Verification method and device for central processor system

A technology for central processing unit and system verification, which is applied in the field of performance verification and can solve the problems of complex circuit structure and workflow of heterogeneous multi-core structure and difficult verification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

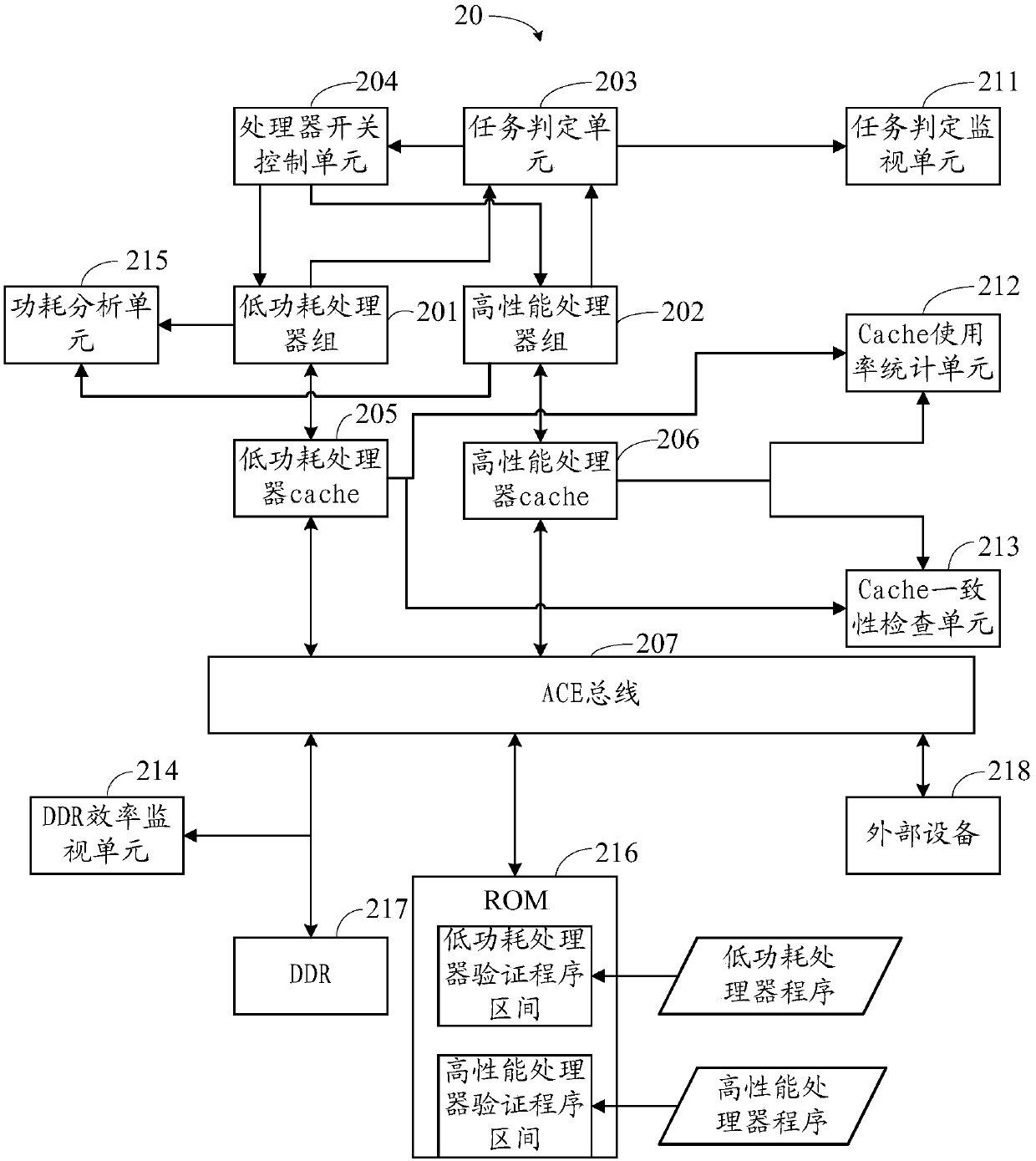

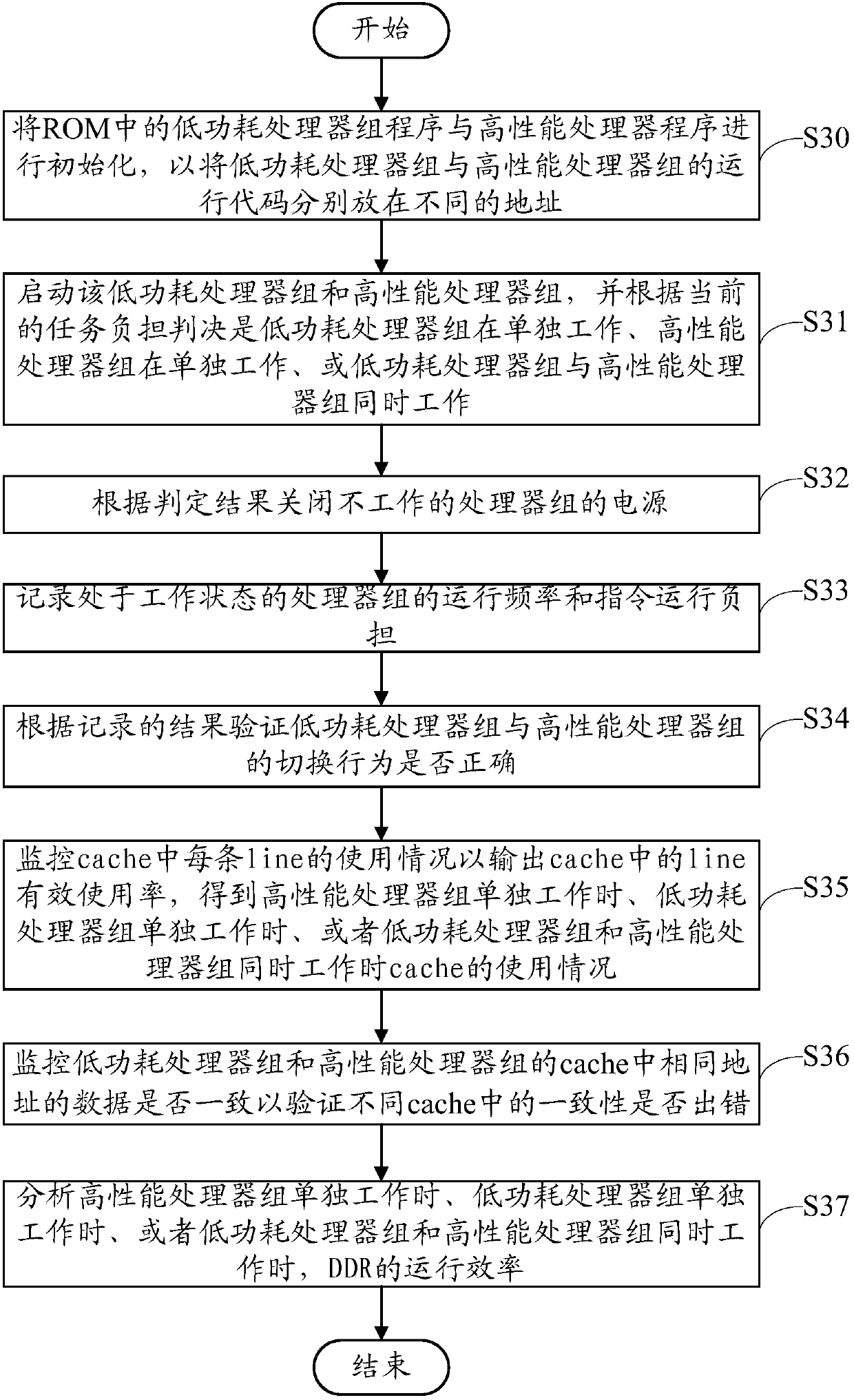

[0035] In order to describe the technical content, structural features, achieved goals and effects of the present invention in detail, the following will be described in detail in conjunction with the embodiments and accompanying drawings.

[0036] ACE bus protocol: ACE protocol is the coherence extension protocol (ACE) of ARM's AMBA 4 bus, which can realize data consistency between multiple CPU processors, better utilize cache memory and simplify software development.

[0037] Cache: Cache memory (cache) is a memory that exists between the main memory and the CPU. It is composed of a static memory chip (SRAM). The capacity is relatively small but the speed is much higher than that of the main memory, and it is close to the speed of the CPU.

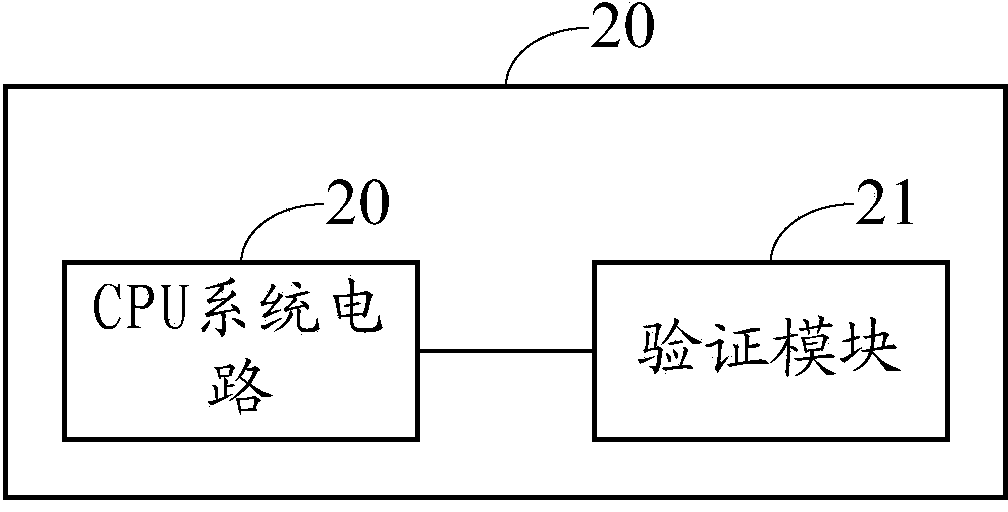

[0038] Please also see figure 1 , 2 , is a schematic structural diagram of a CPU system verification device in an embodiment of the present invention, the device 10 includes a CPU system circuit 20 and a verification module 21 .

[003...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com