Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32 results about "Many-valued logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In logic, a many-valued logic (also multi- or multiple-valued logic) is a propositional calculus in which there are more than two truth values. Traditionally, in Aristotle's logical calculus, there were only two possible values (i.e., "true" and "false") for any proposition. Classical two-valued logic may be extended to n-valued logic for n greater than 2. Those most popular in the literature are three-valued (e.g., Łukasiewicz's and Kleene's, which accept the values "true", "false", and "unknown"), the finite-valued (finitely-many valued) with more than three values, and the infinite-valued (infinitely-many valued), such as fuzzy logic and probability logic.

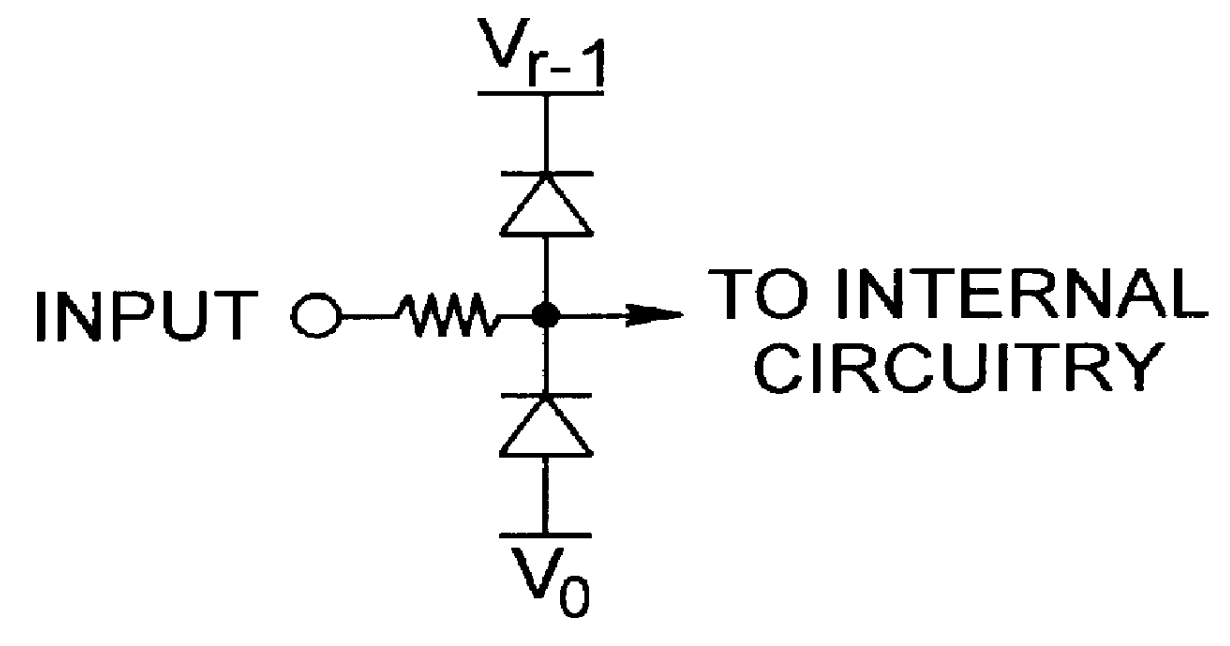

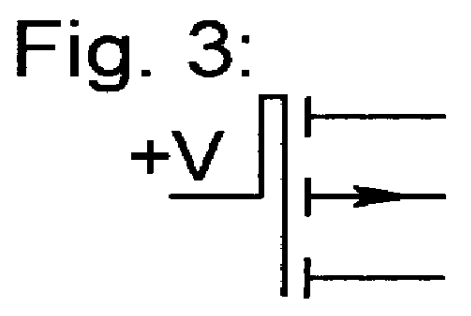

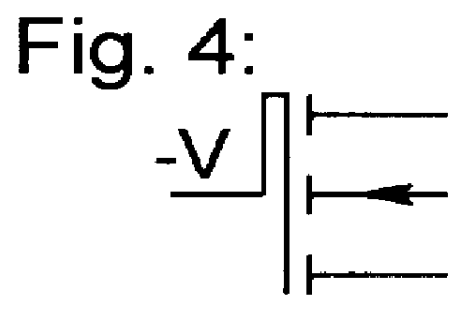

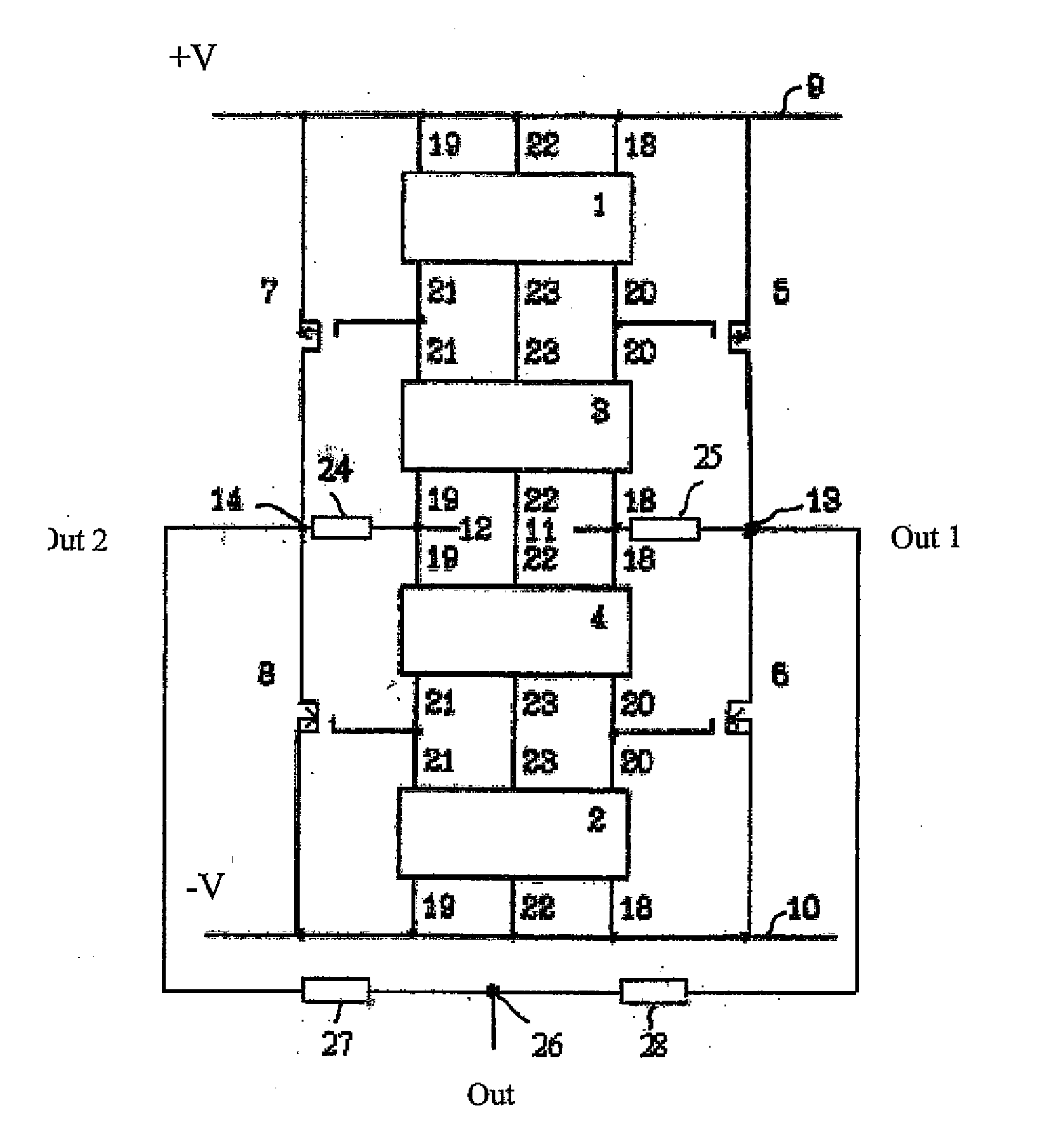

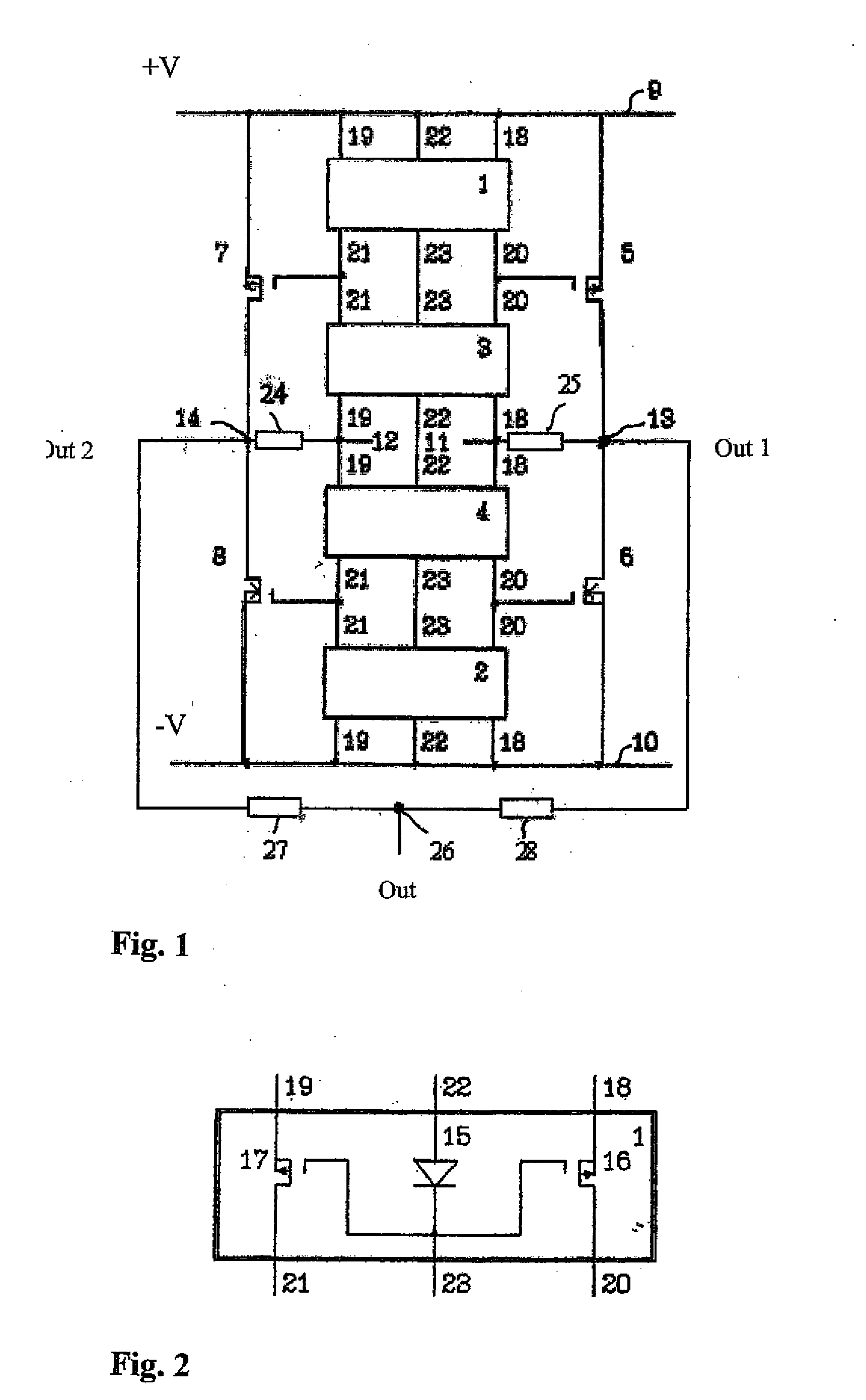

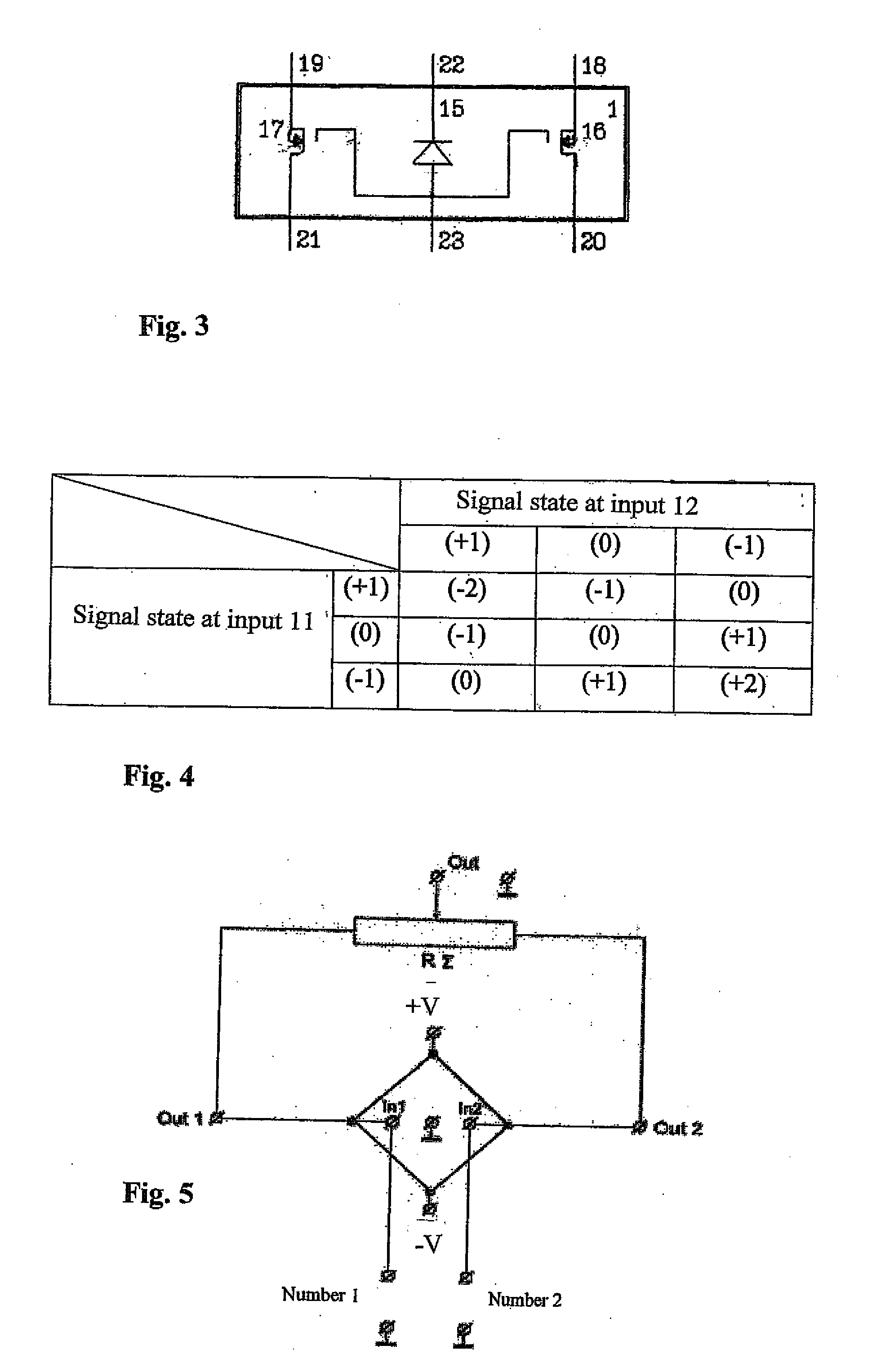

Multiple-valued logic circuit architecture; supplementary symmetrical logic circuit structure (SUS-LOC)

InactiveUS6133754AEasy to copyEasy transferPower consumption reductionLogic circuits characterised by logic functionMany-valued logicLogic synthesis

Circuit structure and resulting circuitry for multiple-valued logic. The circuit structure allows the design and fabrication of any r-valued logic function of n-places where r is an integer greater than 1 and n is an integer greater than 0. This structure is called SUpplementary Symmetrical LOgic Circuit structure (SUS-LOC). In circuits incorporating SUS-LOC, circuit branches are realized that uniquely deliver circuit response and output. For some circuits, and due to the operating characteristics of the switch elements, additional circuit elements, or stages, must be incorporated to prevent "back biasing." SUS-LOC is fully active. Only active elements perform logic synthesis and those components not directly related to logic synthesis, such as resistors and / or other passive loads, are relegated the task of circuit protection. The fabrication of r-valued, multi-valued, or multiple-valued logic circuits, designed using the definitions of the SUS-LOC structure can be accomplished with known techniques, materials, and equipment.

Owner:OMNIBASE LOGIC

Variable threshold transistor for the Schottky FPGA and multilevel storage cell flash arrays

InactiveUS20060044018A1Low powerImprove performanceMultistate logicSolid-state devicesSchottky barrierMulti-level cell

An IC solution utilizing mixed FPGA and MLC arrays is proposed. The process technology is based on the Schottky CMOS devices comprising of CMOS transistors, low barrier Schottky barrier diode (SBD), and multi-level cell (MLC) flash transistors. Circuit architectures are based on the pulsed Schottky CMOS Logic (SCL) gate arrays, wherein a variable threshold NMOS transistor may replace the regular switching transistor. During initialization windows, existing FPGA programming techniques can selectively adjust the VT of the switching transistor, re-configure the intra-connections of the simple SCL gates, complete all global interconnections of various units. Embedded hardware arrays, hardwired blocks, soft macro constructs in one chip, and protocols implementations are parsed. A wide range of circuit applications involving generic IO and logic function generation, ESD and latch up protections, and hot well biasing schemes are presented. The variable threshold transistors thus serve 3 distinctive functions. It acts as an analog device to store directly nonvolatile information in SCL gates. It couples the diode tree logic functions. Finally, it stores and operates large amount of information efficiently. The mixed SCL type FPGA and MLC storages shall emerge as the most compact logic and memory arrays in Si technology. Low power, high performance, and high capacity ICs are designed to mix and replace conventional CMOS-TTL circuits. The idea of multi-value logic composed of binary, ternary, and quaternary hardware and firmware is also introduced.

Owner:SUPER TALENT ELECTRONICS

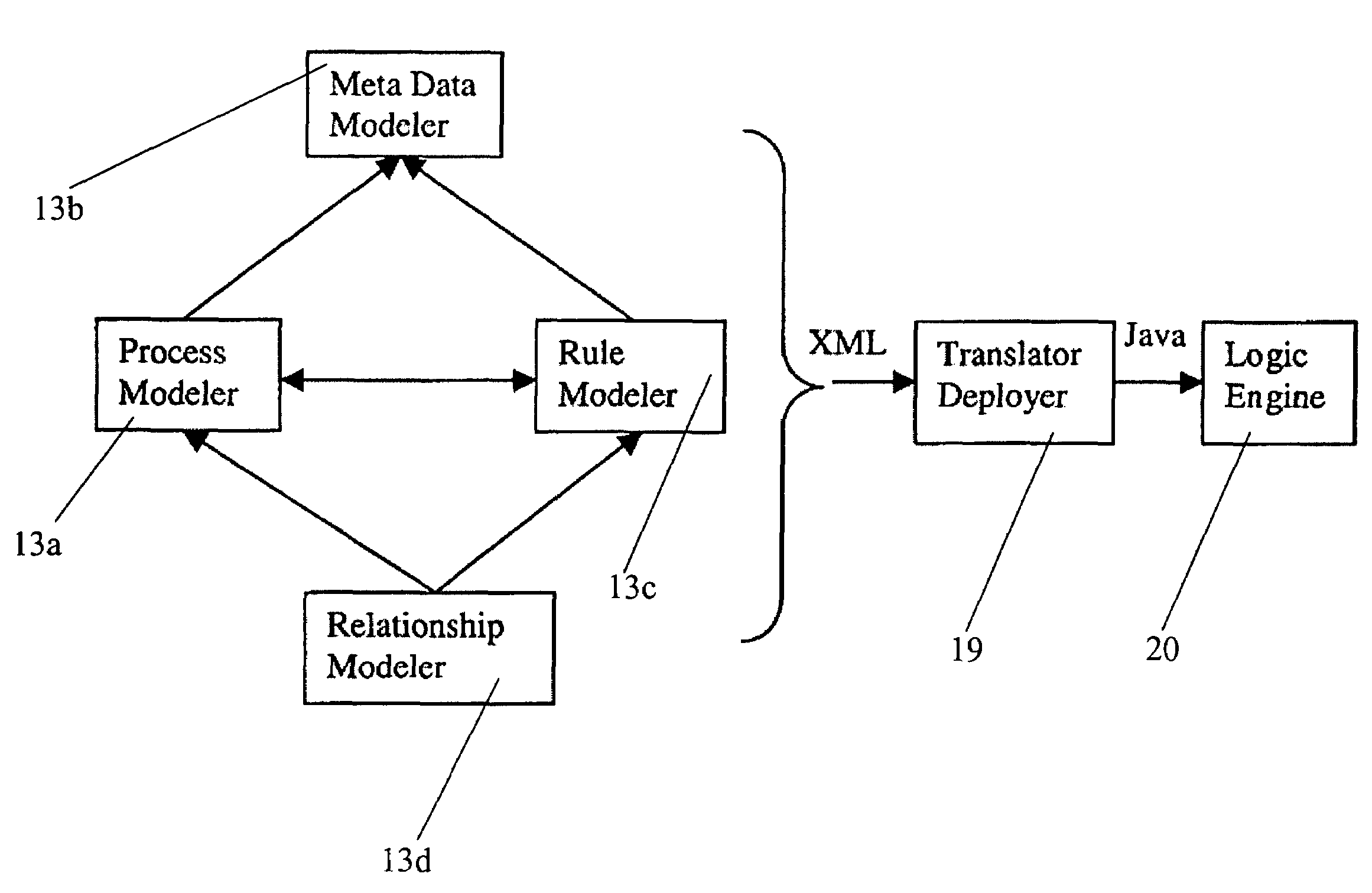

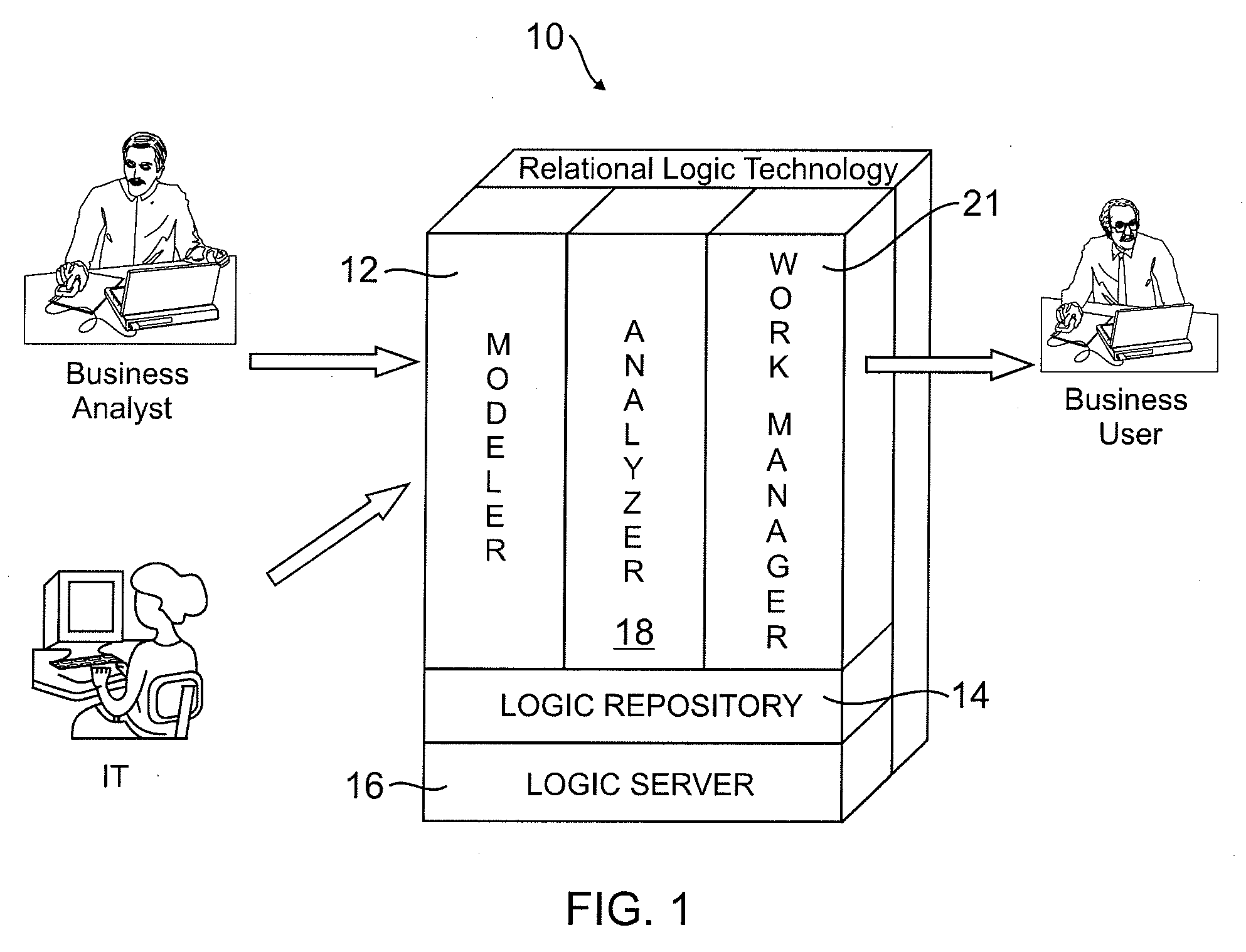

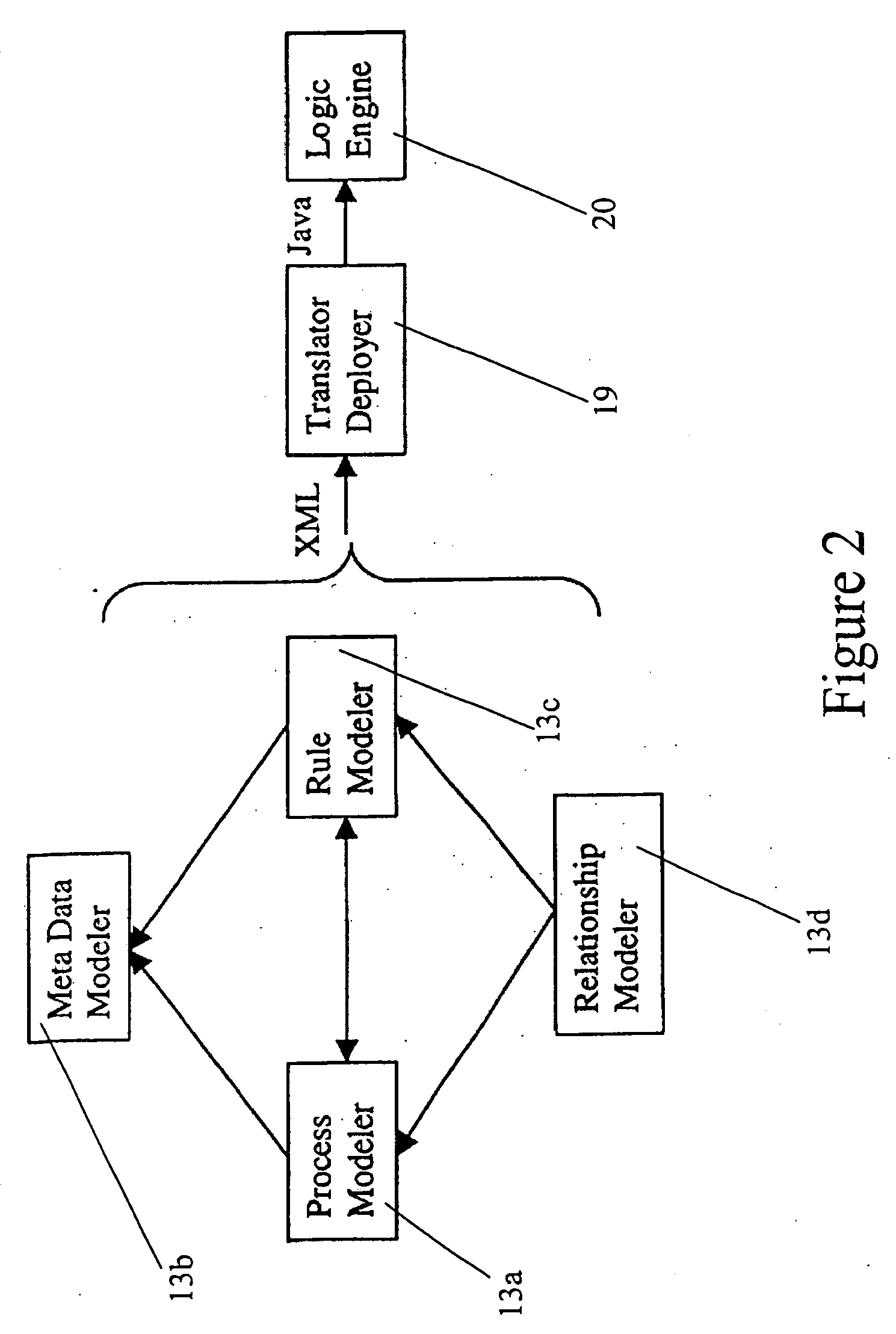

Relational logic management system

ActiveUS7428519B2Easy to trackEasy to reuseKnowledge representationResourcesControl flowWorkflow model

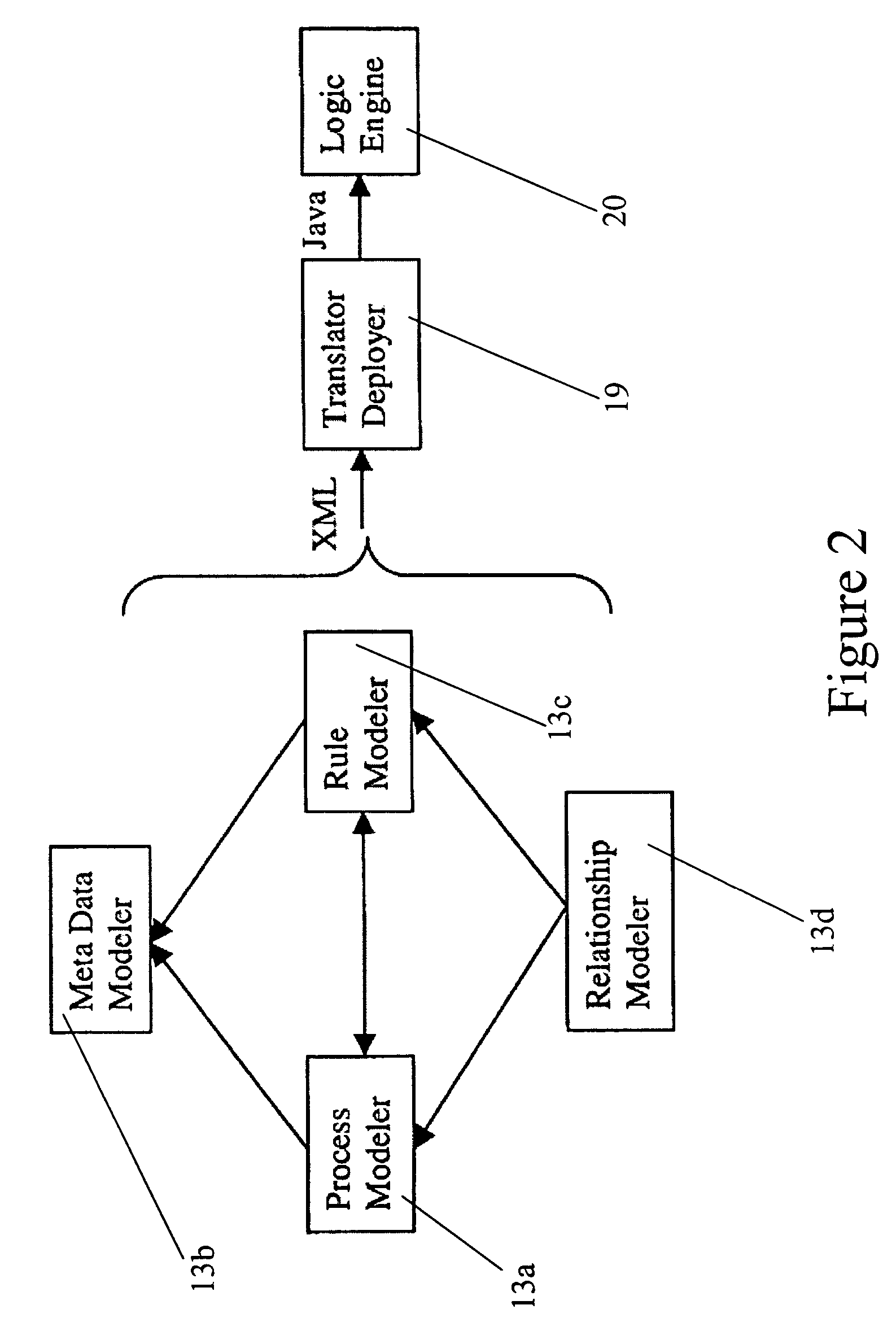

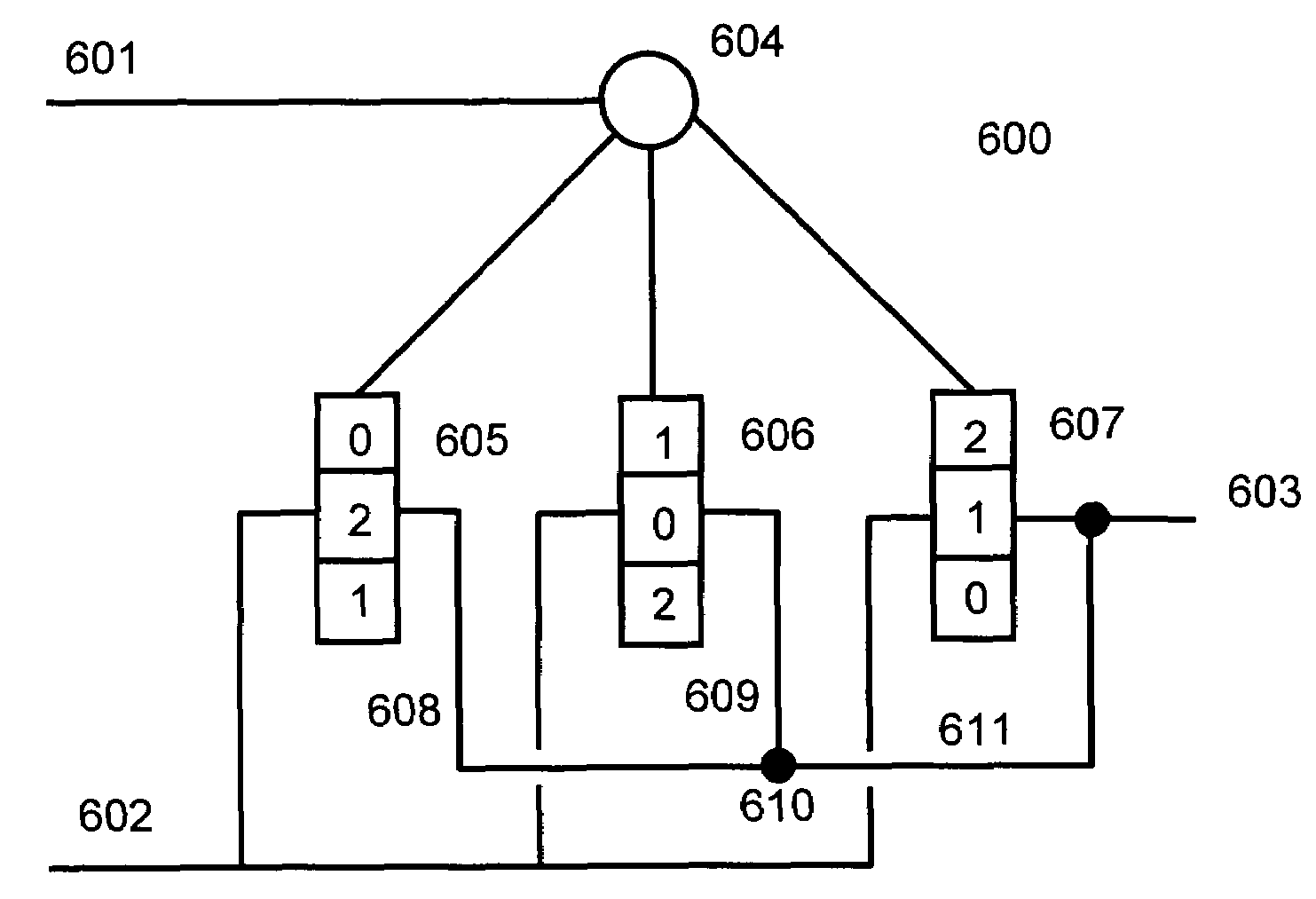

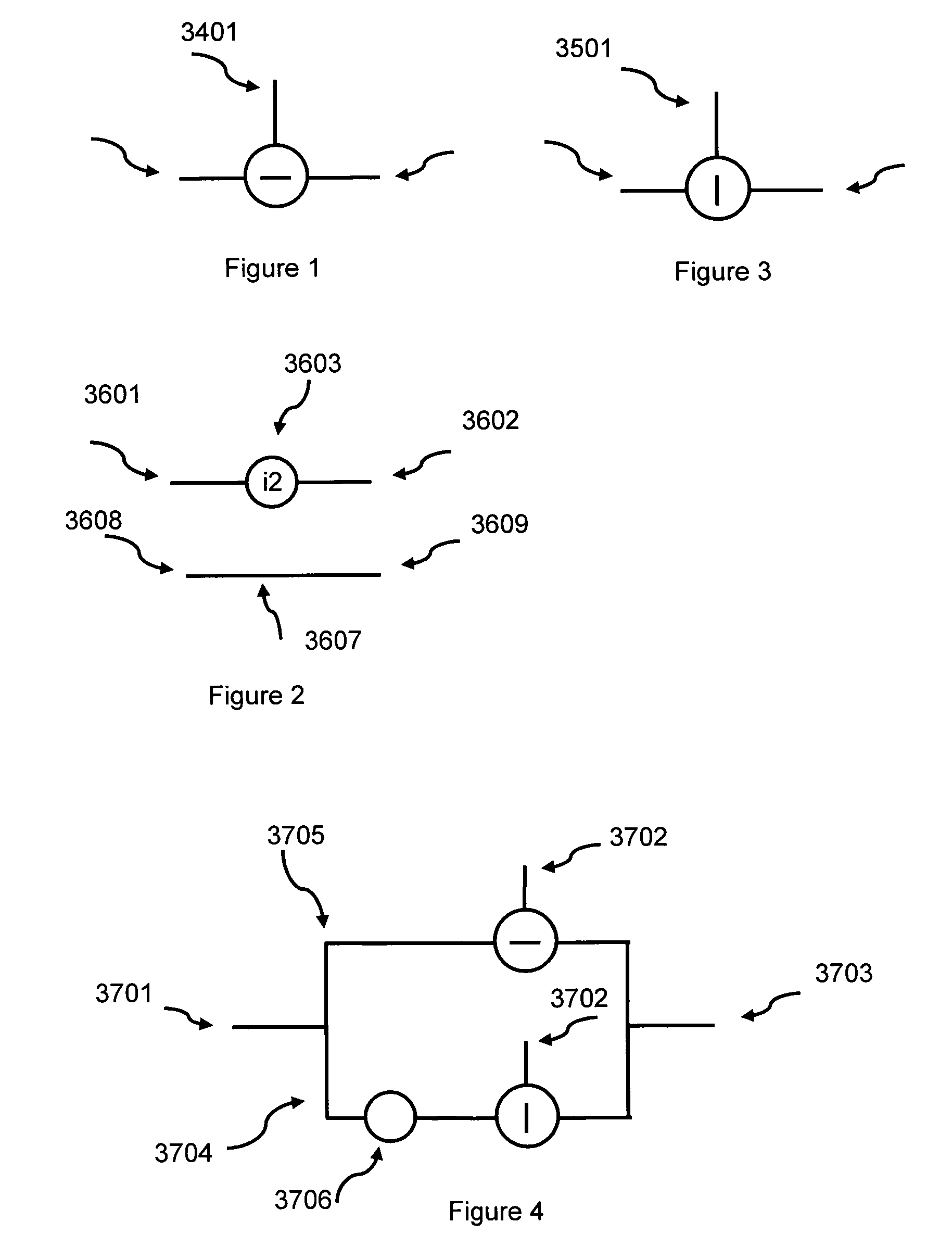

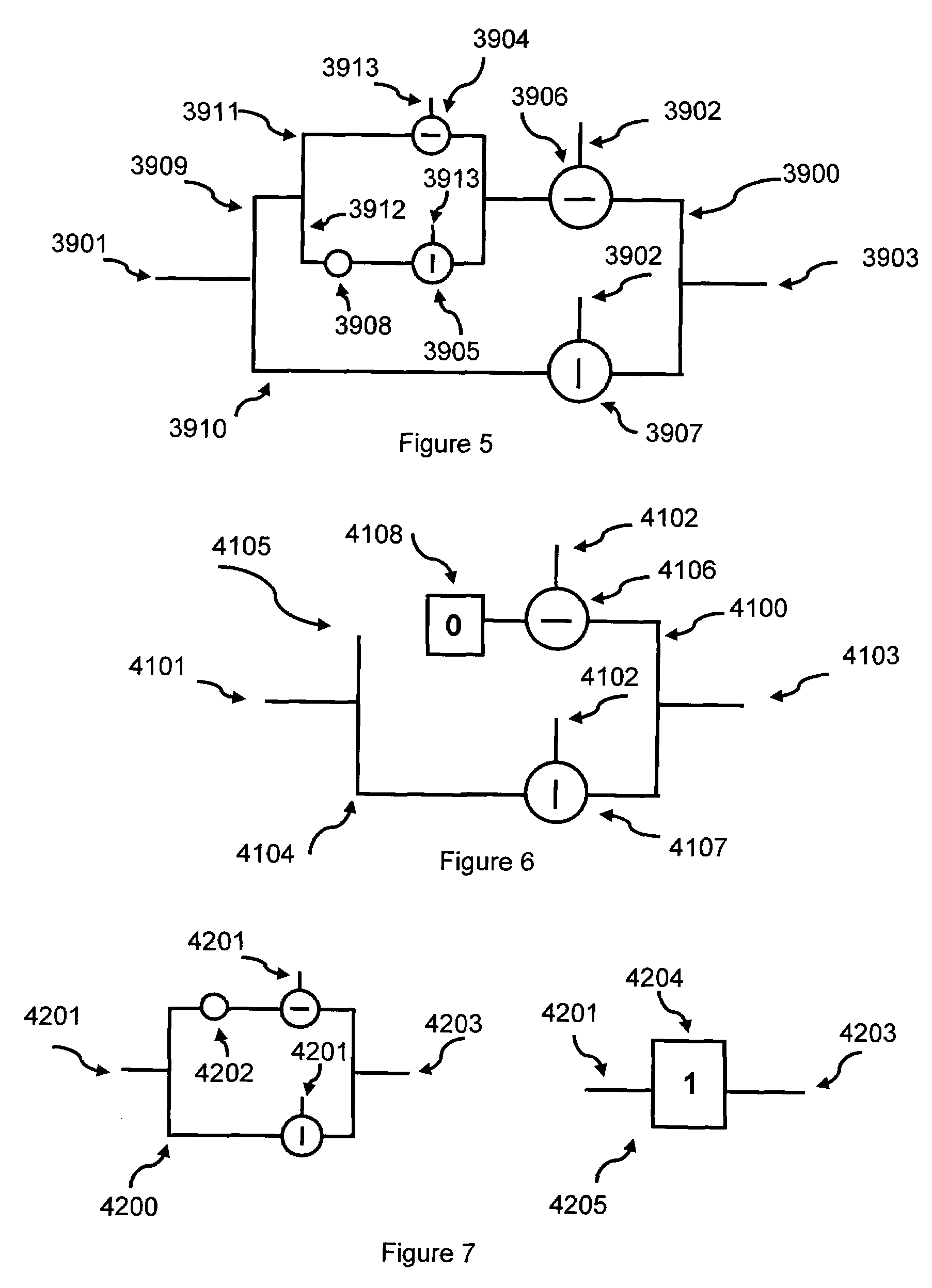

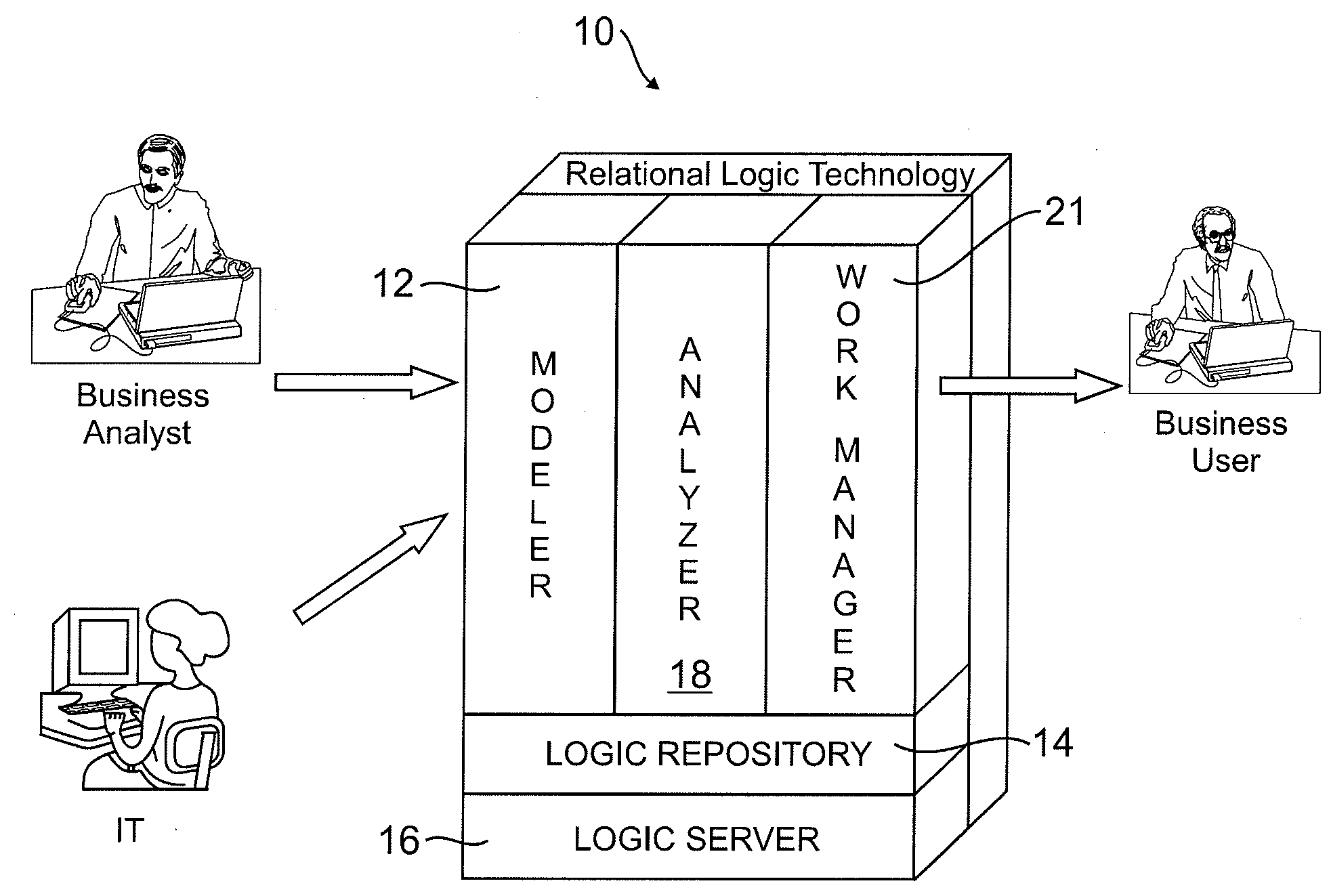

In one aspect, the invention relates to a method to propagate relations between a first rule set and a second rule set wherein the first and second rule sets are invoked by a common workflow model. The method includes tracing paths forward through the workflow model from the first rule set to the second rule set. Enumerating relations that extend forward from the first rule set to the second rule set is another step in the method. Additionally, using multi-valued logic, calculating the effects on the relations of control flow through the workflow model from the first rule set to the second rule set, tracing paths backward through the workflow model from the second rule set to the first rule set, enumerating relations that extend backward from the second rule set to the first rule set, and using multi-valued logic, calculating the effects on the relations of control flow backwards through the workflow model from the second rule set to the first rule set are also steps in the method.

Owner:FAIR ISAAC & CO INC

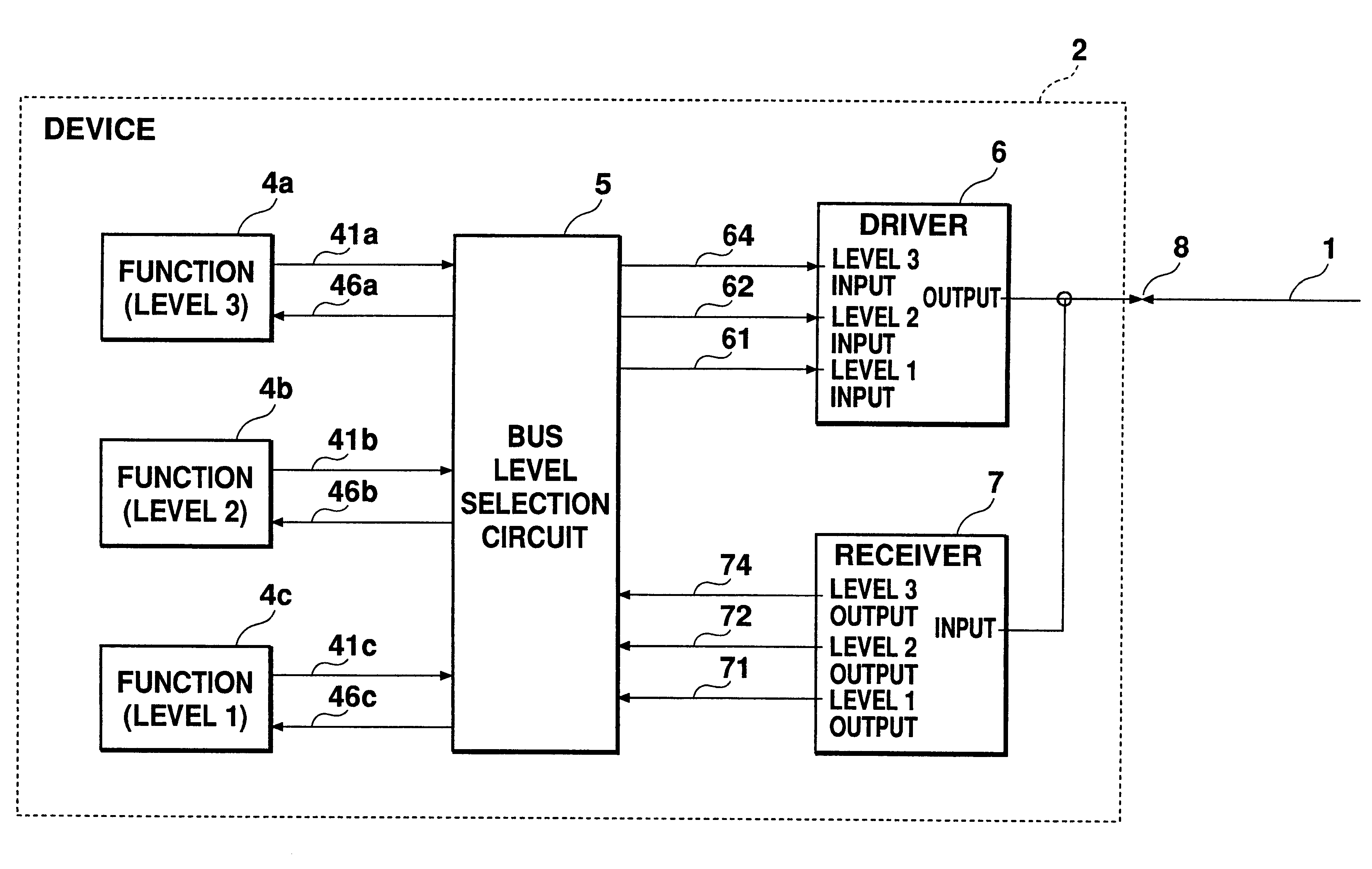

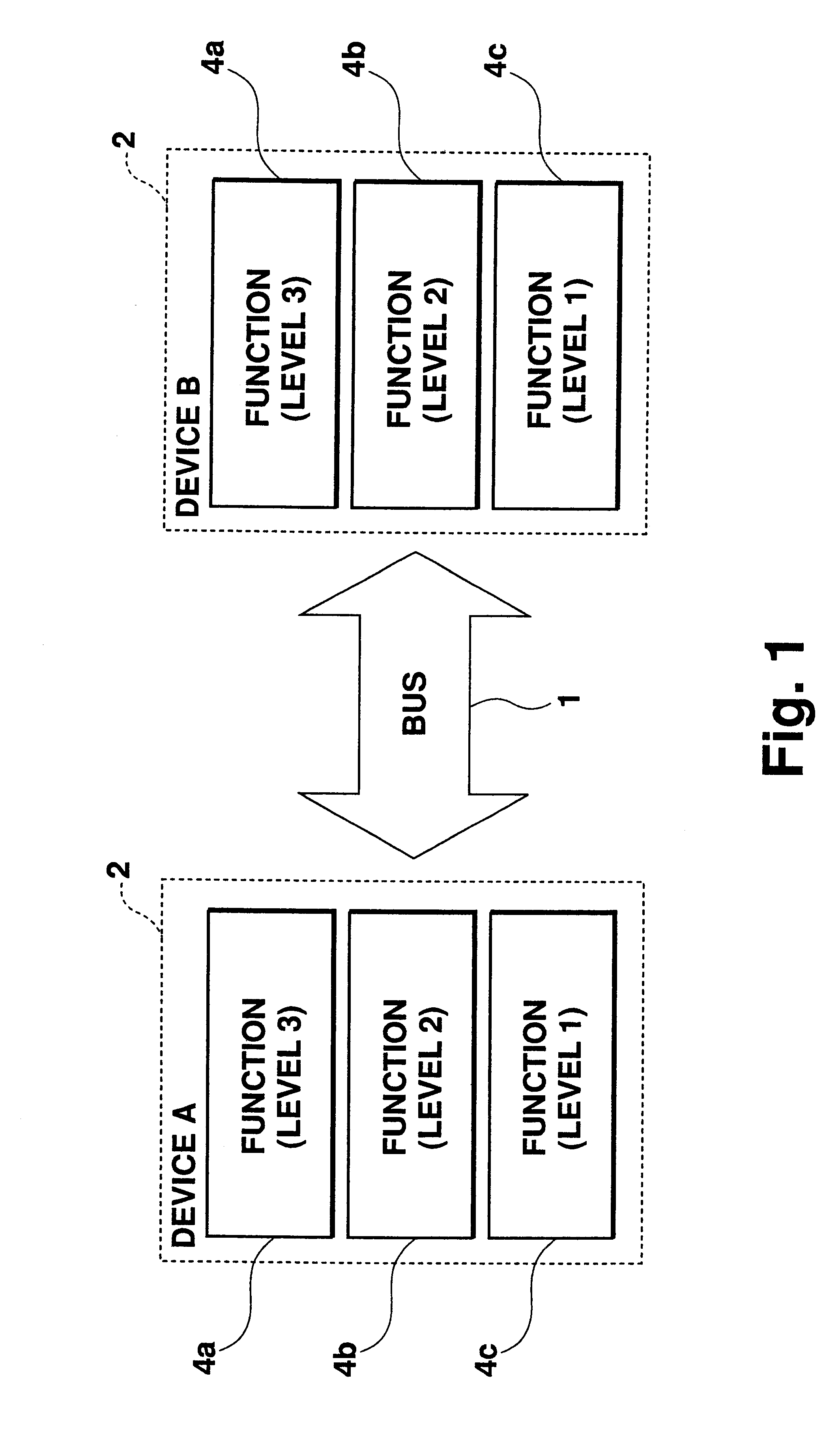

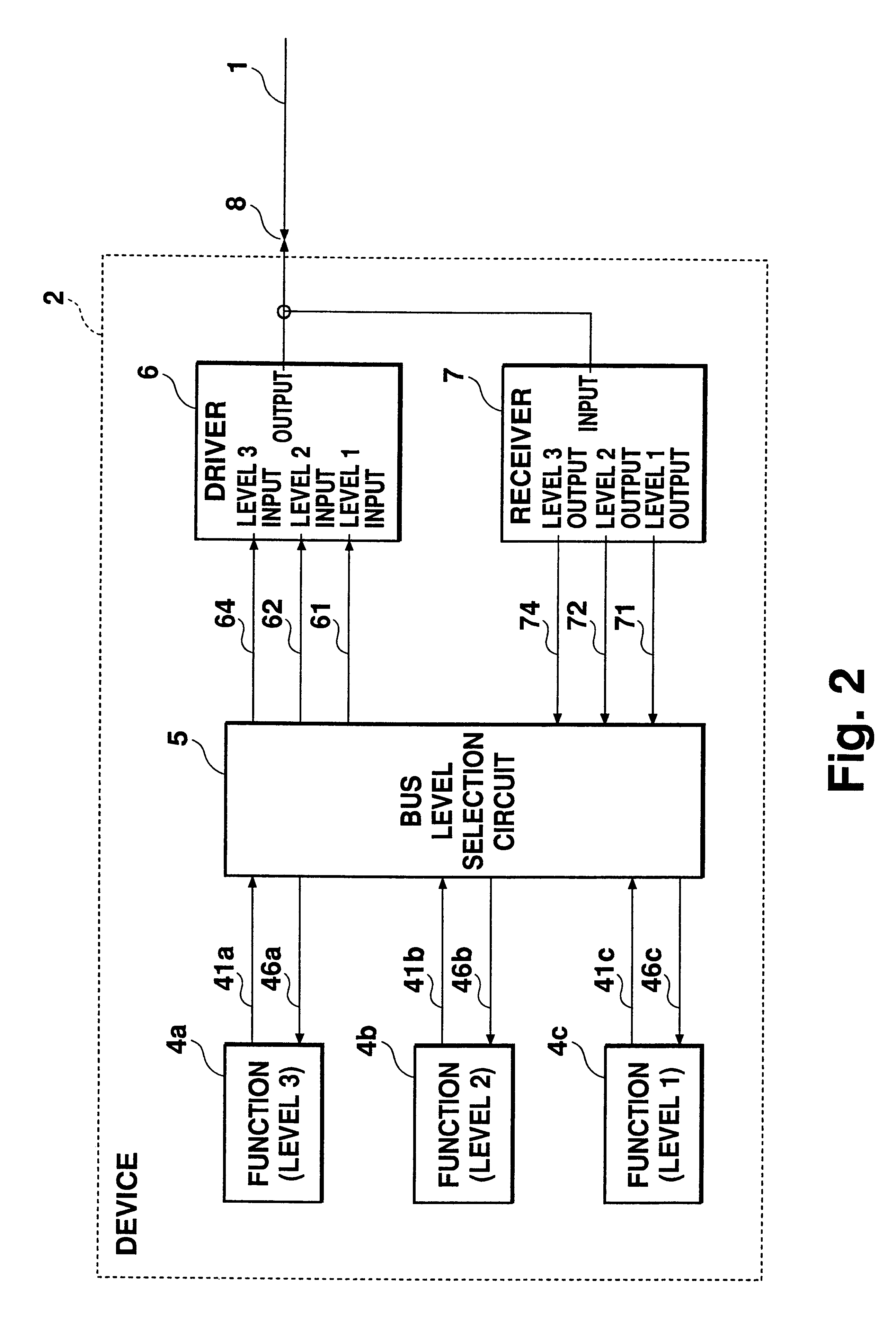

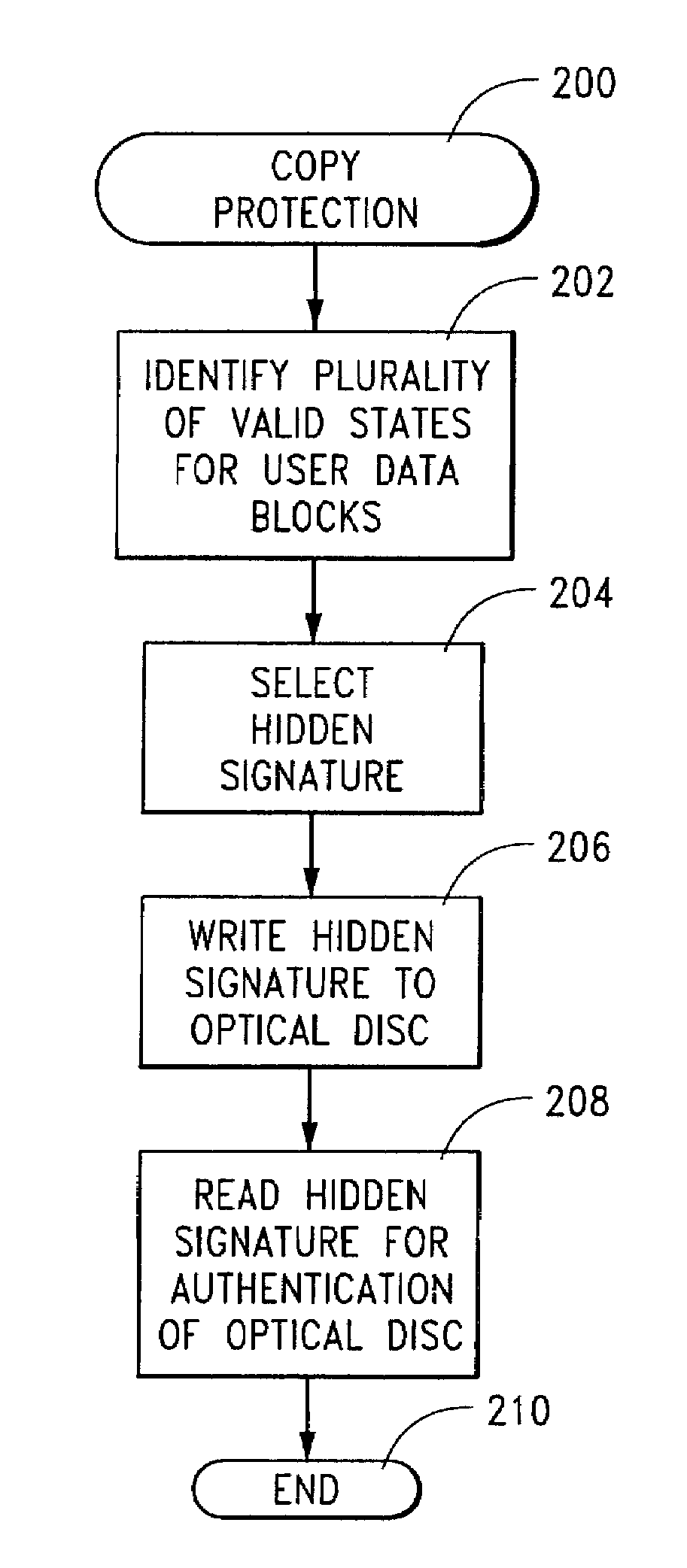

Multi-value logic device, bus system of multi-value logic devices connected with shared bus, and network system of information processors loaded with multi-value logic devices and connected with shared network

InactiveUS6266722B1Logic circuits characterised by logic functionInput/output processes for data processingElectrical conductorNetwork connection

A multi-value logic device in which a unique bus level is allocated beforehand to each binary logic signal outputted by a function of the multi-value logic device. Upon receipt of the binary logic signal via a bus level selection circuit, a driver converts the binary logic signal to an analog signal with a voltage having an amplitude of e.2n-1, in which n is the bus level of the binary logic signal and e is a reference voltage. When a plurality of binary logic signals are simultaneously inputted, the driver superimposes analog signals in accordance with the bus level of each binary logic signal to generate a multi-value logic signal, so that multiplex communication is realized. A receiver performs an operation reverse to the operation of the driver, and encodes a multi-value logic signal received via a bus to convert the signal to a binary logic signal and transmit the signal to each function. In this manner, the multi-value logic device suppresses an increase in the number of bus signal conductors, and enhances throughput by realizing multiplex communication.

Owner:MITSUBISHI ELECTRIC CORP

Single and composite binary and multi-valued logic functions from gates and inverters

InactiveUS7218144B2Minimum propagation timePractical to useLogic circuits characterised by logic functionMultistate logicEngineeringMany-valued logic

Owner:TERNARYLOGIC

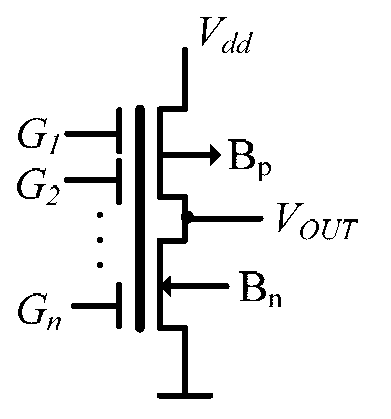

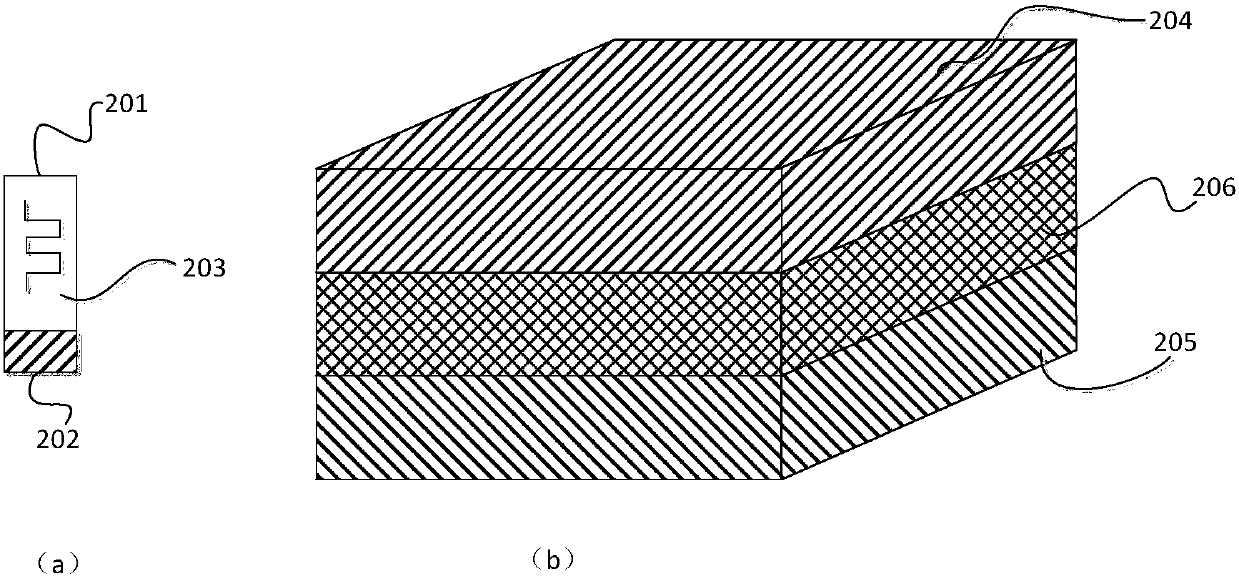

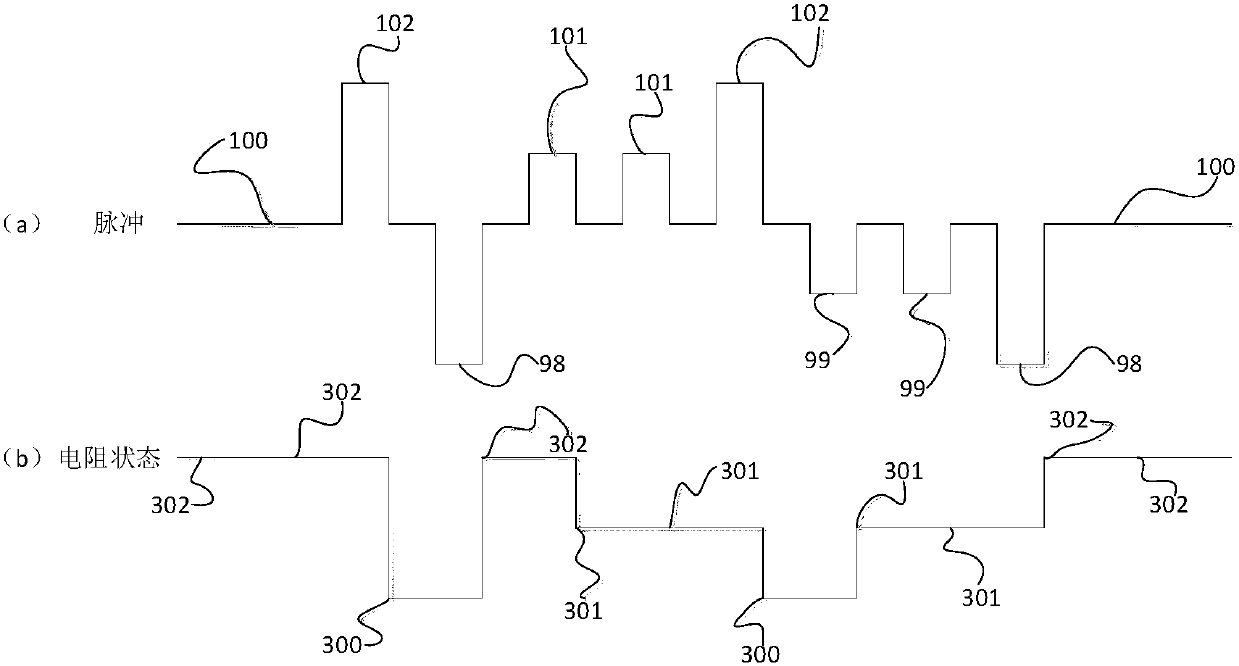

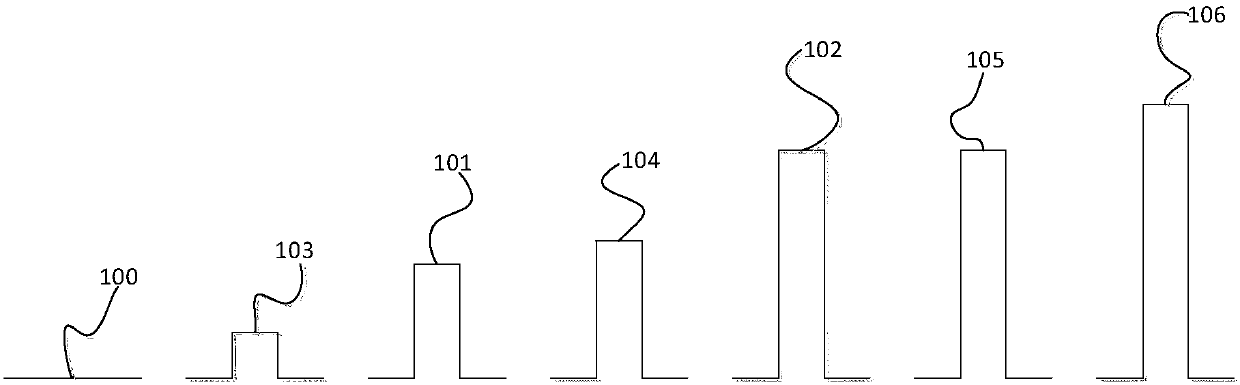

Memristor-based multivalued logic device and operating method thereof

ActiveCN105761750AImplement storageRealize computingDigital storageElectrical resistance and conductanceNegation

The invention discloses a memristor-based nonvolatile multivalued logic device and an operating method thereof. The method provides an operating method for negation and dextrorotation of three-valued logic and multivalued T gate logic, which realizes an exhaustive set of multivalued logic, such as three-valued logic based on the multi-resistance state transition characteristic of a memristor. All the logic operation results are stored in the device in a nonvolatile resistance state, such that a logic operation function and a data storage function are realized simultaneously in the device, i.e., storage and calculation are fused; therefore, a device basis is laid for going beyond the limitation from an information device Moore's law and breaking through the Von Neumann bottleneck in a computer architecture. The memristor-based multivalued logic device disclosed by the invention can be applied to a novel solid-state memory, a logic-arithmetic unit, a programmable gate array, an on-chip system and other fields as a basic unit, and provides a new path for boosting novel computer architecture.

Owner:HUAZHONG UNIV OF SCI & TECH

Relational logic management system

In one aspect, the invention relates to a method to propagate relations between a first rule set and a second rule set wherein the first and second rule sets are invoked by a common workflow model. The method includes tracing paths forward through the workflow model from the first rule set to the second rule set. Enumerating relations that extend forward from the first rule set to the second rule set is another step in the method. Additionally, using multi-valued logic, calculating the effects to the relations of control flow through the workflow model from the first rule set to the second rule set, tracing paths backward through the workflow model from the first rule set to the second rule set, enumerating relations that extend backward form the second rule set to the first rule set, and using multi-valued logic, calculating the effects on the relations of control flow backwards through the workflow model from the second rule set to the first rule set are also steps in the method.

Owner:FAIR ISAAC & CO INC

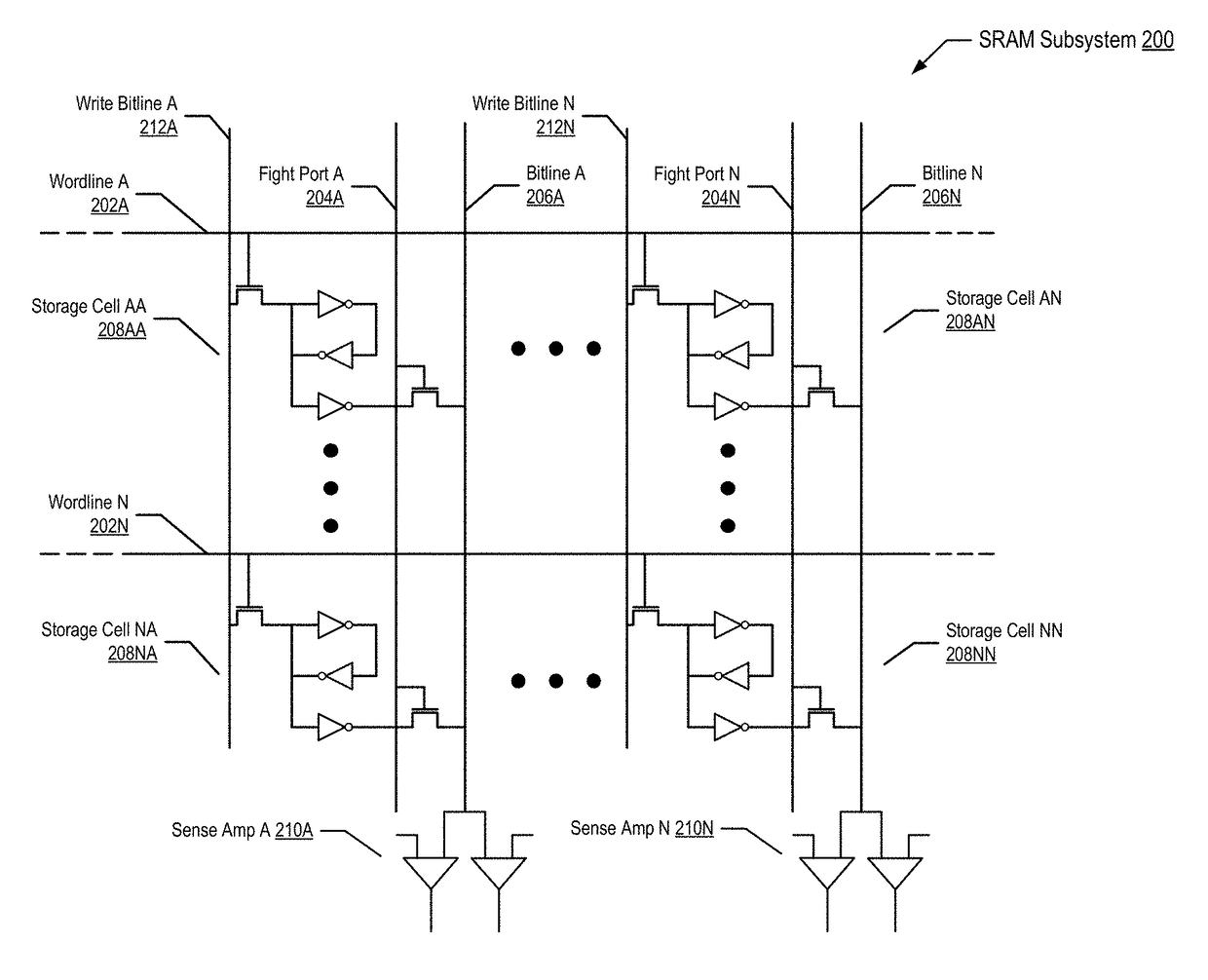

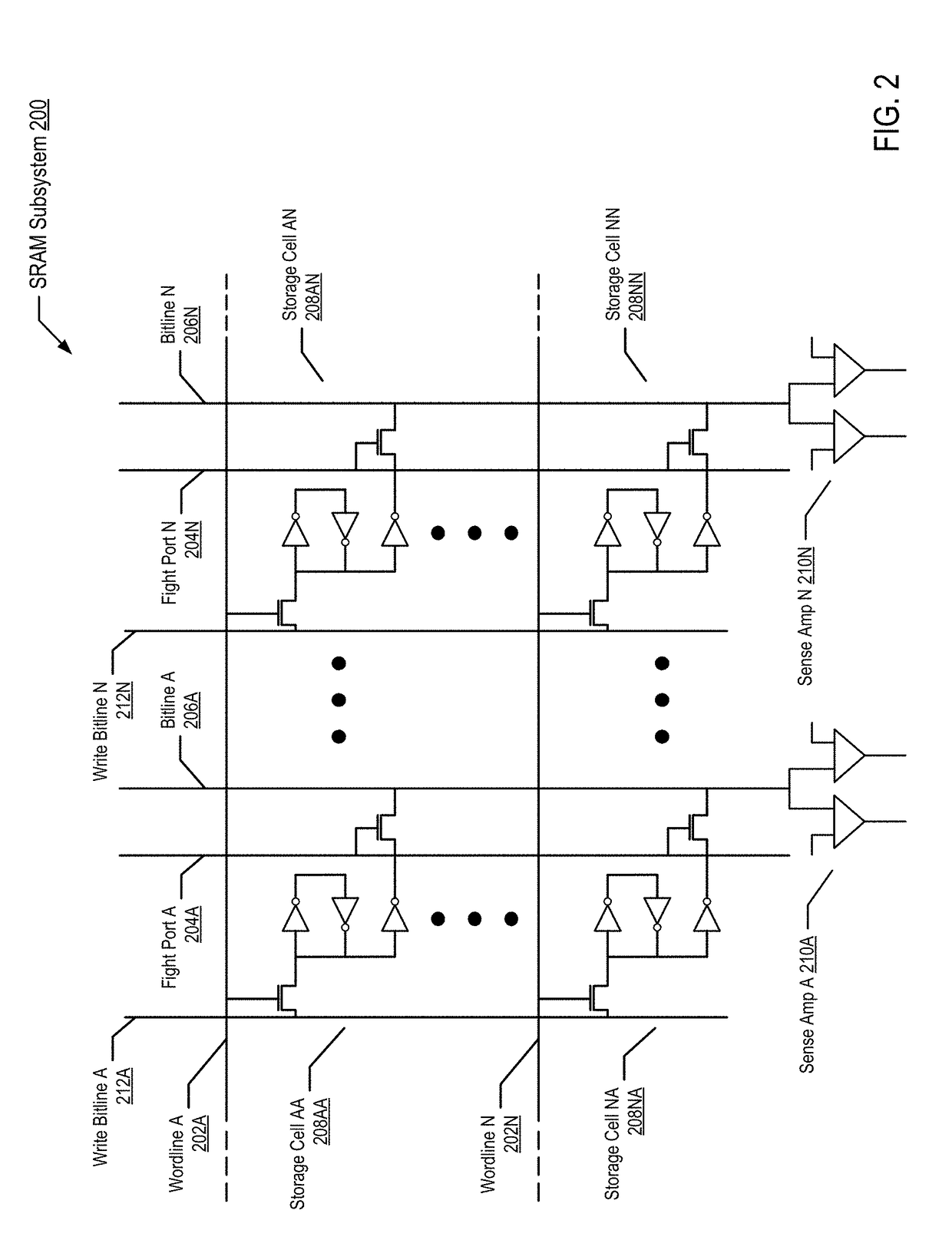

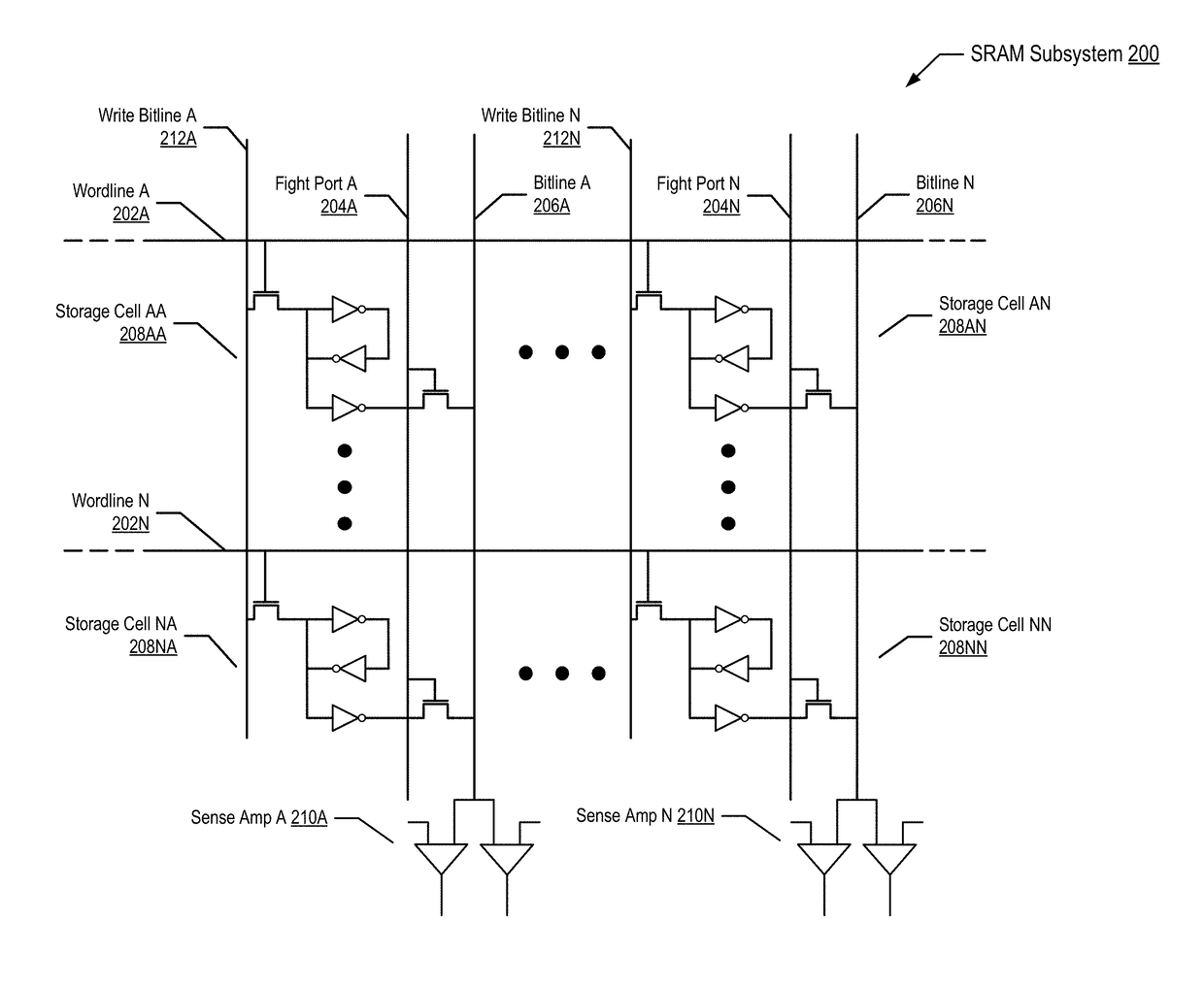

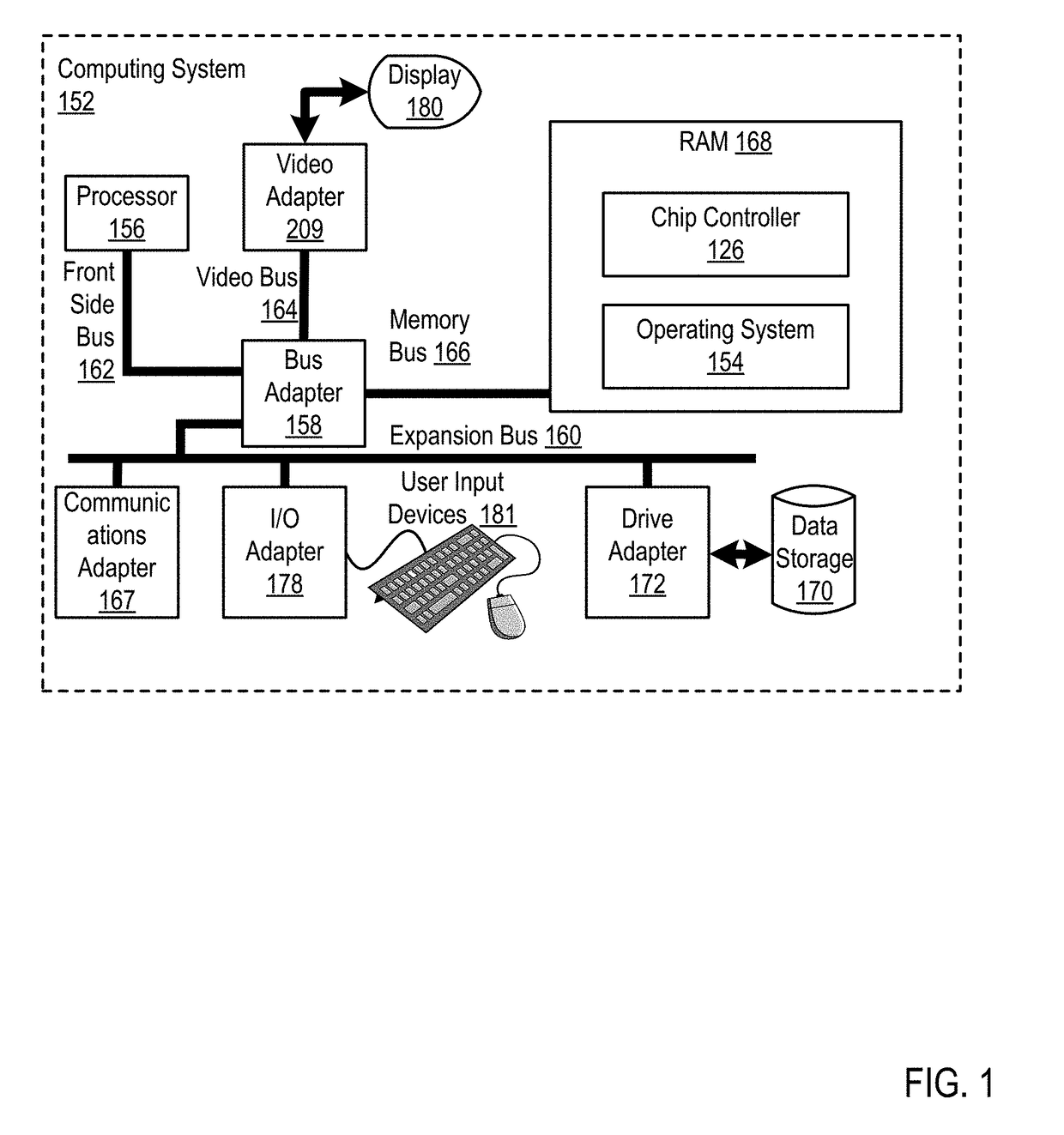

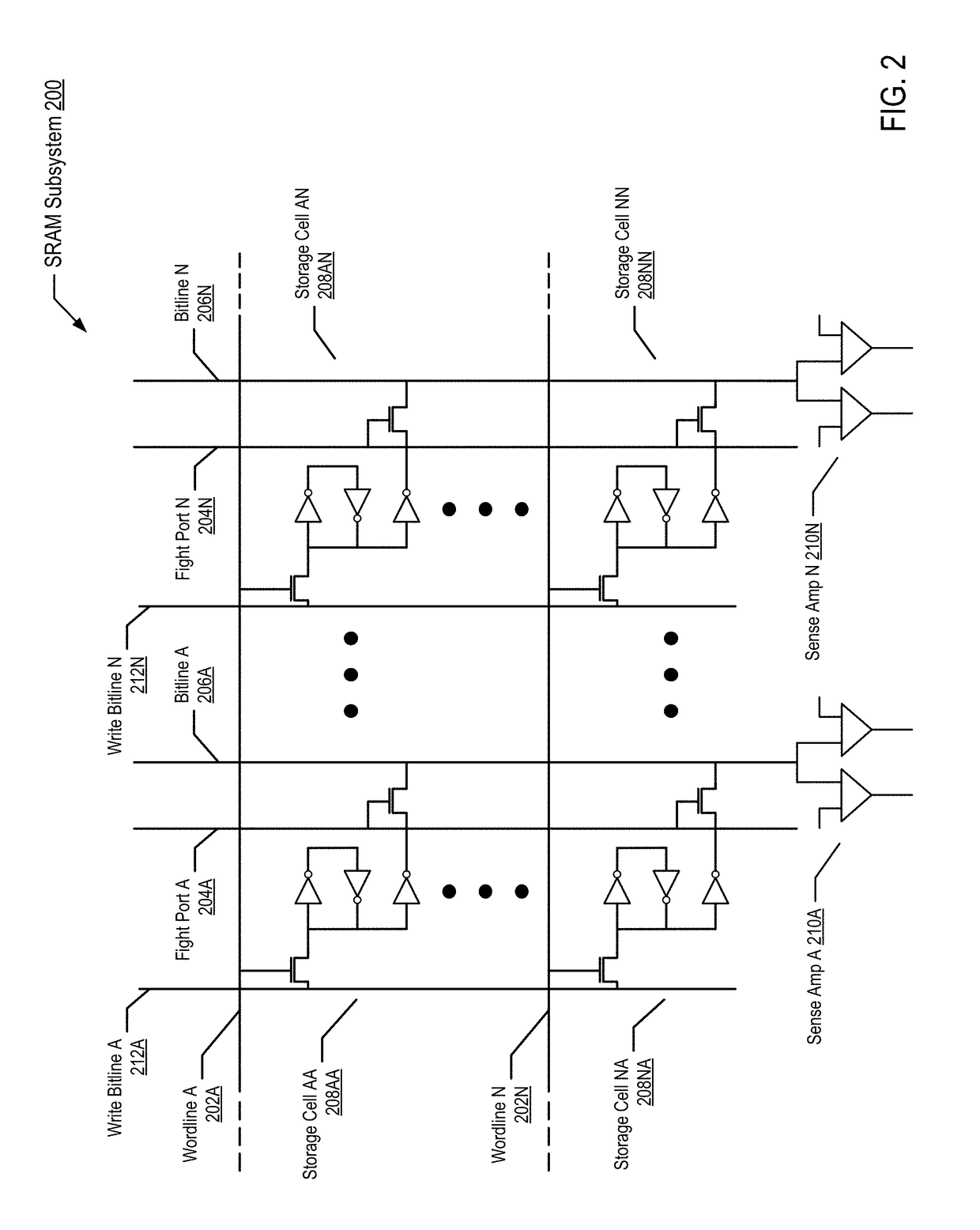

Predicting data correlation using multivalued logical outputs in static random access memory (SRAM) storage cells

ActiveUS9916890B1Natural language data processingDigital storageStatic random-access memoryRandom access memory

Predicting data correlation using multivalued logical outputs in SRAM storage cells including generating a plurality of logical outputs for each of a plurality of variable sets, wherein each variable in each variable set is a data point, and wherein each logical output is a binary indication of a relationship between the data points; writing, into storage cells, each logical output of the plurality of logical outputs for each of the plurality of variable sets; and for each group of corresponding logical outputs of the plurality of logical outputs: activating a fight port for the storage cells storing corresponding logical outputs, wherein activating the fight port causes each corresponding logical output to adjust a resulting voltage based on the logical output stored in each storage cell; and measuring the resulting voltage on a bitline of the activated fight port to determine a correlation probability for the corresponding logical outputs.

Owner:IBM CORP

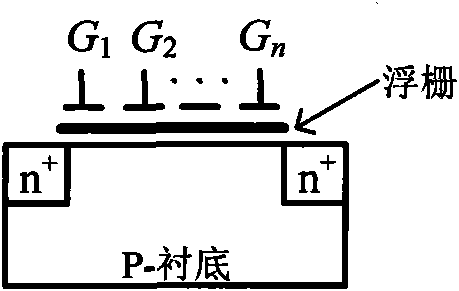

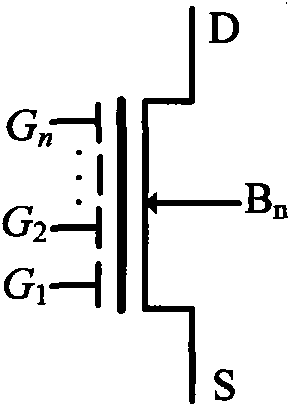

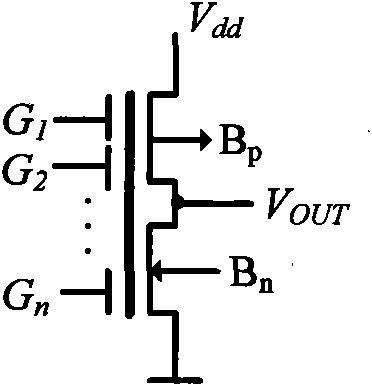

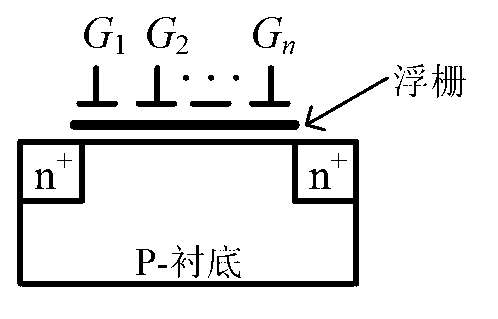

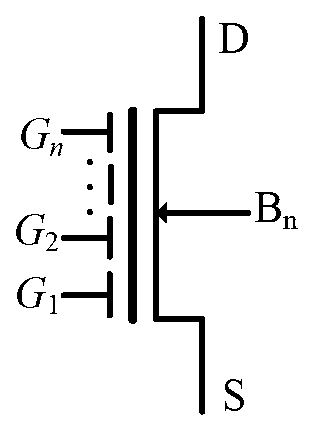

Multiple-valued counter unit based on nerve MOS tube and multi-digit multiple-valued counter

InactiveCN101777139ALow costReduce power consumptionCounting mechanisms/objectsSemiconductor devicesInput controlMany-valued logic

The invention discloses a multiple-valued counter unit based on an MOS tube, which comprises a nerve MOS source electrode follower and at least one unit trigger circuit connected on an input control grid of the nerve MOS source electrode follower, wherein the unit trigger circuit comprises a first binary D flip-flop, a second binary D flip-flop, an And gate and an OR gate. The invention has the advantages that the nerve MOS tube is used to substitute for complex threshold operation in multi-valued logic, thereby realizing multi-valued logic on the true sense, the multi-valued counter with different cardinal numbers can be realized by increasing the number of the unit trigger circuit forming the binary D flip-flops and connecting the unit trigger circuit forming the binary D flip-flops with an idle input control grid of the source electrode follower. Compare with the traditional multi-valued counter, the invention can greatly save the number of the components, and reduce the cost and the energy consumption of circuit design. The invention adopts the mode of asynchronous carry to realize the multi-digit multi-valued counter on the basis of the multi-valued counter unit, and the circuit which is designed by using PSPICE simulation verification has correct logical function.

Owner:NINGBO UNIV

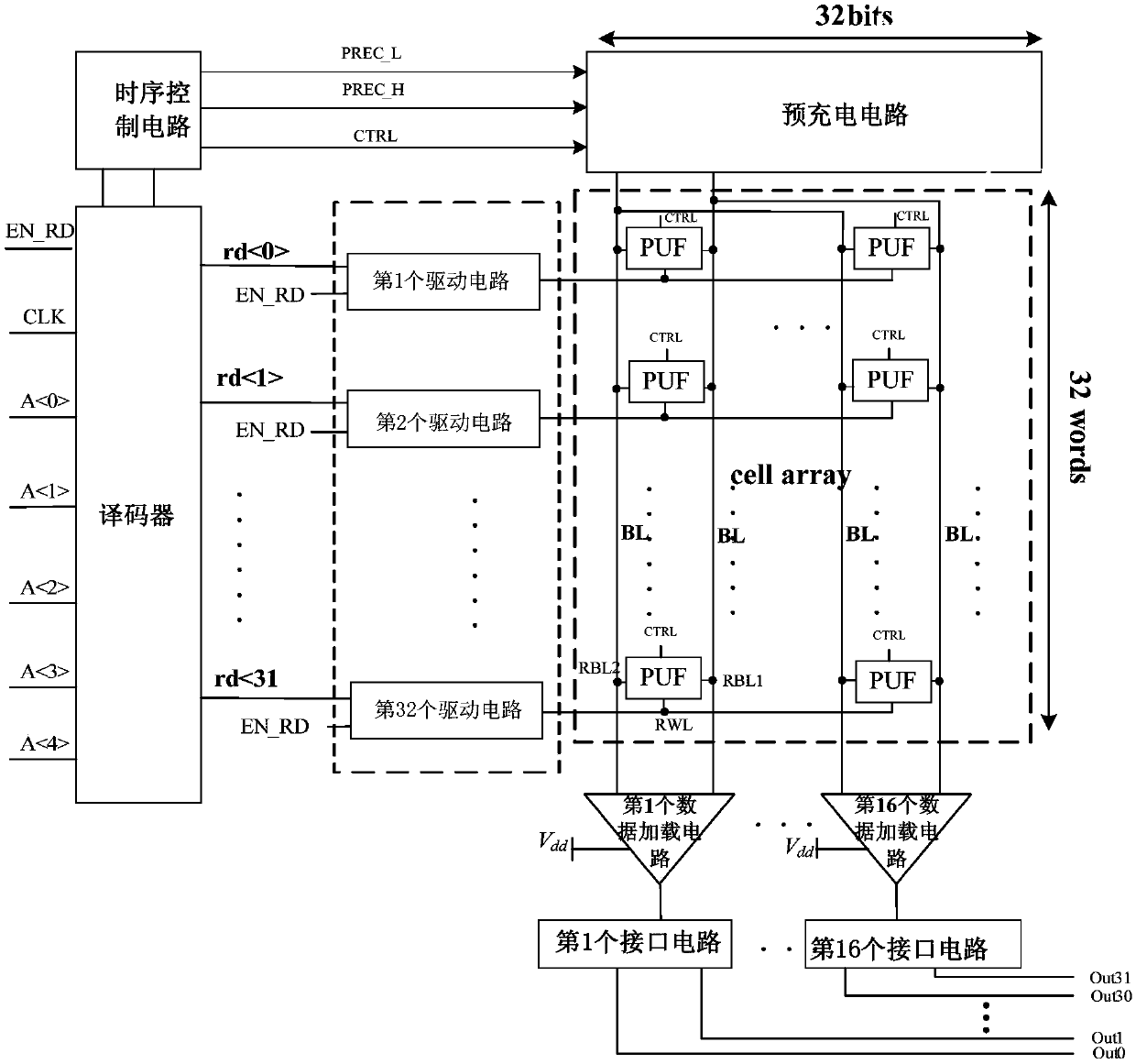

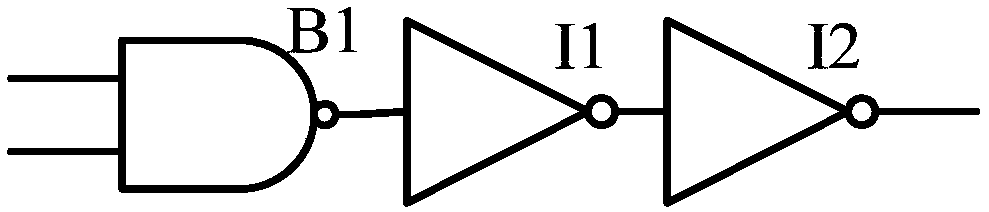

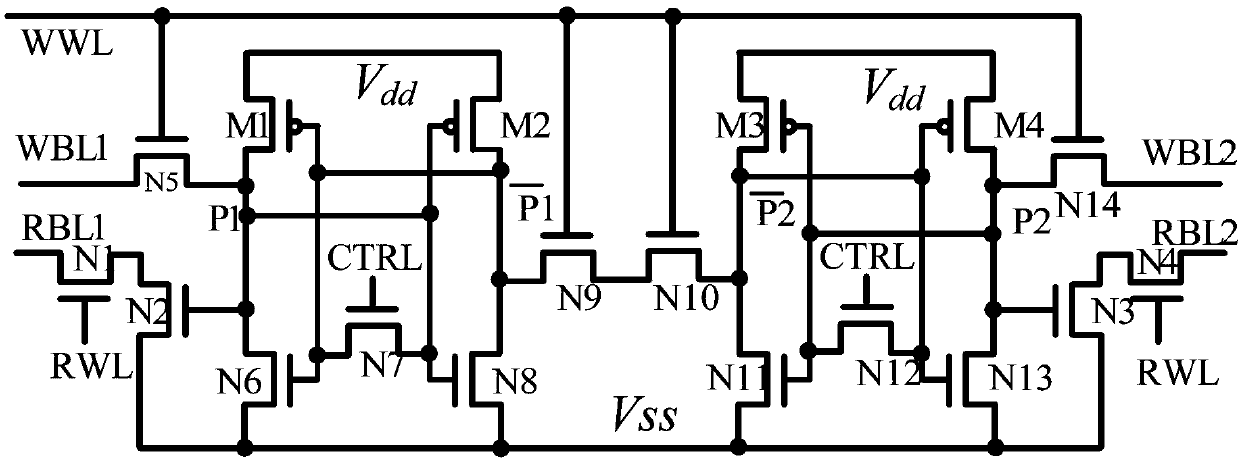

Twin-storage type multi-valued physically unclonable function circuit

ActiveCN107688755AIncrease profitReduce energy consumptionInternal/peripheral component protectionFull customPre-charge

The invention discloses a twin-storage type multi-valued physically unclonable functional circuit which comprises a time sequence control circuit, a decoder, a driver, a pre-charge circuit, a PUF (physically unclonable function) array, 16 data loading circuits and 16 interface circuits. The driver comprises 32 driving circuits with identical structures, and 512 PUF circuits are arranged accordingto a 32 row*16 column mode to form the PUF array. The twin-storage type multi-valued physically unclonable functional circuit has the advantages that 2-bit random source data can be generated by the PUF circuits which are of twin structures, four-valued data can be outputted by multi-valued logic circuits formed by the data loading circuits and the interface circuits, and accordingly the quantities of bit lines can be reduced by 50%; the twin-storage type multi-valued physically unclonable functional circuit is designed in full-custom modes by the aid of TSMC_LP65nm processes, and the area ofthe twin-storage type multi-valued physically unclonable functional circuit is 0.019 mm<2>; as shown by test results, the lowermost work voltages of the twin-storage type multi-valued physically unclonable functional circuit are 320 mV, corresponding work frequencies are 110 kHz, the hardware utilization rate is increased by 15% at least, and energy consumption is reduced by 30%.

Owner:NINGBO UNIV

Predicting data correlation using multivalued logical outputs in static random access memory (SRAM) storage cells

InactiveUS20180240512A1Natural language data processingDigital storageBit lineStatic random-access memory

Owner:INT BUSINESS MASCH CORP

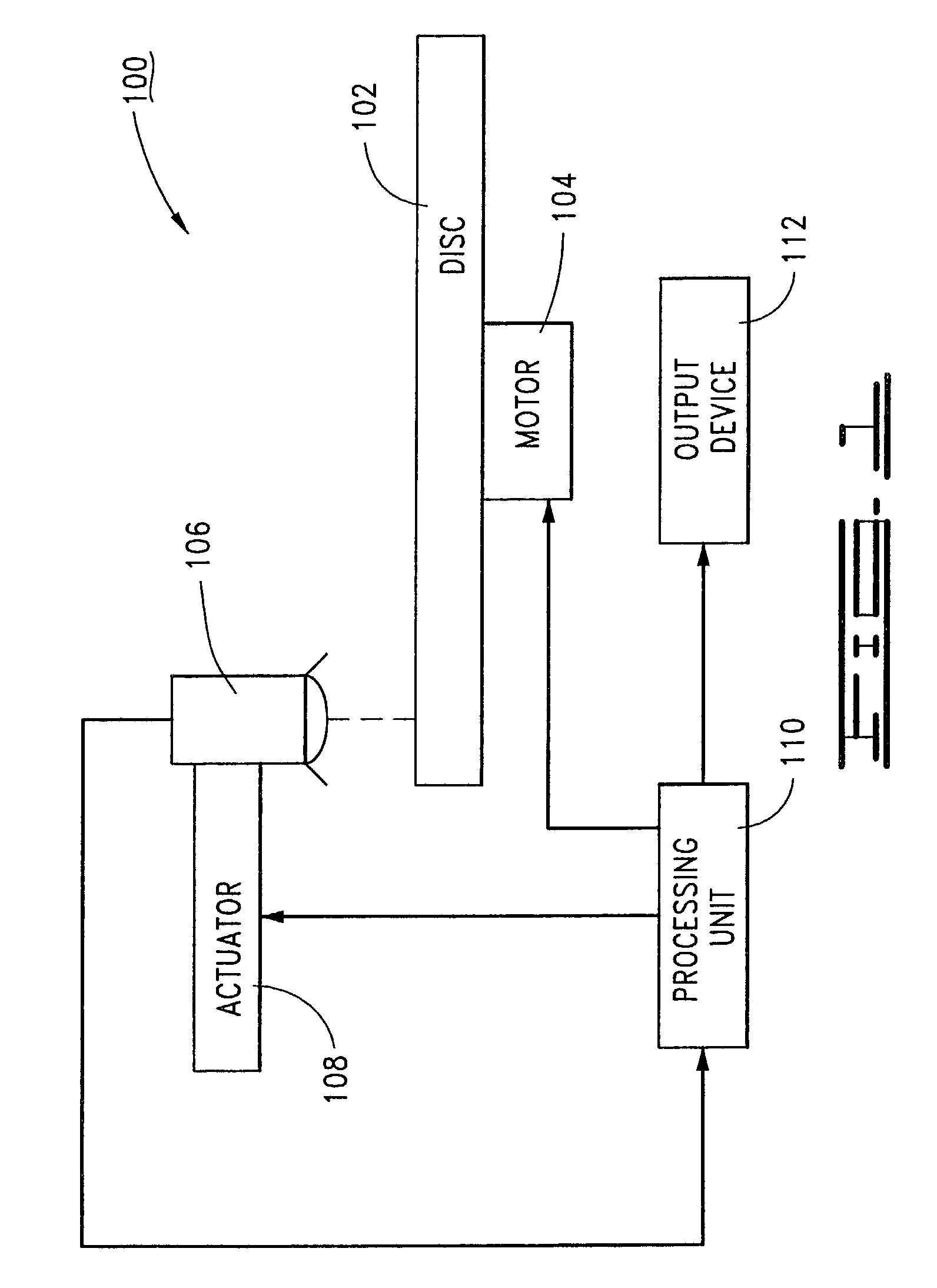

Multivalued logic circuit

InactiveUS20100164596A1Improve the protective effectSimplify workLogic circuits characterised by logic functionComputations using contact-making devicesElectrical resistance and conductancePush–pull output

In a bridge adder circuit, a first and a second complementary pair of current mirrors is connected between the input terminals and a positive and a negative supply voltage bus, respectively, to control a first and a second push-pull output stage. The outputs of the push-pull output stages are connected to the respective inputs through first resistors and to a common output node through second resistors. As a result, a universal circuit element for a multivalued logic element, such as ternary logic or 5-valued logic is provided.

Owner:FUZZY CHIP PTE

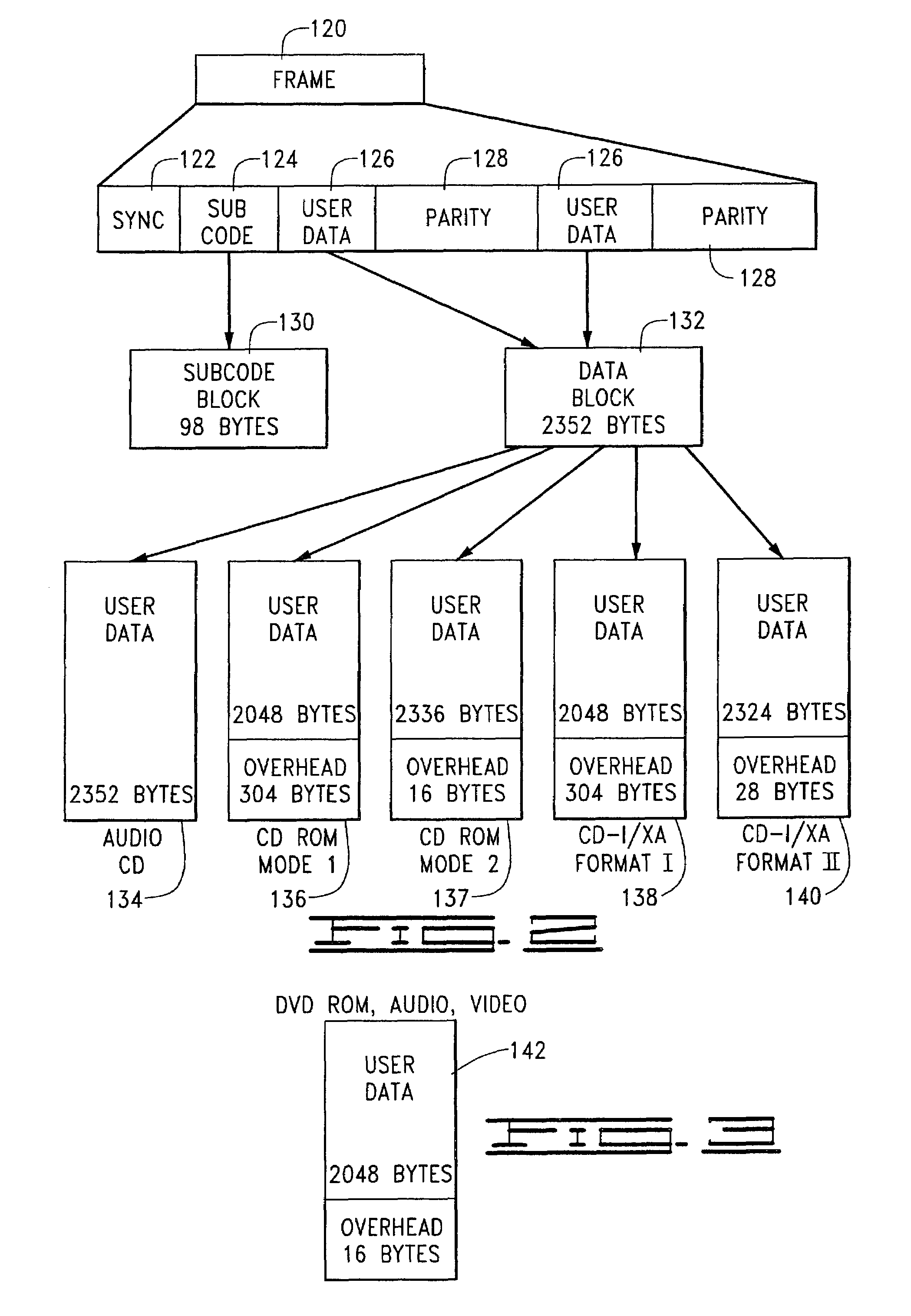

Sequencing data blocks to provide hidden data on a recording medium

InactiveUS7805764B1Easy authenticationFacilitate forensic tracking effortDigital data processing detailsUser identity/authority verificationComputer hardwareHidden data

Method and apparatus for providing a hidden signature to a recording medium, such as an optical disc (102). The hidden signature is generated in relation to the selected sequencing of data blocks (132, 134, 136, 138, 140, 142). A plurality of) mutually exclusive, valid possible states are identified for each of the data blocks (202), each state conforming to requirements set forth by a published standards document to which the optical disc conforms. A different logical value is assigned to each of the possible states, and the hidden signature is selected as a multi-value logical word comprising a sequence of the logical values (204). The hidden signature is thereafter written to the optical disc by writing a set of corresponding data blocks at selected locations on the optical disc having states corresponding to the multi-value logical word (206). The hidden signature thereafter facilitates copy protection or forensic tracking efforts (208).

Owner:DOUG CARSON & ASSOCS

Three-valued thermal-insulation domino direct circulation valve and reverse circulation valve

ActiveCN102857215AHighly integratedHigh densityLogic circuits characterised by logic functionElectric pulse generatorThermal insulationInformation density

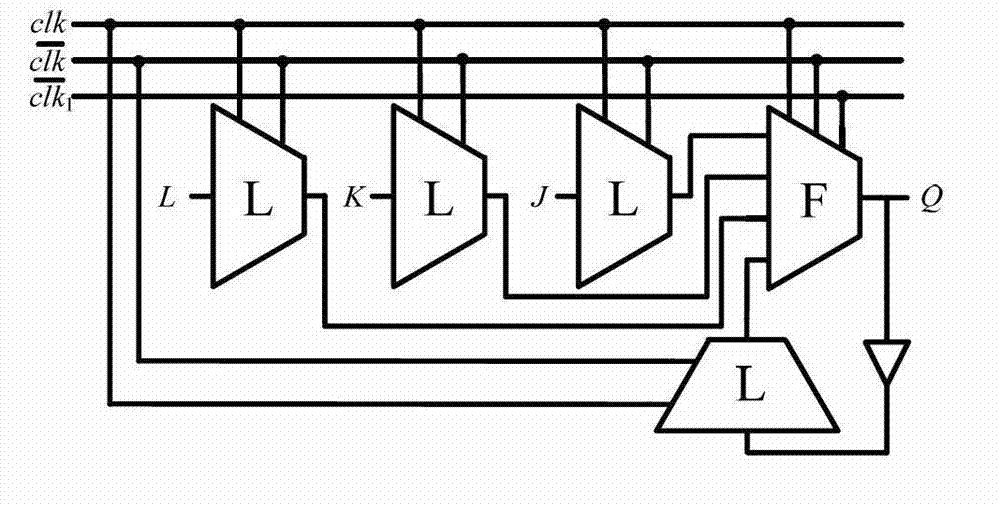

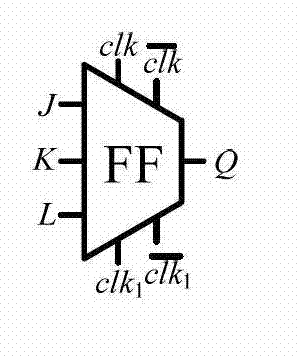

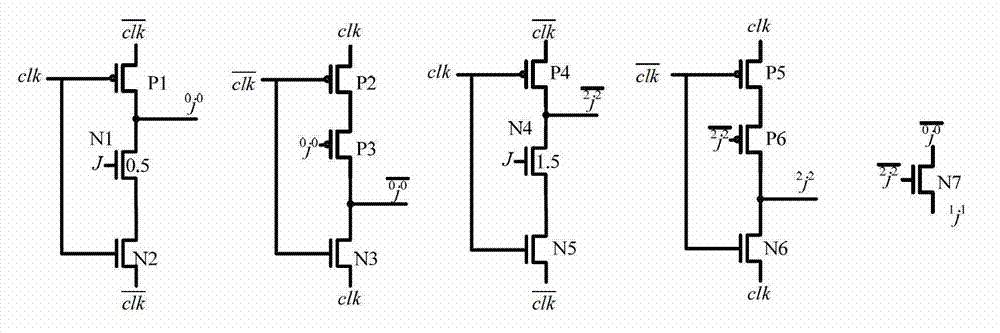

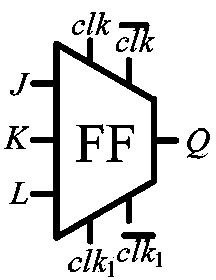

The invention discloses a three-valued thermal-insulation domino direct circulation valve and a three-valued thermal-insulation domino reverse circulation valve which respectively comprise a three-valued low-power dissipation domino JKL trigger, wherein each three-valued low-power dissipation domino JKL trigger consists of a first three-valued thermal-insulation domino text calculation circuit, a second three-valued thermal-insulation domino text calculation circuit, a third three-valued thermal-insulation domino text calculation circuit, a fourth three-valued thermal-insulation domino text calculation circuit and a basic three-valued JKL trigger circuit; thermal-insulation logic, multi-valued logic and multi-domino circuits are combined together through the first to fourth three-valued thermal-insulation domino text calculation circuits, thus realizing a three-valued low-power dissipation domino JKL trigger; and the three-valued thermal-insulation domino direct circulation valve and the three-valued thermal-insulation domino reverse circulation valve have the advantages of being high in circuit integration and information density and low in power dissipation on the basis of the three-valued low-power dissipation domino JKL trigger.

Owner:NINGBO UNIV

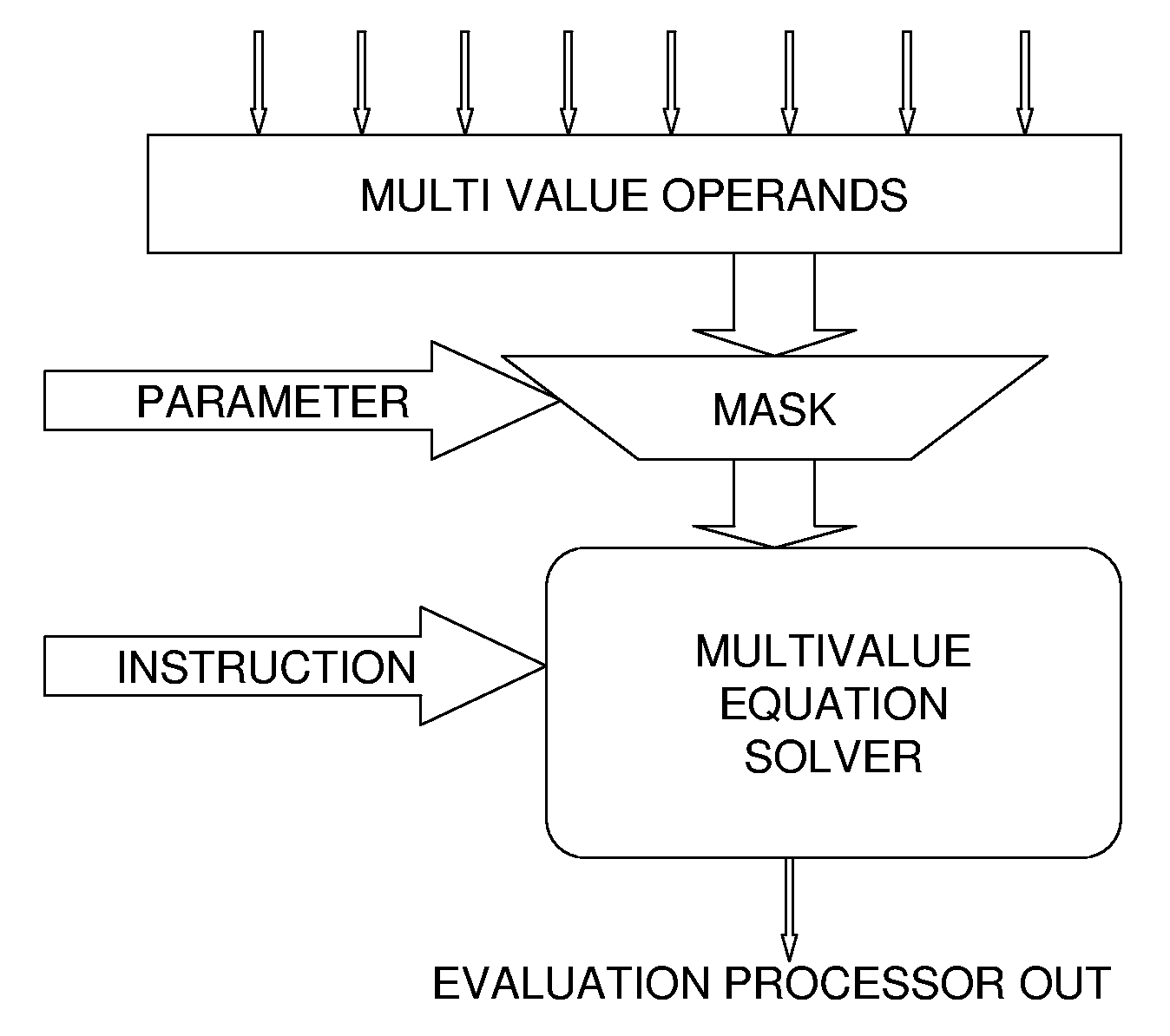

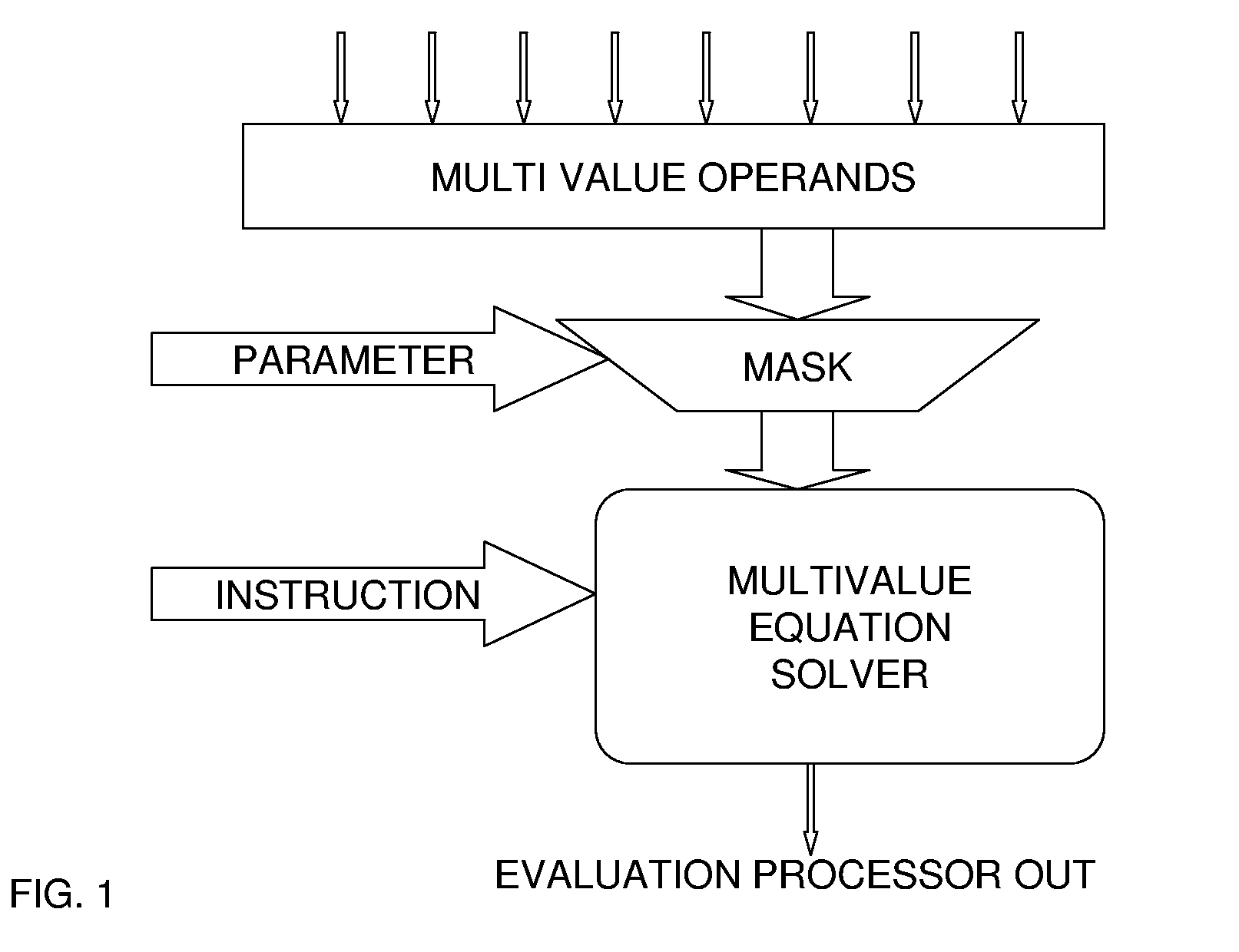

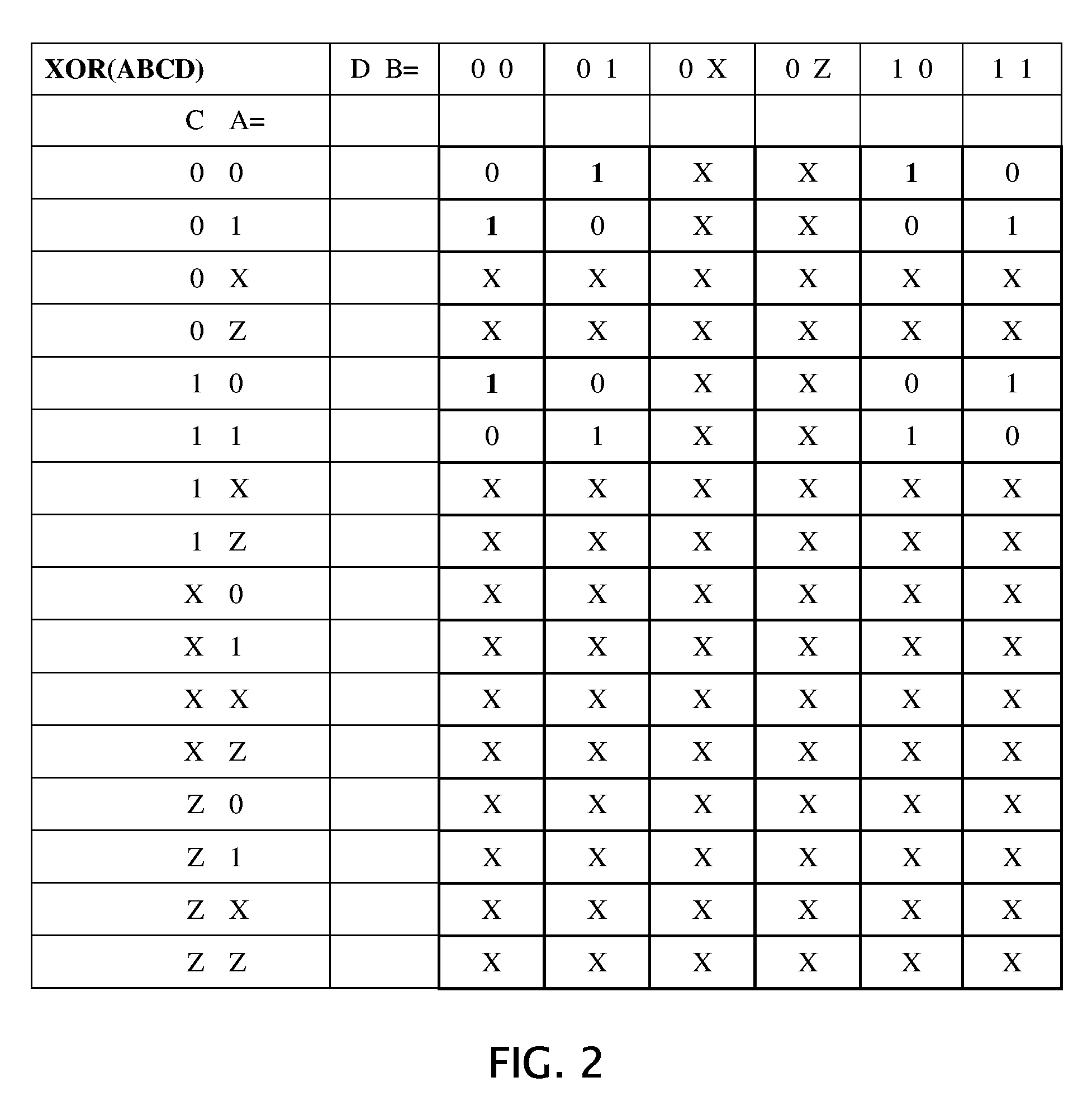

Compact processor element for a scalable digital logic verification and emulation system

ActiveUS7509602B2Effective evaluationLow costCAD circuit designSoftware simulation/interpretation/emulationElectronic systemsProcessor element

Owner:EVE

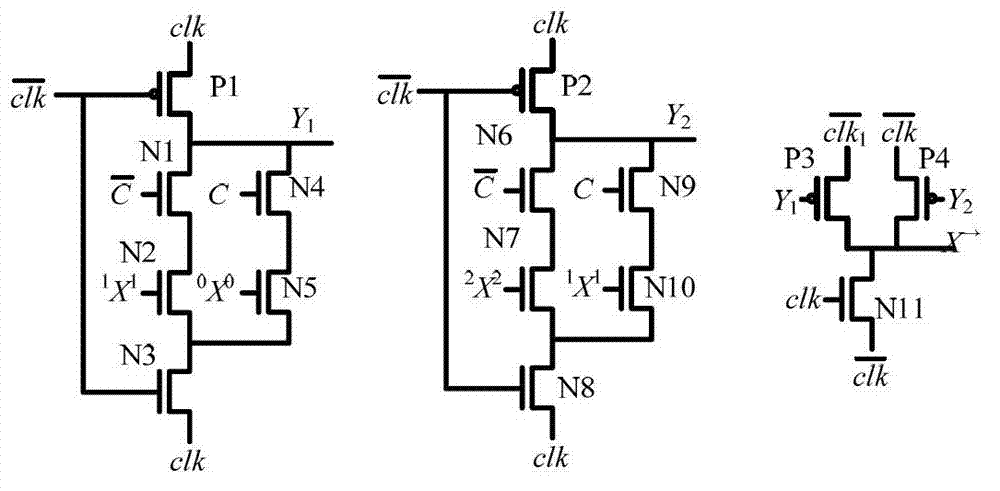

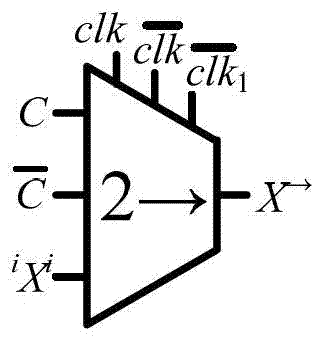

Ultra-low power consumption three-valued counting unit and multi-bit counter based on Domino circuit

ActiveCN103095288ALogical function is correctReduce power consumptionCounting chain pulse countersLevel structureSwitching signal

The invention discloses an ultra-low power consumption three-valued counting unit and a multi-bit counter based on a Domino circuit. The three-valued counter is designed with a switch-signal theory as guidance and combining the heat insulation logic, the multi-value logic and a Domino circuit. A three-valued positive cycle gate circuit switch-level structure with an Enable Pin is deduced first, a three-valued heat insulation Domino text arithmetic circuit and a heat insulation Domino bumper are combined to obtain a three-valued counting unit (namely, a single-bit three-valued counter). Then, a three-valued counter Enable signal generating circuit structural formula is deduced, and the three-valued counting unit and the three-valued counter Enable signal generating circuit are in cascade connection to obtain the three-valued multi-bit counter. According to Spice software simulation, the ultra-low power consumption three-valued four-bit counter based on the Domino circuit has the advantages of being correct in logic function and capable of saving power consumption by approximately 63% compared with a traditional three-valued four-bit Domino counter.

Owner:HANGZHOU HANGUANG ILLUMINATION

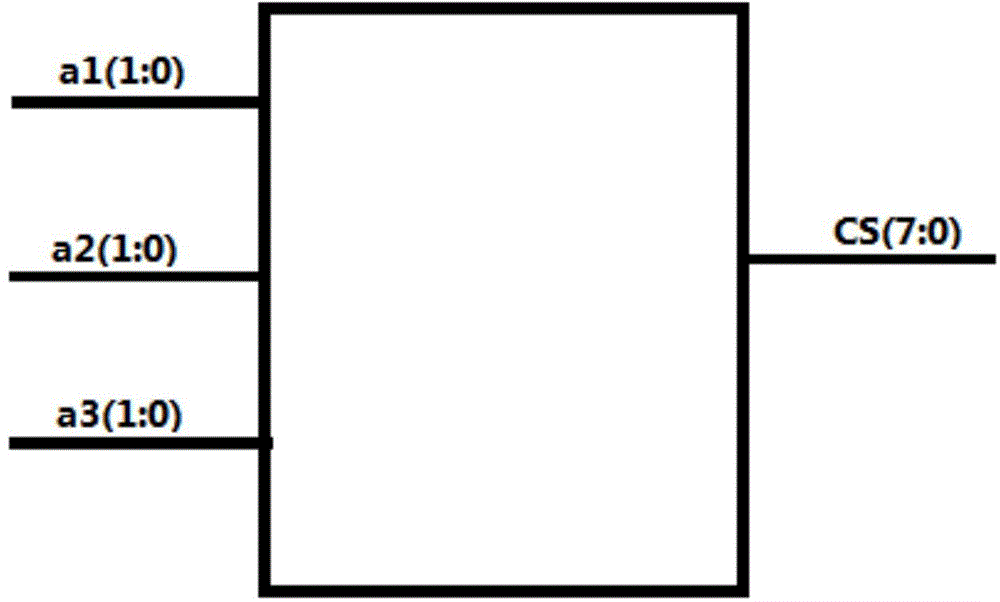

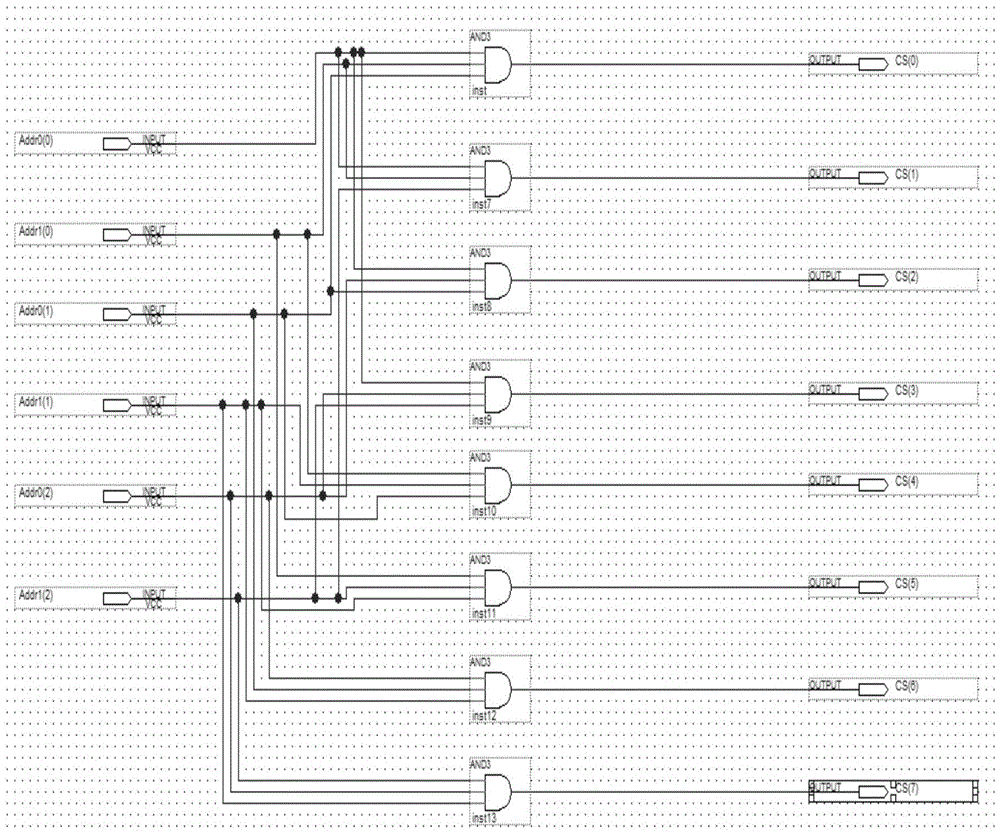

Address decoding method based on multi-valued logic circuit

InactiveCN104090859ASimultaneous readingSupports parallel processingElectric digital data processingDecoding methodsParallel processing

The invention relates to an address decoding method based on a multi-valued logic circuit, in particular relates to an address decoding method for accessing a plurality of storage units once, and belongs to the technical field of digit circuits. The method is characterized in that 2n AND gates are adopted, and the created address decoding method is provided with 2n input ends; 2n address signals of storage units to be selected are respectively sent to the 2n input ends of the address decoding method; the 2n AND gates of the address decoding method are respectively subjected to AND operation; the corresponding storage unit can be selected as result is equal to 1, and thus the corresponding read and write circuit can be driven. The method has the advantages that multi-valued addressing is realized, the storage data can be read and written at the same time, the novel storage or processing devices apply, and parallel processing of data is supported.

Owner:BEIJING UNIV OF POSTS & TELECOMM

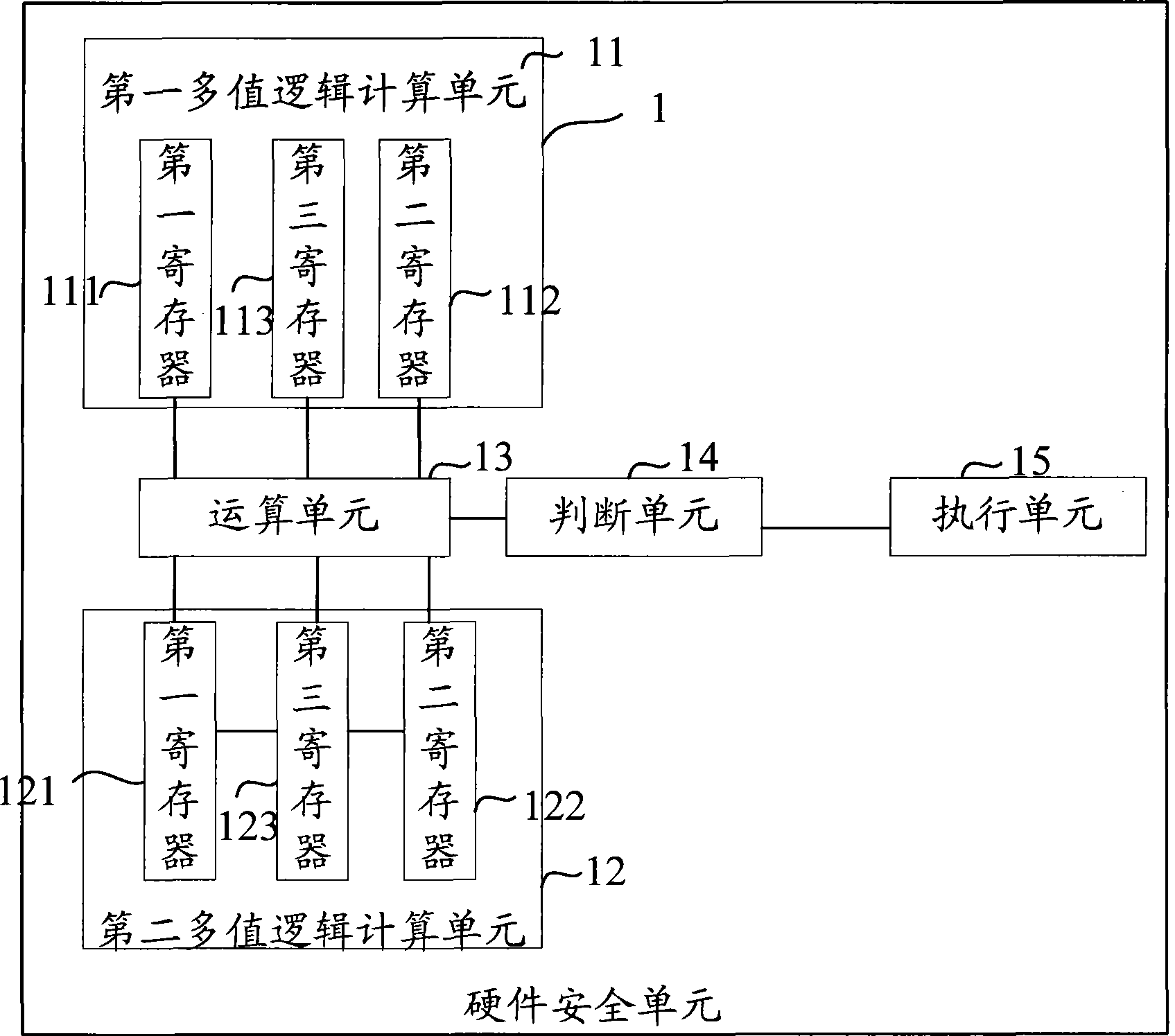

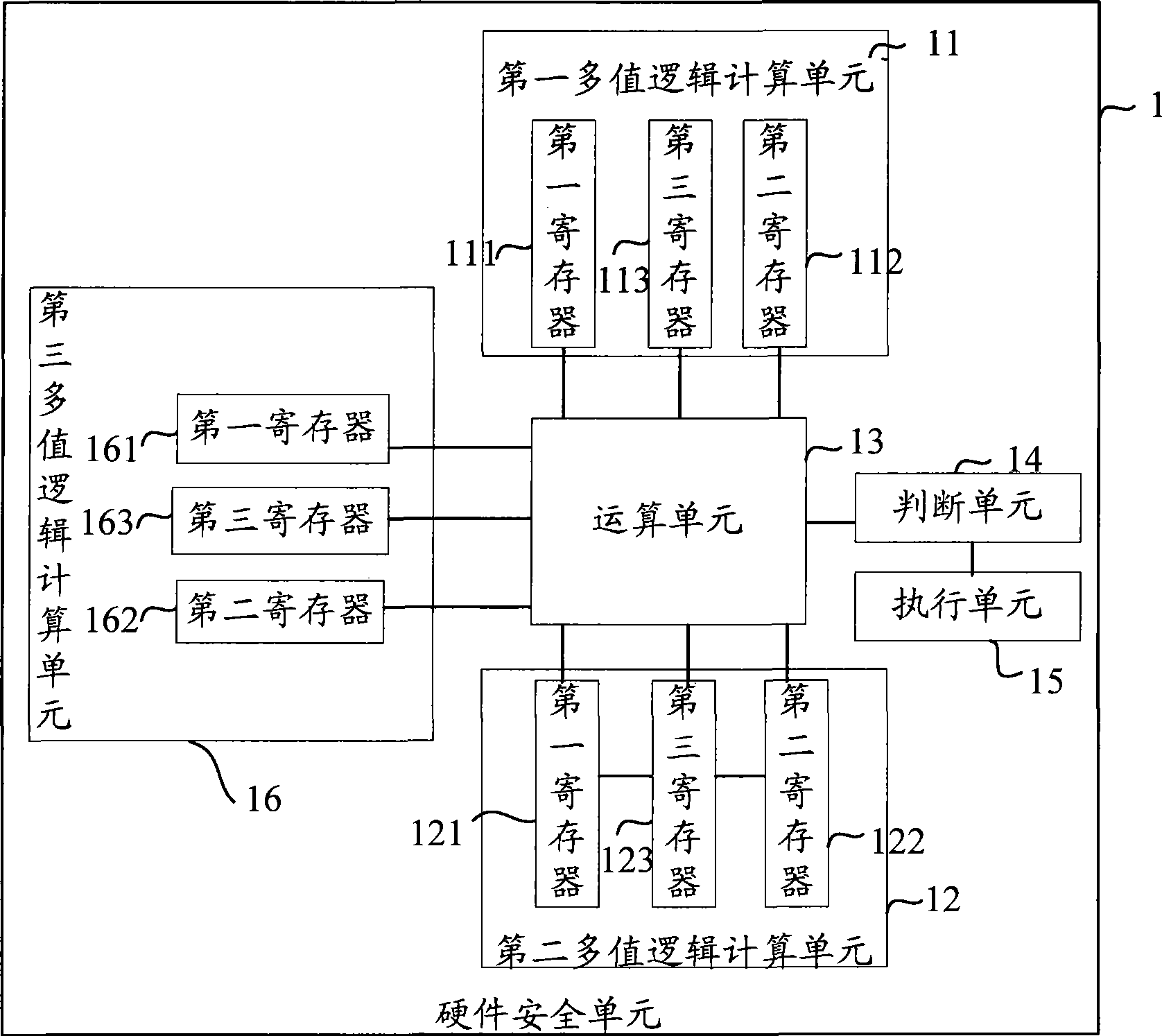

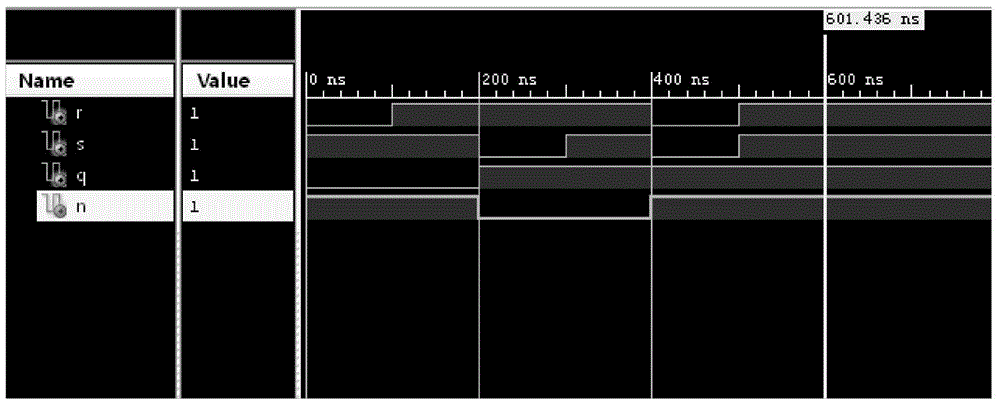

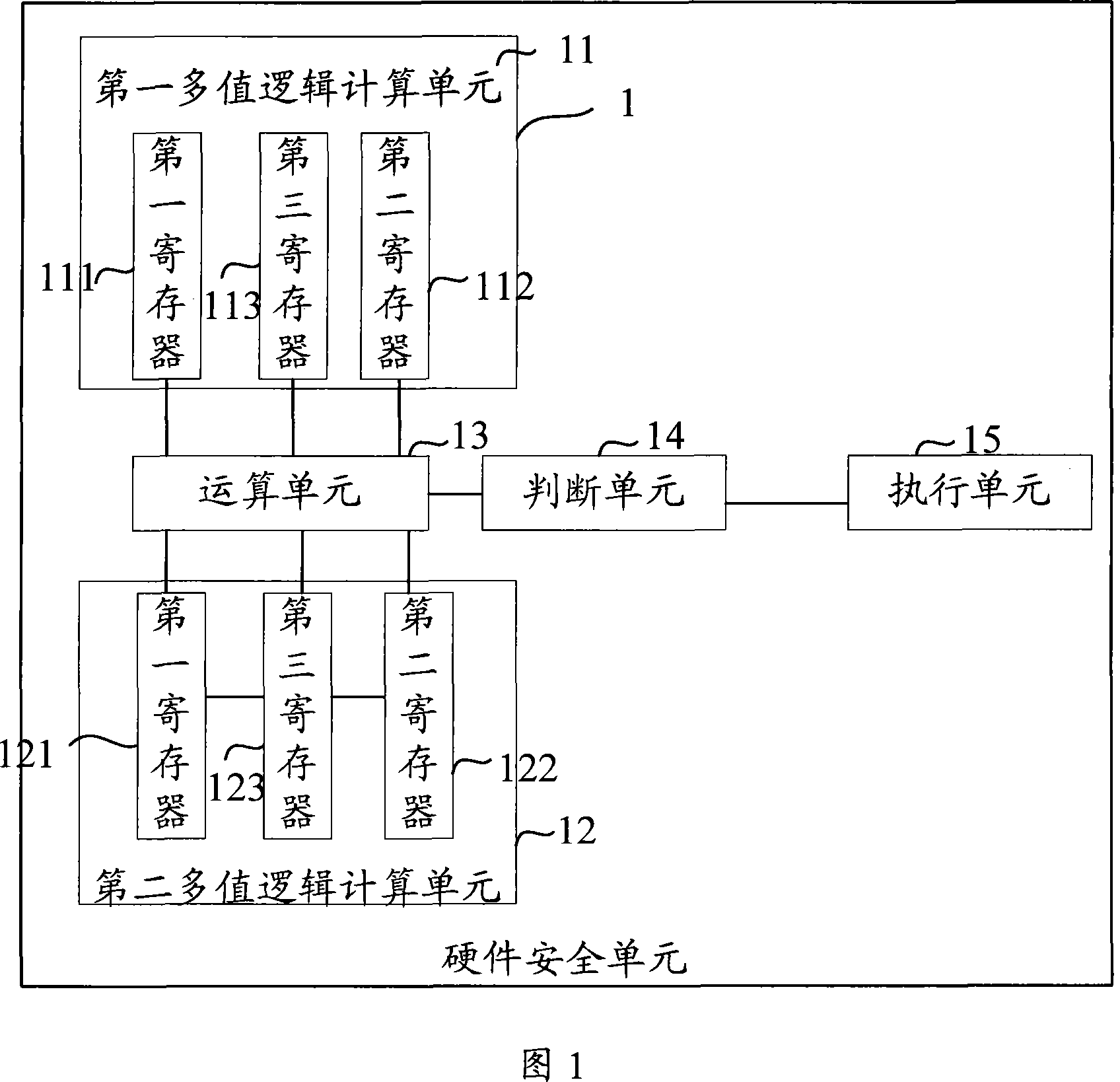

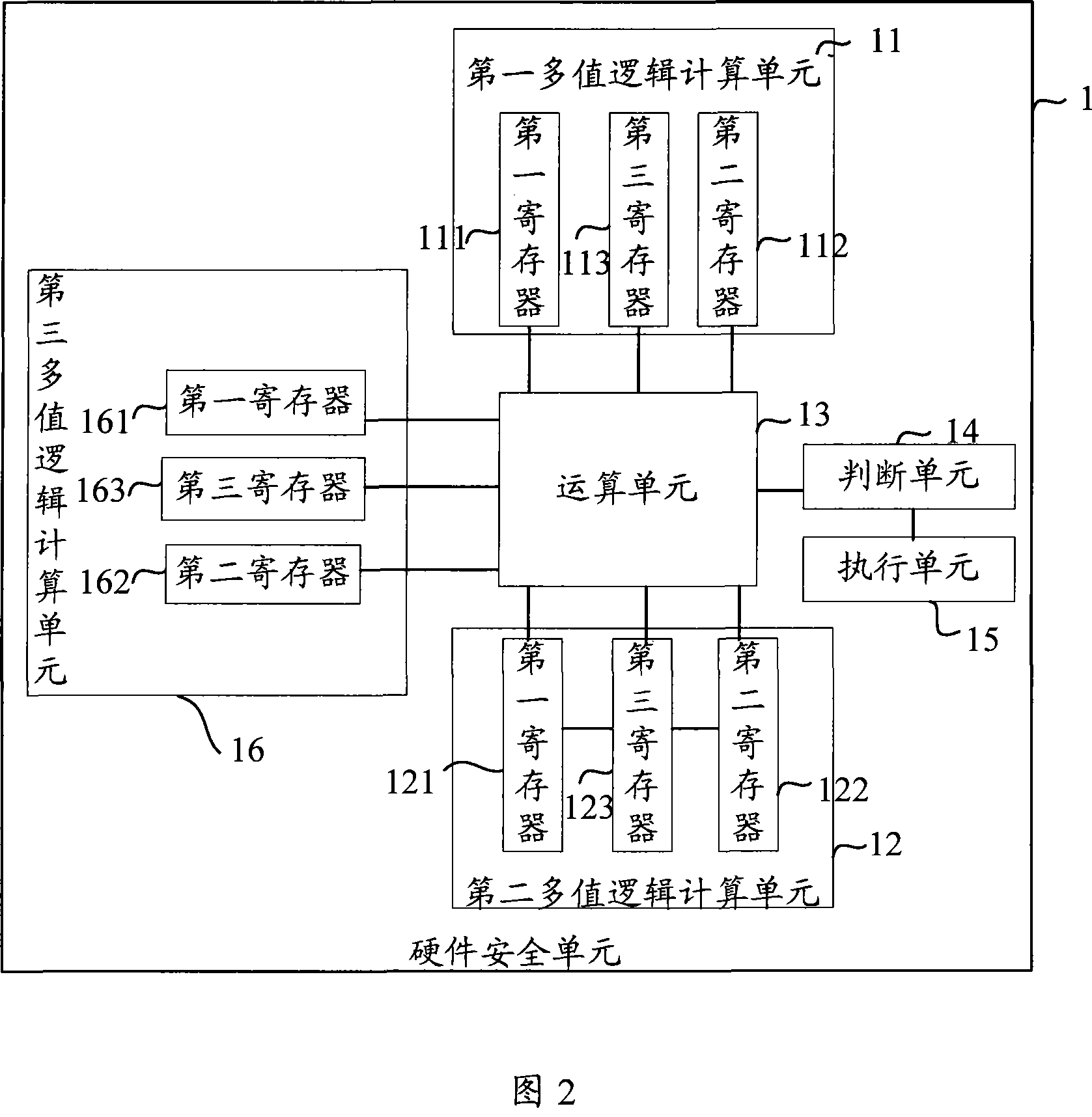

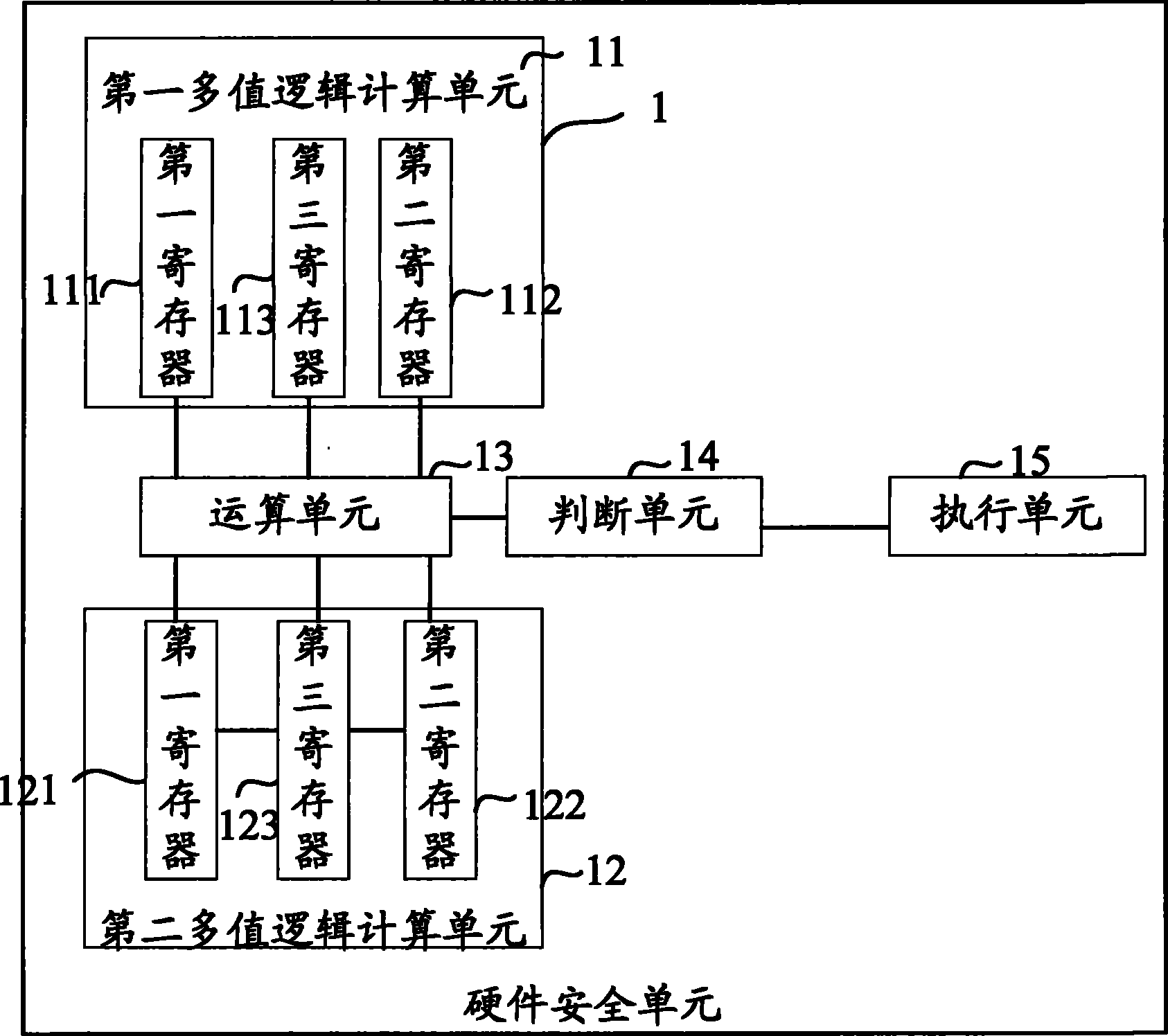

Hardware security unit

ActiveCN101482903AMeet needsFlexible operationPlatform integrity maintainanceProcessor registerLogical operations

The invention relates to a hardware safety unit which at least comprises a first multivalued logic calculating element, a second multivalued logic calculating element, an operation element, a judging element and an implementing element. The first and second multivalued logic calculating elements are respectively connected with the operation element. Each multivalued logic calculating element comprises at least three registers. The operation element calls multivalued logic operators in a third register of the second multivalued logic calculating element, respectively calculates an expected logic state and a current logic state of the second multivalued logic calculating element and the first multivalued logic calculating element according to the multivalued logic operators, and obtains an expected logic operation result and a current logic operation result; the judging element judges if the current logic operation result achieves the expected logic operation result; the implementing element implements the corresponding operation according to the judged result which is judged by the judging element. The invention provides a hardware safety system and solves the problem in the process of adopting two-valued logic judgement to serve for the whole trust chain.

Owner:LENOVO (BEIJING) LTD

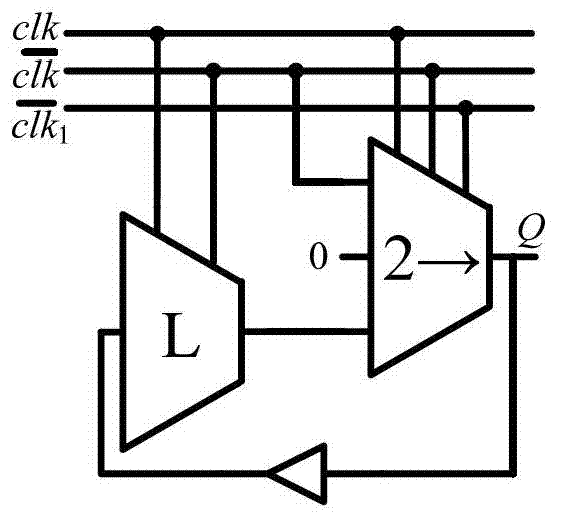

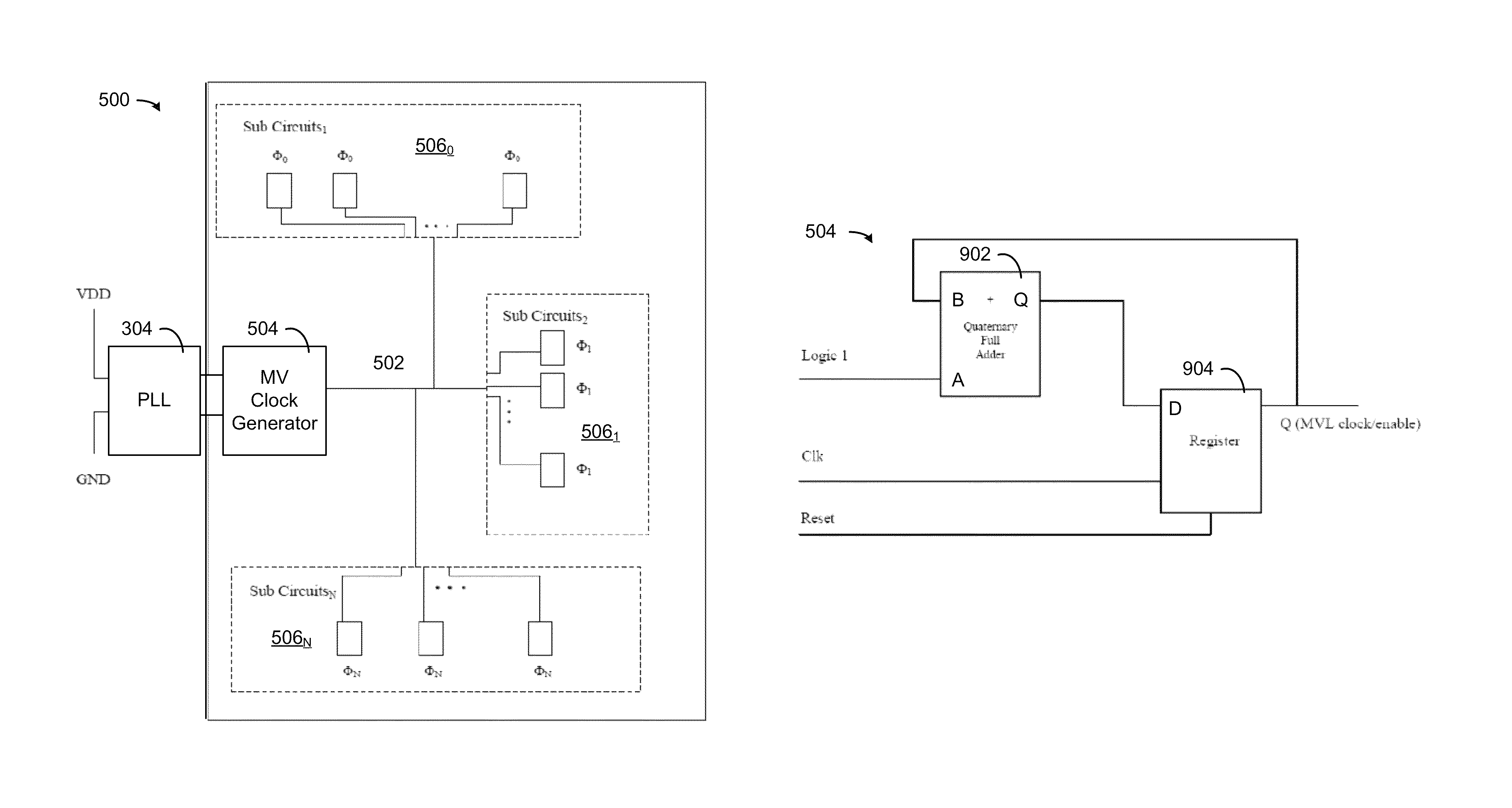

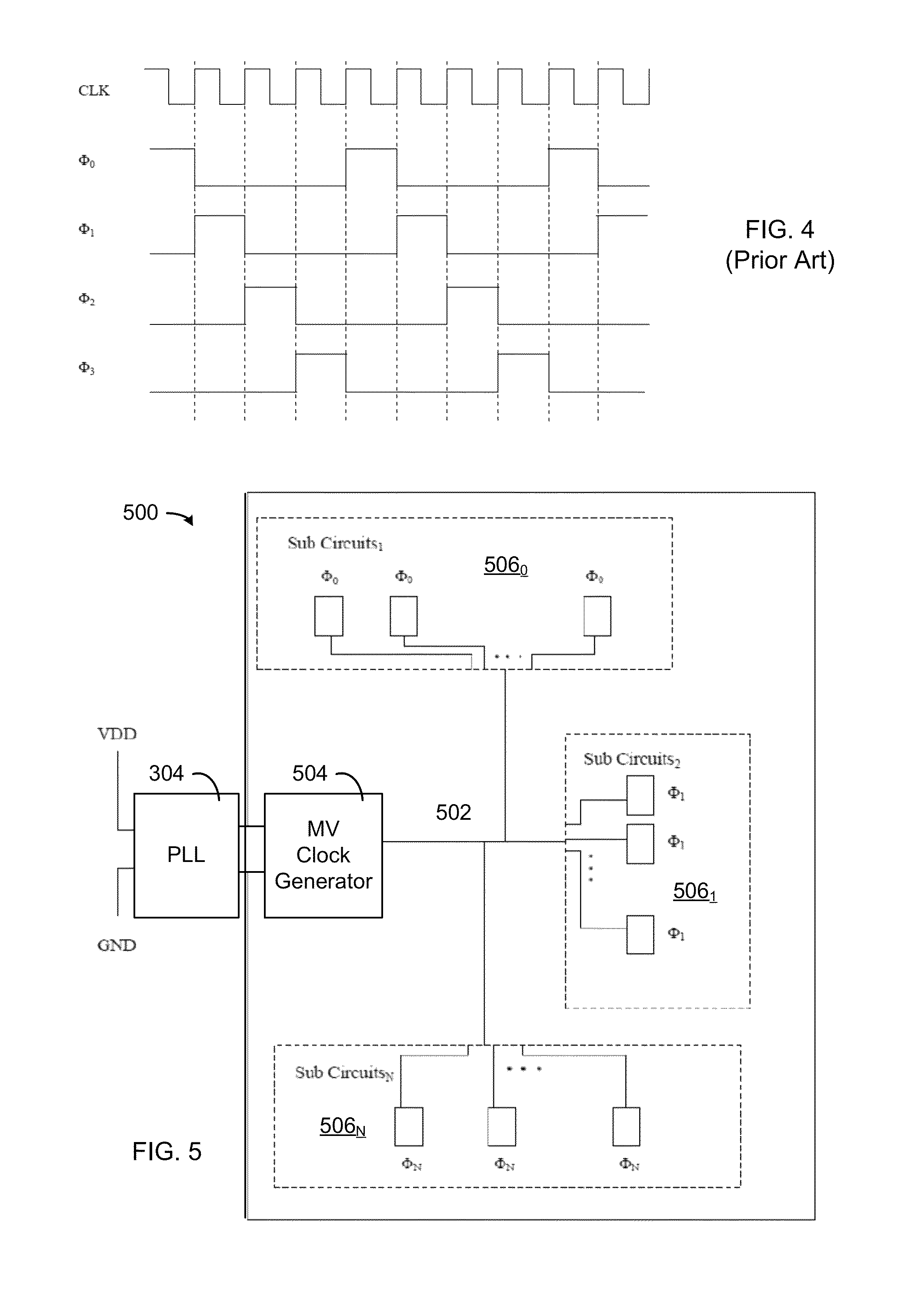

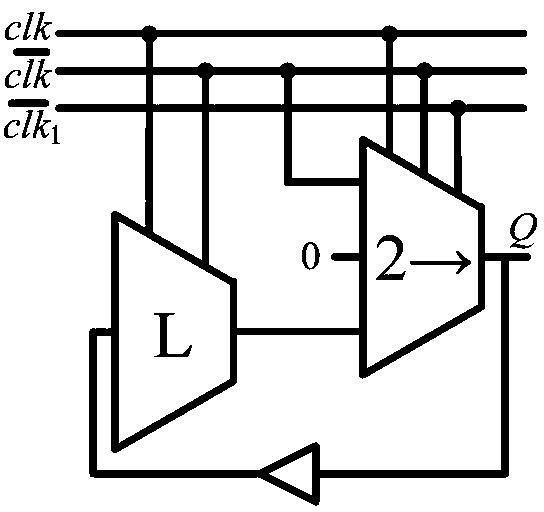

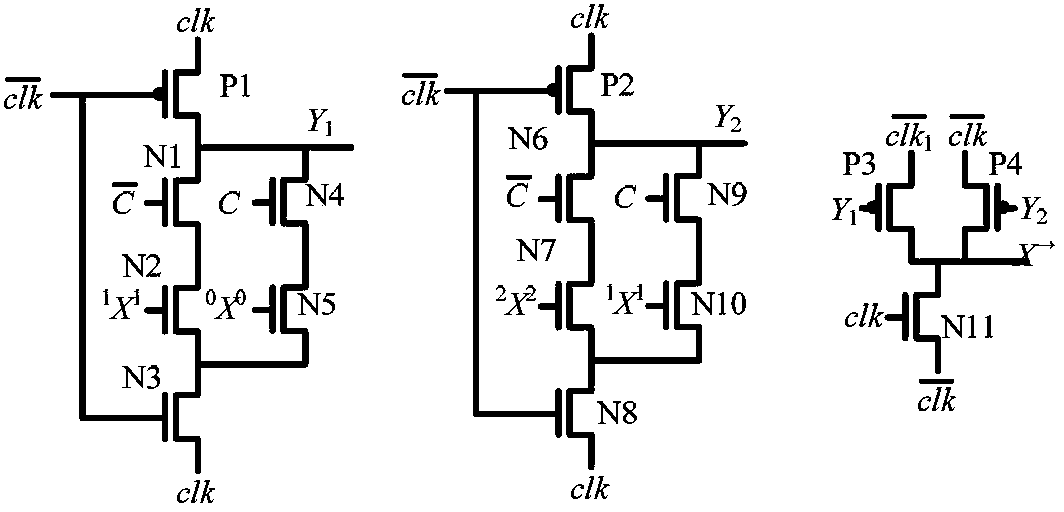

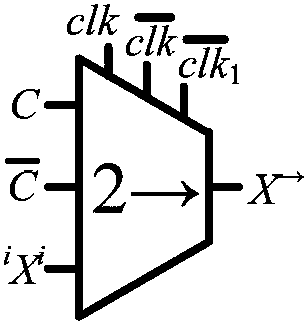

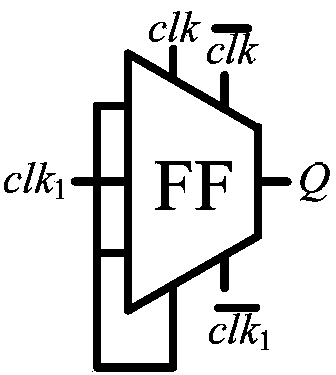

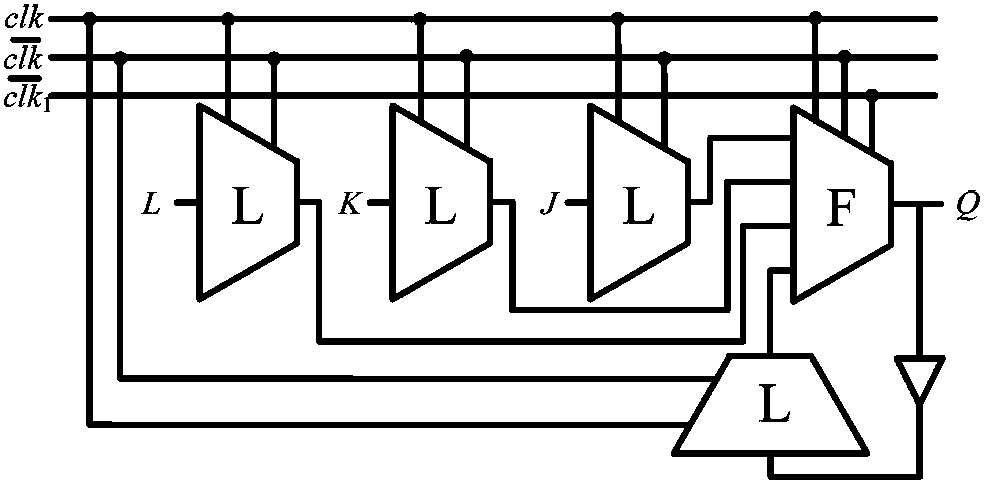

Single clock distribution network for multi-phase clock integrated circuits

A multi-valued logic (MVL) circuit includes a MVL clock generator that generates a MVL clock signal having three or more ith MVL levels, a single MVL clock signal distribution network connected to the MVL clock generator, and three or more ith MVL selection circuits connected to the single MVL clock signal distribution network where i=0 to N and N>=3. Each ith MVL selection circuit corresponds to a specified ith MVL level. The ith MVL selection circuit outputs an ith binary clock signal having: (a) a first logic level whenever the MVL clock signal is equal to the ith MVL level and the ith data input receives the first logic level, (b) a second logic level whenever the MVL clock signal is equal to the ith MVL level and the ith data input receives the second logic level, and (c) a previous logic level of the ith binary clock signal whenever the MVL clock signal is not equal to the ith MVL level.

Owner:IRONWOOD CYBER INC

Three-value low power consumption domino JKL trigger

InactiveCN102790602AHighly integratedHigh densityElectric pulse generatorInformation densityEngineering

The invention discloses a three-value low power consumption domino JKL trigger. The three-value low power consumption domino JKL trigger consists of a first three-value heat-insulating domino character operational circuit, a second three-value heat-insulating domino character operational circuit, a third three-value heat-insulating domino character operational circuit, a fourth three-value heat-insulating domino character operational circuit and a three-value JKL trigger basic circuit, wherein a heat-insulating logic, a multi-value logic and a domino circuit are combined together by the first three-value heat-insulating domino character operational circuit, the second three-value heat-insulating domino character operational circuit, the third three-value heat-insulating domino character operational circuit and the fourth three-value heat-insulating domino character operational circuit. The three-value low power consumption domino JKL trigger has the advantages that the circuit integration level and information density of the JKL trigger are improved; and compared with a conventional three-value domino JKL trigger, the three-value low power consumption domino JKL trigger disclosed by the invention has the characteristic that energy consumption is saved by 69 percent.

Owner:HANGZHOU MAEN TECH

Multiple-valued counter unit based on nerve MOS tube and multi-digit multiple-valued counter

InactiveCN101777139BLow costReduce power consumptionCounting mechanisms/objectsSemiconductor devicesInput controlEngineering

The present invention discloses a neuron MOS based multi-valued counter unit. The counter unit includes a neuron MOS source follower and at least a control gate connected the neuron MOS source follower. The control gate includes a first dual-value D flip-flop, a second dual-value D flip-flop, an AND gate, and an OR gate. The present invention utilizes the neuron MOS to replace the complicated threshold value operations of the multi-value logic. The current invention implements the true multi-value logic and a multi-base multi-value counter by increasing the number of the dual-value D flip-flop, and connecting the dual-value D flip-flop to the input control gate of the neuron MOS follower. Comparing to the conventional multi-value counter, the present invention reduces the necessary components in constructing the counter, and it also reduces the cost and power consumption. The present invention applies the asynchronous carry-over concept to implement the multi-digit multi-value counter, and it also has been verified by the simulation of P Simulation Program with Integrated Circuit Emphasis (SPICE).

Owner:NINGBO UNIV

A memristor-based multi-valued logic device and its operation method

ActiveCN105761750BImplement storageRealize computingDigital storageElectrical resistance and conductanceNegation

The invention discloses a memristor-based nonvolatile multivalued logic device and an operating method thereof. The method provides an operating method for negation and dextrorotation of three-valued logic and multivalued T gate logic, which realizes an exhaustive set of multivalued logic, such as three-valued logic based on the multi-resistance state transition characteristic of a memristor. All the logic operation results are stored in the device in a nonvolatile resistance state, such that a logic operation function and a data storage function are realized simultaneously in the device, i.e., storage and calculation are fused; therefore, a device basis is laid for going beyond the limitation from an information device Moore's law and breaking through the Von Neumann bottleneck in a computer architecture. The memristor-based multivalued logic device disclosed by the invention can be applied to a novel solid-state memory, a logic-arithmetic unit, a programmable gate array, an on-chip system and other fields as a basic unit, and provides a new path for boosting novel computer architecture.

Owner:HUAZHONG UNIV OF SCI & TECH

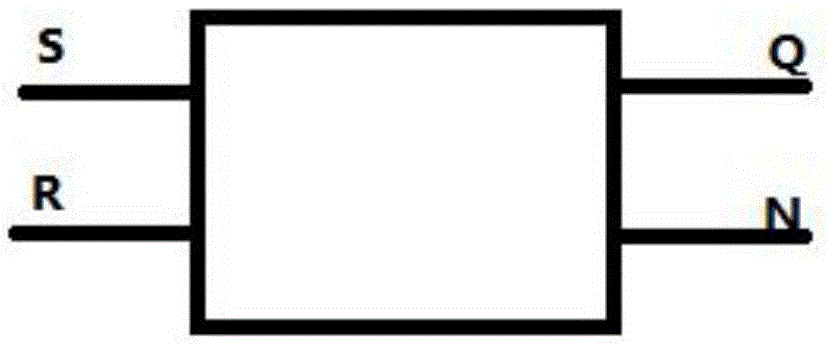

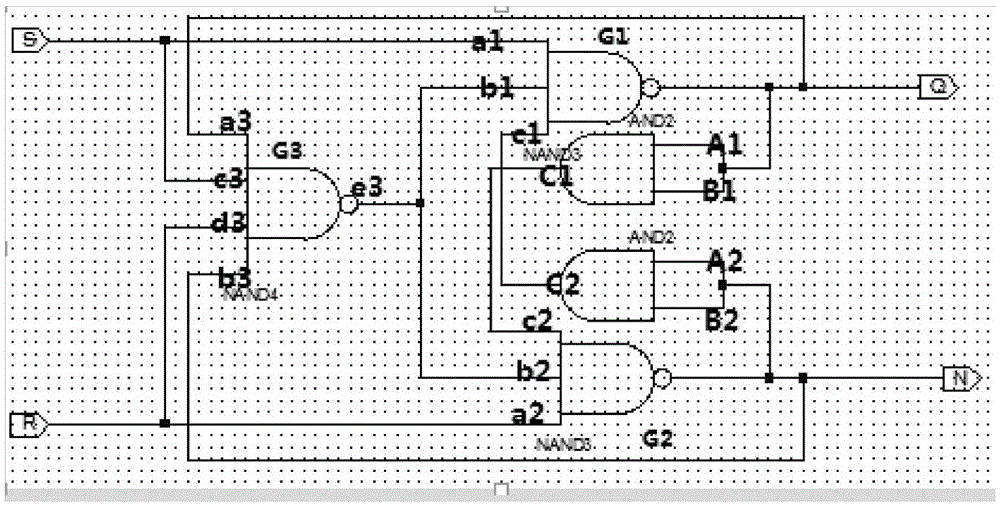

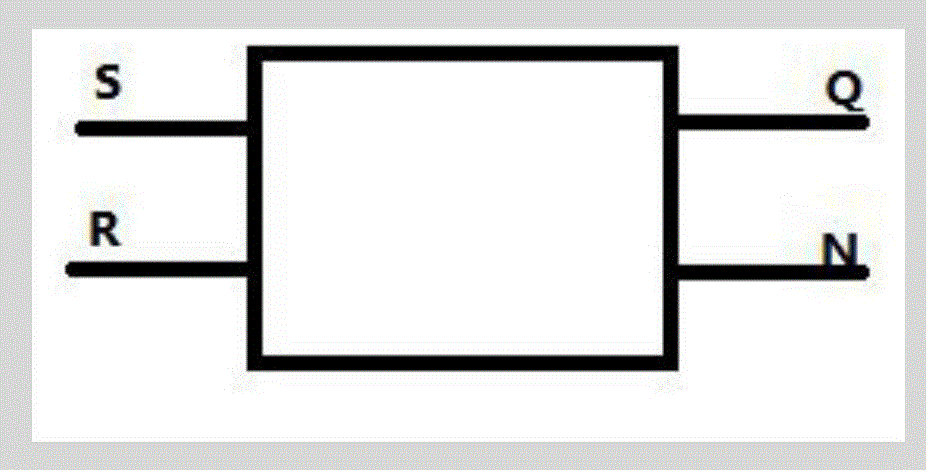

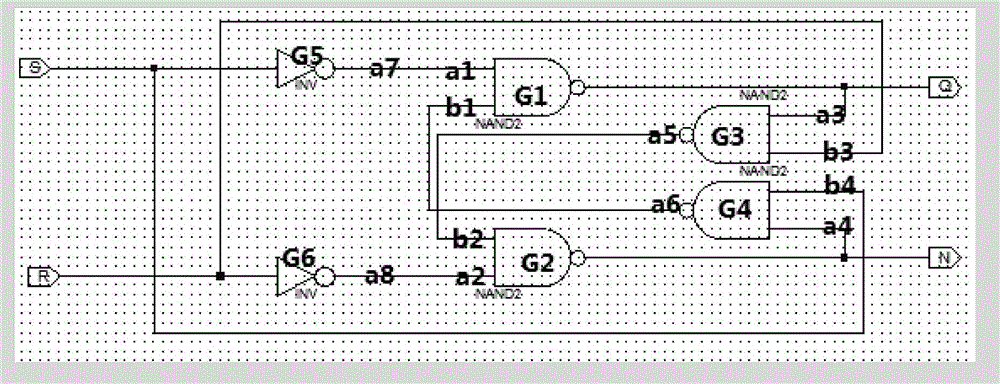

A tri-stable rs flip-flop supporting multi-valued logic

InactiveCN103701450BImplement multivalued logicSimple structureElectric pulse generator detailsLogic circuitsStable stateEngineering

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Hardware security unit

ActiveCN101482903BMeet needsFlexible operationPlatform integrity maintainanceComputer hardwareLogical operations

The invention relates to a hardware safety unit which at least comprises a first multivalued logic calculating element, a second multivalued logic calculating element, an operation element, a judging element and an implementing element. The first and second multivalued logic calculating elements are respectively connected with the operation element. Each multivalued logic calculating element comprises at least three registers. The operation element calls multivalued logic operators in a third register of the second multivalued logic calculating element, respectively calculates an expected logic state and a current logic state of the second multivalued logic calculating element and the first multivalued logic calculating element according to the multivalued logic operators, and obtains an expected logic operation result and a current logic operation result; the judging element judges if the current logic operation result achieves the expected logic operation result; the implementing element implements the corresponding operation according to the judged result which is judged by the judging element. The invention provides a hardware safety system and solves the problem in the process of adopting two-valued logic judgement to serve for the whole trust chain.

Owner:LENOVO (BEIJING) LTD

Ultra-low power consumption three-valued counting unit and multi-bit counter based on Domino circuit

ActiveCN103095288BLogical function is correctReduce power consumptionCounting chain pulse countersLevel structureSwitching signal

The invention discloses an ultra-low power consumption three-valued counting unit and a multi-bit counter based on a Domino circuit. The three-valued counter is designed with a switch-signal theory as guidance and combining the heat insulation logic, the multi-value logic and a Domino circuit. A three-valued positive cycle gate circuit switch-level structure with an Enable Pin is deduced first, a three-valued heat insulation Domino text arithmetic circuit and a heat insulation Domino bumper are combined to obtain a three-valued counting unit (namely, a single-bit three-valued counter). Then, a three-valued counter Enable signal generating circuit structural formula is deduced, and the three-valued counting unit and the three-valued counter Enable signal generating circuit are in cascade connection to obtain the three-valued multi-bit counter. According to Spice software simulation, the ultra-low power consumption three-valued four-bit counter based on the Domino circuit has the advantages of being correct in logic function and capable of saving power consumption by approximately 63% compared with a traditional three-valued four-bit Domino counter.

Owner:HANGZHOU HANGUANG ILLUMINATION

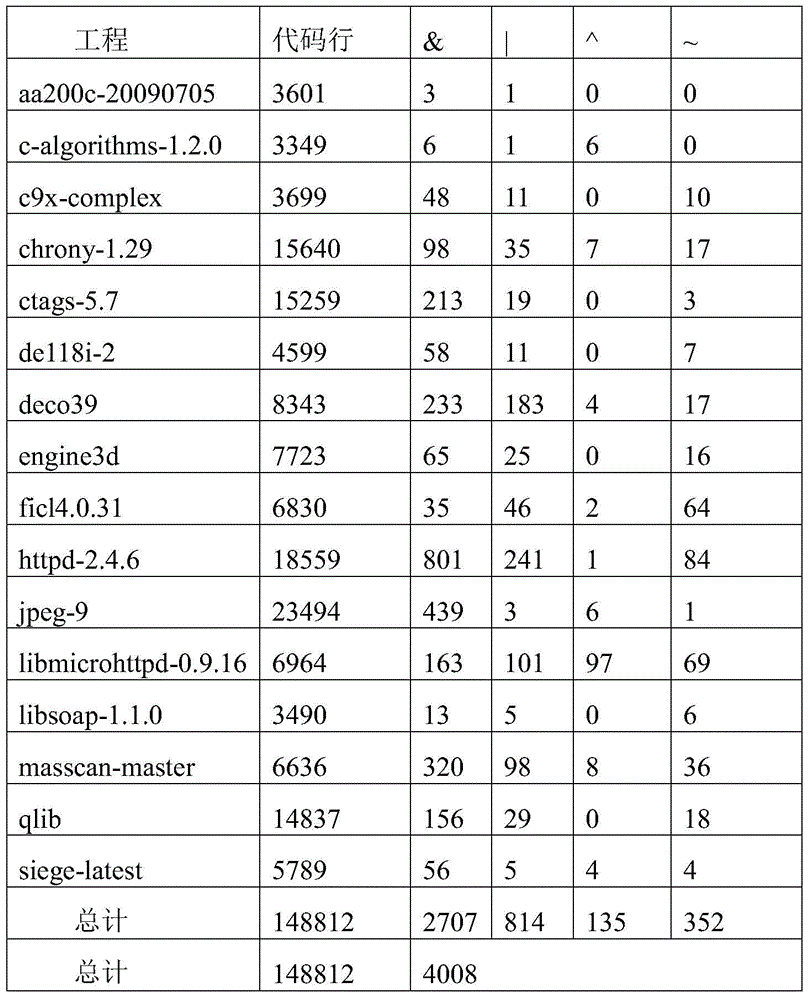

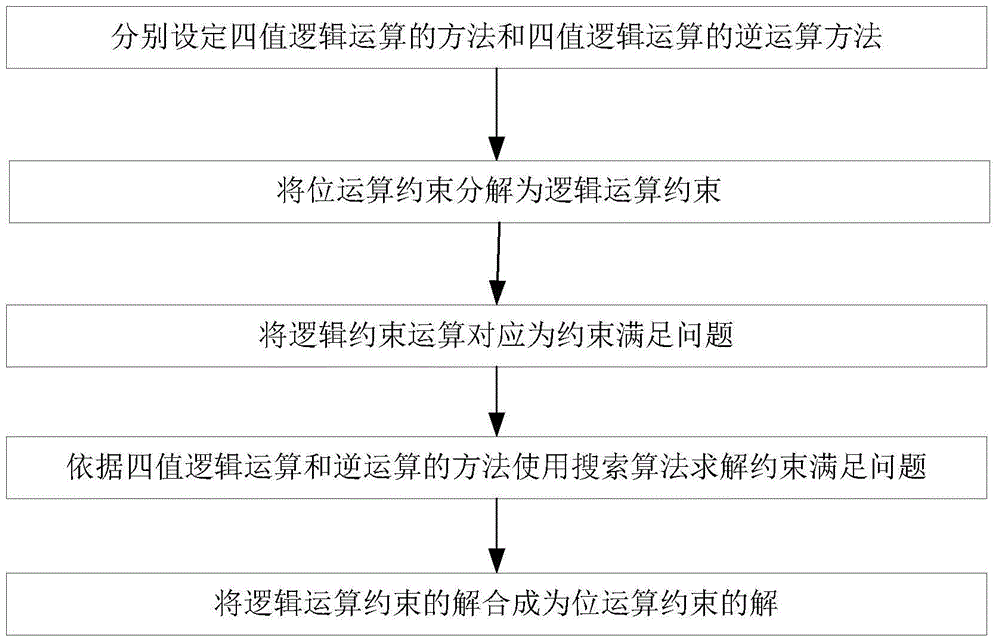

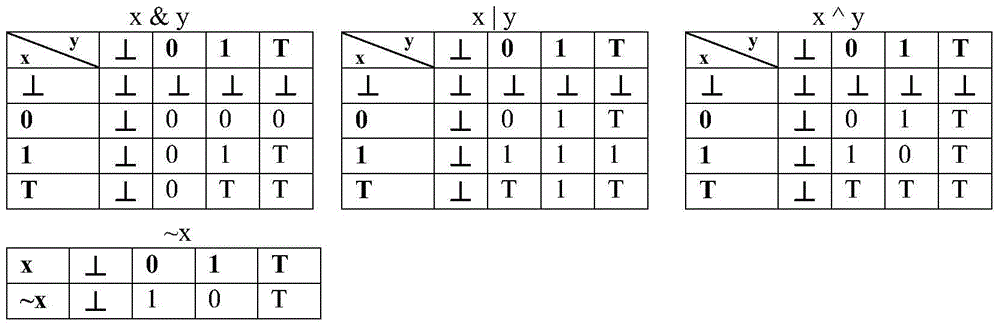

Method for generating bit operation test case based on four-valued logic

InactiveCN105005530AImprove search efficiencySoftware testing/debuggingConstraint satisfaction problemTheoretical computer science

The invention discloses a method for generating a bit operation test case based on four-valued logic, and belongs to the technical field of test case generation in a software test. The method specifically comprises the following steps: a first step of setting a four-valued logic operation method and an inverse operation method of four-valued logic operation; a second step of resolving a bit operation constraint into logic operation constraints; a third step of enabling the logic operation constraints to correspond to constraint satisfaction problems; a fourth step of solving the logic operation constraints by virtue of a search algorithm according to the four-valued logic operation and inverse operation methods; and 5 synthesizing the solutions of the logic operation constraints into a solution of the bit operation constraint. The method has the advantages that the range of a variable is computed by employing the multi-valued logic, so that the search efficiency of the search space and the bit operation is improved; and the test case generation efficiency of the bit operation is further improved.

Owner:BEIJING UNIV OF POSTS & TELECOMM

Three-valued thermal-insulation domino direct circulation valve and reverse circulation valve

ActiveCN102857215BHighly integratedHigh densityLogic circuits characterised by logic functionElectric pulse generatorThermal insulationInformation density

The invention discloses a three-valued thermal-insulation domino direct circulation valve and a three-valued thermal-insulation domino reverse circulation valve which respectively comprise a three-valued low-power dissipation domino JKL trigger, wherein each three-valued low-power dissipation domino JKL trigger consists of a first three-valued thermal-insulation domino text calculation circuit, a second three-valued thermal-insulation domino text calculation circuit, a third three-valued thermal-insulation domino text calculation circuit, a fourth three-valued thermal-insulation domino text calculation circuit and a basic three-valued JKL trigger circuit; thermal-insulation logic, multi-valued logic and multi-domino circuits are combined together through the first to fourth three-valued thermal-insulation domino text calculation circuits, thus realizing a three-valued low-power dissipation domino JKL trigger; and the three-valued thermal-insulation domino direct circulation valve and the three-valued thermal-insulation domino reverse circulation valve have the advantages of being high in circuit integration and information density and low in power dissipation on the basis of the three-valued low-power dissipation domino JKL trigger.

Owner:NINGBO UNIV

Three-value low power consumption domino JKL trigger

InactiveCN102790602BHighly integratedHigh densityElectric pulse generatorEngineeringInformation density

The invention discloses a three-value low power consumption domino JKL trigger. The three-value low power consumption domino JKL trigger consists of a first three-value heat-insulating domino character operational circuit, a second three-value heat-insulating domino character operational circuit, a third three-value heat-insulating domino character operational circuit, a fourth three-value heat-insulating domino character operational circuit and a three-value JKL trigger basic circuit, wherein a heat-insulating logic, a multi-value logic and a domino circuit are combined together by the first three-value heat-insulating domino character operational circuit, the second three-value heat-insulating domino character operational circuit, the third three-value heat-insulating domino character operational circuit and the fourth three-value heat-insulating domino character operational circuit. The three-value low power consumption domino JKL trigger has the advantages that the circuit integration level and information density of the JKL trigger are improved; and compared with a conventional three-value domino JKL trigger, the three-value low power consumption domino JKL trigger disclosed by the invention has the characteristic that energy consumption is saved by 69 percent.

Owner:HANGZHOU MAEN TECH

A quad-stable rs flip-flop supporting multi-valued logic

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

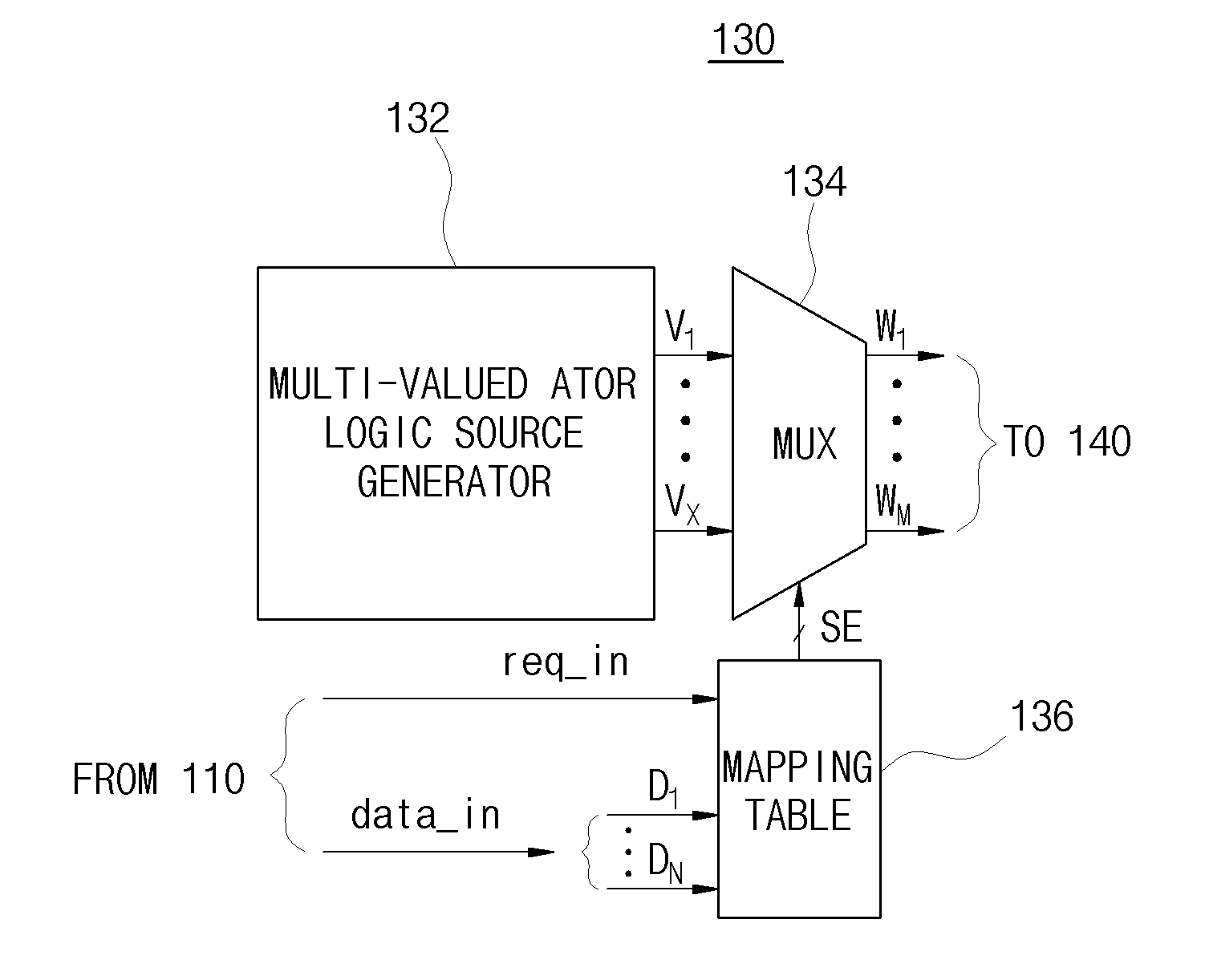

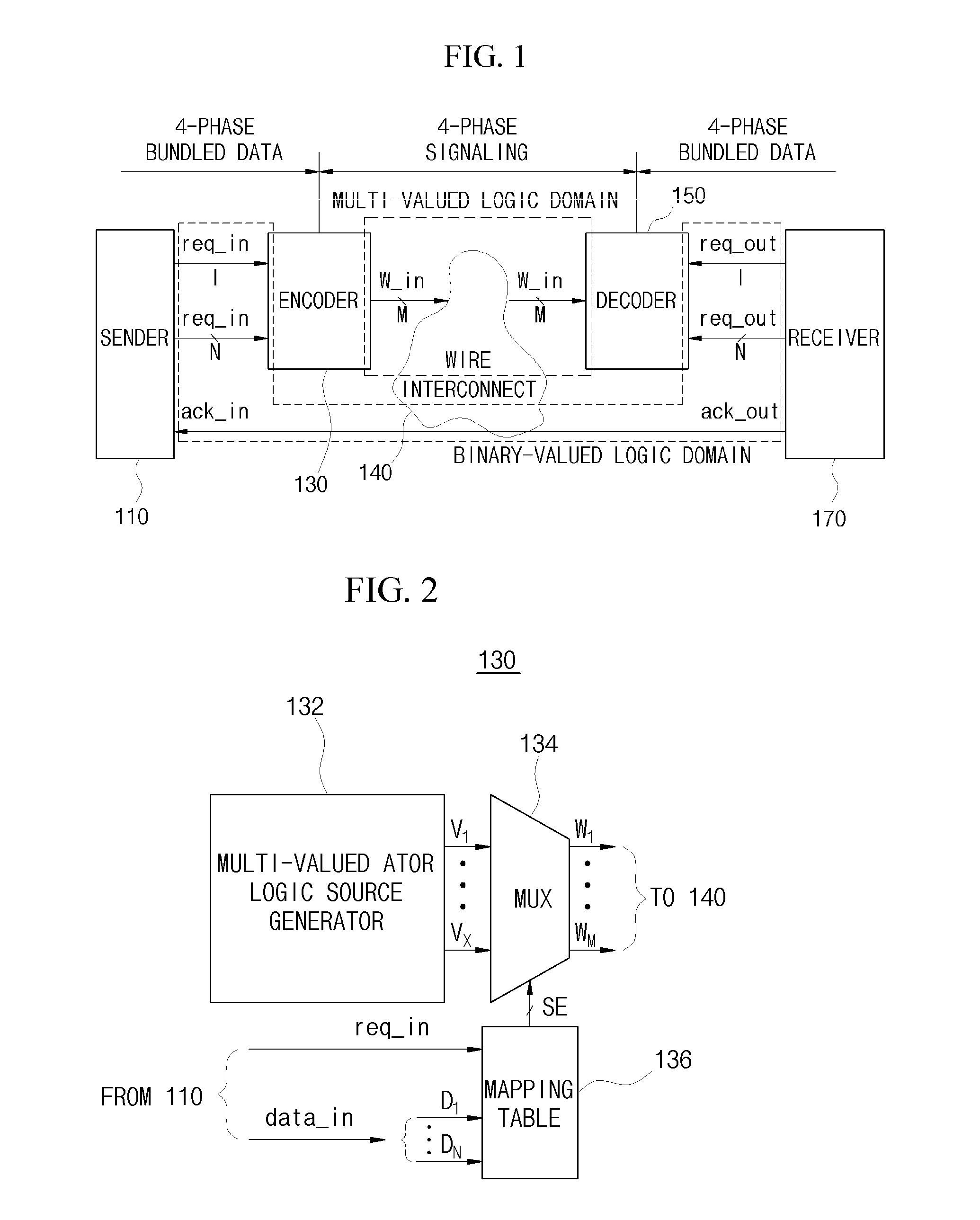

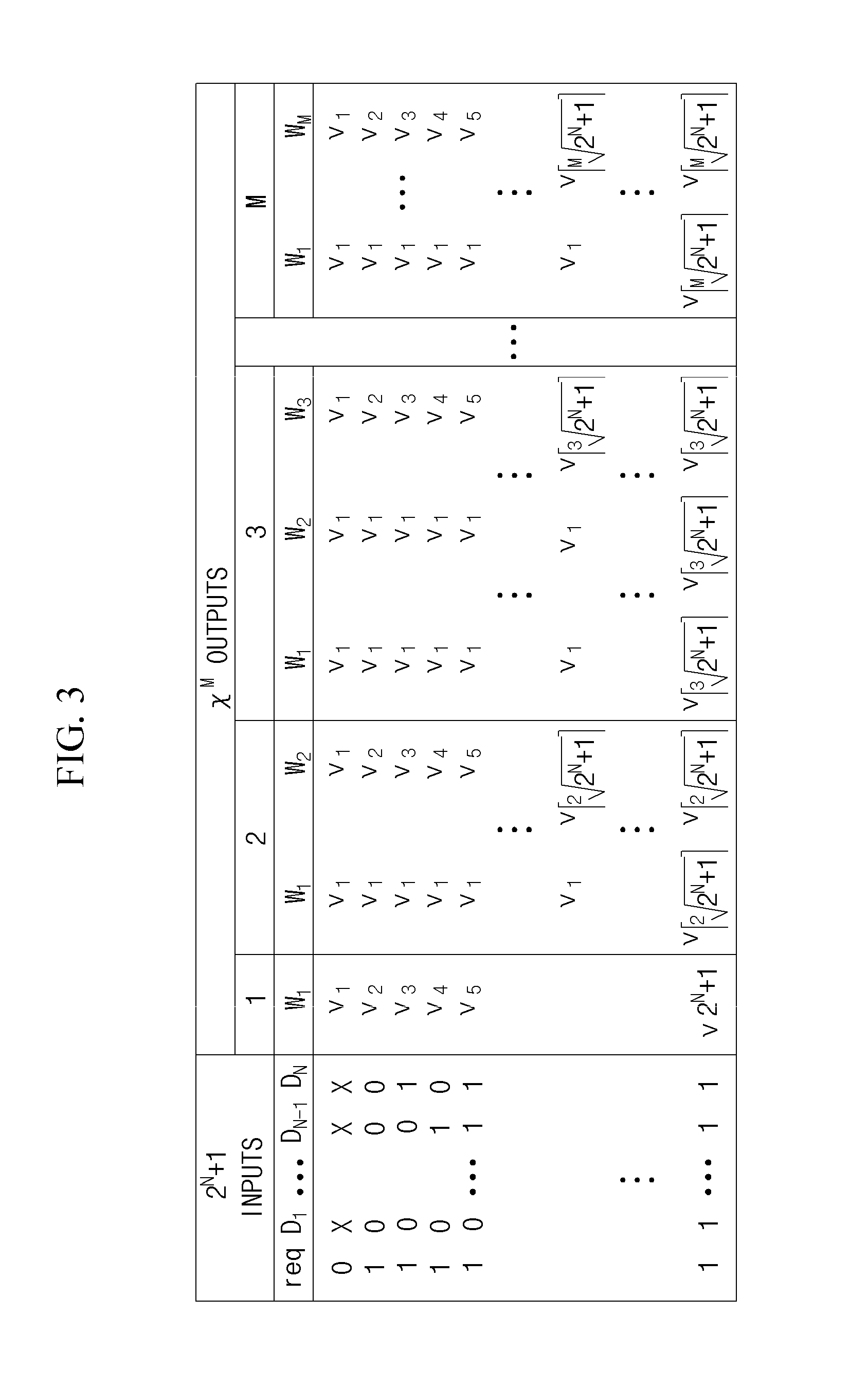

Data transmission apparatus and method for transmitting data in delay-insensitive data transmission method supporting handshake protocol

ActiveUS20160087763A1Reduce in quantityError prevention/detection by using return channelModulated-carrier systemsComputer hardwareData transmission

Provided are a data transmission apparatus and method for transmitting data in a Delay-Insensitive (DI) data transmission method supporting a handshake protocol. The data transmission apparatus includes a sender which outputs a binary-valued logic signal based on binary-valued logic, and an encoder which encodes the binary-valued logic signal input through input wires into a multi-valued logic signal based on multi-valued logic and transmits the encoded multi-valued logic signal to a decoder through output wires. Here, the encoder includes a mapping table which stores input variables including the number of input wires and the number of output wires smaller than the number of input wires and the multi-valued logic signal corresponding to the input variables, and encodes the binary-valued logic signal into the multi-valued logic signal with reference to the mapping table.

Owner:ELECTRONICS & TELECOMM RES INST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com