Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

340 results about "Logical Function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The OR function is a basic logical function that is used to compare any two statements or values. If you’re familiar with any kind of programming language, you have most probably used it before.

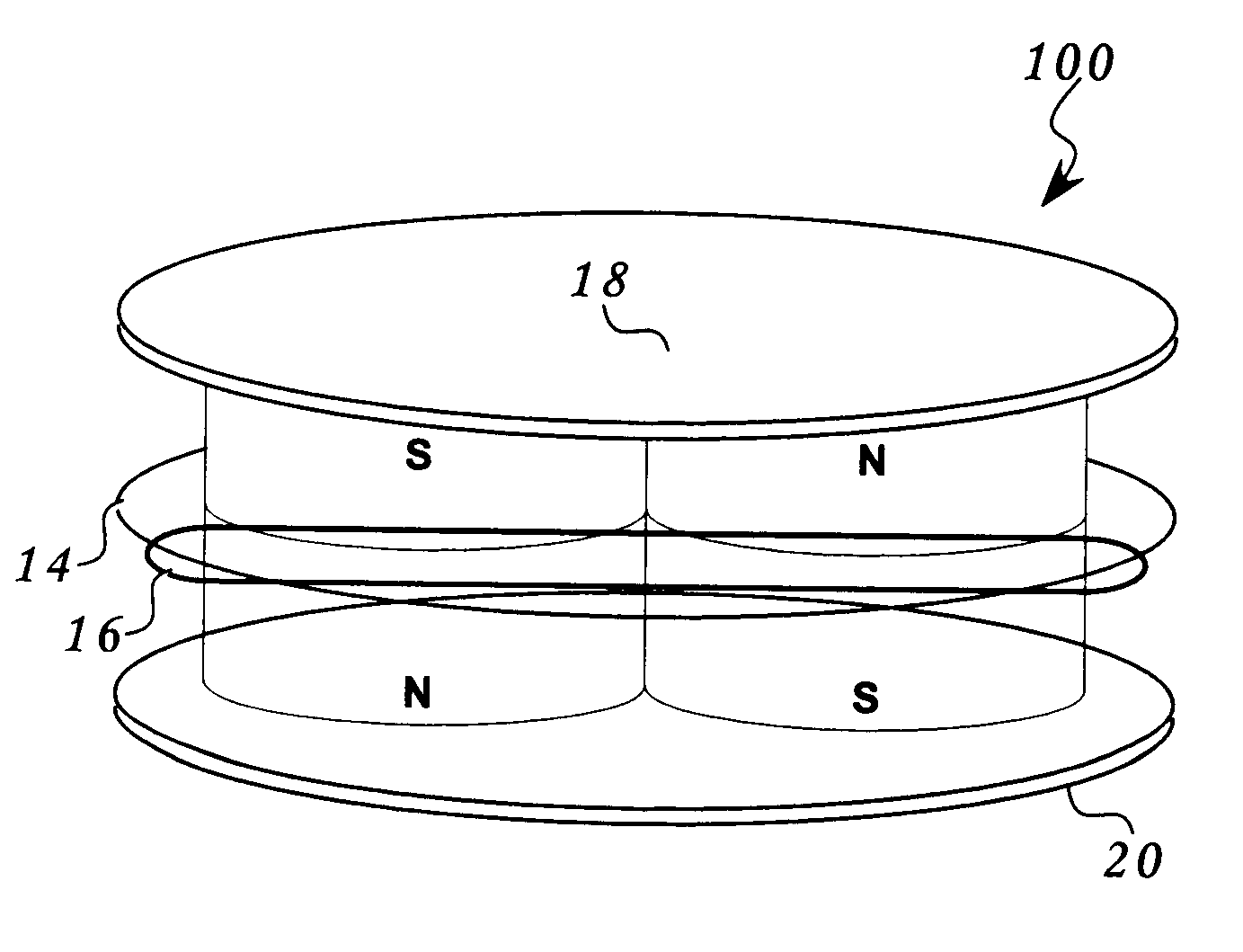

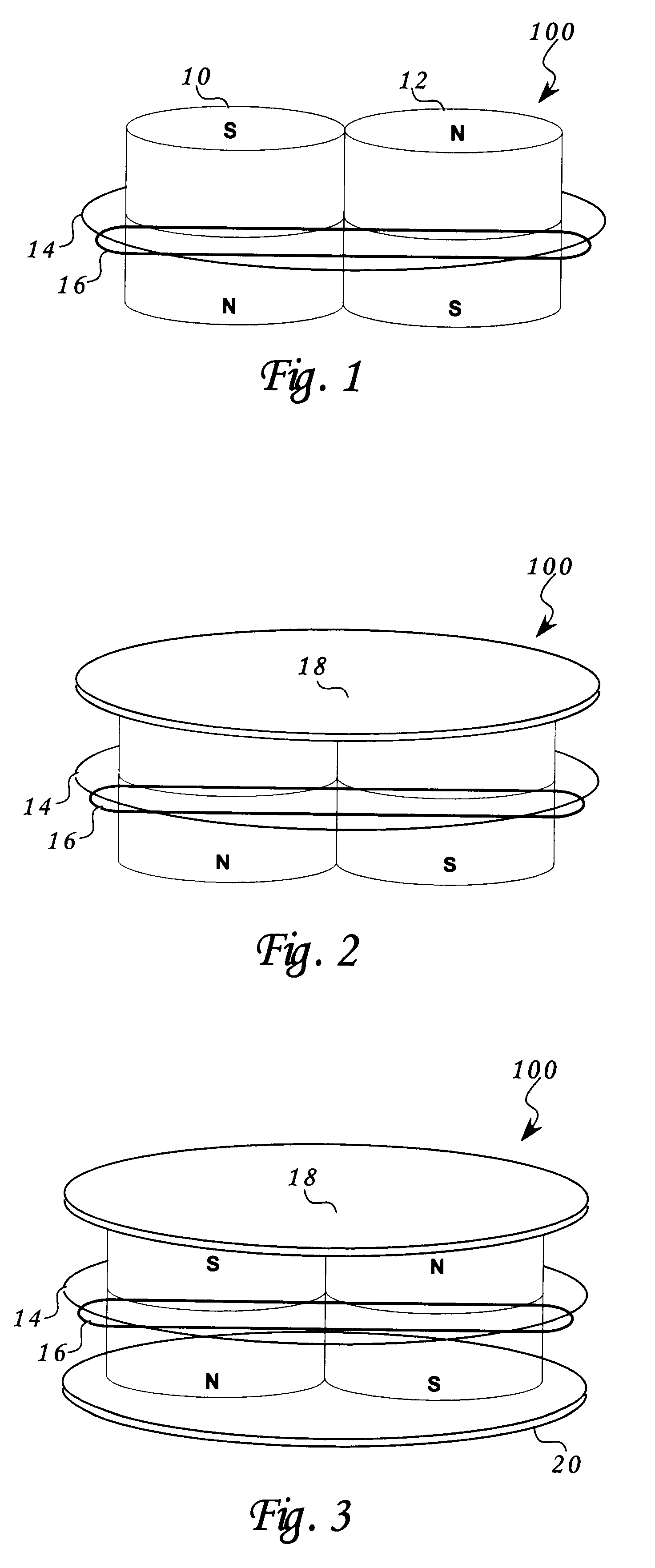

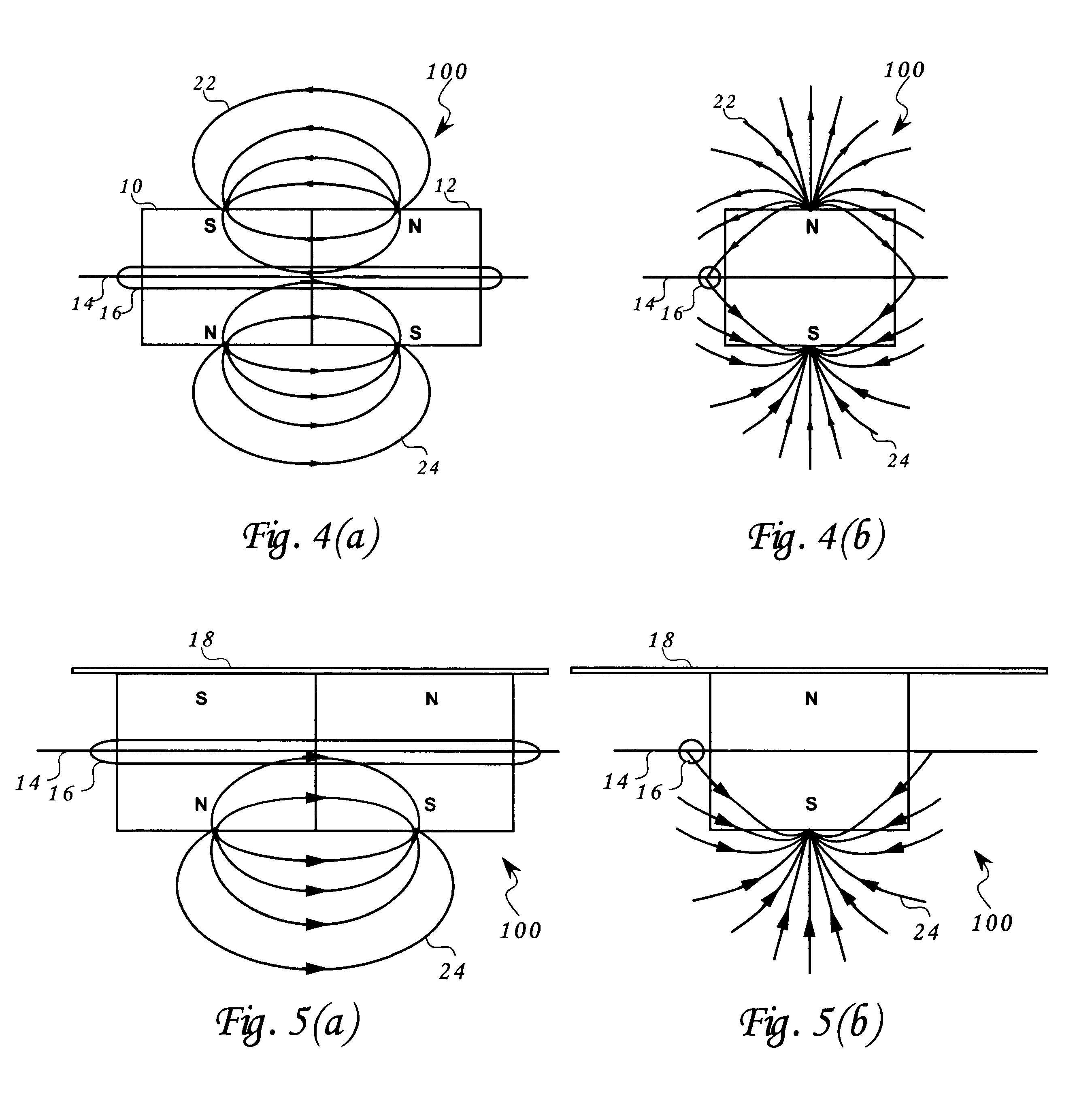

Multifaceted balanced magnetic proximity sensor

An apparatus and method of proximity switch / sensor based generally on a balanceable magnetic pole array. The magnetic pole array contains at least four poles with optional ferromagnetic shunt(s). The proximity of a shunt to a magnetic pole array determines whether the array is balanced or unbalanced. A balanced array is one with a zone where the vector sum of magnetic fields emanating from the array's poles can be made to approach zero. A sensor such as a reed switch is placed in the balanced zone. When the balance of the array is disturbed by the application of one or multiple shunts, the resulting finite magnetic field vector along with the resulting magnetic flux, activates the sensor. This approach can be implemented in a variety of array structures that offer implementation of a variety of logical functions. Multiple shunts and their proximity to the array are used as the logical function's inputs and the sensor's state as the logical function's output.

Owner:OSTERWEIL JOSEF

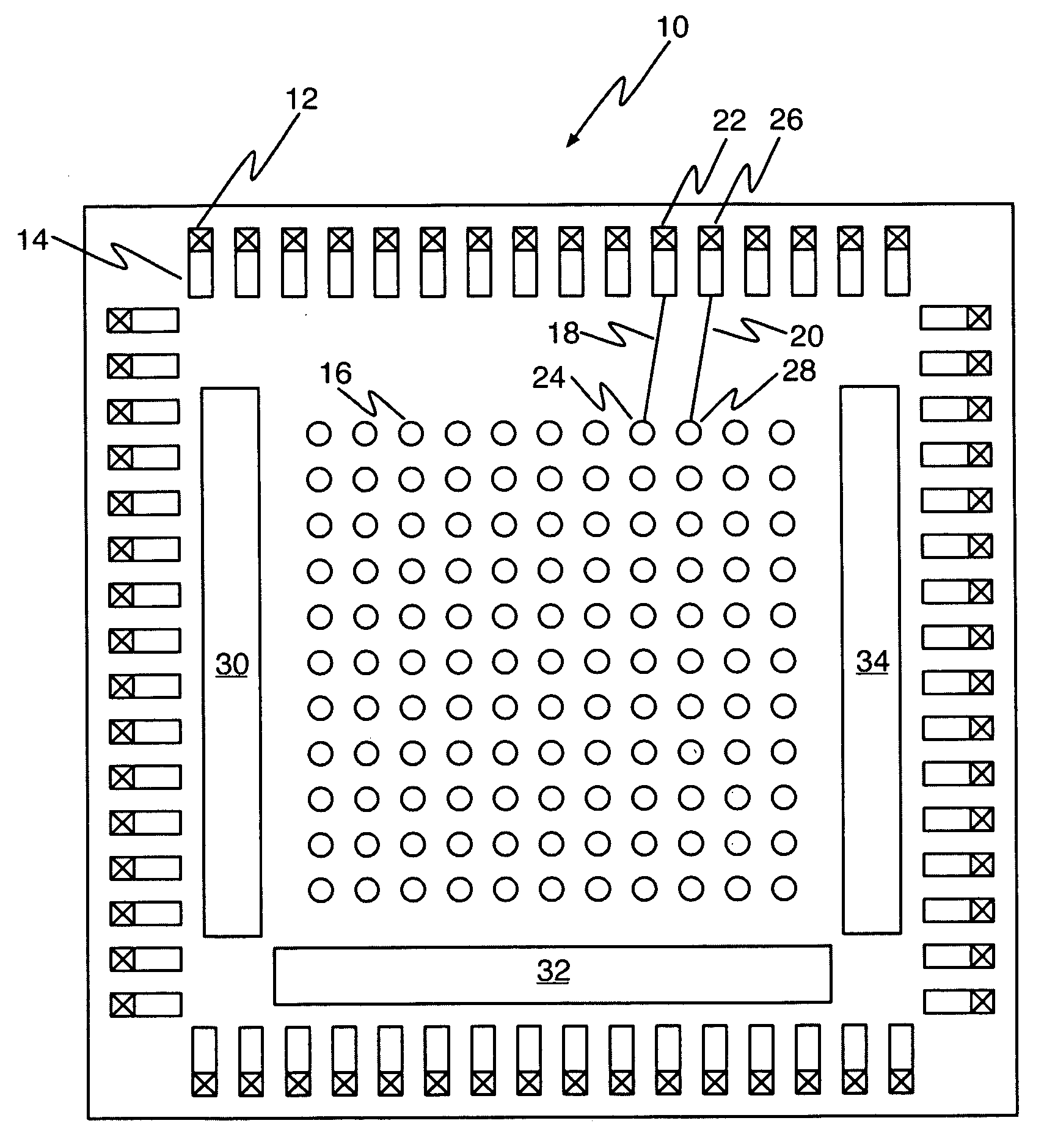

Face-to-face bonded I/O circuit die and functional logic circuit die system

ActiveUS20060071332A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit

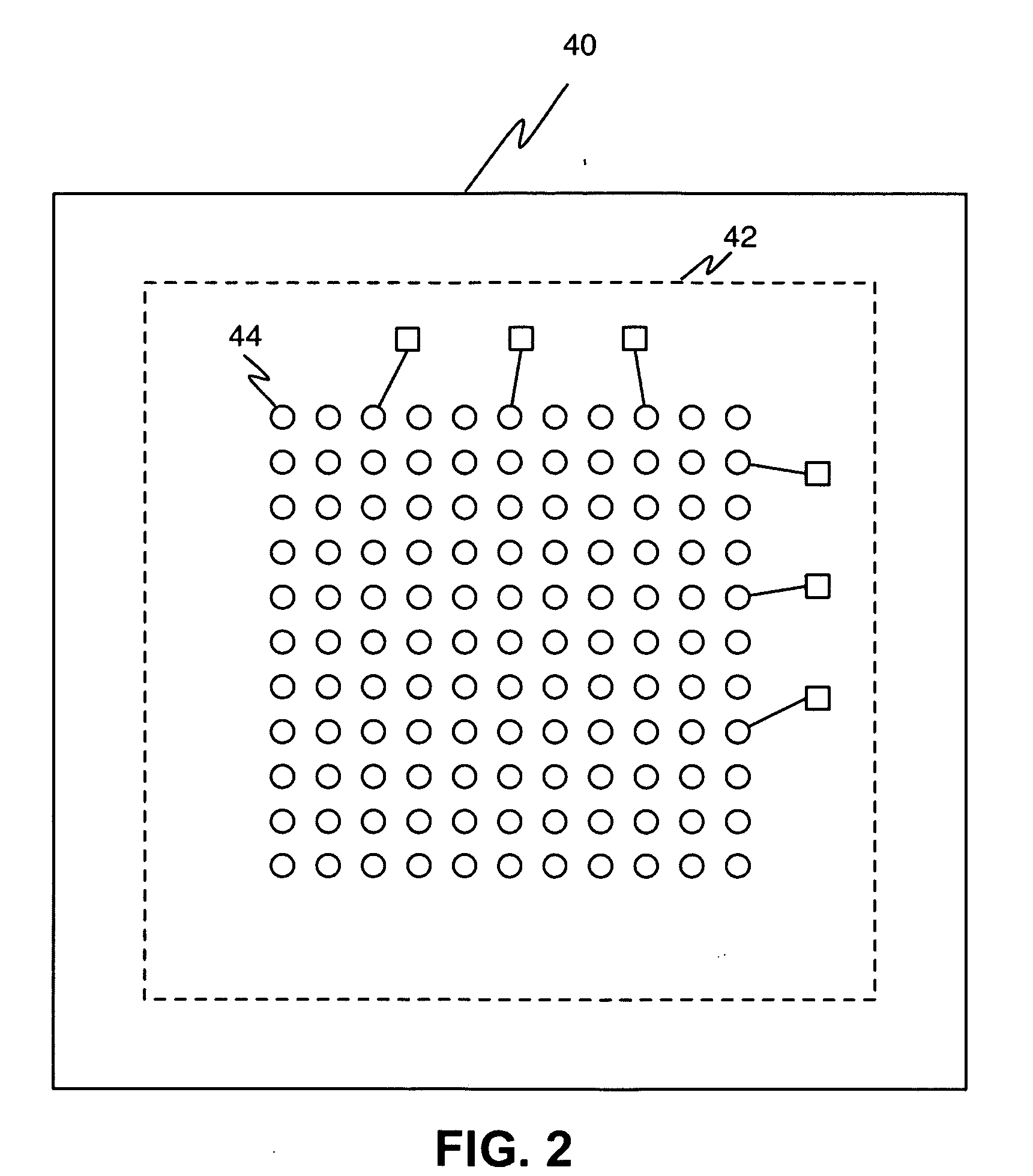

An integrated circuit system includes a first set of integrated circuit dice each member of the set having a different configuration of input / output circuits disposed thereon and a second set of integrated circuit dice each having different logical function circuits disposed thereon. Each member of the first and second sets of integrated circuit dice include an array of face-to-face bonding pads disposed thereon that mate with the array of face-to-face bonding pads of each member of the other set.

Owner:MICROSEMI SOC

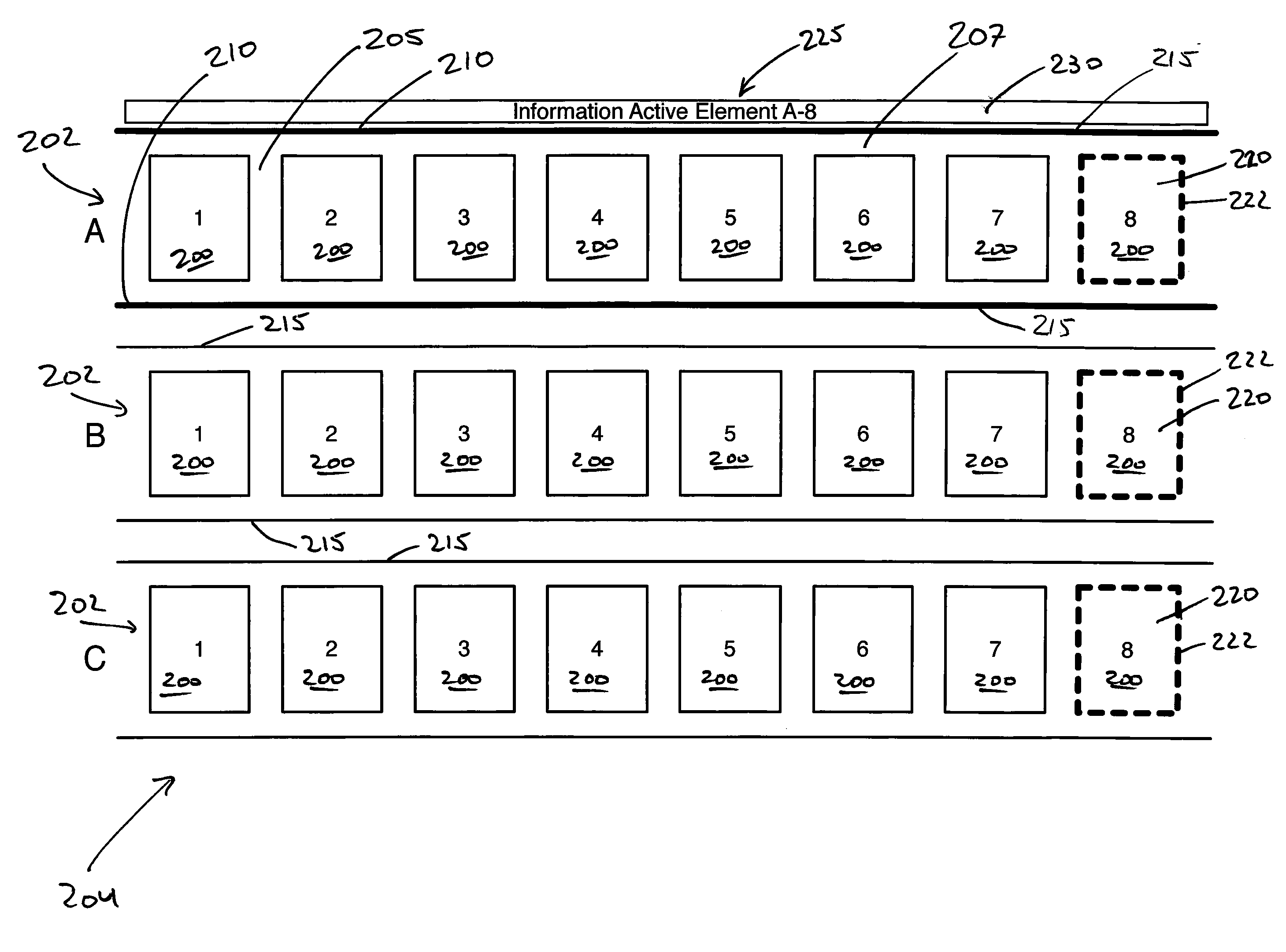

Architecture for face-to-face bonding between substrate and multiple daughter chips

ActiveUS7358601B1Semiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit

An integrated circuit system includes a first integrated circuit die and a family of second integrated circuit dice. The first integrated circuit die have input / output circuits disposed thereon and further have a first array of face-to-face bonding structures disposed on a first face thereof. Each member of the family of second integrated circuit dice have logical function circuits disposed thereon and further have a second array of face-to-face bonding structures disposed on a first face thereof. The second array of face-to-face bonding structures of each member of the family mates with a different portion of the first array of face-to-face bonding structures.

Owner:MICROSEMI SOC

Combined Layer 2 Virtual MAC Address with Layer 3 IP Address Routing

Inbound packets received by a physical network adapter of a processing device are routed by evaluating an inbound frame to determine if an inbound frame destination MAC address is associated with the processing device and determining whether the inbound frame should be routed to a corresponding logical interface or to drop the inbound frame if the inbound frame destination MAC address is equal to a virtual MAC address supported by the processing device. If it is determined that the inbound frame should be routed to the corresponding logical interface, then any necessary layer 3 functions are performed and the inbound frame is routed to the corresponding logical interface, thereby combining both layer 2 and layer 3 routing into a single logical function.

Owner:IBM CORP

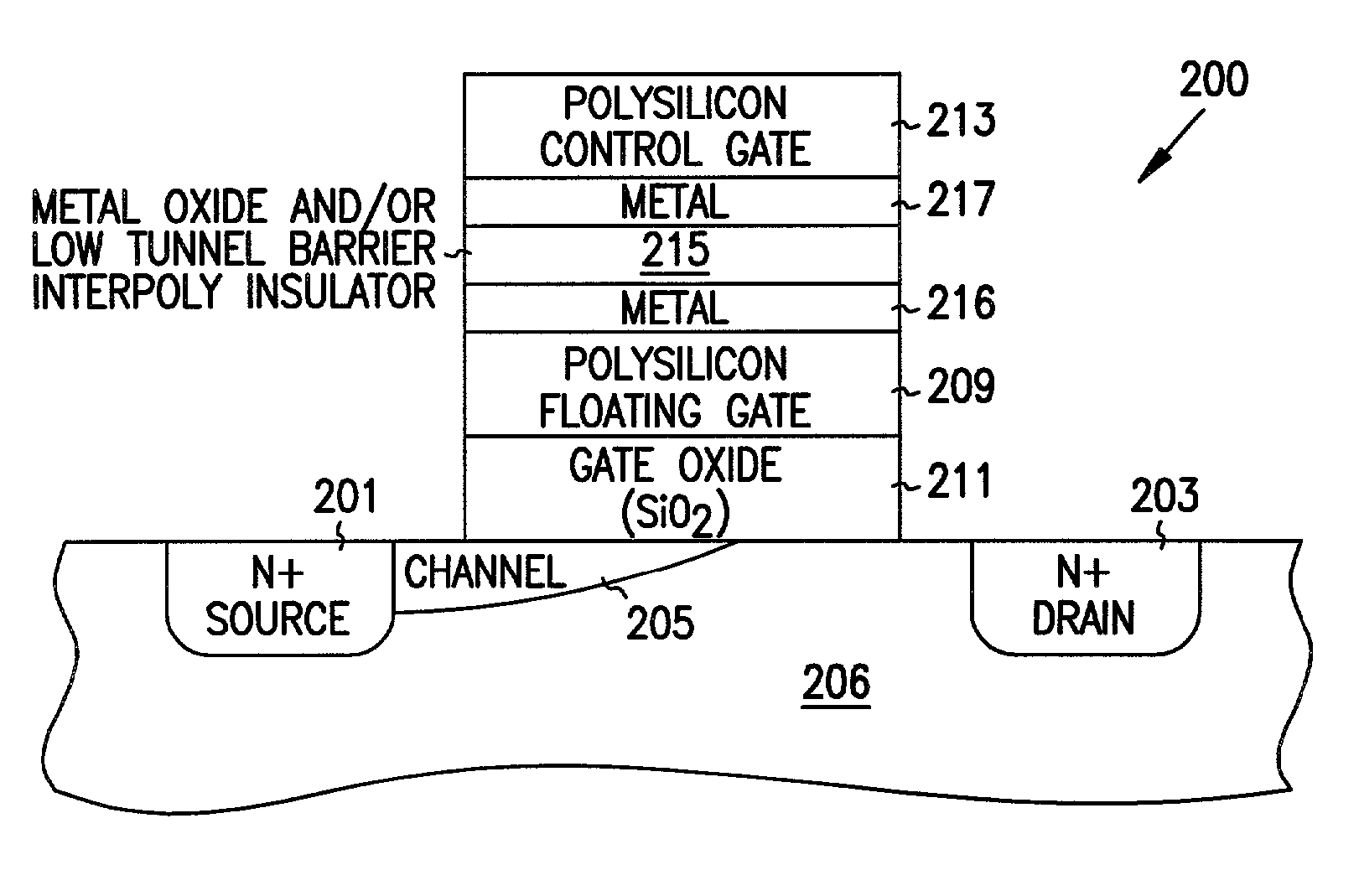

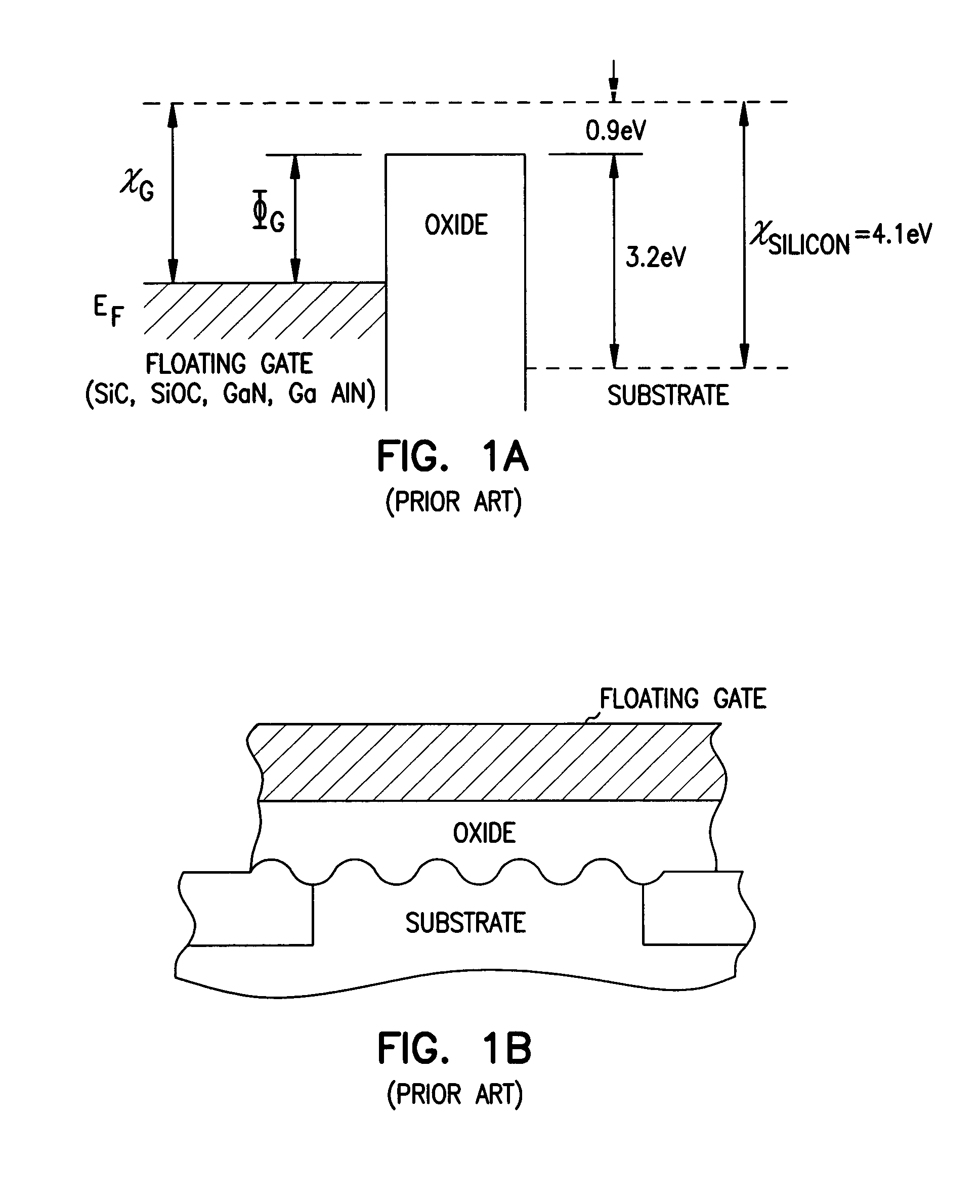

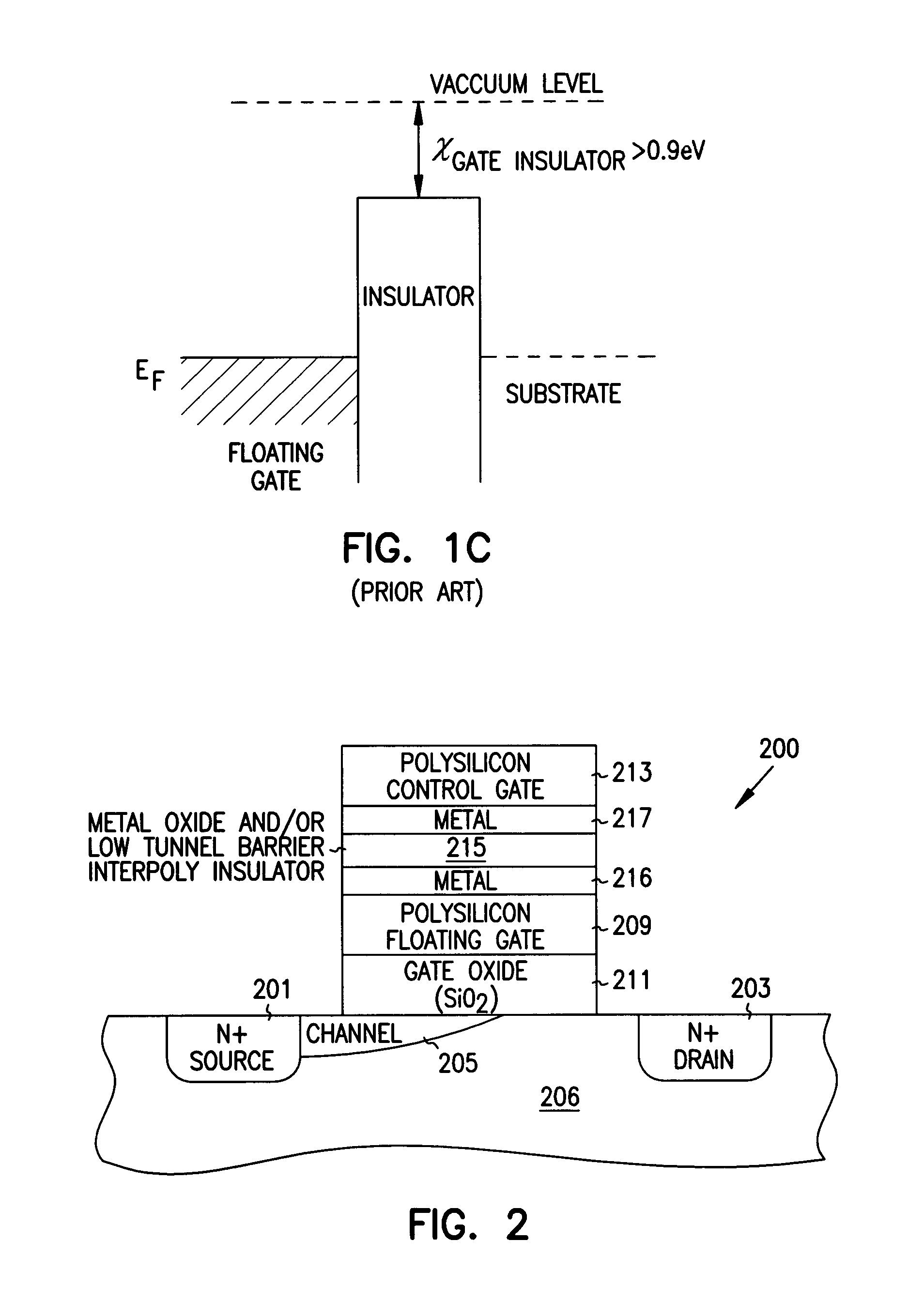

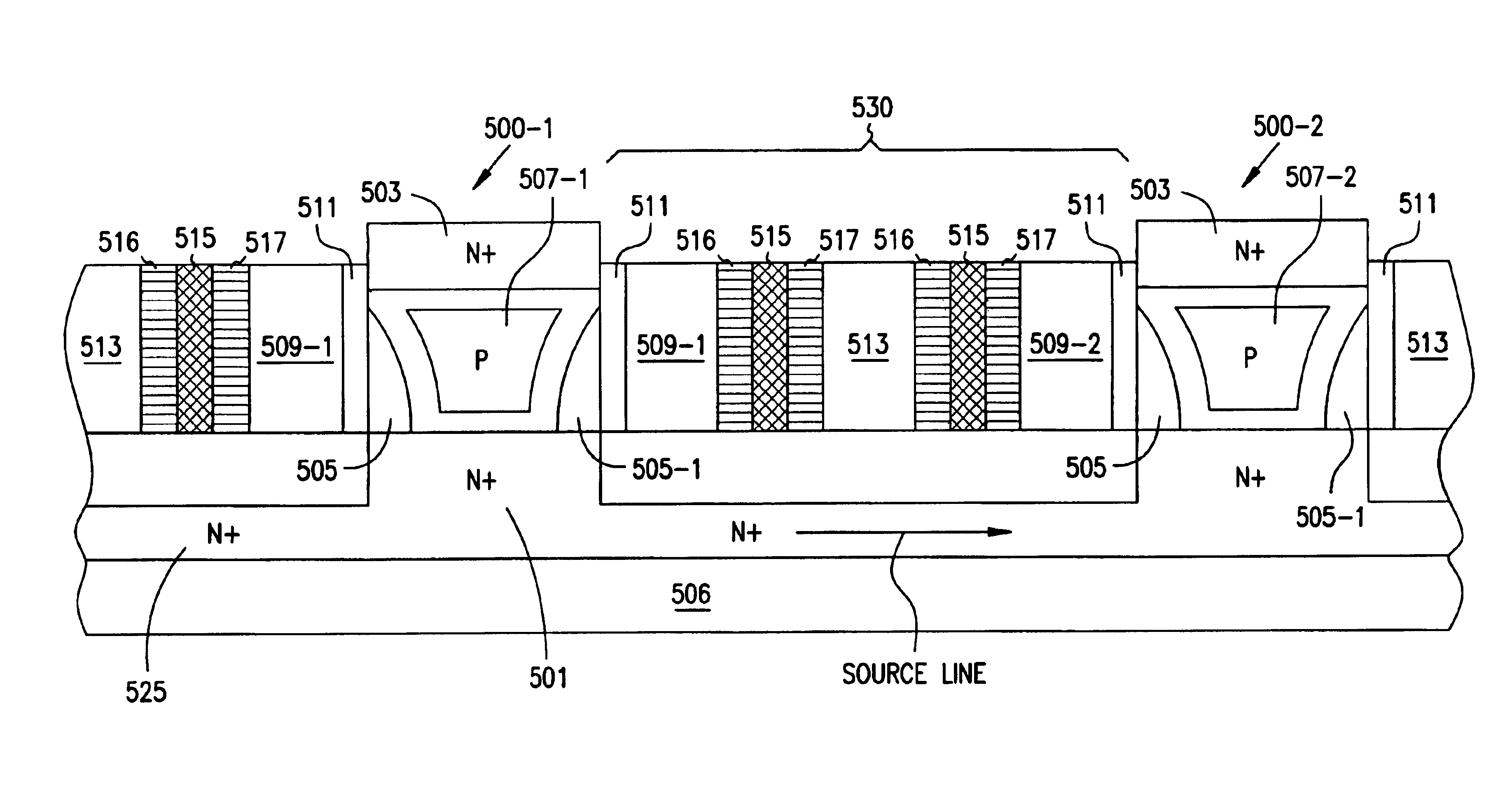

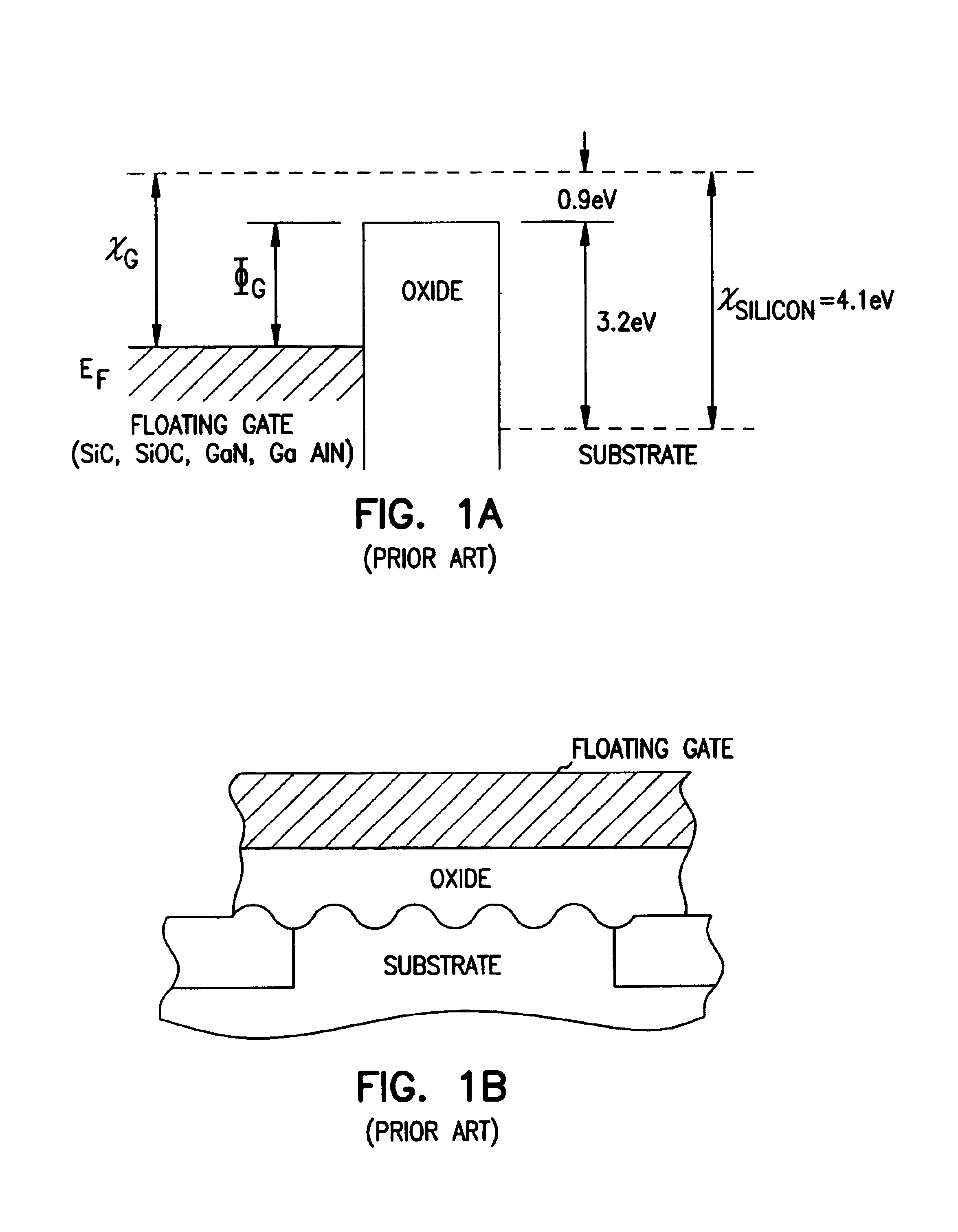

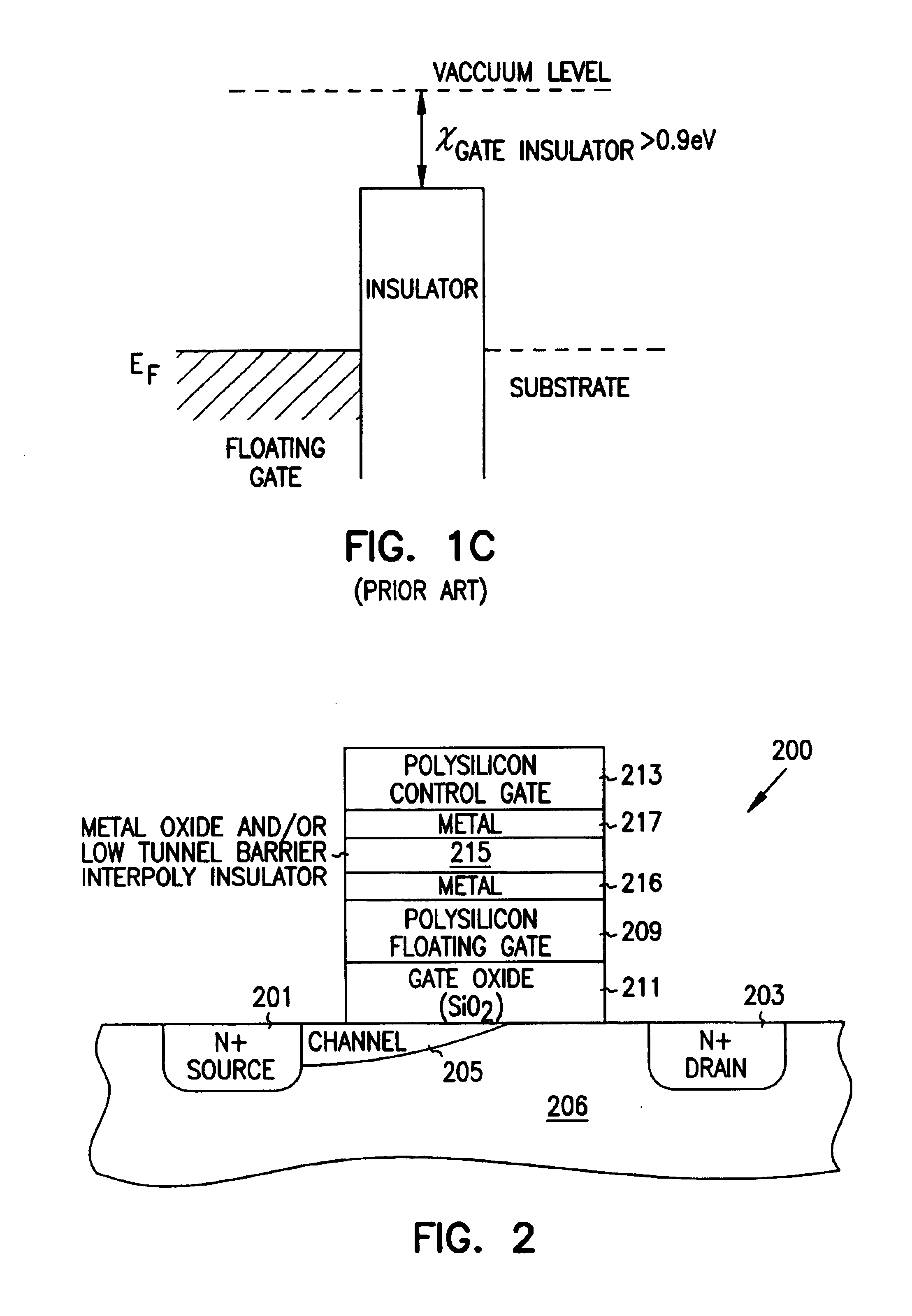

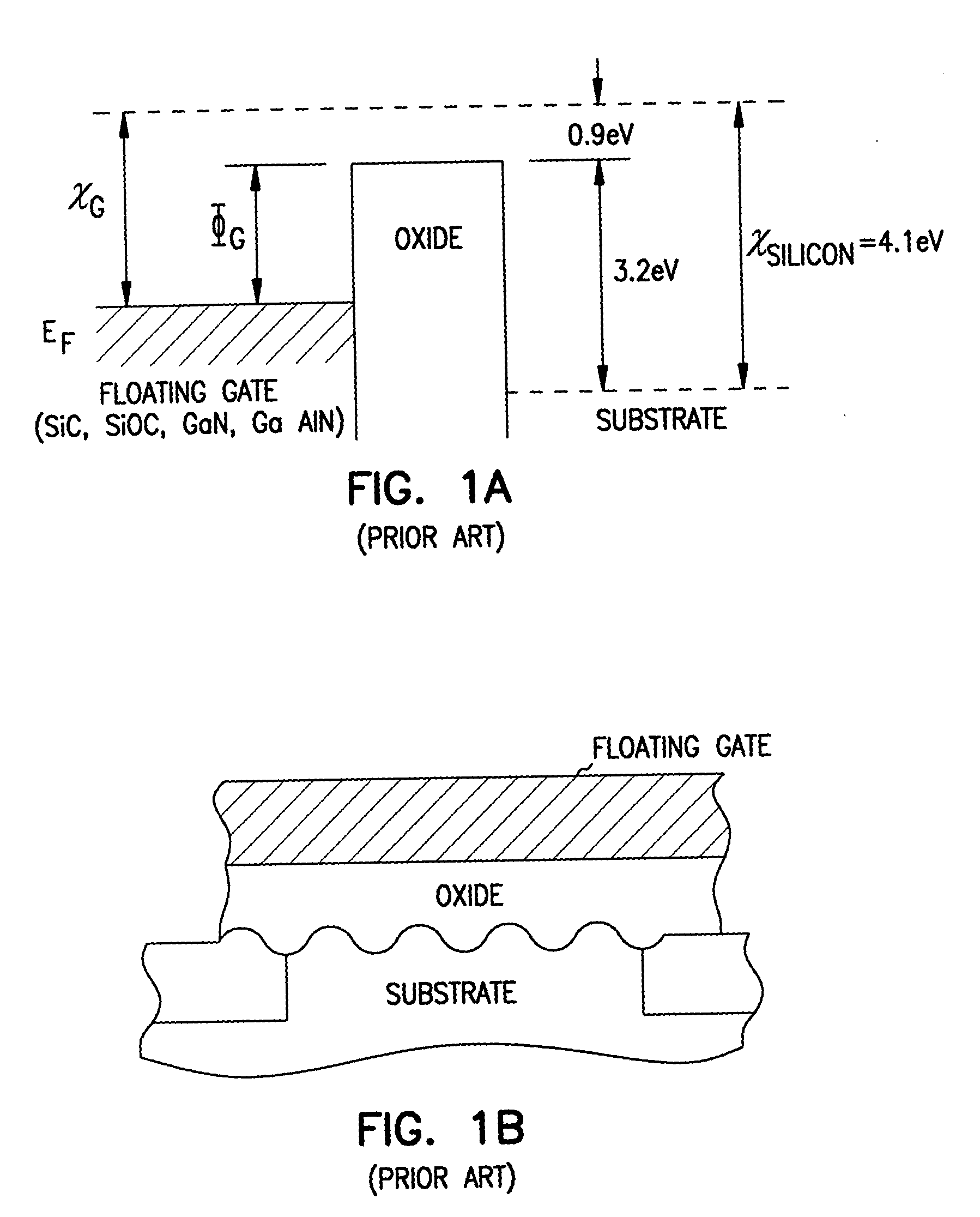

In service programmable logic arrays with low tunnel barrier interpoly insulators

Structures and methods for in service programmable logic arrays with low tunnel barrier interpoly insulators are provided. The in-service programmable logic array includes a first logic and a second logic plan having a number of logic cells arranged in rows and columns that are interconnected to produce a number of logical outputs such that the in service programmable logic array implements a logical function. The logic cell includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5 and / or a Perovskite oxide tunnel barrier.

Owner:MICRON TECH INC

Service programmable logic arrays with low tunnel barrier interpoly insulators

Structures and methods for in service programmable logic arrays with low tunnel barrier interpoly insulators are provided. The in-service programmable logic array includes a first logic and a second logic plan having a number of logic cells arranged in rows and columns that are interconnected to produce a number of logical outputs such that the in service programmable logic array implements a logical function. The logic cell includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5 and / or a Perovskite oxide tunnel barrier.

Owner:MICRON TECH INC

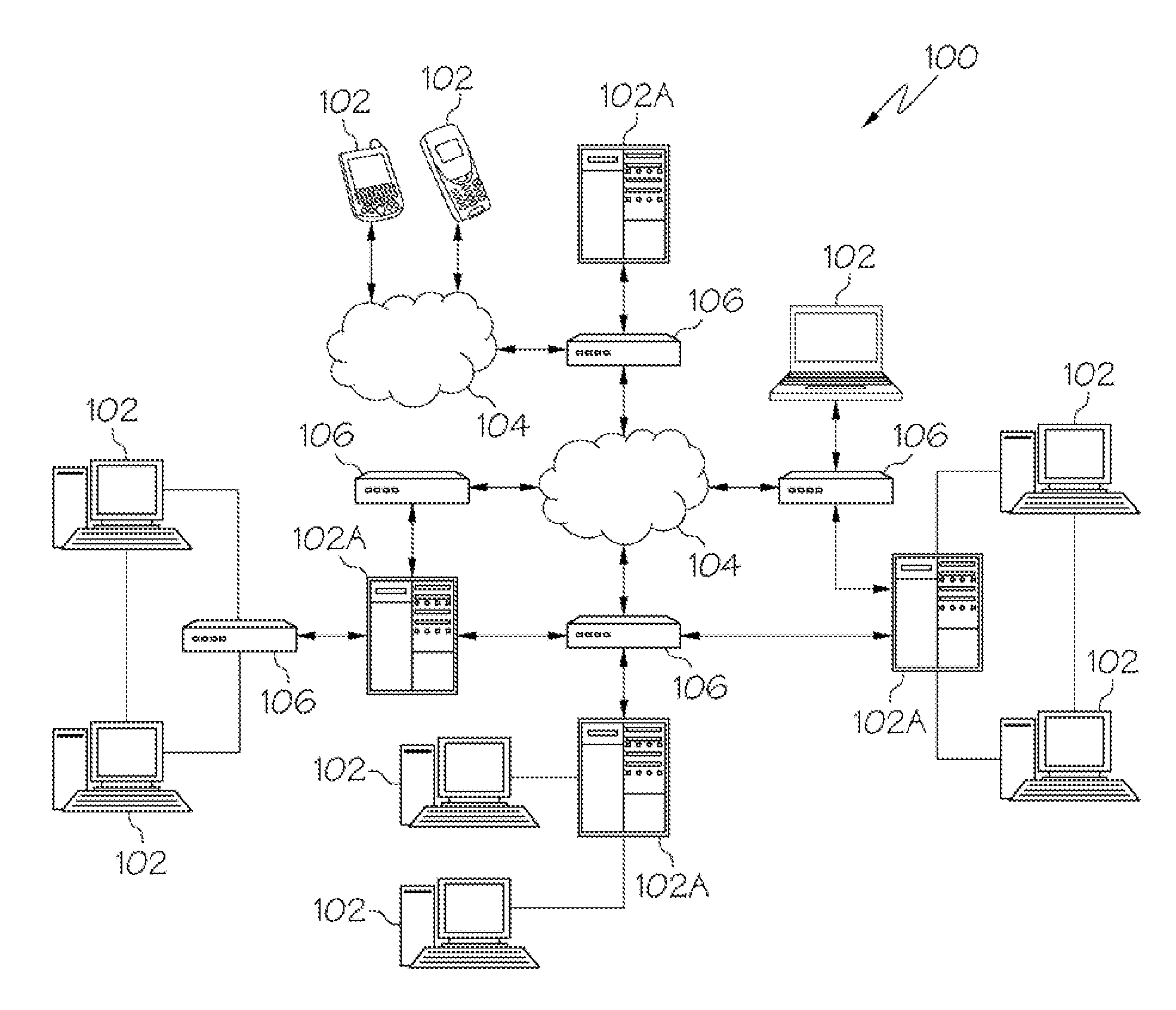

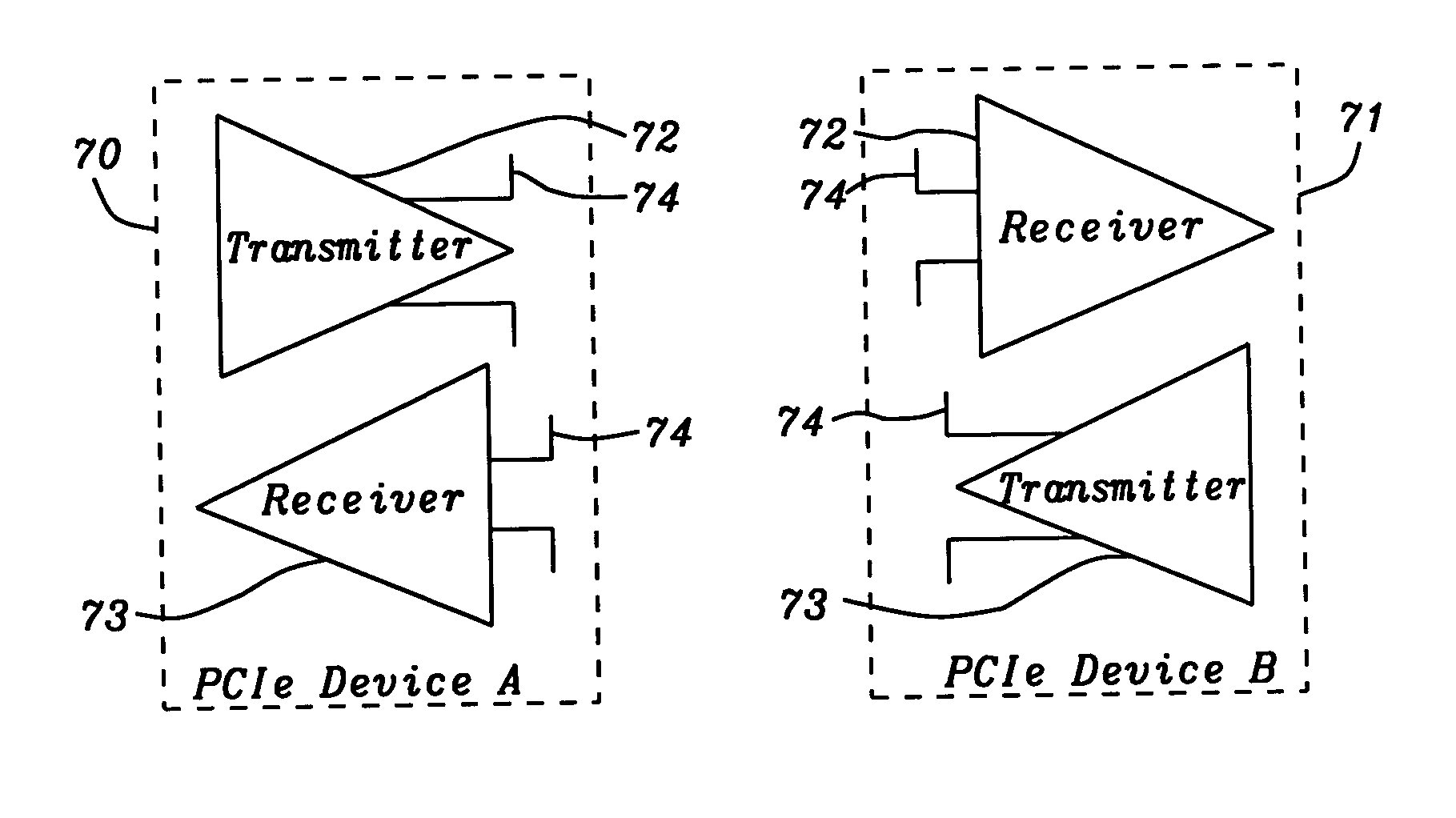

Inter-chip and intra-chip wireless communications systems

InactiveUS20050075080A1Antenna supports/mountingsSemiconductor/solid-state device detailsCommunications systemCoupling

A method and implementation for communicating between logic functions using non-metallic coupling between logic functions on a same chip or separate chip is shown. For communication on the same chip, radiated energy from an antenna coupled to a transmitting logic function is coupled to a receiving antenna and then coupled by an electrical connection to a receiving logic function. Communication between USLI chips mounted on a module is performed by coupling an RF signal from a first chip to a μ-satellite mounted within the module and then coupling the RF signal from the satellite to a second chip. Communication can also be formed between the satellite and different logical functions on the same USLI chip.

Owner:NANYANG TECH UNIV

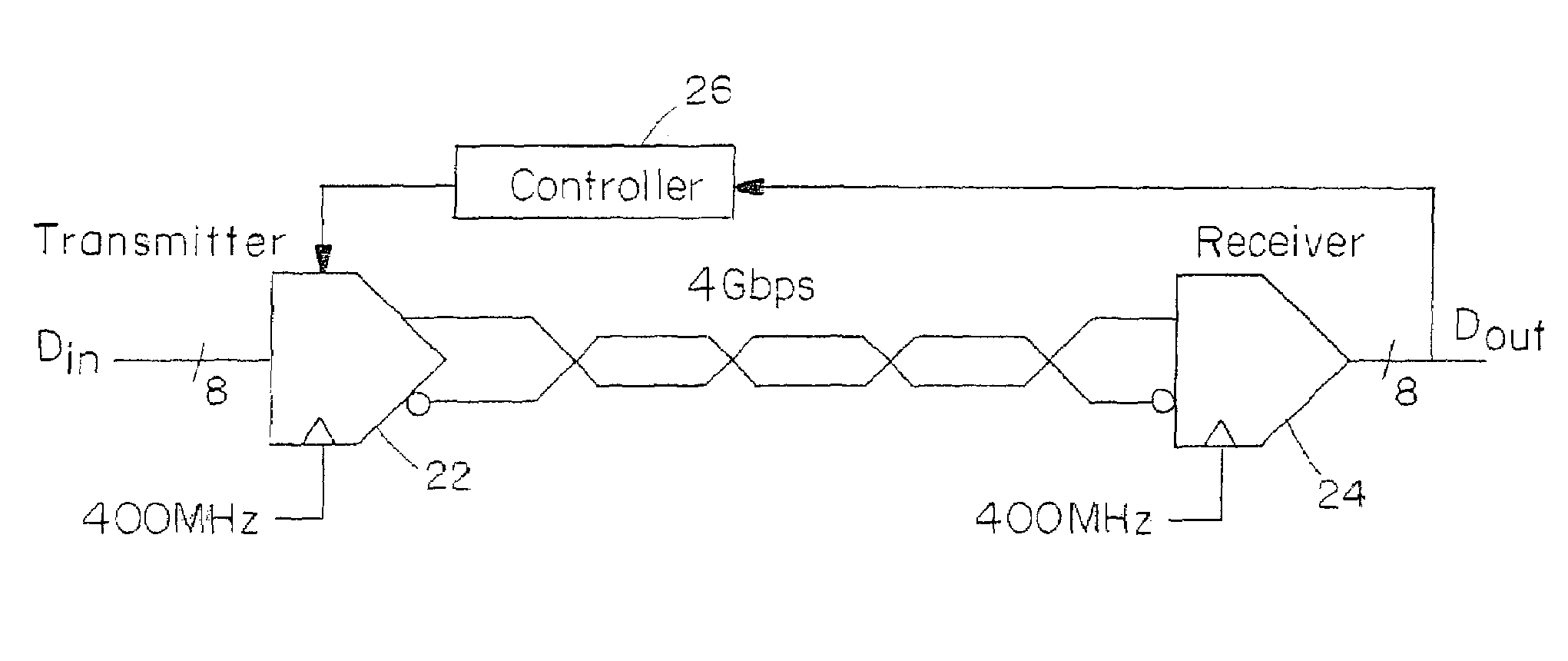

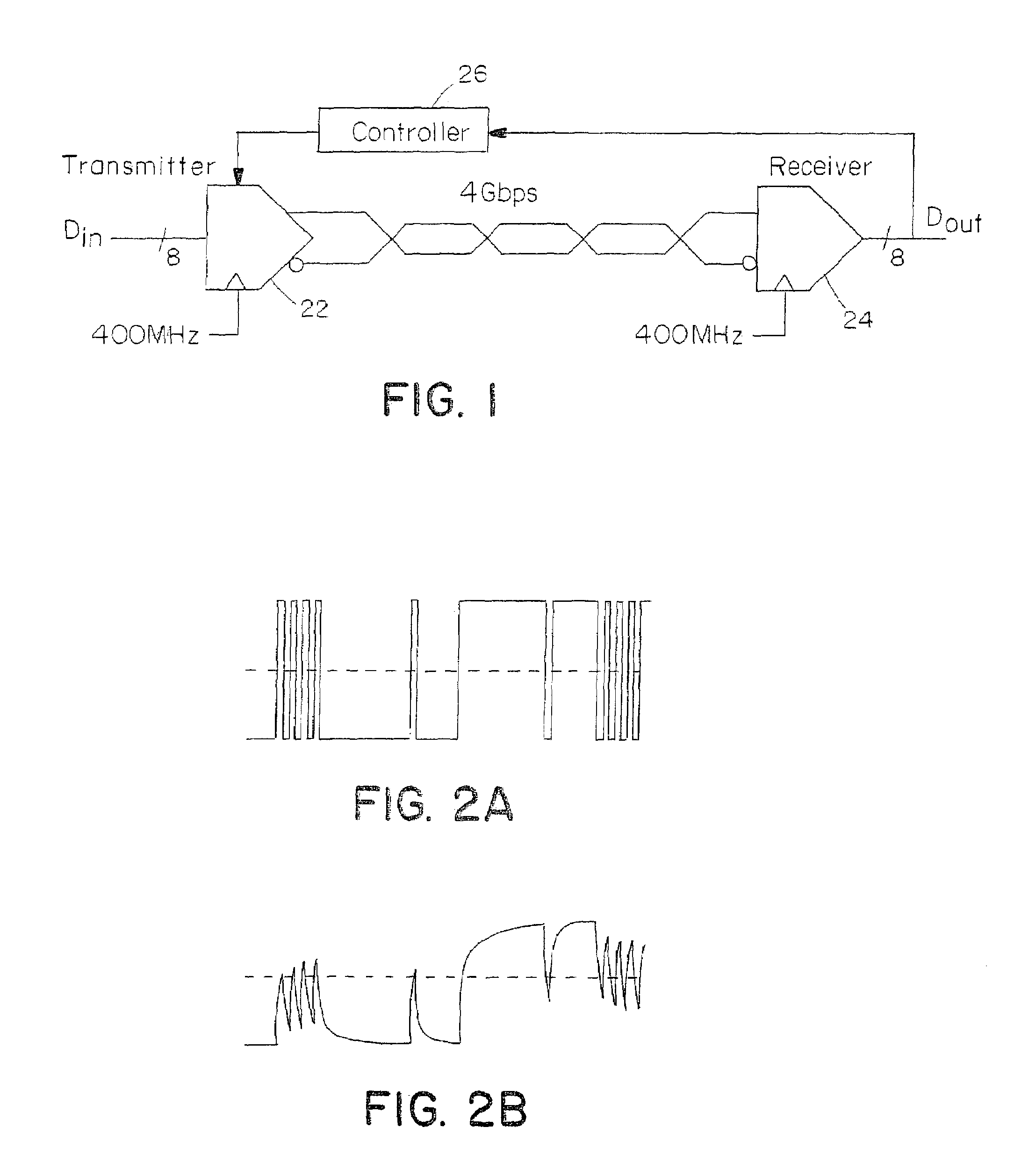

Digital transmitter

InactiveUS7099404B2Large attenuationReduce clock frequencyMultiple-port networksTransmission control/equlisationUltrasound attenuationDigital analog converter

An equalizer provided in a digital transmitter compensates for attenuation in a signal channel to a digital receiver. The equalizer generates signal levels as a logical function of bit history to emphasize transition signal levels relative to repeated signal levels. The preferred equalizer includes an FIR transition filter using a look-up table. Parallel circuits including FIR filters and digital-to-analog converters provide a high speed equalizer with lower speed circuitry. The equalizer is particularly suited to in-cabinet and local area network transmissions where feedback circuitry facilitates adaptive training of the equalizer.

Owner:THE UNIV OF NORTH CAROLINA AT CHAPEL HILL +1

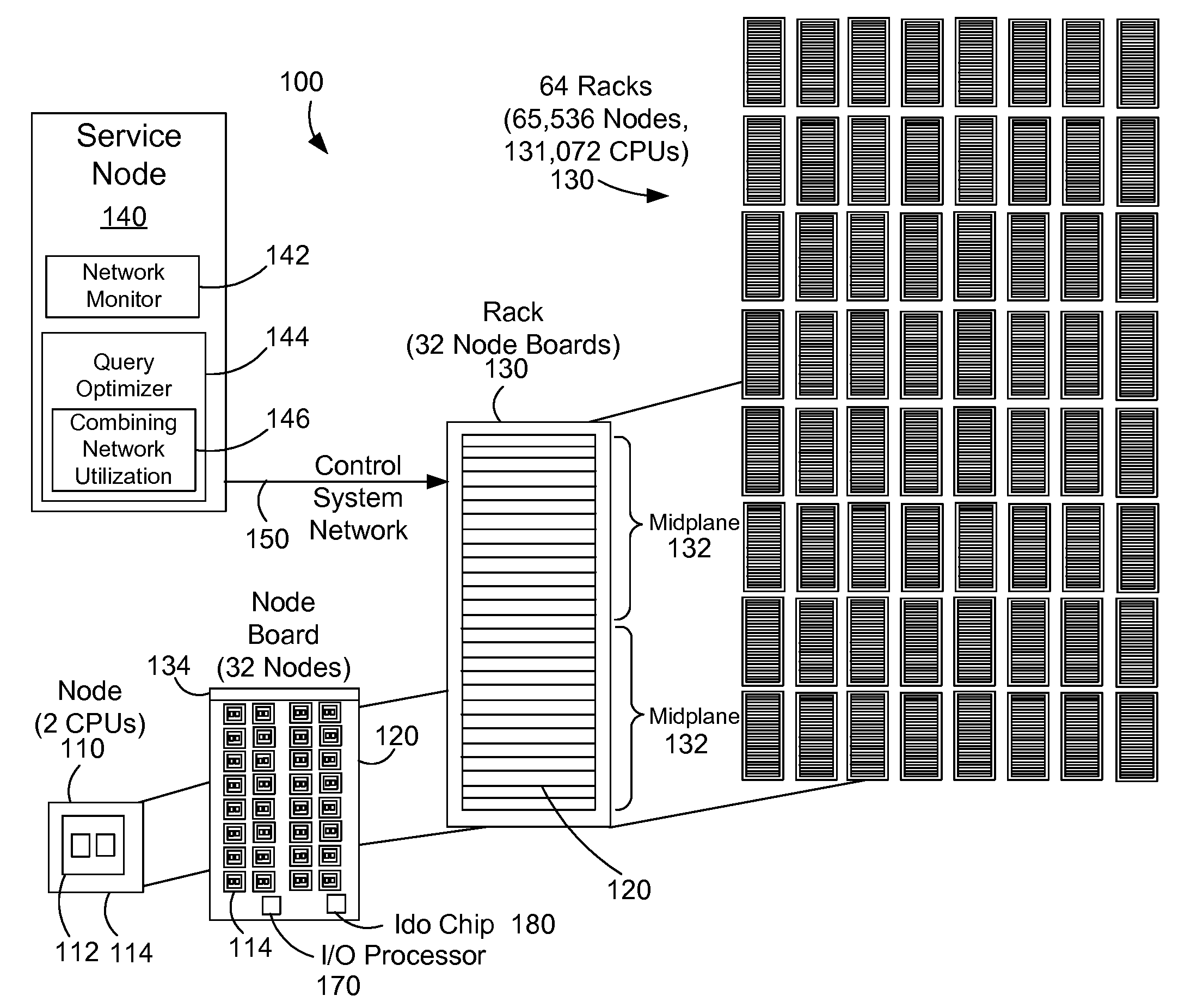

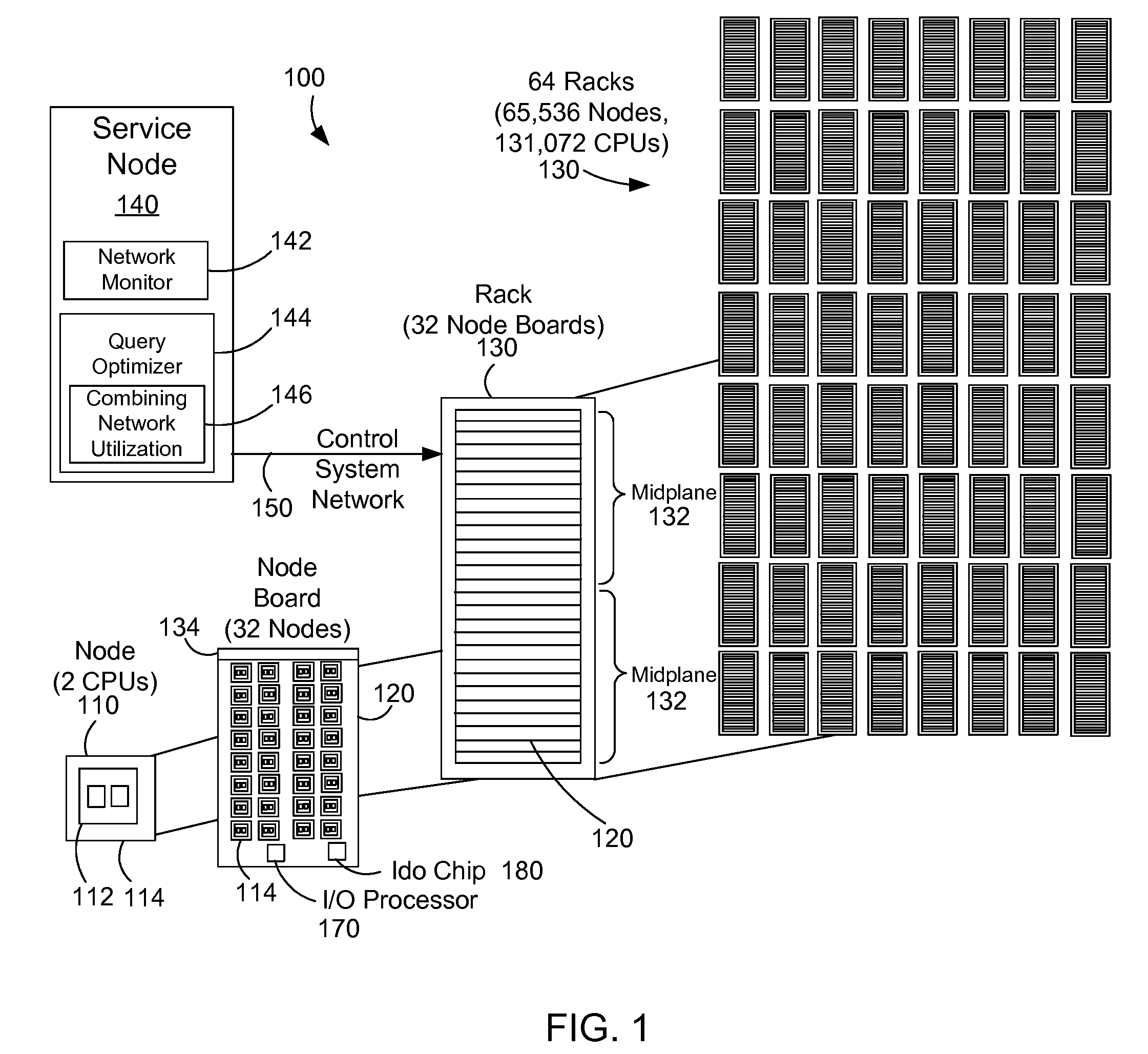

Query Execution and Optimization Utilizing a Combining Network in a Parallel Computer System

InactiveUS20090043910A1Improve parallel efficiencyImprove efficiencyData processing applicationsDigital data information retrievalDatabase queryComputerized system

An apparatus and method for a database query optimizer utilizes a combining network to optimize a portion of a query in a parallel computer system with multiple nodes. The efficiency of the parallel computer system is increased by offloading collective operations on node data to the global combining network. The global combining network performs collective operations such as minimum, maximum, sum, and logical functions such as OR and XOR.

Owner:IBM CORP

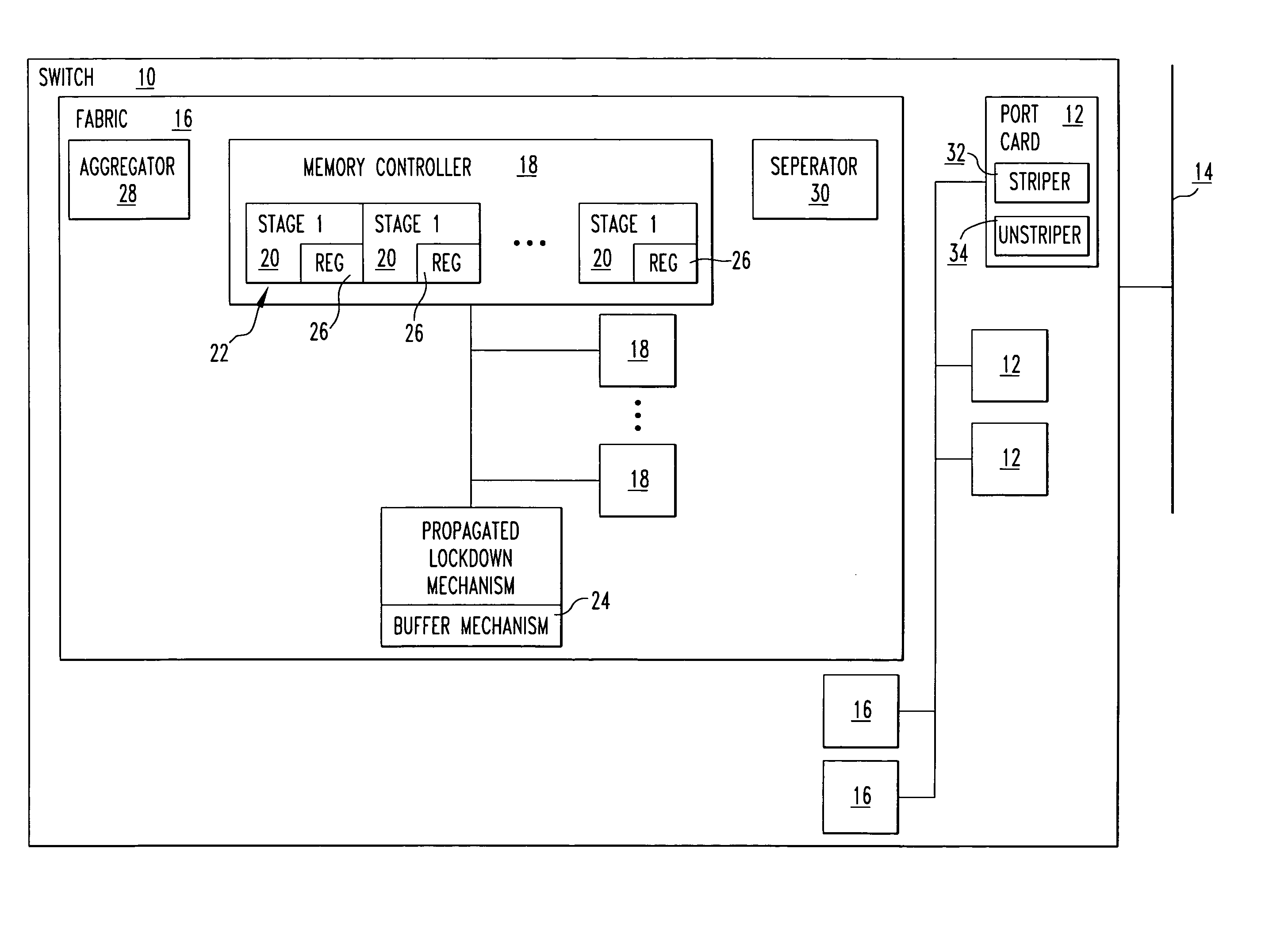

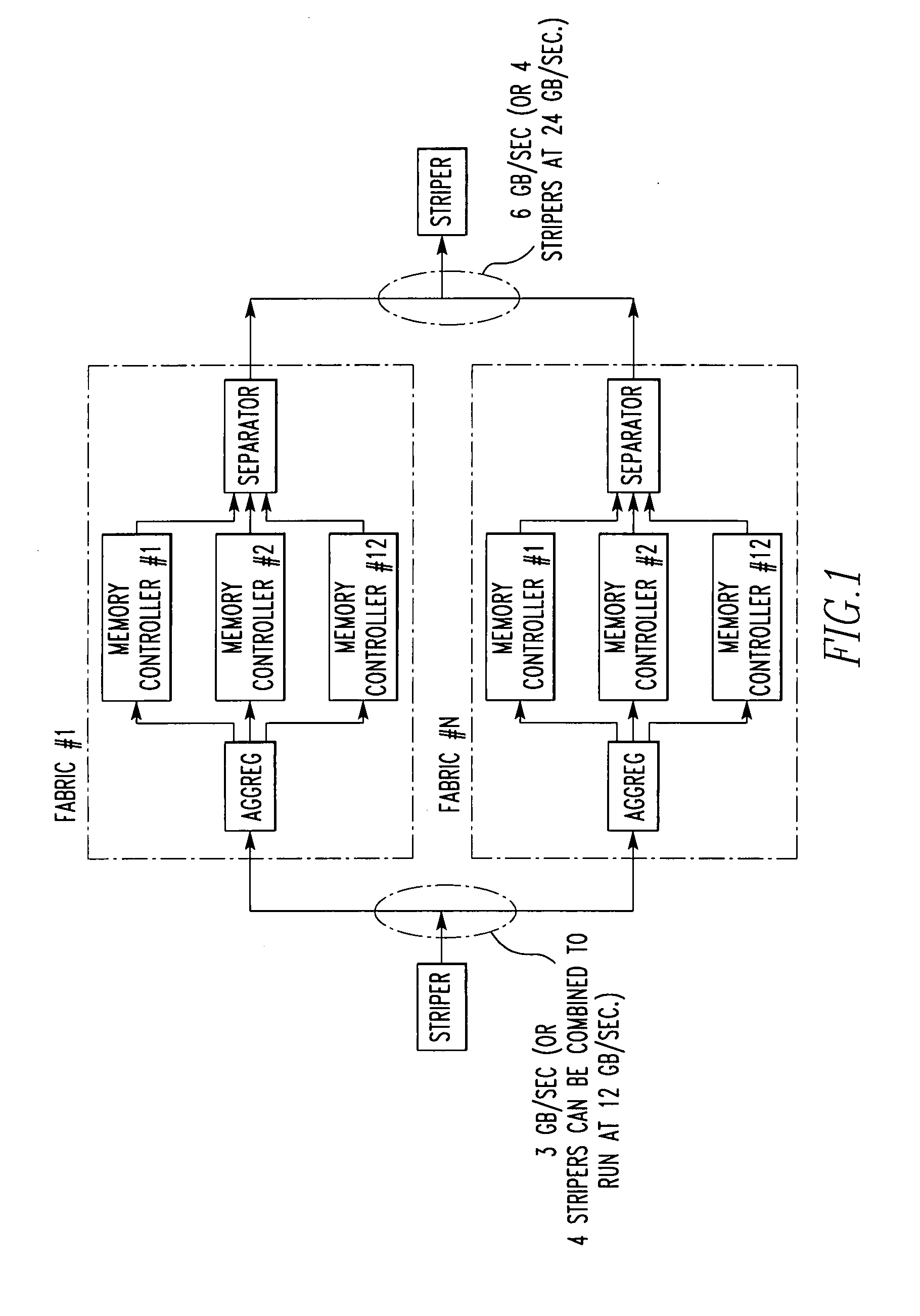

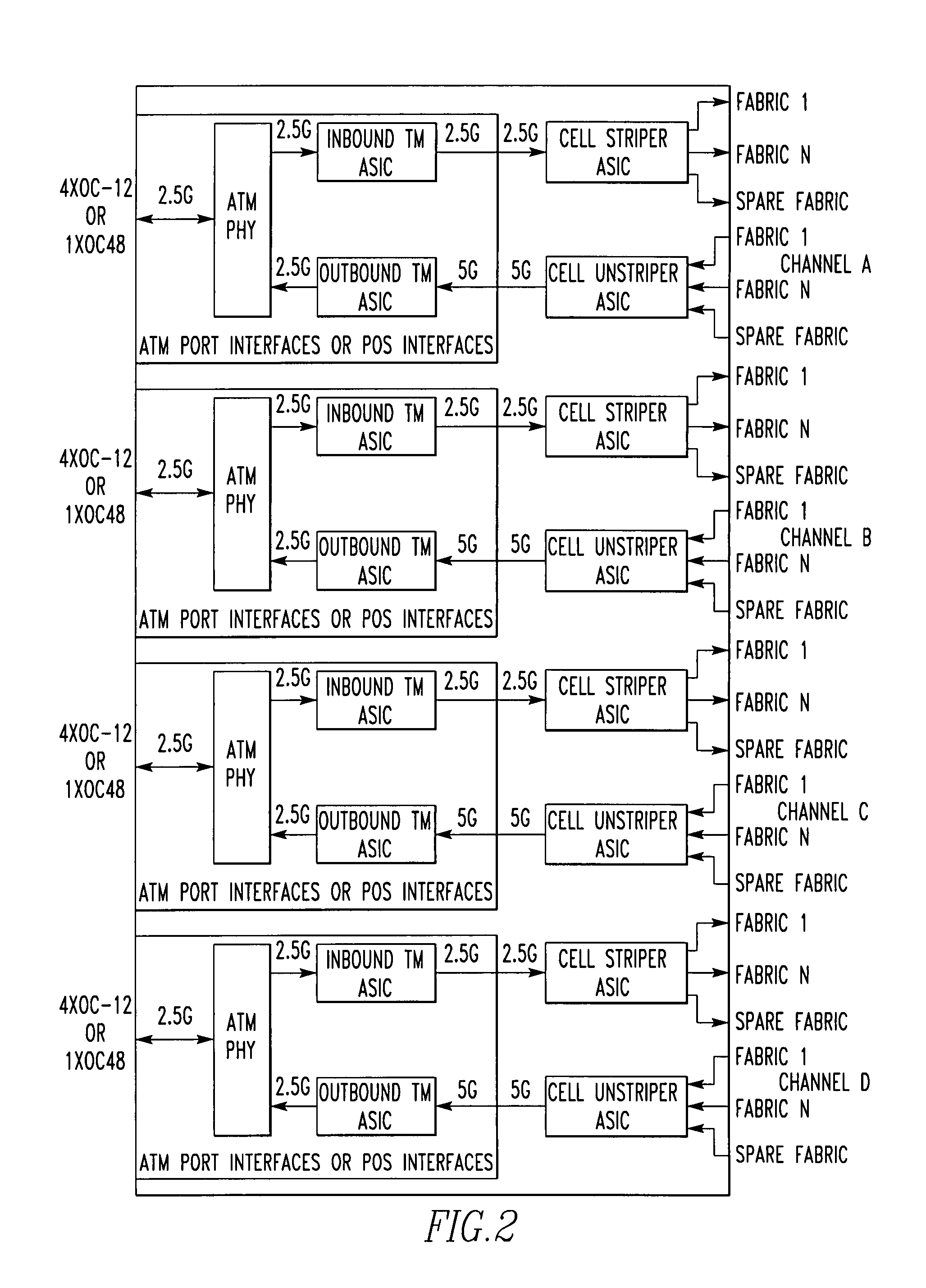

Switch fabrics logical synchronization utilizing propagation lockdown

InactiveUS7283547B1Time-division multiplexData switching by path configurationComputer hardwareMemory controller

A switch includes a port card for receiving packets from and sending packets to a network. The switch includes a fabric connected to the port card for switching the packets. The fabric has memory controllers which perform logical functions and in which portions of the packets are stored. The fabric has stages for switching the portions of the packets. The fabric has a mechanism for propagated lockdown of each stage wherein each stage is idle a correct number of cycles and each memory controller performs the same logical functions the corresponding same logical cycles. A method for switching packets includes the steps of introducing idles a correct number of cycles in each stage of memory controllers in fabrics of a switch to maintain the fabrics in logical synchronization. Then there is the step performing with each memory controller in the fabrics same logical functions at corresponding same logical cycles.

Owner:TELEFON AB LM ERICSSON (PUBL)

Active element

Owner:9224 5489 QUEBEC

Service programmable logic arrays with low tunnel barrier interpoly insulators

Structures and methods for in service programmable logic arrays with low tunnel barrier interpoly insulators are provided. The in-service programmable logic array includes a first logic and a second logic plan having a number of logic cells arranged in rows and columns that are interconnected to produce a number of logical outputs such that the in service programmable logic array implements a logical function. The logic cell includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5 and / or a Perovskite oxide tunnel barrier.

Owner:MICRON TECH INC

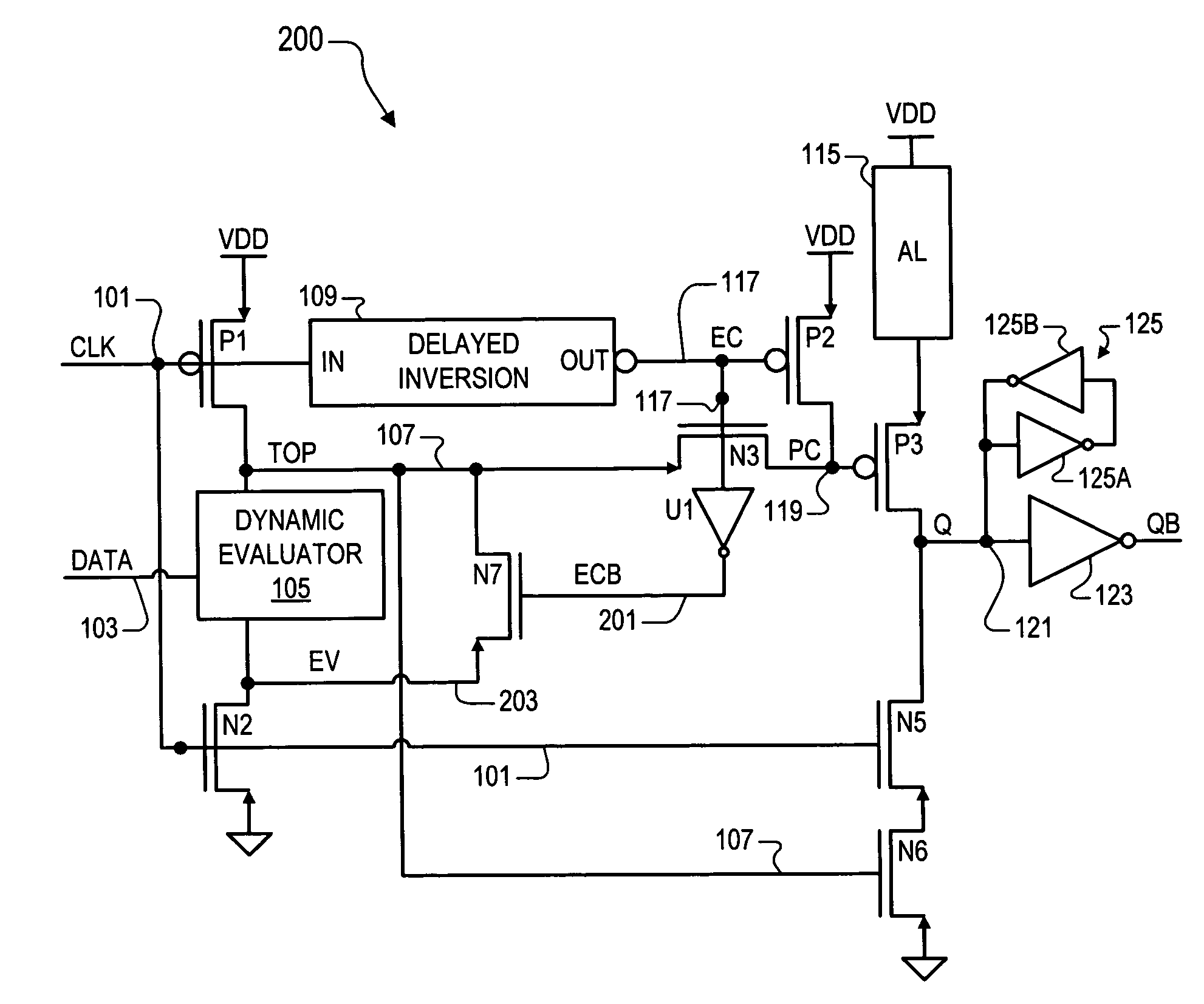

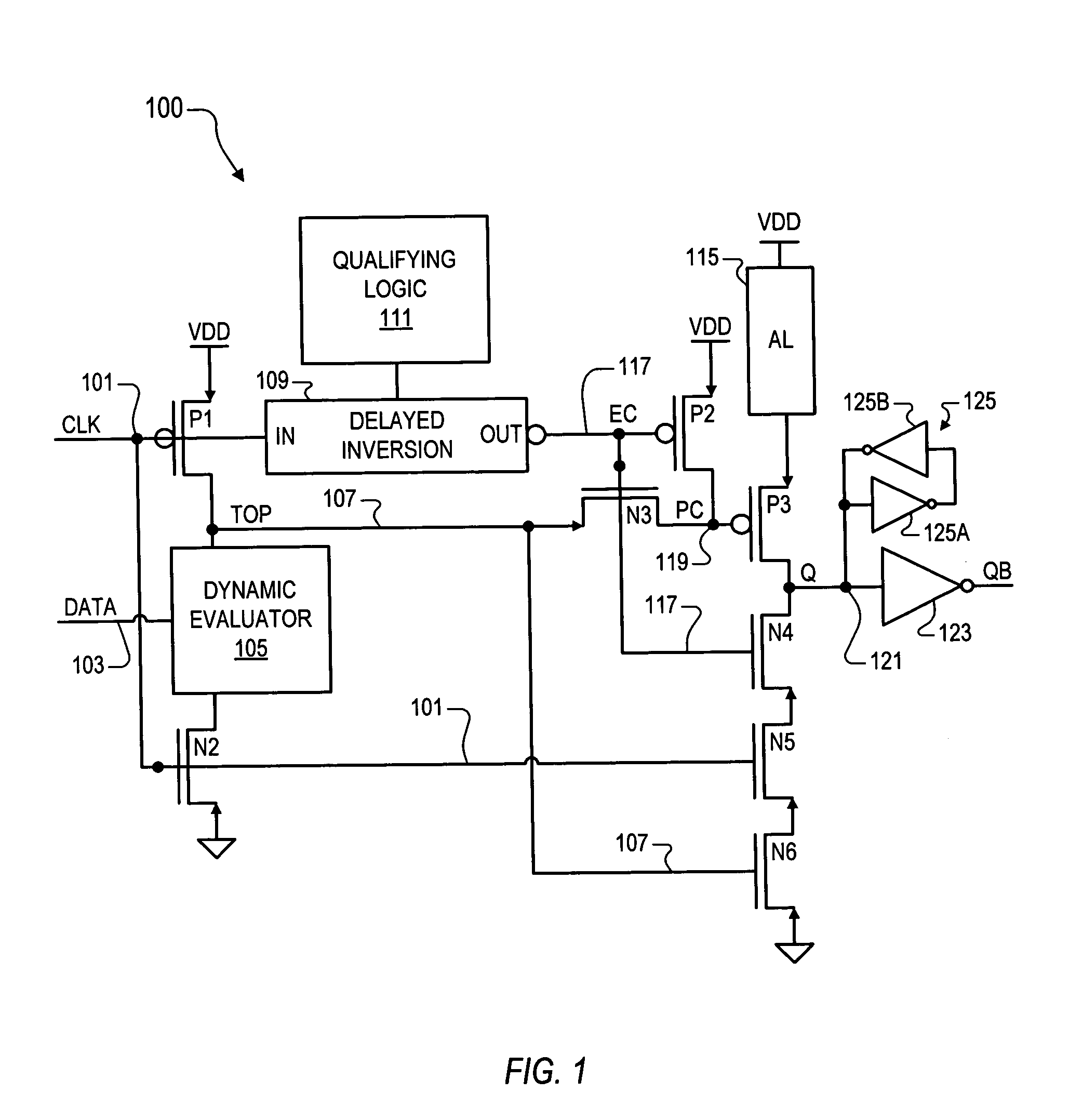

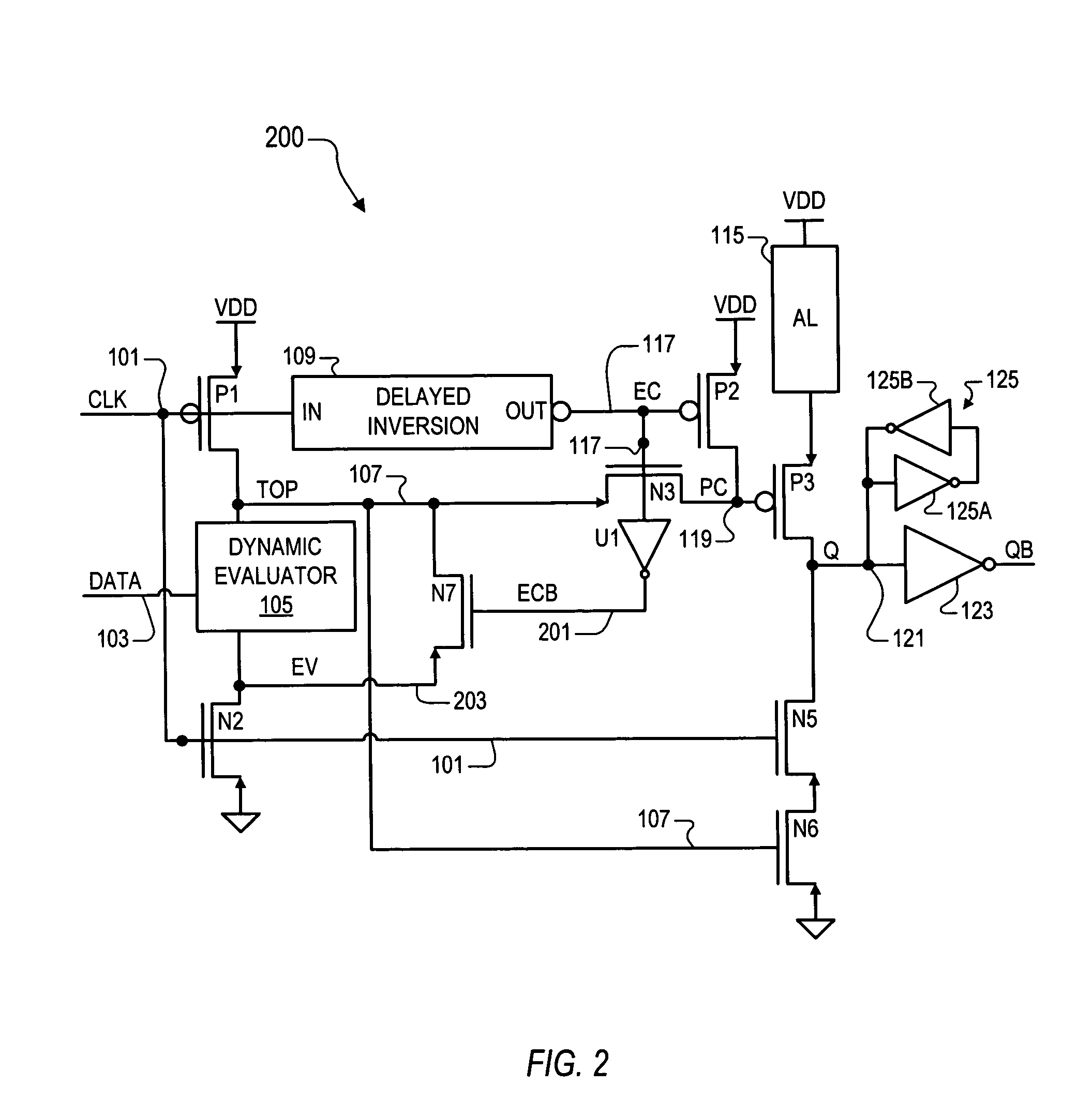

Dynamic logic register

ActiveUS20050046446A1Prevent of data signalAvoid dataDigital storageLogic circuitsPre-chargeData signal

A dynamic logic register including a complementary pair of evaluation devices, delayed inversion logic, a dynamic evaluator, latching logic, and a keeper circuit coupled to the output. The evaluation devices are responsive to a clock signal and provide a pre-charged node and an evaluation node. The delayed inversion logic outputs a complete signal that is a delayed and inverted version of the clock signal. The dynamic evaluator, coupled between the pre-charged and evaluation nodes, evaluates a logic function based on a data signal during an evaluation period between operative edges of the clock and complete signals. The latching logic enables the state of an output node to be determined by the state of the pre-charged node during the evaluation period and otherwise clamps the pre-charged node to prevent perturbations of the data signal from propagating to the output node.

Owner:VIA TECH INC

Digital integrated circuit chip testing system

InactiveCN102540060AImprove stabilityImprove mean time between failuresElectrical testingFpga implementationsTest object

The invention provides a test pattern-based testing system for realizing a functional test on a digital integrated circuit. The functional test is mainly used for testing logical functions of a chip under a certain timing sequence, and a basic principle is that the chip is excited by means of test patterns and whether the response of the chip is consistent with expected response is observed. The functional test can cover failure models of extremely high proportion logic circuits. A debugging technology supported one-step testing system comprises two parts, namely test pattern file conversion software applied to a personal computer (PC) and a digital integrated circuit chip testing machine, wherein the digital integrated circuit chip testing machine consists of architectures of a central processing unit (CPU) and a field programmable gate array (FPGA); the CPU is used for storing and converting pattern files, controlling the testing process, communicating with a host, and the like. A pattern controlling logic circuit is realized by an FPGA, the waveform generation, the control of Pattern random access memory (RAM) and sampling control are finished through the FPGA, and a drive and a comparator are controlled so as to test and control a tested object.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

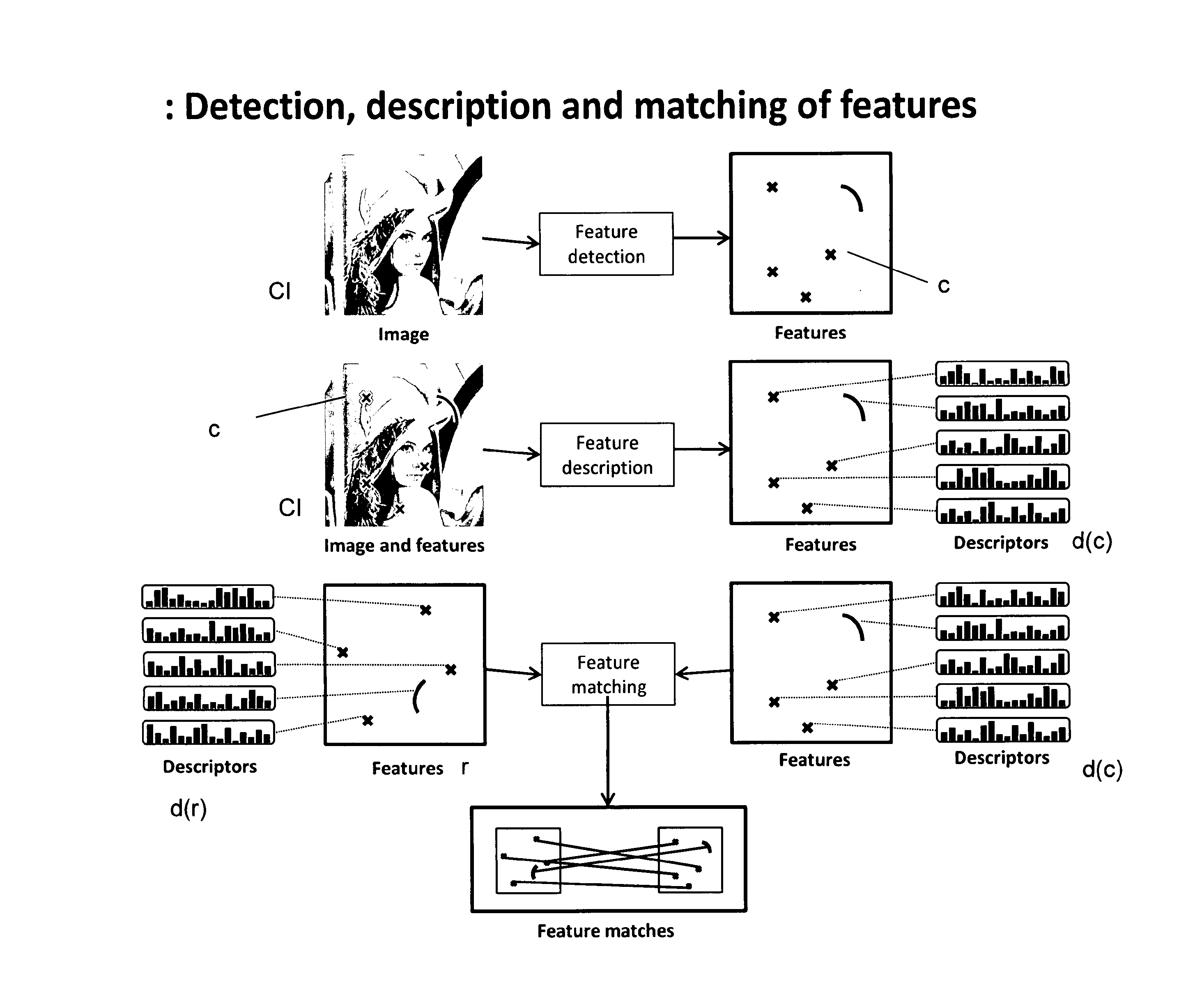

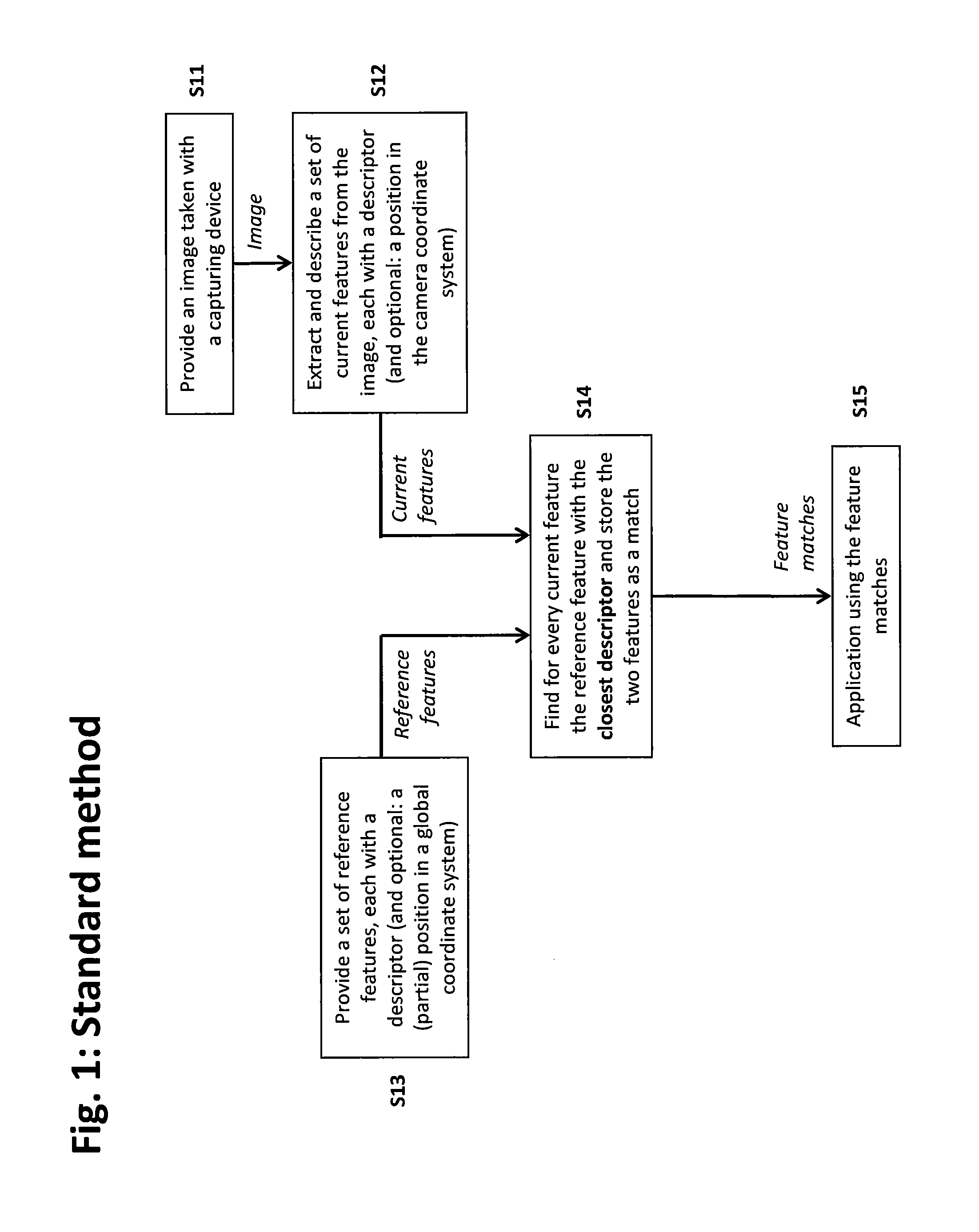

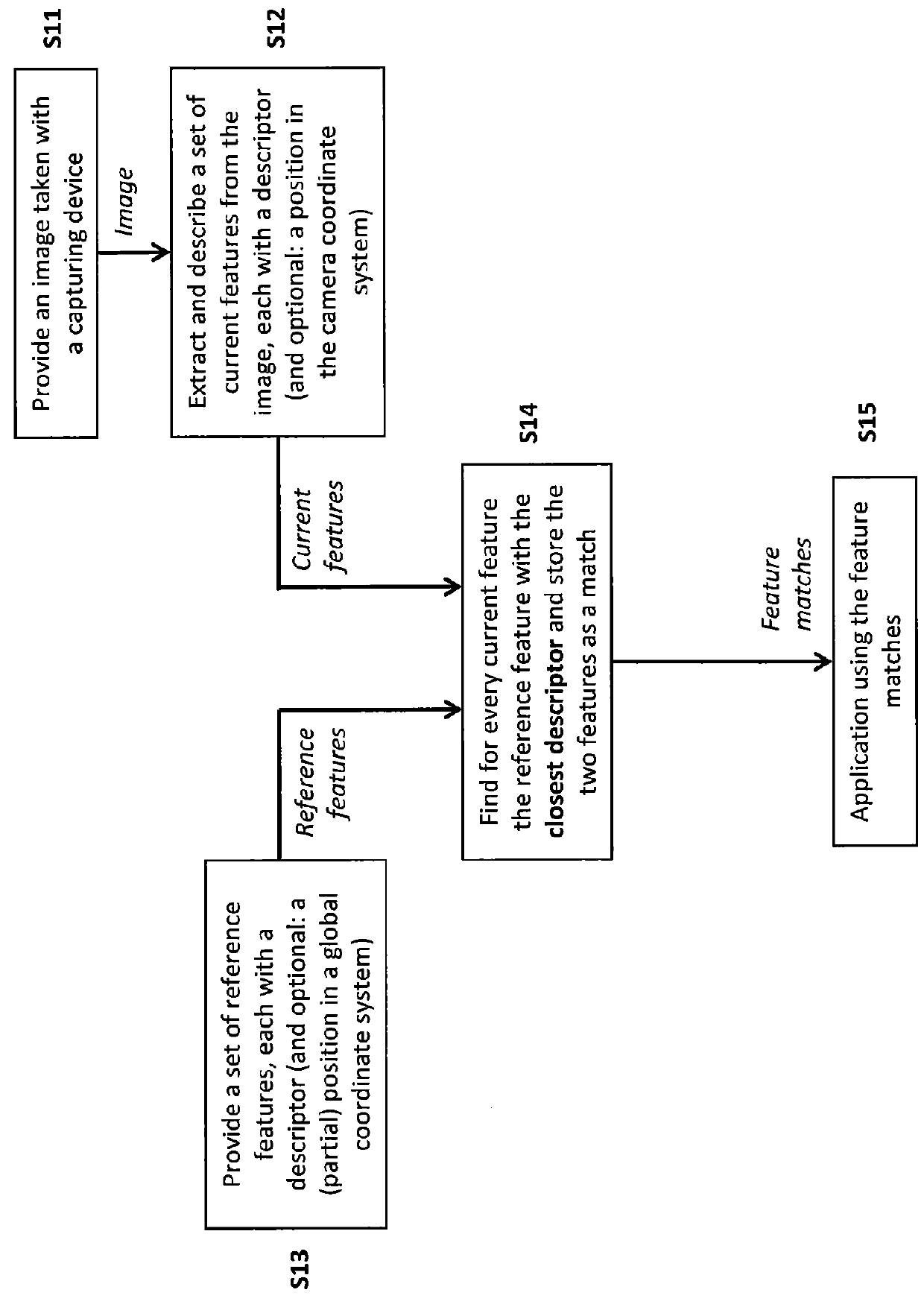

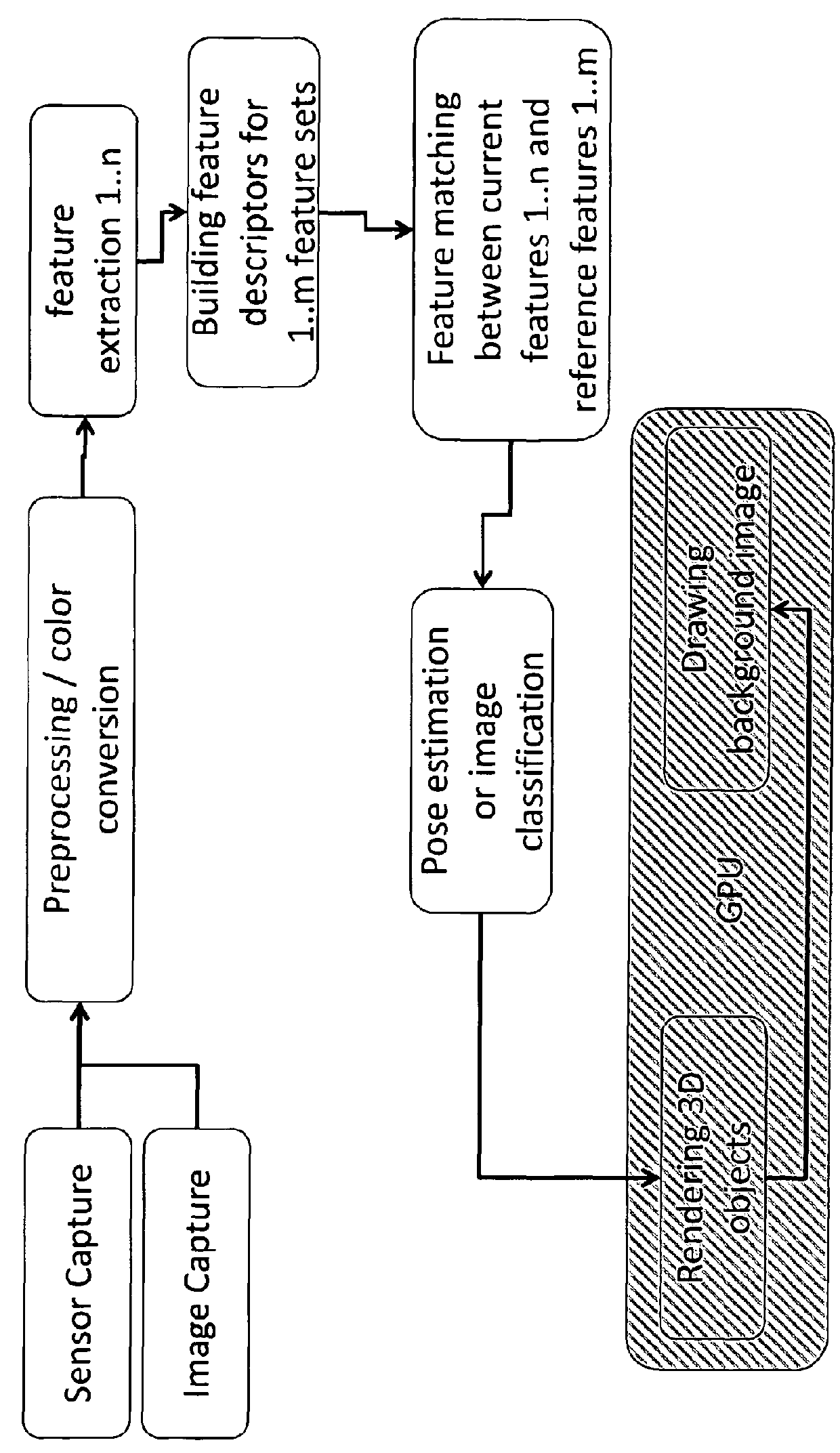

Method of matching image features with reference features and integrated circuit therefor

ActiveUS20150049955A1Easy to initializeImprove performanceCharacter and pattern recognitionStill image data queryingImaging FeatureSimilarity measure

The invention is related to a method of matching image features with reference features, comprising the steps of providing a current image captured by a capturing device, providing reference features (r), wherein each of the reference features comprises at least one reference feature descriptor (d(r)), determining current features (c) in the current image and associating with each of the current features at least one respective current feature descriptor (d(c)), and matching the current features with at least some of the reference features by determining a respective similarity measure (D(c, r)) between each respective current feature descriptor (d(c)) and each respective reference feature descriptor (d(r)). According to the invention, the determination of the similarity measure is performed on an integrated circuit by hardwired logic or configurable logic which processes logical functions for determining the similarity measure. The invention is also concerned with an integrated circuit for matching of image features with reference features.

Owner:APPLE INC

Variable threshold transistor for the Schottky FPGA and multilevel storage cell flash arrays

InactiveUS20060044018A1Low powerImprove performanceMultistate logicSolid-state devicesSchottky barrierMulti-level cell

An IC solution utilizing mixed FPGA and MLC arrays is proposed. The process technology is based on the Schottky CMOS devices comprising of CMOS transistors, low barrier Schottky barrier diode (SBD), and multi-level cell (MLC) flash transistors. Circuit architectures are based on the pulsed Schottky CMOS Logic (SCL) gate arrays, wherein a variable threshold NMOS transistor may replace the regular switching transistor. During initialization windows, existing FPGA programming techniques can selectively adjust the VT of the switching transistor, re-configure the intra-connections of the simple SCL gates, complete all global interconnections of various units. Embedded hardware arrays, hardwired blocks, soft macro constructs in one chip, and protocols implementations are parsed. A wide range of circuit applications involving generic IO and logic function generation, ESD and latch up protections, and hot well biasing schemes are presented. The variable threshold transistors thus serve 3 distinctive functions. It acts as an analog device to store directly nonvolatile information in SCL gates. It couples the diode tree logic functions. Finally, it stores and operates large amount of information efficiently. The mixed SCL type FPGA and MLC storages shall emerge as the most compact logic and memory arrays in Si technology. Low power, high performance, and high capacity ICs are designed to mix and replace conventional CMOS-TTL circuits. The idea of multi-value logic composed of binary, ternary, and quaternary hardware and firmware is also introduced.

Owner:SUPER TALENT ELECTRONICS

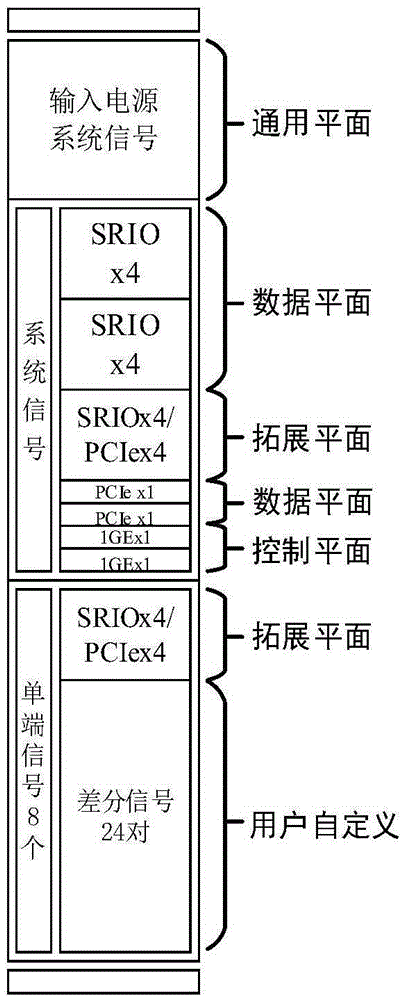

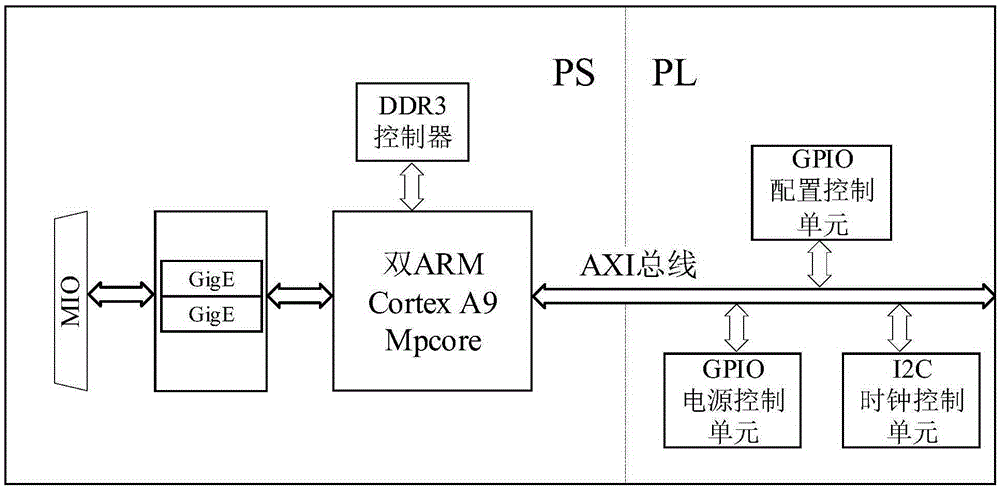

Reconfigurable/dual redundancy VPX3U signal processing carrier board based on Soc

InactiveCN105335327AIncrease flexibilityImprove versatilityElectric digital data processingDigital signal processingBus interface

The invention discloses a reconfigurable / dual redundancy VPX3U signal processing carrier board based on Soc, under VPX control surface 1GEx1 signalization, a carrier board Soc controller can perform control command dynamic loading and logical function on-line reorganization on a high-performance reconfigurable FPGA (Field Programmable Gate Array), and board-level power and timer management and condition monitoring are completed; a reconfigurable FPGA chip is in interaction with front-end received signals through a standard FMC interface, and multi-function real-time digital signal processing is realized according to a loading program. Meanwhile, a dual-redundancy data bus interface is designed in a VPX connector, and a signal processing carrier board can be in data interaction with other board cards such as a master control switch card, an adjacent board card and the like in the system by a VPX dual redundancy data bus interface.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

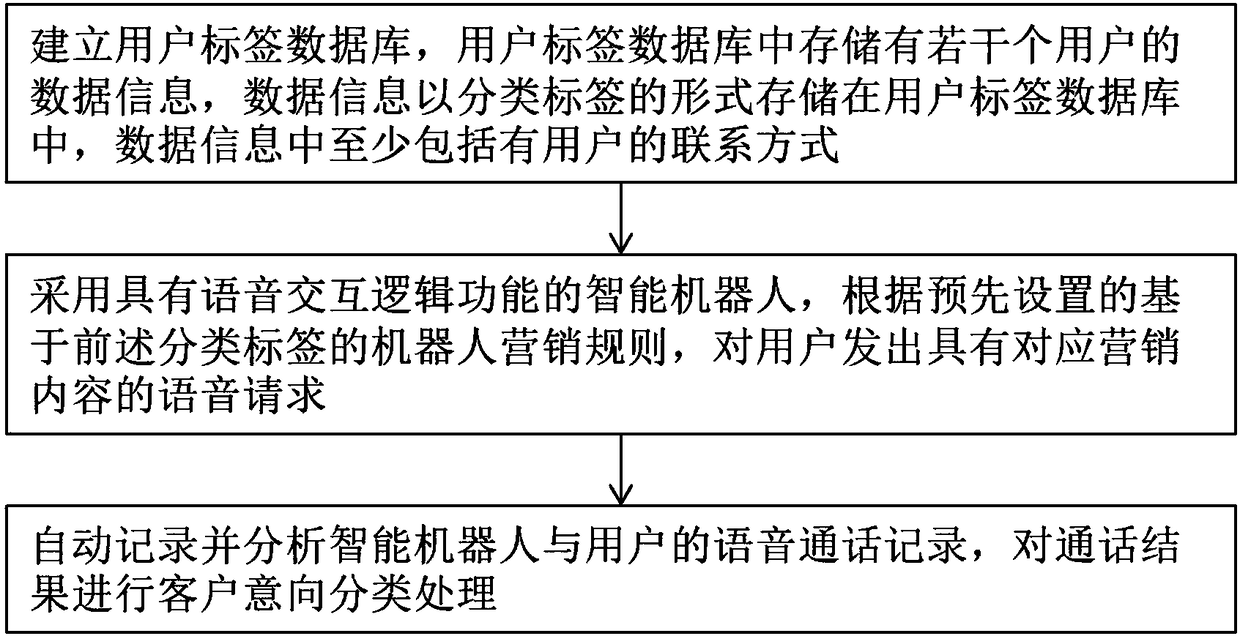

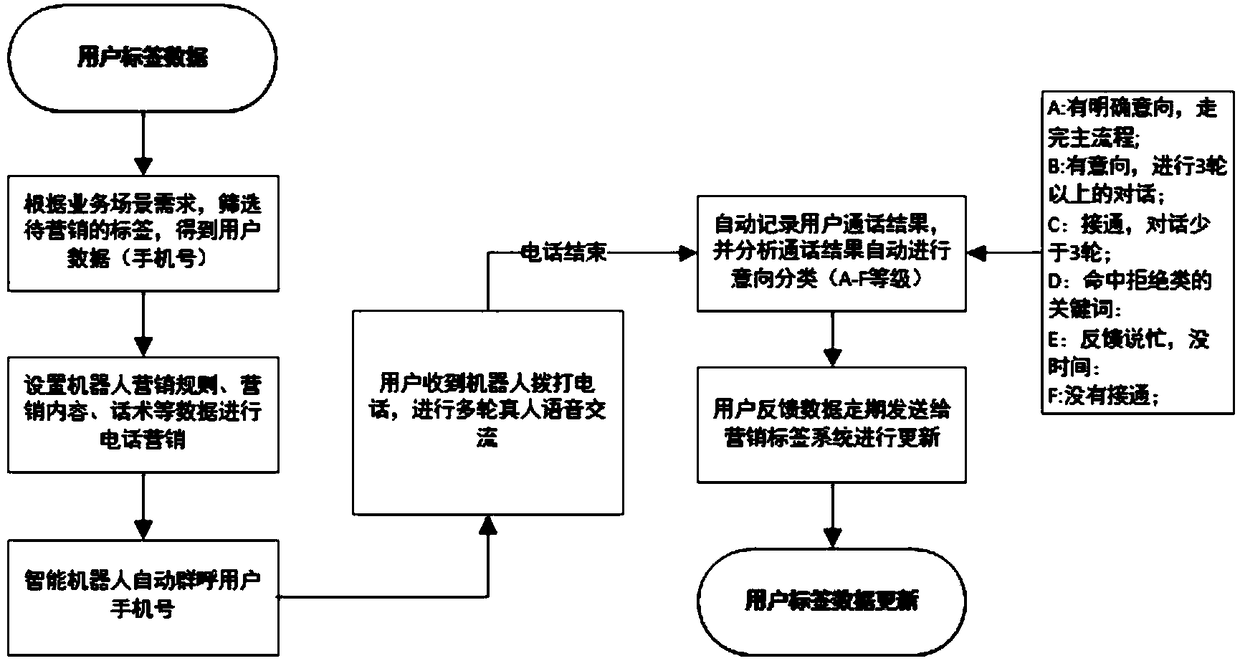

Intelligent robot customer service marketing method and system based on user tag system

PendingCN108521525ARealize automatic marketing serviceSpecial service for subscribersMarketingData informationContact method

The invention provides an intelligent robot customer service marketing method and system based on a user tag system. The intelligent robot customer service marketing method comprises the steps of establishing a user tag database, wherein data information for a plurality of users is stored in the user tag database, the data information is stored in the user tag database in a form of category tags,and the data information at least includes contact ways of the users; sending a voice request having a corresponding marketing content to each of the users by using an intelligent robot having a voiceinteraction logical function according to a robot marketing rule that is set in advance and is based on the category tags; and automatically recording and analyzing a voice call record between the intelligent robot and the each of the users, and performing client will classification processing on call results. According to the intelligent robot customer service marketing method and system, the mechanization of telephone marketing can be implemented, the utilization rate of the time is improved, the manpower cost is saved and the sales performance is improved.

Owner:小视科技(江苏)股份有限公司

Method of matching image features with reference features and integrated circuit therefor

ActiveUS9378431B2Easy to initializeImprove performanceTelevision system detailsImage analysisImaging FeatureSimilarity measure

The invention is related to a method of matching image features with reference features, comprising the steps of providing a current image captured by a capturing device, providing reference features (r), wherein each of the reference features comprises at least one reference feature descriptor (d(r)), determining current features (c) in the current image and associating with each of the current features at least one respective current feature descriptor (d(c)), and matching the current features with at least some of the reference features by determining a respective similarity measure (D(c, r)) between each respective current feature descriptor (d(c)) and each respective reference feature descriptor (d(r)). According to the invention, the determination of the similarity measure is performed on an integrated circuit by hardwired logic or configurable logic which processes logical functions for determining the similarity measure. The invention is also concerned with an integrated circuit for matching of image features with reference features.

Owner:APPLE INC

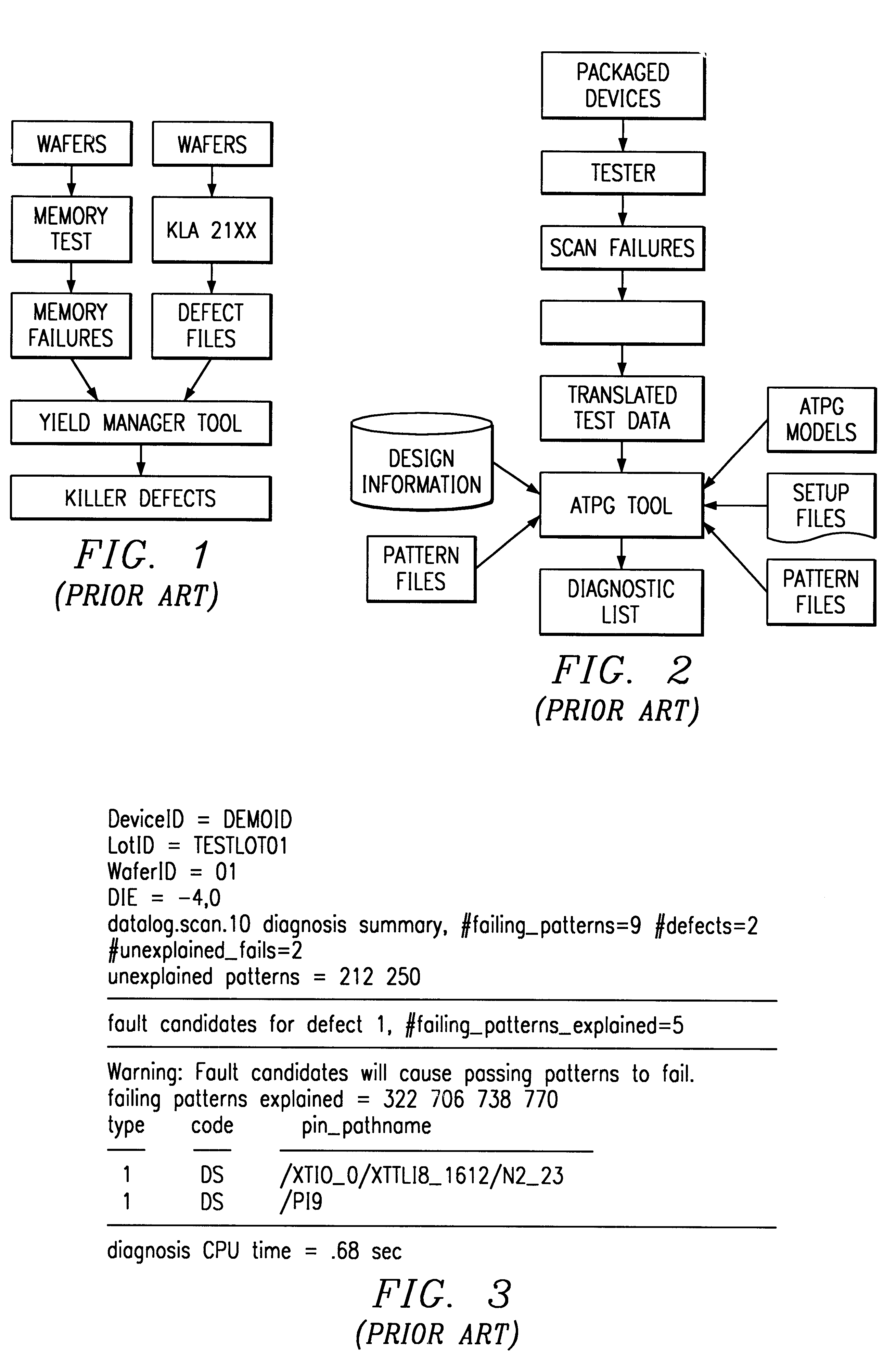

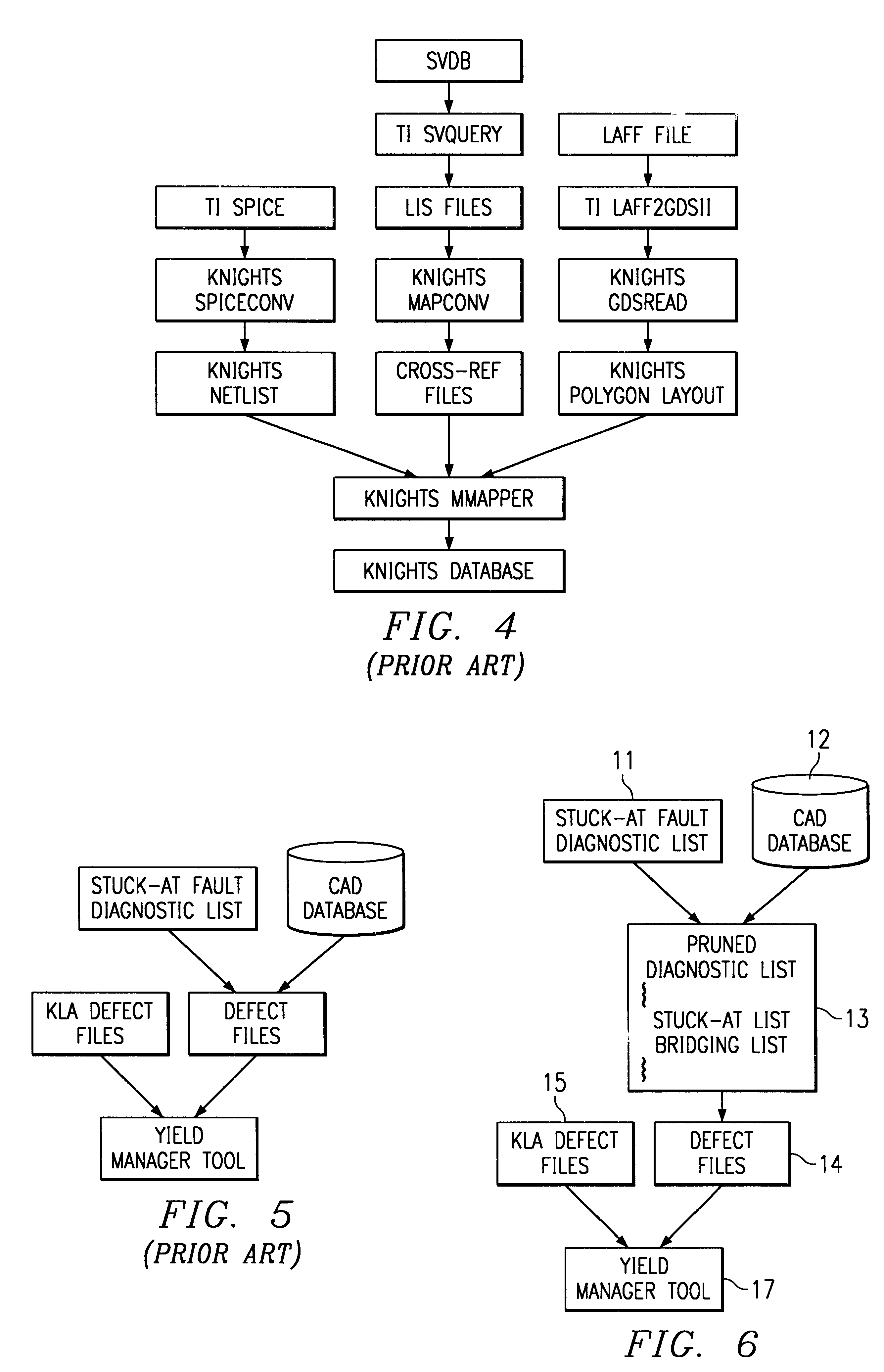

System for mapping logical functional test data of logical integrated circuits to physical representation using pruned diagnostic list

InactiveUS6553329B2Digital circuit testingResistance/reactance/impedenceComputer hardwareFunctional testing

An improved method for mapping logical function test data of logical integrated circuits to physical representations uses a pruned diagnostic list. The steps include creating a final logical diagnostic list of potential bridging faults in response to testing the circuit for stuck-at faults at a plurality of nets of the circuit, receiving the physical data associated with nets of the circuit, applying adjacency criteria to the physical data, generating a pruned diagnostic list of potential bridging faults in response to applying the adjacency criteria, performing in-line inspection to obtain second localized probable defect data and correlating second localized portable defect data with the pruned diagnostic list.

Owner:HARRIS KAYOT +1

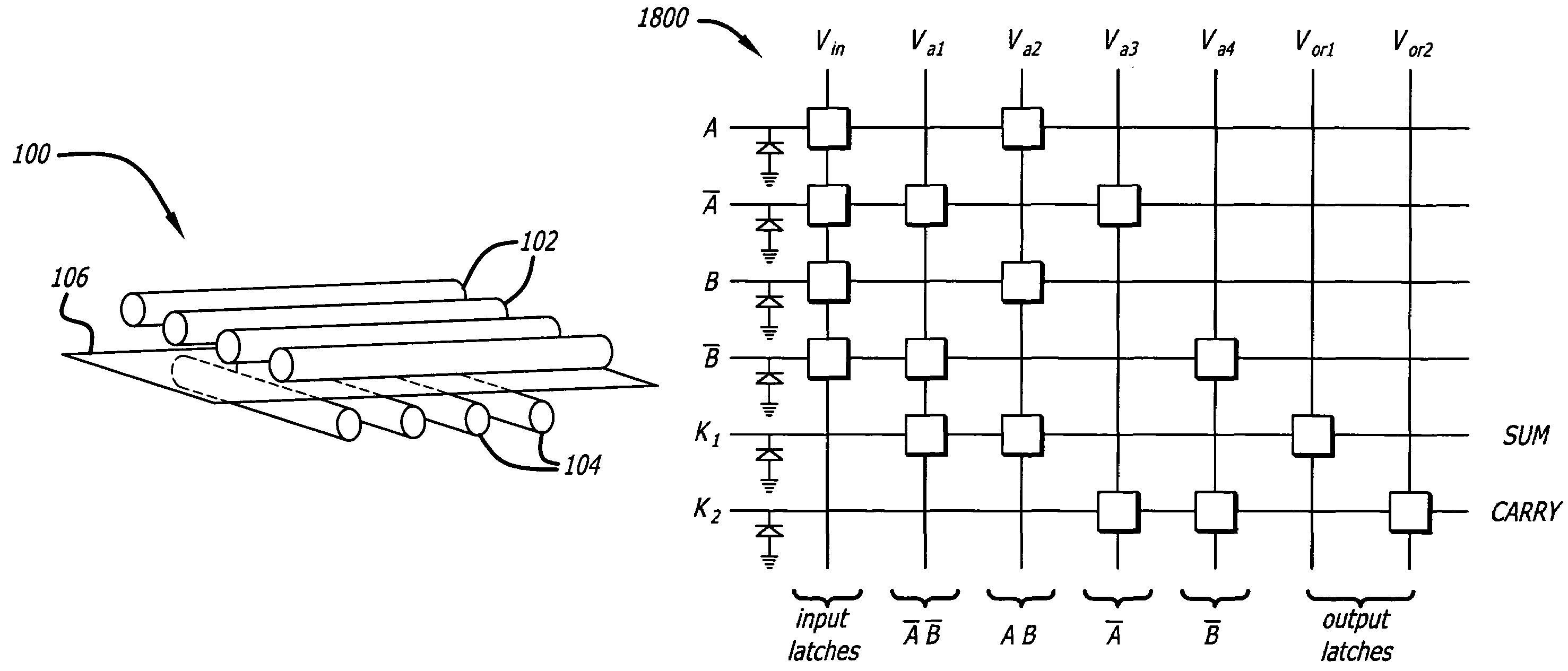

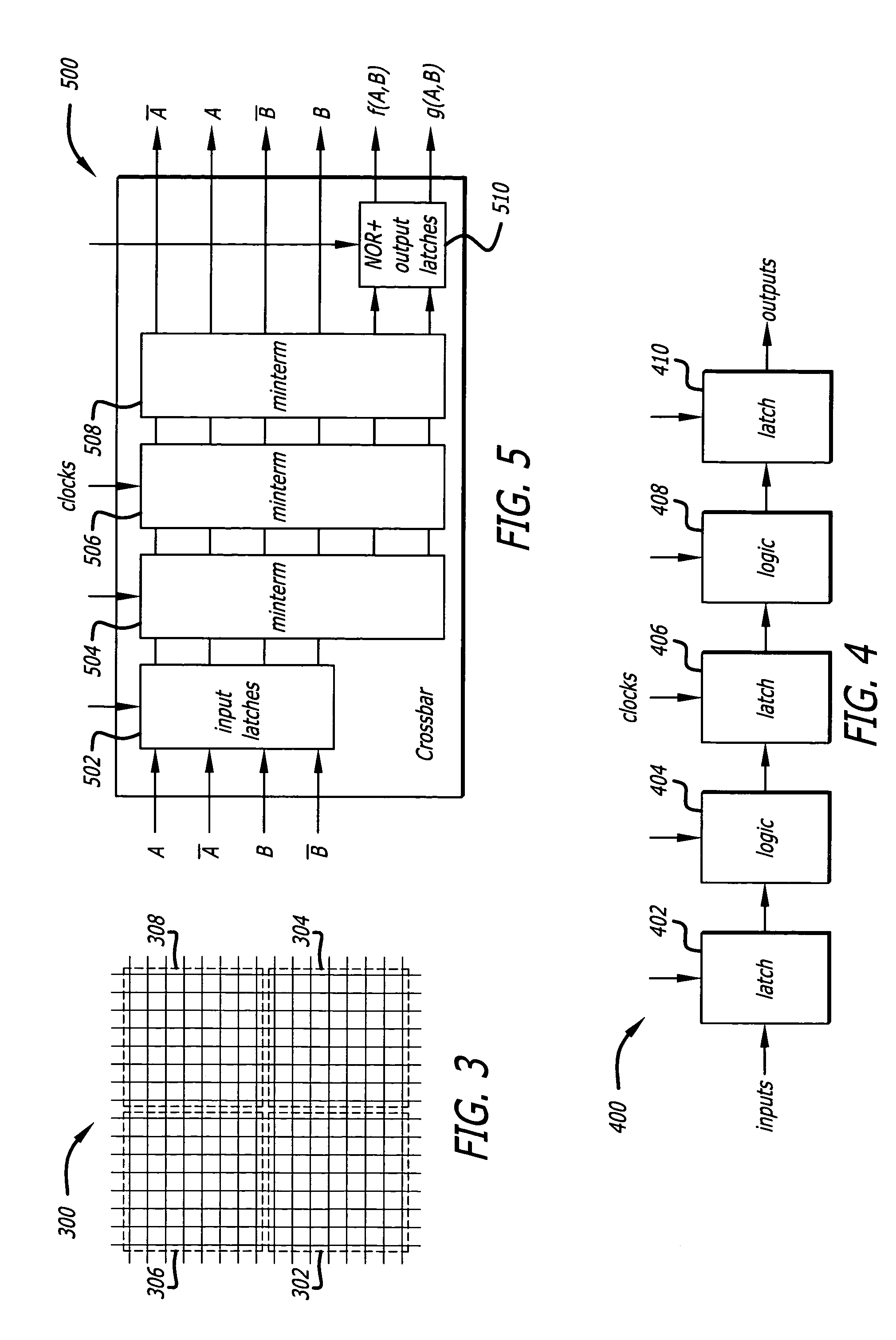

Architecture and methods for computing with reconfigurable resistor crossbars

ActiveUS7203789B2Reliability increasing modificationsLogic circuits characterised by logic functionCrossover switchComputer science

An architecture for computing includes nanometer scale crossbar switches configured to perform a logical function in response to a sequence of pulses that encode logic values in the nanometer scale crossbar switches as impedances.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

System for mapping logical functional test data of logical integrated circuits to physical representation using pruned diagnostic list

InactiveUS20020010560A1Digital circuit testingResistance/reactance/impedenceComputer hardwareFunctional testing

An improved method for mapping logical function test data of logical integrated circuits to physical representations uses a pruned diagnostic list. The steps include creating a final logical diagnostic list of potential bridging faults in response to testing the circuit for stuck-at faults at a plurality of nets of the circuit, receiving the physical data associated with nets of the circuit, applying adjacency criteria to the physical data, generating a pruned diagnostic list of potential bridging faults in response to applying the adjacency criteria, performing in-line inspection to obtain second localized probable defect data and correlating second localized portable defect data with the pruned diagnostic list.

Owner:HARRIS KAYOT +1

Programmable logic arrays with ultra thin body transistors

Structures and methods for programmable logic arrays are provided. In one embodiment, the programmable logic array includes a first logic plane and a second logic plane. The first logic plane receives a number of input signals. The first logic plane has a plurality of logic cells arranged in rows and columns that are interconnected to provide a number of logical outputs. The second logic plane has a number of logic cells arranged in rows and columns that receive the outputs of the first logic plane and that are interconnected to produce a number of logical outputs such that the programmable logic array implements a logical function. Each of the logic cells includes a vertical pillar extending outwardly from a semiconductor substrate. Each pillar includes a single crystalline first contact layer and a second contact layer separated by an oxide layer. Each logic cell further includes at least one single crystalline ultra thin vertical transistor that is selectively disposed adjacent the vertical pillar. The single crystalline vertical transistors have an ultra thin single crystalline vertical first source / drain region coupled to the first contact layer, an ultra thin single crystalline vertical second source / drain region coupled to the second contact layer; and an ultra thin single crystalline vertical body region which opposes the oxide layer and couples the first and the second source / drain regions.

Owner:MICRON TECH INC

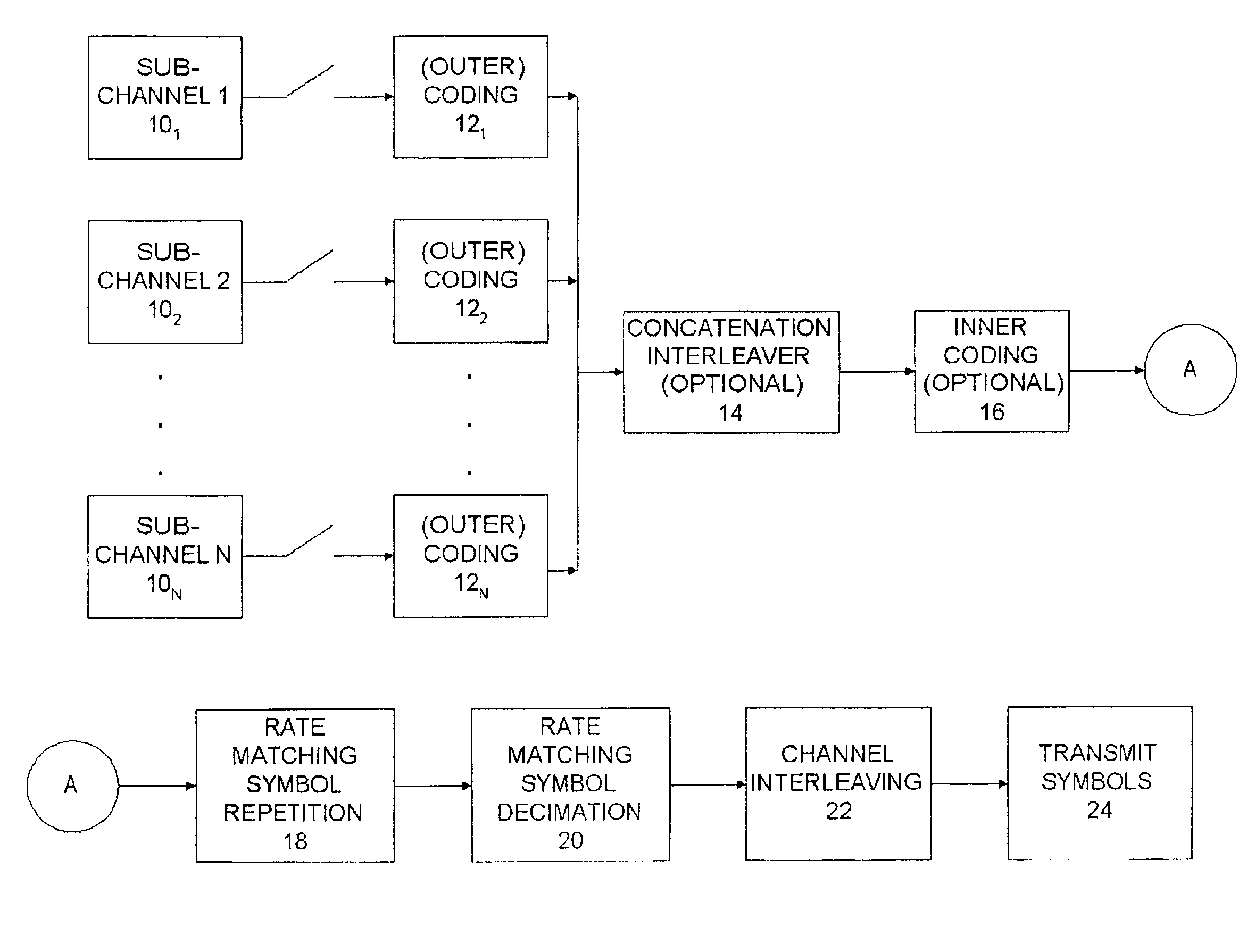

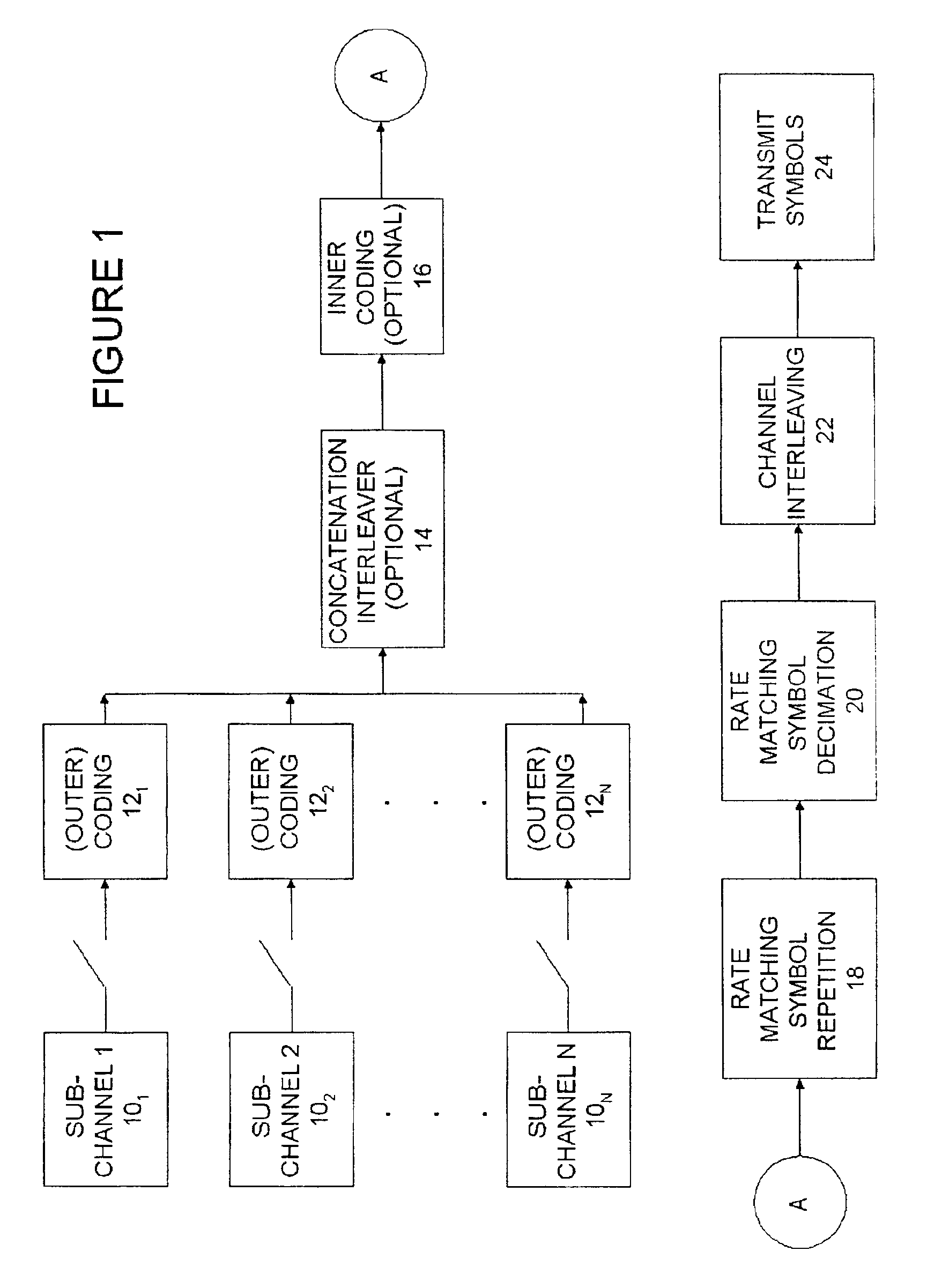

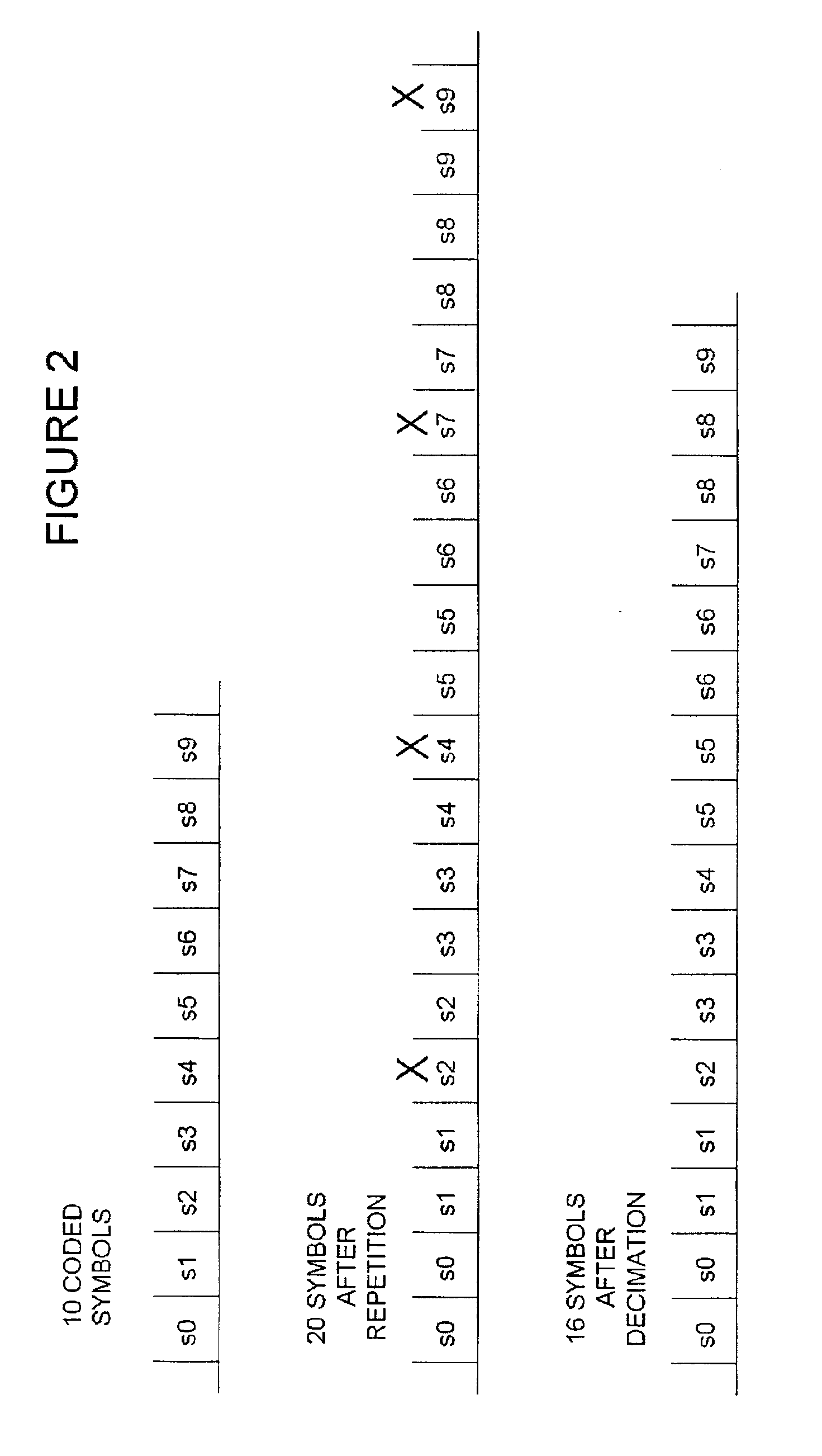

Fast feedback channel with flexible bit reliability for wireless communications

InactiveUS6876641B2Low powerSave powerError prevention/detection by using return channelTime-division multiplexComputer hardwarePerformance enhancement

A single physical channel carries “fast feedback” information in such a way that each type of data is on a physical sub-channel. The sub-channels are not “logical” channels in that they cannot be separated by logical functions alone because some knowledge of the modulation mechanisms is required. Each sub-channel is independently channel coded (this is outer channel coding if an inner code is applied). The resulting code symbols from all sub-channels are then merged into one set of symbols. These code symbols can then optionally be concatenation interleaved and inner channel coded, if the performance enhancement is desired and the complexity is acceptable. The result is then extended by code symbol repetition to provide a total number of symbols greater than or equal to one of the possible quantities of symbols per frame supported by the physical channel, and then decimated (symbols deleted) to provide a number of symbols equal to one of the allowable quantities of symbols per frame. The result is then interleaved, and transmitted over the physical channel.

Owner:APPLE INC

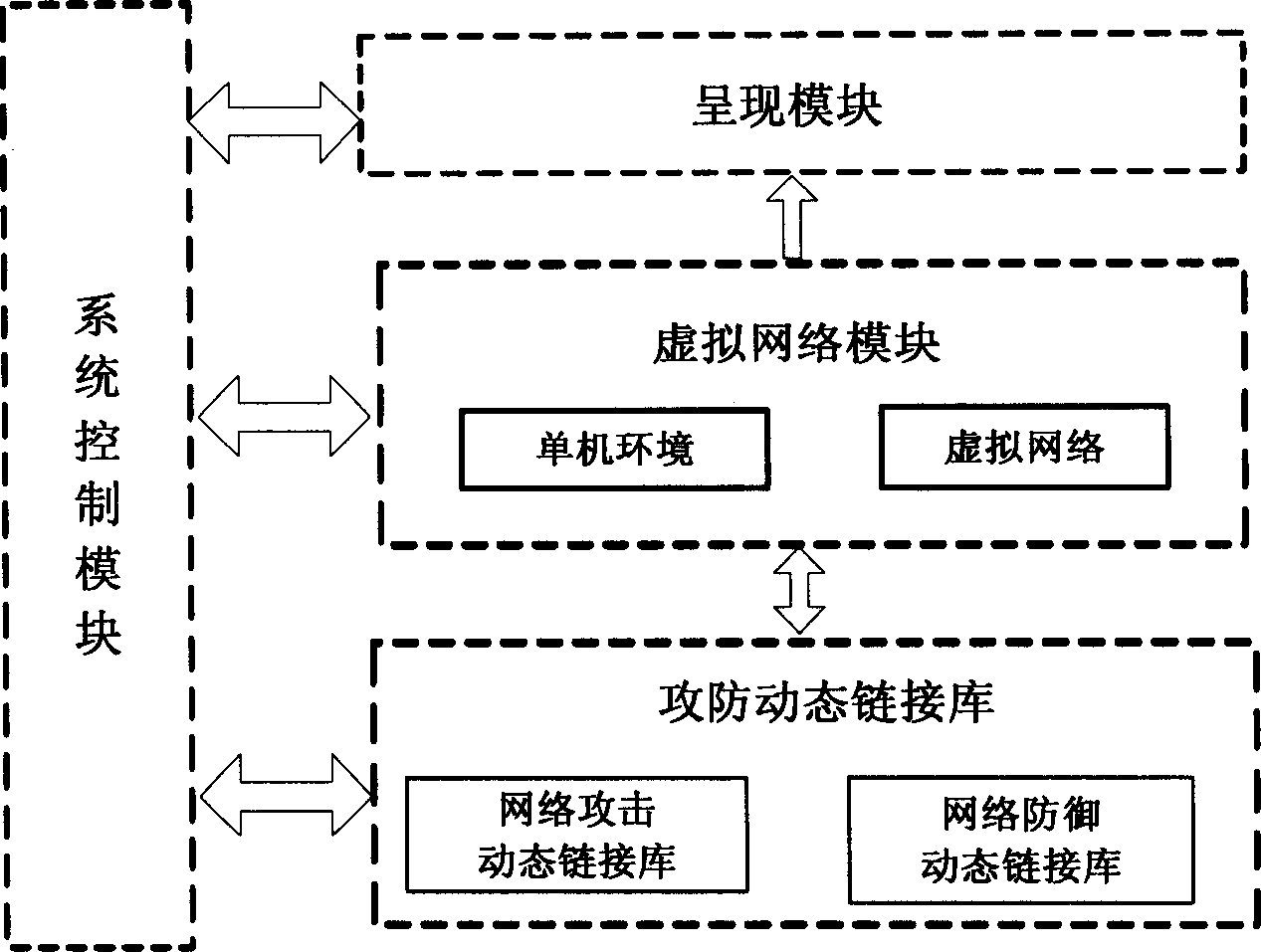

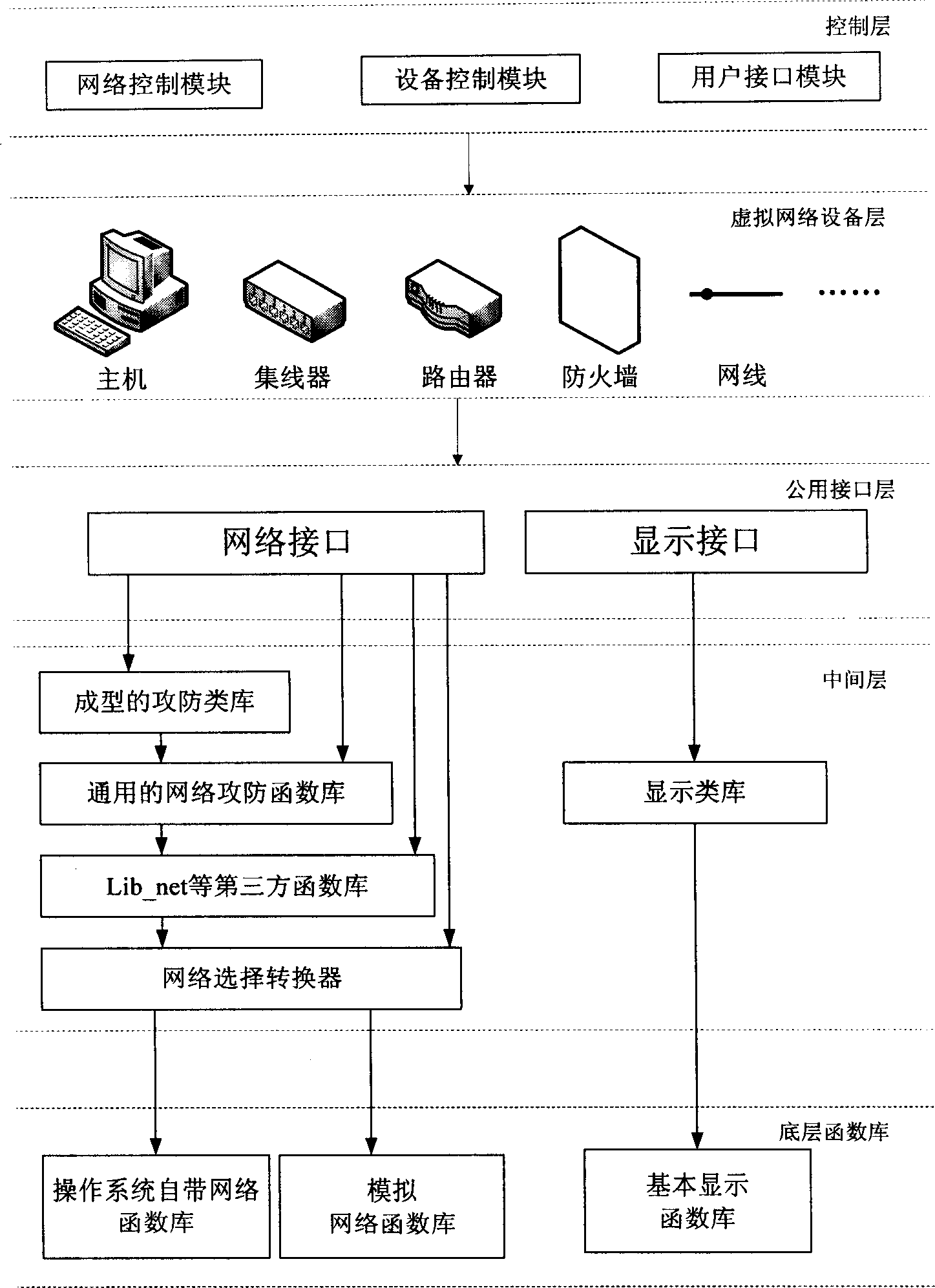

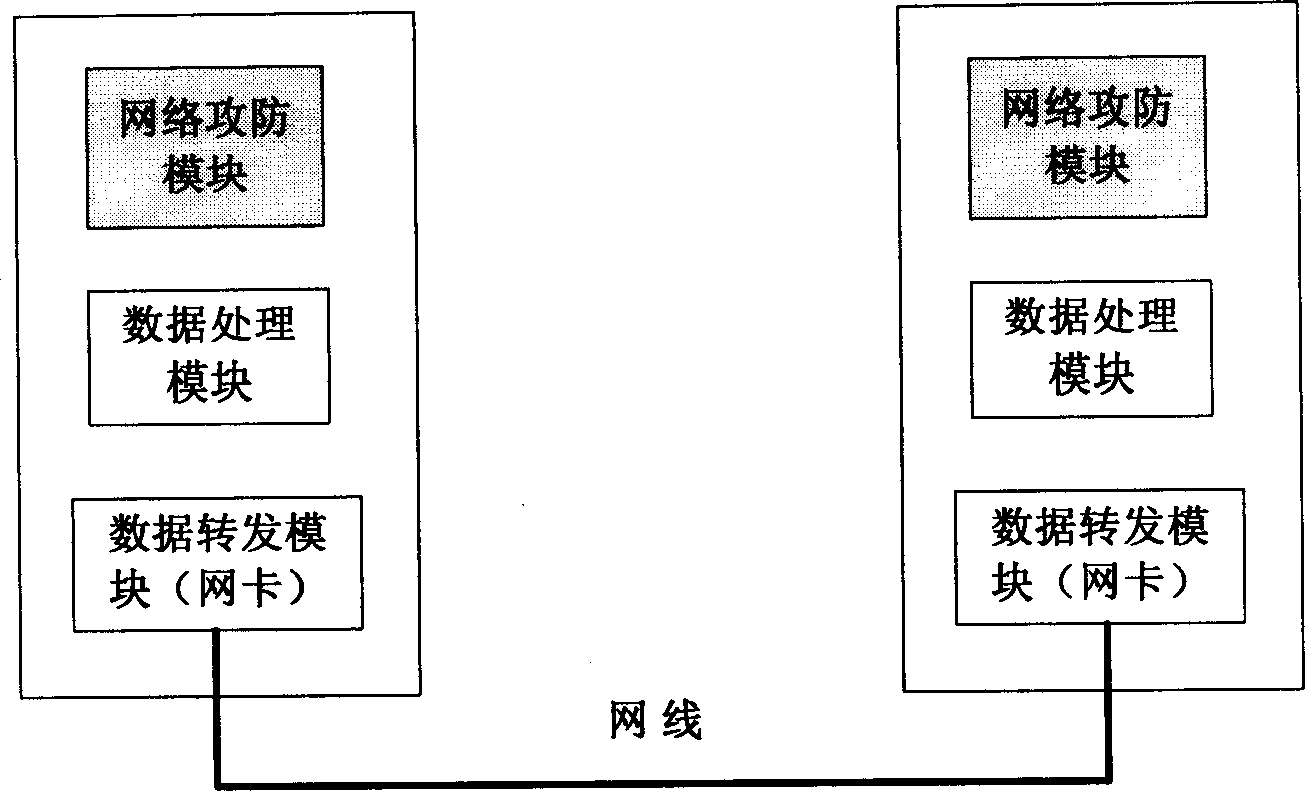

Network security emulation system and its emulation method

InactiveCN1805385ASolve environmental problemsTroubleshooting Emulation Platform IssuesData switching networksSpecial data processing applicationsPublic interfaceControl layer

The invention relates to a network safe simulation system and relative imitation method. The logical function of said network safe simulation system comprises: a virtual network module, a attack-defend dynamic chain connection base, a system control module, and a display module, while said logical functions are displayed by the control layer, virtual network device layer, public interface layer, middle layer and bottom function base. The virtual network device can simulate the host machine, router, firewall, network card, concentrator, and network wire on the single machine to connect each virtual network device to form the virtual network. The process that using said virtual network to process the safe simulation comprises: first, setting the user program; distributing system parameter document; coding the system; imitated operating the coded system in the operating system; at last collecting the simulated data according to which makes the network safety analyst. The invention has easy operation and extended availability, which can be used as network safety research simulation environment and imitation platform.

Owner:KUNSHAN RUIXIANG XUNTONG COMM TECHCO

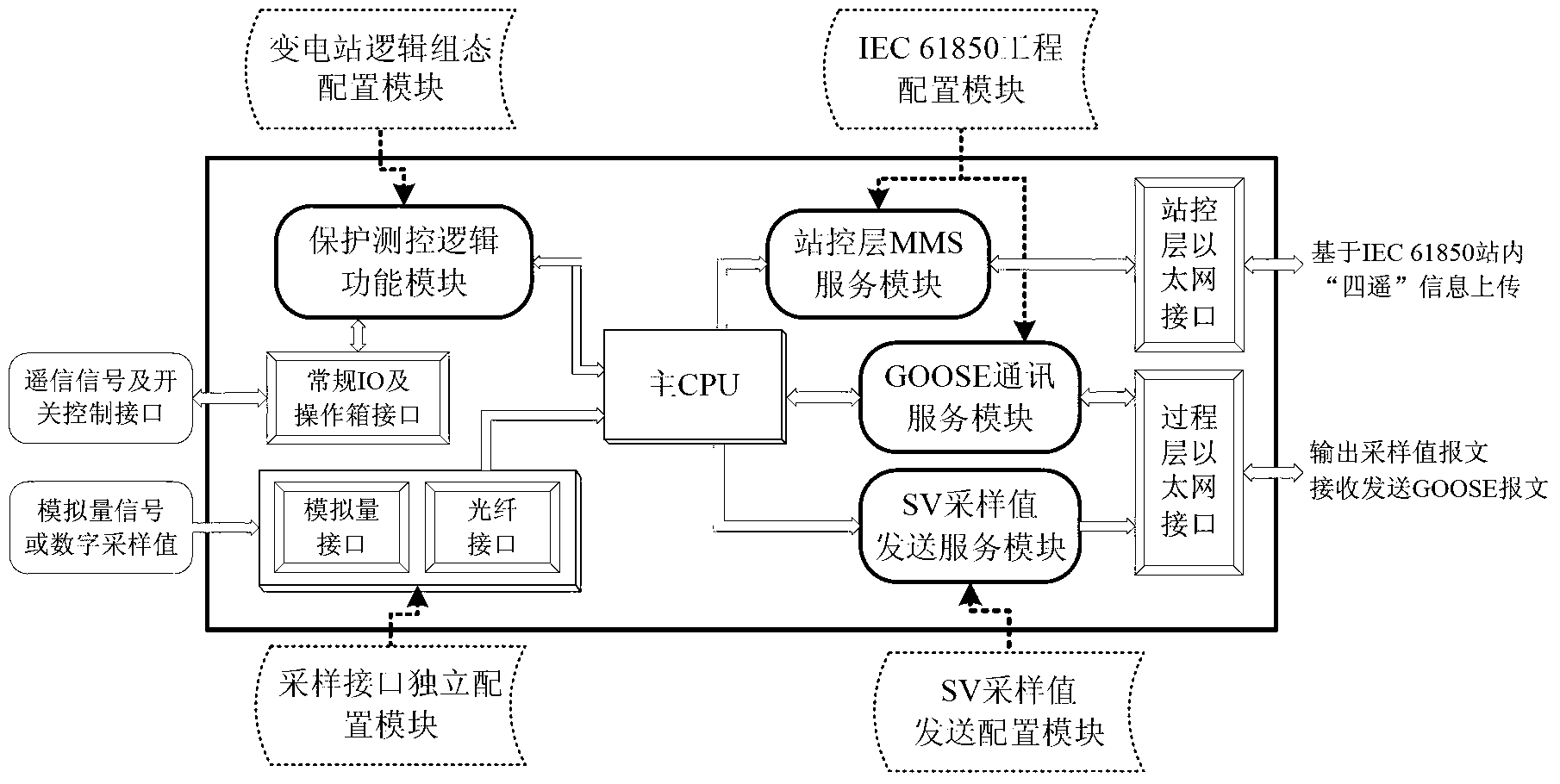

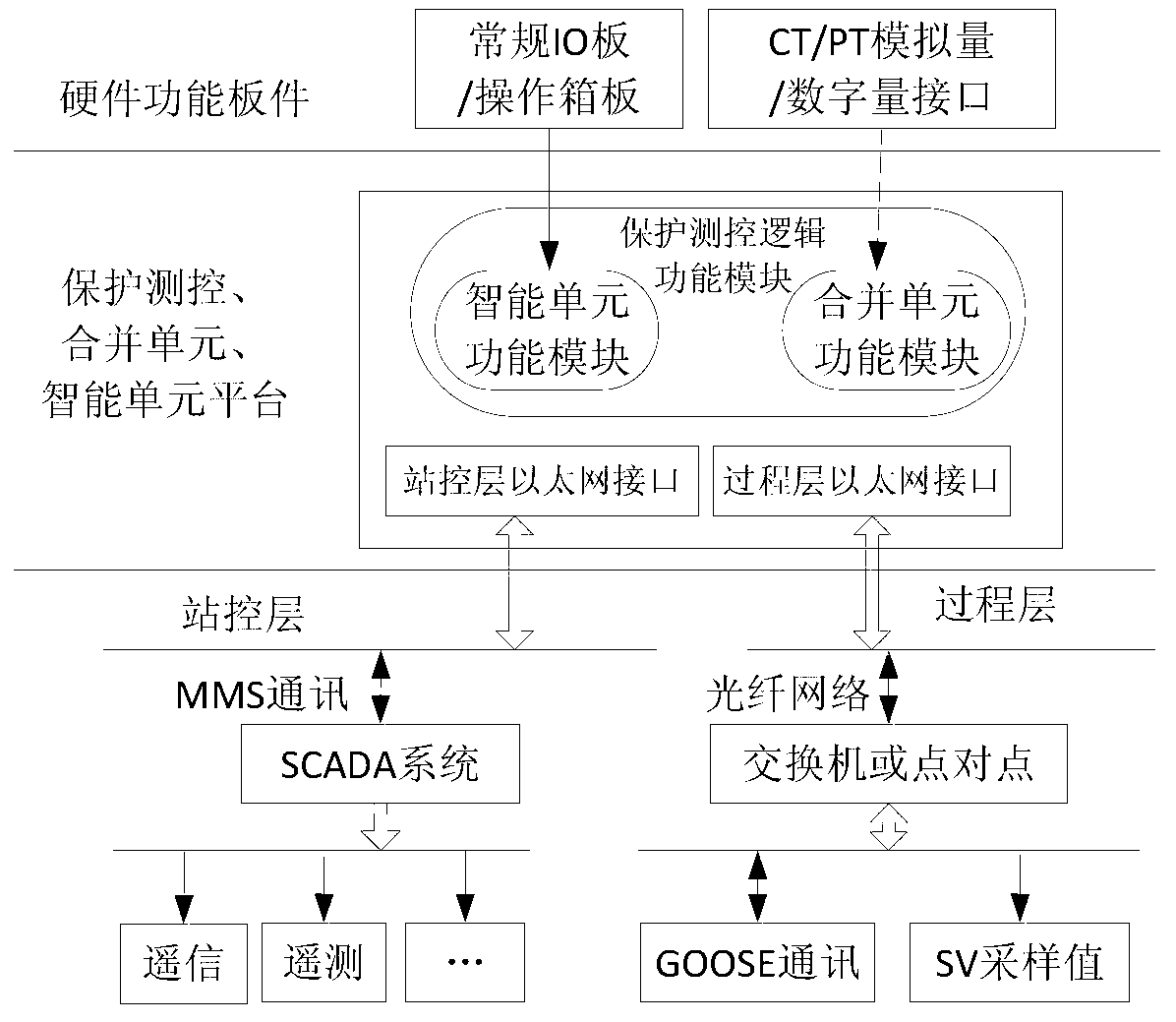

Multifunctional integrated configuration platform system of secondary equipment of intelligent substation

ActiveCN103269125AImprove debugging efficiencyImprove inspection and maintenance efficiencyCircuit arrangementsInformation technology support systemControl layerSmart substation

The invention discloses a multifunctional integrated configuration platform system of secondary equipment of an intelligent substation. The multifunctional integrated configuration platform system of the secondary equipment of the intelligent substation comprises a sampling interface independent configuration module, a substation logical configuration module, an IEC 61850 project configuration module, an SV sampling value sending configuration module and a digital relay protection equipment platform, wherein the digital relay protection equipment platform comprises an analog quantity and fiber interface module, a common IO and operation box interface module, a protection measurement and control logical function module, a station control layer MMS service module, a GOOSE communication service module and an SV sampling value sending service module. The multifunctional integrated configuration platform system can be used in the intelligent substation, realizes the functions of an independent protection, measurement and control device, a merging unit device, an intelligent unit device and a two-to-one or multi-to-one functional device, realizes the integration of the functions of the secondary equipment of the intelligent substation and project configuration, simplifies equipment configuration inside the substation, optimizes a network structure of the intelligent substation, effectively improves the operation reliability and project designing and debugging efficiency of the whole system.

Owner:STATE GRID CORP OF CHINA +3

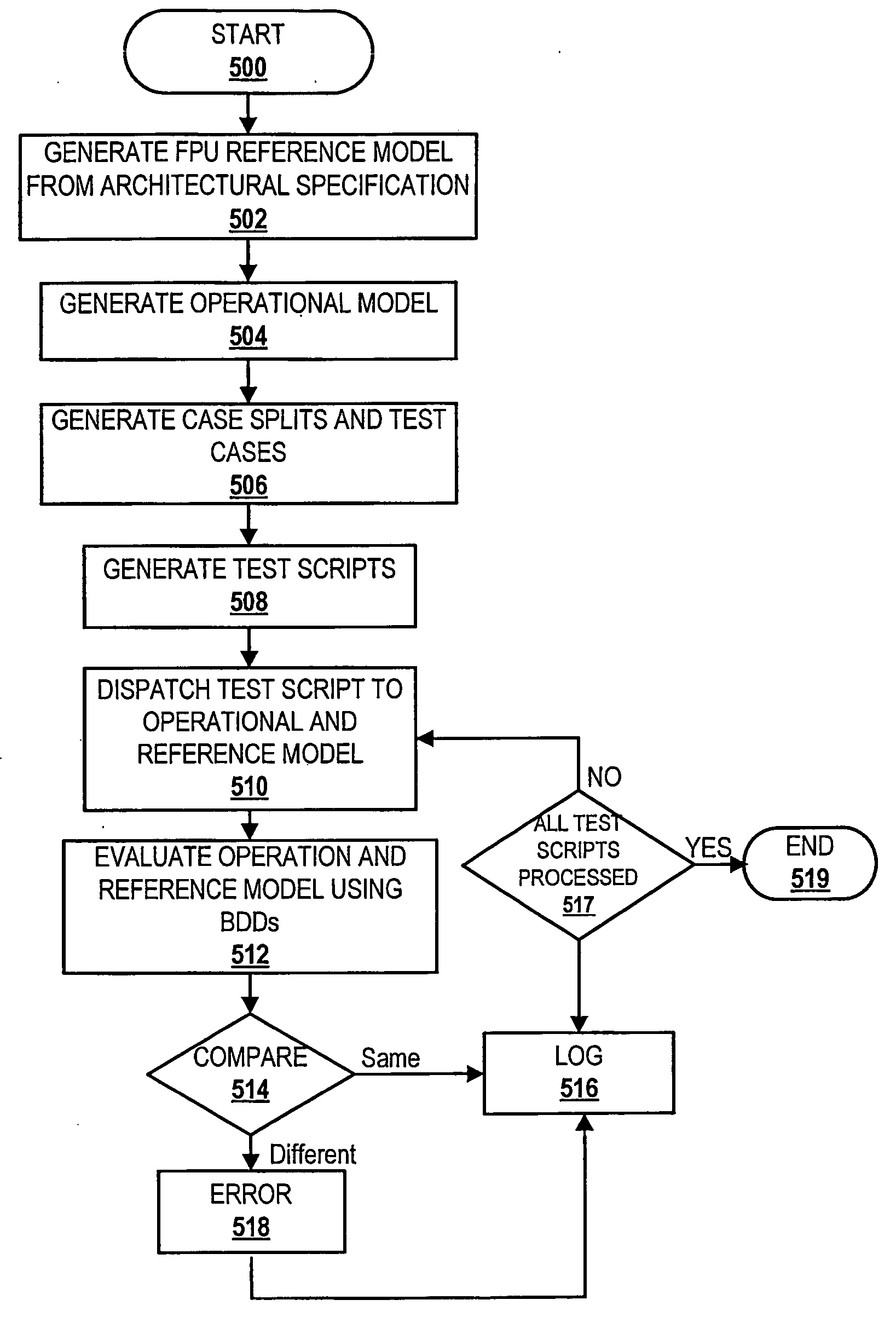

Method, system and computer program product for verification of digital designs using case-splitting via constrained internal signals

InactiveUS20060122817A1CAD circuit designSoftware simulation/interpretation/emulationReference modelTest script

A method of verifying a digital design is disclosed. The method comprises generating a reference model for a first digital design and creating an operational model for a second digital design, wherein the first digital design and the second digital design are intended to have a same logical function. A plurality of testcase types are then created by constraining one or more internal signals, and one or more test scripts representing the plurality of testcase types are produced. The method also includes verifying the second digital design with a testing simulation program by comparing results of the test scripts from the operational model and the reference model.

Owner:GLOBALFOUNDRIES INC

Flexible carry scheme for field programmable gate arrays

InactiveUS7663400B1Exclusive-OR circuitsComputations using contact-making devicesLeast significant bitComputer module

A fast, flexible carry scheme for use in clustered field programmable gate array architectures is described. Each cluster has a cluster carry input node, a cluster carry output node, a cluster carry output circuit having an output coupled to the cluster carry output node, a first input coupled to the cluster carry input node, and a second input and a plurality of logic modules each comprising a logic function generator circuit coupled to a carry circuit. The logic modules are coupled in a series carry arrangement between the cluster carry input node and the second input of the cluster carry output circuit such that the least significant bit of an arithmetic logic circuit can be programmably placed in any of the logic modules.

Owner:MICROSEMI SOC

Commutation locker cabinet electric arc protecting equipment

InactiveCN101141061ALimit durationEliminate hazardsEmergency protective circuit arrangementsLogical FunctionPower module

The invention relates to a rectifying cabinet electric arc protective device, which comprises a power module supplying power to the whole electric arc protective device, an arc detection main unit for managing and controlling the whole electric arc protective device, an arc detection assistant unit for collecting the light information from an arc sensor, an over-current detection unit for generating the tripping logical function, and an arc detection probe. The invention is characterized in that the arc detection probe is connected with the arc detection main unit and the arc detection assistant unit through a long optical fiber with photosensitive property at the front section. Moreover, the invention has advantages of ensuring the rectifying device to quickly and selectively cut the failure set or the feeding breaker when in arc fault, thereby radically limiting the duration of the failure arc and eliminating the harm to various personnel and devices caused by arc short circuit as well as reducing the sever economic loss brought about by accident expansion.

Owner:包头铝业有限公司

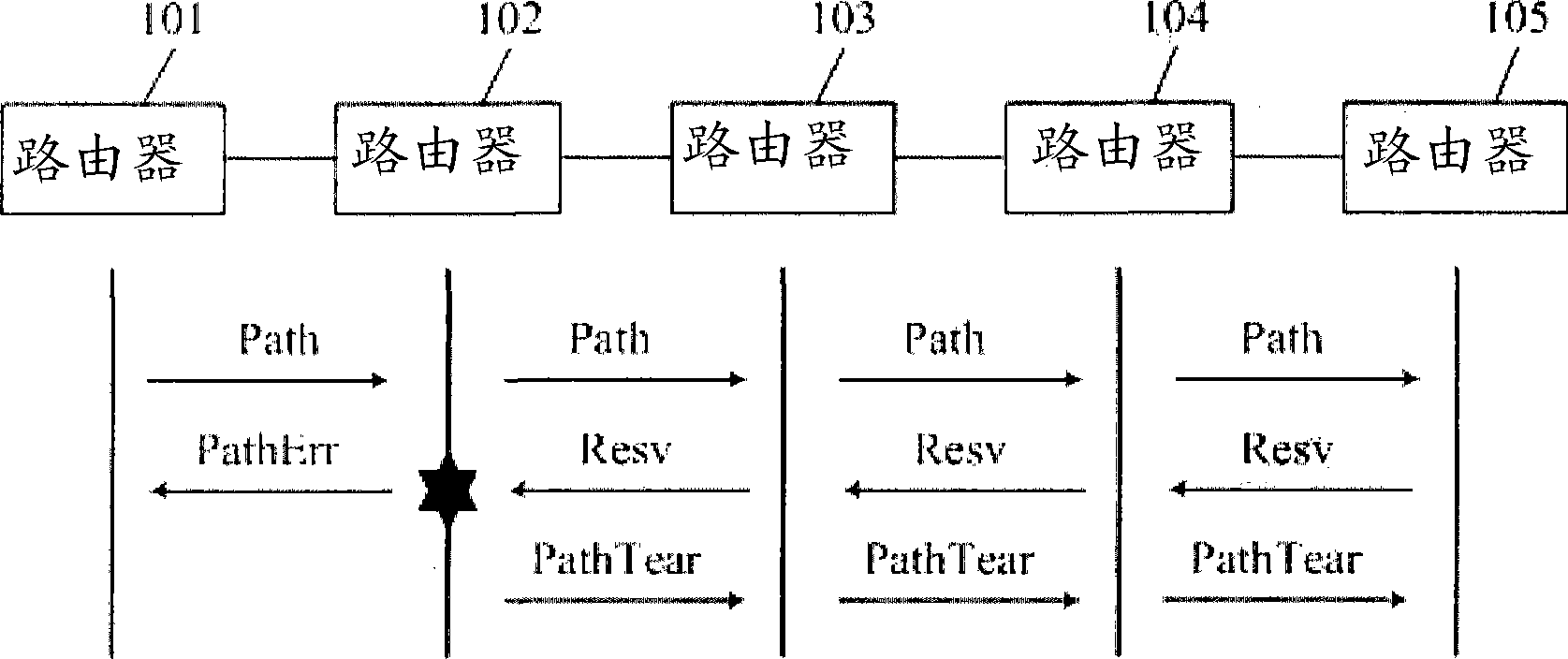

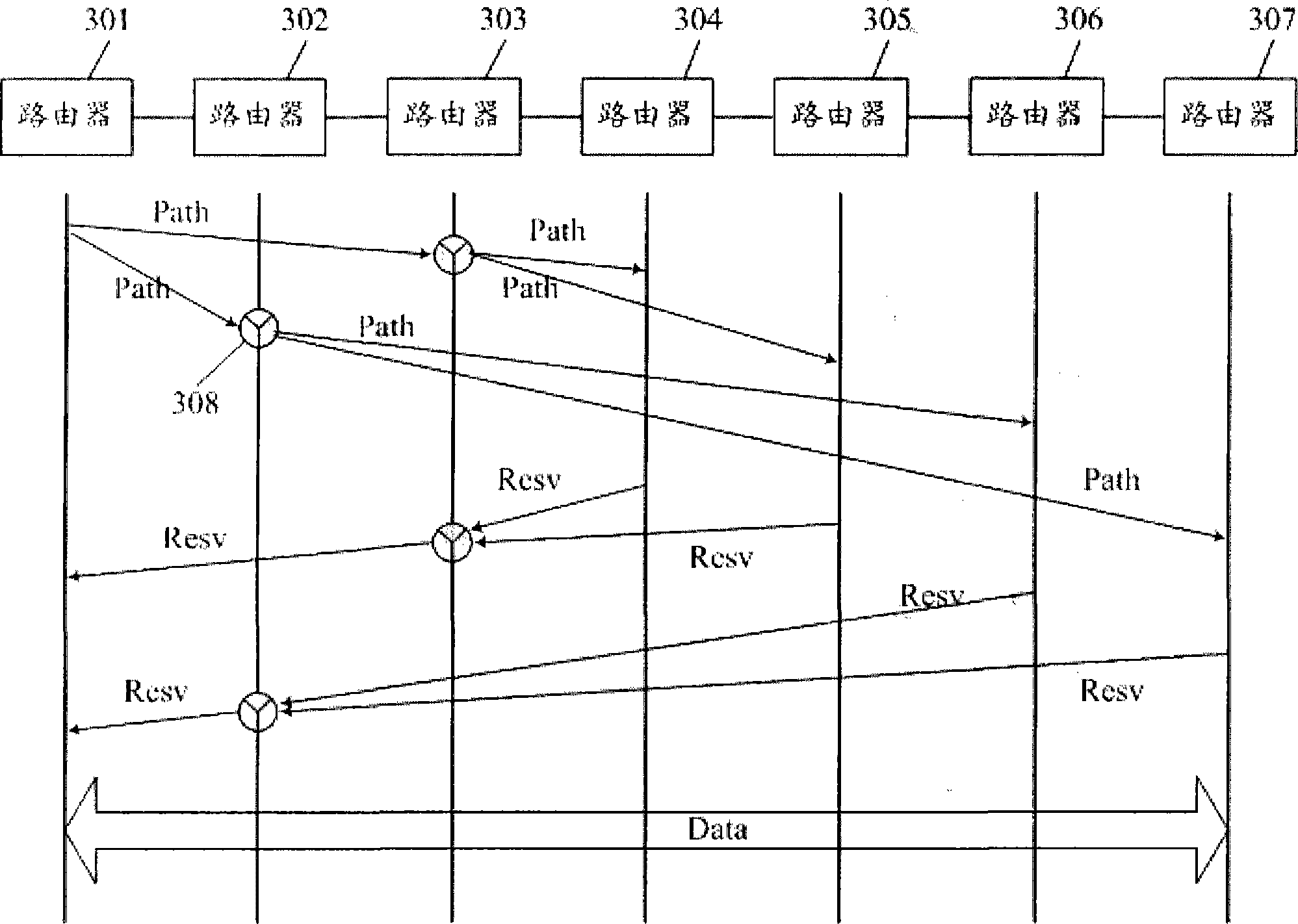

Tree shaped fast connection establishing method based on multi-Agent cooperation

ActiveCN101488898APrevent false reservationsPrevents errors from being preempted by other requestsStar/tree networksStructure of Management InformationConnection control

The invention relates to the communication field, the invention embodiment discloses a tree-shaped fast connecting establishing method based on multiple-Agent cooperation. The method comprises: an integral establishing process flow of single service tree-shaped signaling; a signaling expanding abstraction logical function in a network with control plane; a topological abstract method of multiple-Agent collaboration signaling forwarding tree; a traversing mode of tree-shaped signaling forwarding tree based on non-balance type binary forwarding tree; a traversing mode of tree-shaped signaling forwarding tree based on non-balance type N-branch forwarding tree; a resource invalidation processing method in the tree-shaped signaling service process flow. According to the method of the invention, the entity logical function can be forwarded by expanding the signaling, the connection control operation can be performed between a plurality of Agents to establish a layered structure for a calling connection controller, the higher grade calling connection controller implements the control function for a first stage calling connection controller to rapidly implement the connection establishment and respectively provide processing flows for different resource invalidation conditions. After considering the queue processing and exterior transmission time delay, the connection can be optimized by a non-standard binary forwarding tree structure. The tree-shaped signaling implementing interface of the multiple-Agent system comprises a GUI interface for taking charge of the transmitting of the control command, the real-time data detection, the data filtering, the center resource database access and the Agent information report and so on operations.

Owner:BEIJING UNIV OF POSTS & TELECOMM +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com