Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

31 results about "Defect prevention" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The purpose of Defect Prevention is to identify the cause of defects and prevent them from recurring. Defect Prevention involves analyzing defects that were encountered in the past and taking specific actions to prevent the occurrence of those types of defects in the future.

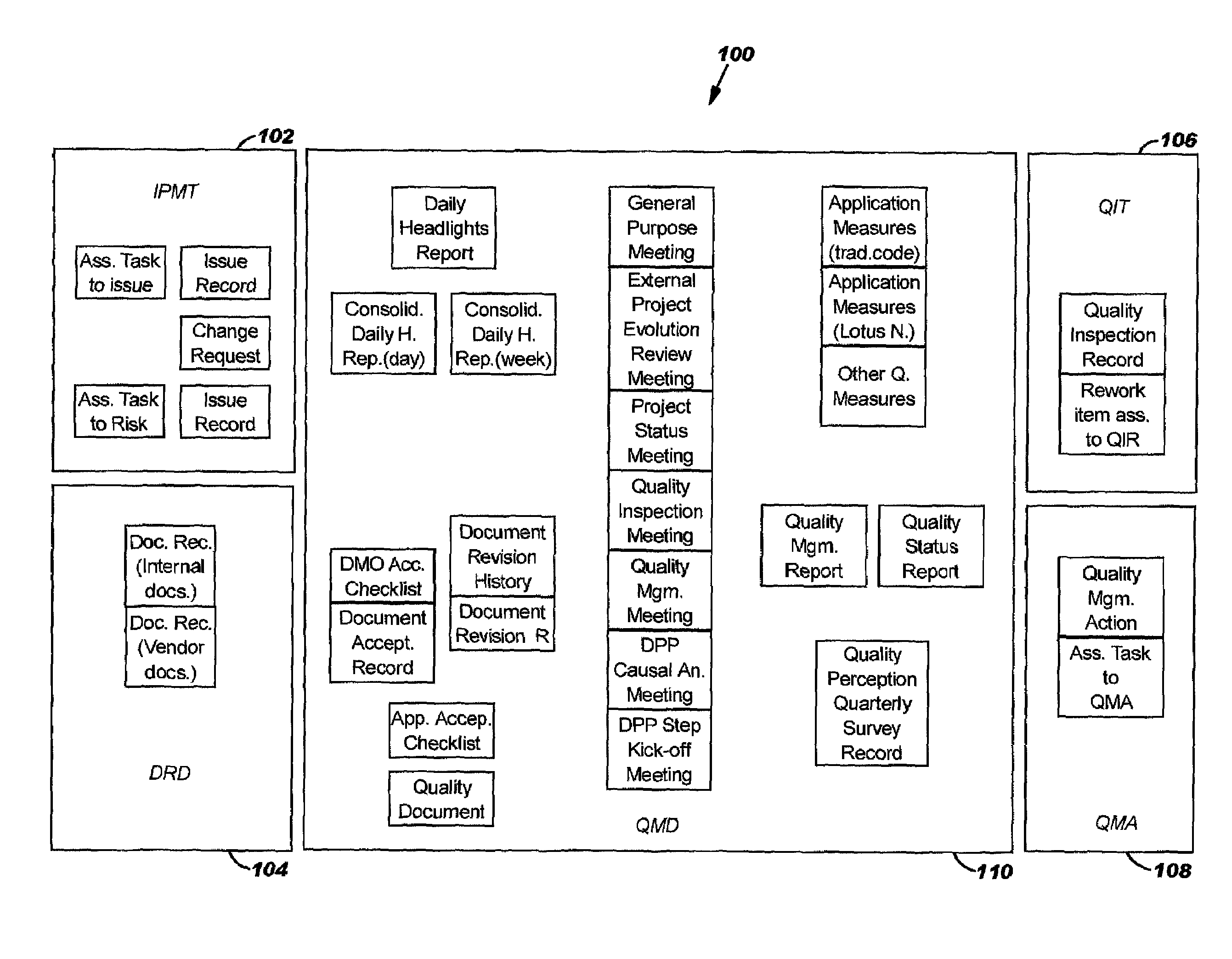

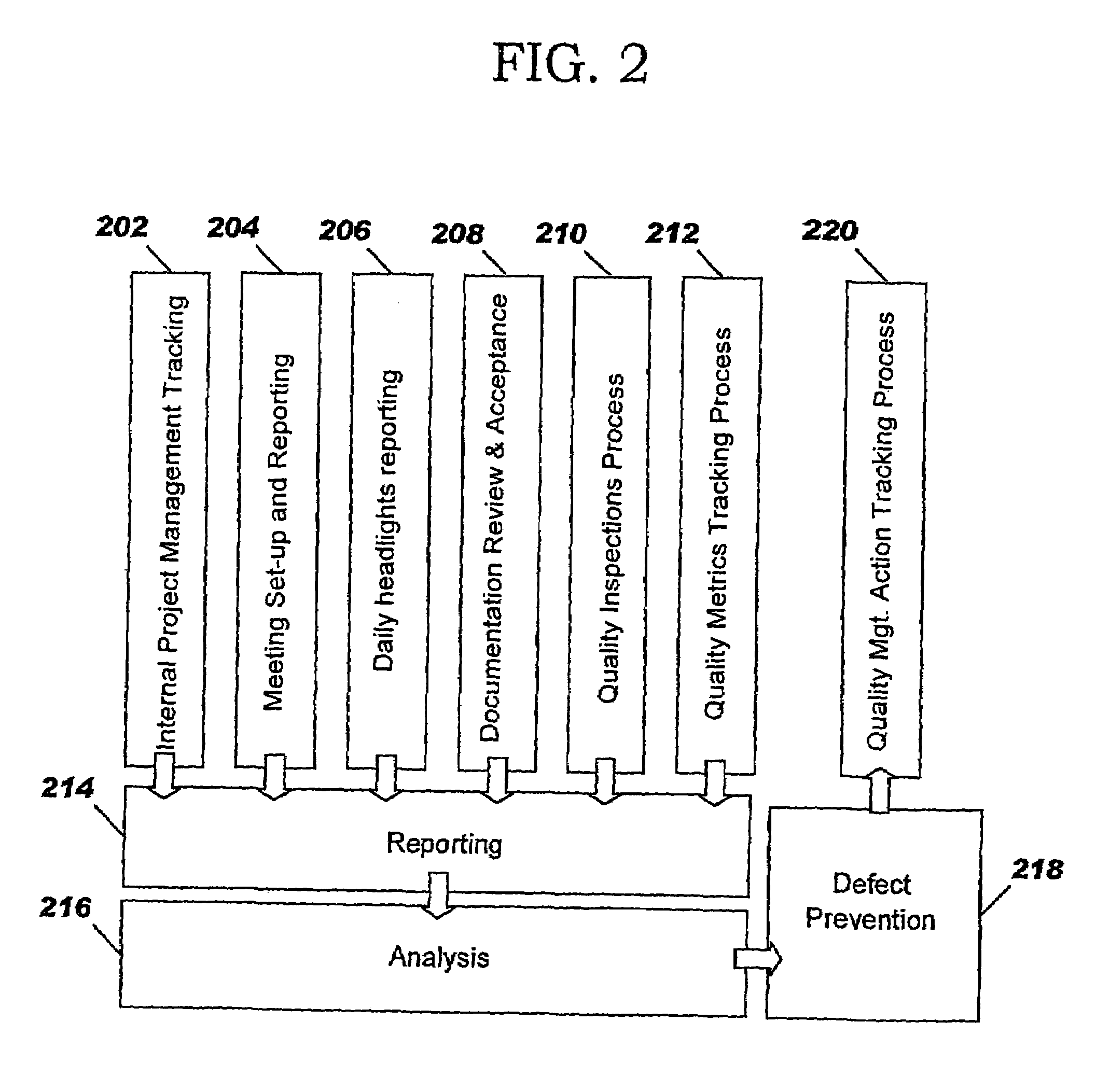

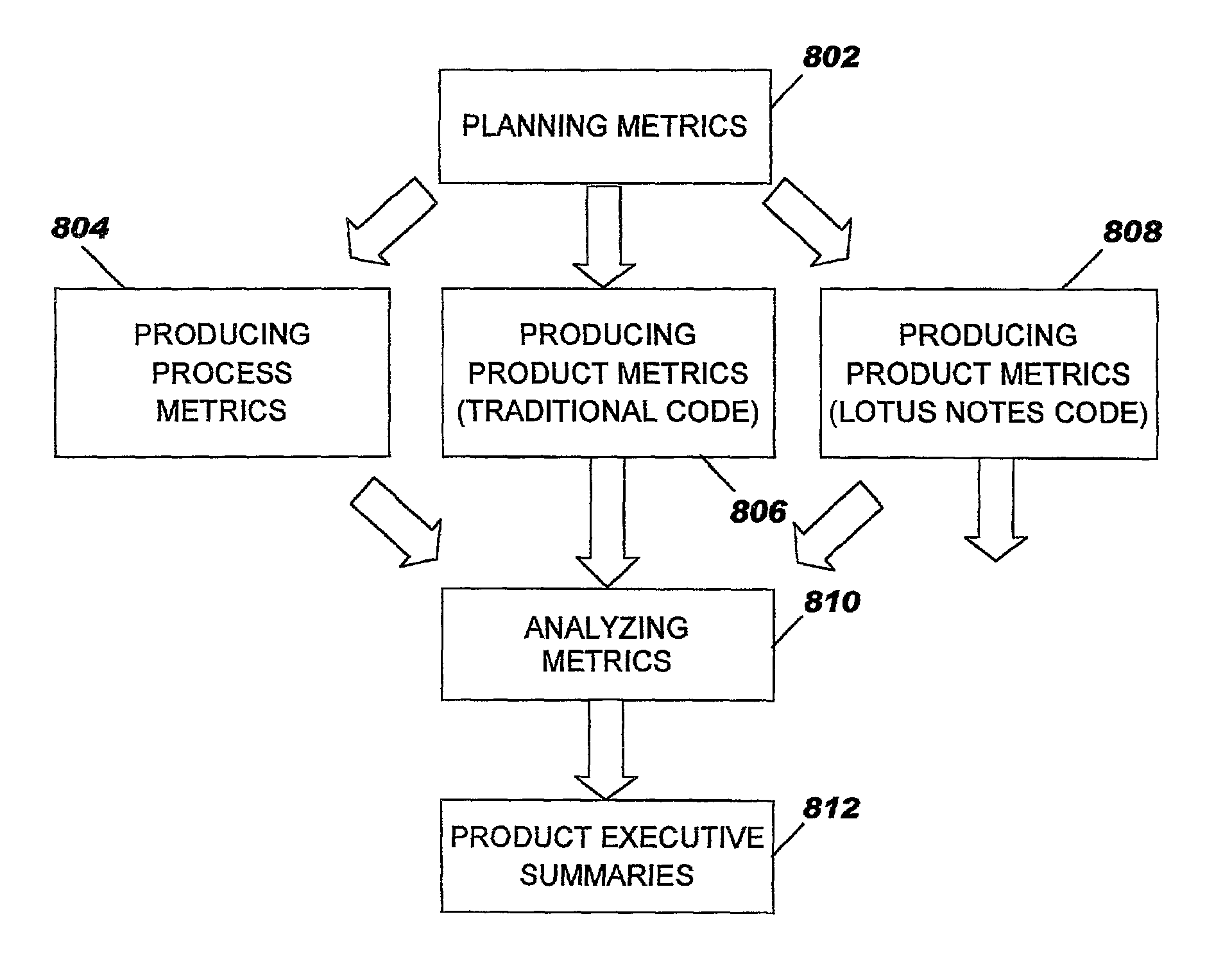

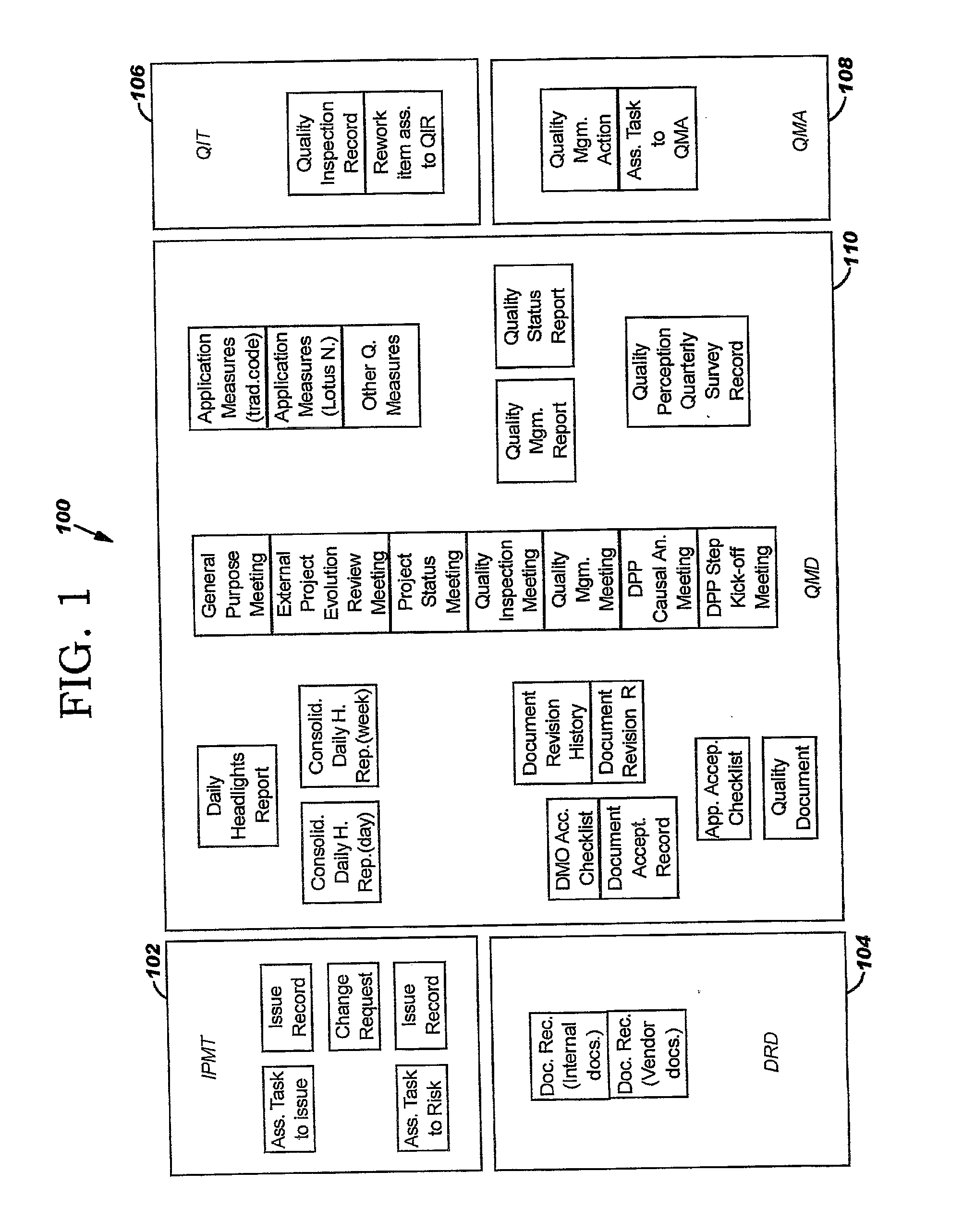

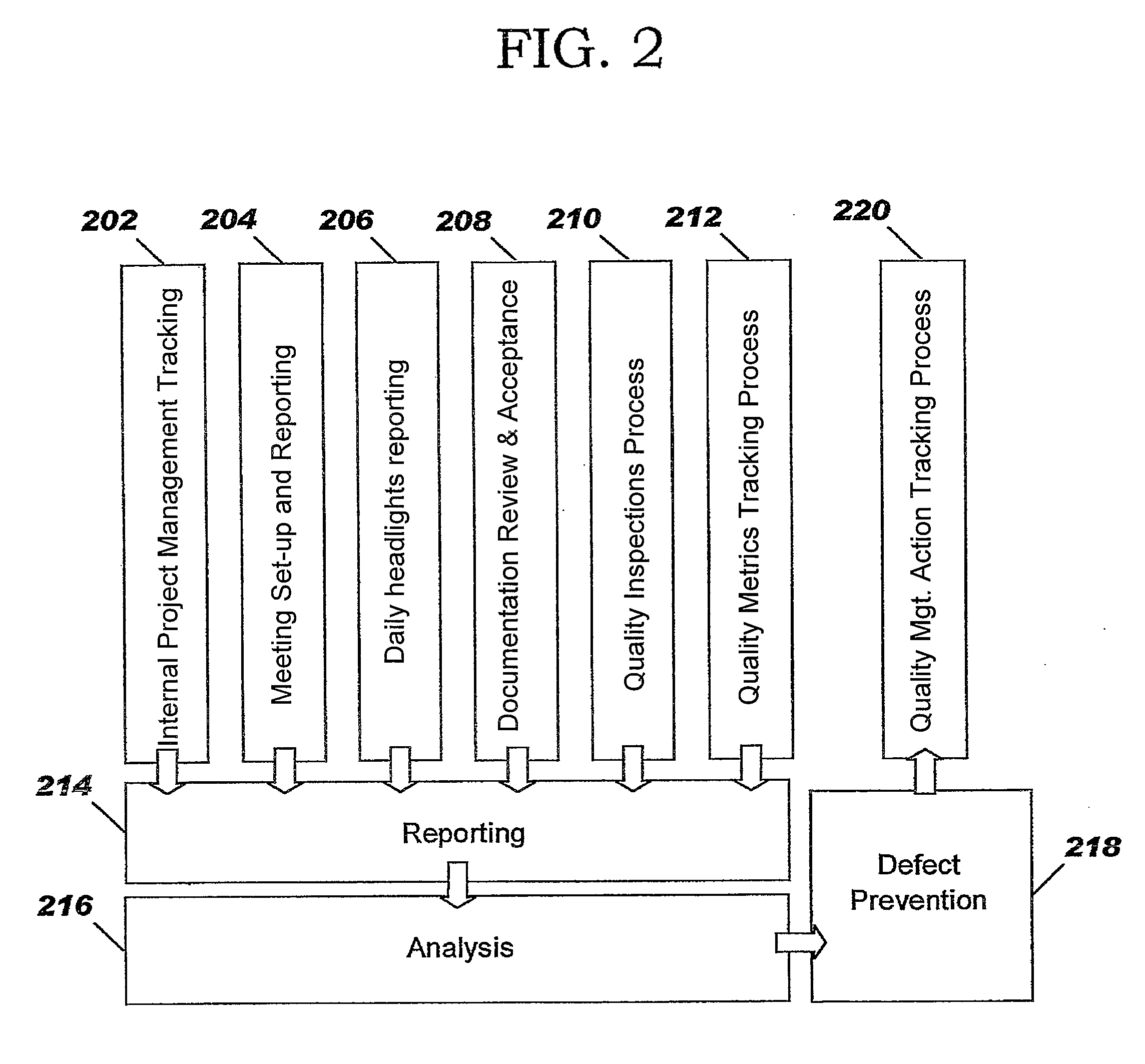

Method and system for a quality software management process

InactiveUS7337124B2Easy to deploySpeed up the processFinanceMultiprogramming arrangementsQuality processManagement process

A quality management framework system and method for operating a quality plan in a product development organization having quality objectives. The system includes a plurality of computer implemented tools accessible by users for operating a plurality of quality processes. Data relative to the quality processes is collected and aggregated to generate quality reports. Reports are analyzed and problems are detected through a defect prevention process. Quality actions are initiated in a feedback quality management action tracking process.

Owner:IBM CORP

Method and System for a Quality Software Management Process

InactiveUS20080092108A1Easy to deployOptimize workflowOffice automationResourcesQuality processManagement process

Owner:INT BUSINESS MASCH CORP

Real time closed-loop process control system for defect prevention

InactiveUS20050033464A1Avoid defectsElectric testing/monitoringElectric controllersControl systemClosed loop

A method is provided for executing a monitoring process during a manufacturing process to produce products. The method measures, in real time, performance variables of an upstream portion of a present manufacturing process, analyzes, with a processor, trends in the performance variables of the present manufacturing process together with data that models a portion of a subsequent manufacturing process, that occurs after the present manufacture process, to predict performance of the subsequent manufacturing process, sends trend analysis information to the present manufacturing process, and sends information to the subsequent manufacturing process.

Owner:SIEMENS DEMATIC ELECTRONICS ASSEMBLY SYST

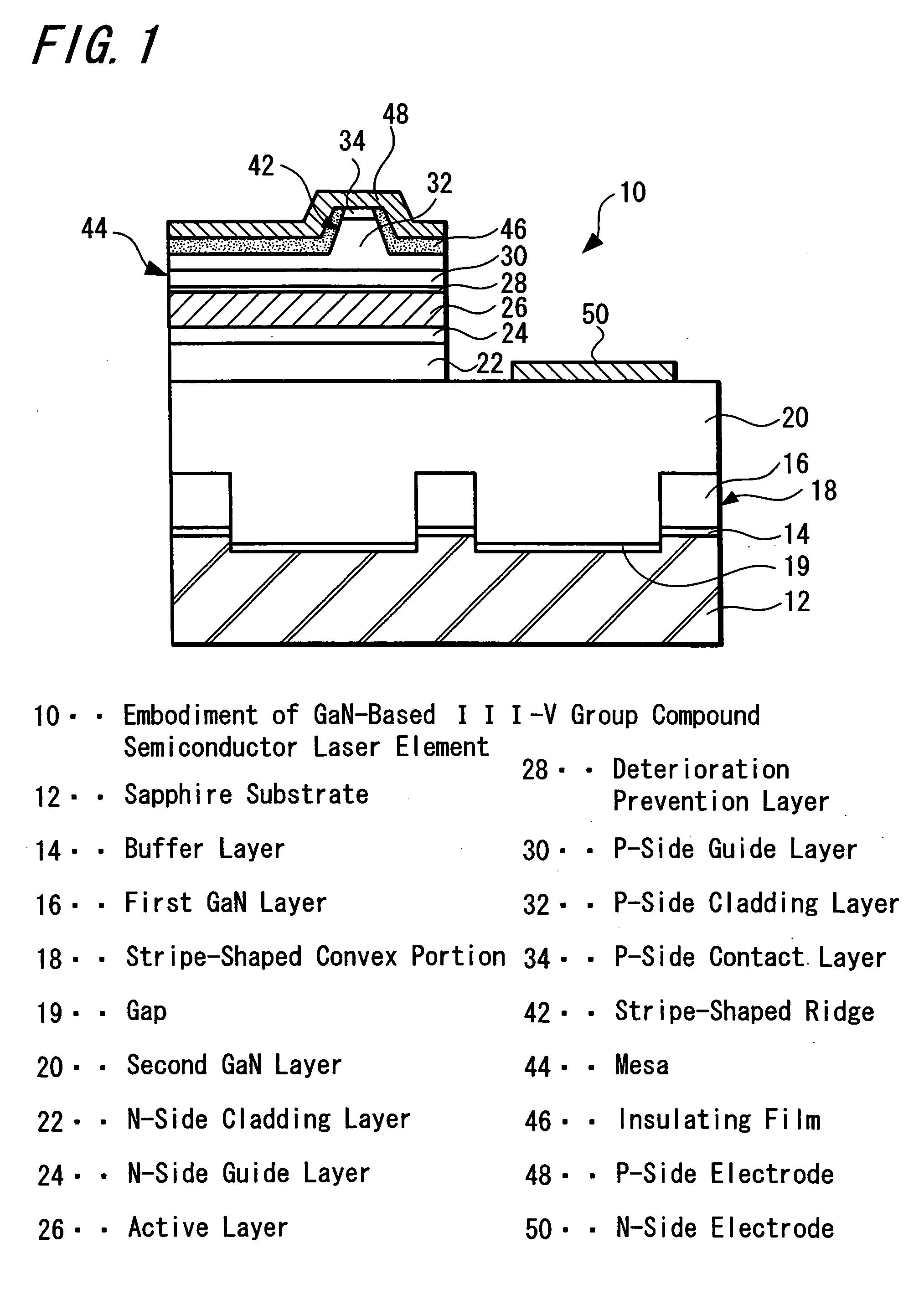

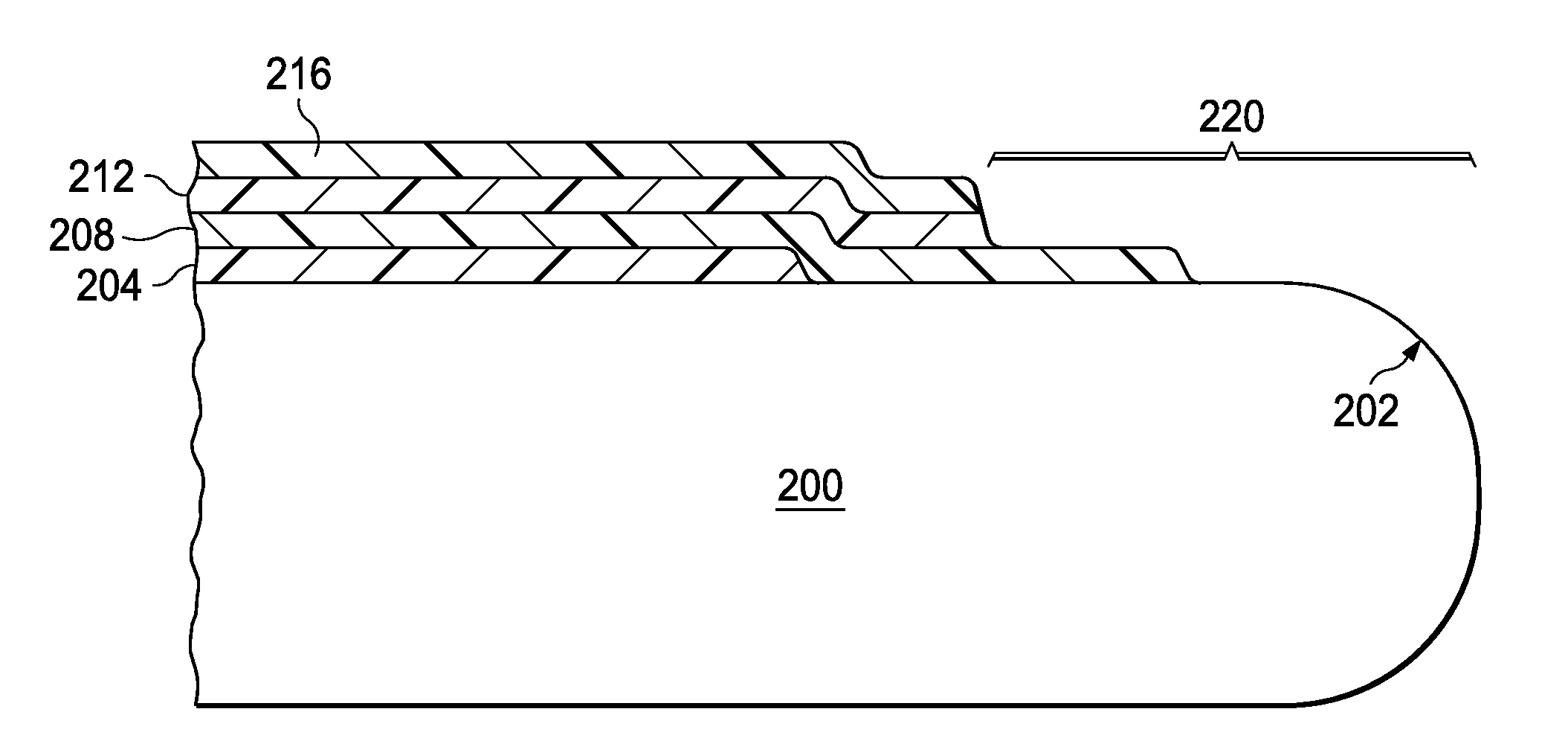

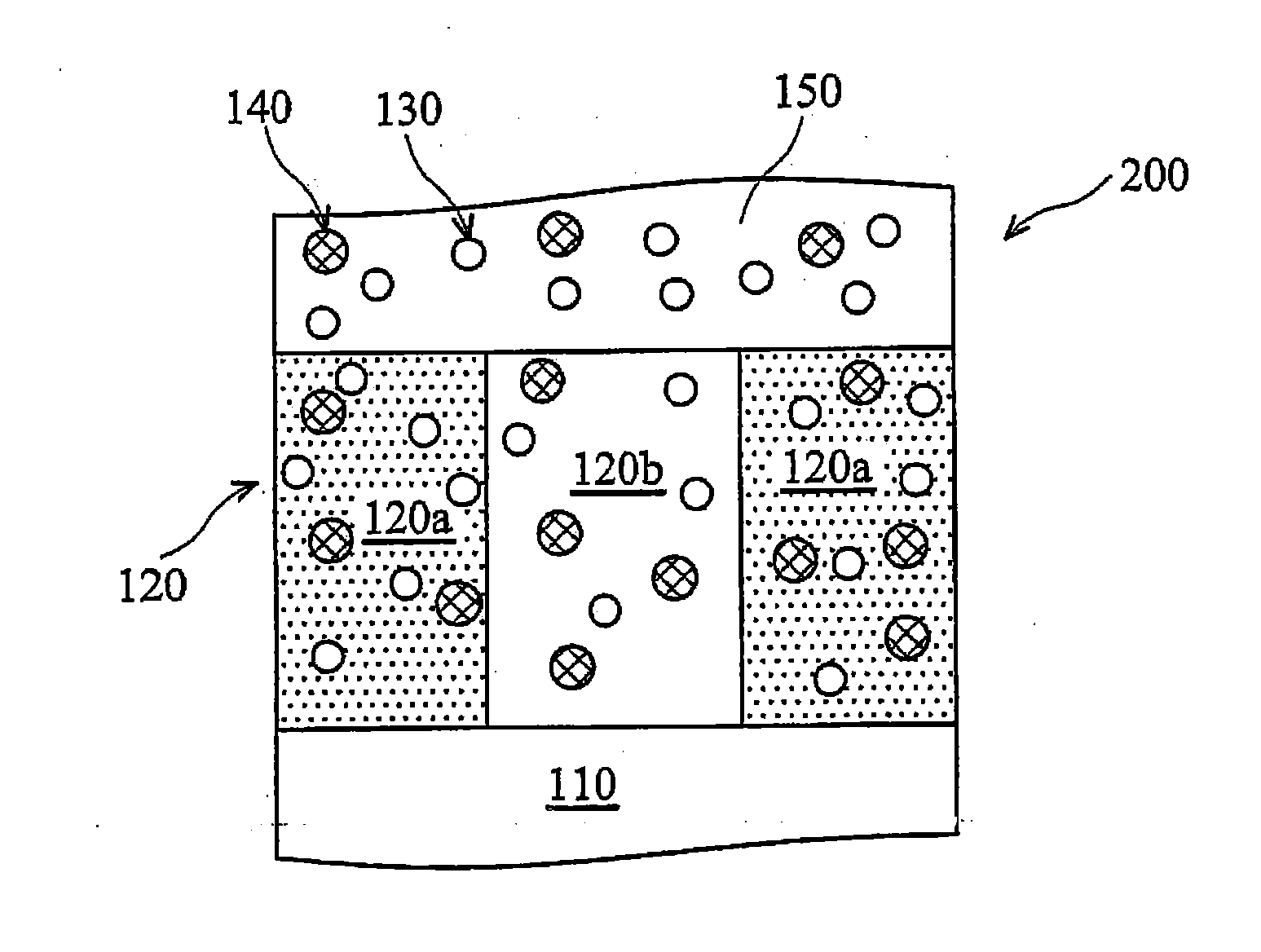

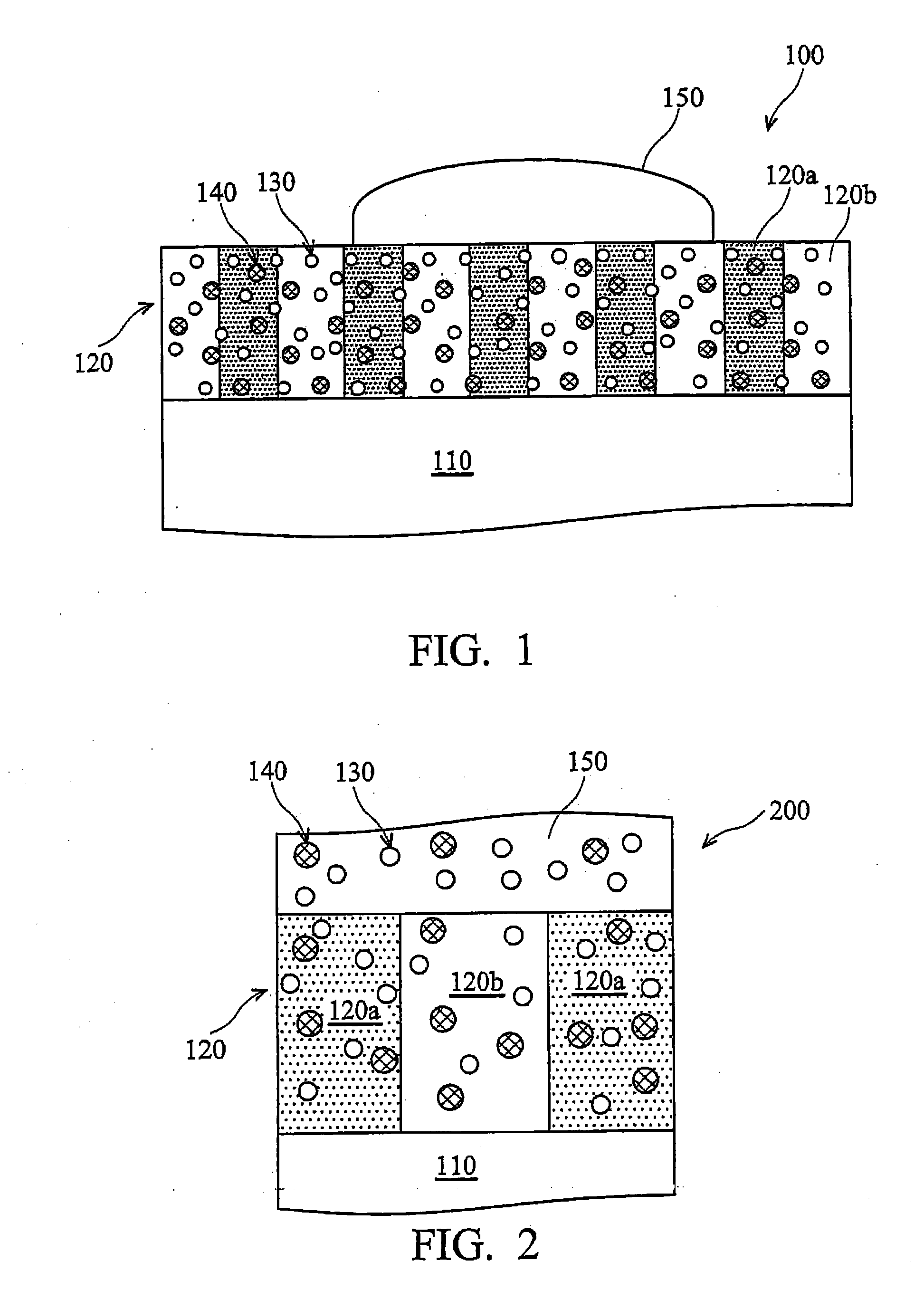

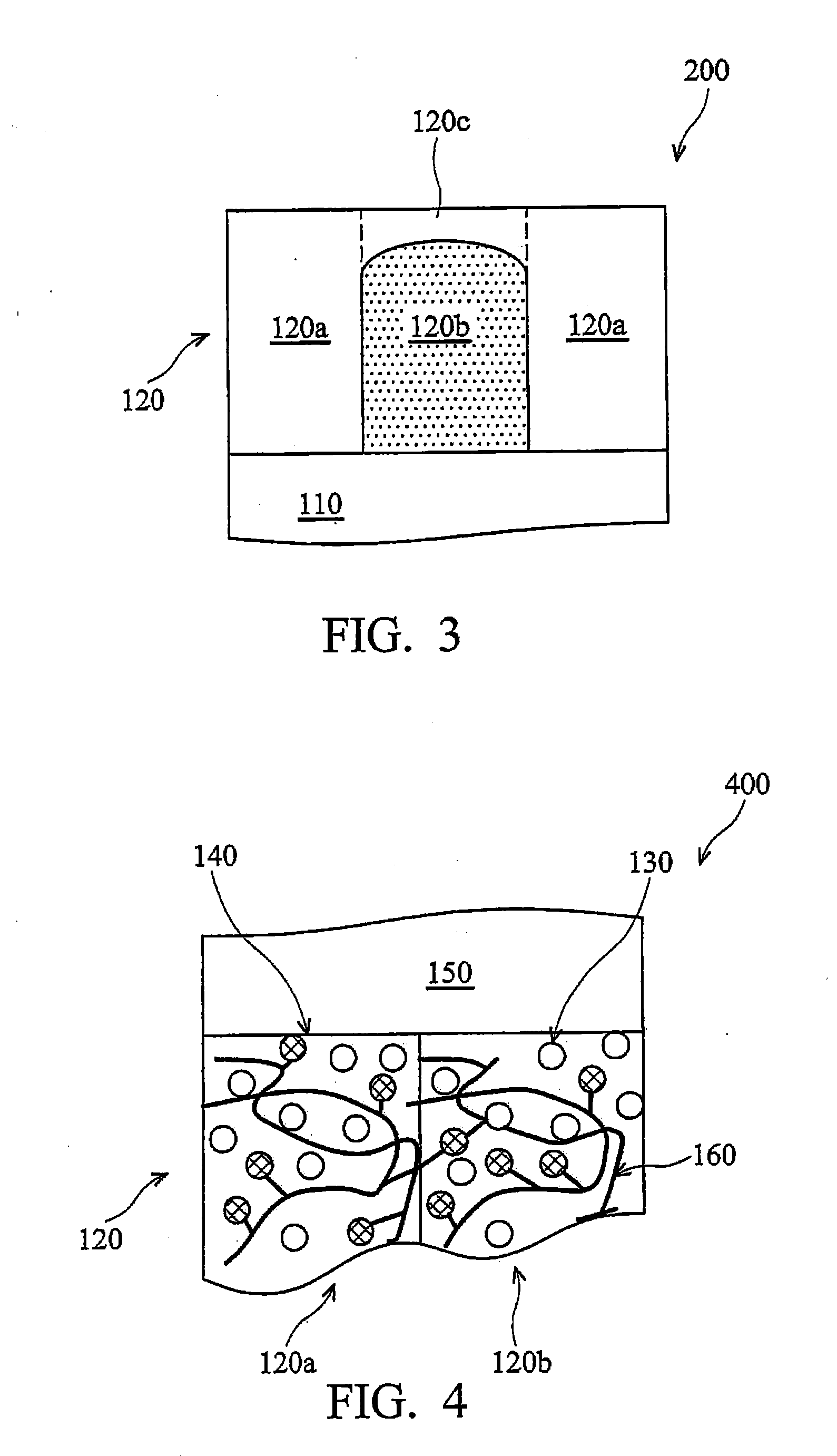

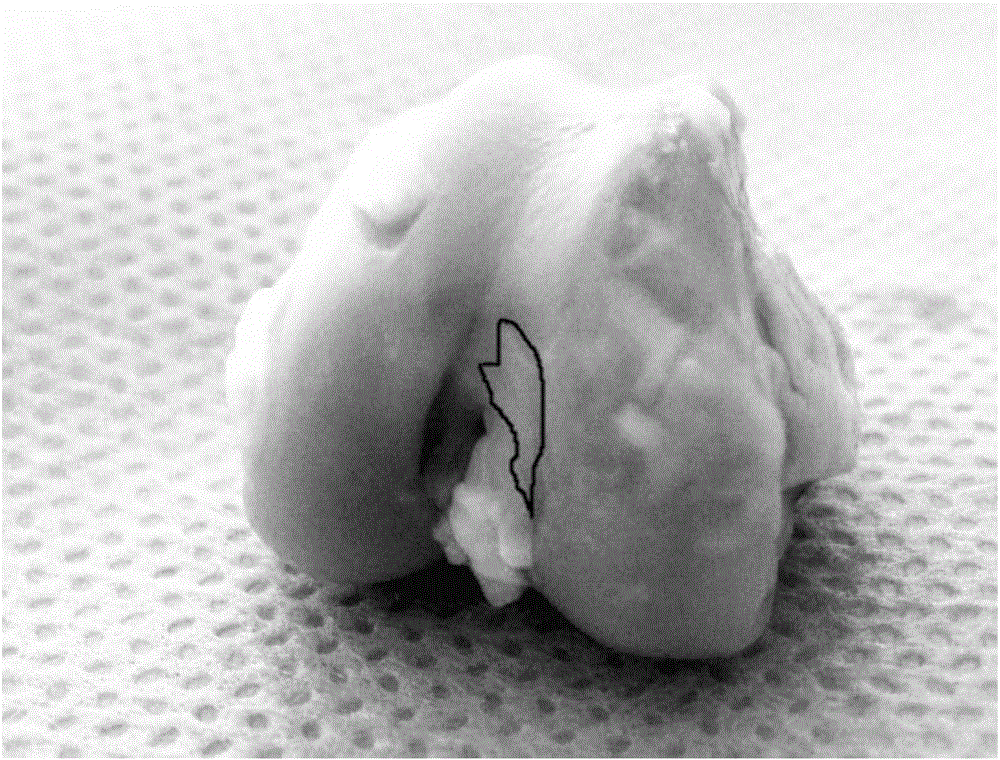

Gan-Based III-V Compound Semiconductor Light-Emitting Element and Method for Manufacturing Thereof

InactiveUS20080217632A1Improve efficiencyAvoid it happening againOptical wave guidanceLaser detailsSurface layerQuantum well

A GaN-based III-V group compound semiconductor light-emitting element having high light-emitting efficiency and high reliability at a light-emitting wavelength of 440 nm or more is provided.A GaN-based semiconductor laser element 10 has a laminated structure of: a stripe-shaped convex portion 18 made of a surface layer of a sapphire substrate 12, a buffer layer 14 and a first GaN layer 16, and on the sapphire substrate, a second GaN layer 20, an n-side cladding layer 22, an n-side guide layer 24, an active layer 26, a deterioration prevention layer 28, a p-side guide layer 30, a p-side cladding layer 32 and a p-side contact layer 34. The active layer is formed of a quantum well structure including a GaInN barrier layer 36 and a GaInN well layer 38, and a planar crystal defect prevention layer 40 made of an AlGaN layer is provided on the upper surface or lower surface, or between both the surfaces of the barrier layer and the well layer. Upper portions of the p-side contact layer and the p-side cladding layer are formed as a stripe-shaped ridge 42 and a mesa 44 is formed in parallel with the ridge.

Owner:SONY CORP

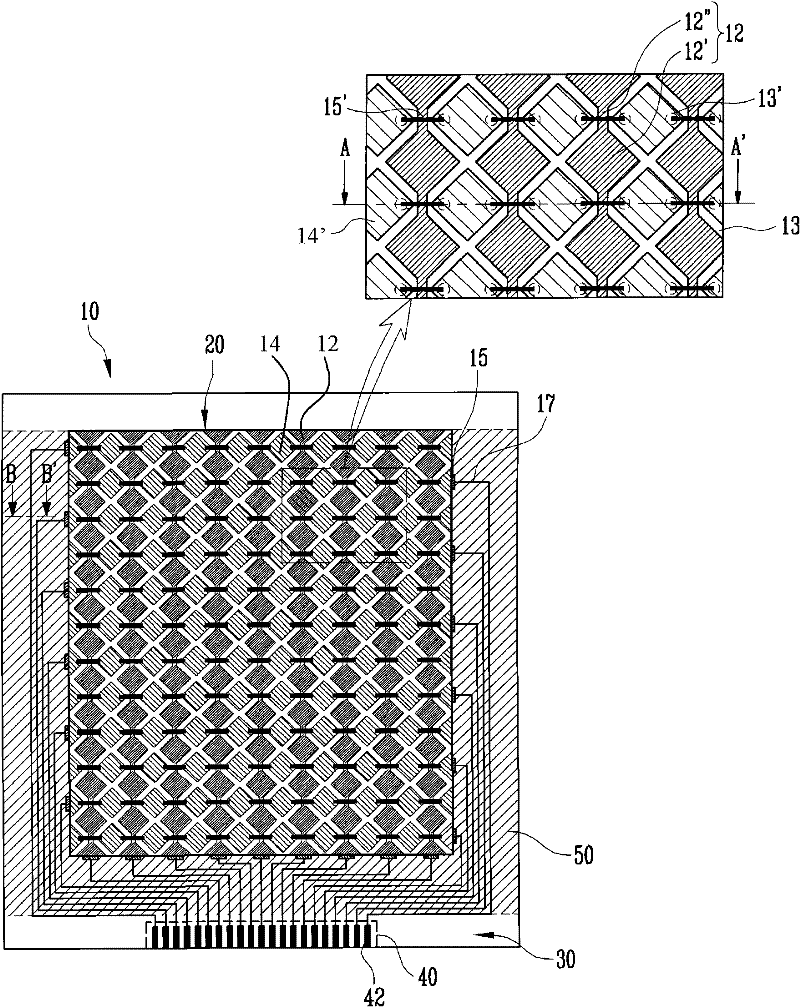

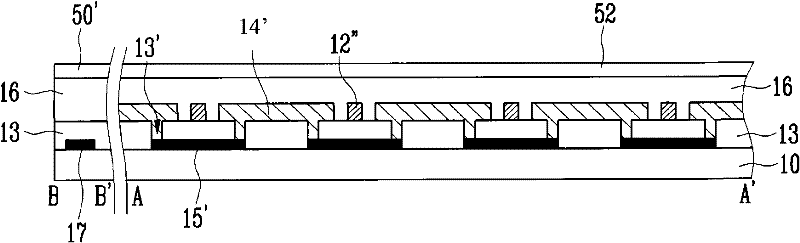

Flat panel display integrated with touch screen panel

InactiveCN102193671ANon-linear opticsInput/output processes for data processingDisplay deviceEngineering

The invention provides a flat panel display integrated with touch screen panel. The touch screen panel is directly formed on an upper substrate of a flat panel display which provides a flat panel display integrated with the touch screen panel with an improved yield and reliability by improving ESD defect prevention due to the introduction of electrostatic by using a shield member covering sensing lines so that the sensing lines formed in a non-display region of the touch screen panel are not exposed to the outside.

Owner:SAMSUNG DISPLAY CO LTD

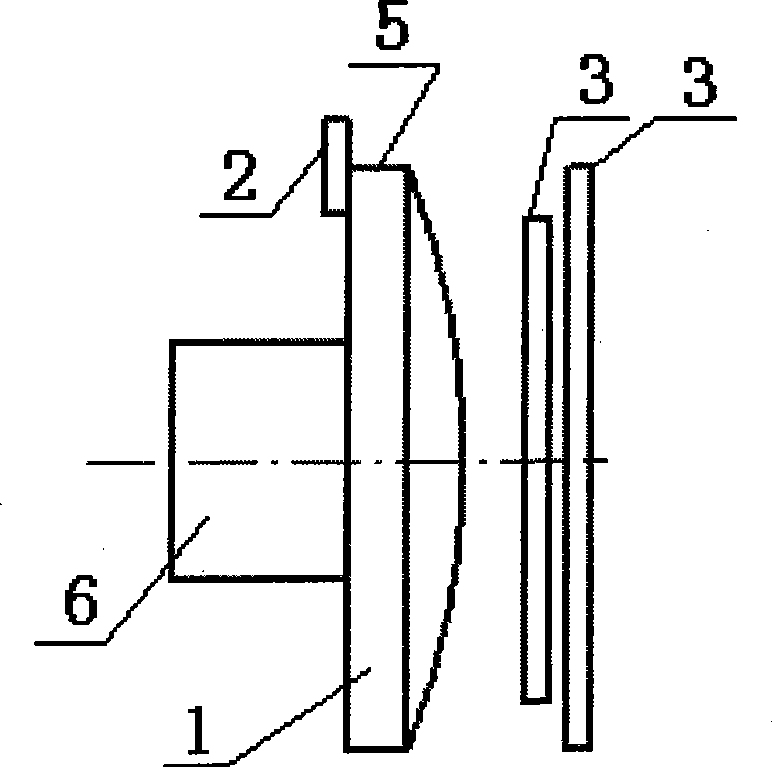

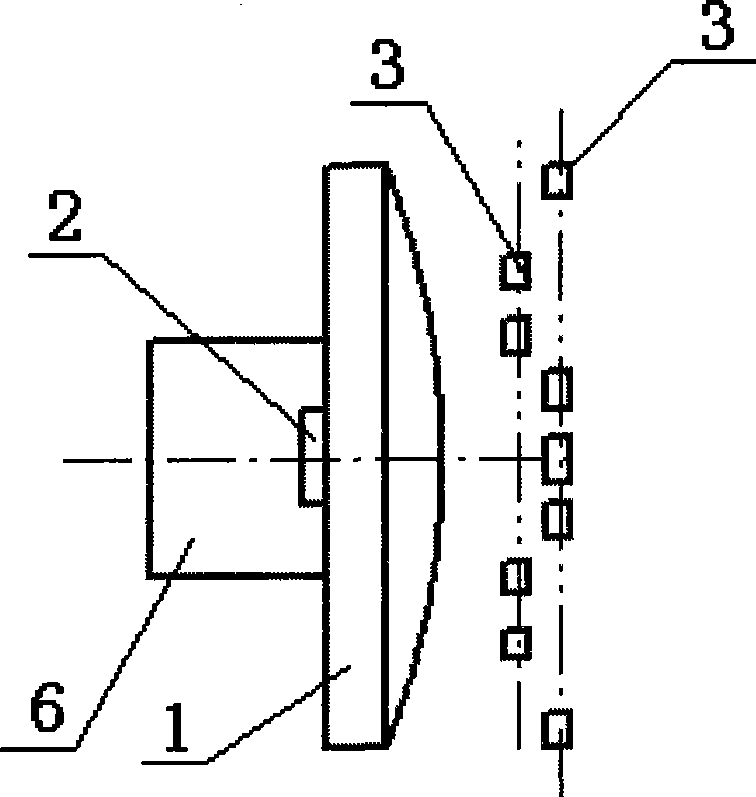

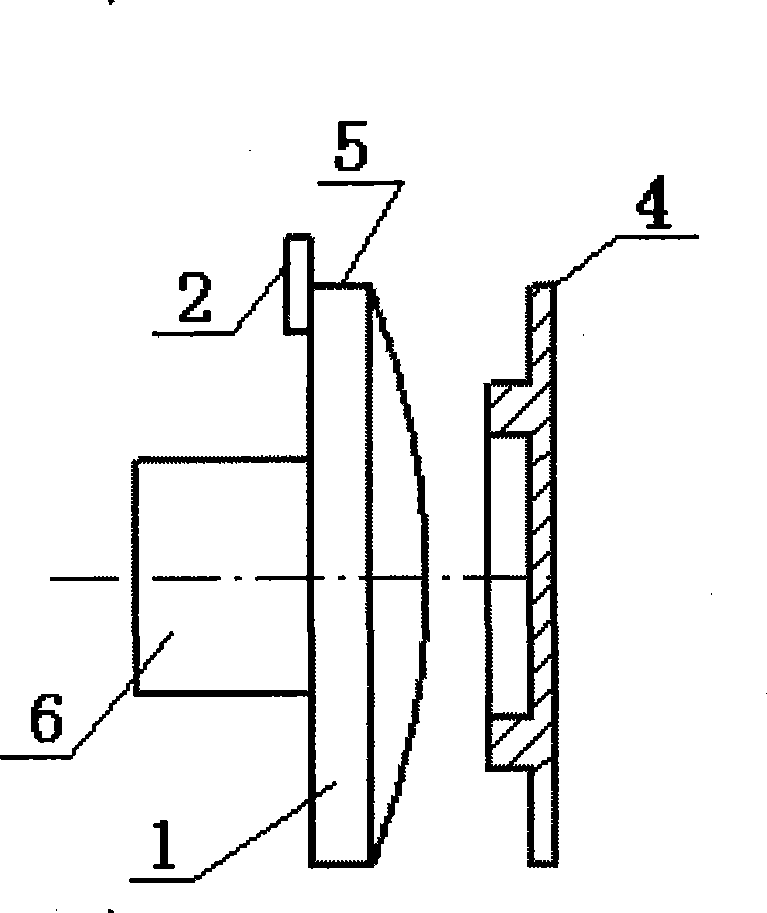

Chrome plating method for spherical crown surface of major diameter spherical crown workpiece

The invention provides a method for plating chromium on a spherical cap surface of a large-diameter spherical cap workpiece. In a step of immersing and positioning, the arrangement mode or structure of an anode strap or an anode plate is changed; in a step of plating chromium, opacified chromium is plated under the conditions that the temperature of the plating solution is 70 to 75 DEG C and the current density is 20 to 25A / decimeter<2>; and then, hard chromium is plated under the conditions that the temperature of the plating solution is 50 to 55 DEG C and the current density is 25 to 30A / decimeter<2>. The polishing processing is carried out on the spherical cap surface of the workpiece, which has the advantages of good evenness of chromium plated coating, defect prevention, high electroplating efficiency, fast speed of cladding deposit, high surface finish of the spherical cap surface after chromium is plated, and subsequent mechanical processing workload reduction.

Owner:LUOYANG SUNRUI SPECIAL EQUIP

Immersion lithography wafer edge bead removal for wafer and scanner defect prevention

ActiveUS20090163026A1Reduce particulate pollutionDecorative surface effectsSemiconductor/solid-state device manufacturingMonomethyl etherSolvent

A method of performing a single step / single solvent edge bead removal (EBR) process on a photolithography layer stack including a photoresist layer and a top coat layer using propylene glycol monomethyl ether acetate (PGMEA) or a mixture of PGMEA and gamma-butyrolactone (GBL) is disclosed. The single step / single solvent EBR process is compatible with organic and inorganic BARC layers.

Owner:TEXAS INSTR INC

Water mark defect prevention for immersion lithography

ActiveUS8415091B2Semiconductor/solid-state device manufacturingPhotosensitive material processingReduced mobilityPolymer

A photoresist material having a polymer that turns soluble to a base solution in response to reaction with acid. The material includes a photo-acid generator (PAG) that decomposes to form acid in response to radiation energy and a quencher capable of neutralizing acid and having a reduced mobility. The photoresist material can thereby prevent water mark defects from immersion lithography.

Owner:TAIWAN SEMICON MFG CO LTD

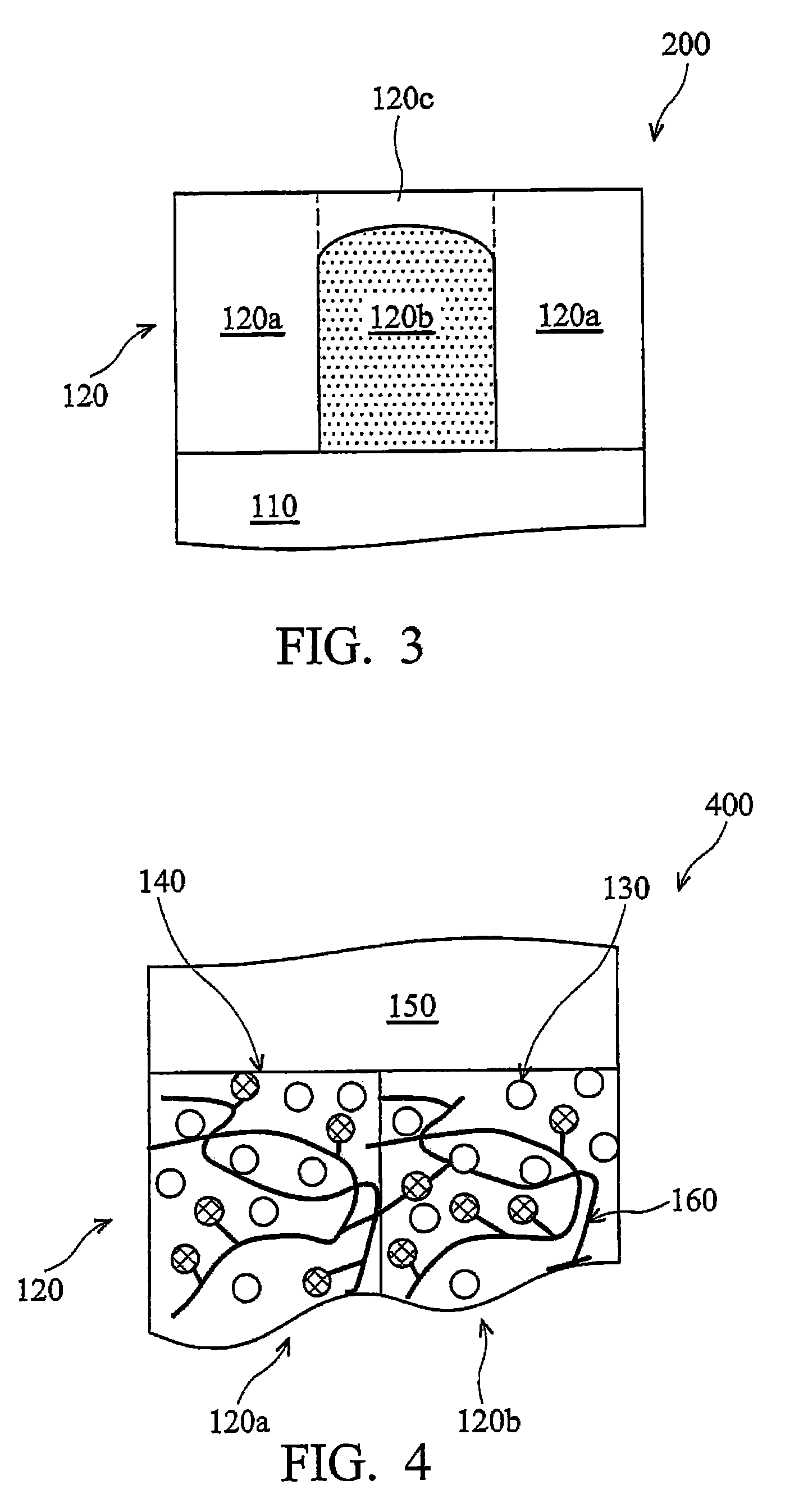

Method for preventing defects of electric-power information hardware

PendingCN106776316AImprove build qualityReduce the risk of failureSoftware testing/debuggingSoftware systemFailure risk

The invention provides a method for preventing defects of electric-power information software. The method comprises the following steps of: inputting measurement information for the electric-power information at all stages in the life cycle and measurement information of the development process into an AODE prediction model, and calculating the defect densities of all stages; then searching a defect knowledge base of the electric-power information software and acquiring defect introduction reasons and corresponding prevention measures at all the stages; and finally carrying out defect prevention in a targeted manner to reduce the defect density. The method provided by the invention has the advantages that the method and the technical basis can be provided for preventing the defects in construction of an electric information system, the introduction of the defects can be prevented at the early construction of the electric information system, the defect introduction rate can be reduced, the repeated work of 'defect introduction-testing-modification' can be reduced, the targeted property for preventing the defects can be effectively improved, the project development expense of the information system can be saved, the failure risk of a software system can be reduced and the whole construction quality of the electric-power information software can be wholly improved.

Owner:CHINA ELECTRIC POWER RES INST +1

Apparatus for cooling hot-dip plated steel sheet

PendingUS20210332468A1Increase productivityQuality improvementHot-dipping/immersion processesMetallurgyAir knife

Provided is an apparatus for cooling a hot-dip plated steel sheet, the apparatus being capable of reducing comb-pattern surface defects occurring on the edge portion of the hot-dip plated steel sheet. The apparatus includes: a gas knife for spraying wiping gas to a steel sheet that has passed through a plating bath, thereby adjusting the plating thickness thereof; a defect prevention portion installed downstream of the gas knife so as to spray cooling gas to the steel sheet, thereby cooling same; and a moving portion for driving the defect prevention portion such that same moves.

Owner:POHANG IRON & STEEL CO LTD

Immersion lithography wafer edge bead removal for wafer and scanner defect prevention

ActiveUS8318607B2Reduce particulate pollutionDecorative surface effectsSemiconductor/solid-state device manufacturingMonomethyl etherSolvent

A method of performing a single step / single solvent edge bead removal (EBR) process on a photolithography layer stack including a photoresist layer and a top coat layer using propylene glycol monomethyl ether acetate (PGMEA) or a mixture of PGMEA and gamma-butyrolactone (GBL) is disclosed. The single step / single solvent EBR process is compatible with organic and inorganic BARC layers.

Owner:TEXAS INSTR INC

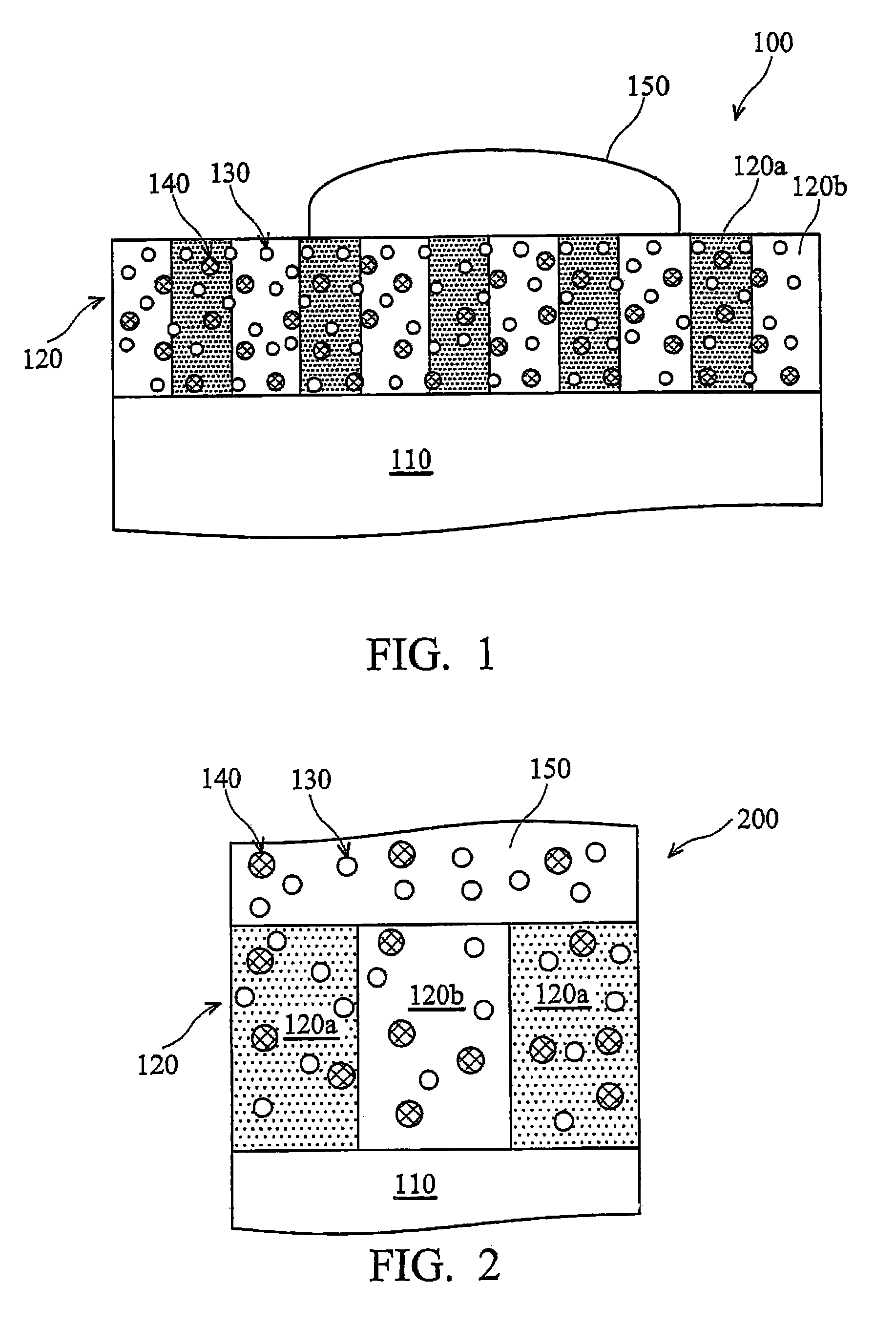

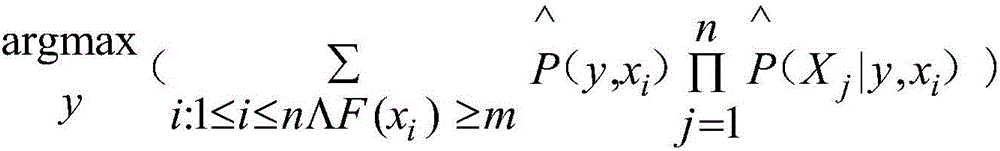

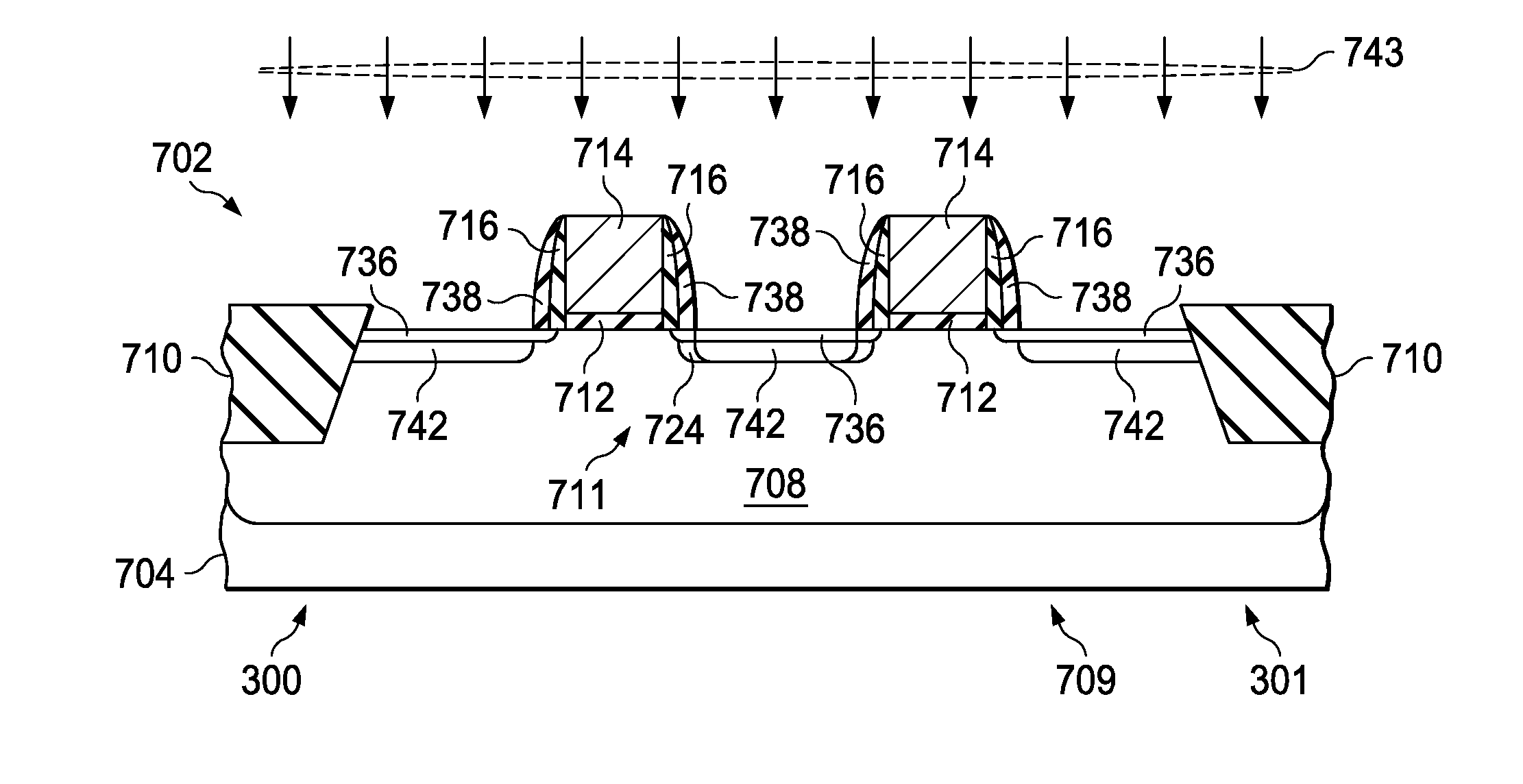

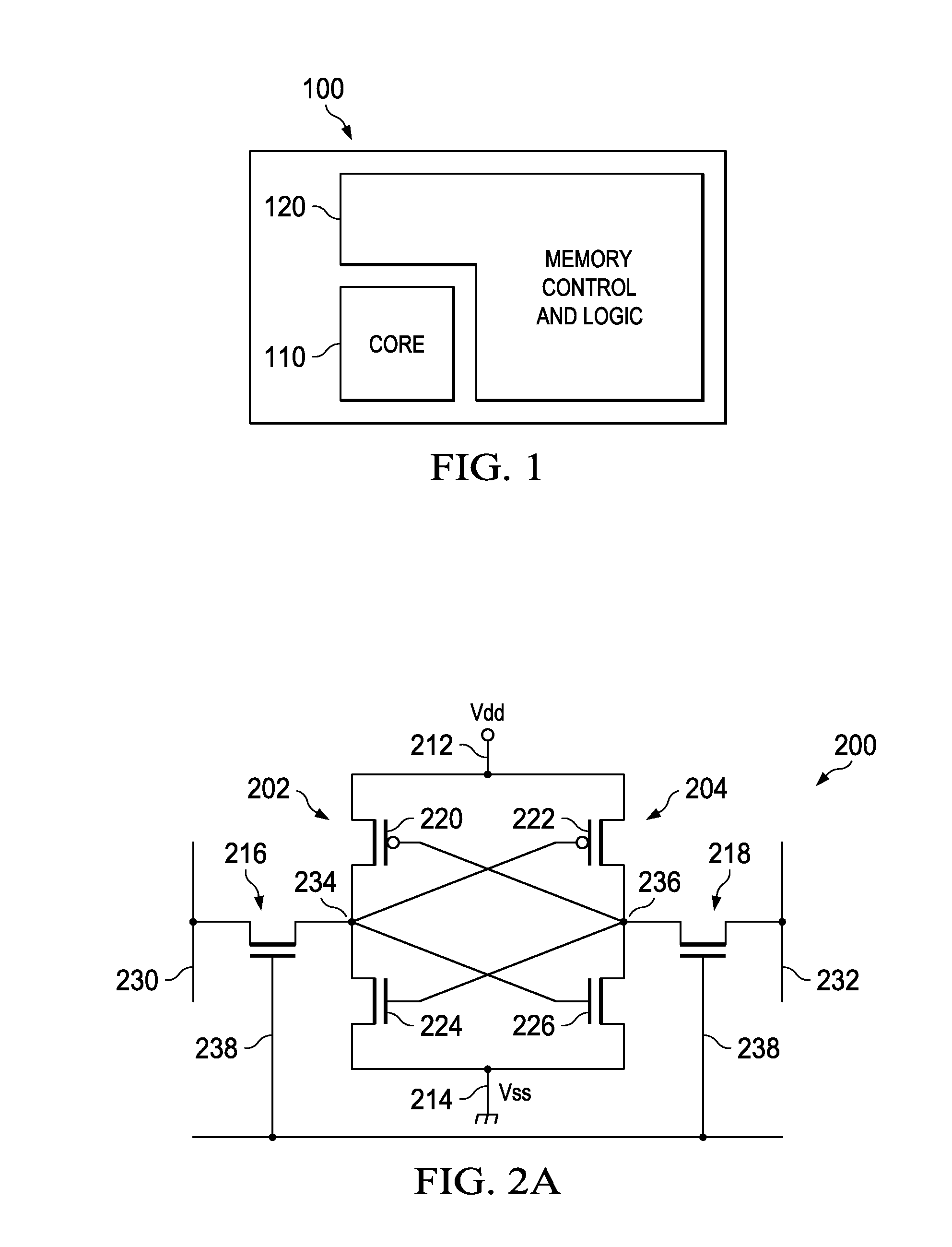

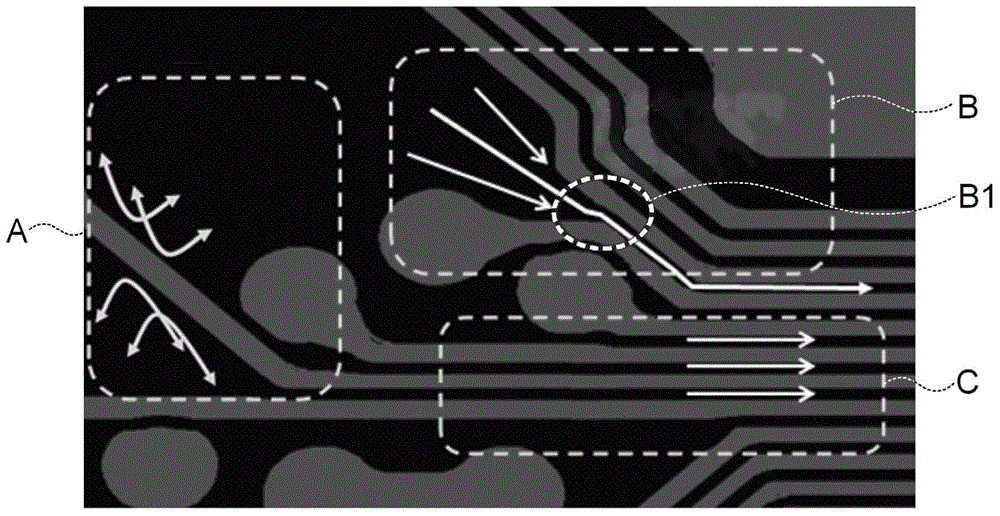

Defect prevention on SRAM cells that incorporate selective epitaxial regions

ActiveUS8384138B2Improved mobility and drive currentReduce defectsTransistorSolid-state devicesEngineeringSram cell

An SRAM device and method of forming MOS transistors of the device having reduced defects associated with selective epitaxial growth in moat tip regions is discussed. The SRAM device comprises a core region and a logic region, logic transistors within the logic region of the SRAM, and selective epitaxial regions grown on both source and drain regions; and memory cell transistors within the core region of the SRAM, and having the selective epitaxial regions grown on only one of the source and drain regions. One method of forming the MOS transistors of the SRAM cell comprises forming a gate structure over a first conductivity type substrate to define a channel therein, masking one of the source and drain regions in the core region, forming a recess in the substrate of the unmasked side of the channel, epitaxially growing SiGe in the recess, removing the mask, and forming the source and drain extension regions in source / drain regions.

Owner:TEXAS INSTR INC

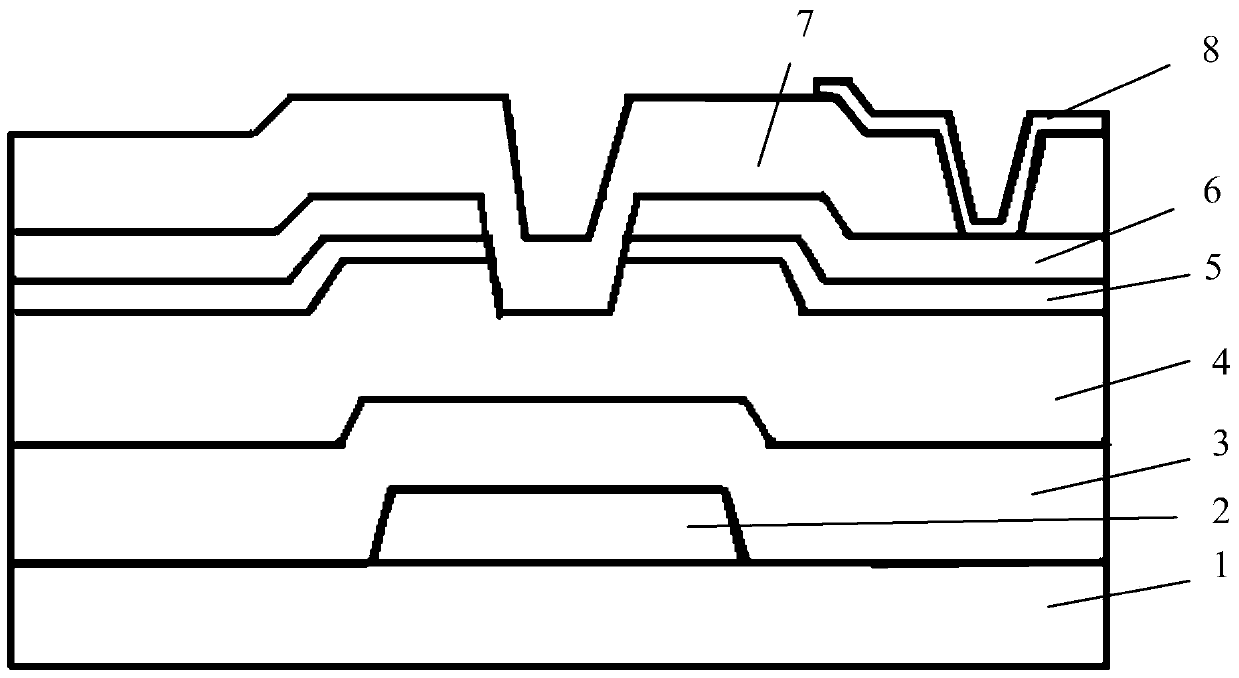

Thin film transistor, manufacturing method thereof, array substrate and display device

ActiveCN104966740AReduce driftImprove stabilityTransistorSolid-state devicesInsulation layerCharge carrier

The invention discloses a thin film transistor, a manufacturing method thereof, an array substrate and a display device, which belongs to the technical field of thin film transistors. The thin film transistor comprises a substrate, a gate electrode, a gate insulation layer and an active layer. The gate insulation layer comprises an inner defect prevention layer and an interface defect prevention layer, wherein the inner defect prevention layer is located between the interface defect prevention layer and the gate electrode; the inner defect prevention layer is used for reducing inner defects of the gate insulation layer; and the interface defect prevention layer is used for reducing defects of a contact interface between the gate insulation layer and the active layer. Through arranging the gate insulation layer in the above mode, the defect number of the inner part of the gate insulation layer and the defect number of the contact surface between the gate insulation layer and the active layer can be reduced, accumulation of carriers (positrons) inside the gate insulation layer and on the contact surface between the gate insulation layer and the active layer can thus be reduced, thin film transistor threshold voltage offset phenomena can be effectively reduced, and the defect rate of the thin film transistors is reduced.

Owner:BOE TECH GRP CO LTD

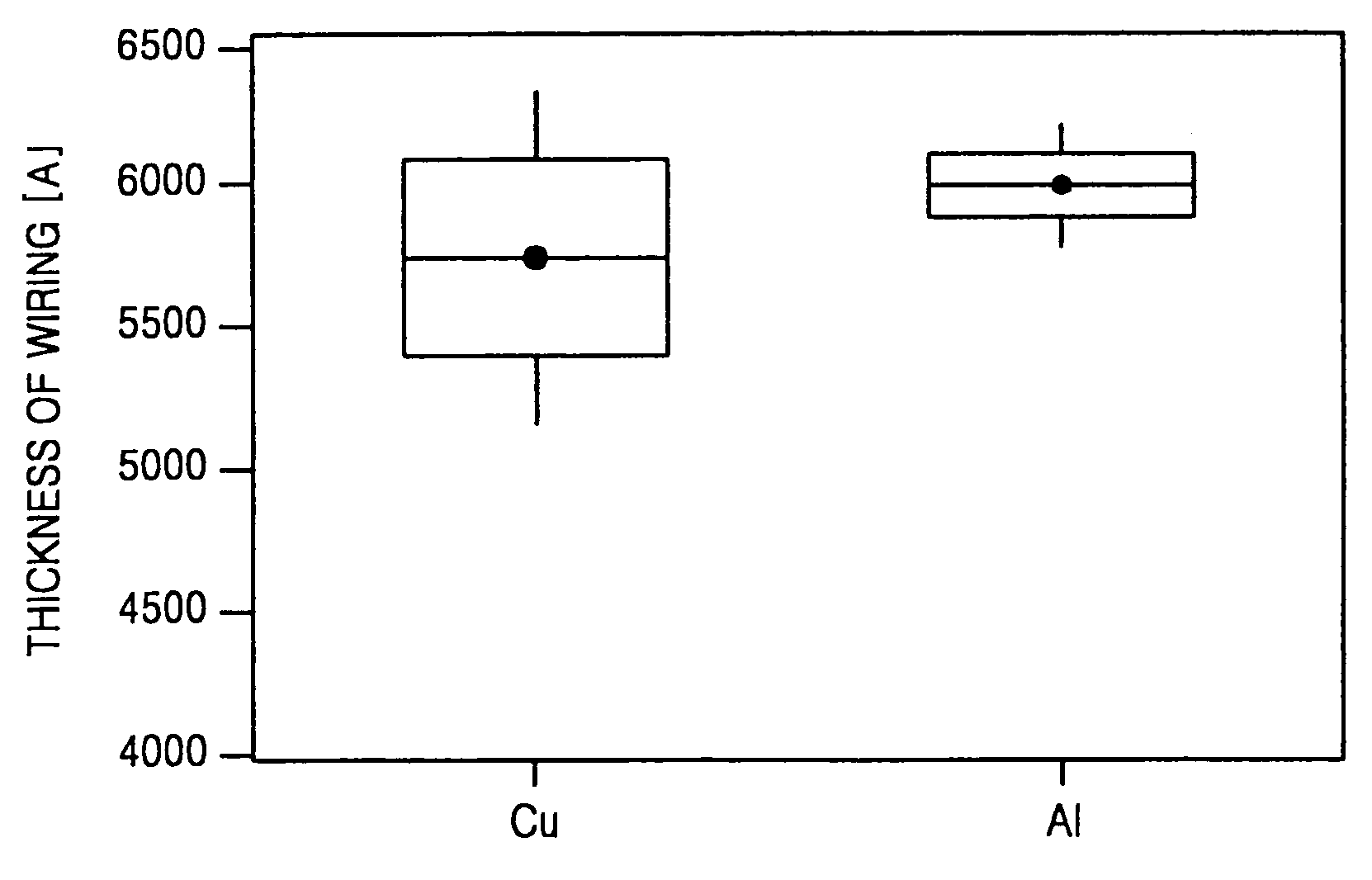

CMP slurry for forming aluminum film, CMP method using the slurry, and method for forming aluminum wiring using the CMP method

ActiveUS7247256B2Removal rateReduce removal rateDecorative surface effectsSemiconductor/solid-state device manufacturingPh controlCompound (substance)

Owner:SAMSUNG ELECTRONICS CO LTD

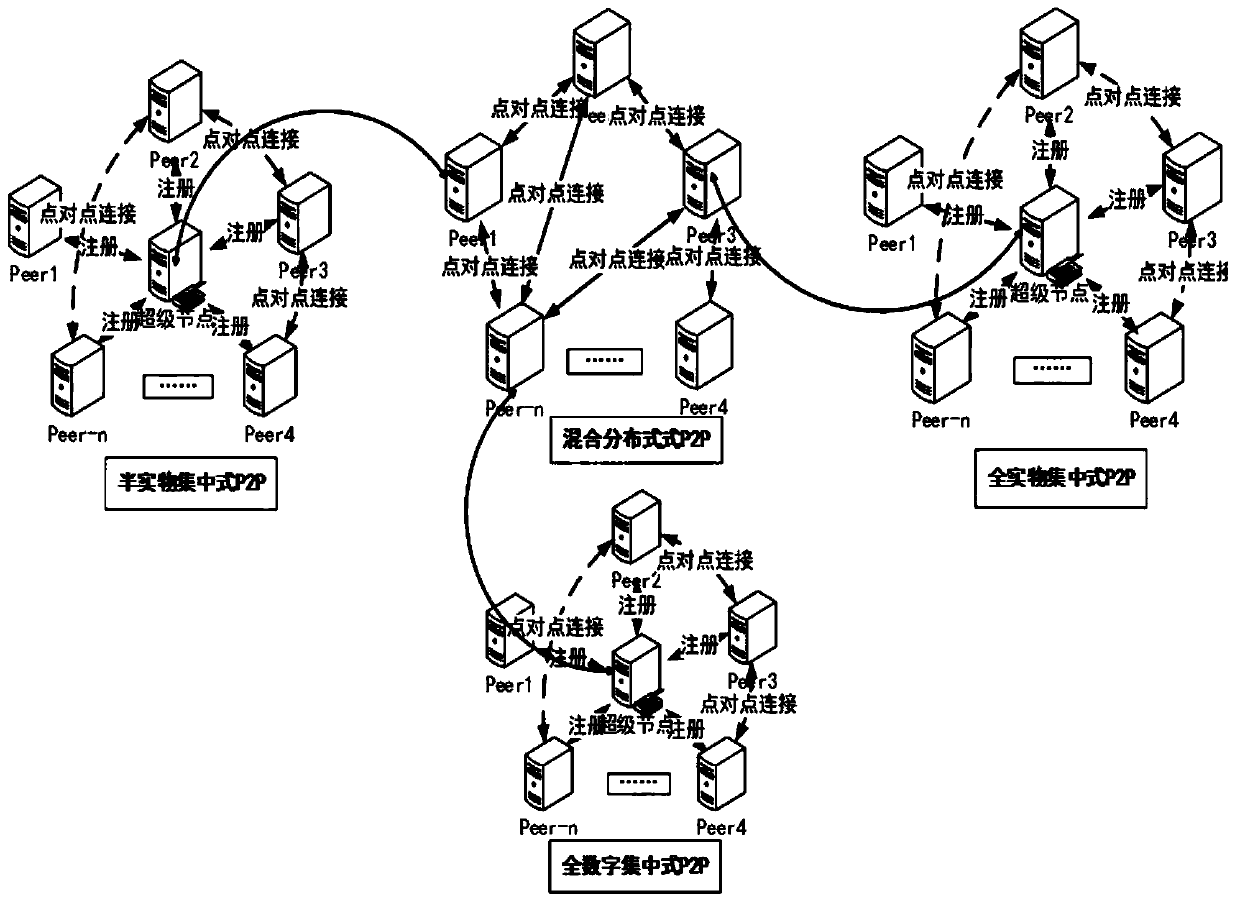

Multi-source heterogeneous embedded software co-simulation test method

ActiveCN110569615AMake sure to advance correctlyTroubleshooting Time Consistency IssuesSpecial data processing applicationsProblem of timeSlide window

The invention discloses a multi-source heterogeneous embedded software co-simulation test method. The method comprises a hybrid P2P-based co-simulation test method, a sliding window-based clock synchronization method and a time coefficient matrix-based dynamic time advancing method. The hybrid P2P-based collaborative simulation test method adopted by the invention can realize hybrid collaborativesimulation of all-physical, semi-physical, all-digital and other nodes in multi-source heterogeneous embedded software, so as to completely simulate a software application scene as soon as possible todiscover potential defects for defect prevention. According to the clock synchronization method based on the sliding window, efficient synchronization of node clocks can be achieved in the collaborative simulation execution process, and the problem of time consistency is solved. According to the dynamic time advancing method based on the time coefficient matrix, correct advancing of a simulationtime sequence is ensured.

Owner:COMP APPL RES INST CHINA ACAD OF ENG PHYSICS

Water Mark Defect Prevention for Immersion Lithography

ActiveUS20110183273A1Photomechanical exposure apparatusMicrolithography exposure apparatusReduced mobilityPolymer

A photoresist material having a polymer that turns soluble to a base solution in response to reaction with acid. The material includes a photo-acid generator (PAG) that decomposes to form acid in response to radiation energy and a quencher capable of neutralizing acid and having a reduced mobility. The photoresist material can thereby prevent water mark defects from immersion lithography.

Owner:TAIWAN SEMICON MFG CO LTD

Pharmaceutical combination for preventing birth-defect and improving memory

InactiveCN101278984ASufficient sourceLow costHeavy metal active ingredientsNervous disorderDefect preventionAdverse effect

A medicine composition used for preventing and treating birth defect and improving memory consists of atractylodes, radix polygoni multiflori preparata, compound Vitamin B and trace elements, including zinc, selenium, ferrite, chromium, copper, molybdenum, iodine and manganese. The medicine composition is applicable to pregestational women, pregnant women and lactating mothers and has good effect on birth defect prevention and memory improvement. In addition, the medicine composition has the function of health care and benefit and does not cause any adverse effect after long term administration.

Owner:BEIJING GUANWUZHOU BIOSCIENCE INSTITUTION (CN)

Medicine composition for preventing birth defect and improving memory

InactiveCN101288717ASufficient sourceLow costHeavy metal active ingredientsNervous disorderDefect preventionAtractylodes ovata

A medicine composite is used for preventing birth defect and improving memory, which comprises atractylodes ovata, radix rehmanniae preparata, Vitamin B compound, Vitamin E and trace elements, including zinc, selenium, ferrum, chromium, copper, molybdenum and manganese. The medicine composite is applicable for pregestational women, pregnant women and wet nurse and has good effect on birth defect prevention and memory improvement. In addition, the medicine composite has the functions of health care and benefit without causing any toxicity or side effect after being used for a long term.

Owner:BEIJING GUANWUZHOU BIOSCIENCE INSTITUTION (CN)

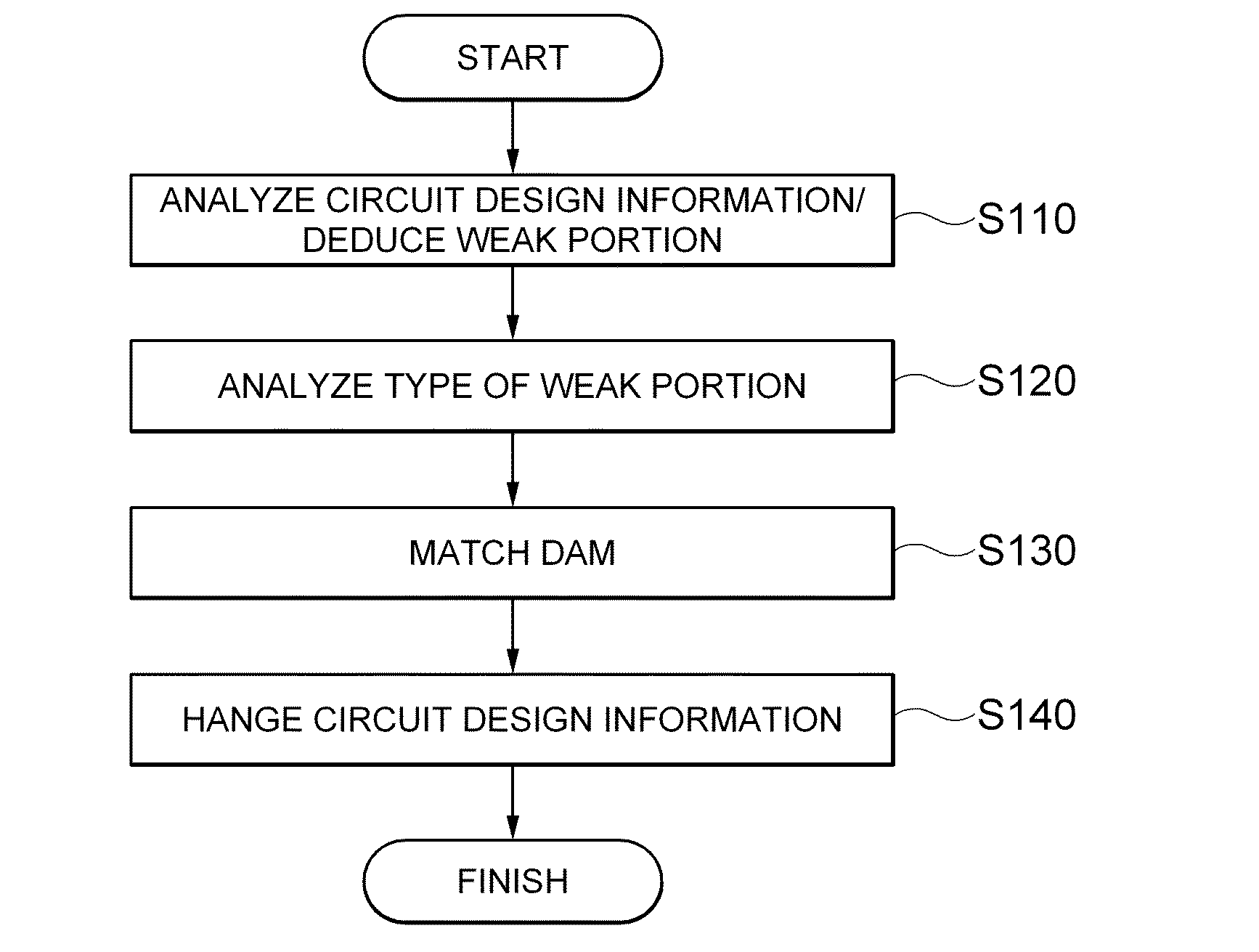

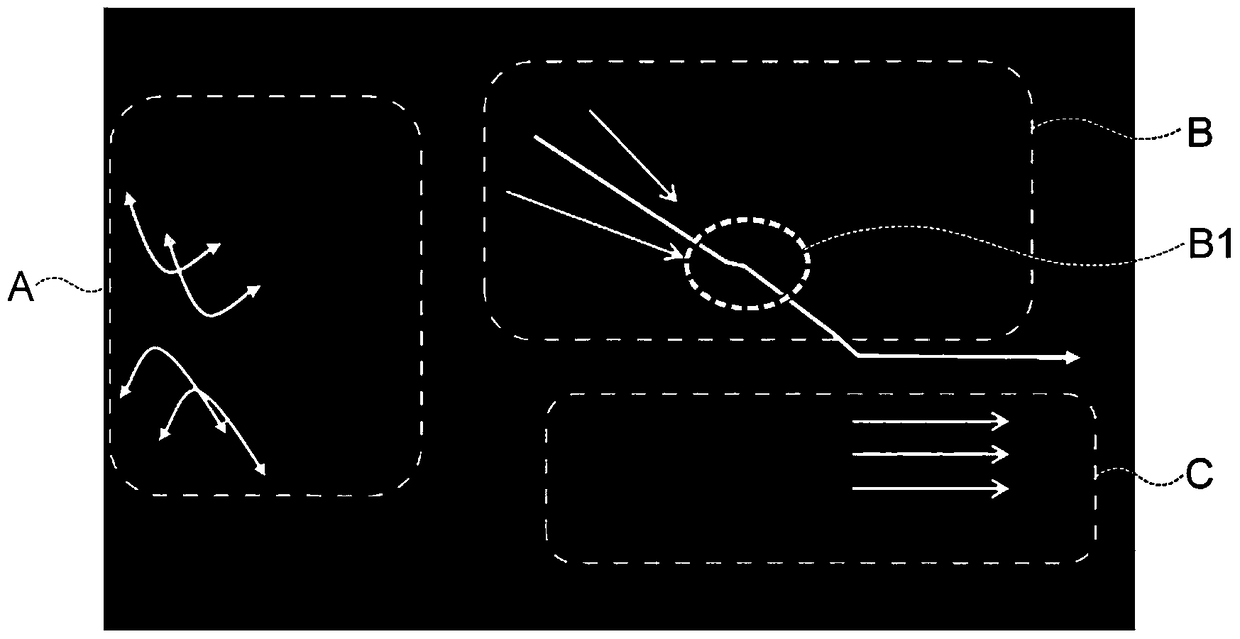

Circuit width thinning defect prevention device and method of preventing circuit width thinning defect

InactiveUS20140189626A1Avoid widthMaterial analysis by optical meansUsing optical meansEtchingDesign information

The present invention relates to a circuit width thinning defect prevention device and a method of preventing a circuit width thinning defect, and can prevent a circuit width thinning defect, that is, a reduction in circuit width due to excessive etching on a specific portion by including a storage means for storing dam design information classified according to the type of a weak portion; an analysis means for analyzing first design information to deduce the type and position of the weak portion; a matching means for extracting the dam design information corresponding to the type of the weak portion from the dam design information stored in the storage means; and a change means for changing the first design information to add a dam according to the dam design information extracted by the matching means to the position of the weak portion deduced by the analysis means.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Method and device for building electric power information software defect prevention knowledge database

PendingCN106708735AEnsure comprehensivenessGuaranteed to be scientificSoftware testing/debuggingData miningDatabase

The invention provides a method and device for building an electric power information software defect prevention knowledge database. The method includes: respectively acquiring metric unit information and a defect mode; respectively using a machine learning reasoning mode and a production system reasoning mode to perform reasoning analysis on the acquired metric unit information and the defect mode. The method has the advantages that the input of the metric unit information and the defect mode which are different in features is considered while the corresponding reasoning modes are used, and accordingly the comprehensiveness, scientificity, pertinence and applicability of the building method of the electric power information software defect prevention knowledge database are fully guaranteed.

Owner:CHINA ELECTRIC POWER RES INST +1

Medicine composition for preventing birth defect and improving memory

InactiveCN101288730ASufficient sourceLow costHeavy metal active ingredientsNervous disorderObstetricsSide effect

A medicine composition is used for preventing birth defect and improving memory, which comprises atractylis ovata, Chinese yam, Vitamin B compound, Vitamin E and trace elements, including zinc, selenium, ferrum, chromium, copper, molybdenum, iodine and manganese. The medicine composition is applicable for pregestational women, pregnant women and wet nurse and has good effect on birth defect prevention and memory improvement. In addition, the medicine composition has the function of health care and benefit without causing any toxicity or side effects after being used for a long term.

Owner:BEIJING GUANWUZHOU BIOSCIENCE INSTITUTION (CN)

Circuit Width Thinning Defect Prevention Device and Method

ActiveCN103917051BPrevent width narrowing defectPrevent Thinning DefectsMaterial analysis by optical meansUsing optical meansEtchingDesign information

The present invention relates to a circuit width thinning defect prevention device and a method of preventing a circuit width thinning defect, and can prevent a circuit width thinning defect, that is, a reduction in circuit width due to excessive etching on a specific portion by including a storage means for storing dam design information classified according to the type of a weak portion; an analysis means for analyzing first design information to deduce the type and position of the weak portion; a matching means for extracting the dam design information corresponding to the type of the weak portion from the dam design information stored in the storage means; and a change means for changing the first design information to add a dam according to the dam design information extracted by the matching means to the position of the weak portion deduced by the analysis means.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Chrome plating method for spherical crown surface of major diameter spherical crown workpiece

The invention provides a method for plating chromium on a spherical cap surface of a large-diameter spherical cap workpiece. In a step of immersing and positioning, the arrangement mode or structure of an anode strap or an anode plate is changed; in a step of plating chromium, opacified chromium is plated under the conditions that the temperature of the plating solution is 70 to 75 DEG C and the current density is 20 to 25A / decimeter<2>; and then, hard chromium is plated under the conditions that the temperature of the plating solution is 50 to 55 DEG C and the current density is 25 to 30A / decimeter<2>. The polishing processing is carried out on the spherical cap surface of the workpiece, which has the advantages of good evenness of chromium plated coating, defect prevention, high electroplating efficiency, fast speed of cladding deposit, high surface finish of the spherical cap surface after chromium is plated, and subsequent mechanical processing workload reduction.

Owner:LUOYANG SUNRUI SPECIAL EQUIP

Thin film transistor and preparation method thereof, array substrate, display device

ActiveCN104966740BReduce driftImprove stabilityTransistorSolid-state devicesInsulation layerCharge carrier

The invention discloses a thin film transistor, a manufacturing method thereof, an array substrate and a display device, which belongs to the technical field of thin film transistors. The thin film transistor comprises a substrate, a gate electrode, a gate insulation layer and an active layer. The gate insulation layer comprises an inner defect prevention layer and an interface defect prevention layer, wherein the inner defect prevention layer is located between the interface defect prevention layer and the gate electrode; the inner defect prevention layer is used for reducing inner defects of the gate insulation layer; and the interface defect prevention layer is used for reducing defects of a contact interface between the gate insulation layer and the active layer. Through arranging the gate insulation layer in the above mode, the defect number of the inner part of the gate insulation layer and the defect number of the contact surface between the gate insulation layer and the active layer can be reduced, accumulation of carriers (positrons) inside the gate insulation layer and on the contact surface between the gate insulation layer and the active layer can thus be reduced, thin film transistor threshold voltage offset phenomena can be effectively reduced, and the defect rate of the thin film transistors is reduced.

Owner:BOE TECH GRP CO LTD

Health food for preventing and treating articular cartilage defects and use thereof

InactiveCN106256233AFix bug fixesAvoid complicationsSkeletal disorderFood ingredient functionsLicorice rootsSemen

The invention discloses a health food for preventing and treating articular cartilage defects and a use thereof. The health food comprises, by mass, 4-51 parts of brown rice, 0-20 parts of purple sweet potatoes, 5-10 parts of fructus psoraleae, 0-8 parts of achyranthes root, 0-8 parts of bark of eucommia, 5-10 parts of rhizoma drynariae, 1-5 parts of semen cuscutae, 5-10 parts of dry rehmannia root, 1-5 parts of white peony root, 1-5 parts of radix astragali, 5-15 parts of radix angelicae sinensis, 5-10 parts of dried orange peel, 0-5 parts of peach seeds and 1-5 parts of licorice root. An experiment proves that the health food has a function of obvious restoration of articular cartilage defects, can be used for preventing and treating articular cartilage defects, can protect joints and improving physique through long-term eating and provides the optimal approach for articular cartilage defect prevention and treatment.

Owner:济南敬德昌生物科技有限公司

Drift fault recognition method of hot-rolling strip steel based on sound signals

ActiveCN101829689BHigh detection and recognition rateEffective judgmentMeasuring devicesMetal rolling arrangementsMel-frequency cepstrumProduction line

Owner:UNIV OF SCI & TECH BEIJING

Defect prevention on SRAM cells that incorporate selective epitaxial regions

ActiveUS20130196479A1Improved mobility and drive currentReduce defectsTransistorSolid-state devicesEngineeringSram cell

An SRAM device and method of forming MOS transistors of the device having reduced defects associated with selective epitaxial growth in moat tip regions is discussed. The SRAM device comprises a core region and a logic region, logic transistors within the logic region of the SRAM, and selective epitaxial regions grown on both source and drain regions; and memory cell transistors within the core region of the SRAM, and having the selective epitaxial regions grown on only one of the source and drain regions. One method of forming the MOS transistors of the SRAM cell comprises forming a gate structure over a first conductivity type substrate to define a channel therein, masking one of the source and drain regions in the core region, forming a recess in the substrate of the unmasked side of the channel, epitaxially growing SiGe in the recess, removing the mask, and forming the source and drain extension regions in source / drain regions.

Owner:TEXAS INSTR INC

Circuit width thinning defect prevention device and method of preventing circuit width thinning defect

ActiveCN103917051APrevent width narrowing defectPrevent Thinning DefectsMaterial analysis by optical meansUsing optical meansEtchingDesign information

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

A control method and application of anti-tower defect of asymmetrical side guide plate of coiler

The invention relates to an anti-tower shaped defect control method for a coiler's asymmetric side guide plate. The method includes: deflecting the transfer rollers of a coiler's transfer roller group, keeping the opening of a driving side guide plate at the level of strip steel width / 2 and the opening of a work side guide plate in the range of strip steel width / 2+60mm-strip steel width / 2+100mm, making a roll table rotate to push the strip steel forward and generate a divergent pushing force simultaneously so as to make the strip steel operate closely to the driving side guide plate, when the strip steel head completely enter the side plates, letting the work side guide plate quickly draw close to the driving side guide plate to realize close, and keeping the driving side guide plate still till the strip steel head is bitten into a subsequent pinch roll group. The method provided by the invention can reduce tower shaped defects of the strip steel, improve coil quality, has no need for recoiling and repair, and saves manpower and material resources. And the method has small investment in equipment hardware transformation, only needs to make angular adjustment on part of the roll table, and other improvements can be achieved by modifying software. Thus, the method is suitable to the field of preventing steel coil tower shaped defects by coilers in various steel production.

Owner:BAOSHAN IRON & STEEL CO LTD

Device for preventing medium around underground pipeline from collapsing

PendingCN109404609APrevent collapseStop lossPipe laying and repairPipe protection against damage/wearWater leakageSolid particle

The invention relates to a device for preventing a medium around an underground pipeline from collapsing, and belongs to the technical field of underground pipeline defect prevention, and diagnosis and treatment. The device mainly comprises a fixing chain, fixing supports, geotechnical cloth, a reverse filter layer and lock catches, wherein the fixing supports are located on the inner side of thefixing chain and are connected with the fixing chain, the reverse filter layer wrapped in the geotechnical cloth is arranged between the fixing supports, and the lock catches are arranged at the two ends of the fixing chain. The device for preventing the medium around the underground pipeline from collapsing is installed on the periphery of the underground pipeline, the geotechnical cloth and thereverse filter layer are arranged on the device, so that when a leakage point occurs in the pipeline, only water is allowed to flow back and forth around the pipeline, and solid particles are prevented from being lost. According to the device, when the leakage point and water leakage of the underground pipeline occur, surrounding soil bodies and other media are guaranteed not to be lost along withflowing of the water, so that the device plays an essential role in protection of the underground pipeline and a road, a bridge and a building above the pipeline.

Owner:CENT RES INST OF BUILDING & CONSTR CO LTD MCC GRP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com