Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

34results about How to "Solve the speed bottleneck" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Data processing method and device

ActiveCN101799750AIncrease profitImplement multiple launchesResource allocationConcurrent instruction executionProduction lineParallel computing

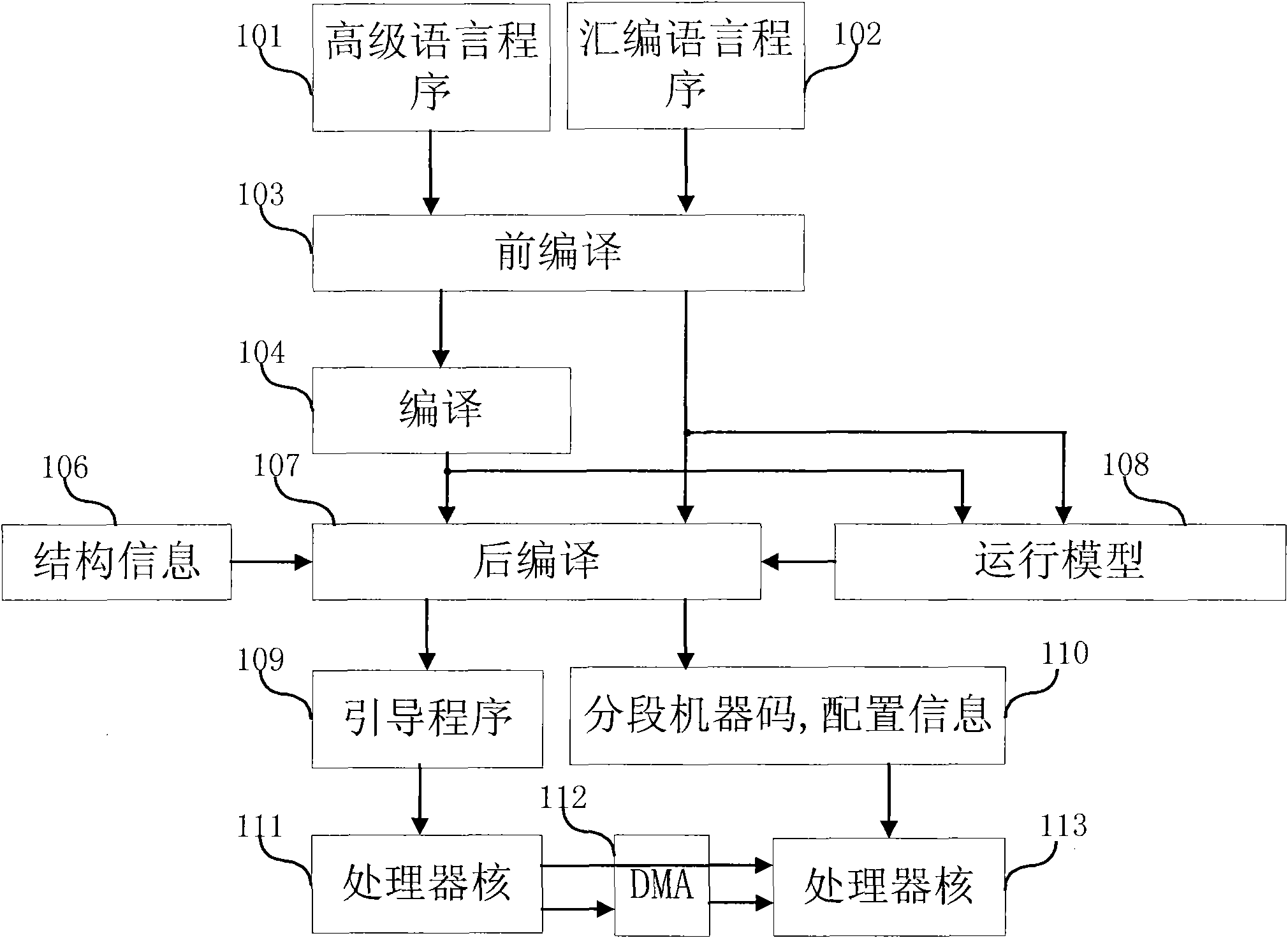

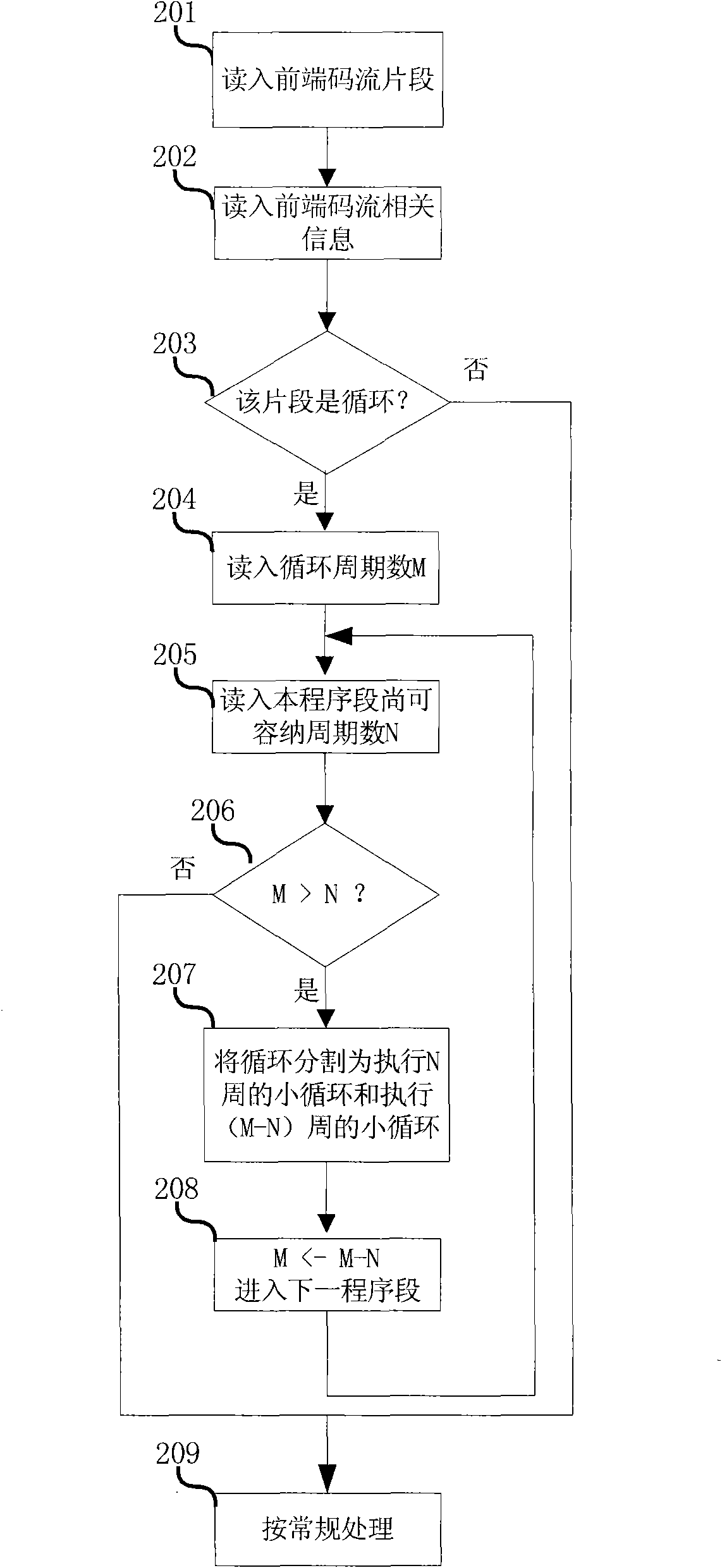

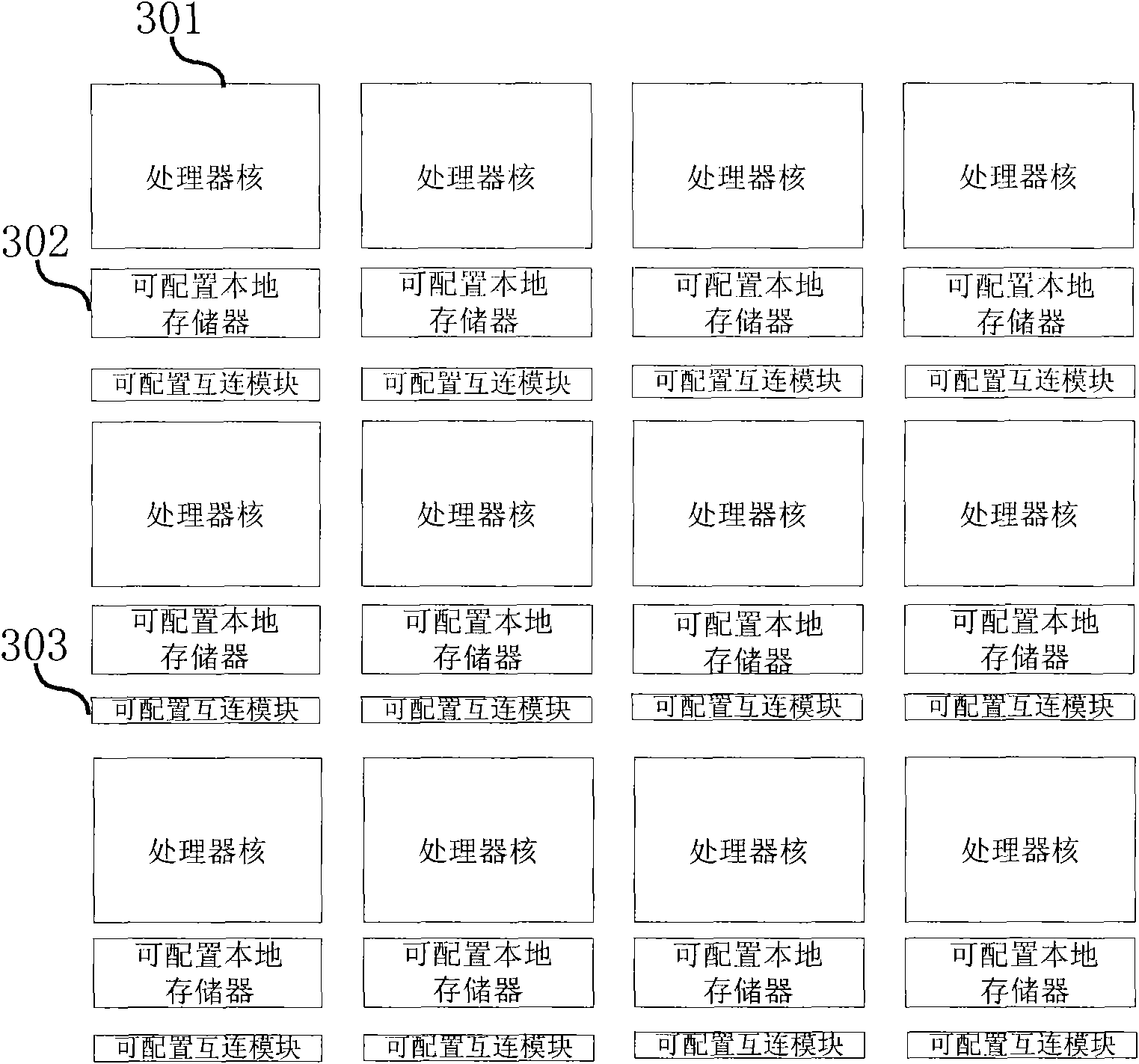

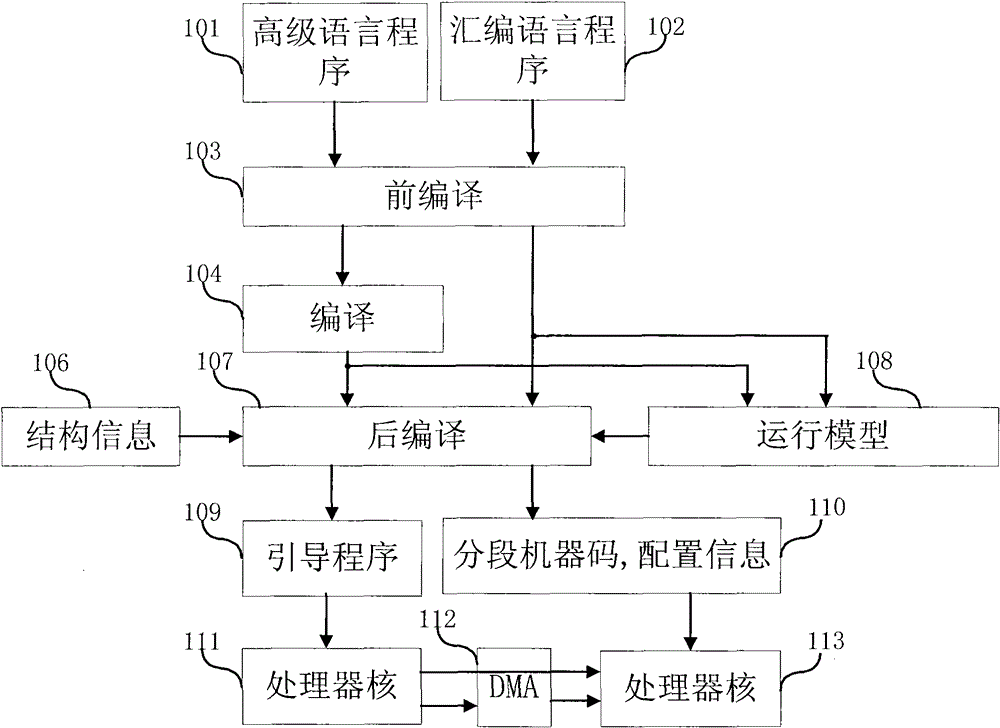

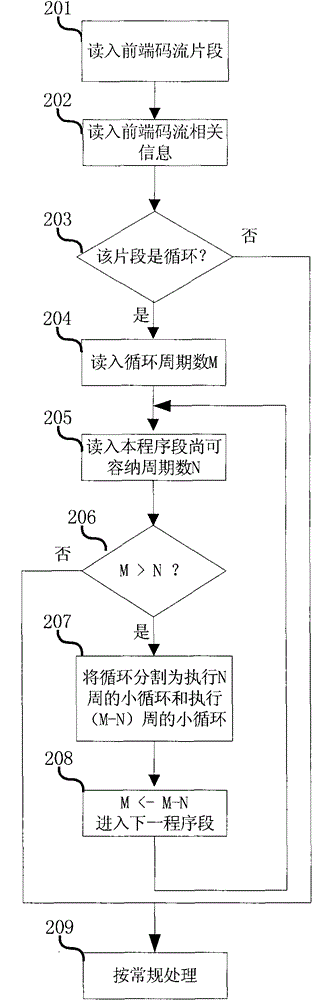

The invention relates to a data processing method and a device. Program codes running on a serially connected multiprocessor nuclear structure are partitioned according to specific rules, so that the serially connected multiprocessor nuclear structure forms a serial multi-emitting and production line layered structure, and the time required for running corresponding code fragments obtained by partitioning on each nucleus is equal as much as possible, thereby realizing the load balance of internuclear workload.

Owner:SHANGHAI XINHAO MICROELECTRONICS

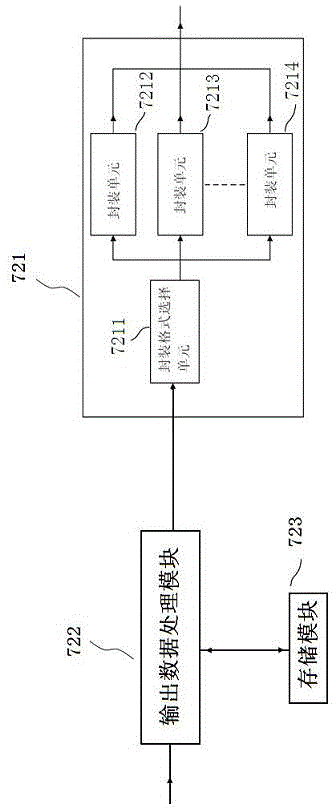

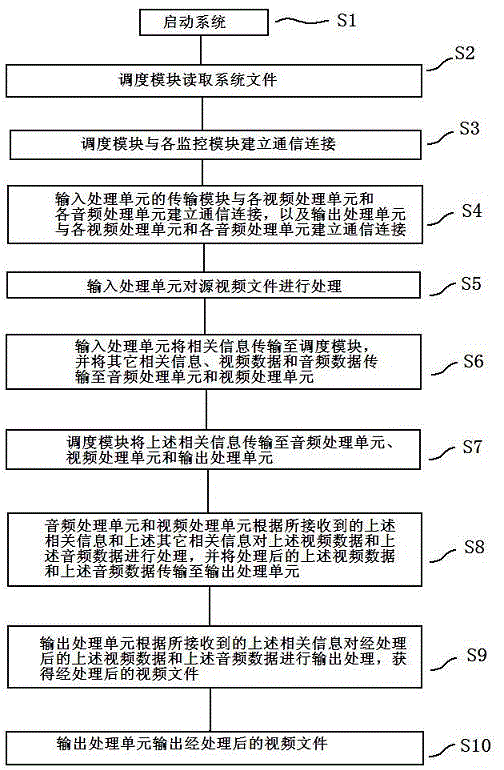

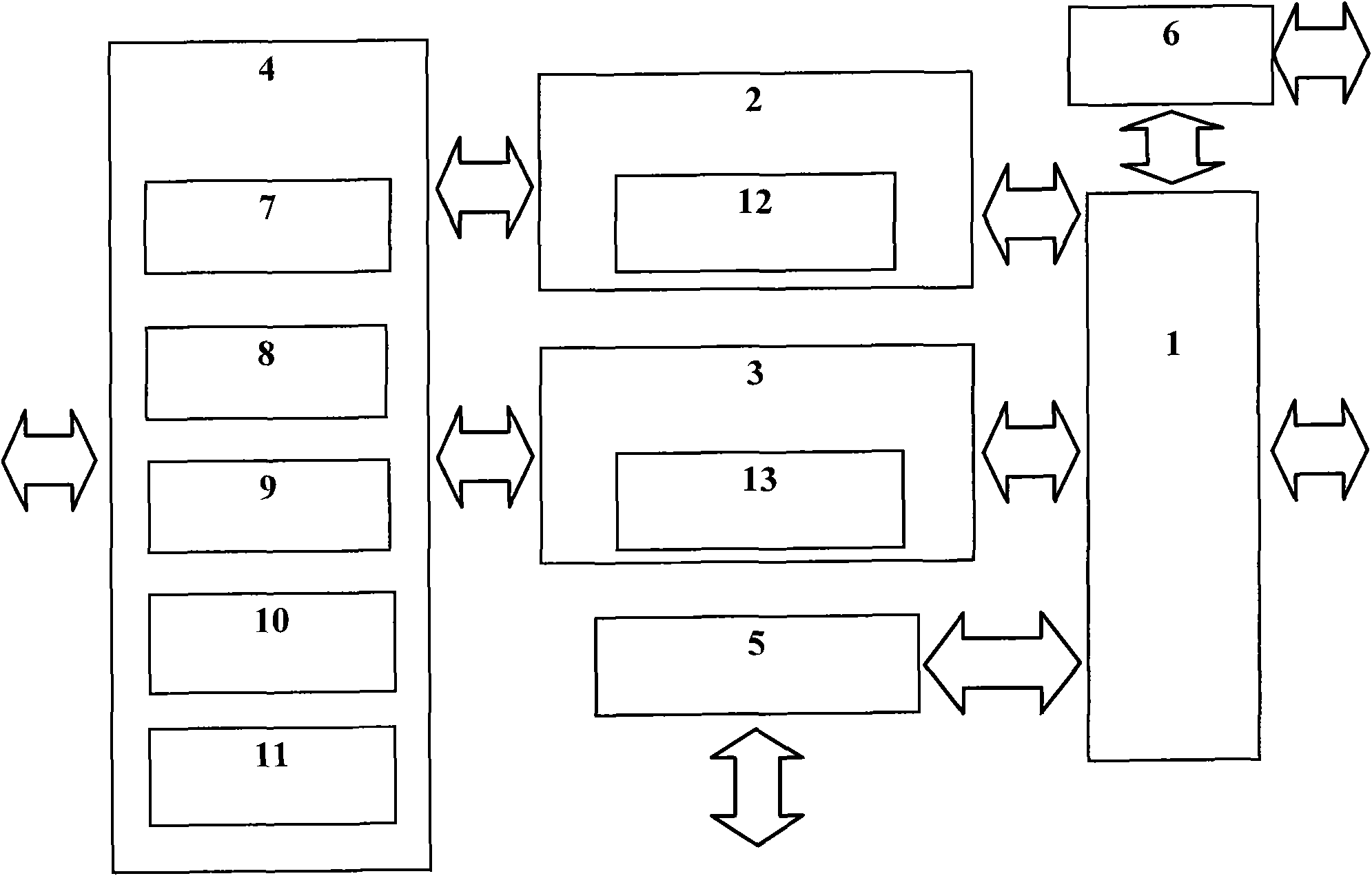

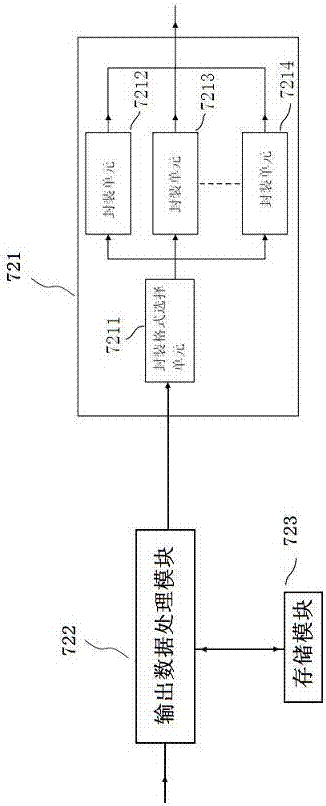

Distributed audio and video processing device and distributed audio and video processing method

InactiveCN103605709ASolve the speed bottleneckShorten the timeAudio data retrievalProgram controlData subjectData processing

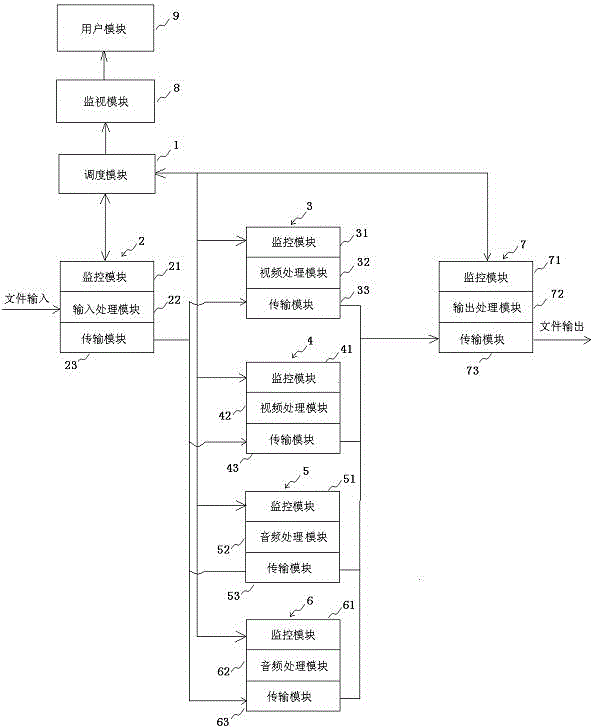

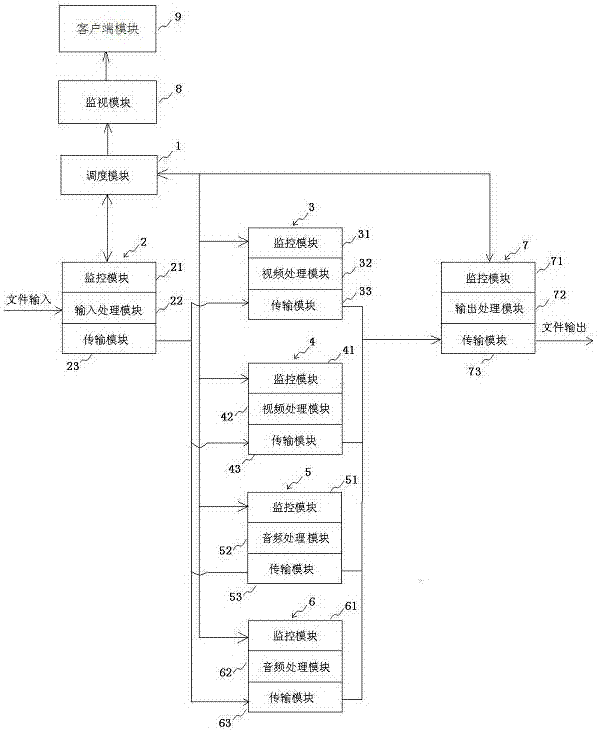

The invention relates to a distributed audio and video file processing system which comprises an input processing unit, multiple video data processing units, multiple audio data processing units, an output processing unit and a dispatching unit. The input processing unit is used for receiving and processing source video files to acquire video data and audio data, and the video data and the audio data are respectively subjected to segmentation process; the video data processing units are respectively used for processing the video data subjected to the segmentation process; the audio data processing units are respectively used for processing the audio data subjected to the segmentation process; the output processing unit is used for processing and outputting the processed video data and audio data; the dispatching unit is used for coordinating operation of the input processing unit, the video data processing units, the audio data processing units and the output processing unit. Meanwhile, the invention further provides a distributed audio and video file processing method and a distributed audio and video file processing device.

Owner:TVMINING BEIJING MEDIA TECH

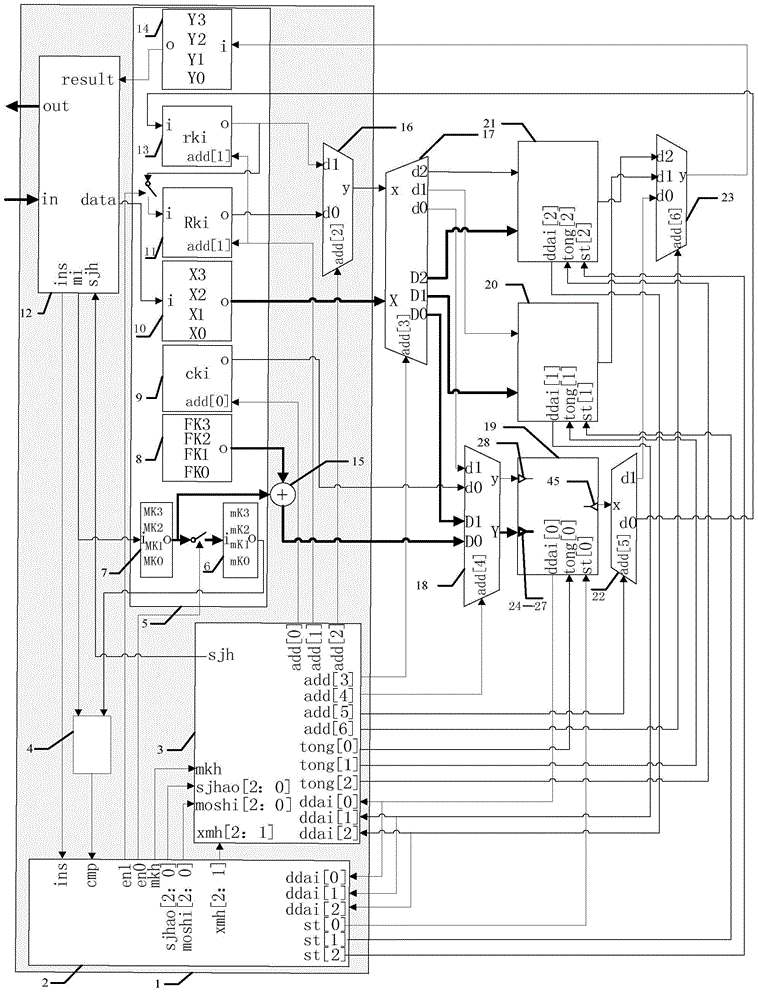

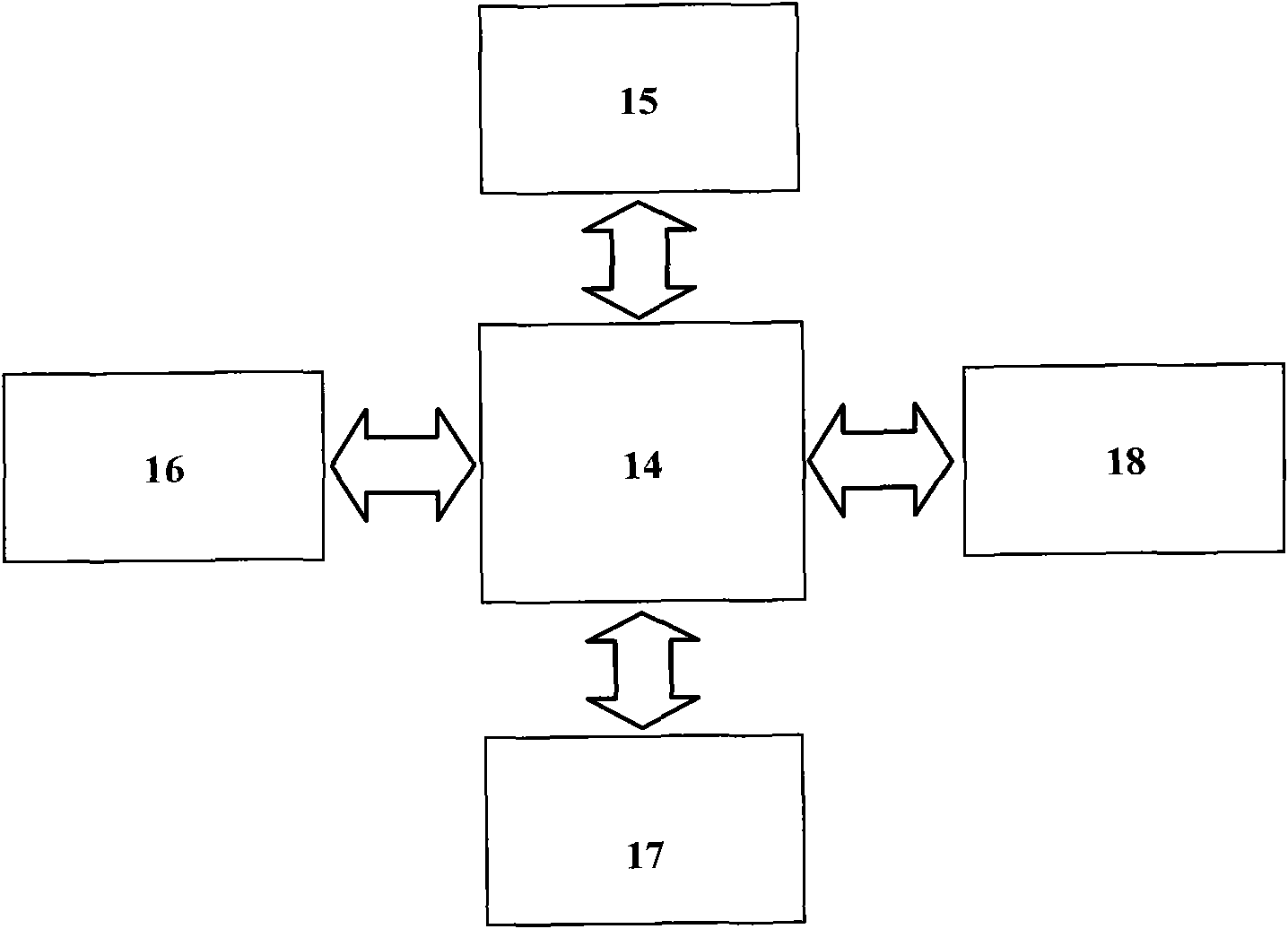

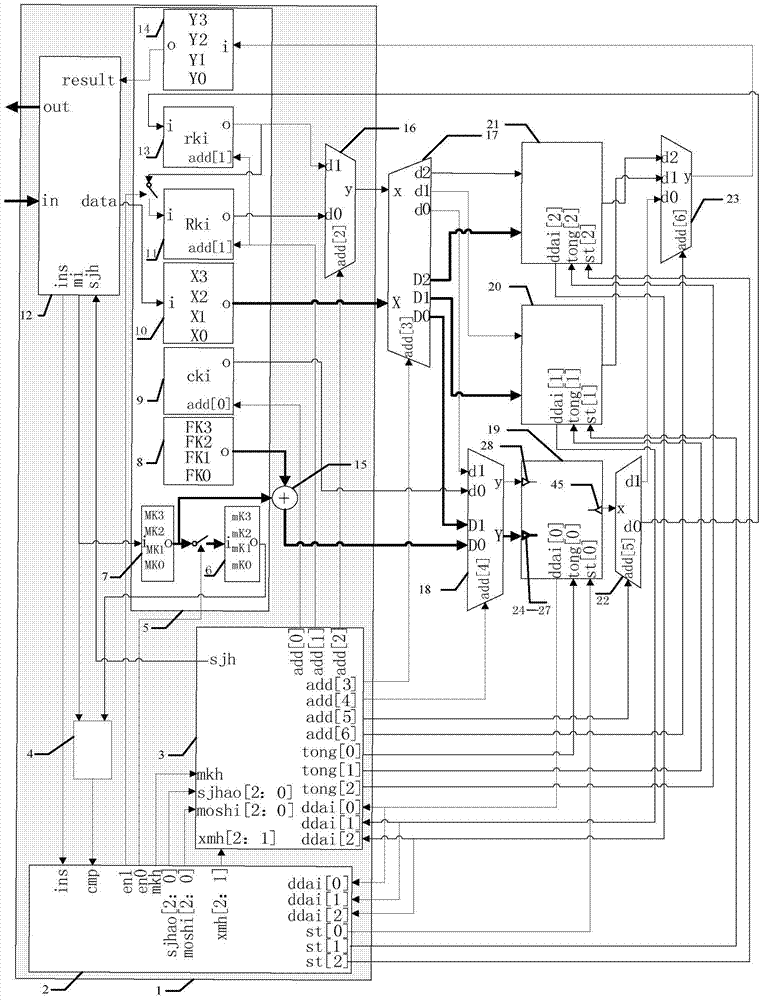

System for realizing SM4 algorithm at super-speed as well as operating method of system

ActiveCN104579636ASolve the speed bottleneckRealize collaborative flowEncryption apparatus with shift registers/memoriesData channelSingle task

The invention relates to a system for realizing SM4 algorithm at a super-speed. The system comprises a control module, a cipher-expanding / ciphering / deciphering module, a ciphering / deciphering module, a ciphering / deciphering module, a data channel subdivider, a cipher-expanding / ciphering and deciphering selector, a round cipher / result channel subdivider and a result selector. The system provided by the invention solves the problem that the speed is low in the existing hardware system as 32 round keys are computed to cipher, and during single task operation, the treatment speed can reach nearly two folds of the existing hardware system. Based on the thought of module reusability, three tasks are synchronously ciphered and deciphered, and the problem that a deciphering module is idle during frequent ciphering tasks in conventional design is solved, so that the utilization ratio and operating speed of the system are effectively improved; during multi-task operation without changing the keys, the processing speed reaches three times that of the single-task operation, the fastest six times that of the existing hardware system.

Owner:BINZHOU POLYTECHNIC

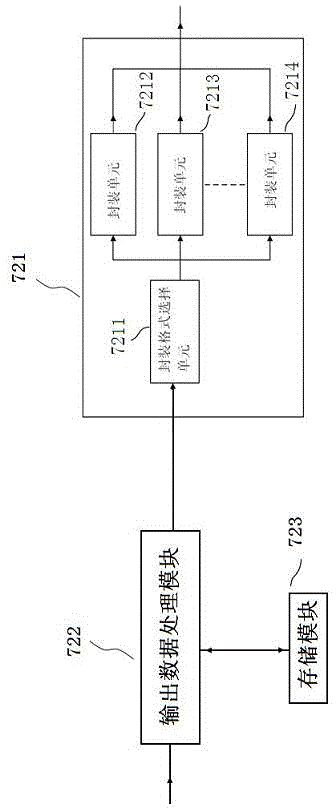

Distributed audio and video processing device and distributed audio and video processing method

InactiveCN103605710ASolve the speed bottleneckShorten the timeAudio data retrievalVideo data retrievalVideo processingData processing

The invention provides a distributed audio and video file processing system which comprises an input processing unit, multiple video data processing units, multiple audio data processing units, an output processing unit and a dispatching unit. The input processing unit is used for receiving and processing source video files to acquire audio and video data, the audio and video data are respectively segmented into audio and video data fragments which are dispatched to corresponding audio and video data processing units for processing according to a certain dispatching rule; the video data processing units are respectively used for processing the segmented video data fragments; the audio data processing units are respectively used for processing the segmented audio data fragments; the output processing unit is used for processing and outputting the processed audio and video data fragments; the dispatching unit is used for coordinating operation of the input processing unit, the audio and video data processing units and the output processing unit. The invention further provides a distributed audio and video file processing method and a distributed audio and video file processing device.

Owner:TVMINING BEIJING MEDIA TECH

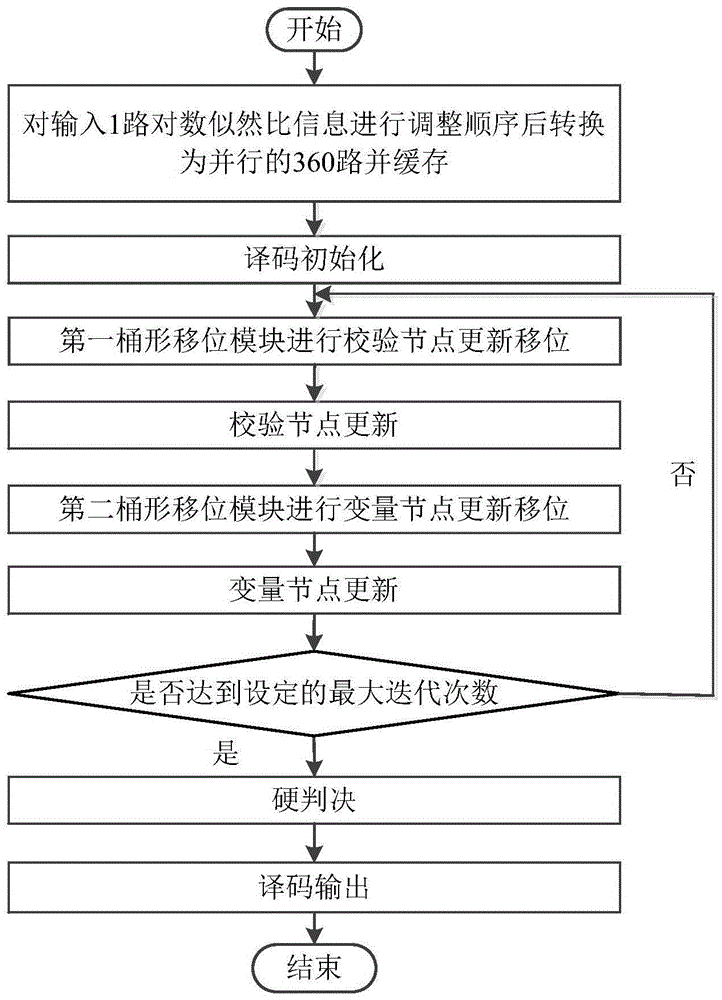

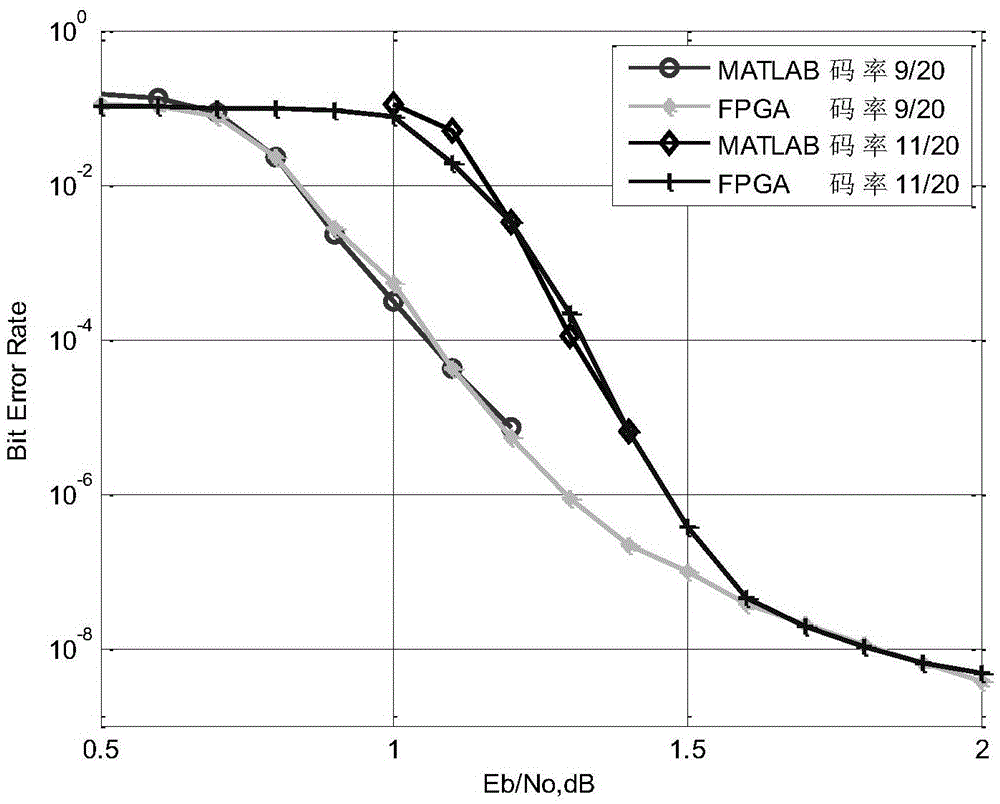

Design method of LDPC (Low-Density Parity-Check Code) decoder compatible with DVB-S2X standard

ActiveCN105680879AImprove throughputShorten the timeError correction/detection using multiple parity bitsCode conversionComputer architectureLow-density parity-check code

The invention discloses a design method of an LDPC (Low-Density Parity-Check Code) decoder compatible with a DVB-S2X standard, which mainly solves the problem of long iteration time of a decoder in an existing system. The design method of the LDPC decoder compatible with the DVB-S2X standard comprises the implementing steps of 1, designing a data buffer, converting input single-path data into 360-path parallel data after the input single-path data are subjected to sequence adjustment, buffering the 360-path parallel data and carrying out decoding initiation for the data; 2, designing a first barrel-shaped shifting module, shifting the 360-path data after variable node updating and carrying out check node updating; 3, designing a second barrel-shaped shifting module, and shifting the 360-path data after the check node updating is finished and then carrying out variable node updating; 4, after the number of decoding iterations reaches to the set maximum number of iterations, calculating hard decision information for the 360-path data; and 5, after the hard decision information is subjected to the decoding decision, outputting the hard decision information in sequence so as to finish the decoding. According to the design method of the LDPC decoder compatible with the DVB-S2X standard, the iteration time of the LDPC decoder is reduced, and the throughput of the decoder is increased by one time.

Owner:XIDIAN UNIV

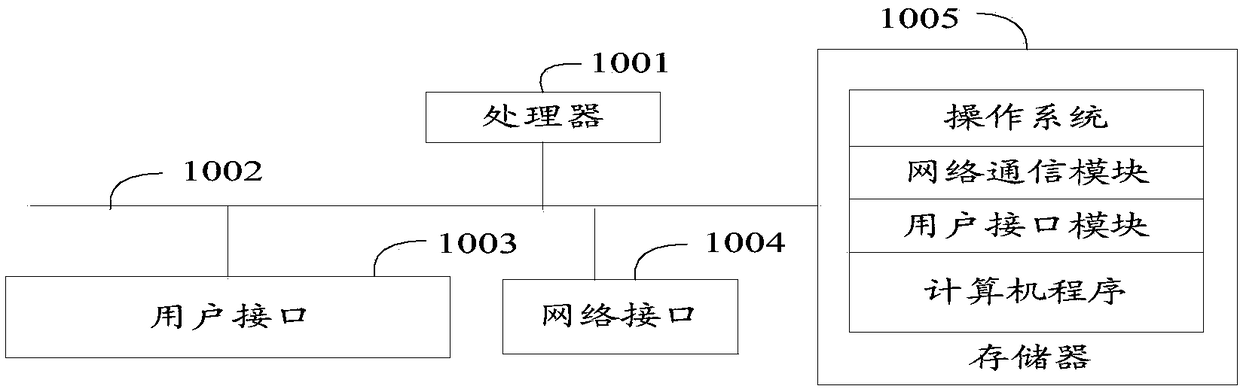

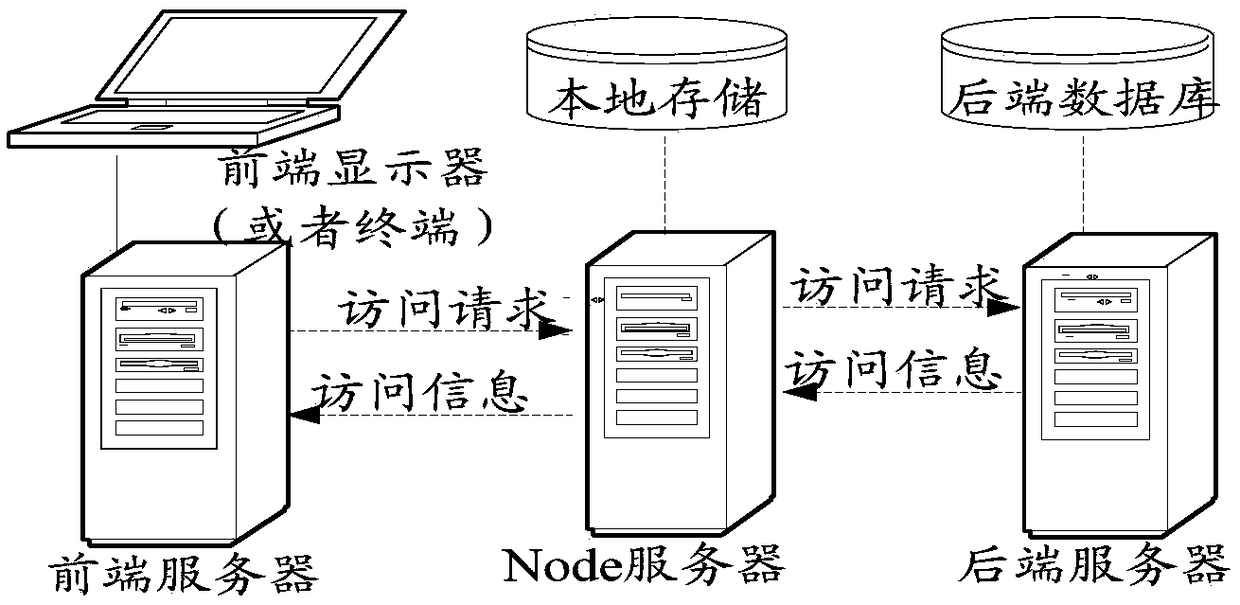

Network data loading method, device and equipment and computer memory medium

ActiveCN108881396ARelieve stressRealize millisecond-level data transmissionTransmissionSpecial data processing applicationsBack end serverNetwork data

The invention discloses a network data loading method. The method is applied to a Node server and comprises the following steps of receiving an access request sent by a front end server, and judging whether the access request is a page access request or not; obtaining a page identity in the page access request if the access request is the page access request; judging whether a preset static page identity set comprises the page identity or not; processing the page access request if the preset static page identity set comprises the page identity, and sending page data to the front end server; sending the page access request to a rear end server if the preset static page identity set does not comprise the page identity; and receiving feedback information sent by the rear end server based on the page access request, and sending the feedback information to the front end server, thereby enabling the front end server to carry out rendering to generate a corresponding network page. The invention also discloses a network data loading device and equipment and a computer memory medium. According to the method, the device, the equipment and the computer memory medium, data processing efficiency is improved.

Owner:PINGAN PUHUI ENTERPRISE MANAGEMENT CO LTD

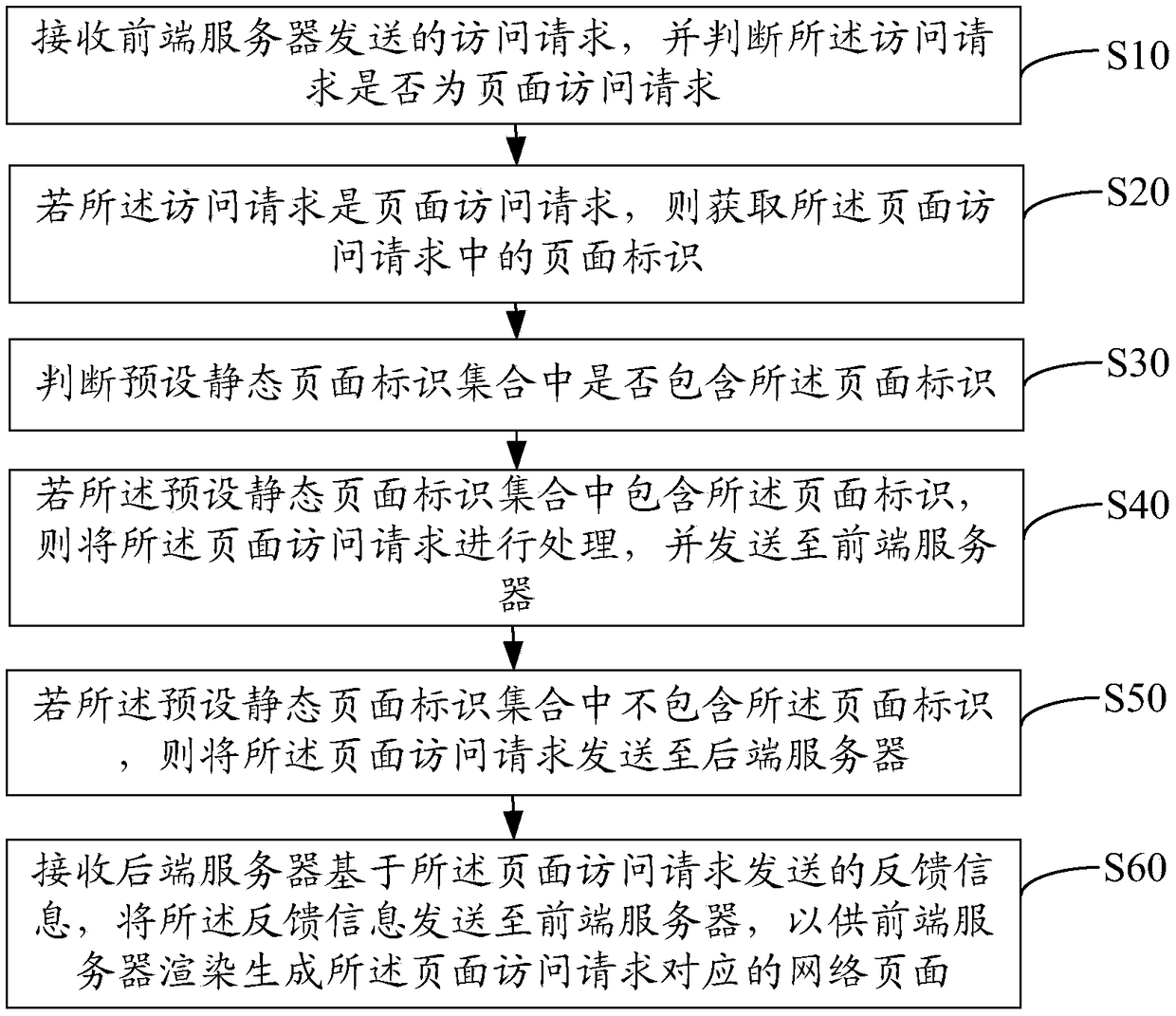

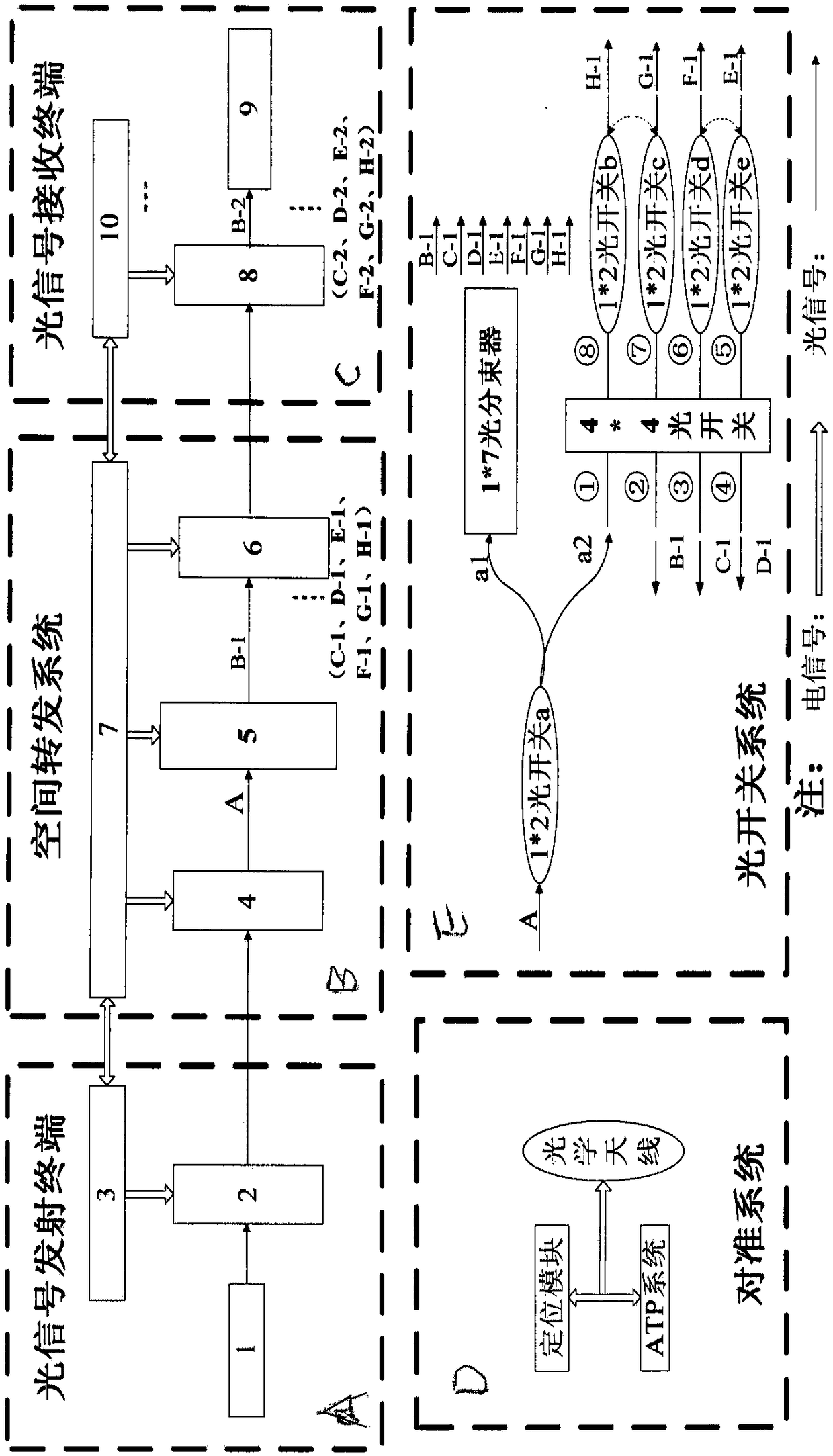

Space laser communication forwarding system based on passive optical switch

ActiveCN105490727ASolve the speed bottleneckTo achieve high-speed transmission requirementsRadio transmissionElectromagnetic transmittersOptical burst switchingBroadcasting

The invention discloses a space laser communication forwarding system based on a passive optical switch. The system consists of a ground optical signal transmitting terminal, a space forwarding system and a ground optical signal receiving terminal. A transmitting end and a receiving end for space optical communications are placed on the ground, and the space forwarding system is carried by an aircraft and only forwards optical signals without processing such as amplification, modulation, demodulation and the like, so that the complexity of a space system is lowered greatly, and the sizes, weights and power consumption of space loads are lowered. Moreover, point-to-point or broadcasting-mode forwarding of the optical signals is realized through an optical switching system. The signals are modulated on the transmitting end, and demodulated on the receiving end, so that ground-space-ground forwarding communications are realized.

Owner:山东中科际联光电集成技术研究院有限公司

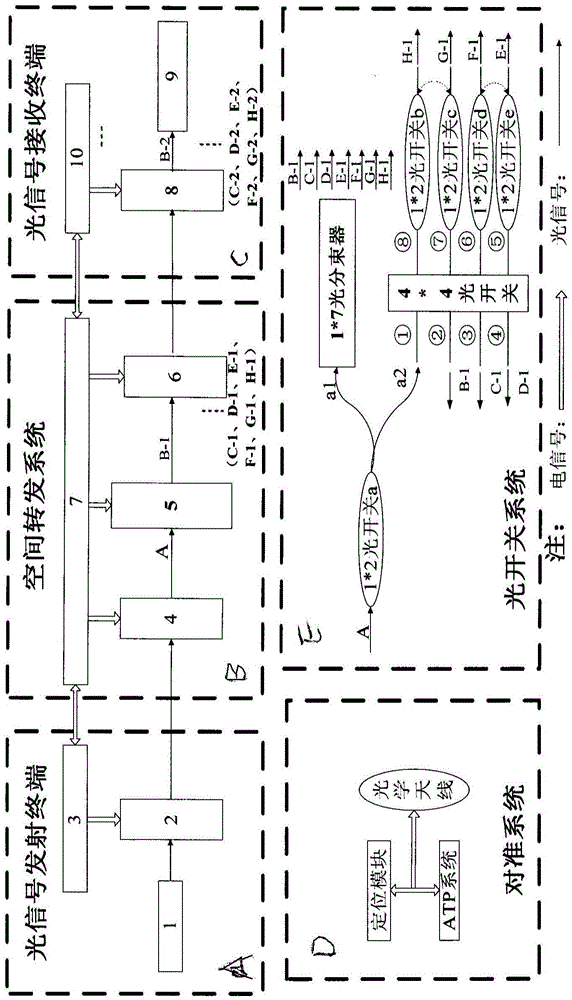

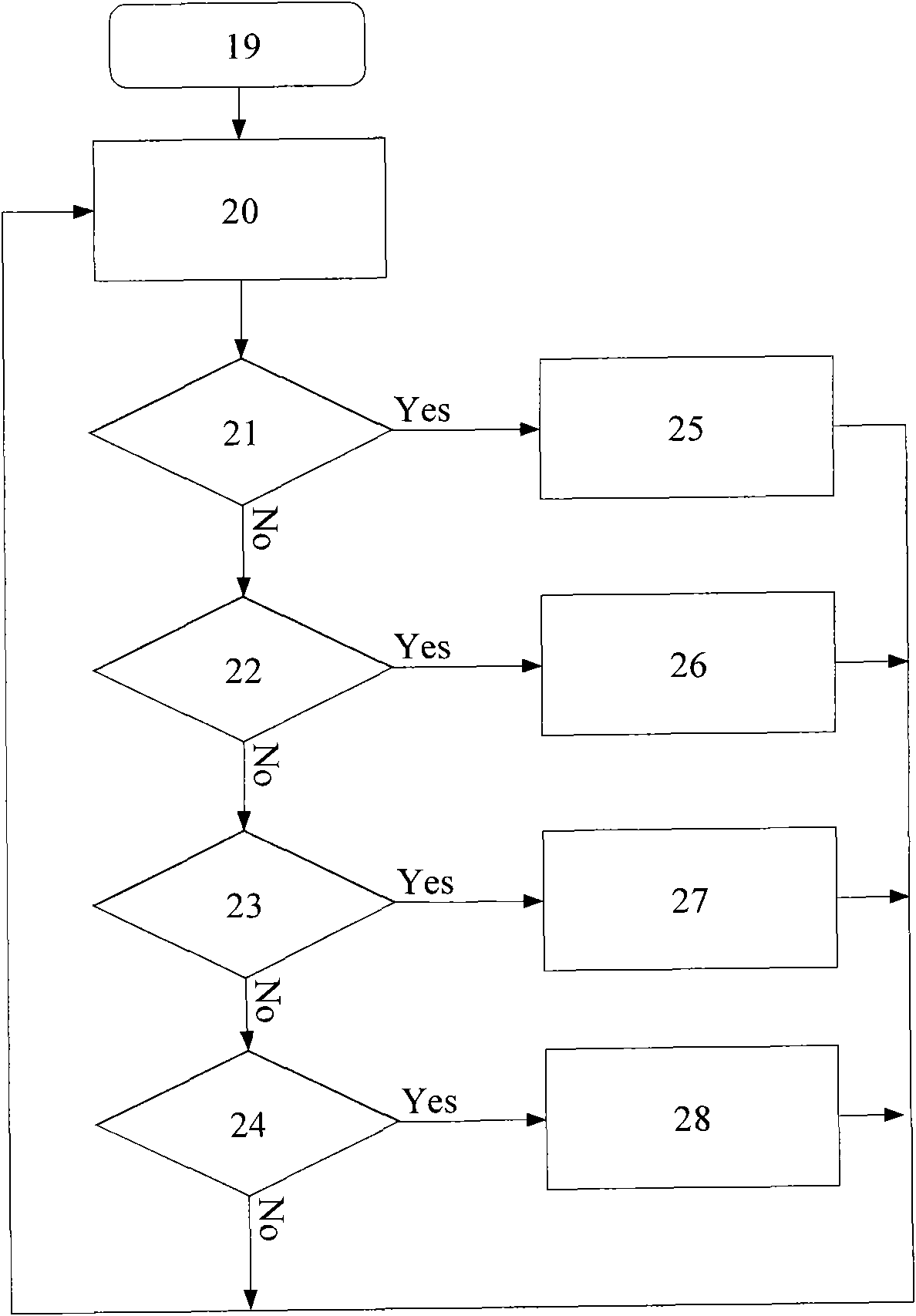

Device for breaking through nonvolatile semiconductor memory member speed bottle-neck

InactiveCN101097562AAvoid complex mechanismsReduce complexityMemory adressing/allocation/relocationACCESS.busBottle neck

A kind of device to breach the speed bottleneck of non-volatile memory is disclosed, which includes buffering device, instruction bus and the access bus of non-volatile memory; the buffering device is mounted between the CPU the non-volatile memory, the buffering device and microprocessor CPU are connected by instruction bus, the buffering device and the non-volatile memory are connected by the access bus of non-volatile memory to expand the bit width of access bus of non-volatile memory connected with buffering device; the instruction bus includes state bus, information bus of instruction address and instruction code bus; the access bus of non-volatile memory includes address bus of non-volatile memory and data bus of non-volatile memory; the buffering device includes buffering controller and buffering unit, and the buffering unit can be controlled by buffering controller via control bus.

Owner:NATIONZ TECH INC

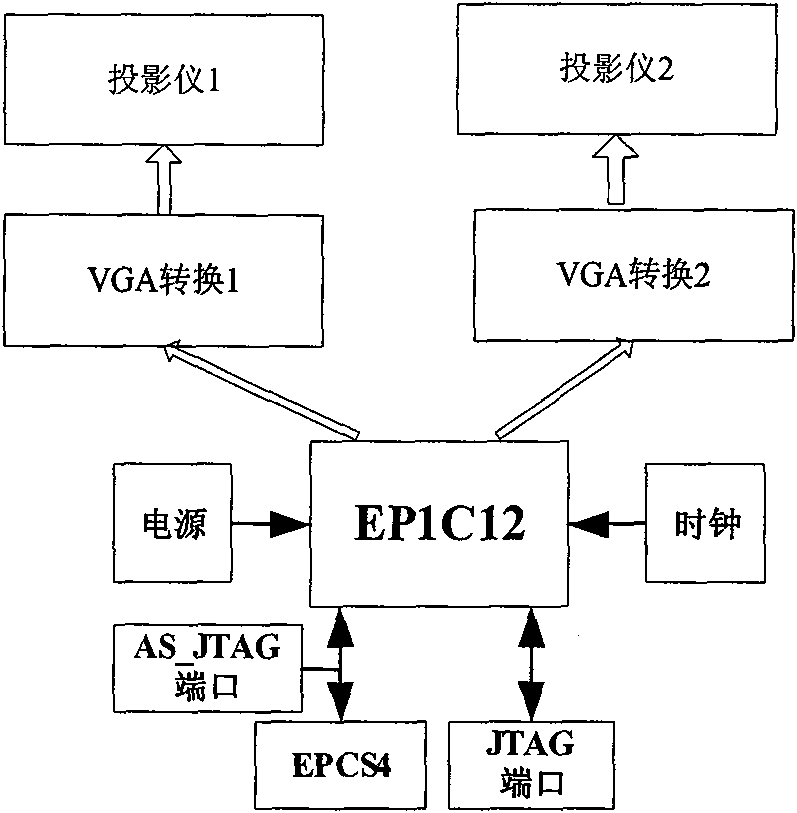

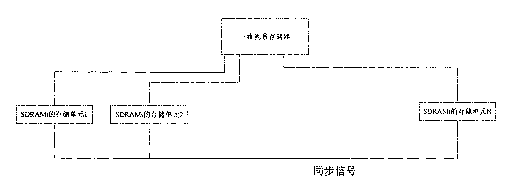

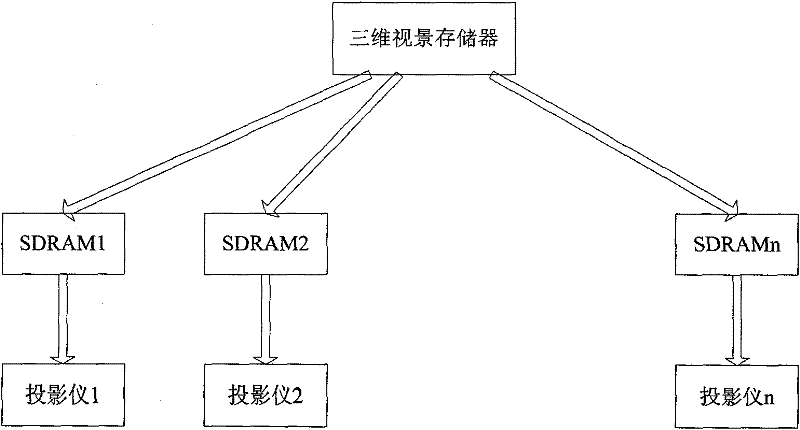

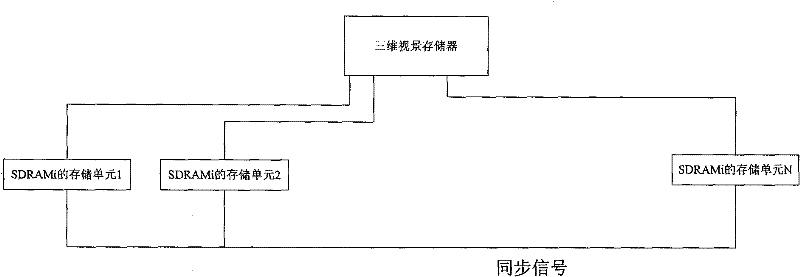

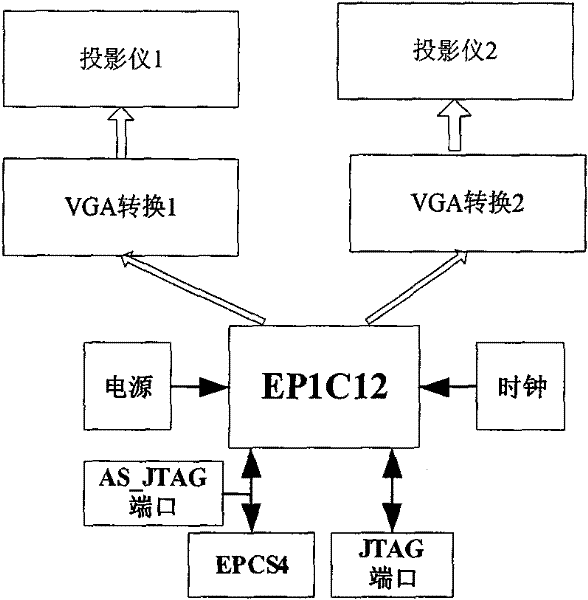

Method for directly assigning and displaying true three-dimensional simulation regions

InactiveCN102087465ASolve the speed bottleneckStereoscopic photographySteroscopic systemsThree dimensional simulationSimulation

The invention provides a method for directly assigning and displaying true three-dimensional simulation regions. The method comprises the following steps of: directly connecting a storage unit of a three-dimensional visual image storage with a display storage region of each projector, which is divided in advance, and carrying out assignment control by a synchronous signal; simultaneously assigning all the display storage regions which are divided in advance by contents which are stored in the three-dimensional visual image storage and respectively correspond to the display storage region of each projector according to the synchronous signal; and after completing assigning the display storage regions of all the projectors, synchronously controlling and displaying to realize rapid and synchronous display of a plurality of projectors. By the method, on-line assignment and image calling of the divided display regions are realized by hardware, rapid and synchronous display of a plurality of projectors is reliably realized and the problem of the speed bottleneck of a method for performing simulation by a software method is solved.

Owner:XIAN FEISIDA AUTOMATION ENG

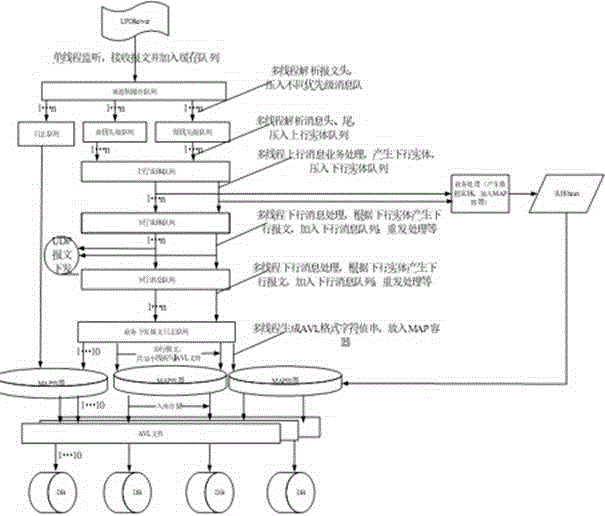

Data input method based on OBD equipment

ActiveCN105208004AStable performanceEfficient storageData switching networksData processingMessage queue

The embodiment of the invention discloses a data input method based on OBD equipment, relates to the technical field of high-concurrency data processing, and can ensure timeliness of the real-time monitoring process of the OBD equipment and ease data congestion. The data input method based on the OBD equipment comprises the steps that data transmitted to a server by the OBD equipment according to a UDP / IP protocol are received by the server; the received data are taken out of a memory queue through the multi-service processing thread, the header of the received data is parsed, uplink entities are correspondingly generated according to the key words of the header, and the uplink entities are added to an uplink entity queue; downlink entities are generated according to the processing result of the uplink entity queue and pressed in a downlink entity queue, downlink messages are generated according to the downlink entities, and the downlink messages are added to a downlink information queue; and downlink information is issued to the OBD equipment according to the downlink information queue. The data input method based on the OBD equipment is suitable for data interaction with the OBD equipment.

Owner:联创汽车服务有限公司

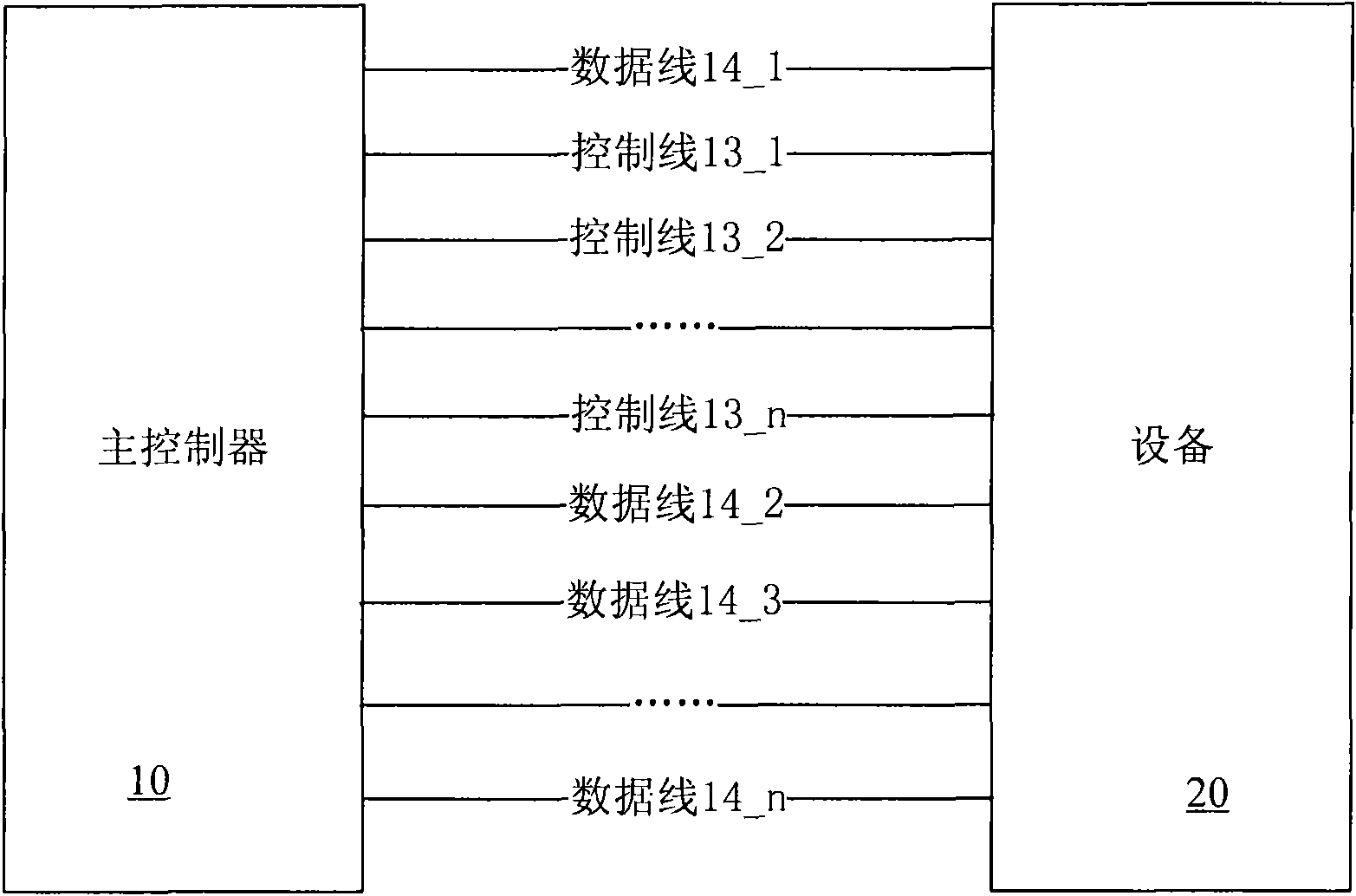

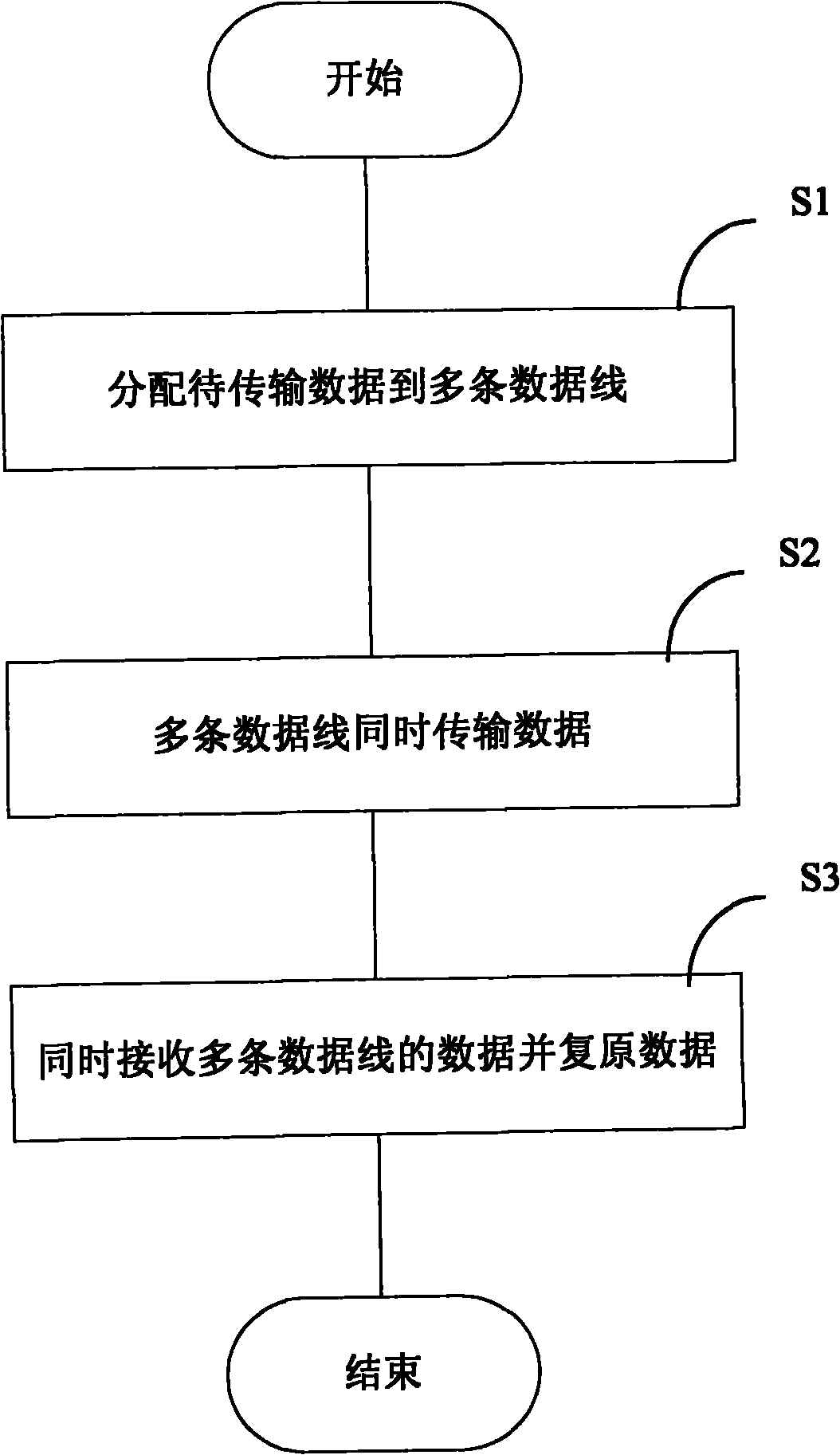

Data transmission method and device

InactiveCN101789915ASolve the speed bottleneckOvercoming the disadvantage of limited transmissionBaseband system detailsComputer hardwareOriginal data

The invention discloses a data transmission method and a data transmission device for providing a serial and parallel combination transmission mode between a transmitting end and a receiving end. A plurality of control lines and a plurality of data lines are connected between the transmitting end and the receiving end, and the data lines can be increased based on a primary serial structure. The method comprises the following steps: packing data to be transmitted into a plurality of data packets according to the data lines and the data transmission mode at the transmitting end and distributing the data packets onto the plurality of data lines respectively; transmitting the plurality of data packets through the plurality of data lines respectively, wherein the data lines transmit the data packets in a serial mode; and receiving a plurality of data blocks at the receiving end respectively and recovering the data blocks into original data.

Owner:YINGHUADA (SHANGHAI) ELECTRONIC CO LTD

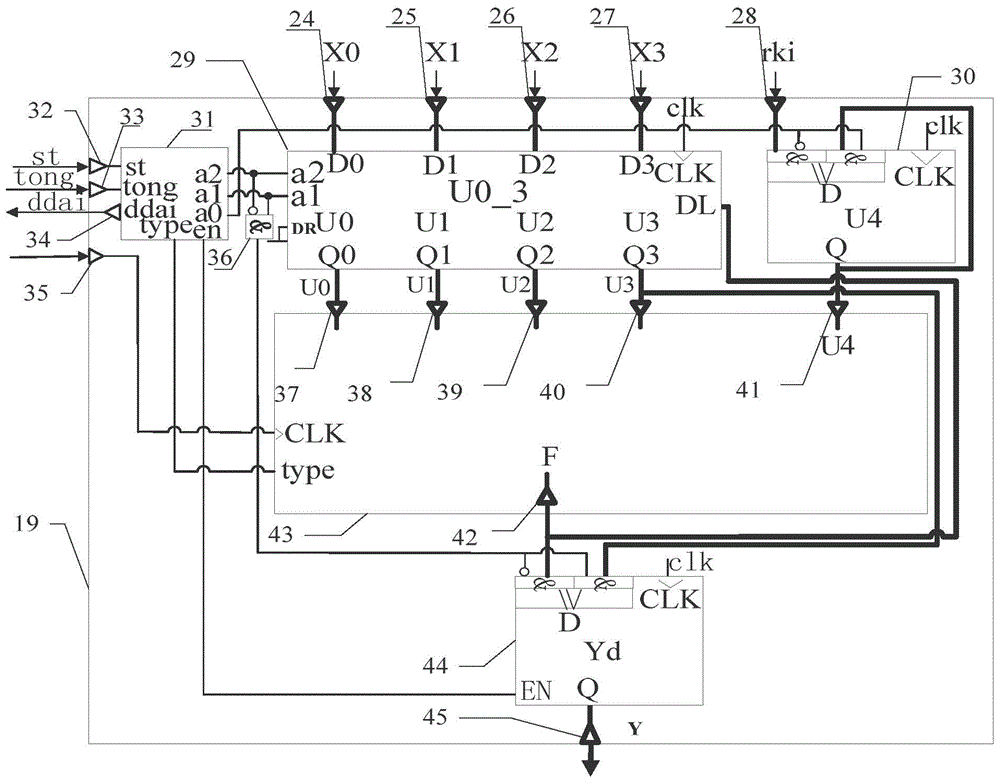

FPGA based IPv6 data packet high-speed processing device and operational method thereof

InactiveCN101567844AEasy to handleSolve the speed bottleneckData switching networksModularityBus interface

The invention provides an FPGA based IPv6 data packet high-speed processing device and an operational method thereof, and belongs to the technical field of transceiving processing of the data packet. The device comprises a microprocessor interface module, an IPv6 data packet encapsulating transmission module, an IPv6 data packet decapsulation analysis module, an Ethernet MAC controller module, an SRAM controller module and a user interactive module, wherein the microprocessor interface module is connected with an external microprocessor, the IPv6 data packet encapsulating transmission module, the IPv6 data packet decapsulation analysis module, the SRAM controller module and the user interactive module respectively; and the IPv6 data packet encapsulating transmission module and the IPv6 data packet decapsulation analysis module are connected with the Ethernet MAC controller module respectively. The device has the advantages that: the IPv6 is fully supported, the speed of processing the network data is greatly improved, the modularization design is adopted, and various microprocessors or bus interfaces are adapted only by modifying the microprocessor interface module, so that the device is high in expansibility, versatility and flexibility.

Owner:SHANDONG UNIV

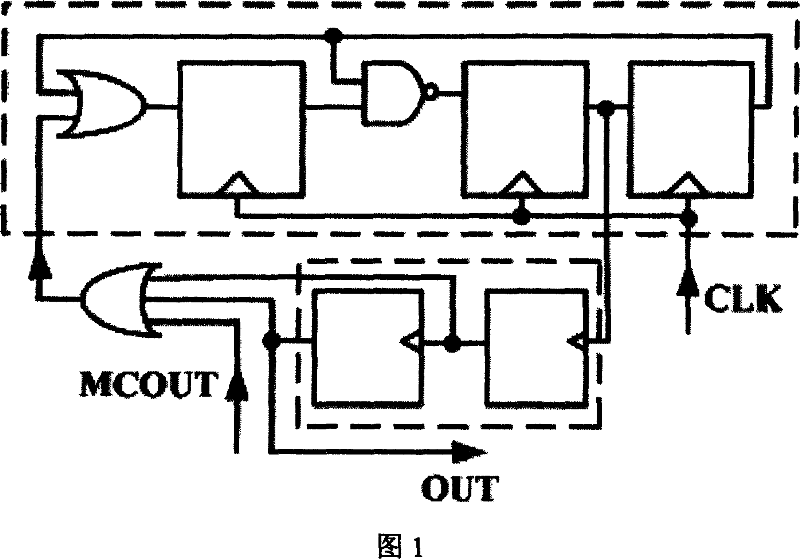

High-speed dual mode 16/17 pre-divider

InactiveCN101039116AEliminate the effect of speedHigh speedCounting chain pulse countersTransceiverDual mode

Provided is a high speed two-mode16 / 17 prescaler circuit belonging to high speed frequency synthesizer and high frequency transceiver technology field. The prescaler circuit comprises three positive edge triggers, a two input or a door, a two input or a non-door, a three input and a non-door and two negative edge triggers. The synchronization frequency division unit composed by the three positive edge trigger, the two input or door and the two input and the non-door adopts rising edge trigger except 4 / 5. The asynchronization frequency division unit composed by the two negative edge triggers adopts fall edge trigger except 4. The feedback control unit adopts the three input and the non-door. The prescaler circuit prevents the influence of the feedback path to the speed of the prescale in 17 frequency division in the existing technology and reduces the delay of the feedback path thus preventing the influence of the feedback state to the synchronization 4 / 5 frequency division speed, increasing the speed of the prescaler, solving the bottleneck problem of speed of the frequency synthesizer and realizing well the 16 / 17 high frequency division of the prescaler.

Owner:SOUTHEAST UNIV

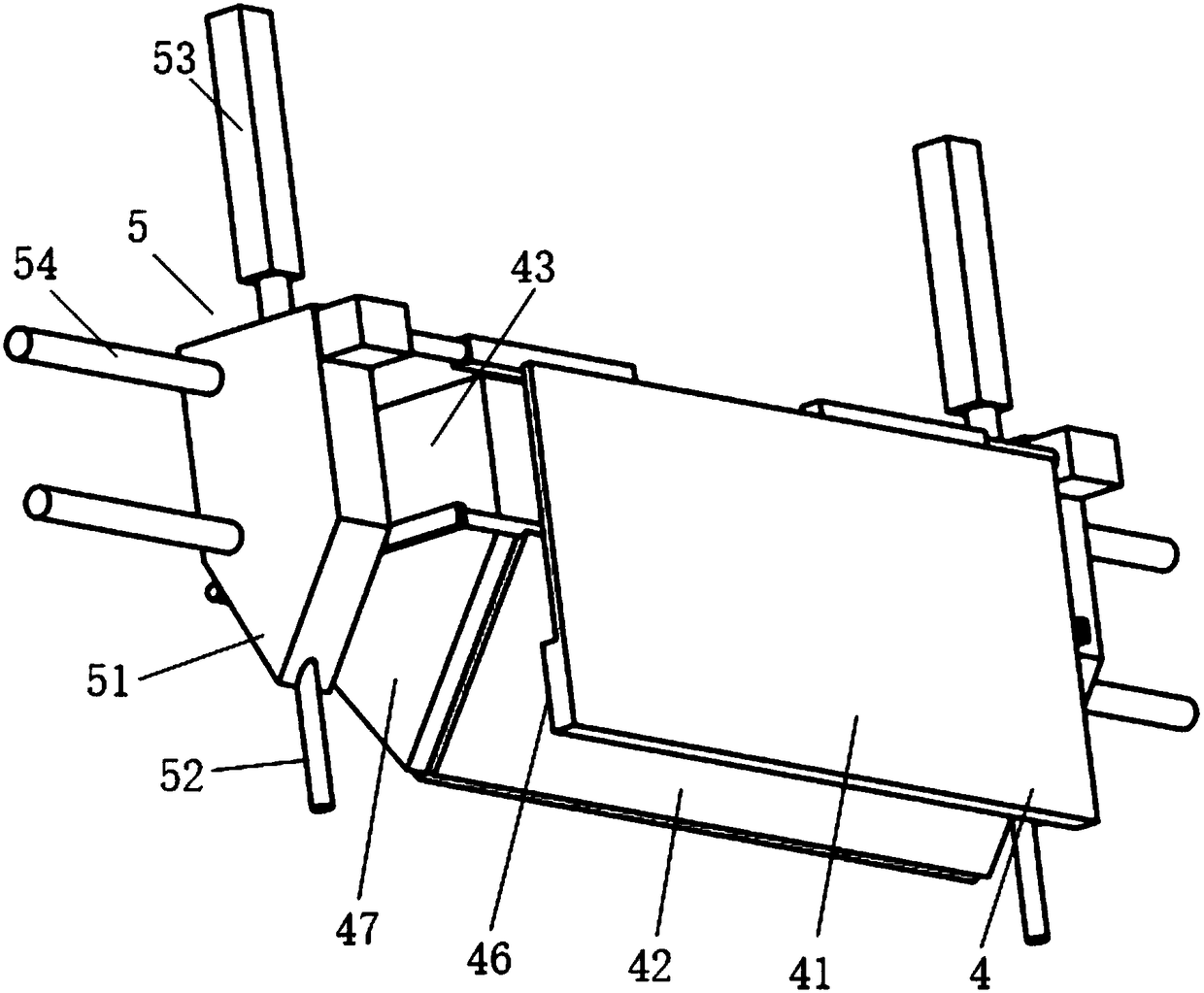

Full-automatic discharge bagging machine

The embodiment of the invention discloses a full-automatic discharge bagging machine which comprises a bag opening clamping mechanism and bag opening sealing mechanisms. The bag opening clamping mechanism is arranged below a discharge mechanism, the bag opening sealing mechanisms are arranged on the left side and the right side of the bag opening clamping mechanism, and the bag opening clamping mechanism comprises a fixed clamping plate and a movable clamping plate located on the inner side of the fixed clamping plate. Each bag opening sealing mechanism comprises a bag opening sealing slidingblock, wherein a sealing rod is arranged in the bag opening sealing sliding block, the upper end of the sealing rod is connected with a telescopic air cylinder, the lower end of the sealing rod stretches out of the lower portion of the bag opening sealing sliding block, and the bag opening sealing sliding block is arranged on a horizontal sliding column and can be driven by a sealing air cylinderto slide along the horizontal sliding column. A packaging bag is fixed below a discharge outlet through the bag opening clamping mechanism for facilitating charging; and the bag opening of the packaging bag filled with materials is arranged through the bag opening sealing mechanisms, the bag opening is kept in a vertical plane shape, and follow-up sealing operation is facilitated.

Owner:伍光永

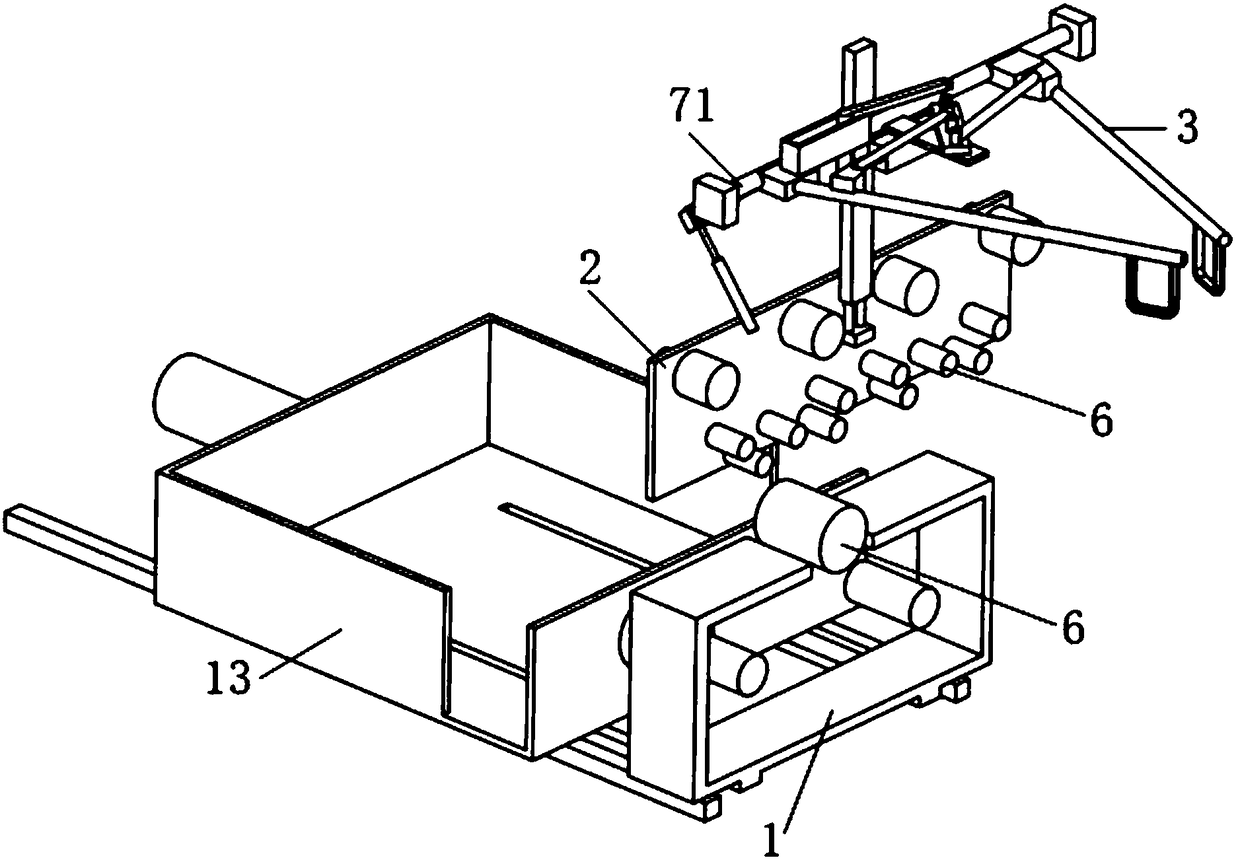

Servo motor mold opening and closing mechanism for rotary bottle blowing machine

The invention relates to the field of bottle blowing machines, in particular to a servo motor mold opening and closing mechanism for a rotary bottle blowing machine. A hanging-lug-type mold carrier is adopted. The servo motor mold opening and closing mechanism comprises a connecting assembly connected to the hanging-lug-type mold carrier, and the connecting assembly is connected with a servo motor through a lead-screw and bushing transmitting mechanism. According to the servo motor mold opening and closing mechanism for the rotary bottle blowing machine, as the hanging-lug-type mold carrier, the connecting assembly, the lead-screw and bushing transmitting mechanism and the servo motor are arranged, track-free mold opening and closing control is achieved, and the multiple defects of a rotating speed bottleneck, serious abrasion, poor mold assembling-disassembling precision and poor mechanical stability of a track mold opening and closing mechanism in the prior art are overcome.

Owner:SHANDONG HUABAOLONG LIGHT IND MACHINERY

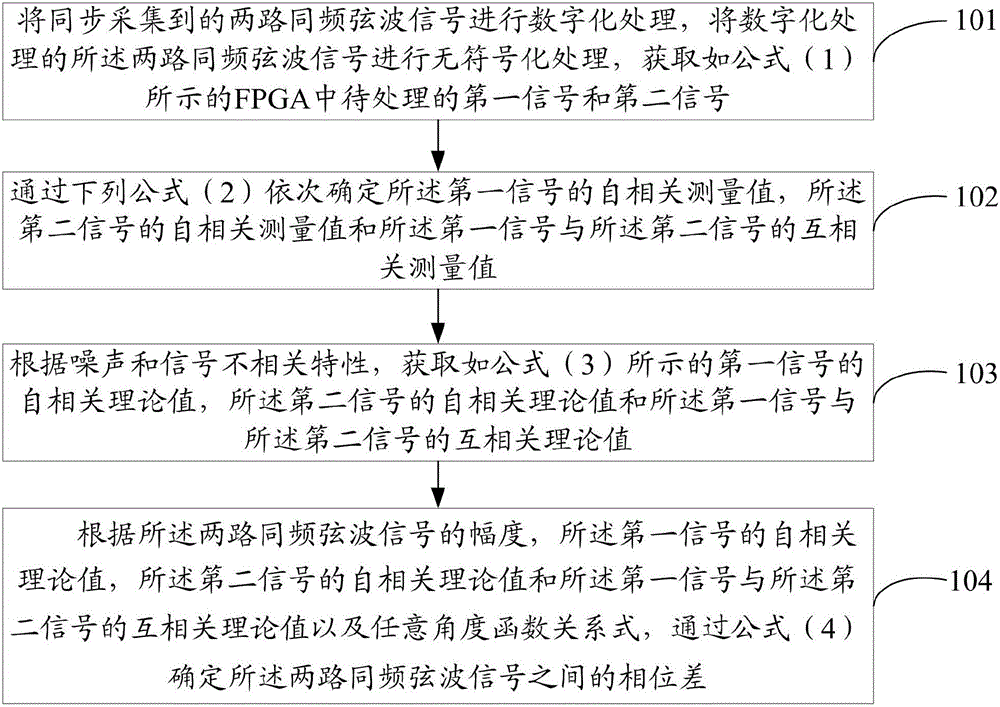

Low-frequency string-wave signal phase difference measurement method

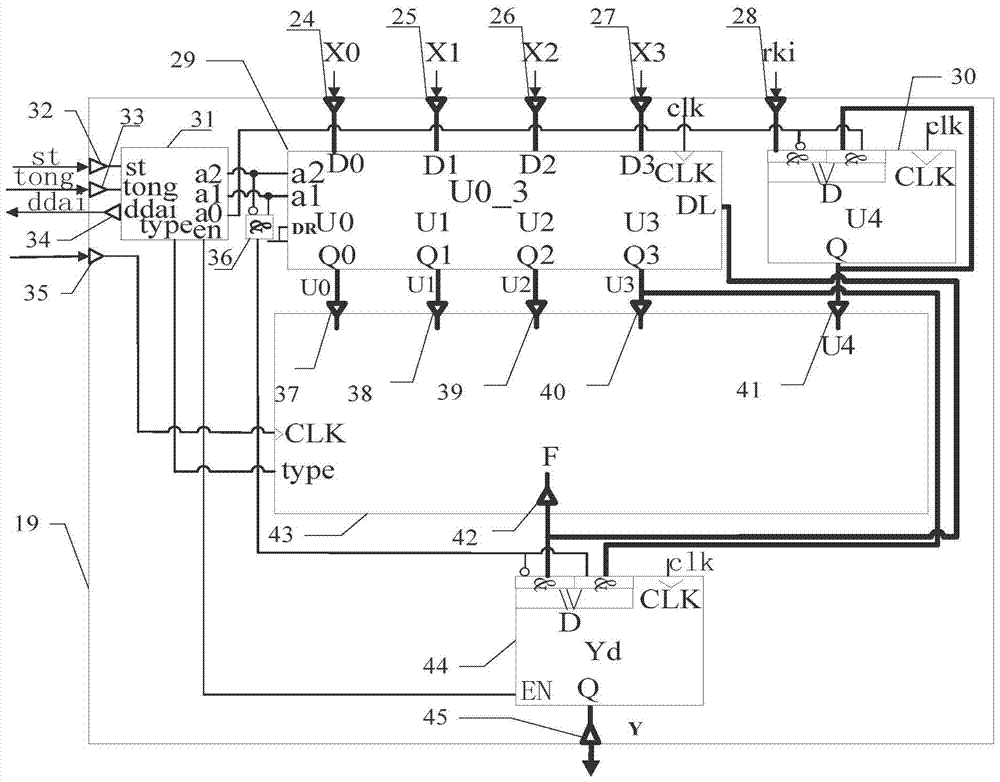

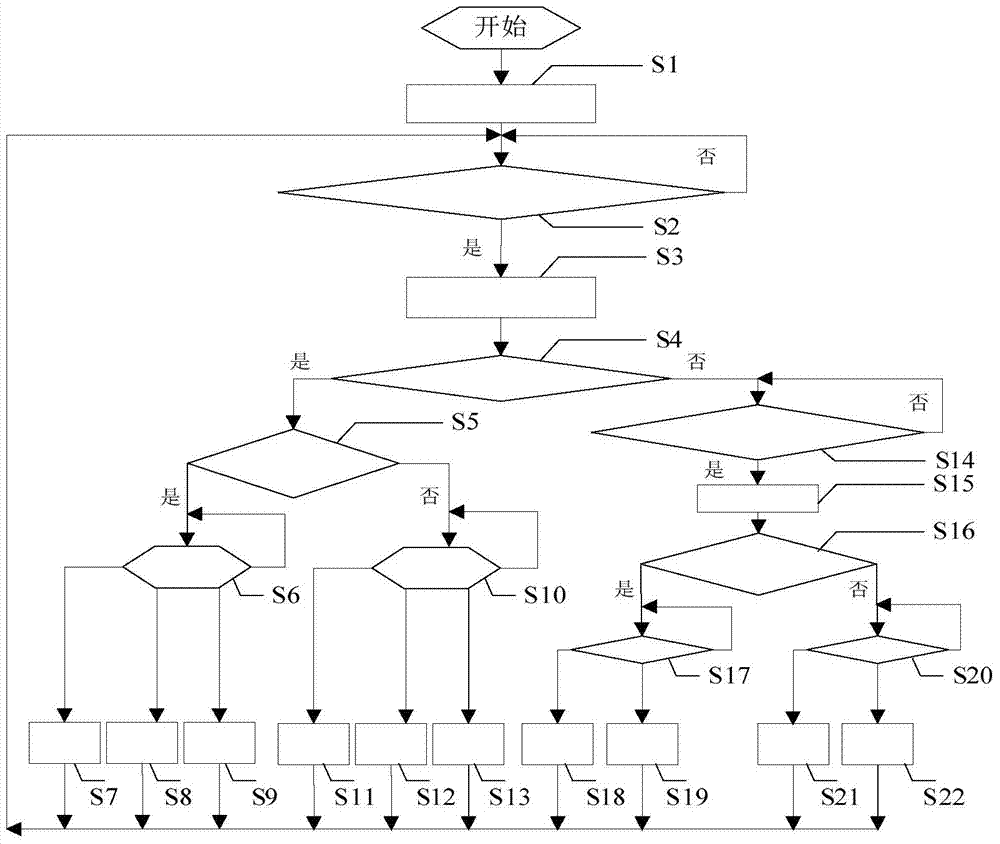

InactiveCN106353596AReduce volumeSolve the speed bottleneckVoltage-current phase anglePhase differenceSelf correlation

The invention provides a low-frequency string-wave signal phase difference measurement method and belongs to the field of phase different measurement with an aim to solve problems that existing phase difference measurement is complex in circuit structure and low in measurement accuracy. The low-frequency string-wave signal phase difference measurement method includes: subjecting two same-frequency string-wave signals acquired synchronously to no-signifying processing to acquire a first signal and a second signal which are to be process in an FPGA (field programmable gate array); sequentially determining self-correlation measurement value of the first signal, self-correlation measurement value of the second signal and cross-correlation measurement value of the first and second signals; according to noise and signal correlation features, acquiring self-correlation theoretical value of the first signal, self-correlation theoretical value of the second signal and cross-correlation theoretical value of the first and second signals; according to amplitude of the two same-frequency string-wave signals, the self-correlation theoretical value, the self-correlation theoretical value, the cross-correlation theoretical value of the first and second signals and an arbitrary-angle function relation formula, determining the phase difference of the same-frequency string-wave signals.

Owner:NORTHWEST UNIV(CN)

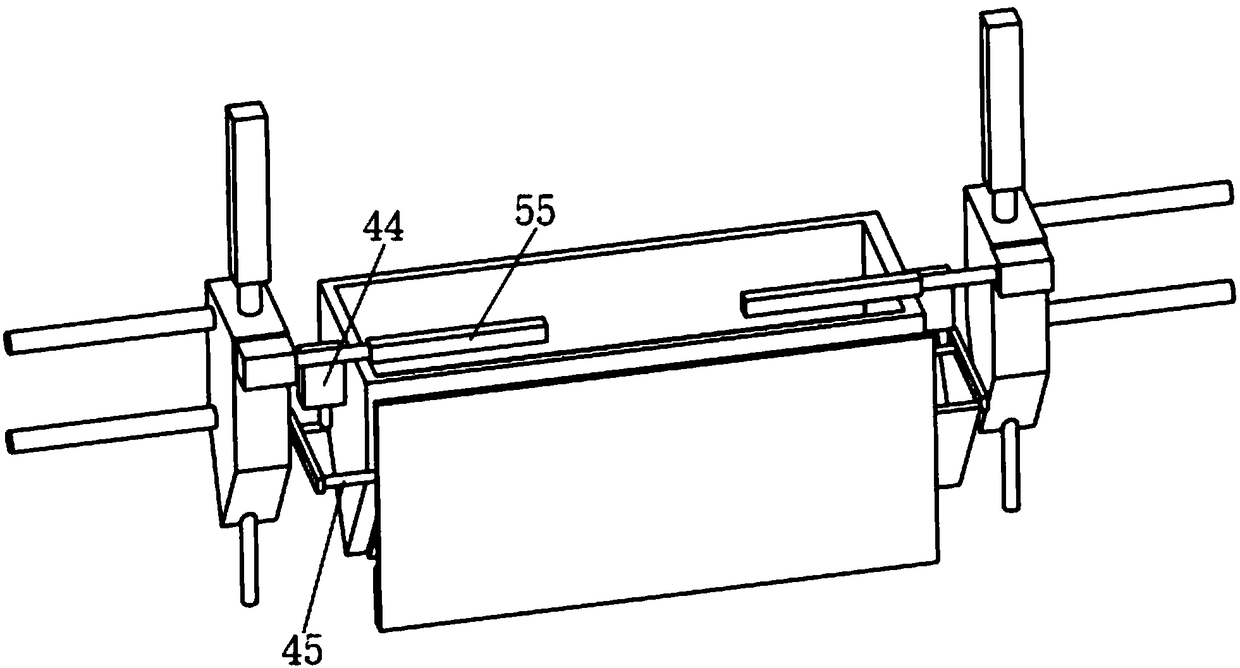

Fully-automatic bag fetching and opening machine

The embodiment of the invention discloses a fully-automatic bag fetching and opening machine. The fully-automatic bag fetching and opening machine comprises a lower opening mechanism, an upper openingmechanism and a bag fetching arm. A bag storage unit is fixedly arranged behind the lower opening mechanism and can move back and forth along with the lower opening mechanism. The upper opening mechanism is arranged on a longitudinal movement mechanism. The lower opening mechanism and the upper opening mechanism are each provided with a gluing mechanism. Each gluing mechanism comprises gluing wheels. Each gluing wheel is provided with adhesive tape. The adhesive face of each piece of adhesive tape faces the side away from the corresponding gluing wheel. The bag fetching arm is connected witha swing shaft through a hinge-joint seat and can be driven by the swing shaft to swing forwards and backwards. According to the fully-automatic bag fetching and opening machine, by means of the loweropening mechanism, the upper opening mechanism and the bag fetching arm, packaging bags can be fetched, opened and connected into a discharging mechanism in a sleeved manner fully automatically; the discharging speed is greatly increased while manpower is saved; and the main speed bottleneck problem found in the material packaging process is solved.

Owner:伍光永

Direct assignment display method in true three-dimensional simulation area

InactiveCN103048871ASolve the speed bottleneckStereoscopic photographySteroscopic systemsDimensional simulationComputer graphics (images)

The invention provides a direct assignment display method in a true three-dimensional simulation area. The method comprises the following steps of: directly connecting storage units of a three-dimensional visual image memory with pre-divided display storage areas of each projector, and performing assignment control by using synchronizing signals; assigning the contents, corresponding to the display storage areas of each projector, of the three-dimensional visual image memory to all pre-divided display storage areas at the same time according to the synchronizing signals; and when the assignment of the display storage areas of all projectors is completed, synchronously controlling the display to realize the rapid and synchronous display of a plurality of projectors. By the method, the assignment and the image call of the divided display areas are realized on line by hardware; the rapid and synchronous display of the plurality of projectors is realized reliably; and the problem of the simulation speed bottleneck of a software method is solved.

Owner:上海日浦信息技术有限公司

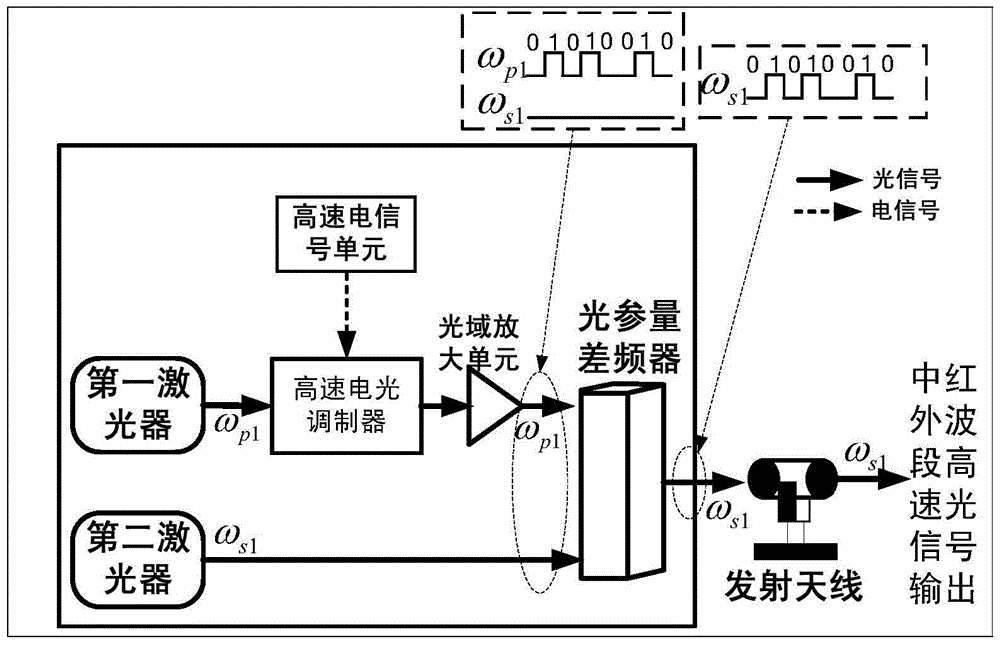

High-speed mid-infrared space laser communication system and communication method

ActiveCN103701525BSolve the speed bottleneckRealize transmissionClose-range type systemsPhotovoltaic detectorsCommunications system

The invention discloses a high-speed intermediate-infrared laser space communication system and a communication method. The system comprises a first laser device, a near-infrared high-speed electrooptical modulator, an optical parameter difference frequency device and a transmitting antenna which are connected sequentially, a second laser device connected with the optical parameter difference frequency device, a receiving antenna, an optical parameter sum frequency device, a near-infrared high-speed photodetector and a high-speed electrical signal processing unit which are connected sequentially, and a third laser device connected with the optical parameter sum frequency device, wherein the near-infrared high-speed electrooptical modulator is connected with the high-speed electrical signal processing unit; the optical wave frequency generated by the first laser device is omega p1; the optical wave frequency generated by the second laser device is omega s1; and the optical wave frequency generated by the third laser device is omega p2. According to the system and the method, restriction of immaturity of a high-speed intermediate-infrared communication device to an intermediate-infrared laser space communication rate is avoided, and space communication transmission and processing of high-speed (tens to hundreds of Gbits / s) and high-capacity optical information can be achieved.

Owner:西安中科天塔科技股份有限公司

A system for implementing SM4 algorithm at ultra-high speed and its operation method

ActiveCN104579636BSolve the speed bottleneckRealize collaborative flowEncryption apparatus with shift registers/memoriesMultiplexingUltra high speed

The invention relates to an ultra-high-speed system for realizing the SM4 algorithm, including a control module, a cryptographic expansion / encryption / decryption module, an encryption / decryption module, a decryption / encryption module, a data splitter, a cryptographic expansion / encryption / decryption selector, and a round encryption / result splitter and result selector, the present invention solves the problem of low speed caused by having to wait for 32 round keys to be calculated before encryption in the existing hardware system, and the processing speed can reach Nearly twice that of the existing hardware system; based on the idea of module reuse, the present invention realizes the synchronous encryption / decryption operation of three groups of tasks, solves the problem that the decryption module is idle during frequent encryption tasks in the traditional design, and effectively improves The utilization rate and operation speed of the system are improved, and the processing speed is three times that of single-task operation when the key is not changed in multi-task operation, and the fastest is six times that of the existing hardware system.

Owner:BINZHOU POLYTECHNIC

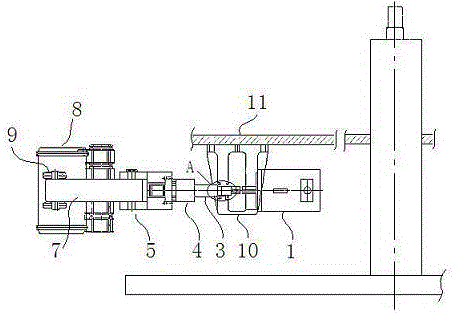

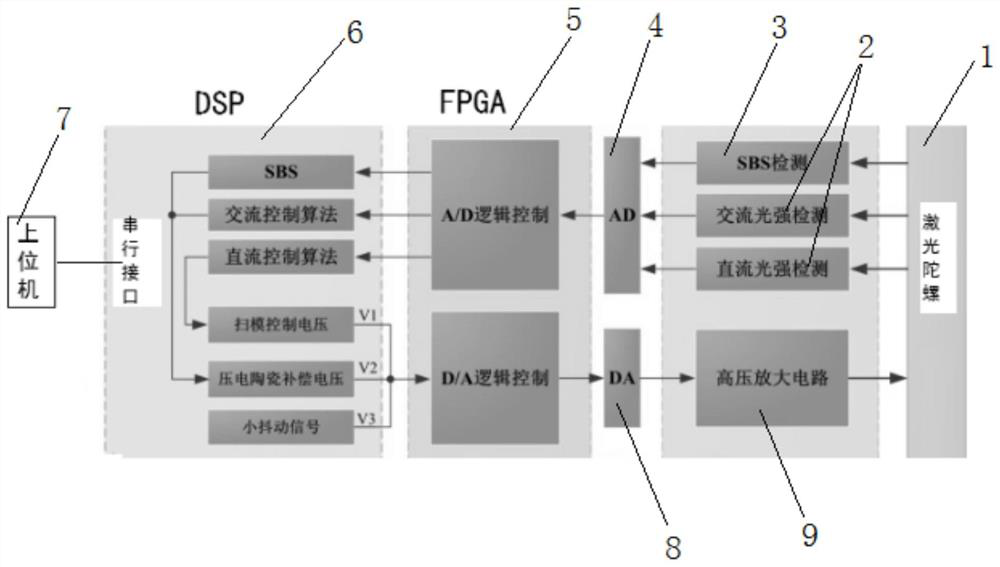

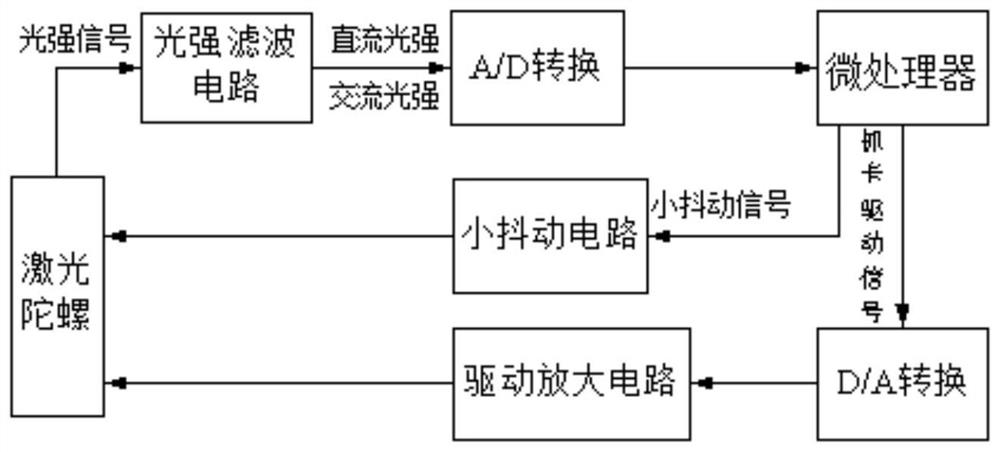

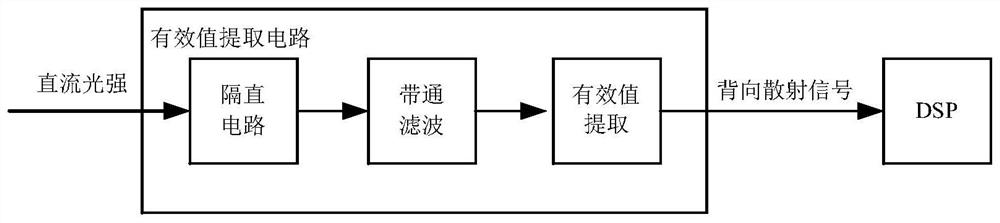

Laser gyroscope frequency stabilization control system and method based on DSP and FPGA

PendingCN111856987AEasy to observeSolve the speed bottleneckProgramme controlComputer controlPhysicsEngineering

The invention discloses a laser gyroscope frequency stabilization control system and method based on a DSP and an FPGA. The system comprises piezoelectric ceramic and an annular resonant cavity, and further comprises a light intensity detection device, an SBS detection device, a light intensity filter circuit, an A / D converter, a D / A converter, a high-voltage amplification circuit and a microprocessor, and the microprocessor comprises a DSP main processor and an FPGA coprocessor; the light intensity detection device is connected with the light intensity filter circuit, the light intensity filter circuit and the SBS detection device are electrically connected with the A / D converter, the A / D converter is connected with the FPGA coprocessor, the FPGA coprocessor is communicated with the DSP main processor, and the DSP main processor is connected with the upper computer; and the FPGA coprocessor is electrically connected with an input port of the D / A converter. The laser gyroscope frequency stabilization control system and method based on the DSP and the FPGA have the differential push-pull frequency stabilization function, and the measurement precision of the laser gyroscope is improved.

Owner:NANJING UNIV OF SCI & TECH

FPGA based IPv6 data packet high-speed processing device and operational method thereof

InactiveCN101567844BEasy to handleSolve the speed bottleneckData switching networksNetwork packetModularity

The invention provides an FPGA based IPv6 data packet high-speed processing device and an operational method thereof, and belongs to the technical field of transceiving processing of the data packet. The device comprises a microprocessor interface module, an IPv6 data packet encapsulating transmission module, an IPv6 data packet decapsulation analysis module, an Ethernet MAC controller module, anSRAM controller module and a user interactive module, wherein the microprocessor interface module is connected with an external microprocessor, the IPv6 data packet encapsulating transmission module,the IPv6 data packet decapsulation analysis module, the SRAM controller module and the user interactive module respectively; and the IPv6 data packet encapsulating transmission module and the IPv6 data packet decapsulation analysis module are connected with the Ethernet MAC controller module respectively. The device has the advantages that: the IPv6 is fully supported, the speed of processing thenetwork data is greatly improved, the modularization design is adopted, and various microprocessors or bus interfaces are adapted only by modifying the microprocessor interface module, so that the device is high in expansibility, versatility and flexibility.

Owner:SHANDONG UNIV

Data processing method and device

ActiveCN101799750BIncrease profitImplement multiple launchesResource allocationConcurrent instruction executionProduction lineParallel computing

The invention relates to a data processing method and a device. Program codes running on a serially connected multiprocessor nuclear structure are partitioned according to specific rules, so that the serially connected multiprocessor nuclear structure forms a serial multi-emitting and production line layered structure, and the time required for running corresponding code fragments obtained by partitioning on each nucleus is equal as much as possible, thereby realizing the load balance of internuclear workload.

Owner:SHANGHAI XINHAO MICROELECTRONICS

True three-dimensional simulation angle description and direct projection display method

ActiveCN102375325BQuick displaySynchronous displayStereoscopic photographySteroscopic systemsThree dimensional simulationProjection screen

The invention provides a true three-dimensional simulation angle description and direct projection display method. The method comprises the following steps: defining a spherical surface in an angular altitude alpha and an azimuth angle beta according to the projection effect, wherein the angular altitude ranges from minus alpha 0 to 90 DEG, and the alpha 0 can be directly determined according to a three-dimensional projection screen, and the azimuth angle ranges from 0-360 DEG, so that accurate coordinates can be provided for of all points on the spherical surface; describing a true world coordinate and each projector coordinate to be displayed by using the uniform angular altitude and azimuth angle, thereby determining all different angular altitude and azimuth angle coordinates (alpha i, beta i) of projectors corresponding to the projection regions on the screen after the projector is mounted and debugged; and reading the corresponding coordinate (alpha i, beta i) of the real world on line without on-line computation, and becoming a rectangular region in a proportion to be directly projected. The real world is realized through the angular altitude and the azimuth angle, the unification of the projector coordinator systems solves the speed bottleneck problem of simulation with a software method.

Owner:XIAN FEISIDA AUTOMATION ENG

A distributed audio and video processing device and processing method

InactiveCN103605710BSolve the speed bottleneckShorten the timeAudio data retrievalVideo data retrievalVideo processingData processing

The invention provides a distributed audio and video file processing system which comprises an input processing unit, multiple video data processing units, multiple audio data processing units, an output processing unit and a dispatching unit. The input processing unit is used for receiving and processing source video files to acquire audio and video data, the audio and video data are respectively segmented into audio and video data fragments which are dispatched to corresponding audio and video data processing units for processing according to a certain dispatching rule; the video data processing units are respectively used for processing the segmented video data fragments; the audio data processing units are respectively used for processing the segmented audio data fragments; the output processing unit is used for processing and outputting the processed audio and video data fragments; the dispatching unit is used for coordinating operation of the input processing unit, the audio and video data processing units and the output processing unit. The invention further provides a distributed audio and video file processing method and a distributed audio and video file processing device.

Owner:TVMINING BEIJING MEDIA TECH

Space Laser Communication Transmitter System Based on Passive Optical Switch

ActiveCN105490727BSolve the speed bottleneckTo achieve high-speed transmission requirementsRadio transmissionElectromagnetic transmittersOptical burst switchingEngineering

The invention discloses a space laser communication forwarding system based on a passive optical switch. The system consists of a ground optical signal transmitting terminal, a space forwarding system and a ground optical signal receiving terminal. A transmitting end and a receiving end for space optical communications are placed on the ground, and the space forwarding system is carried by an aircraft and only forwards optical signals without processing such as amplification, modulation, demodulation and the like, so that the complexity of a space system is lowered greatly, and the sizes, weights and power consumption of space loads are lowered. Moreover, point-to-point or broadcasting-mode forwarding of the optical signals is realized through an optical switching system. The signals are modulated on the transmitting end, and demodulated on the receiving end, so that ground-space-ground forwarding communications are realized.

Owner:山东中科际联光电集成技术研究院有限公司

A data storage method based on obd equipment

ActiveCN105208004BGuaranteed timelinessSolve the speed bottleneckData switching networksMessage queueProtocol for Carrying Authentication for Network Access

The embodiment of the invention discloses a data input method based on OBD equipment, relates to the technical field of high-concurrency data processing, and can ensure timeliness of the real-time monitoring process of the OBD equipment and ease data congestion. The data input method based on the OBD equipment comprises the steps that data transmitted to a server by the OBD equipment according to a UDP / IP protocol are received by the server; the received data are taken out of a memory queue through the multi-service processing thread, the header of the received data is parsed, uplink entities are correspondingly generated according to the key words of the header, and the uplink entities are added to an uplink entity queue; downlink entities are generated according to the processing result of the uplink entity queue and pressed in a downlink entity queue, downlink messages are generated according to the downlink entities, and the downlink messages are added to a downlink information queue; and downlink information is issued to the OBD equipment according to the downlink information queue. The data input method based on the OBD equipment is suitable for data interaction with the OBD equipment.

Owner:南京联创数字科技有限公司

Design method of ldpc decoder compatible with dvb-s2x standard

ActiveCN105680879BImprove throughputShorten the timeError correction/detection using multiple parity bitsCode conversionComputer architectureLow-density parity-check code

Owner:XIDIAN UNIV

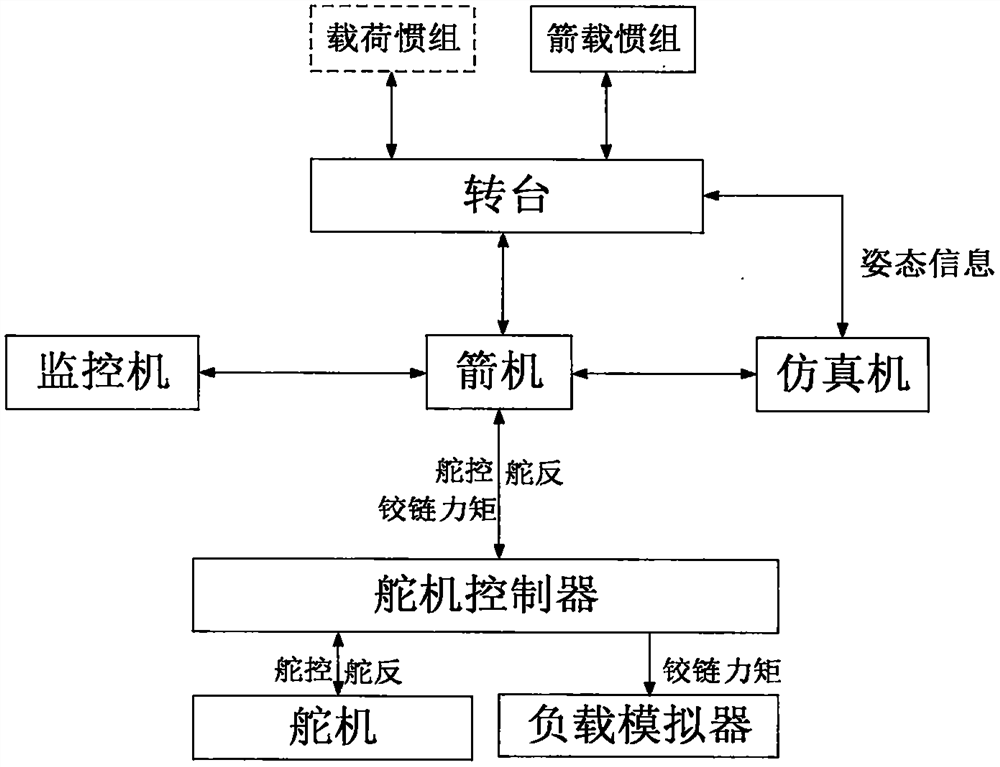

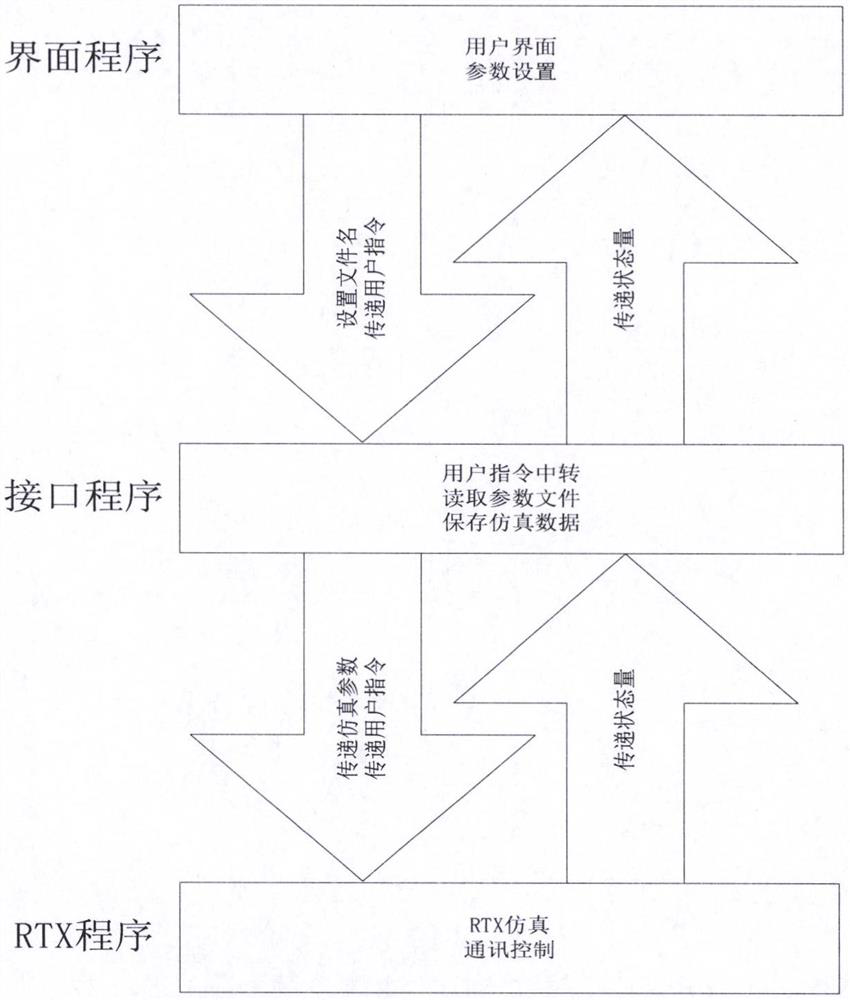

Implementation method for guaranteeing real-time performance of semi-physical simulation through three-layer structure

InactiveCN113110108AFix unexpected delaysSolve the waiting problemResource allocationSimulator controlComputer architectureEngineering

The invention discloses an implementation method for guaranteeing the real-time performance of semi-physical simulation by a three-layer structure, which aims at the real-time performance requirement of a semi-physical simulation system, starts from the top design and software and hardware, and is implemented by adopting a mode of reasonable division and mutual cooperation of hardware and software functions. A multi-core CPU is divided into two parts, wherein one part is that under RTX, threads where codes with high requirements for real-time performance are located independently occupy one CPU physical core respectively; the other part of the CPU is reserved in Windows to execute the codes that are time-consuming but not high in real-time requirement; the codes are divided into three layers on software, wherein the first layer is simulation and communication codes with high requirements on real-time performance; the second layer is a low-speed IO operation code; and the third layer is user interface codes. The division mode fully ensures that the real-time requirement of the semi-physical simulation is met, and ensures that threads where codes with high real-time requirement in the semi-physical simulation software are located can occupy CPU resources at any time and scheduling waiting does not occur. The third layer in the three-layer structure also provides a wide space for the design of the user interface, and the user interface of the third layer can use various UI design and programming languages based on the isolation effect of the second layer.

Owner:北京星途探索科技有限公司

Method for directly assigning and displaying true three-dimensional simulation regions

InactiveCN102087465BSolve the speed bottleneckStereoscopic photographySteroscopic systemsThree dimensional simulationSynchronous control

The invention provides a method for directly assigning and displaying true three-dimensional simulation regions. The method comprises the following steps of: directly connecting a storage unit of a three-dimensional visual image storage with a display storage region of each projector, which is divided in advance, and carrying out assignment control by a synchronous signal; simultaneously assigning all the display storage regions which are divided in advance by contents which are stored in the three-dimensional visual image storage and respectively correspond to the display storage region of each projector according to the synchronous signal; and after completing assigning the display storage regions of all the projectors, synchronously controlling and displaying to realize rapid and synchronous display of a plurality of projectors. By the method, on-line assignment and image calling of the divided display regions are realized by hardware, rapid and synchronous display of a plurality of projectors is reliably realized and the problem of the speed bottleneck of a method for performing simulation by a software method is solved.

Owner:XIAN FEISIDA AUTOMATION ENG

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com