System for realizing SM4 algorithm at super-speed as well as operating method of system

An ultra-high-speed, algorithmic technology, applied in the direction of encryption devices with shift registers/memory, etc., can solve the problems of reducing the operation processing speed, reducing the data processing speed, and failing to meet the requirements.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

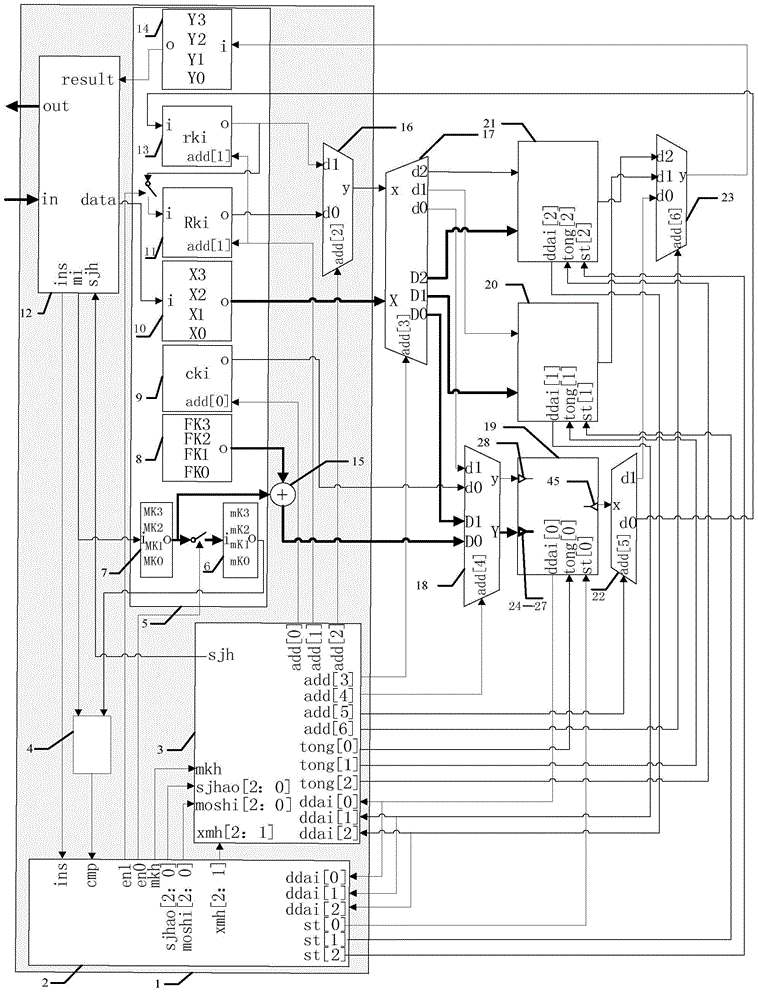

[0155] An ultra-high-speed system for implementing the SM4 algorithm, comprising: a control module 1, a cryptographic expansion / encryption / decryption module 19, an encryption / decryption module 20, a decryption / encryption module 21, a data splitter 17, and a cryptographic expansion / encryption / decryption selector 18. Wheel secret / result splitter 22, result selector 23, the control module 1 includes a microprocessor interface 12, a startup module 2, a data path module 3, a data cache area 5, a comparator 4, and an exclusive OR operation module 15 and new / old round secret selector 16, described data cache area 5 comprises old key storage area 6, new key storage area 7, system parameter storage area 8, intrinsic parameter storage area 9, original data storage area 10, Old round secret storage area 11, new round secret storage area 13 and result data storage area 14;

[0156] The microprocessor interface 12 is connected to the microprocessor; the three groups of iterations input of ...

Embodiment 2

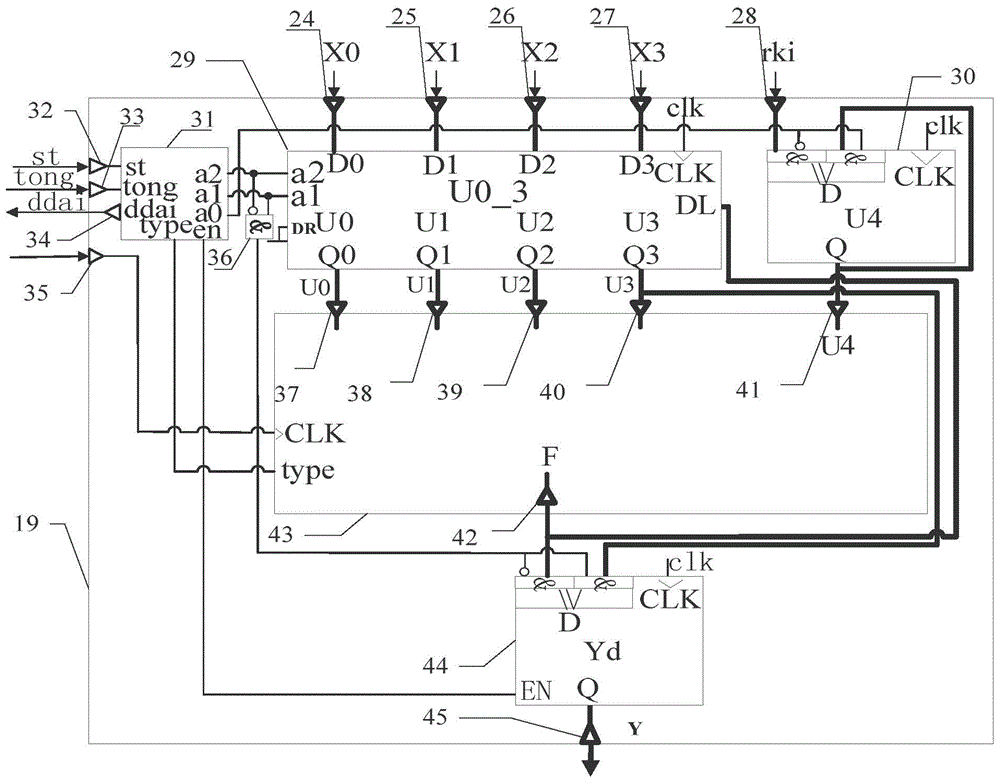

[0159] According to the system described in Embodiment 1, the difference is that the dense expansion / encryption / decryption module 19 includes a bidirectional shift register group, a D flip-flop group with retention, a state machine module 31, an F / F' transformation module 43, Band enable optional D flip-flop group, the bidirectional shift register group is a four-input 32-bit bidirectional shift register U0_332, and the four-input 32-bit bidirectional shift register U0_332 includes four 32-bit registers, namely U0 — U3, the D flip-flop group with hold is a 32-bit D flip-flop U430 with hold function, and the D flip-flop group with enable option is a 32-bit D flip-flop with an optional input for output enable Device Yd44;

[0160] The data input module of described dense expansion / encryption / decryption module 19 comprises described four input 32-bit bidirectional shift register U0_332 and the 32-bit D flip-flop U430 of described band holding function, and described dense expansi...

Embodiment 3

[0163] According to the system described in embodiment 1 or embodiment 2, the difference is that the instruction output, key output, and data output of the microprocessor interface 12 are respectively connected to the instruction input and the new key storage area 7 of the startup module 2 And the input of comparator 4, the input of original data storage area 10; The input of described comparator 4 connects the key output of described microprocessor interface 12 and the output of old round secret storage area 11; The output of described comparator 4 The output is connected to the comparison signal input of the startup module 2; the enable signal output en1 and en0 of the startup module 2 are respectively connected to the enable input and new password of the new round secret storage area 13 assigned to the old round secret storage area 11. The key storage area 7 is assigned to the enable input of the old key storage area 6; the three module data number outputs of the startup mod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com