Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

204results about How to "Shorten write time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

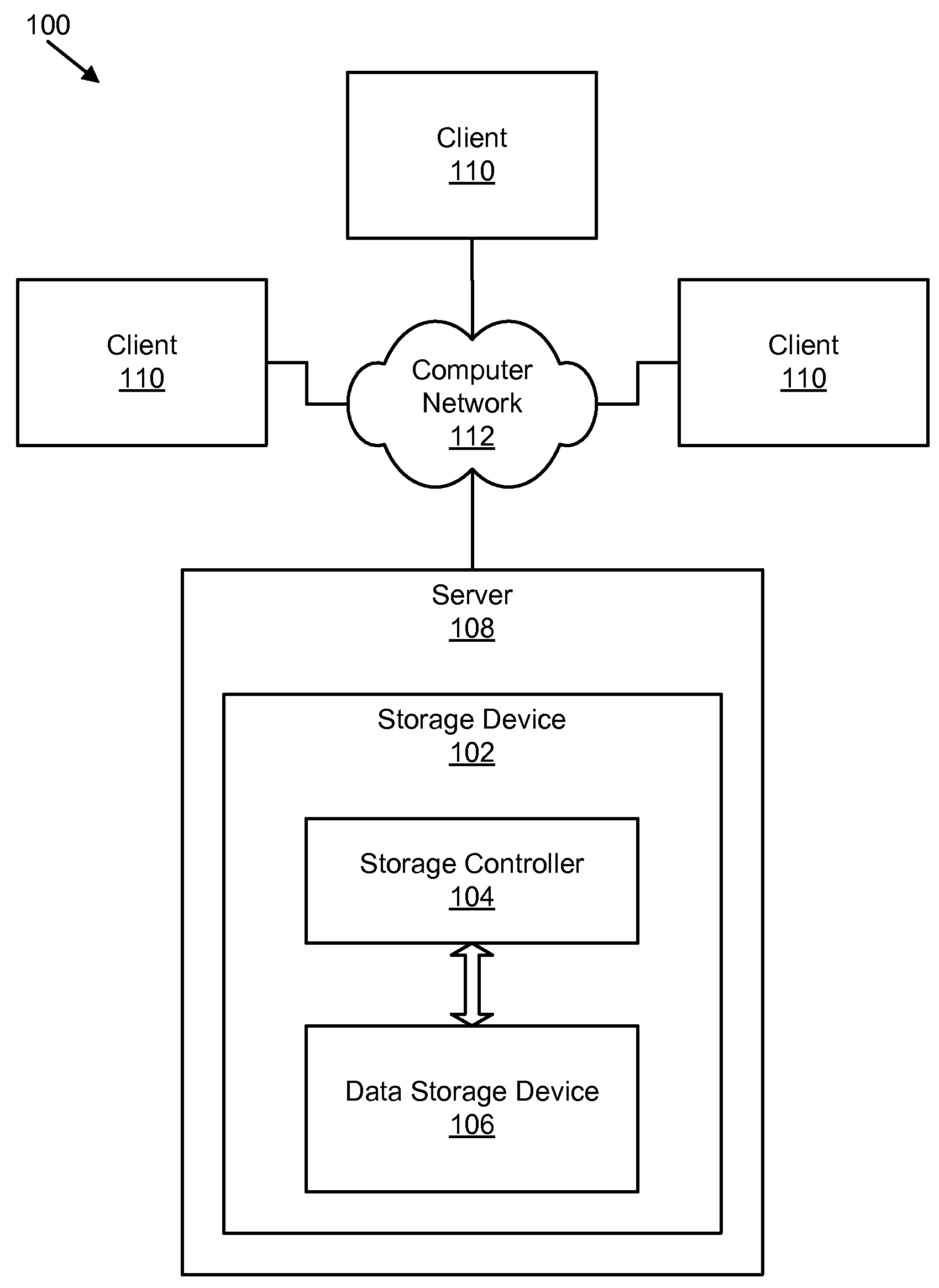

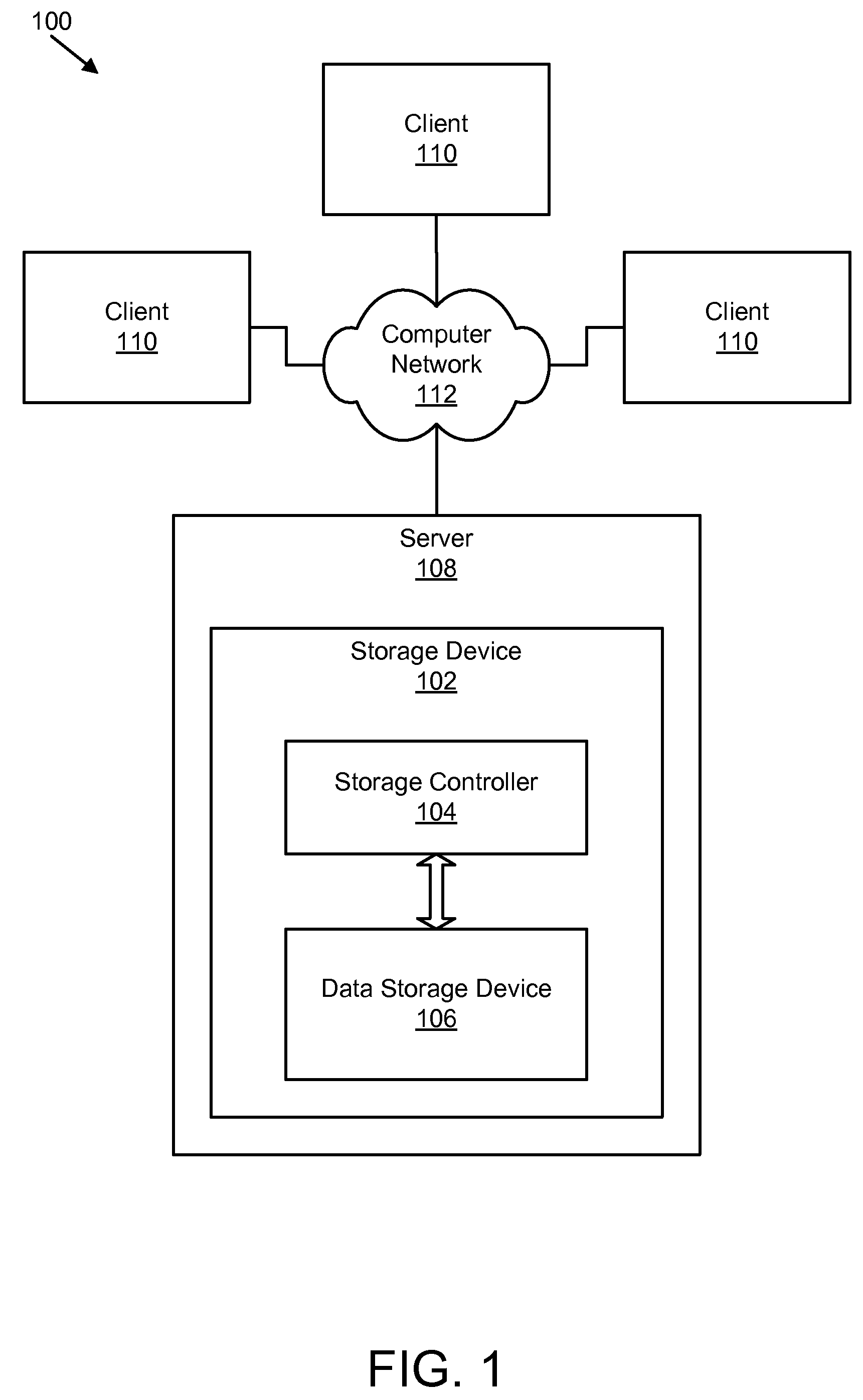

Apparatus, system, and method for converting a storage request into an append data storage command

ActiveUS20090150605A1Shorten write timeImprove efficiencyMemory architecture accessing/allocationProgram synchronisationData segmentNetwork packet

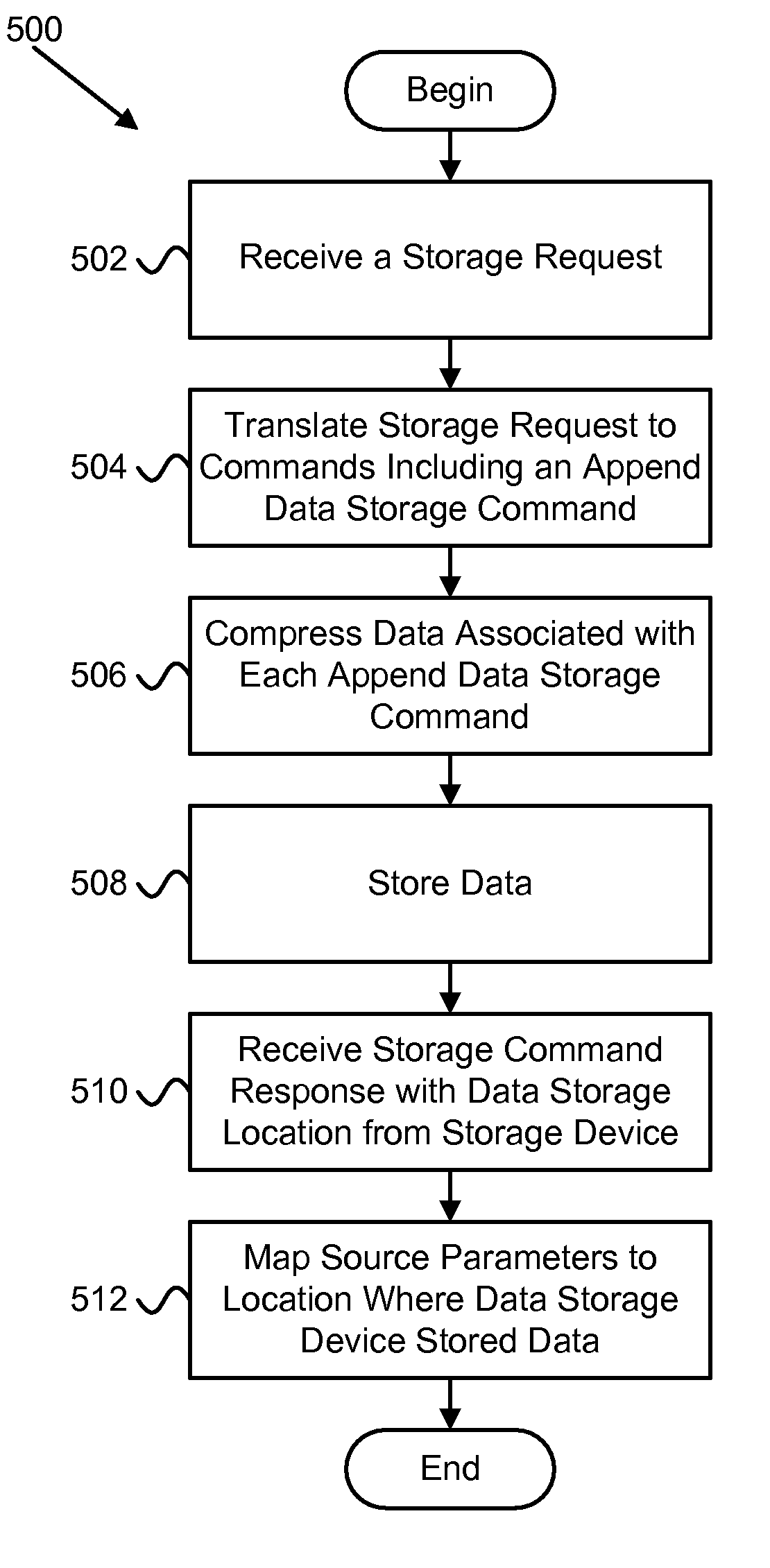

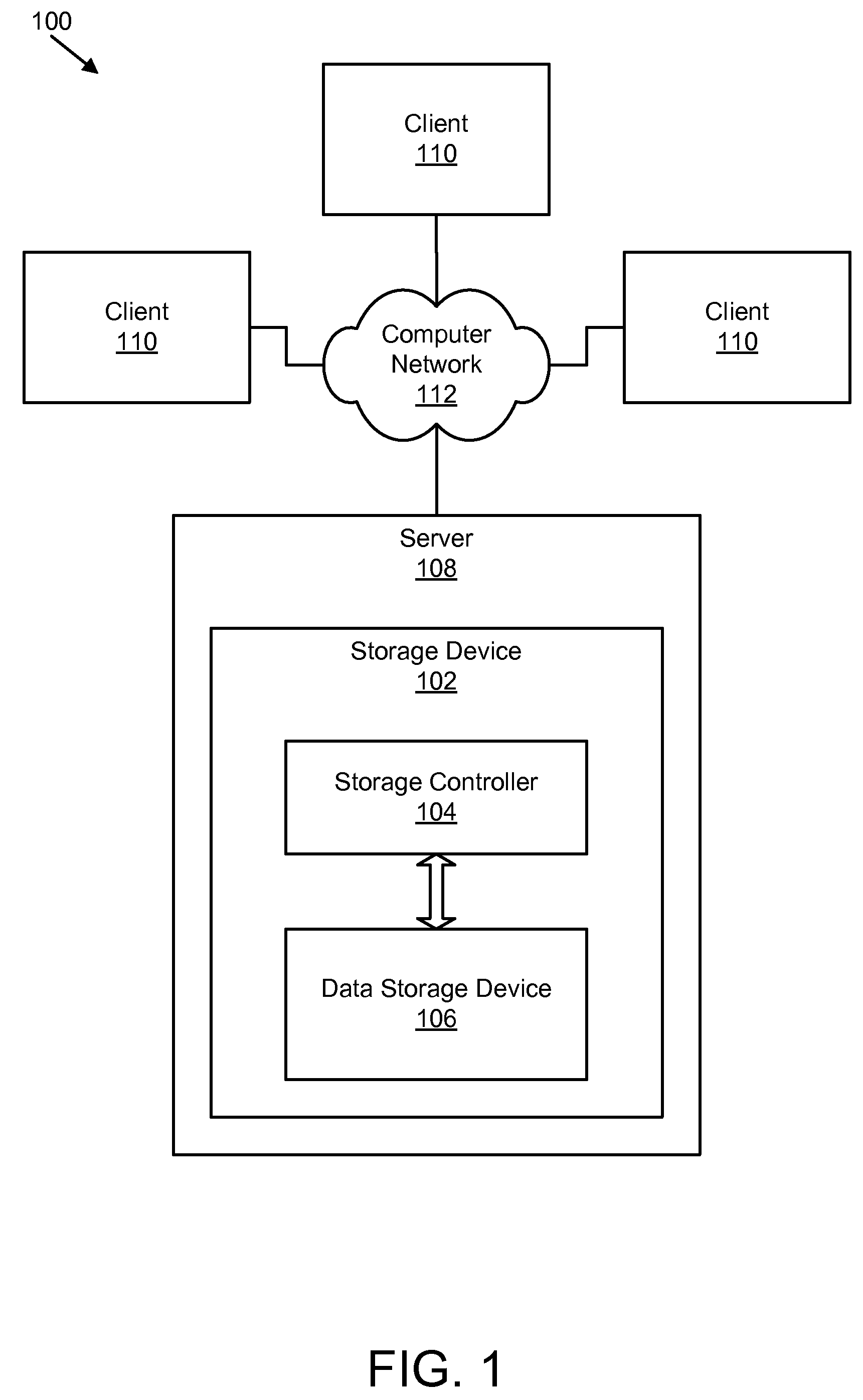

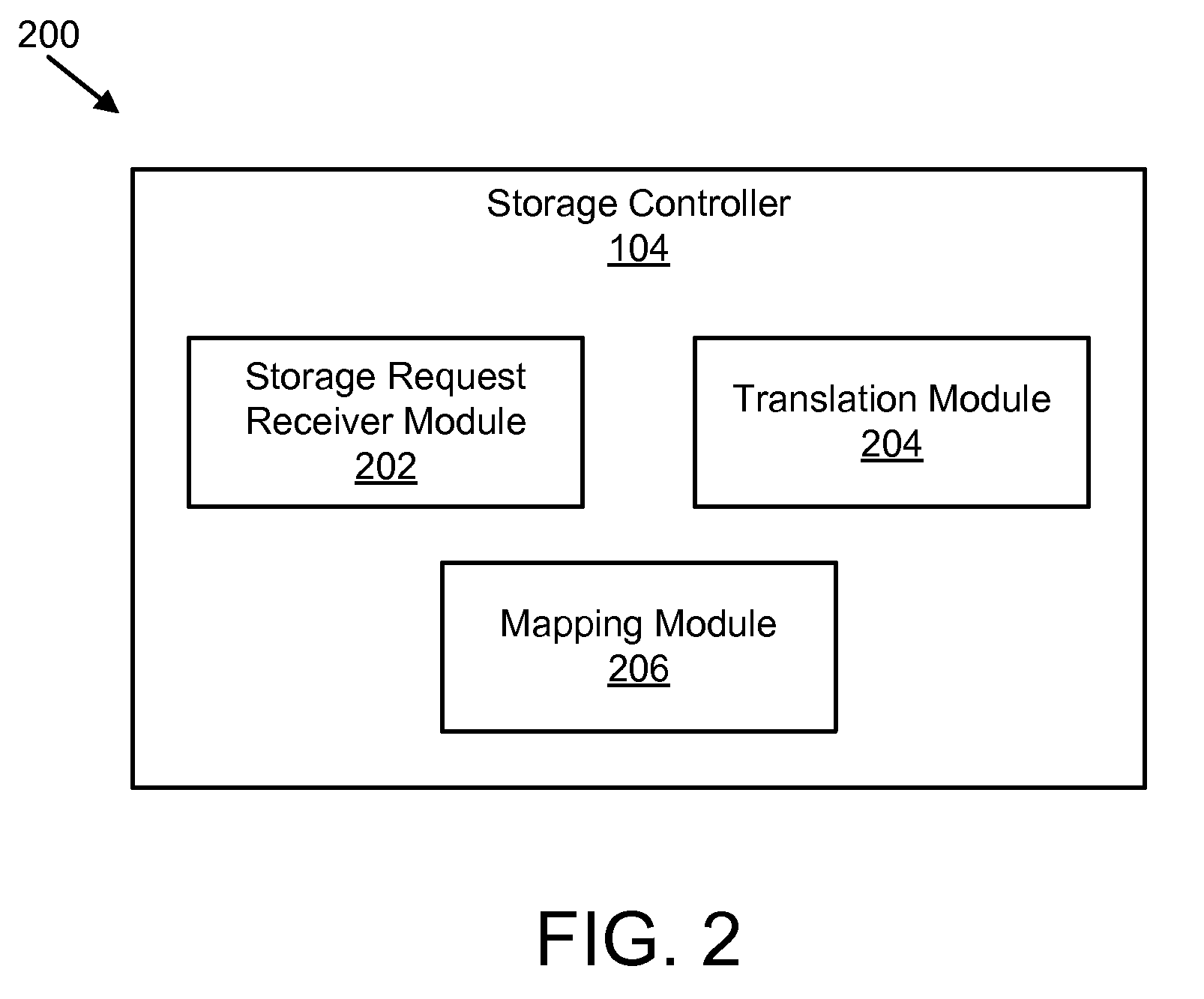

An apparatus, system, and method are disclosed for converting a storage request to an append data storage command. A storage request receiver module receives a storage request from a requesting device. The storage request is to store a data segment onto a data storage device. The storage request includes source parameters for the data segment. The source parameters include a virtual address. A translation module translates the storage request to storage commands. At least one storage command includes an append data storage command that directs the data storage device to store data of the data segment and the one or more source parameters with the data, including a virtual address, at one or more append points. A mapping module maps source parameters of the data segment to locations where the data storage device appended the data packets of the data segment and source parameters.

Owner:UNIFICATION TECH LLC

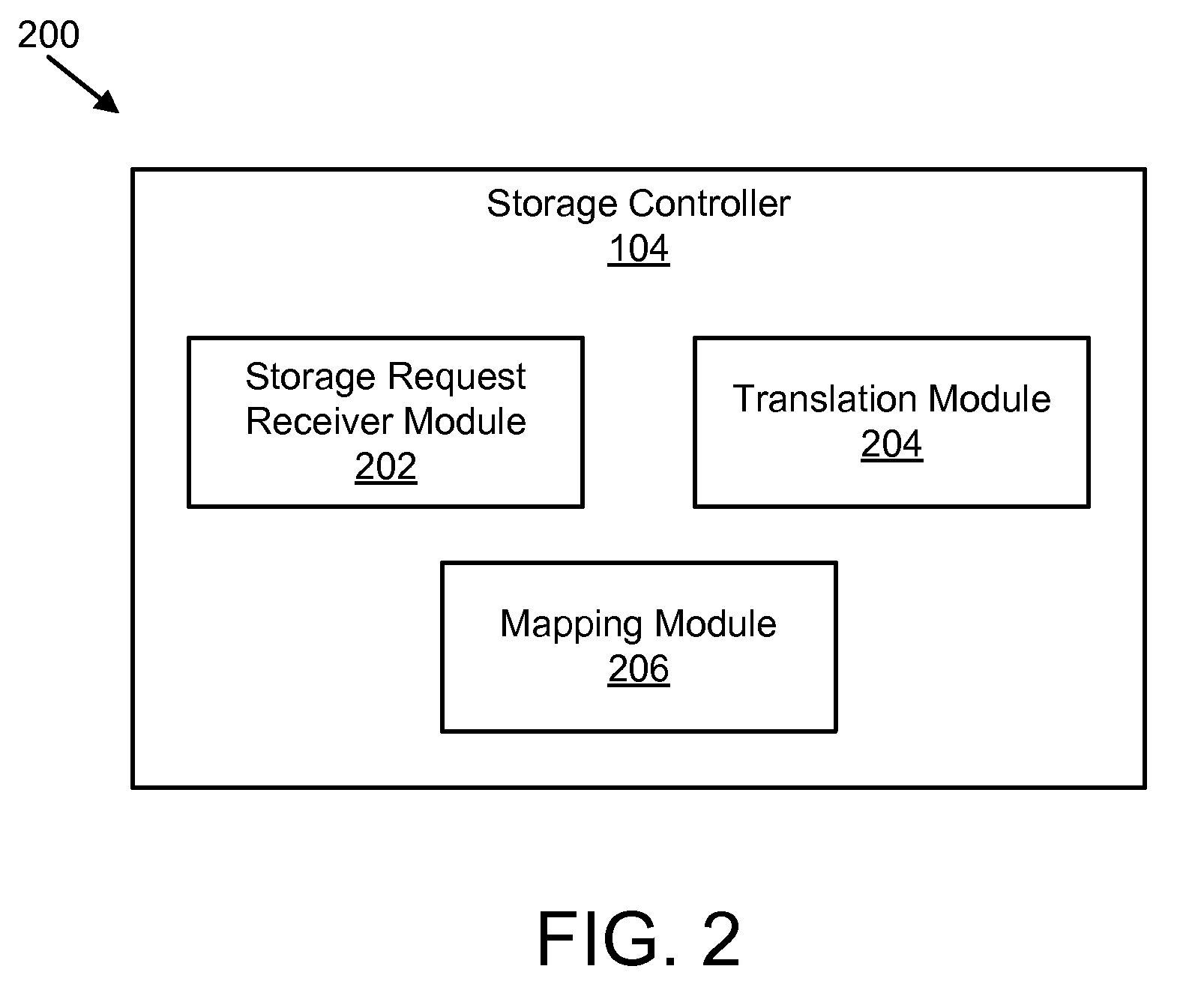

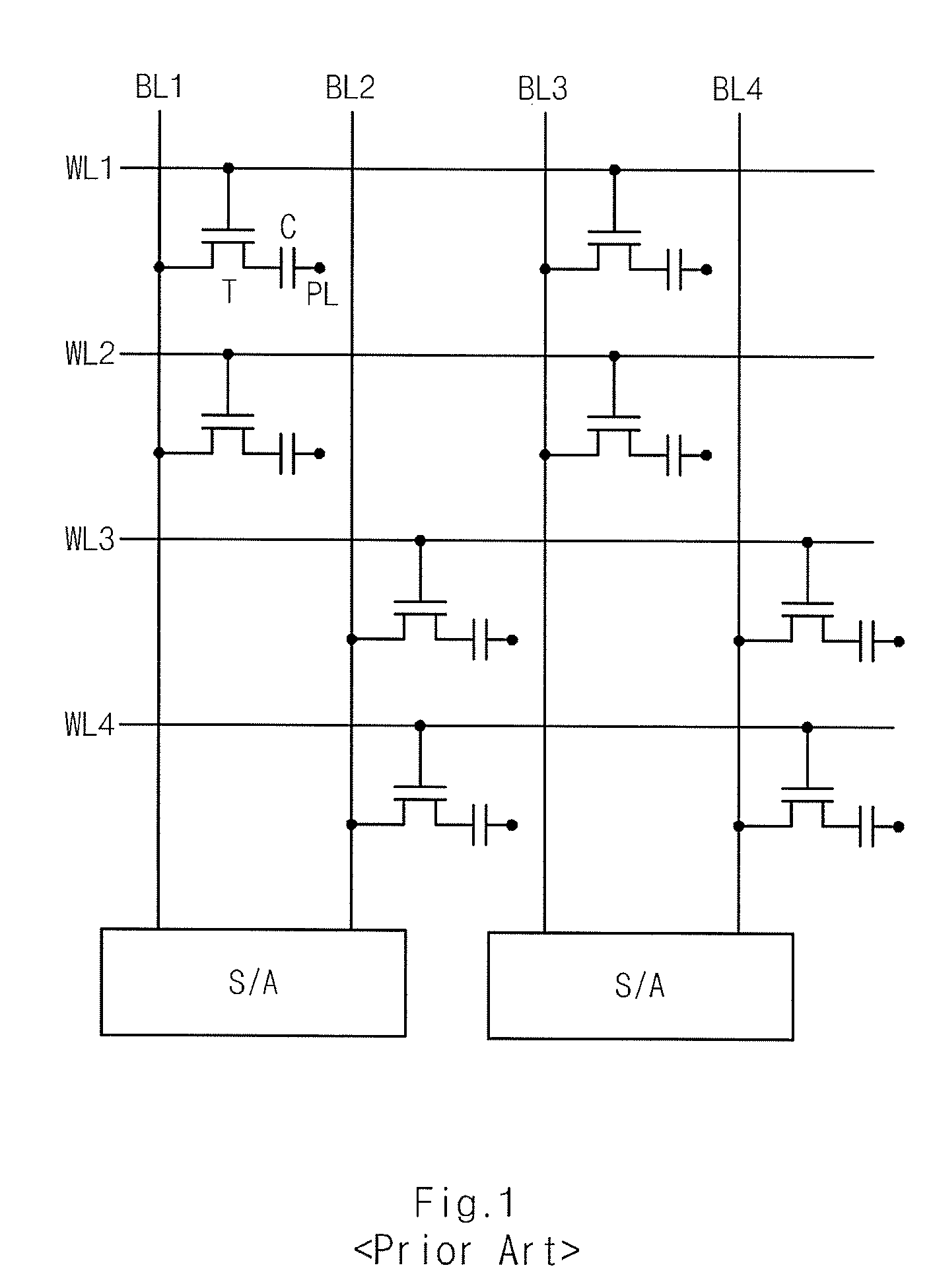

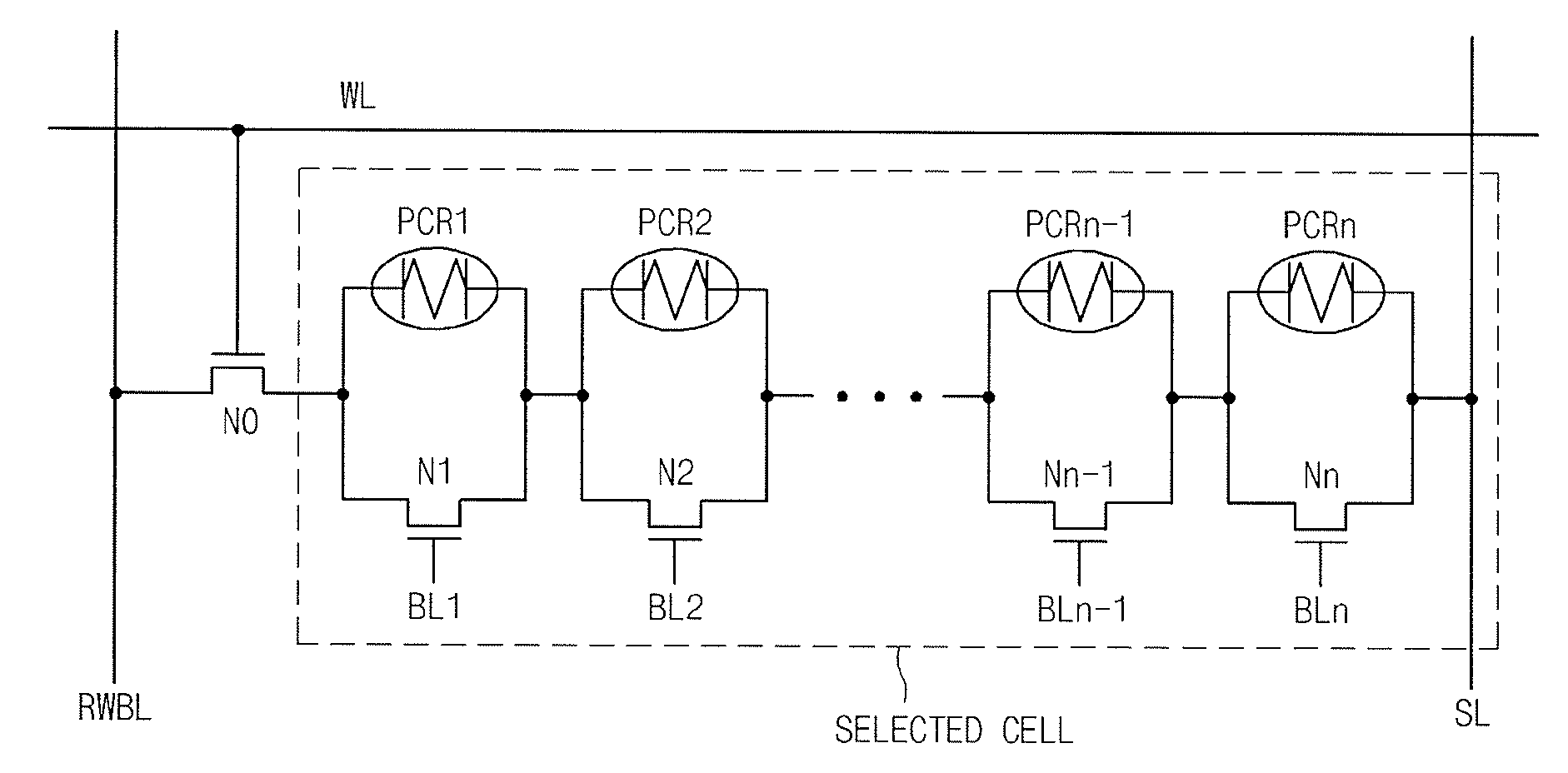

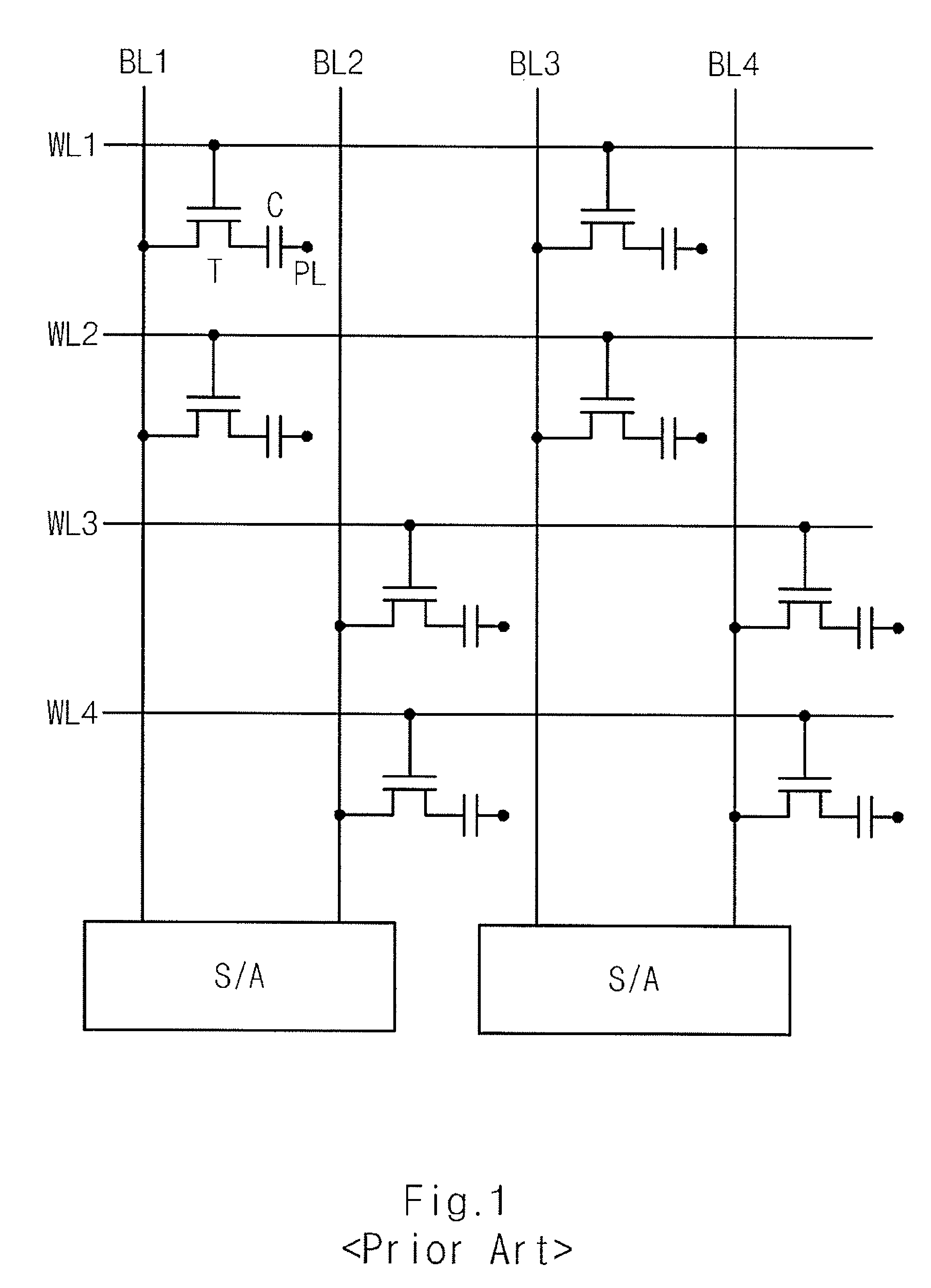

Semiconductor memory device for writing data to multiple cells simultaneously and refresh method thereof

ActiveUS20090067229A1Improve data retentionShorten write timeRead-only memoriesDigital storageWrite bitComputer architecture

A semiconductor memory device includes a read / write bit line configured to supply a cell driving voltage. A selecting unit is connected to the read / write bit line and is controlled by a word line. A plurality of cells are connected between the selecting unit and a source line, and the cells are configured to read and write data according to a cell driving voltage. Each switching element of a plurality of switching elements are connected in parallel with a single cell of the plurality of cells, and the plurality of switching elements are controlled selectively by a plurality of bit lines.

Owner:SK HYNIX INC

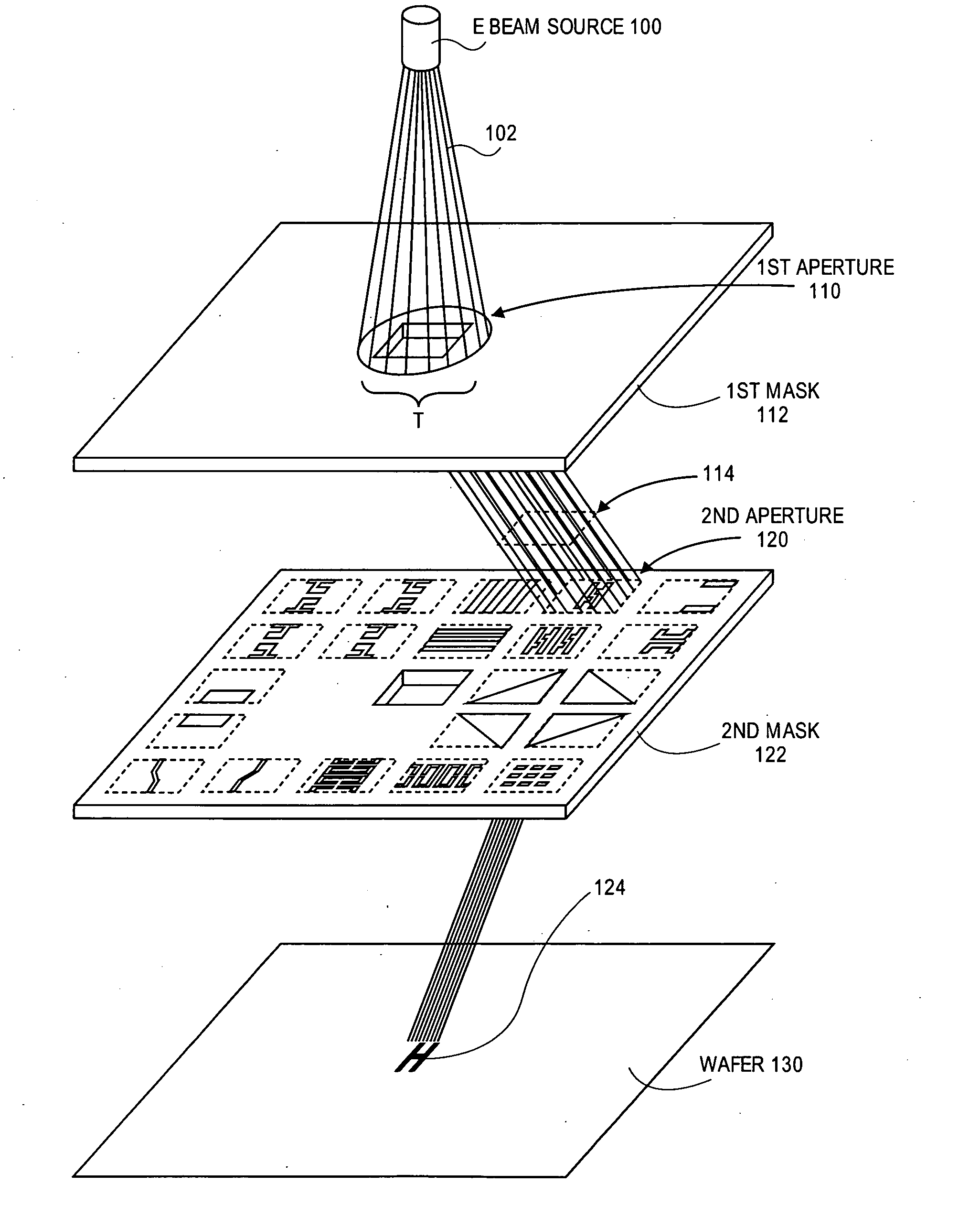

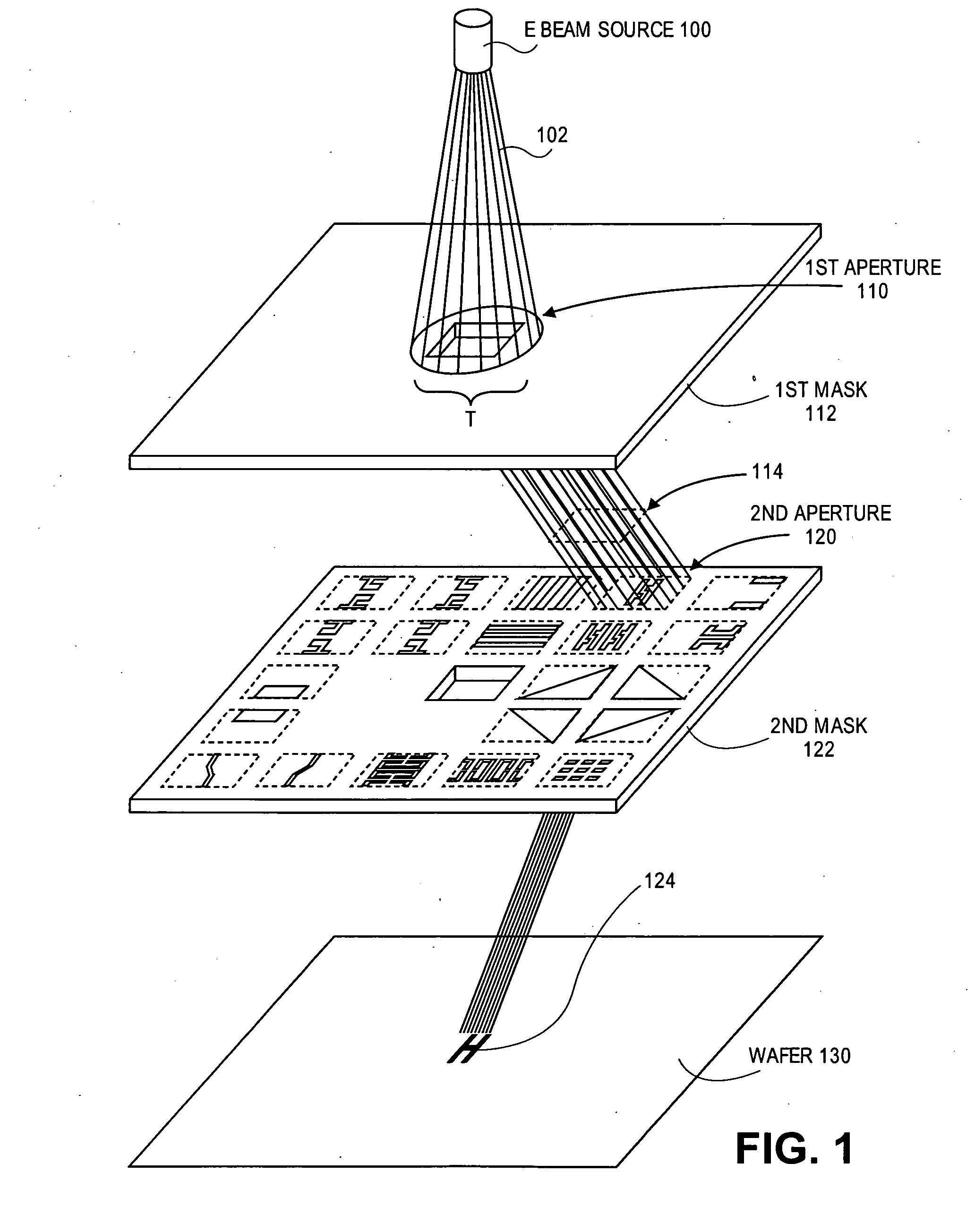

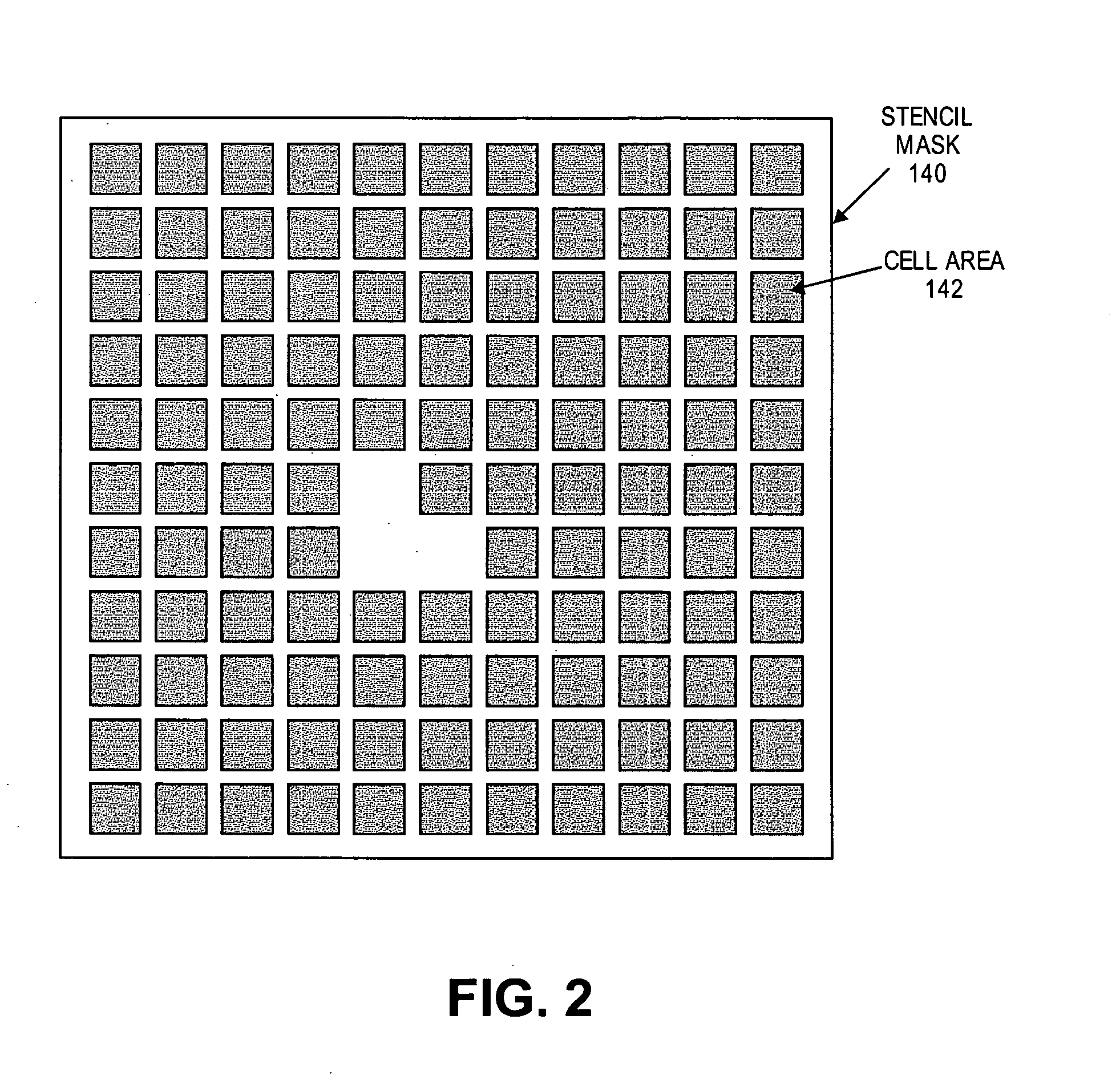

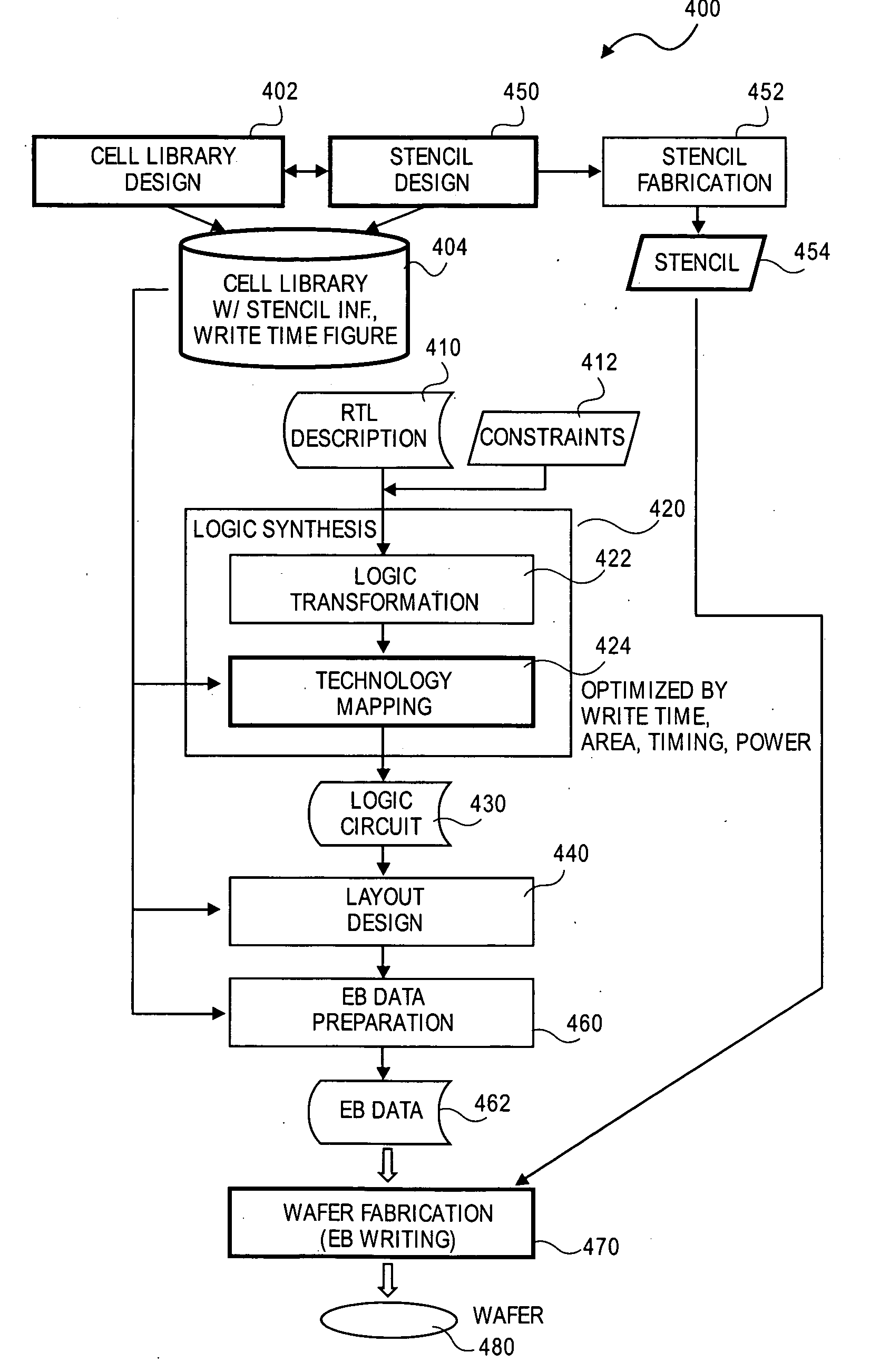

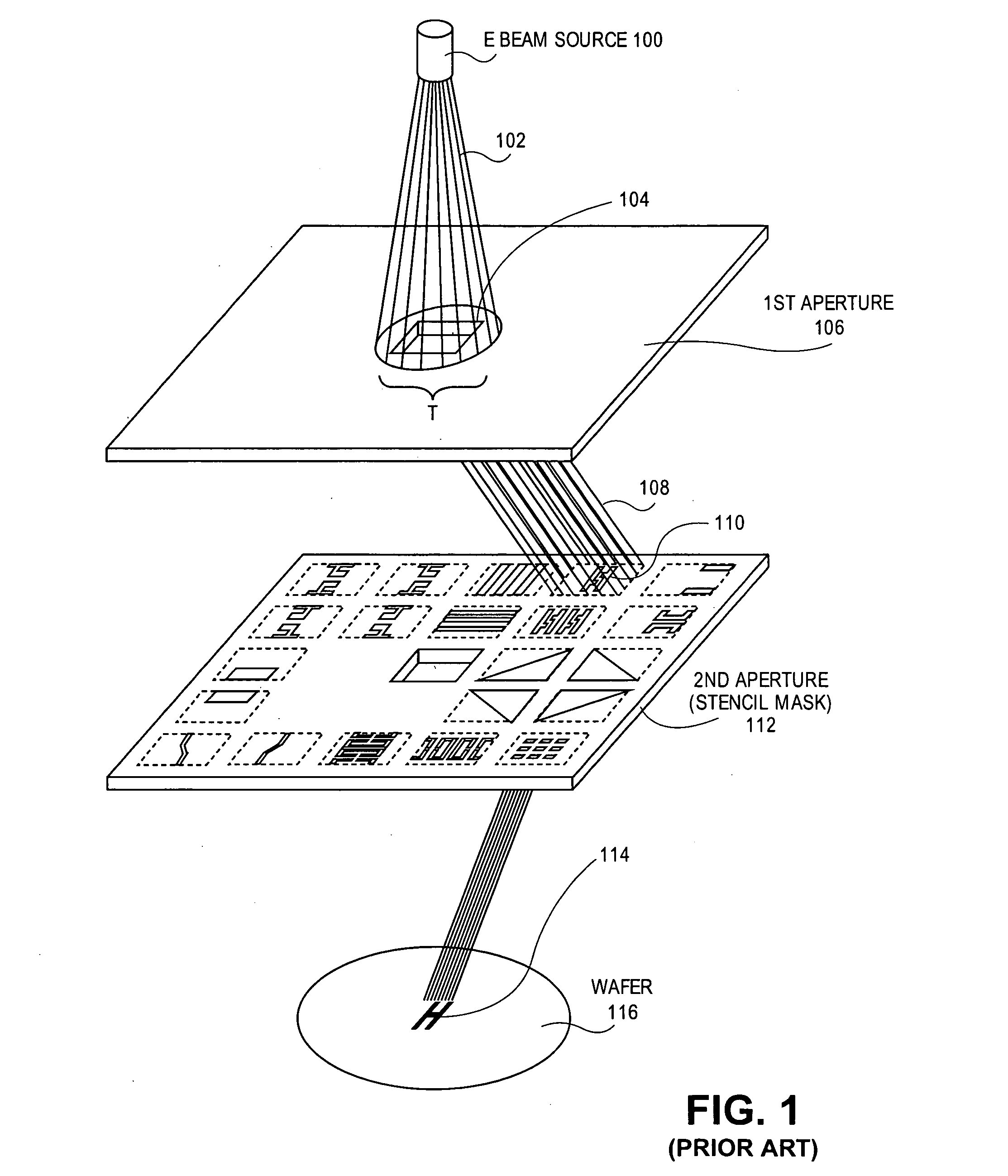

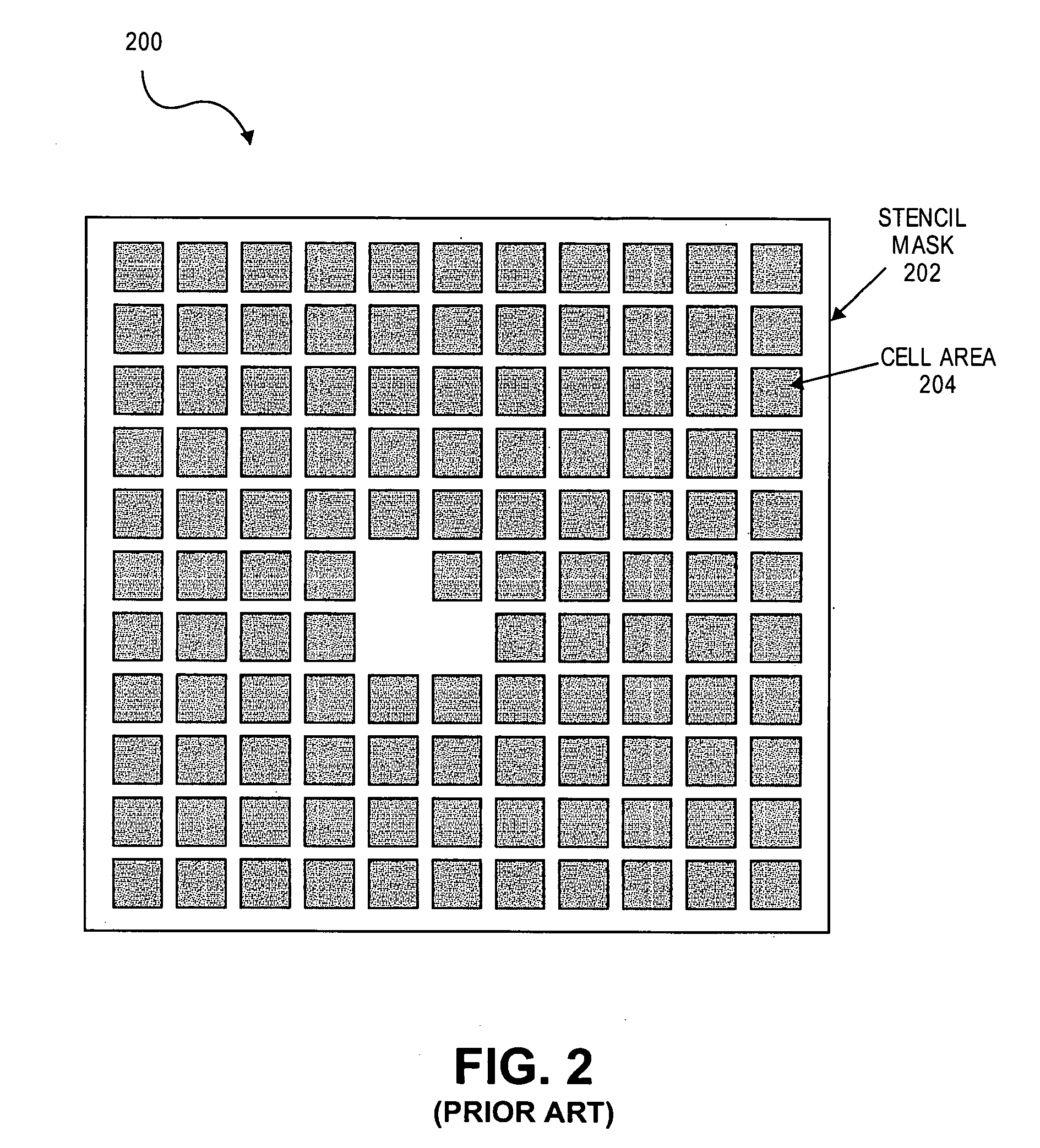

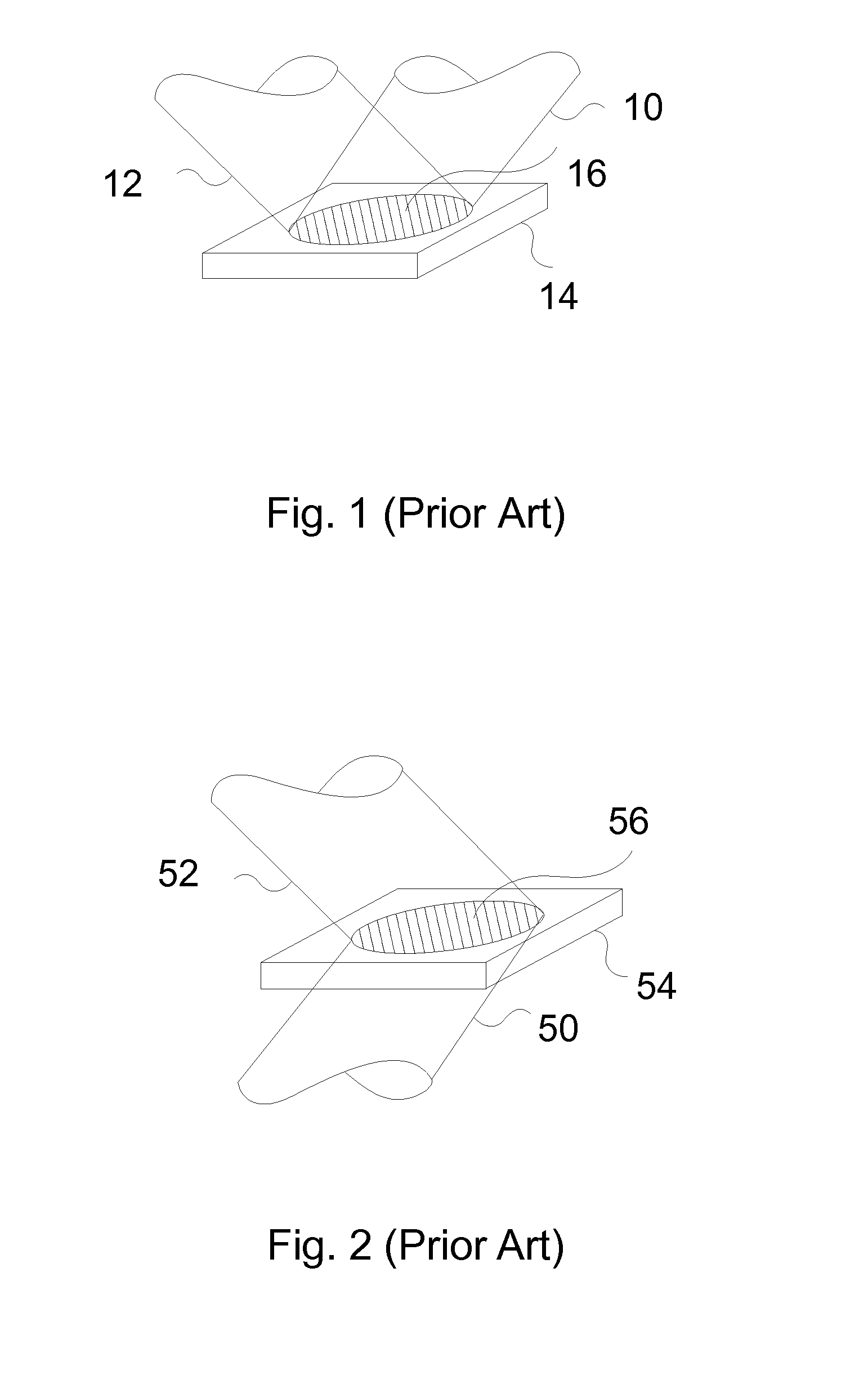

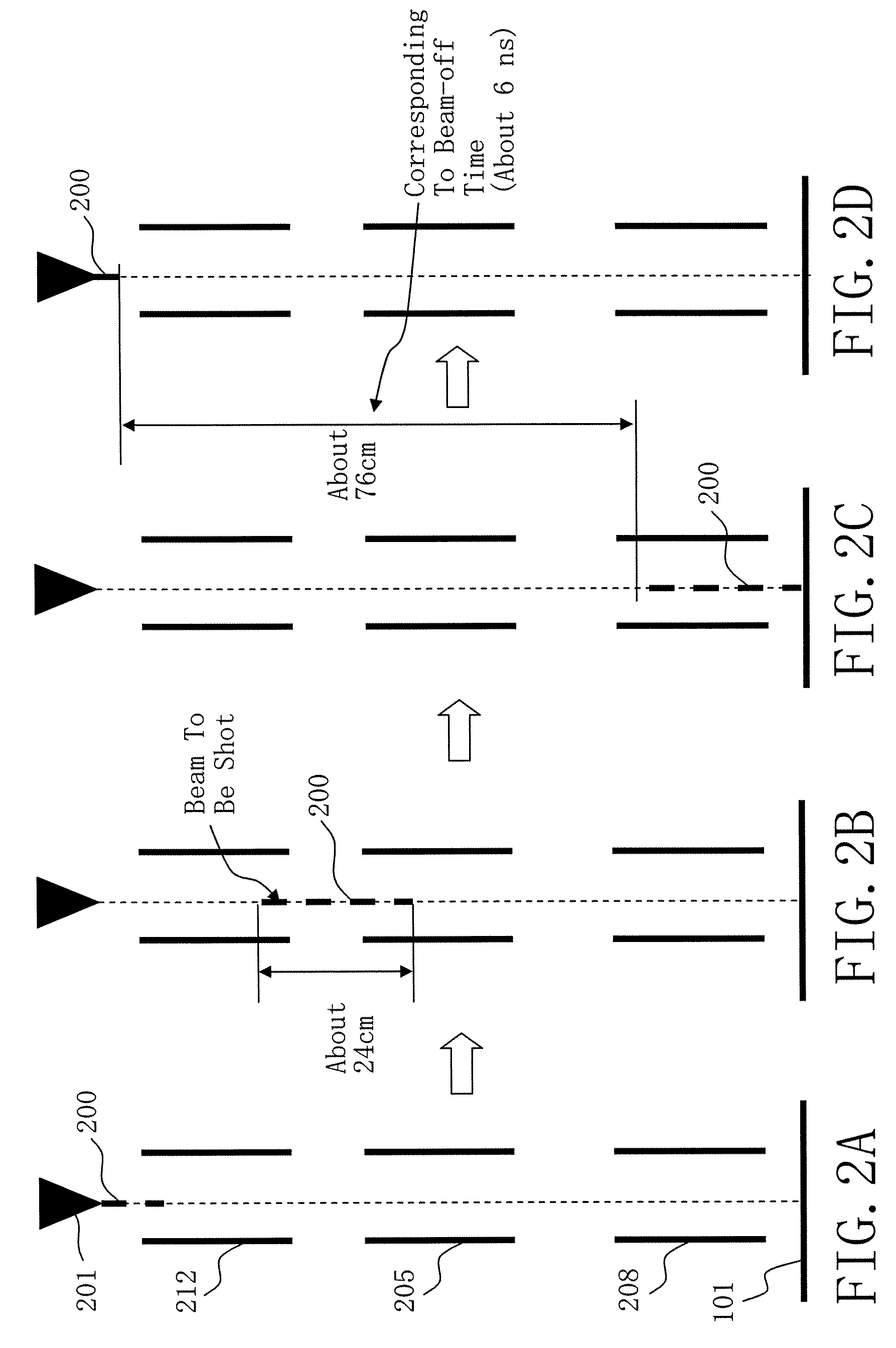

Stencil design and method for cell projection particle beam lithography

ActiveUS20080116397A1Reduce EB writing timeShorten write timeNanoinformaticsElectrode and associated part arrangementsCell patternParticle beam

A method and system for particle beam lithography, such as electron beam (EB) lithography, is disclosed. The method and system include selecting one of a plurality of cell patterns from a stencil mask and partially exposing the cell pattern to a particle beam, such as an electron beam, so as to selectively project a portion of the cell pattern on a substrate.

Owner:ADVANTEST CORP

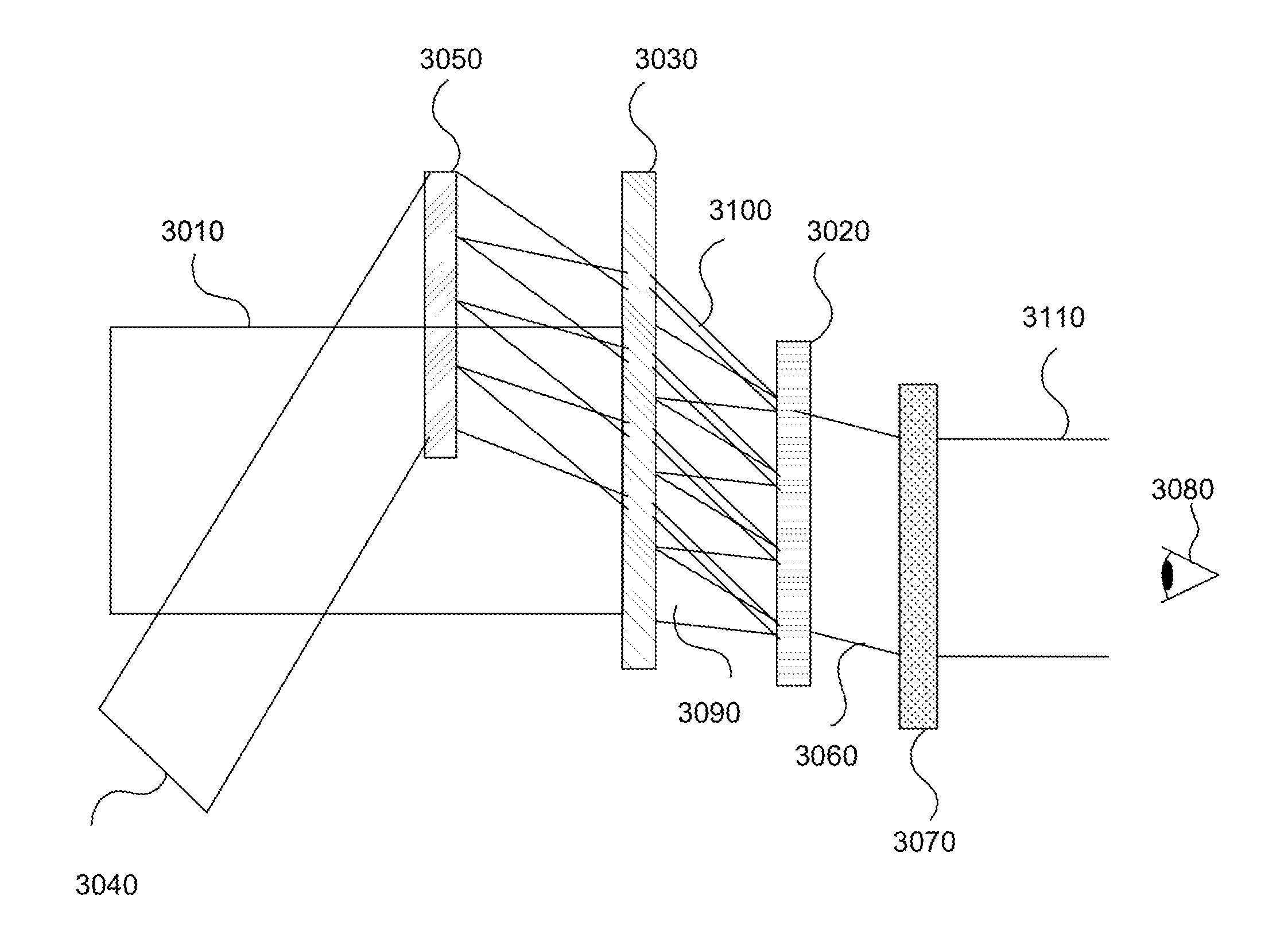

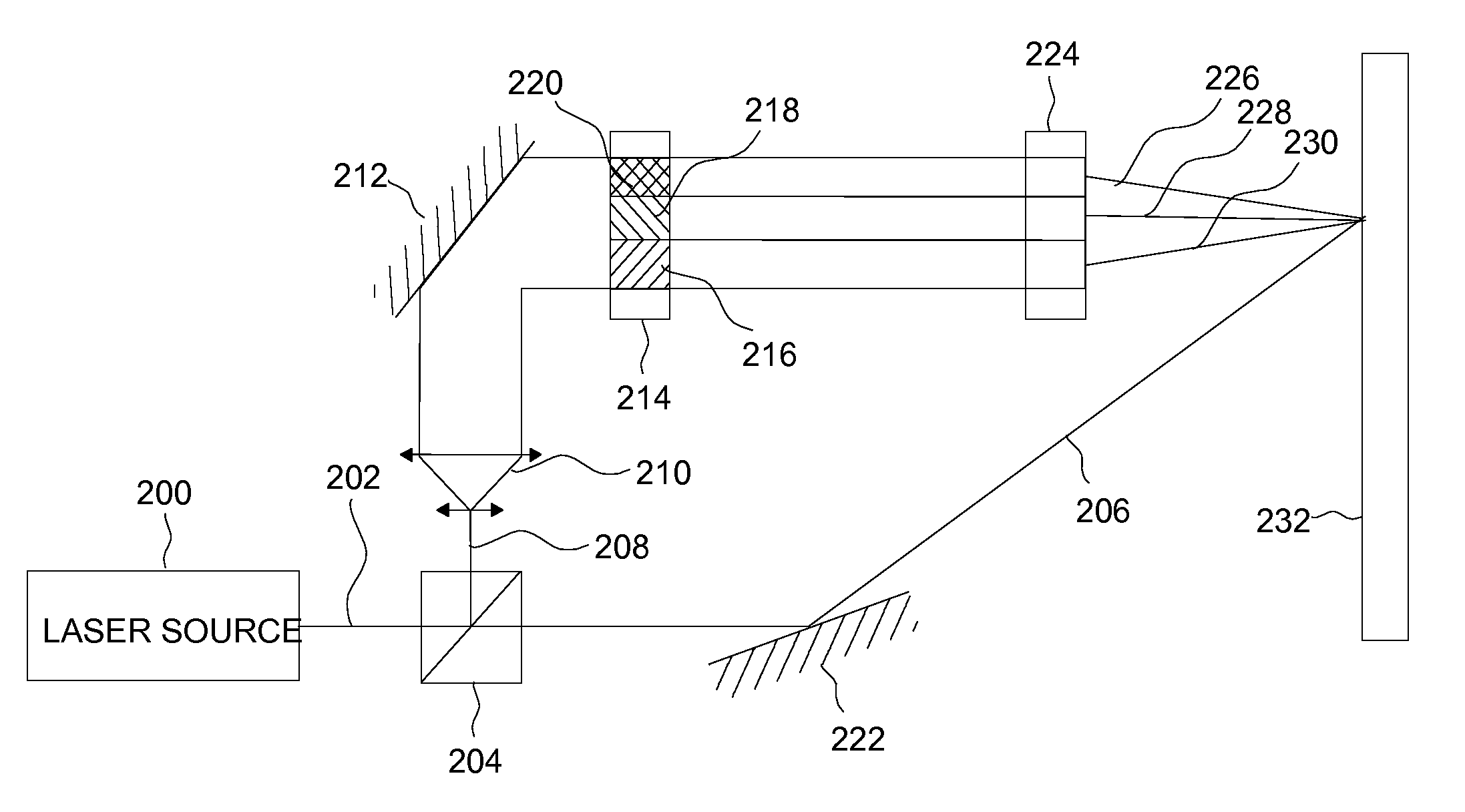

System for holography

ActiveUS8634119B2Shorten write timeImprove efficiencyHolographic optical componentsRecord information storageImage resolutionDisplay device

Owner:TIPD

Apparatus, system, and method for converting a storage request into an append data storage command

ActiveUS8151082B2Shorten write timeImprove efficiencyMemory architecture accessing/allocationProgram synchronisationData segmentNetwork packet

An apparatus, system, and method are disclosed for converting a storage request to an append data storage command. A storage request receiver module receives a storage request from a requesting device. The storage request is to store a data segment onto a data storage device. The storage request includes source parameters for the data segment. The source parameters include a virtual address. A translation module translates the storage request to storage commands. At least one storage command includes an append data storage command that directs the data storage device to store data of the data segment and the one or more source parameters with the data, including a virtual address, at one or more append points. A mapping module maps source parameters of the data segment to locations where the data storage device appended the data packets of the data segment and source parameters.

Owner:UNIFICATION TECH LLC

Method and system for logic design for cell projection particle beam lithography

InactiveUS20080128637A1Short EB writing timeShorten write timeElectric discharge tubesNanoinformaticsCell patternLithographic artist

A method for particle beam lithography, such as electron beam (EB) lithography, includes predefining a stencil design having a plurality of cell patterns with information from a cell library, fabricating the stencil design, synthesizing a functional description into a logic circuit design after predefining the stencil design so that one or more characteristics of the stencil design are considered during synthesizing of the functional description into the logic circuit design, optimizing the logic circuit design, generating a layout design from the optimized logic circuit design, and forming the logic circuit on a substrate according to the stencil design and the layout design.

Owner:D2S

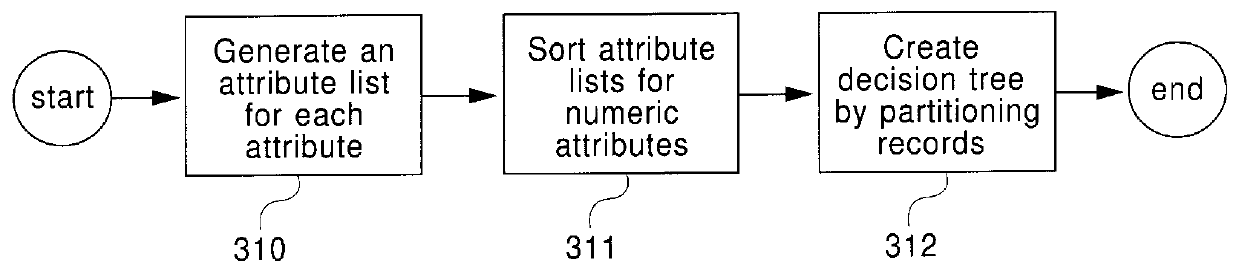

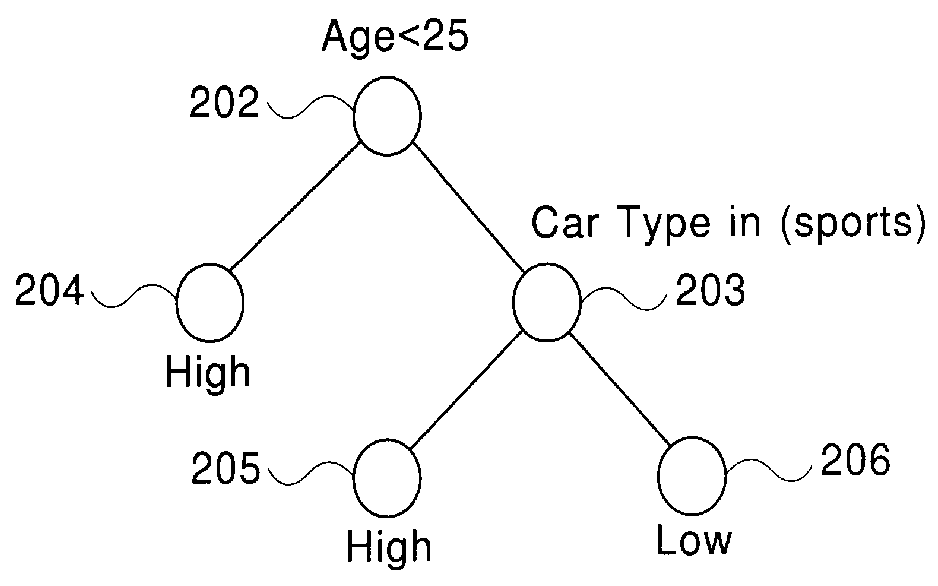

Method to reduce I/O for hierarchical data partitioning methods

InactiveUS6055539AGenerate efficientlyShort training timeData processing applicationsDigital data information retrievalRecordsetMulti processor

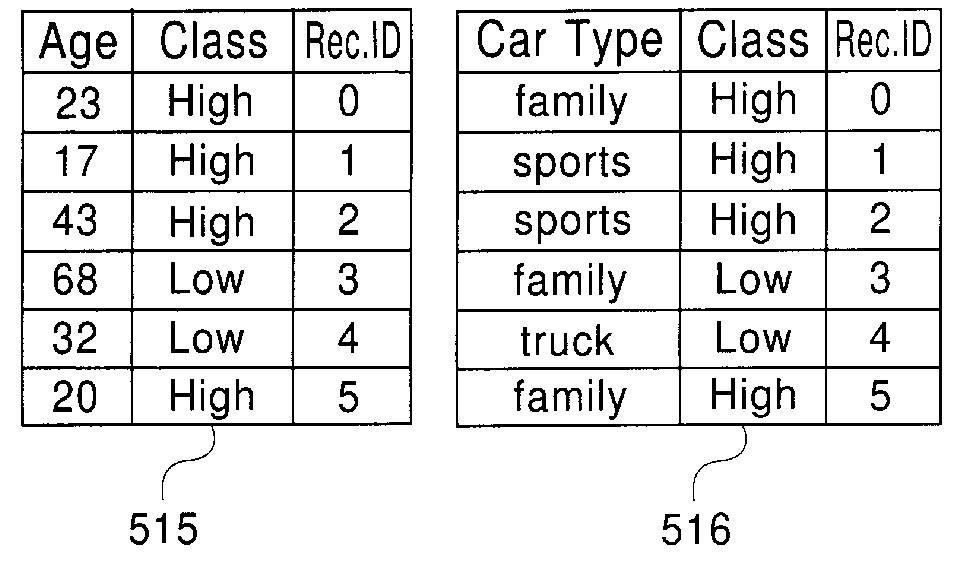

A method and system for generating a decision-tree classifier from a training set of records, independent of the system memory size. The method includes the steps of: generating an attribute list for each attribute of the records, sorting the attribute lists for numeric attributes, and generating a decision tree by repeatedly partitioning the records using the attribute lists. For each node, split points are evaluated to determine the best split test for partitioning the records at the node. Preferably, a gini index and class histograms are used in determining the best splits. The gini index indicates how well a split point separates the records while the class histograms reflect the class distribution of the records at the node. Also, a hash table is built as the attribute list of the split attribute is divided among the child nodes, which is then used for splitting the remaining attribute lists of the node. The method reduces I / O read time by combining the read for partitioning the records at a node with the read required for determining the best split test for the child nodes. Further, it requires writes of the records only at one out of n levels of the decision tree where n> / =2. Finally, a novel data layout on disk minimizes disk seek time. The I / O optimizations work in a general environment for hierarchical data partitioning. They also work in a multi-processor environment. After the generation of the decision tree, any prior art pruning methods may be used for pruning the tree.

Owner:IBM CORP

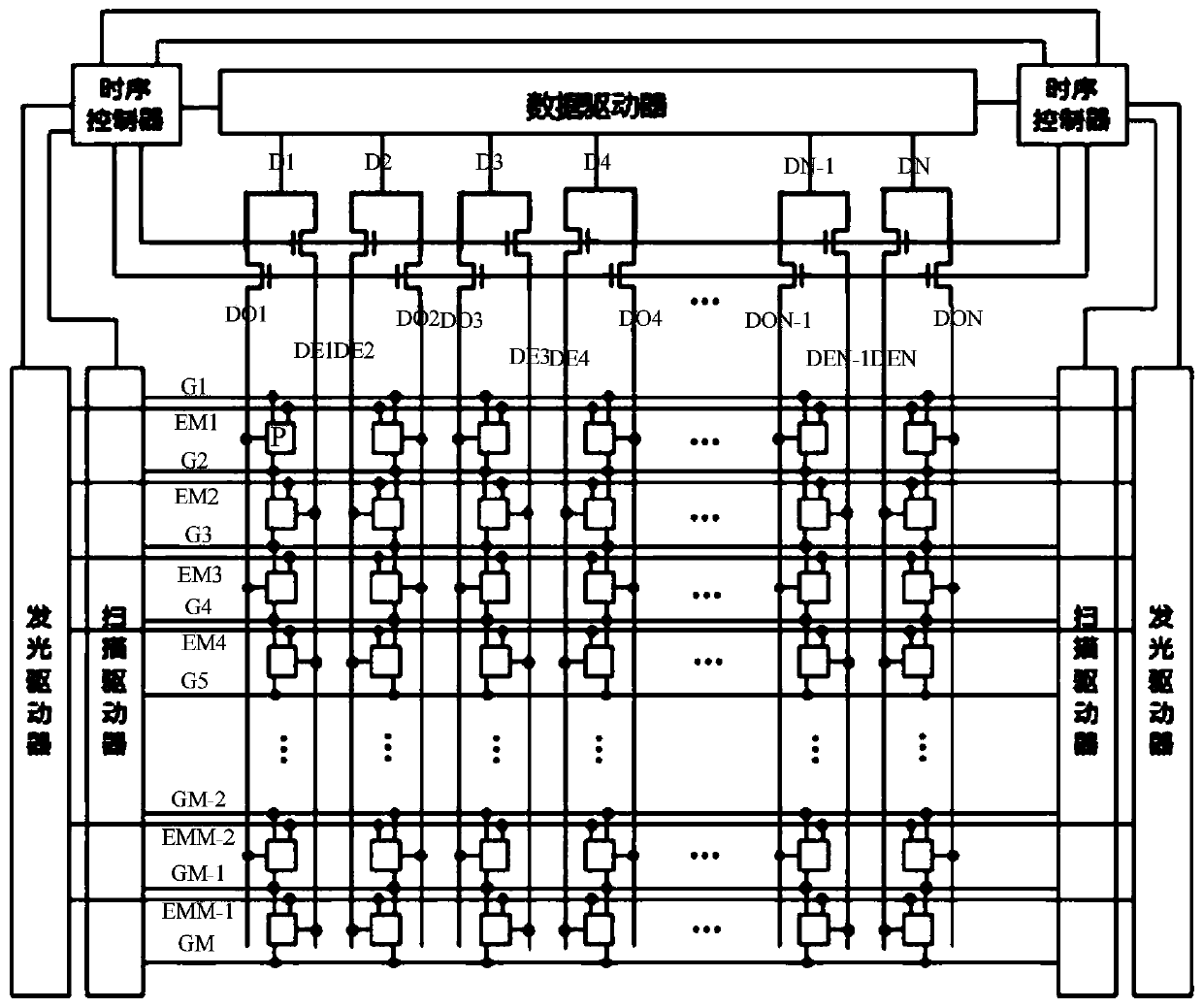

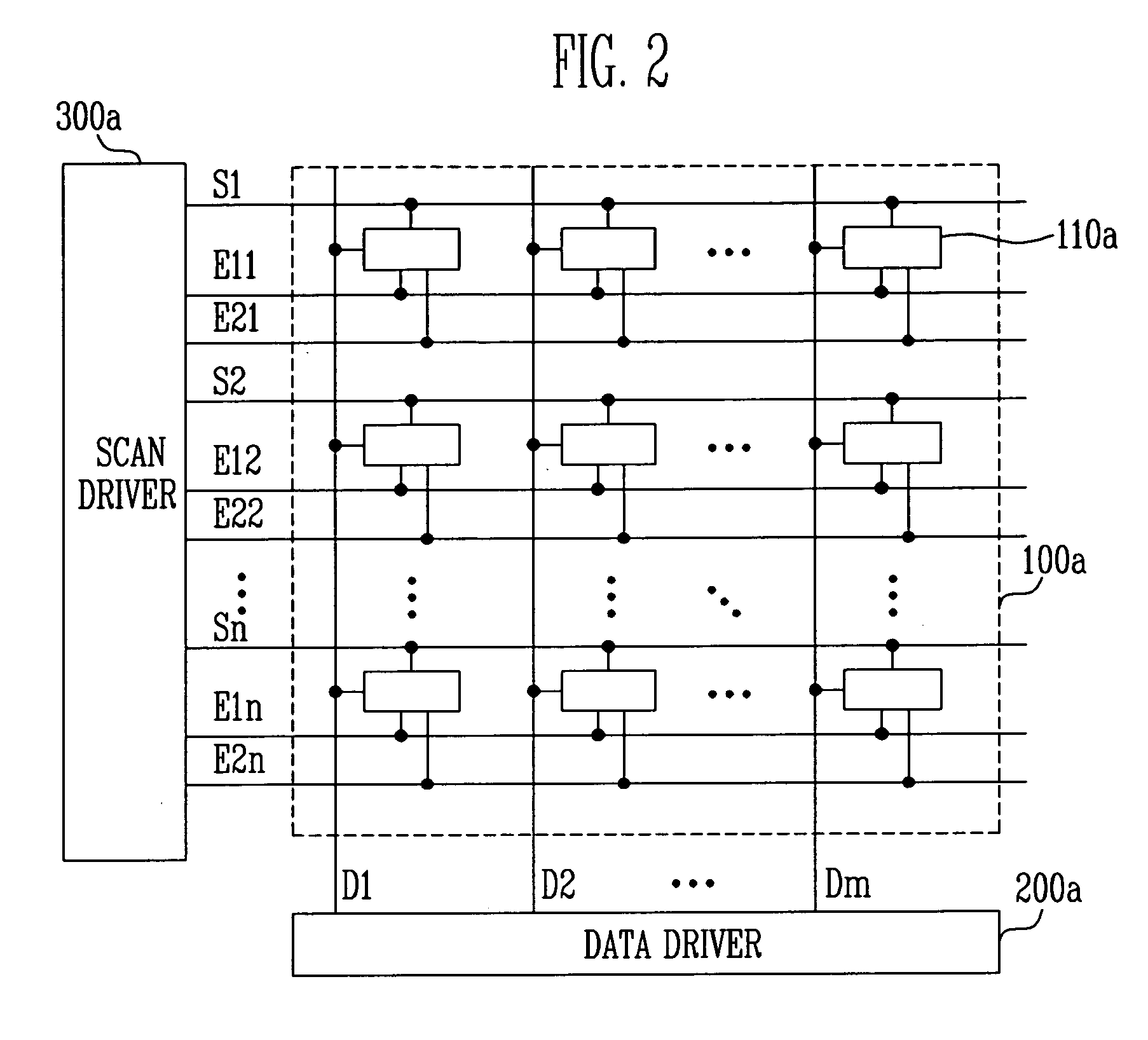

Display device

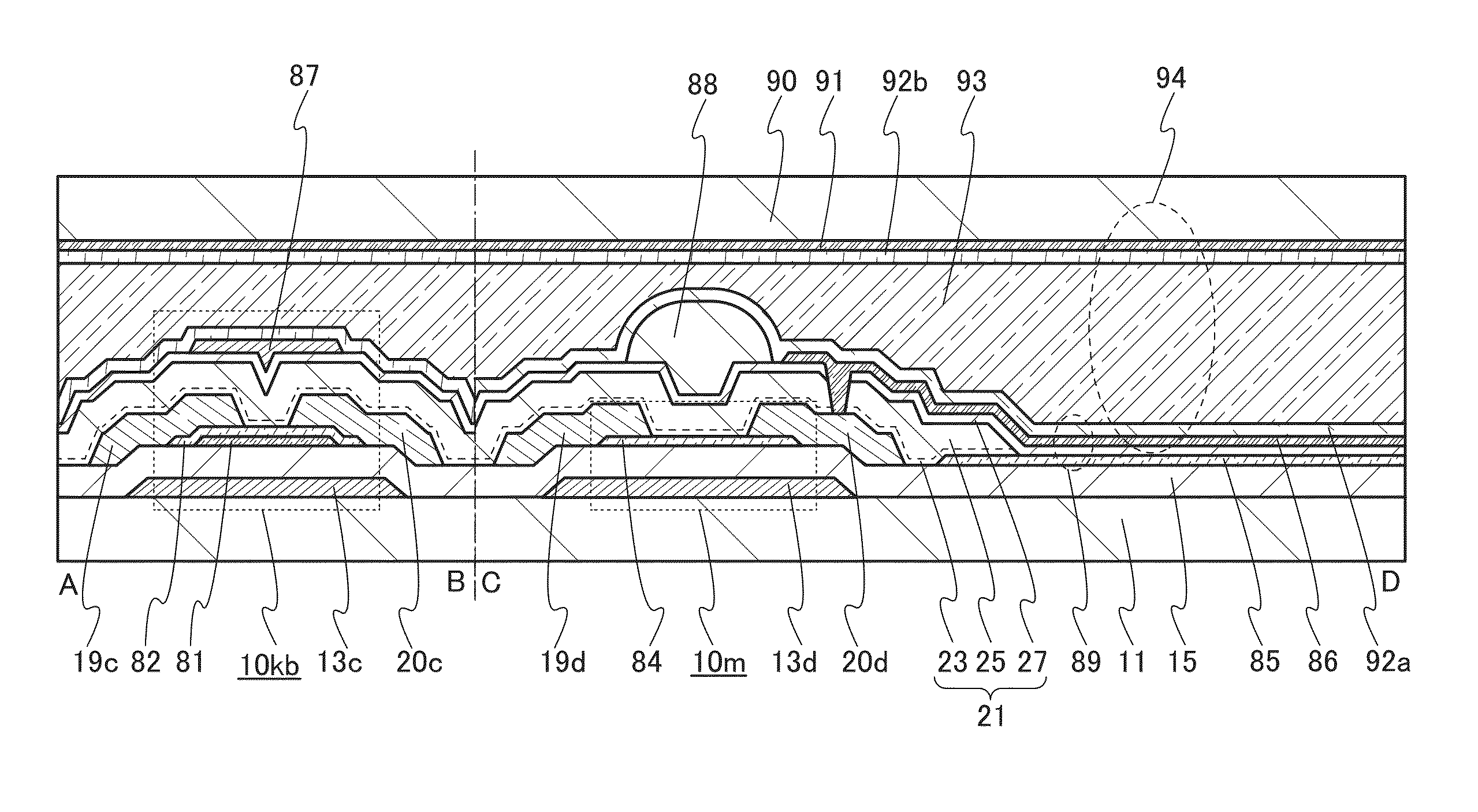

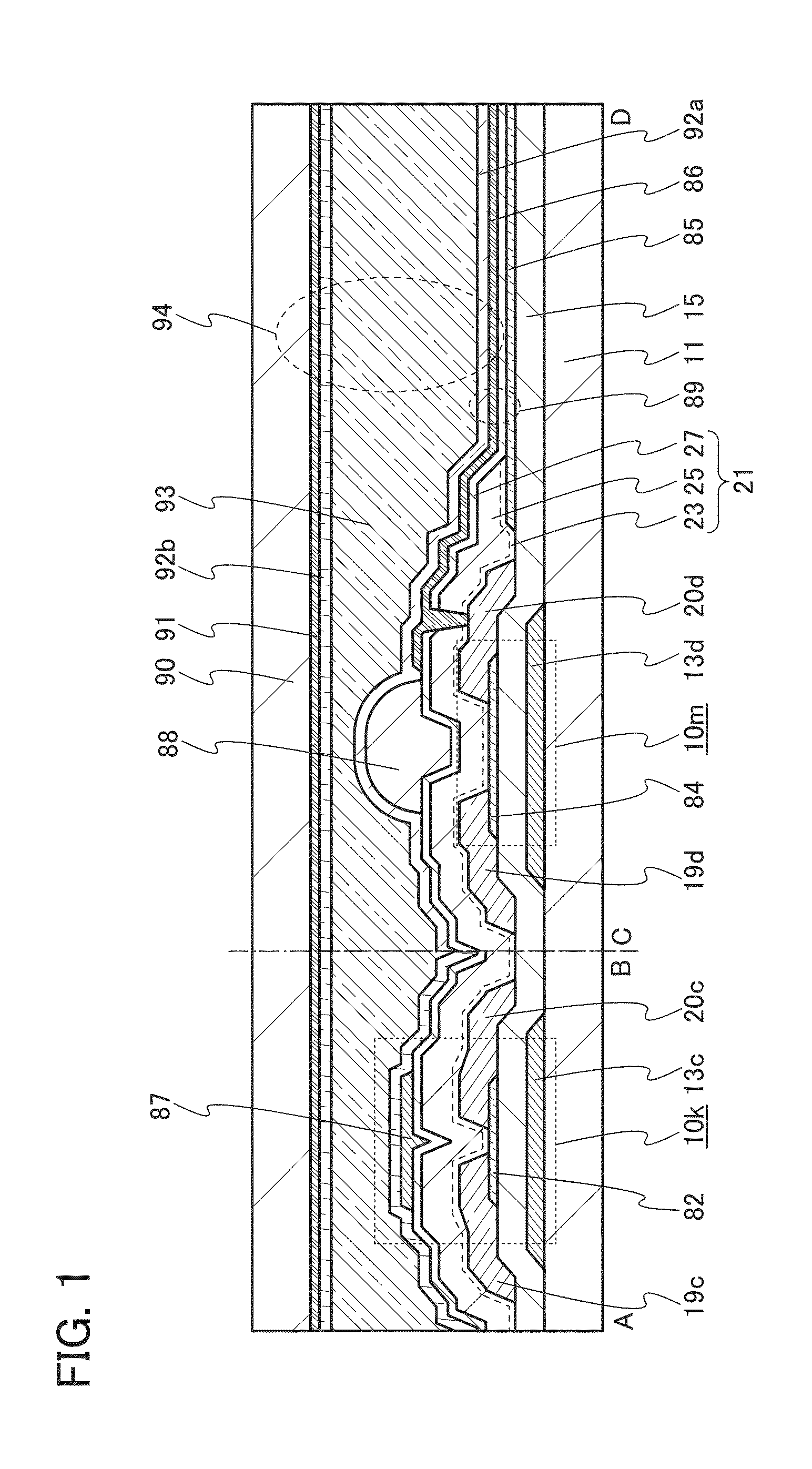

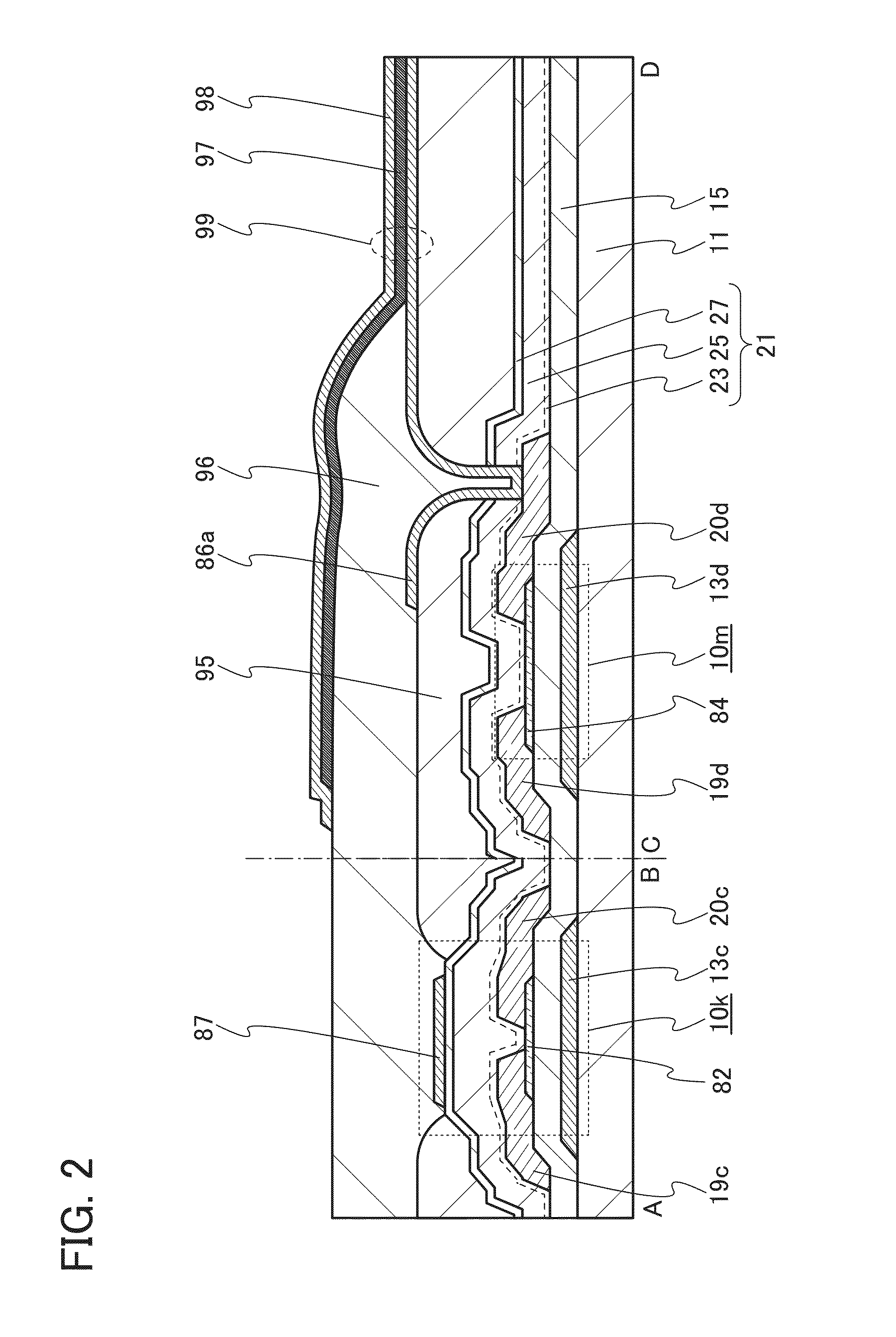

ActiveUS20150153599A1Improve image qualityFew external connection terminalStatic indicating devicesSolid-state devicesDriver circuitMicrometer

To provide a display device in which plural kinds of circuits are formed over one substrate and plural kinds of transistors corresponding to characteristics of the plural kinds of circuits are provided. The display device includes a pixel portion and a driver circuit that drives the pixel portion over one substrate. The pixel portion includes a first transistor including a first oxide semiconductor film. The driver circuit includes a second transistor including a second oxide semiconductor film. The first oxide semiconductor film and the second oxide semiconductor film are formed over one insulating surface. A channel length of the first transistor is longer than a channel length of the second transistor. The channel length of the first transistor is greater than or equal to 2.5 micrometer.

Owner:SEMICON ENERGY LAB CO LTD

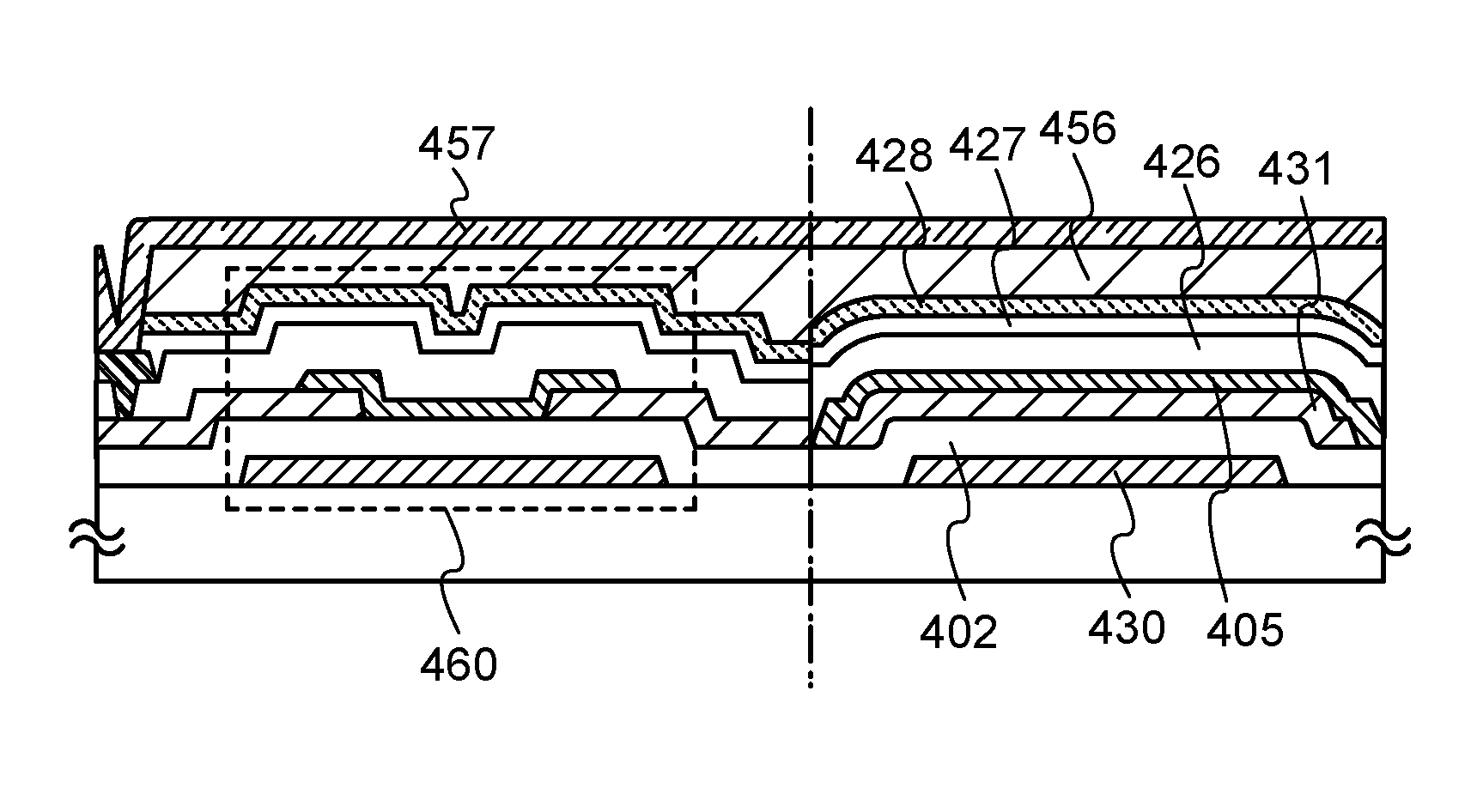

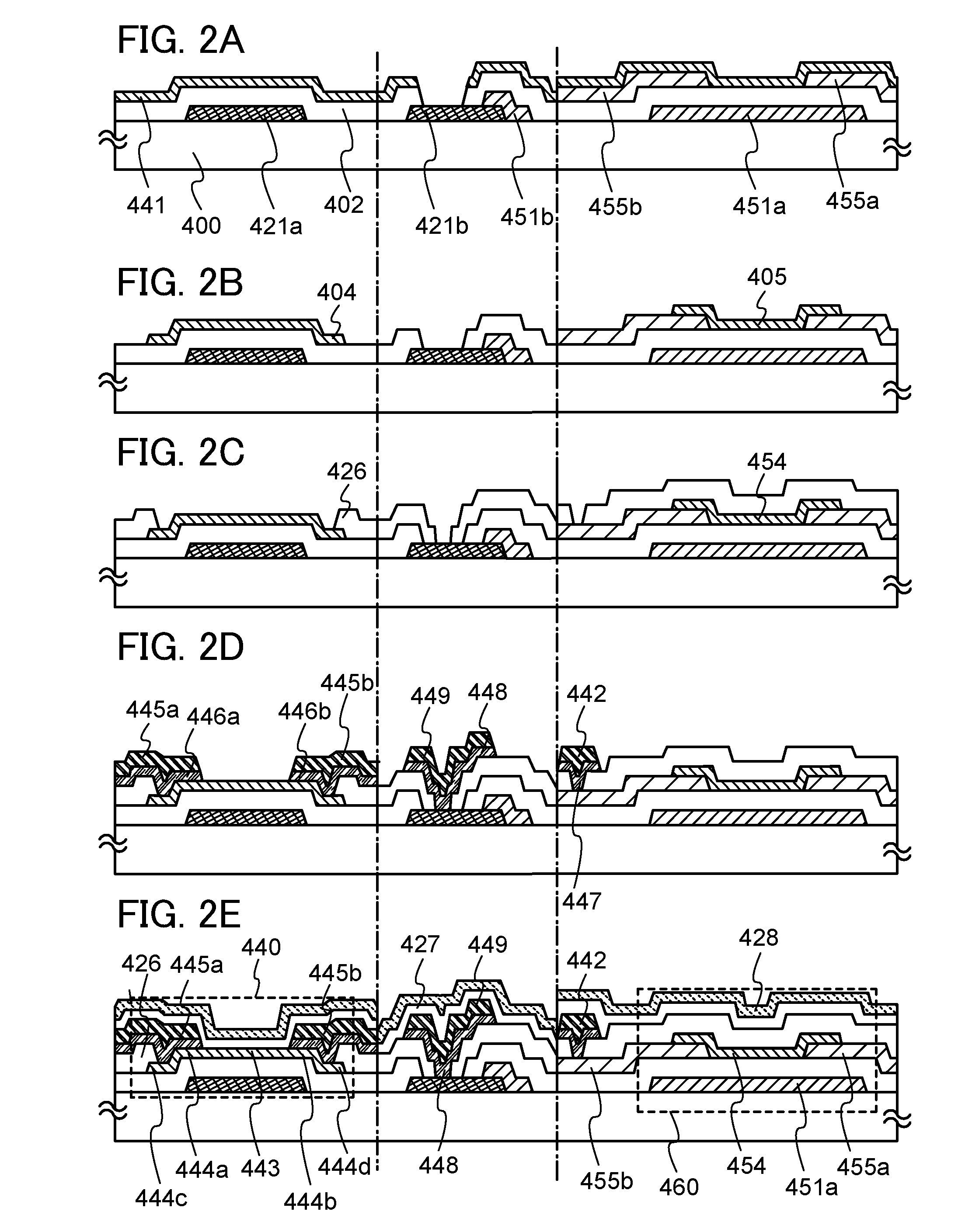

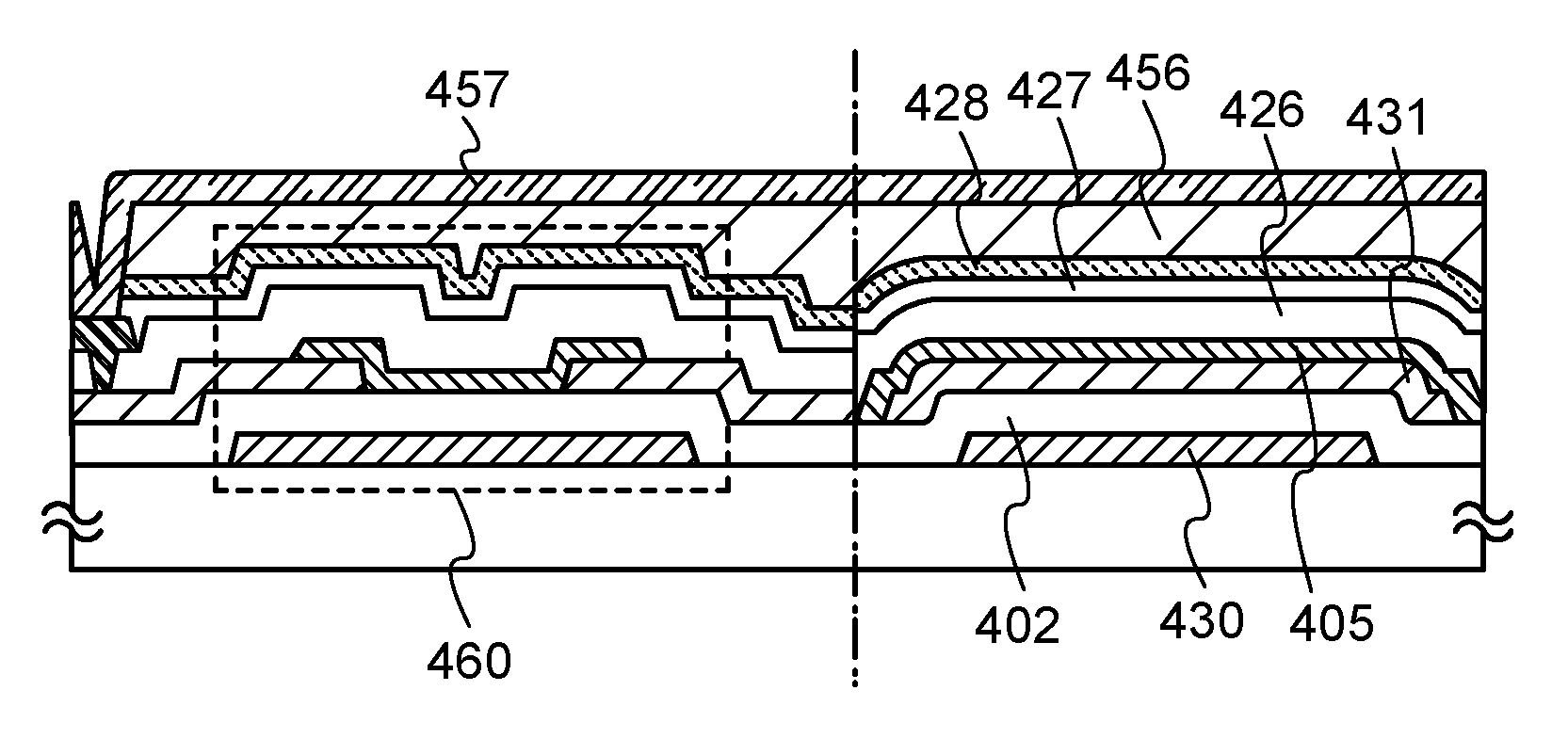

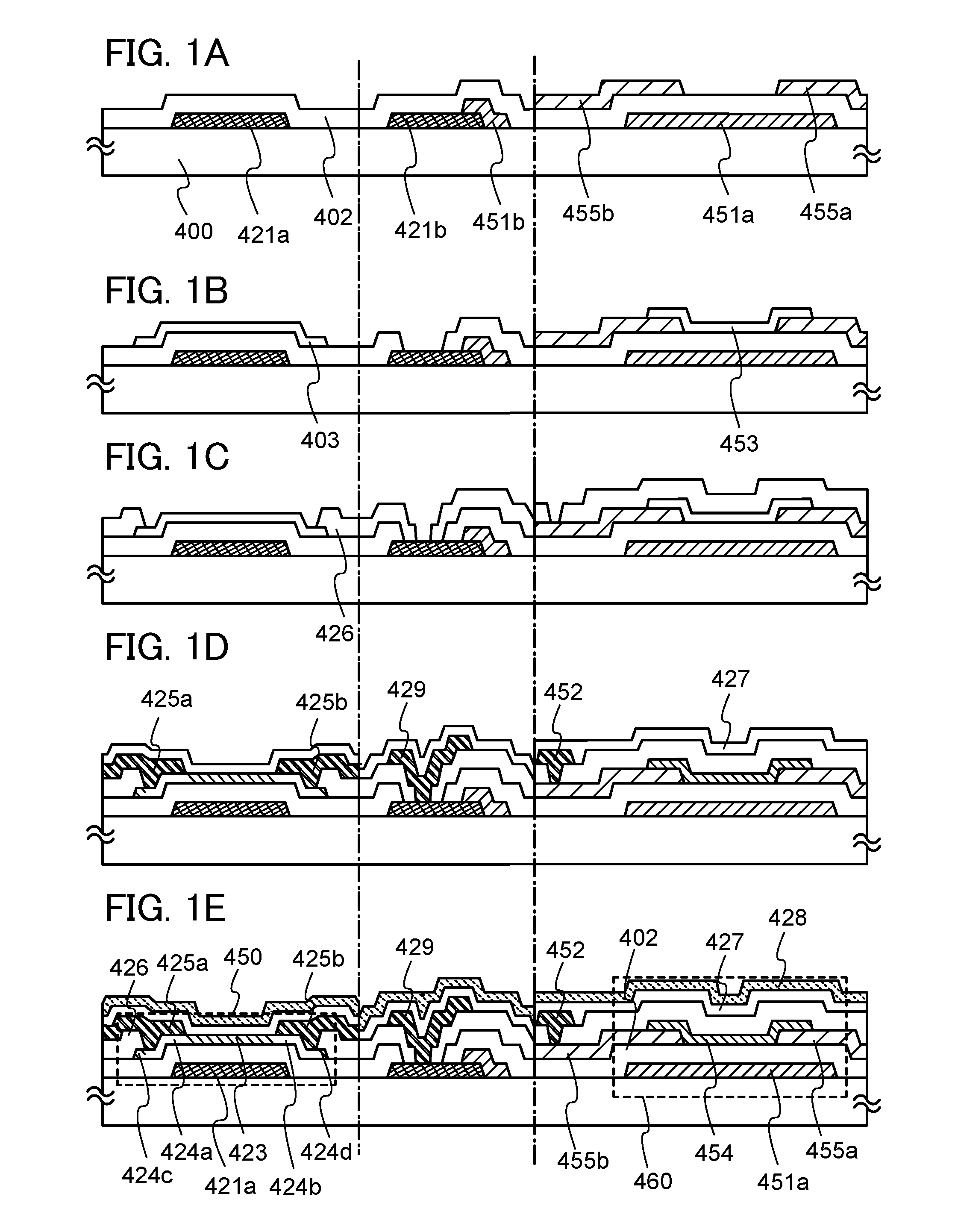

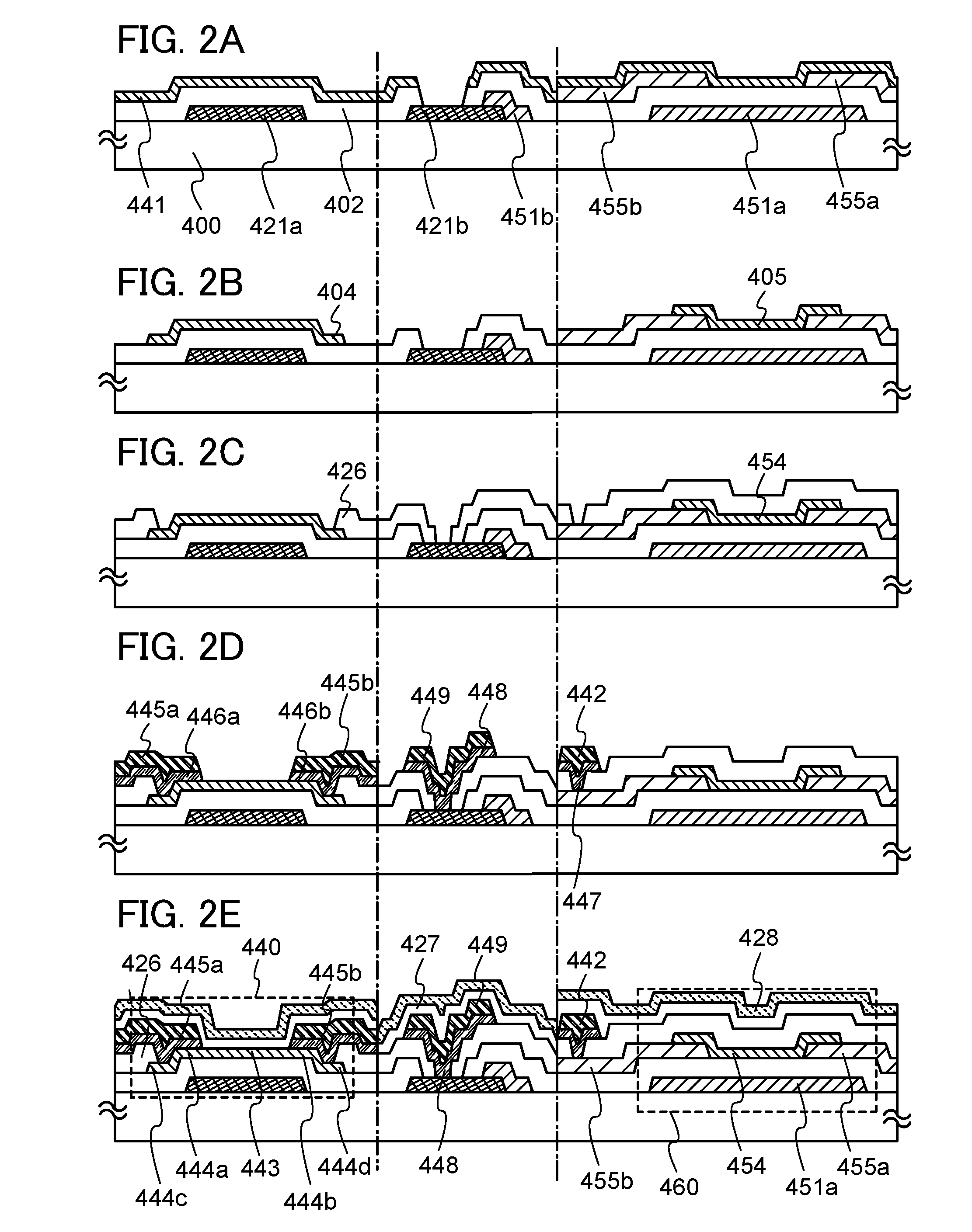

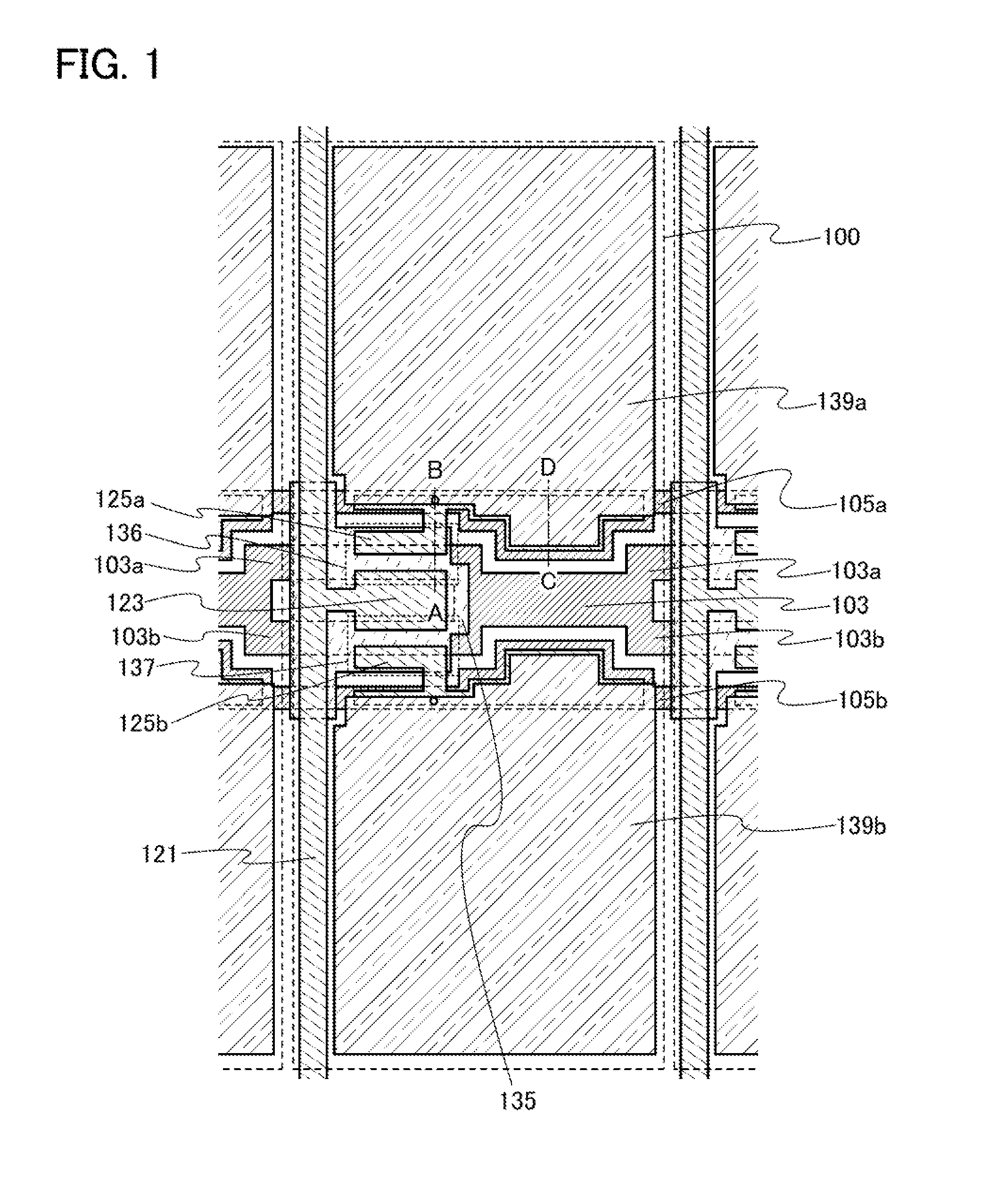

Display device and method for manufacturing the same

ActiveUS8115883B2High densityShorten display timeStatic indicating devicesSolid-state devicesDriver circuitElectrical conductor

An object is to provide a display device with excellent display characteristics, where a pixel circuit and a driver circuit provided over one substrate are formed using transistors which have different structures corresponding to characteristics of the respective circuits. The driver circuit portion includes a driver circuit transistor in which a gate electrode layer, a source electrode layer, and a drain electrode layer are formed using a metal film, and a channel layer is formed using an oxide semiconductor. The pixel portion includes a pixel transistor in which a gate electrode layer, a source electrode layer, and a drain electrode layer are formed using an oxide conductor, and a semiconductor layer is formed using an oxide semiconductor. The pixel transistor is formed using a light-transmitting material, and thus, a display device with higher aperture ratio can be manufactured.

Owner:SEMICON ENERGY LAB CO LTD

Display device and method for manufacturing the same

ActiveUS20110049510A1Easily brokenLower display costsSolid-state devicesSemiconductor/solid-state device manufacturingDriver circuitElectrical conductor

An object is to provide a display device with excellent display characteristics, where a pixel circuit and a driver circuit provided over one substrate are formed using transistors which have different structures corresponding to characteristics of the respective circuits. The driver circuit portion includes a driver circuit transistor in which a gate electrode layer, a source electrode layer, and a drain electrode layer are formed using a metal film, and a channel layer is formed using an oxide semiconductor. The pixel portion includes a pixel transistor in which a gate electrode layer, a source electrode layer, and a drain electrode layer are formed using an oxide conductor, and a semiconductor layer is formed using an oxide semiconductor. The pixel transistor is formed using a light-transmitting material, and thus, a display device with higher aperture ratio can be manufactured.

Owner:SEMICON ENERGY LAB CO LTD

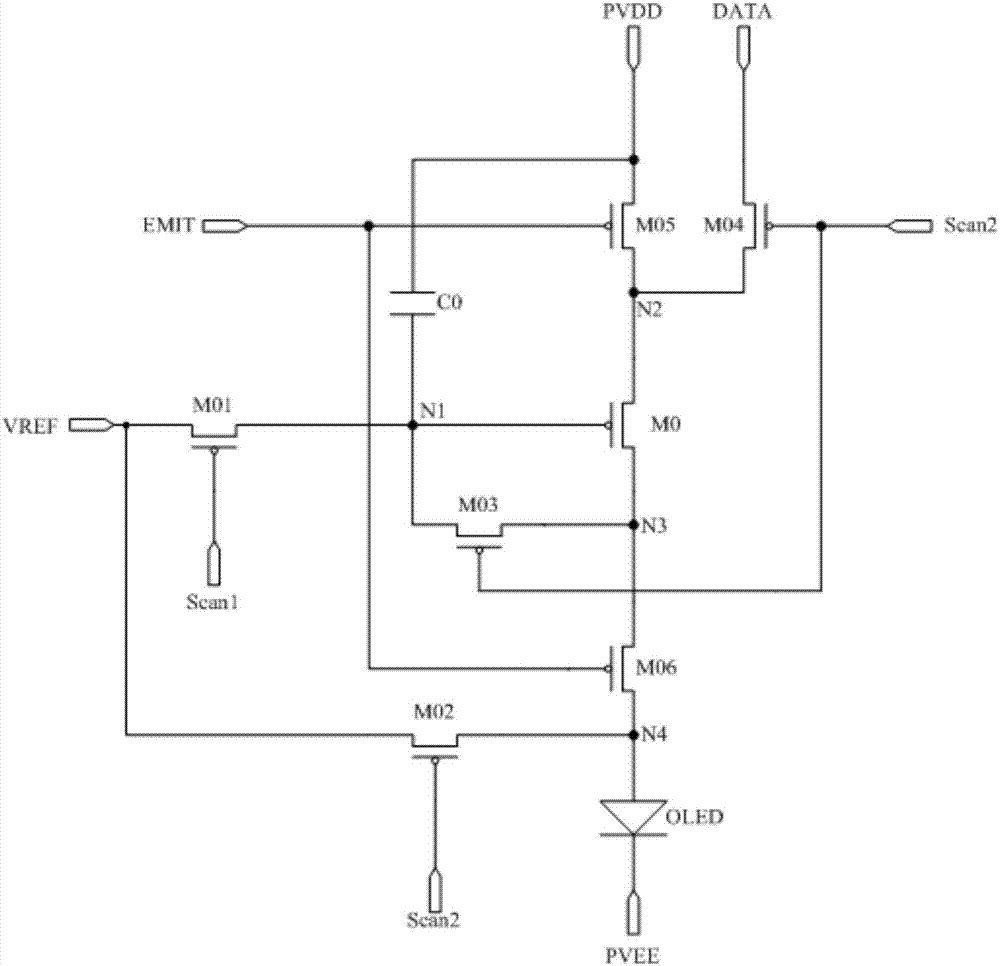

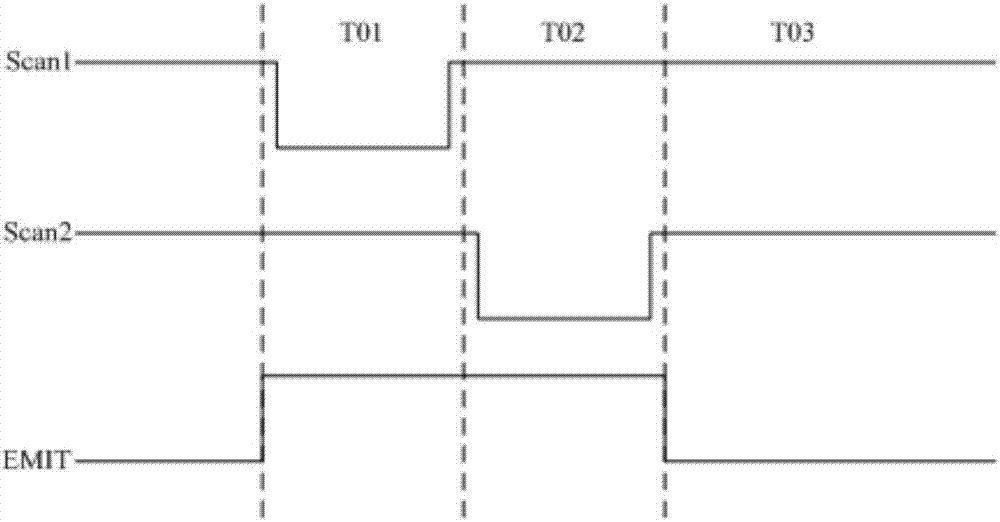

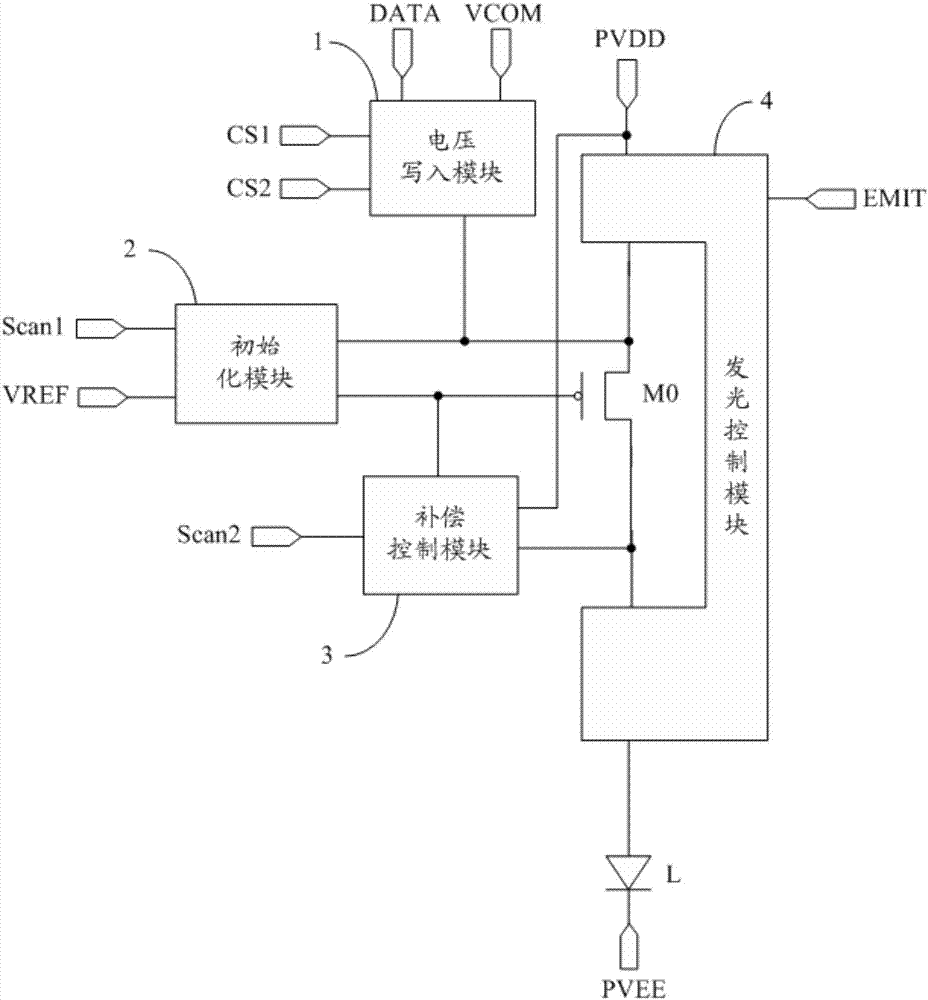

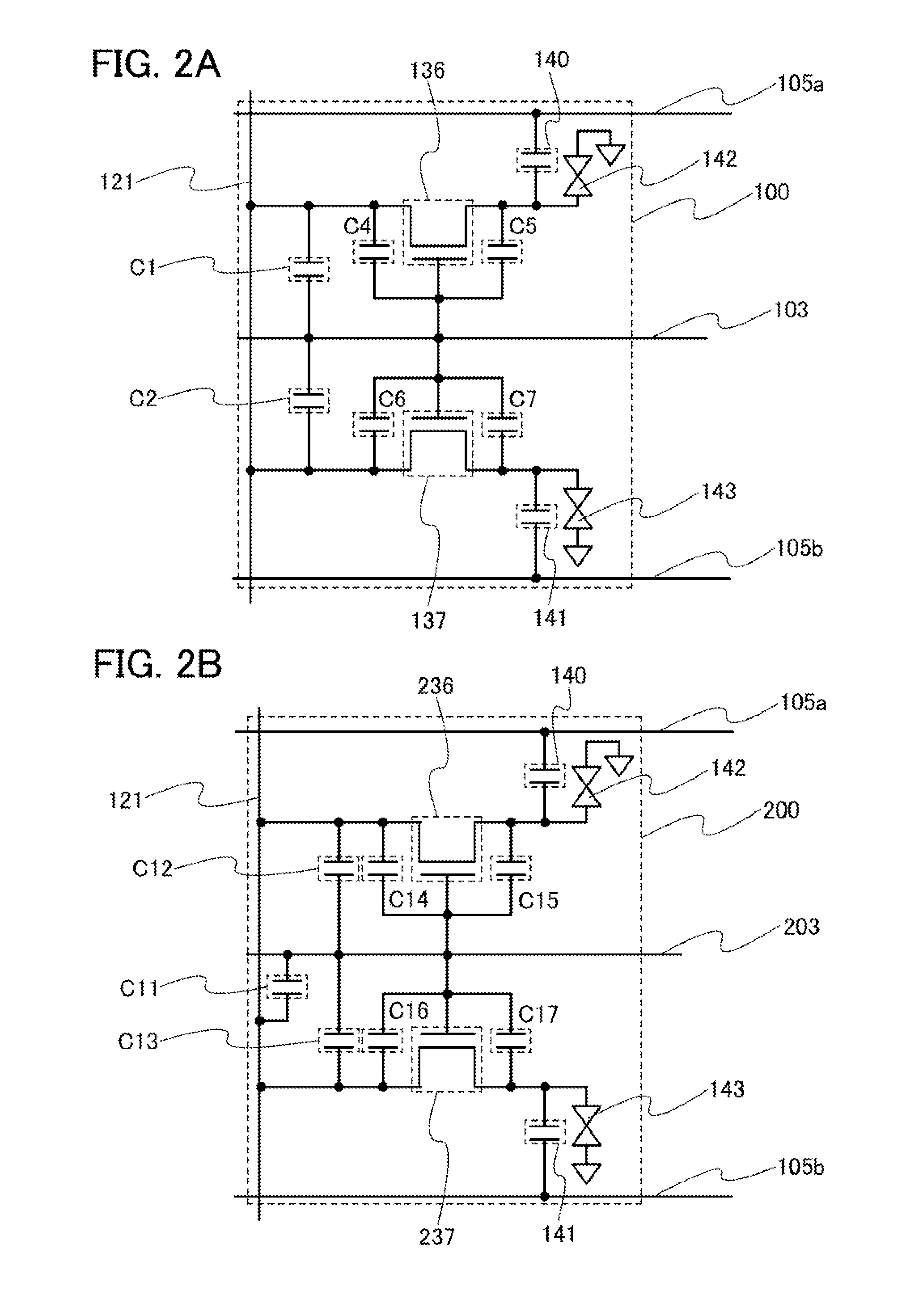

Pixel circuit, driving method of pixel circuit, organic light-emitting display panel and display device

ActiveCN107452339AShorten write timeRecovery Threshold Voltage ShiftStatic indicating devicesSolid-state devicesDisplay deviceParasitic capacitance

The invention discloses a pixel circuit, a driving method of the pixel circuit, an organic light-emitting display panel and a display device. A unified public voltage signal is inputted to a first electrode of a drive transistor before a data signal is written into a control electrode of the drive transistor; the public voltage signal and a threshold voltage of the drive transistor are written into a control electrode of the drive transistor, so that relatively high current can pass through the drive transistor, threshold voltage deviation, which is caused by bias stress, of the drive transistor can be recovered, a retarding effect of the drive transistor can be improved and the occurrence of a ghosting phenomenon can be prevented; in addition, when the data signal is written into the control electrode of the drive transistor, a time of writing the data signal can be shortened, and the control electrode and the first electrode of the drive transistor can achieve jump through a unified potential, so that a difference, which is caused by stray capacitance between the control electrode and the first electrode of the drive transistor, can be prevented, the problem that threshold voltage grabbing is inconsistent due to voltage jump can be avoided and consistent brightness of the first frame after high-low grayscale switching can be guaranteed.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

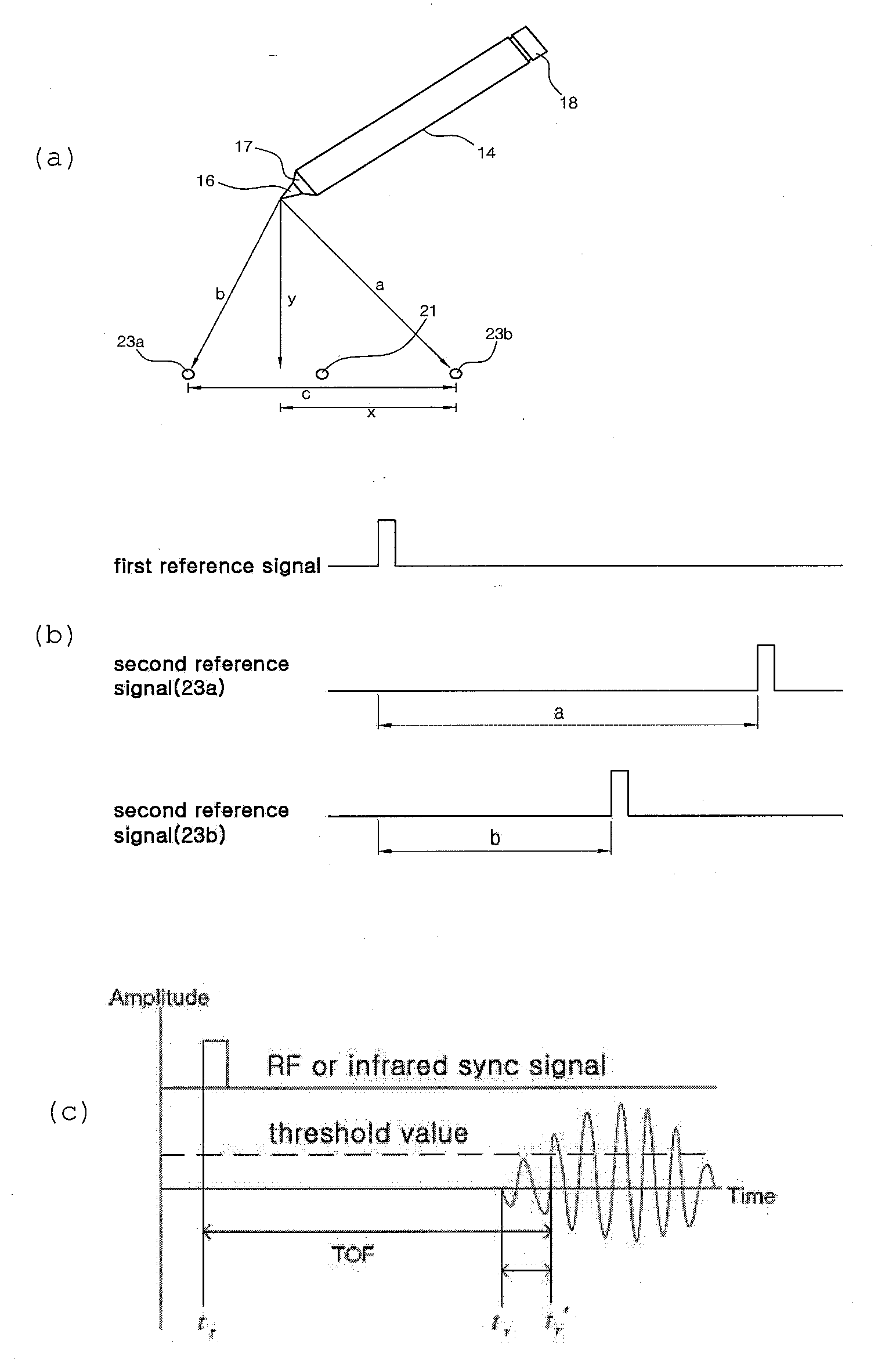

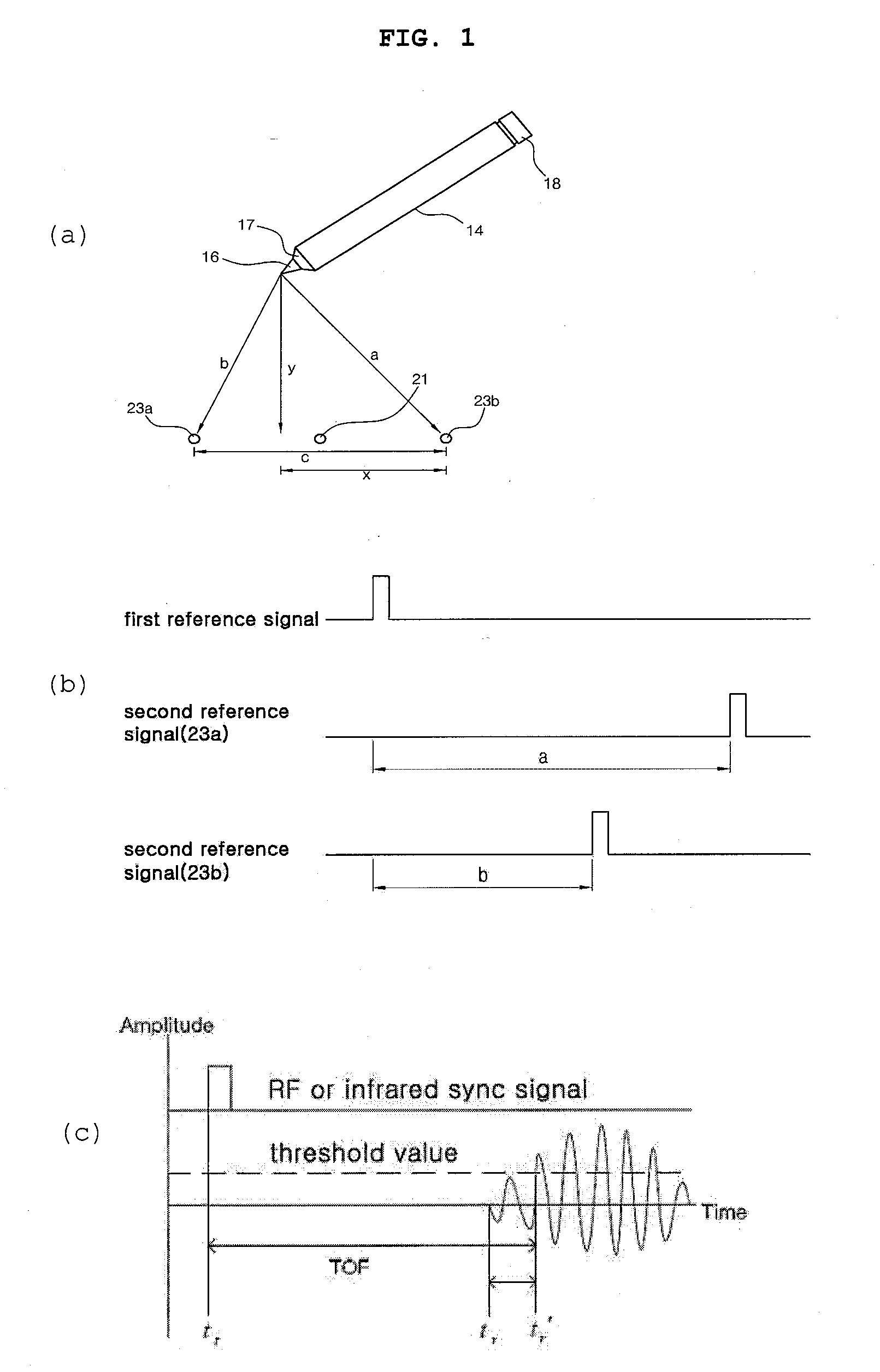

Portable Apparatus and Method for Inputing Data With Electronic Pen and Transmitting Data

InactiveUS20090009489A1Shorten write timeTransmissionInput/output processes for data processingComputer scienceImaging data

Disclosed is a portable apparatus and a method for inputting data with an electronic pen and transmitting data. More particularly, there is provided a portable apparatus for creating image data with an electronic pen and transmitting the created image data, or inputting data with an electronic pen, which allows a user to input numerals, characters, etc. without a keypad, and transmitting the input data, and to a data input and transmission method using such a portable apparatus.

Owner:LEE YONG JIK

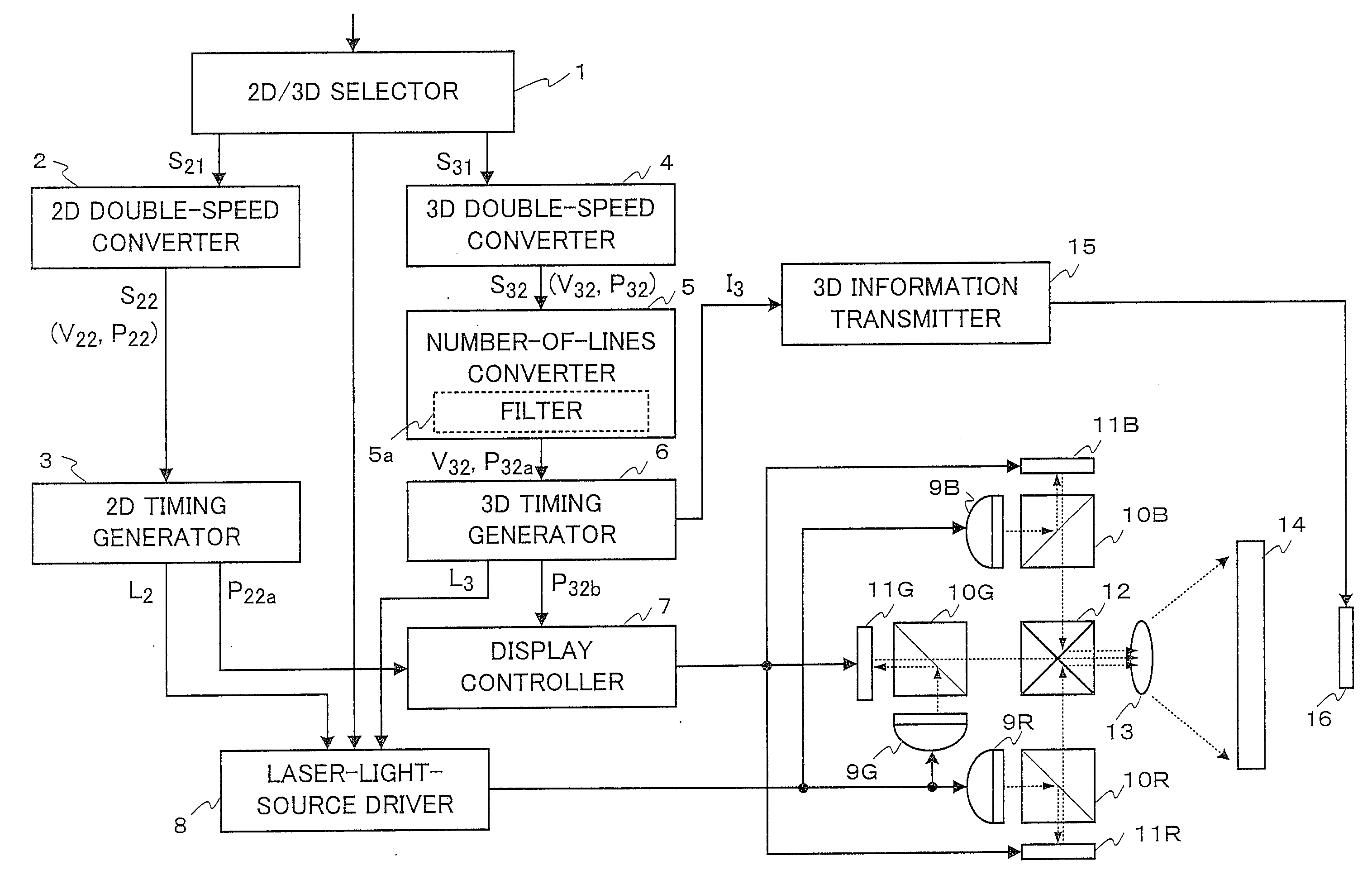

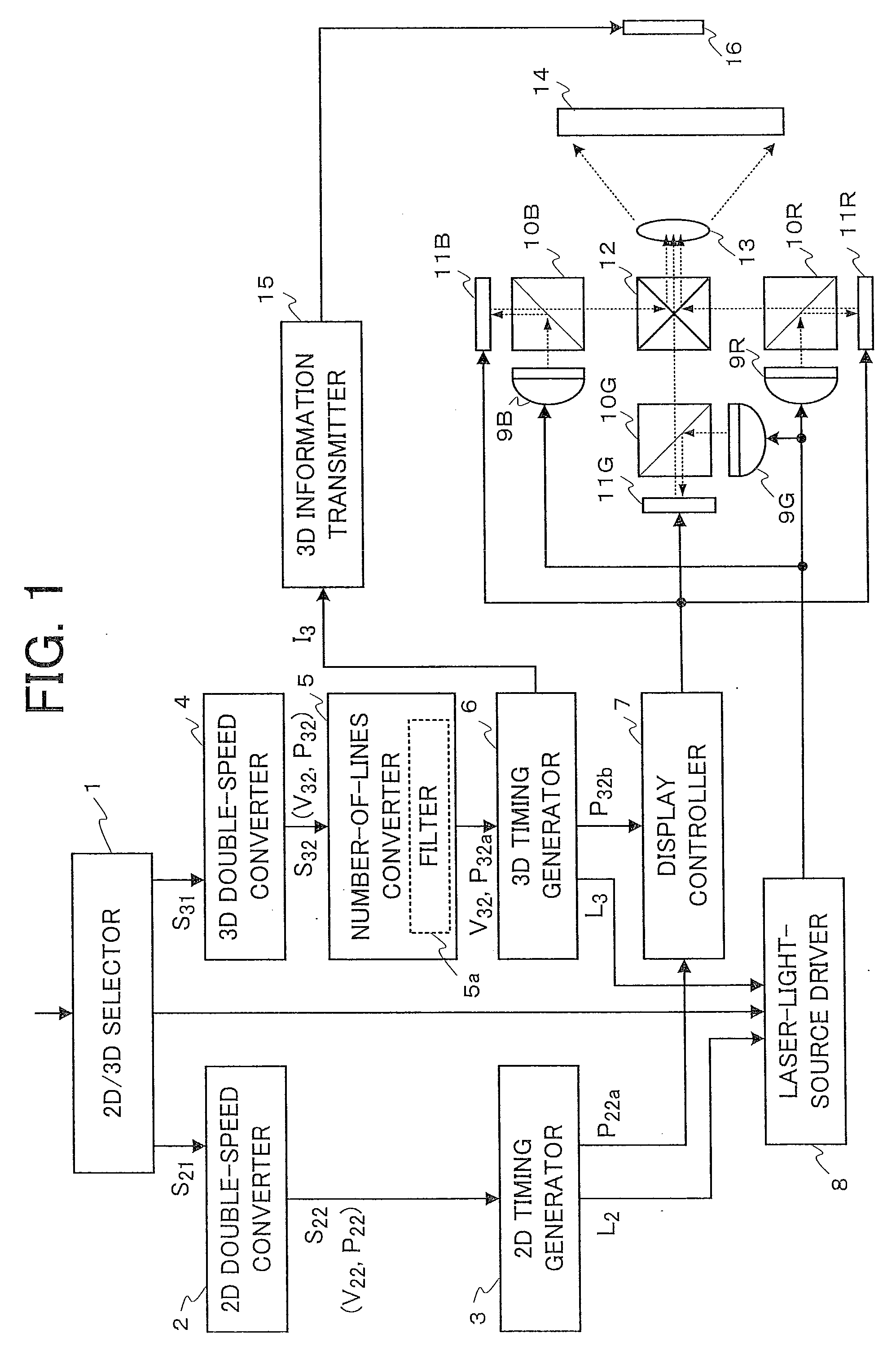

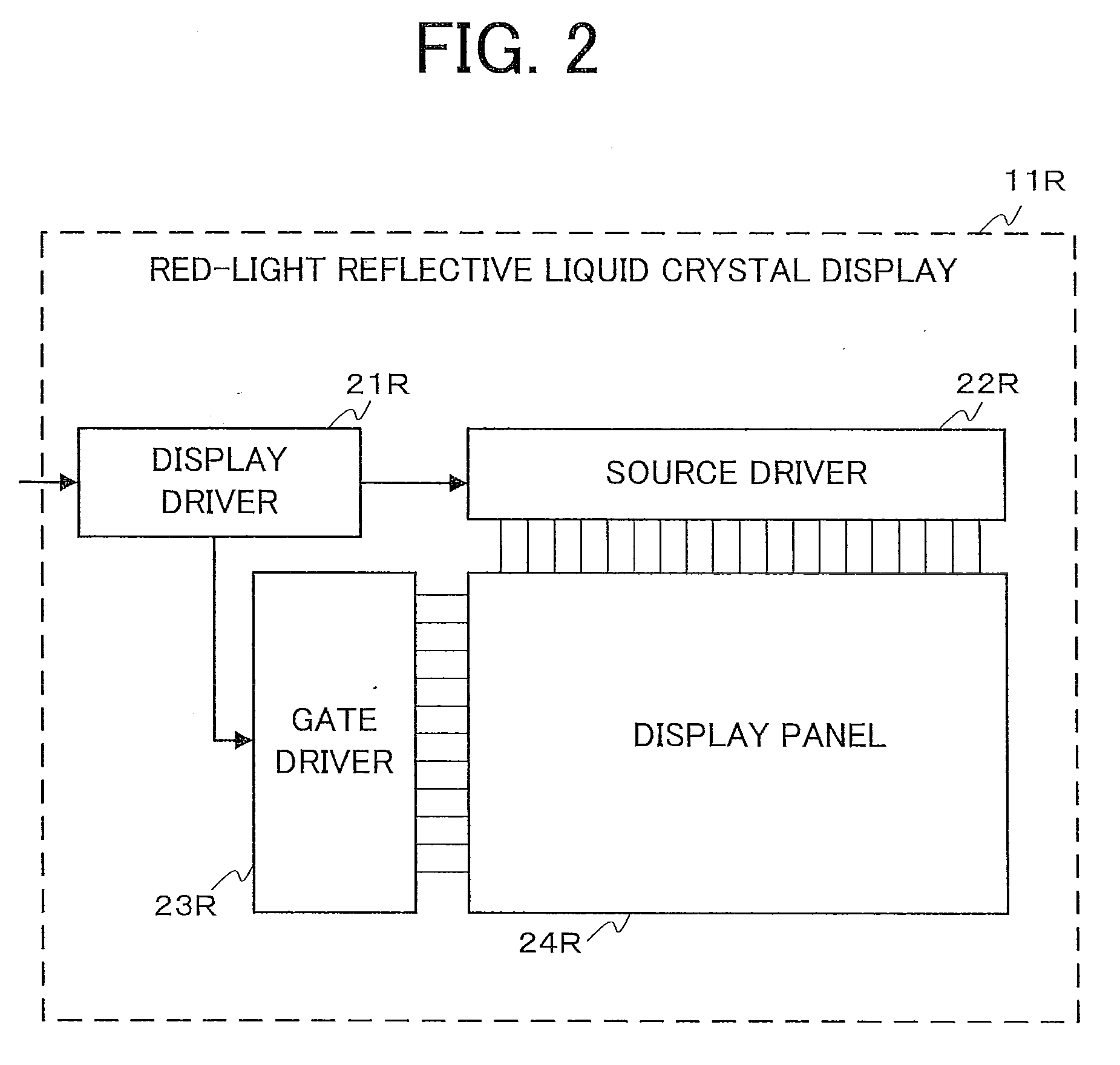

Image display apparatus and image display method

InactiveUS20100045784A1Shorten receiving timeShorten write timeStatic indicating devicesColor television detailsTiming generatorImage signal

An image display apparatus including a display unit having a display panel; an illuminator; a number-of-lines converter for changing each of number of lines in one frame of an image-for-left-eye signal and number of lines in one frame of an image-for-right-eye signal to a reduced number of lines; a timing generator for generating a display timing signal and an illuminating timing signal; a display controller; and an illuminator driver for causing the illuminator to apply light to the display panel at timing synchronized with the display timing signal every one frame; wherein the display unit duplicates an image signal of each line of the image-for-left-eye signal of the reduced number of lines and the image-for-right-eye signal of the reduced number of lines to produce the same plural image signals for plural lines and simultaneously writes the produced signals for plural lines in the display panel to display an image.

Owner:MITSUBISHI ELECTRIC CORP

Display device

ActiveUS20120154346A1Parasitic capacitanceAperture ratioTransistorSolid-state devicesElectrical resistance and conductanceLiquid-crystal display

To provide a display device in which parasitic capacitance between wirings can be reduced while preventing increase in wiring resistance. To provide a display device with improved display quality. To provide a display device with low power consumption. A pixel of the liquid crystal display device includes a signal line, a scan line intersecting with the signal line, a first electrode projected from the signal line, a second electrode facing the first electrode, and a pixel electrode connected to the second electrode. Part of the scan line has a loop shape, and part of the first electrode is located in a region overlapped with an opening of the scan line. In other words, part of the first electrode is not overlapped with the scan line.

Owner:SEMICON ENERGY LAB CO LTD

System for holography

ActiveUS20120008482A1High diffraction efficiencyImprove diffractionHolographic optical componentsRecord information storageImage resolutionDisplay device

The present invention provides systems of recording holograms that reduce the writing time, increase the diffraction efficiency, improve the resolution, or restitute color. These systems are well suited for use with an updateable 3D holographic display using integral holography and photorefractive polymer.

Owner:TIPD

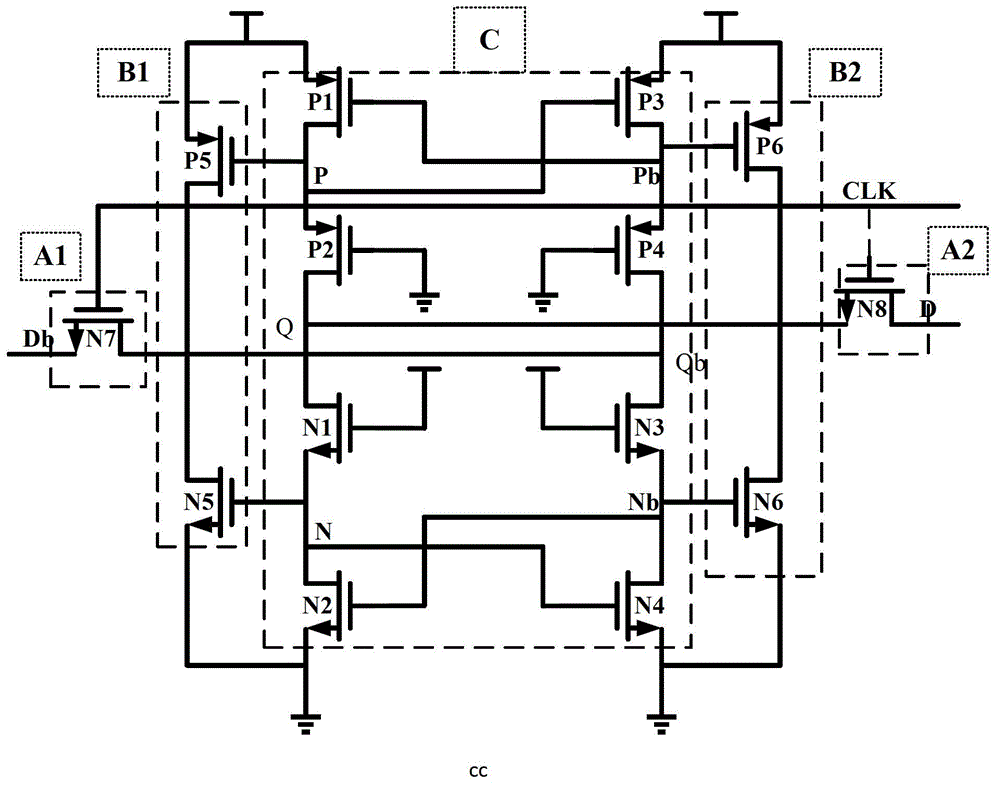

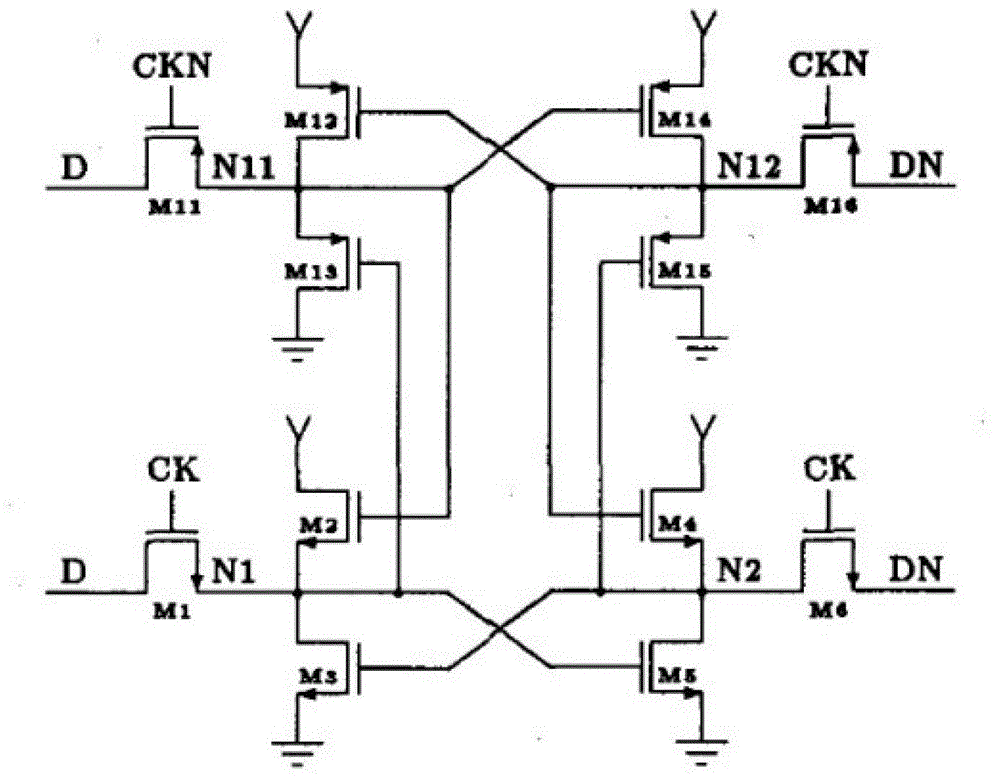

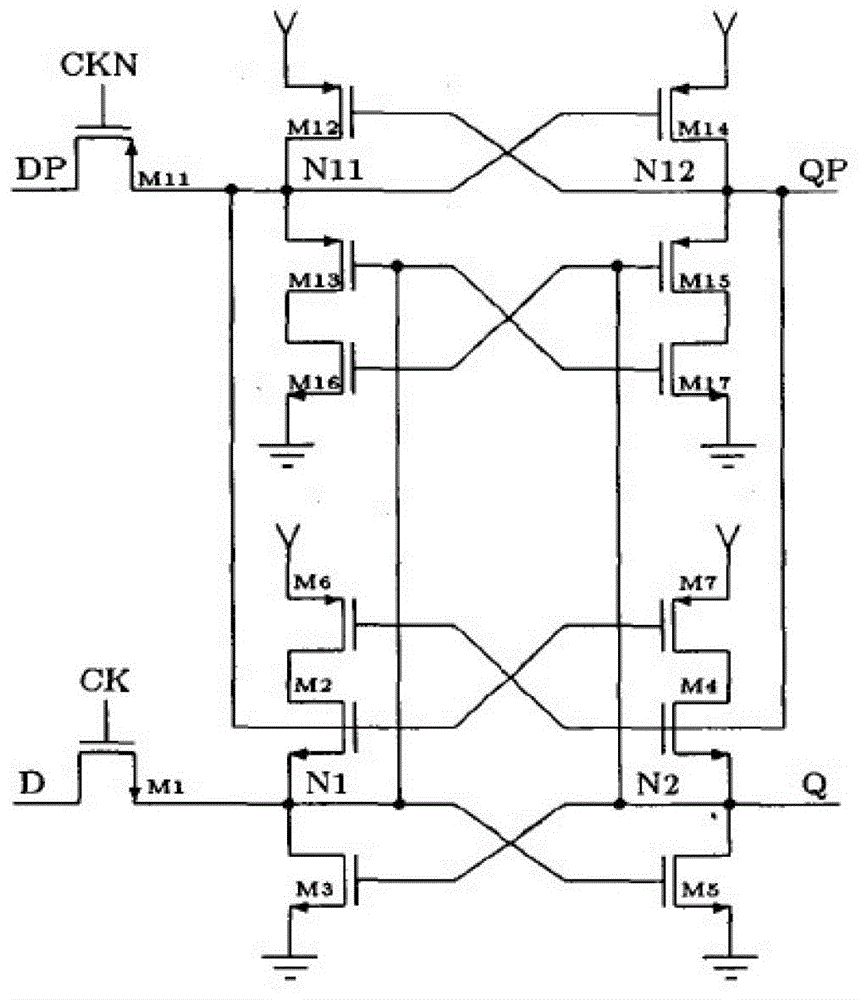

Novel static random access memory (SRAM) storage unit preventing single particle from turning

ActiveCN102723109ARealize the ability of flip reinforcementReduce rollover recovery timeDigital storageStatic random-access memoryClock network

The invention discloses a novel static random access memory (SRAM) storage unit preventing a single particle from turning. The storage unit comprises a first input / output port, a first potential turning recovery driving circuit, a voltage retaining circuit, a second potential turning recovery driving circuit and a second input / output port which are connected in series with one another sequentially. An automatic recovery function for voltage turning when a sensitive node is impacted by a high-energy particle can be realized; according to a simulation result of a TSMC 0.18 mu_m process, a turning threshold value LETth is more than 500 MeV / (mg.cm<2>); compared with the conventional storage unit preventing the single particle from turning, the SRAM storage unit has the characteristic of high writing speed; the recovery time can be effectively shortened; by adopting a unidirectional clock and a small-clock amplitude, a clock network is relatively simple and relatively high in reliability; the clock is only connected with the gate of a read-write transistor, and the clock load is relatively small; and the sensitive node can be used for reinforcing multi-node turning of the single particle, which is caused by drains positioned on a P-type tube and an N-type tube..

Owner:XI AN JIAOTONG UNIV

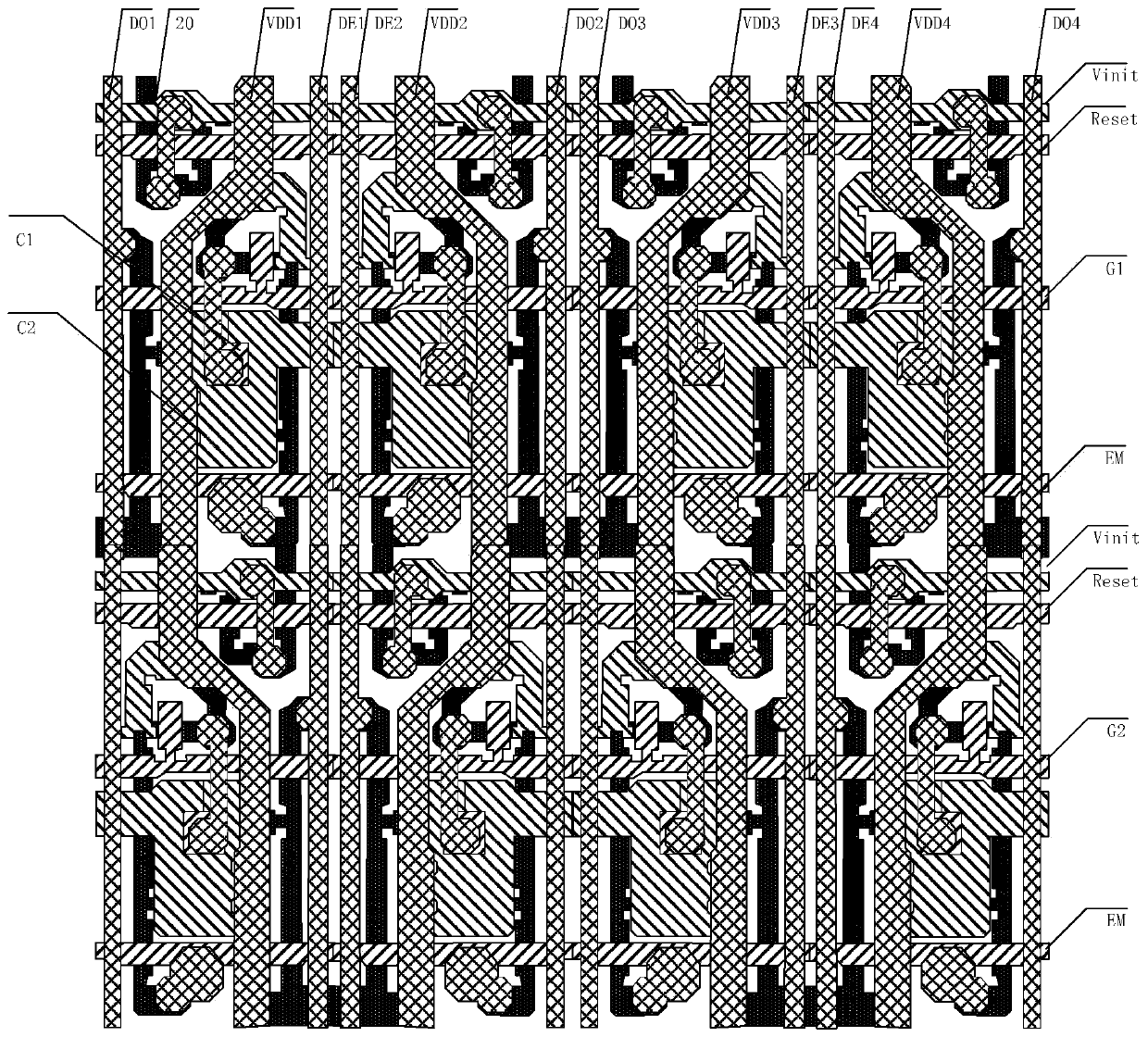

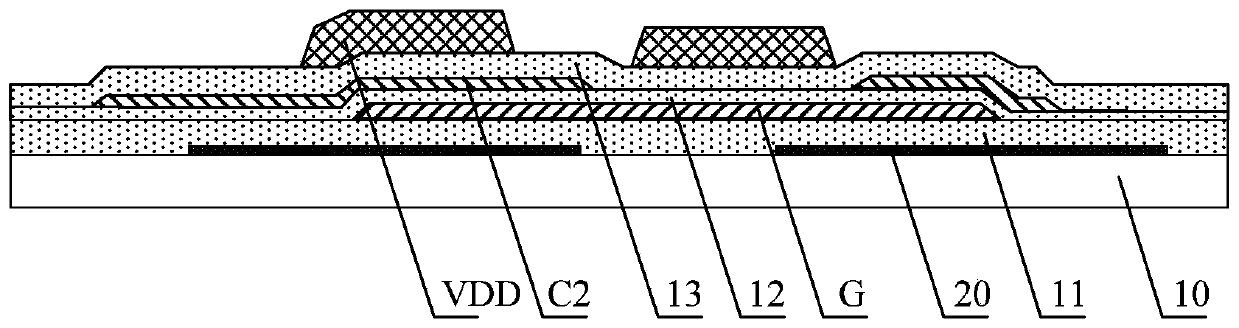

Display substrate, manufacturing method thereof, and display device

ActiveCN110690265AReduce power consumptionReduce loadSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDisplay device

A display substrate, a manufacturing method thereof, and a display device are disclosed. The display substrate includes a substrate, and a plurality of sub-pixels, a plurality of columns of power lines and data lines which are disposed on the substrate. Each sub-pixel includes: a driving circuit. The driving circuit includes a transistor and a capacitor. The capacitor includes a first electrode plate and a second electrode plate opposite to each other. The active layer of the transistor is located on a side of the second electrode plate of the capacitor close to the substrate. The power linesare located on a side of the second electrode plate of the capacitor away from the substrate. For each sub-pixel, the power lines are connected to the second electrode plate of the capacitor and the active layer of the transistor. The second electrode plate of the capacitor of each sub-pixel is connected to the second electrode of the capacitor of an adjacent sub-pixel located in the same row. Theactive layer of the transistor of each sub-pixel is connected to the active layer of the transistor of another adjacent sub-pixel located in the same row. The display substrate can reduce the load ofthe data lines, thereby reducing the power consumption of the display substrate and shortening the writing time of a data signal.

Owner:BOE TECH GRP CO LTD

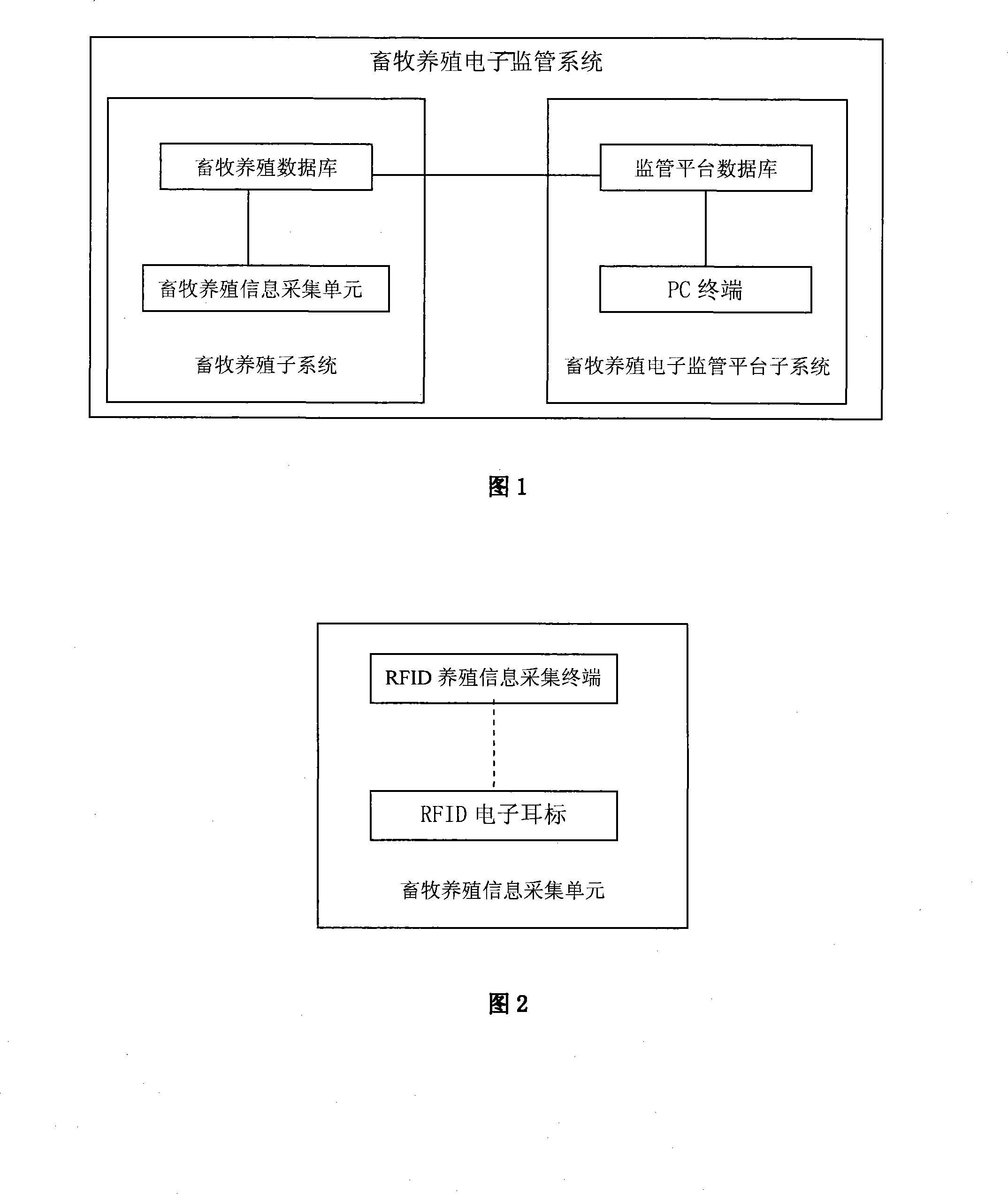

Electric monitoring system for farming cultivation

InactiveCN101221649AExtended service lifeLong reading distanceData processing applicationsCo-operative working arrangementsWeb browserMonitoring system

The invention discloses a stock raising electronic supervision system, which comprises a stock raising subsystem and a stock raising supervision platform subsystem, wherein the stock raising subsystem comprises a stock raising information acquisition unit and a stock raising database, and the stock raising electronic supervision platform subsystem comprises a supervision platform database and a PC terminal. The stock raising subsystem and the stock raising supervision platform subsystem are connected with each other through the stock raising database and the supervision platform database, the stock raising information acquisition unit is connected with the stock raising database, and a user has access to the supervision platform database through a web browser in the PC terminal. The invention enables the government to supervise stock raising enterprises, live pig butcheries, meat wholesale enterprises and retail stalls, and also enables the public to enquiry the source of pork, the process control and the meat prices through the platform.

Owner:SHANDONG TAIBAO PREVENTING COUNTERFEIT

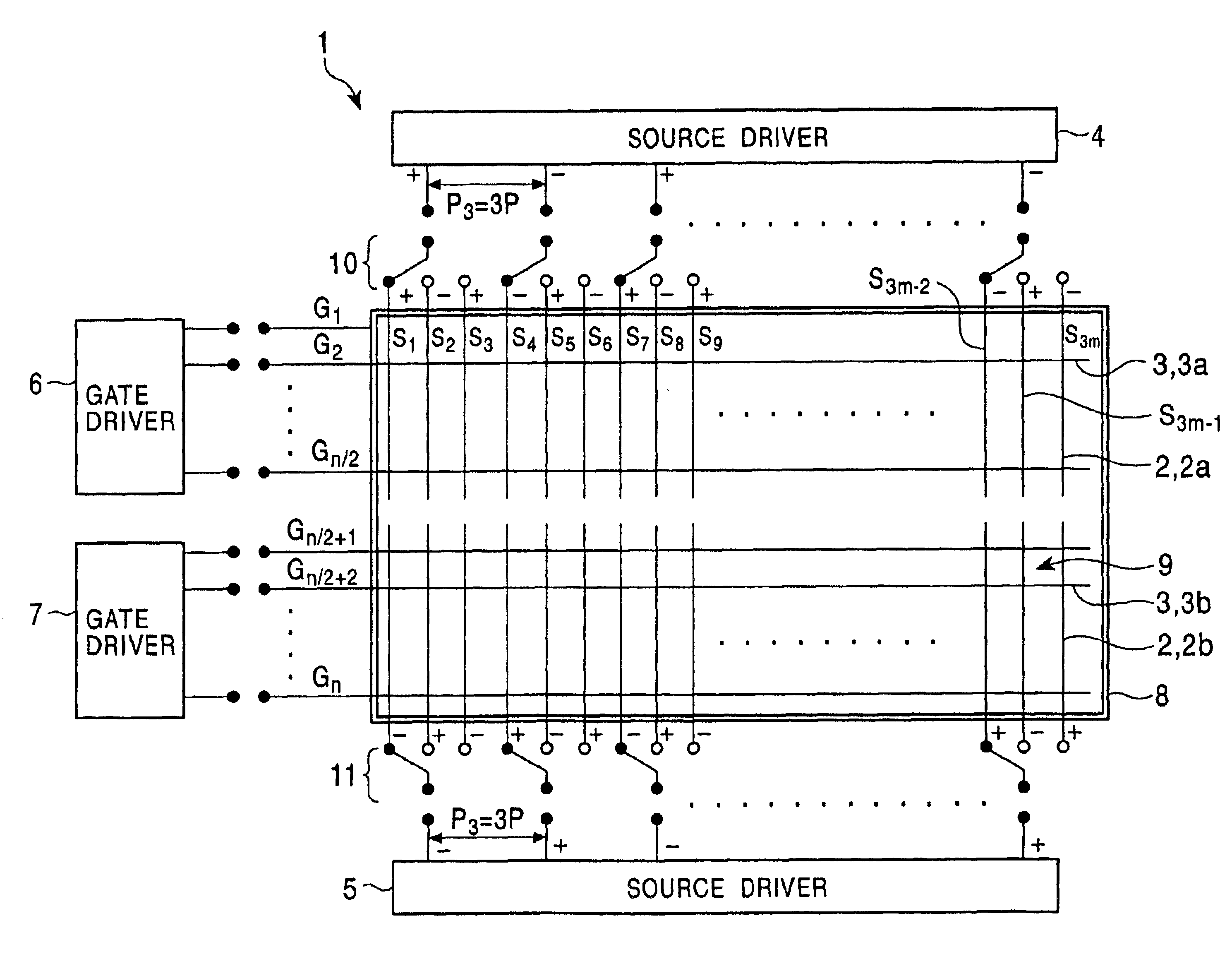

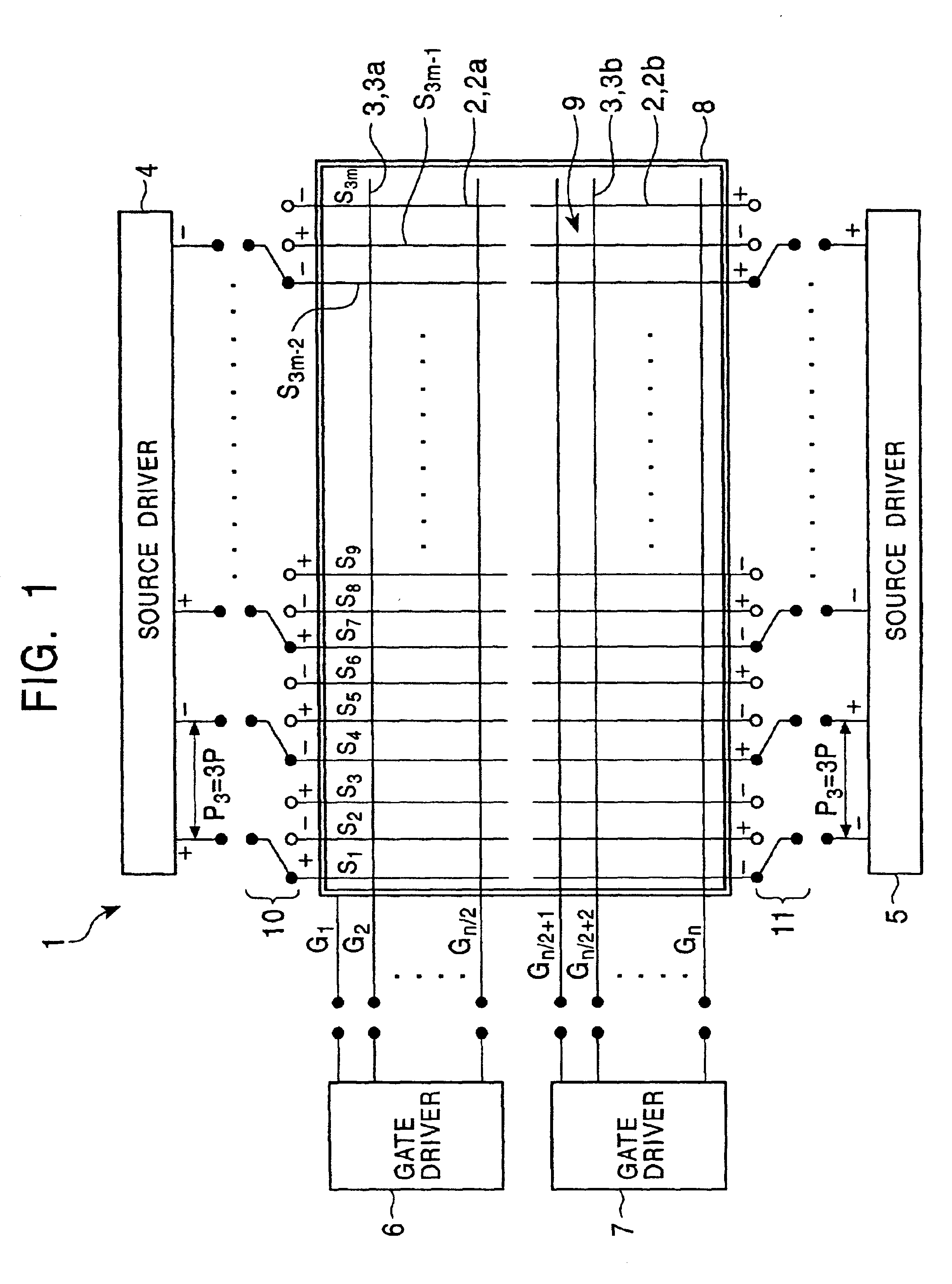

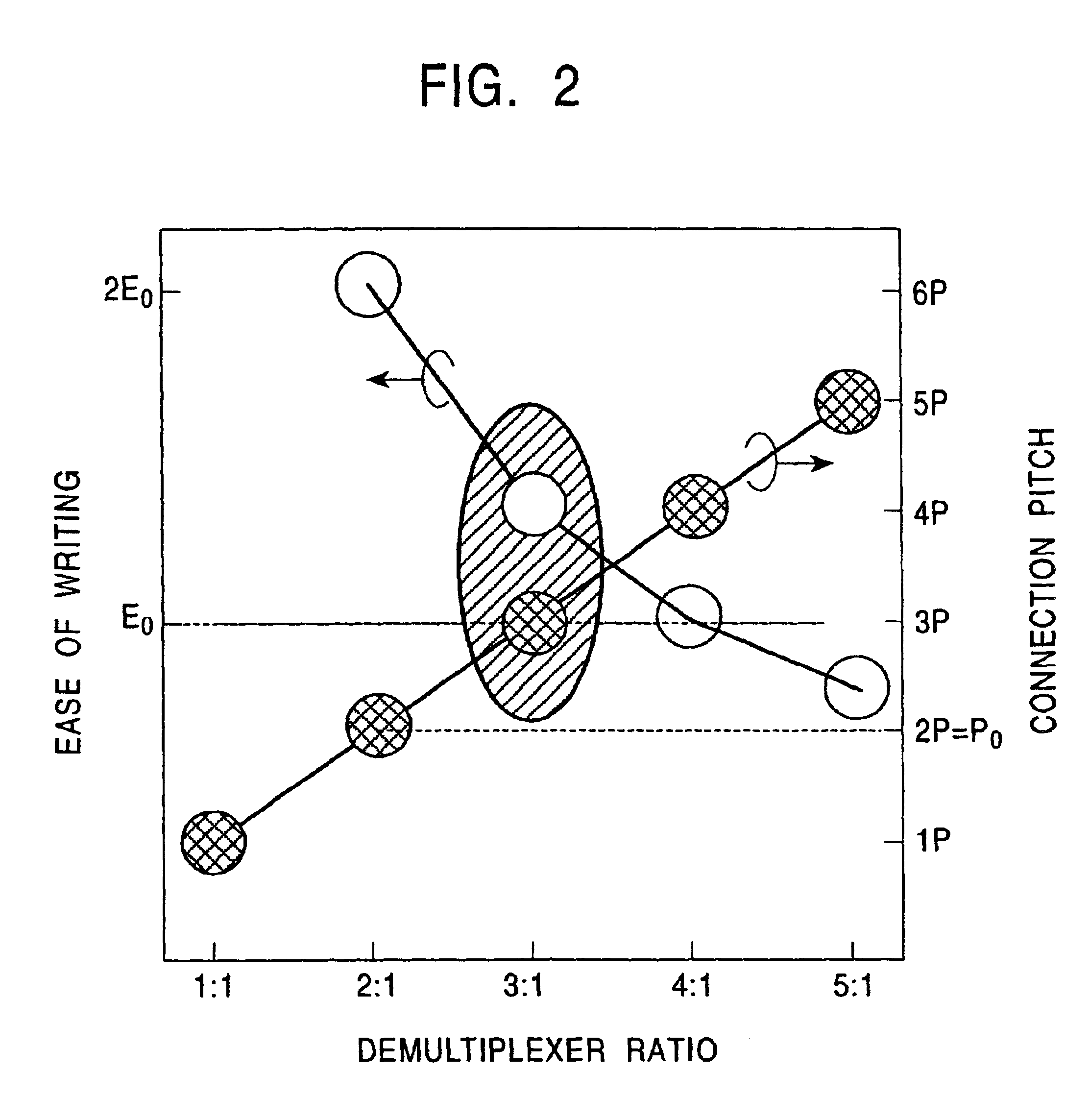

Active-matrix liquid crystal display suitable for high-definition display, and driving method thereof

InactiveUS6924786B2Easy to achieveSmooth connectionStatic indicating devicesNon-linear opticsGate driverLiquid-crystal display

A liquid crystal display having a plurality of source lines which are each divided into two groups includes a first source driver for applying image signals to a first group of the divided source lines, a second source driver for applying image signals to a second group, a first gate driver operative to apply scanning signals to one segment of a plurality of gate lines that extends across the first group of the divided source lines, and a second gate driver for applying scanning signals to the other segment of a plurality of gate lines that extends across the second group of the divided source lines. The liquid crystal display further includes 3:1 demultiplexers to switch and allocate an image signal from each of the first and second source drivers to three source lines.

Owner:INTELLECTUAL VENTURES ASSETS 186 LLC

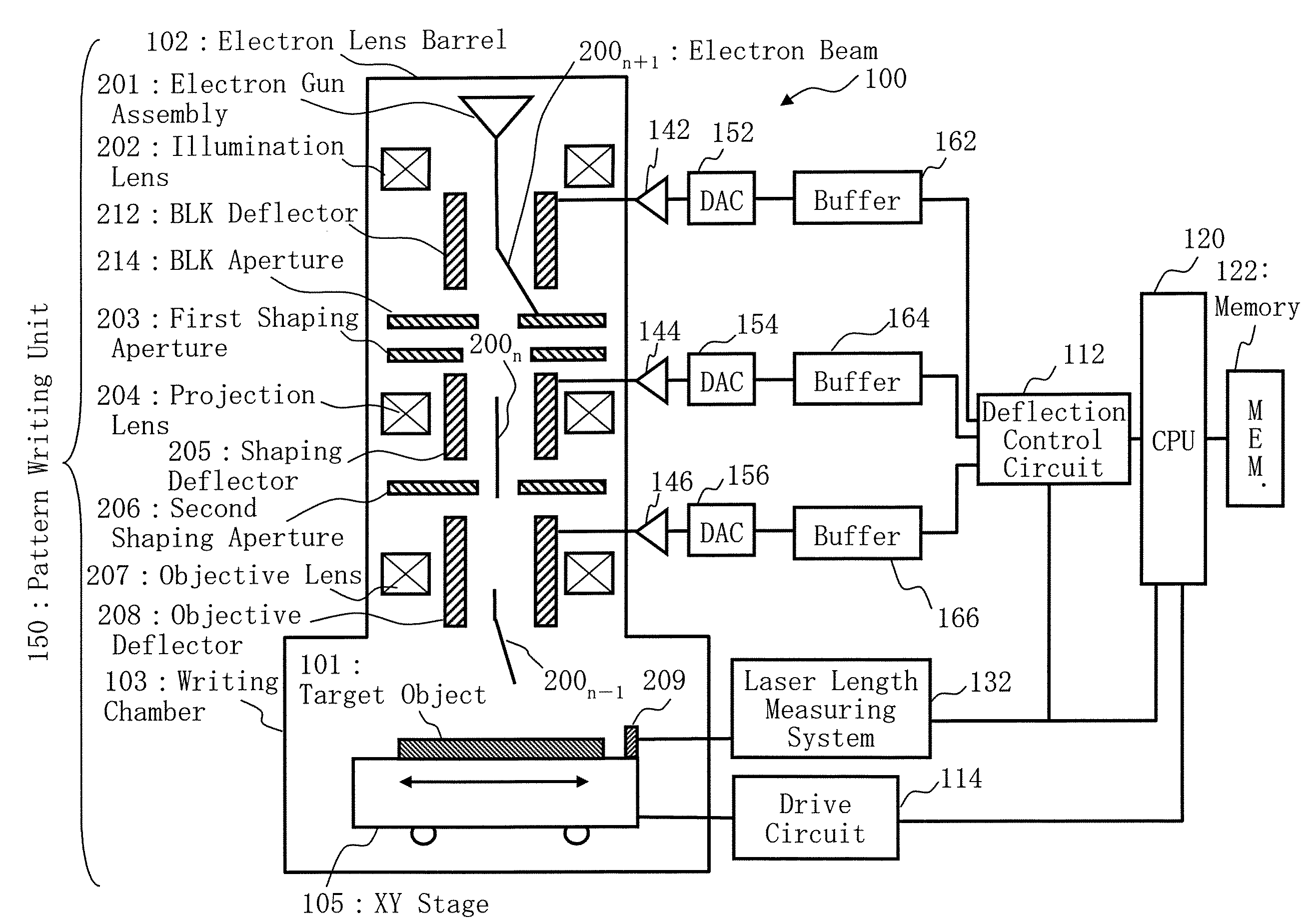

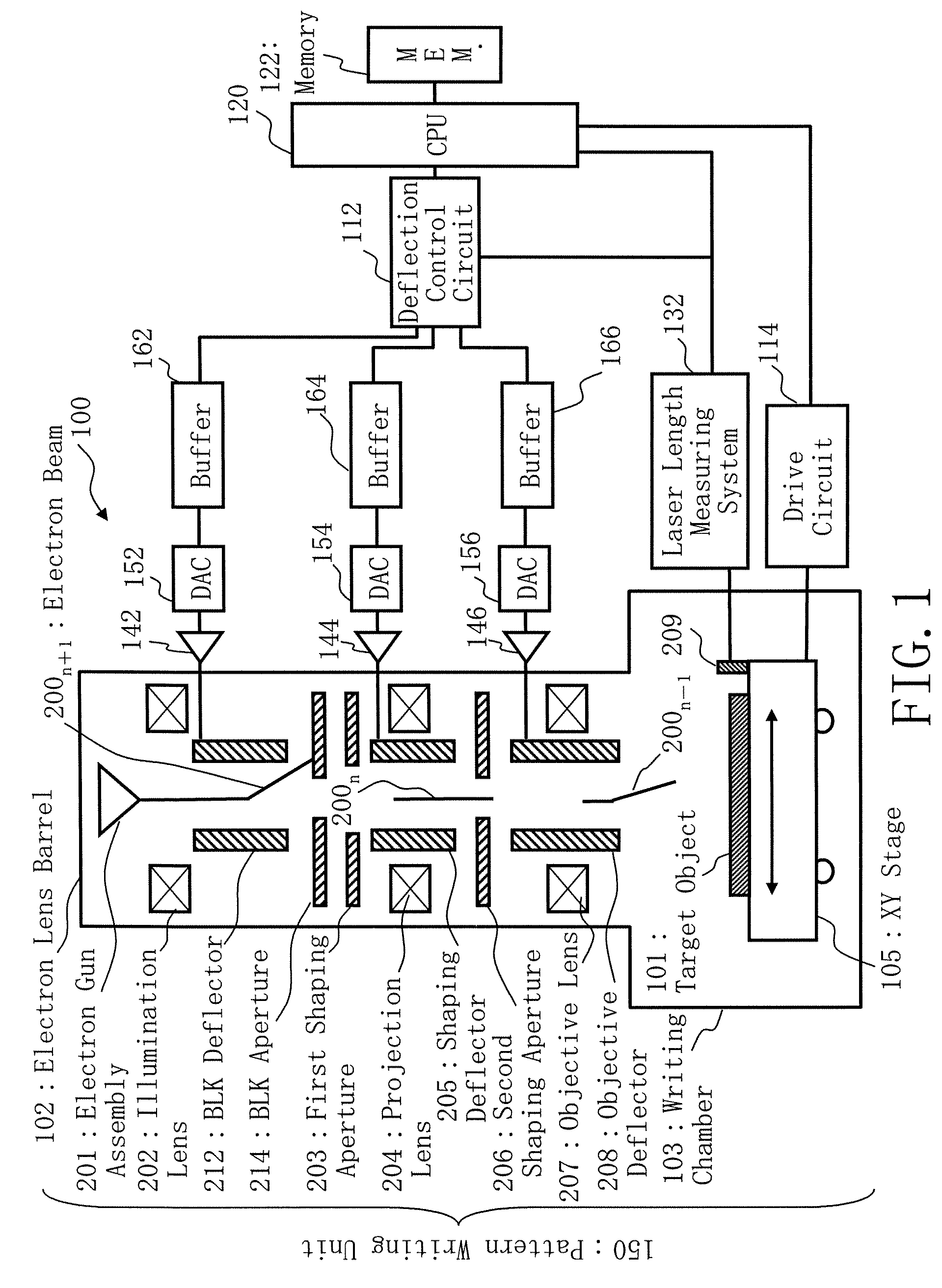

Charged particle beam writing method and apparatus

ActiveUS7601968B2Shorten write timeStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsParticle physicsCharged particle beam

A charged particle beam writing method includes irradiating a shot of a charged particle beam, and deflecting the charged particle beam of the shot using a plurality of deflectors arranged on an optical path of the charged particle beam to write a pattern on a target object, wherein any one of the plurality of deflectors controls deflection of a charged particle beam of a shot different from a shot which is controlled in deflection by another deflector in the same period.

Owner:NUFLARE TECH INC

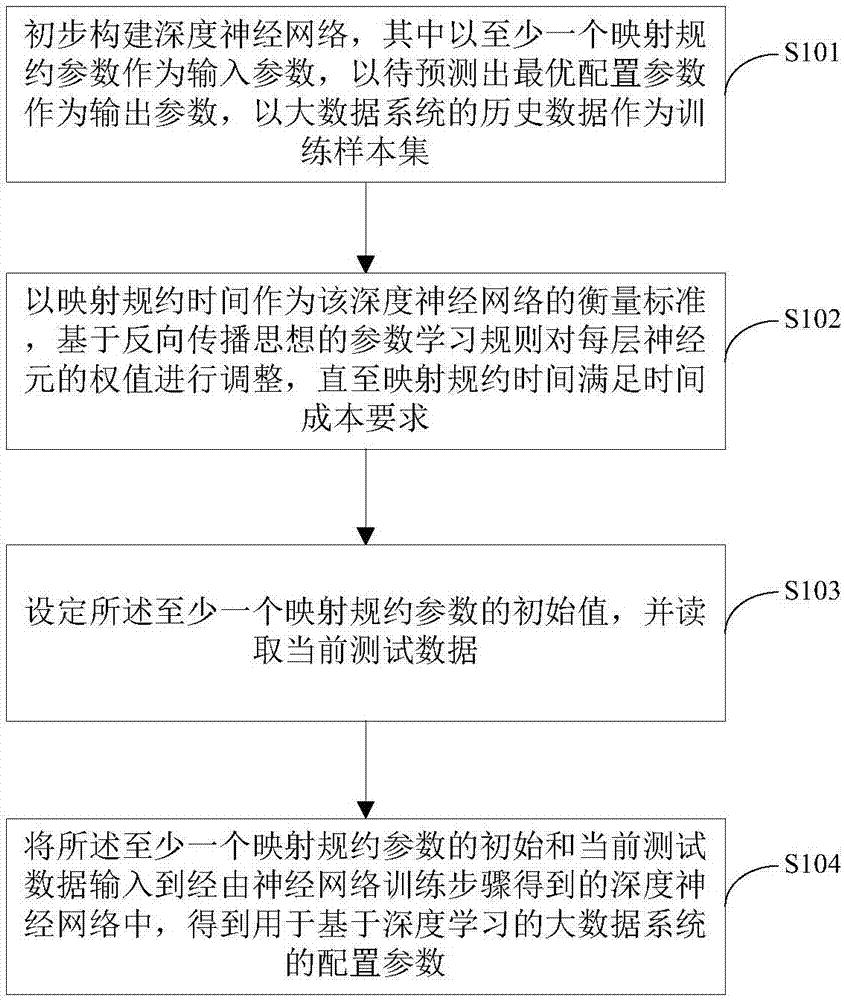

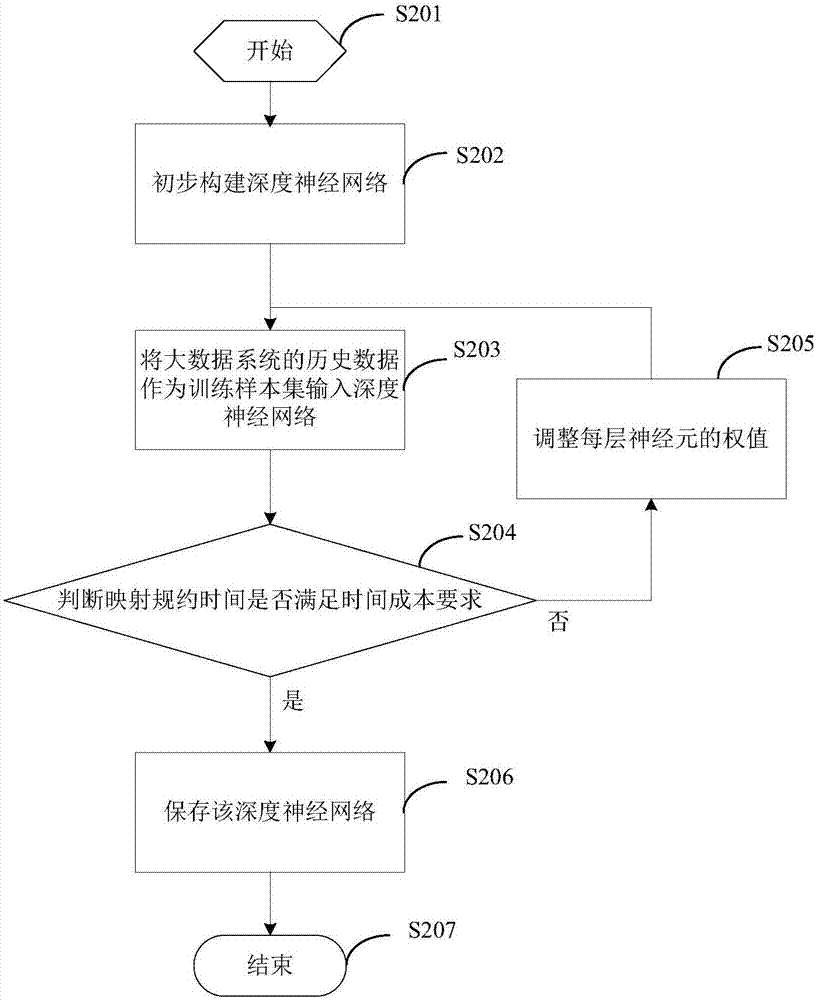

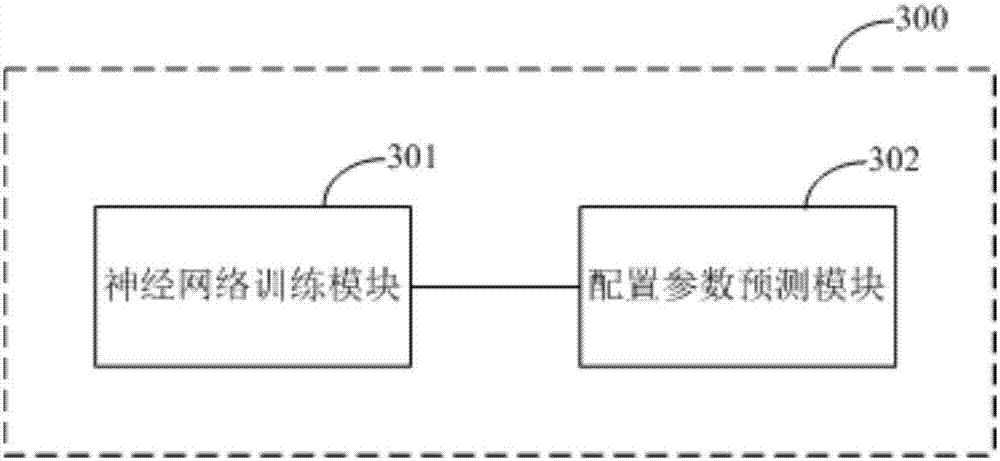

Big data system configuration parameter adjusting and optimizing method and system based on deep learning

ActiveCN107229693AShorten the timeAvoid manual adjustment and find the problem of optimal parametersDatabase distribution/replicationNeural learning methodsNerve networkLearning rule

The invention provides a big data system configuration parameter adjusting and optimizing method and system based on deep learning. The a big data system configuration parameter adjusting and optimizing method comprises a nerve network training step of preliminarily constructing a deep neural network, taking at least one MapReduce parameter as an input parameter, taking an optimal configuration parameter to be predicted as an output parameter, and taking historical data of a big data system as a training sample set; taking the MapReduce time as the measuring standard of the deep neural network, and adjusting the weight of each layer of nerve cells based on the parameter learning rule of the back propagation idea until the MapReduce time satisfies the time cost demand; and a configuration parameter prediction step of setting the initial value of the at least one MapReduce parameter, reading the current test data, inputting the current test data into the deep neural network obtained in the nerve network training step, and obtaining the configuration parameter. According to the invention, the configuration parameter in the MapReduce framework is adjusted and optimized by means of the deep neural network, manual adjustment is avoided, and the predicted parameter is good in application effect.

Owner:工创集团有限公司

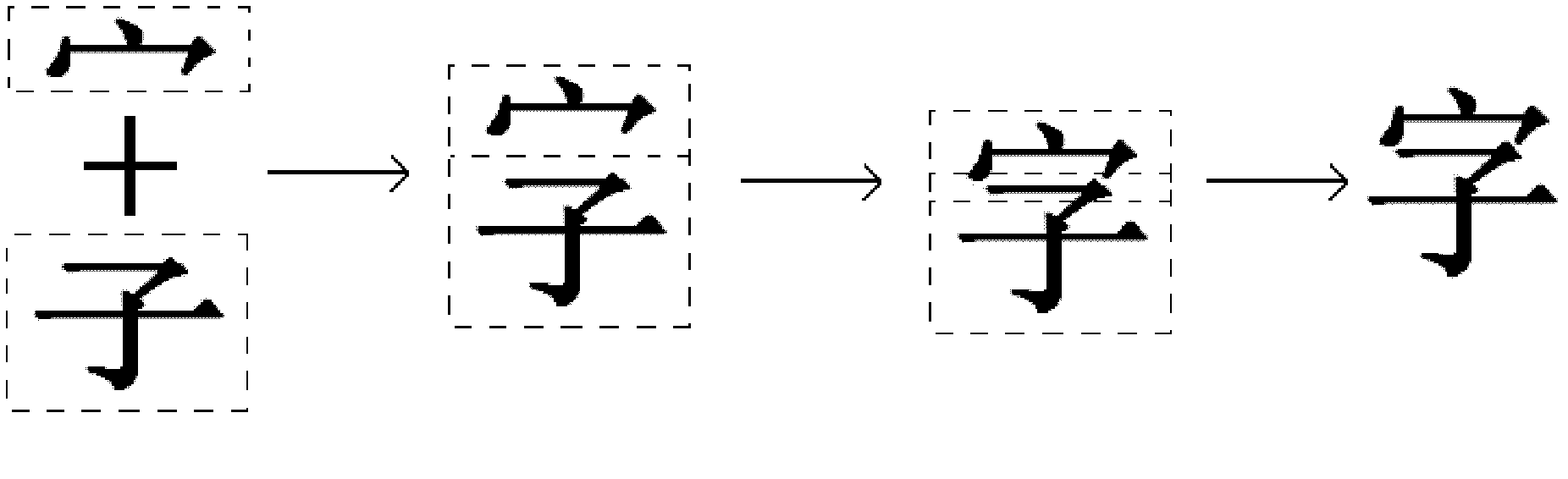

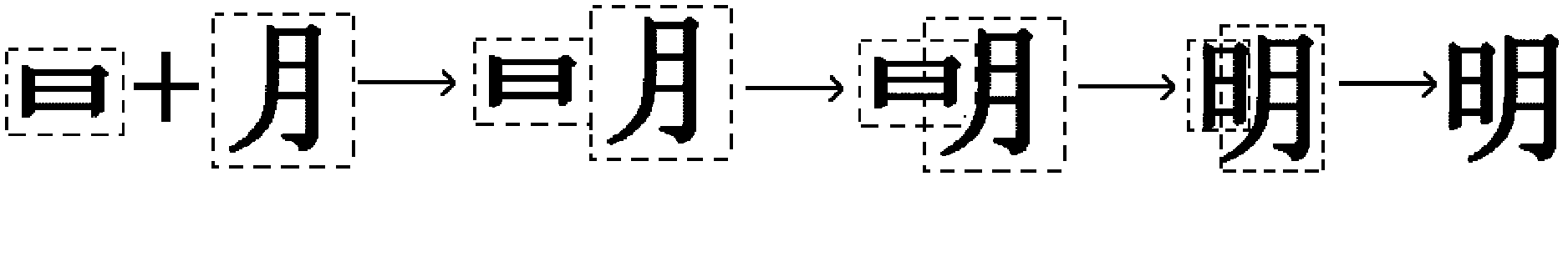

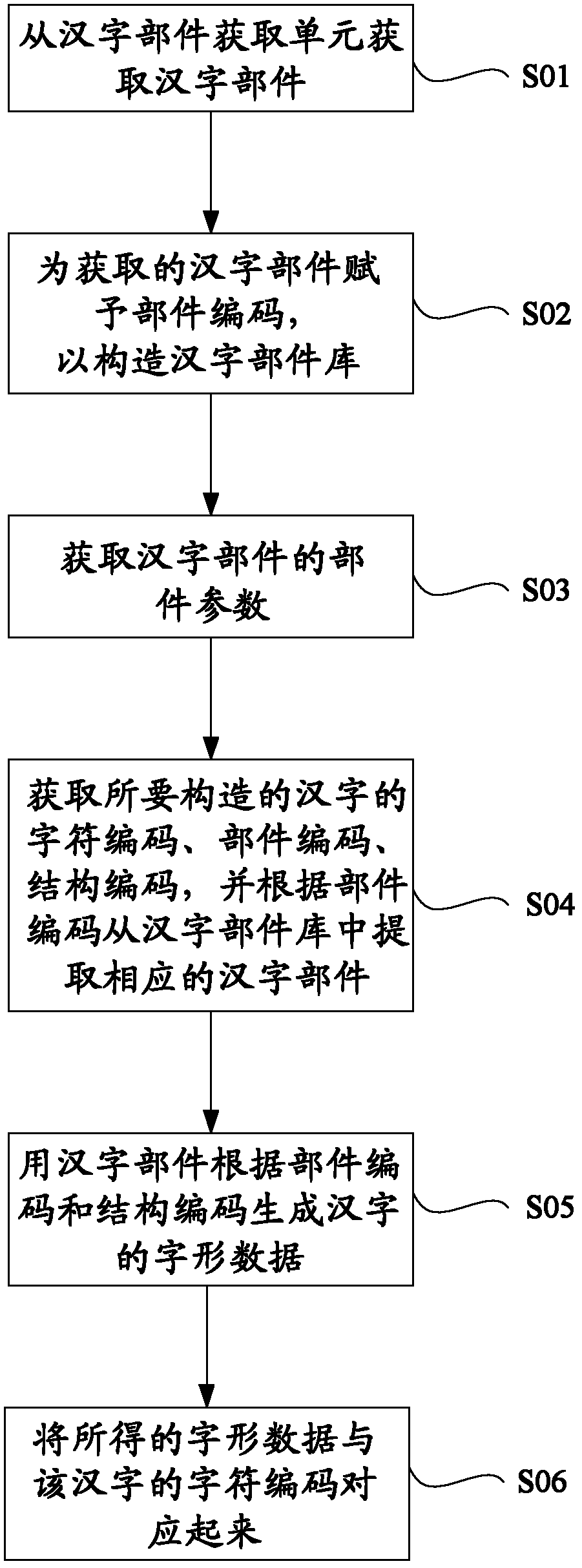

Method and equipment for word formation of Chinese characters, and method for constructing font object library

ActiveCN103186511AImprove the efficiency of word makingShorten write timeNatural language data processingSpecial data processing applicationsChinese charactersGlyph

The invention provides a method and equipment for word formation of Chinese characters, and a method for constructing a font object library, and can solve the problem of low efficiency, high cost and incapability of real time word formation in the conventional word formation technology of Chinese characters. The method for word formation of Chinese characters comprises the followings: acquiring the character codes, component codes and structural codes, of Chinese characters to be constructed, abstracting components of the Chinese characters from a Chinese character component library, wherein structural codes prescribe the structures of the Chinese characters and the positions of the Chinese character components in the Chinese characters; generating font data of the Chinese characters by using Chinese character components according to structural codes and allowing the font data to correspond to the character codes. The method for constructing the font object library comprises the followings: generating corresponding font data and character code of the Chinese characters by using the method for word formation of the Chinese characters and constructing the font object library by using the obtained font data. The equipment for word formation of the Chinese characters comprises units corresponding to the method. The method provided by the invention is used for constructing a huge-font object library.

Owner:PEKING UNIV +2

Semiconductor memory device for writing data to multiple cells simultaneously and refresh method thereof

ActiveUS7961534B2Shorten write timeImprove data retentionRead-only memoriesDigital storageComputer architectureSemiconductor

A semiconductor memory device includes a read / write bit line configured to supply a cell driving voltage. A selecting unit is connected to the read / write bit line and is controlled by a word line. A plurality of cells are connected between the selecting unit and a source line, and the cells are configured to read and write data according to a cell driving voltage. Each switching element of a plurality of switching elements are connected in parallel with a single cell of the plurality of cells, and the plurality of switching elements are controlled selectively by a plurality of bit lines.

Owner:SK HYNIX INC

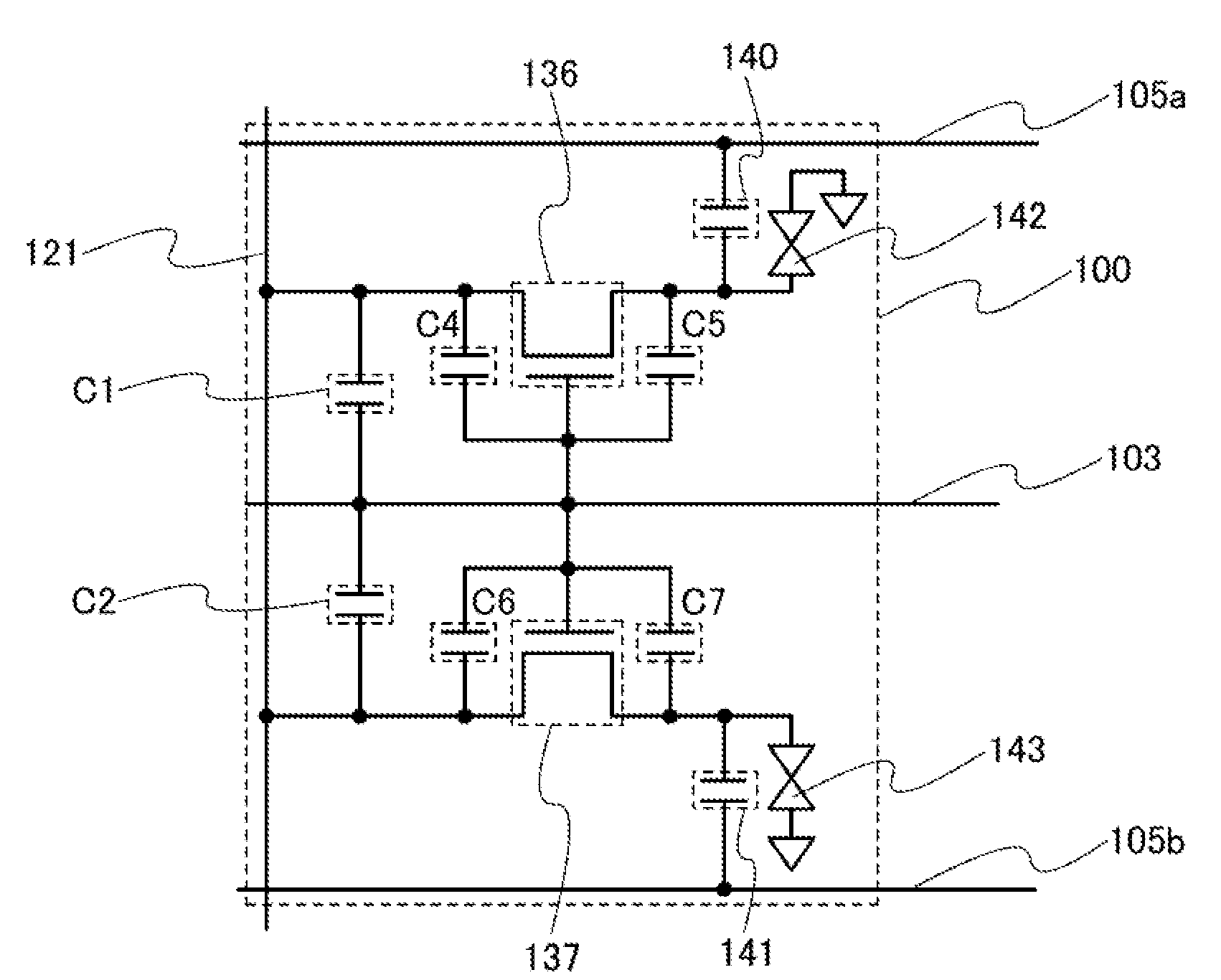

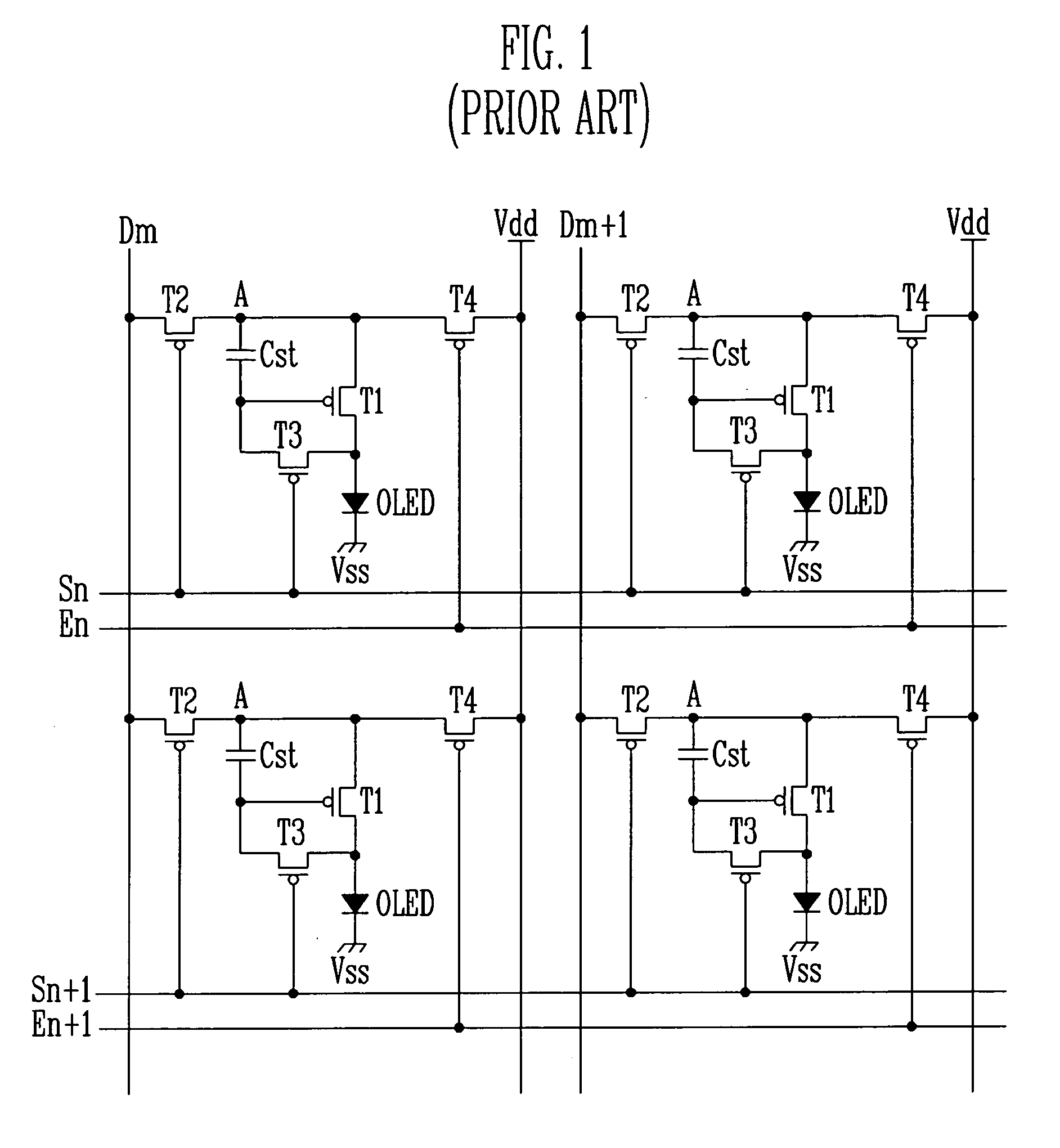

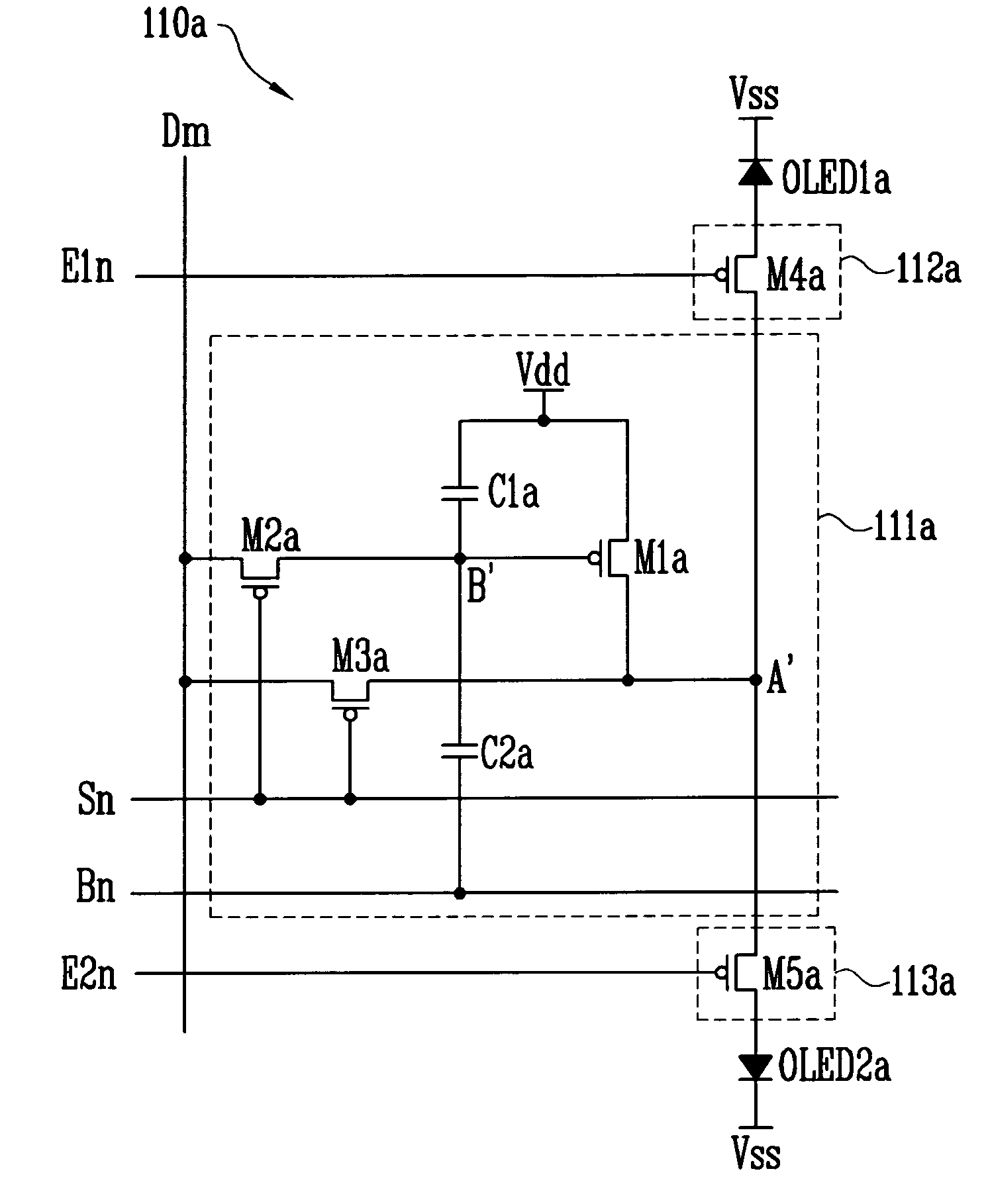

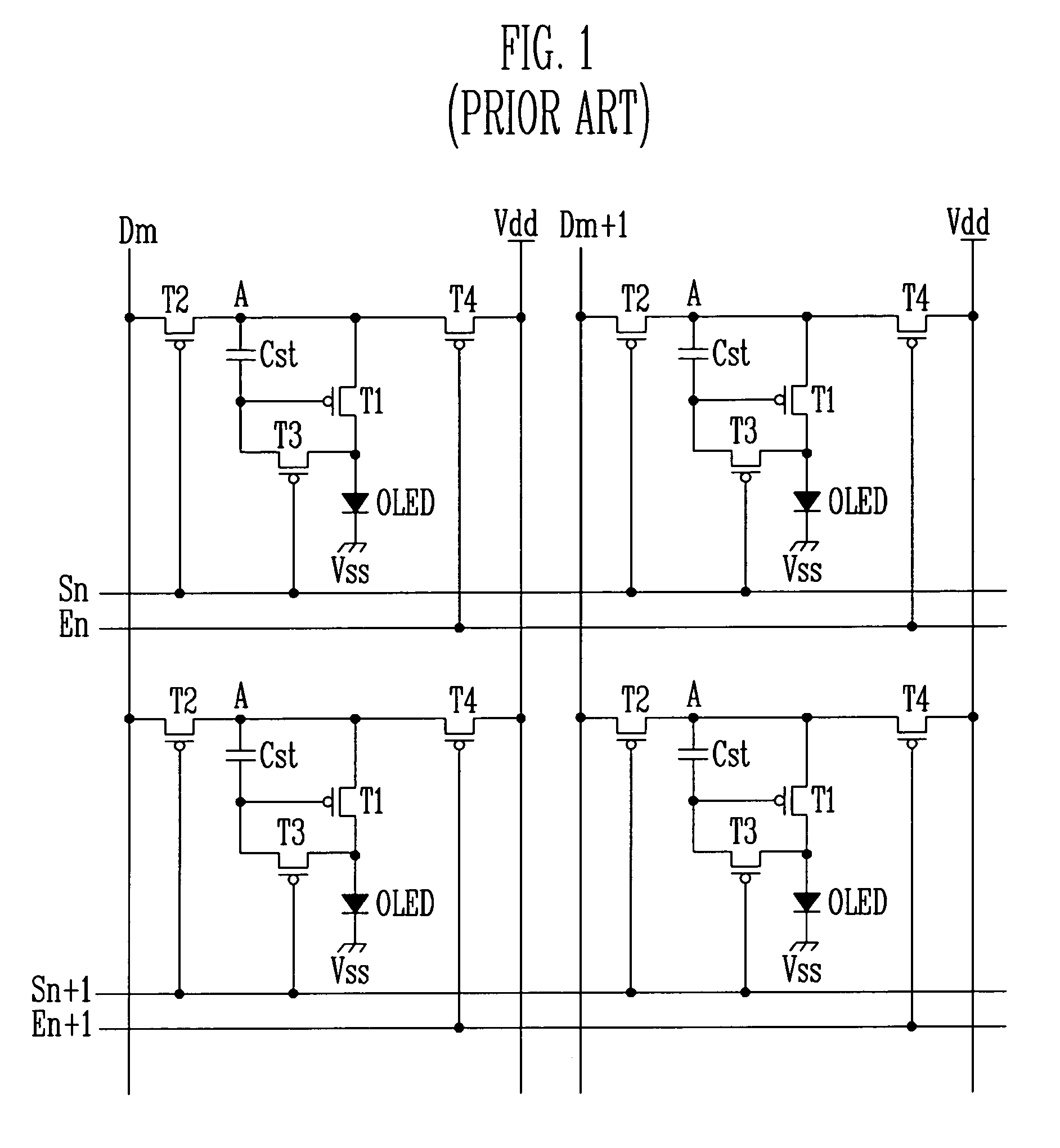

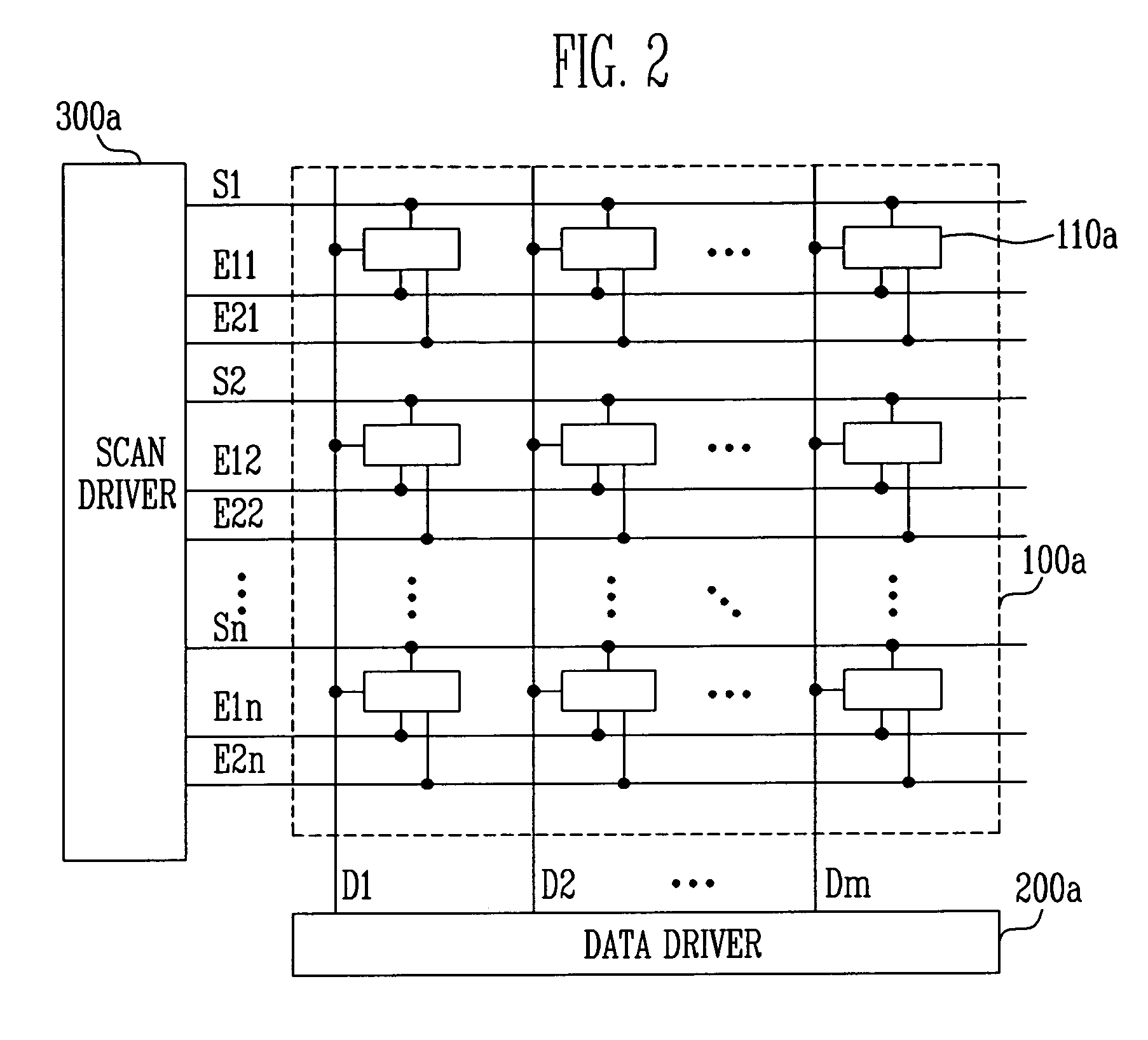

Pixel circuit and light emitting display using the same

ActiveUS20060124944A1Reduce write timeReduce numberStatic indicating devicesElectroluminescent light sourcesDisplay deviceDriving current

A light emitting display includes a plurality of light emitting diodes within a pixel. A drive circuit is coupled to the plurality of light emitting diodes and generates a drive current flowing through the light emitting diodes corresponding to a data current. A switch circuit assembly is coupled to the plurality of light emitting diodes and the drive circuit and sequentially transfers the drive current from the drive circuit to the plurality of light emitting diodes. The light emitting diodes sequentially emit light. When all the light emitting diodes emit light, one frame is formed.

Owner:SAMSUNG DISPLAY CO LTD

Pixel circuit and light emitting display using the same

ActiveUS7679587B2Increase volumeReduce in quantityStatic indicating devicesElectroluminescent light sourcesDisplay deviceLight-emitting diode

A light emitting display includes a plurality of light emitting diodes within a pixel. A drive circuit is coupled to the plurality of light emitting diodes and generates a drive current flowing through the light emitting diodes corresponding to a data current. A switch circuit assembly is coupled to the plurality of light emitting diodes and the drive circuit and sequentially transfers the drive current from the drive circuit to the plurality of light emitting diodes. The light emitting diodes sequentially emit light. When all the light emitting diodes emit light, one frame is formed.

Owner:SAMSUNG DISPLAY CO LTD

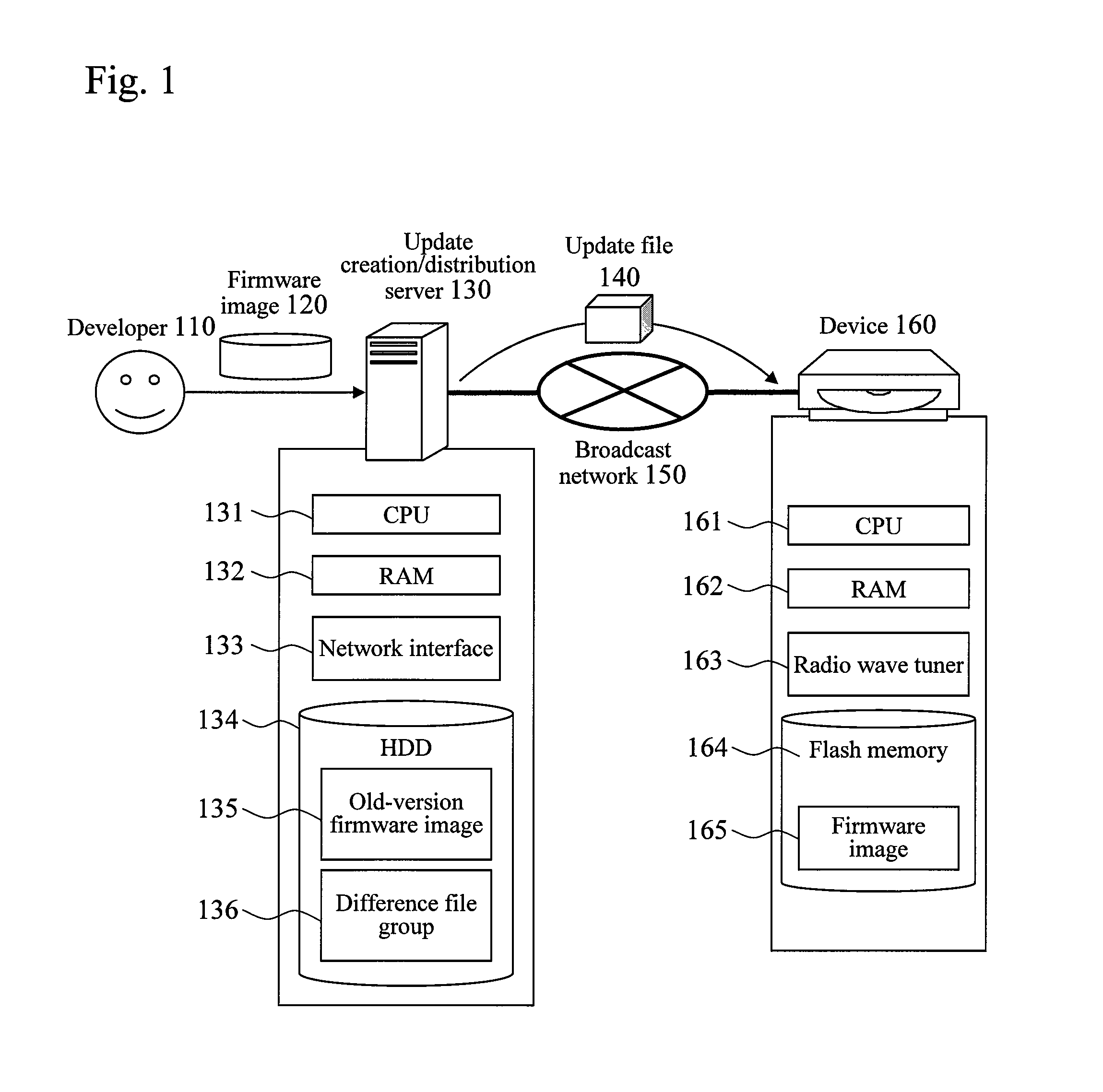

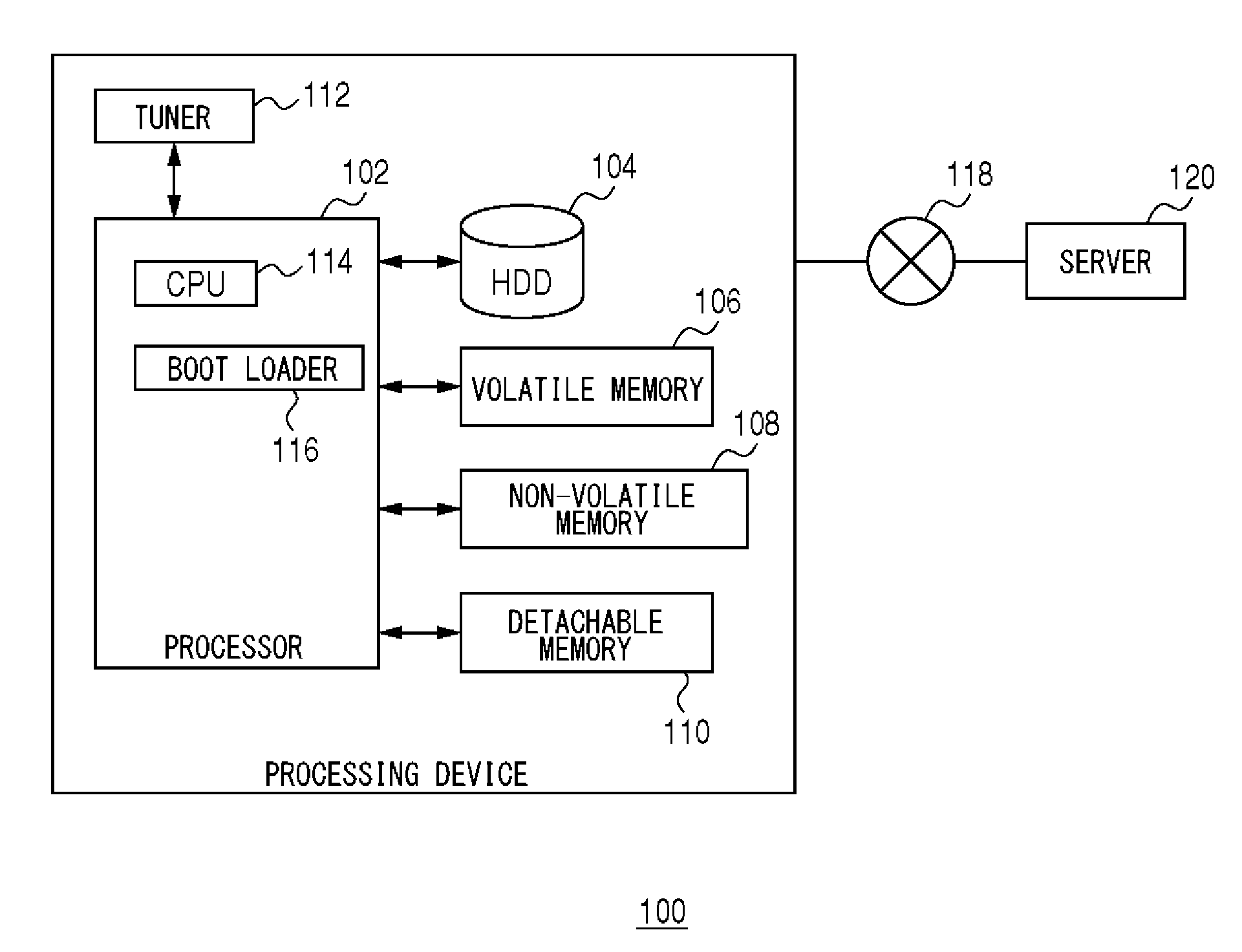

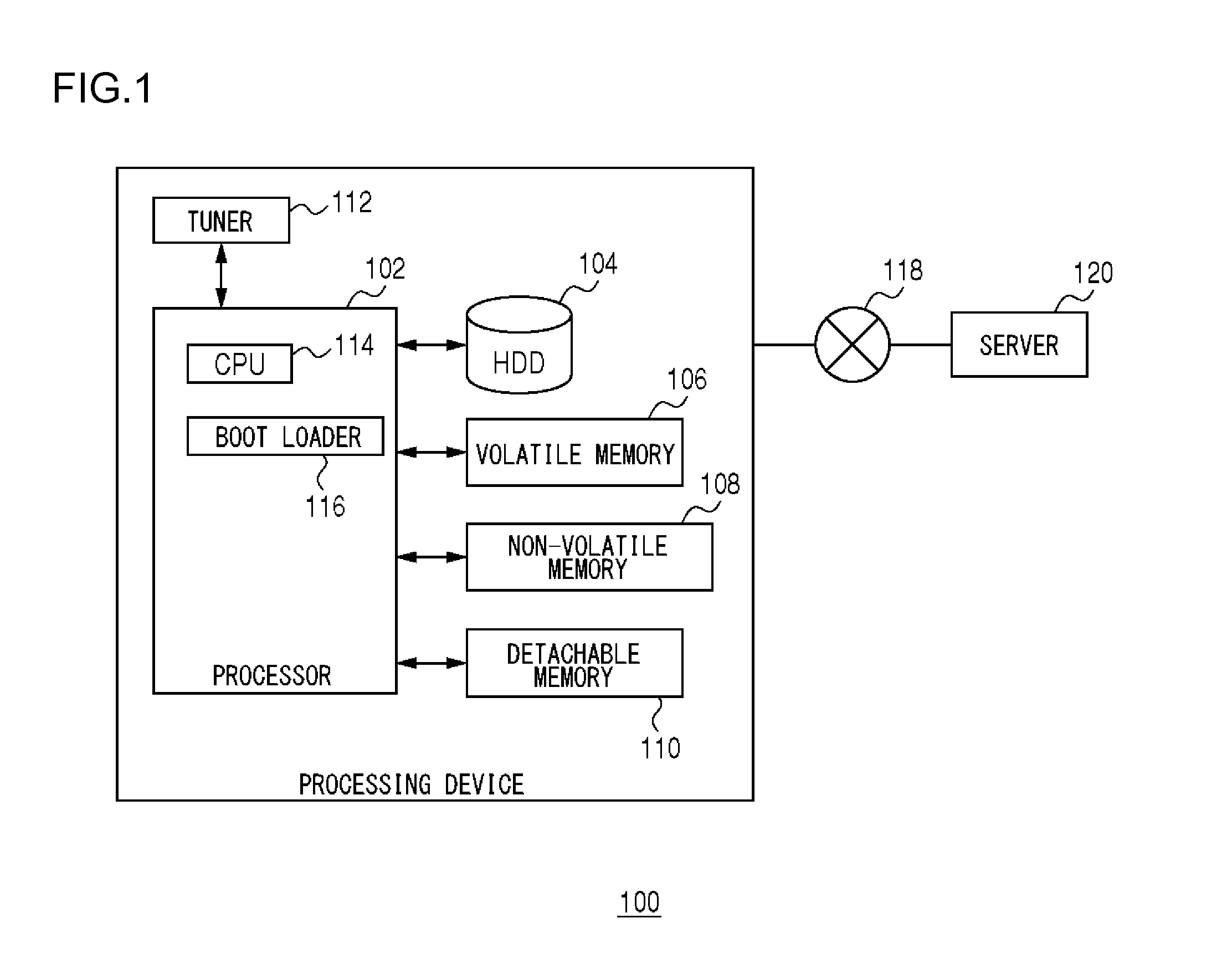

Firmware update data generating apparatus and information device

InactiveUS8904374B2Reduce memory capacityShorten write timeProgram loading/initiatingMemory systemsFirmware versionInformation device

There is provided a firmware updating technique for which consumed memory and writing time are small for devices subject to a firmware update, for which the distributed update size is small, and which is performed via a broadcast network. To this end, assuming that the latest firmware version is N, there is provided a means that extracts differences between firmware of version j−i and firmware of version i (j−1→j differences) for j=2 to N, and that distributes these differences together via the broadcast network. With respect to a device subject to an update comprising firmware of version i, there is provided a means that saves, of the distributed j−1→j differences (where 2≦j≦N), only the differences for which j<i in a storage area, generates an i→N difference based on the saved j−1→j differences (where i≦j≦N), and updates the firmware in flash memory based on the content of the i→N difference (see FIG. 1).

Owner:HITACHI SOFTWARE ENG

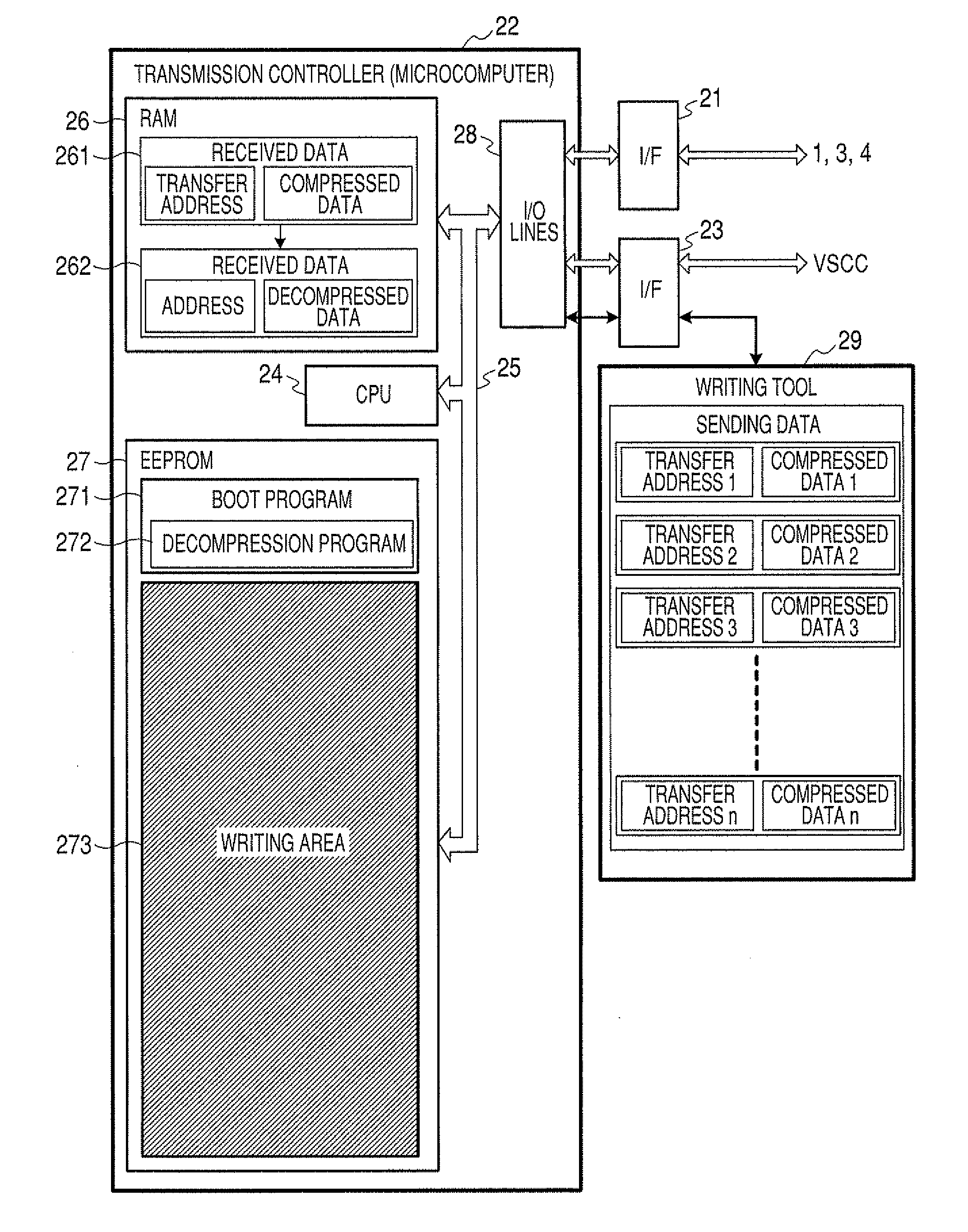

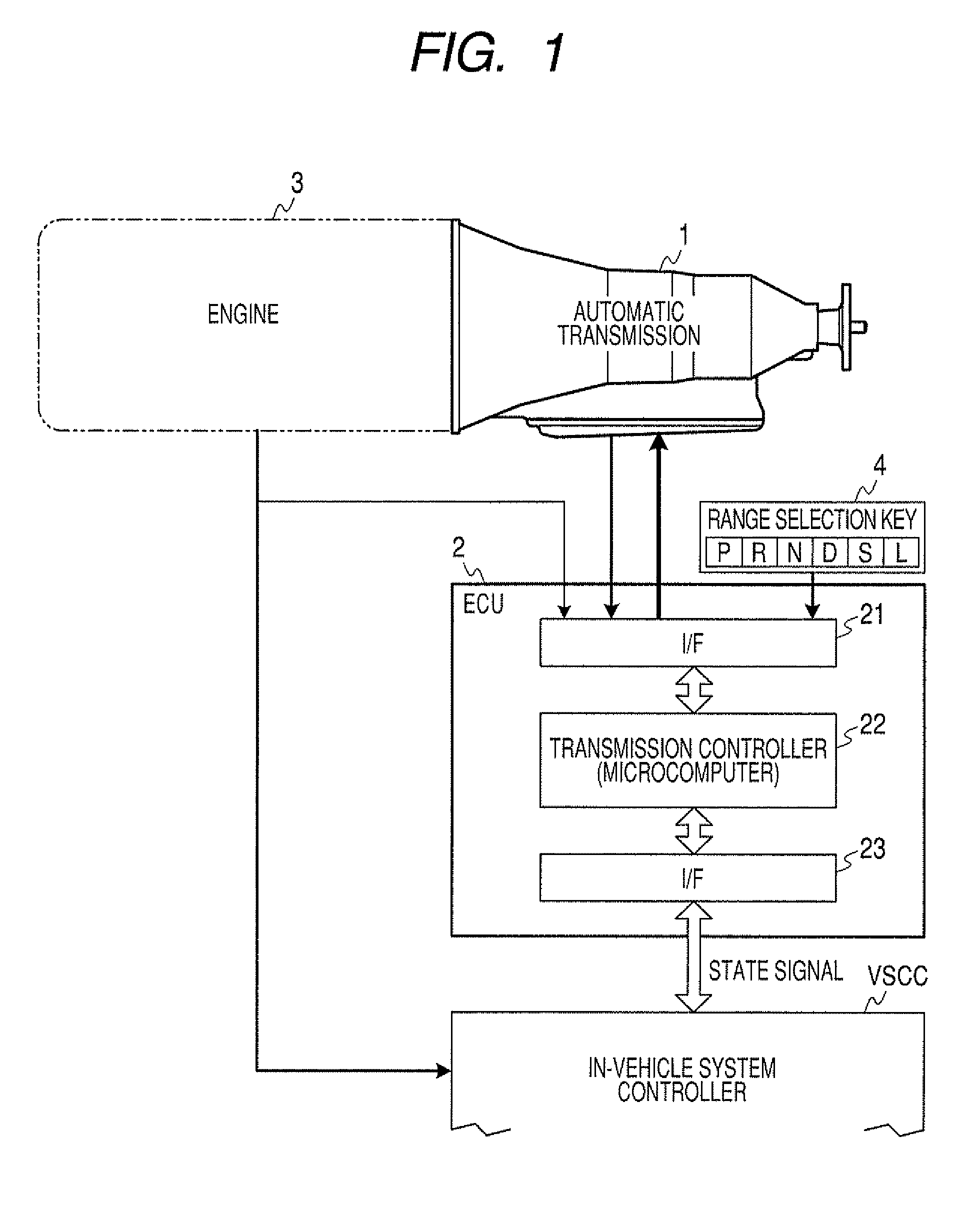

Method of writing control data into on-board vehicle control unit and the control unit

InactiveUS20090248912A1Avoid the needIncrease capacityMemory architecture accessing/allocationDigital data processing detailsOn boardControl data

A first-type data transfer frame for uncompressed transfer of a control program and control data including reference data, and a second-type data transfer frame for compressed transfer have the same fixed size, and each transfer frame includes compression identification information indicating uncompressed or compressed data. When an on-board vehicle control unit receives a transfer frame with uncompressed control data, the control unit stores the uncompressed control data of the frame in a nonvolatile memory. When the transfer frame has compressed control data, the control unit writes the compressed control data of the frame into RAM, and decompresses control data in the RAM. The control unit sequentially accumulates decompressed control data in the RAM, and when amount of the accumulated control data reaches a setting amount, the control unit halts the decompressing, and transfers the decompressed control data from the RAM into the nonvolatile memory, and restarts decompressing for the next received data transfer frame from the halt point.

Owner:AISIN AW CO LTD

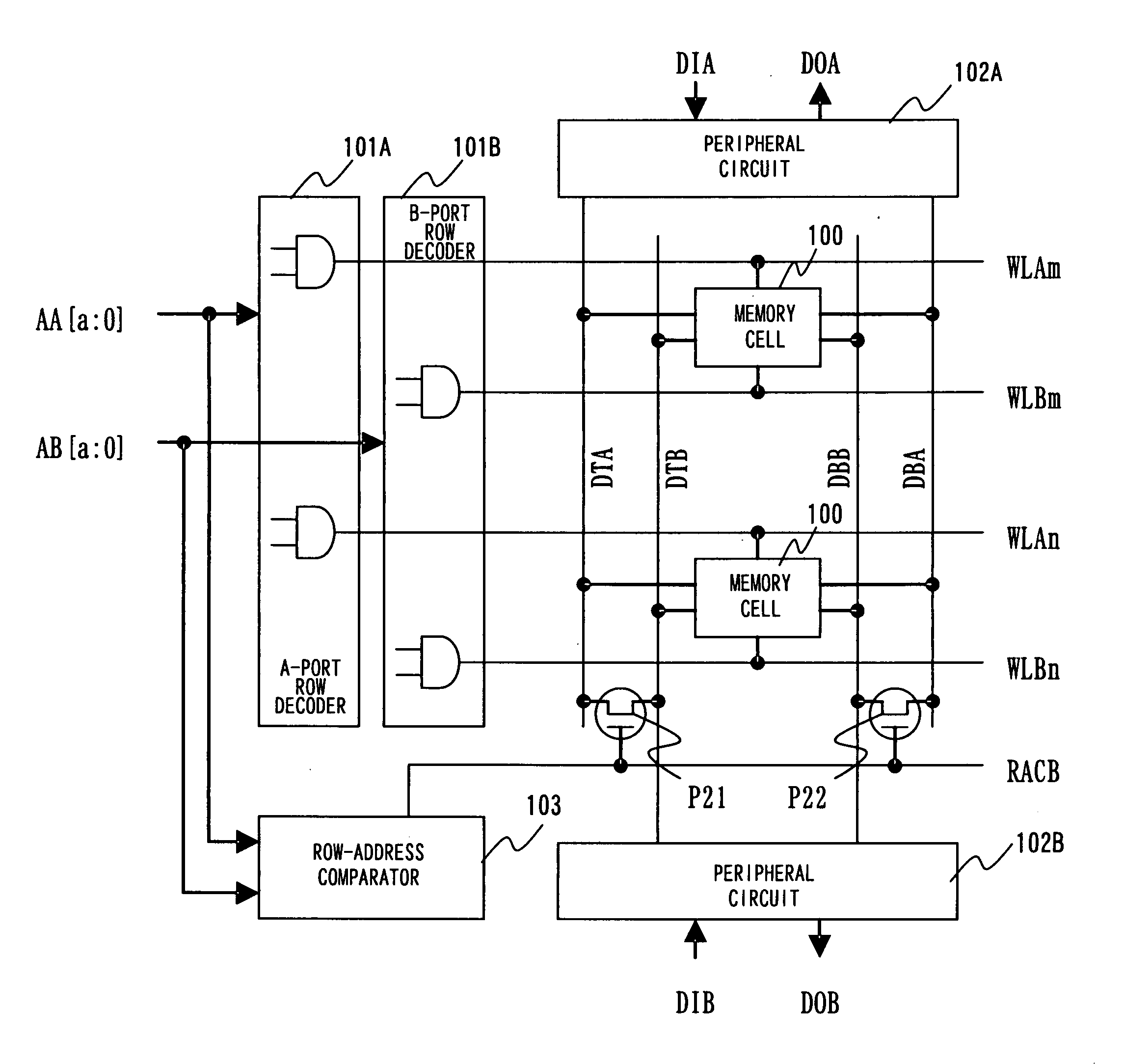

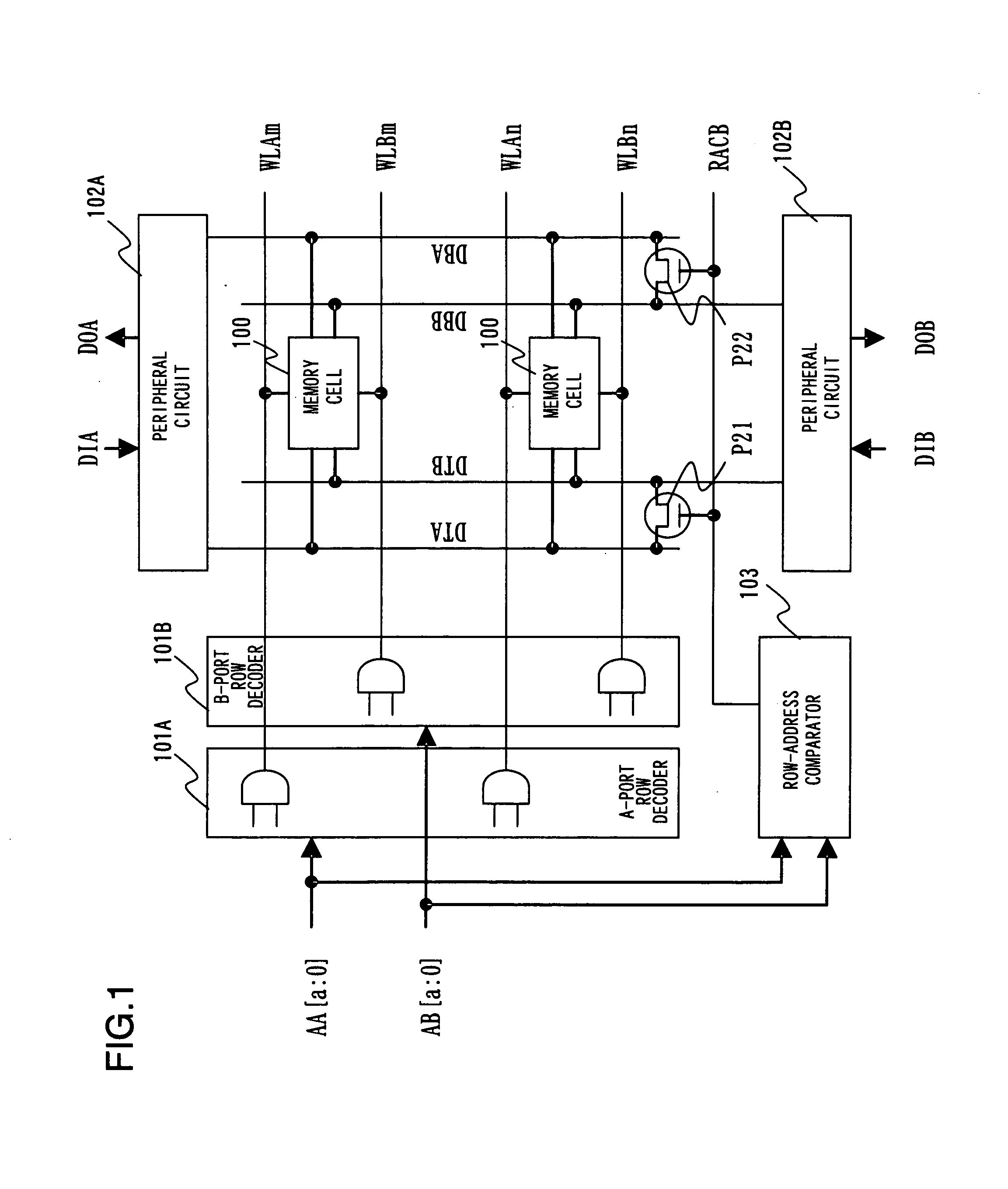

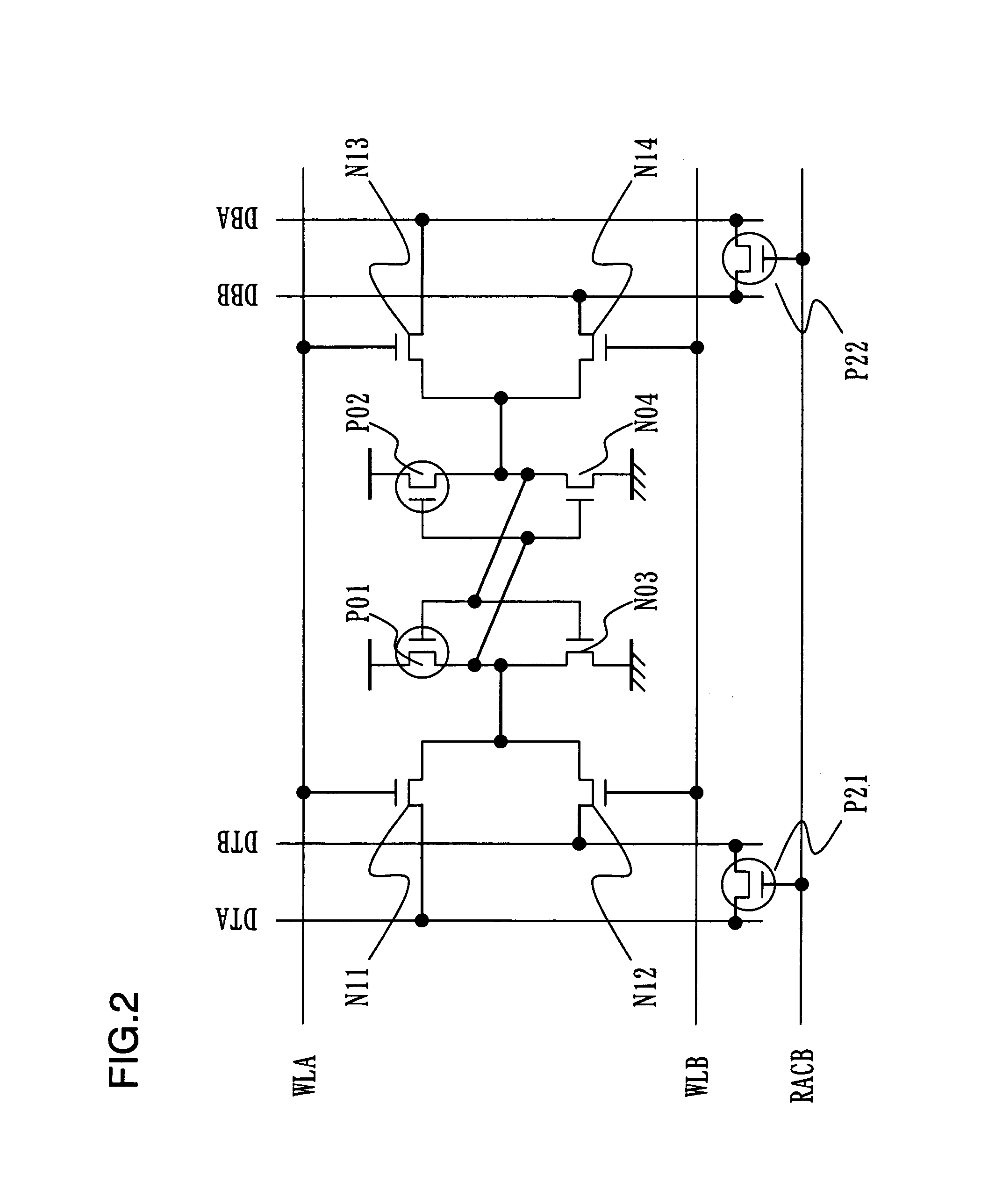

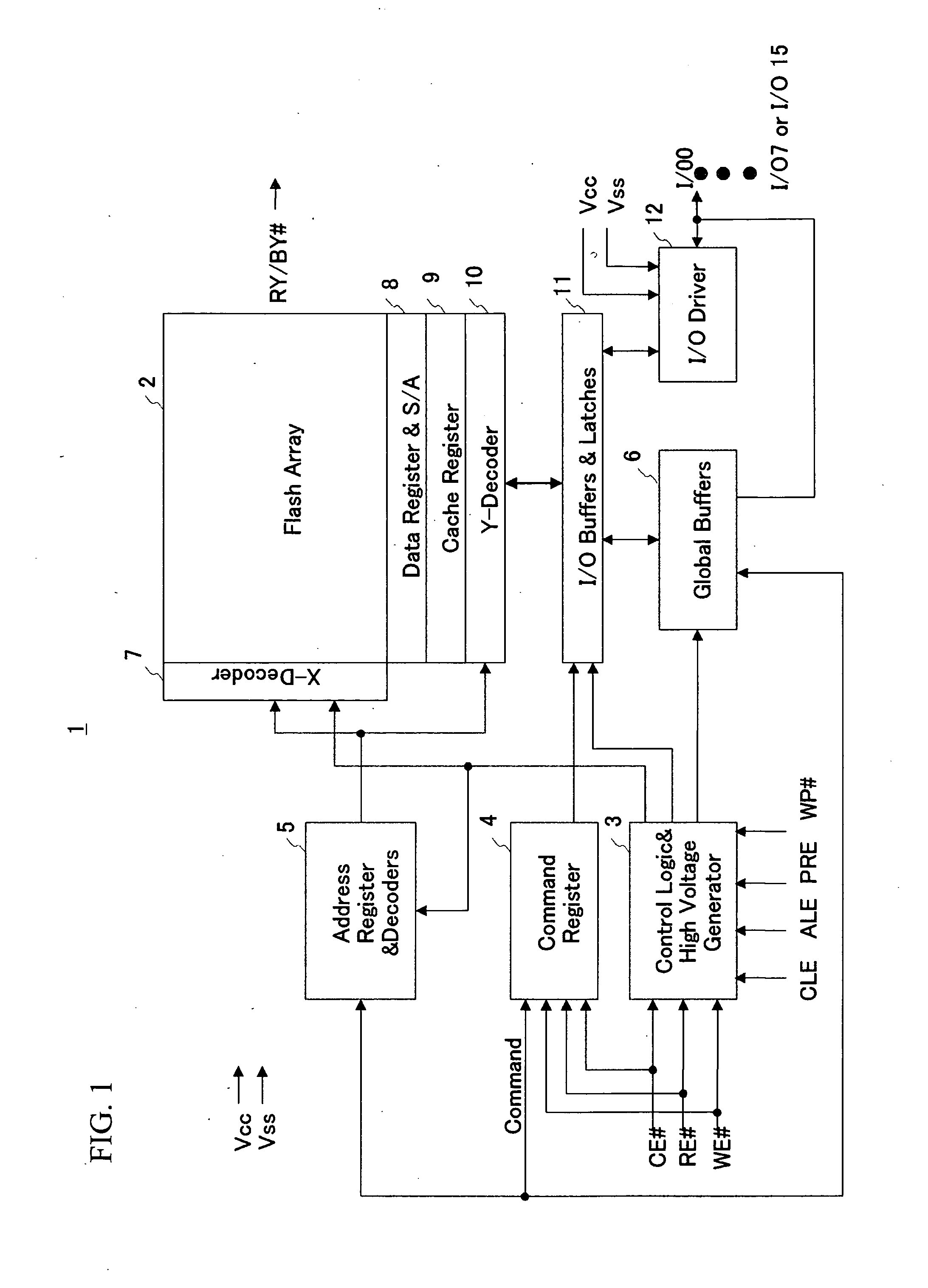

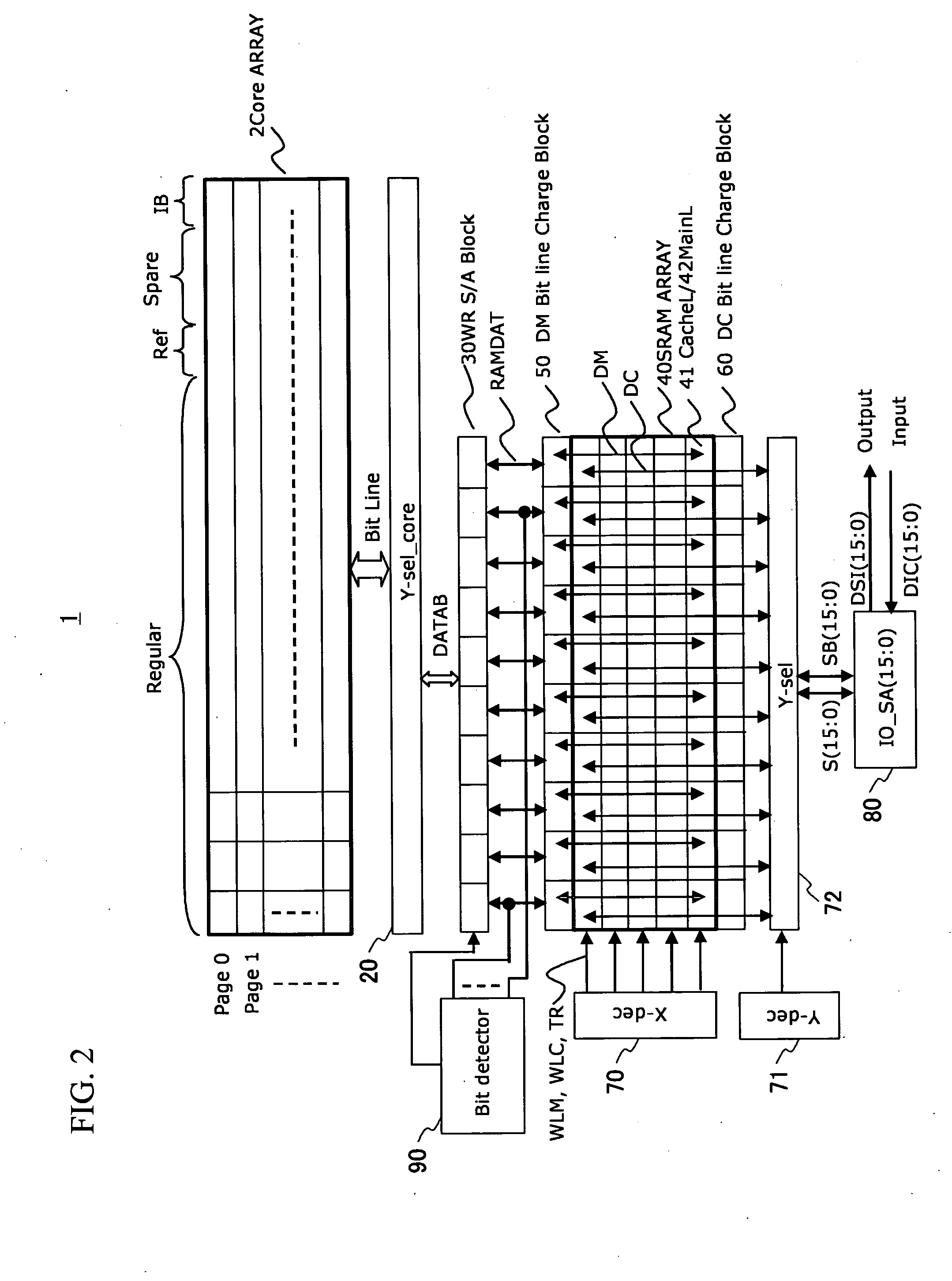

Semiconductor memory device

InactiveUS20080316851A1Improve data reading speedDecrease in malfunctionDigital storageBit lineComputer science

Disclosed is a semiconductor memory device including a plurality of memory cells, each of which is connected to word lines of first and second ports and to bit lines of the first and second ports, and first and second inter-port switches for electrically connecting first bit lines of the first port and second bit lines of the second port when row addresses of the first and second ports match each other.

Owner:NEC ELECTRONICS CORP

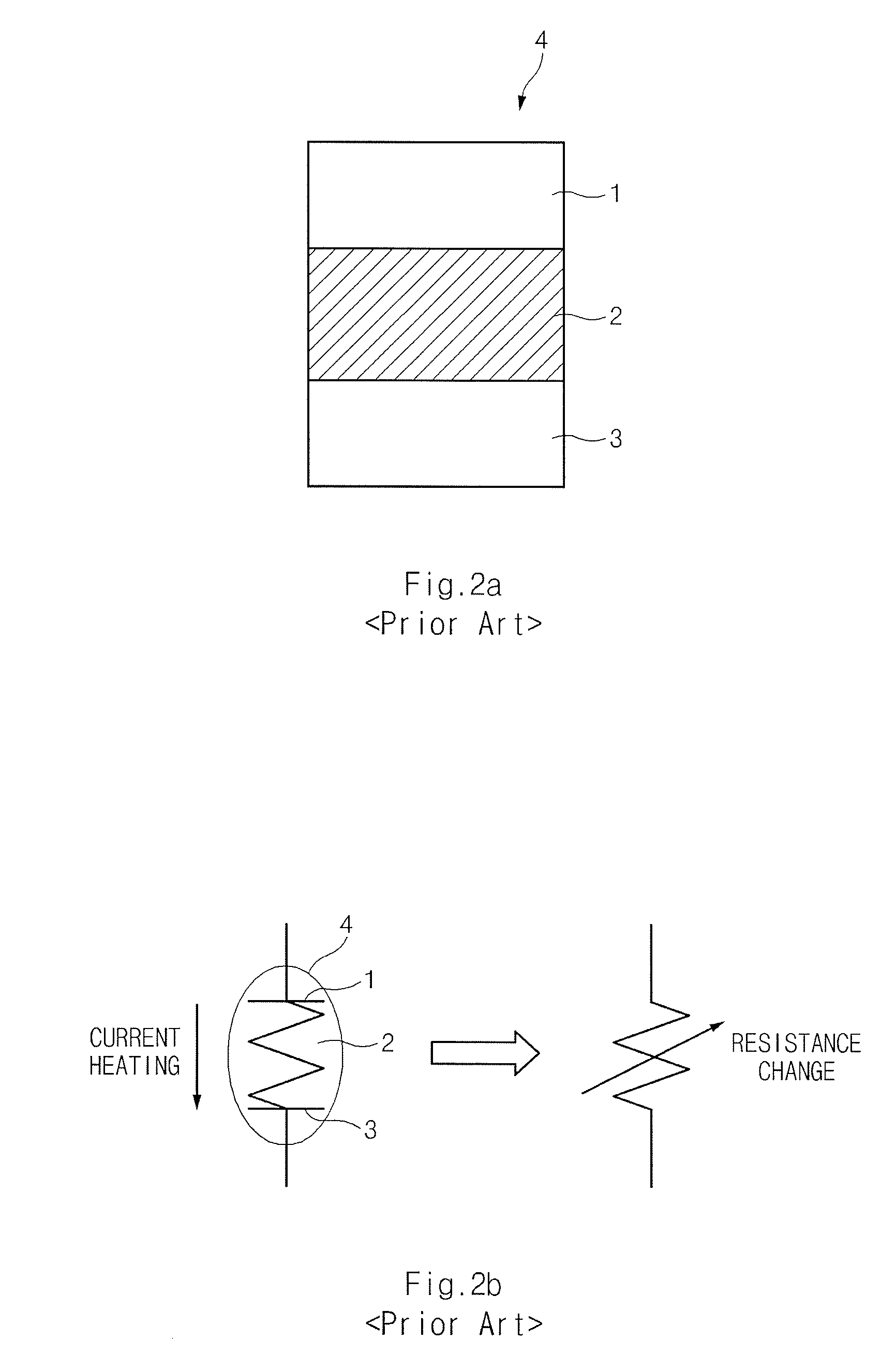

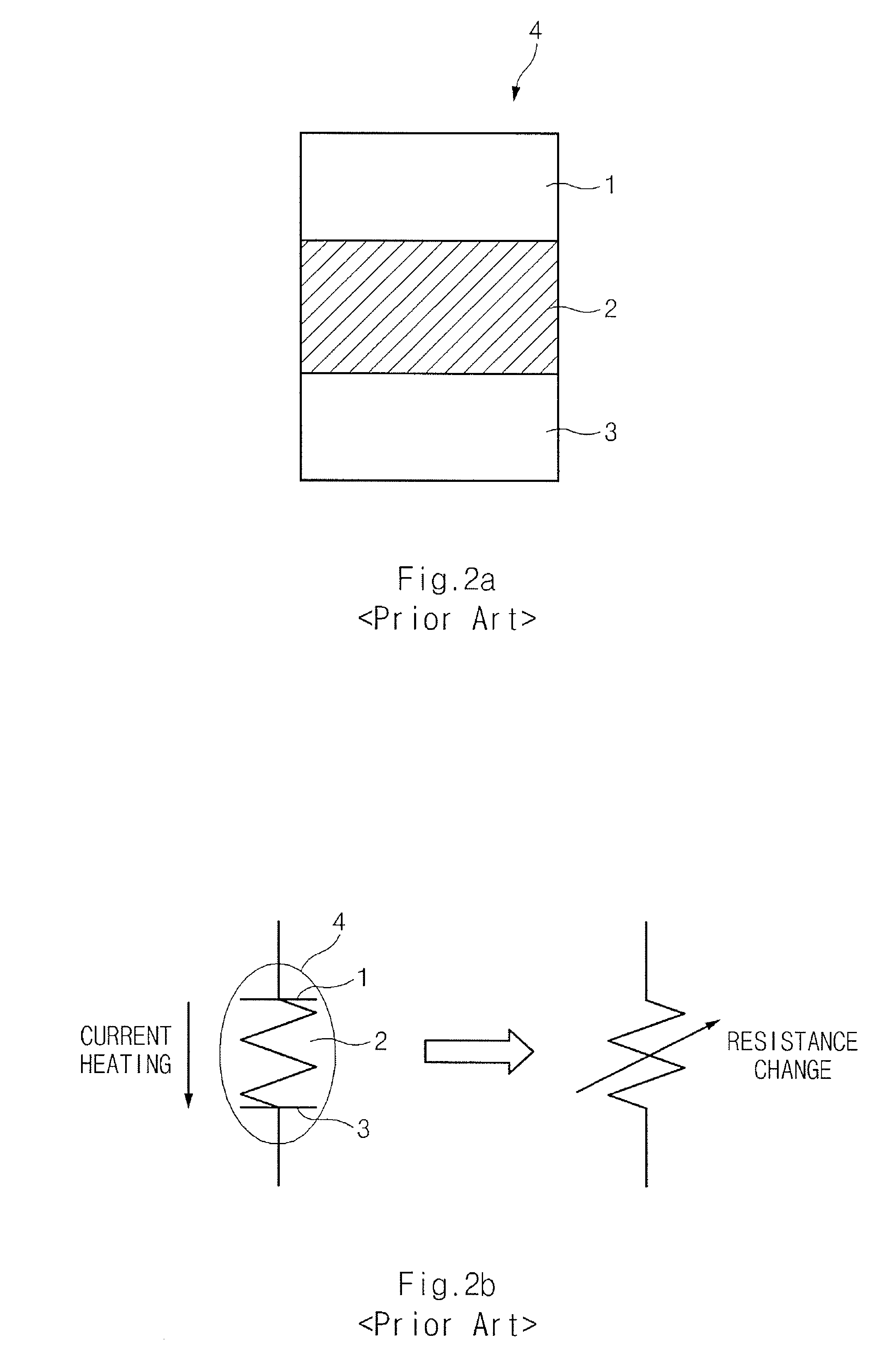

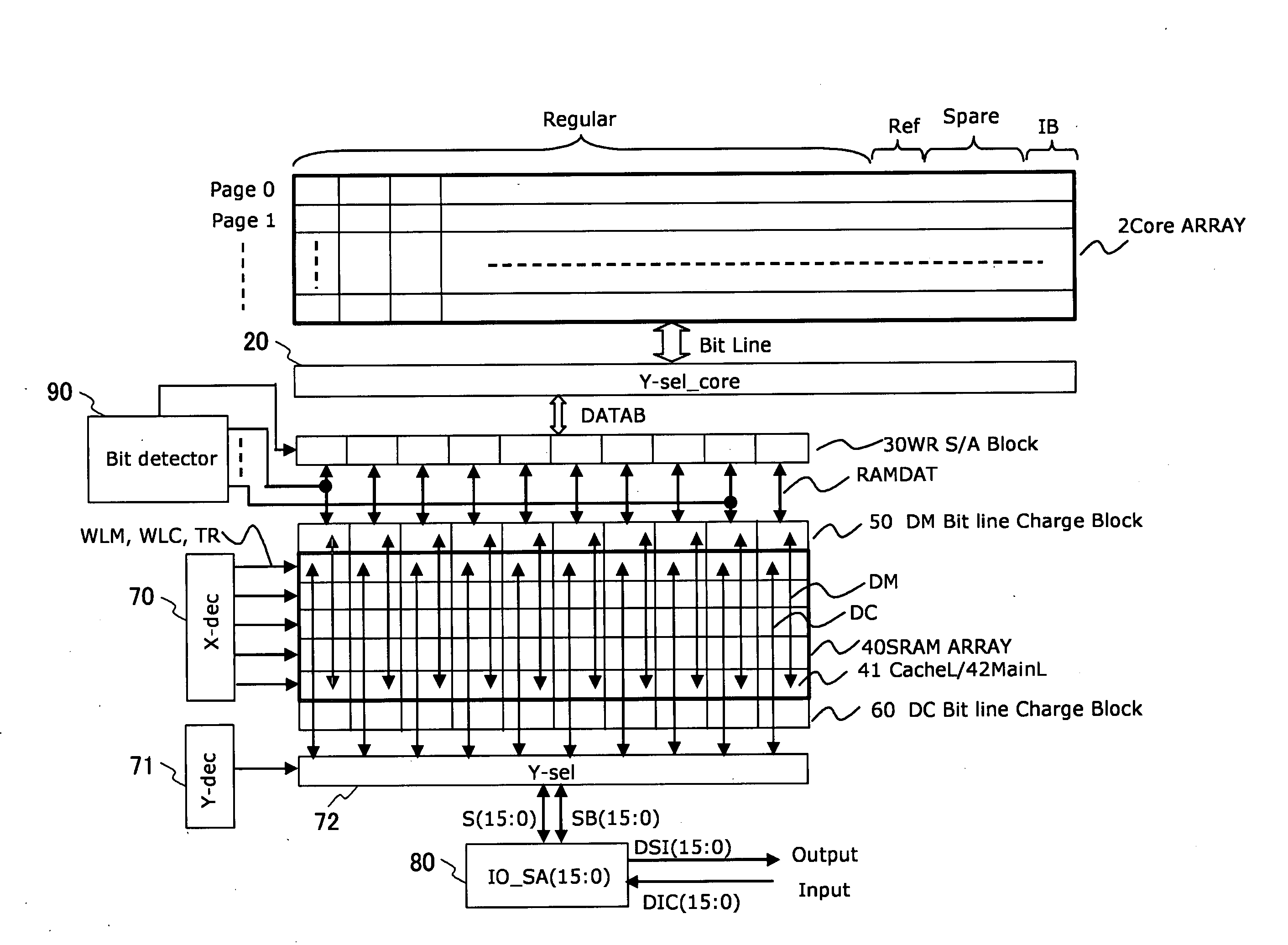

Semiconductor device and method of controlling the same

ActiveUS20060245247A1Writing time becomes shortReduce circuit areaRead-only memoriesDigital storageDevice materialControl circuit

A semiconductor device (1) includes a non-volatile memory cell array (2), a write / read circuit (30) writing data into and reading data from the non-volatile memory cell array (2), a data input / output circuit (80), and a volatile memory cell array (40) including a first latch circuit (41) that is connected to the write / read circuit (30) and latches first data, and a second latch circuit (42) that is connected to the data input / output circuit (80) and latches second data. The device (1) may further include an inverter circuit (310) that inverts the first data in accordance with the number of bits to be actually written among the first data, and a control circuit (3) that causes the second data to be latched in the second latch circuit (42) while the first data is being written into the non-volatile memory cell array (2). This semiconductor device (1) has a shorter writing time and a smaller circuit area.

Owner:VALLEY DEVICE MANAGEMENT

Processing device and writing method for writing a file to a storage medium

InactiveUS20120317349A1Reduce processing latencyShorten write timeInput/output to record carriersLink editingOperating systemNon-volatile memory

An acquiring unit acquires, from a storage device capable of storing a file by dividing the file into a plurality of blocks, managing information indicating an address of each block configuring the file. A creating unit creates a table indicating a start address and a size of each continuous region by extracting the address of each block from the acquired managing information, and aggregating blocks having continuous addresses as a continuous region. A reading unit reads a file stored in a non-volatile memory. A dividing unit divides the read file into a plurality of blocks. A writing unit writes the divided file to the storage device in units of the continuous region, which is from the start address over the size, based on the table, so as to maintain the addresses indicated in the managing information.

Owner:JVC KENWOOD CORP A CORP OF JAPAN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com