Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

142results about How to "Reduce circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

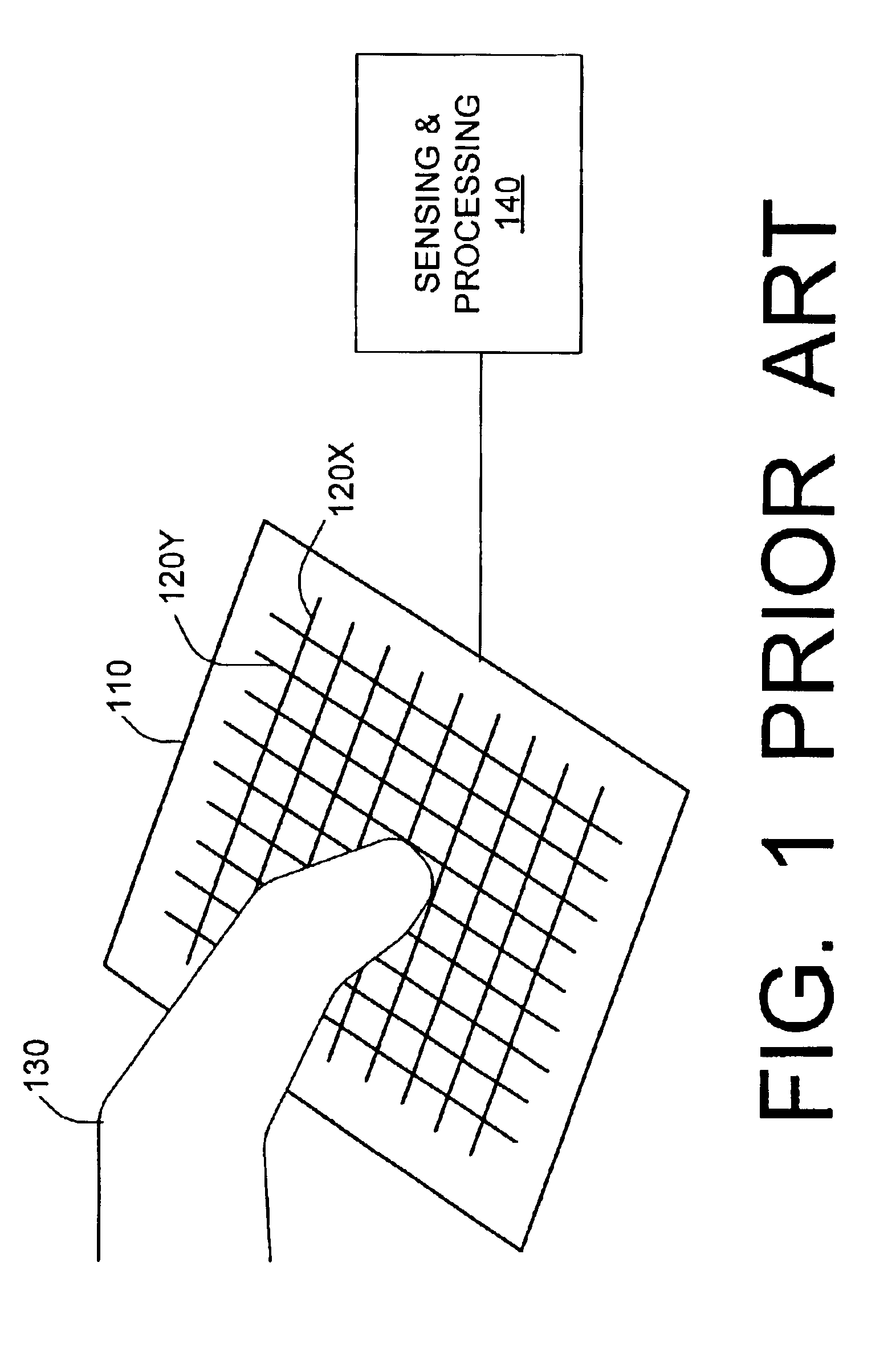

Touch sensor

InactiveUS7154481B2Reduce circuitSimple controllerTransmission systemsUsing electrical meansCapacitanceTouch Senses

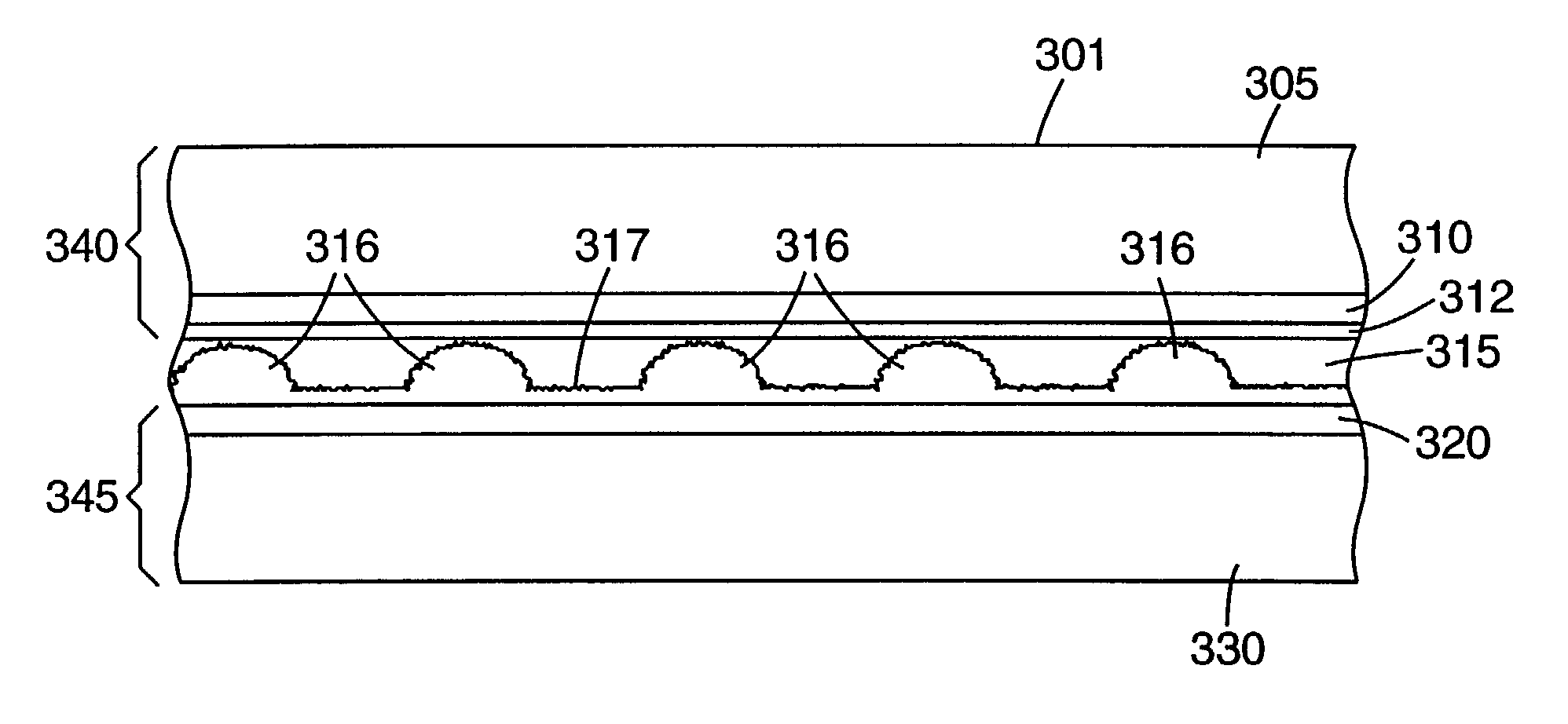

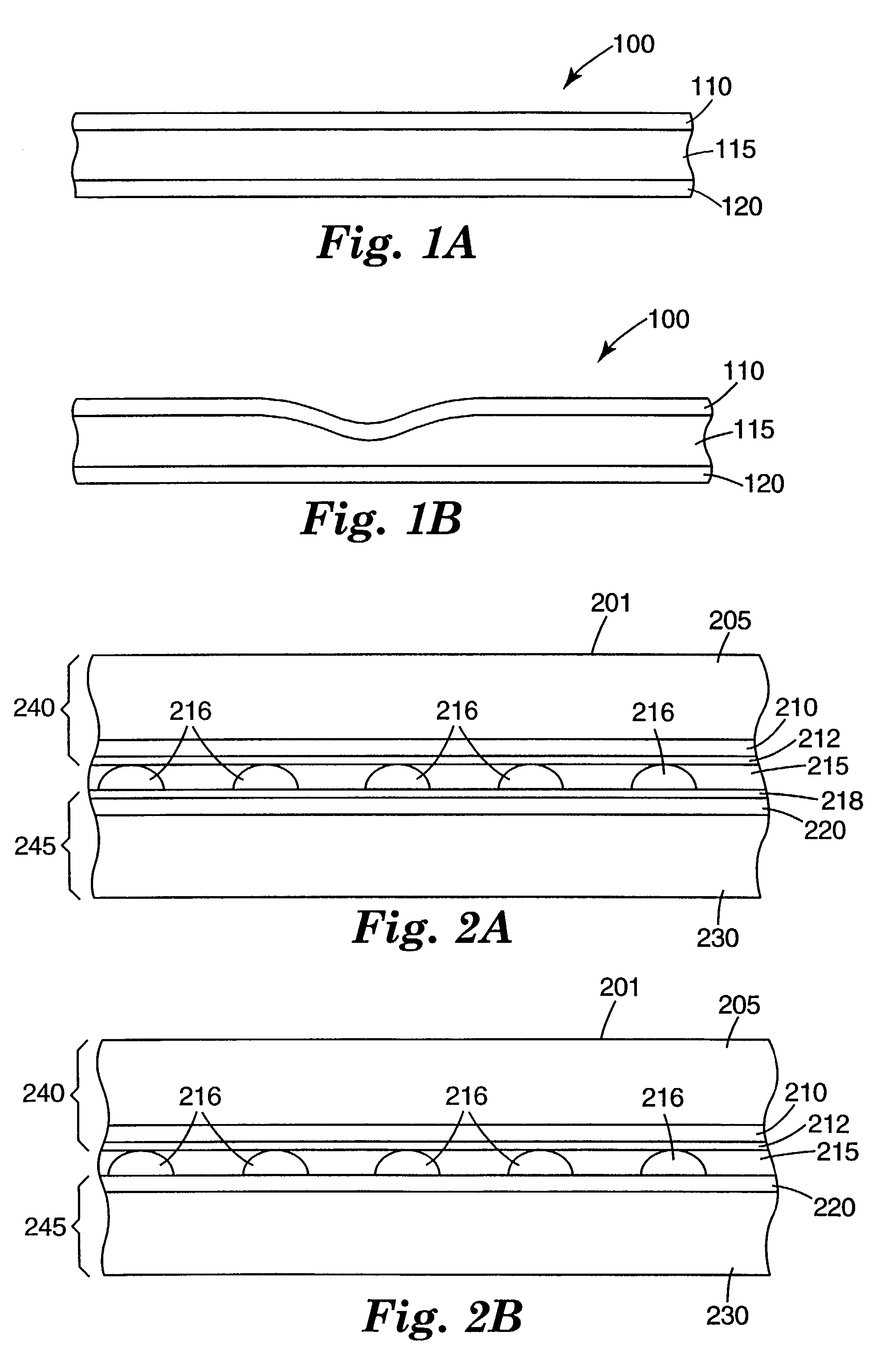

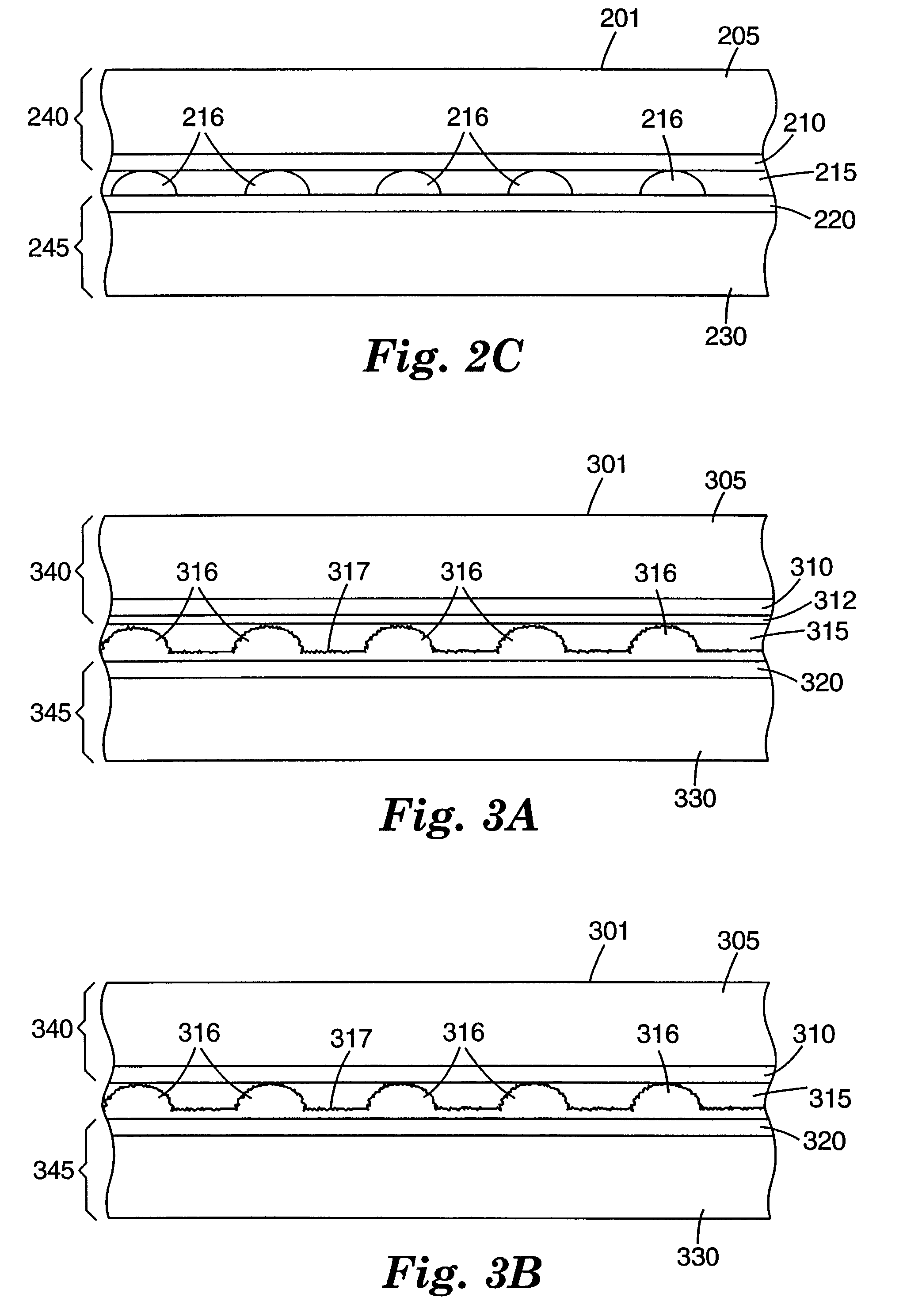

A touch sensing method and a touch sensing device are described for sensing a location of a touch. When the touch sensing device is touched, a first conductive layer disposed on a supporting layer is deflected toward a second conductive layer. The touch location is determined by sensing the change in capacitance at the location of the touch. A change in capacitance at the touch location is sensed by driving one of the conductive layers with an electrical signal referenced to the other conductive layer and measuring the current flow between the conductive layers. The sensed change in capacitance is greater than a change in the external capacitance of the touch sensor.

Owner:3M INNOVATIVE PROPERTIES CO

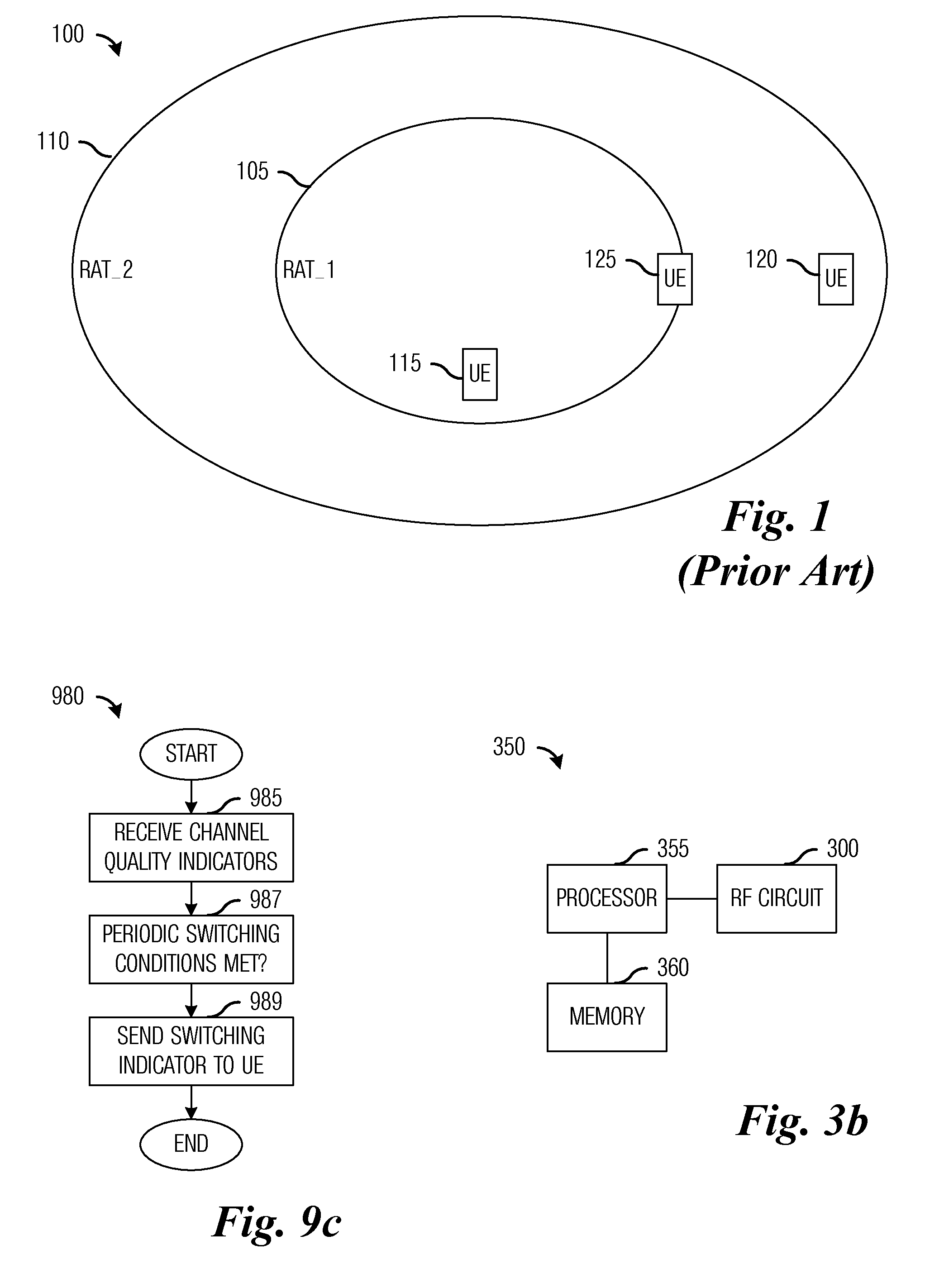

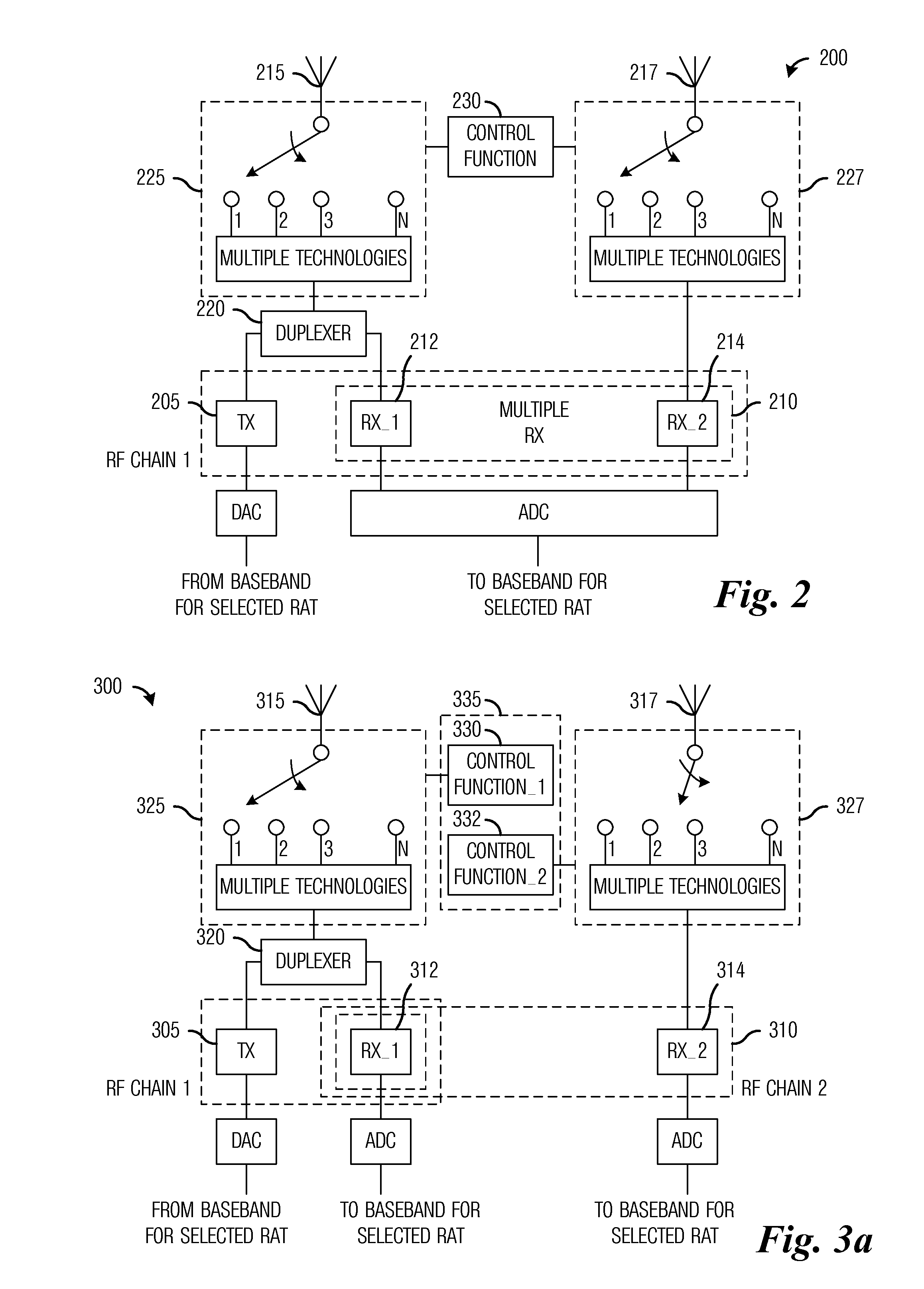

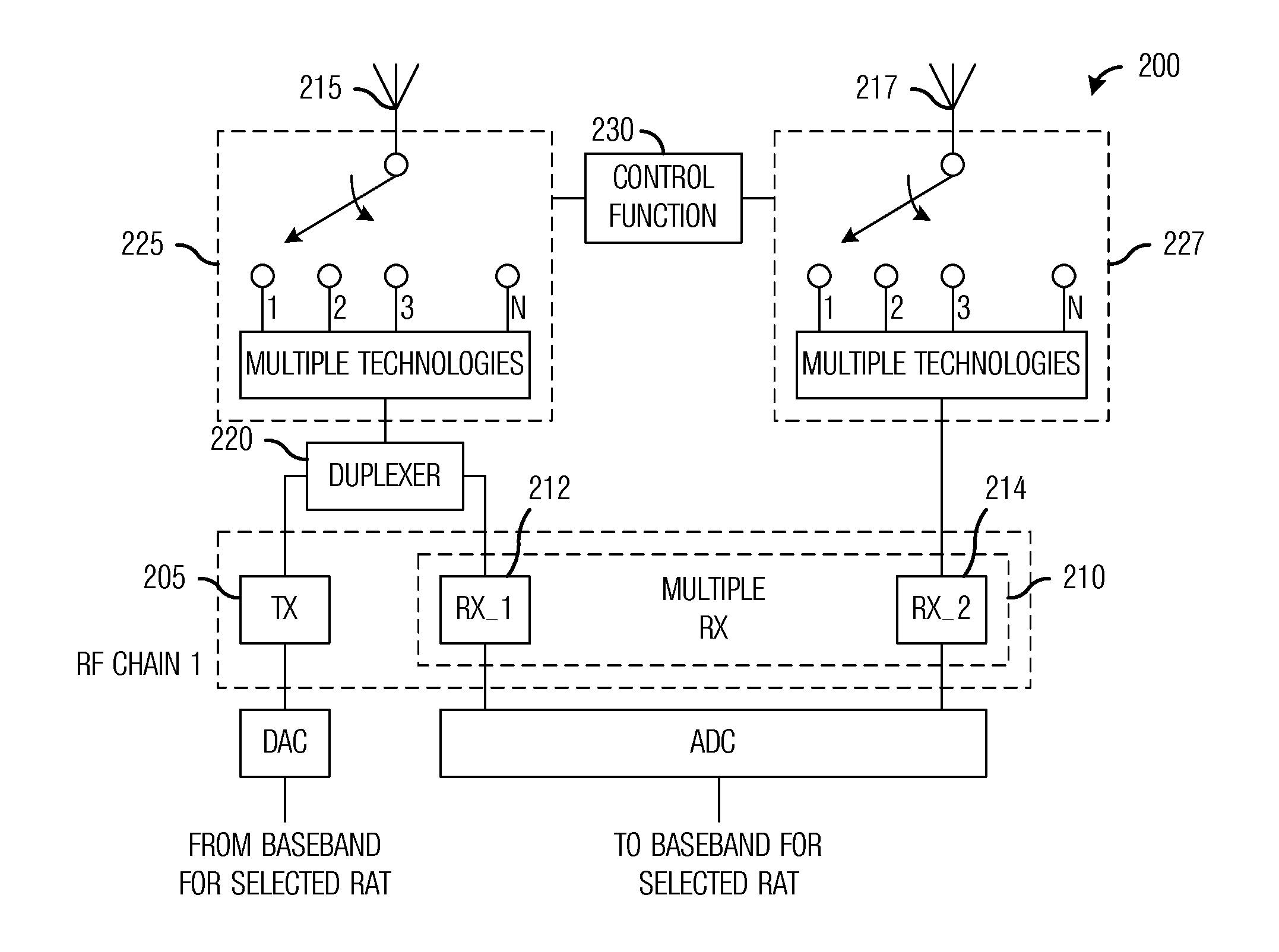

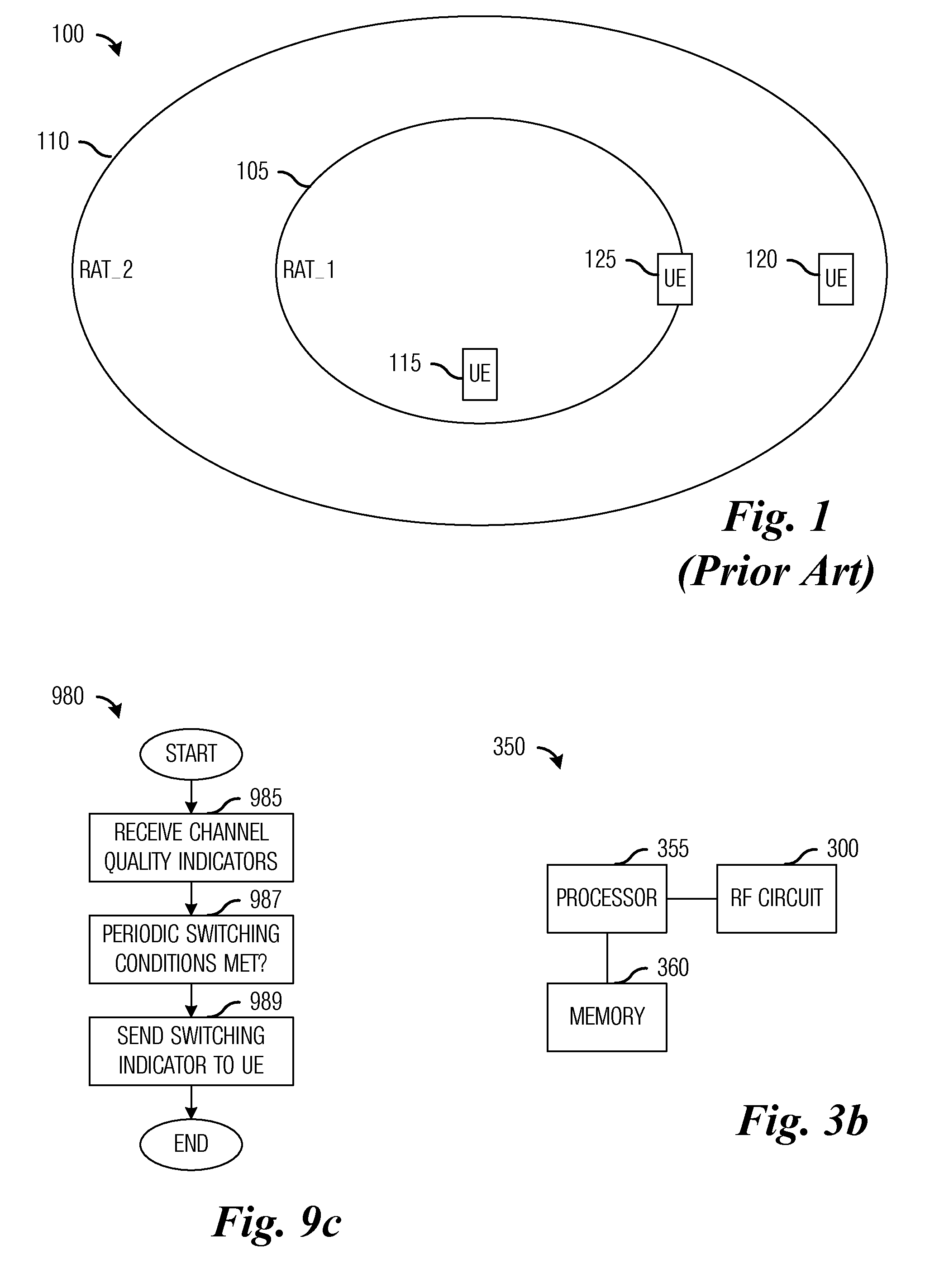

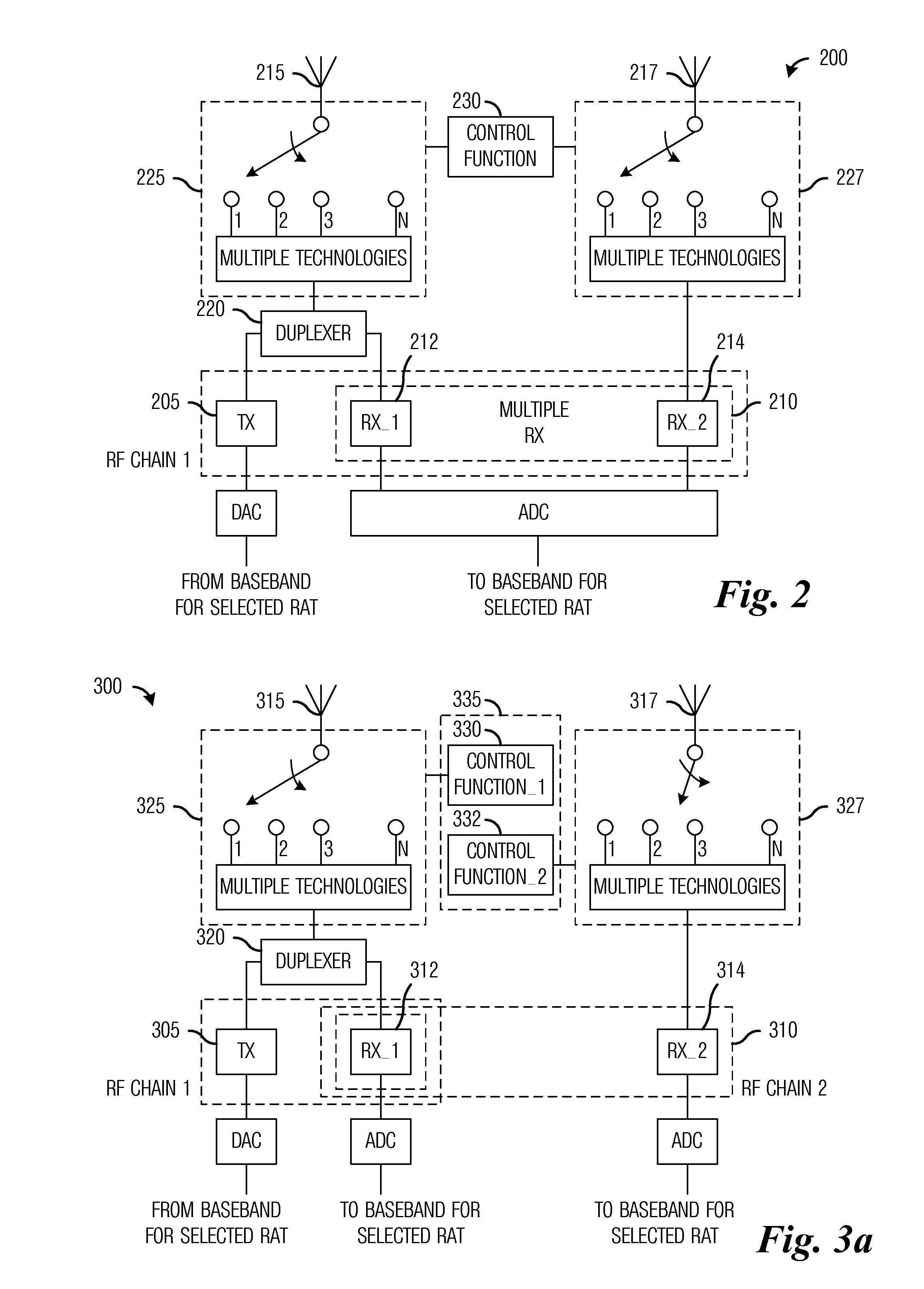

System and Method for Supporting Handovers Between Different Radio Access Technologies of a Wireless Communications System

ActiveUS20100260147A1Cost reductionReduction of circuitryTime-division multiplexSecret communicationRadio accessRadio access technology

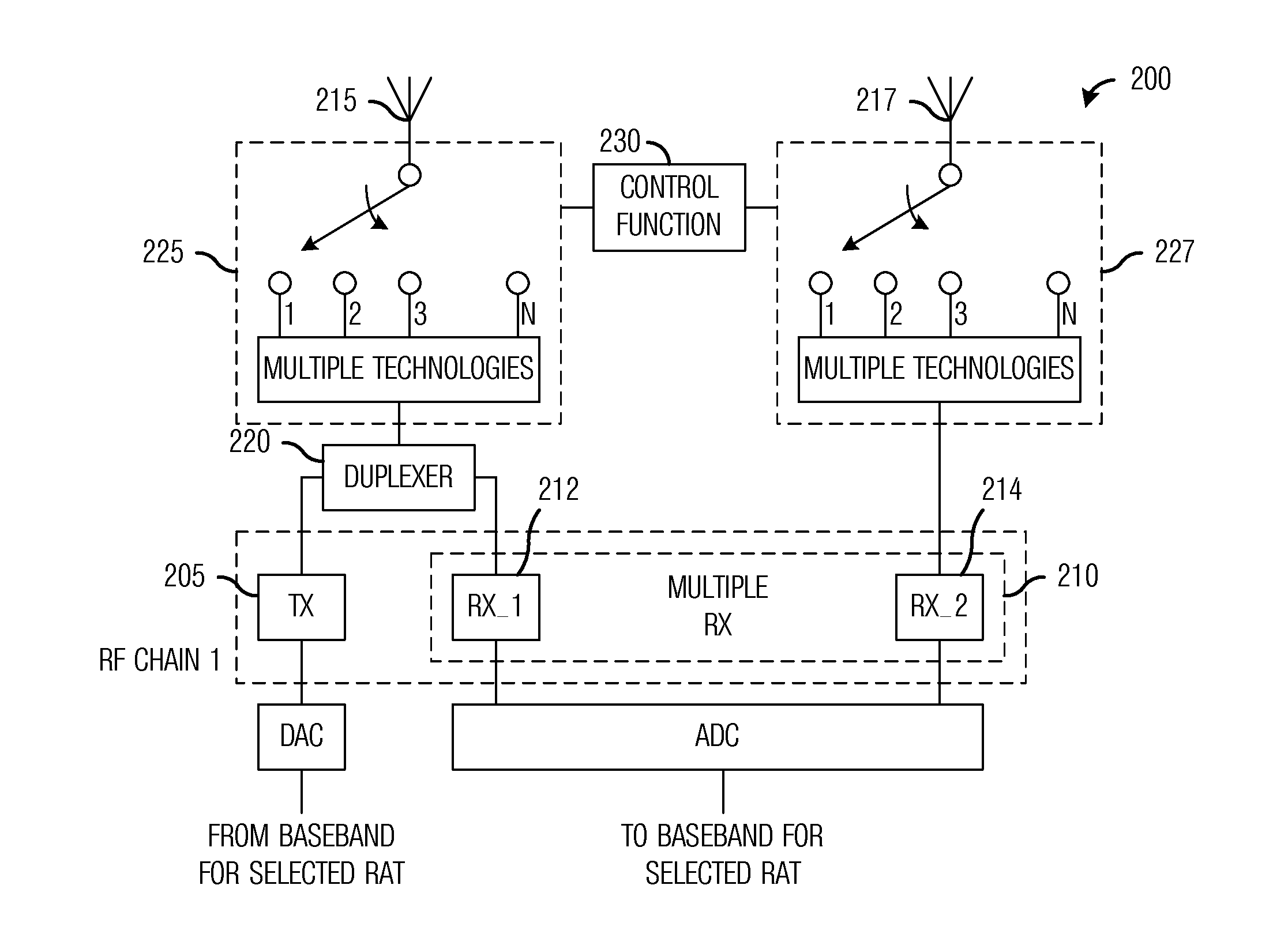

A system and method for supporting handovers between different radio access technologies is provided. A method for communications device operations includes sending a request to a controller of the communications device to change an operating mode of the communications device, and receiving a transmission responsive to the request. The method also includes in response to determining that the controller has granted the request to change the operating mode and that the communications device is operating in a border cell, changing the operating mode of the communications device, tuning at least one receiver of the communications device to an alternate radio access technology (RAT), and initiating a handover with the alternate RAT.

Owner:FUTUREWEI TECH INC

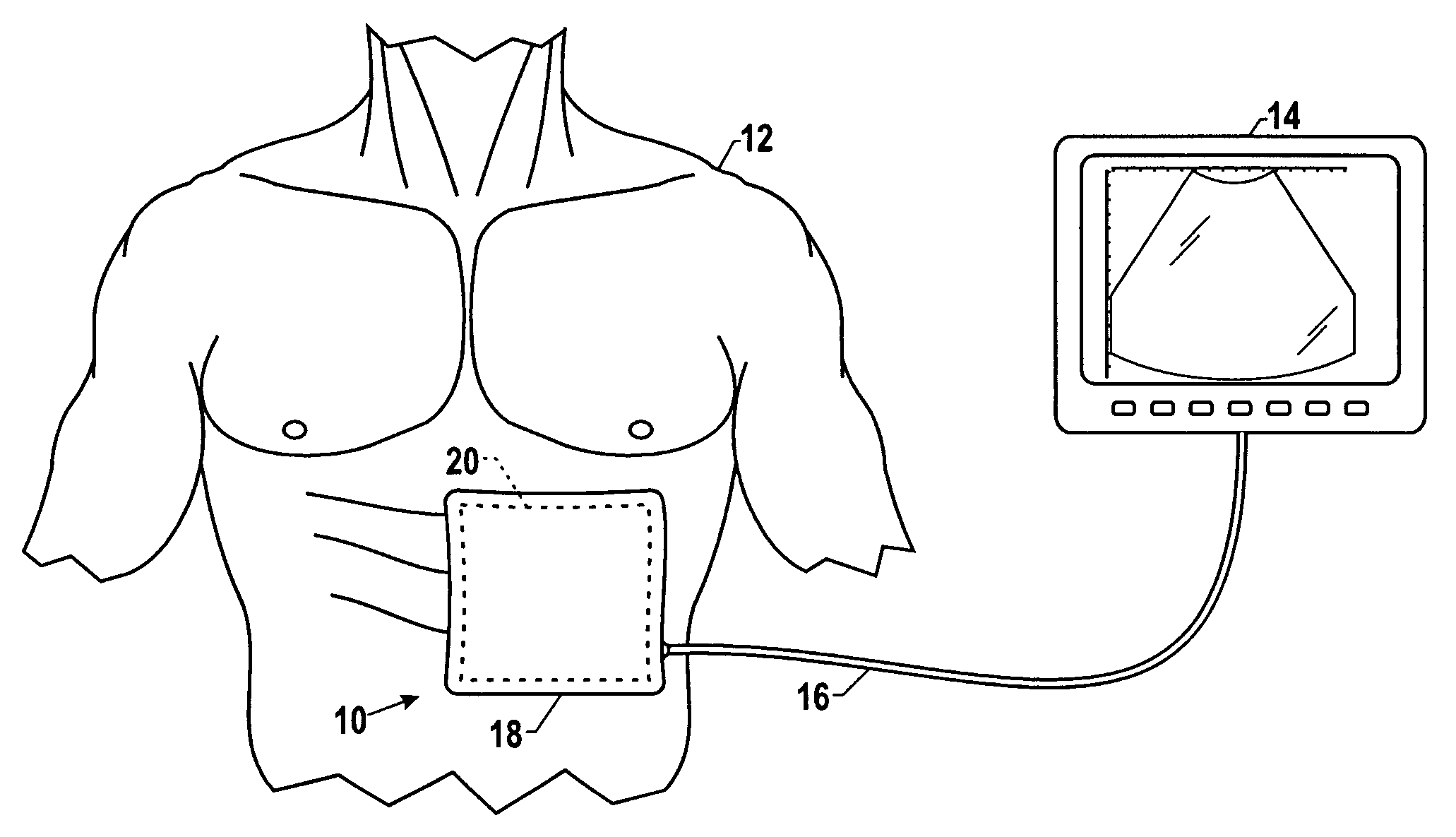

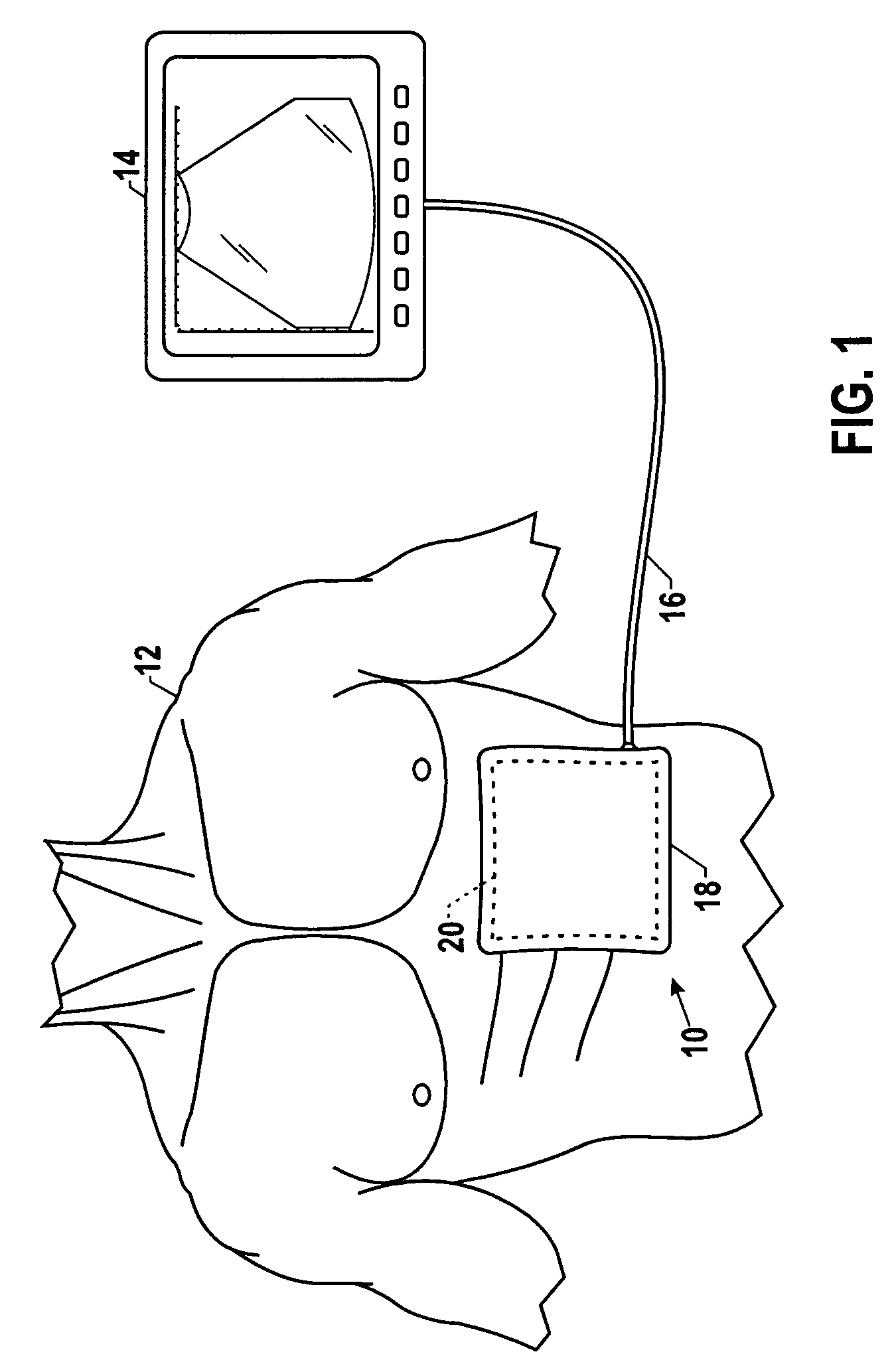

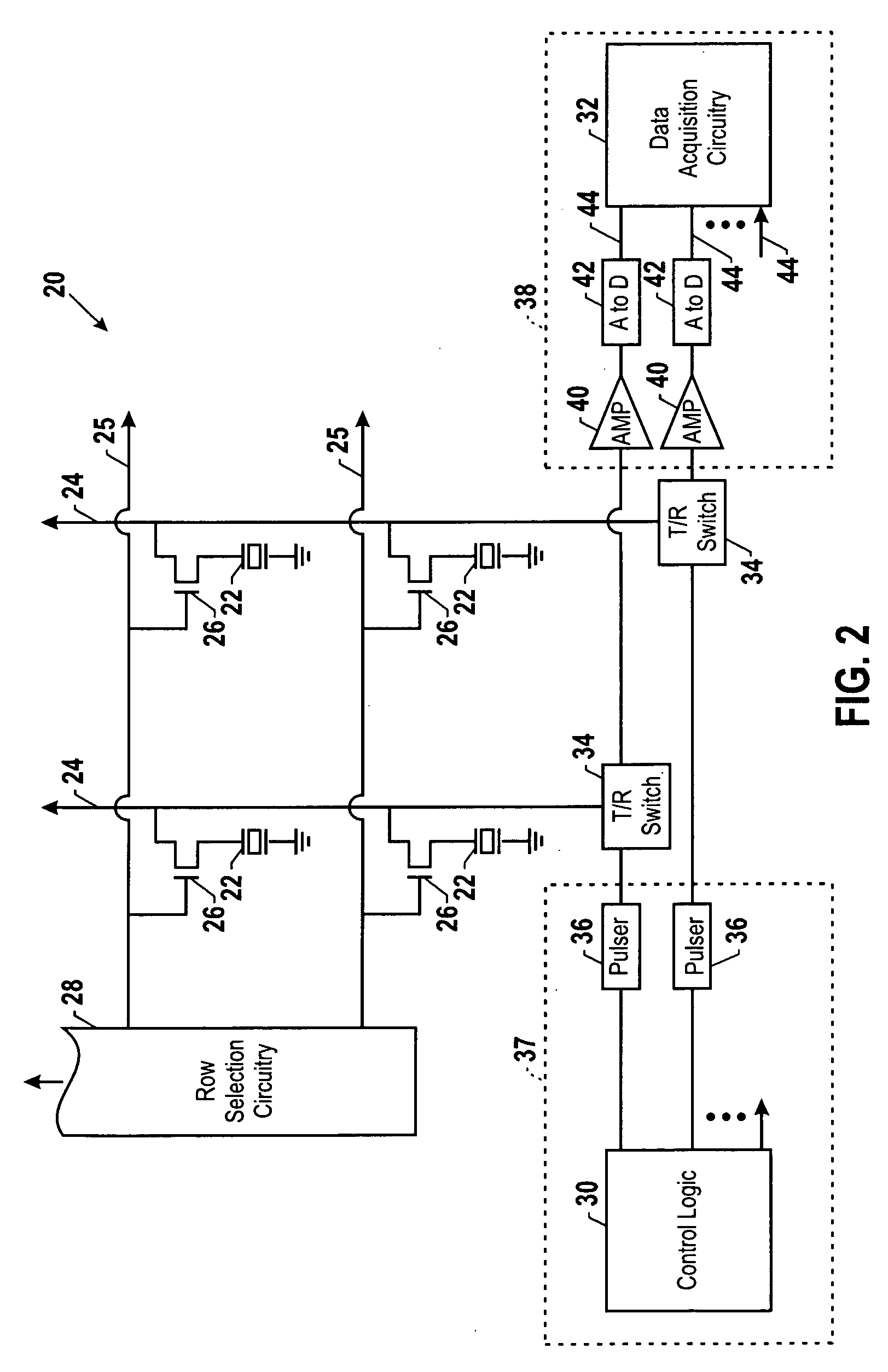

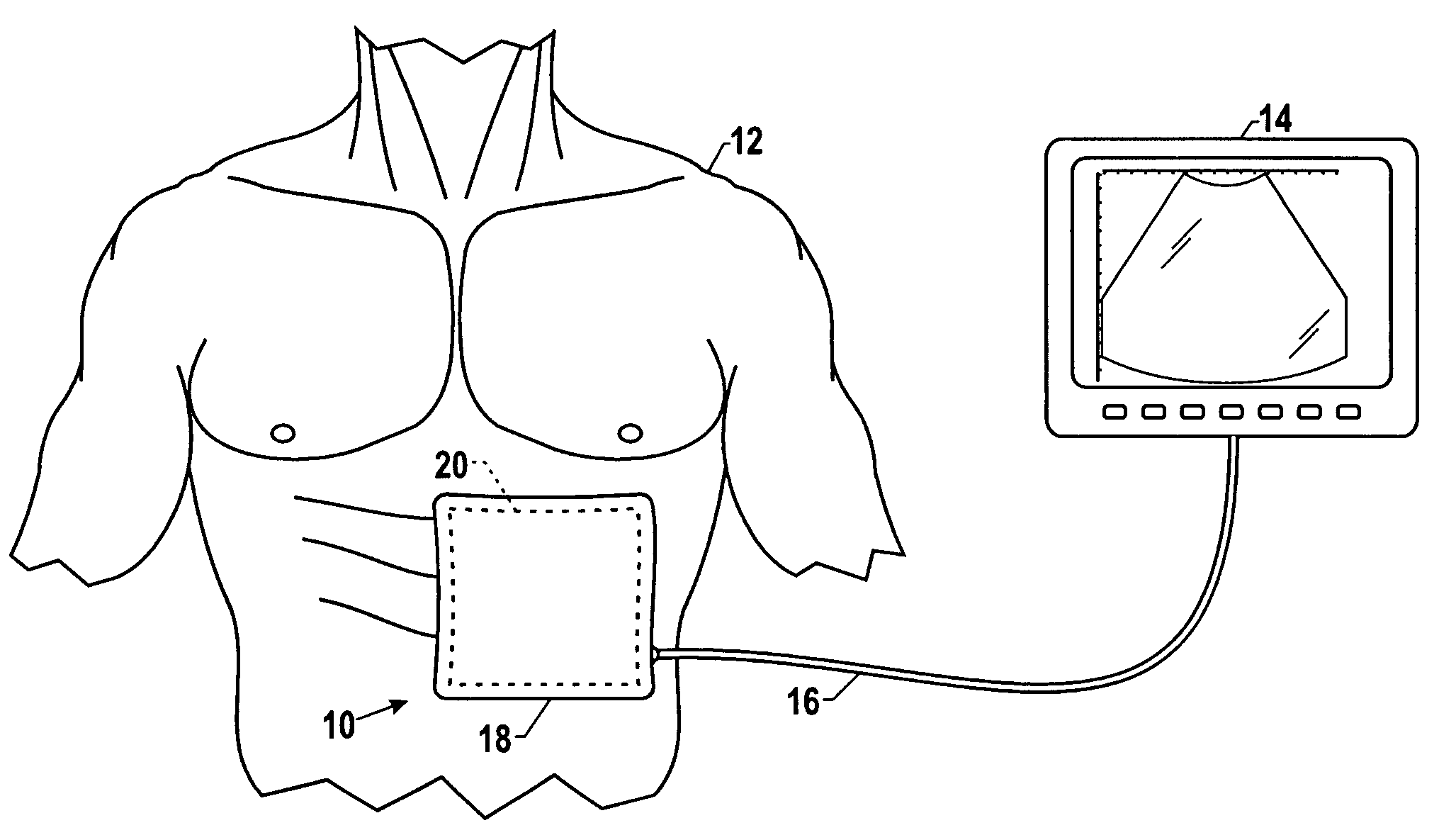

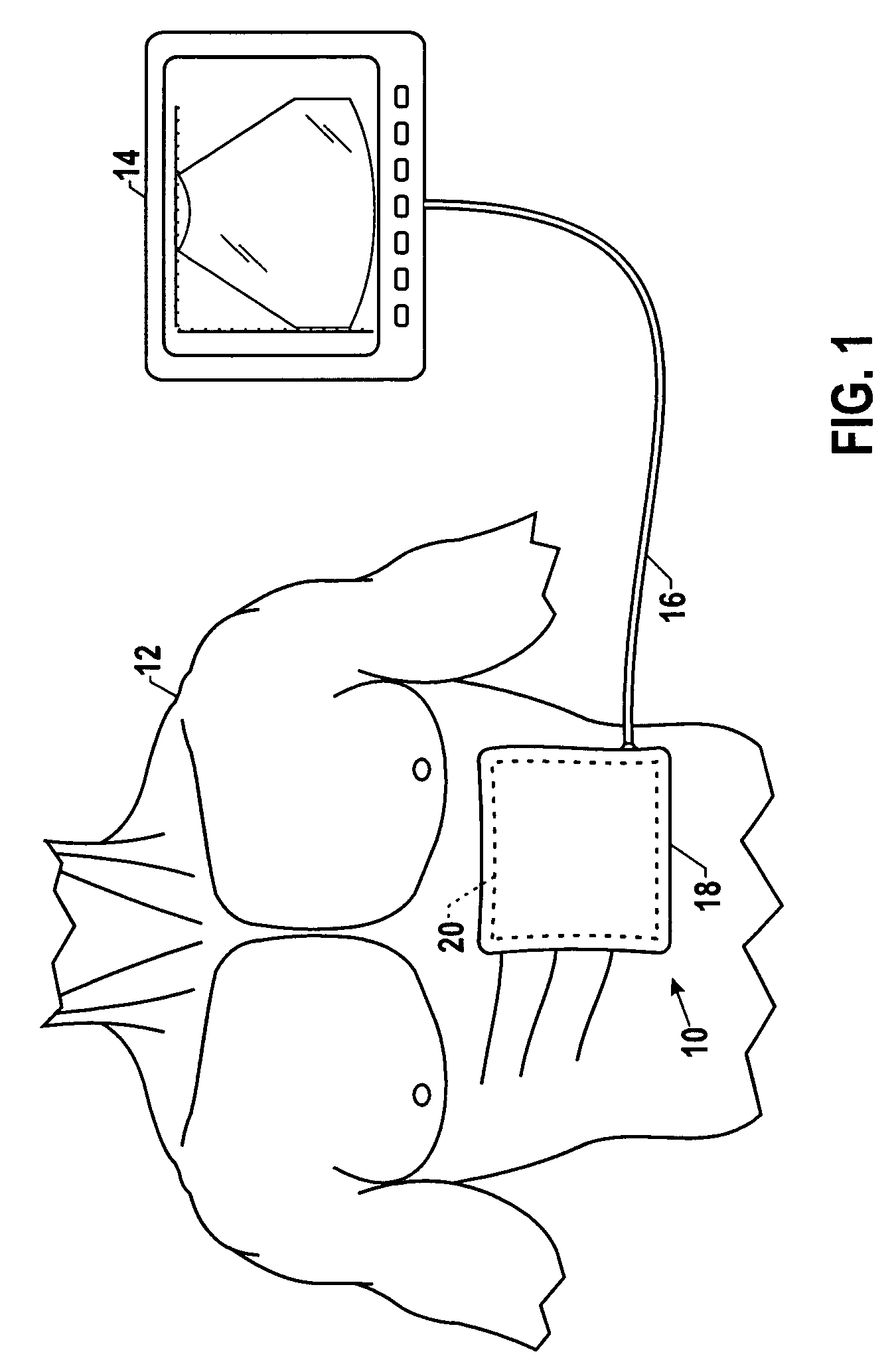

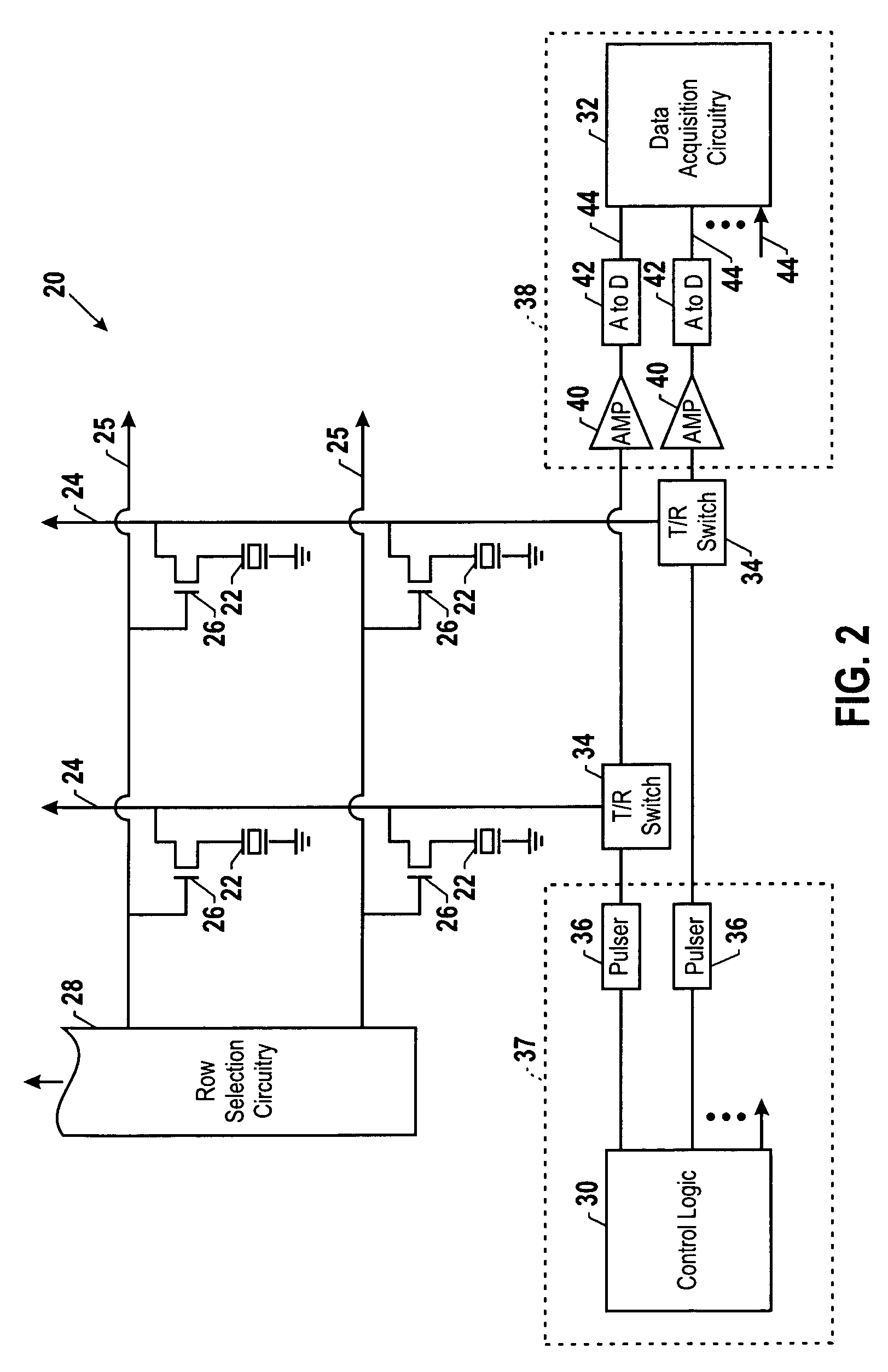

Systems and methods for operating a two-dimensional transducer array

ActiveUS20100152587A1Reduce circuitReduce the numberUltrasonic/sonic/infrasonic diagnosticsAnalysing solids using sonic/ultrasonic/infrasonic wavesEngineeringTransducer

According to embodiments of the present technique, a system and a method for addressing transducers in a two-dimensional transducer array is disclosed. According to one aspect of the present technique, the transducers are arranged in rows and columns, and the columns are coupled to a shared transmit and receive circuitry while the rows are coupled to a row selection circuitry. In another embodiment, each transducer is coupled to a separate, dedicated transmit circuitry and the columns are coupled to a shared receive circuitry.

Owner:GENERAL ELECTRIC CO

Motion estimation architecture for area and power reduction

InactiveUS6020934AReduce power consumptionReduce circuitTelevision system detailsPicture reproducers using cathode ray tubesMotion vectorChipset

A method for compensating for reduced picture quality when combining a multi-chip encoding chipset into a single integrated semiconductor IC. The method includes additional functions provided on the single IC to compensate for the negative effects on picture quality produced as a result of rounding 8 bit luminance pixel data to 5 bits, where the luminance data values are supplied as input to the search function. The additional functions are collectively referred to as motion biasing and are applied to influence the choice of a "best match" motion type, which is well known in the art. The biasing is performed by the addition of a weight factor to a total difference result that is calculated by the search function. The biasing is applied only for the purpose of influencing the choice of a reference frame that is not necessarily the frame which produces an optimal motion vector, but rather will result in using fewer bits to encode macroblocks.

Owner:IBM CORP

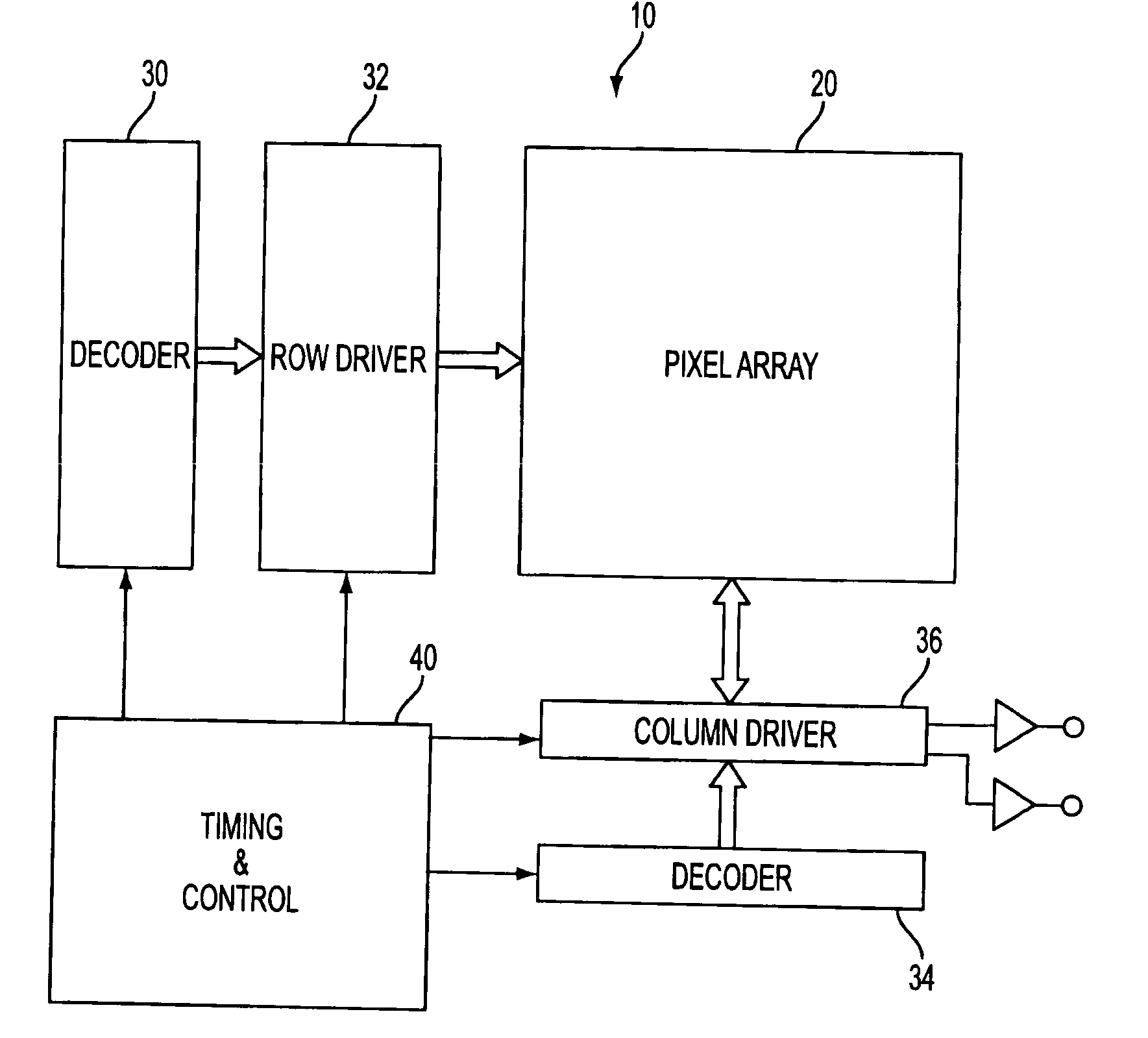

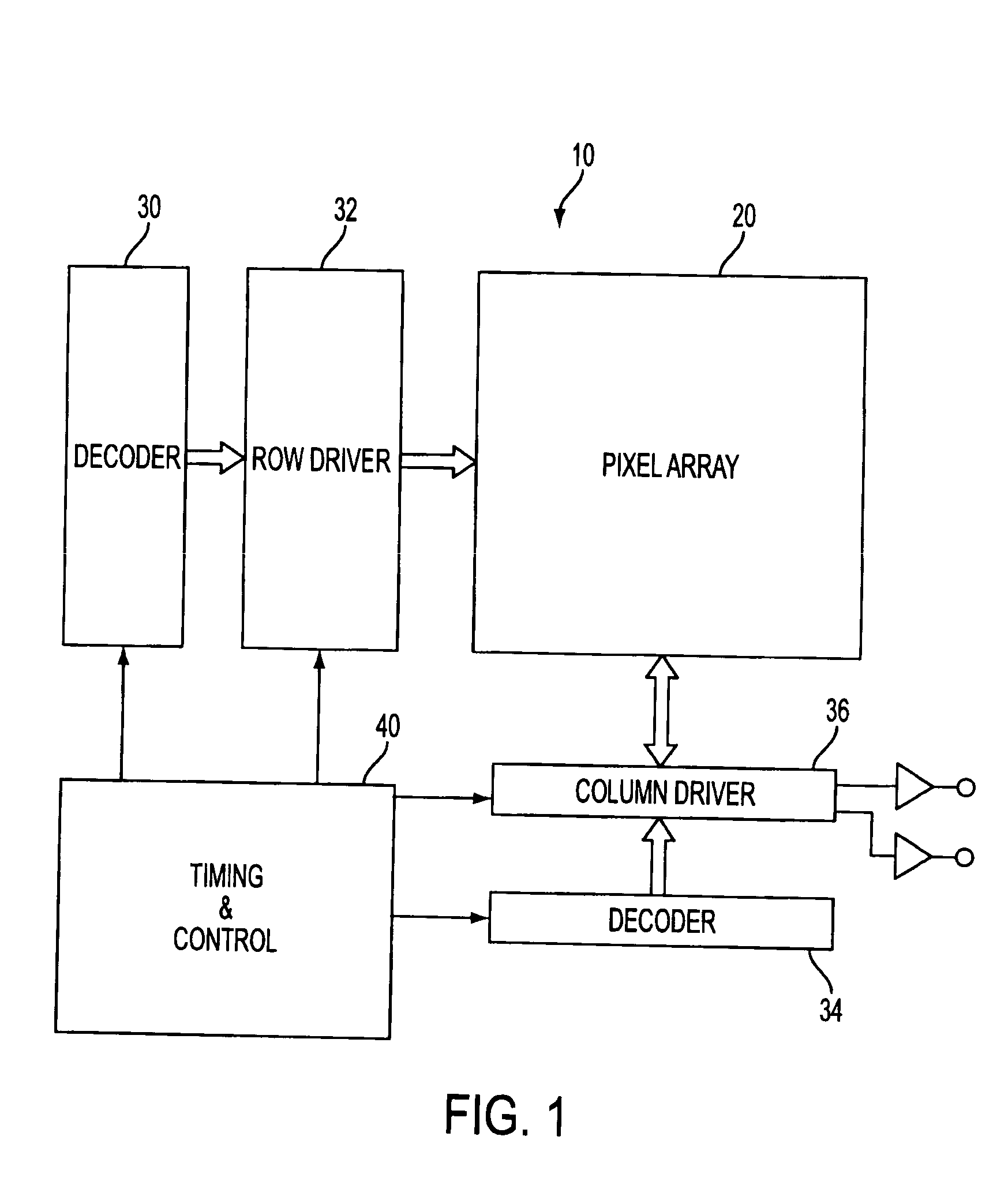

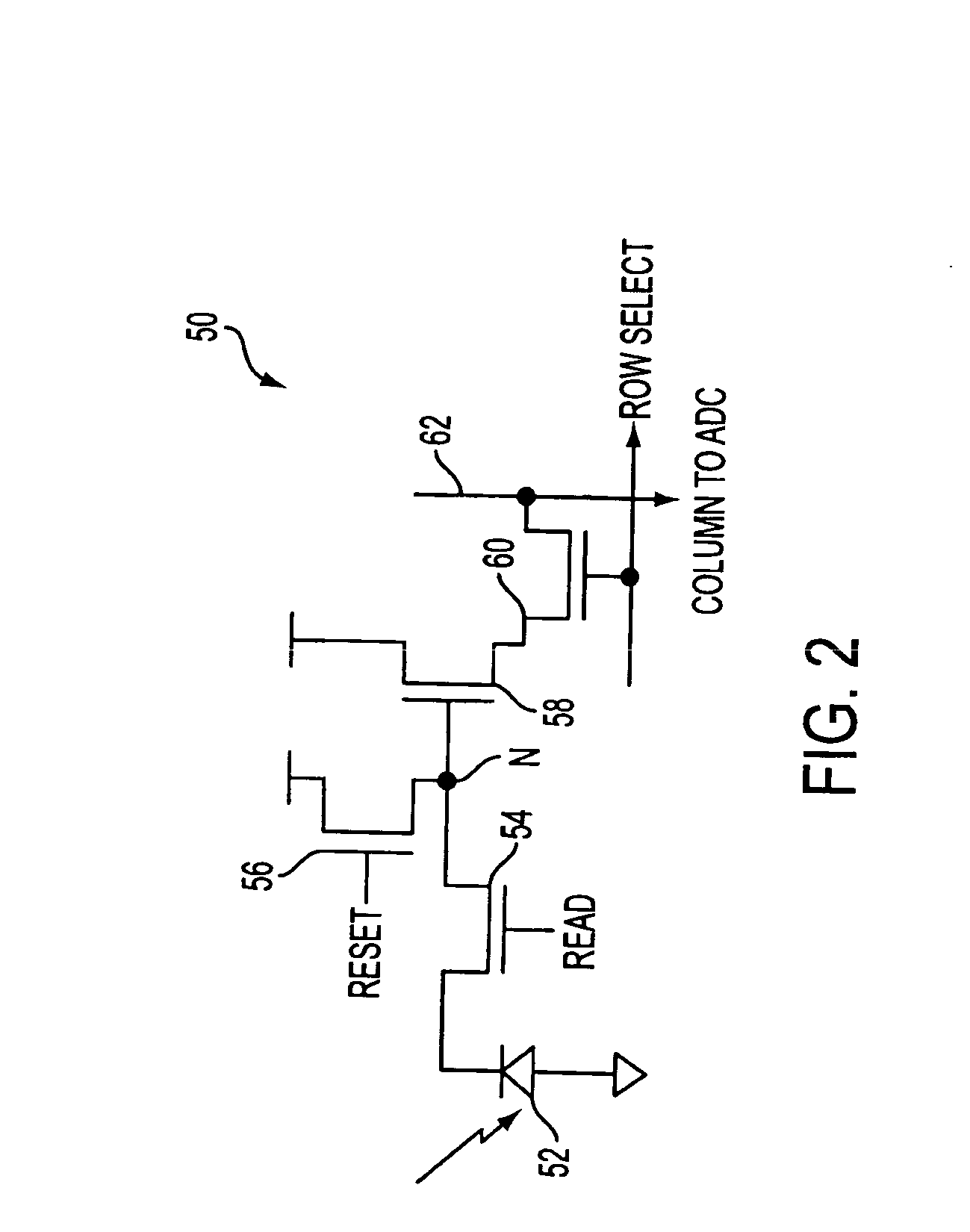

Per column one-bit ADC for image sensors

ActiveUS20050041128A1Reduces circuitry and power consumptionEfficient and simple mannerAnalogue/digital conversionTelevision system detailsA d converterImage sensor

A per column one-bit analog-to-digital converter for an image sensor. The analog-to-digital converter utilizes the difference between a reference signal current and a pixel signal current to obtain a digital output representative of the analog pixel signal in an efficient and simple manner. The output of the one-bit analog-to-digital converter is fed to a counter to give a representation of the brightness of the light-to-charge conversion in the associated pixel. The analog-to-digital converter does not use a reference voltage and precision elements and thus, does not suffer from power supply, noise and precision variations.

Owner:MICRON TECH INC

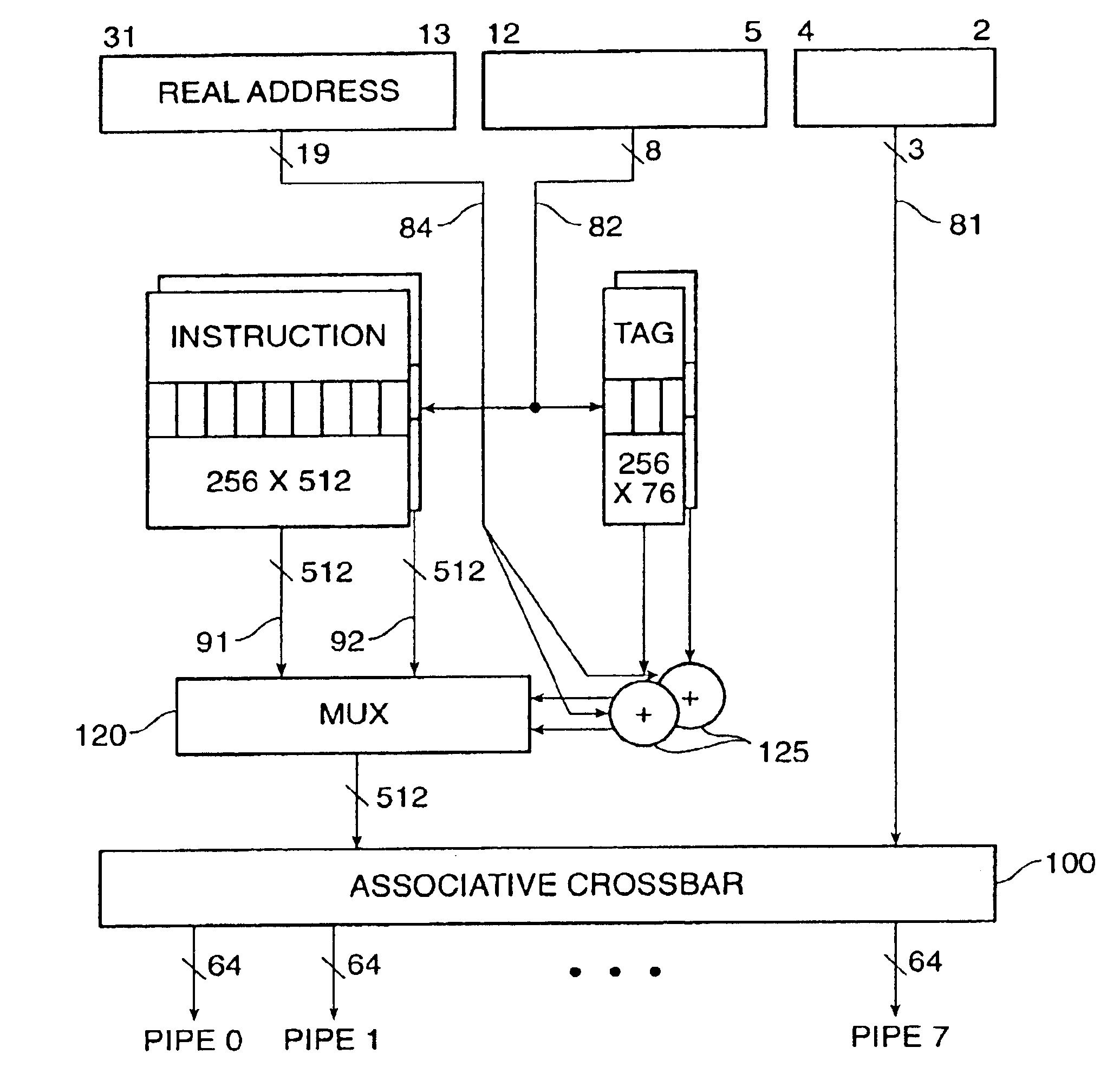

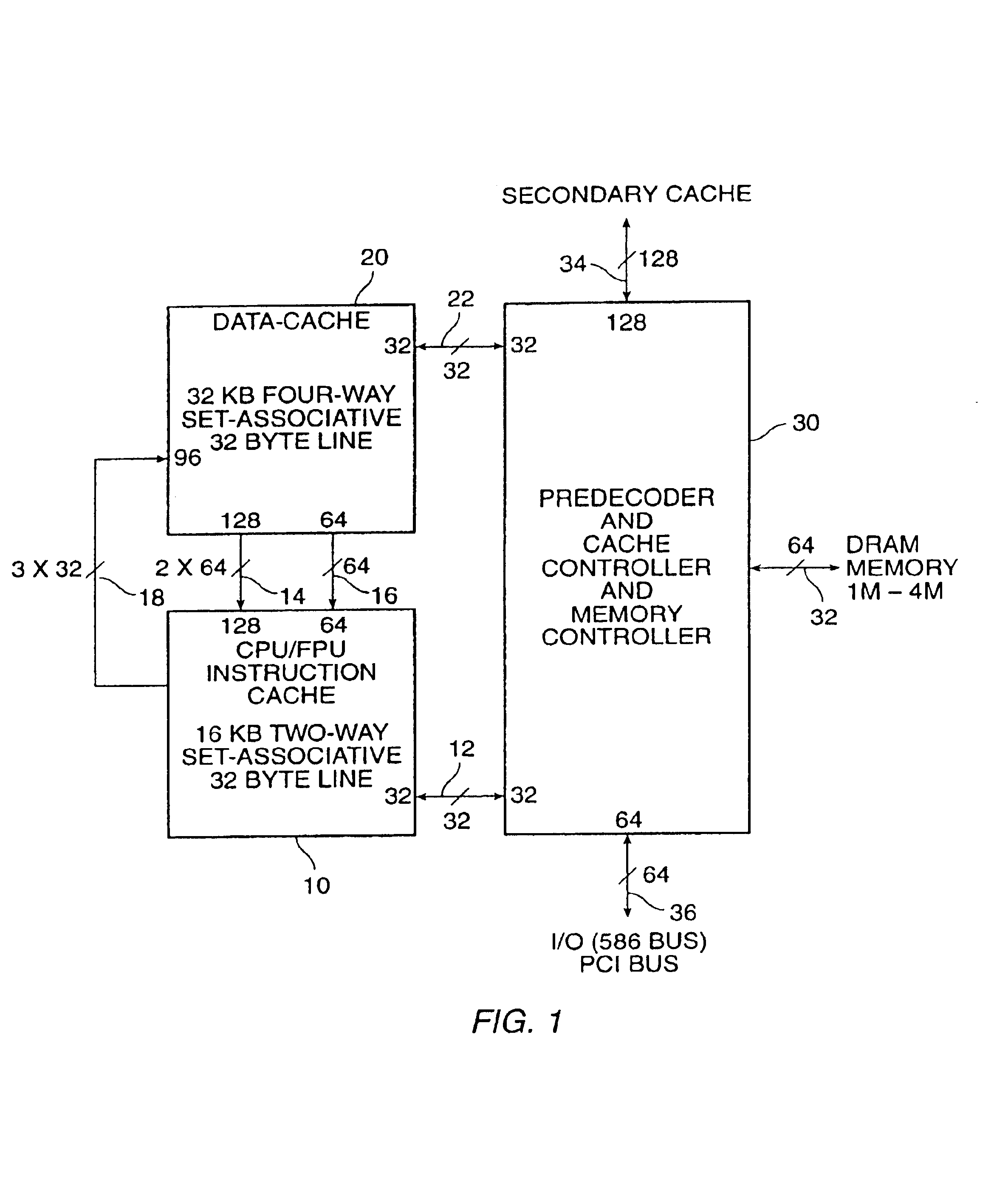

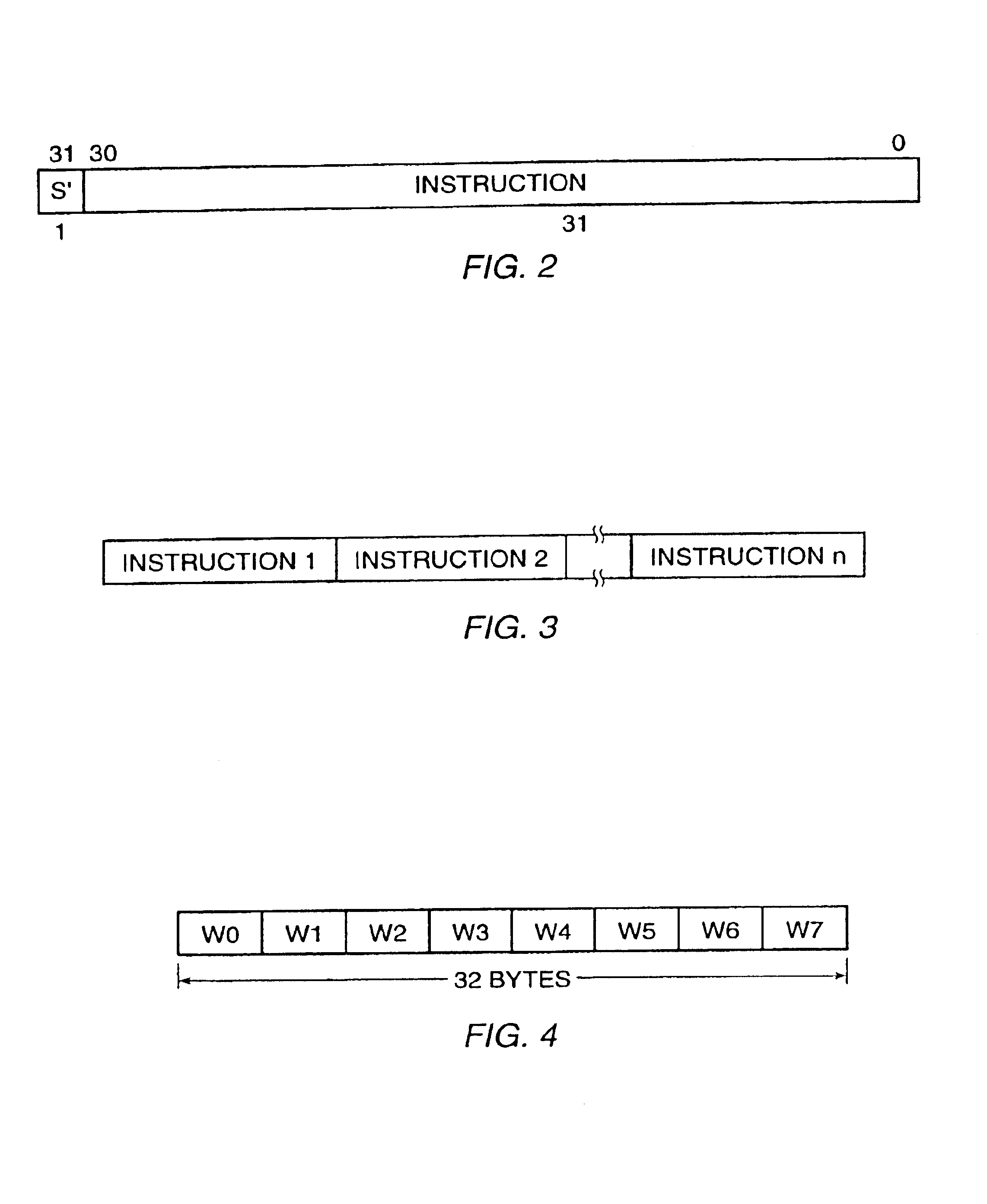

VLIW processor and method therefor

InactiveUS6892293B2Low powerSimple circuitGeneral purpose stored program computerConcurrent instruction executionCrossbar switchParallel computing

A computing system as described in which individual instructions are executable in parallel by processing pipelines, and instructions to be executed in parallel by different pipelines are supplied to the pipelines simultaneously. The system includes storage for storing an arbitrary number of the instructions to be executed. The instructions to be executed are tagged with pipeline identification tags indicative of the pipeline to which they should be dispatched. The pipeline identification tags are supplied to a system which controls a crossbar switch, enabling the tags to be used to control the switch and supply the appropriate instructions simultaneously to the differing pipelines.

Owner:INTERGRAPH HARDWARE TECH

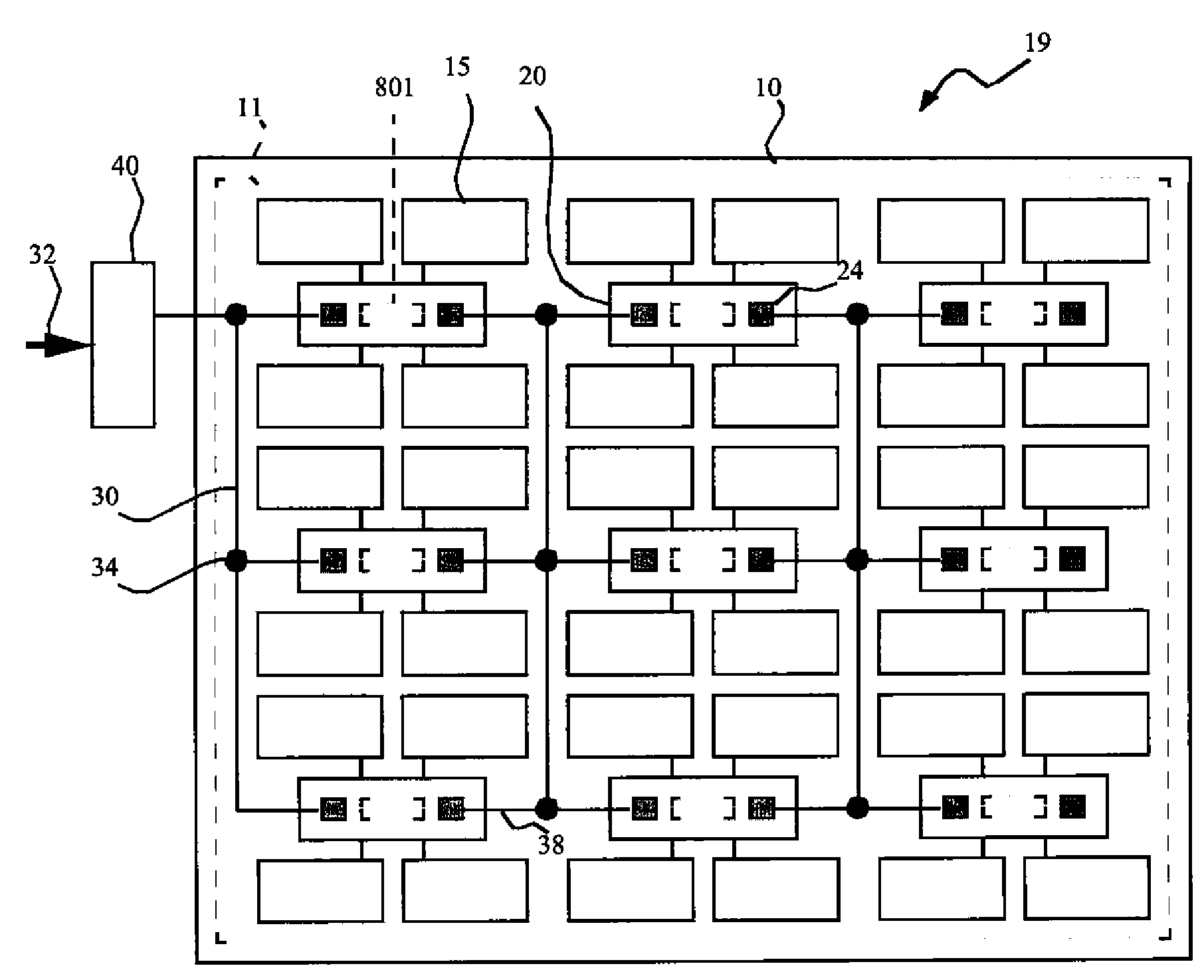

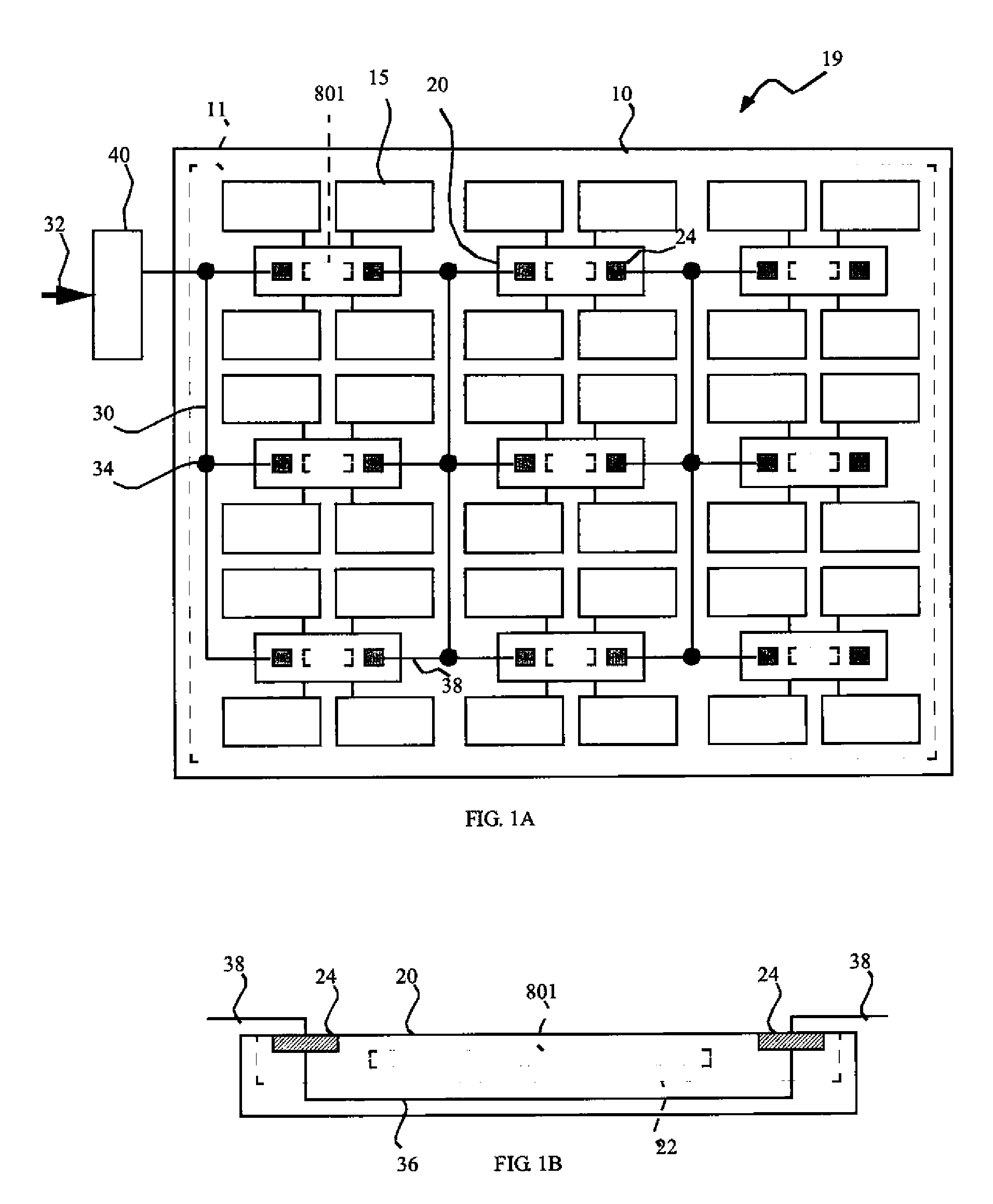

Display device with parallel data distribution

ActiveUS20100309100A1Reduced Routing ComplexityReducing bond-out requirementElectrical apparatusCathode-ray tube indicatorsElectricityInformation control

A display device responsive to a controller, including a substrate having a display area; a two-dimensional array of pixels formed on the substrate in the display area, each pixel comprising an optical element and a driving circuit for controlling the optical element in response to selected pixel information; a two-dimensional array of selection circuits located in the display area, each associated with one or more pixels, for selecting pixel information provided by the controller, wherein each selection circuit receives the provided pixel information, selects pixel information corresponding to its associated pixel(s) in response to the provided pixel information, and provides the selected pixel information to the corresponding driving circuit(s); and a parallel signal conductor electrically connecting the selection circuits in common for transmitting pixel information provided by the controller to each of the selection circuits.

Owner:GLOBAL OLED TECH

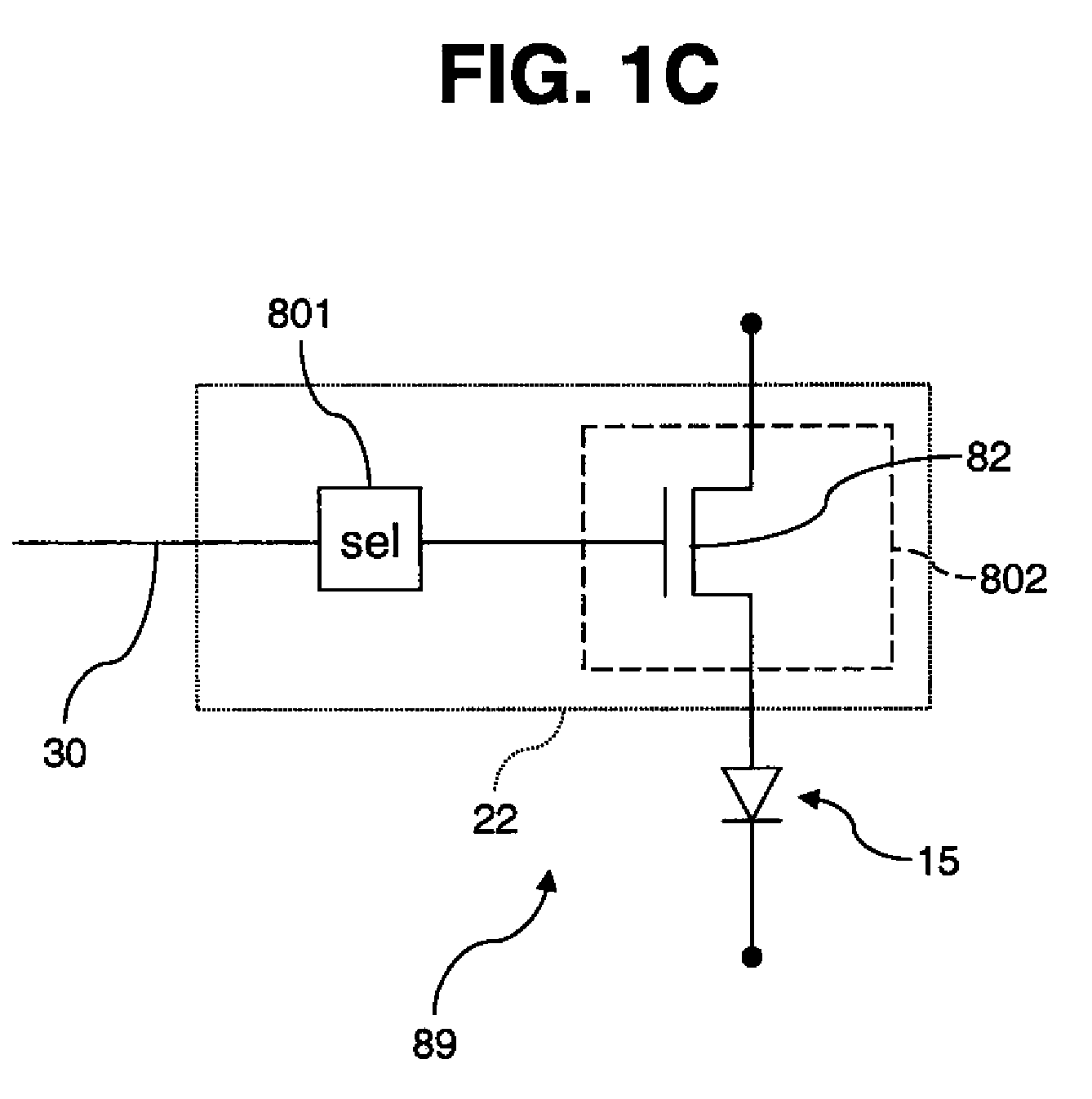

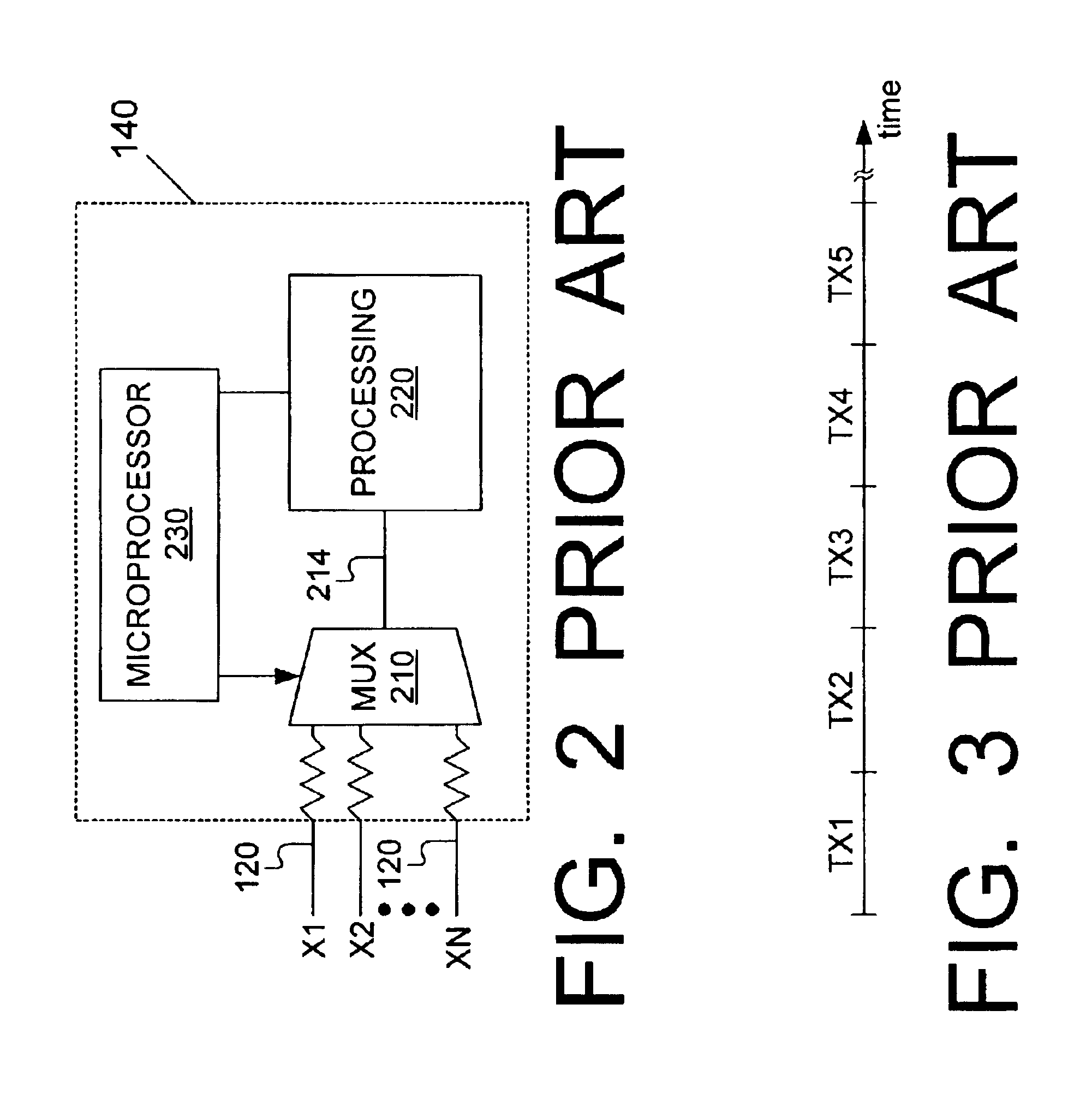

Sensing an object with a plurality of conductors

InactiveUS6891531B2Short response timeMany timesTransmission systemsCathode-ray tube indicatorsElectrical conductorEngineering

An object (130), e.g. a human finger or a stylus, is sensed with a plurality of conductors (120, X1, . . . XN). The conductor processing times (TX1, TX2, . . . TXN) but are shifted relative to one other.

Owner:SENTELIC HLDG CO LTD

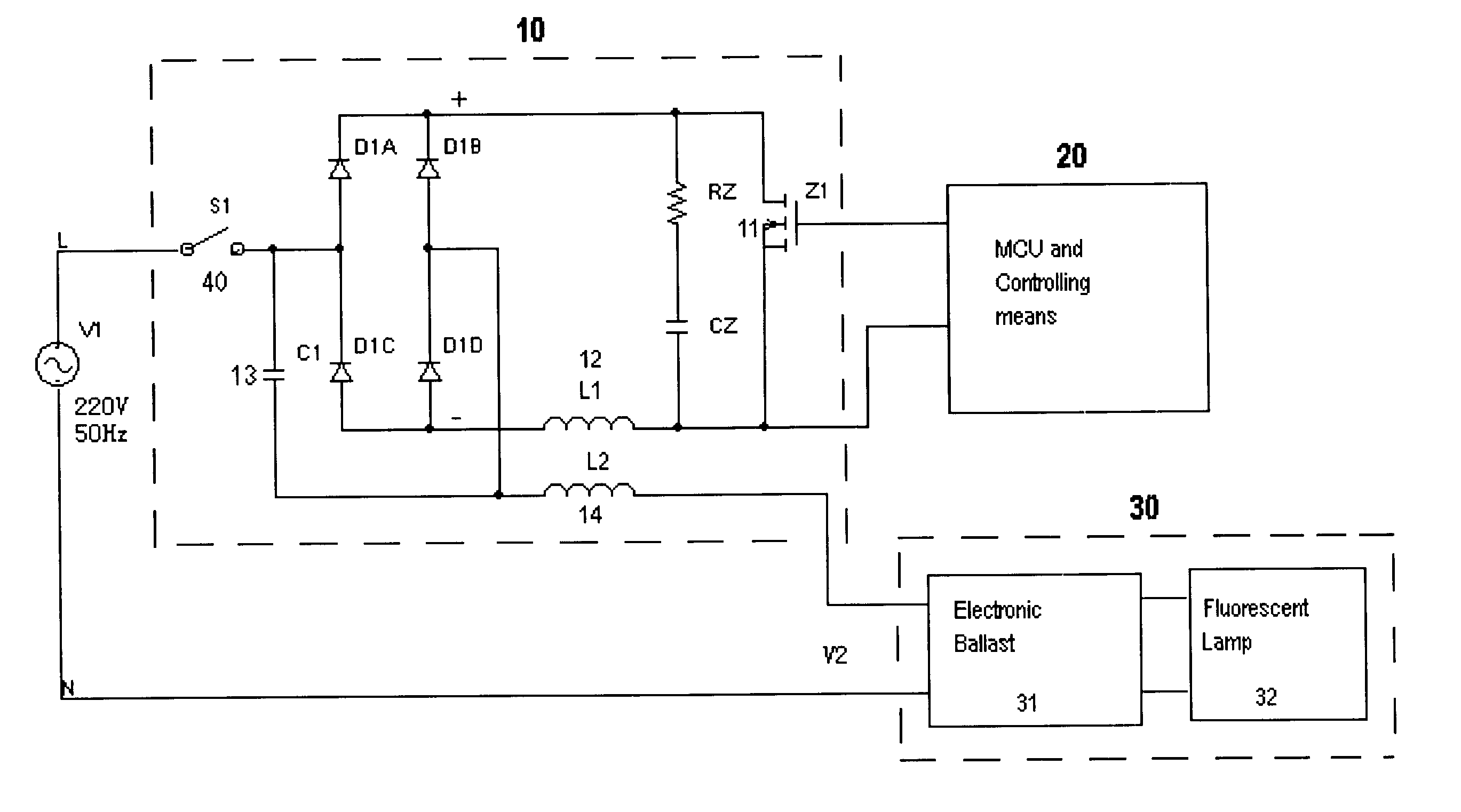

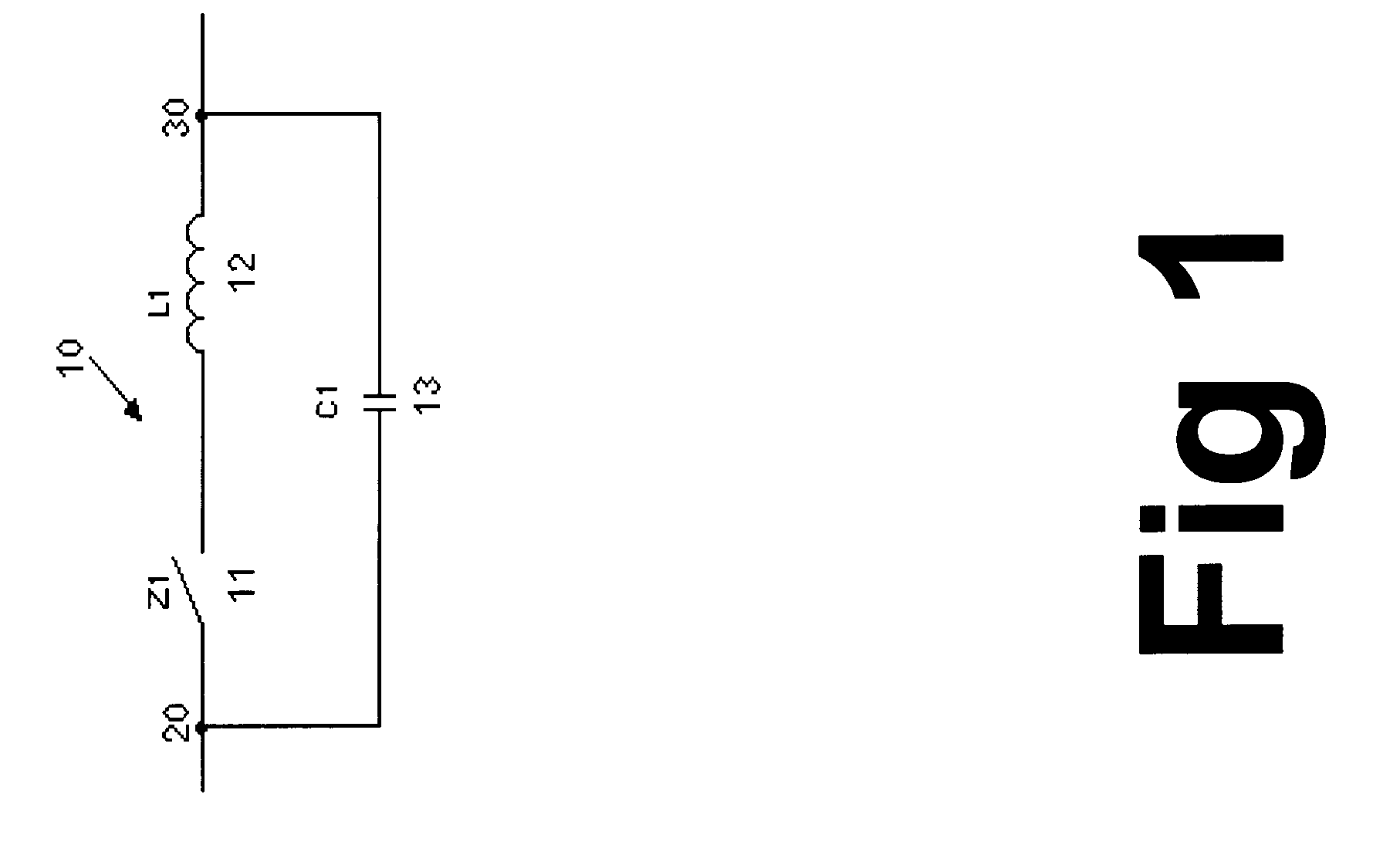

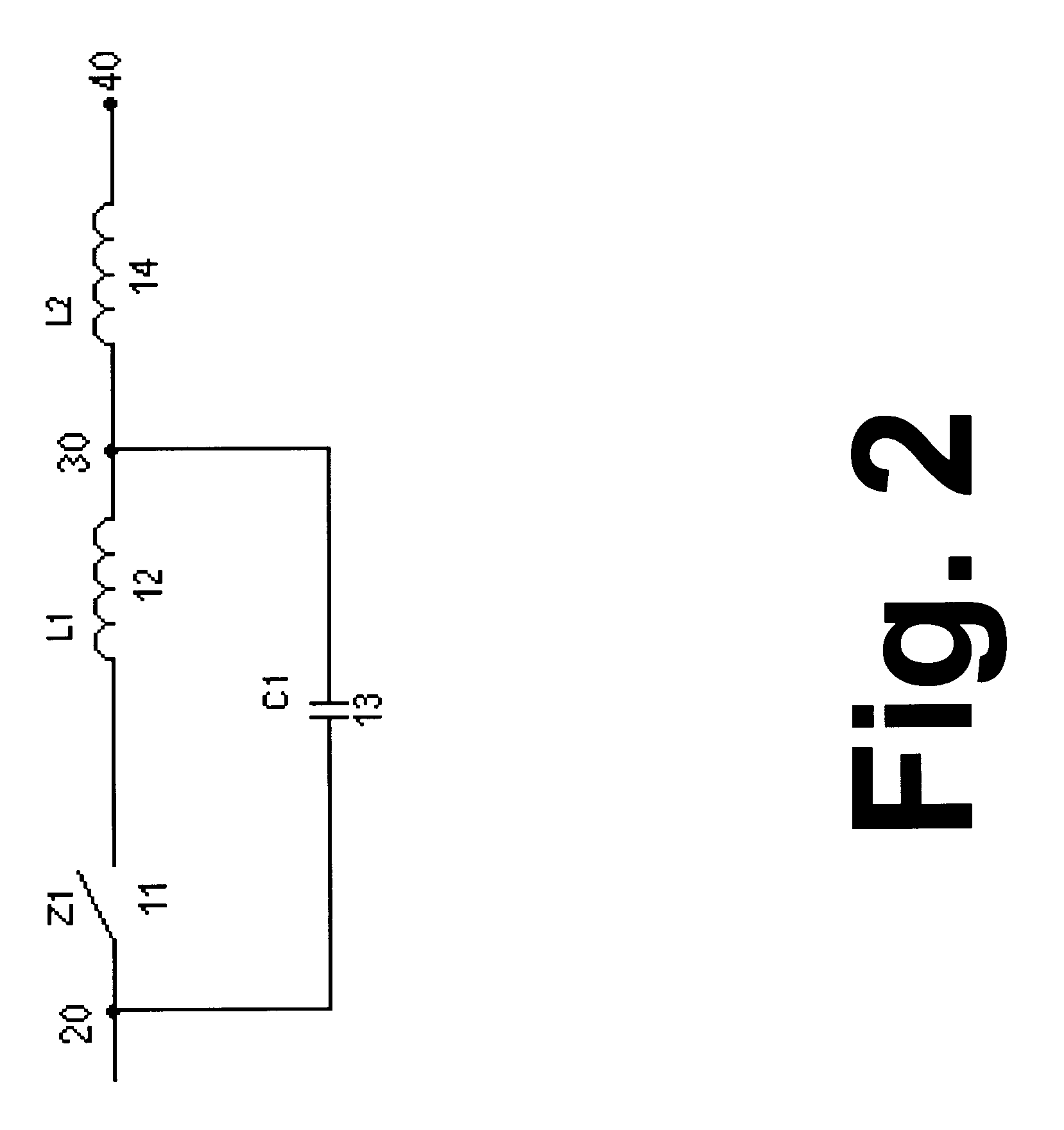

Dimmer for energy saving lamp

InactiveUS6727665B2Simple circuitReduce circuitElectrical apparatusElectric light circuit arrangementControl signalDimmer

Owner:CLIPSAL ASIA HLDG

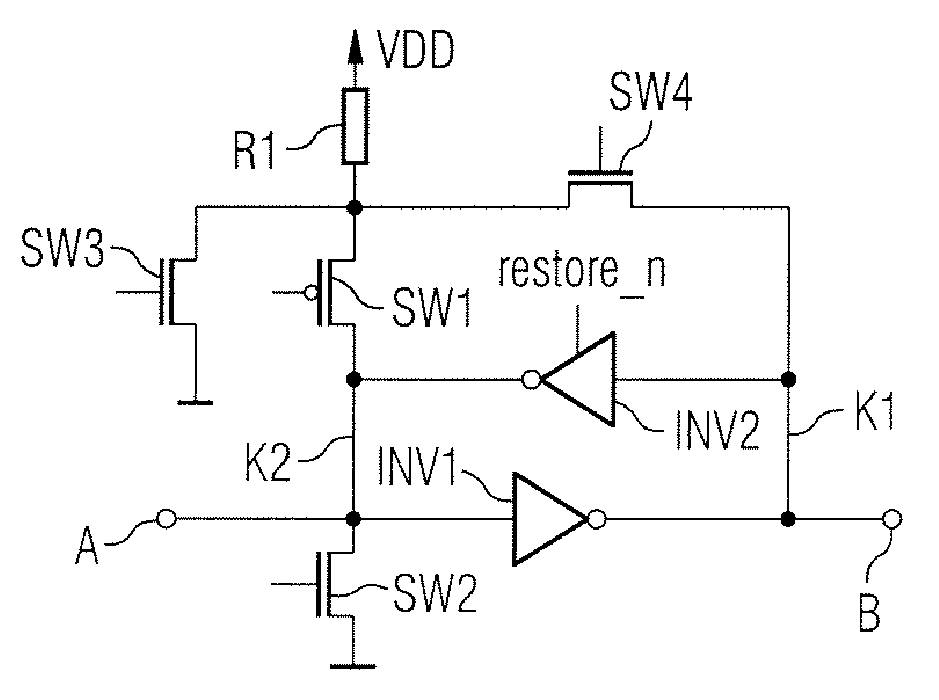

Bistable multivibrator with non-volatile state storage

InactiveUS20070002619A1Restrict power loss consumptionSufficient magnitudeDigital storageBinary informationMultivibrator

The non-volatile memory cell has a volatile memory means for storing an item of binary information. Furthermore, the memory cell comprises only a single programmable resistance element for non-volatile saving of the stored information and a means for saving the information in the resistance element. A means for retrieving the saved information is additionally present.

Owner:INFINEON TECH AG

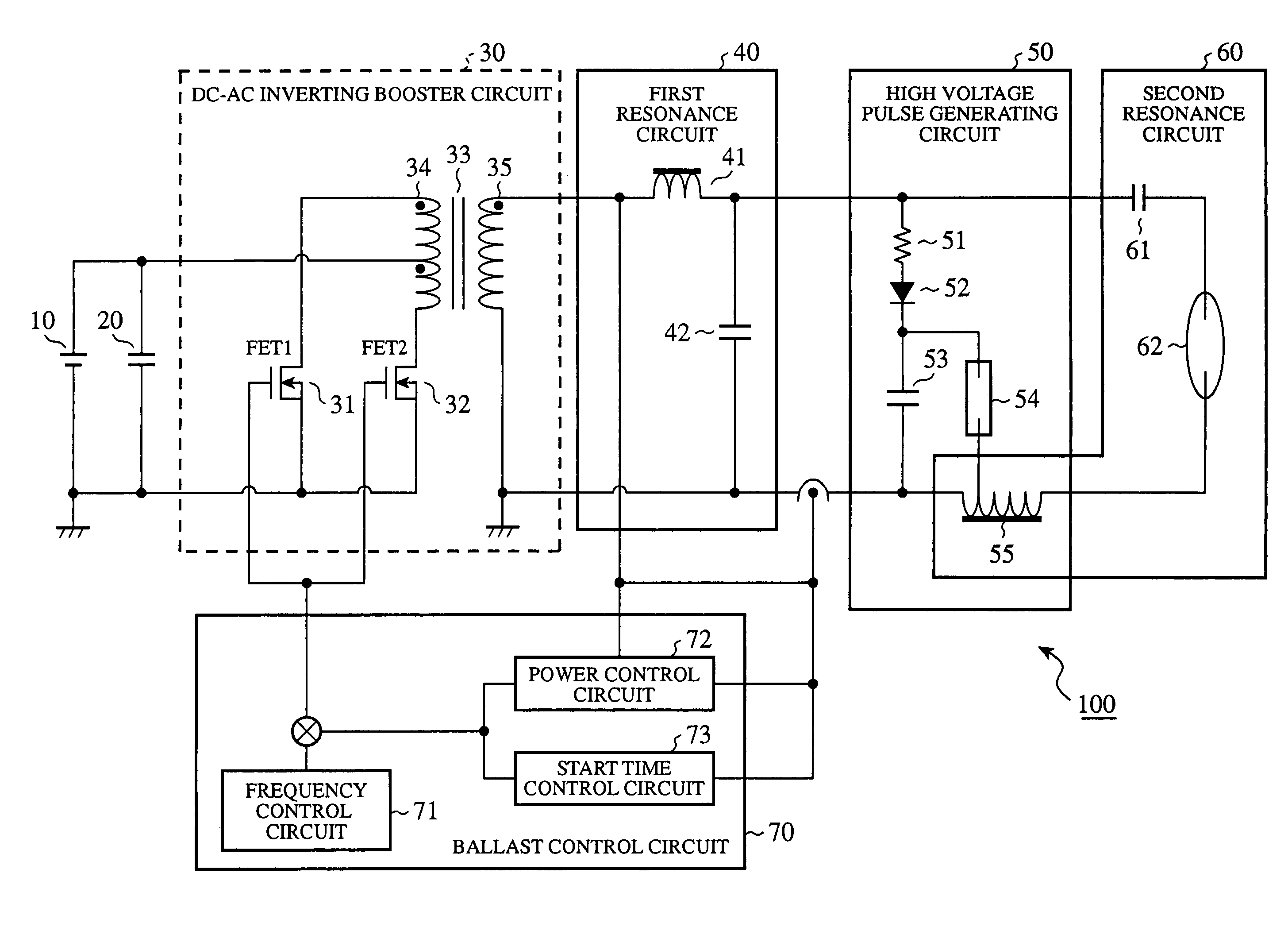

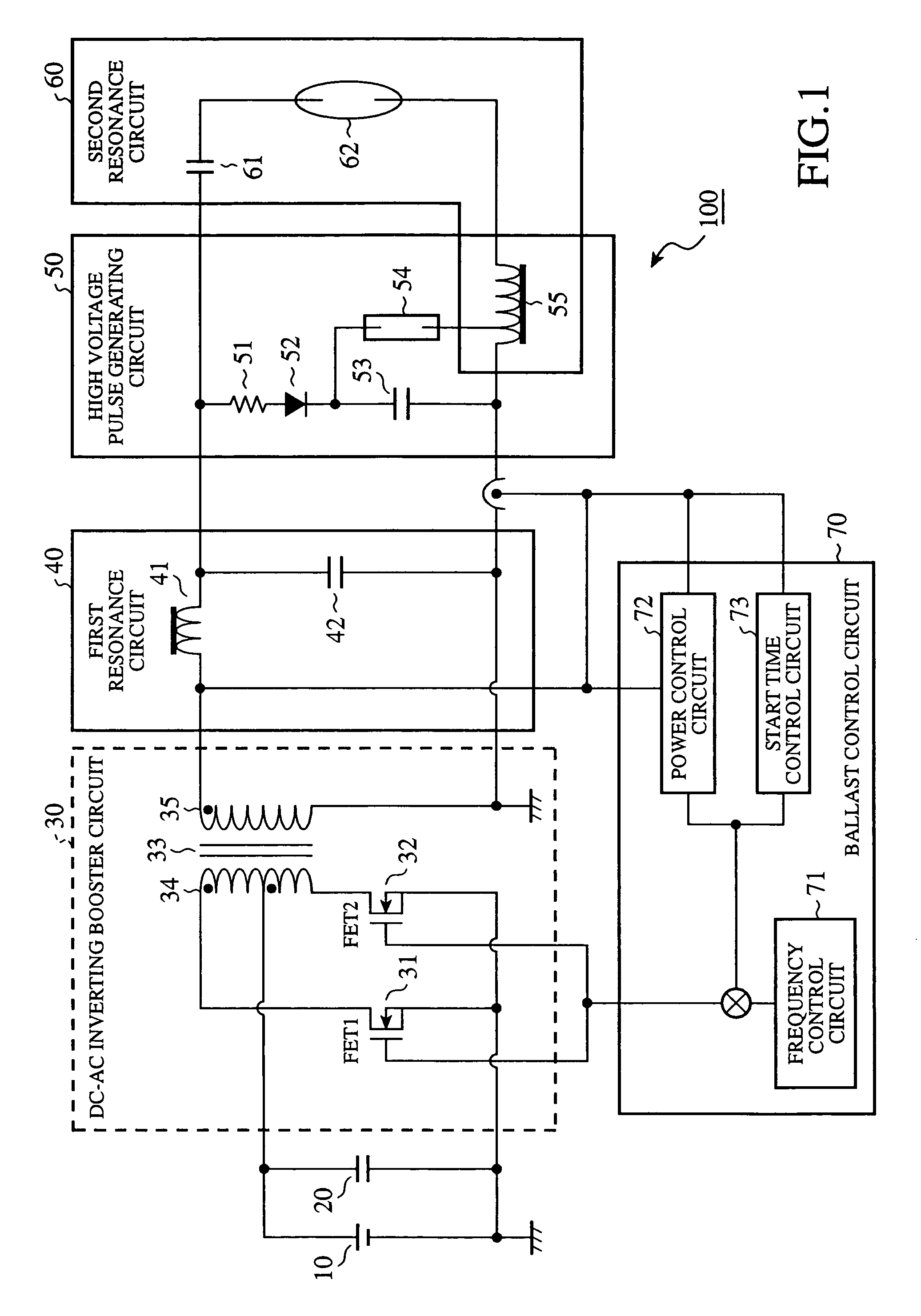

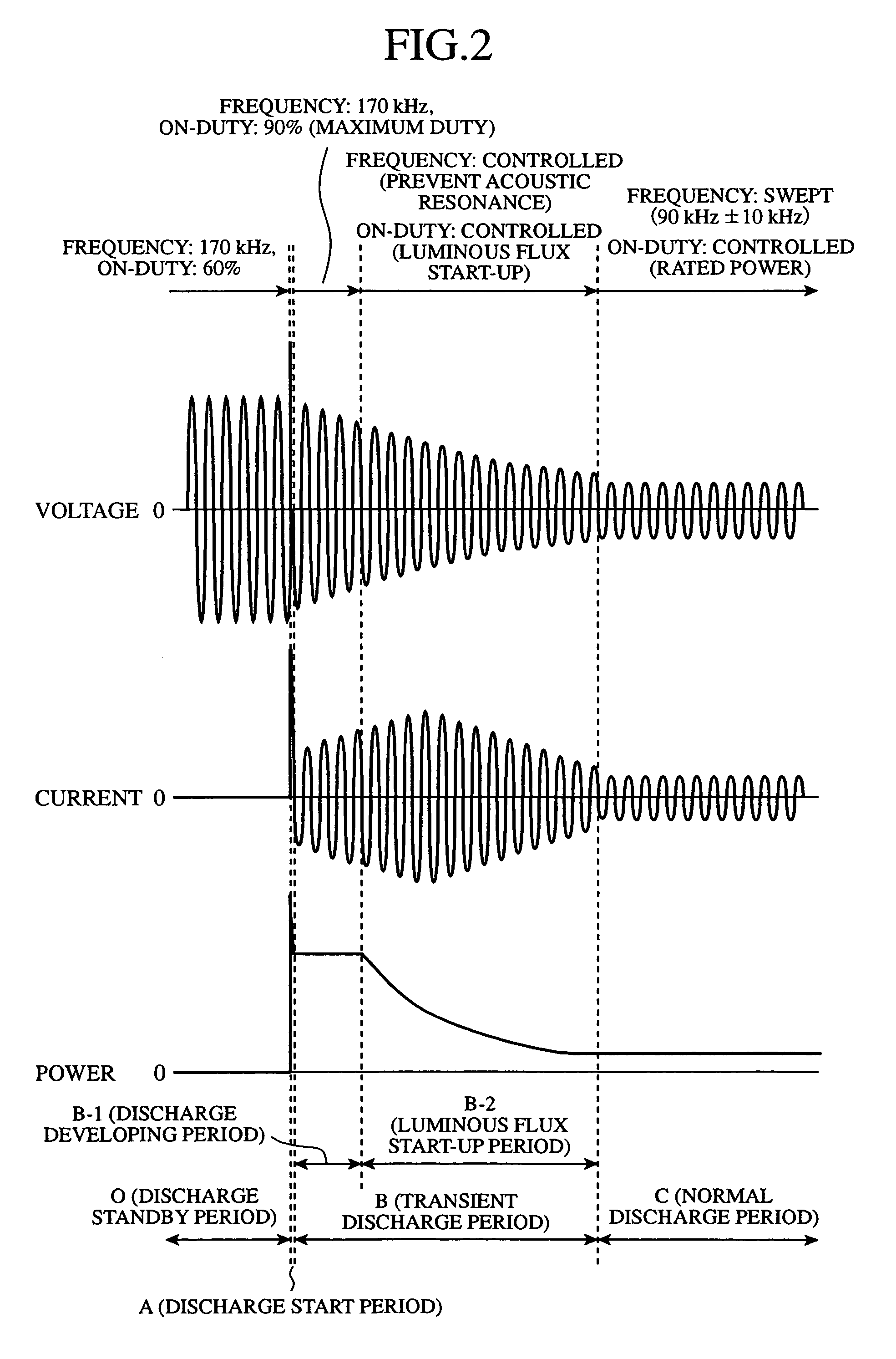

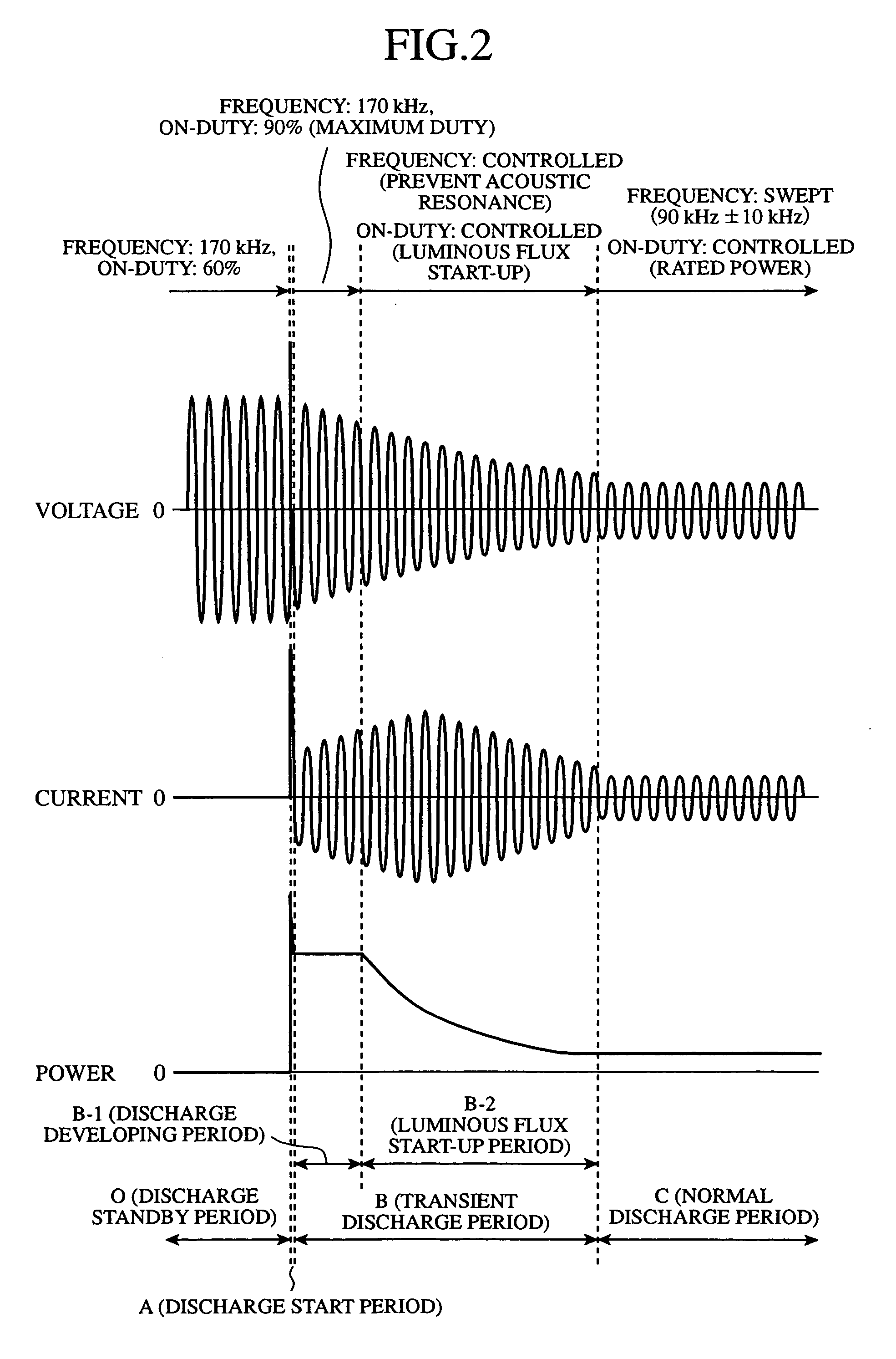

High intensity discharge lamp ballast apparatus

InactiveUS6975077B2Sufficient energySmall sizeElectric light circuit arrangementGas discharge lamp usageEngineeringDc ac converter

A compact, low cost high intensity discharge lamp ballast apparatus which can carry out normal ballasting without extinction at discharge start includes a DC-AC inverting booster circuit, a first resonance circuit, and a second resonance circuit. The DC-AC inverting booster circuit includes a DC-AC converter transformer for converting a DC voltage fed from a DC power supply to an AC voltage in response to switching on and off of FETs, boosting the voltage. The first resonance circuit includes a leakage inductance connected in series with the secondary winding of the DC-AC converter transformer, and a first resonant capacitor connected in parallel with the secondary winding. The second resonance circuit includes a metal halide lamp, an ignitor transformer for producing a voltage to start lighting of the metal halide lamp, and a second resonant capacitor.

Owner:MITSUBISHI ELECTRIC CORP

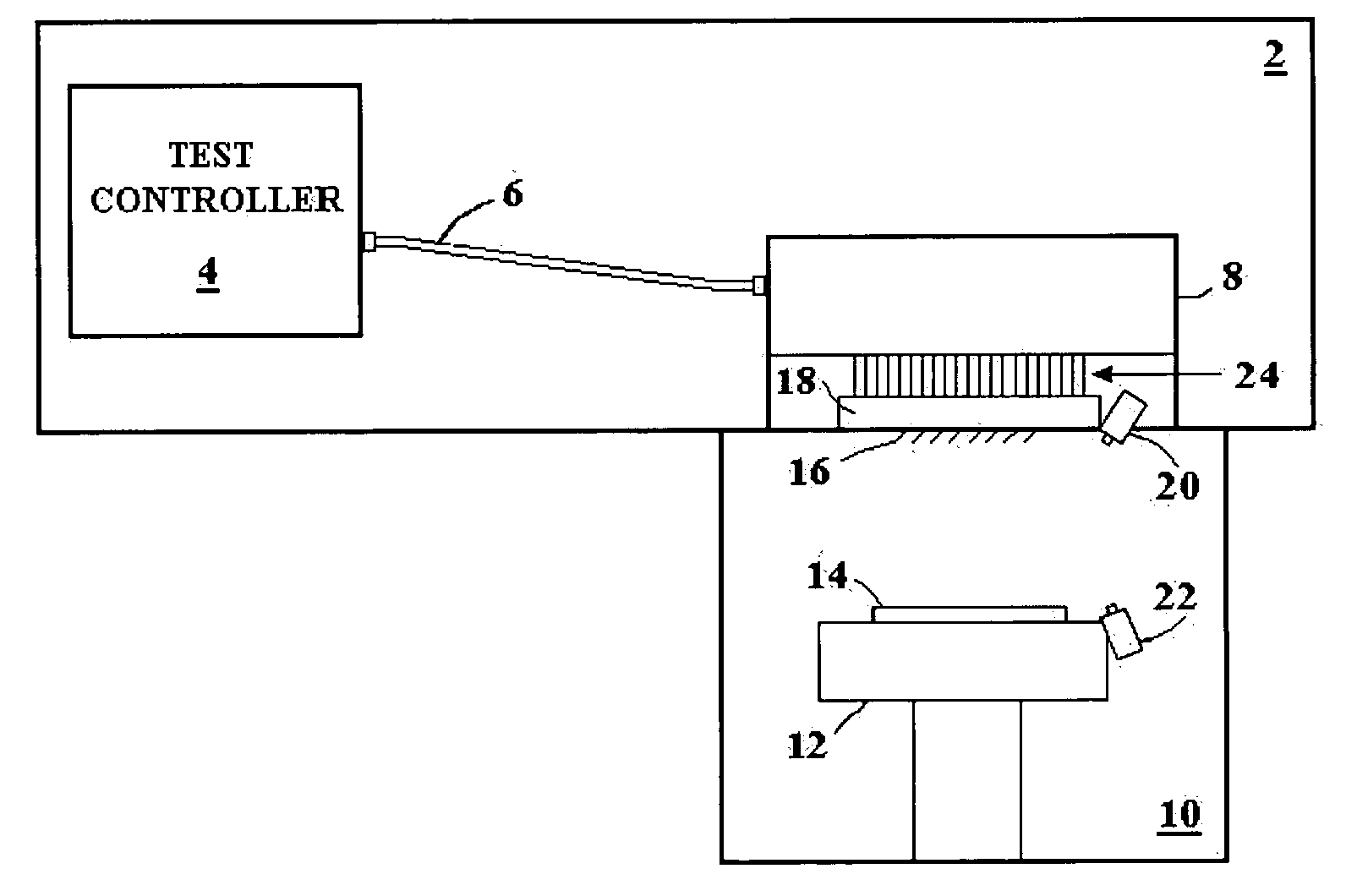

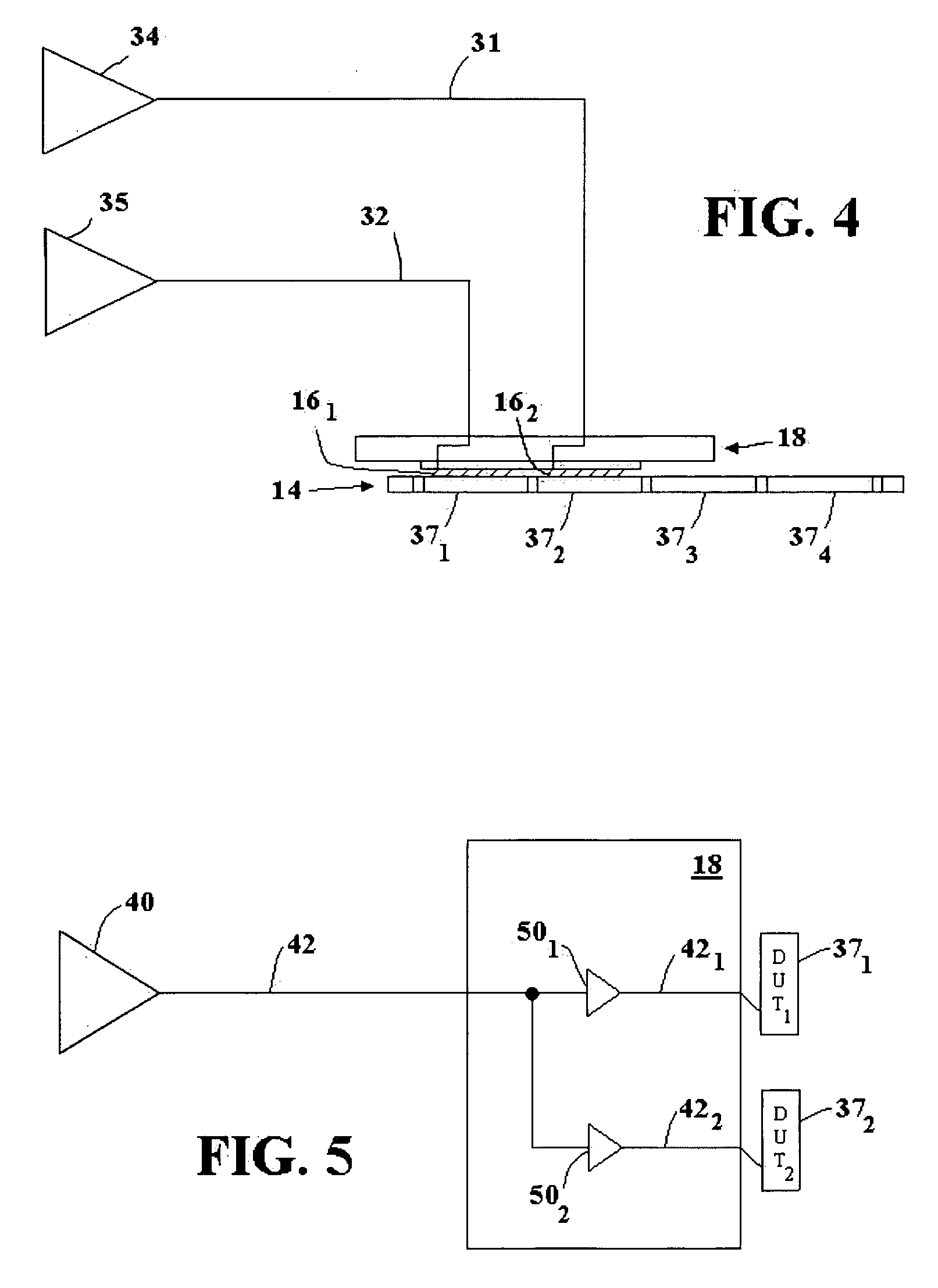

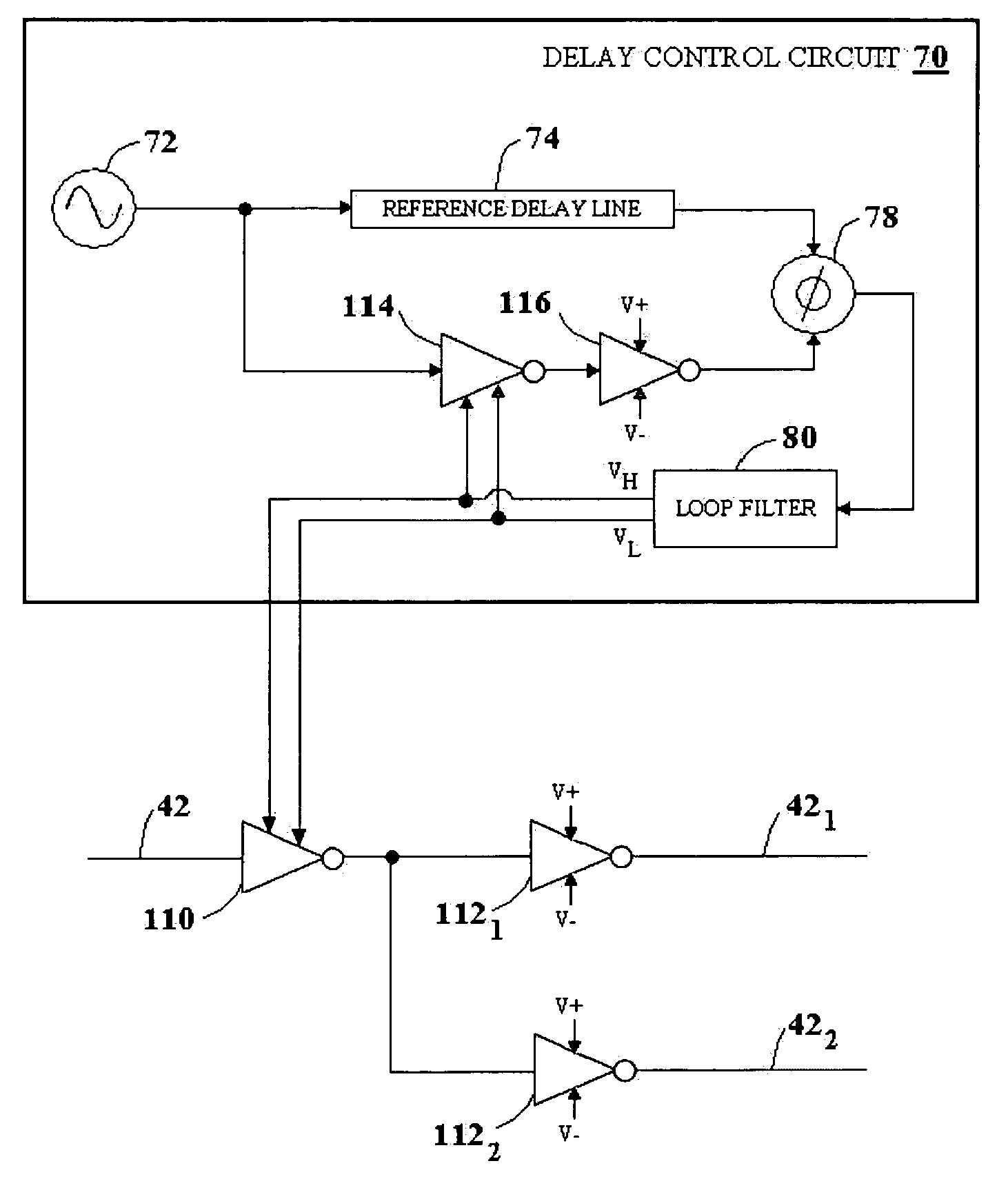

Isolation buffers with controlled equal time delays

InactiveUS20050088167A1Equal line delaysReduce circuitSemiconductor/solid-state device testing/measurementElectronic circuit testingControl signalDelay-locked loop

A system is provided for controlling the delay in an isolation buffer. Multiple such isolation buffers are used to connect a single signal channel to multiple lines and controlled to provide an equal delay. Isolation buffer delay is controlled to be uniform by varying either power supply voltage or current. A single delay control circuit forming a delay-lock loop supplies the delay control signal to each buffer to assure the uniform delay. Since controlling delay can also vary the output voltage of each isolation buffer, in one embodiment buffers are made from two series inverters: one with a variable delay, and the second without a variable delay providing a fixed output voltage swing. To reduce circuitry needed, in one embodiment an isolation buffer with a variable power supply is provided in a channel prior to a branch, while buffers having a fixed delay are provided in each branch. A wafer test system can be configured using the isolation buffers having equal delays to enable concurrently connecting one tester channel to multiple wafer test probes.

Owner:FORMFACTOR INC

Isolation buffers with controlled equal time delays

InactiveUS7154259B2Equal line delaysReduce circuitSemiconductor/solid-state device testing/measurementElectronic circuit testingControl signalDelay-locked loop

A system is provided for controlling the delay in an isolation buffer. Multiple such isolation buffers are used to connect a single signal channel to multiple lines and controlled to provide an equal delay. Isolation buffer delay is controlled to be uniform by varying either power supply voltage or current. A single delay control circuit forming a delay-lock loop supplies the delay control signal to each buffer to assure the uniform delay. Since controlling delay can also vary the output voltage of each isolation buffer, in one embodiment buffers are made from two series inverters: one with a variable delay, and the second without a variable delay providing a fixed output voltage swing. To reduce circuitry needed, in one embodiment an isolation buffer with a variable power supply is provided in a channel prior to a branch, while buffers having a fixed delay are provided in each branch. A wafer test system can be configured using the isolation buffers having equal delays to enable concurrently connecting one tester channel to multiple wafer test probes.

Owner:FORMFACTOR INC

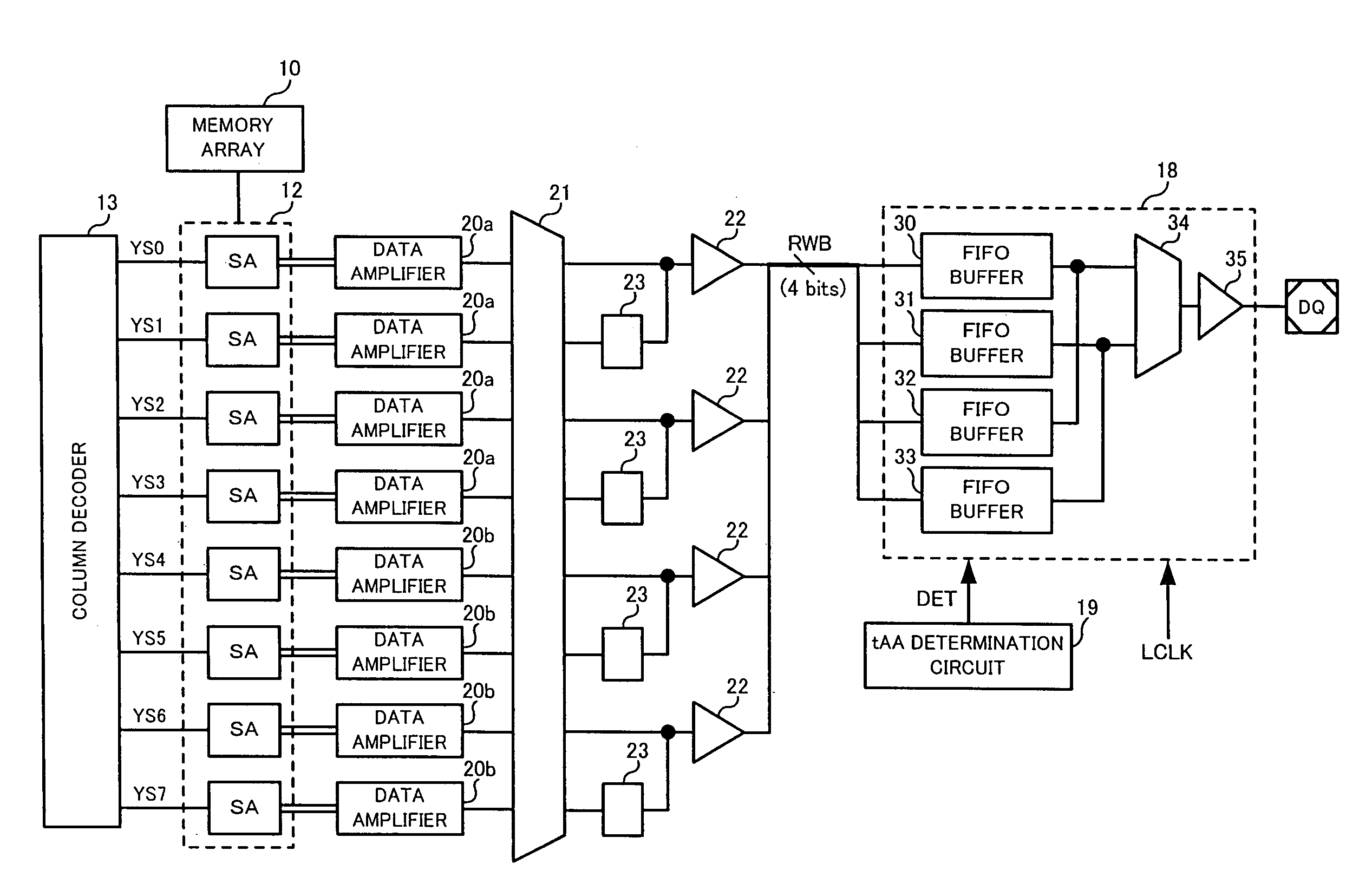

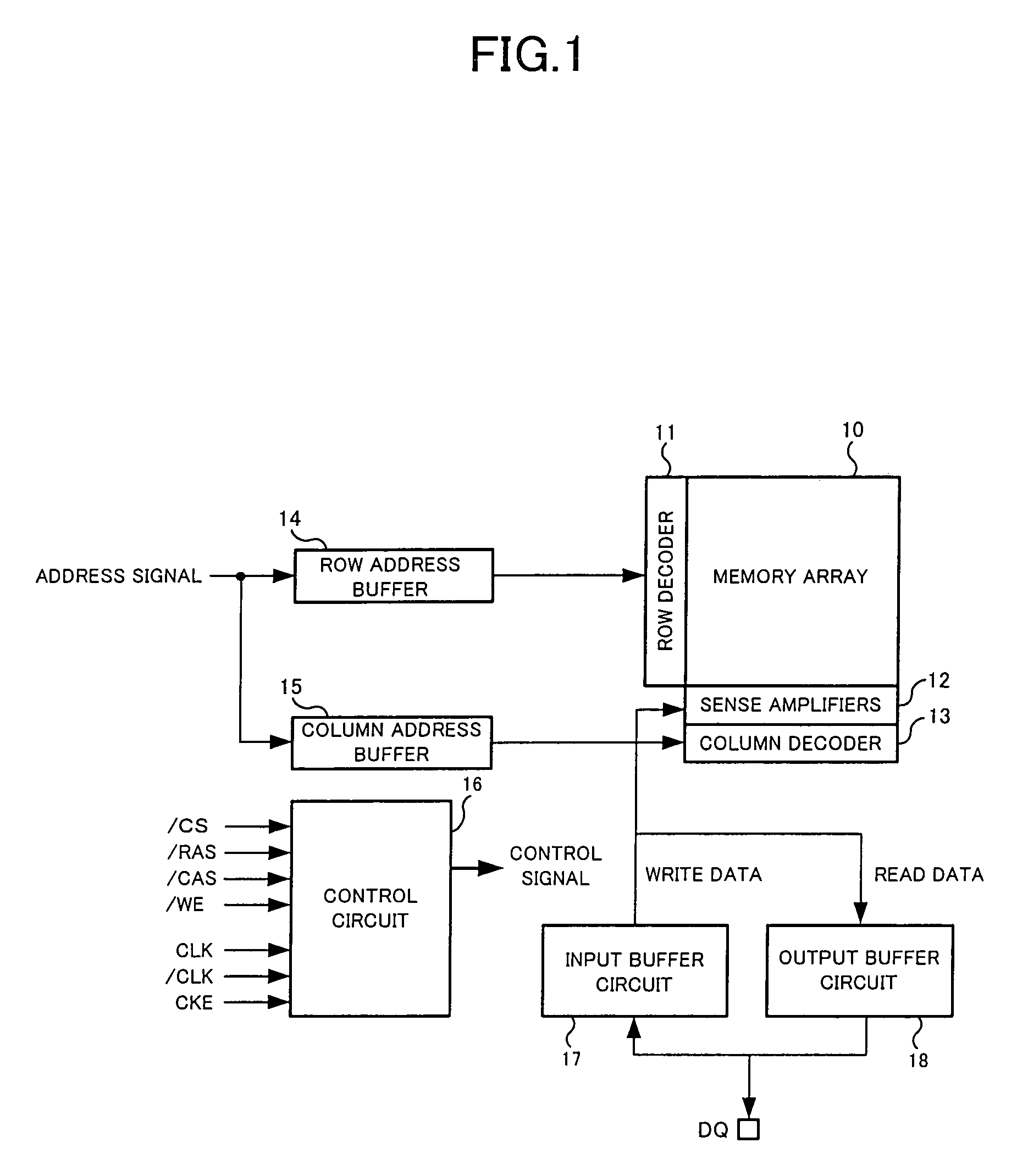

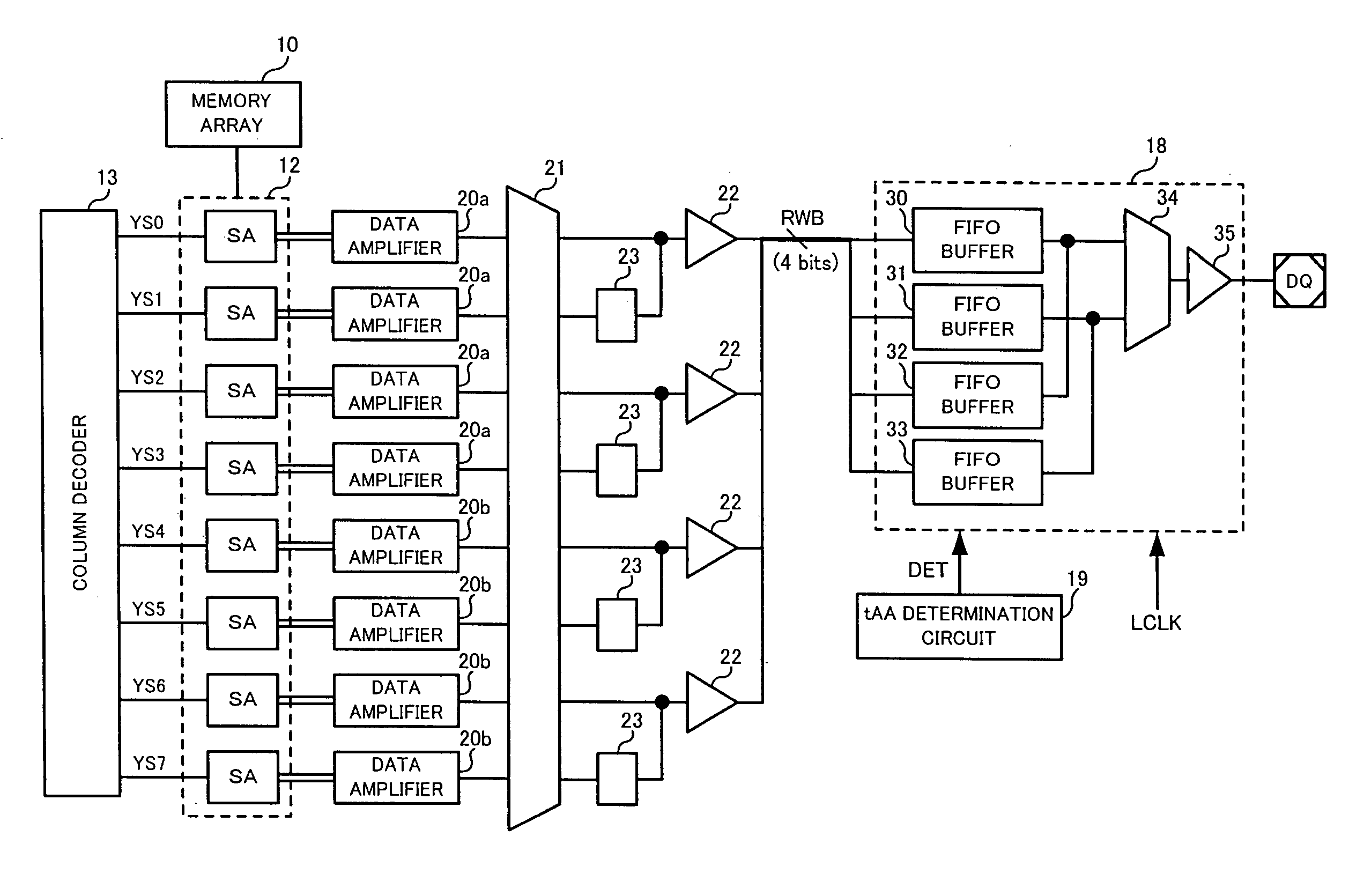

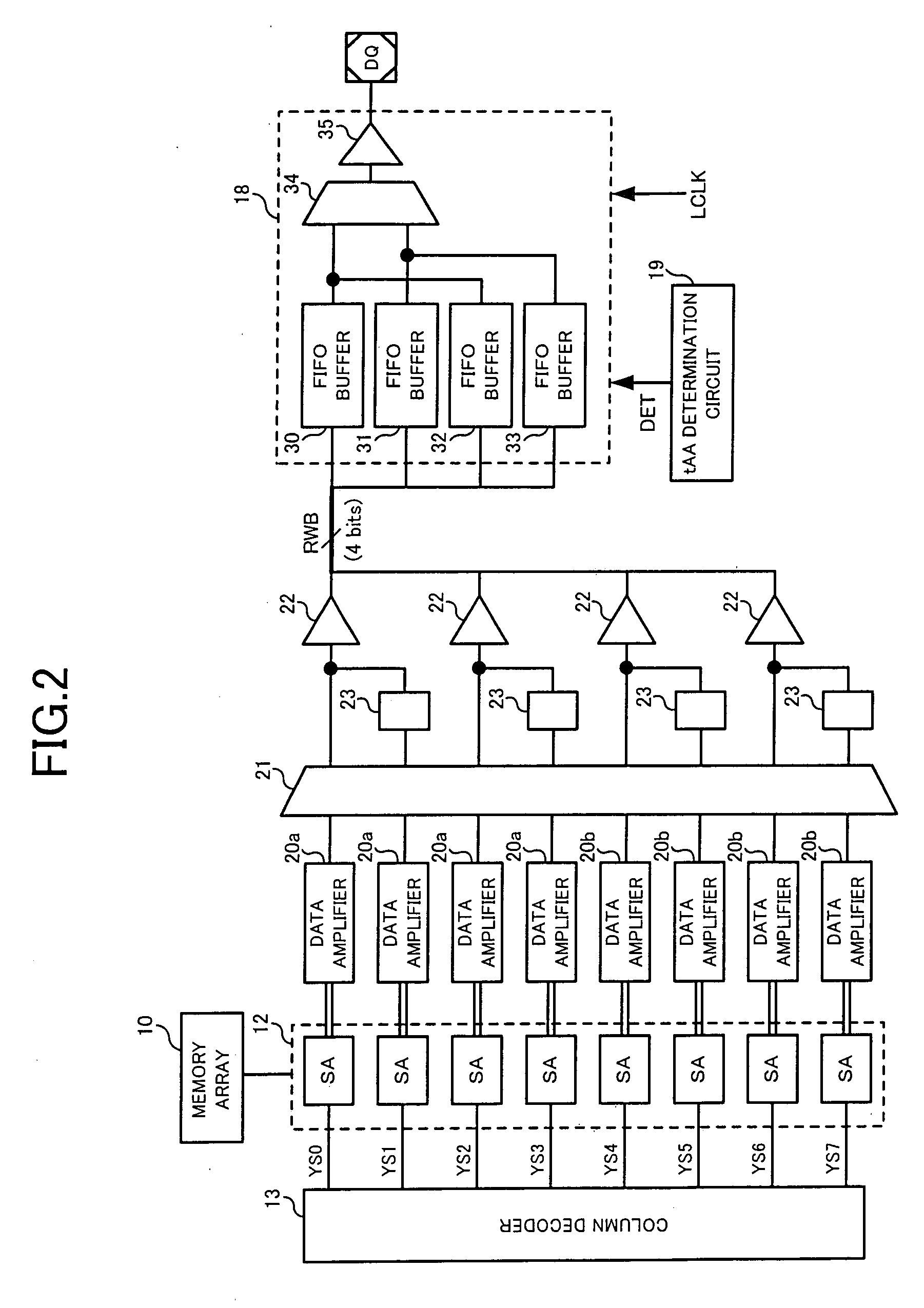

Semiconductor storage device

ActiveUS7426144B2Increased current consumptionReduce circuitRead-only memoriesDigital storageSemiconductor storage devicesControl circuit

A semiconductor storage device comprising: a transfer control circuit for prefetching data of a predetermined number of bits stored in a memory array in response to a read command, and transferring L bits of the prefetched data in parallel to an internal bus in synchronization with an internal clock; and an output buffer circuit which includes L FIFO buffers each for latching each bit of the L bits input from the internal bus and extracts stored data from each of the L FIFO buffers in accordance with an input sequence in synchronization with an external clock so as to transfer the data serially to outside, wherein each of the L FIFO buffers includes an M-bit latch circuit and an N-bit latch circuit, and paths of the M-bit and N-bit latch circuits can be selectively switched.

Owner:MICRON TECH INC

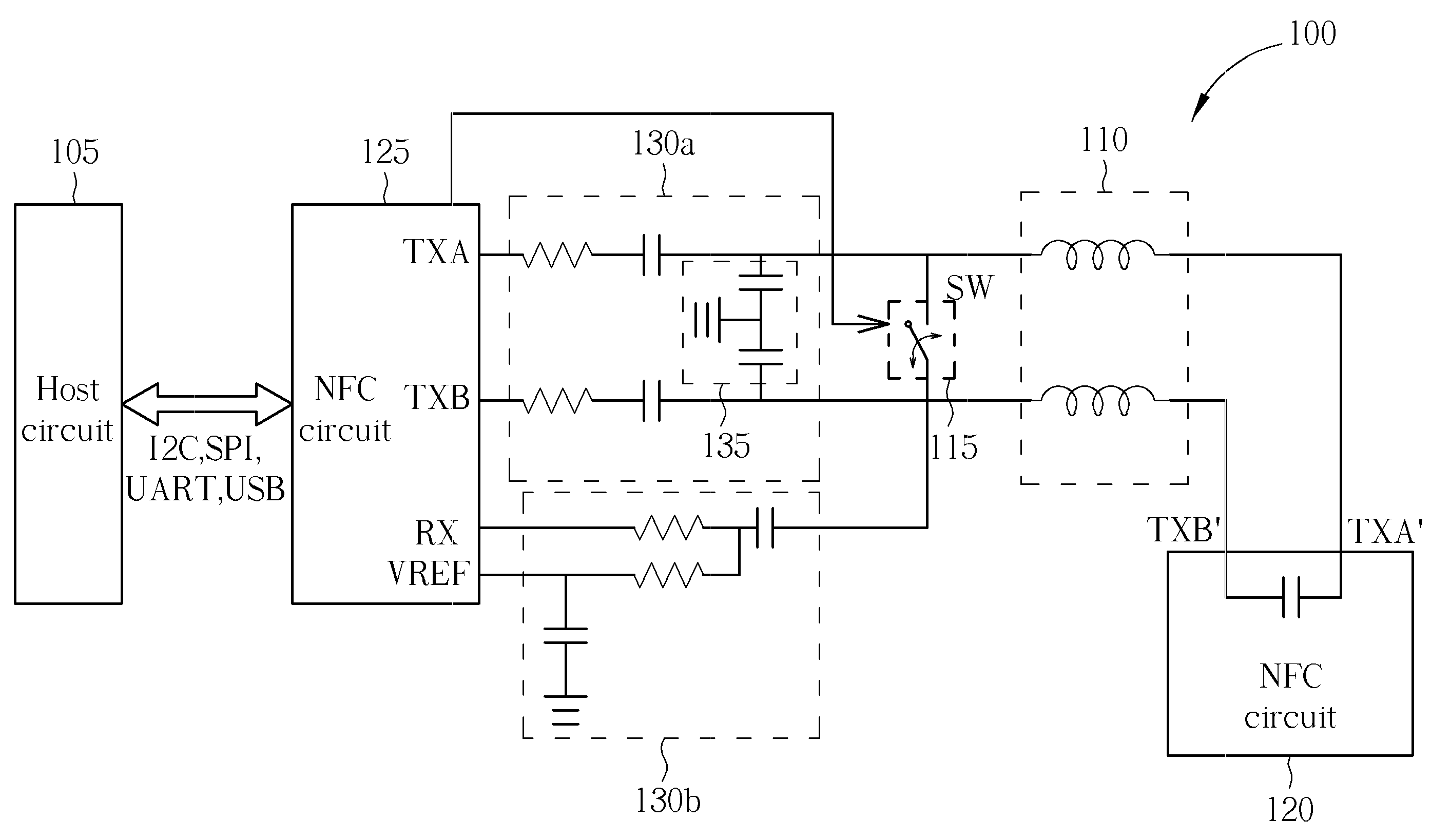

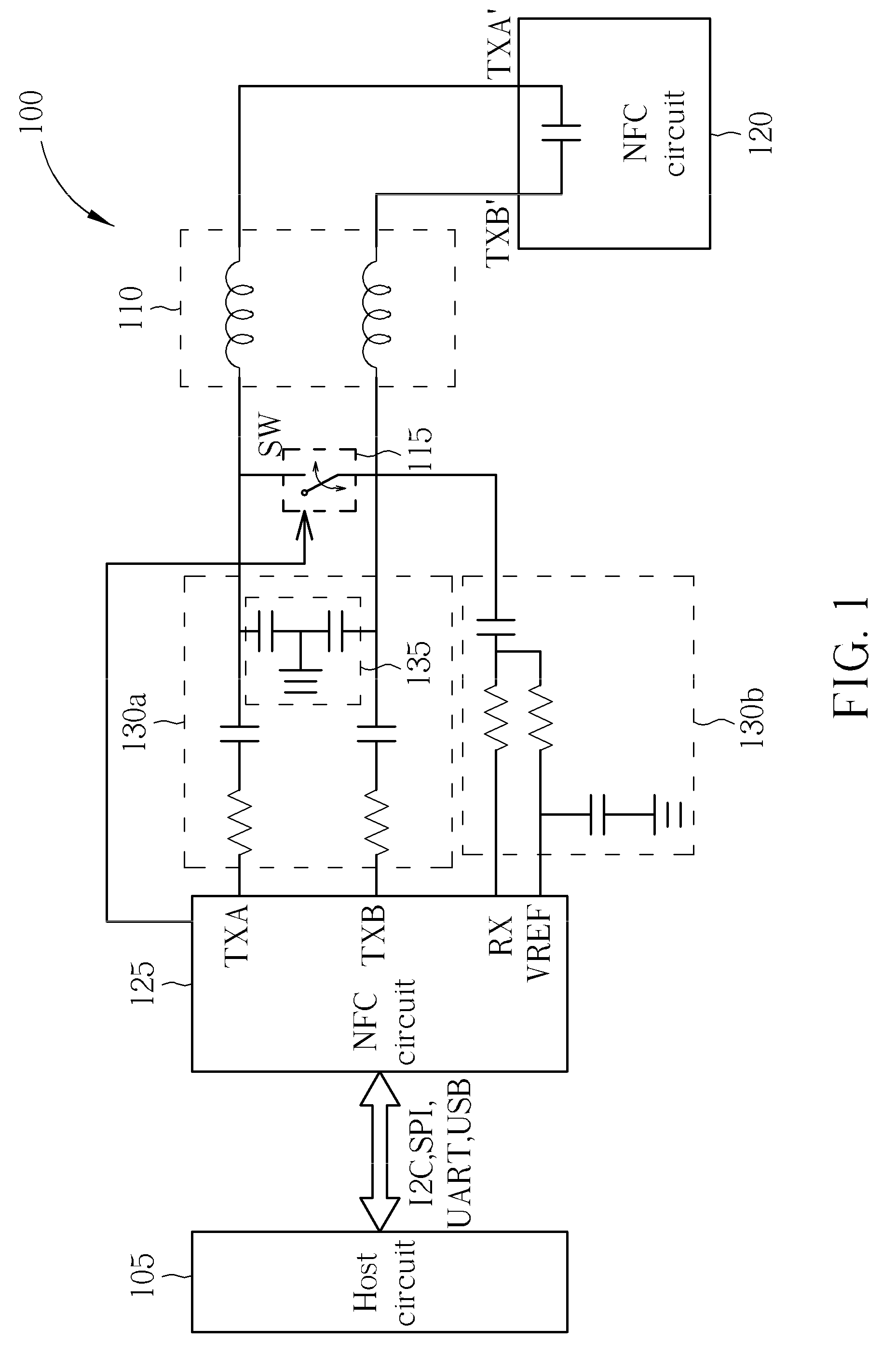

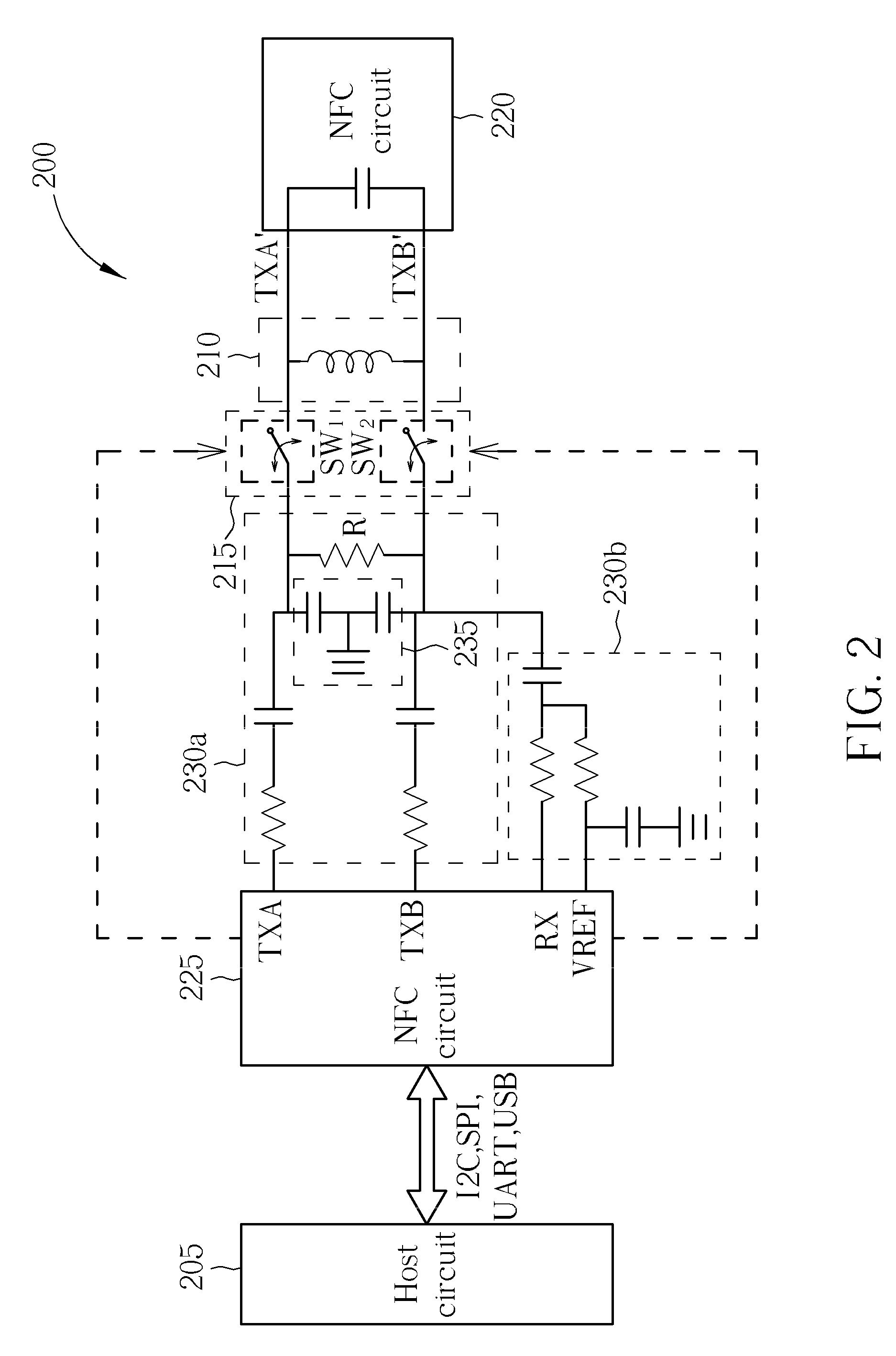

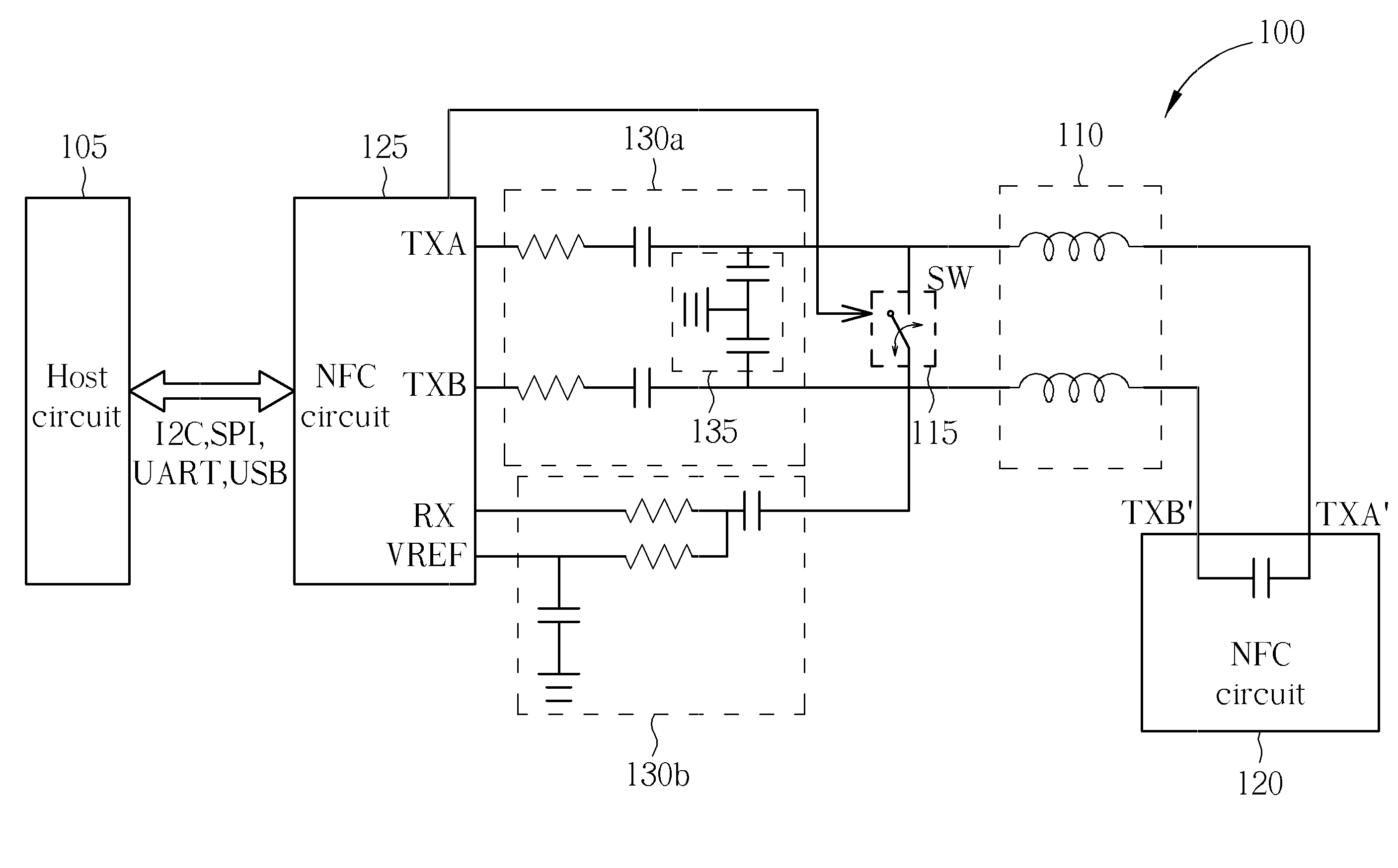

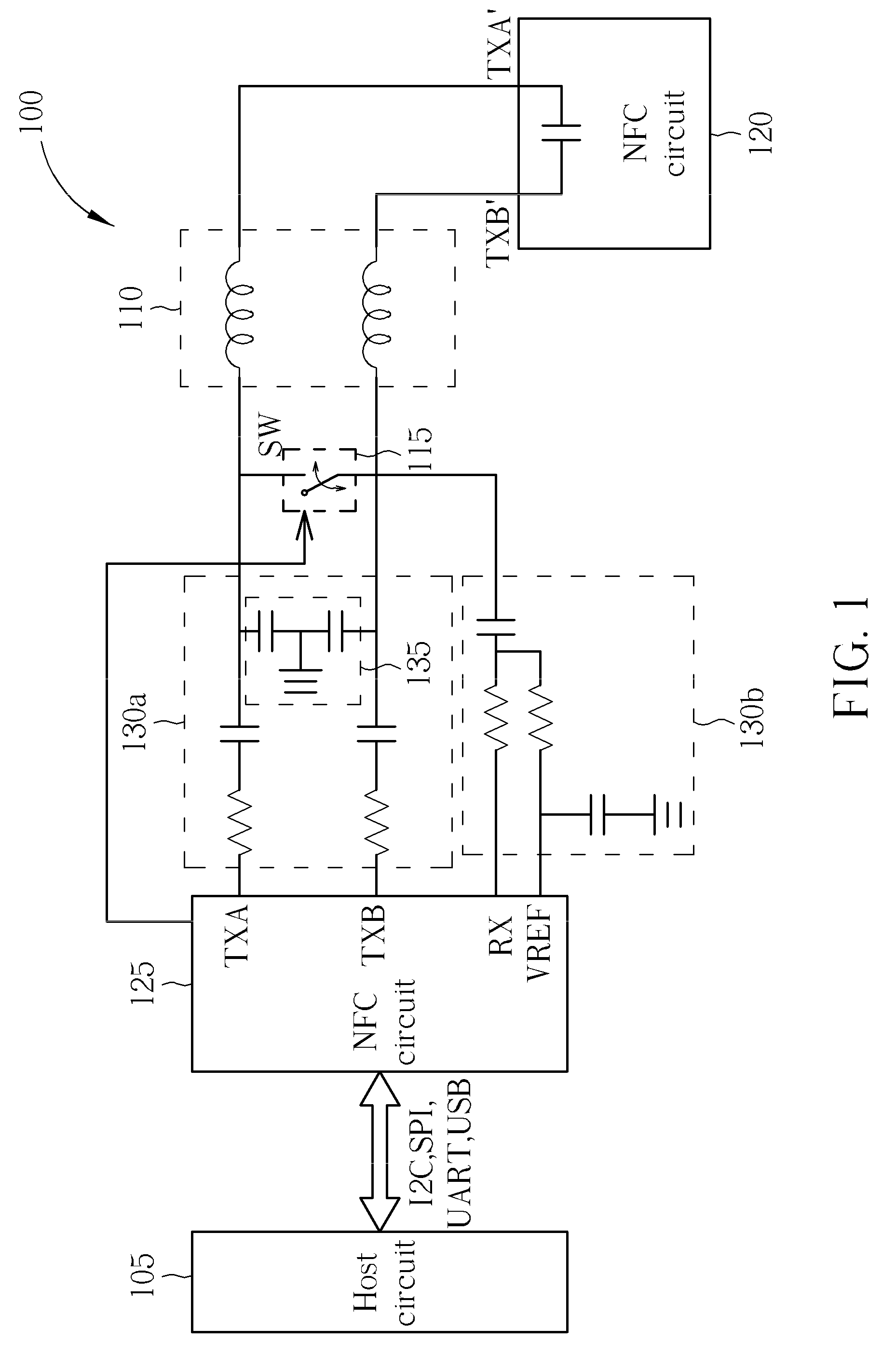

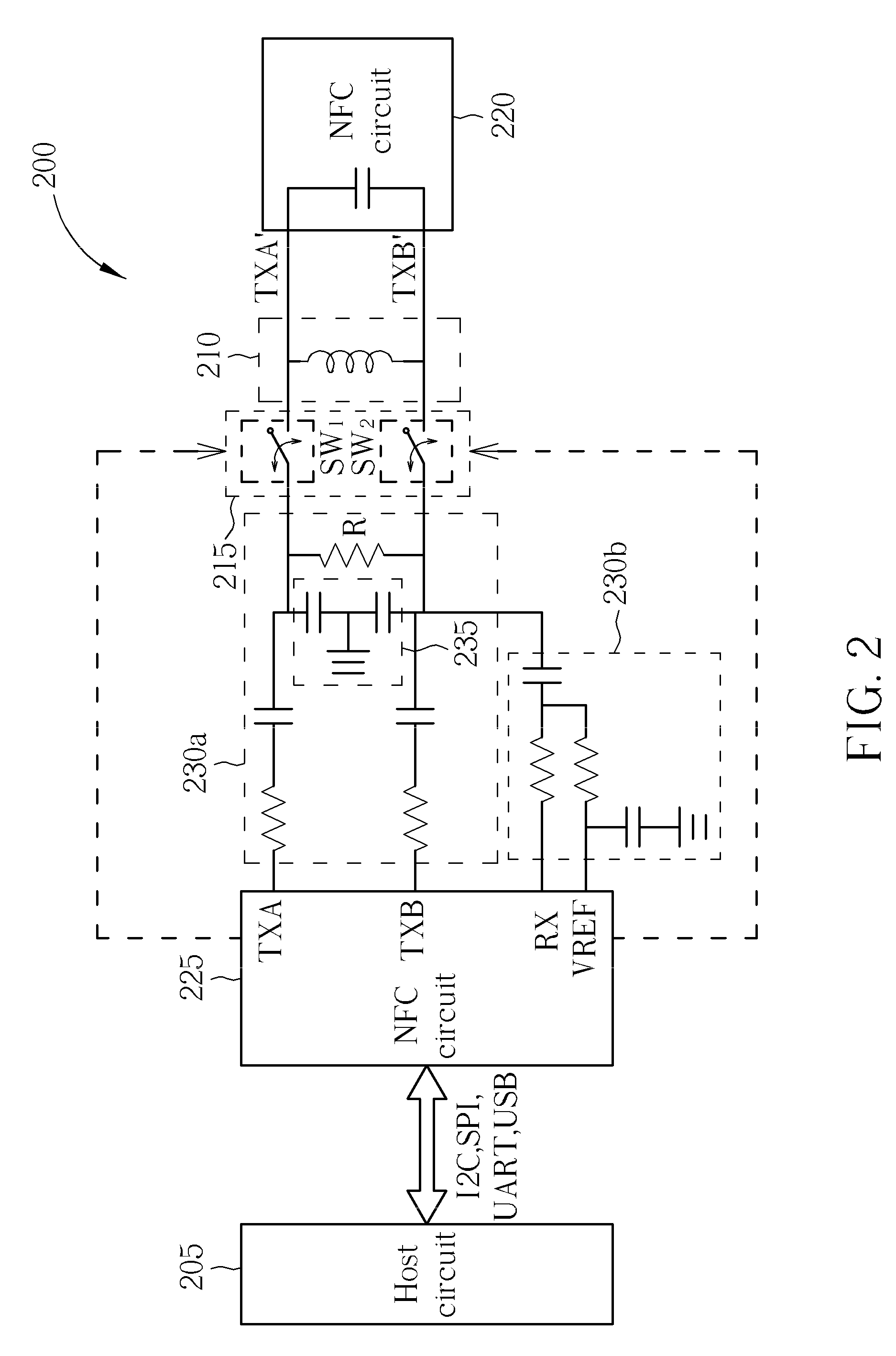

Wireless communication apparatus and method thereof

ActiveUS20090212917A1Reduce circuitLow costMultiplex system selection arrangementsElectric signal transmission systemsTelecommunicationsCommunication circuits

A wireless communication method utilizing a wireless communication apparatus is provided. The method includes: providing an antenna unit being used by both a first wireless communication circuit and a second wireless communication circuit, using the first wireless communication circuit for RFID communication via the antenna unit in a first mode, and utilizing the second wireless communication circuit for RFID communication via the antenna unit in a second mode.

Owner:XUESHAN TECH INC

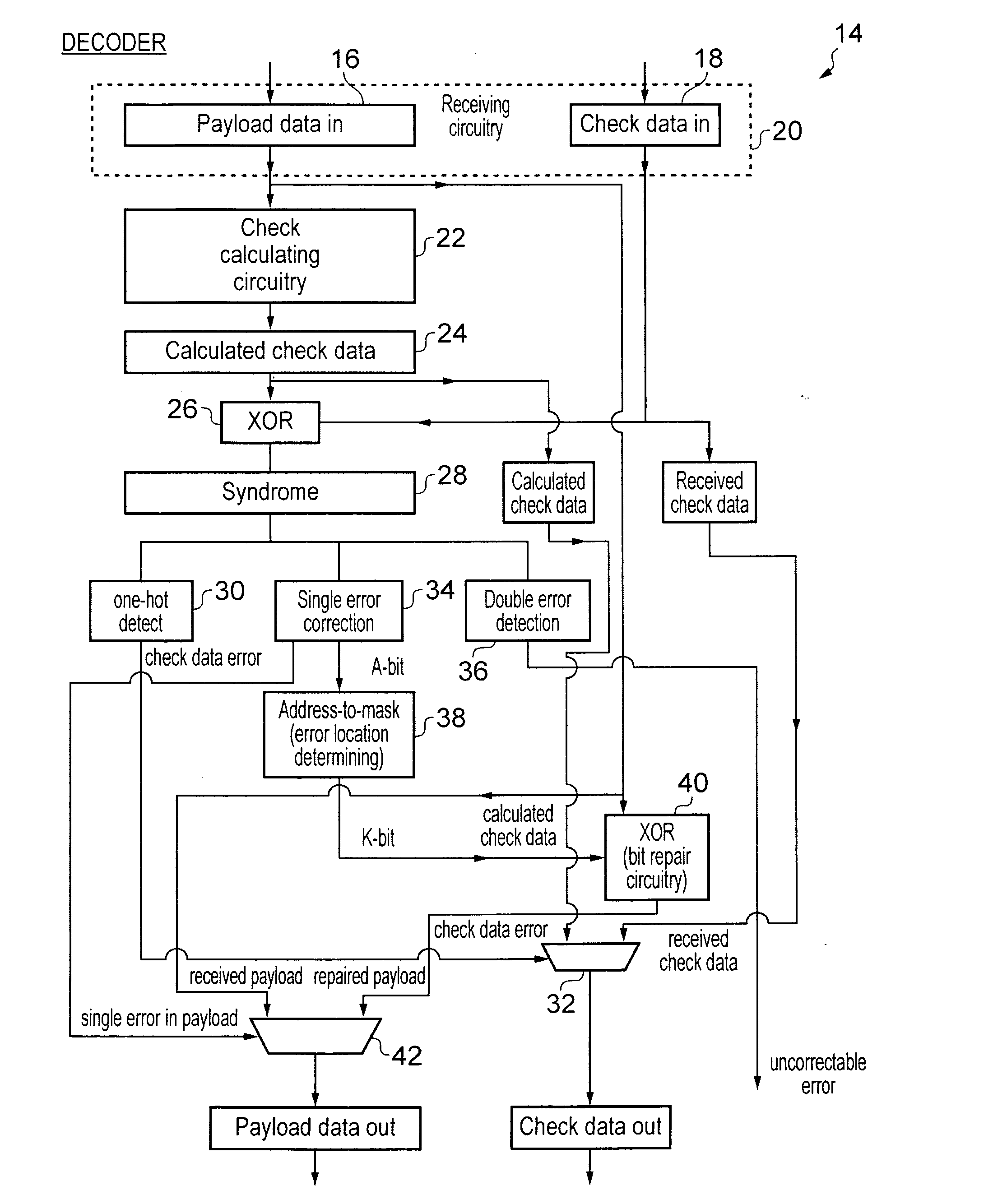

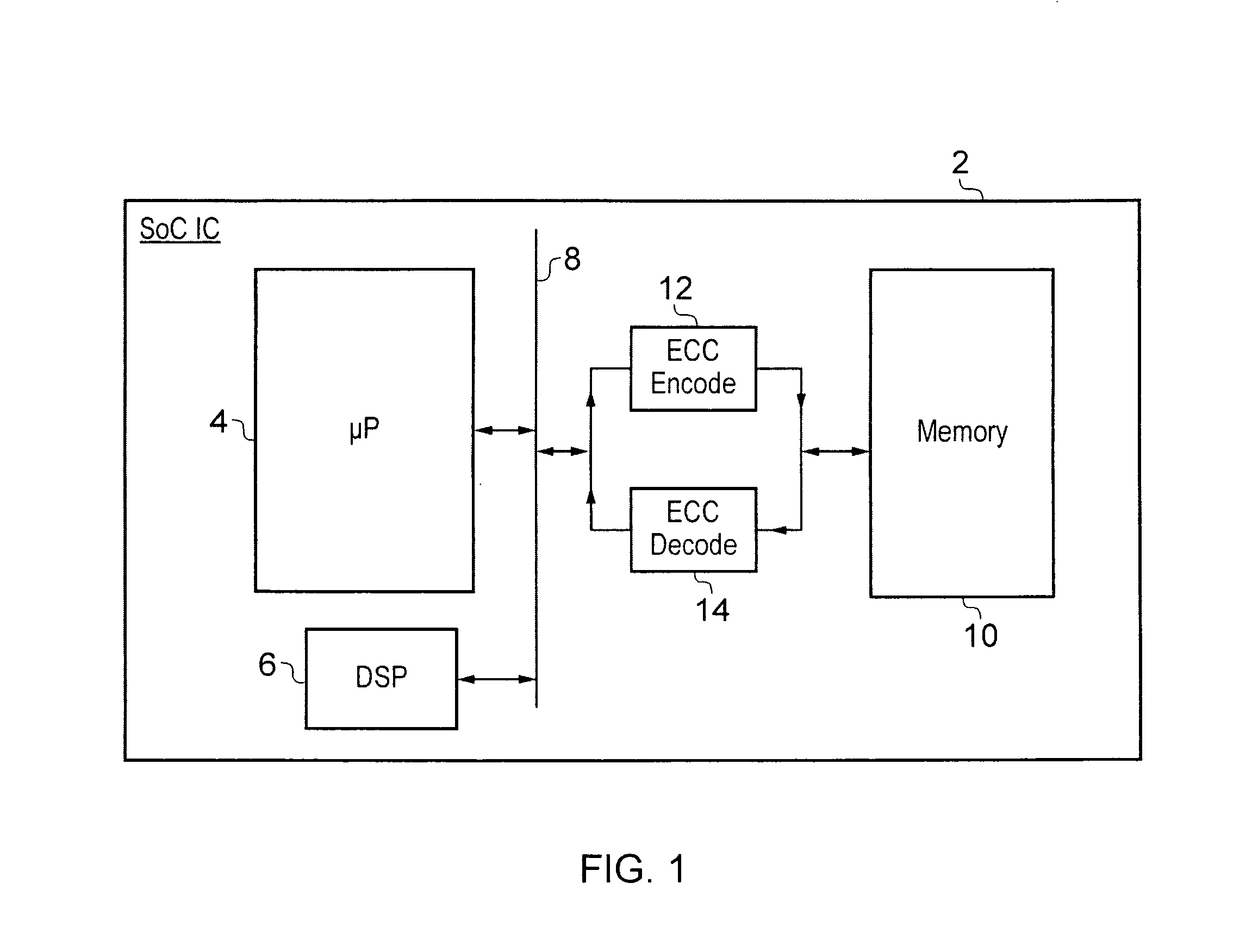

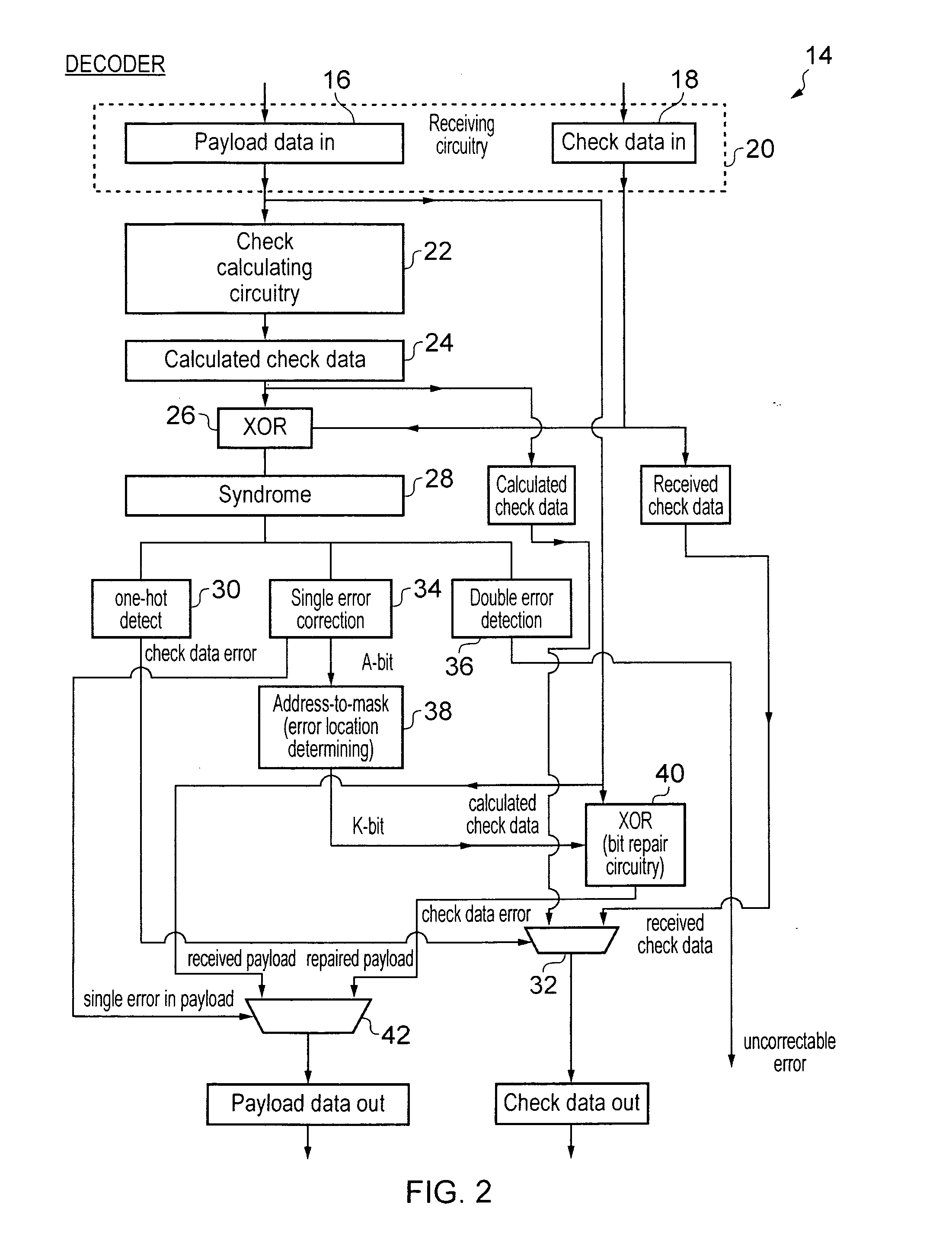

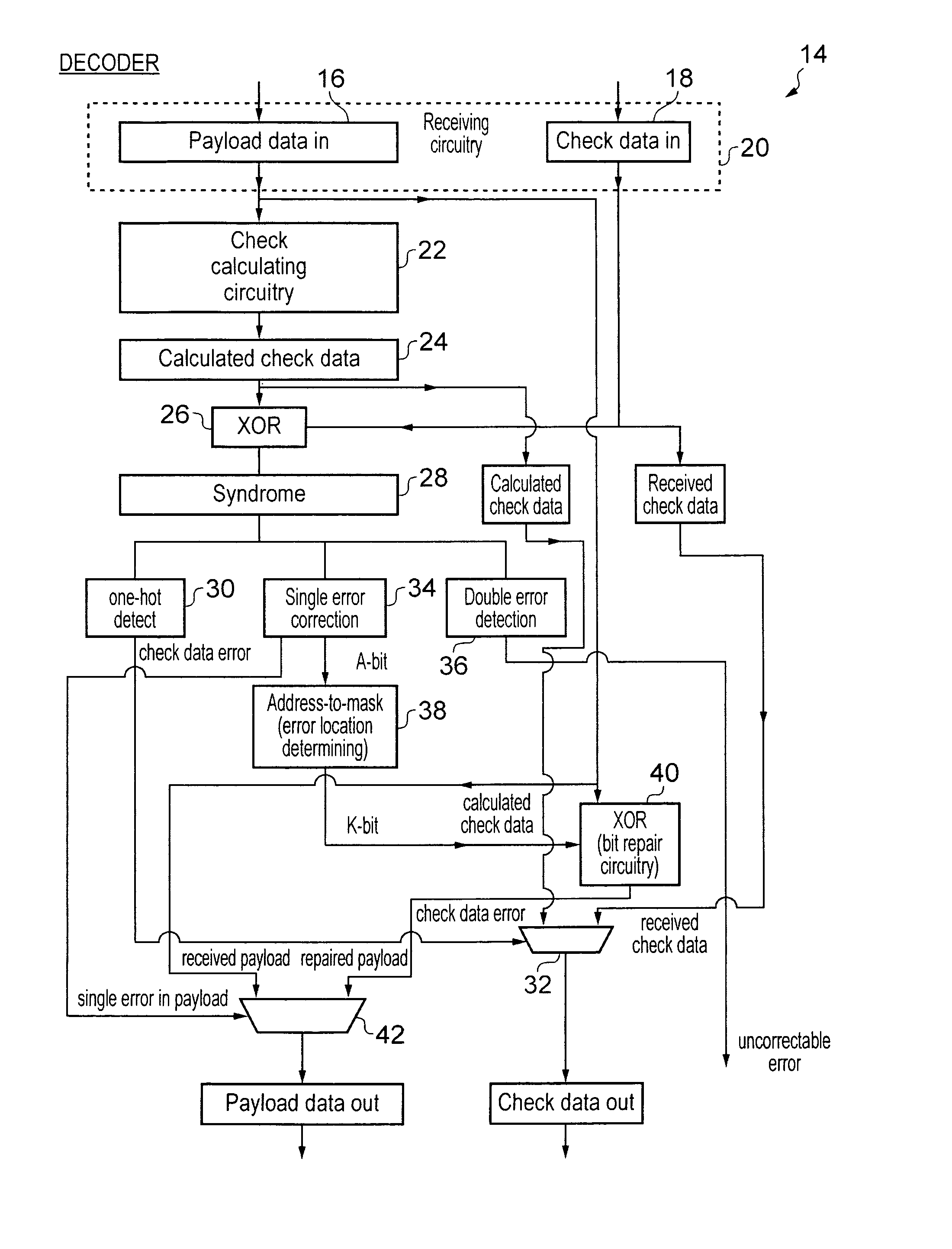

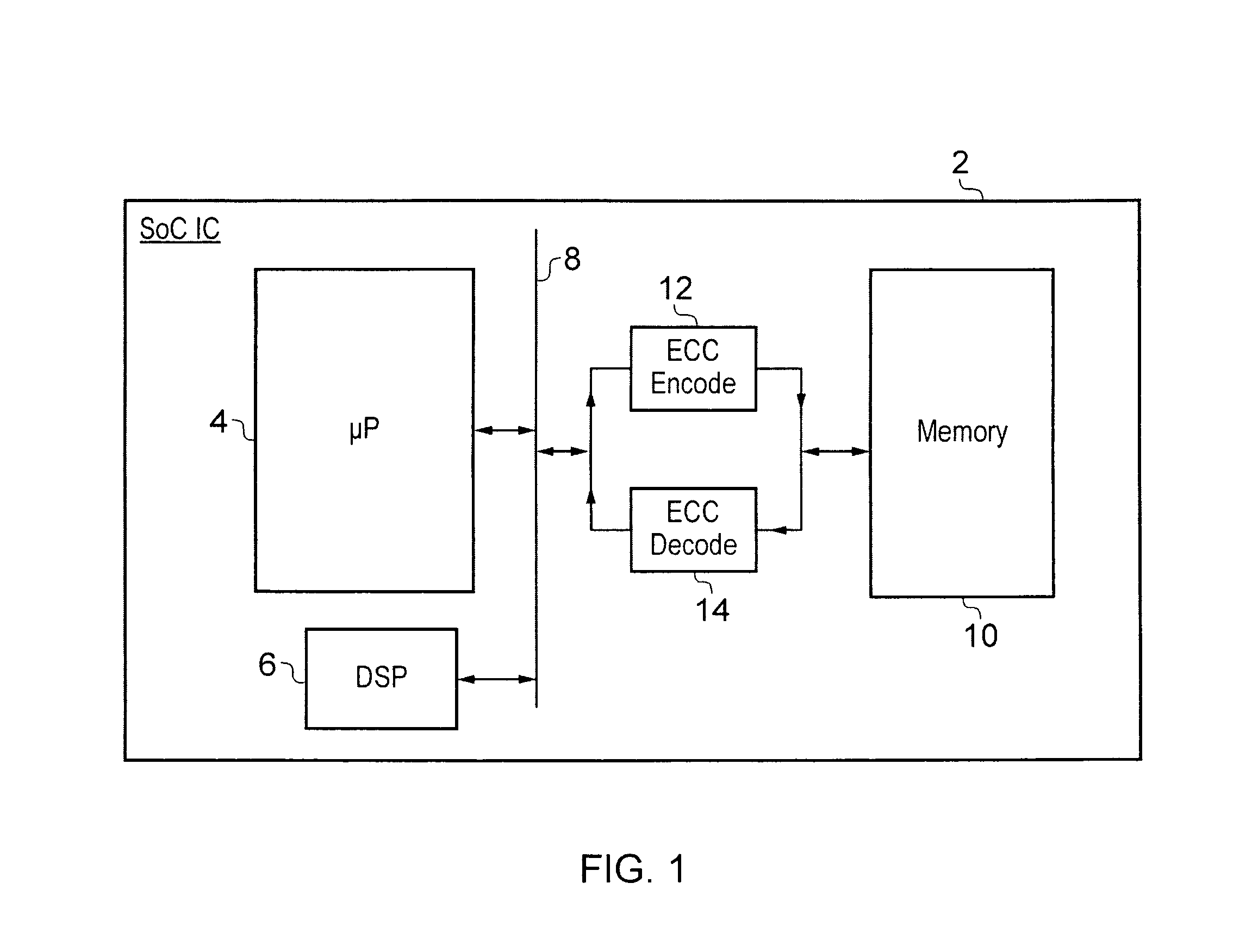

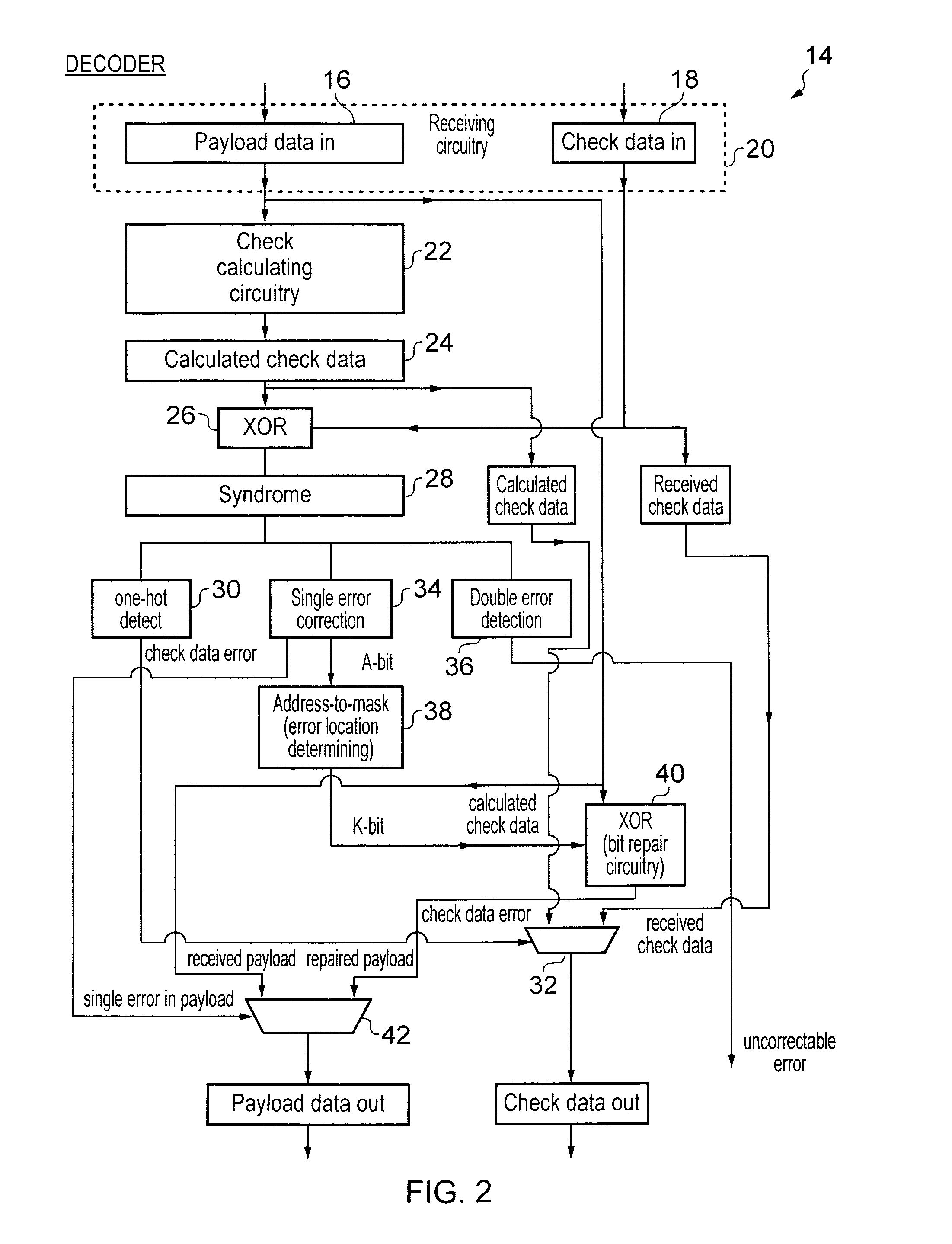

Error control coding for single error correction and double error detection

ActiveUS20110099451A1Good error correction/detectionLow overhead implementationReed-muller codesChecking code calculationsComputer hardwareChecksum

An error correction coding is provided that generates P bits of check data from K M-bit words of payload data. The P bits of check data include an address field A, a bit error indicating field E and an auxiliary field P−(E+A). The address field encodes a set of error addresses which has a cardinality equal to the bit size K of the payload data and providing a one-to-one mapping between values of the address field and the locations of a single bit error within the payload data. The bit error indicating field indicates if a bit error is present. The auxiliary field is a minimum size bit vector such that together with the address field and the bit area indicating field it provides a checksum for a systematic code for the payload data with a minimum Hamming distance serving to provide either single error correction capability or single error correction and double error detection capability.

Owner:ARM LTD

Semiconductor storage device

ActiveUS20070076474A1Increased current consumptionReduce circuitRead-only memoriesDigital storageSemiconductor storage devicesControl circuit

A semiconductor storage device comprising: a transfer control circuit for prefetching data of a predetermined number of bits stored in a memory array in response to a read command, and transferring L bits of the prefetched data in parallel to an internal bus in synchronization with an internal clock; and an output buffer circuit which includes L FIFO buffers each for latching each bit of the L bits input from the internal bus and extracts stored data from each of the L FIFO buffers in accordance with an input sequence in synchronization with an external clock so as to transfer the data serially to outside, wherein each of the L FIFO buffers includes an M-bit latch circuit and an N-bit latch circuit, and paths of the M-bit and N-bit latch circuits can be selectively switched.

Owner:MICRON TECH INC

High intensity discharge lamp ballast apparatus

InactiveUS20050057181A1DownsizeSufficient energyElectric light circuit arrangementGas discharge lamp usageResonant capacitorHigh intensity

A compact, low cost high intensity discharge lamp ballast apparatus which can carry out normal ballasting without extinction at discharge start includes a DC-AC inverting booster circuit, a first resonance circuit, and a second resonance circuit. The DC-AC inverting booster circuit includes a DC-AC converter transformer for converting a DC voltage fed from a DC power supply to an AC voltage in response to switching on and off of FETs, boosting the voltage. The first resonance circuit includes a leakage inductance connected in series with the secondary winding of the DC-AC converter transformer, and a first resonant capacitor connected in parallel with the secondary winding. The second resonance circuit includes a metal halide lamp, an ignitor transformer for producing a voltage to start lighting of the metal halide lamp, and a second resonant capacitor.

Owner:MITSUBISHI ELECTRIC CORP

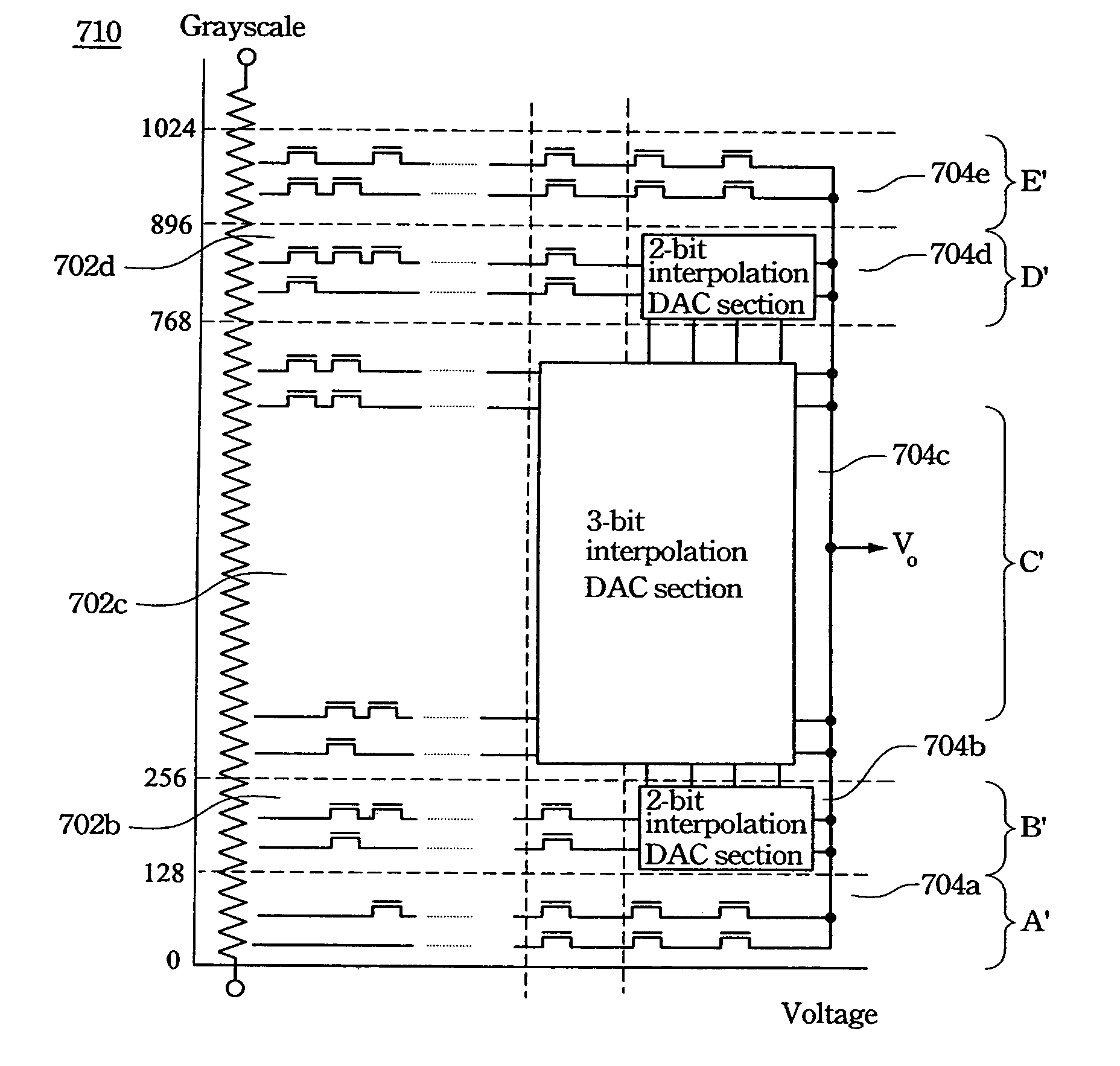

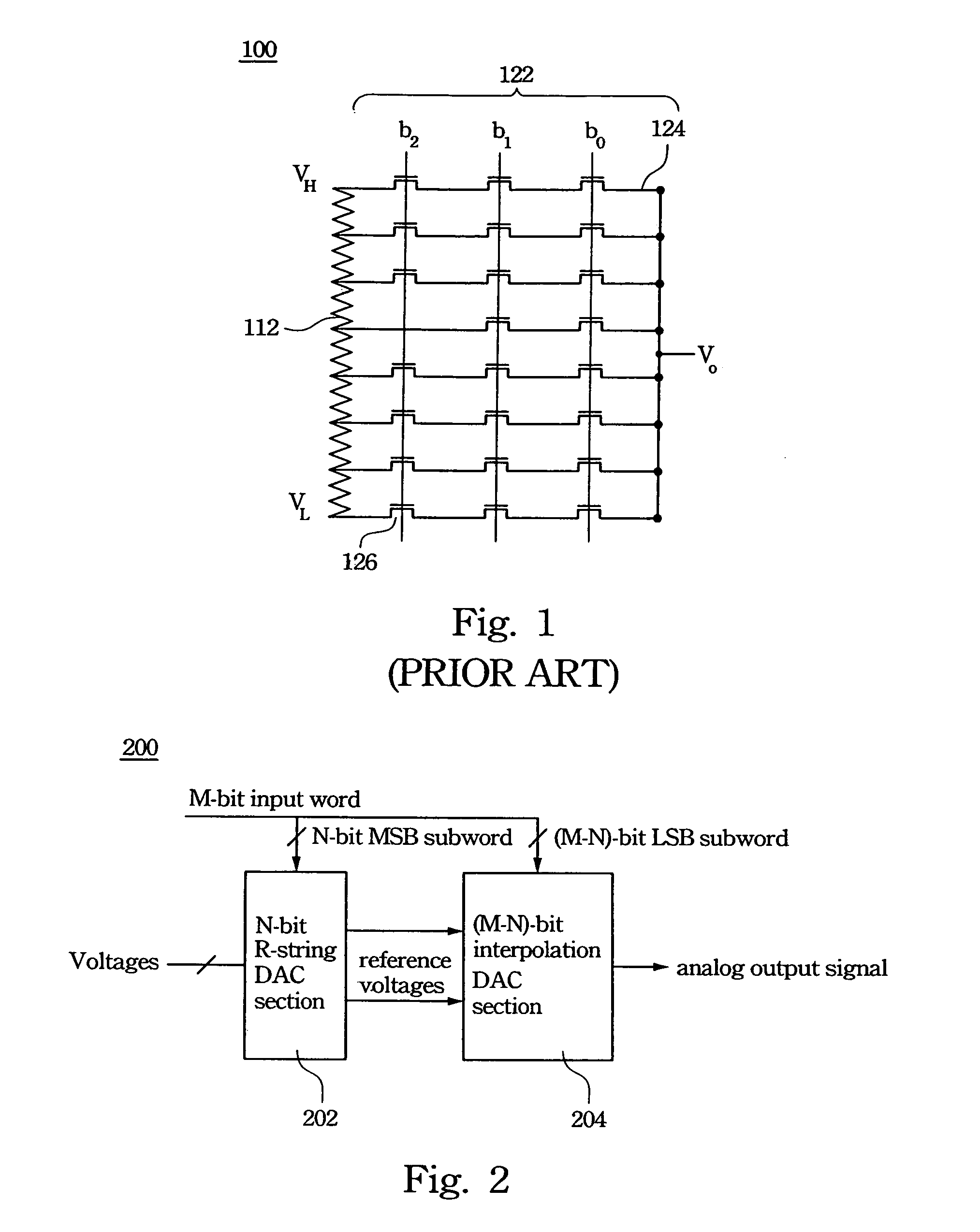

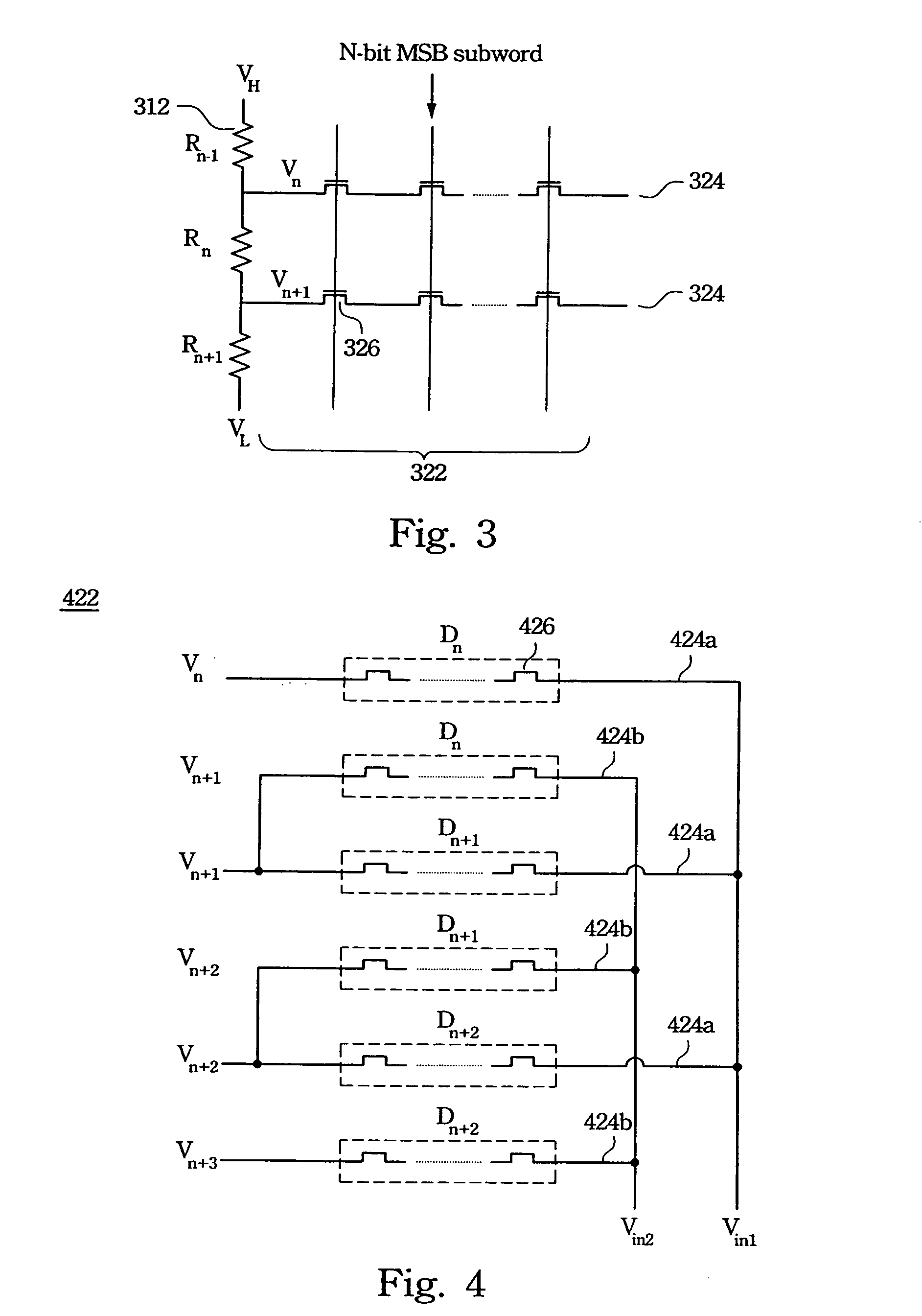

Digital-to-analog converter

ActiveUS7161517B1Reduce loadReduce layout areaElectric signal transmission systemsDigital-analogue convertorsDigital analog converterEngineering

Owner:HIMAX TECH LTD

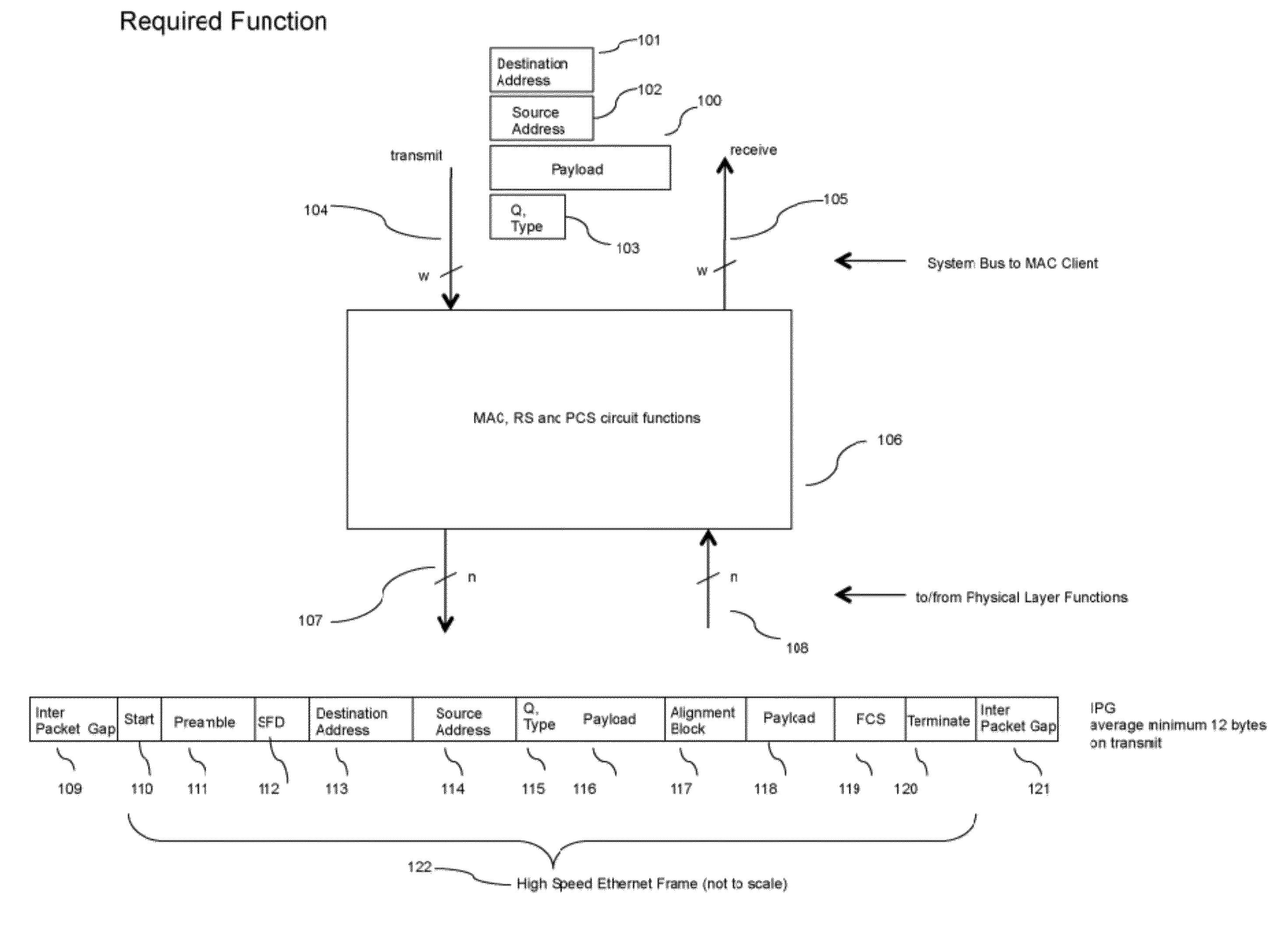

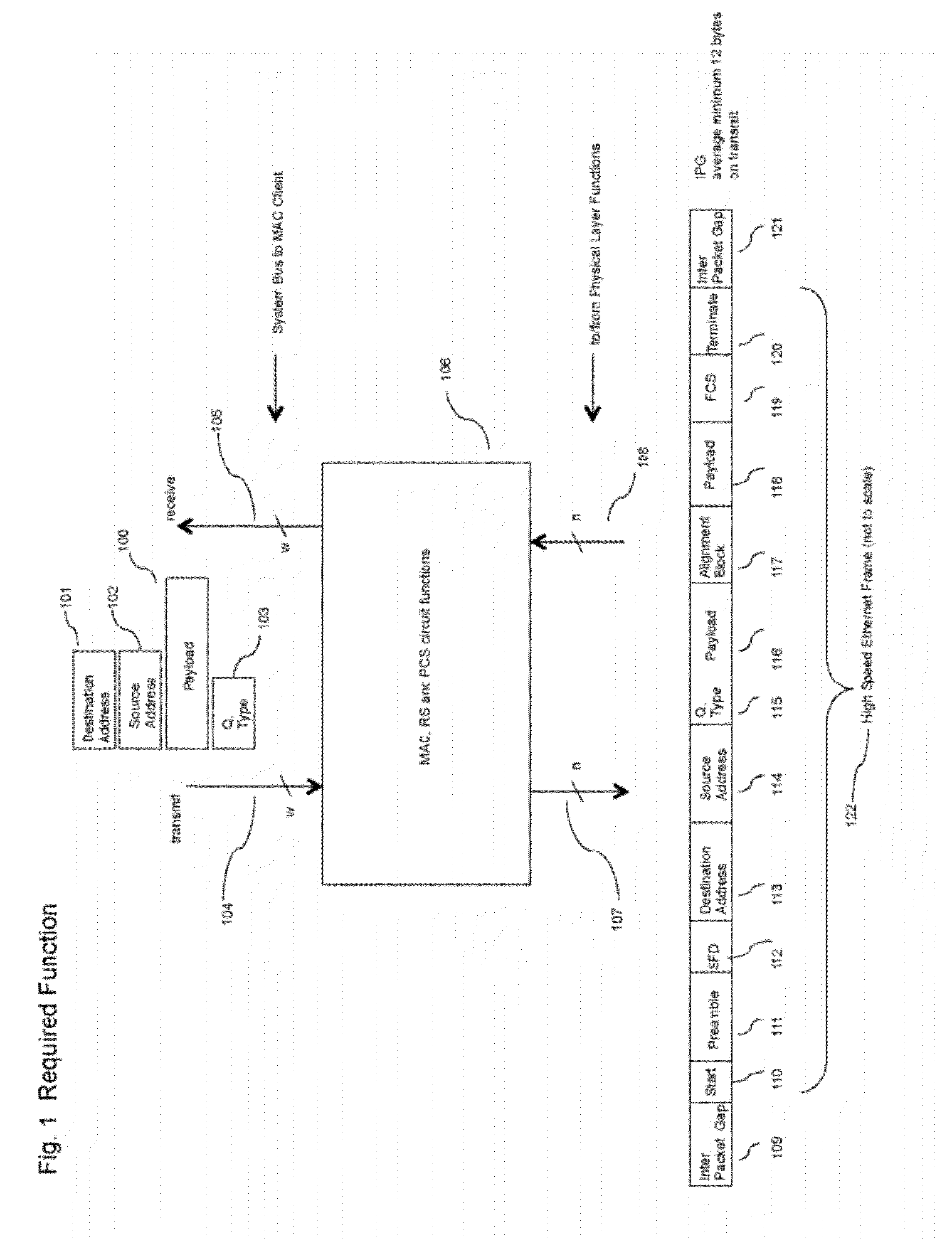

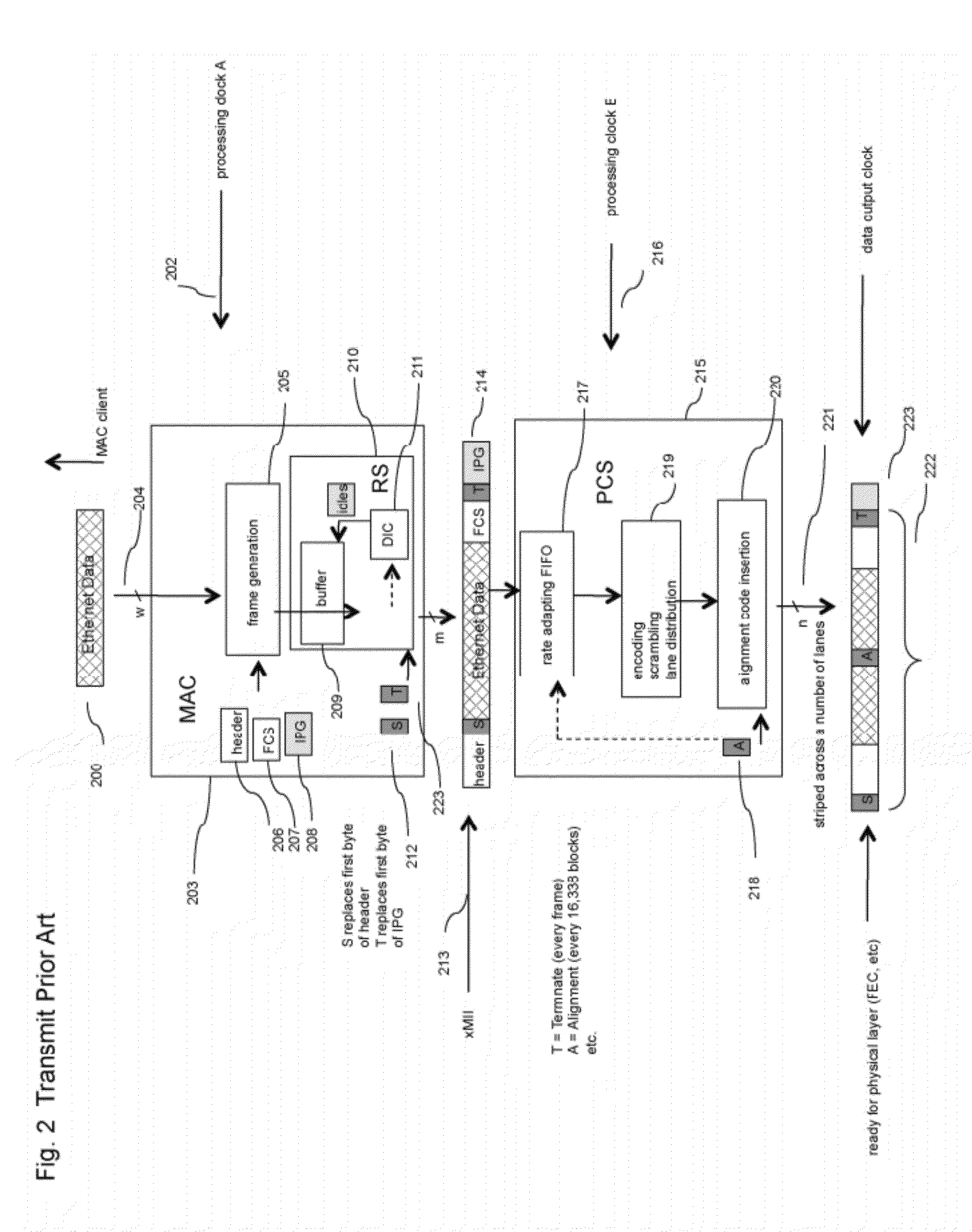

Packet Network Interface Apparatus and Method

ActiveUS20120236878A1Small circuitReduce circuitTime-division multiplexTransmissionTime domainNetwork interface device

A packet network interface apparatus includes a media access control (MAC) module for constructing a packet for transmission over a packet network and a physical coding sublayer (PCS) module for encoding the packet for transmission over a physical interface. An inter packet gap module located between the MAC module and the PCS module directly transfers data to the PCS module while maintaining a certain inter packet gap by deleting or inserting idle characters. The inter packet gap module has at least one memory module for temporary storage of packet data. The modules preferably operate in a common time domain.

Owner:XILINX INC

Wireless communication apparatus and method thereof

ActiveUS8018344B2Reduce circuitLow costMultiplex system selection arrangementsElectric signal transmission systemsTelecommunicationsCommunication circuits

A wireless communication method utilizing a wireless communication apparatus is provided. The method includes: providing an antenna unit being used by both a first wireless communication circuit and a second wireless communication circuit, using the first wireless communication circuit for RFID communication via the antenna unit in a first mode, and utilizing the second wireless communication circuit for RFID communication via the antenna unit in a second mode.

Owner:XUESHAN TECH INC

Systems and methods for operating a two-dimensional transducer array

ActiveUS8176787B2Reduce circuitReduce the numberUltrasonic/sonic/infrasonic diagnosticsAnalysing solids using sonic/ultrasonic/infrasonic wavesTransducerEngineering

According to embodiments of the present technique, a system and a method for addressing transducers in a two-dimensional transducer array is disclosed. According to one aspect of the present technique, the transducers are arranged in rows and columns, and the columns are coupled to a shared transmit and receive circuitry while the rows are coupled to a row selection circuitry. In another embodiment, each transducer is coupled to a separate, dedicated transmit circuitry and the columns are coupled to a shared receive circuitry.

Owner:GENERAL ELECTRIC CO

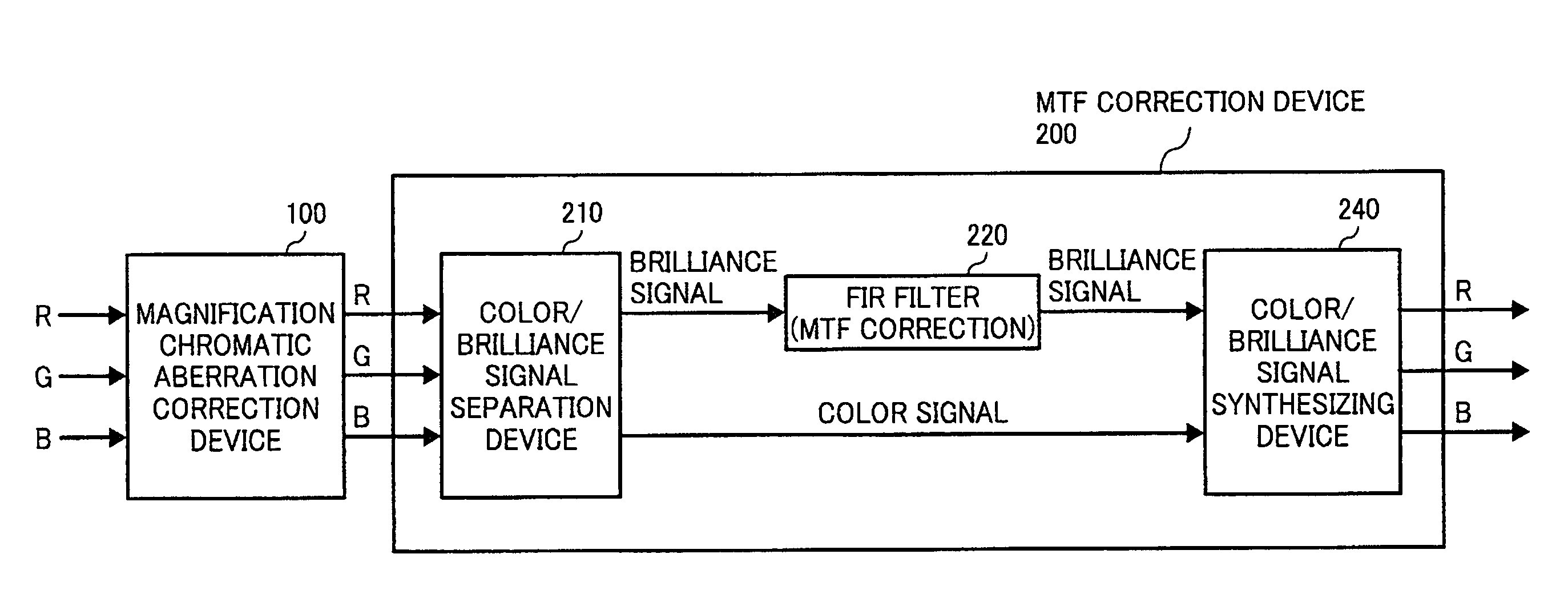

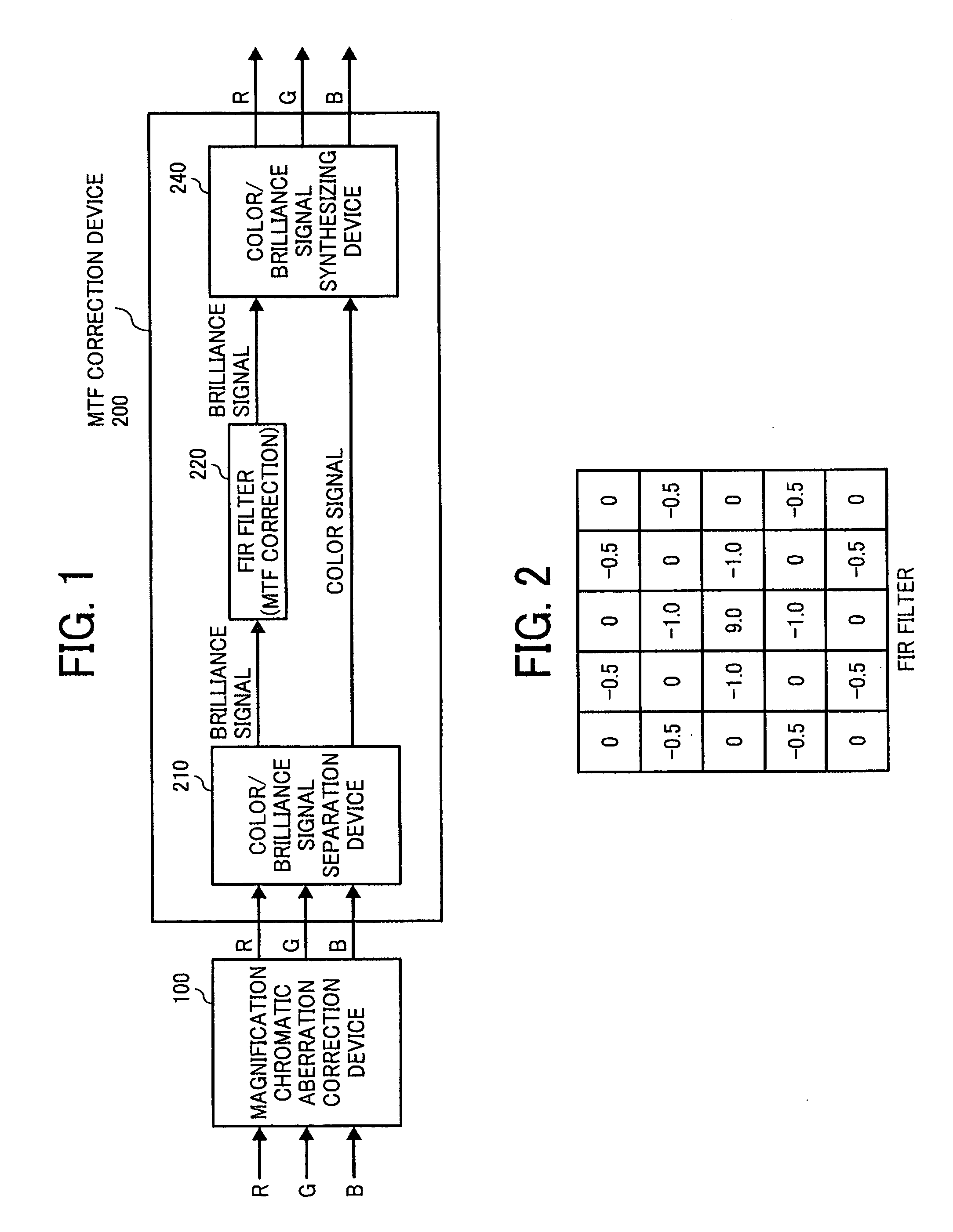

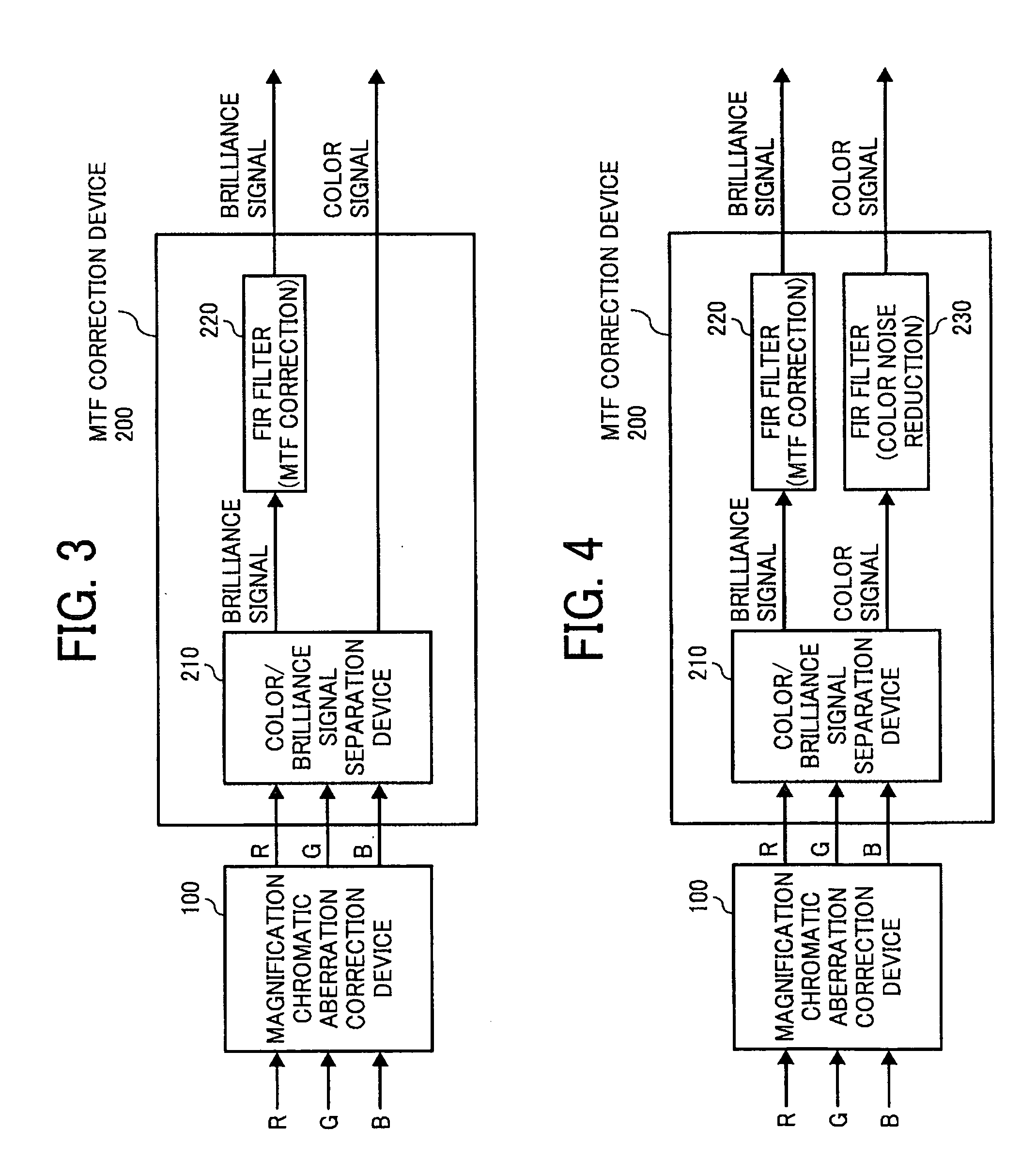

Image processing apparatus and method

ActiveUS20090226086A1Prevent image degradationCorrect chromatic aberrationTelevision system detailsCharacter and pattern recognitionImaging processingWide field

An image processing method of processing an image obtained by using an optical system having a wide field angle and a large magnification chromatic aberration includes the steps of applying magnification chromatic aberration correction processing to the image, applying separation processing to the image after the step of applying the magnification chromatic aberration correction for separating the image into a brightness signal and a color signal, and applying a high band emphasis processing only to the brightness signal after the step of applying the separation processing.

Owner:RICOH KK

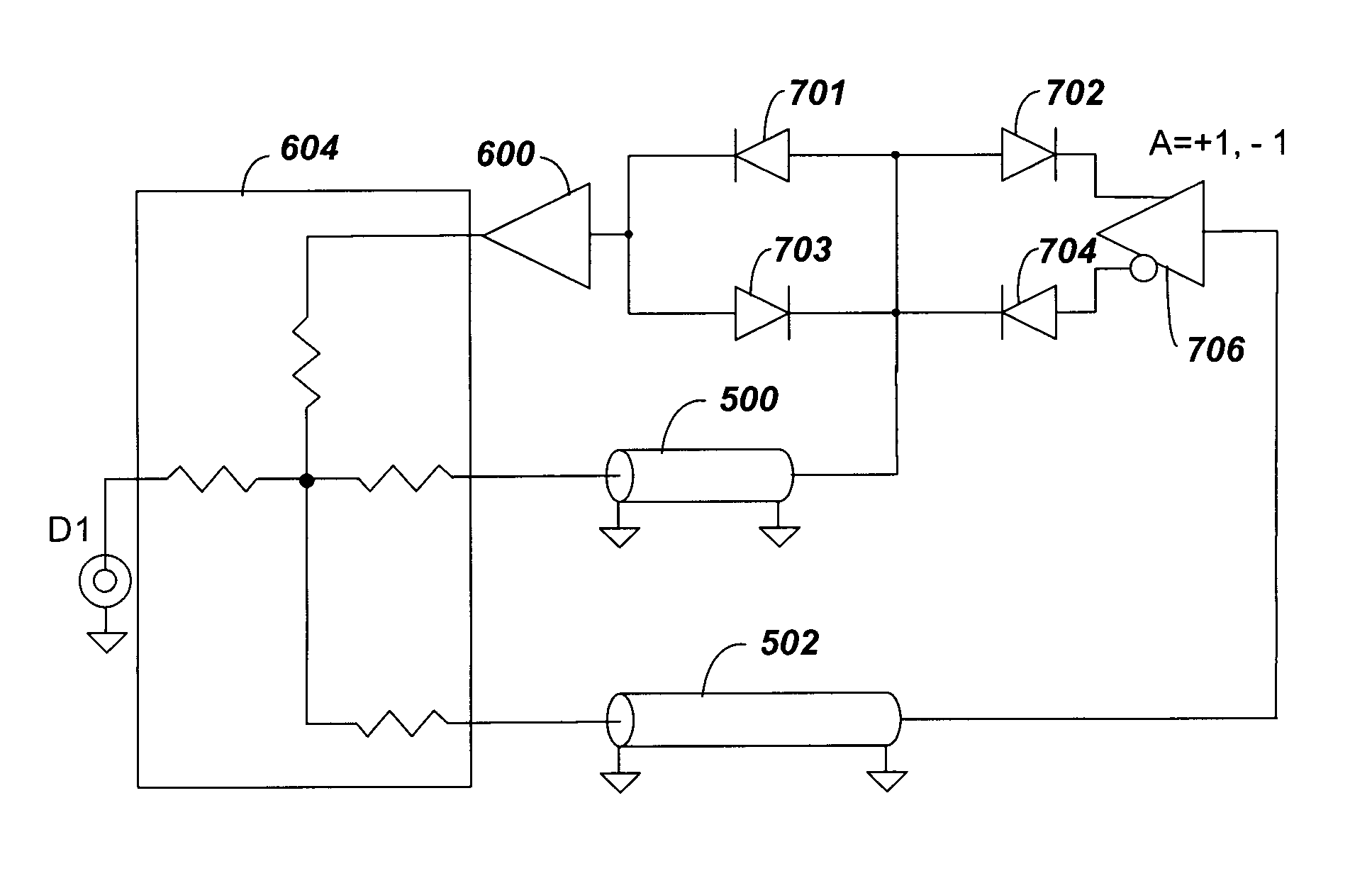

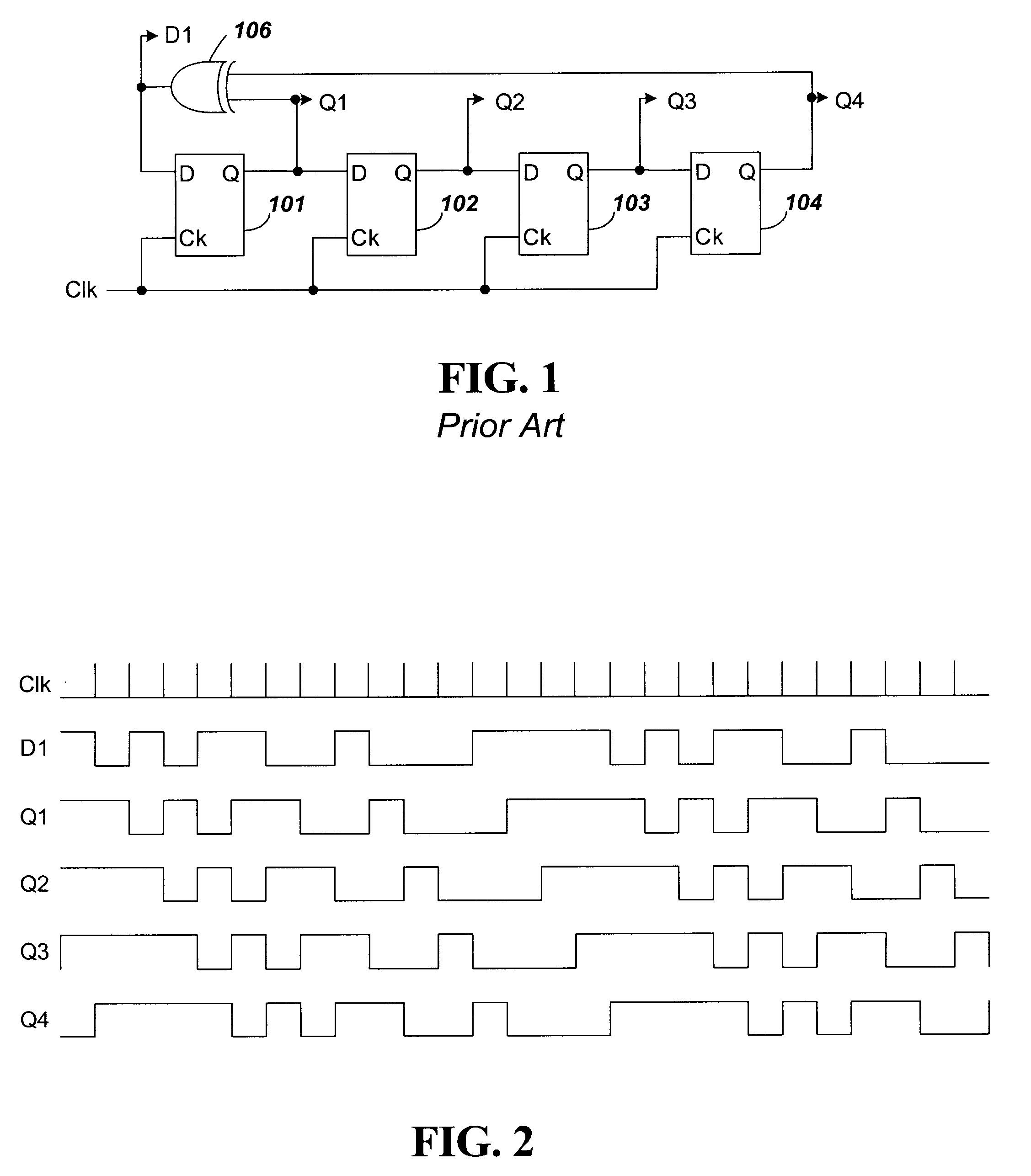

Analog pseudo random bit sequence generator

InactiveUS8156167B2Reduce circuitRandom number generatorsOscillations generatorsAudio power amplifierGilbert cell

A Pseudo Random Bit Sequence (PRBS) generator is provided with components to enable operation at very high microwave frequencies with inexpensive components. The PRBS generator initially replaces the D flip-flops of a conventional PRBS generator with delay lines connected in a similar manner. Further, an exclusive OR (EXOR) gate used in a conventional device is replaced in one embodiment by a mixer and amplifier. In another embodiment, the EXOR gate is replaced by a Gilbert Cell. In some embodiments, complementary outputs of an EXOR gate are connected to separate delay lines to reduce components needed for the PRBS generator.

Owner:ANRITSU CO

System and method for supporting handovers between different radio access technologies of a wireless communications system

ActiveUS8369290B2Reduce circuitLow costTime-division multiplexCommunication jammingRadio access technologyCommunications system

A system and method for supporting handovers between different radio access technologies is provided. A method for communications device operations includes sending a request to a controller of the communications device to change an operating mode of the communications device, and receiving a transmission responsive to the request. The method also includes in response to determining that the controller has granted the request to change the operating mode and that the communications device is operating in a border cell, changing the operating mode of the communications device, tuning at least one receiver of the communications device to an alternate radio access technology (RAT), and initiating a handover with the alternate RAT.

Owner:FUTUREWEI TECH INC

Error control coding for single error correction and double error detection

ActiveUS8381083B2Reduce overheadReduce circuitReed-muller codesError detection/correctionComputer hardwareChecksum

An error correction coding is provided that generates P bits of check data from K M-bit words of payload data. The P bits of check data include an address field A, a bit error indicating field E and an auxiliary field P−(E+A). The address field encodes a set of error addresses which has a cardinality equal to the bit size K of the payload data and providing a one-to-one mapping between values of the address field and the locations of a single bit error within the payload data. The bit error indicating field indicates if a bit error is present. The auxiliary field is a minimum size bit vector such that together with the address field and the bit area indicating field it provides a checksum for a systematic code for the payload data with a minimum Hamming distance serving to provide either single error correction capability or single error correction and double error detection capability.

Owner:ARM LTD

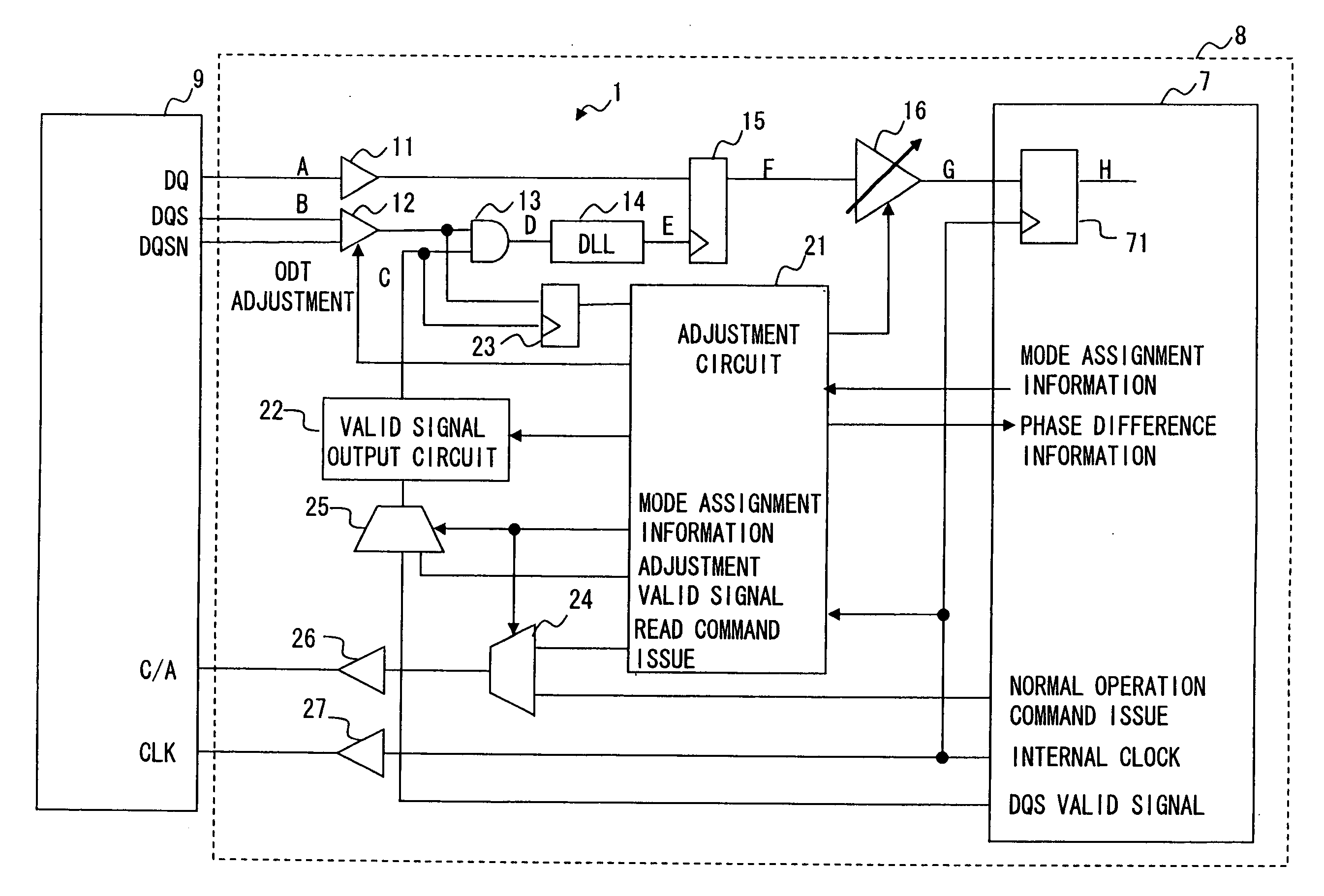

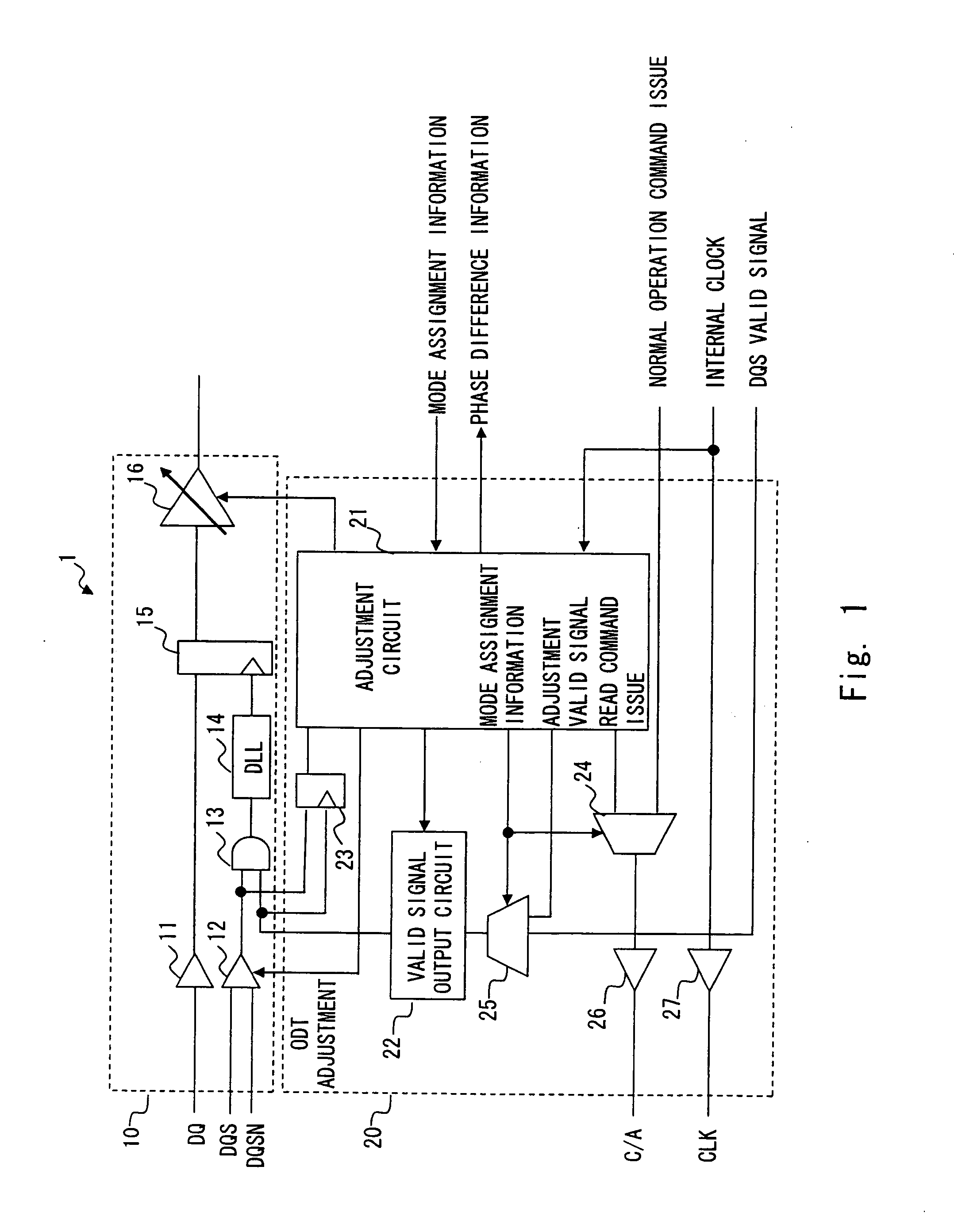

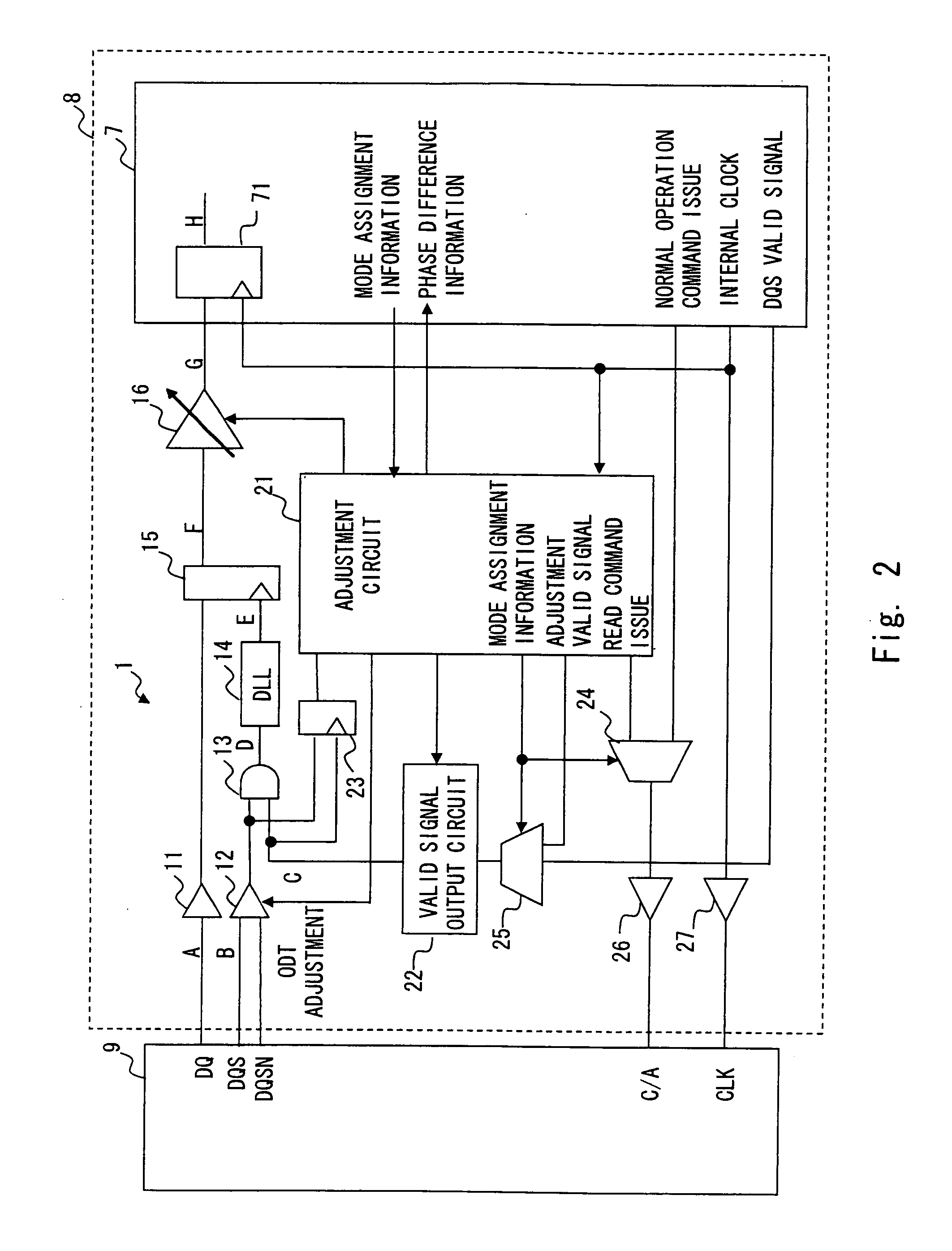

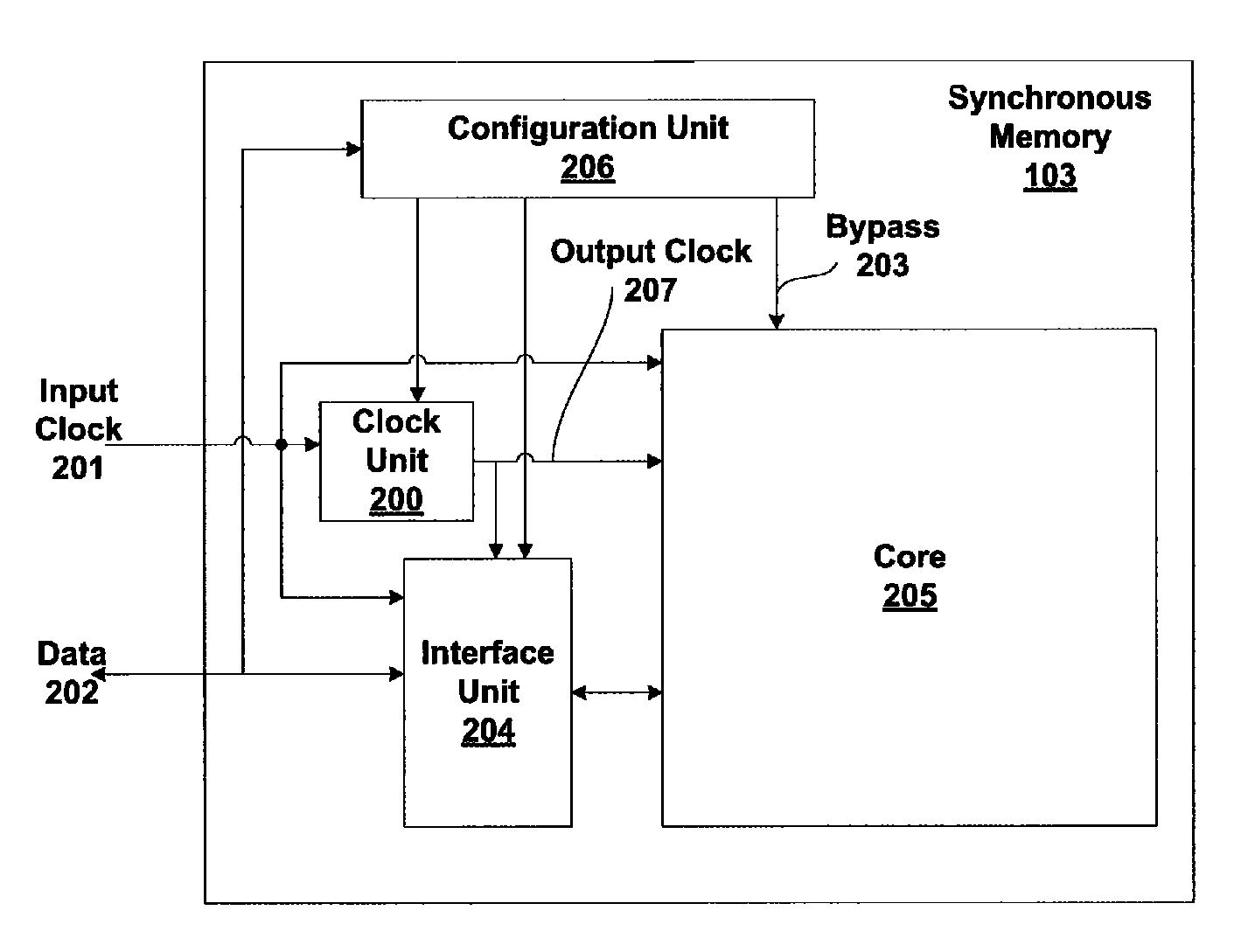

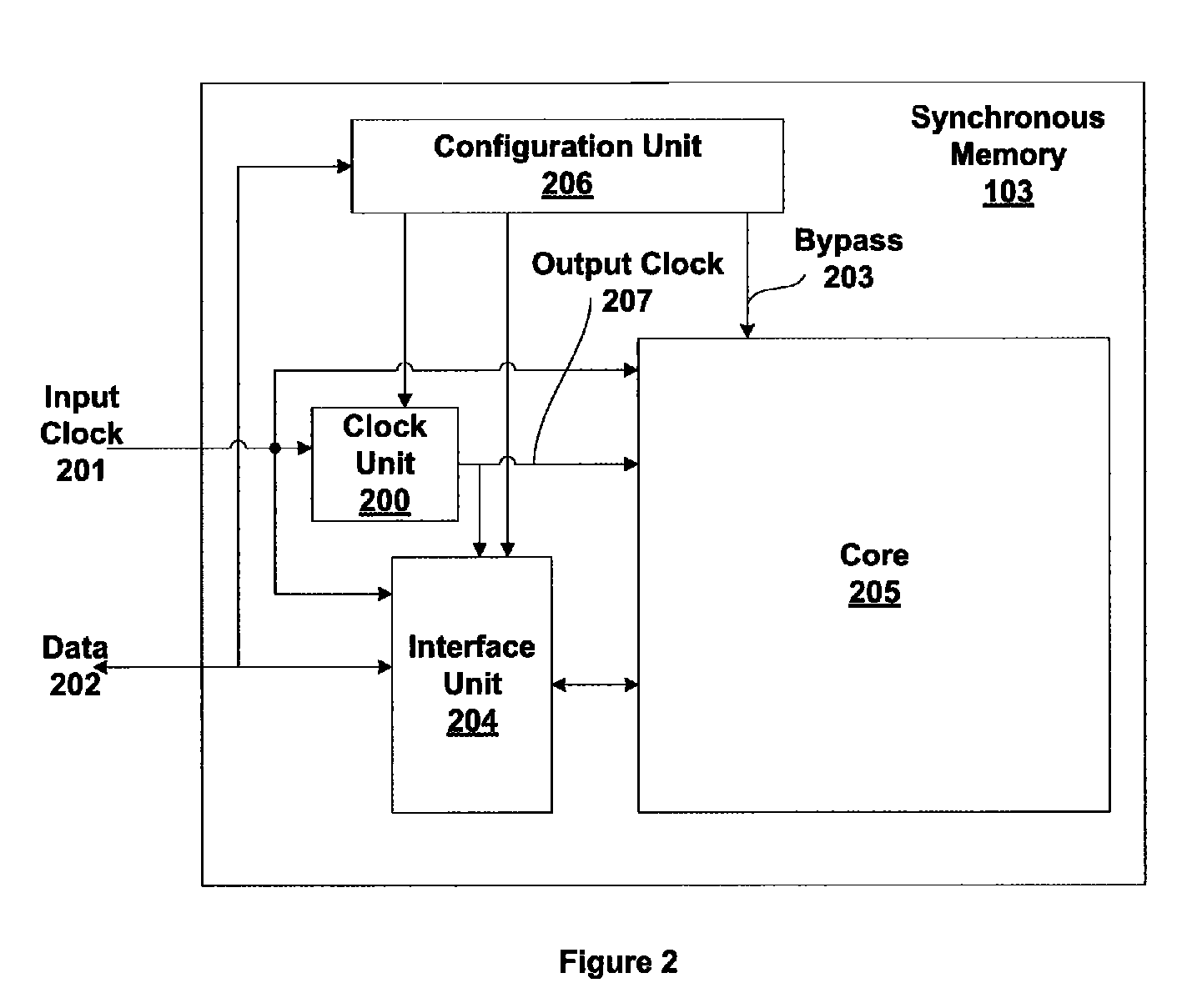

Delay adjustment device, semiconductor device and delay adjustment method

ActiveUS20100124131A1Reduce chip sizeLow costDigital storageGenerating/distributing signalsData retrievalData signal

Provided is a delay adjustment device that contributes to downsizing the circuit that adjusts a flight time. The delay adjustment device is connected to a memory, and adjusts a timing to retrieve data with a data signal and a data strobe signal output from the memory. The delay adjustment device includes a data retrieve unit that receives the data signal and the data strobe signal, and outputs a data value of the data signal in accordance with the data strobe signal; and a control unit that issues a read command to the memory, calculates a flight time, and controls a valid period of the data strobe signal based on the flight time.

Owner:RENESAS ELECTRONICS CORP

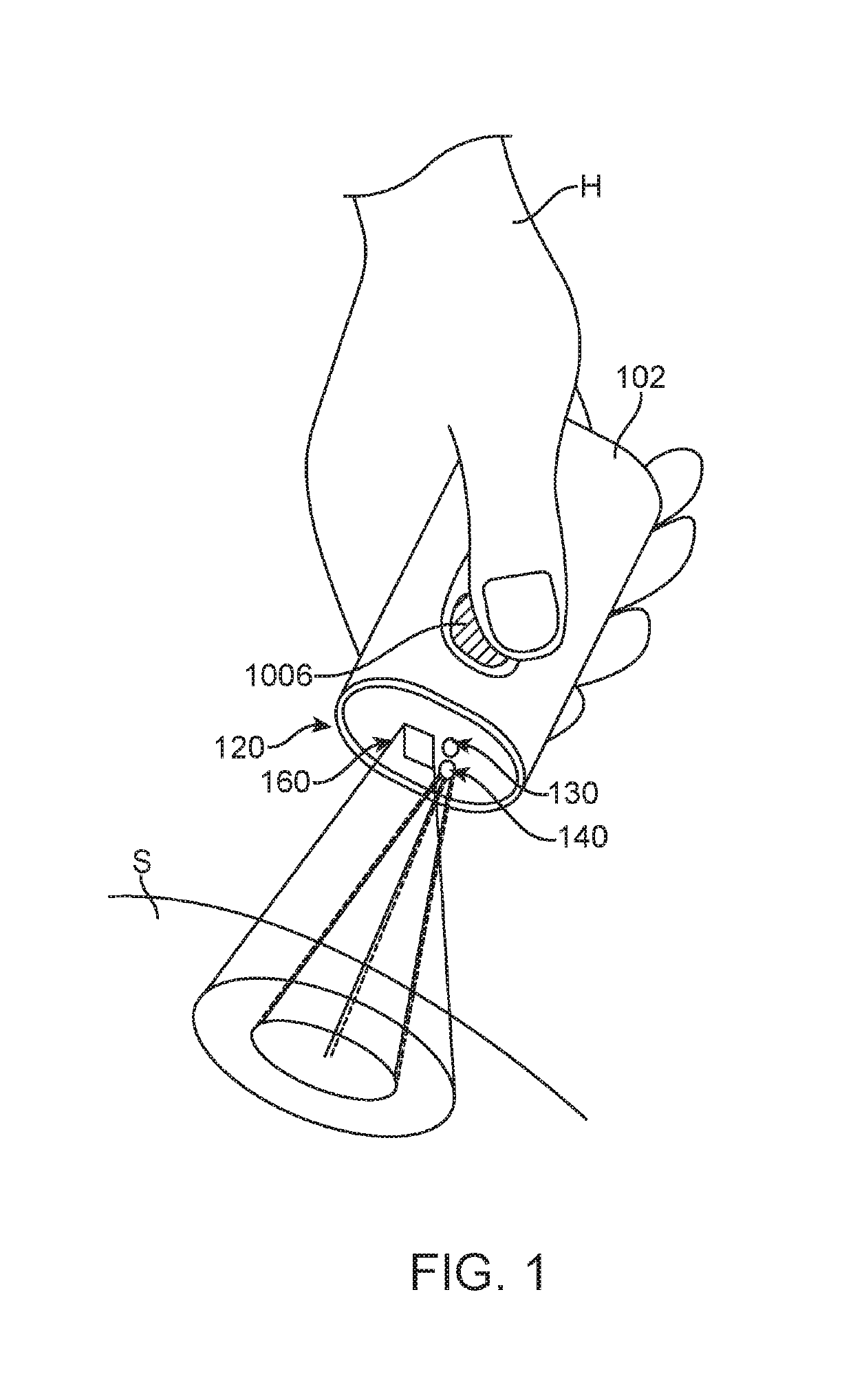

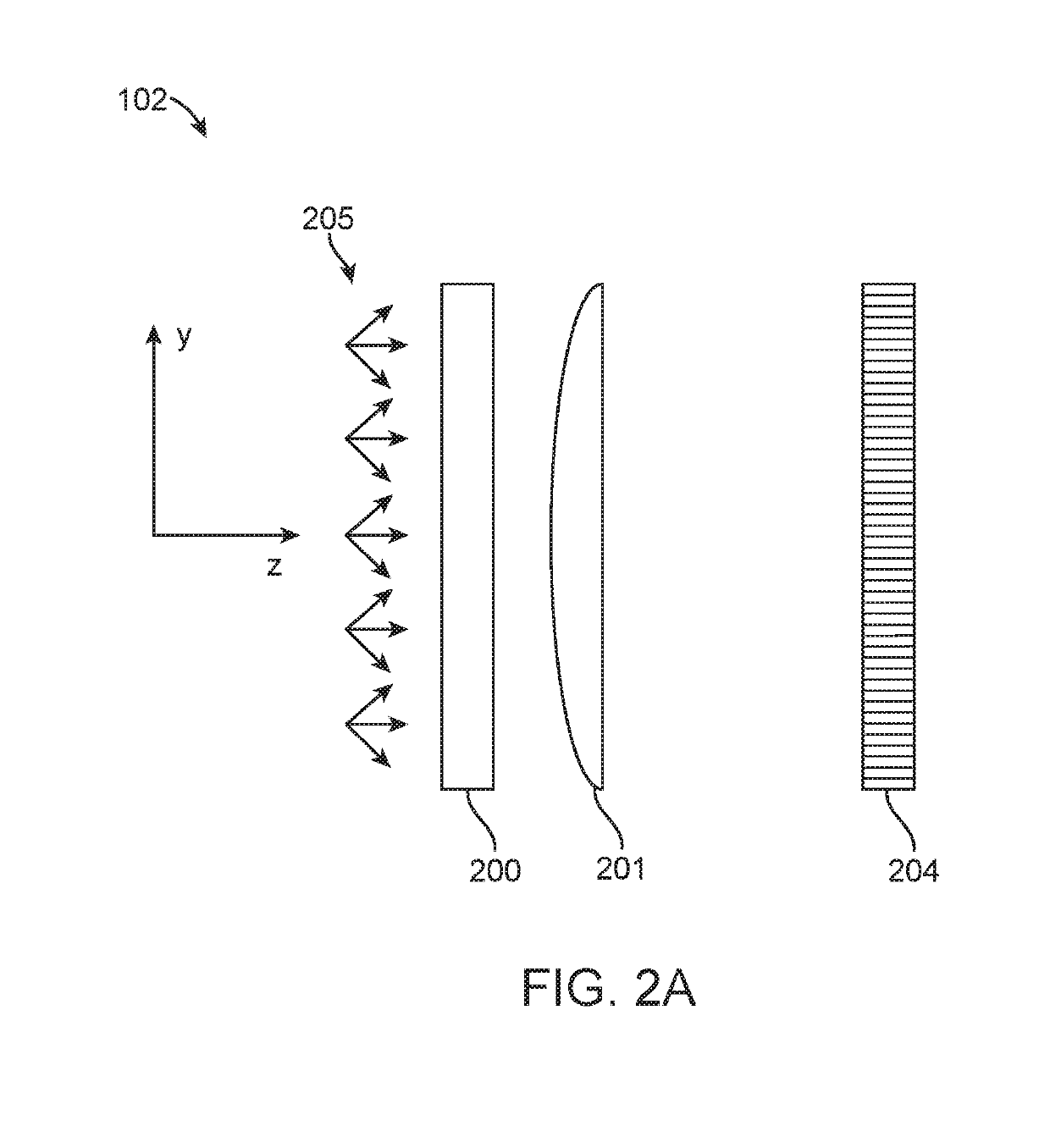

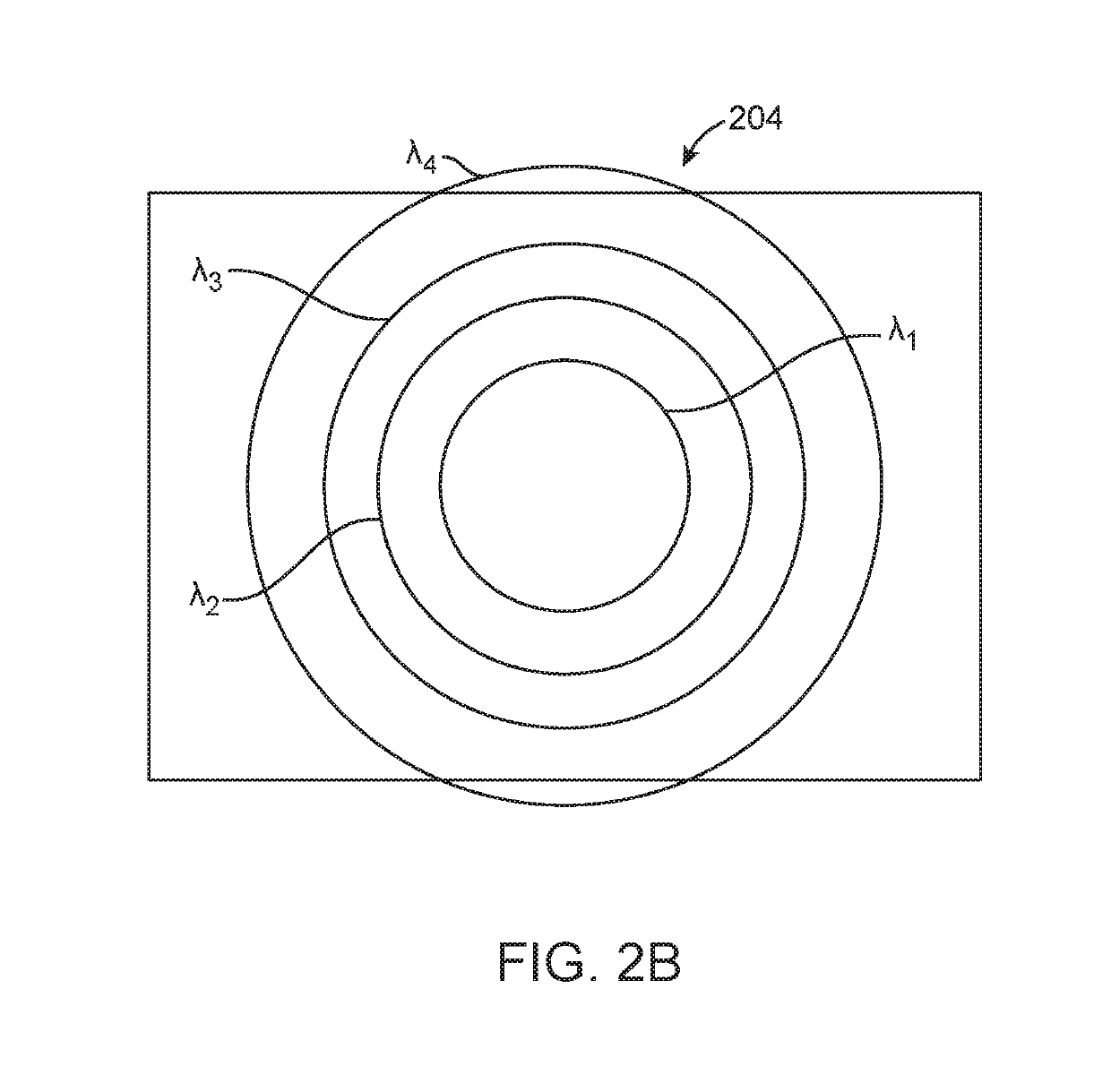

Detector for spectrometry system

ActiveUS10502679B2Decreasing size and weight and complexitySimple and inexpensive to manufactureRadiation pyrometrySpectrum investigationElectricityElectrical connection

A compact spectrometer system comprising an improved detector is provided herein. The spectrometer system herein disclosed can comprises a filter, a Fourier transform optical element, and a detector. The detector can comprise a custom detector having a shape that corresponds to the pattern of light incident on the detector. The custom detector may comprise a plurality of separate detection areas, each area configured to detect a portion of the light pattern incident on the detector. The custom detector may comprise a material capable of detecting wavelengths in the short-wavelength infrared (SWIR) range. The custom detector may be configured to require a relatively low number of electrical connections such that it may be implemented using standard, low-cost electronic packaging techniques. An improved, custom detector as described herein can provide the functionality of a two-dimensional pixel array detector while being relatively simple and inexpensive to manufacture.

Owner:VERIFOOD

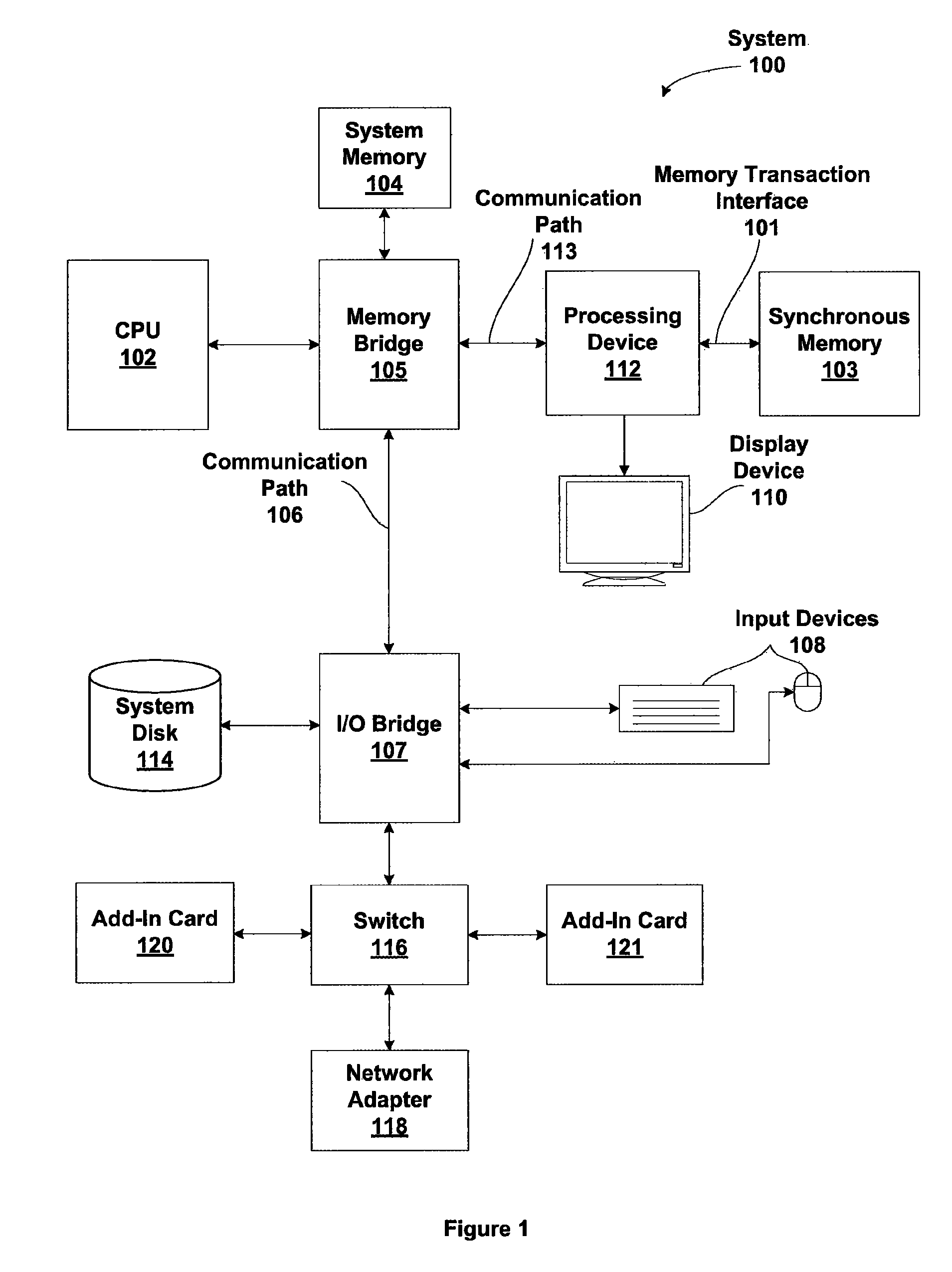

Low latency synchronous memory performance switching using update control

ActiveUS8055871B1Reduce power consumptionImprove performanceEnergy efficient ICTDigital data processing detailsLatency (engineering)Memory performance

A synchronous memory device is configured to switch into and out of a full speed mode to change speed the speed of data transactions without significantly disturbing the frequency of a clock input to a PLL or DLL that provides the internal clock for the synchronous memory device. Since the PLL or DLL receives a clock signal whether or not the synchronous memory device is in a non-full speed mode, the PLL or DLL does not need to settle or relock when the clock signal is reapplied to exit a different speed mode and return to the full speed mode. Therefore, the latency incurred to switch into and out of different speed modes is reduced by eliminating or substantially reducing the time for settling or relocking the PLL or DLL.

Owner:NVIDIA CORP

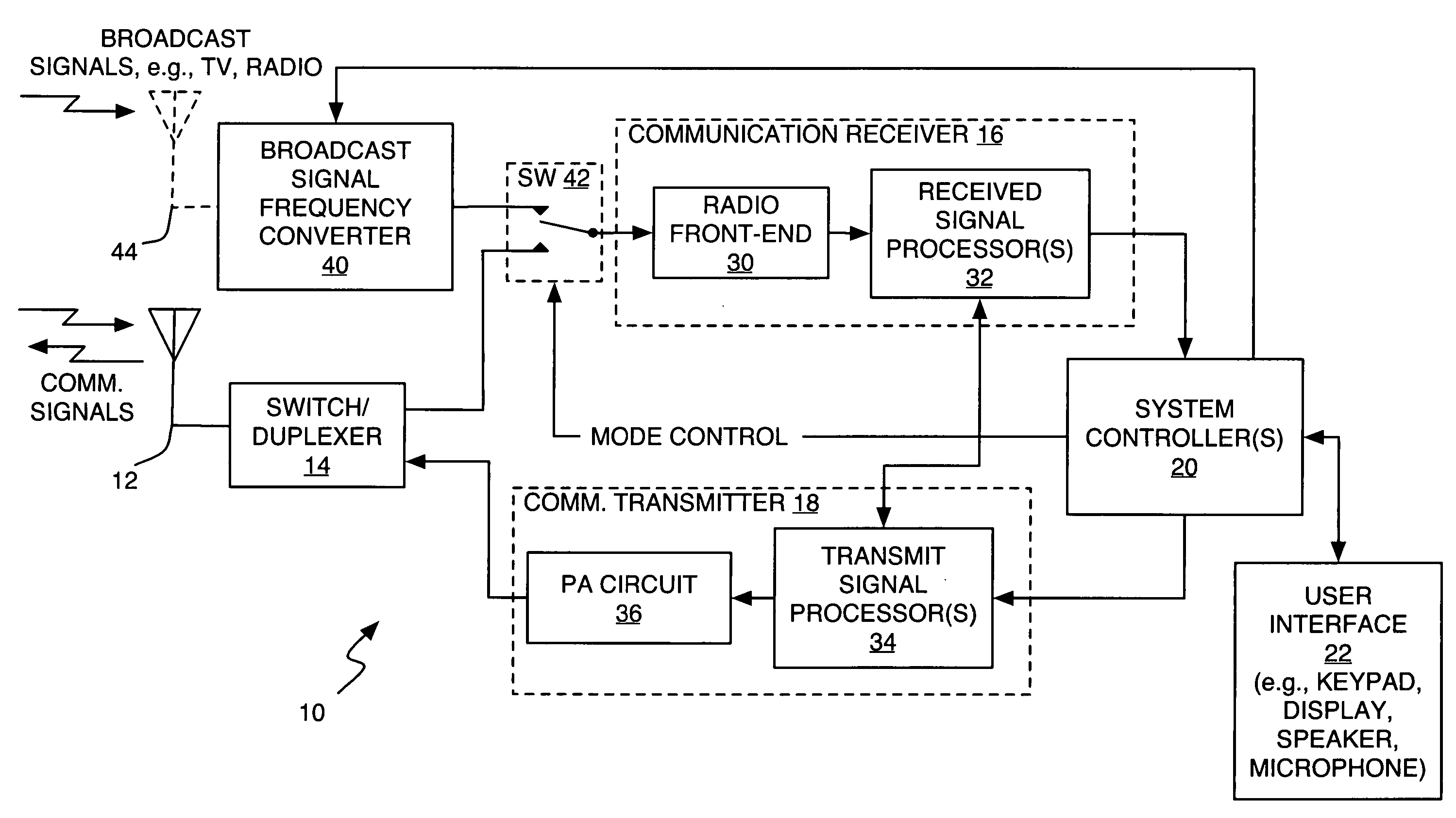

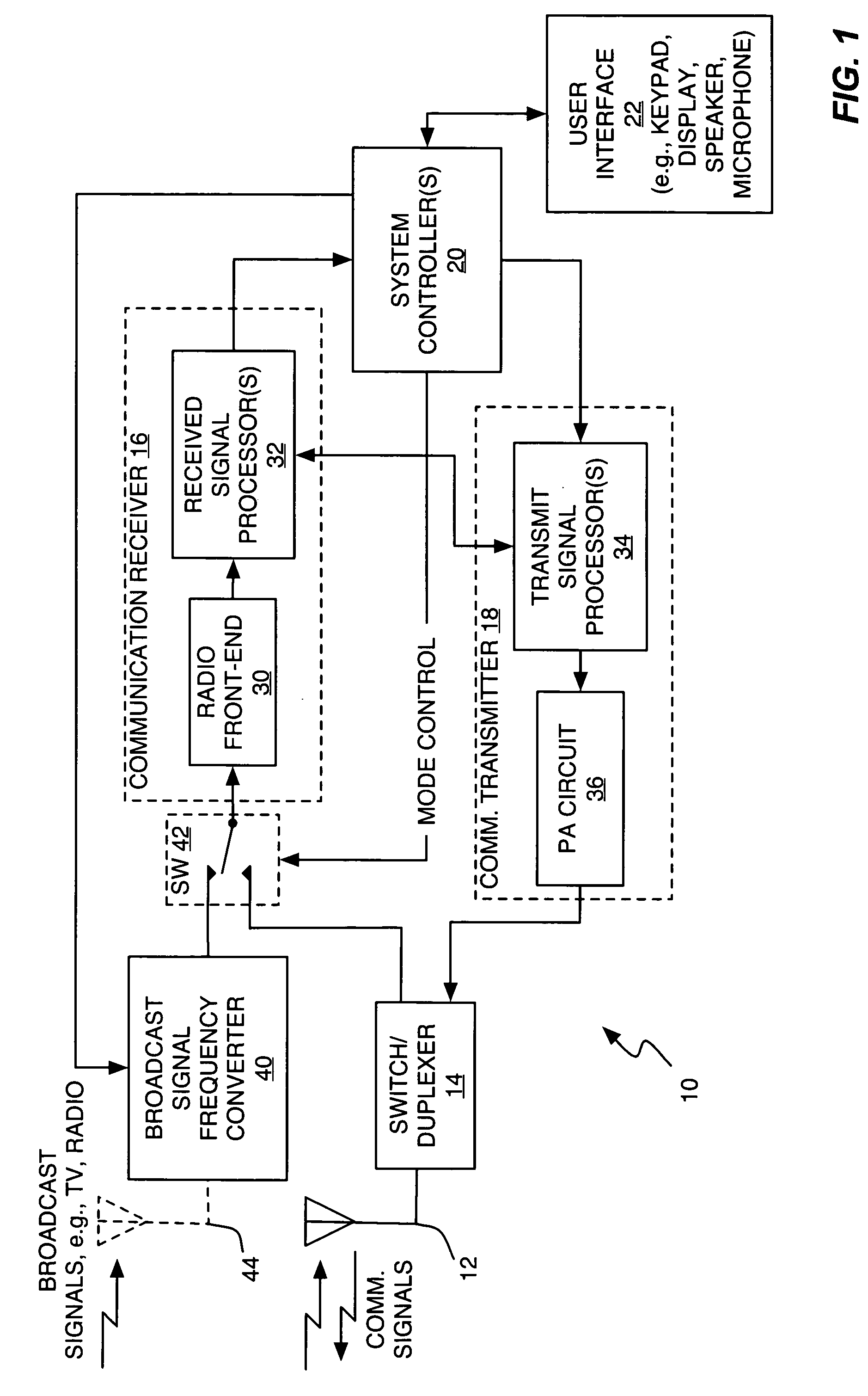

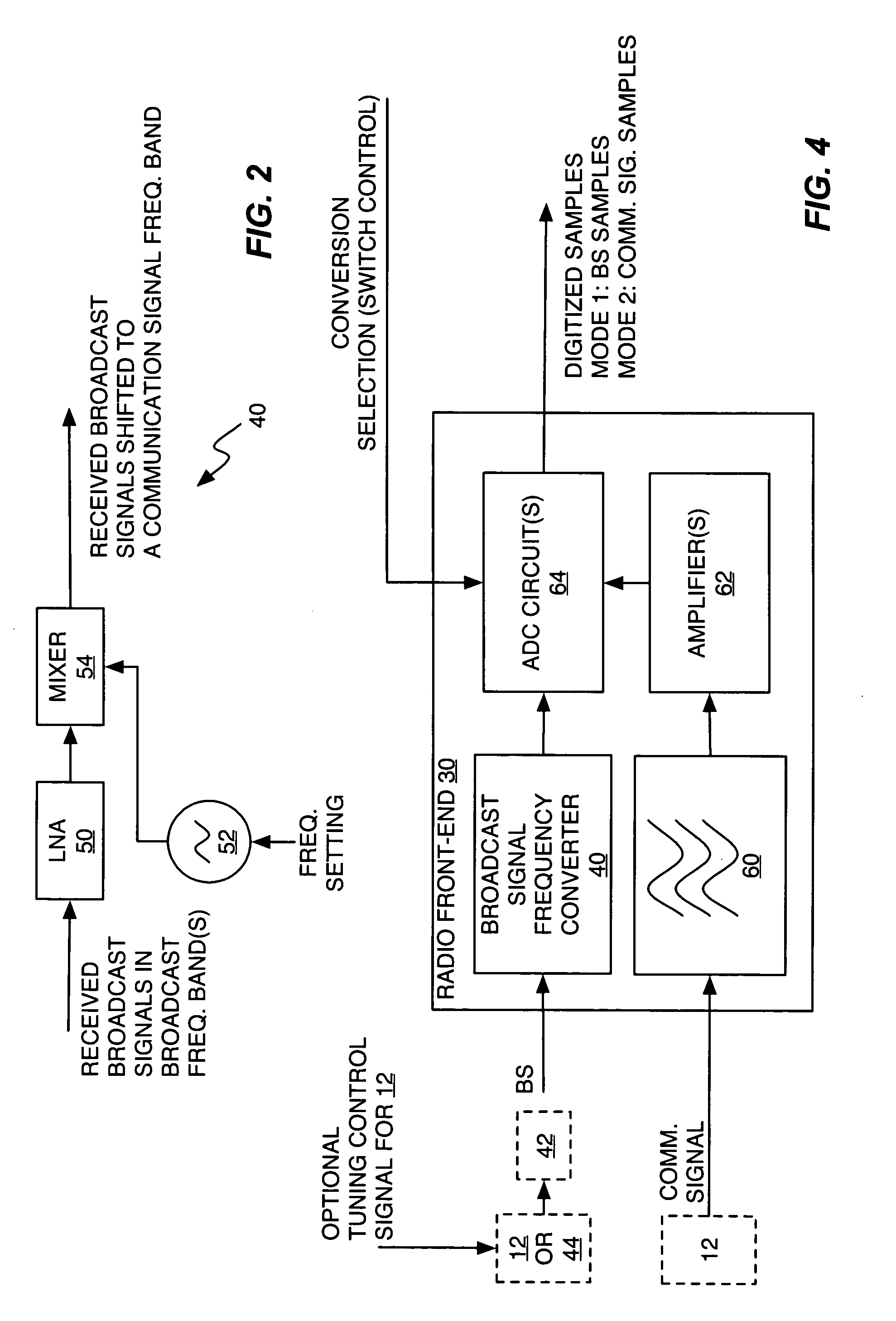

Low cost method for receiving broadcast channels with a cellular terminal

InactiveUS20050233765A1Reduce decreaseQuality improvementSimultaneous amplitude and angle demodulationSubstation equipmentBroadcast channelsFrequency shift

A wireless communication terminal includes a broadcast signal frequency converter that is communicatively coupled to the terminal's communication signal receiver and is configured to use its communication receiver to process received broadcast signals. In an exemplary embodiment, the converter includes a frequency shifting circuit, e.g., a block frequency converter, that shifts broadcast signal bands into communication signal bands, such that received broadcast signals are shifted into a frequency range compatible with the communication receiver's signal path. Moreover, the significant digital domain signal processing capability of the communication receiver can be used to receive broadcast television and / or radio signals, provide signal enhancements, and extract other types of information such as RDBS, IBOC, etc. Further, the terminal can be configured to maintain communication network monitoring while receiving broadcast signals by switching the receiver back to a communication network signal long enough to check for pages, etc.

Owner:SONY ERICSSON MOBILE COMM AB

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com