Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Reduce body effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

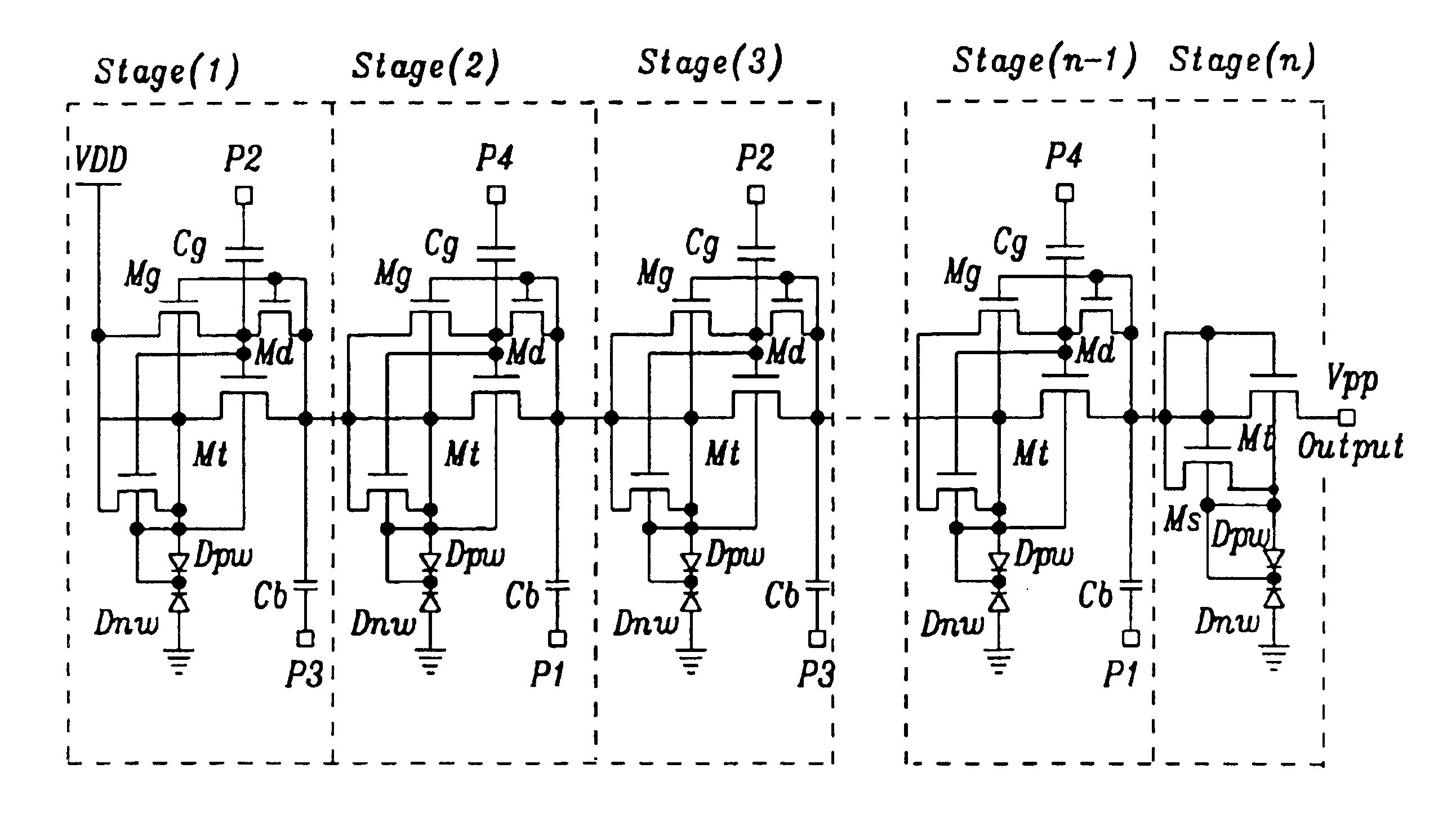

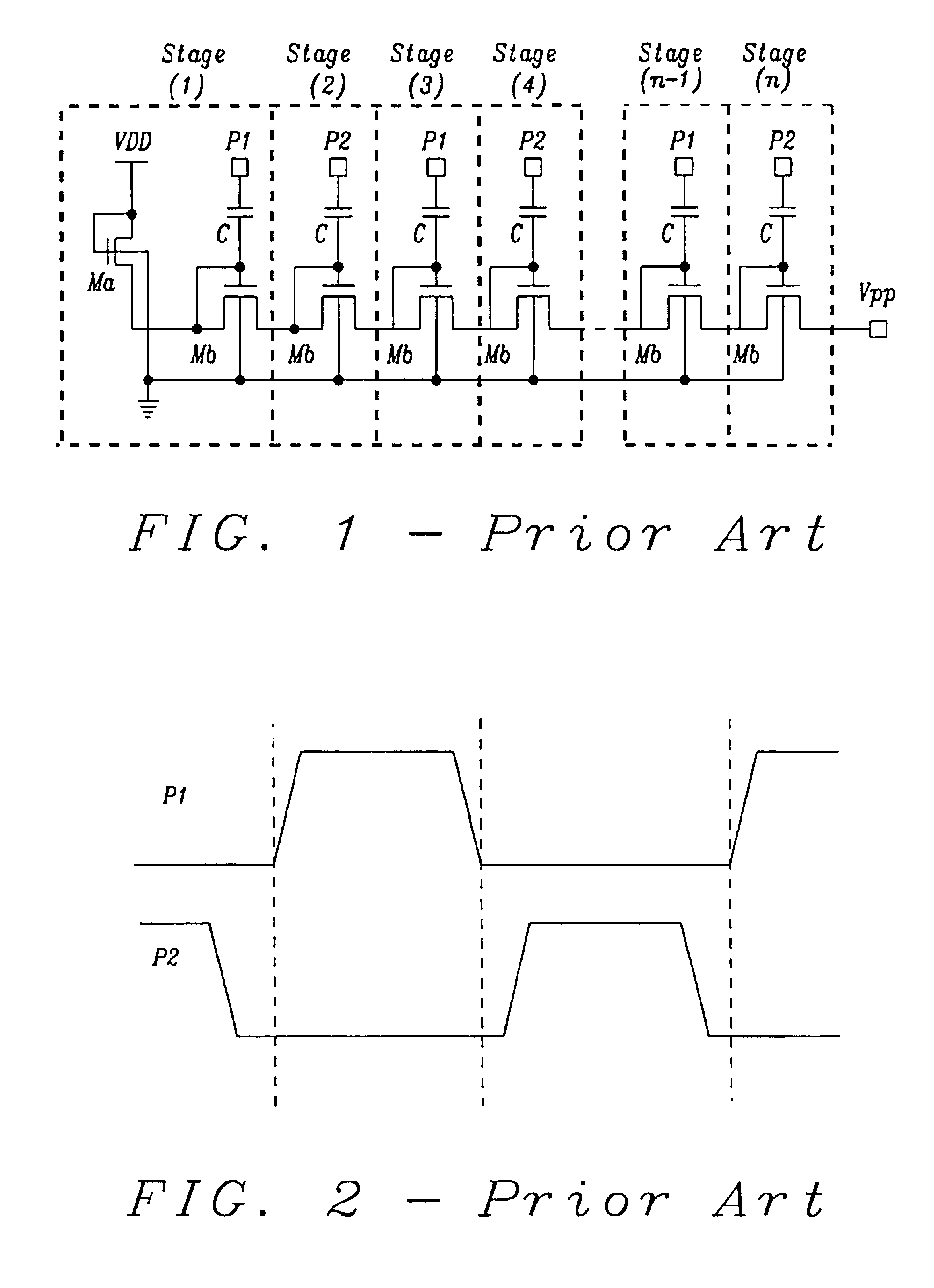

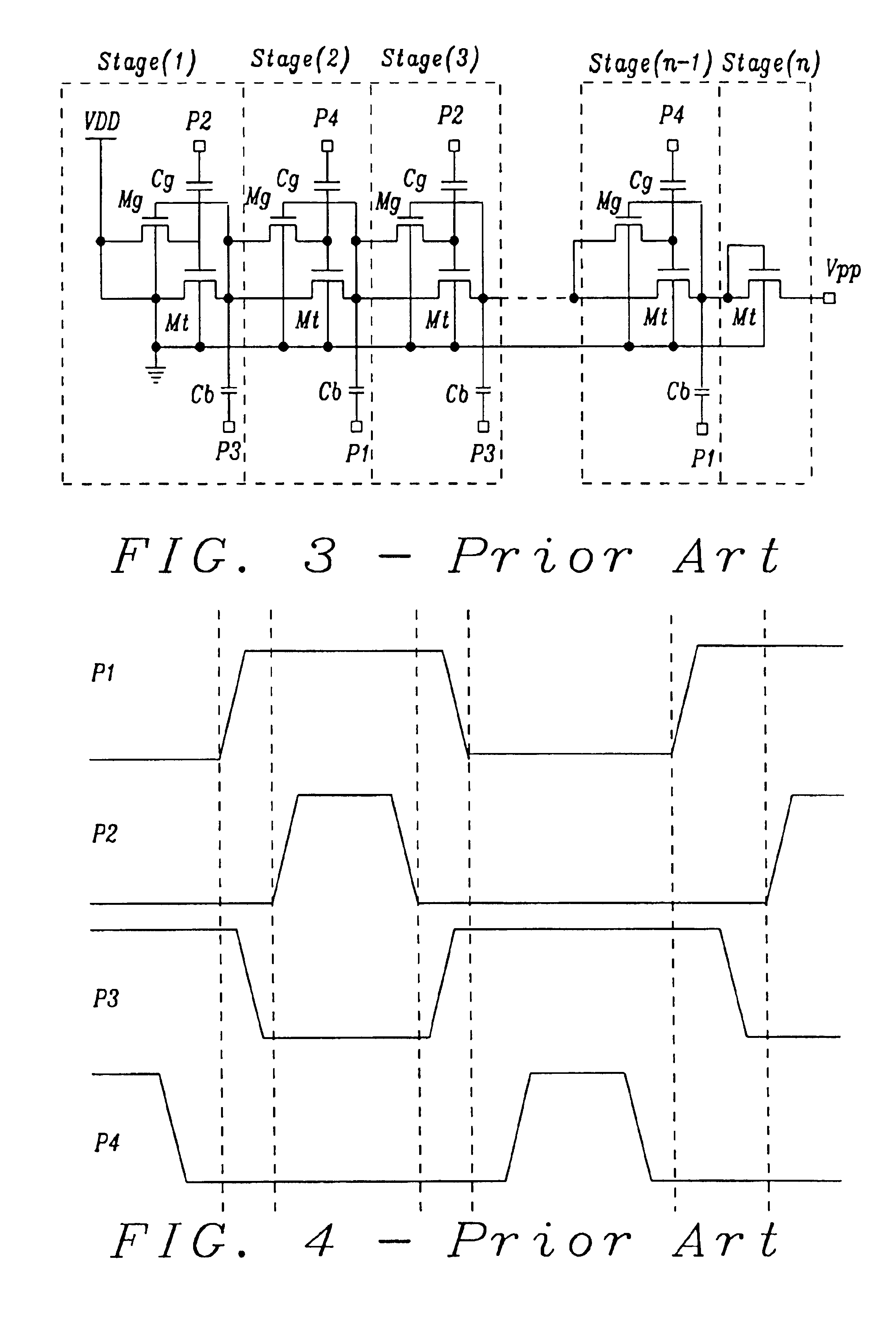

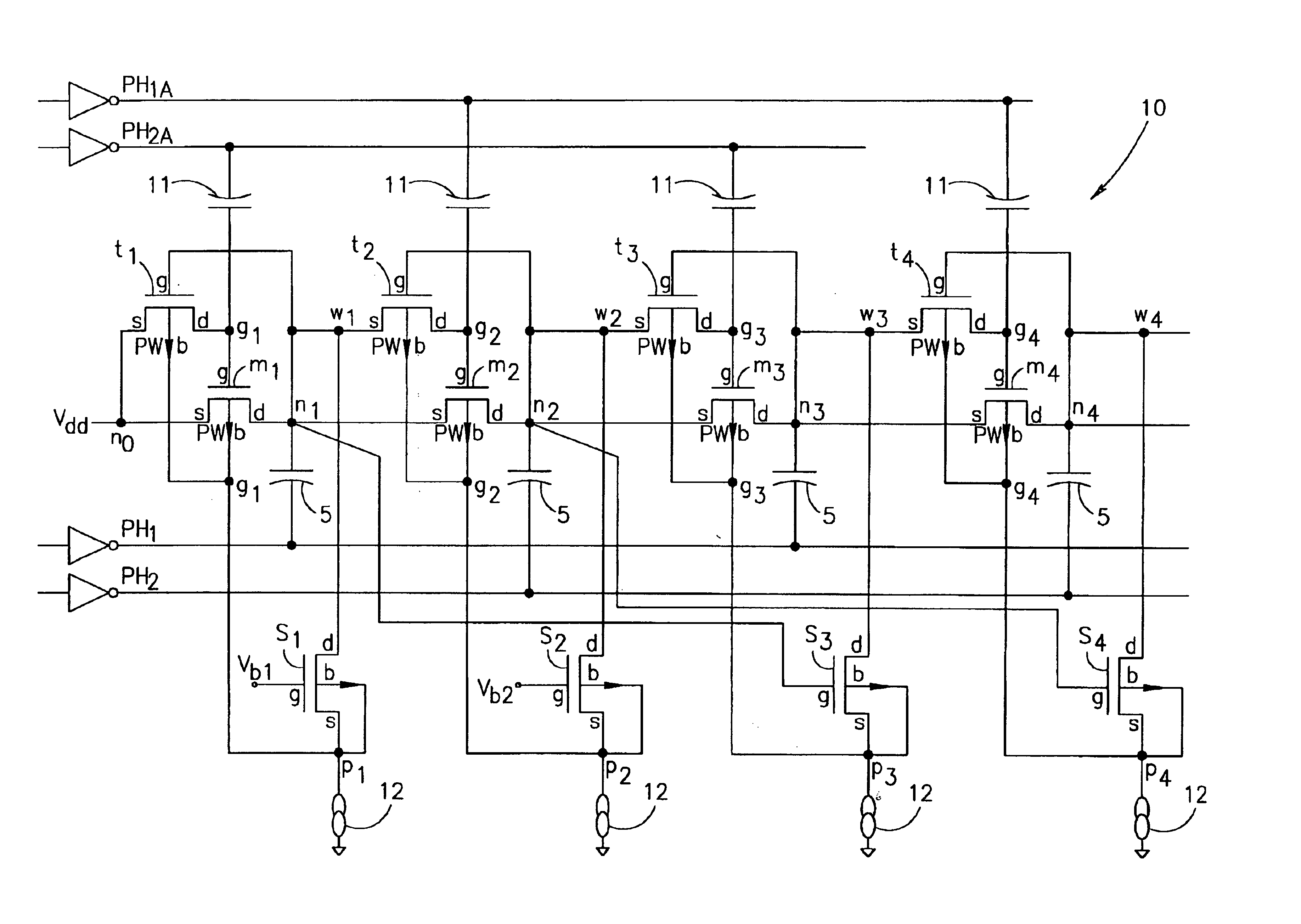

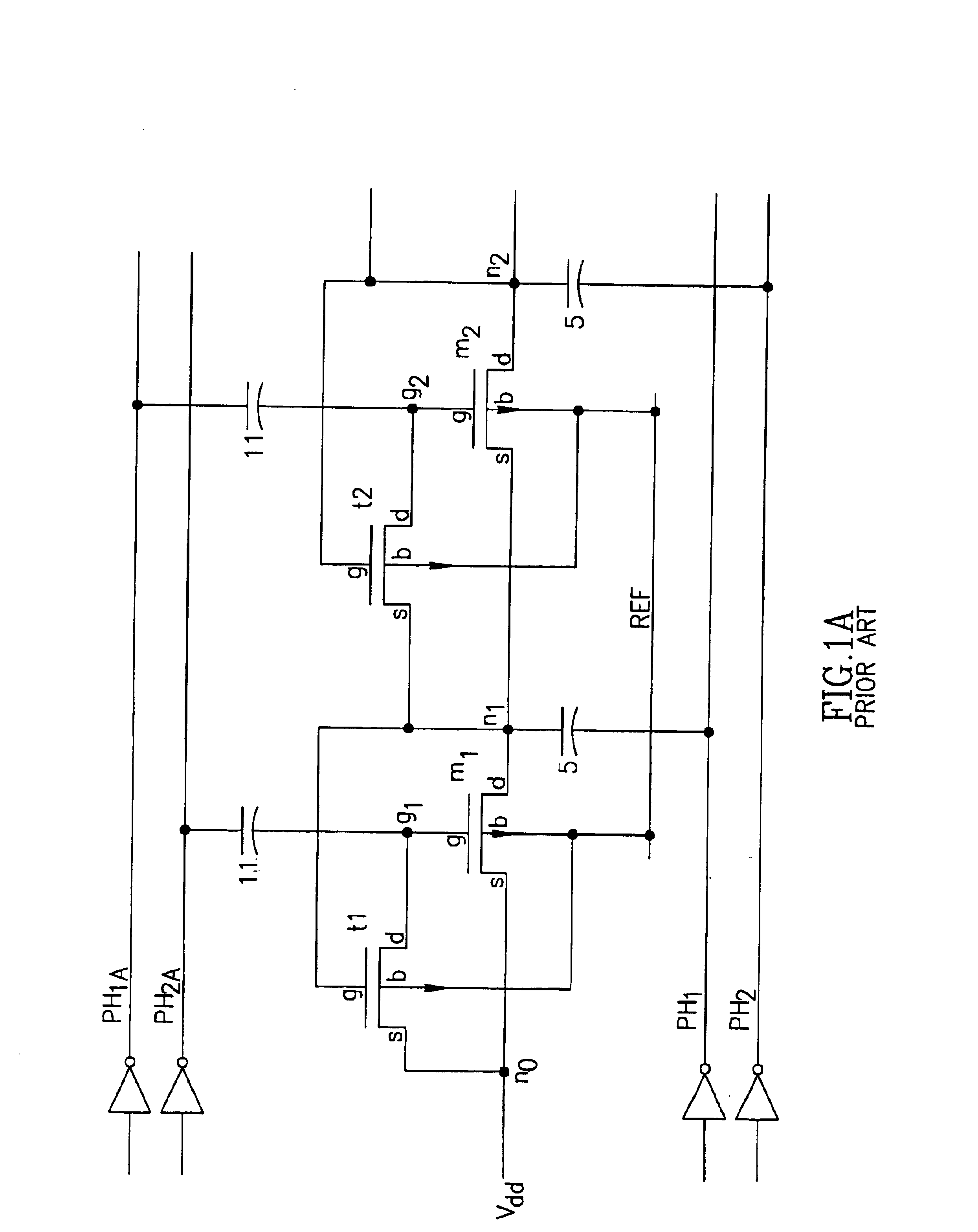

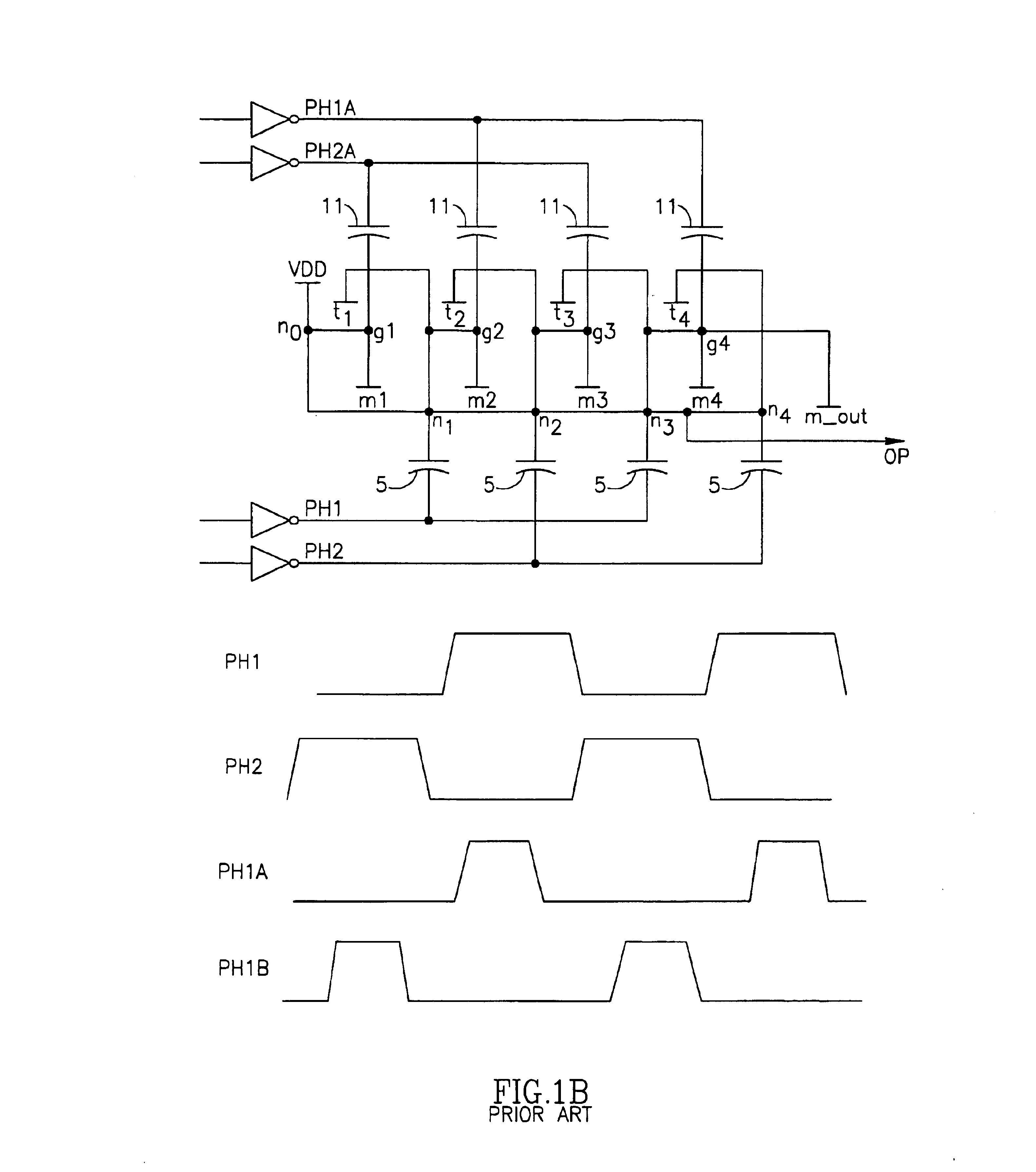

High efficiency triple well charge pump circuit

InactiveUS6914791B1Reduce body effectIncreases boost coupling effectAc-dc conversionApparatus without intermediate ac conversionCapacitanceMOSFET

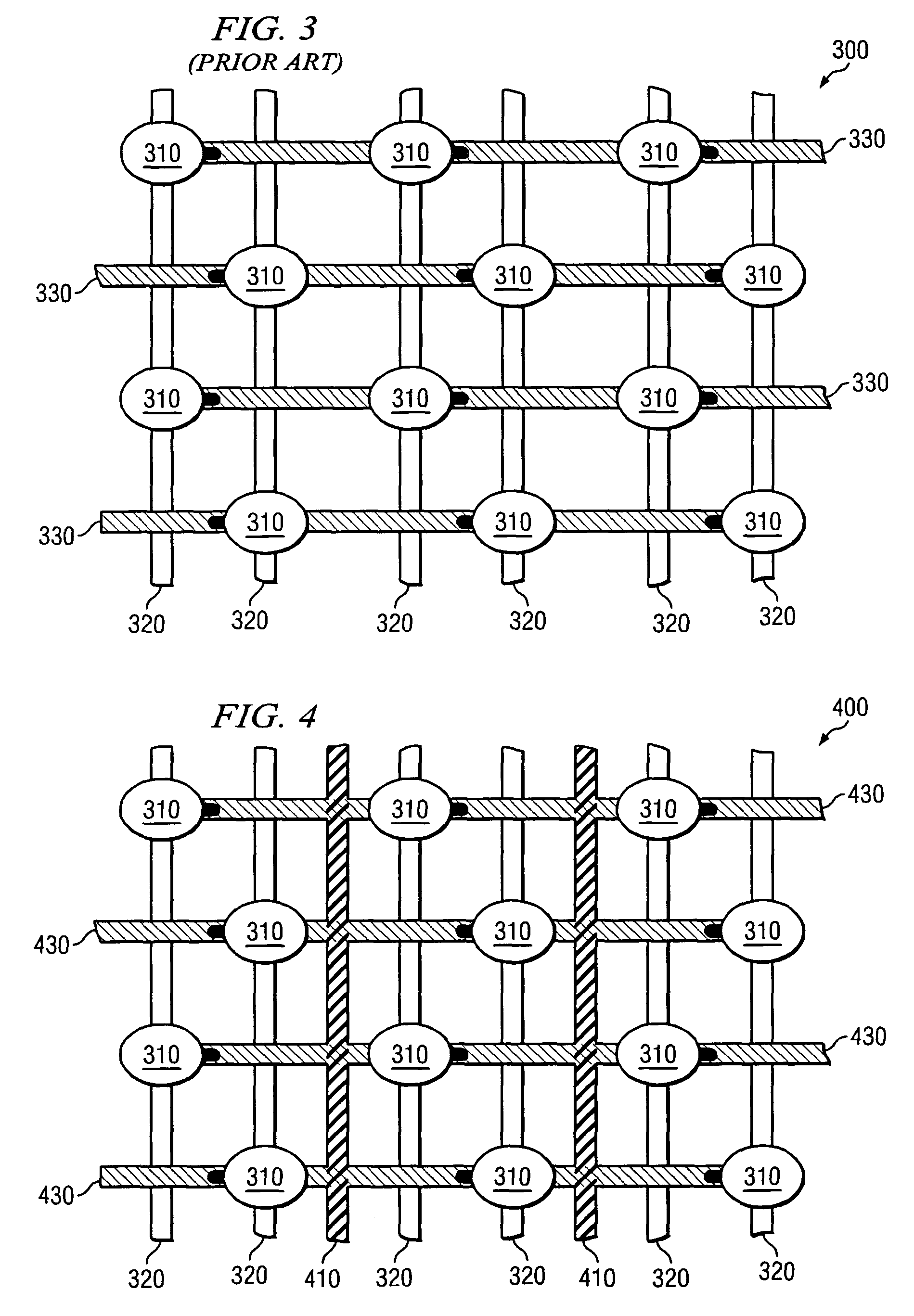

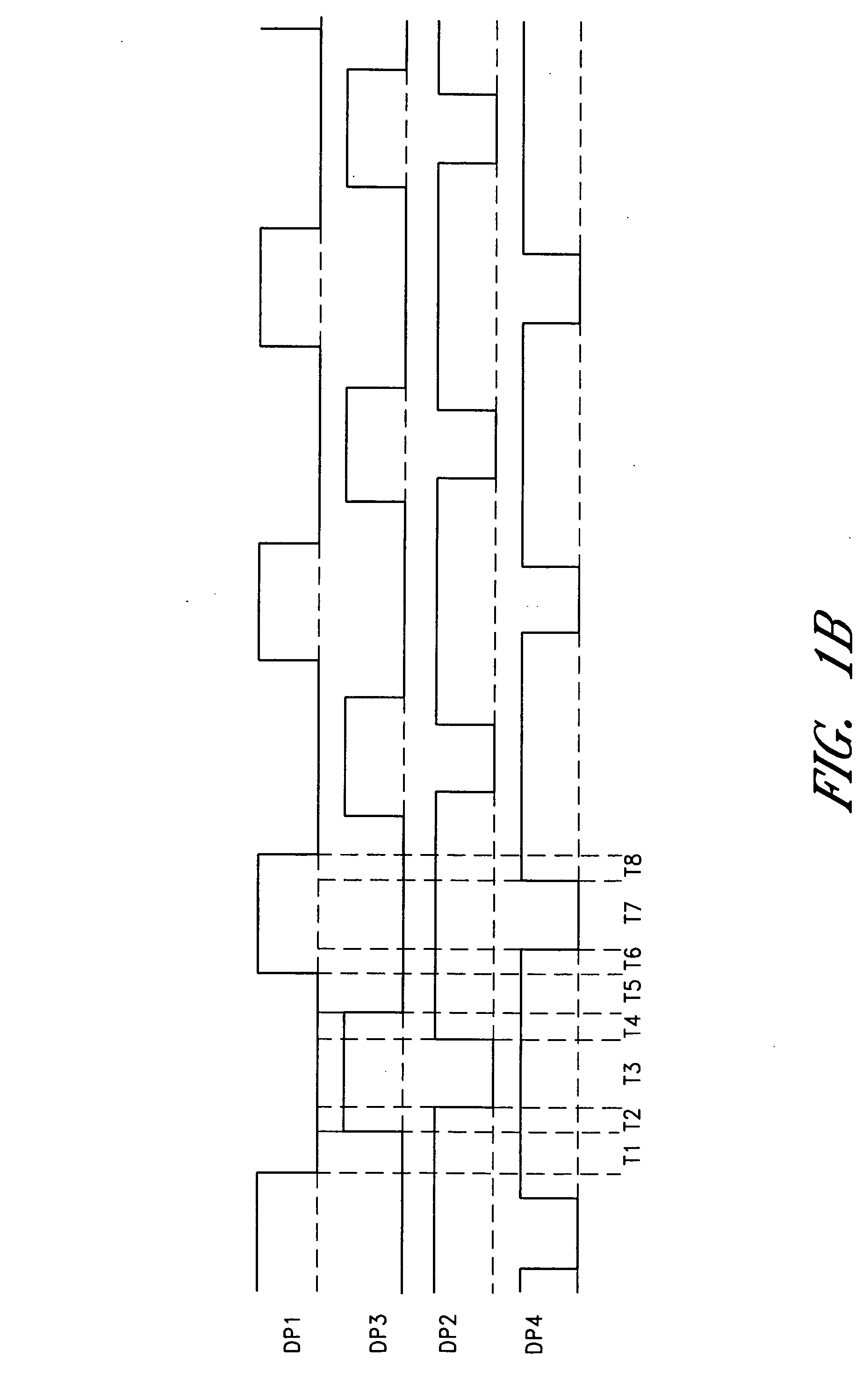

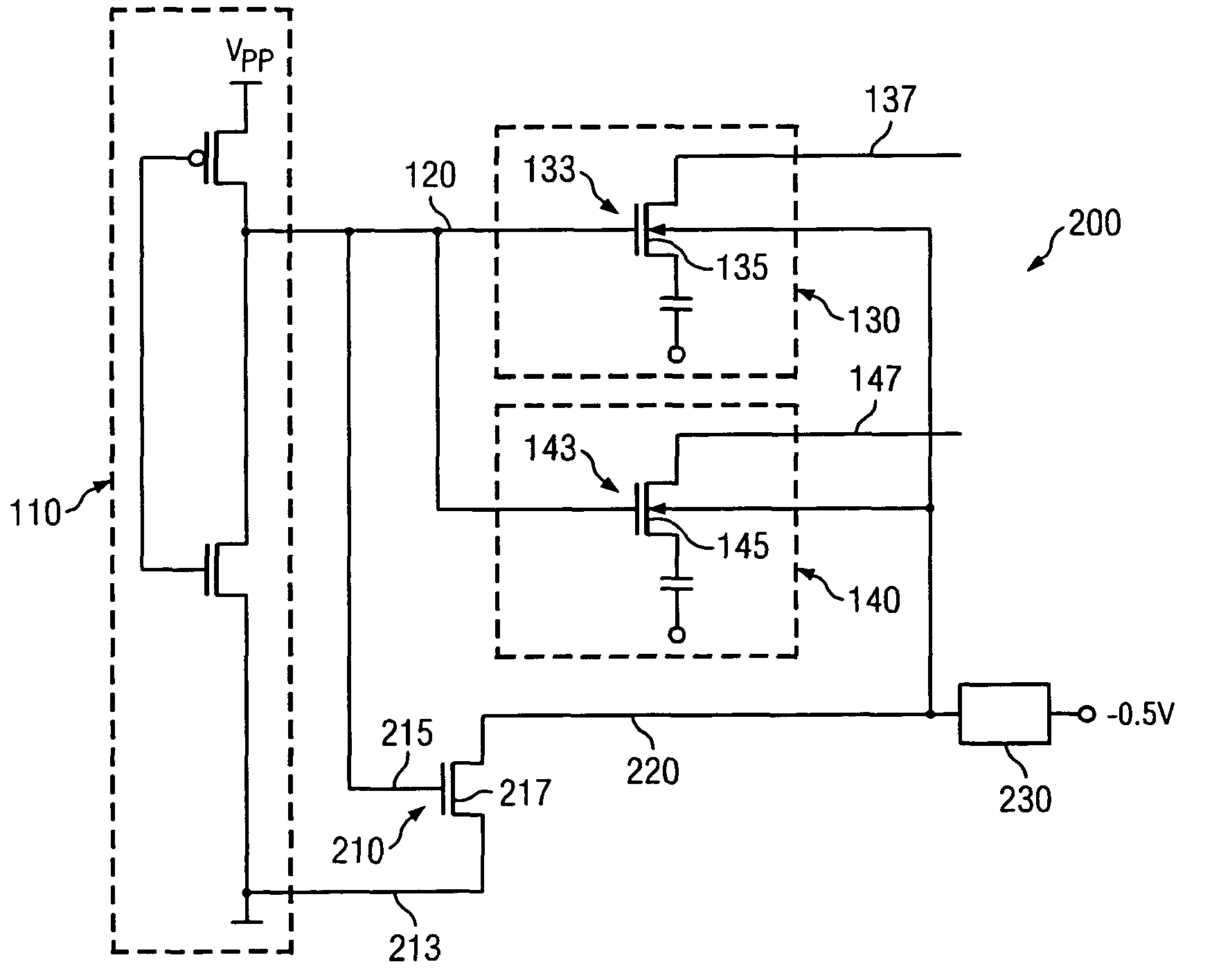

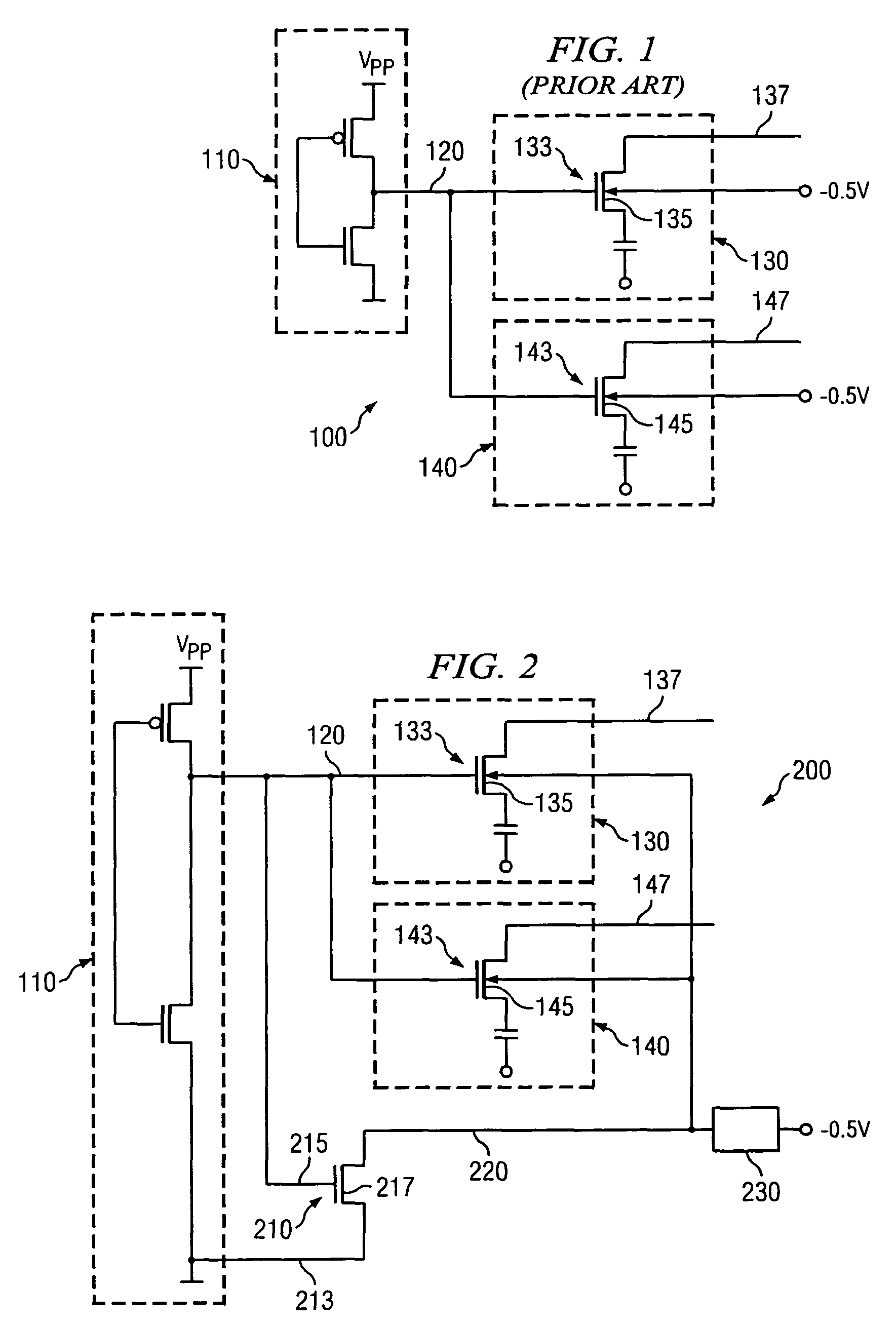

An improved charge pump circuit is provided using a triple-well structure where the charge pump circuit has a plurality of stages containing N-channel MOSFET devices in which each stage is contained in a P-well within a Deep N-well residing on a P-substrate. Each pump stage is formed in its own P-well and the pumping stages are serially connected from power supply source to the output terminal. Each pumping stage includes a charge transfer device, a first auxiliary device to precharge the gate of the charge transfer device with a voltage from the previous stage, and a second auxiliary device to switch coupling between the charge transfer device and its substrate region to reduce the body effect and increases the capacitive boosting effect. The multiple stages of circuitry are clocked from either a four-phase clock or a two-phase clock.

Owner:HALO LSI INC

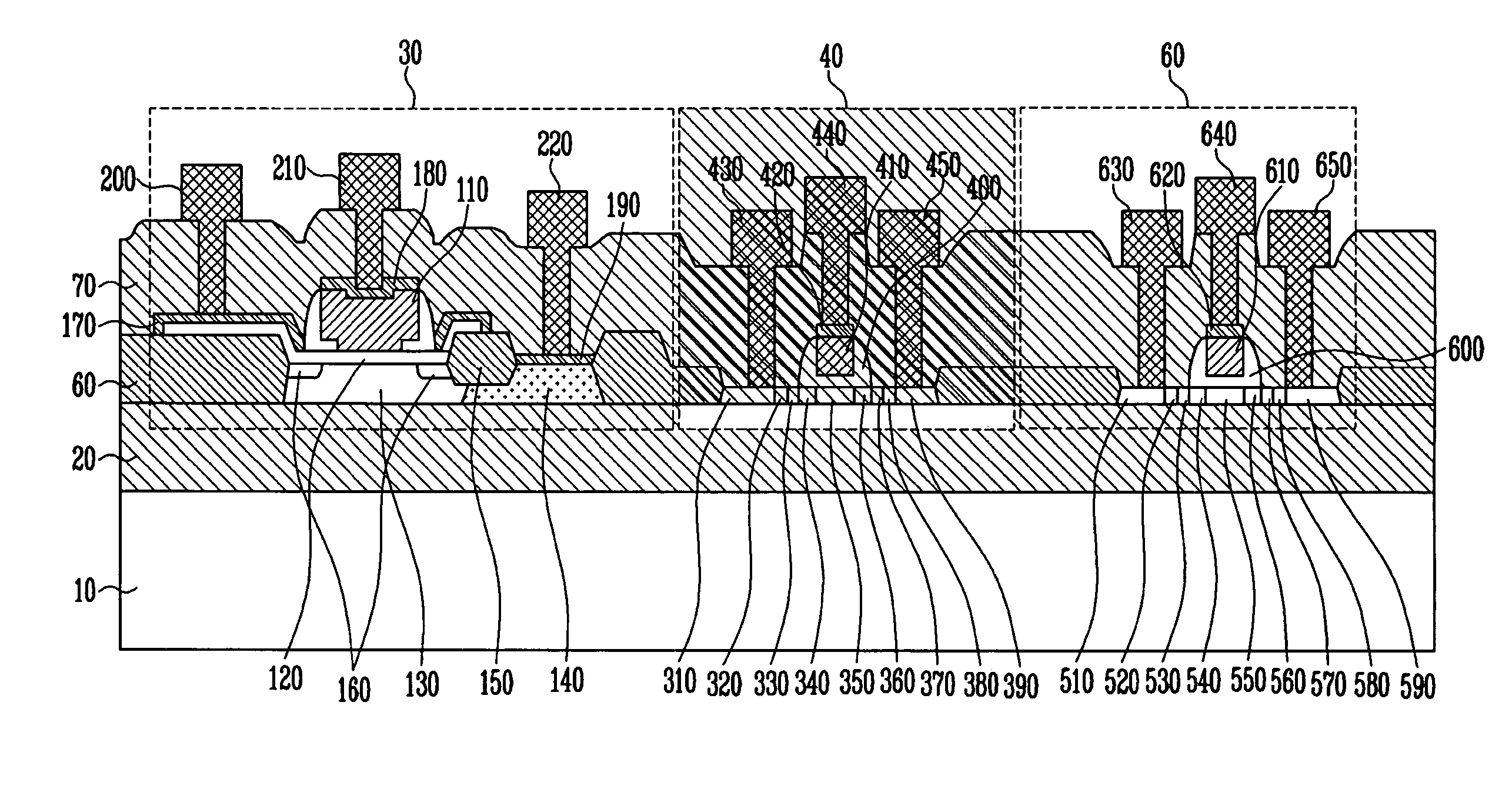

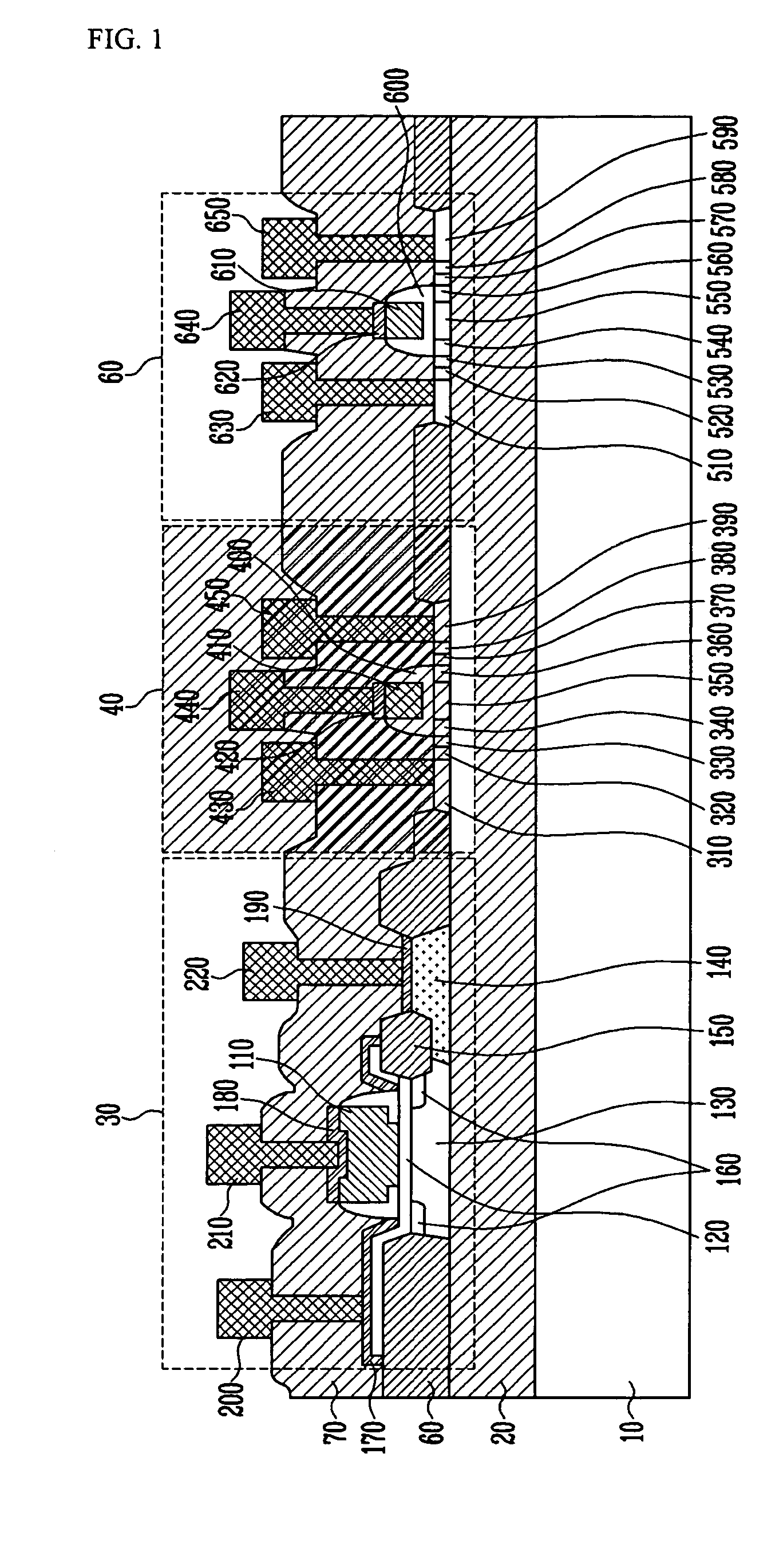

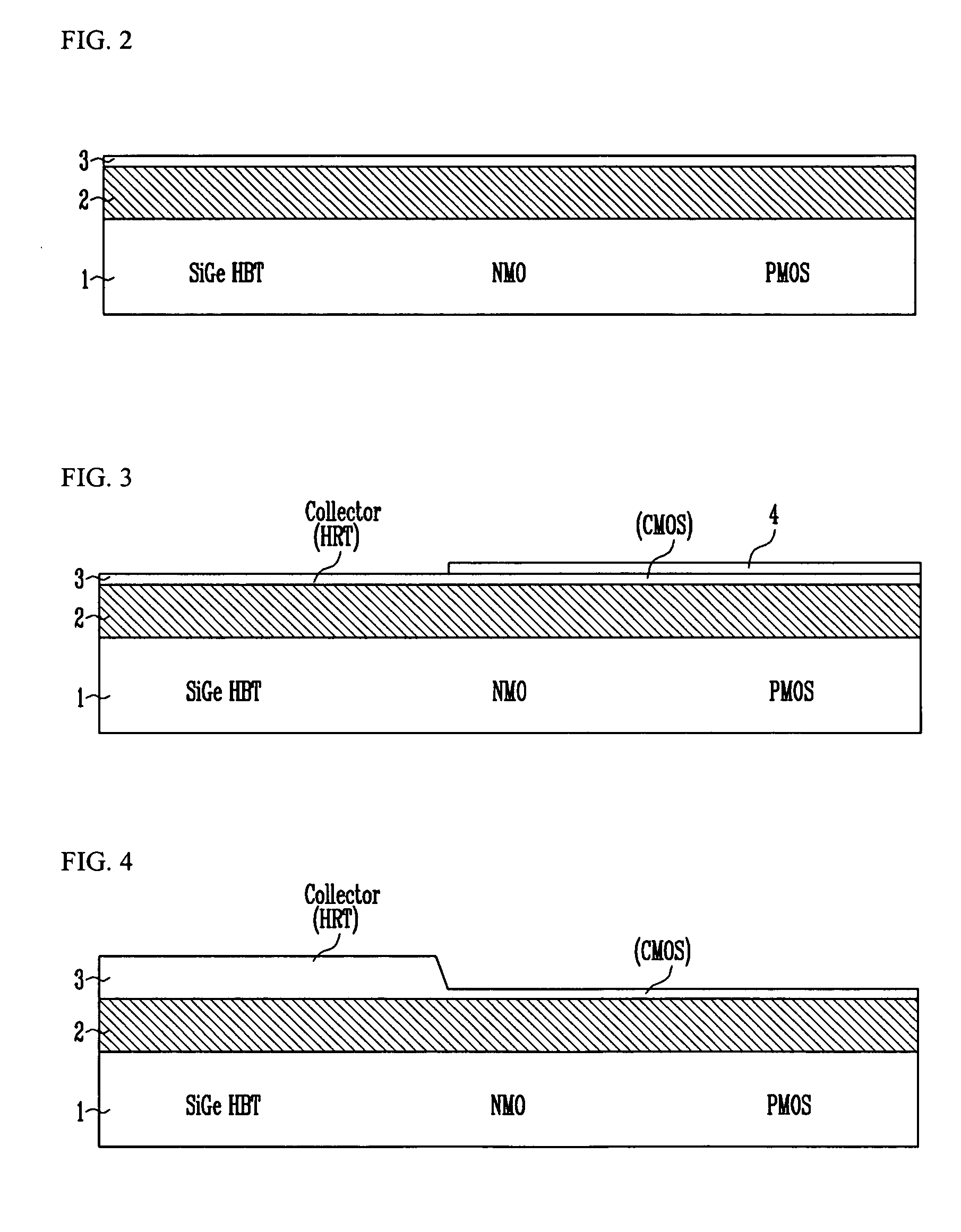

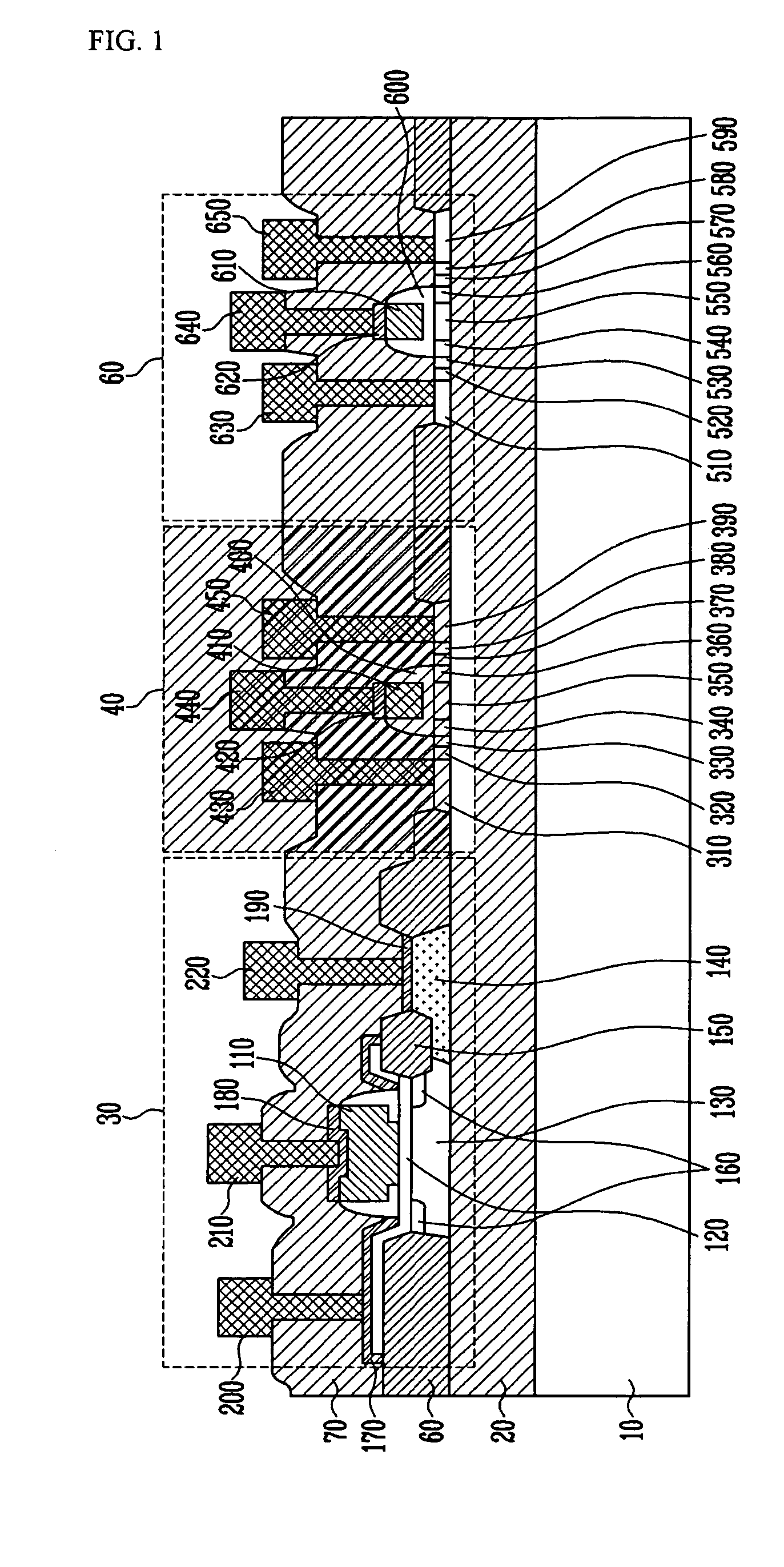

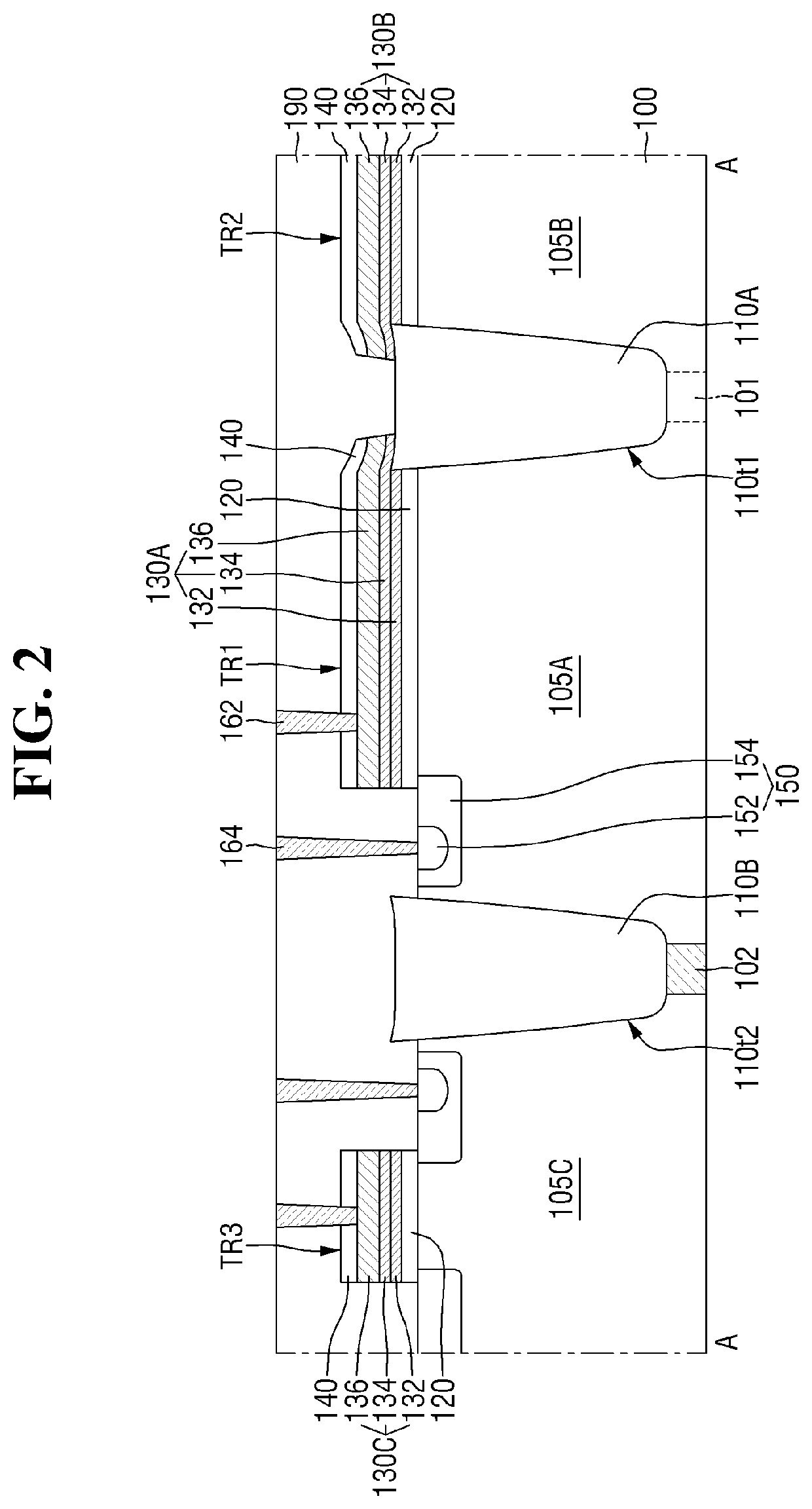

NMOS device, PMOS device, and SiGe HBT device formed on SOI substrate and method of fabricating the same

Provided are an NMOS device, a PMOS device and a SiGe HBT device which are implemented on an SOI substrate and a method of fabricating the same. In manufacturing a Si-based high speed device, a SiGe HBT and a CMOS are mounted on a single SOI substrate. In particular, a source and a drain of the CMOS are formed of SiGe and metal, and thus leakage current is prevented and low power consumption is achieved. Also, heat generation in a chip is suppressed, and a wide operation range may be obtained even at a low voltage.

Owner:ELECTRONICS & TELECOMM RES INST

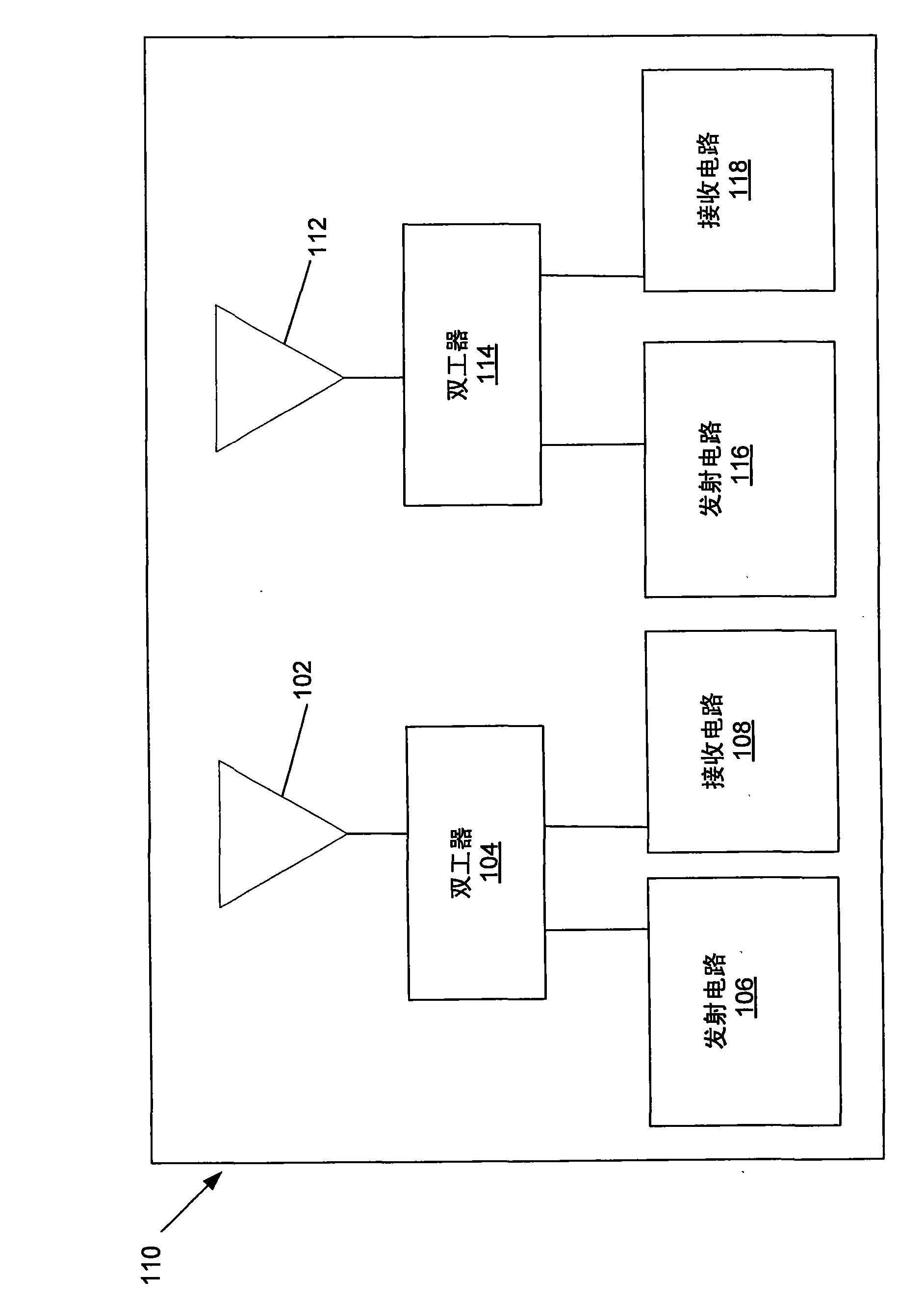

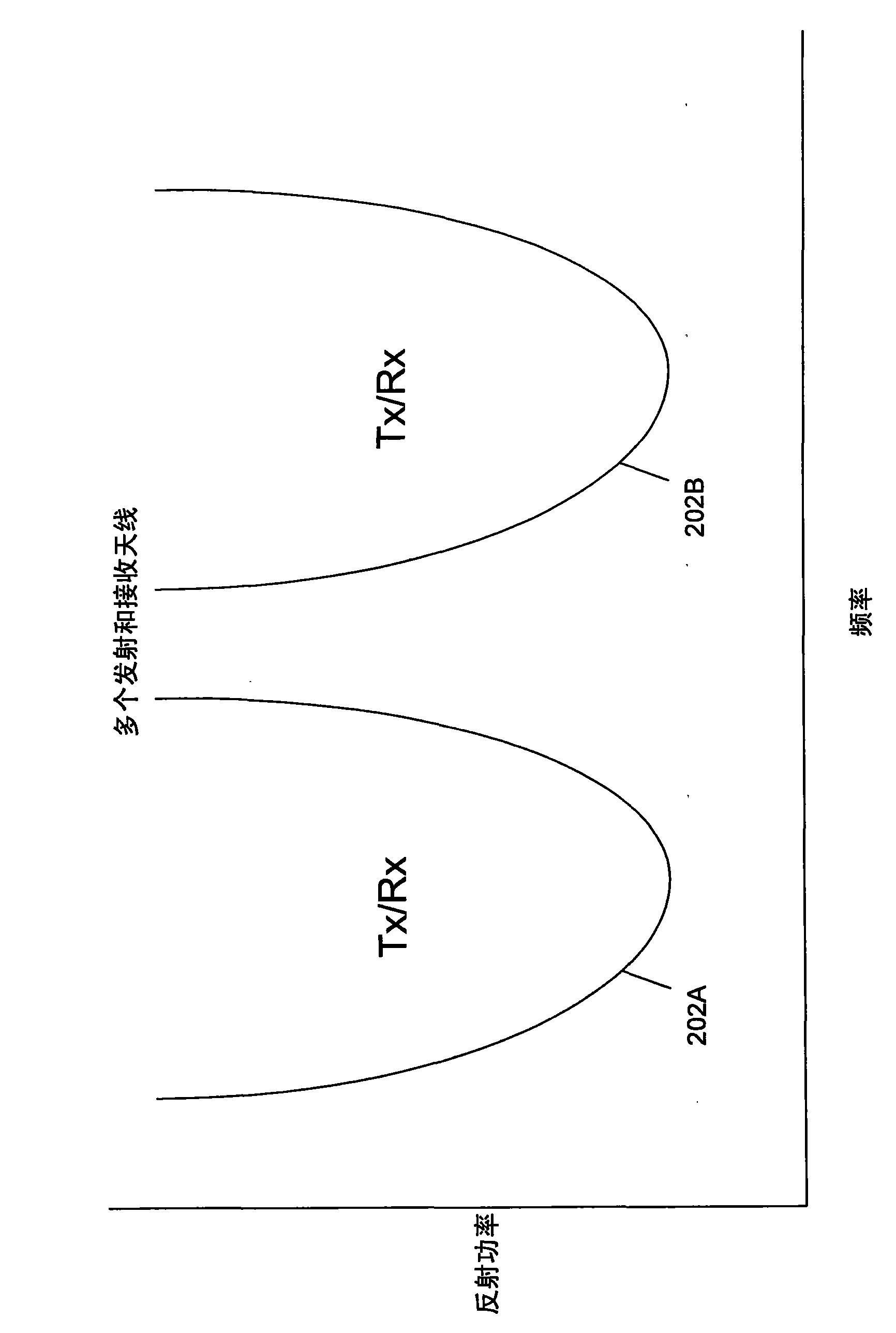

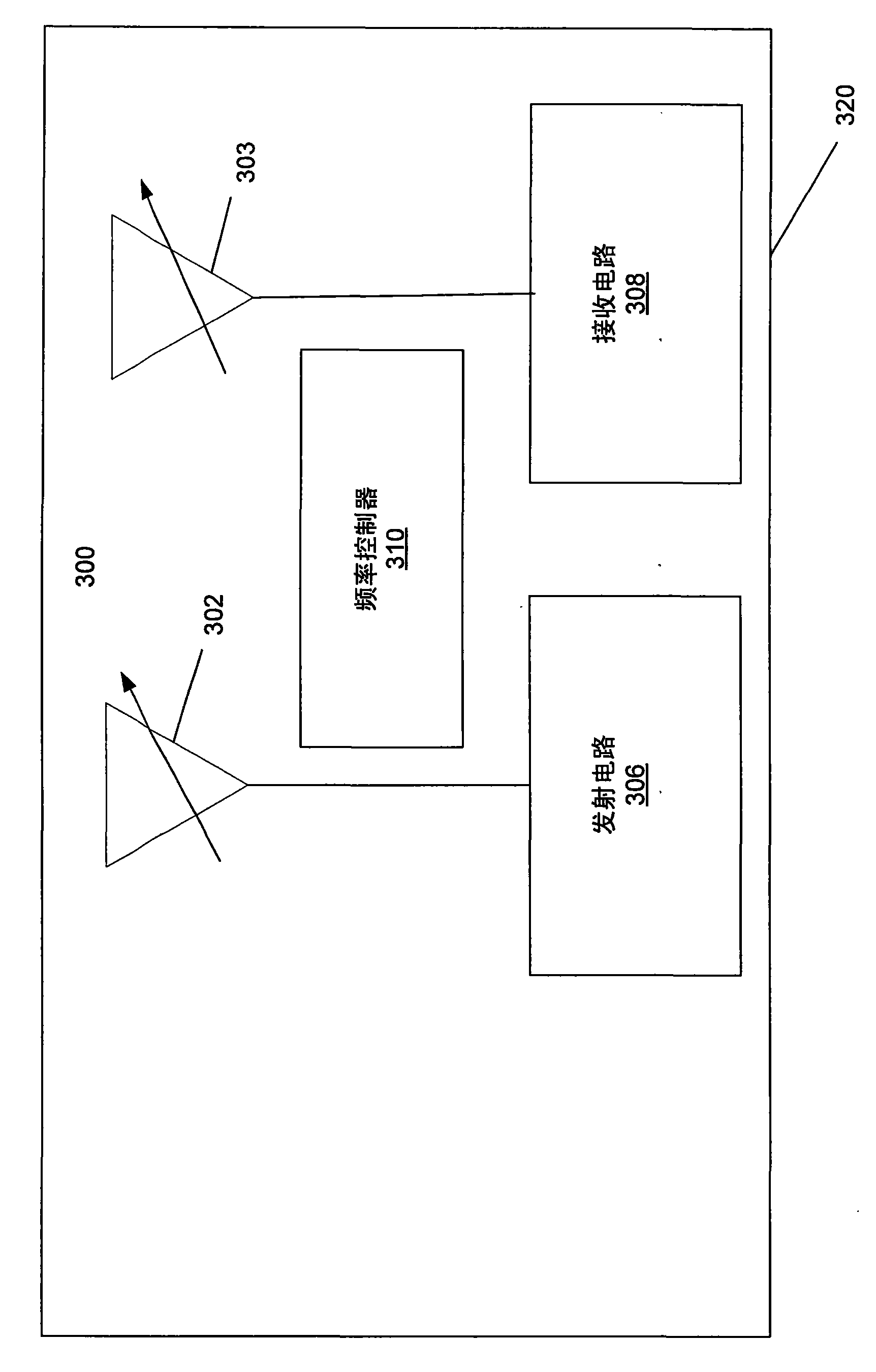

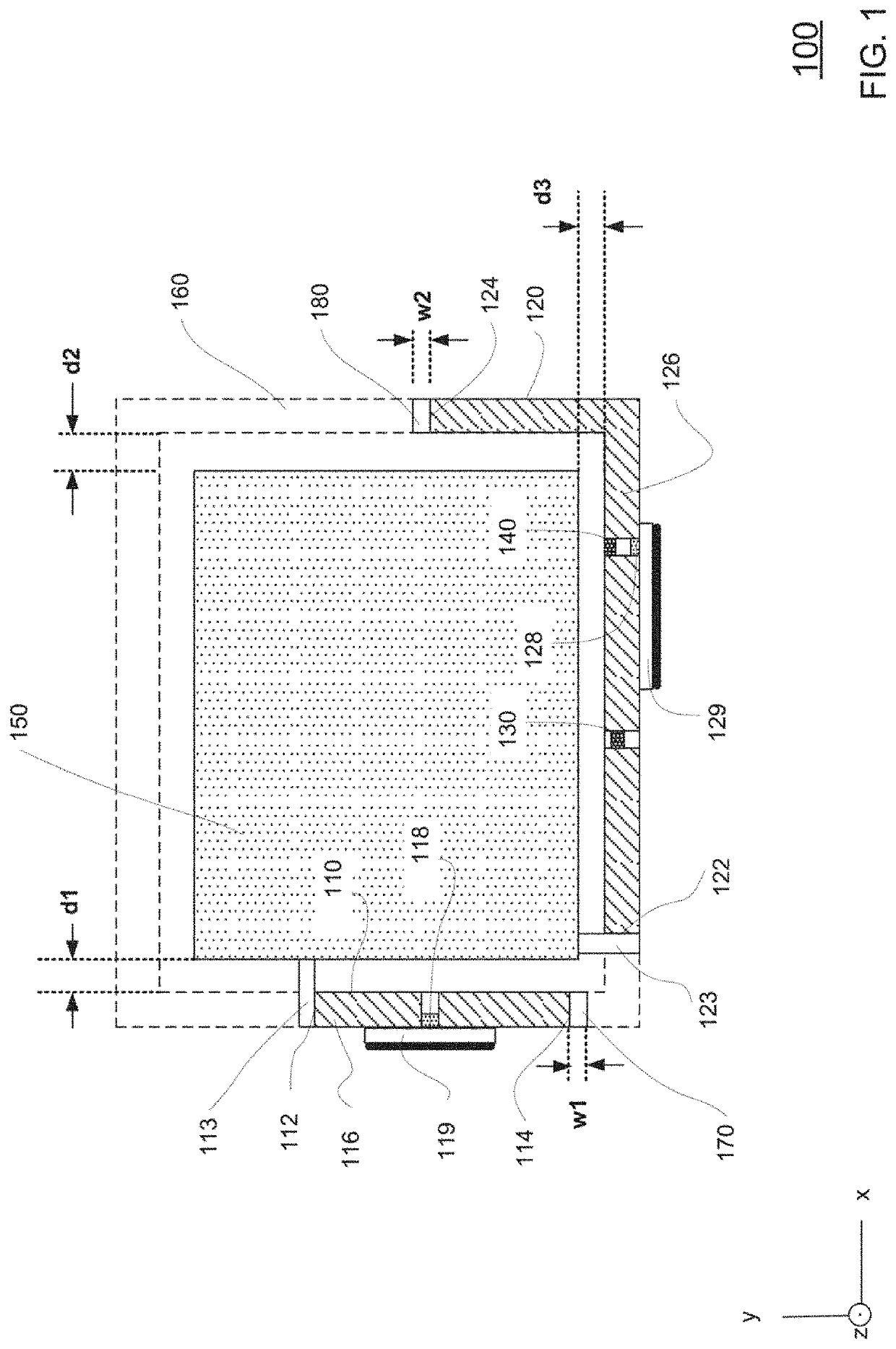

Adaptable antenna system

ActiveCN101529657ALow costReduce sizeSimultaneous aerial operationsAntenna supports/mountingsSmall form factorWide band

The invention utilizes small, narrow-band and frequency adaptable antennas to provide coverage to a wide range of wireless modes and frequency bands on a host wireless device. The antennas have narrow pass-band characteristics, require minimal space on the host device, and allow for smaller form factor. The frequency tunability further allows for a fewer number of antennas to be used. The operation of the antennas may also be adaptably relocated from unused modes to in-use modes to maximize performance. These features of the antennas result in cost and size reductions. In another aspect, the antennas may be broadband antennas.

Owner:QUALCOMM INC

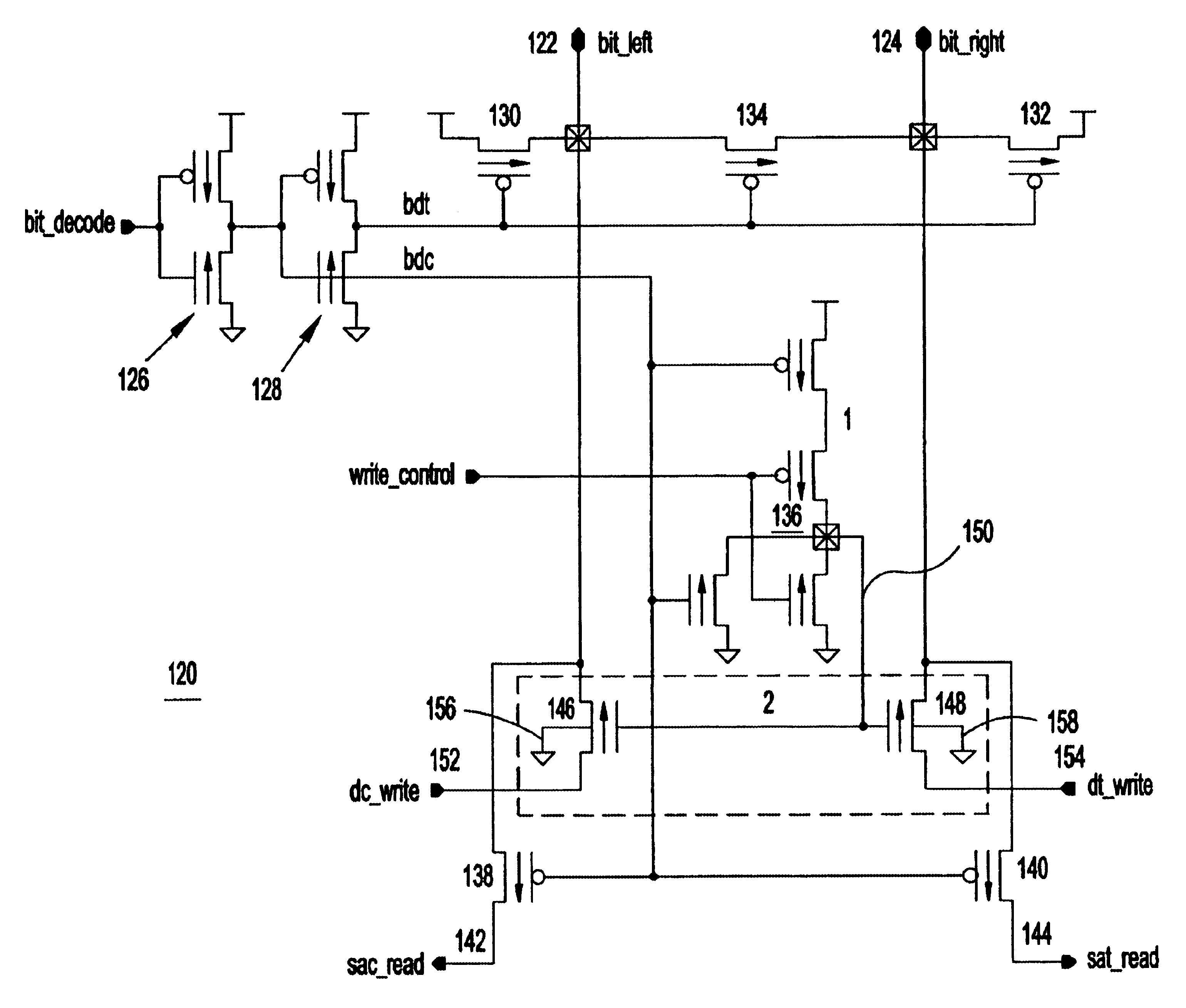

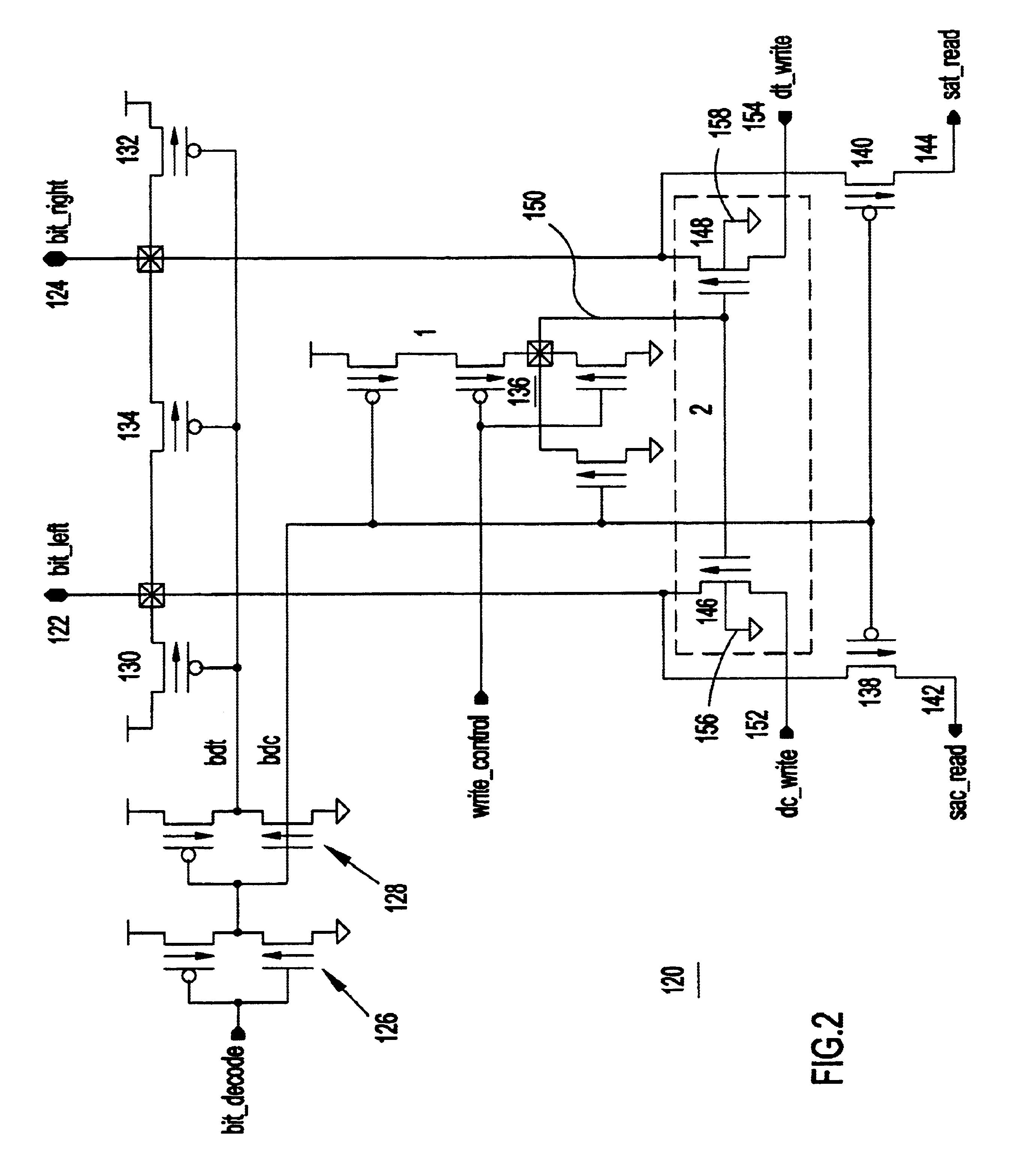

Coupled body contacts for SOI differential circuits

A silicon on insulator (SOI) CMOS circuit, macro and integrated circuit (IC) chip. The chip or macro may include be an SRAM in partially depleted (PD) SOI CMOS. Most field effect transistors (FETs) do not have body contacts. FETs otherwise exhibiting a sensitivity to history effects have body contacts. The body contact for each such FET is connected to at least one other body contact. A back bias voltage may be provided to selected FETs.

Owner:GLOBALFOUNDRIES US INC

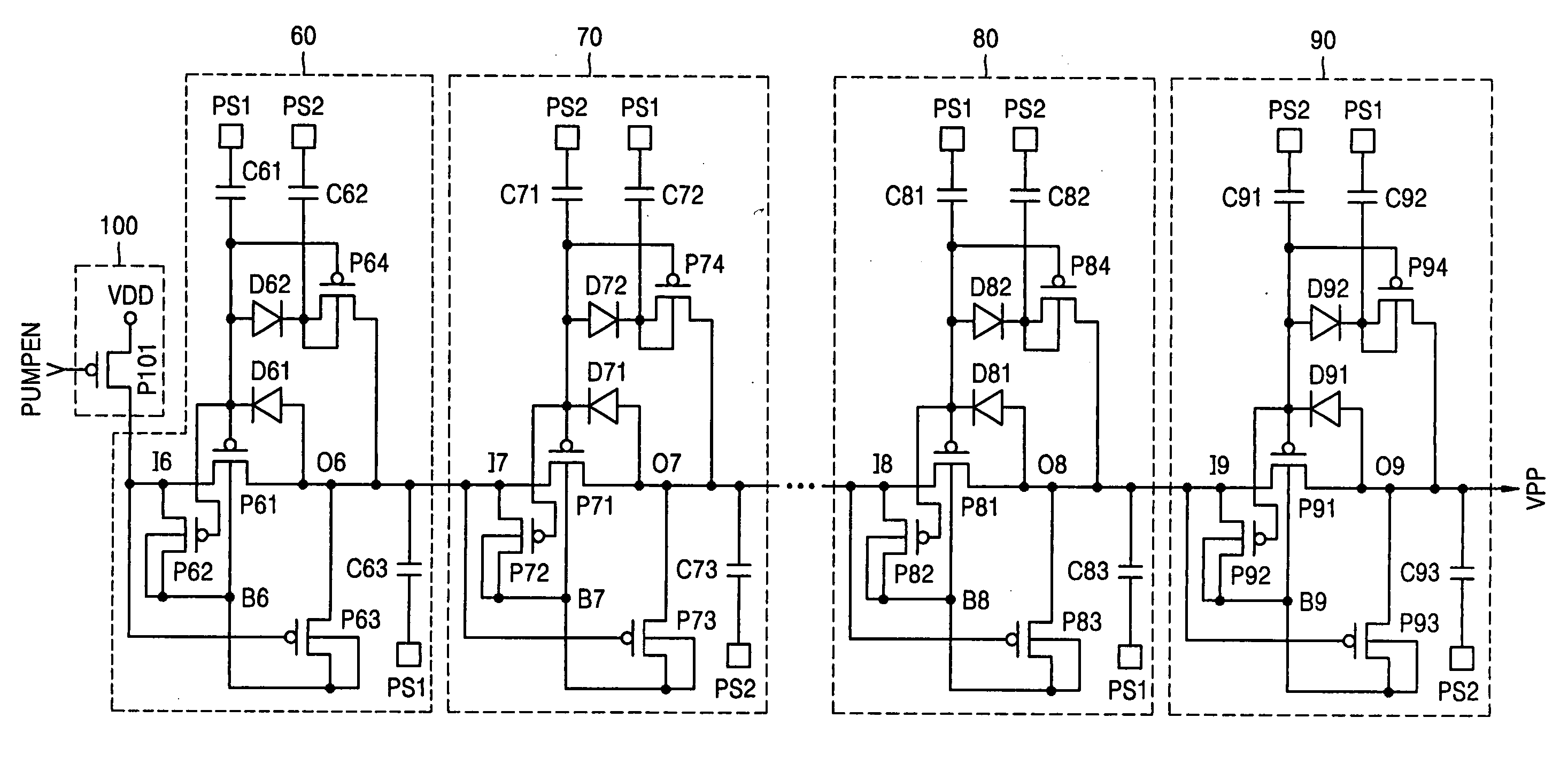

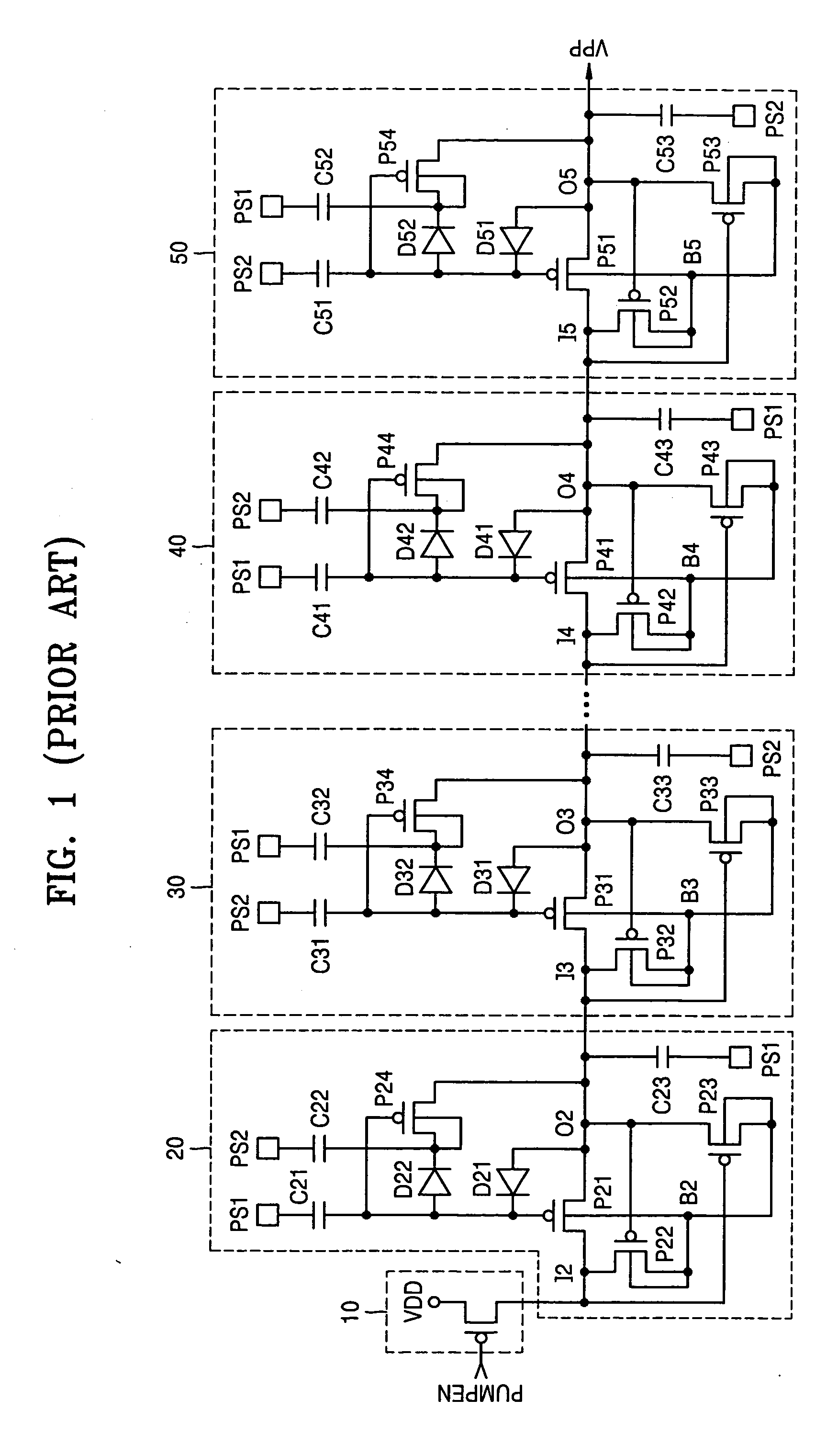

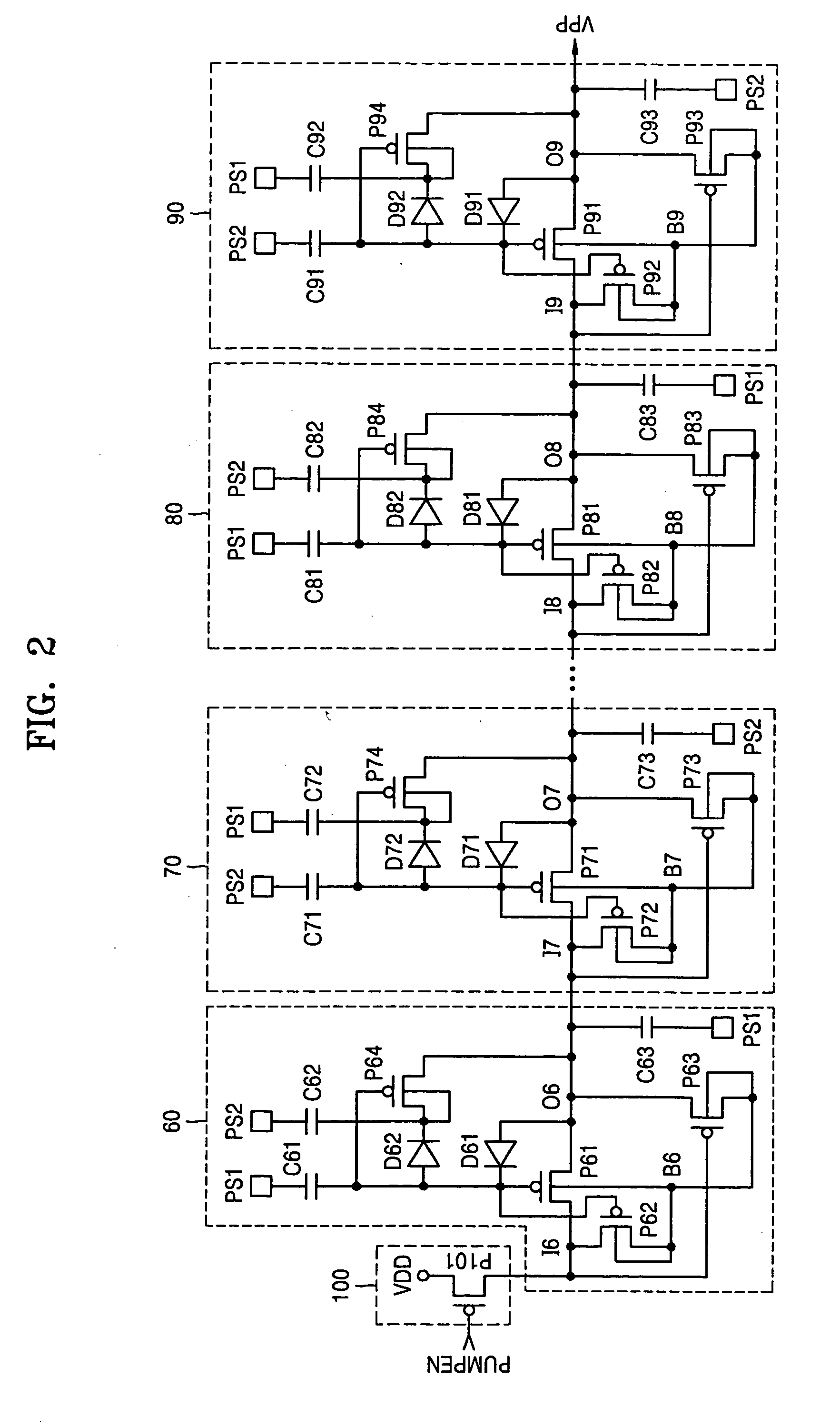

Charge pump circuit having high charge transfer efficiency

InactiveUS20050088220A1Improve pumping efficiencyEnhanced charge transferRead-only memoriesApparatus without intermediate ac conversionCharge transfer efficiencyCharge pump

A charge pump circuit alleviates the body effect of a charge transfer transistor, thereby improving the charge transfer efficiency of the charge transfer transistor and thus pumping efficiency. The charge pump circuit includes a plurality of boosting stages that have input nodes and boosting nodes that are connected in series. Each of the boosting stages includes a charge transfer transistor and a first switch transistor, their respective gates being connected together. A first terminal of the charge transfer transistor is connected to one of the input nodes, and a second terminal of the charge transfer transistor is connected to one of the boosting nodes. The first switch transistor makes the voltage level at the bulk of the charge transfer transistors equal to the voltage level at the first terminal of the charge transfer transistor while charges are being transferred through the charge transfer transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

Charge pump stage with body effect minimization

InactiveUS6864739B2Minimizes body effectReduce body effectAc-dc conversionApparatus without intermediate ac conversionEngineeringReducing bodies

A method for operating a charge pump, the method including biasing a bulk of a charge pump stage so as to reduce body effect without forward biasing diodes of the charge pump stage.

Owner:SAIFUN SEMICON

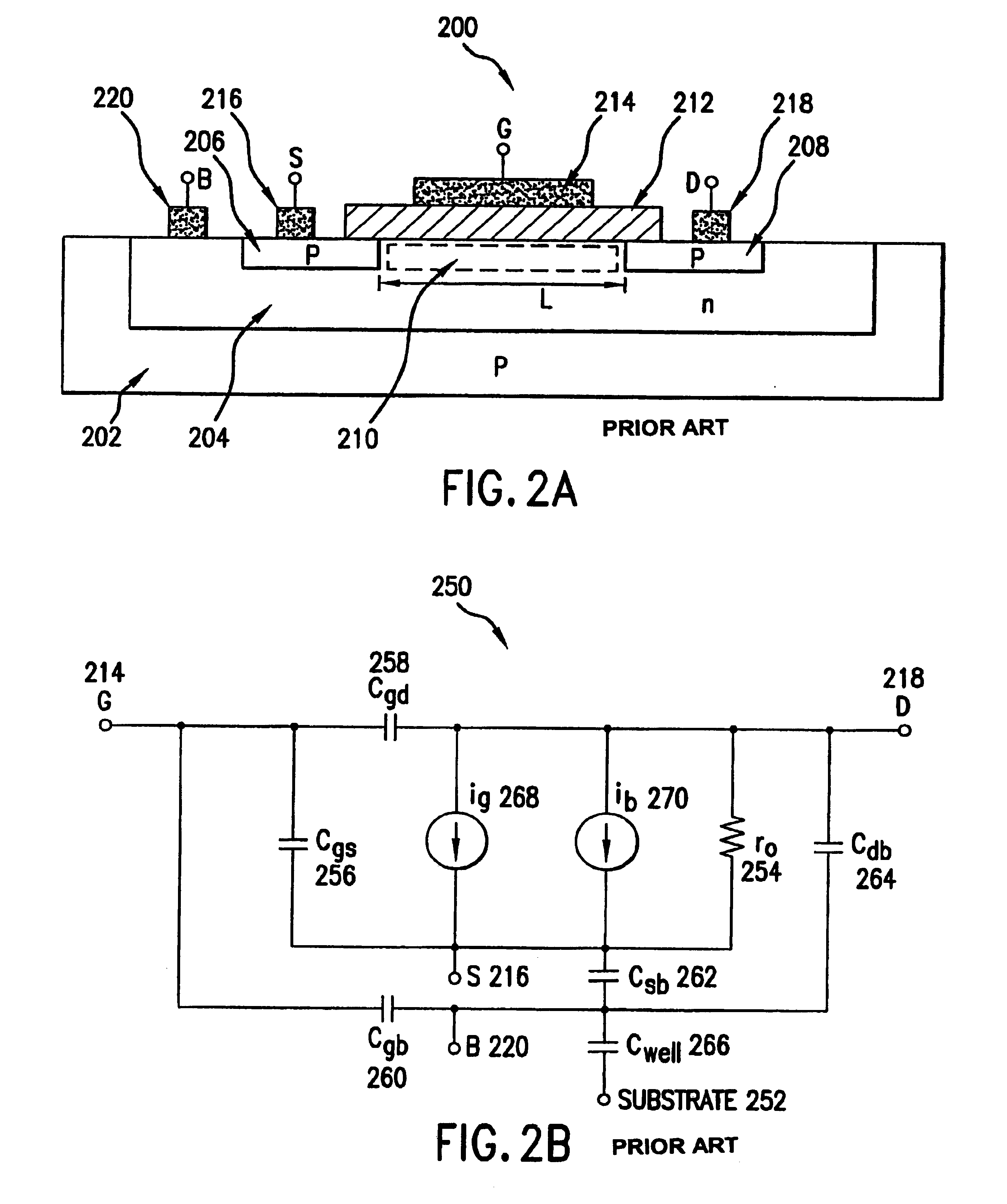

NMOS device formed on SOI substrate and method of fabricating the same

Provided are an NMOS device, a PMOS device and a SiGe HBT device which are implemented on an SOI substrate and a method of fabricating the same. In manufacturing a Si-based high speed device, a SiGe HBT and a CMOS are mounted on a single SOI substrate. In particular, a source and a drain of the CMOS are formed of SiGe and metal, and thus leakage current is prevented and low power consumption is achieved. Also, heat generation in a chip is suppressed, and a wide operation range may be obtained even at a low voltage.

Owner:ELECTRONICS & TELECOMM RES INST

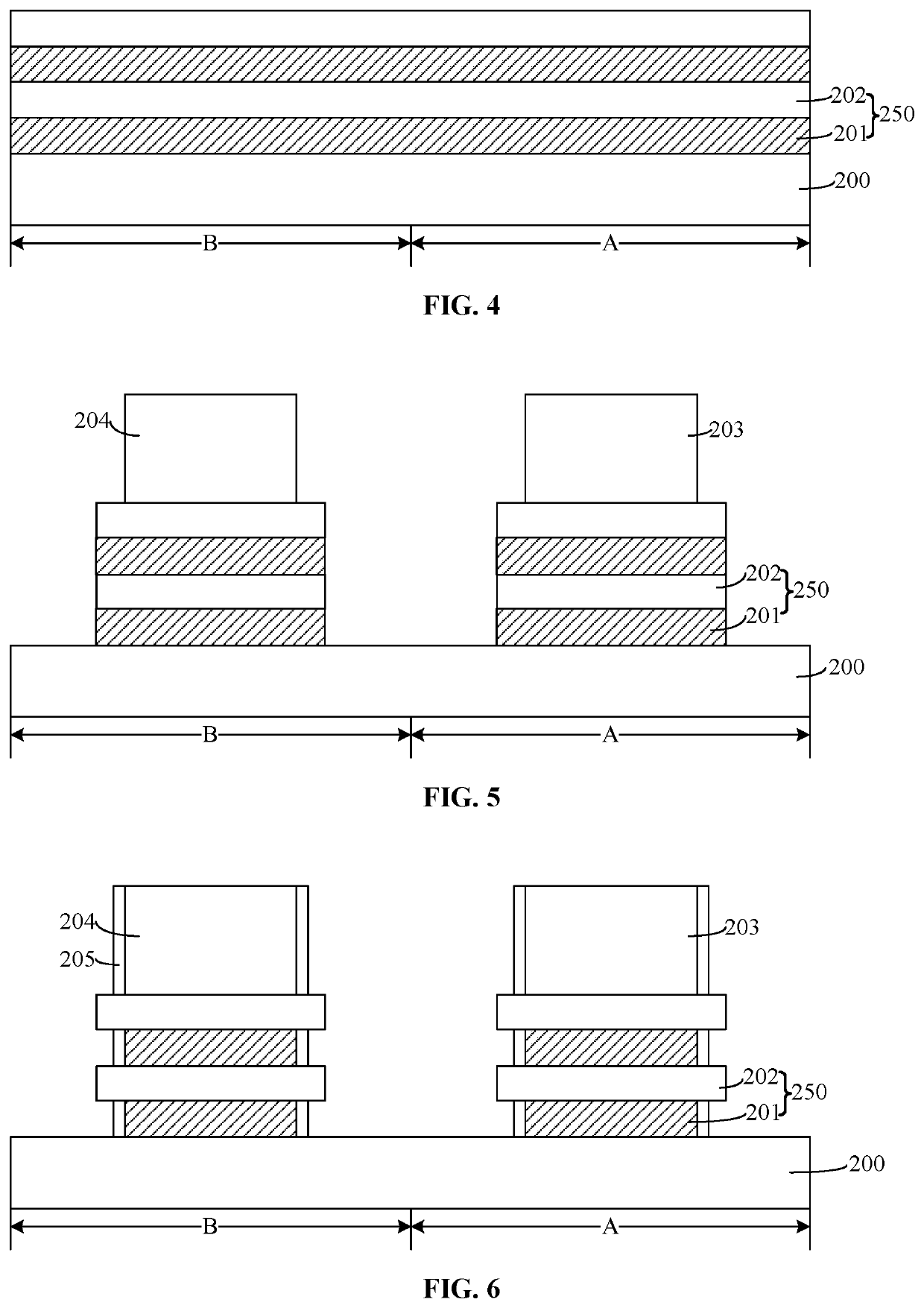

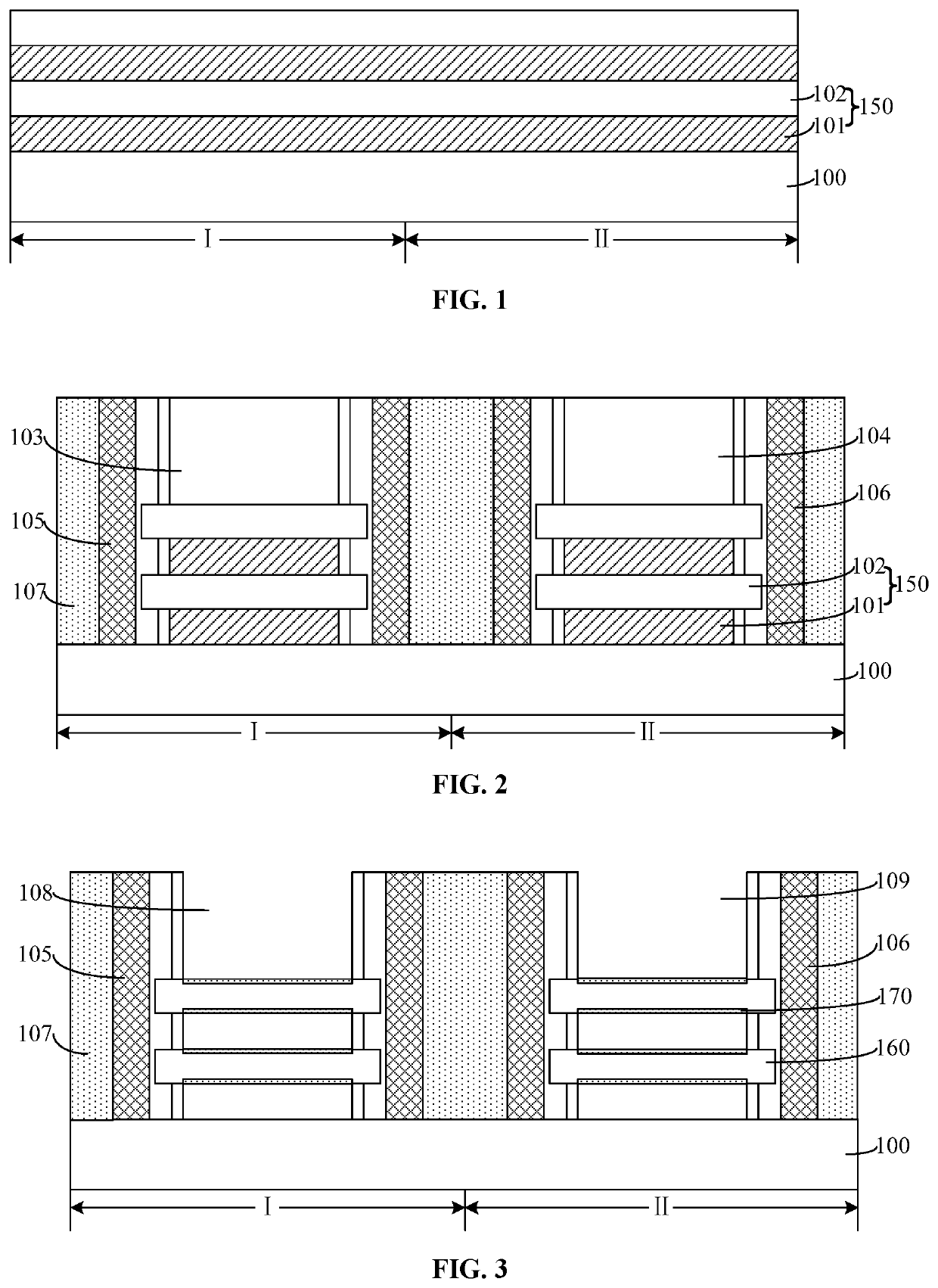

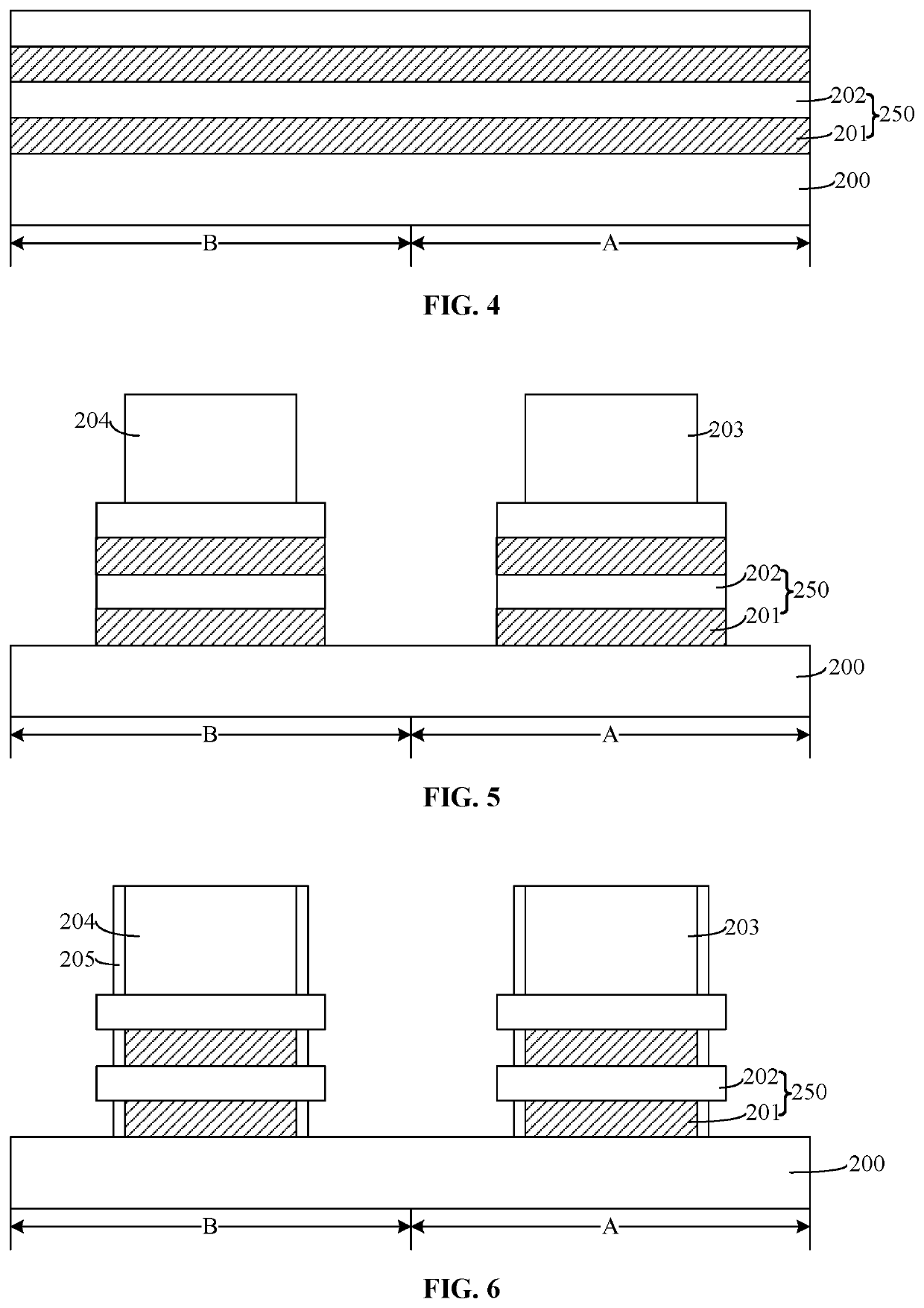

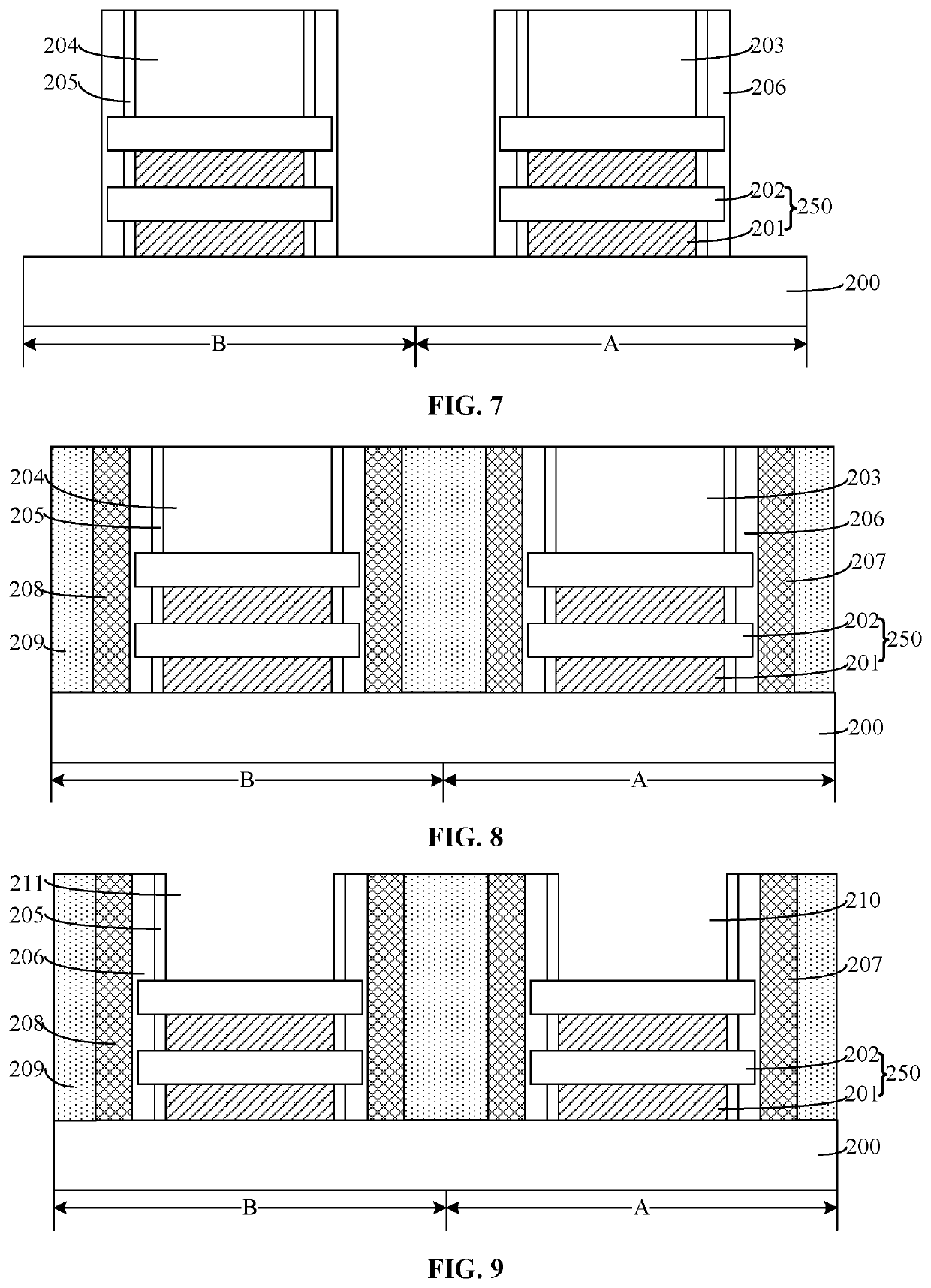

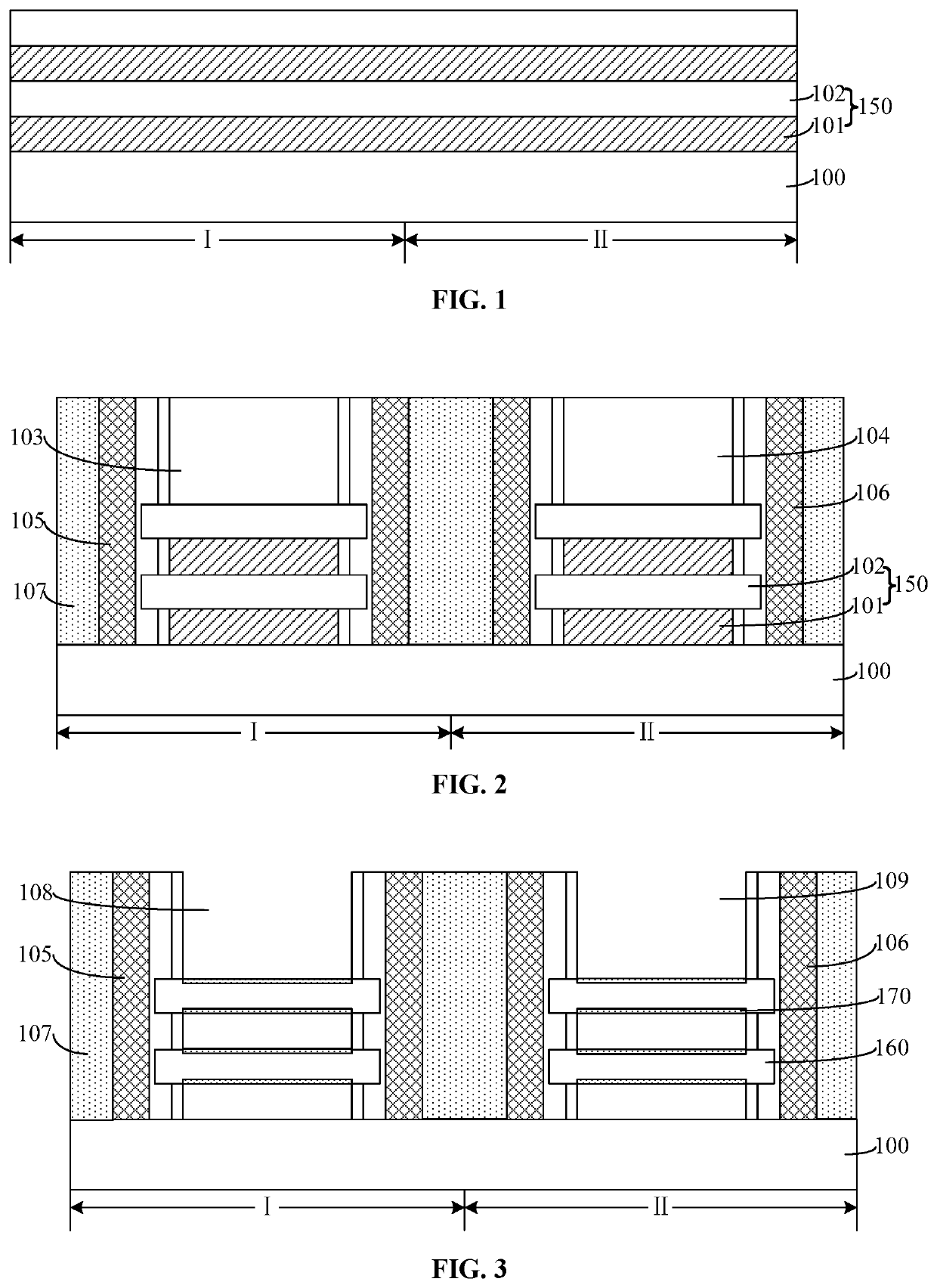

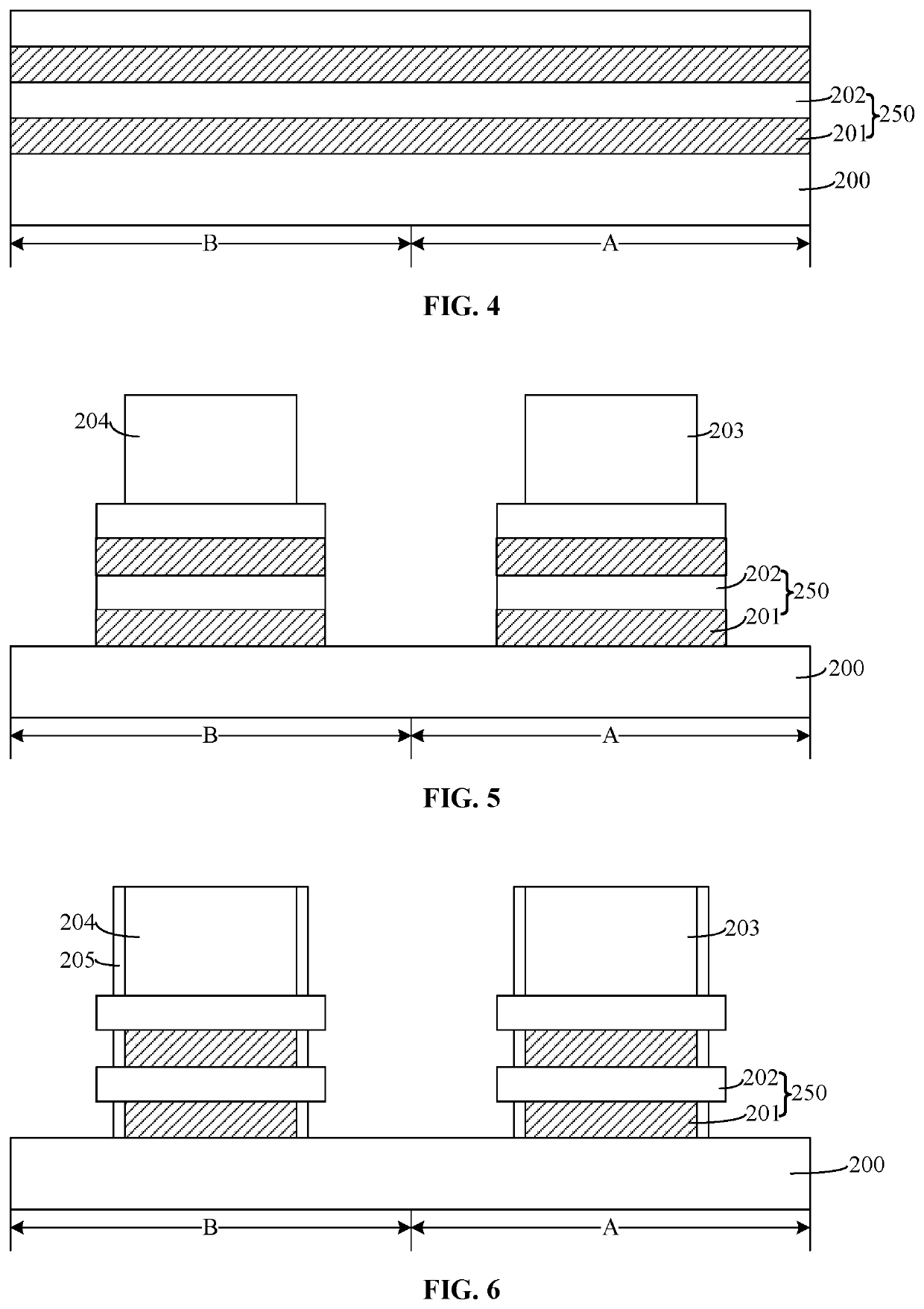

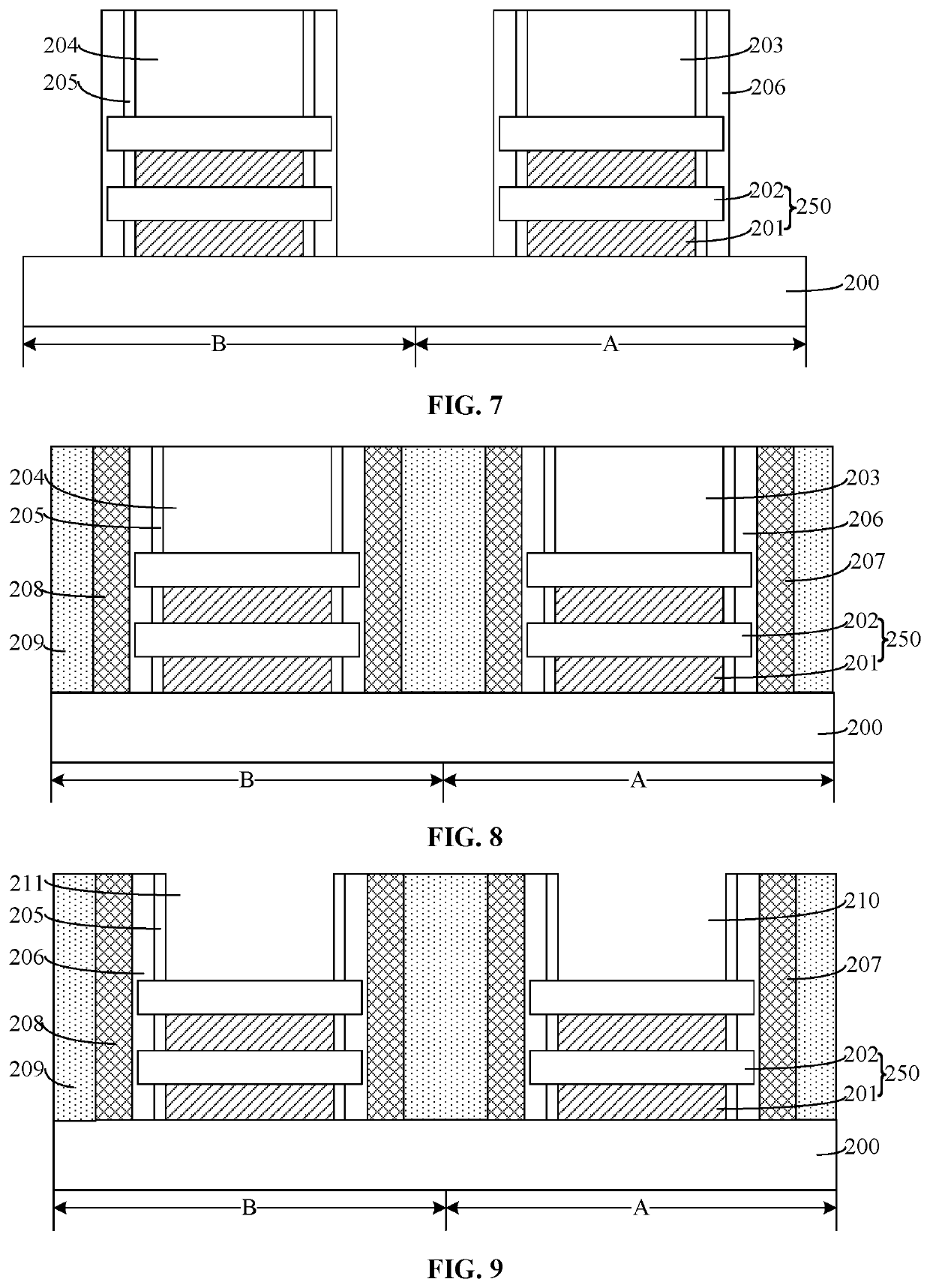

Semiconductor structure and fabrication method

ActiveUS20190371888A1Reduce body effectFacilitate complete depletion of depletion layerTransistorNanoinformaticsNanowireSemiconductor structure

Semiconductor structures and fabrication methods are provided. An exemplary fabrication method includes providing a semiconductor substrate having a first region and a second region; forming first nanowires over the first region of the semiconductor substrate; forming second nanowires with a diameter smaller than a diameter of the first nanowires over the second region of the semiconductor substrate; forming a first gate layer around the first nanowires; and forming a second gate layer around the second nanowires.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

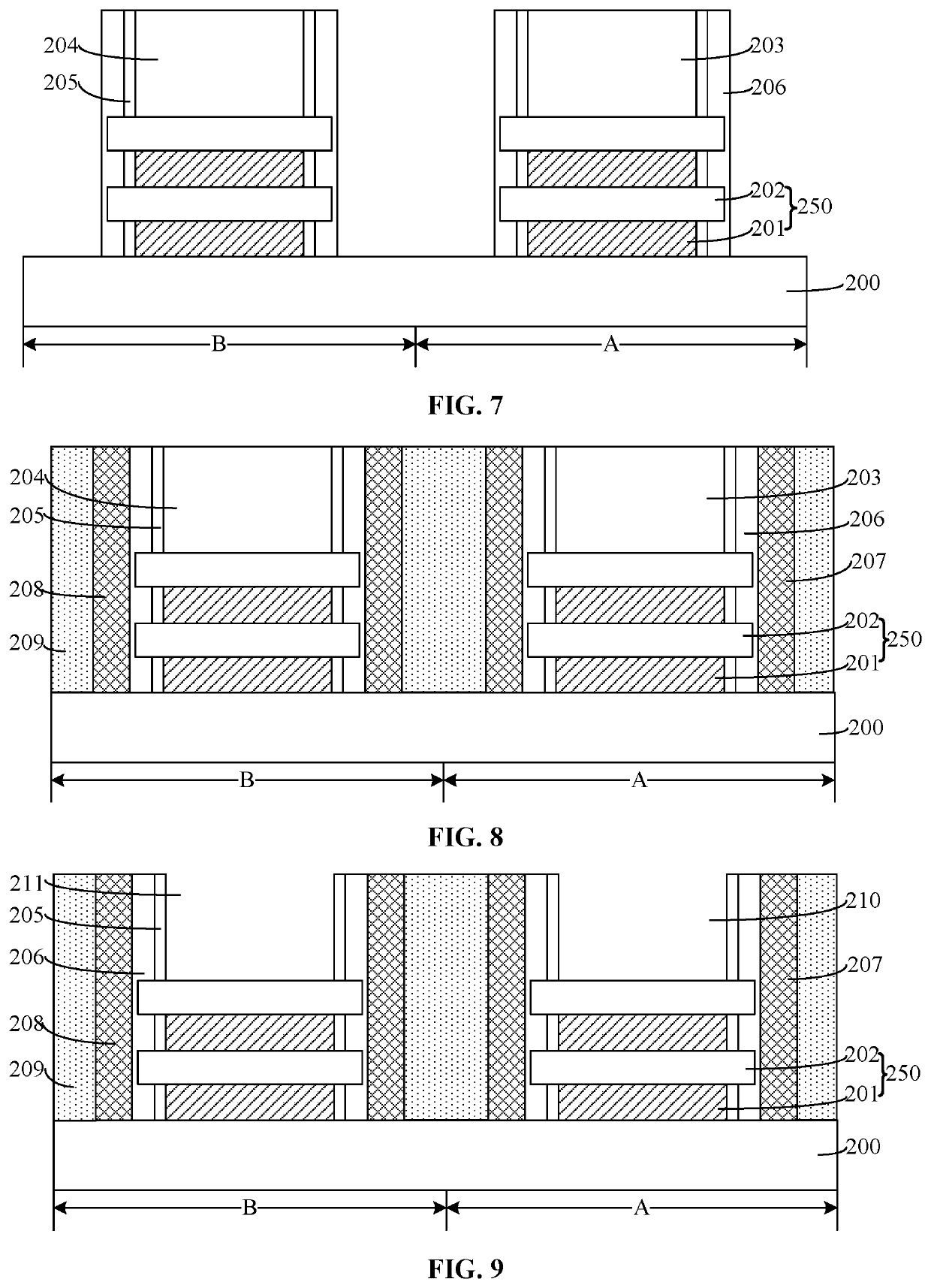

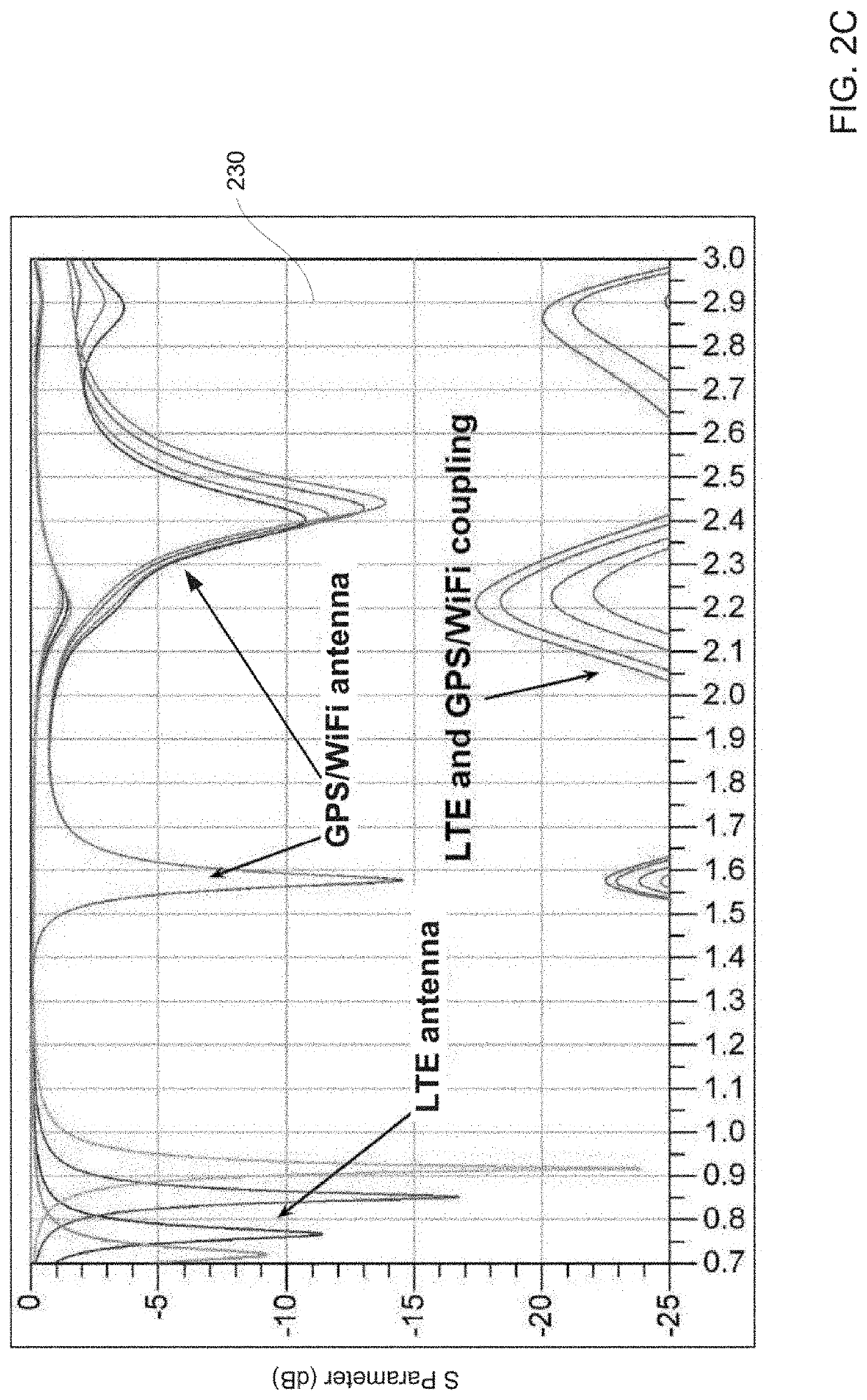

Tunable Antenna System for Smart Watch

ActiveUS20190363428A1Reduce body effectEasy to separateSimultaneous aerial operationsAntenna adaptation in movable bodiesEngineeringGround plane

A tunable antenna system is provided for a wearable personal computing device, such as a smartwatch. The tunable antenna system includes at least two antennas configured for respective sets of frequency ranges. One or more radiating elements of the antennas are formed from portions of a metal bezel of the wearable personal computing device. For at least one of the antennas, an aperture tuner and an impedance tuner positioned within the metal bezel are provided, e.g., to tune between various communication bands. Non-conductive slits may be positioned within the metal bezel to provide isolation between the antennas. A ground plane of the antenna system may be formed by a metallic component of the wearable personal computing device. The antenna system can be insulated from a wearer's skin by a non-metallic back cover and optionally a glass back plate arranged to contact the wearer's skin or clothing during use.

Owner:GOOGLE LLC

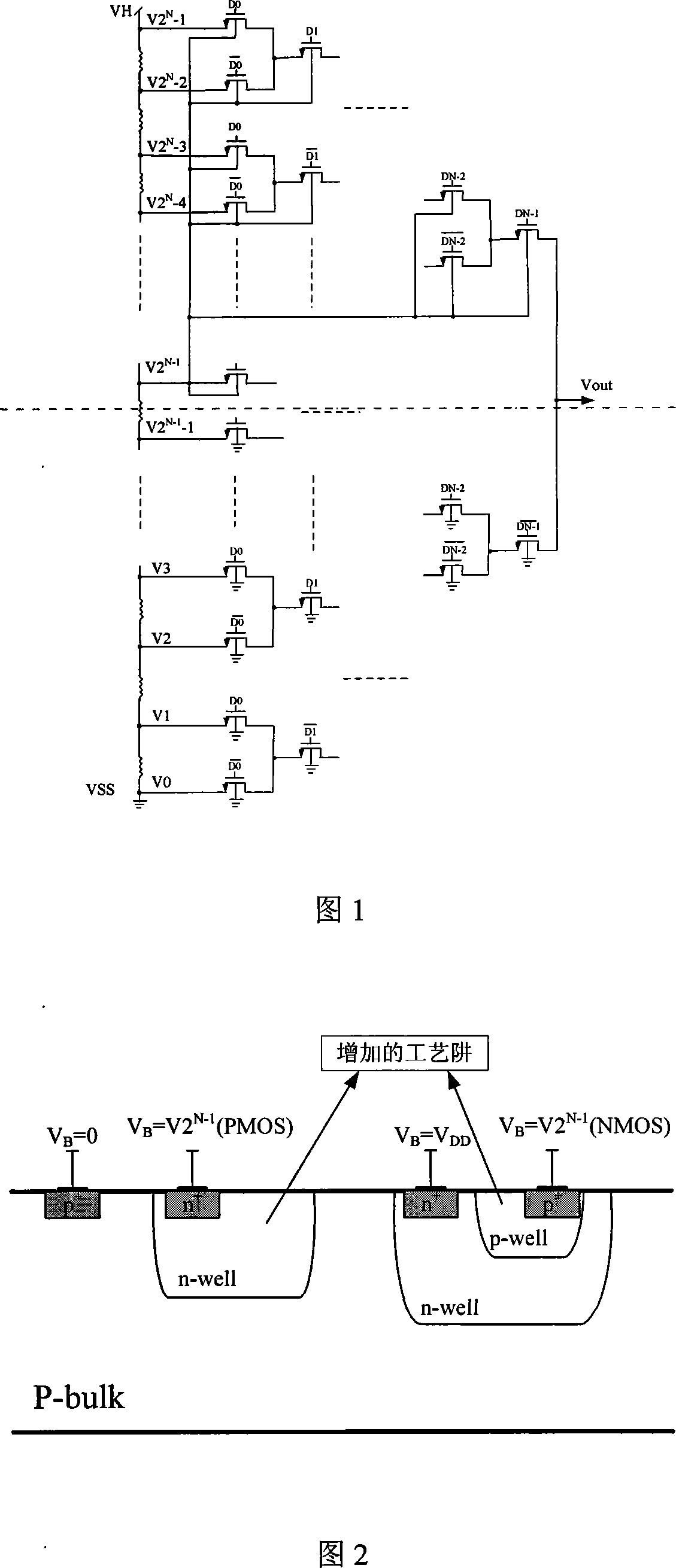

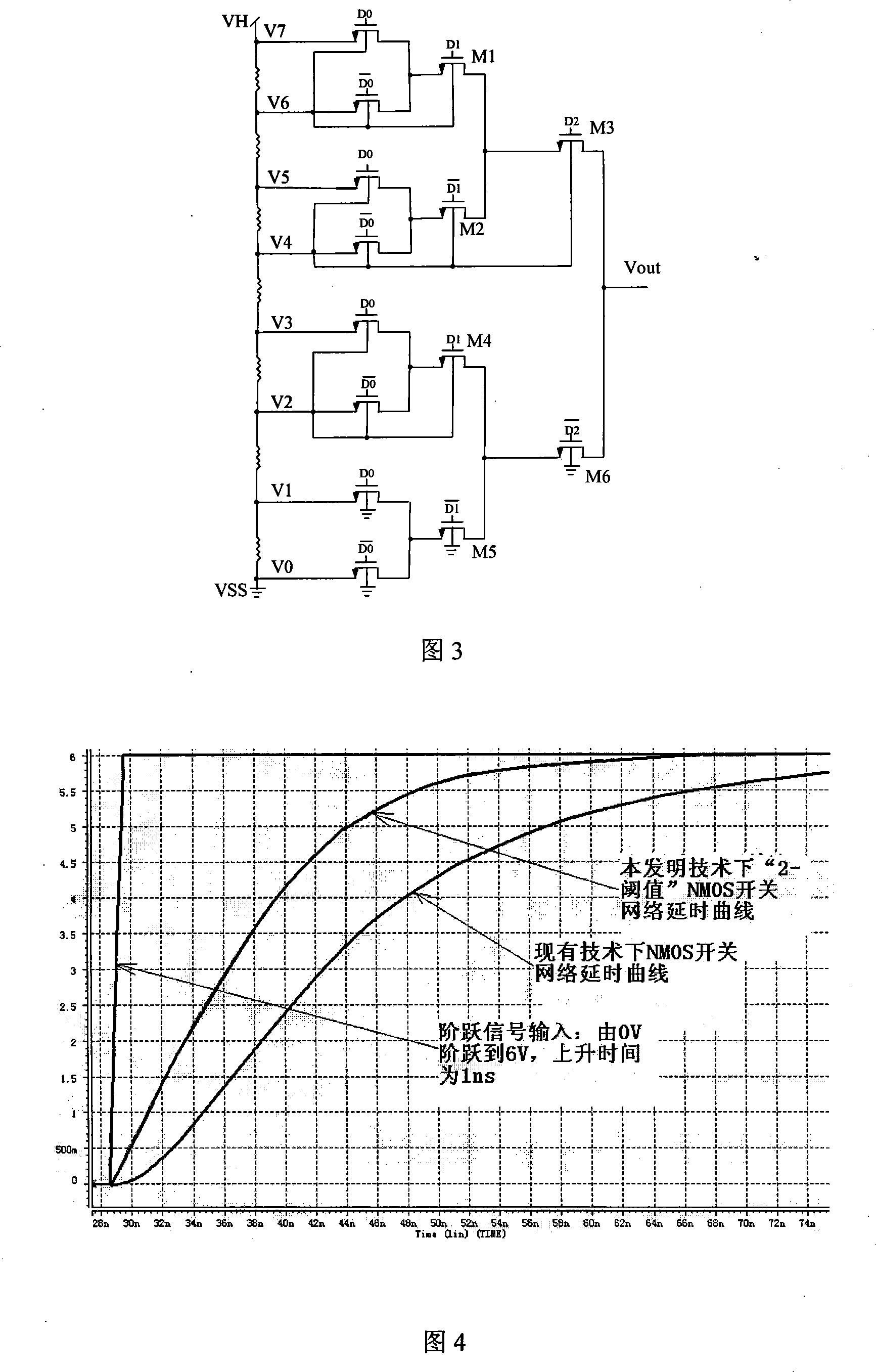

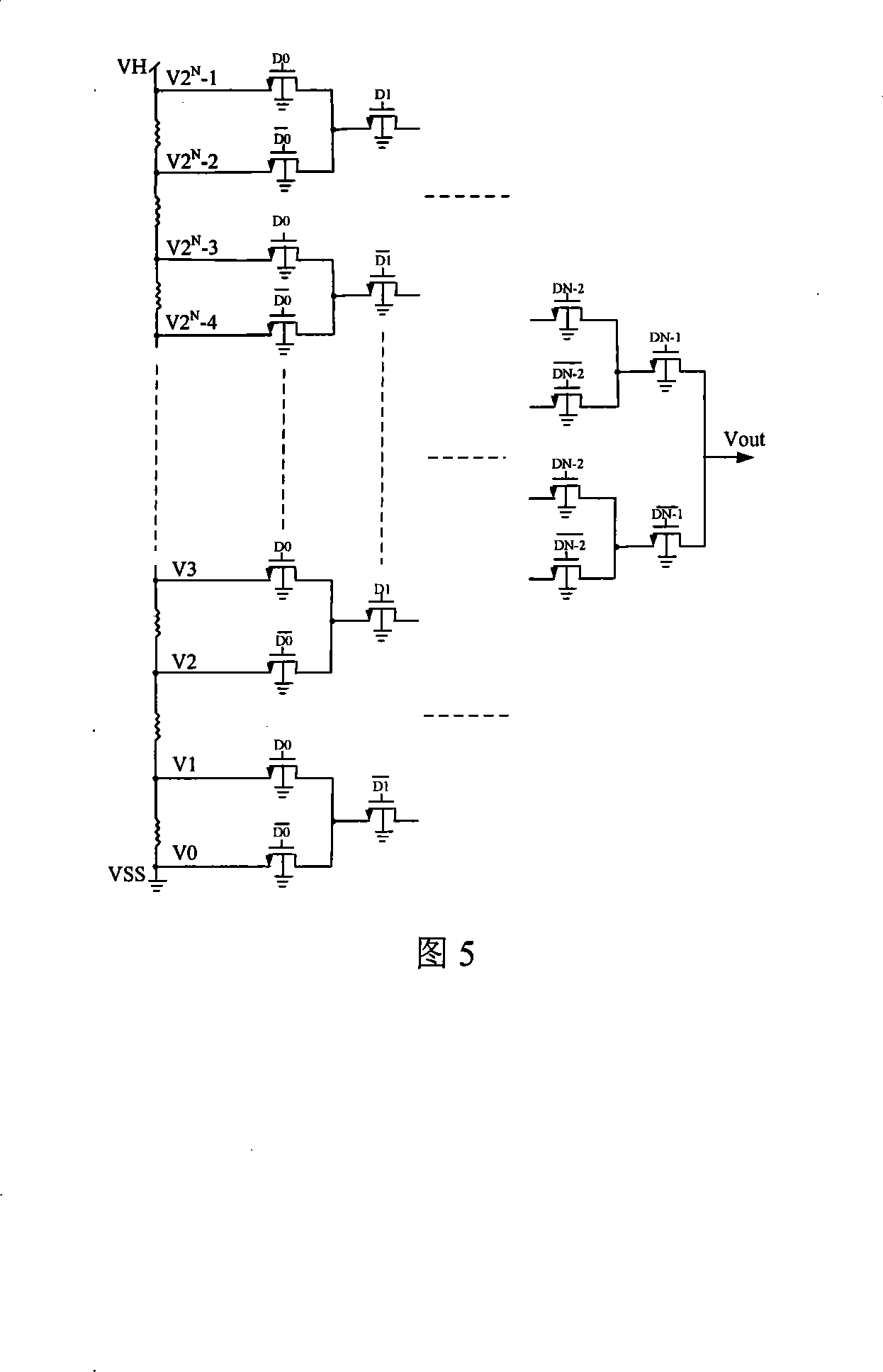

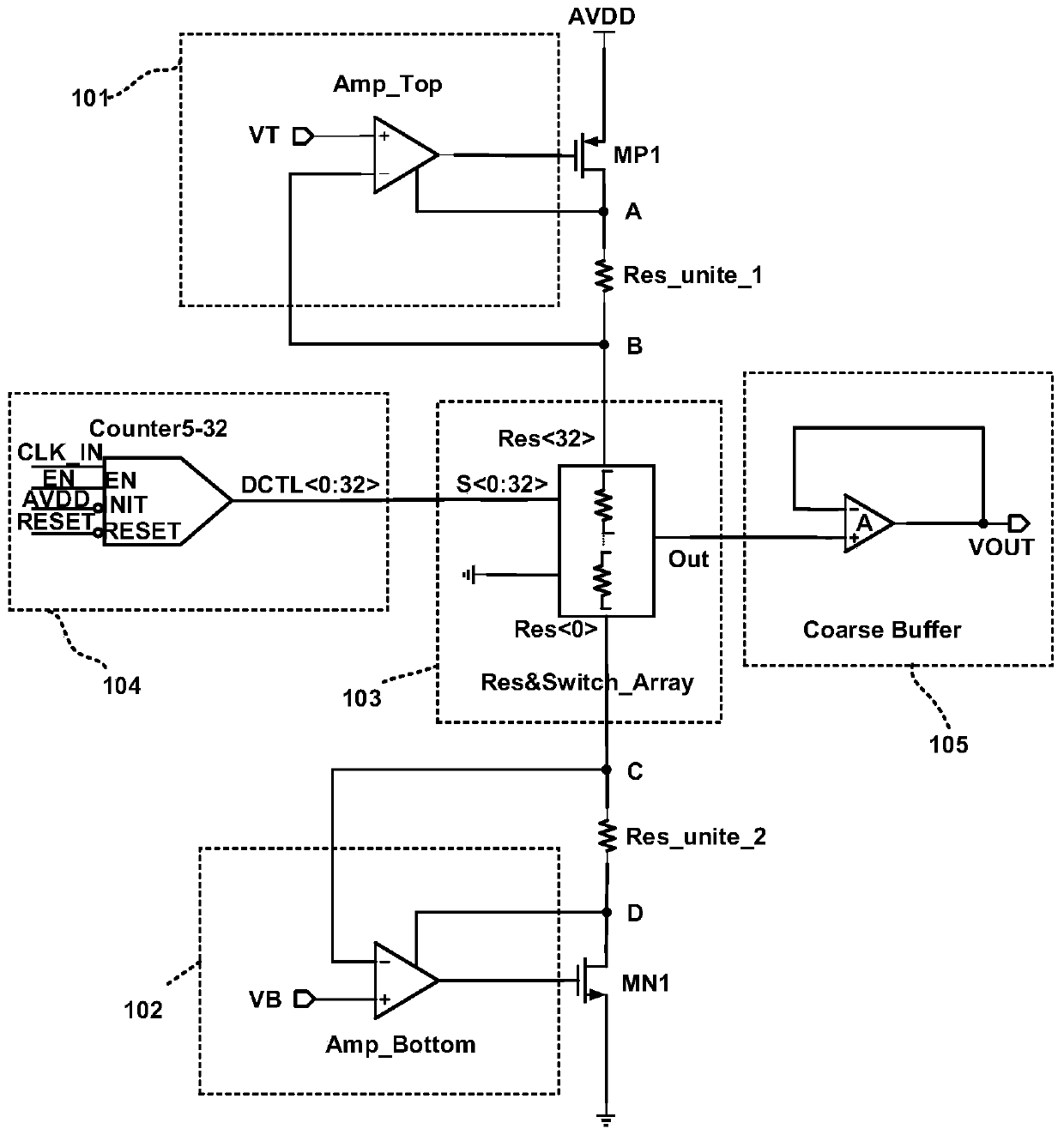

Multi-threshold digital/analog converter for thin film transistor LCD driven chip

InactiveCN101102113AReduce voltageLower latencyStatic indicating devicesDigital-analogue convertorsCMOSDigital analog converter

The invention is concerned with the multi-threshold digital-analog converter (DAC) of the source drive chip of the thin film transistor model liquid crystal display screen, that is: It can reduces the bulk effect by setting up different voltage substrate VB through the CMOS tube of the DAC separately, to reduce the resistance guiding through and time delay of the CMOS tube decoding switch and improve the speed of the DAC. The voltage substrate VB is no more than the voltage of the 3 terminals of the NMOS tube, and is no less than the voltage of the 3 terminals of the PMOS tube to make the substrate of each the NMOS tube or the PMOS tube off-set in reverse direction. Under the condition of non-improving the complexity of the circuit and the area of the chip, it reduces the delay time of the digital-analog converter and improves the speed by reducing the voltage of the substrate of the CMOS tube and the source electrode, and the bulk effect of the CMOS tube.

Owner:西安龙腾微电子科技发展有限公司

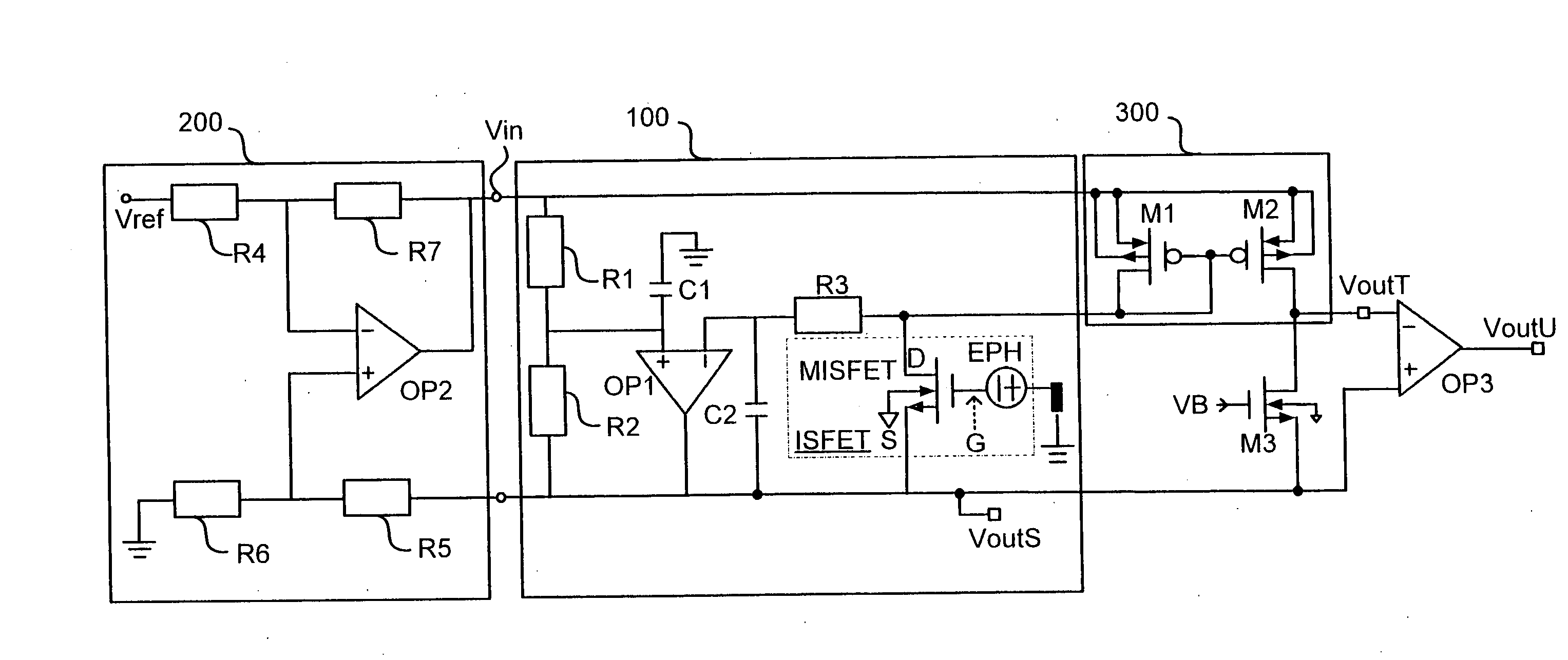

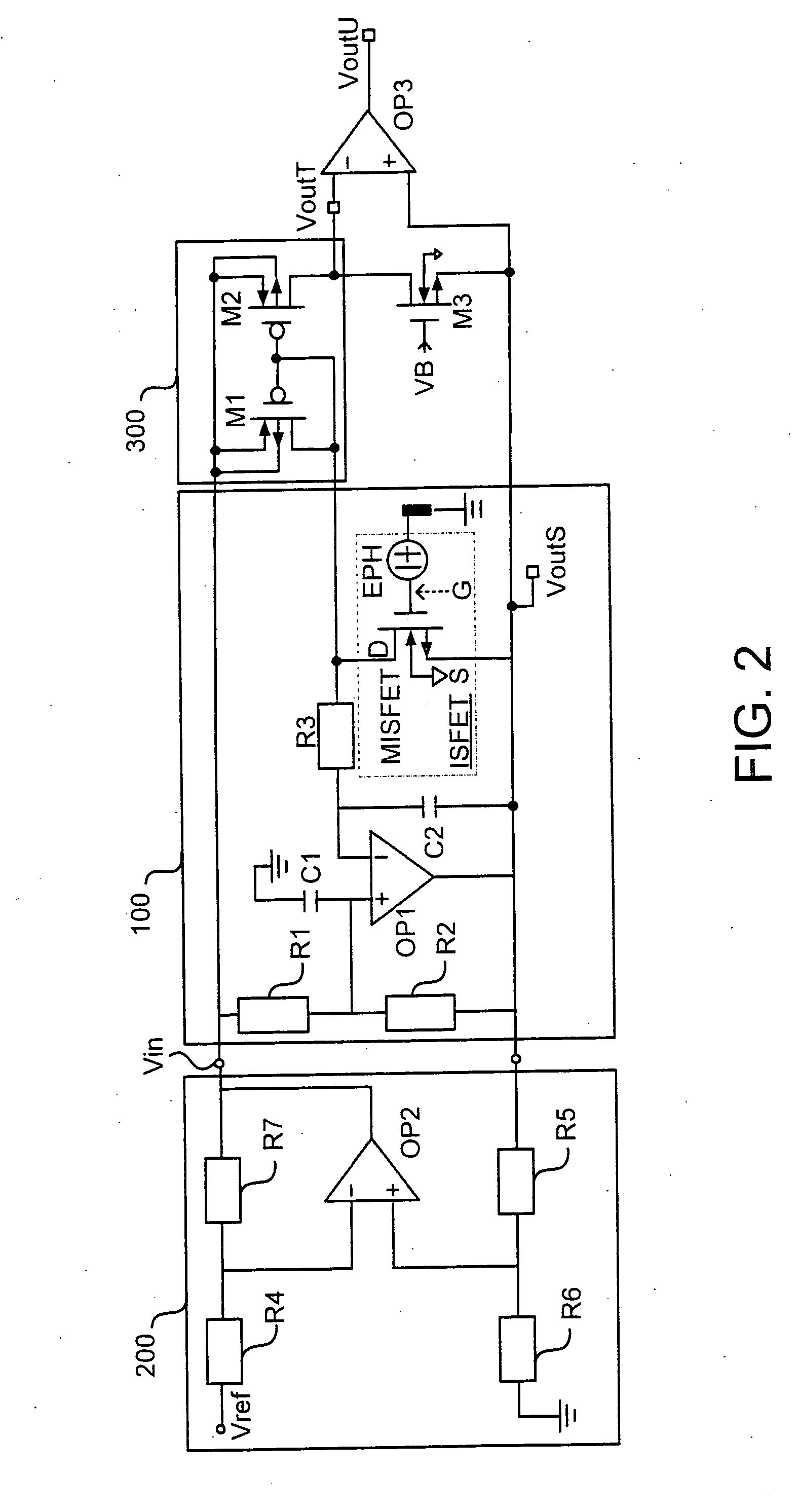

Electronic circuit for ion sensor with body effect reduction

ActiveUS20070089988A1Reduce body effectSuitable for useSpecial data processing applicationsChemical methods analysisVoltage referenceTime drift

An electronic circuit for ion sensor with the body effect reduction includes a bridge-type floating source circuit provided with an input terminal, an output terminal reflecting the change in the potential dependent on ion concentration, and an ion-sensitive field effect transistor (ISFET) wherein one terminal of the ISFET is coupled with the output terminal; a current mirror for providing a current to the bridge-type circuit; a third transistor for receiving the operating current provided by the current mirror, identical to the current provided to the ISFET; a differential amplifying circuit, wherein one input terminal of the amplifying circuit is input with a reference voltage, and the other input terminal is coupled with the output of the bridge-type readout circuit; and a third amplifier to generate a differential output voltage compensated for the body effect, temperature and time drift effects.

Owner:CHUNG YUAN CHRISTIAN UNIVERSITY

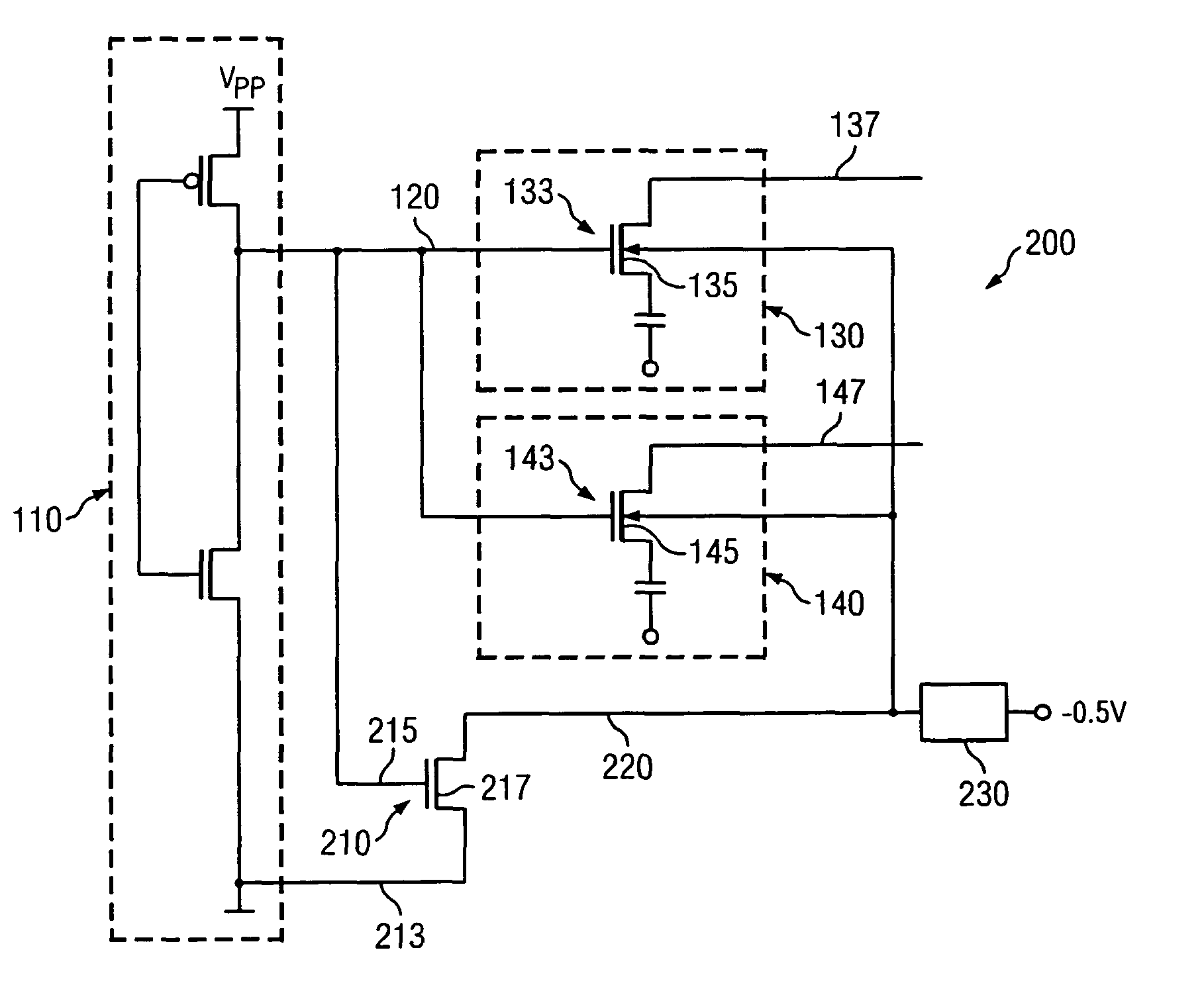

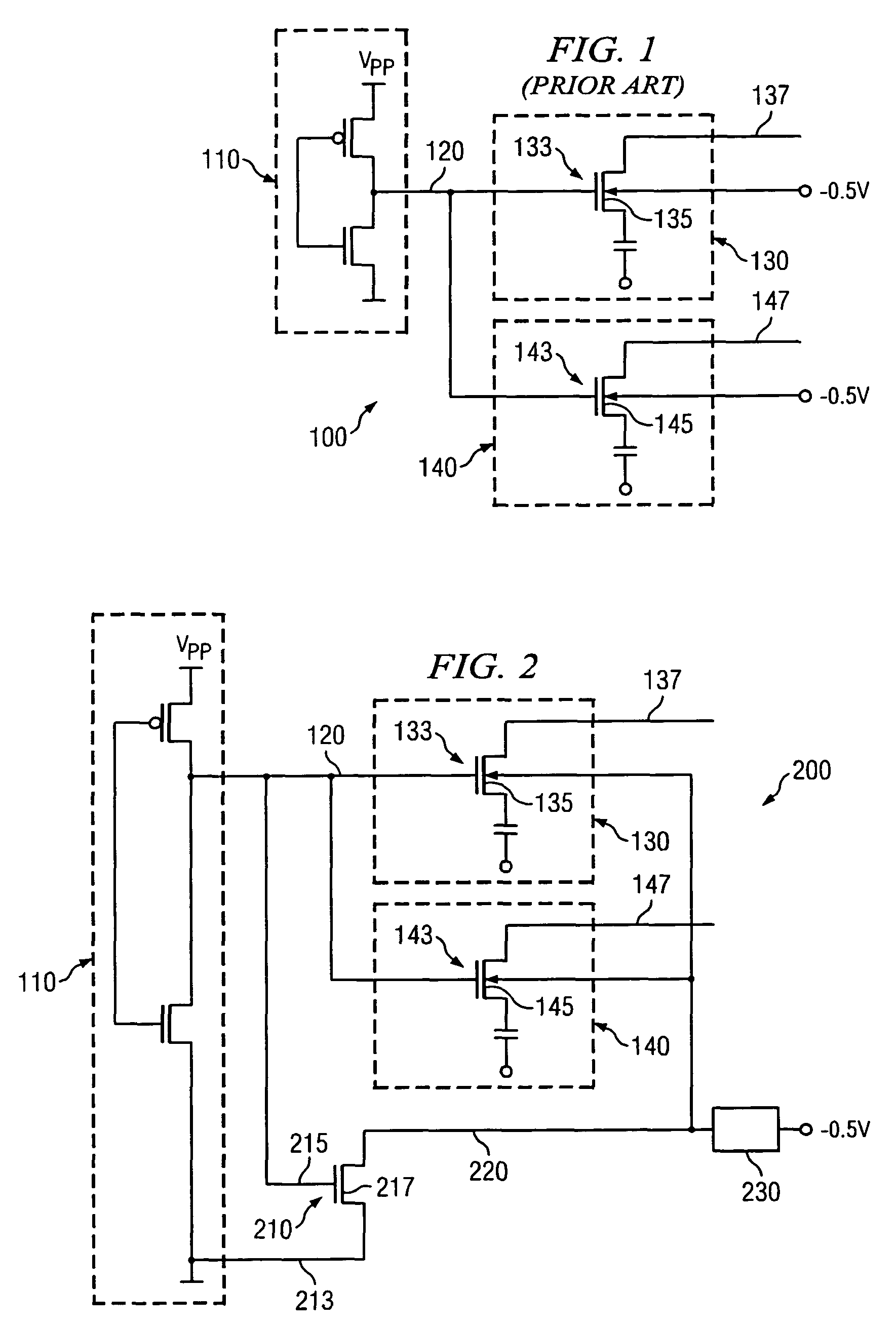

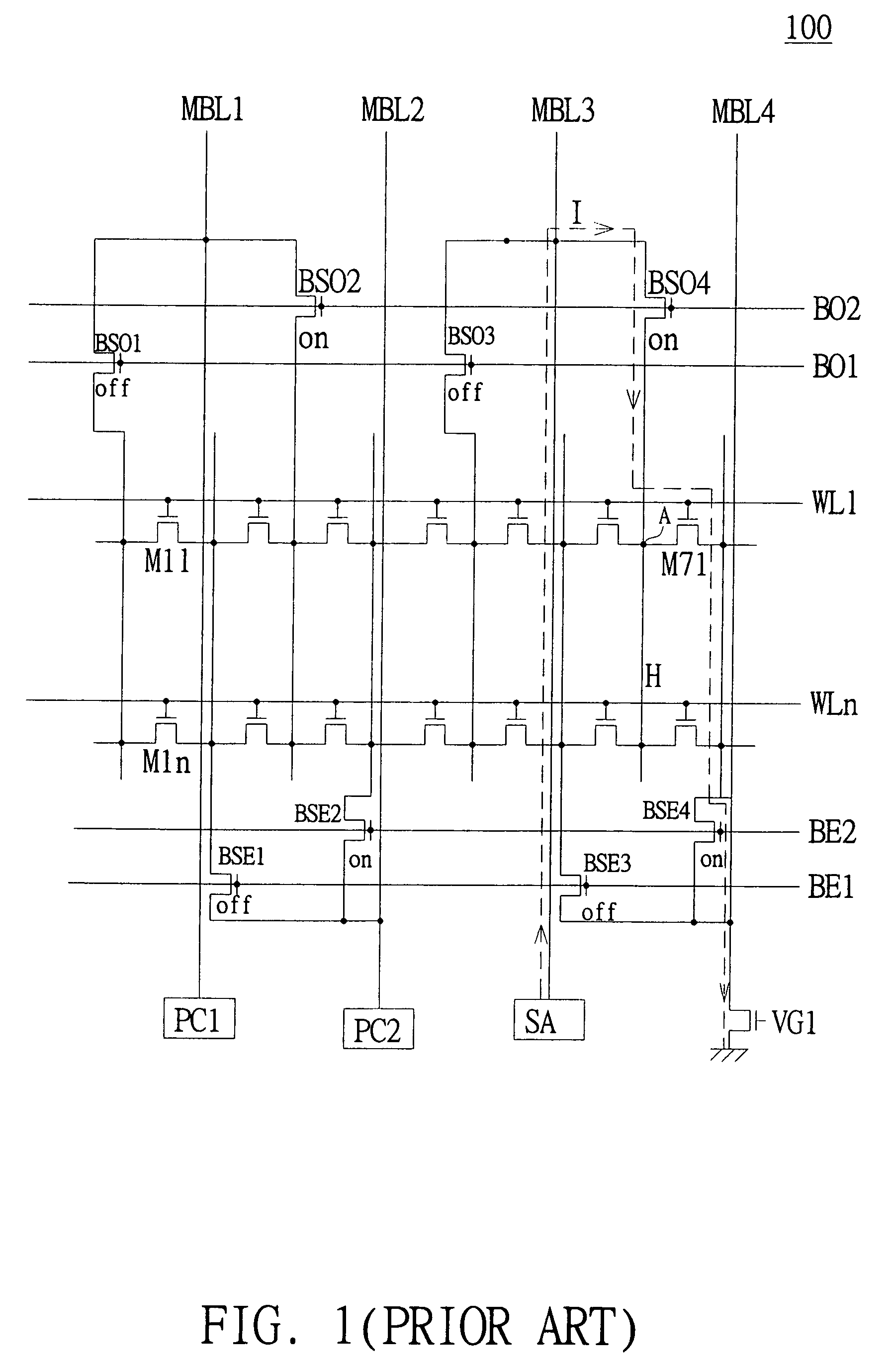

Controlled substrate voltage for memory switches

InactiveUS7170798B2Reduce the overall heightEasy to operateRead-only memoriesDigital storageBody contactData Corruption

Owner:POLARIS INNOVATIONS LTD

Voltage generating circuit and semiconductor device having the same

ActiveUS8067977B2Increase powerImprove reliabilityApparatus without intermediate ac conversionDigital storageControl signalDevice material

Owner:SAMSUNG ELECTRONICS CO LTD

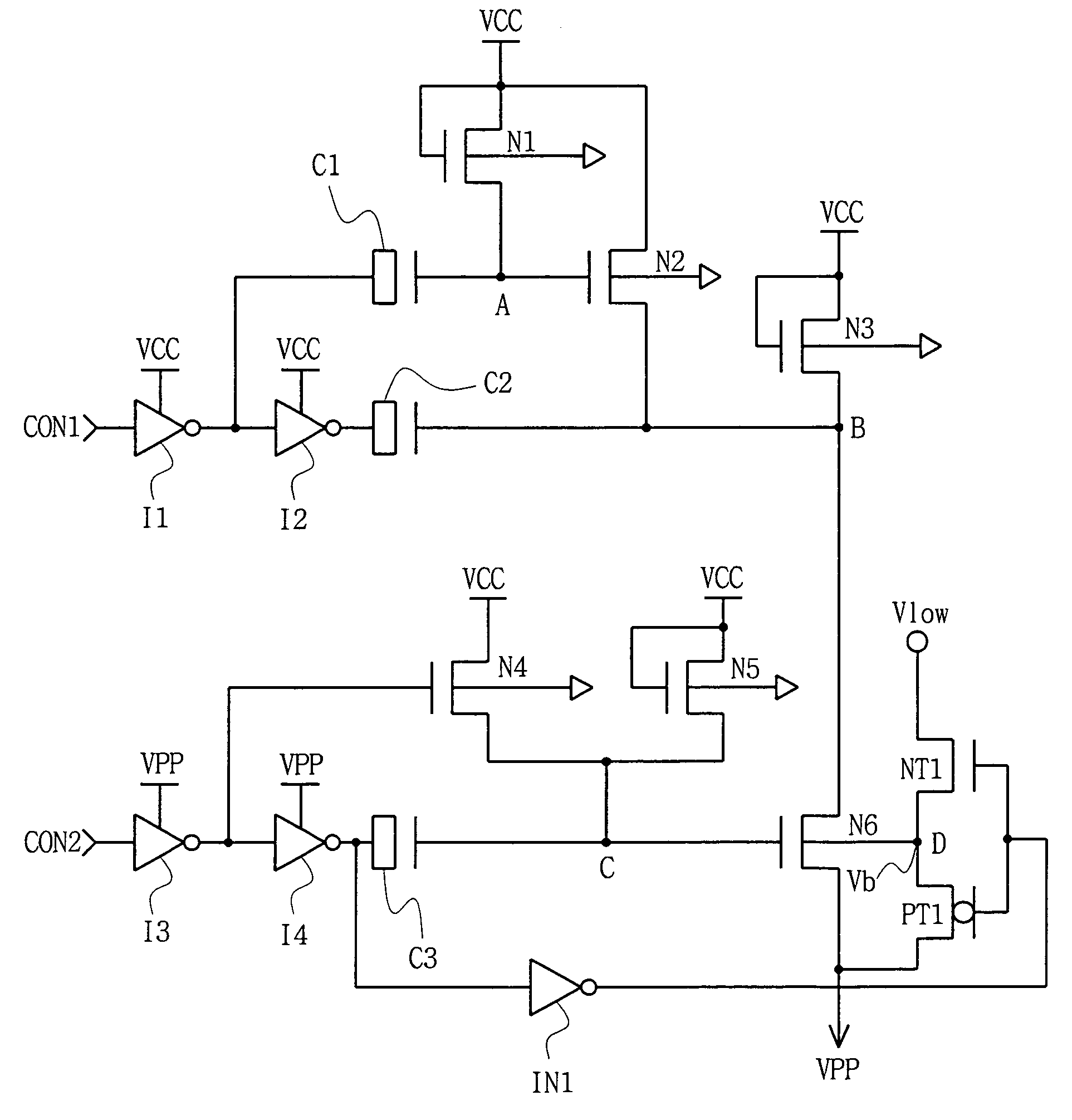

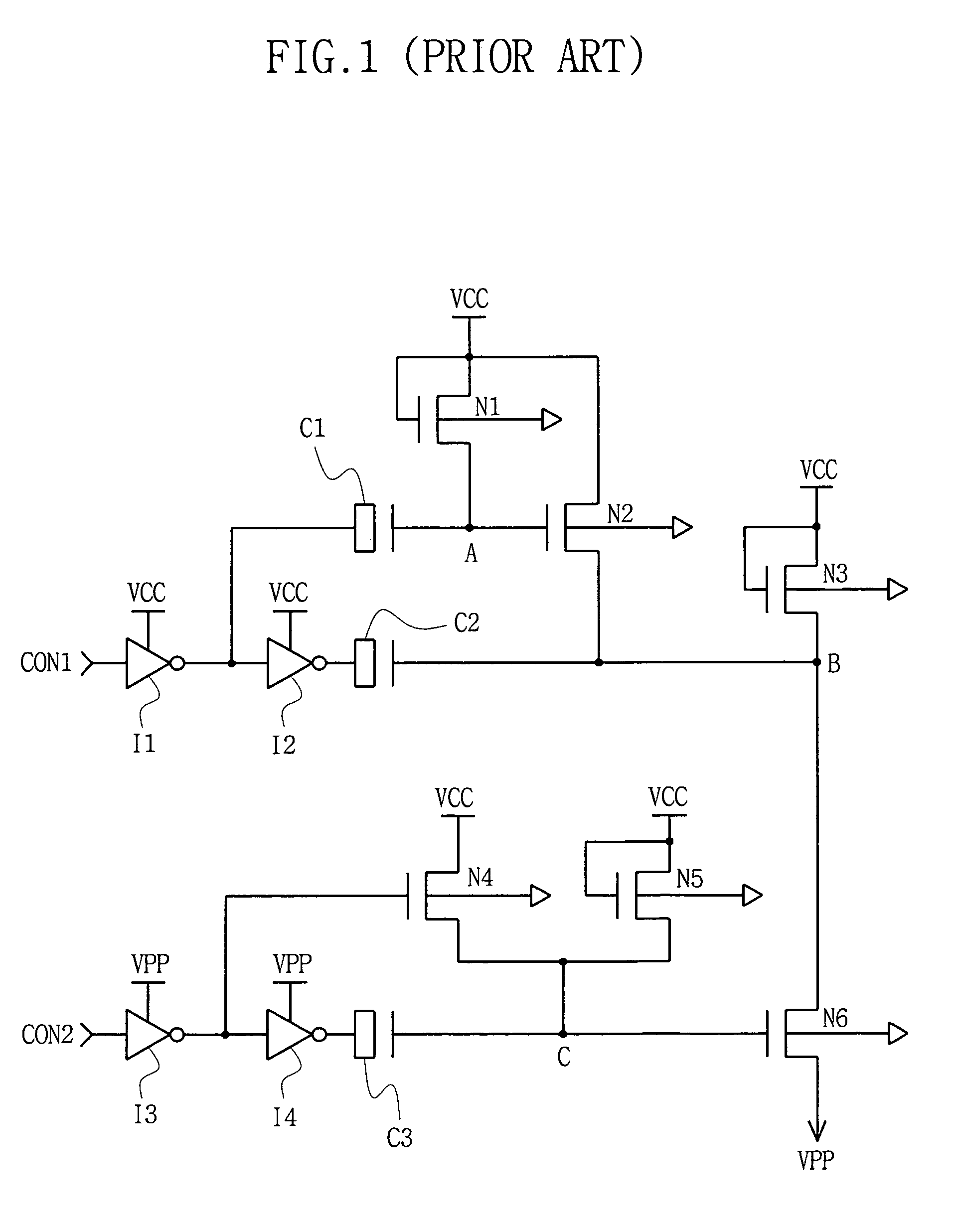

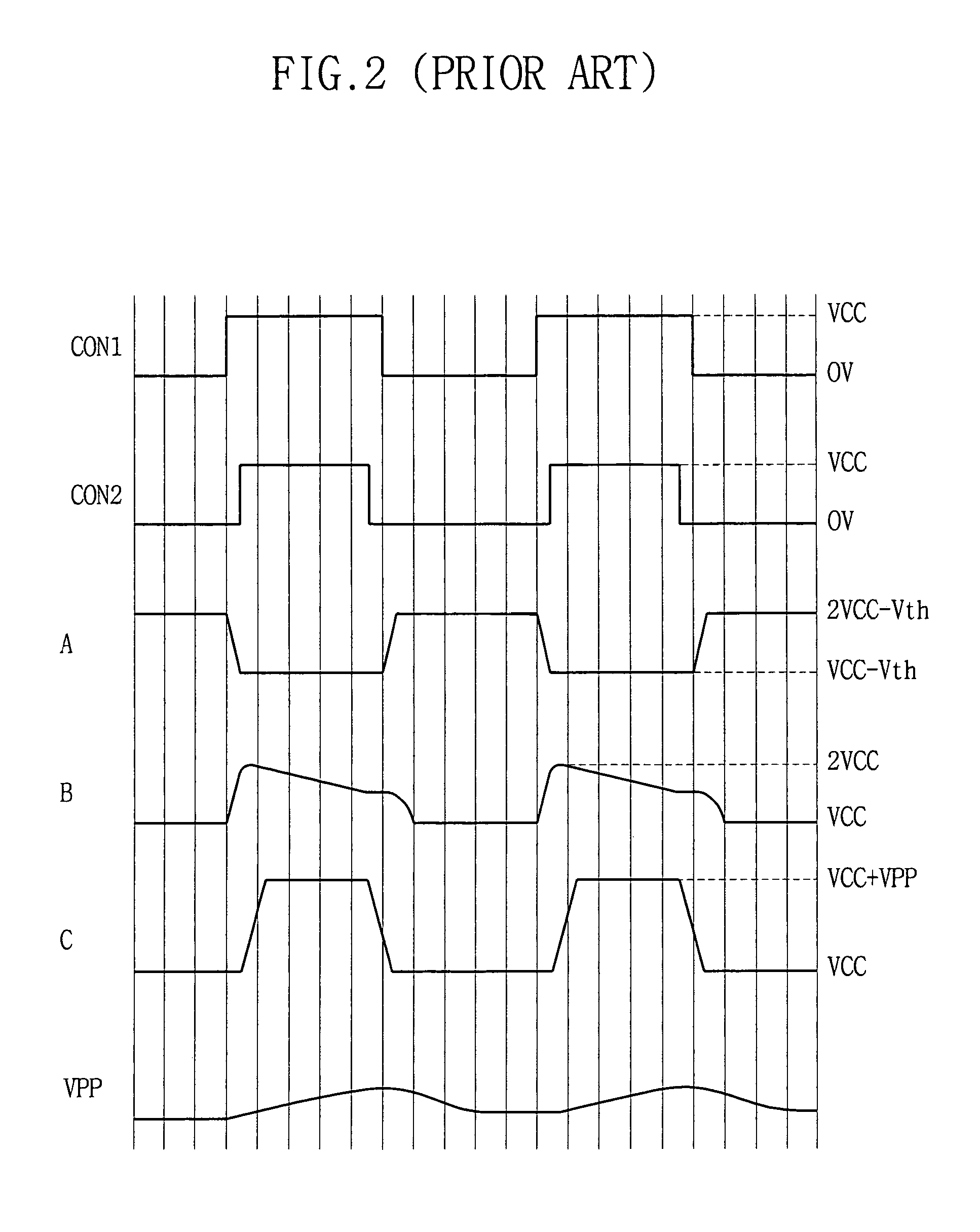

Charge pump for use in a semiconductor memory

In an embodiment, an improved charge pump circuit is provided to control a threshold voltage increase of a charge transmission transistor during a charge transfer period, and to prevent a latch-up generation during a charge non-transfer period. A charge transmission transistor transmits the voltage of a boosting node to a high voltage generation terminal in response to the voltage of a control node. In a bulk connection switch, during the charge transfer period the high voltage generation terminal is connected to the bulk of the charge transmission transistor and during the charge non-transfer period the bulk is connected to the low voltage, being lower than that of the voltage appearing at the boosting node of the charge transmission transistor or the high voltage generation terminal. Charge transmission efficiency and pumping operation reliability are improved, increasing the reliability of data access operations in a semiconductor memory device, for example.

Owner:SAMSUNG ELECTRONICS CO LTD

High-speed and high-linearity grid voltage bootstrap switching circuit

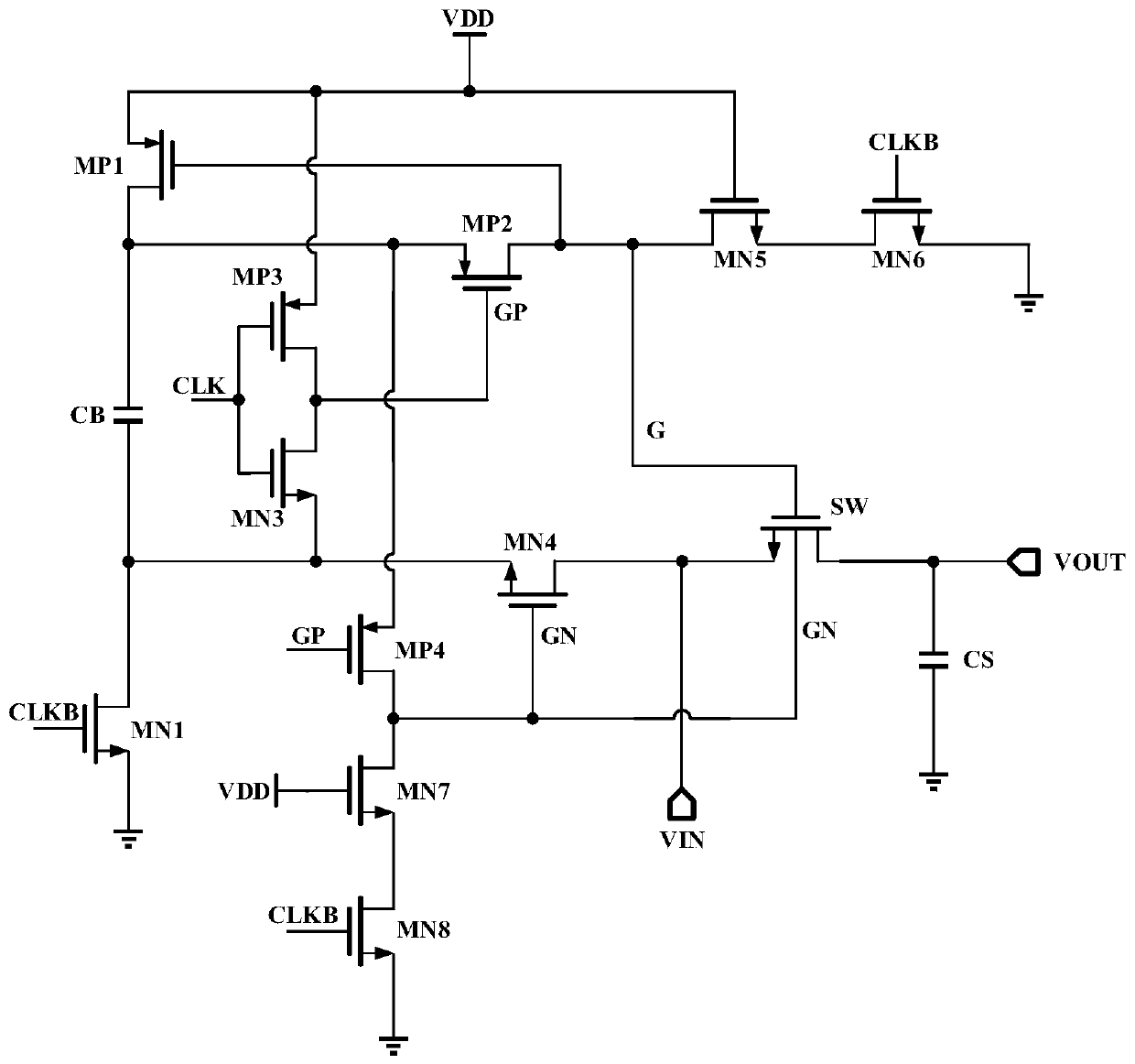

ActiveCN111245413AReduce body effectImprove linearityEfficient power electronics conversionElectronic switchingParasitic capacitanceHemt circuits

The invention, which belongs to the technical field of analog circuit, discloses a high-speed and high-linearity grid voltage bootstrap switching circuit. According to the invention, GN node signals generated by a fourth PMOS transistor, an eighth NMOS transistor and a seventh NMOS transistor are used for controlling the grid electrode of the fourth NMOS transistor; in addition, the same signal, namely a GN node signal, is used for controlling a substrate of a sampling switch tube, so that the substrate potential of the sampling switch tube is kept consistent with the grid potential during sampling, and thus the speed of the circuit is increased; the parasitic capacitance of the grid terminal of the sampling switch tube is reduced by reducing the number of the tubes connected with the gridterminal of the sampling switch tube; meanwhile, the bulk effect in the secondary effect of the MOS tube is reduced, the linearity of the sampling switch tube is ensured, and finally, the precisionof the sampling switch circuit is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

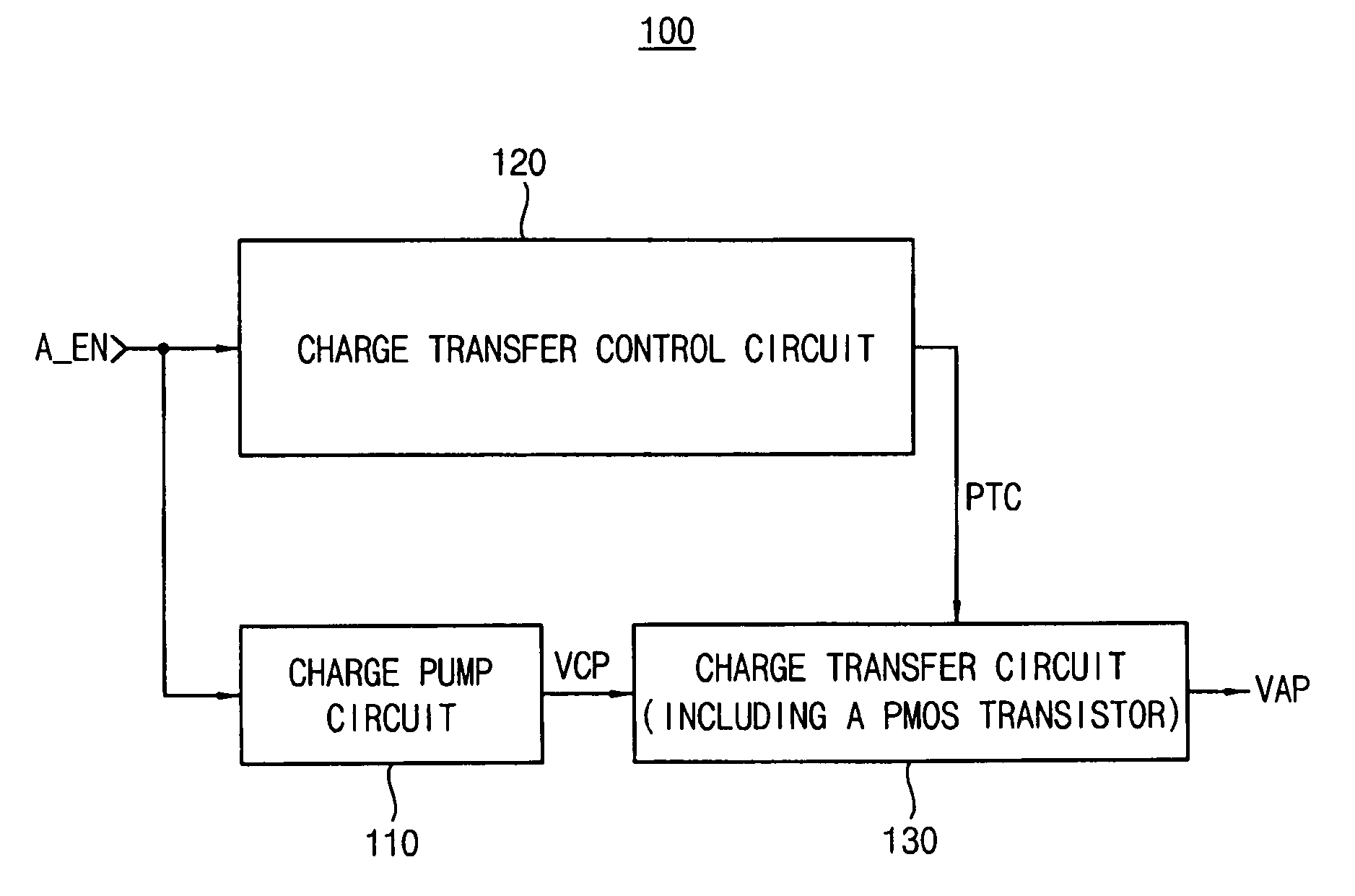

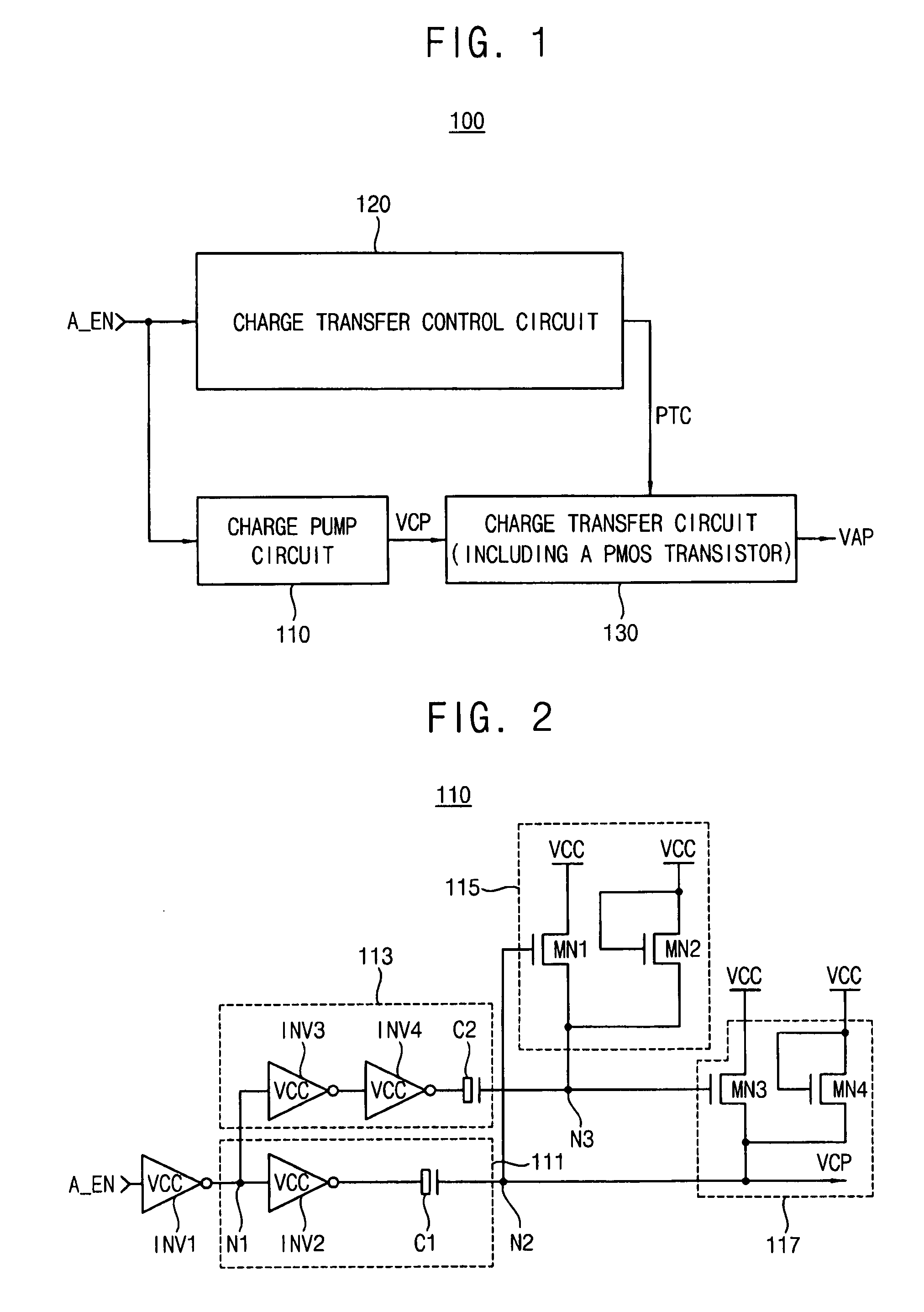

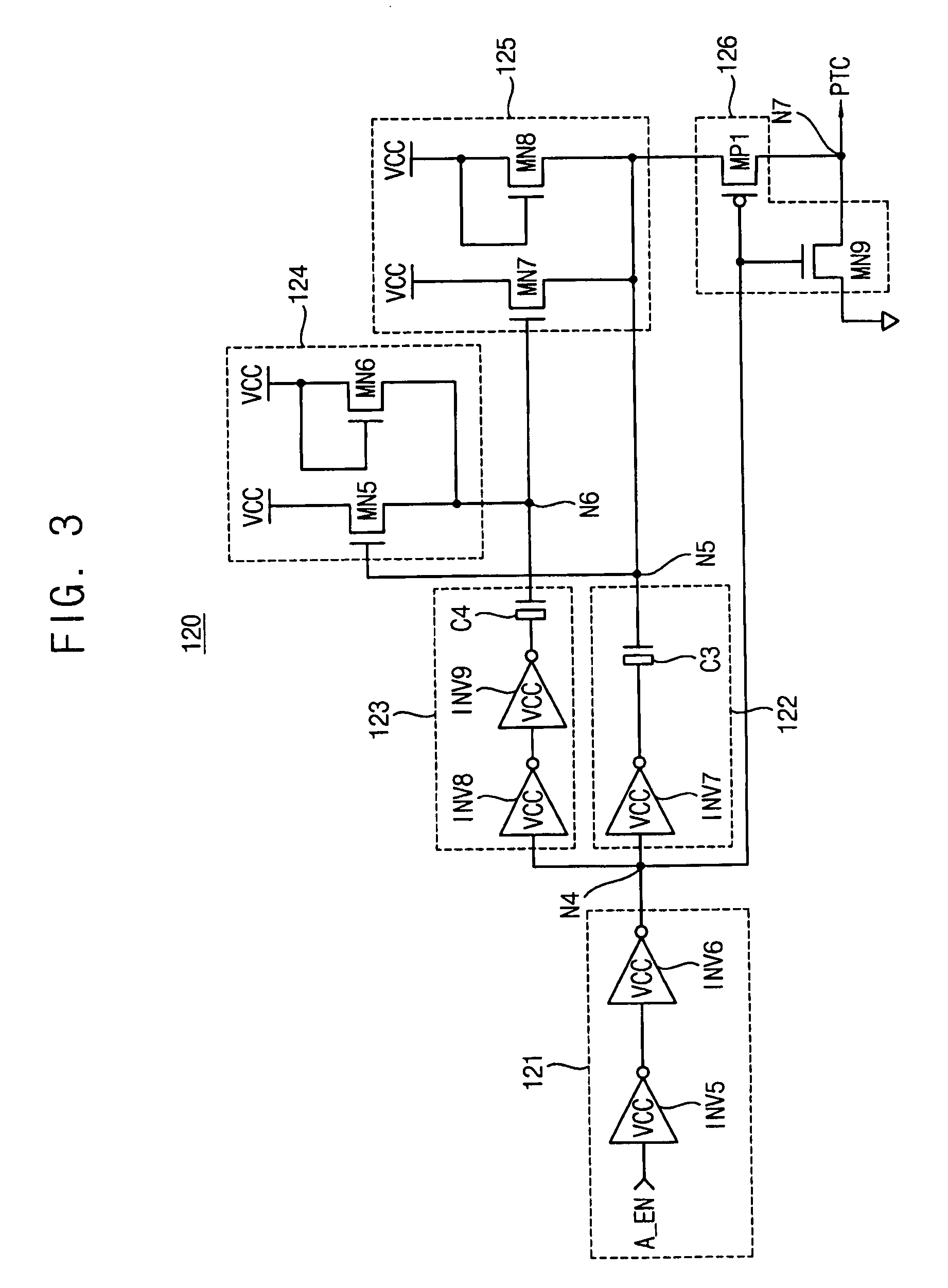

Voltage generating circuit and semiconductor device having the same

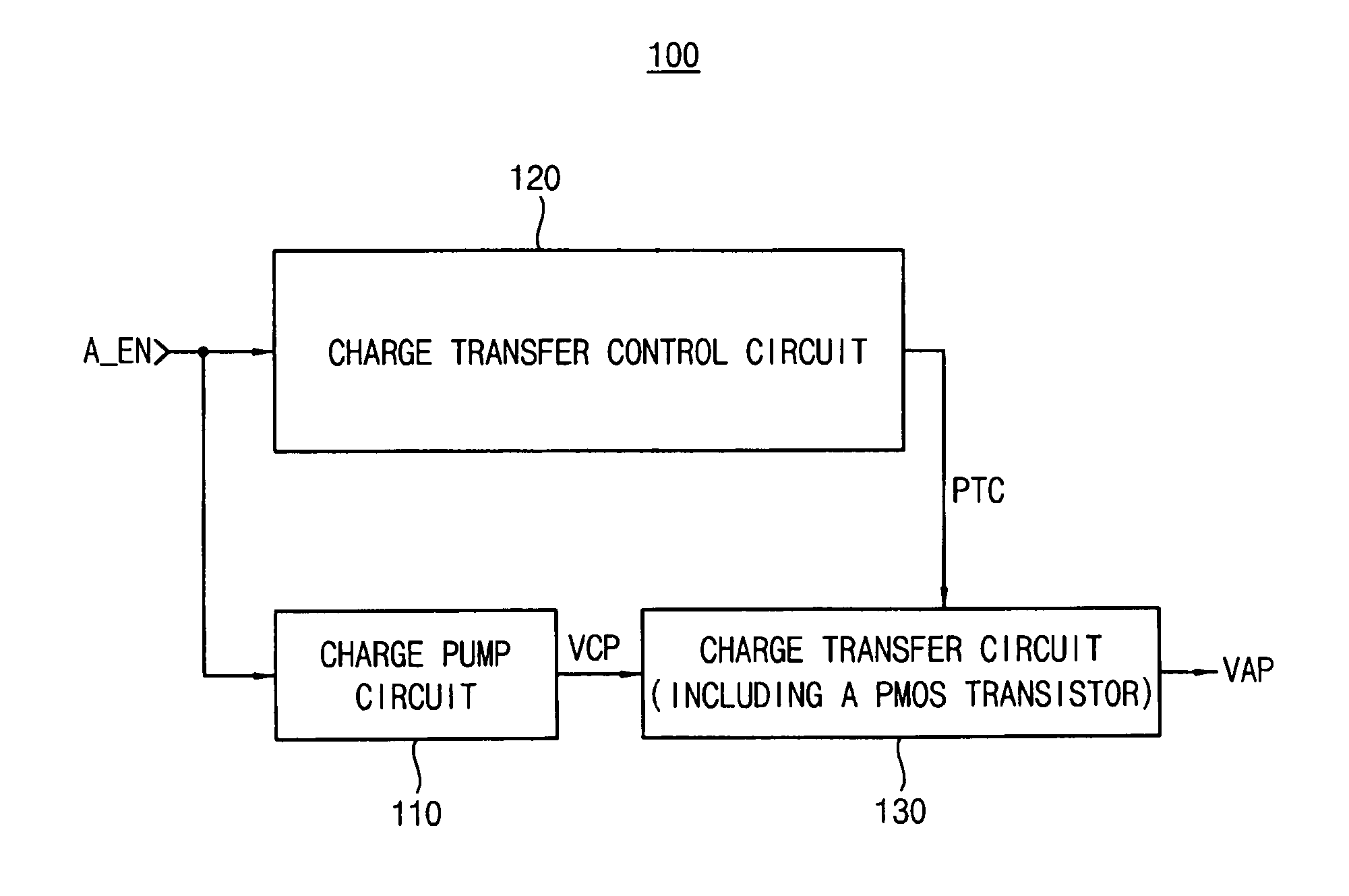

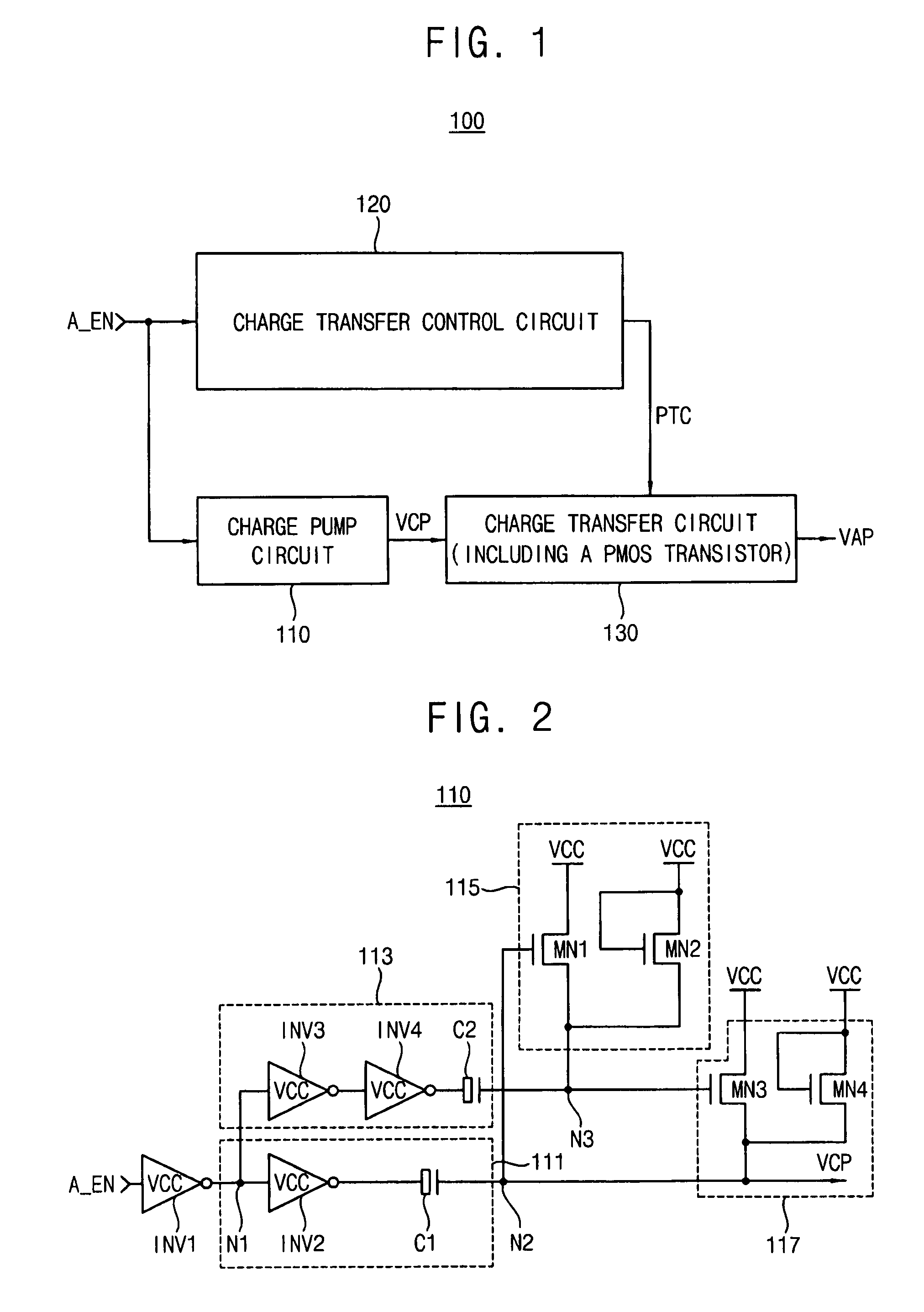

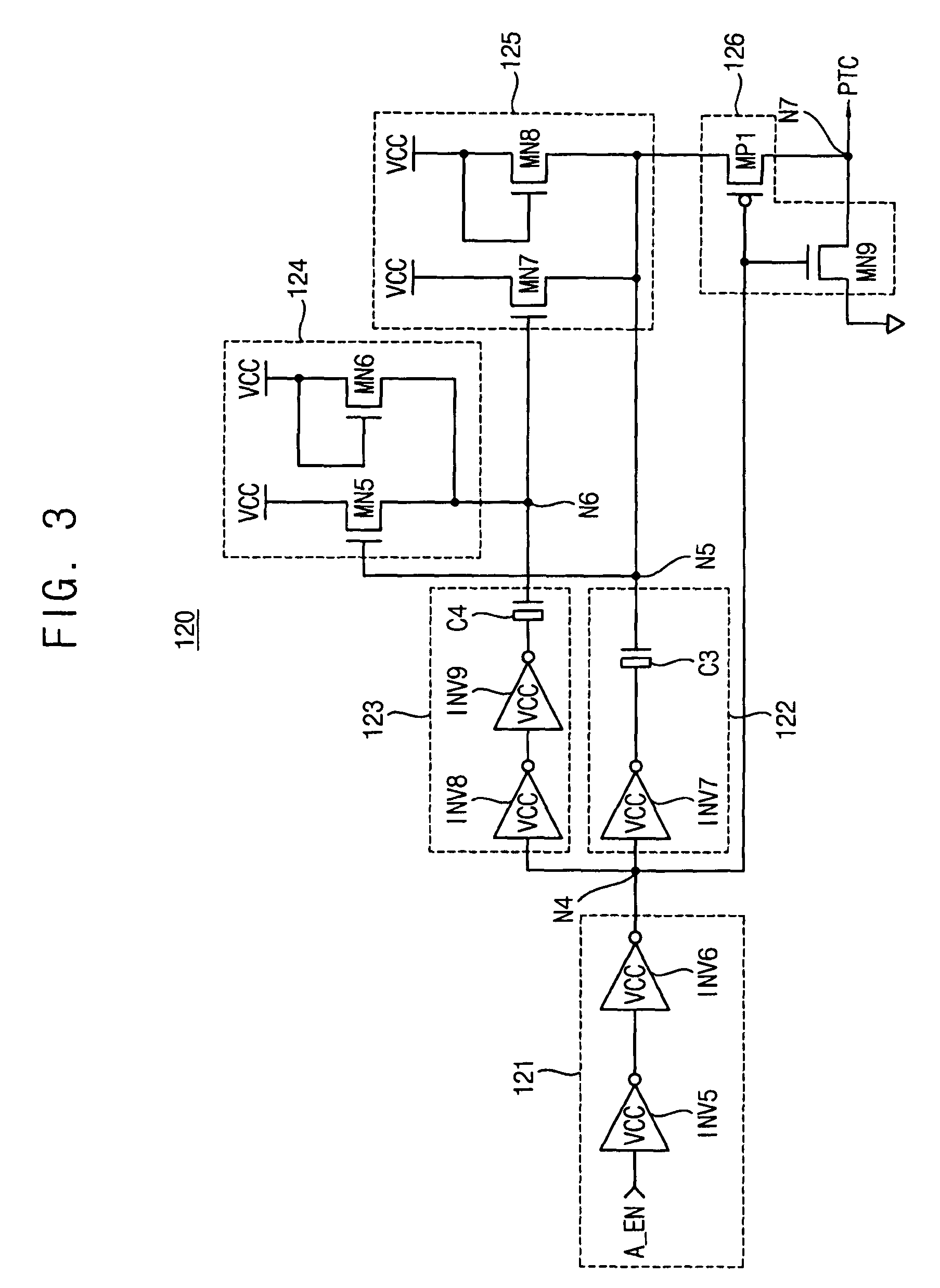

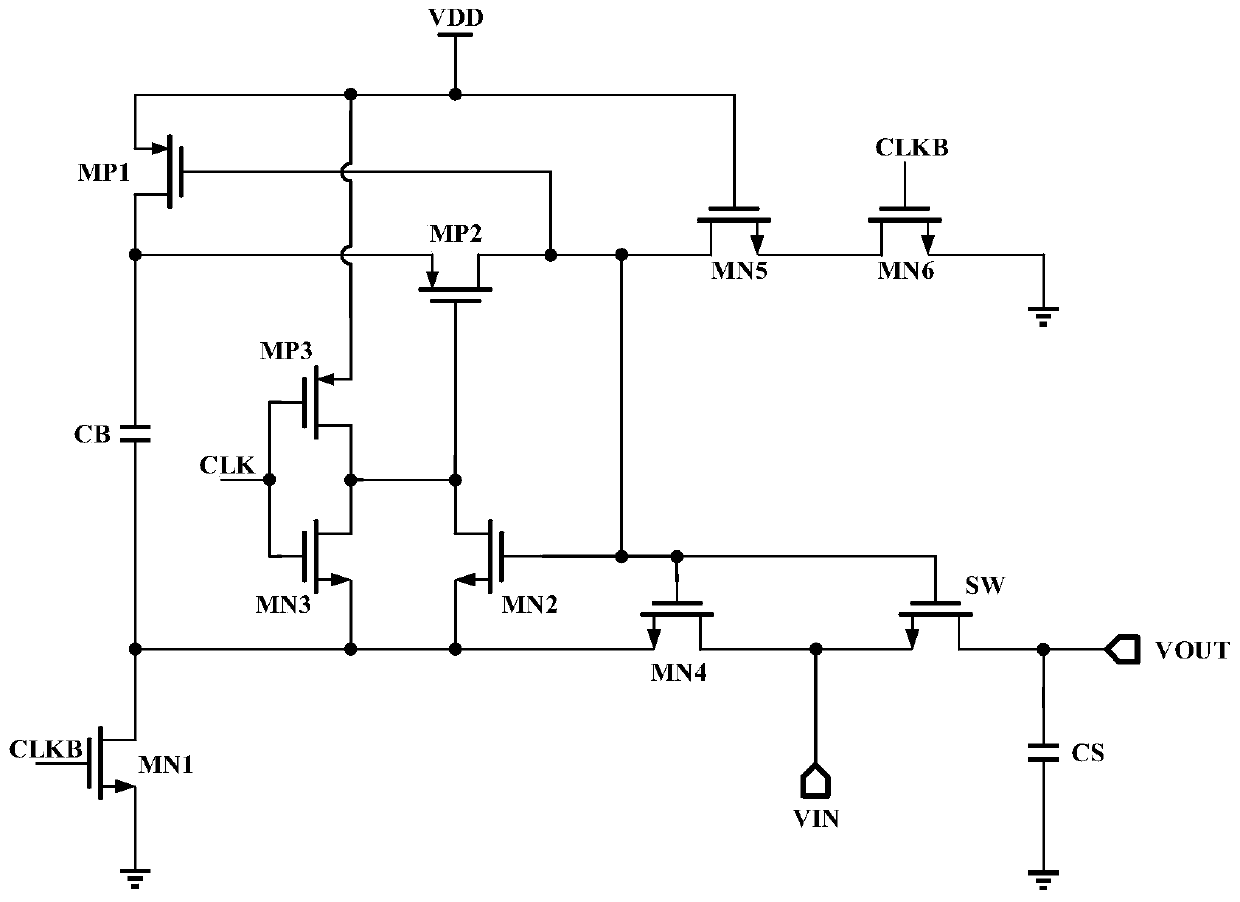

ActiveUS20090261892A1Improve reliabilityReduce power consumptionApparatus without intermediate ac conversionDigital storageControl signalDevice material

An active charge pump circuit may include a charge pump circuit, a control circuit, and a charge transfer circuit. The charge pump circuit may generate a charge pumping voltage in response to an active enable signal. The control circuit may generate a charge transfer control signal varying between a ground voltage and a boosted power supply voltage that is twice as much as a power supply voltage in response to the active enable signal. The charge transfer circuit may output the charge pumping voltage as an active voltage in response to the charge transfer control signal.

Owner:SAMSUNG ELECTRONICS CO LTD

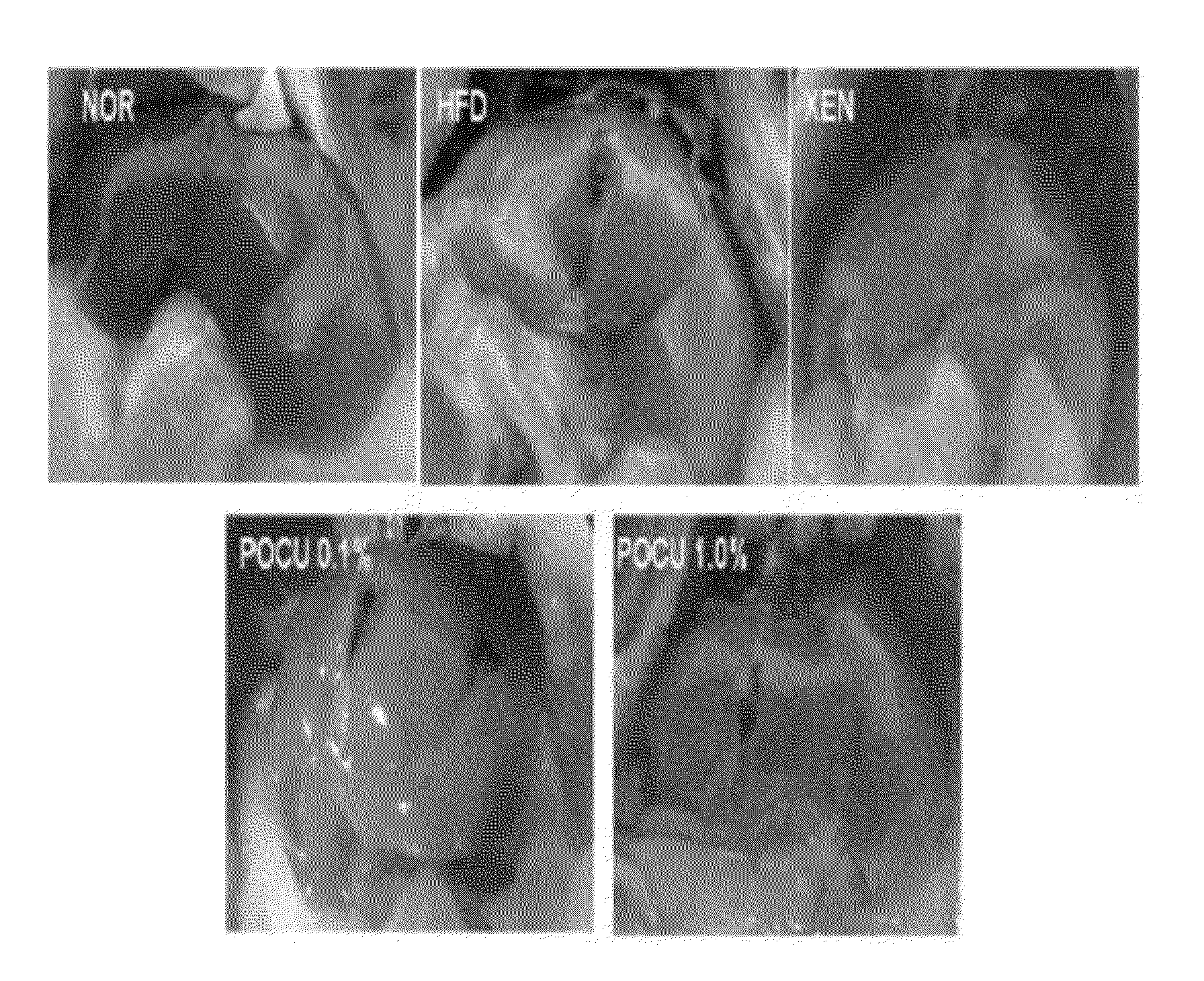

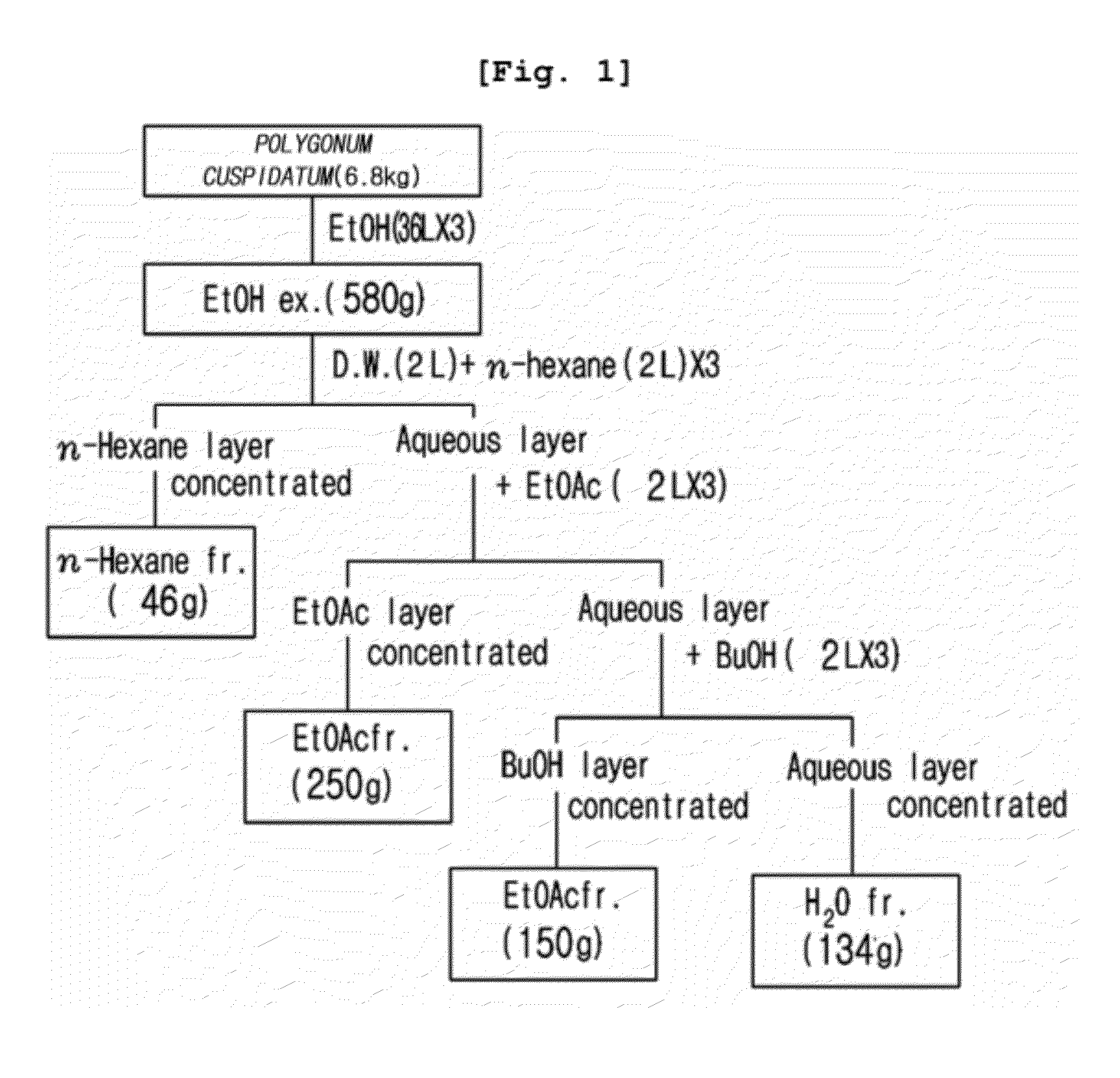

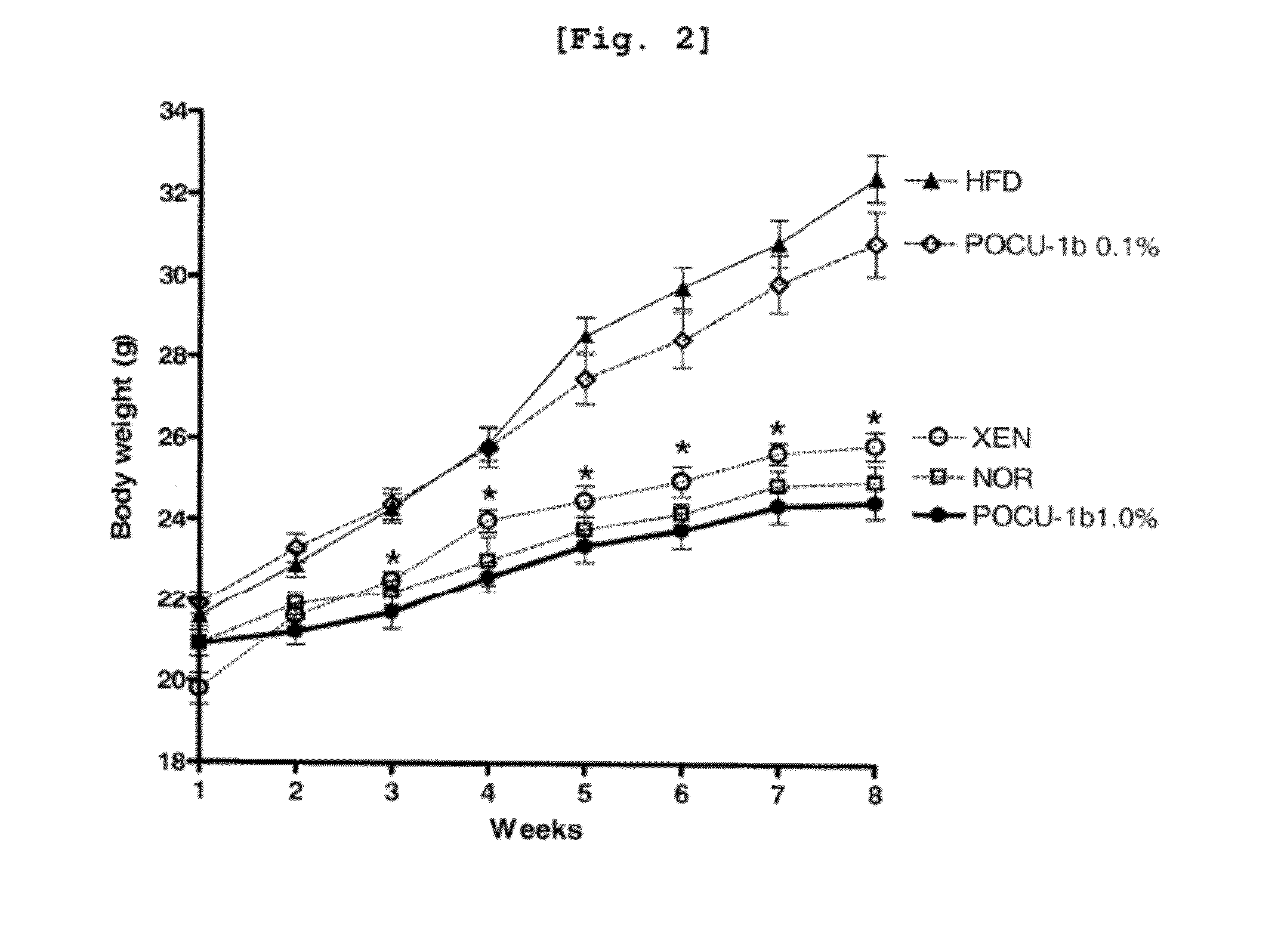

Compositions and functional foods for treating and preventing obesity using polygonum cuspidatum butanol fraction and ethyl acetate fraction

ActiveUS20120183633A1Reduce obesityToxic reductionBiocideMetabolism disorderEthyl acetateBULK ACTIVE INGREDIENT

The present invention relates to the obesity-curative or obesity-preventive effect of a Polygonum cuspidatum butanol fraction and a Polygonum cuspidatum ethylacetate fraction, and more particularly, to a pharmaceutical composition and a functional food for treating obesity, the pharmaceutical composition and the functional food comprising a Polygonum cuspidatum butanol fraction (POCU-1b) and an ethylacetate fraction as active ingredients, wherein the Polygonum cuspidatum butanol fraction and the ethylacetate fraction inhibit effectively the activity of pancreatic lipase, an important enzyme involving in fat absorption in a living body, and have excellent inhibitory effect on fat absorption in the short term fat absorption-inhibitory animal experiments using lipid emulsions.

Owner:KOREA INST OF ORIENTAL MEDICINE

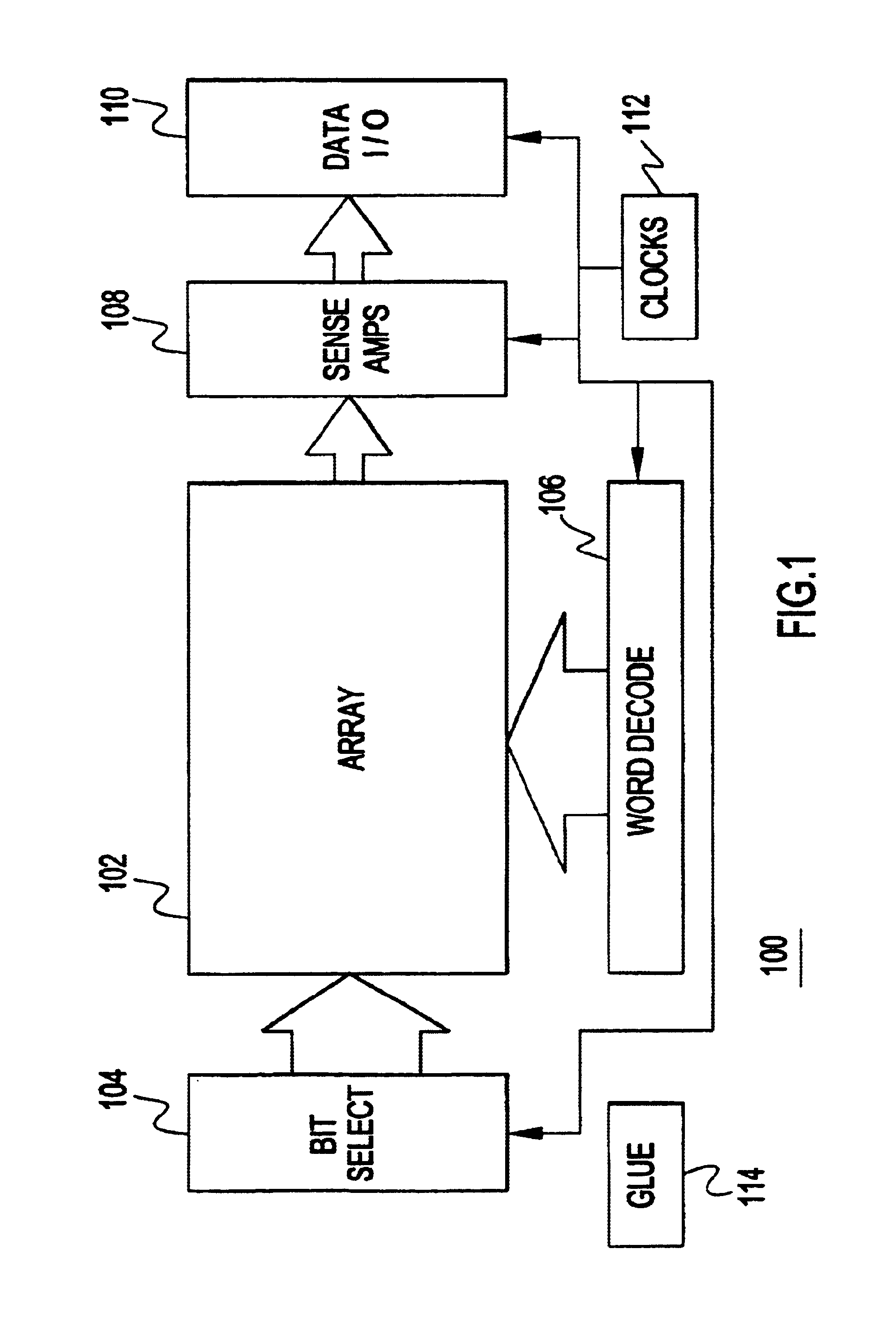

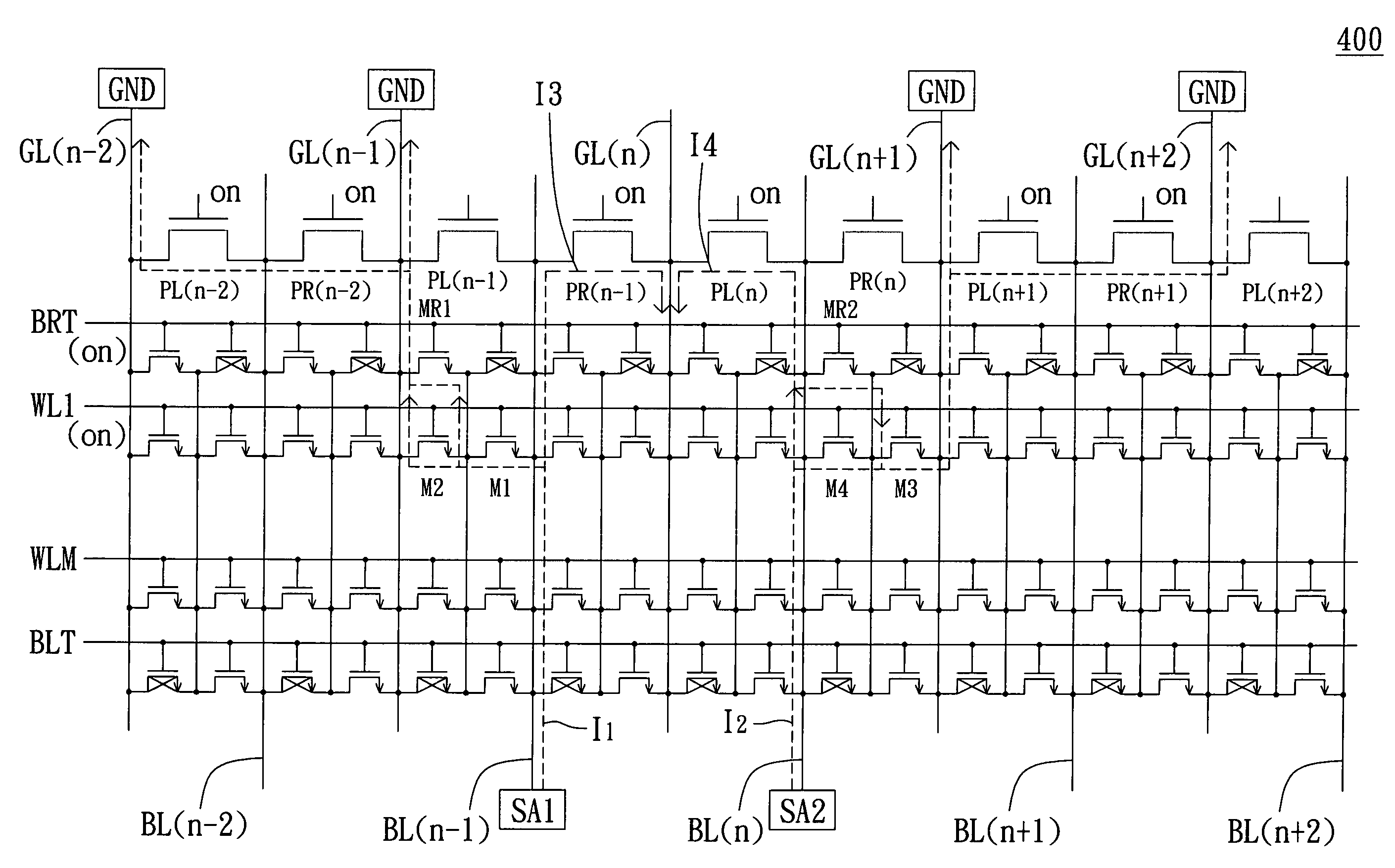

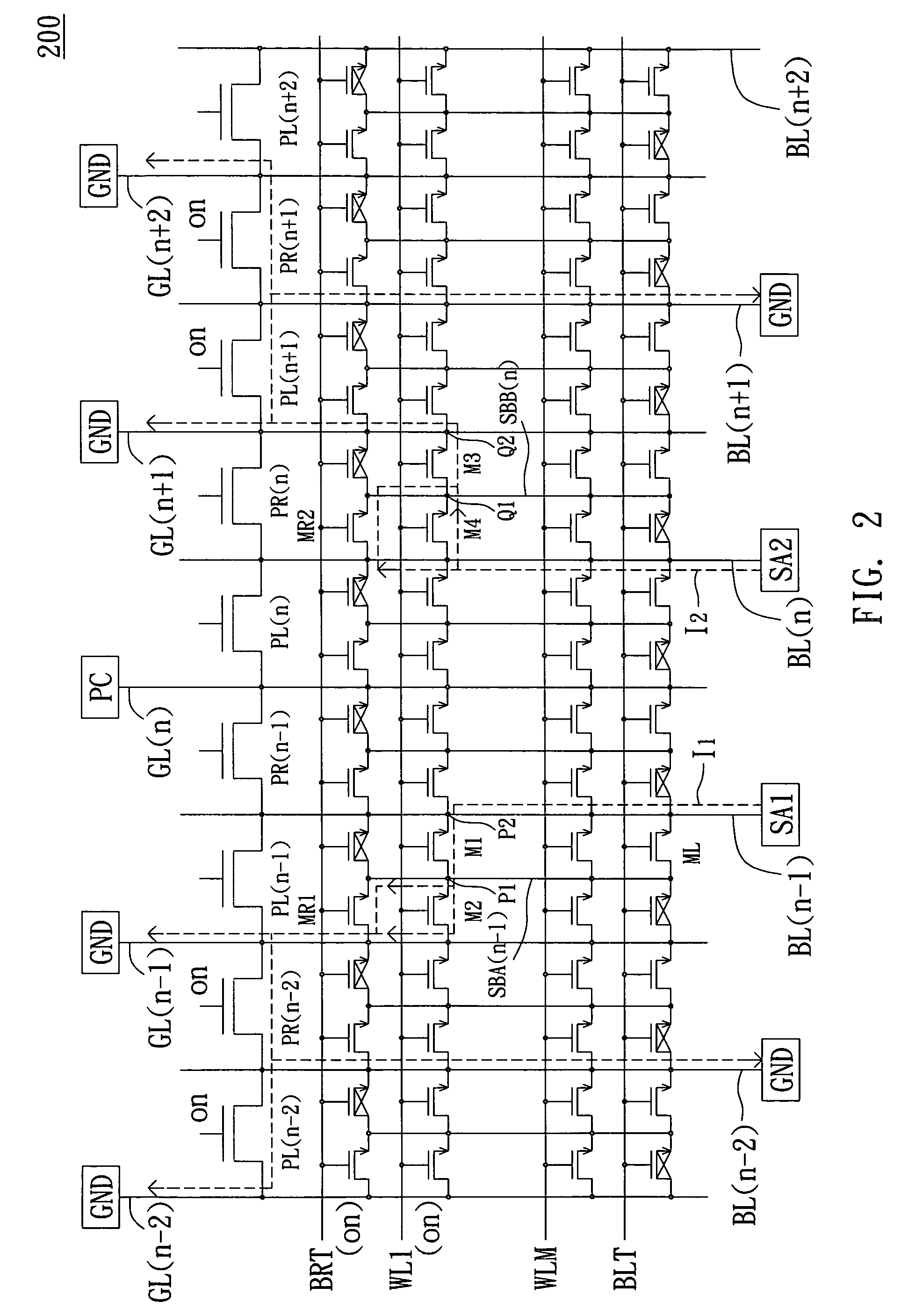

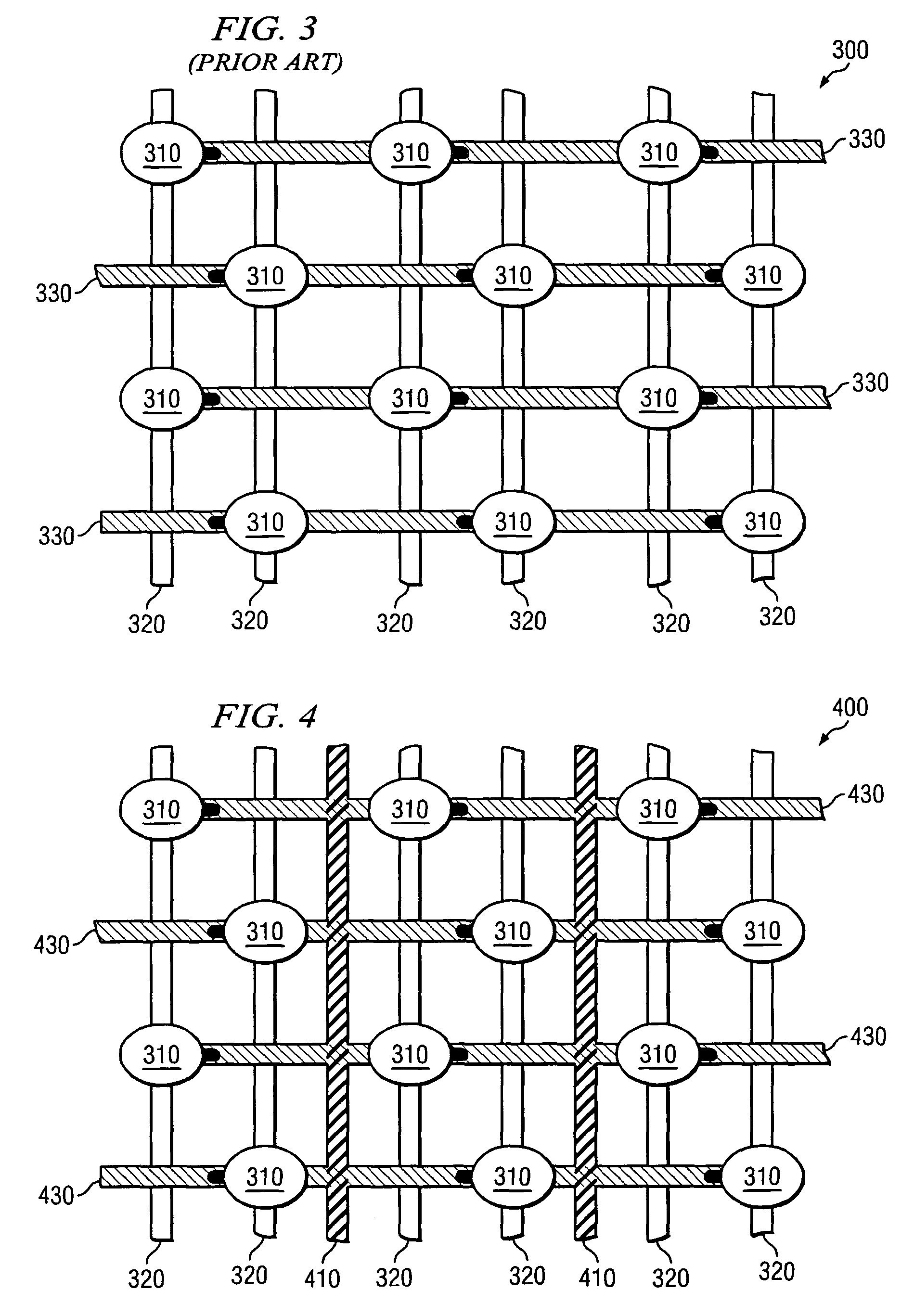

Memory with low and fixed pre-charge loading

ActiveUS6980456B2Load largeReduce power consumptionRead-only memoriesSemiconductor/solid-state device manufacturingAudio power amplifierPre-charge

A virtual ground memory with low and fixed pre-charge loading is provided. First metal lines GL(n−1), GL(n), and GL(n+1) and second metal lines BL(n−1) and BL(n) are disposed in the sequence GL(n−1), BL(n−1), GL(n), BL(n) and GL(n+1). Each first metal line and the adjacent second metal line are coupled respectively to two ends of the corresponding memory cell. Word lines are used for controlling memory cells. The second metal lines BL are in high level when the memory cells which the second metal lines BL are coupled to are chosen. A first and second sense amplifier are coupled to the second metal line BL(n−1) and BL(n) respectively, and the first metal lines GL(n−1) and GL(n+1) are coupled to ground level. One of the word lines is enabled to read the corresponding memory cells. A virtual ground memory loading can be fixed by this invention.

Owner:MACRONIX INT CO LTD

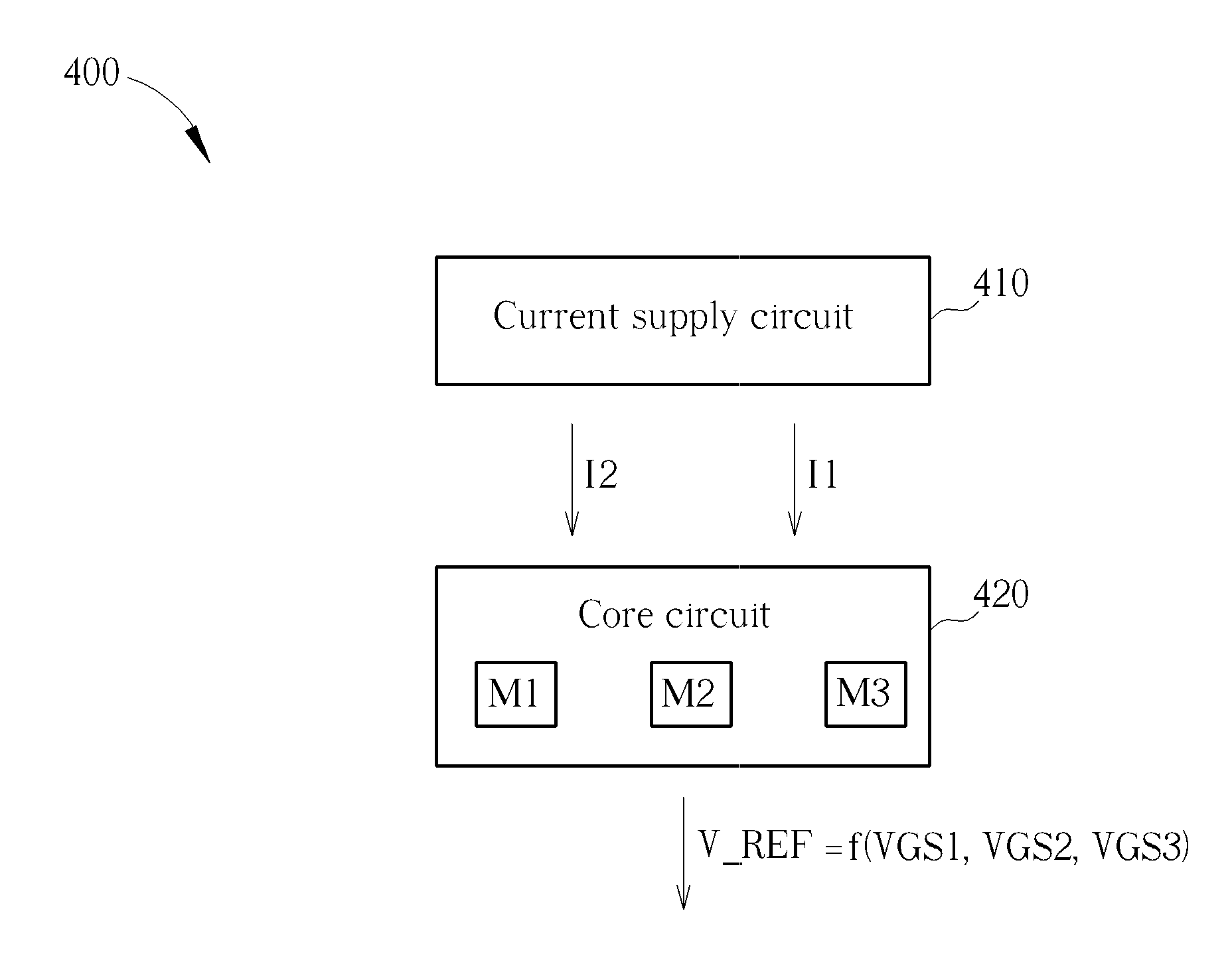

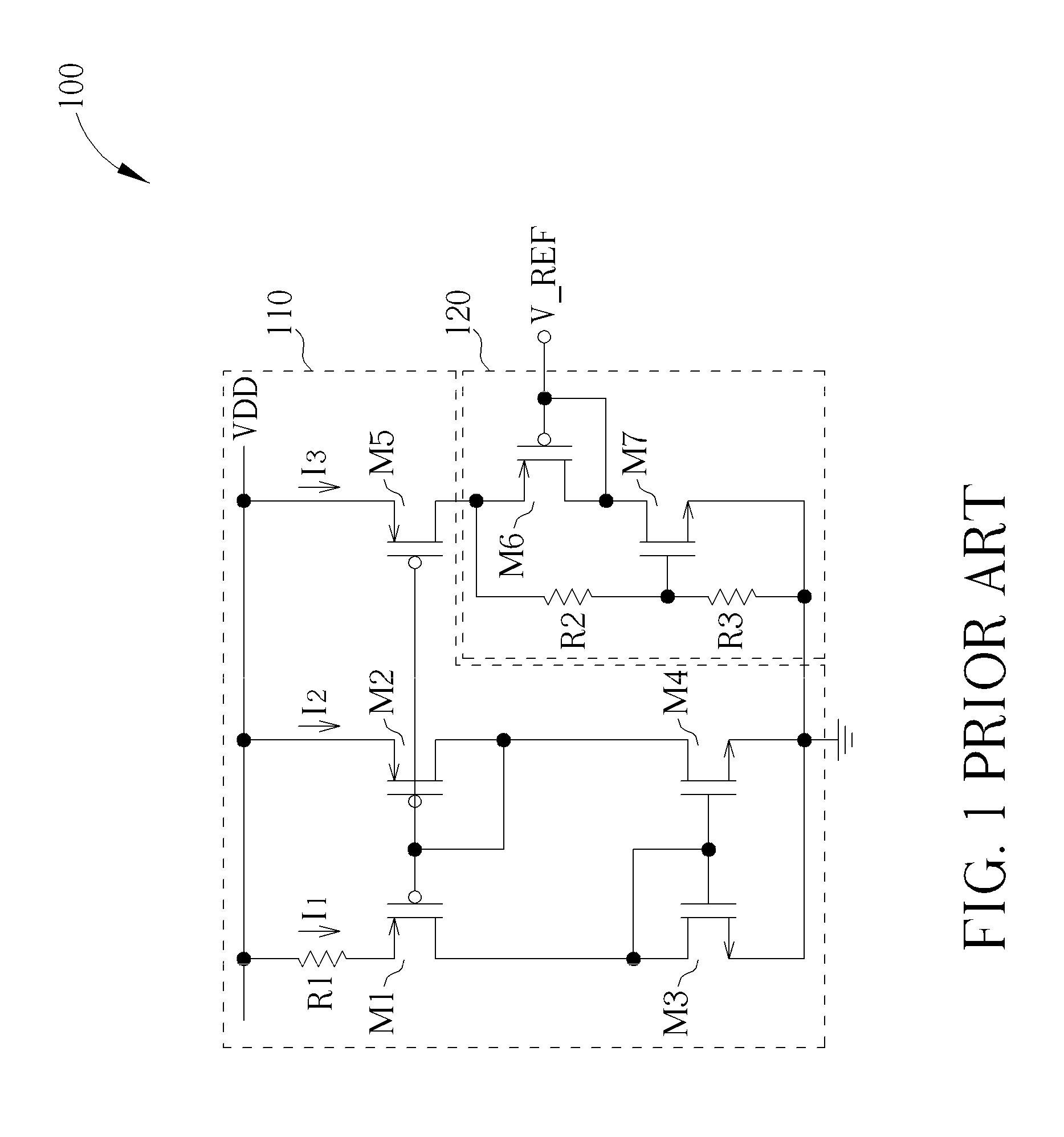

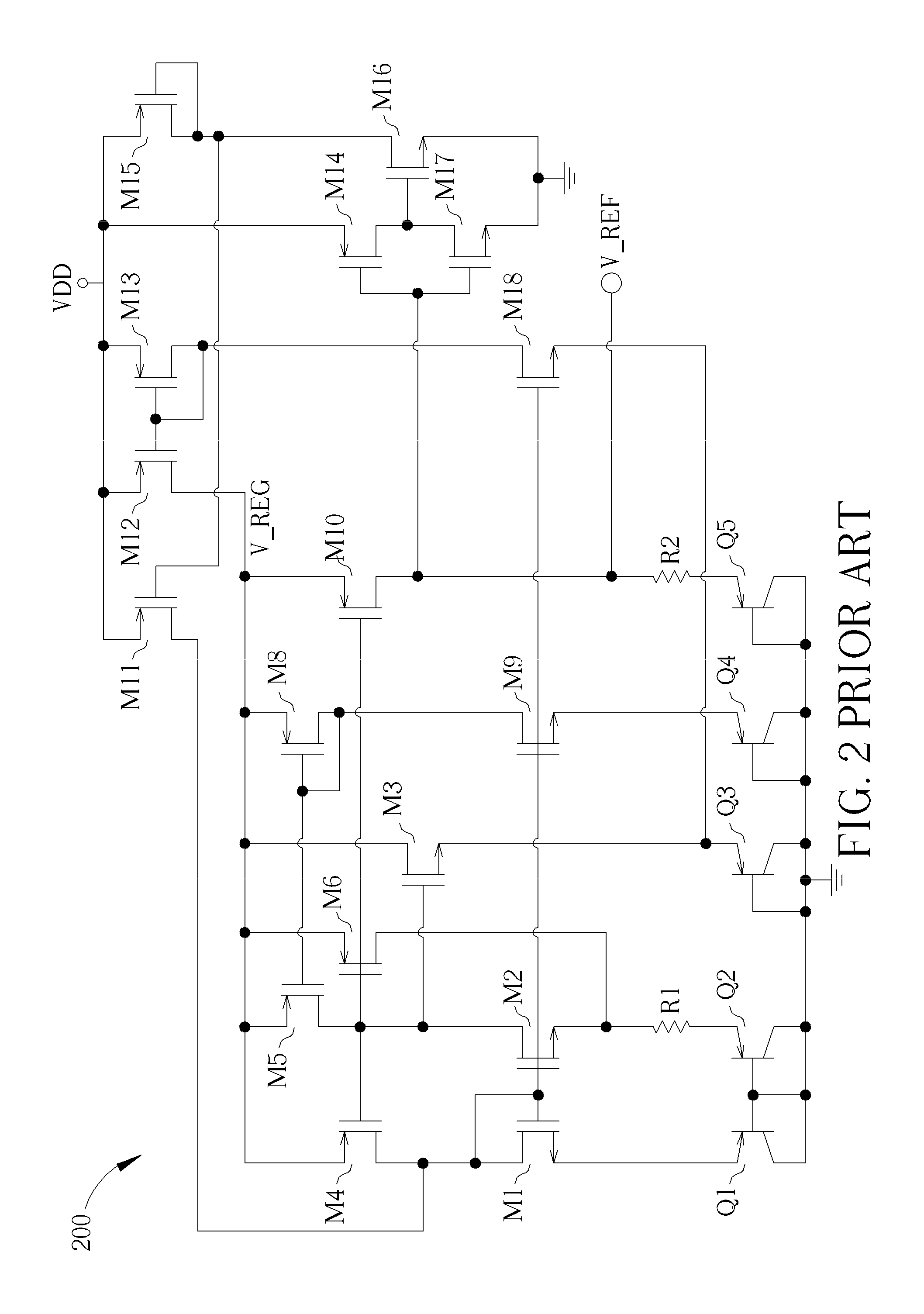

Voltage reference generation circuit using gate-to-source voltage difference and related method thereof, and voltage regulation circuit having common-source configuration and related method thereof

ActiveUS20130193935A1Reduction factorWideband high PSRRElectric variable regulationVoltage regulationHemt circuits

A voltage reference generation circuit includes a current supply circuit and a core circuit. The current supply circuit is arranged to provide a plurality of currents. The core circuit is coupled to the current supply circuit, and arranged to receive the currents and accordingly generate a voltage reference. The core circuit includes a first transistor, a second transistor and a third transistor, wherein the first transistor and the third transistor generate a first gate-to-source voltage and a third gate-to-source voltage, respectively, according to a first current of the received currents; the second transistor generates a second gate-to-source voltage according to a second current of the received currents; and the voltage reference is generated according to the first gate-to-source voltage, the second gate-to-source voltage and the third gate-to-source voltage.

Owner:SPI ELECTRONICS

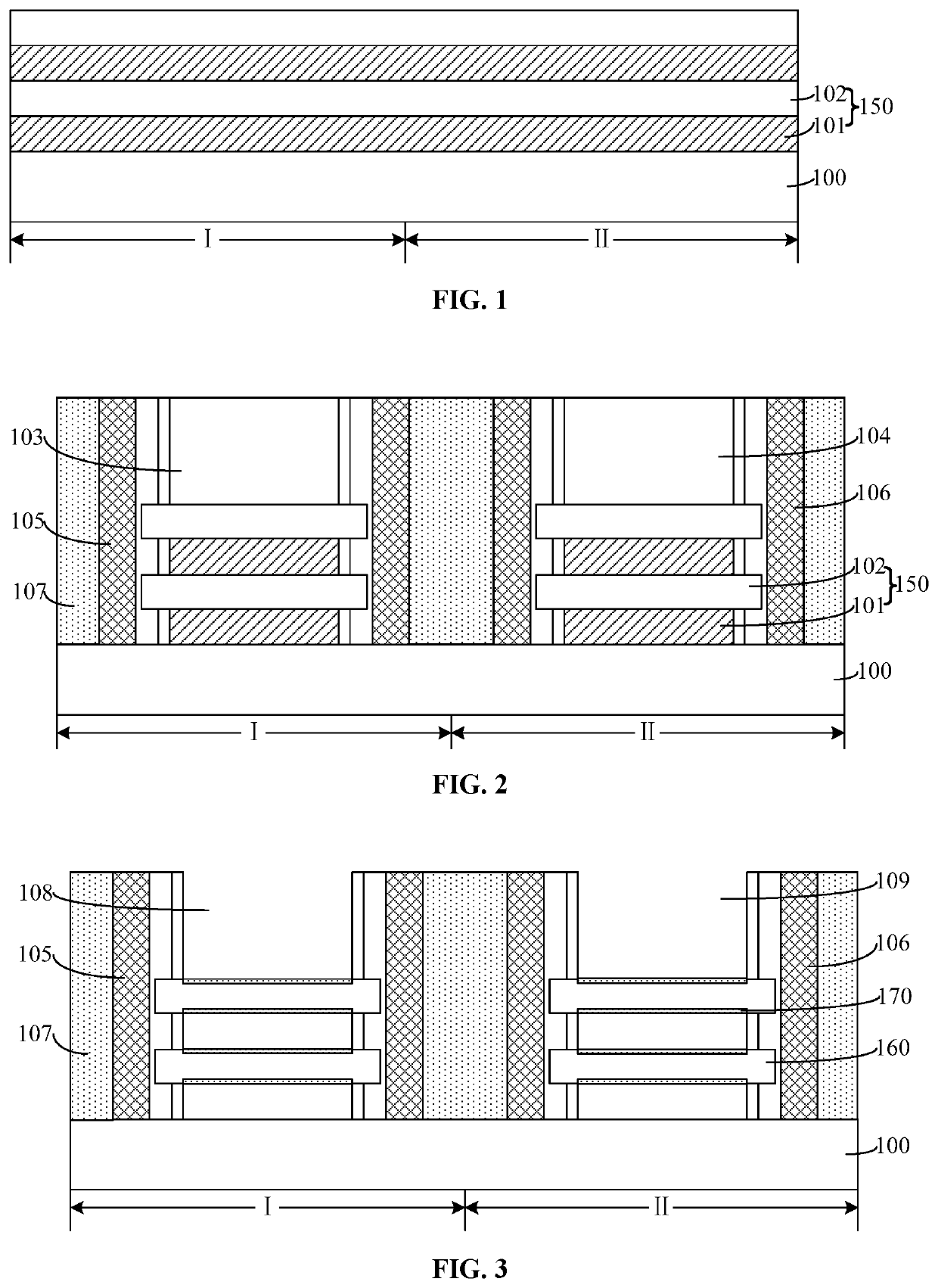

Semiconductor structure and fabrication method

ActiveUS11164941B2Reduce body effectFacilitate complete depletion of depletion layerTransistorNanoinformaticsNanowireSemiconductor structure

Semiconductor structures and fabrication methods are provided. An exemplary fabrication method includes providing a semiconductor substrate having a first region and a second region; forming first nanowires over the first region of the semiconductor substrate; forming second nanowires with a diameter smaller than a diameter of the first nanowires over the second region of the semiconductor substrate; forming a first gate layer around the first nanowires; and forming a second gate layer around the second nanowires.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

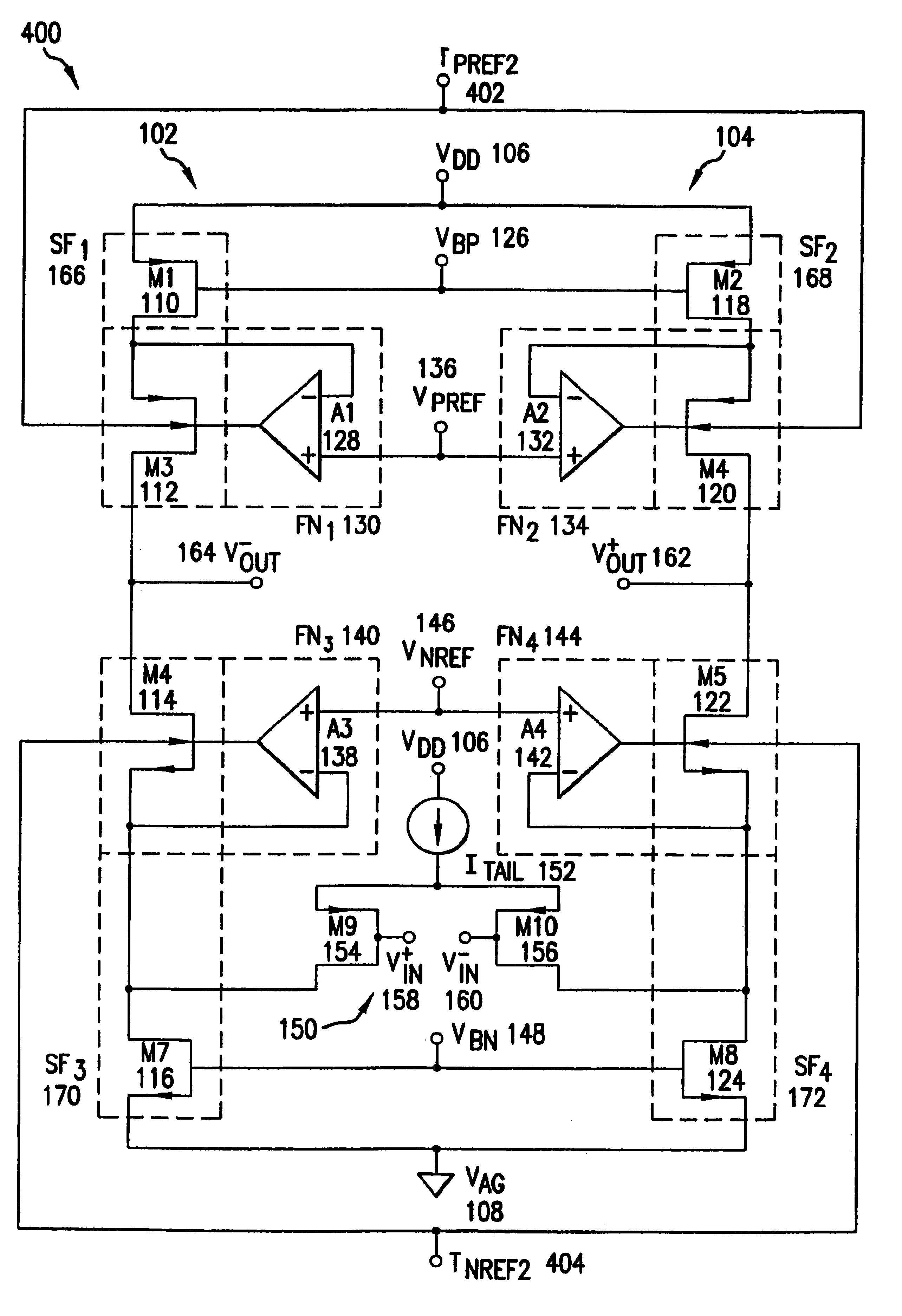

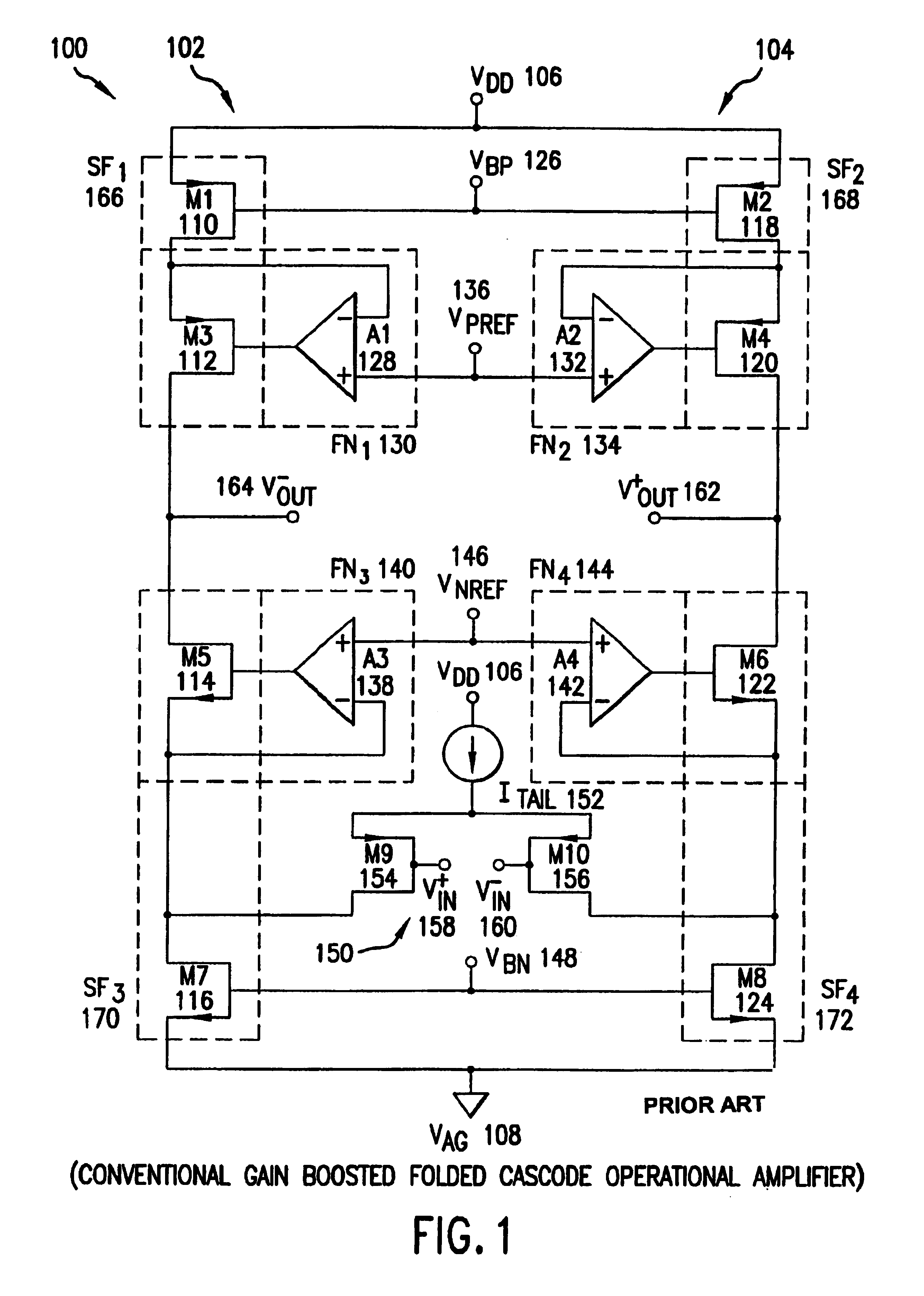

MOSFET well biasing scheme that mitigates body effect

InactiveUS6956434B2Reduce power consumptionReduce body effectAmplifier modifications to reduce temperature/voltage variationDifferential amplifiersMOSFETAudio power amplifier

A biasing scheme for a MOSFET that mitigates the MOSFET body effect. The biasing scheme can be realized replicating the voltage at the source terminal of a MOSFET and applying this replicated voltage to the body terminal. In this manner, the effect of the body transconductance, at high frequencies, becomes a function of the ratio of the well-to-substrate capacitance of the MOSFET to the sum of the well-to-substrate capacitance and the source-to-body capacitance of the transistor. At high frequencies, the biasing scheme mitigates the reduction in gain of a source follower caused by the body effect of a driven MOSFET within the source follower, improves the stability of a feedback network established by a gain boosting amplifier and the driven MOSFET by contributing a negative half plane zero to the transfer function of the feedback network, and reduces the power consumed by the gain boosting amplifier.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Semiconductor structure

ActiveUS20210408236A1Reduce body effectFacilitate complete depletion of depletion layerTransistorNanoinformaticsNanowireSemiconductor structure

A semiconductor structure is provided. The semiconductor structure includes a semiconductor substrate having a first region and a second region; first nanowires formed over the first region of the semiconductor substrate; second nanowires with a diameter smaller than a diameter of the first nanowires formed over the second region of the semiconductor substrate; a first gate layer formed around the first nanowires; and a second gate layer formed around the second nanowires.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

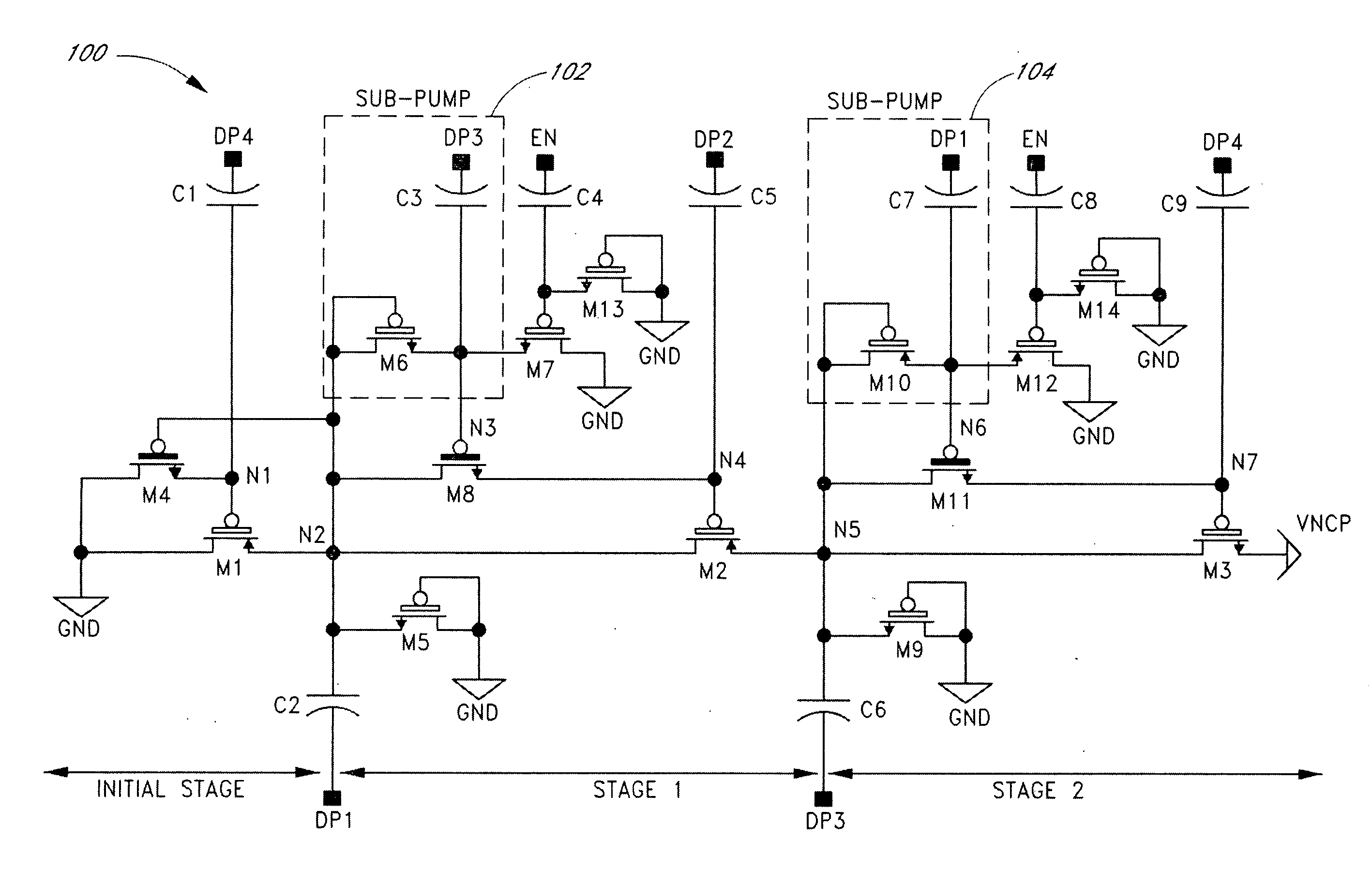

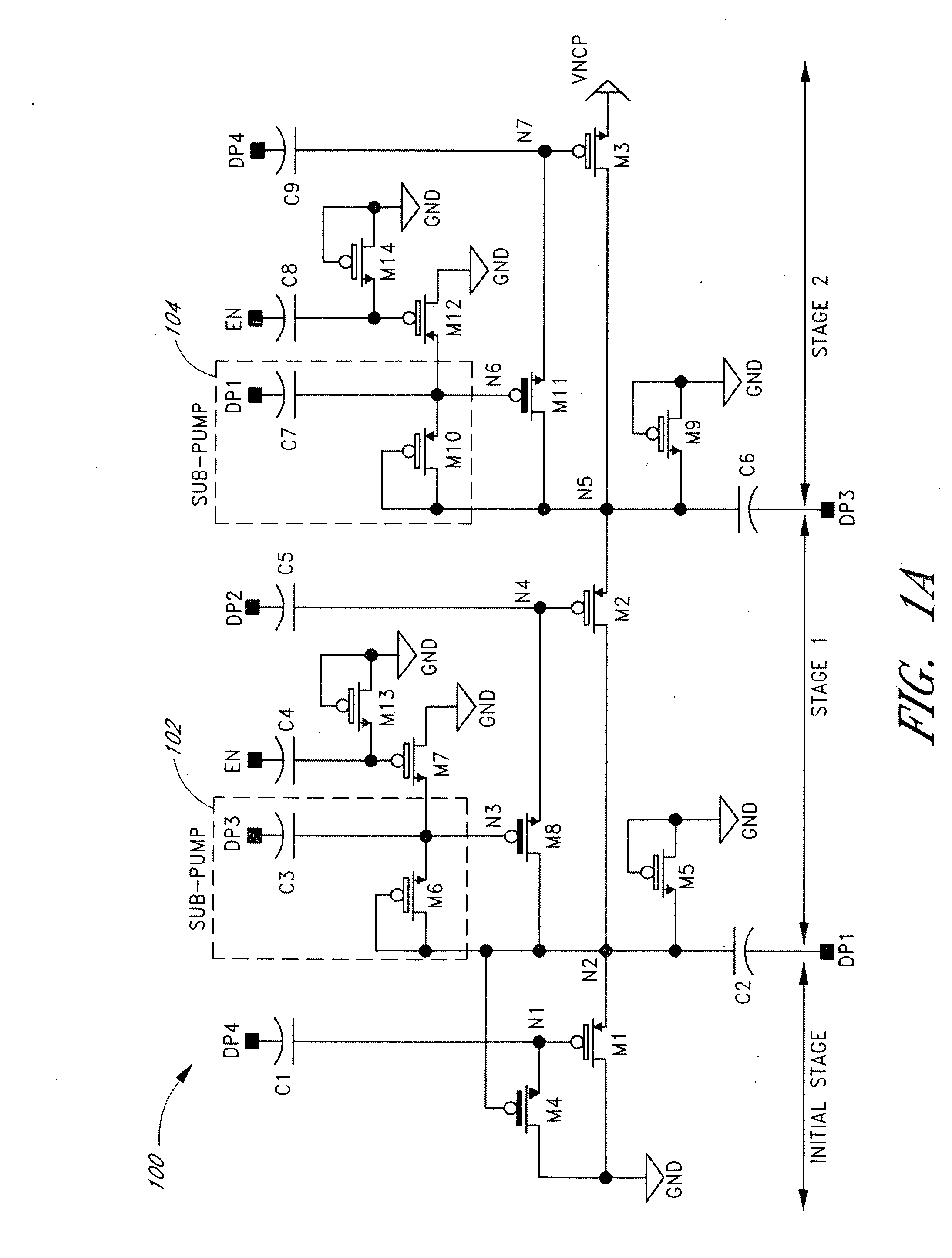

Charge pump circuit

ActiveUS20060132219A1Reduce body effectImprove precharge efficiencyAc-dc conversionApparatus without intermediate ac conversionMOSFETPre-charge

In an embodiment, a charge pump circuit comprises a first pump stage, including a first sub-pump coupled to a first pre-charge MOSFET transistor, wherein the first sub-pump is used to pump down a gate of the first pre-charge MOSFET transistor to thereby increase the pre-charge efficiency of the first pre-charge MOSFET transistor. The higher efficiency the re-charge MOSFET is, the lower the gate level of pass transistor is. Thus, the charge sharing efficiency becomes better, and the body effect will be eliminated. The following pump stage is the same as the first pump stage. In addition, this embodiment is implemented by PMOSFET only; therefore, only single well is needed and then a small layout area can be achieved. Consequently, a high efficiency negative pump can be obtained.

Owner:MACRONIX INT CO LTD

Supplementary Food Composition For Reducing Body Odor

InactiveUS20090192232A1Reducing body odorImprove reducibilityBiocidePharmaceutical non-active ingredientsFood supplementAdditive ingredient

This invention relates to a food supplement for reducing body odor; it is a mixture of edible carriers with chitin aqueous solution lyophilized powder, chitosan aqueous solution lyophilized powder, chitin powder, chitosan powder, or the composition of these ingredients, and it comes in the form of tablets or pills. The invention has an outstanding effect in reducing various types of body odors, including Koreans' unique body odor, such as Kimchi smell or garlic smell, westerners' unique body odor, such as cheese smell or butter smell, Arabs' unique body odor, such as mutton smell, armpit odor and body odor that is unique in the aged.

Owner:KIM JIN MAN

Controlled substrate voltage for memory switches

InactiveUS20050050262A1Reduce the overall heightEasy to operateDigital storageMemory systemsBody contactData Corruption

Active control of body contacts in memory devices can provide variable substrate voltages during device operation. The body contacts can be used to adjust the body bias of switches in activated memory cells, while maintaining the body bias of switches in inactive memory cells. This can reduce the body effect (i.e., variation of the threshold voltage due to a variation of the substrate or bulk voltage) and can therefore provide improved array device performance (e.g., reduced data corruption) while the word line (“WL”) is activated.

Owner:POLARIS INNOVATIONS

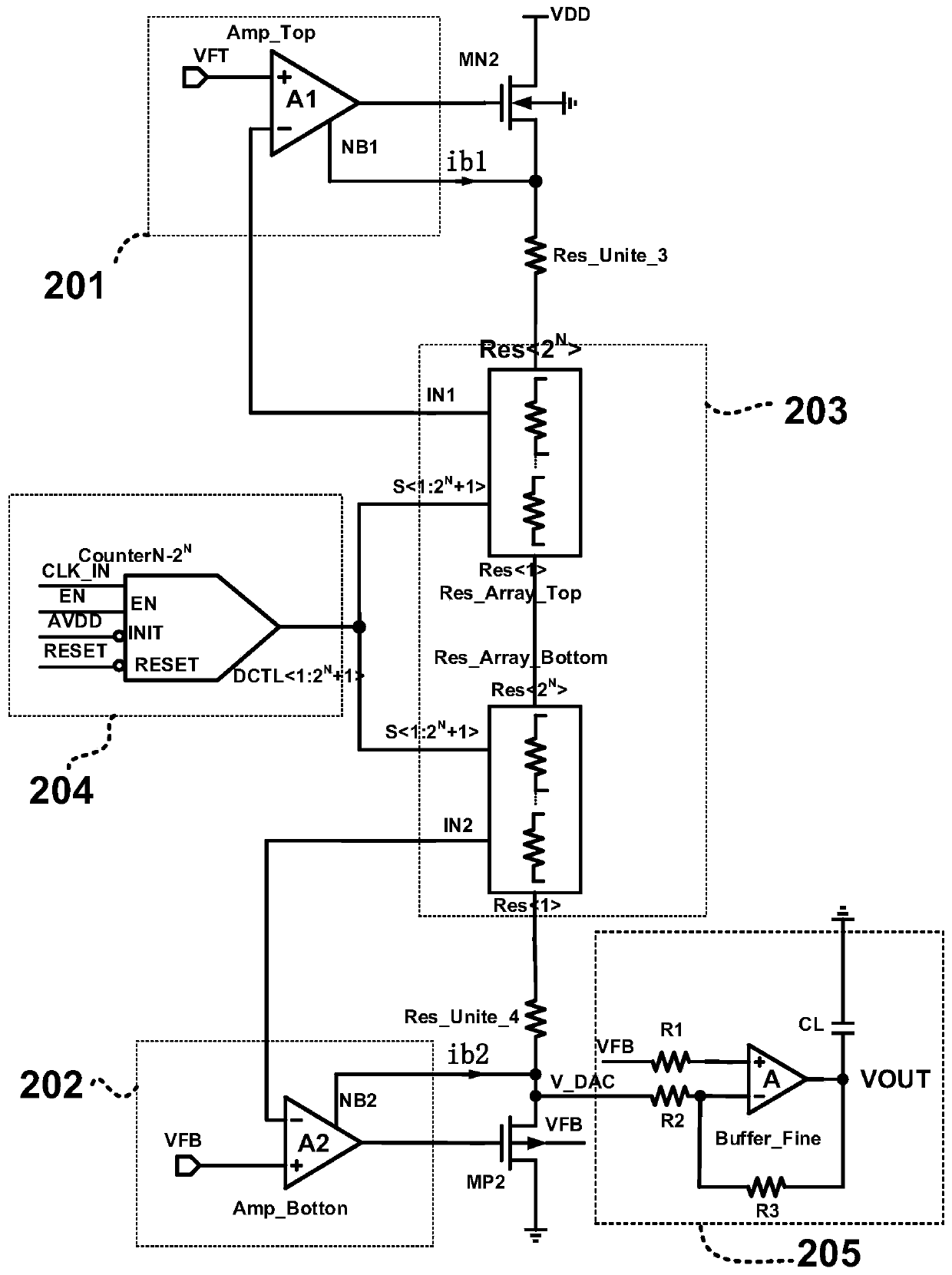

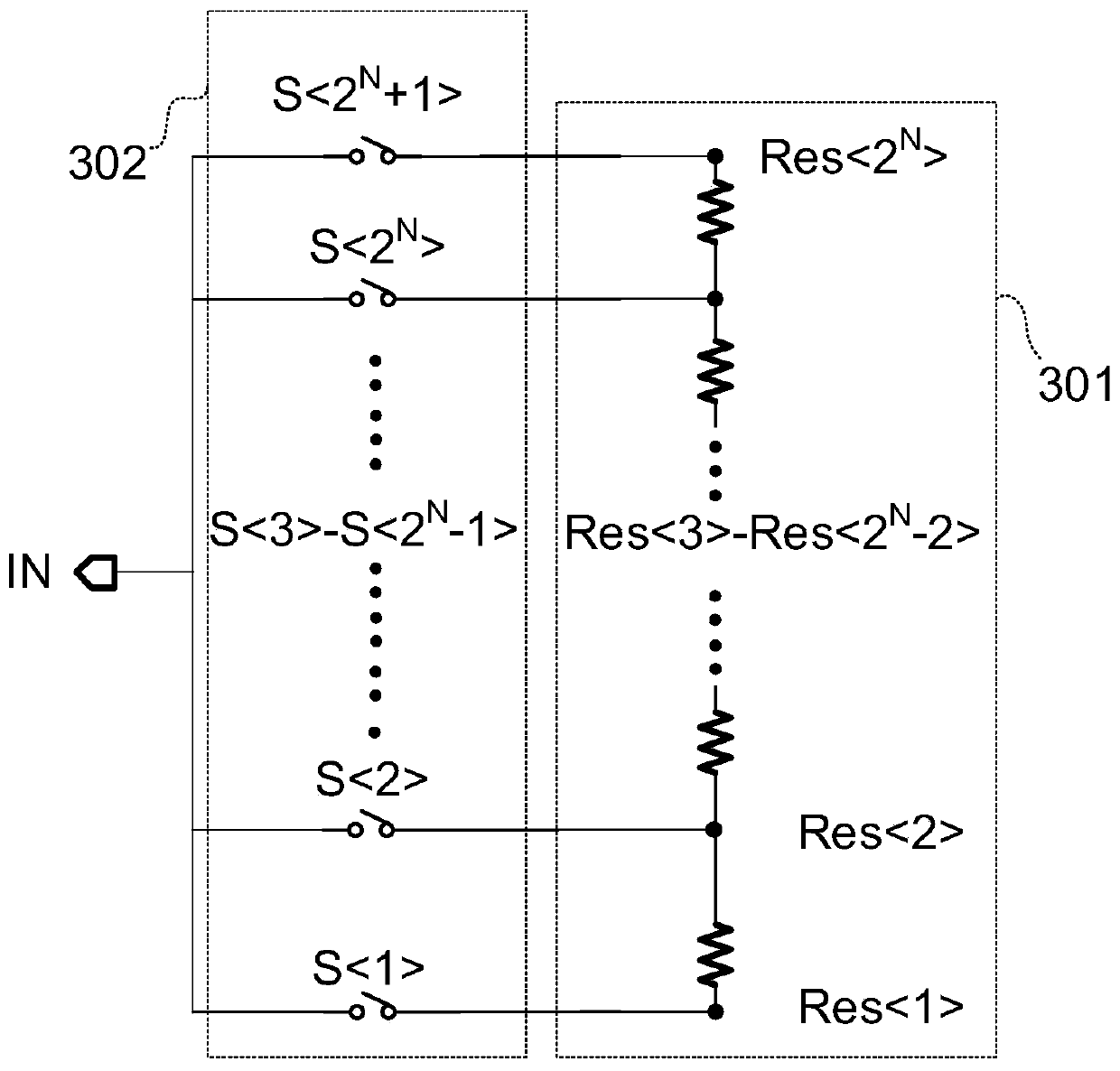

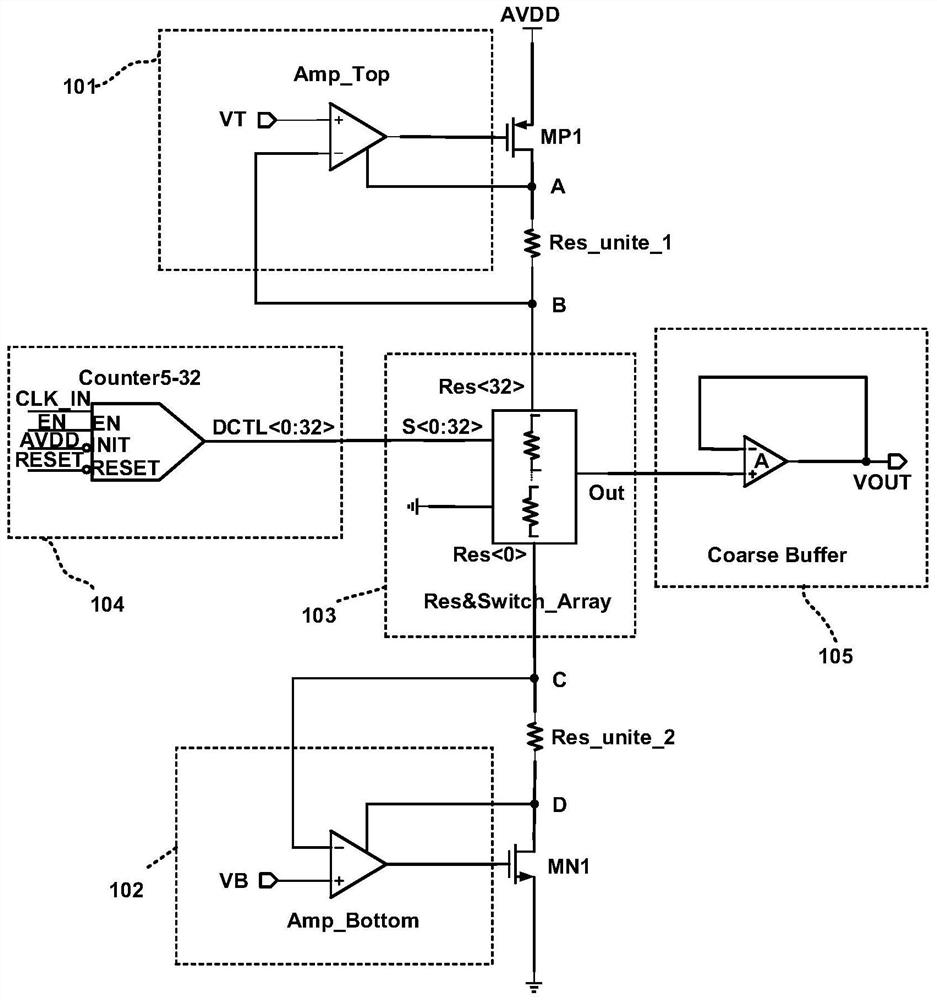

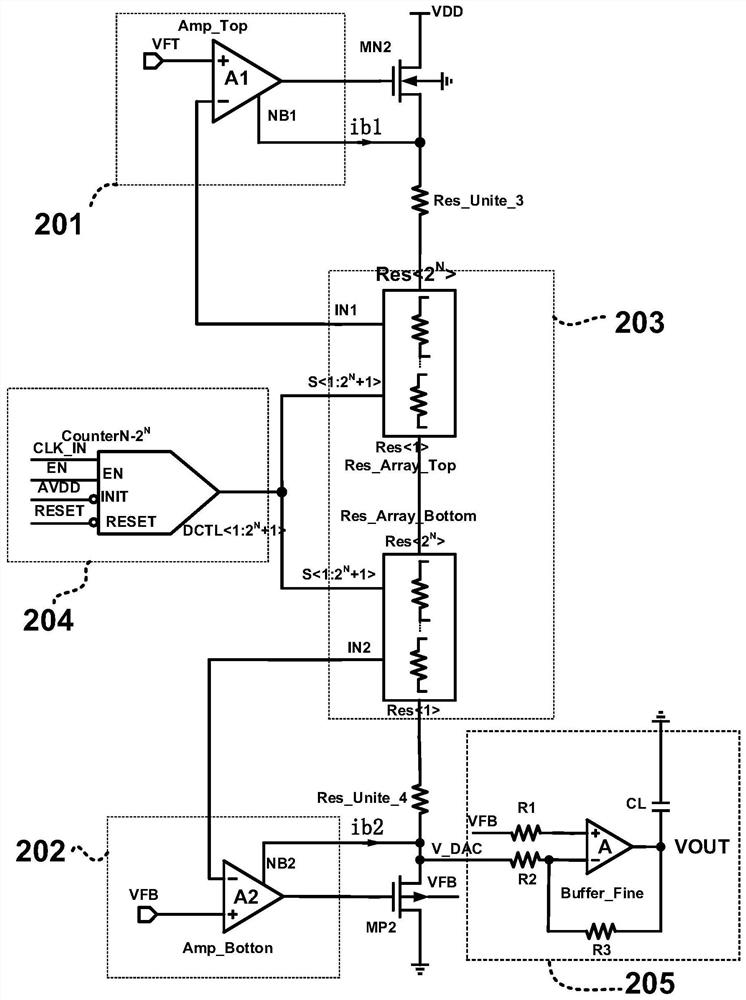

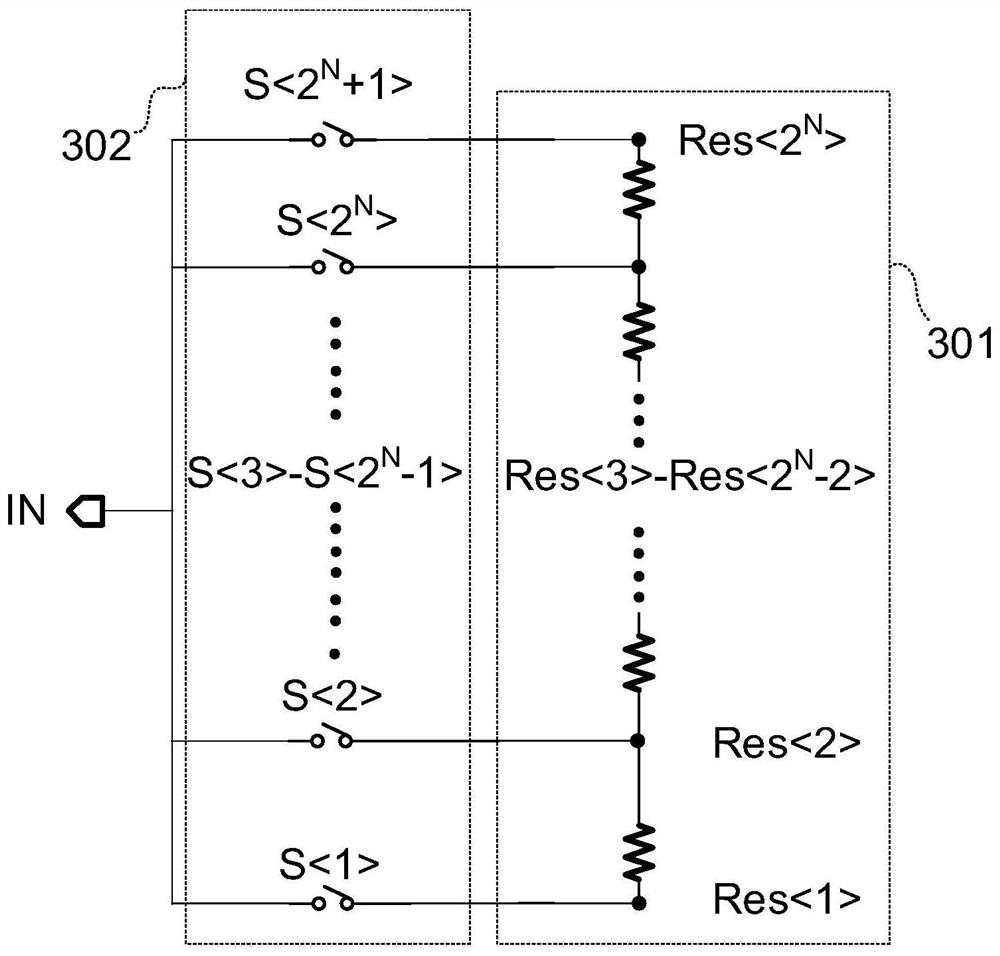

Fine quantization ramp generator for two-step monoclinic analog-to-digital converter

ActiveCN111224667ASolve Integral Nonlinearity (INL)Solving Differential Nonlinearity (DNL)Analogue-digital convertersDifferential nonlinearityEngineering

The invention belongs to the technical field of analog-to-digital conversion, and particularly relates to a fine quantization ramp generator for a two-step monoclinic analog-to-digital converter. According to the fine quantization ramp generator, an output buffer module 205 adopts a common-mode invariant mode, so that the problem that the performances such as integral nonlinearity (INL), differential nonlinearity (DNL) and spurious-free dynamic range (SFDR) of the slope generator become poor due to the change of the common-mode level of the output buffer of the slope generator in the establishing process is solved; meanwhile, the problem that substrate parasitic capacitance is introduced into a loop by adopting substrate source short circuit is avoided, and a good effect of improving the linearity of an output signal of the ramp generator is achieved; in addition, a feedforward transconductance path structure and a resistance-capacitance compensation structure are adopted, so that thepurpose of zero-pole cancellation of an operational amplifier of the output buffer module 205 of the fine-quantization ramp generator is achieved, and the linearity, the loop stability and the establishing stabilization time of the output buffer module 205 of the fine quantization ramp generator are optimized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Charge pump device and operating method thereof

InactiveUS20090066406A1Reduce body effectImprove the level ofPulse automatic controlAc-dc conversionEngineeringCapacitor

A charge pump device and an operating method thereof are proposed. The charge pump device is composed of a plurality of stages of charge transfer units and an output unit that are cascaded together. Each stage of the charge transfer units includes a first node for input, a second node for output, a first circuit and a first capacitor. The first node or the second node is biased at a bias provided for the first circuit. Thereby, the first capacitors of the odd-numbered stage and the even-numbered stage of charge transfer units can respectively receive two clock signals that are mutually opposite in phase for complementary switching operating. Collocated with the switching of the output unit, an output voltage with a high negative level can be generated.

Owner:YIELD MICROELECTRONICS CORP

A Refinement Ramp Generator for Two-Step Single-Slope Analog-to-Digital Converter

ActiveCN111224667BReduce body effectAvoid problems introduced into the loopAnalogue-digital convertersCapacitanceEngineering

The invention belongs to the technical field of analog-to-digital conversion, and in particular relates to a fine-grained ramp generator for a two-step single-slope analog-to-digital converter. The present invention solves the problem of integral non-linearity (INL) and differential non-linearity (INL) of the ramp generator due to changes in the common-mode level of the output buffer of the ramp generator during the establishment of the ramp generator by adopting a mode invariant to the common mode of the output buffer module 205. Linearity (DNL), spurious-free dynamic range (SFDR) and other performance degradation problems; and at the same time avoid the problem of using substrate-source short circuit to introduce substrate parasitic capacitance into the loop, which is helpful for improving the output signal of the ramp generator The linearity has a good effect; also by adopting a feed-forward transconductance path structure and a resistor-capacitor compensation structure, the purpose of pole-zero cancellation of the output buffer module 205 of the refinement ramp generator is realized, and the refinement is optimized. The linearity, loop stability and settling time of the ramp generator output buffer module 205 are quantized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Supplementary food composition for reducing body odor

InactiveUS20100273737A1Reducing body odorReduce body effectBiocideOrganic active ingredientsFood supplementAdditive ingredient

A food supplement for reducing body odor which includes a mixture of edible carriers with chitin aqueous solution lyophilized powder, chitosan aqueous solution lyophilized powder, chitin powder, chitosan powder, or a combination of these ingredients, in the form of tablets or pills. The food supplement has the outstanding effect of reducing various types of body odors, including Koreans' unique body odor, such as Kimchi smell or garlic smell; westerners' unique body odor, such as cheese smell or butter smell, Arabs' unique body odor, such as mutton smell, armpit odor and body odor that is unique to the aged.

Owner:KIM JIN MAN +2

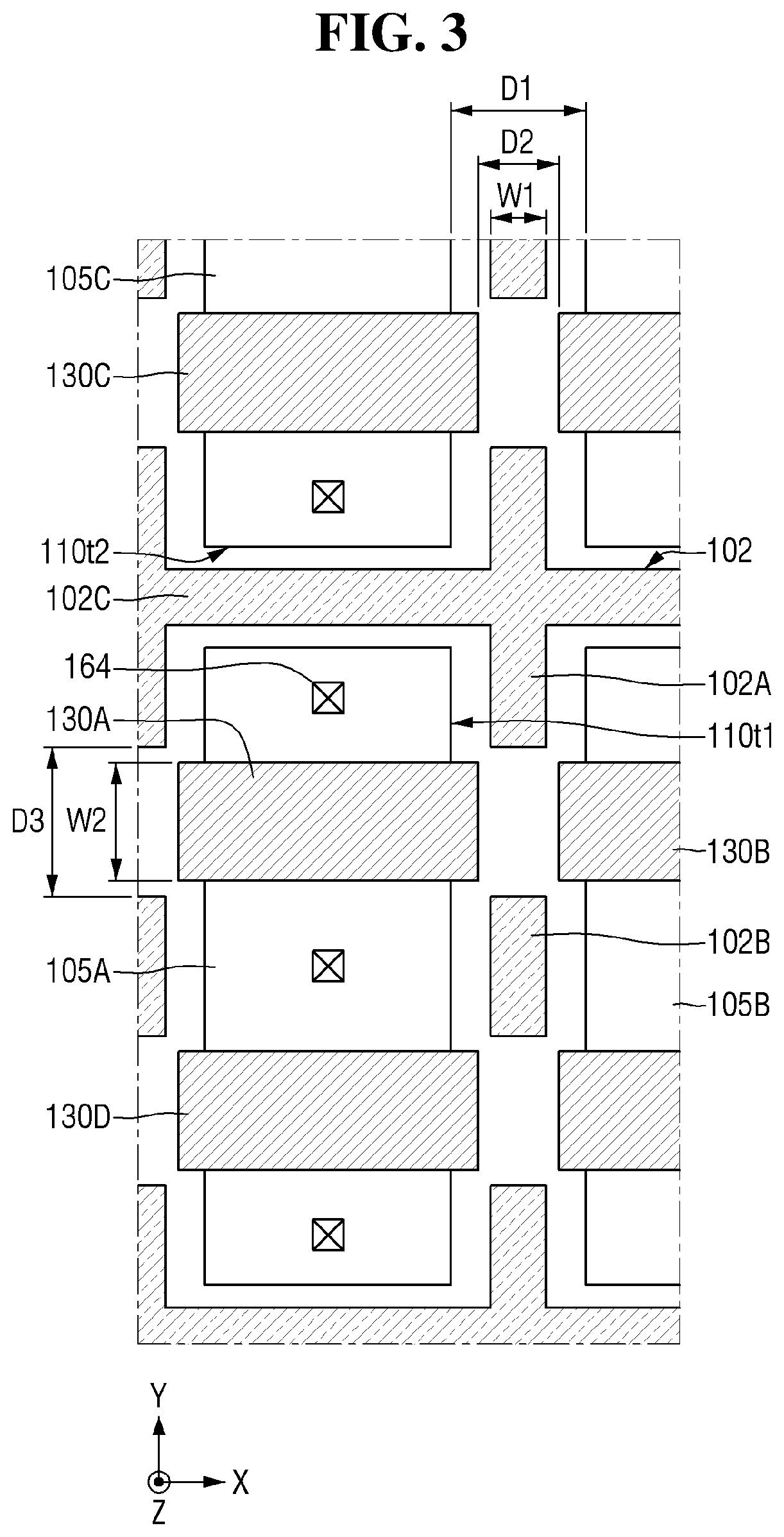

Semiconductor device, nonvolatile memory device including the same, electronic system including the same, and method for fabricating the same

PendingUS20220208779A1Improve performanceImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingElectronic systemsDevice material

A semiconductor device includes a first active region and a second active region arranged along a first direction in a substrate, an element isolation layer extending in a second direction in the substrate to isolate the first active region and the second active region, a first gate electrode extending in the first direction on the first active region, a second gate electrode extending in the first direction on the second active region, and an isolation impurity region containing impurities of a first conductivity type in the substrate and disposed below the element isolation layer, in which the isolation impurity region includes a first isolation region and a second isolation region spaced apart from each other in the second direction, and at least a part of the substrate interposed between the first gate electrode and the second gate electrode is interposed between the first isolation region and the second isolation region.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com