Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

106 results about "Integral nonlinearity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

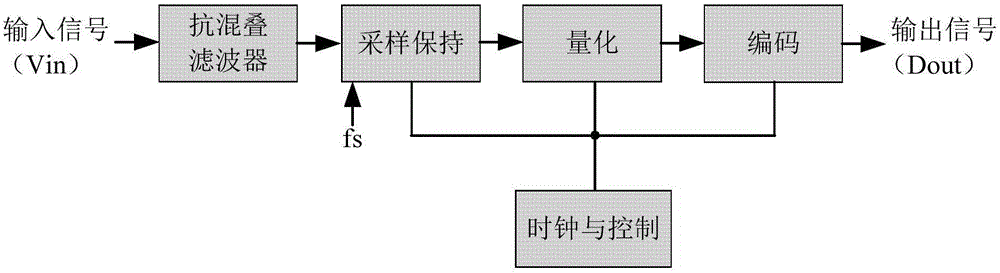

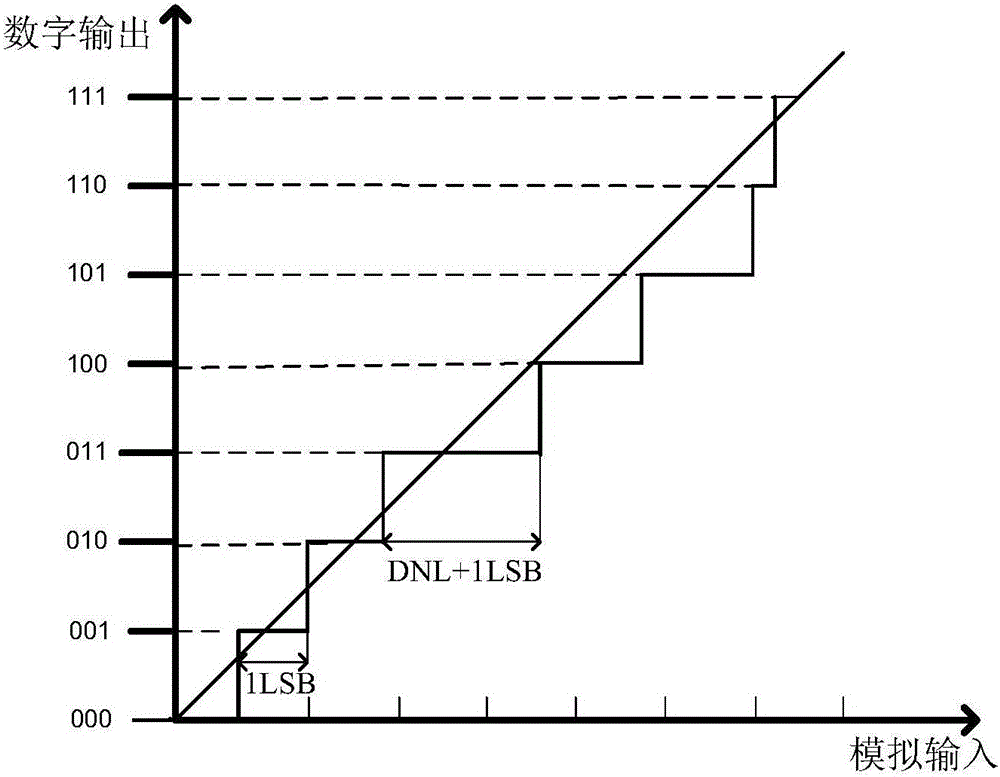

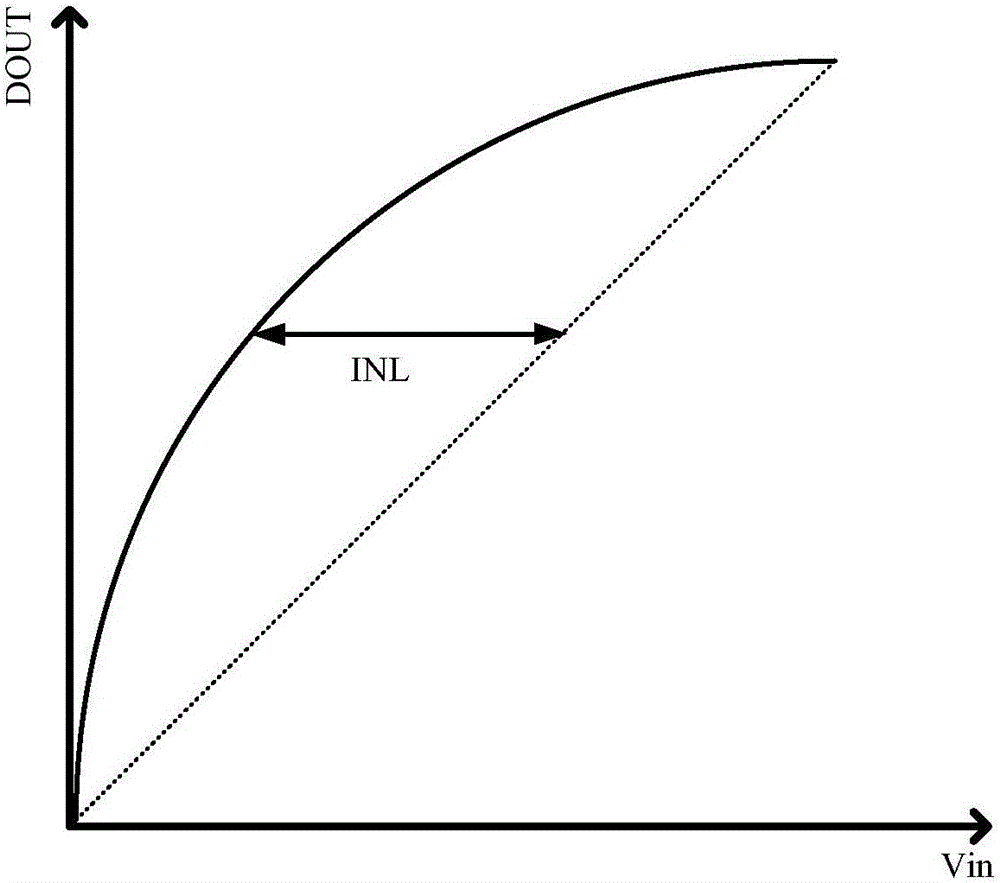

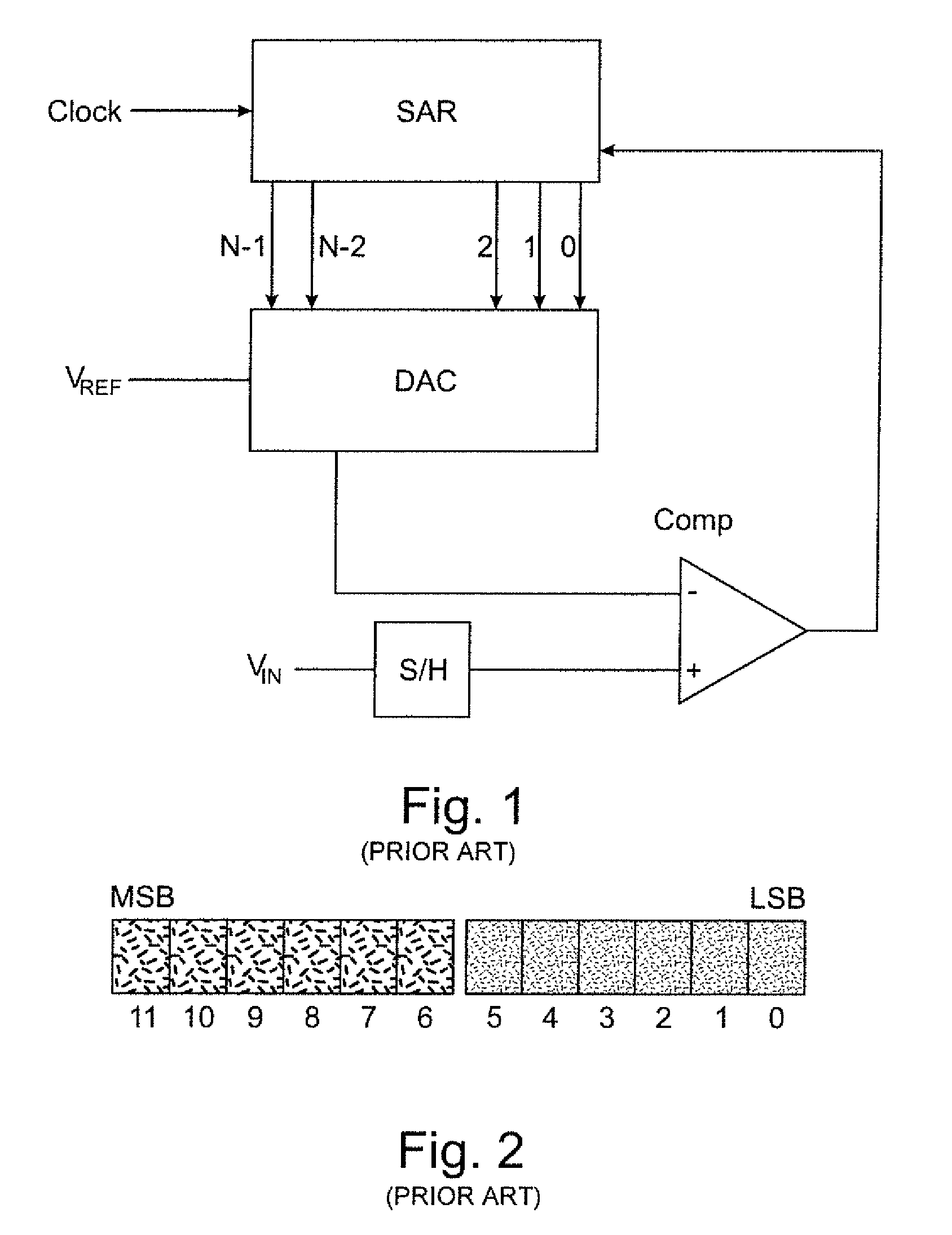

Integral nonlinearity (acronym INL) is a commonly used measure of performance in digital-to-analog (DAC) and analog-to-digital (ADC) converters. In DACs, it is a measure of the deviation between the ideal output value and the actual measured output value for a certain input code. In ADCs, it is the deviation between the ideal input threshold value and the measured threshold level of a certain output code. This measurement is performed after offset and gain errors have been compensated.

All-analog calibration of sting-DAC linearity: application to high voltage processes

ActiveUS6897794B2Quantity minimizationLow costElectric signal transmission systemsDigital-analogue convertorsVoltage referenceHigh pressure

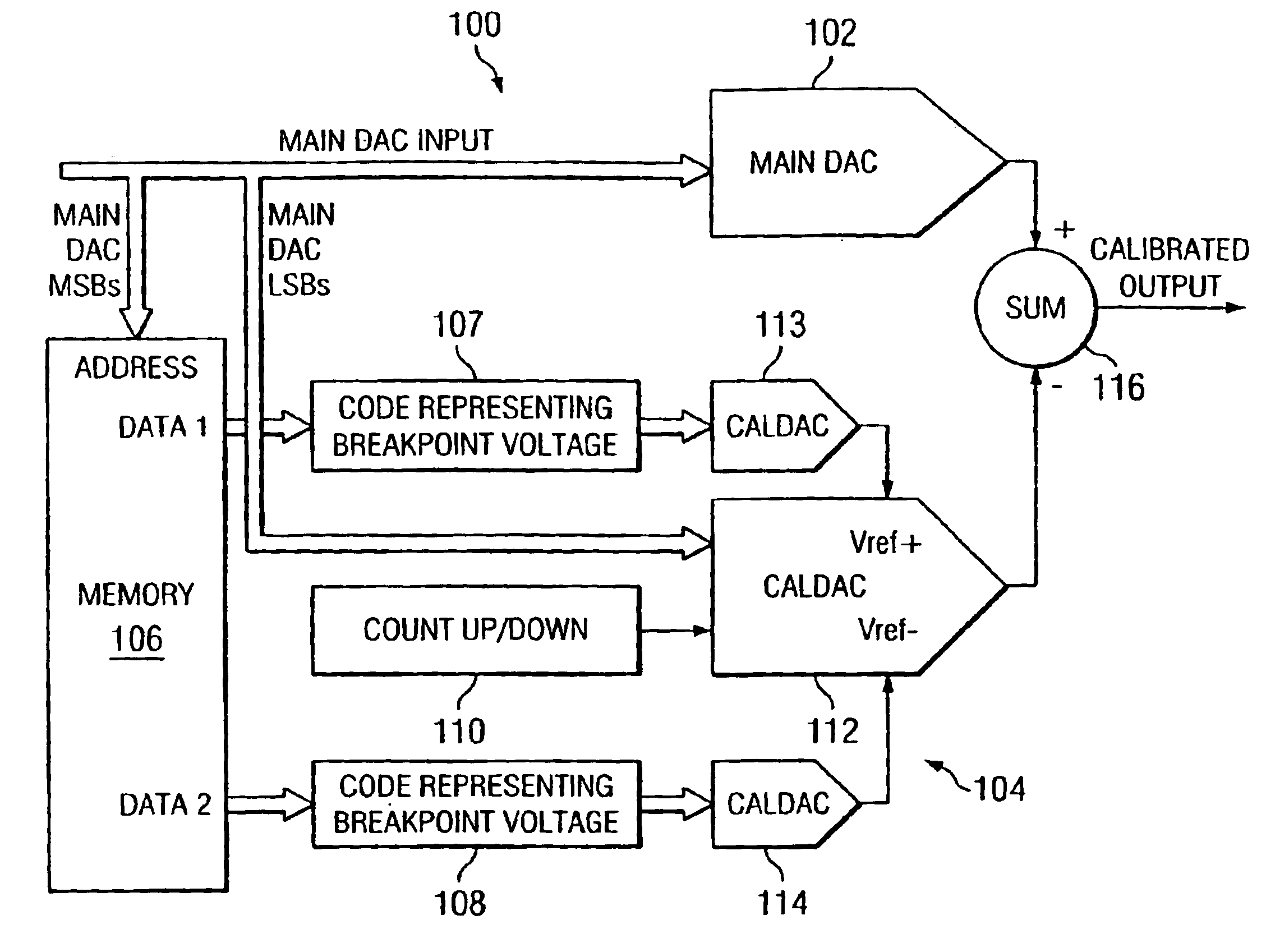

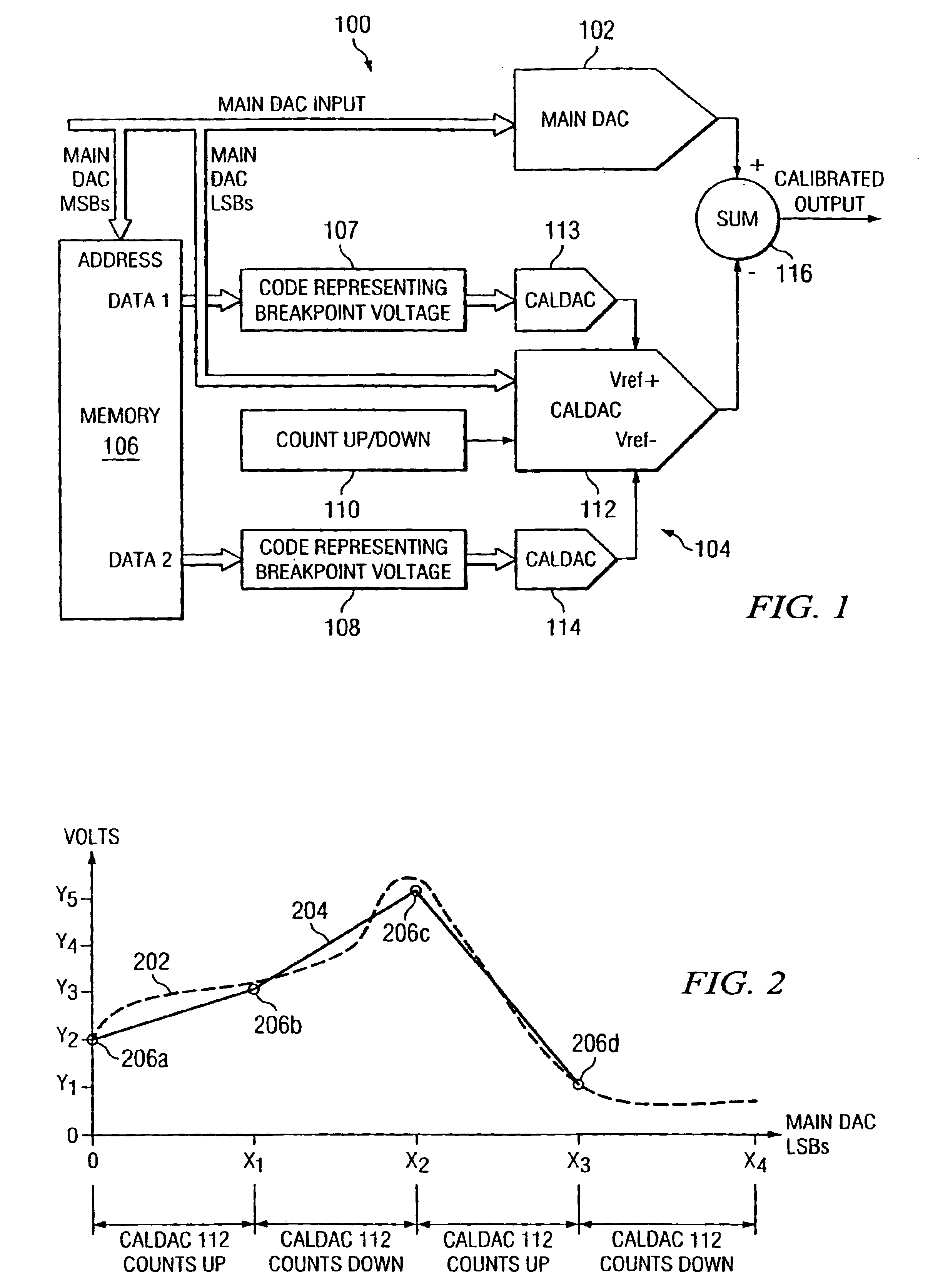

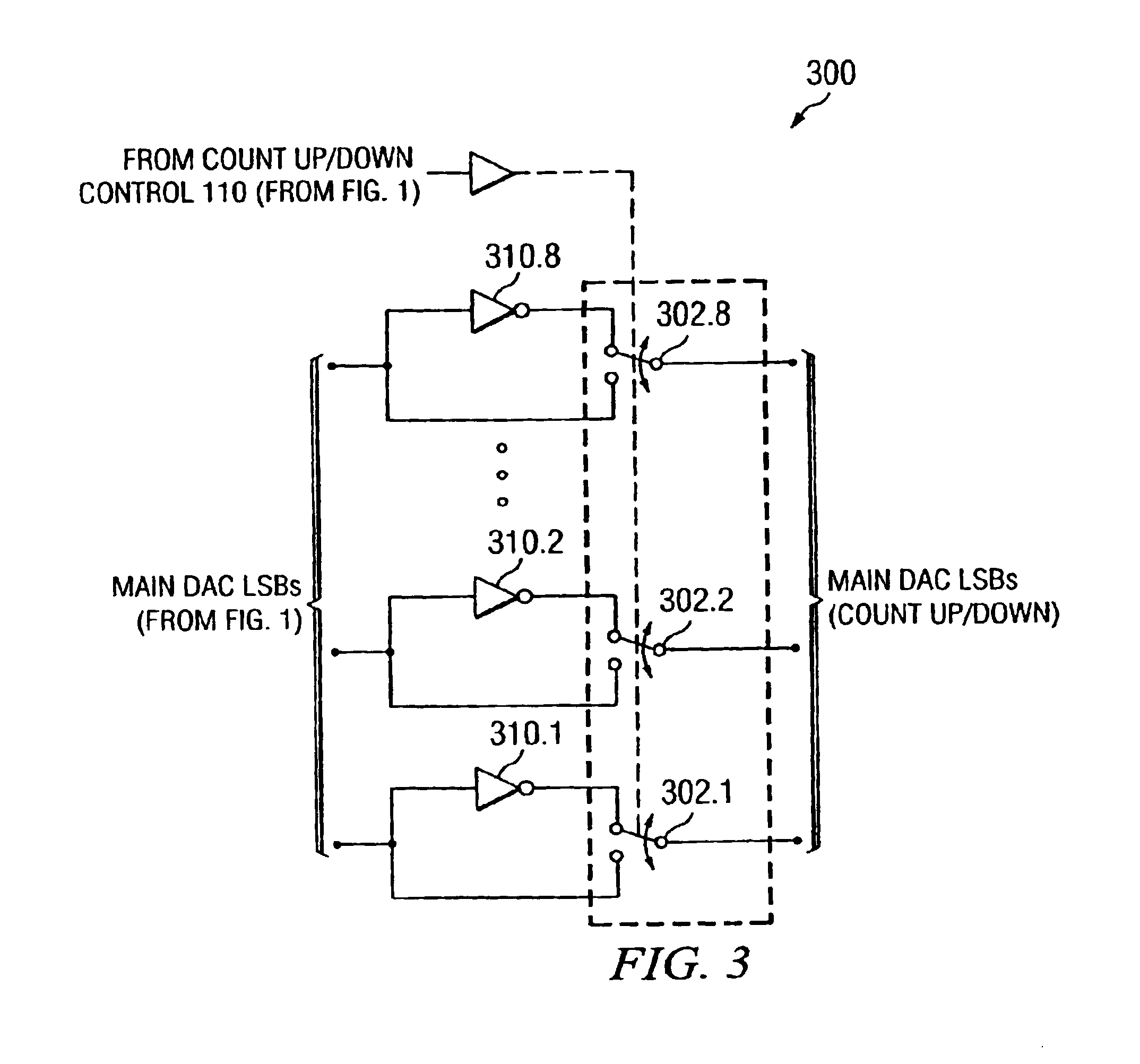

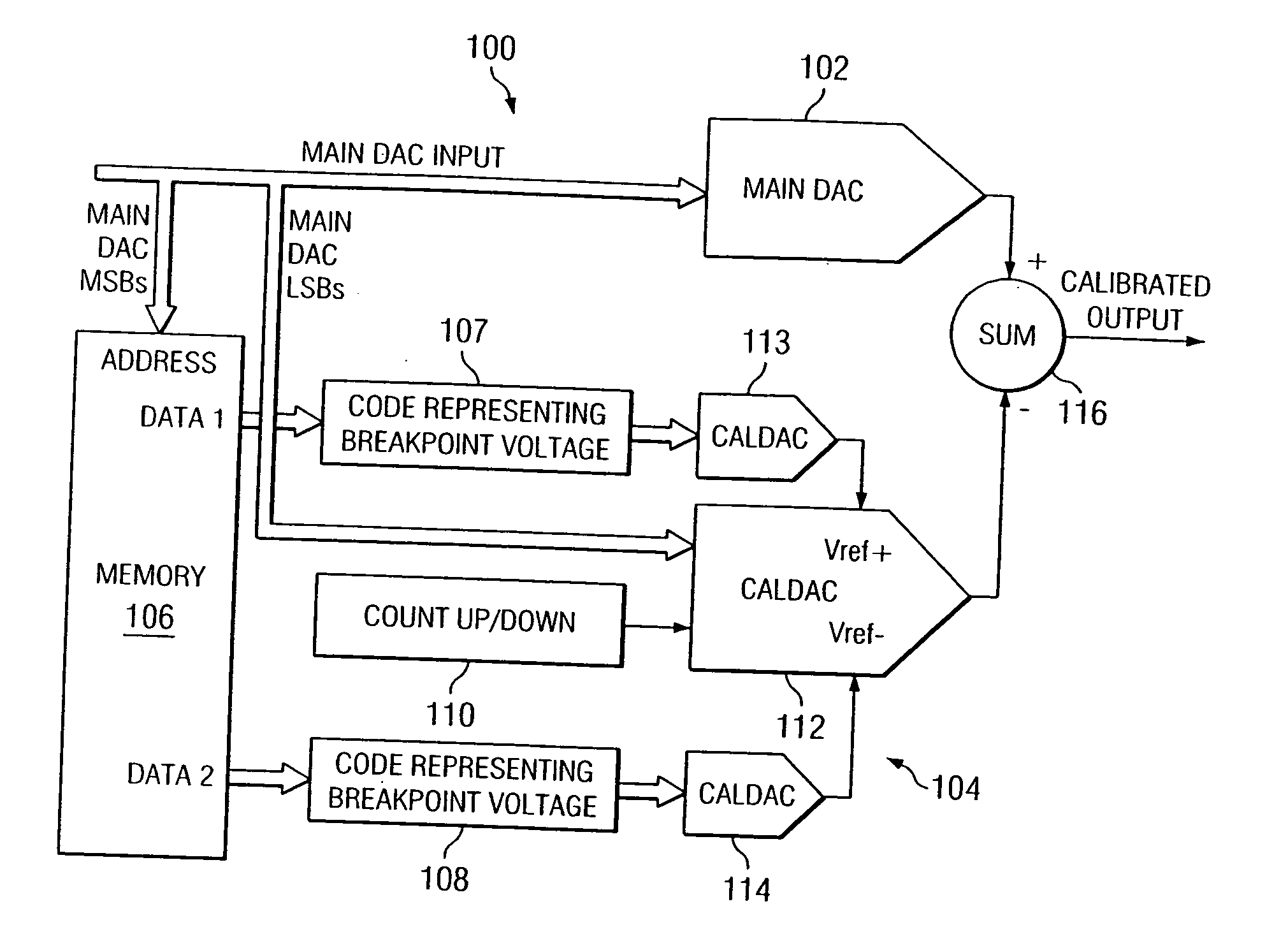

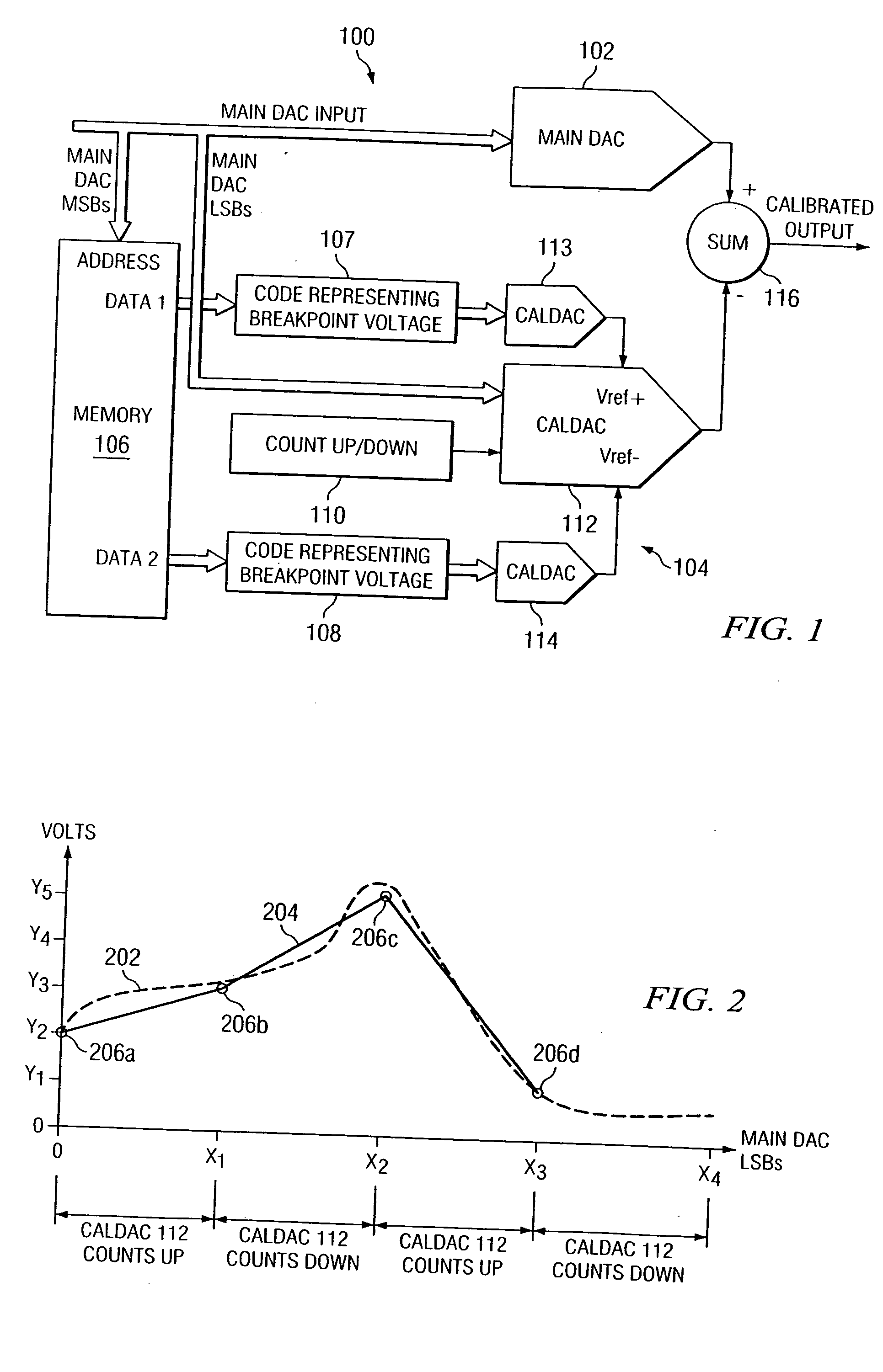

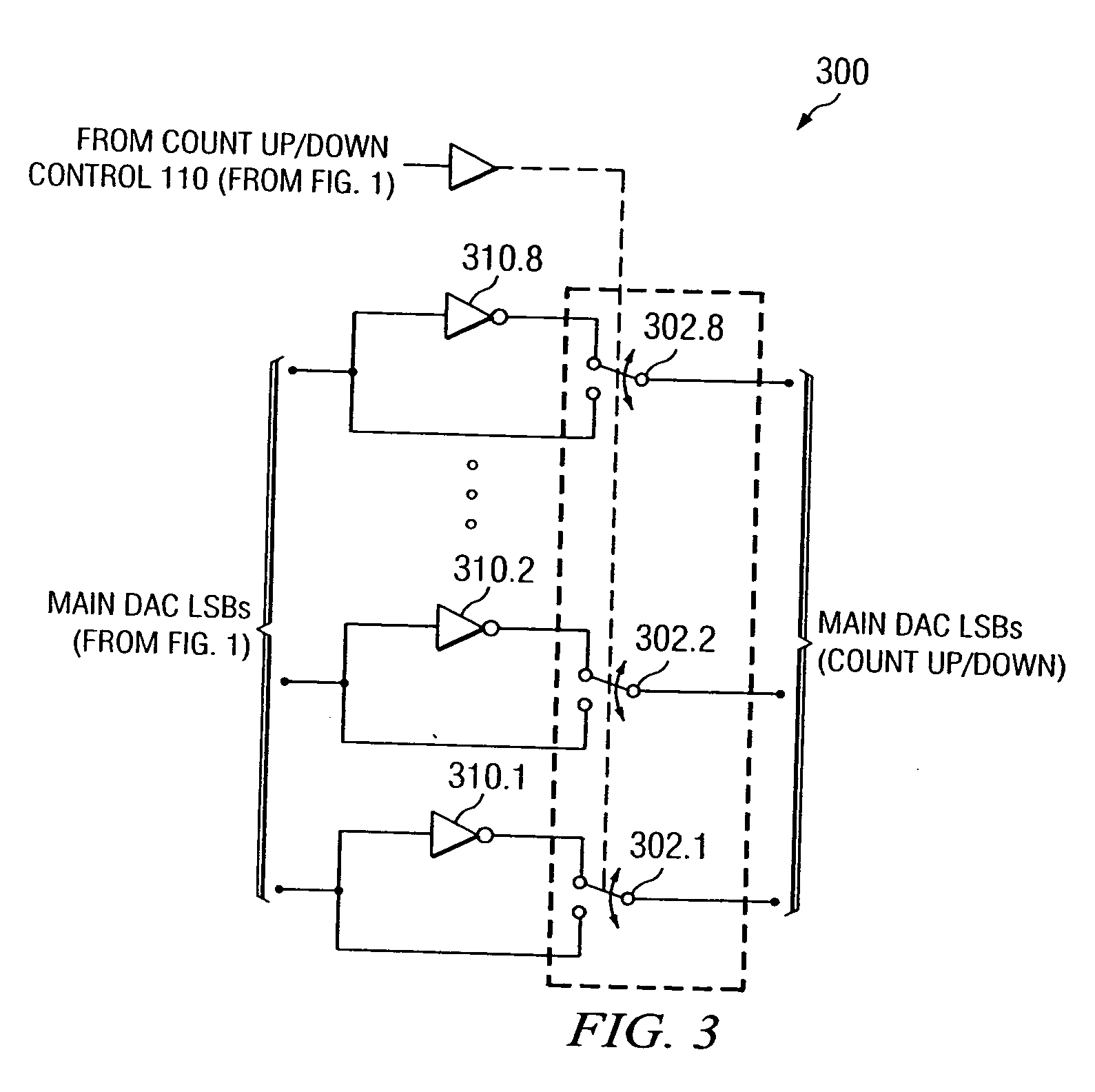

A system and method of calibrating a digital-to-analog converter (DAC) such as a resistor string DAC that reduces costs by making more efficient use of semiconductor die area. A digital-to-analog converter includes a main DAC to be calibrated, a memory, a plurality of calibration DACs, and an analog summing circuit. The main DAC receives digital input code values, and converts the respective input code values into an analog signal. A first calibration DAC receives a predetermined number of lower order bits of the respective input code values, and interpolates between a positive reference voltage and a negative reference voltage to generate linear waveforms for the PWL approximation. A second calibration DAC generates the positive reference voltage, and a third calibration DAC generates the negative reference voltage. The memory stores a plurality of PWL breakpoint code values representing respective integral non-linearity error values of the main DAC, and applies consecutive PWL breakpoint code values to the second and third calibration DACs, respectively, to generate the positive and negative reference voltages for the first calibration DAC.

Owner:TEXAS INSTR INC

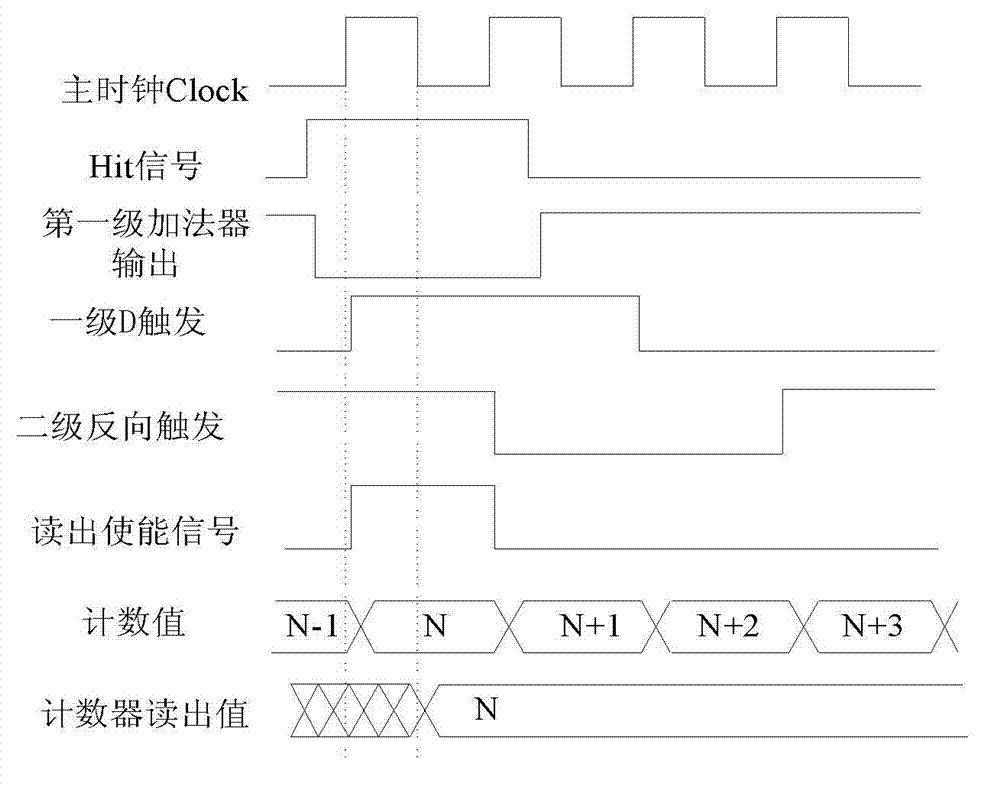

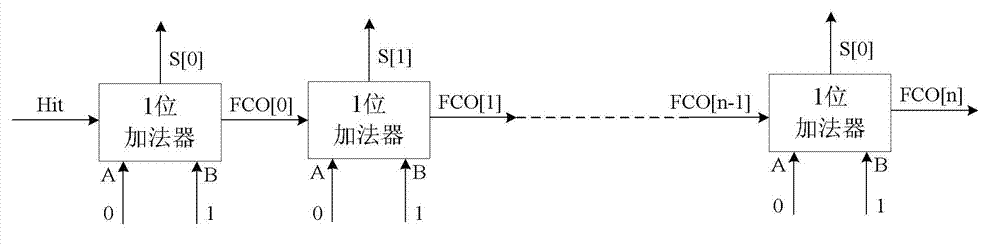

Time digital converter based on antifuse field programmable gata array (FPGA) and temperature drift correcting method thereof

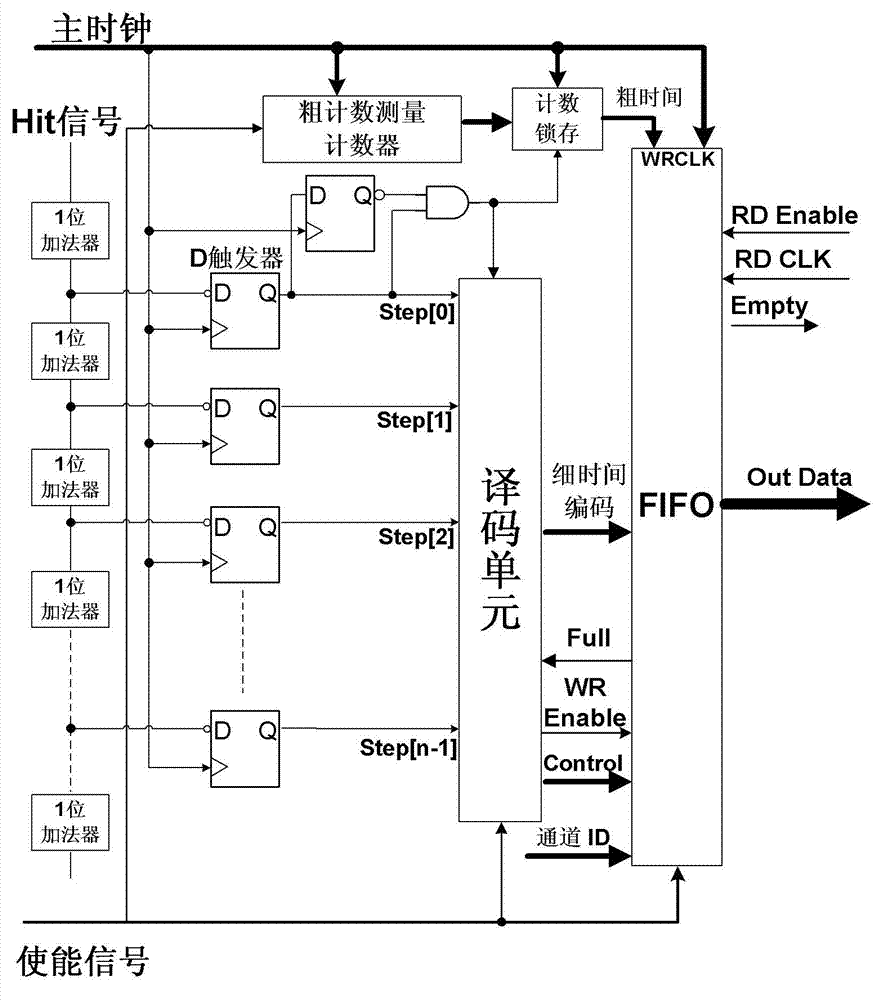

ActiveCN103092059AFlexible useLow costAnalogue/digital conversionElectric signal transmission systemsLeast significant bitEngineering

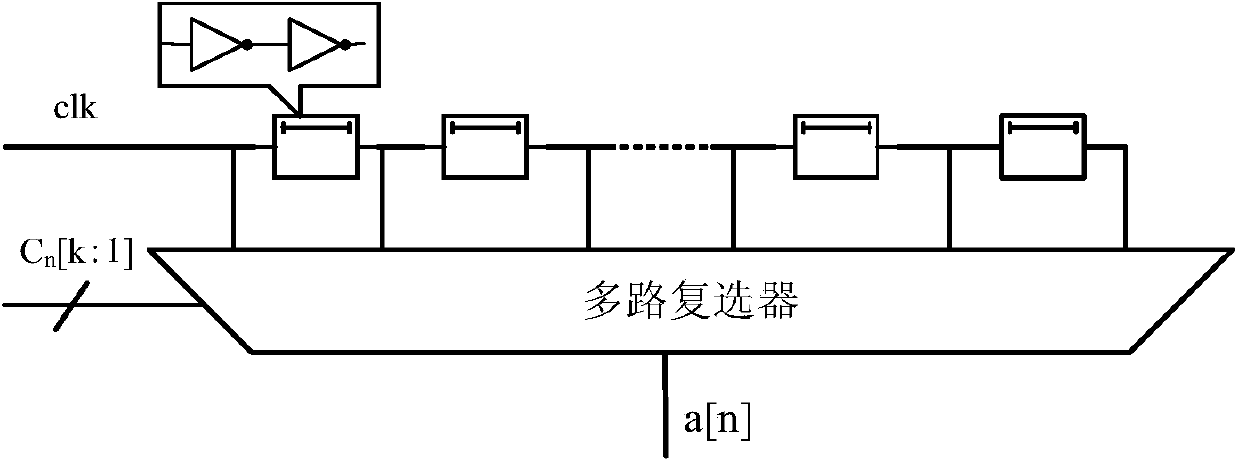

The invention discloses a high-precision time digital converter based on antifuse field programmable gata array (FPGA) and a temperature drift correcting algorithm thereof. The time digital converter based on antifuse FPGA is divided into two parts: (1) carrying out rough time measuring by means of a counting method; (2) achieving time interpolation by means of carry cascade connection in the FPGA, namely achieving fine time measuring by means of an interpolation method, and correcting a measuring result of the fine time according to the operating ambient temperature of the FPGA combined with temperature drift correcting algorithms when the measuring are completed, and therefore measurement accuracy of time digital converter in a large temperature range can be guaranteed. The digital converter based on antifuse FPGA and temperature drift correcting method thereof are characterized by comprising the following steps: achieving rough counting measuring by utilizing a high-speed counter which works under master clock, measuring fine time by means of the carry cascade connection to achieve time interpolation, calibrating the least significant bit (LSB) of the time digital converter, and obtaining a function relation of the LSB with temperature changes, and correcting fine time measuring results according to the function relation and integral nonlinearity of the time digital converter.

Owner:UNIV OF SCI & TECH OF CHINA

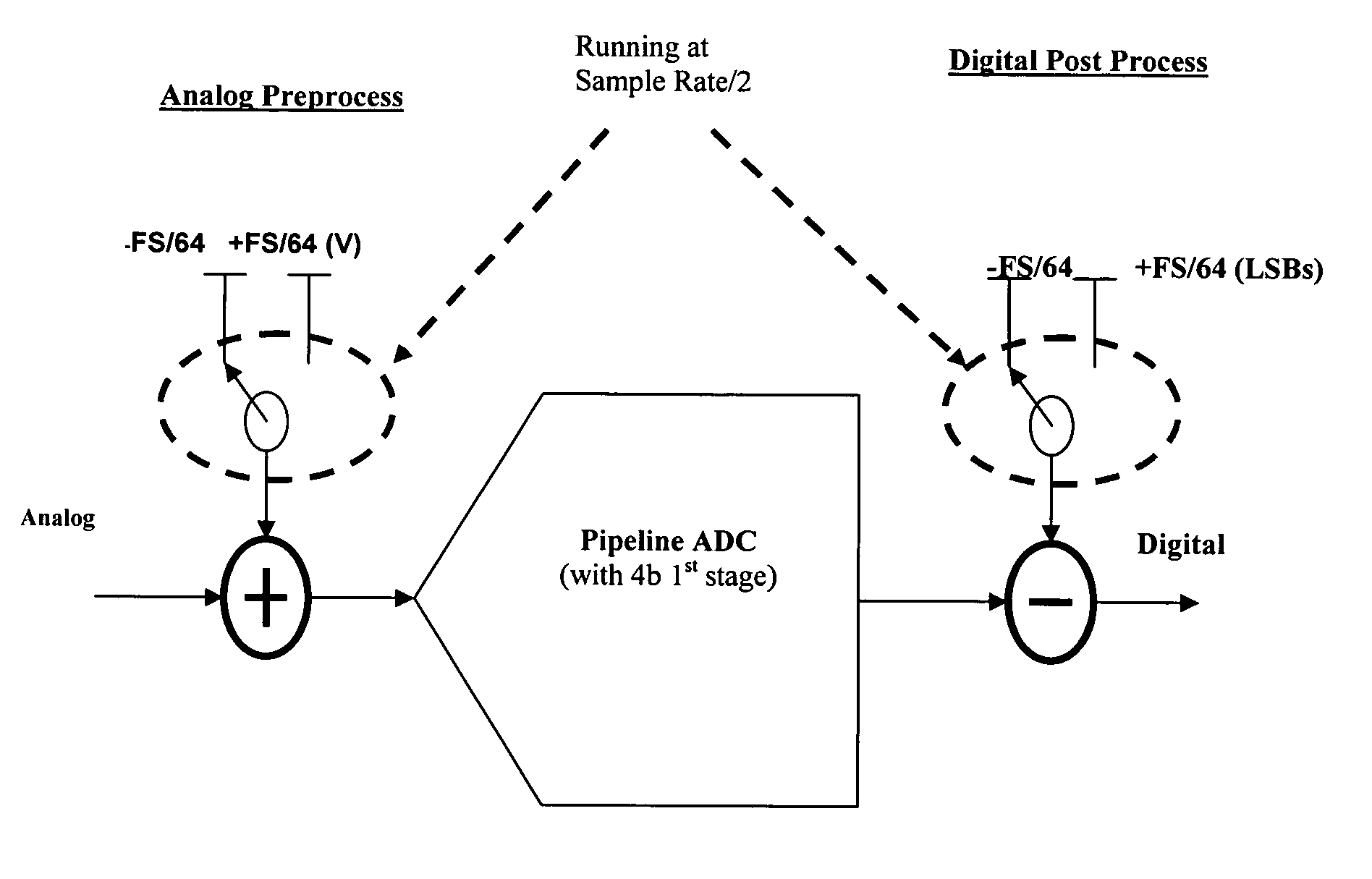

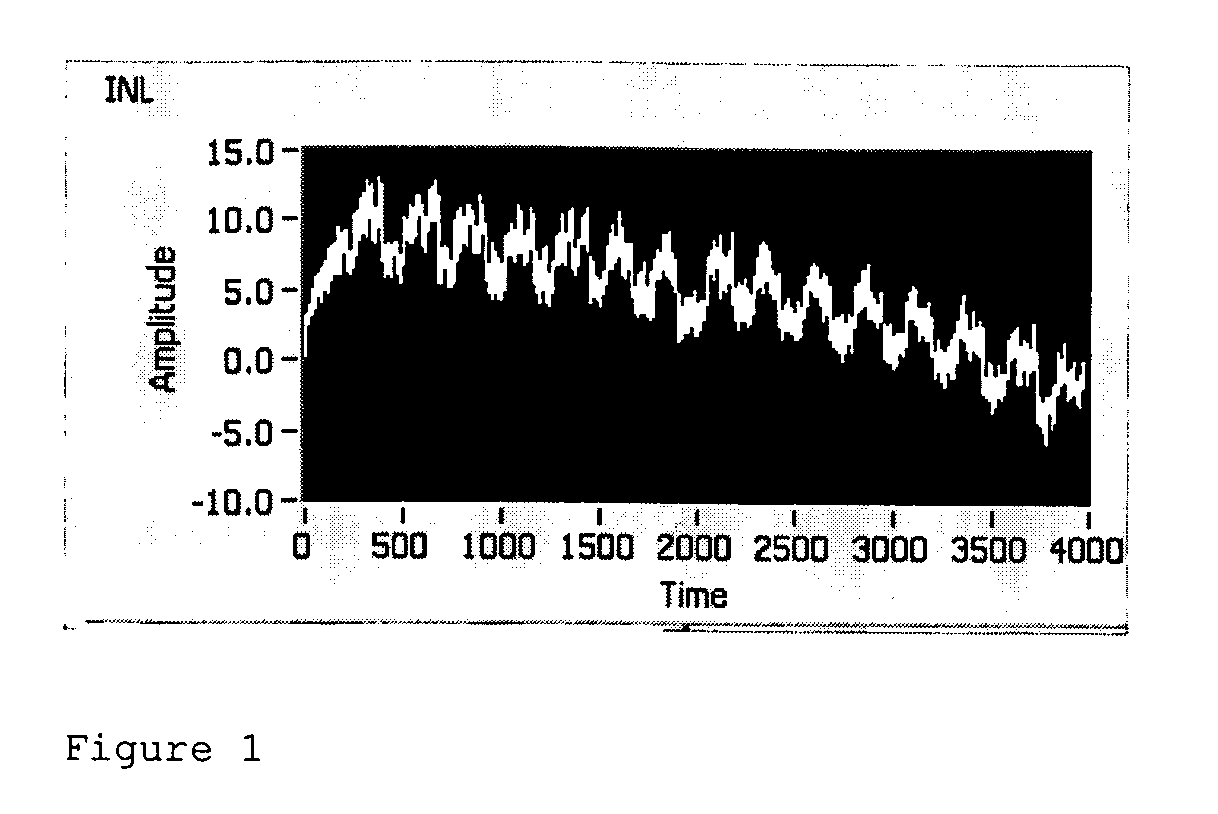

INL curve correction in a pipeline ADC

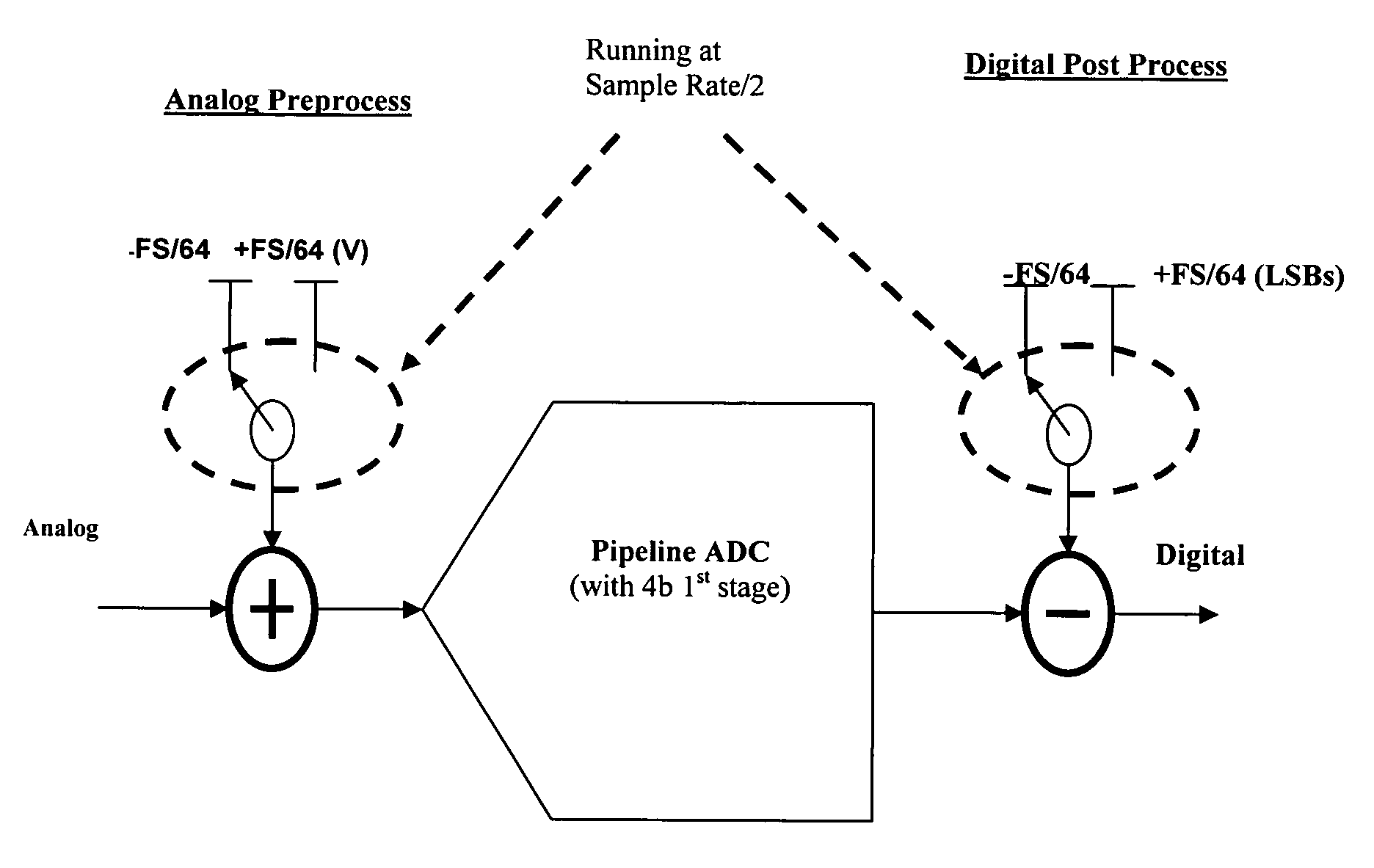

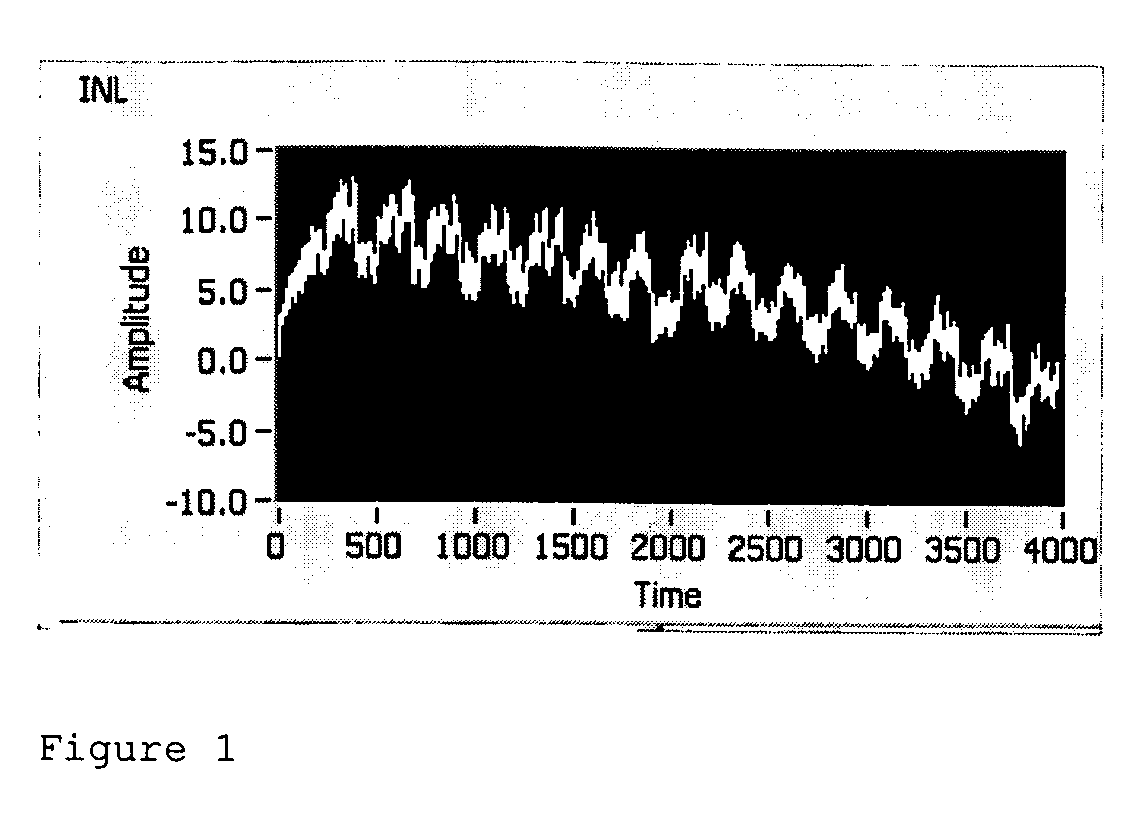

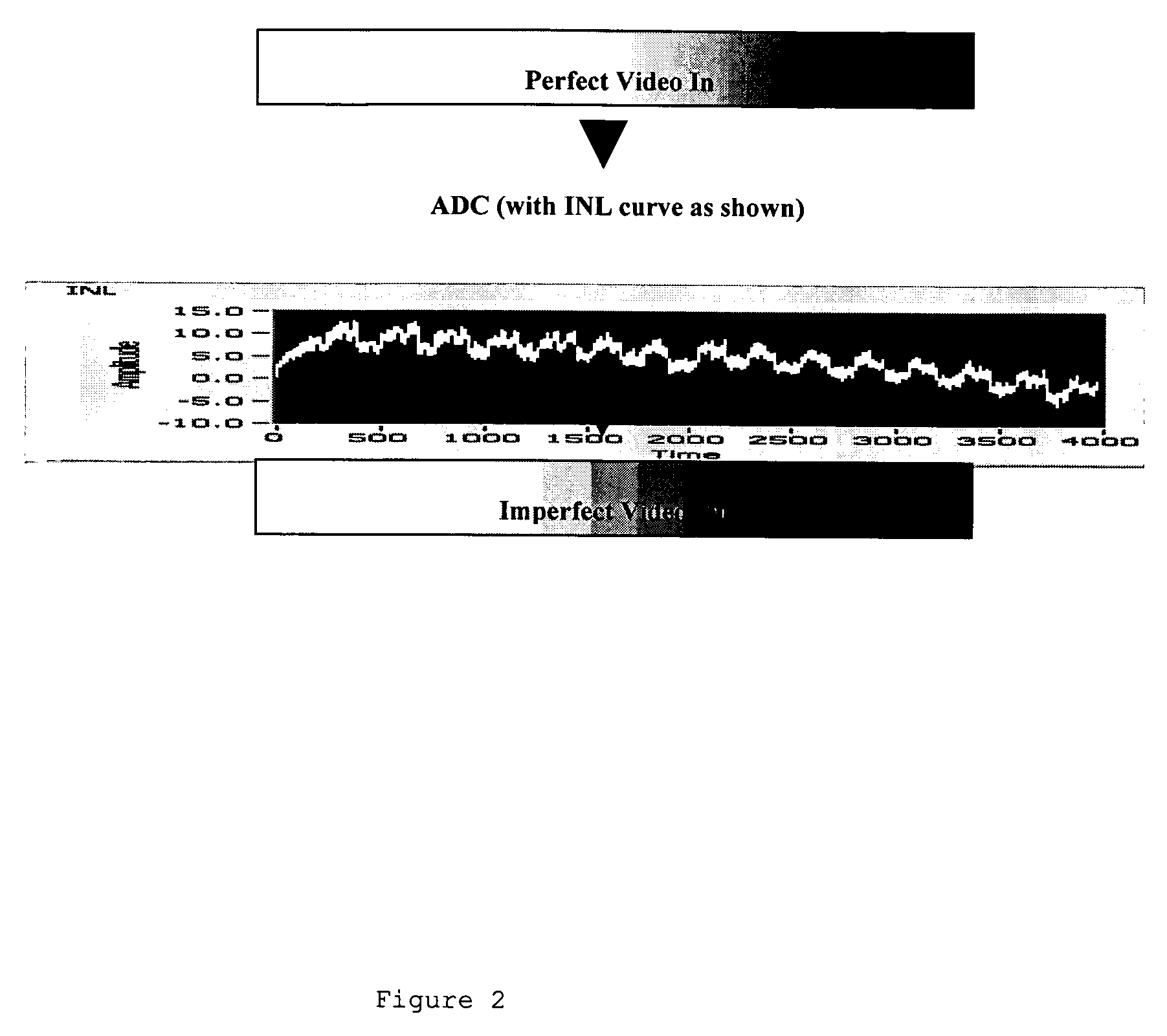

ActiveUS20060114144A1Reduce nonlinear errorMinimize impactElectric signal transmission systemsAnalogue conversionA d converterFeedback circuits

The present invention relates to a method and system for reducing integral non linearity errors in a pipeline Analog to Digital Converter (ADC). The invention provides in a first embodiment a method comprising the steps of: adding an analog dither signal to the analog input signal of a pipeline Analog to Digital Converter, and converting the analog input signal to a digital output signal by means of the pipeline Analog to Digital Converter. The amplitude of the analog dither signal is determined by the architecture of the Analog to Digital Converter. The invention also provides in a second embodiment a circuit comprising a pipeline analog to digital converter for converting an analog input signal to a digital output signal and a feedback circuit coupled to the converter such that the digital output signal is adapted to have an average non linearity error value of about zero LSBs.

Owner:ANALOG DEVICES INC

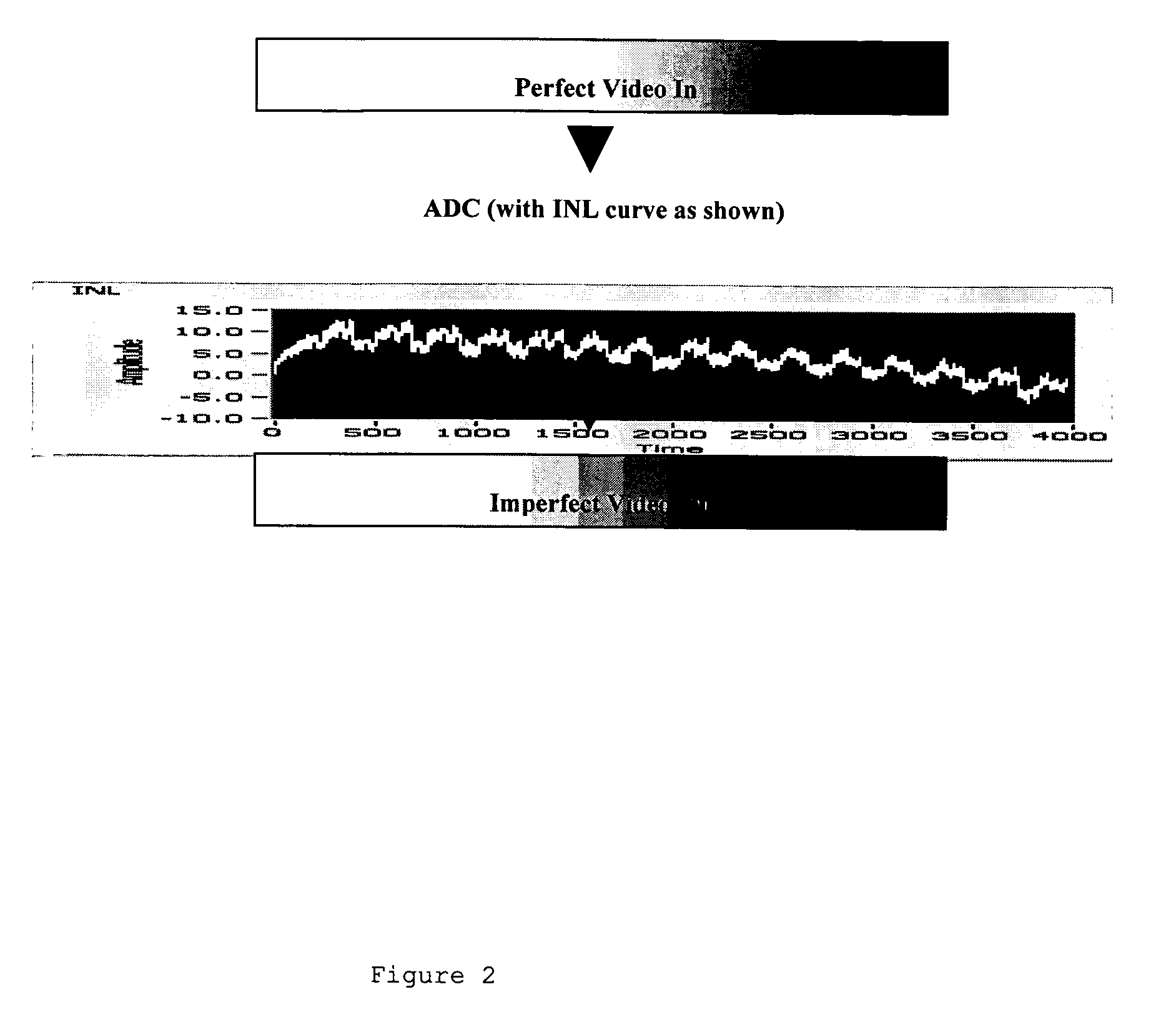

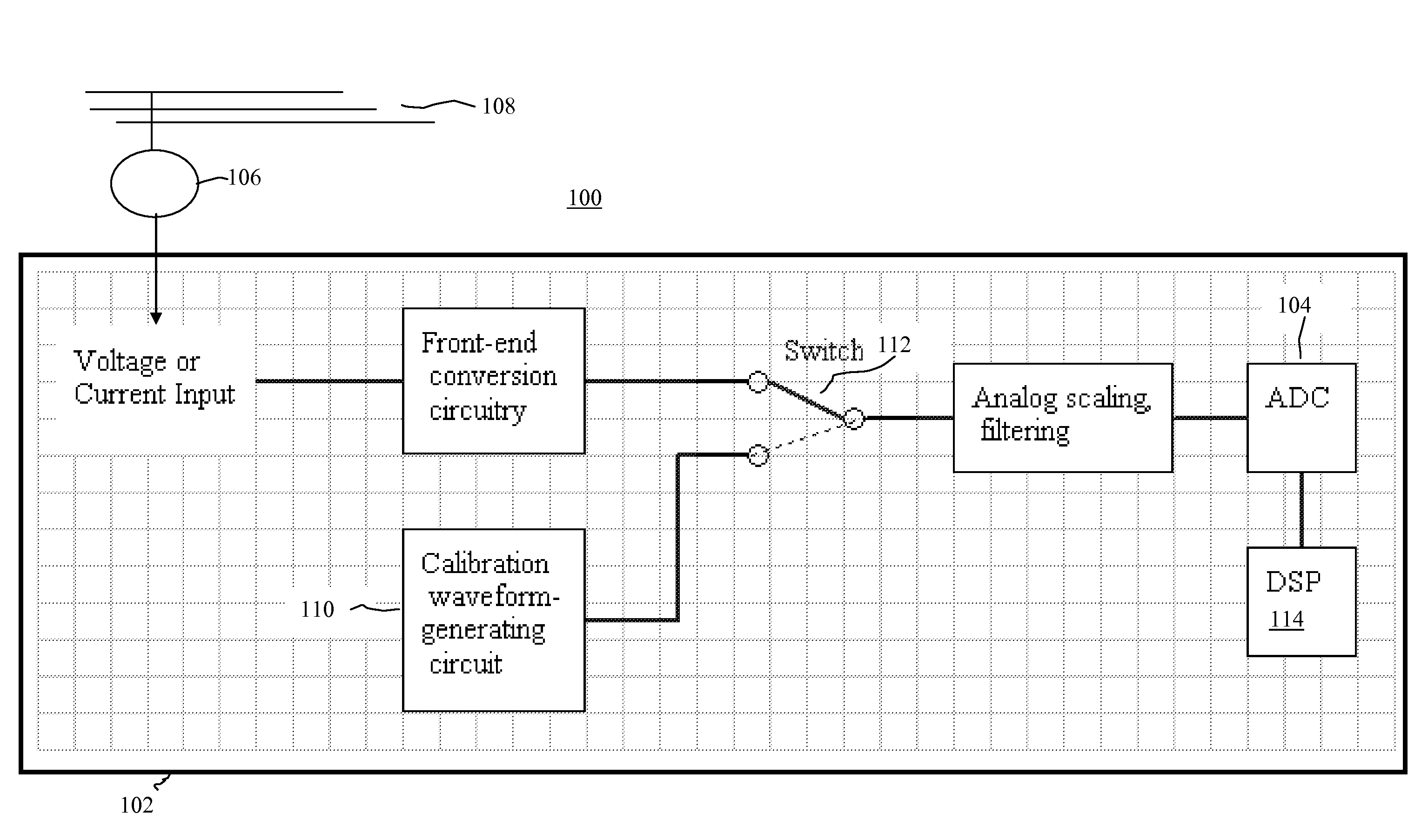

Non-linearity calibration using an internal source in an intelligent electronic device

ActiveUS20120191395A1Tariff metering apparatusCurrent/voltage measurementElectrical conductorAnalog-to-digital converter

An intelligent electronic device, and in particular, an electrical power meter, featuring an internal calibration system capable of calibrating its measurement mechanisms for the integral nonlinearities introduced by the components which make up those mechanisms, in particular, the analog-to-digital converter, is disclosed. The analog-to-digital converter is coupled with at least one sensor which is operable to sense electrical energy in one or more conductors and output a corresponding electrical signal indicative thereof, the analog-to-digital converter being operative to convert the electrical signal output by the sensor to at least one corresponding digital signal. Integral non-linearity (“INL”) is a term describing the deviation between the ideal output of an analog-to-digital converter and the actual output (after offset and gain errors have been removed). The disclosed embodiments further relate to an electrical power meter having internal INL calibration using a relatively low cost, low accuracy internal signal source, obviating the need for costly external signal sources or measurement systems, which quickly calibrates the electrical power meter for such INL substantially across its entire measurement range and significantly improves the measurement accuracy thereby.

Owner:SCHNEIDER ELECTRIC USA INC

All-analog calibration of string-DAC linearity: application to high voltage processes

ActiveUS20050001747A1Quantity minimizationEasy to useElectric signal transmission systemsDigital-analogue convertorsVoltage referenceHigh pressure

A system and method of calibrating a digital-to-analog converter (DAC) such as a resistor string DAC that reduces costs by making more efficient use of semiconductor die area. A digital-to-analog converter includes a main DAC to be calibrated, a memory, a plurality of calibration DACs, and an analog summing circuit. The main DAC receives digital input code values, and converts the respective input code values into an analog signal. A first calibration DAC receives a predetermined number of lower order bits of the respective input code values, and interpolates between a positive reference voltage and a negative reference voltage to generate linear waveforms for the PWL approximation. A second calibration DAC generates the positive reference voltage, and a third calibration DAC generates the negative reference voltage. The memory stores a plurality of PWL breakpoint code values representing respective integral non-linearity error values of the main DAC, and applies consecutive PWL breakpoint code values to the second and third calibration DACs, respectively, to generate the positive and negative reference voltages for the first calibration DAC.

Owner:TEXAS INSTR INC

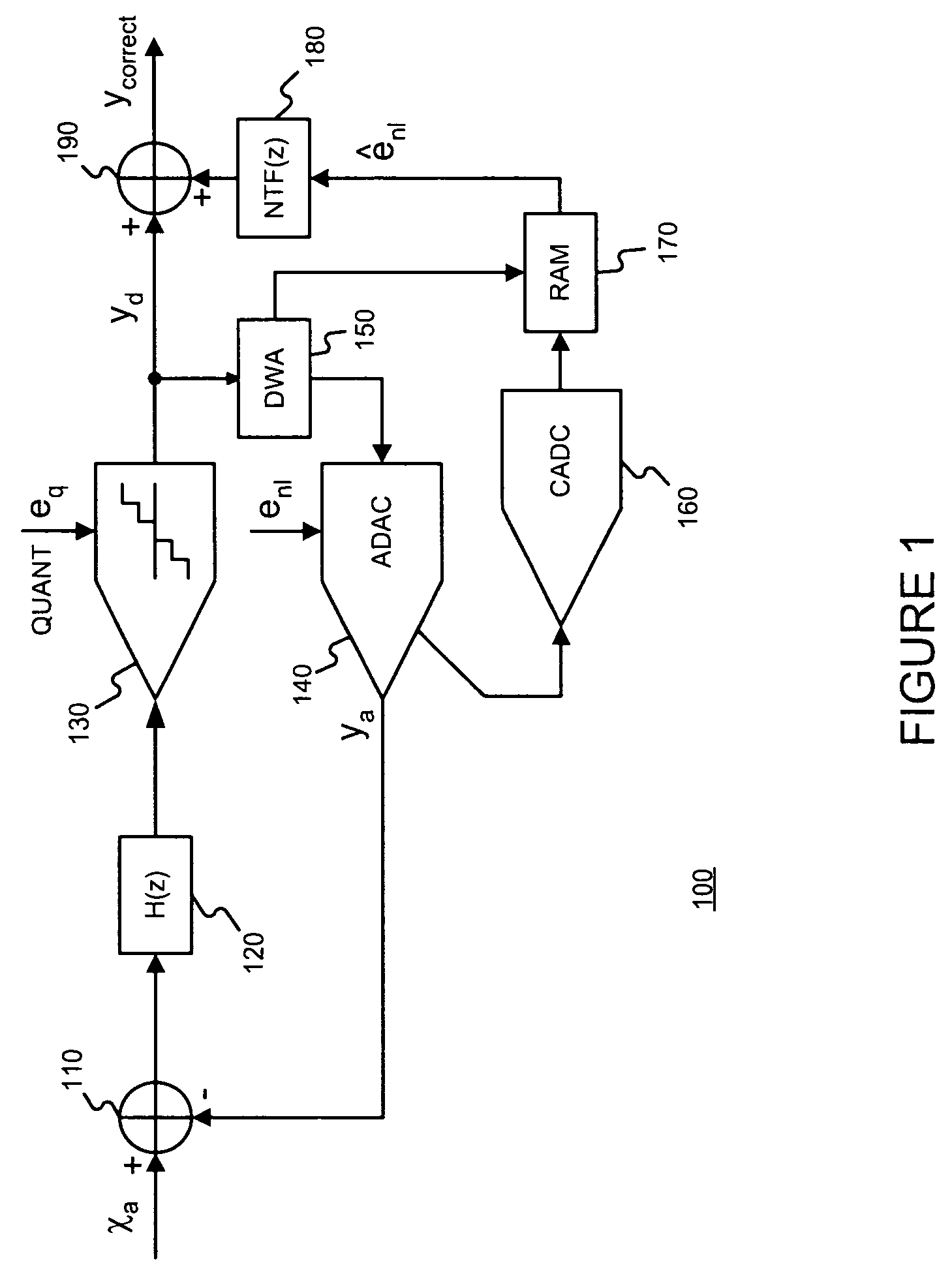

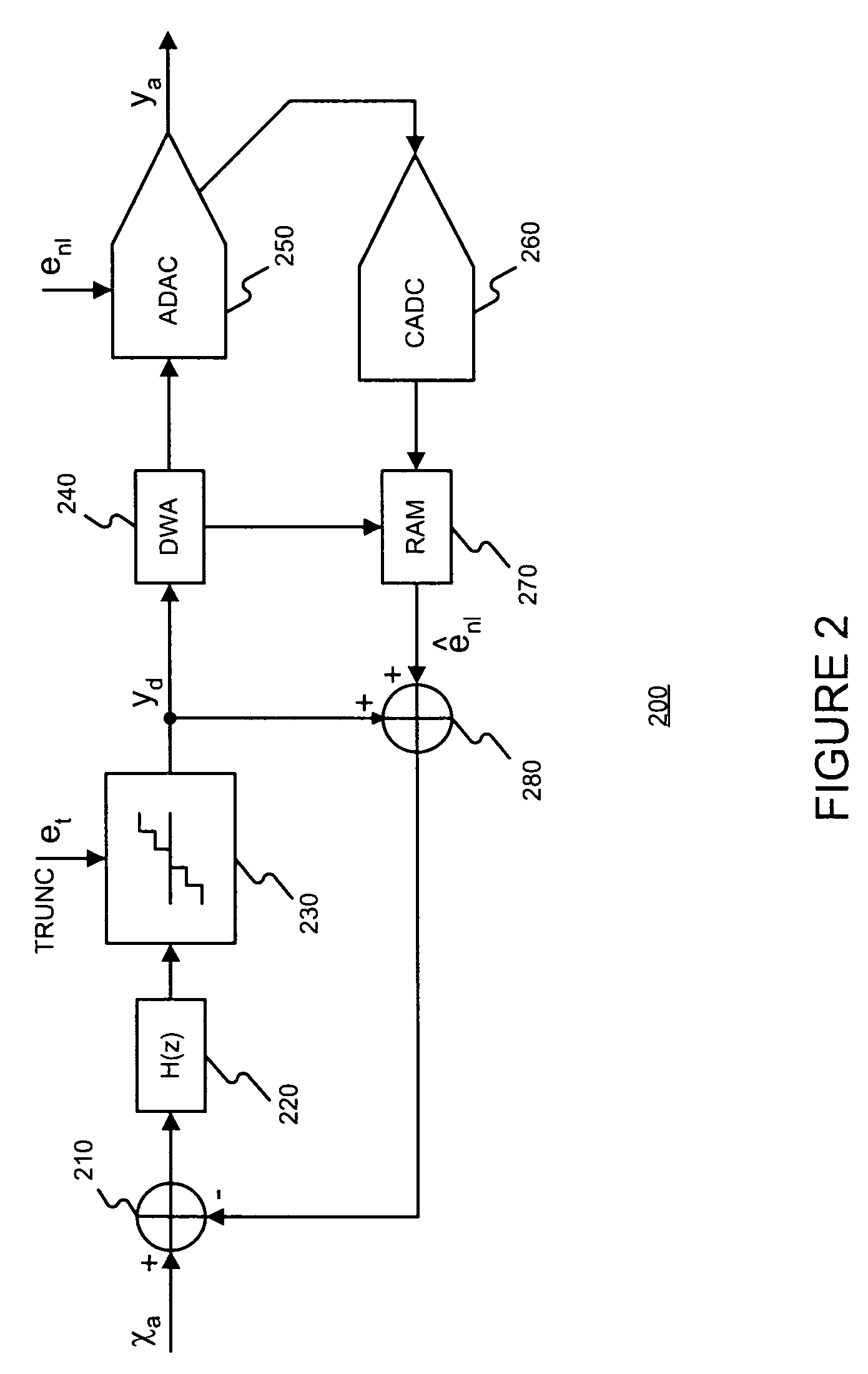

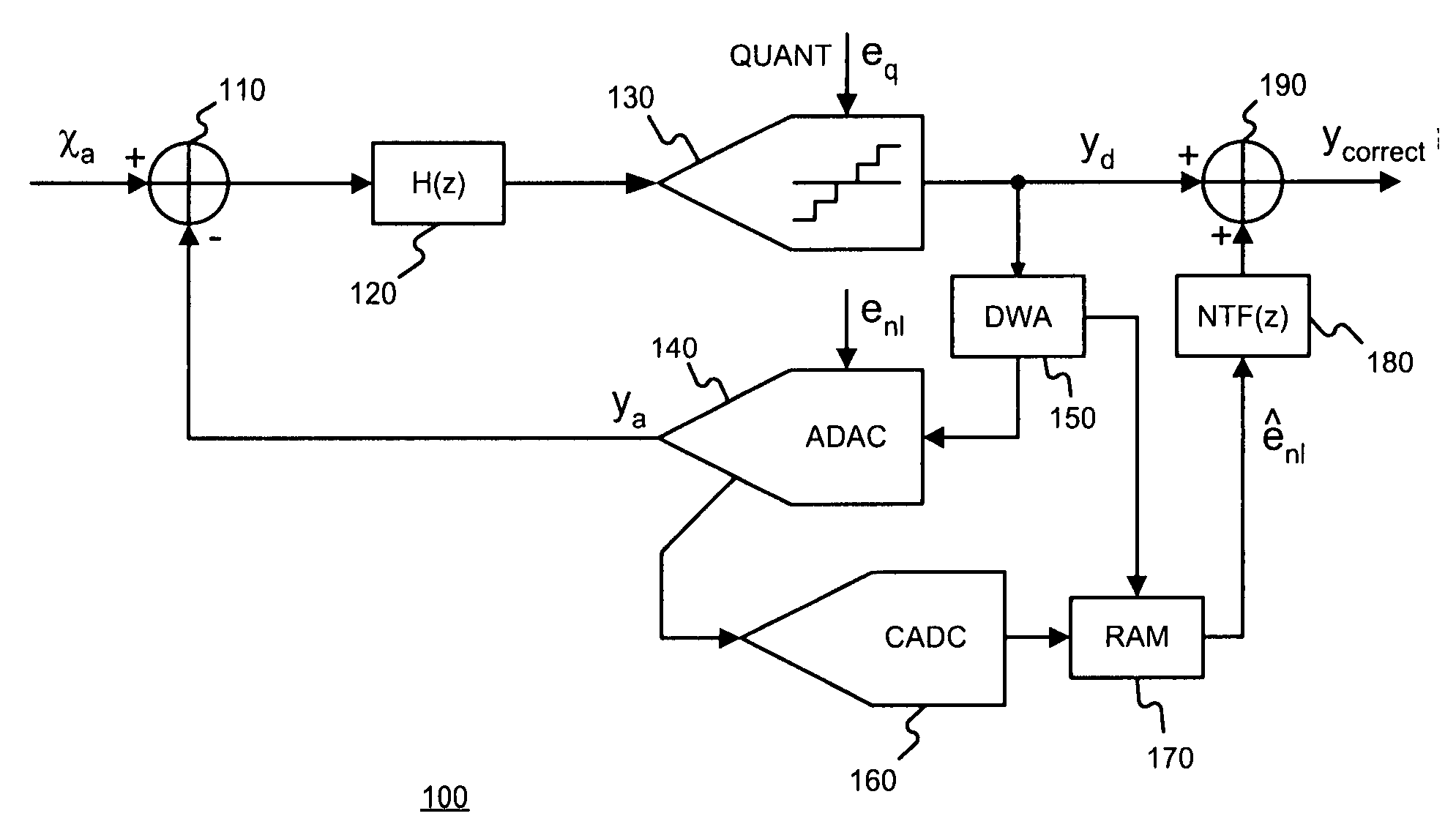

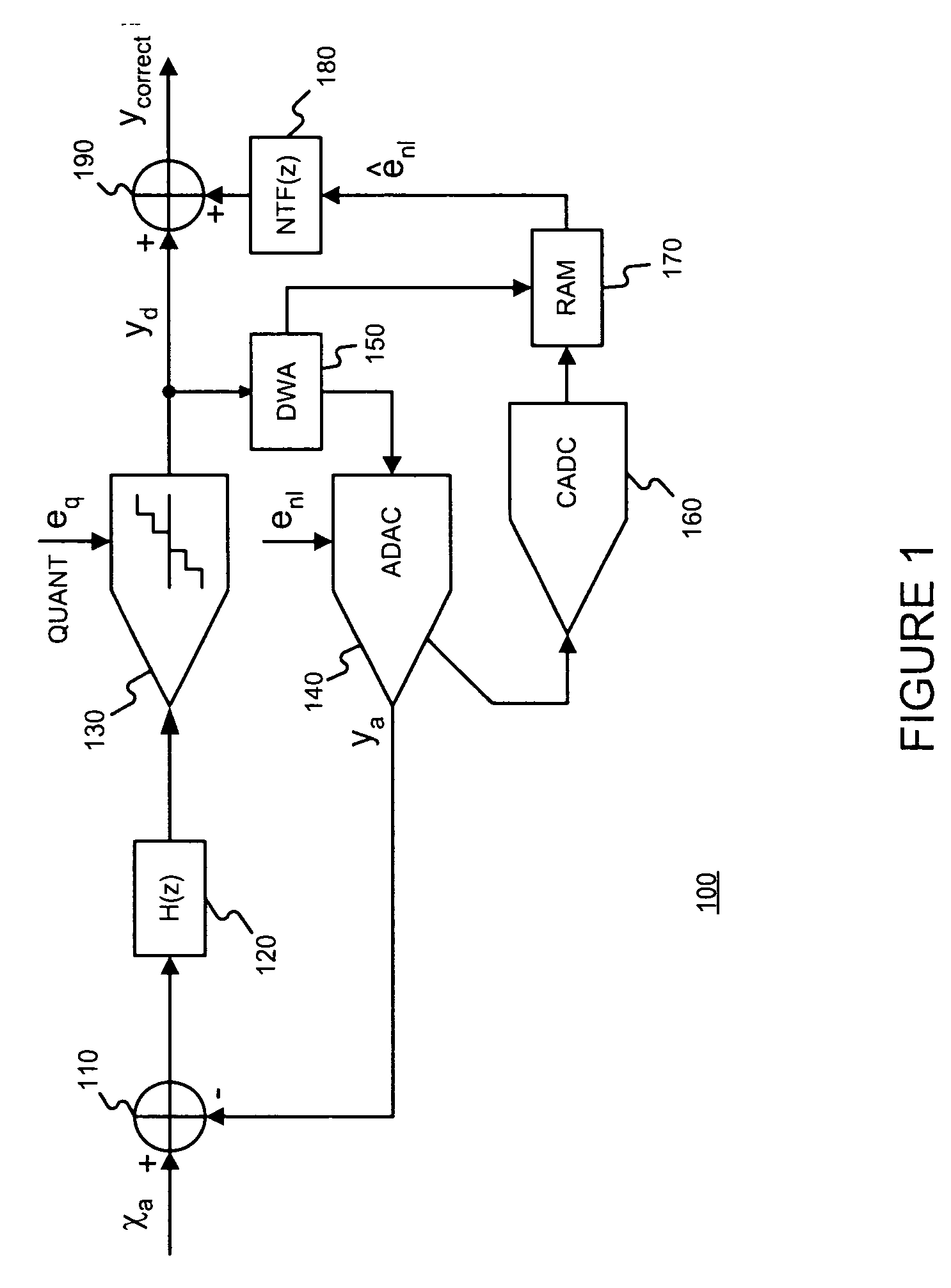

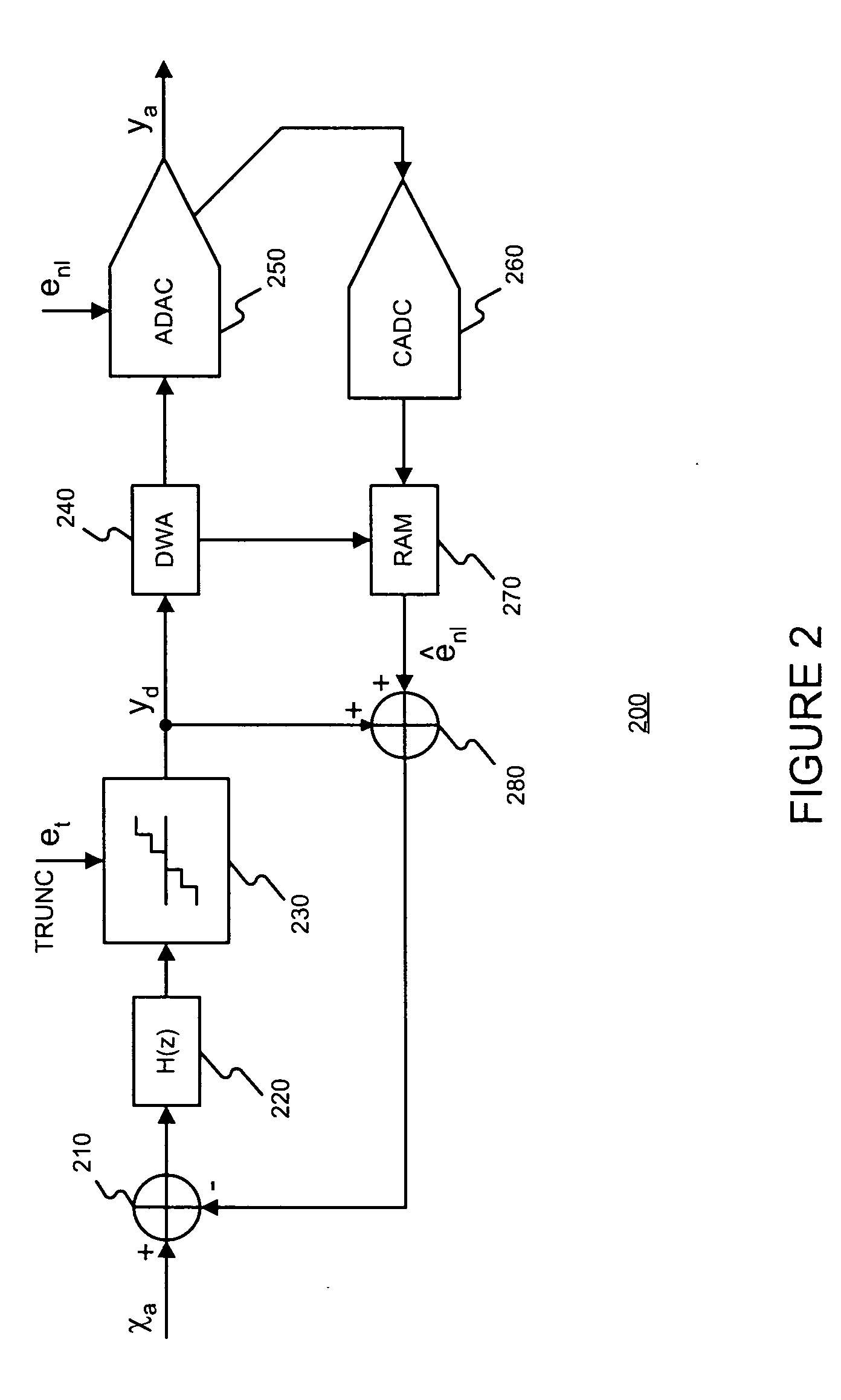

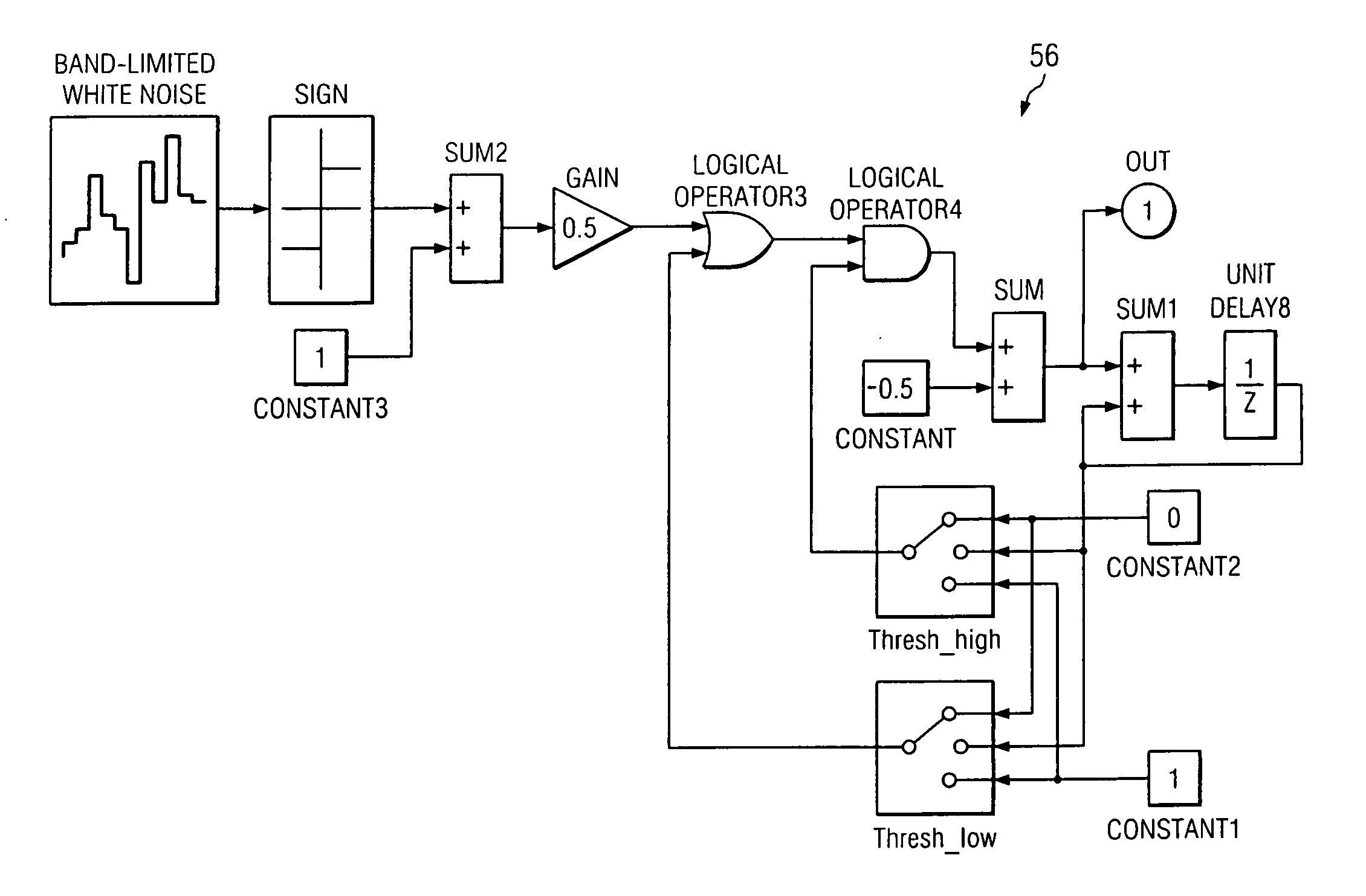

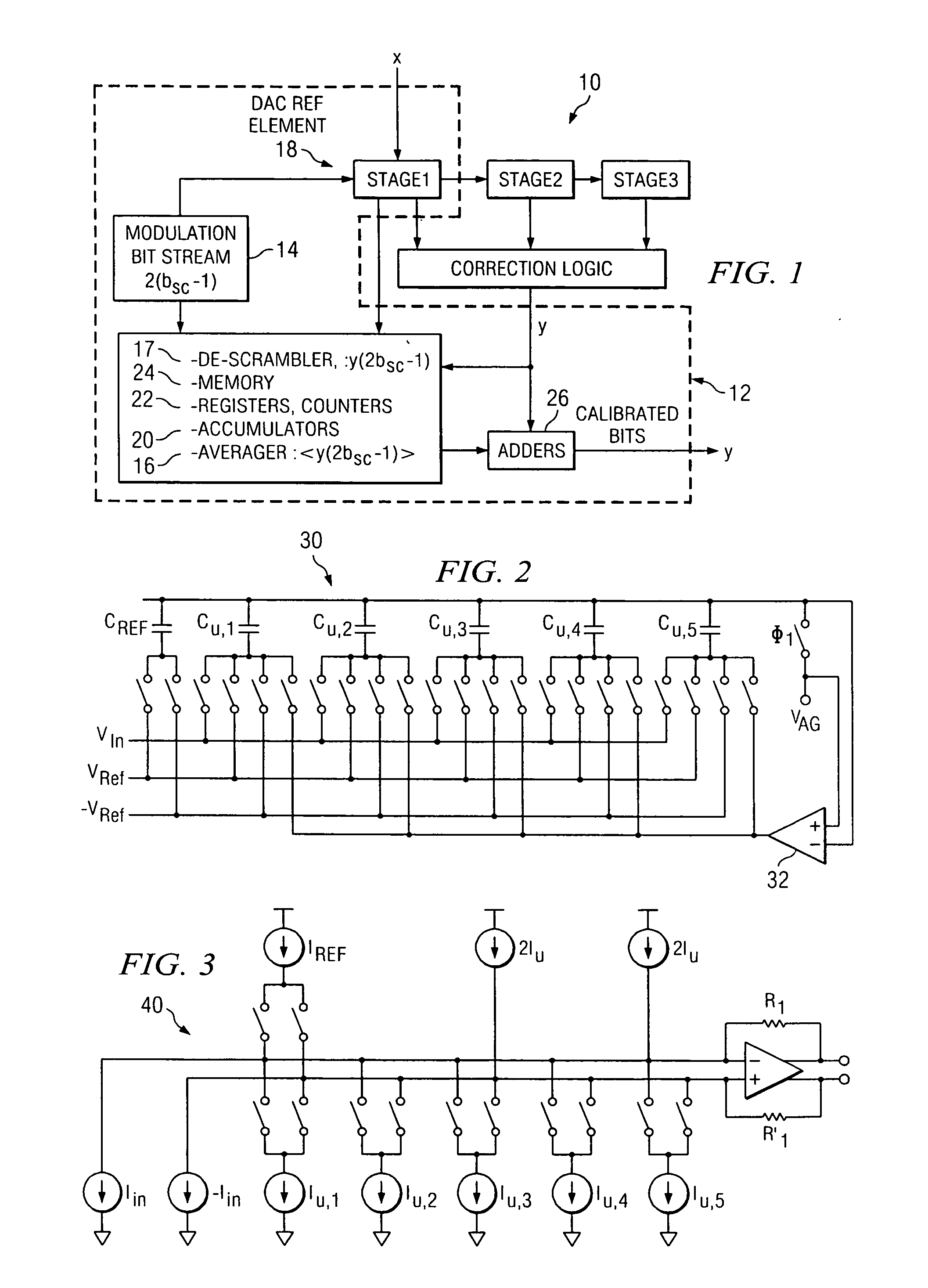

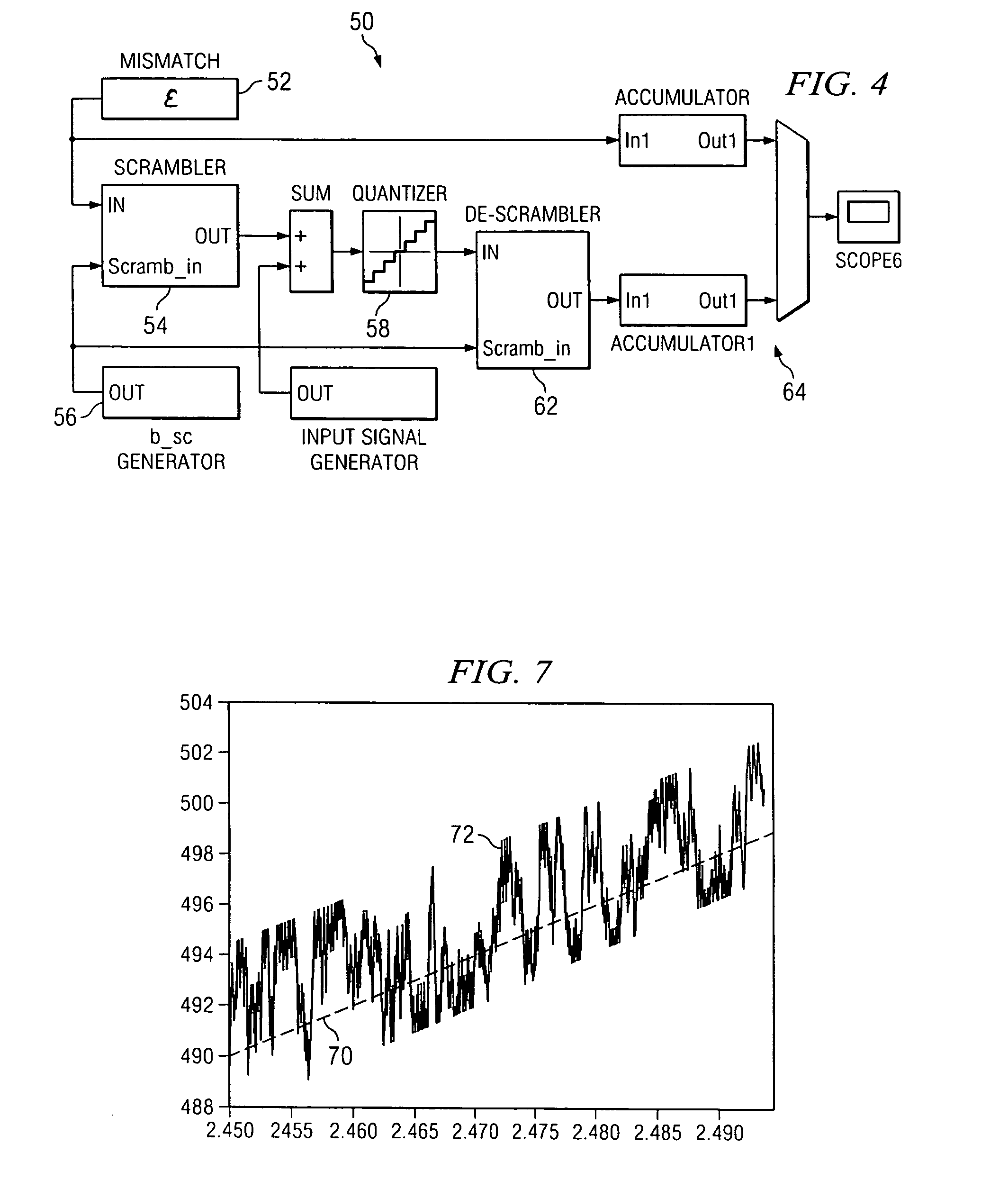

Digital correction of nonlinearity errors of multibit delta-sigma digital to analog converters

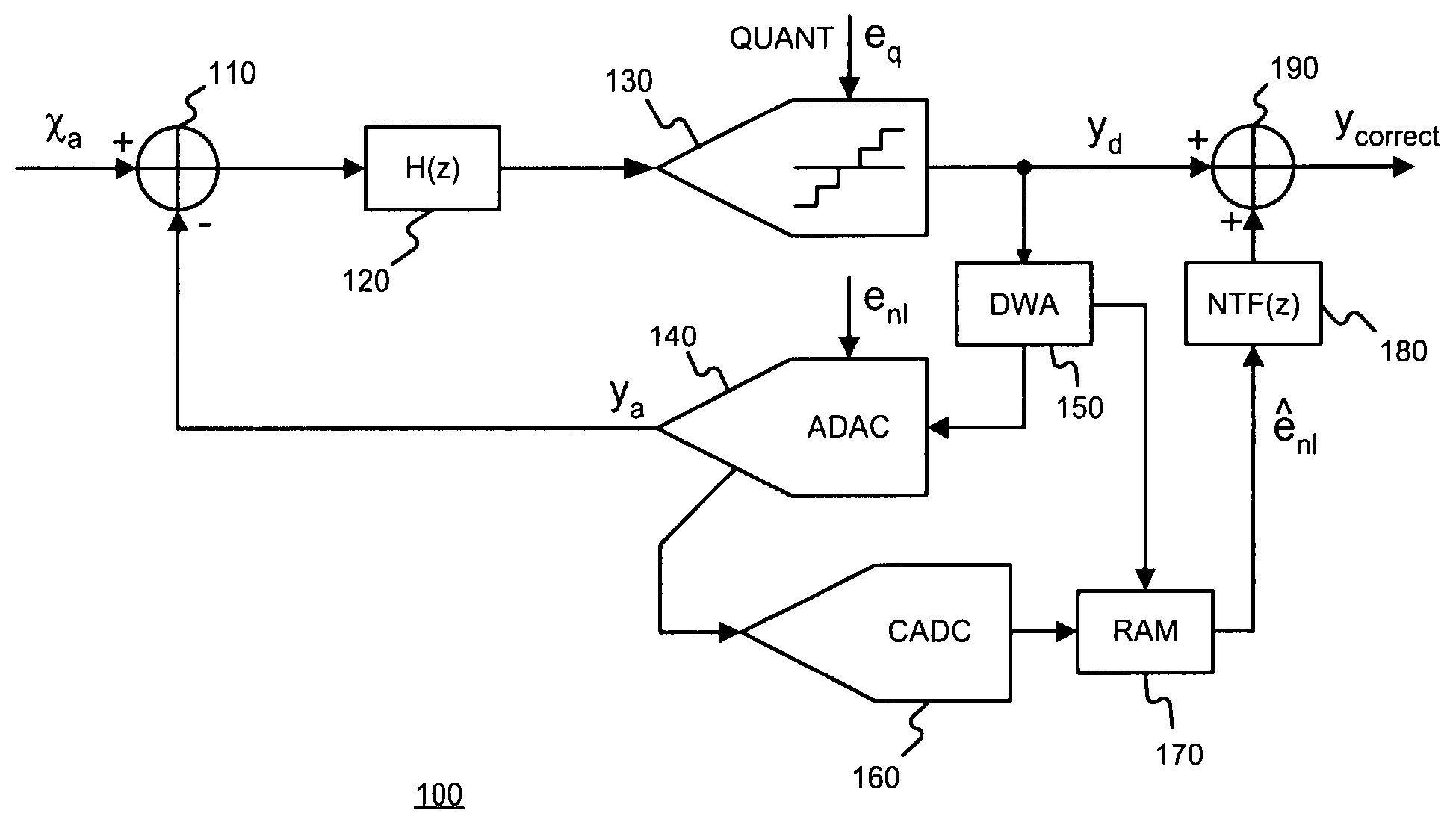

ActiveUS7362247B2Resolution requirement for CADC can be relaxed significantlyEasy to implementElectric signal transmission systemsAnalogue conversionImage resolutionRandom access memory

Digital correction of multibit ADAC nonlinearities for error feedback DACs is provided. The integral nonlinearity (INL) error of the multibit ADAC is estimated (on line or off line) by a low-resolution calibration ADC (CADC) and stored in a random-access memory (RAM) table. The INL values are then used to compensate for the ADAC's distortion in the digital domain. When this compensation is combined with mismatch-shaping techniques such as DWA, the resolution requirement for CADC can be relaxed significantly. The implementation of the proposed correction circuit for error-feedback modulators is inherently simple, since the correction only needs a digital summation without any additional digital filtering.

Owner:AVAGO TECH INT SALES PTE LTD

Circuits and methods to minimize nonlinearity errors in interpolating circuits

Owner:TEXAS INSTR INC

Capacitor exchange method for improving DNL (Differential Nonlinearity)/INL (Integral Nonlinearity) of successive approximation analog to digital converter

InactiveCN105049049AReduce areaSimple structureAnalogue/digital conversionElectric signal transmission systemsCapacitanceCorrection algorithm

The invention discloses a capacitor exchange method for improving the DNL (Differential Nonlinearity) / INL (Integral Nonlinearity) of a successive approximation analog to digital converter (ADC), and relates to the fields of microelectronics and solid-state electronics, in particular to the field of high-performance ADCs. The DNL / INL error caused by judgment of a secondary high order can be offset by exchange of a secondary high-order capacitor with all subsequent capacitors between two conversions without introduction of any extra ADC, introduction of any correction algorithm or splitting of any capacitor. Compared with a conventional correction method for improving the DNL / INL with dependence on an auxiliary ADC, a correction algorithm or capacitor splitting, the capacitor exchange method has the effects of simpler structure, smaller chip occupation area and higher easiness in on-chip implementation.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Digital correction of nonlinearity errors of multibit delta-sigma digital to analog converters

ActiveUS20070109164A1Resolution requirement for CADC can be relaxed significantlyImprove performanceElectric signal transmission systemsAnalogue conversionImage resolutionRandom access memory

Digital correction of multibit ADAC nonlinearities for error feedback DACs is provided. The integral nonlinearity (INL) error of the multibit ADAC is estimated (on line or off line) by a low-resolution calibration ADC (CADC) and stored in a random-access memory (RAM) table. The INL values are then used to compensate for the ADAC's distortion in the digital domain. When this compensation is combined with mismatch-shaping techniques such as DWA, the resolution requirement for CADC can be relaxed significantly. The implementation of the proposed correction circuit for error-feedback modulators is inherently simple, since the correction only needs a digital summation without any additional digital filtering.

Owner:AVAGO TECH INT SALES PTE LTD

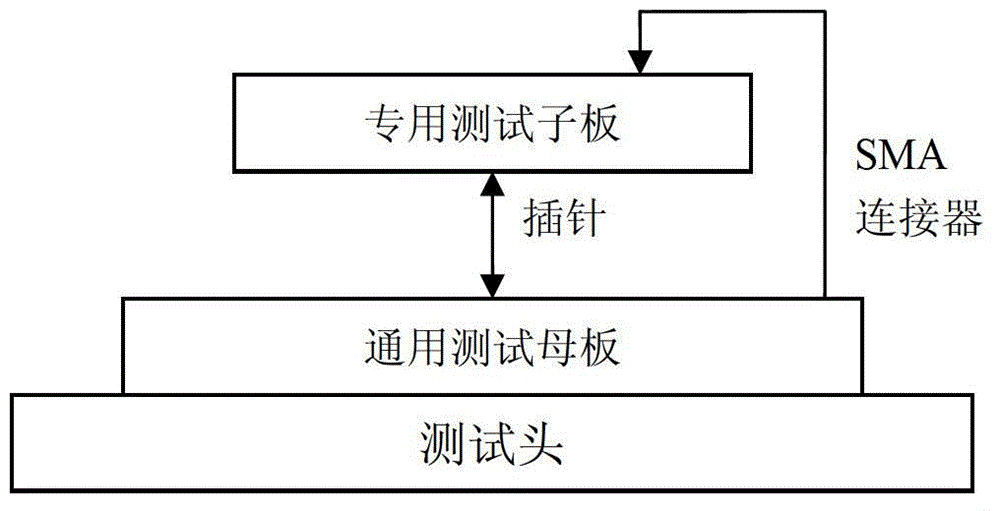

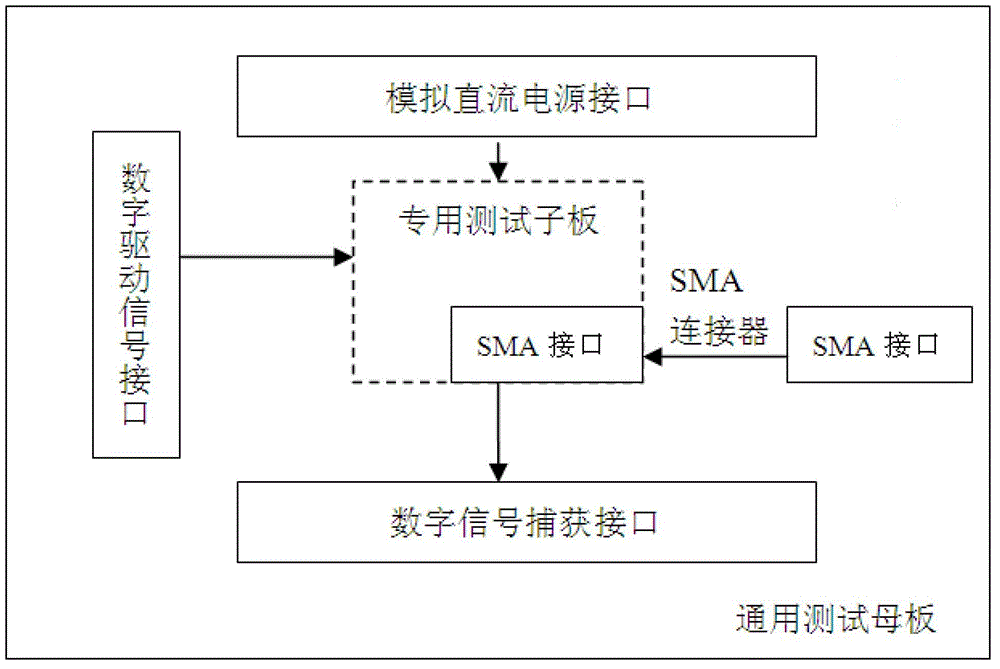

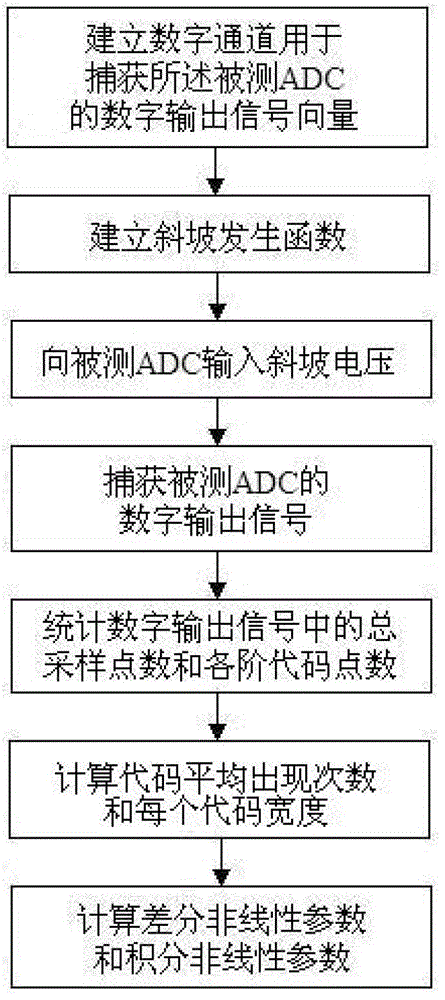

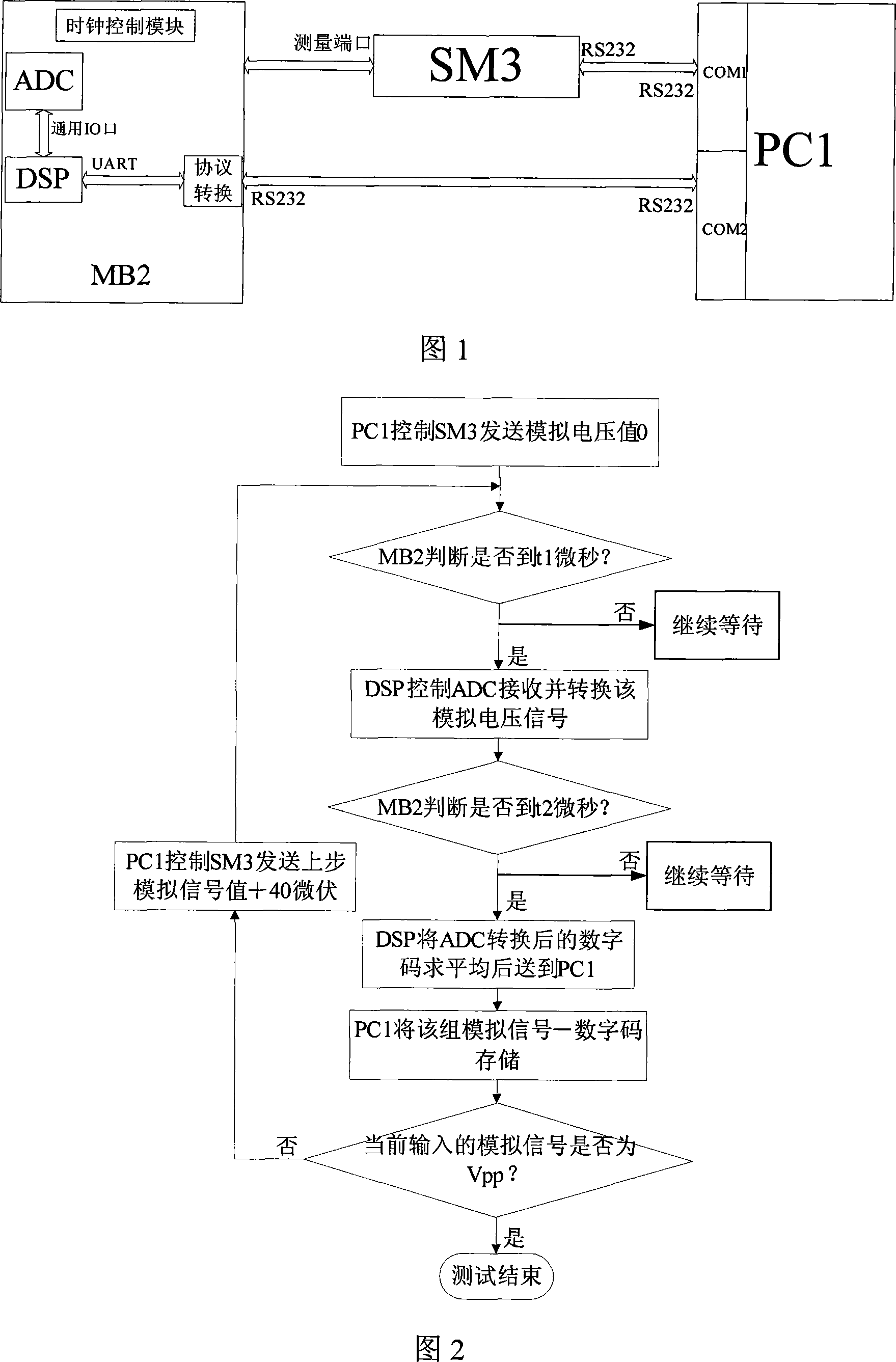

Test adapter and test method for analog-to-digital converter nonlinear parameters

ActiveCN102723950AHigh precisionEasy to operateAnalogue/digital conversion calibration/testingNonlinear parametersEngineering

The invention discloses a test adapter for analog-to-digital converter nonlinear parameters. The test adapter comprises a general test mother board and a special test sub board. The invention further discloses a test method for analog-to-digital converter nonlinear parameters. The test method includes the following steps: building a slope generating function; inputting slope analog voltage into an analog-to-digital converter to be tested; capturing digital output signals of the analog-to-digital converter to be tested; counting the number of total sampling points and all stages of codes in the digital output signals; calculating the average occurrence number of the codes; and calculating differential nonlinear parameters and integral nonlinear parameters. According to the test adapter and the test method for analog-to-digital converter nonlinear parameters, the differential nonlinear parameters and the integral nonlinear parameters of the high-speed and high-accuracy analog-to-digital converter are accurately measured through a linear slope histogram and the natural statistical property of the analog-to-digital converter. The test method is higher than the conventional method and easy to operate, and reduces inaccuracy degree of measurement error to a certain extent.

Owner:CASIC DEFENSE TECH RES & TEST CENT

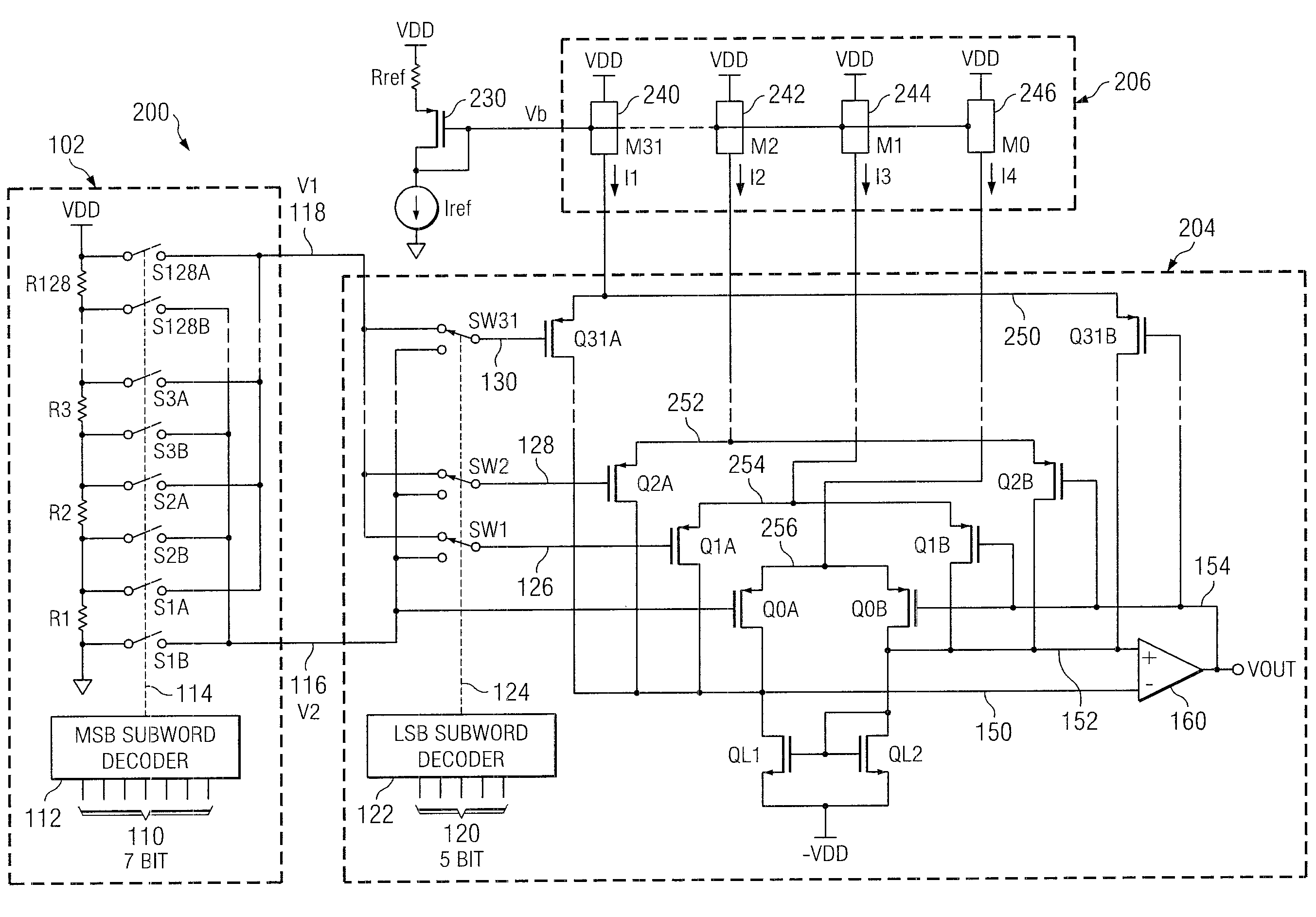

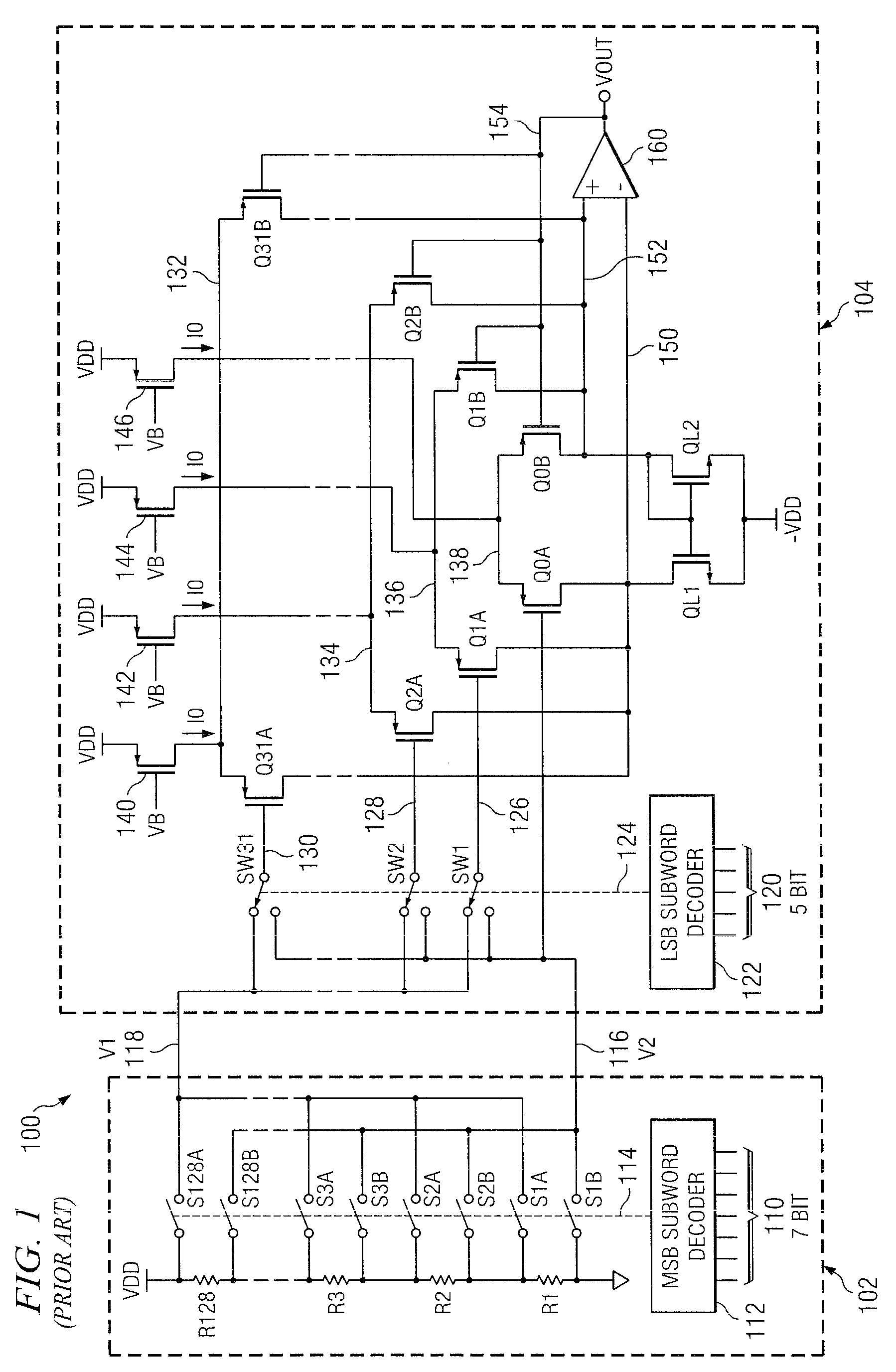

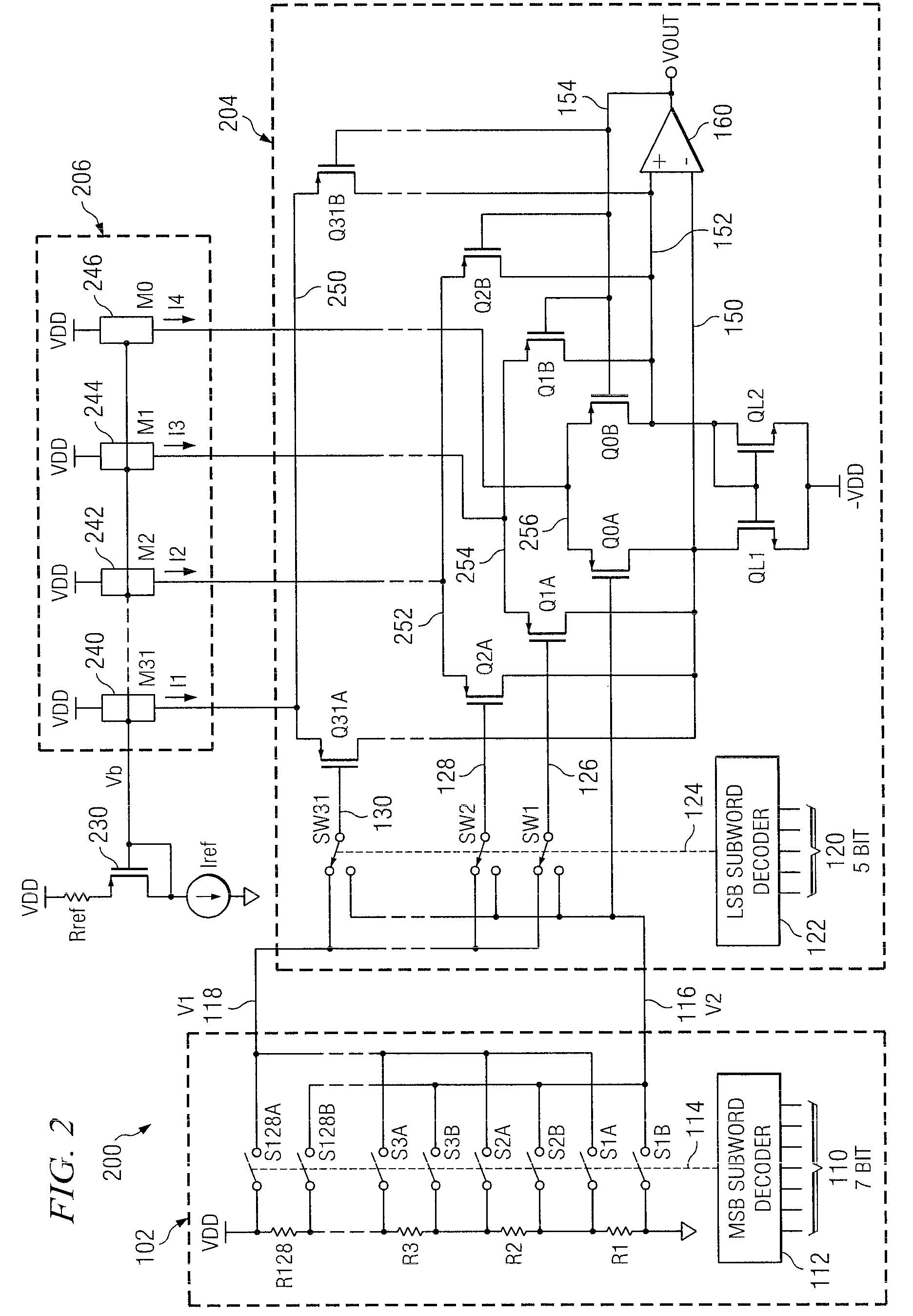

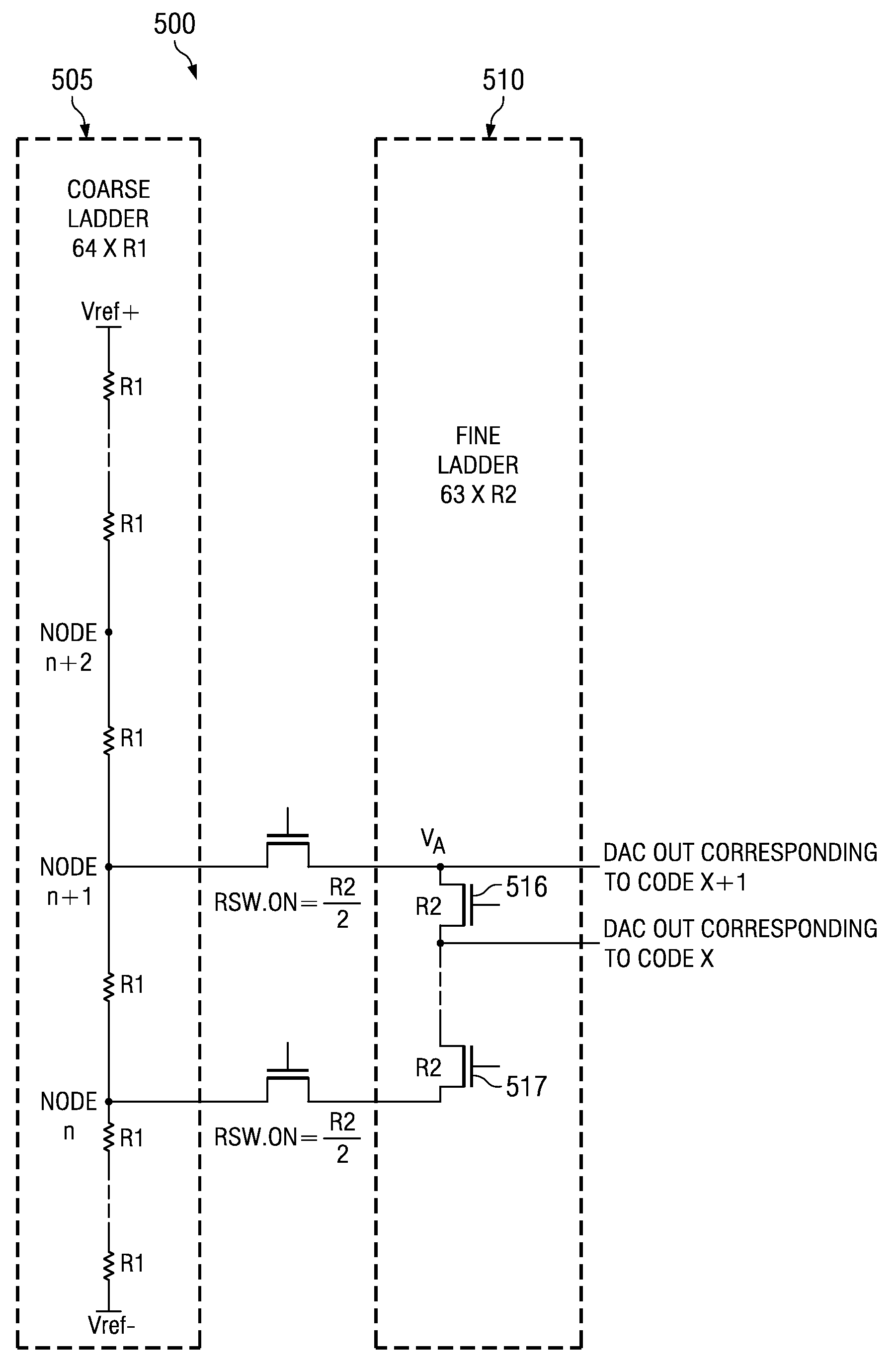

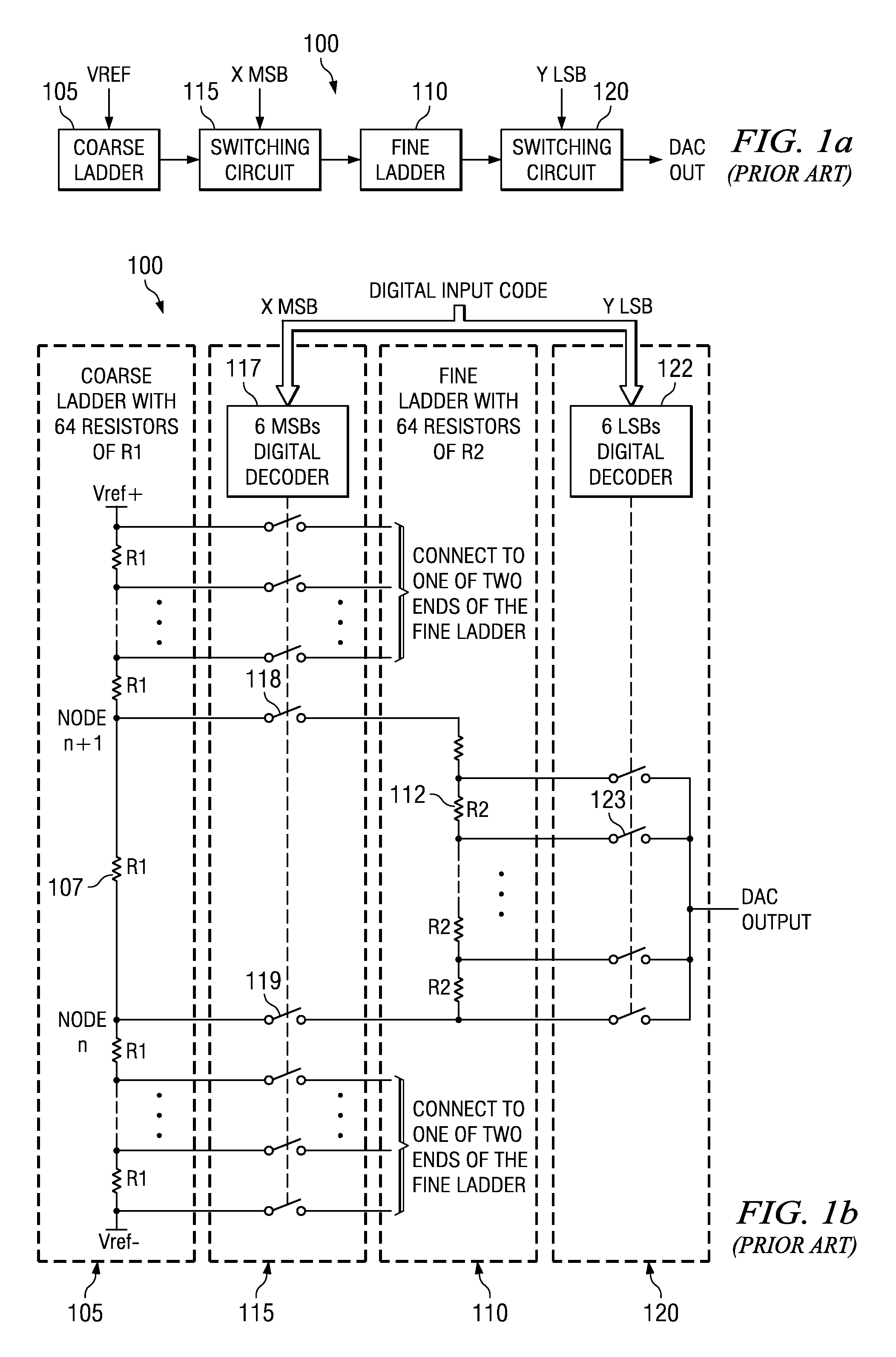

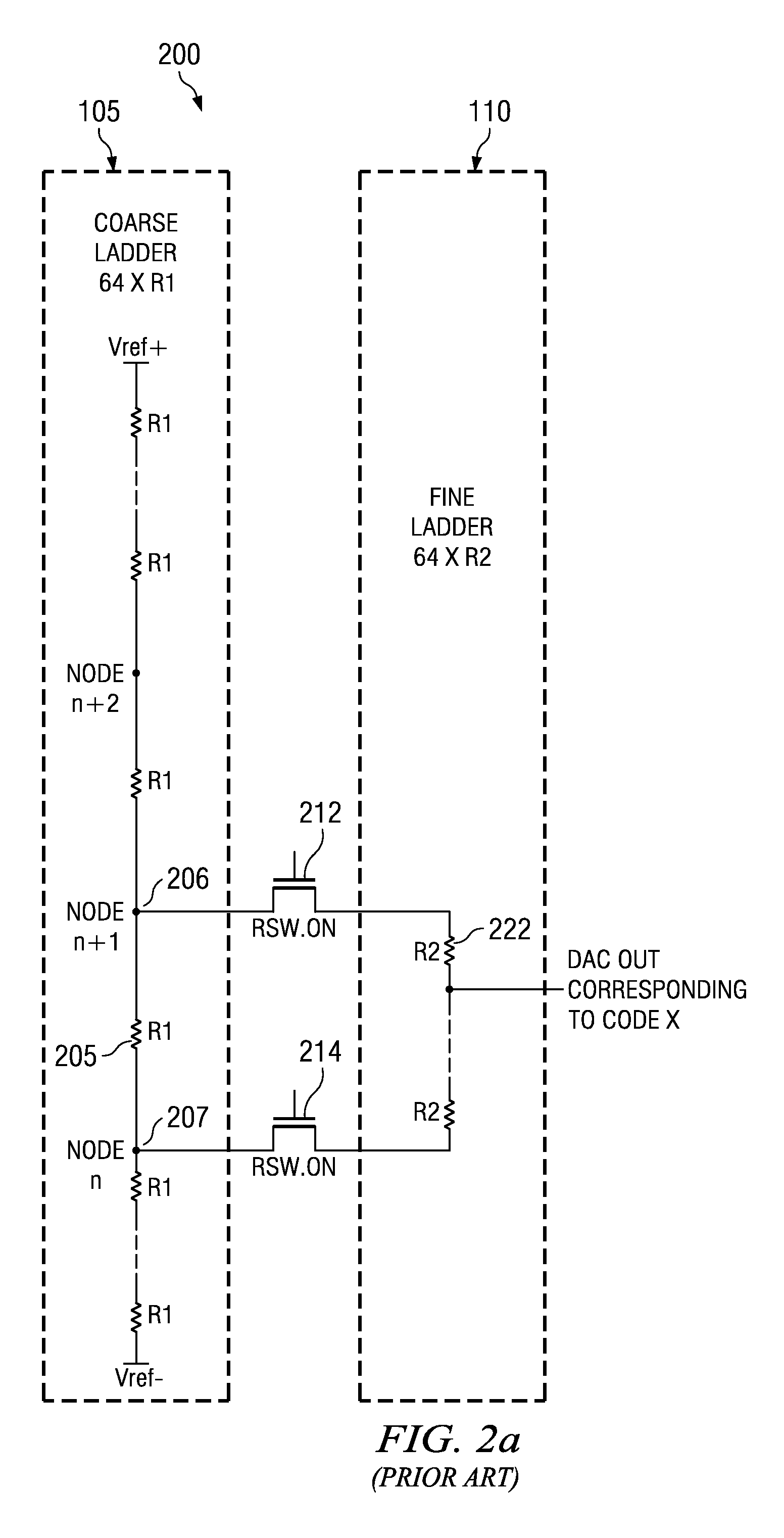

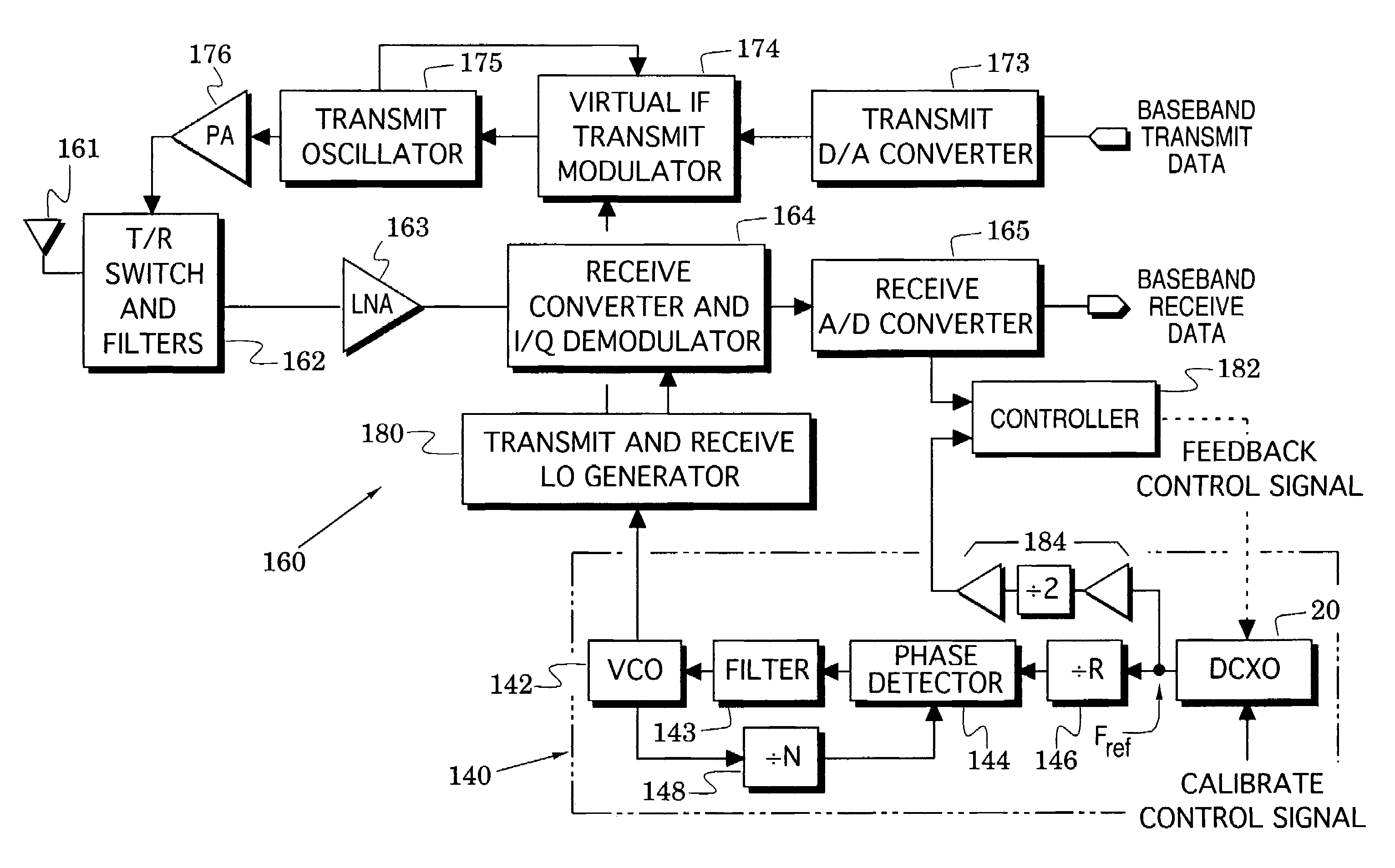

Digital-to-analog converter with triode region transistors in resistor/switch network

ActiveUS20080055135A1Improving DNLImpedance mismatchElectric signal transmission systemsDigital-analogue convertorsElectrical resistance and conductanceResistor ladder

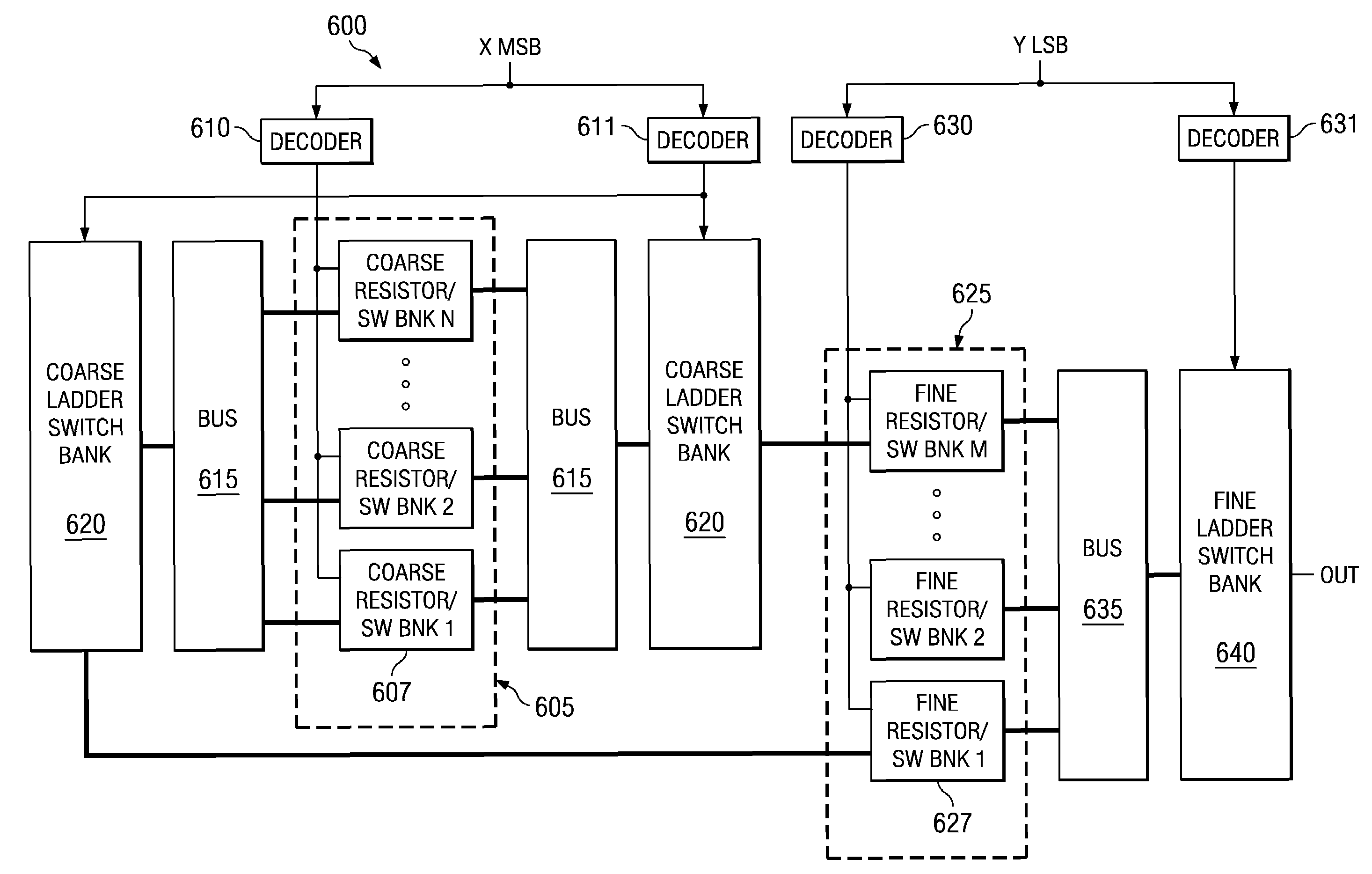

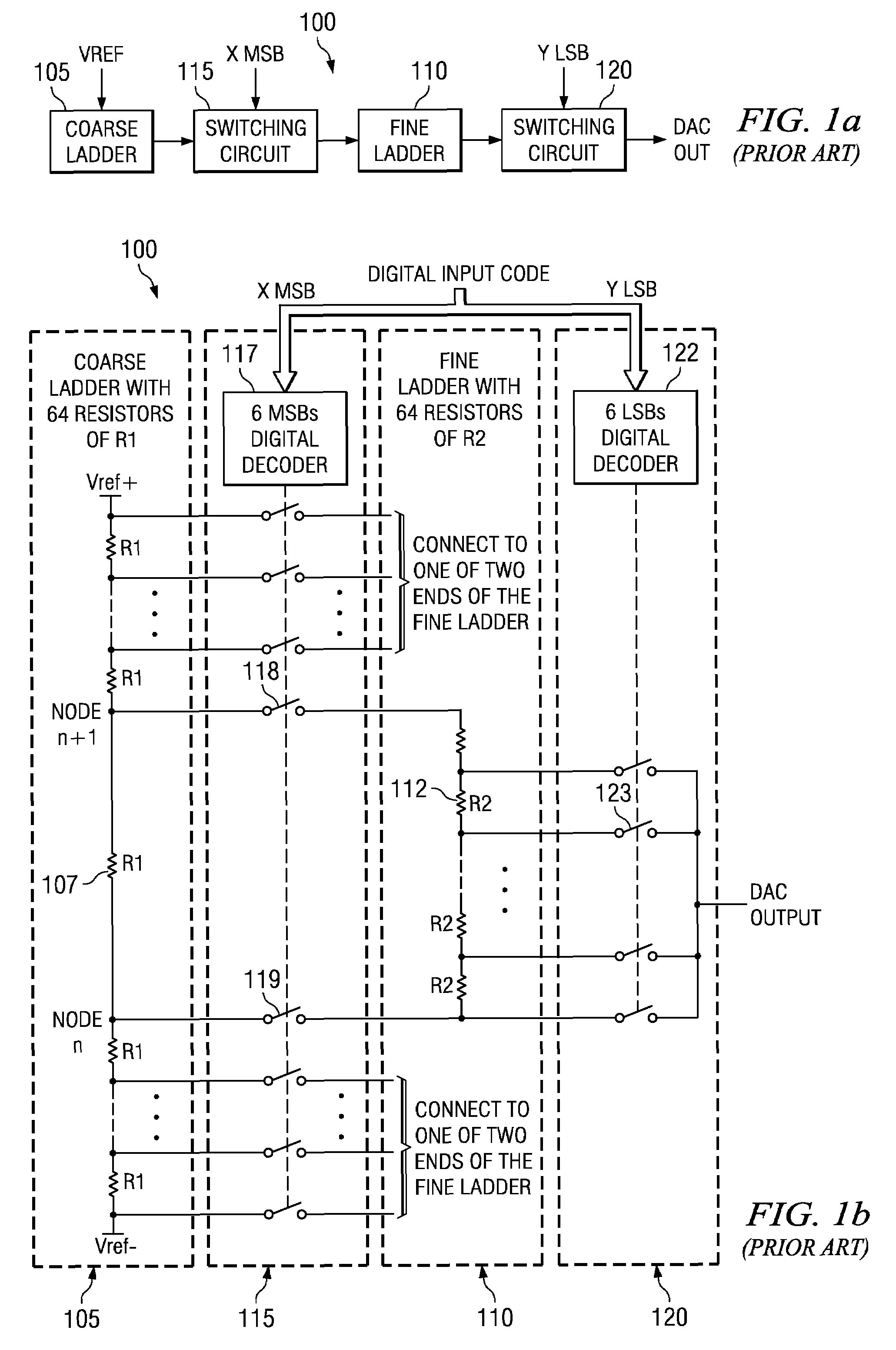

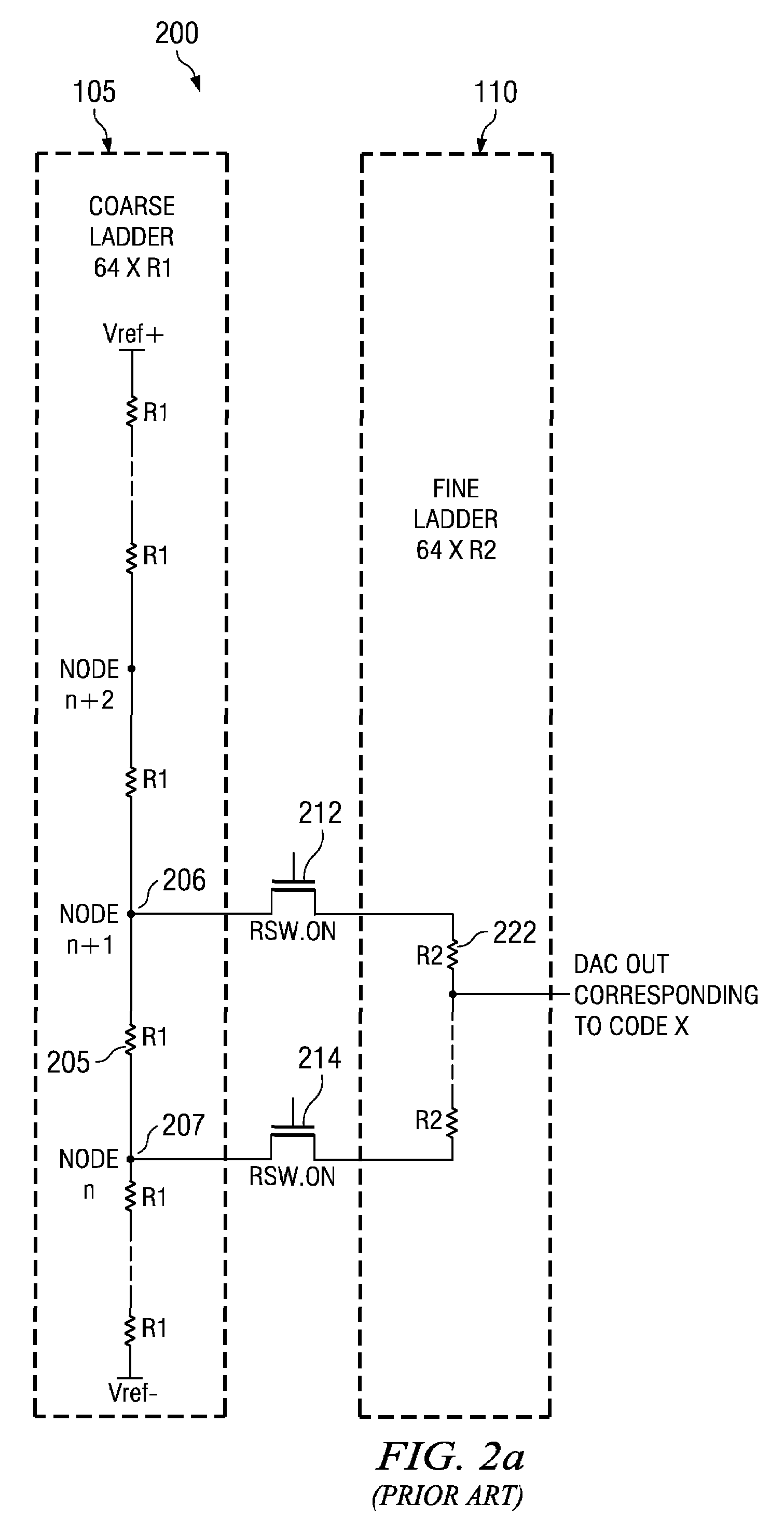

System and method for high-speed and high-precision digital to analog conversion. A preferred embodiment comprises a dual-resistor ladder digital-to-analog converter with a coarse resistor ladder and a fine resistor ladder, wherein resistors in the fine resistor ladder are implemented using transistors. When the effective resistances of switches used in a switching circuit are properly matched with the resistance of the resistors, the differential non-linearity and the integral non-linearity of the digital-to-analog converter can be minimized. The use of transistors to implement switches and resistors can help to eliminate mismatches arising from different fabrication steps and materials, further improving the performance of the digital-to-analog converter.

Owner:TEXAS INSTR INC

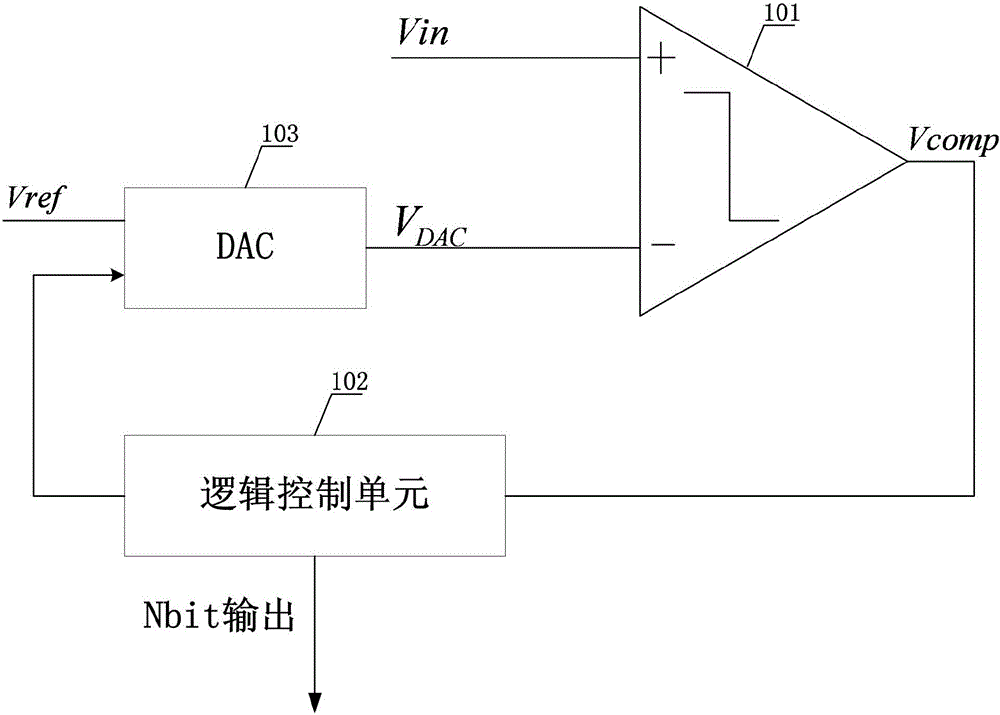

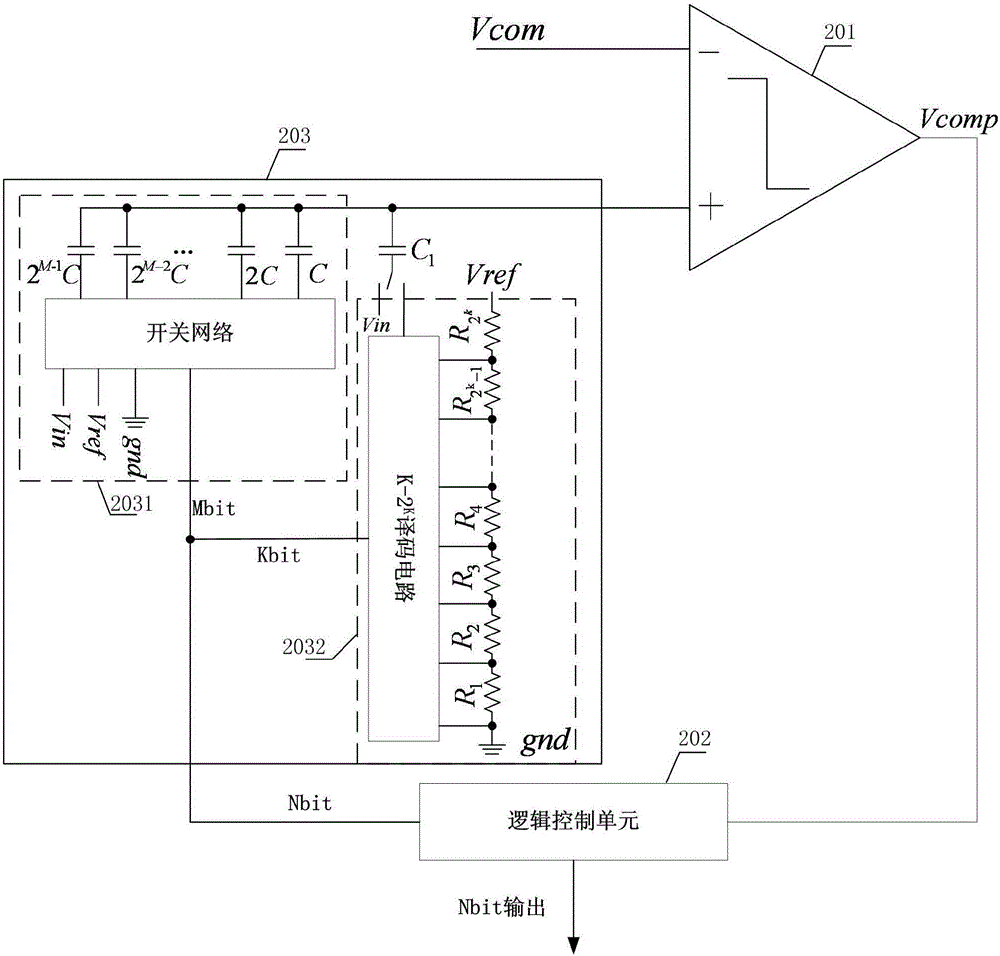

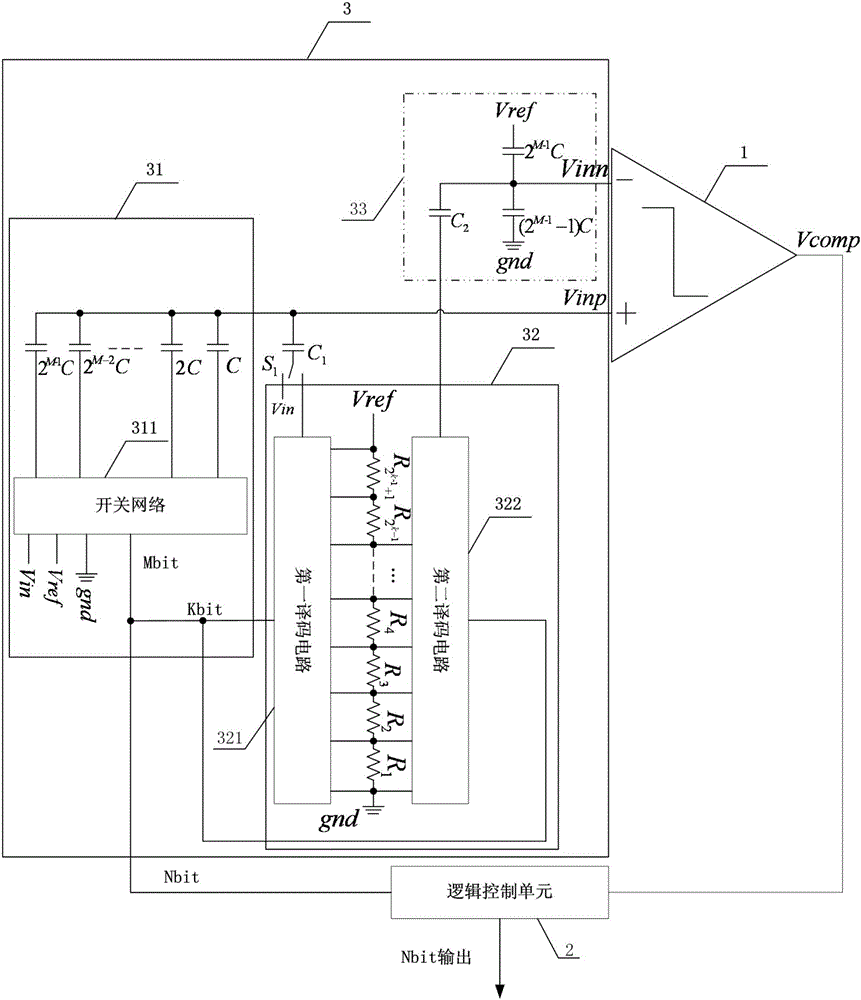

Successive approximation type analog-to-digital converter structure

ActiveCN105827245AReduce Integral NonlinearityReduce differential nonlinearityElectric signal transmission systemsAnalogue-digital convertersCapacitanceDifferential nonlinearity

The invention relates to a successive approximation type analog-to-digital converter (ADC) structure which comprises a comparator, a logic control unit and a digital to analog converter (DAC). The DAC comprises a capacitive sub DA structure, a resistive sub DA structure and an input common-mode setting circuit; and the resistive sub DA structure comprises a first decoding circuit, a second decoding circuit and a resistor string. The resistor string is formed by connecting 2<k-1>+1 resistors in series, the lower end of the resistor string is connected with reference ground level, the upper end of the resistor string is connected with a reference level, a lower-end tapping of each resistor of the resistor string is led out and connected with the first decoding circuit, an upper-end tapping of a (2<k-1>+1)th resistor is led out and connected with the first decoding circuit, lower-end tappings of the first to (2<k-1>)th resistors are led out and connected with the second decoding circuit, the first decoding circuit is connected to the positive input end of the comparator via a first switch, and the second decoding circuit is connected with the input common-mode setting circuit via a second capacitor. The resistor string multiplexing structure is used to reduce integral and differential nonlinearity caused by mismatching of resistors.

Owner:58TH RES INST OF CETC

Method of testing digital-to-analog and analog-to-digital converters

InactiveUS20120075130A1Electric signal transmission systemsAnalogue-digital convertersElectrical resistance and conductanceDigital analog converter

A method of testing a digital-to-analog or analog-to-digital converter including coarse and fine voltage dividers corresponding respectively to more and less significant bits of the digital signal. Reference input signals are applied corresponding to a first selection of the fine resistor elements with each selection of the coarse resistor elements in succession, corresponding output signals of the converter are measured, and differential non-linearity values and integral non-linearity values for these selections of fine and coarse resistor elements are calculated. Similar measurements and calculations are made for a first selection of the coarse resistor elements with each of the selections of the fine resistor elements in succession. Differential non-linearity values and integral non-linearity values for other combinations of the coarse resistor elements with the fine resistor elements are then calculated using combinations of the calculated differential non-linearity values and the calculated integral non-linearity values.

Owner:NXP USA INC

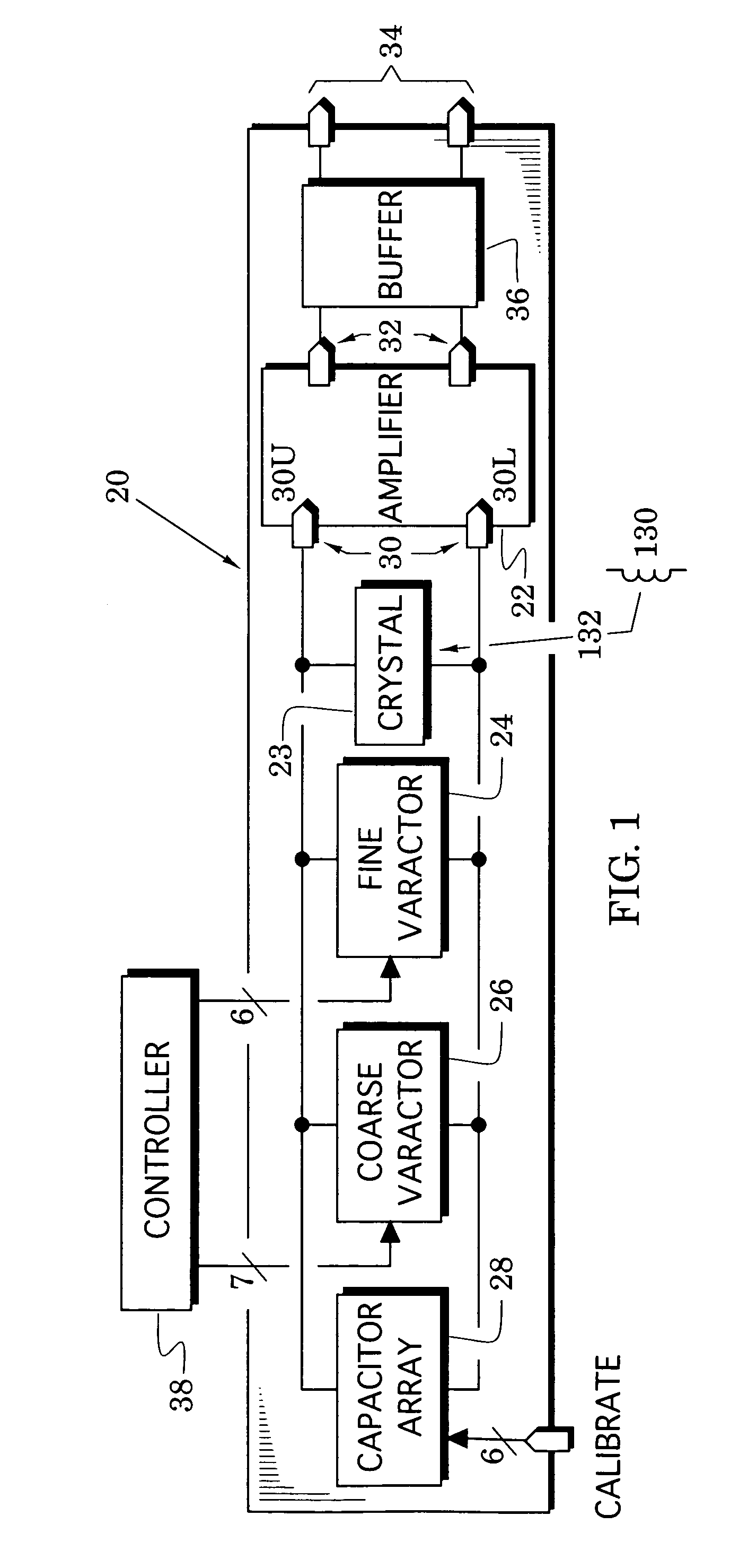

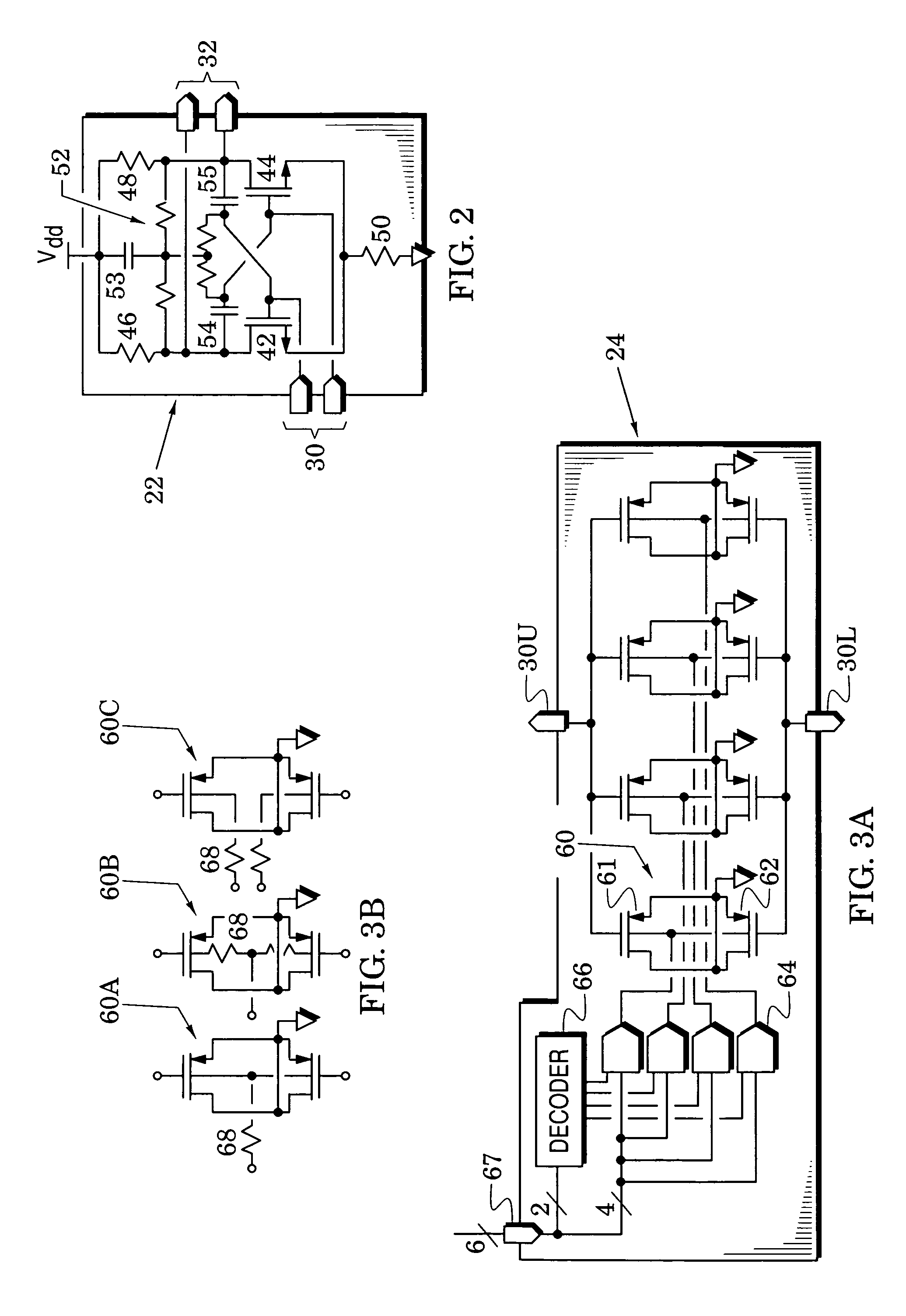

Digitally-controlled reference oscillators

InactiveUS7199698B1Low costSmall sizeAngle modulation by variable impedenceAngle modulation detailsPhase noiseEngineering

Varactor and reference oscillator structures are provided that are particularly suited for integrated circuit fabrication and which provide excellent parameter performance (e.g., monotonicity, linearity, low phase noise and low differential and integral non-linearity) so that they are useful in a variety of wireless communication structures (e.g., cellular telephones).

Owner:MEDIATEK INC

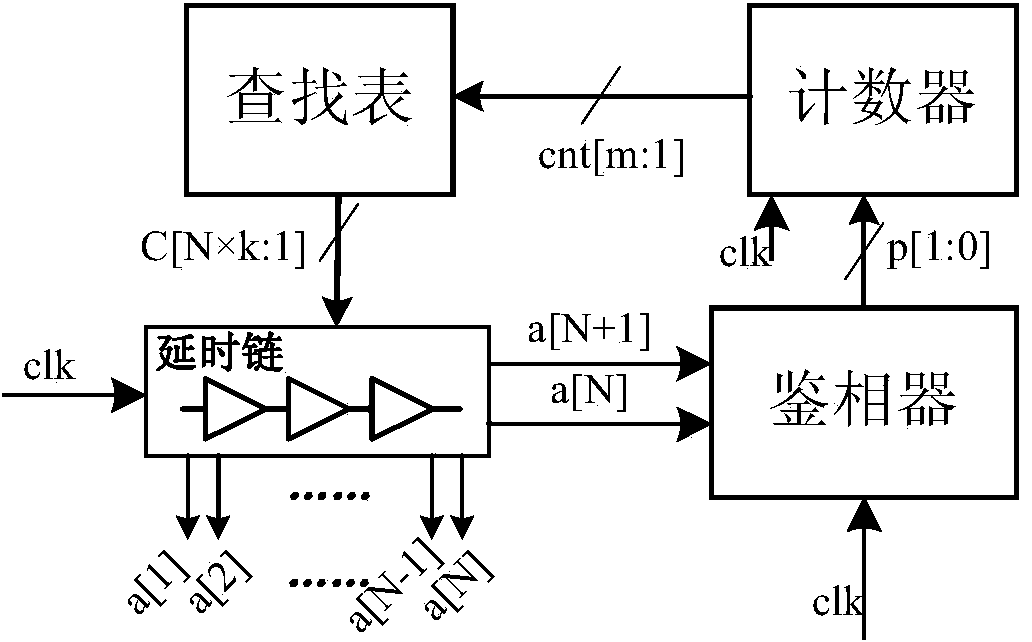

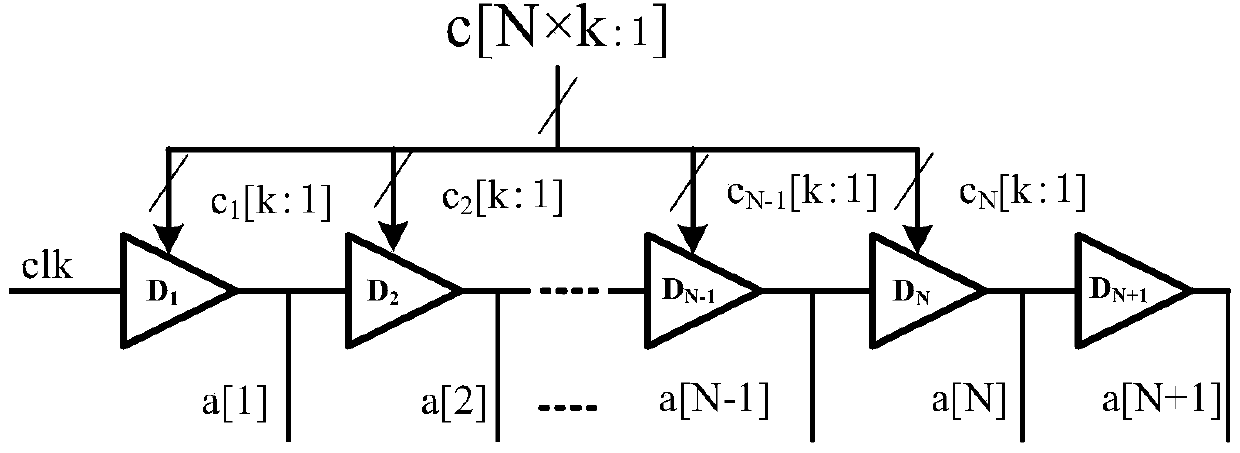

Multiphase clock generation circuit

InactiveCN103427798AEvenly distributed phase differenceSimple structureElectric pulse generator circuitsPhase detectorDiscriminator

The invention discloses a multiphase clock generation circuit, and belongs to the technical field of electronics. The multiphase clock generation circuit comprises a delay chain, a phase discriminator, a counter and a lookup table module. The phase discriminator judges whether delay of the delay chain is equal to a reference clock period or not, and the delay of delay units of the delay chain is adjusted according to output results of the phase discriminator, so that the delay of the delay chain is equal to the reference clock period. In the adjusting process and N delay units, the delay of k delay units is smaller than an ideal value, the delay of N-k delay units is larger than the ideal value, and both N and k are integers. The delay units are divided into 2*min [k, (N-k)] +1 groups, and the difference of control codes of the delay units in adjacent groups is 1, so that an optimized linearity result is obtained. The multiphase clock generation circuit has the advantages of simple structure, high reliability, low differential nonlinearity and integral nonlinearity and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

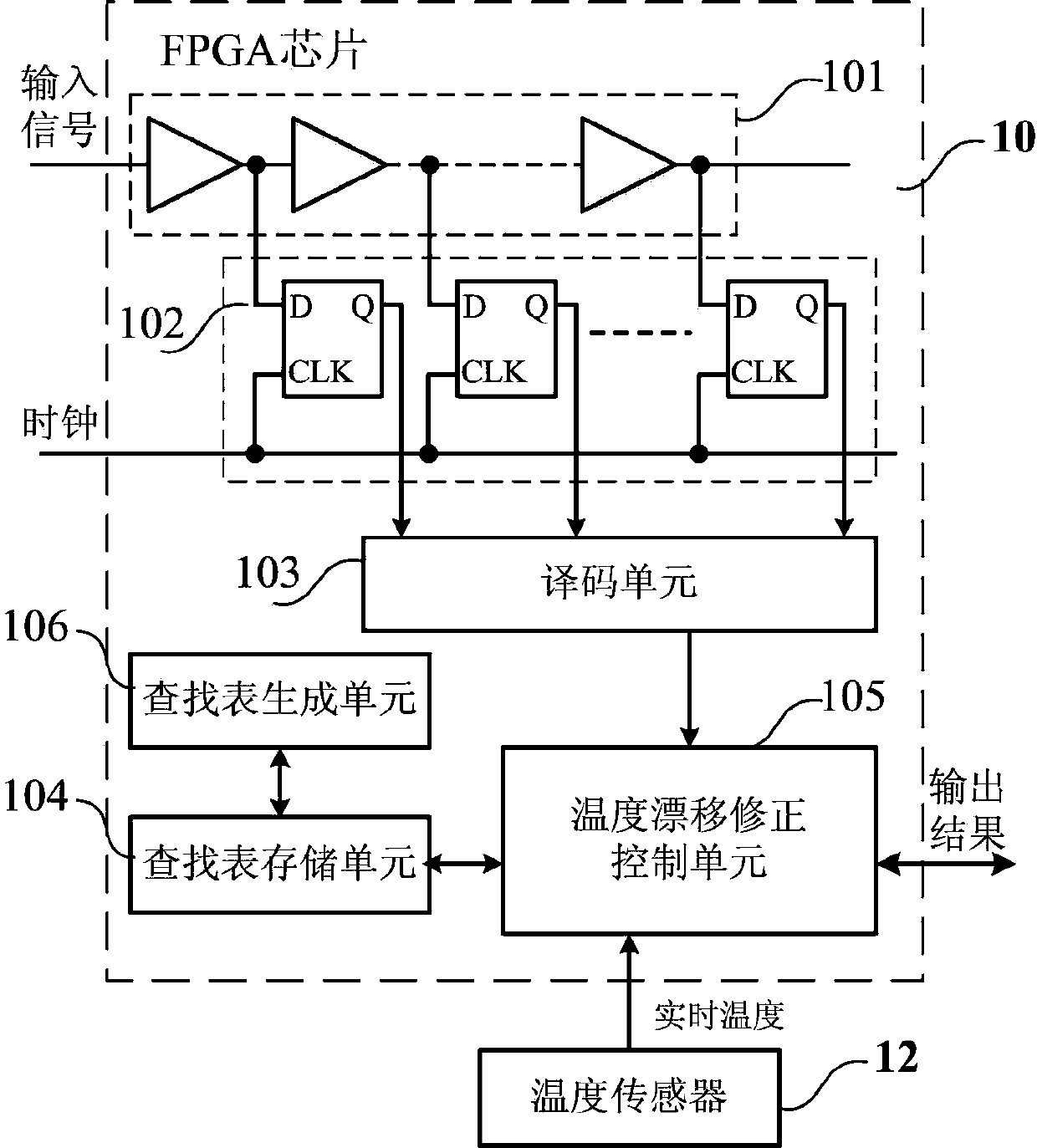

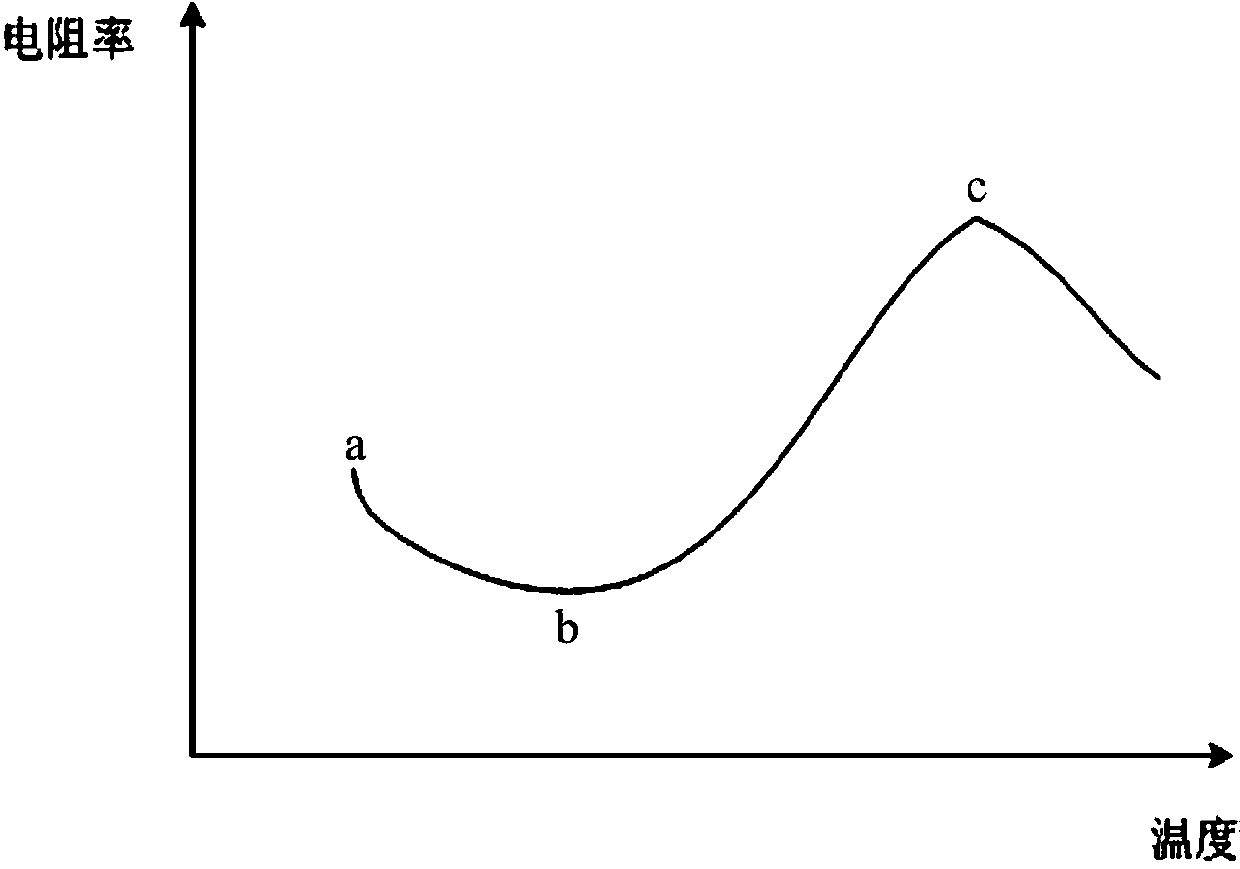

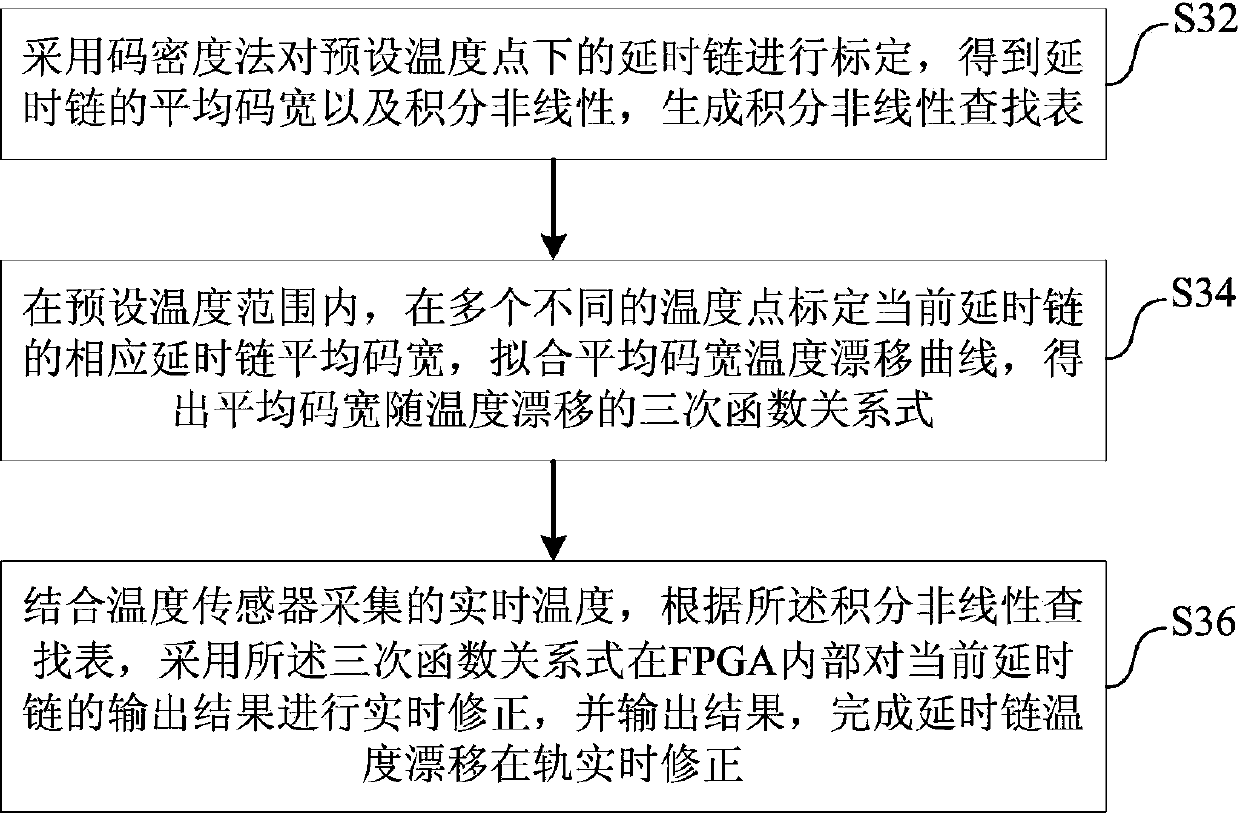

Delay chain temperature drift on-orbit correction device and method based on FPGA

InactiveCN104199481AUpload in real timeFlexible useTemperatue controlTime informationOrbit correction

The invention discloses a delay chain temperature drift on-orbit correction device and a delay chain temperature drift on-orbit correction method based on FPGA. The device comprises a temperature sensor, a delay chain, a D trigger array, a decoding unit, a lookup table storage unit and a temperature drift correction control unit, wherein the temperature sensor is used for collecting real-time temperature; the delay chain is used for reading out time information of an input signal relating to a clock edge; the D trigger array is connected to the delay chain, for locking an output state of each delay unit in the delay chain when arriving the clock edge and outputting temperature coding data; the decoding unit is connected to the D trigger array, for converting the temperature coding data into binary code data and outputting; the lookup table storage unit is used for storing integral nonlinear lookup table data of the delay chain marked at a preset temperature point; the temperature drift correction control unit is connected to the temperature sensor, the decoding unit and the lookup table storage unit respectively, for achieving on-orbit correction of delay chain temperature drift. According to the delay chain temperature drift on-orbit correction device and method based on FPGA, correction of the delay chain temperature drift is achieved by fewer sources, and high time resolution capacity is ensured.

Owner:SHANGHAI ENG CENT FOR MICROSATELLITES

INL curve correction in a pipeline ADC

ActiveUS7348906B2Minimize impactReduce the amount of noiseElectric signal transmission systemsAnalogue conversionFeedback circuitsAnalog signal

The present invention relates to a method and system for reducing integral non linearity errors in a pipeline Analog to Digital Converter (ADC). The invention provides in a first embodiment a method comprising the steps of: adding an analog dither signal to the analog input signal of a pipeline Analog to Digital Converter, and converting the analog input signal to a digital output signal by means of the pipeline Analog to Digital Converter. The amplitude of the analog dither signal is determined by the architecture of the Analog to Digital Converter. The invention also provides in a second embodiment a circuit comprising a pipeline analog to digital converter for converting an analog input signal to a digital output signal and a feedback circuit coupled to the converter such that the digital output signal is adapted to have an average non linearity error value of about zero LSBs.

Owner:ANALOG DEVICES INC

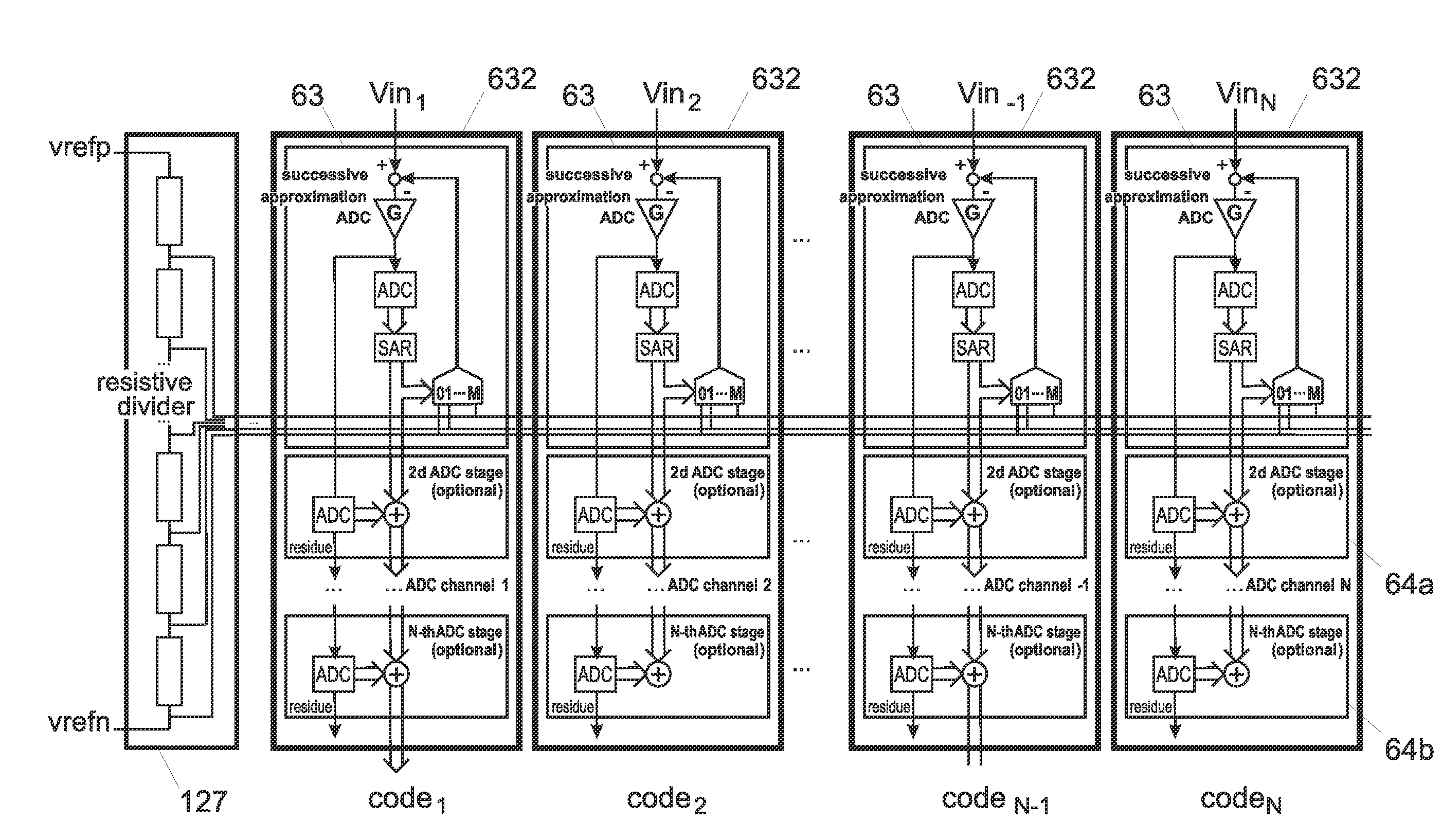

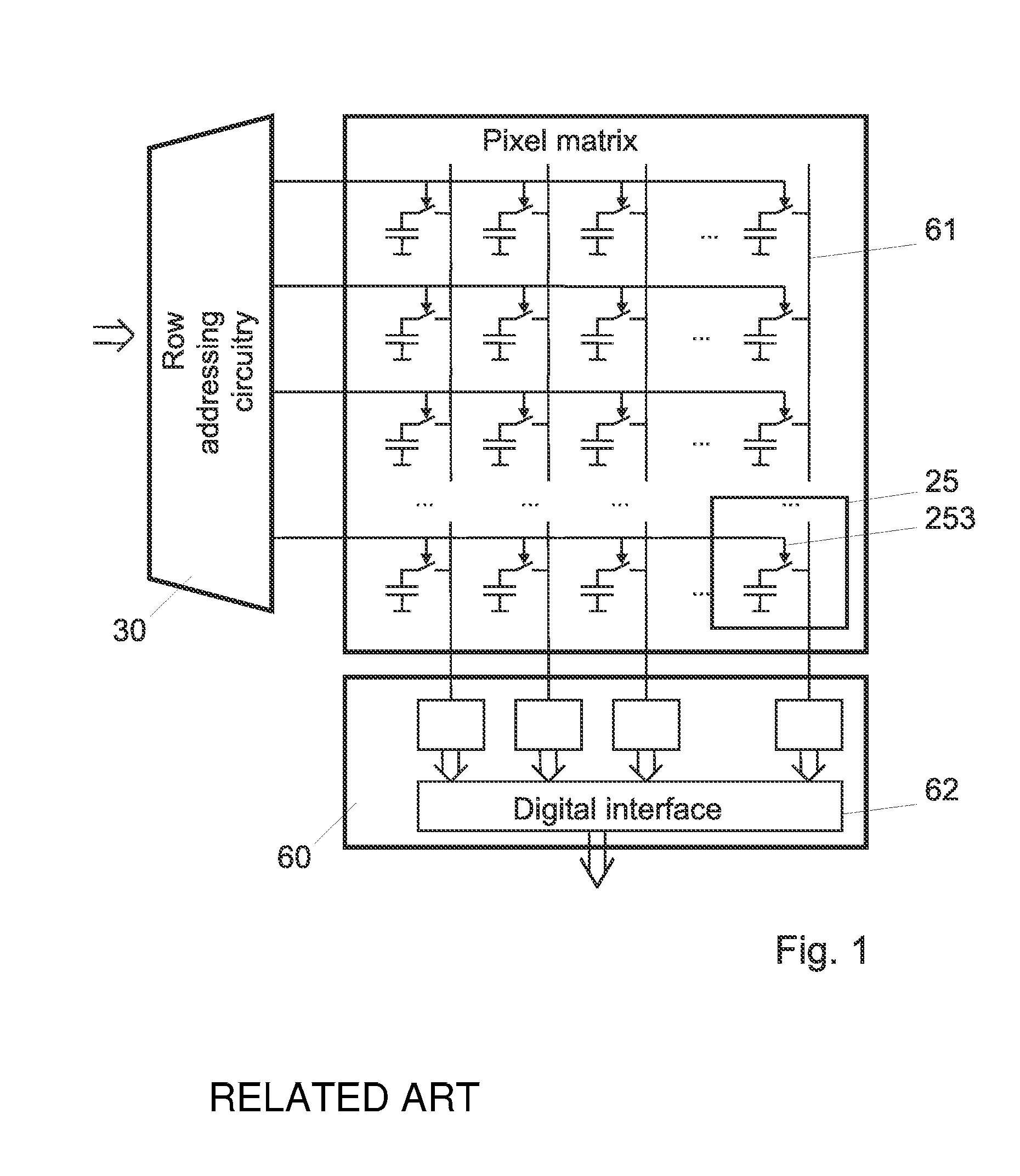

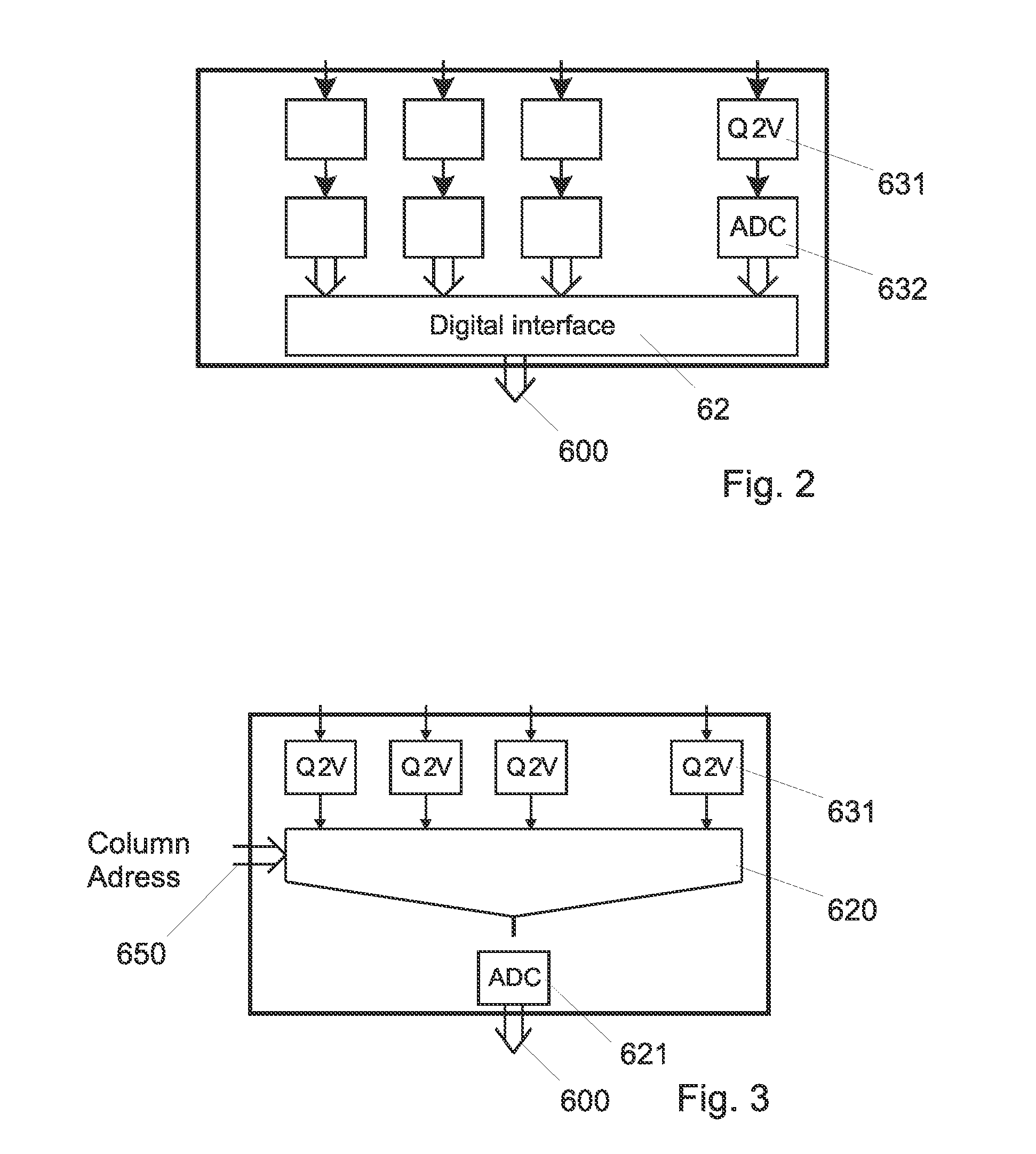

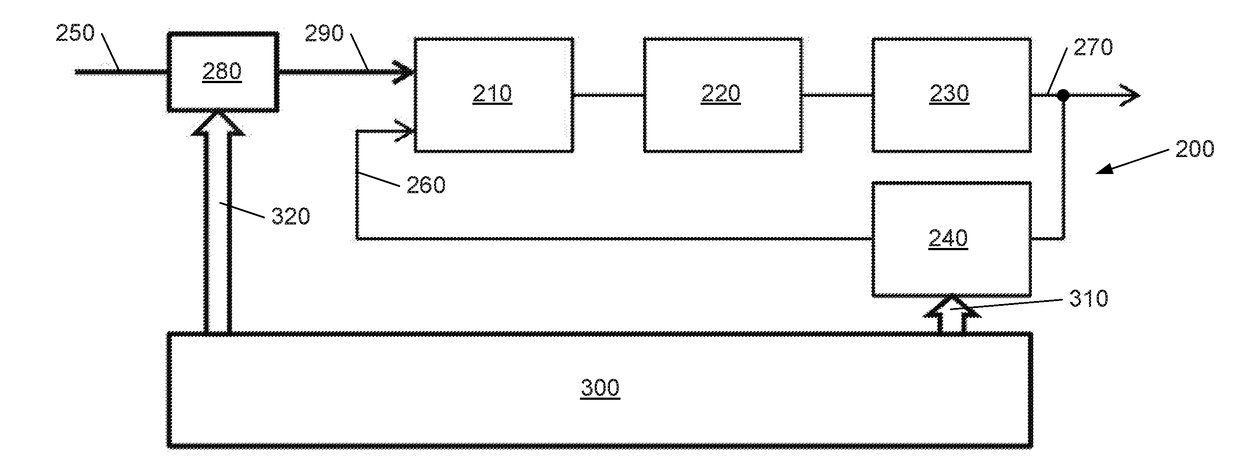

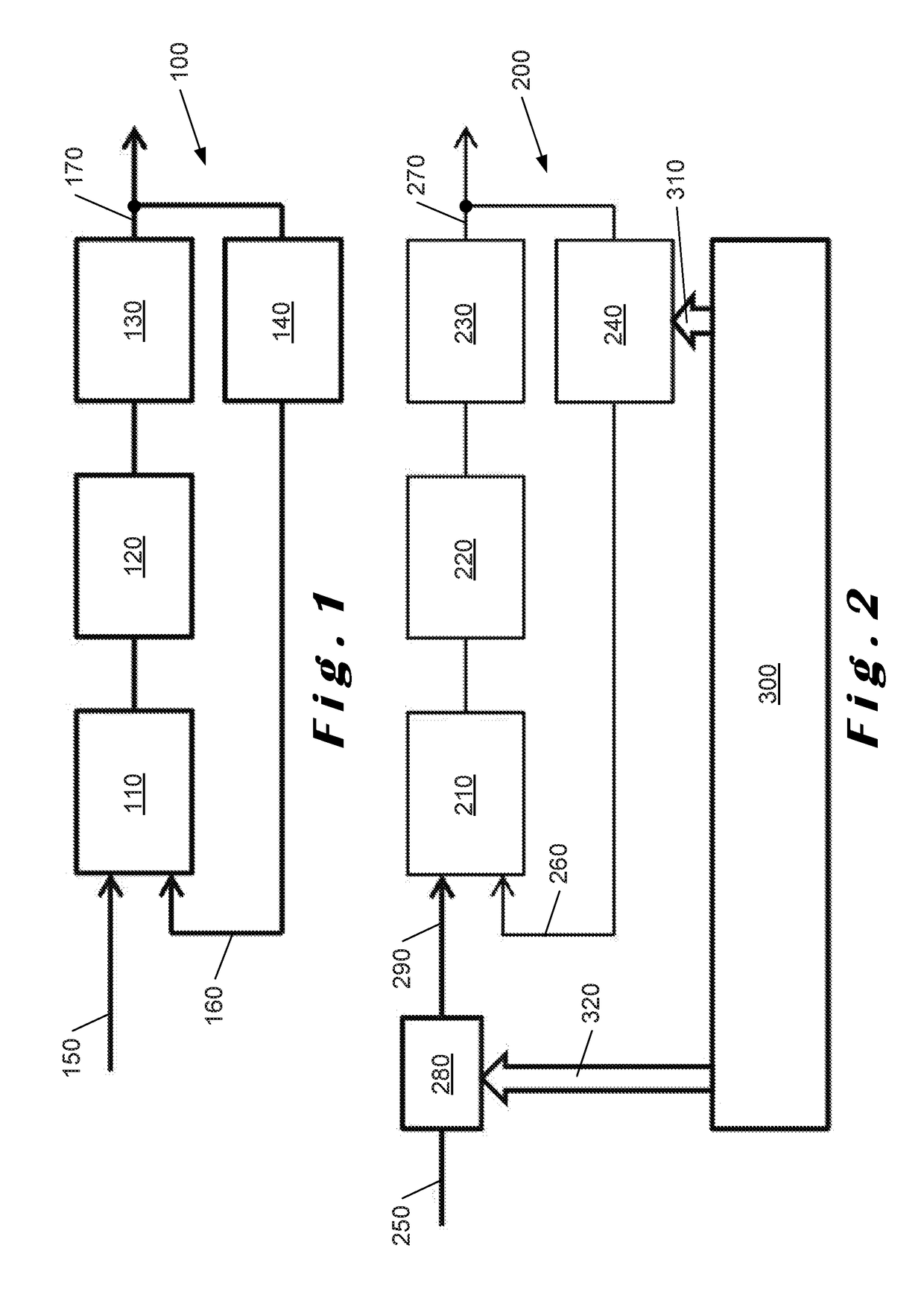

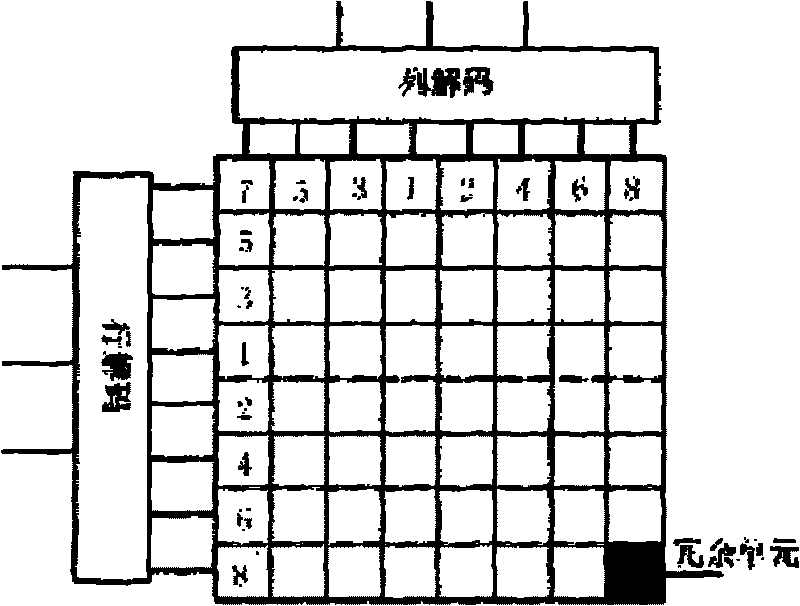

X-Ray Imaging Readout and System

An innovative readout circuit for a pixel detector, for example a solid-state X-ray pixel array, The invention includes a bank of successive approximation ADCs with a DAC in a feedback path. The integral non-linearity of the DACs and of the ADC is reduced to very low levels by providing a common resistive ladder for all the channels. In this way, the conversion law is sensibly the same for all the ADC, thus avoiding stripes or artefacts on the acquired image.

Owner:ADVANCED SILICON

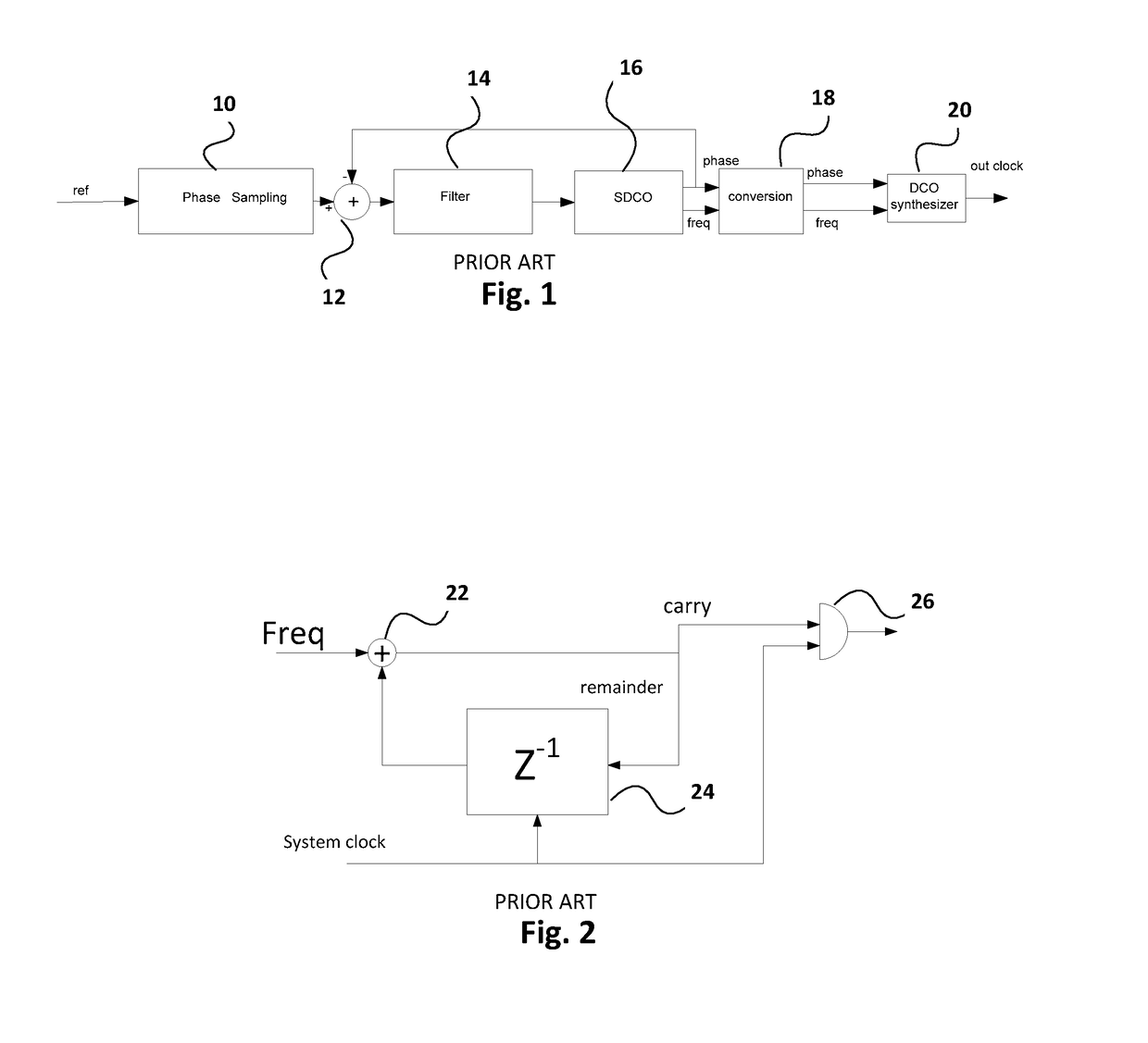

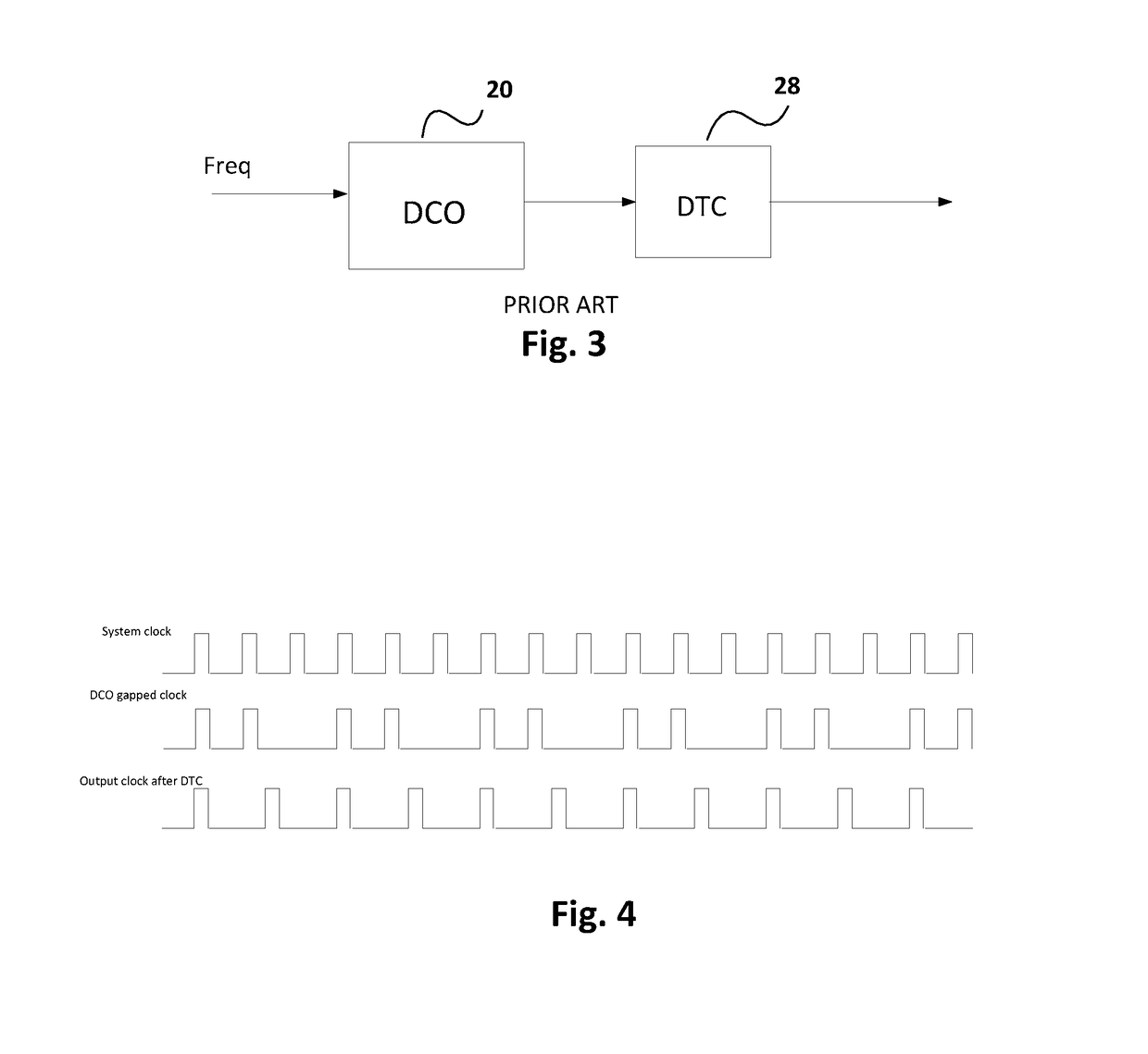

Phase-Locked Loop

ActiveUS20180337683A1Improve linearityReduce noiseError preventionPulse automatic controlDigital converterLinearity

Systems and methods for providing improved linearity and reduced noise in a digital phase-locked loop in which a differential time-to-digital converter is implemented. Digital-to-time converters are used for adjusting a reference clock signal based on a fractional change signal and for adjusting a feedback signal based on another fractional change signal. Each fractional change signal is centered about a midpoint, M, and offset from the midpoint by a fraction, x, such that the fractional change signals can be described as (M+x) and (M−x), respectively. By implementing a differential time-to-digital converter, the sum of delays in each input path is kept constant so that integral non-linearity is improved. Supply sensitivity is also reduced, as the same supply is applied to both differential input paths. Since the differential delay can be both positive and negative, the delay range of a differential digital-to-time converter is half that of a single input digital-to-time converter.

Owner:STICHTING IMEC NEDERLAND

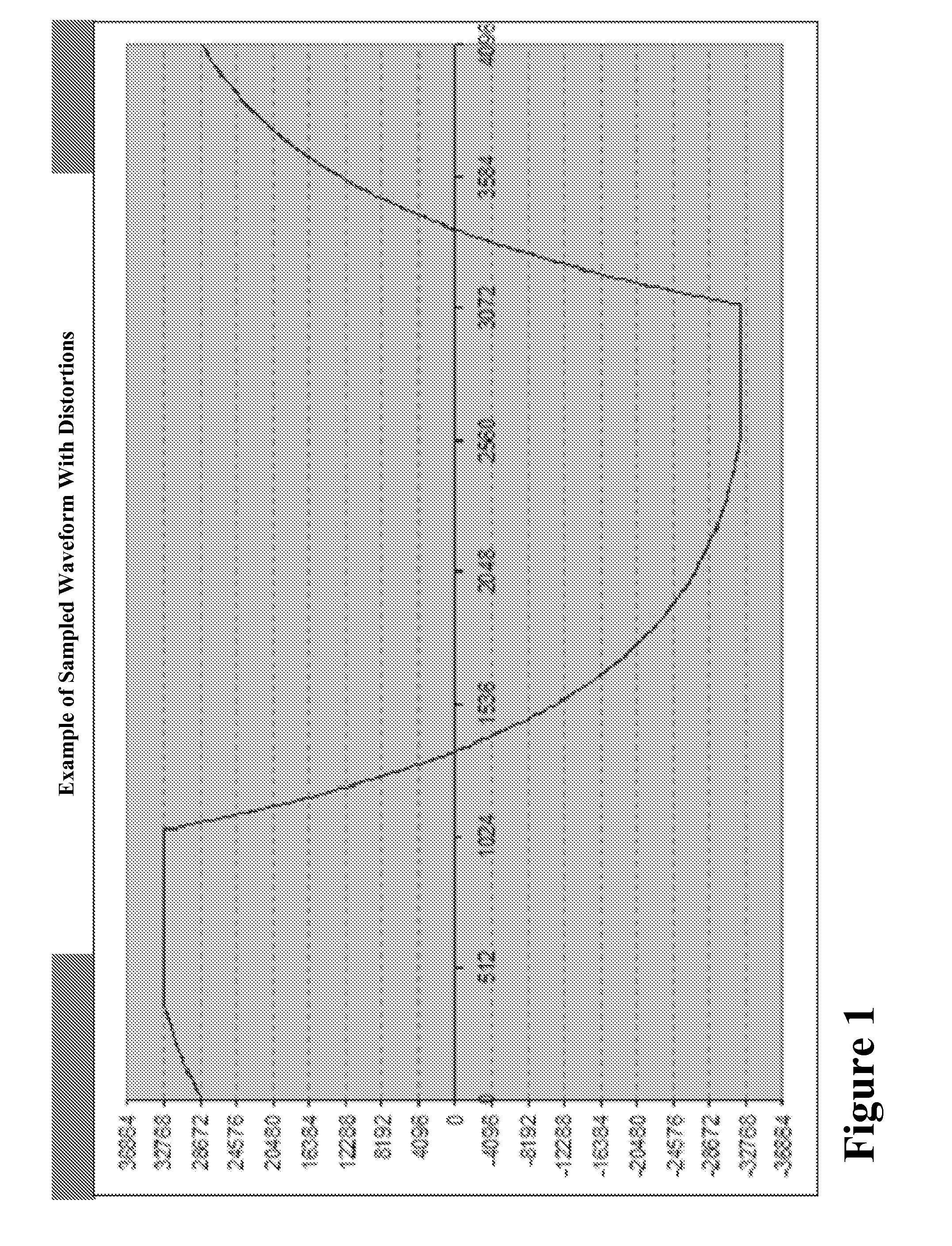

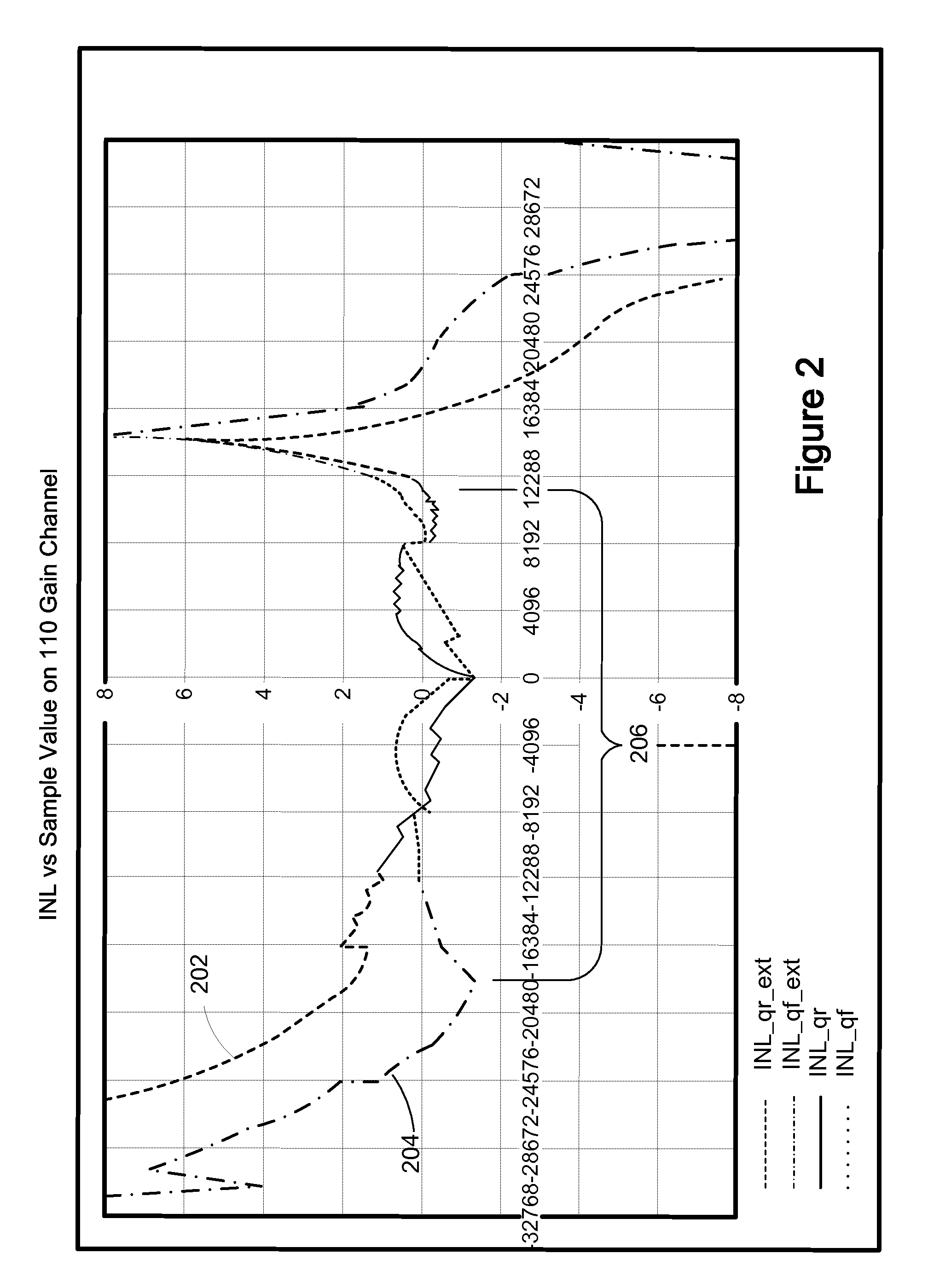

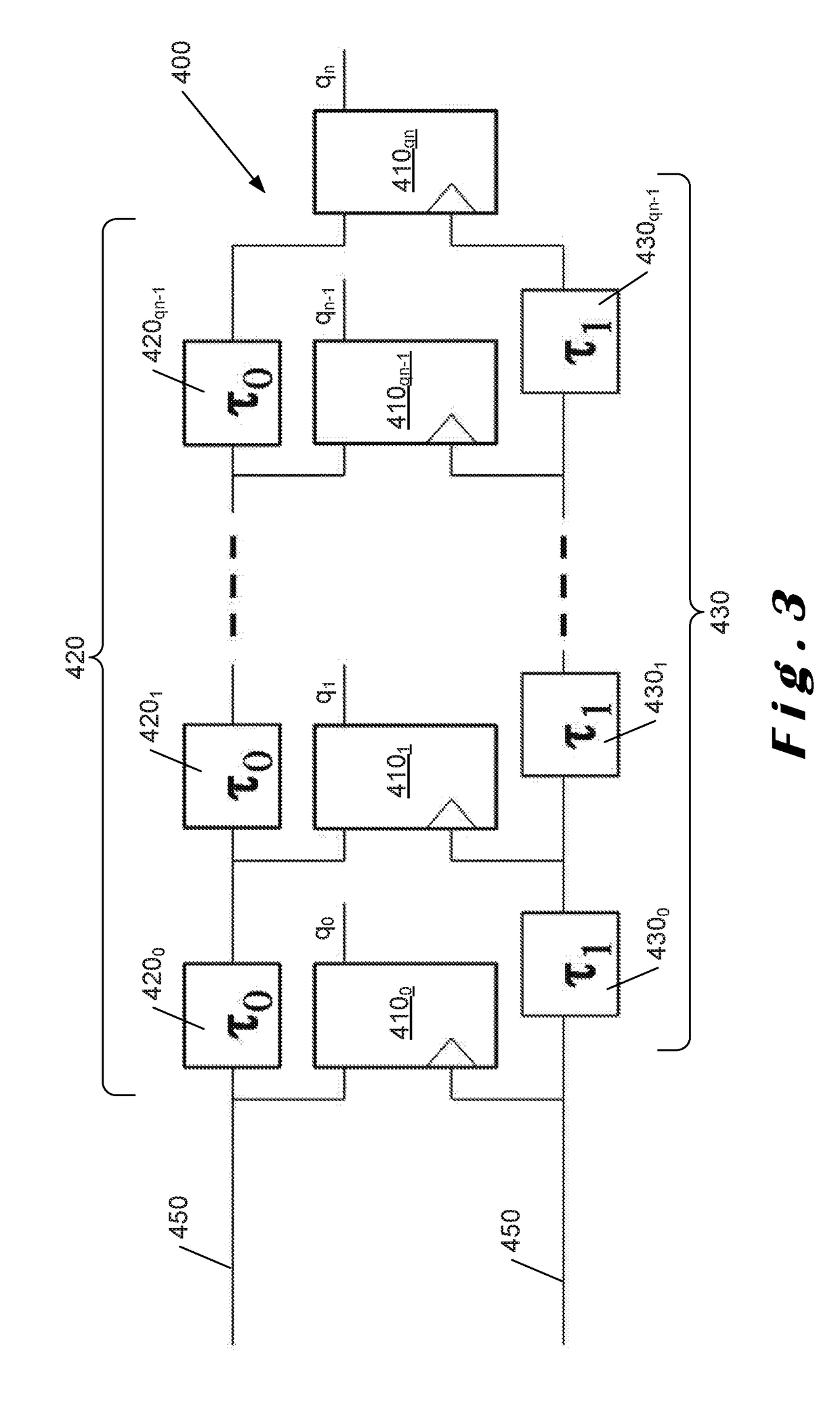

Continuous digital background calibration in pipelined ADC architecture

ActiveUS20050137802A1Addressing slow performanceElectric signal transmission systemsMeasurement arrangements for variableComputer scienceIntegral nonlinearity

Disclosed are new methods and systems for achieving calibration in a pipelined ADC system. The methods and systems may be used to provide continuous digital background calibration in a pipelined ADC. Component mismatch error from each DAC in the pipeline is tabulated to provide an integral nonlinearity profile, which is subtracted from the ADC transfer characteristic.

Owner:TEXAS INSTR INC

Unbalanced design method of high-position current source unit of current rudder-type digital-to-analog converter

ActiveCN101694843AHigh precisionSecond order error cancellationTransistorDigital-analogue convertorsDigital analog converterEngineering

The invention relates to an unbalanced design method of a high-position current source unit of a current rudder-type digital-to-analog converter, which can effectively reduce integral nonlinearity errors, thus improving the accuracy of the high-speed and high-accuracy current rudder-type digital-to-analog converter. The unbalanced design method comprises a high-position current source unit structure under the existing sequence of specific switches and is characterized in that the current intensity can be regulated by adjusting width-to-length ratio (W / L) of a row MOS tube at the outmost edge of two sides of each quadrant current source unit matrix, thus leading the current to be unequal with the current generated by other row current source units in the same quadrant, and using unbalanced current difference to counteract second-order errors brought by a system.

Owner:杭州思泰微电子有限公司

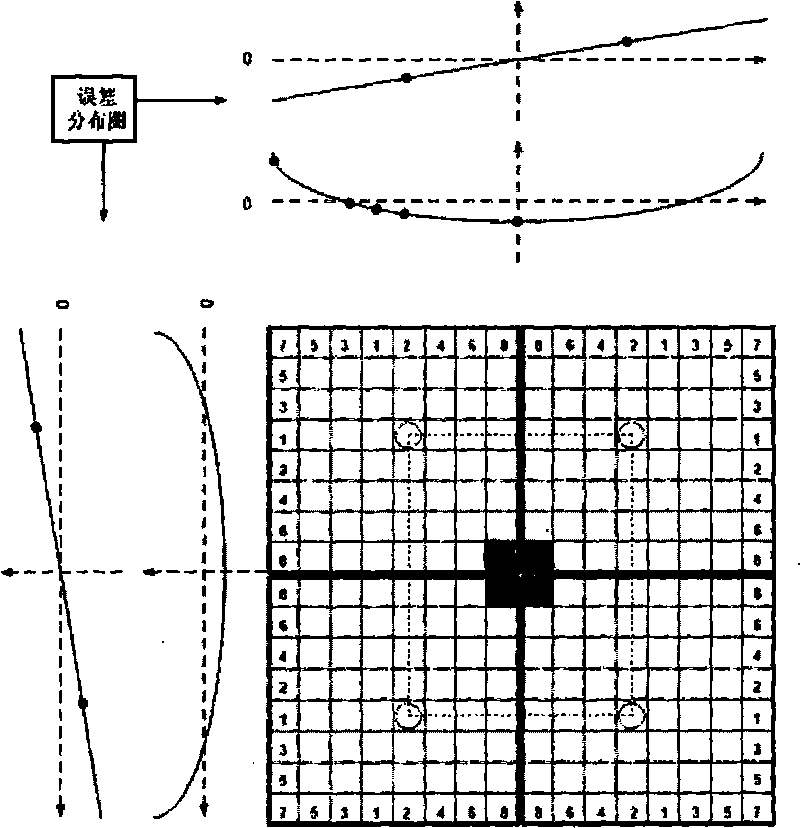

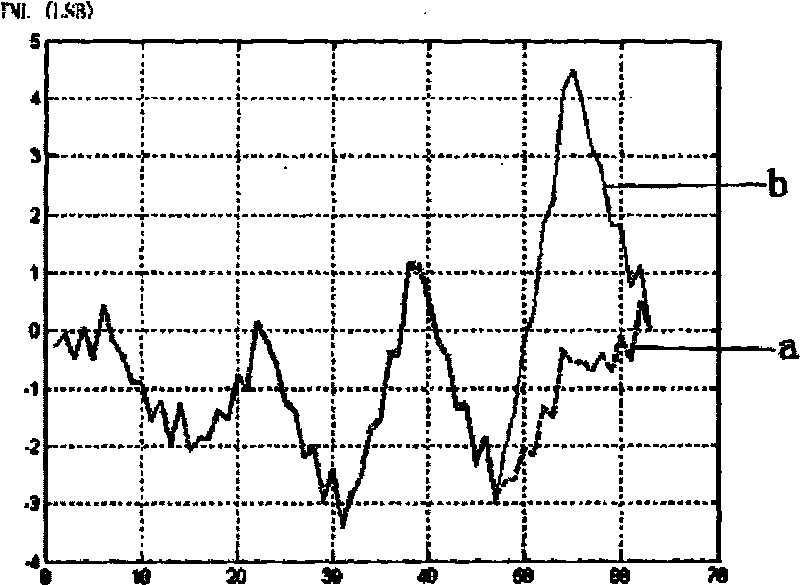

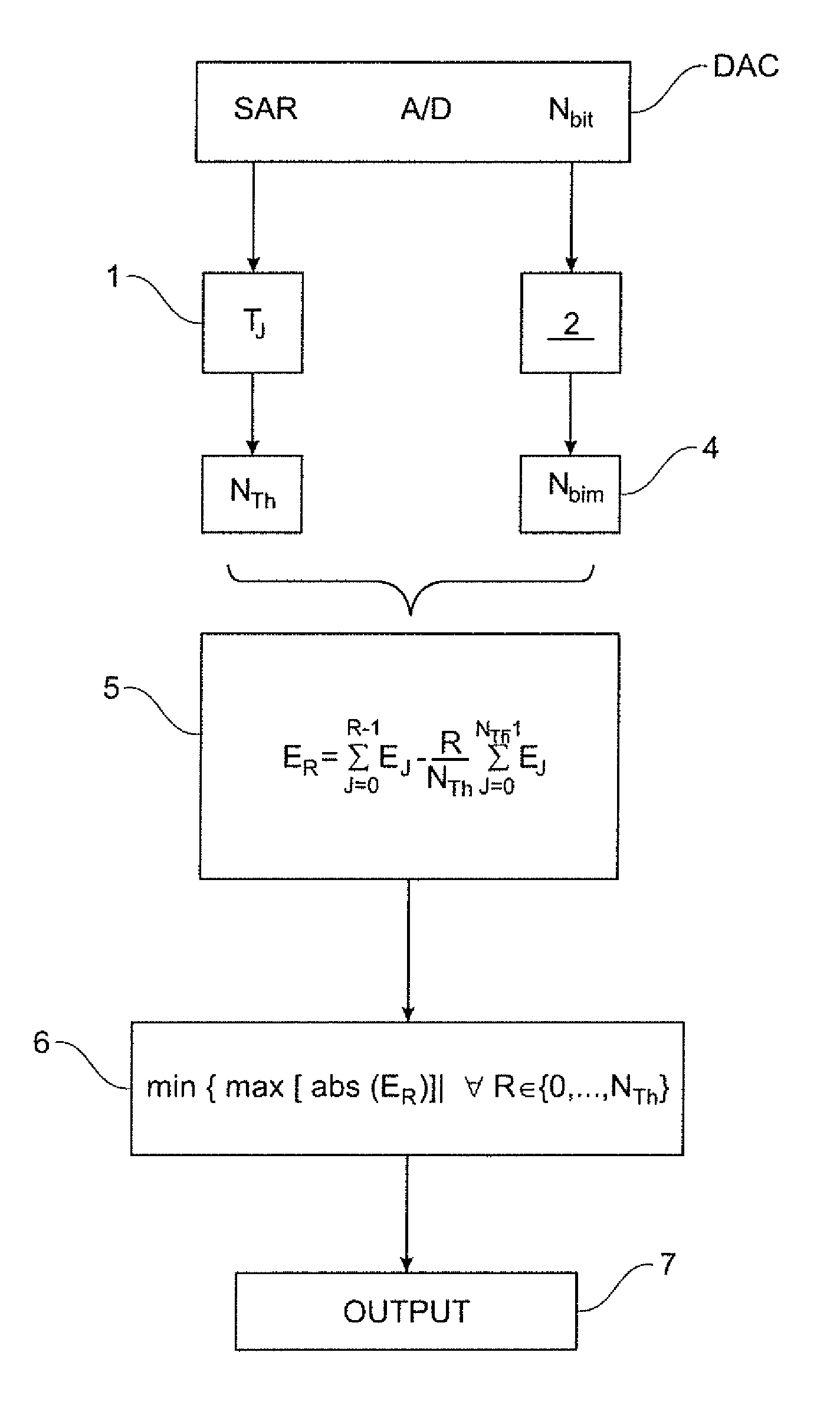

Method of calibrating a thermometer-code SAR A/D converter and thermometer-code SAR-A/D converter implementing said method

ActiveUS9432041B2Electric signal transmission systemsAnalogue-digital convertersDigital analog converterEngineering

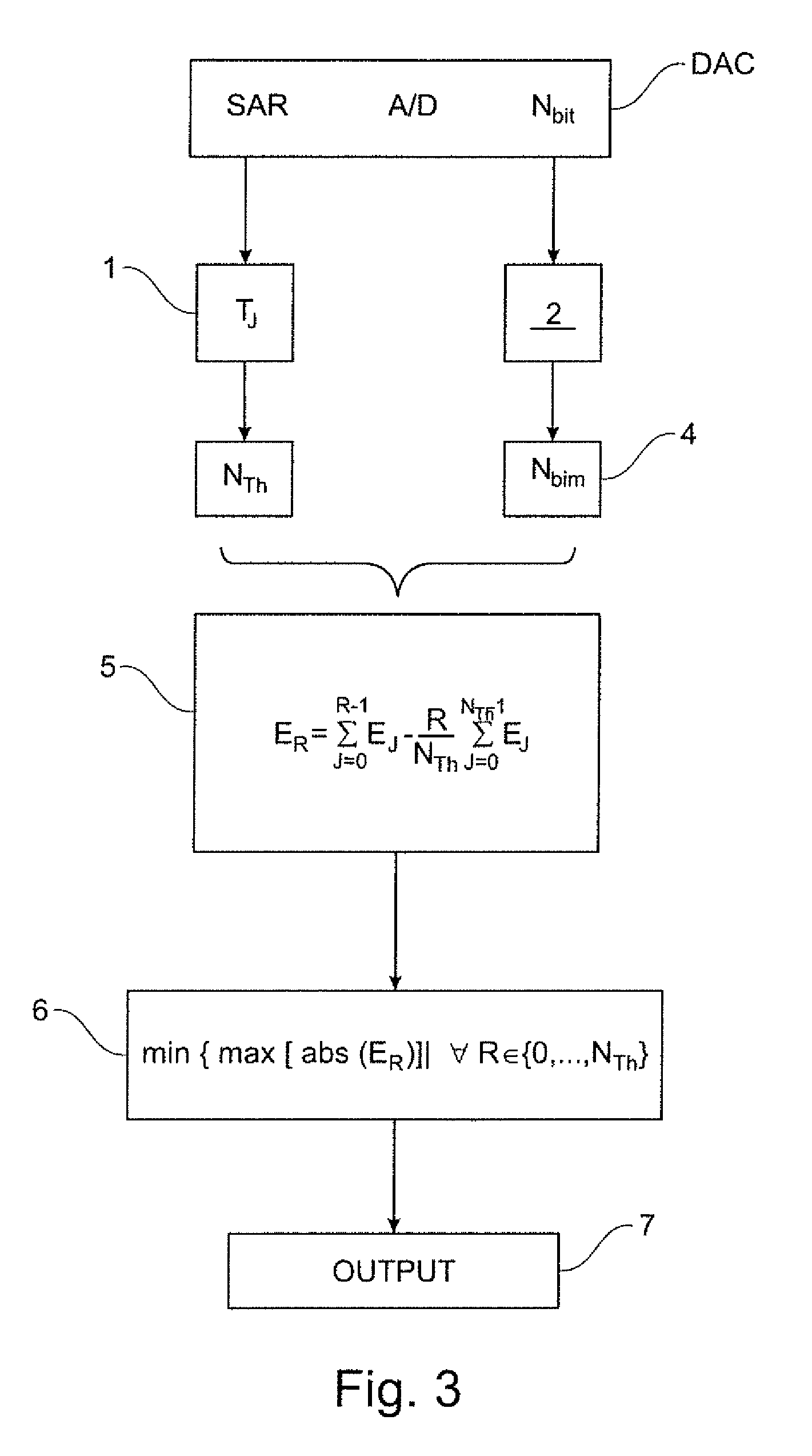

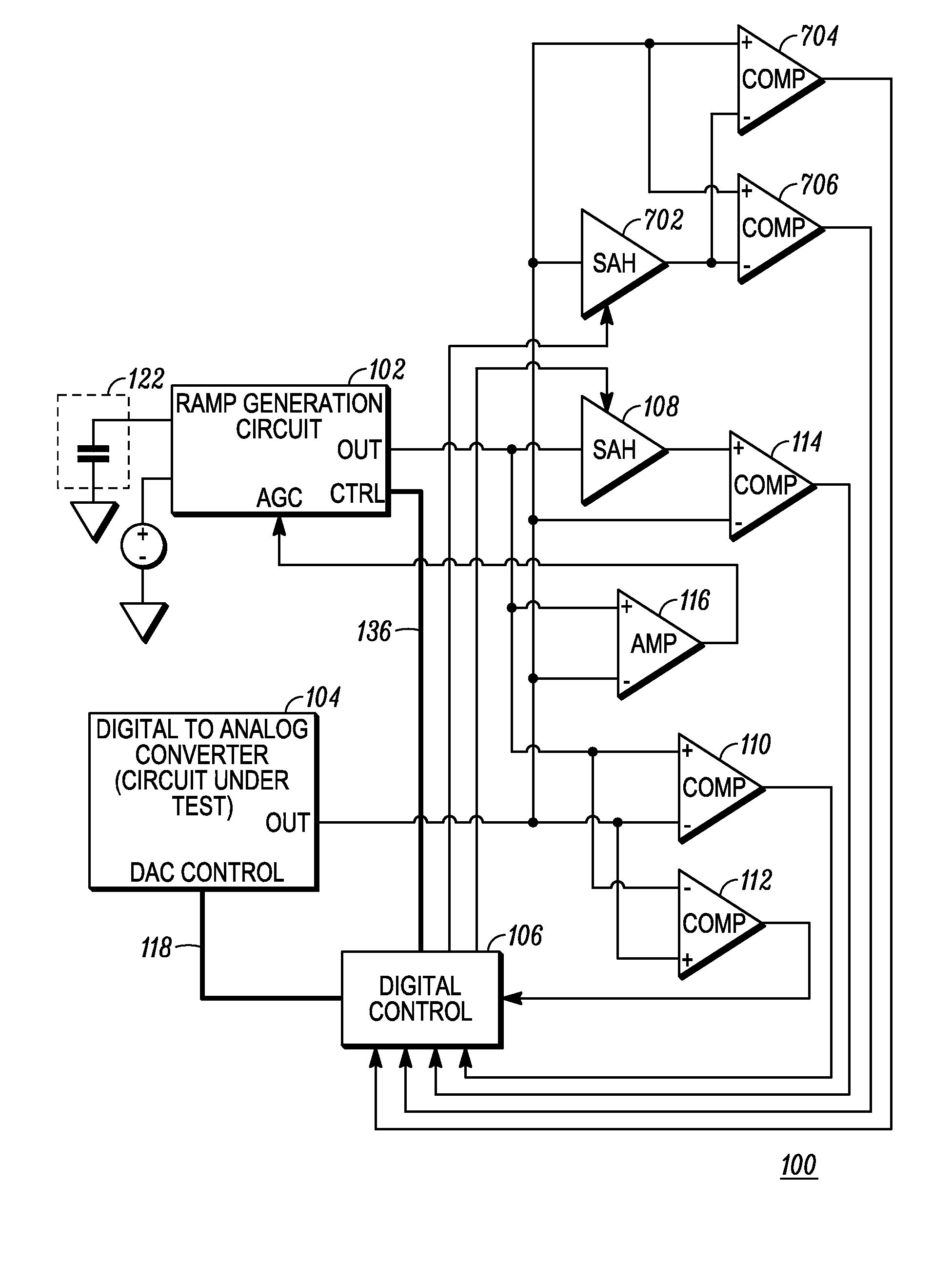

A method of calibrating a thermometer-code SAR-A / D converter is provided. The thermometer-code SAR-A / D converter includes an Nbit-bit digital-to-analog converter (DAC) for outputting an Nbit-bit output code. The DAC includes a first subconverter having a plurality of NTh thermometer elements Tj and a second subconverter having a plurality of NBin binary-weighted elements. The Nbit output code is equal to the sum of NBitTh and NBitBin where NTh=2NBitTh and NBitBin is equal to NBin=NBitBin. The calibration method includes determining an Integral Non-Linearity error value (εR) of an Rth thermometer-code level of the thermometer elements. The method further includes reducing the highest of the error value εR to obtain a reduced error value, and generating the output code according to said reduced error.

Owner:STMICROELECTRONICS INT NV

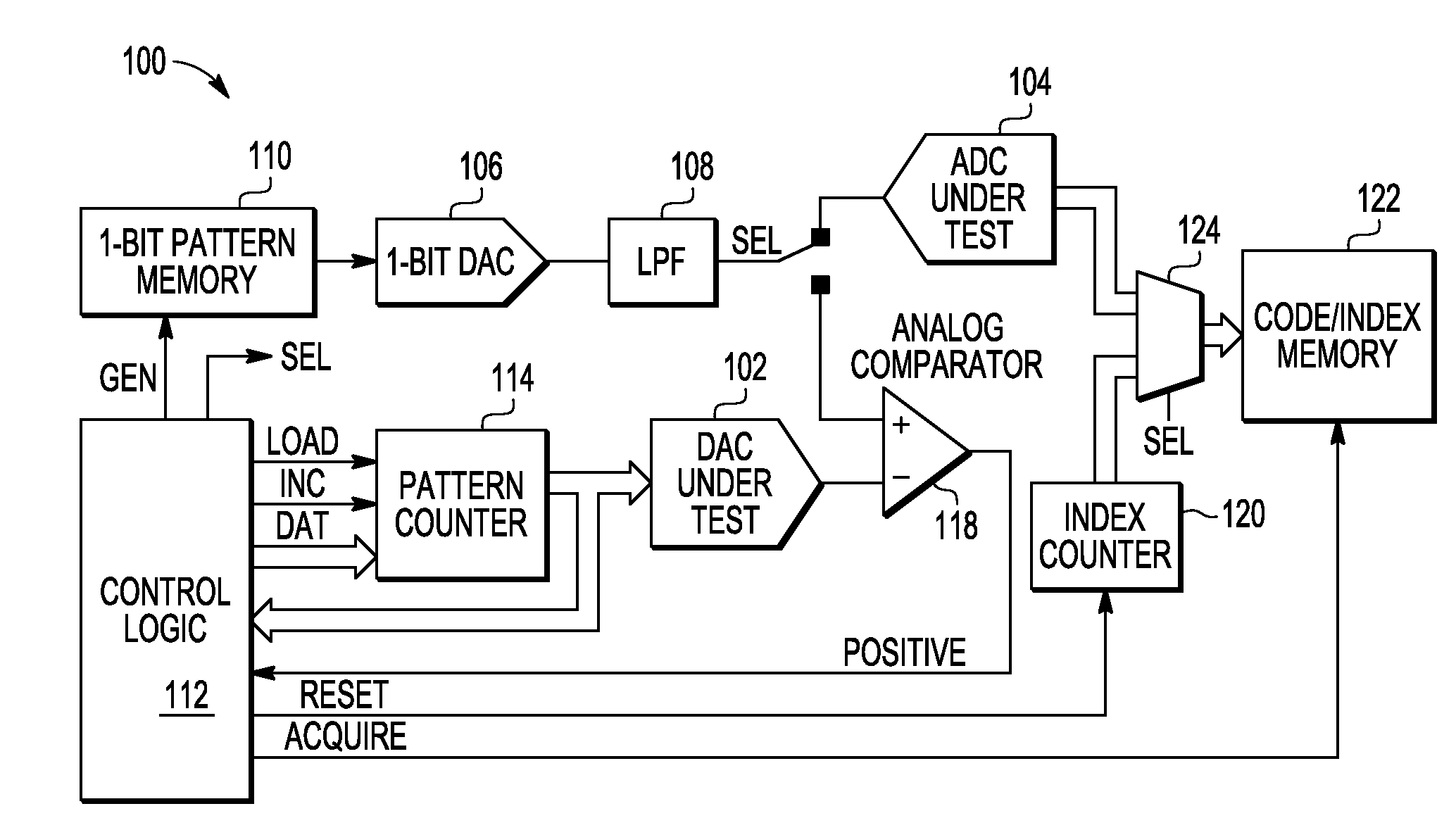

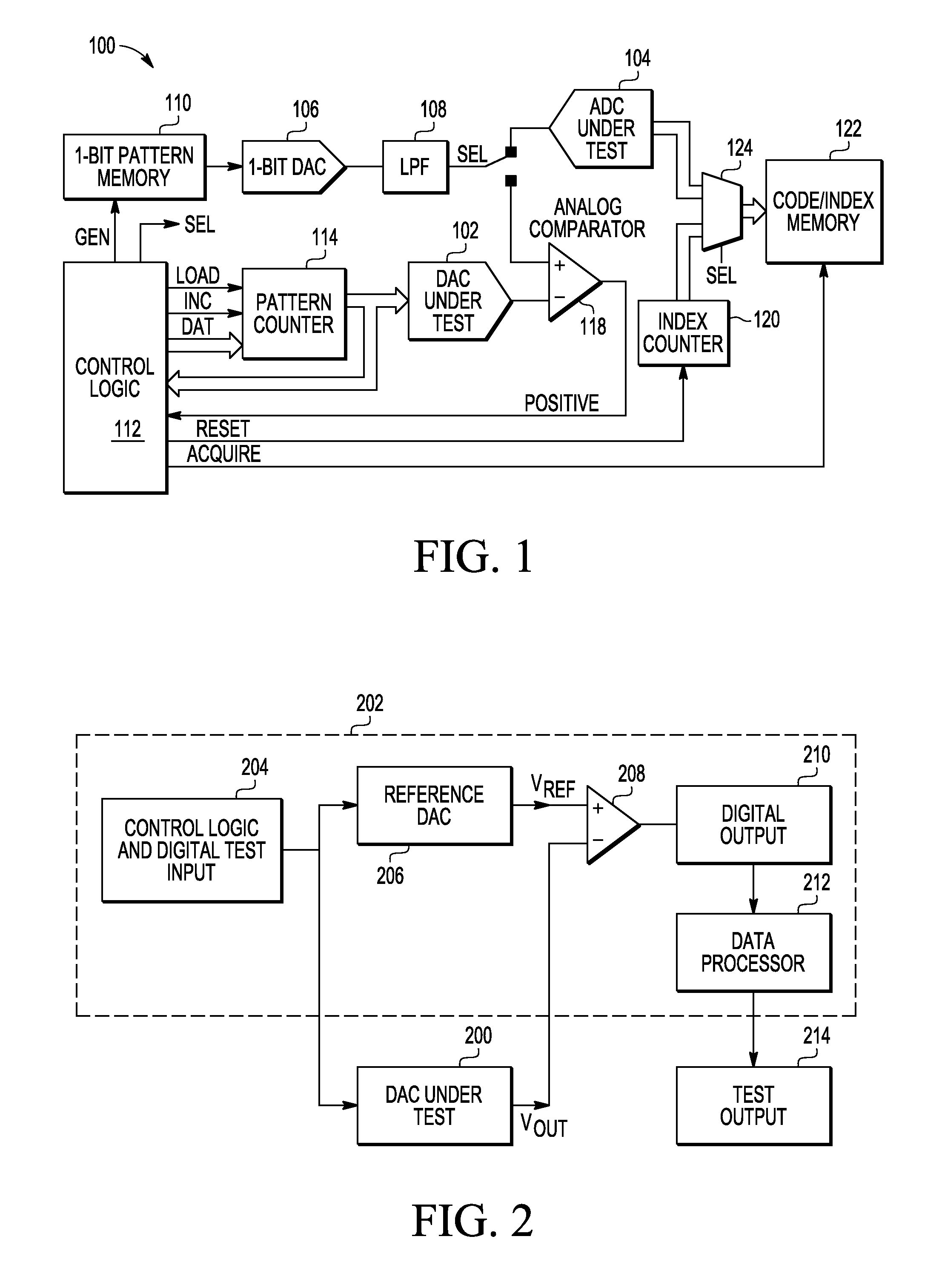

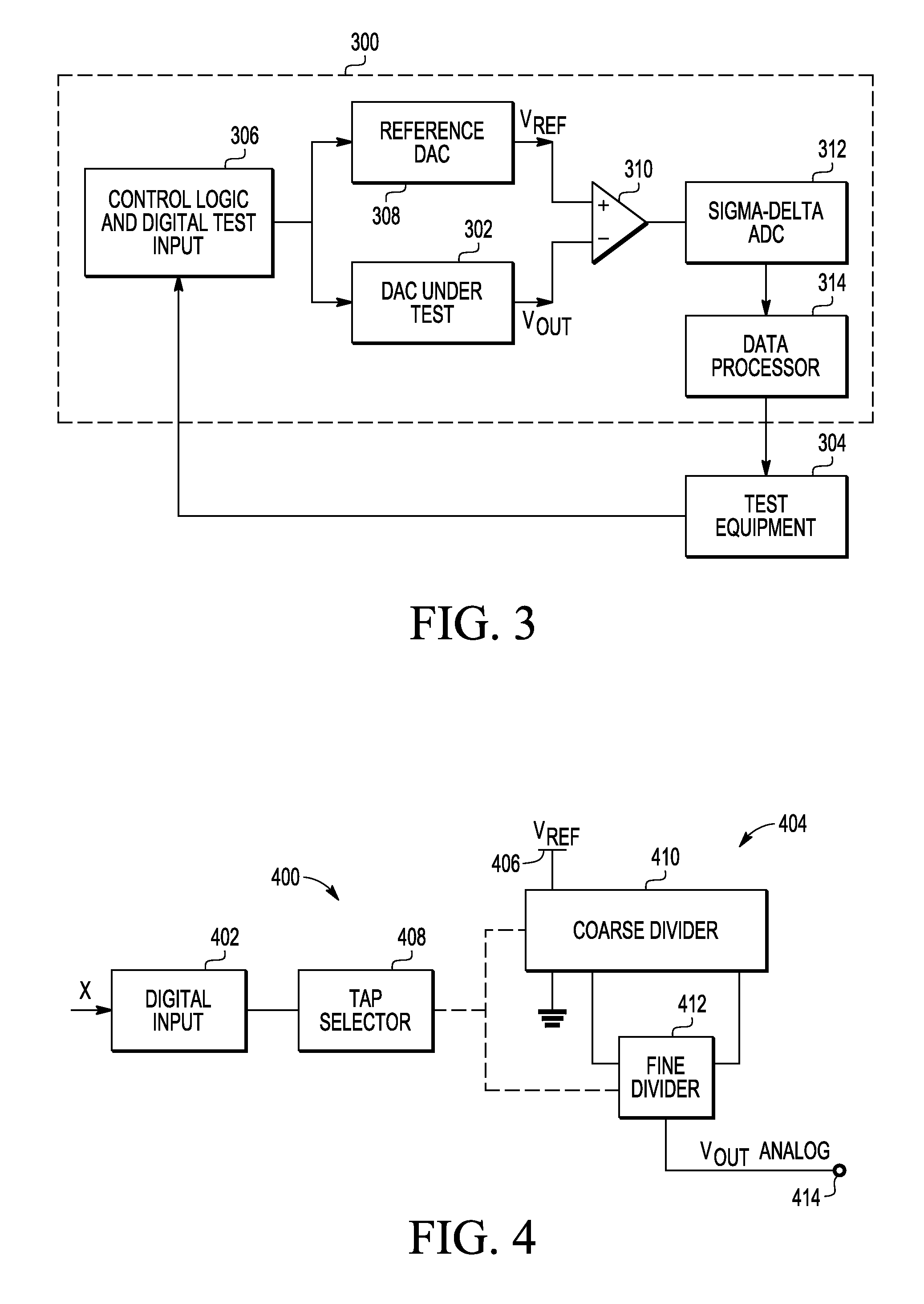

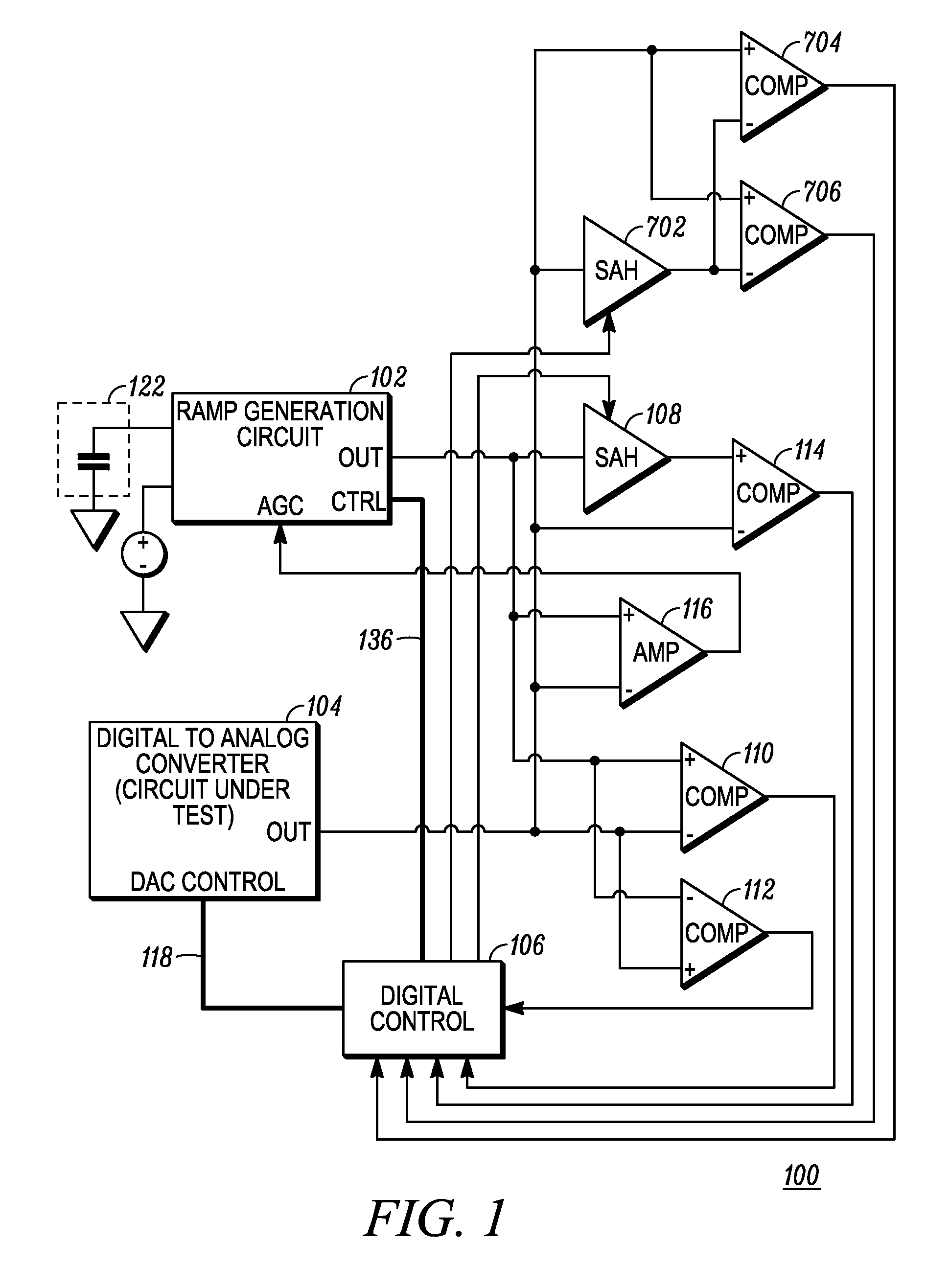

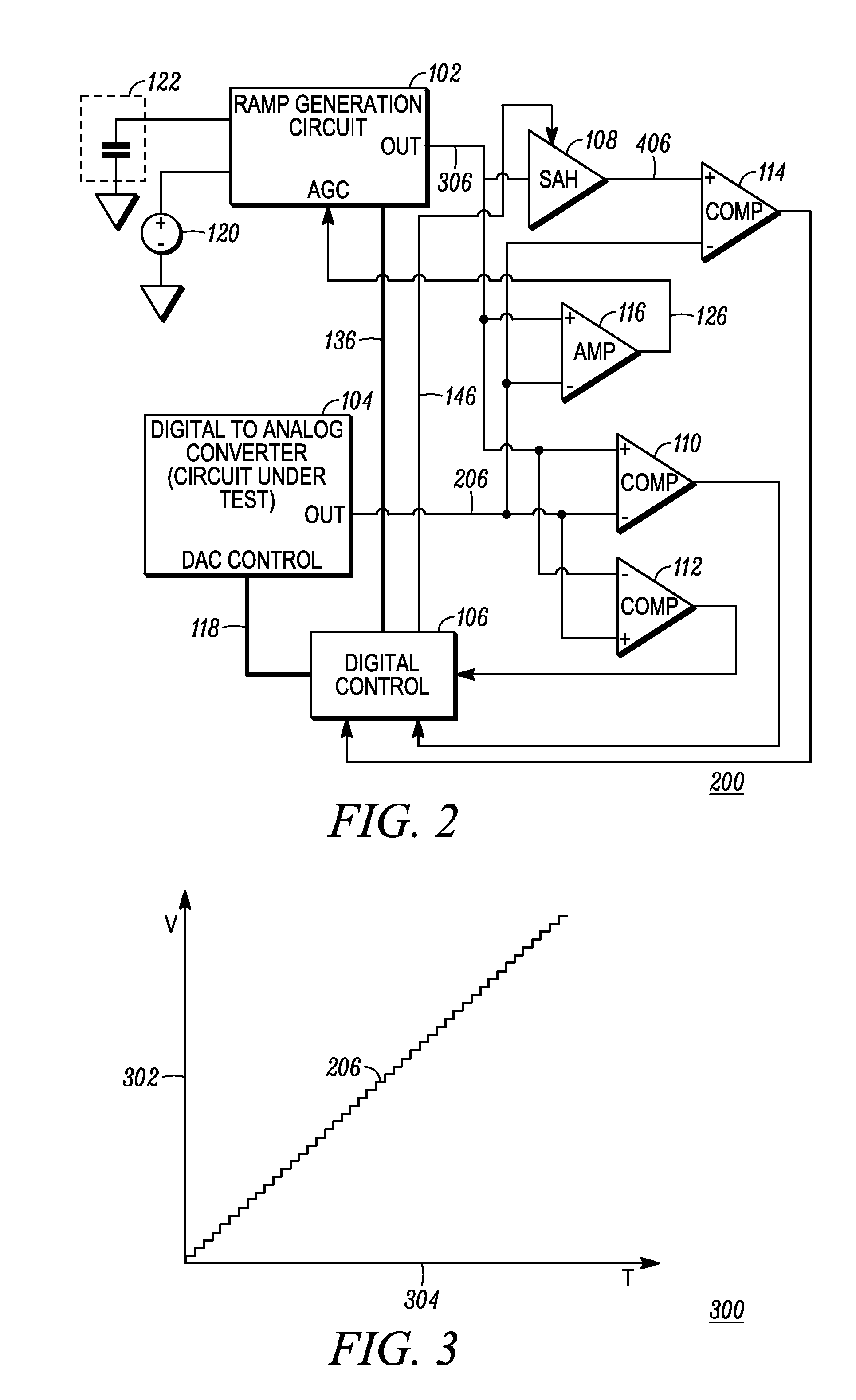

Method and apparatus for self-testing a digital-to-analog converter (DAC) in an integrated circuit

ActiveUS8223048B2Electric signal transmission systemsDigital-analogue convertorsIntegral nonlinearityDigital-to-analog converter

An on-chip self testing digital-to-analog converter (DAC) is provided. The functionality of the DAC is measured using a combination of integral non-linearity (INL) and differential non-linearity (DNL). Parts may pass or be rejected based on the testing. When a DAC passes the testing, the process continues to the next DAC or quits if all the DACs have been tested.

Owner:MOTOROLA SOLUTIONS INC

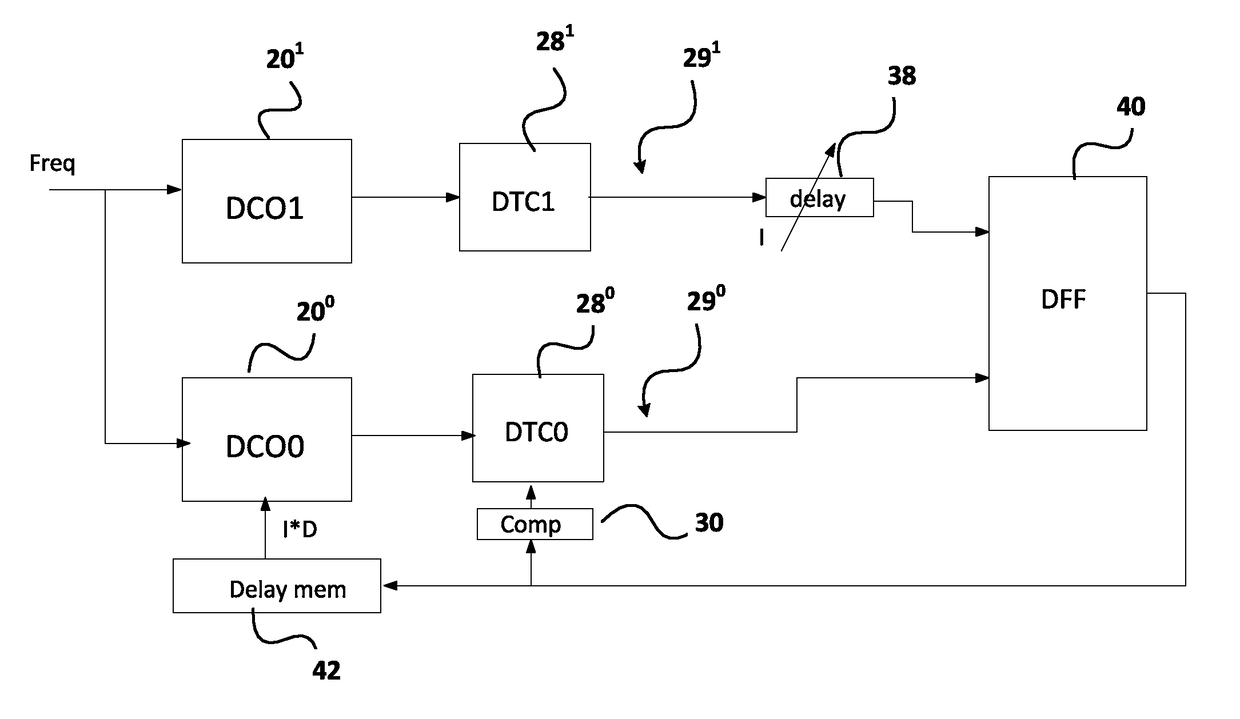

Clock synthesizer with integral non-linear interpolation (INL) distortion compensation

ActiveUS10128826B2Accurate methodQuickly and adaptively adjust the non-linear distortionPulse automatic controlOscillations generatorsDigital control oscillatorComputer module

A method of compensating for integral nonlinear interpolation (INL) distortion in a clock synthesizer driven by a system clock running at a frequency fsys, involves introducing a selected nominal analog delay I*dt with an actual delay of I*dt+δ at the output of the a first path with a digital controlled oscillator (DCO) and a digital-to-time converter (DTC) and a nominal digital delay I*D with an actual delay of I*D+Δ at the input of a second path with a DCO and a DTC that offsets the actual analog delay in the first path, adjusting the contents x(k) of a compensation module in the second path to align the output pulses of the first and second paths for different values of k, where k represents an interpolation point, iteratively repeating the two preceding steps for all N values of I, and averaging the contents x(k) of the compensation module to derive the compensation values to be applied to a one of the DTCs to correct for INL distortion.

Owner:MICROSEMI SEMICON

Digital-to-analog converter with triode region transistors in resistor/switch network

ActiveUS7372387B2Improving DNLImpedance mismatchElectric signal transmission systemsDigital-analogue convertorsElectrical resistance and conductanceDigital analog converter

System and method for high-speed and high-precision digital to analog conversion. A preferred embodiment comprises a dual-resistor ladder digital-to-analog converter with a coarse resistor ladder and a fine resistor ladder, wherein resistors in the fine resistor ladder are implemented using transistors. When the effective resistances of switches used in a switching circuit are properly matched with the resistance of the resistors, the differential non-linearity and the integral non-linearity of the digital-to-analog converter can be minimized. The use of transistors to implement switches and resistors can help to eliminate mismatches arising from different fabrication steps and materials, further improving the performance of the digital-to-analog converter.

Owner:TEXAS INSTR INC

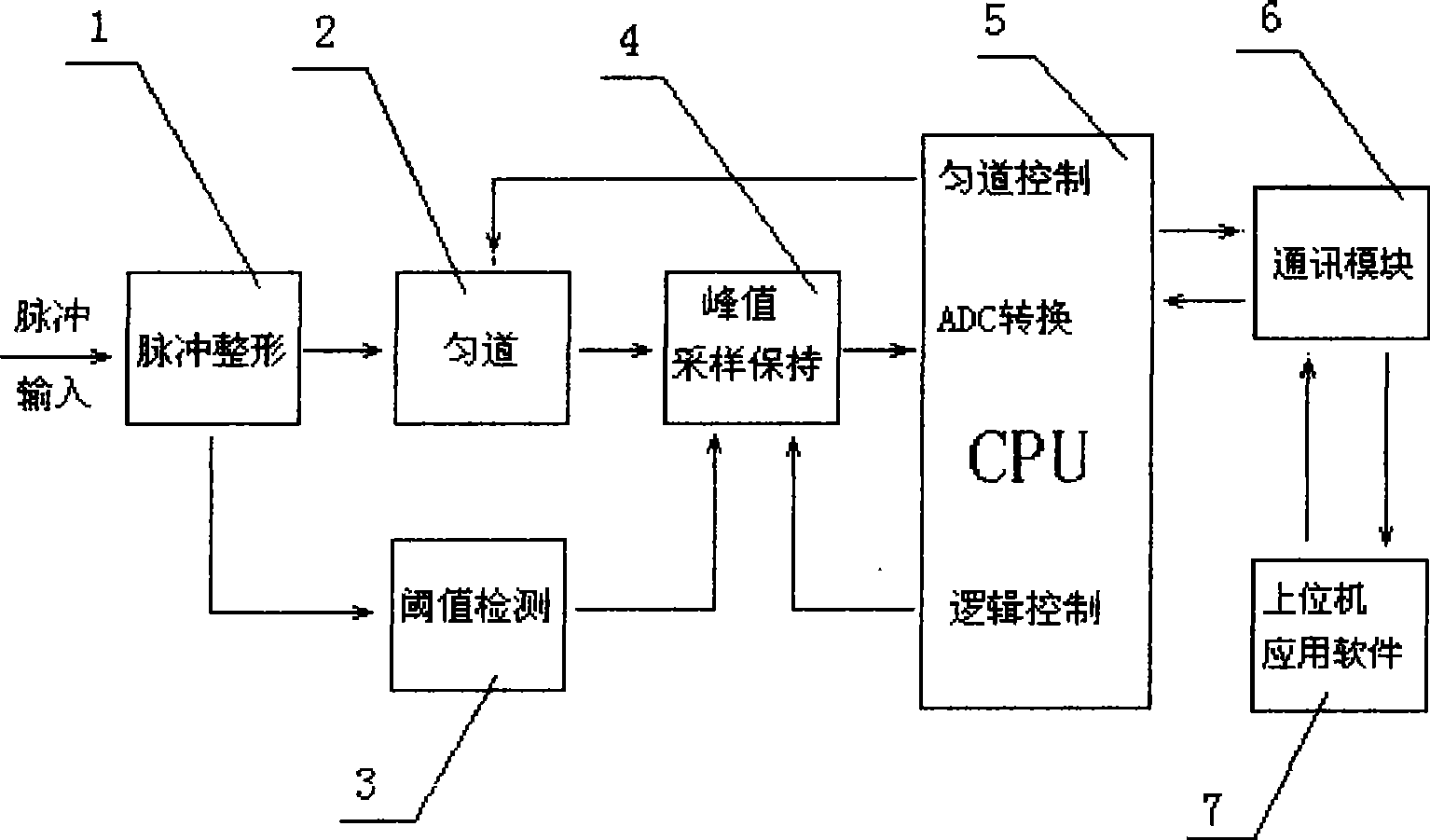

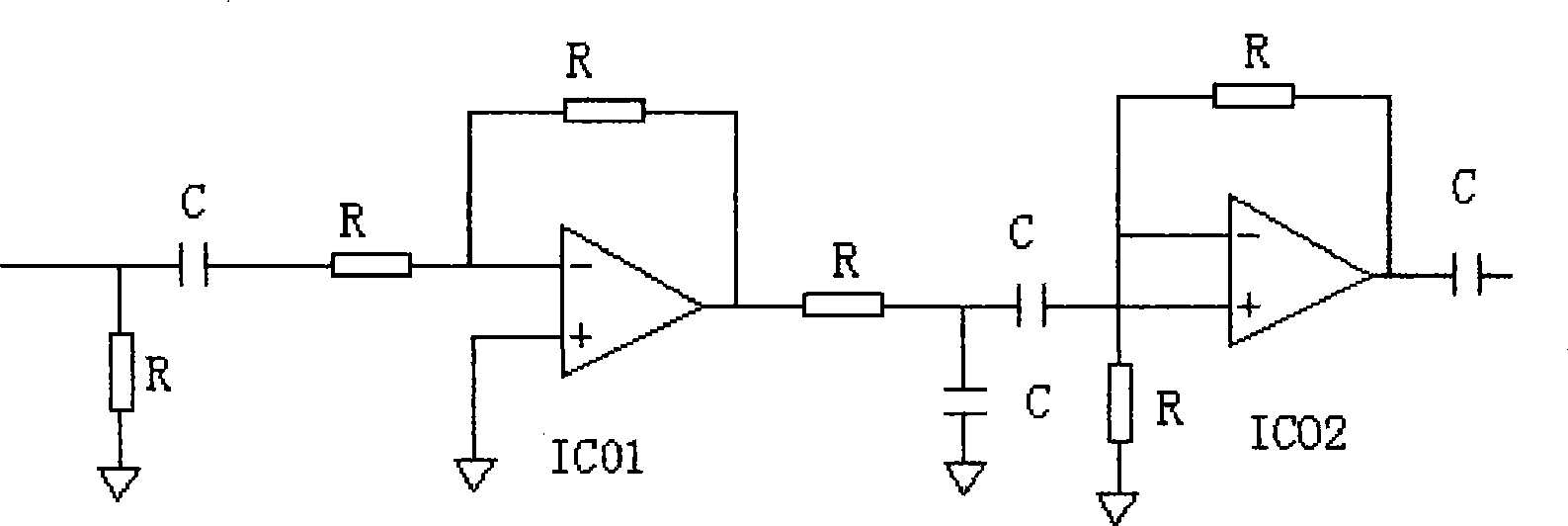

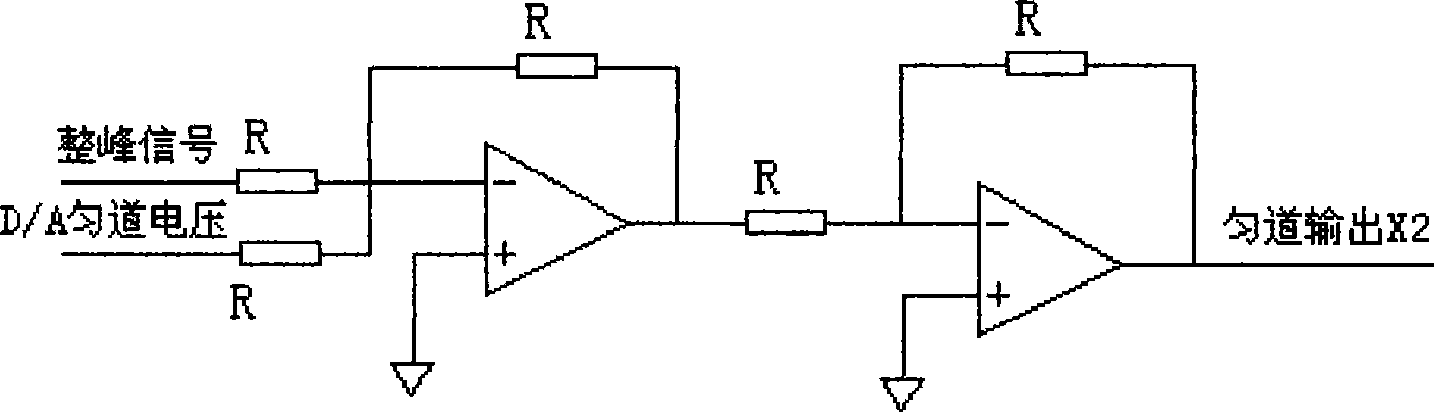

Portable high-speed multi-channel energy spectrometer

InactiveCN101464420AEnhanced interactionReduce acquisition timeMaterial analysis by measuring secondary emissionMicrocontrollerCollection period

The invention provides a device for using rays to detect elements. The device is characterized in that a pulse signal input terminal is connected with a pulse shaping unit circuit; the output terminal of the pulse shaping unit circuit is connected in parallel with an uniform path unit circuit and a threshold detecting unit circuit; the output terminal of the uniform path unit circuit and the output terminal of the threshold detecting unit circuit are connected with a peak value sample-holding unit circuit separately; the output terminal of the peak value sample-holding unit circuit is connected with a singlechip which is connected with a memorizer; and a communication unit is connected with the output interface of the singlechip. By adopting the high speed A / D conversion technology, the pulse peak voltage detecting and holding technology, a high speed linear gate circuit and a complete machine logic control system in the circuit, the invention ensures that integral nonlinear index attains 0.025%, the maximum output frequency exceeds 30kHz, the collection period is shortened, the range of application is expanded, the Chinese interface of application software is more convenient to be operated, and the interaction between data output and other application programs is facilitated.

Owner:DANDONG DONGFANG MEASUREMENT&CONTROL TECHCO

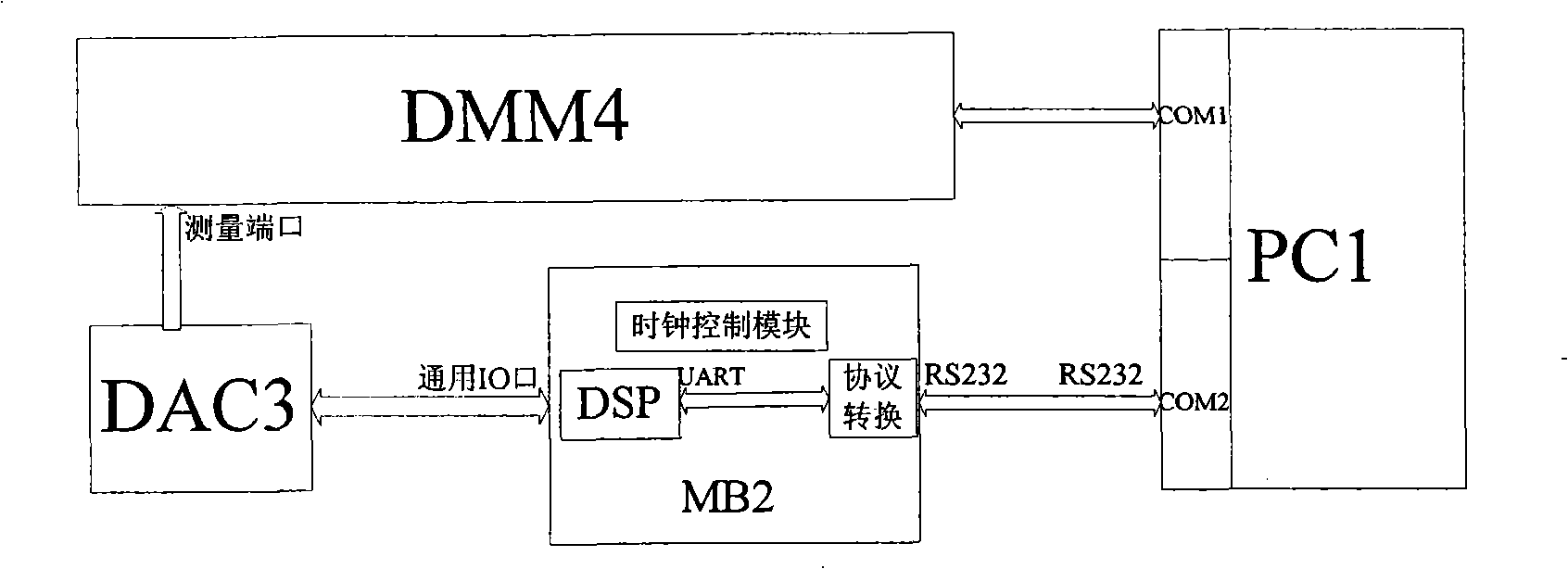

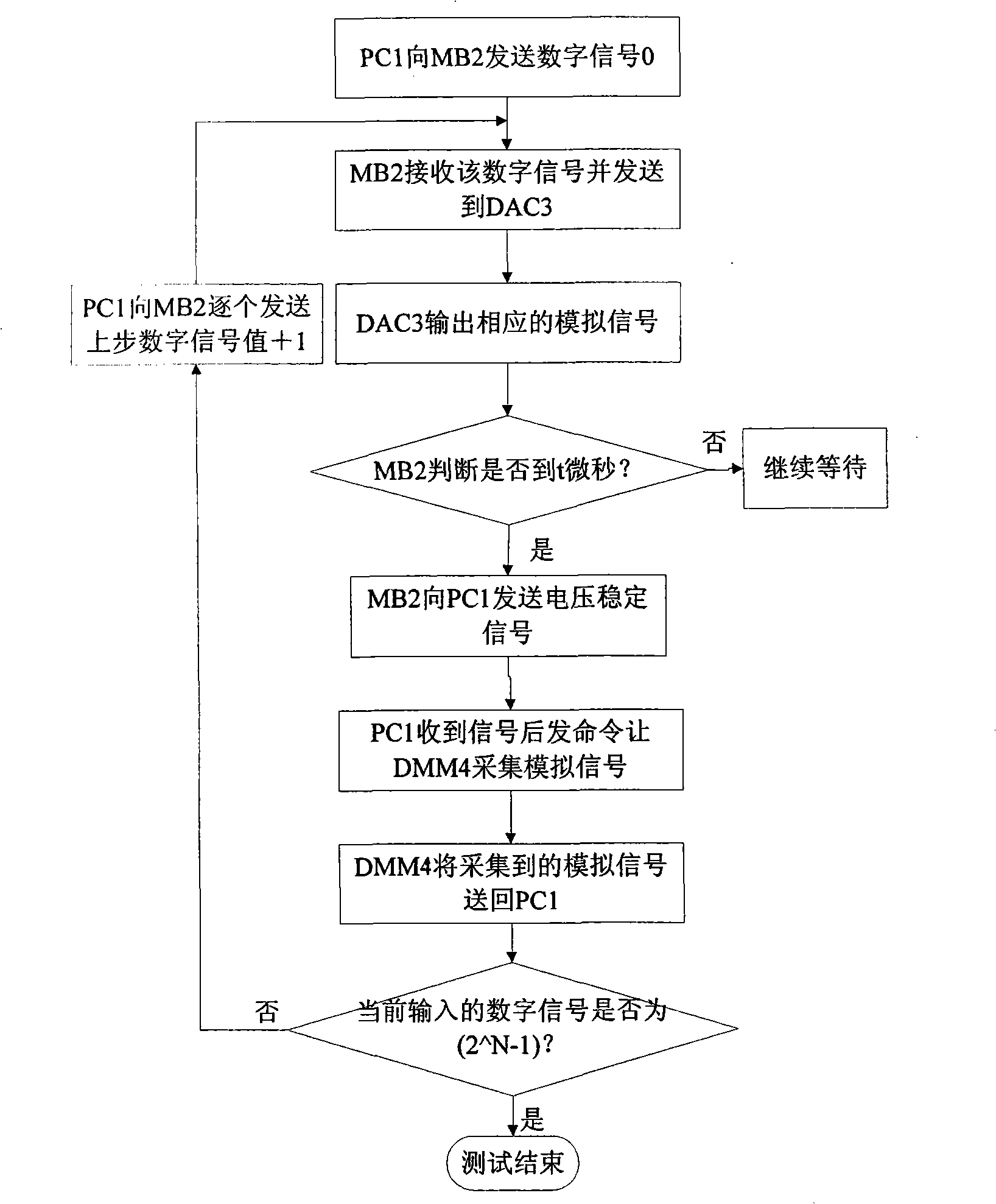

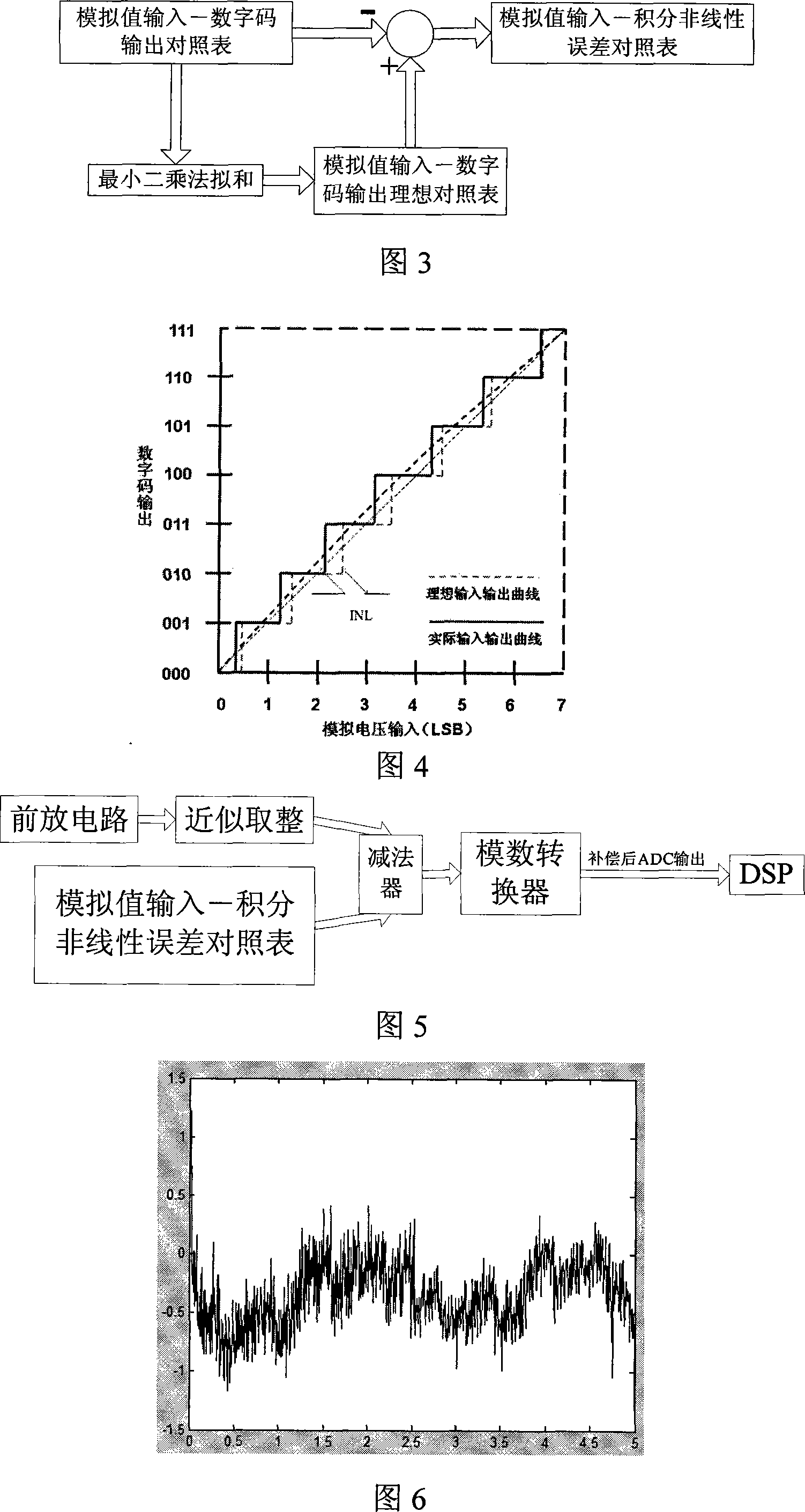

Method for enhancing optical fibre gyroscope output accuracy

The invention discloses a method for increasing the fiber optic gyro scope output precision. The method comprises the steps of: constructing a testing system which inputs digital codes and outputs simulated values of the analog-digital converter; obtaining a comparison table which is output through inputting responded simulated values of different digital codes from 0 to 2N-1 of the analog-digital converter; calculating to obtain an integration non-linear error comparison table corresponding to different digital code input of the analog-digital converter; compensating integration non-linear errors of the analog-digital converter through a hardware compensating method of adding a subtracter; and obtaining accurate analog-digital converter output. The method effectively lowers false output which is caused by the integration non-linear errors of the analog-digital converter, guarantees the accuracy of fiber optic gyro scope feedback and offset voltage, can regulate compensated integration non-linear error parts according to parameter differences of the analog-digital converter, and effectively improves the output precision of the fiber optic gyro scope.

Owner:ZHEJIANG UNIV

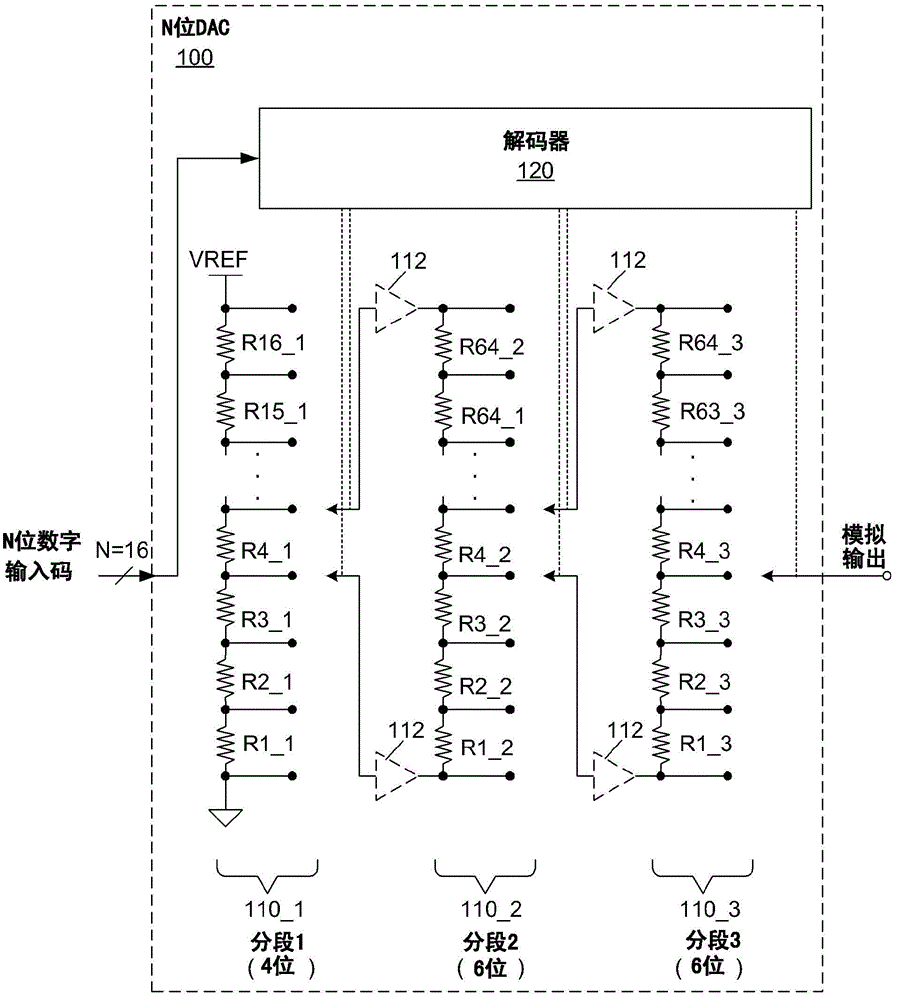

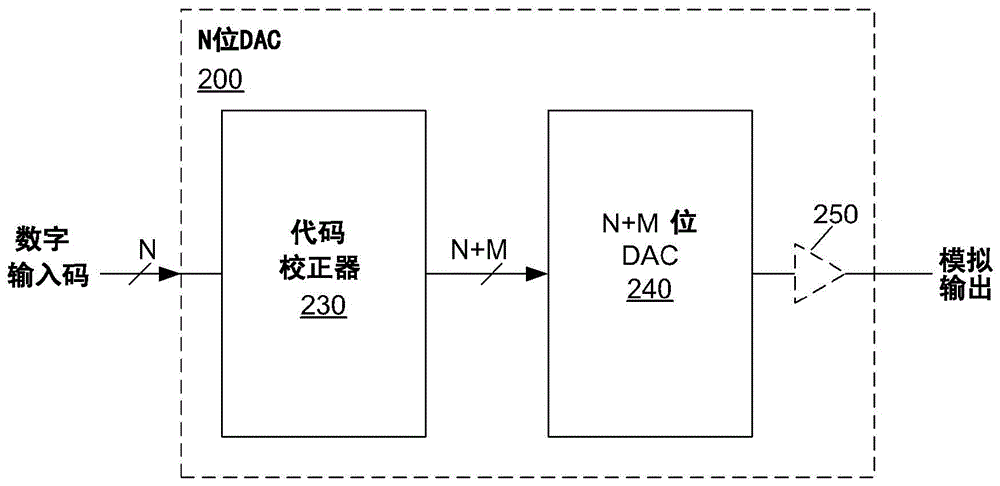

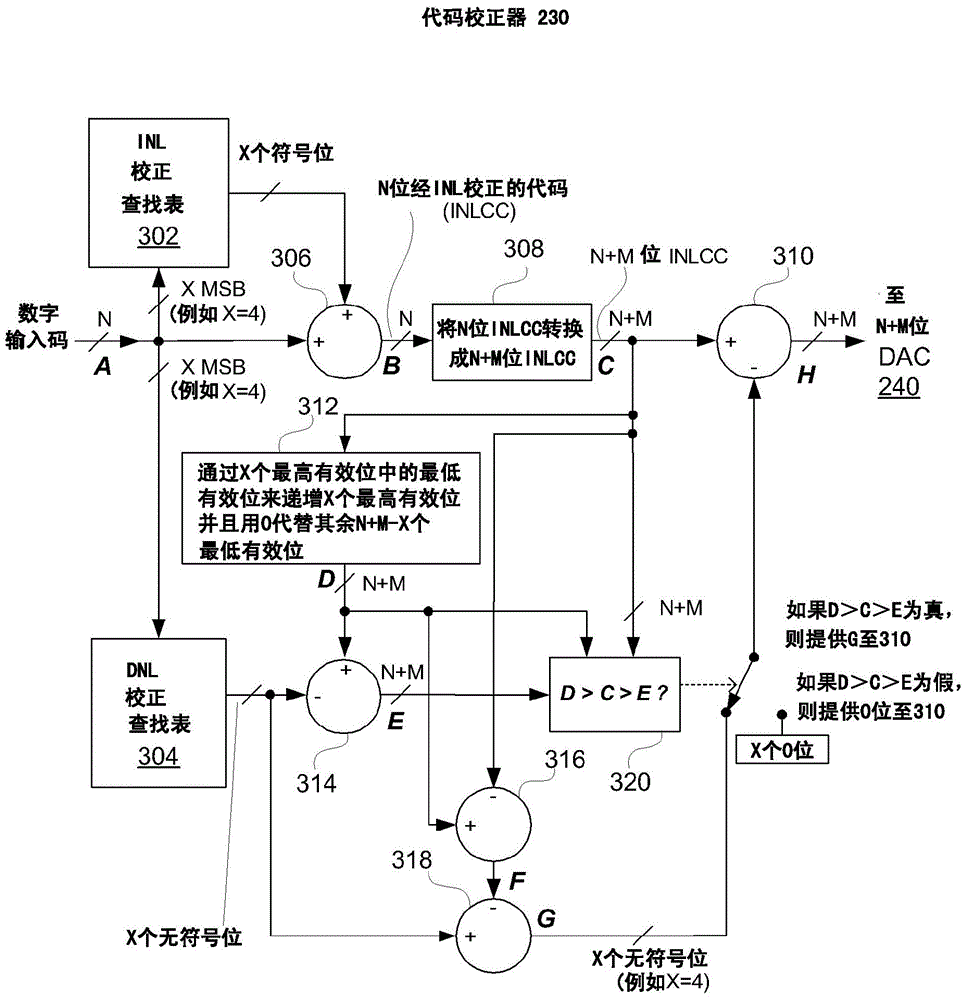

Integrated non-linearity (INL) and differential non-linearity (DNL) correction techniques for digital-to-analog converters (DACS)

ActiveCN103986471ADigital-analogue convertorsAnalogue/digital conversion calibration/testingDifferential nonlinearityImage resolution

INL values are determined for a plurality of sub-segments of a DAC that is adapted to accept N bit digital input codes, and a first set of correction codes that can be used to reduce to a range of INL values (to thereby improve linearity of the DAC) are determined and stored. Additionally, DNL values are determined for the plurality of sub-segments for which INL values were determined, and a second set of correction codes that can be used to ensure that all values of DNL >-1 (to thereby ensure that the DAC is monotonic) are determined and stored. This can include using one or more extra bits of resolution to remap at least some of the 2N possible digital input codes (that can be accepted by the DAC) to more than 2N possible digital output codes, to ensure that all values of DNL >-1. Such stored first and second sets are thereafter used when performing digital to analog conversions.

Owner:INTERSIL INC

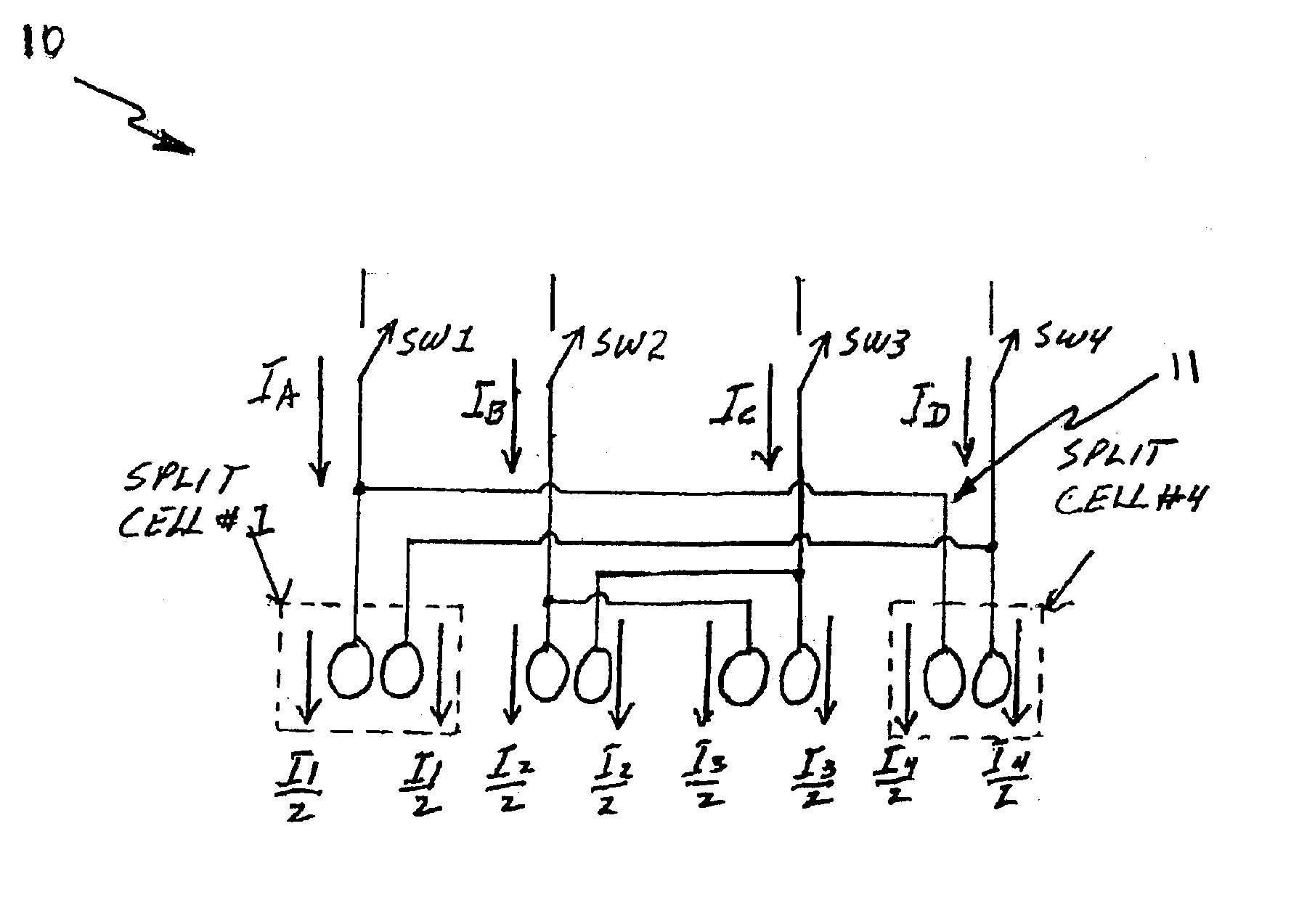

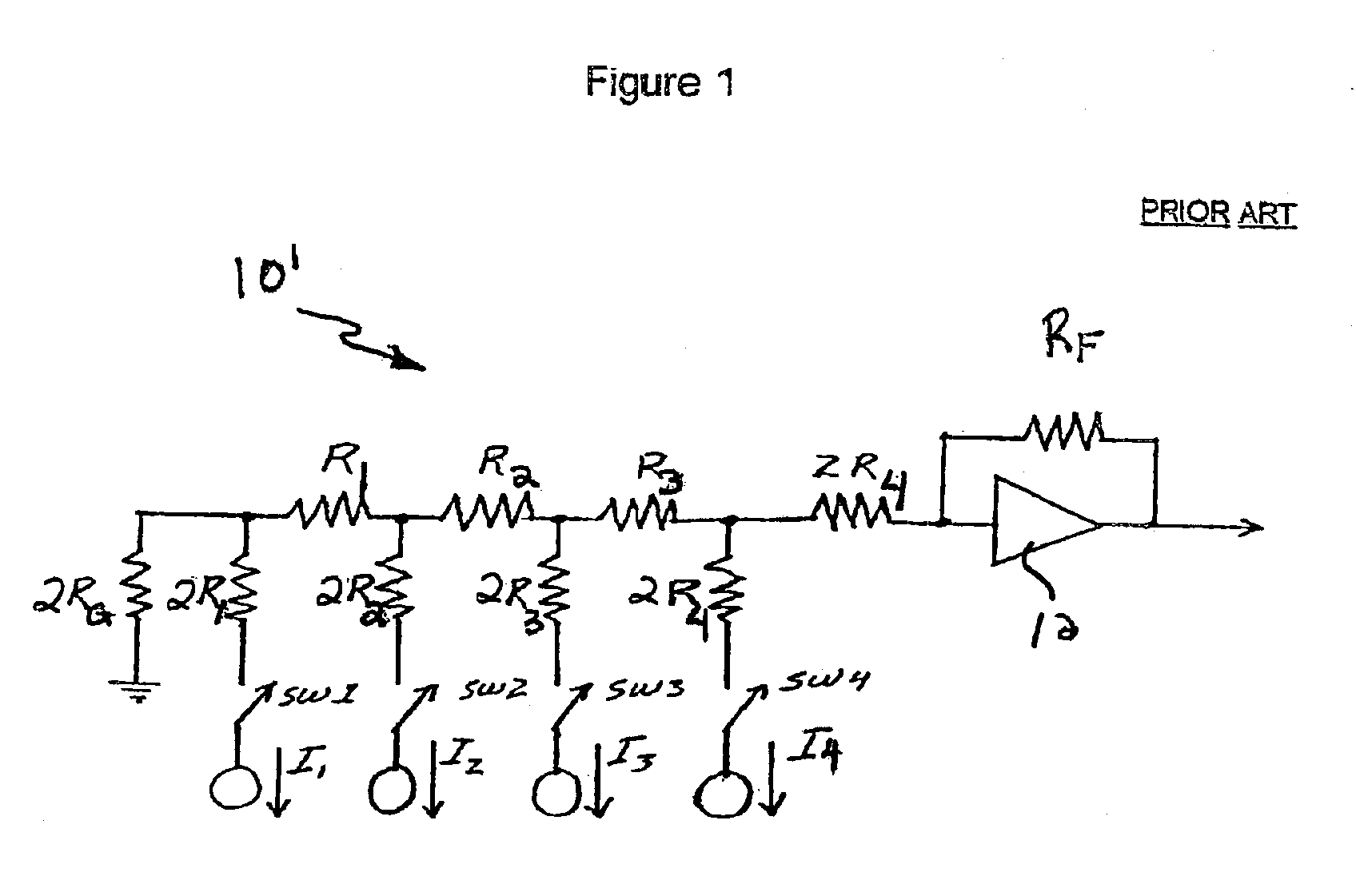

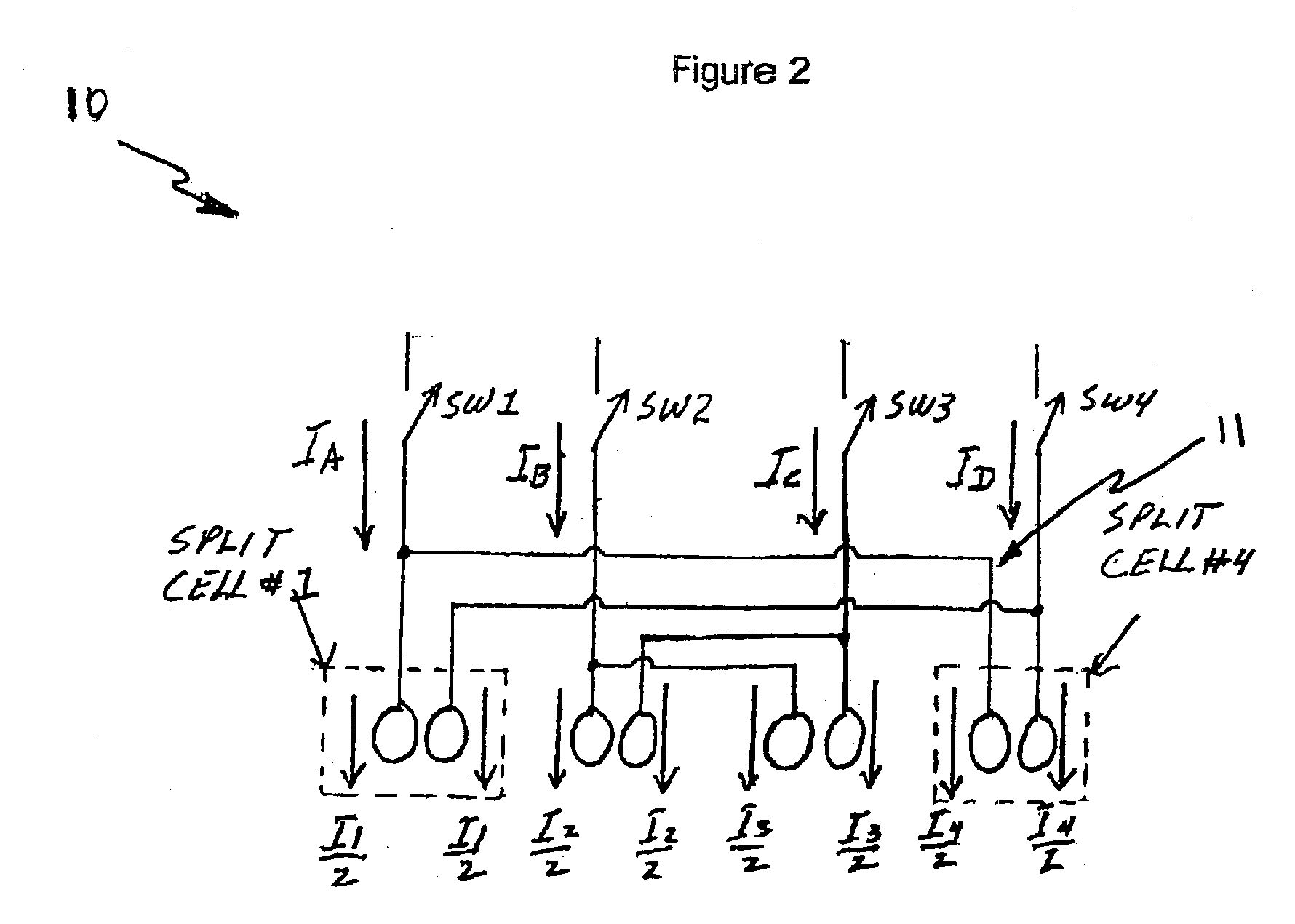

Split cell bowtie digital to analog converter and method

ActiveUS6879276B2Promote lowerElectric signal transmission systemsDigital-analogue convertorsAudio power amplifierDifferential nonlinearity

A DAC (10) including an operational amplifier (12) having an input terminal; a plurality of current paths coupled to the input terminal; a plurality of current sources (I1 / 2 -I4 / 2); and an arrangement (11) for switchably coupling current from at least two of the cells to a respective one of the paths in response to an input signal. In a specific embodiment, the inventive DAC (10) further includes a first resistive element (2R1-2R4) disposed in each of the current paths, a second resistive element (R1-R4) disposed between the current paths, and a feedback resistor (RF) disposed between an output terminal of the amplifier and the input terminal thereof. In the illustrative embodiment, the coupling arrangement includes a plurality of switches (SW1-SW4); each of the switches is adapted to switch half of the current from a first source and half of the current from a second source into a respective one of the paths. The invention is adapted to lower the distortion of digital to analog converters by improving differential nonlinearities and integral nonlinearities, caused primarily by current source gradient errors, without the need for trimming.

Owner:MICROELECTRONICS TECH INC

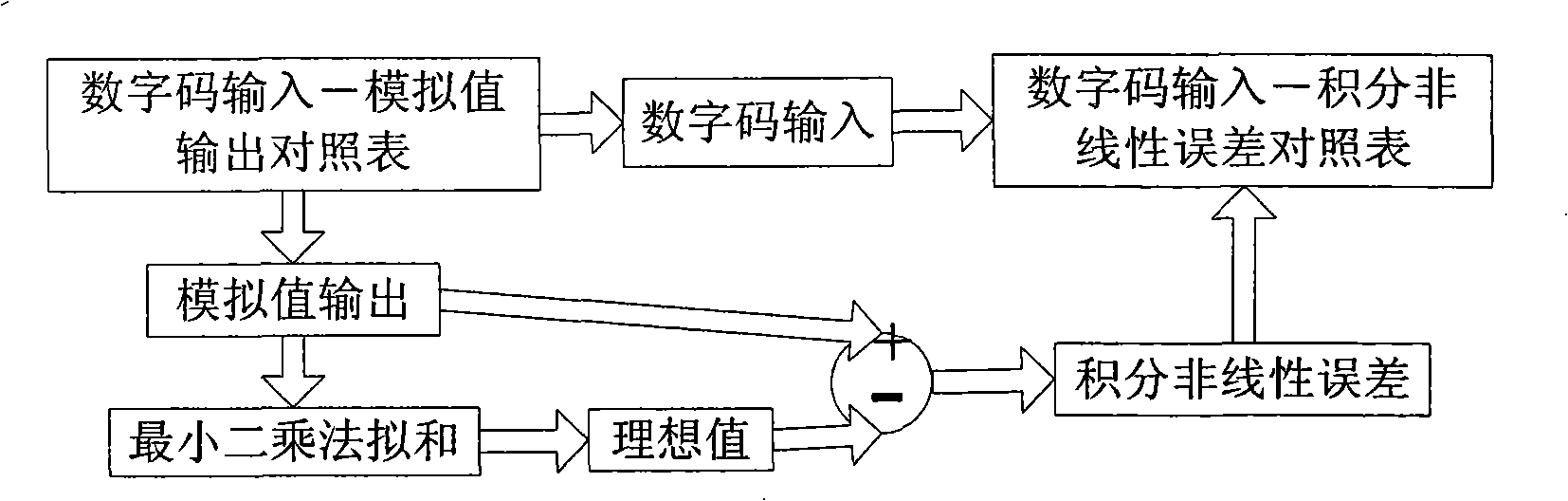

Method for improving open cycle digital optical fiber gyroscope scale factor linearity

InactiveCN101216323AImprove linearityEasy to operateSagnac effect gyrometersAnalogue/digital conversion calibration/testingError checkGyroscope

The invention discloses a method for improving linearity of scale factors of a digital open loop optical fiber gyroscope, which comprises the following steps of: constructing a test system for analog value input-digital code output of an analog-to-digital converter; obtaining a check list output in digital coded responding to different analog value inputs of the analog-to-digital converter from 0 to Vpp; calculating to obtain a nonlinear integral error check list of digital code steps corresponding to different analog value inputs of the analog-to-digital converter; and compensating the nonlinear integral error of the analog-to-digital converter by addition of a subtracter, and obtaining accurate outputs of the analog-to-digital converter. The invention effectively reduces pseudo output arising from the nonlinear integral error of the analog-to-digital converter, so as to ensure the accuracy of the output signal of the digital open loop optical fiber gyroscope; and can compensate the nonlinear integral error according to different parameters of the analog-to-digital converter, so as to effectively improve the linearity of the scale factor of the digital open loop optical fiber gyroscope.

Owner:ZHEJIANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com