Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

36results about How to "Increased circuit complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

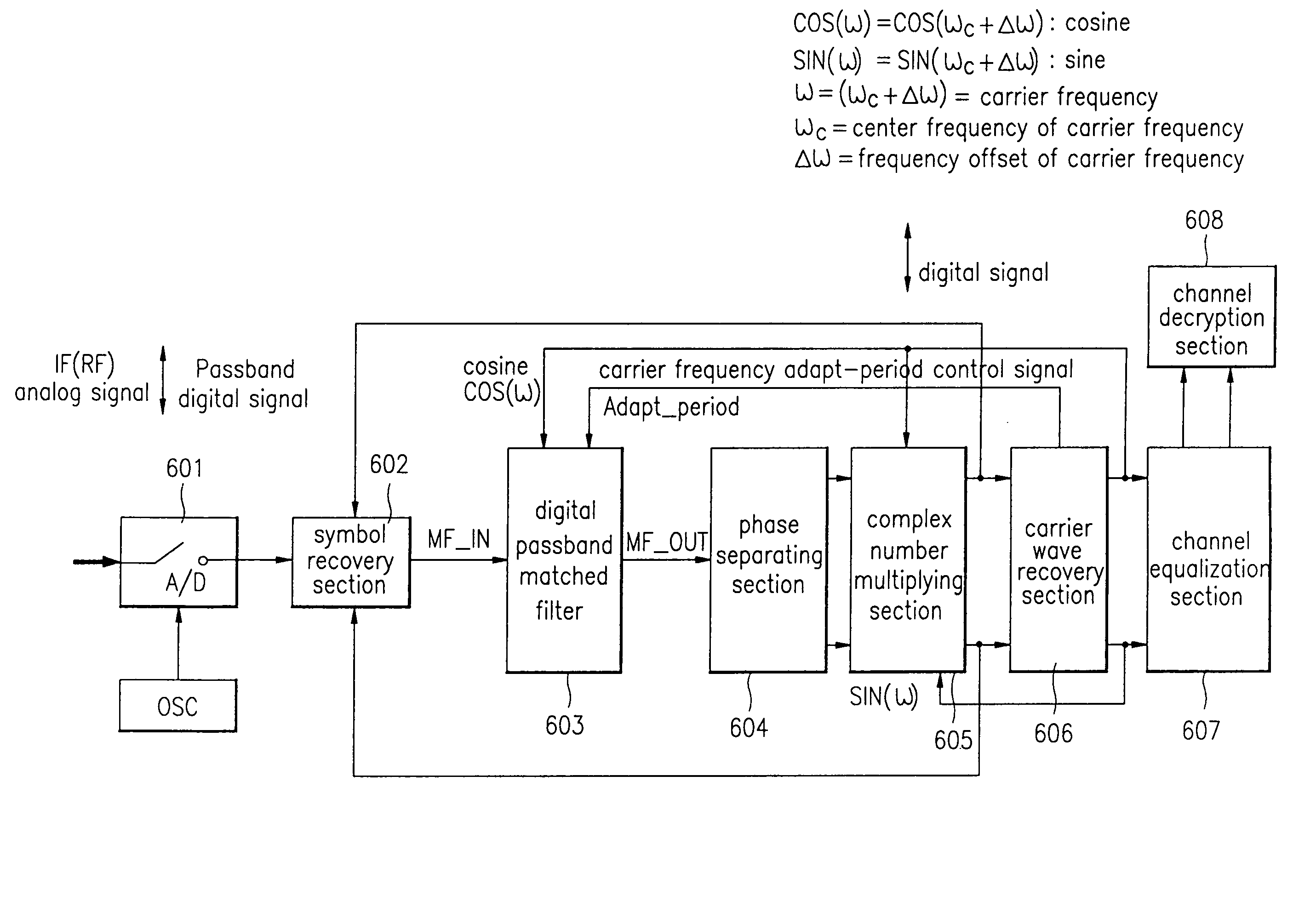

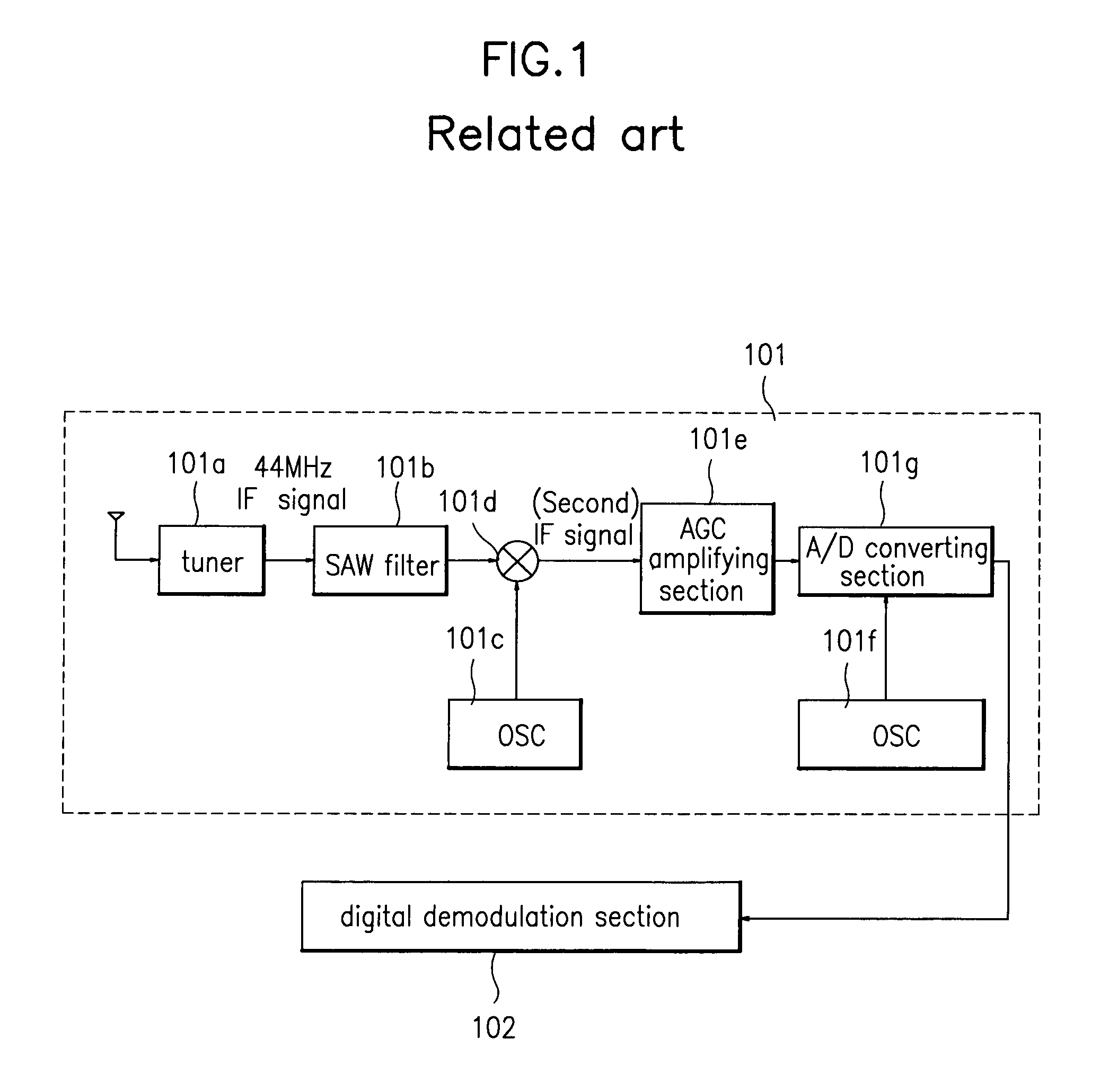

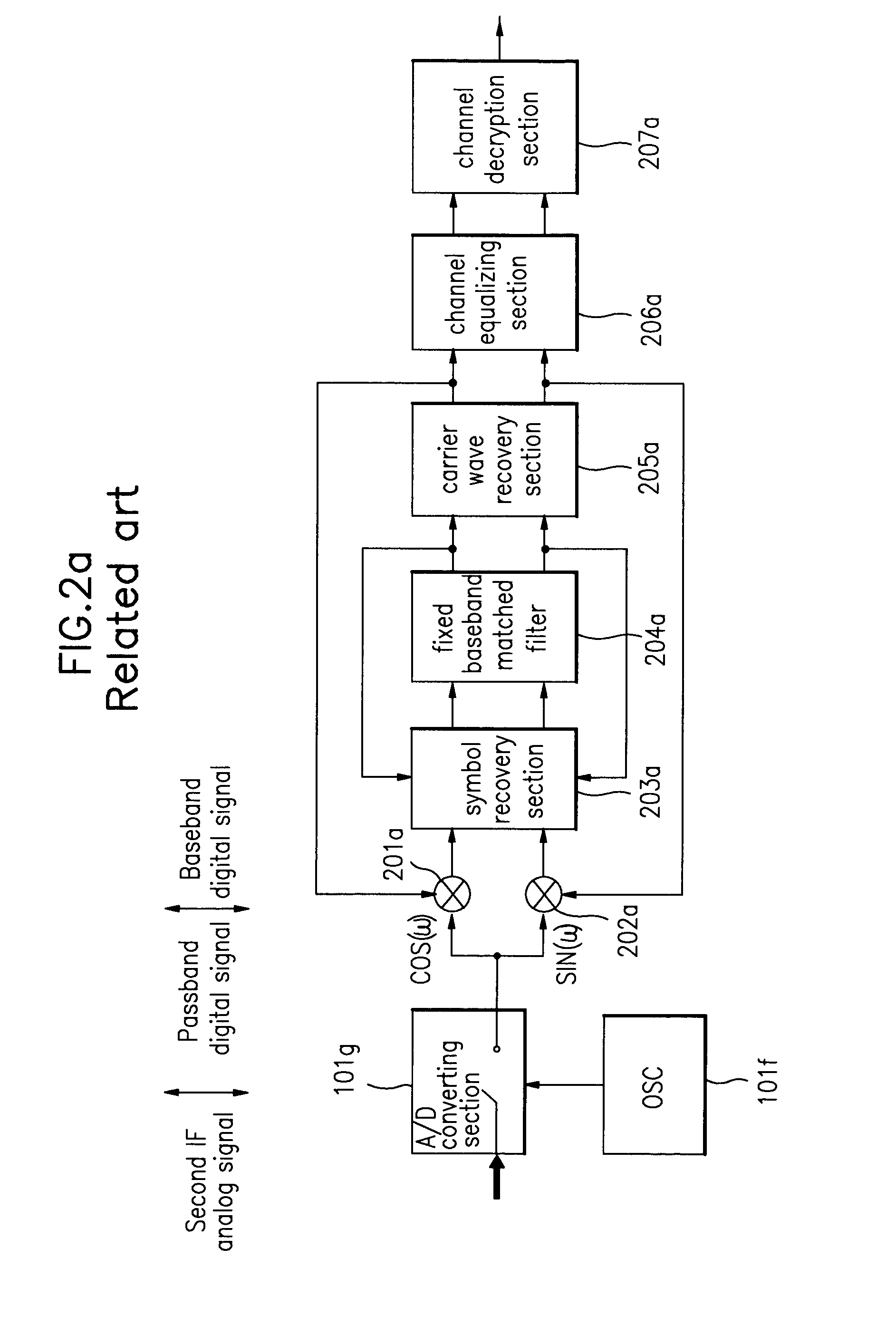

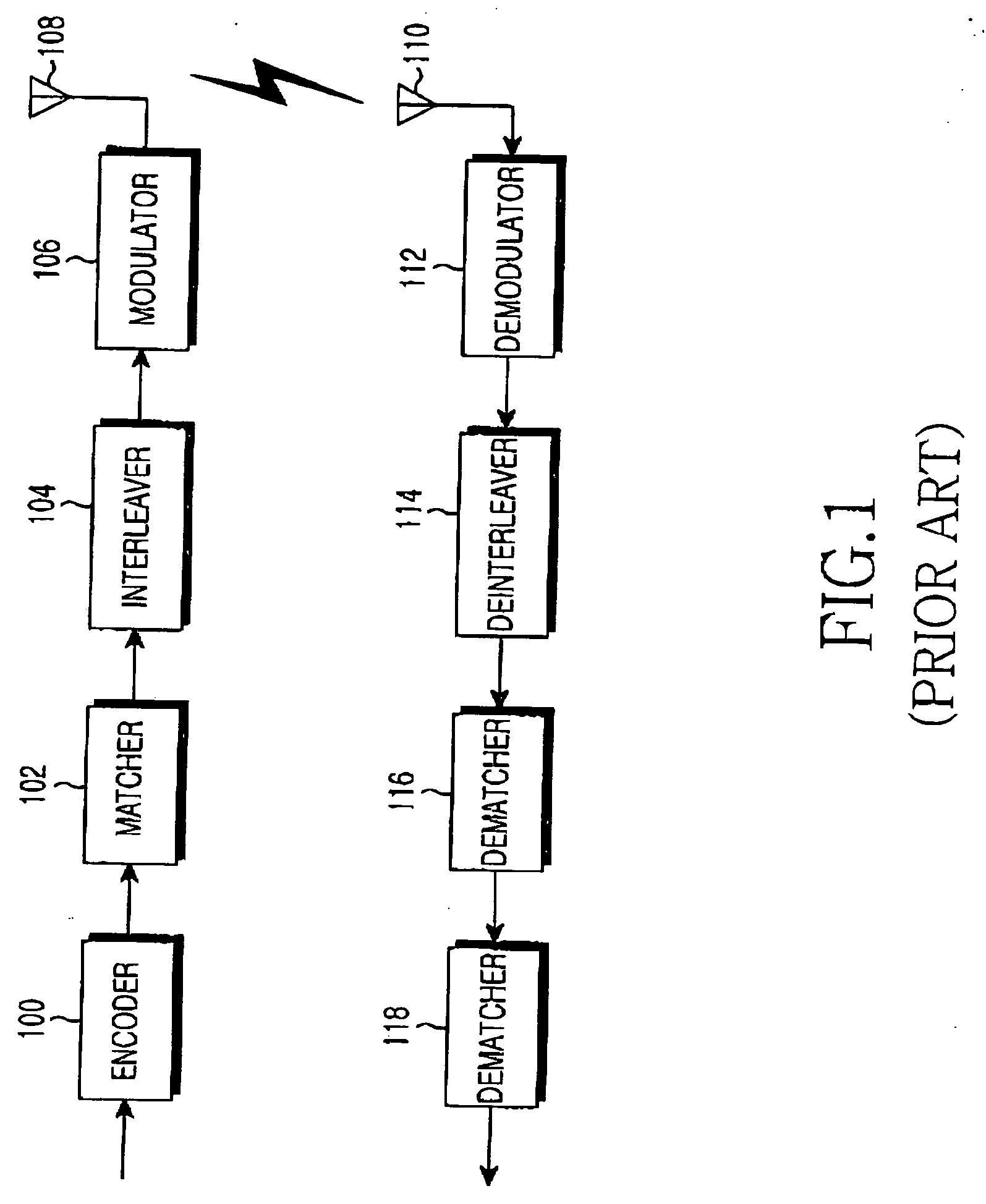

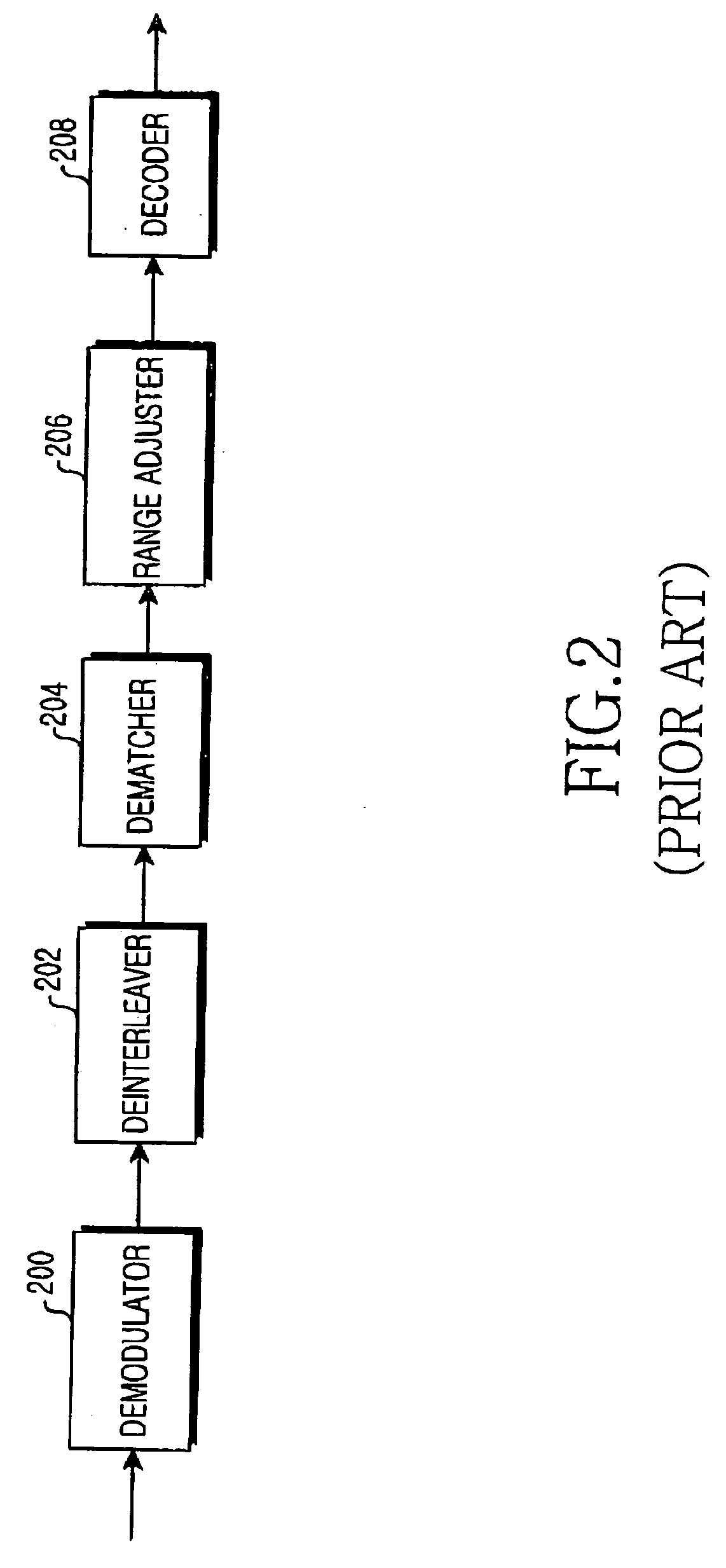

Matched filter, filtering method and digital broadcast receiver using the same

InactiveUS6980609B1Deterioration of SNR performanceIncreased circuit complexityCarrier regulationAmplitude-modulated carrier systemsCircuit complexityCarrier signal

A digital passband matched filter is automatically adapted to a carrier wave ω in accordance with a frequency offset of the carrier wave, to obtain a passband digital signal having no frequency distortion due to the frequency offset. Thus, a receiver in which drawbacks such as decrease of SNR and increase of circuit complexity caused by the fixed baseband / passband matched filter is obtained. Since a cosine wave generating section operates in a carrier wave frequency restoring mode and a carrier wave frequency adaptive mode, respectively, a single cosine wave ROM table can be used regardless of the respective operating modes, thereby reducing circuit complexity. Since the digital passband matched filter acts to renew the filter coefficients adapted to the carrier wave adaptive mode only, power consumption required to operate the filter can be minimized.

Owner:LG ELECTRONICS INC

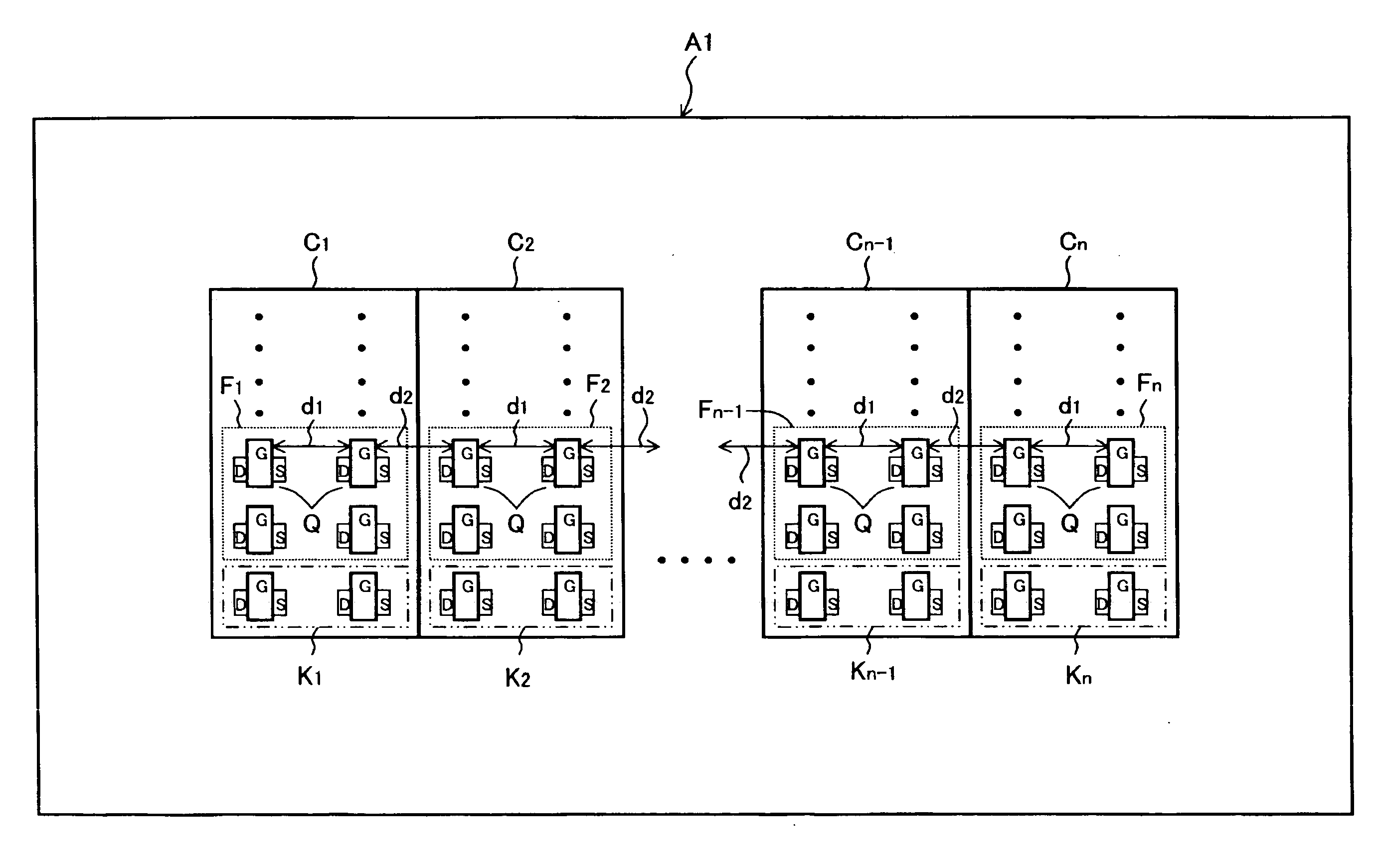

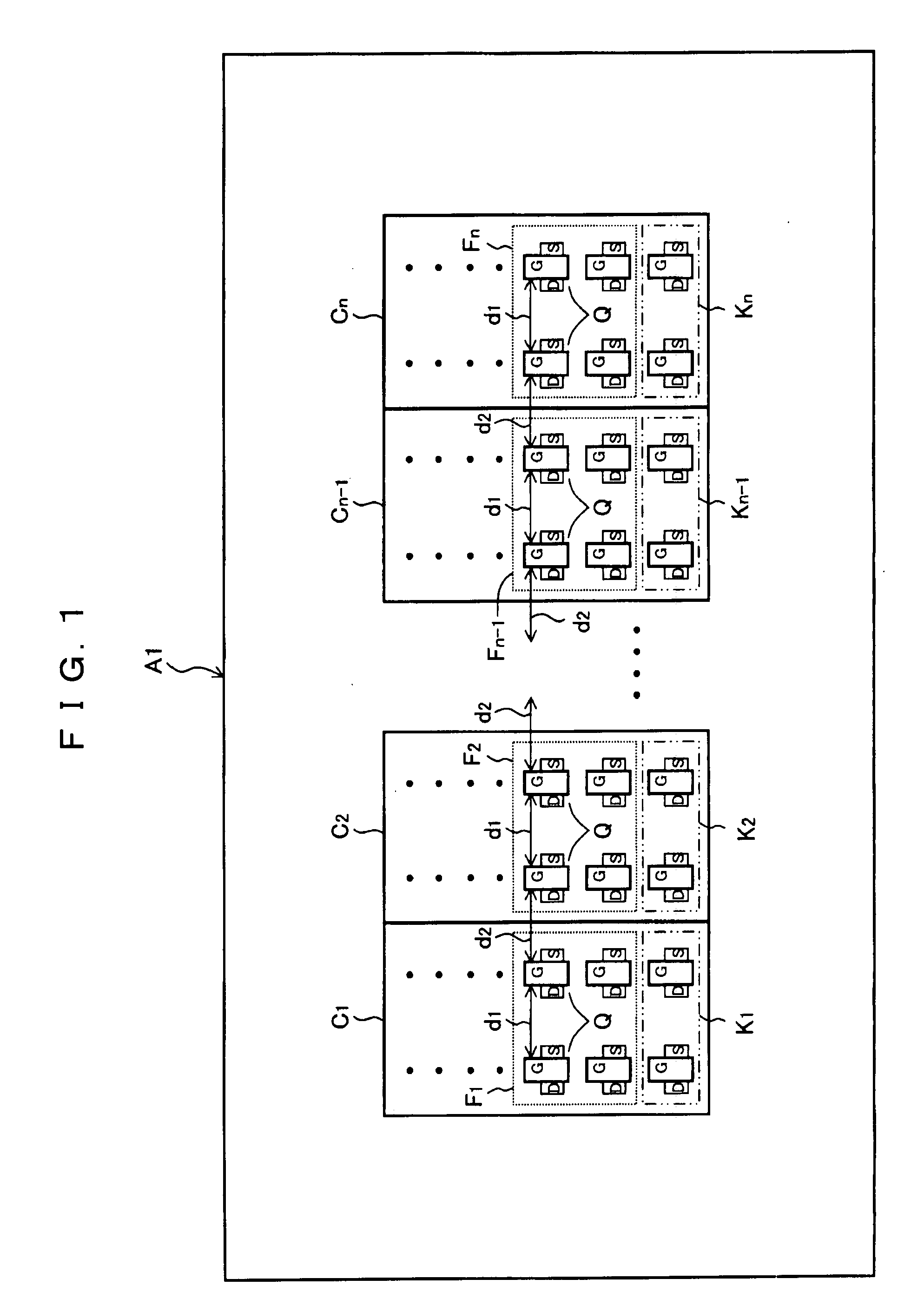

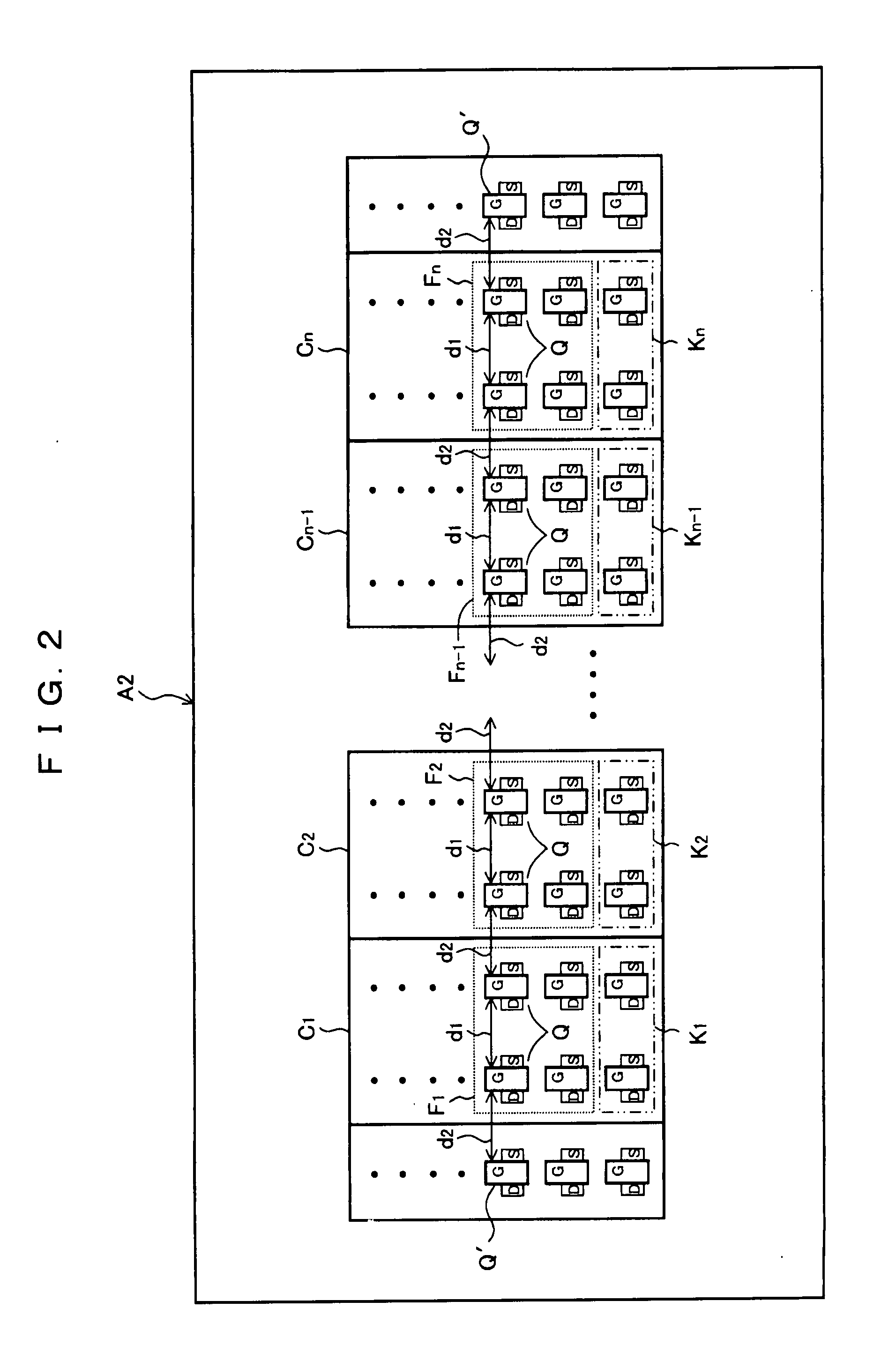

Layout method and semiconductor device

InactiveUS20080022247A1Size of cellIncrease the areaTransistorSolid-state devicesEngineeringSemiconductor

The present invention is provided with a plural cell including a transistor pair. The plural cells are arranged at equal intervals so as to configure a cell group. A inter-cell distance between a transistor in one of the cell and a transistor the other cell in each of adjacent cells in the cell group is equal to a intra-cell distance between one of the transistor and the other transistor in the transistor pair.

Owner:PANASONIC CORP

Power consumption stabilization system & method

InactiveUS20050078016A1Reduce maximum power consumptionLimiting designReliability increasing modificationsCode conversionNumber generatorComputer science

A source signal is provided. The source signal is XORed with a scrambling random signal to generate a scrambled signal. The scrambled signal is transmitted through the digital logic circuit. The scrambled signal is XORed with the descrambling random signal logically identical to the scrambling random signal to produce a descrambled signal identical to the source signal. In one embodiment, the scrambling random signal is transmitted through the digital logic circuit and used as the descrambling random signal. In another embodiment, the scrambling random signal and descrambling random signal are generated independently using pseudo-random number generators. In yet another embodiment, the scrambling random signal is self-synchronizing and is contained within the pattern of the scrambled signal.

Owner:AGILENT TECH INC

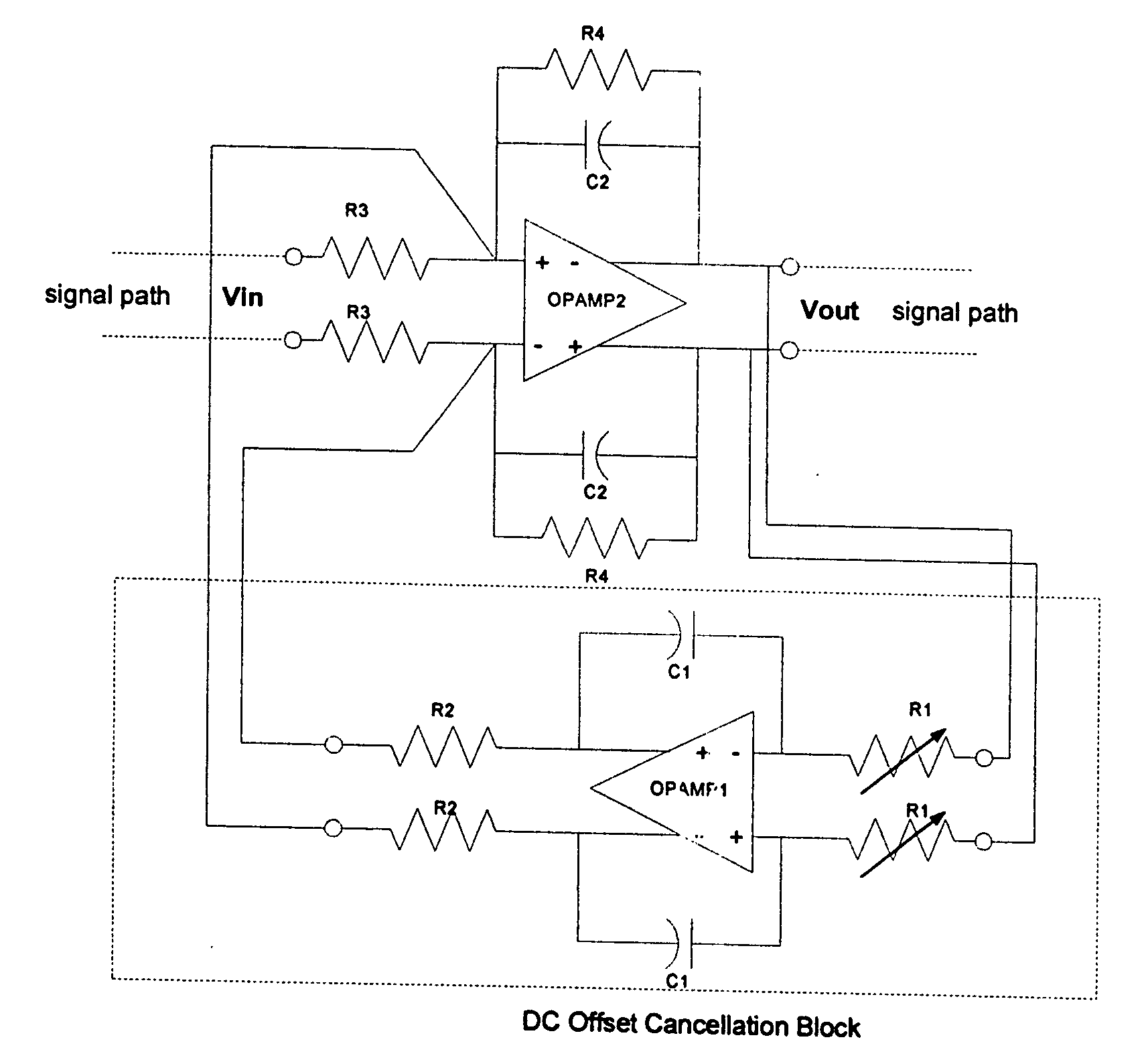

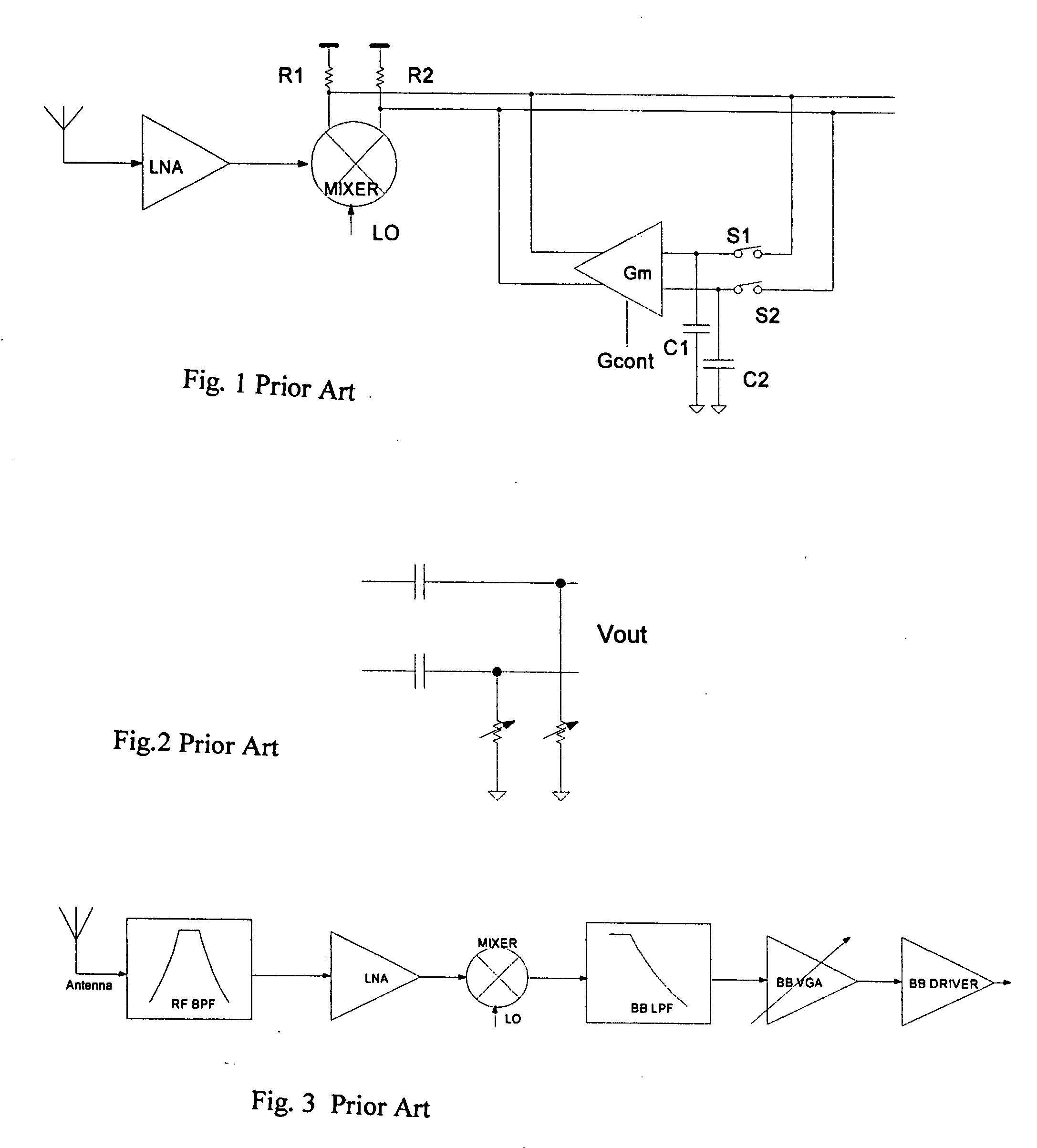

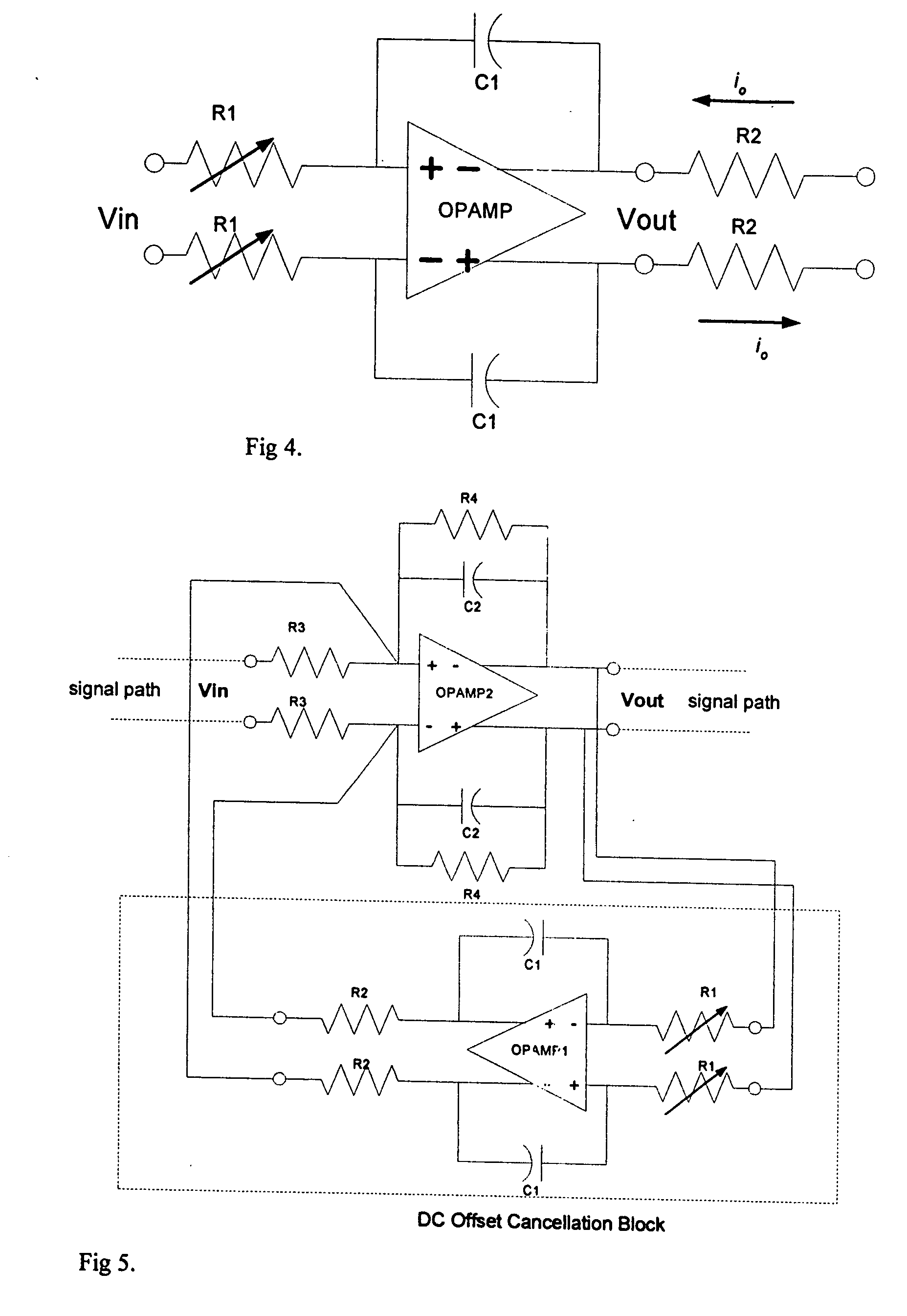

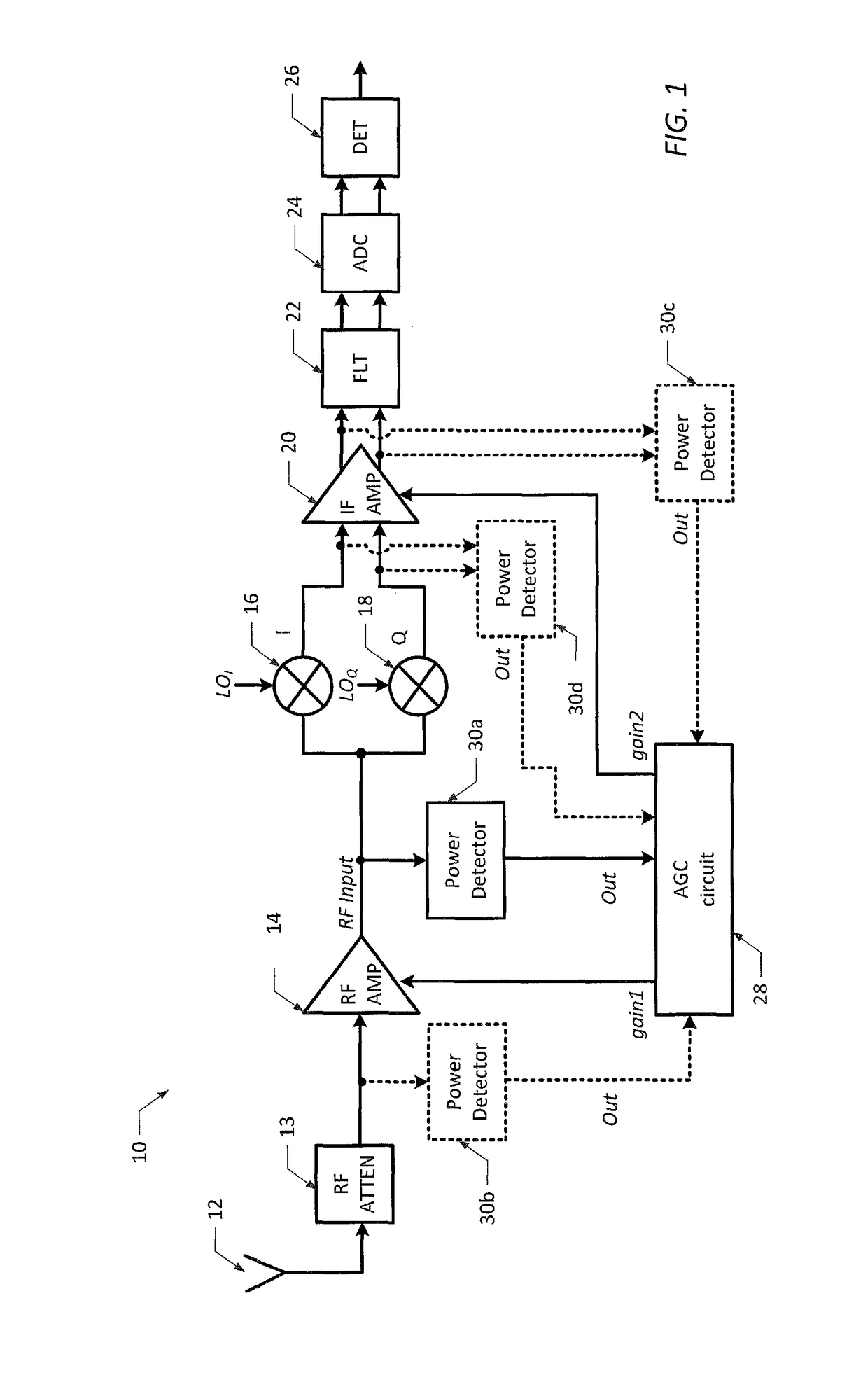

DC offset cancellation in a direct-conversion receiver

InactiveUS20050110550A1Reduce silicon areaSave powerPulse automatic controlDifferential amplifiersCapacitanceIntegrator

The DCOC block is used in ZIF BB to form HPF function to cancel dc offset with a penalty of small silicon area and low power consumption. It is a LPF plus a voltage to current conversion (VIC) resistor, and can hook up with any BB opamp used in signal path, to form a feedback loop, with or without signal gain stages in the loop. The BB opamp is used as a summing point. The summing method is input current summing. The cutoff frequency of the HPF function is thus defined by the integrator, the VIC resistor, and the feedback resistor in the summing opamp. The presence of the VIC resistor can drastically reduce the integrator capacitor and resistor values and thus save silicon area or improve receiver performance.

Owner:PROMINENT COMM

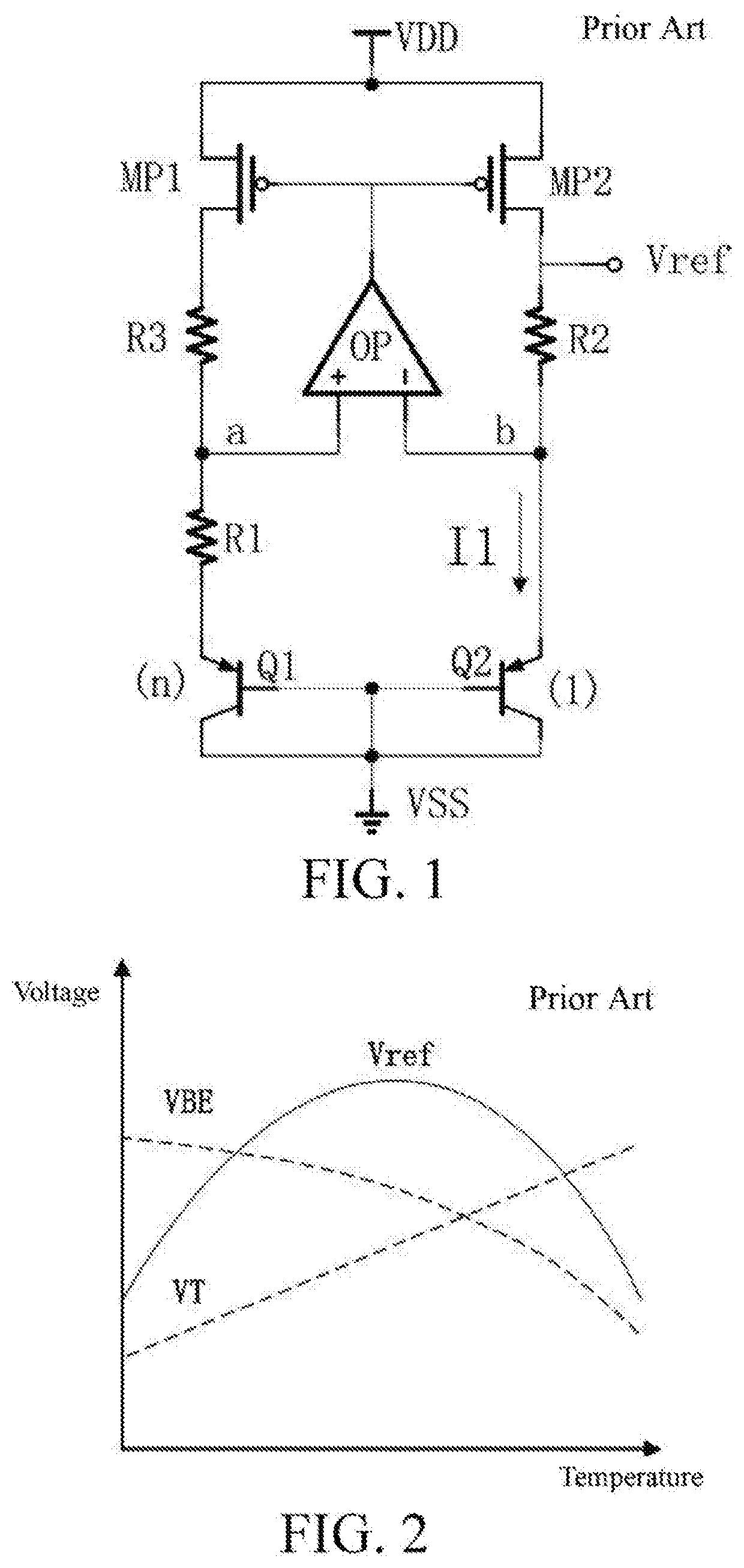

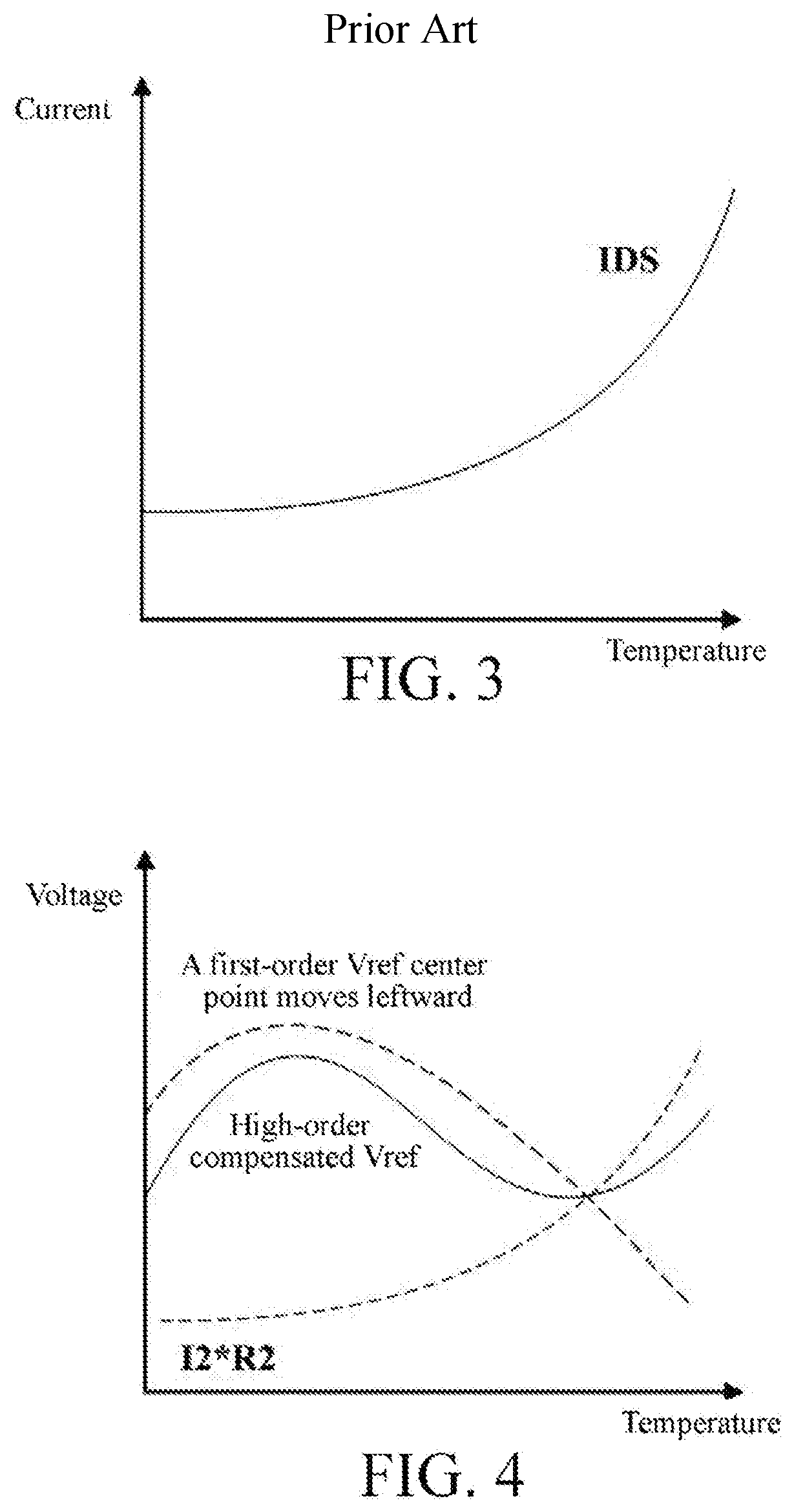

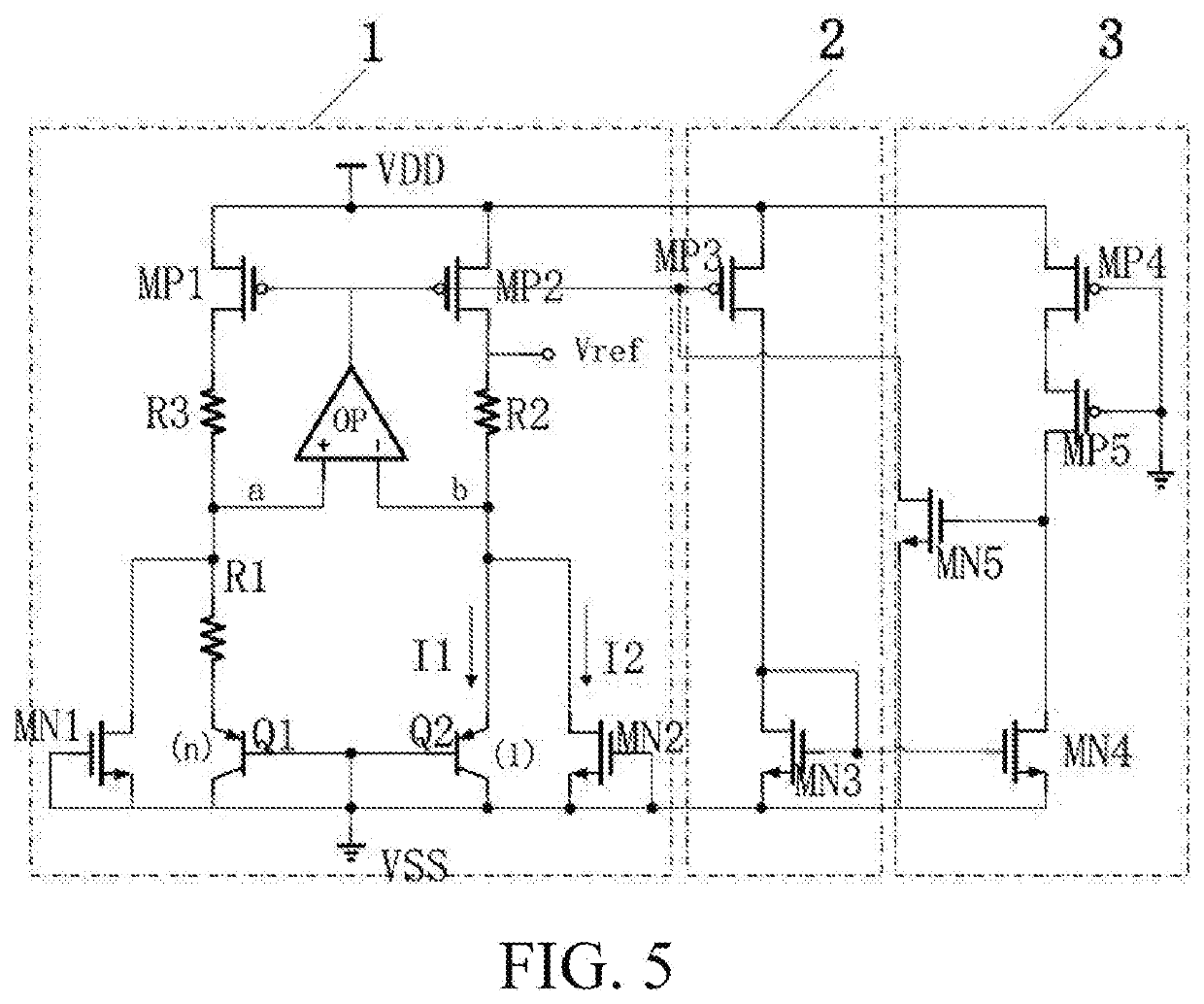

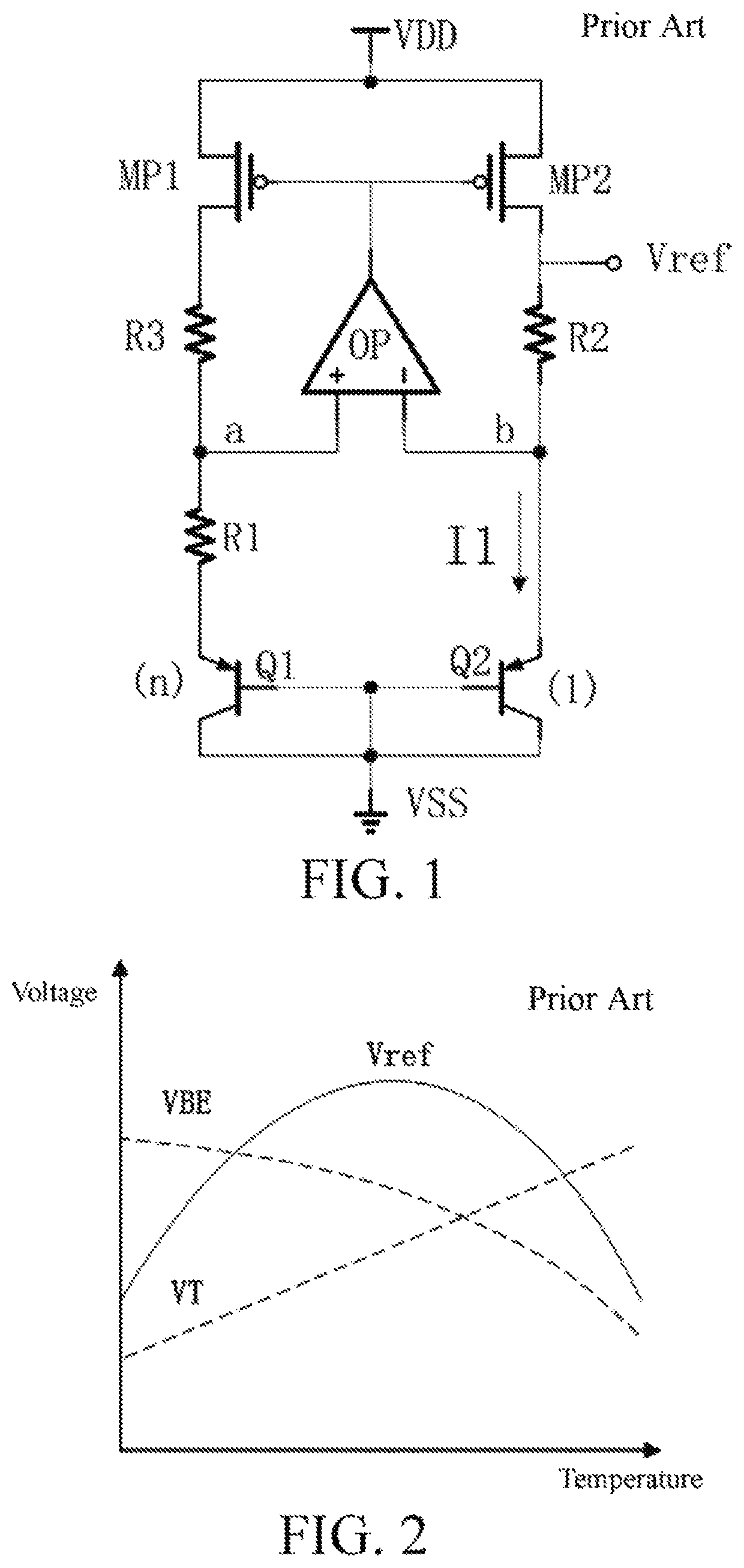

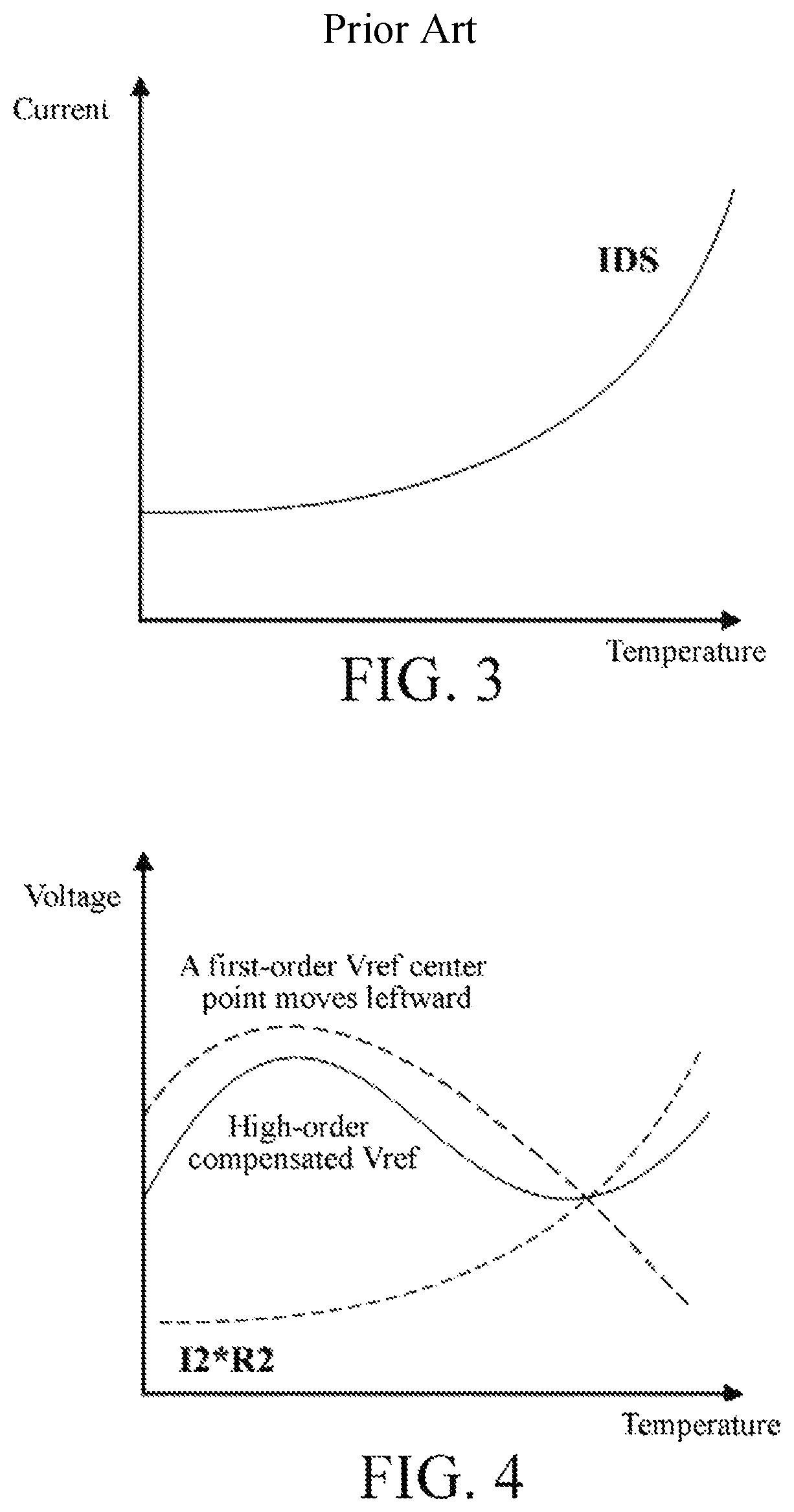

Bandgap reference circuit and high-order temperature compensation method

ActiveUS20200073429A1Improve accuracyReduce power consumptionEfficient power electronics conversionElectric variable regulationCMOSHemt circuits

A bandgap reference circuit and a high-order temperature compensation method are disclosed. The bandgap reference circuit includes: a starting circuit, a bias circuit and a high-order compensated bandgap reference voltage generating circuit, where a compensation method of the high-order compensated bandgap reference voltage generating circuit is to perform curvature correction by using a sub-threshold current of a CMOS transistor to obtain a high-order temperature-compensated bandgap reference voltage source circuit. The present circuit has the advantages that a manner not increasing circuit complexity can be adopted for implementation, the accuracy of a bandgap reference source can be greatly improved, and power consumption, chip area and cost are reduced.

Owner:PURESEMI CO LTD

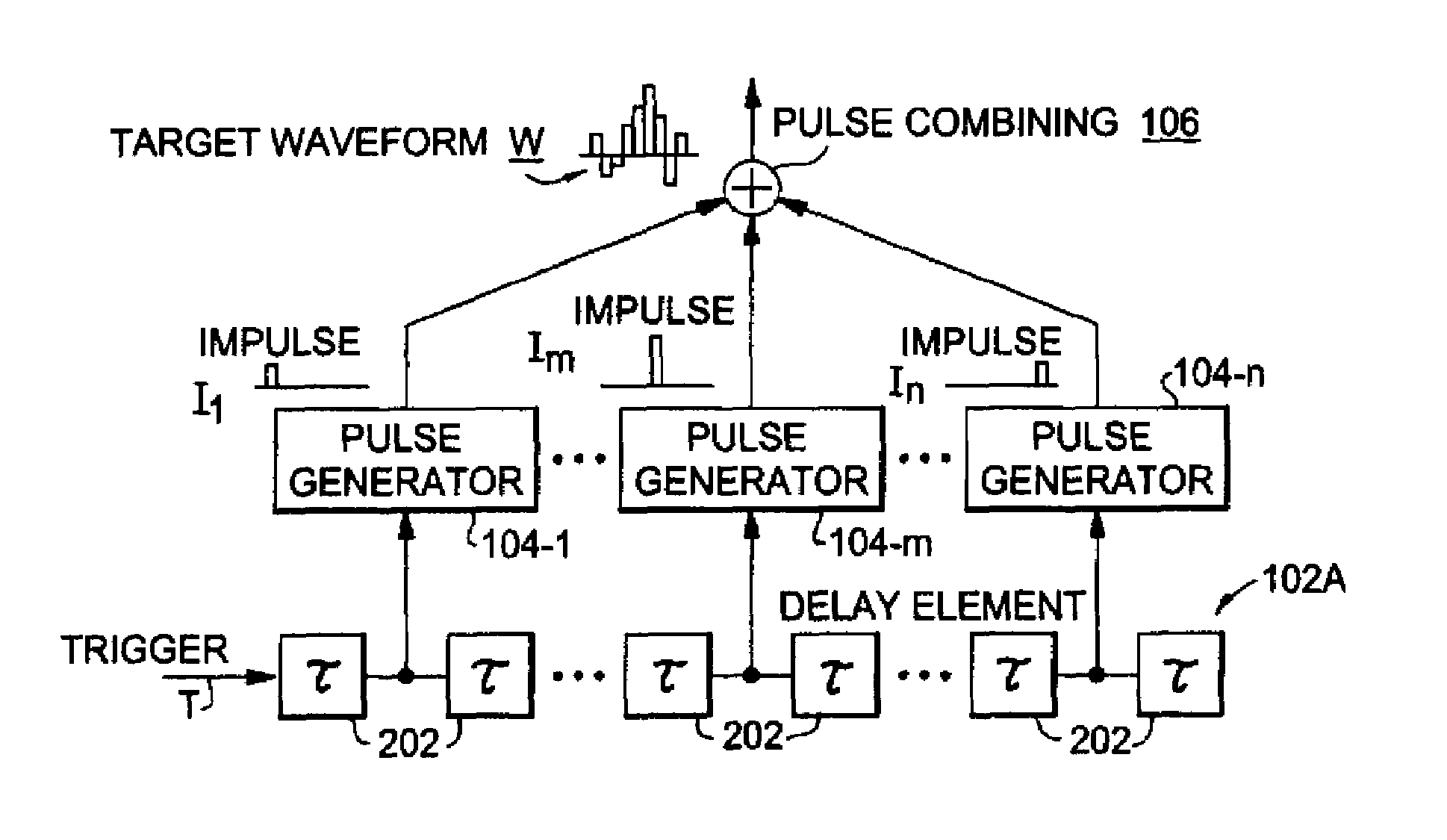

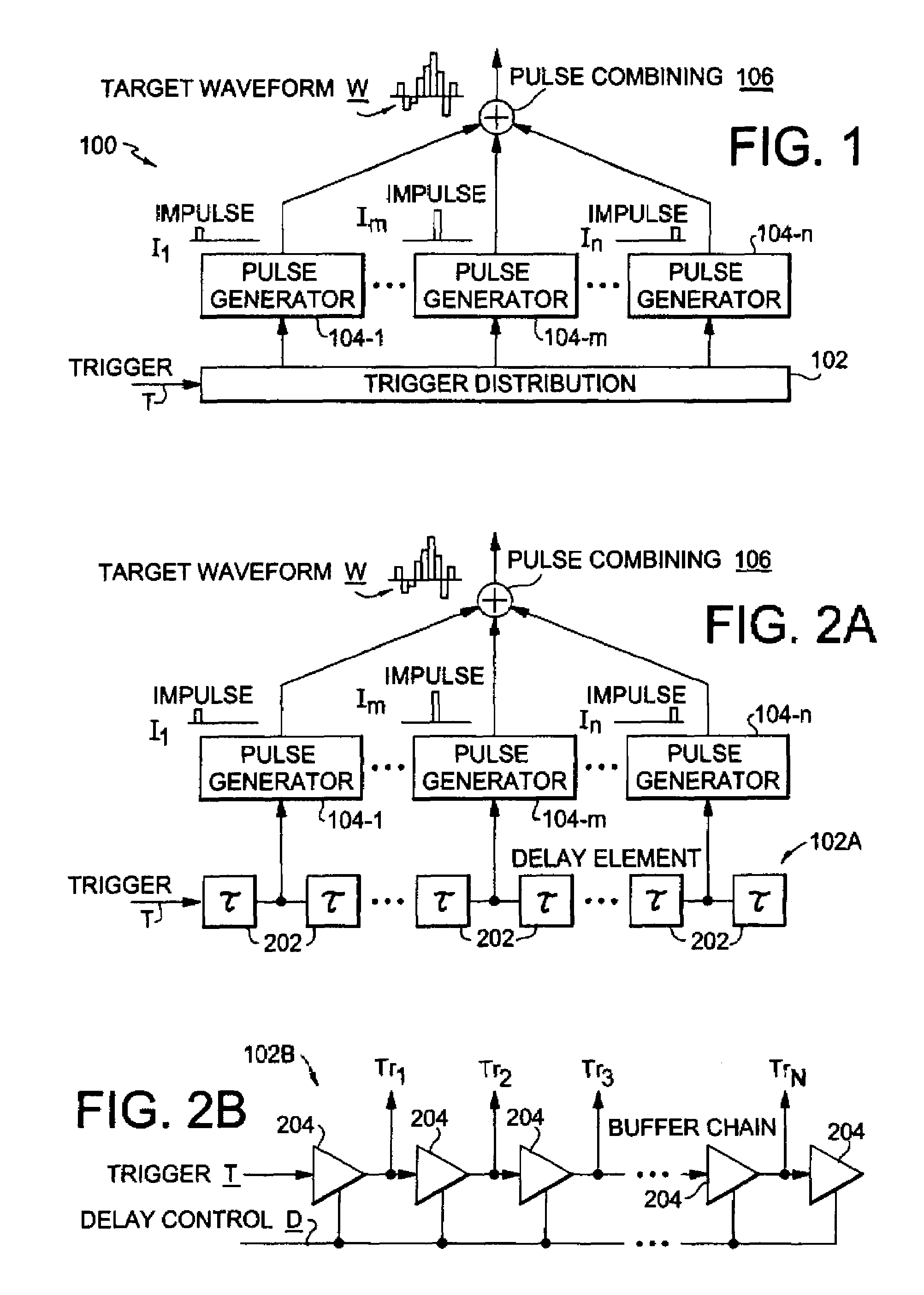

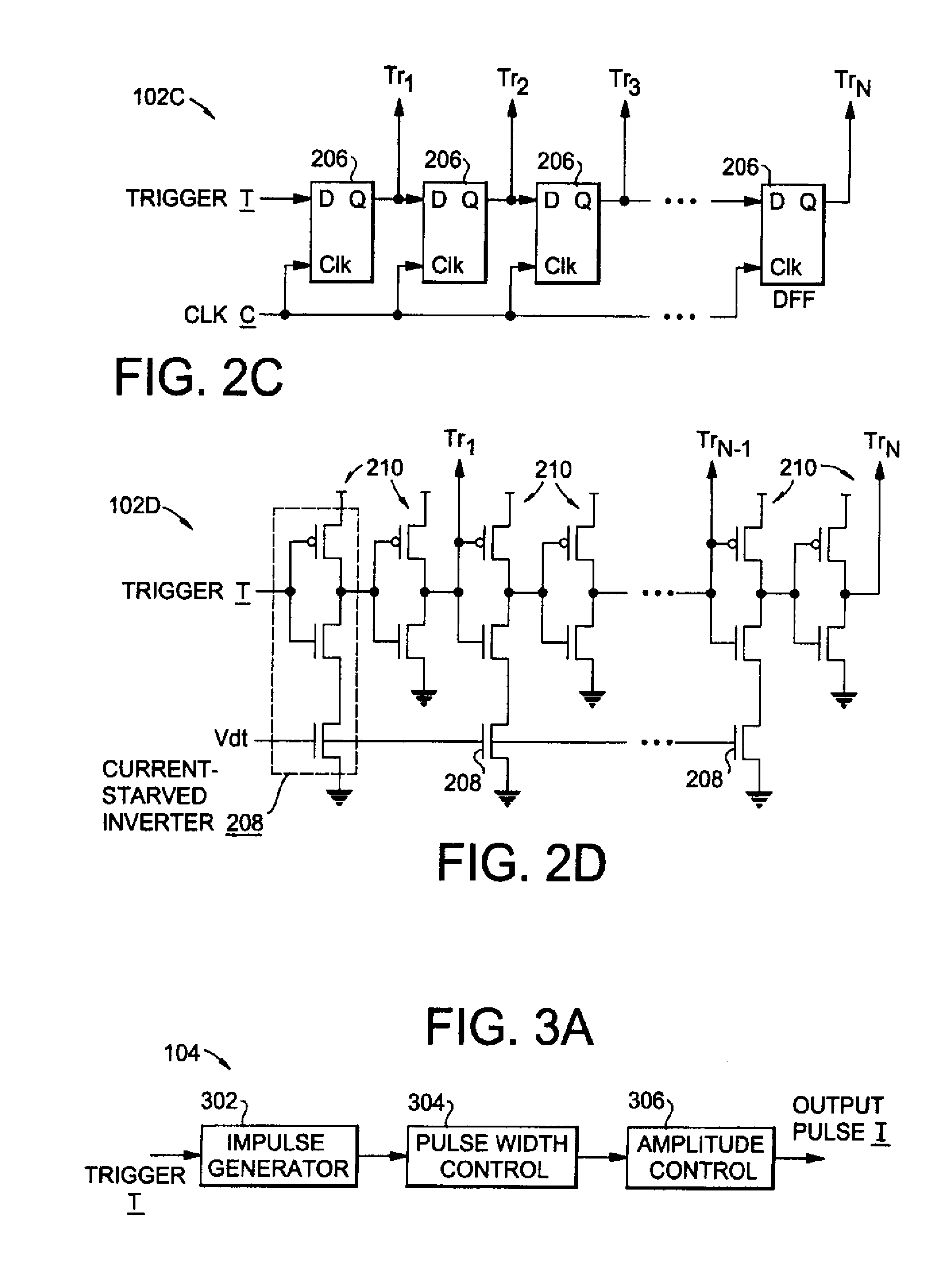

Distributed arbitrary waveform generator

InactiveUS7545304B1Low lossEasily accommodateElectric signal transmission systemsPulse generatorPhysicsWave shape

A distributed arbitrary waveform generator (DAWG) synthesizes the target waveform using a series of narrow pulses generated by a number of pulse generators. To achieve this, it uses an input trigger signal to control all the pulse generators, each of which generates a narrow pulse (impulses) at a specific sample time, and then all the impulses are combined to generate the output waveform. The input trigger signal is distributed to each pulse generator by a trigger distribution network. Impulses generated by pulse generators can be tuned in both pulse amplitude and width, and the spacing between them can be tuned by the trigger distribution network. Therefore the waveforms generated are completely reconfigurable.

Owner:UNIVERSITY OF ROCHESTER

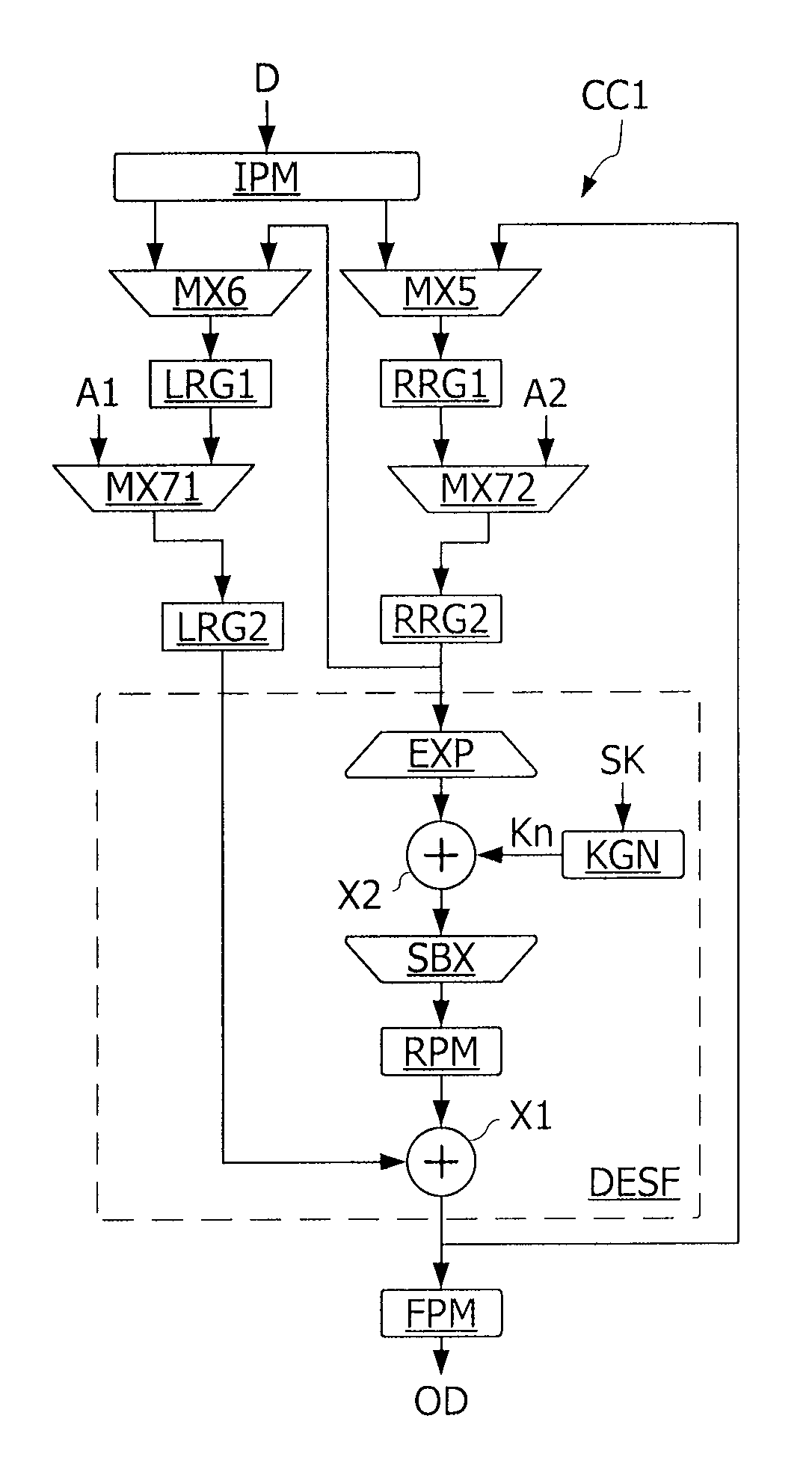

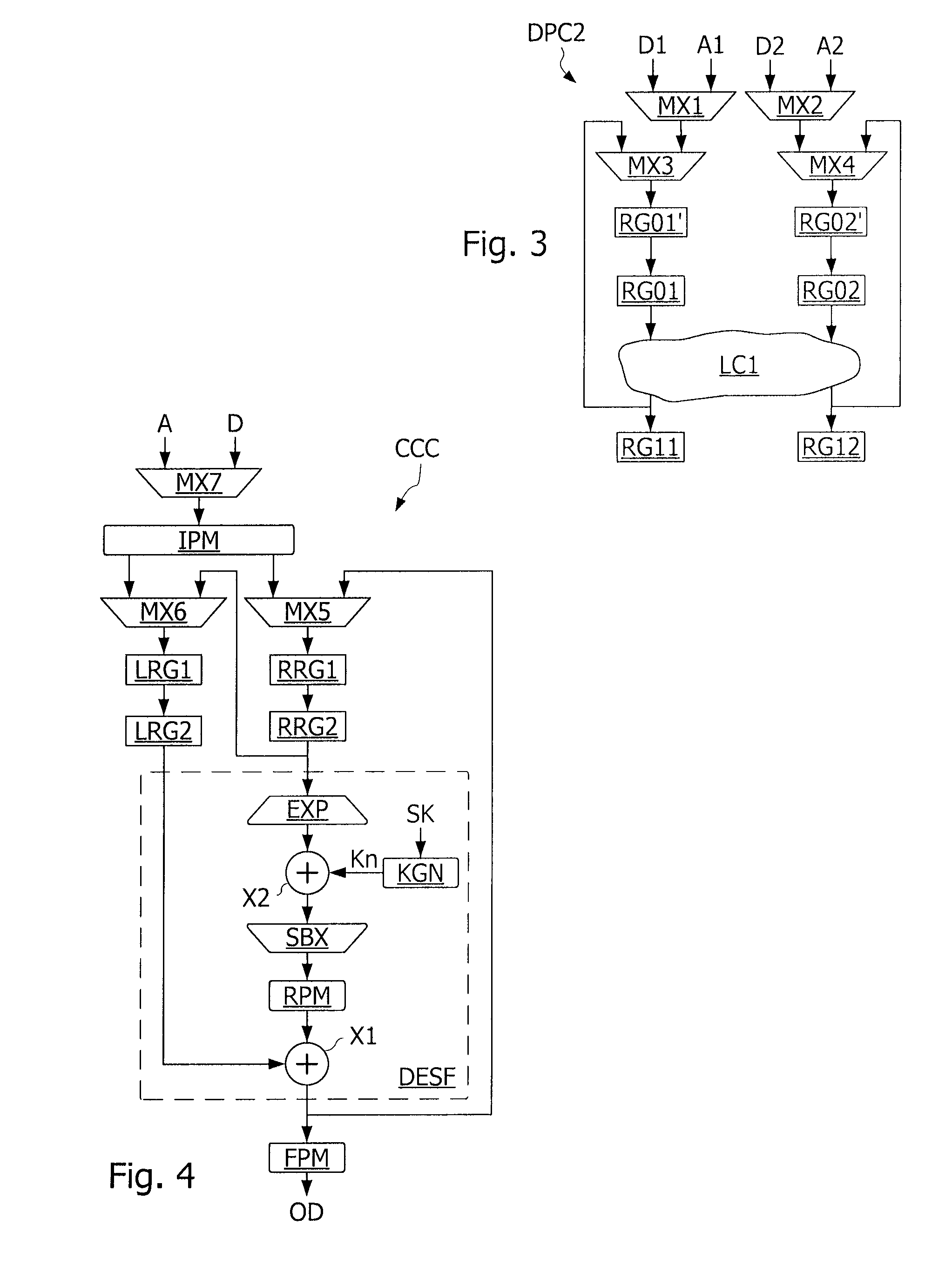

Countermeasure method and device for protecting data circulating in an electronic component

ActiveUS20110176674A1Increased circuit complexityDigital data processing detailsAnalogue secracy/subscription systemsCountermeasureProcessor register

The present disclosure relates to a countermeasure method in an integrated circuit comprising at least one first logic circuit and at least one first input register supplying the first logic circuit with a datum, the method comprising steps of introducing a random datum into each first input register of the first logic circuit and of the first logic circuit reading the random datum in each first input register, then of introducing a datum to be processed into each first input register, and of the first logic circuit processing the datum in each first input register.

Owner:STMICROELECTRONICS (ROUSSET) SAS

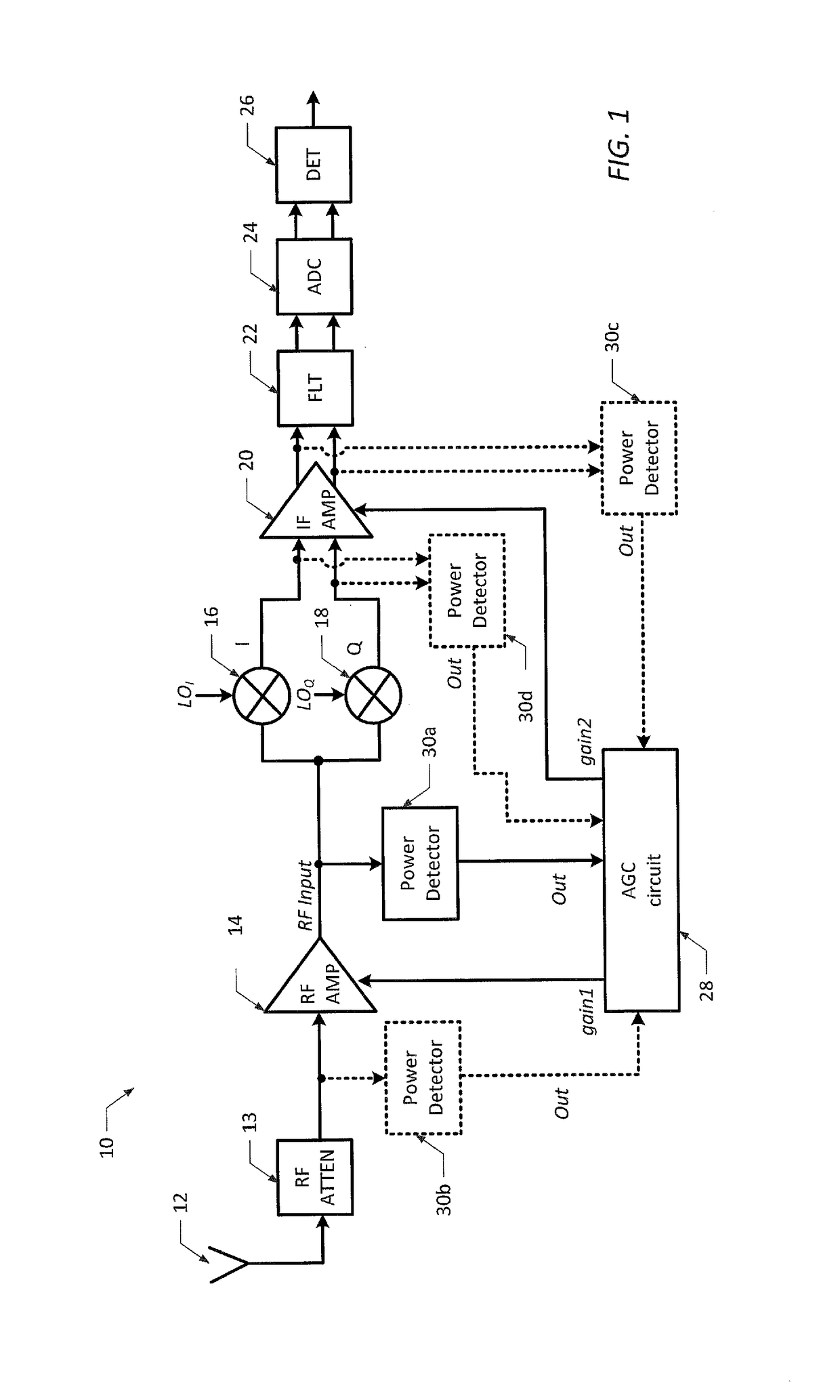

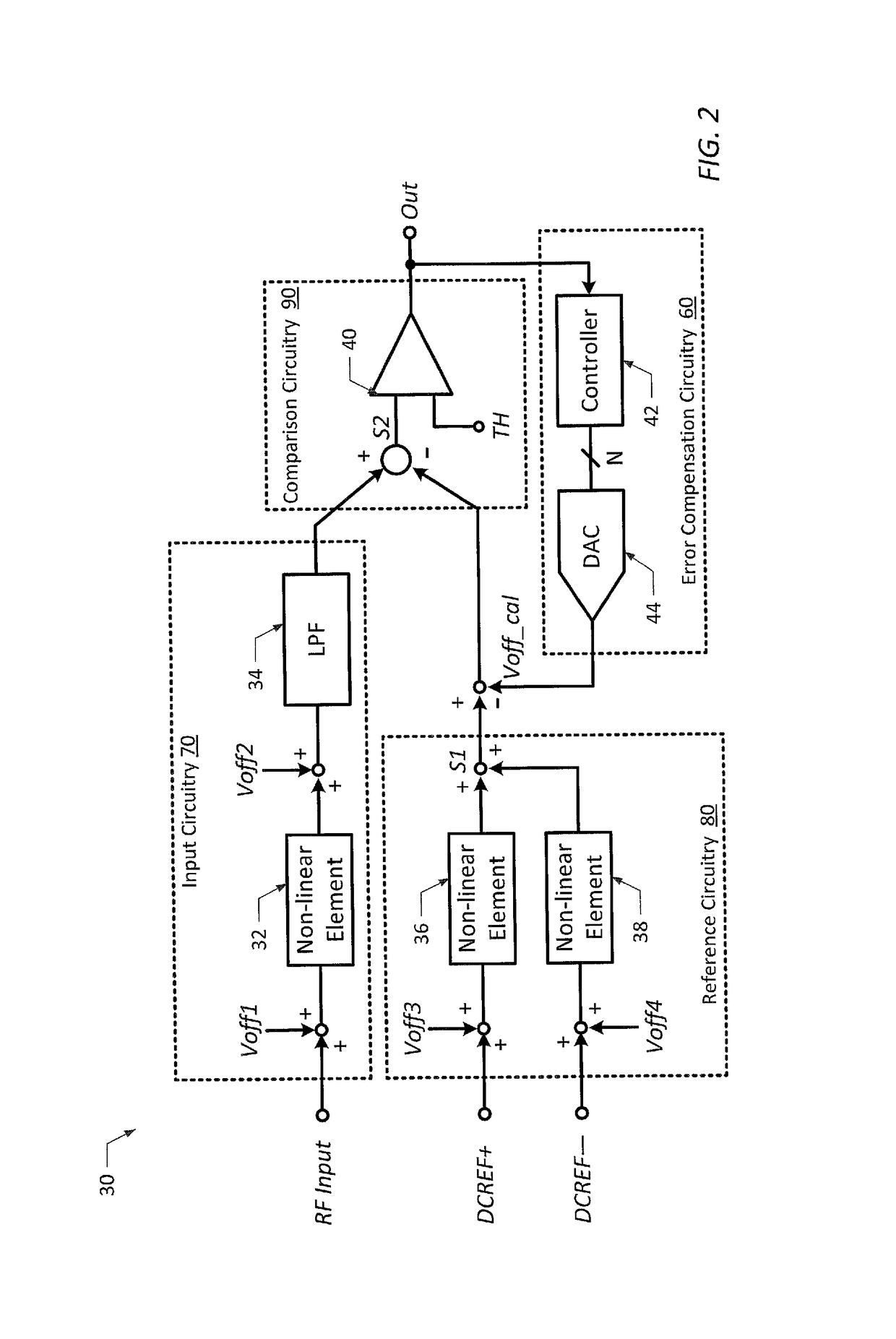

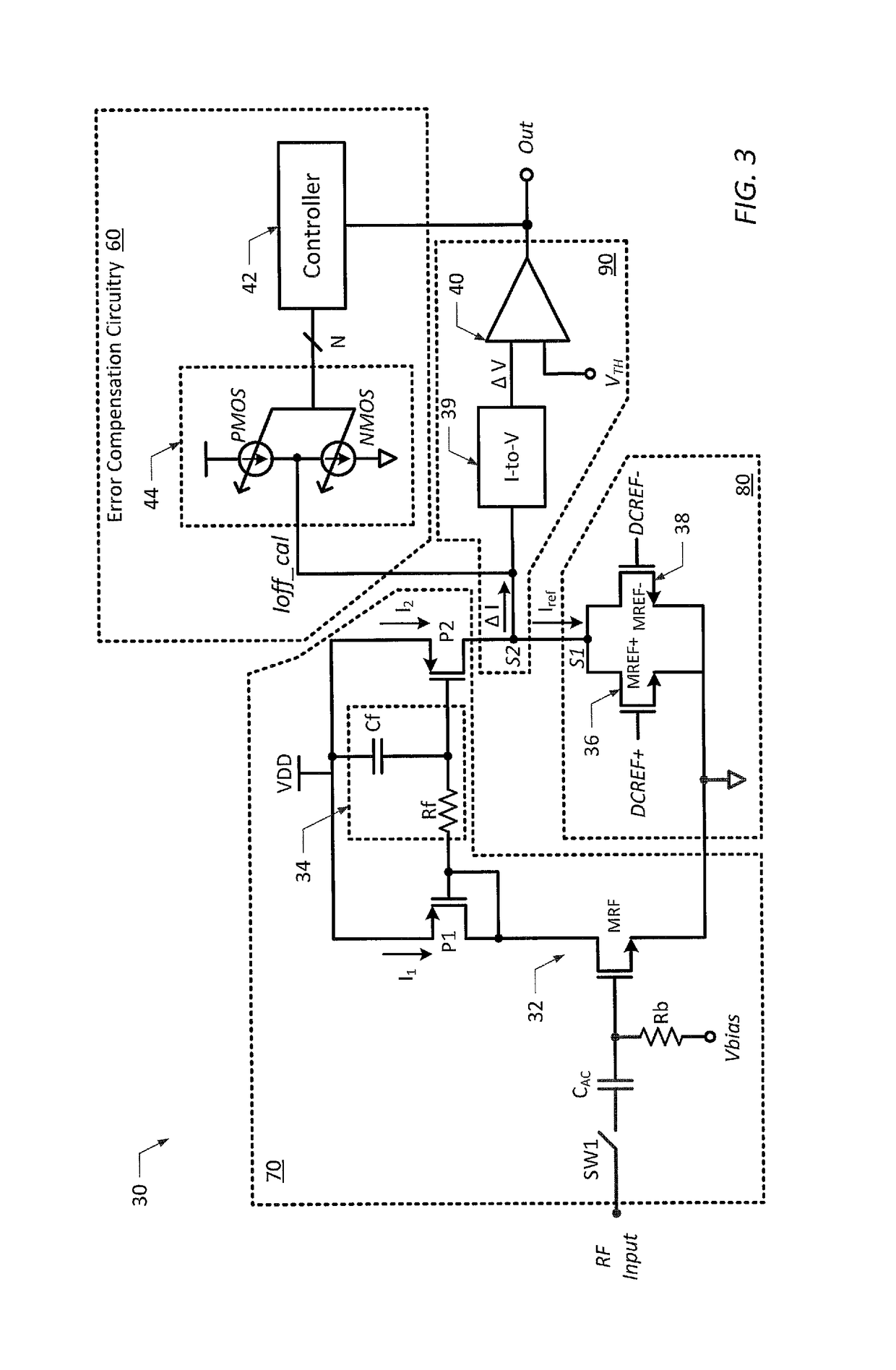

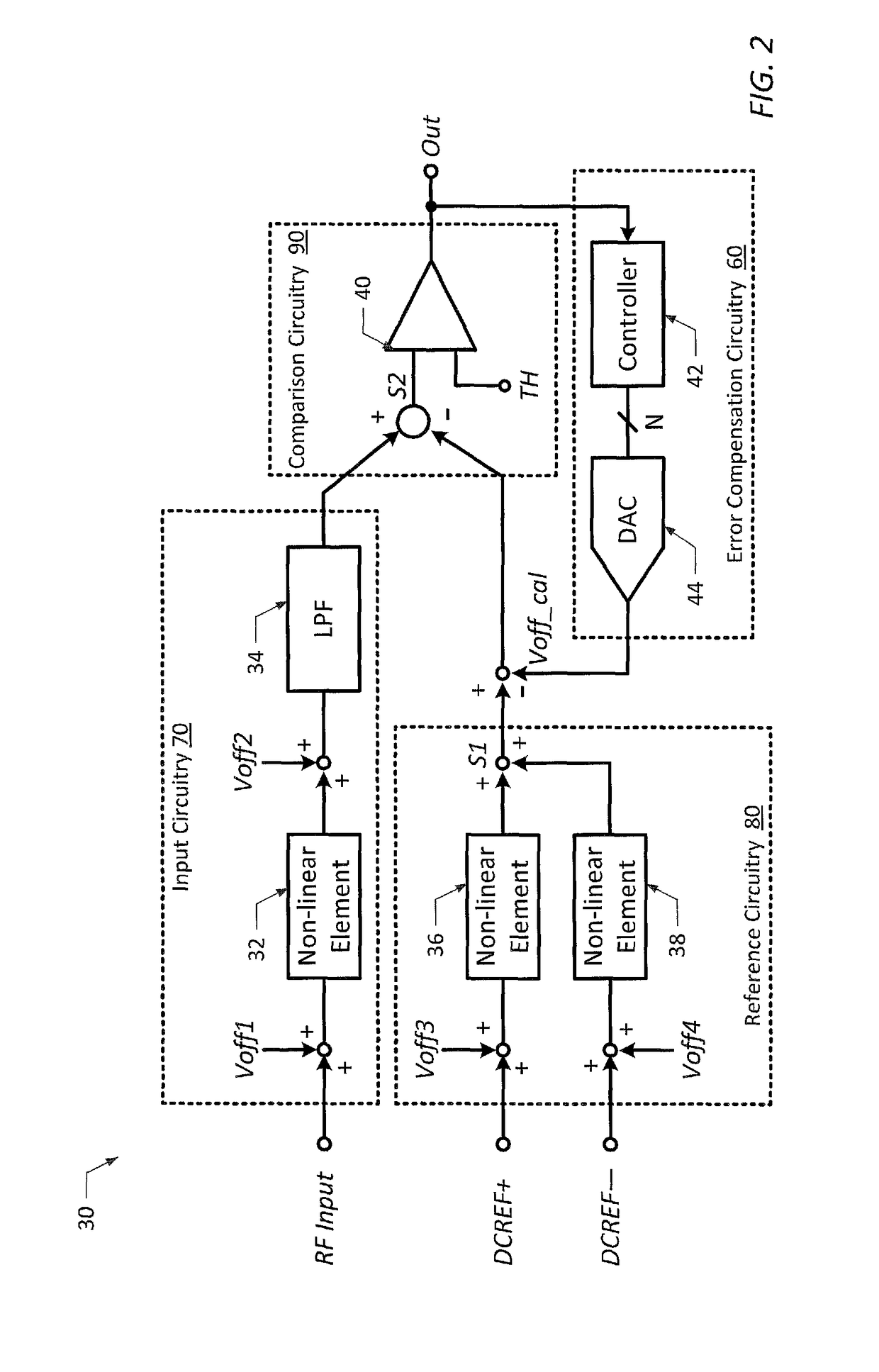

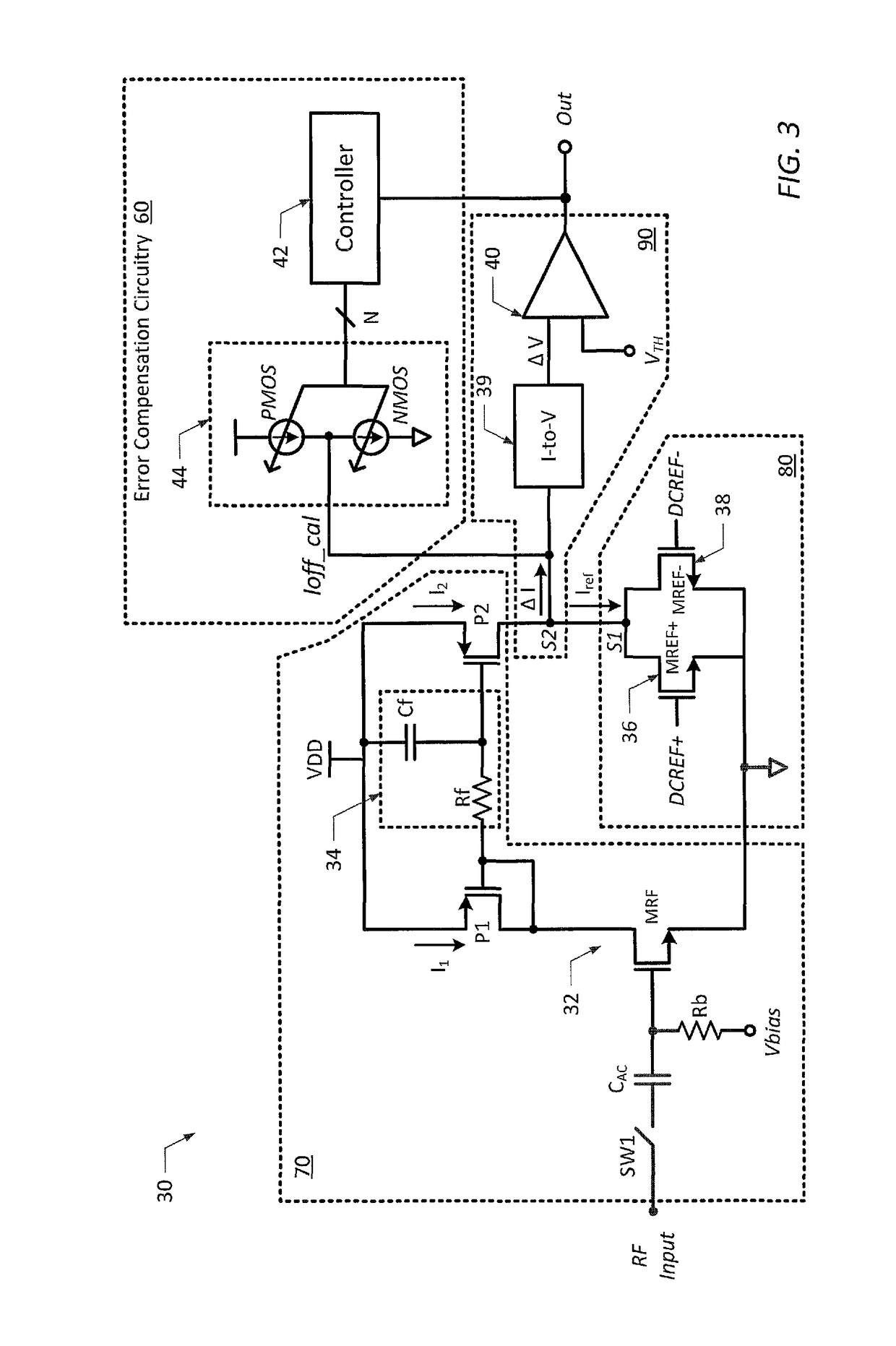

Accurate, low-power power detector circuits and related methods using programmable reference circuitry

ActiveUS10164593B1Improve accuracyIncrease power and area consumptionGain controlDc-dc conversionVIT signalsNormal mode

Embodiments of power detector circuits and related methods to compensate for undesired DC offsets generated within power detector circuits are disclosed. Input signals having input frequencies are received and converted to a magnitude signal, and reference signals are also generated. The magnitude signal may include a DC component proportional to a power of the input signal along with undesired DC offsets. The reference signal may include a DC component proportional to a power of at least one input reference signal along with undesired DC offsets. To compensate for errors introduced by the DC offsets, a programmable digital input signal is determined in a calibration mode and then applied to reference circuitry in a normal mode to compensate for the DC offsets. For the calibration mode, a difference between the magnitude signal and the reference signal is compared to a threshold value to generate a power detection output signal.

Owner:SILICON LAB INC

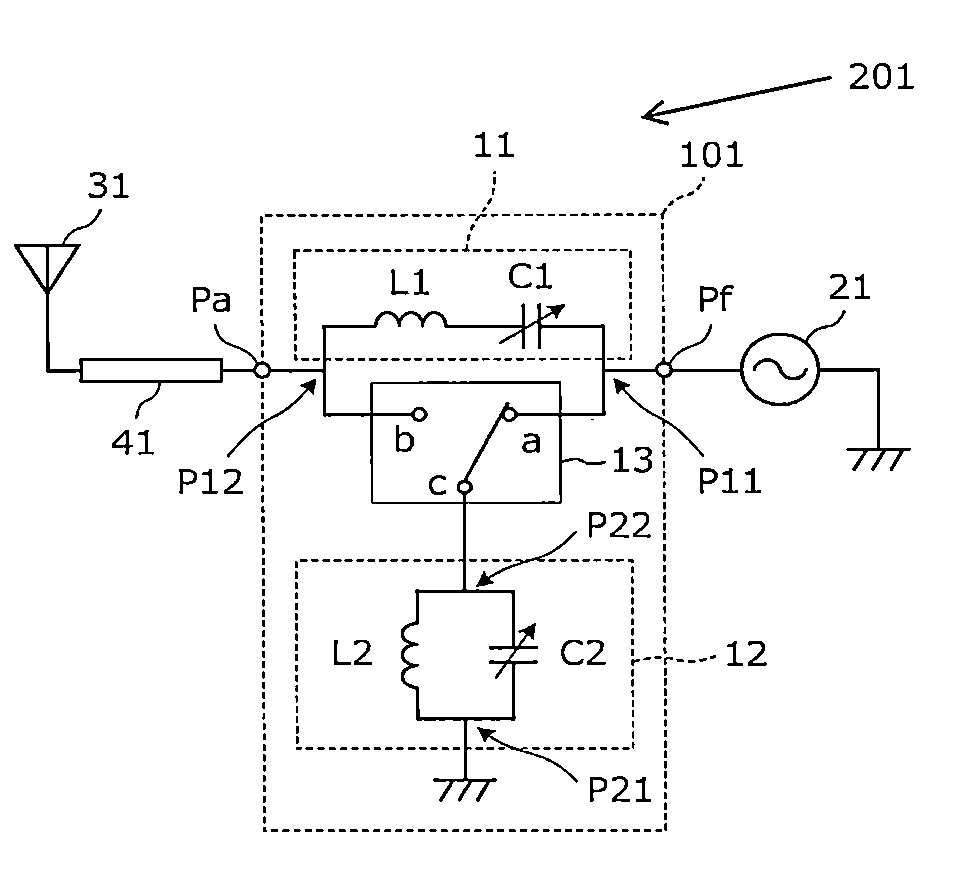

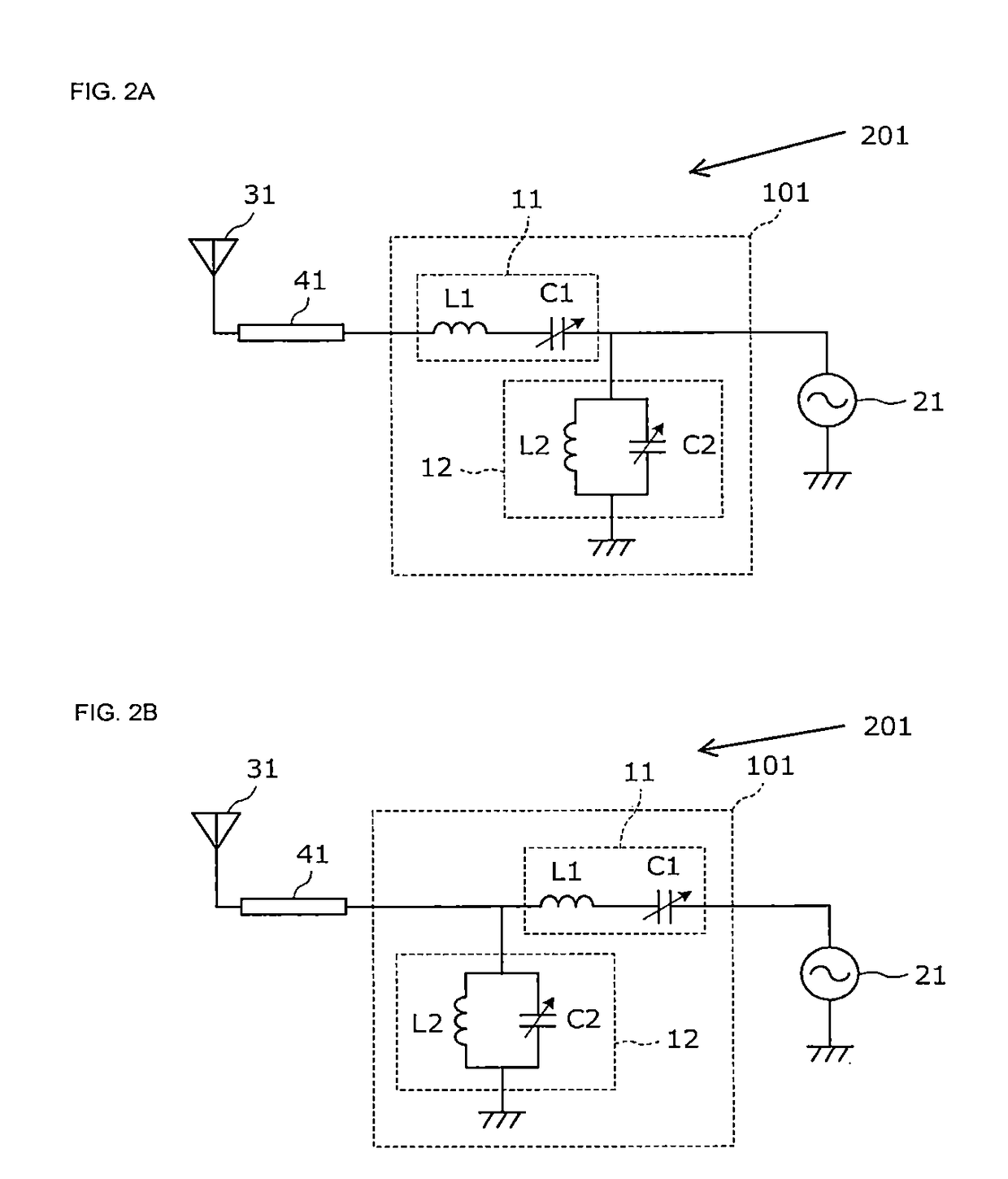

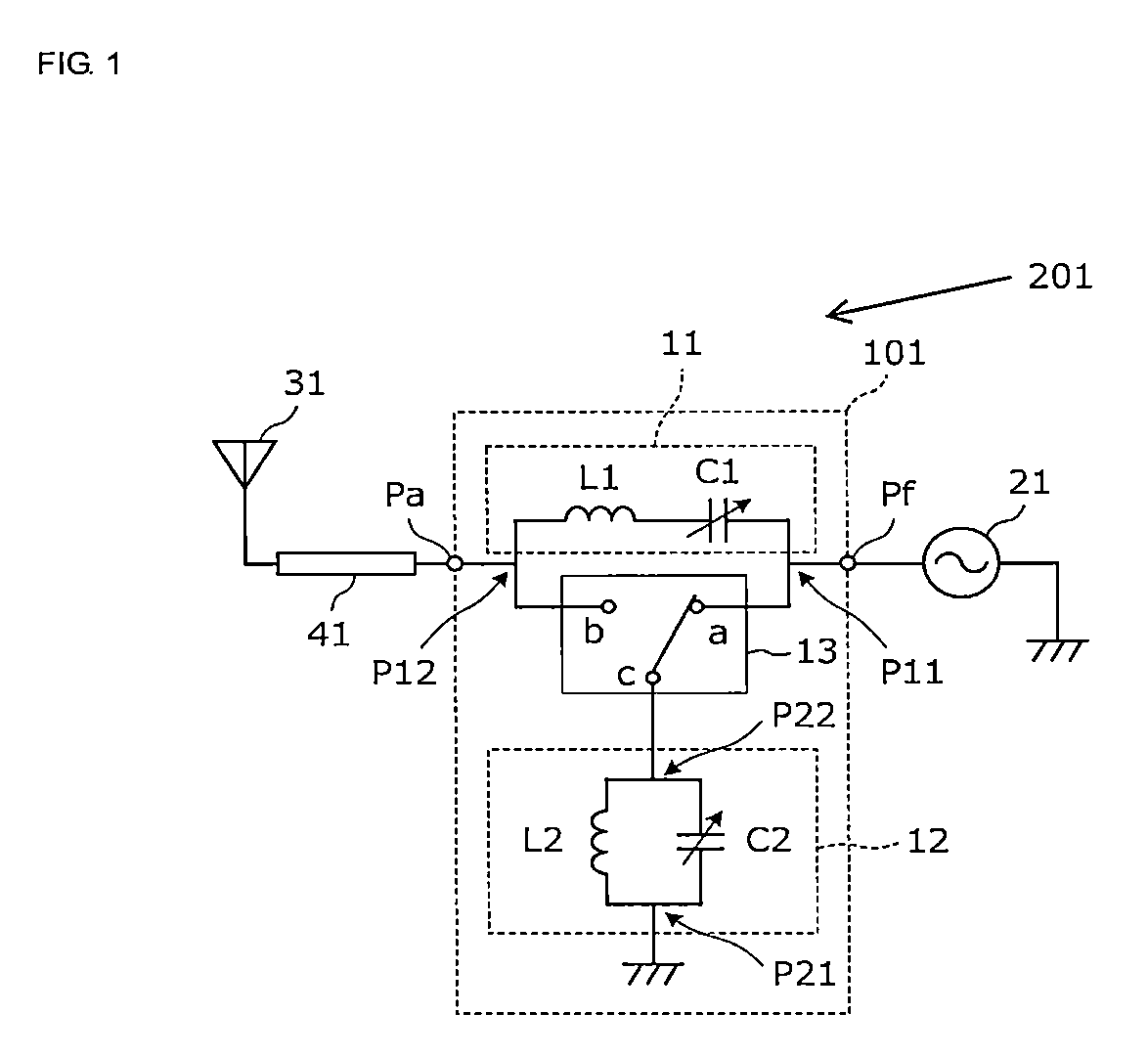

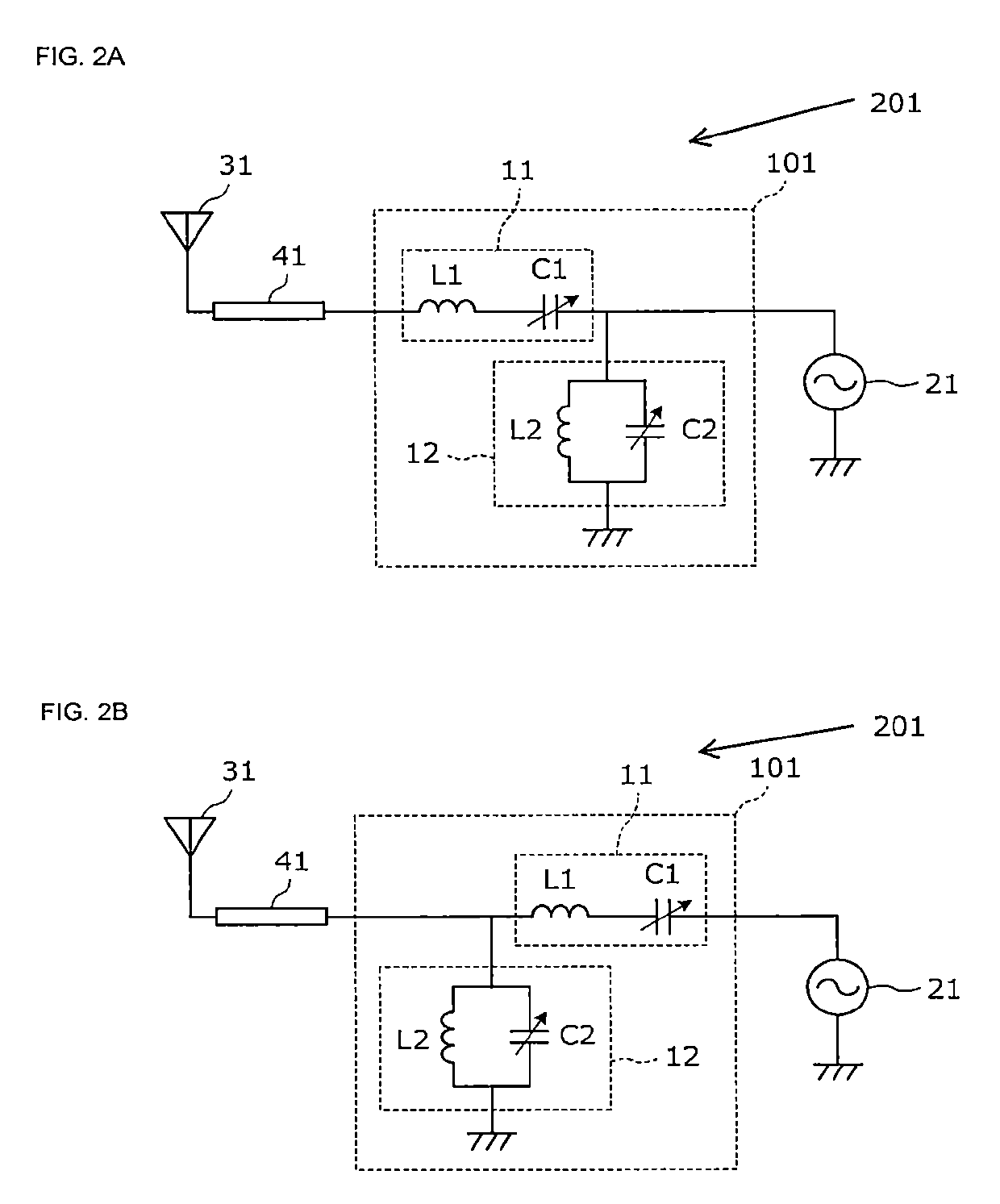

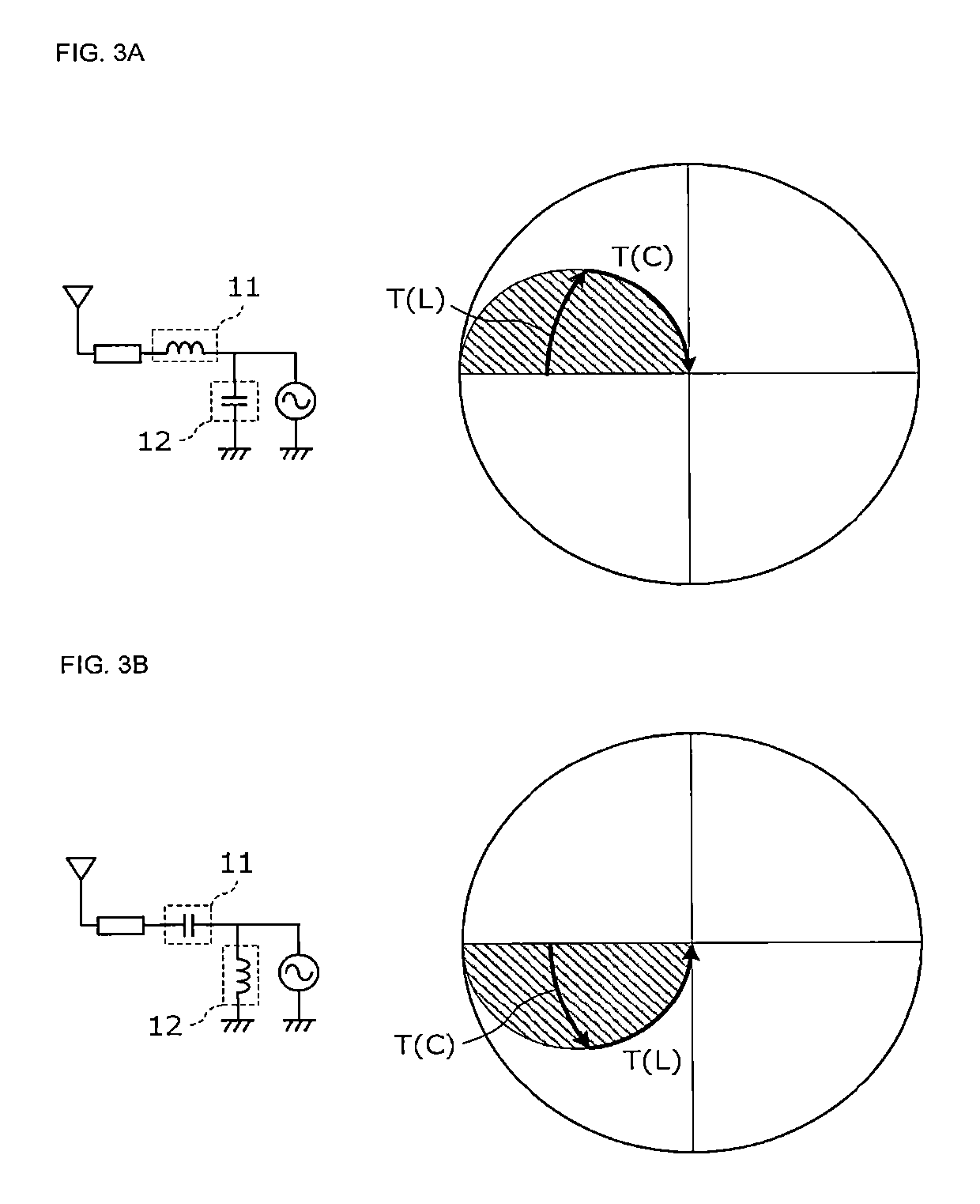

Antenna matching circuit, antenna circuit, front-end circuit, and communication apparatus

ActiveUS20180159220A1Increased circuit complexityReduce component countMultiple-port networksSimultaneous aerial operationsCapacitanceInductor

The present disclosure includes a first circuit that is connected between a power feed port and an antenna port, and a second circuit that is connected between the power feed port and the ground or between the antenna port and the ground. The first circuit is a circuit in which for example a first variable capacitance element is connected in series with a first inductor, and the second circuit is a circuit in which for example a second variable capacitance element is connected in parallel with a second inductor. A switch performs switching at least between a first state in which a second end of the second circuit is connected to a first end of the first circuit and a second state in which the second end of the second circuit is connected to a second end of the first circuit.

Owner:MURATA MFG CO LTD

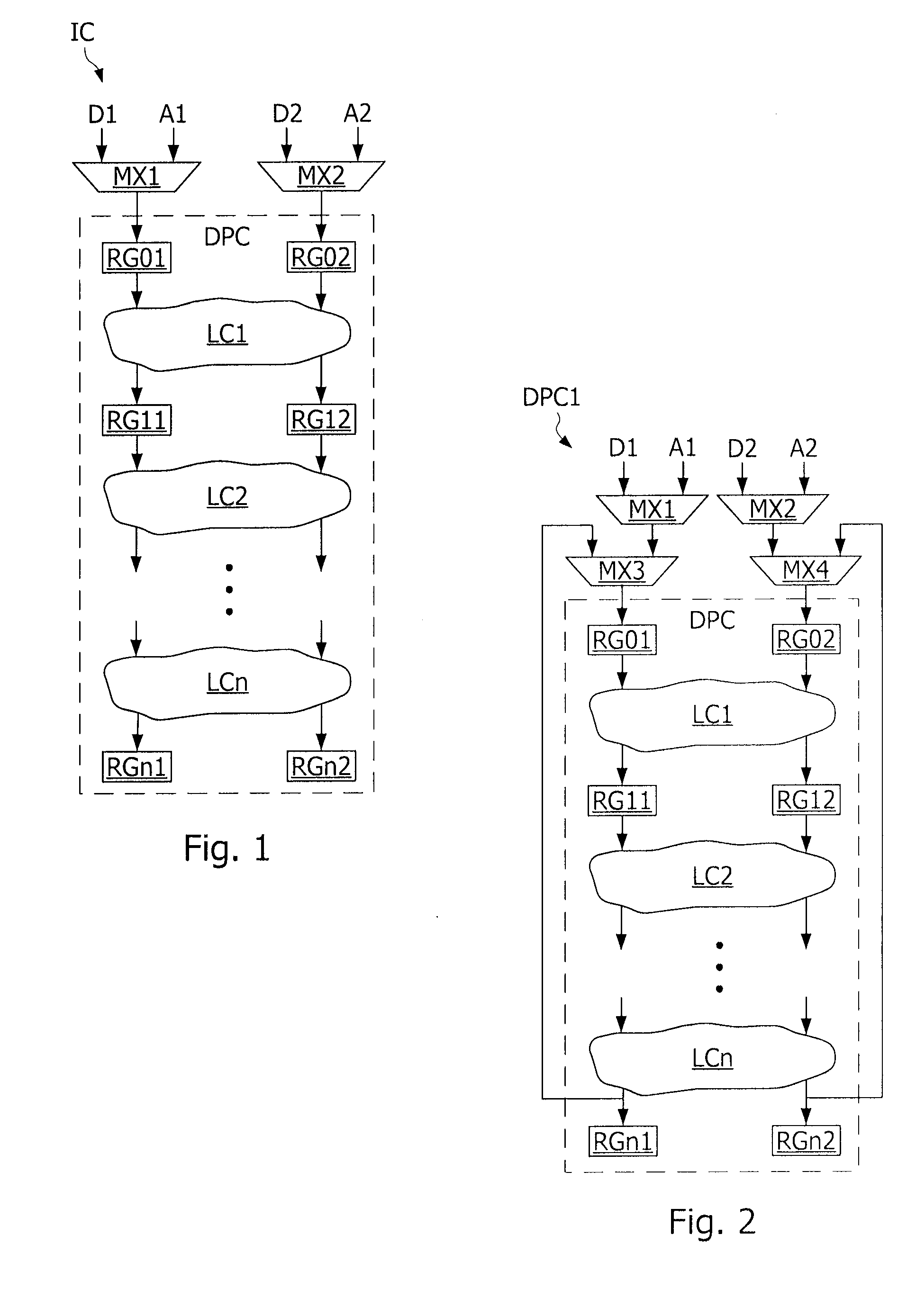

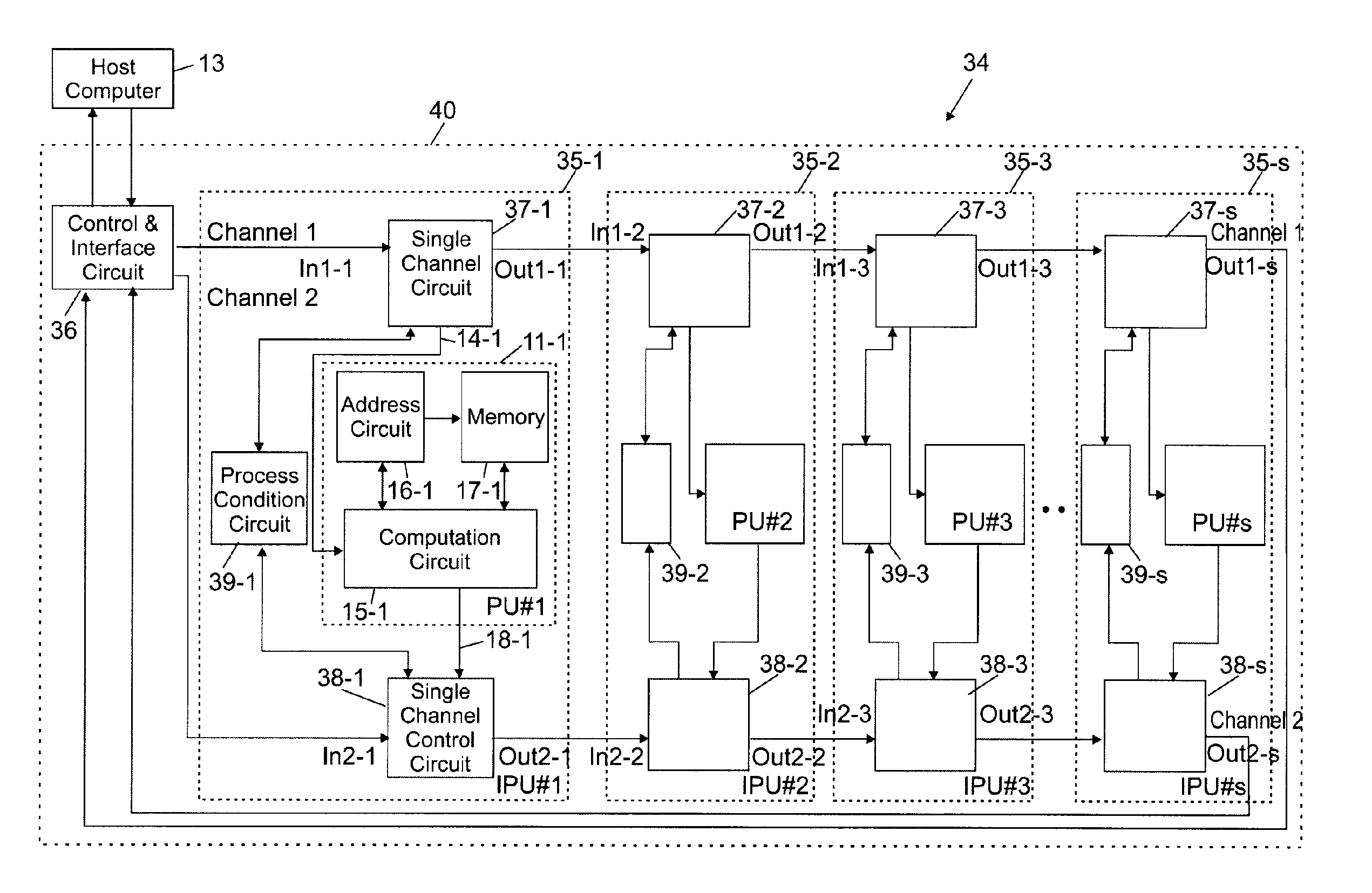

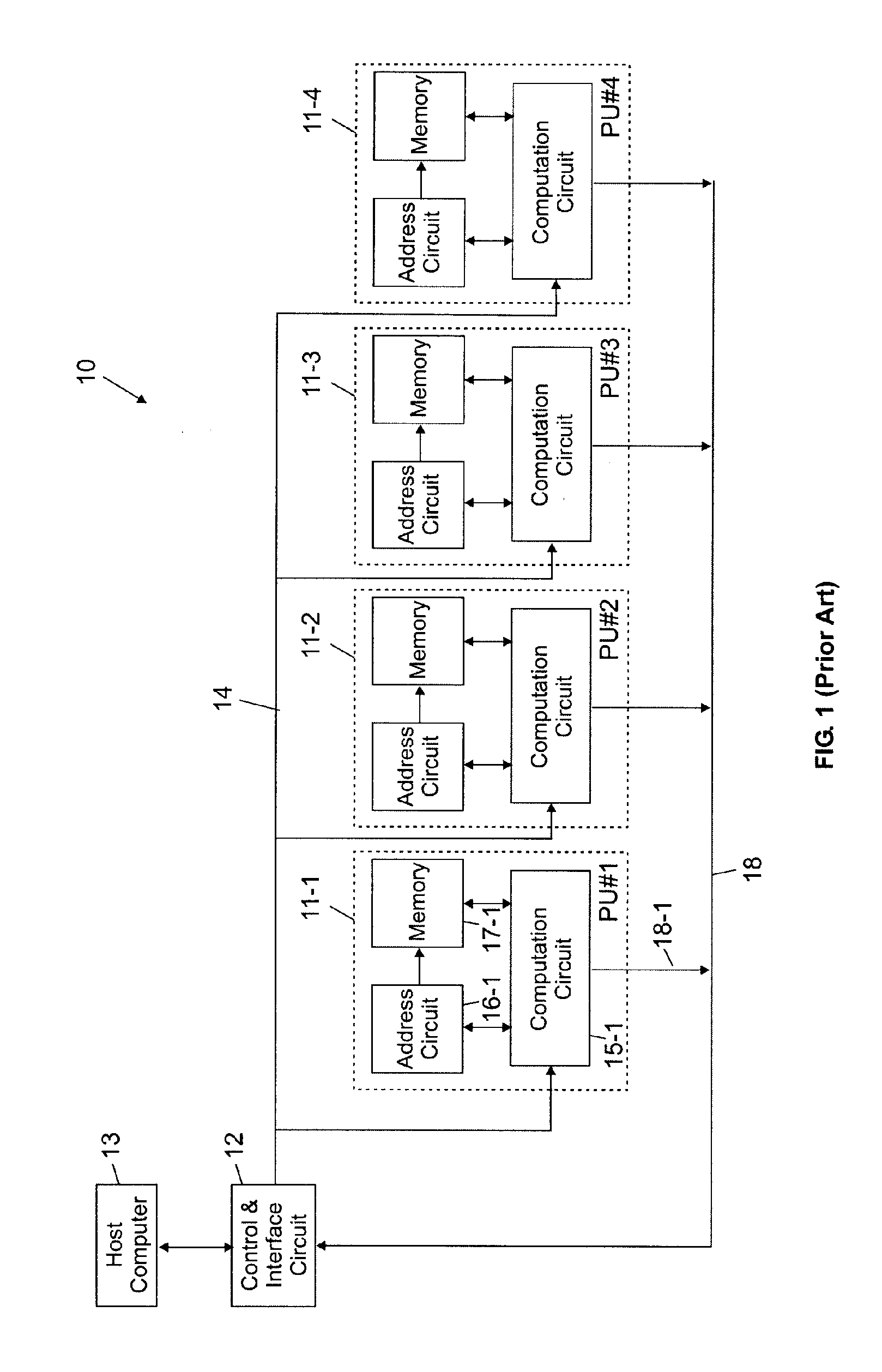

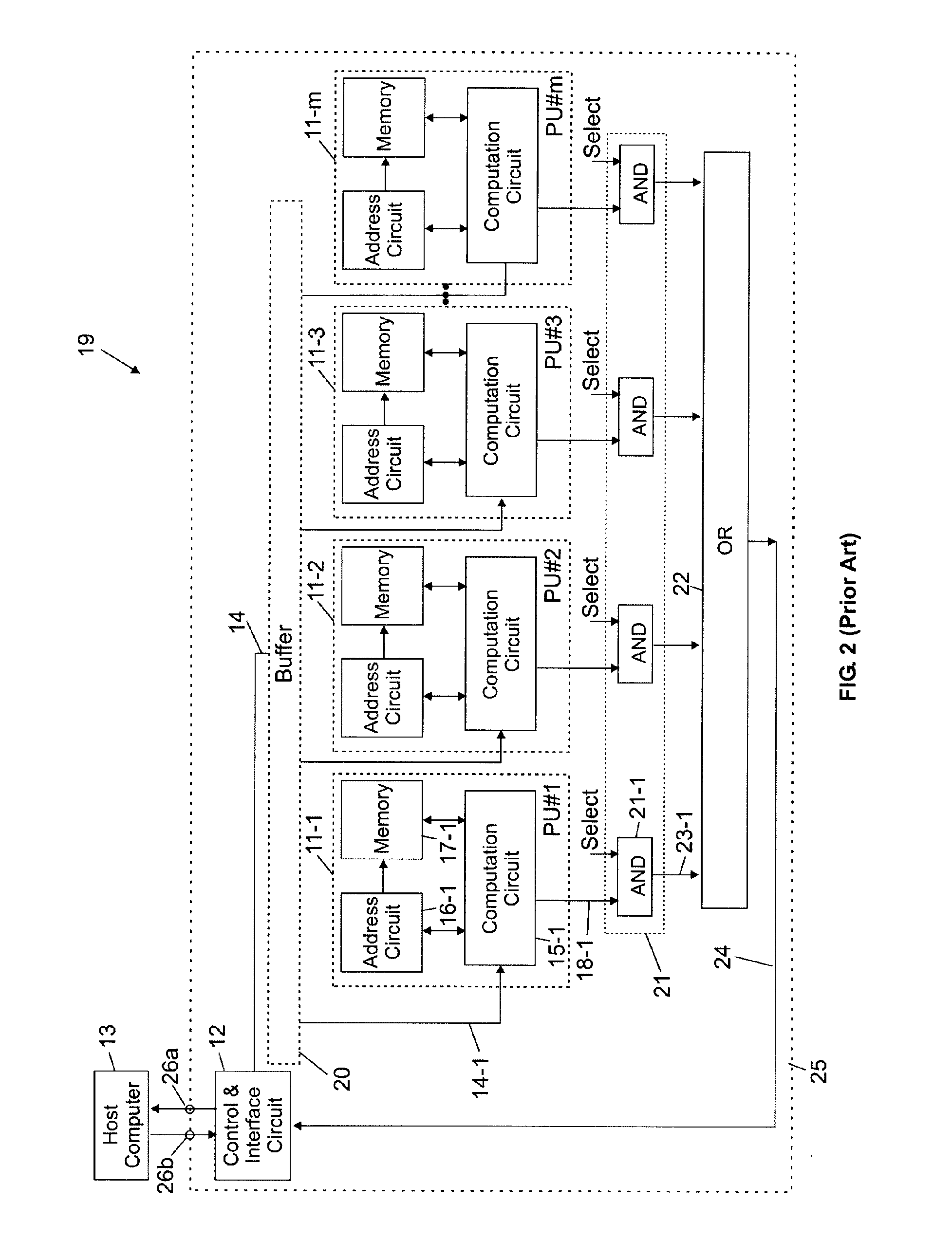

Processing unit having a dual channel bus architecture

InactiveUS20050138324A1Improve performanceImprove scalabilityGeneral purpose stored program computerElectric digital data processingProcessing elementInstruction set

A processing unit having a dual channel bus architecture associated with a specific instruction set, configured to receive an input message and transmit an output message that is identical or derived therefrom. A message consists of one opcode, with or without associated data, used to control each processing unit depending on logic conditions stored in dedicated registers in each unit. Processing units are serially connected but can work simultaneously for a total pipelined operation. This dual architecture is organized around two channels labeled Channel 1 and Channel 2. Channel 1 mainly transmits an input message to all units while Channel 2 mainly transmits the results after processing in a unit as an output message. Depending on the logic conditions, an input message not processed in a processing unit may be transmitted to the next one without any change.

Owner:IBM CORP

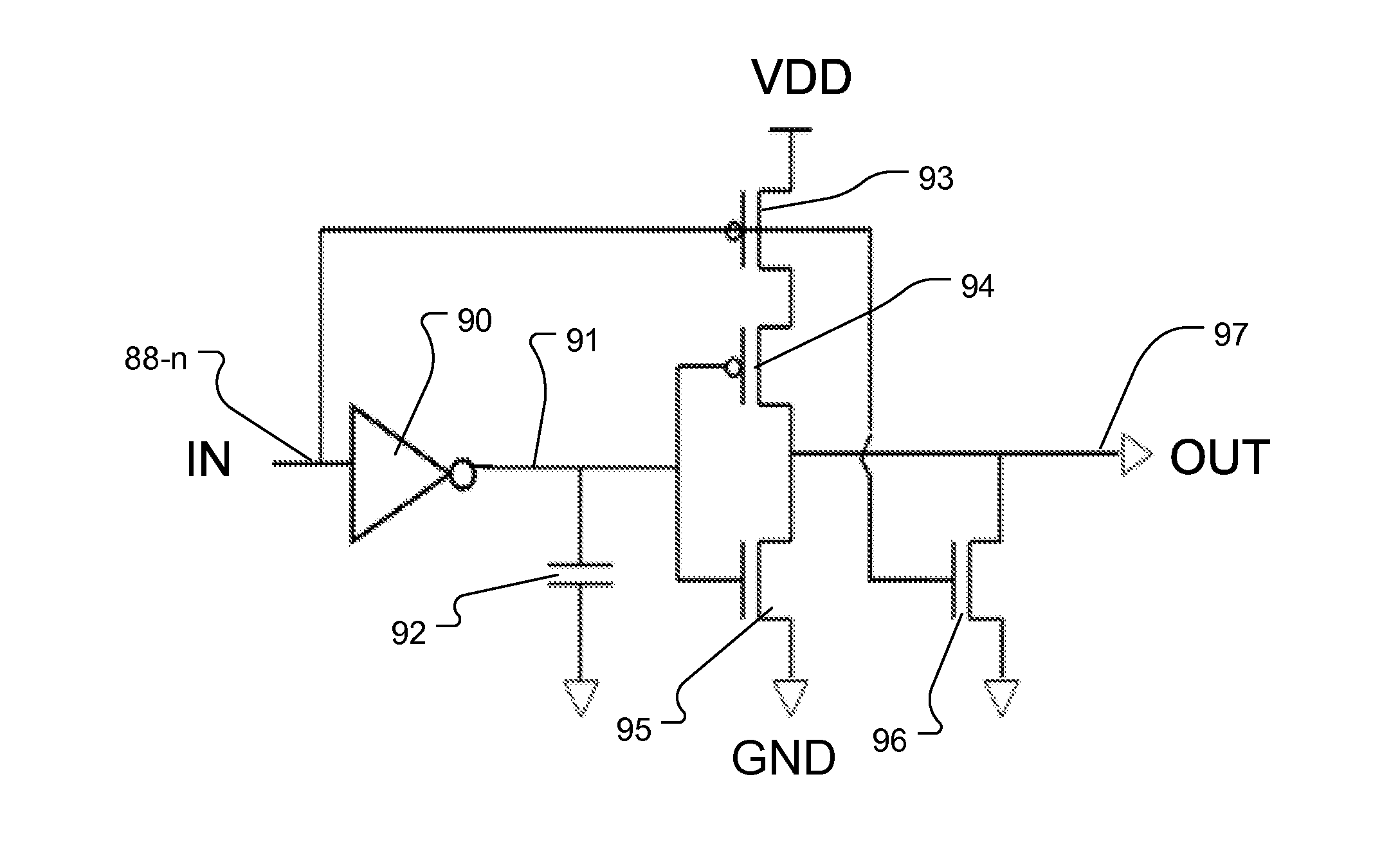

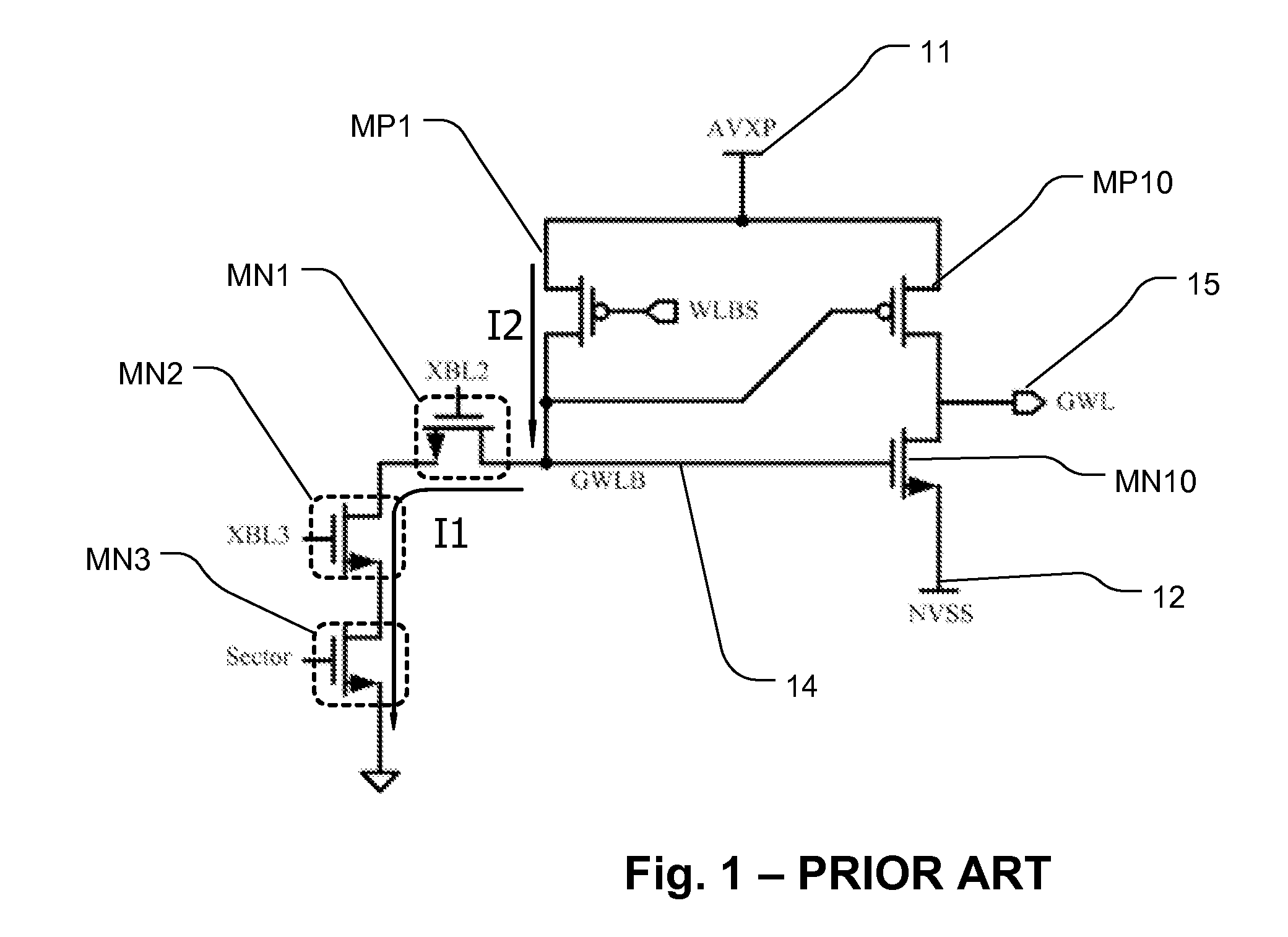

Dynamic driver circuit

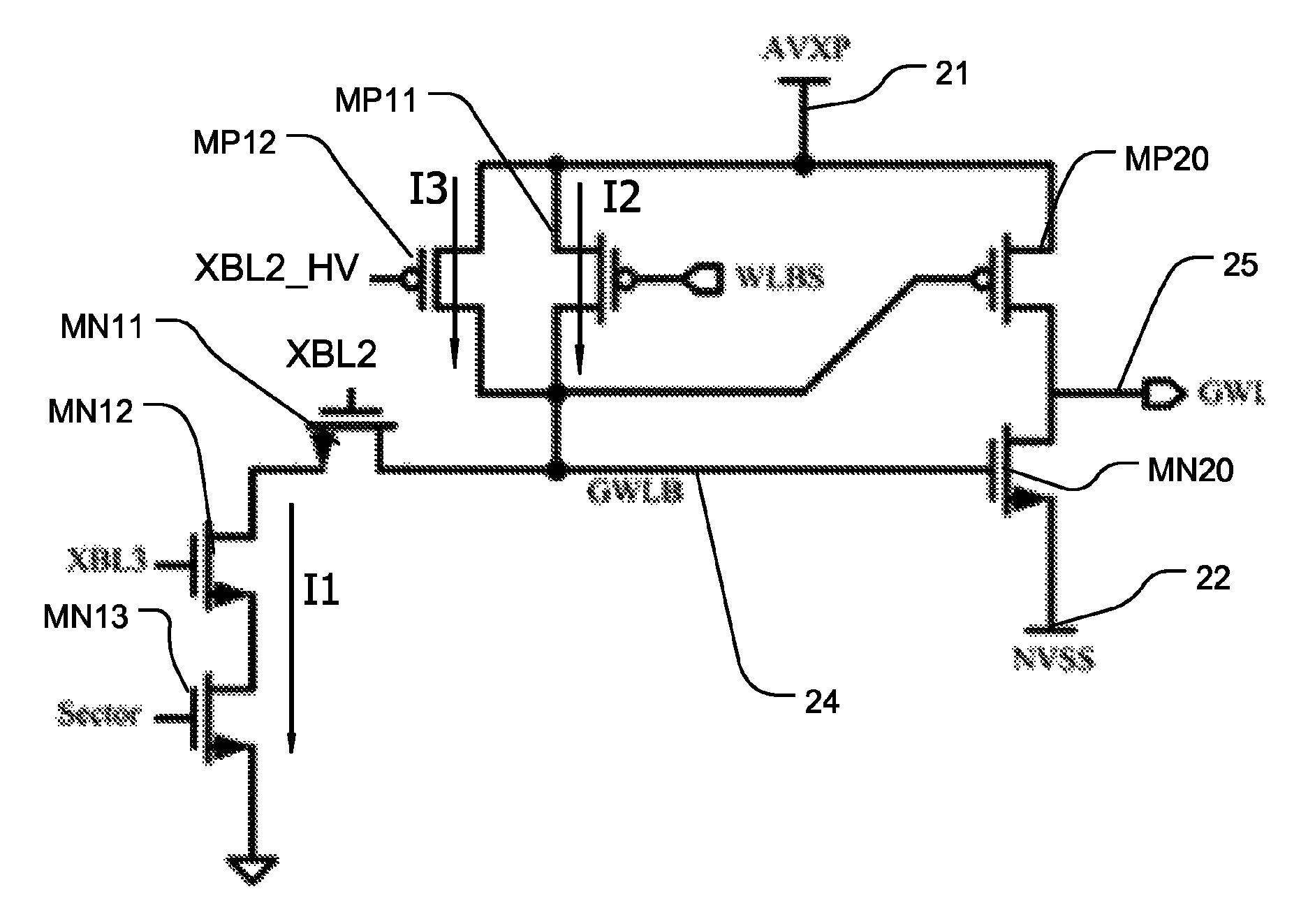

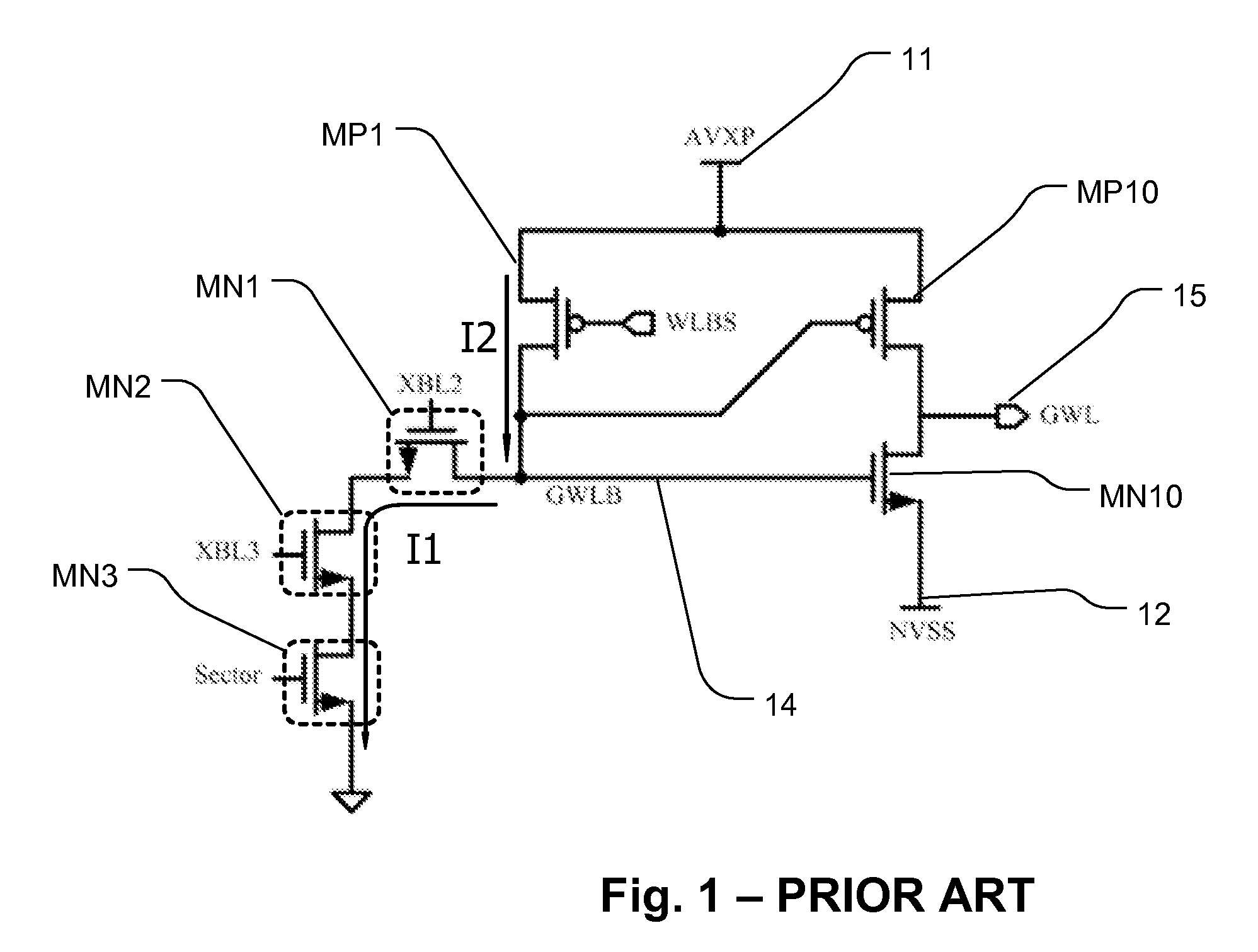

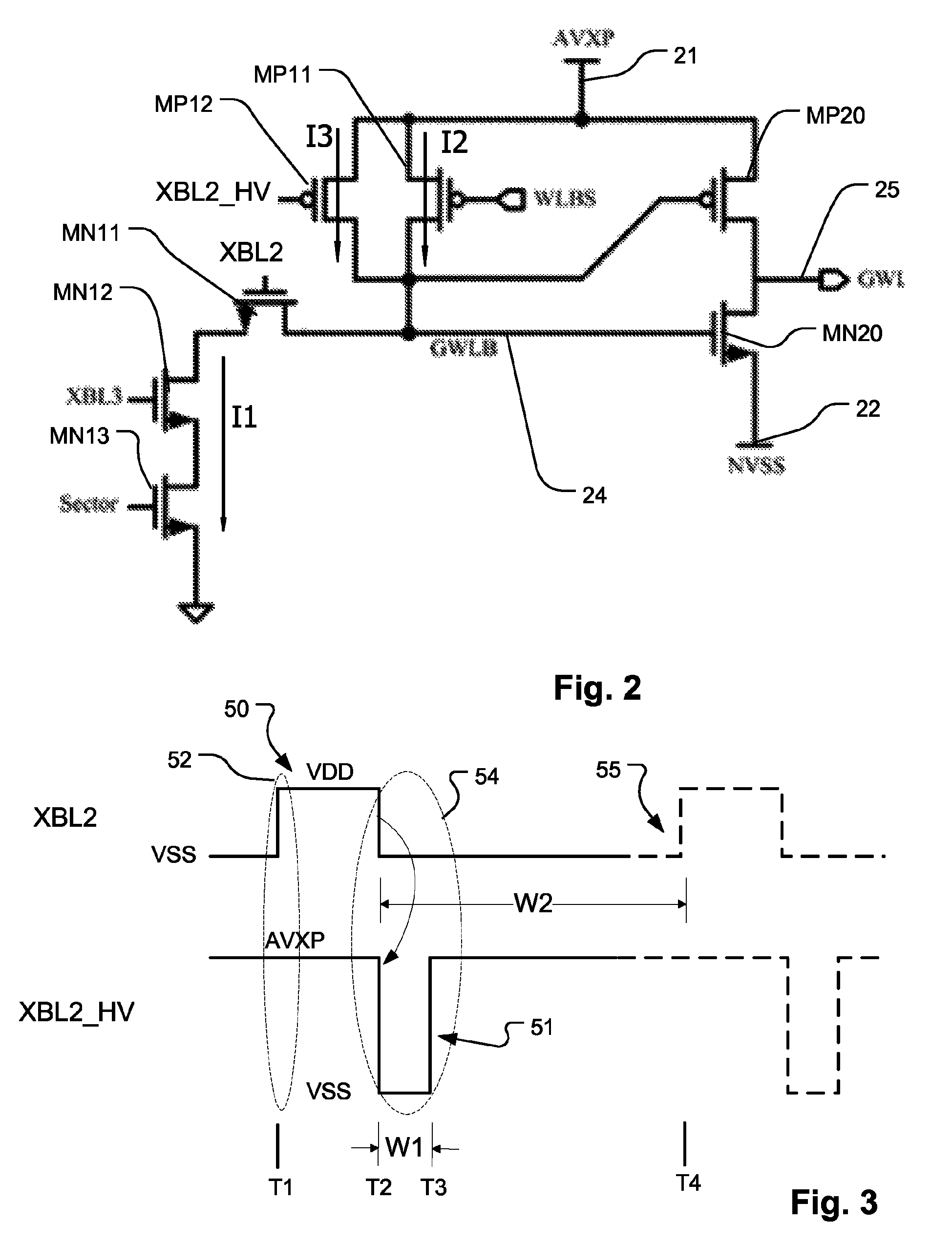

ActiveUS8723559B2Low costIncreased circuit complexityRead-only memoriesDigital storageDriver circuitPower flow

A circuit usable as a word line driver includes a driver that switches in response to a voltage on a control node, and a circuit supplying a voltage to the control node. The circuit that applies a voltage to control node provides a first static current tending to pull the control node up to a first source voltage, and provides a fighting current pulse in response to a signal selecting the driver to pull the control node down to a second source voltage, overcoming the first static current. In addition, a circuit provides a pull-up boost current on a transition of the signal selecting the driver that turns off the fighting current, and applies a boosting current pulse to the control node to assist pulling the control node quickly to the first source voltage.

Owner:MACRONIX INT CO LTD

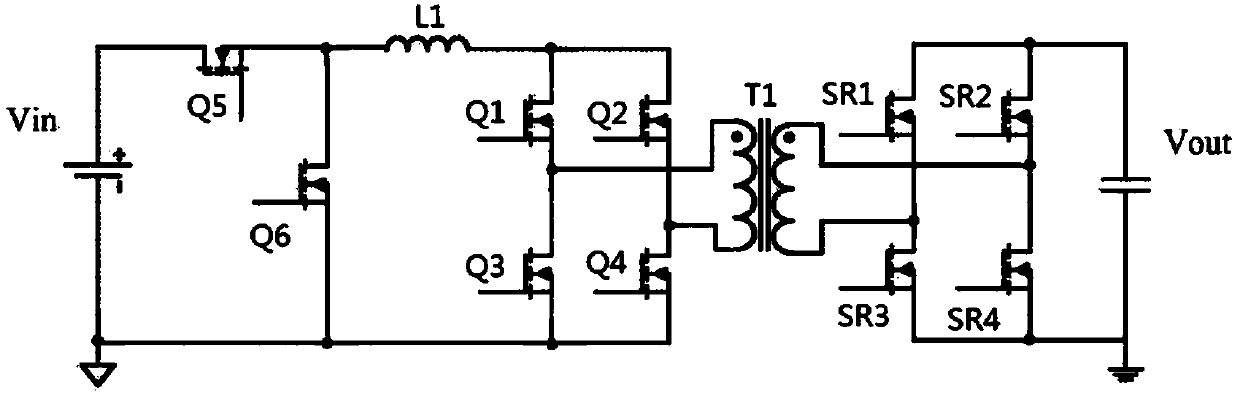

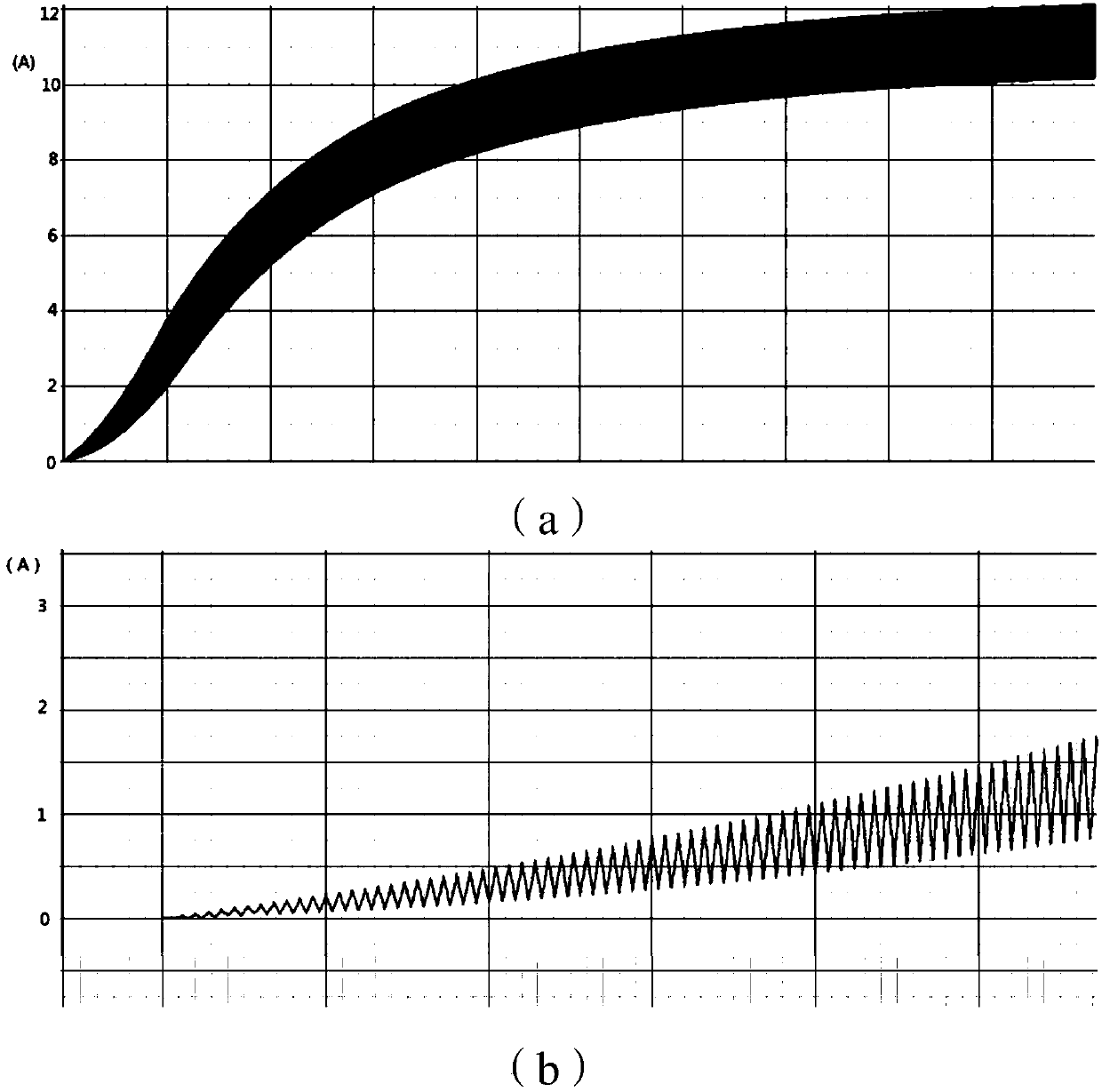

Magnetic bias restraining method and device

ActiveCN109980937AEasy to implementBias suppressionDc-dc conversionElectric variable regulationEngineeringTransformer

The embodiment of the invention discloses a magnetic bias restraining method and device. The method comprises the steps of: obtaining a bus voltage U1 when a transformer is subjected to forward excitation and a bus voltage U2 when the transformer is subjected to reverse excitation in a direct current-direct current transformer; determining the magnetic bias compensation amount [Delta]d1 when the transformer is subjected to forward excitation and the magnetic bias compensation amount [Delta]d2 when the transformer is subjected to reverse excitation according to the bus voltage U1 when the transformer is subjected to forward excitation and the bus voltage U2 when the transformer is subjected to reverse excitation; superposing the magnetic bias compensation amount [Delta]d1 when the transformer is subjected to forward excitation and the direct current-direct current transformer loop output duty ratio signal amount to output the superposition value to a switch tube exciting in a forward direction, and superposing the magnetic bias compensation amount [Delta]d2 when the transformer is subjected to reverse excitation and the direct current-direct current transformer loop output duty ratio signal amount to output the superposition value to a switch tube exciting in a reverse direction. According to the embodiment, the magnetic bias restraining of the transformer can be effectively achieved.

Owner:ZTE CORP

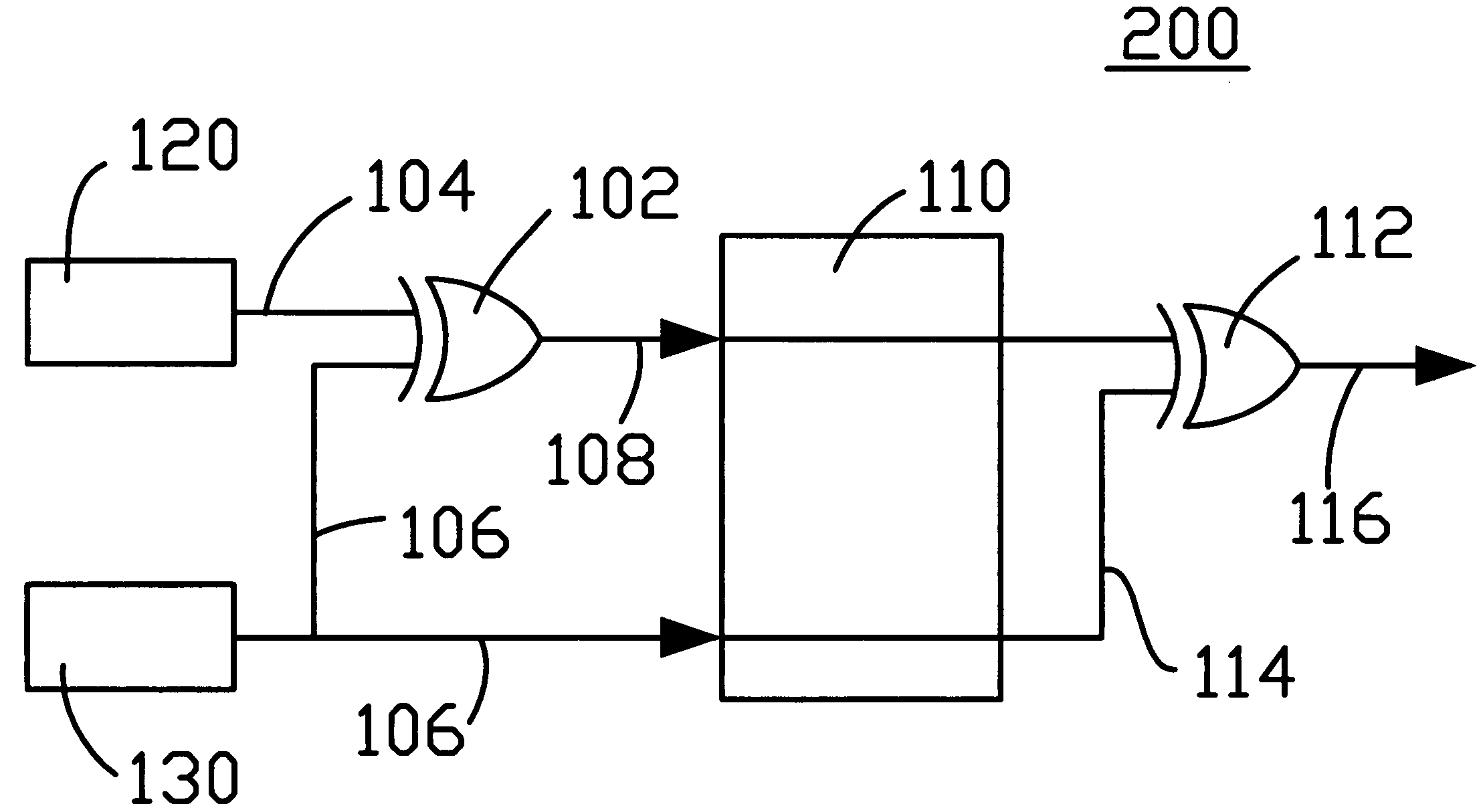

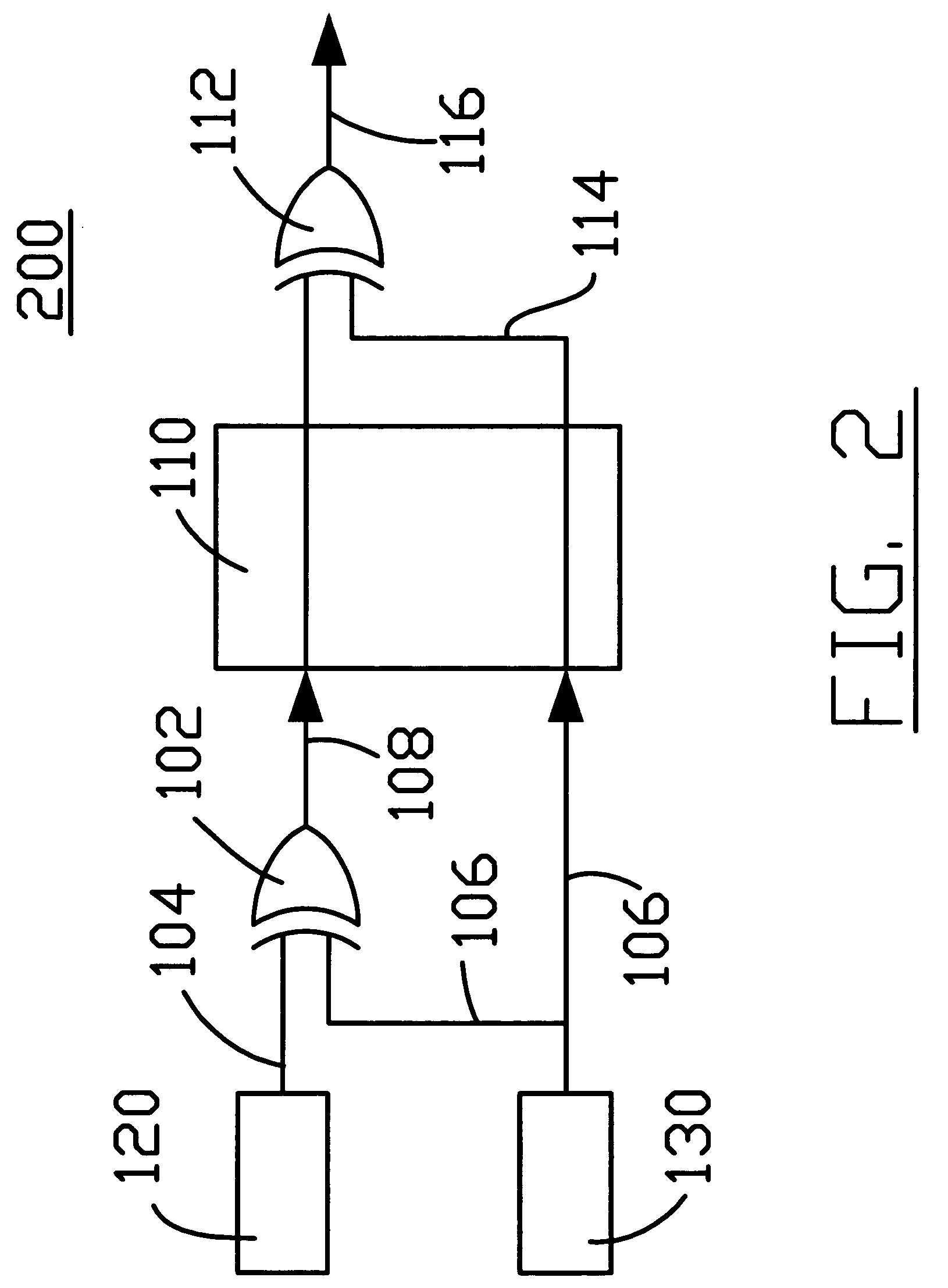

Power consumption stabilization system and method

InactiveUS6933862B2Maximum power consumption can be reducedWithout limiting design and layoutReliability increasing modificationsCode conversionNumber generatorComputer science

A source signal is provided. The source signal is XORed with a scrambling random signal to generate a scrambled signal. The scrambled signal is transmitted through the digital logic circuit. The scrambled signal is XORed with the descrambling random signal logically identical to the scrambling random signal to produce a descrambled signal identical to the source signal. In one embodiment, the scrambling random signal is transmitted through the digital logic circuit and used as the descrambling random signal. In another embodiment, the scrambling random signal and descrambling random signal are generated independently using pseudo-random number generators. In yet another embodiment, the scrambling random signal is self-synchronizing and is contained within the pattern of the scrambled signal.

Owner:AGILENT TECH INC

Accurate, low-power power detector circuits and related methods

ActiveUS10063203B1Improve accuracyIncrease the areaGain controlDc-dc conversionDetector circuitsNormal mode

Embodiments of power detector circuits and related methods to compensate for undesired DC offsets generated within power detector circuits are disclosed. Input signals having input frequencies are received and converted to a magnitude signal, and reference signals are also generated. The magnitude signal may include a DC component proportional to a power of the input signal along with undesired DC offsets. The reference signal may include a DC component proportional to a power of at least one input reference signal along with undesired DC offsets. To compensate for errors introduced by the DC offsets, a DC offset calibration signal or a gain are determined in a calibration mode and then applied in a normal mode to compensate for the DC offsets. For the calibration mode, a difference between the magnitude signal and the reference signal is compared to a threshold value to generate a power detection output signal.

Owner:SILICON LAB INC

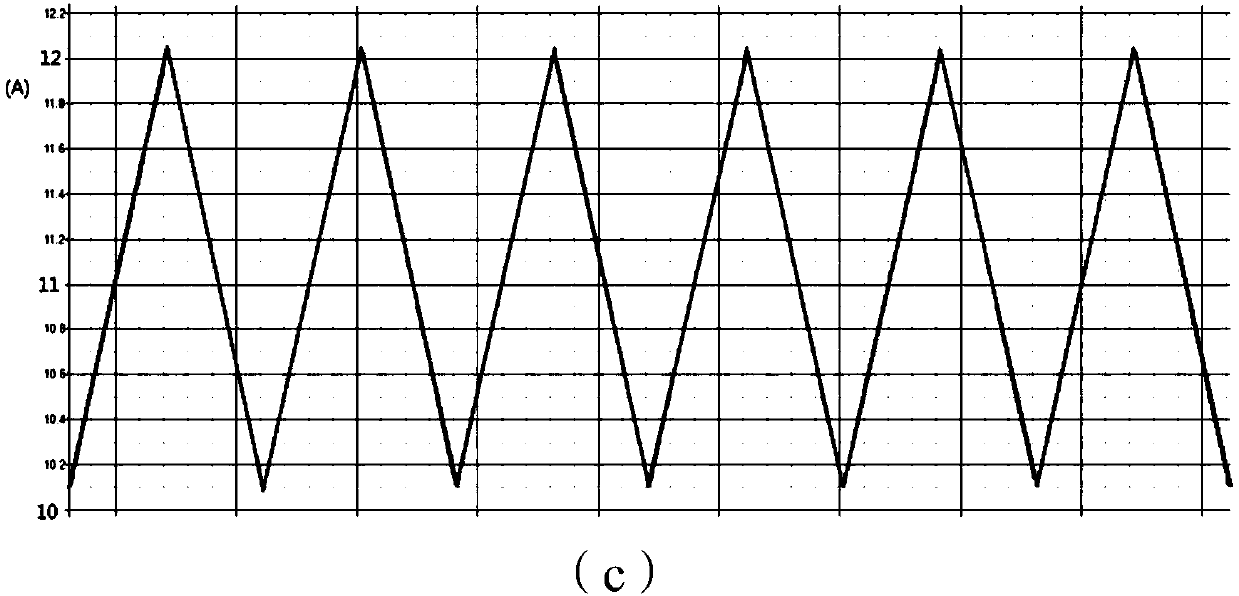

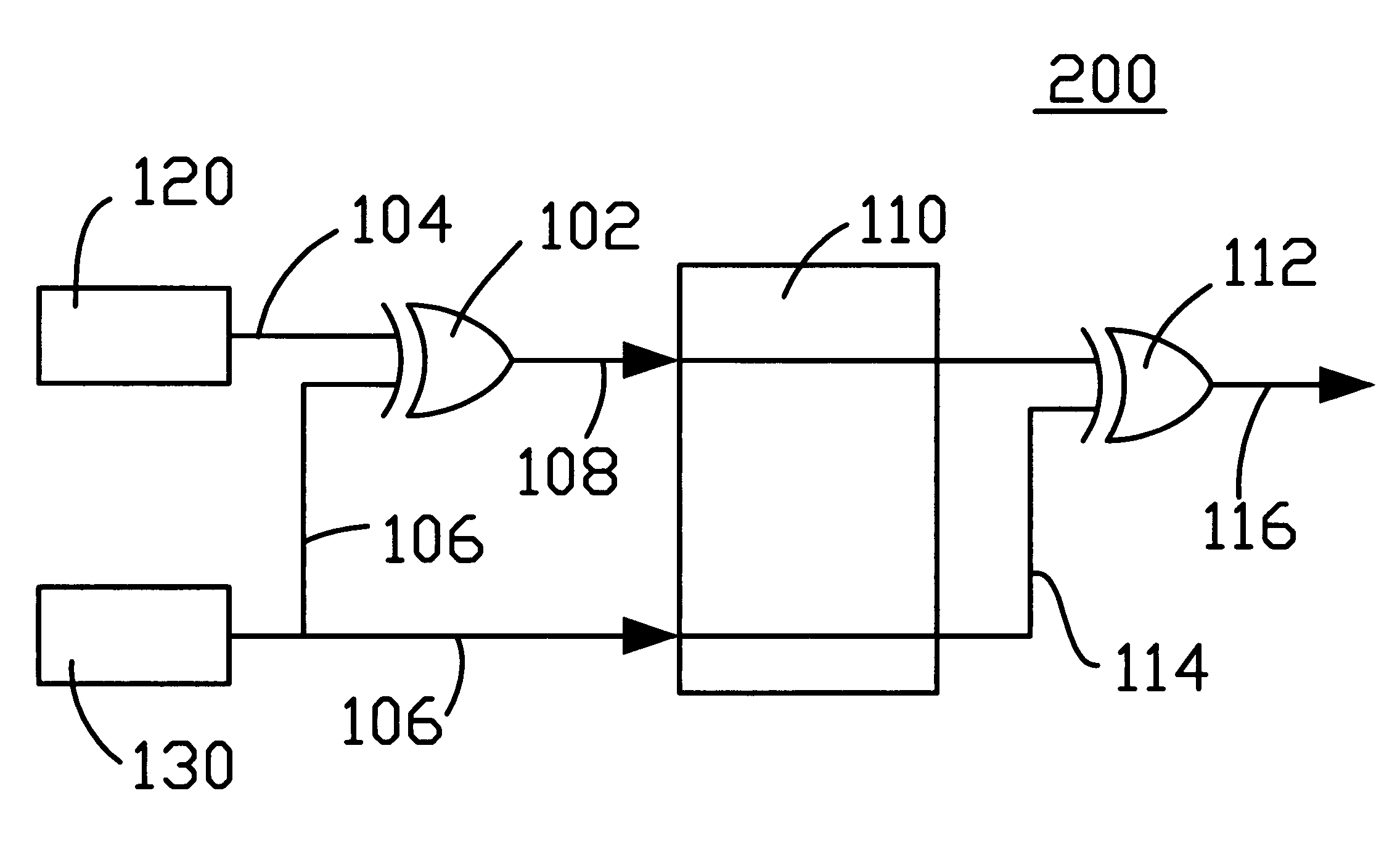

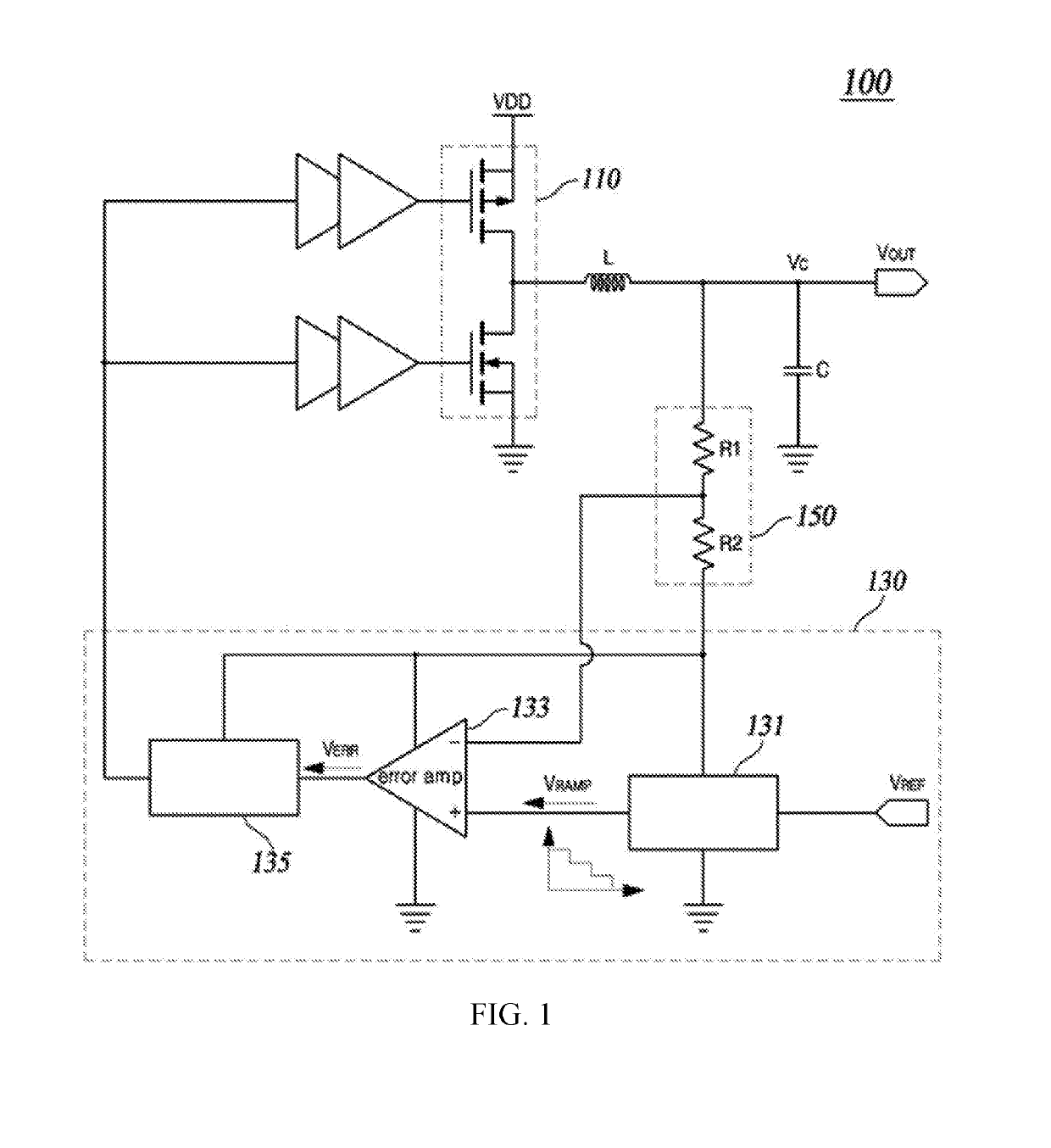

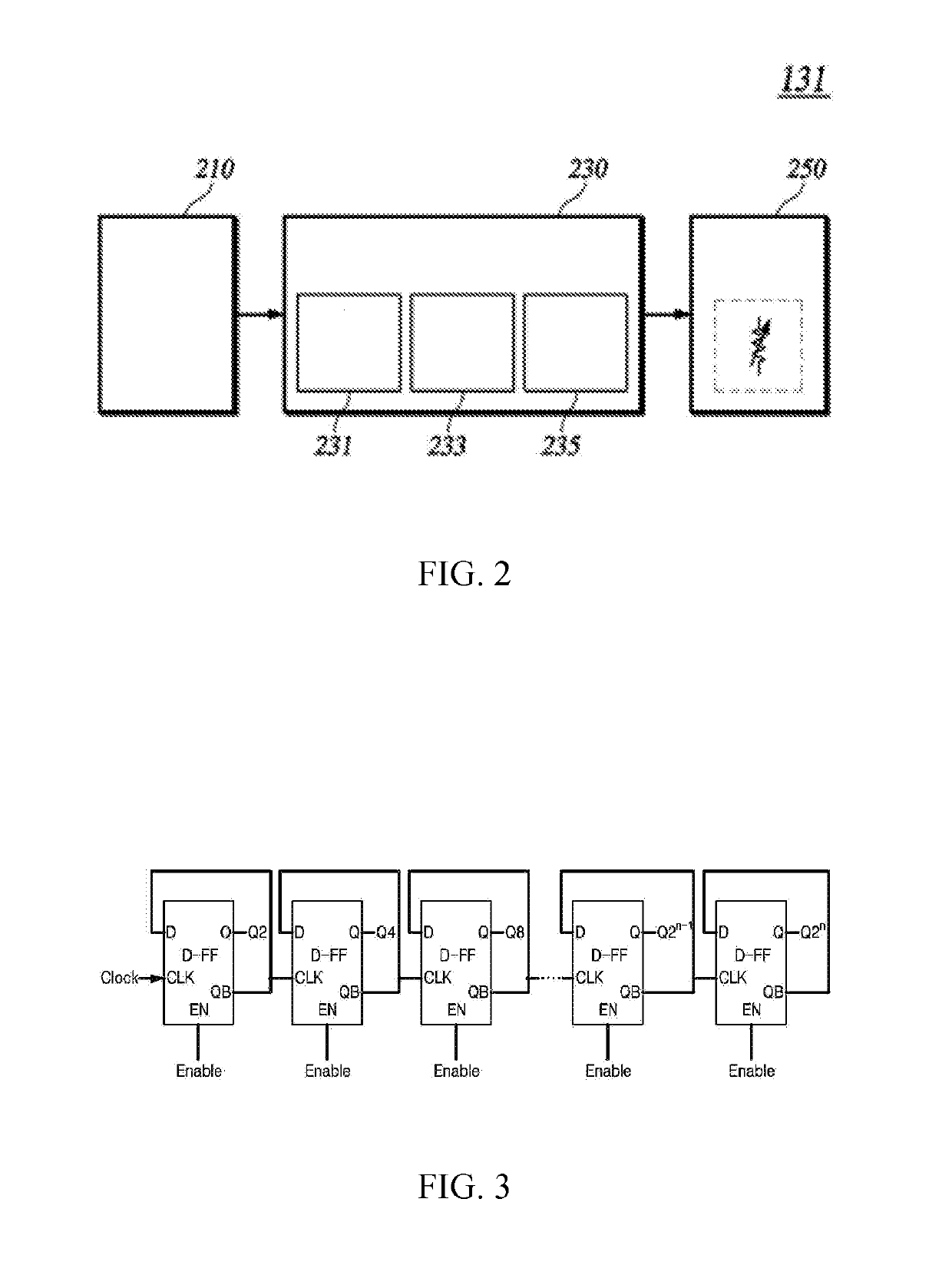

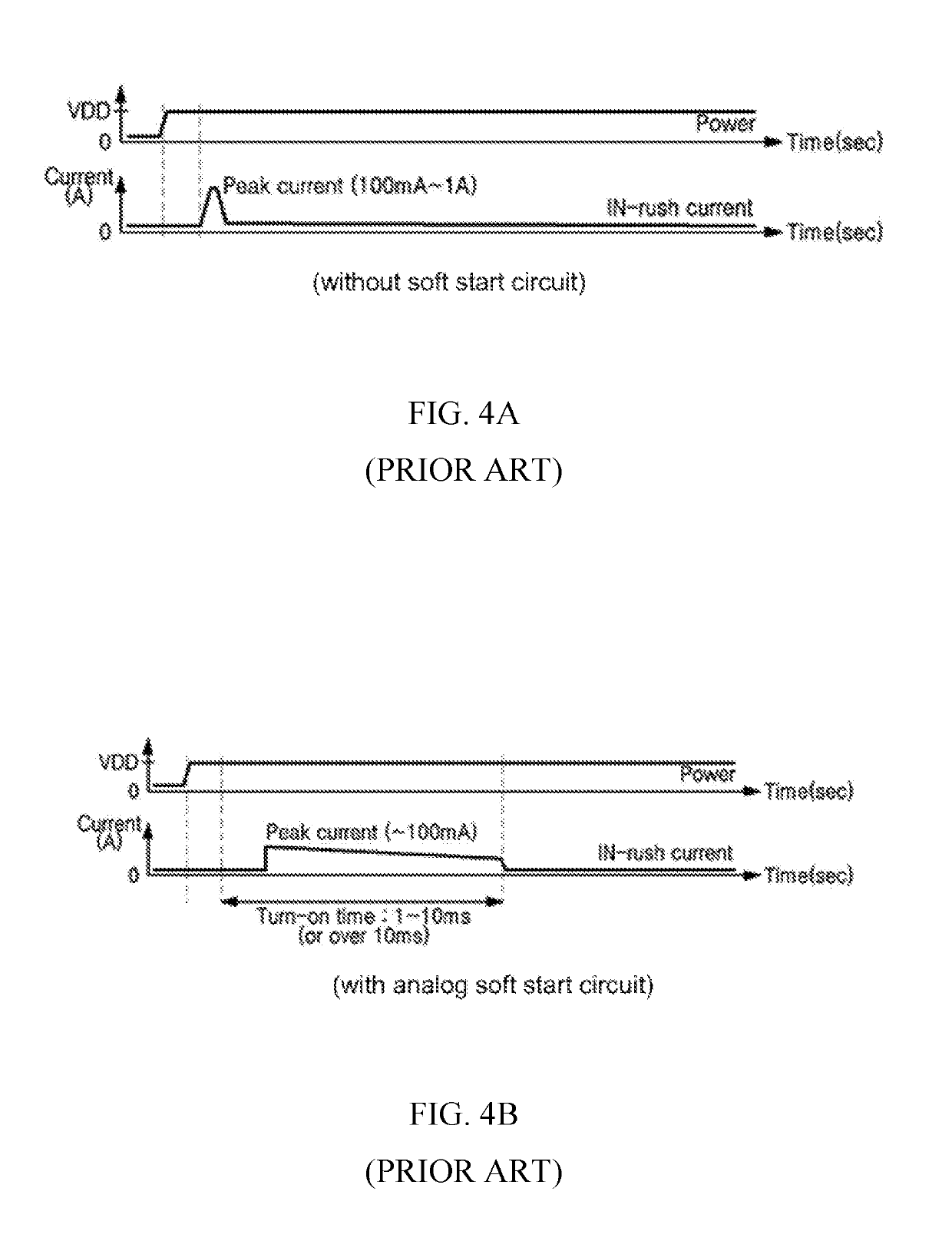

Switching regulator with soft start circuit and operation method thereof

ActiveUS10459467B1Increased circuit complexityIncreasing complexityDc-dc conversionElectric variable regulationStart timeVoltage reference

Disclosed herein is a switching regulator with a soft start circuit for suppressing an in-rush current. The switching regulator includes a peak detector configured to receive a clock signal and detect a peak voltage of the clock signal, a comparator configured to generate a soft start signal for controlling a soft start of the switching regulator based on a result of comparing a level of the peak voltage of the clock signal to a preset reference voltage level, a counter configured to switch a state of the soft start signal at a time point when a preset soft start time arrives, and a ramp voltage generation unit configured to generate a ramp voltage by adjusting a resistance of a variable resistor based on the soft start signal.

Owner:DIALOG SEMICON KOREA INC

Antenna matching circuit, antenna circuit, front-end circuit, and communication apparatus

ActiveUS10424841B2Increased circuit complexityReduce component countMultiple-port networksSimultaneous aerial operationsCapacitanceEngineering

The present disclosure includes a first circuit that is connected between a power feed port and an antenna port, and a second circuit that is connected between the power feed port and the ground or between the antenna port and the ground. The first circuit is a circuit in which for example a first variable capacitance element is connected in series with a first inductor, and the second circuit is a circuit in which for example a second variable capacitance element is connected in parallel with a second inductor. A switch performs switching at least between a first state in which a second end of the second circuit is connected to a first end of the first circuit and a second state in which the second end of the second circuit is connected to a second end of the first circuit.

Owner:MURATA MFG CO LTD

Dynamic driver circuit

ActiveUS20140062543A1Low costIncreased circuit complexityRead-only memoriesDigital storageDriver circuitLine driver

A circuit usable as a word line driver includes a driver that switches in response to a voltage on a control node, and a circuit supplying a voltage to the control node. The circuit that applies a voltage to control node provides a first static current tending to pull the control node up to a first source voltage, and provides a fighting current pulse in response to a signal selecting the driver to pull the control node down to a second source voltage, overcoming the first static current. In addition, a circuit provides a pull-up boost current on a transition of the signal selecting the driver that turns off the fighting current, and applies a boosting current pulse to the control node to assist pulling the control node quickly to the first source voltage.

Owner:MACRONIX INT CO LTD

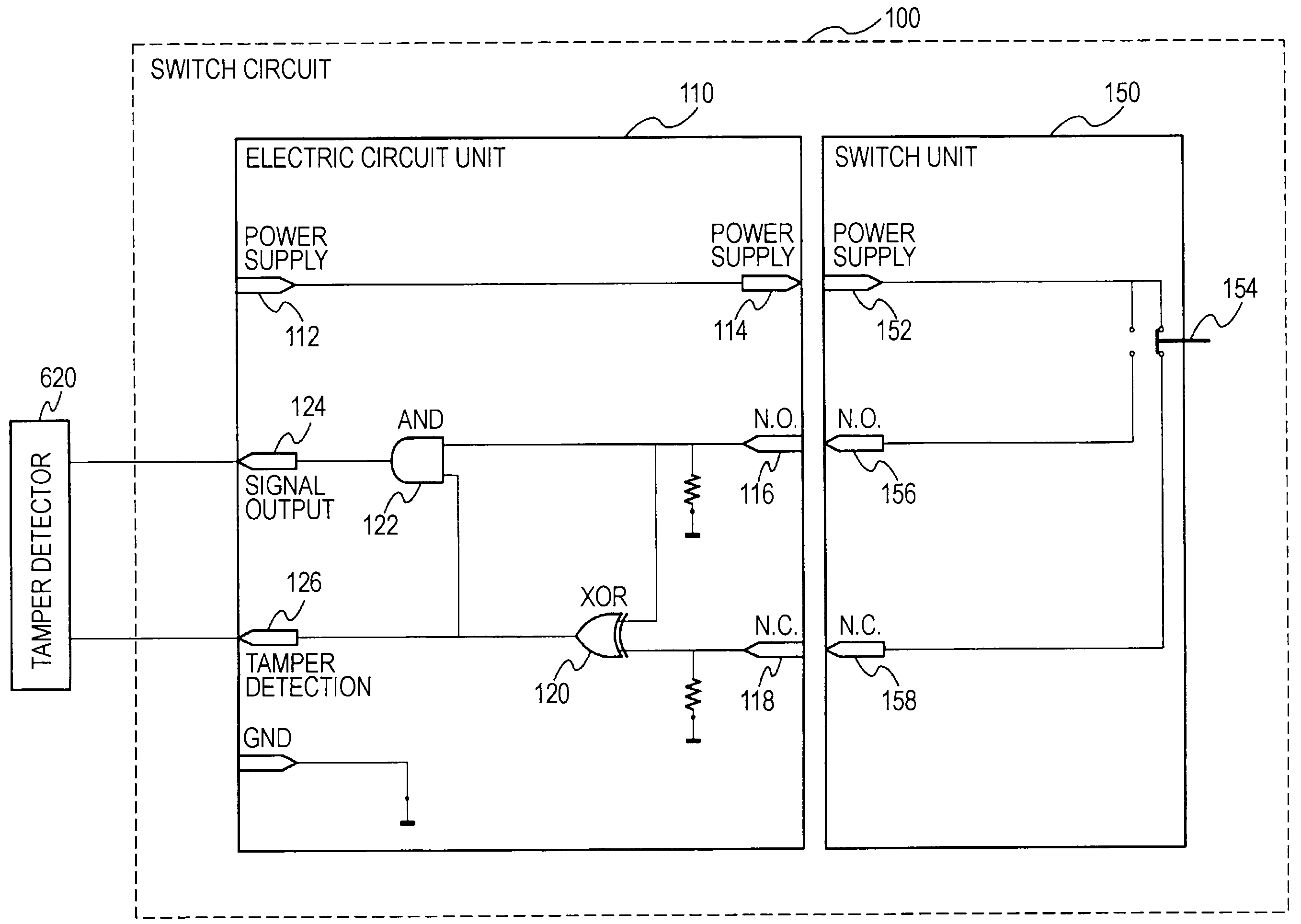

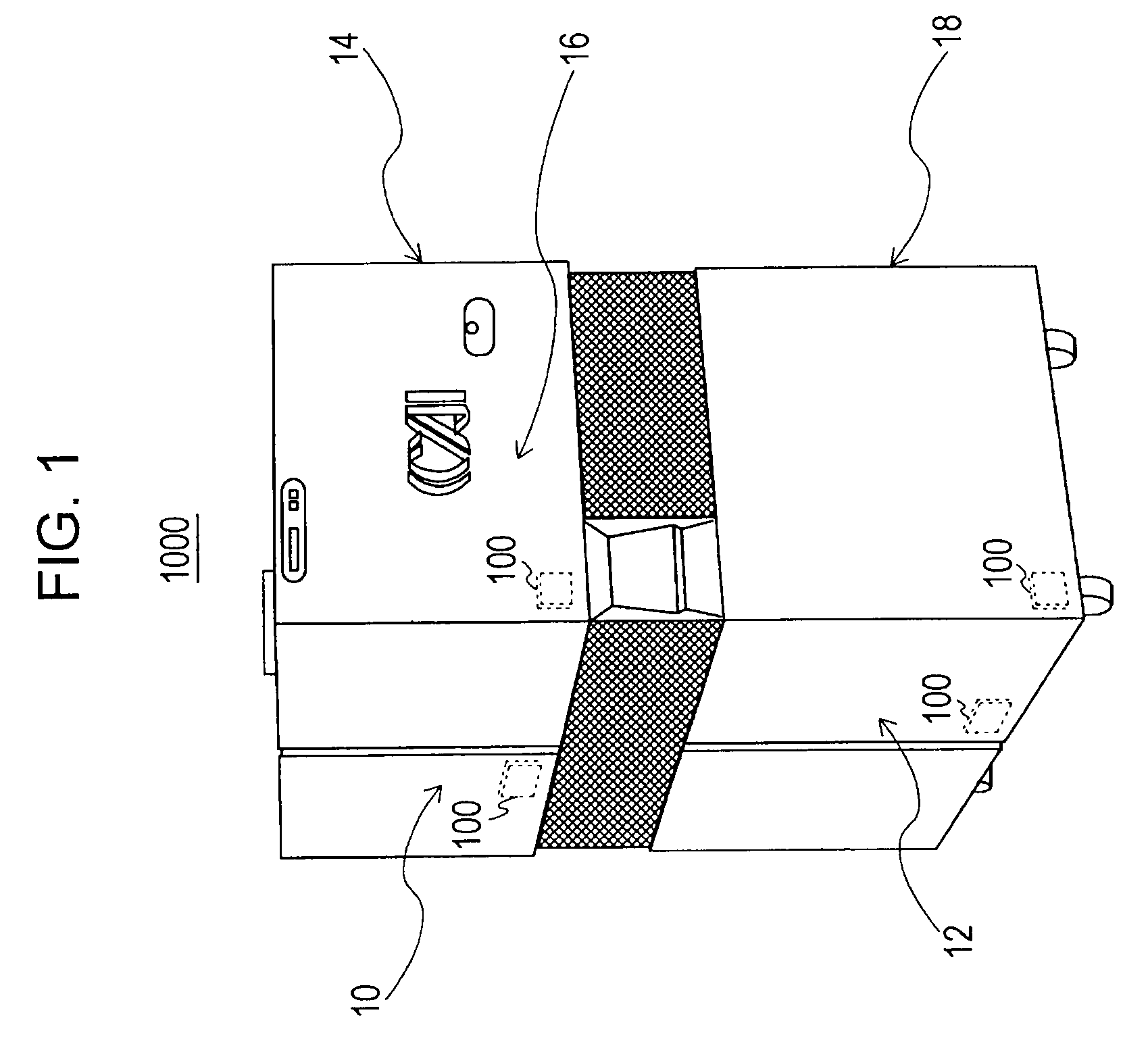

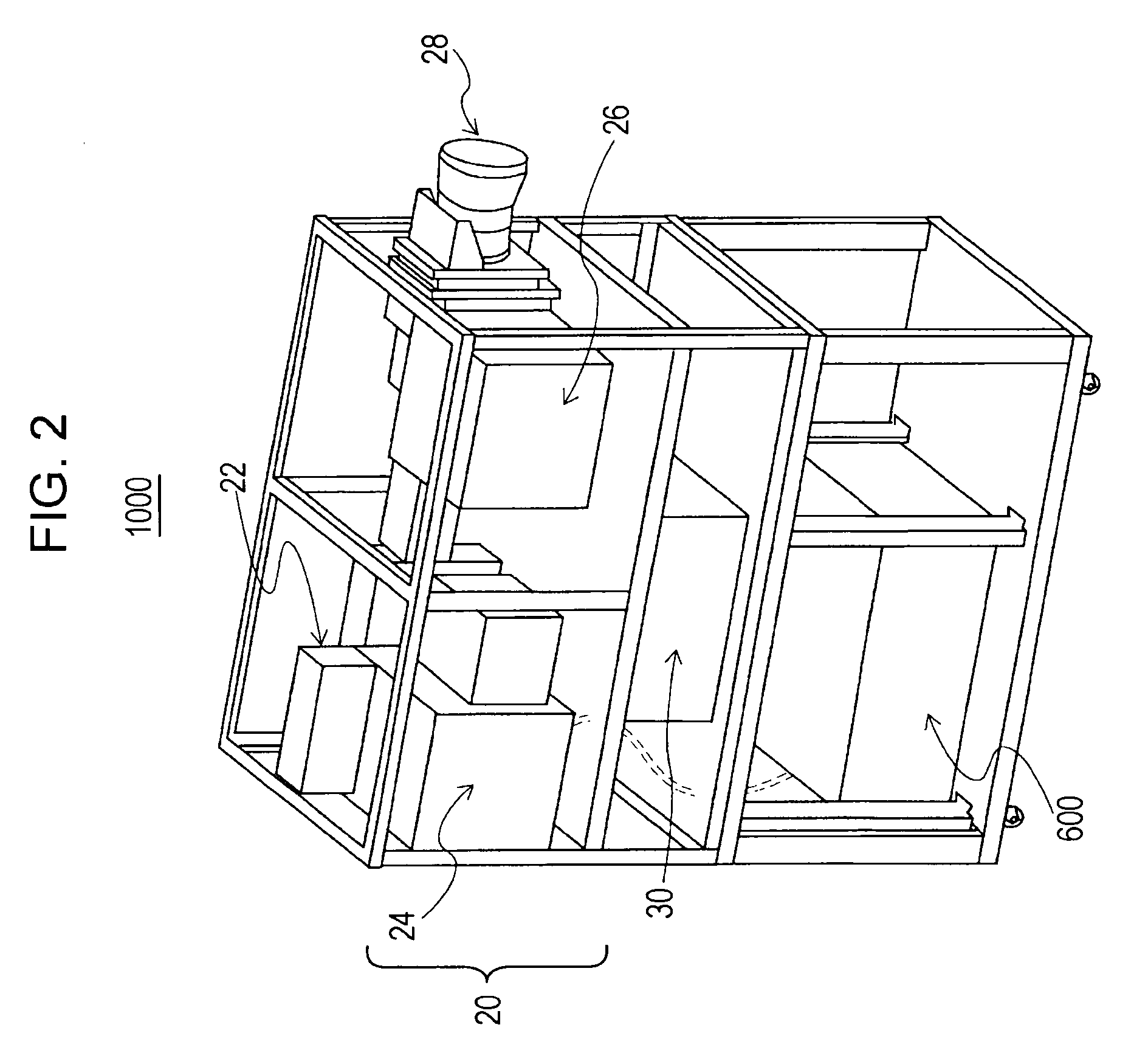

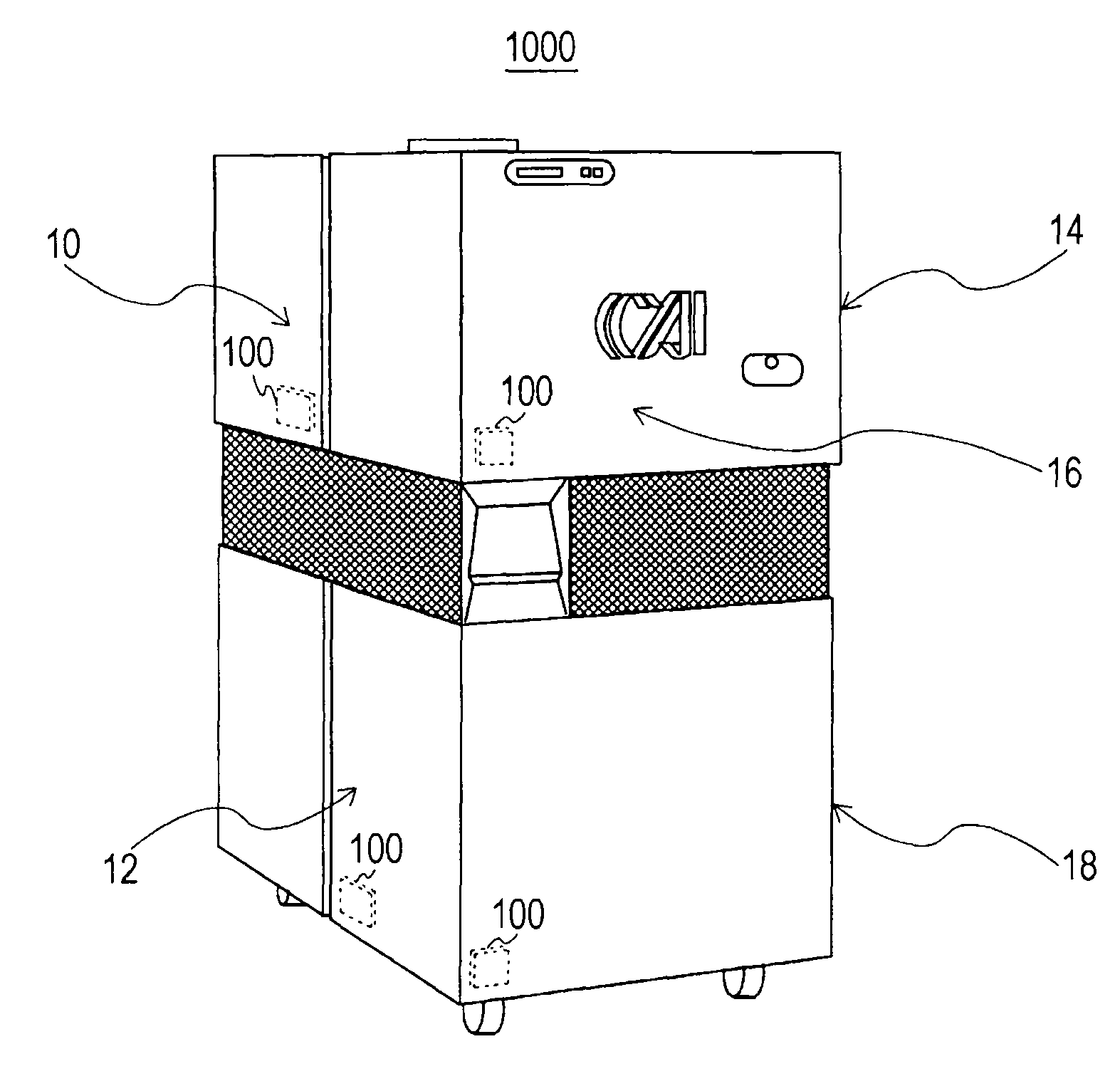

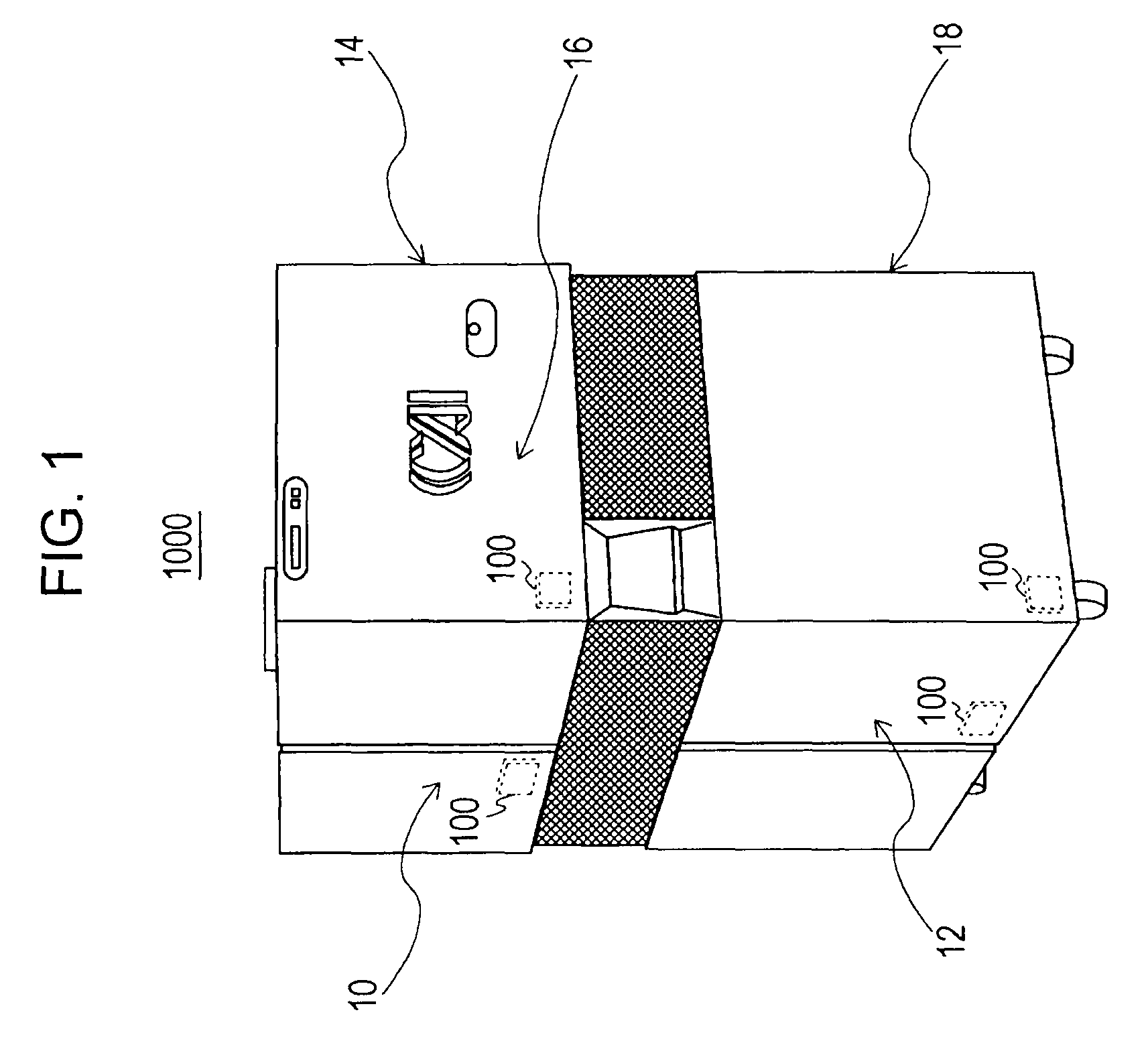

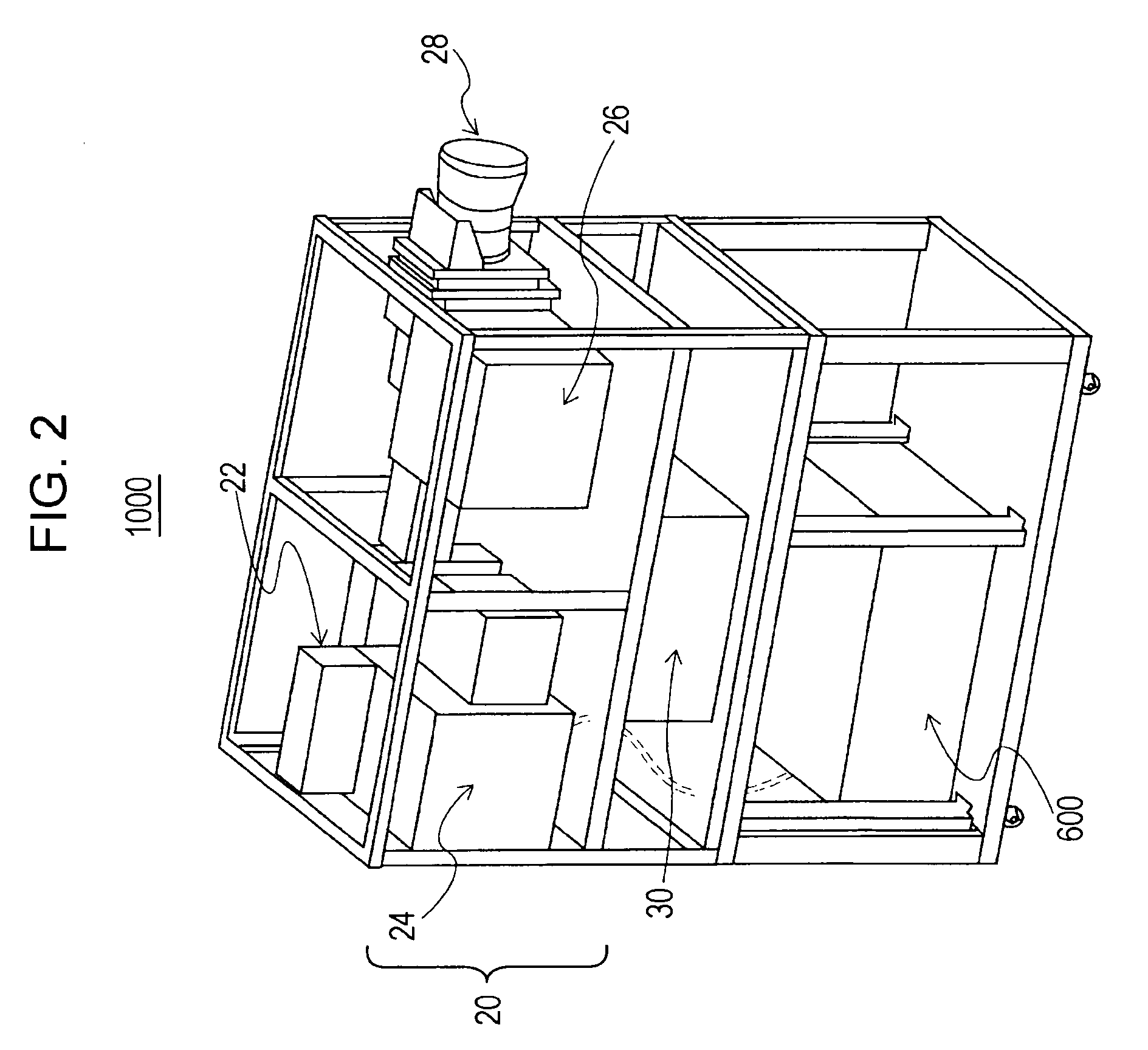

Movie projection system

ActiveUS20080272912A1Improve securityImprove the immunityBurglar alarm by openingAnalogue secracy/subscription systemsProjection systemVideo server

In a movie projection system, a switch circuit is disposed on a door of a case in which a video server is disposed. A tamper detector detects a state of the door as to whether the door is open or not and a state of the switch circuit as to whether the switch circuit has been tampered with or not, on the basis of an output signal provided by the switch circuit. A projecting operation controller controls the operation of the movie projection system such that when the door is detected to be in the open state or the switch circuit is detected to have been tampered with, the projecting operation controller stops inputting and outputting video data to or from the video server.

Owner:SONY CORP

Bandgap reference circuit and high-order temperature compensation method

ActiveUS10599176B1Improve accuracyReduce power consumptionEfficient power electronics conversionElectric variable regulationCMOSHemt circuits

A bandgap reference circuit and a high-order temperature compensation method are disclosed. The bandgap reference circuit includes: a starting circuit, a bias circuit and a high-order compensated bandgap reference voltage generating circuit, where a compensation method of the high-order compensated bandgap reference voltage generating circuit is to perform curvature correction by using a sub-threshold current of a CMOS transistor to obtain a high-order temperature-compensated bandgap reference voltage source circuit. The present circuit has the advantages that a manner not increasing circuit complexity can be adopted for implementation, the accuracy of a bandgap reference source can be greatly improved, and power consumption, chip area and cost are reduced.

Owner:PURESEMI CO LTD

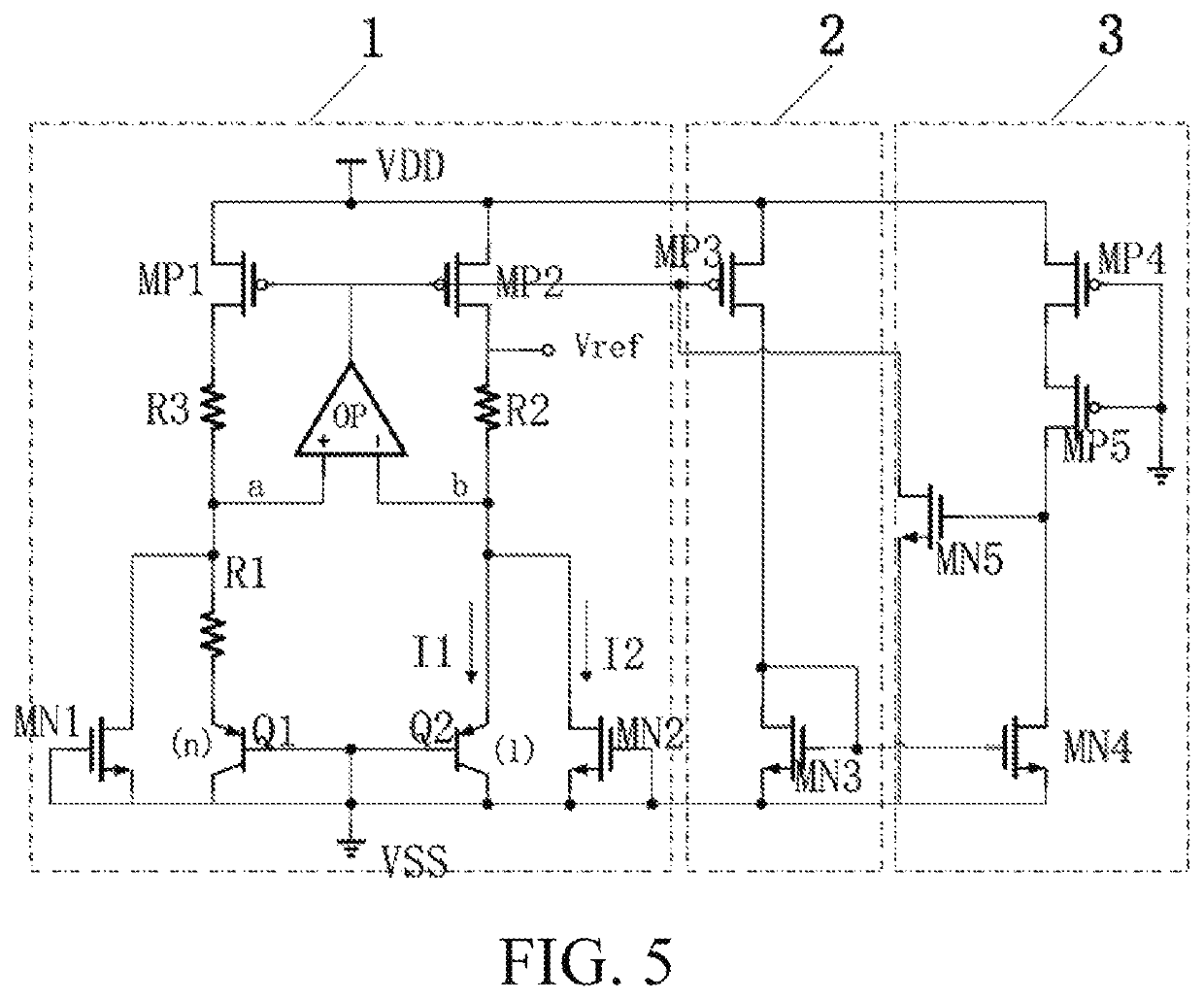

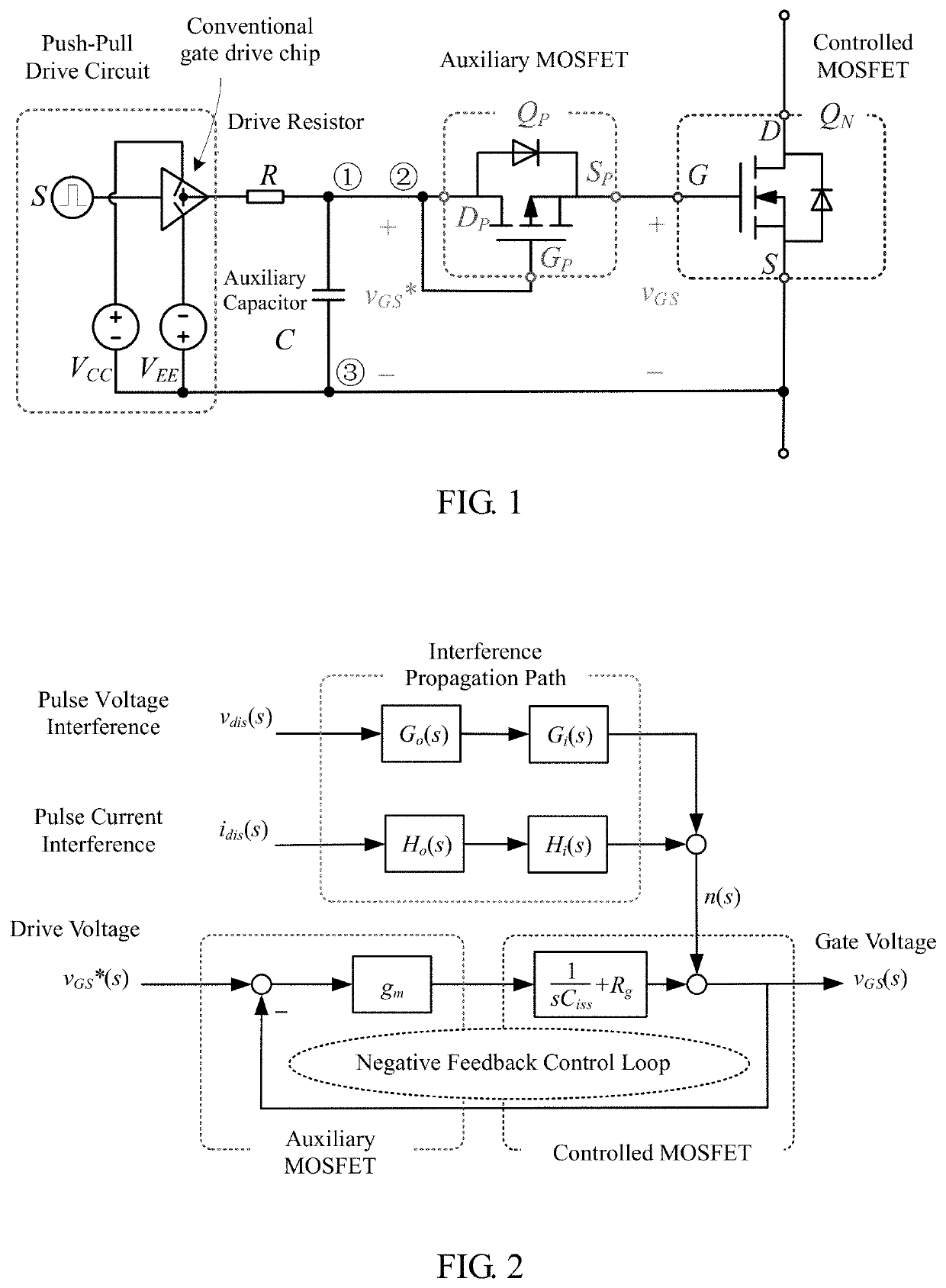

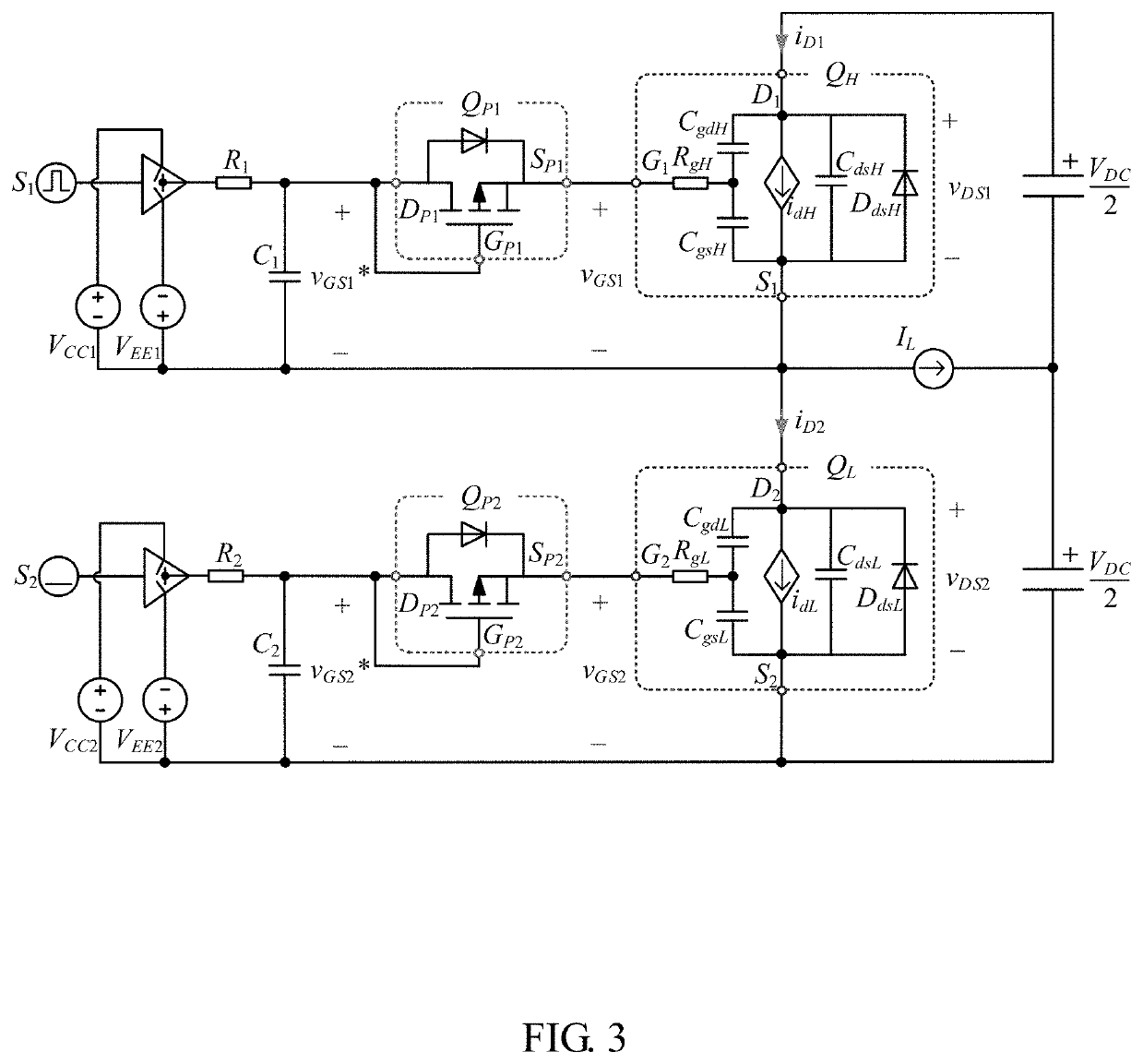

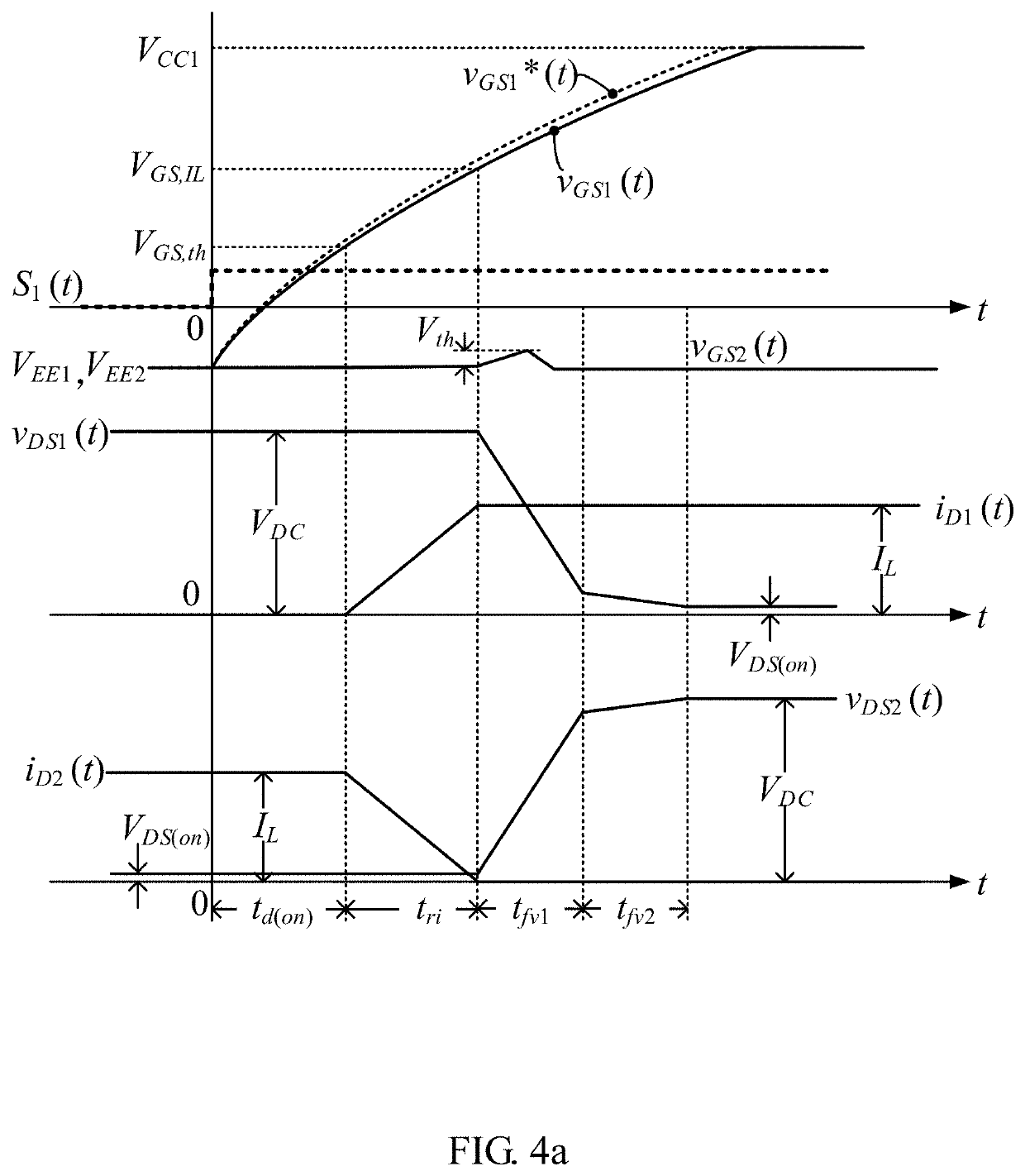

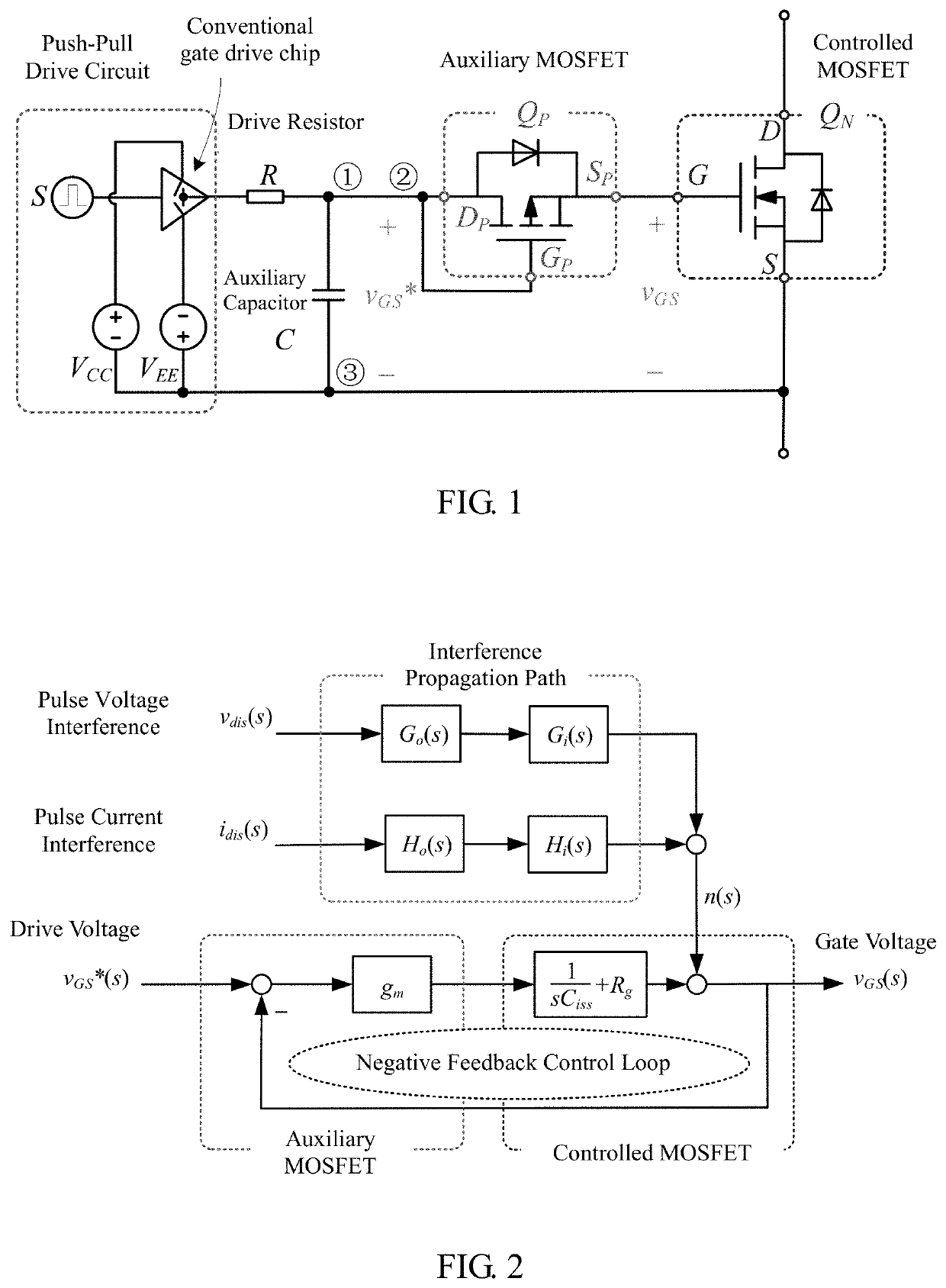

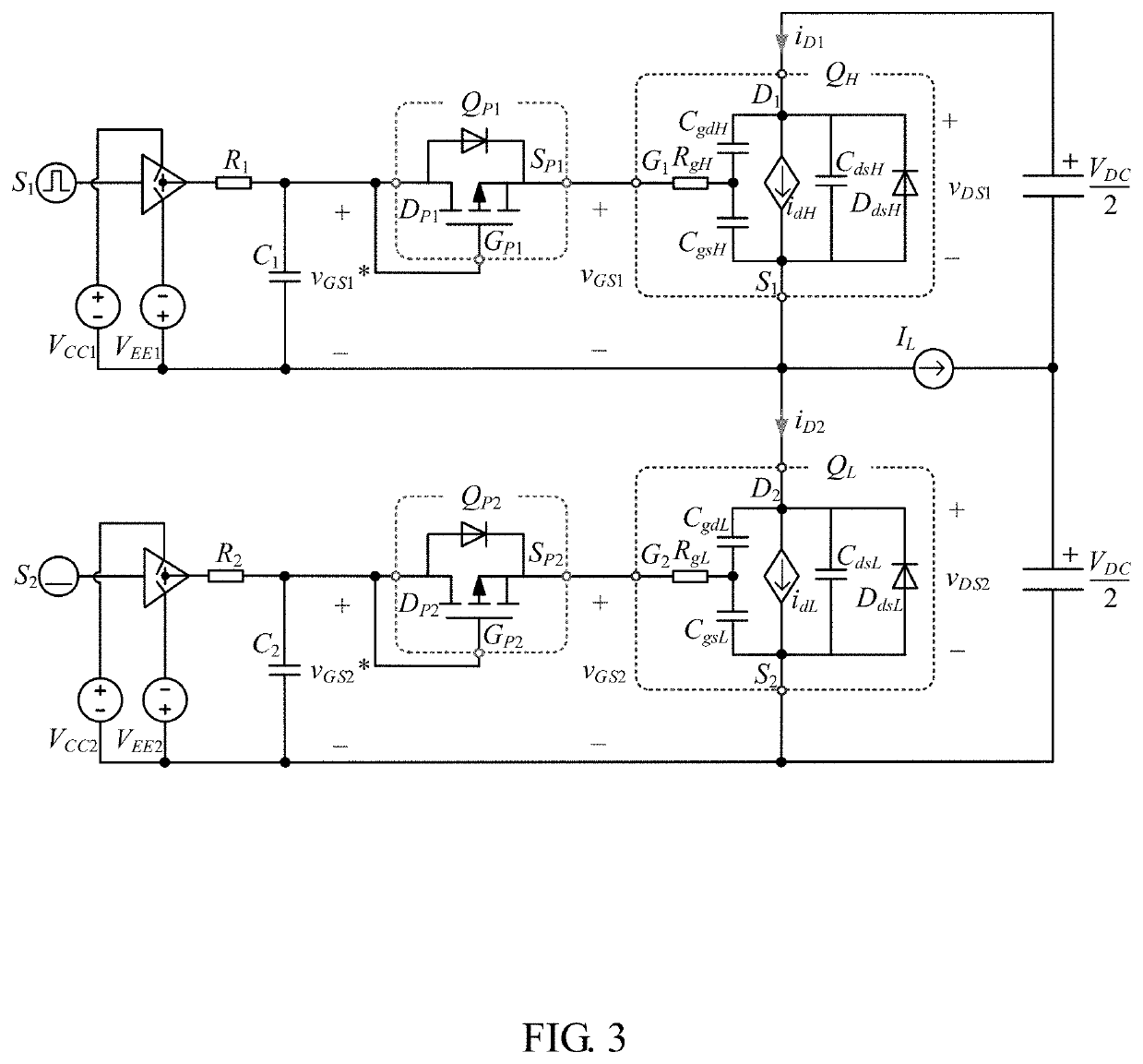

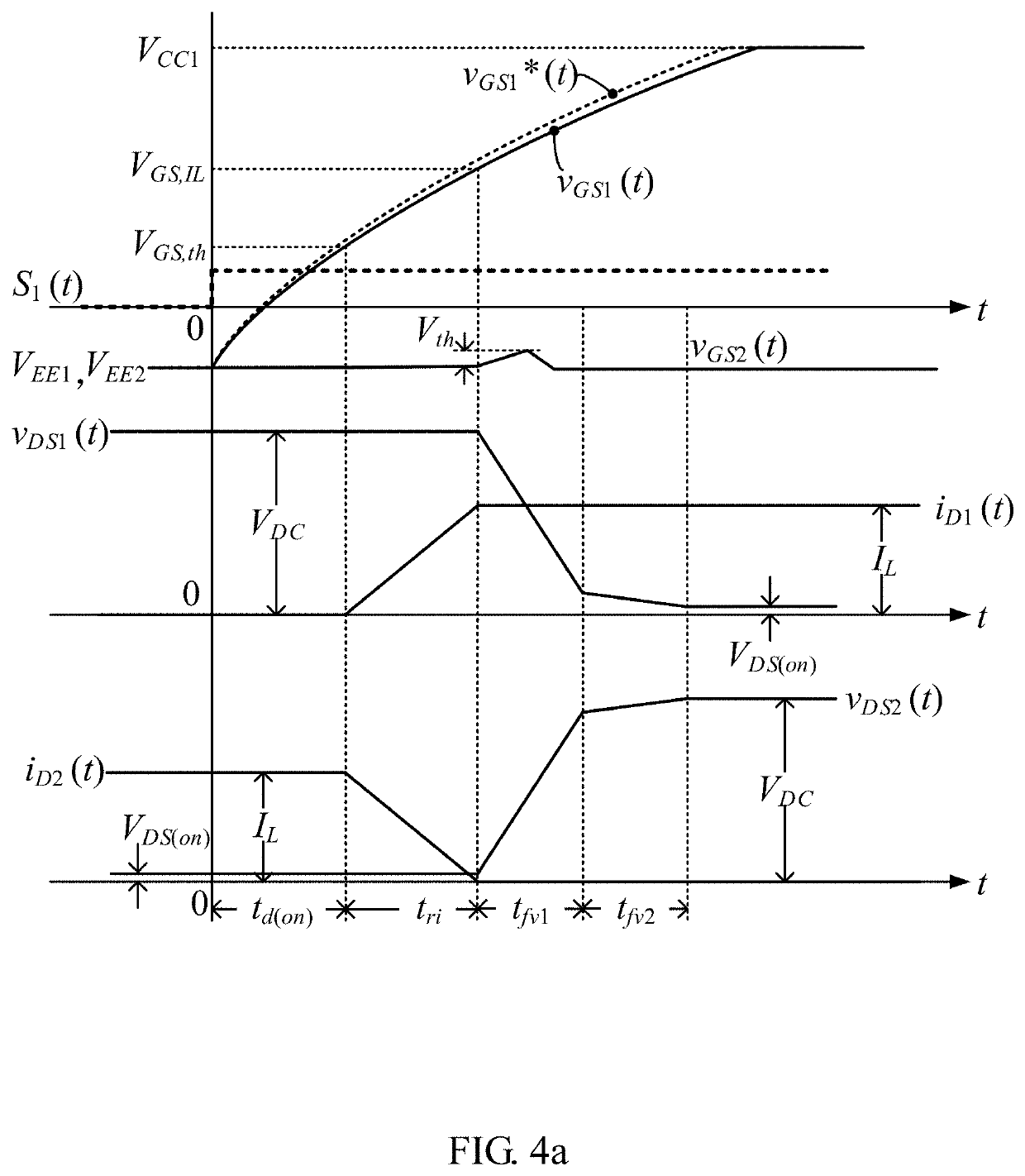

Power MOSFET Active Gate Drive Based on Negative Feedback Mechanism

ActiveUS20220123741A1Simple structureEasily realizedTransistorElectronic switchingCapacitanceDevice material

This invention introduces the negative feedback into the gate drive. It proposes a negative feedback active gate drive (NFAGD) for silicon carbide (SiC) and gallium nitride (GaN) semiconductor devices to fully utilize their potential of high switching-speed capability in a phase-leg configuration. An auxiliary P-channel MOSFET is introduced to construct a negative feedback control mechanism. Due to the negative feedback mechanism, the proposed drive can automatically attenuate the disturbance from the complementary device of the phase-leg. The negative feedback active gate drive (NFAGD) has a simple structure and easy to be realized using a push-pull drive circuit, a drive resistor, an auxiliary MOSFET and an auxiliary capacitor, without involving any additional logical circuits. Functionally, the negative feedback active gate drive (NFAGD) can automatically suppress the induced gate-source voltage and make the gate voltage of the MOSFET stable even during high-speed switching operation without sacrificing the switching speed of the MOSFET.

Owner:BEIJING JIAOTONG UNIV +1

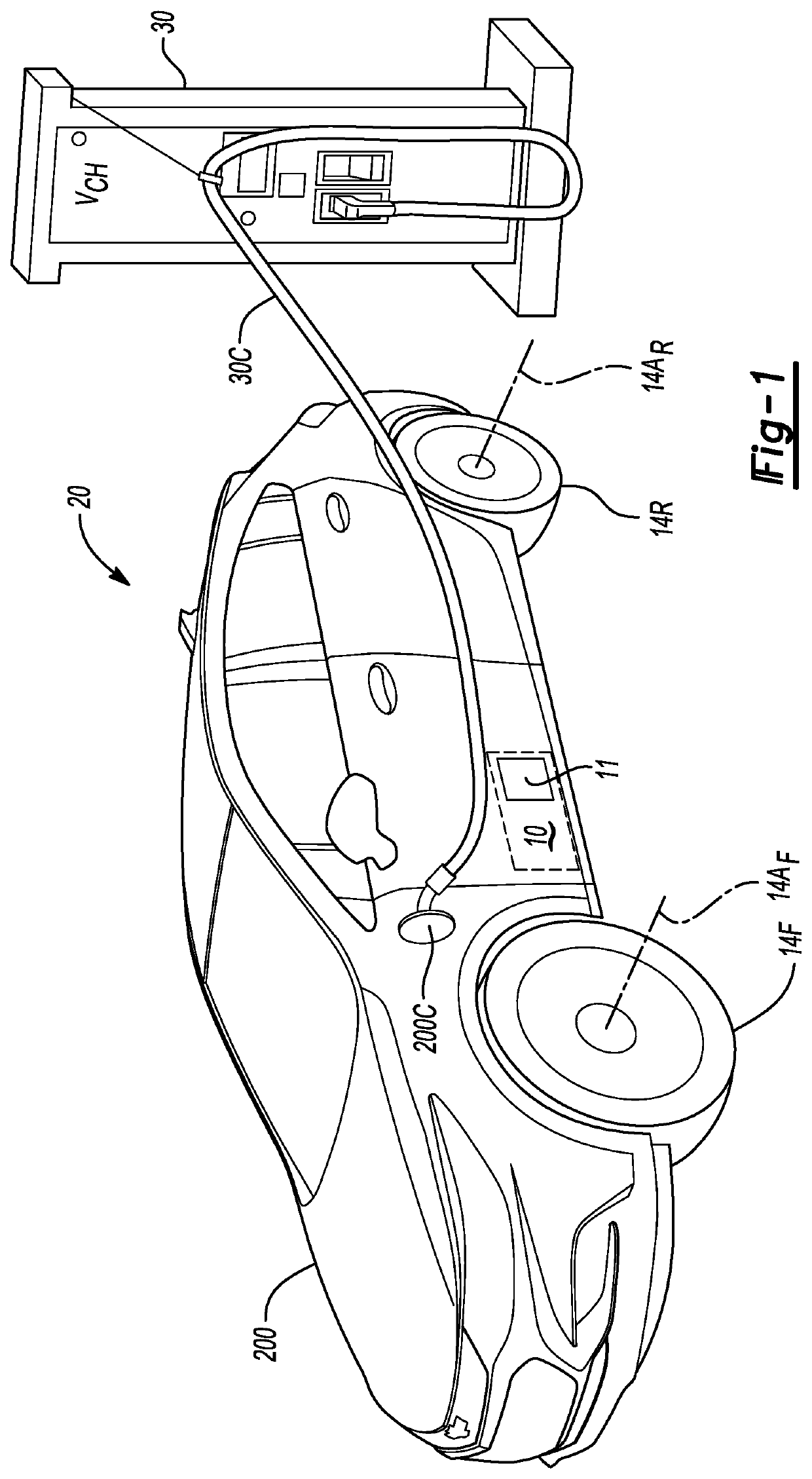

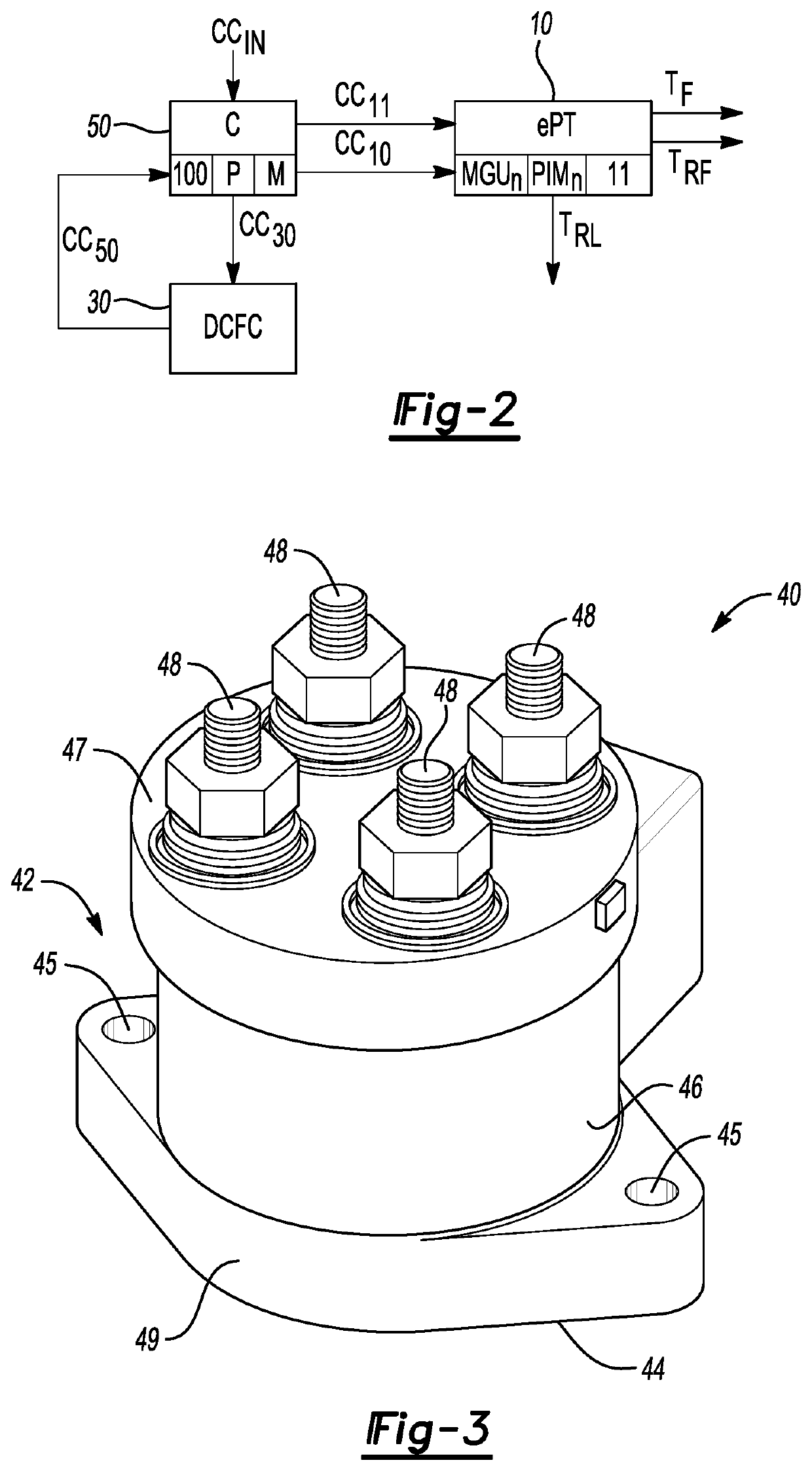

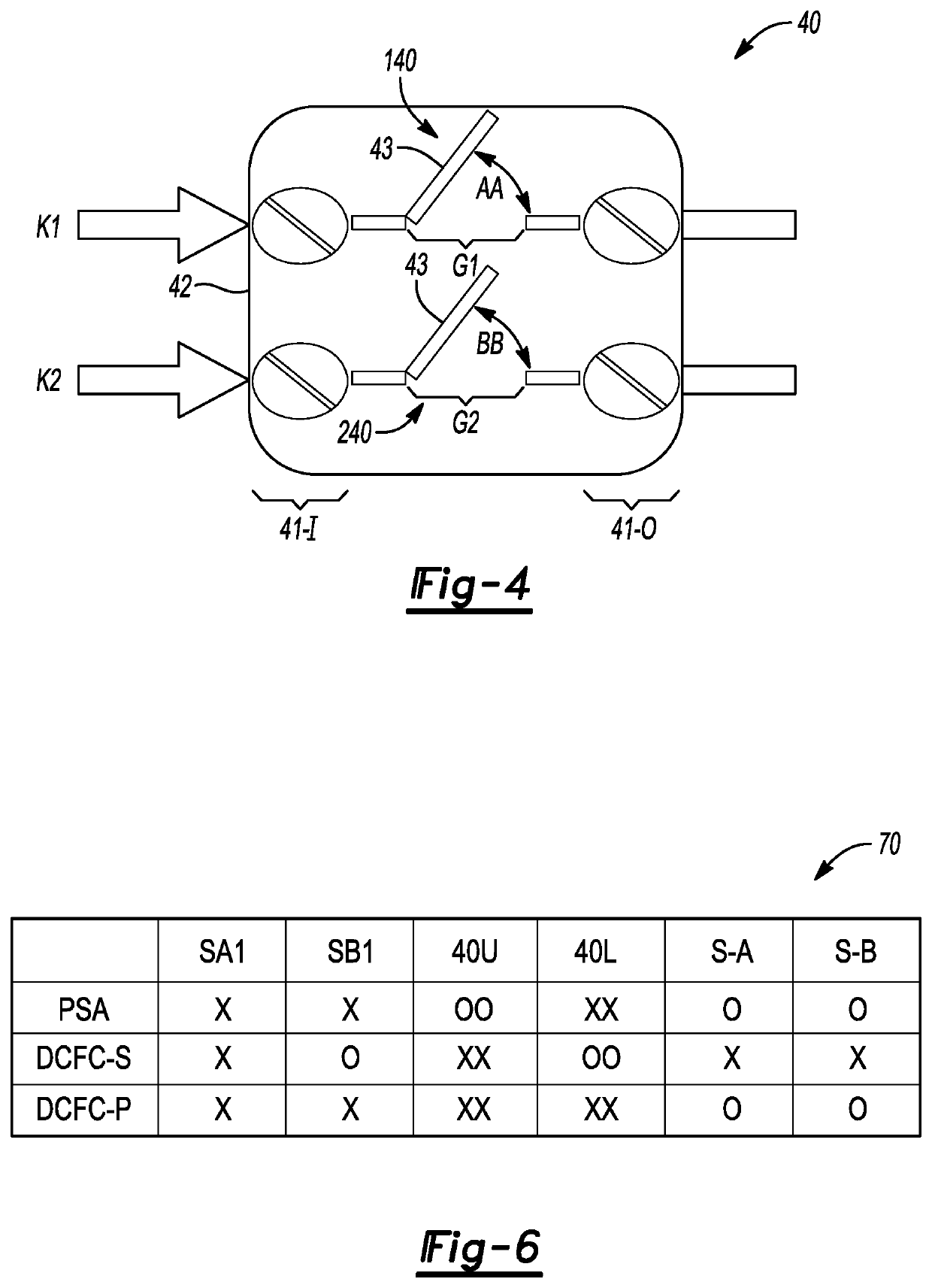

Electric powertrain with battery system having multi-pole high-voltage contactor

ActiveUS20220097538A1Increased circuit complexityIncrease costCharge equalisation circuitCharging stationsContactorPower inverter

A battery system includes high-voltage switches, including a multi-pole contactor. Multiple packs are connectable in a series or parallel configuration via the switches. The contactor includes first and second pairs of electrical terminals separated by a respective circuit gap, with respective contactor arms simultaneously closing or opening the gaps. At all times, internal switches formed by the gaps and arms have the same ON / OFF state corresponding to the circuit gaps both being closed or both being open. Two of the contactors may be used to connect the battery packs to a DC fast-charging station, and to connect electrode terminals of the battery packs to a bus rail, respectively. An electric powertrain includes the battery system and an electrical load, including a rotary electric machine, that is connected to a power inverter and to a mechanical load.

Owner:GM GLOBAL TECH OPERATIONS LLC

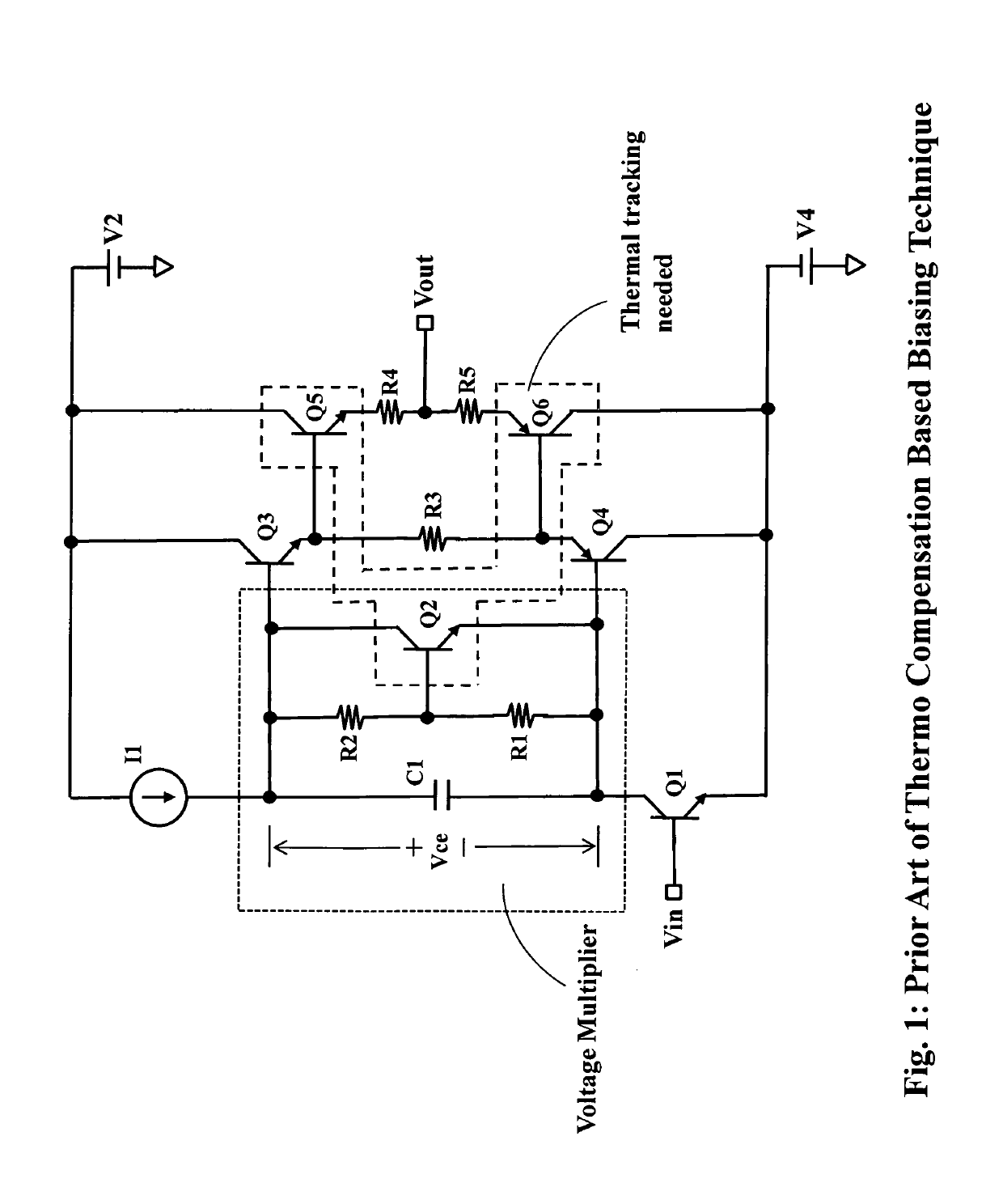

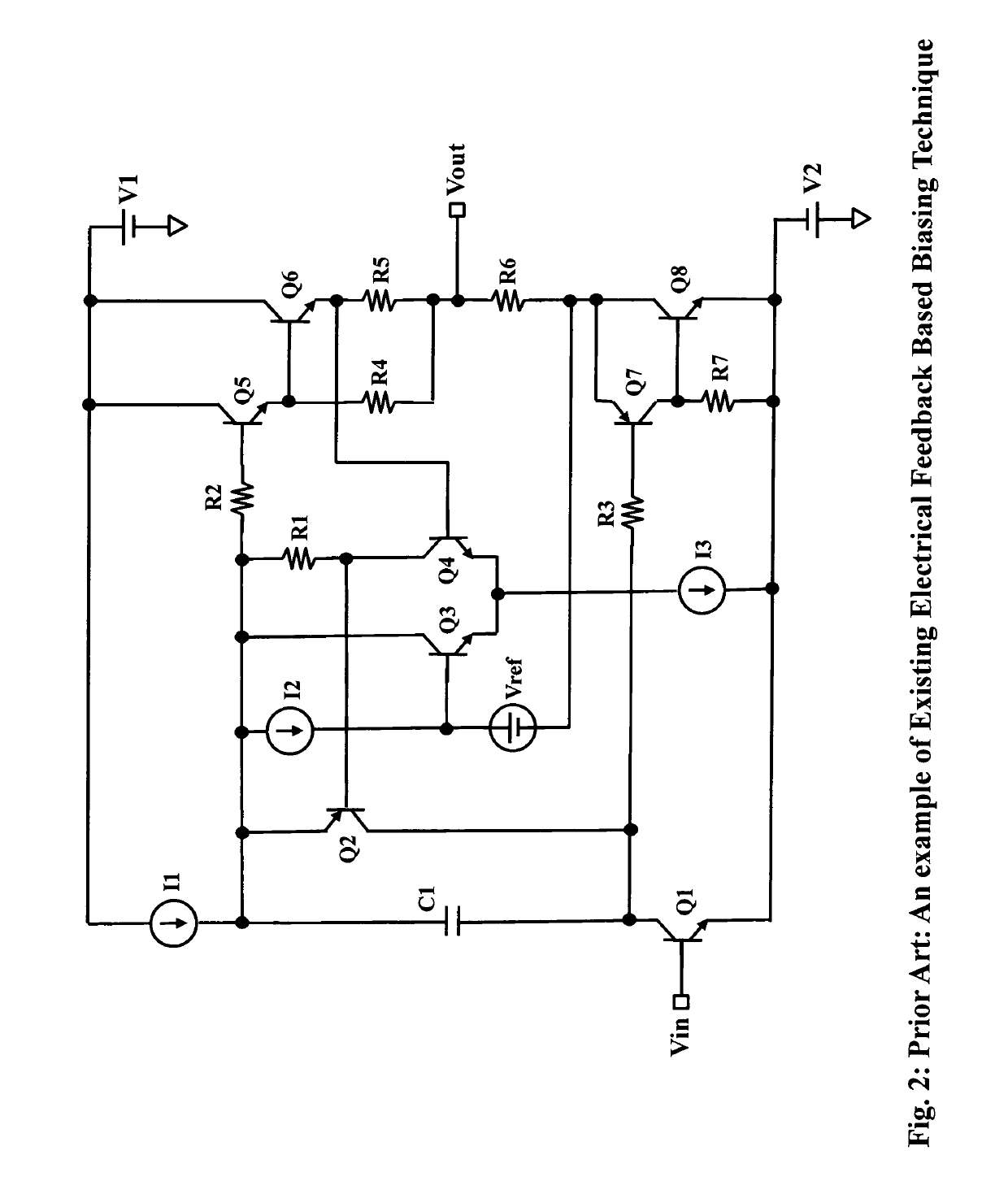

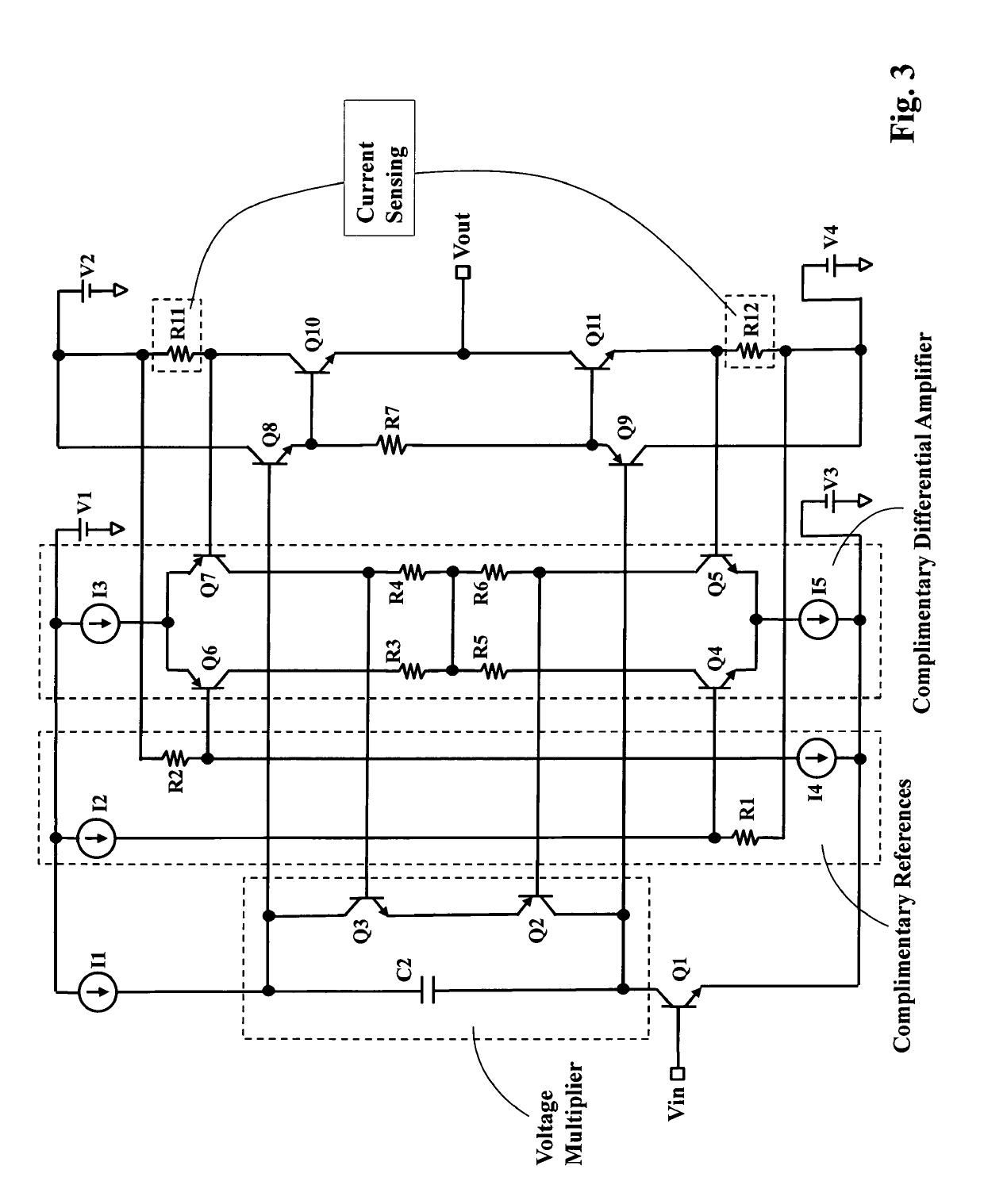

Biasing method without using thermal compensation applicable for both class-A and class-AB audio power amplifier

InactiveUS10432153B2Reduce sensitivityBiasing issueAmplifier modifications to reduce temperature/voltage variationPower amplifiersElectricityVoltage multiplier

The present invention reveals a new biasing method which can be used in solid state audio power amplifier design despite of the Class of operation. The proposed biasing technology relies only on traditional electrical feedback to build up and maintain the desired biasing current and doesn't need thermal coupling or thermal tracking techniques in order to overcome power transistor device's temperature dependent input-output characteristics as required by traditional approach. An ingenious current sensing and amplification circuit is devised in order to generate an voltage output which is only corresponding to the quiescent biasing current of the output stage. This voltage output is then used as an representative of the power stage biasing current to be regulated by a feedback loop comprising a traditional voltage multiplier, the output stage and the aforementioned current sensing and amplification circuit.

Owner:WANG ZHENWU

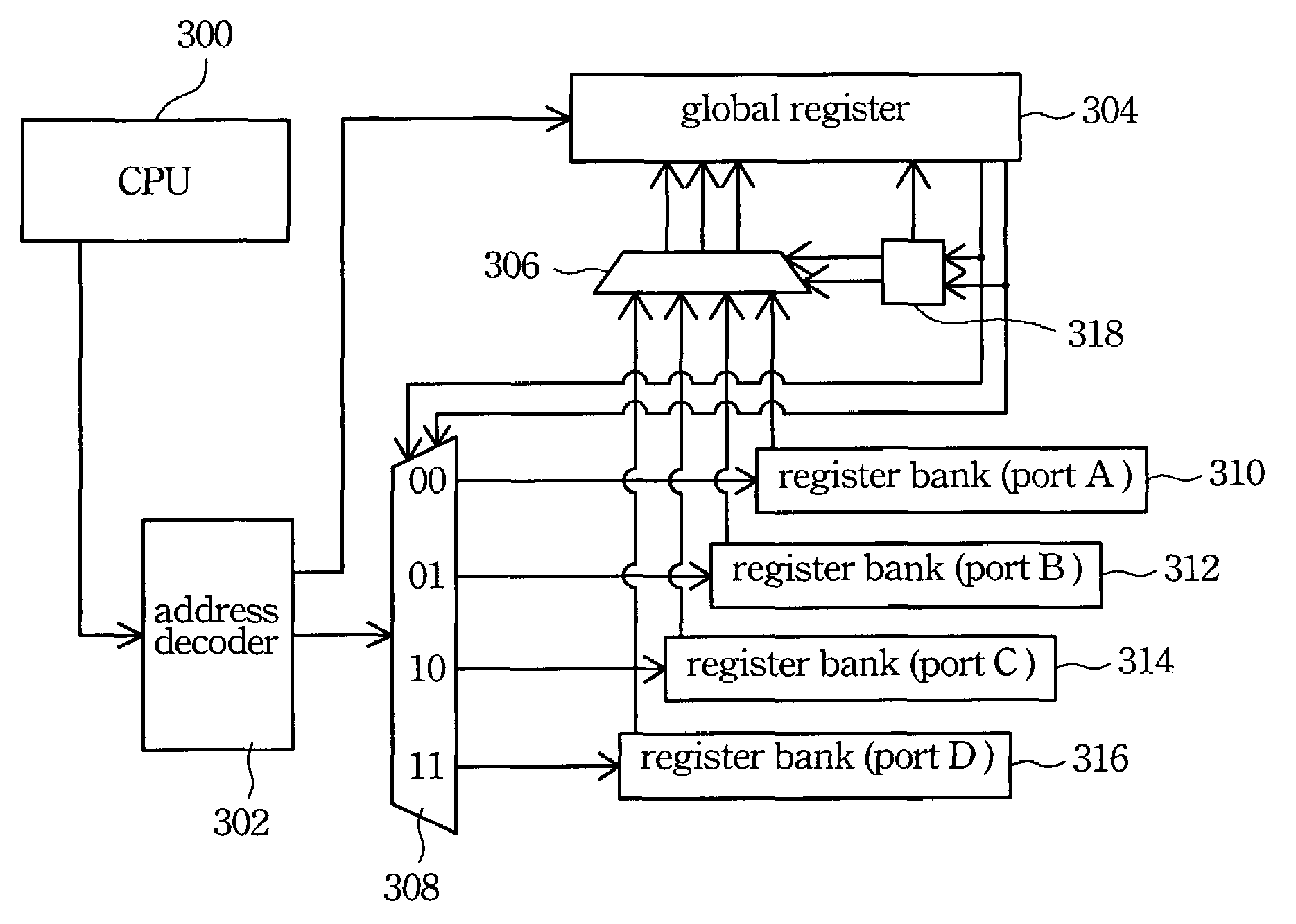

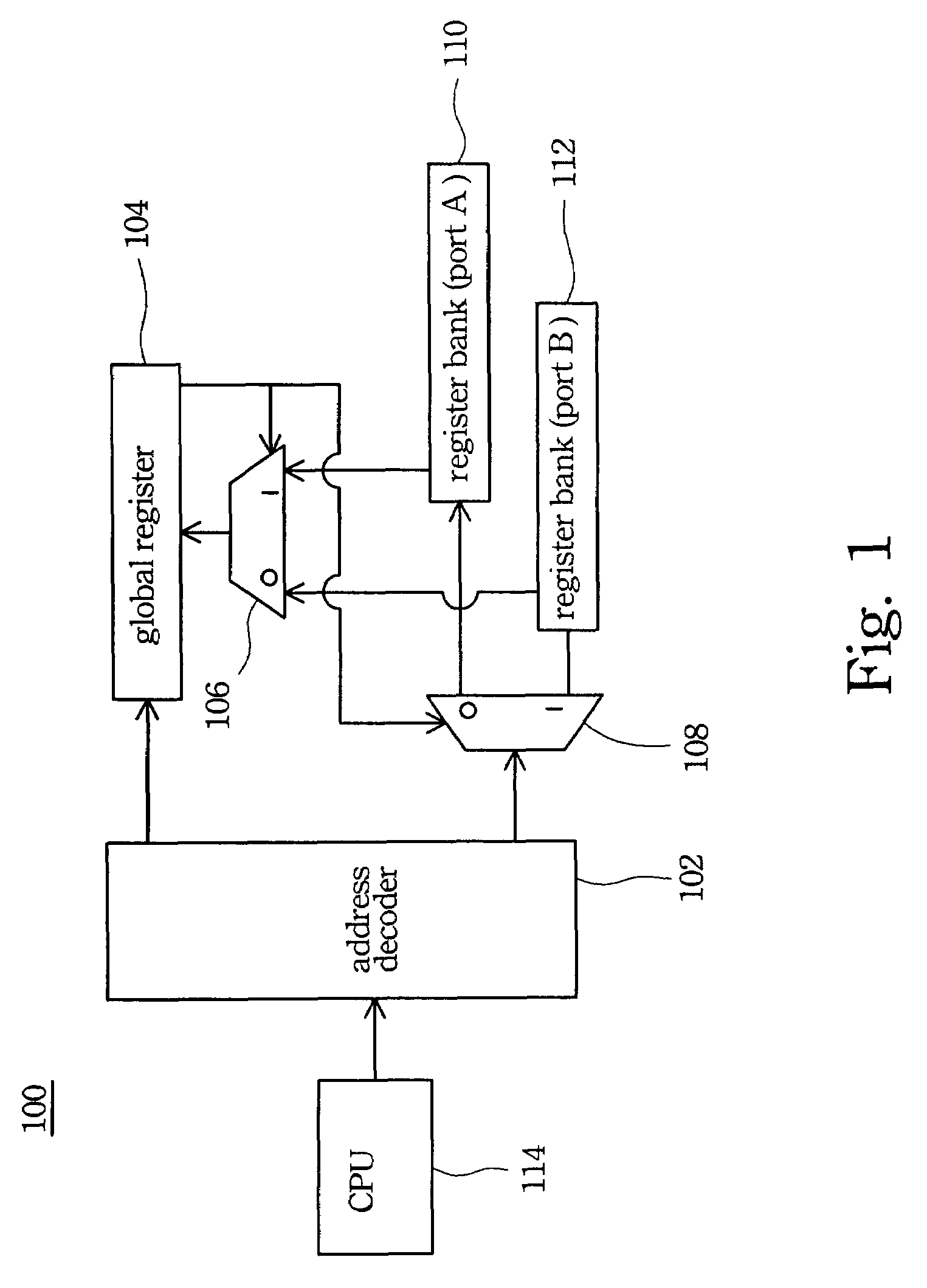

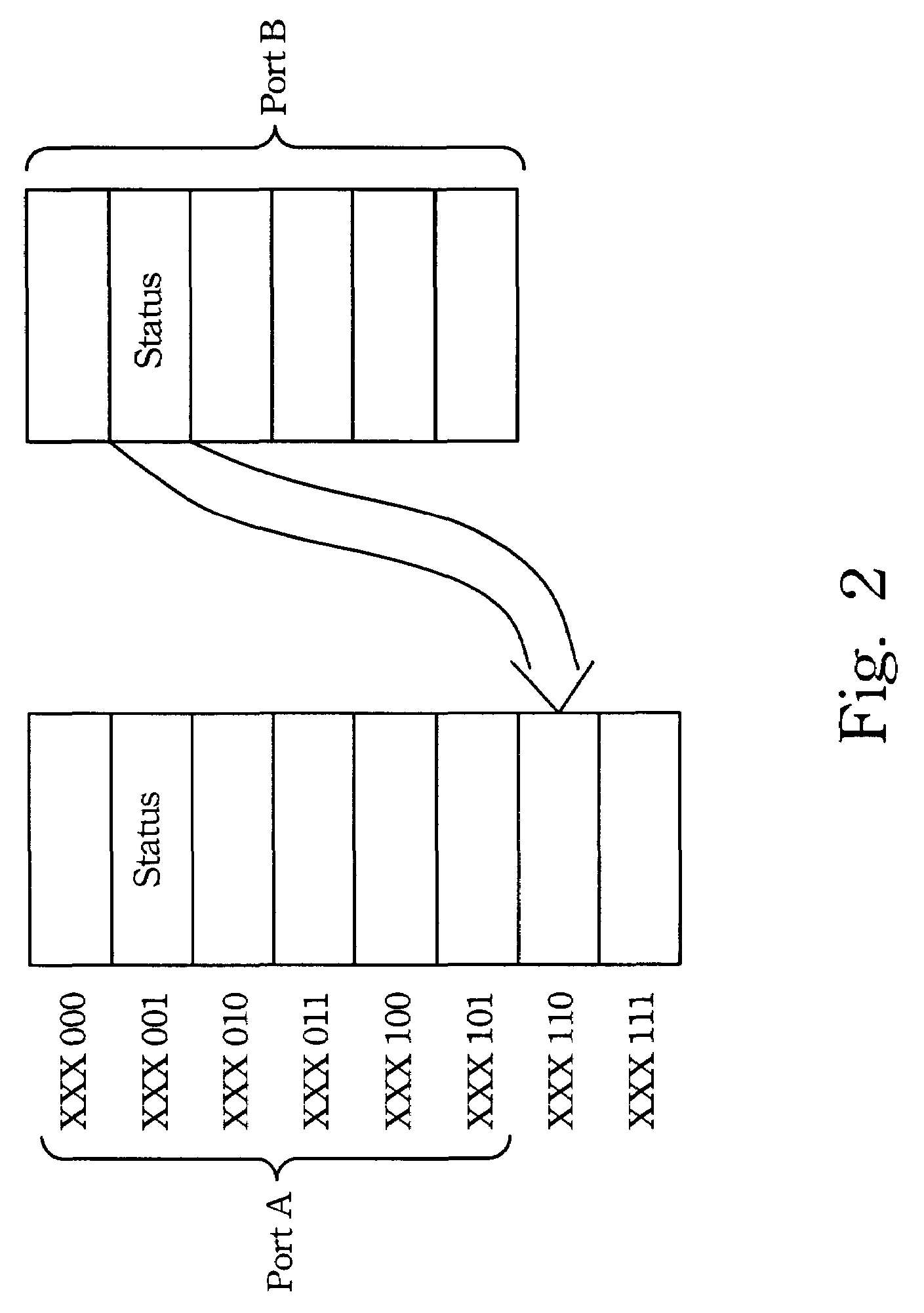

Easy access port structure and access method

InactiveUS7185139B2Increased circuit complexityImprove maintenance convenienceMemory adressing/allocation/relocationAccess methodProcessor register

Owner:WINBOND ELECTRONICS CORP

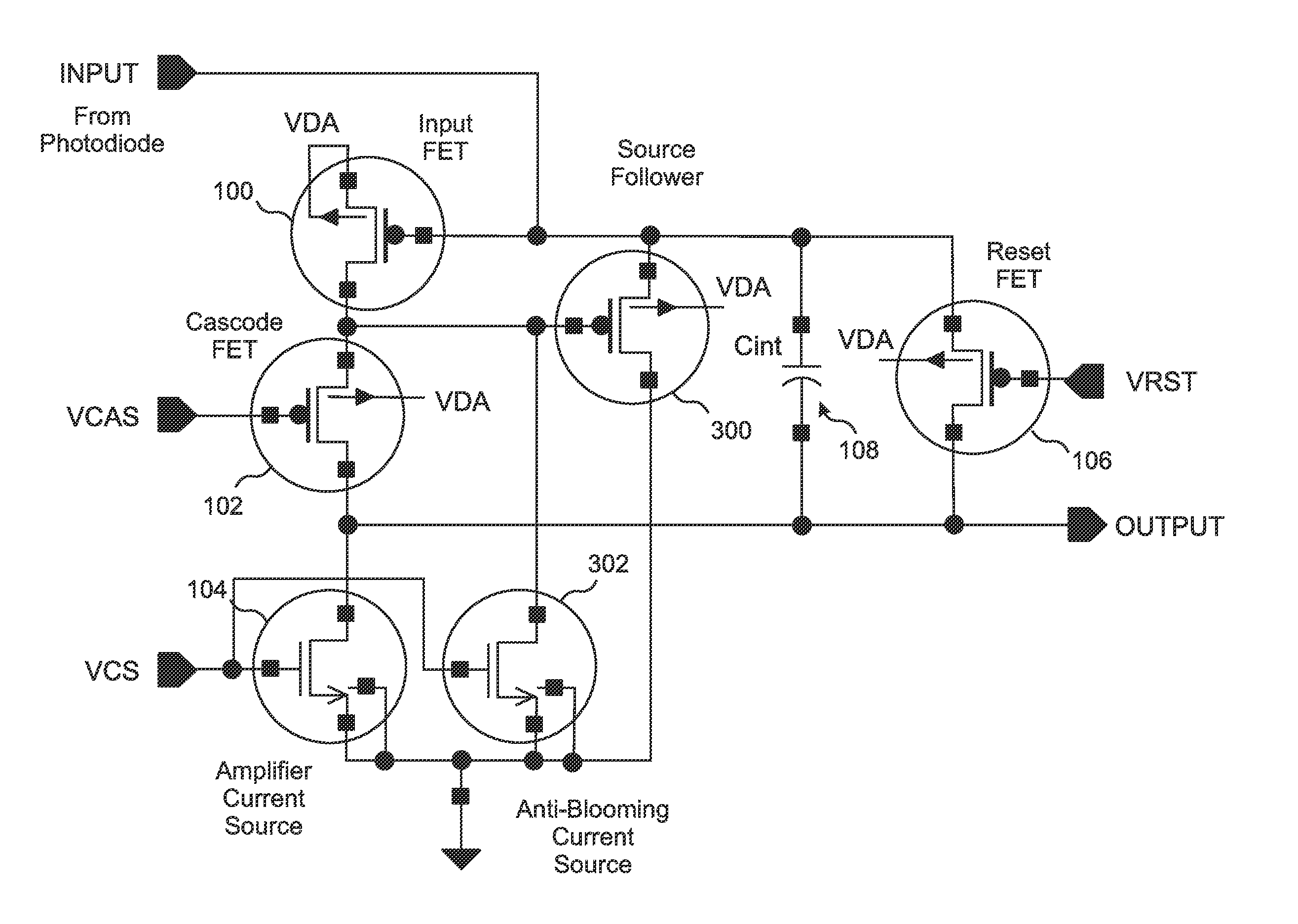

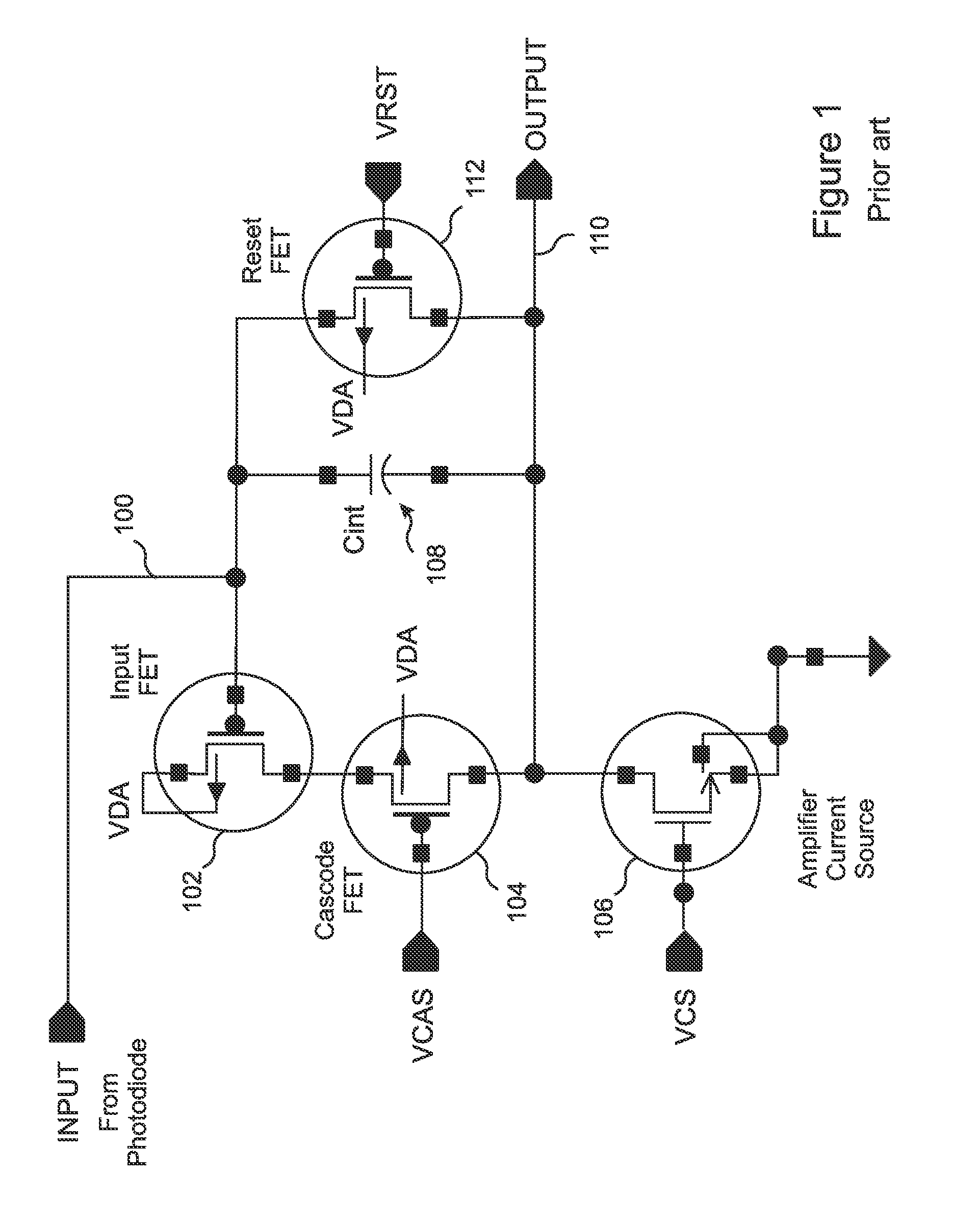

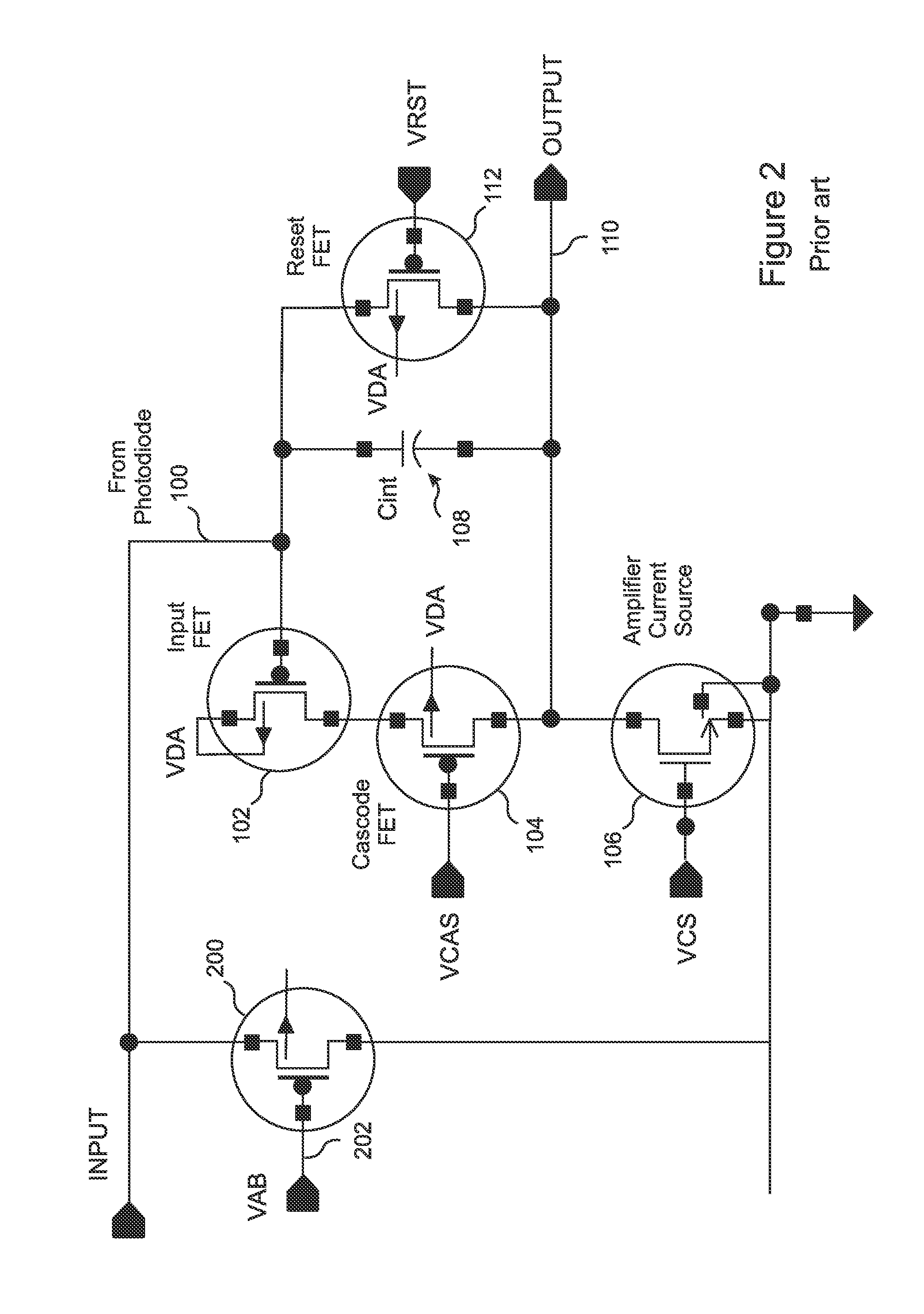

Anti-blooming circuit for integrating photodiode pre-amplifiers

ActiveUS8921757B2Performance maximizationMinimize complexityMaterial analysis by optical meansAmplifiers controlled by lightCircuit complexityAudio power amplifier

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTEGRATION INC

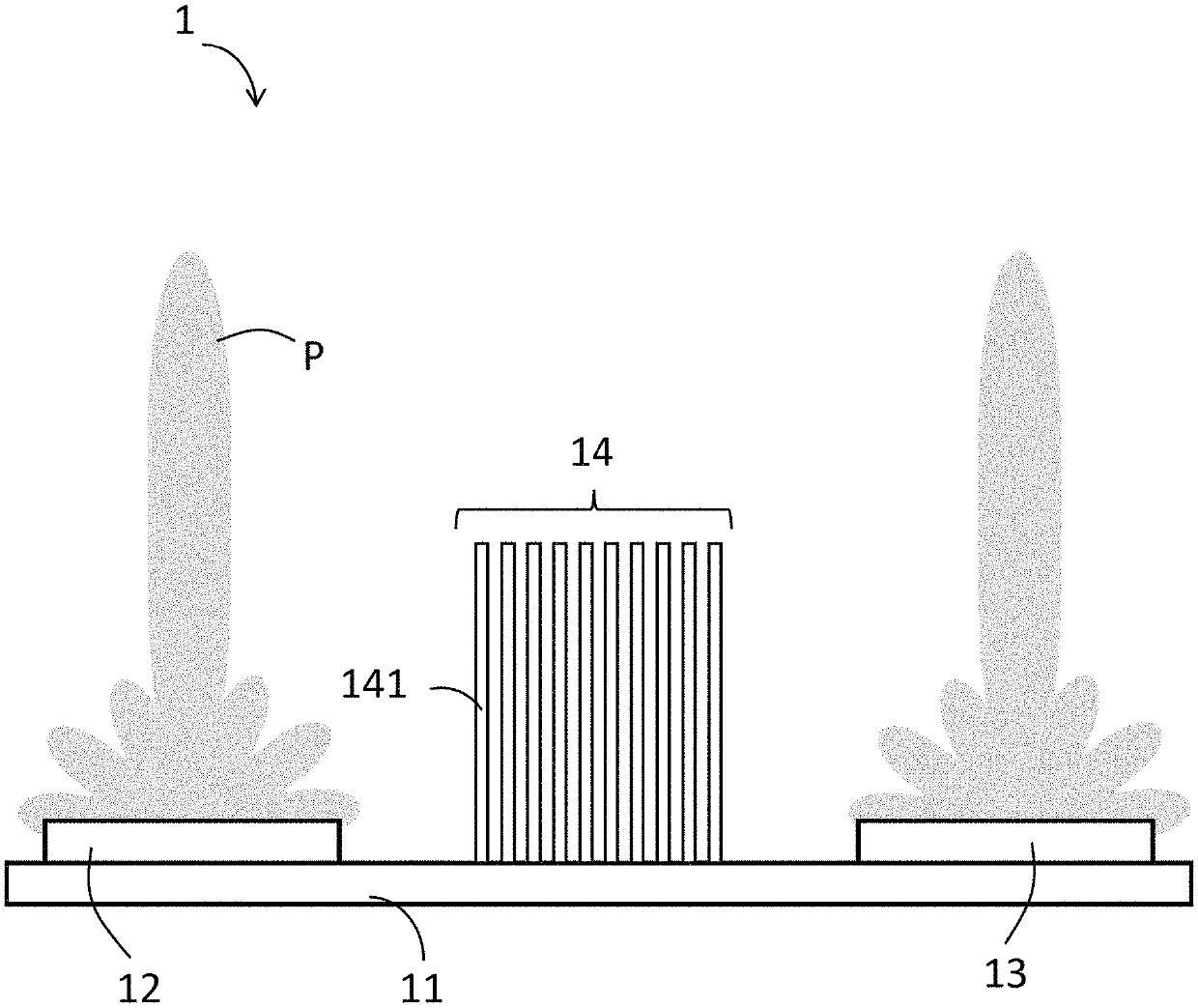

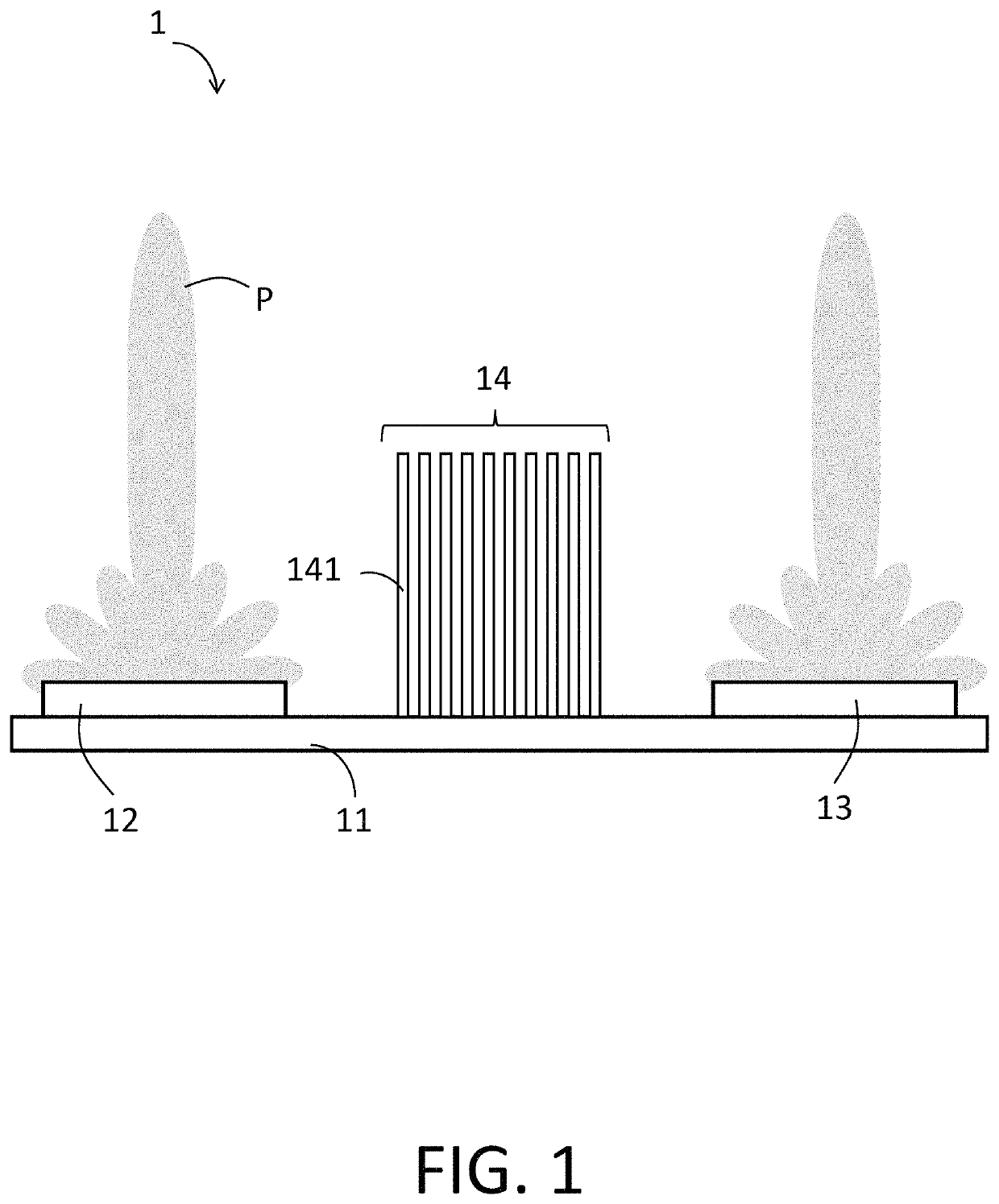

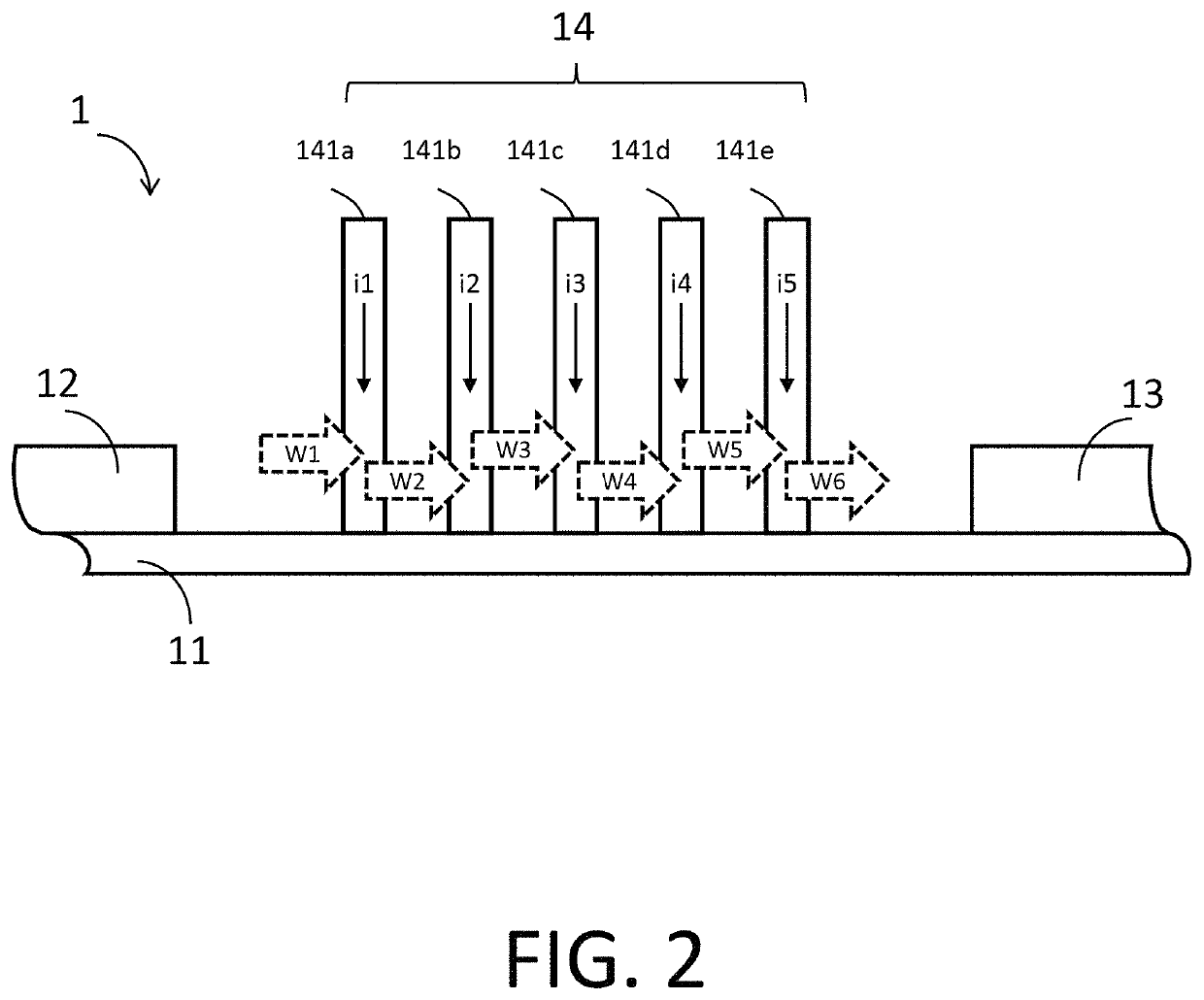

Continuous wave radar system

ActiveUS11372080B2Effective attenuationReduce signal leakageWave based measurement systemsTelecommunicationsElectrical connection

A continuous wave radar system comprises a substrate, a transmitter disposed on the substrate, a receiver disposed on the substrate, and an isolating device comprising a plurality of metal plates parallelly disposed on the substrate between the transmitter and the receiver for isolating leakage signal transmitted from the transmitter to the receiver. The metal plates are grounded with the transmitter and the receiver via electrical connection between the metal plates and the substrate. The metal plates are so arranged that an eddy current induced in each of the metal plates is directed away by grounding when the leakage signal passes through the metal plates.

Owner:NAT CHUNG SHAN INST SCI & TECH

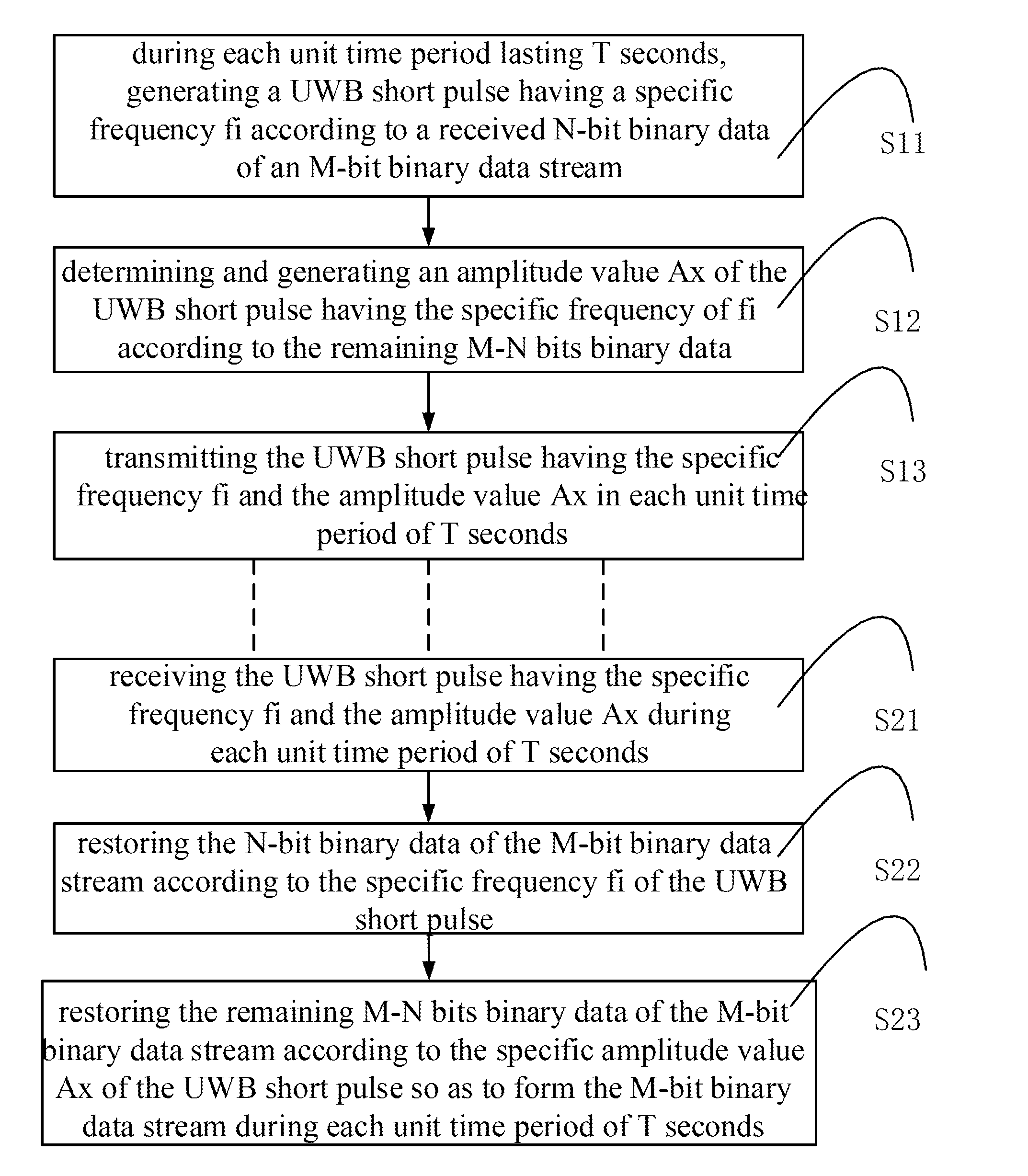

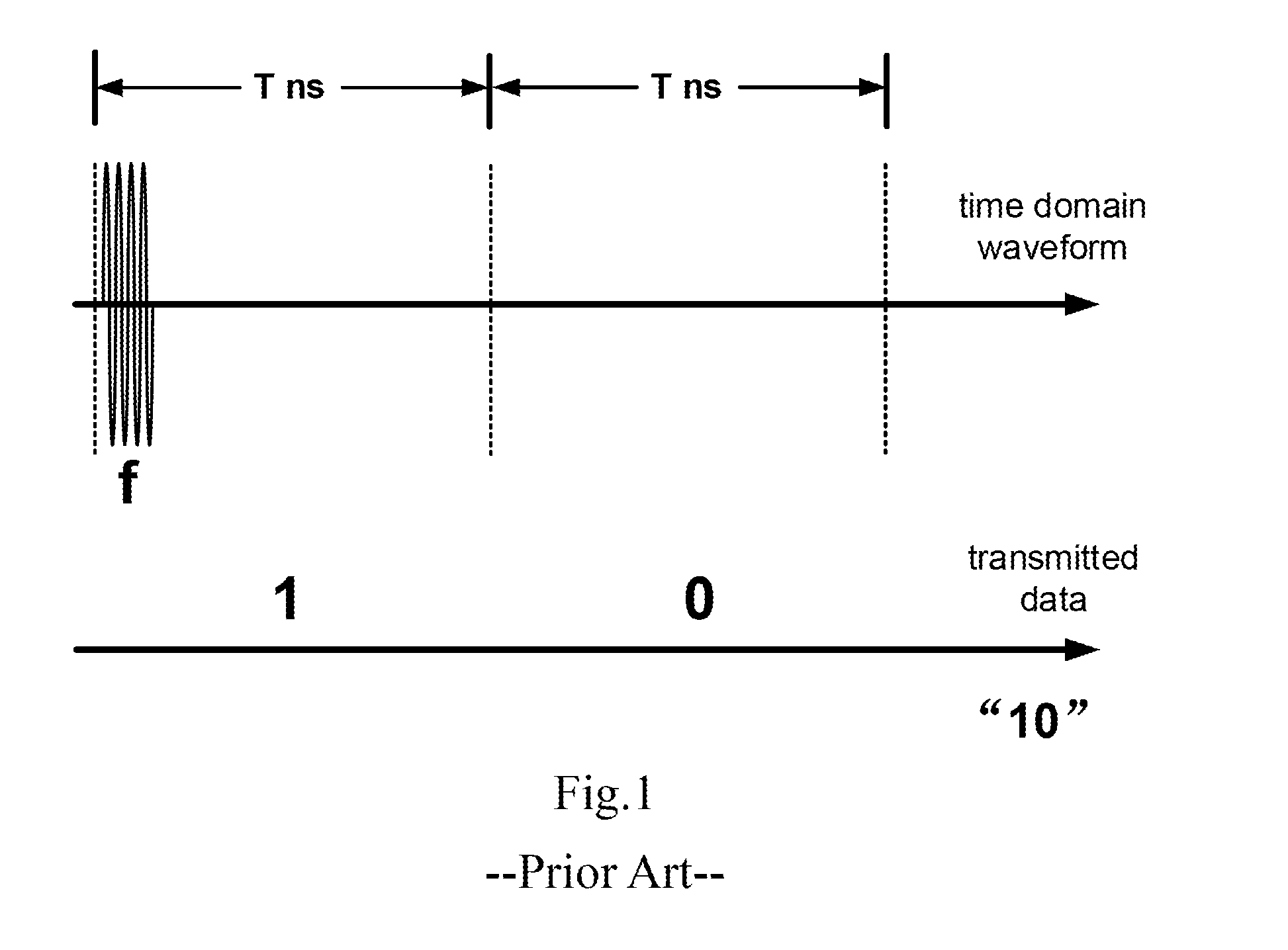

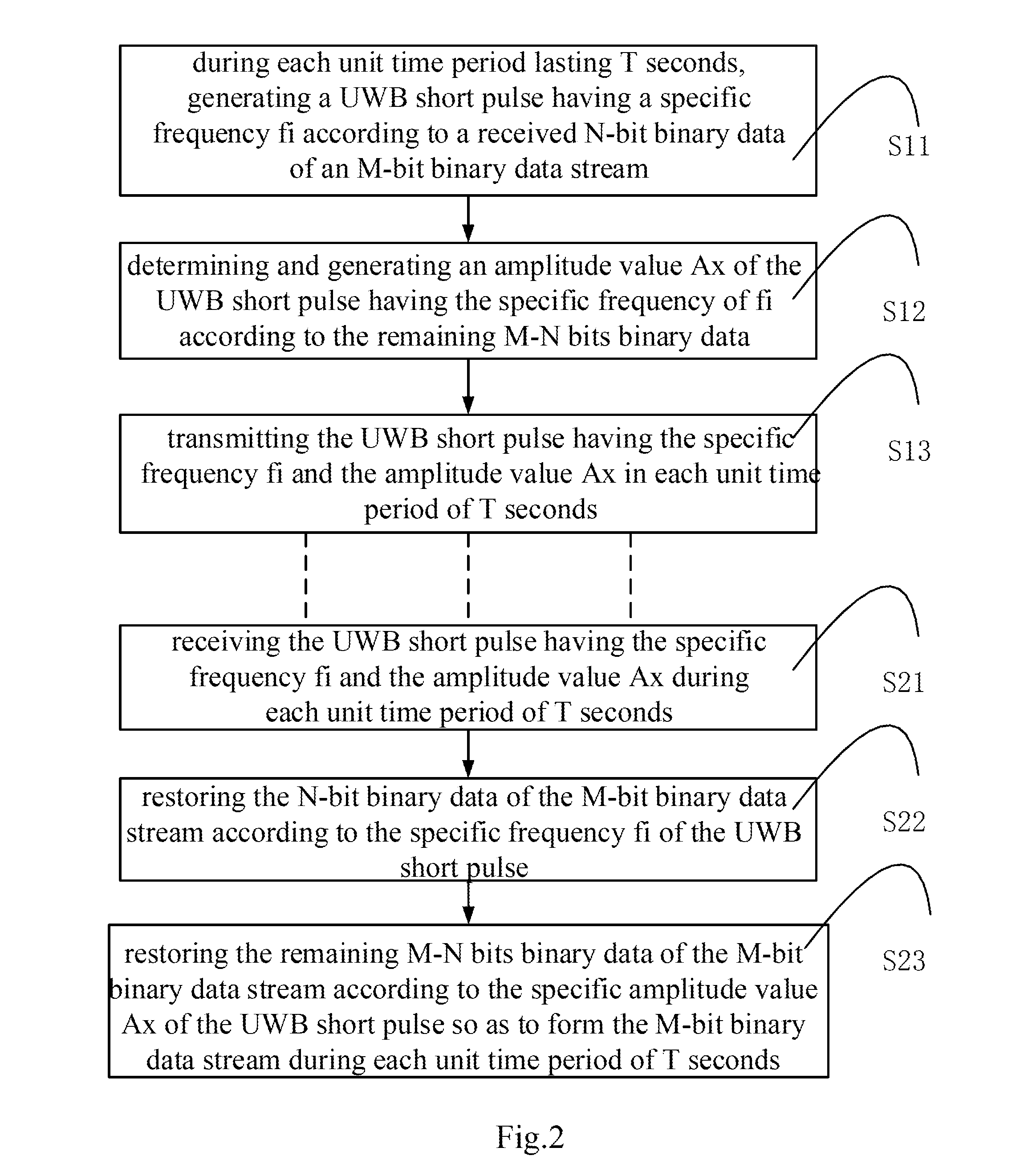

Impulse radio ultra wide bandwidth data transmission encoding/decoding method and encoding/decoding module

ActiveUS20150010042A1Improve time utilizationIncreased circuit complexityAmplitude-modulated carrier systemsFrequency-modulated carrier systemsDecoding methodsCircuit complexity

The present invention provides an IR-UWB data transmission encoding / decoding method and module. The encoding method comprises: in each unit time period lasting T seconds, receiving an N-bit of binary data of an M-bit binary data stream and generating UWB impulse radio signal having a specific frequency fi, determining and generating an amplitude value Ax of the UWB impulse radio signal having the specific frequency fi according to the remaining M-N bits binary data, and finally transmitting the UWB impulse radio signal having the specific frequency fi and the amplitude value. The decoding method corresponds to the encoding method. According to the present invention, the data transmission rate can be increased by four times compared with the conventional data transmission rate without increasing the circuit complexity, which is useful and attractive to the IR-UWB system.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

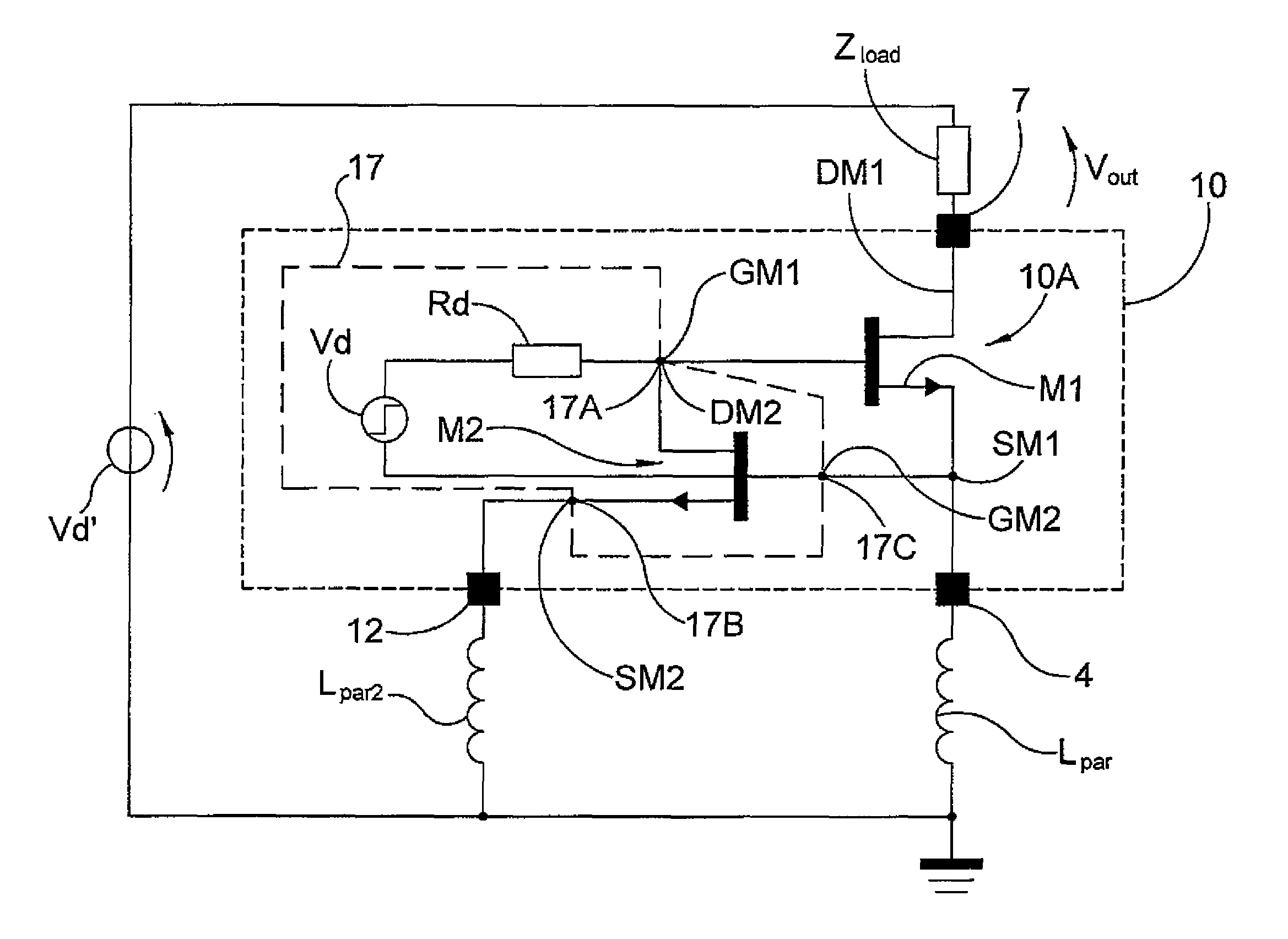

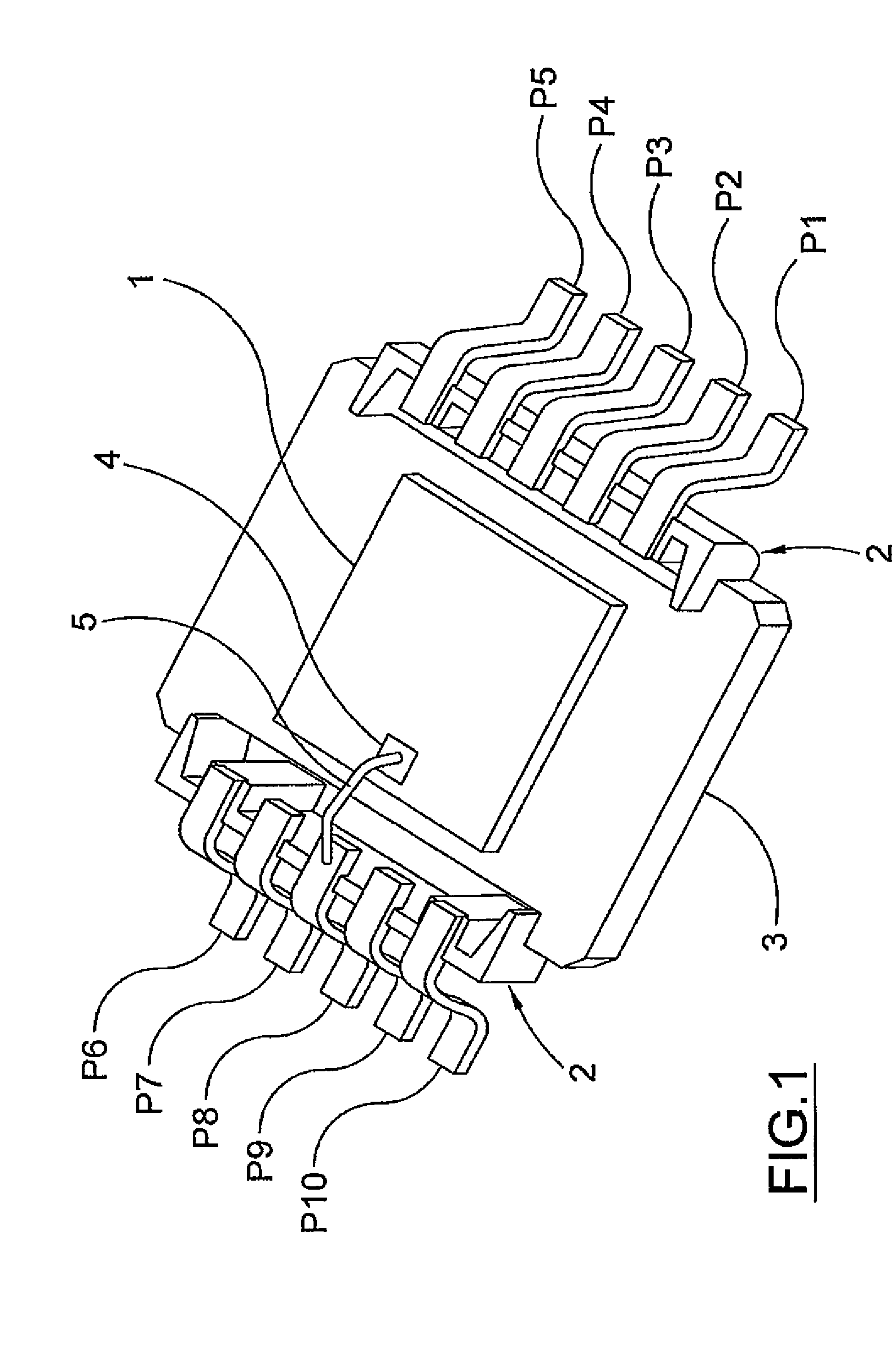

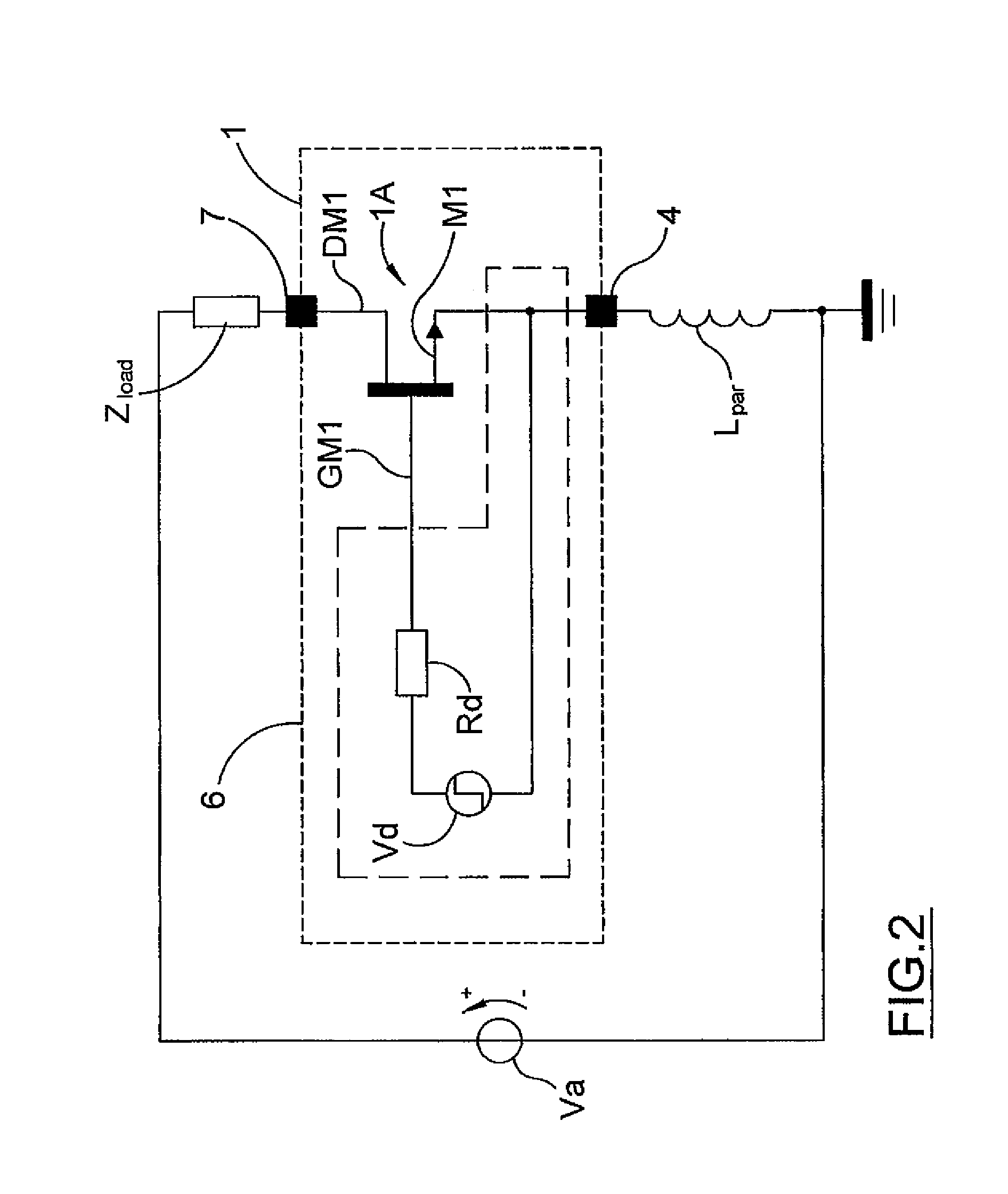

Power integrated circuit with high insensitivity to parasitic inductances of wires for connection to a package and package for said integrated circuit

ActiveUS8159796B2Reduce and minimize overvoltagesIncreased circuit complexitySemiconductor/solid-state device detailsSolid-state devicesElectricityEngineering

The present disclosure relates to an integrated circuit and a package on which such integrated circuit is placed, the latter having a power output stage, at least one first pad, one second pad and one drive circuit for driving said power output stage, wherein the integrated circuit is characterized in that it has at least one additional third pad, other than said at least one first and said at least one second pads, said drive circuit being electrically coupled between said at least one third pad and said power output stage.

Owner:STMICROELECTRONICS SRL

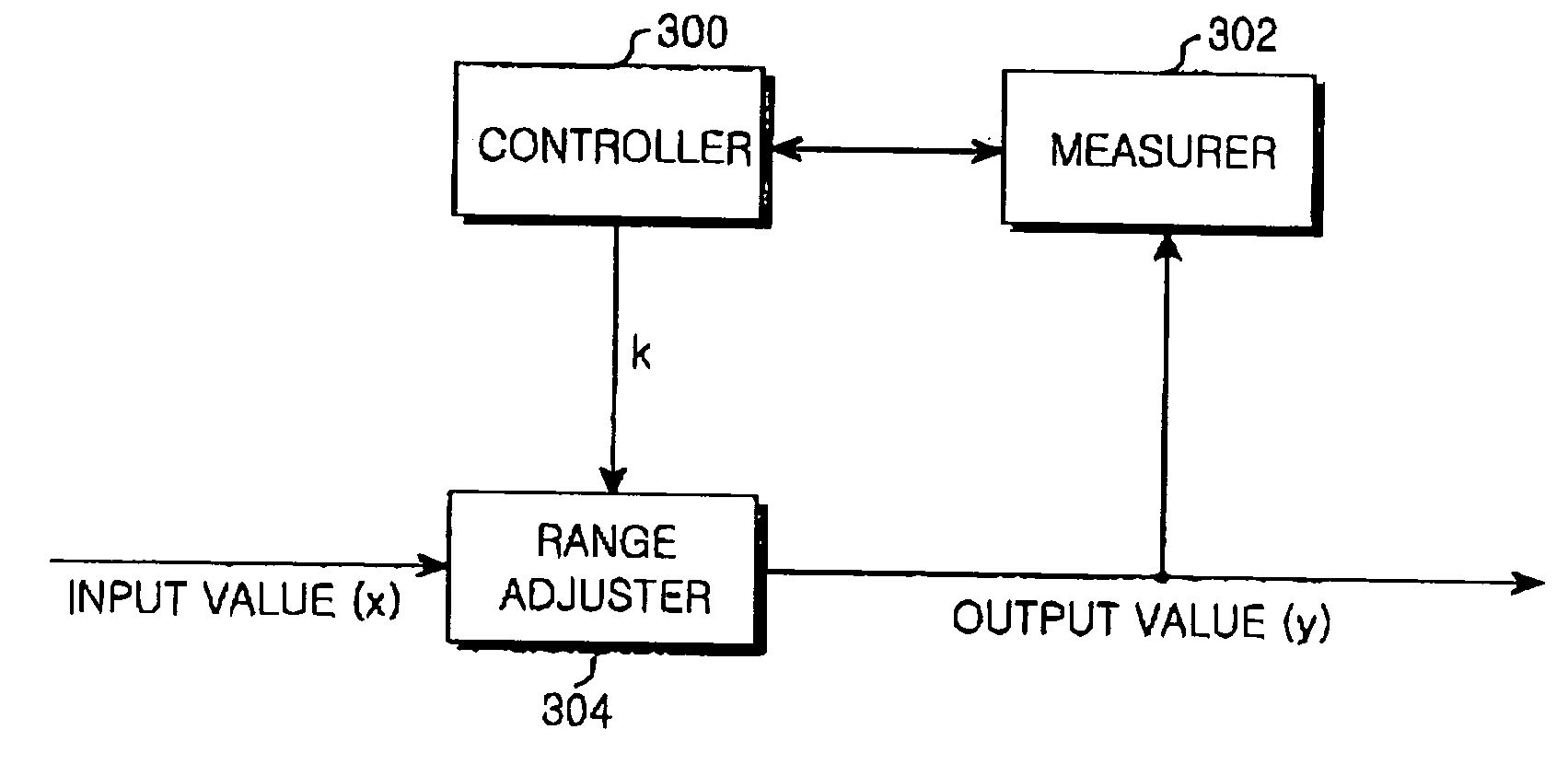

Apparatus and method for adjusting an input range for a soft-decision decoder

ActiveUS20050174980A1Increase memory capacityIncreased circuit complexityError preventionOther decoding techniquesMeasuring outputSoft-decision decoder

An apparatus and method for adjusting a desired expression section according to input bit values in a mobile communication system that expresses only a defined partial section of the input bit values in order to make the number of output bits be less than the number of the input bits, and maps bit values included in unexpressed sections to a specific value is provided. In the apparatus and method, a measurer divides possible output bit values into at least three sections, and measures output frequencies of output bits for the respective sections for a predetermined time. A controller adjusts the desired expression section, when an output frequency for a specific section is greater than output frequencies for other sections.

Owner:SAMSUNG ELECTRONICS CO LTD

Power MOSFET active gate drive based on negative feedback mechanism

ActiveUS11336277B2Sacrificing switching speedIncreased circuit complexityTransistorElectronic switchingCapacitanceDevice material

This invention introduces the negative feedback into the gate drive. It proposes a negative feedback active gate drive (NFAGD) for silicon carbide (SiC) and gallium nitride (GaN) semiconductor devices to fully utilize their potential of high switching-speed capability in a phase-leg configuration. An auxiliary P-channel MOSFET is introduced to construct a negative feedback control mechanism. Due to the negative feedback mechanism, the proposed drive can automatically attenuate the disturbance from the complementary device of the phase-leg. The negative feedback active gate drive (NFAGD) has a simple structure and easy to be realized using a push-pull drive circuit, a drive resistor, an auxiliary MOSFET and an auxiliary capacitor, without involving any additional logical circuits. Functionally, the negative feedback active gate drive (NFAGD) can automatically suppress the induced gate-source voltage and make the gate voltage of the MOSFET stable even during high-speed switching operation without sacrificing the switching speed of the MOSFET.

Owner:BEIJING JIAOTONG UNIV +1

Movie projection system

ActiveUS7884716B2Improve securityImprove the immunityBurglar alarm by openingAnalogue secracy/subscription systemsEngineeringProjection system

In a movie projection system, a switch circuit is disposed on a door of a case in which a video server is disposed. A tamper detector detects a state of the door as to whether the door is open or not and a state of the switch circuit as to whether the switch circuit has been tampered with or not, on the basis of an output signal provided by the switch circuit. A projecting operation controller controls the operation of the movie projection system such that when the door is detected to be in the open state or the switch circuit is detected to have been tampered with, the projecting operation controller stops inputting and outputting video data to or from the video server.

Owner:SONY CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com