Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

54results about How to "Improve data transfer bandwidth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

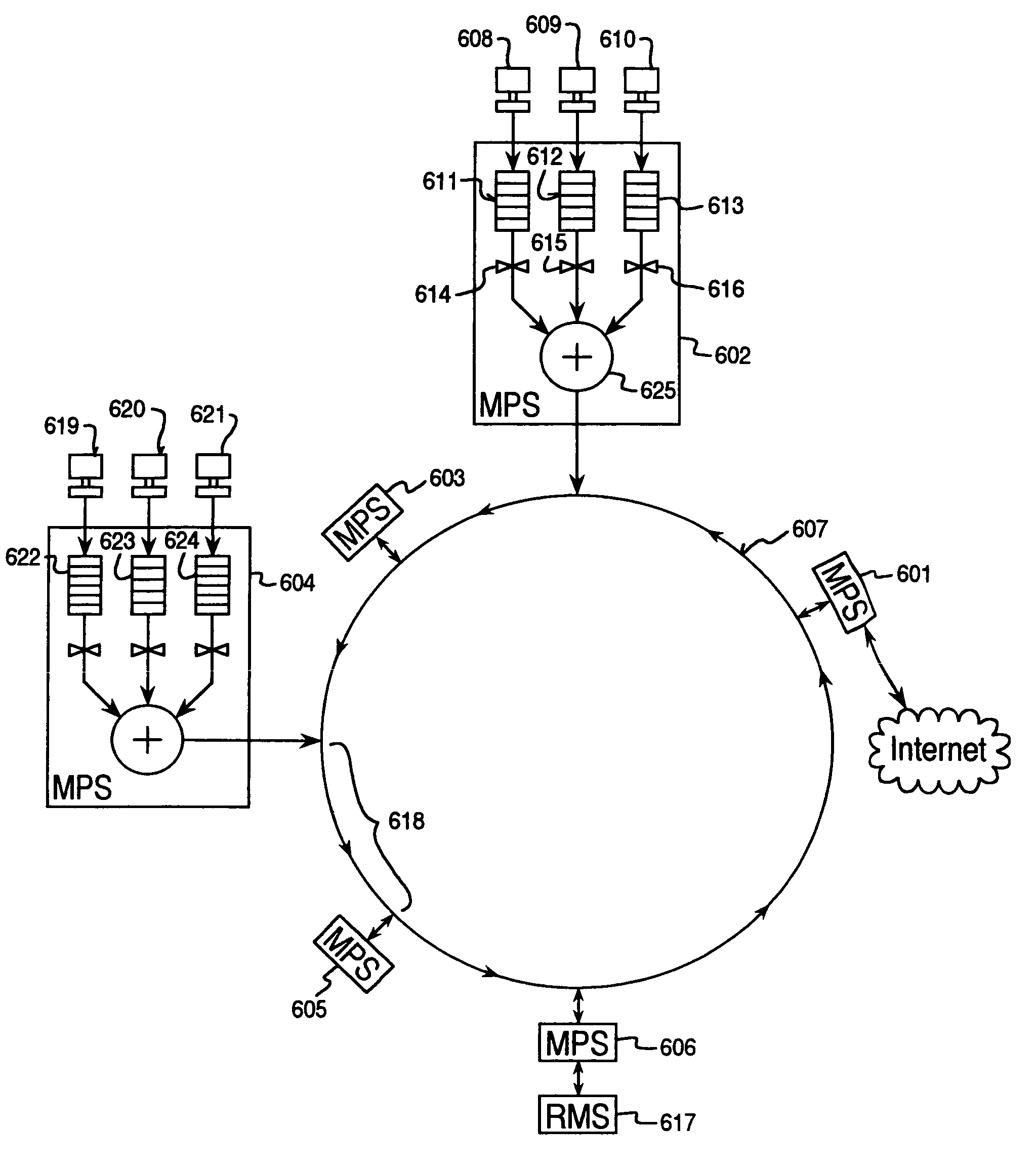

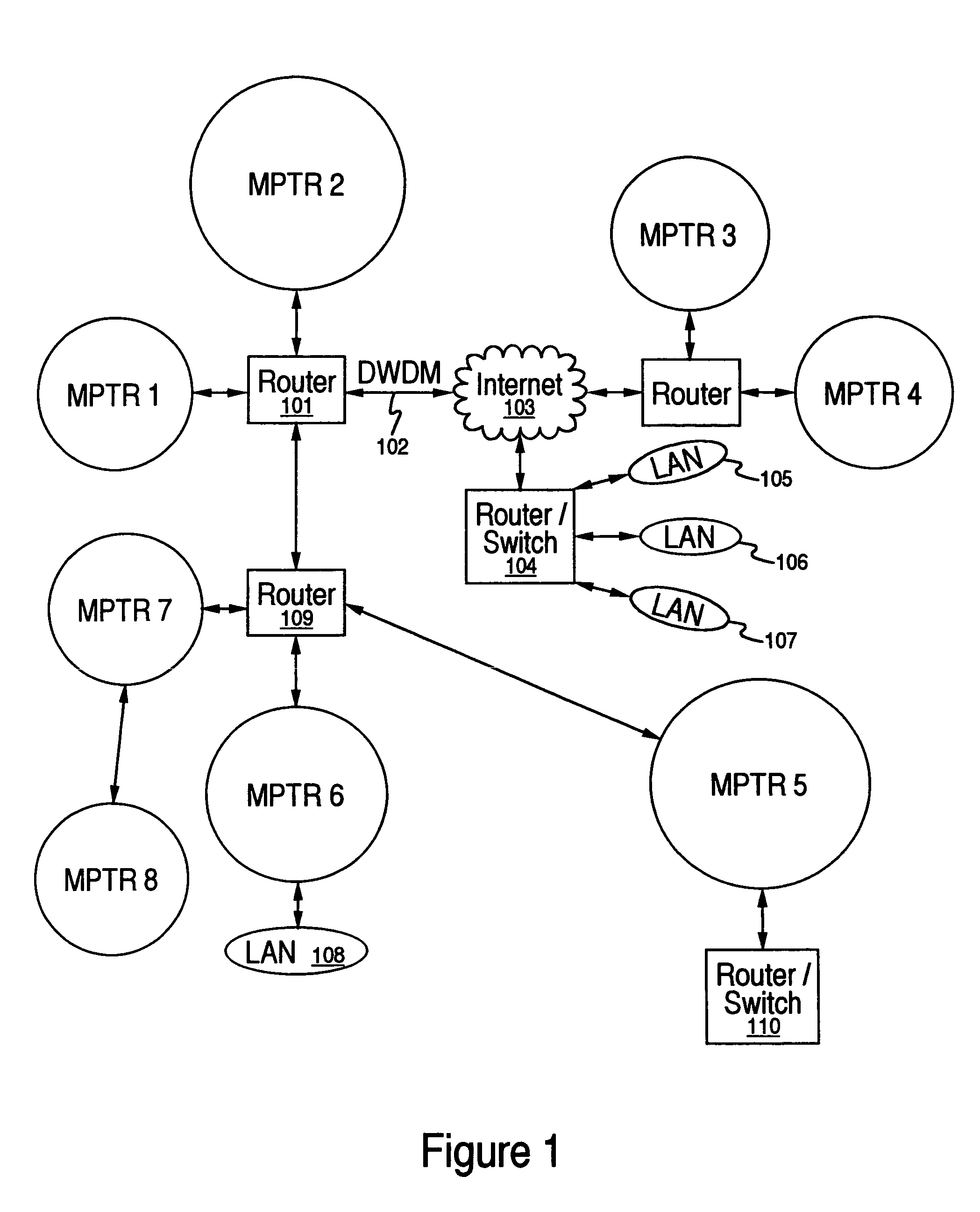

Method and system for weighted fair flow control in an asynchronous metro packet transport ring network

InactiveUS7061861B1Large amount of available bandwidthExcessive buffering delayError preventionFrequency-division multiplex detailsQuality of serviceRing network

A method and system for implementing weighted fair flow control on a metropolitan area network. Weighted fair flow control is implemented using a plurality of metro packet switches (MPS), each including a respective plurality of virtual queues and a respective plurality of per flow queues. Each MPS accepts data from a respective plurality of local input flows. Each local input flow has a respective quality of service (QoS) associated therewith. The data of the local input flows are queued using the per flow queues, with each input flow having its respective per flow queue. Each virtual queue maintains a track of the flow rate of its respective local input flow. Data is transmitted from the local input flows of each MPS across a communications channel of the network and the bandwidth of the communications channel is allocated in accordance with the QoS of each local input flow. The QoS is used to determine the rate of transmission of the local input flow from the per flow queue to the communications channel. This implements an efficient weighted bandwidth utilization of the communications channel. Among the plurality of MPS, bandwidth of the communications channel is allocated by throttling the rate at which data is transmitted from an upstream MPS with respect to the rate at which data is transmitted from a downstream MPS, thereby implementing a weighted fair bandwidth utilization of the communications channel.

Owner:ARRIS ENTERPRISES LLC

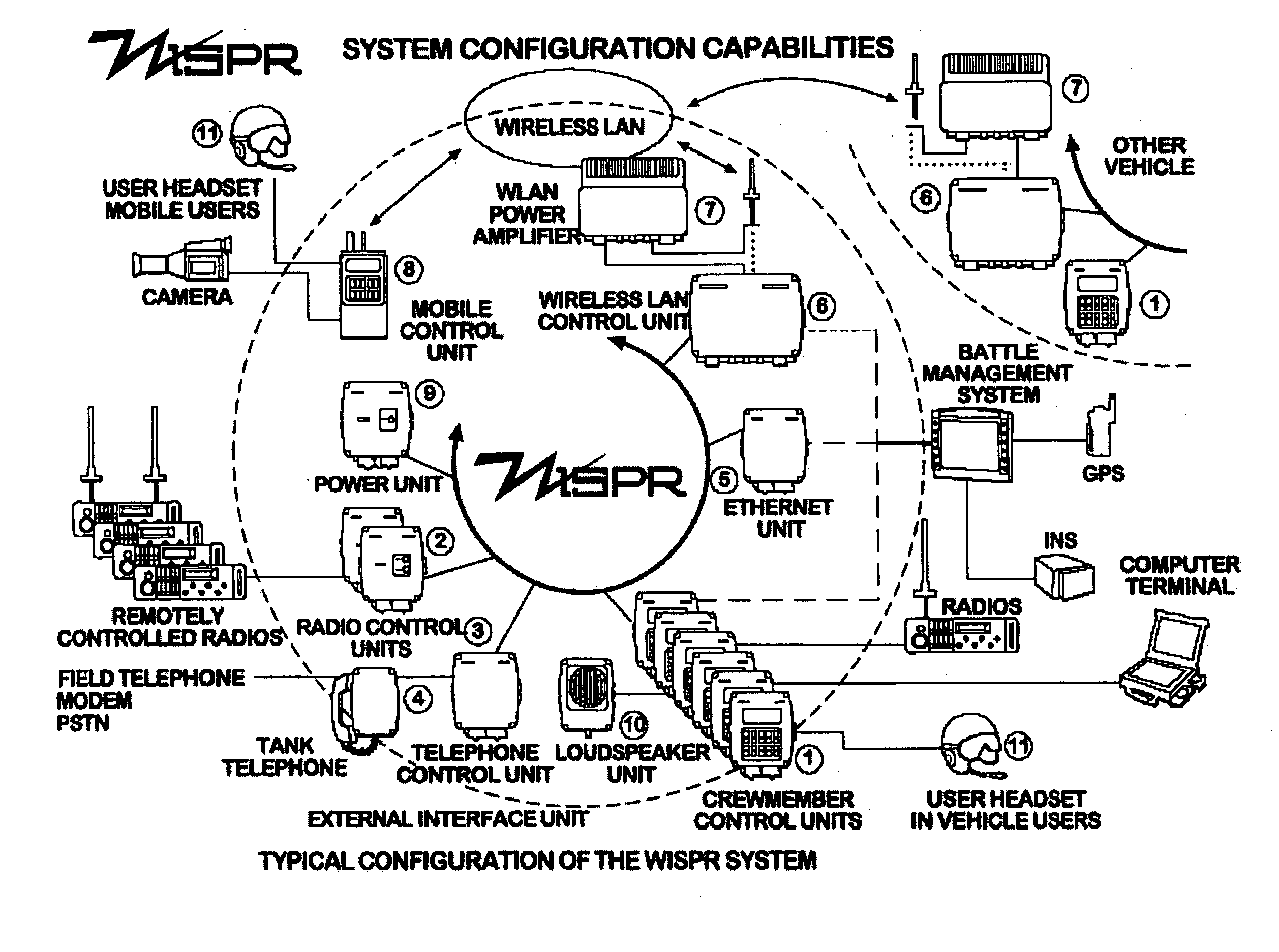

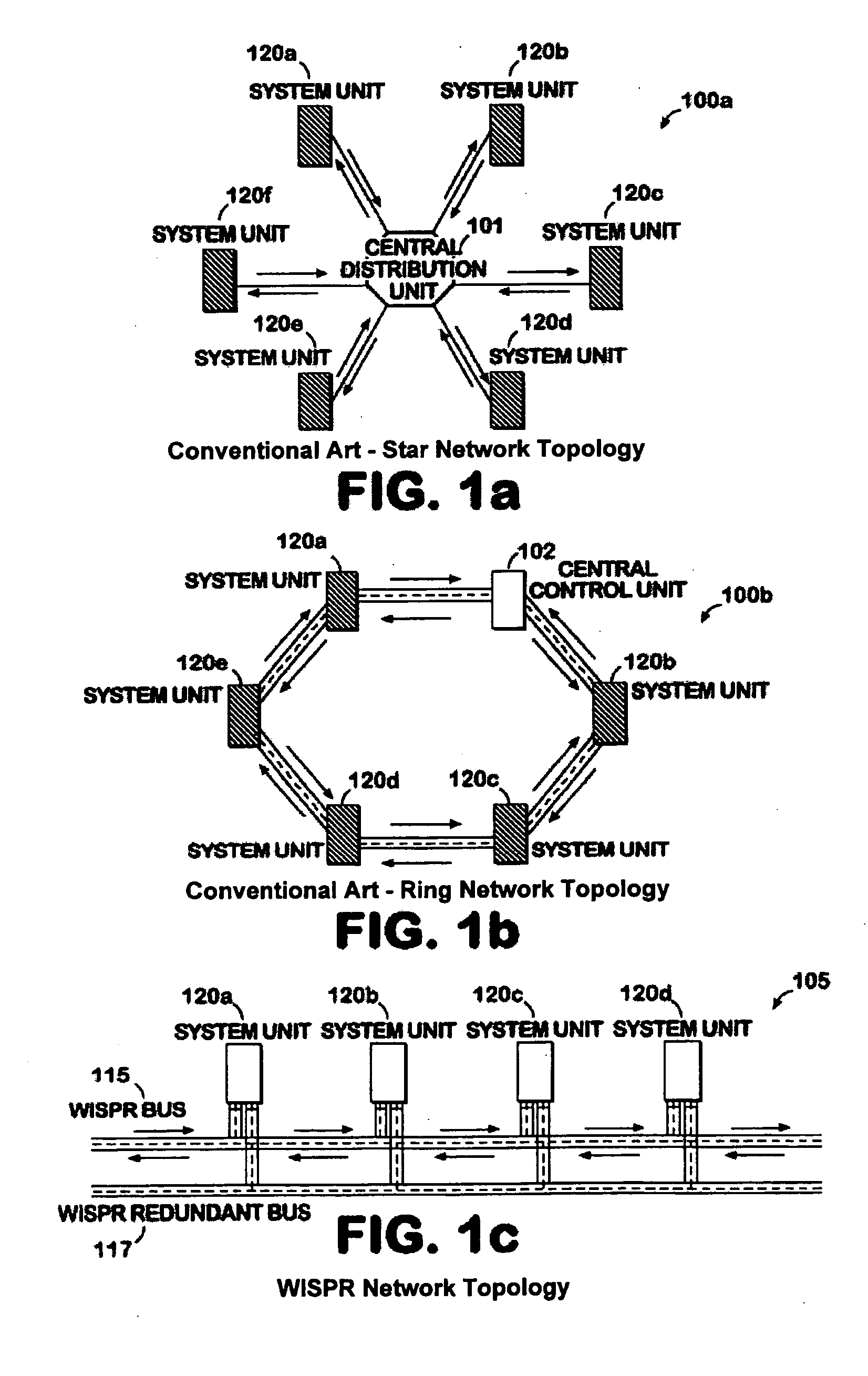

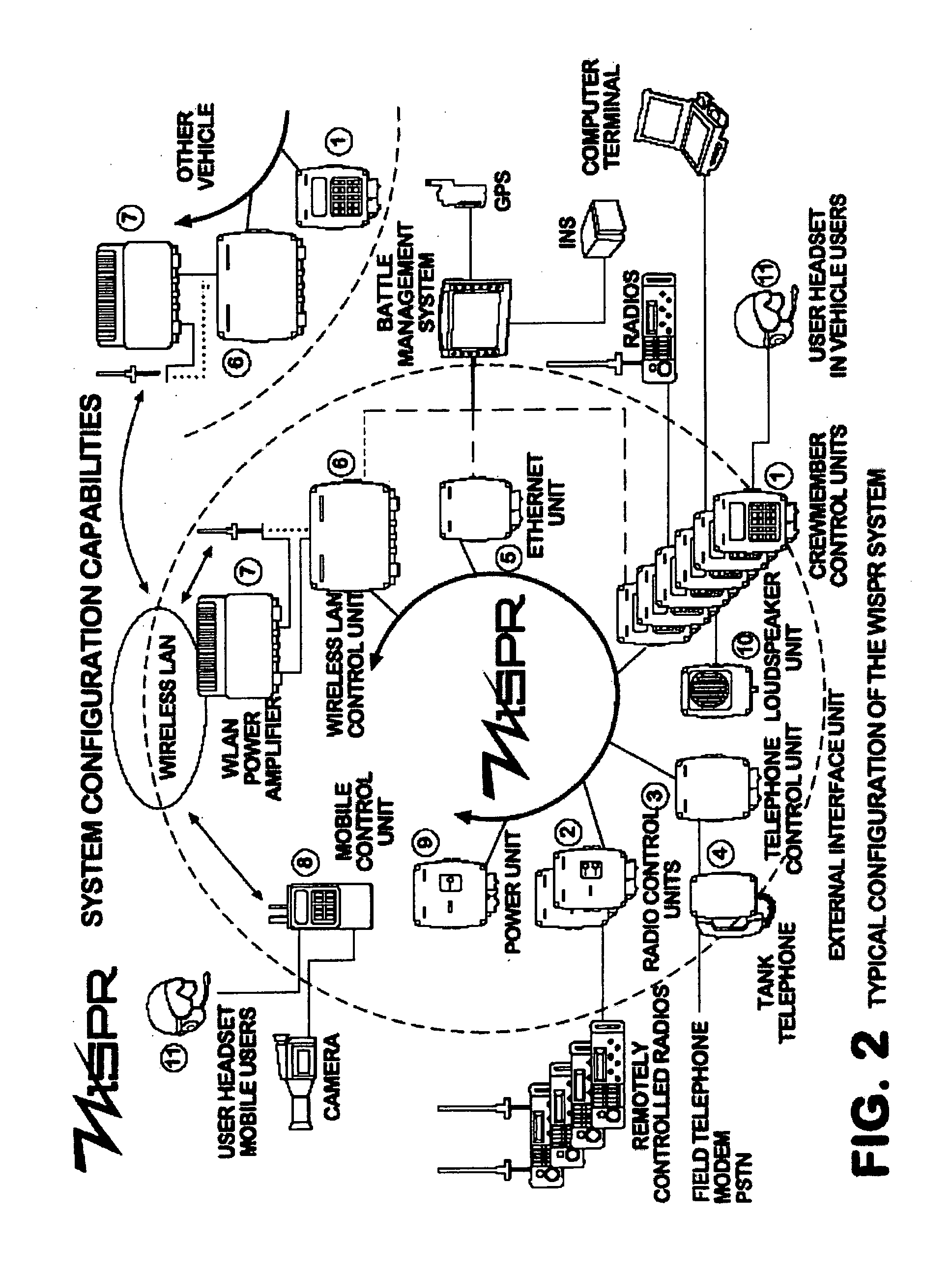

Wideband intercom and secure packet radio (WISPR)

InactiveUS20050232207A1Improve operational capabilitiesHigh degreeTransmission systemsNetwork topologiesAnti jammingSystem configuration

A Wideband Intercom and Secure Packet Radio (WISPR) system includes a state-of-the-art digital, fully programmable communication system that provides internal and external communication to the operators of any type of vehicle. The WISPR system includes a dedicated secure radio with anti-jamming capabilities in order to support a Wireless Local Area Network (WLAN) and is able to provide voice and data communication over radios, analog wires and data / voice over field telephones and tank telephones. The system supports a variety of user specified operational requirements (e.g. hierarchy plans, closed group conference, wired or wireless remote radio control, tactical data reception, independent listen / talk functions) and has the capacity for dynamic adaptation to field requirements and the potential for expansion in order to fulfill the future needs of the Armed Forces. The WISPR system configuration is adaptable according to the type of platform and the particular operational requirements for a specific application.

Owner:INTRACOM DEFENSE ELECTRONICS SYST

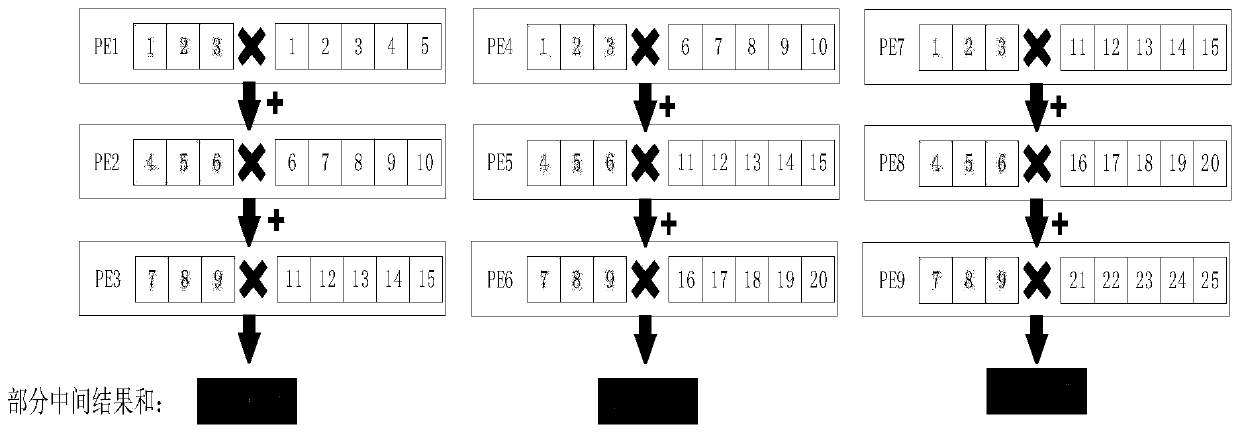

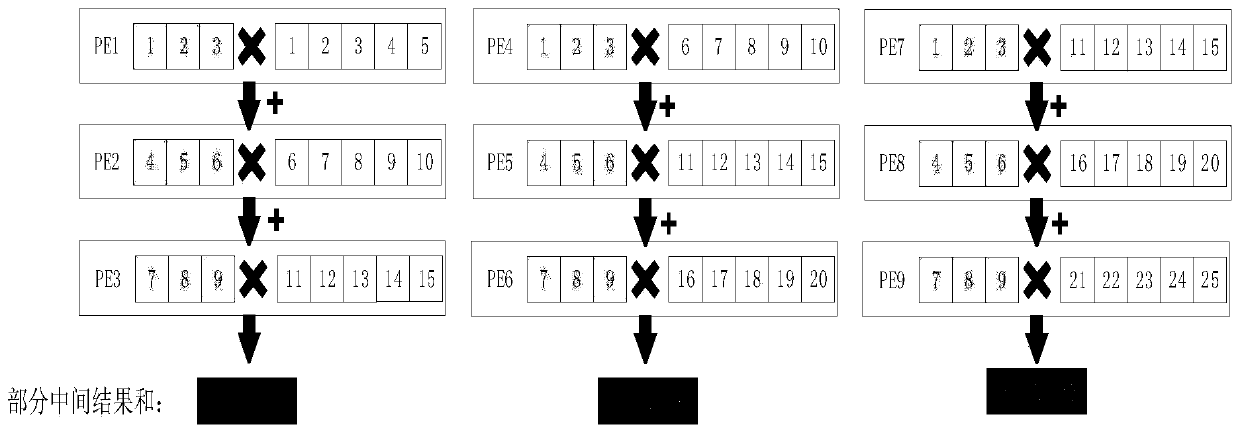

Convolutional neural network acceleration engine, convolutional neural network acceleration system and method

ActiveCN111178519AReduce data accessImprove performanceNeural architecturesPhysical realisationAlgorithmTerm memory

The invention discloses a convolutional neural network acceleration engine, a convolutional neural network acceleration system and a convolutional neural network acceleration method, and belongs to the field of heterogeneous computing acceleration, wherein the physical PE matrix comprises a plurality of physical PE units, and the physical PE units are used for executing row convolution operation and related partial sum accumulation operation; the XY interconnection bus is used for transmitting the input feature image data, the output feature image data and the convolution kernel parameters from the global cache to the physical PE matrix, or transmitting an operation result generated by the physical PE matrix to the global cache; the adjacent interconnection bus is used for transmitting anintermediate result between the same column of physical PE units; the system comprises a 3D-Memory, and a convolutional neural network acceleration engine is integrated in a memory controller of eachVault unit and used for completing a subset of a convolutional neural network calculation task; the method is optimized layer by layer on the basis of the system. According to the invention, the performance and energy consumption of the convolutional neural network can be improved.

Owner:HUAZHONG UNIV OF SCI & TECH

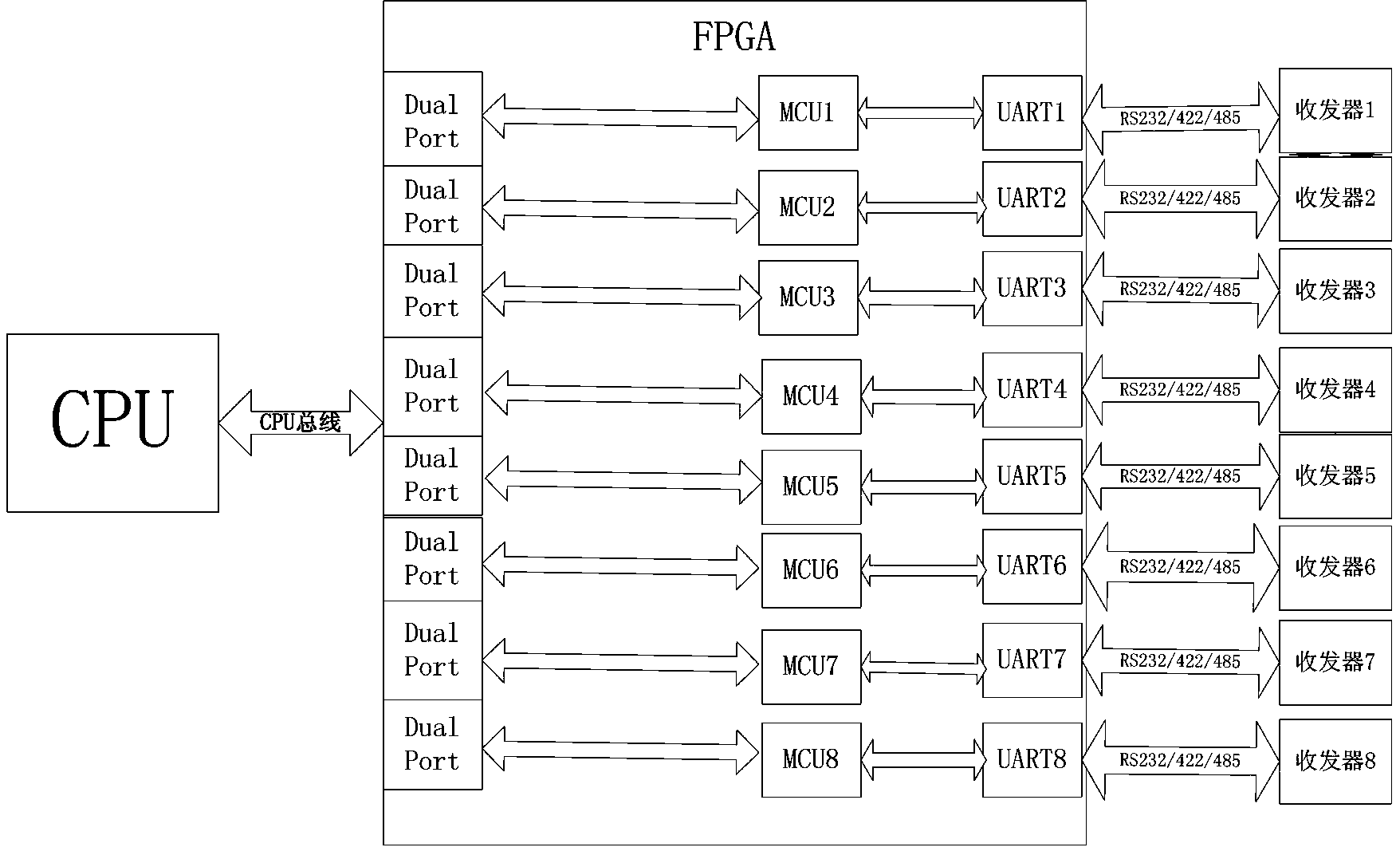

Multi-serial-port parallel processing framework based on FPGA

InactiveCN103713543AReduce loadFlexibility to increase or decrease the quantityProgramme controlComputer controlTransceiverFpga chip

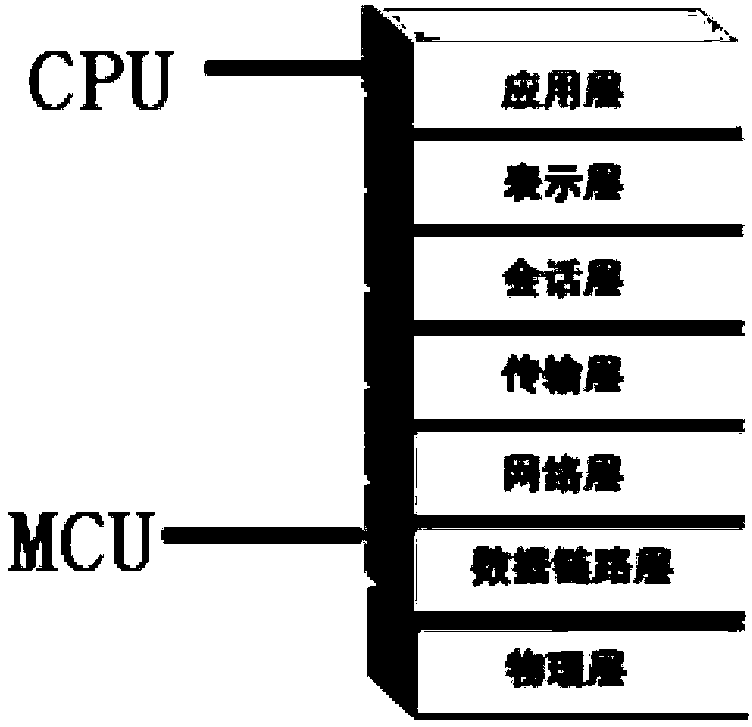

The invention belongs to the technical field of distributed industrial control, and relates to a multi-serial-port parallel processing framework based on an FPGA. The framework comprises transceivers, an FPGA programmable logic chip and a processor CPU. The CPU is connected with the FPGA chip via a CPU interface bus. The framework is characterized in that: multiple UART cores and multiple co-processor MCUs which are corresponding to all the UART cores are designed in the FPGA chip via a hardware description language; multiple embedded type storage devices which are corresponding to all the co-processor MCUs are embedded in the FPGA, and each embedded type storage device is configured to be a dual-port mode capable of performing read-write operation; and the multiple UART cores are connected with the multiple corresponding transceivers via RS232 / RS422 / RS485 interfaces. The framework is low in hardware design cost so that a CPU load can be effectively reduced, serial bus data transmission bandwidth can be enhanced and multipath serial channels can be flexibly expanded.

Owner:STATE NUCLEAR POWER AUTOMATION SYST ENGCO

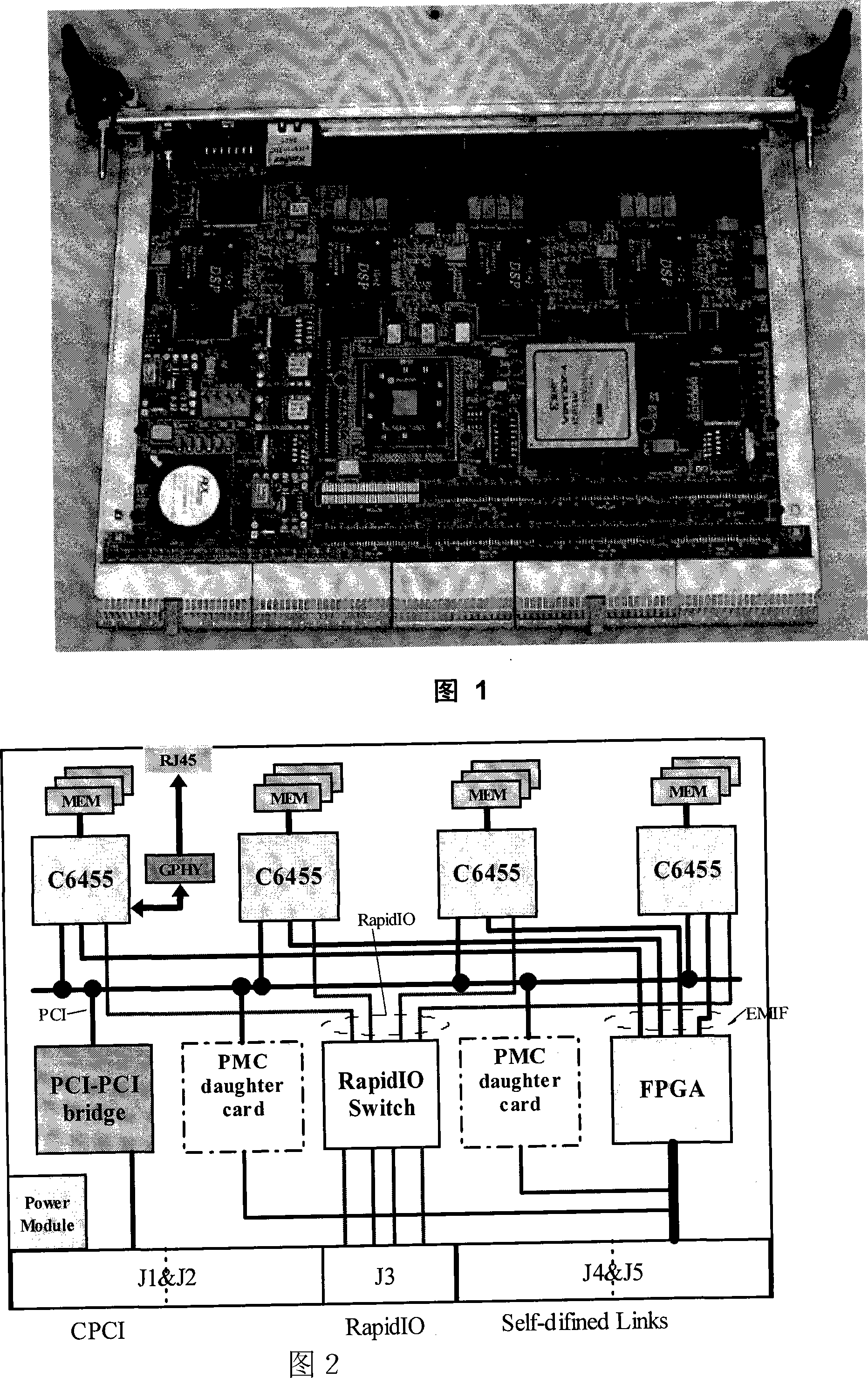

Scalable DSPEED-DSP_Q6455 signal processing board based on switcher

InactiveCN101102197AEasy to handleLarge storage capacityData switching detailsData switching by path configurationExtensibilityThe Internet

The card thereof comprises seven power modules, four processing nodes, a chipset for interconnecting said processing nodes and a gigabit Ethernet port. The communication protocol comprises PCI protocol, serial RapidIO protocol and gigabit Ethernet protocol. The board type is cPCI standard board type. The working platform is an engineering control computer platform. The method for constructing internet is: based on the switch mode under serial RapidIO protocol, based on the sync transmission mode of FPGA, based on cPCI protocol bus mode, and based on gigabit Ethernet mode. The invention can be used in radar signal process, image process and base station.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

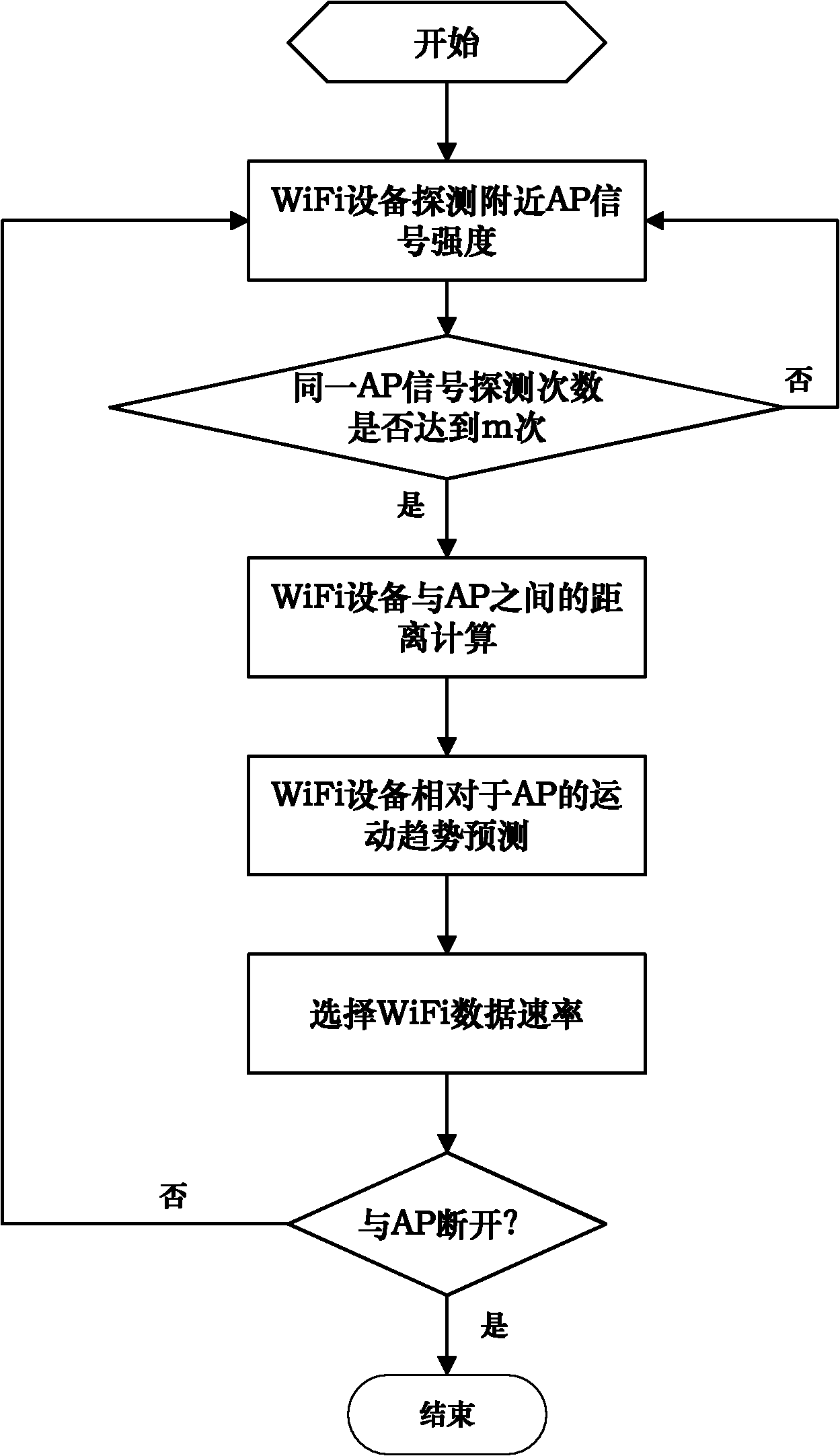

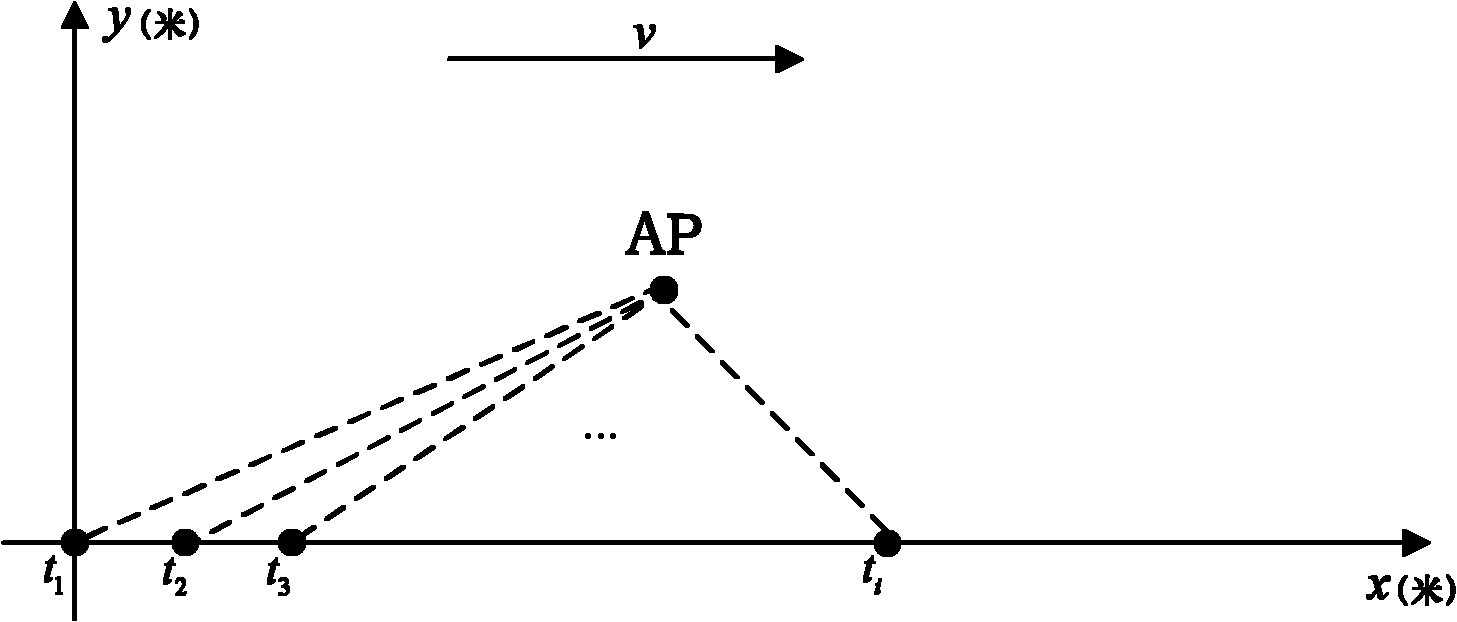

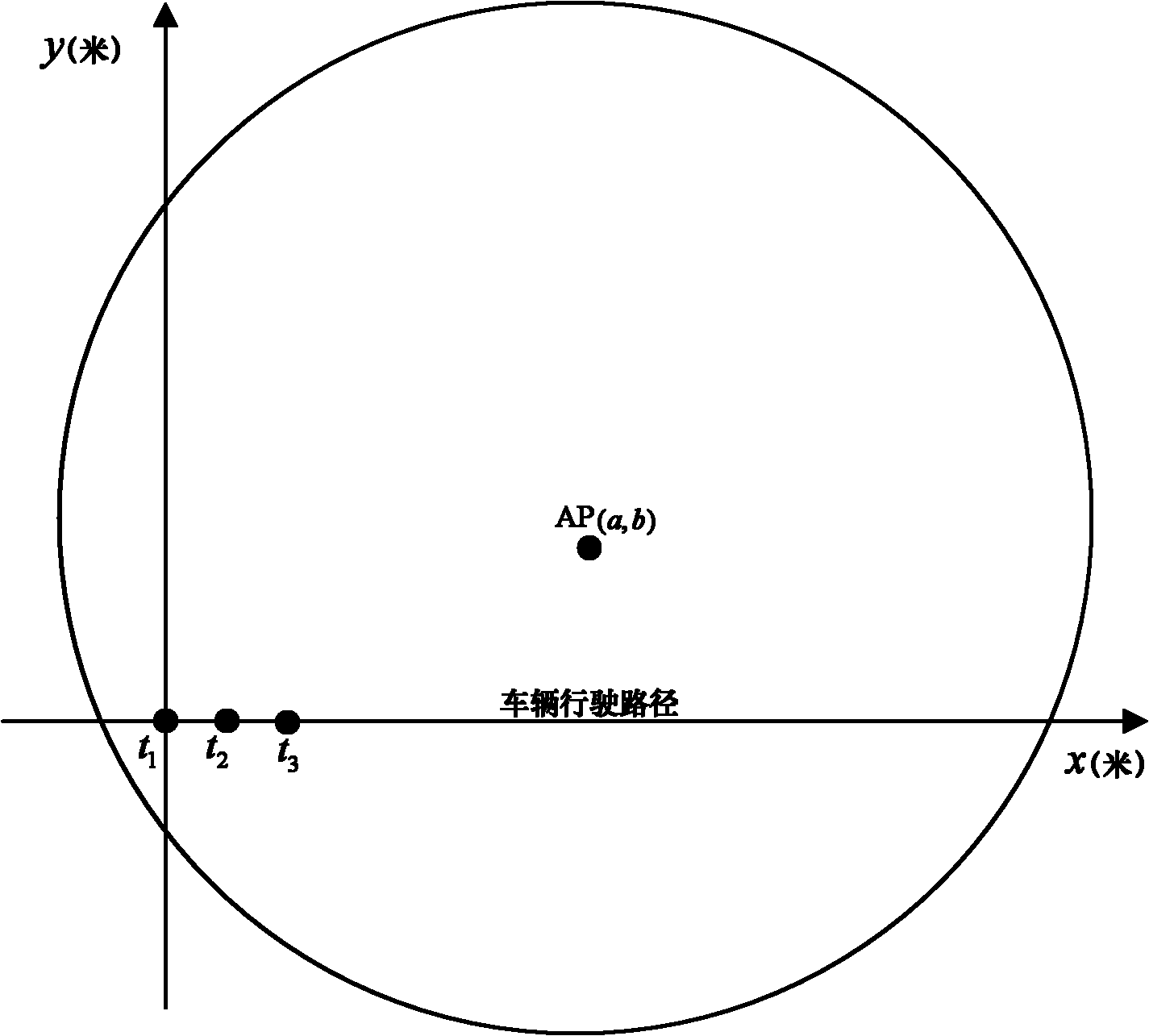

Mobility-prediction-based wireless fidelity (WiFi) speed self-adapting selecting method

InactiveCN102075297AImprove data transfer bandwidthChange sending rate in real timeError preventionNetwork traffic/resource managementData rateEngineering

The invention provides a mobility-prediction-based wireless fidelity (WiFi) speed self-adapting selecting method, which belongs to the communication field. Firstly a vehicle WiFi device continuously detects the strength of access point (AP) signals nearby, the strength value of the detected AP signal is converted to a corresponding distance value, and the movement trend of the vehicle WiFi deviceis predicted according to a plurality of distance values; and a data speed of the WiFi device is selected according to the movement trend of the vehicle WiFi device and a distance-data speed table which is obtained through the experiment. By the method provided by the invention, the shaking of the data speed of the WiFi device during the moving process of a vehicle can be reduced, and the data transmission efficiency can be improved.

Owner:BEIHANG UNIV

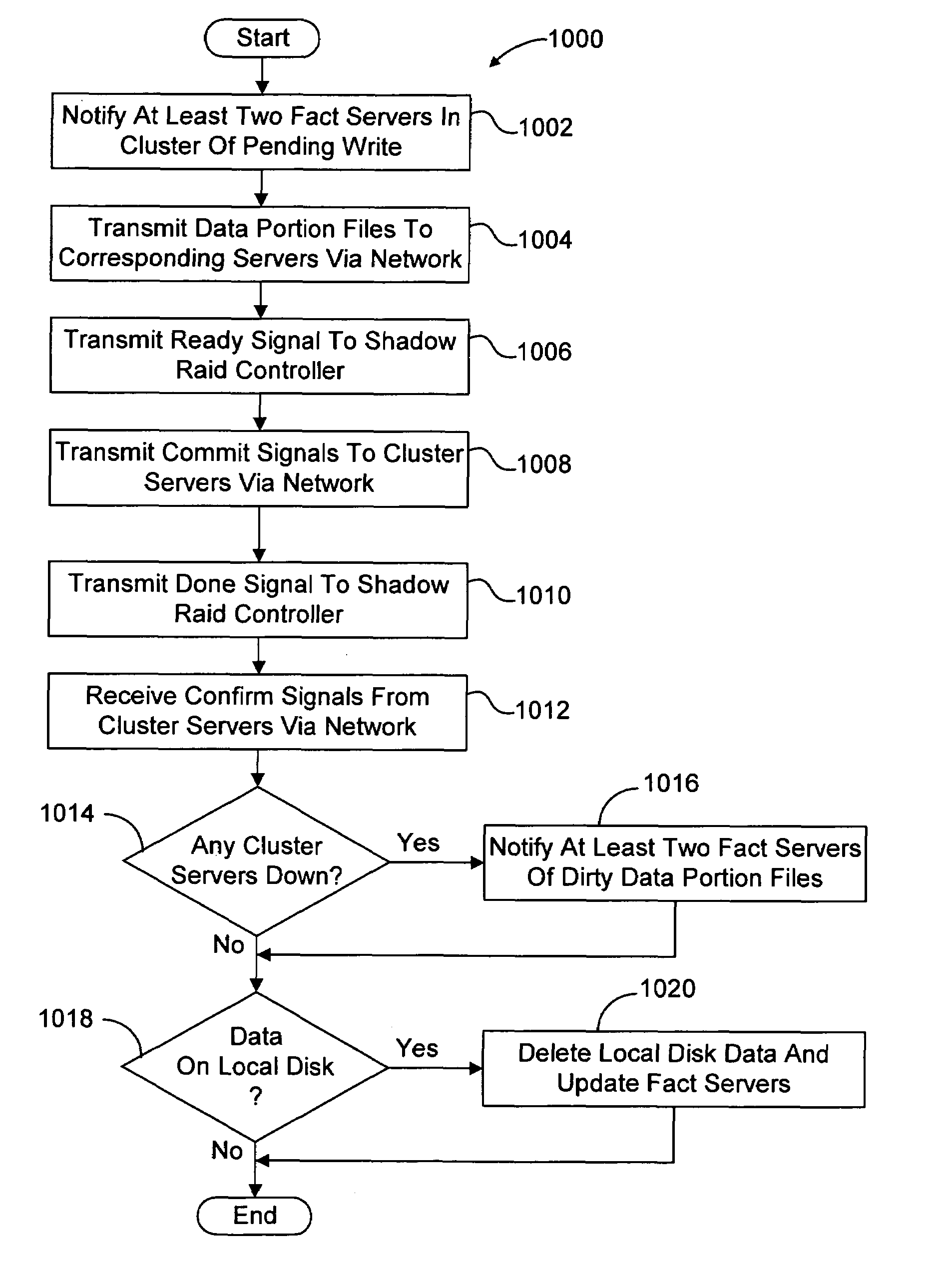

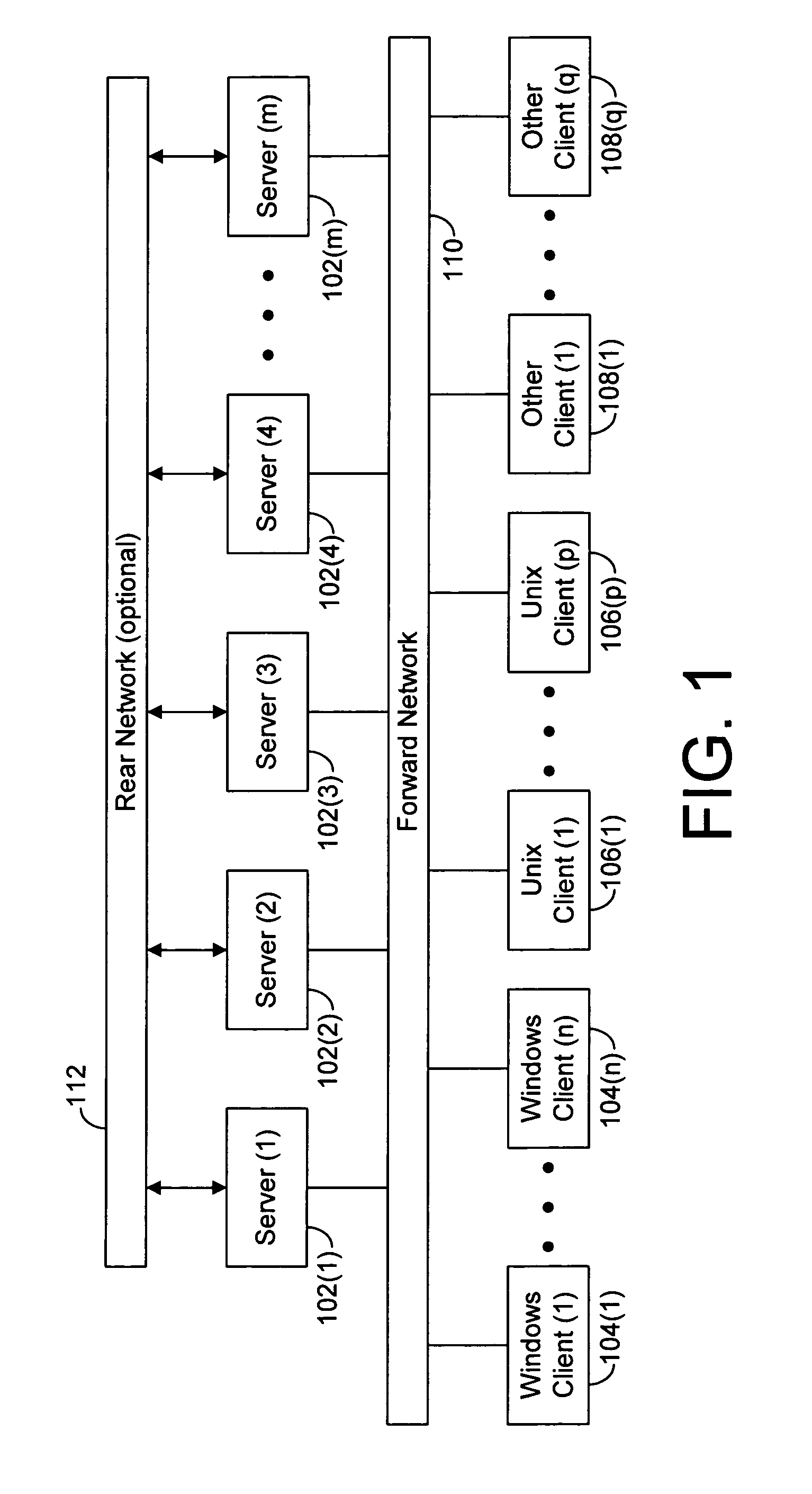

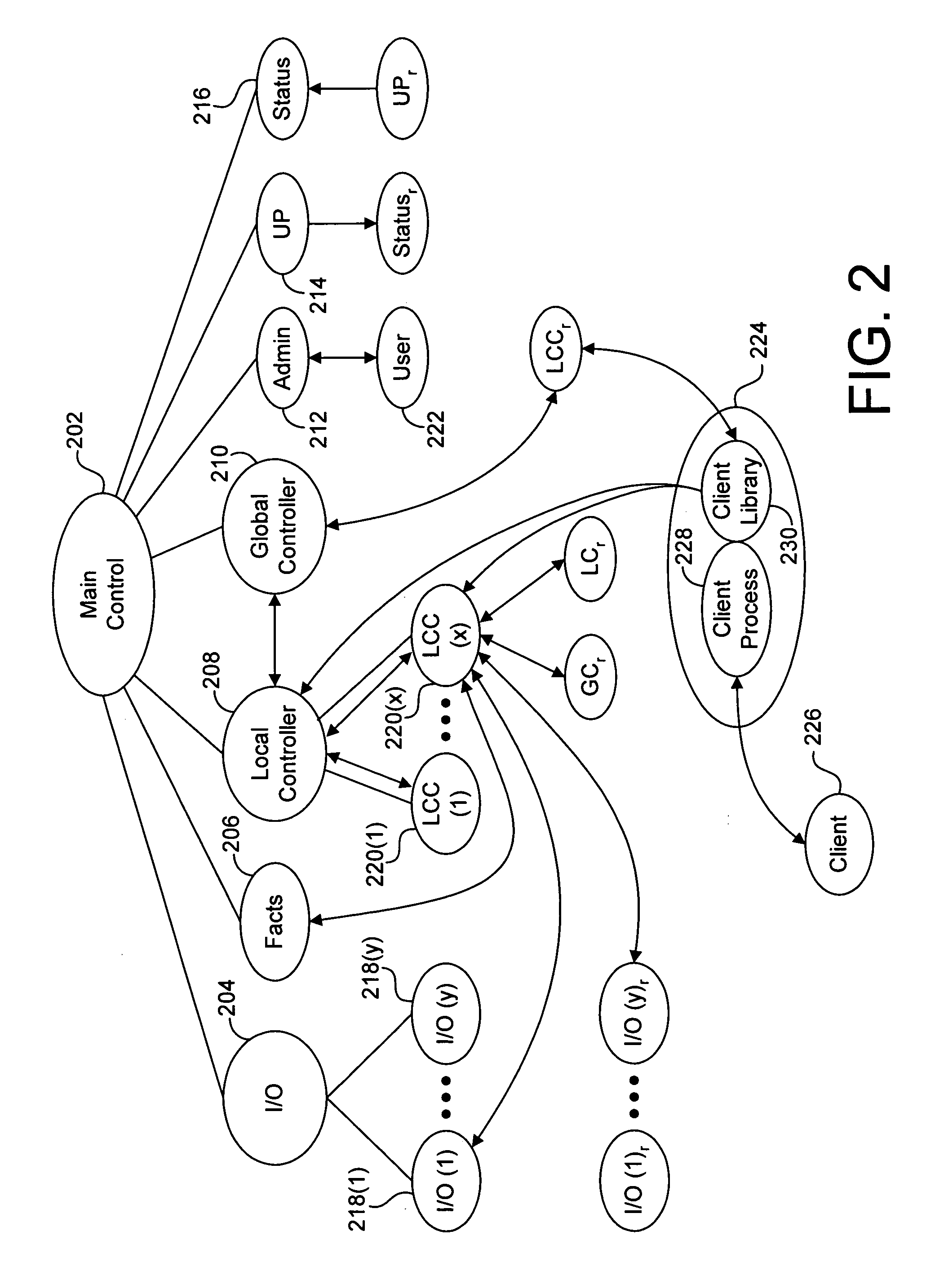

System and method for distributed network data storage

InactiveUS7085819B2Facilitate writing dataFacilitates incremental augmentationInput/output to record carriersMultiple digital computer combinationsRAIDData set

A distributed network data storage method includes receiving a data set from a client, defining a virtual device to include a plurality of device portions each on one of a plurality of network servers, parsing the data set into a plurality of data portions, and writing each of the data portions to a corresponding one of the virtual device portions. Methods are also disclosed for securely writing data to the virtual devices, and for identifying and reconstructing corrupt data. A system for implementing the data storage / retrieval method includes a plurality of network servers, each running a distributed RAID server application. The servers communicate with clients via a first network, and with each other via a second network.

Owner:SIGMA STORAGE

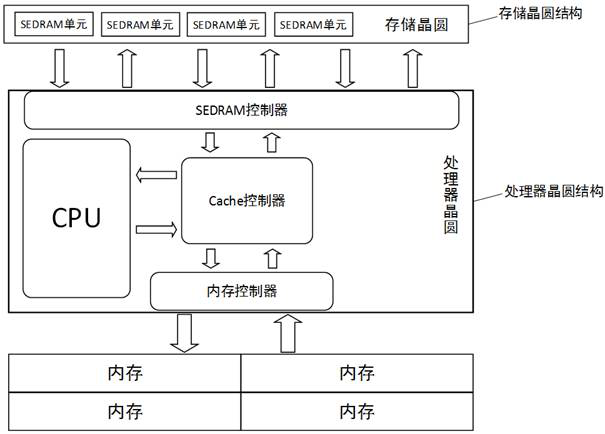

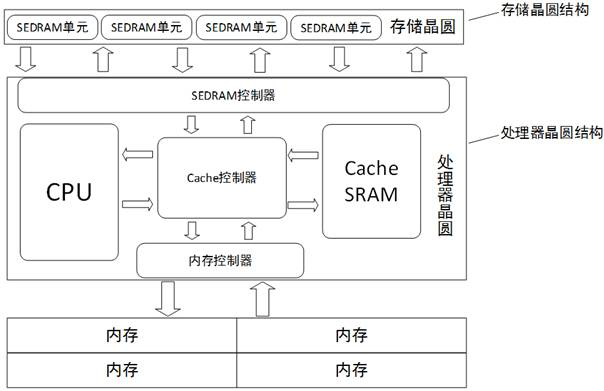

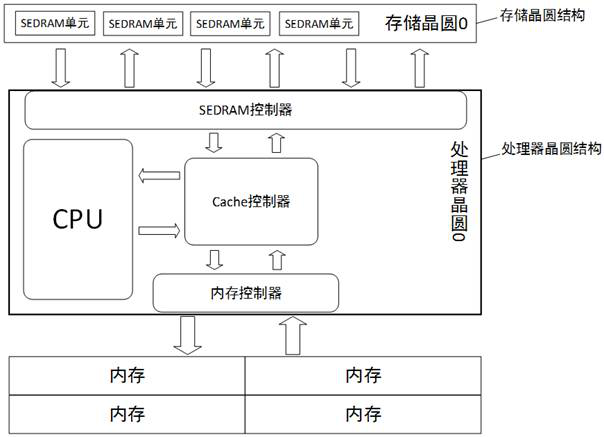

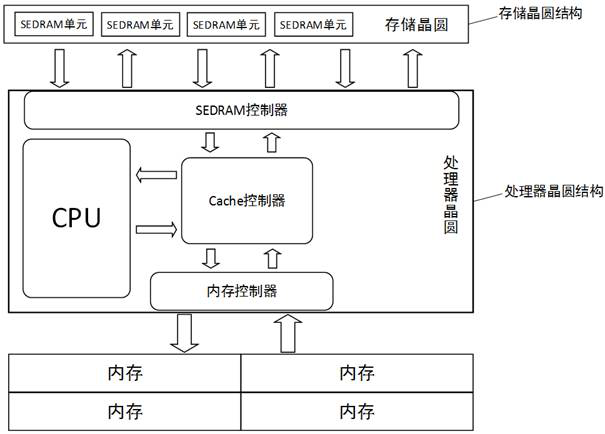

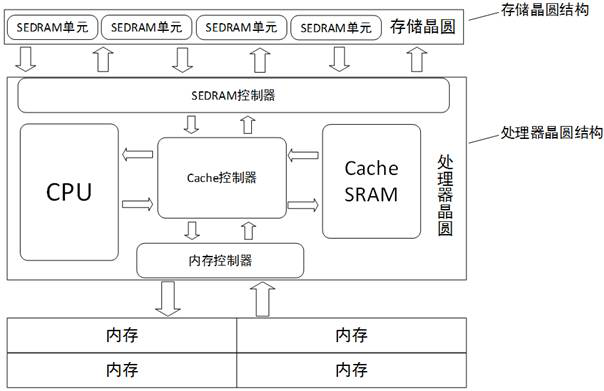

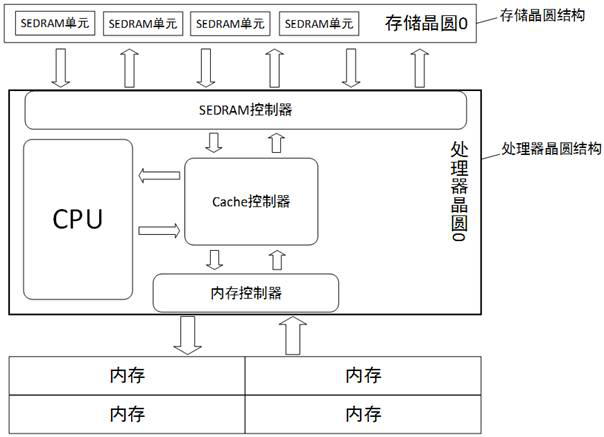

Stacked Cache system based on SEDRAM, control method and Cache device

ActiveCN112558889ALarge capacityBreak outInput/output to record carriersResource allocationWaferTerm memory

The invention relates to a stacked Cache system based on an SEDRAM, a control method and a Cache device, the stacked Cache system is integrated on a multi-layer bonding wafer and comprises a cache memory, a Cache controller and an SEDRAM controller; wherein the multi-layer bonding wafer comprises a storage wafer structure and a processor wafer structure; the SEDRAM unit is integrated in each layerof storage wafer in the storage wafer structure and is used as a storage space of the high-speed buffer memory; the processor wafer structure is integrated with a CPU, a Cache controller, an SEDRAM controller and a memory controller. According to the Cache system, the SEDRAM unit integrated on each layer of storage wafer of the storage wafer structure is used as the storage space of the cache memory, so that the capacity and bandwidth of the cache memory can be greatly improved, the hit rate of the cache memory is increased, the reading speed of hot spot data is increased, the hit rate of data read in a CPU is increased, and meanwhile, storage resources of the processor chip can be saved.

Owner:BEIJING VCORE TECH CO LTD

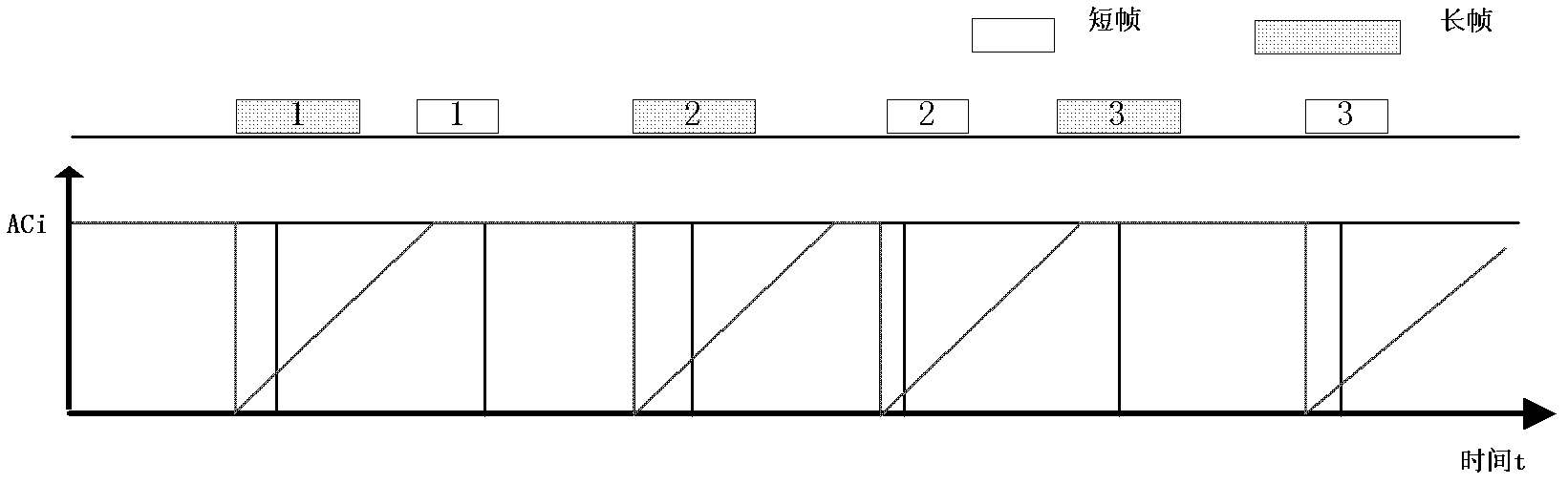

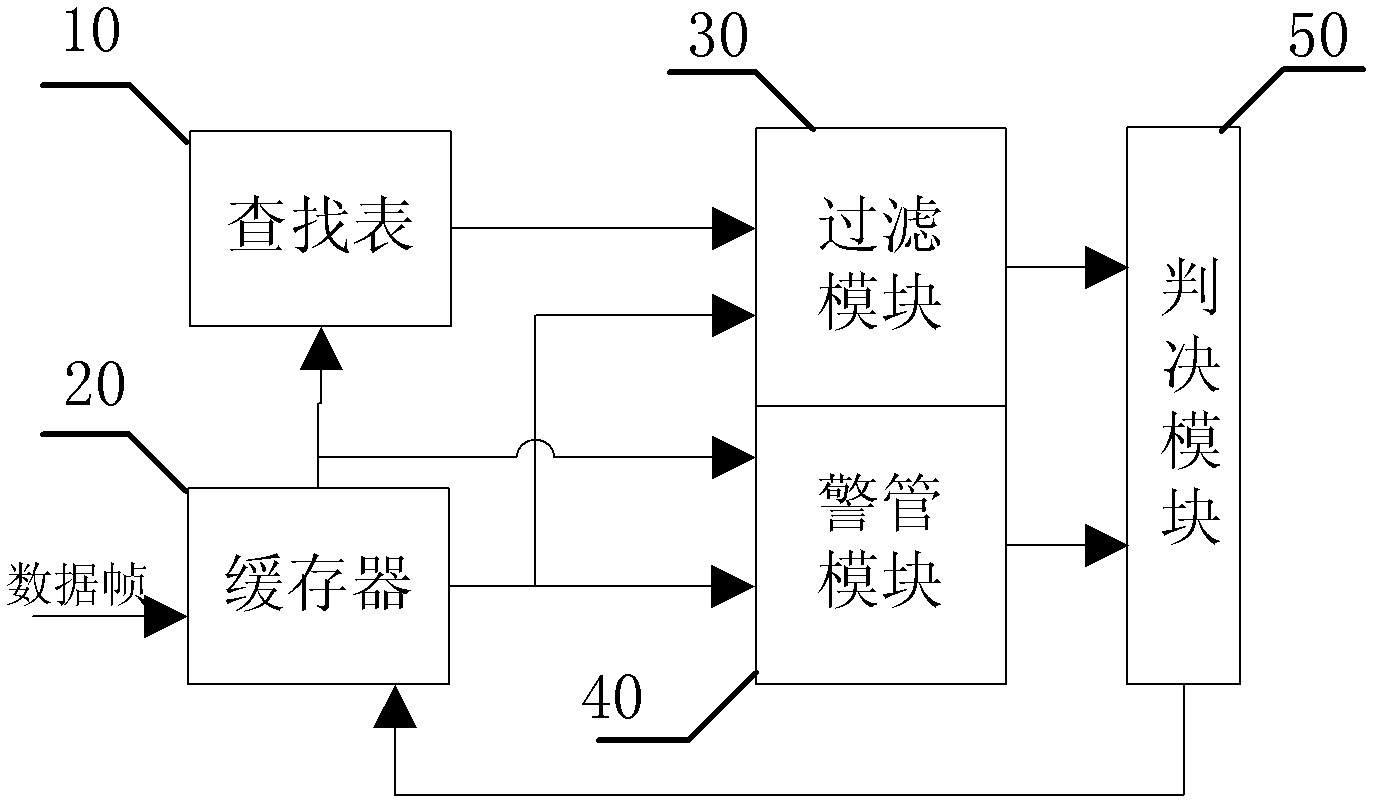

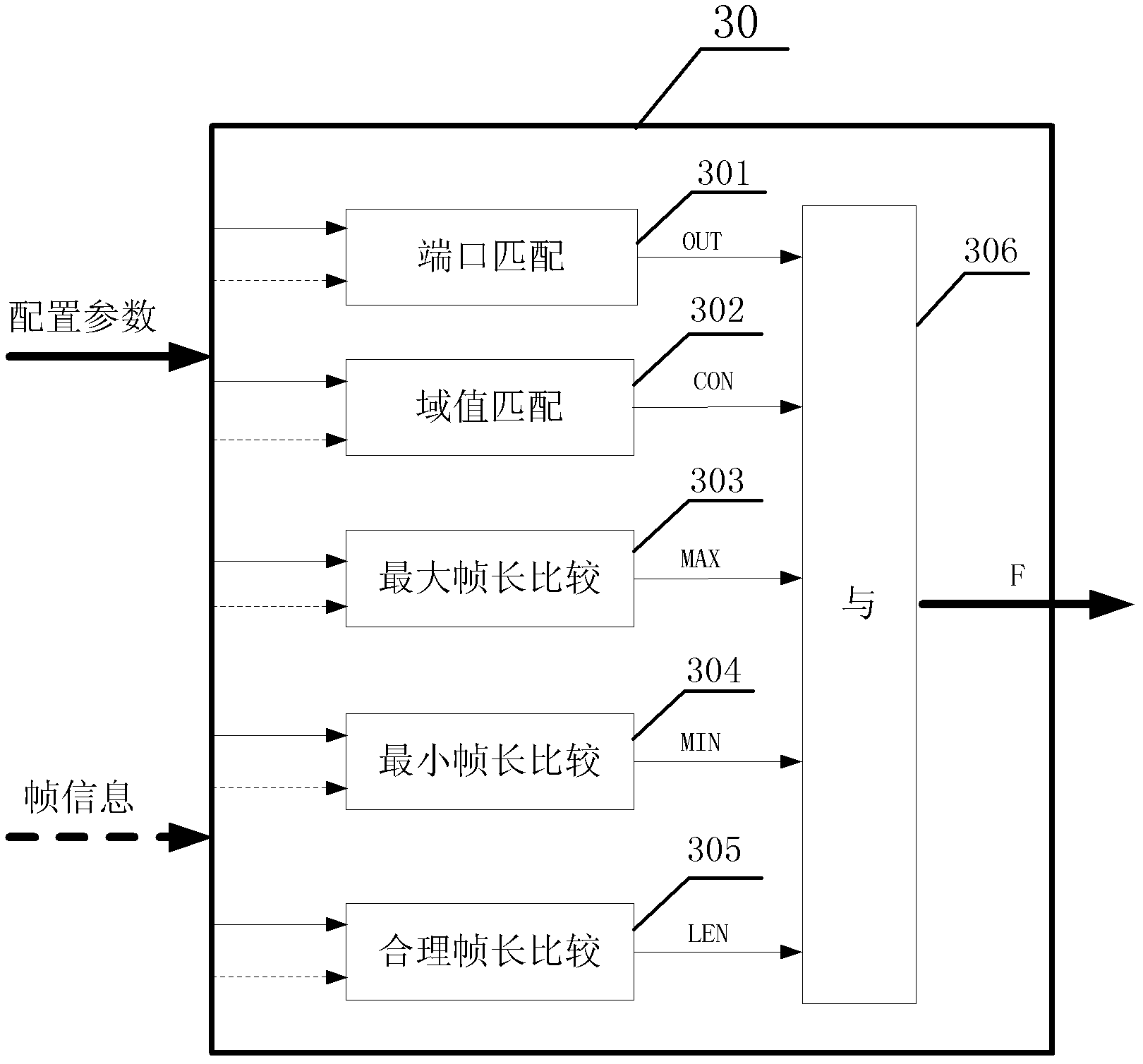

Byte-based filtering and policing system and method of avionics full duplex switched Ethernet (AFDX) switch

InactiveCN102497285ASolve the lossMeet data transfer requirementsData switching networksExchange networkPass rate

The invention discloses a byte-based filtering and policing tube system and a byte-based filtering and policing tube method of an avionics full duplex switched Ethernet (AFDX) switch, mainly solves the problem of frame loss under the condition of larger jitter and different frame lengths. The system comprises a cache, a lookup table, a filtering module, a policing tube module and a determination module, wherein the cache stores data frames and extracts the virtual link (VL) and the frame information of the data frames; the VL is used for searching for the filtering parameters of the data frames in the lookup table; the filtering parameters are compared with the frame information in the filtering module to determine whether the data frames meet a filtering requirement; a byte leaky bucket algorithm is used for controlling data frame traffic in the policing tube module simultaneously; and finally, the determination module is used for determining whether the data frames are permitted to enter a switched network. According to the invention, the implementation method is simple, system resources are saved, the pass rate of the data frames is high, the network switching performance can be improved, and the system and method can be used for filtering data frames and controlling flow rate in an AFDX.

Owner:XIDIAN UNIV

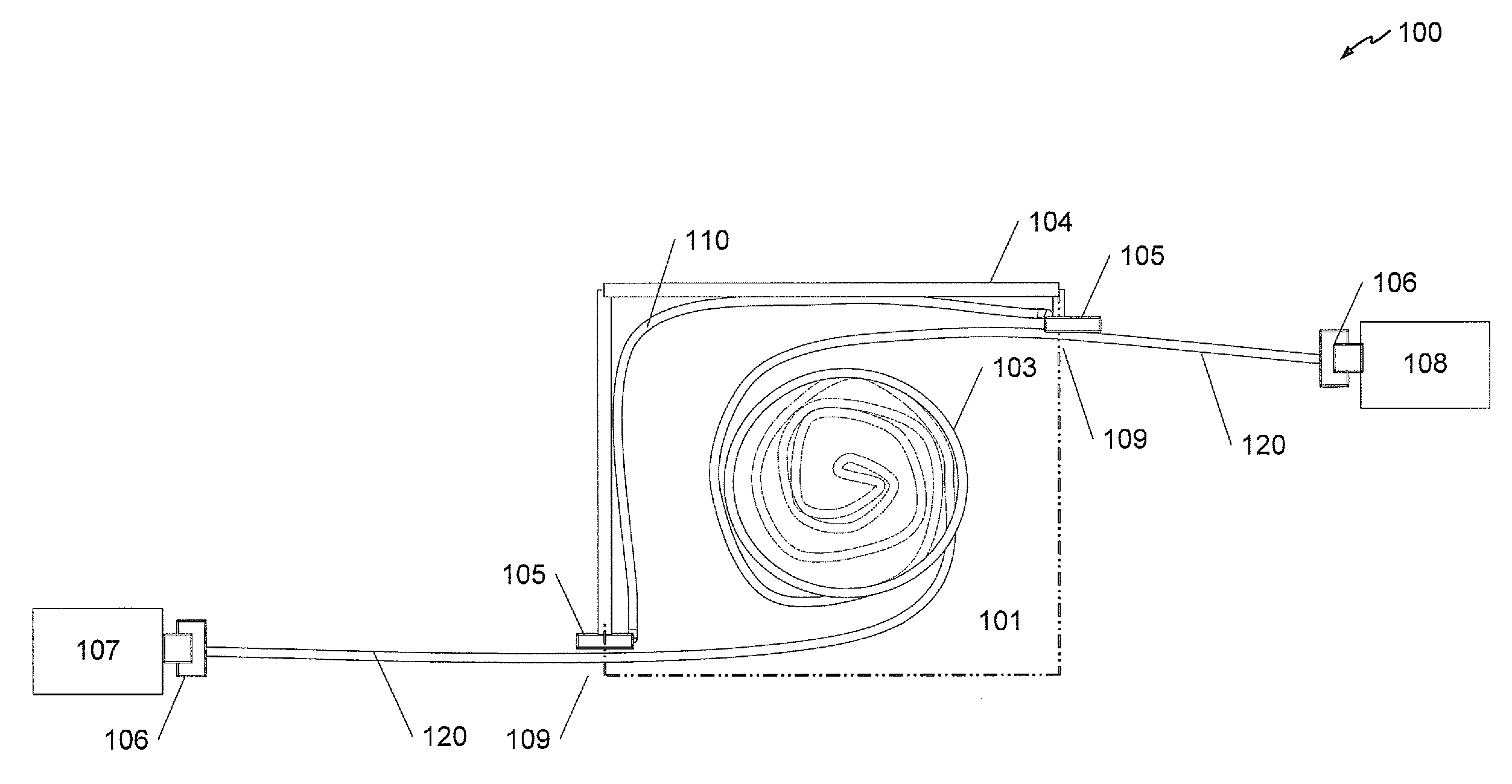

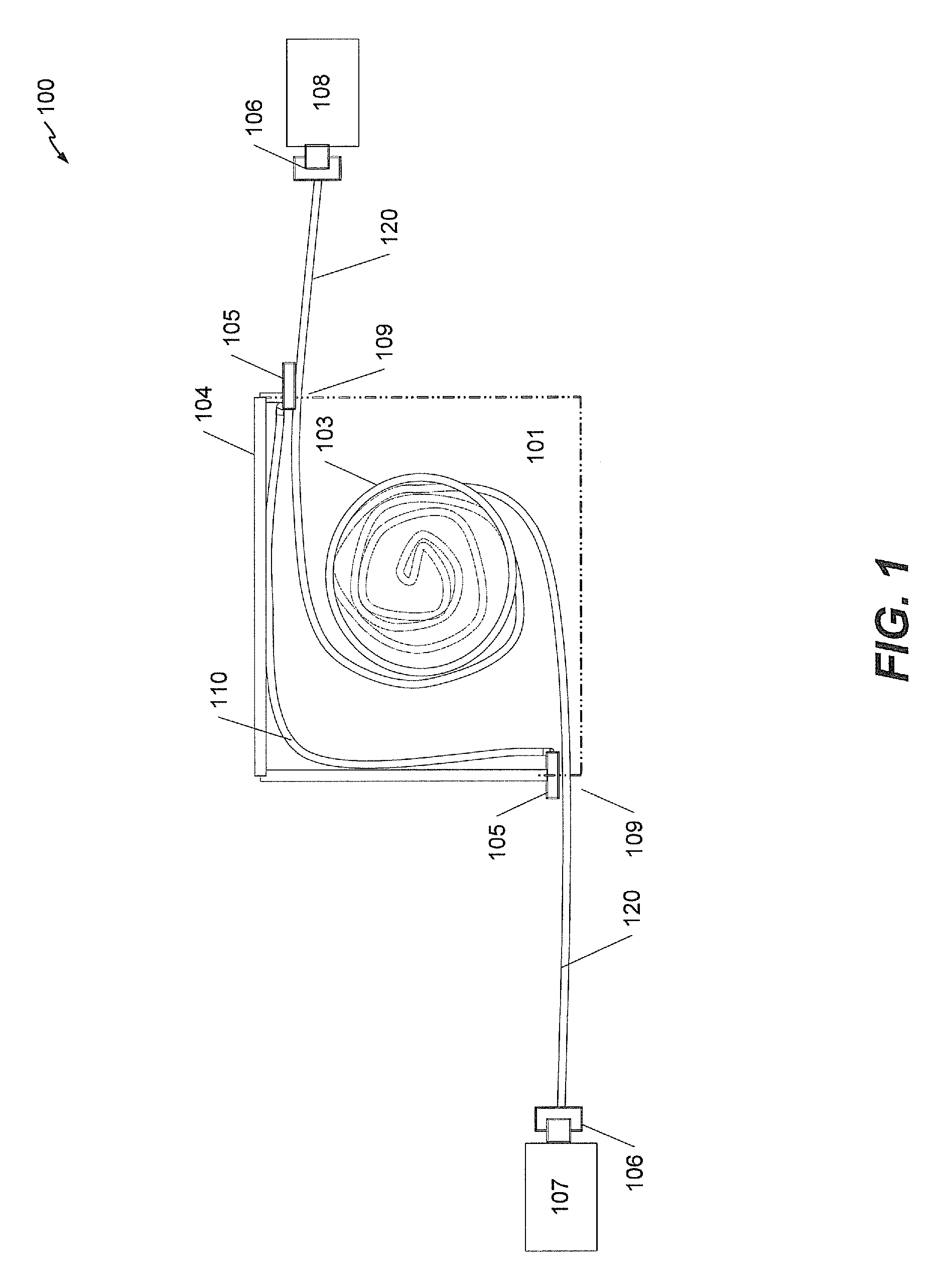

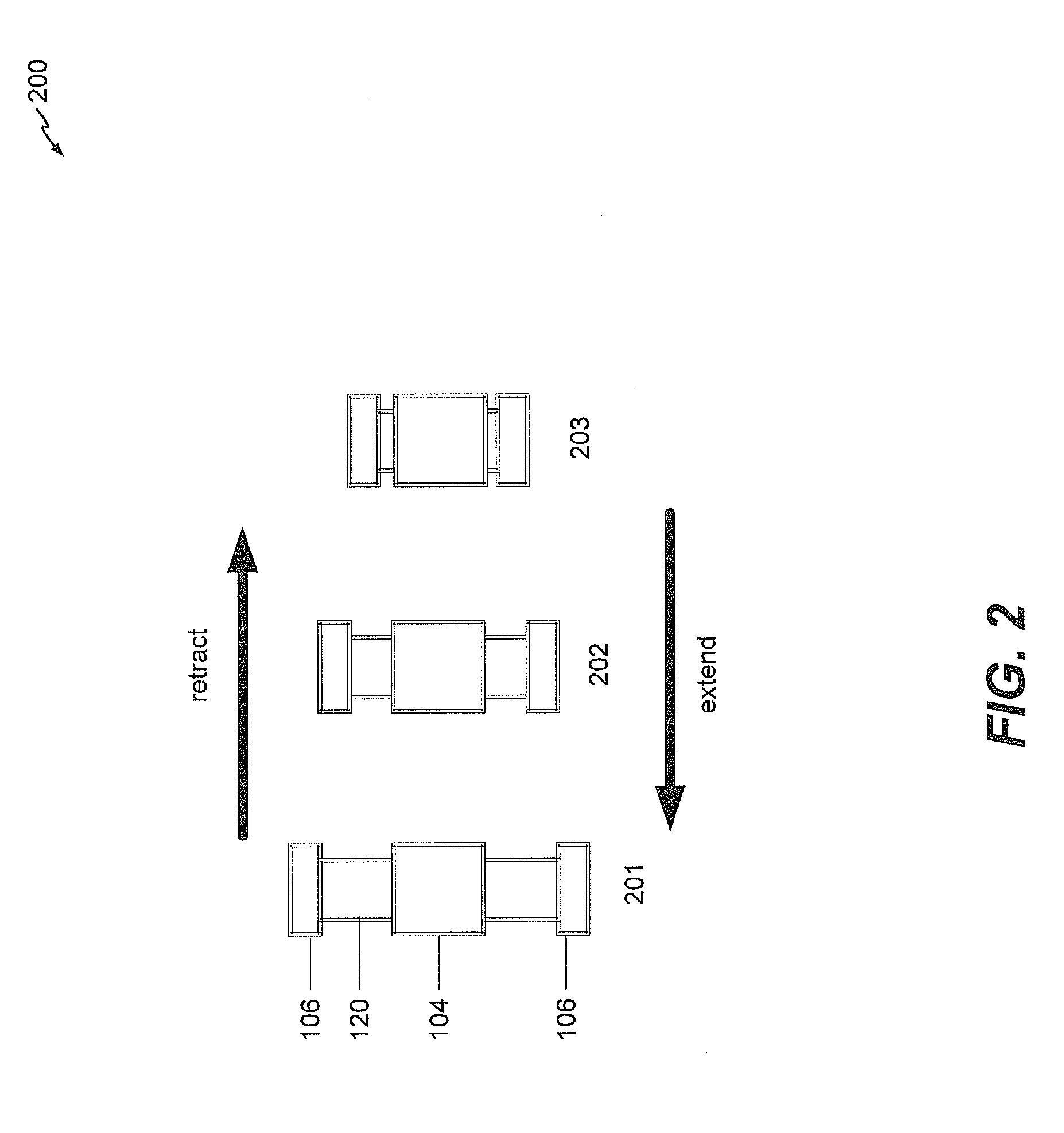

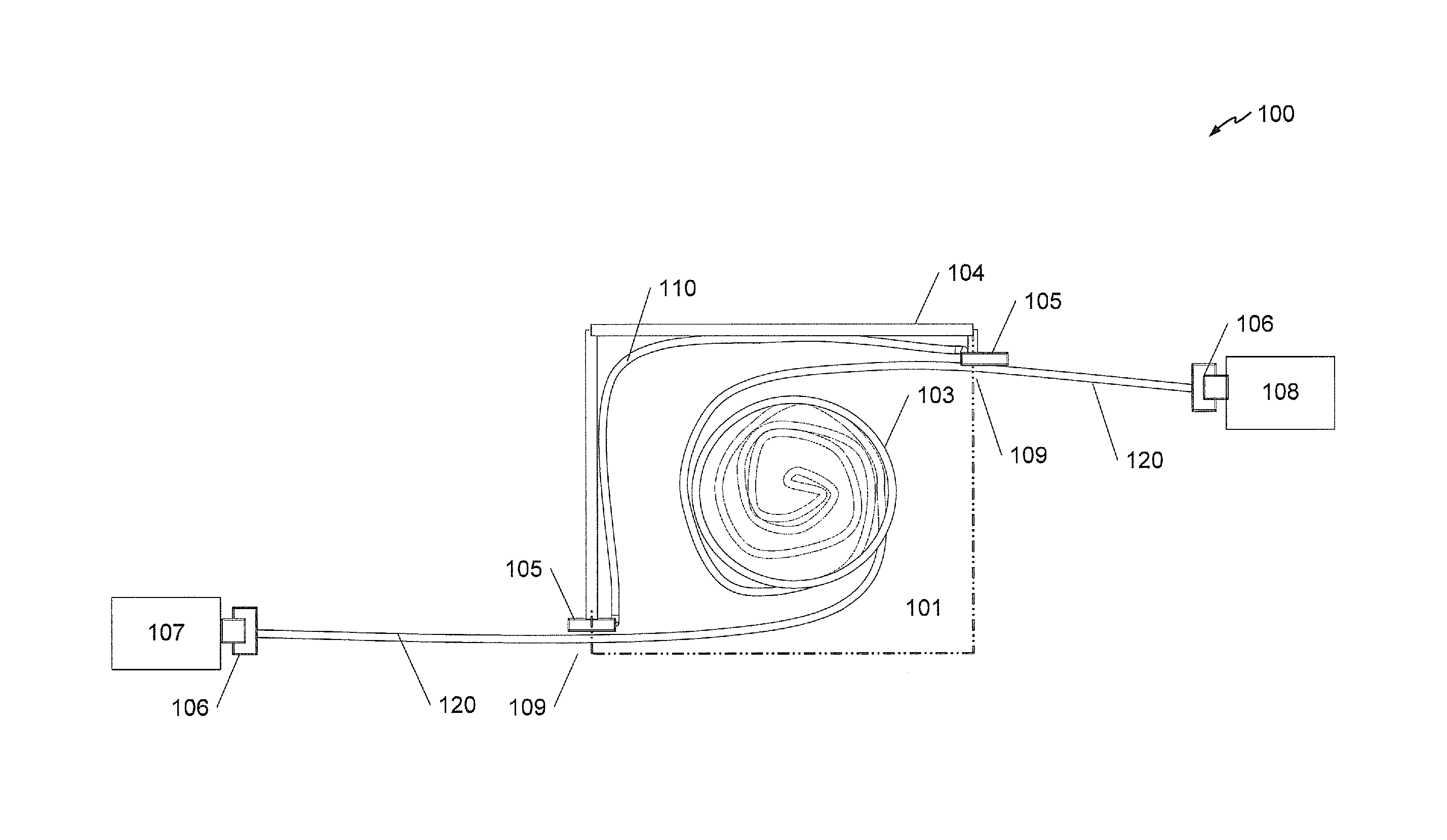

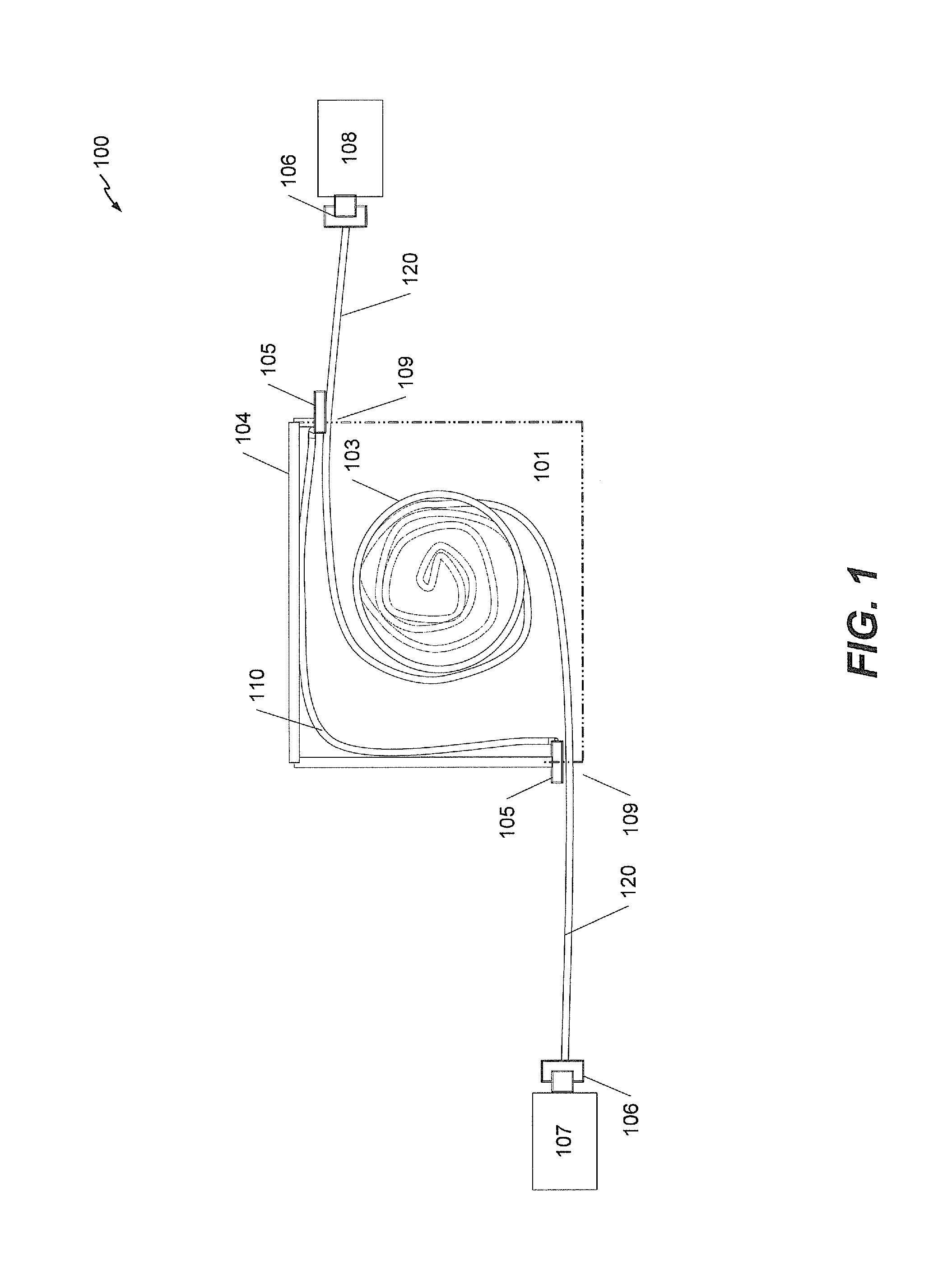

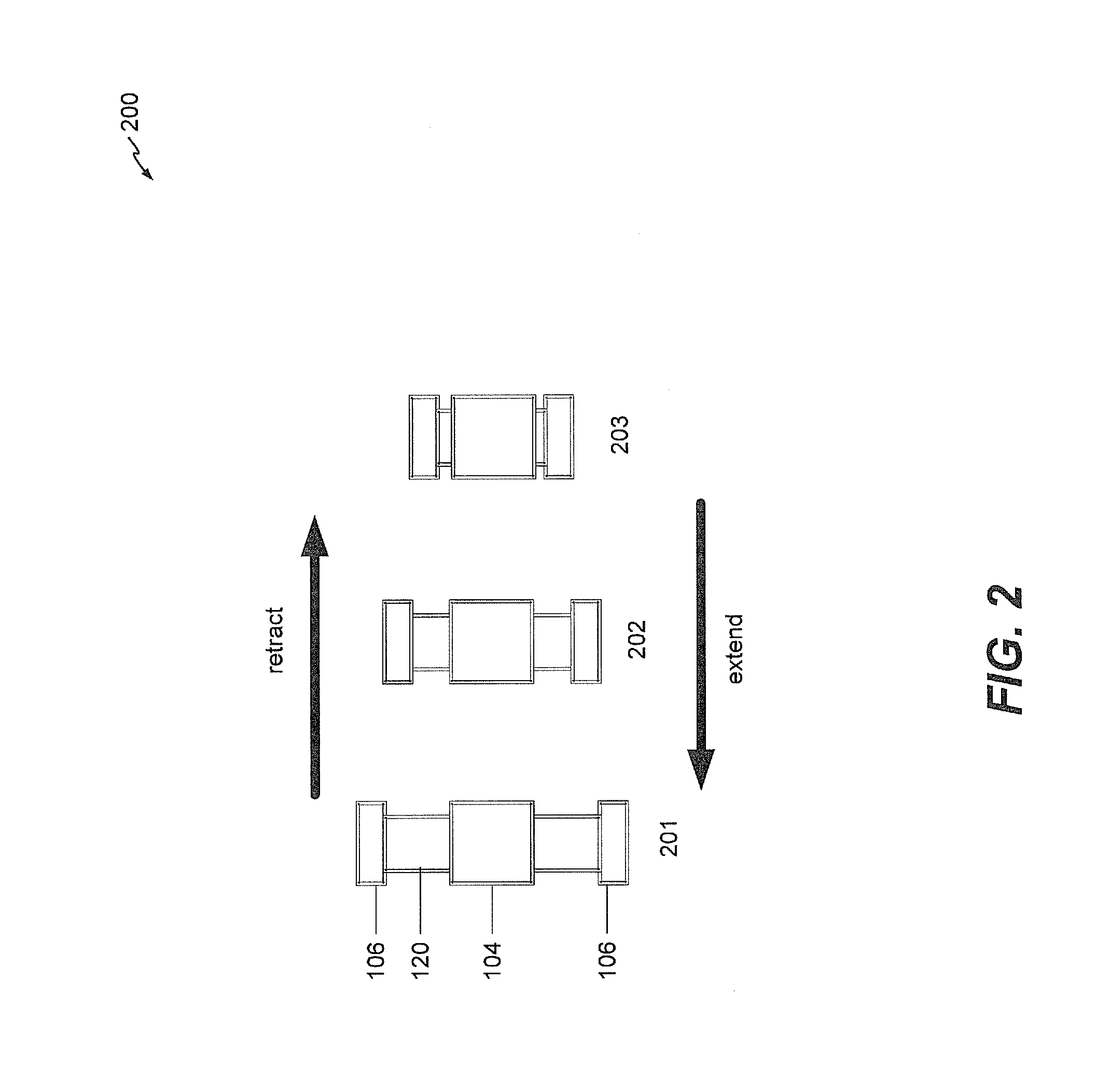

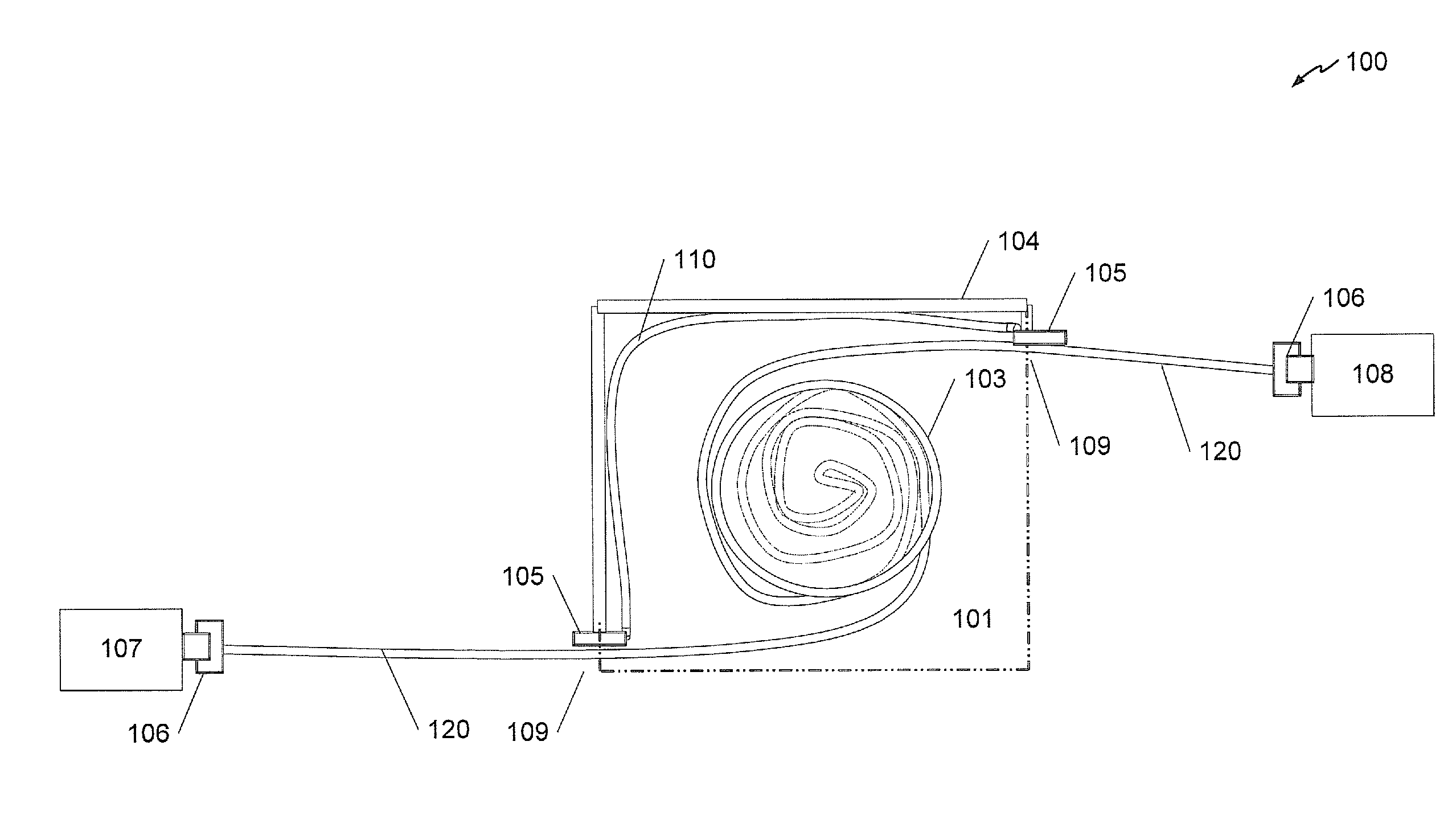

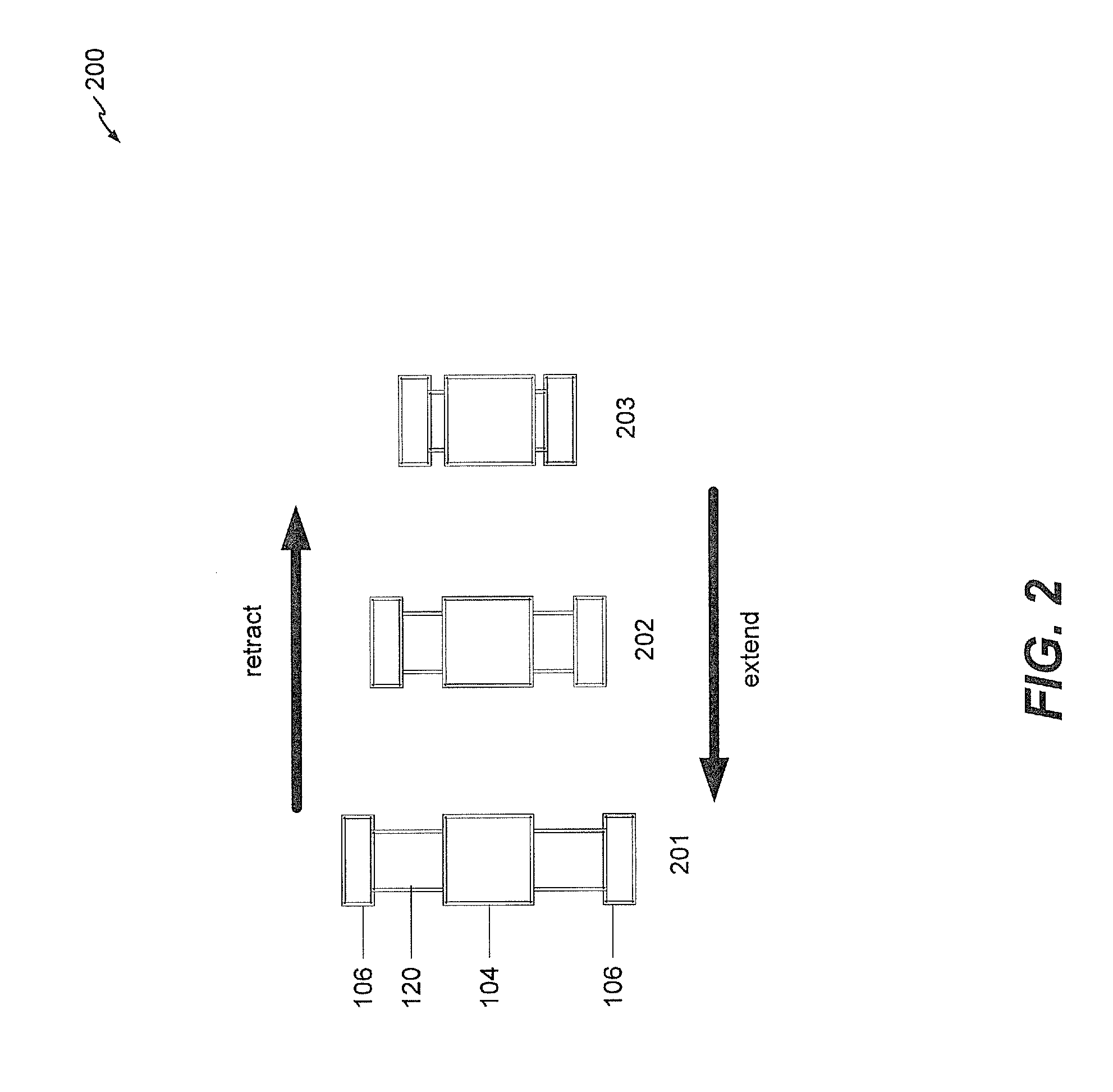

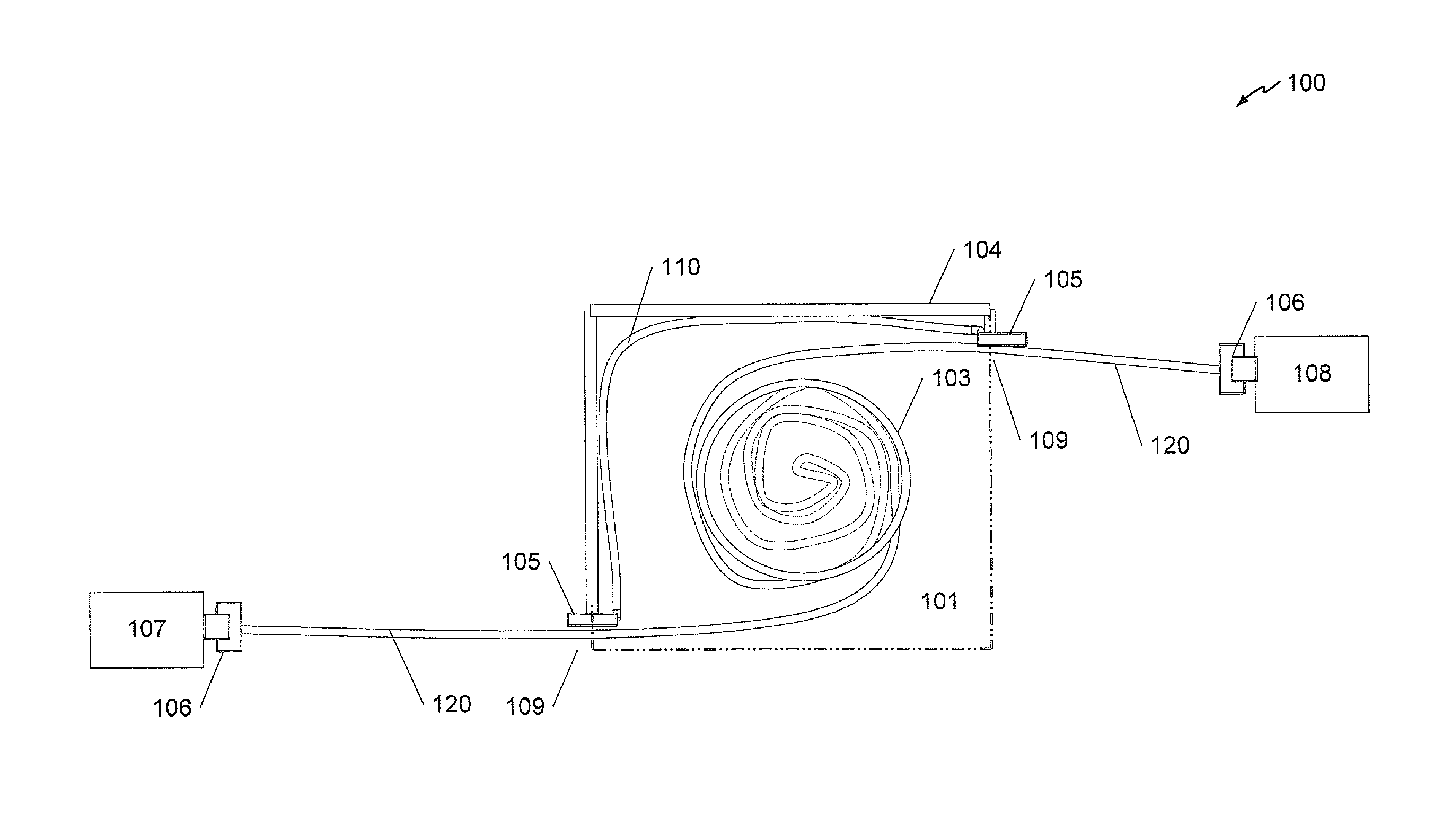

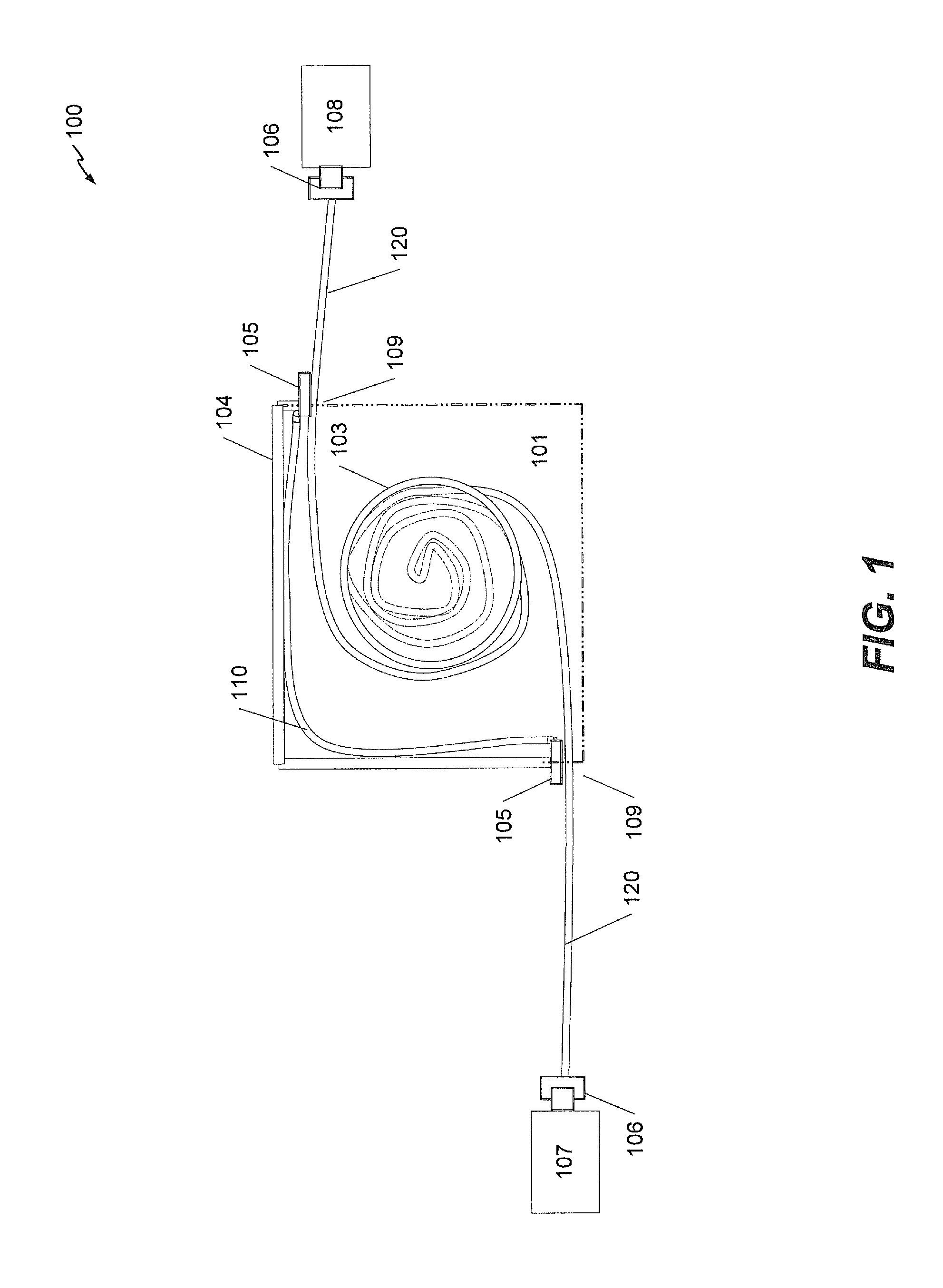

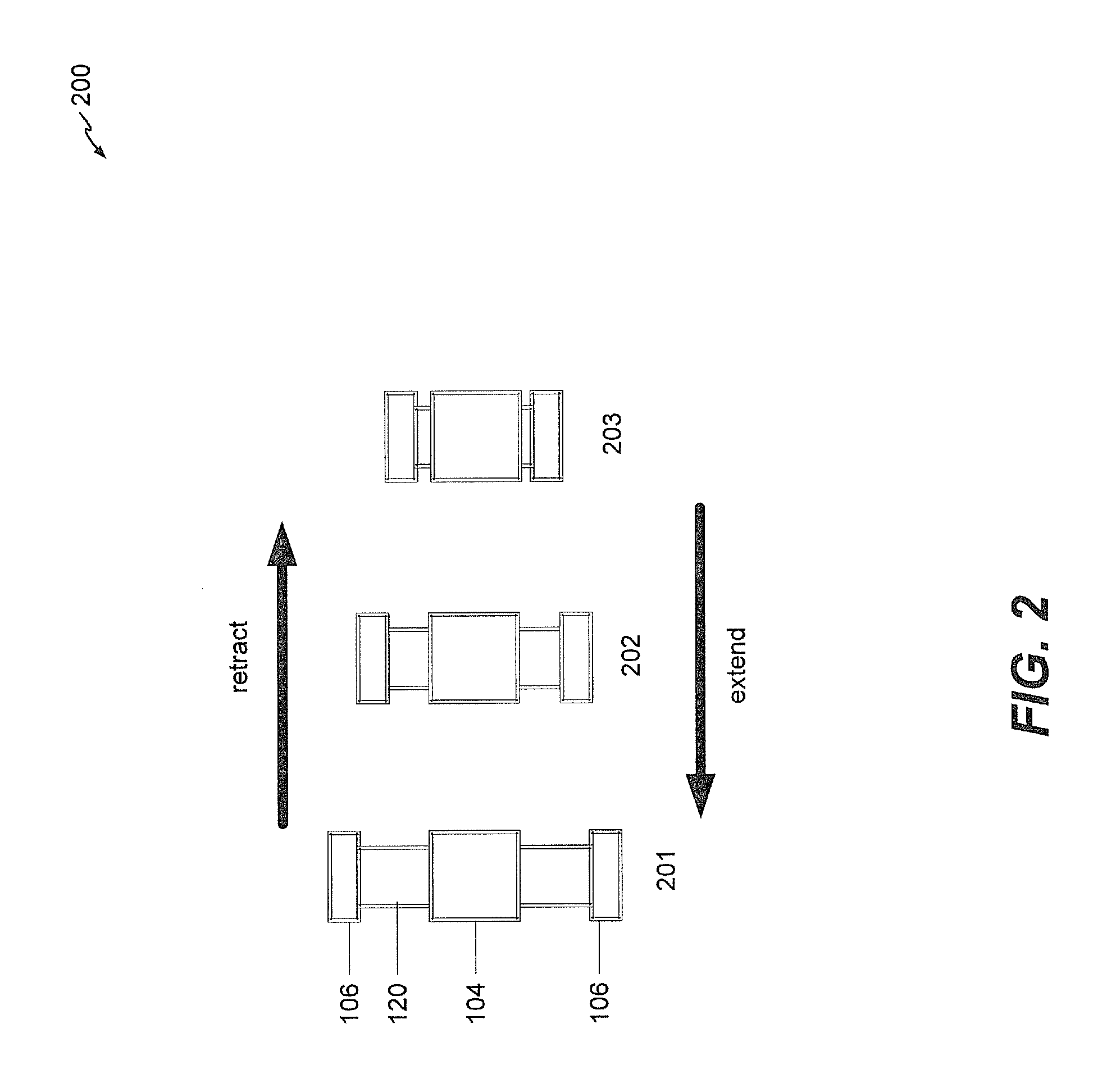

Retractable interconnect device including multiple electrical paths

ActiveUS20150200528A1Data transfer speed is fastImprove data transfer bandwidthLine/current collector detailsArrangements using take-up reel/drumElectricityEngineering

Owner:IBM CORP

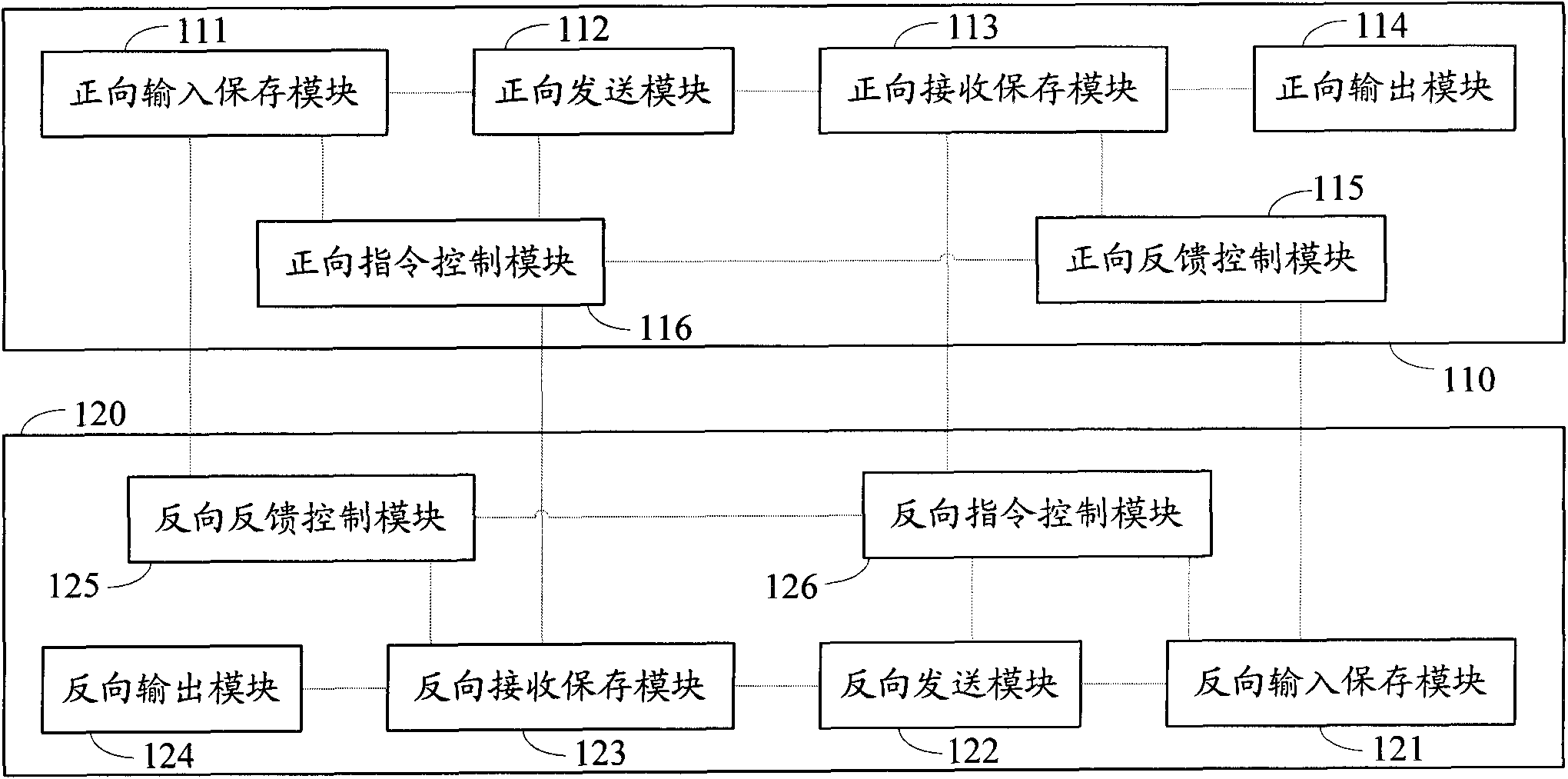

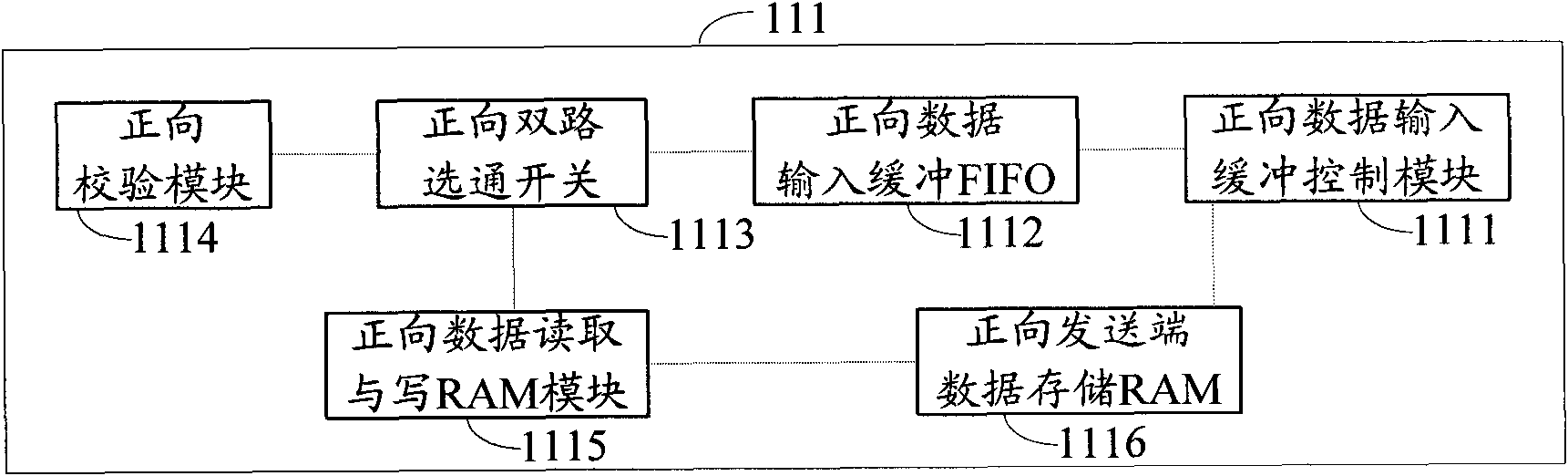

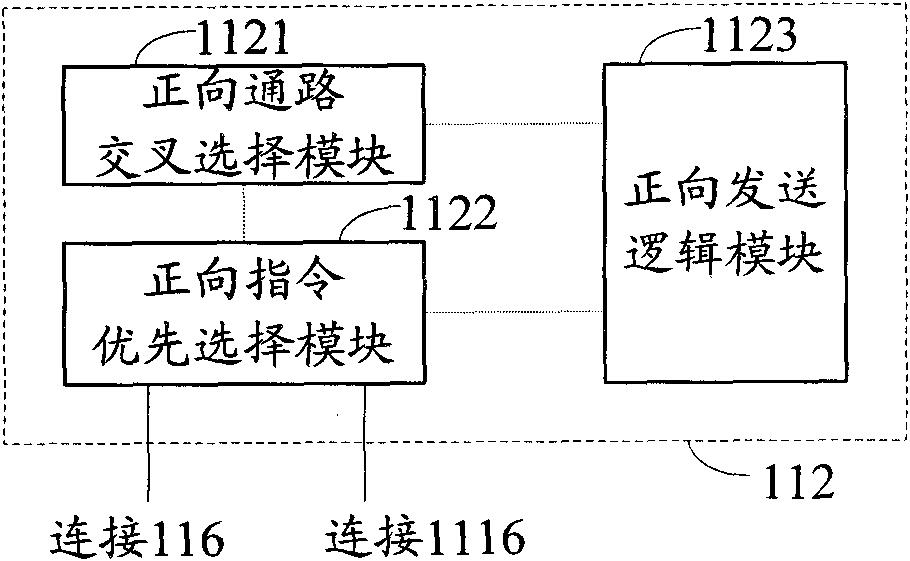

Self-adaptive multi-path serial redundant high-speed bus

InactiveCN101834695AReliable error correctionIncrease speedError preventionBus networksFeedback controlData transmission

The invention discloses bus equipment, comprising two composition structures and sub equipment including a forward subsystem and a backward subsystem, wherein the two composition structures are used for transmitting data in two transmission directions; the forward subsystem and the backward subsystem have the same connecting relationships; the forward subsystem comprises a forward input saving module, a forward transmitting module, a forward receiving and saving module, a forward output module, a forward feedback control module and a forward instruction control module; and the backward subsystem comprises a backward input saving module, a backward transmitting module, a backward receiving and saving module, a backward output module, a backward feedback control module and a backward instruction control module. The bus equipment can simultaneously realize the work with high speed and high reliability and the capacity of bus nodes is higher.

Owner:ZHONGBEI UNIV

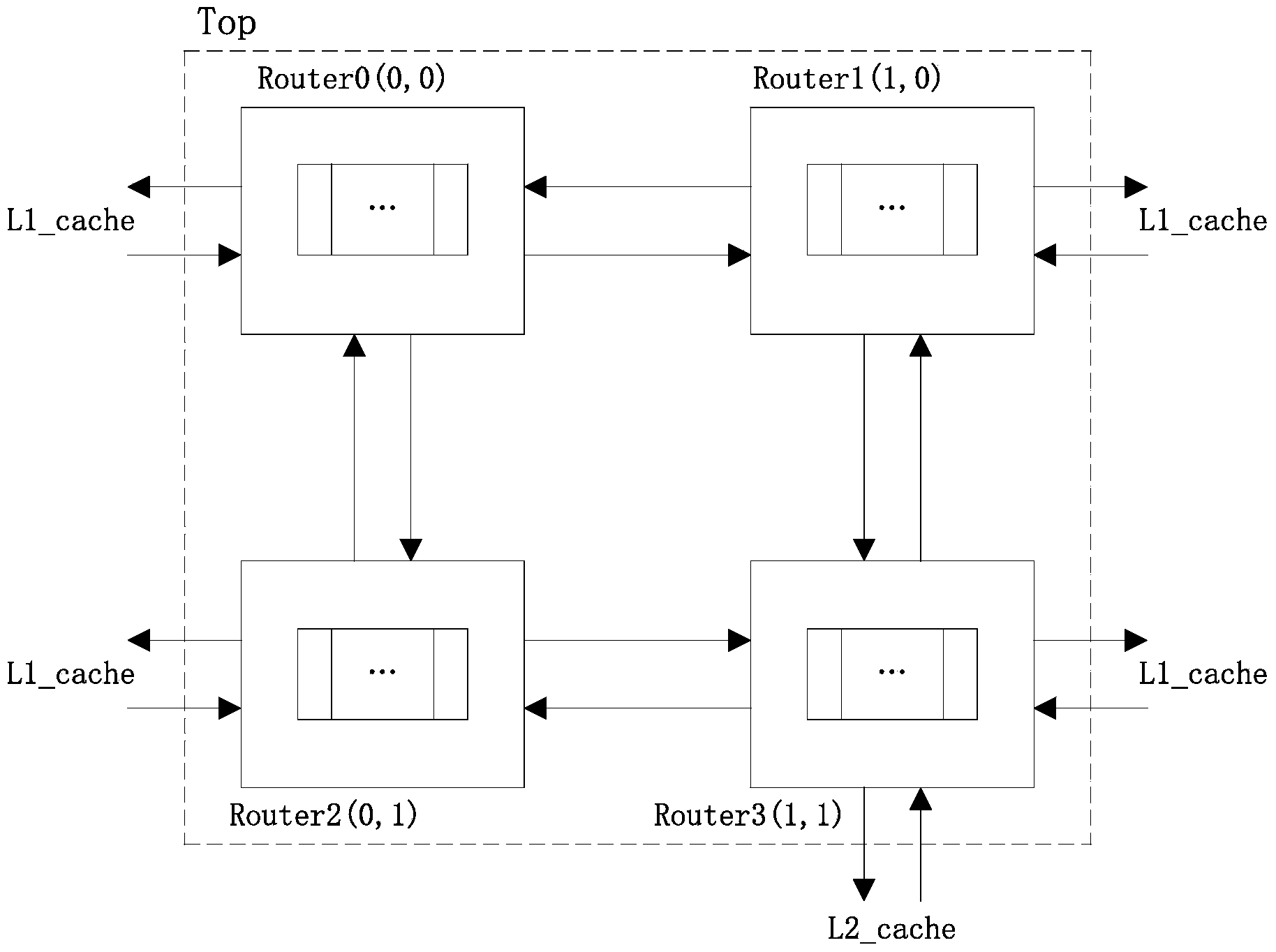

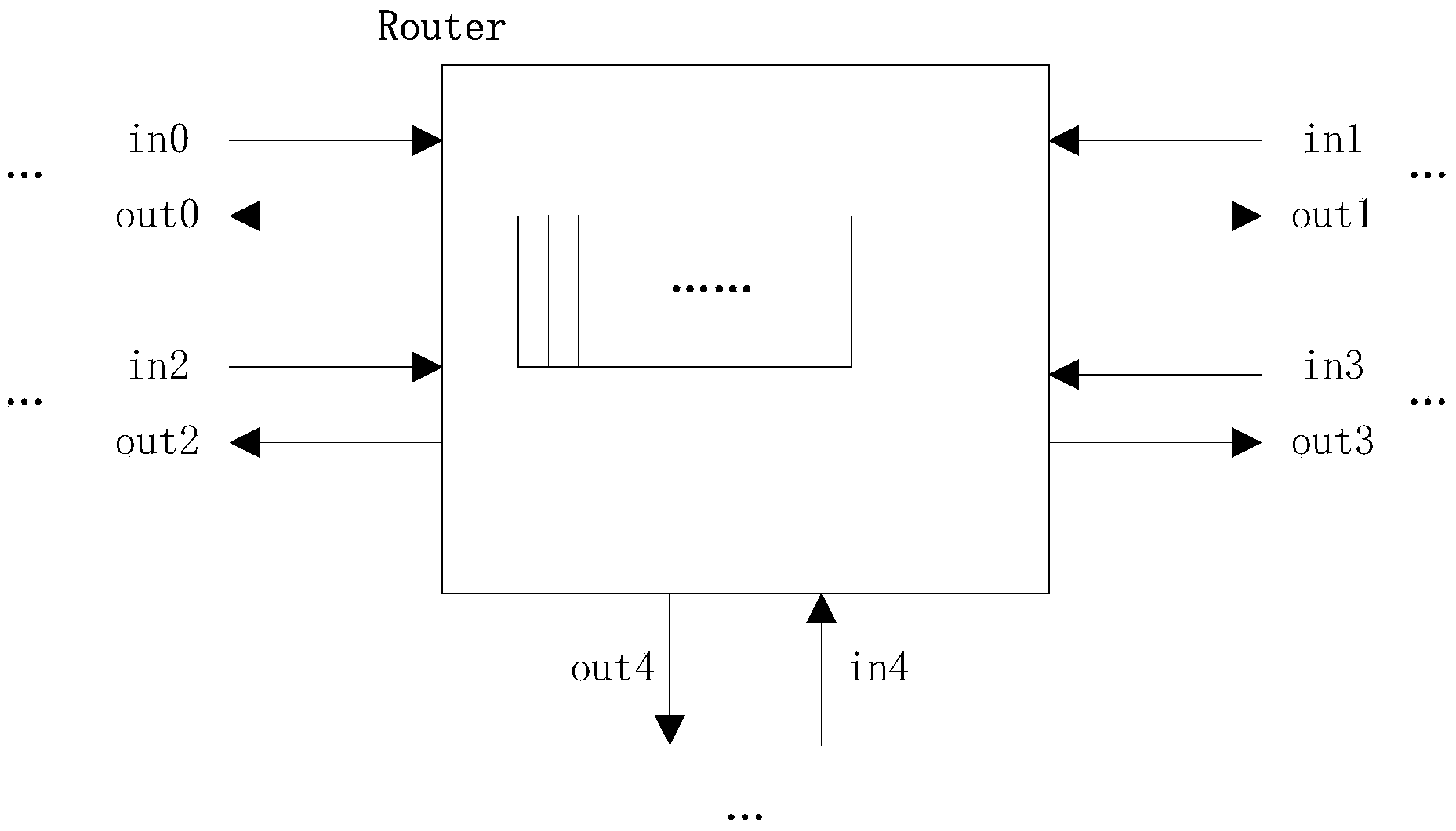

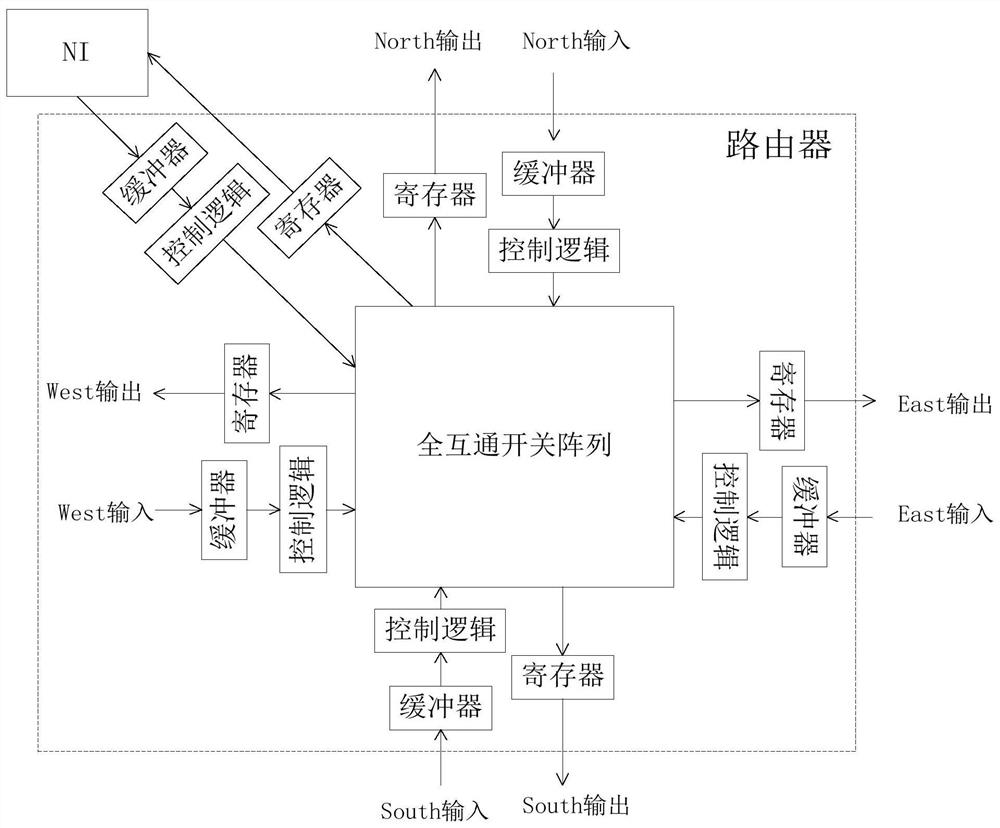

Multi-core memory system simulator on basis of network-on-chip interconnection

ActiveCN103914333ASpeed up developmentShort interconnectSoftware simulation/interpretation/emulationSystemCParallel computing

The invention discloses a multi-core memory system simulator on the basis of network-on-chip interconnection. The multi-core memory system simulator is characterized in that a core of SystemC is used as a driving core of the integral simulator, the multi-core memory system simulator comprises cache modules, a plurality of route modules and QEMU modules, the cache modules are used for simulating primary high-speed caches of cores of various processors, the route modules are used for simulating secondary high-speed caches of the cores of the various processors, and the QEMU modules are used for realizing functional simulation effects; the various route modules are interconnected with networks-on-chip which are formed by the secondary high-speed caches shared by the cores of the simulation processors, and each route module is provided with a group of signal lines connected with the corresponding cache modules; pkt (packet) messages which are transmitted by one cache module or one route module are distributed to another cache module or another route module. The multi-core memory system simulator has the advantages that system software of target systems can be developed by the aid of the simulator, the software and hardware can be simultaneously developed, and accordingly the system development speed can be increased.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

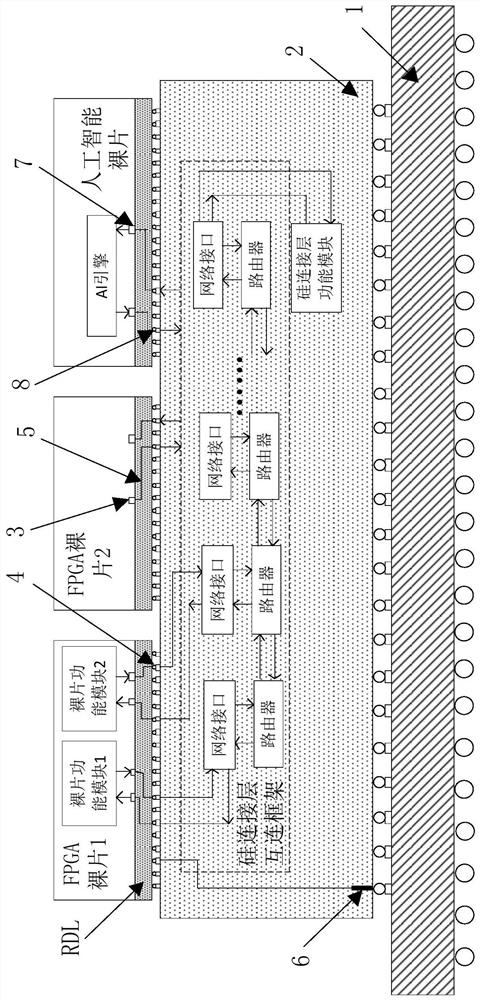

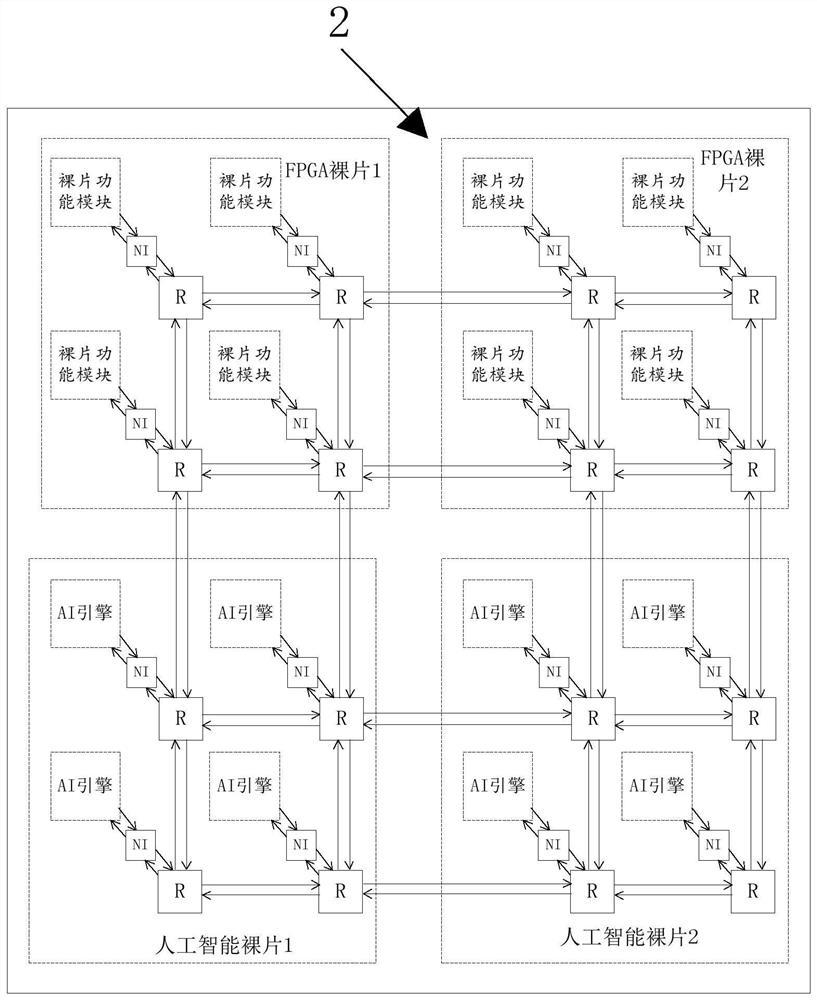

FPGA device of network-on-chip is formed using silicon connection layer

ActiveCN111755437AImprove data transfer bandwidthImprove performanceSemiconductor/solid-state device detailsSolid-state devicesNetworks on chipData transmission

The invention discloses an FPGA device for forming a network-on-chip by using a silicon connection layer, relating to the technical field of FPGA. An active silicon connection layer is designed in theFPGA device. A silicon connection layer interconnection frame is arranged in the silicon connection layer, and each bare chip function module in the FPGA bare chip is accessed to the silicon connection layer interconnection framework to form an on-chip network together with the silicon connection layer interconnection framework; each bare chip function module, a network interface in the silicon connection layer interconnection framework and the router form an NOC node; and the NOC nodes are communicated with each other, so that the bare chip function modules in the FPGA bare chip without thebuilt-in NOC network can be efficiently interconnected and communicated through the silicon connection layer interconnection framework, and the processing difficulty is reduced on the basis of improving the data transmission bandwidth and performance in the FPGA device.

Owner:WUXI ESIONTECH CO LTD

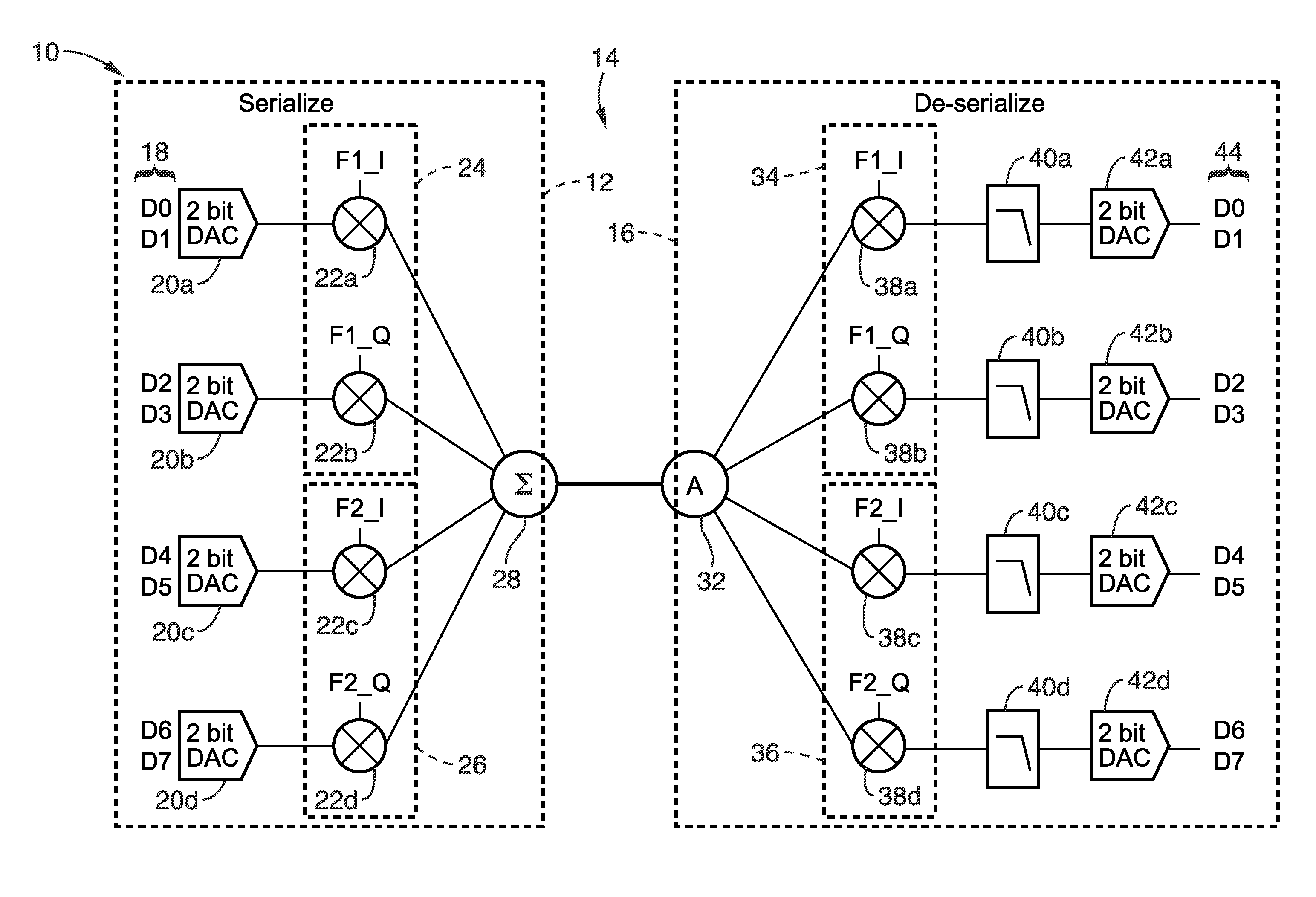

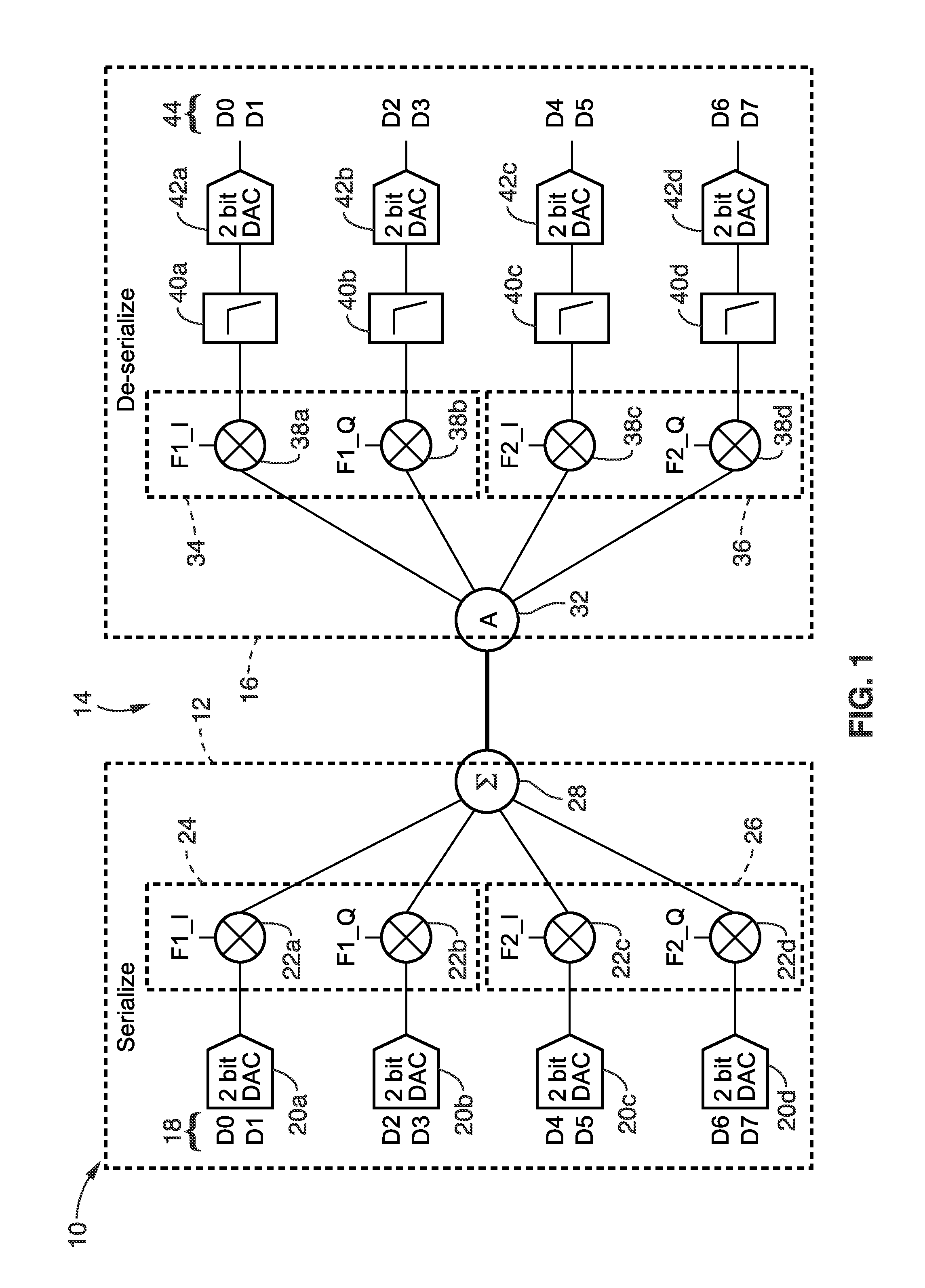

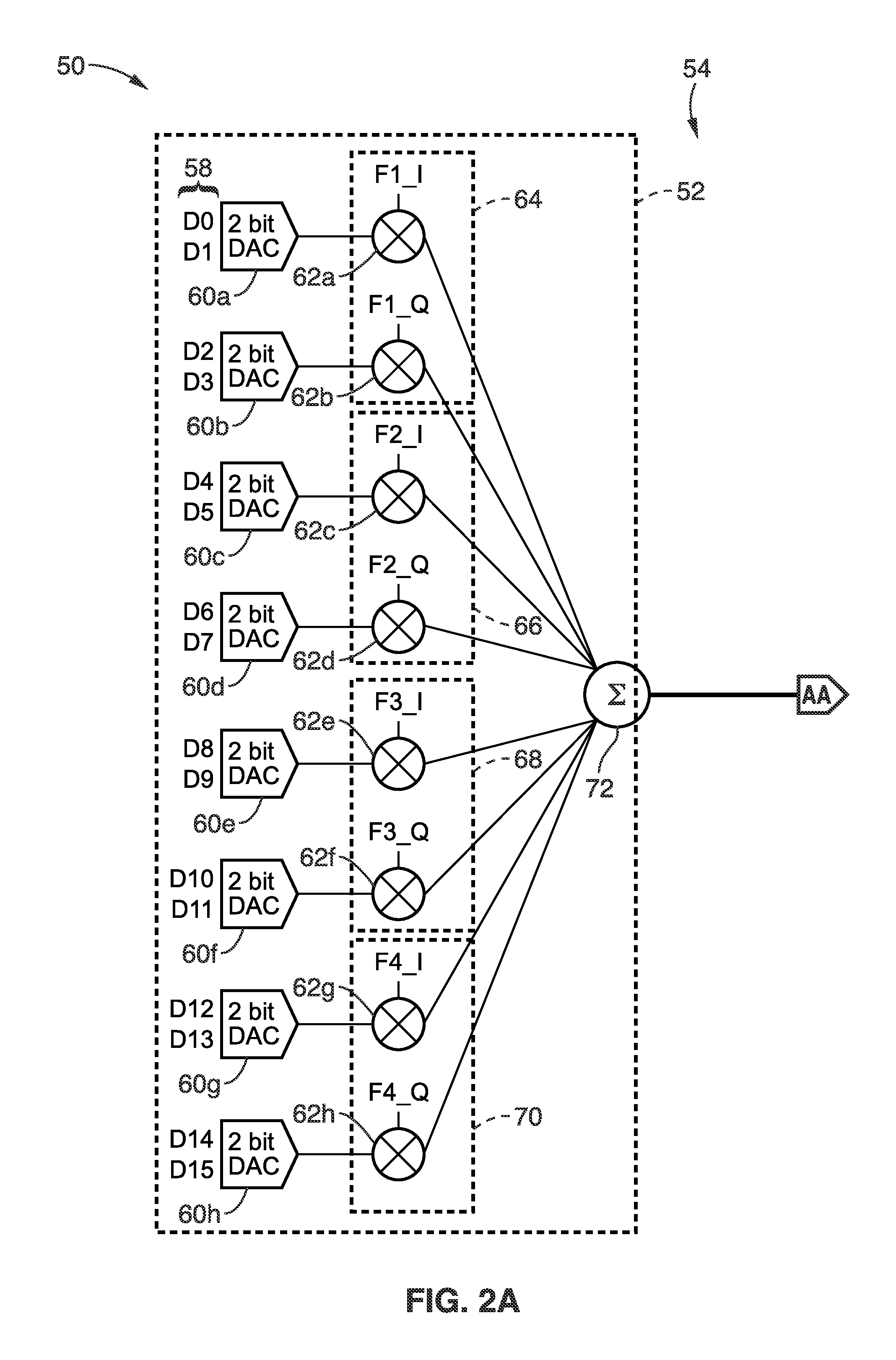

Scalable serial/de-serial I/O for chip-to-chip connection based on multi-frequency QAM scheme

ActiveUS9369318B2Low costImprove data transfer bandwidthParallel/series conversionMultiple carrier systemsDigital dataLow-pass filter

A serializer and de-serializer circuit which is particularly well-suited for use in communicating digital data from one integrated circuit (chip) to another for implementing chip-to-chip communications is presented. The circuits are scalable and utilize a multi-frequency quadrature amplitude modulation (QAM) mechanism for converting digital data bits from a parallel form into a serial analog stream for communication over a chip I / O connection. The serializer has multiple digital-to-analog converters (DACs) whose outputs are directed to QAM mixer inputs, within QAMs at multiple frequencies, whose outputs are summed into a single analog signal for communication over an I / O connection. The de-serializer amplifies the analog signal which is received by QAM mixers at different frequencies, whose outputs are low pass filtered and converted back to parallel digital data bits.

Owner:RGT UNIV OF CALIFORNIA

Retractable interconnect device including multiple electrical paths

ActiveUS9197053B2Data transfer speed is fastImprove data transfer bandwidthArrangements using take-up reel/drumFlexible lead accommodationElectricityEngineering

Owner:IBM CORP

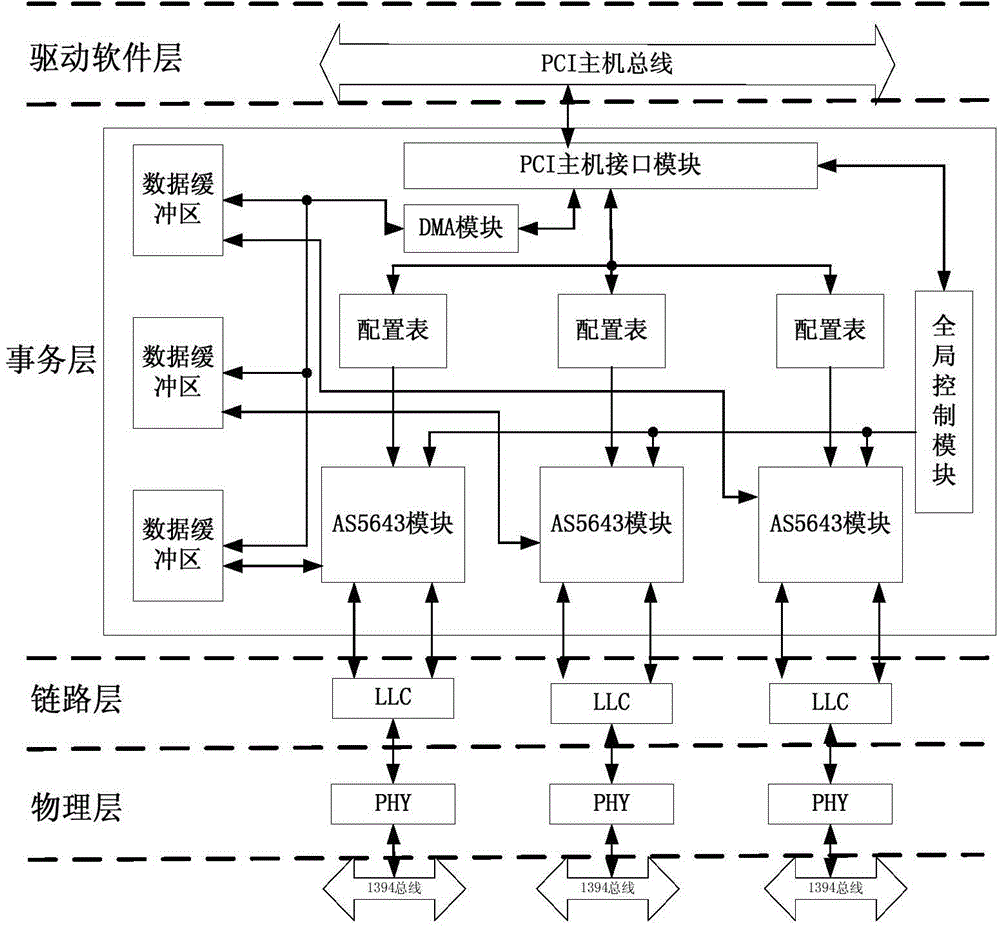

Multichannel synchronization and offset controllable circuit in single logic chip

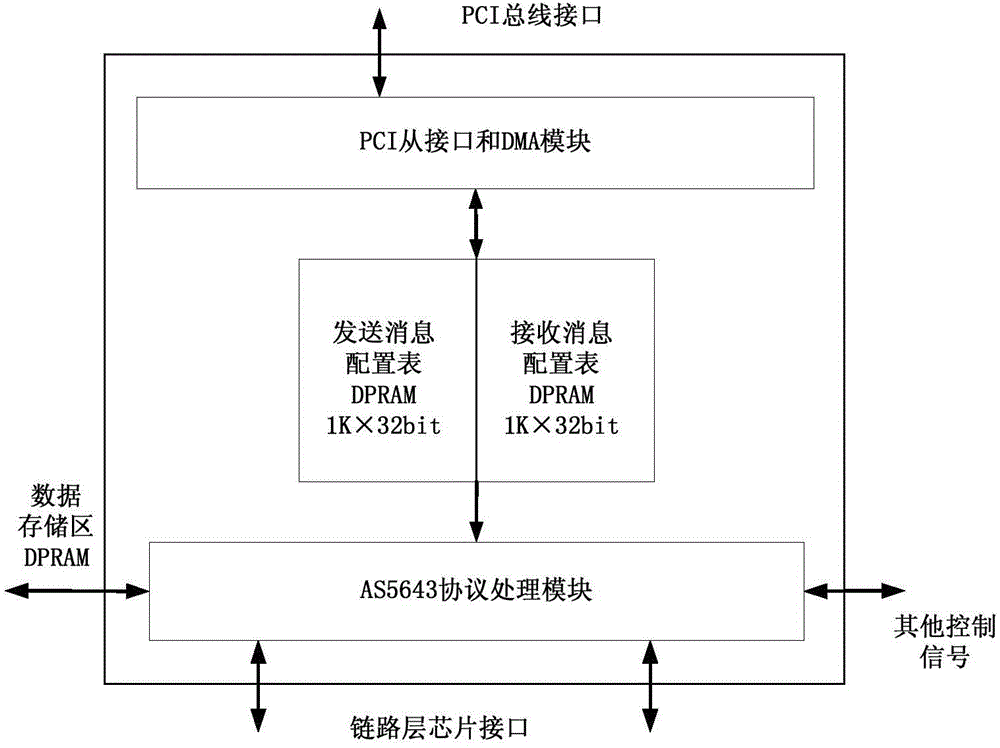

InactiveCN104461969AImprove data transfer bandwidthImprove certaintyElectric digital data processingDirect memory accessProtocol processing

The invention provides a multichannel synchronization and offset controllable circuit in a single logic chip. The multichannel synchronization and offset controllable circuit comprises a main unit interface module, a DMA (direct memory access) module, a configuration table transmitting and receiving list DPRAM (dual port random access memory) module, a data DPRAM module, an AS5643 protocol processing module and a global control module. The configuration table transmitting and receiving list DPRAM module, the data DPRAM module, the AS5643 protocol processing module can realize three AS5643 node functions, a global register can dispatch uniformly and start transmission, synchronous control of the three nodes is realized, and the multichannel synchronization and offset controllable circuit can be realized and used for AS5643 protocol node communication.

Owner:AVIC NO 631 RES INST

System and method for a high speed, bi-directional, zero turnaround time, pseudo differential bus capable of supporting arbitrary number of drivers and receivers

InactiveUS6686774B1Reduce pre-charge timeMaximizing evaluation timeReliability increasing modificationsElectronic switchingElectric Charge UnitPre-charge

A method and system for high speed bussing in microprocessors and microelectronic devices is disclosed. The method and system implement a type of differential bus with distributed bus pre-charge units designed to decrease bus pre-charge time. The method and system utilize a universal self-tracking clock signal to determine the minimum required bus pre-charge time. The time saved by decreasing the bus pre-charge time can be directly applied to the bus evaluation period thereby increasing system performance and reliability.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Power line communication equipment and power line communication method

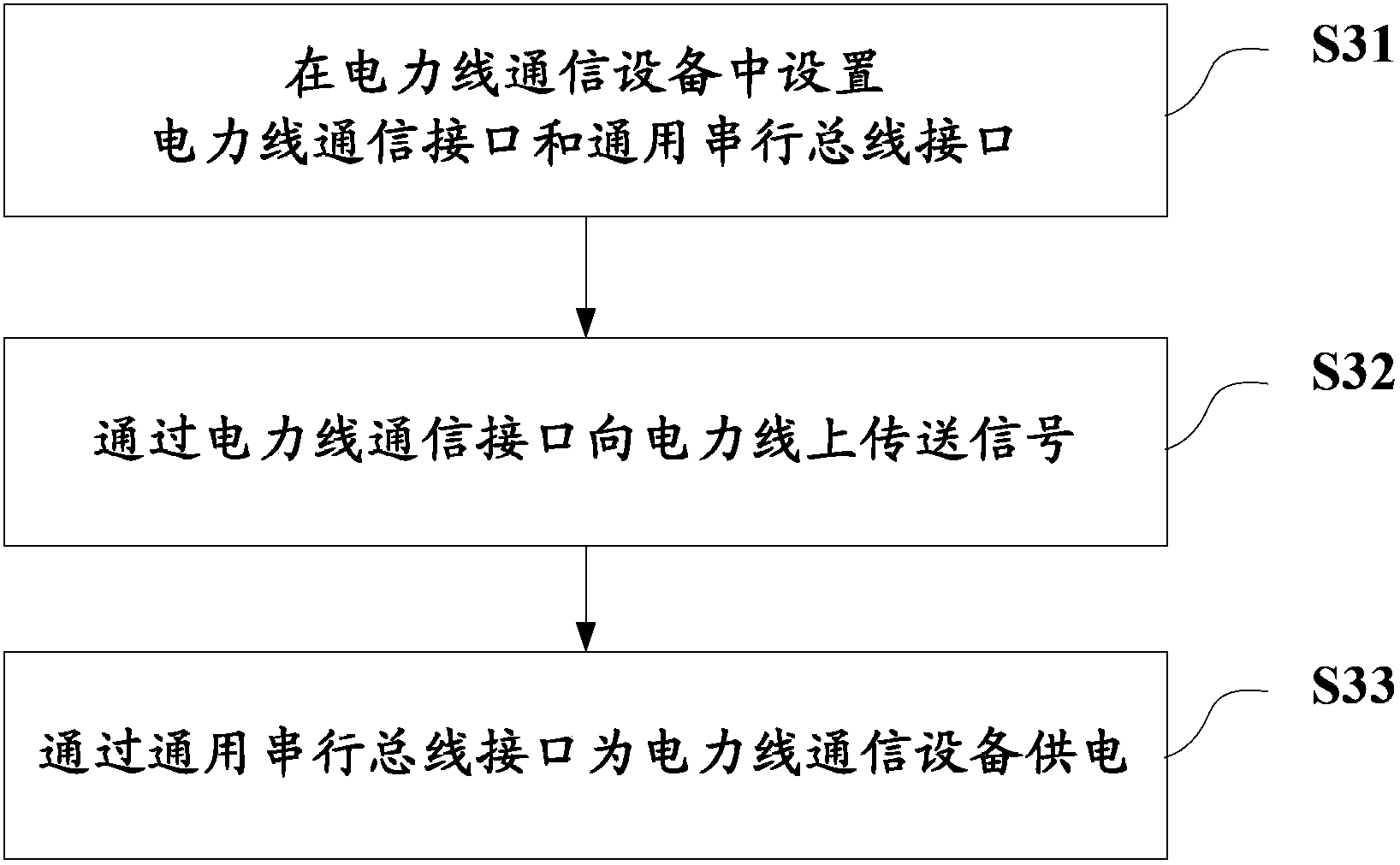

ActiveCN103905090AReduce Conducted InterferenceLow costPower distribution line transmissionTransformerCoupling

The invention discloses a piece of power line communication equipment and a power line communication method, and relates to the field of terminals. The power line communication equipment comprises a power line communication interface, a universal serial bus interface and a signal coupling unit. The power line communication interface is connected with the signal coupling unit and is used for transmitting a signal to the signal coupling unit. The signal coupling unit is used for coupling or decoupling the signal. The universal serial bus interface is used for supplying power to the power line communication equipment. According to the invention, weak power supply is carried out based on the USB interface. On one hand, compared with strong power supply, power consumption of the equipment can be reduced, fewer transformers are required, the device cost is reduced, the product size is reduced, the difficulty in wiring design is reduced, the access threshold for equipment design and production is lowered, and the rise of the power line communication market is benefited. On the other hand, power supply interfaces are separated and an information interface is independently arranged, conductive interference on the power line communication interface is reduced, and the equipment can easily meet the electromagnetic compatibility certification requirements.

Owner:CHINA TELECOM CORP LTD

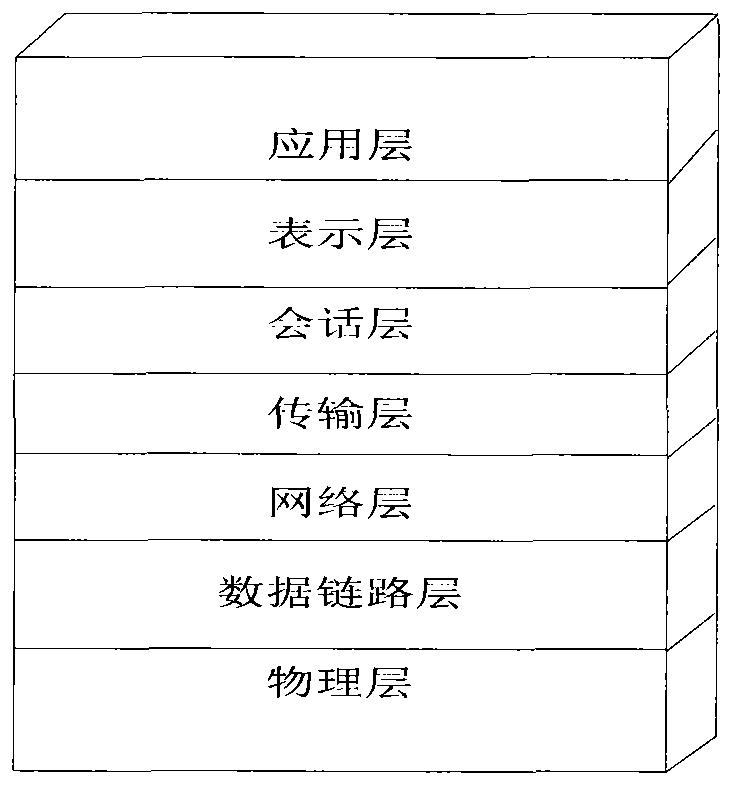

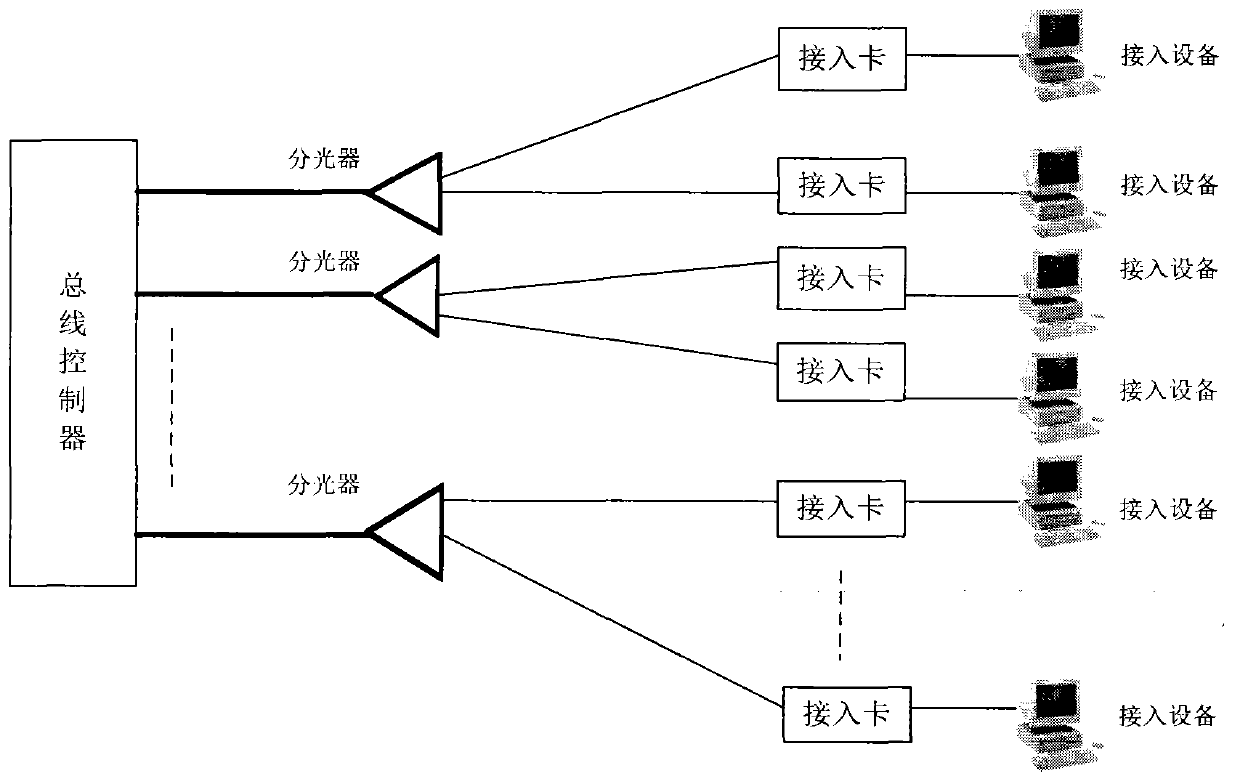

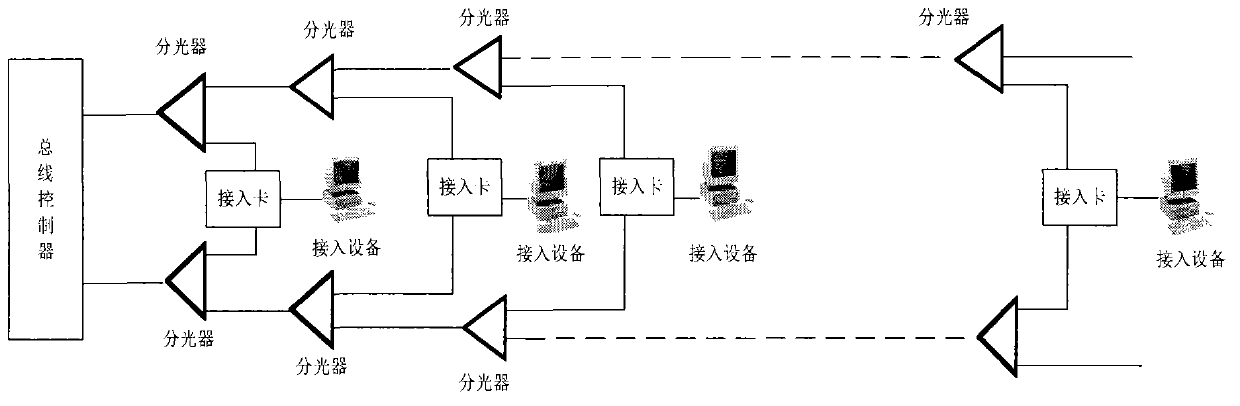

Design method for realizing high-speed data bus by optical fiber channel

InactiveCN104796199AImprove reliabilityImprove data transfer bandwidthBus-type electromagnetic networksAviationForeign technology

The invention relates to a design method for realizing a high-speed data bus by an optical fiber channel, comprising an Ethernet passive optical network configuration method, a three-layer exchange mechanism, a topology of optical fiber bus design, a bus controller, an access unit, a photoelectric conversion module, a light splitter, and an optical fiber. Before the invention, technologies related to an optical fiber high-speed data transmission bus use foreign standards, and as the technologies and chips for realizing the technologies belong to the scope of embargo of the west to China, China could not directly use the standards. According to the invention, a new method is used to replace a similar foreign technology, and an optical fiber high-speed data transmission bus product standard system of our own is established, so that the optical fiber high-speed data transmission bus technology can be widely applied to spaceflight, aviation, war industry, electronic industry and other fields.

Owner:KANGYUXING TECH BEIJING

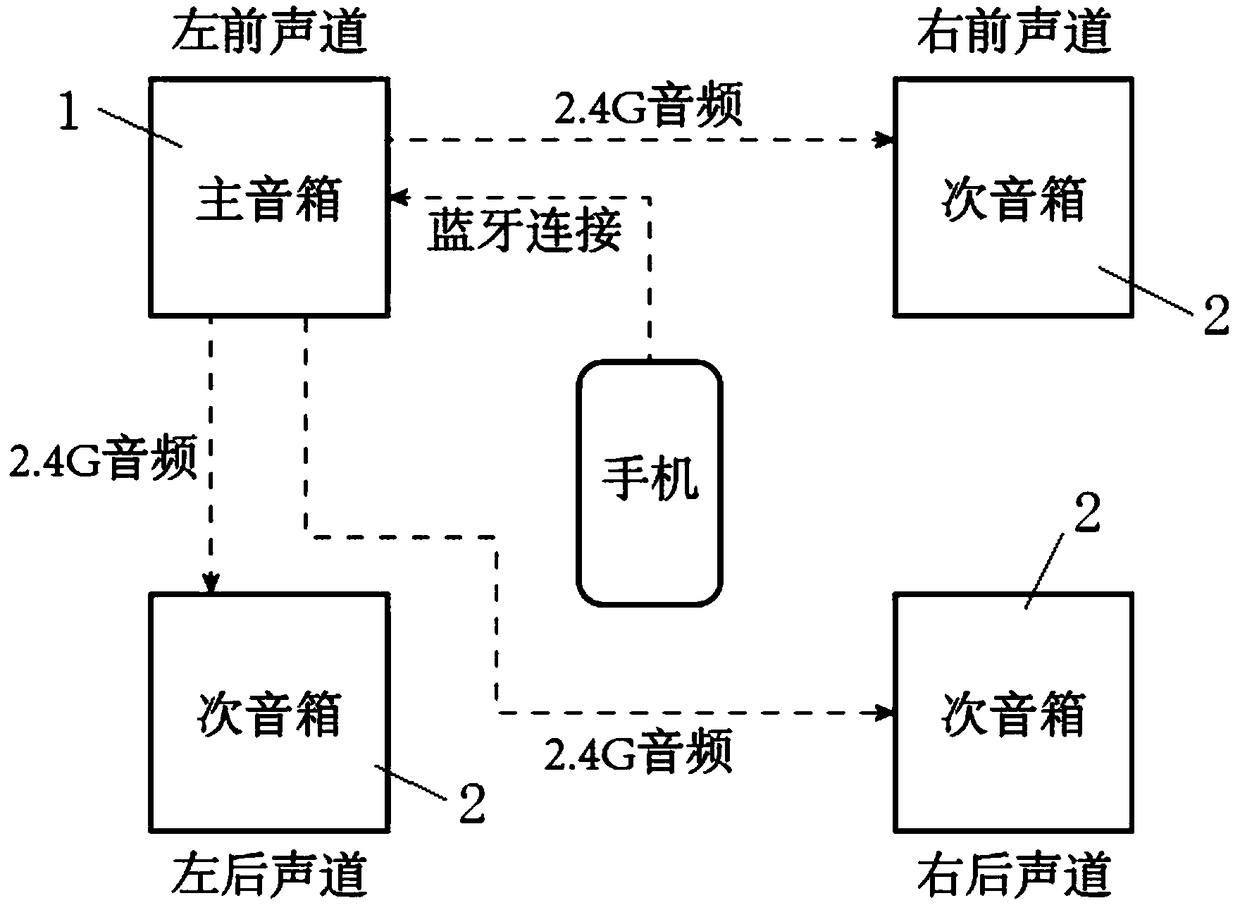

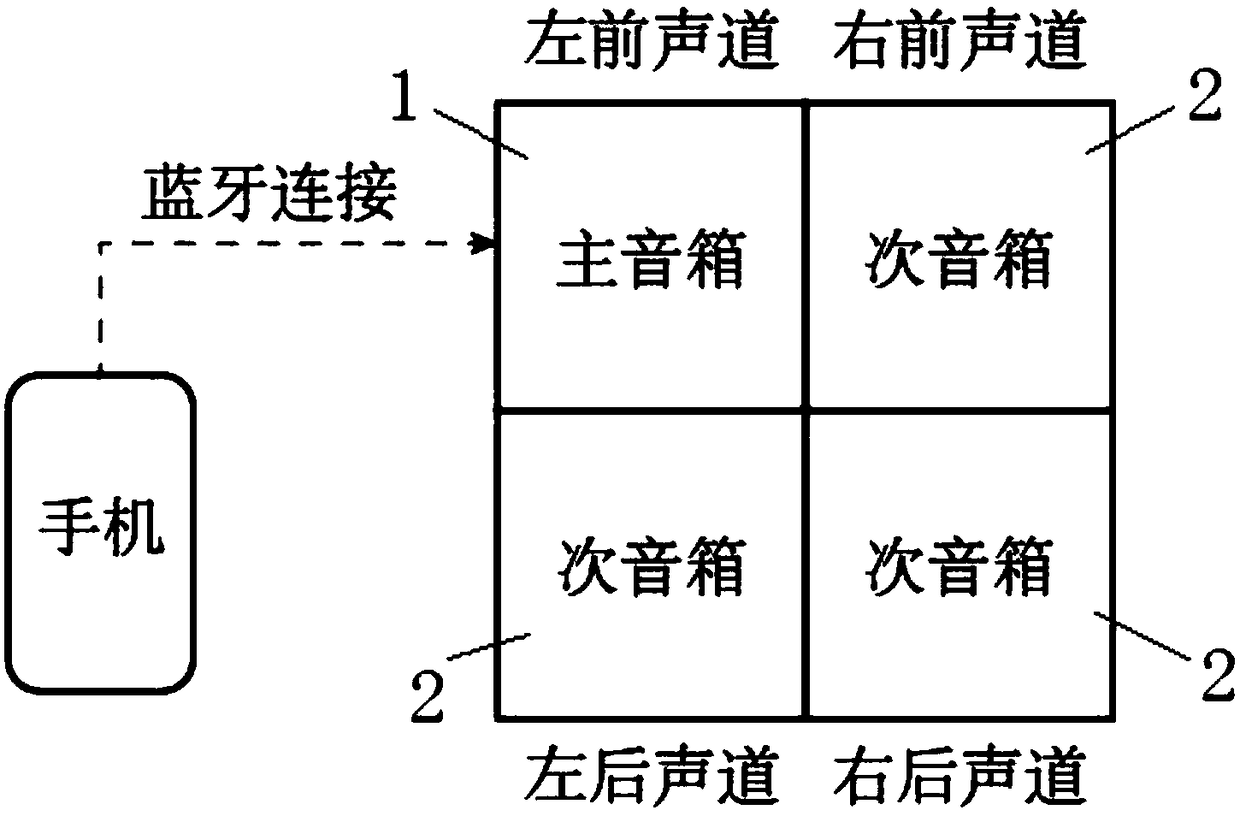

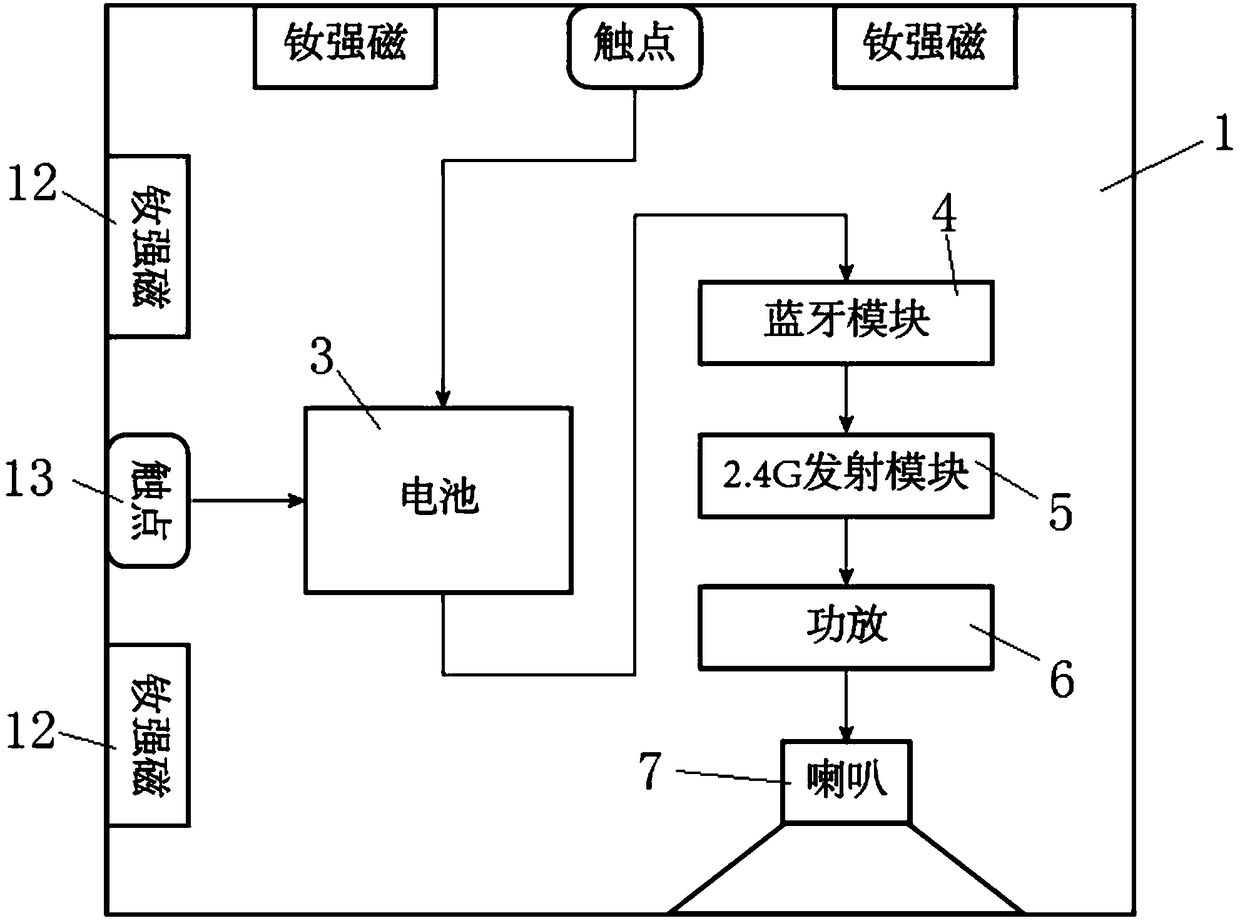

Modular stereo speaker

InactiveCN108989955AAchieve stereo field effectEasy to combineLoudspeaker transducer fixingLoudspeaker spatial/constructional arrangementsWireless transmissionModularity

The invention relates to the technical field of wireless blue portable speakers.A modular stereo speaker is disclosed, includes a primary speaker and several secondary speakers, the main loudspeaker and the secondary loudspeaker, and the secondary loudspeakersare connected through separable fixing mechanisms. The main sound box comprises an internal power module, an audio input module, an audio emission module, a power amplifier module and a horn. After receiving the audio signal, the audio input module transmits a part of the audio signal to the horn external amplifier output through the power amplifier module, and transmits a part of the audio signal through the audio emission module. The subloudspeaker box comprises a power module, an audio receiving module, a power amplifier module anda horn arranged in the subloudspeaker box. The audio receiving module receives the audio signal emitted by the audio emitting module of the main loudspeaker box, and sends the audio signal to the external amplifier output of the horn through the power amplifier module. The invention changes the wireless transmission mode, realizes modular separation and combination, the modular stereo speaker notonly is portable but also has good stereoscopic field effect.

Owner:钱军成

Retractable interconnect device configured to switch between electrical paths

InactiveUS20150200500A1Data transfer speed is fastImprove data transfer bandwidthFlexible lead accommodationElectricityEngineering

Owner:IBM CORP

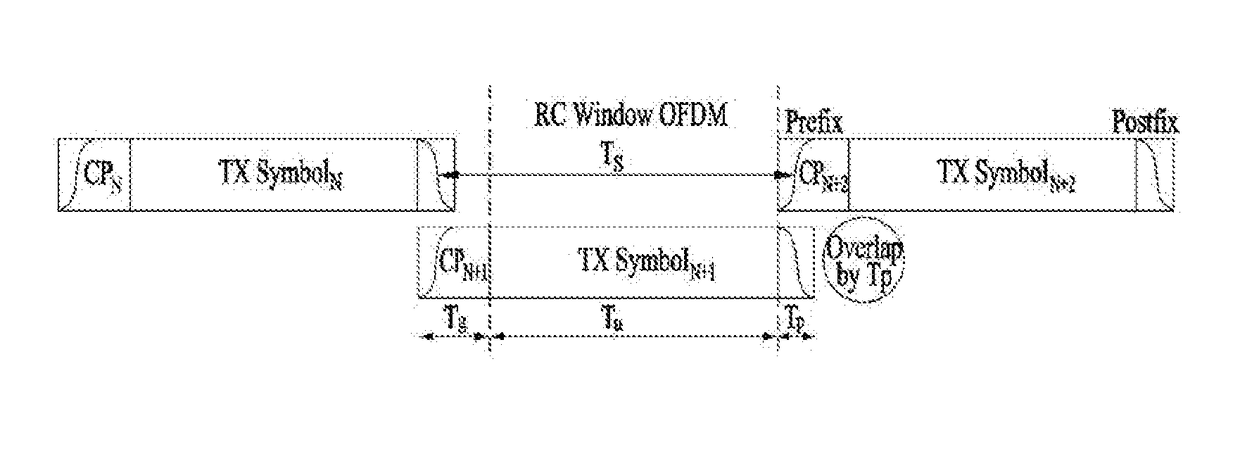

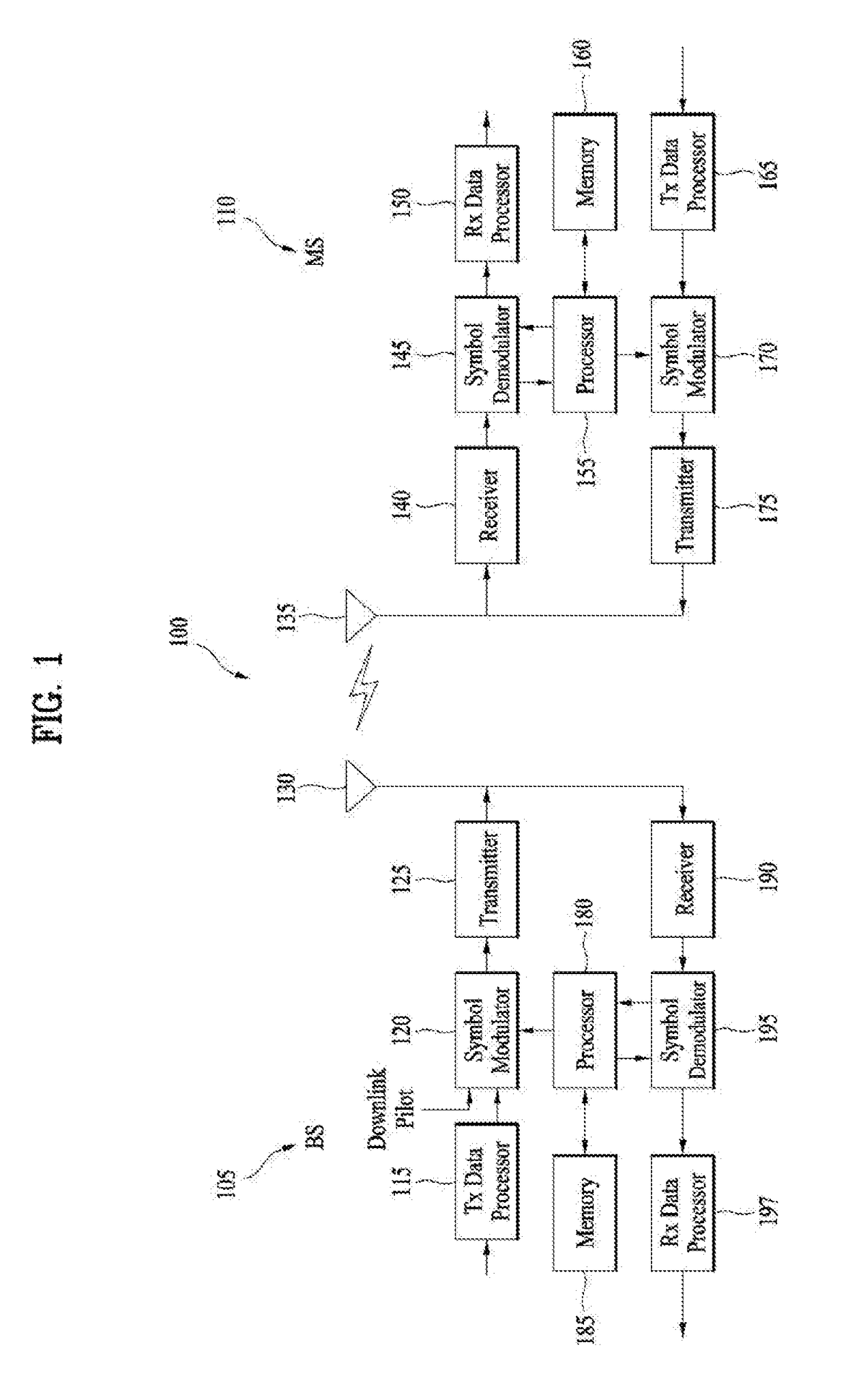

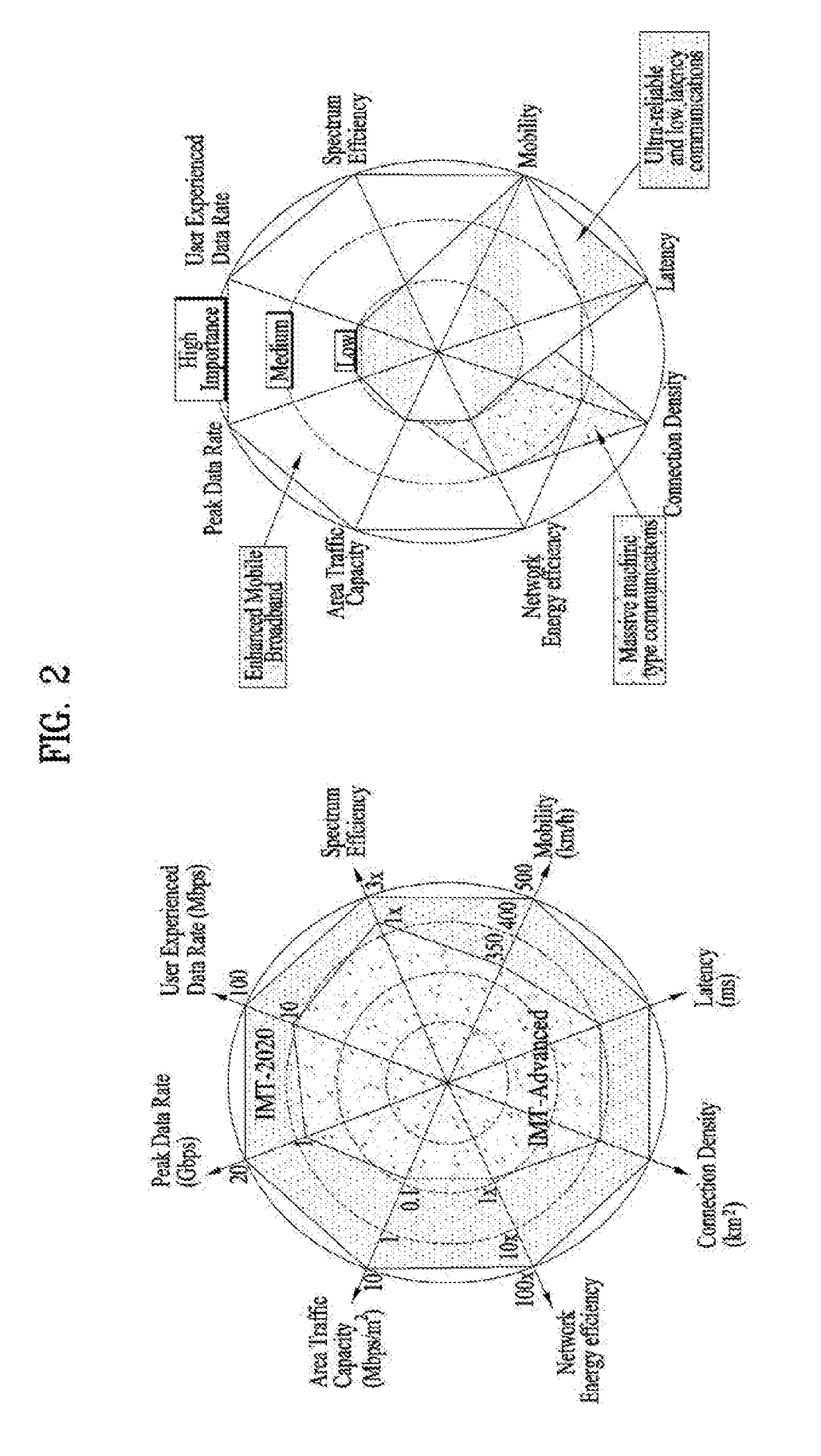

Method of transmitting signal by adaptively controlling windowing or filtering in wireless communciation system and apparatus therefor

ActiveUS20180213501A1Improve data transfer bandwidthImprove abilitiesSynchronisation arrangementNetwork traffic/resource managementCommunications systemUser equipment

A method of transmitting a signal by adaptively controlling windowing or filtering by a user equipment in a wireless communication system, includes the steps of receiving a message including a timing advance (TA) value from a base station, determining a windowing type or a filtering type corresponding to the TA value, and transmitting an uplink signal to which the determined windowing type is applied. In this case, the windowing type is distinguished according to a length of a valid symbol and the filtering type can be distinguished according to a filter coefficient value.

Owner:LG ELECTRONICS INC

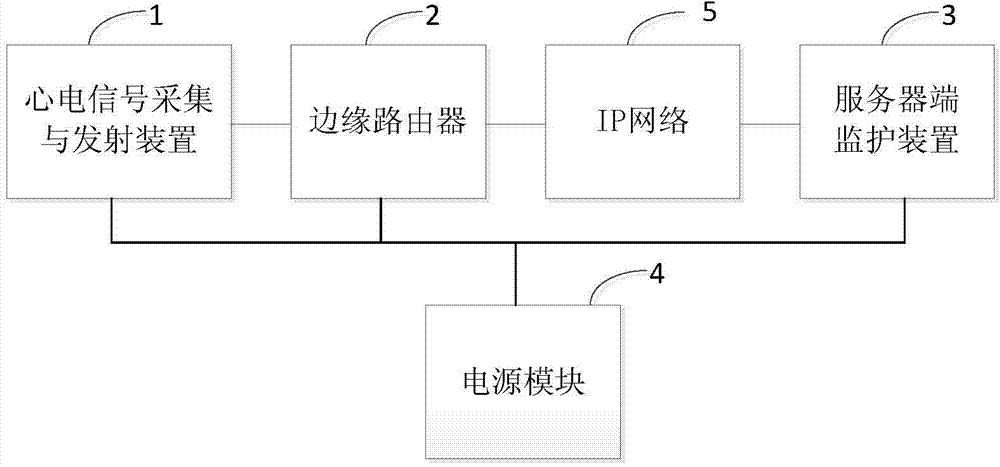

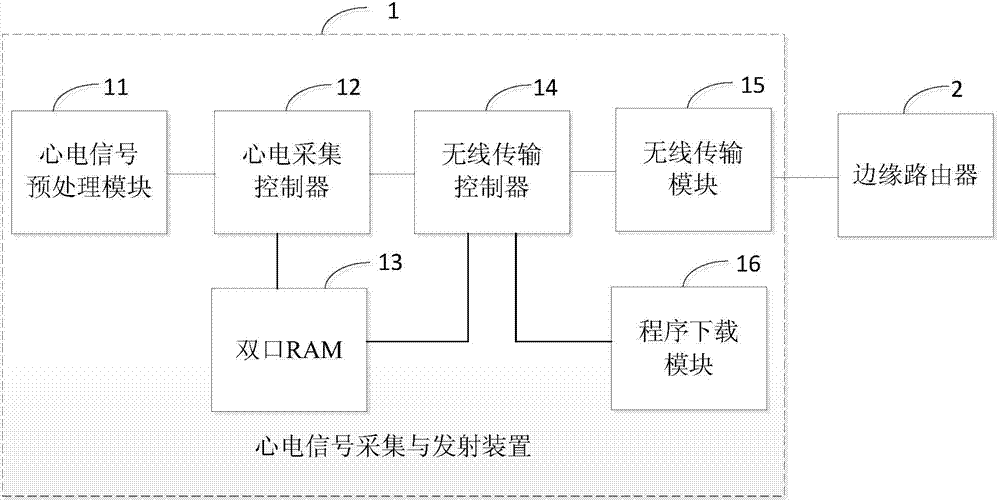

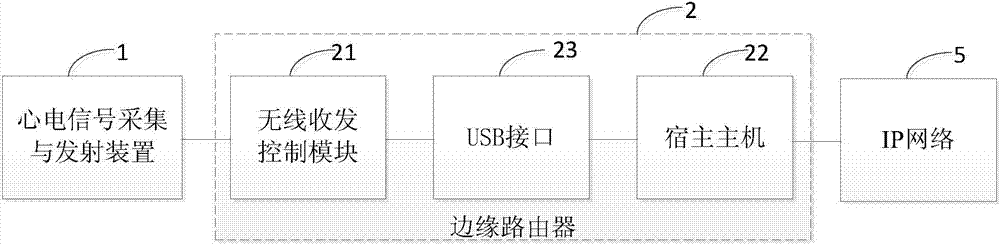

Wireless remote electrocardiograph monitoring system

InactiveCN104720791AReduce invalid occupancyImprove data transfer bandwidthSensorsTelemetric patient monitoringEcg signalAnti jamming

The invention relates to the field of electrocardiograph monitoring, and provides a wireless remote electrocardiograph monitoring system. The problems that an electrocardiograph monitoring system at present is weak in anti-jamming capability, large in power dissipation and larger in occupancy of network resources are solved. The wireless remote electrocardiograph monitoring system comprises an electrocardiograph signal collecting and transmitting device, an edge router and a server end monitoring device, wherein the electrocardiograph signal collecting and transmitting device comprises an electrocardiograph signal pre-processing module, an electrocardiograph collecting controller, a dual-port RAM, a wireless transmission controller and a wireless transmission module. According to the technical scheme, a ping-pong storage structure based on the dual-port RAM is adopted, the data transmission bandwidth is improved, and invalid occupation of a wireless channel is reduced; in addition, the wireless transmission mode based on the 6LoWPAN protocol is adopted, so that complicated networking protocol conversion is effectively avoided while the anti-jamming capability of wireless transmission is improved and the power consumption of the system is reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Retractable interconnect device configured to switch between electrical paths

InactiveUS9166346B2Data transfer speed is fastImprove data transfer bandwidthClamped/spring connectionsFlexible lead accommodationEngineeringElectrical and Electronics engineering

Owner:IBM CORP

Method for designing optical fiber bus based on Ethernet passive optical network

InactiveCN103281131AImprove reliabilityThere is no problem of electromagnetic interferenceBus-type electromagnetic networksFibre transmissionAviationTopological graph

The invention relates to a method for designing an optical fiber bus based on an Ethernet passive optical network. The method includes a configuration method of the Ethernet passive optical network, a three-tier exchange mechanism, a topological graph of optical fiber bus design, a bus controller, access units, a photovoltaic conversion module, optical dividers and optical fibers. In the prior art, foreign standards are adopted for all technologies related to the optical fibers, and due to the fact that the technologies and chips used for realizing the technologies belong to an embargo range which the west imposes on China, China can not directly adopt the standards. The novel method replaces an abroad homogeneous technology, and a set of autonomous standard systems of optical fiber bus products is established in China. Therefore, the optical fiber bus technology can be widely applied to the fields of aerospace, aviation, a military industry, an electronic industry and the like.

Owner:慈溪市京慈通信科技有限公司

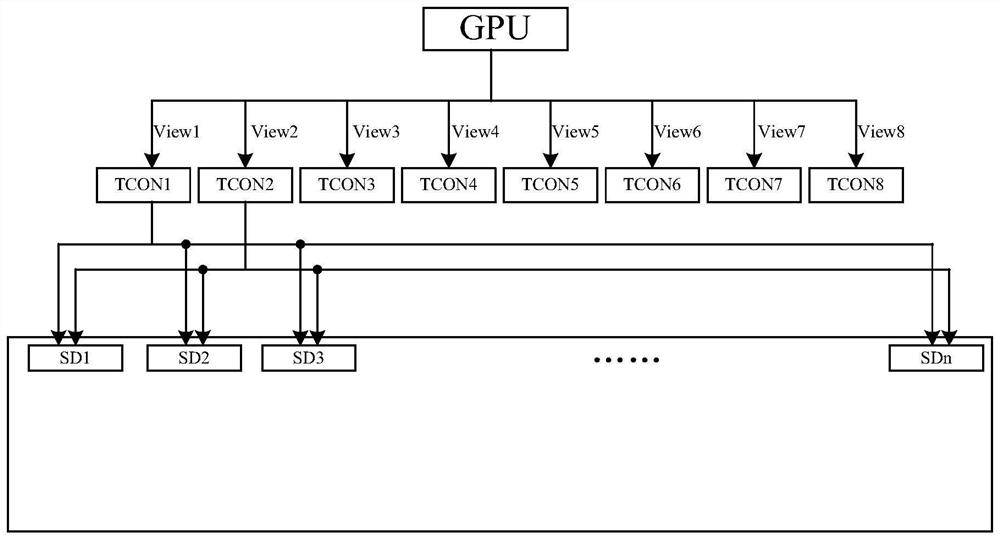

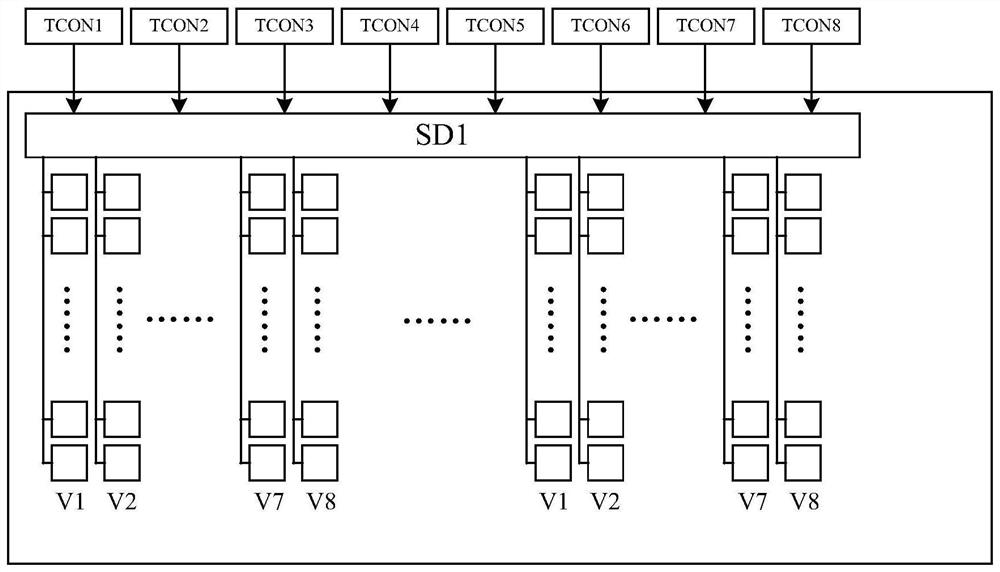

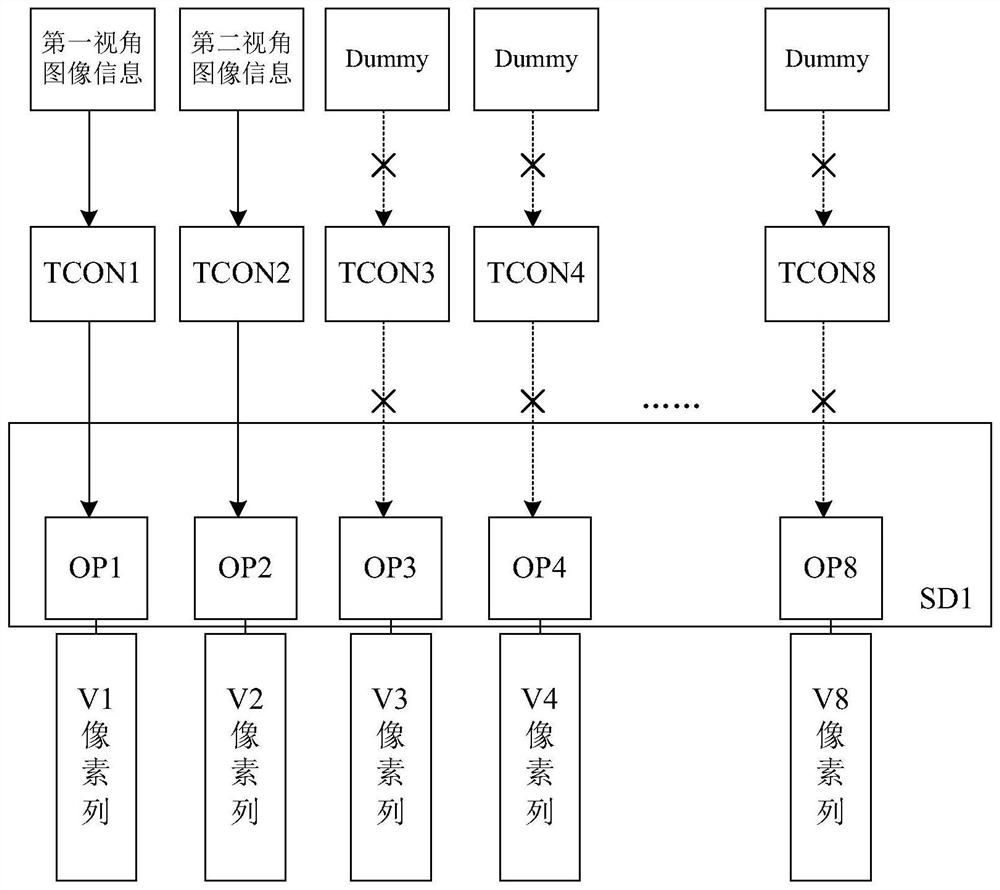

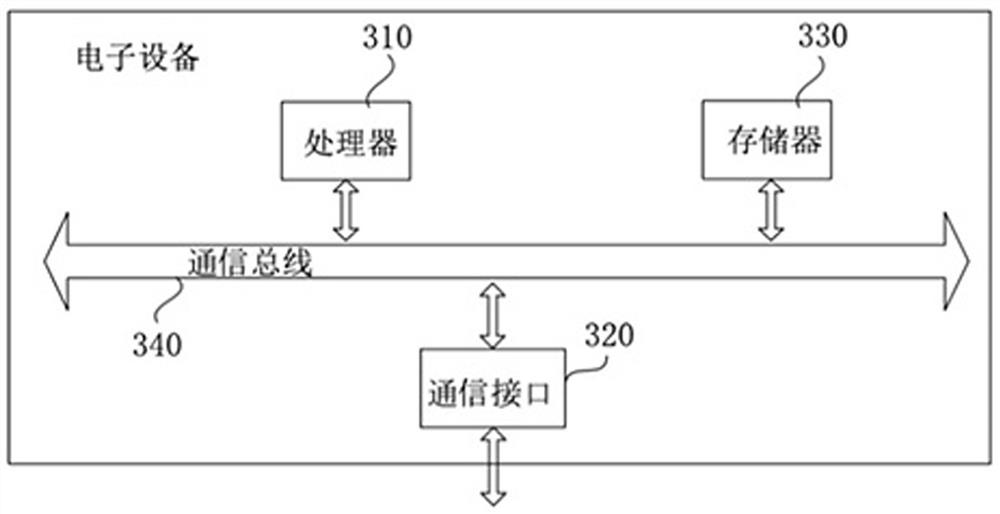

Display control system, display control method, electronic device, and storage medium

PendingCN113282175AIncrease the number ofIncrease refresh rateInput/output for user-computer interactionGraph readingData transmissionData channel

The invention provides a display control method, a display control system, electronic equipment and a storage medium. The method comprises the steps: determining at least one piece of target view angle image information to be displayed from multiple pieces of view angle image information based on at least one piece of target view angle information, wherein the target view angle image information corresponds to the target view angle information; and dividing the target view angle image information into at least two groups of data, transmitting the data to a display panel through at least two target data channels, further enabling the display panel to display the data based on the received data. The display control system comprises a plurality of data channels in one-to-one correspondence with the plurality of pieces of view angle image information, the at least two target data channels comprise a data channel corresponding to the target view angle image information and at least one multiplexing data channel not corresponding to the target view angle image information. According to the scheme, the number of data channels and the data transmission bandwidth are increased, and the refresh rate and the display effect can be improved.

Owner:BOE TECH GRP CO LTD

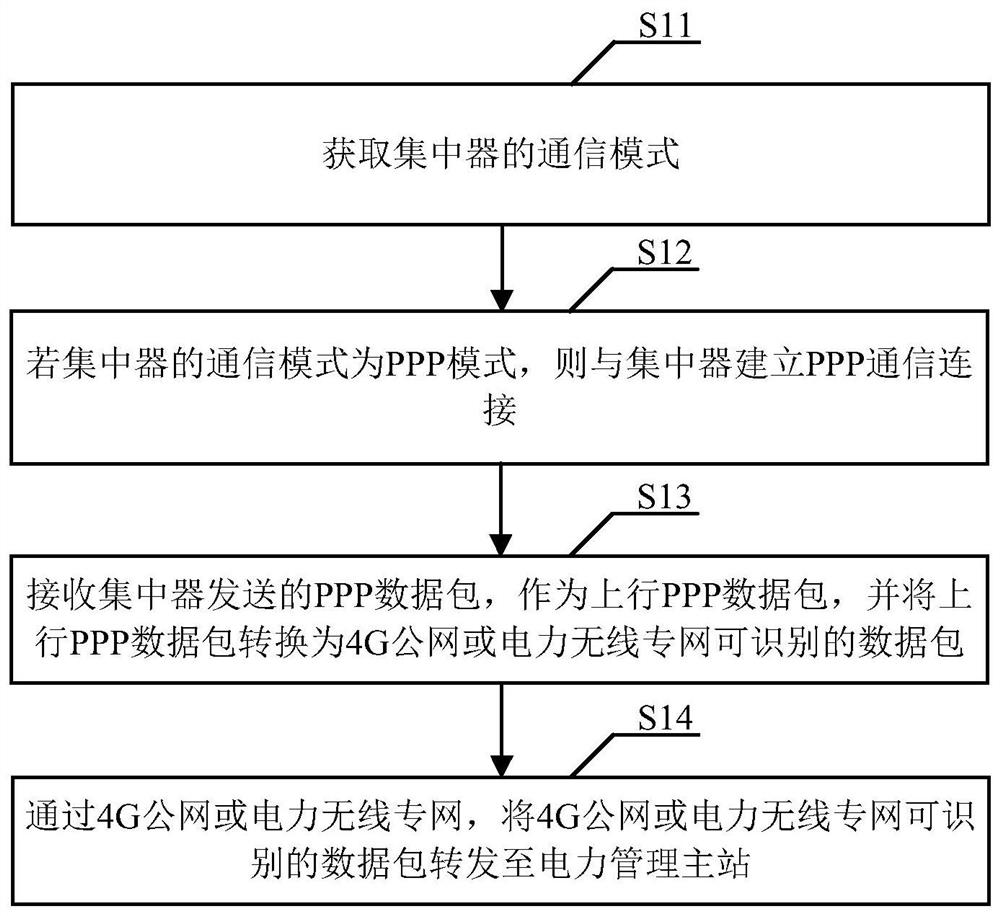

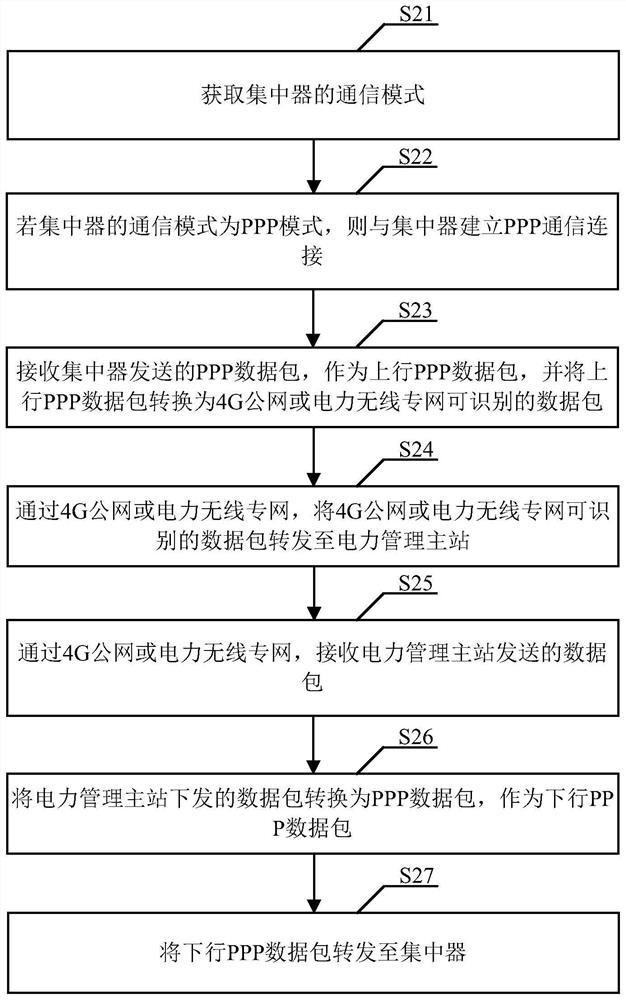

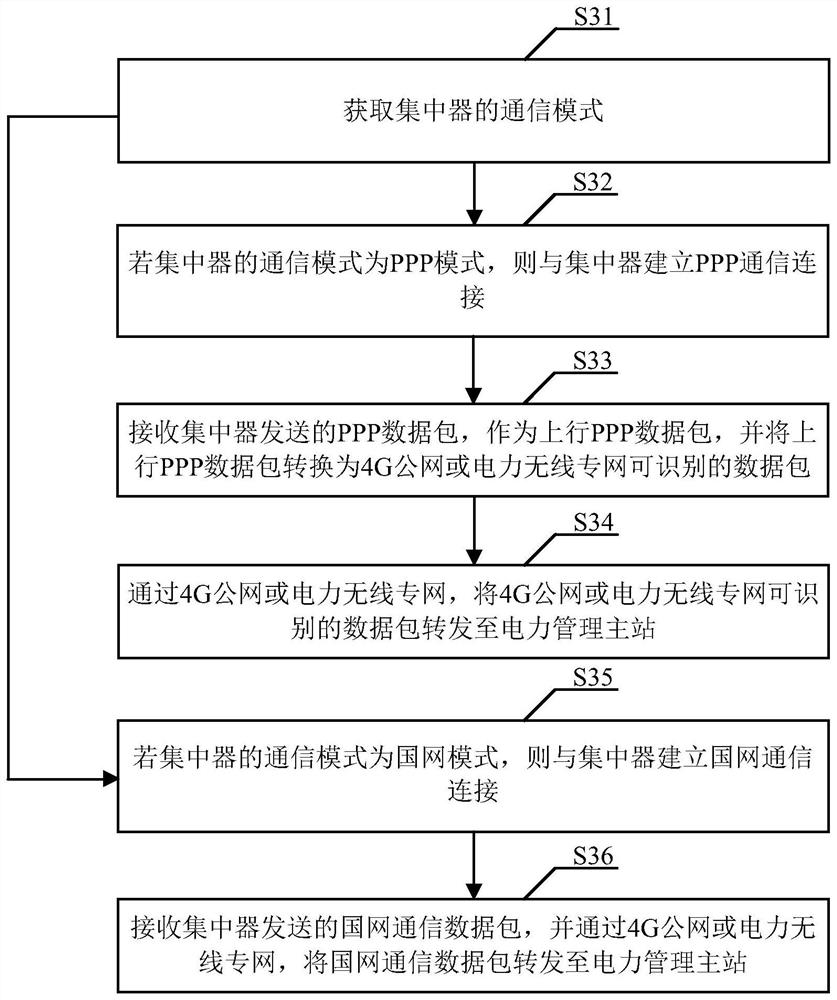

A remote communication method and device

ActiveCN108566404BImprove coverage qualityImprove communication qualityCircuit arrangementsTransmissionPrivate networkMaster station

The application provides a remote communication method and device. The remote communication method includes: obtaining the communication mode of the concentrator; if the communication mode of the concentrator is PPP mode, establishing a PPP communication connection with the concentrator; receiving the PPP data sent by the concentrator packet, as an uplink PPP data packet, and convert the uplink PPP data packet into a data packet recognizable by the 4G public network or the power wireless private network; through the 4G public network or the power wireless private network, the 4G public network or the power wireless private network Network-identifiable data packets are forwarded to the power management master station. In this application, the quality and rate of remote communication between the concentrator and the power management master station can be improved through the above methods.

Owner:STATE GRID INFORMATION & TELECOMM GRP +1

A stacked cache system, control method and cache device based on sedram

ActiveCN112558889BLarge capacityBreak outInput/output to record carriersResource allocationWaferMemory controller

Owner:BEIJING VCORE TECH CO LTD

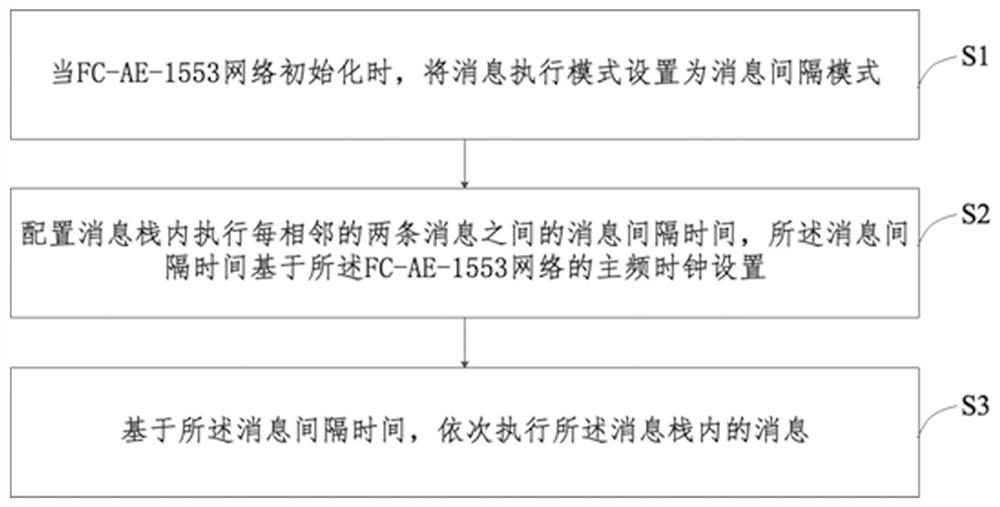

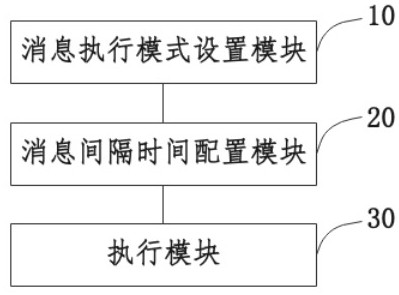

FC-ae-1553 Network Optimization Method and System

ActiveCN112995808BIncrease flexibilityImprove data transfer bandwidthMultiplex system selection arrangementsFibre transmissionEngineeringData transmission

The present invention provides a FC-AE-1553 network optimization method and system, including: when the FC-AE-1553 network is initialized, the message execution mode is set to the message interval mode; every adjacent two messages are executed in the configuration message stack The message interval time between, the message interval time is set based on the main frequency clock of the FC-AE-1553 network; based on the message interval time, execute the messages in the message stack in sequence. The present invention does not need to consider the message execution time, and by designing the execution interval between two messages, the data transmission bandwidth and the flexibility of the user's use can be effectively improved, and the best performance can be achieved, which is beneficial to the actual scene use.

Owner:BEIJING TASSON SCI & TECH CO LTD

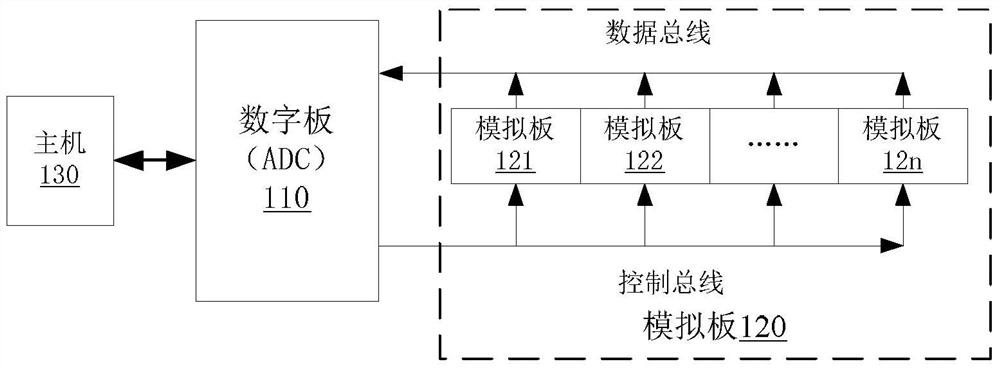

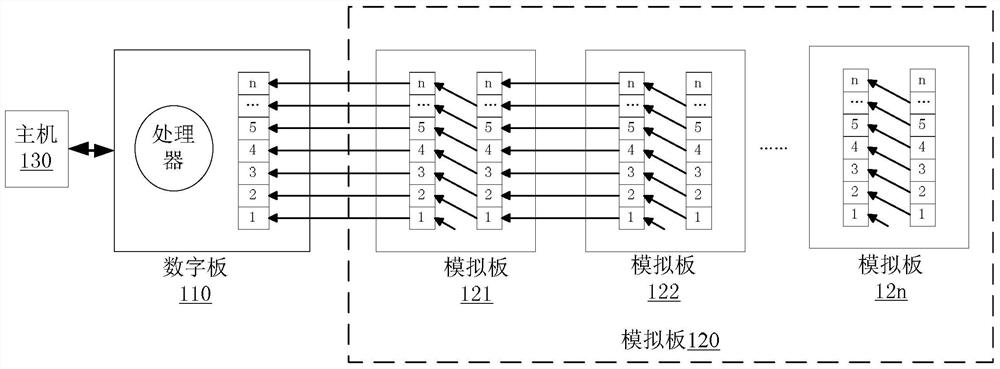

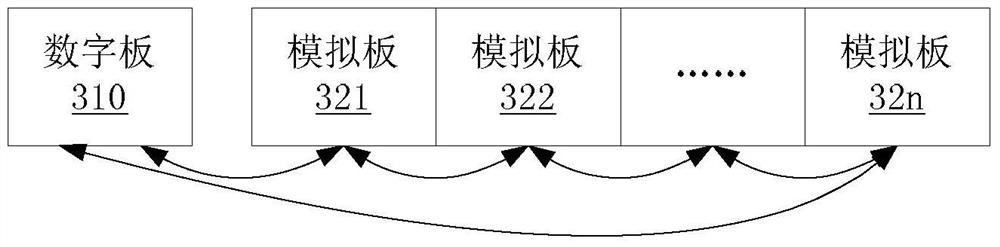

Data acquisition device, data acquisition system and method

ActiveCN105487997BSatisfy large-scaleSolve the shortcomings of poor anti-interference abilityElectric digital data processingData packData acquisition

A data collection device is disclosed, which is used to collect data according to received instructions, including: N analog boards, the N analog boards are sequentially connected in series, and N is a natural number greater than or equal to 1 for collecting data; digital boards , connected to the first analog board in the N analog boards, for forwarding the received instructions to the N analog boards, and uploading the data collected by the N analog boards according to the instructions; wherein, The first analog board among the N analog boards receives the instructions forwarded by the digital board, and sequentially forwards them to the next-level analog boards, and the N analog boards collect data according to the received instructions, and forward them sequentially to the upper The primary analog board is sent to the digital board through the first analog board among the N analog boards. The invention also provides a data acquisition system and method thereof, which have strong anti-interference ability, strong real-time data transmission ability, high data transmission bandwidth, convenient fault diagnosis and high reliability.

Owner:XNDT TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com