Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Adequate drive capacity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

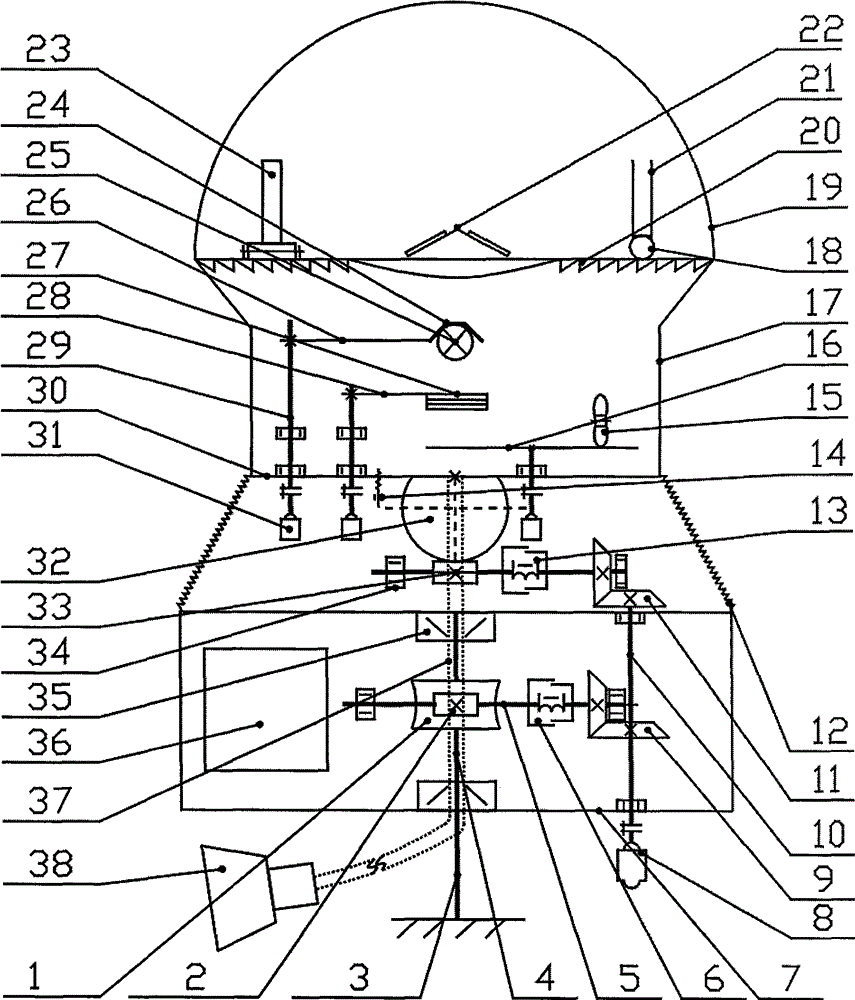

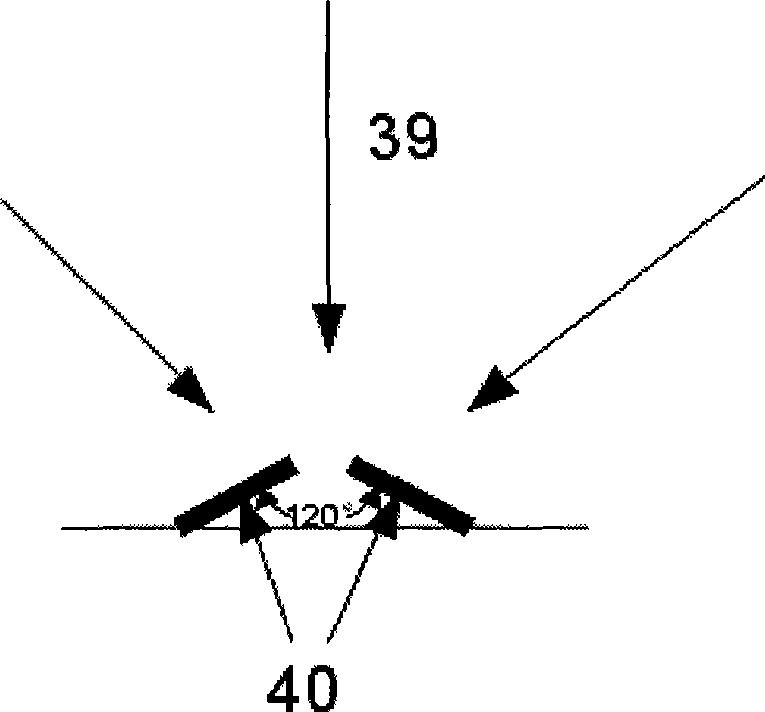

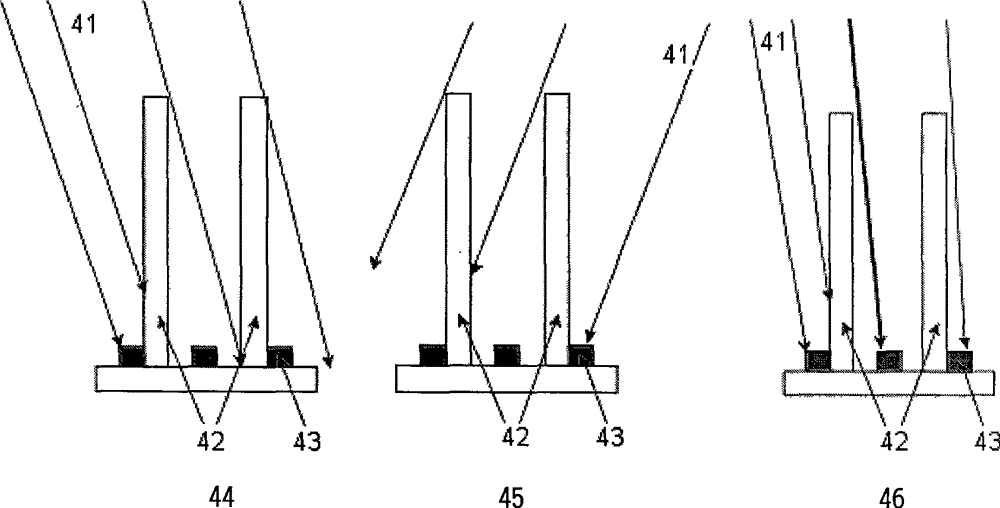

Light source gatherer

ActiveCN101672452AAchieve isolationAdequate drive capacityLighting applicationsMechanical apparatusElectromagnetic clutchControl system

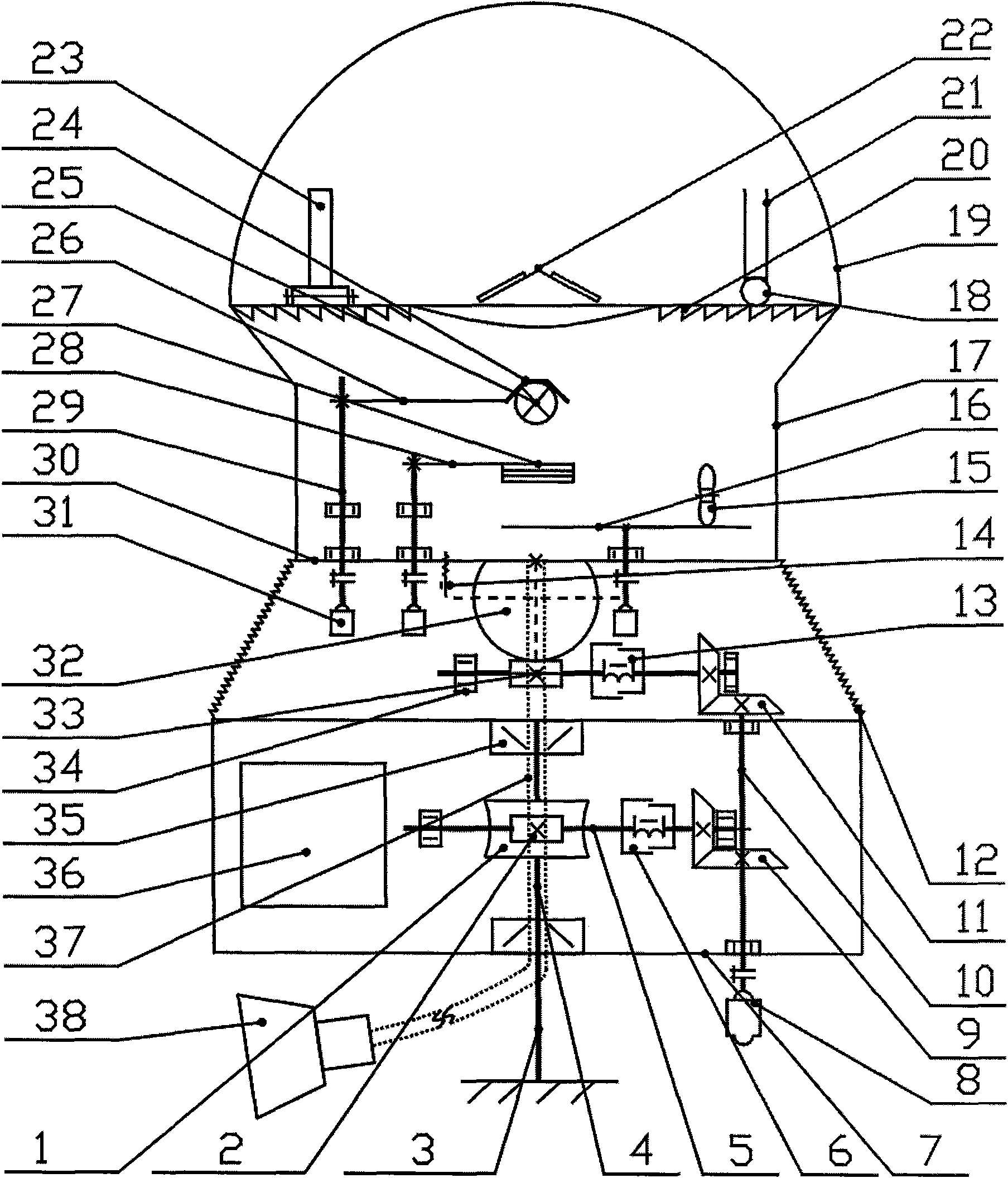

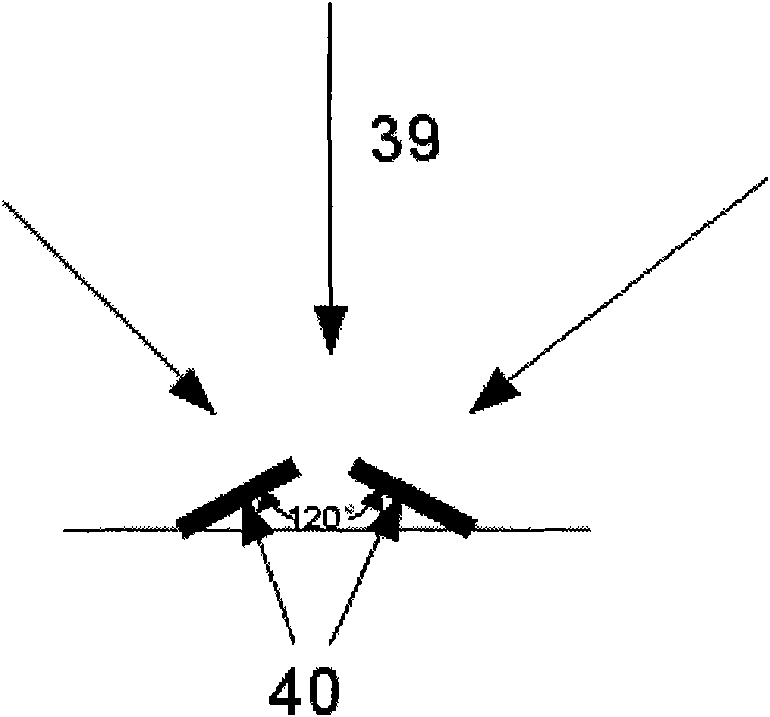

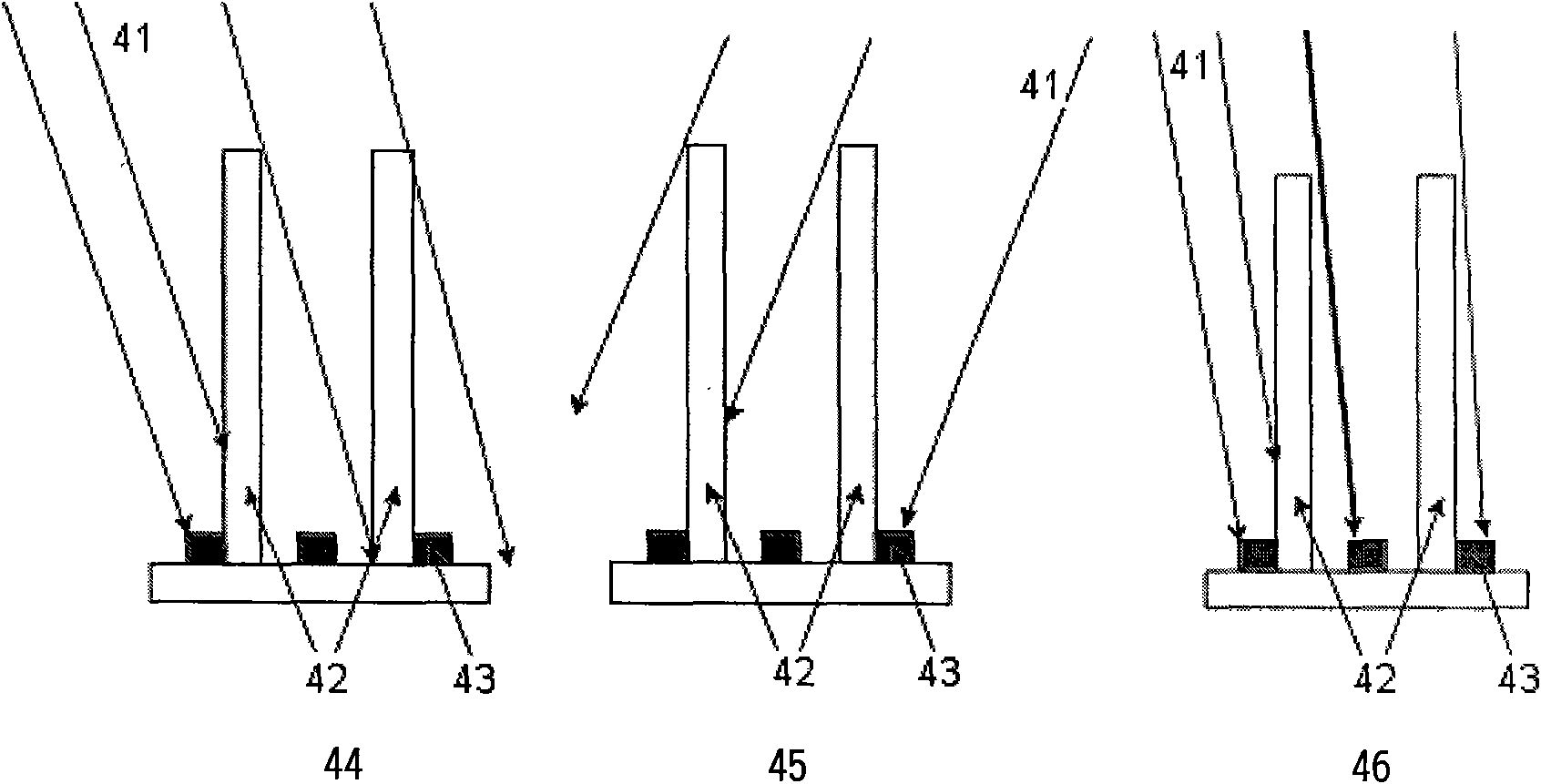

The invention discloses an improvement on a light source gatherer device for automatically tracing sun light, and belongs to the new field of an illumination technique of optical fiber use and solar energy utilization. The device comprises a light gathering device, an electromechanical driving device, a sensor, a control system, a lamp light source, optical fibers, a switch and a luminous back lamp. The improvement on the device is characterized in that under the attraction of an magnetic clutch and the worm and gear engagement, the light gathering device is driven to rotate in the plane direction and the vertical direction in a self-locking way; the light gathering device adopts a circular belt type screw lens to gather light, and is provided with an axial fan at the side of a light filter to blow, exhaust and radiate heat; the sensor arranged at the position for checking the sun light sends a control command to a motor and the magnetic clutch of the electromechanical driving device through the control system, and the control command is used for controlling and driving the light gathering device to complete the motion adjustment for tracing any space angle required by the sun light, and controlling the lamp light source, the light filter and a color disc to do rotation at inlet and outlet positions in the horizontal direction, so the device can automatically gather light, collect the sun light source, and convert the lamp light source in sun-shading days.

Owner:NANJING SCI RES TECH

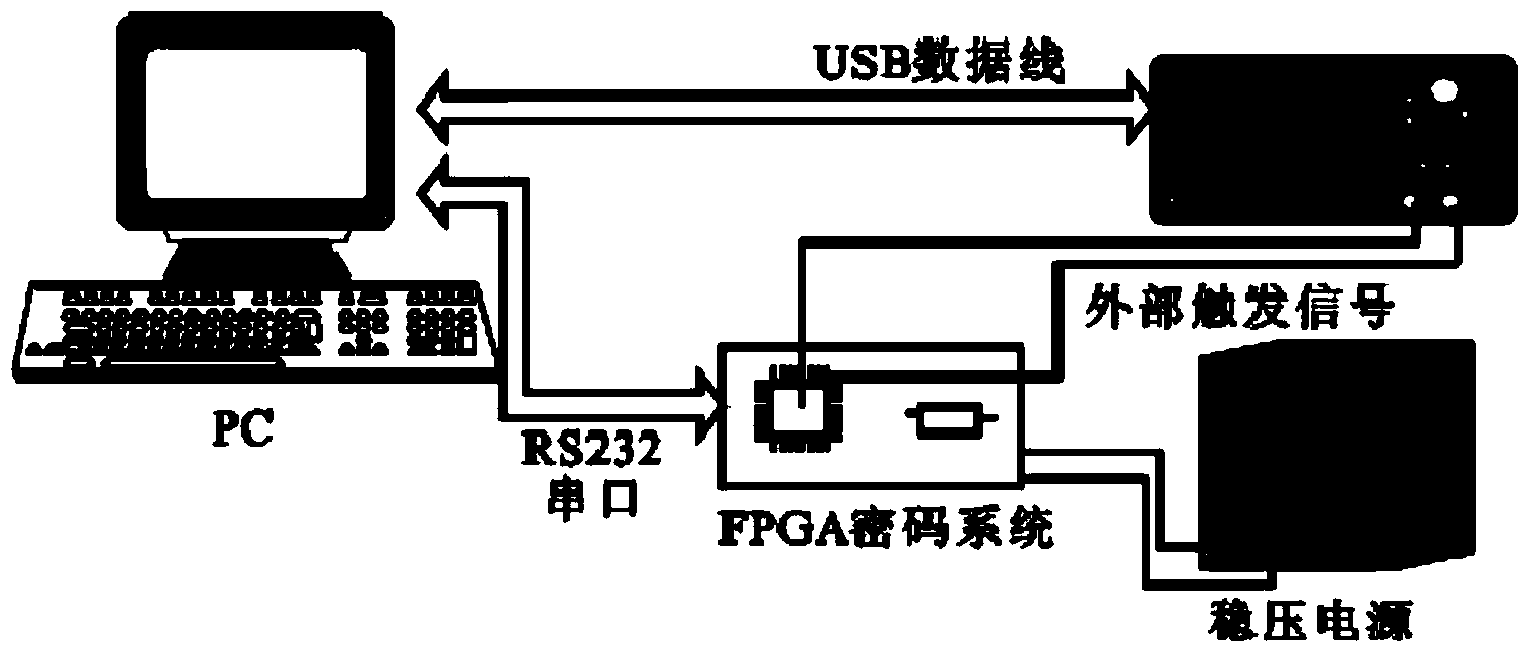

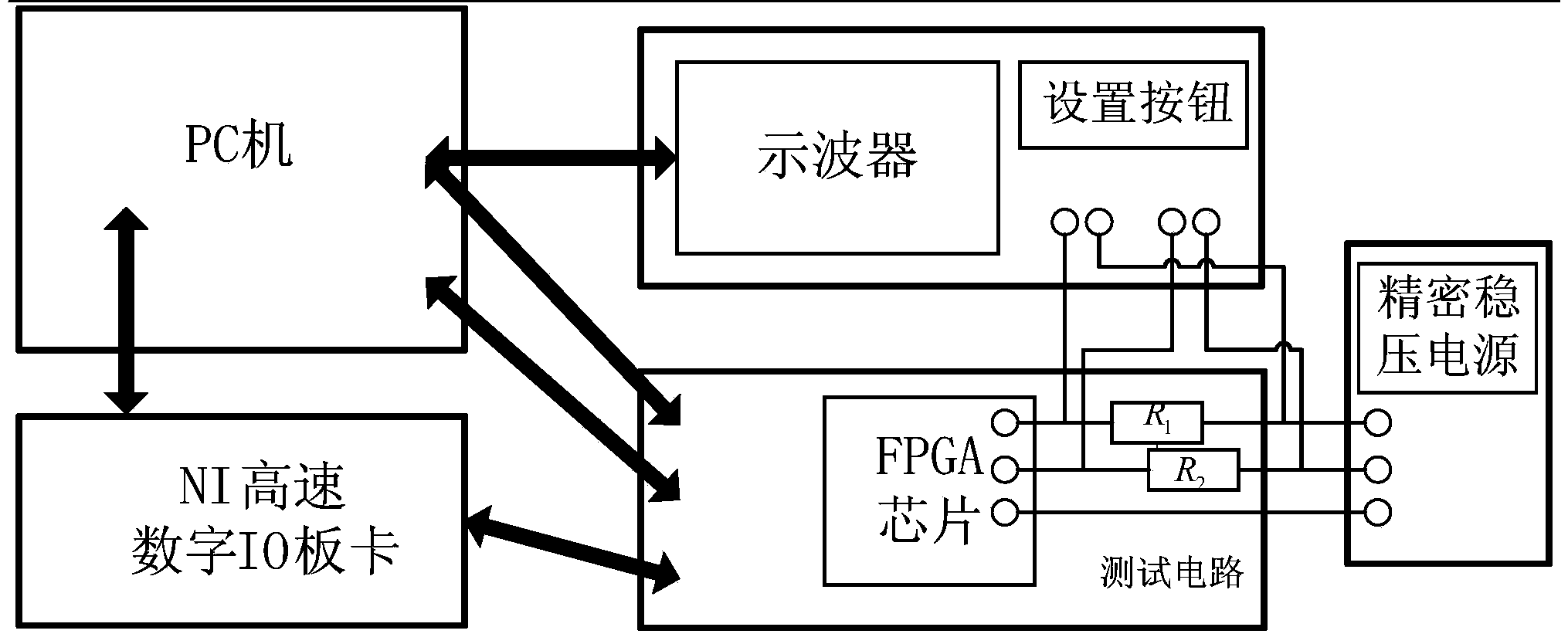

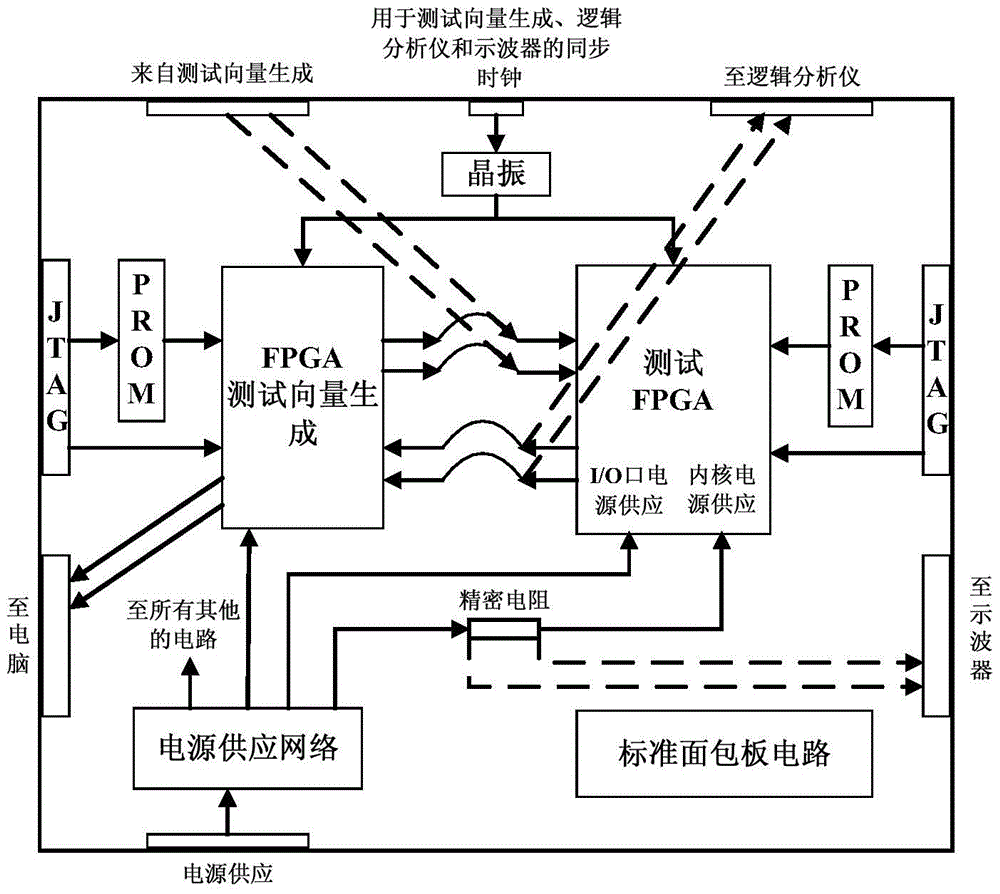

Hardware Trojan horse test system

ActiveCN103954904AImprove the level of automated testingEasy to handleDigital circuit testingElectrical resistance and conductanceFpga chip

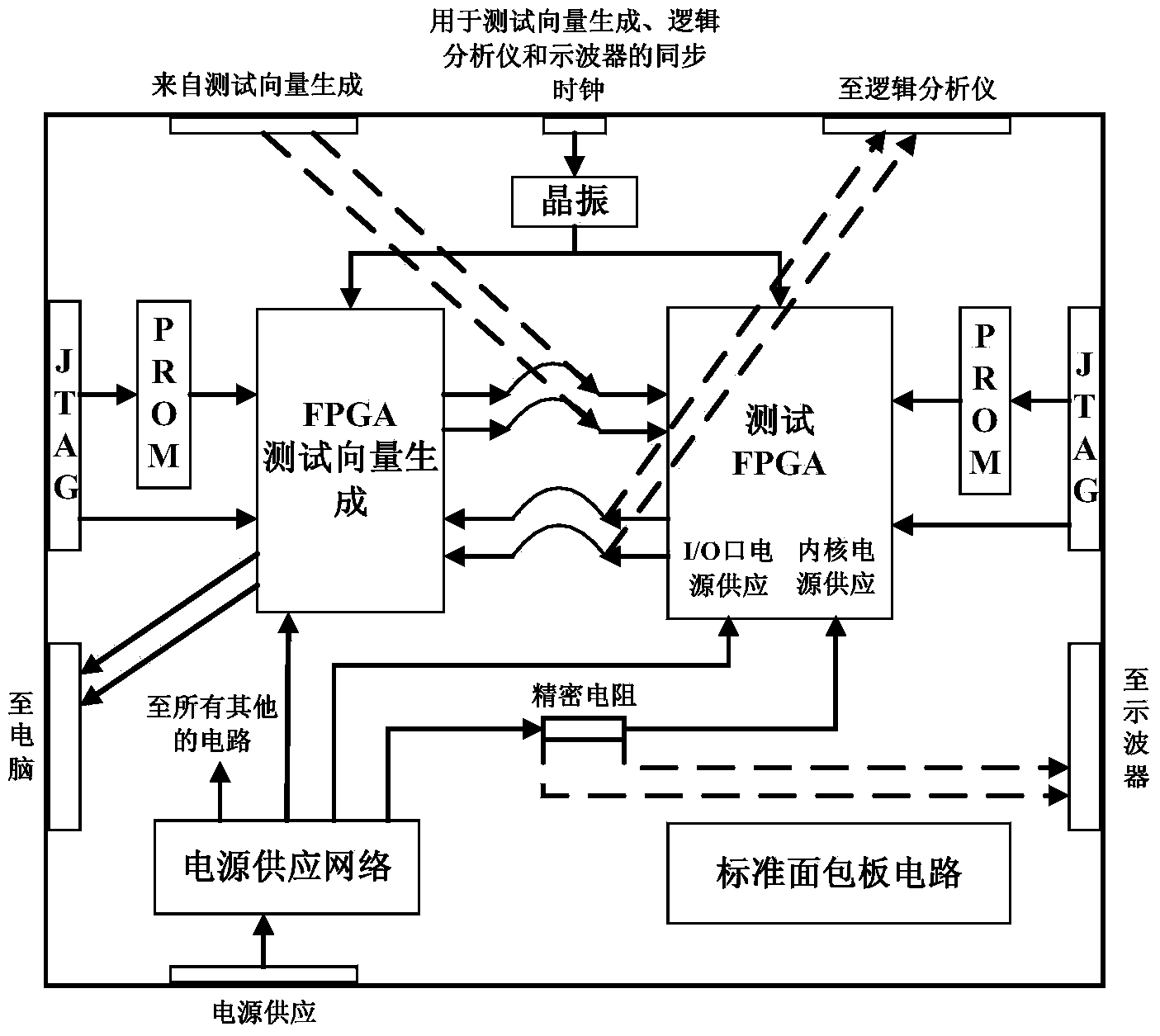

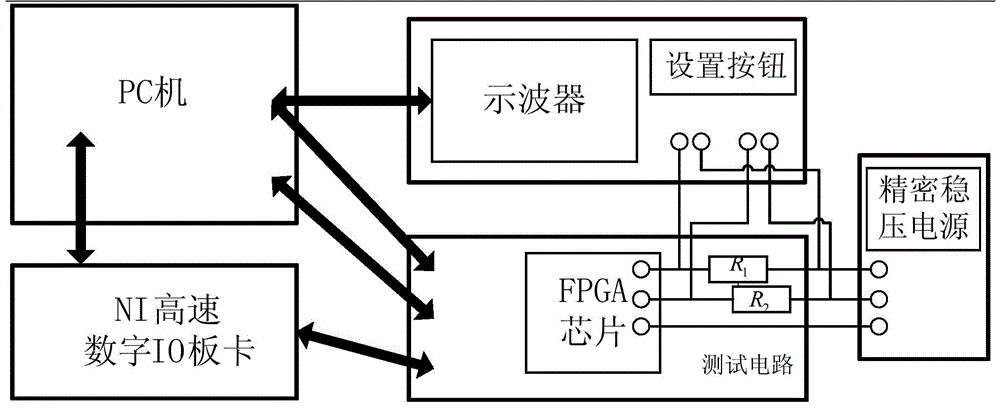

The invention discloses a hardware Trojan horse test system. The hardware Trojan horse test system comprises a PC, an NI high-speed digital I / O board and a test circuit, wherein the PC is used for generating a test vector, conducting programming on an FPGA chip, controlling the NI high-speed digital I / O board, an oscilloscope and the FPGA chip and receiving signals sent by the NI high-speed digital I / O board and the oscilloscope; the NI high-speed digital I / O board is used for outputting the test vector to the FPGA chip, collecting an FPGA response signal and sending back the FPGA response signal to the PC; the testing circuit comprises the FPGA chip and receives the test vector output by the NI high-speed digital I / O board. The hardware Trojan horse test system further comprises a precise resistor R1, a precise resistor R2, the oscilloscope and a precise voltage-stabilized source, wherein the precise resistor R1 and the precise resistor R2 monitor the power consumption change of the kernel voltage and the auxiliary voltage of the FPGA chip, the oscilloscope is used for automatically triggering and collecting signals of power consumption change of the kernel voltage and the auxiliary voltage of the FPGA chip and sending the signals to the PC; the precise voltage-stabilized source is used for supplying power to the test circuit. The hardware Trojan horse test system conducts automatic tests, improves the precision of logic testing and bypass analysis and is high in application value.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

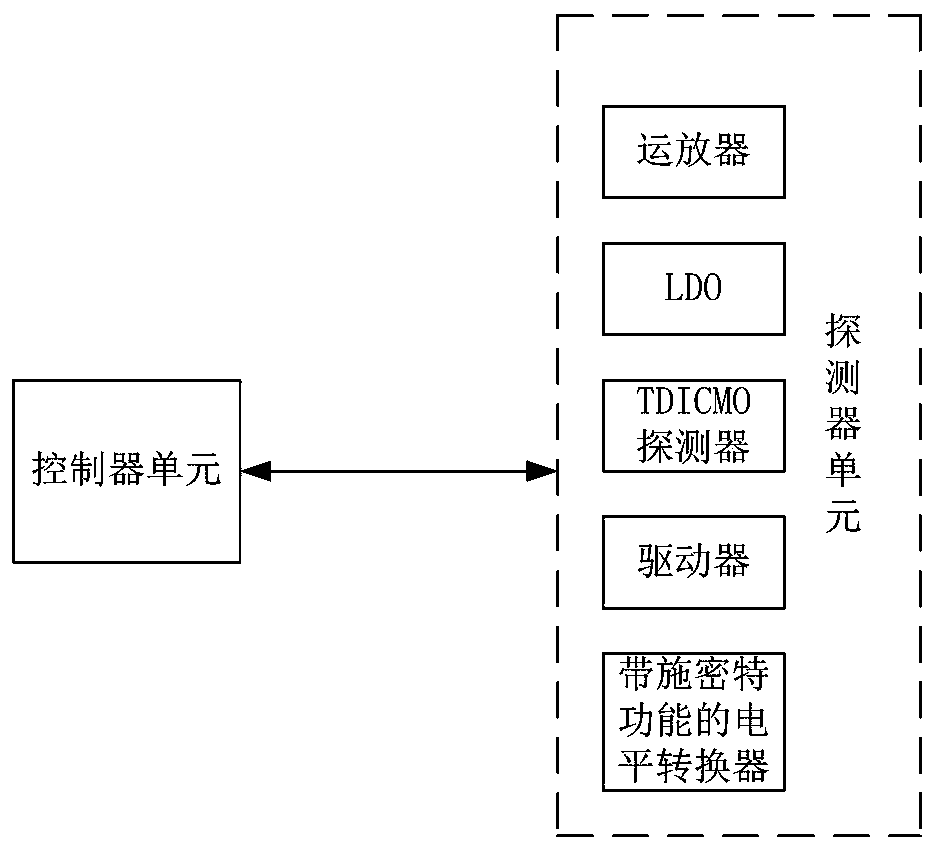

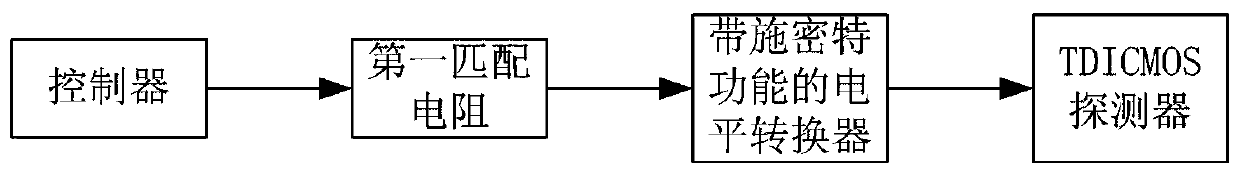

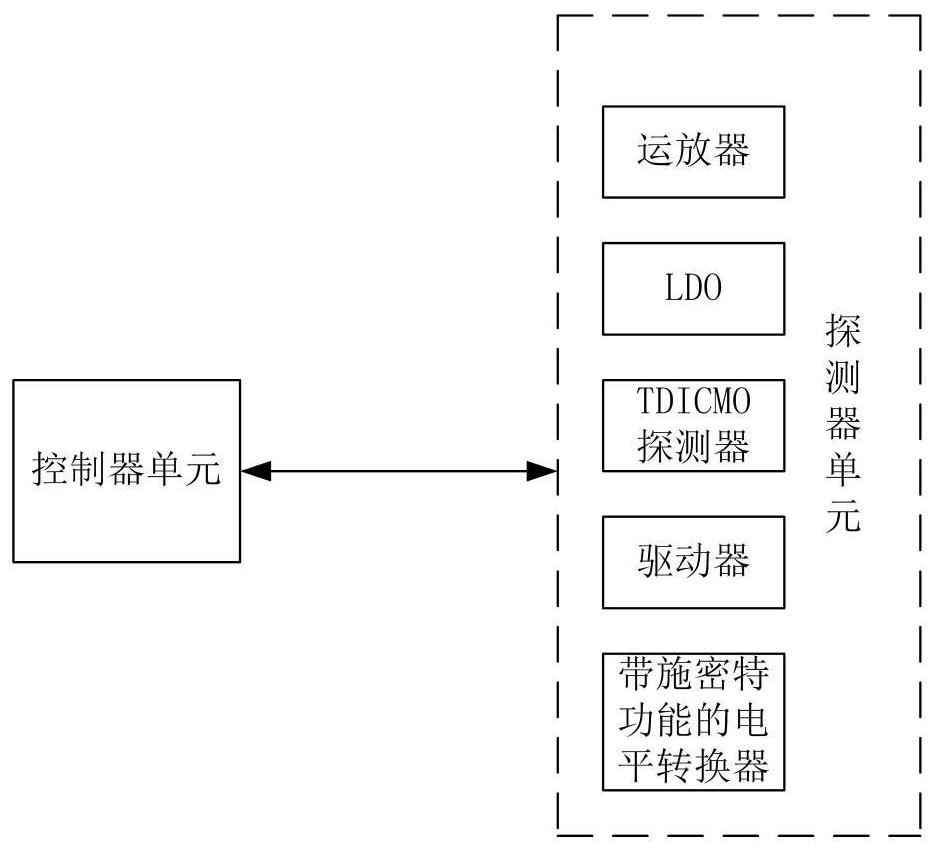

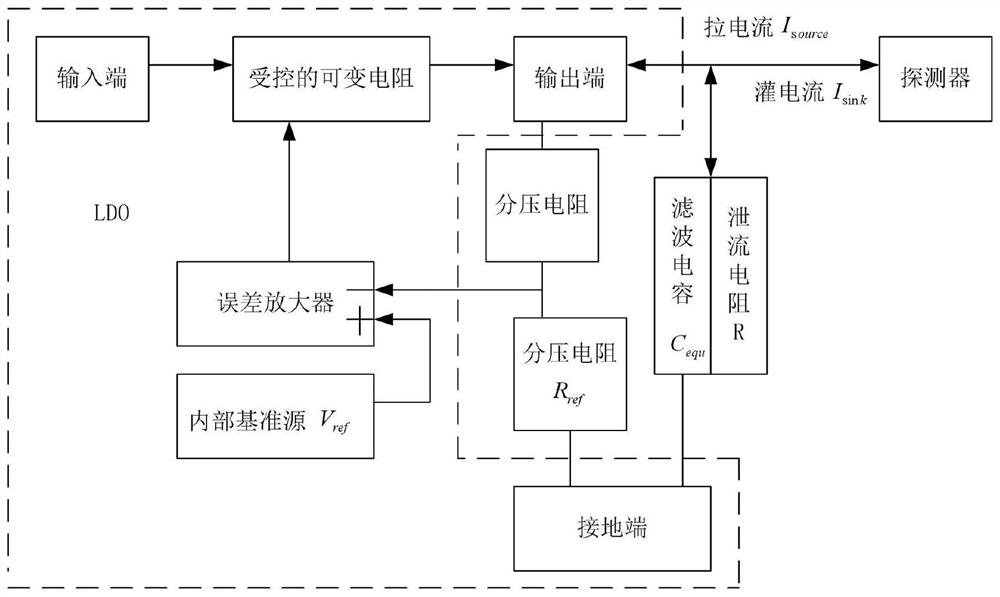

Design method of TDICMOS imaging unit

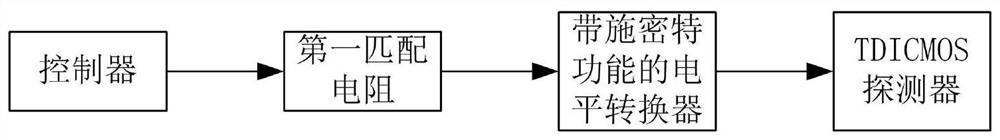

InactiveCN110034748AAvoid access difficultiesEasy accessElectric pulse generatorRadiation controlled devicesSolderingDigital input

The invention discloses a design method of a TDICMOS imaging unit, relates to a design method of a TDICMOS imaging unit, solves the problems that the existing TDICMOS imaging unit is complex in designand poor in stability. A controller unit and a detector unit are included, the controller unit generates a control signal required by the detector unit and receives the digital image data output by the detector unit; the detector unit comprises a TDICMOS detector, an operational amplifier, an LDO, a driver with a Schmidt function and a level shifter with a Schmidt function. According to the invention, power supply of a pixel part with pull-fill current, transmission of a digital input control signal, a generation mode of a charge transfer driving signal, a placement mode of a via hole in a high-density region and processing of a multilayer grounding plane are designed respectively; the utilization area of the circuit board is increased to the maximum extent, the integrity of control driving signals and a power supply is improved, and meanwhile voltage breakdown, pseudo soldering and other risks are avoided.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

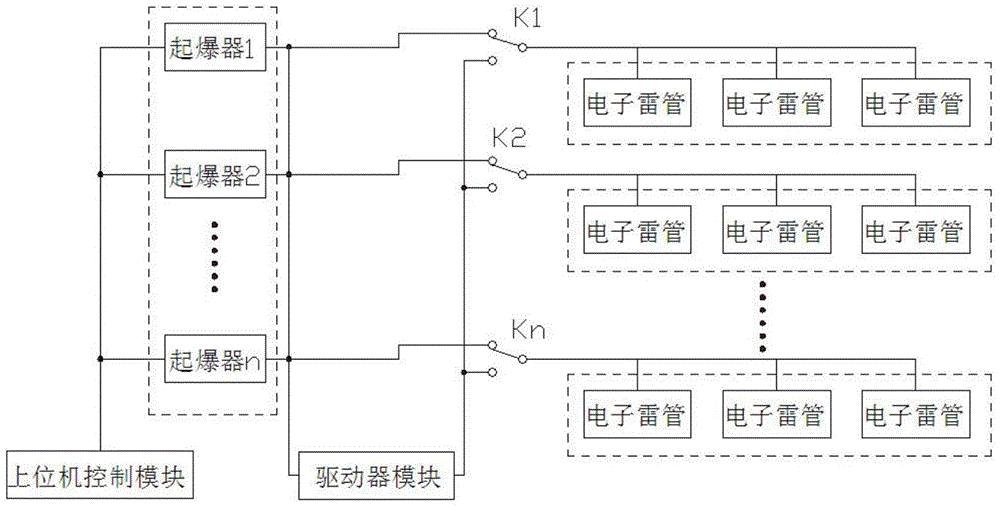

Control system for initiation networks of electronic detonators

InactiveCN104457462AAdequate drive capacityNo loss of detonation accuracyBlastingAmmunition fuzesDetonatorControl system

The invention provides a control system of initiation networks of electronic detonators. The control system comprises an upper computer control module, an actuator module, an initiator control module, changeover switches and the initiation networks. A signal input end of the initiator control module is connected with the upper computer control module, an output end of the initiator control module is connected with the initiation networks by the corresponding changeover switches and is further connected with an input end of the actuator module, and an output end of the actuator module is connected with the corresponding changeover switches. The control system has the advantages that various initiators are respectively connected with corresponding initiation networks before initiation instructions are issued, and accordingly initiation network detection, delay setting and the like can be completed; the initiation networks are completely connected with actuators in a changeover manner during initiation, the initiation instructions are amplified via the actuators, accordingly, all the initiation networks can be actuated by the aid of sufficient actuation capacity, initiation precision loss due to the system can be prevented, and the control system is simple and is high in reliability.

Owner:GUIZHOU JIULIAN IND EXPLOSIVE MATERIALS DEV +1

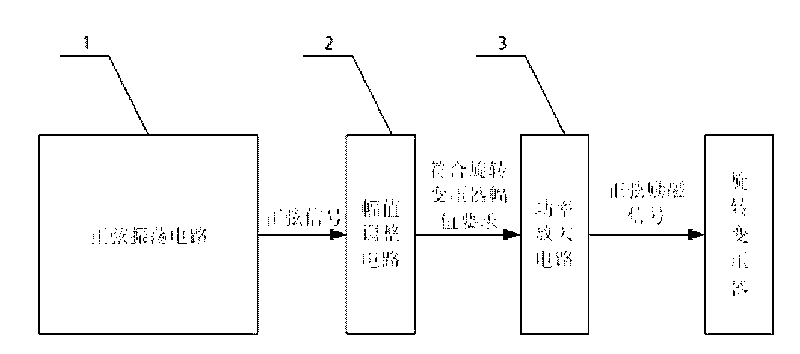

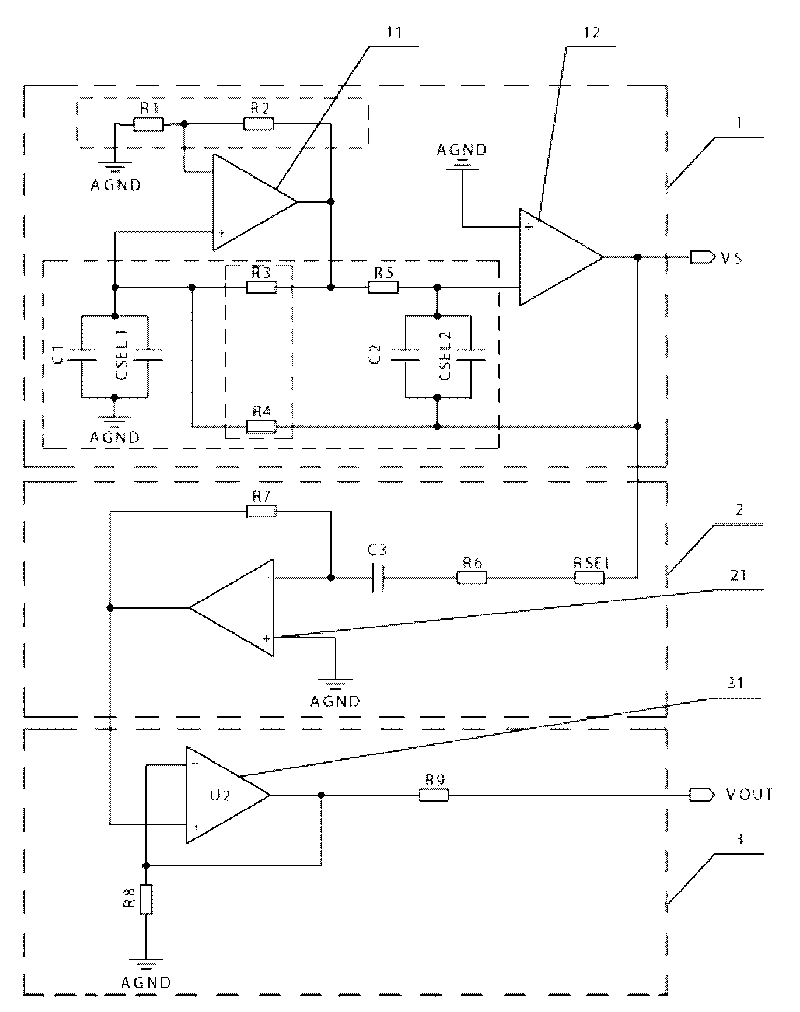

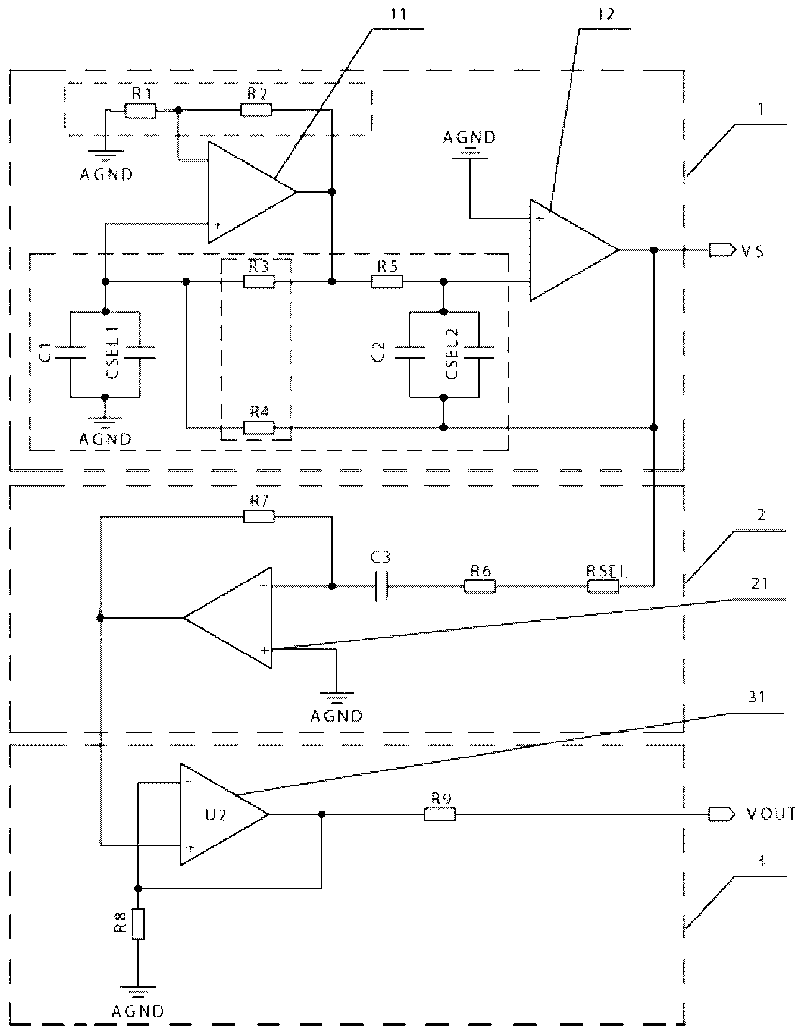

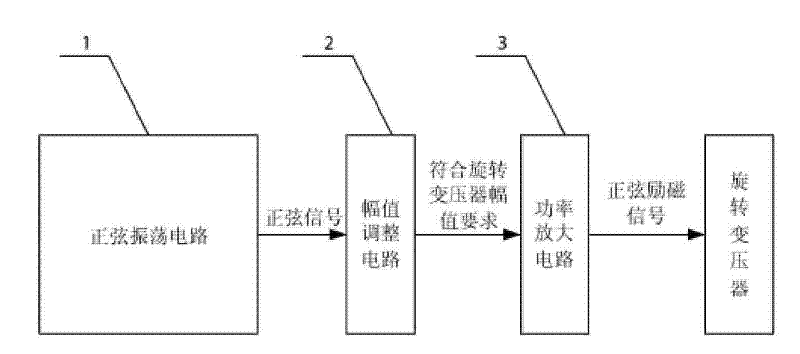

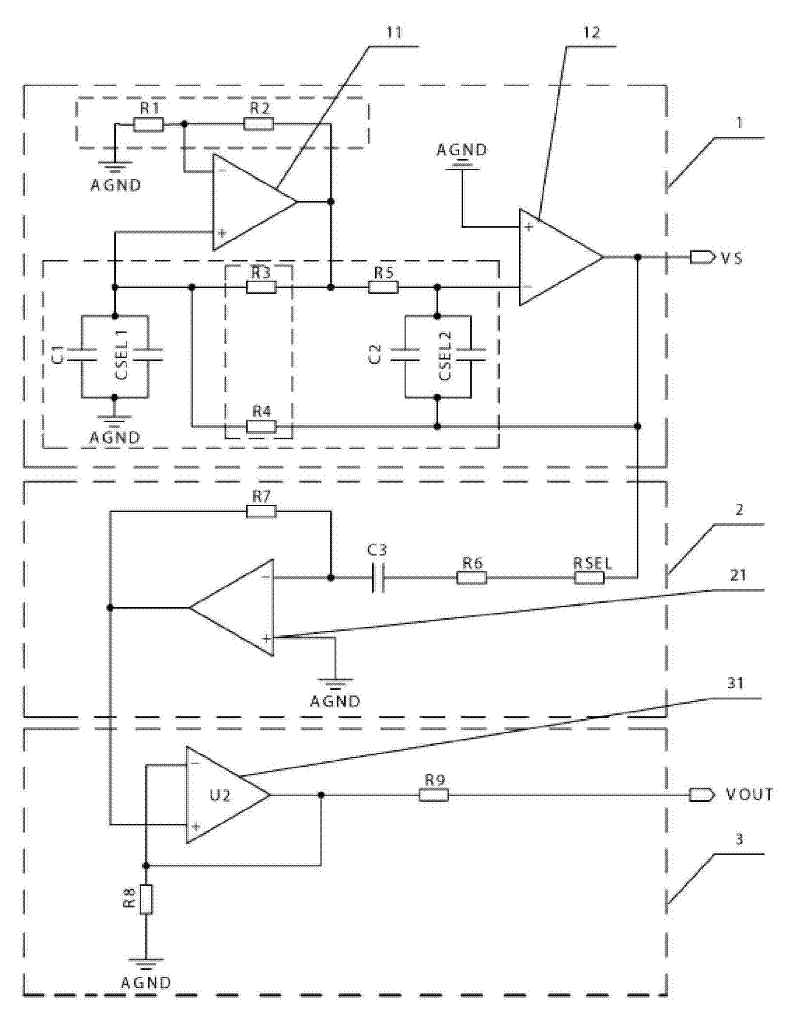

Excitation power circuit of rotary transformer

InactiveCN101714821AImprove reliabilityLow costConversion without intermediate conversion to dcCapacitanceAudio power amplifier

The invention discloses an excitation power circuit of a rotary transformer, belongs to the field of drive power sources, and solves the problems of complex circuit and incapability of independently working in the traditional excitation power of the rotary transformer. The excitation power circuit consists of a sinusoidal oscillation circuit, an amplitude adjusting circuit and a power amplifying circuit, wherein the sinusoidal oscillation circuit consists of a resistor R1, a resistor R2, a resistor R3, a resistor R4, a resistor R5, a capacitor C1, a capacitor C2, a capacitor CSEL1, a capacitor CSEL2, a first operational amplifier and a second operational amplifier; the amplitude adjusting circuit consists of a resistor R6, a resistor R7, a resistor RSEL, a capacitor C3 and a third operational amplifier; and the power amplifying circuit comprises a resistor R8 and a power amplifier. The frequency of a sinusoidal excitation power source generated by the circuit of the invention is modulated by selecting a capacitance value of the capacitor CSEL1 and the capacitor CSEL2, and the amplitude value of the sinusoidal excitation power source is adjusted by changing the resistance value of the resistor RSEL. The excitation power circuit of the invention serves as the drive power source of the rotary transformer.

Owner:HARBIN INST OF TECH

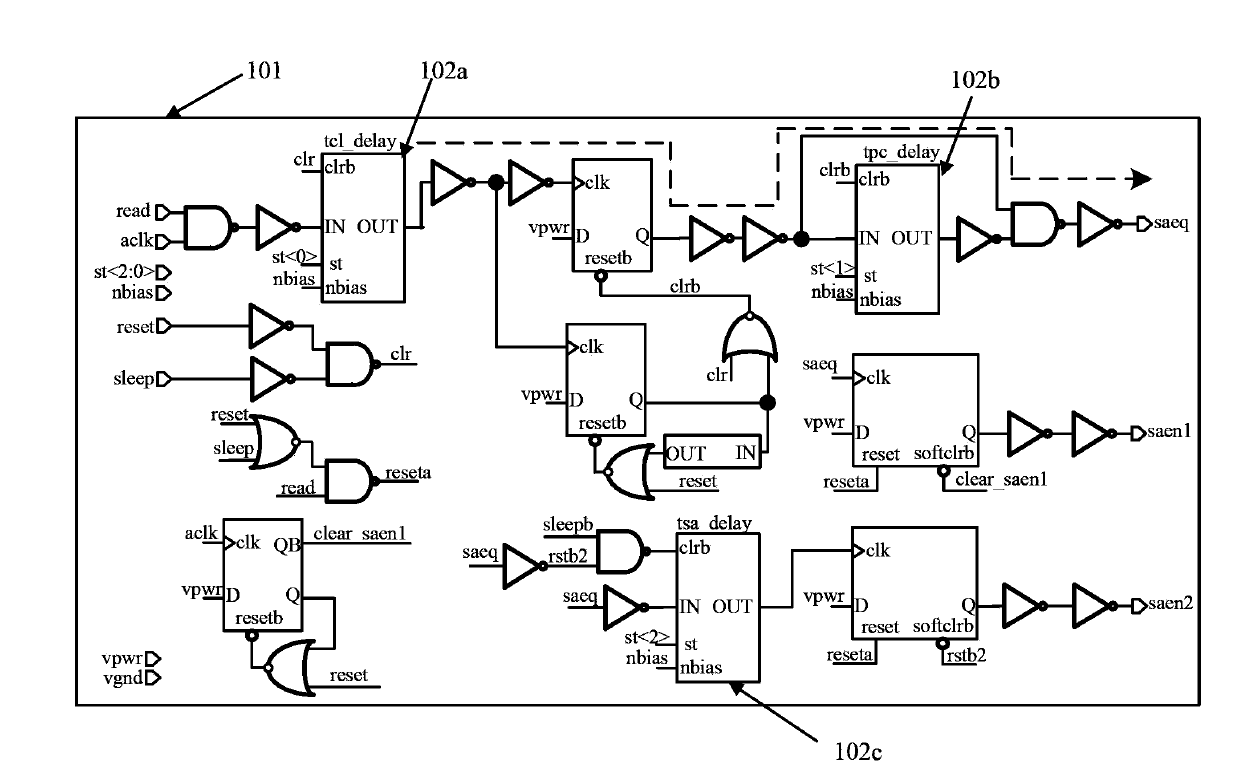

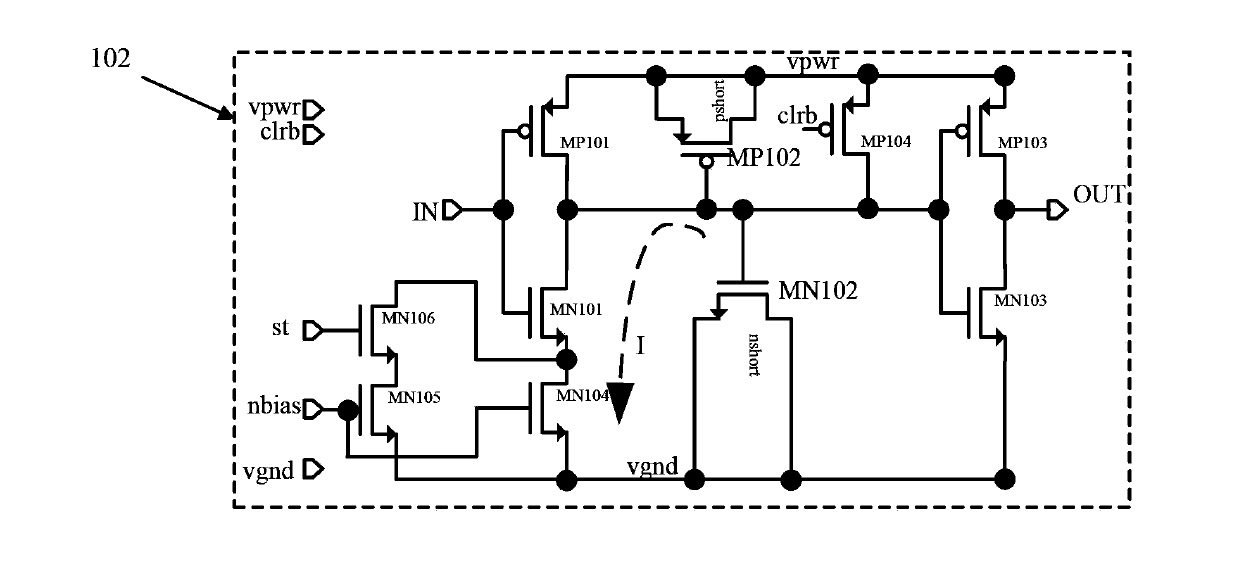

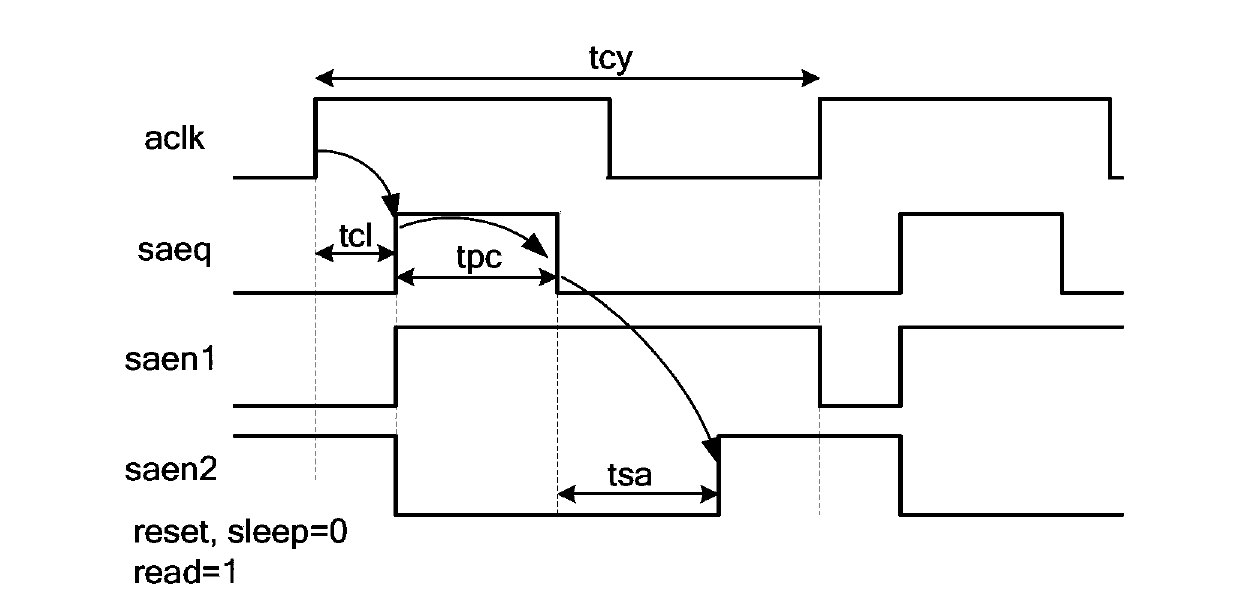

Read operation control signal generator and operating method thereof

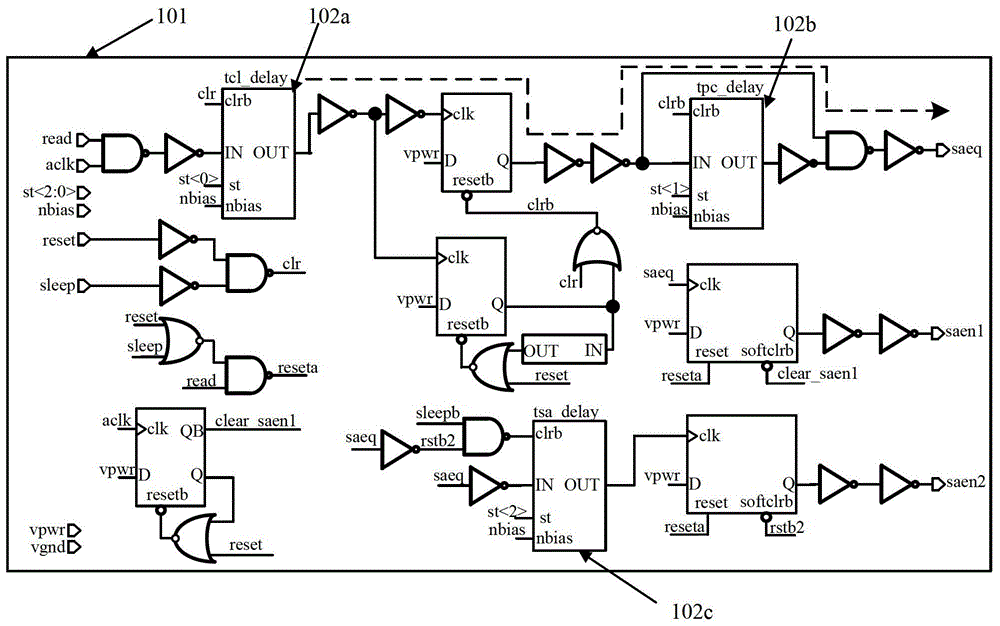

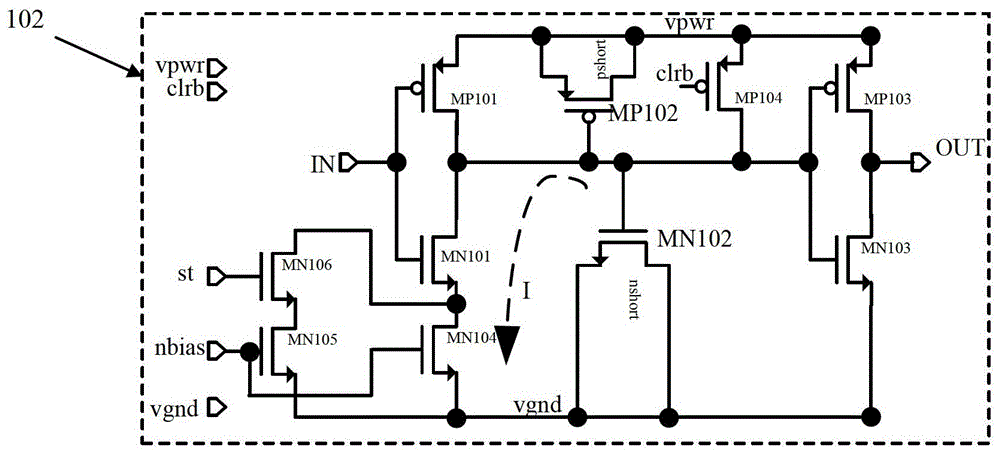

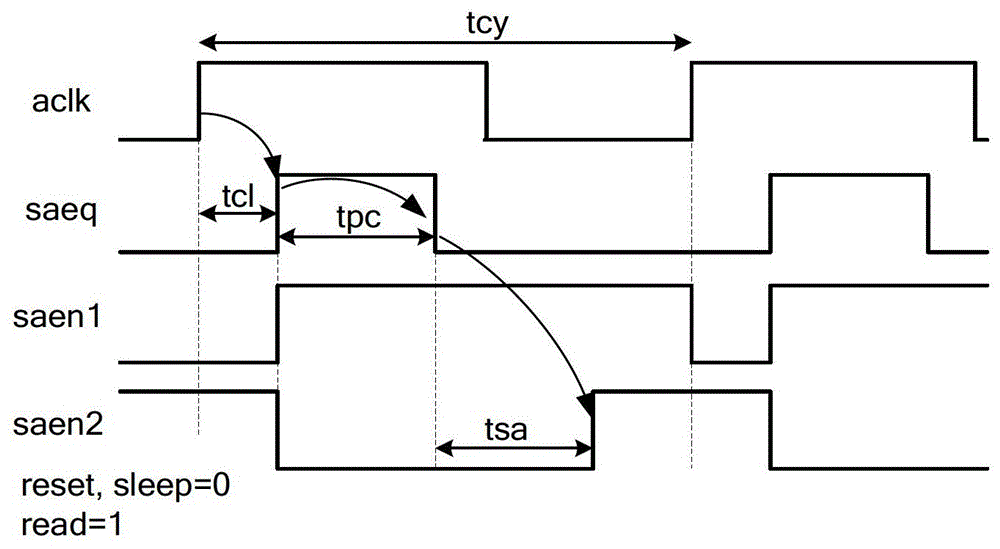

The invention discloses a read-operation control signal generator. The read-operation control signal generator comprises three delay circuits with same structures and different delay time setting; the input terminal of a first delay circuit is connected with internal clock signals, three delayed output signals are generated successively by the delay circuits because of rising edge trigger of external clock signals, and signal saeq is subjected to miteinander with nonsignals of second output signals and first output signals, and then is output via a noninverting amplifier; signal saen1 is output by a noninverting amplifie via first output signals; signal saen2 is output by a noninverting amplifie via third output signals; zero clearing of the three delay circuits can be realized via rising edge trigger of external clock signals, third output signals can be delaed by a fourth delay circuit, and zero clearing signals are lower by the fourth delay circuit so as to realize zero clearing of the three delay circuits. The invention also discloses an operation method of the read-operation control signal generator. The read-operation control signal generator is simple in circuit structure, and is capable of reducing delay skew, domain area, and circuit powder consumption.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

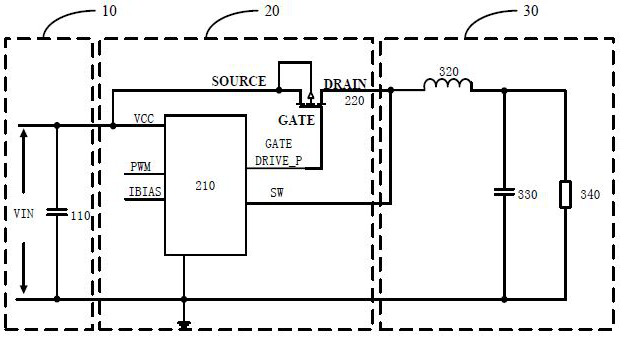

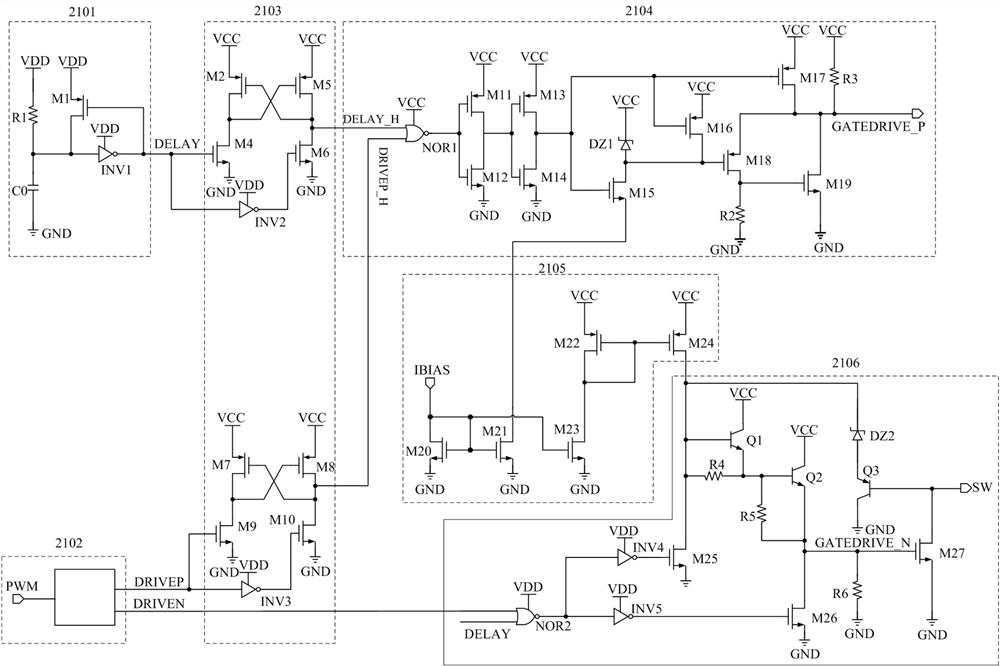

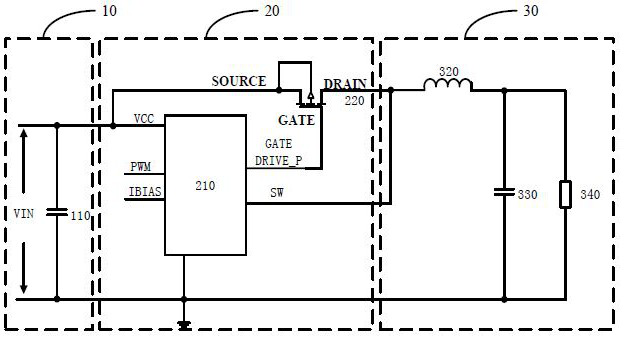

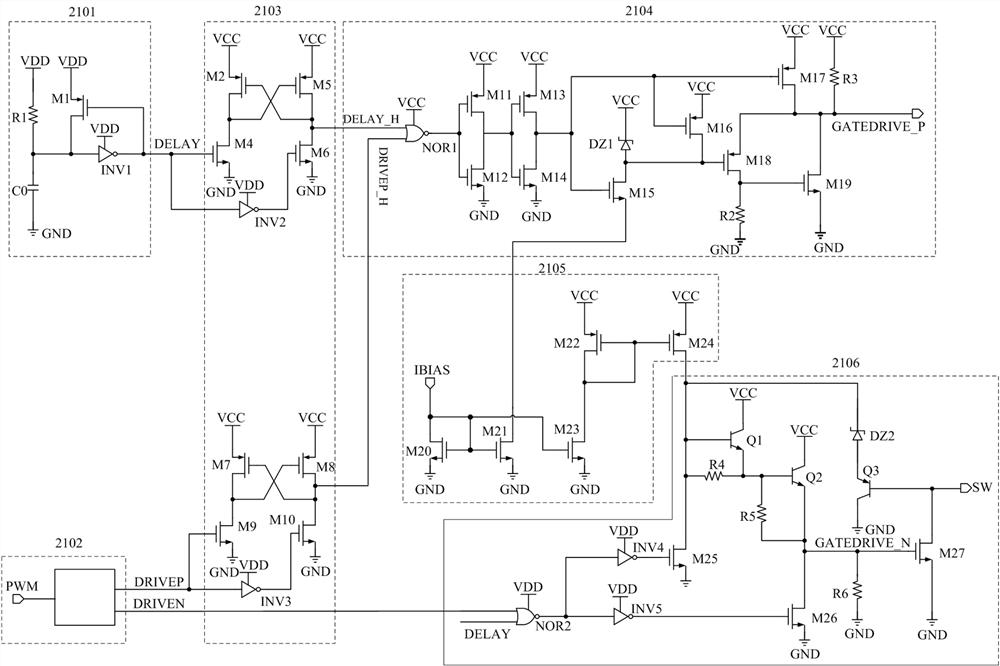

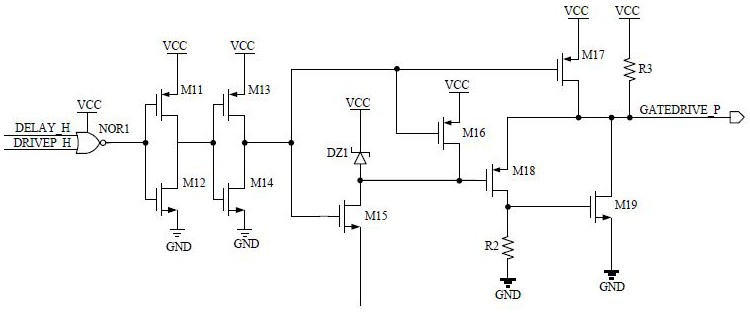

Synchronous rectification driving module, synchronous rectification driving circuit and BUCK type voltage reduction circuit

ActiveCN112421937ALow costImprove system efficiencyDc-dc conversionElectric variable regulationDriver circuitHemt circuits

The invention provides a synchronous rectification driving module, a synchronous rectification driving circuit and a BUCK type voltage reduction circuit. A PMOS power tube is used as an upper tube ofthe synchronous rectification circuit, an NMOS power tube is used as a lower tube, and a PMOS power tube driving circuit and an NMOS power tube driving circuit are improved; wherein the PMOS driving circuit is powered by adopting a direct VCCGND; according to the PMOS drive circuit, the voltage of the grid drive end of the PMOS power tube is limited by adopting a method of limiting the voltage ofan M18 grid and enabling M18 and M19 to be matched for discharging, so the circuit structure is simplified while the drive capability is ensured; the NMOS driving circuit stabilizes the voltage of a grid driving end of the NMOS power tube by limiting the voltage of the base of the triode Q1, and ensures that the grid driving end of the NMOS power tube has enough drive capability by amplifying thecurrent flowing out of the M24 through the Q1 and Q2.

Owner:SHANGHAI XINLONG SEMICON TECH CO LTD

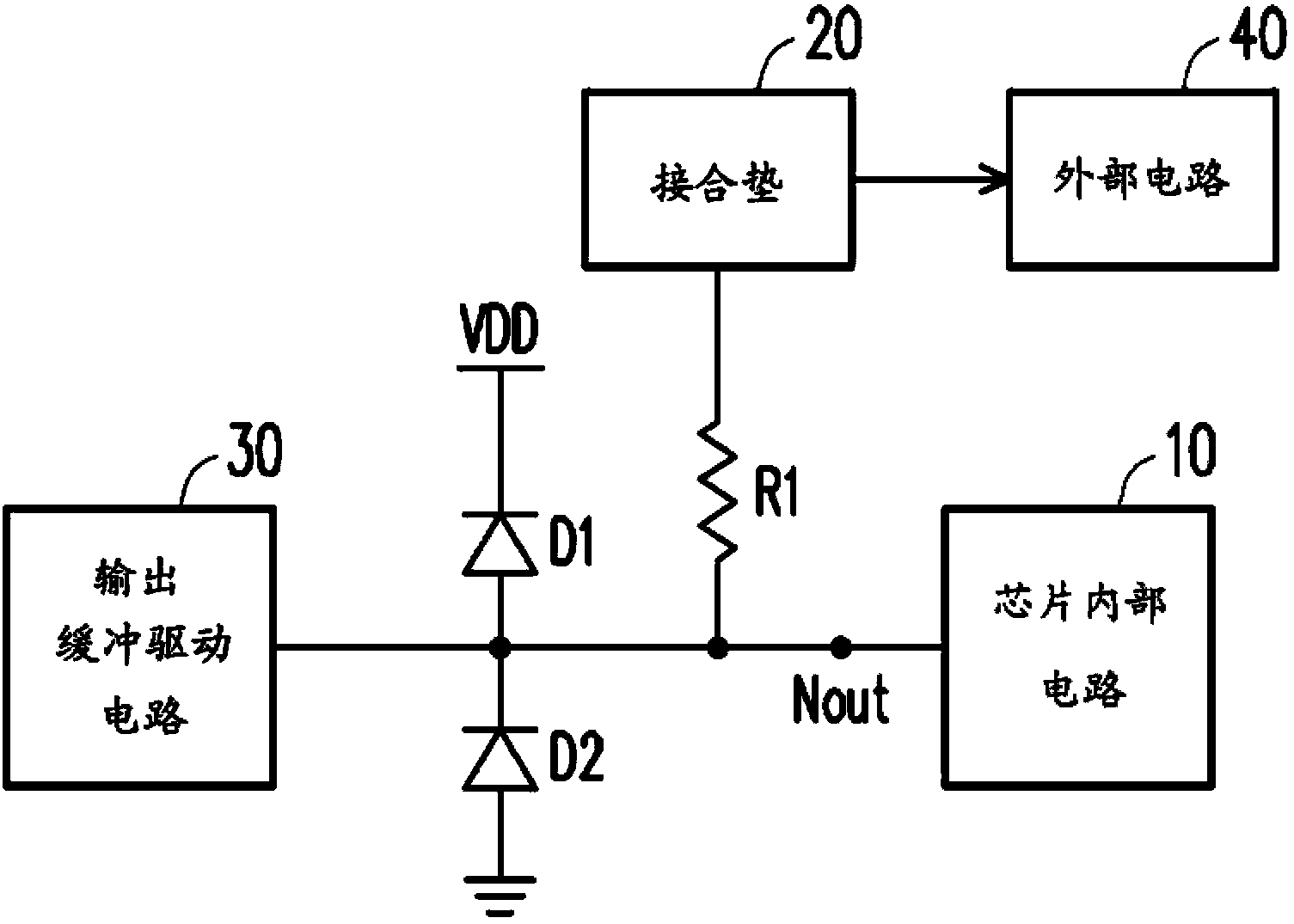

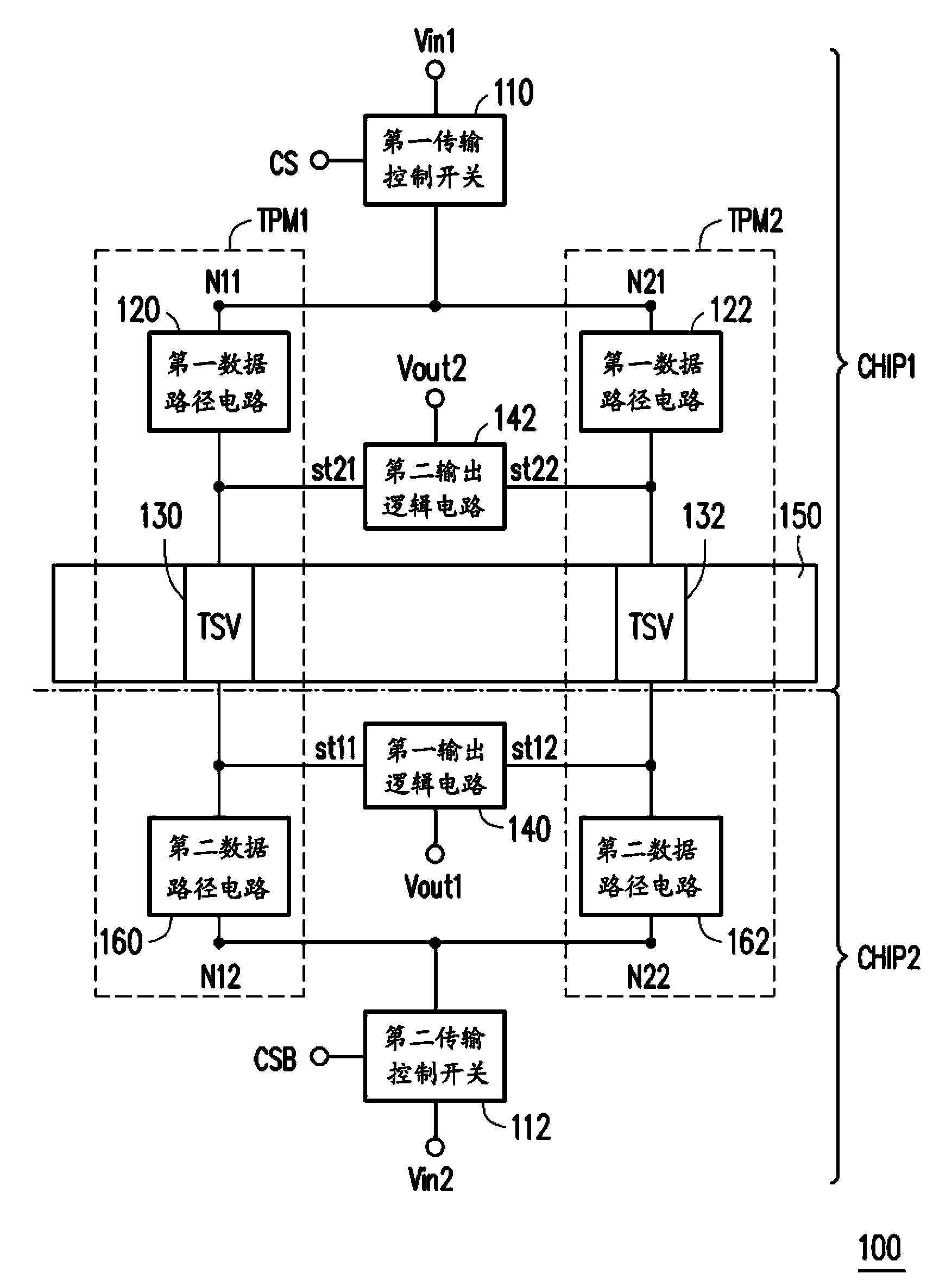

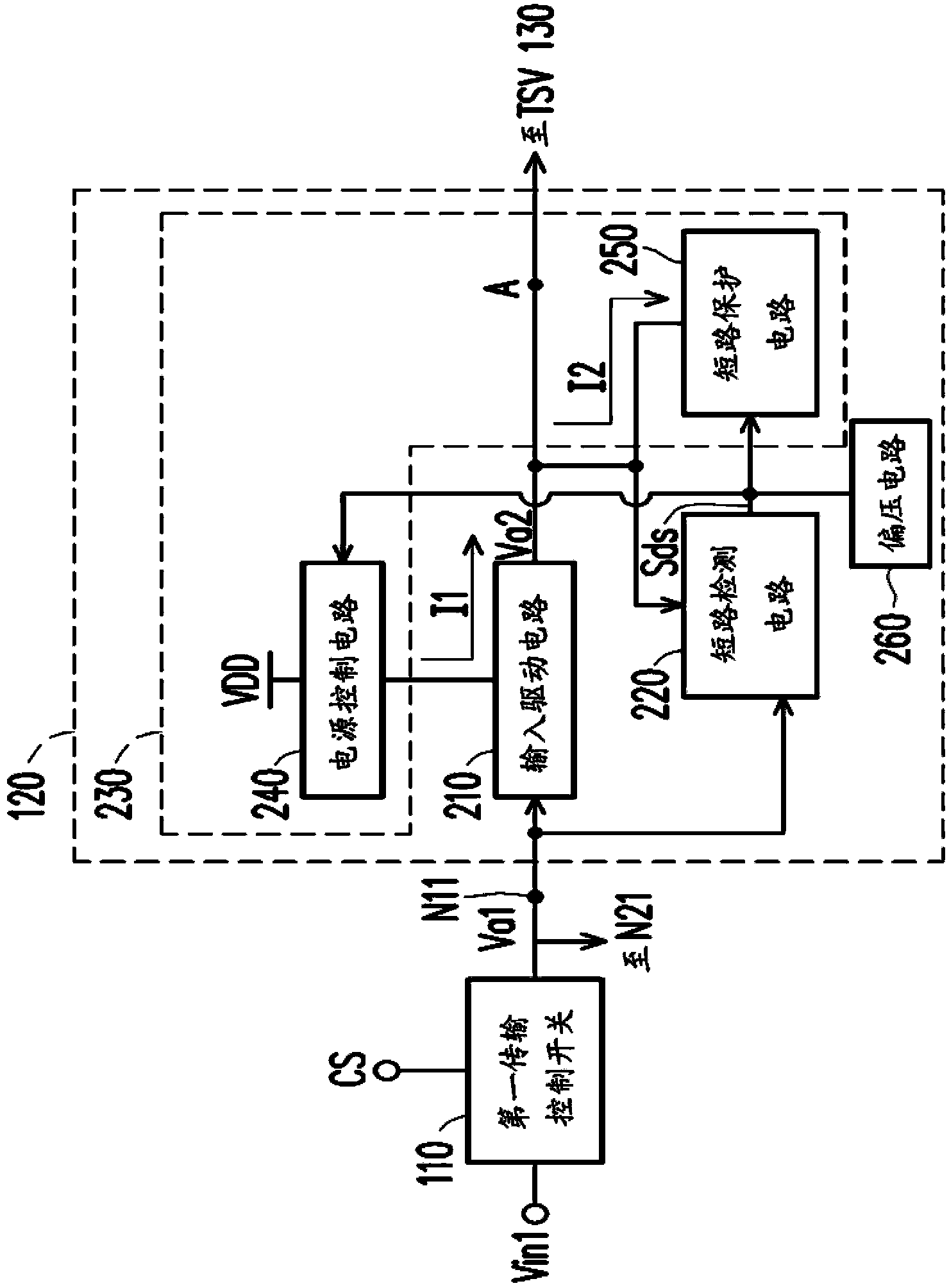

Through silicon via repair circuit

InactiveCN103904064APrevent inflowAvoid driftingSemiconductor/solid-state device detailsSolid-state devicesDatapath circuitsSwitching signal

A through silicon via (TSV) repair circuit is provided. The TSV repair circuit includes at least two transmission control switches and at least two transmission path modules. Two transmission control switches transmit an input signal of a first chip or a second chip to one of two terminals in each of the transmission path modules according to a switch signal. Each transmission path module includes at least two data path circuits and corresponding TSVs. Each data path circuit includes an input driving circuit, a short-circuit detection circuit and a leakage current cancellation circuit. The short-circuit detection circuit detects whether to detect whether short-circuit on the TSV and a silicon substrate is present and generate a short-circuit detection output signal. The leakage current cancellation circuit to avoid a leakage current generated by a first level voltage to flow into the silicon substrate according to the short-circuit detection output signal.

Owner:IND TECH RES INST

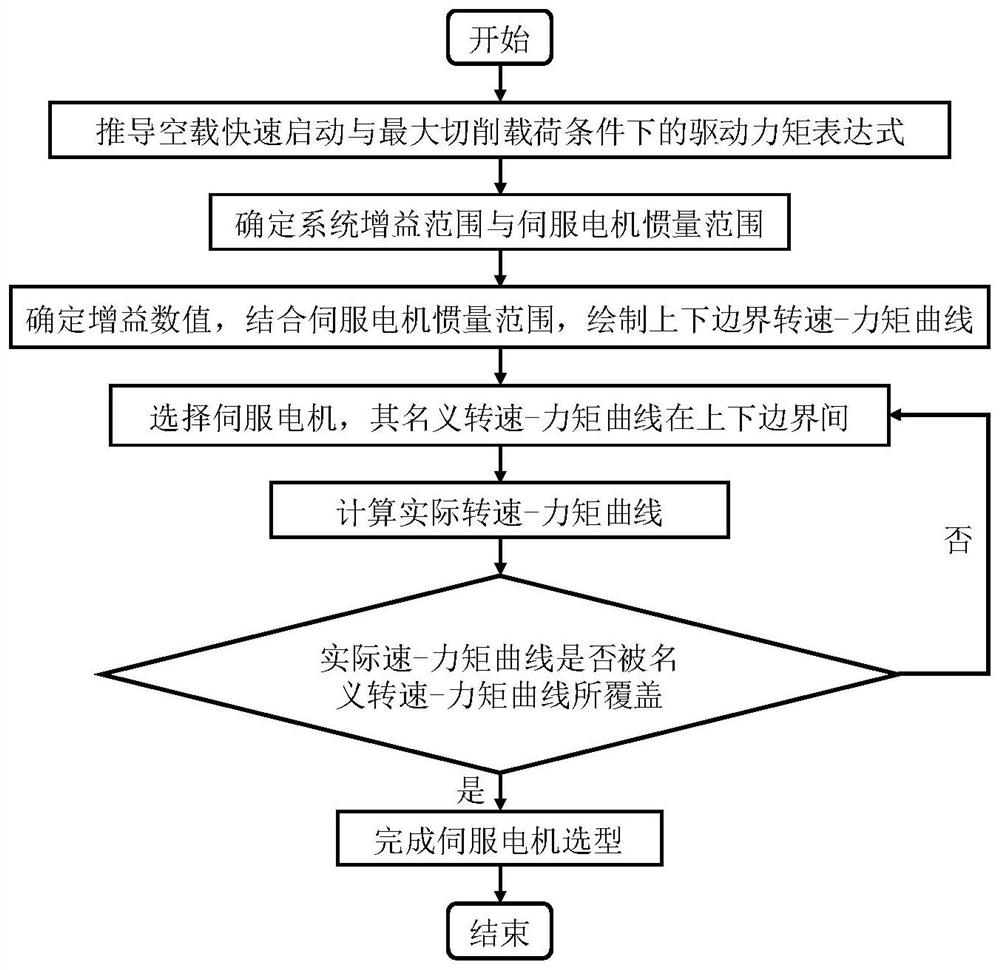

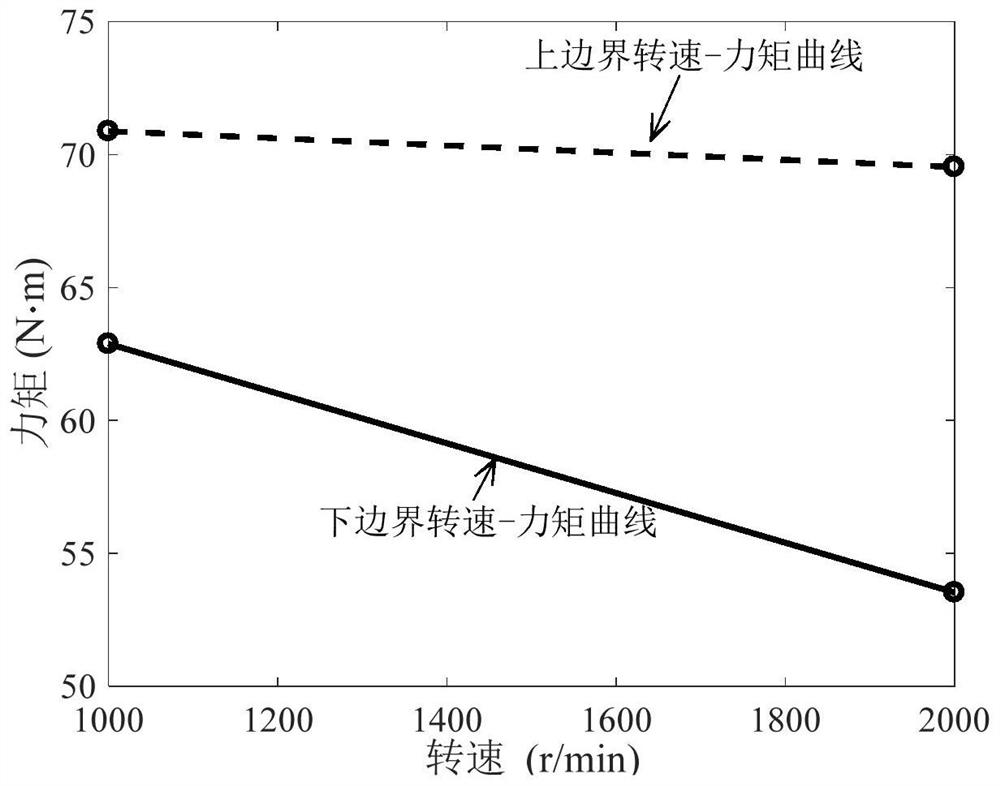

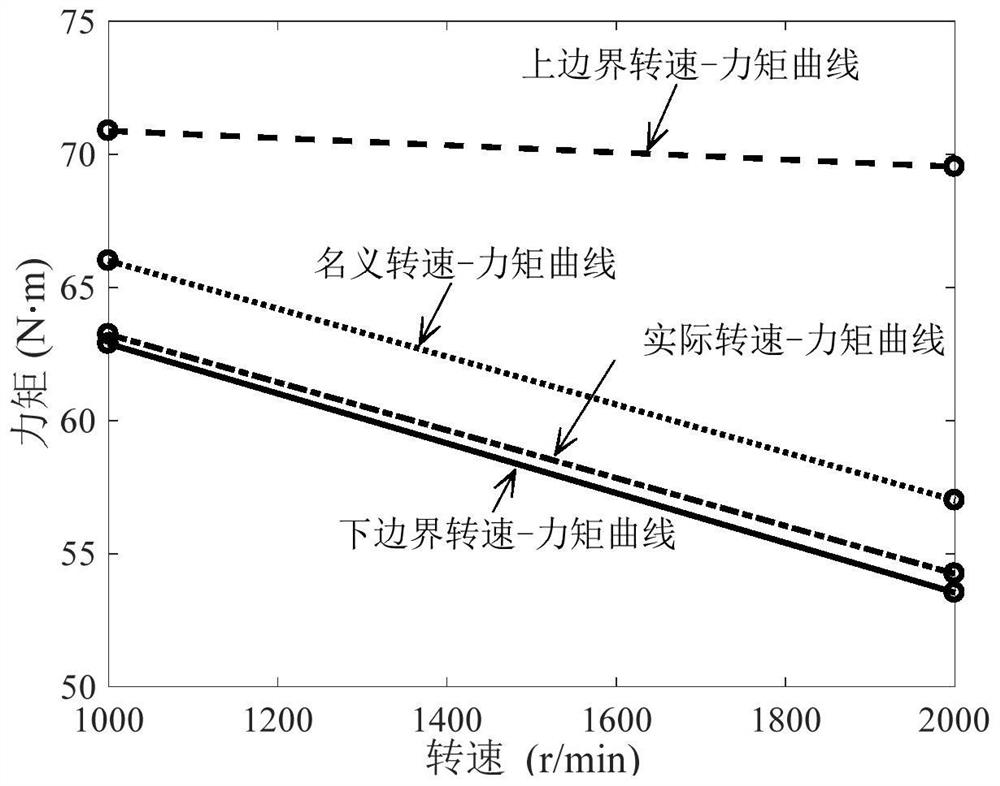

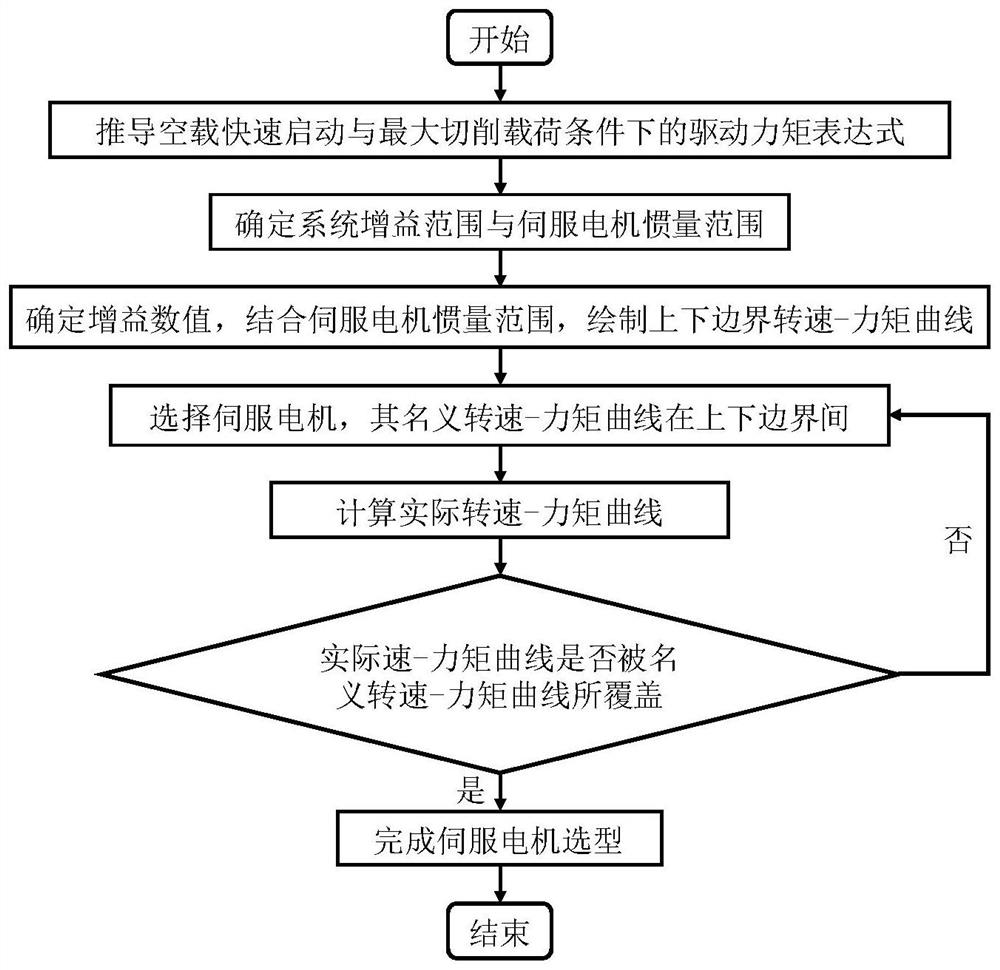

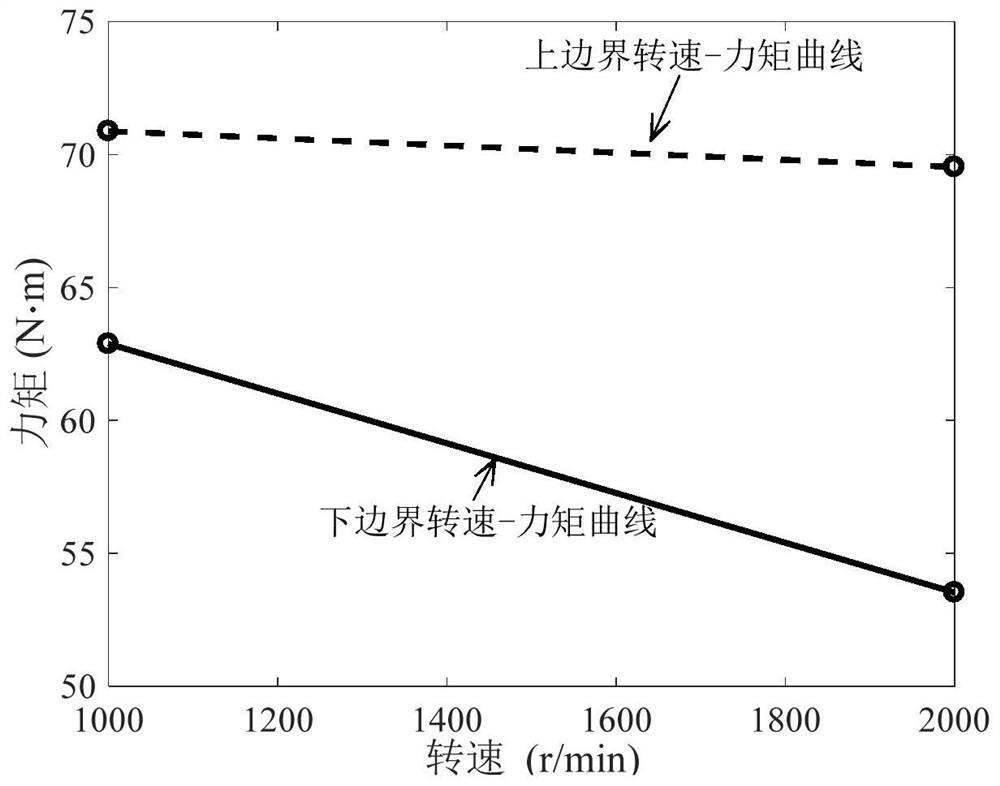

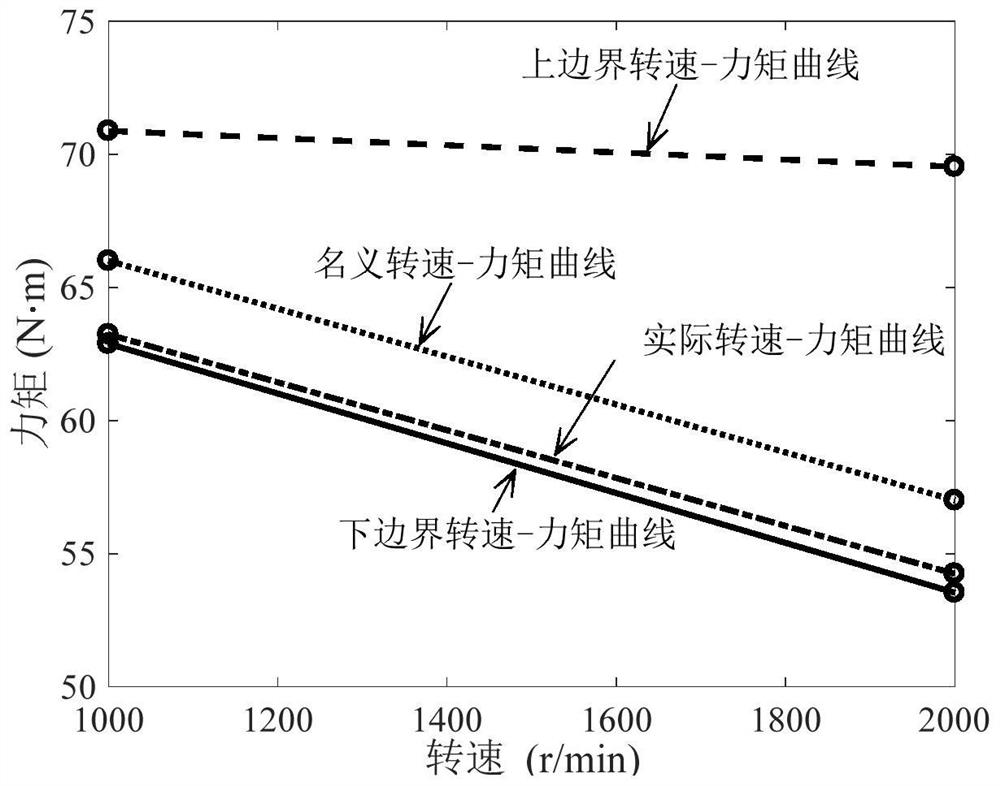

Servo motor type selection method for ball screw feeding system

ActiveCN112835325AAdequate drive capacityQuick selectionProgramme controlComputer controlElectric machineBall screw

The invention belongs to the technical field of mechatronics, and particularly relates to a servo motor type selection method for a ball screw feeding system. The method comprises the following steps: firstly, deducing a driving torque expression under the conditions of no-load quick start and maximum cutting load; further determining a system gain range and a servo motor inertia range; and finally, completing servo motor model selection according to the rotating speed-torque curve. According to the method, various typical working conditions are fully considered, it is guaranteed that the ball screw feeding system has enough driving capacity, meanwhile, the motor-load inertia ratio is concerned, and the servo motor obtains good dynamic performance. According to the method, rapid and accurate type selection of the servo motor of the ball screw feeding system is achieved, the problems that a traditional method depends on experience and is low in efficiency and inaccurate are solved, the servo motor is rapidly and accurately selected for the ball screw feeding system, and meanwhile the accurate and convenient type selection method for the servo motor is provided for field engineering technicians.

Owner:TSINGHUA UNIV

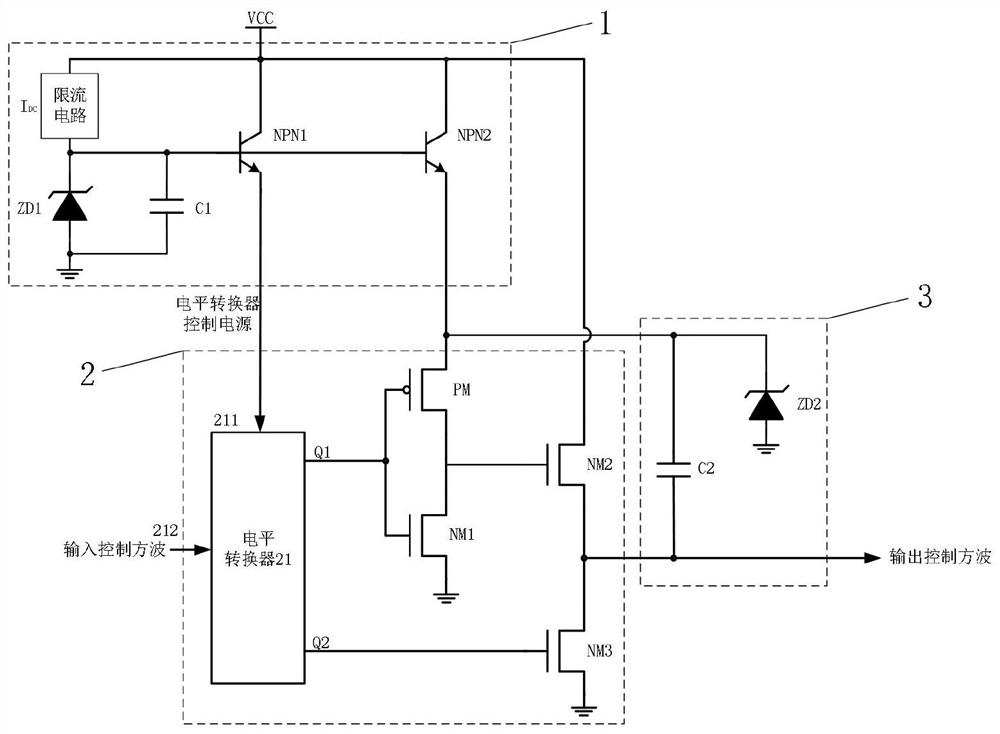

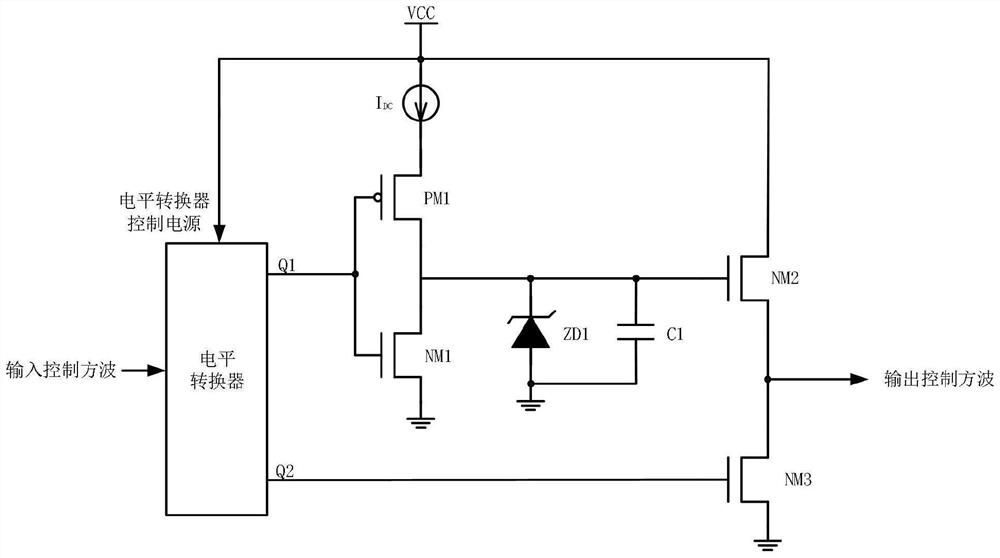

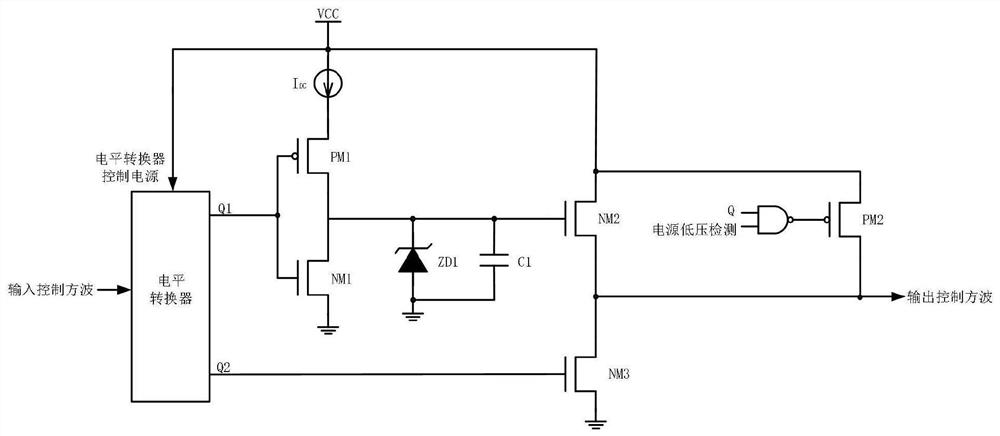

Power MOS drive circuit

The invention discloses a power MOS (Metal Oxide Semiconductor) driving circuit, which comprises a second NMOS (N-channel Metal Oxide Semiconductor) transistor NM2, a third NMOS transistor NM3 and a clamping circuit 3 arranged between the second NMOS transistor NM2 and the third NMOS transistor NM3, and is characterized in that a source electrode of the second NMOS transistor NM2 is connected with a drain electrode of the third NMOS transistor NM3 and is used for generating an output control square wave; and the clamping circuit 3 is used for limiting the output of the high level of the control square wave.

Owner:西安鼎芯微电子有限公司

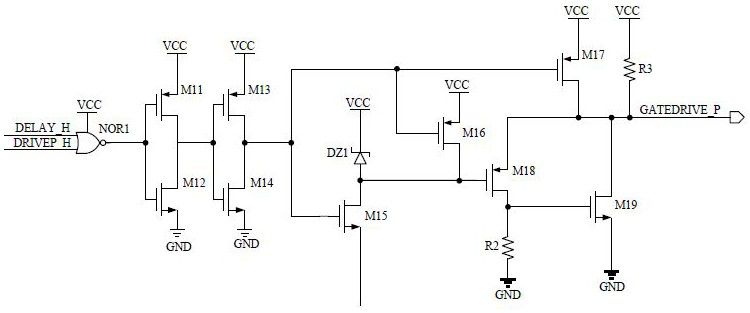

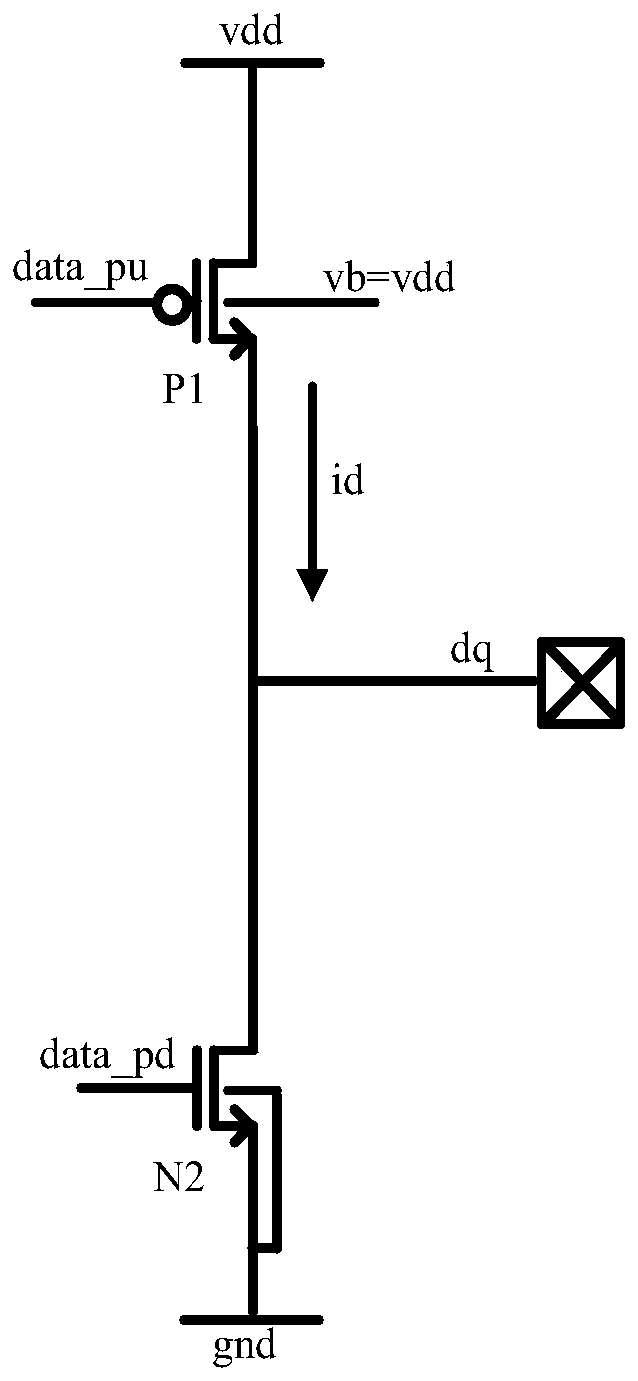

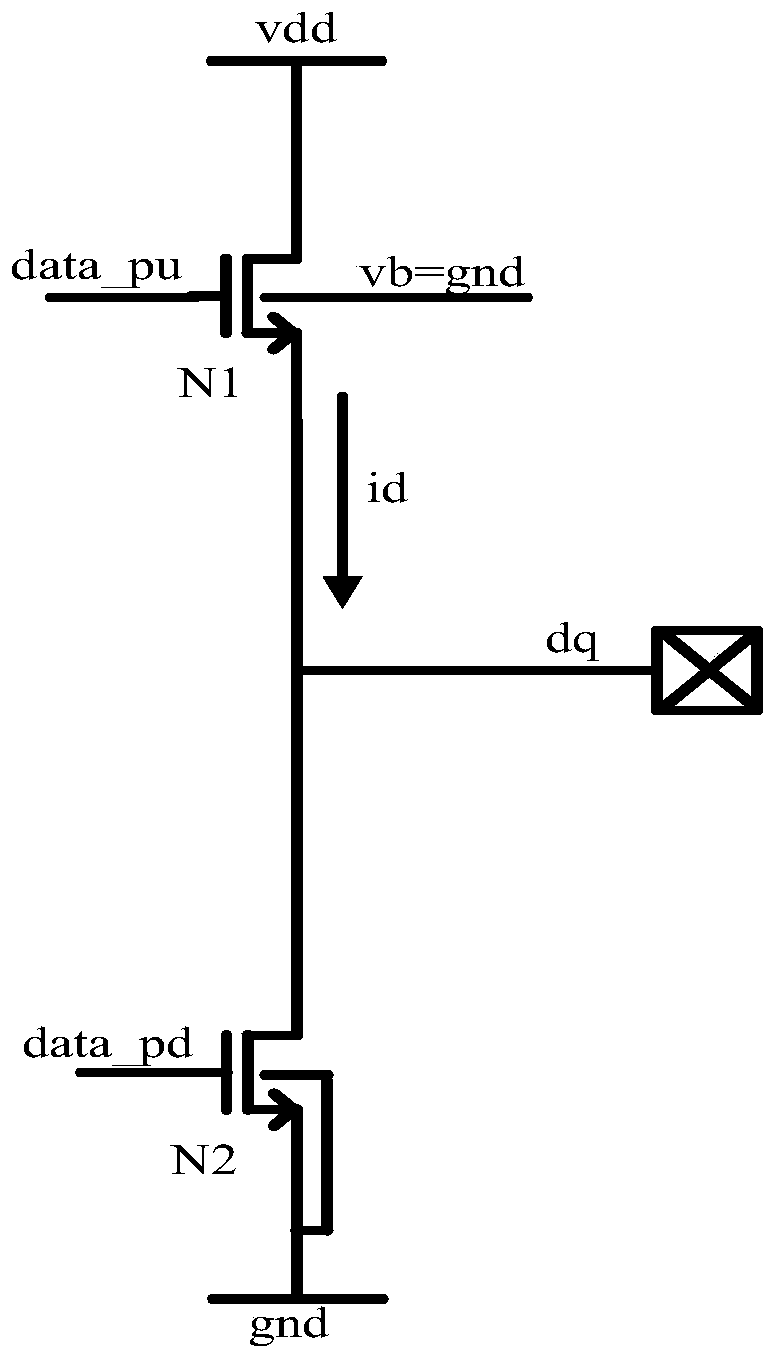

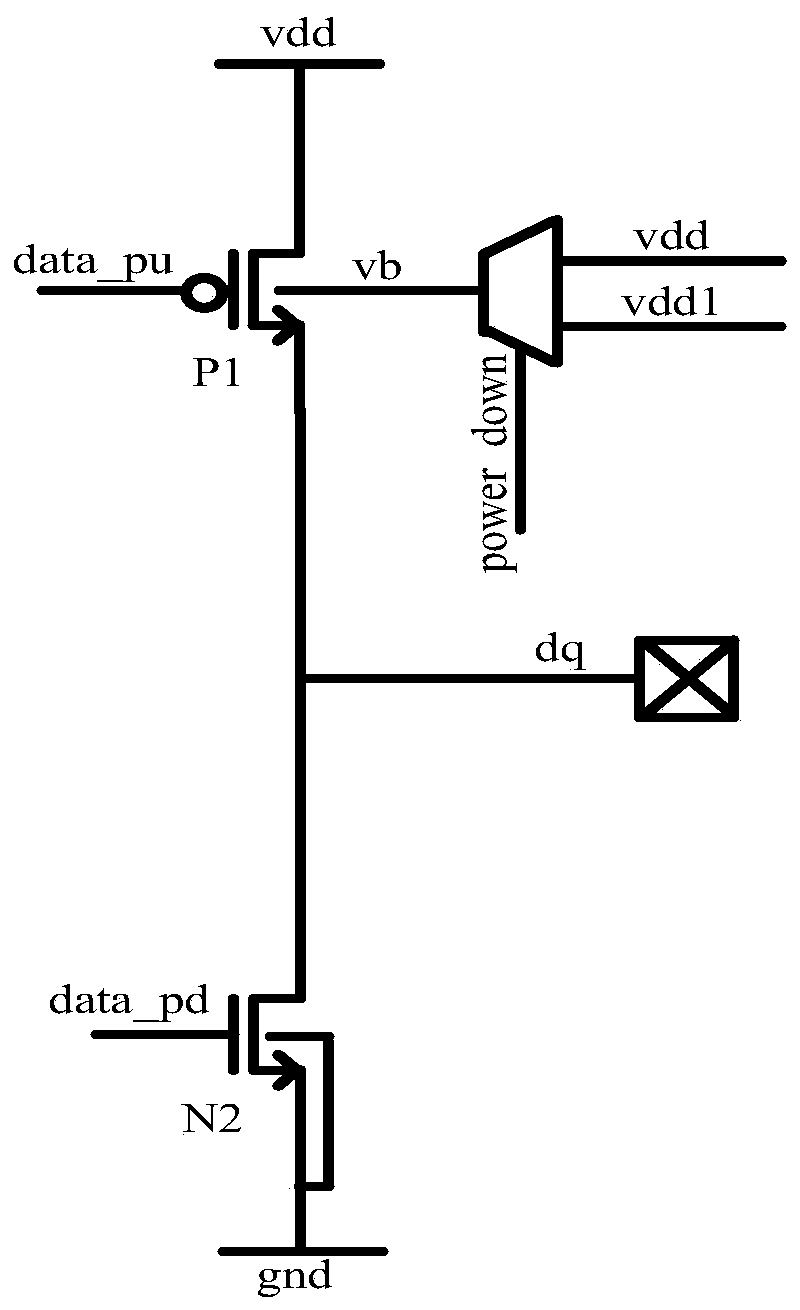

A DRAM output driving circuit and a method for reducing electric leakage thereof

InactiveCN109741775AReduce leakage currentAdequate drive capacityDigital storageEngineeringDrain current

The DRAM output driving circuit comprises a pull-up transistor and a pull-down transistor which are sequentially connected to a working voltage end and a grounding voltage end, and a driving voltage output end dq is arranged between the pull-up transistor and the pull-down transistor; wherein the substrate of the pull-up transistor is connected with the output end of the voltage selector, the input end of the voltage selector is respectively connected with corresponding loading voltage and additional loading voltage, and the control end of the voltage selector is connected with a voltage selection signal. The voltage selector is arranged to aim at different pull-up transistors; Substrate voltages of different sizes are selected under different states, so that the leakage current of the output driving circuit can be reduced in a power-saving mode according to the correlation between the leakage current of different pull-up transistors and threshold voltage, the electric leakage is reduced, and enough driving capability can be provided for an output stage under the condition of normal work; and the leakage current of the DRAM output driving circuit in a power-saving mode is effectively reduced.

Owner:XI AN UNIIC SEMICON CO LTD

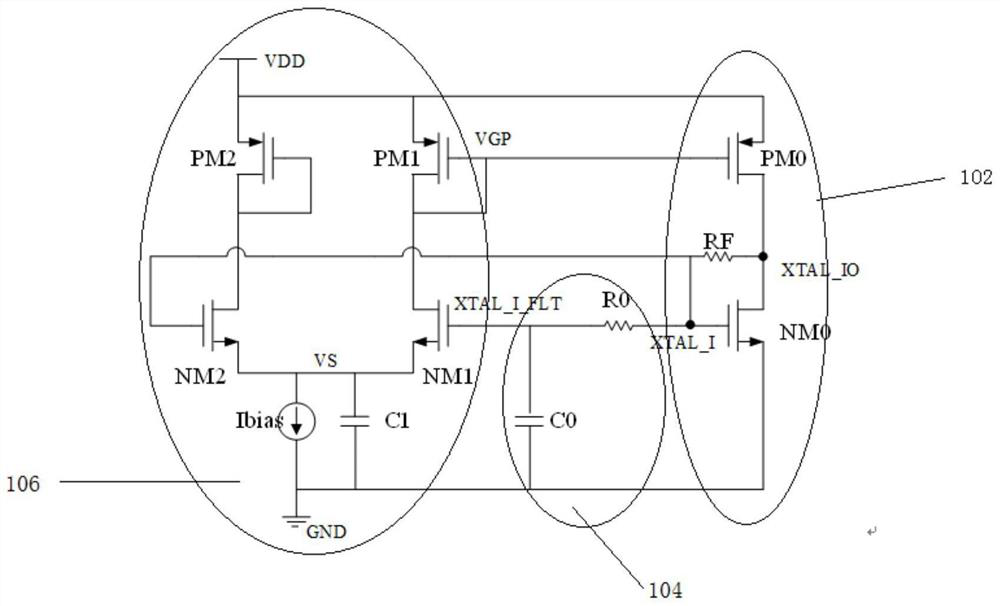

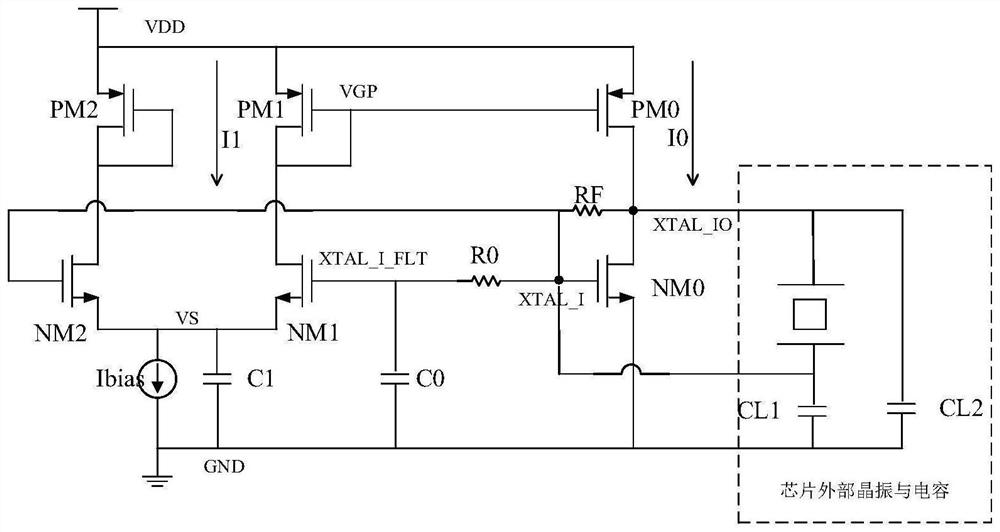

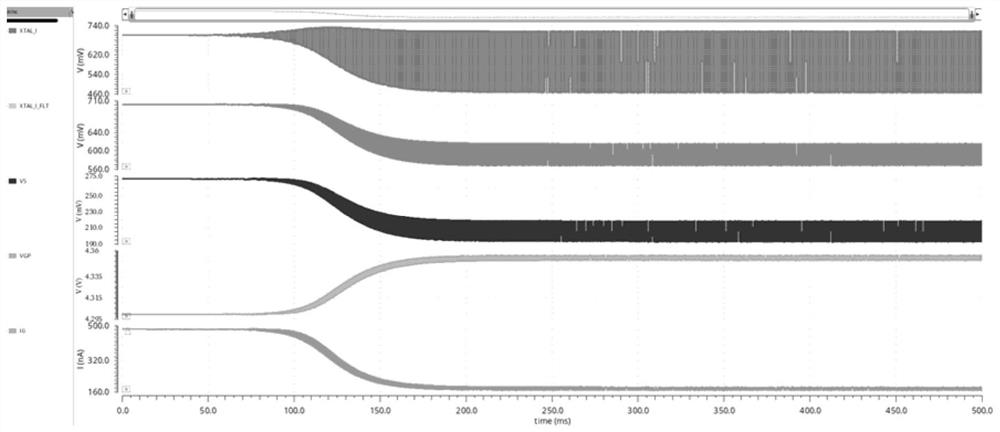

Crystal oscillator circuit

PendingCN114337654AAdequate drive capacityImprove driving abilityPulse automatic controlGenerator starterSoftware engineeringHemt circuits

The invention discloses a crystal oscillator circuit. The crystal oscillator circuit comprises an oscillator driving module, a first-order filtering module and an amplitude detection and current bias adjustment module, the oscillator driving module is respectively connected with the first-order filtering module and the amplitude detection and current bias adjustment module, and is used for driving the crystal oscillator; the first-order filtering module is respectively connected with the oscillator driving module and the amplitude detection and current bias adjustment module and is used for filtering an alternating current signal of a first connecting end of the crystal oscillator; and the amplitude detection and current bias adjustment module is respectively connected with the first-order filtering module and the oscillator driving module, and is used for detecting the oscillation amplitude of the crystal oscillator and dynamically adjusting the bias current of the oscillator driving module. According to the invention, the bias current of the driver at the initial moment is relatively large, so that enough driving capability is ensured. As the oscillation signal gradually rises, the bias current gradually drops, automatic gain control is realized, the power consumption of the circuit also gradually drops, and meanwhile, the crystal oscillator circuit is high in driving capability and wide in application scene.

Owner:苏州领慧立芯科技有限公司

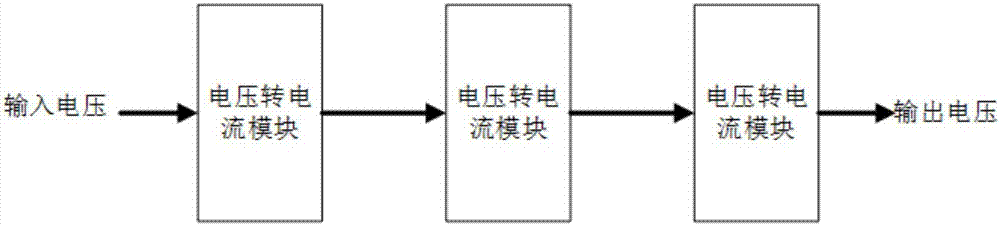

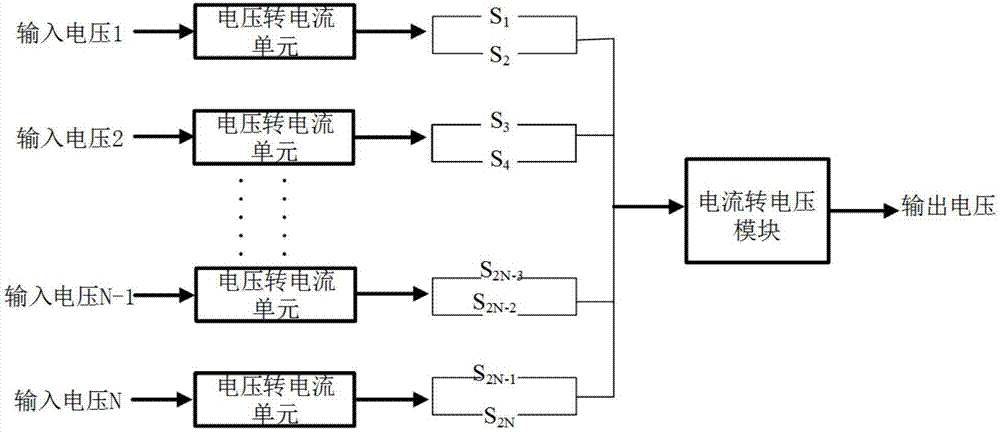

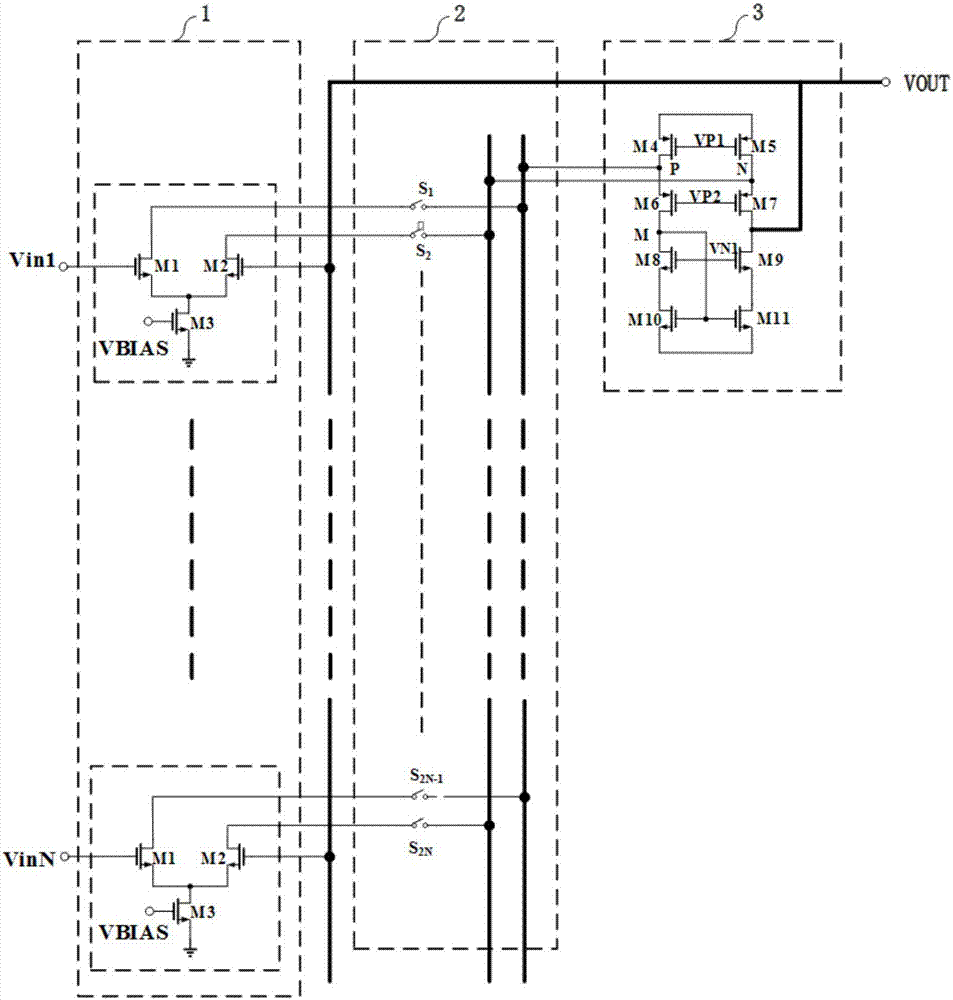

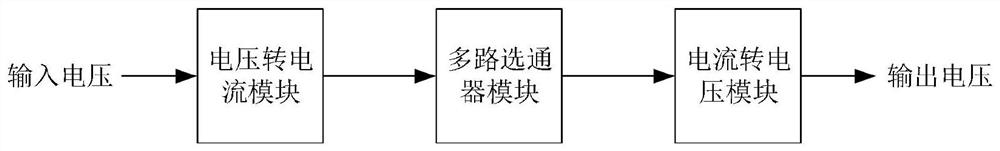

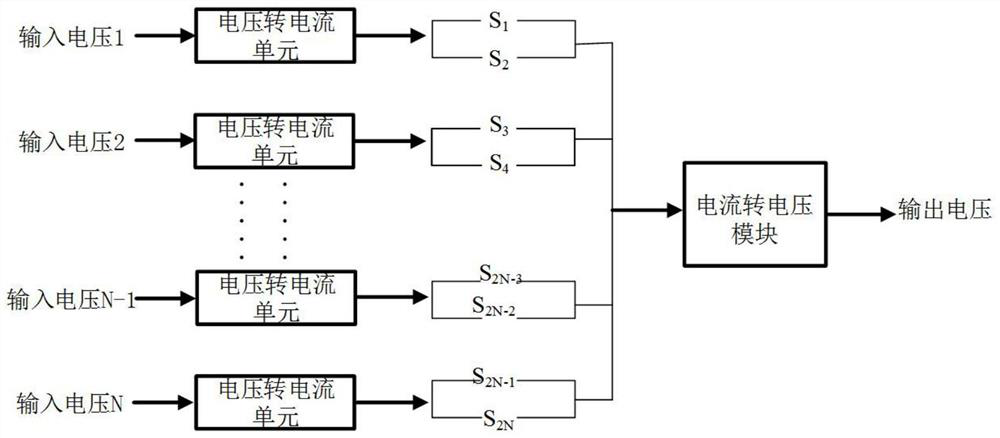

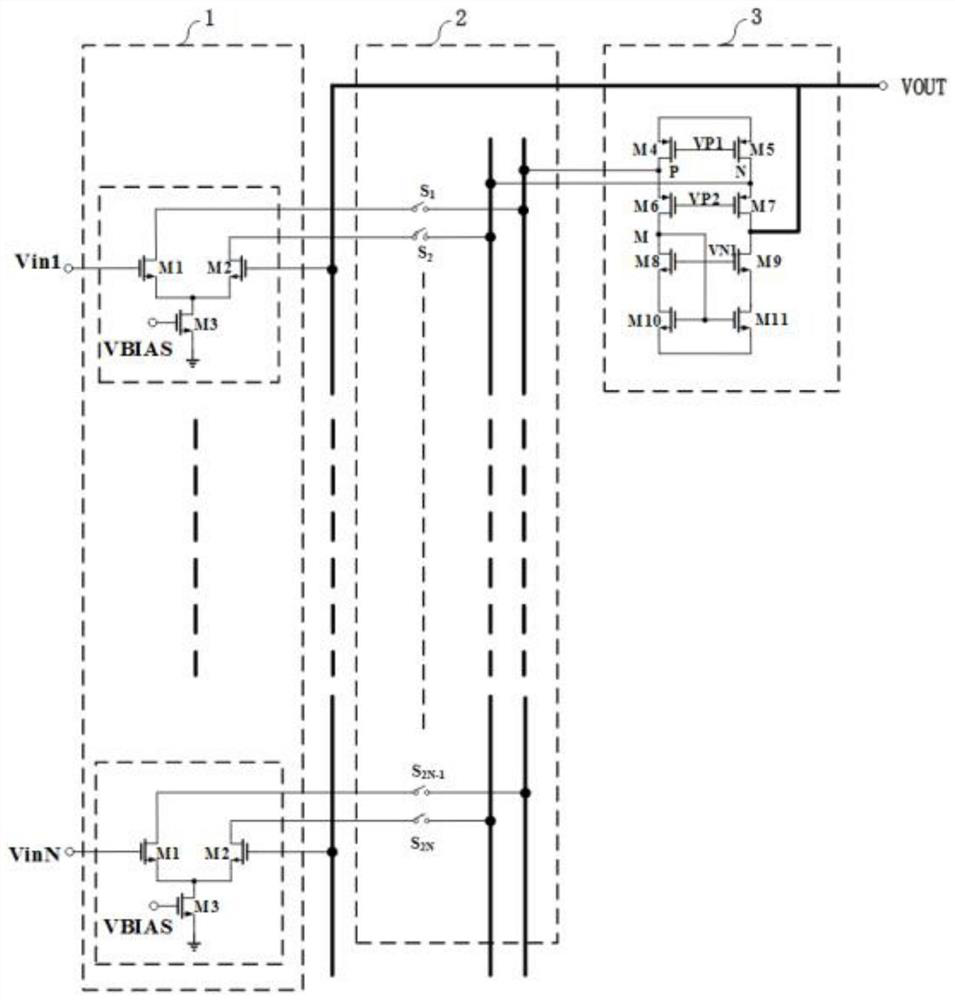

Multi-input high-speed CMOS buffer circuit

ActiveCN107070447AImprove usabilityAdequate drive capacityLogic circuits coupling/interface using field-effect transistorsElectronic switchingCMOSMulti input

The invention discloses a multi-input high-speed CMOS buffer circuit. The buffer circuit comprises a voltage-to-current module, a multipath selector module, and a current-to-voltage module, wherein two sides of the multipath selector module are respectively connected with the voltage-to-current module and the current-to-voltage module, the other side of the voltage-to-current module is used for inputting the voltage, and the other side of the current-to-voltage module is used for outputting the voltage; the voltage-to-current module is used for converting multiple input voltage into a current signal; the multipath selector module is used for conducting the voltage-to-current module and the current-to-voltage module; the current-to-voltage module is used for converting the input current signal into a voltage signal and outputting the voltage signal. The multi-input high-speed CMOS buffer circuit disclosed by the invention has the excellent characteristics of being fast in buffering speed, small in delay, free from using a bootstrapping switch, and strong in usability.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

Light source gatherer

ActiveCN101672452BAchieve isolationAdequate drive capacityLighting applicationsMechanical apparatusControl systemElectromagnetic clutch

The invention discloses an improvement on a light source gatherer device for automatically tracing sun light, and belongs to the new field of an illumination technique of optical fiber use and solar energy utilization. The device comprises a light gathering device, an electromechanical driving device, a sensor, a control system, a lamp light source, optical fibers, a switch and a luminous back lamp. The improvement on the device is characterized in that under the attraction of an magnetic clutch and the worm and gear engagement, the light gathering device is driven to rotate in the plane direction and the vertical direction in a self-locking way; the light gathering device adopts a circular belt type screw lens to gather light, and is provided with an axial fan at the side of a light filter to blow, exhaust and radiate heat; the sensor arranged at the position for checking the sun light sends a control command to a motor and the magnetic clutch of the electromechanical driving device through the control system, and the control command is used for controlling and driving the light gathering device to complete the motion adjustment for tracing any space angle required by the sun light, and controlling the lamp light source, the light filter and a color disc to do rotation at inlet and outlet positions in the horizontal direction, so the device can automatically gather light, collect the sun light source, and convert the lamp light source in sun-shading days.

Owner:NANJING SCI RES TECH

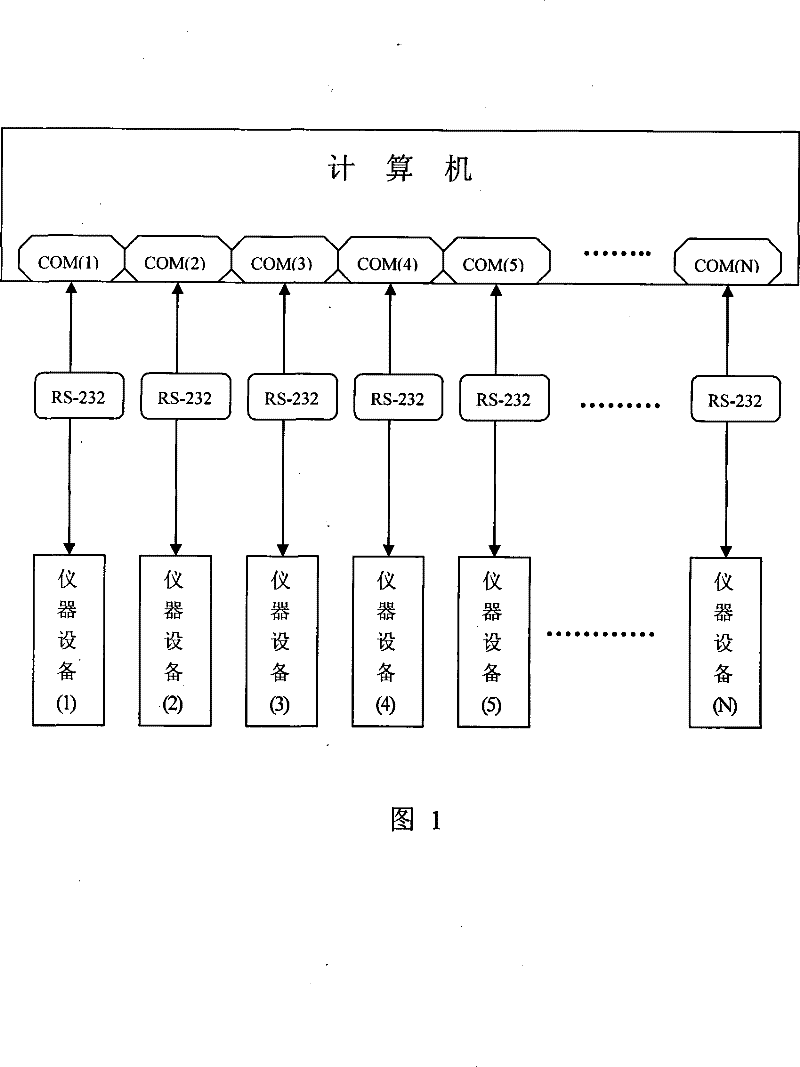

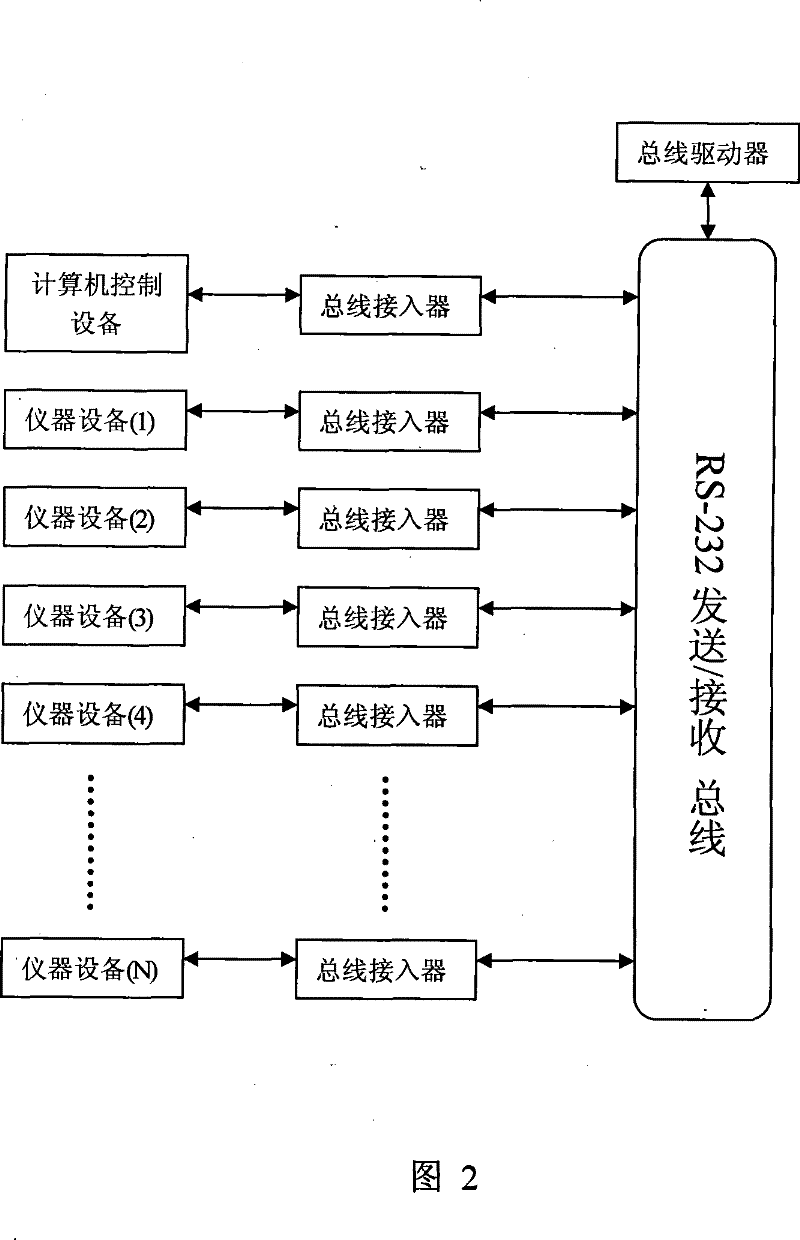

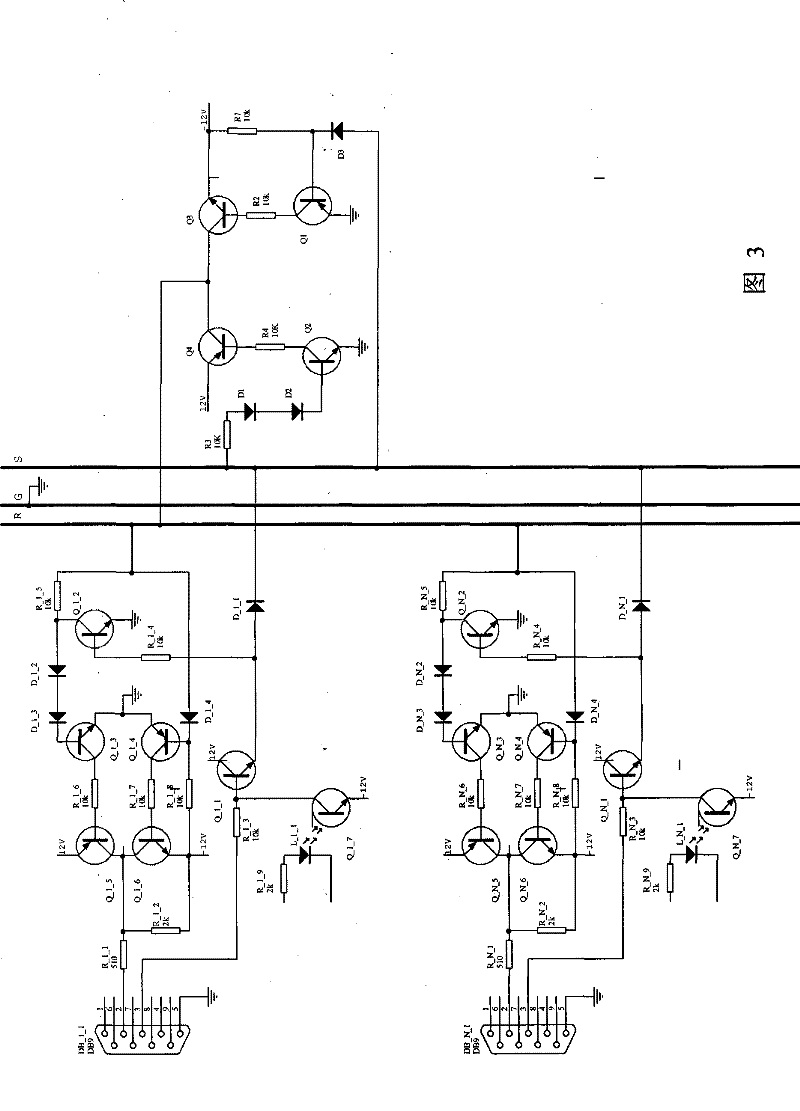

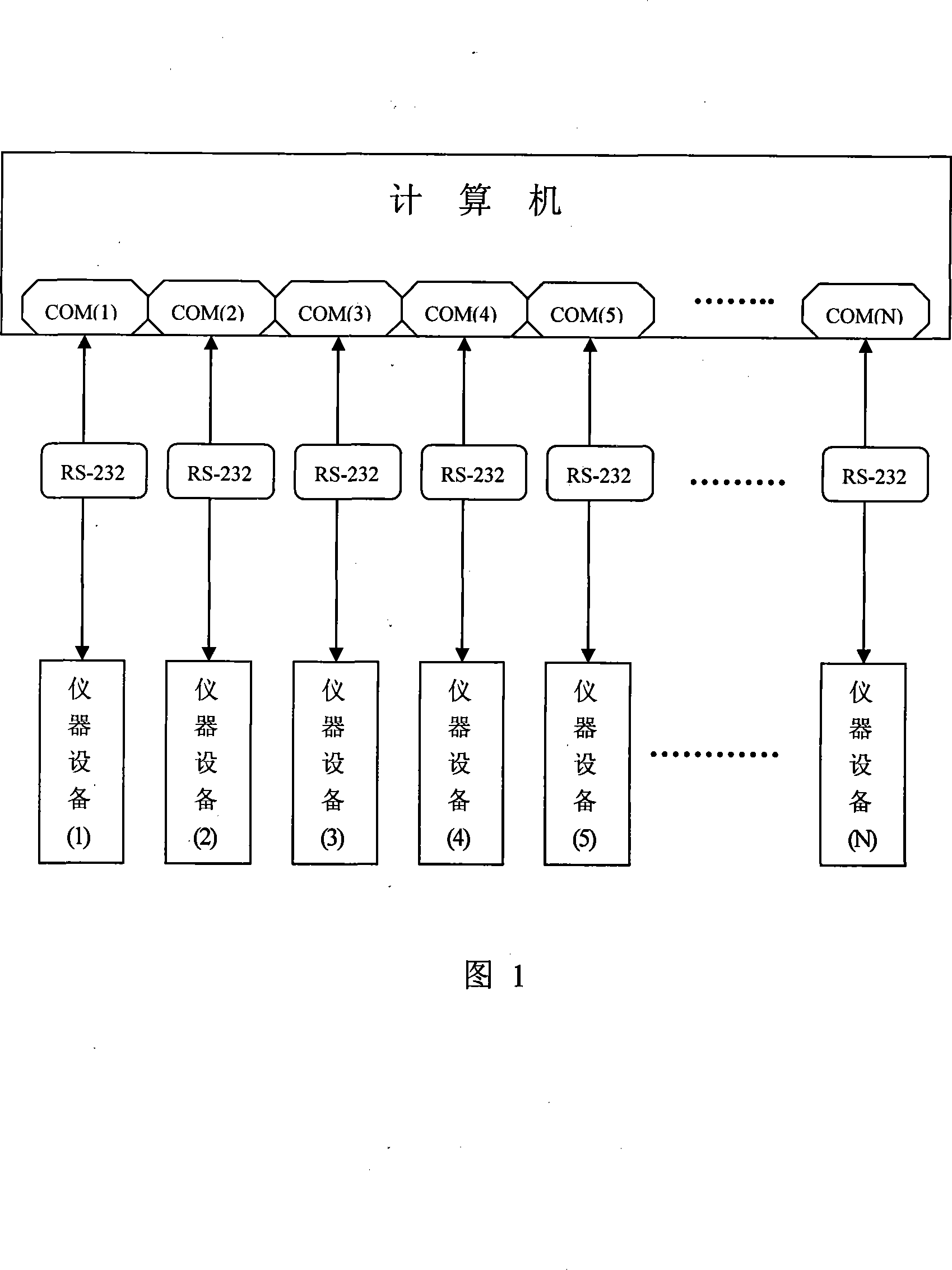

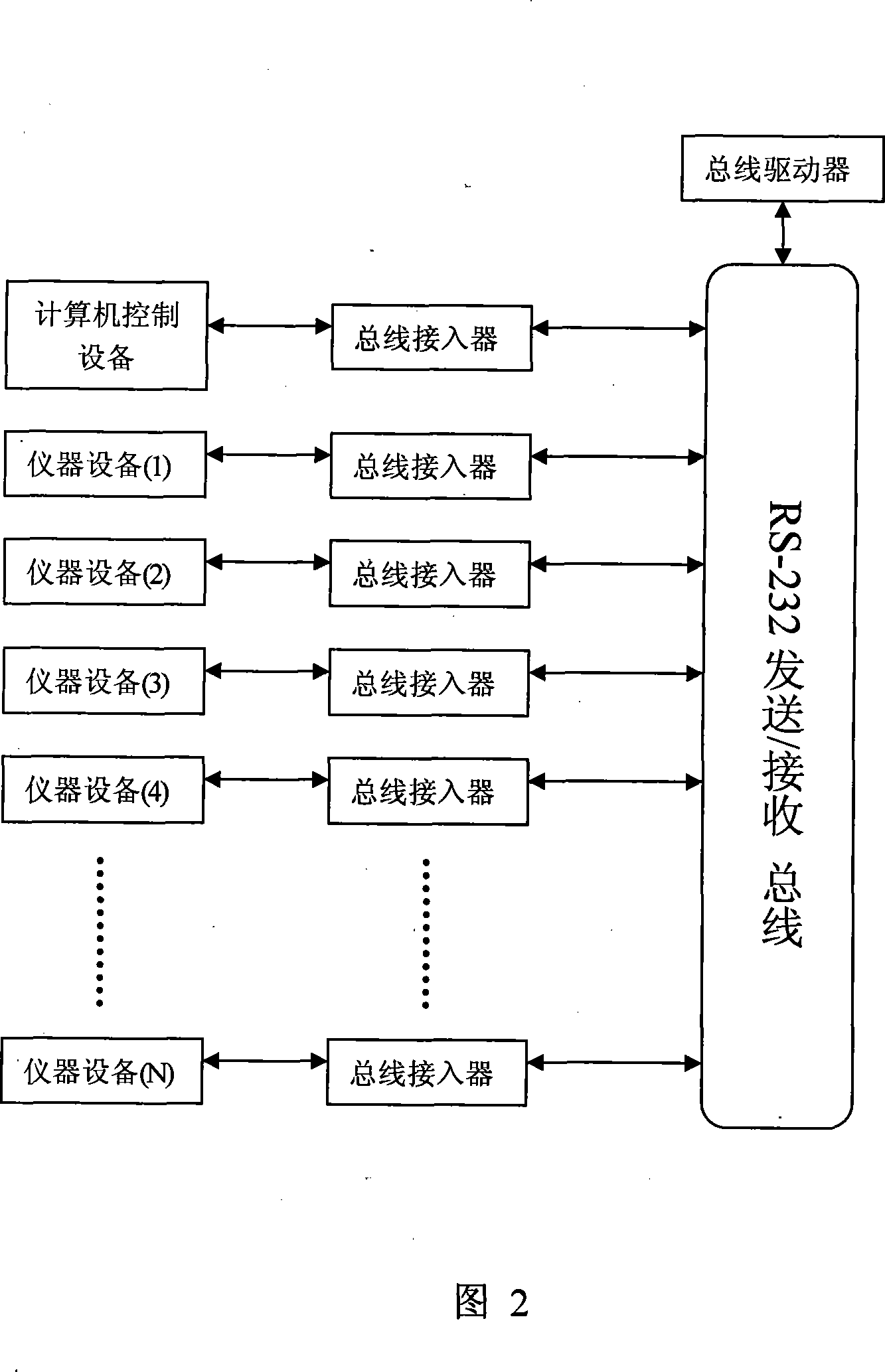

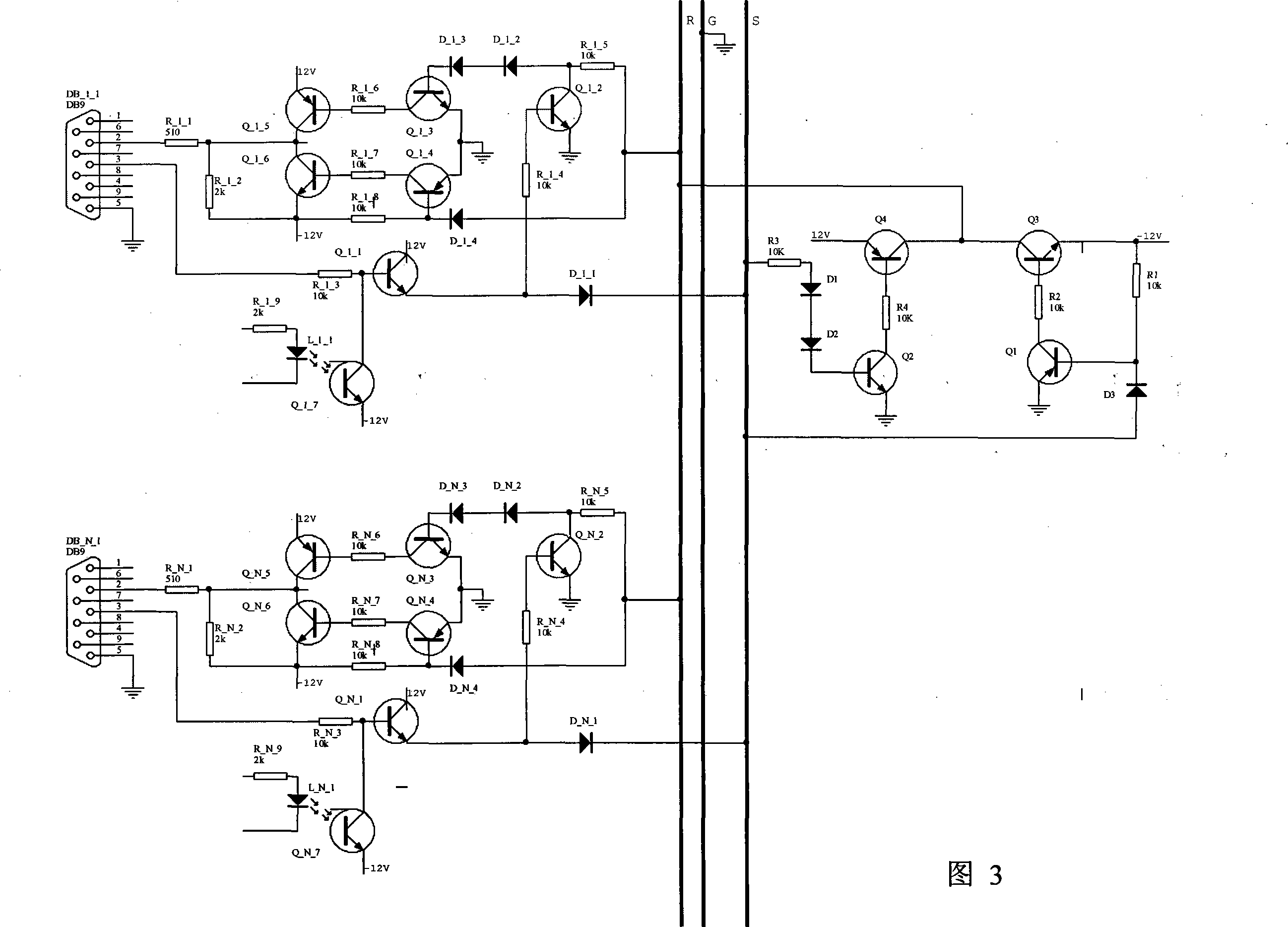

Duplex interconnection device based on standard RS-232 interface and its control method

InactiveCN101221549BMeet the full-duplex communication requirementsAdequate drive capacityElectric digital data processingComputer hardwareInterconnection

The invention discloses a multi-access interconnection device based on the standard RS-232 interface and the control method thereof. The multi-access interconnection device comprises an RS-232 sending / receiving bus and a bus driver as well as a bus connector used to be connected with computer controlled equipment and instrument equipment; the computer controlled equipment and the instrument equipment are connected with the RS-232 sending / receiving bus through the bus connector. The control method is that: a control instruction is sent to the RS-232 sending / receiving bus through the computer controlled equipment in a mode of sending a broadcast message, and the related instrument equipment automatically receives the control instruction, executes a task related to the control instrument, and then returns the execution result to the computer controlled equipment. The invention solves the problem that various different kinds of instrument equipment products of different manufacturers adopt the connection of the standard RS-232 interface with the computers to meet the requirements of modern automatic surveillance / monitoring stations being more and more huge and complicated.

Owner:广东省环境监测中心

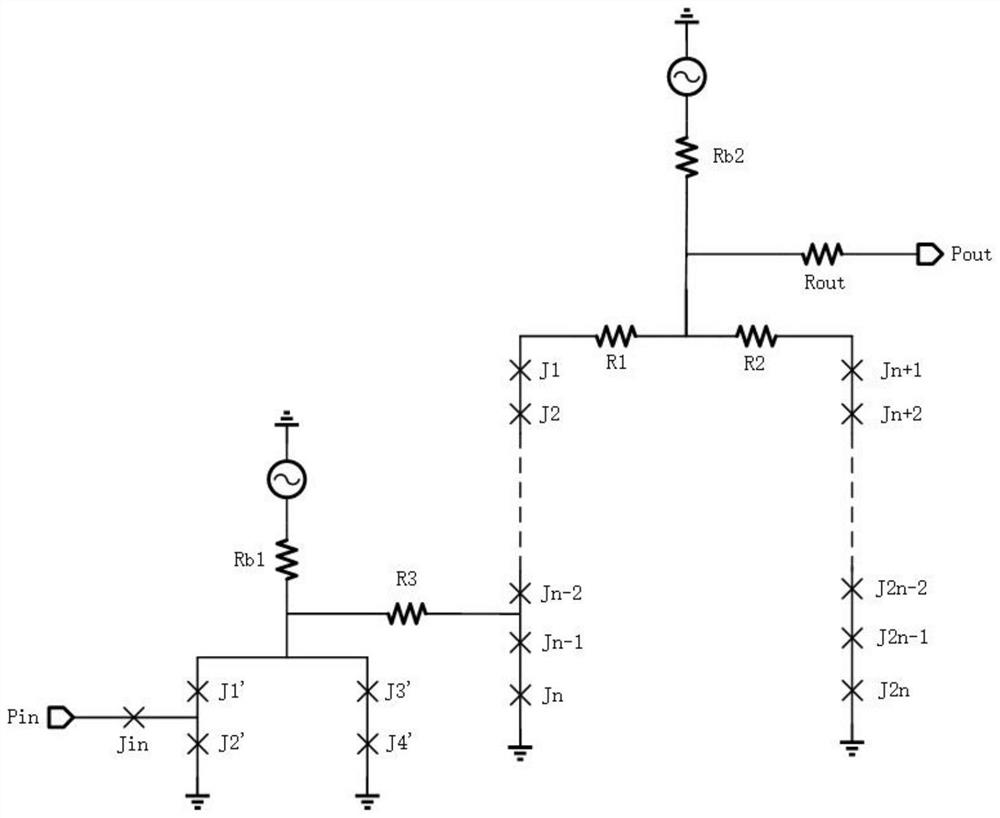

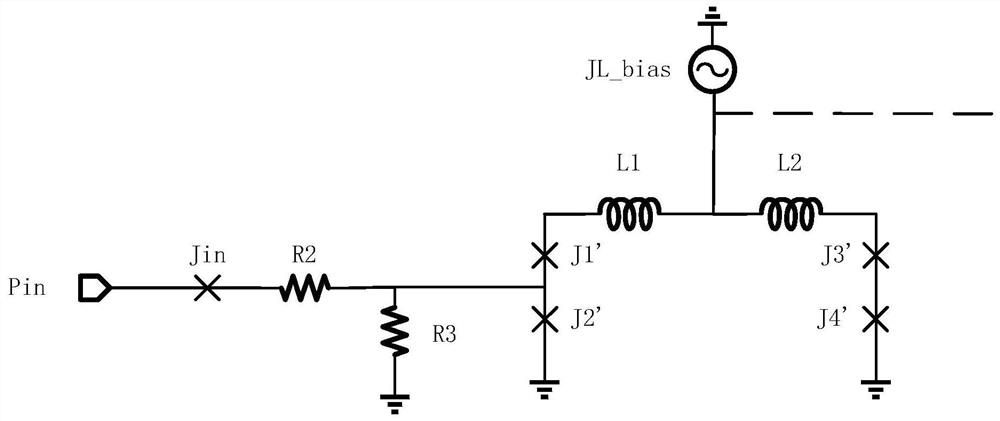

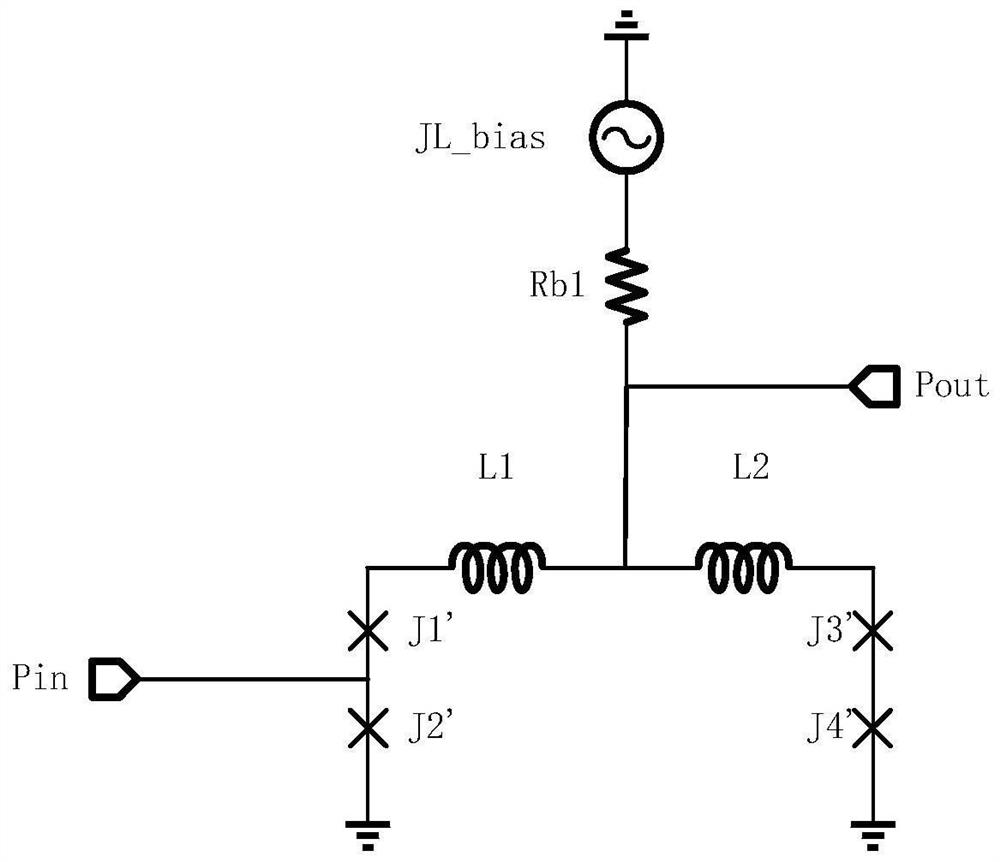

Superconducting interface circuit

PendingCN114301446AIncrease flexibilityReduce areaLogic circuits using superconductive devicesSoftware engineeringHemt circuits

The invention belongs to the technical field of superconducting integrated circuits, and particularly relates to a superconducting interface circuit. The superconducting interface circuit comprises a front-stage amplification circuit 4 Josephson latch which is used as an input detection circuit and is used for detecting microampere-level output current of a superconducting digital integrated circuit; and the Suzuki stack is used as a subsequent amplifier, receives the driving current generated by the 4JL, and generates dozens of millivolts of output voltage to drive a subsequent semiconductor integrated circuit under the action of alternating current bias. According to the superconducting interface circuit, the magnitude and proportion of the critical current of the Josephson junction of the pre-stage amplification circuit 4JL are adjusted, so that the superconducting interface circuit can detect about dozens of microamperes of input current, and the detection precision of the superconducting interface circuit is ensured; in addition, a method of connecting Josephson junctions in series is adopted, and backflow after the superconducting interface circuit is triggered is reduced. The superconducting interface circuit can be independently packaged, and the flexibility and the application prospect of the interface circuit in a superconducting circuit are greatly improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Excitation power circuit of rotary transformer

InactiveCN101714821BImprove reliabilityLow costConversion without intermediate conversion to dcCapacitanceAudio power amplifier

The invention discloses an excitation power circuit of a rotary transformer, belongs to the field of drive power sources, and solves the problems of complex circuit and incapability of independently working in the traditional excitation power of the rotary transformer. The excitation power circuit consists of a sinusoidal oscillation circuit, an amplitude adjusting circuit and a power amplifying circuit, wherein the sinusoidal oscillation circuit consists of a resistor R1, a resistor R2, a resistor R3, a resistor R4, a resistor R5, a capacitor C1, a capacitor C2, a capacitor CSEL1, a capacitor CSEL2, a first operational amplifier and a second operational amplifier; the amplitude adjusting circuit consists of a resistor R6, a resistor R7, a resistor RSEL, a capacitor C3 and a third operational amplifier; and the power amplifying circuit comprises a resistor R8 and a power amplifier. The frequency of a sinusoidal excitation power source generated by the circuit of the invention is modulated by selecting a capacitance value of the capacitor CSEL1 and the capacitor CSEL2, and the amplitude value of the sinusoidal excitation power source is adjusted by changing the resistance value of the resistor RSEL. The excitation power circuit of the invention serves as the drive power source of the rotary transformer.

Owner:HARBIN INST OF TECH

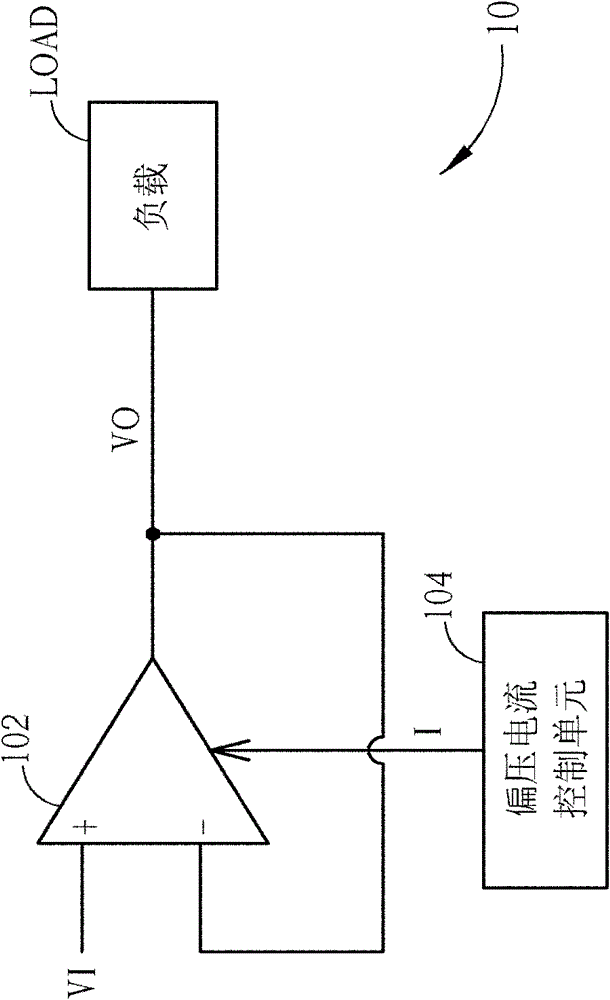

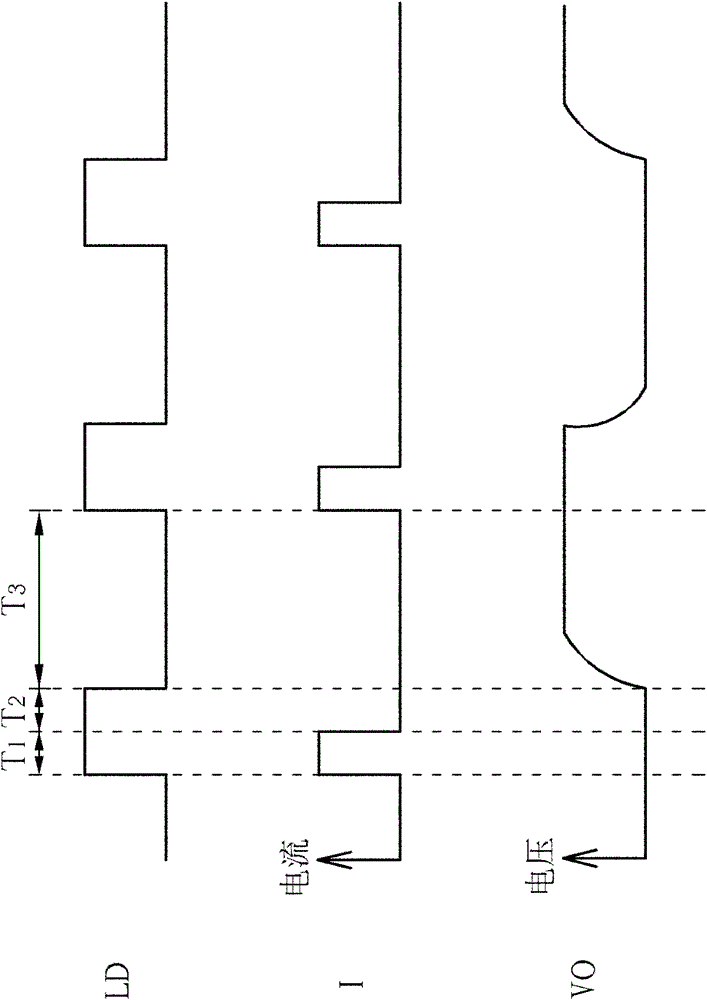

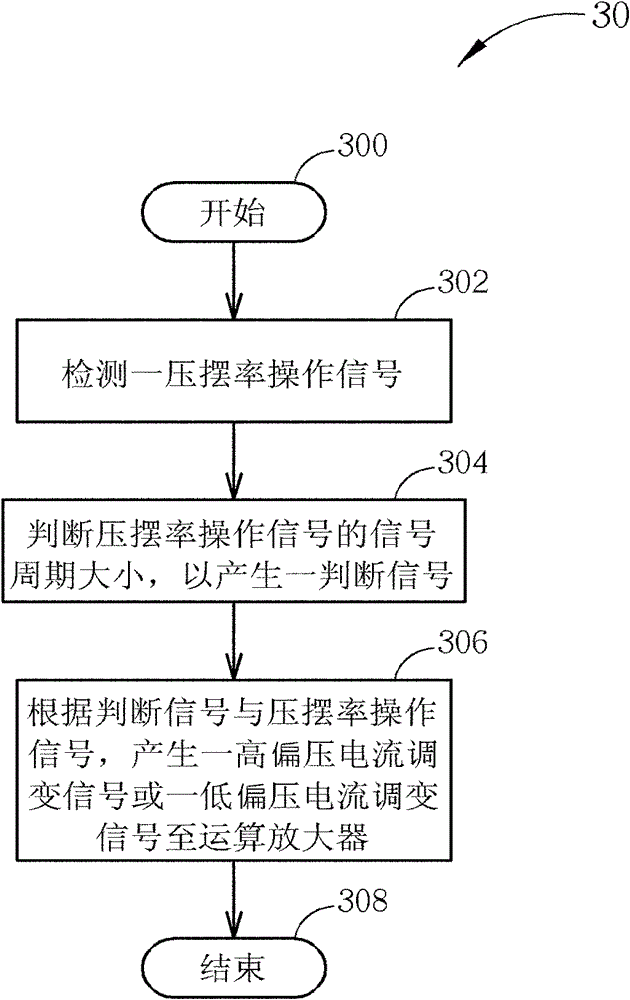

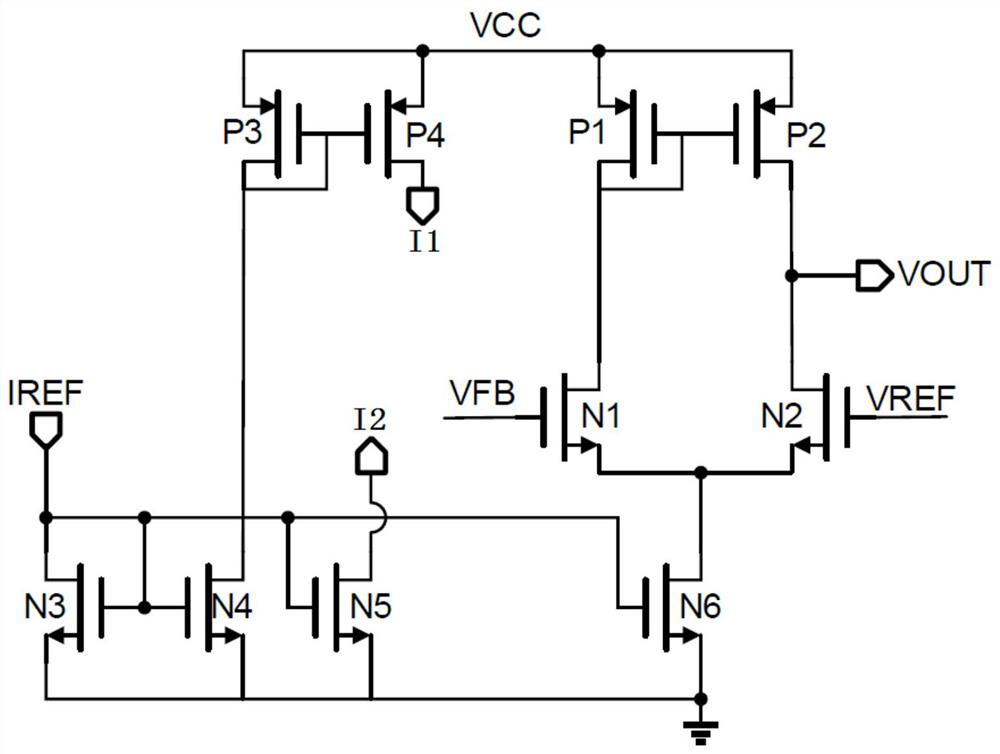

Bias Current Control Method and Driving Circuit of Operational Amplifier

ActiveCN102571006BIncrease internal slew rateReduce consumptionStatic indicating devicesDifferential amplifiersDriver circuitAudio power amplifier

Owner:NOVATEK MICROELECTRONICS CORP

Duplex interconnection device based on standard RS-232 interface and its control method

InactiveCN101221549AMeet the full-duplex communication requirementsAdequate drive capacityElectric digital data processingRs 232 interfaceInterconnection

The invention discloses a multi-access interconnection device based on the standard RS-232 interface and the control method thereof. The multi-access interconnection device comprises an RS-232 sending / receiving bus and a bus driver as well as a bus connector used to be connected with computer controlled equipment and instrument equipment; the computer controlled equipment and the instrument equipment are connected with the RS-232 sending / receiving bus through the bus connector. The control method is that: a control instruction is sent to the RS-232 sending / receiving bus through the computer controlled equipment in a mode of sending a broadcast message, and the related instrument equipment automatically receives the control instruction, executes a task related to the control instrument, and then returns the execution result to the computer controlled equipment. The invention solves the problem that various different kinds of instrument equipment products of different manufacturers adopt the connection of the standard RS-232 interface with the computers to meet the requirements of modern automatic surveillance / monitoring stations being more and more huge and complicated.

Owner:广东省环境监测中心

Design method of tdicmos imaging unit

InactiveCN110034748BSolve access difficultiesEasy accessElectric pulse generatorRadiation controlled devicesHigh densityControl signal

The design method of a TDICMOS imaging unit relates to a design method of a TDICMOS imaging unit, which solves the problems of complex design and poor stability of the existing TDICMOS imaging unit, including a controller unit and a detector unit; the controller unit generates a detector unit The required control signal, and receive the digital image data output by the detector unit; the detector unit includes a TDICMOS detector, an operational amplifier, an LDO, a driver with a Schmitt function, and a level shifter with a Schmitt function device; the present invention is respectively designed for the power supply of the pixel part with the sinking current, the transmission of the digital input control signal, the generation method of the charge transfer driving signal, the placement method of the via hole in the high-density area and the processing of the multi-layer ground plane, the maximum Maximize the utilization area of the circuit board, improve the integrity of the control drive signal and power supply, and avoid risks such as voltage breakdown and virtual soldering.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

Synchronous rectification drive module, synchronous rectification drive circuit and buck type step-down circuit

ActiveCN112421937BLow costImprove system efficiencyDc-dc conversionElectric variable regulationHemt circuitsElectric drive

The invention provides a synchronous rectification driving module, a synchronous rectification driving circuit and a buck-type step-down circuit, which adopts a PMOS power tube as the upper tube of the synchronous rectification circuit, and an NMOS power tube as the lower tube, and improves the PMOS power tube driving circuit and the NMOS power tube. tube drive circuit; the PMOS drive circuit uses direct VCC‑GND power supply; the PMOS drive circuit uses the method of limiting the gate voltage of M18 and making M18 and M19 discharge together to limit the voltage of the gate drive terminal of the PMOS power tube, so as to ensure the driving ability. At the same time, the circuit structure is simplified; the NMOS drive circuit stabilizes the voltage of the gate drive terminal of the NMOS power tube by limiting the base voltage of the transistor Q1, and ensures the gate drive terminal of the NMOS power tube by amplifying the current flowing out of M24 through Q1 and Q2. There is enough driving capacity.

Owner:SHANGHAI XINLONG SEMICON TECH CO LTD

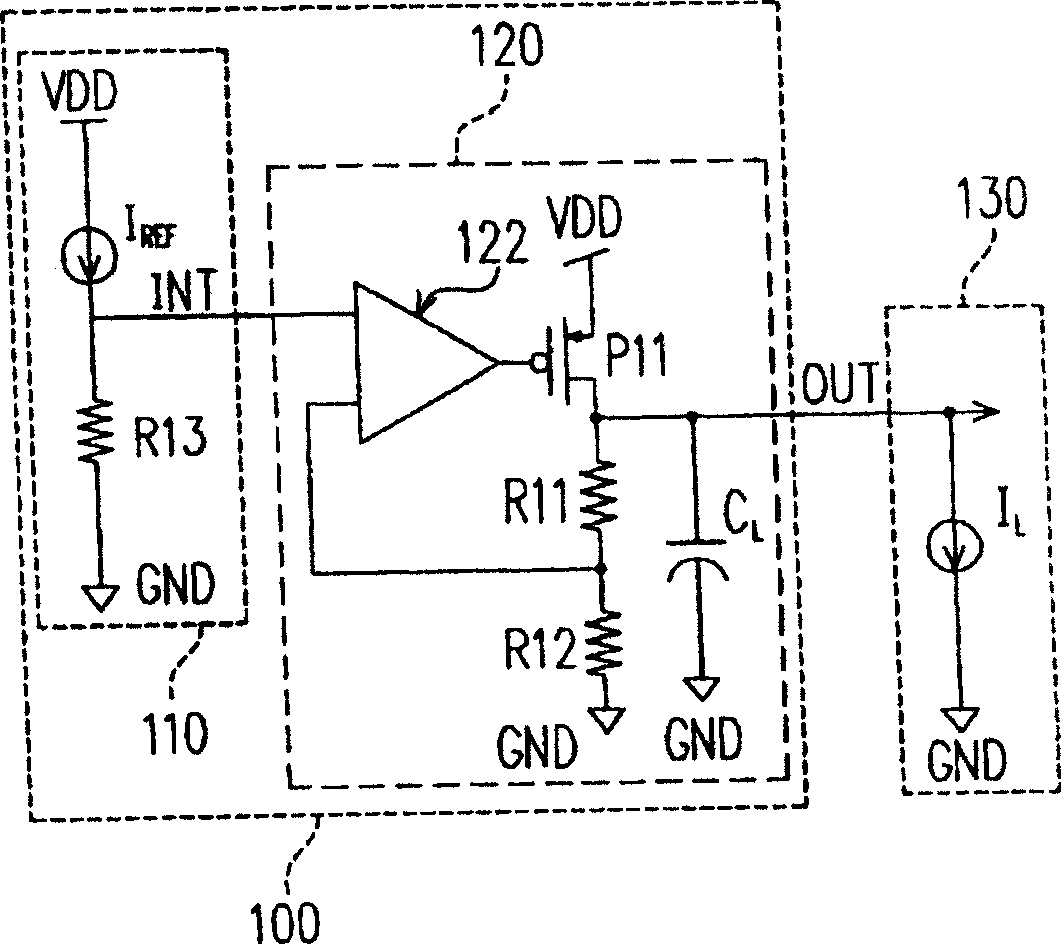

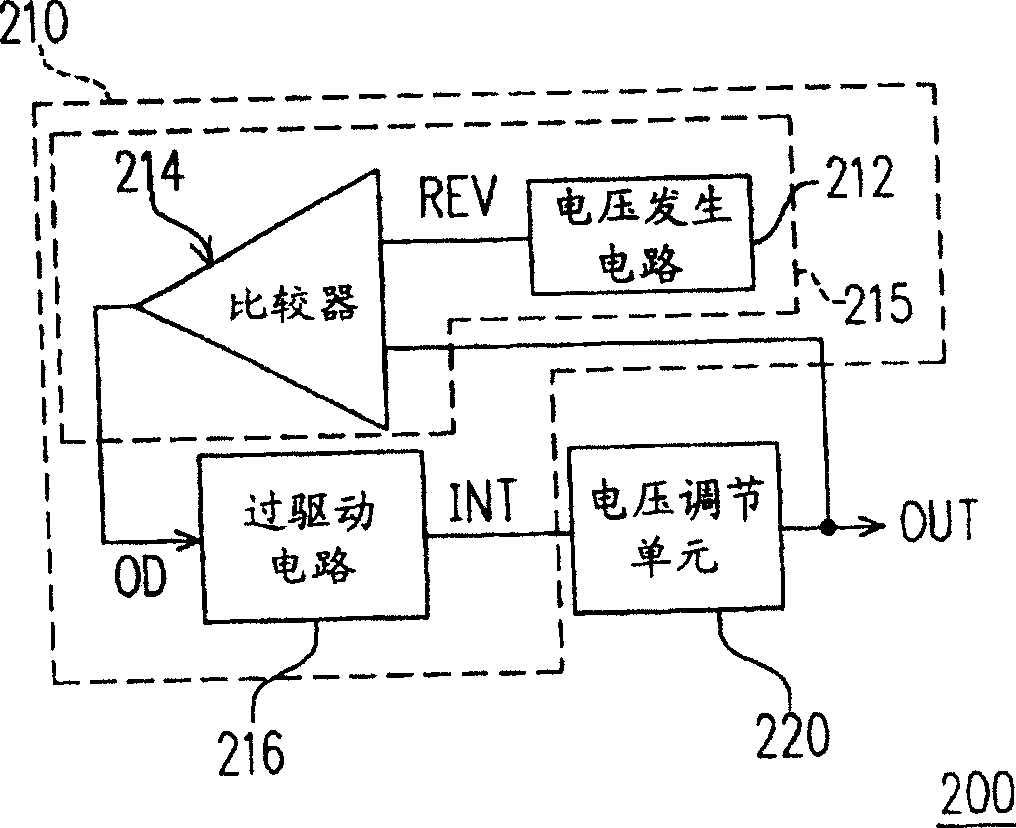

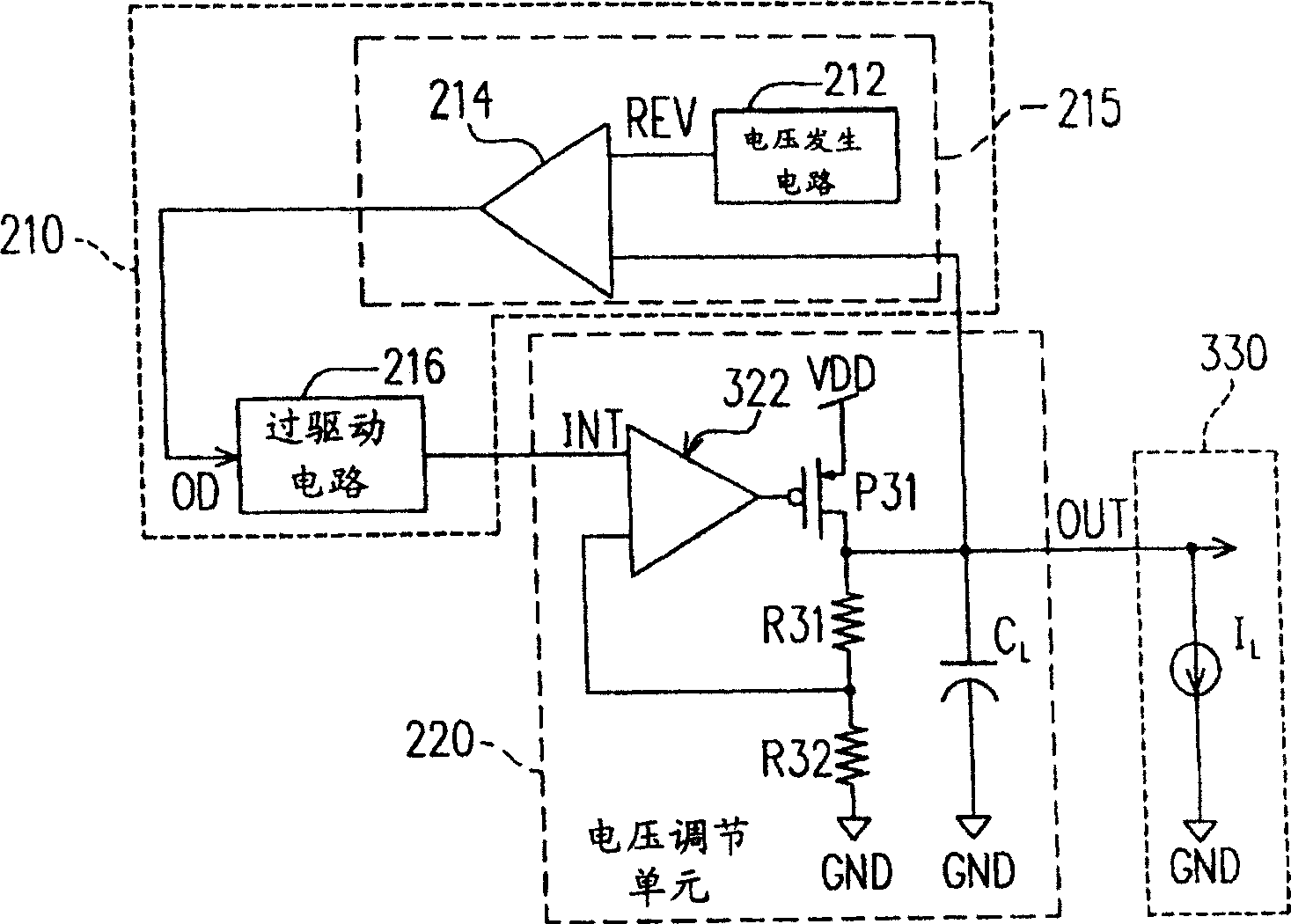

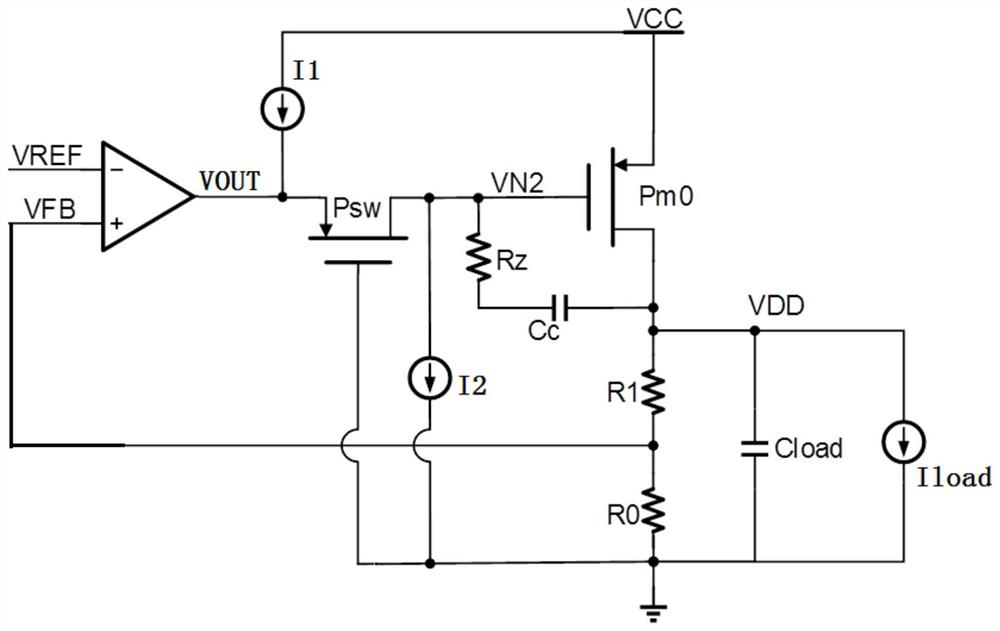

Voltage regulator

InactiveCN100514245CReal-time adjustment of input voltageAdequate drive capacityElectric variable regulationDriver circuitVoltage regulation

A voltage regulator, which includes a voltage regulation unit and an overdrive unit. The voltage regulating unit outputs a corresponding output voltage according to the input voltage. The overdrive unit includes a voltage comparison circuit, coupled to the output terminal of the voltage regulator, for comparing the output voltage of the voltage regulator with a reference voltage, and outputting an overdrive signal; and an overdrive circuit, coupled to the voltage comparison circuit and the voltage between the input terminals of the adjustment unit, and adjust the input voltage of the voltage adjustment unit according to the overdrive signal, wherein if the output voltage is greater than the reference voltage, the overdrive signal is a low logic level, and the input voltage is a normal level; if the output If the voltage is lower than the reference voltage, the overdrive signal is at a high logic level, and the overdrive unit increases the level of the input voltage.

Owner:NOVATEK MICROELECTRONICS CORP

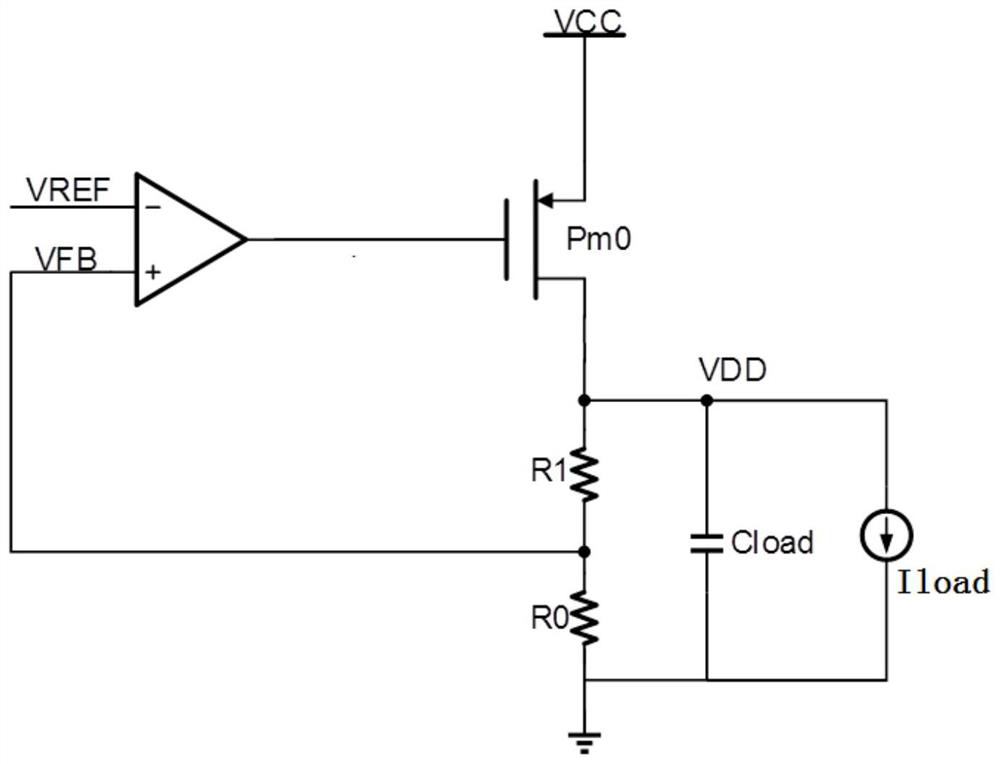

Linear voltage regulator circuit

ActiveCN113741608ANormal working conditionStable outputElectric variable regulationPhysicsEngineering

The invention discloses a linear voltage regulator circuit. A first current source, a second current source and a switch PMOS tube which are equal are added, the output of an operational amplifier provides gate-source voltage for the switch PMOS tube, the first current source and the second current source enable constant current to flow through the switch PMOS tube, and when the input voltage is lower and the linear voltage regulator circuit is heavily loaded, due to the fact that large current flows through the driving PMOS tube, the grid voltage of the driving PMOS tube is reduced, the switching PMOS tube is switched on, the output end of the operational amplifier is raised to the grid-source voltage of the switching PMOS tube, and meanwhile the grid voltage of the driving PMOS tube is not limited by the output of the operational amplifier, the output of the operational amplifier is not affected by the grid voltage of the driving PMOS tube under the low input voltage. The linear voltage regulator circuit can still output stable output voltage under the conditions of low input voltage and heavy load.

Owner:PUYA SEMICON SHANGHAI CO LTD

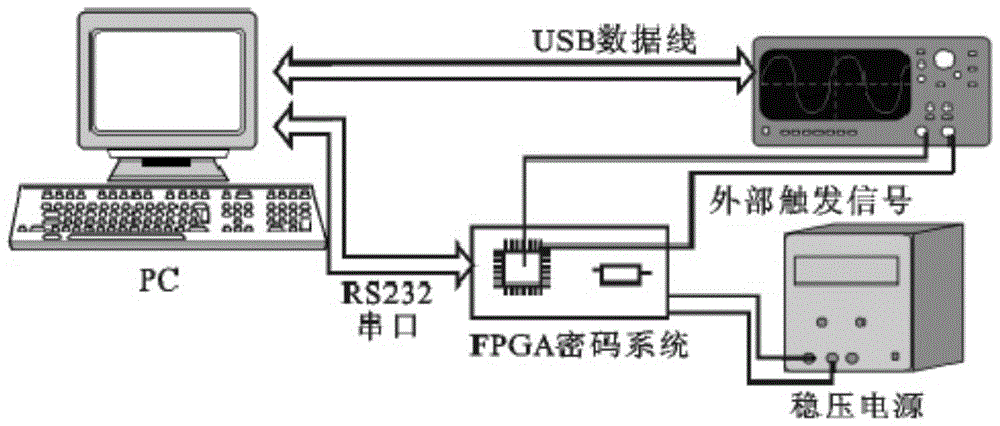

Hardware Trojan Test System

ActiveCN103954904BImprove the level of automated testingEasy to handleDigital circuit testingElectrical resistance and conductanceLogic testing

The invention discloses a hardware Trojan horse test system. The hardware Trojan horse test system comprises a PC, an NI high-speed digital I / O board and a test circuit, wherein the PC is used for generating a test vector, conducting programming on an FPGA chip, controlling the NI high-speed digital I / O board, an oscilloscope and the FPGA chip and receiving signals sent by the NI high-speed digital I / O board and the oscilloscope; the NI high-speed digital I / O board is used for outputting the test vector to the FPGA chip, collecting an FPGA response signal and sending back the FPGA response signal to the PC; the testing circuit comprises the FPGA chip and receives the test vector output by the NI high-speed digital I / O board. The hardware Trojan horse test system further comprises a precise resistor R1, a precise resistor R2, the oscilloscope and a precise voltage-stabilized source, wherein the precise resistor R1 and the precise resistor R2 monitor the power consumption change of the kernel voltage and the auxiliary voltage of the FPGA chip, the oscilloscope is used for automatically triggering and collecting signals of power consumption change of the kernel voltage and the auxiliary voltage of the FPGA chip and sending the signals to the PC; the precise voltage-stabilized source is used for supplying power to the test circuit. The hardware Trojan horse test system conducts automatic tests, improves the precision of logic testing and bypass analysis and is high in application value.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

Read operation control signal generator and its working method

The invention discloses a read-operation control signal generator. The read-operation control signal generator comprises three delay circuits with same structures and different delay time setting; the input terminal of a first delay circuit is connected with internal clock signals, three delayed output signals are generated successively by the delay circuits because of rising edge trigger of external clock signals, and signal saeq is subjected to miteinander with nonsignals of second output signals and first output signals, and then is output via a noninverting amplifier; signal saen1 is output by a noninverting amplifie via first output signals; signal saen2 is output by a noninverting amplifie via third output signals; zero clearing of the three delay circuits can be realized via rising edge trigger of external clock signals, third output signals can be delaed by a fourth delay circuit, and zero clearing signals are lower by the fourth delay circuit so as to realize zero clearing of the three delay circuits. The invention also discloses an operation method of the read-operation control signal generator. The read-operation control signal generator is simple in circuit structure, and is capable of reducing delay skew, domain area, and circuit powder consumption.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A type selection method of servo motor for ball screw feed system

ActiveCN112835325BAdequate drive capacityQuick selectionProgramme controlComputer controlBall screwElectric machinery

The invention belongs to the technical field of mechatronics, and in particular relates to a method for selecting a servo motor for a ball screw feed system. This method first deduces the driving torque expression under the conditions of no-load quick start and maximum cutting load; further determines the range of system gain and the range of inertia of the servo motor; finally completes the selection of the servo motor according to the speed-torque curve. This method fully considers various typical working conditions to ensure that the ball screw feed system has sufficient driving capacity. At the same time, it also pays attention to the motor-load inertia ratio, so that the servo motor can obtain better dynamic performance. This method realizes the fast and accurate selection of the servo motor of the ball screw feeding system, overcomes the problems of relying on experience, low efficiency and inaccuracy of the traditional method, and quickly and accurately selects the servo motor for the ball screw feeding system, and at the same time It provides an accurate and convenient servo motor selection method for on-site engineers and technicians.

Owner:TSINGHUA UNIV

A Multi-input High Speed CMOS Buffer Circuit

ActiveCN107070447BImprove usabilityAdequate drive capacityLogic circuits coupling/interface using field-effect transistorsElectronic switchingCMOSHemt circuits

The invention discloses a multi-input high-speed CMOS buffer circuit. The buffer circuit comprises a voltage-to-current module, a multipath selector module, and a current-to-voltage module, wherein two sides of the multipath selector module are respectively connected with the voltage-to-current module and the current-to-voltage module, the other side of the voltage-to-current module is used for inputting the voltage, and the other side of the current-to-voltage module is used for outputting the voltage; the voltage-to-current module is used for converting multiple input voltage into a current signal; the multipath selector module is used for conducting the voltage-to-current module and the current-to-voltage module; the current-to-voltage module is used for converting the input current signal into a voltage signal and outputting the voltage signal. The multi-input high-speed CMOS buffer circuit disclosed by the invention has the excellent characteristics of being fast in buffering speed, small in delay, free from using a bootstrapping switch, and strong in usability.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

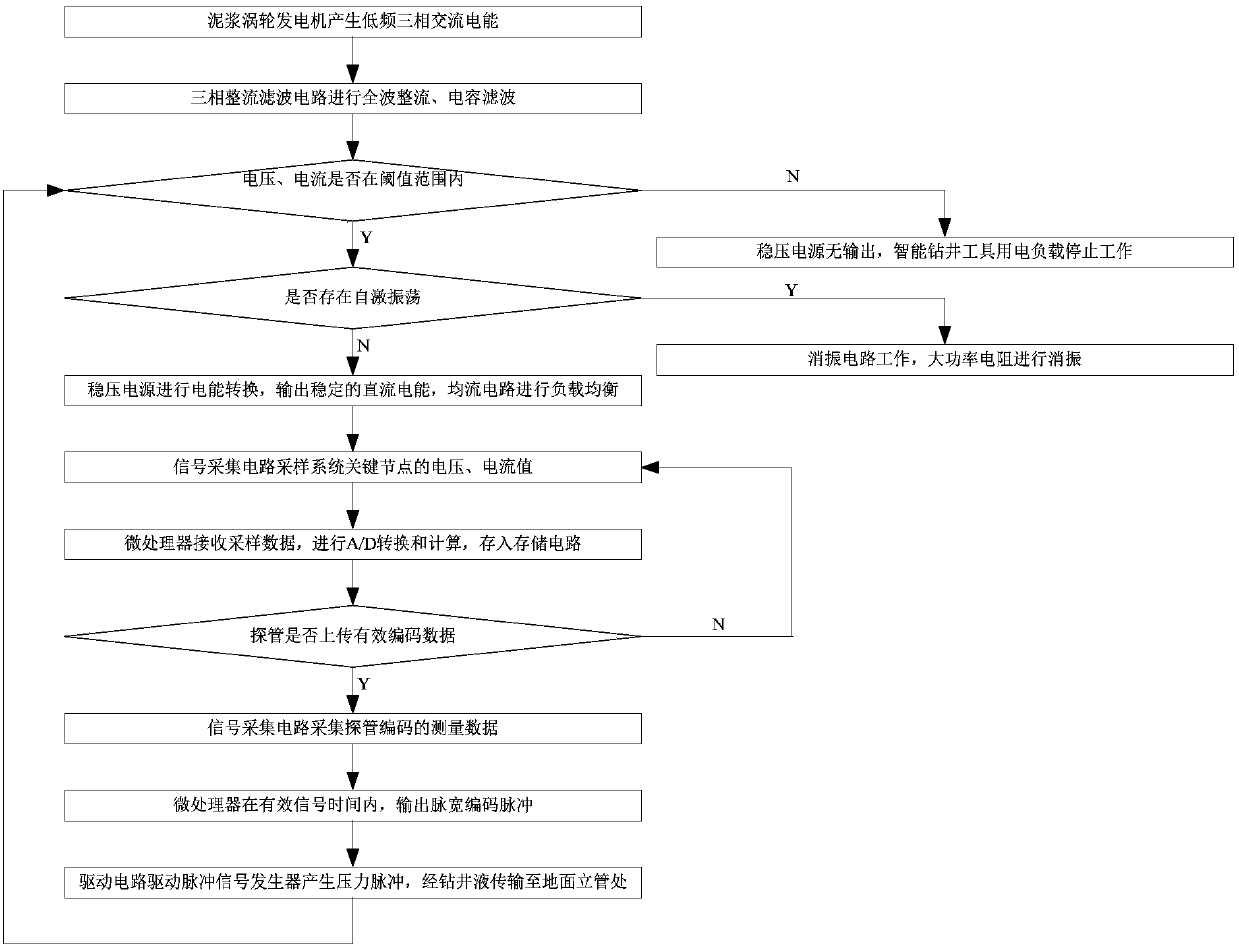

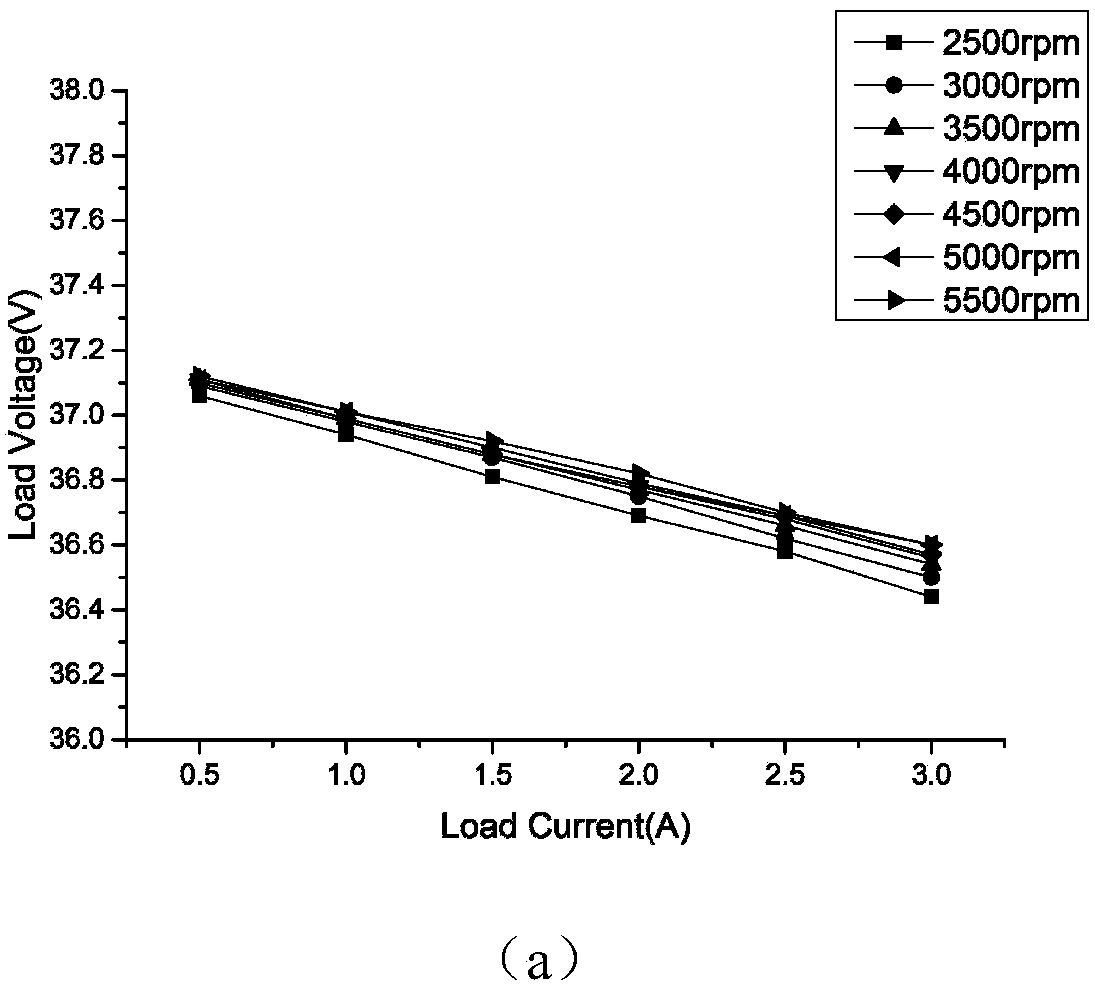

Intelligent drilling tool downhole power supply realization method and pulse driving method and circuit

ActiveCN105634307BStable drive currentAdequate drive capacityAc-dc conversion without reversalElectric generator controlFeedback circuitsEngineering

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

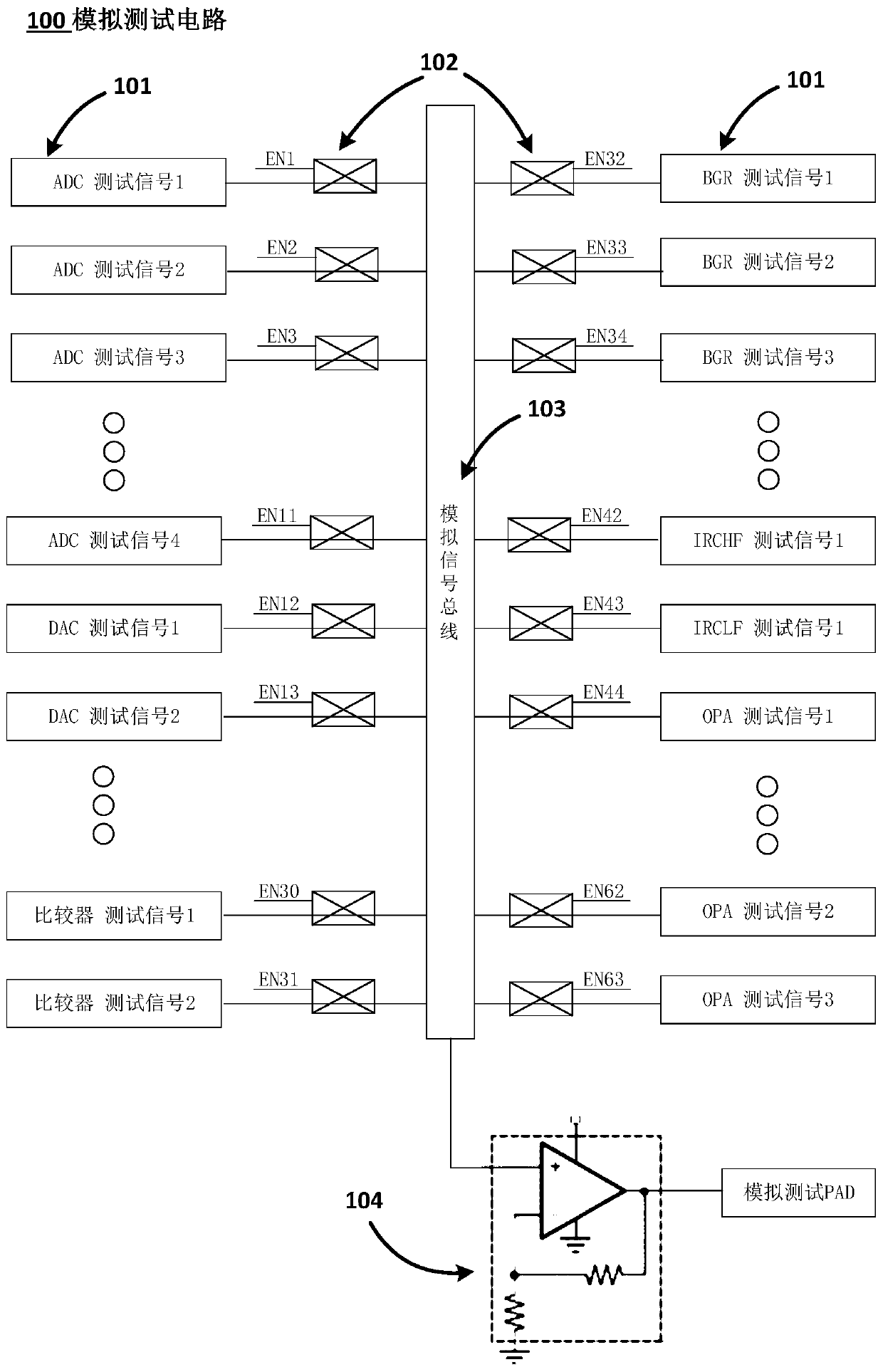

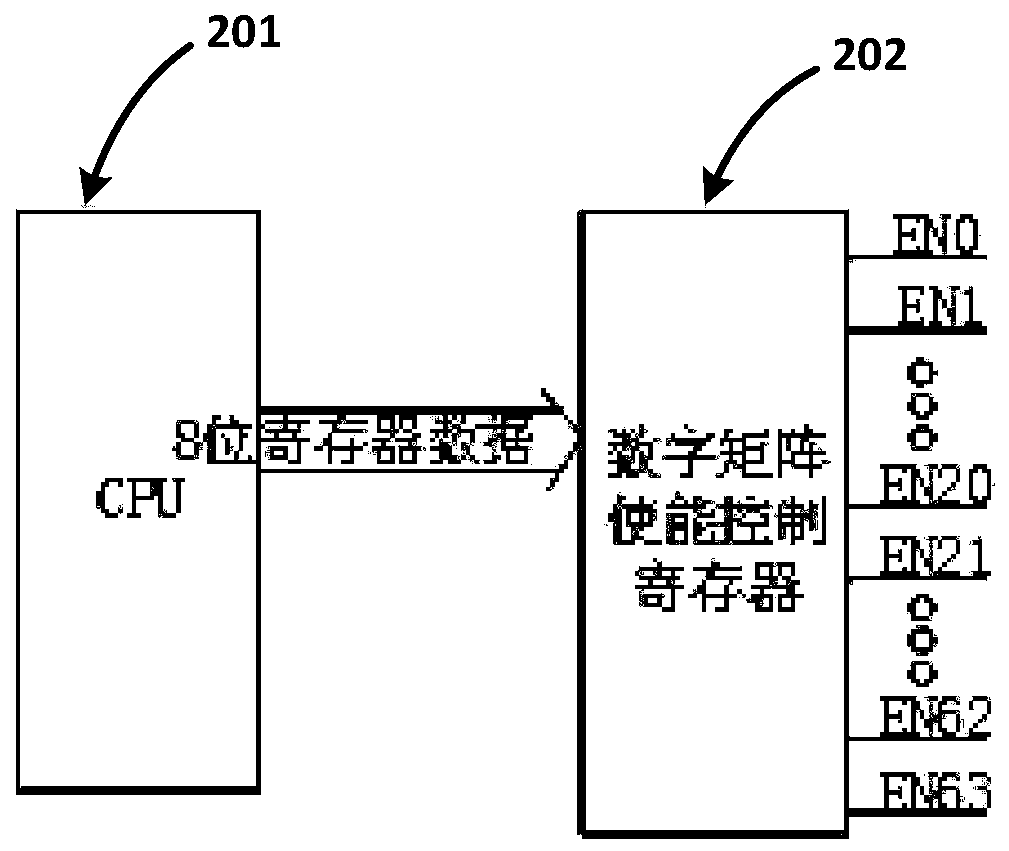

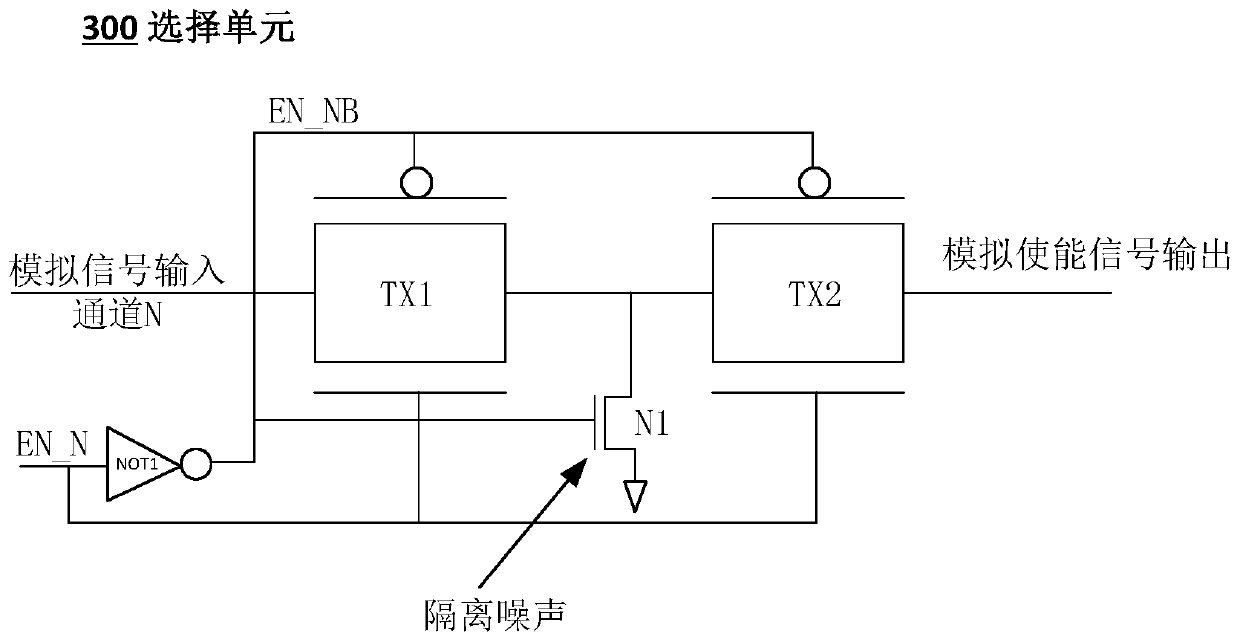

Analog signal test circuit

The present invention relates to an analog signal test circuit. The analog signal test circuit comprises: a plurality of analog signal input channels configured to receive an analog test signal; a channel gating circuit having an input end connected with the analog signal input channels and having an output end connected with an analog signal bus, wherein the channel gating circuit is configured to selectively connect or disconnect with the analog signal input channels; the analog signal bus connected with the channel gating circuit and connected with a buffer, wherein the analog signal bus isconfigured to transmit the selectively connected analog test signal to the buffer; and a buffer circuit having an input end connected with the analog signal bus and having an output end being the output end of the analog test signal, wherein the buffer circuit is configured to perform buffer and output on the analog test signal transmitted by the analog signal bus. The analog signal test circuitcan reduce the mutual interference between test nodes, can reduce the number of buffers and can ensure the high drive capability.

Owner:HUADA SEMICON CO LTD

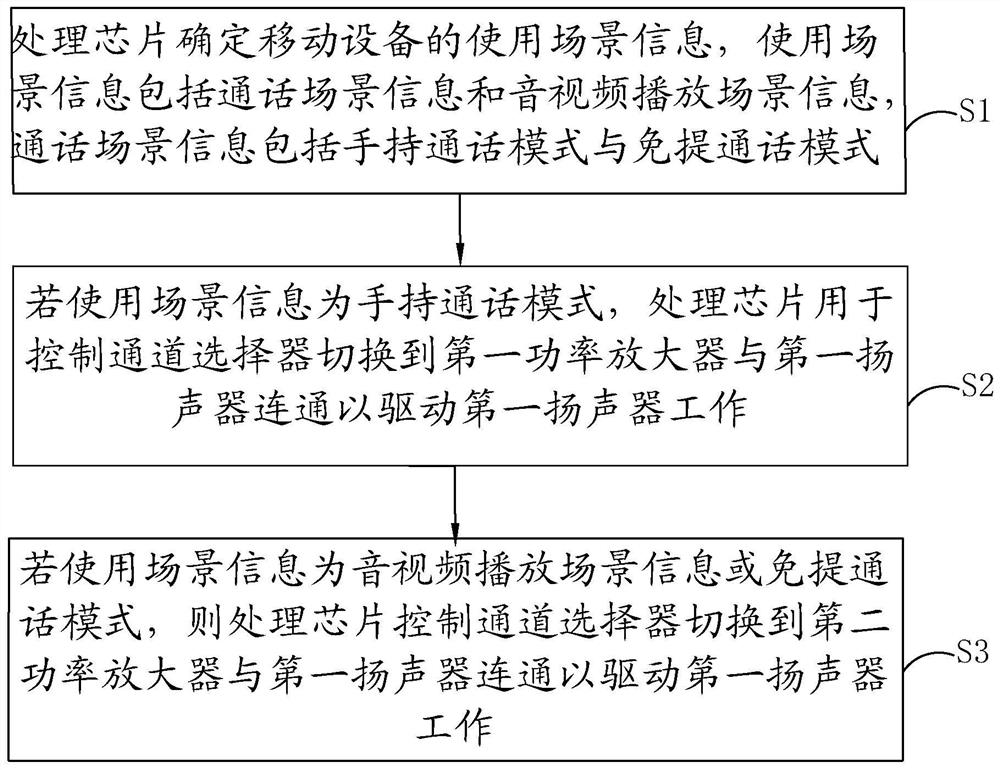

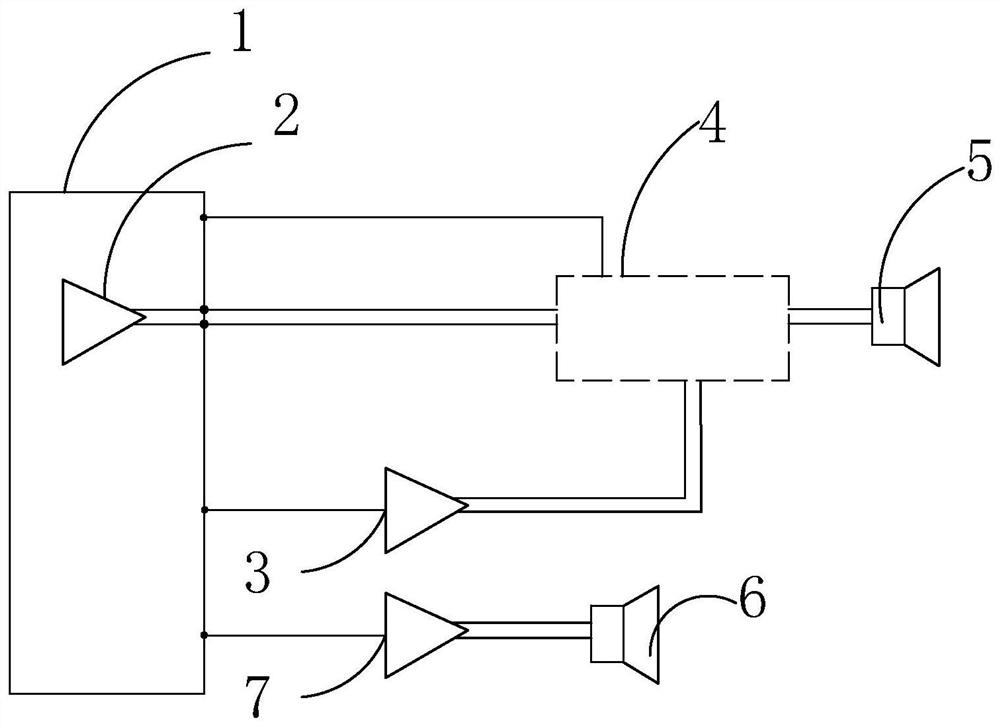

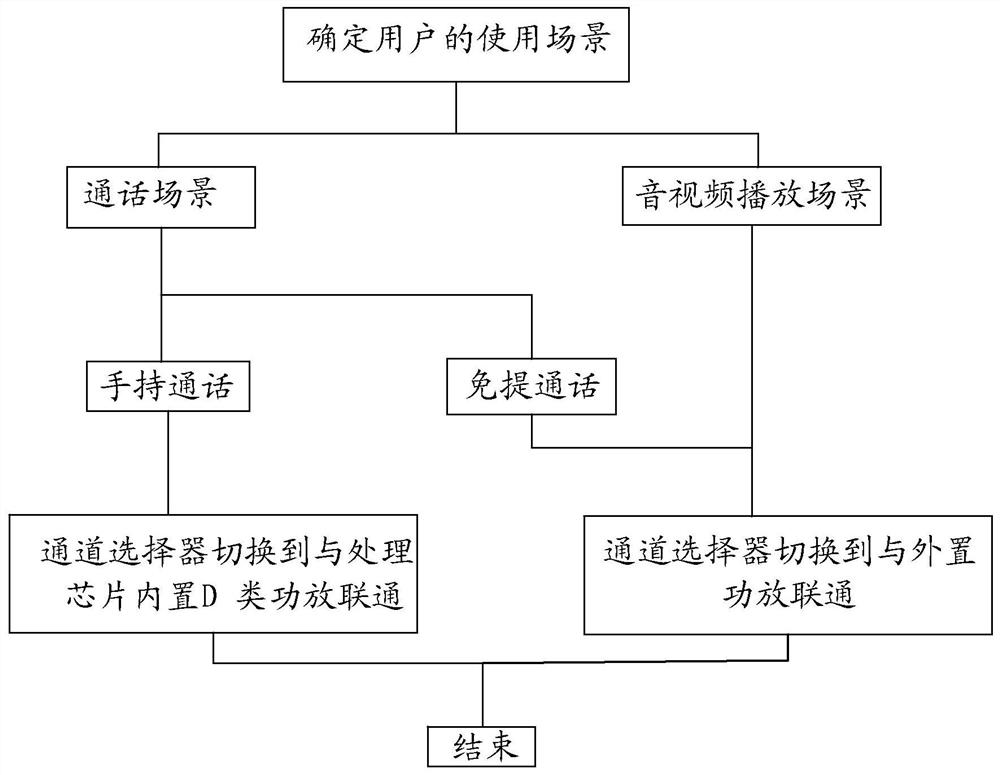

Loudspeaker driving method and circuit for mobile equipment

PendingCN113014706AReduce noise floorImprove sound qualityTelephone set constructionsAudio power amplifierLoudspeaker

The invention provides a loudspeaker driving method and circuit for mobile equipment. The equipment comprises a mobile equipment processing chip, a first power amplifier and a second power amplifier which are connected with the processing chip, a channel selector connected with the processing chip, and a first loudspeaker connected with the channel selector. The method comprises the steps that the processing chip determines use scene information of the mobile equipment; if the use scene information is in a handheld call mode, the processing chip controls the channel selector to be switched to the first power amplifier to be communicated with the first loudspeaker so as to drive the first loudspeaker to work; and if the use scene information is audio and video playing scene information or a hands-free call mode, the processing chip controls the channel selector to be switched to the second power amplifier to be communicated with the first loudspeaker so as to drive the first loudspeaker to work. According to the embodiment of the invention, by switching different power amplifiers for driving, the background noise of the system is ensured to be as low as possible when a user carries out a handheld call, and meanwhile, the method has enough driving capability when the user carries out the hand-free call and plays music.

Owner:AAC MICROTECH CHANGZHOU

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com