Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

40results about How to "Stress" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

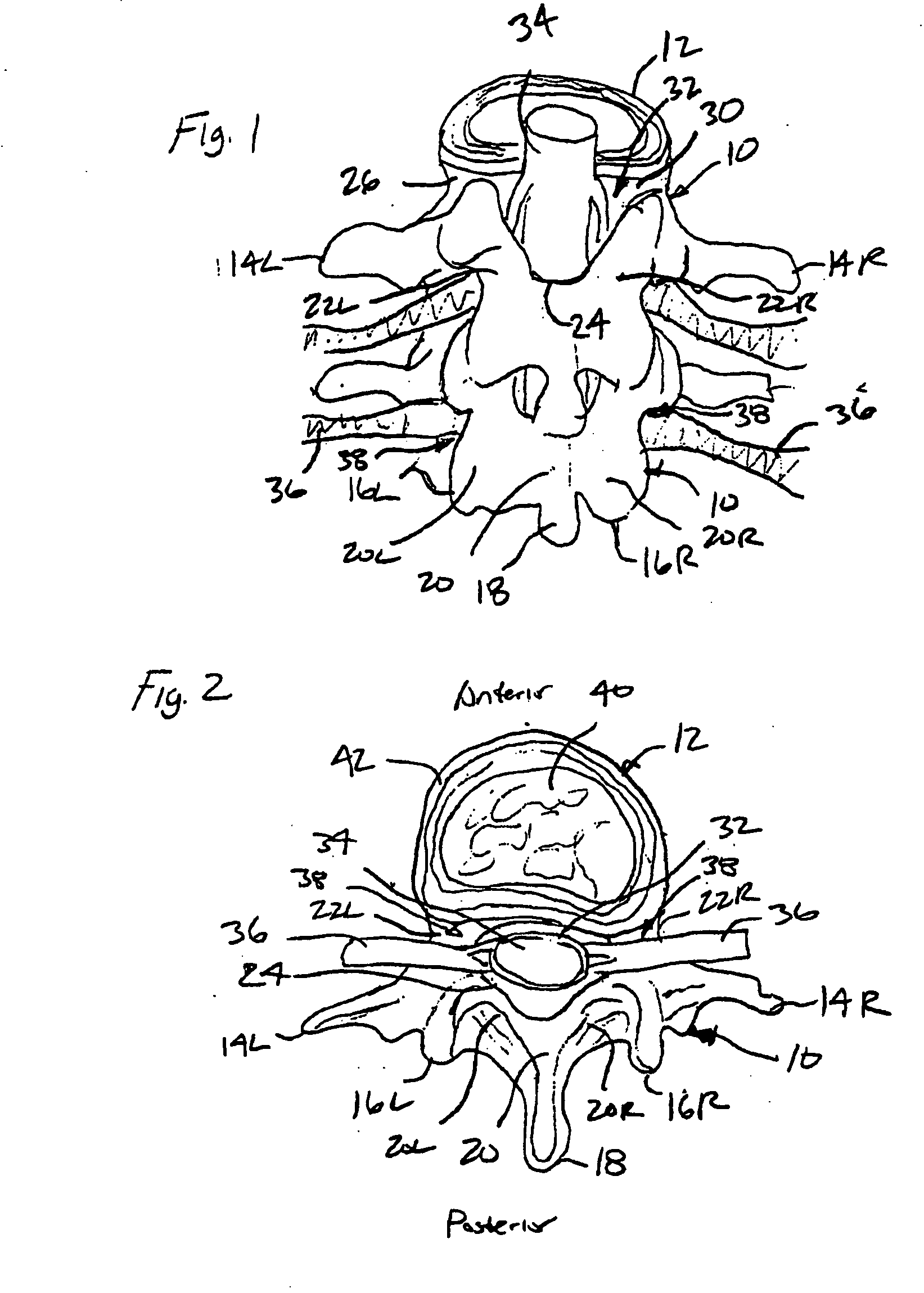

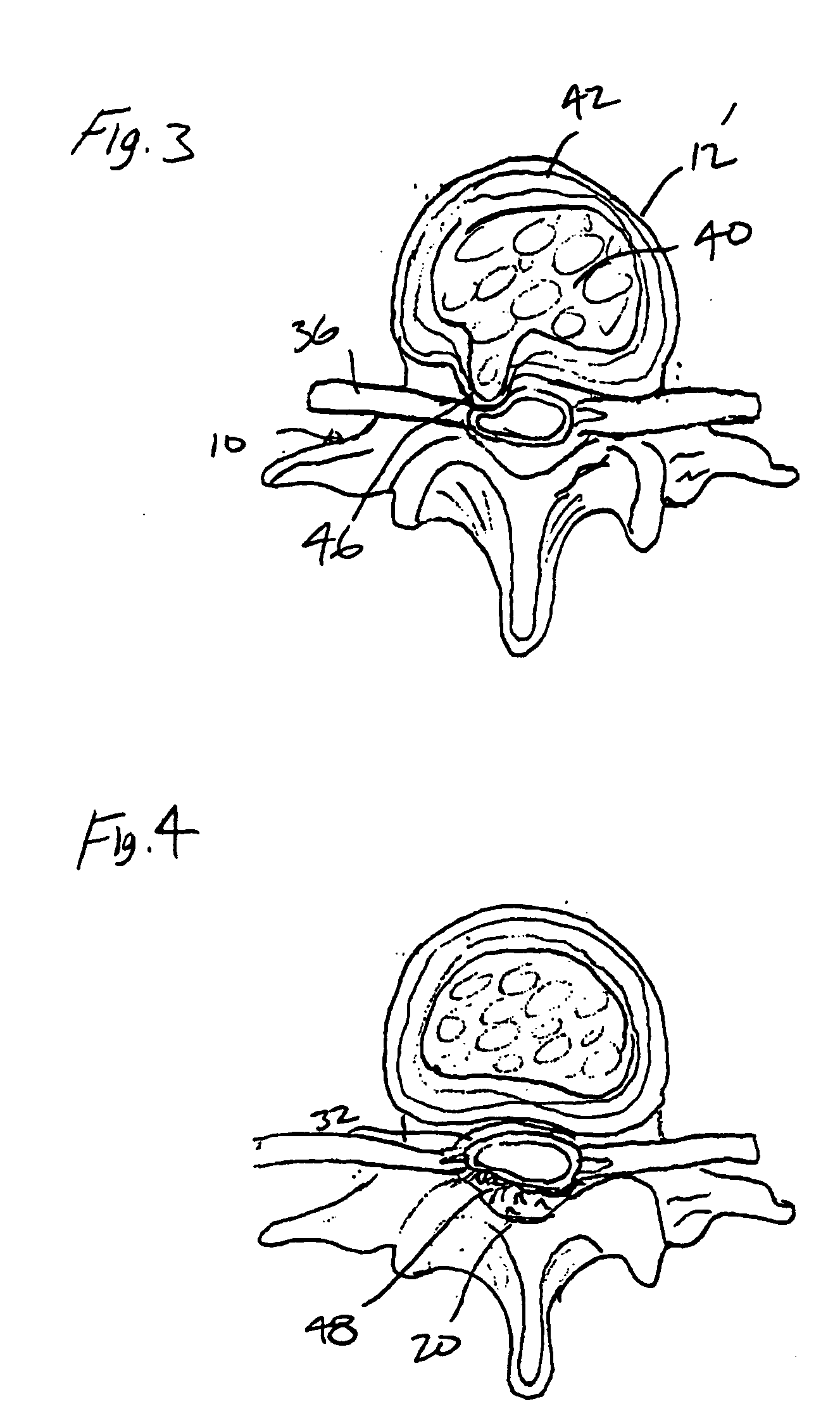

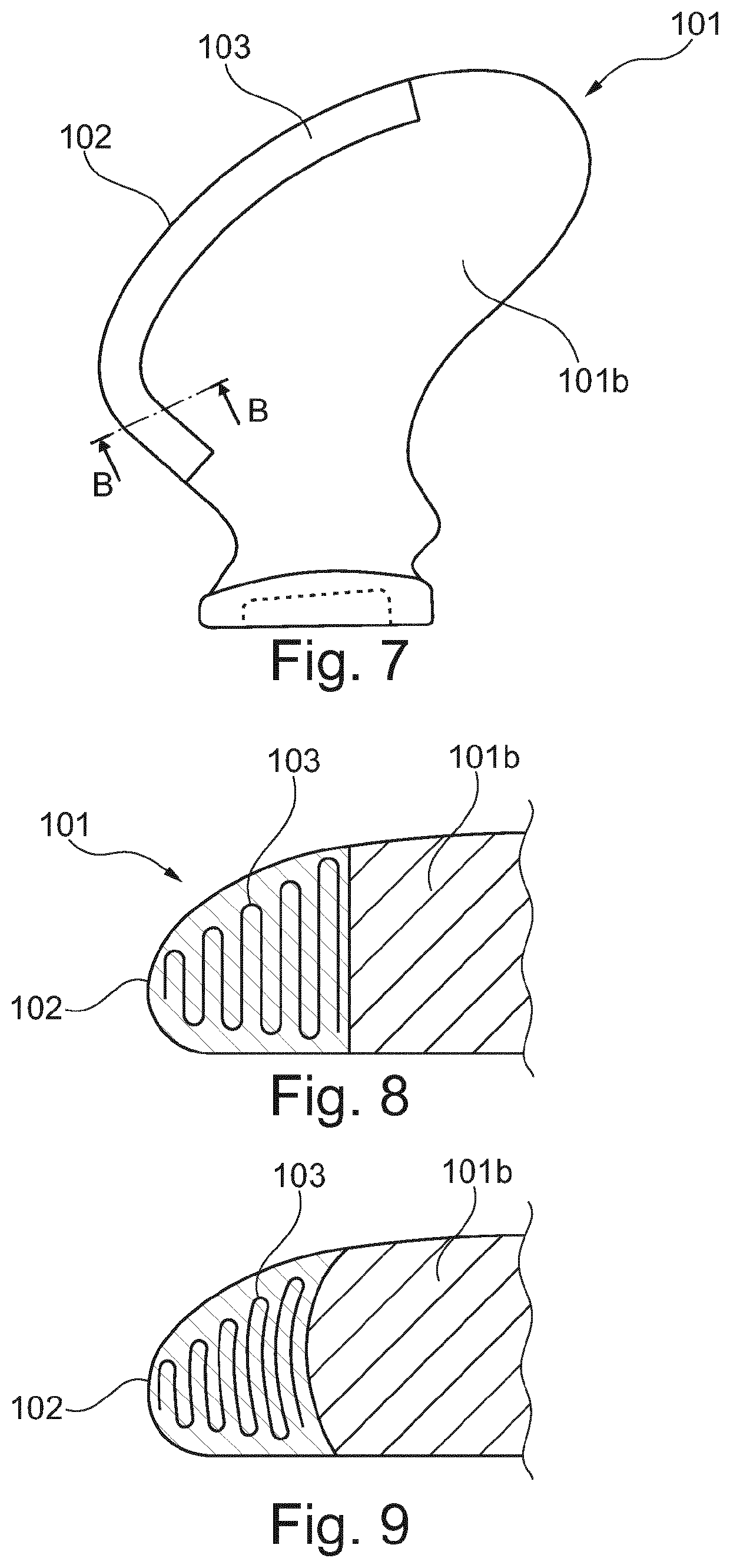

Articulating tissue removal probe and methods of using the same

InactiveUS20050261692A1StressStress minimizationEndoscopic cutting instrumentsSurgical forcepsMedicineDrive shaft

A medical probe comprises a probe shaft having proximal and distal shaft portions, and an operative element, such as a tissue removal element, associated with the distal shaft portion. The proximal and distal shaft portions can be positioned relative to each other in an axially aligned relationship and an axially non-aligned relationship at the interface between the shaft portions. For example, the ends of the shaft portions that engage each other can be beveled, in which case, relative rotation of the shaft portions will cause the angle between the portions to vary. Or, the shaft portions can hinge relative to each other to vary the angle between them. Thus, it can be appreciated that the probe can be introduced along a straight path via a small opening within the patient, and then the probe shaft portions can be moved relative to each other to reach off-axis tissue. The probe may have a drive shaft that extends within the probe shaft and on which the operative element is mounted. The drive shaft may have proximal and distal rigid shaft portions and a linkage between the drive shaft portions, so that the drive shaft can bend when the probe shaft portions are placed in their axially non-aligned relationship.

Owner:BOSTON SCI SCIMED INC

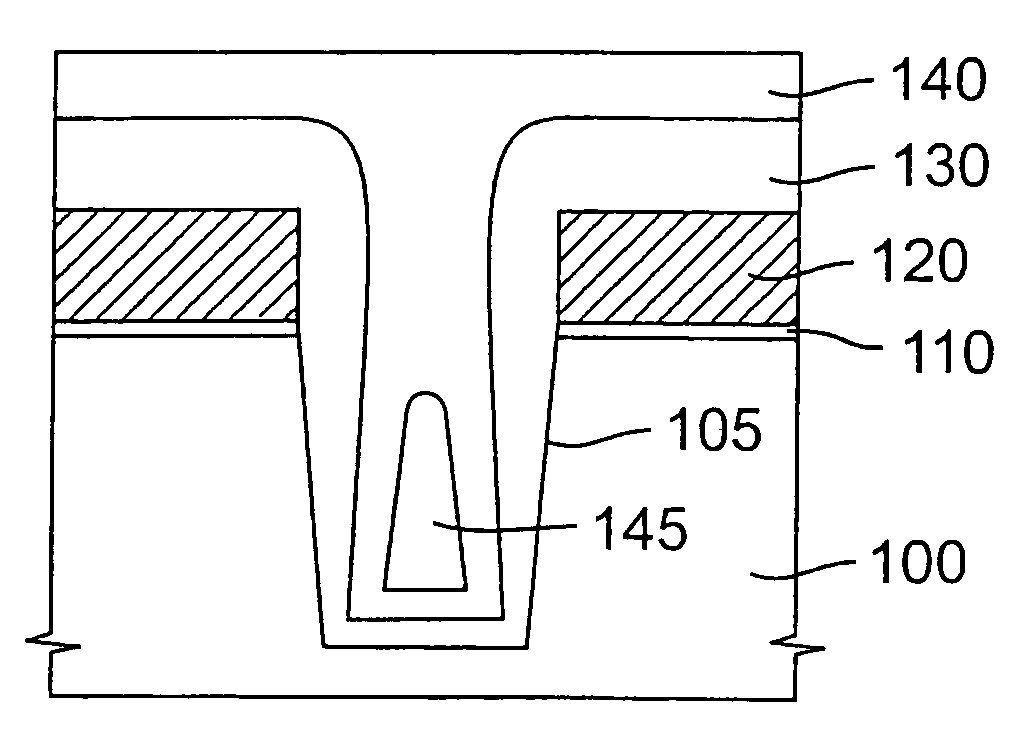

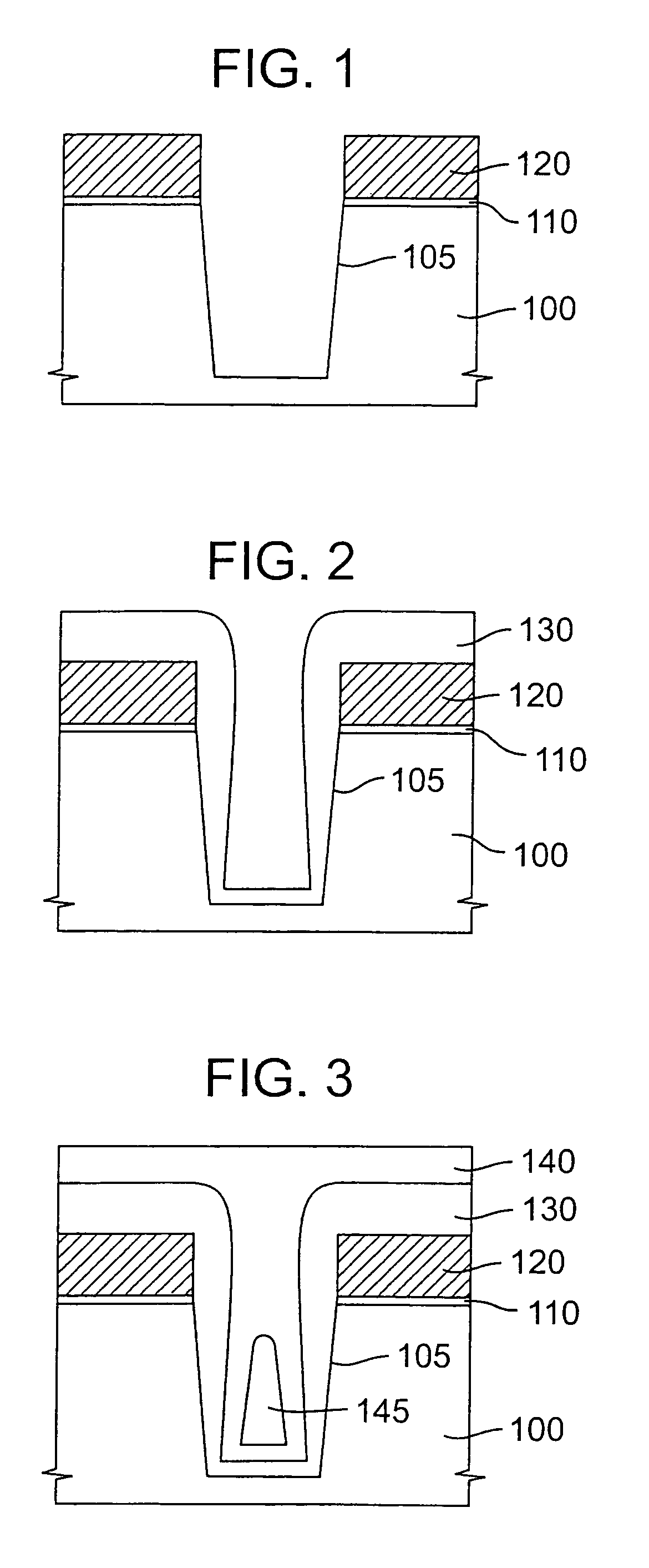

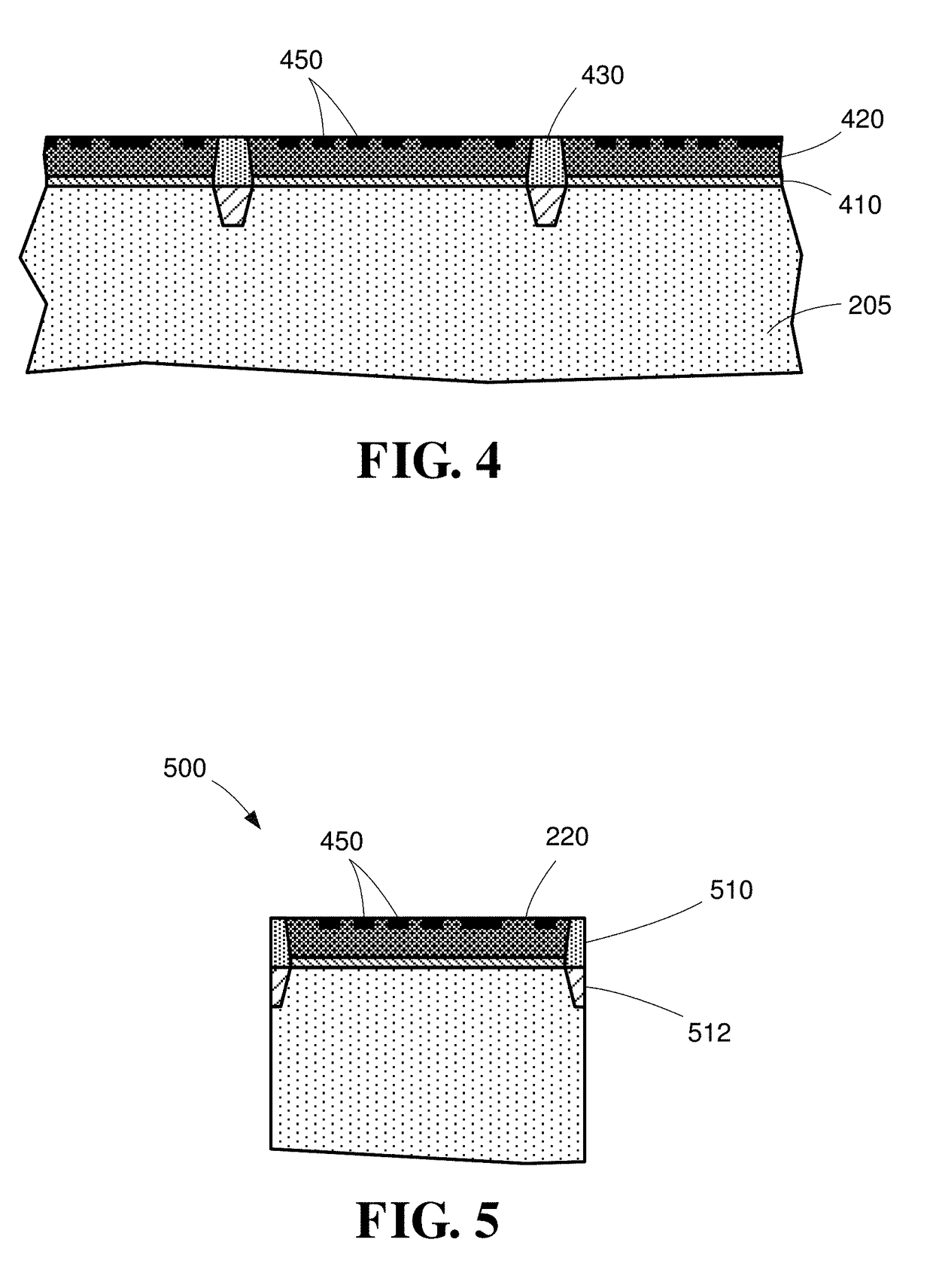

Stress-relieved shallow trench isolation (STI) structure and method for forming the same

InactiveUS7015116B1StressRelieve pressureSemiconductor/solid-state device manufacturingDielectric layerSemiconductor

A shallow trench isolation (STI) structure in a semiconductor substrate and a method for forming the same are provided. A trench is formed in a semiconductor substrate. A first dielectric layer is formed on sidewalls of the trench. The first dielectric layer is formed thicker at a top portion of the sidewalls than a bottom portion of the sidewalls and leaving an entrance of the trench open to expose the trench. A second dielectric layer is conformally formed on the first dielectric layer to close the entrance, thus forming a void buried within the trench. Thus, the stress between the trench dielectric layer and the surrounding silicon substrate during thermal cycling can be substantially reduced.

Owner:INTEGRATED DEVICE TECH INC

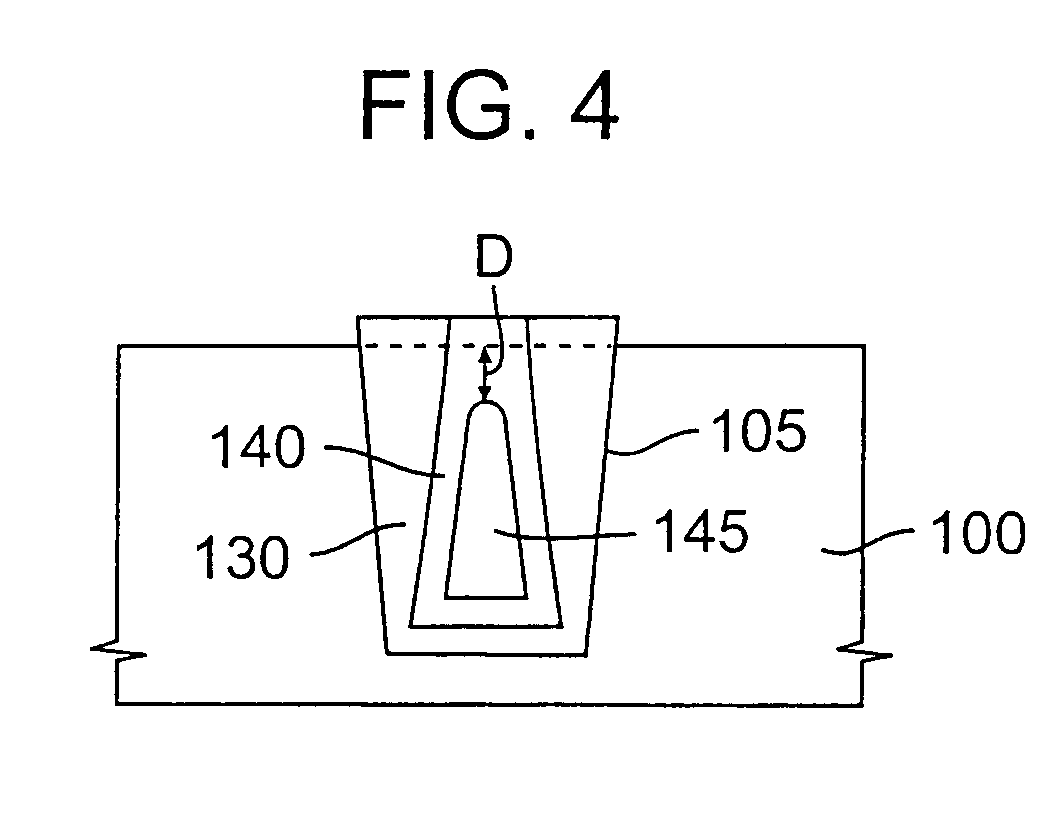

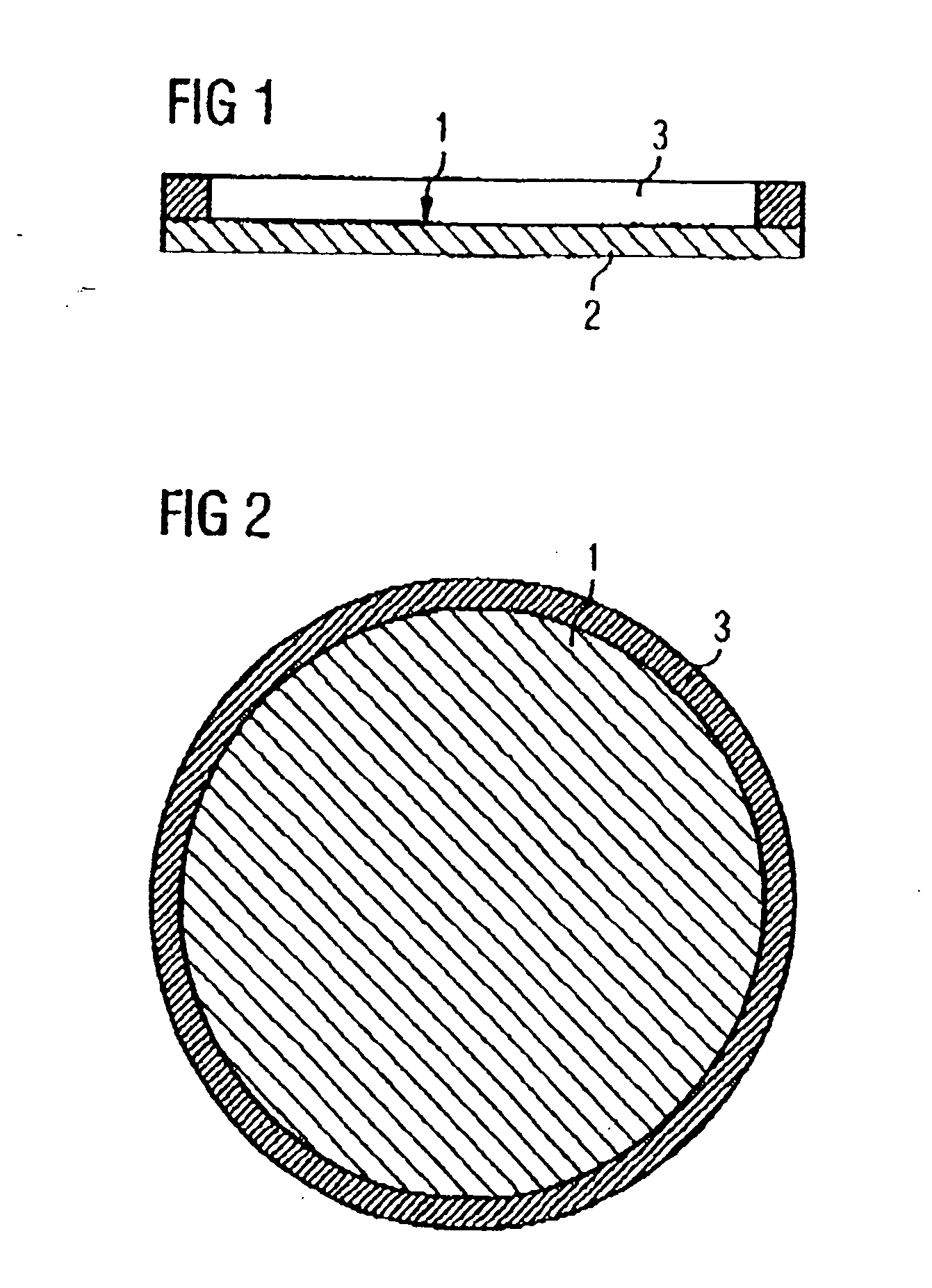

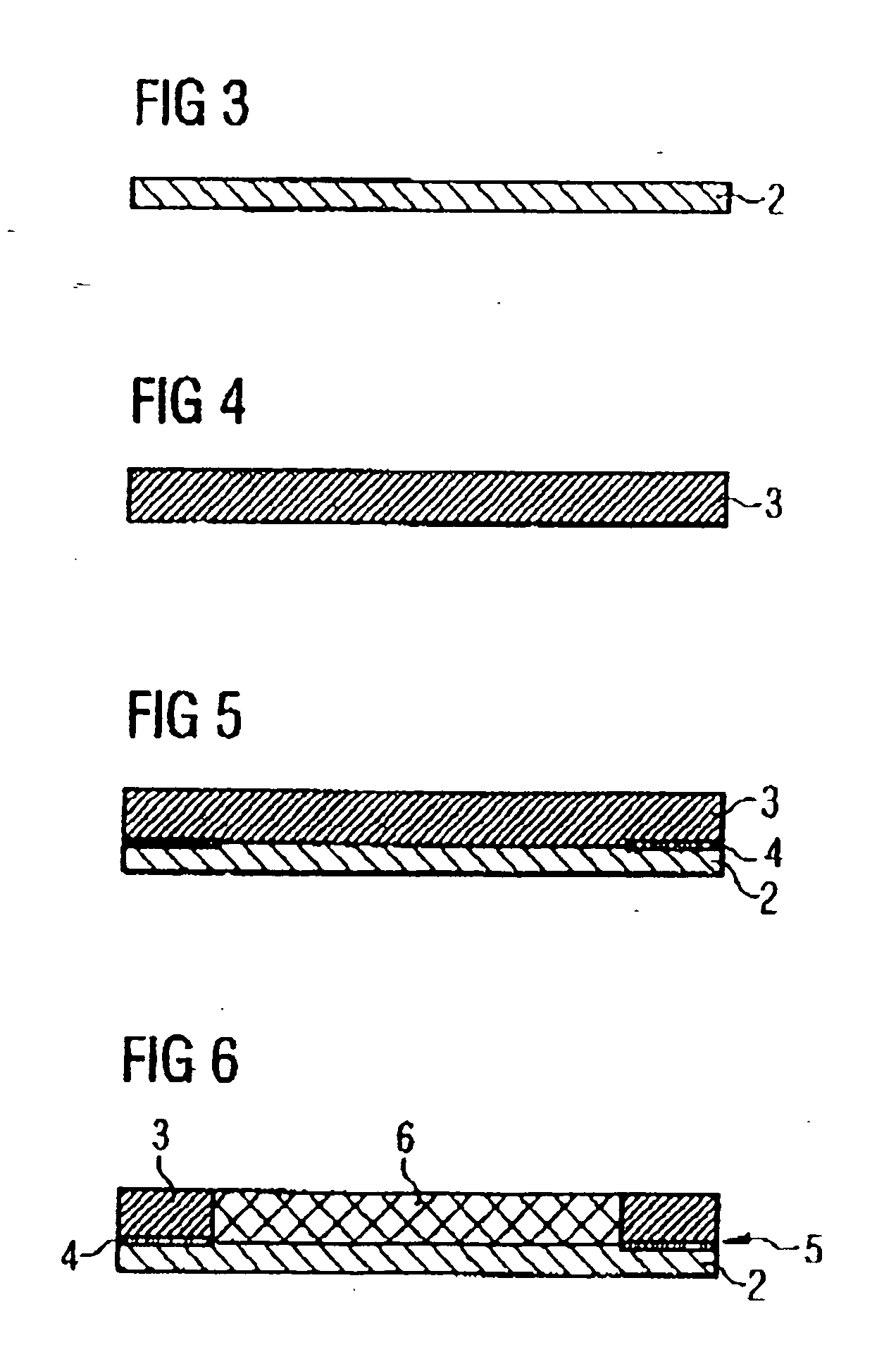

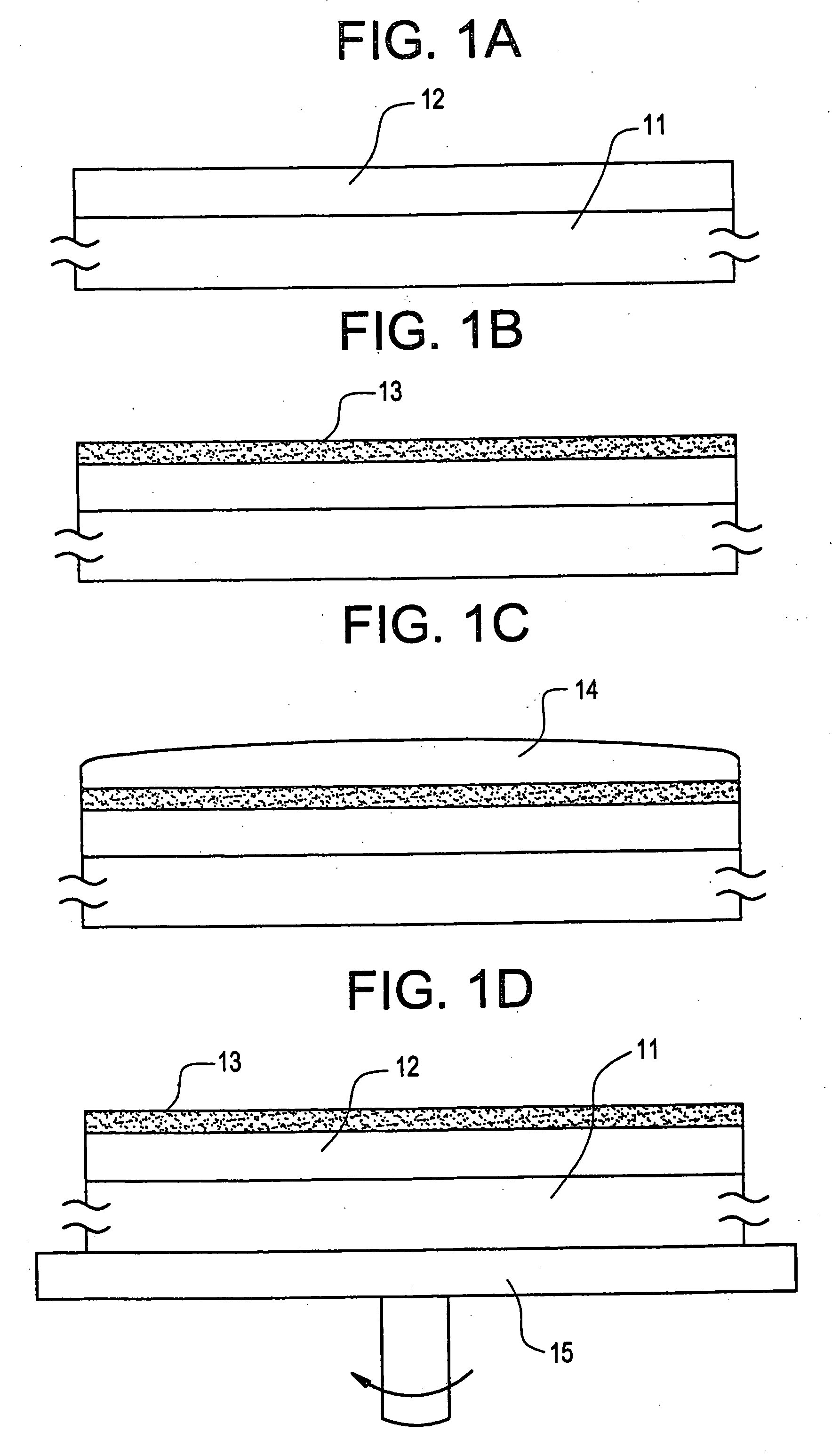

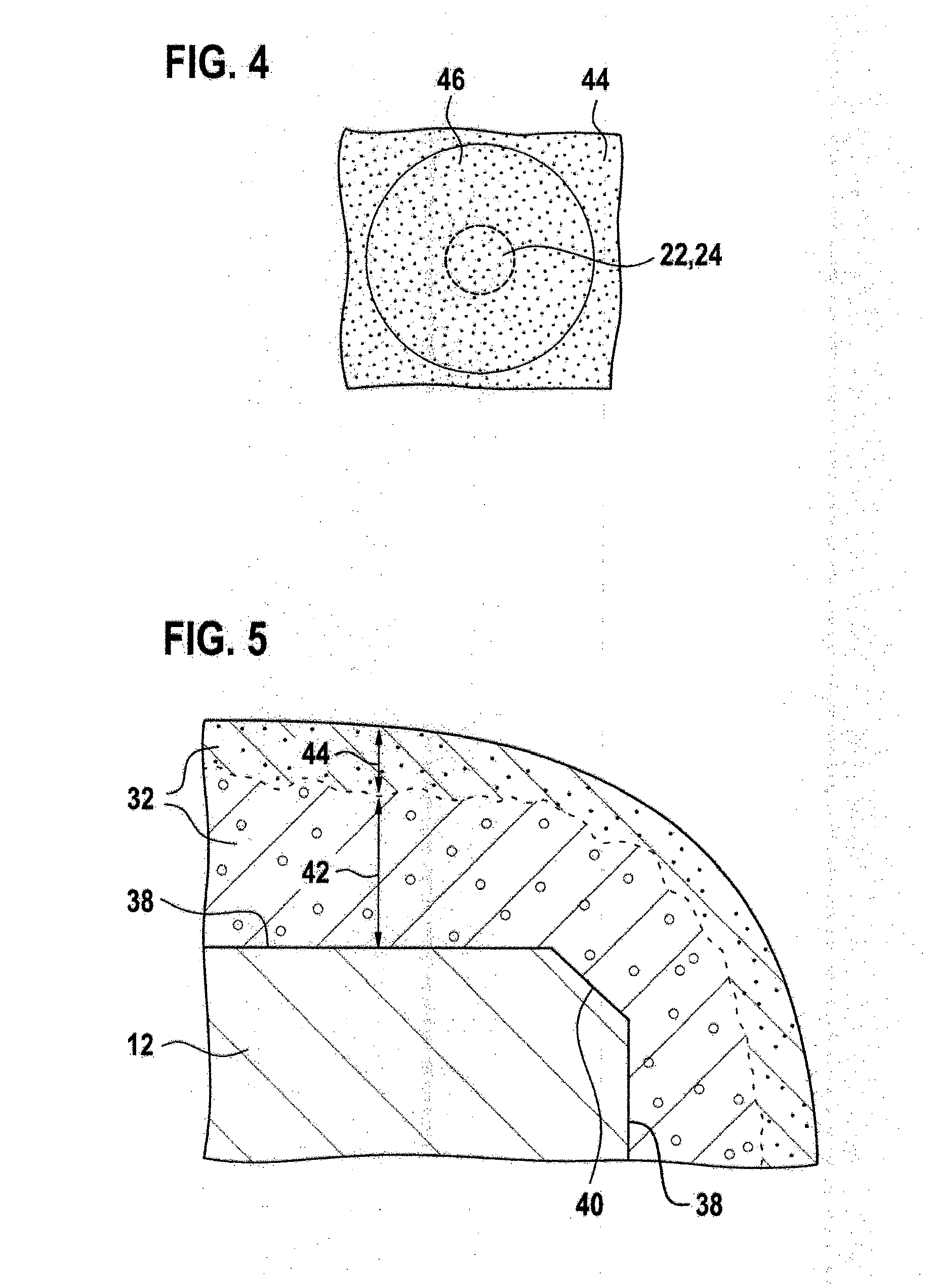

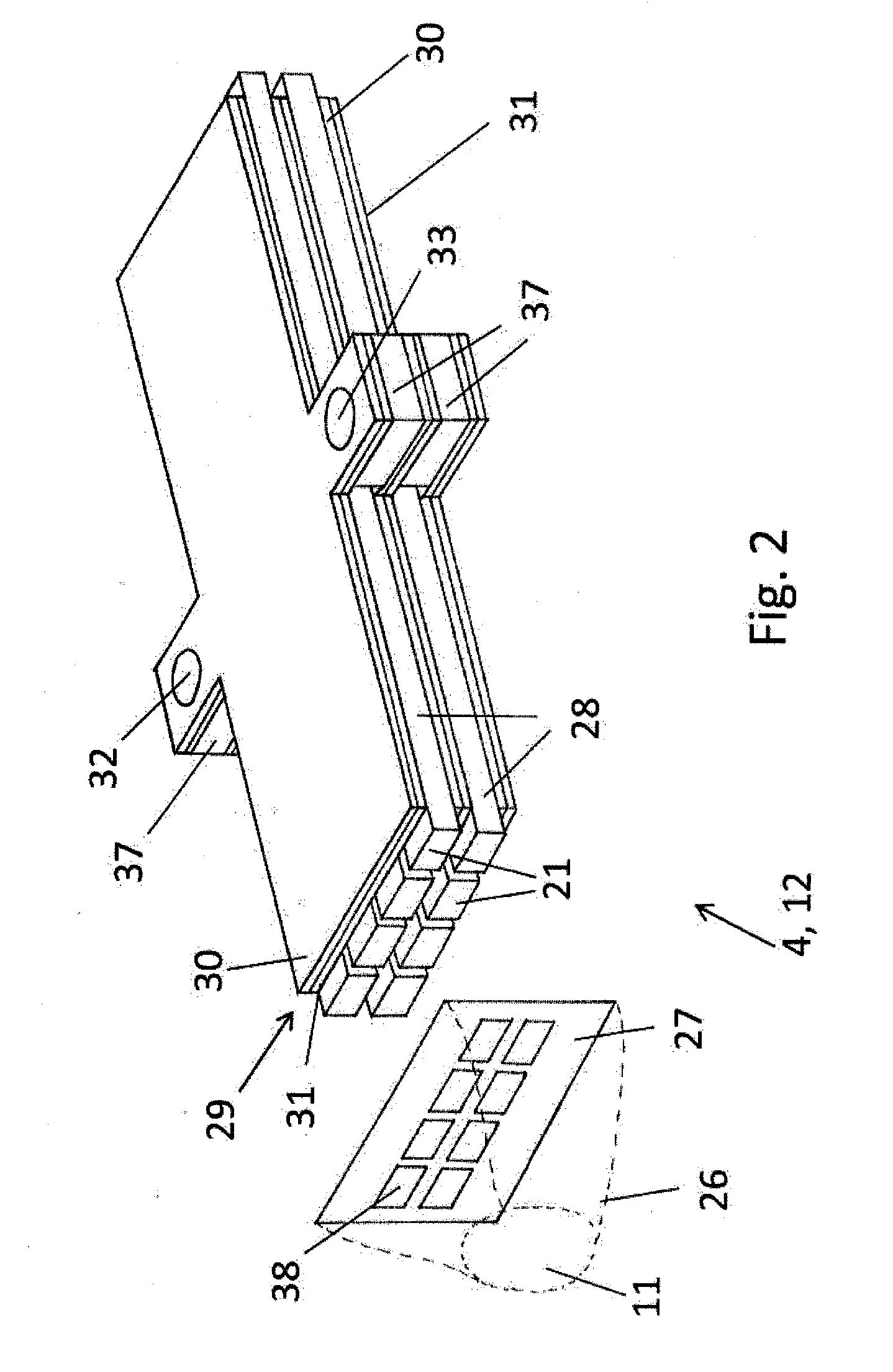

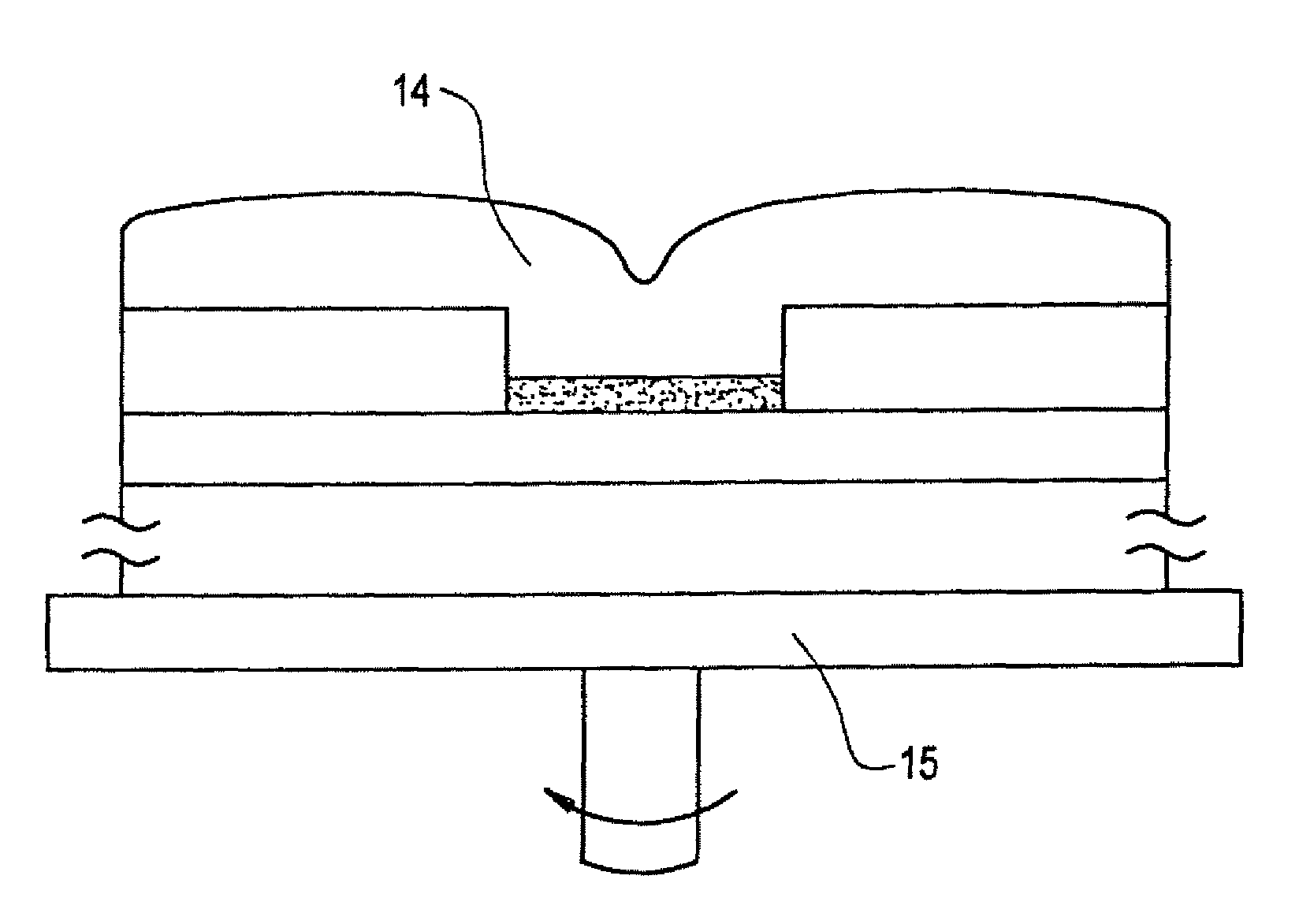

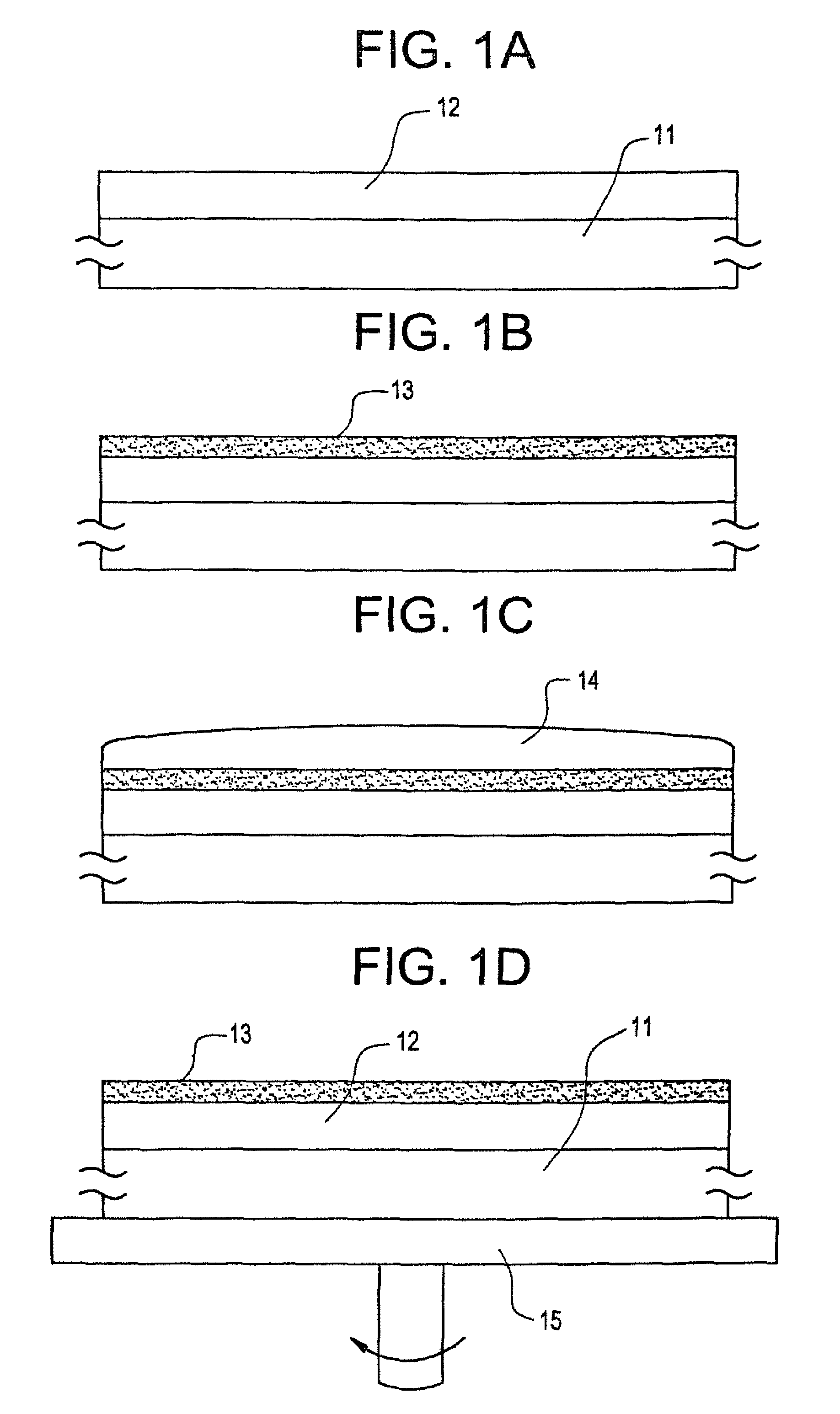

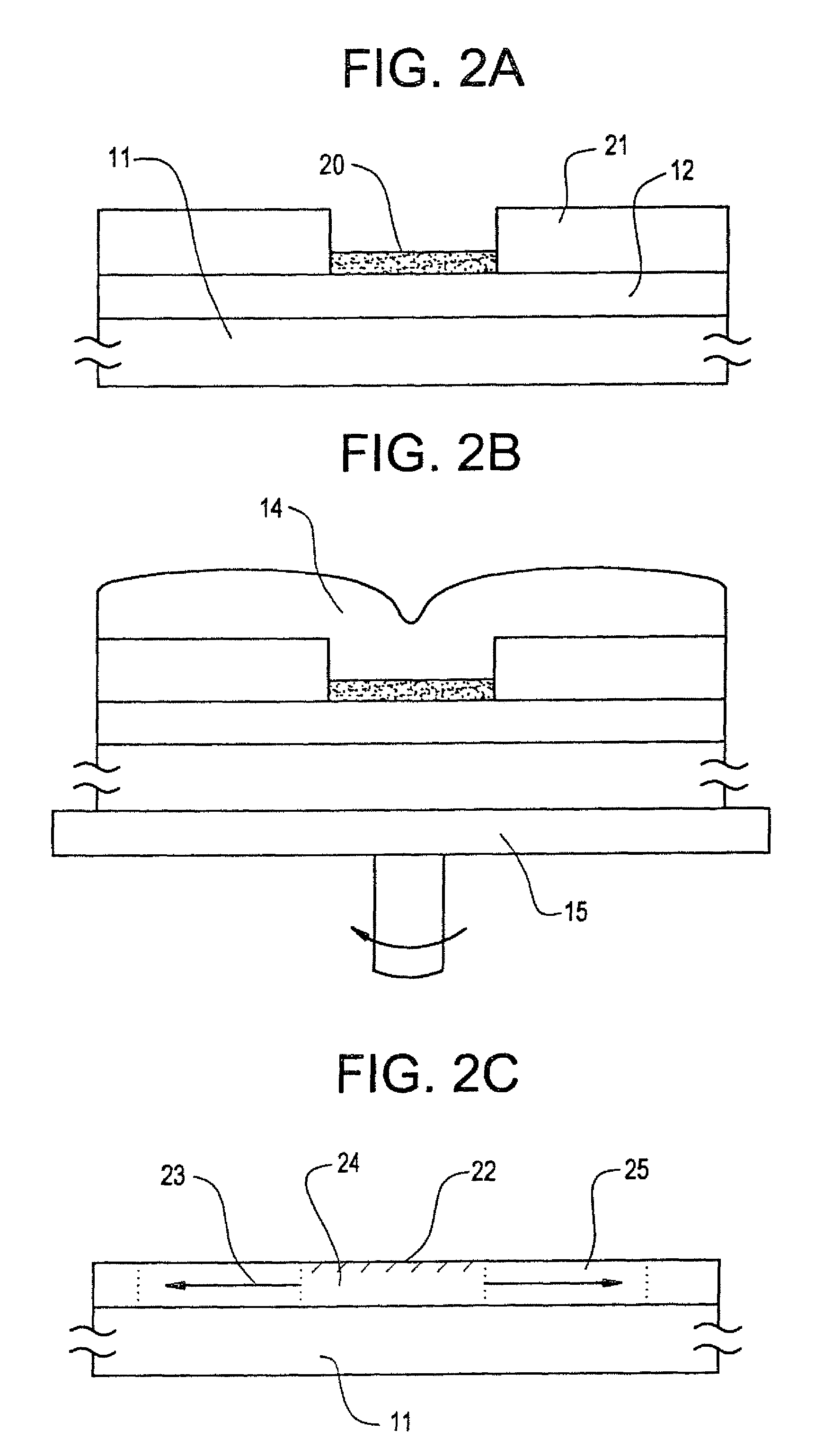

Wafer stabilization device and associated production method

InactiveUS20050236693A1Eliminate deformationFunction can be ensuredSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsAdhesive

A stabilization device and method for stabilizing a workpiece such as a thin film wafer is presented. The thin wafer is fixed and oriented in planar fashion. The stabilization device is realized by a profiled ring which is arranged on the periphery of the wafer and is intimately connected thereto. The stabilization device and wafer are connected via negative pressure or by means of an adhesive having high thermal stability. The wafer and device are formed from similar semiconductor materials and have the same outline contour. The stabilization device remains on the wafer during process steps in the course of production and processing of the wafer.

Owner:INFINEON TECH AG

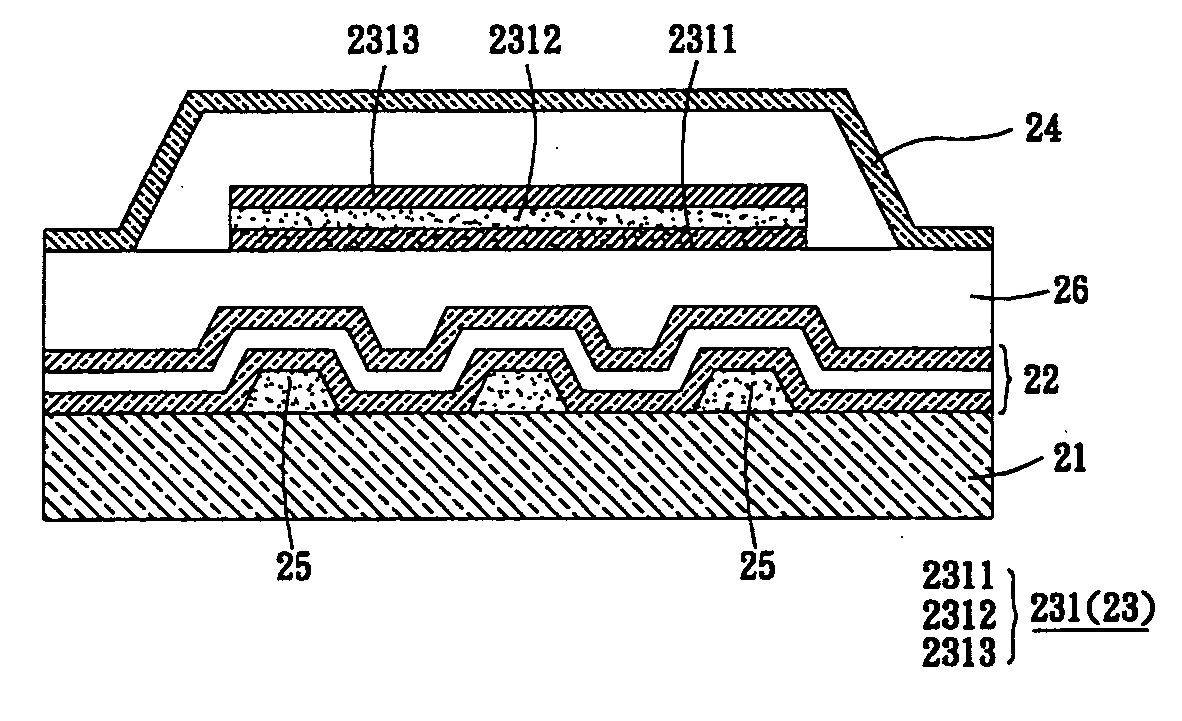

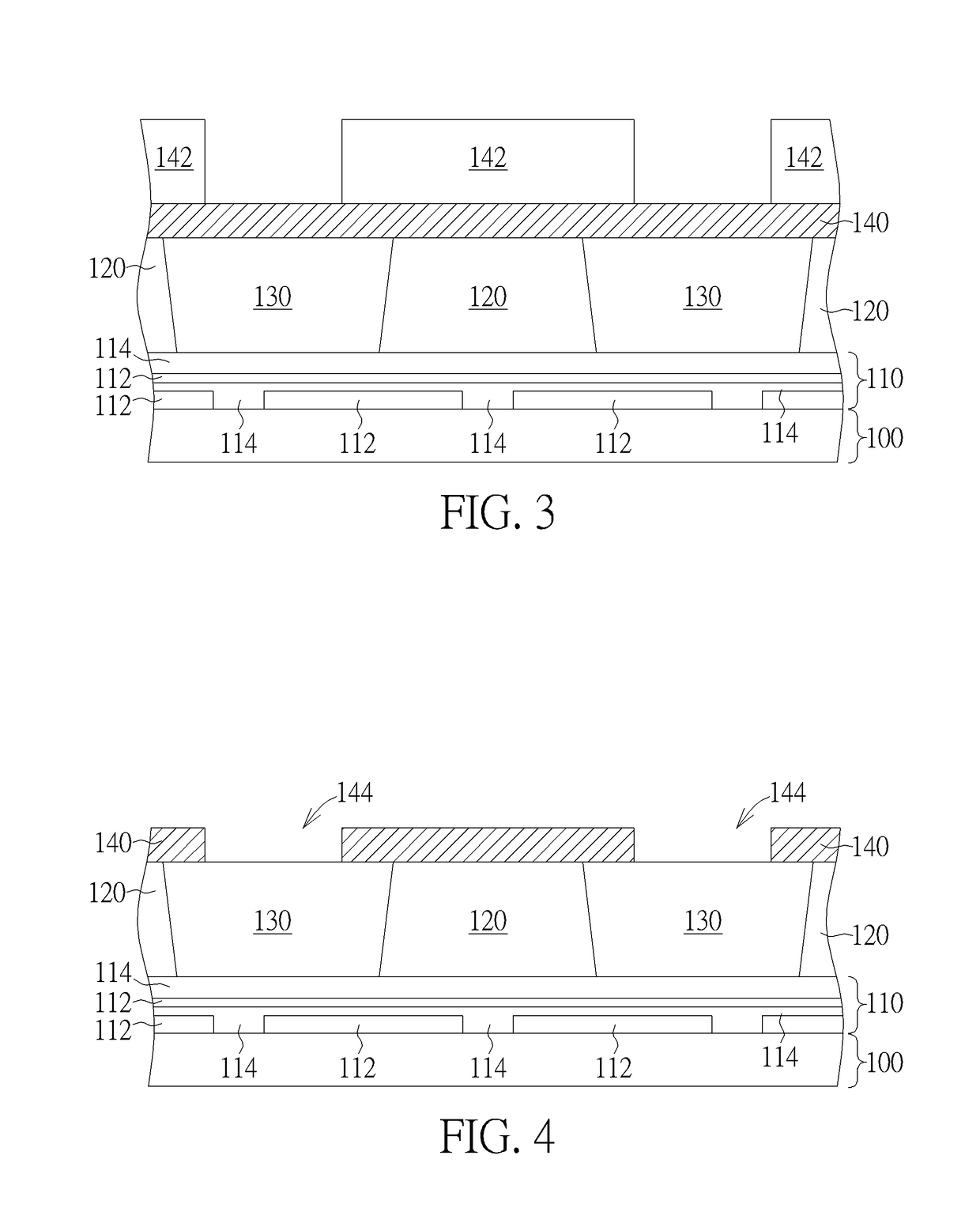

Panel of organic electroluminescent display

InactiveUS20050062052A1Decrease stressMore contact areaSolid-state devicesSemiconductor/solid-state device manufacturingOrganic electroluminescenceElectroluminescent display

An organic electroluminescent display panel comprises a substrate, at least one organic light-emitting area, at least one protecting layer, at least one isolation layer and at least one protrusion. In this case, the organic light-emitting area comprises a plurality of pixels and is disposed over the substrate. The protecting layer is disposed over the substrate and the organic light-emitting area. The isolation layer is disposed over the protecting layer.

Owner:RITDISPLAY

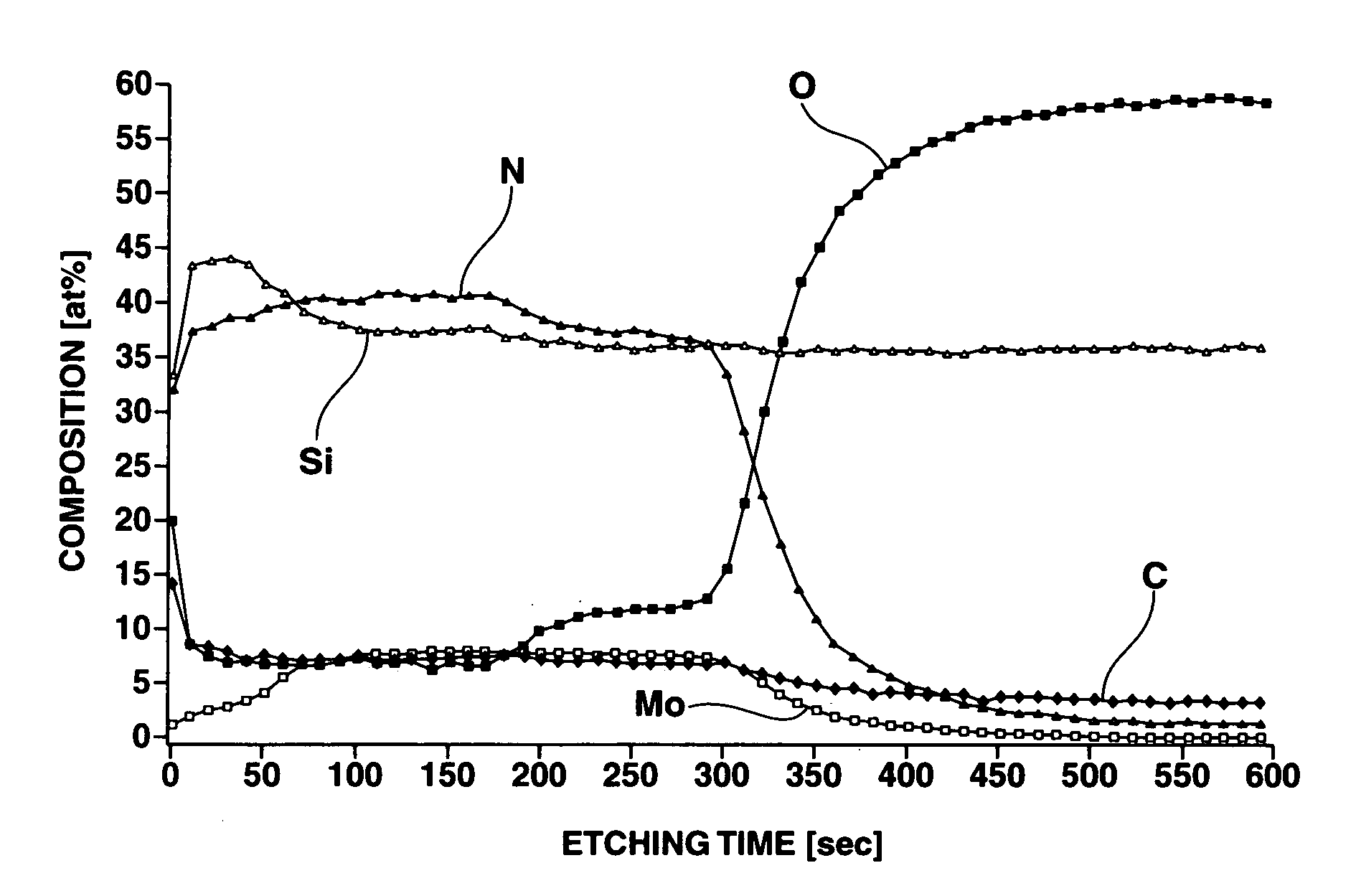

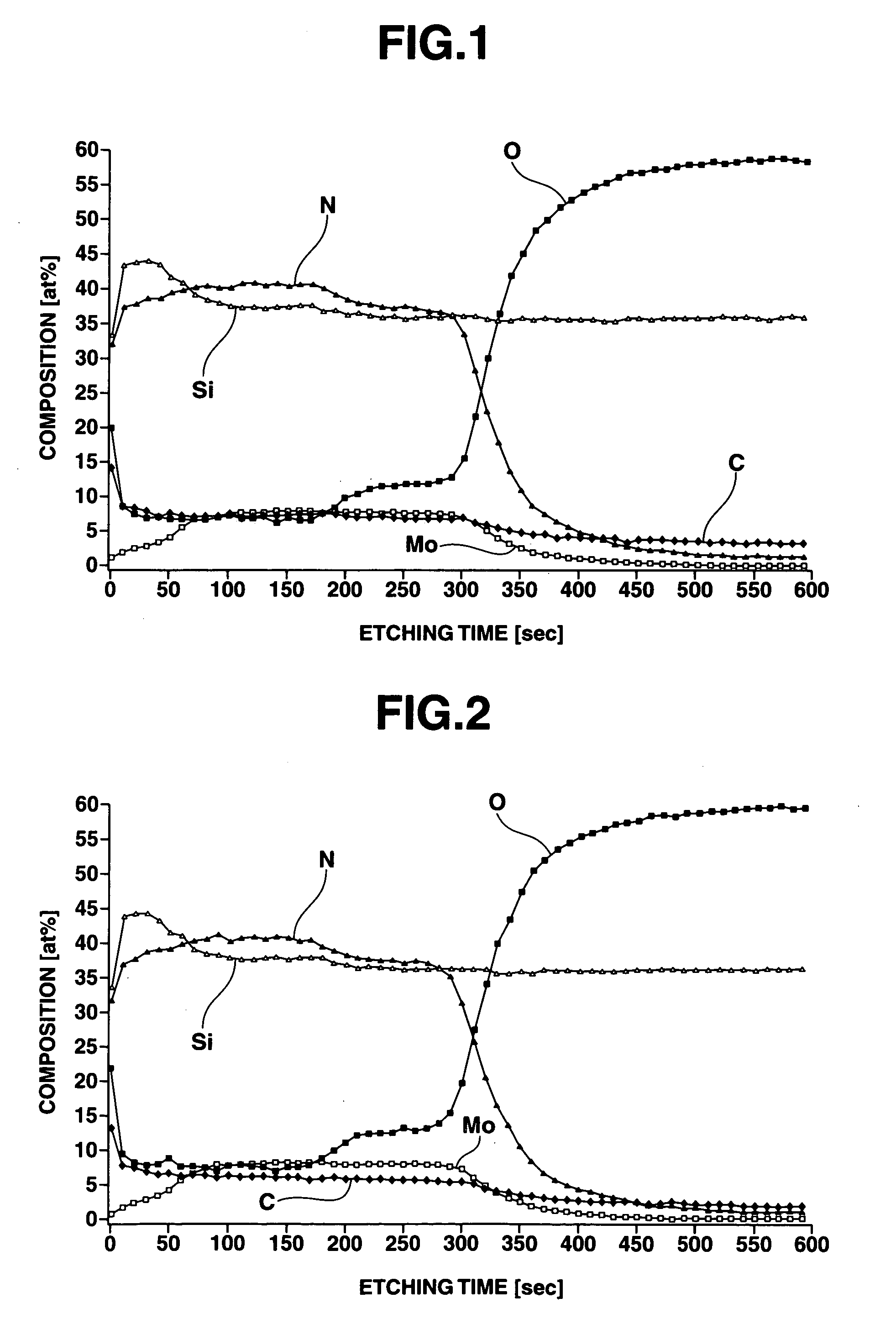

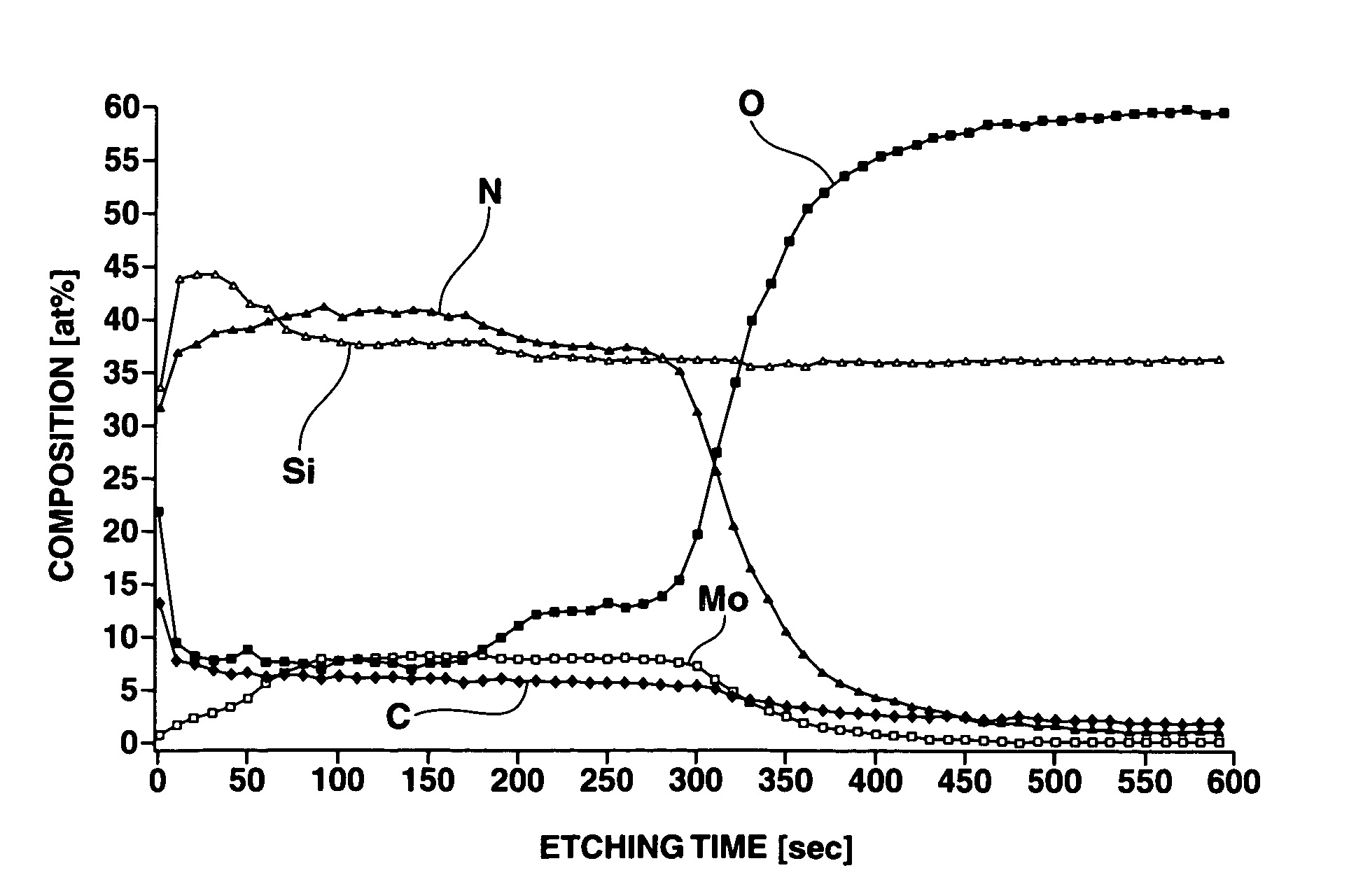

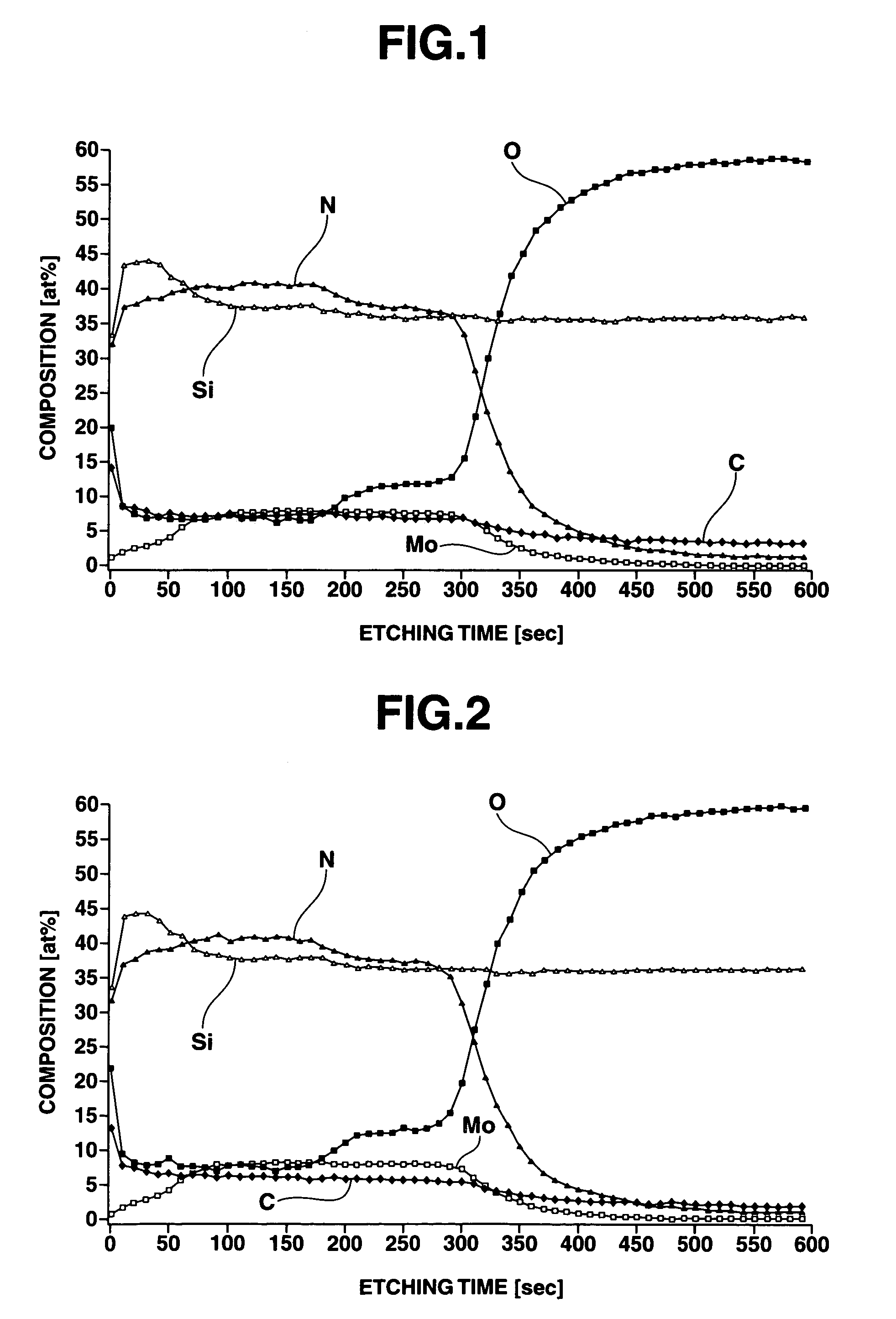

Preparation of photomask blank and photomask

ActiveUS20050260505A1Improve chemical resistanceSuppress changesCellsVacuum evaporation coatingFlash-lampResist

A photomask blank is prepared by forming a light-absorbing film on a transparent substrate, and irradiating the light-absorbing film with light from a flash lamp at an energy density of 3 to 40 J / cm2. A photomask is prepared by forming a resist pattern on the photomask blank by photolithography, etching away those portions of the light-absorbing film which are not covered with the resist pattern, and removing the resist.

Owner:SHIN ETSU CHEM IND CO LTD

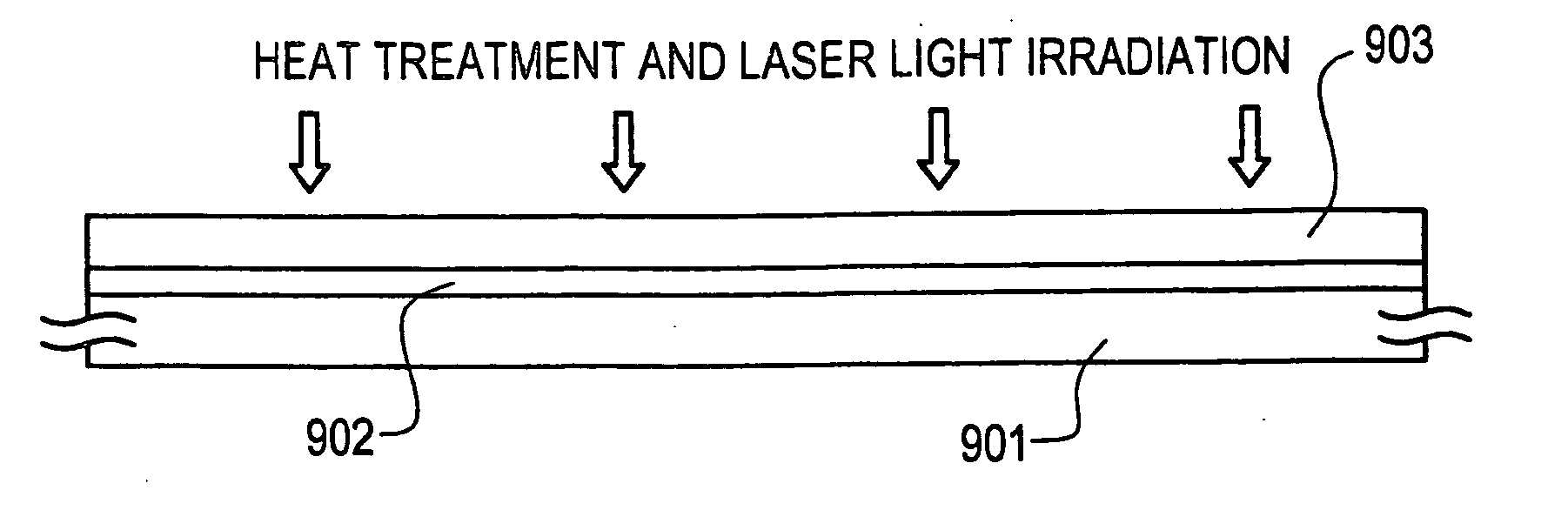

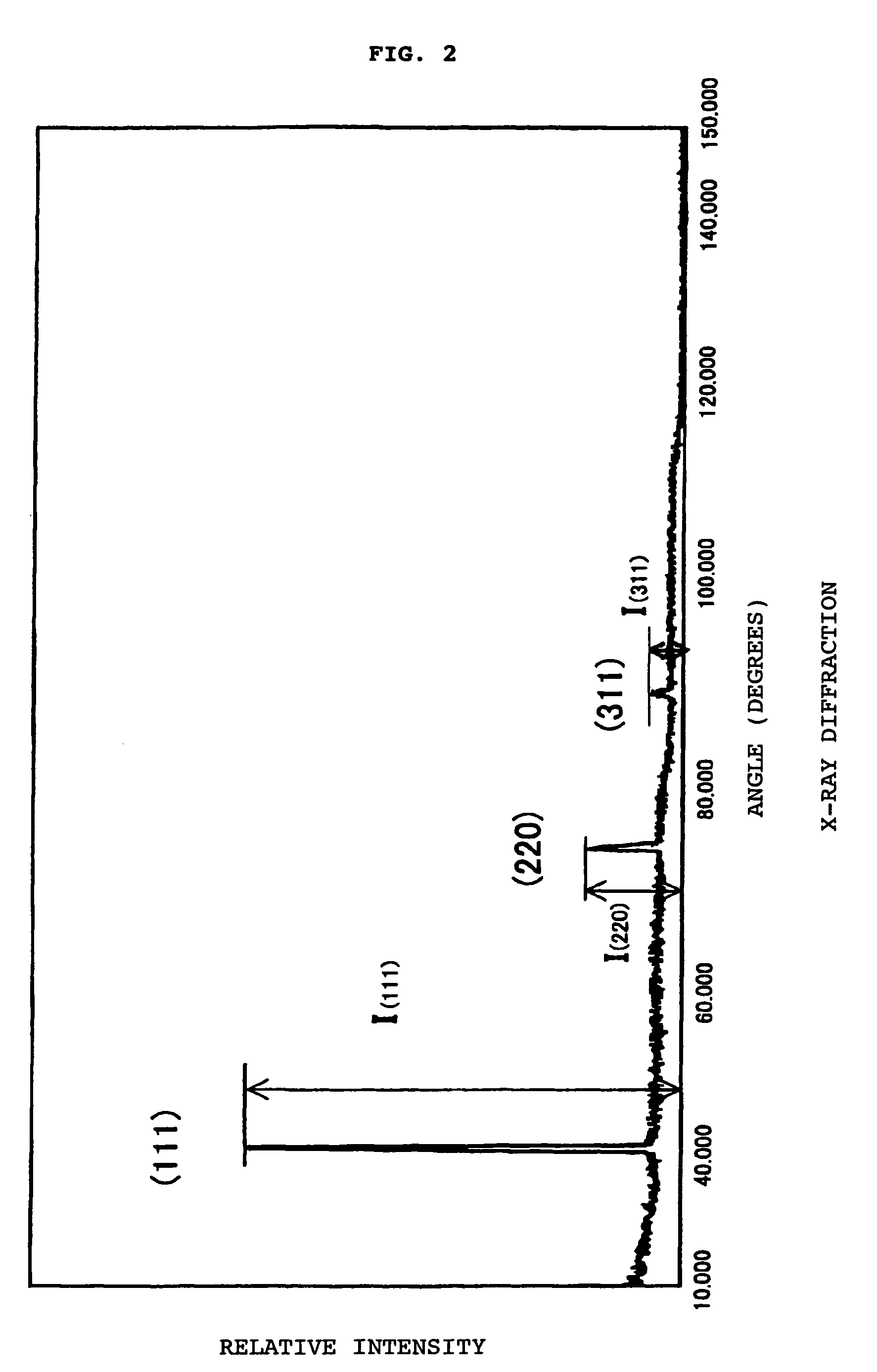

Process for fabricating semiconductor device

InactiveUS20050239240A1Efficient introductionExcellent electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialAmorphous silicon

A process for fabricating a semiconductor device comprising the steps of: introducing into an amorphous silicon film, a metallic element which accelerates the crystallization of the amorphous silicon film; applying heat treatment to the amorphous silicon film to obtain a crystalline silicon film; irradiating a laser beam or an intense light to the crystalline silicon film; and heat treating the crystalline silicon film irradiated with a laser beam or an intense light.

Owner:SEMICON ENERGY LAB CO LTD

Method for manufacturing a solid electrolyte sensor element for detecting at least one property of a measuring gas in a measuring gas chamber, containing two porous ceramic layers

InactiveUS20160061767A1Increasing thermal massImprove robustnessWave amplification devicesMaterial analysis by electric/magnetic meansMetallurgyGas chamber

A method for manufacturing a sensor element is provided for detecting at least one property of a measuring gas in a measuring gas chamber, in particular for detecting a proportion of a gas component in the measuring gas or a temperature of the measuring gas. The method includes the following steps: providing at least one solid electrolyte which includes at least one functional element; applying, at least in sections, at least one first layer made of a ceramic material to the solid electrolyte, the first layer having a first porosity after the application; and applying, at least in sections, at least one second layer made of a ceramic material, the second layer having a second porosity after the application, and the first layer differing from the second layer with respect to at least one material property. Moreover, a sensor element which is manufacturable according to this method is provided.

Owner:ROBERT BOSCH GMBH

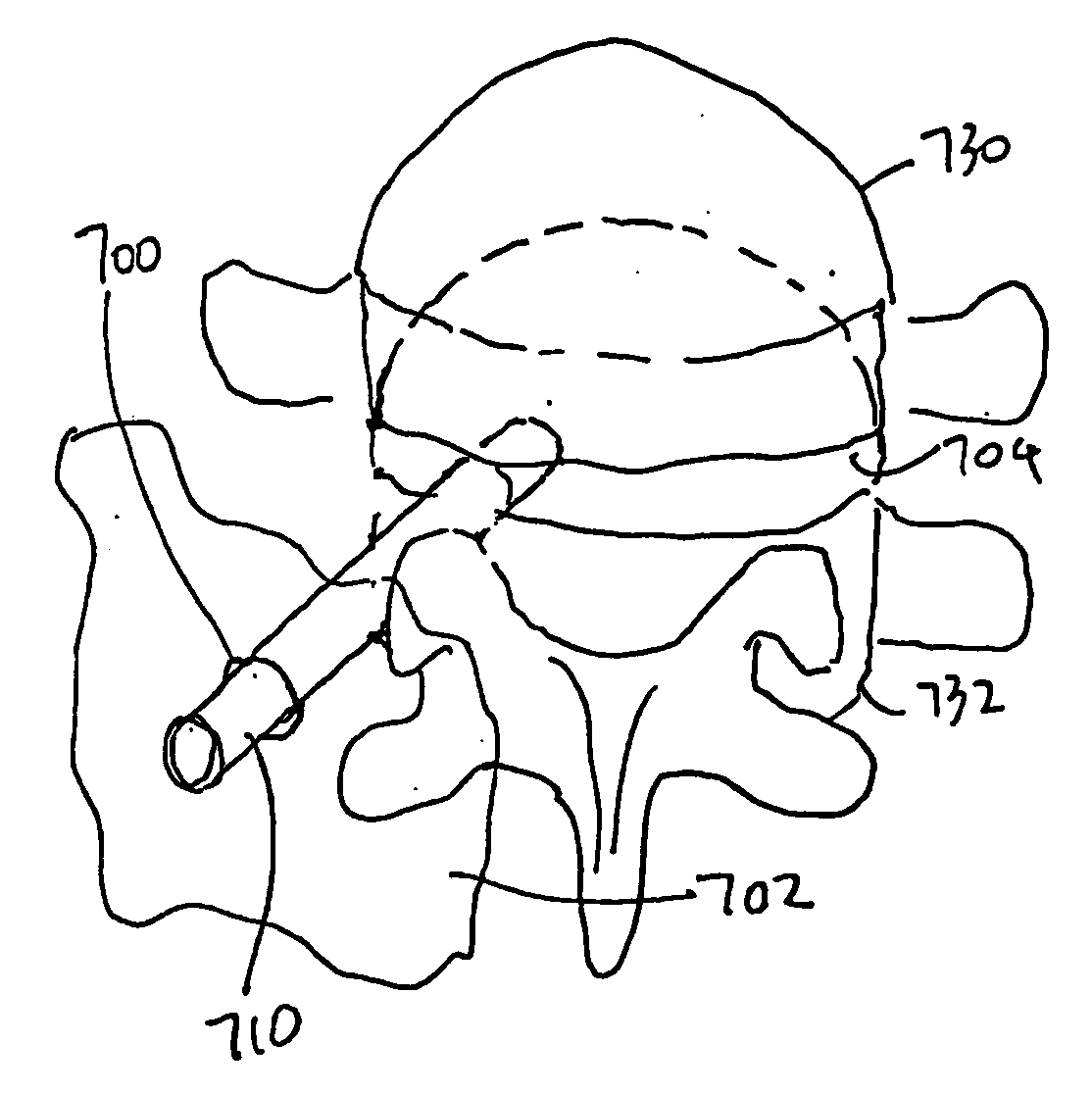

Elastomeric intervertebral disc prosthesis

An intervertebral disc prosthesis includes upper and lower rigid endplates and an elastomeric core structure located between the endplates and attached thereto, wherein the elastomeric core structure has a centroid positioned posterior to a centroid of at least one of the endplates.

Owner:K2M

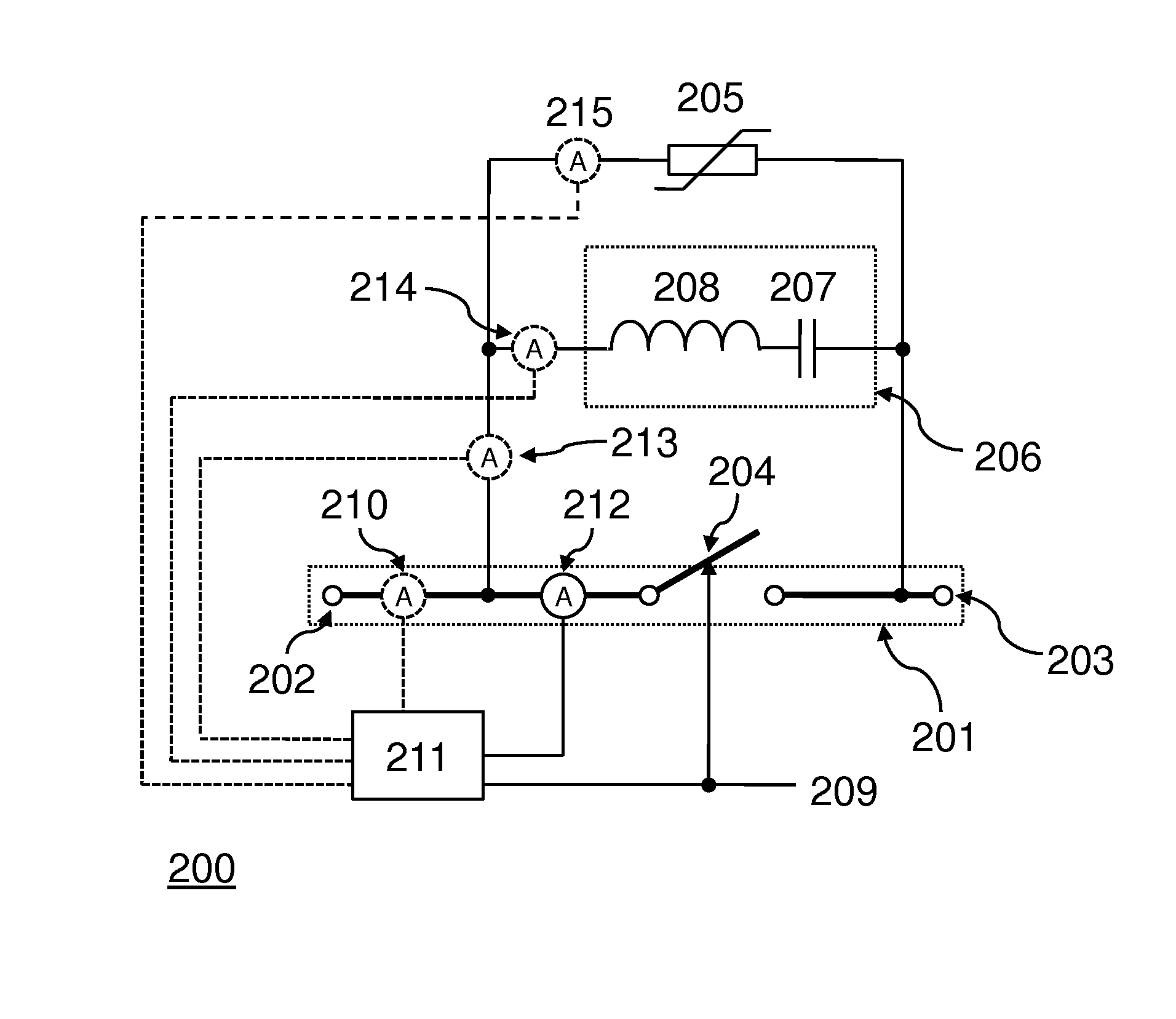

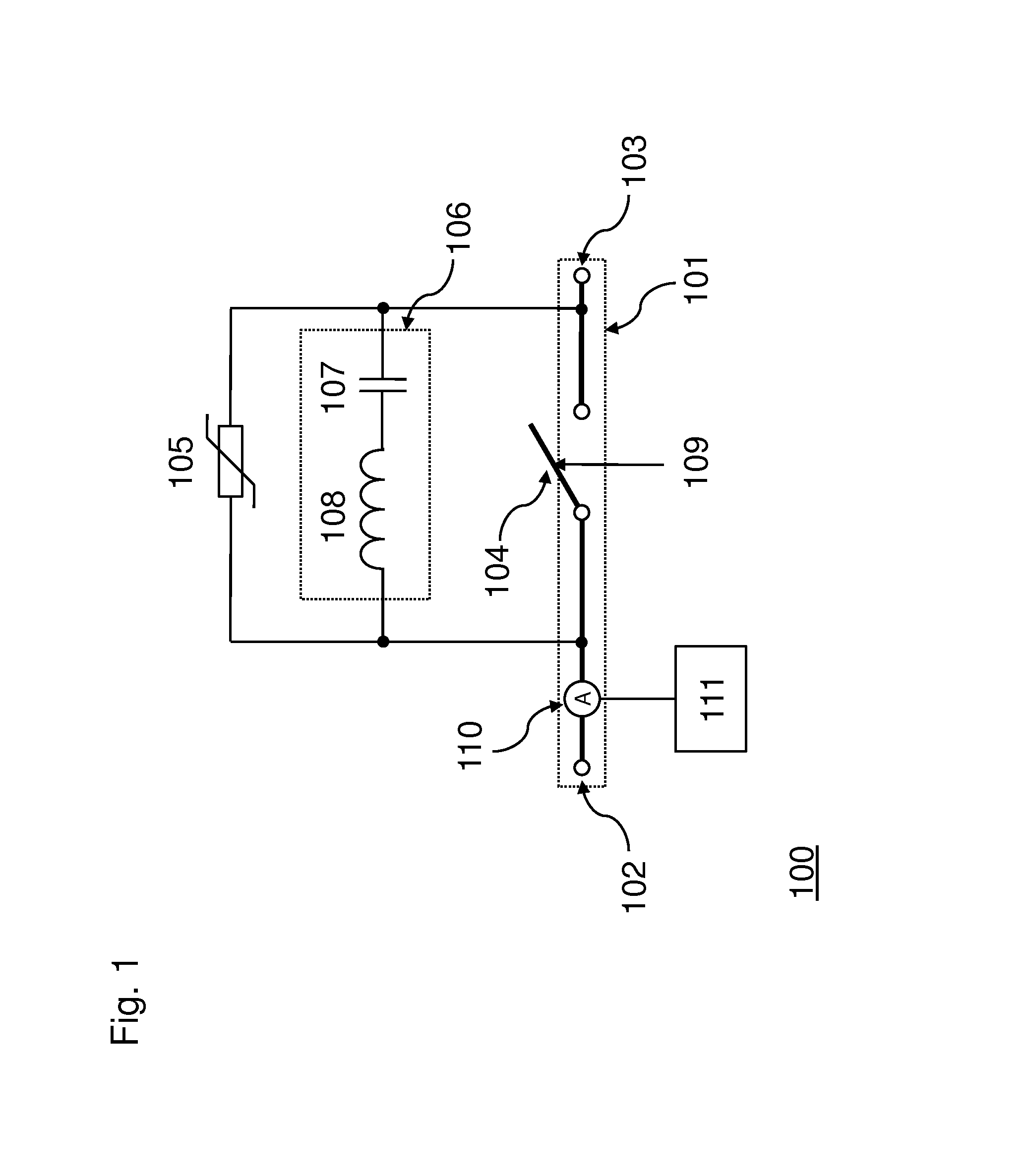

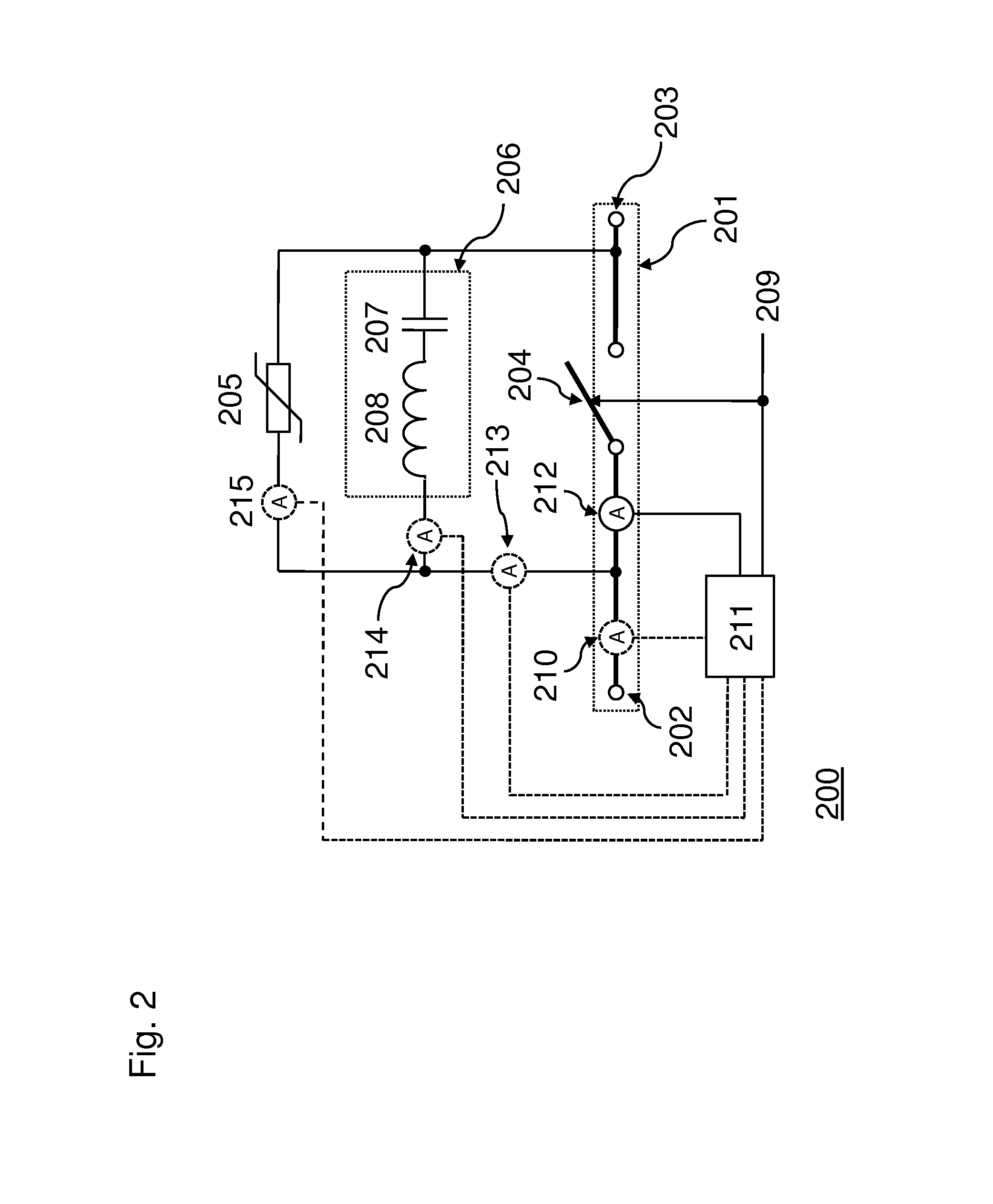

Fast breaker failure detection for HVDC circuit breakers

ActiveUS20140055903A1Reduce riskAvoid arcingProtective switch detailsCircuit-breaking switches for excess currentsNonlinear resistorPower flow

Owner:HITACHI ENERGY SWITZERLAND AG

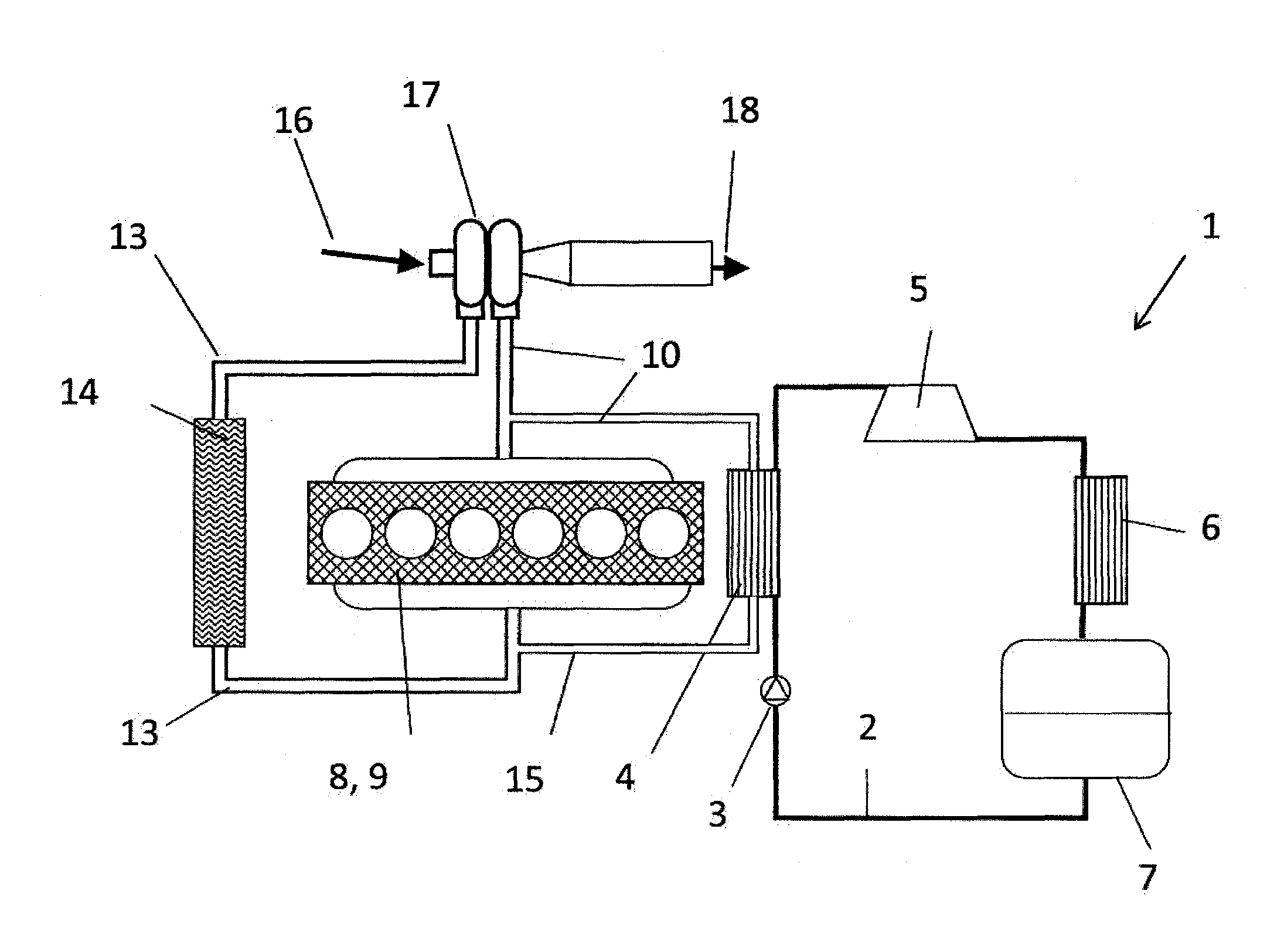

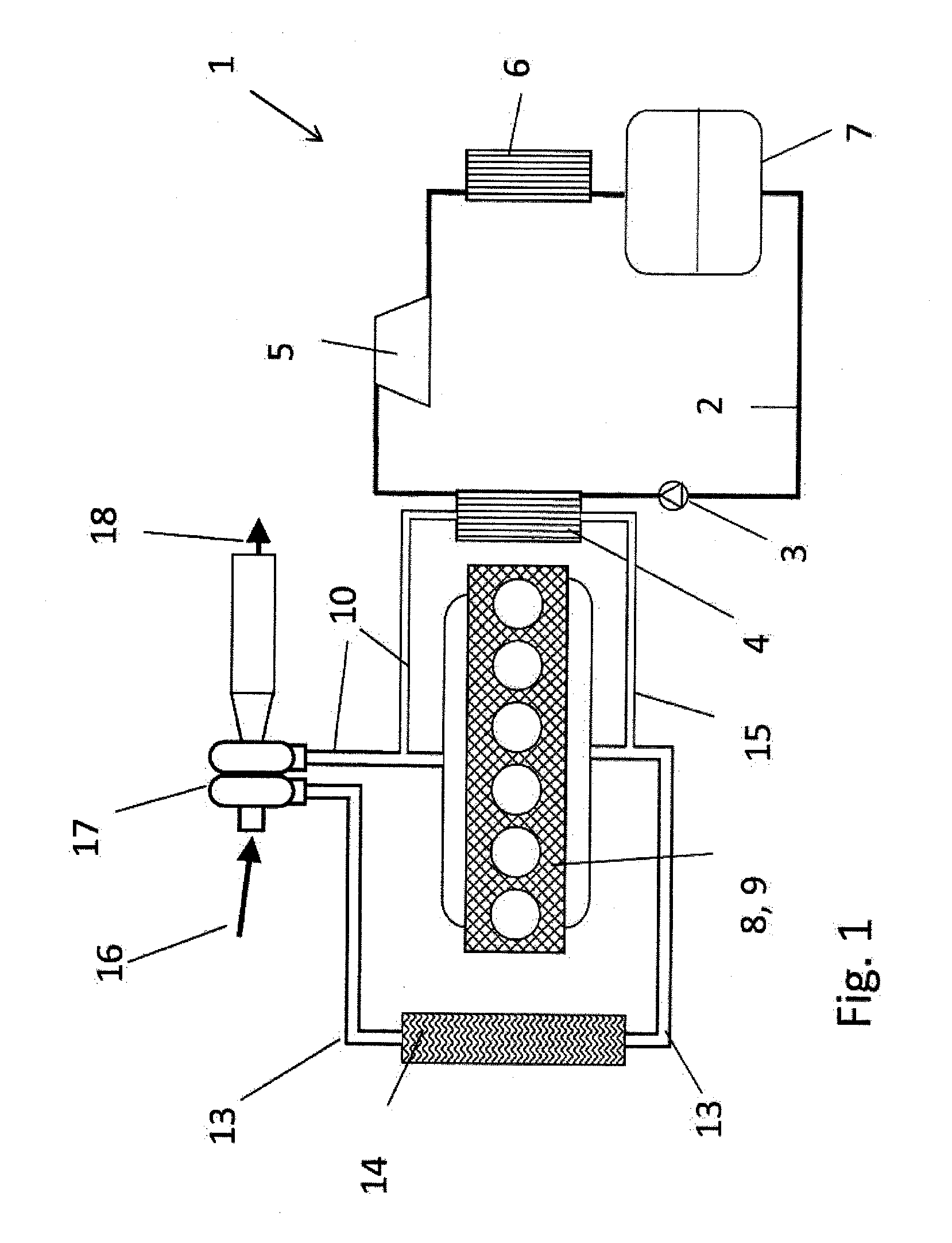

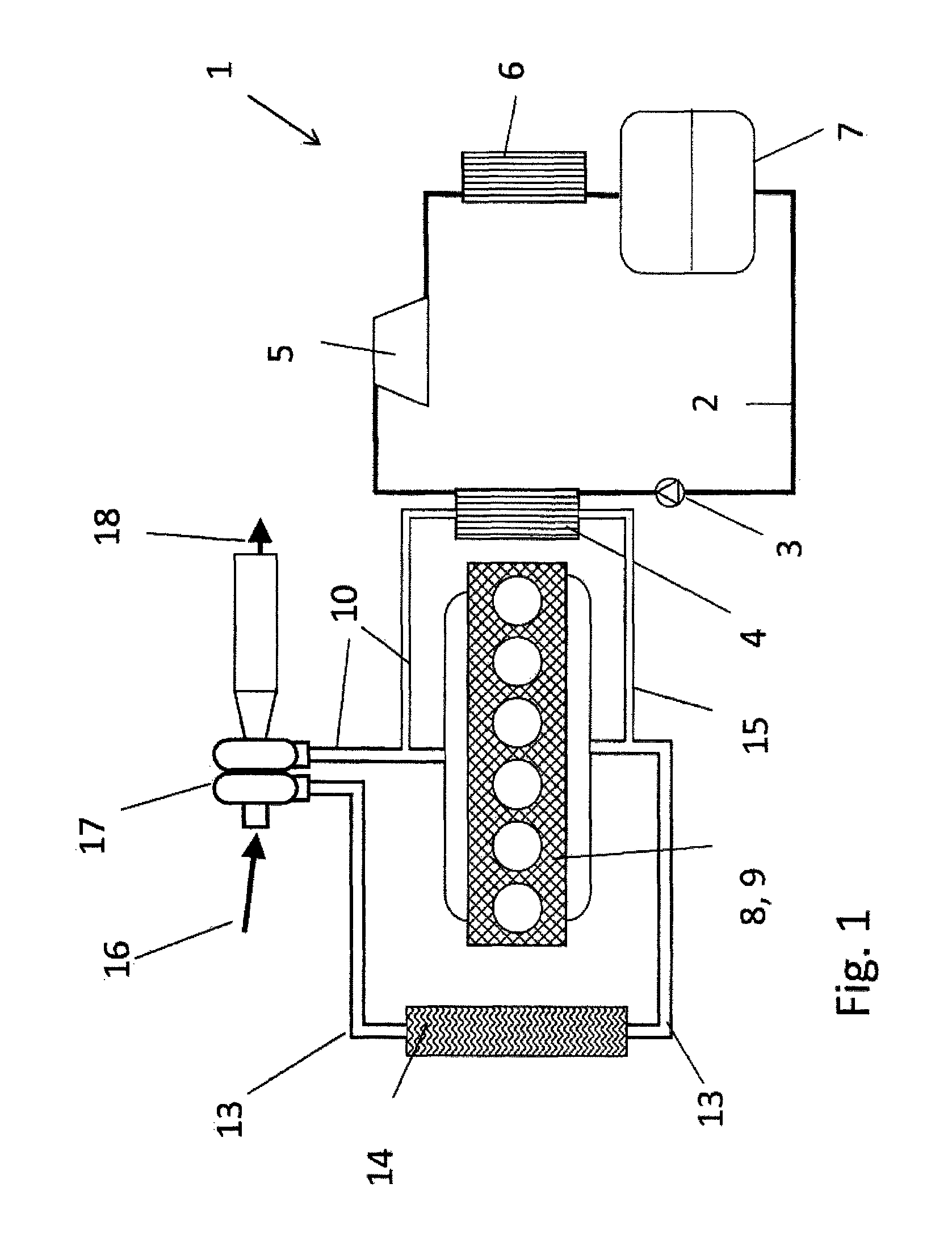

Heat exchanger

InactiveUS20130219880A1High thermalHigh thermal and mechanical loadRecuperative heat exchangersSafety devices for heat exchange apparatusEngineeringExpansion joint

Owner:BEHR GMBH & CO KG

Diamond-coated electrode and method for producing same

InactiveUS7314540B2Lower resistanceImprove adhesionPhysical/chemical process catalystsUltra-high pressure processesElectrical resistance and conductanceDiamond electrodes

A diamond electrode having a sufficiently low resistance is disclosed which is realized by increasing the amount of boron added thereto. A method for producing a high-performance, high-durability electrode is also disclosed by which adhesiveness between a diamond coating and a substrate and separation resistance during electrolysis are sufficiently increased. An electrode composed of a substrate and a diamond layer coating the substrate is characterized in that the electrode is composed of a base coated with diamond and the diamond contains boron in such an amount that the boron concentration is not less than 10,000 ppm but not more than 100,000 ppm. The base is preferably made of an insulating material.

Owner:SUMITOMO ELECTRIC IND LTD

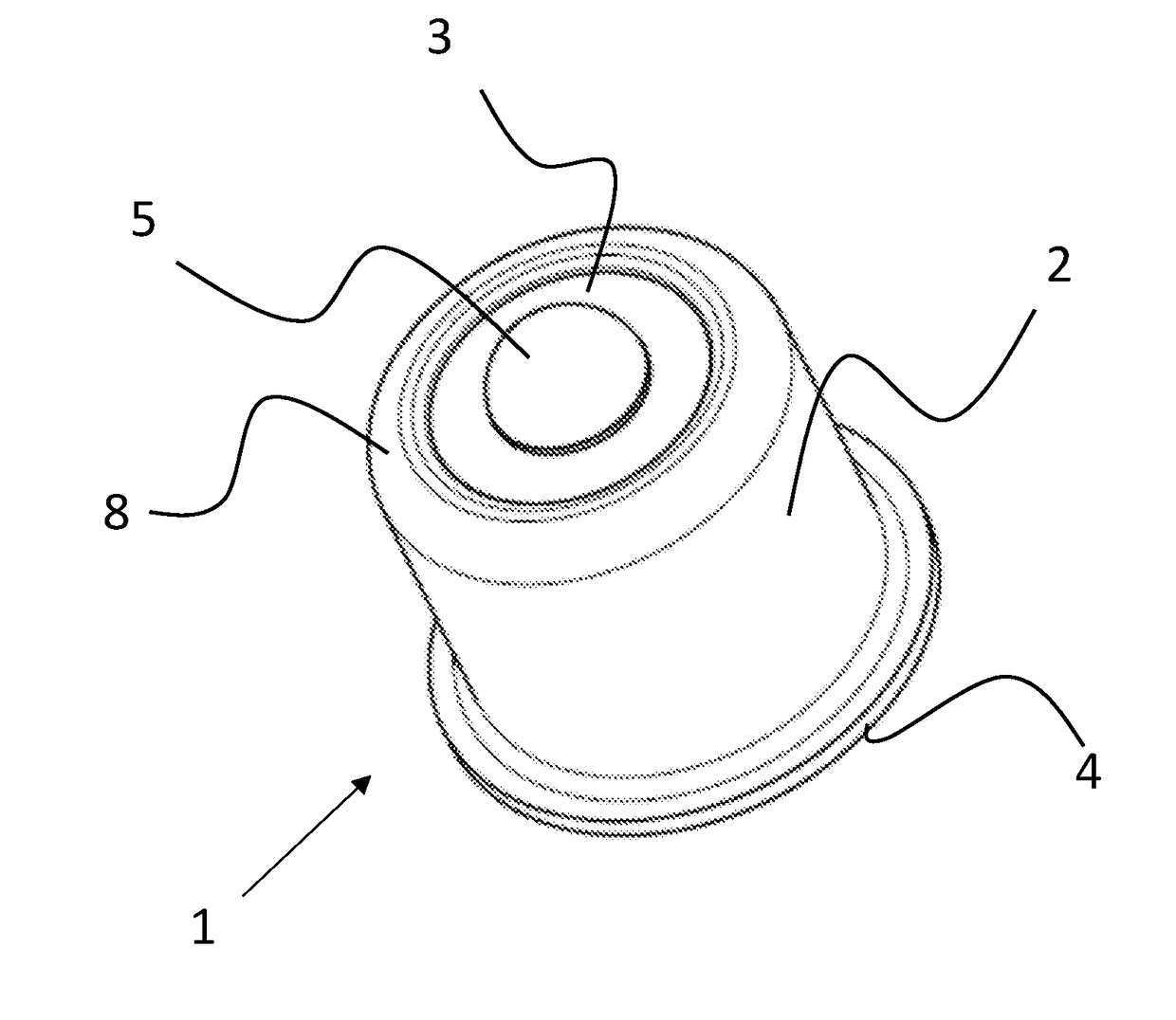

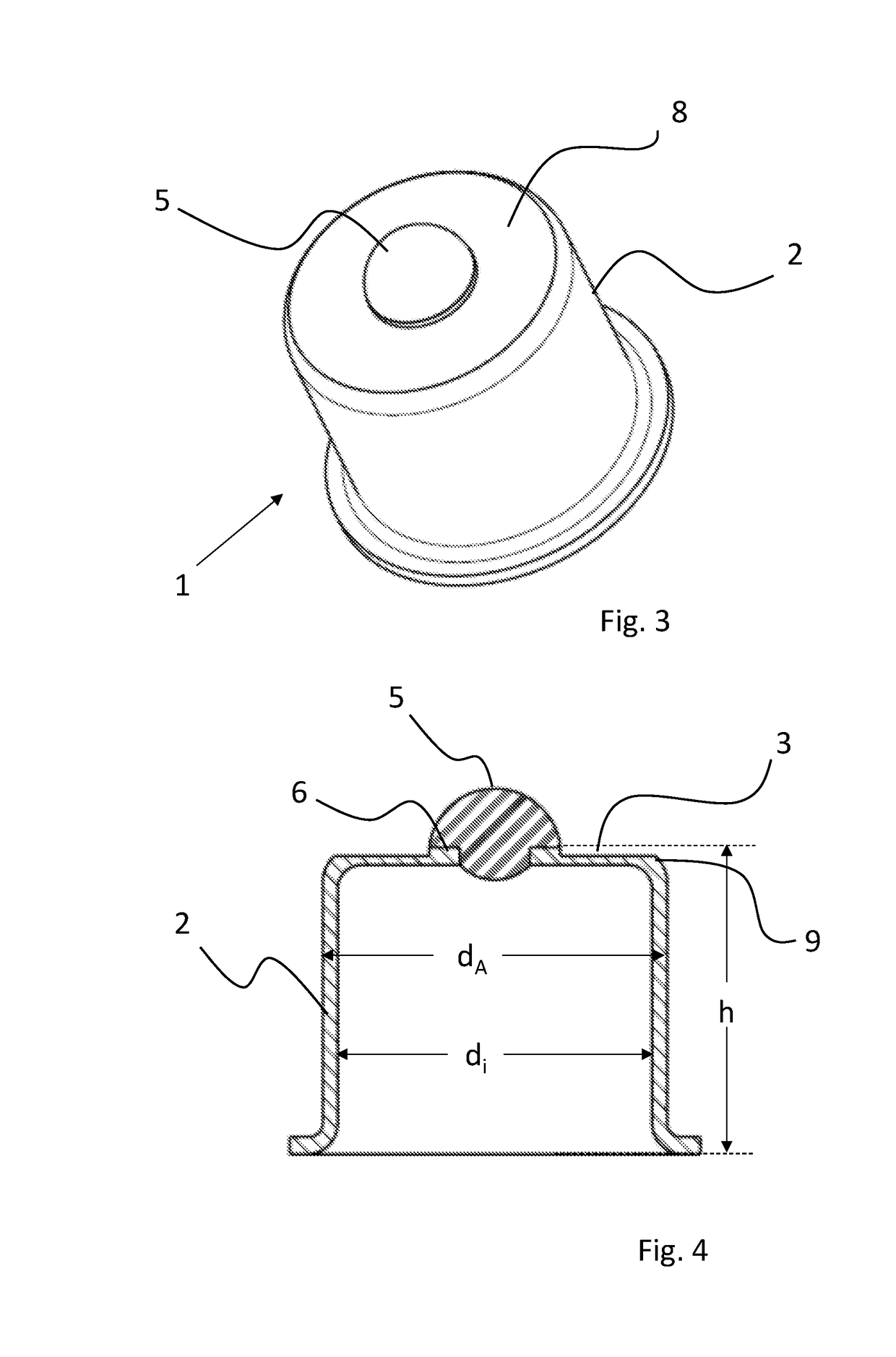

Lens cap for a transistor outline package

ActiveUS20170294390A1Reduce mechanical stressStressSemiconductor/solid-state device detailsSolid-state devicesEngineeringTransistor

A lens cap for a transistor outline (TO) package is provided that has an inner diameter of less than 4 mm. The lens cap includes a metal shell with a wall thickness of less than 0.2 mm and a thinned area surrounding the lens so that in the thinned area the wall thickness is reduced by at least 35%.

Owner:SCHOTT AG

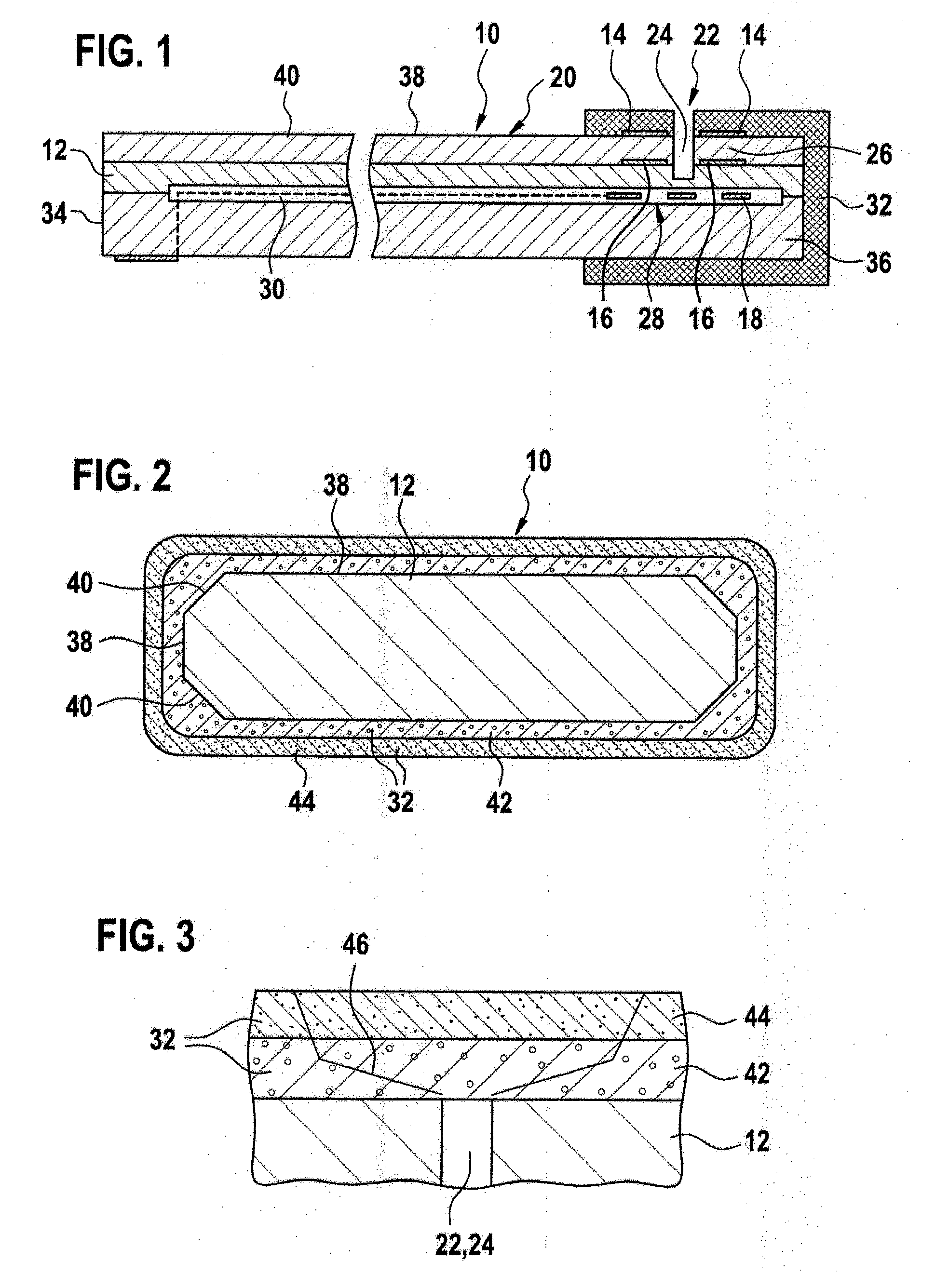

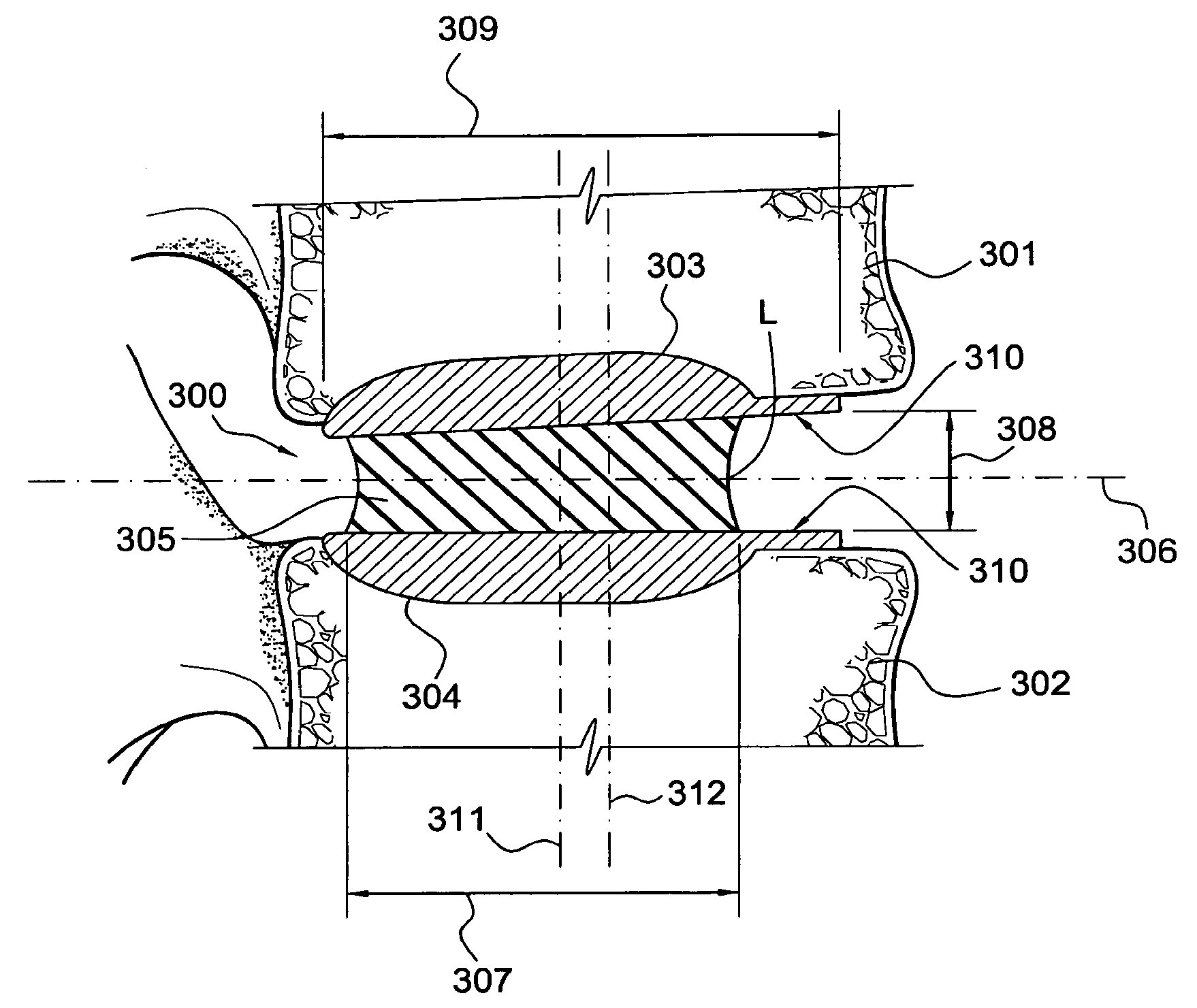

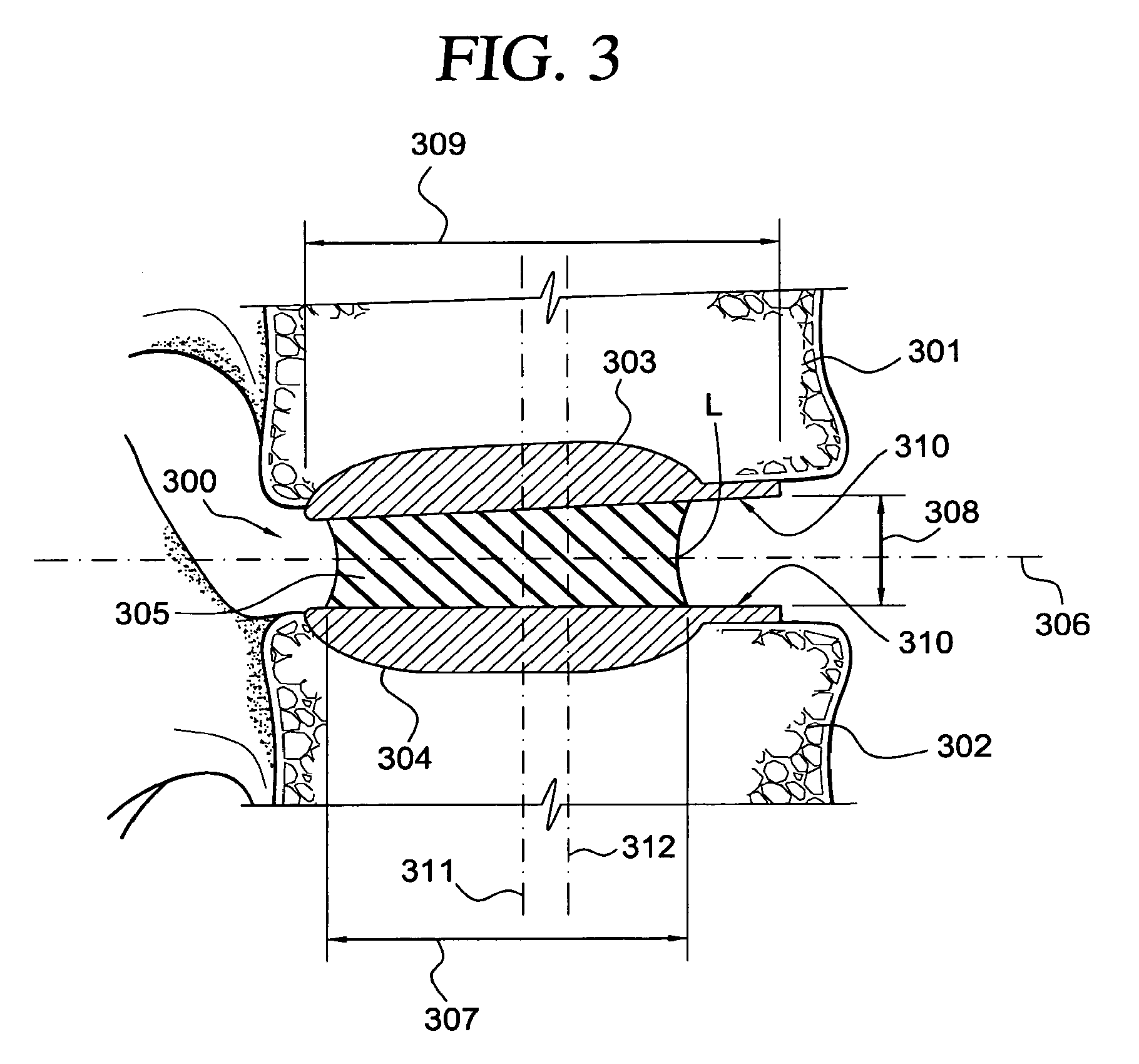

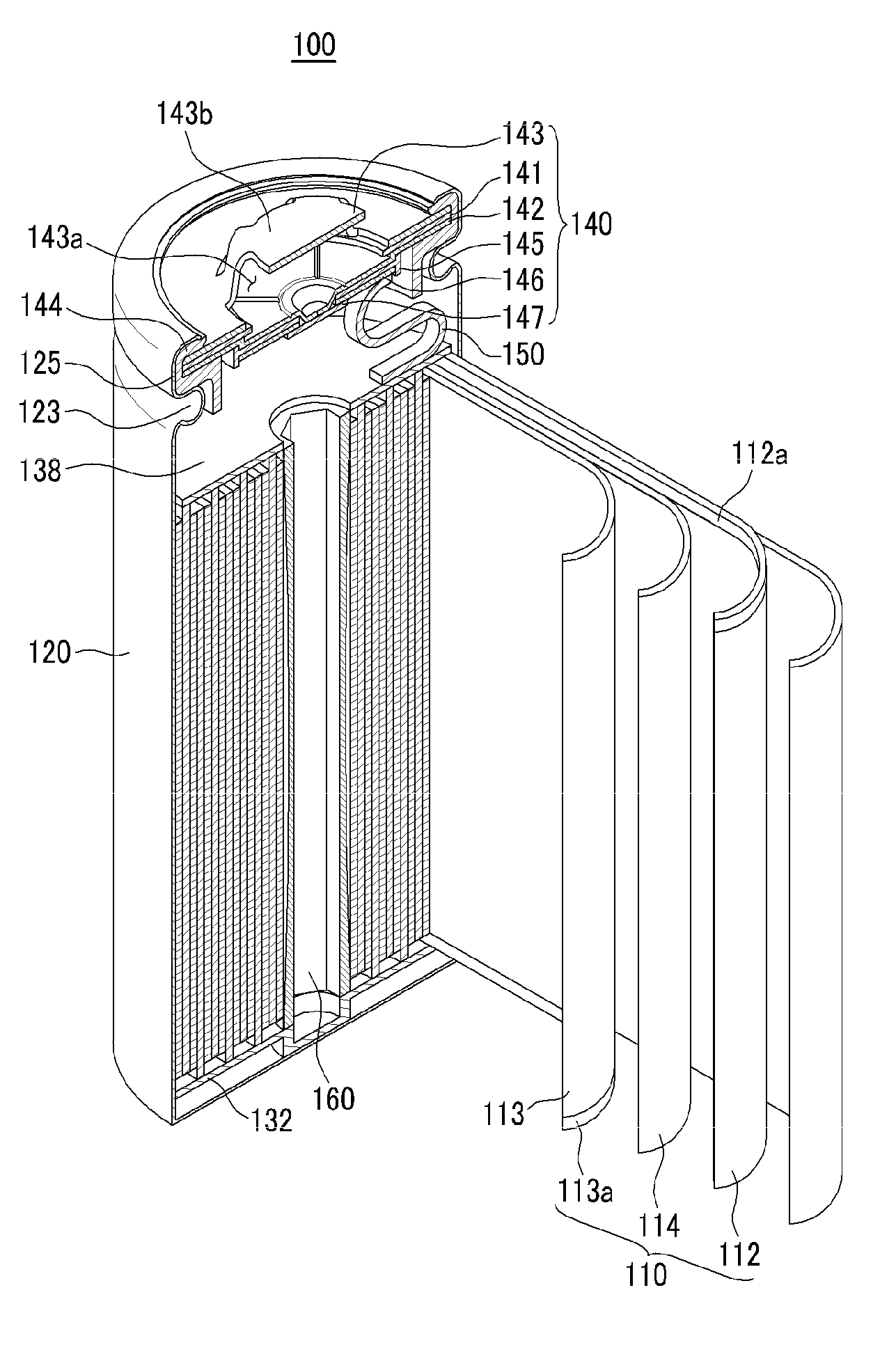

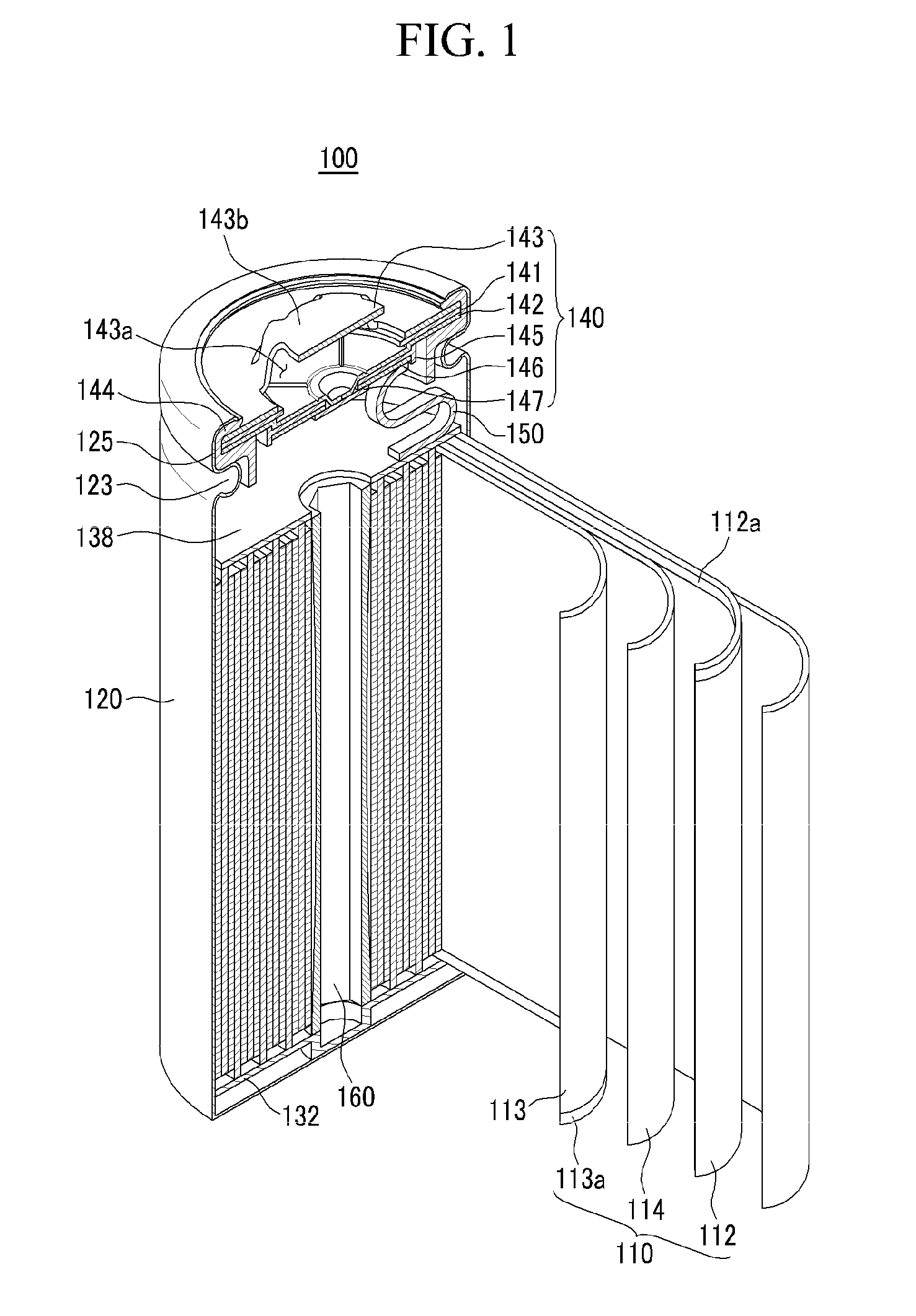

Rechargeable battery

InactiveUS20090280403A1Simple structureMinimize stressCell seperators/membranes/diaphragms/spacersFinal product manufactureRechargeable cellBiomedical engineering

A rechargeable battery including an electrode assembly, a case, a cap assembly, and a core. The electrode assembly includes an anode, a cathode, and a separator interposed between the anode and the cathode. The case has a space for housing the electrode assembly. The cap assembly is connected to the case and electrically connected to the electrode assembly. The core is disposed inside the electrode assembly, and has a distance between the exterior and the center thereof at one end in a length direction that is greater than a distance between the exterior and the center thereof at the center in the length direction.

Owner:SAMSUNG SDI CO LTD

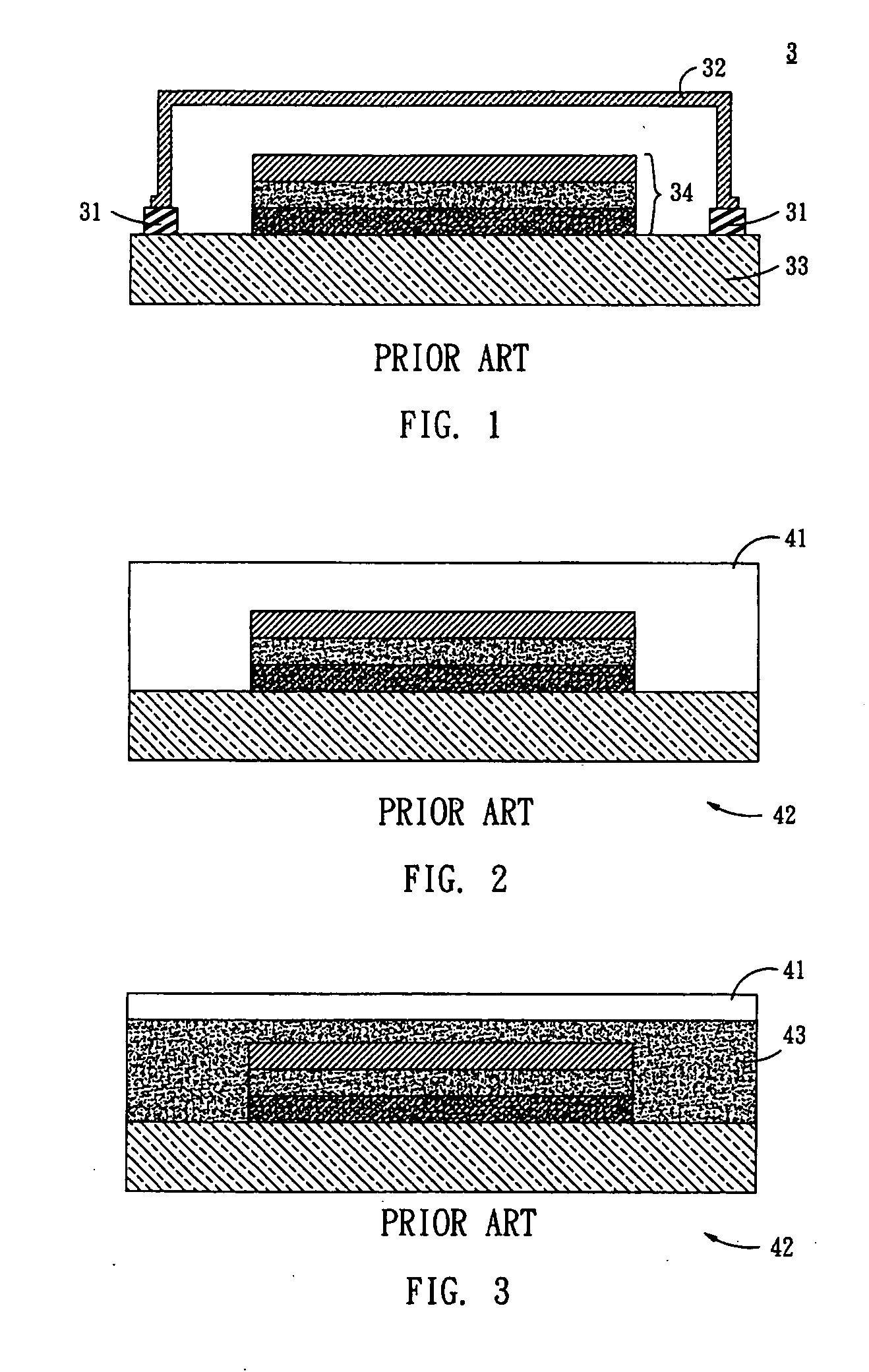

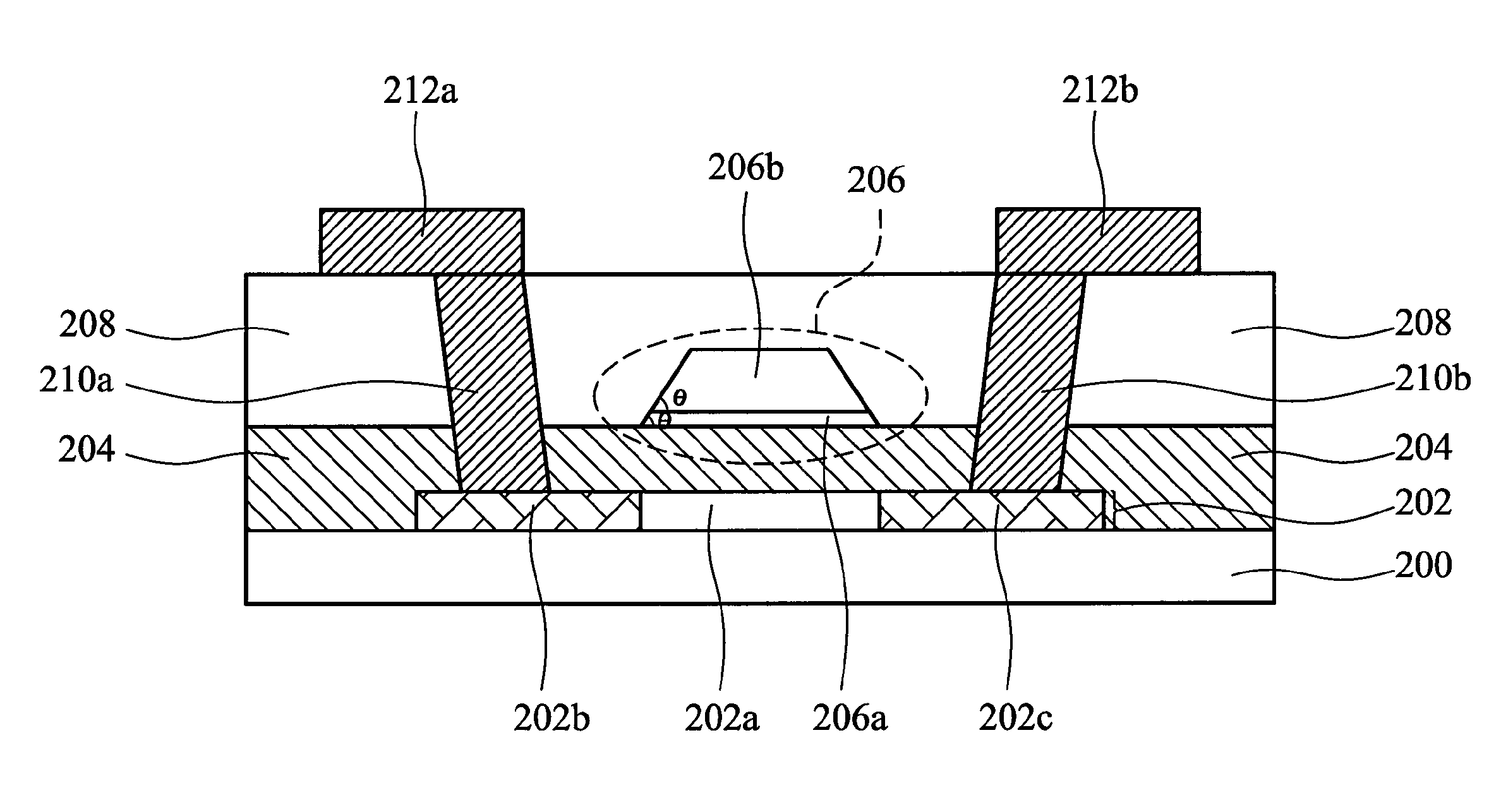

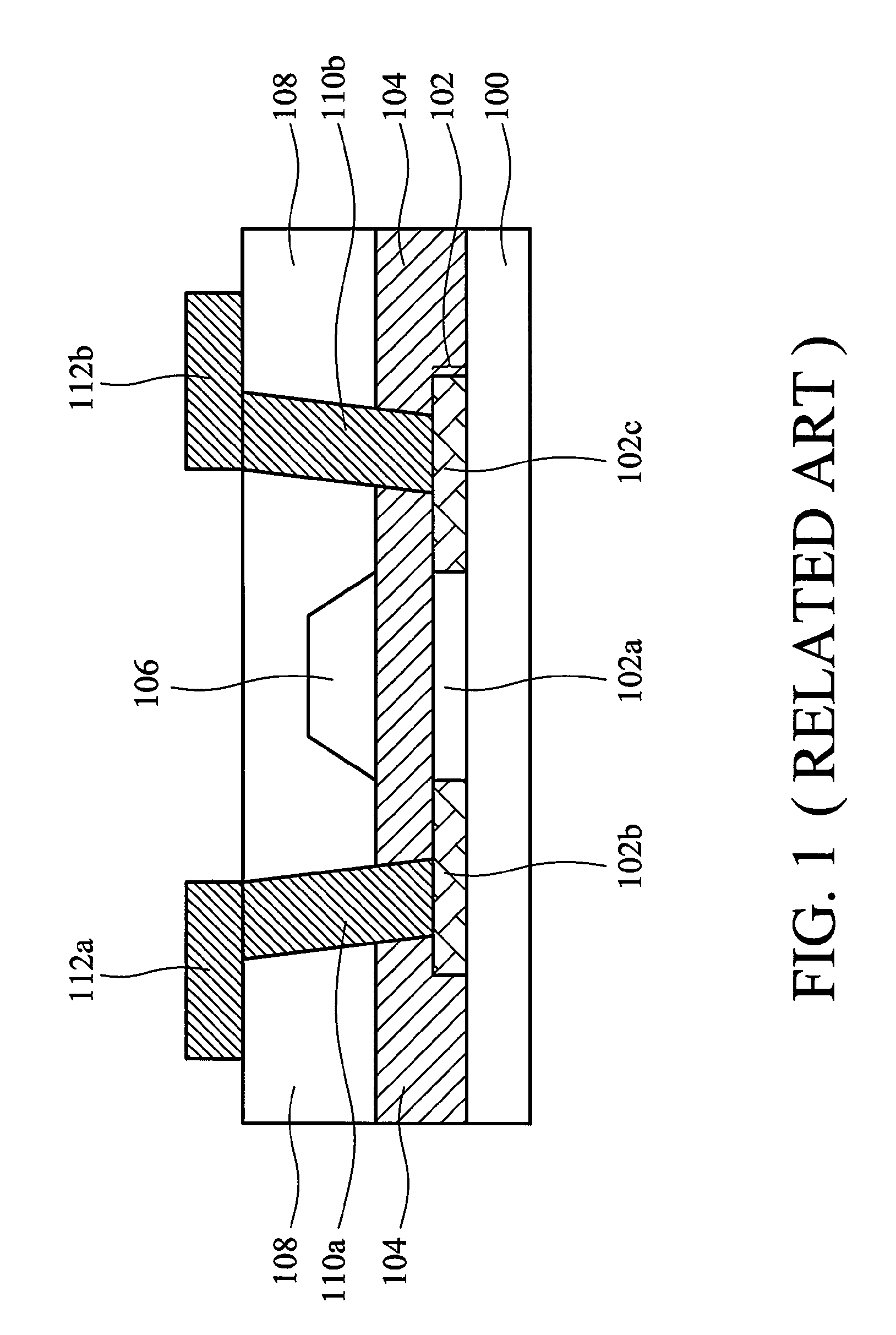

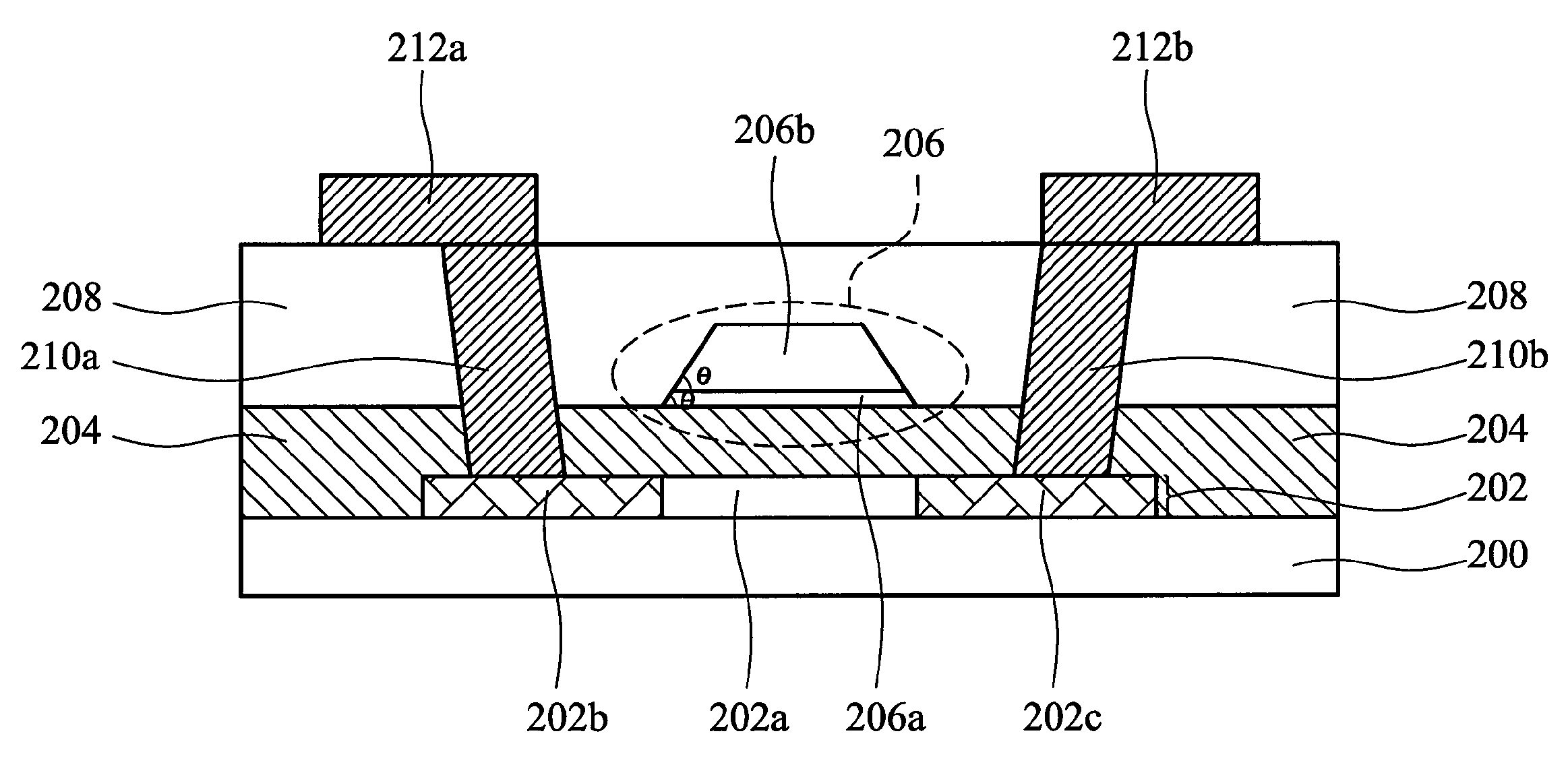

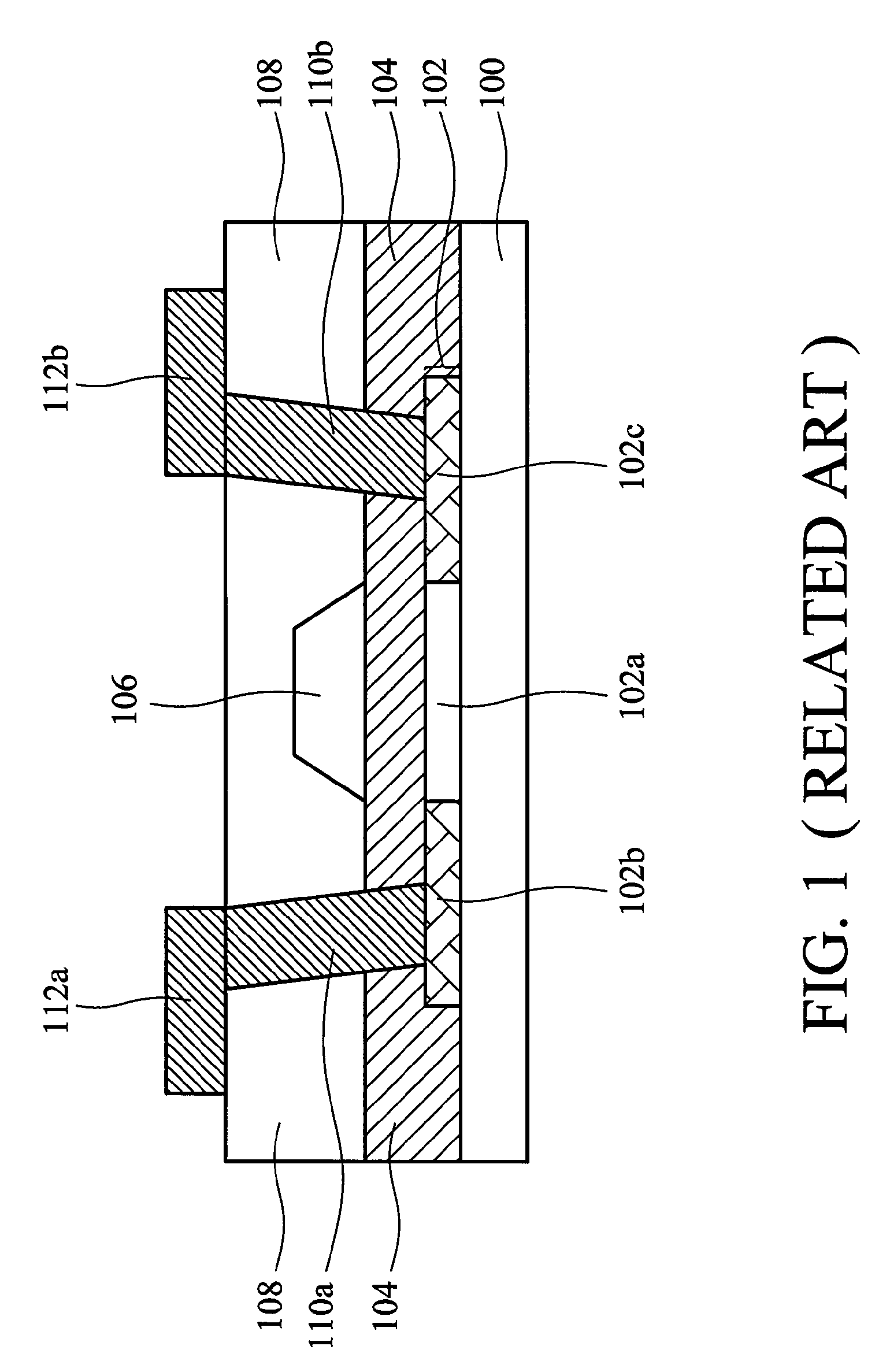

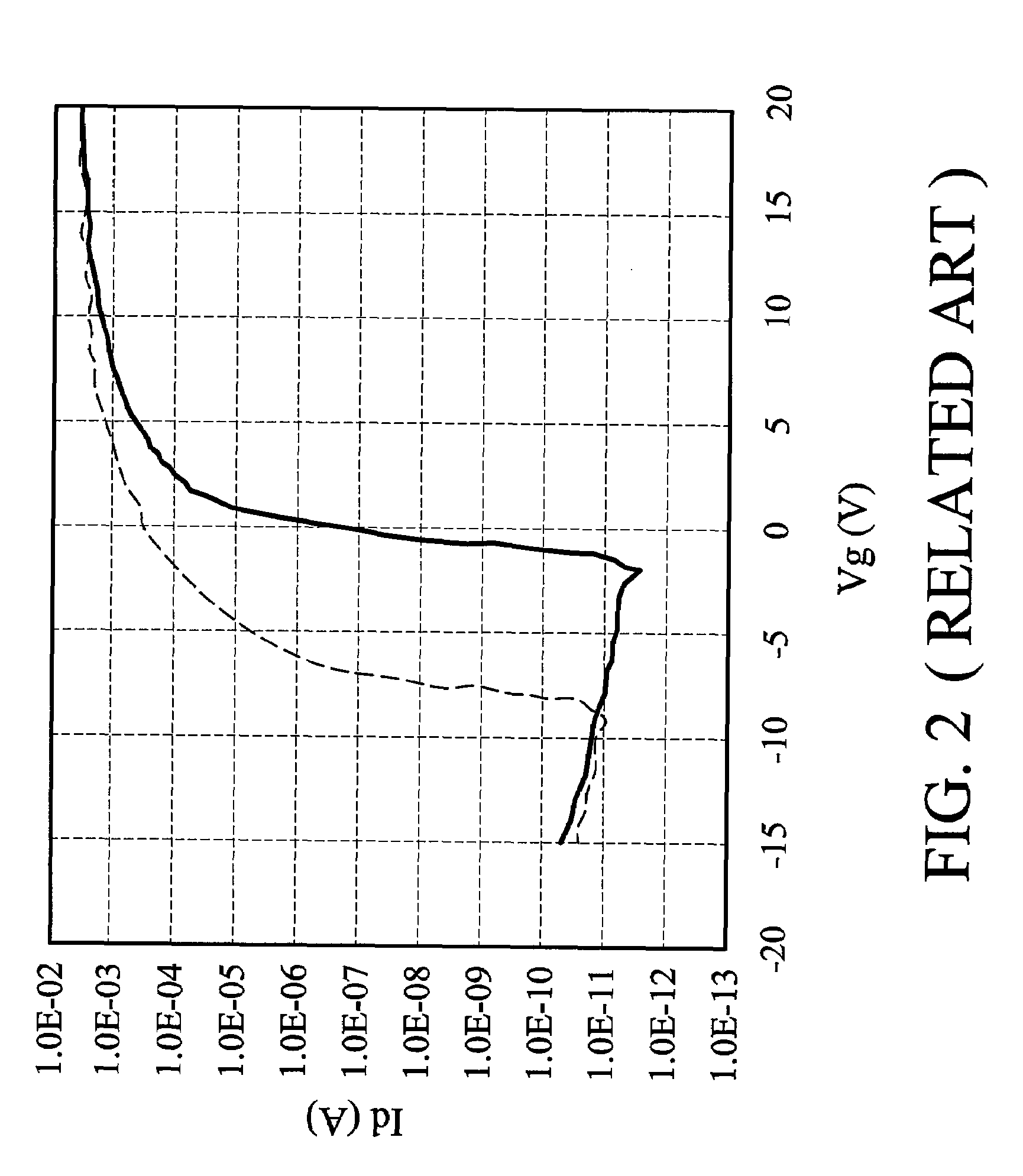

Thin film transistor

ActiveUS20070267635A1Relieve pressureImprove stabilitySolid-state devicesSemiconductor devicesTransistorAND gate

A thin film transistor is disclosed, comprising a substrate, a polysilicon layer overlying the substrate, a gate insulating layer overlying the polysilicon layer, a gate electrode, a dielectric interlayer overlying the gate electrode and gate insulating layer, and a source / drain electrode overlying the dielectric interlayer. Specifically, the gate electrode comprises a first electrode layer overlying the gate insulating layer and a second electrode layer essentially overlying an upper surface of the first electrode layer. The first and second electrode layers each has substantially the same profile with a taper angle of less than about 90 degrees.

Owner:AU OPTRONICS CORP

Preparation of photomask blank and photomask

Owner:SHIN ETSU CHEM IND CO LTD

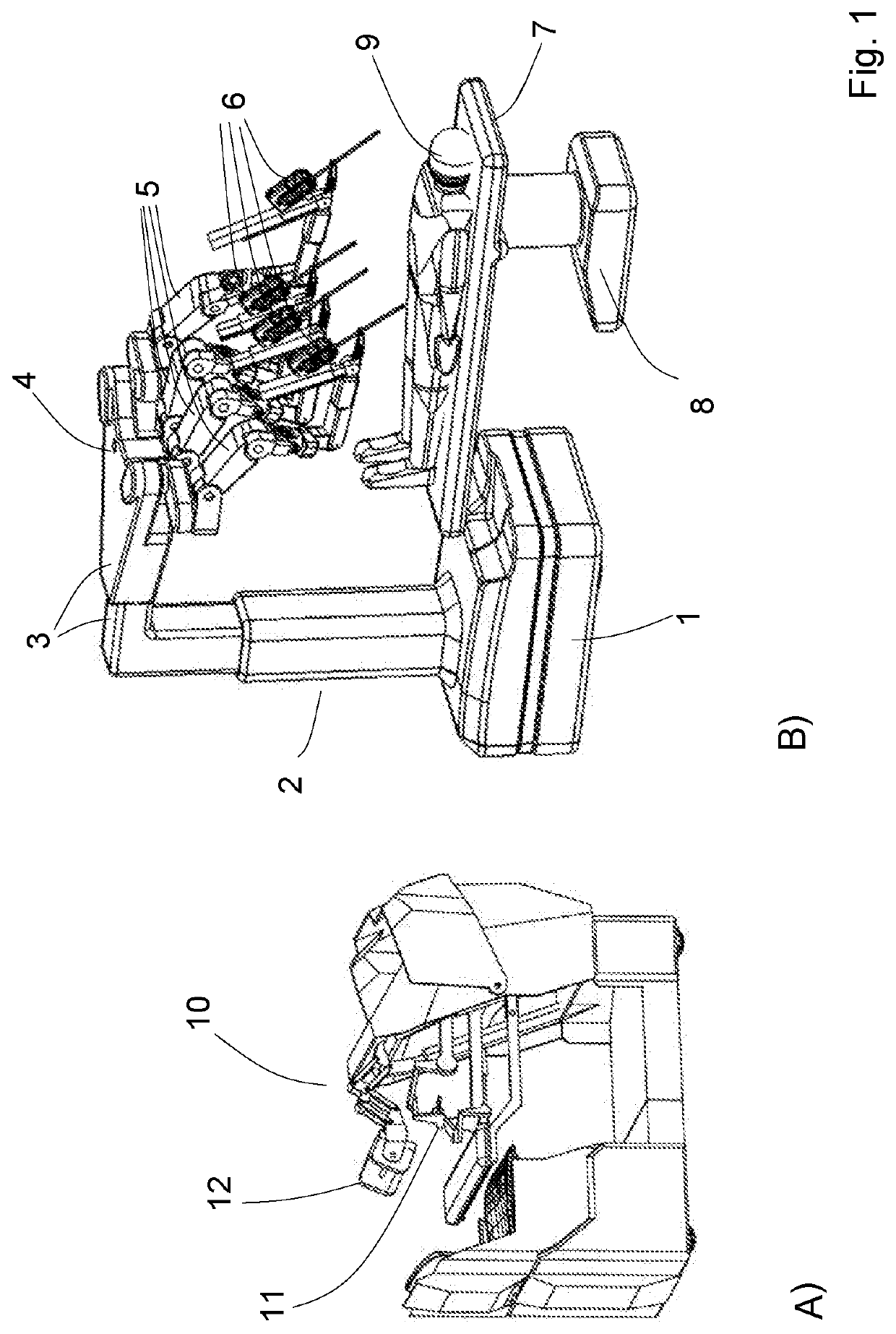

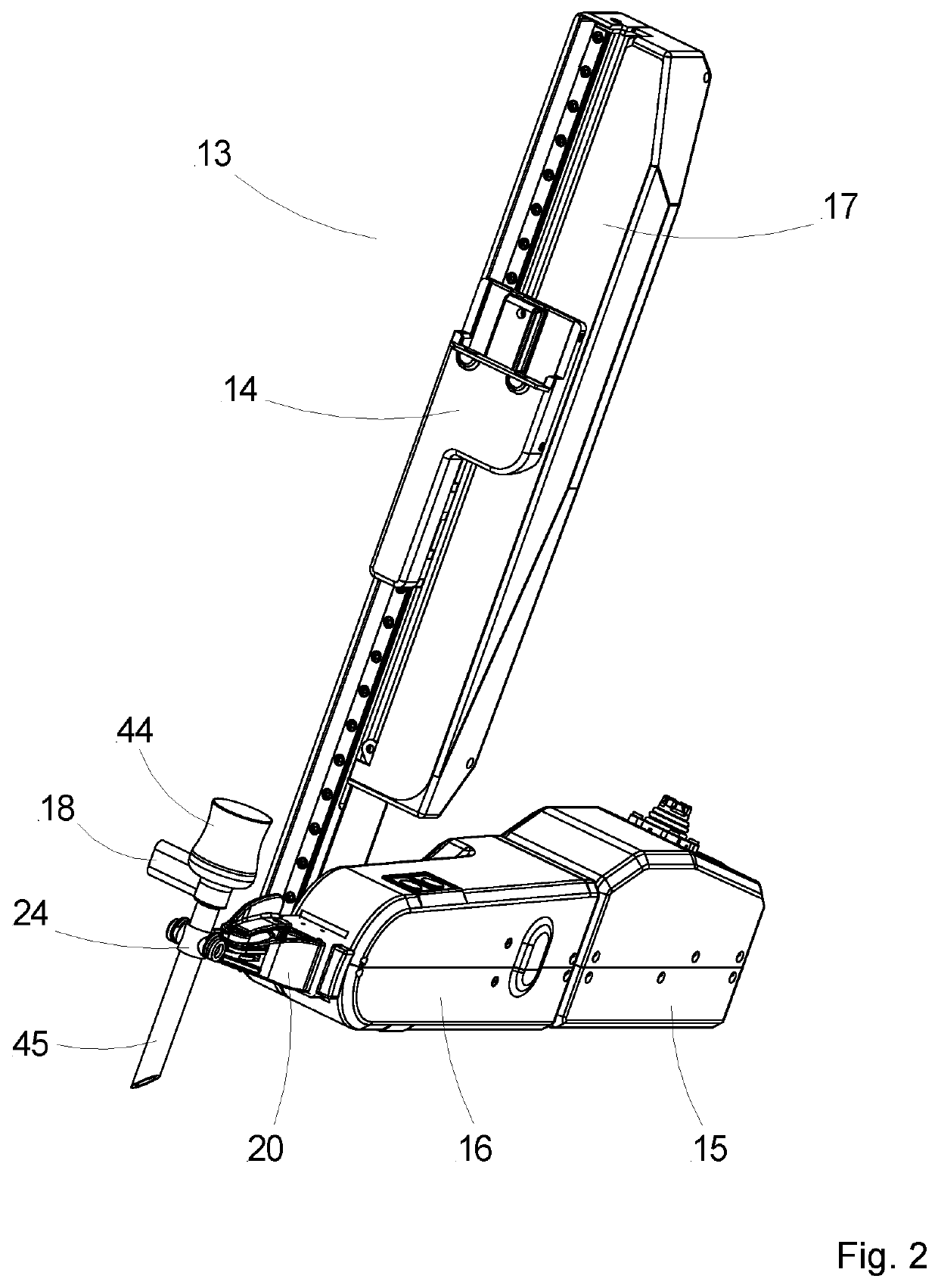

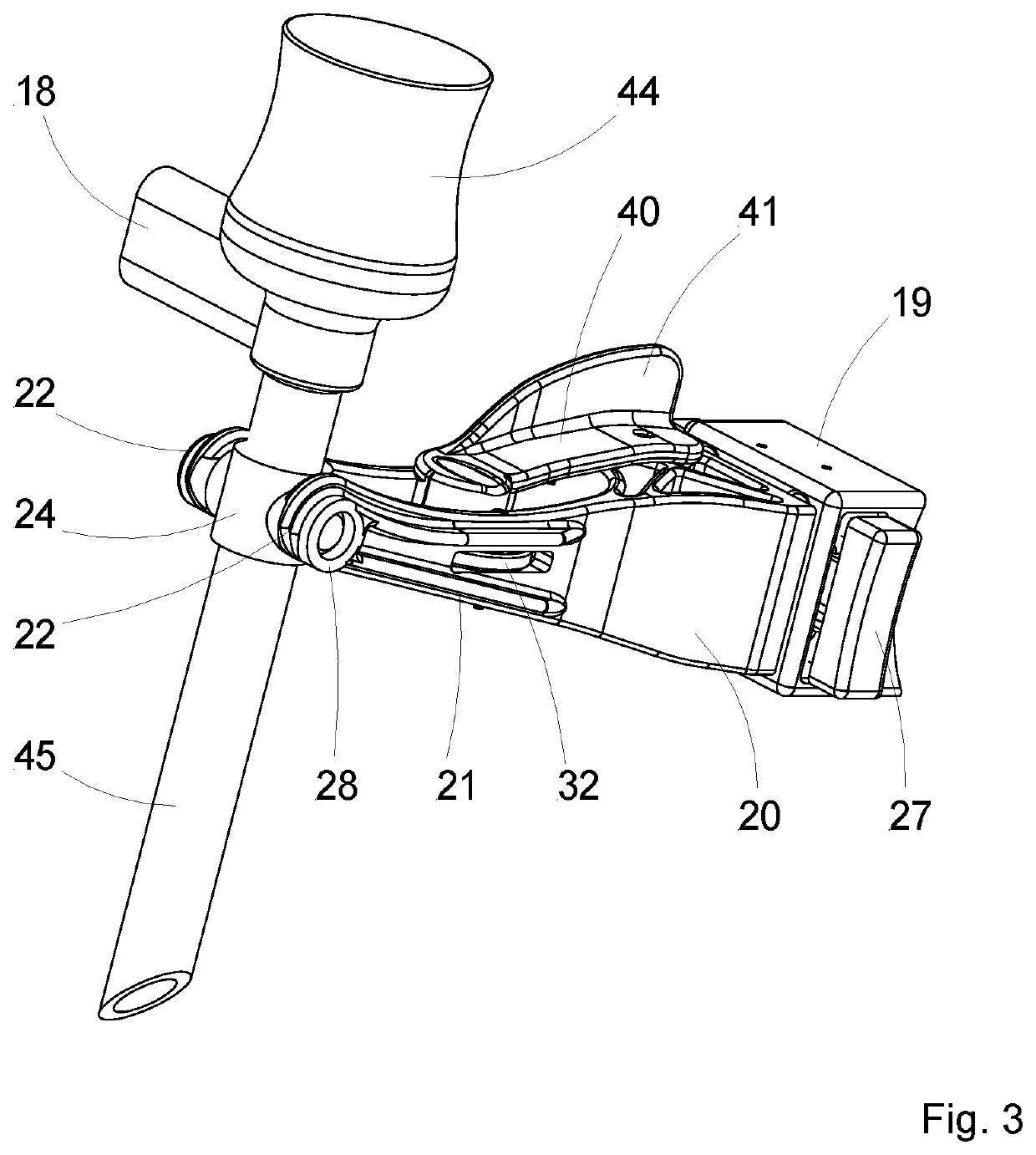

Trocar holder

ActiveUS20200000532A1Simple replaceabilityEasily adaptedCannulasDiagnosticsSpinal columnMechanical engineering

A trocar holder for a manipulator of a robotic surgical system. The trocar holder comprises a base element for securing the trocar holder to the manipulator and a clamp element which is replaceably connected to the base element via a coupling mechanism. Two limbs movable relative to each other in a clamp plane are formed on the clamp element. The limbs are connected via a spine and have free tips. The trocar holder also has a clamp mechanism for opening and closing the limbs and a receiving element for a trocar.

Owner:AVATERAMEDICAL GMBH

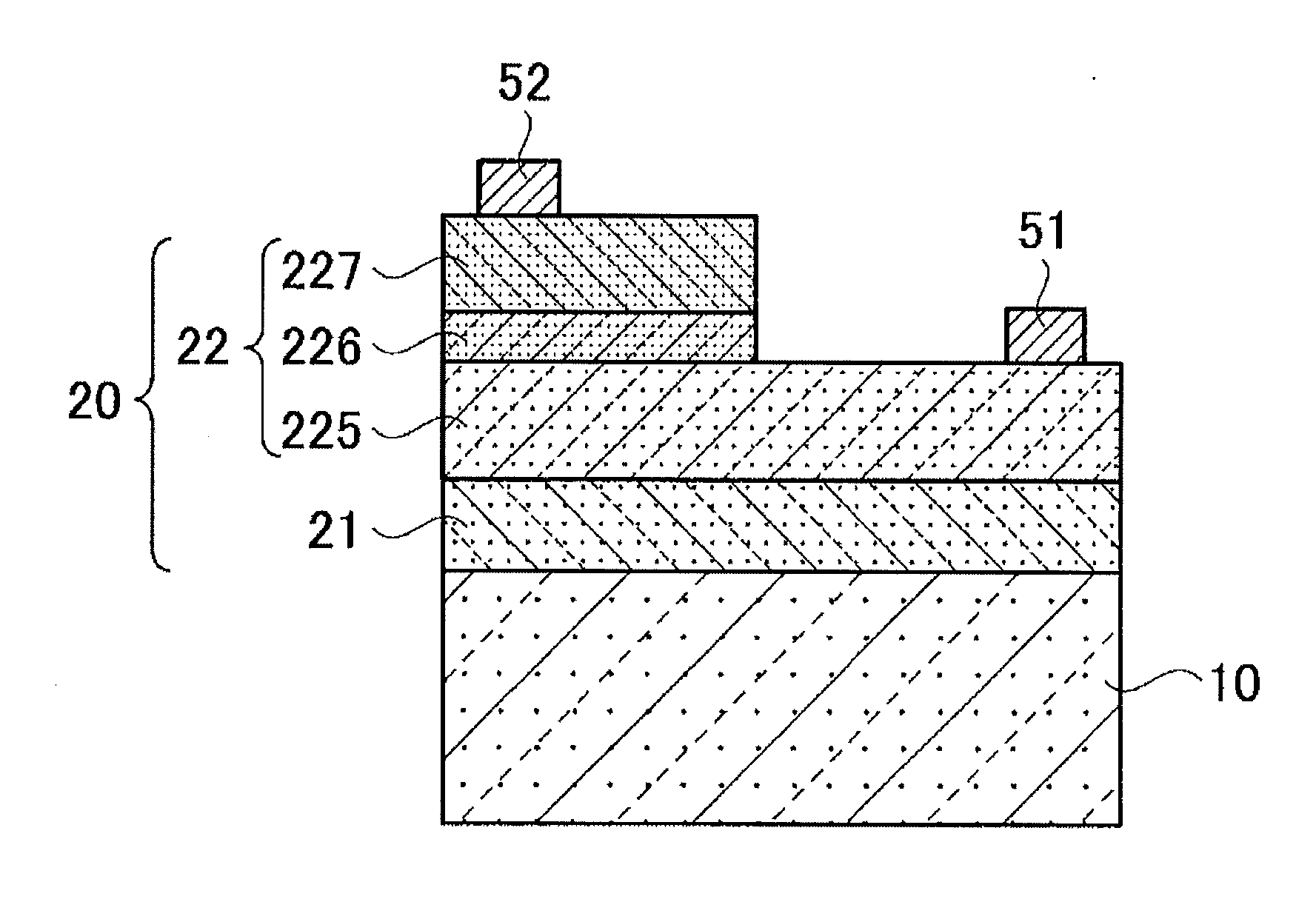

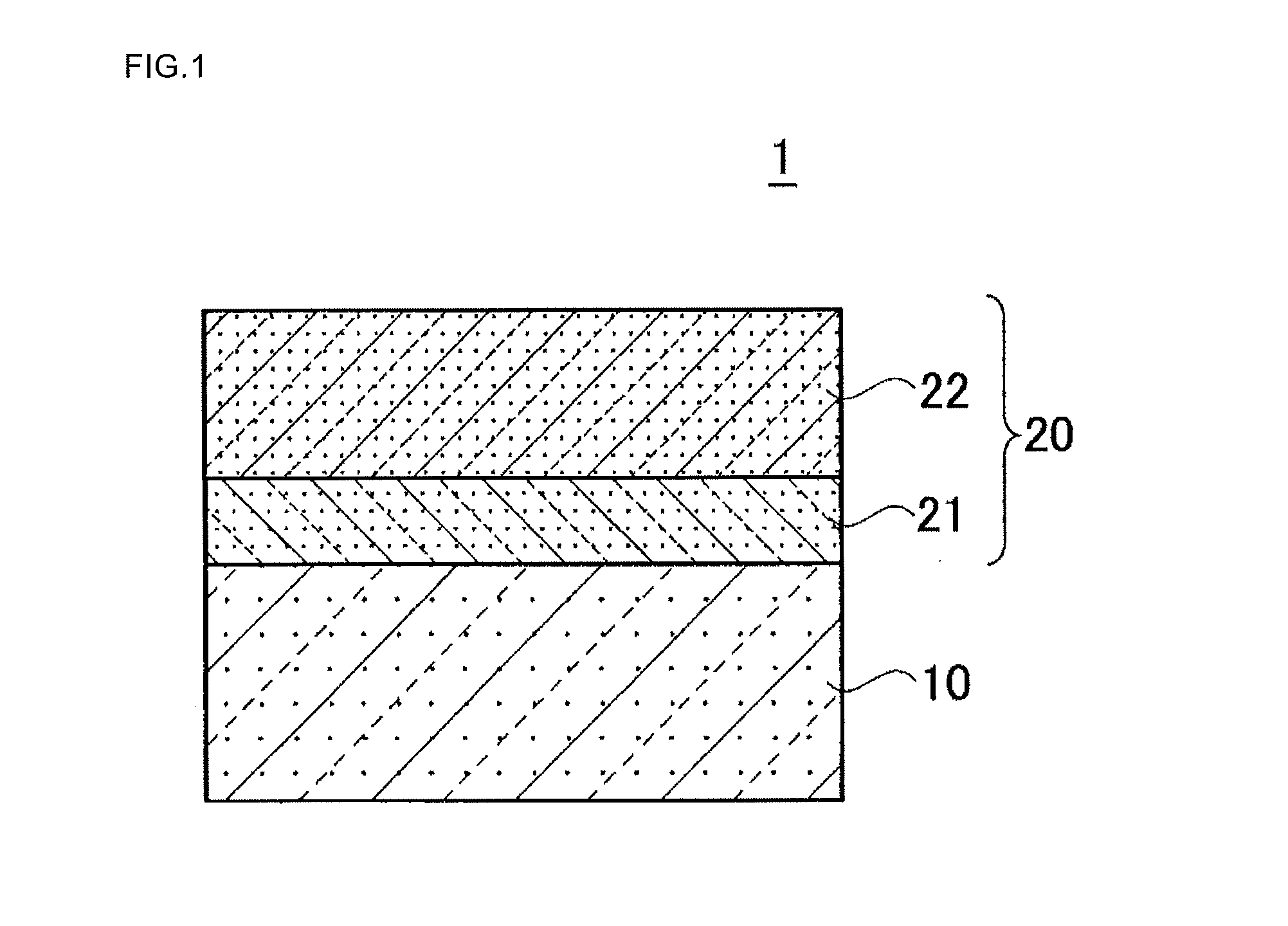

Epitaxial substrate, semiconductor device, and method for manufacturing semiconductor device

InactiveUS20150084163A1StressSemiconductor/solid-state device detailsSolid-state devicesThermal expansionBoron

The present invention provides an epitaxial substrate including a silicon substrate containing oxygen atoms in concentrations of 4×1017 cm−3 or more and 6×1017 cm−3 or less and containing boron atoms in concentrations of 5×1018 cm−3 or more and 6×1019 cm−3 or less and a semiconductor layer that is placed on the silicon substrate and is made of a material having a thermal expansion coefficient different from the thermal expansion coefficient of the silicon substrate. As a result, the epitaxial substrate in which the occurrence of warpage caused by the stress between the silicon substrate and the semiconductor layer is suppressed is provided.

Owner:SANKEN ELECTRIC CO LTD +1

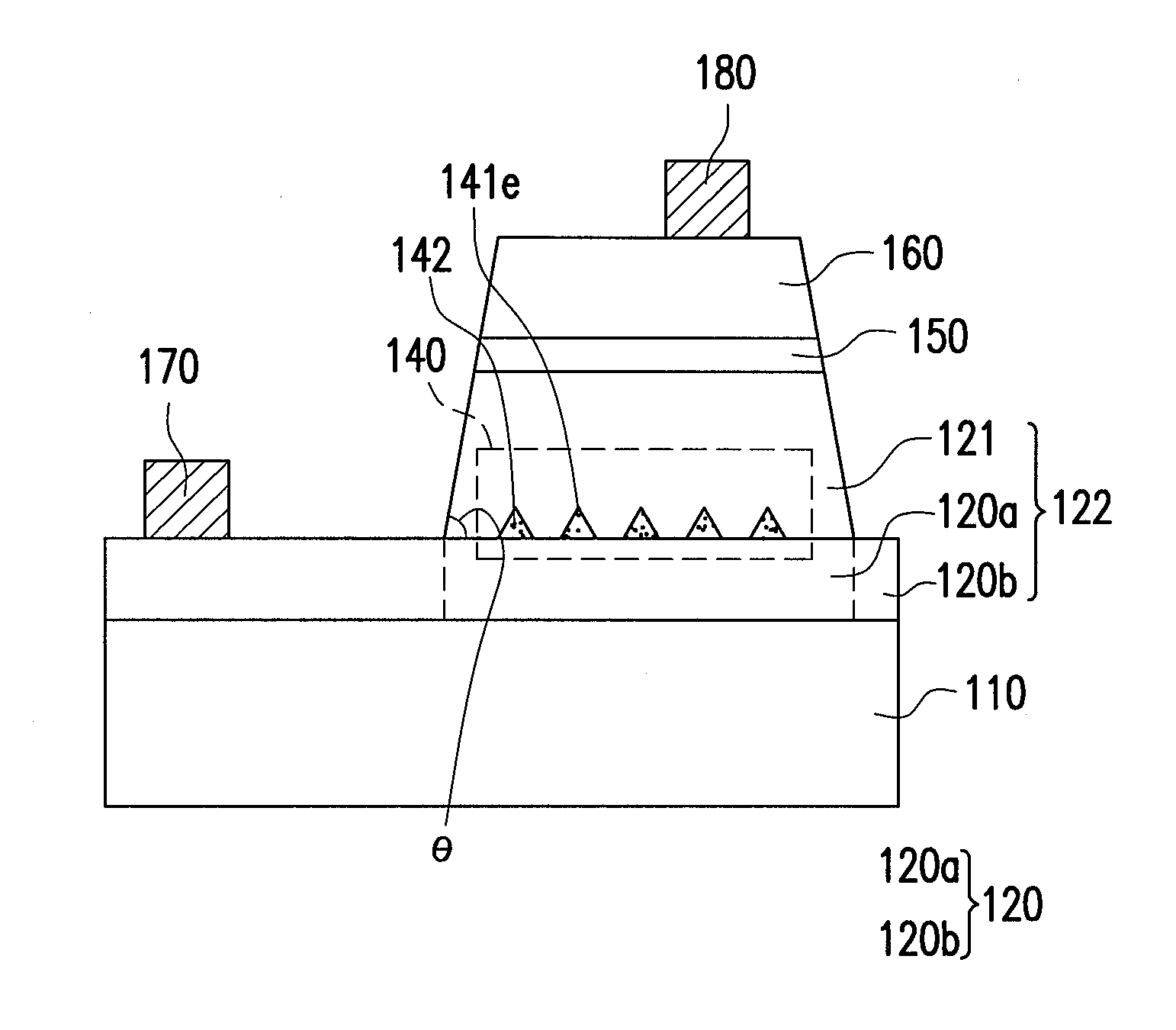

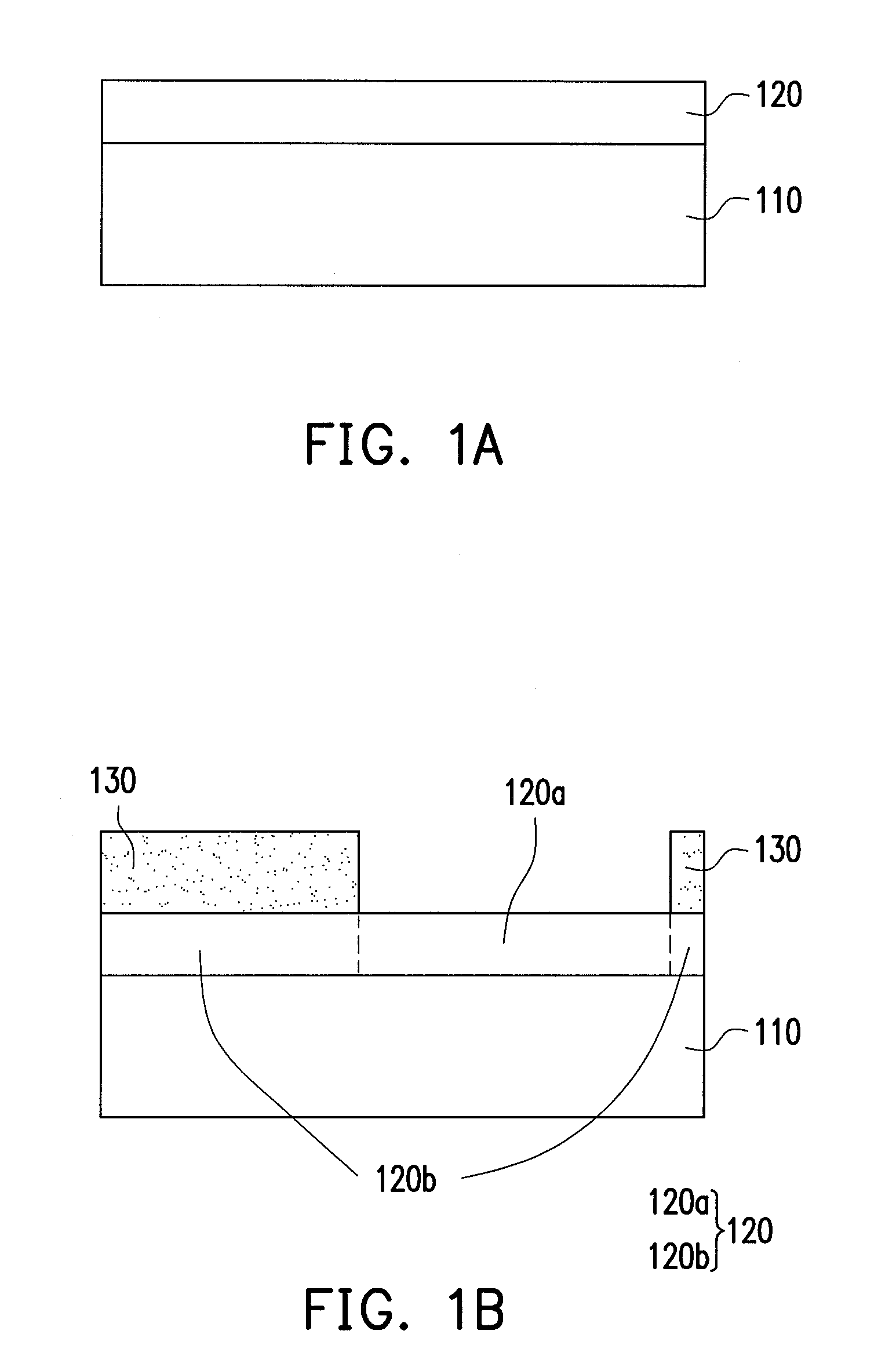

Semiconductor light-emitting device and manufacturing method thereof

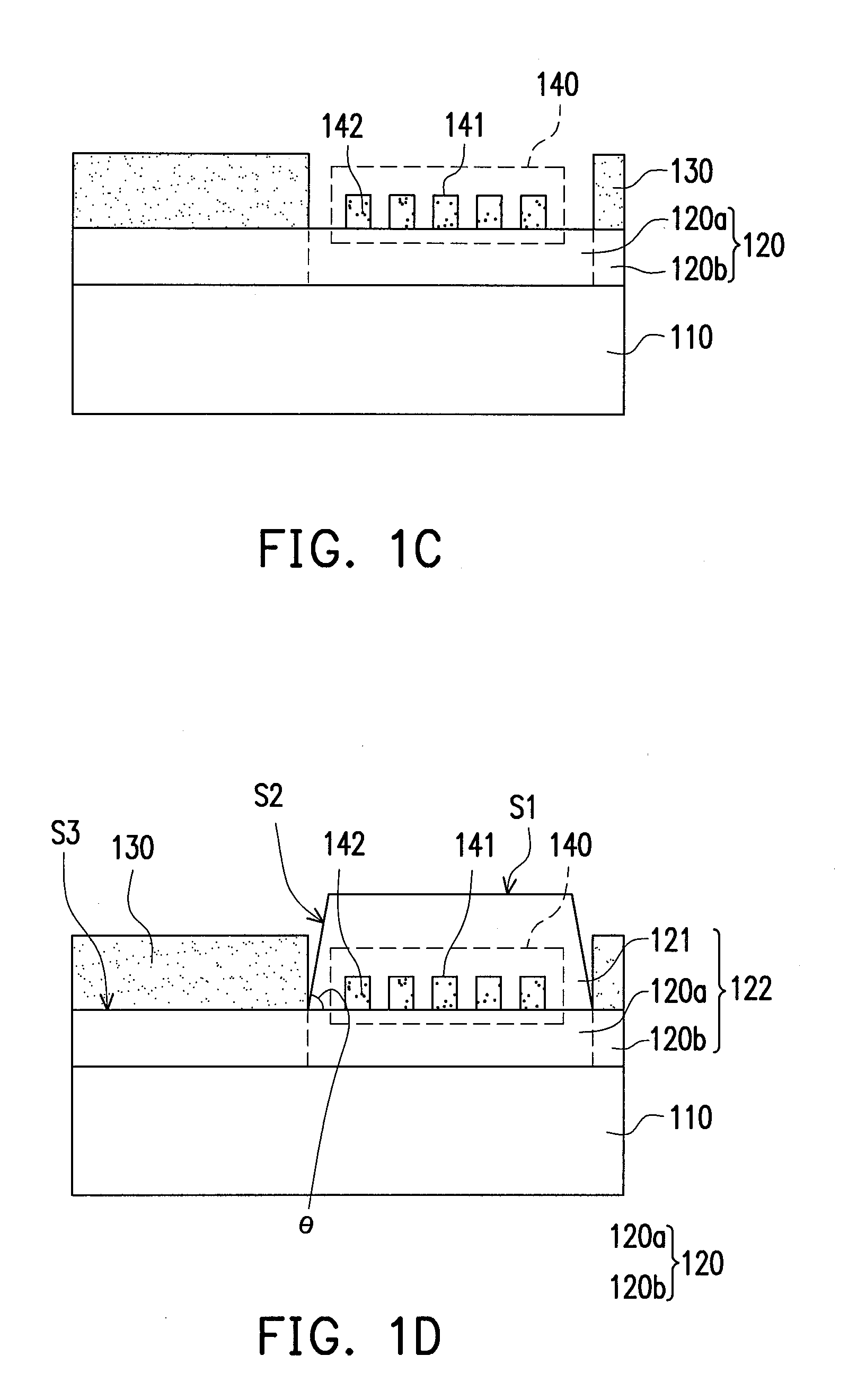

InactiveUS20130240932A1Improve light extraction efficiencyImprove extraction efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorMaterials science

A semiconductor light-emitting device and a manufacturing method thereof are provided, wherein the semiconductor light-emitting device includes a substrate, a first type doped semiconductor layer, a light-emitting layer, a second type doped semiconductor layer and an optical micro-structure layer. The first type doped semiconductor layer is disposed on the substrate and includes a base portion and a mesa portion. The base portion has a top surface, and the mesa portion is disposed on the top surface of the base portion. The light-emitting layer is disposed on the first type doped semiconductor layer. The second type doped semiconductor layer is disposed on the light-emitting layer. The optical micro-structure layer is embedded in the first type doped semiconductor layer.

Owner:GENESIS PHOTONICS

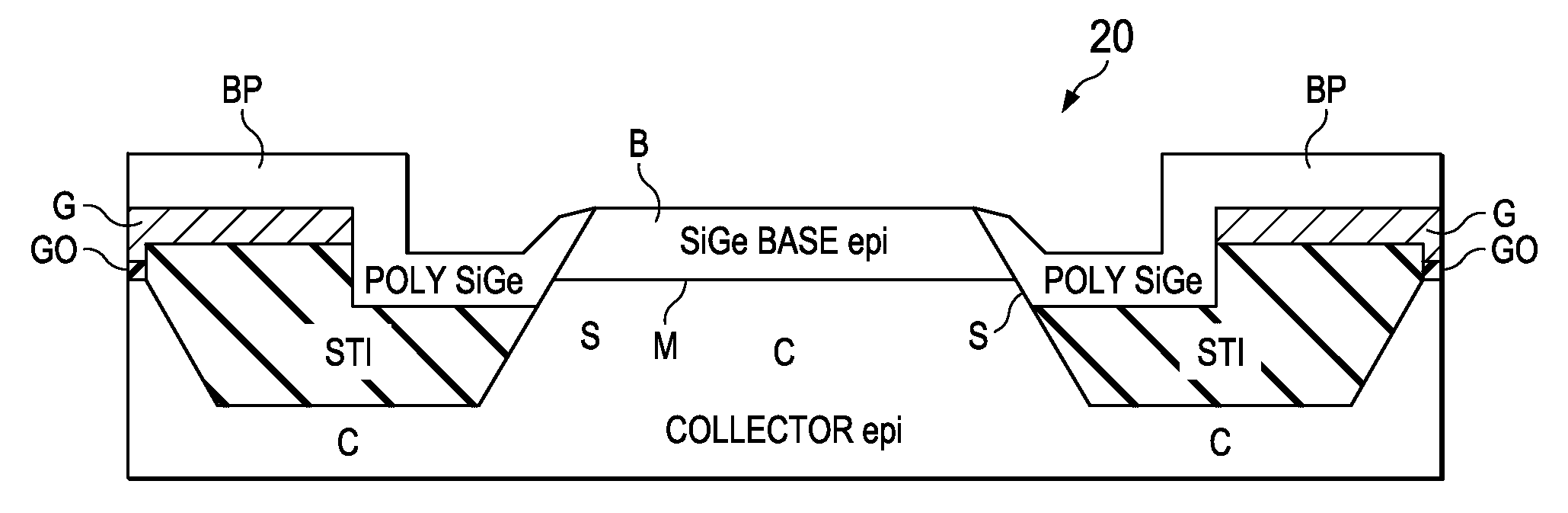

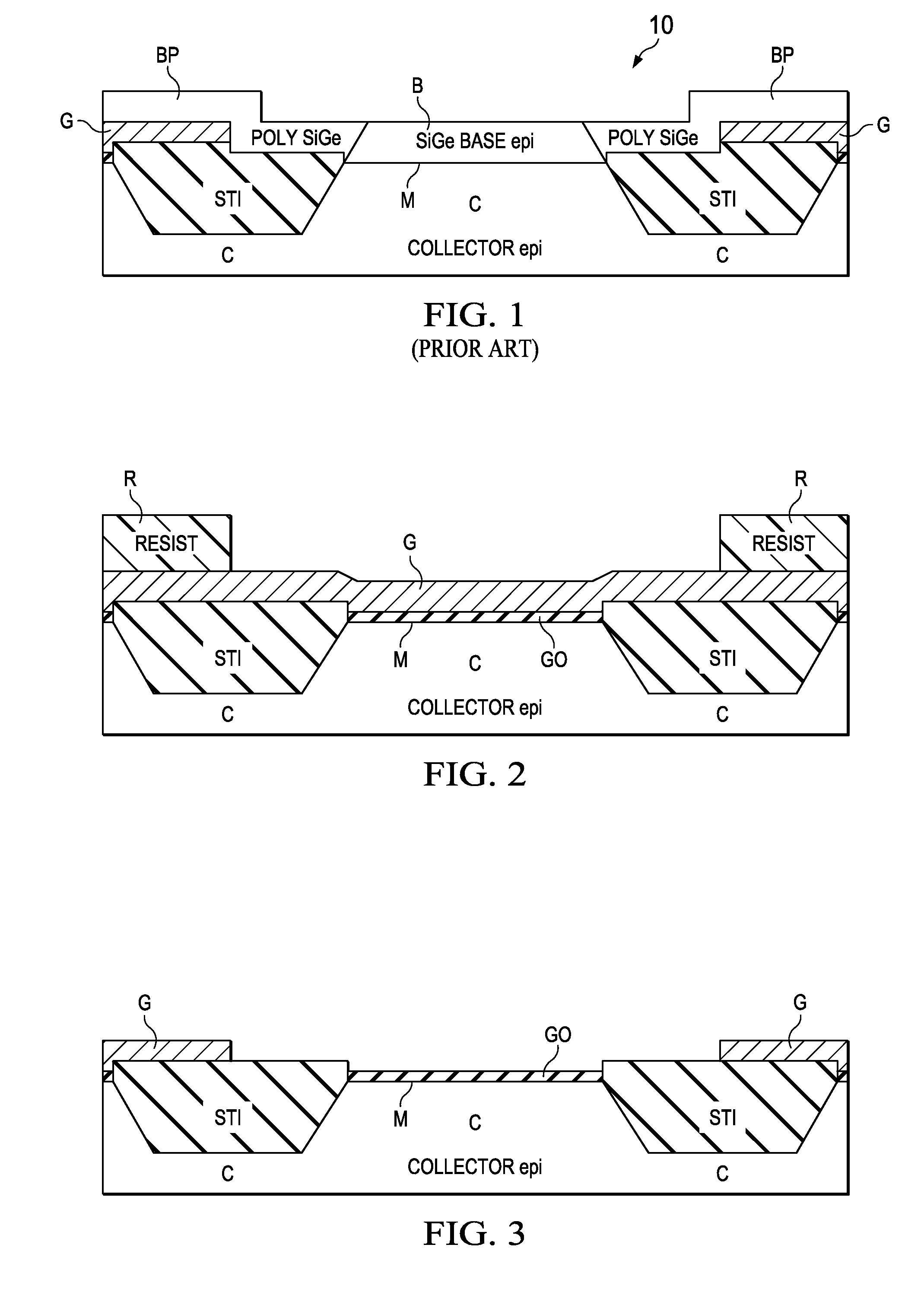

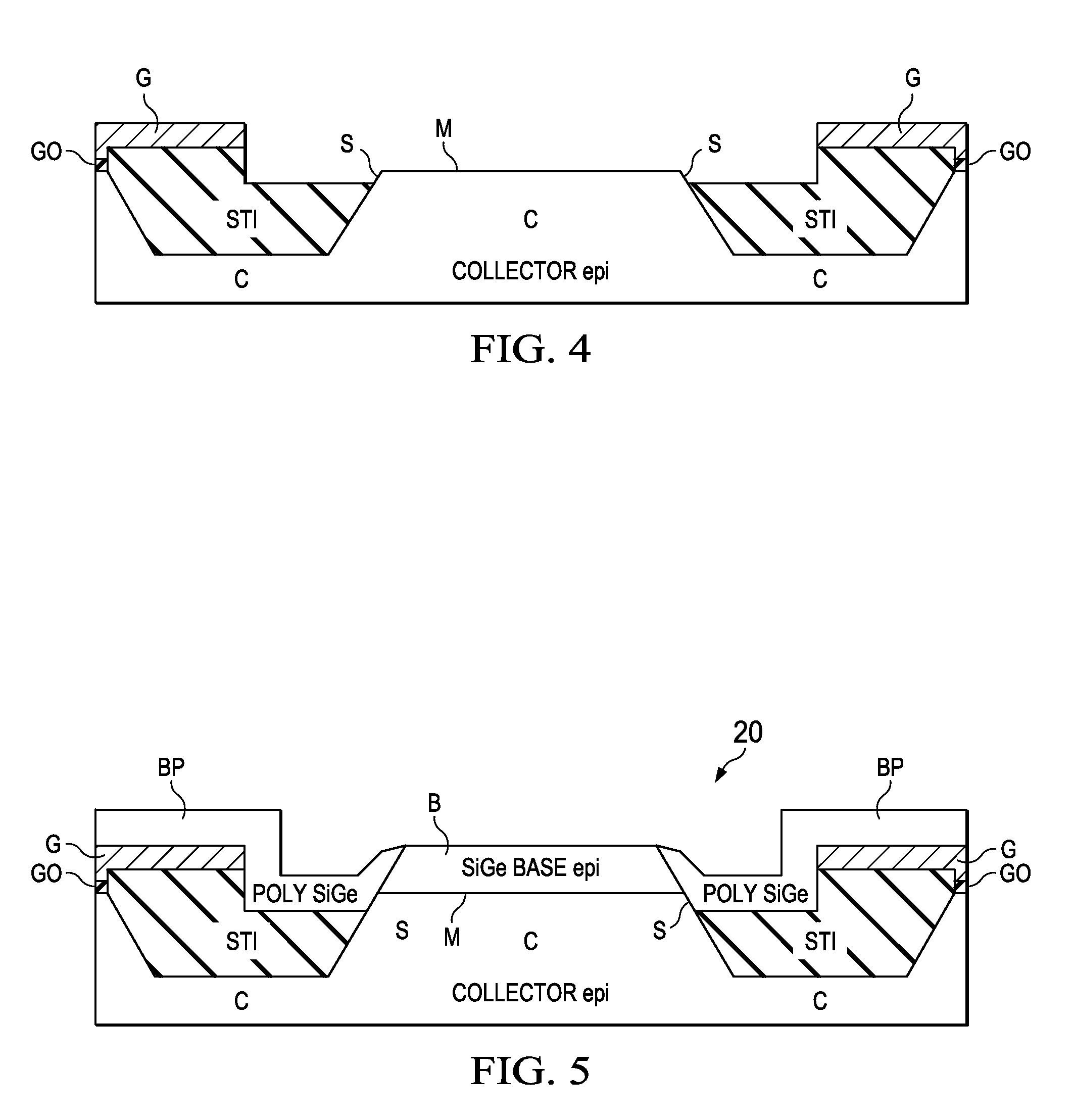

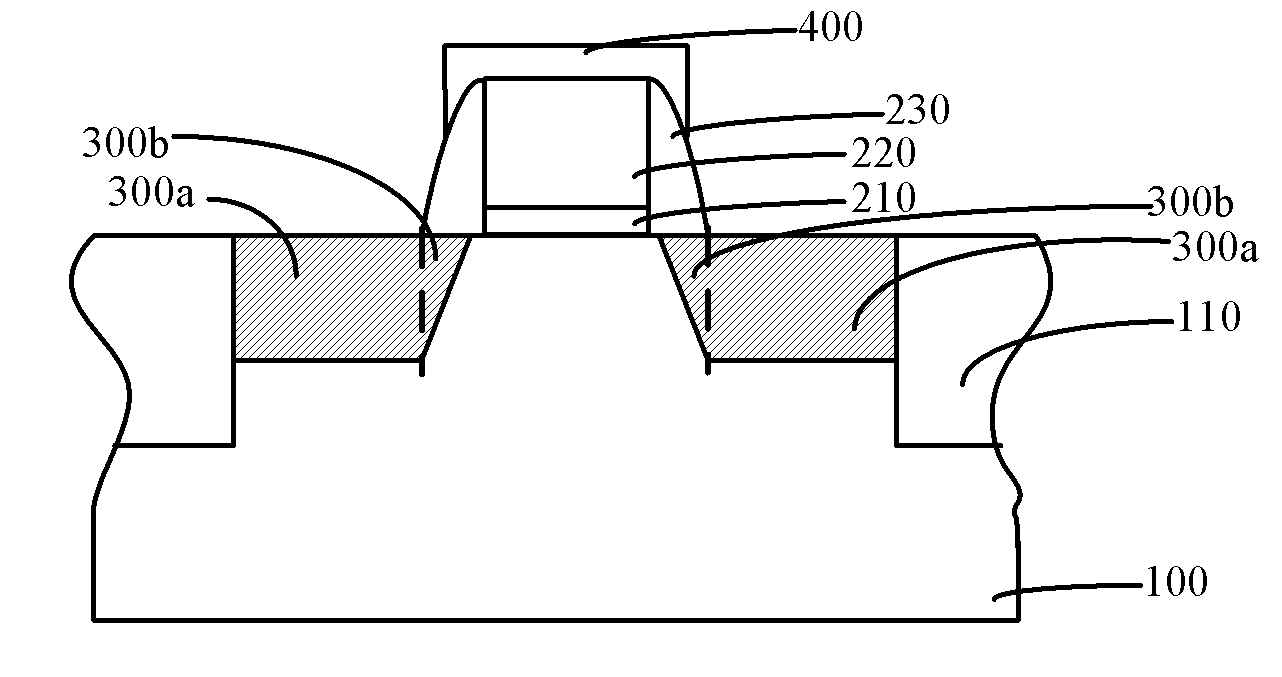

Bipolar transistor

ActiveUS20110049517A1Reduce thicknessStressTransistorSolid-state devicesEngineeringElectrical and Electronics engineering

A bipolar transistor has a collector having a base layer provided thereon and a shallow trench isolation structure formed therein. A base poly layer is provided on the shallow trench isolation structure. The shallow trench isolation structure defines a step such that a surface of the collector projects from the shallow trench isolation structure adjacent the collector.

Owner:TEXAS INSTR INC

Reduction of wafer bow during growth of epitaxial films

InactiveUS20180358221A1Reducing wafer bowRelieve in-plane stressOptical wave guidancePolycrystalline material growthWaferingWafer bow

Structures and methods for reducing wafer bow during heteroepitaxial growth are described. Micro-trenches may be formed across a surface of a substrate and filled with polycrystalline material. Stress-relieving regions of material can be grown over the polycrystalline material in a layer of semiconductor material during heteroepitaxy.

Owner:MACOM TECH SOLUTIONS HLDG INC

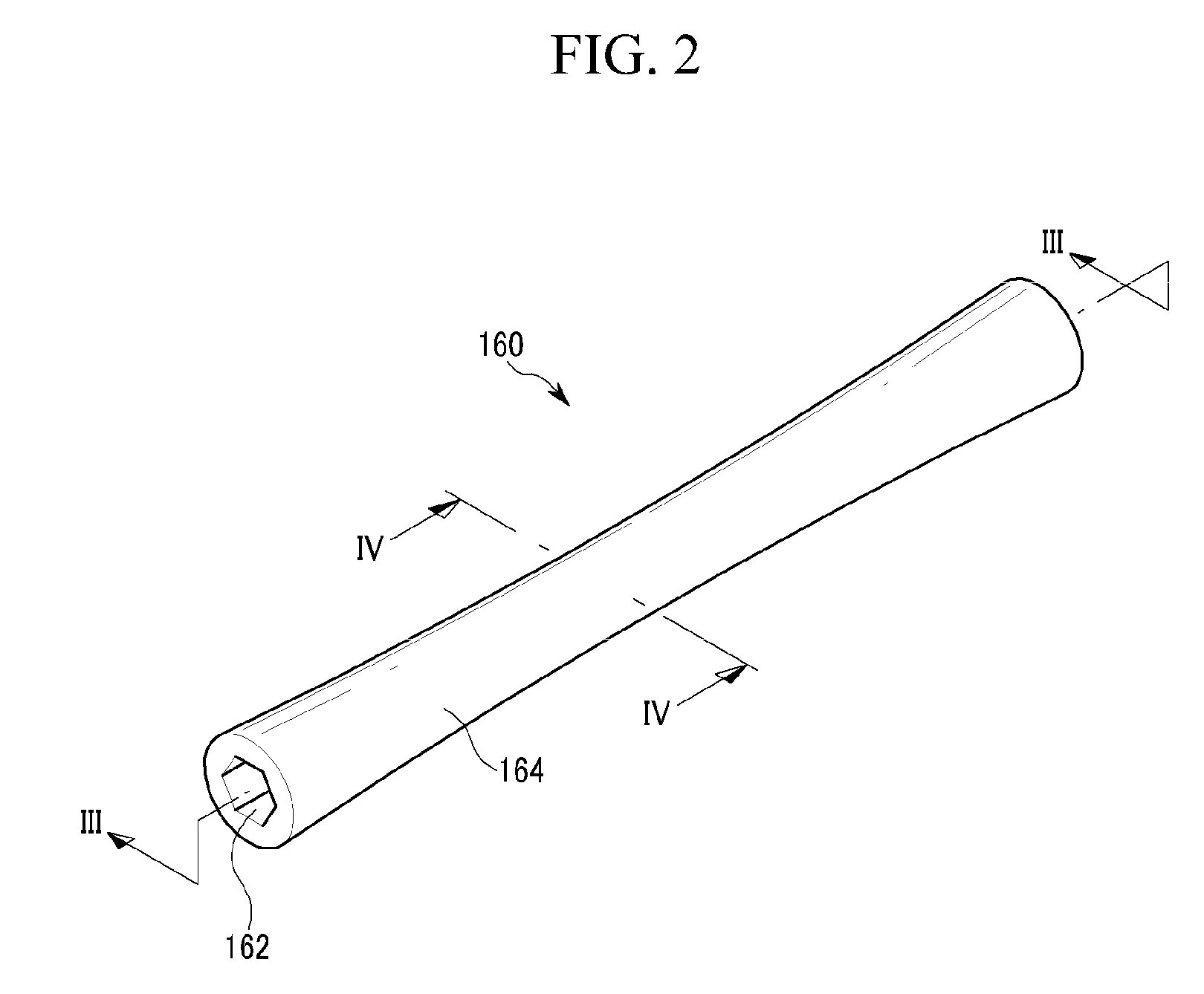

Tube target

The invention relates to a tube target (50) for sputtering, with a target (46) disposed on a cylindrical carrier tube. This target (46) is divided into several segments. The target (46) includes at least one groove (51-54) extending obliquely with respect to its rotational axis.

Owner:PROTECH MATERIALS INC

Process for fabricating semiconductor device

InactiveUS7767559B2Efficient introductionExcellent electrical propertiesTransistorSolid-state devicesAmorphous siliconCrystalline silicon

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor integrated circuit structure including dielectric having negative thermal expansion

ActiveUS9633955B1Reduce stressMitigate and eliminateSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitNegative thermal expansion

A semiconductor IC structure includes a semiconductor substrate, a multi-layered dielectric structure disposed on the semiconductor substrate, a first conductive layer disposed in the multi-layered dielectric structure, and a second conductive layer disposed on the multi-layered dielectric structure. The multi-layered dielectric structure further includes a first dielectric layer disposed on the semiconductor substrate, and a second dielectric layer disposed on the first dielectric layer. A coefficient of thermal expansion (CTE) of the first dielectric layer is larger than zero, and a CTE of the second dielectric layer is smaller than zero.

Owner:UNITED MICROELECTRONICS CORP

Semiconductor device and method for forming the same

ActiveUS20120139016A1Increase pressureEnhanced transistor performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor

A semiconductor device and a method for forming the same are provided. The method includes: providing a substrate having a gate structure and first spacers on both sidewalls of the gate structure formed on a top surface of the substrate; forming first openings in the substrate by using the first spacers as a mask, wherein the first openings are located on both sides of the gate structure; forming second openings by etching the first openings with an etching gas, wherein each of the second openings is an expansion of a corresponding one of the first openings toward the gate structure and extends to underneath an adjacent first spacer; and forming epitaxial layers in the first openings and the second openings.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Heat exchanger

InactiveUS8826663B2Relieve pressureImprove carrying capacityRecuperative heat exchangersSafety devices for heat exchange apparatusPlate heat exchangerEngineering

Owner:BEHR GMBH & CO KG

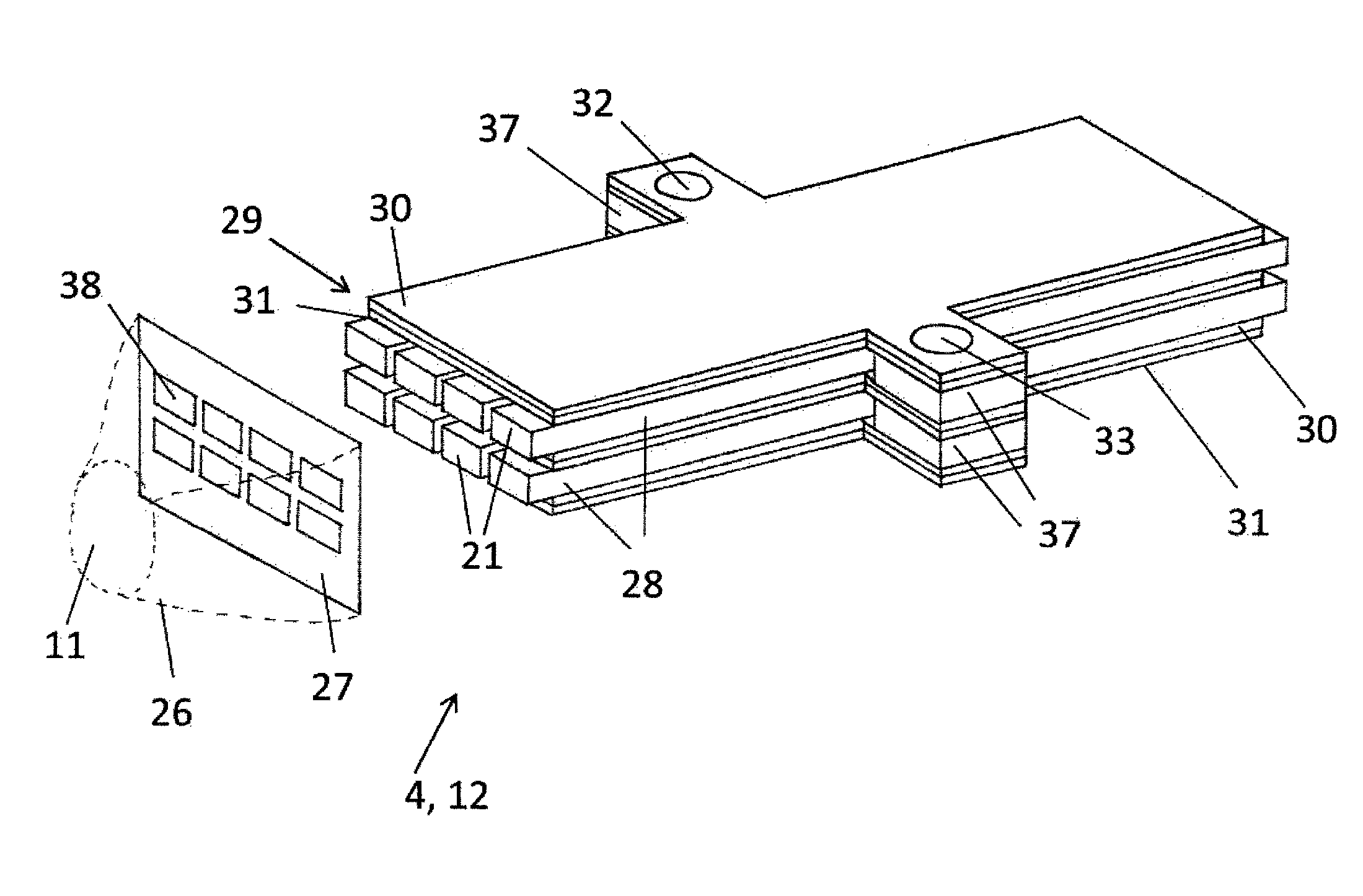

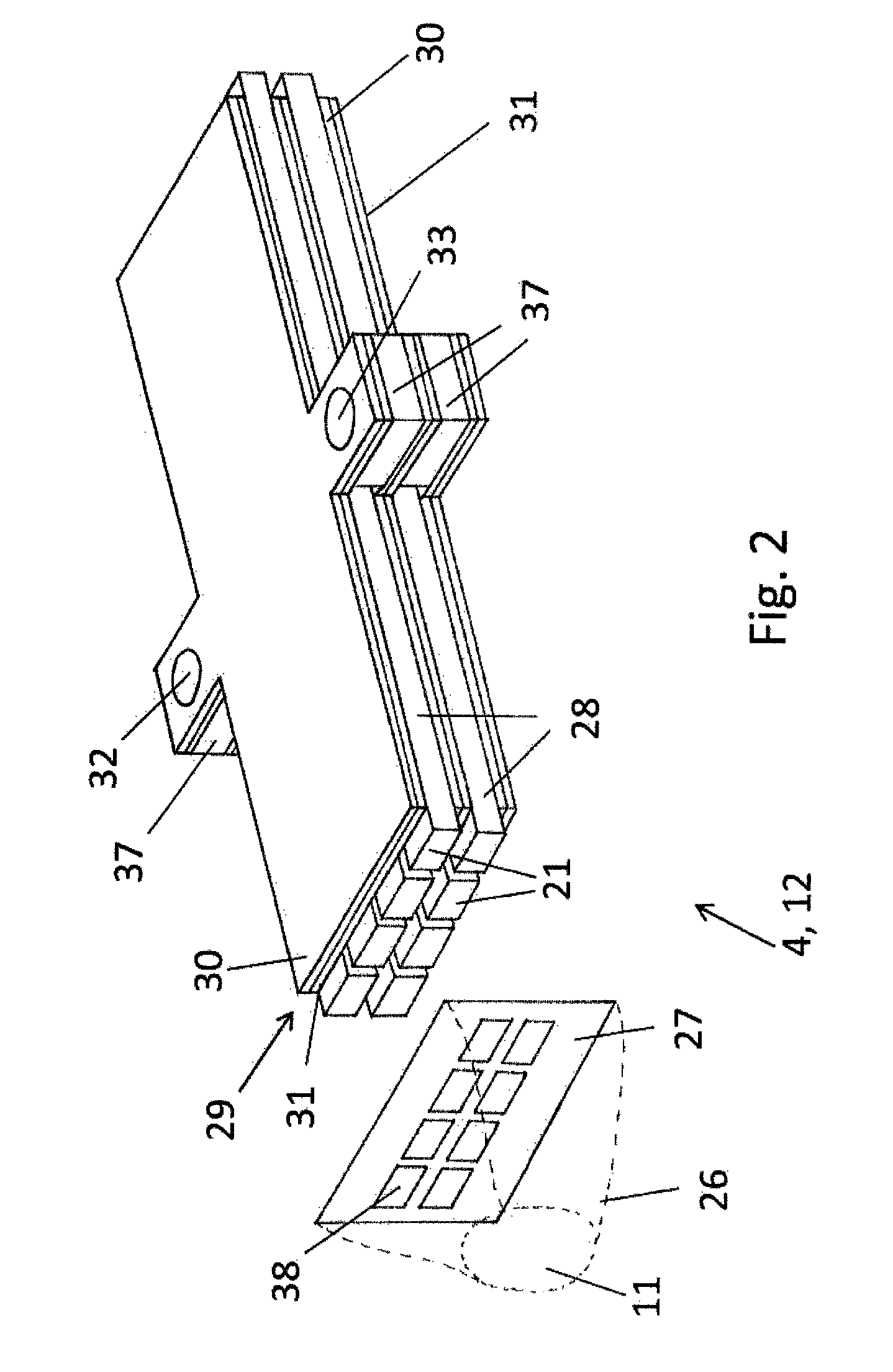

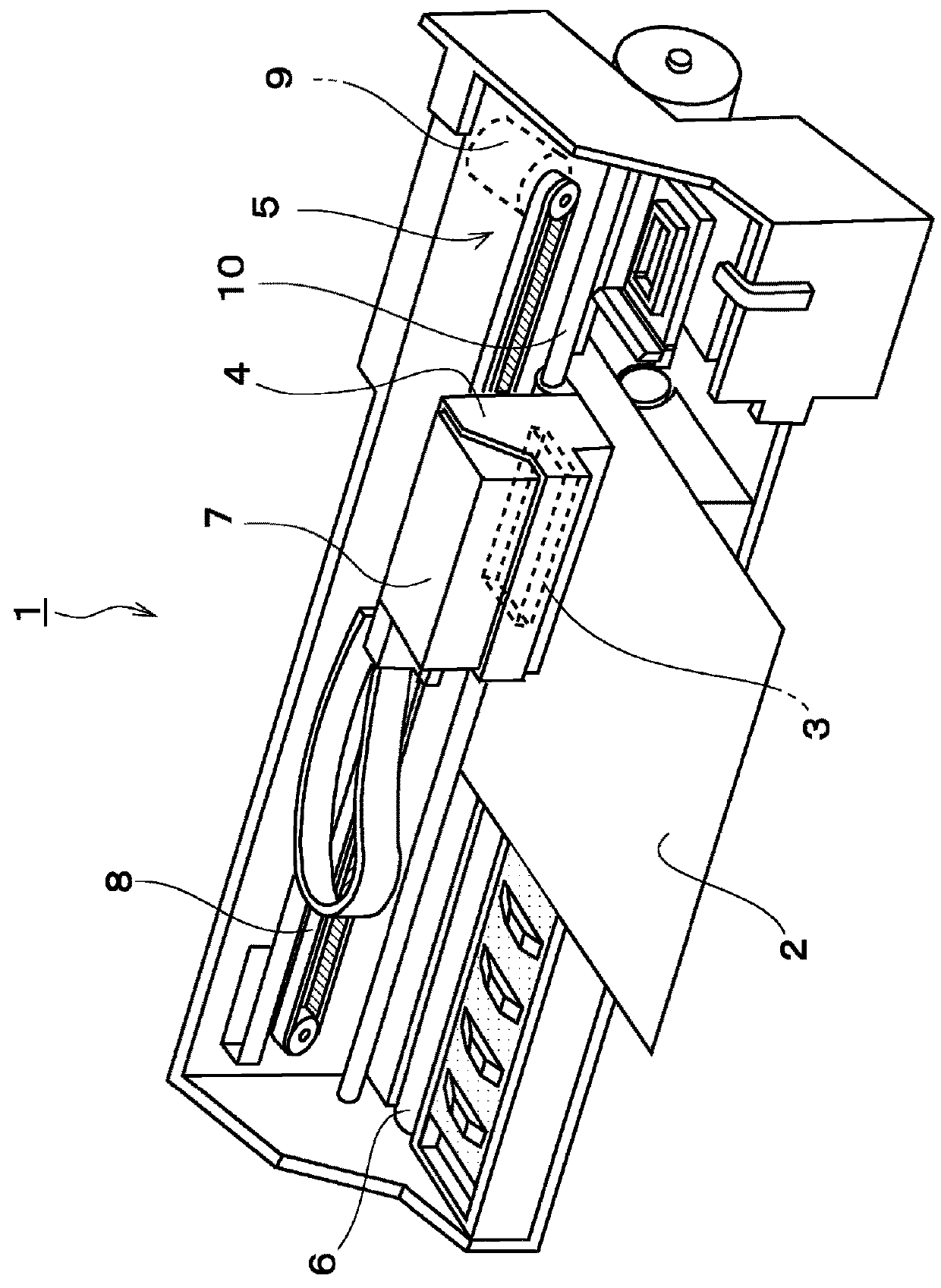

Liquid ejecting head and liquid ejecting apparatus

ActiveUS20180178513A1Reduction in reliability is suppressedLow costInking apparatusLiquid jetEngineering

A liquid ejecting head (recording head) includes a structure (flow path member) having a plurality of stacked plates (a nozzle plate, a flow path plate, and a diaphragm) in which end surfaces at both sides in one direction are aligned. At least two plates of the plates (the nozzle plate, the flow path plate, and the diaphragm) have different coefficients of linear expansion in the one direction, and holding members are fixed to the end surfaces of the structure (flow path member) at both sides in the one direction, the holding members having stiffness higher than stiffness of a plate having the highest coefficient of linear expansion in the one direction among the plates (the nozzle plate, the flow path plate, and the diaphragm).

Owner:SEIKO EPSON CORP

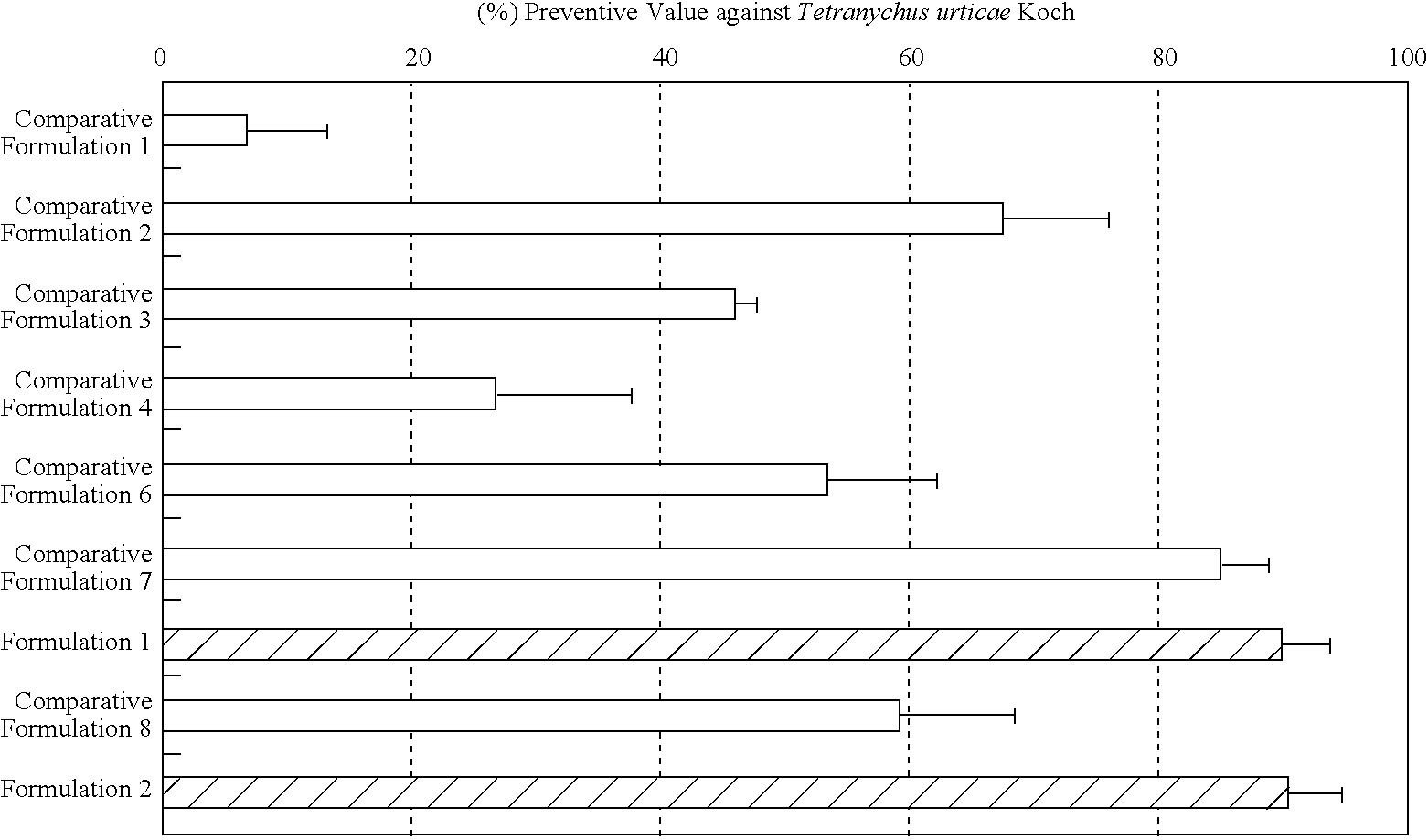

Pesticidal/ovicidal composition and pesticidal/ovicidal method

InactiveUS20090286877A1StressNo risk of drug resistance inductionBiocideOrganic active ingredientsGlycerol DerivativesChemical composition

A pesticidal / ovicidal composition comprising (a) 50-99.9 parts by mass of a triglyceride containing not less than 50% of oleic acid as a fatty acid component; (b) 0.1-20 parts by mass of a nonionic surface active agent; and (c) 0-30 parts by mass of a glycerin derivative. The composition according to the invention has not only a pesticidal activity but also an ovicidal activity on crop pests, and provides a safe and high pesticidal / ovicidal effect.

Owner:RIKEN

Thin film transistor

ActiveUS7649207B2StressStability of thin film transistor can be enhancedSolid-state devicesSemiconductor devicesPolycrystalline siliconTransistor

A thin film transistor is disclosed, comprising a substrate, a polysilicon layer overlying the substrate, a gate insulating layer overlying the polysilicon layer, a gate electrode, a dielectric interlayer overlying the gate electrode and gate insulating layer, and a source / drain electrode overlying the dielectric interlayer. Specifically, the gate electrode comprises a first electrode layer overlying the gate insulating layer and a second electrode layer essentially overlying an upper surface of the first electrode layer. The first and second electrode layers each has substantially the same profile with a taper angle of less than about 90 degrees.

Owner:AU OPTRONICS CORP

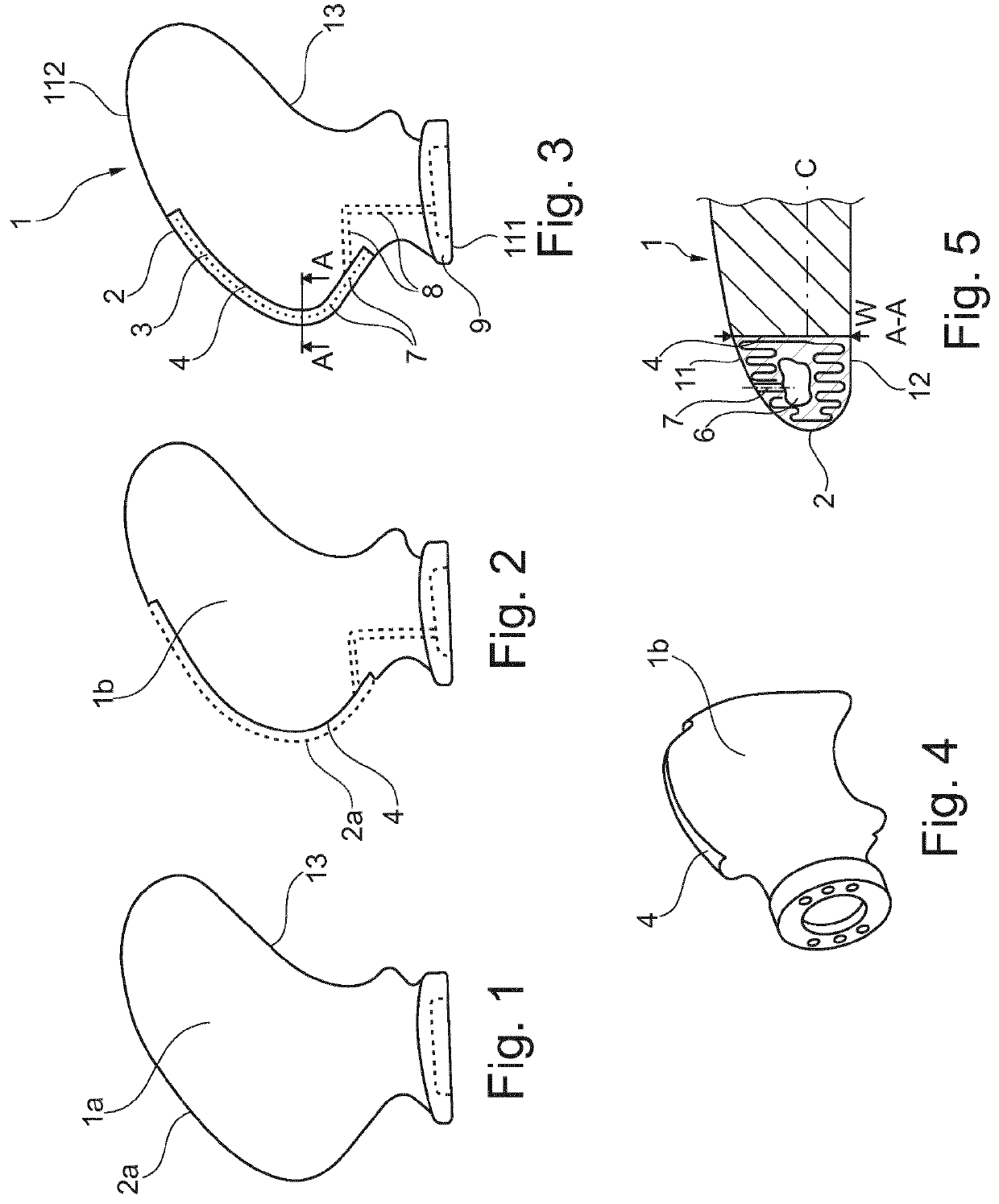

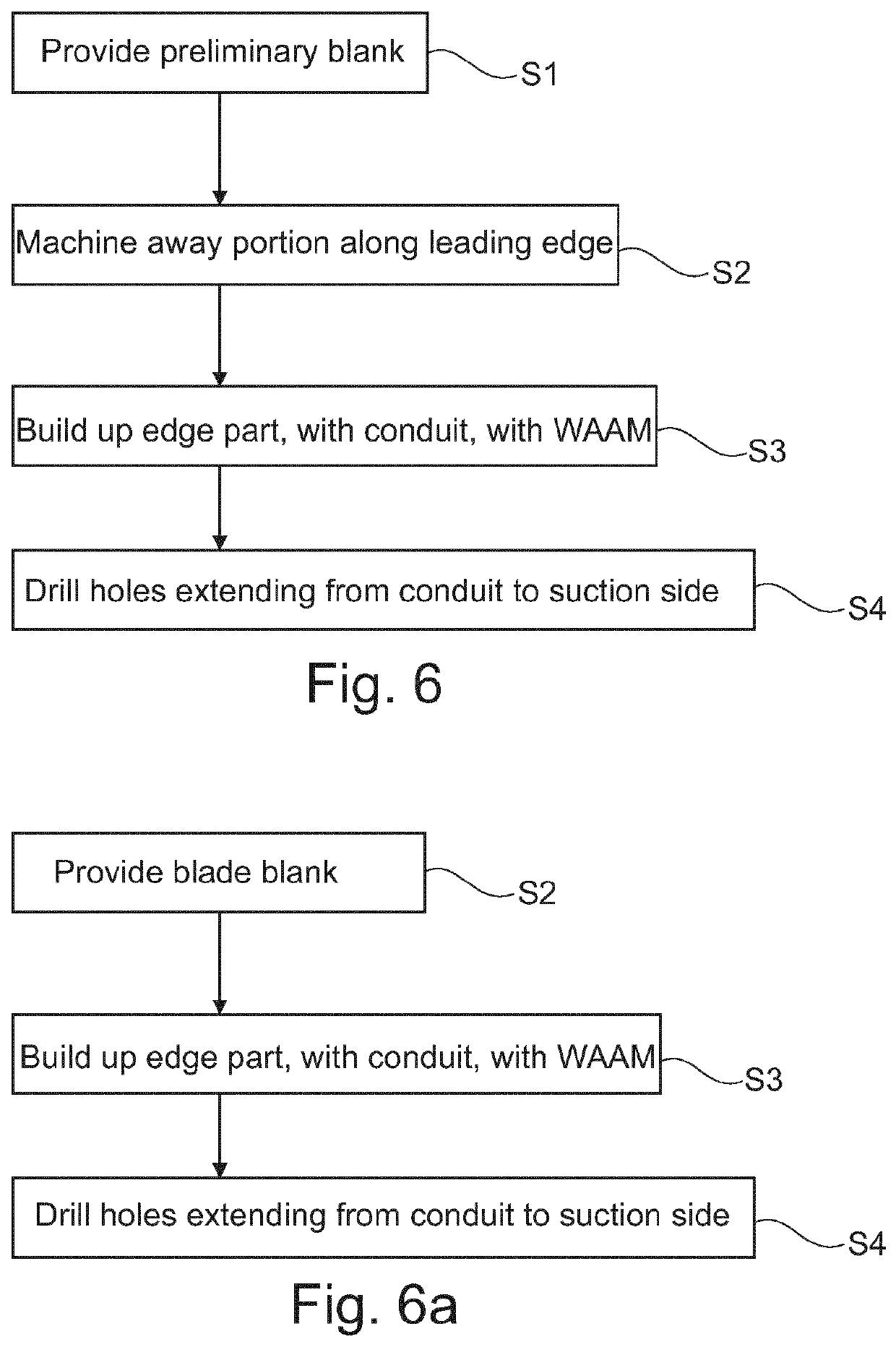

A method for manufacturing a propeller blade and a propeller blade

ActiveUS20210031901A1Simple and cost-effectiveReduce crackingTurbinesAdditive manufacturing apparatusLeading edgeWire rod

The present invention involves a method for manufacturing a blade (1) for a propeller, which blade (1) has a leading edge (2) and a trailing edge, the method comprising the steps of: forming a conduit in the blade (1), making a plurality of holes (7) through which the conduit (6) communicates with the exterior of the blade (1), and providing a blade blank having an edge part receiving surface (4) extending along at least a major part of the leading edge (2) of the blade (1) to be manufactured, wherein forming a conduit (6) comprises building up an edge part (3) onto the edge part receiving surface (4) by a wire-based additive manufacturing process, wherein the additive manufacturing process is adapted to form the conduit (6) at least partly delimited by the edge part (3) and extending along the leading edge (2) of the blade (1) to be manufactured.

Owner:KONGSBERG MARITIME SWEDEN AB

Pesticidal/ovicidal composition and pesticidal/ovicidal method

InactiveUS20090061028A1No risk of drug resistance inductionSufficient pesticidalBiocideDead animal preservationGlycerol DerivativesChemical composition

A pesticidal / ovicidal composition comprising: (a) 50-97.9 parts by mass of a triglyceride containing not less than 50% of oleic acid as a fatty acid component; (b) 0.1-20 parts by mass of a cationic surface active agent; and (c) 2-30 parts by mass of a glycerin derivative, and a pesticidal / ovicidal method using the same. The composition according to the invention has not only a pesticidal activity but also an ovicidal activity on crop pests, and provides a safe and high pesticidal / ovicidal effect.

Owner:RIKEN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com