Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

34 results about "Wafer bow" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

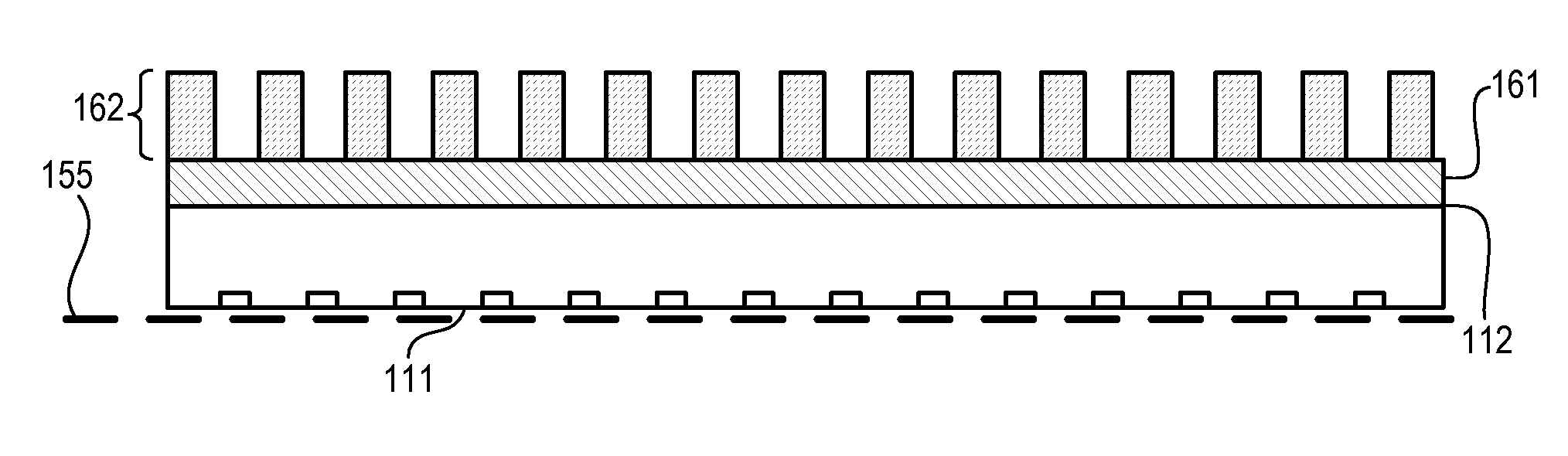

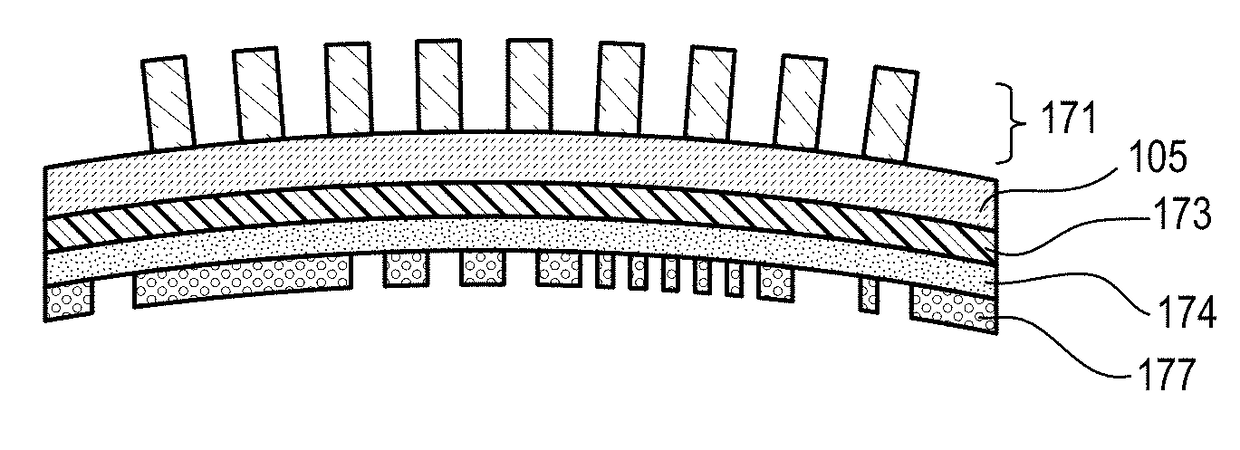

Processes for Making Reliable VCSEL Devices and VCSEL arrays

ActiveUS20150255955A1Easy to controlMinimized volumeLaser detailsSolid-state devicesWafer bowEngineering

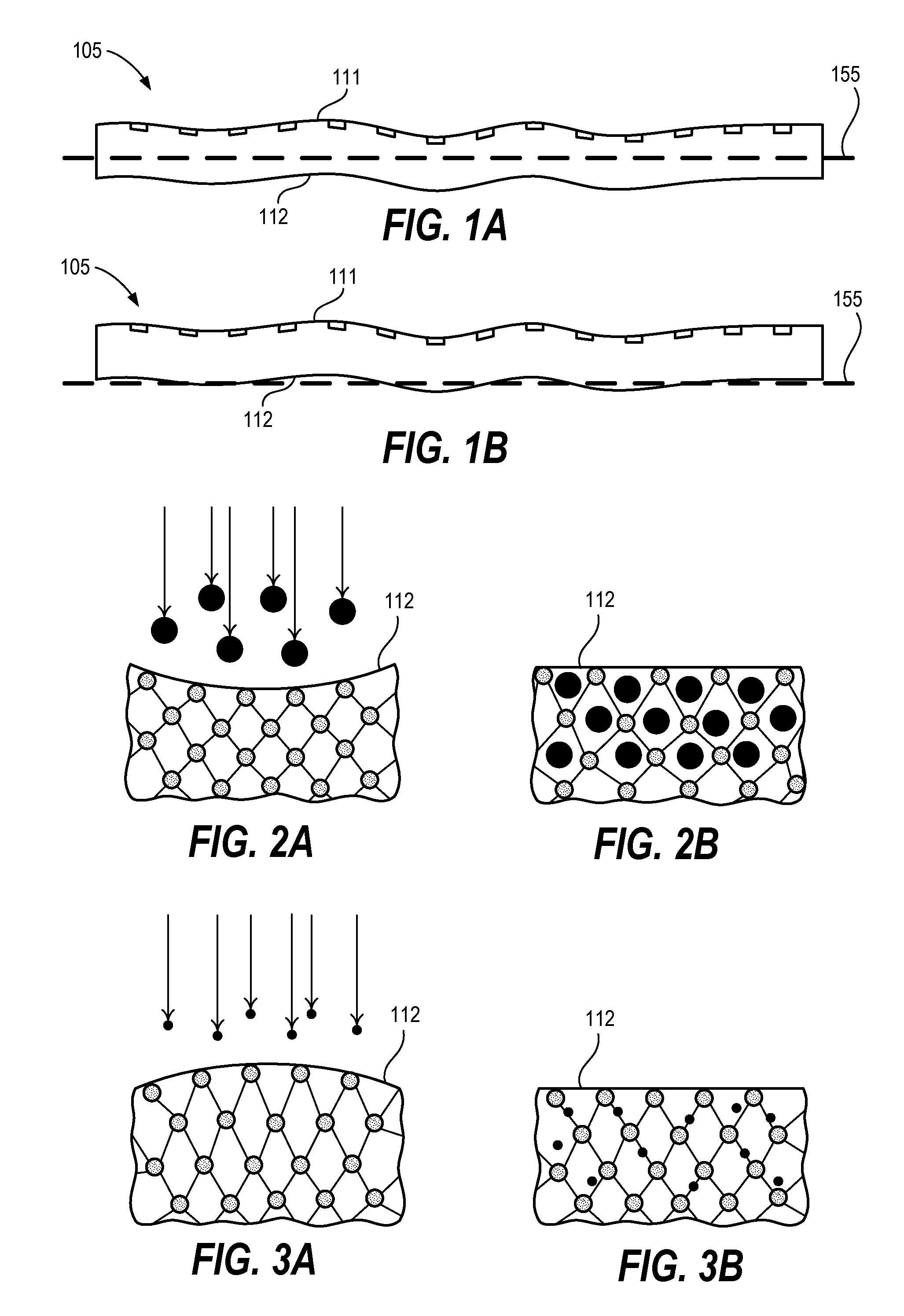

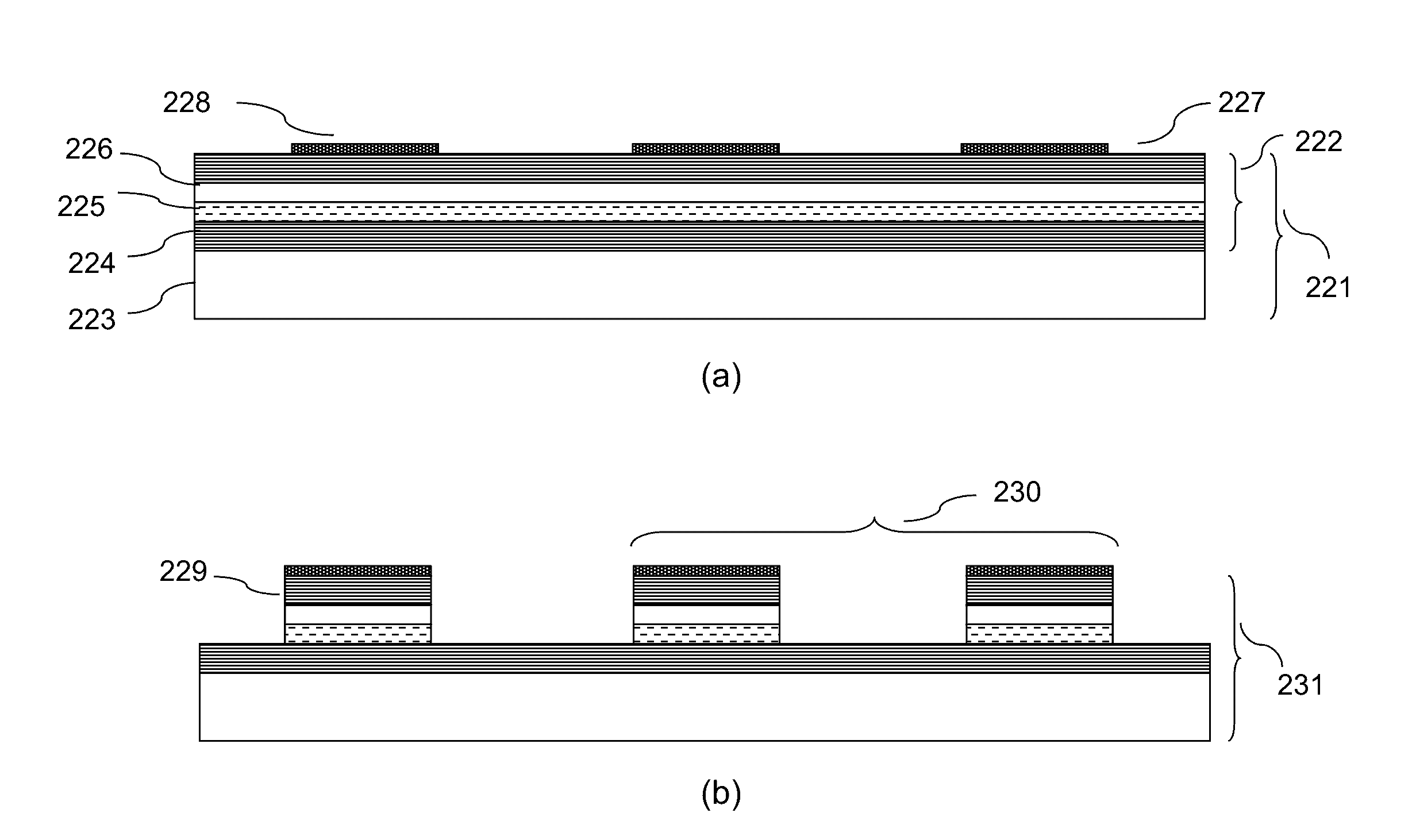

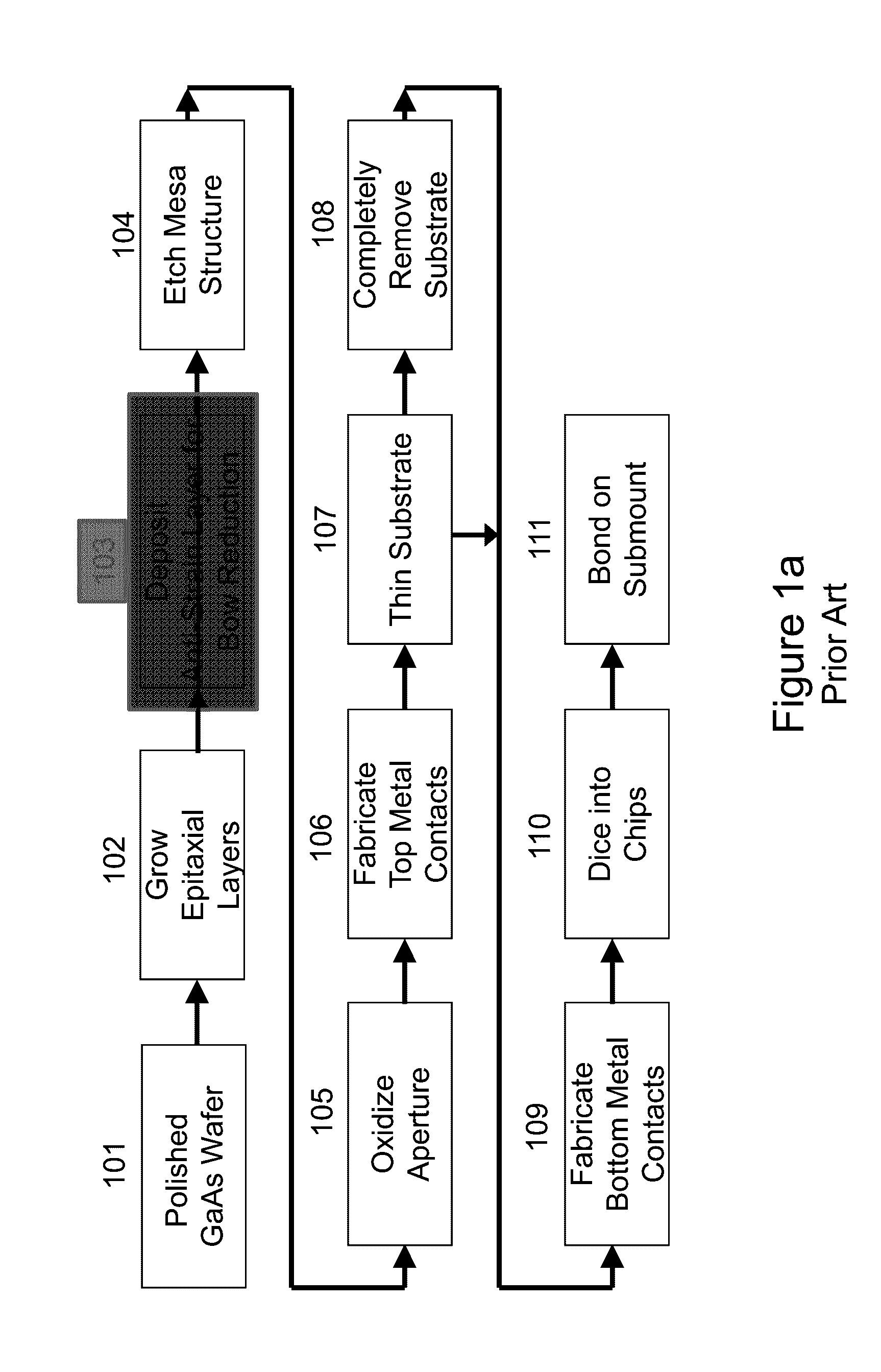

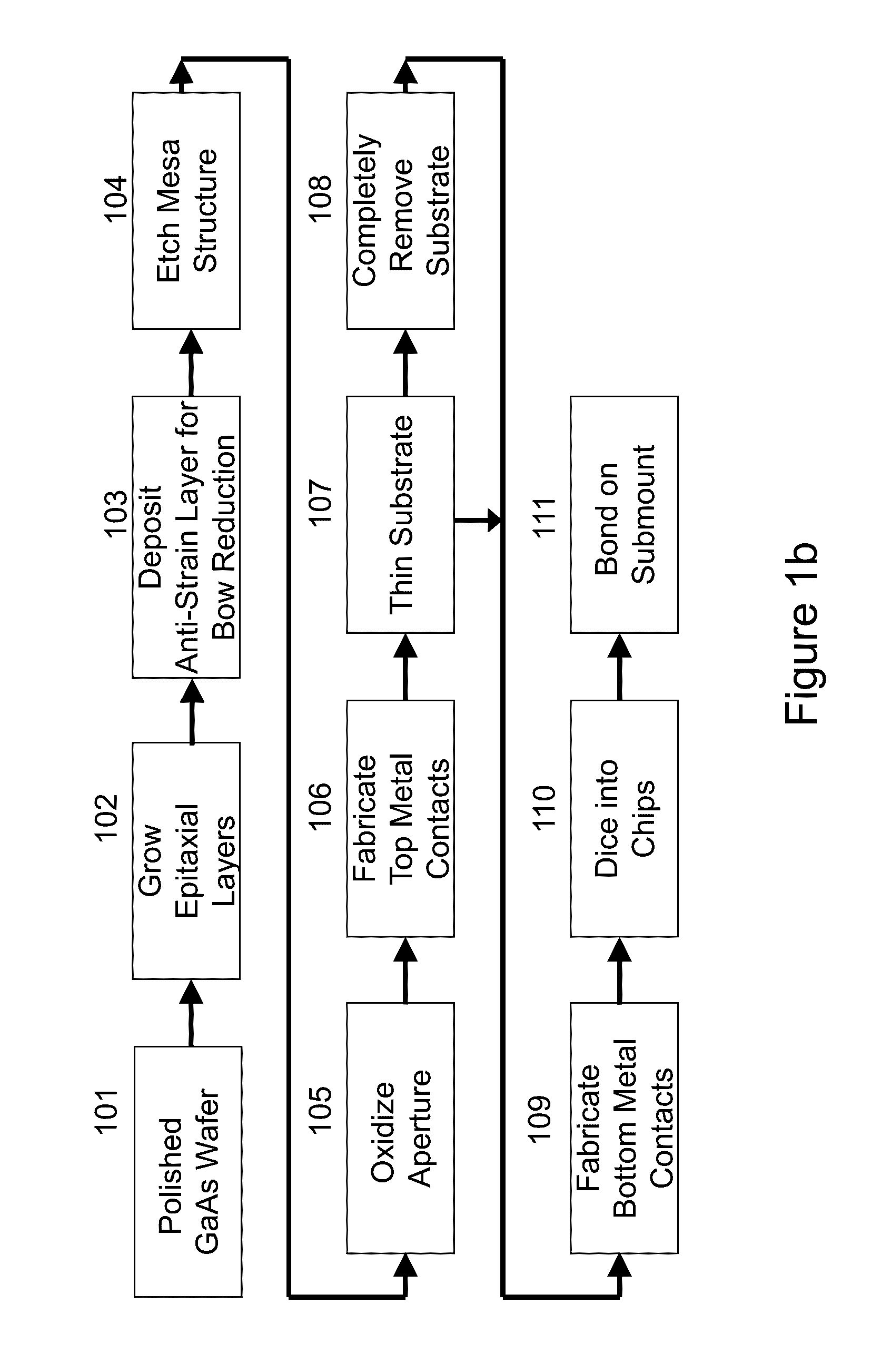

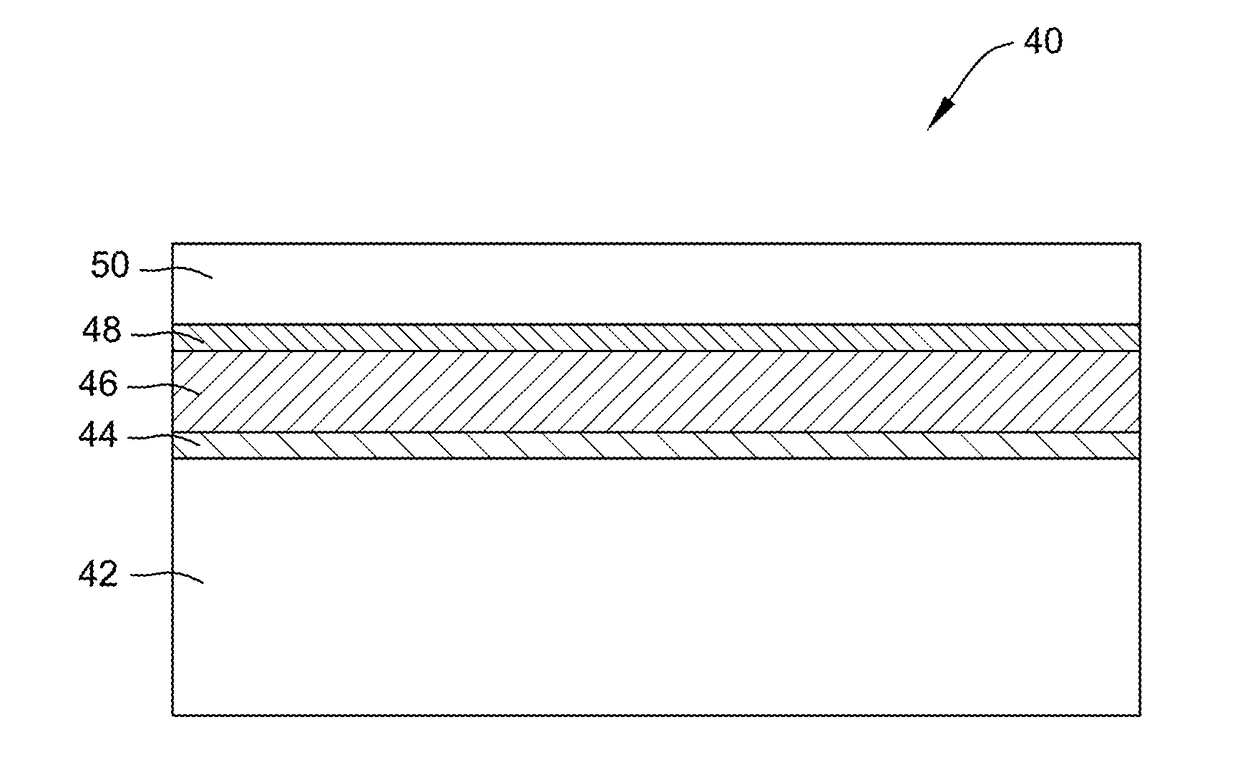

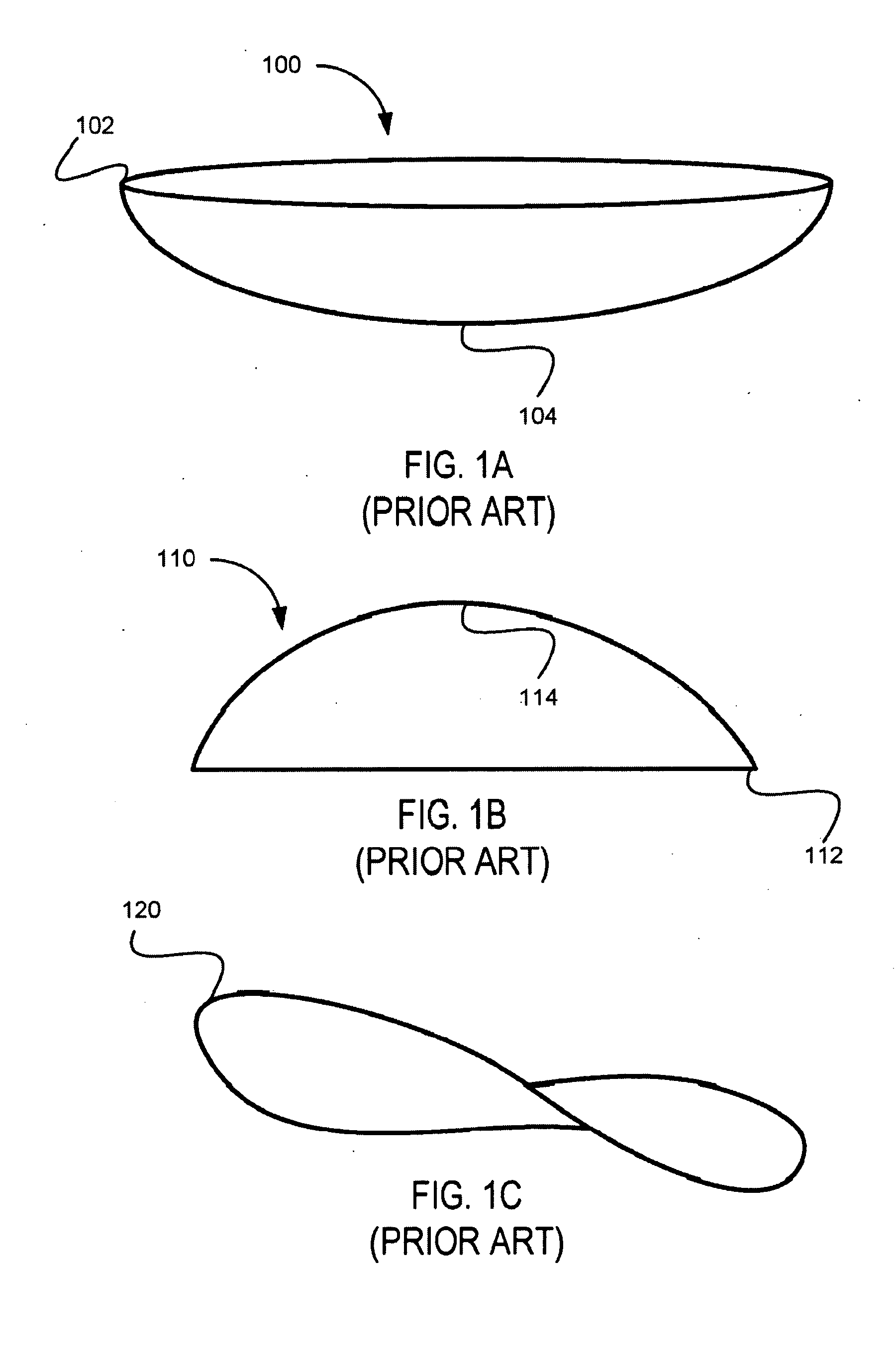

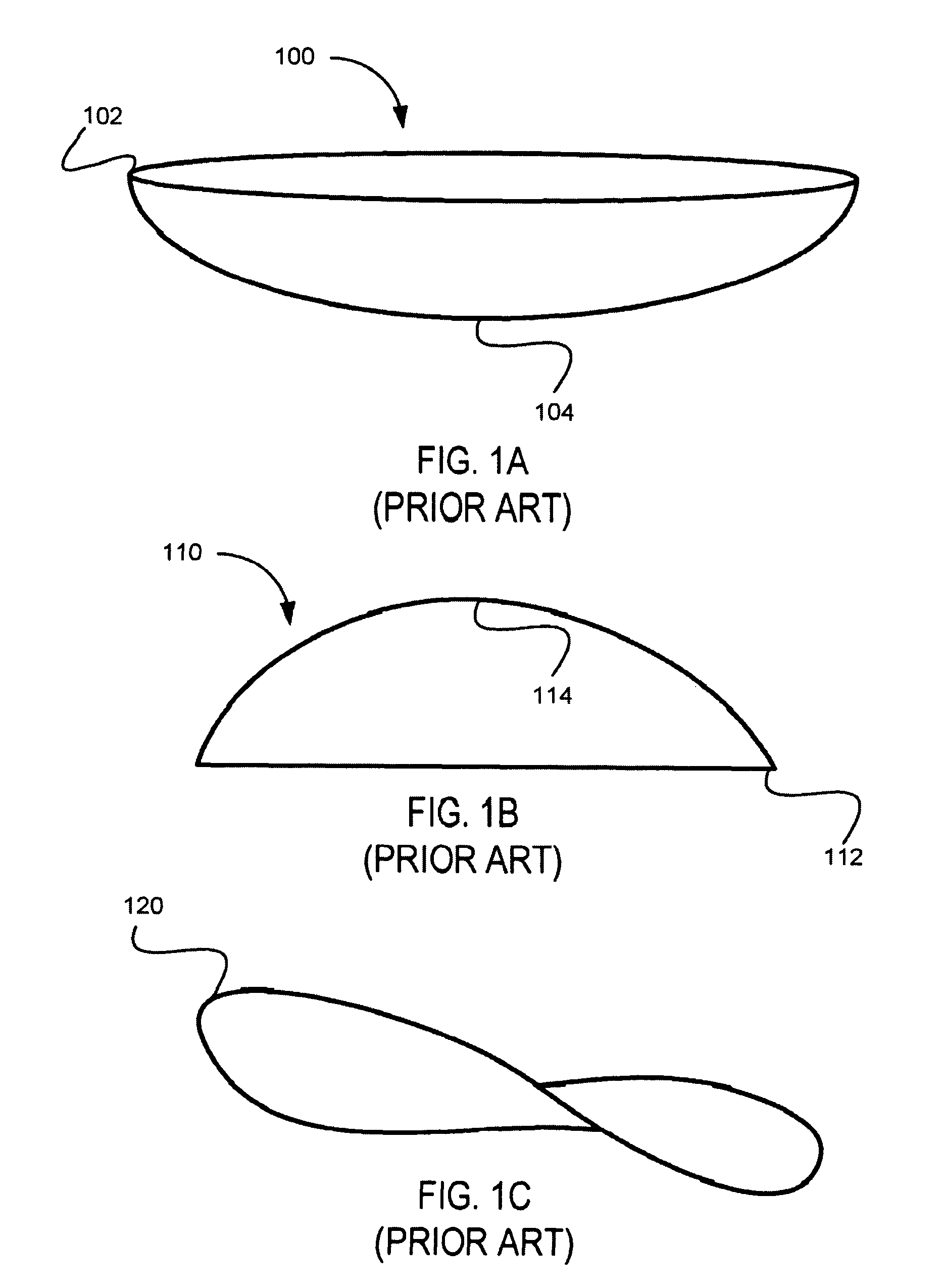

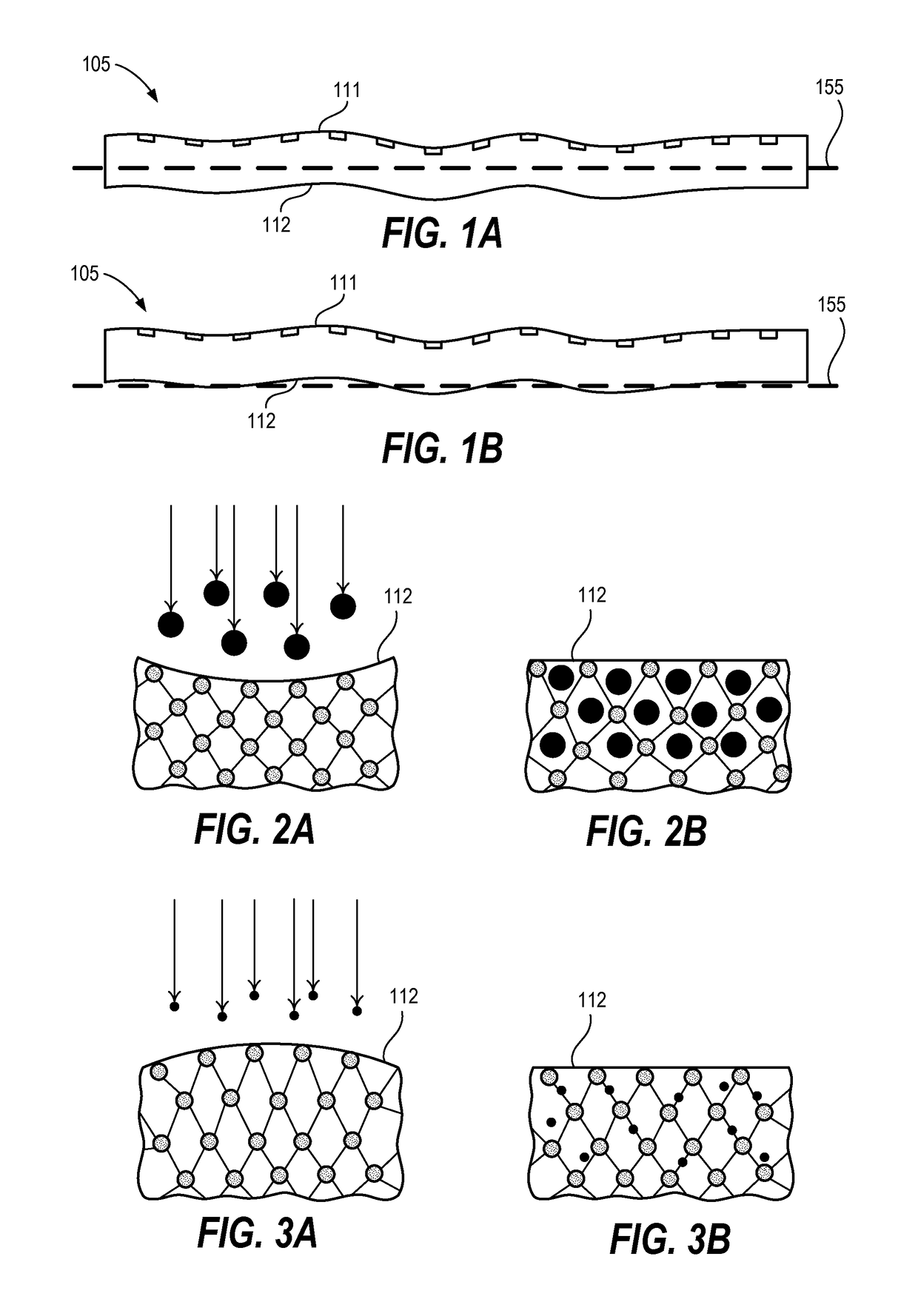

A set of VCSEL fabrication methods has been invented which enhance the performance and long time reliability of VCSEL devices and arrays of devices. Wafer bow caused by growing a large number of epitaxial layers required to fabricate VCSEL device generates strain and results in bowing / warping of the device wafer. The stress so generated is eliminated by applying a stress compensation layer on the substrate to a surface opposite to the epitaxial layer surface. New oxidation equipment designs and process parameters are described which produce more precision apertures and reduce stress in the VCSEL device. An ultrathin fabrication procedure is described which enables high power VCSELs to be made for high power operation at many different wavelengths. A low temperature electrical contacting process improves VCSEL long term reliability.

Owner:PRINCETON OPTRONICS

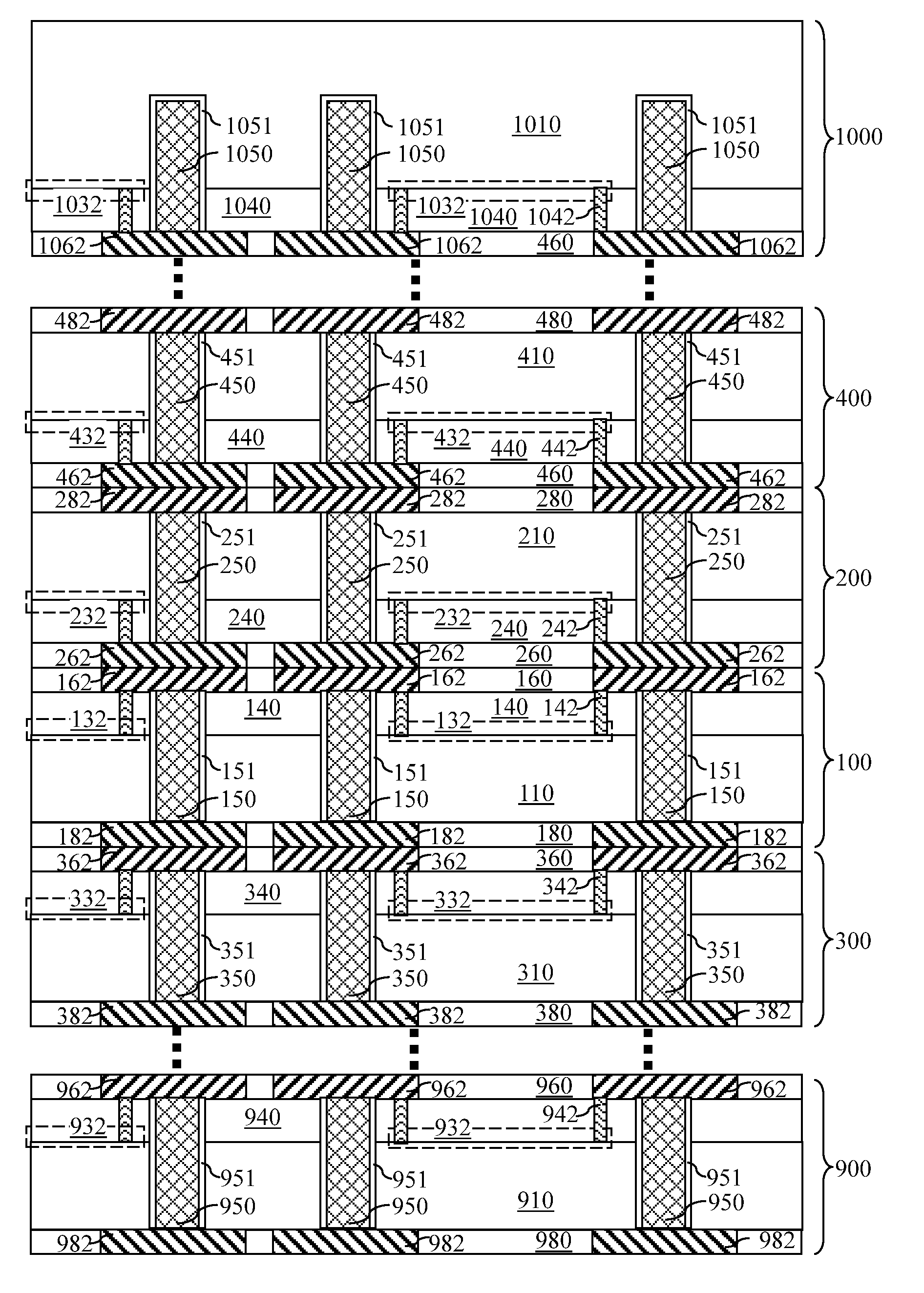

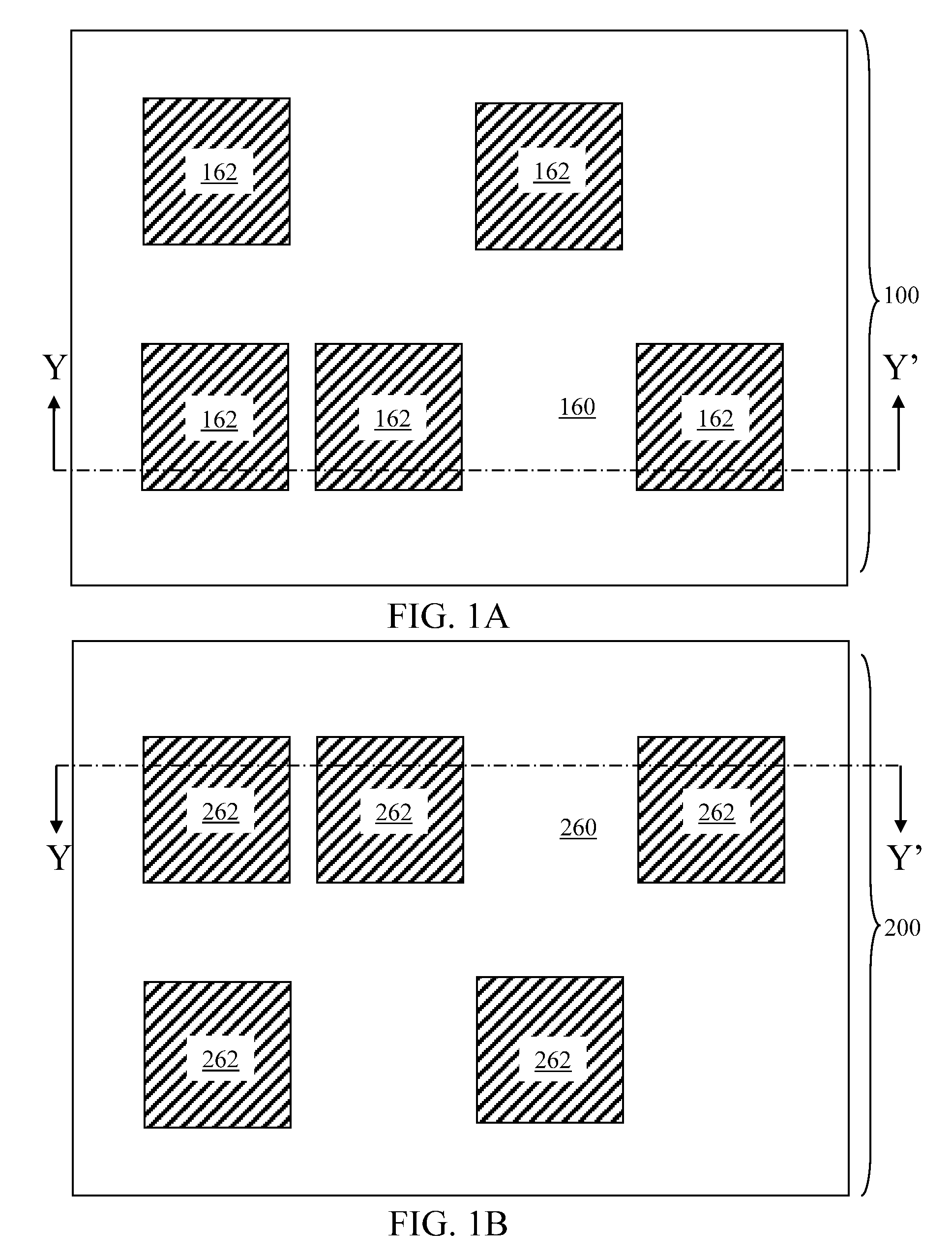

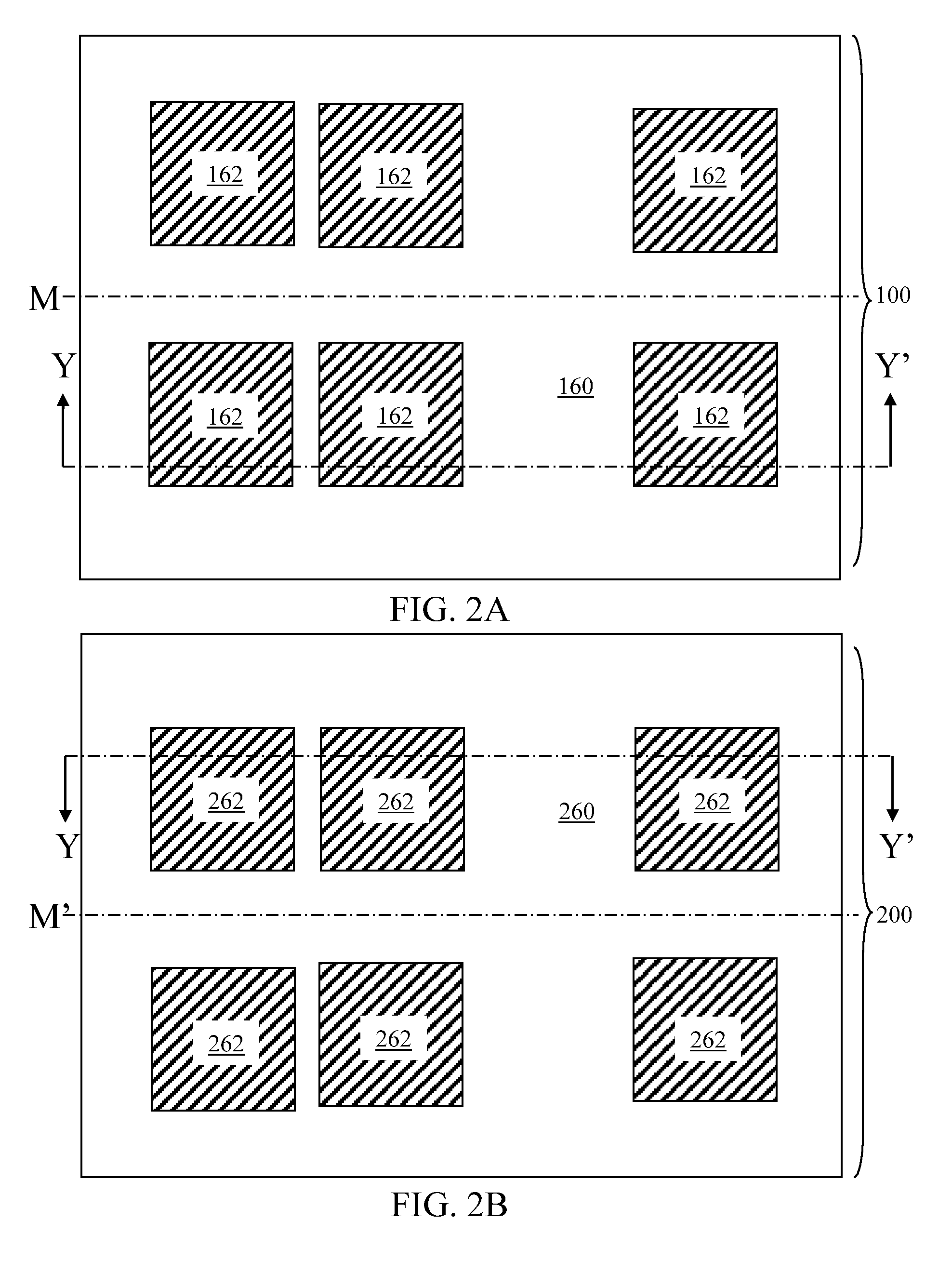

Bow-balanced 3D chip stacking

InactiveUS8546188B2Maximal cancellationSemiconductor/solid-state device detailsSolid-state devicesWafer bowSemiconductor chip

A first set of semiconductor substrates includes semiconductor chips having bonding pads arranged in a primary pattern. A second set of semiconductor substrates includes semiconductor chips having bonding pads arranged in a mirror-image pattern. A first semiconductor substrate from the first set is bonded to a second semiconductor substrate from the second set such that each bonding pads is bonded to a mirror-image bonding pad. Additional substrates are bonded sequentially such that the bonded structure includes an even number of semiconductor substrates of which one half have bonding pads of the primary pattern and are bonded to the side of the first semiconductor substrate, while the other half have bonding pads of the mirror-image pattern and are bonded to the side of the second semiconductor substrate. The mirror-image patterns of the bonding pads enable maximal cancellation of wafer bow.

Owner:IBM CORP

Method for Correcting Wafer Bow from Overlay

ActiveUS20150294917A1Easy to stackReduce yieldSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingWafer bowSemiconductor

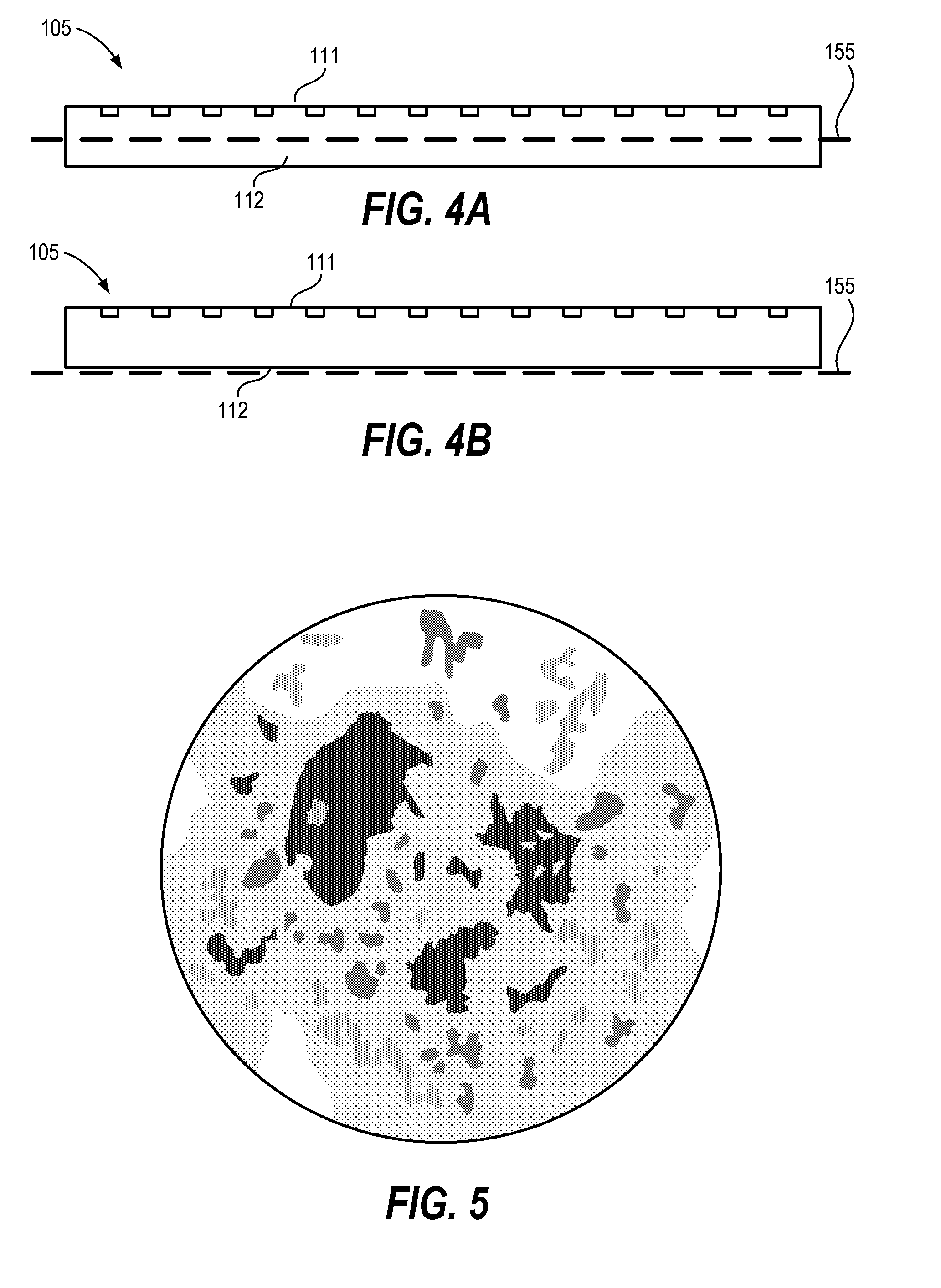

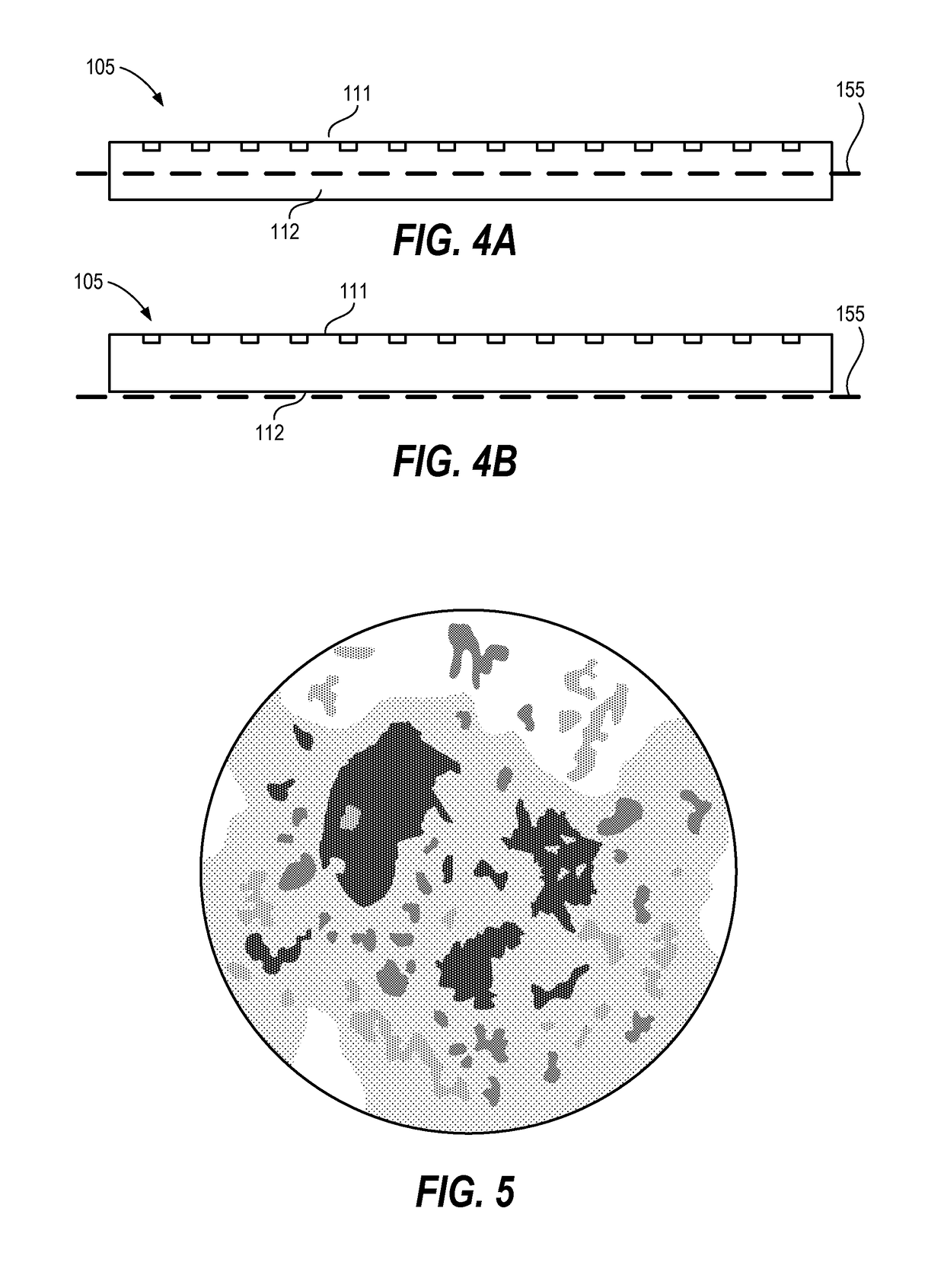

Described herein are methods for flattening a substrate, such as a semiconductor wafer, to reduce bowing in such substrates. Methods include treating or bombarding a backside surface of a substrate with particles of varying doses, densities, and spatial locations. Particle bombardment and selection is such that the substrate becomes more planar by selectively increasing or decreasing z-height points to reduce overall deflection. One or more tensile or compressive films can be added to the backside surface to be selectively relaxed at specific point locations. Such methods can correct bowing in substrates resulting from various fabrication processes such as thermal annealing.

Owner:TOKYO ELECTRON LTD

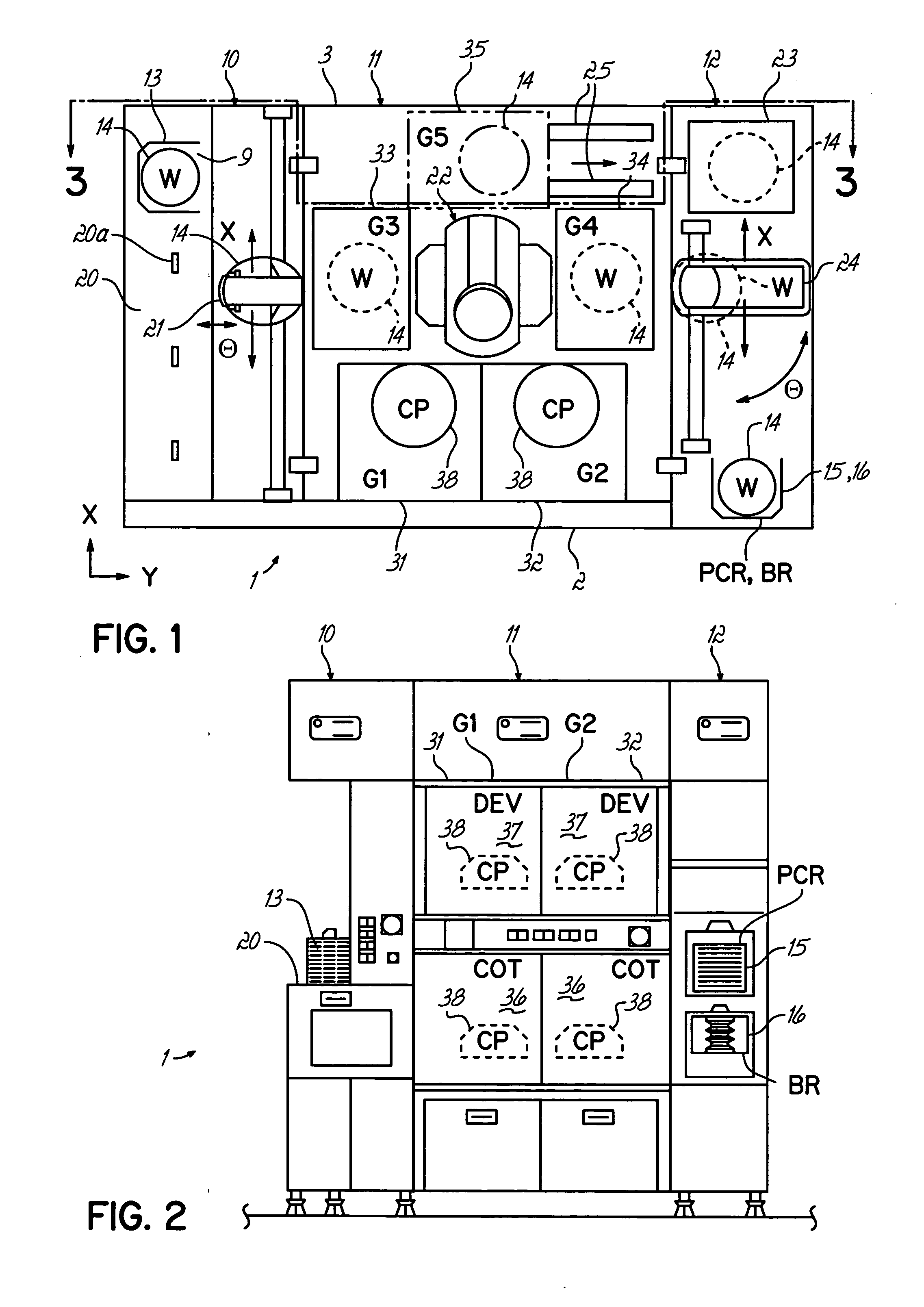

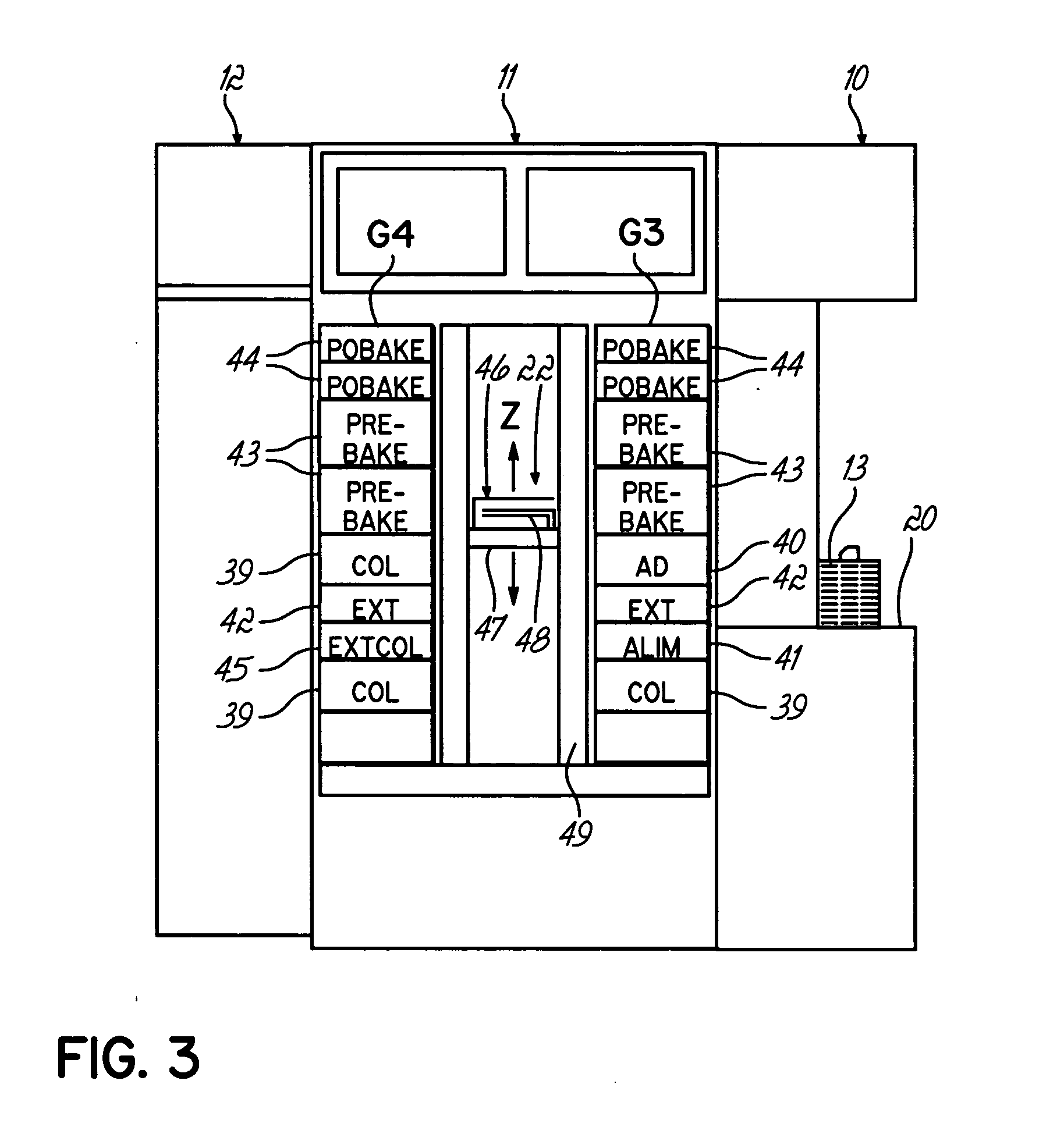

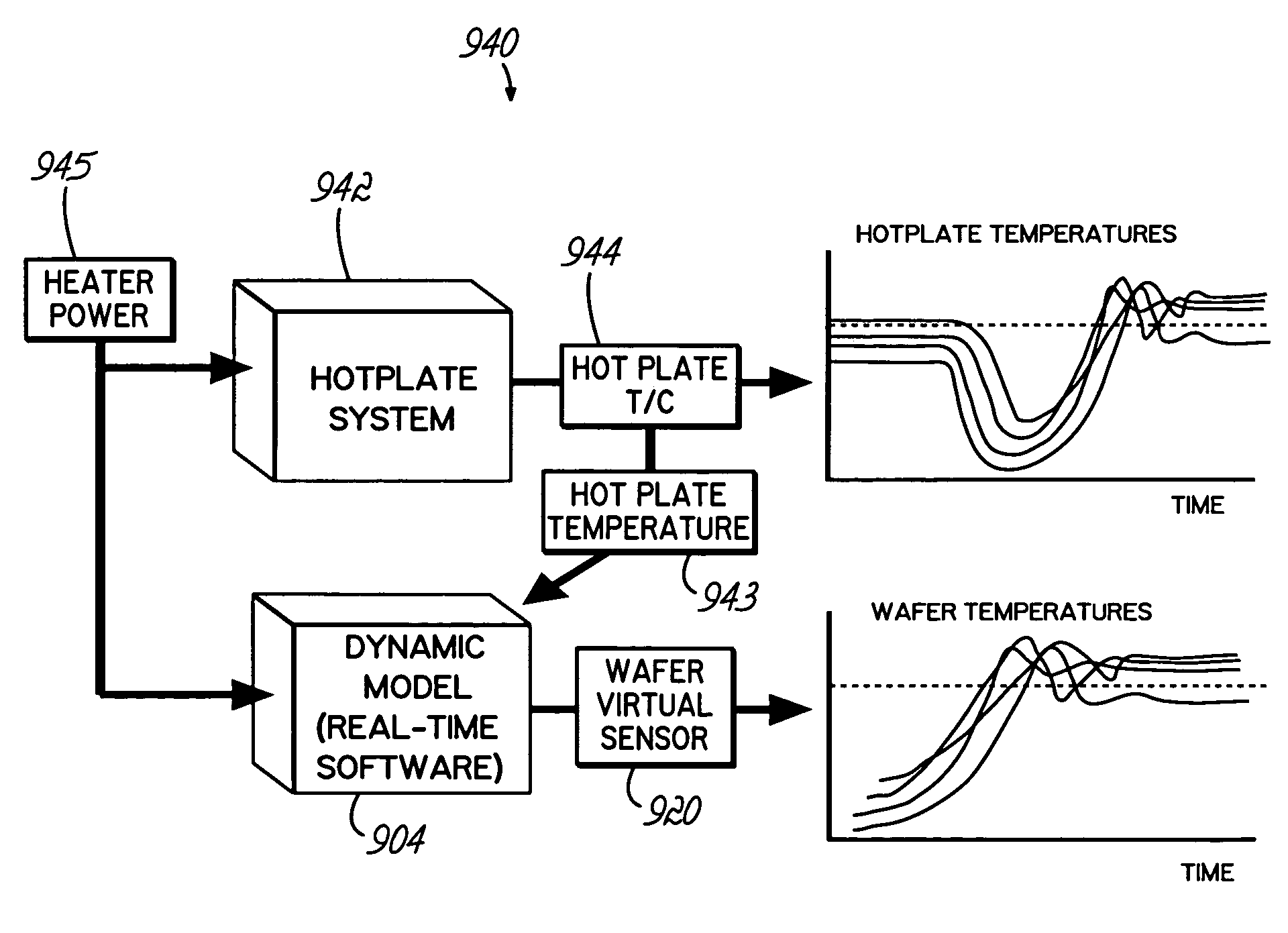

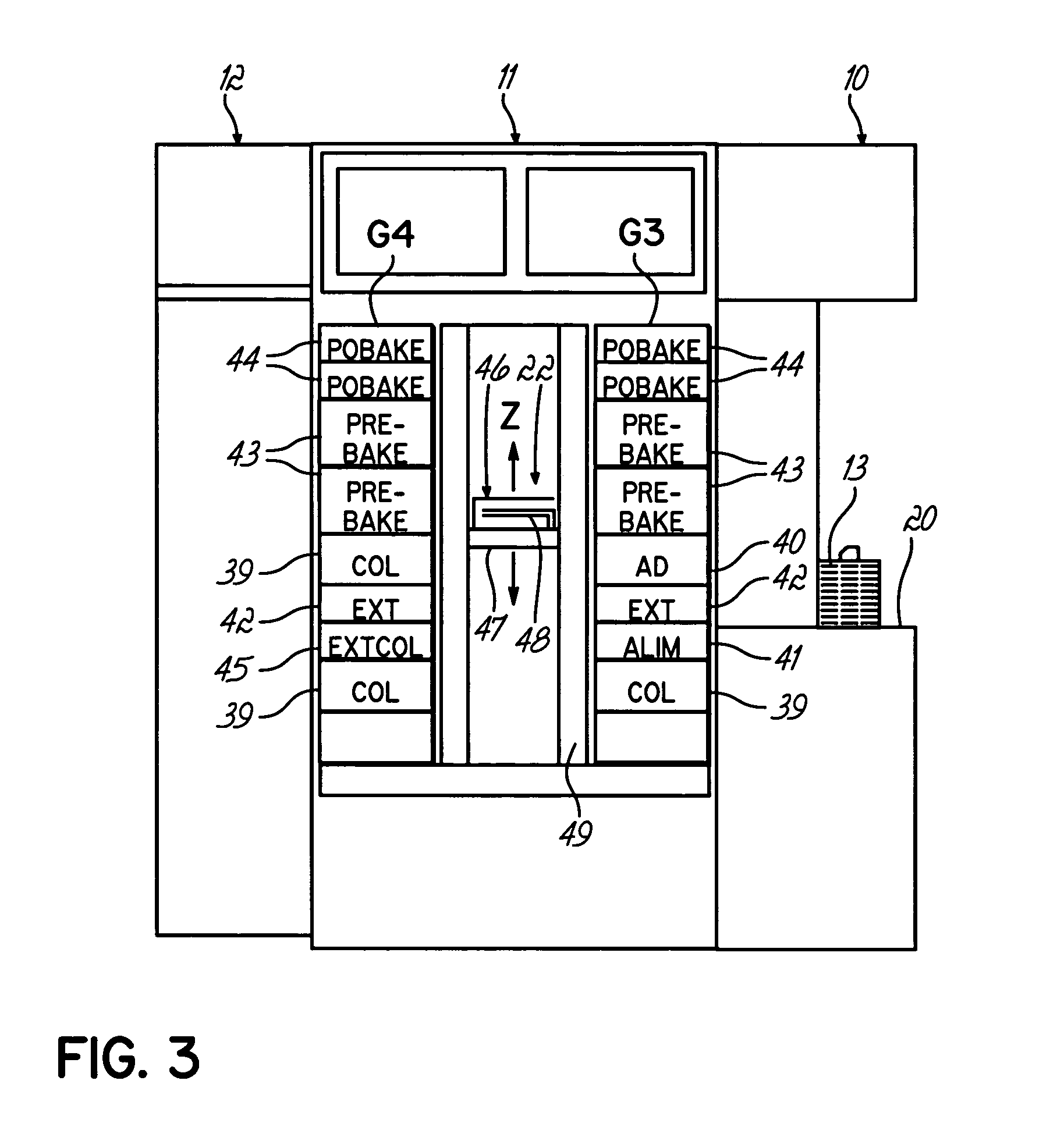

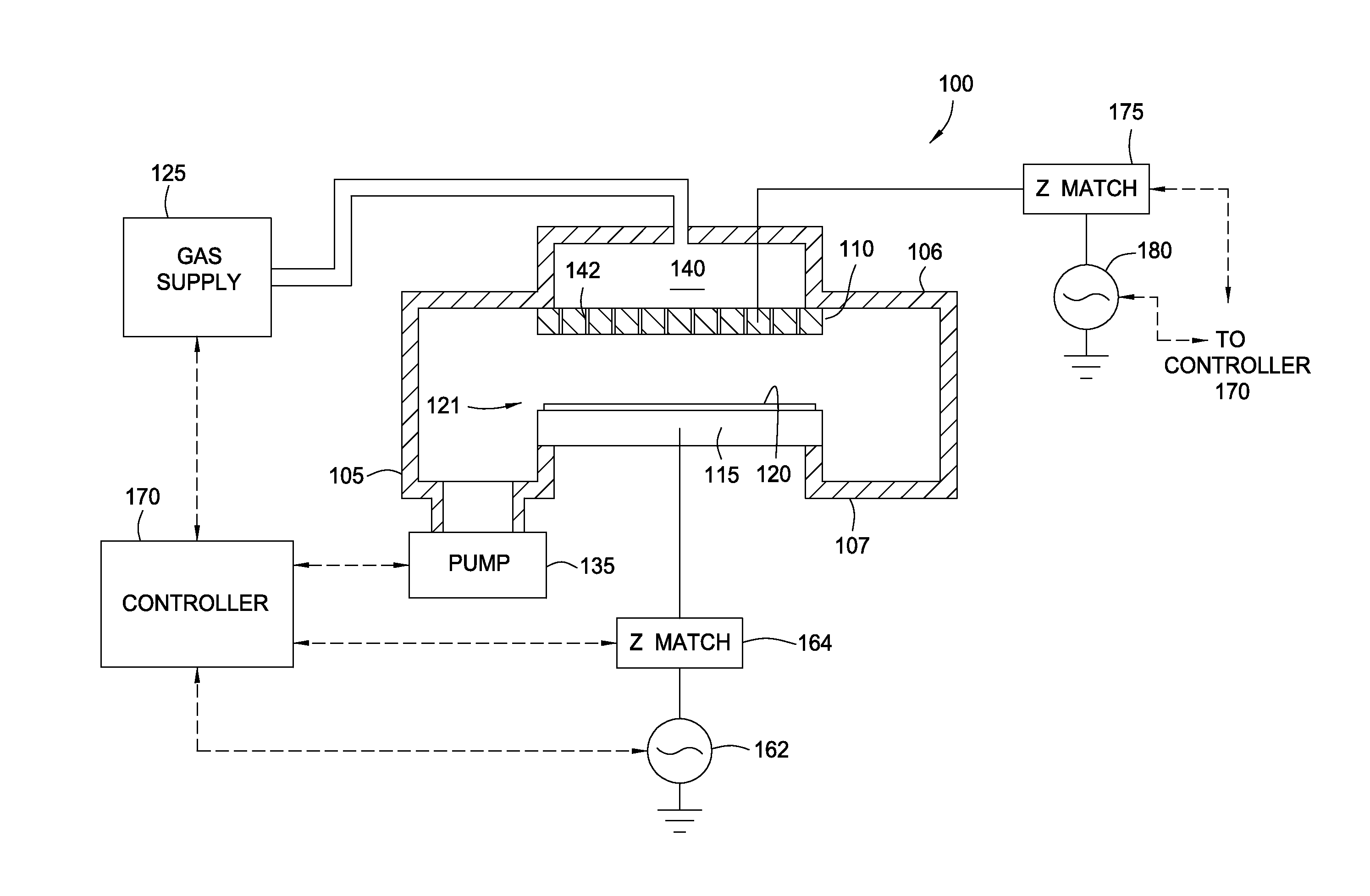

Methods for adaptive real time control of a thermal processing system

InactiveUS20050149886A1Easy to controlUniform temperature profileForce measurementSemiconductor/solid-state device manufacturingWafer bowDynamic models

Methods for adaptive real time control of a system for thermal processing substrates, such as semiconductor wafers and display panels. Generally, the method includes creating a dynamic model of the thermal processing system, incorporating wafer bow in the dynamic model, coupling a diffusion-amplification model into the dynamic thermal model, creating a multivariable controller, parameterizing the nominal setpoints, creating a process sensitivity matrix, creating intelligent setpoints using an efficient optimization method and process data, and establishing recipes that select appropriate models and setpoints during run-time.

Owner:TOKYO ELECTRON LTD

Methods for adaptive real time control of a thermal processing system

InactiveUS7101816B2Force measurementSemiconductor/solid-state device manufacturingWafer bowDynamic models

Methods for adaptive real time control of a system for thermal processing substrates, such as semiconductor wafers and display panels. Generally, the method includes creating a dynamic model of the thermal processing system, incorporating wafer bow in the dynamic model, coupling a diffusion-amplification model into the dynamic thermal model, creating a multivariable controller, parameterizing the nominal setpoints, creating a process sensitivity matrix, creating intelligent setpoints using an efficient optimization method and process data, and establishing recipes that select appropriate models and setpoints during run-time.

Owner:TOKYO ELECTRON LTD

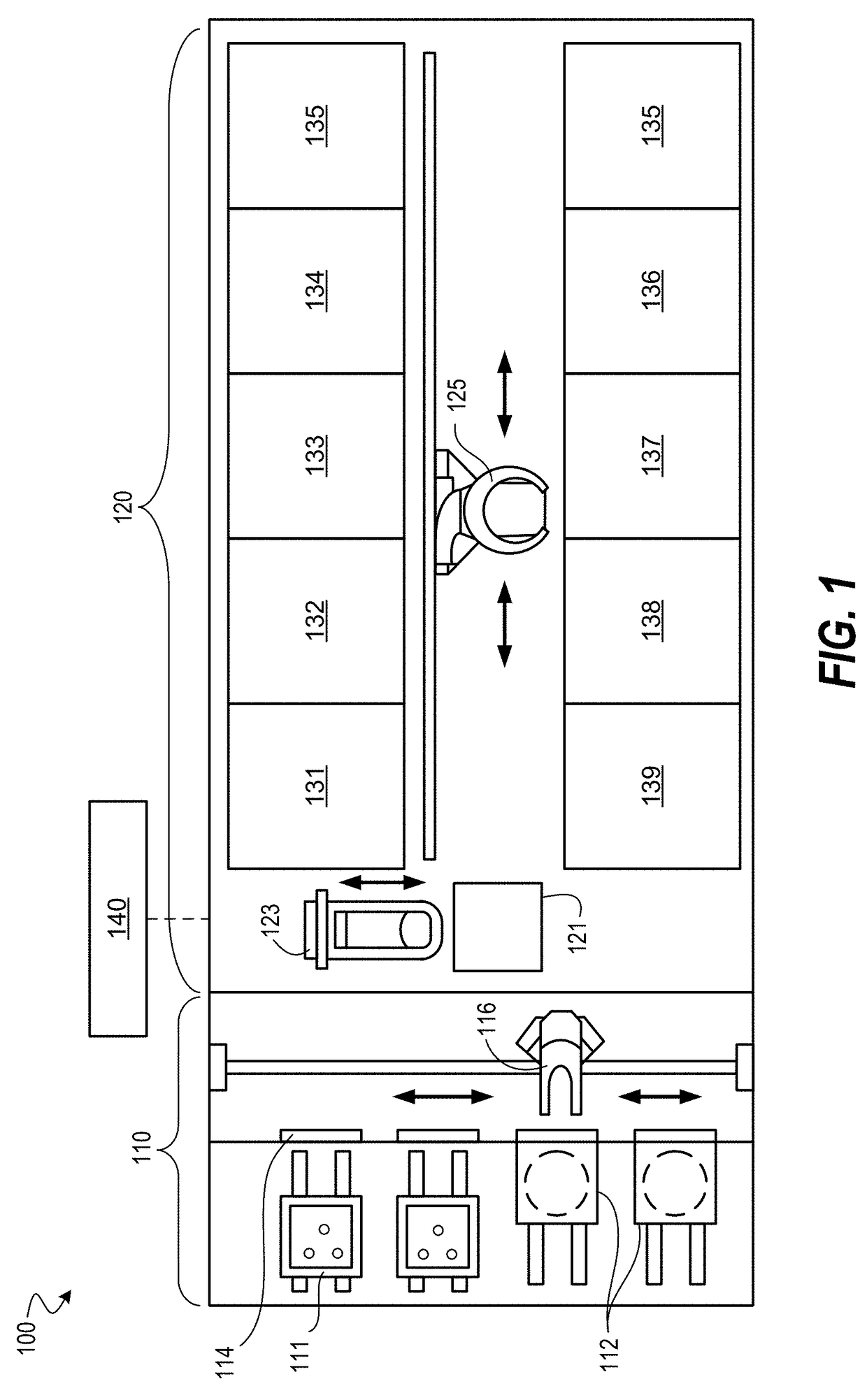

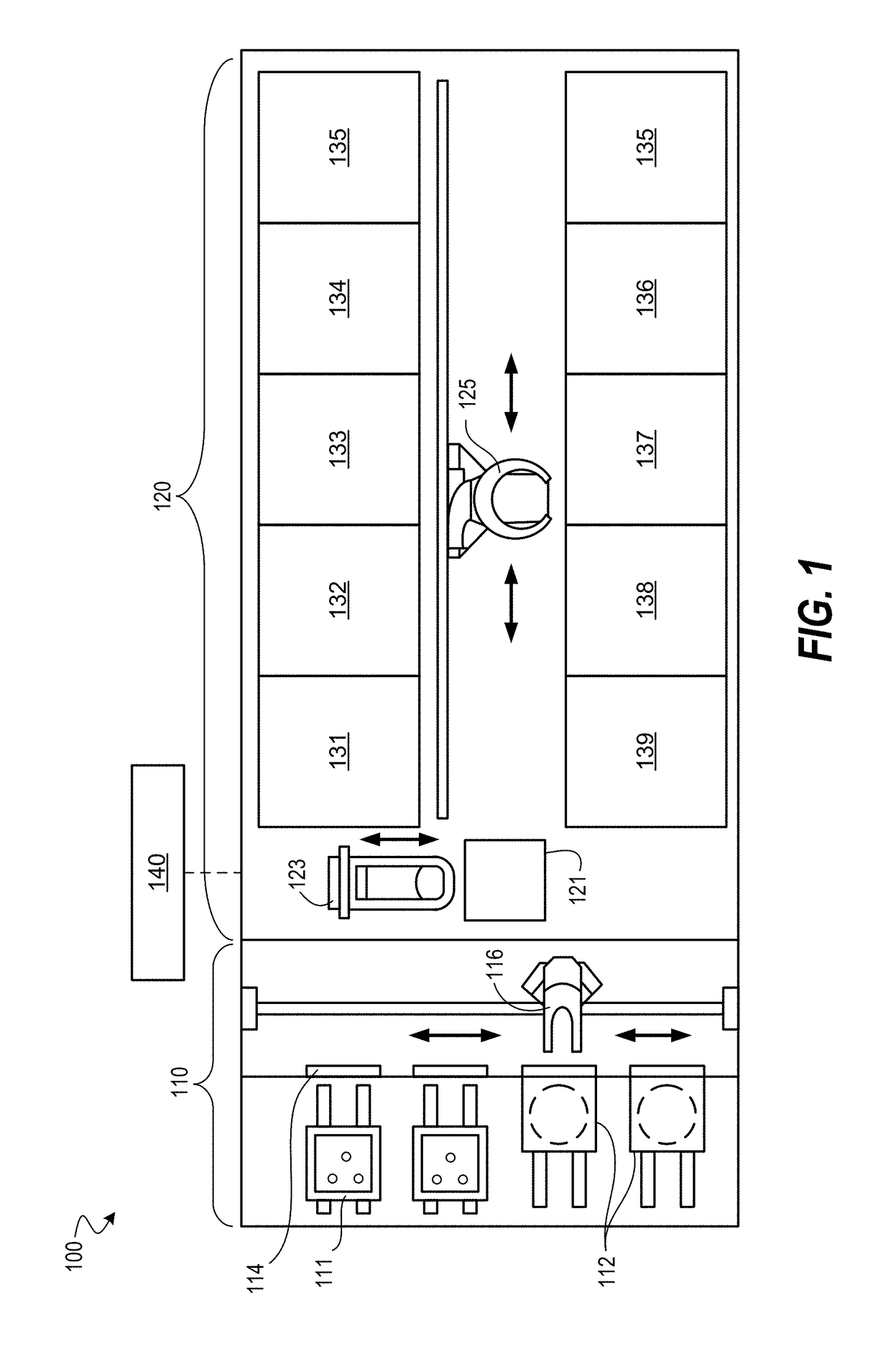

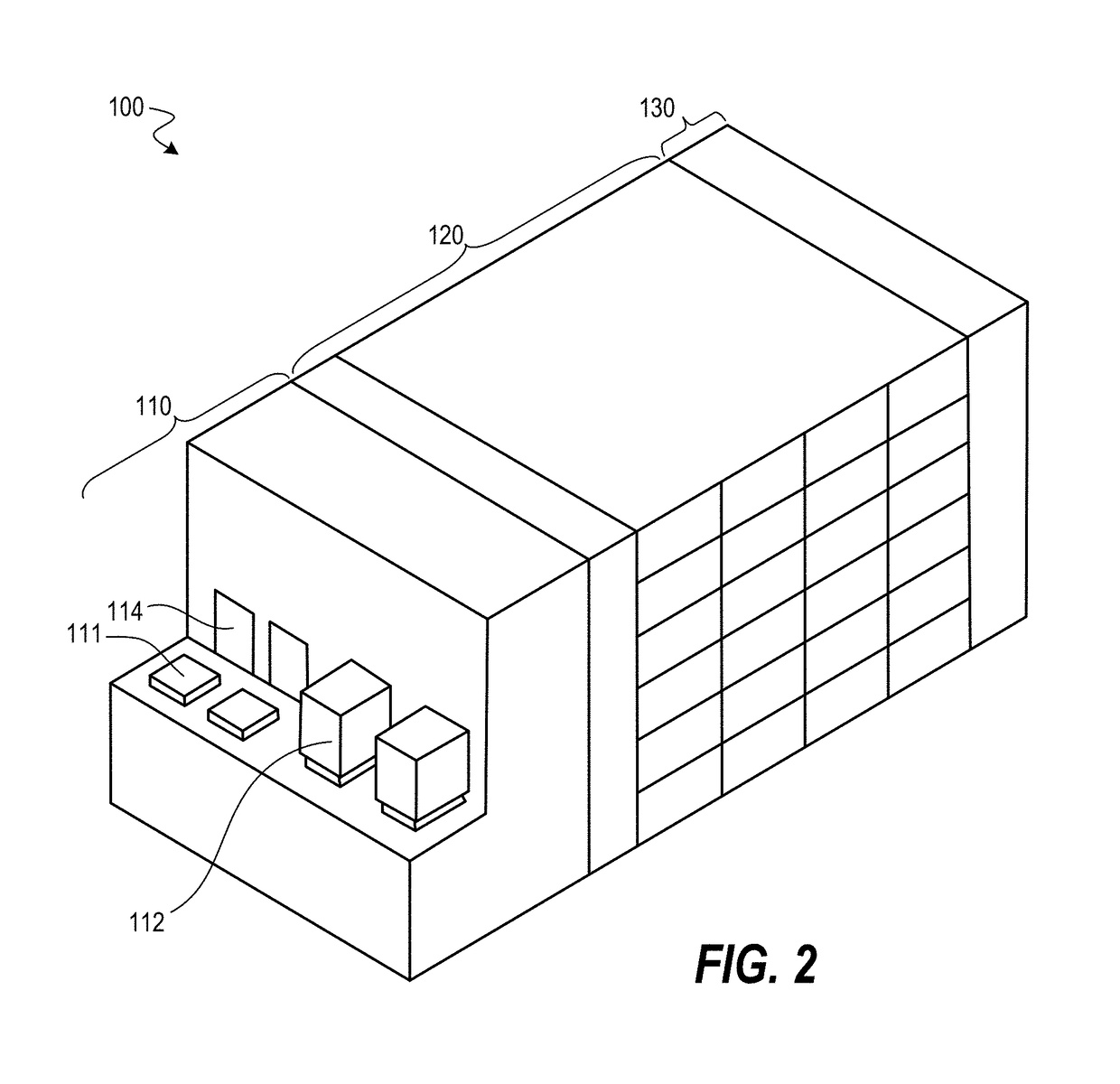

Location-Specific Tuning of Stress to Control Bow to Control Overlay In Semiconductor Processing

Techniques herein include systems and methods for correcting pattern overlay errors by correcting or adjusting bowing of wafers. Location-specific tuning of stress on semiconductor substrates reduces overlay error. Location-specific tuning of stress independently modifies specific regions, areas, or point locations on a substrate to change wafer bow at those specific locations, which reduces overlay error on substrates, which in turn improves overlay of subsequent patterns created on the substrate. Techniques herein include receiving a substrate with some amount of overlay error, measuring bow of the substrate to map z-height deviations across the substrate, generating an overlay correction pattern, and then physically modifying internal stresses on the substrate at specific locations with modifications independent of other coordinate locations. Such modifications can include etching a backside surface of the substrate. One or more processing modules can be used for such processing.

Owner:TOKYO ELECTRON LTD

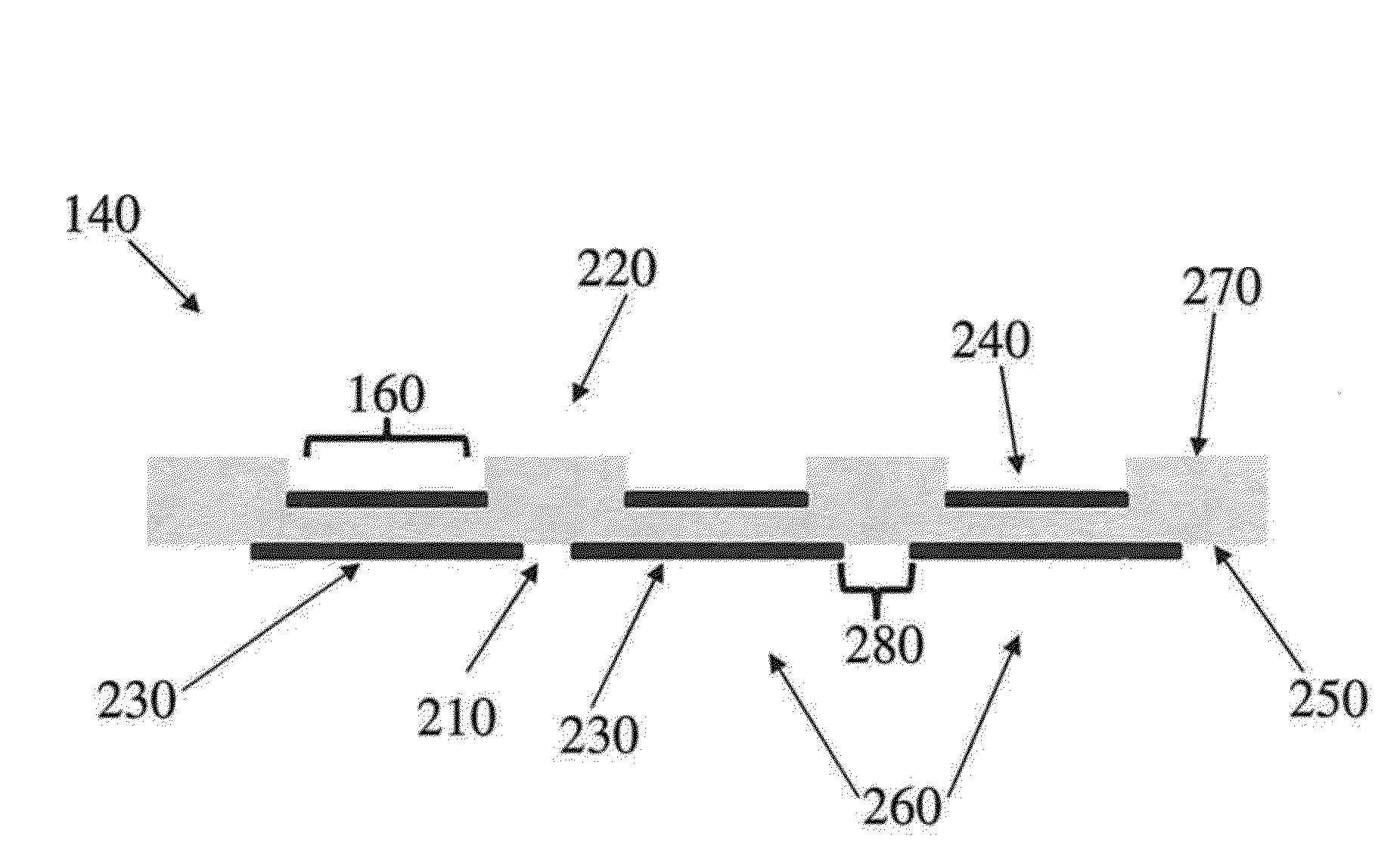

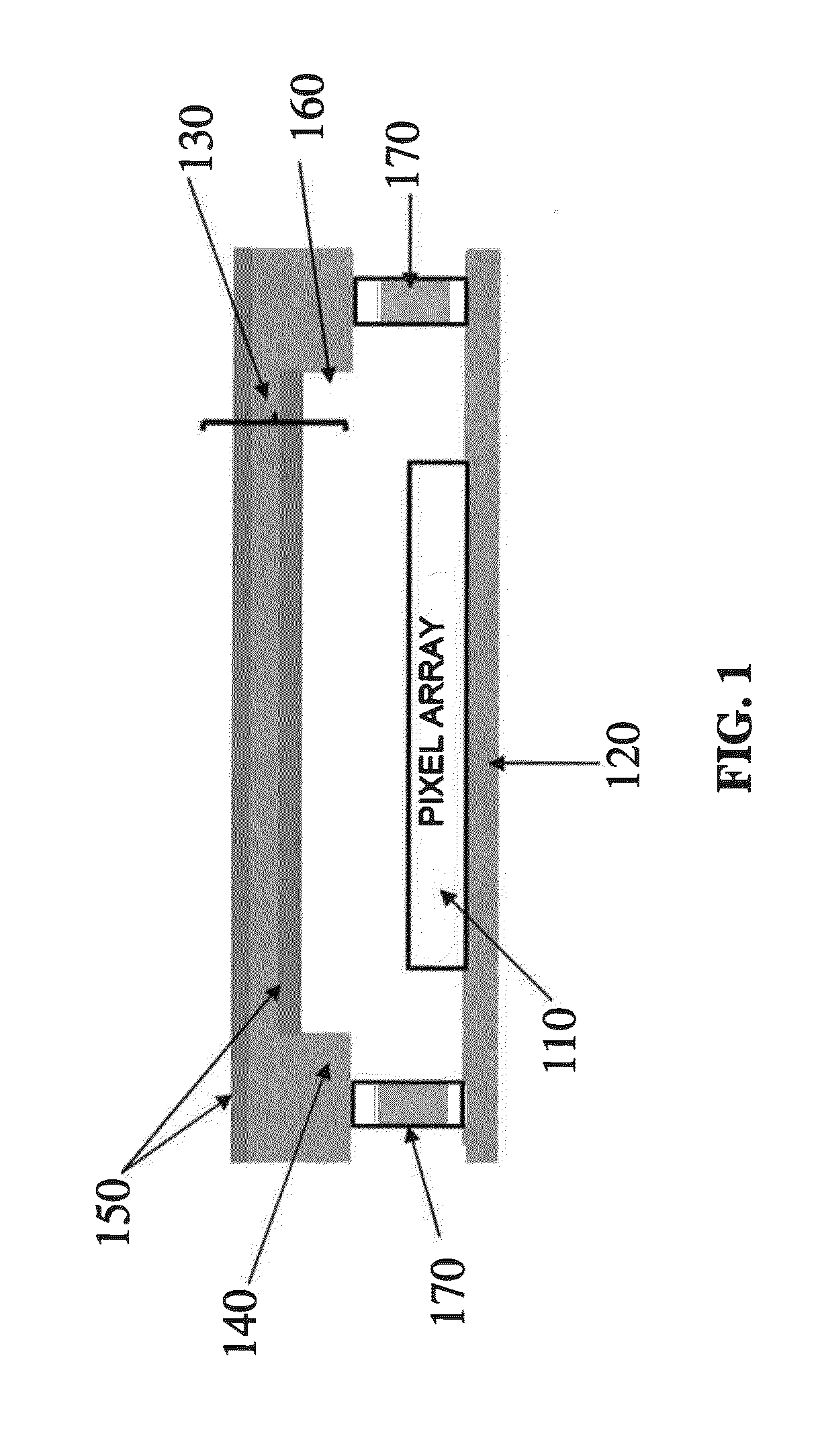

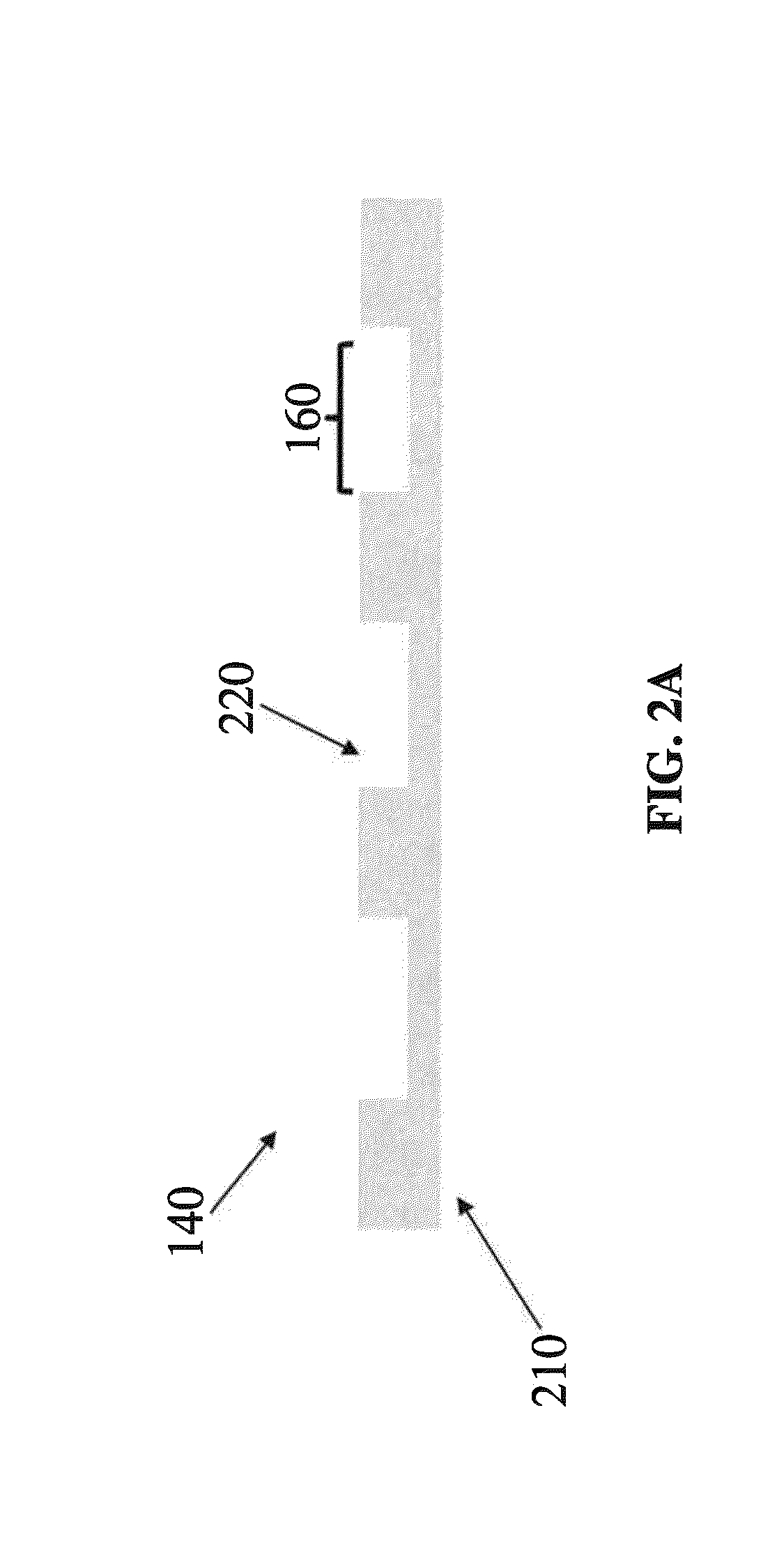

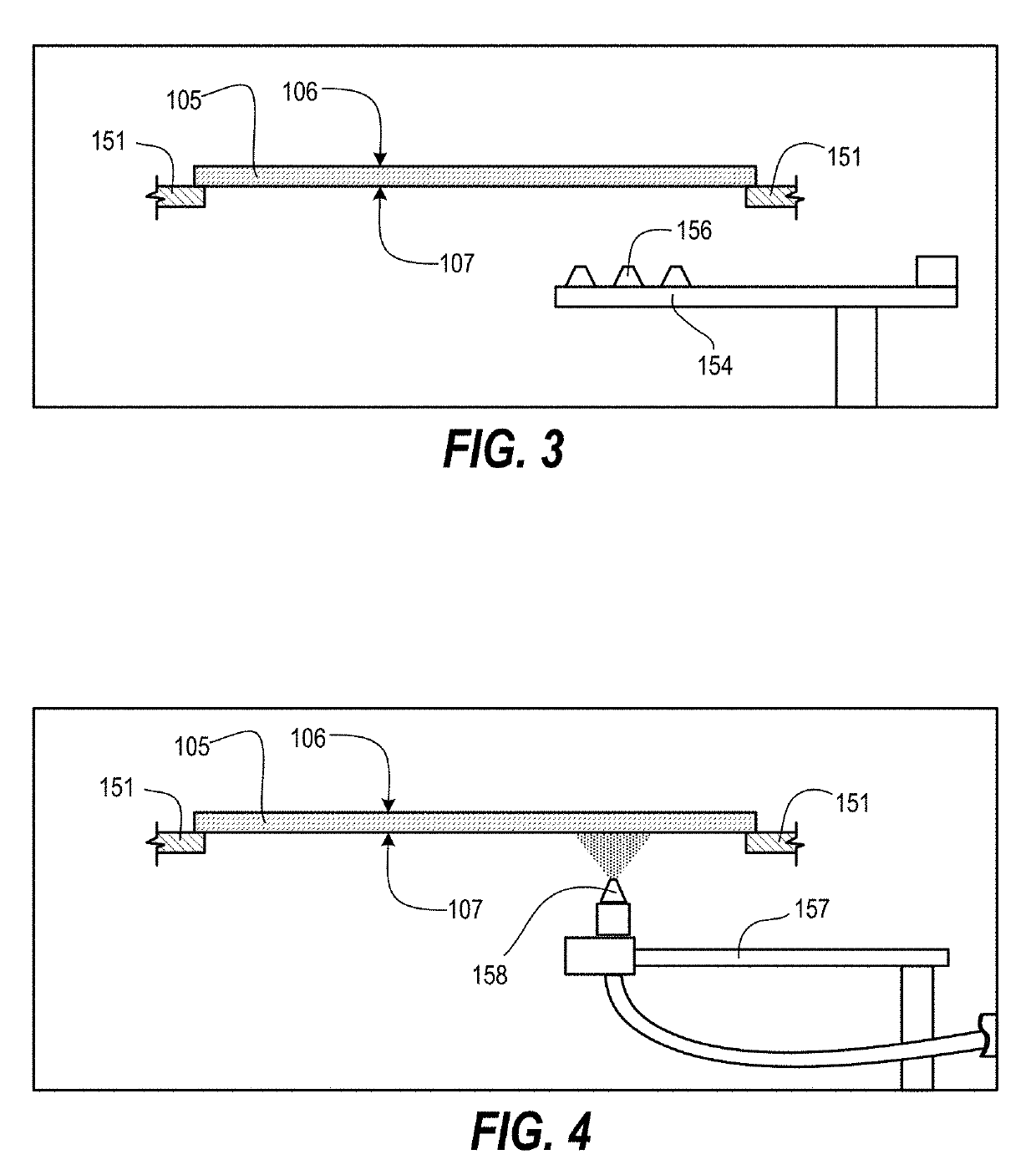

Processes for making reliable VCSEL devices and VCSEL arrays

ActiveUS9520696B2Improve reliabilityCounteract significant bowing and warpingLaser detailsSemiconductor laser structural detailsElectricityWafer bow

A set of VCSEL fabrication methods has been invented which enhance the performance and long time reliability of VCSEL devices and arrays of devices. Wafer bow caused by growing a large number of epitaxial layers required to fabricate VCSEL device generates strain and results in bowing / warping of the device wafer. The stress so generated is eliminated by applying a stress compensation layer on the substrate to a surface opposite to the epitaxial layer surface. New oxidation equipment designs and process parameters are described which produce more precision apertures and reduce stress in the VCSEL device. An ultrathin fabrication procedure is described which enables high power VCSELs to be made for high power operation at many different wavelengths. A low temperature electrical contacting process improves VCSEL long term reliability.

Owner:PRINCETON OPTRONICS

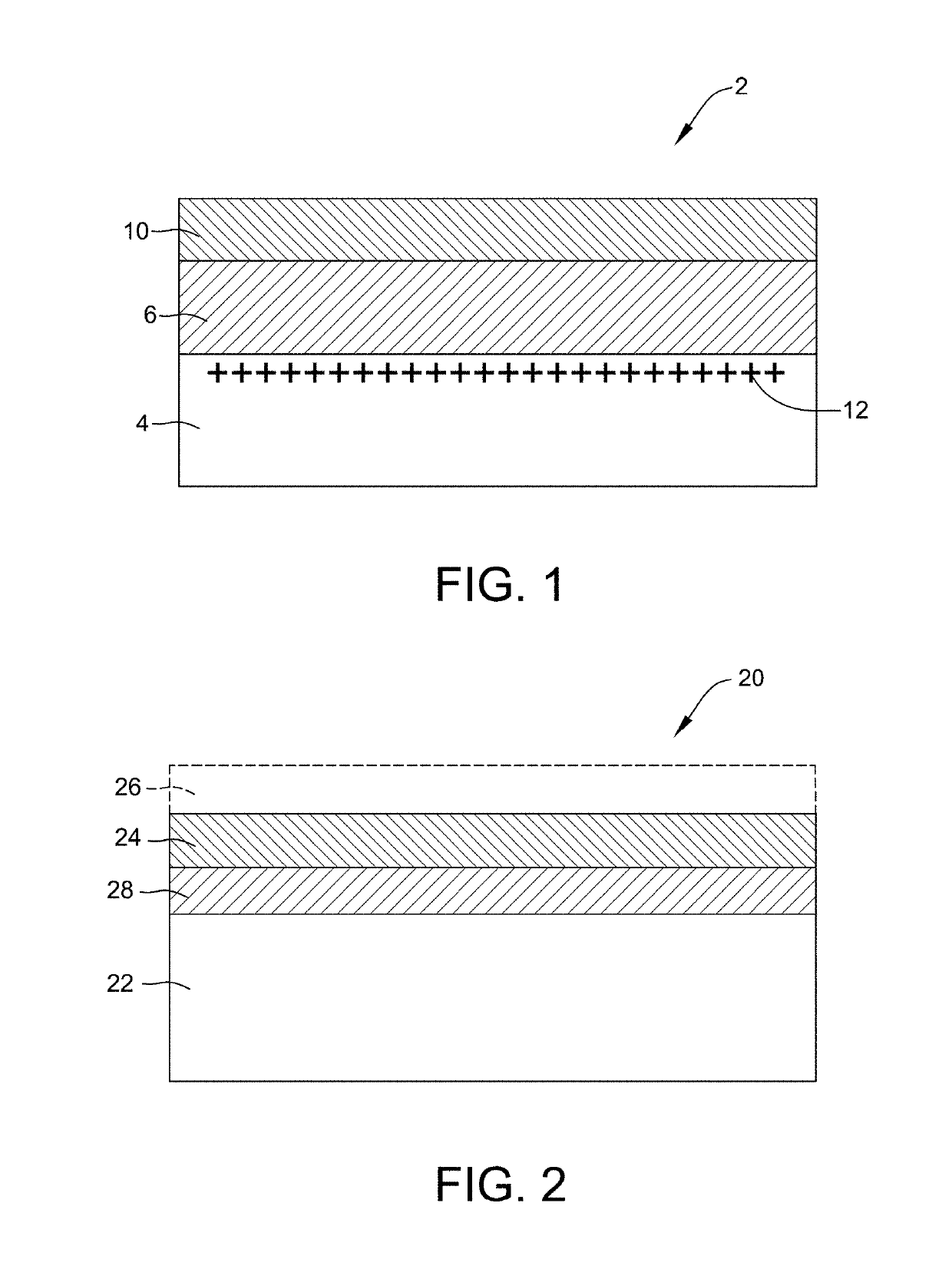

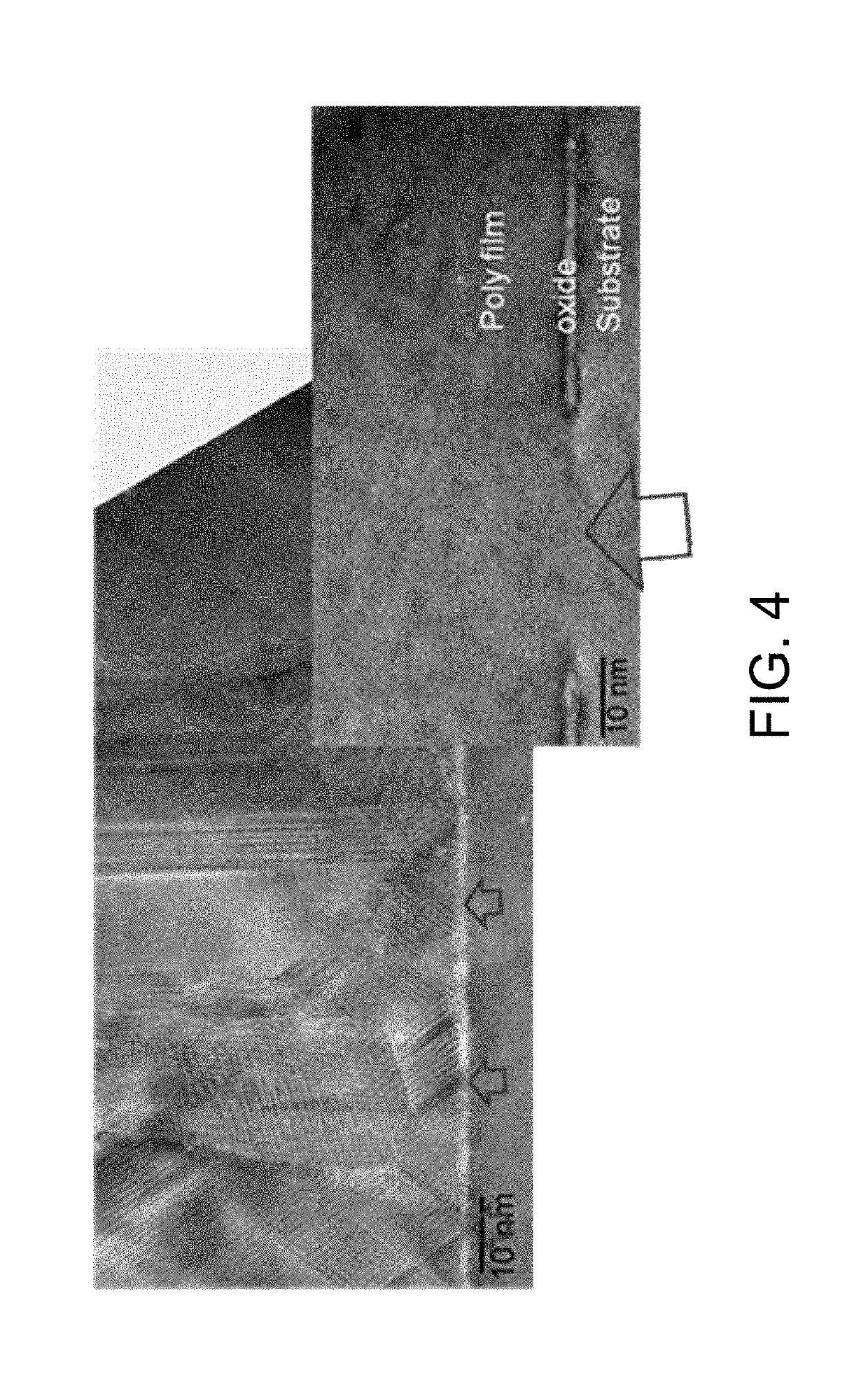

Method of depositing charge trapping polycrystalline silicon films on silicon substrates with controllable film stress

ActiveUS20180233400A1Solid-state devicesSemiconductor/solid-state device manufacturingWafer bowWafering

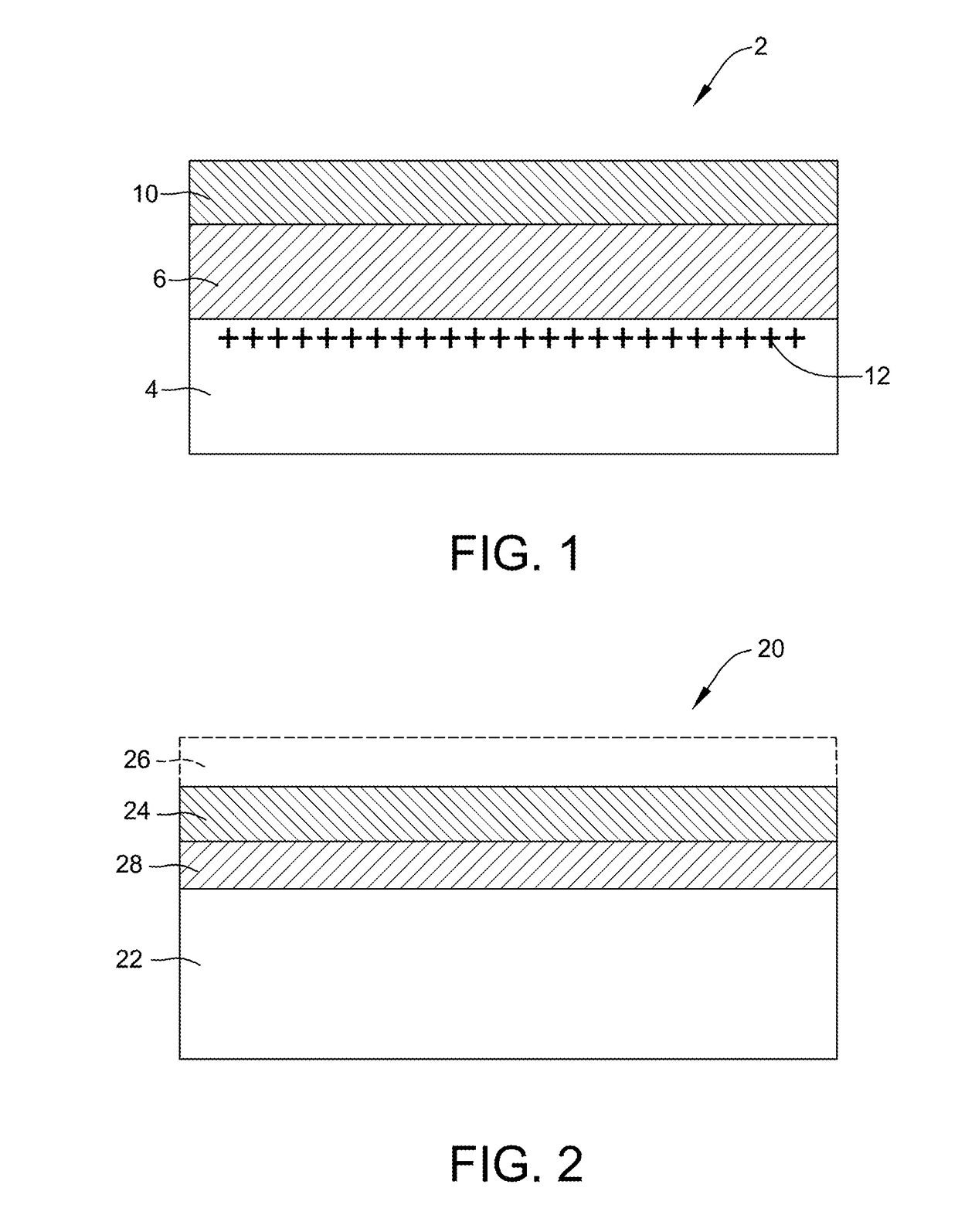

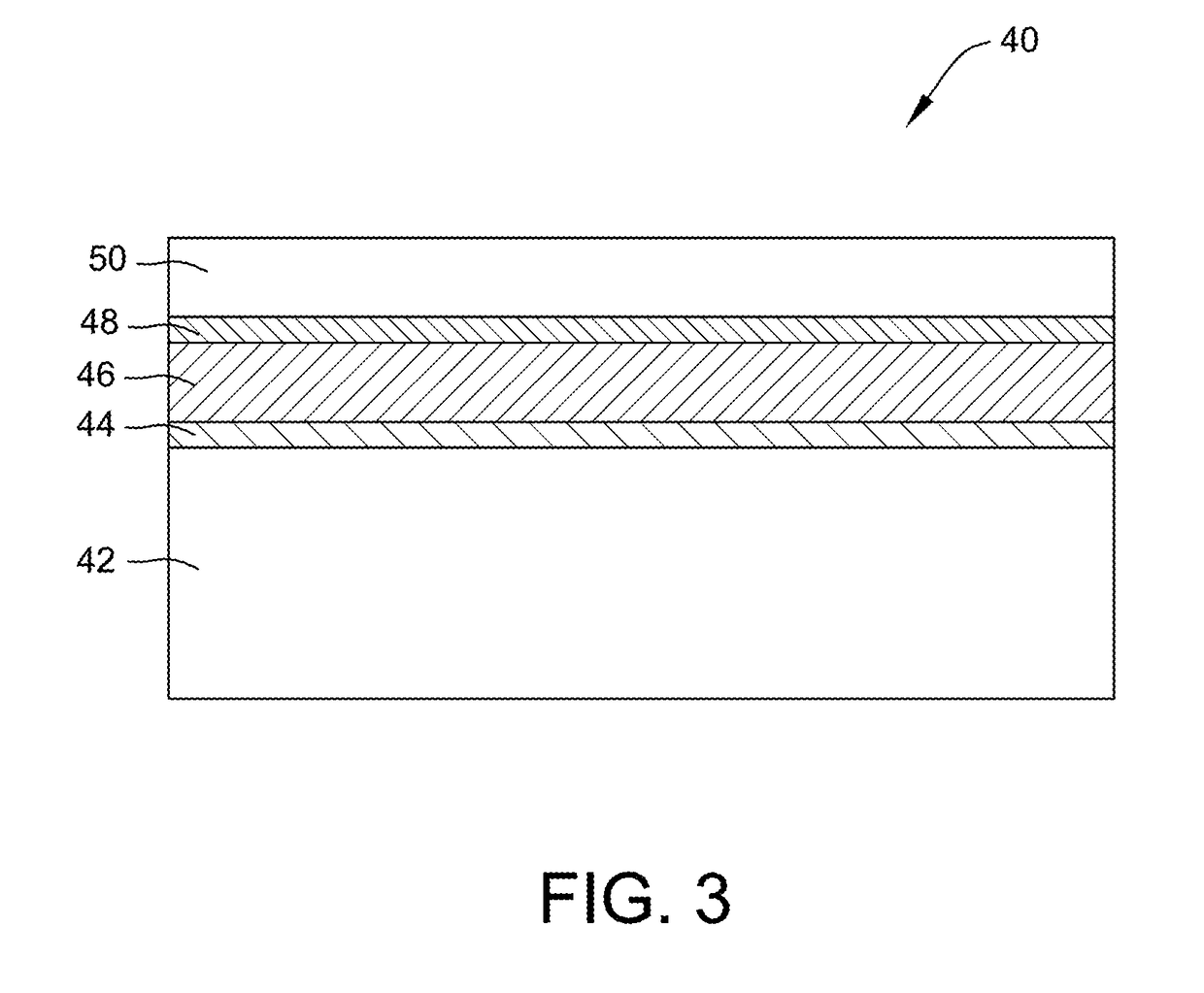

A semiconductor on insulator multilayer structure is provided. The multilayer comprises a high resistivity single crystal semiconductor handle substrate, a textured oxide, nitride, or oxynitride layer, a polycrystalline silicon layer, a dielectric layer, and a single crystal semiconductor device layer. The multilayer structure is prepared in a manner that reduces wafer bow.

Owner:GLOBALWAFERS CO LTD

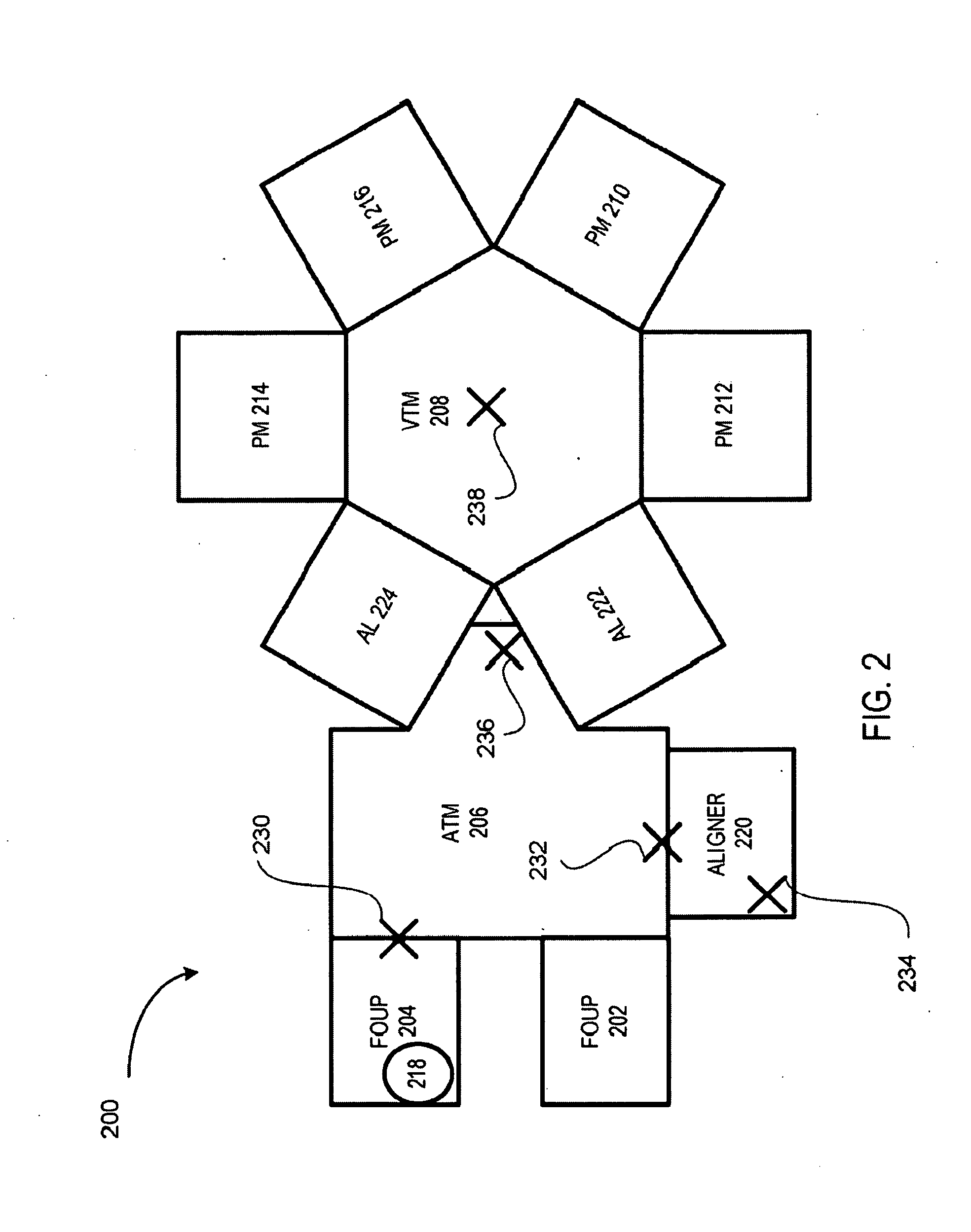

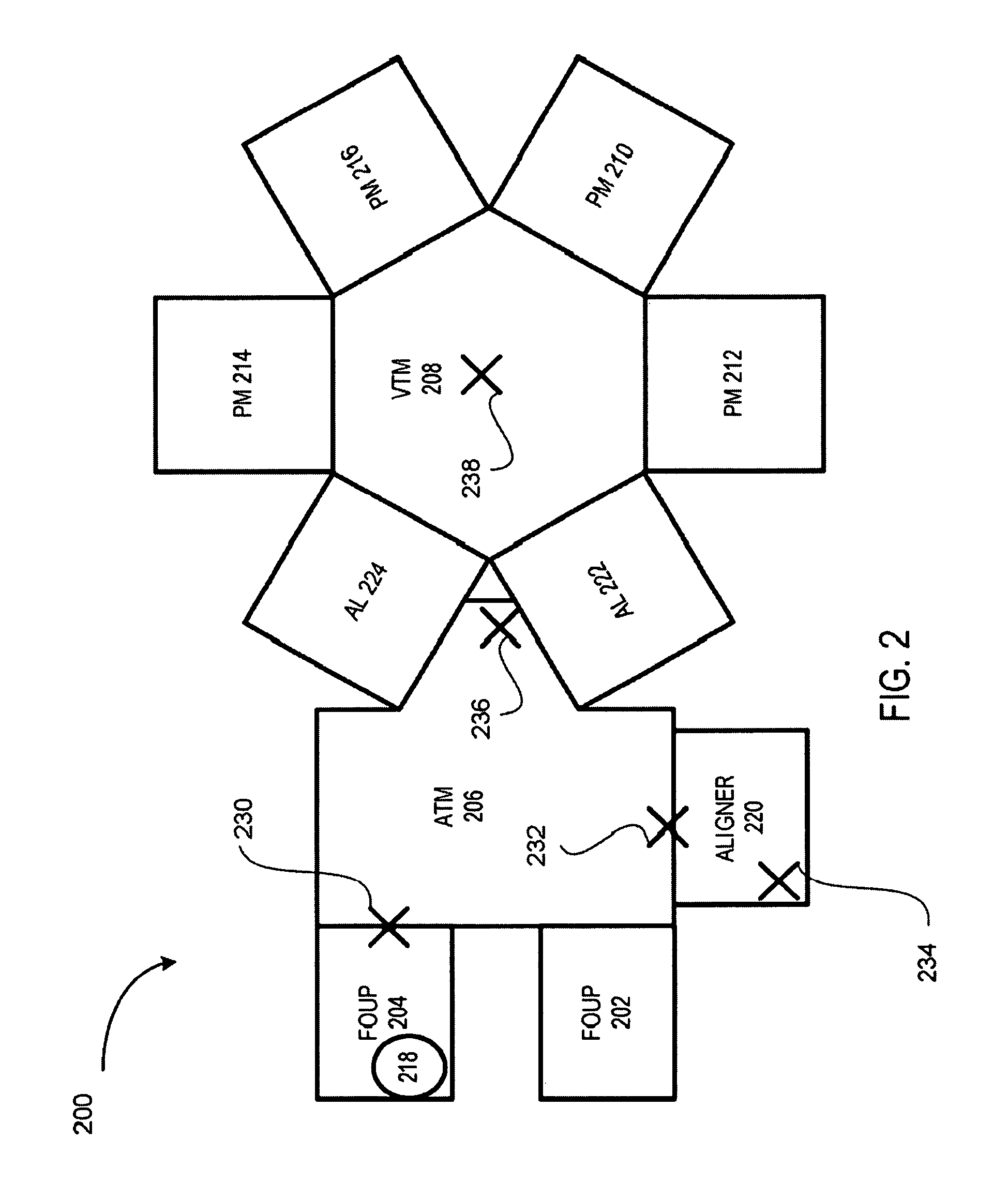

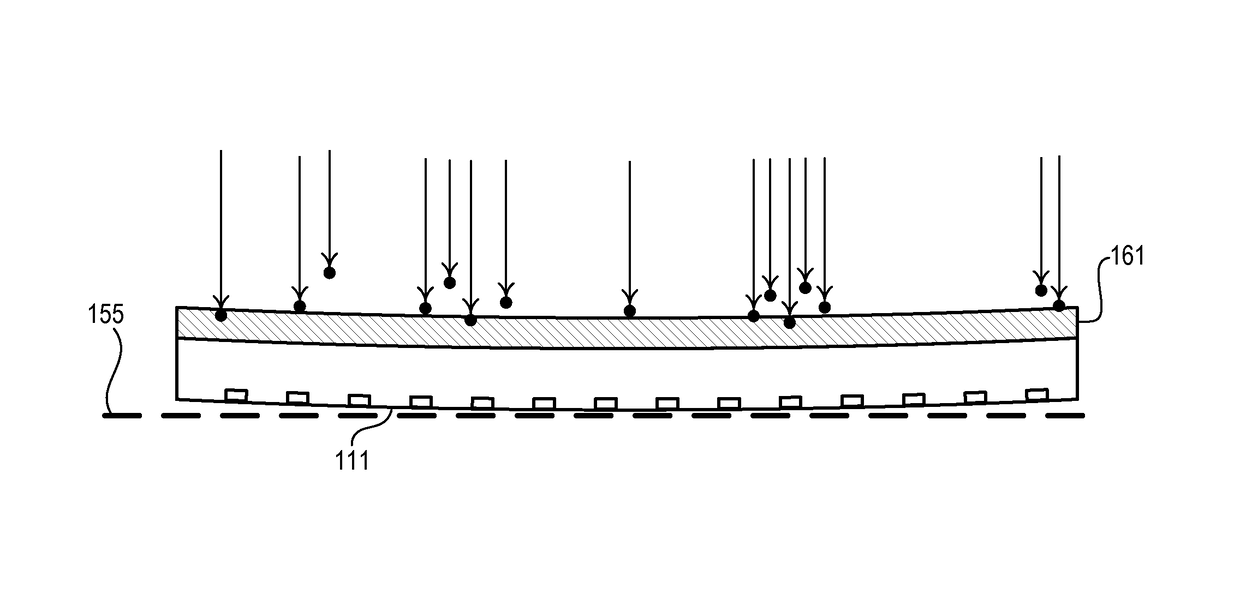

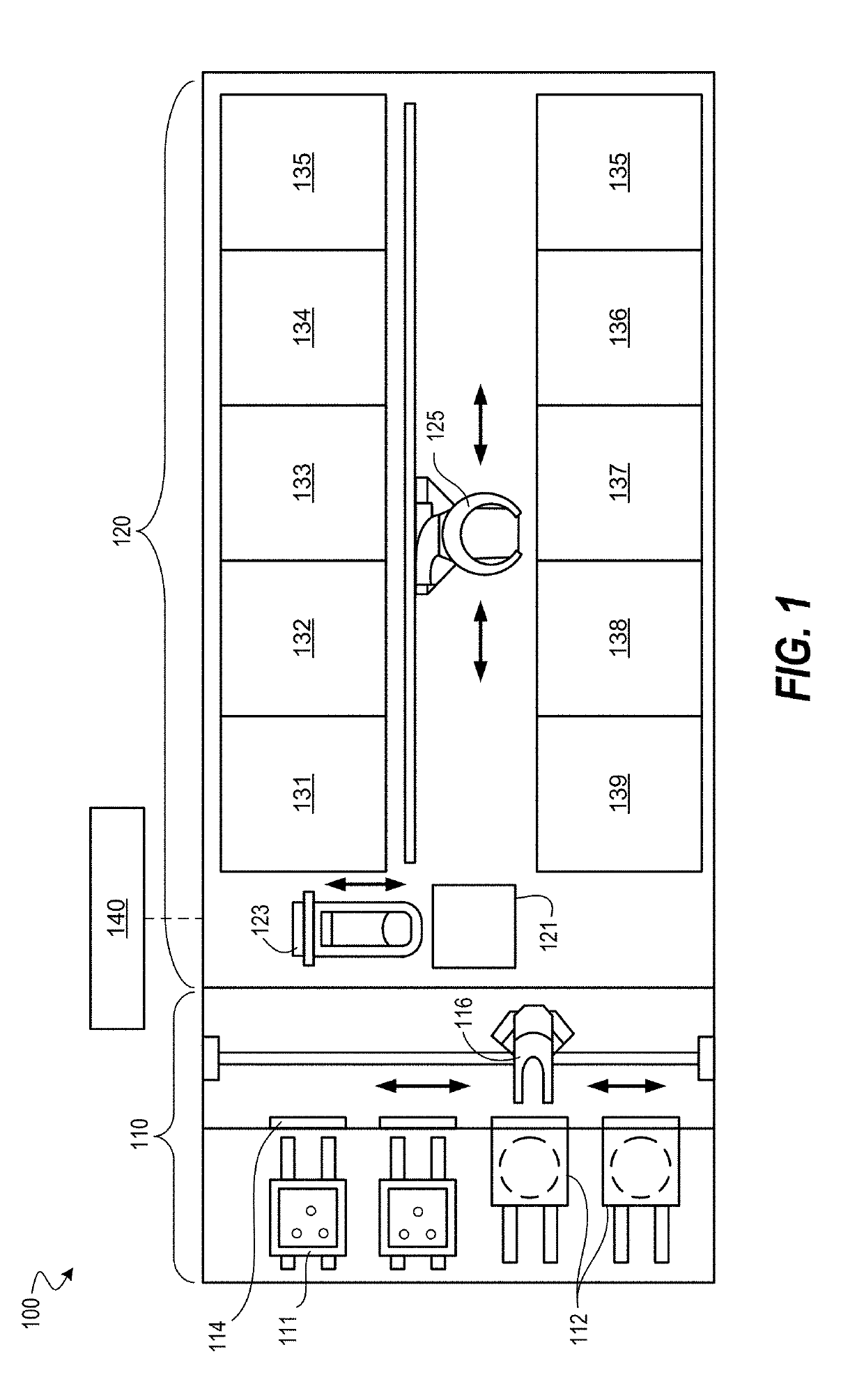

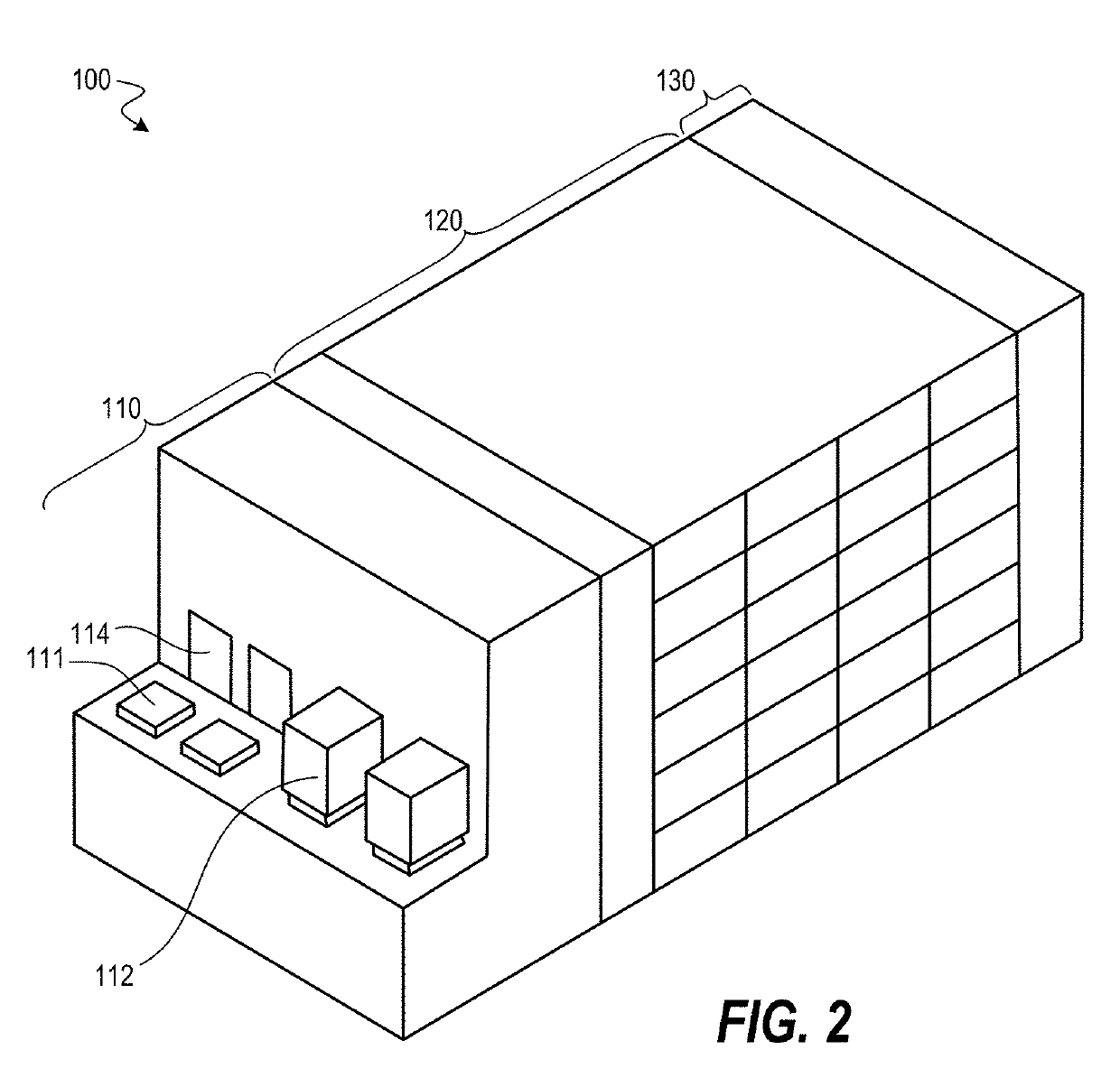

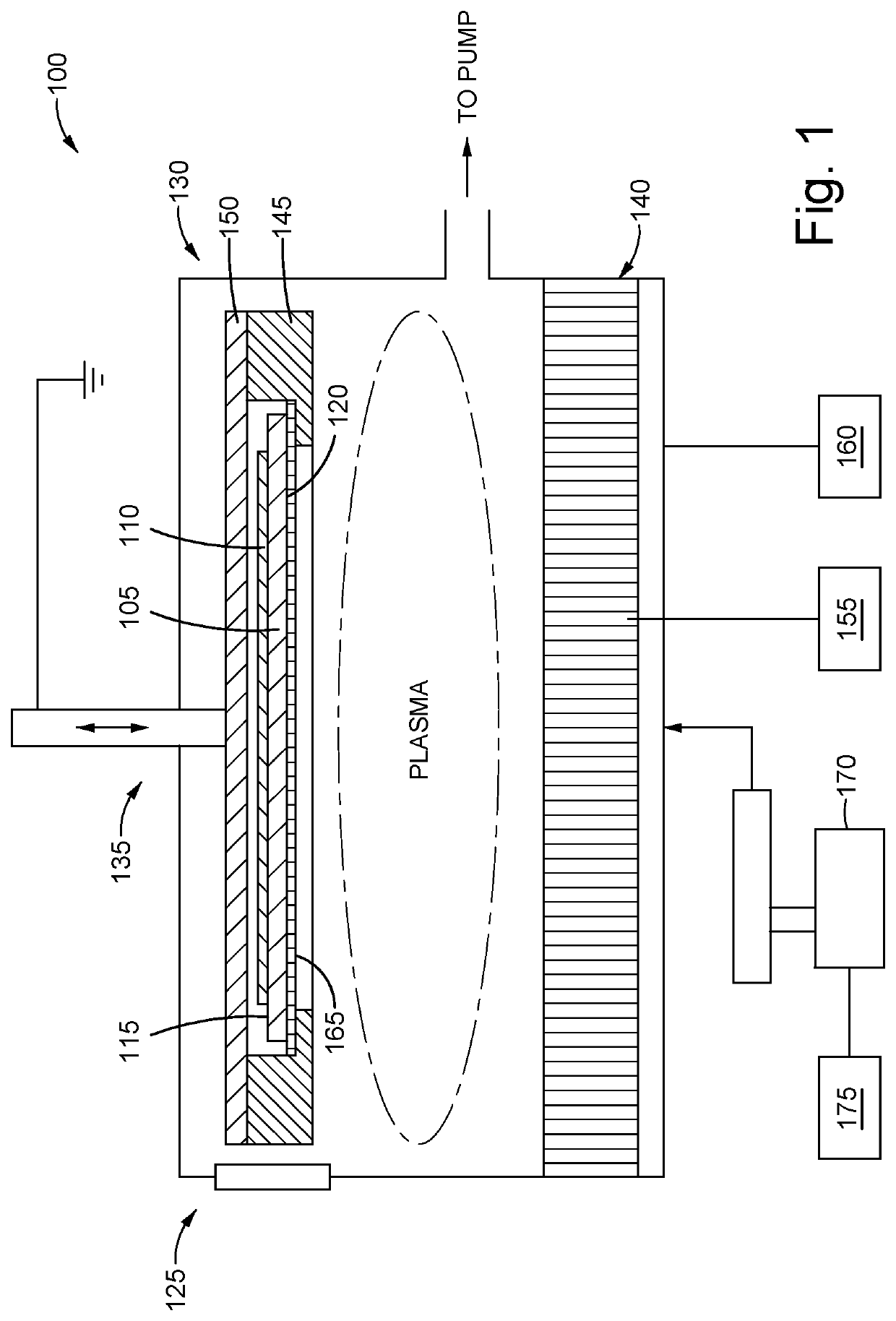

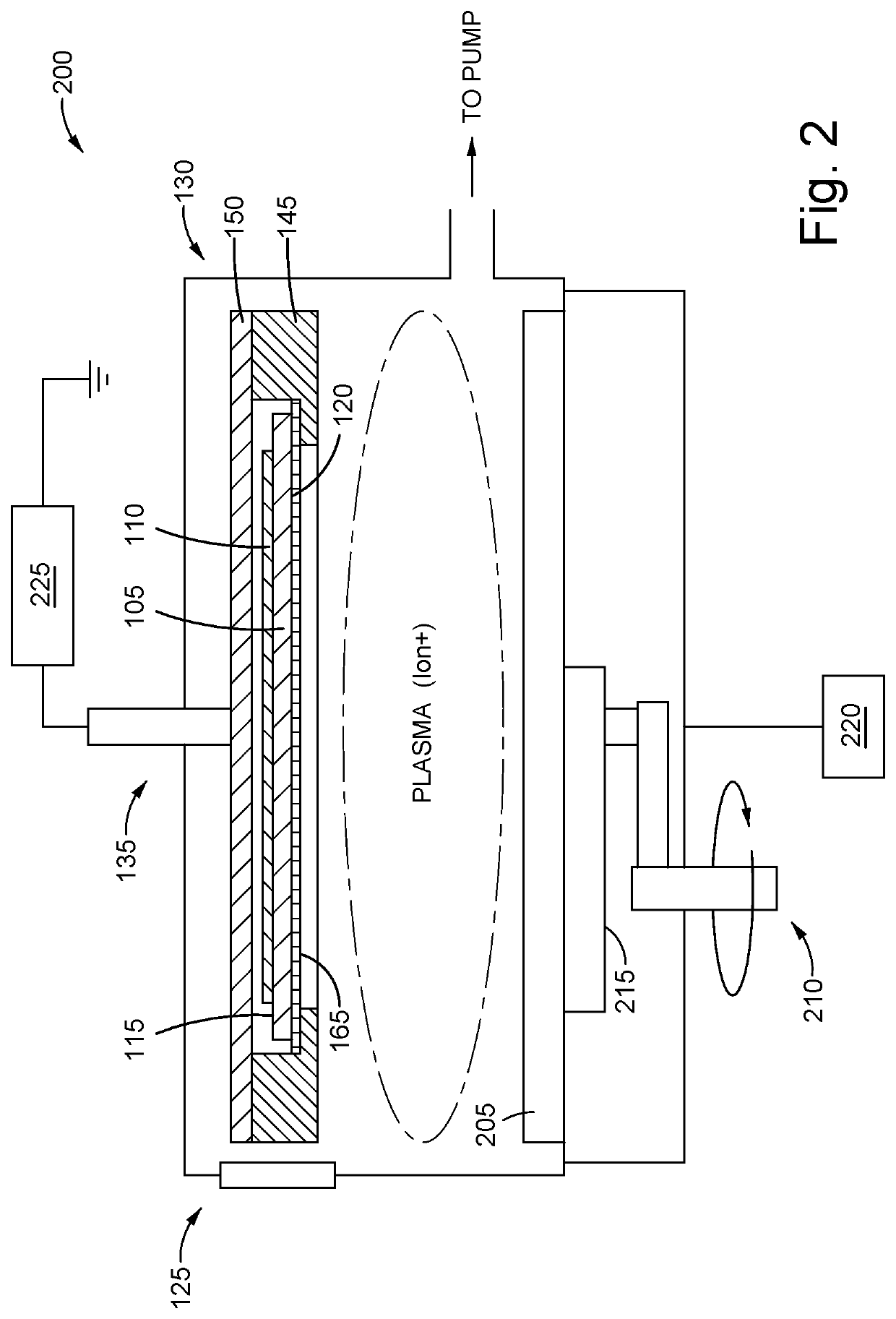

Methods of in-situ measurements of wafer bow

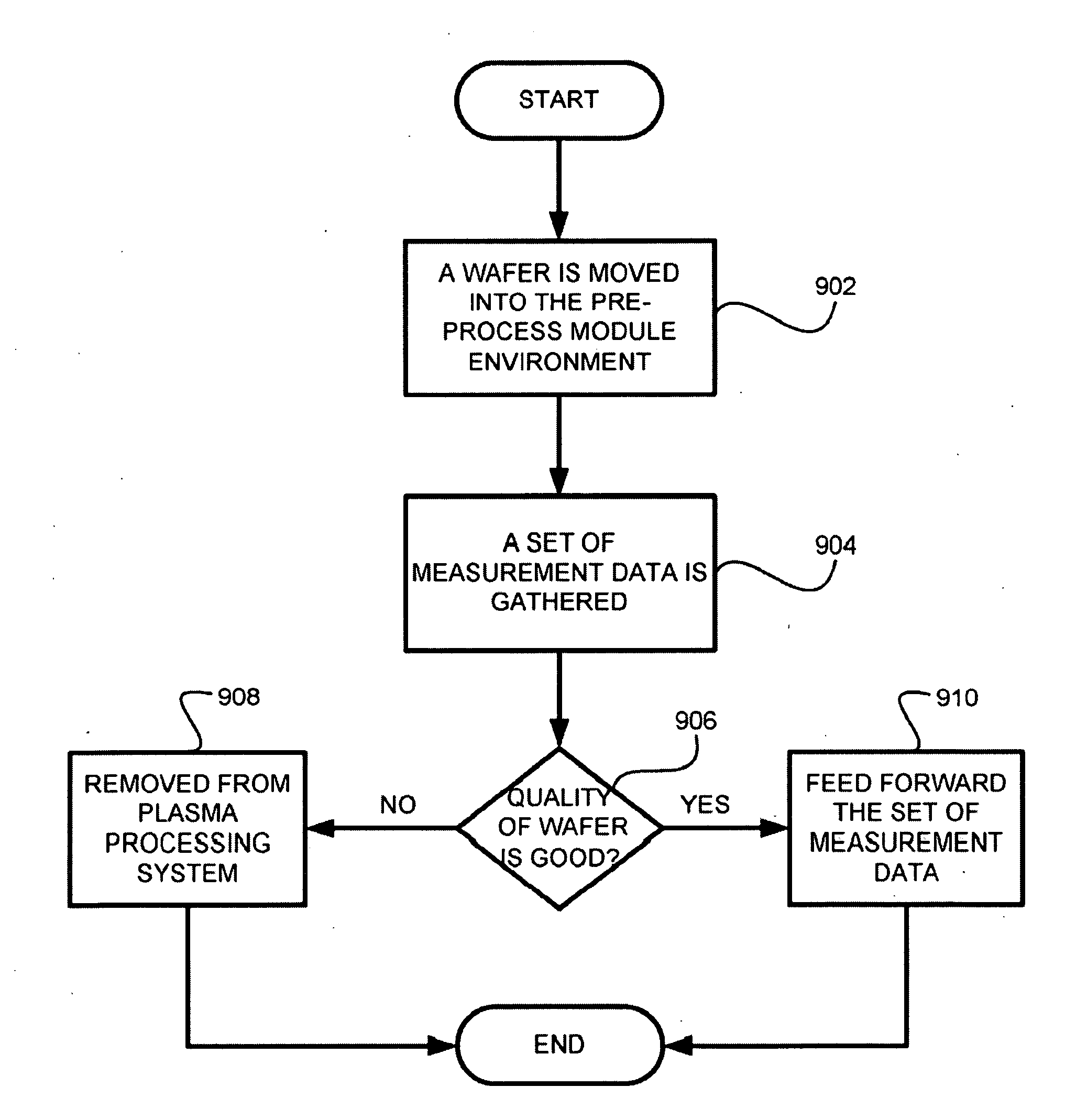

ActiveUS20120283865A1Accurately determinedSemiconductor/solid-state device testing/measurementDigital computer detailsWafer bowProcess module

Various embodiments describe a method of quantifying bow in a wafer. In one embodiment, the method includes measuring a first plurality of distances from a first sensor to a first surface of the wafer to calculate the bow in the wafer. The first sensor is positioned outside of a set of process modules of the plasma processing system. A determination is made whether the calculated bow of the wafer is within a pre-determined range. If the calculated bow of the wafer is within the pre-determined range, the wafer is moved into a process module of the set of process modules for processing and a recipe for processing the wafer is adjusted based on the calculated bow of the wafer. If the calculated bow of the wafer is outside the pre-determined range, the wafer is removed from the plasma processing system. Other methods are described as well.

Owner:LAM RES CORP

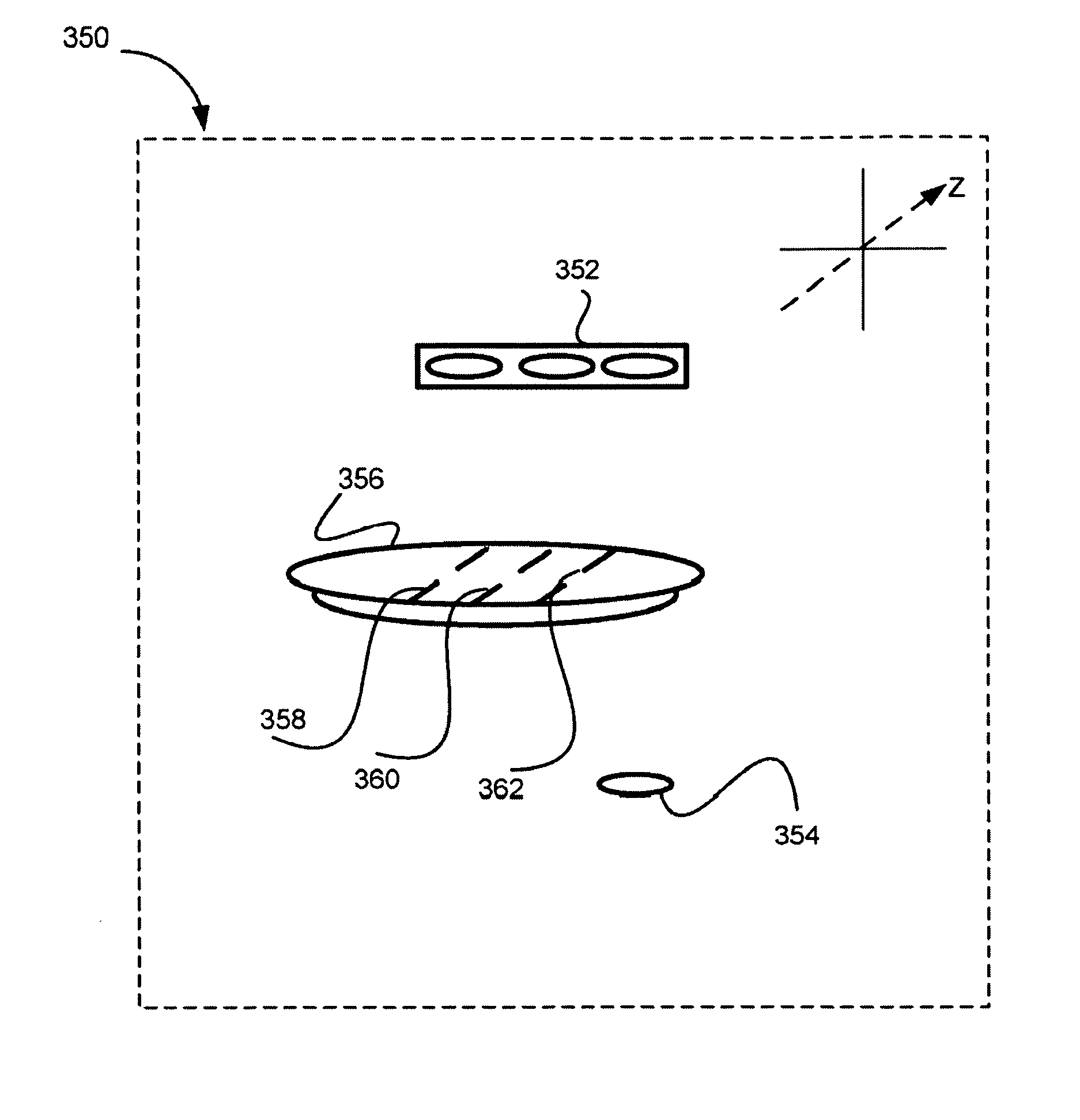

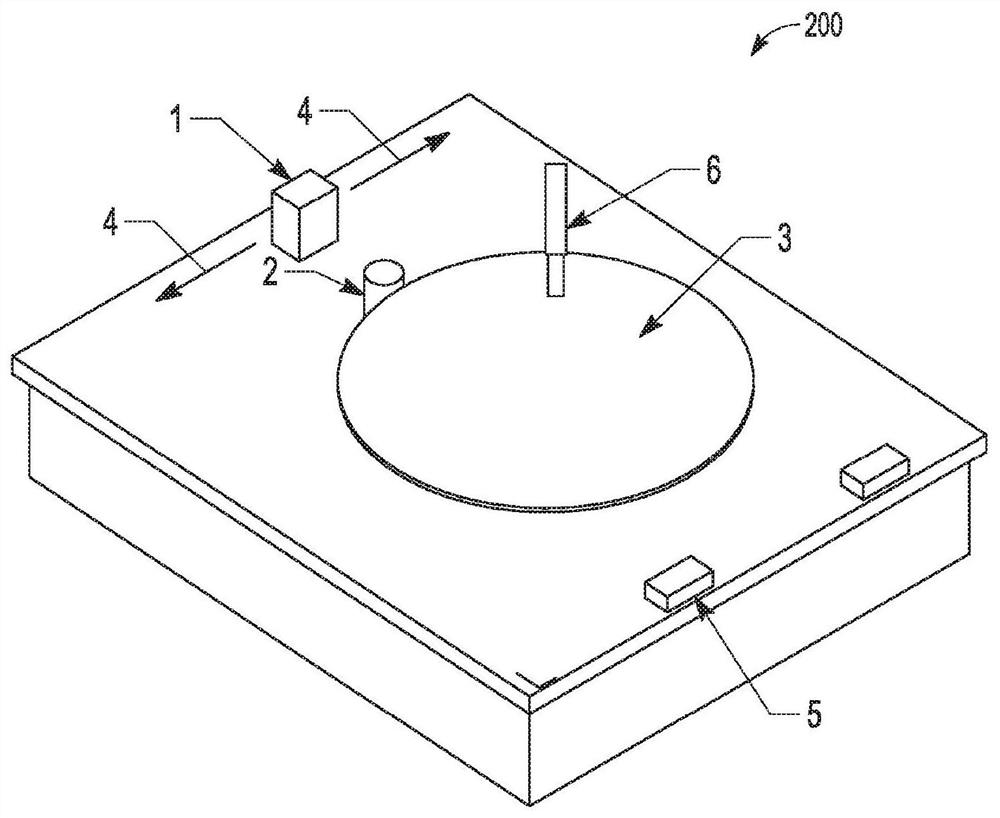

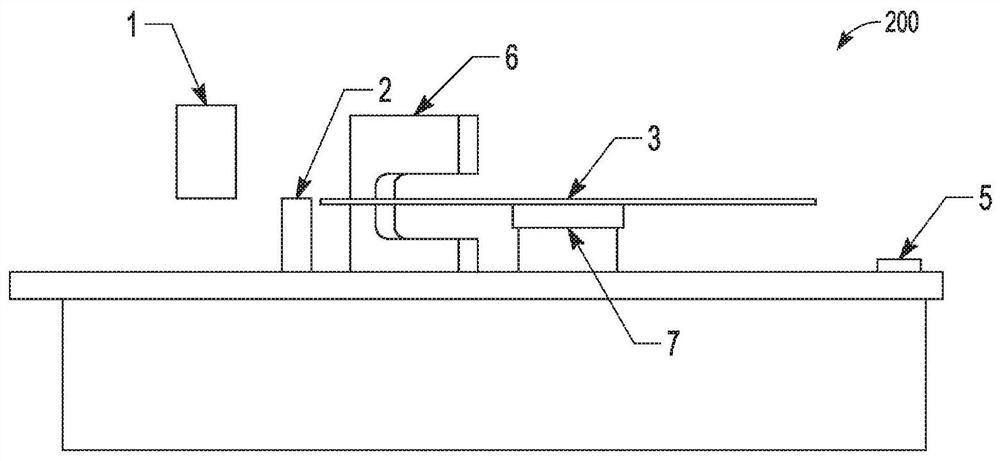

Wafer bow metrology arrangements and methods thereof

ActiveUS8225683B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMetrologyWafer bow

An arrangement for quantifying a wafer bow. The arrangement is positioned within a plasma processing system is provided. The arrangement includes a support mechanism for holding a wafer. The arrangement also includes a first set of sensors, which is configured to collect a first set of measurement data for a plurality of data points on the wafer. The first set of measurement data indicates a minimum gap between the first set of sensors and the wafer. The first set of sensors is positioned in a first location, which is outside of a set of process modules of the plasma processing system.

Owner:LAM RES CORP

Method of depositing charge trapping polycrystalline silicon films on silicon substrates with controllable film stress

ActiveUS20190096745A1Solid-state devicesSemiconductor/solid-state device manufacturingWafer bowWafering

A semiconductor on insulator multilayer structure is provided. The multilayer comprises a high resistivity single crystal semiconductor handle substrate, a textured oxide, nitride, or oxynitride layer, a polycrystalline silicon layer, a dielectric layer, and a single crystal semiconductor device layer. The multilayer structure is prepared in a manner that reduces wafer bow.

Owner:GLOBALWAFERS CO LTD

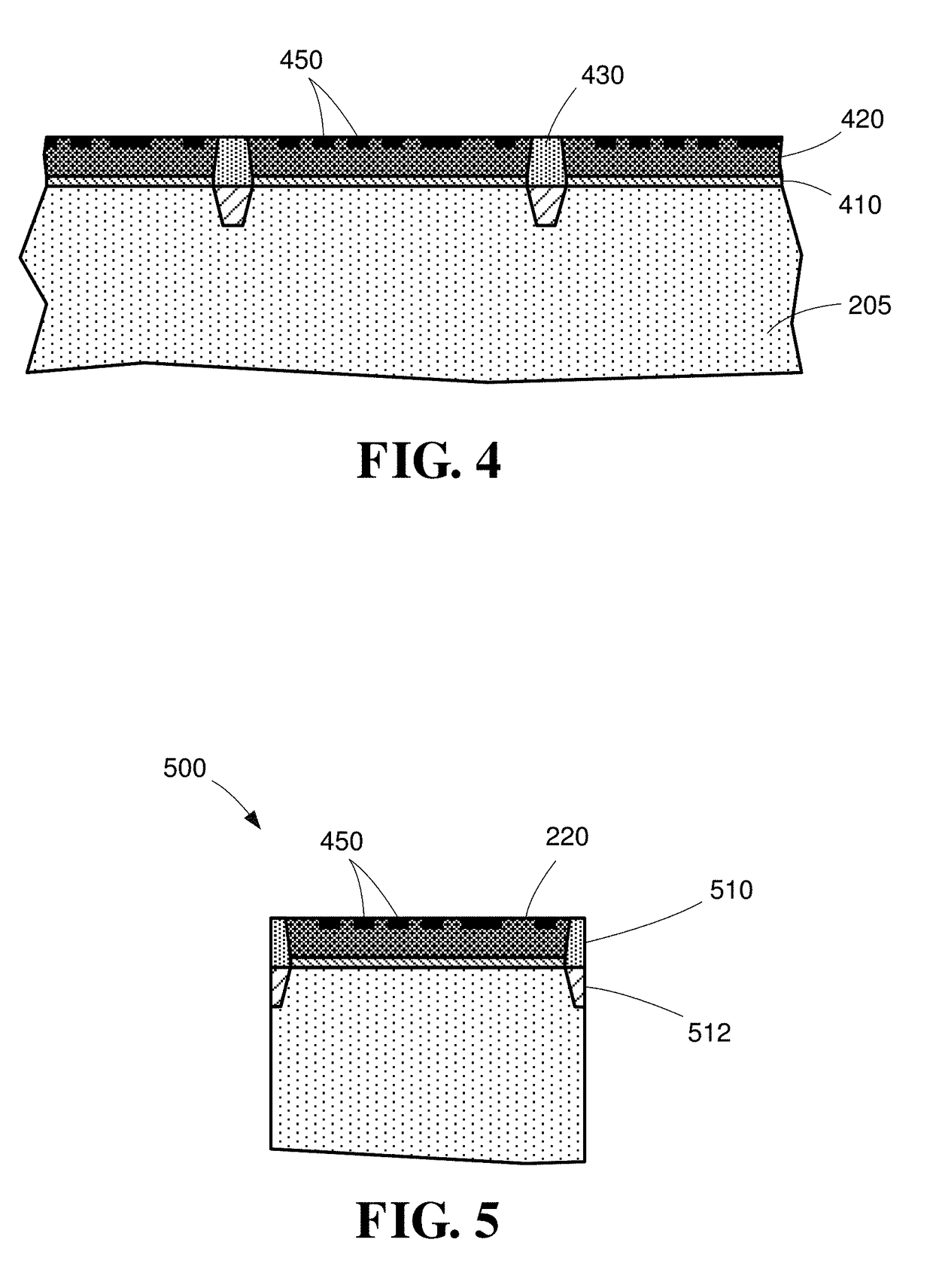

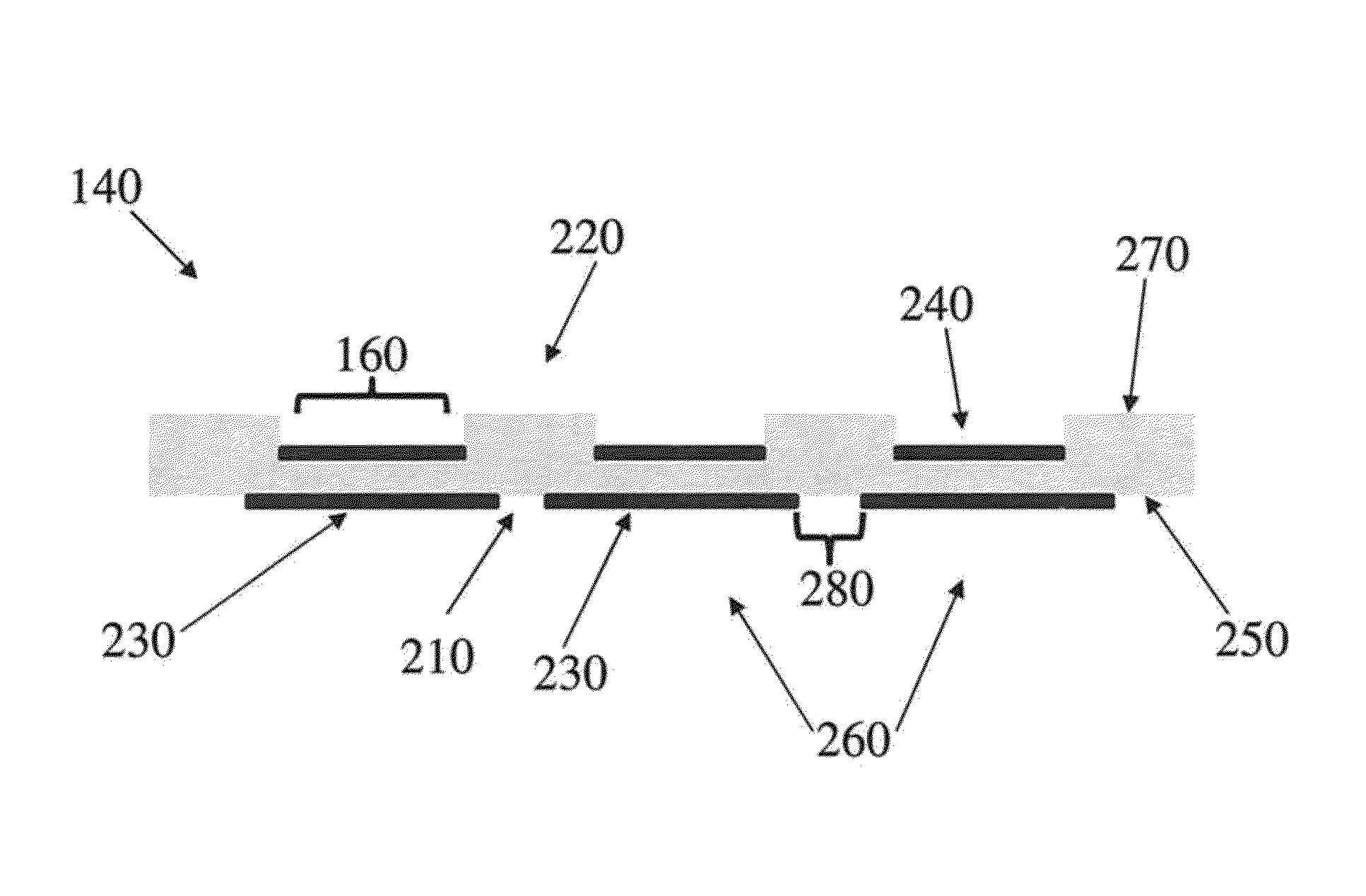

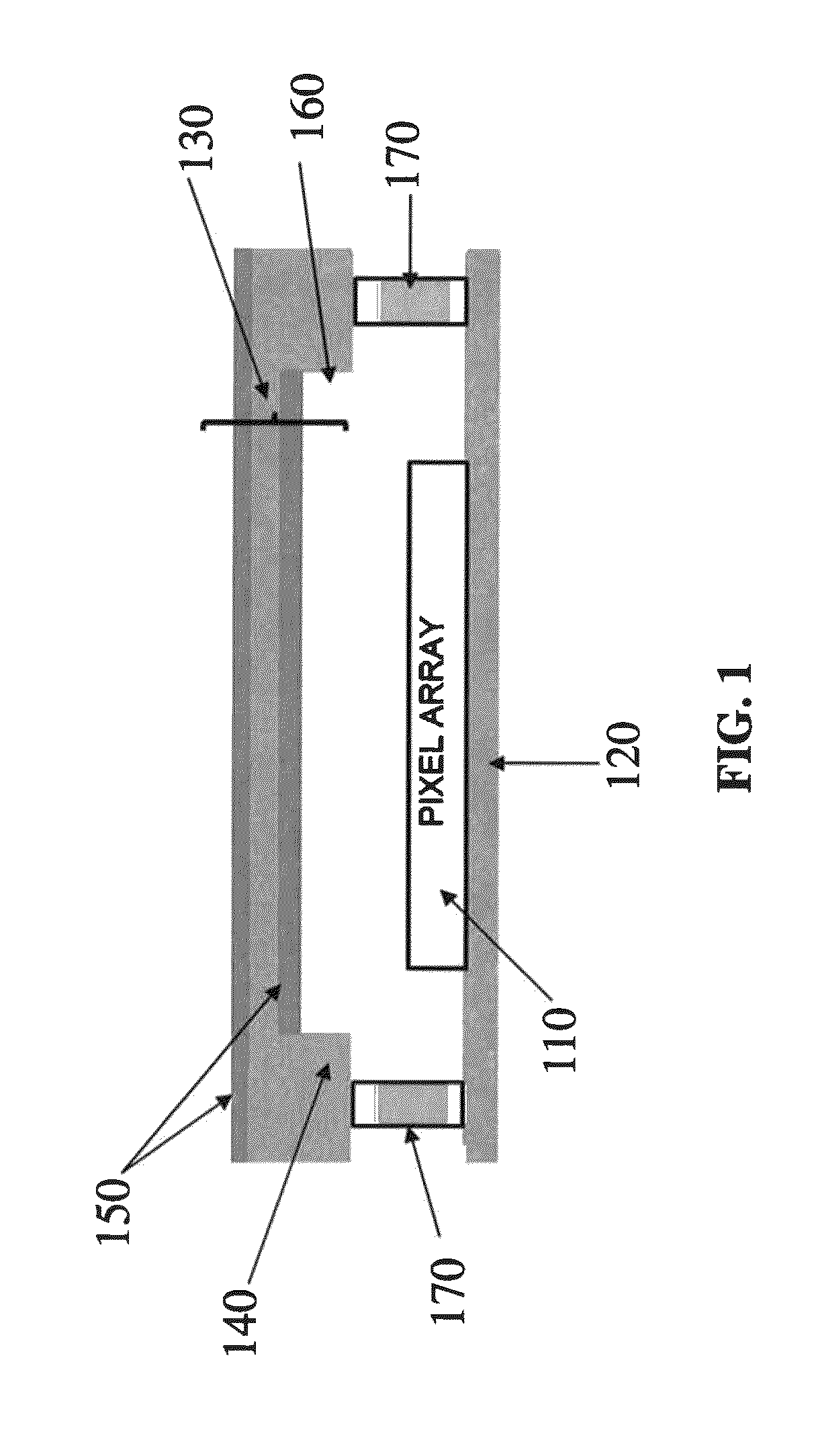

Method of stress relief in Anti-reflective coated cap wafers for wafer level packaged infrared focal plane arrays

ActiveUS20140053966A1Reducing wafer bowLamination ancillary operationsSynthetic resin layered productsAnti-reflective coatingWafer bow

Methods for reducing wafer bow induced by an anti-reflective coating of a cap wafer are provided. The method may utilize a shadow mask having at least one opening therein that is positioned opposite recessed regions in a cap wafer. The method may further include depositing at least one layer of an anti-reflective coating material through the shadow mask onto a planar side of a cap wafer to provide a discontinuous coating on the planar side.

Owner:RAYTHEON CO

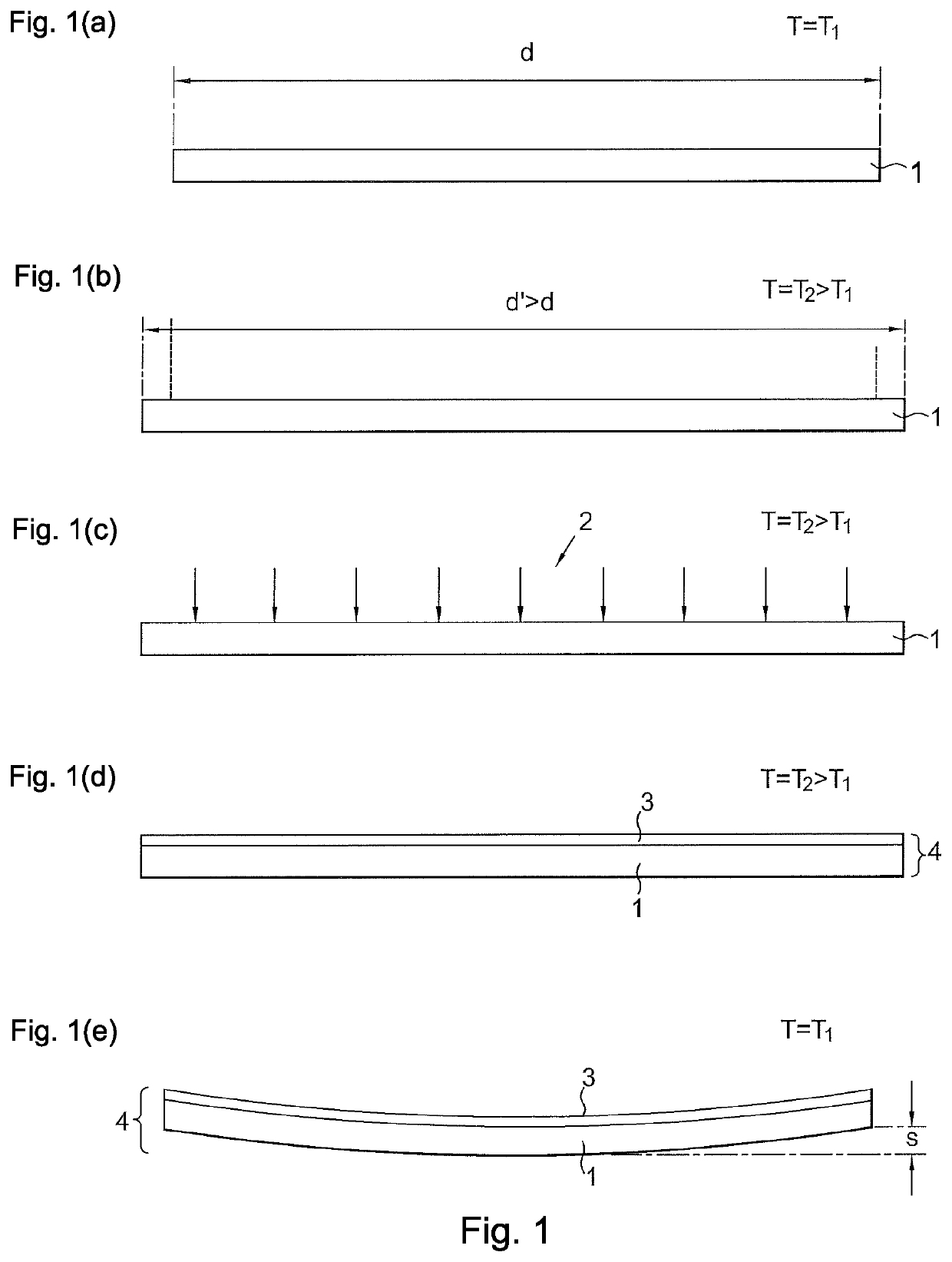

Reduction of wafer bow during growth of epitaxial films

InactiveUS20180358221A1Reducing wafer bowRelieve in-plane stressOptical wave guidancePolycrystalline material growthWaferingWafer bow

Structures and methods for reducing wafer bow during heteroepitaxial growth are described. Micro-trenches may be formed across a surface of a substrate and filled with polycrystalline material. Stress-relieving regions of material can be grown over the polycrystalline material in a layer of semiconductor material during heteroepitaxy.

Owner:MACOM TECH SOLUTIONS HLDG INC

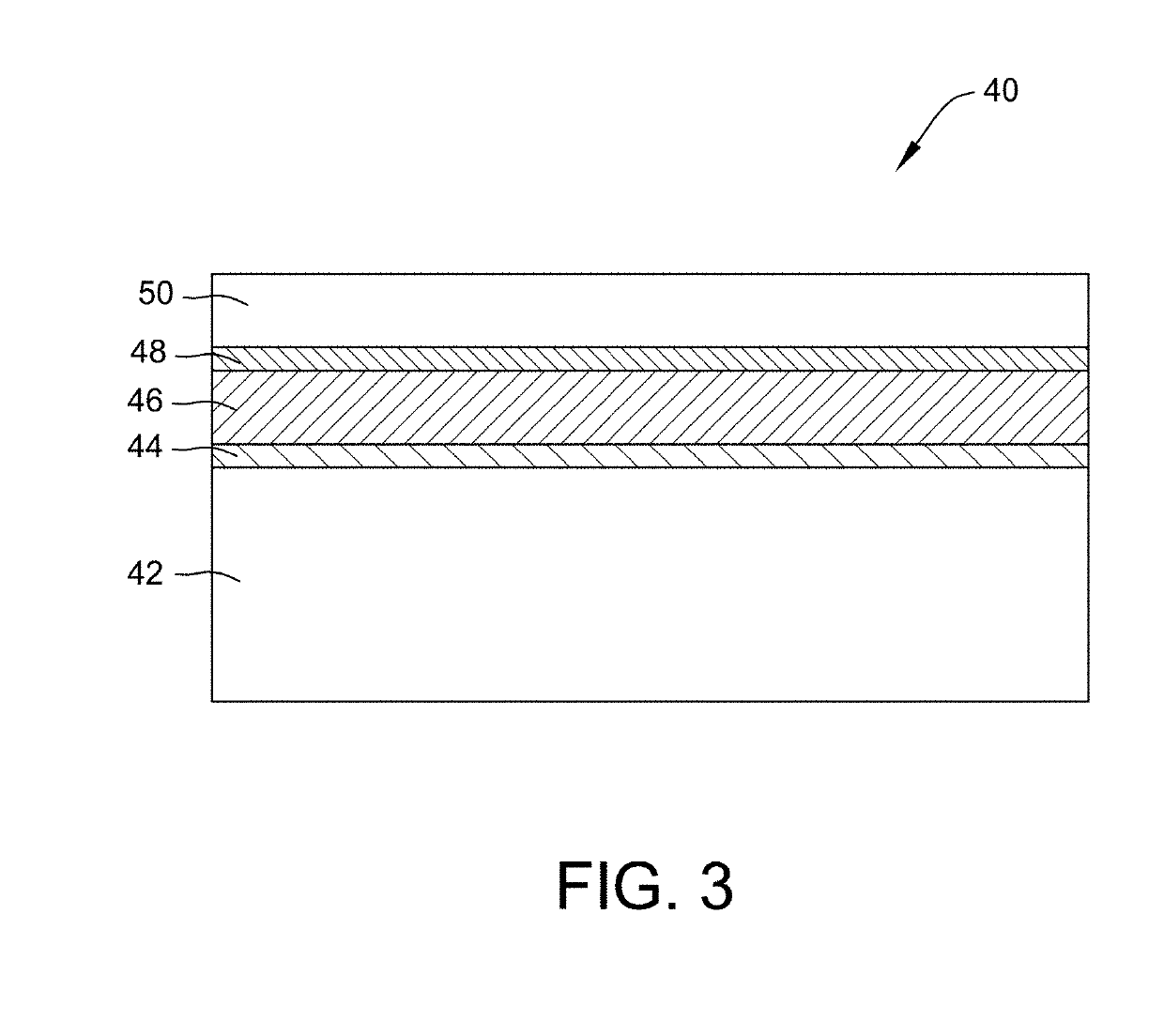

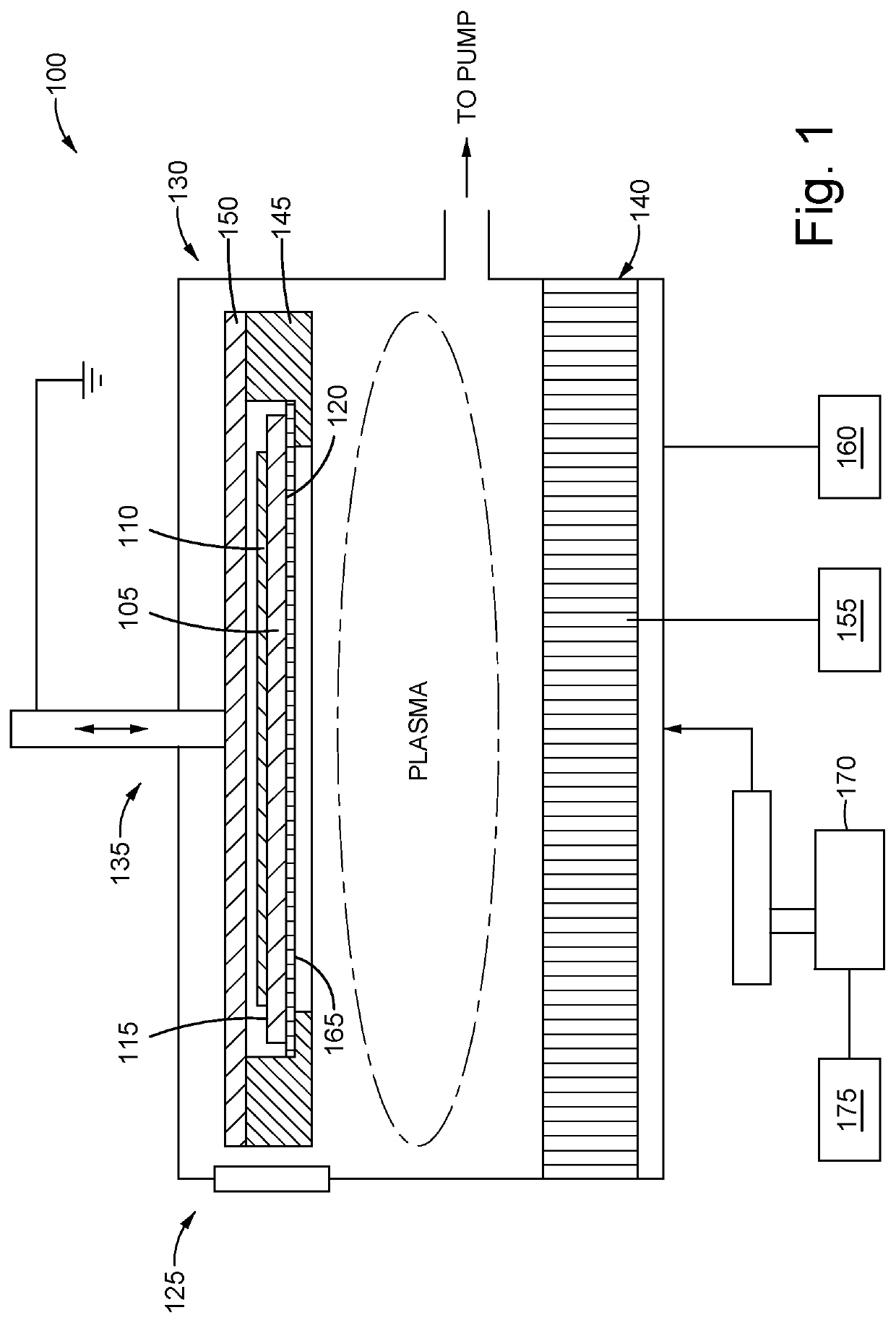

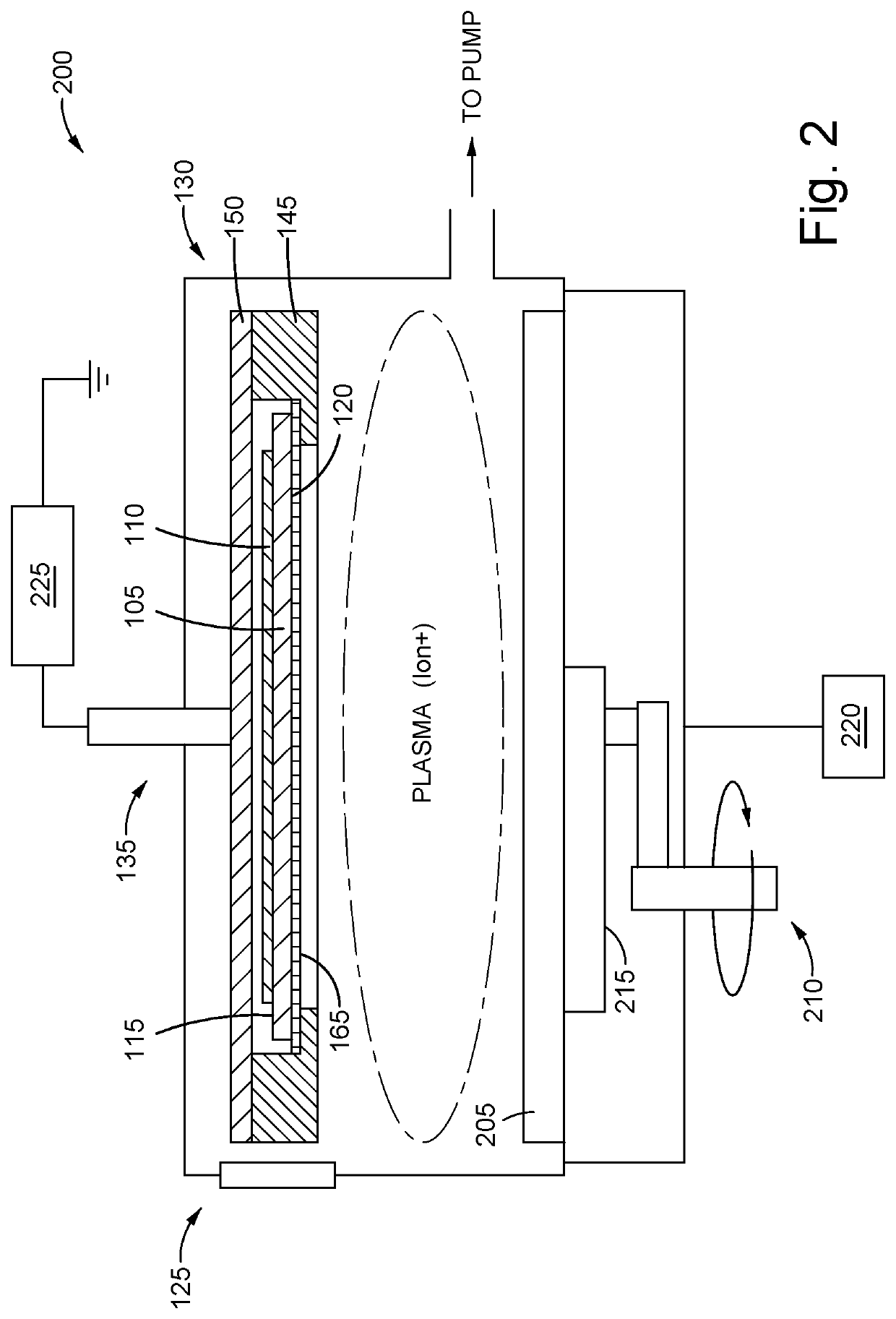

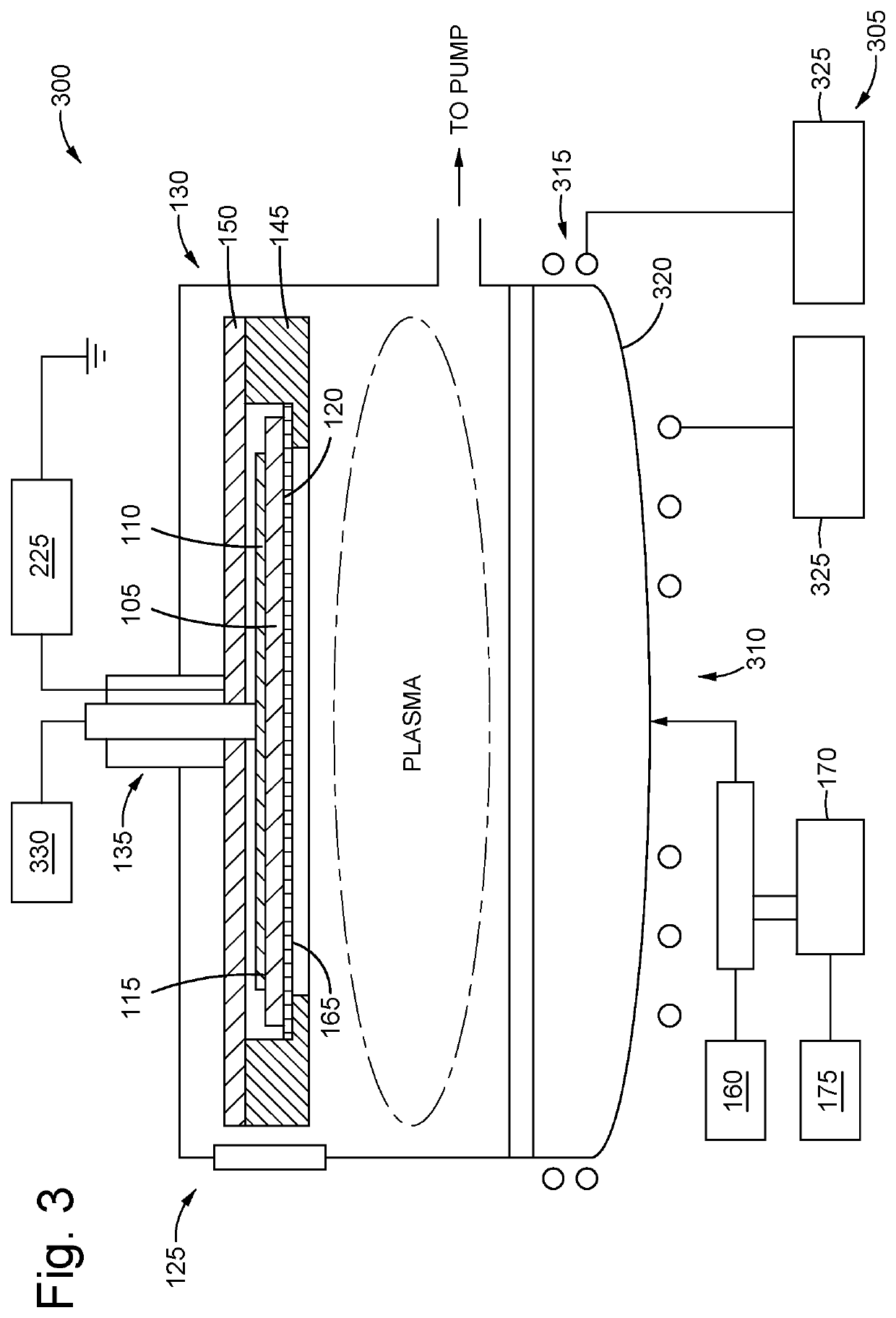

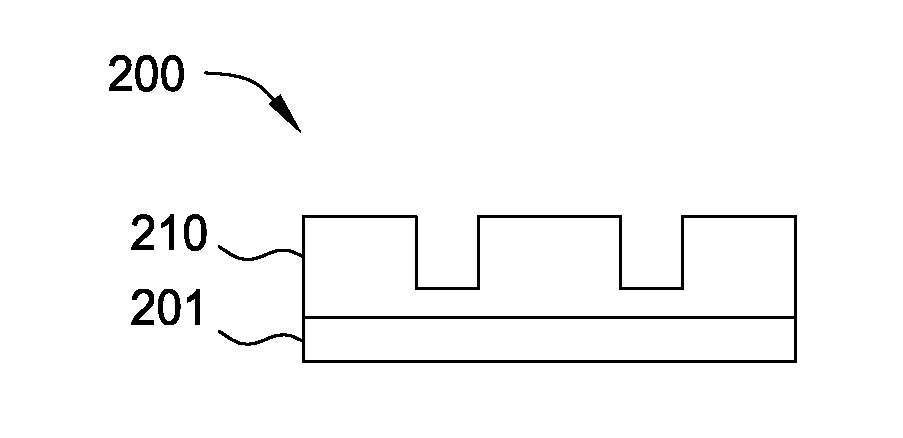

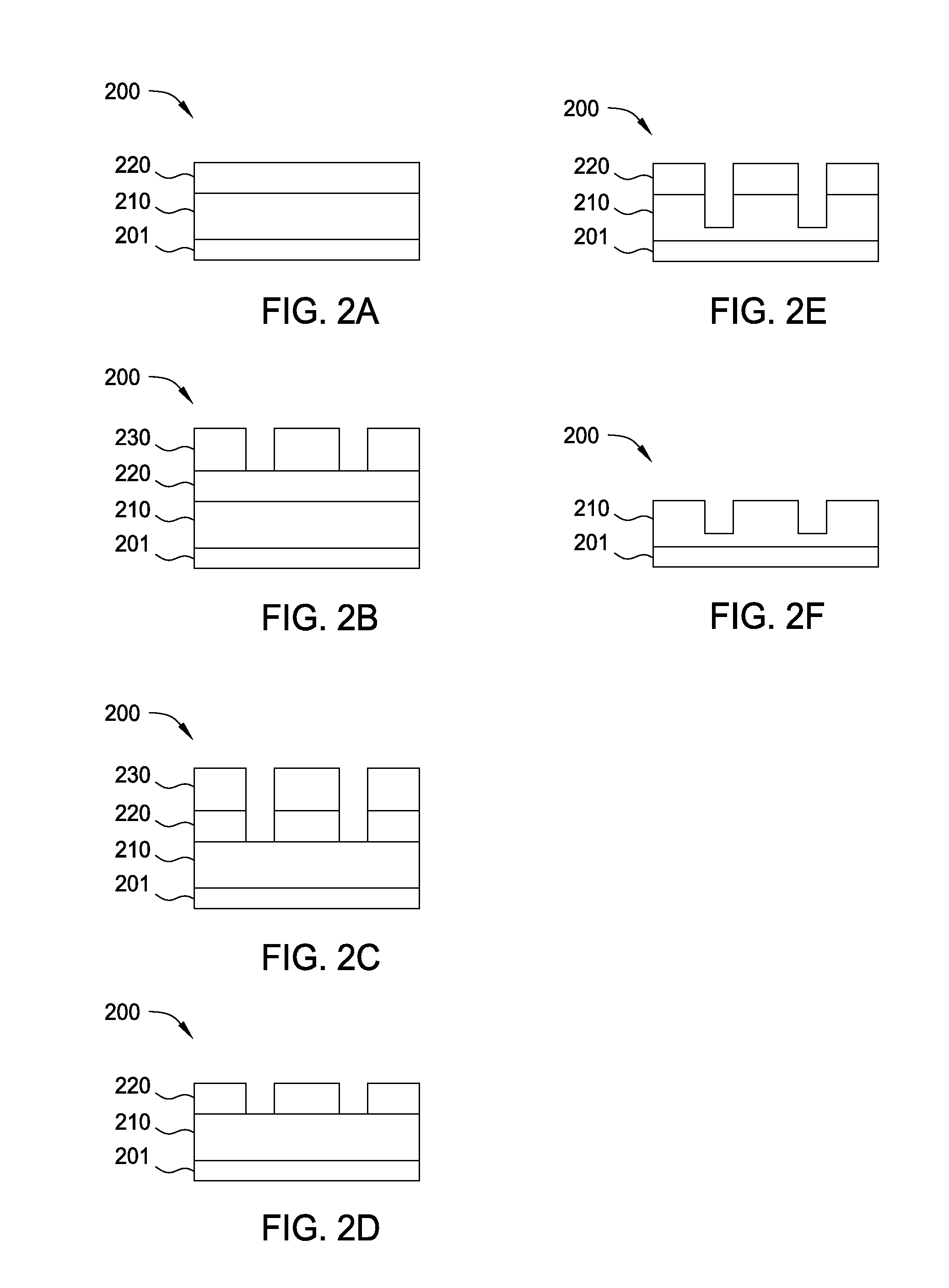

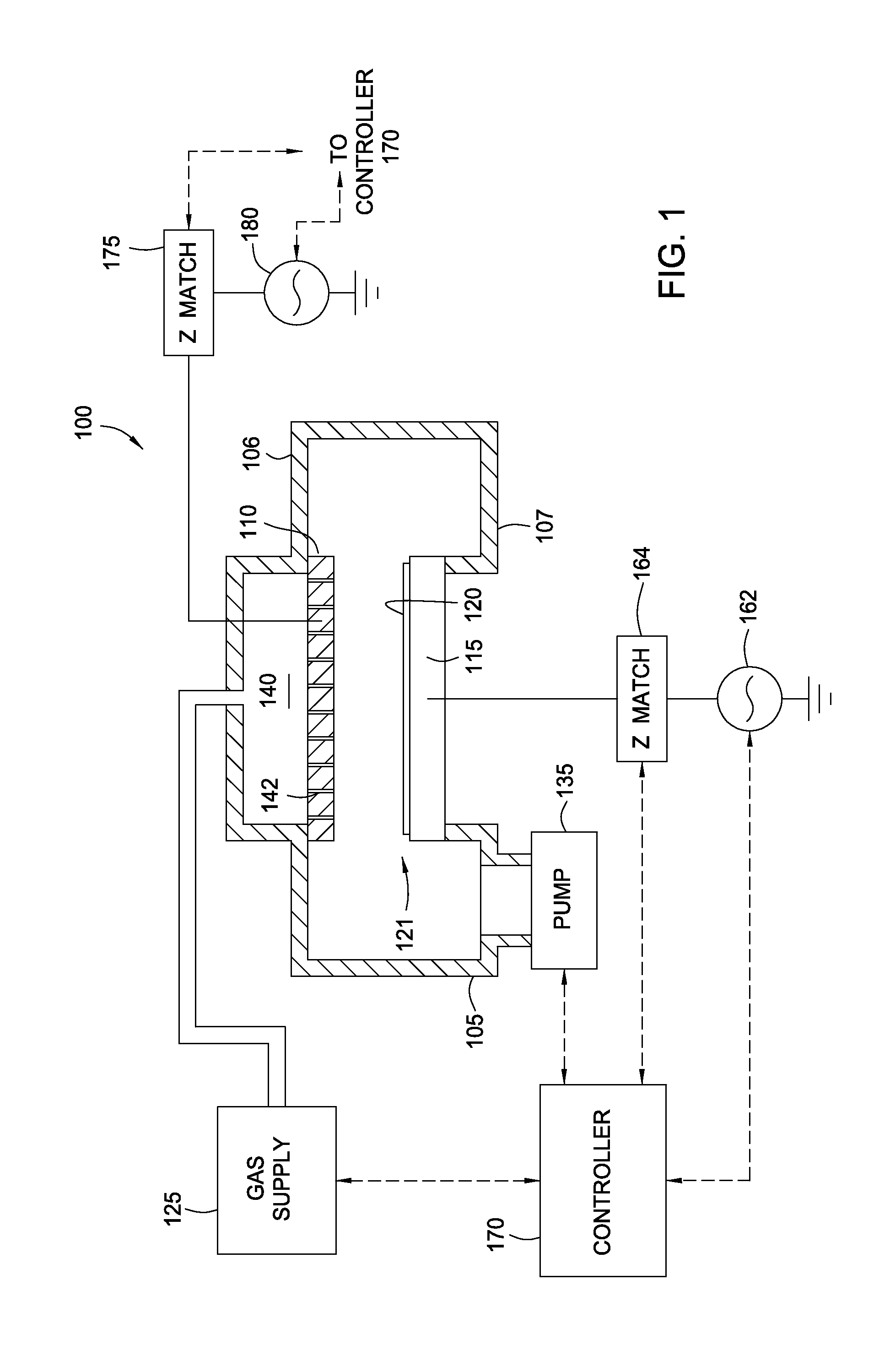

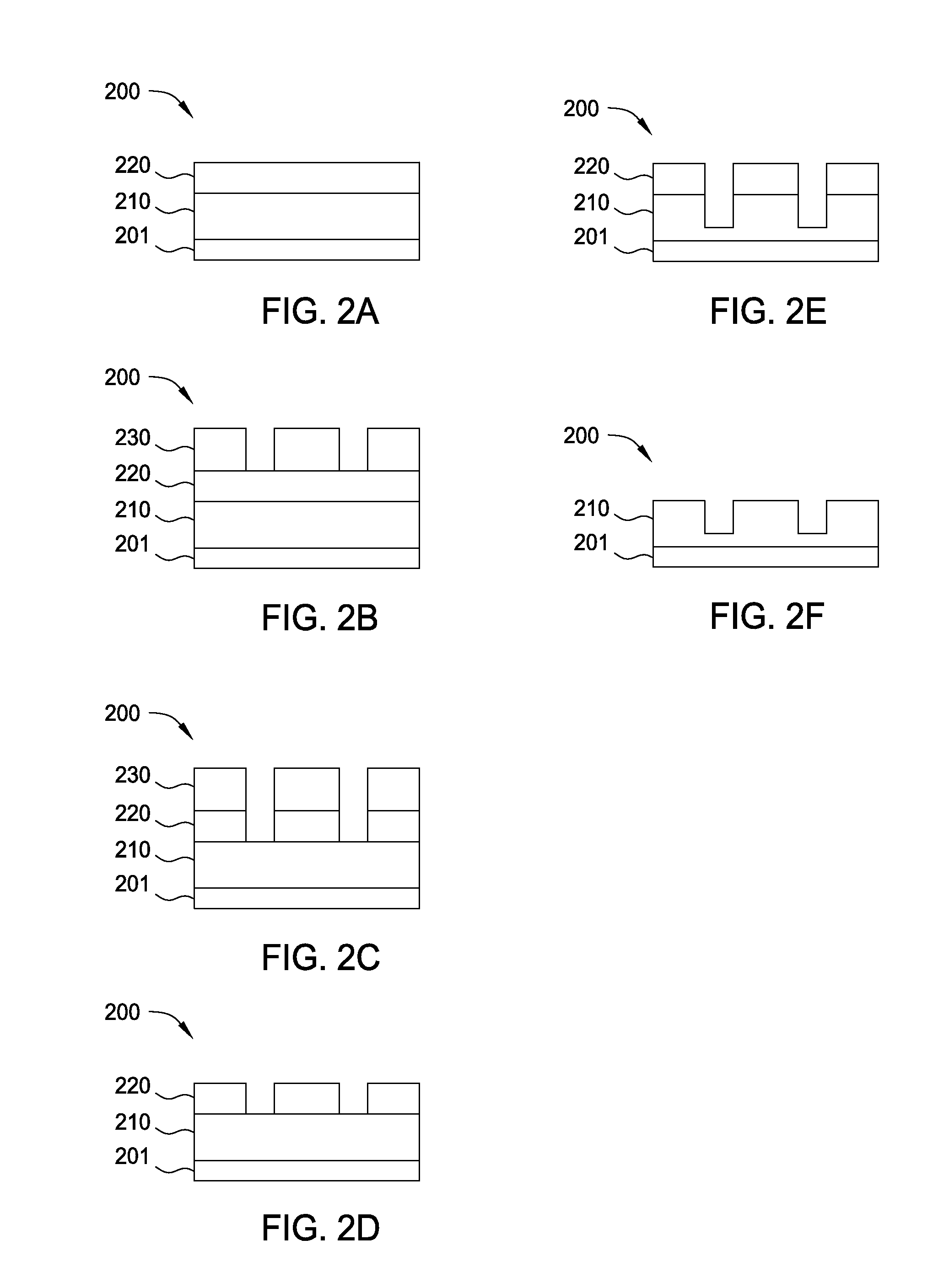

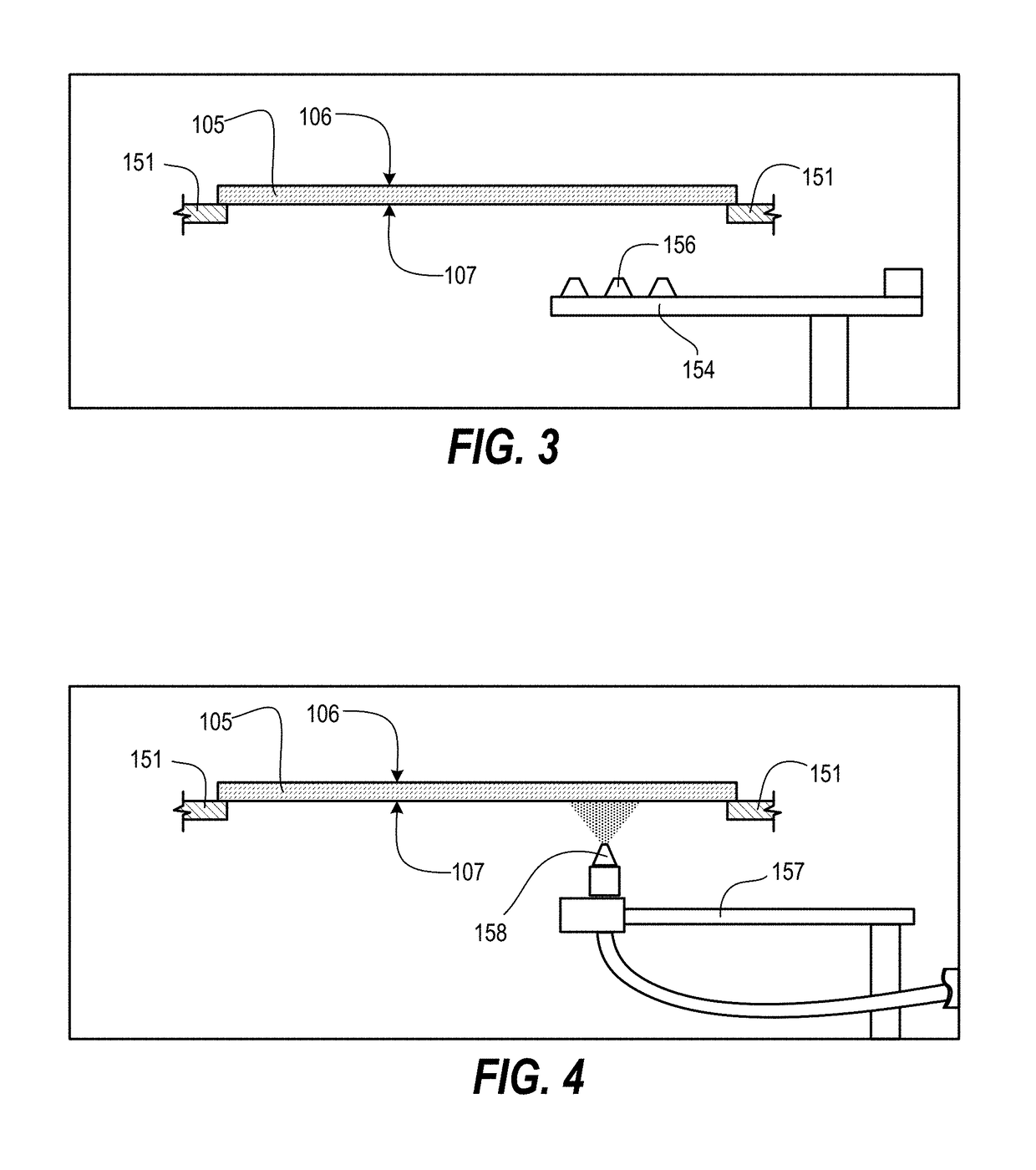

Methods and apparatus to eliminate wafer bow for CVD and patterning hvm systems

ActiveUS20200098702A1Minimize controlHigh densityElectric discharge tubesSemiconductor/solid-state device detailsWafer bowWafering

A method and apparatus for forming a backside coating on a substrate to counteract stresses from a previously deposited film is disclosed. In one embodiment, a method for flattening a bowed substrate includes providing a substrate having a film stack formed on a first major surface thereof, wherein the substrate comprises a bowed orientation, and forming a coating a second major surface of the substrate, wherein the coating is configured to counter stresses produced by the film stack and flattens the substrate from the bowed orientation.

Owner:APPLIED MATERIALS INC

Method for correcting wafer bow from overlay

ActiveUS9824894B2Reduce yieldEasy to stackSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingWafer bowSemiconductor

Described herein are methods for flattening a substrate, such as a semiconductor wafer, to reduce bowing in such substrates. Methods include treating or bombarding a backside surface of a substrate with particles of varying doses, densities, and spatial locations. Particle bombardment and selection is such that the substrate becomes more planar by selectively increasing or decreasing z-height points to reduce overall deflection. One or more tensile or compressive films can be added to the backside surface to be selectively relaxed at specific point locations. Such methods can correct bowing in substrates resulting from various fabrication processes such as thermal annealing.

Owner:TOKYO ELECTRON LTD

Deposition of heteroatom-doped carbon films

ActiveUS20150206739A1High densityImprove etch selectivityDecorative surface effectsDuplicating/marking methodsCarbon layerCarbon film

Easily removable heteroatom-doped carbon-containing layers are deposited. The carbon-containing layers may be used as hardmasks. The heteroatom-doped carbon-containing hardmasks have high etch selectivity and density and also a low compressive stress, which will reduce or eliminate problems with wafer bow. Heteroatoms incorporated into the hardmask include sulfur, phosphorous, nitrogen, oxygen, and fluorine, all of which have low reactivity towards commonly used etchants. When sulfur is used as the heteroatom, the hardmask is easily removed, which simplifies the fabrication of NAND devices, DRAM devices, and other devices.

Owner:APPLIED MATERIALS INC

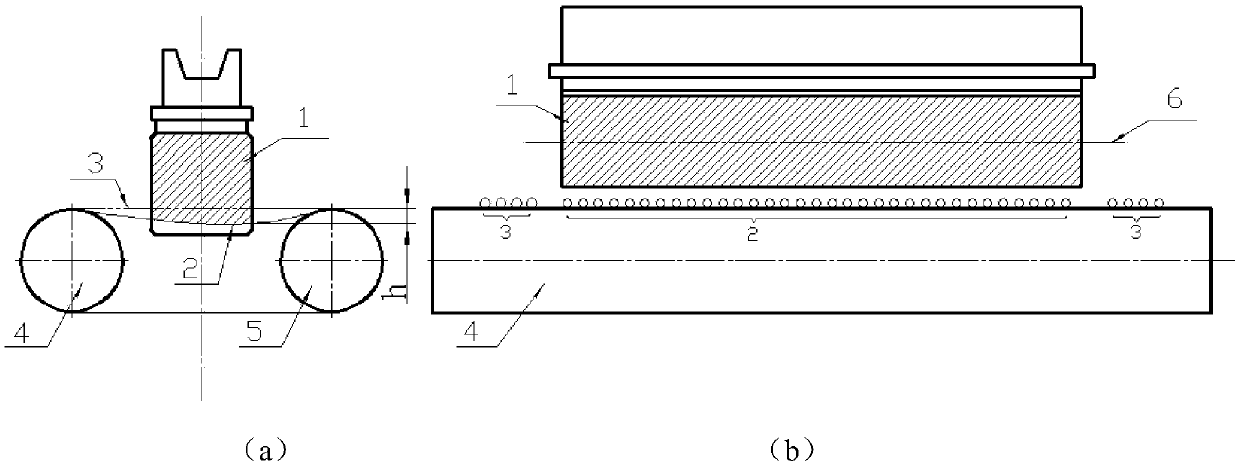

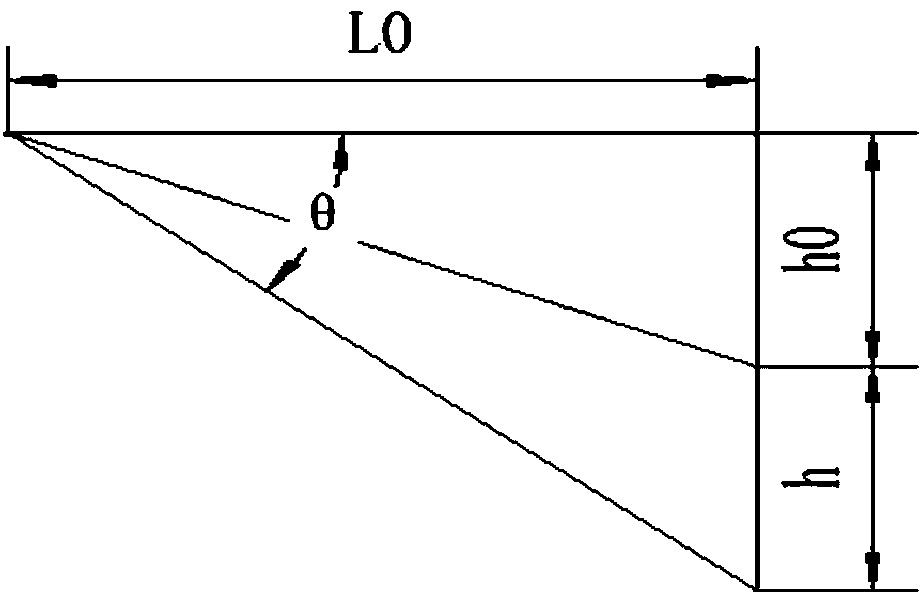

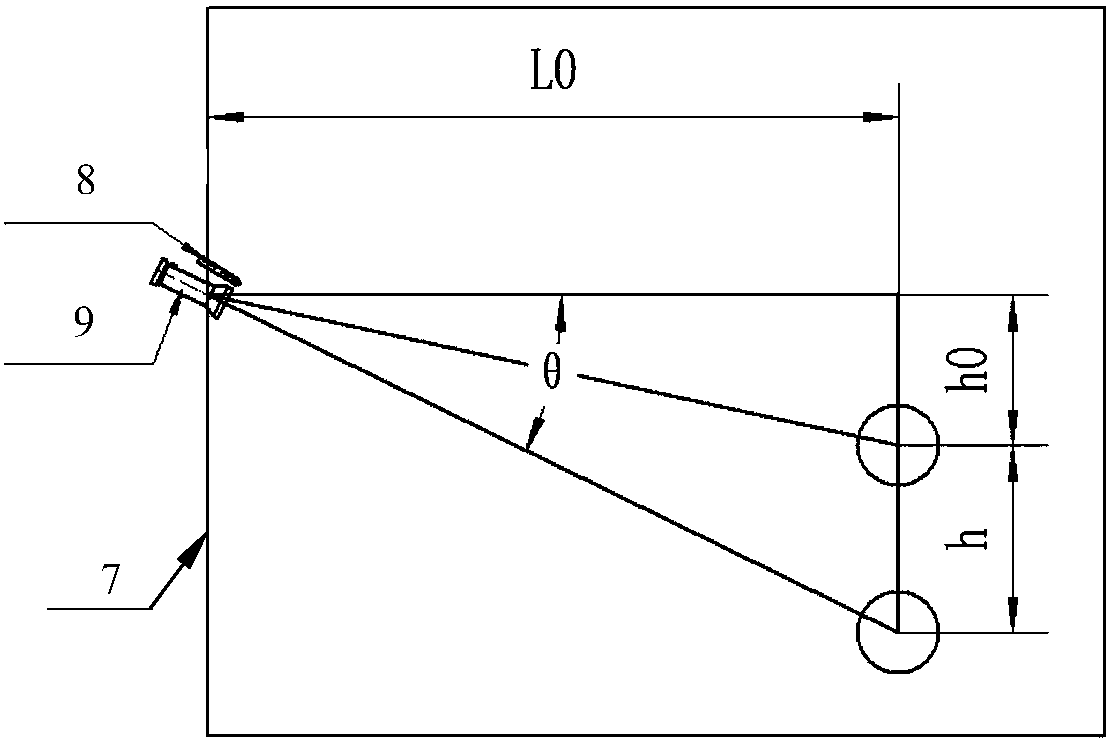

Wire arch detecting method and device in photovoltaic silicon wafer cutting process

PendingCN107672071AReduce the difficulty of detectionThe result is accurateWorking accessoriesFine working devicesWafer bowDirect observation

The invention provides a line arch detecting method and device in the photovoltaic silicon wafer cutting process, and the problems that in the prior art, precision is insufficient, and operation is not convenient can be solved. According to the line arch detecting device, a telephoto lens with a transparent scaleplate is fixedly arranged outside a photovoltaic silicon wafer cutting work area, anda cross-shaped mark is arranged in the center of the lens. The line arch observation view angle of the telephoto lens is set as theta, calculation is conducted through measurement of the horizontal distance L0 between the telephoto lens and the intersection point of a cutting line net and a silicon bar and the height h0 relative to the cutting line net and the theta and h corresponding relation embodied according to the formula: h=L0tan<theta>-h0, the longitudinal height value is marked on the transparent scaleplate, direct observation is conducted, and the line arch value h is obtained. According to the line arch detecting method and device, the detection result is accurate, wherein precision is 1mm; during detection, repeated cutting bin opening and closing in the cutting process are notneeded; and meanwhile, continuous observation is achieved, and the detection difficulty of technicists is greatly lowered.

Owner:杨凌美畅新材料股份有限公司

Deposition of heteroatom-doped carbon films

ActiveUS9406509B2High densityHigh selectivitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingCarbon filmWafer bow

Easily removable heteroatom-doped carbon-containing layers are deposited. The carbon-containing layers may be used as hardmasks. The heteroatom-doped carbon-containing hardmasks have high etch selectivity and density and also a low compressive stress, which will reduce or eliminate problems with wafer bow. Heteroatoms incorporated into the hardmask include sulfur, phosphorous, nitrogen, oxygen, and fluorine, all of which have low reactivity towards commonly used etchants. When sulfur is used as the heteroatom, the hardmask is easily removed, which simplifies the fabrication of NAND devices, DRAM devices, and other devices.

Owner:APPLIED MATERIALS INC

Location-specific tuning of stress to control bow to control overlay in semiconductor processing

Techniques herein include systems and methods for correcting pattern overlay errors by correcting or adjusting bowing of wafers. Location-specific tuning of stress on semiconductor substrates reduces overlay error. Location-specific tuning of stress independently modifies specific regions, areas, or point locations on a substrate to change wafer bow at those specific locations, which reduces overlay error on substrates, which in turn improves overlay of subsequent patterns created on the substrate. Techniques herein include receiving a substrate with some amount of overlay error, measuring bow of the substrate to map z-height deviations across the substrate, generating an overlay correction pattern, and then physically modifying internal stresses on the substrate at specific locations with modifications independent of other coordinate locations. Such modifications can include etching a backside surface of the substrate. One or more processing modules can be used for such processing.

Owner:TOKYO ELECTRON LTD

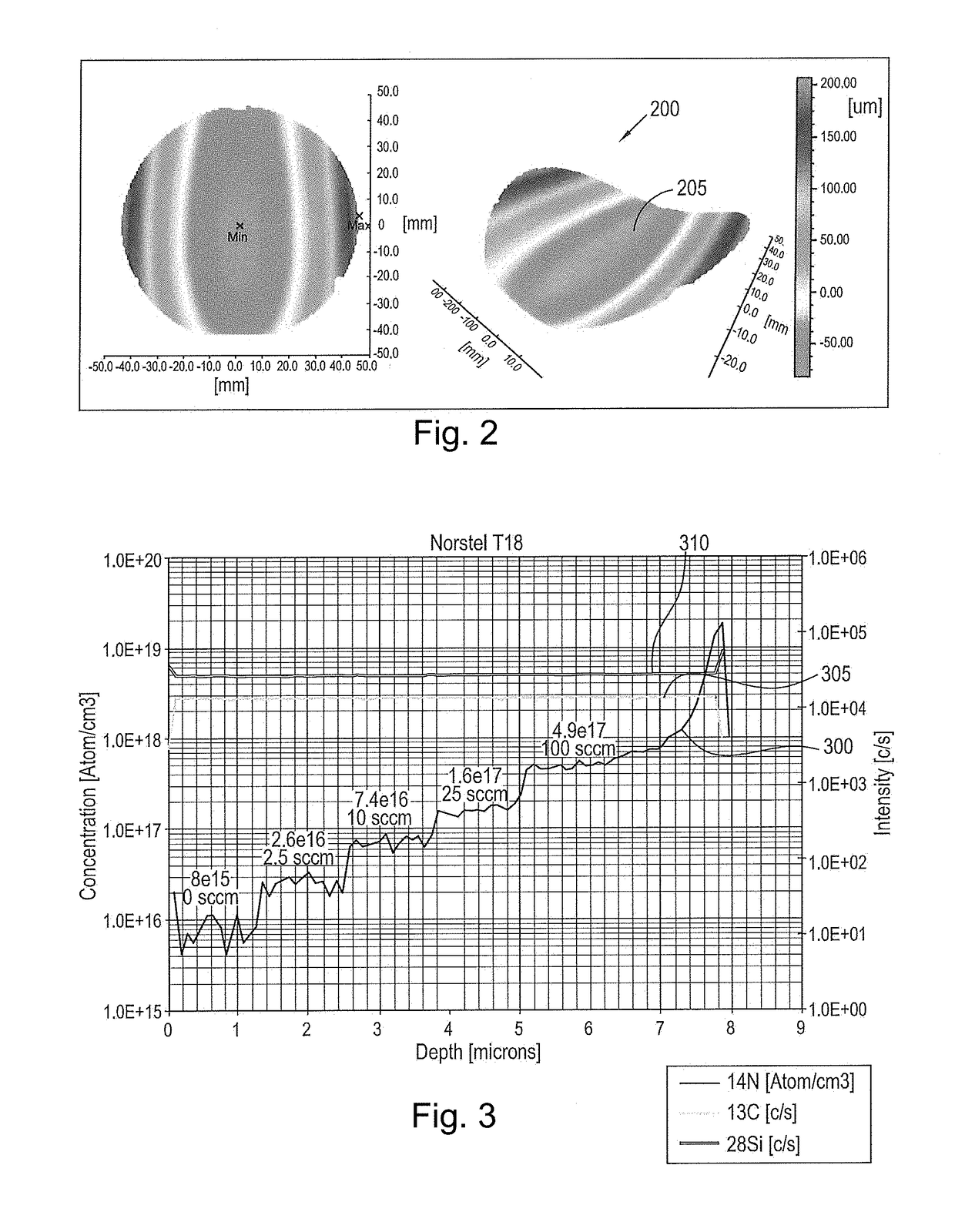

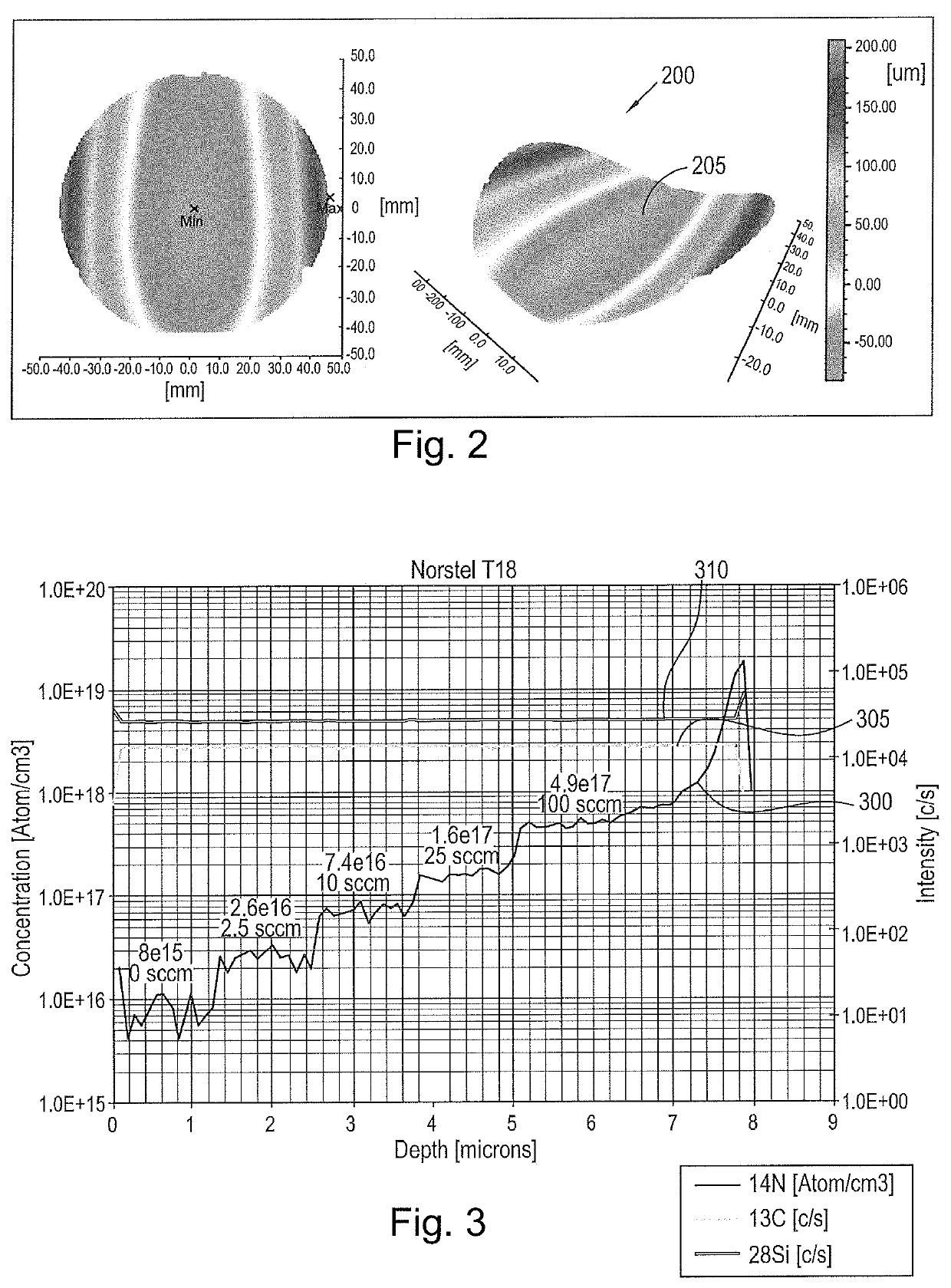

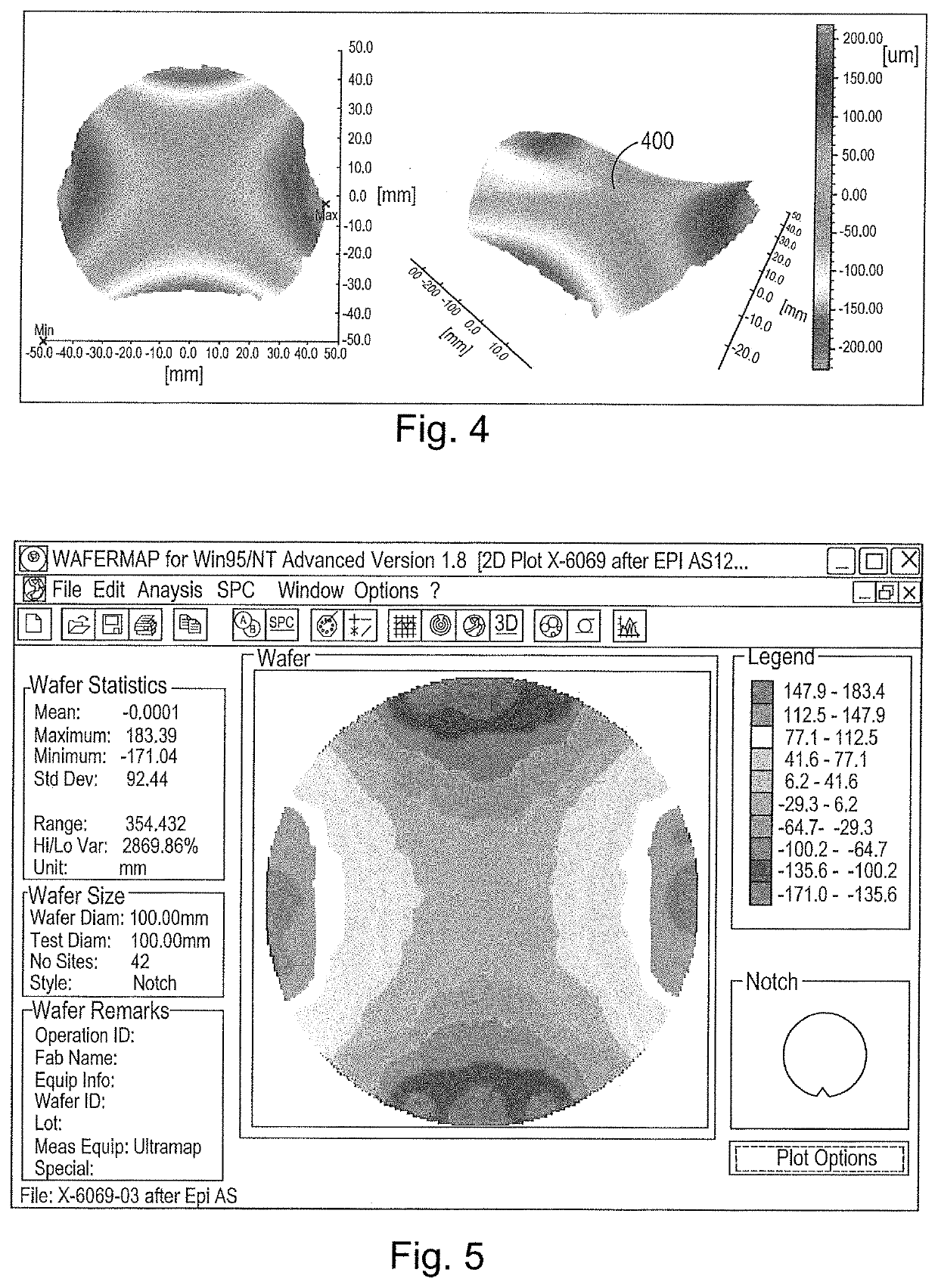

Wafer bow reduction

ActiveUS20170323790A1Reduces wafer bowImprove robustnessPolycrystalline material growthSemiconductor/solid-state device manufacturingWafer bowNitrogen

We describe a method for reducing bow in a composite wafer comprising a silicon wafer and a silicon carbide layer grown on the silicon wafer. The method includes applying nitrogen atoms during the growth process of the silicon carbide layer on the silicon wafer so as to generate a compressive stress within the composite wafer.

Owner:ANVIL SEMICON

Method of stress relief in anti-reflective coated cap wafers for wafer level packaged infrared focal plane arrays

ActiveUS9427776B2Reducing wafer bowDecorative surface effectsSolid-state devicesAnti-reflective coatingWafer bow

Methods for reducing wafer bow induced by an anti-reflective coating of a cap wafer are provided. The method may utilize a shadow mask having at least one opening therein that is positioned opposite recessed regions in a cap wafer. The method may further include depositing at least one layer of an anti-reflective coating material through the shadow mask onto a planar side of a cap wafer to provide a discontinuous coating on the planar side.

Owner:RAYTHEON CO

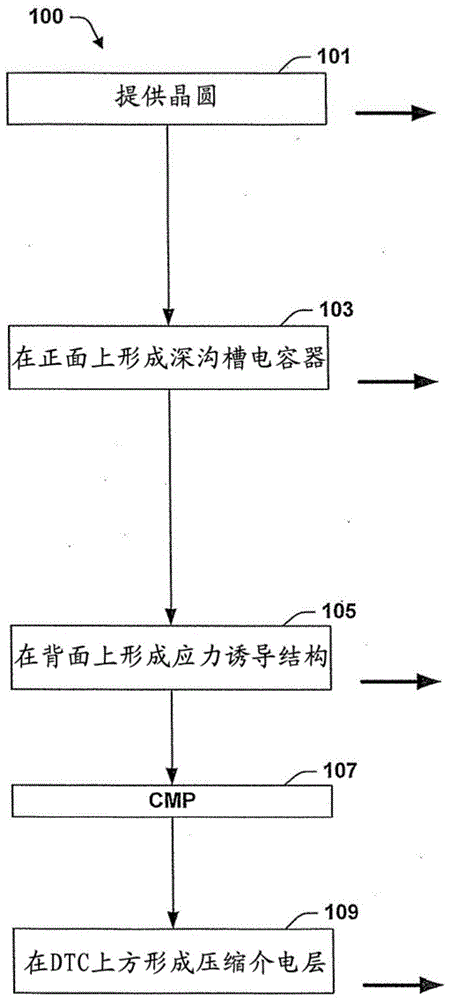

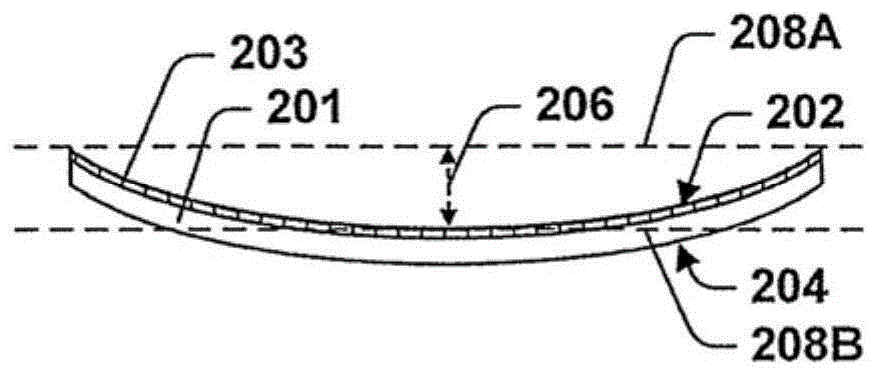

Integrated circuit with backside structure reducing substrate warpage

ActiveCN104253127BSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsWafer bowEngineering

The present invention improves wafer warpage caused by deep trench capacitors through structures formed on the reverse side of the wafer. The structure on the reverse side includes a tensioned membrane. A tension film can be formed in the trenches on the backside of the wafer, which enhances its effect. In some embodiments, wafers are used to form 3D-IC devices. In some embodiments, a 3D-IC device includes high voltage or high power circuitry. The invention also discloses an integrated circuit with a backside structure that reduces substrate warpage.

Owner:TAIWAN SEMICON MFG CO LTD

Location-specific tuning of stress to control bow to control overlay in semiconductor processing

Techniques herein include systems and methods for correcting pattern overlay errors by correcting or adjusting bowing of wafers. Location-specific tuning of stress on semiconductor substrates reduces overlay error. Location-specific tuning of stress independently modifies specific regions, areas, or point locations on a substrate to change wafer bow at those specific locations, which reduces overlay error on substrates, which in turn improves overlay of subsequent patterns created on the substrate. Techniques herein include receiving a substrate with some amount of overlay error, measuring bow of the substrate to map z-height deviations across the substrate, generating an overlay correction pattern, and then physically modifying internal stresses on the substrate at specific locations with modifications independent of other coordinate locations. Such modifications can include etching a backside surface of the substrate. One or more processing modules can be used for such processing.

Owner:TOKYO ELECTRON LTD

Methods and apparatus to eliminate wafer bow for CVD and patterning HVM systems

ActiveUS11094647B2Minimize controlHigh densityElectric discharge tubesSemiconductor/solid-state device detailsWafer bowWafering

A method and apparatus for forming a backside coating on a substrate to counteract stresses from a previously deposited film is disclosed. In one embodiment, a method for flattening a bowed substrate includes providing a substrate having a film stack formed on a first major surface thereof, wherein the substrate comprises a bowed orientation, and forming a coating a second major surface of the substrate, wherein the coating is configured to counter stresses produced by the film stack and flattens the substrate from the bowed orientation.

Owner:APPLIED MATERIALS INC

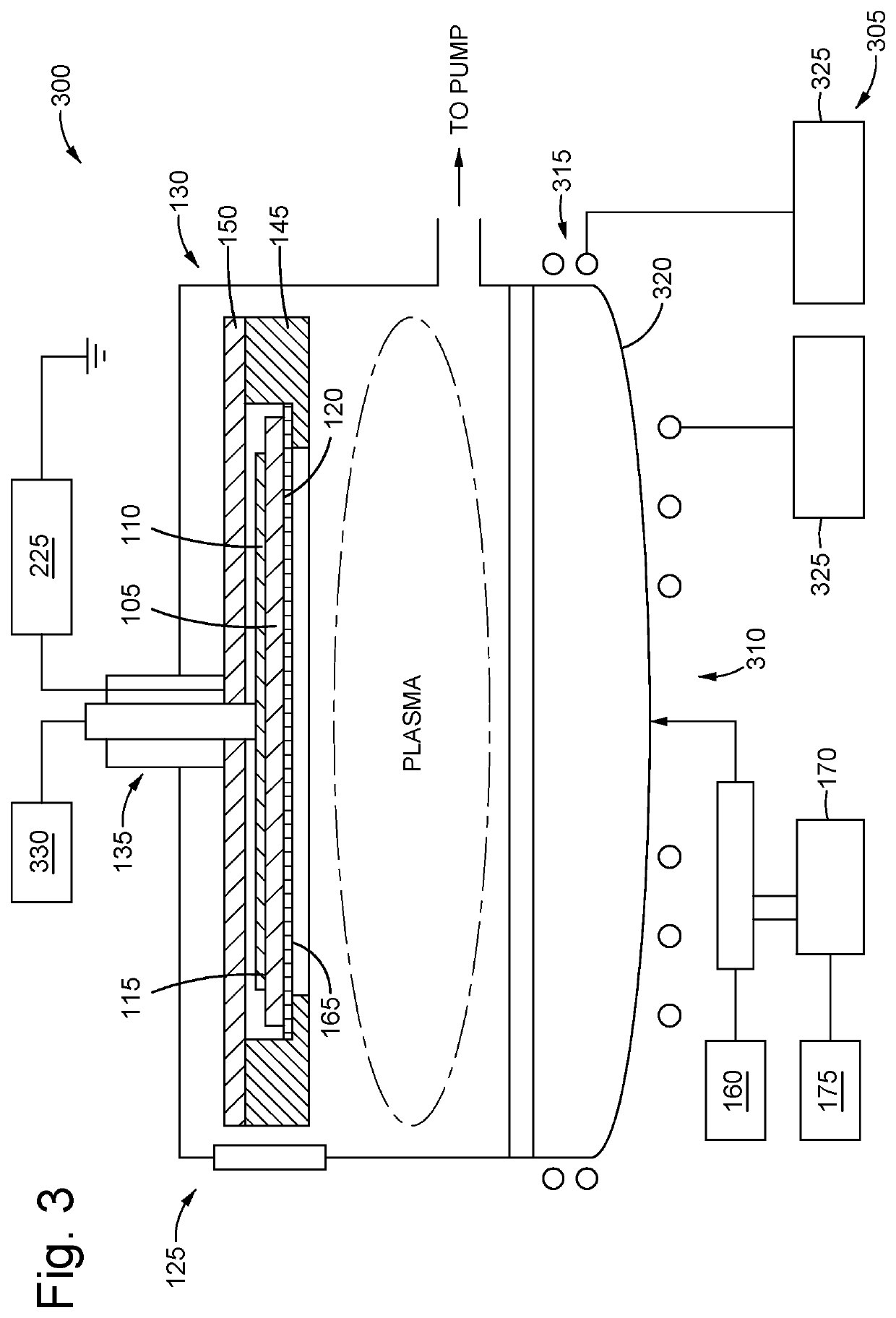

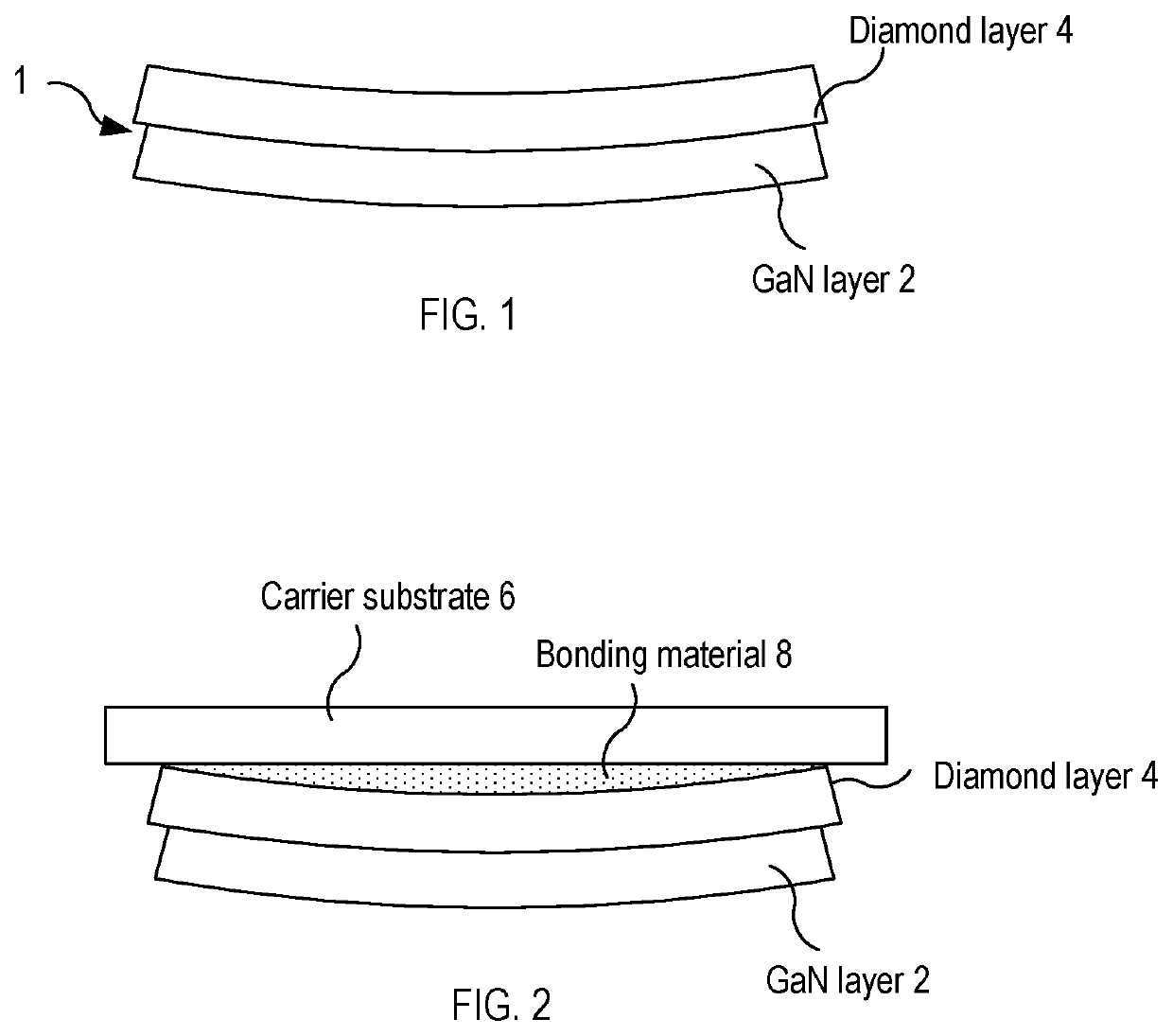

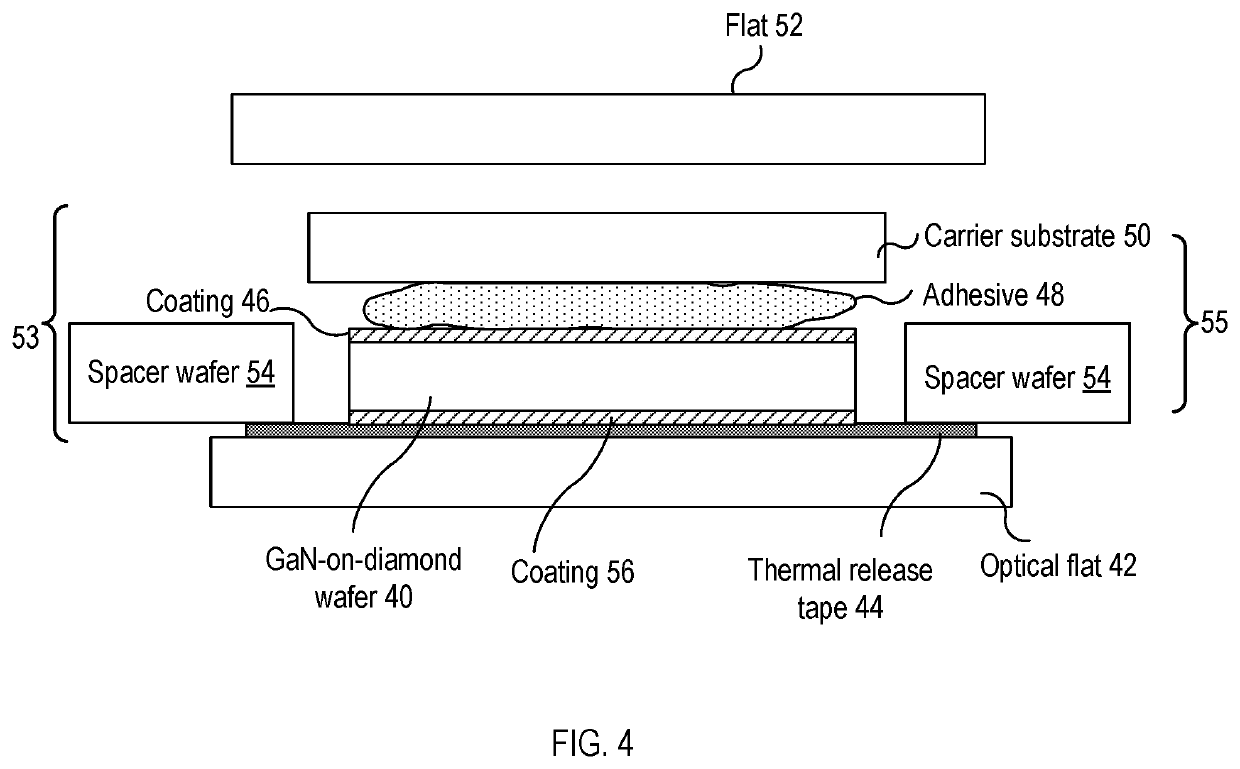

Mounting of semiconductor-on-diamond wafers for device processing

ActiveUS20200227301A1Semiconductor/solid-state device detailsSolid-state devicesThermal dilatationWafer bow

Owner:RFHIC

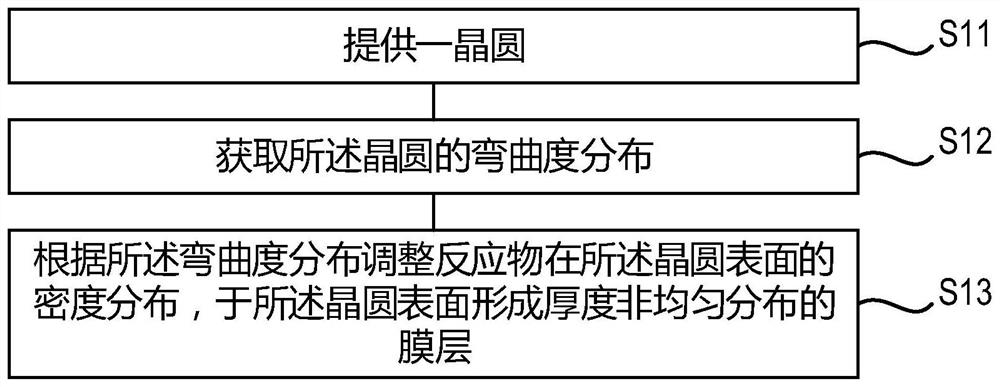

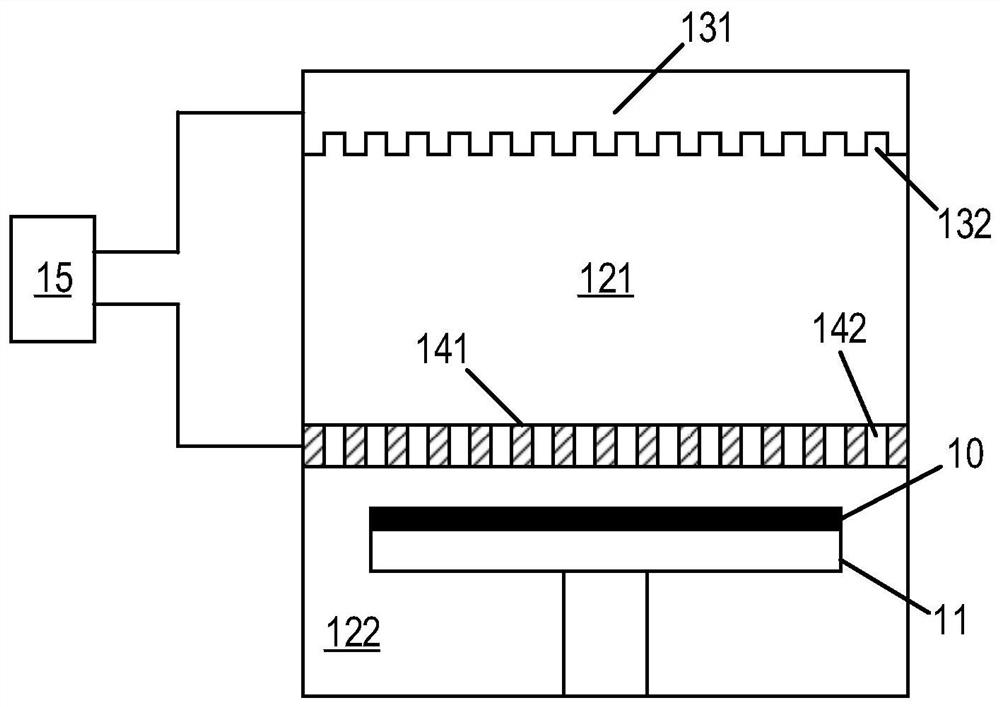

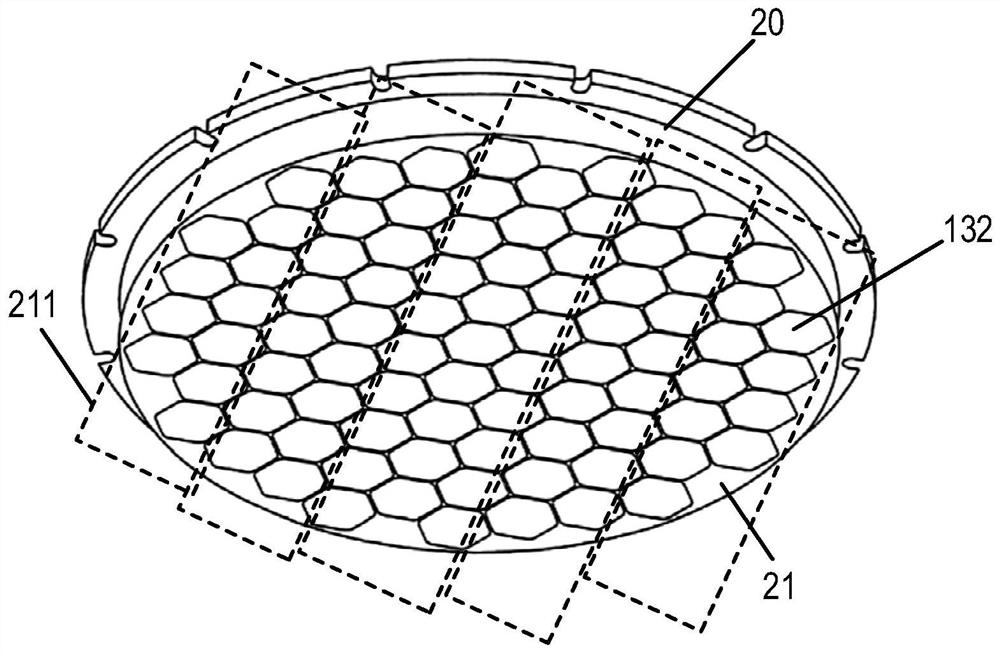

Methods for Balanced Wafer Bow Distribution

ActiveCN109273378BBalanced Curvature DistributionQuality improvementSemiconductor/solid-state device testing/measurementChemical vapor deposition coatingWafer bowEngineering

The invention relates to the technical field of semiconductor manufacturing, in particular to a method for balancing the curvature distribution of a wafer. The method for balancing wafer curvature distribution includes the following steps: providing a wafer; obtaining the curvature distribution of the wafer; adjusting the density distribution of reactants on the surface of the wafer according to the curvature distribution; A film layer with non-uniform thickness distribution is formed on the surface of the wafer. The invention can form a film layer with non-uniform thickness distribution on the surface of the wafer, realize the balance of the curvature distribution of the wafer, is applicable to wafers of various shapes, and effectively improves the quality of wafer products.

Owner:YANGTZE MEMORY TECH CO LTD

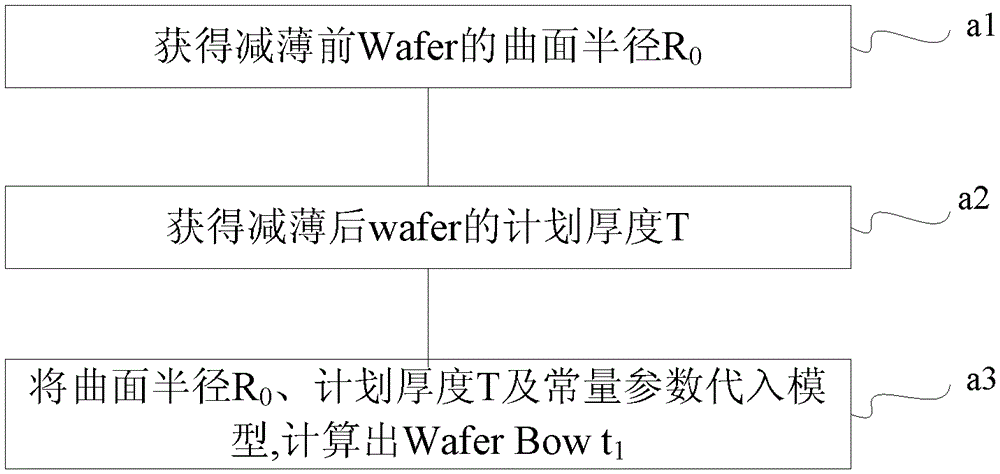

Wafer Bow Measurement Method

ActiveCN102394225BAvoid lostMeasurement devicesSemiconductor/solid-state device testing/measurementWafer curvatureWafer bow

The invention provides a Wafer Bow calculation method to measure and calculate the Wafer Bow before the thinning process, so as to avoid various losses caused by discovering that the Wafer Bow does not meet the requirements after the thinning process is completed. A method for calculating Wafer Bow provided by the present invention comprises the steps of: obtaining the curved surface radius R of the Wafer before thinning 0 and the planned thickness T of the wafer after thinning; according to the surface radius R 0 and the planned thickness T, calculate the Wafer Bow of the thinned wafer as t 1 , the model used in this calculation is: t 1 =[R 0 T 2 -(R 0 2 T 4 -r 2 T 0 4 ) 1 / 2 ] / T 0 2 +C( T 0 / T) 1.58 , where T 0 For the wafer thickness before thinning, r is the radius of the wafer, and C is the curvature of the wafer caused by the gravity of the wafer before thinning.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

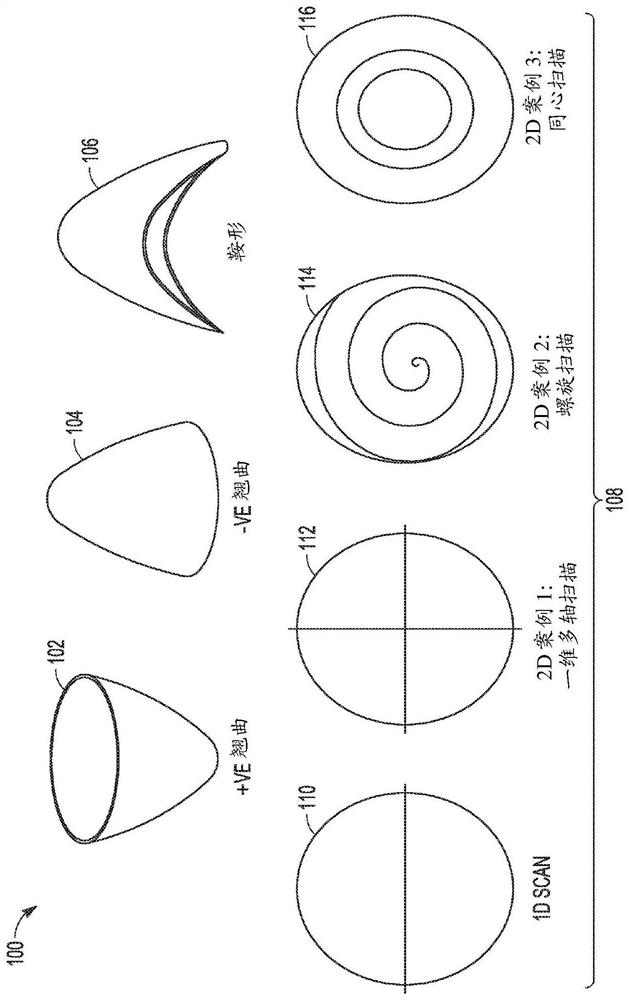

Integrated wafer bow measurements

PendingCN113330543ASemiconductor/solid-state device testing/measurementMaterial analysis by optical meansLinear motionWafer bow

In some examples, a wafer bow measurement system comprises a measurement unit including: a wafer support assembly to impart rotational movement to a measured wafer supported in the measurement unit; an optical sensor; a calibration standard to calibrate the optical sensor; a linear stage actuator to impart linear direction of movement to the optical sensor; a wafer centering sensor to determine a centering of the measured wafer supported in the measurement unit; and a wafer alignment sensor to determine an alignment of the measured wafer supported in the measurement unit.

Owner:LAM RES CORP

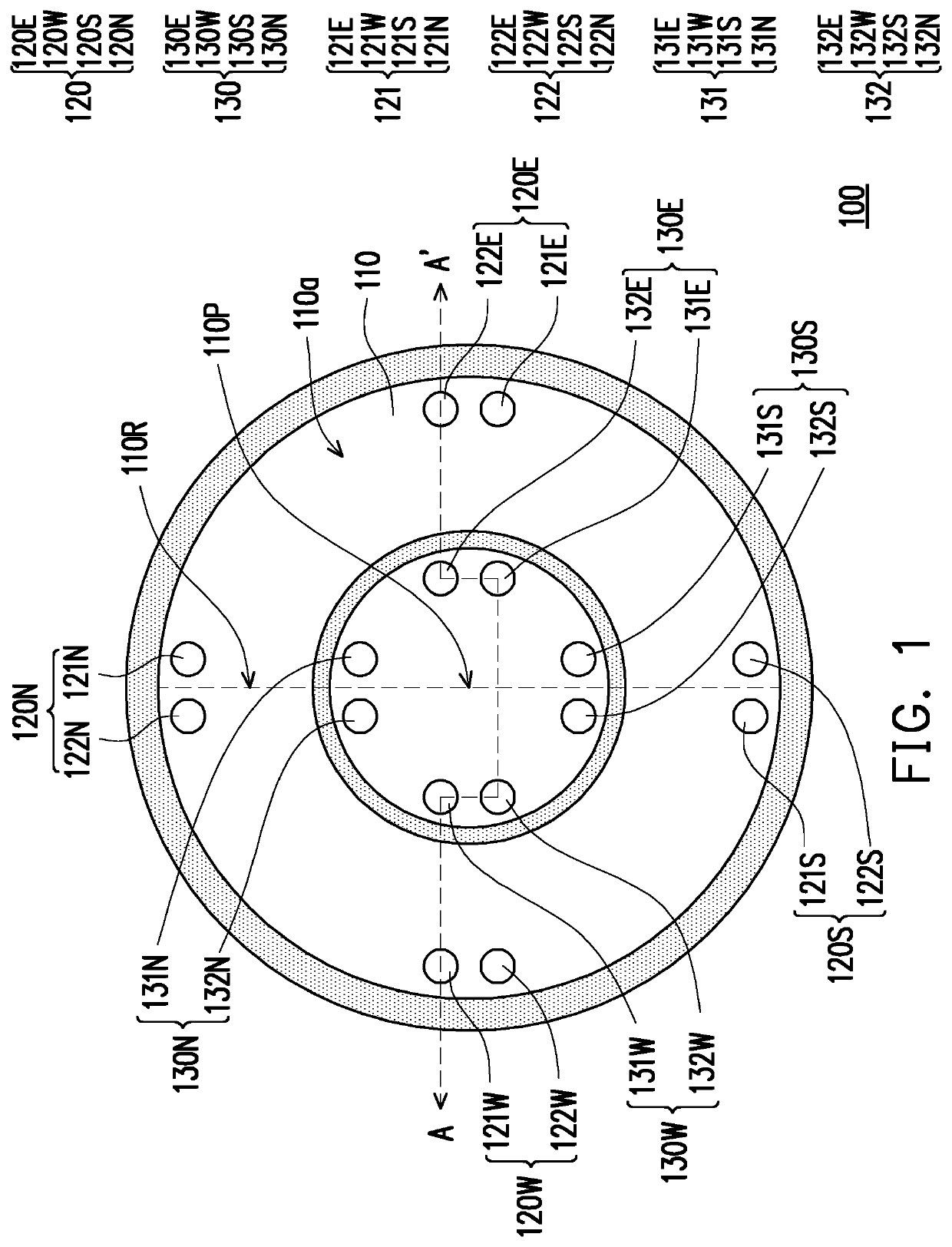

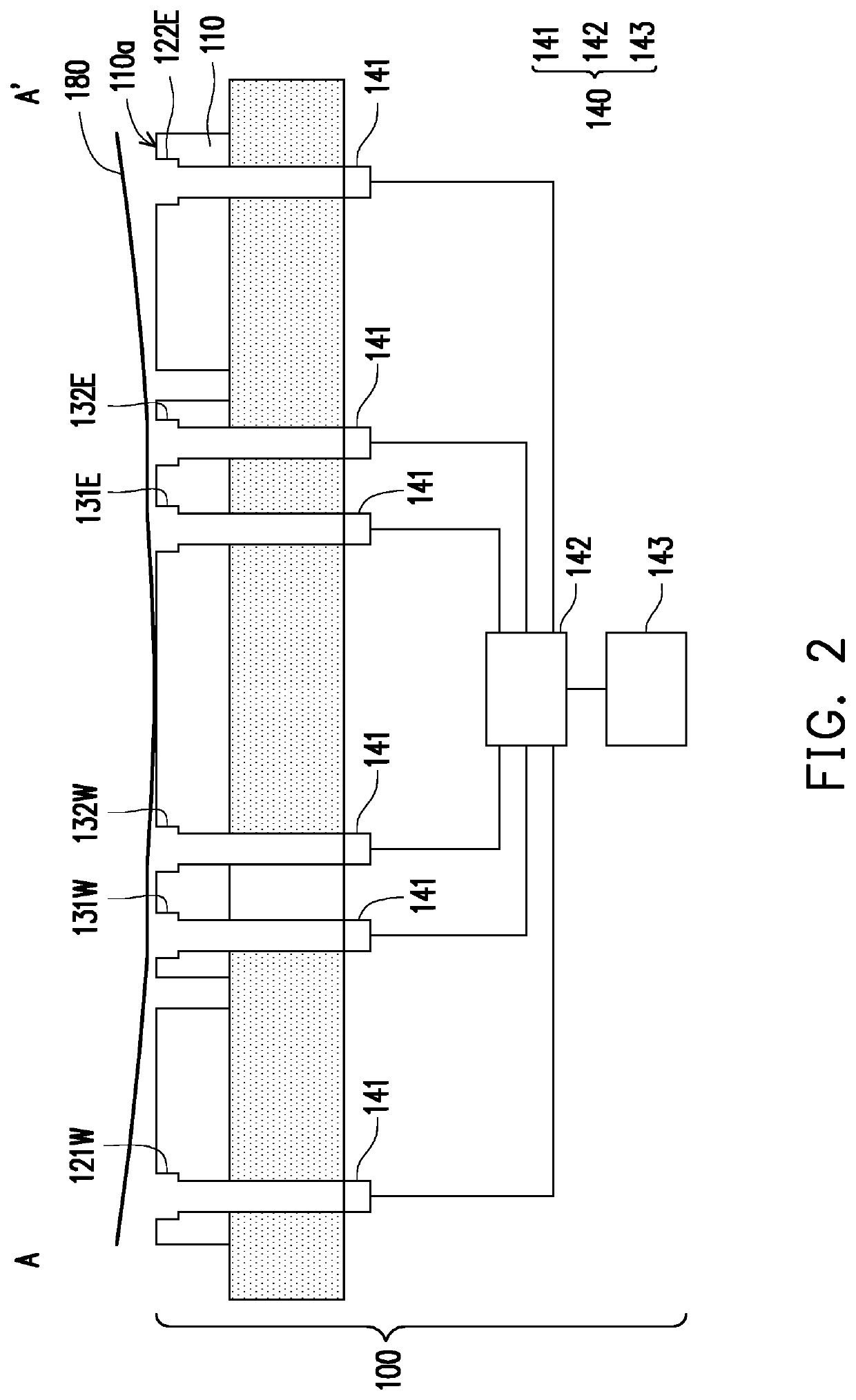

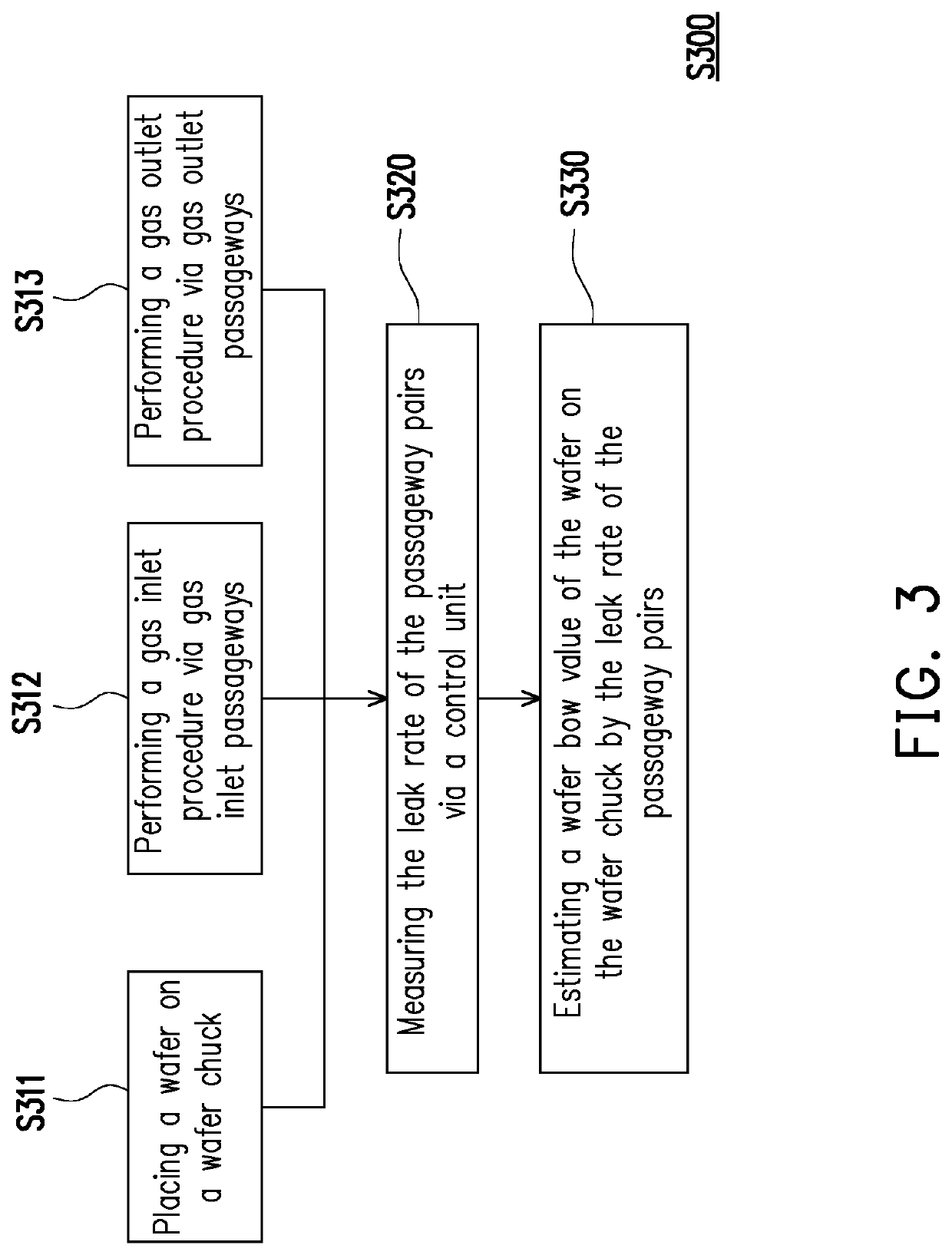

Wafer chuck apparatus, method for measuring wafer bow value and semiconductor process flow

ActiveUS11282726B2The process is simple and fastReduce riskMeasurement of fluid loss/gain rateSemiconductor/solid-state device testing/measurementWafer bowWafering

A method for measuring wafer bow value comprising the following steps is provided. Place a wafer on a wafer chuck apparatus. A gas inlet process is performed on gas inlet passageways of a passageway pair of the wafer chuck apparatus. A gas outlet process is performed on gas outlet passageways of a passageway pair of the wafer chuck apparatus. A leak rate of each channel pair is measured by the control unit when the wafer is placed on the wafer chuck apparatus and during the gas inlet process and gas outlet process are performed. A wafer bow value of the wafer on the wafer chuck apparatus is estimated by the leak rate of the passageway pair. A wafer chuck apparatus is provided. A semiconductor process flow is provided.

Owner:POWERCHIP SEMICON MFG CORP

Wafer bow reduction

ActiveUS10714338B2Improve robustnessEasy to processPolycrystalline material growthSemiconductor/solid-state device manufacturingCarbide siliconWafer bow

We describe a method for reducing bow in a composite wafer comprising a silicon wafer and a silicon carbide layer grown on the silicon wafer. The method includes applying nitrogen atoms during the growth process of the silicon carbide layer on the silicon wafer so as to generate a compressive stress within the composite wafer.

Owner:ANVIL SEMICON

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com