Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

59results about How to "Resistance value" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

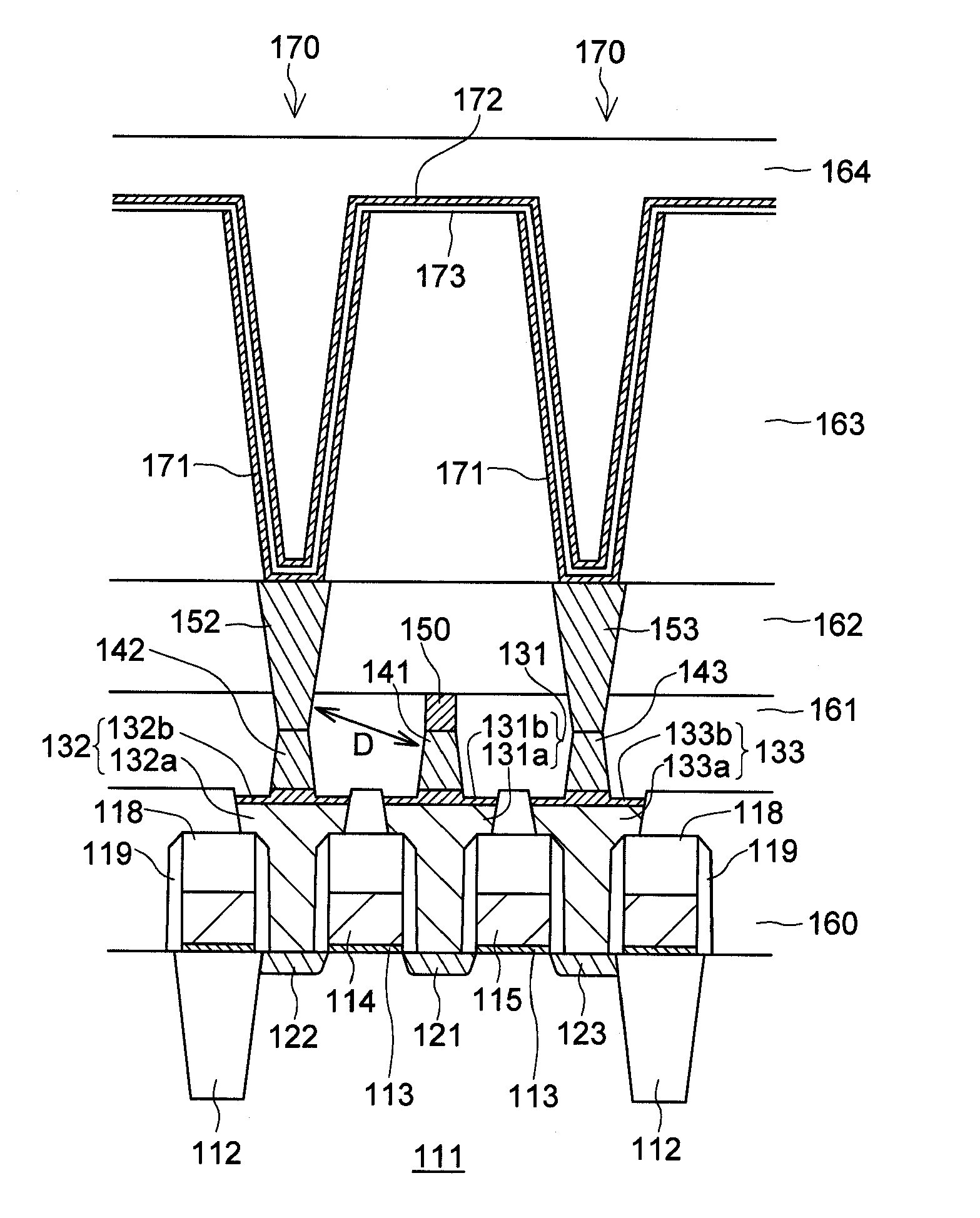

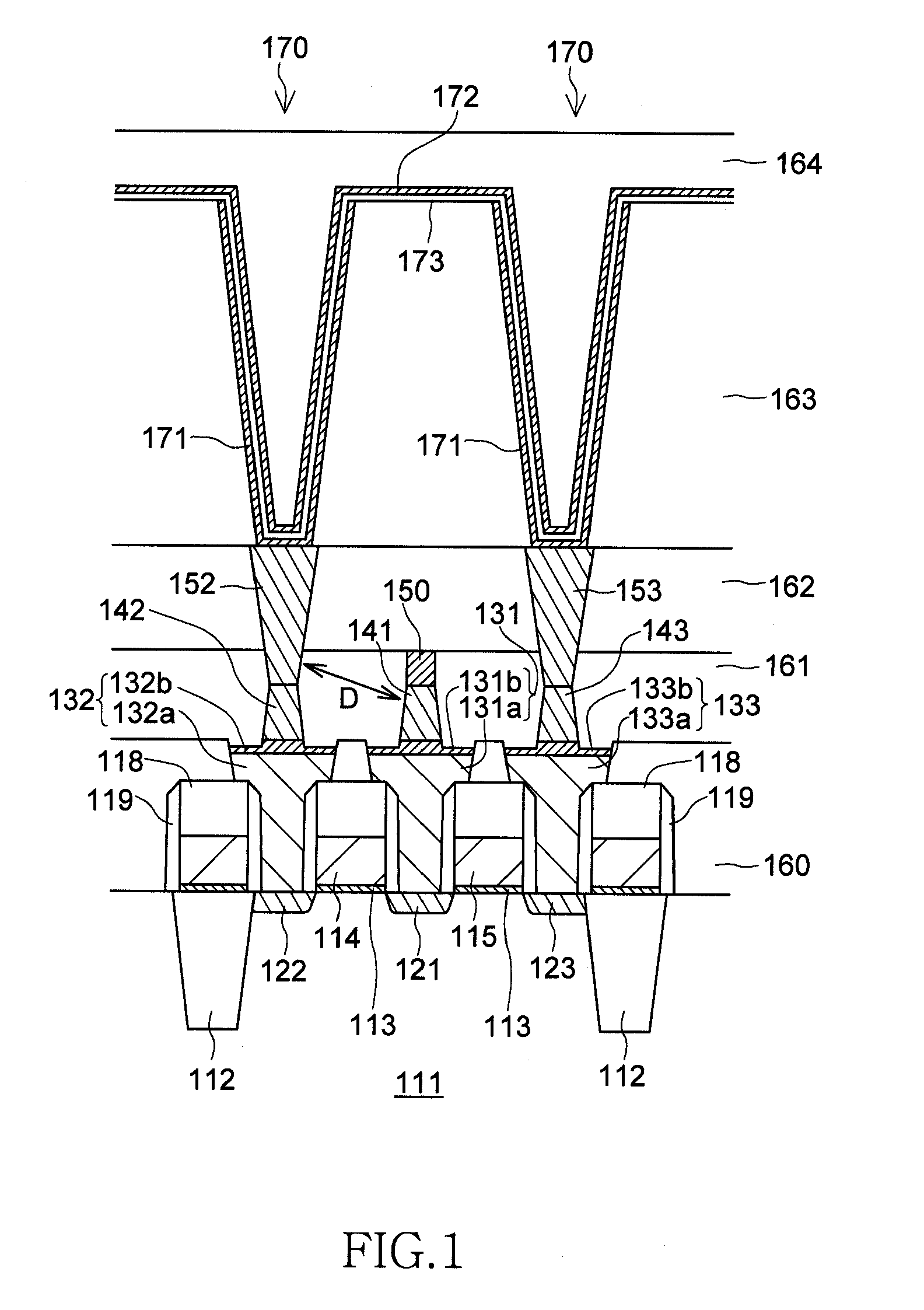

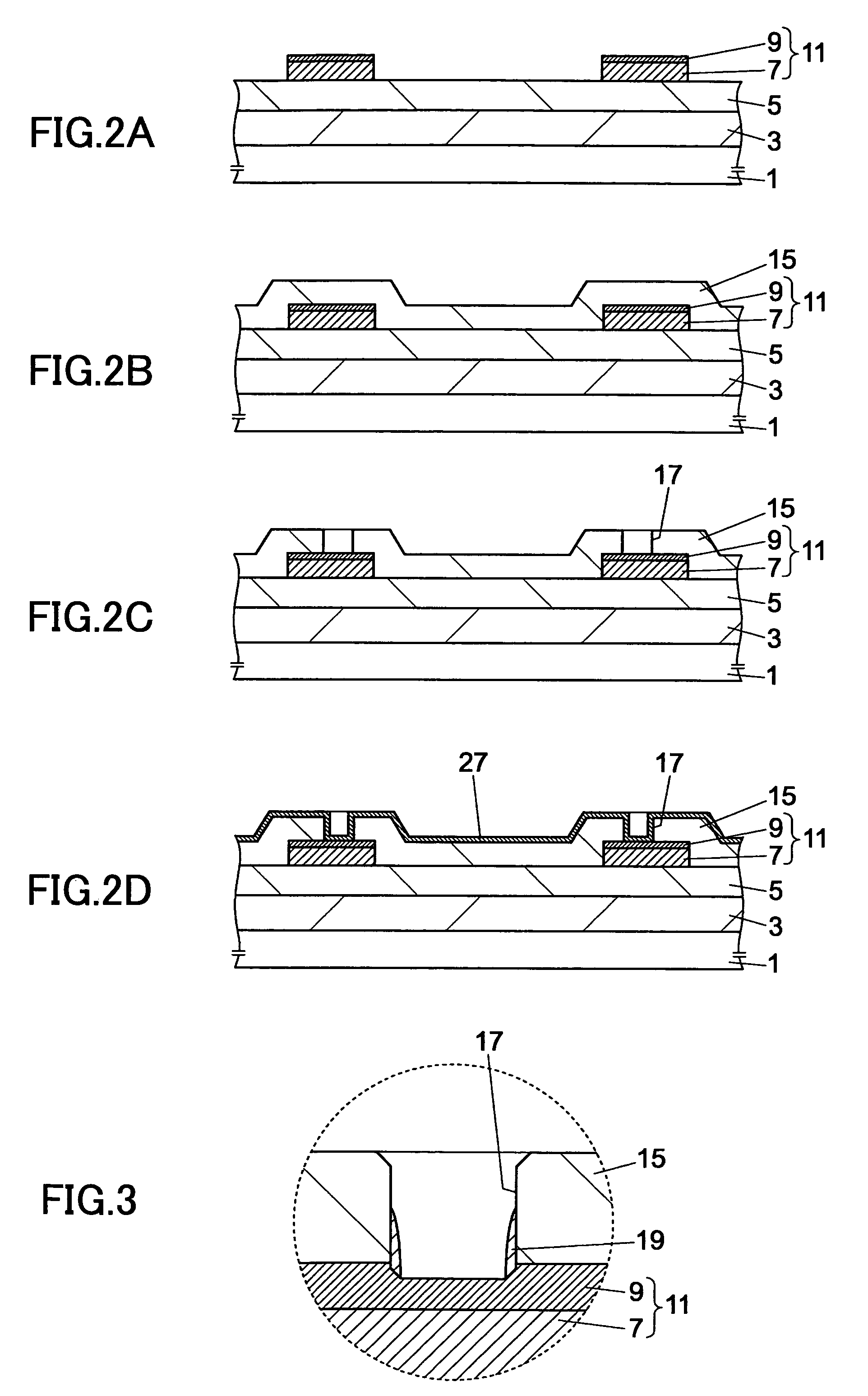

Semiconductor device and manufacturing method therof

InactiveUS20070145591A1Lower the resistance valueImprove the immunitySemiconductor/solid-state device detailsSolid-state devicesDielectricDevice material

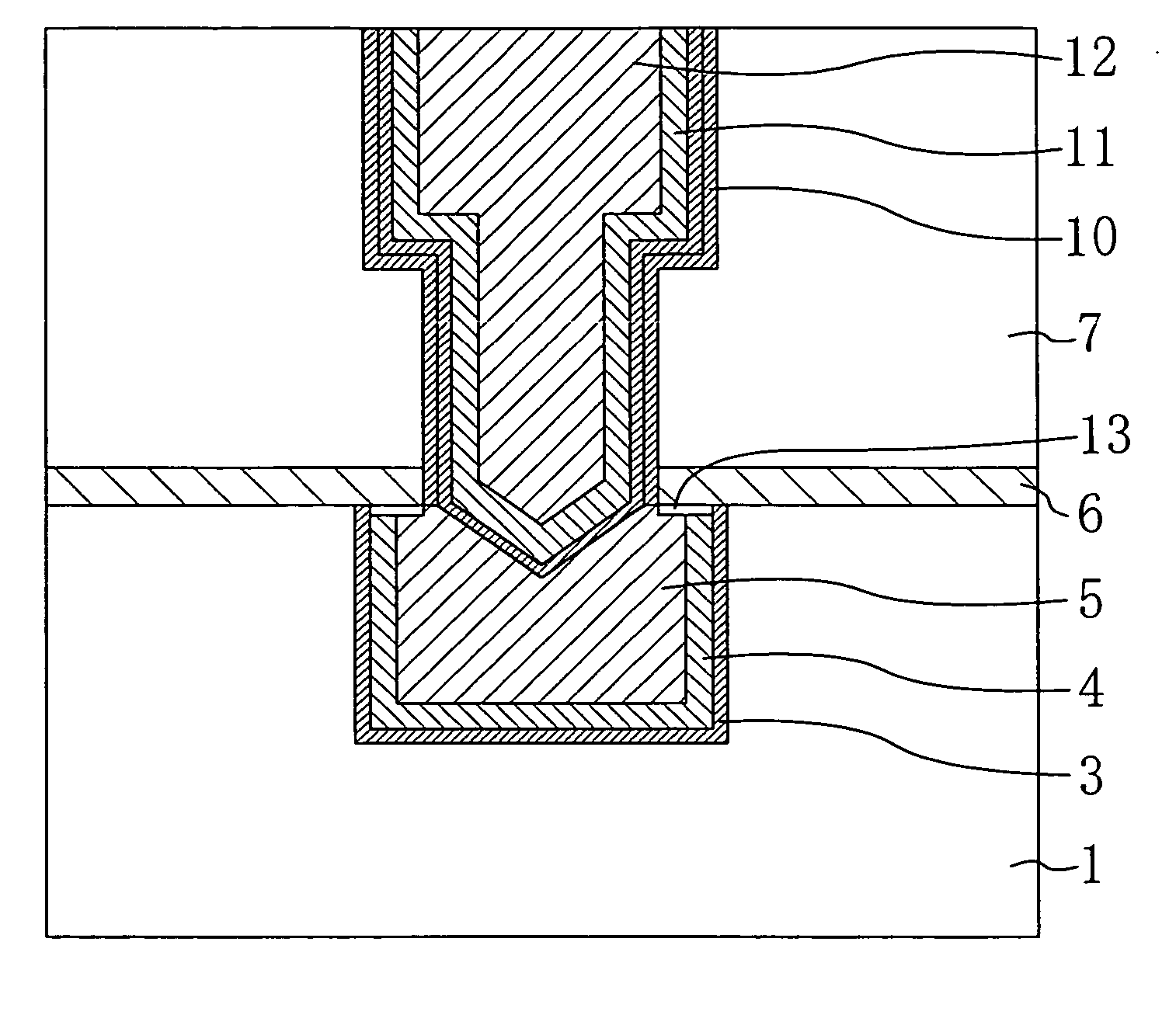

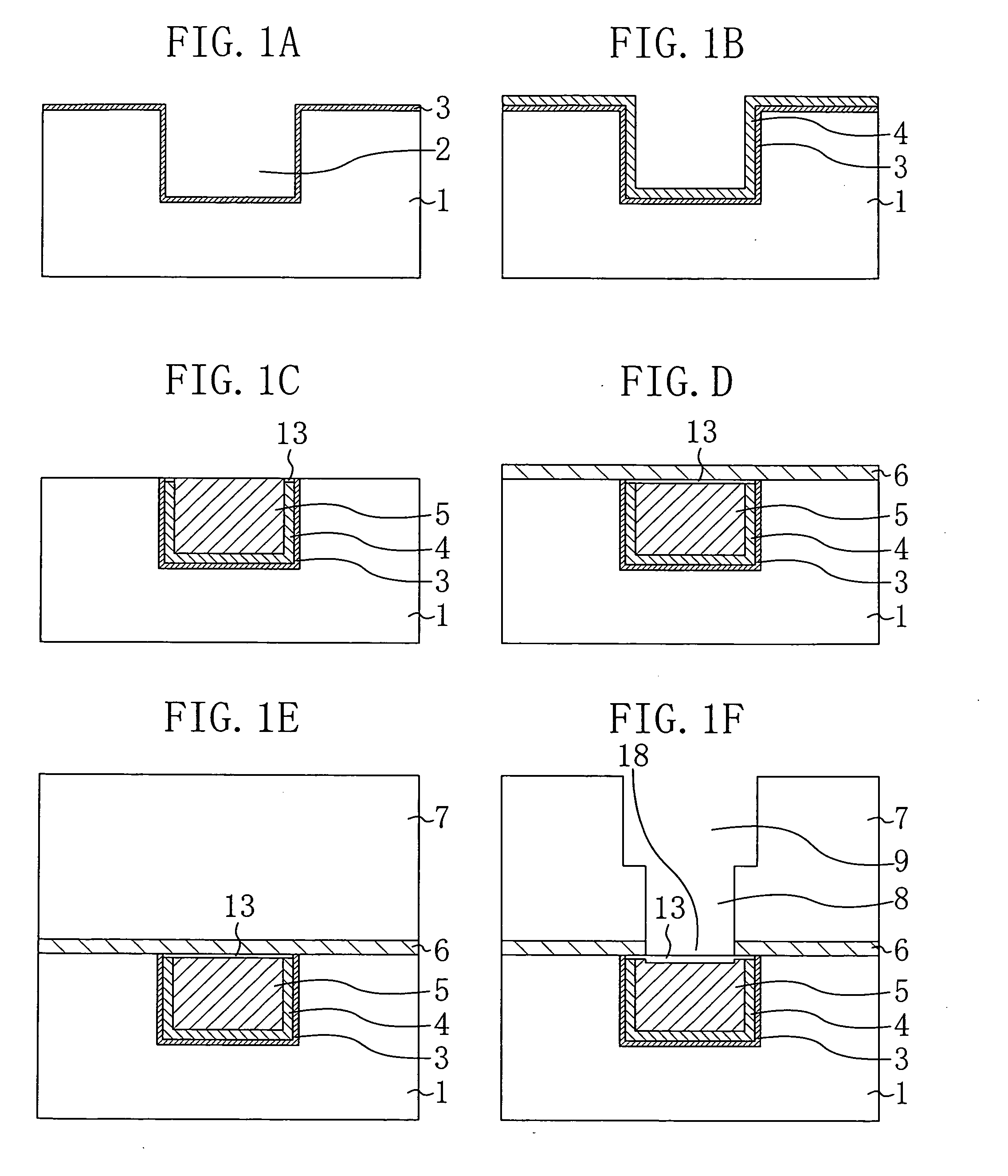

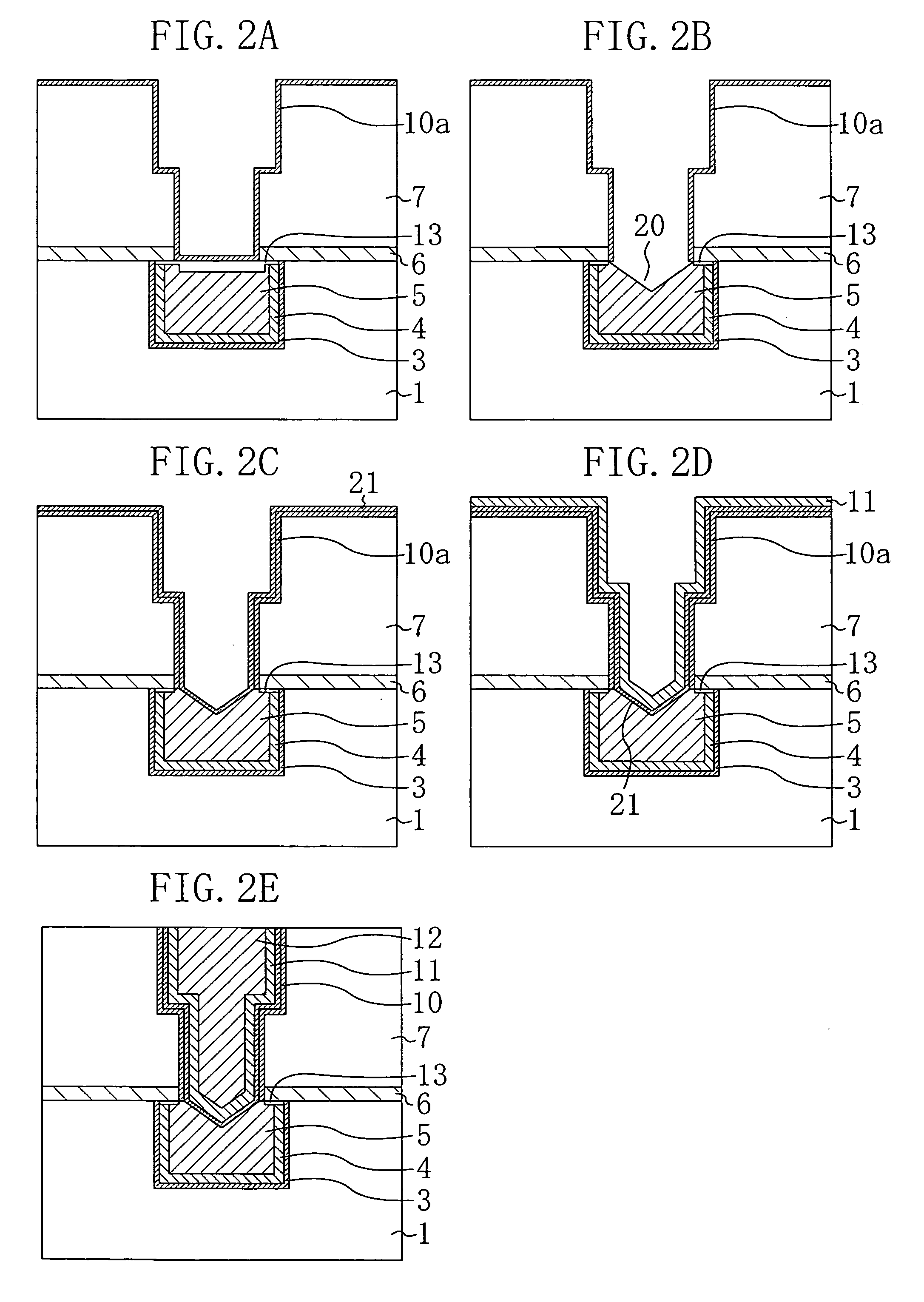

The semiconductor device manufacturing method includes the steps of: applying a first wire including a barrier metal film, a seed film, and a wiring material film in a first wire trench formed in a first interlayer dielectric film; after a second interlayer dielectric film is formed on the first interlayer dielectric film, forming a via hole and a second wire trench in the second interlayer dielectric film so as to expose the wiring material film; applying a barrier metal film on the semiconductor device; and after the barrier metal film on the wiring material film is removed by using, for example, a re-sputtering process, applying a barrier metal film on the wiring material film. The re-sputtering process can remove an oxide film of impurity metal in the seed film applied on the wiring material film.

Owner:PANASONIC CORP +1

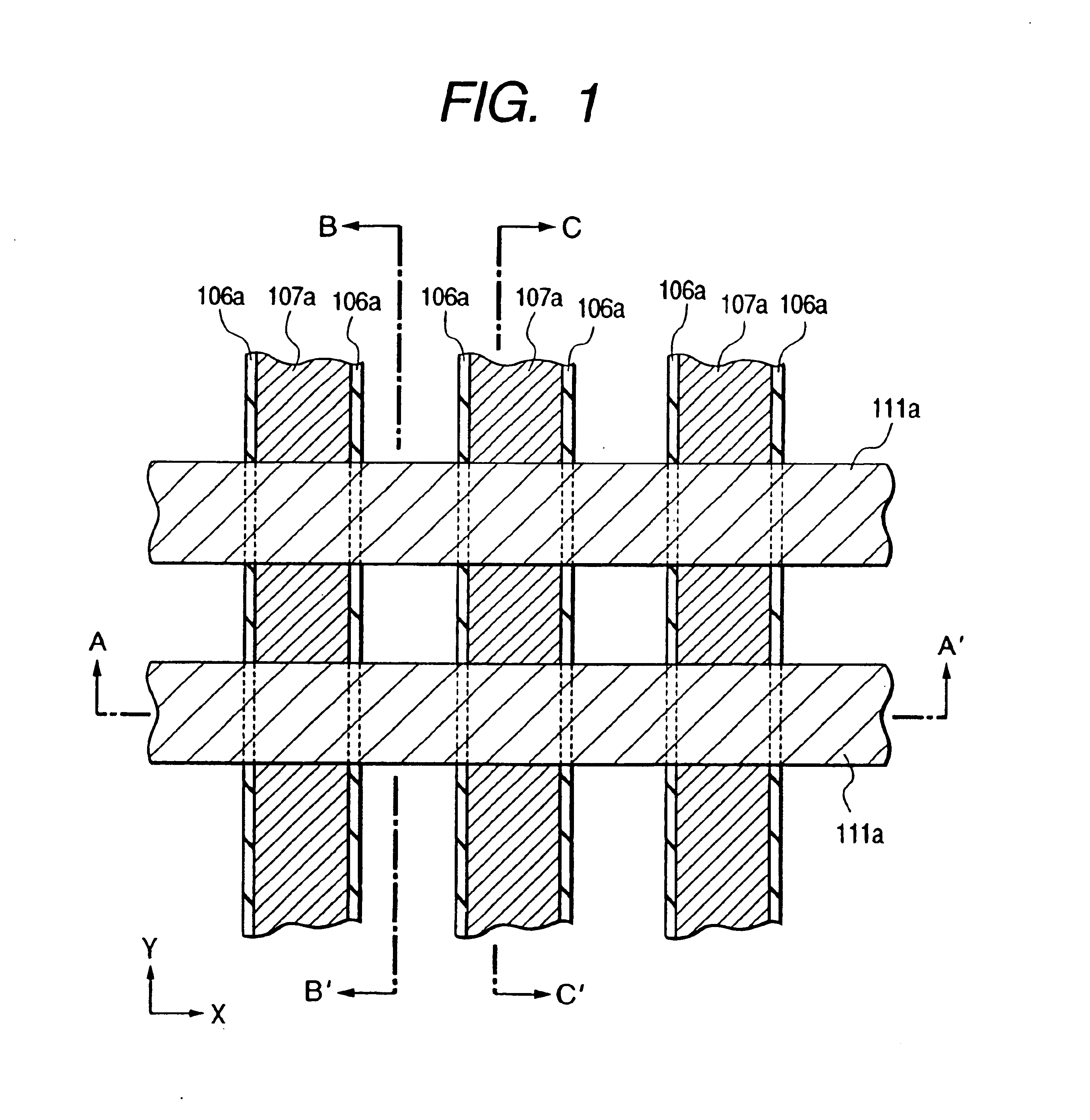

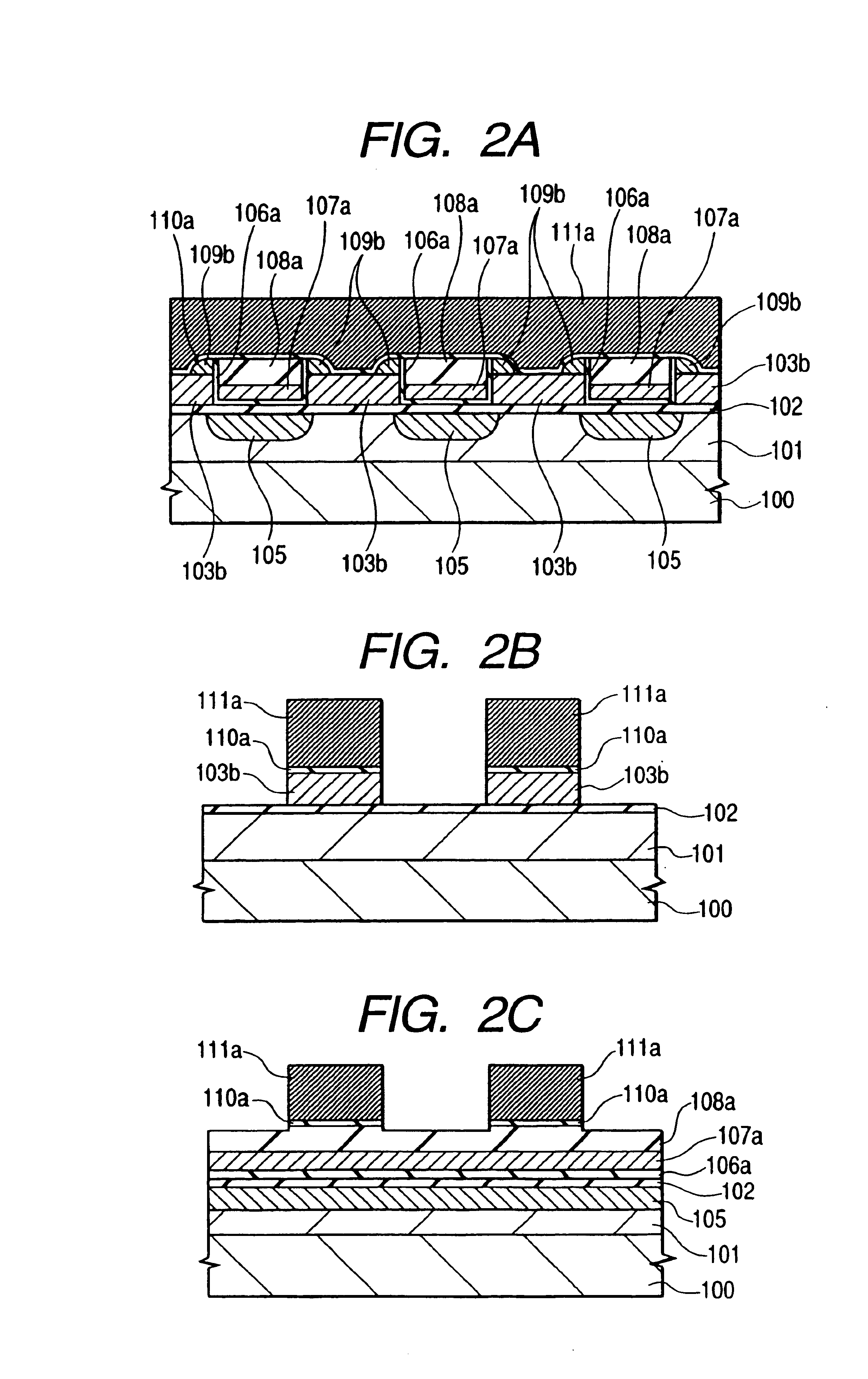

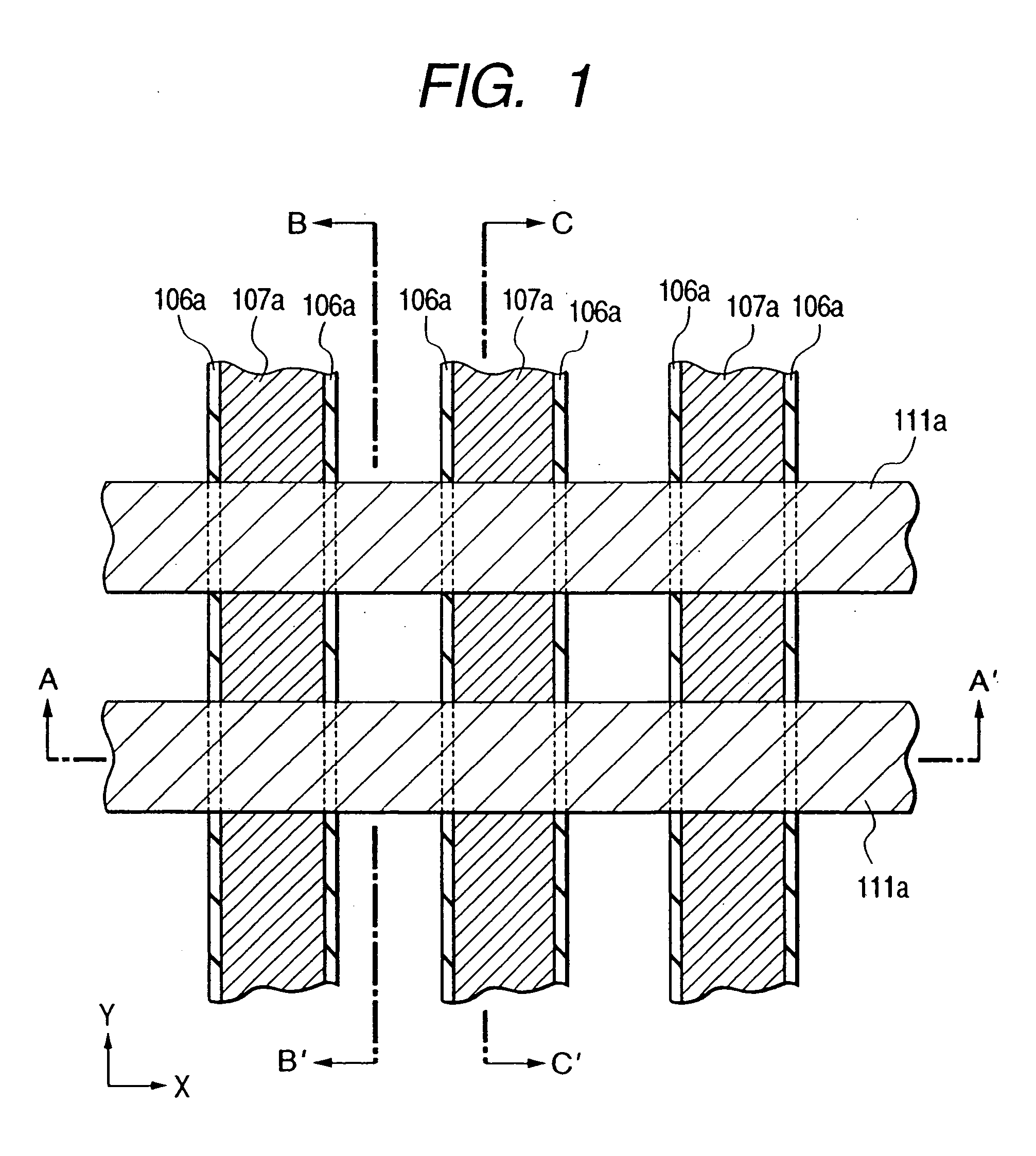

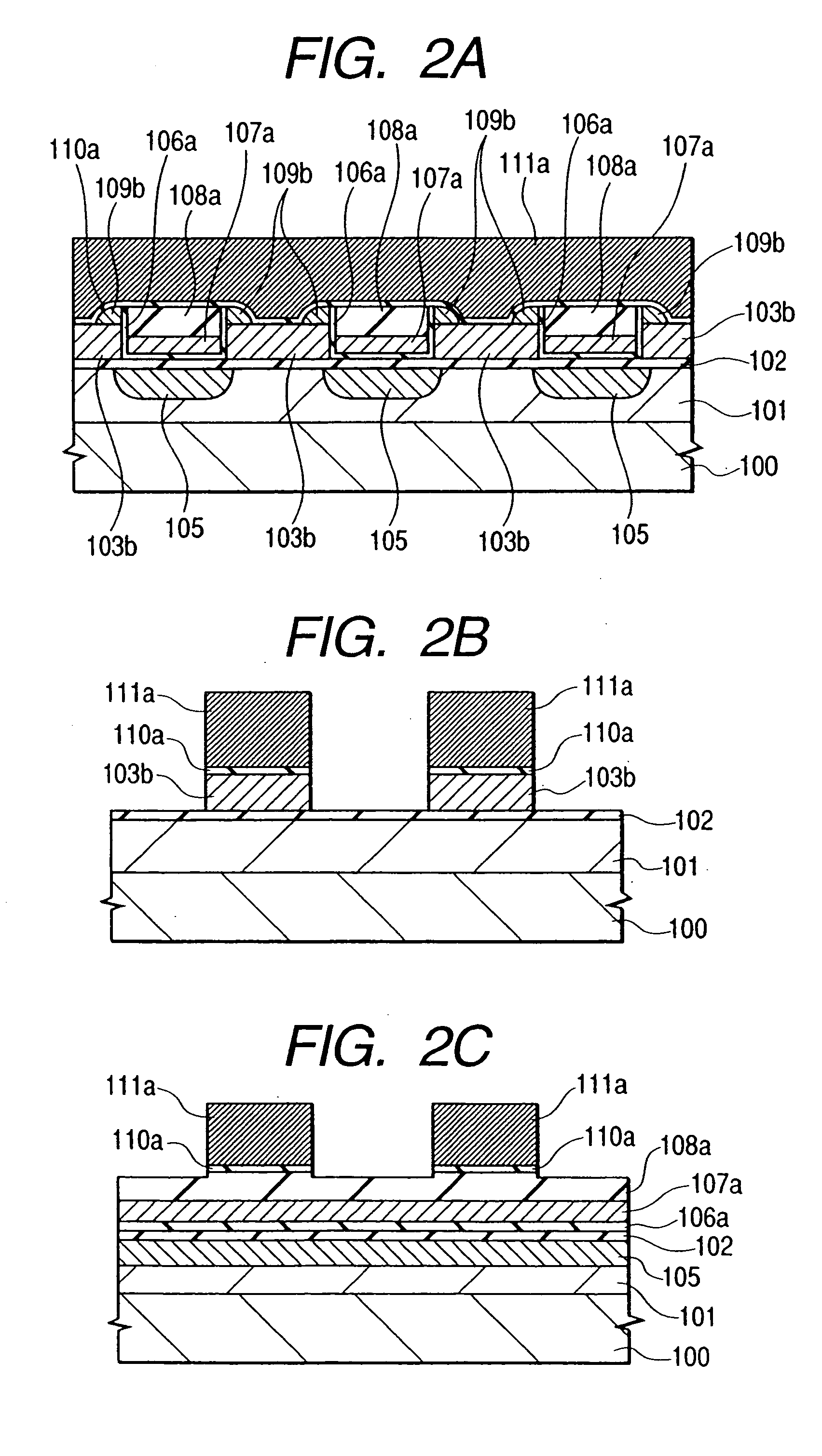

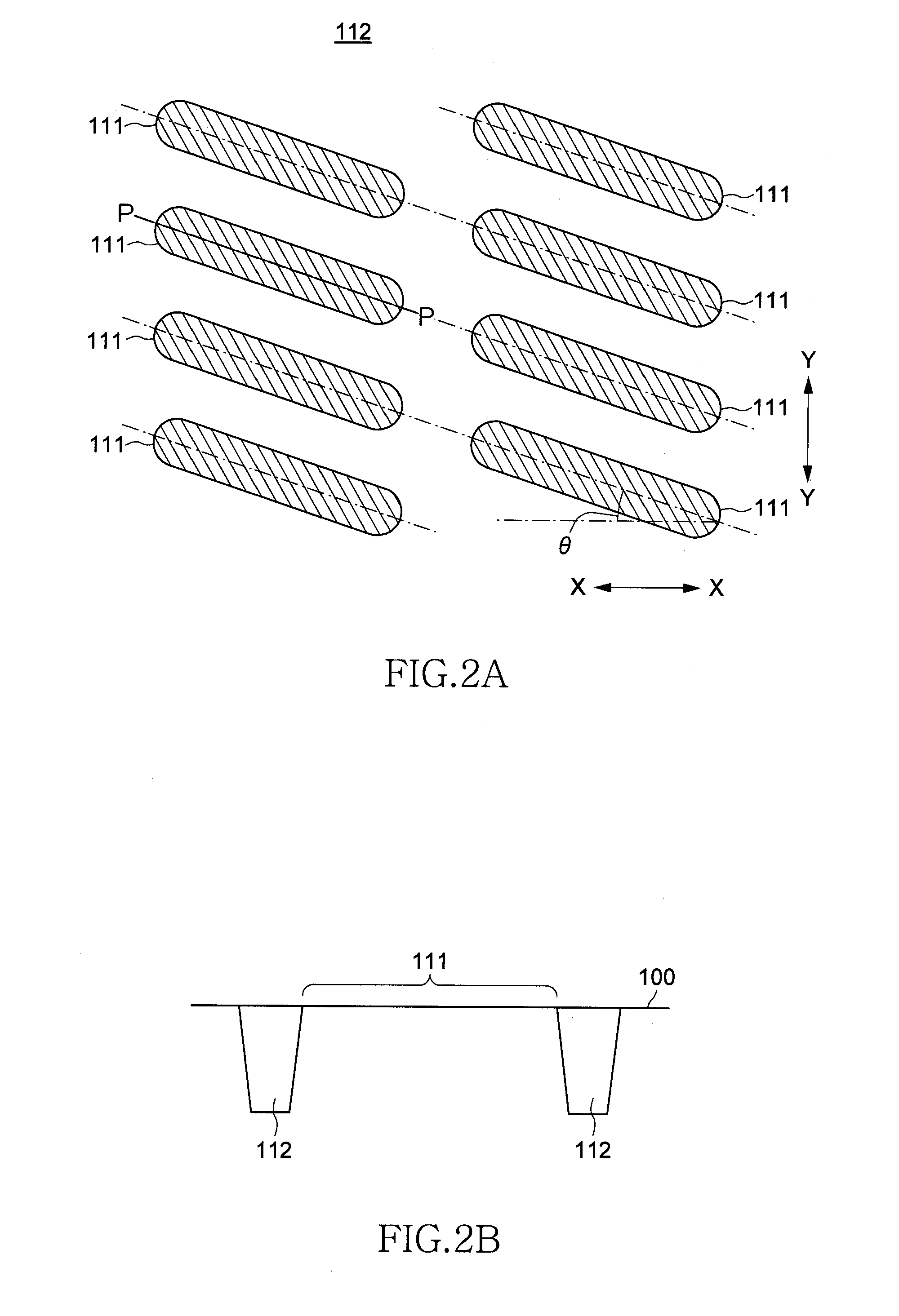

Semiconductor integrated circuit device including first, second and third gates

InactiveUS6901006B1Increase computing speedReduce defect densityTransistorSolid-state devicesMiniaturizationConnection control

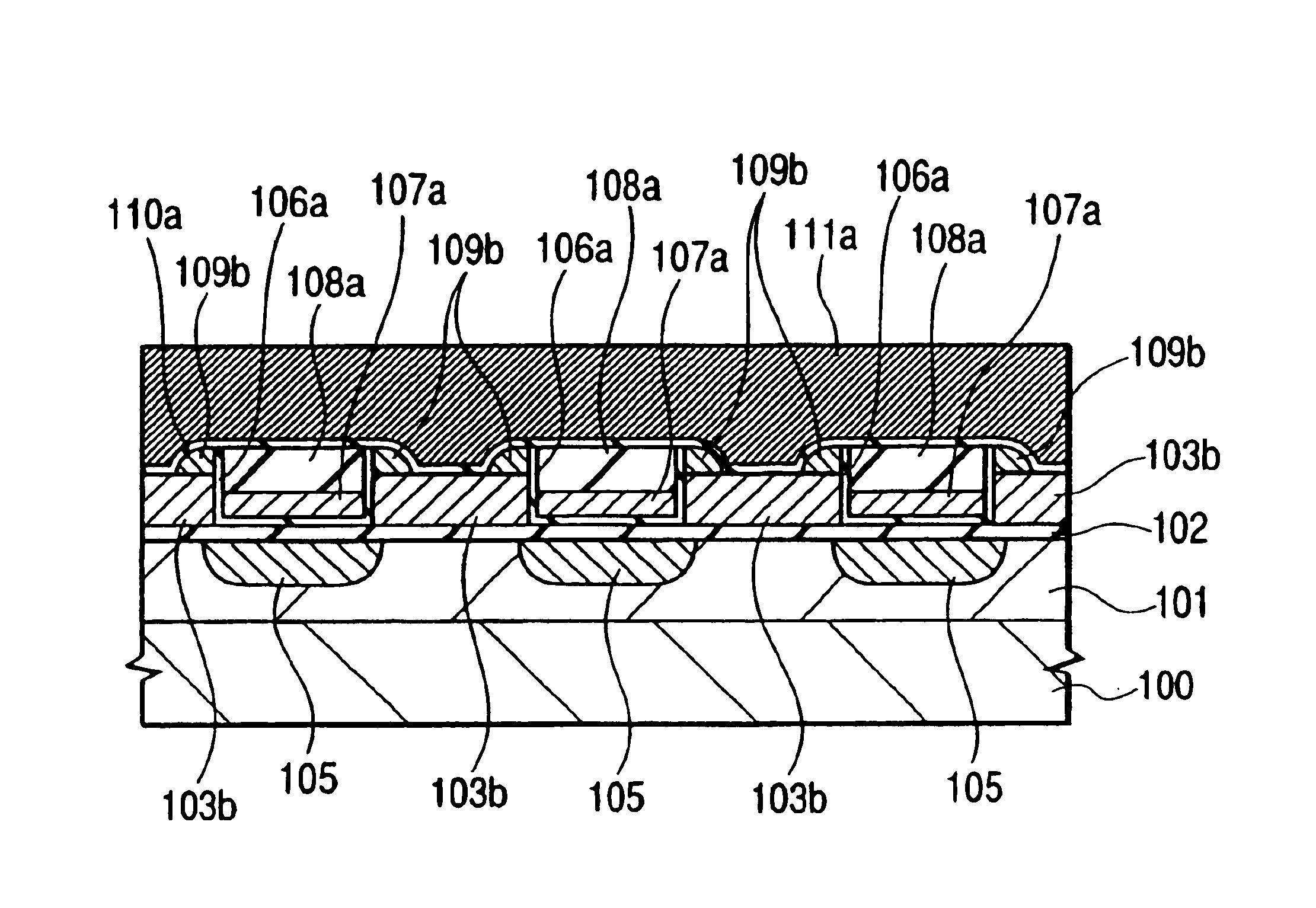

In a semiconductor integrated circuit device including a third gate, the present invention improves miniaturization and operation speed and reduces a defect density of an insulator film. In a semiconductor integrated circuit device including a well of a first conductivity type formed in a semiconductor substrate, a source / drain diffusion layer of a second conductivity type inside the well, a floating gate formed over the semiconductor substrate through an insulator film, a control gate formed and isolated from the floating gate through an insulator film, word lines formed by connecting the control gates and a third gate formed and isolated from the semiconductor substrate, the floating gate and the control gate through an insulator film and different from the floating gate and the control gate, the third gate is buried into a space of the floating gates existing in a direction vertical to the word line and a channel.

Owner:RENESAS ELECTRONICS CORP

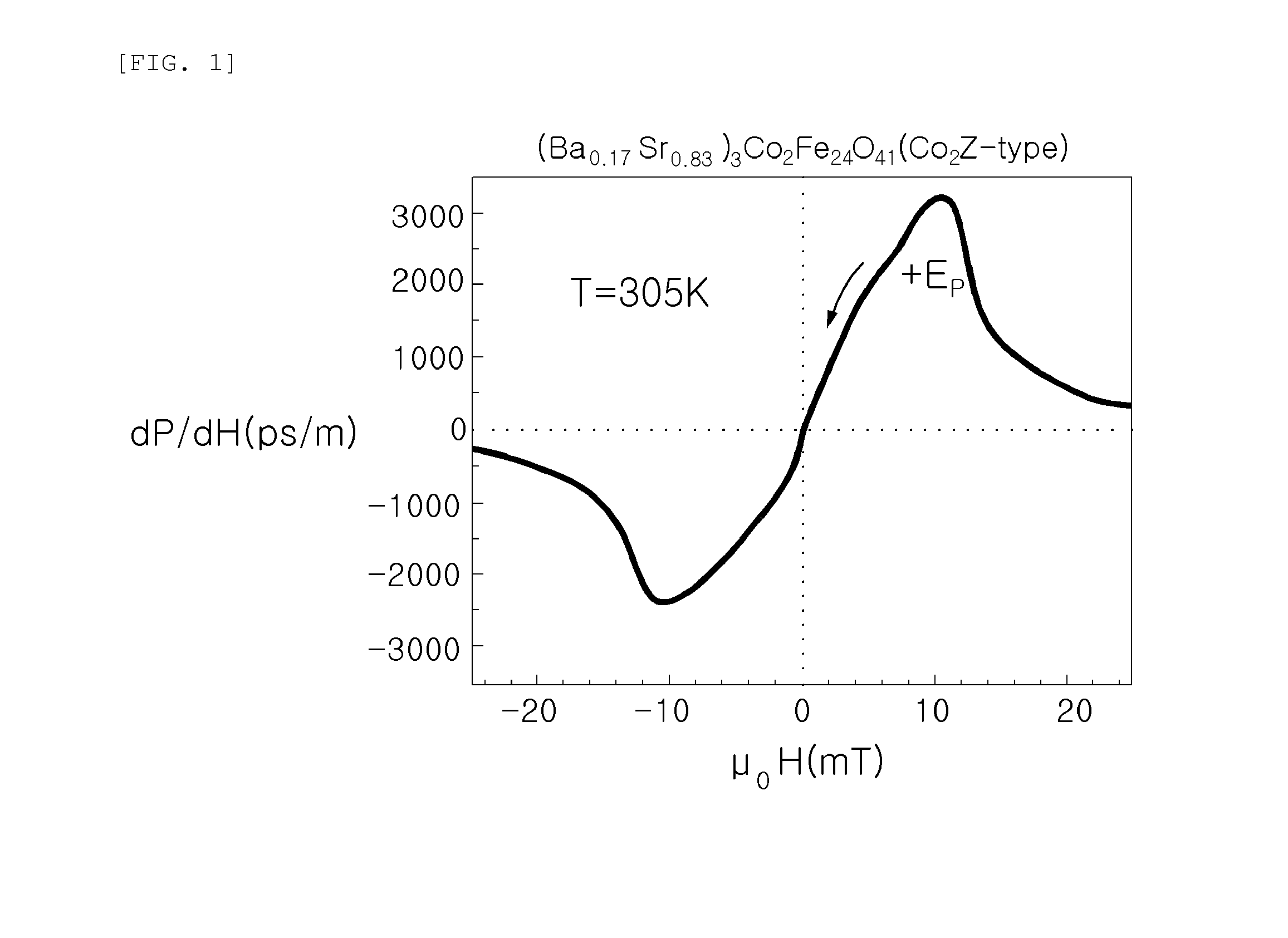

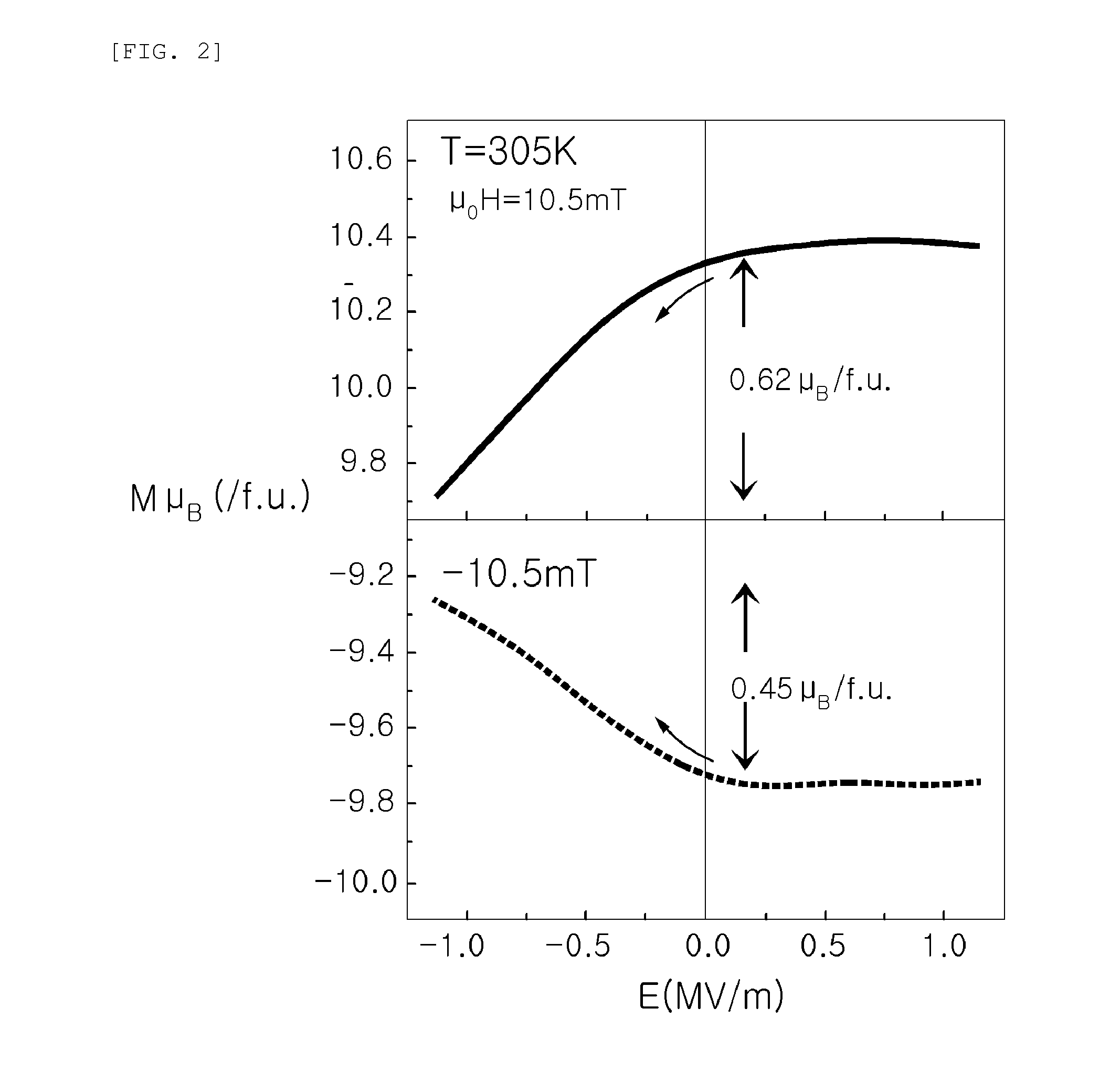

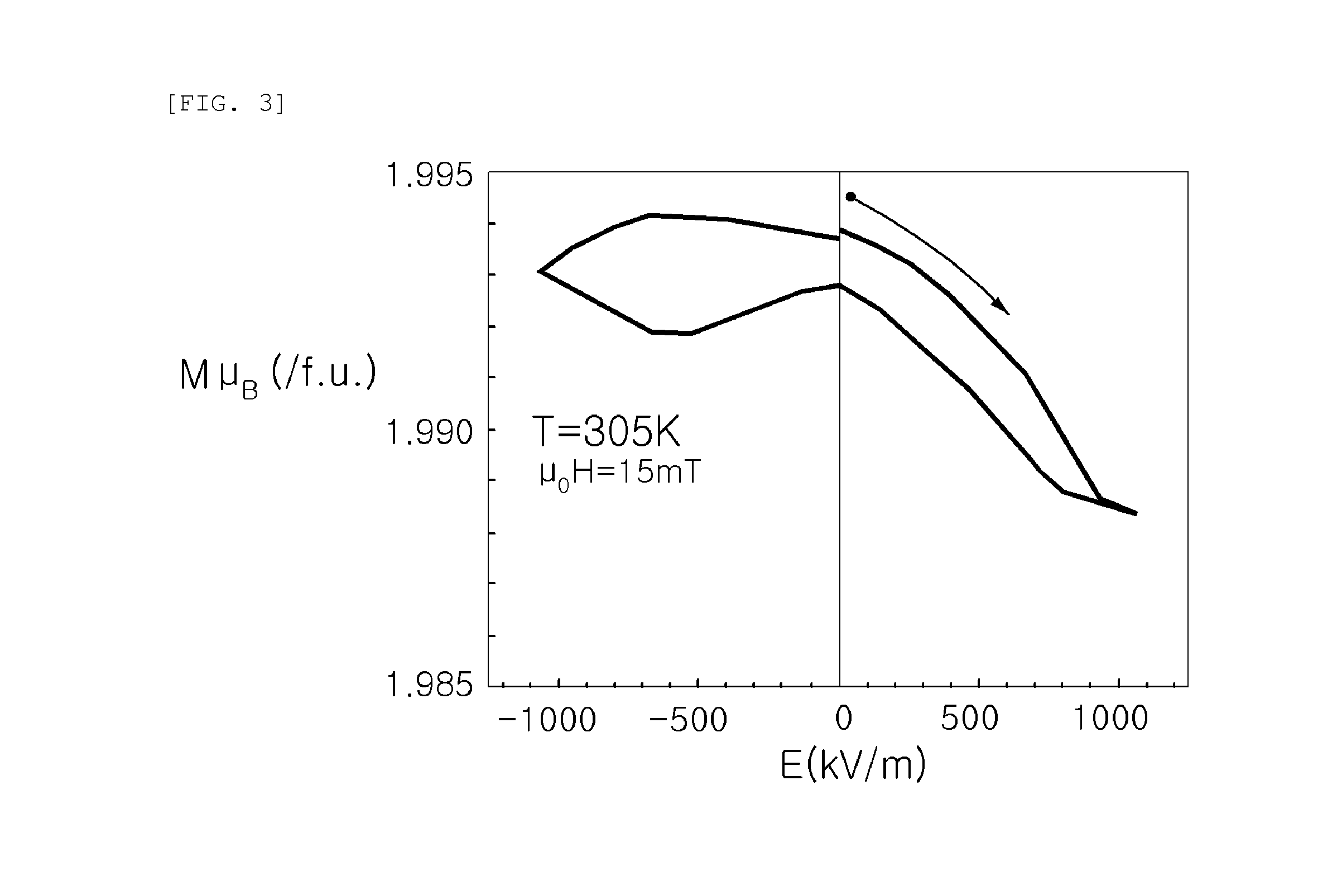

Magnetoelectric material and method of manufacturing the same

ActiveUS20140138571A1Function increaseChange in magnetic susceptibilityPolycrystalline material growthFrom melt solutionsElectricityAlkaline earth metal

The present invention provides a magnetoelectric material in which an electric property is capable of being controlled by a magnetic field or a magnetic property is capable of being controlled by an electric field, and a method of manufacturing the same. Particularly, the present invention provides a magnetoelectric material in which a distance between magnetic ions interacting with each other is controlled by using non-magnetic ions or alkaline earth metal ions, and a method of manufacturing the same.

Owner:SEOUL NAT UNIV R&DB FOUND

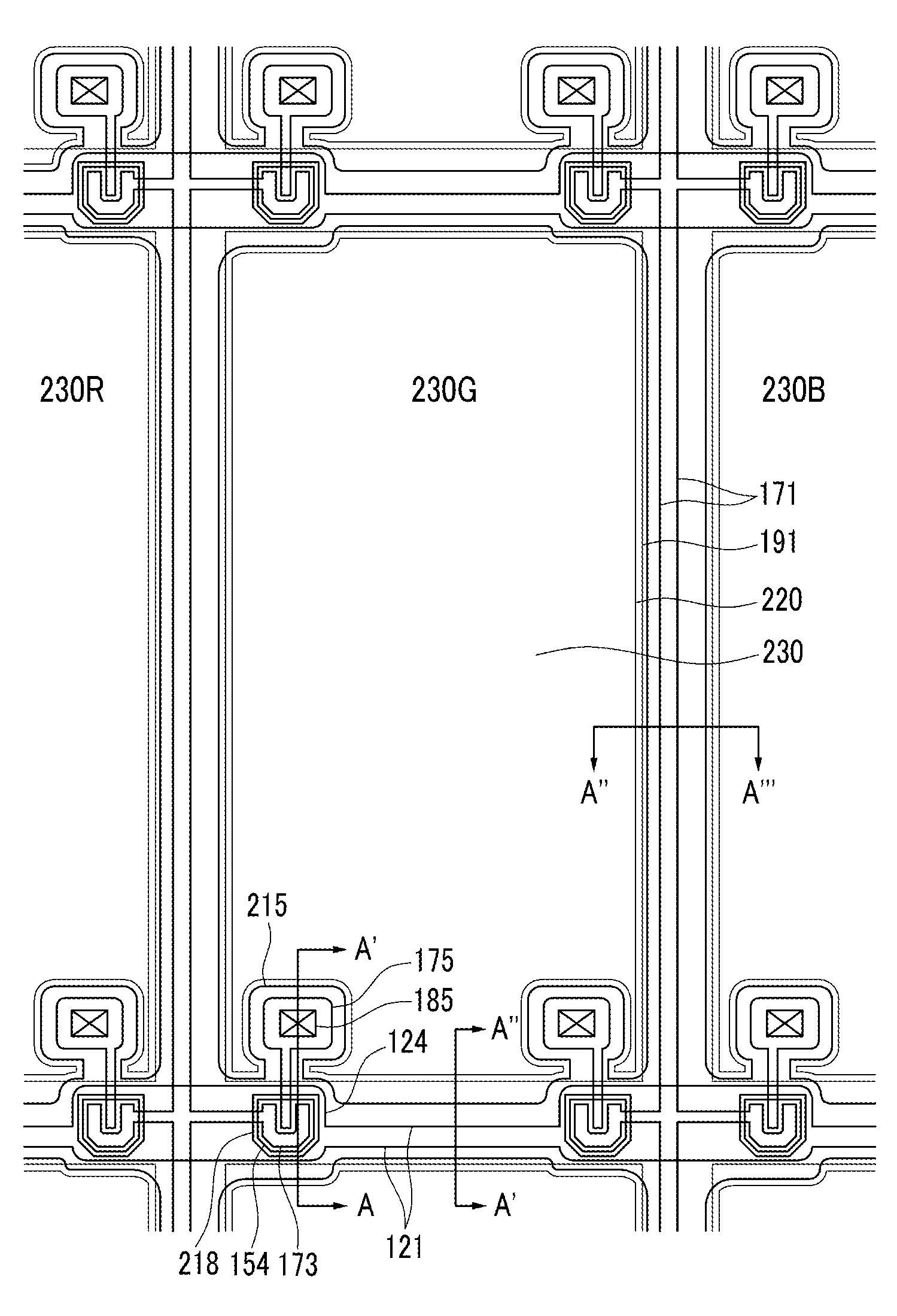

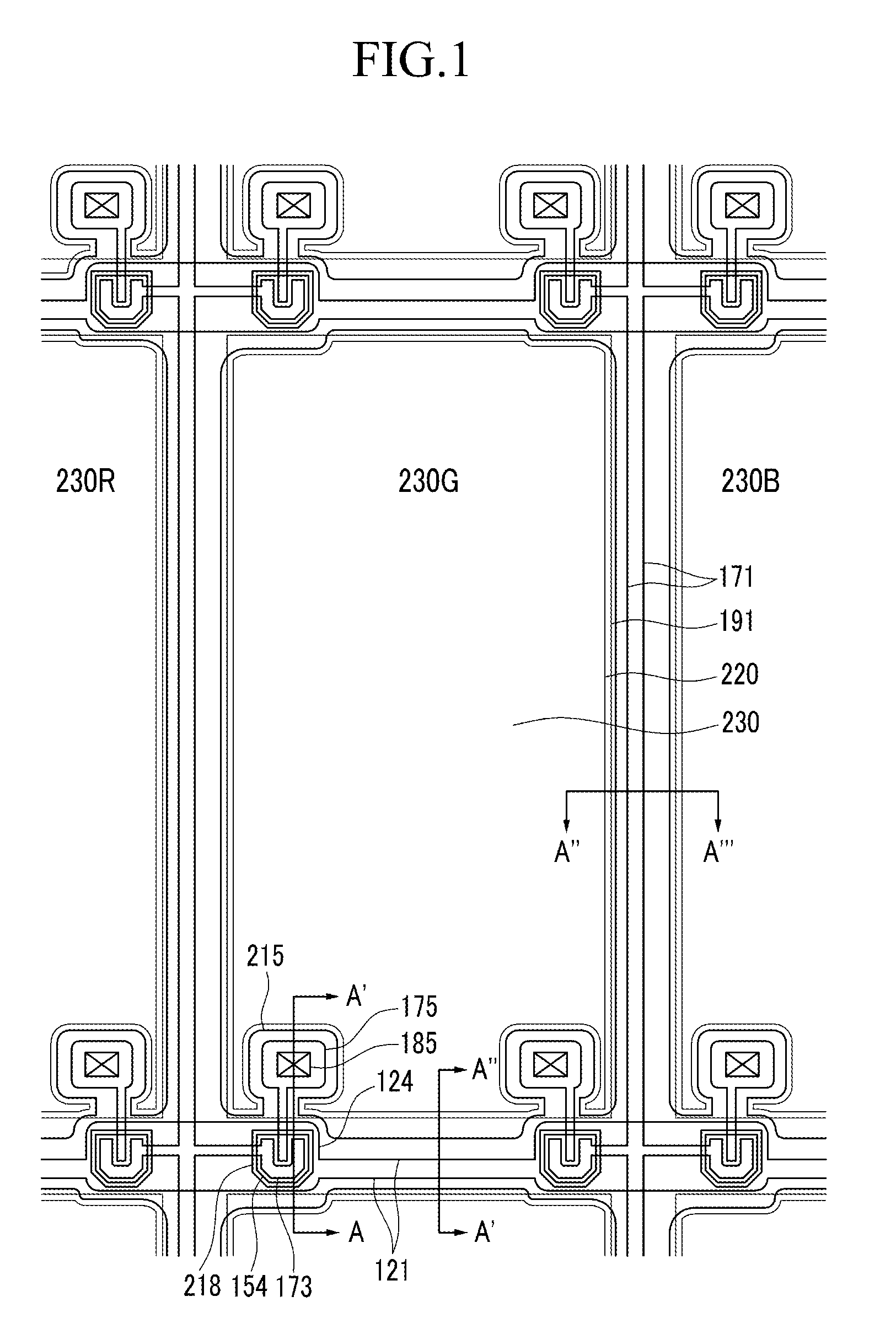

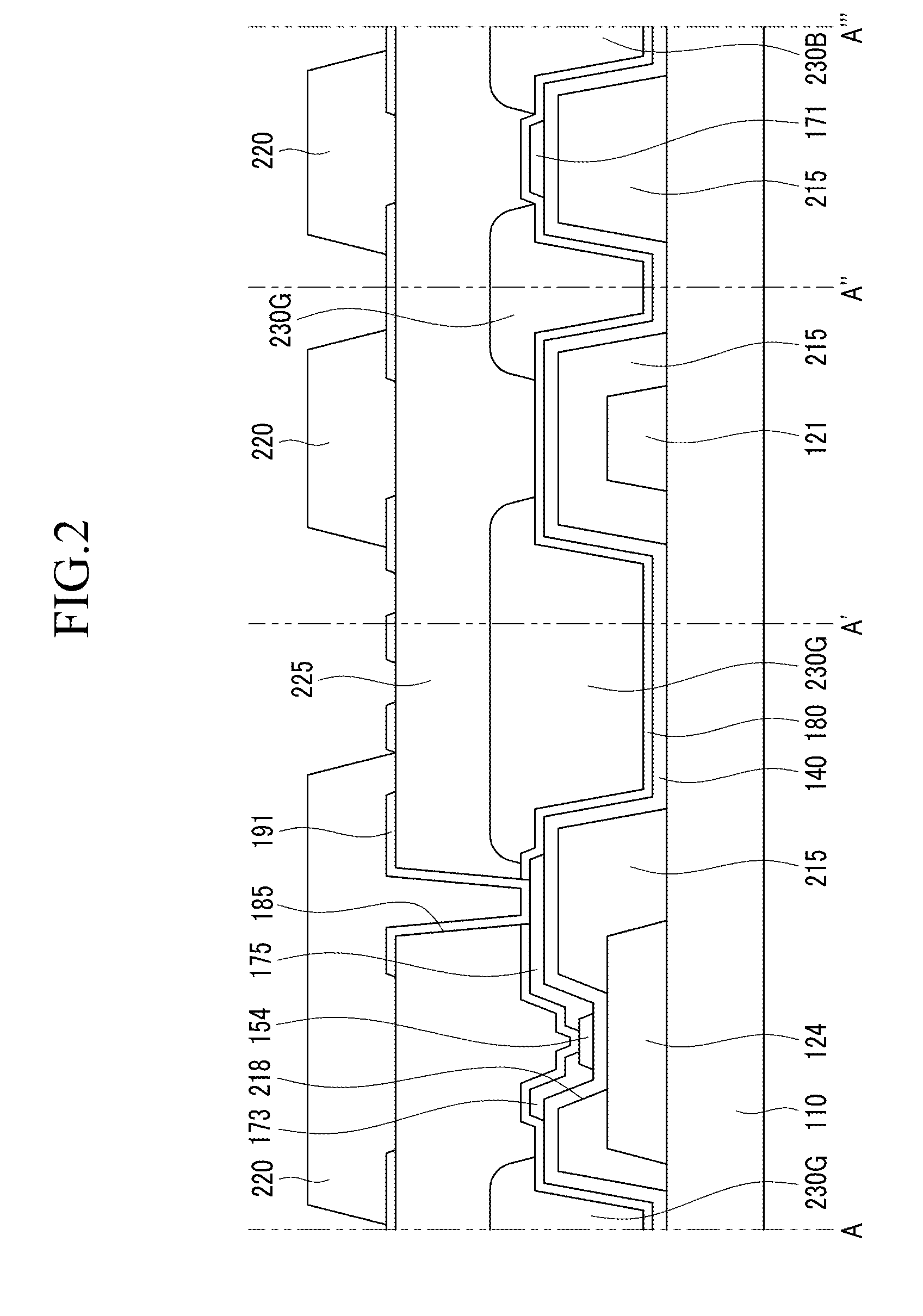

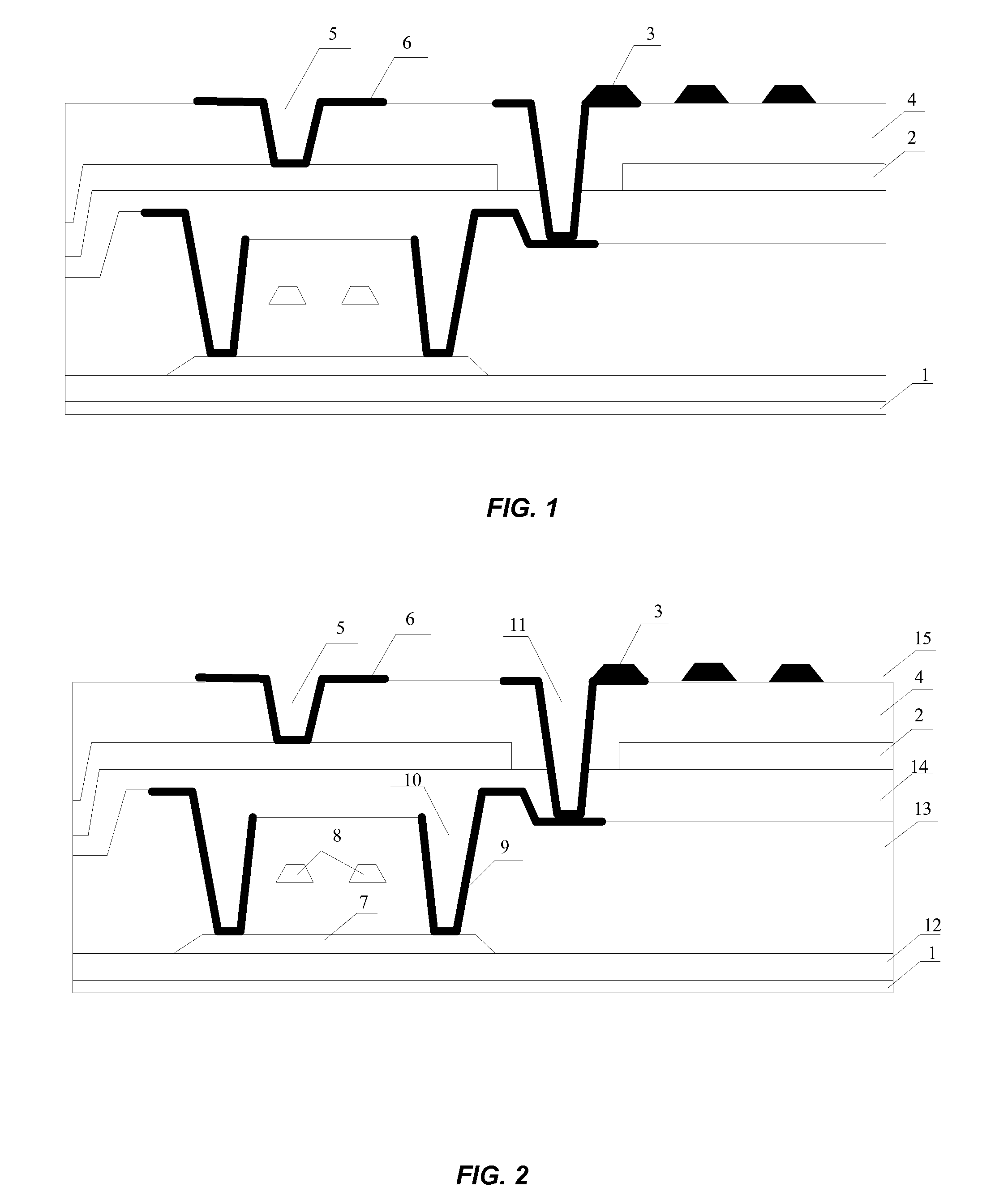

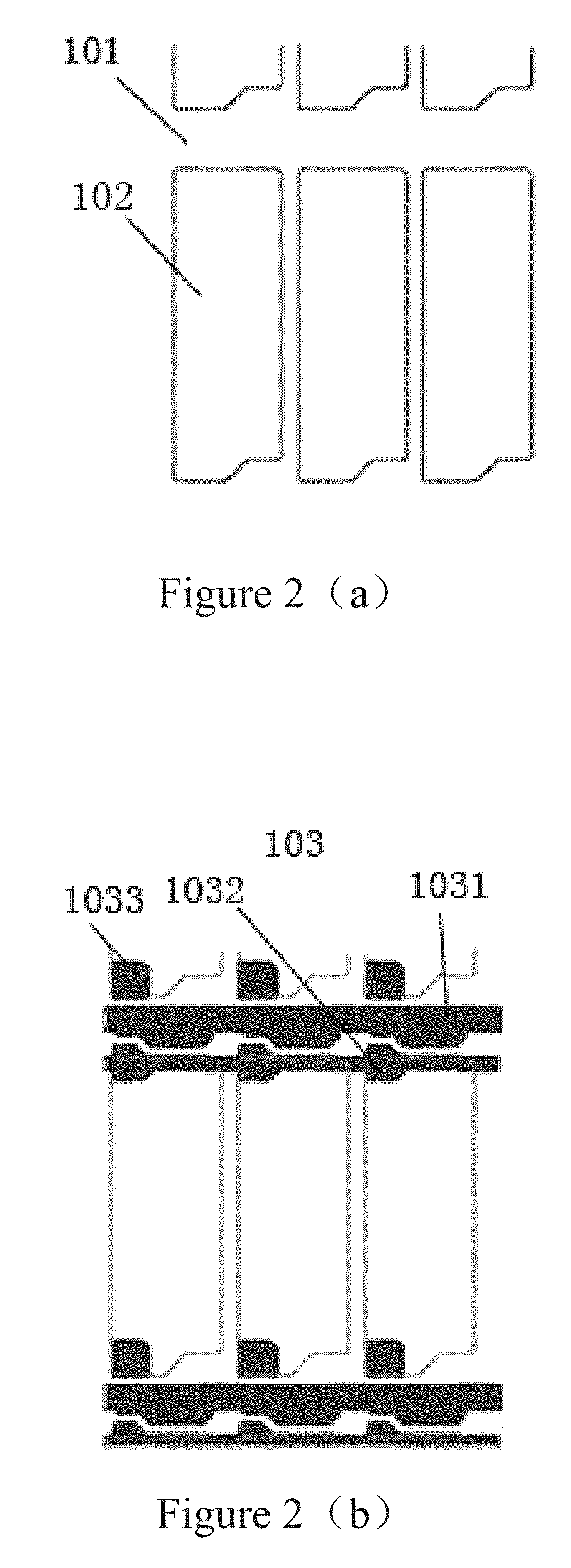

Thin film transistor array panel and method of manufacturing the same

InactiveUS20100053507A1Reduce signal delayIncreasing the thicknessInking apparatusSolid-state devicesEngineeringSignal delay

After increasing the thickness of a gate line and forming a barrier rib that is made of an organic material, a gate insulating layer is formed and then a color filter is formed with an Inkjet method using the barrier rib. By increasing a thickness of the gate line, even if the size of a substrate increases, problems due to signal delay are reduced, and by forming a barrier rib with an organic material, the height of the barrier rib increases, and a taper angle increases and thus a color filter is stably formed.

Owner:SAMSUNG DISPLAY CO LTD

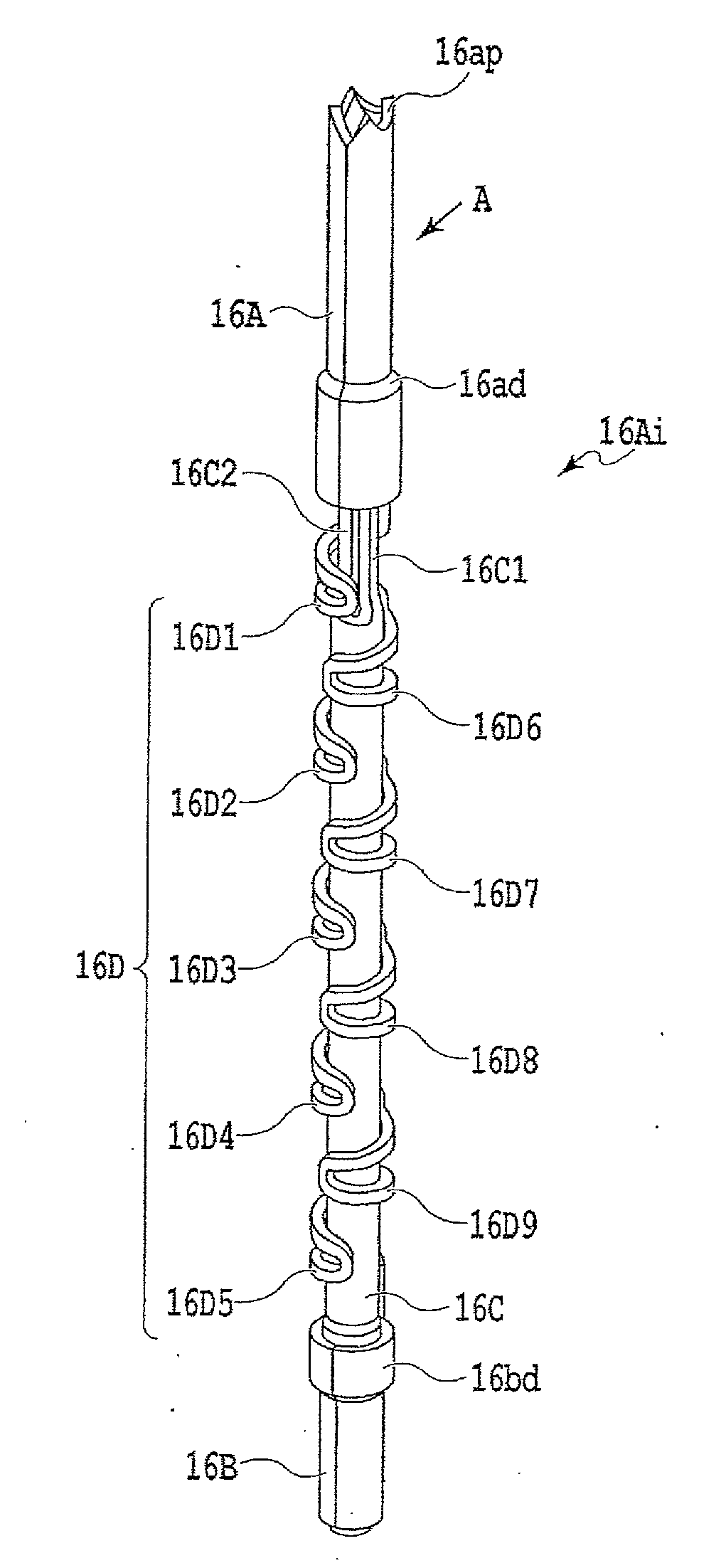

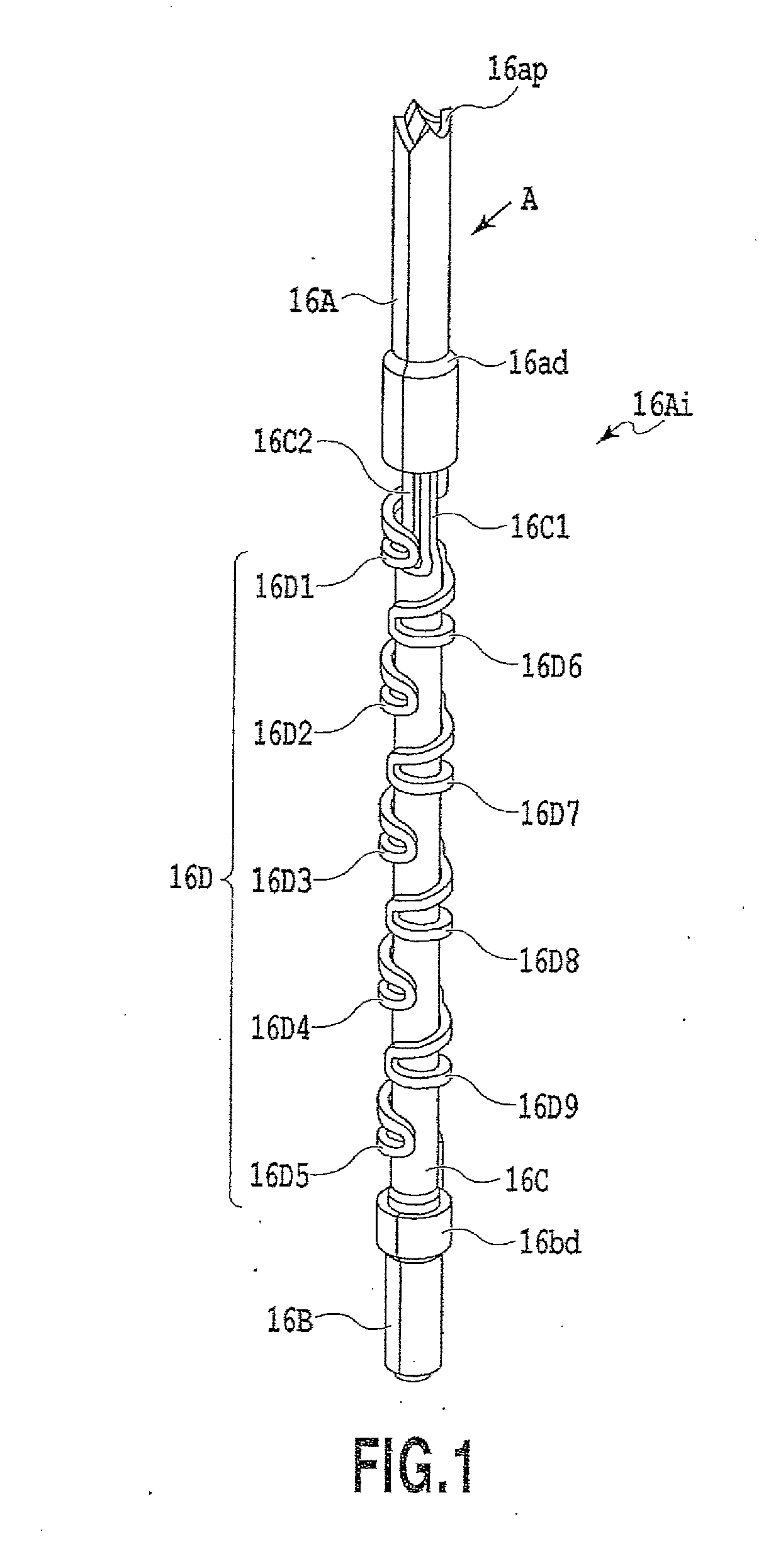

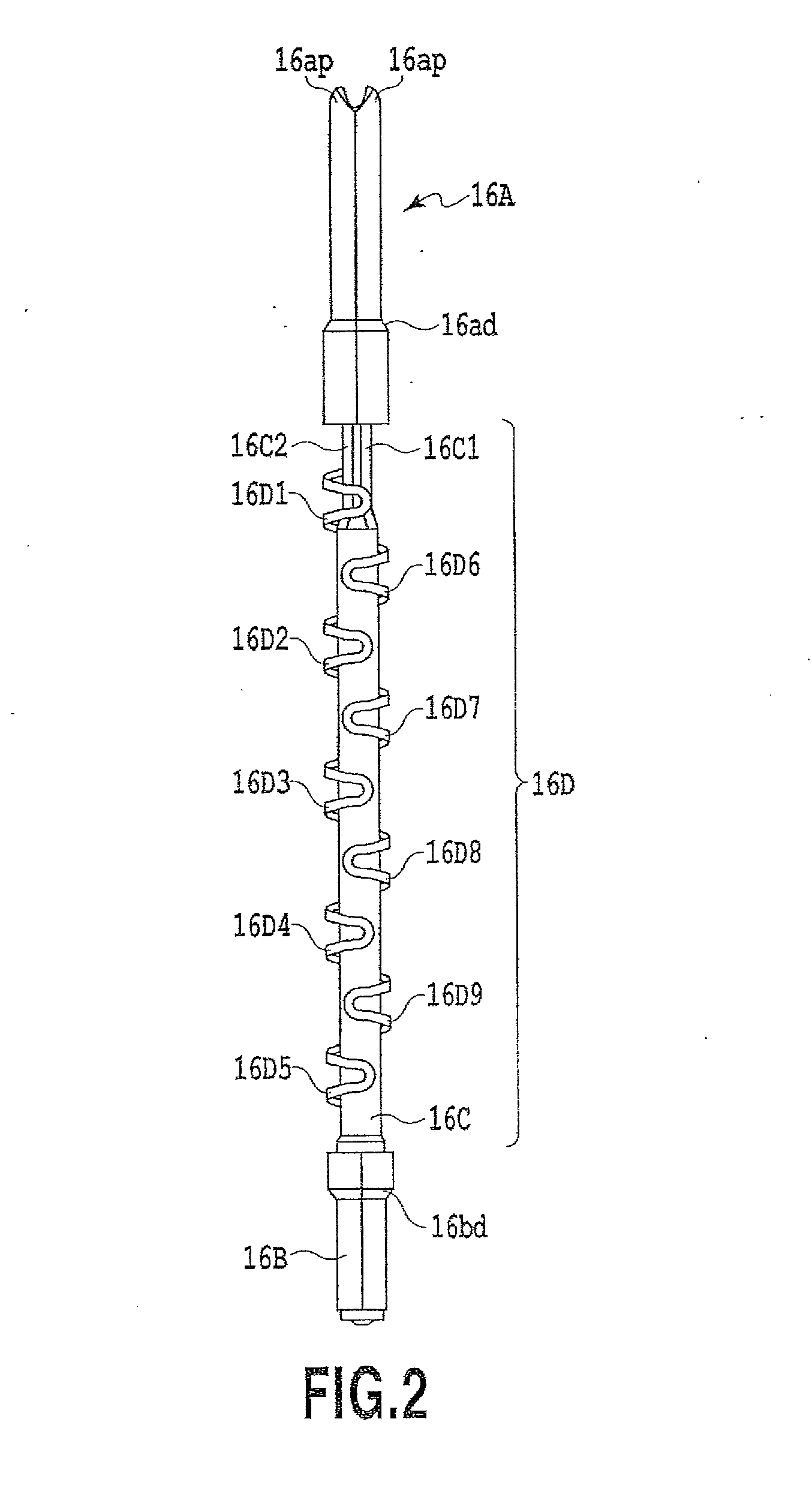

Inspection probe and an IC socket with the same

ActiveUS20140253163A1Reliably and stably reducePrevent bucklingElectrical measurement instrument detailsElectrical testingContact padThin sheet

An inspection probe 16Ai is formed by subjecting a thin sheet material made of a copper alloy to press working. The inspection probe 16Ai includes: a device side plunger 16A having a contact point which selectively comes into contact with an electrode portion DVb of a semiconductor device DV; a board side plunger 16B having a contact point which selectively comes into contact with a contact pad of a printed wiring board 18; a spring portion 16D which biases the device side plunger 16A and the board side plunger 16B in a direction away from each other; and a cylindrical support stem 16C being disposed inside the spring portion 16D, making the spring portion 16D slidable thereon, and being configured to retain straight advancing property of the spring portion 16D.

Owner:YAMAICHI ELECTRONICS

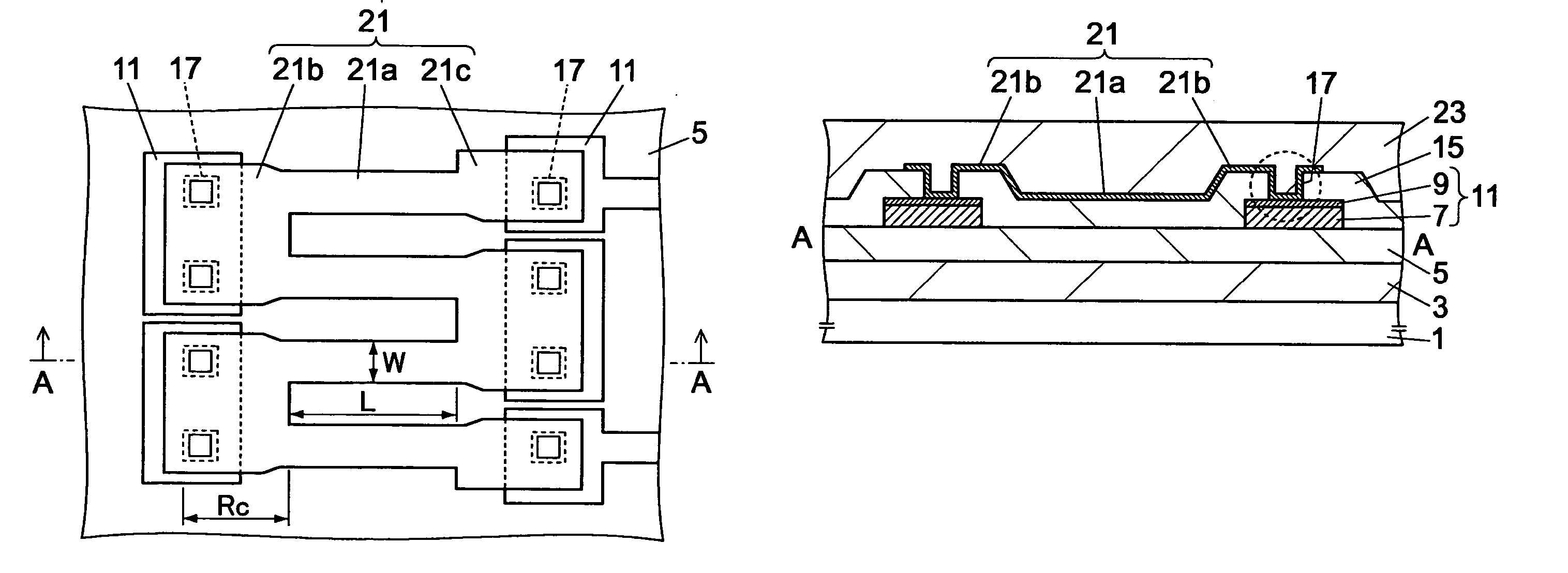

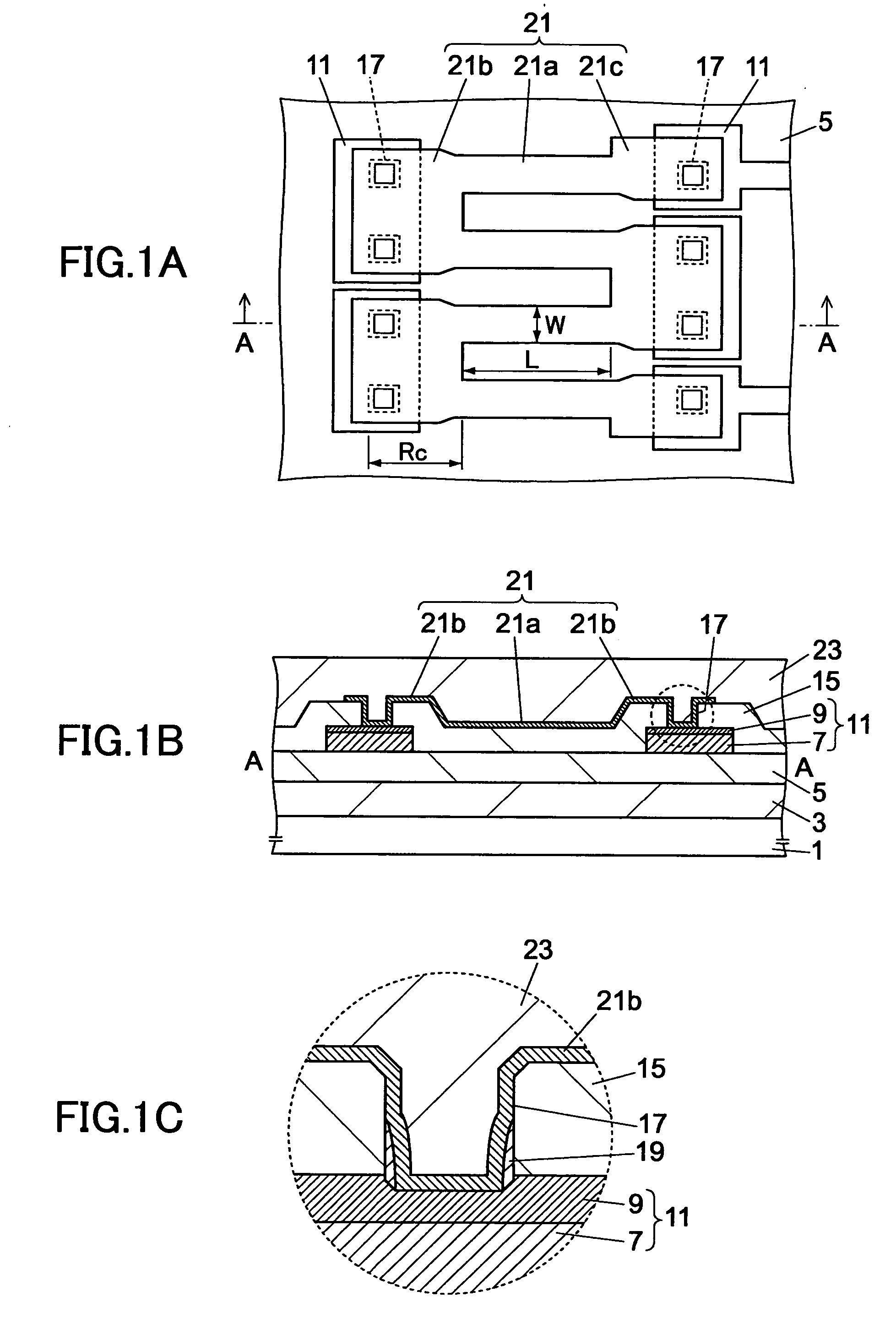

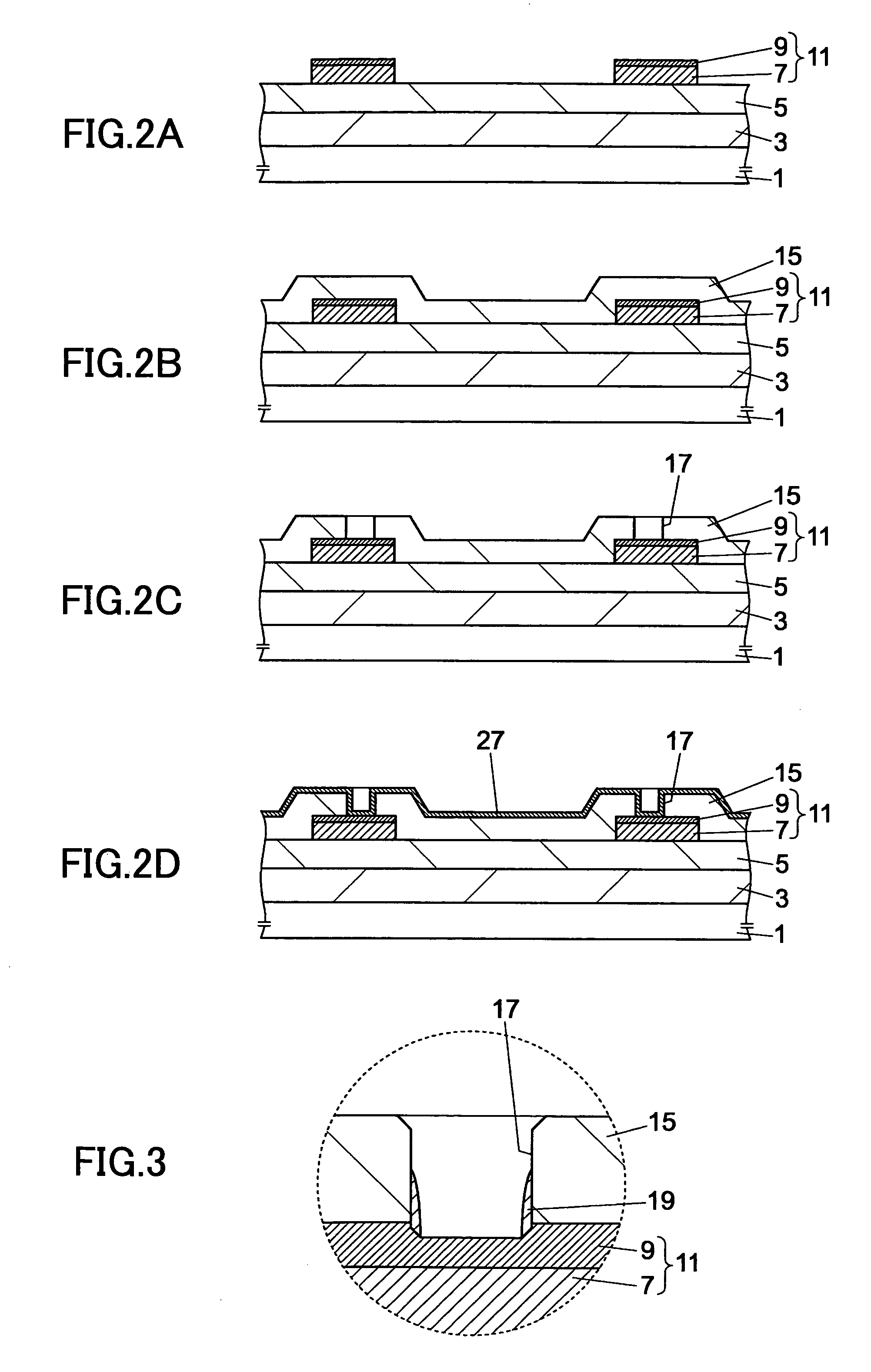

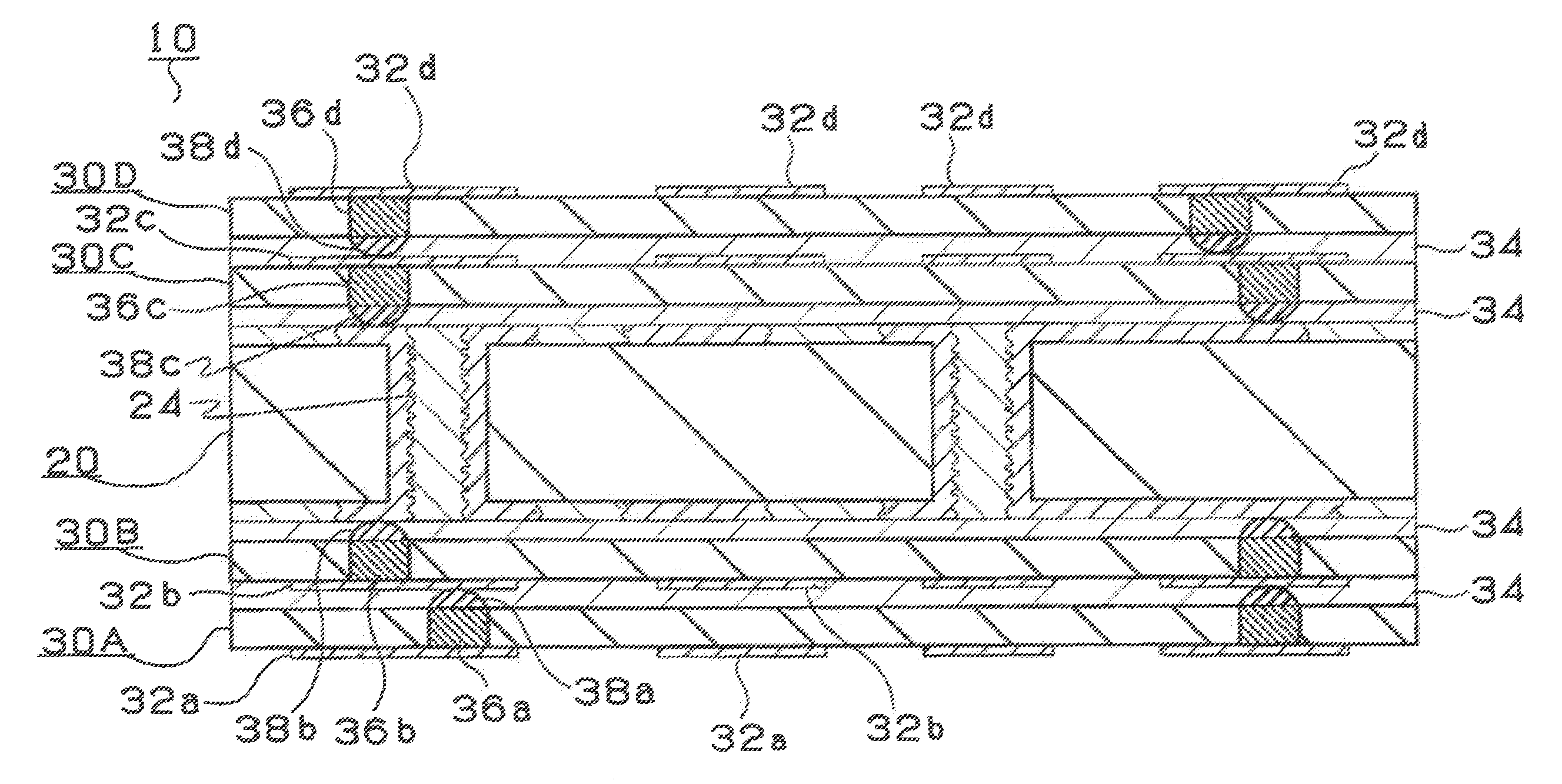

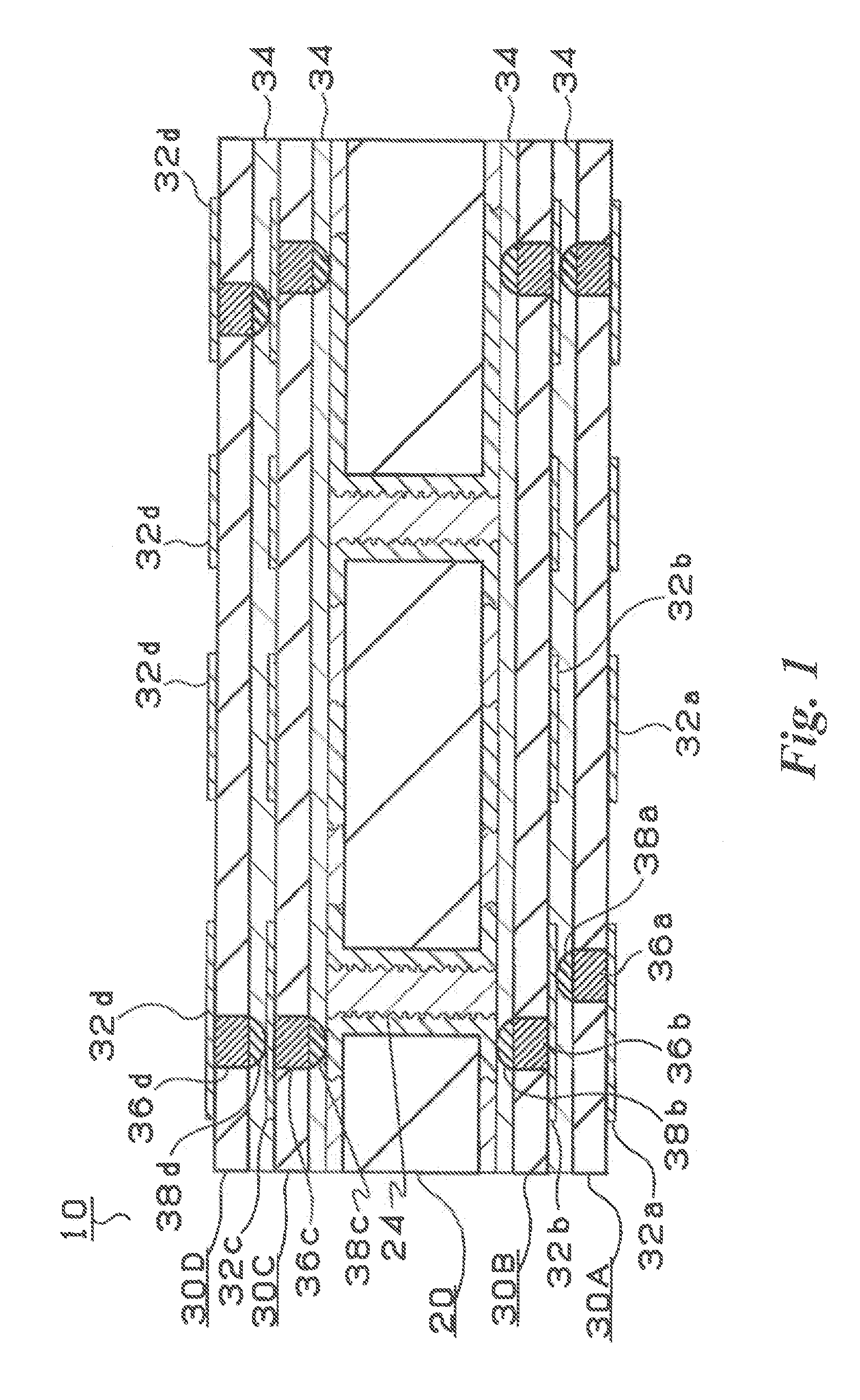

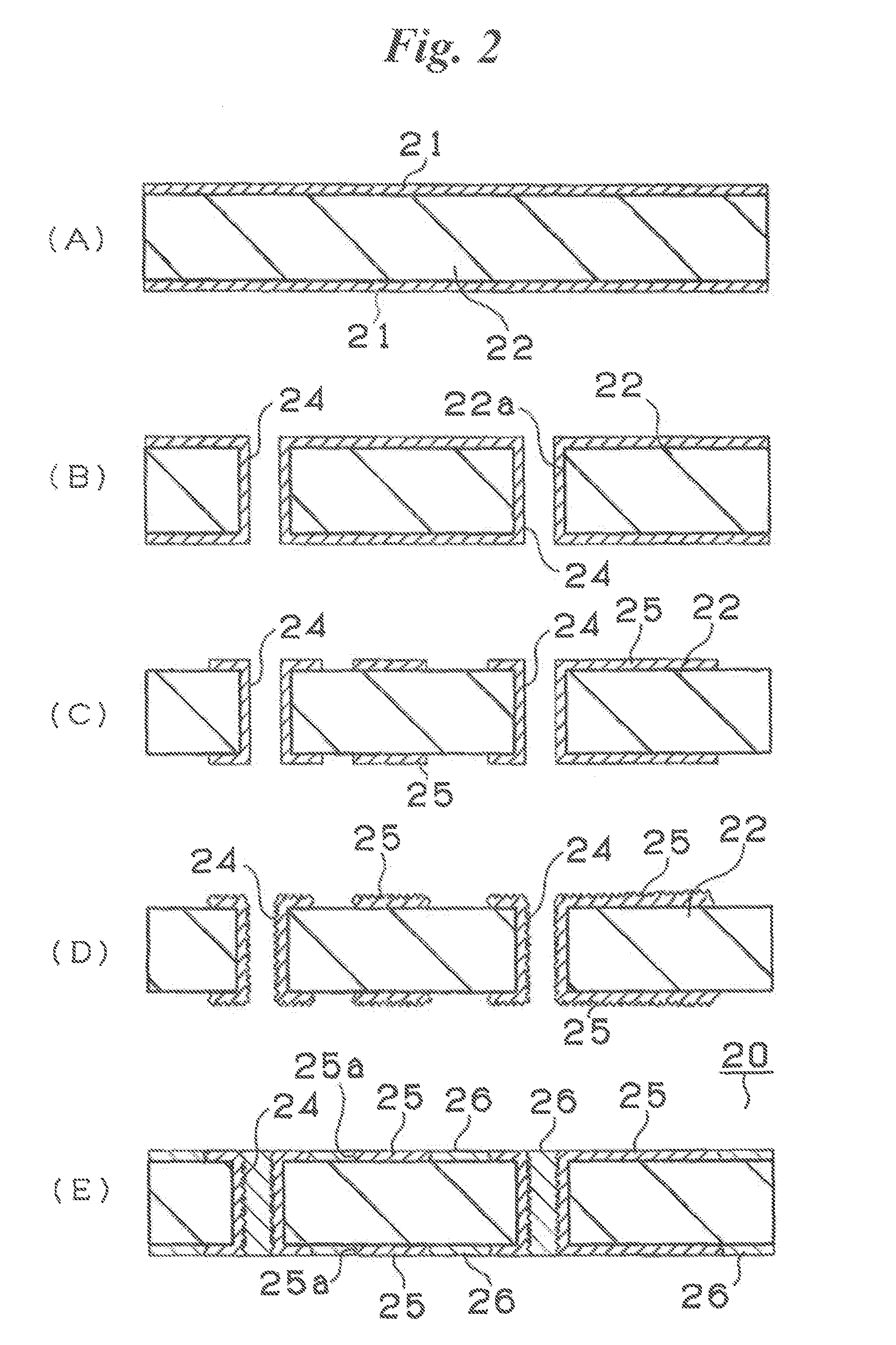

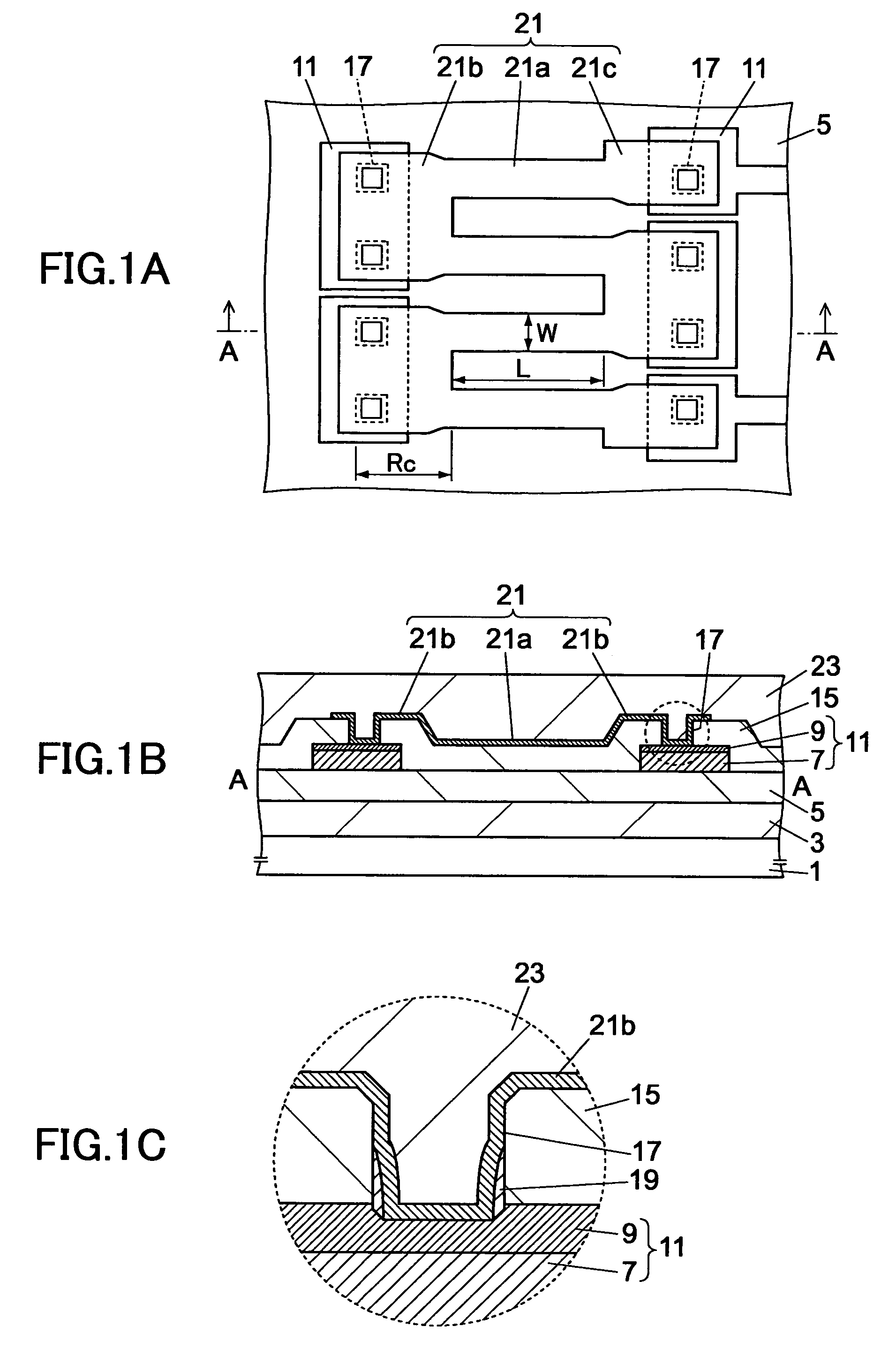

Semiconductor device

InactiveUS20050218478A1Accurate resistanceHigh yieldSemiconductor/solid-state device detailsSolid-state devicesDevice materialBand shape

A semiconductor device is provided that includes: a base insulating film; a metal thin-film resistor that is provided on the base insulating film; a lower-layer insulating film that is formed under the base insulating film; and a wiring pattern that is formed on the lower-layer insulating film. In this semiconductor device, the base insulating film is formed on the lower-layer insulating film and the wiring pattern, and connecting holes are formed in the base insulating film located on the wiring patterns. The metal thin-film resistor has at least two belt-like portions and a return portion that continues to the belt-like portions. The belt-like portions are located at a distance from the region on the wiring pattern. The return portion connects at least two belt-like portions in a position at a distance from the region on the wiring pattern. The return portion is formed in a connecting hole via the region on the wiring pattern.

Owner:RICOH KK

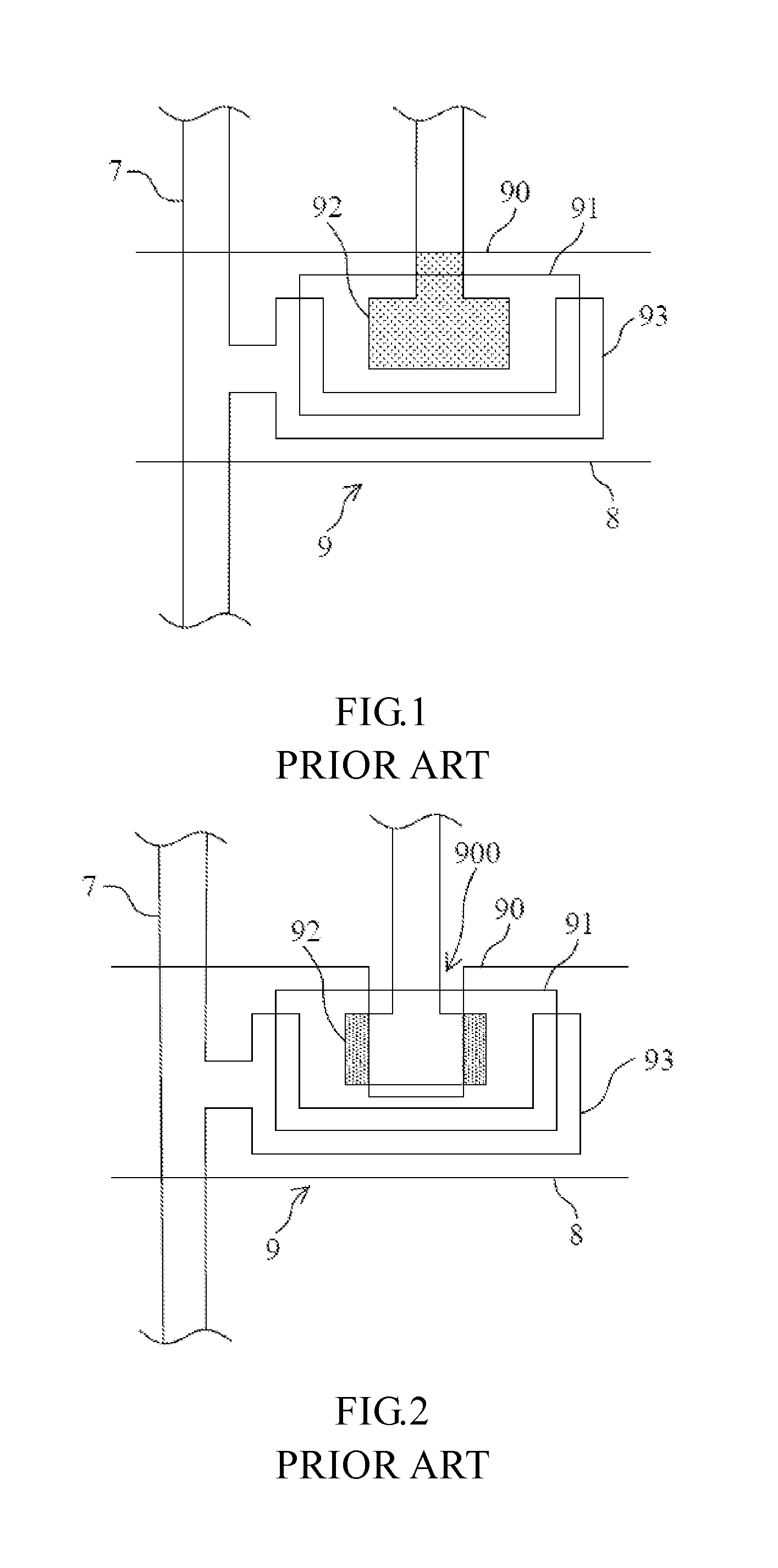

TFT array substrate and manufacturing method thereof and liquid crystal display device

ActiveUS20140211118A1Resistance valueRaise the ratioSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

The present invention discloses a TFT array substrate and a manufacturing method thereof and a liquid crystal display device, which is aiming at lowering the resistance value of a common electrode and not diminishing the aperture ratio of pixels on the premise that the manufacturing cost is not additionally increased. The TFT array substrate includes: a substrate, a common electrode layer arranged on the substrate, a first insulating layer arranged on the common electrode layer and a plurality of pixel electrodes arranged in an array on the first insulating layer, wherein via holes penetrating through the first insulating layer are formed between adjacent pixels in some of a plurality of pixels, and common electrode lines are grown between rows and / or columns of pixels in some of the plurality of pixels, and in parallel with the common electrode layer below the first insulating layer through the via holes.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

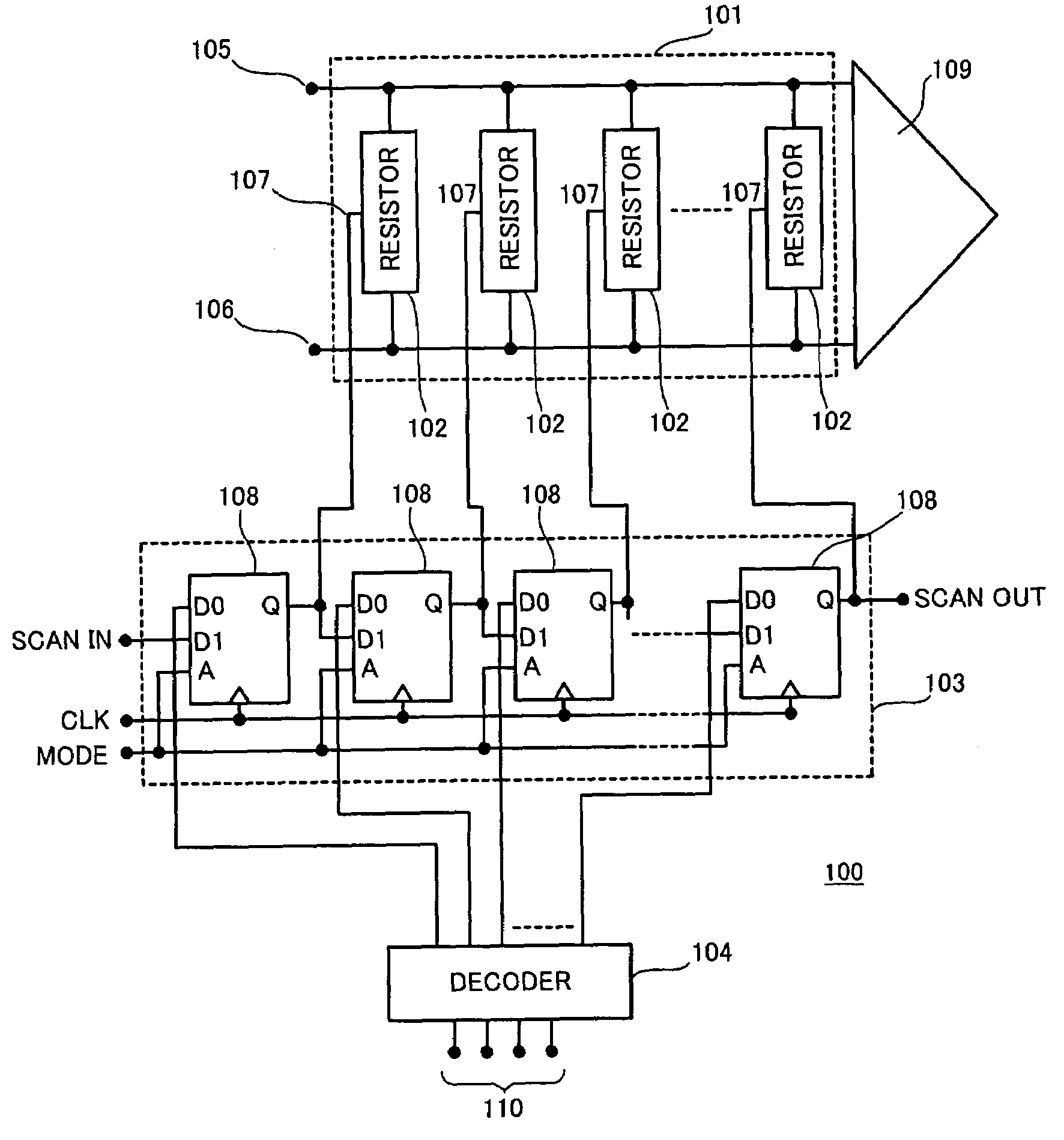

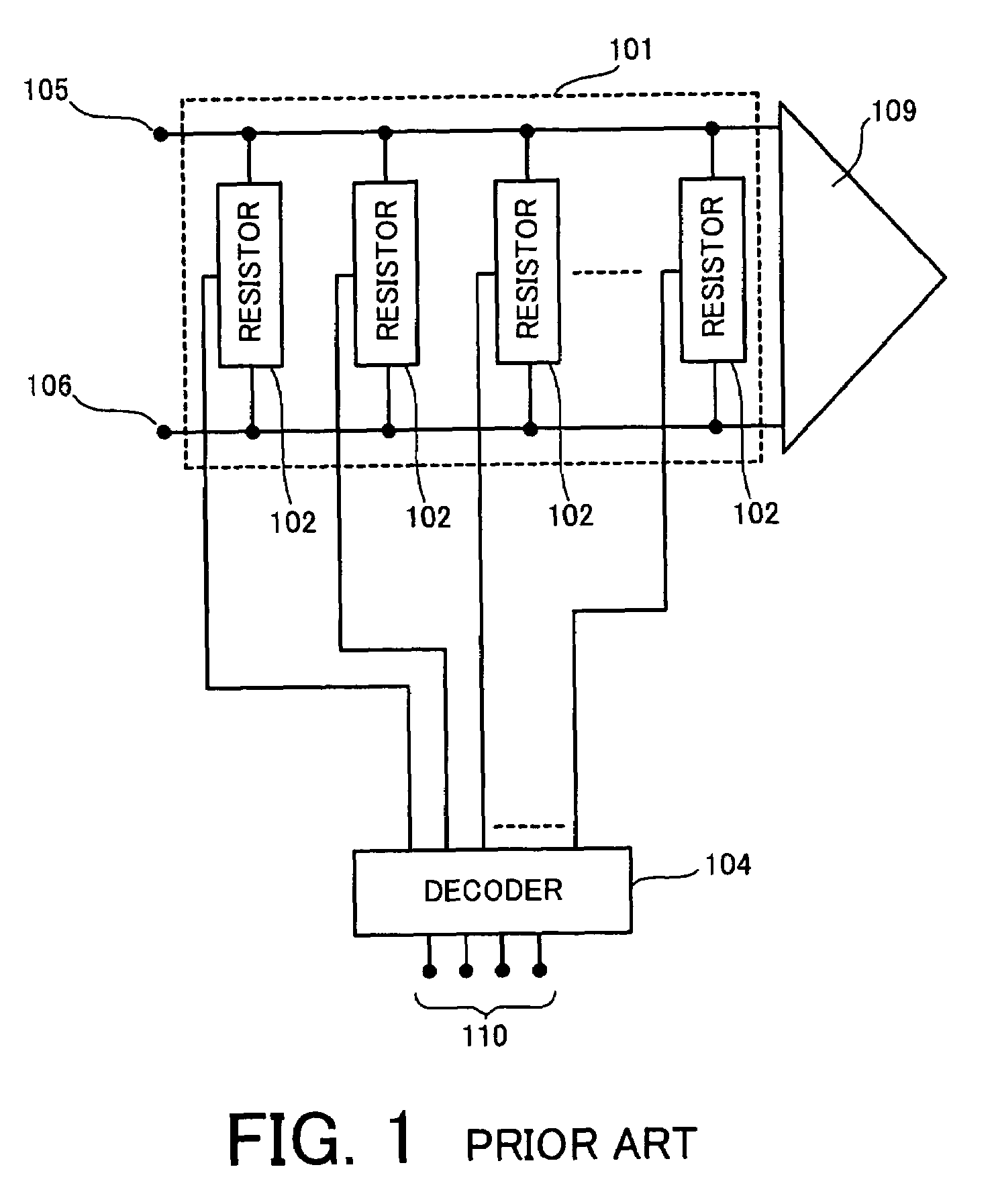

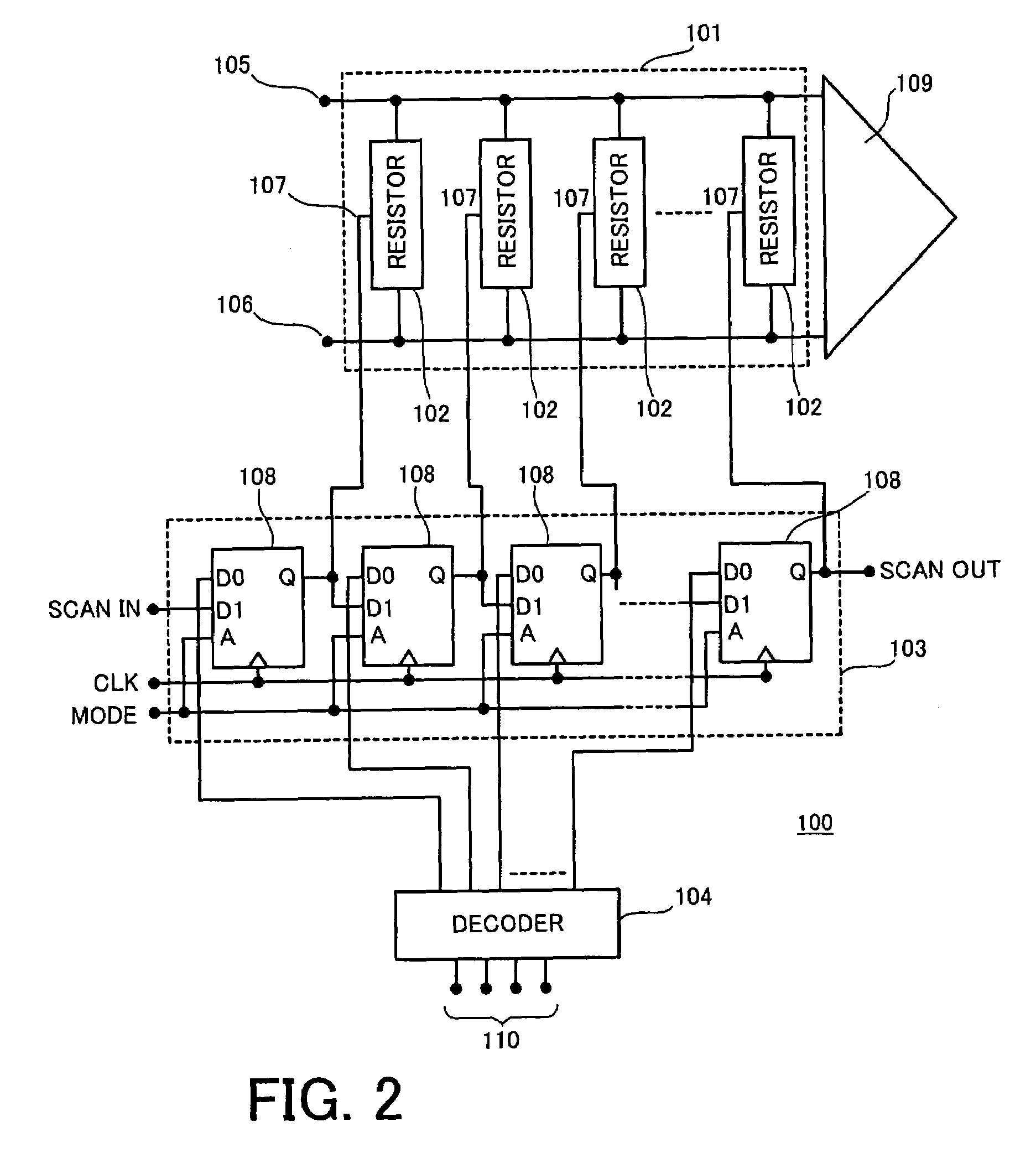

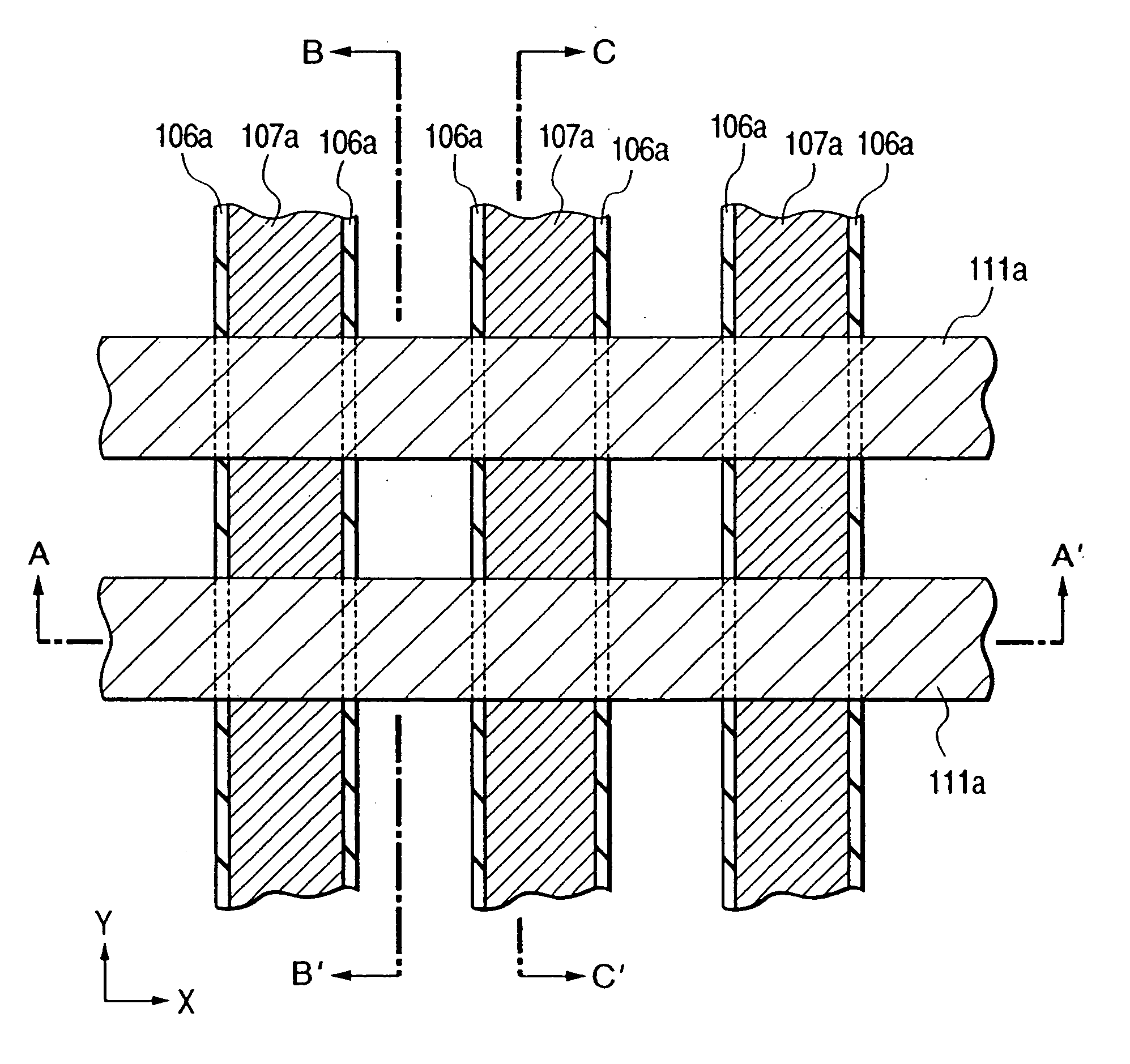

Terminating resistor device and a method for testing a terminating resistor circuit

InactiveUS7038485B2Improve test accuracyImprove accuracyReliability increasing modificationsBaseband system detailsElectrical resistance and conductanceTest procedures

An object of the present invention is to provide a terminating resistor device and a testing method, by which the resistance value of a terminating resistor circuit can be test effectively. The test procedure starts with setting a MUXSCANFF circuit which functions as a selecting circuit in scan mode for test. Then, input a test signal to the scan input and / or clock input. Thereby, a particular resistor element for one bit only is set ON. By detecting the resistance value of this resistor element that has been set ON, it is test whether the one-bit resistance element conforms to manufacturing specification. Select another one of the one-bit resistor elements in order and test each one-bit resistor element, thereby testing all resistor elements.

Owner:RENESAS ELECTRONICS CORP

Semiconductor integrated circuit device including first, second and third gates

InactiveUS20050243603A1Lower resistanceLimiting riseSolid-state devicesRead-only memoriesEngineeringSemiconductor

A semiconductor integrated device having a plurality of memory cells, each including a floating gate, a control gate and an auxiliary gate formed over a side surface of the floating gate through an insulator film. Auxiliary gates coupled to selected memory cells function to generate hot electrons and are alternately arranged with other auxiliary gates functioning to prevent write errors in the non-selected memory cells.

Owner:RENESAS ELECTRONICS CORP

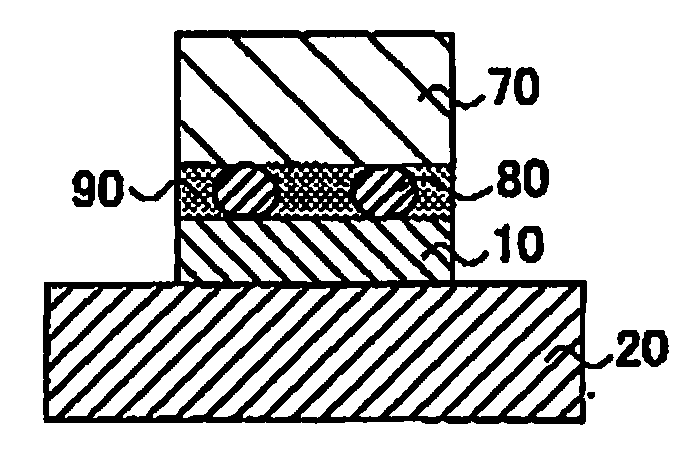

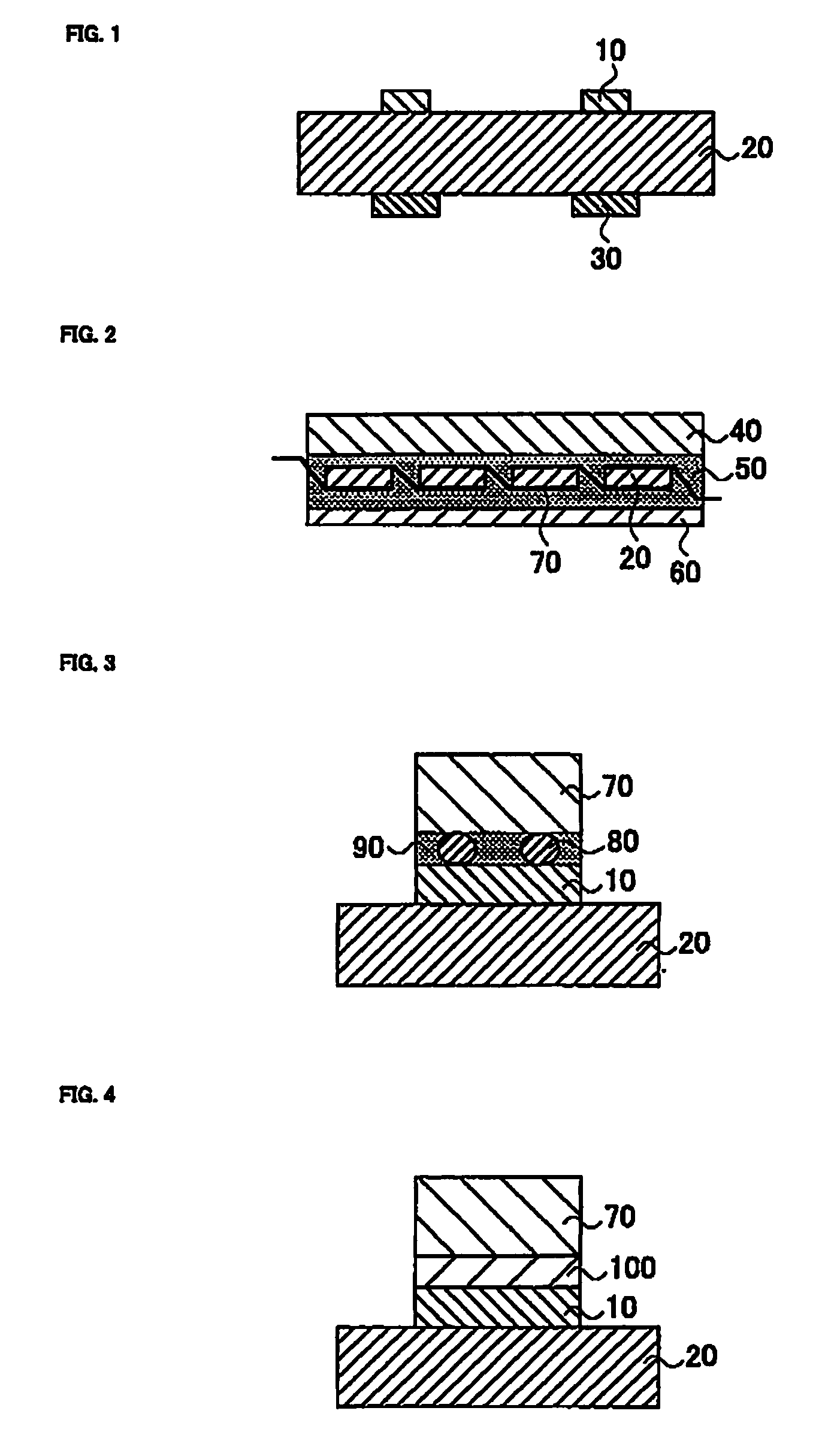

Solar cell module

ActiveUS20100032000A1Increase the resistance valueReduce outputPV power plantsPhotovoltaic energy generationConductive pasteEngineering

Provided is a solar cell module capable of restraining a decrease in the module output. In the solar cell module, a plurality of solar cells are arranged between a light-receiving surface protection member 40 and a back-surface protection member 60, and electrodes 10, 30 of the solar cells are electrically connected to each other through wiring members 70. Each of the electrodes 10, 30 includes a bus bar electrode formed of a resin-type conductive paste. The solar cell module includes an adhesive layer made of a resin 90 between the bus bar electrode and the wiring member 70. Moreover, the residual stress of the resin 90 of the adhesive layer is smaller than the residual stress of a resin contained in the bus bar electrode.

Owner:SANYO ELECTRIC CO LTD

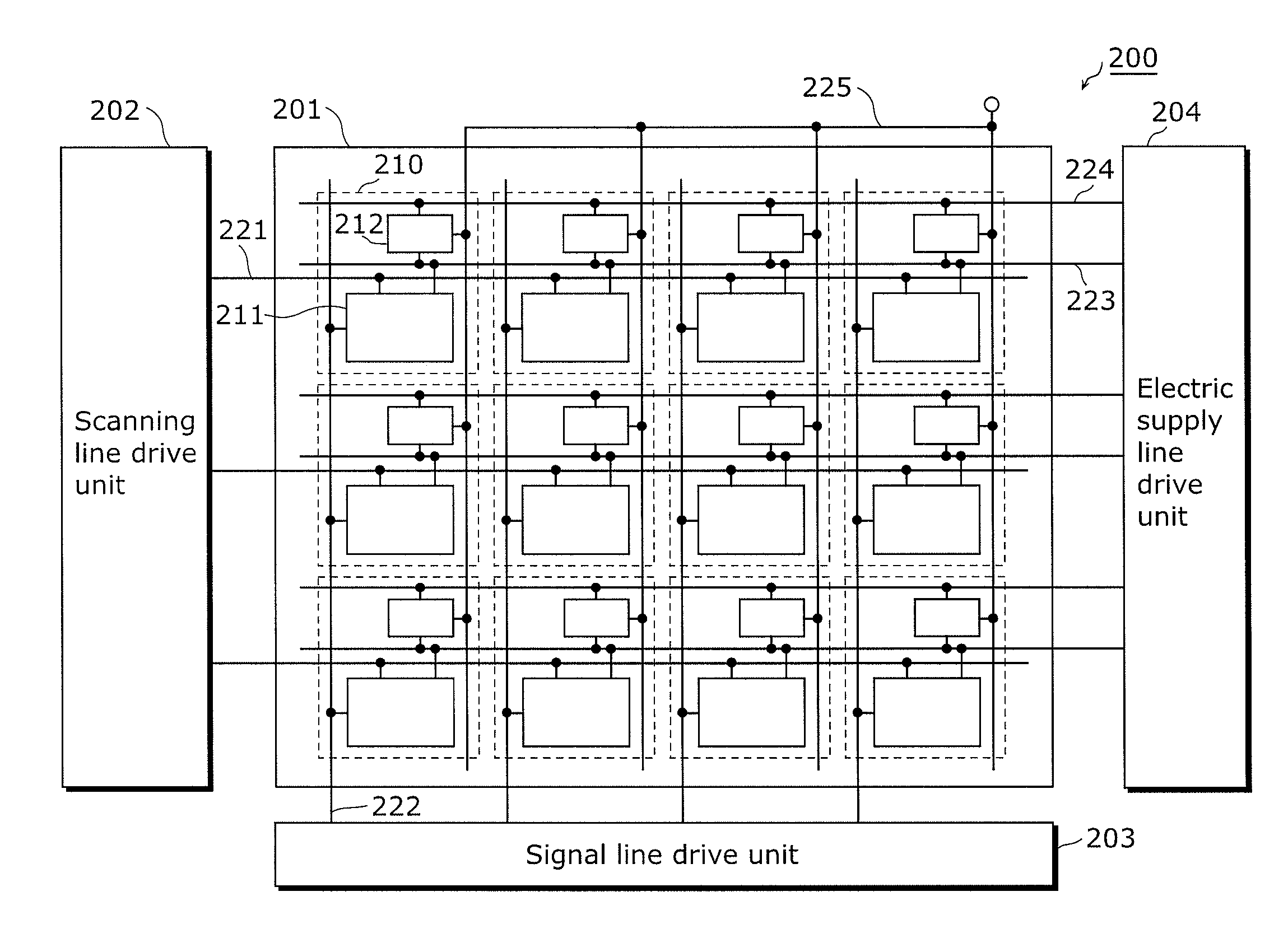

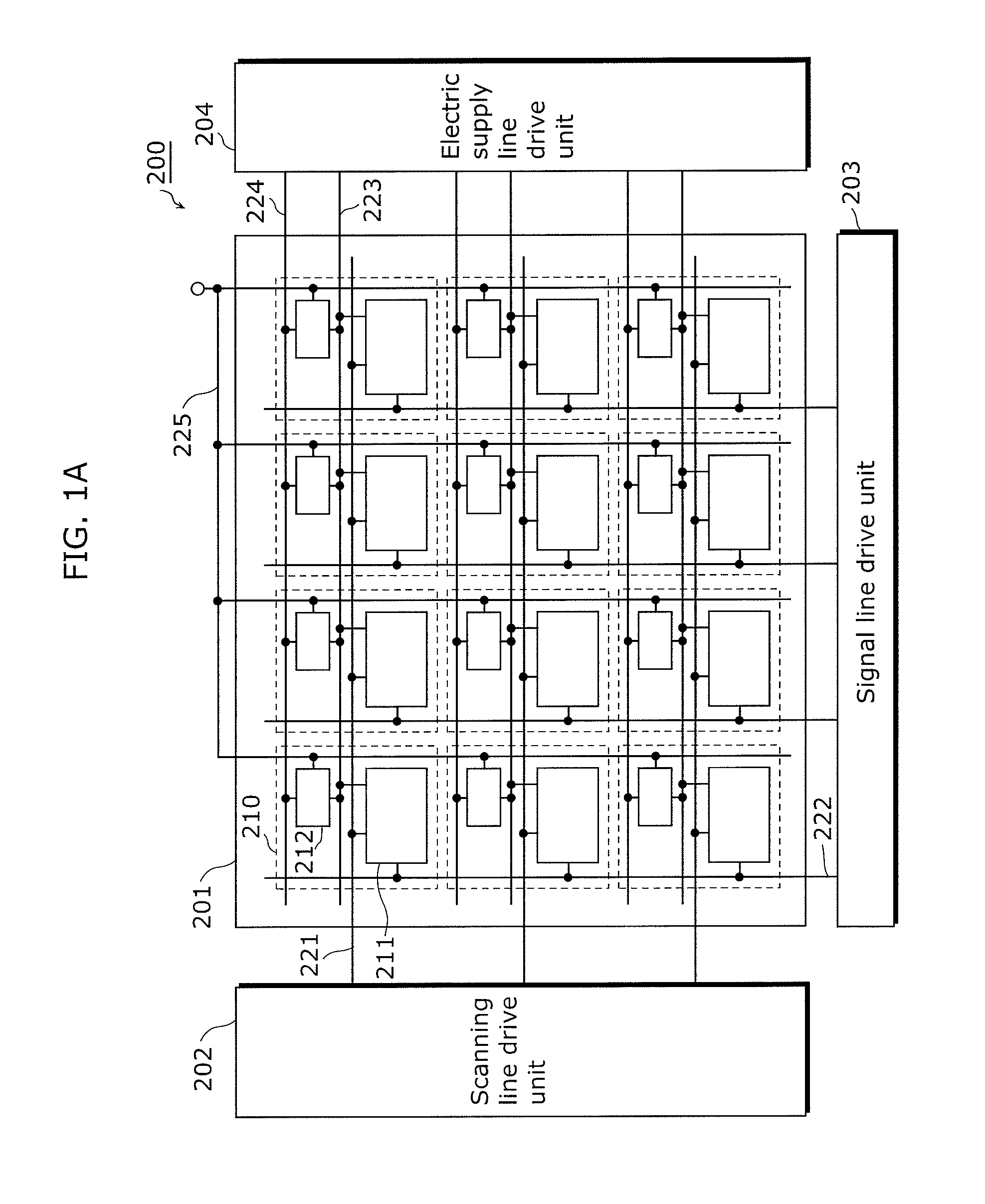

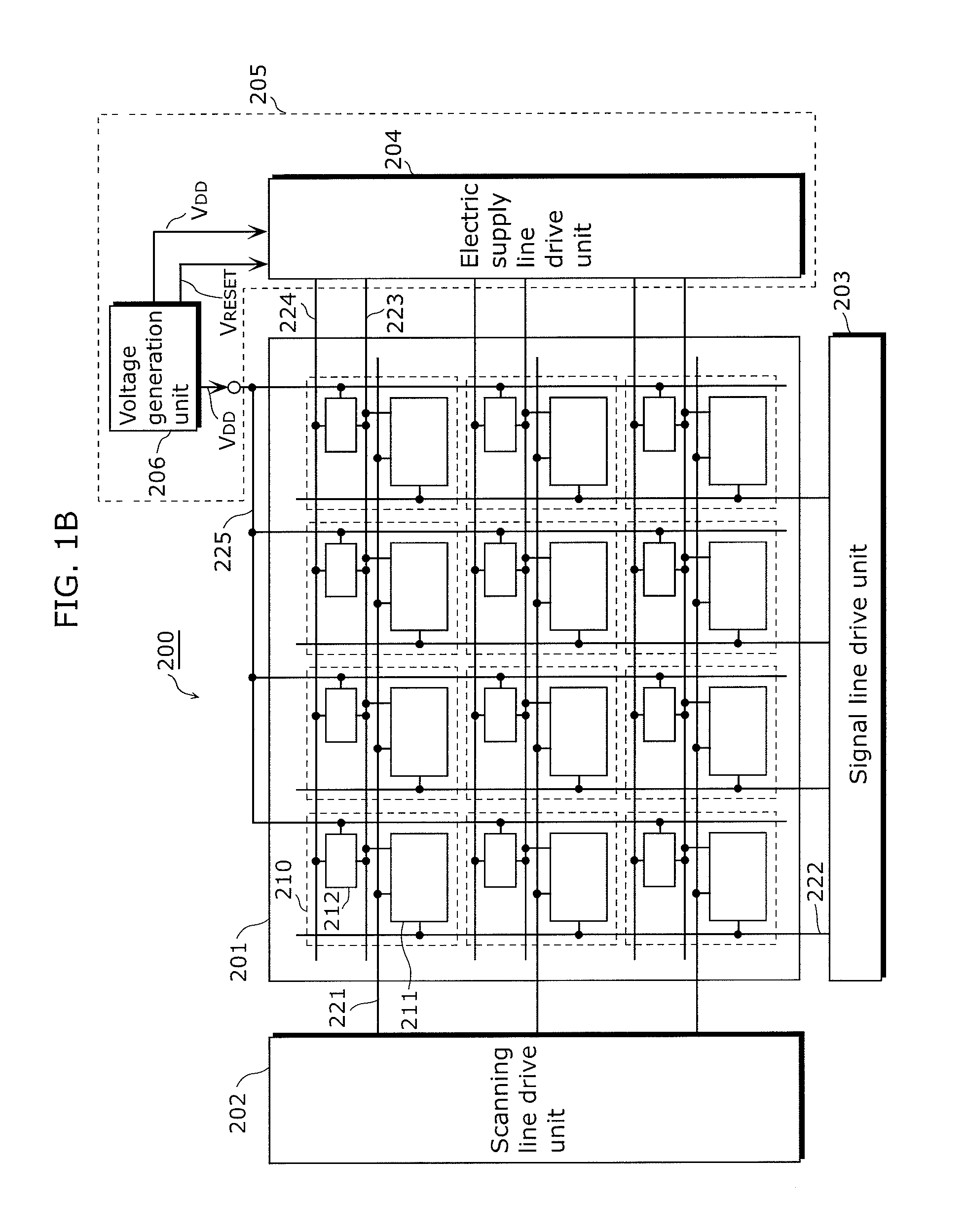

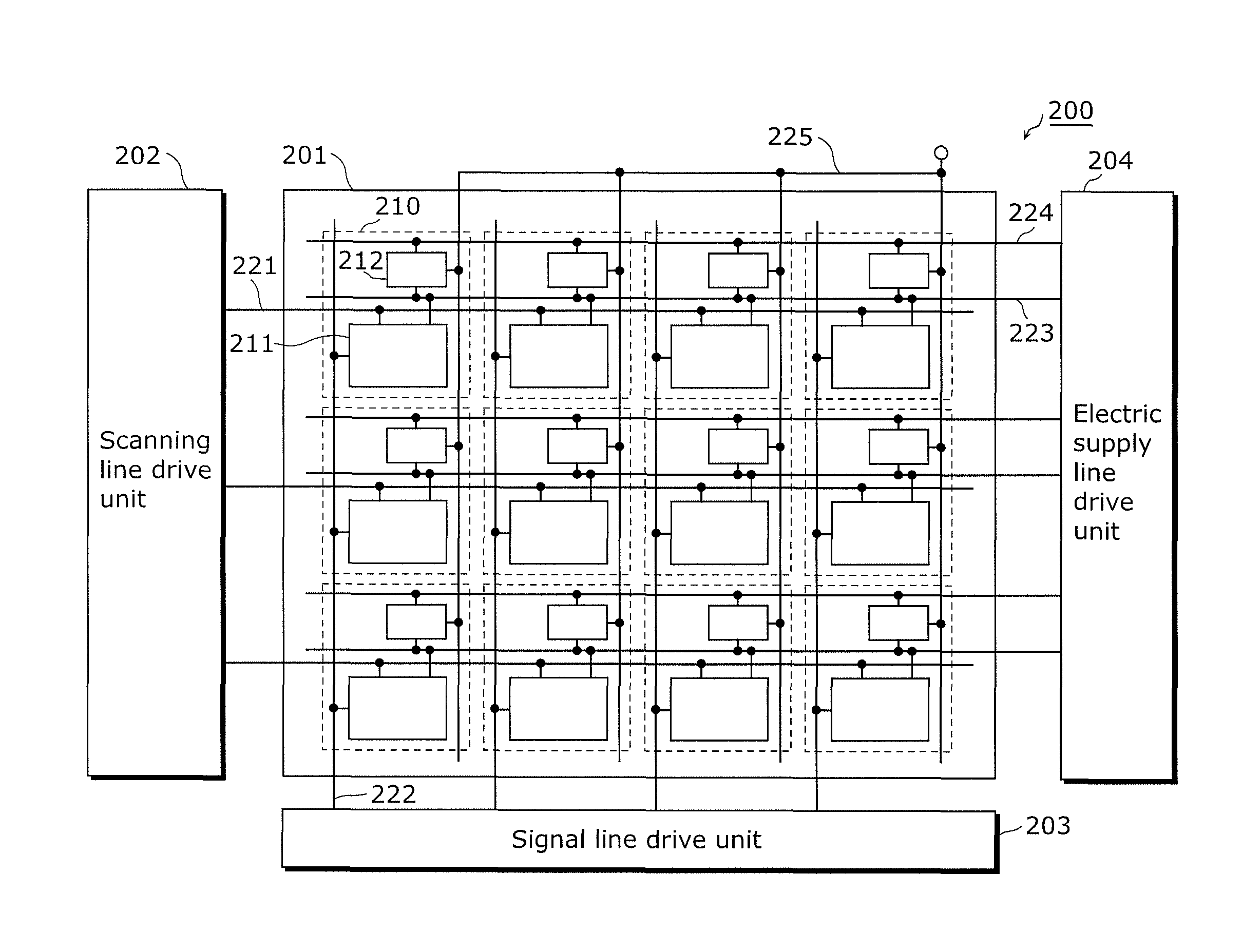

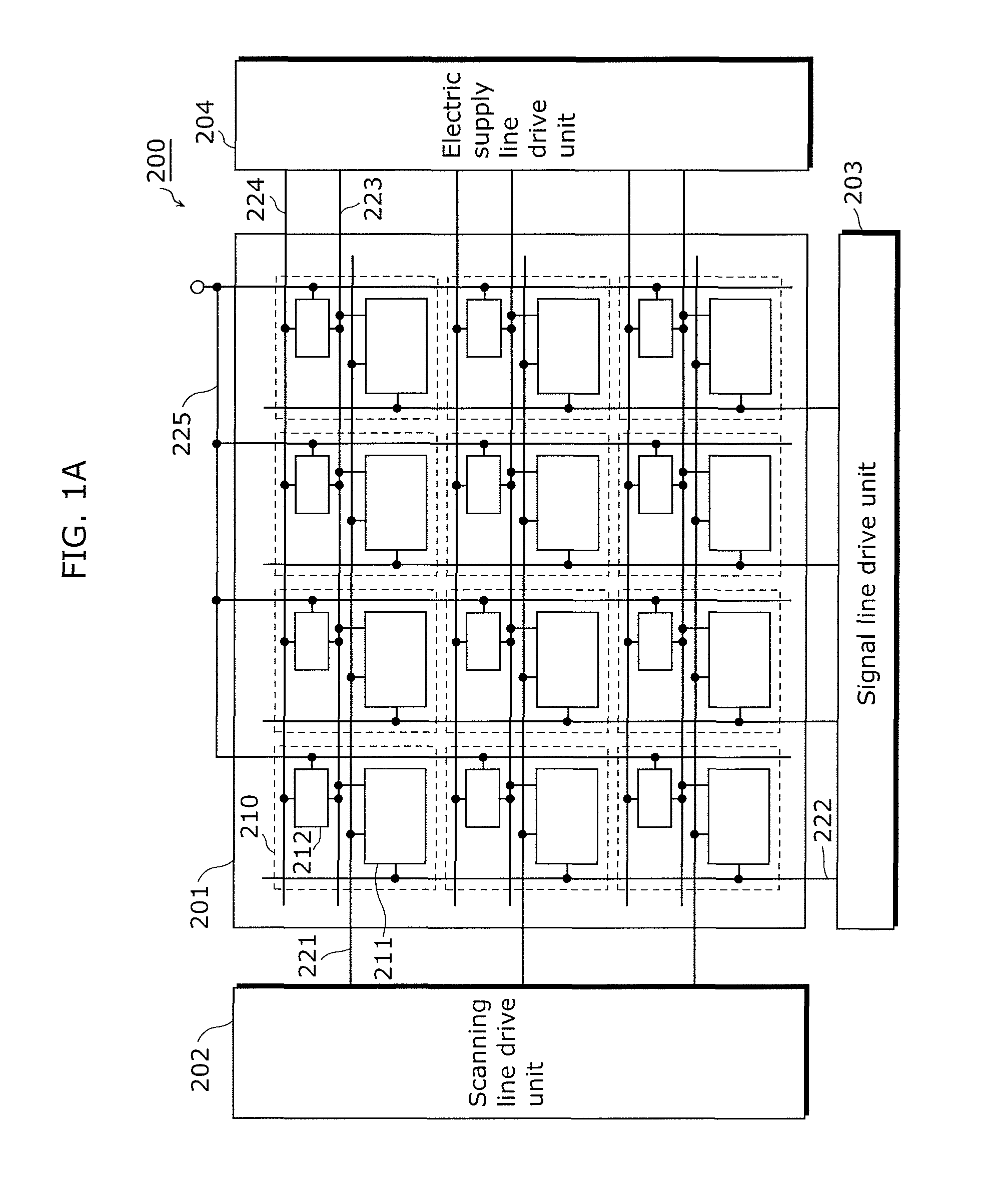

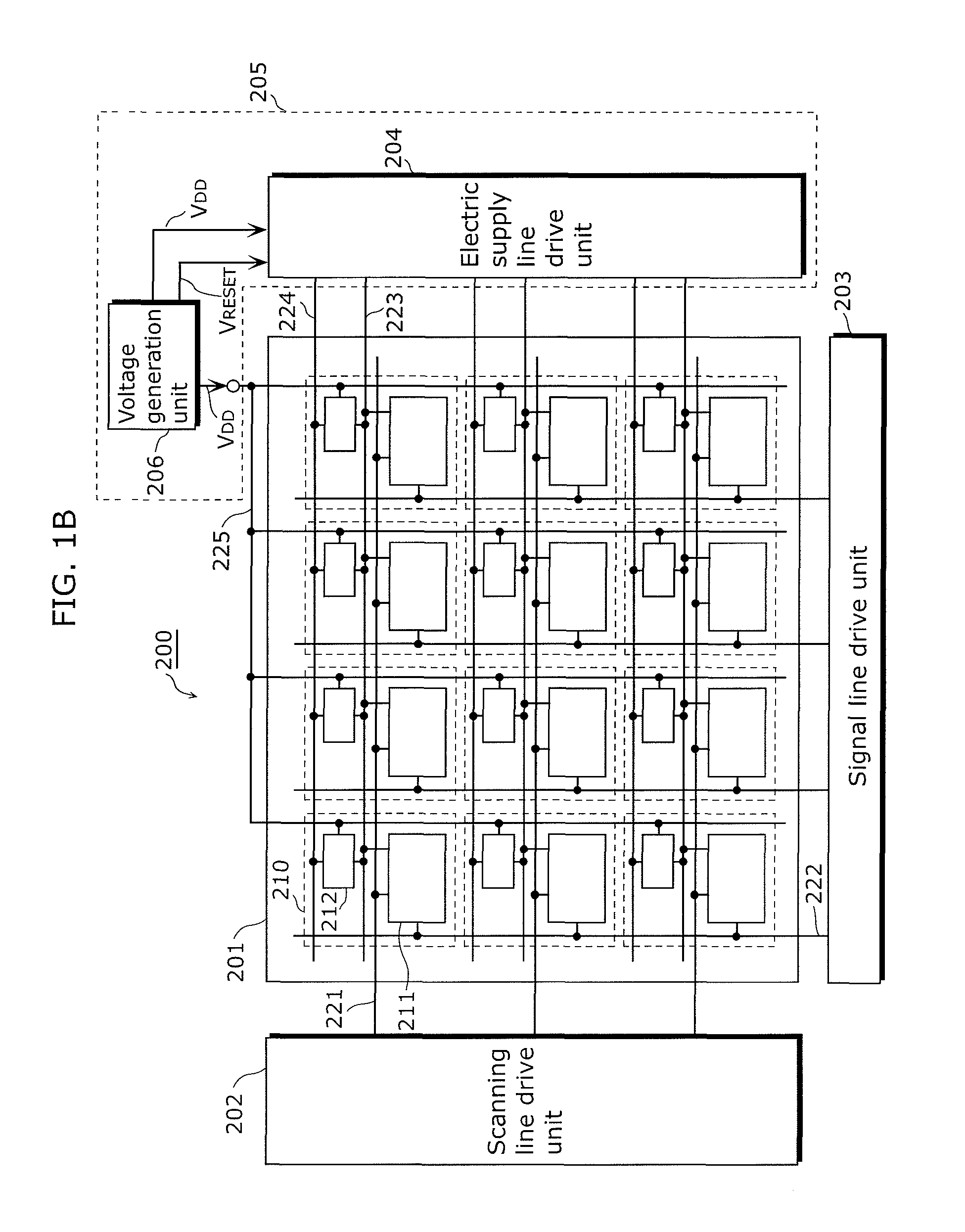

Image display apparatus

ActiveUS20120062130A1Suppress crosstalkResistance valueElectrical apparatusStatic indicating devicesControl lineEngineering

An image display apparatus according to an implementation of the present invention includes: pixel circuits disposed in rows and columns; first power lines and control lines disposed in respective rows; a third power line; second switching transistors disposed at least one for each of the rows and each having a gate terminal connected to the control line disposed in the corresponding row, one of a source terminal and a drain terminal connected to the first power line disposed in the corresponding row, and the other of the source terminal and the drain terminal connected to the third power line; and a power supply unit which supplies the same voltage to the first power lines and the third power line when the second switching transistors are turned ON.

Owner:JOLED INC

Image display apparatus

ActiveUS8552655B2Suppress crosstalkResistance valueElectrical apparatusStatic indicating devicesControl lineEngineering

Owner:JOLED INC

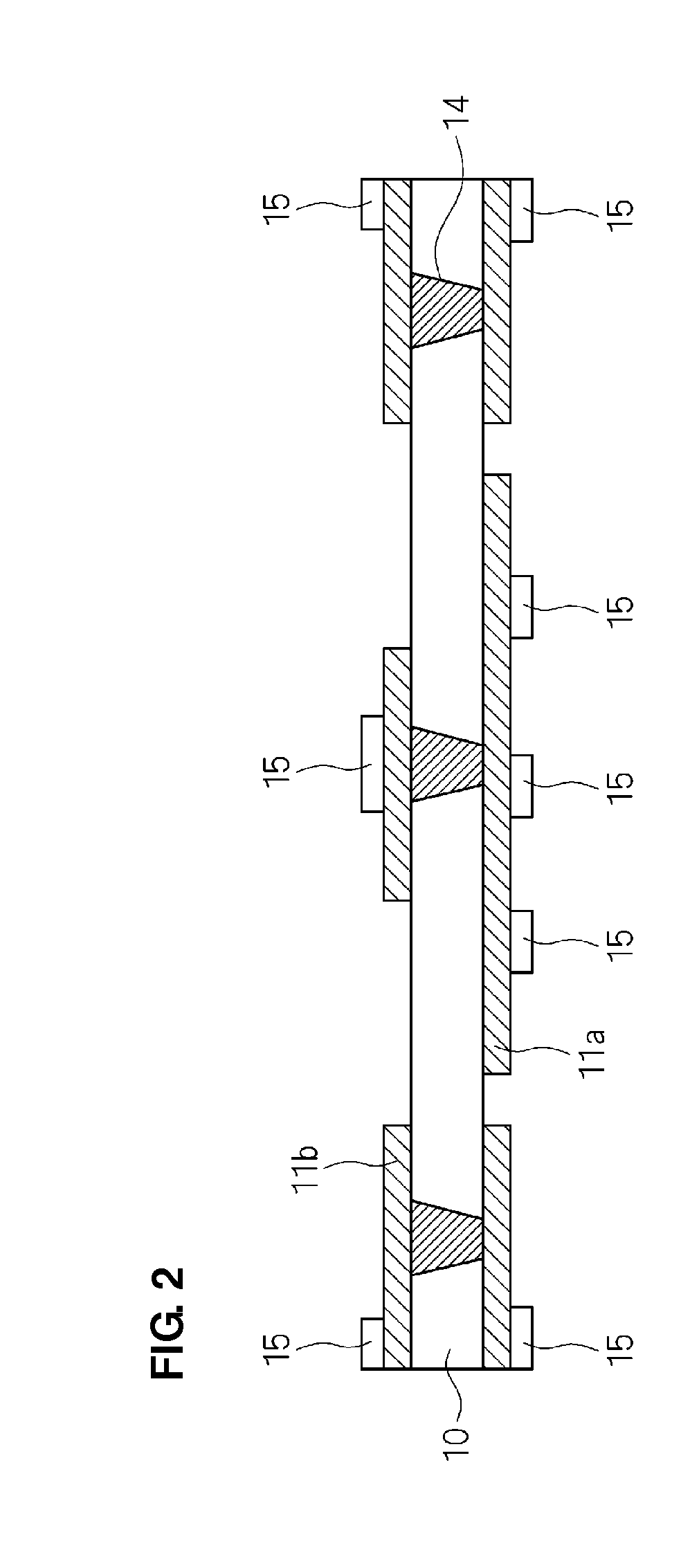

Resin multilayer substrate and method for manufacturing the resin multilayer substrate

InactiveUS20120145445A1Reduce the possibilityIncrease the areaFinal product manufactureSemiconductor/solid-state device detailsElectrical conductorSurface electrode

A resin multilayer substrate includes a component-containing layer and a thin resin layer stacked on a surface of the component-containing layer. The resin multilayer substrate further includes a surface electrode located on a surface opposite to the surface of the thin resin layer stacked on the component-containing layer, a first via conductor provided in the component-containing layer, which includes an end reaching one surface of the component-containing layer, and a second via conductor provided in the thin resin layer, which includes a first end electrically connected to the surface electrode and a second end electrically connected to the via conductor. A portion of the thin resin layer in contact with the second via conductor defines a projection projecting into the first via conductor.

Owner:MURATA MFG CO LTD

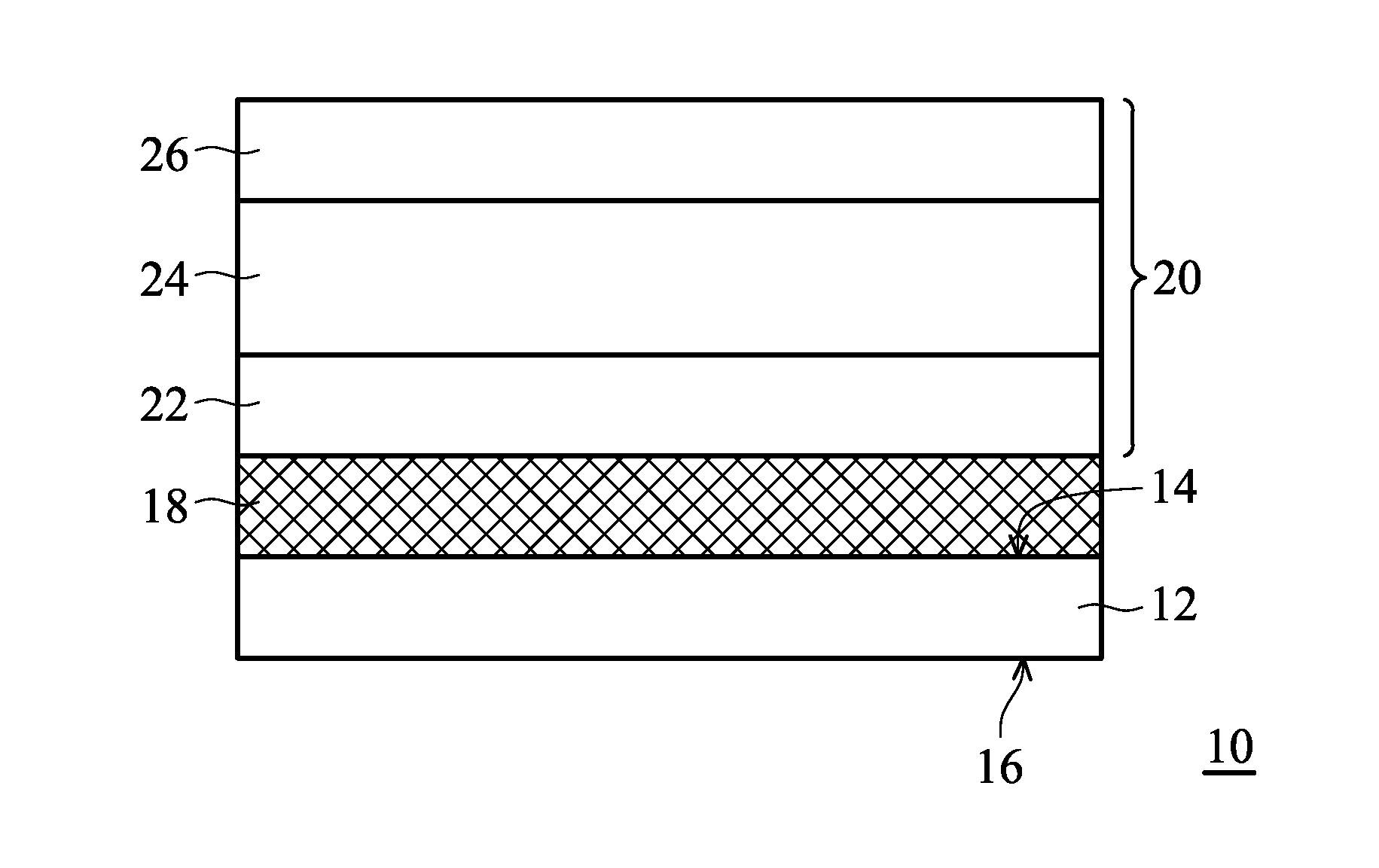

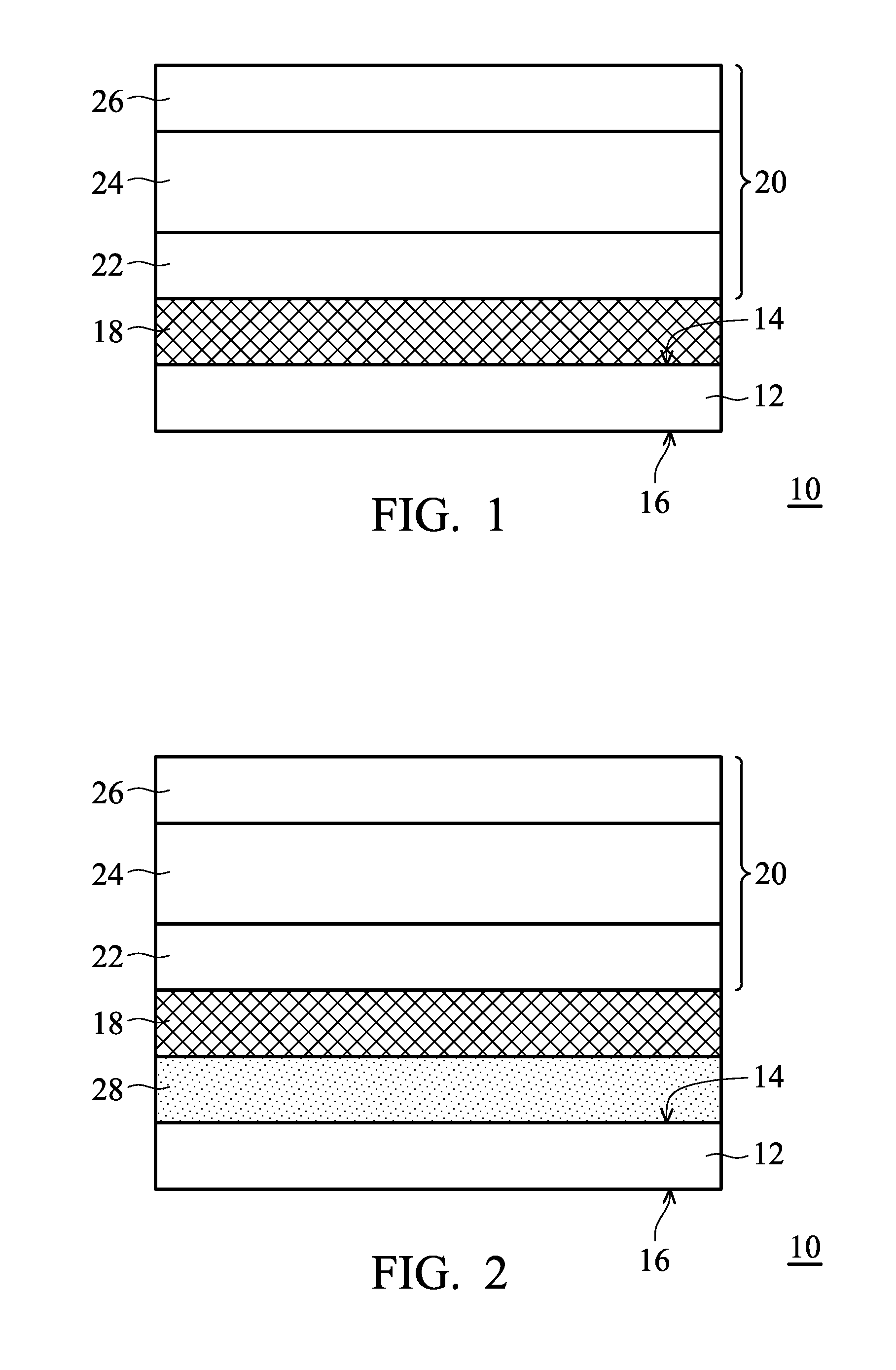

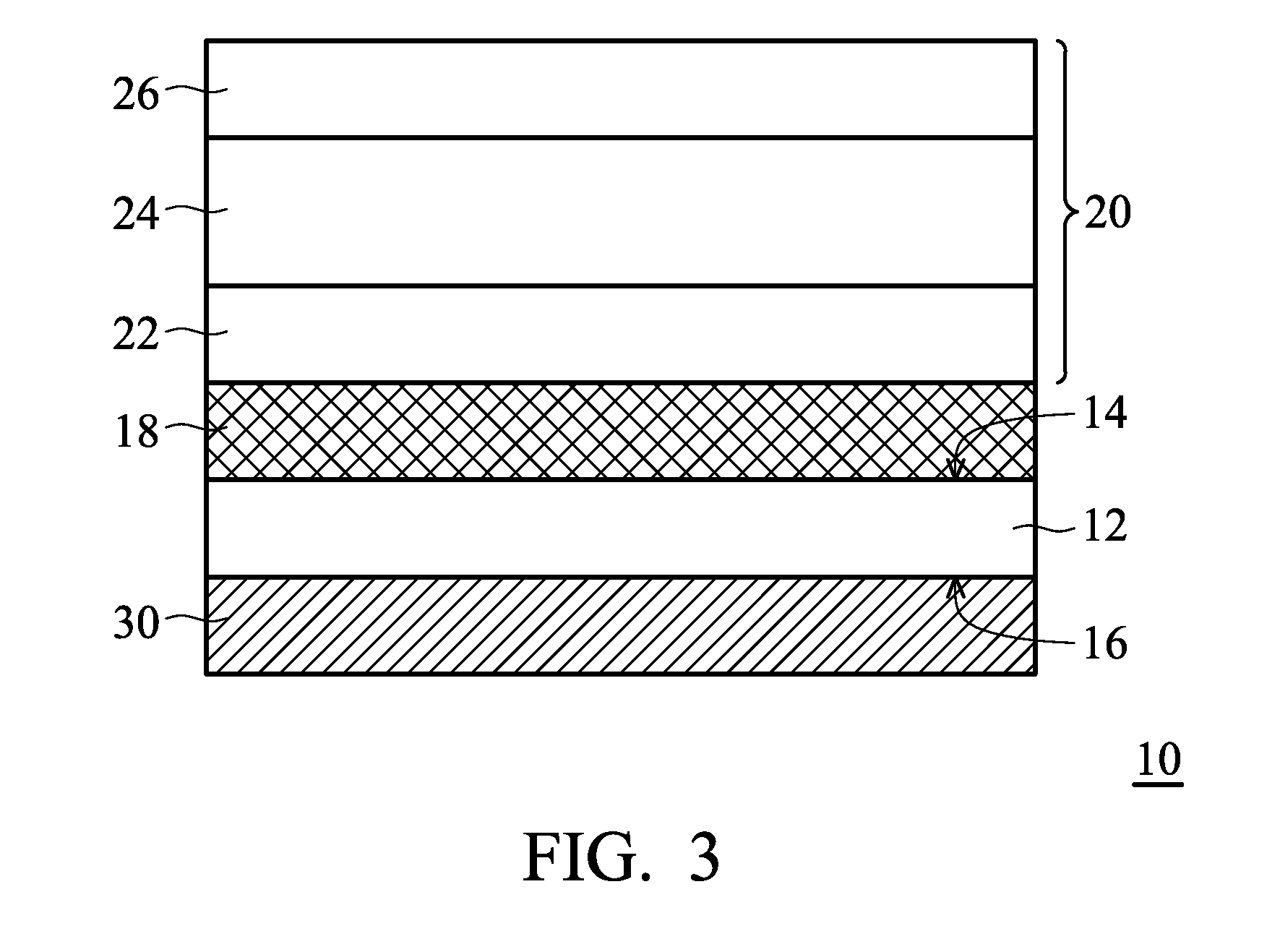

Optical device structures with the light outcoupling layers

ActiveUS20130170224A1Improve Outcoupling EfficiencyImprove luminous efficiencySynthetic resin layered productsSolid-state devicesImideCopolymer

An optical device structure with a light outcoupling layer is provided. The optical device structure includes a substrate having a first surface and a second surface, and a layer of polyimide (PI) or its copolymer formed on the first surface of the substrate, wherein the layer of polyimide or its copolymer is prepared from at least one aromatic diamine and at least one cycloaliphatic dianhydride, and an optical component formed on the layer of polyimide or its copolymer.

Owner:IND TECH RES INST

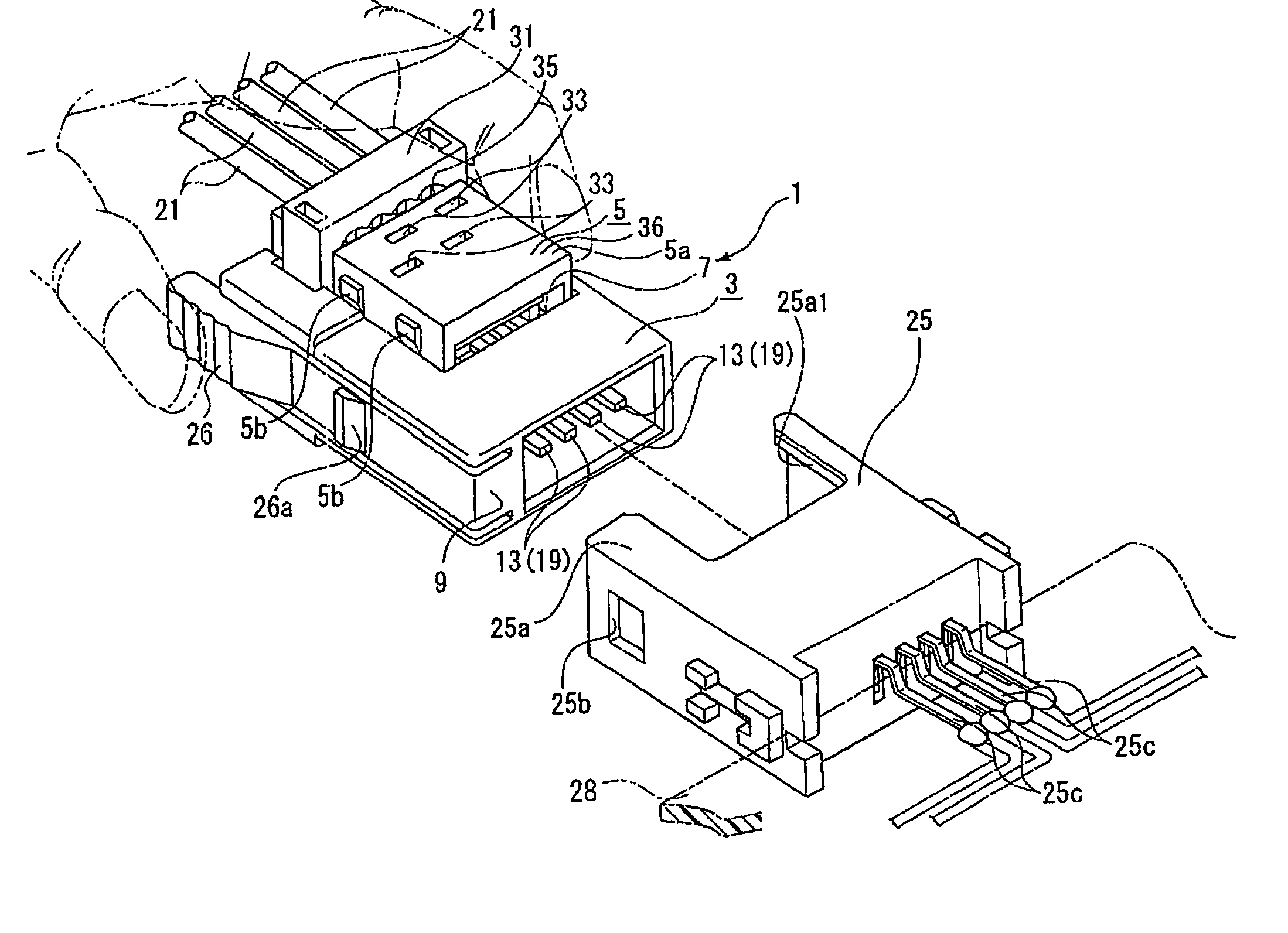

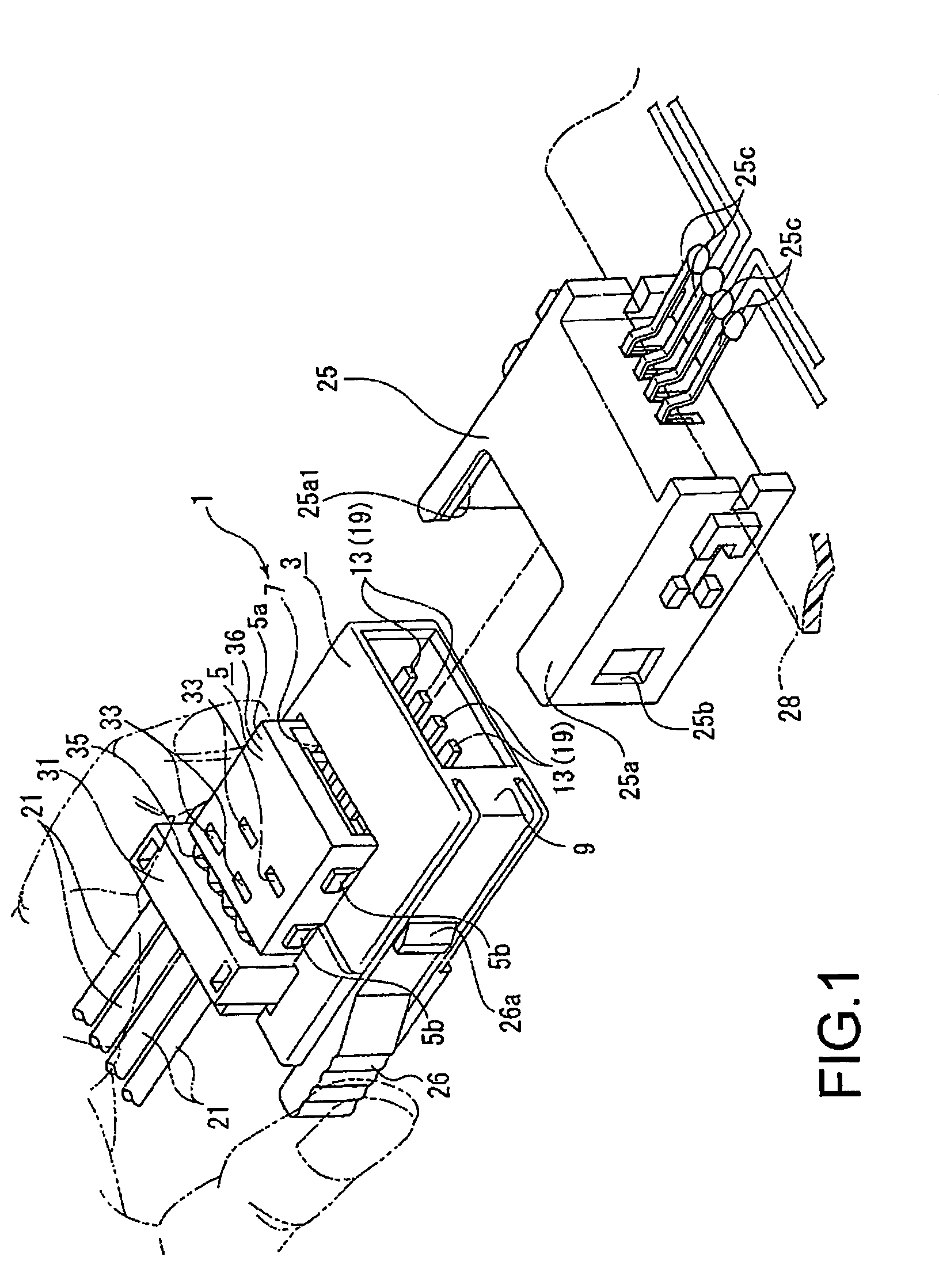

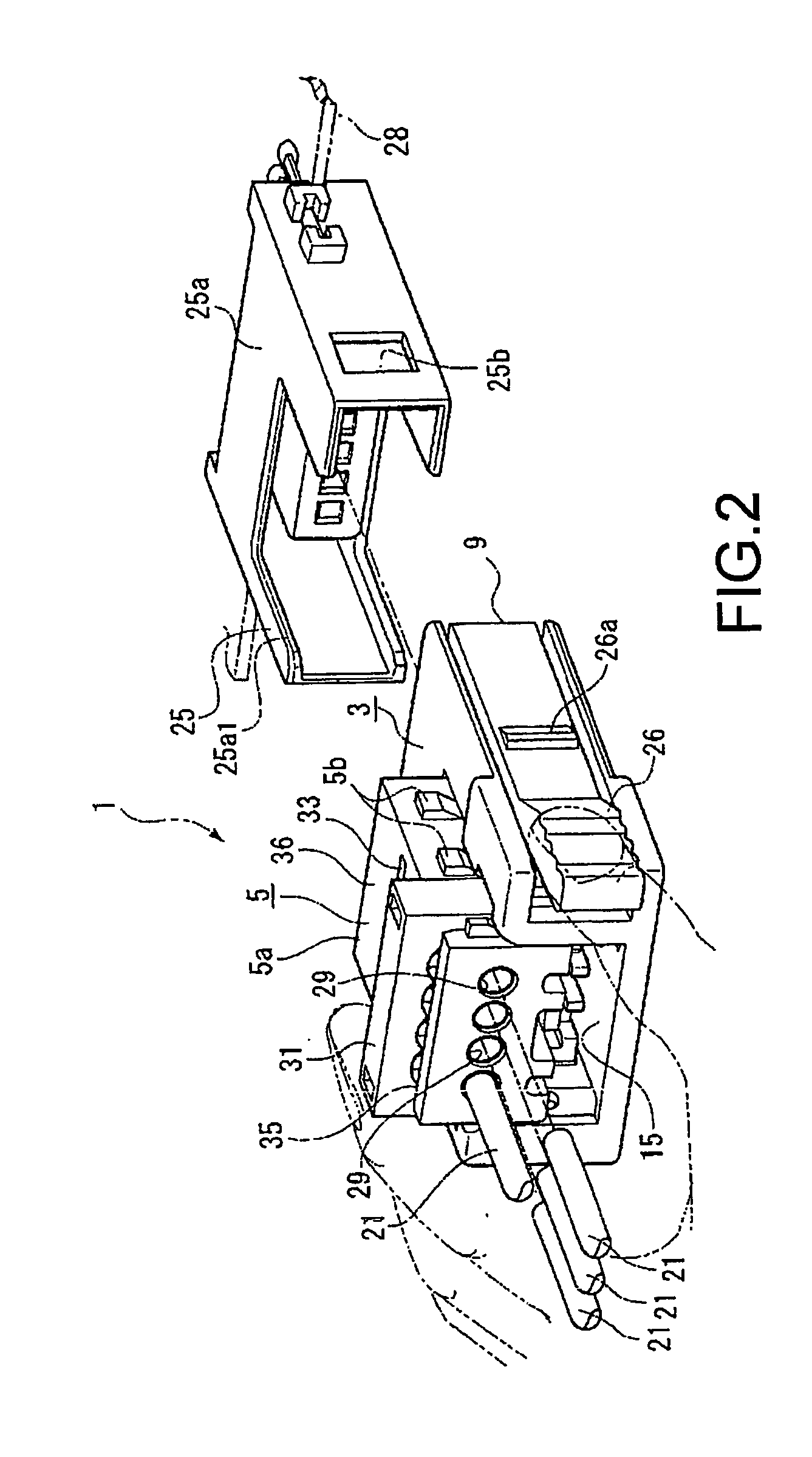

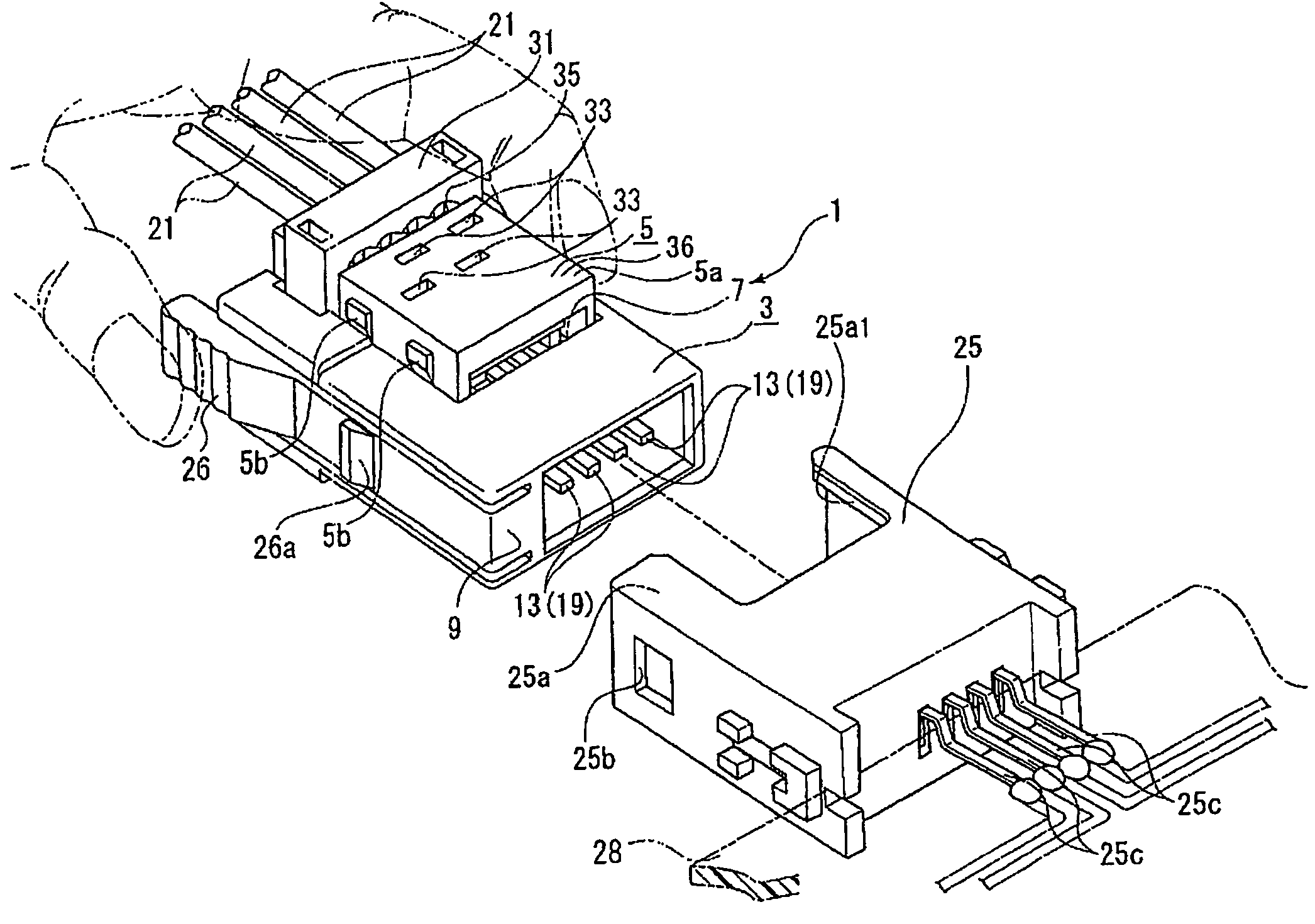

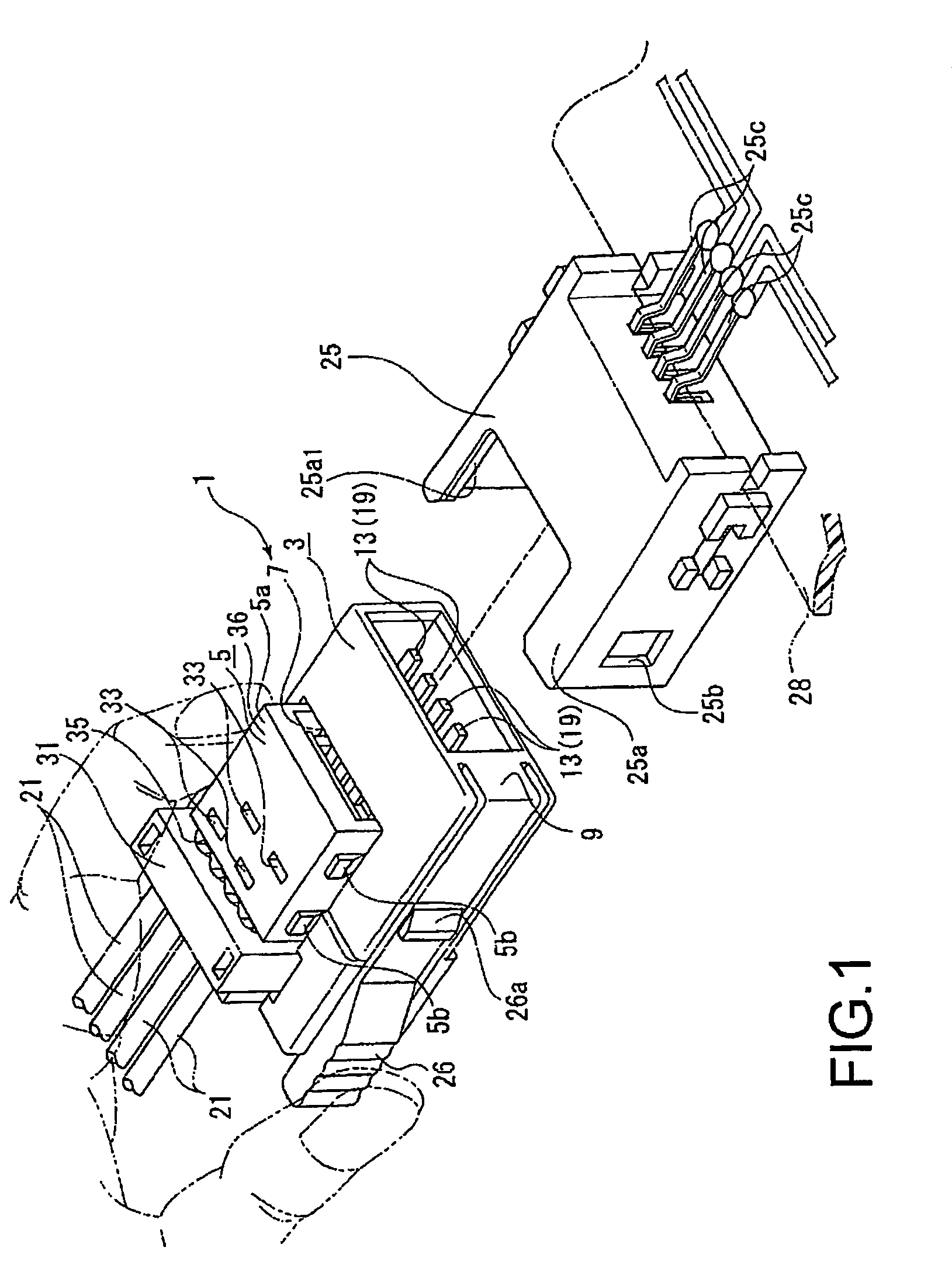

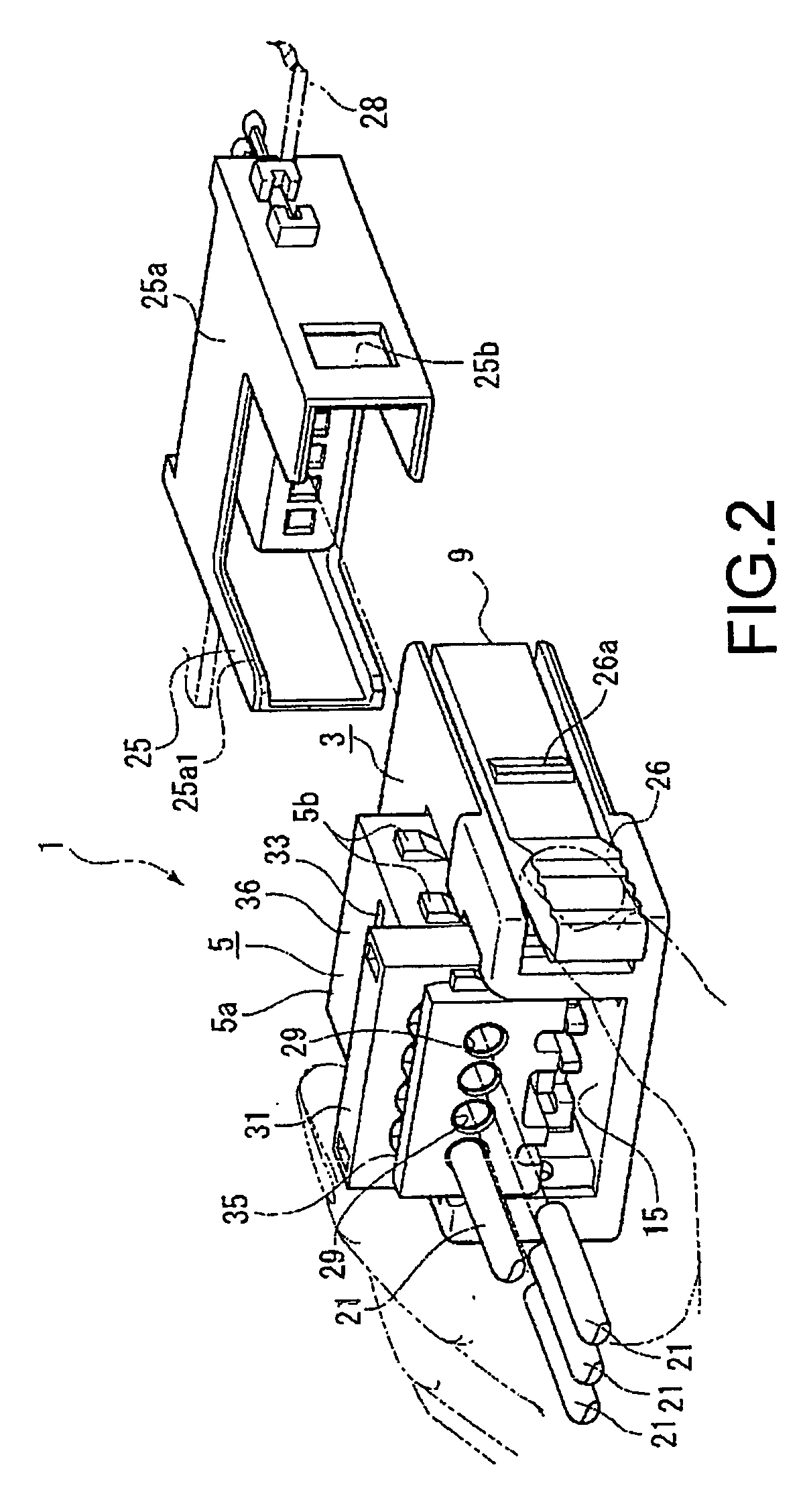

Insulation displacement connector

InactiveUS20050250373A1Reduce tensionResistance degradationCoupling device detailsContact members penetrating/cutting insulation/cable strandsEngineeringMechanical engineering

An IDT connector (1) is provided which includes: a base housing (3) having a terminal (19) to which a wire (21) is press-fit; a cover housing (5) mounted to the base housing (3) and having a wire insertion hole (29) into which the wire (21) is inserted; a wire holder (31) which is provided to the cover housing, for pressing the wire that is to be press-fitted to the terminal; and an IDT contact slot extending orthogonal to the wire insertion hole and formed adjacent to the wire holder with respect to the longitudinal direction of the wire insertion hole.

Owner:MOLEX INC

Semiconductor memory device and manufacturing method thereof

InactiveUS20080185683A1Prevent occurrenceDecrease in resistance valueTransistorSolid-state devicesEngineeringCell contact

A semiconductor memory device includes diffusion regions formed in an active region; cell contacts connected to the diffusion regions, respectively; pillars connected to the cell contacts, respectively; a bit line connected to the pillar; capacitor contacts connected to the pillars, respectively; and storage capacitors connected to the capacitor contacts, respectively. Accordingly, the pillars exist between the cell contacts and the capacitor contacts, and thus, depths of the capacitor contacts are made correspondingly shorter. Therefore, it becomes possible to prevent occurrence of shorting defects while decreasing resistance values of the capacitor contacts.

Owner:LONGITUDE SEMICON S A R L

Insulation displacement connector

InactiveUS7156688B2Reduce tensionResistance degradationCoupling device detailsContact members penetrating/cutting insulation/cable strandsEngineeringElectric wire

An IDT connector (1) is provided which includes: a base housing (3) having a terminal (19) to which a wire (21) is press-fit; a cover housing (5) mounted to the base housing (3) and having a wire insertion hole (29) into which the wire (21) is inserted; a wire holder (31) which is provided to the cover housing, for pressing the wire that is to be press-fitted to the terminal; and an IDT contact slot extending orthogonal to the wire insertion hole and formed adjacent to the wire holder with respect to the longitudinal direction of the wire insertion hole.

Owner:MOLEX INC

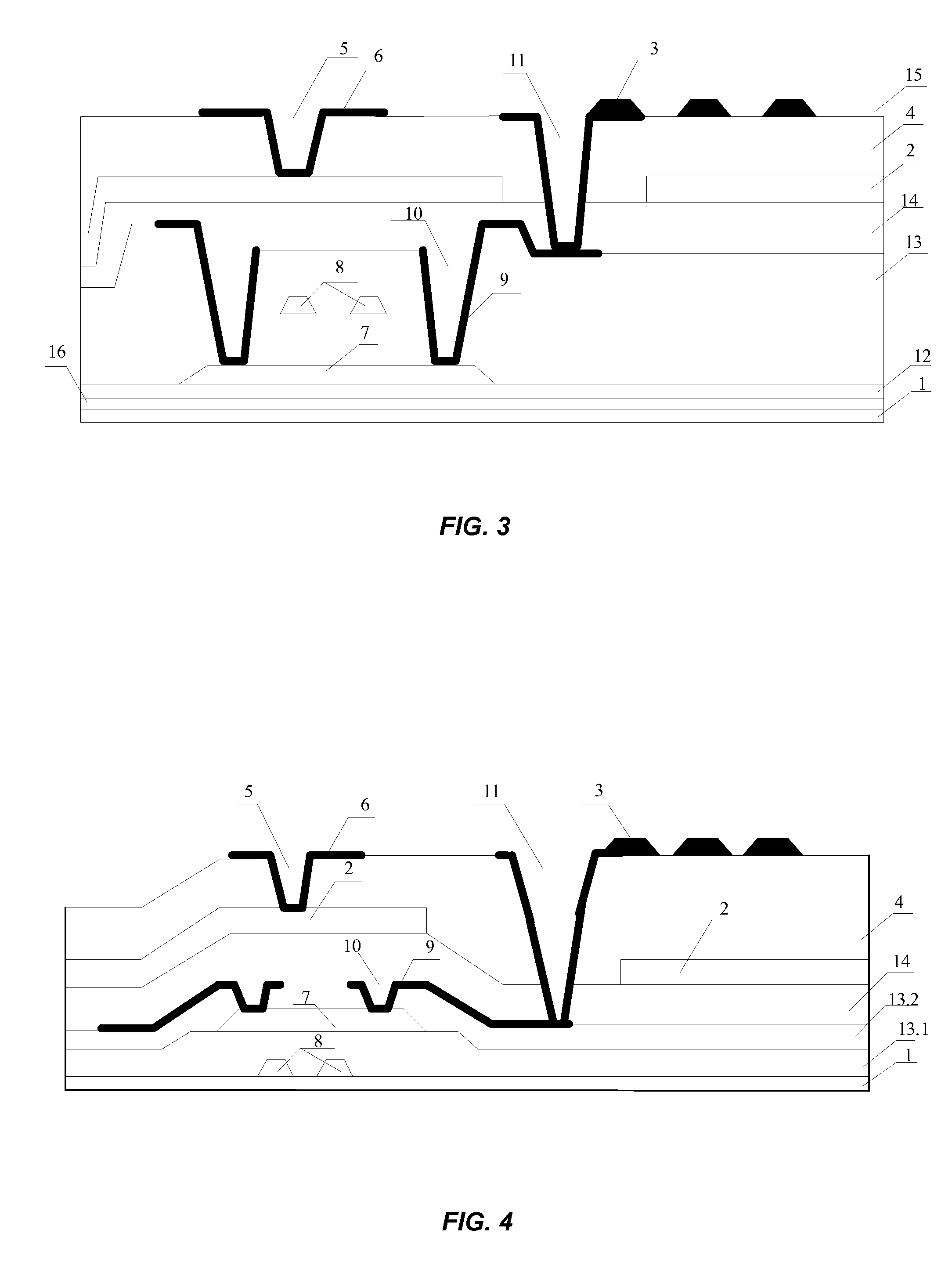

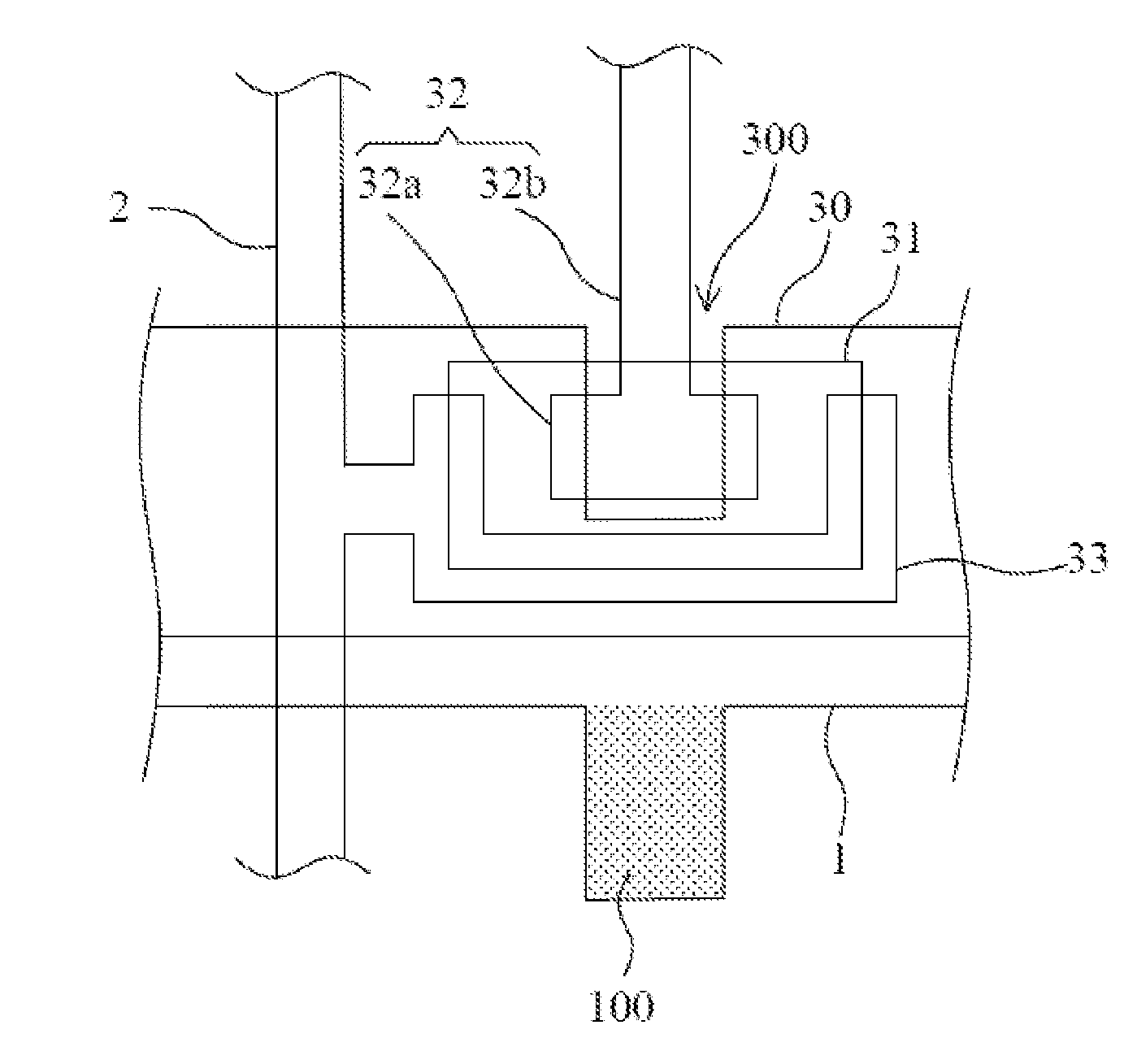

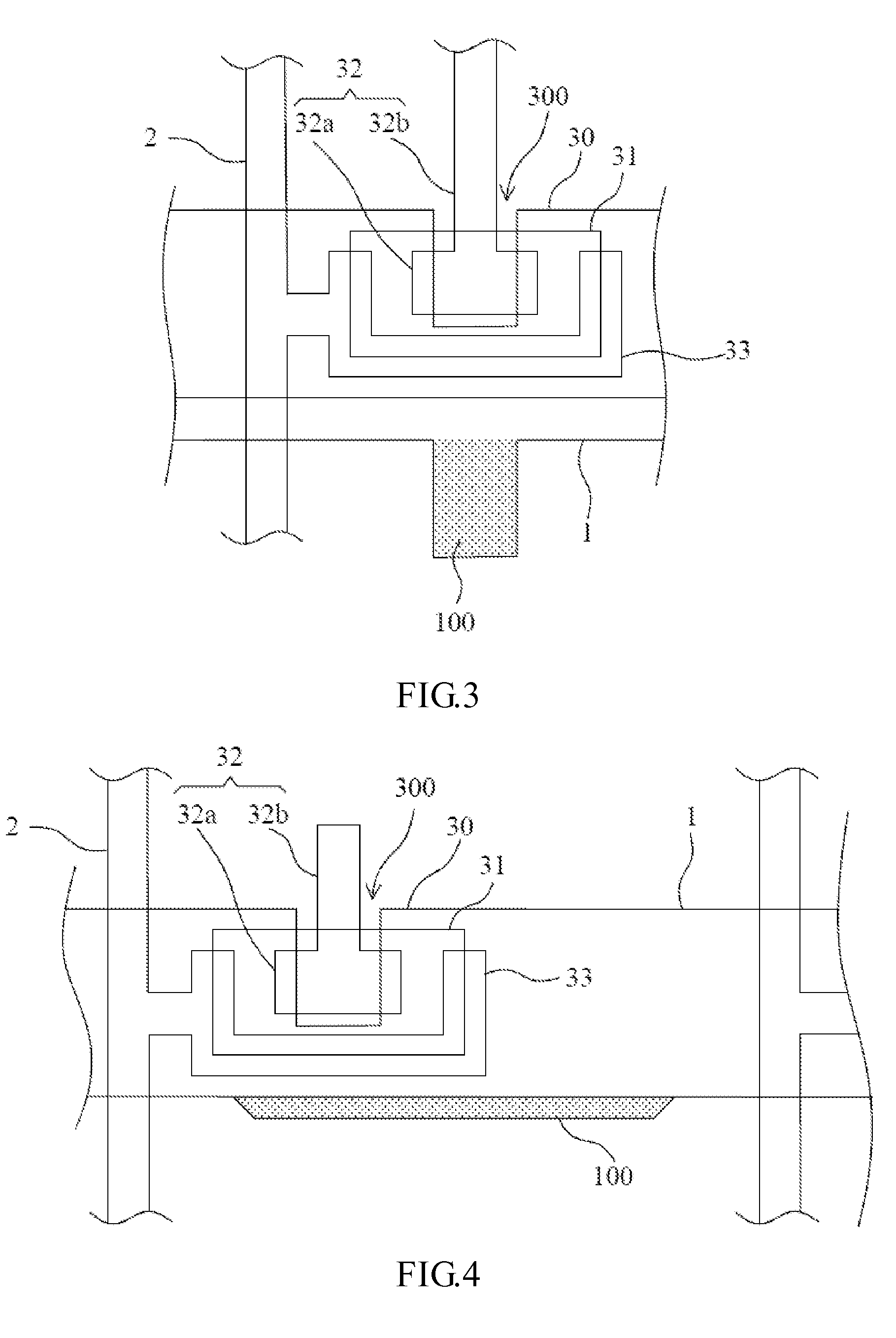

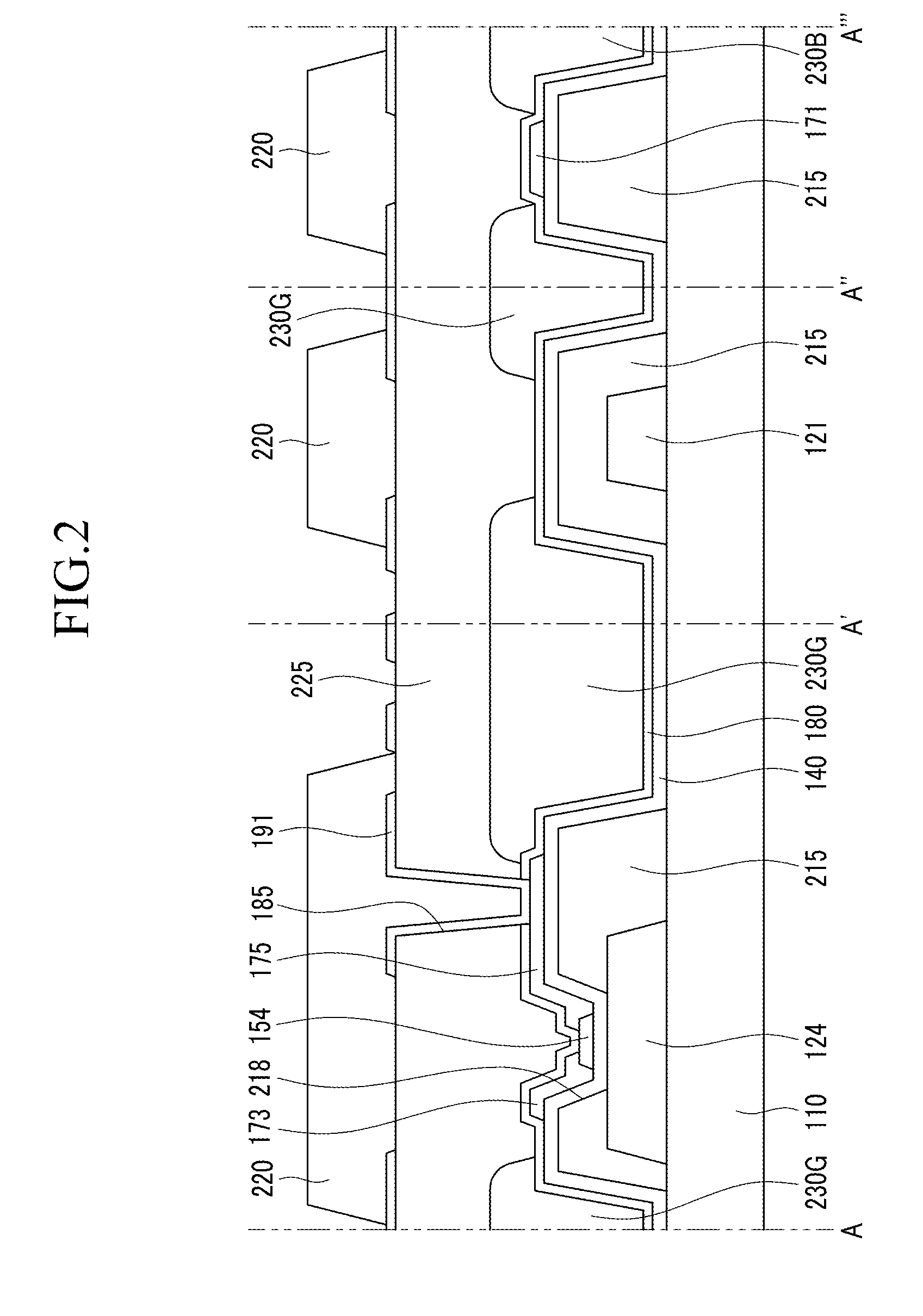

Thin-Film-Transistor Array Substrate and Manufacturing Method Thereof

ActiveUS20130009155A1Reduce parasitic capacitanceResistance valueSolid-state devicesSemiconductor/solid-state device manufacturingTransistor arrayParasitic capacitance

The present invention discloses a thin-film-transistor array substrate and a manufacturing method thereof. The array substrate includes a thin-film transistor and a compensation electrode. A gate electrode of the thin-film transistor is a portion of a scan-signal line and has an opening, and the opening extends to a side of the scan-signal line. A drain electrode of the thin-film transistor is disposed correspondingly to the opening. A source electrode of the thin-film transistor extends from a side of a data-signal line and surrounds the drain electrode. The compensation electrode extends from another side of the scan-signal line and corresponds to the gate electrode. Therefore, the present invention is capable of reducing parasitic capacitance between the drain electrode and the gate electrode without increasing the resistance value of the scan-signal line.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Method for manufacturing single sided substrate

InactiveUS7721427B2Reduce defectsImprove production yieldPrinted circuit assemblingLine/current collector detailsLaser beamsPrinted circuit board

Owner:IBIDEN CO LTD

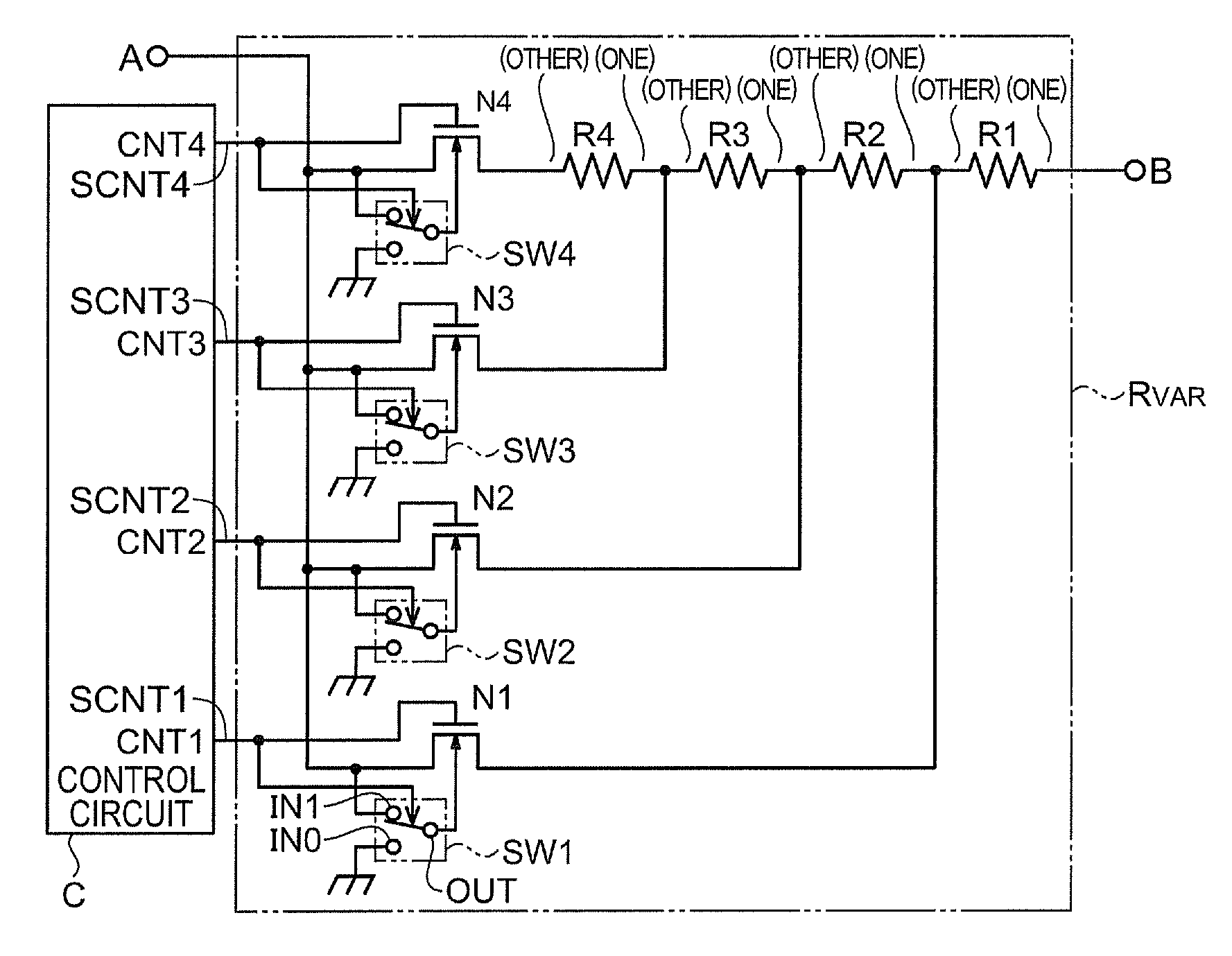

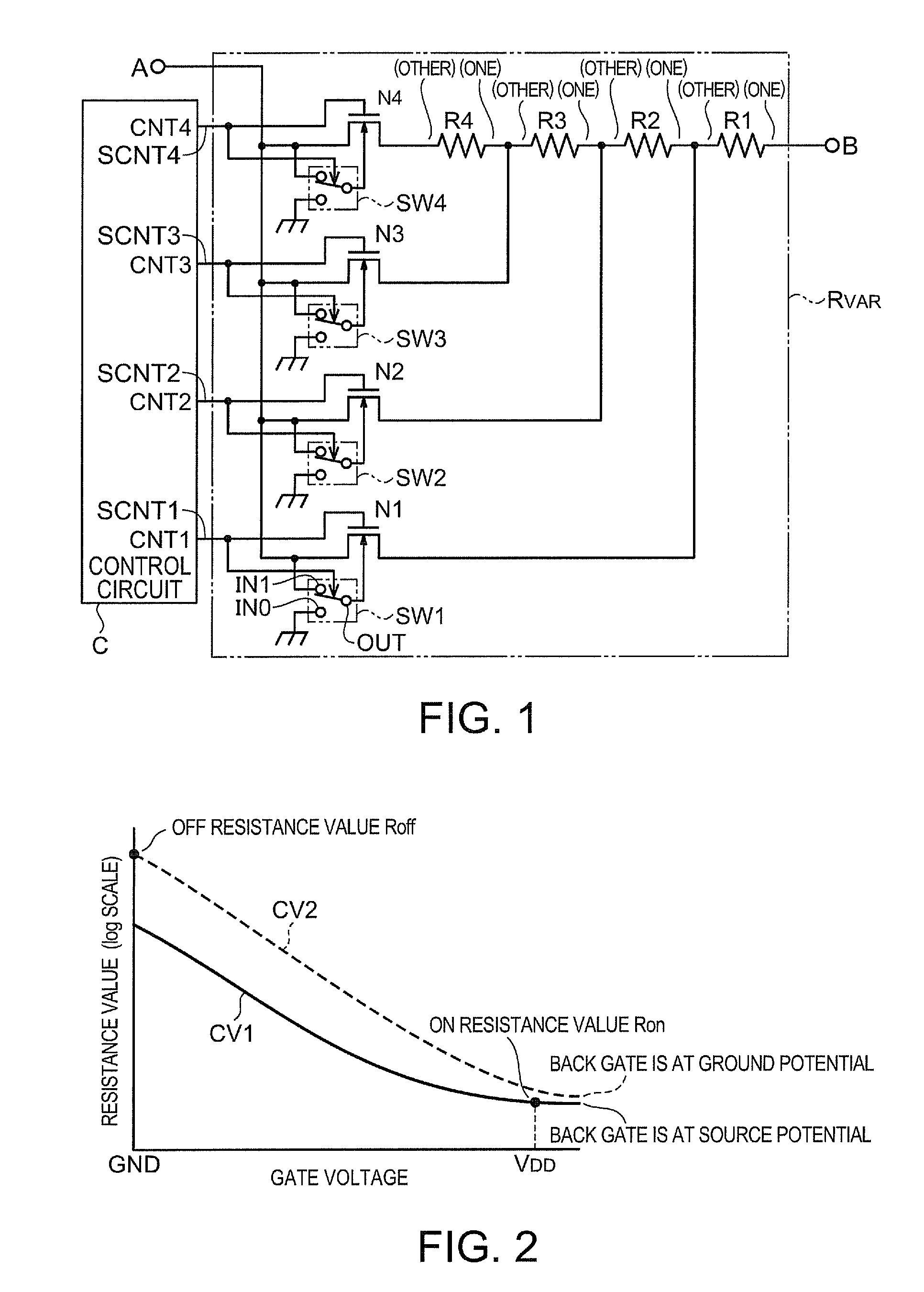

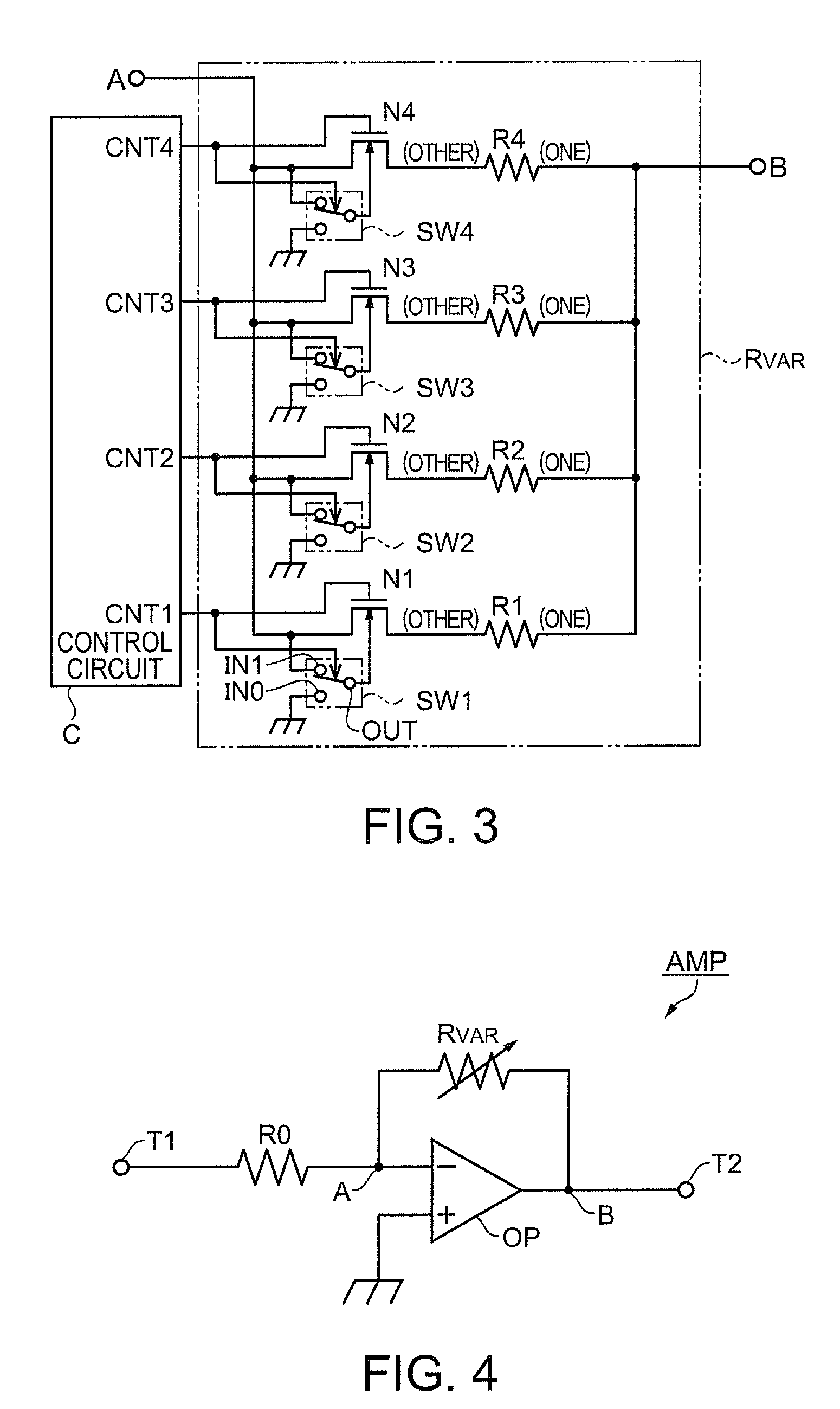

Variable resistor array and amplifier circuit

InactiveUS20090243726A1Resistance valueMultiple-port networksDc network circuit arrangementsAudio power amplifierControl signal

A variable resistor array adapted to make a resistance value between a first terminal and a second terminal variable, includes a plurality of resistors connected in series, first through nth MOS transistors selectively connected to the resistors, and first through nth switches having one input terminal connected to the source of the ith MOS transistor, another input terminal connected to a predetermined voltage, and an output terminal connected to a back gate of the ith MOS transistor, and connecting either one of the one input terminal and the other input terminal to the output terminal under control of the ith control signal. The ith switch connects the other input terminal to the output terminal, and the ith switch also connects the one input terminal to the output terminal.

Owner:SEIKO EPSON CORP

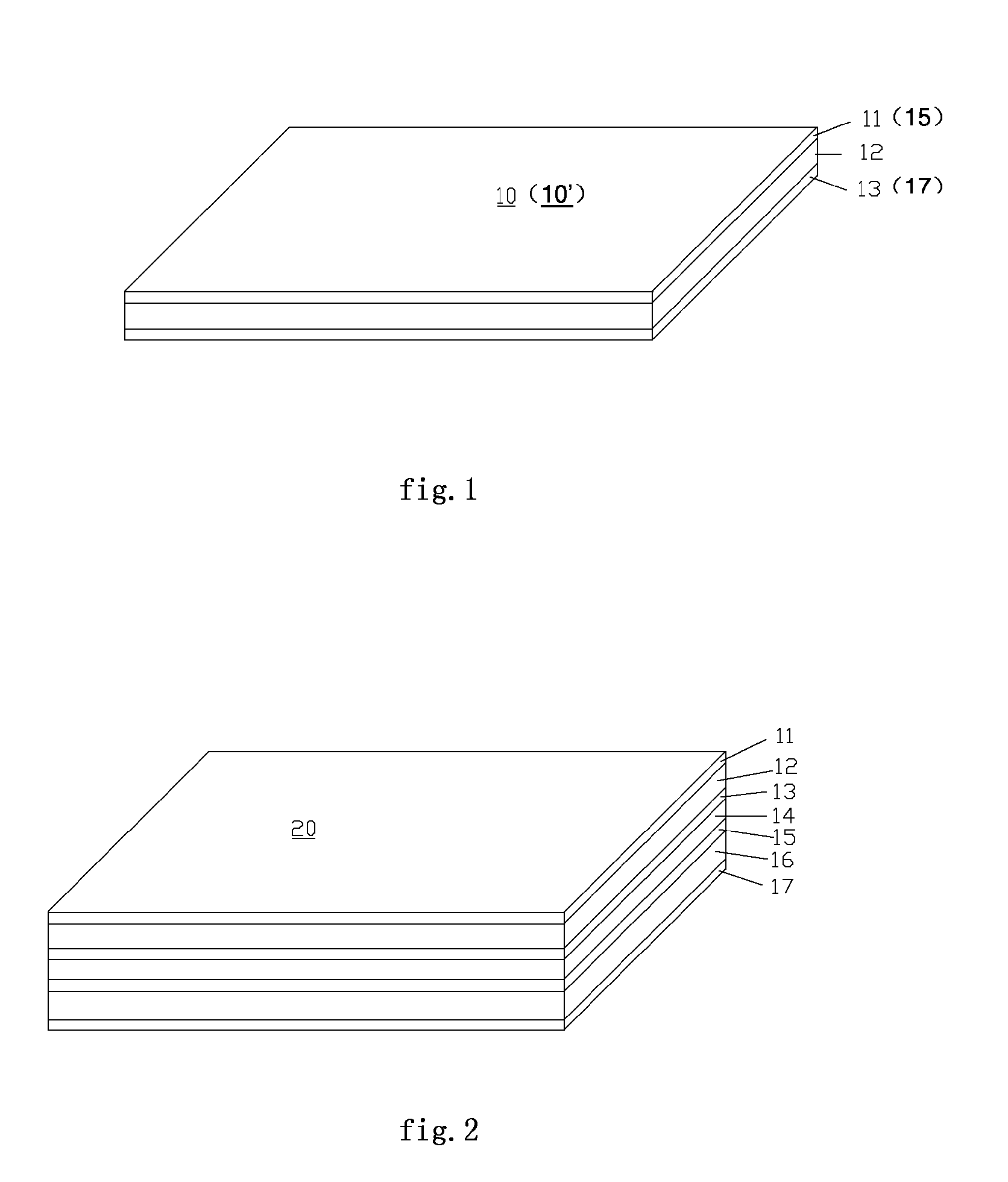

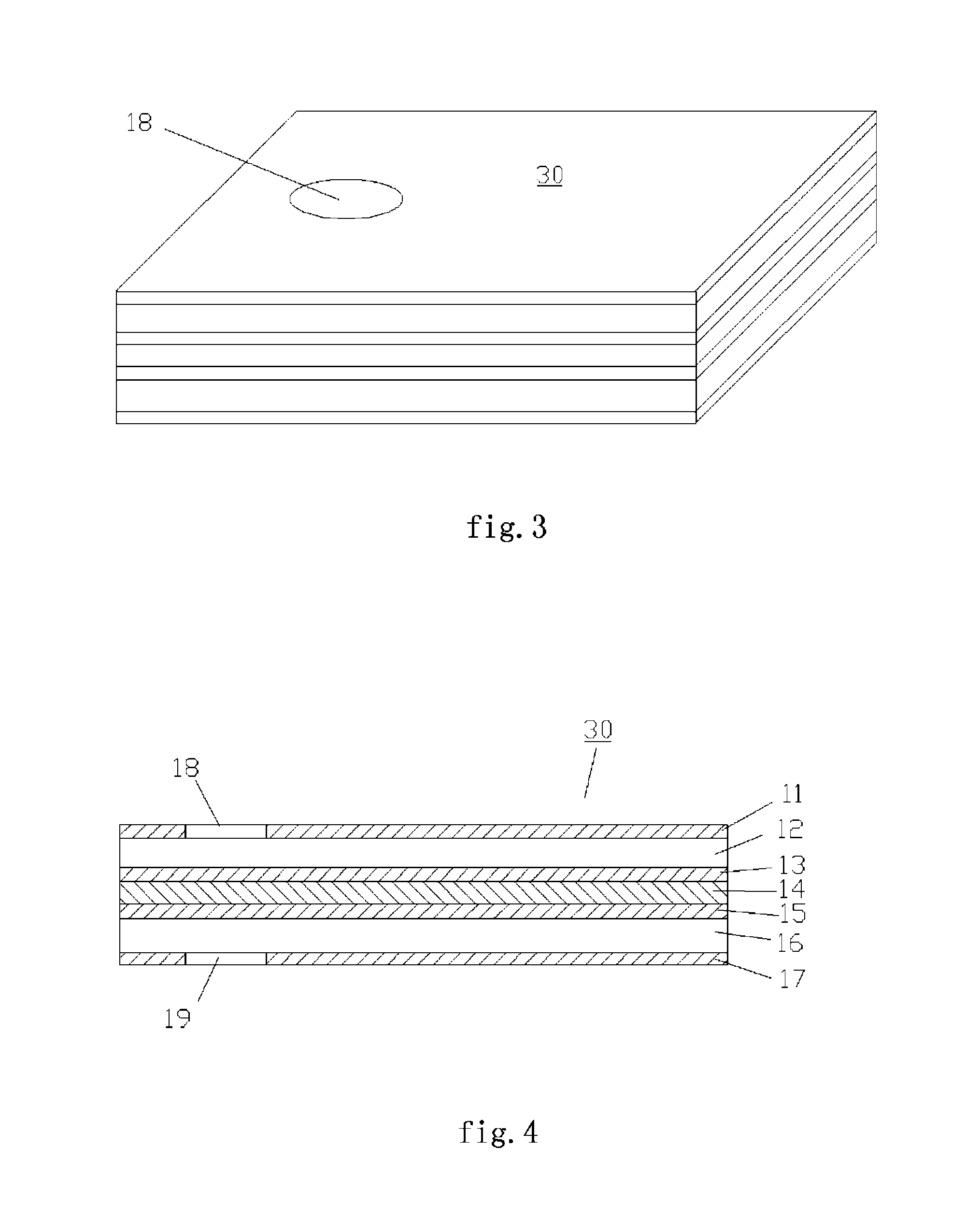

Surface-mount type overcurrent protection element

ActiveUS8576043B2Lower resistanceHigh currentCurrent responsive resistorsPositive temperature coefficient thermistorsMetallic foilSurface mounting

A surface-mount type over-current protection element includes two single-layer composite chips, wherein one chip is made of a first core material and a first and a second metallic foil layer attached on the two surfaces of the first core material, the other chip is made of a second core material and a third and a fourth metallic foil layer attached to the two surfaces of the second core material. The protection element also has an insulating layer arranged between the two chips to electrically insulate and bond to the second and third metallic layers to form a bi-layer composite chip. Part of the first metallic foil layer and the corresponding part of the fourth metallic foil layer are etched to expose part of the first core material and correspond part of the second core material. One or more through-holes are made on the bi-layer composite chip for mounting.

Owner:SHANGHAI CHANGYUAN WAYON CIRCUIT PROTECTION CO LTD

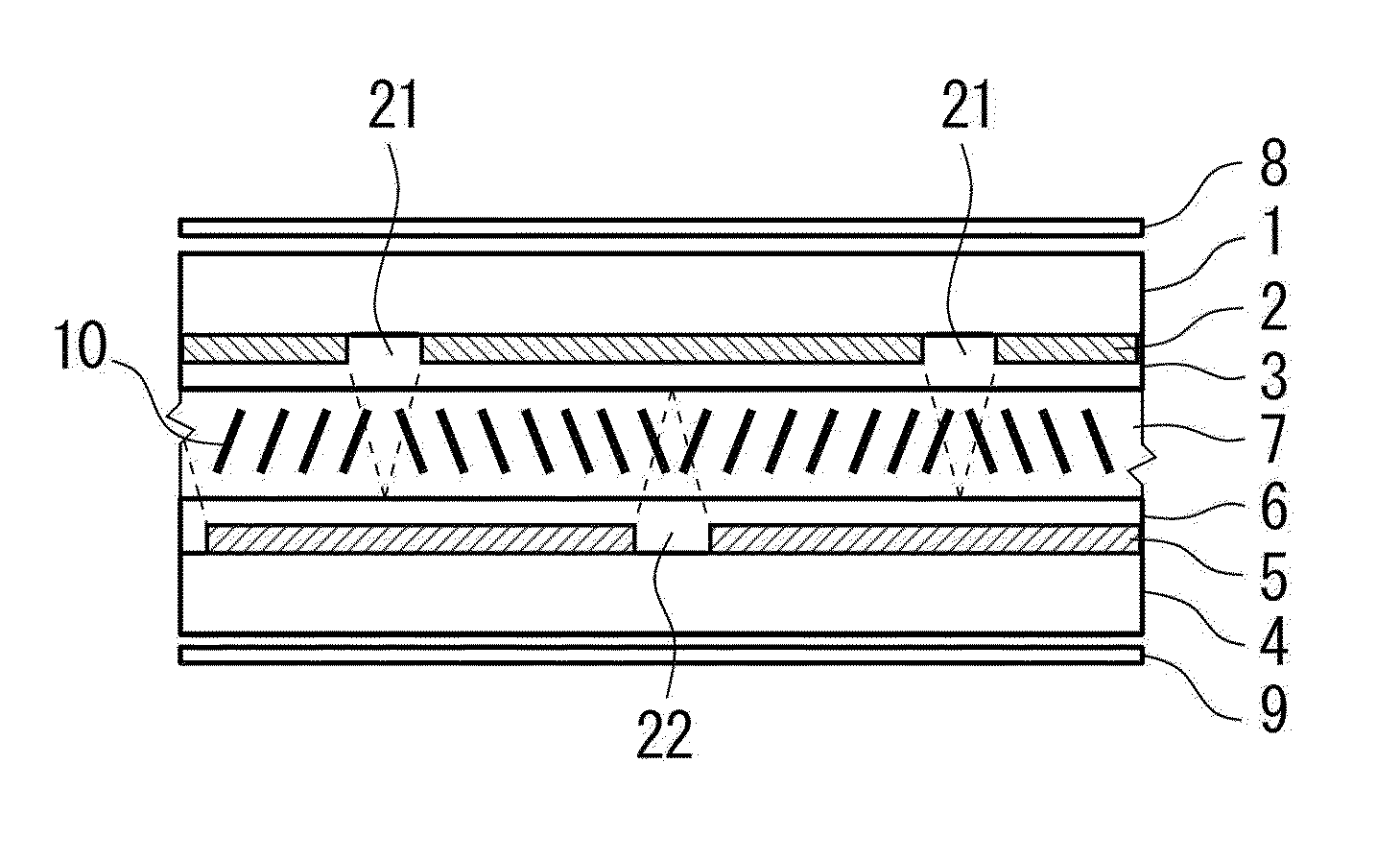

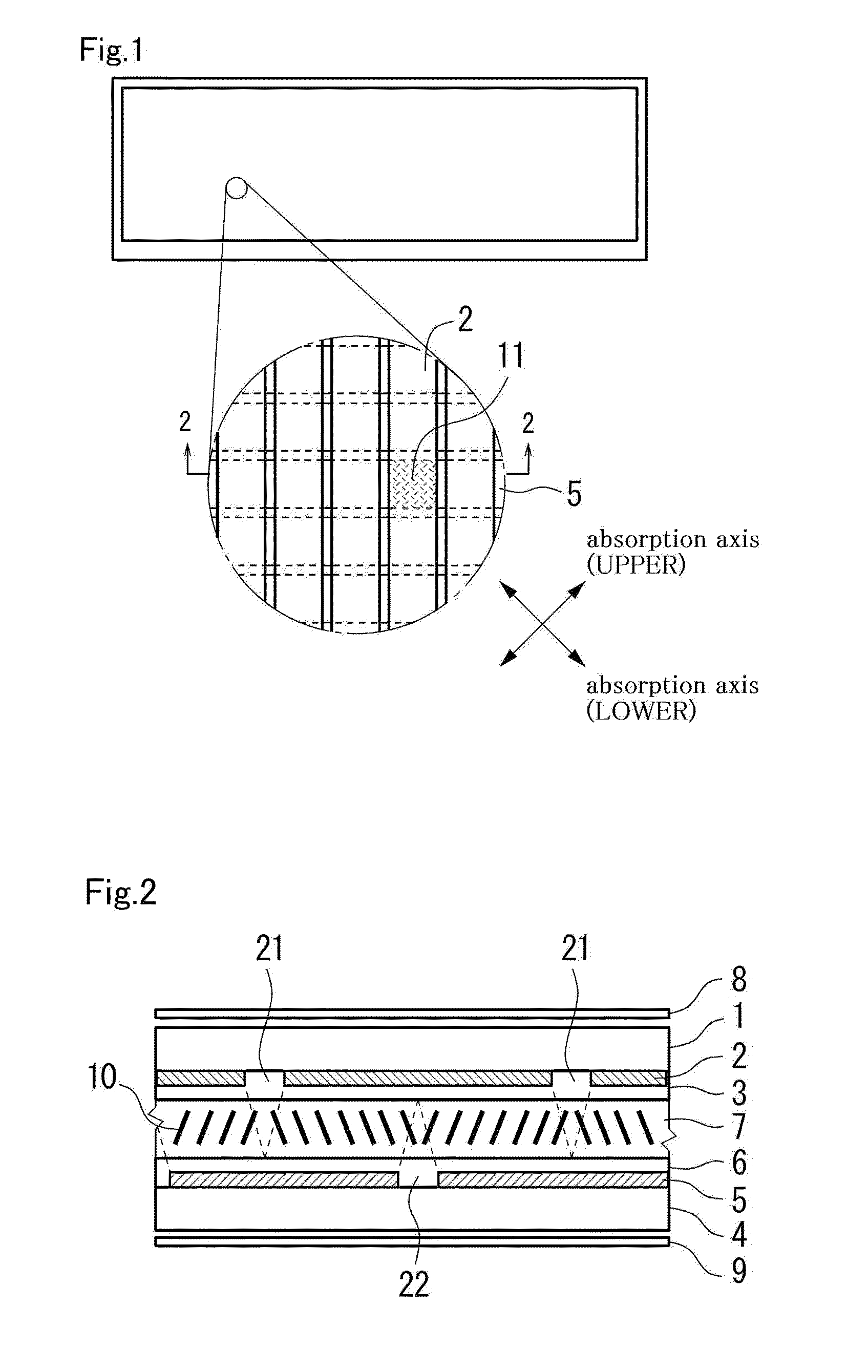

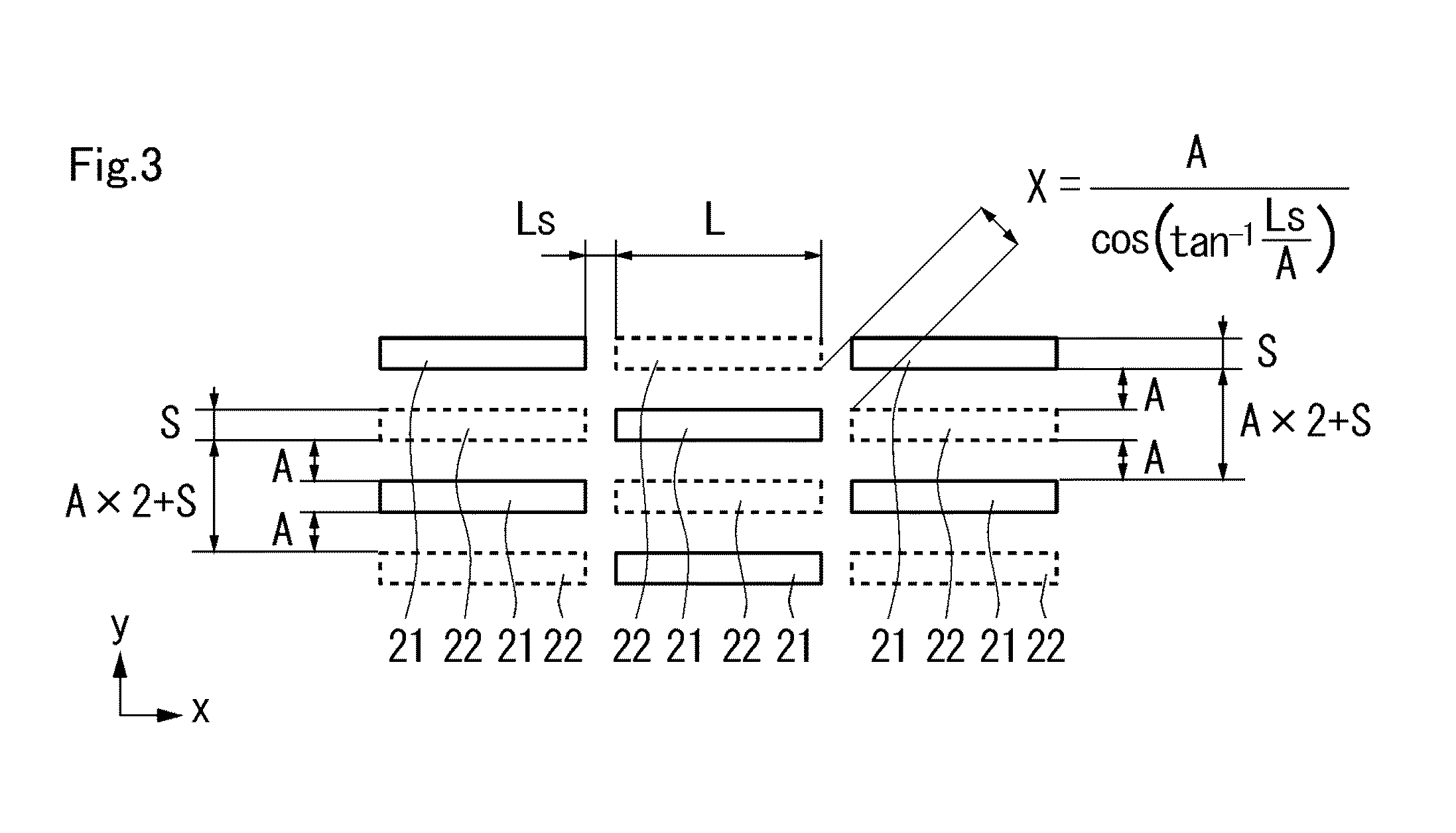

Liquid crystal display

ActiveUS20110242477A1Resistance disconnectionResistance valueNon-linear opticsLiquid-crystal displayEngineering

The liquid crystal display comprises a first substrate having a first electrode formed on one side, and a second substrate having a second electrode formed on one side and which is placed opposite to the first substrate so that the second electrode and the first electrode of the first substrate face each other. A liquid crystal layer is provided between the first substrate and the second substrate. The first electrode includes a plurality of first openings provided in a regular checkered pattern with each first opening having a shape extending in a first direction. The second electrode includes a plurality of second openings provided in a regular checkered pattern with each second opening having a shape extending in the first direction. The plurality of first openings and the plurality of second openings are relatively arranged so that each of the plurality of first openings is positioned between two second openings which are adjacent in a planar view among the plurality of second openings.

Owner:STANLEY ELECTRIC CO LTD

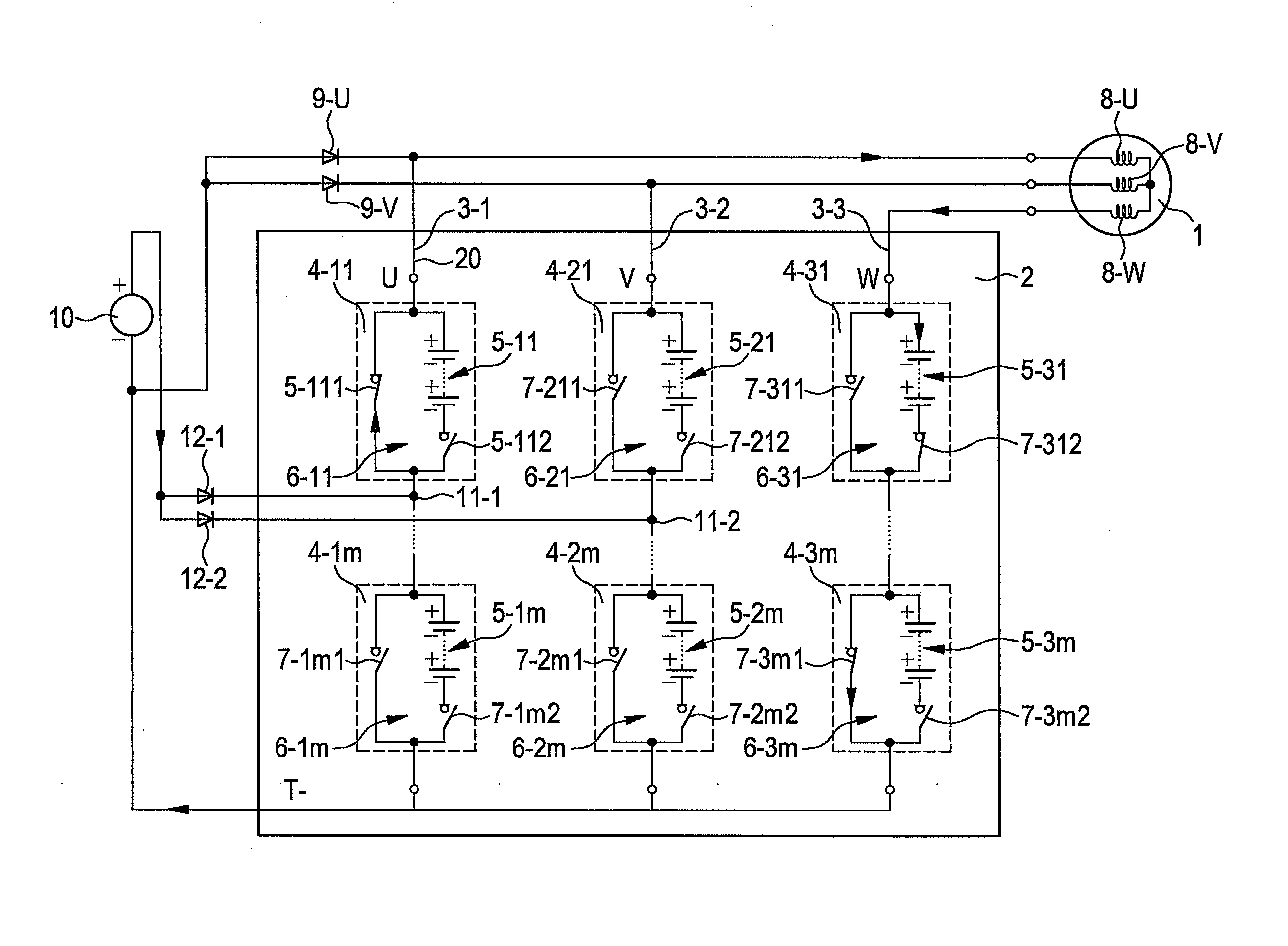

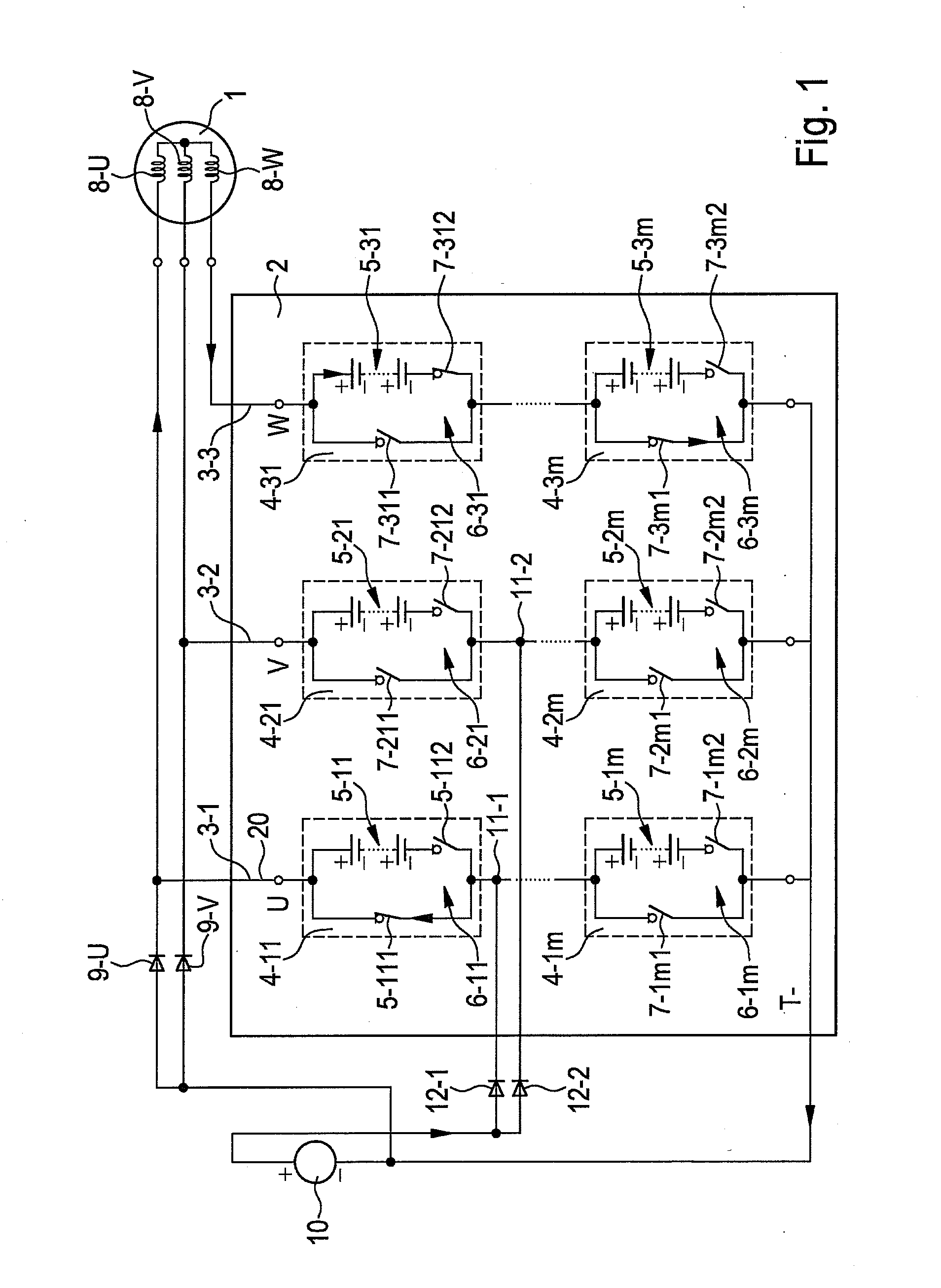

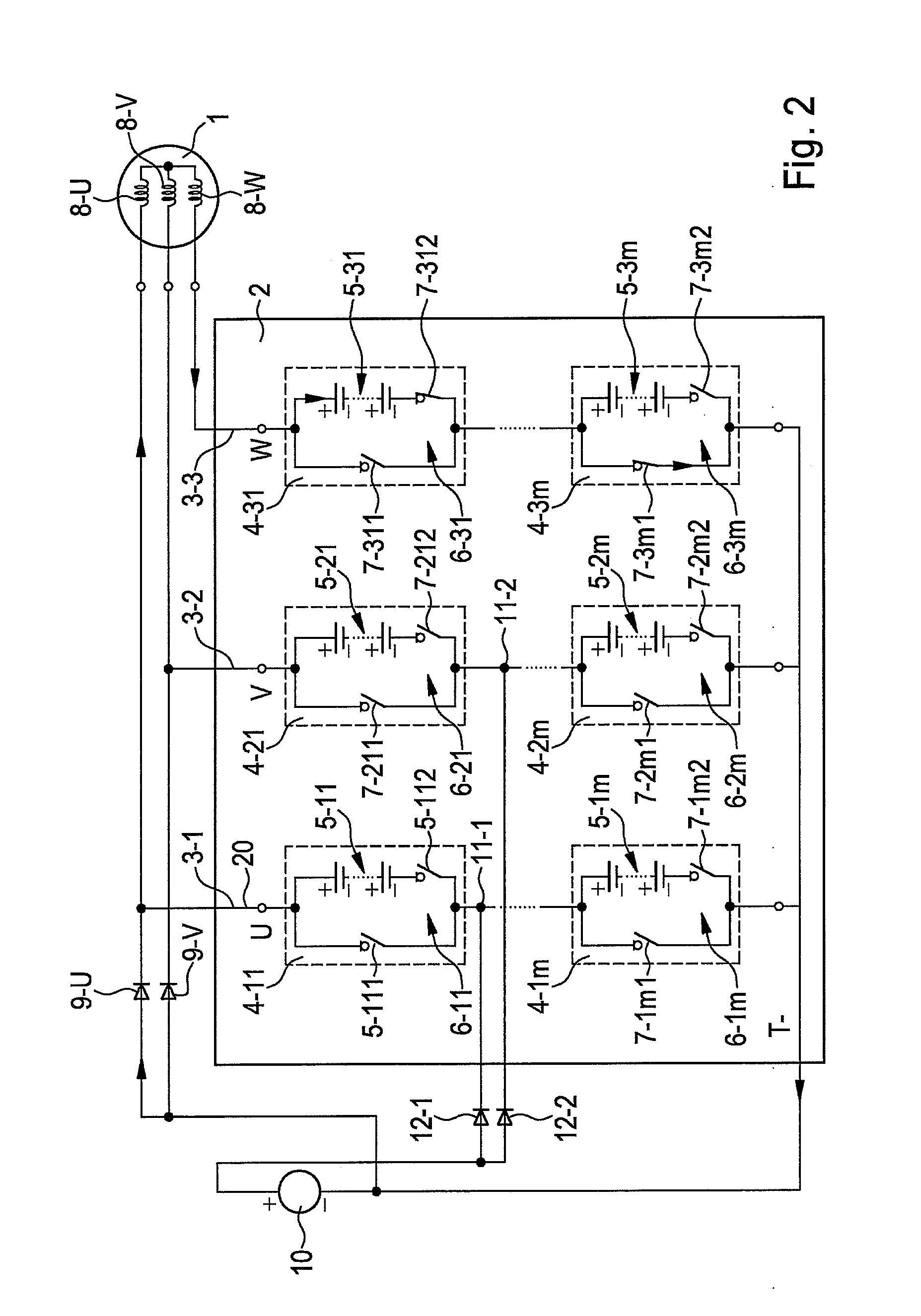

System for Charging an Energy Store, and Method for Operating the Charging System

ActiveUS20130249474A1Good effectResistance valueParallel/serial switchingSequential battery dischargeCouplingControl signal

A system for charging at least one energy reservoir cell in a controllable energy reservoir serving to control / supply electrical energy to an n-phase electrical machine (n≧2). The controllable energy reservoir has n parallel energy supply branches each having at least two series connected energy reservoir modules, each encompassing at least one electrical energy reservoir cell having an associated controllable coupling unit, are connected to a reference bus, and are connected to a respective phase of the machine. As a function of control signals, the coupling units interrupt the respective energy supply branch or bypass the associated reservoir cells or switch the associated reservoir cells into the respective energy supply branch. To charge at least one cell, at least two phases of the machine are connectable via at least one respective free-wheeling diode to a negative pole of a charging device. The reference bus is connectable to the negative pole of the device. Those energy supply branches connected to those phases which are connectable to the negative pole of the device each have a contact point disposed between two energy reservoir modules and is connectable via at least one free-wheeling diode to a positive pole of the device.

Owner:ROBERT BOSCH GMBH

Heating oximeter

ActiveUS20180199872A1High measurement accuracyAccurate measurementSensorsMeasuring/recording heart/pulse rateThermodynamicsLiving body

A heating oximeter includes a heat insulation portion, a heat generation portion including a resistor generating heat by energization, a first temperature detector including a first temperature sensor detecting a temperature of the heat generation portion, an oxygen saturation acquisition assembly including light emitting elements and a light receiving element, and acquiring oxygen saturation in blood optically, and a third temperature detector including a third temperature sensor detecting a temperature of a living body. The heating oximeter is provided by stacking the third temperature detector, the oxygen saturation acquisition assembly, the first temperature detector, the heat generation portion, and the heat insulation portion in this order.

Owner:MURATA MFG CO LTD

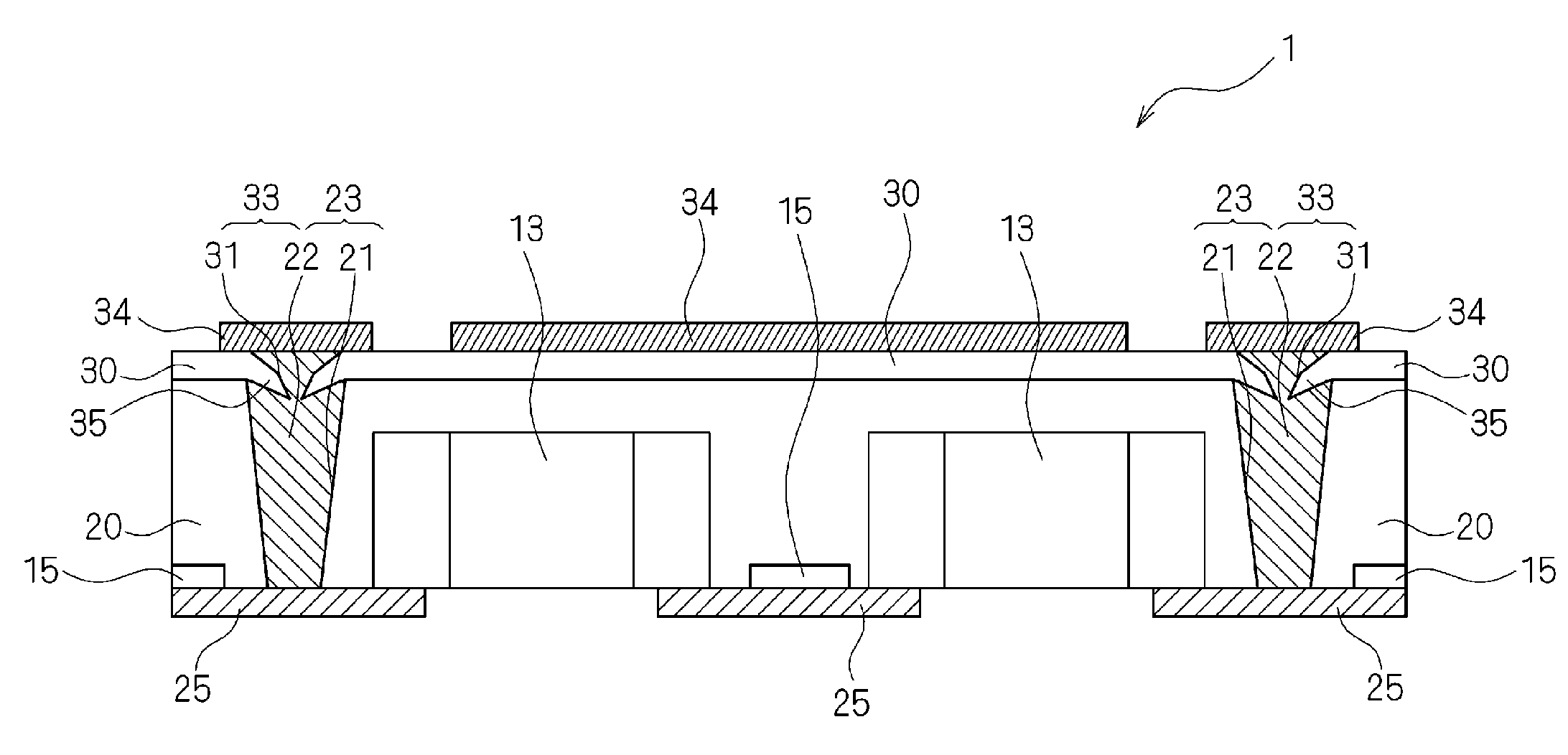

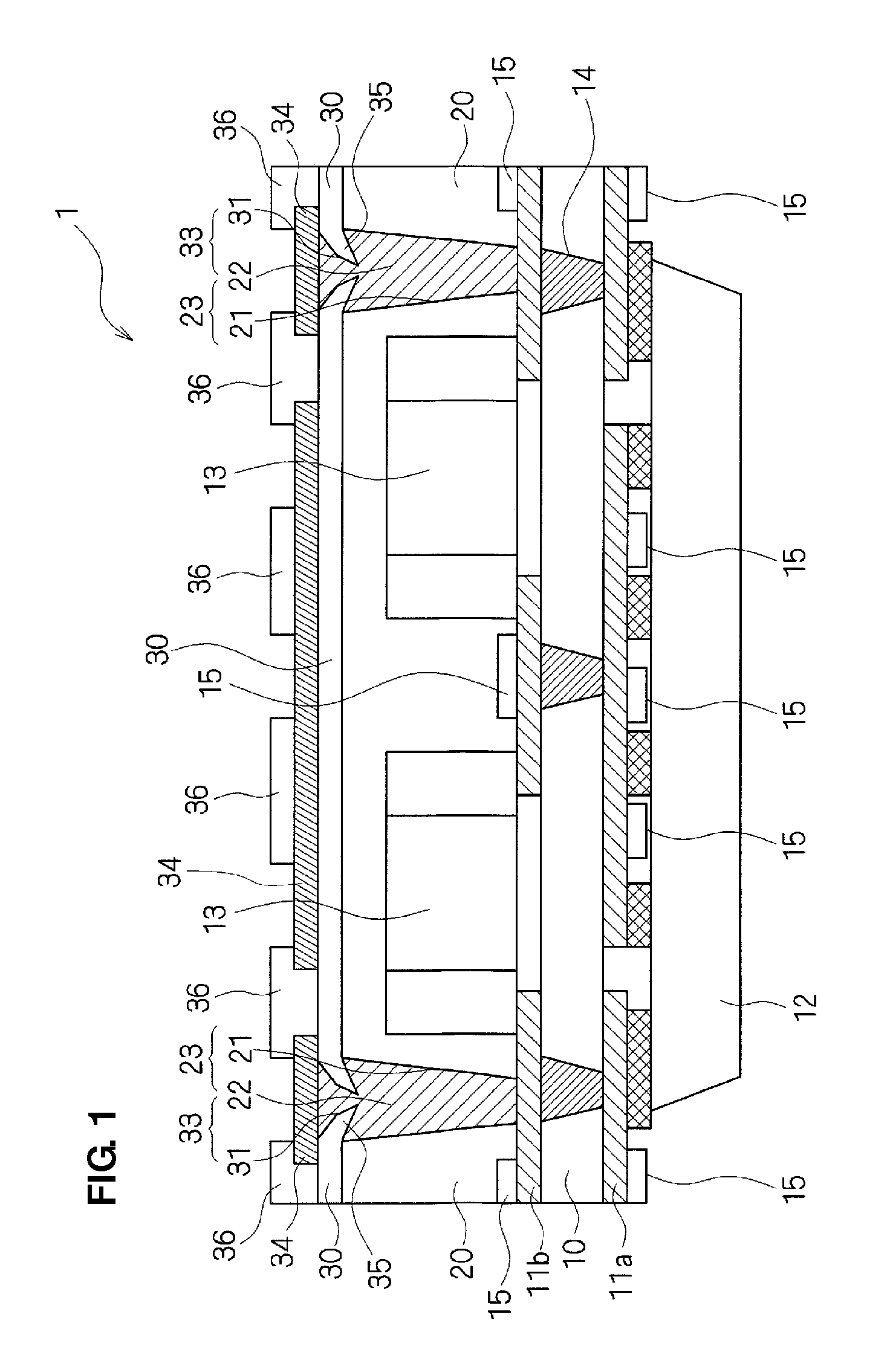

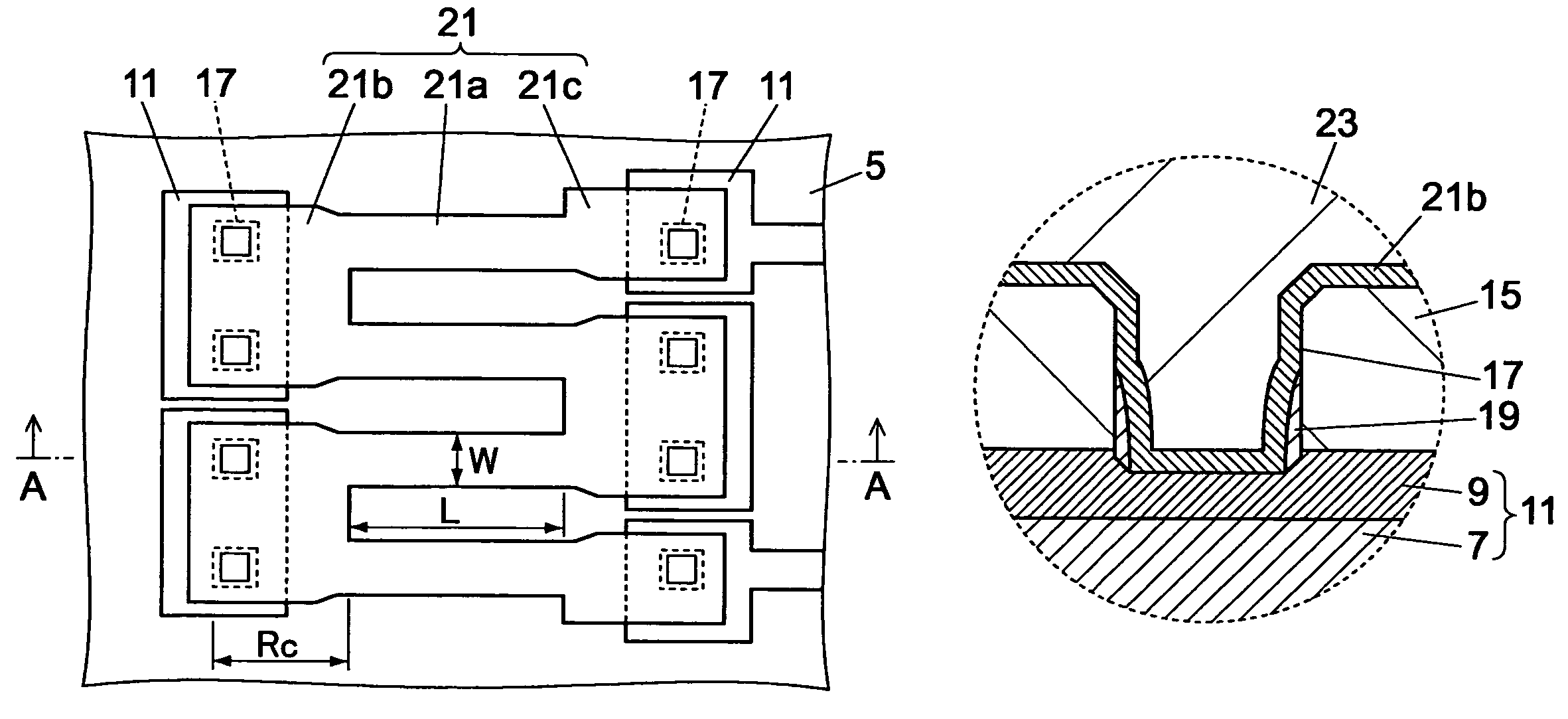

Semiconductor device

InactiveUS7335967B2Resistance valueImprove accuracySemiconductor/solid-state device detailsSolid-state devicesBand shapeSemiconductor

A semiconductor device is provided that includes: a base insulating film; a metal thin-film resistor that is provided on the base insulating film; a lower-layer insulating film that is formed under the base insulating film; and a wiring pattern that is formed on the lower-layer insulating film. In this semiconductor device, the base insulating film is formed on the lower-layer insulating film and the wiring pattern, and connecting holes are formed in the base insulating film located on the wiring patterns. The metal thin-film resistor has at least two belt-like portions and a return portion that continues to the belt-like portions. The belt-like portions are located at a distance from the region on the wiring pattern. The return portion connects at least two belt-like portions in a position at a distance from the region on the wiring pattern. The return portion is formed in a connecting hole via the region on the wiring pattern.

Owner:RICOH KK

Trench-gate type semiconductor device and manufacturing method therefor

ActiveUS9224860B2Avoid contactResistance valueTransistorSemiconductor/solid-state device manufacturingTrench gateDiffusion layer

Owner:MITSUBISHI ELECTRIC CORP

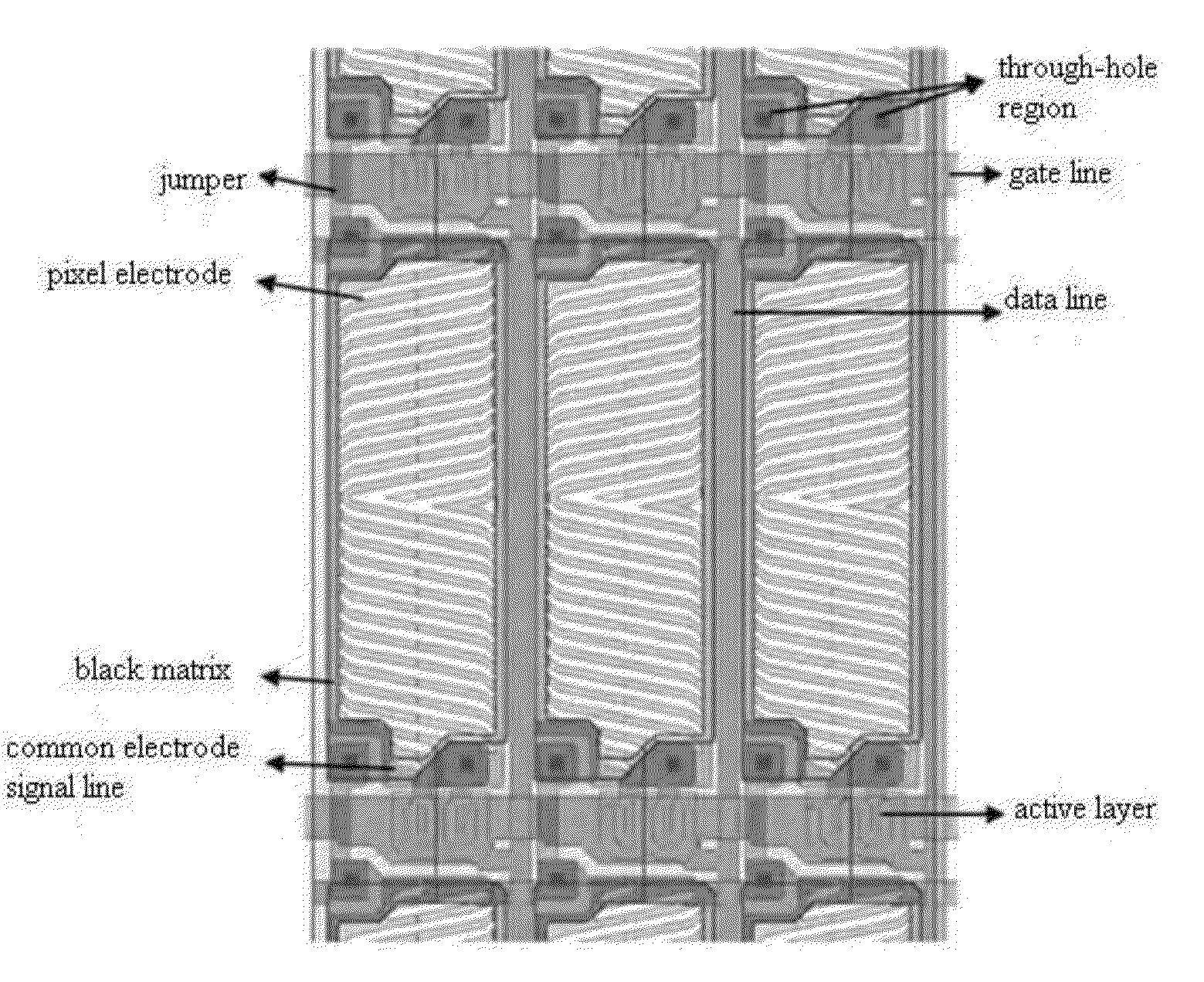

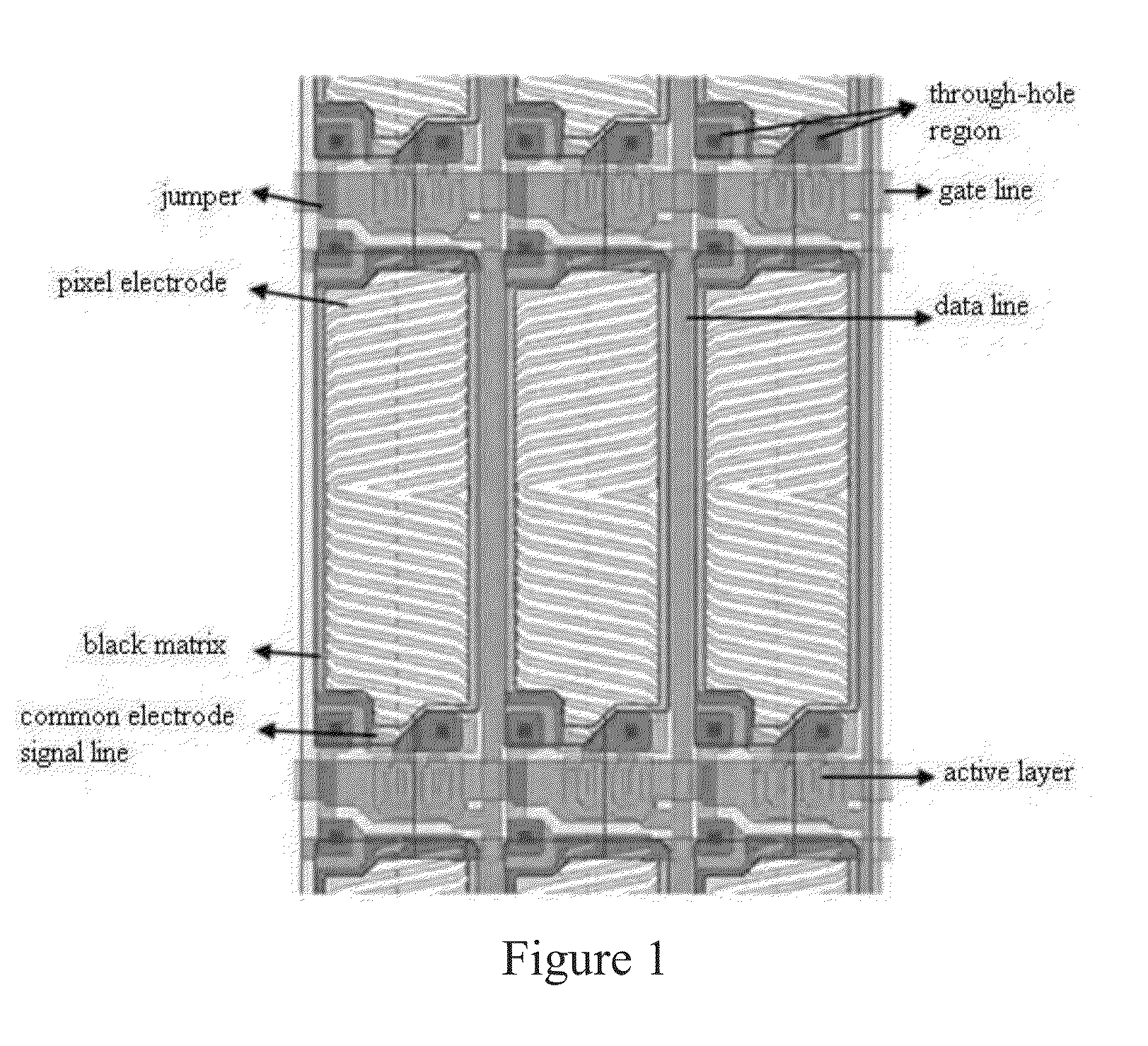

Array substrate and method of manufacturing the same, and liquid crystal display screen

ActiveUS20160148951A1Resistance valueLower the resistance valueSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

Embodiments of the present invention disclose an array substrate and a method of manufacturing the same, and a liquid crystal display screen. The array substrate comprises gate lines, data lines arranged to intersect the gate lines, common electrode signal lines, and a plurality of pixels defined by the gate lines and the data lines, wherein each pixel comprises a drive transistor, a pixel electrode connected with one of a source electrode and a drain electrode of the drive transistor while the other one of the source electrode and the drain electrode of the drive transistor is connected with the respective data line, and a common electrode electrically connected with the respective common electrode signal line, and, the common electrode signal lines and the gate lines are formed in the same layer and extend in the same direction as the gate lines, wherein each pixel further comprises a common electrode connection line formed in the same layer as the respective common electrode signal line and extending in a direction of the respective data line, and the common electrode connection line is electrically connected with the respective common electrode signal line and the respective common electrode. Embodiments of the present invention is made so that the pixel resistance value is reduced, reducing the phenomenon of partial green picture in the liquid crystal display screen as a whole.

Owner:BOE TECH GRP CO LTD +1

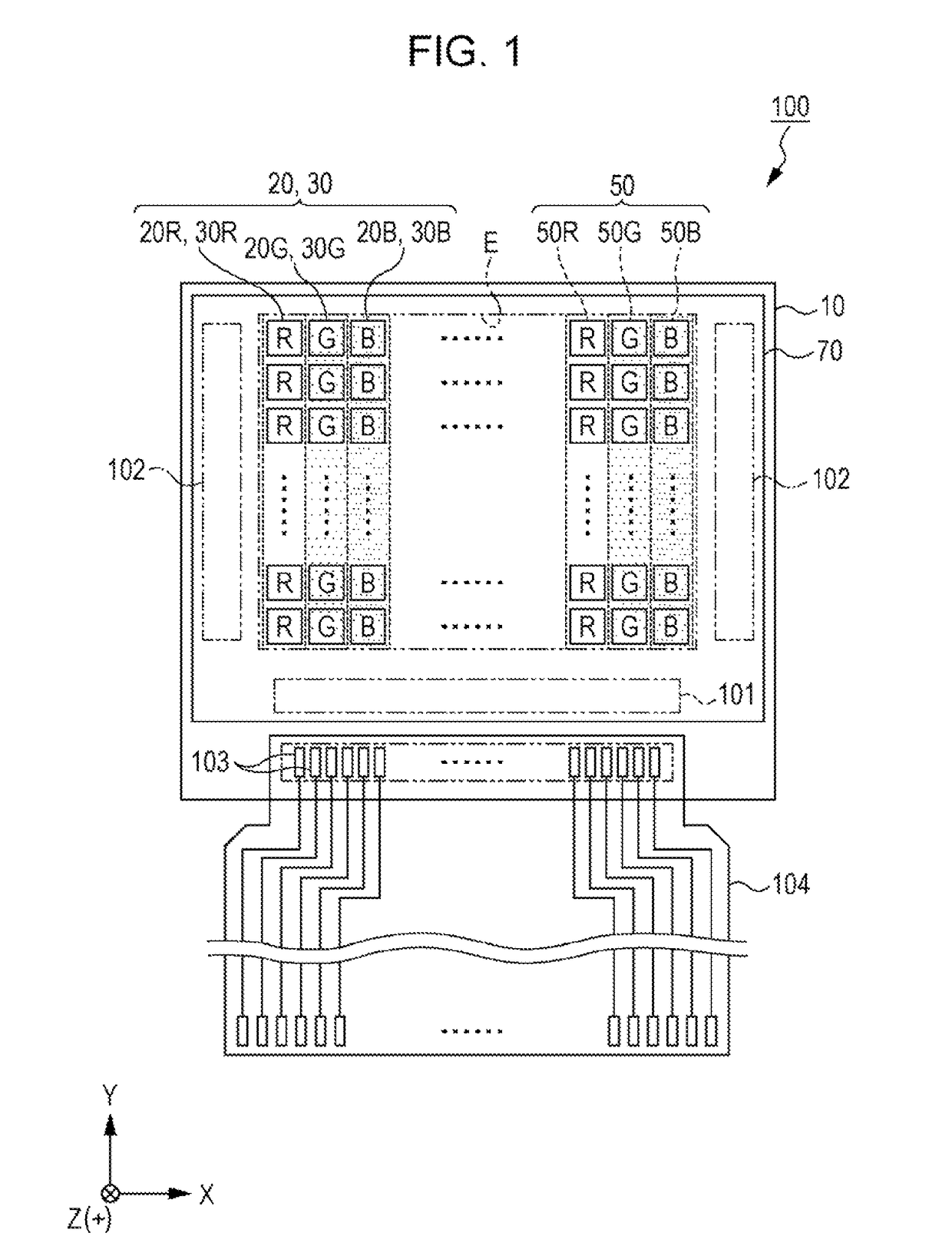

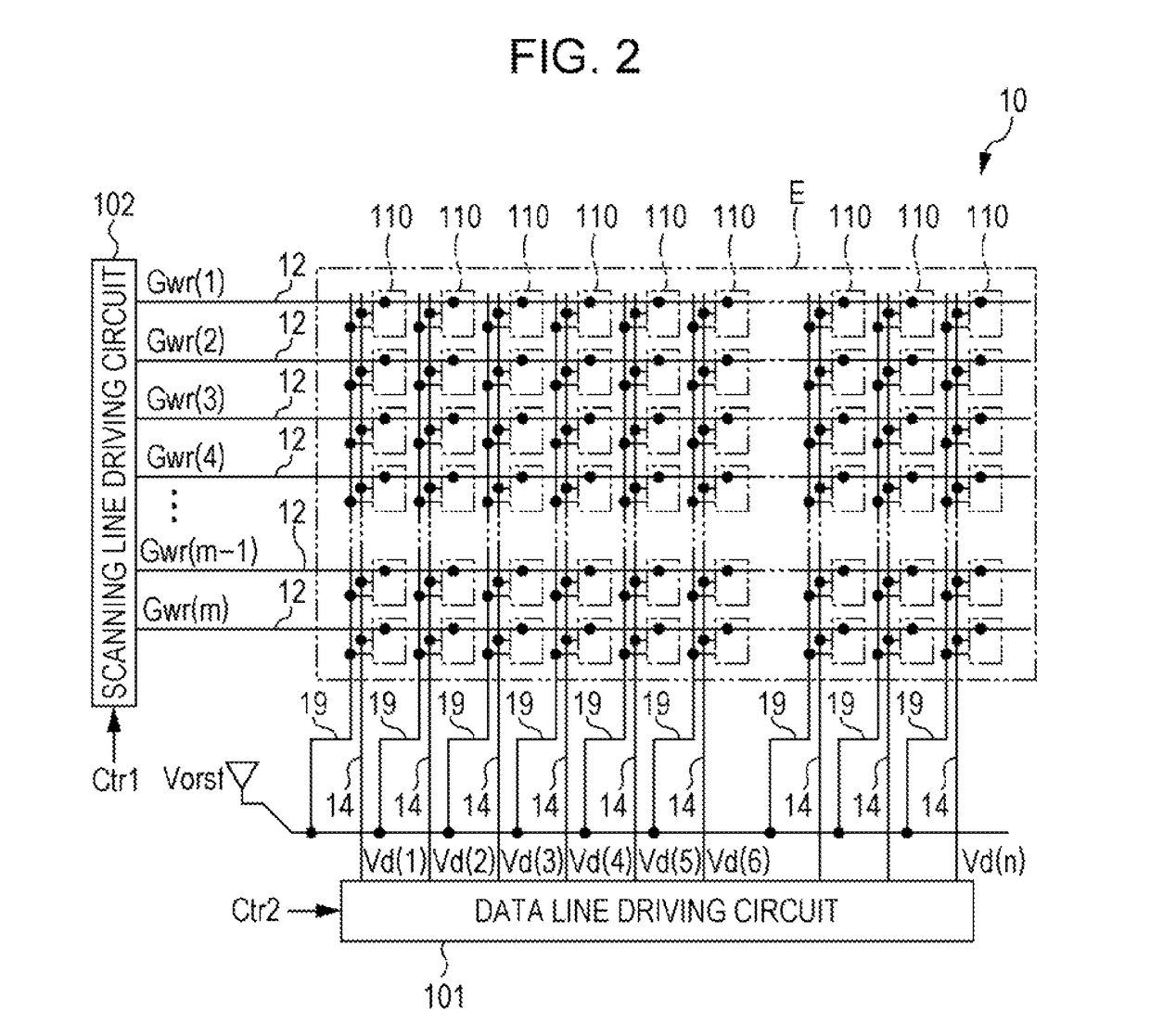

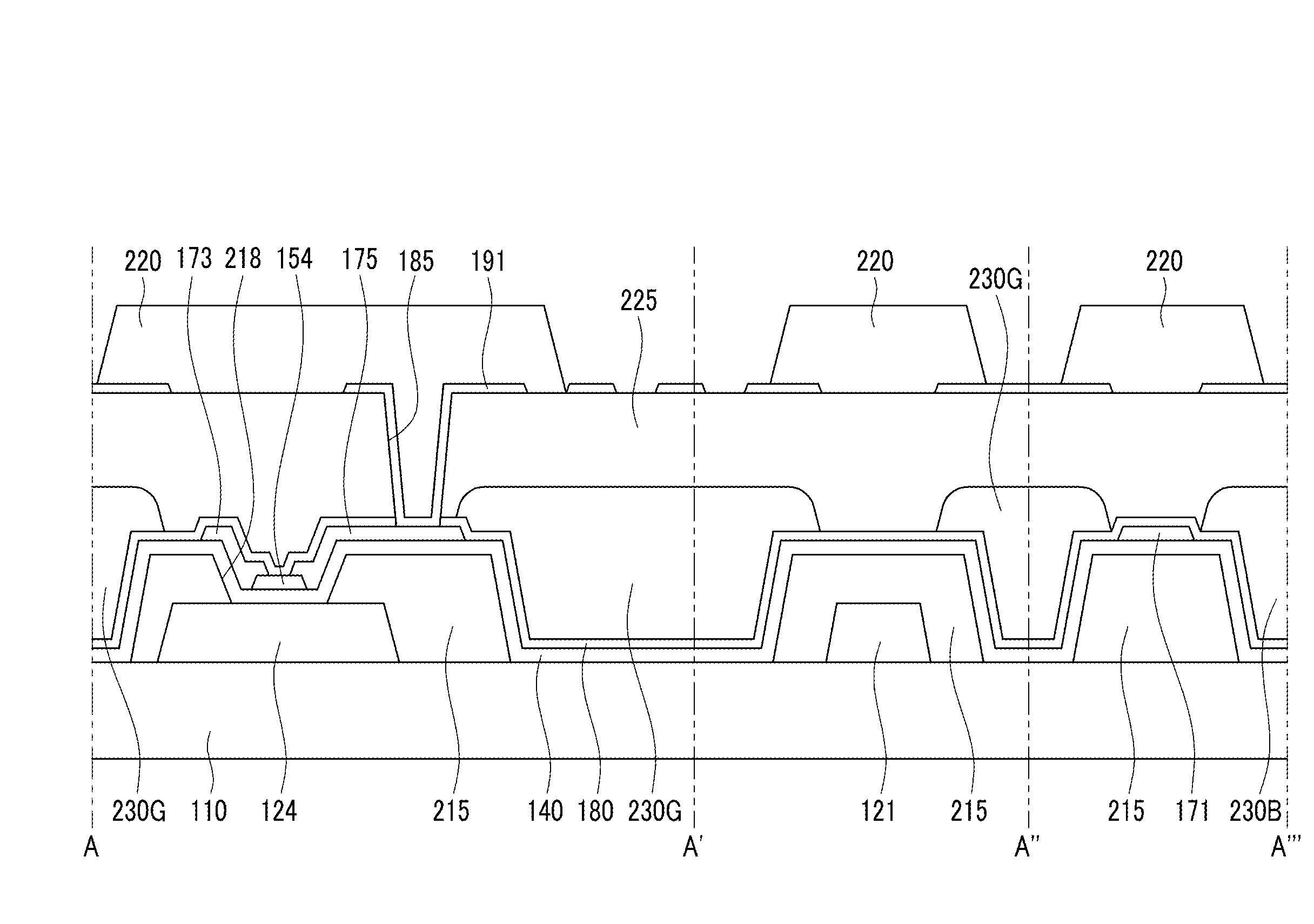

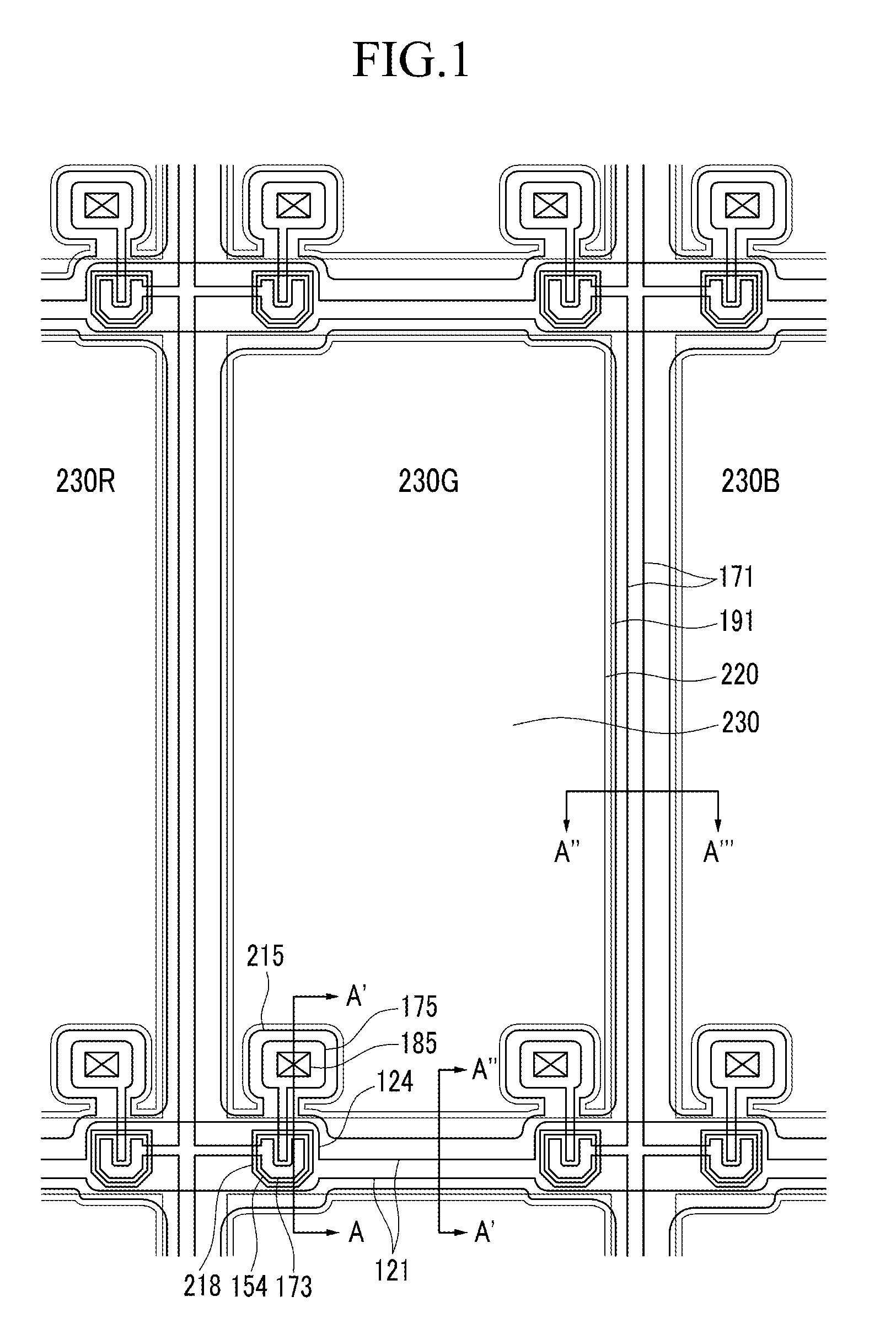

Electro-optical apparatus, manufacturing method thereof, and electronic device

ActiveUS9673416B2Resistance valuePrevent reflectivity from decreasingSolid-state devicesSemiconductor/solid-state device manufacturingElectricityEngineering

There is provided an electro-optical apparatus including an element substrate that includes a display region in which a plurality of light-emitting elements are arranged, and a peripheral region in which a terminal is disposed. The light-emitting element has a structure in which a reflective electrode, an optical adjustment layer, a first electrode, a light-emitting layer, and a second electrode are laminated, and the first electrode is electrically connected to a contact electrode. The terminal has a structure in which a first terminal layer that is formed by a first conductive film which is the same as the reflective electrode, a second terminal layer that is formed by a second conductive film which is the same as the contact electrode, and a third terminal layer that is formed by a third conductive film which is the same as the first electrode are laminated.

Owner:LUMITEK DISPLAY TECH LTD

Thin film transistor array panel and method of manufacturing the same

InactiveUS8218110B2More surelyResistance valueInking apparatusSolid-state devicesEngineeringSignal delay

Owner:SAMSUNG DISPLAY CO LTD

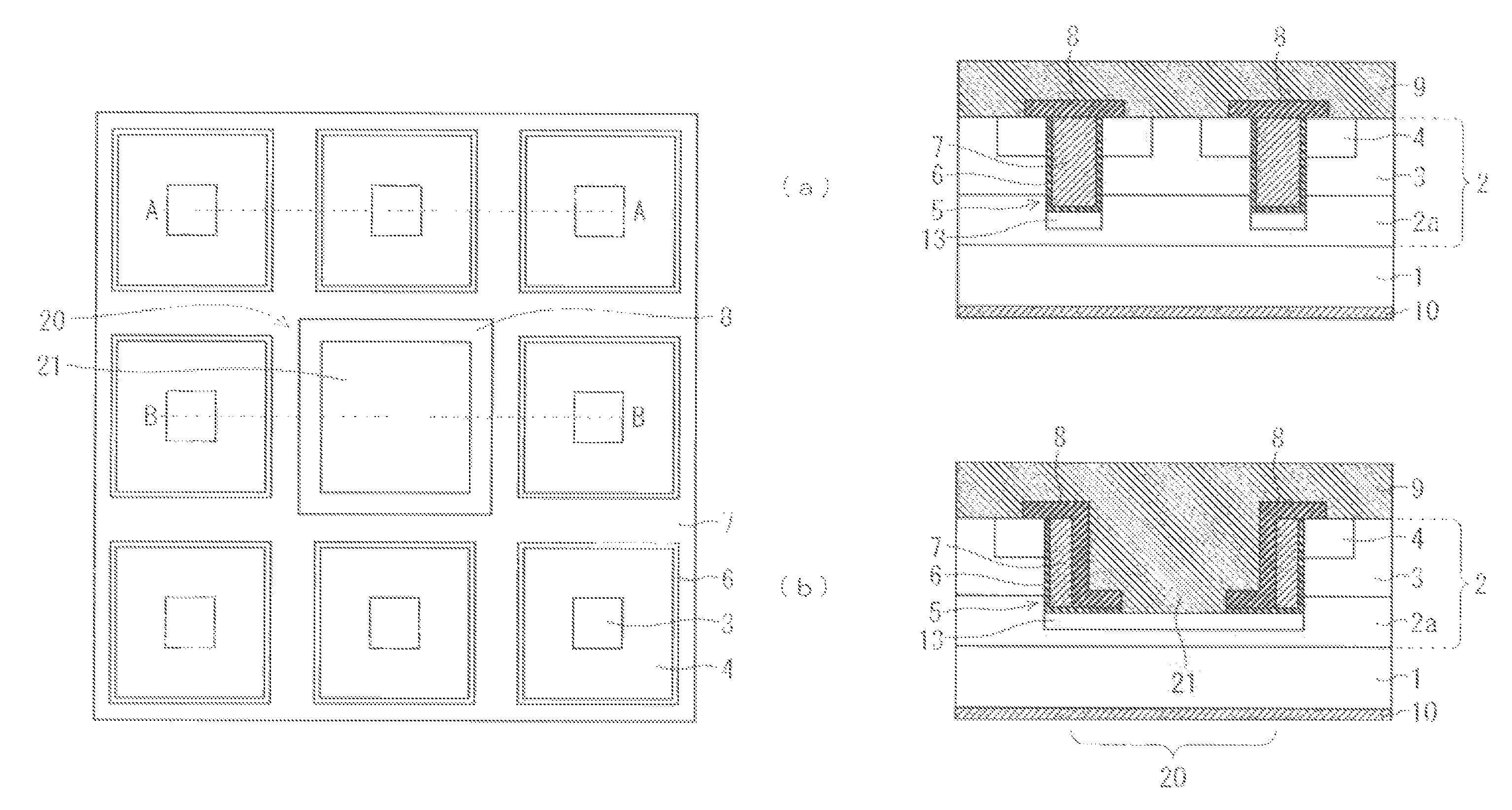

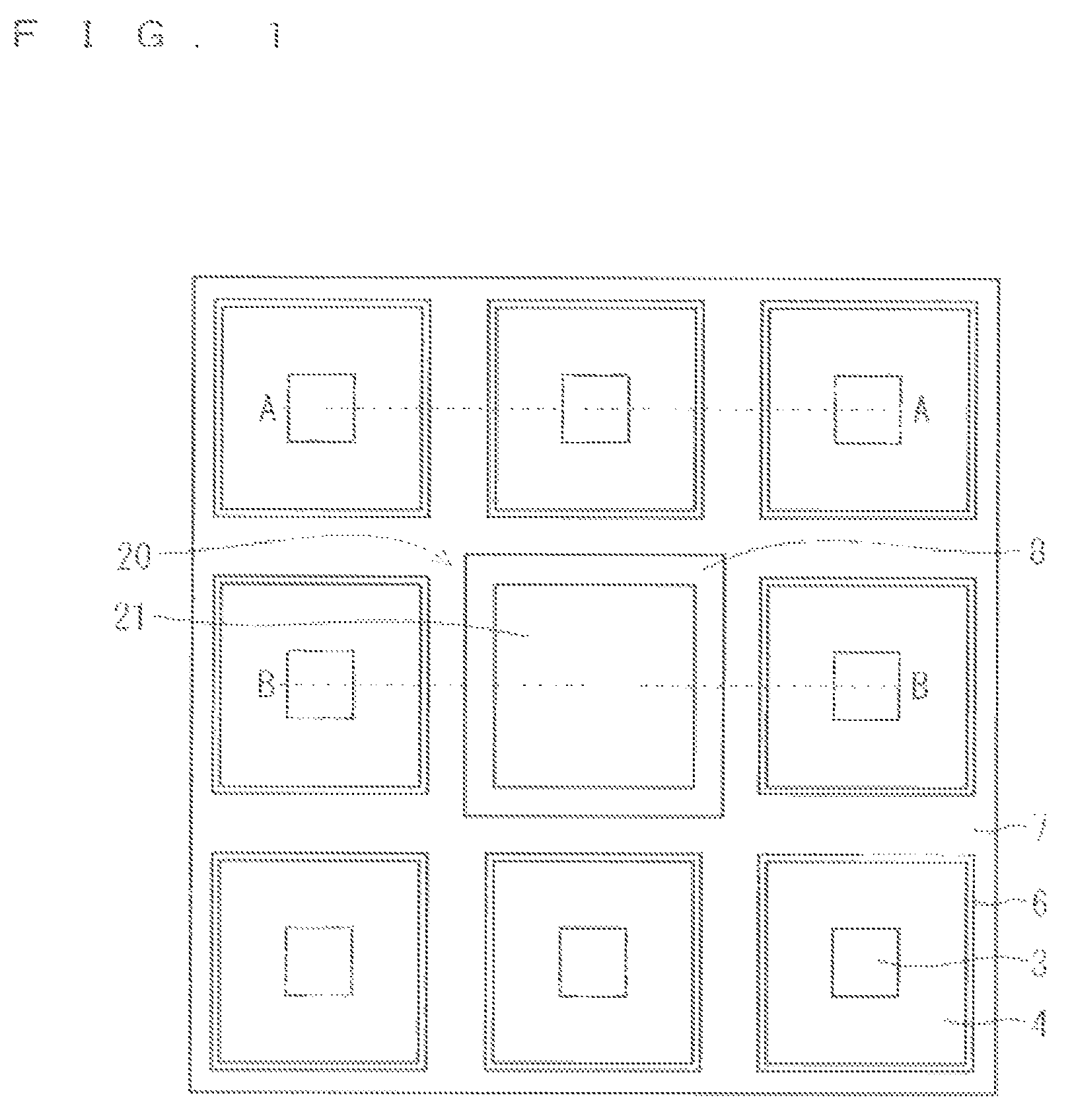

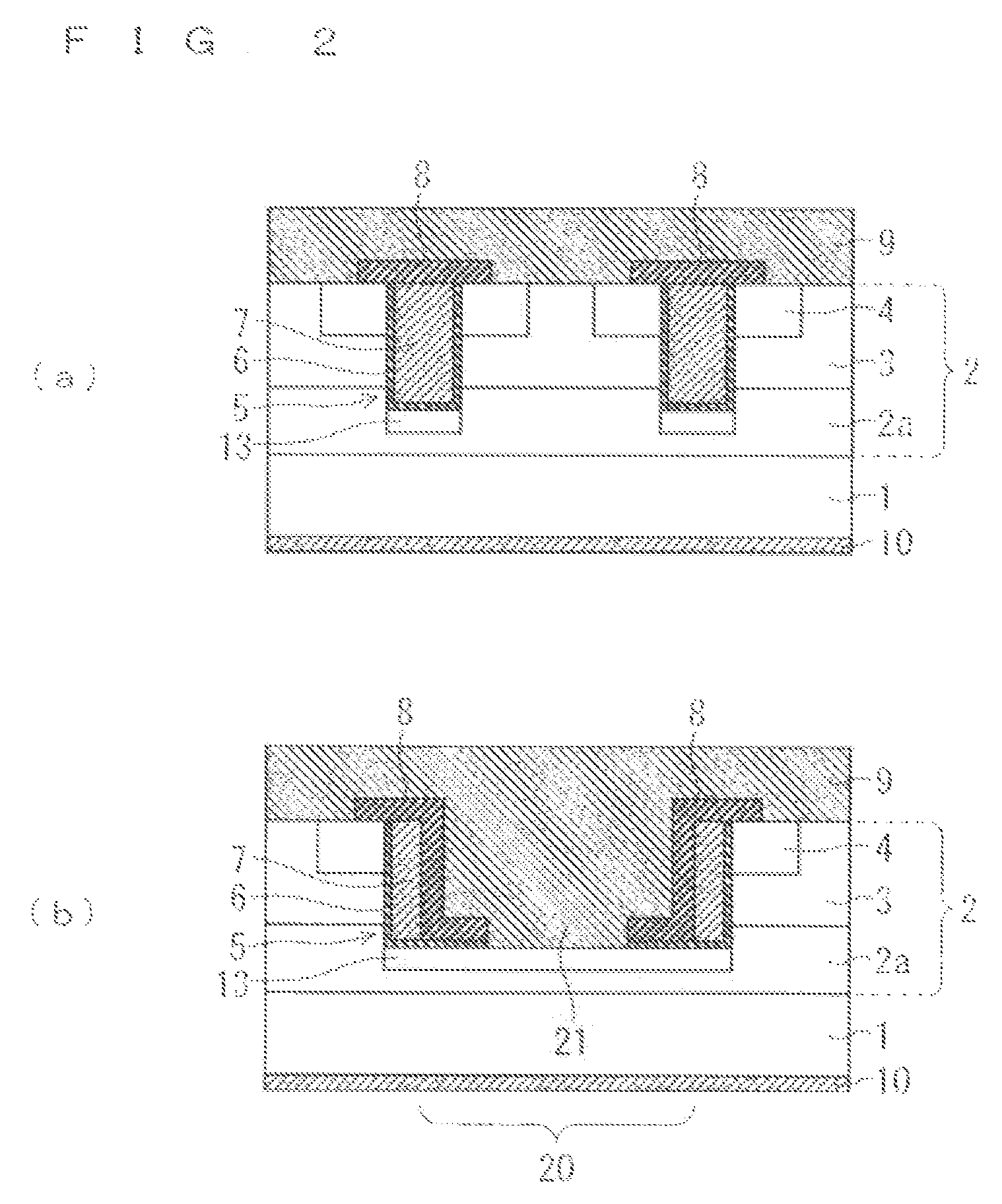

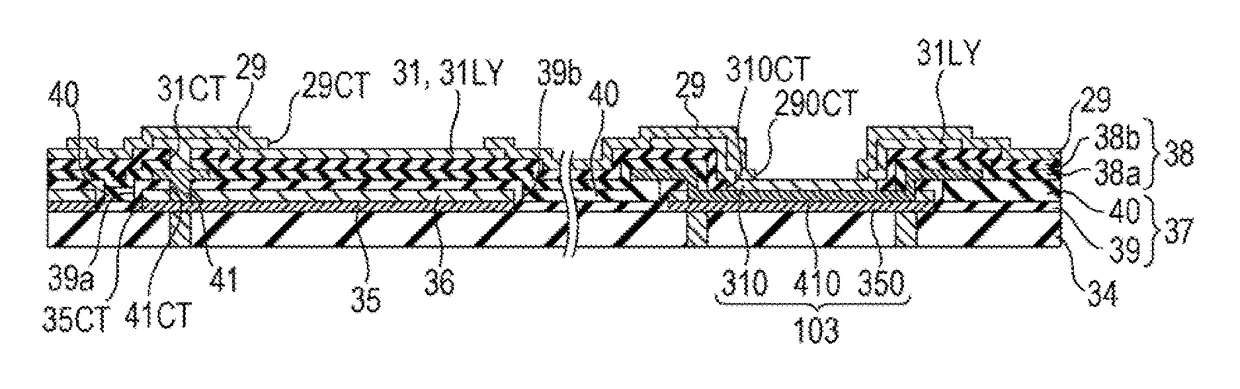

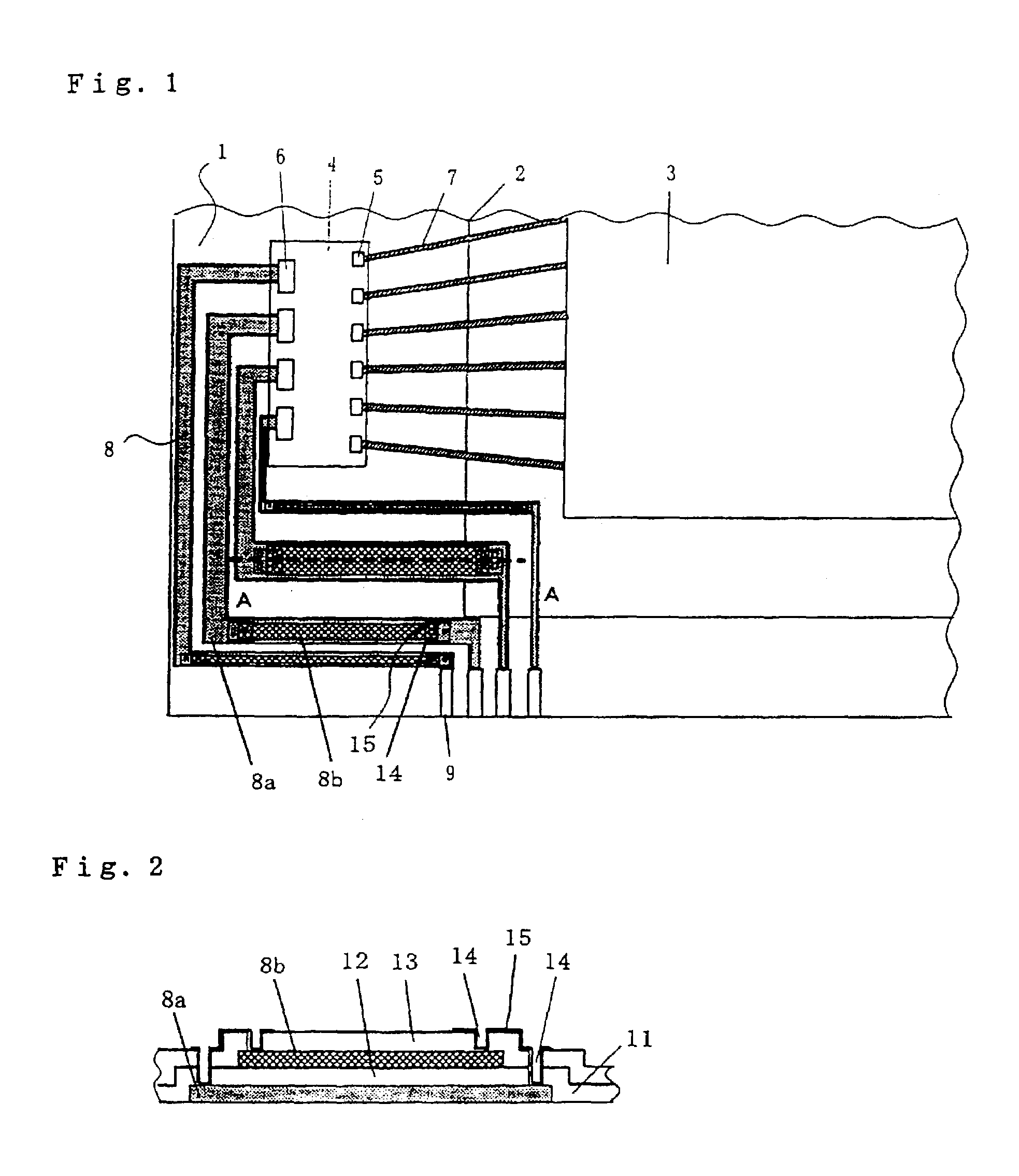

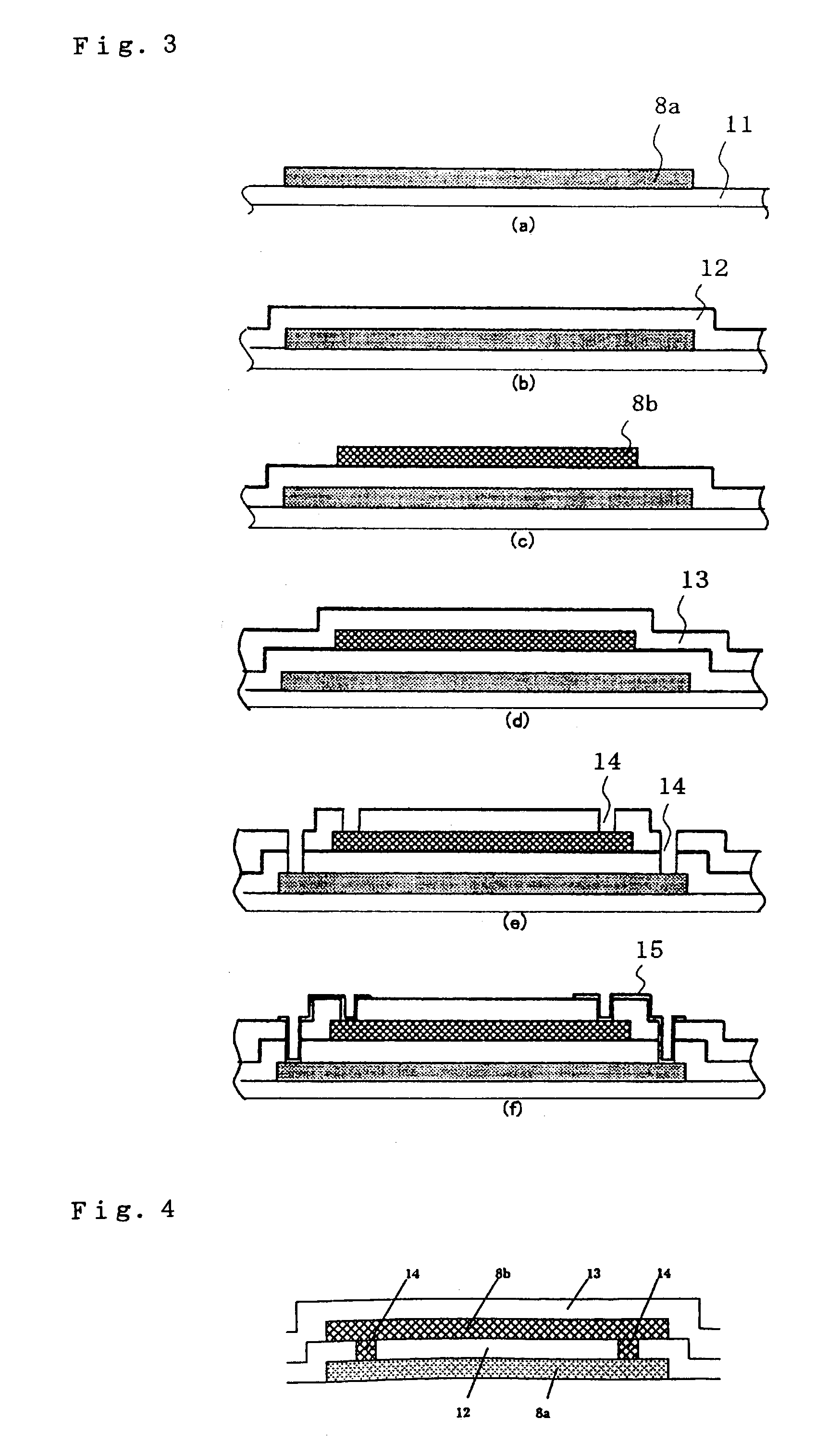

Image display having internal wiring with multi-layer structure and manufacturing method thereof having particular wiring connection

InactiveUS7113246B2Resistance valueQuality improvementSemiconductor/solid-state device detailsSolid-state devicesElectricityDisplay device

An image display in which a resistance value of internal wiring for inputting a signal and a power supply to a driving IC COG-packaged on an insulating substrate composing a display panel is reduced without enlarging external size of the display panel, and a method of manufacturing the image display. In internal wiring 8 for inputting a signal and a power supply to a driving IC 4 COG-packaged on a first insulating substrate 1, first layer internal wiring 8a is composed of a first conductive film forming a scanning line, etc., and second layer internal wiring 8b is composed of a second conductive film forming a signal line, etc. Connecting wiring 15 for connecting the first layer internal wiring 8a and the second layer internal wiring 8b is formed simultaneously with formation of a display electrode, and the internal wiring 8 is formed into a multi-layer structure connected electrically parallel.

Owner:MITSUBISHI ELECTRIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com