Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

165results about How to "Reliable alignment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

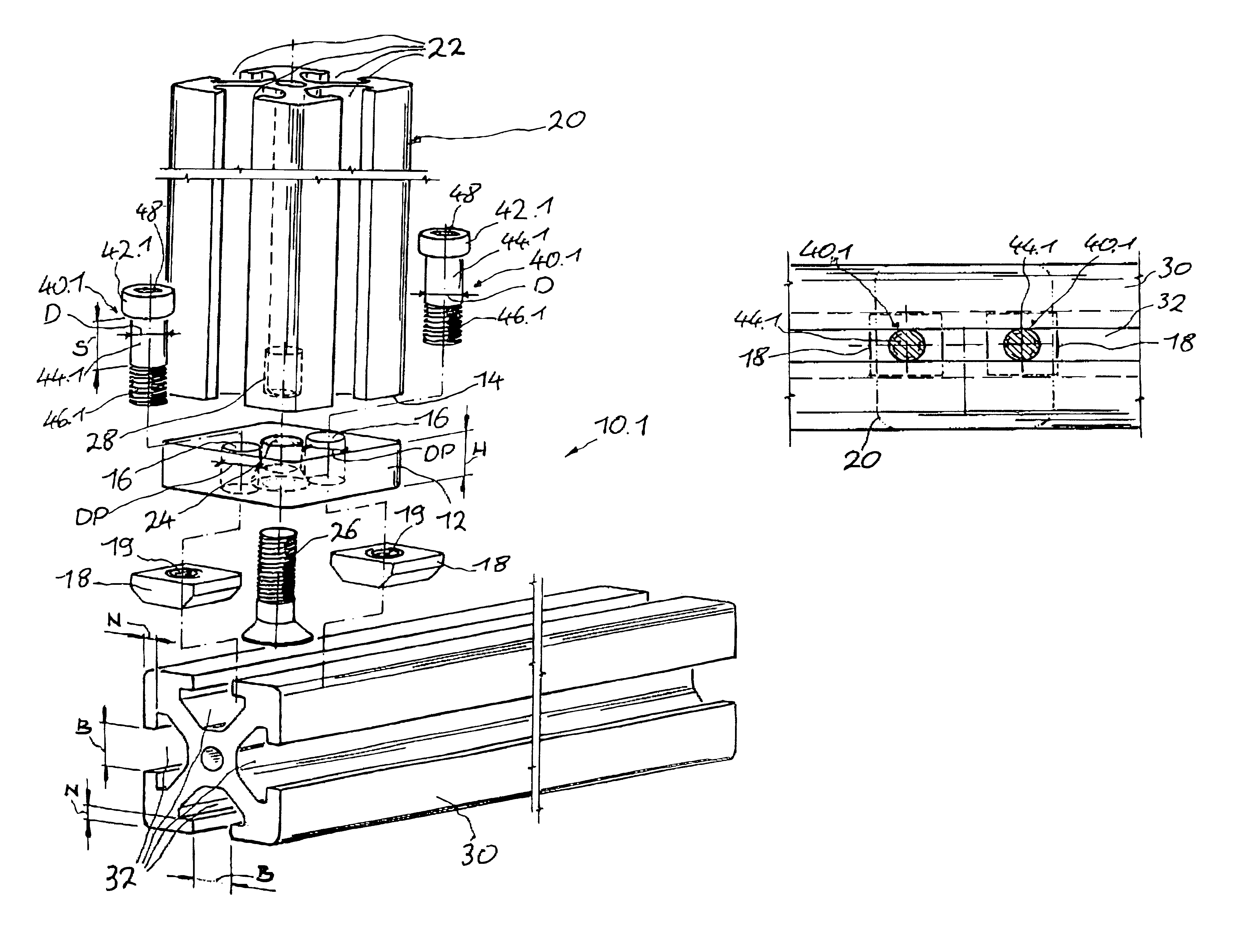

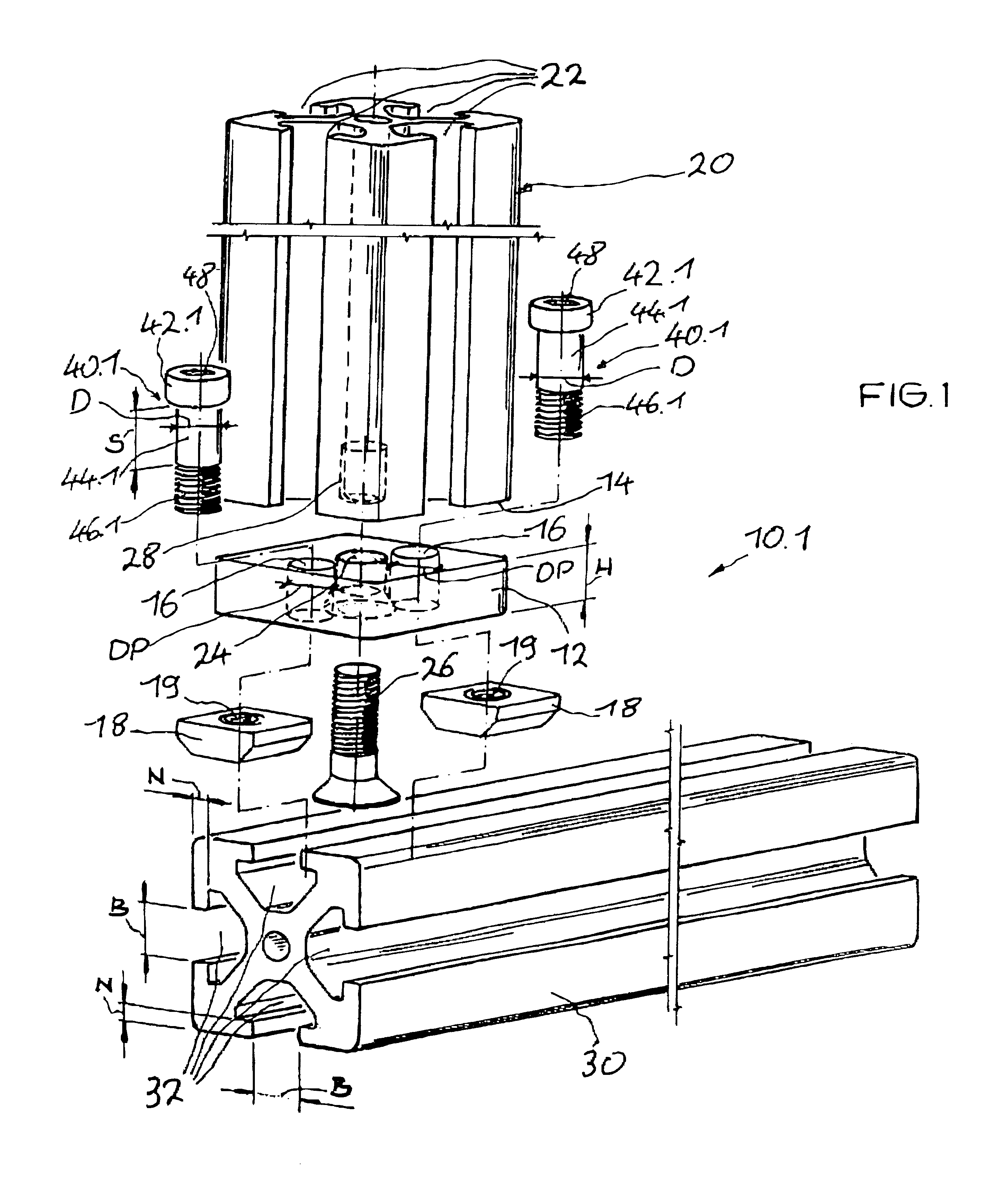

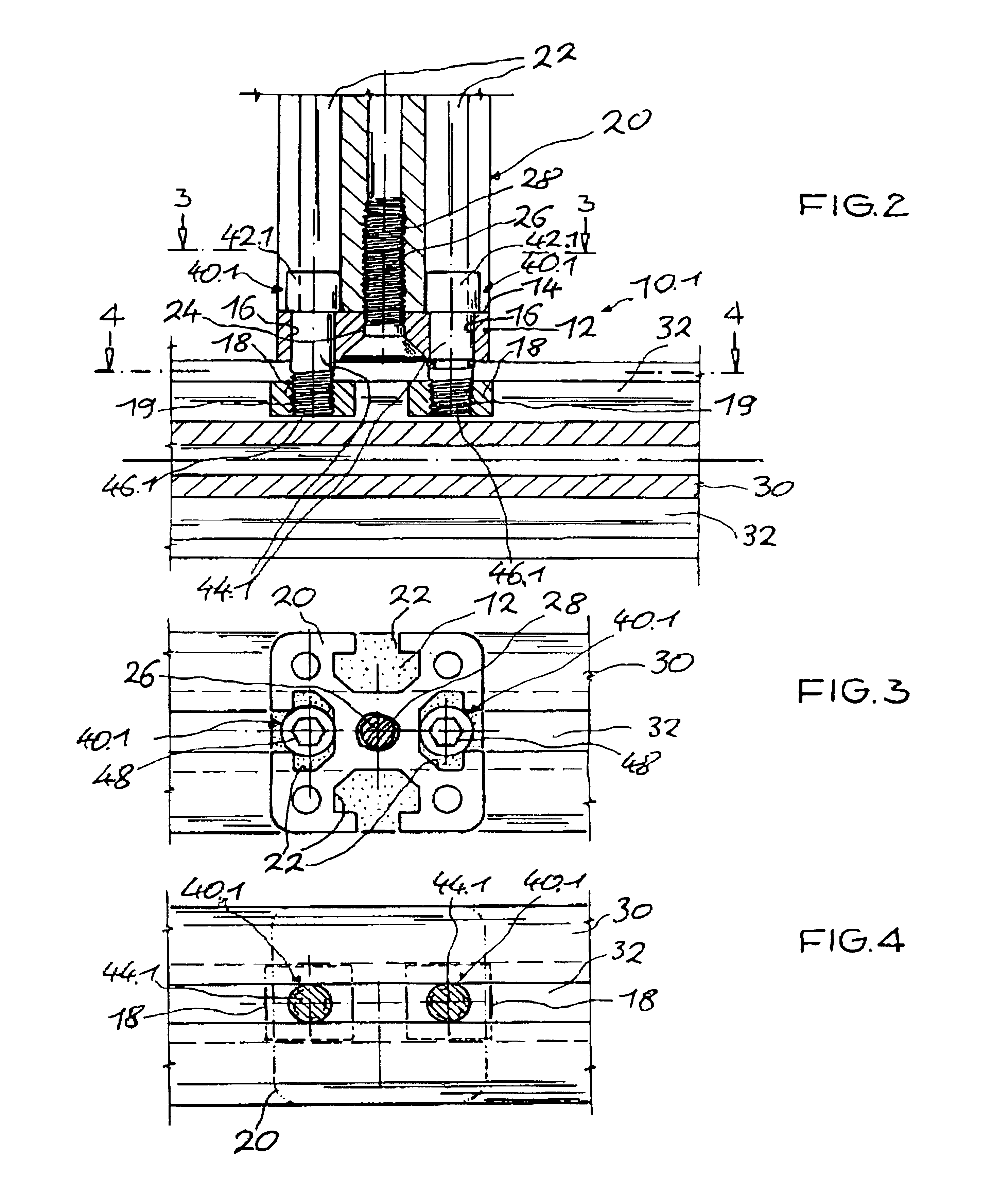

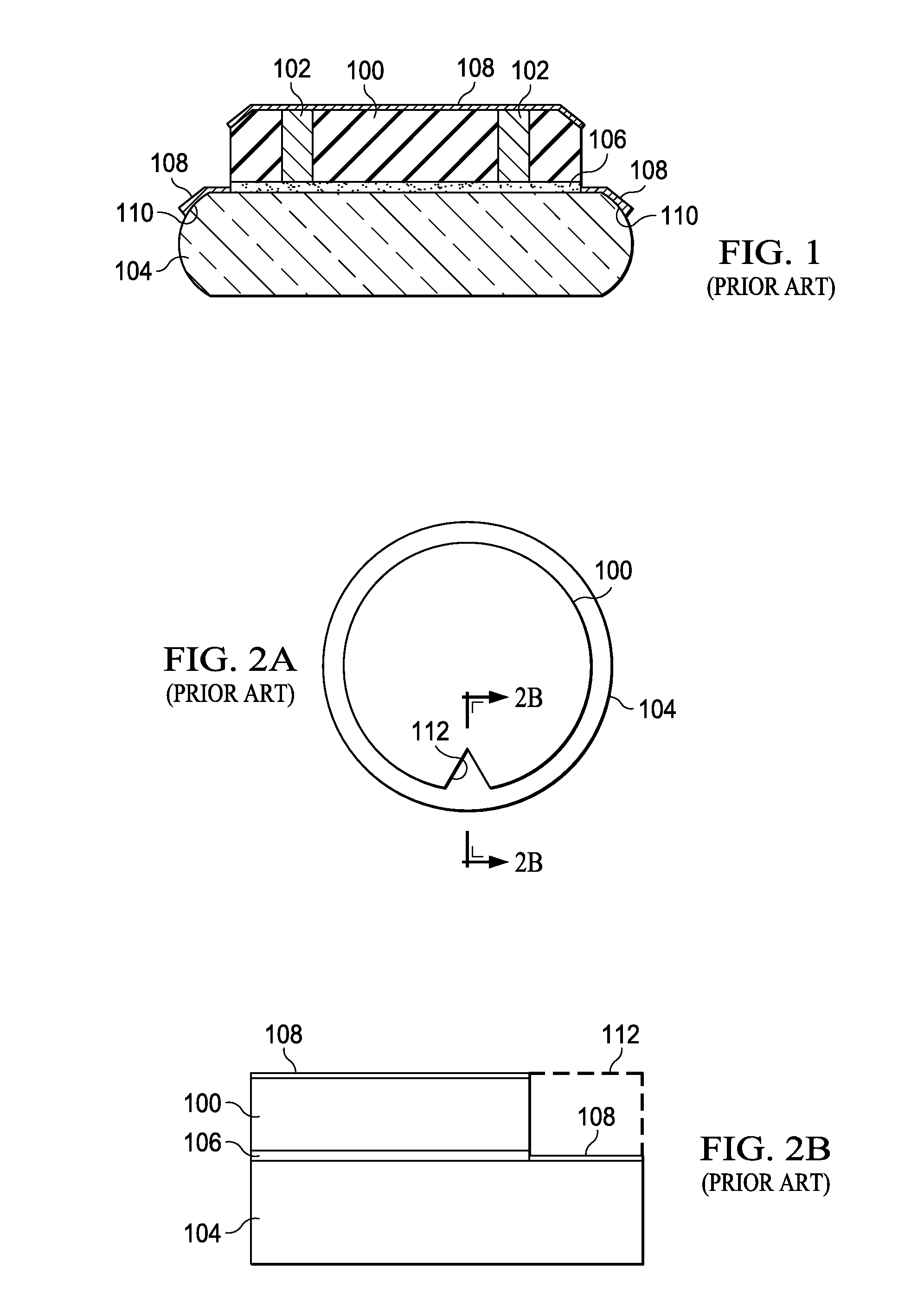

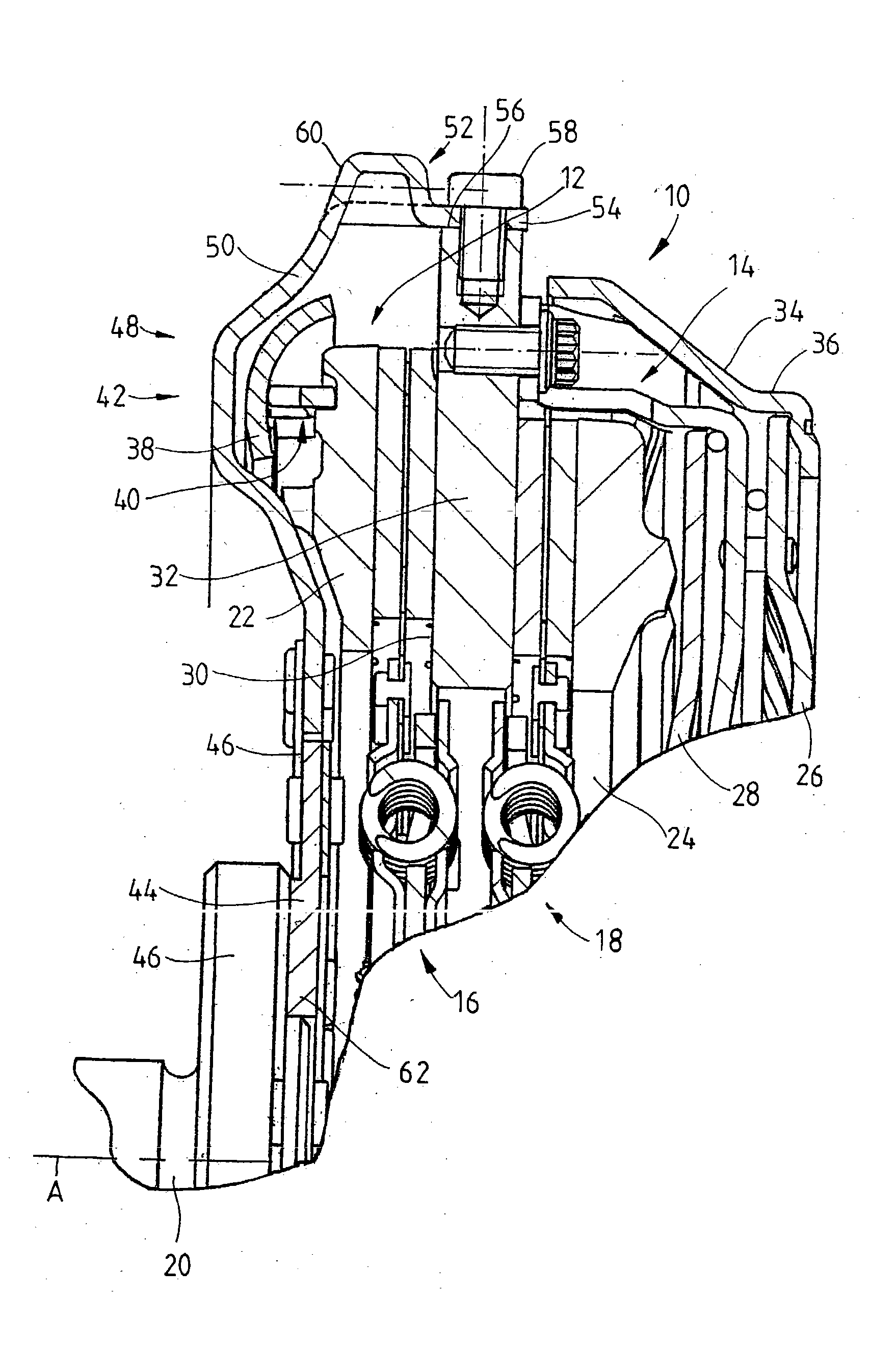

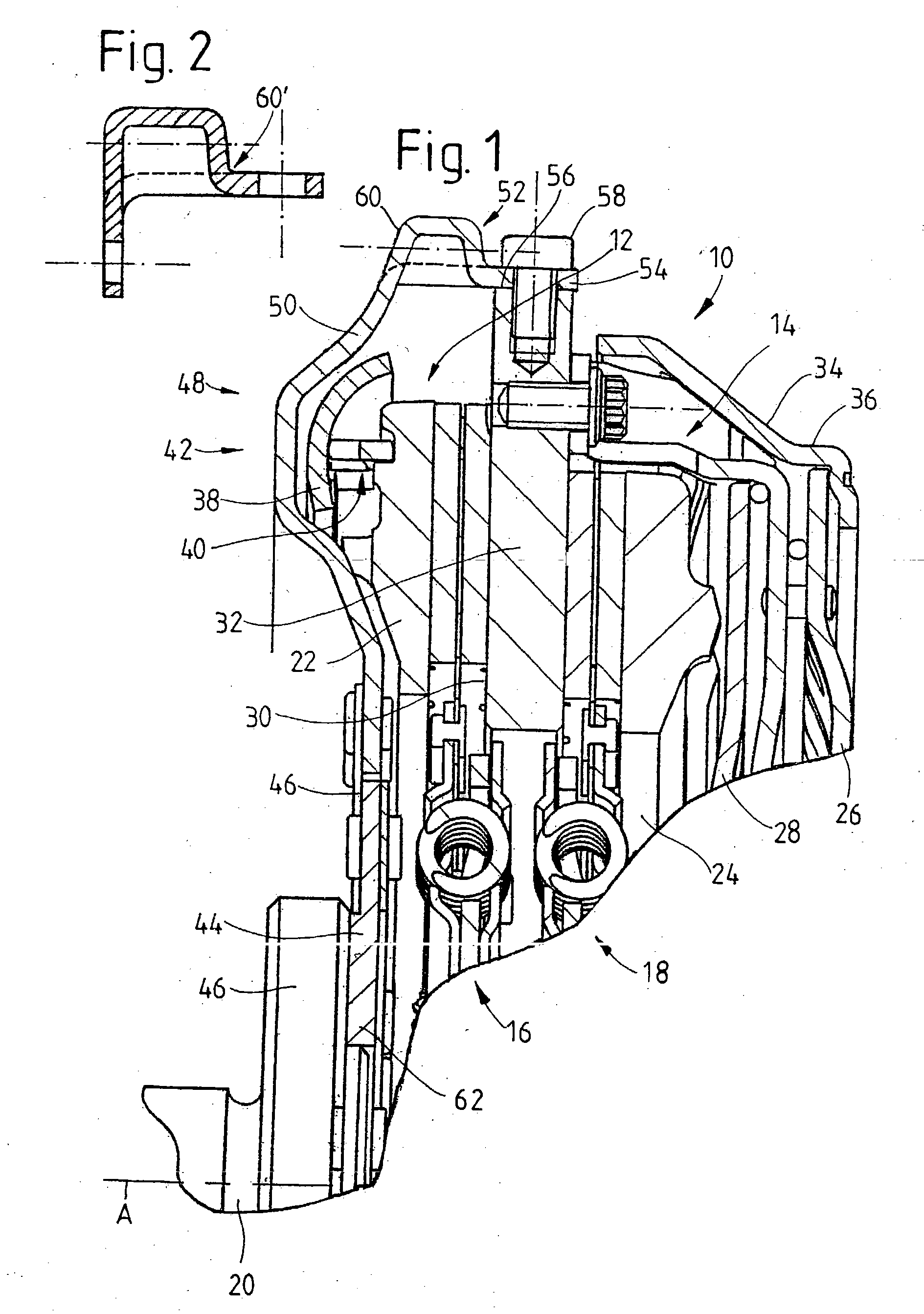

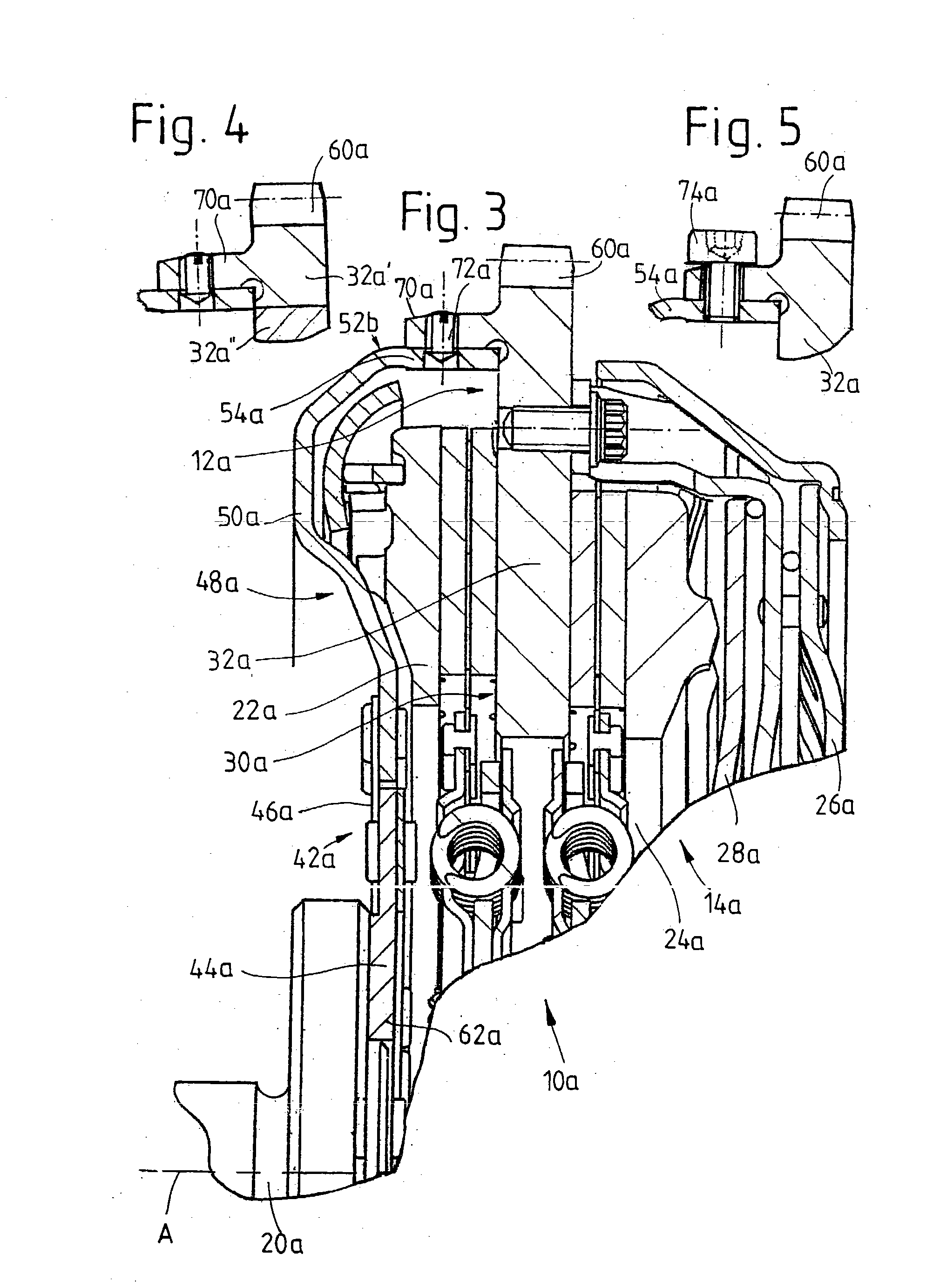

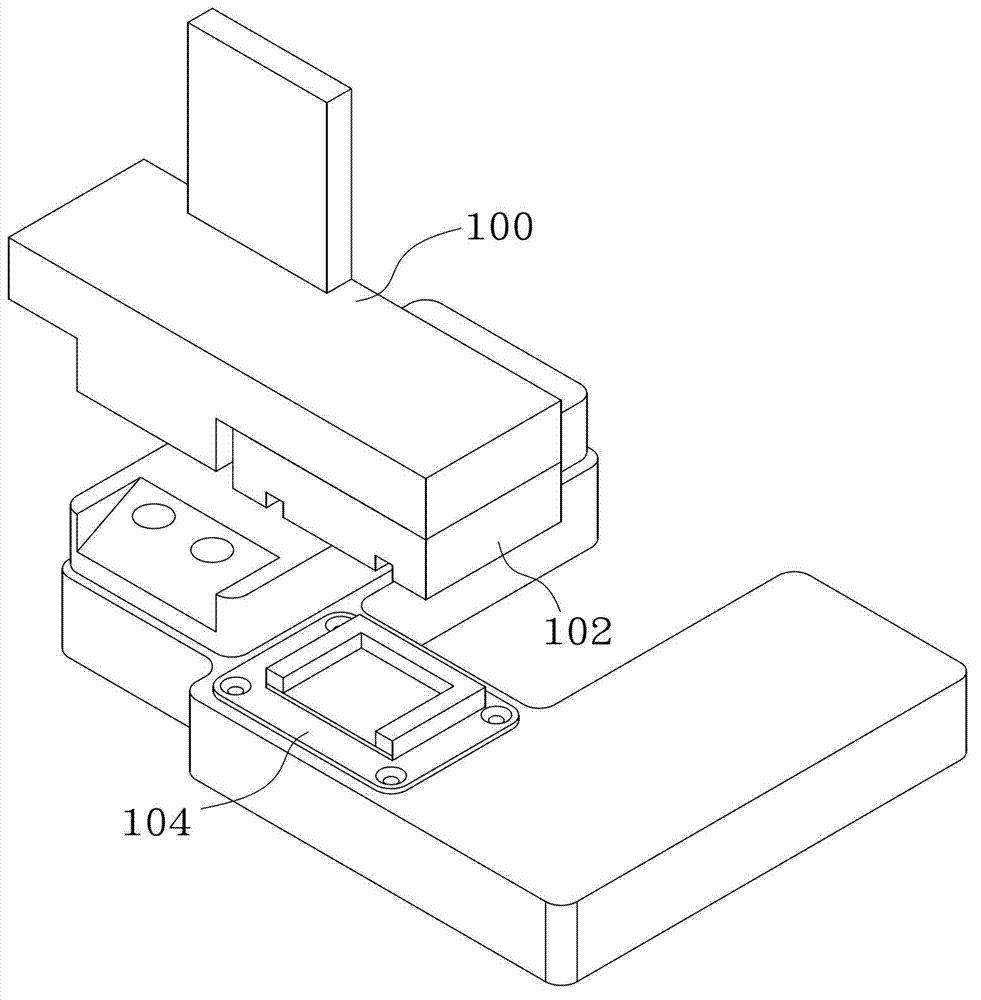

Connecting device for profiled bars with grooves

A connecting device for connecting at least two profiled bars that are essentially perpendicular to one another and have grooves, in conjunction with sliding blocks, one plate connector unit is fastened to the end of a first profiled bar and anchored in a groove in the second profiled bar by way of screw units they extend in recesses in the plate connector unit. The geometry of the screw head of the screw unit is configured such that it centers the screw unit within the groove in the first profiled bar and the engages with a centering effect in the groove in the second profiled bar.

Owner:FMS FORDER UND MONTAGE SYST SCHMALZHOFER

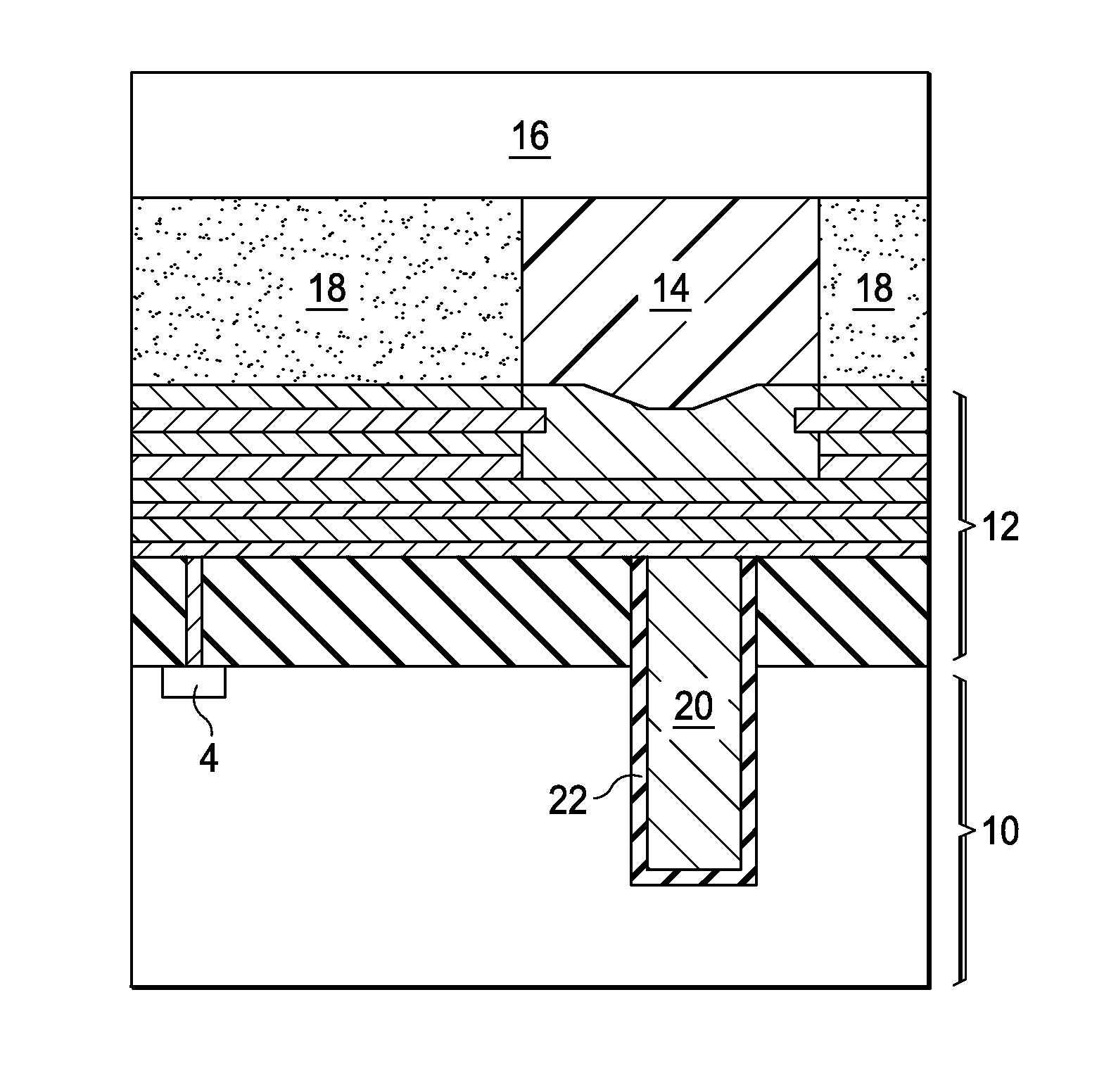

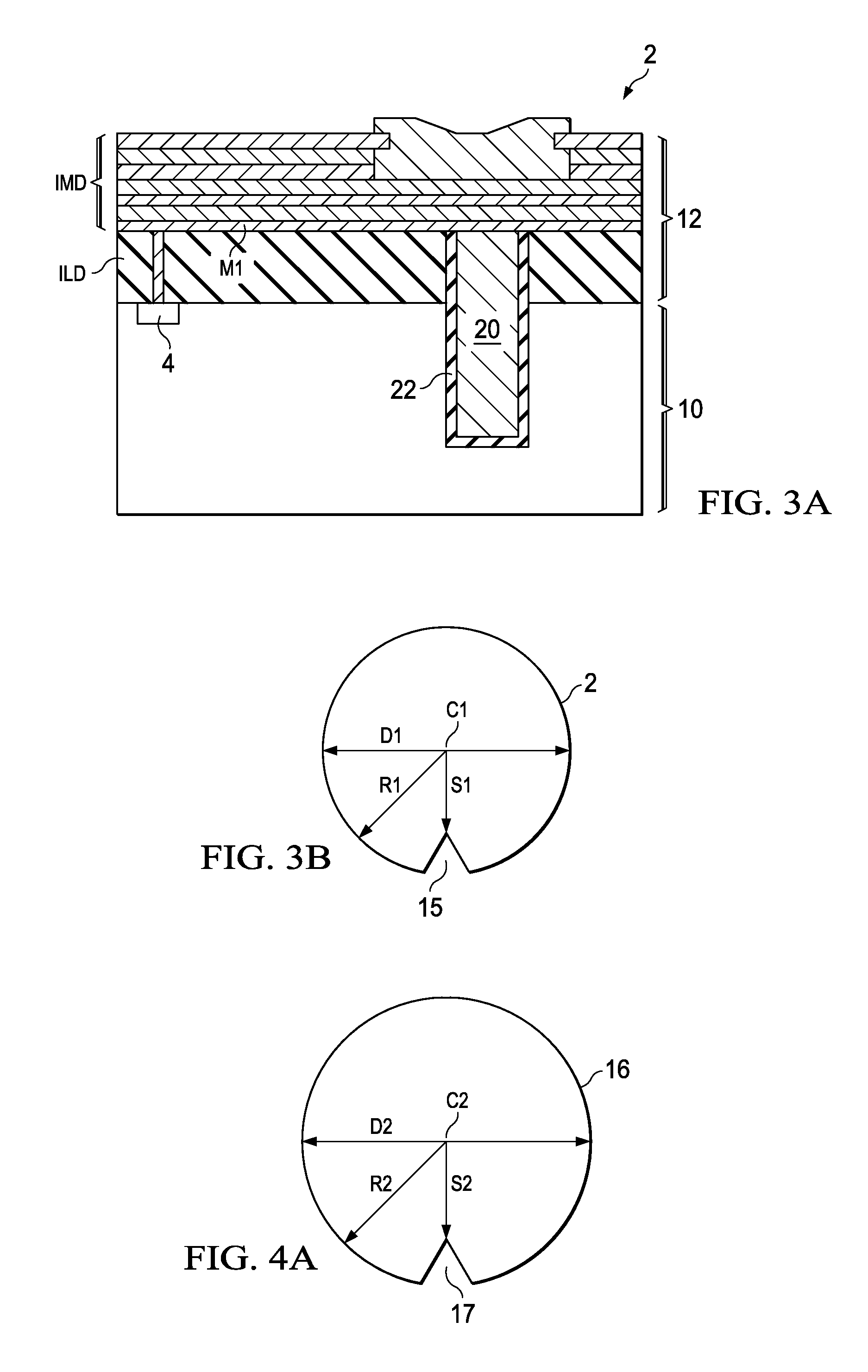

Formation of TSV Backside Interconnects by Modifying Carrier Wafers

ActiveUS20100330798A1Reliable alignmentReduce Particle GenerationSemiconductor/solid-state device detailsSolid-state devicesWaferingSemiconductor

An integrated circuit structure includes a semiconductor wafer, which includes a first notch extending from an edge of the semiconductor wafer into the semiconductor wafer. A carrier wafer is mounted onto the semiconductor wafer. The carrier wafer has a second notch overlapping at least a portion of the first notch. A side of the carrier wafer facing the semiconductor wafer forms a sharp angle with an edge of the carrier wafer. The carrier wafer has a resistivity lower than about 1×108 Ohm-cm.

Owner:TAIWAN SEMICON MFG CO LTD

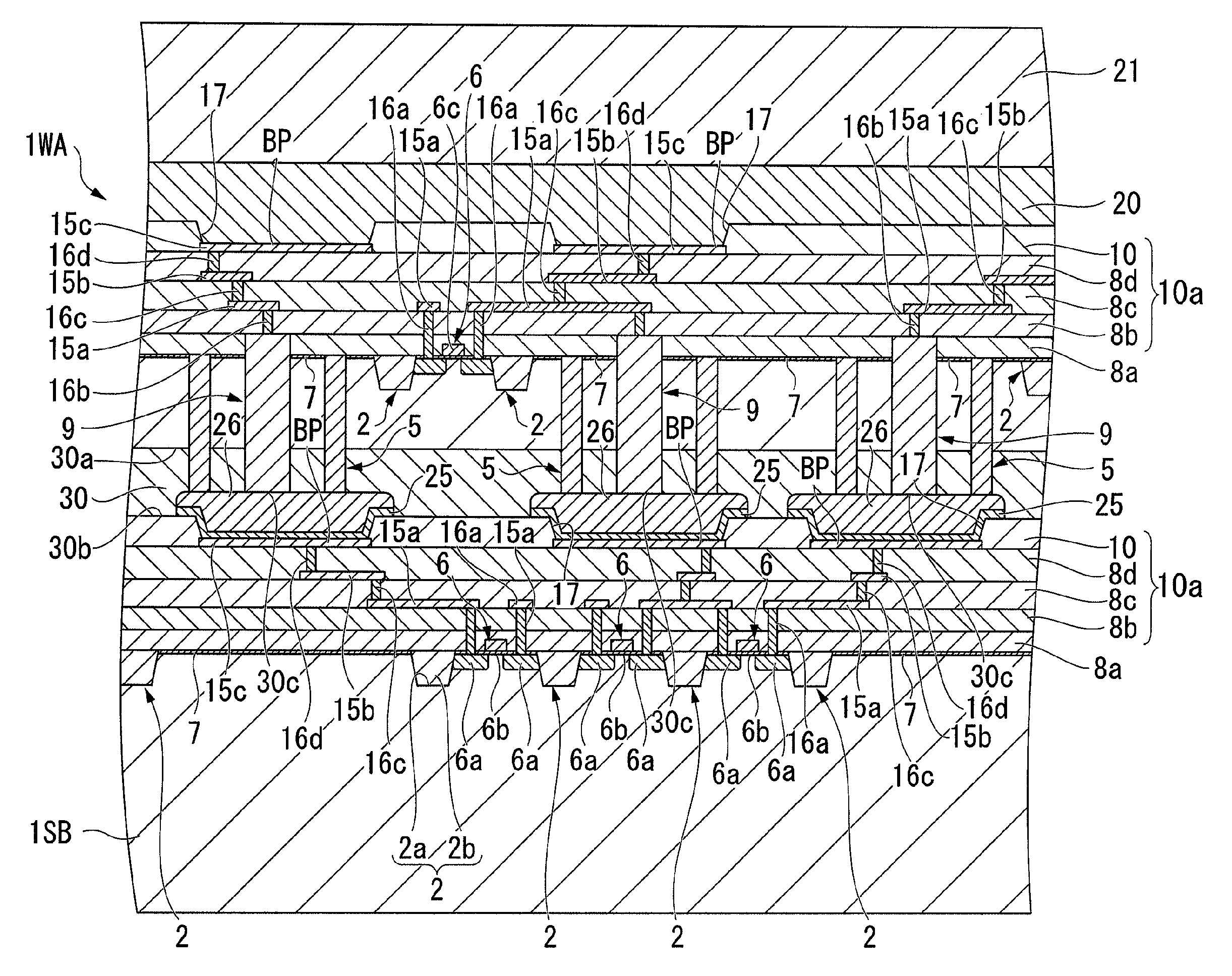

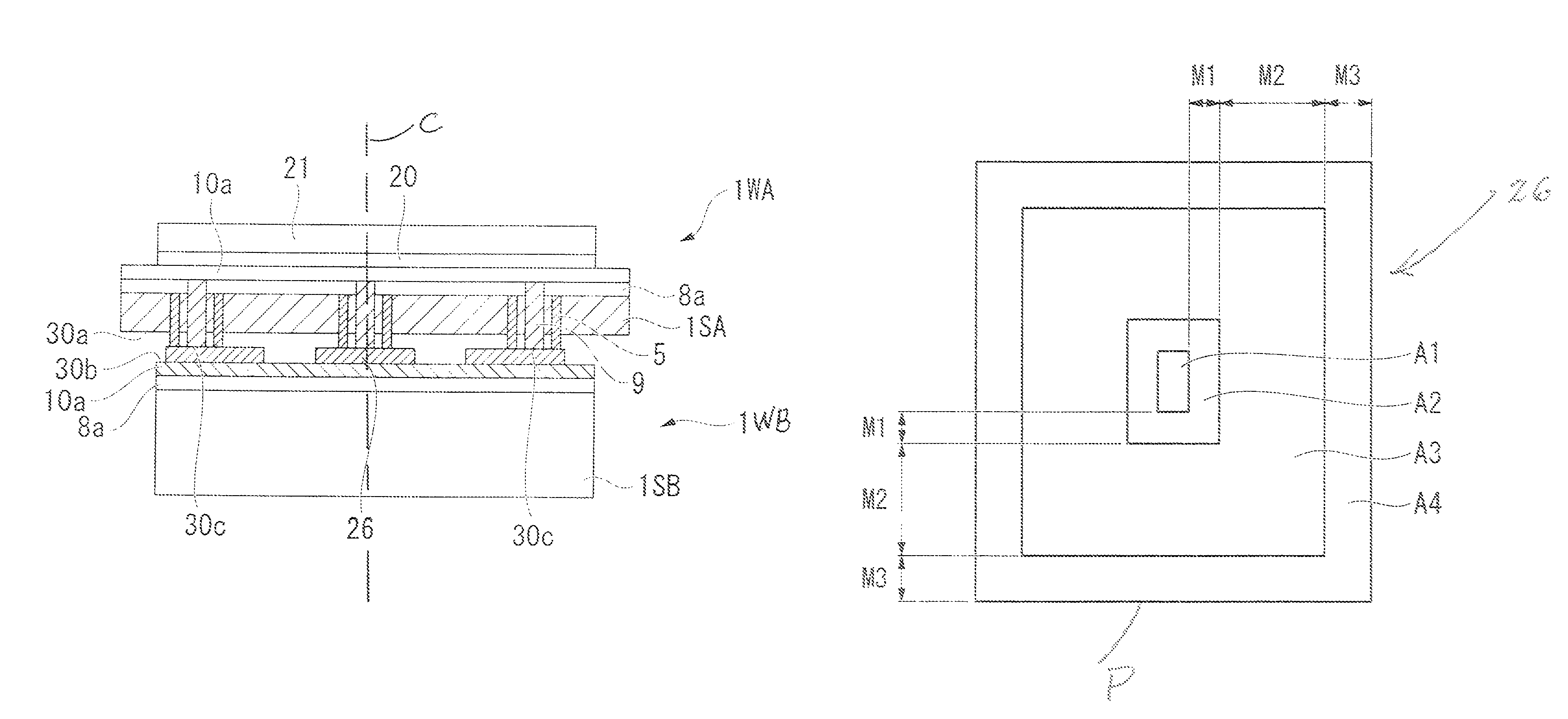

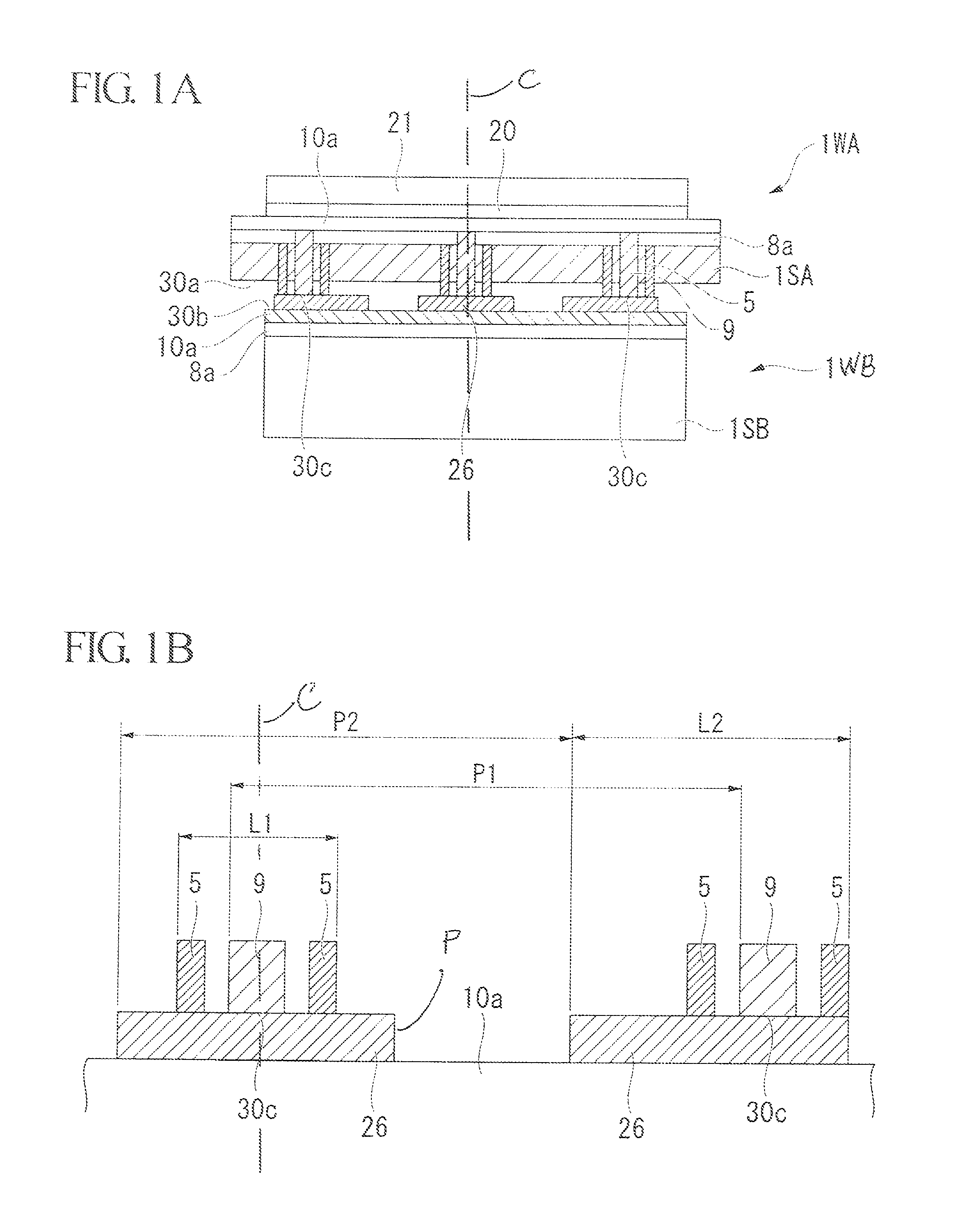

Semiconductor device

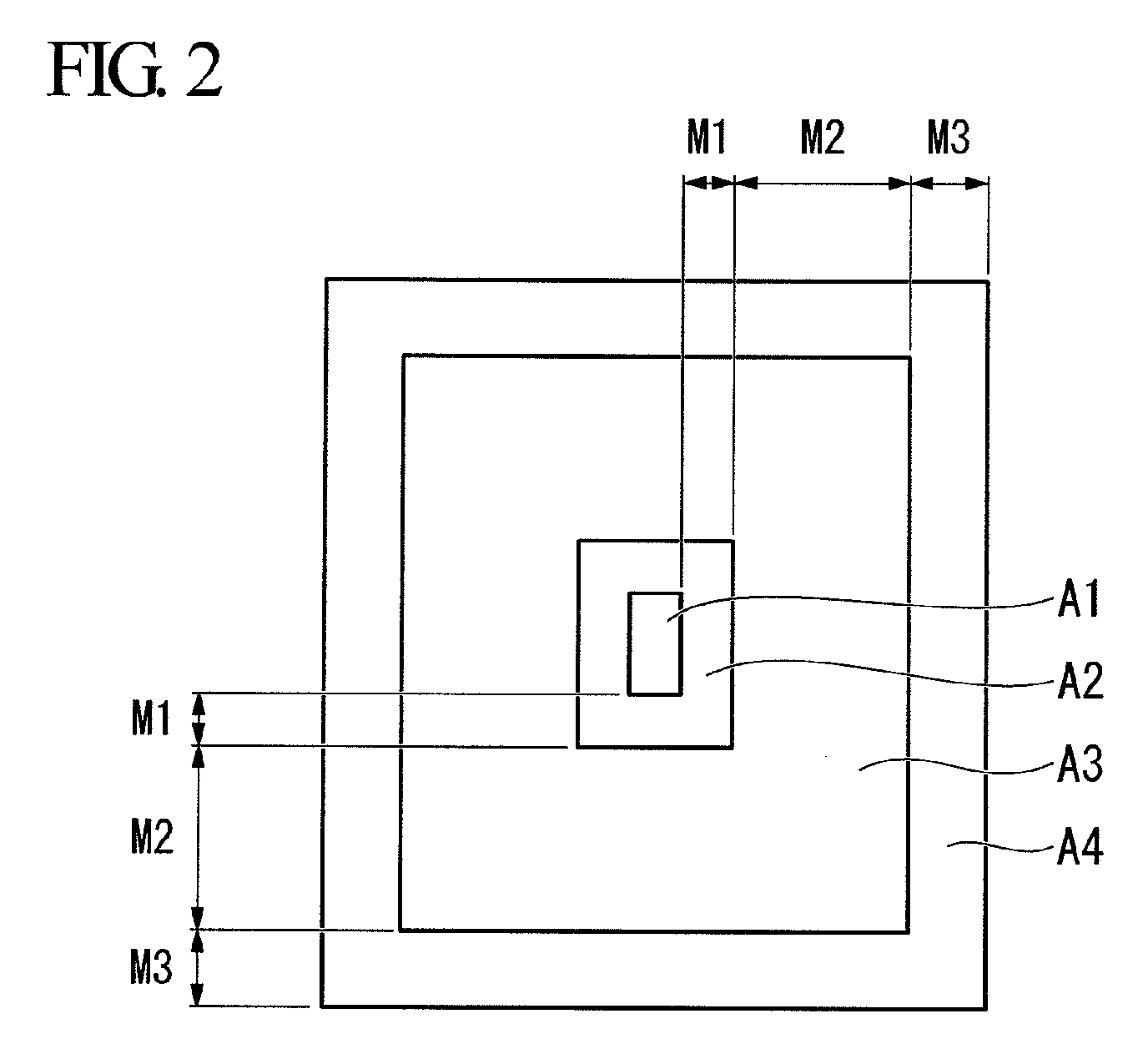

InactiveUS20090057890A1High reliability in electrical connectionIncrease the areaSemiconductor/solid-state device detailsSolid-state devicesEngineeringFace shape

In this semiconductor device, connection parts between wafers are electrically insulated from each other, and a junction face shape of second electrical signal connection parts is larger than the shape of a positioning margin face that is formed by an outer shape when the periphery of a minimum junction face, which has half the area of a junction area of the first electrical signal connection part, is enclosed by a same width dimension as a positioning margin dimension between the first wafer and the second wafer.

Owner:HONDA MOTOR CO LTD

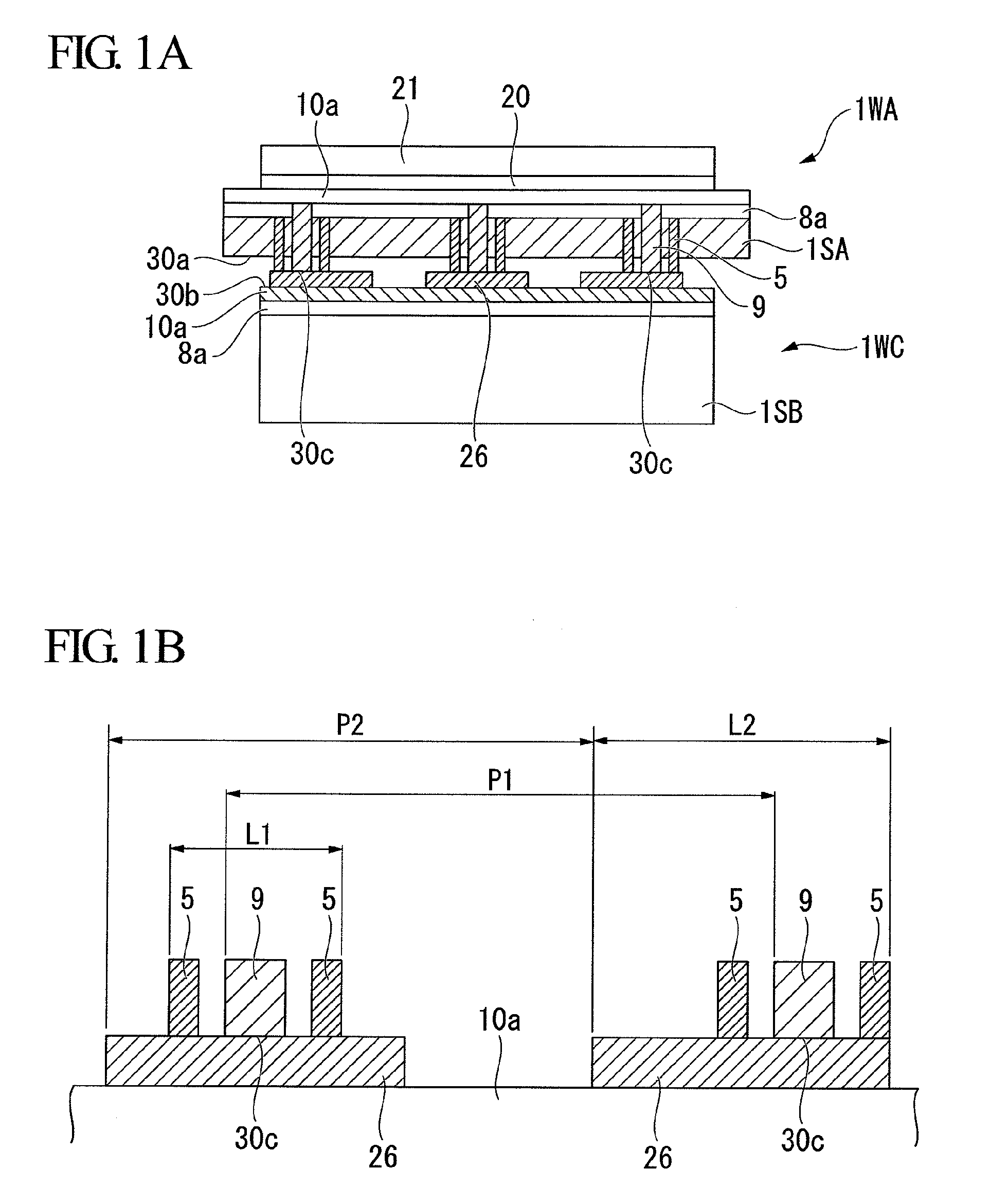

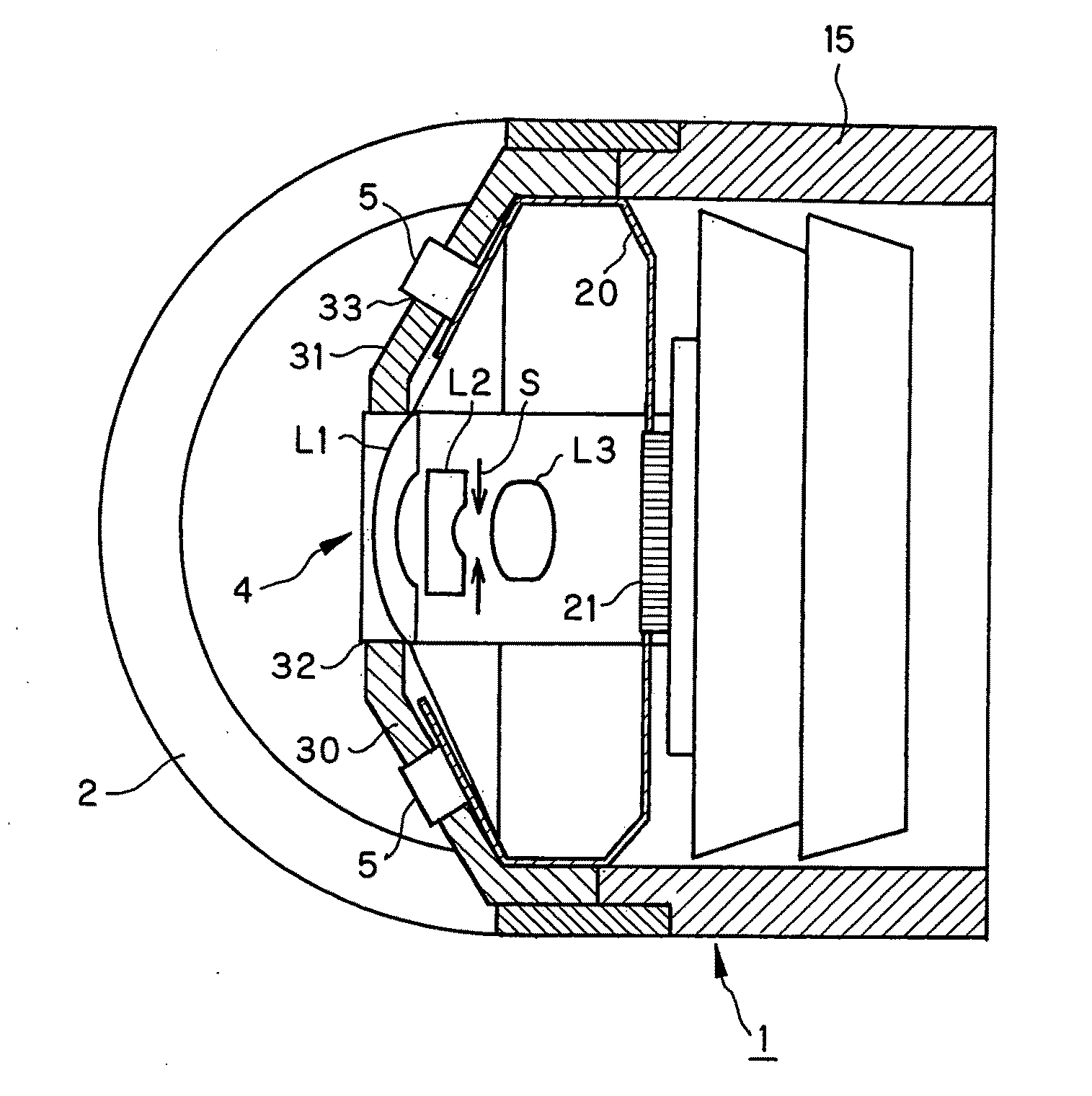

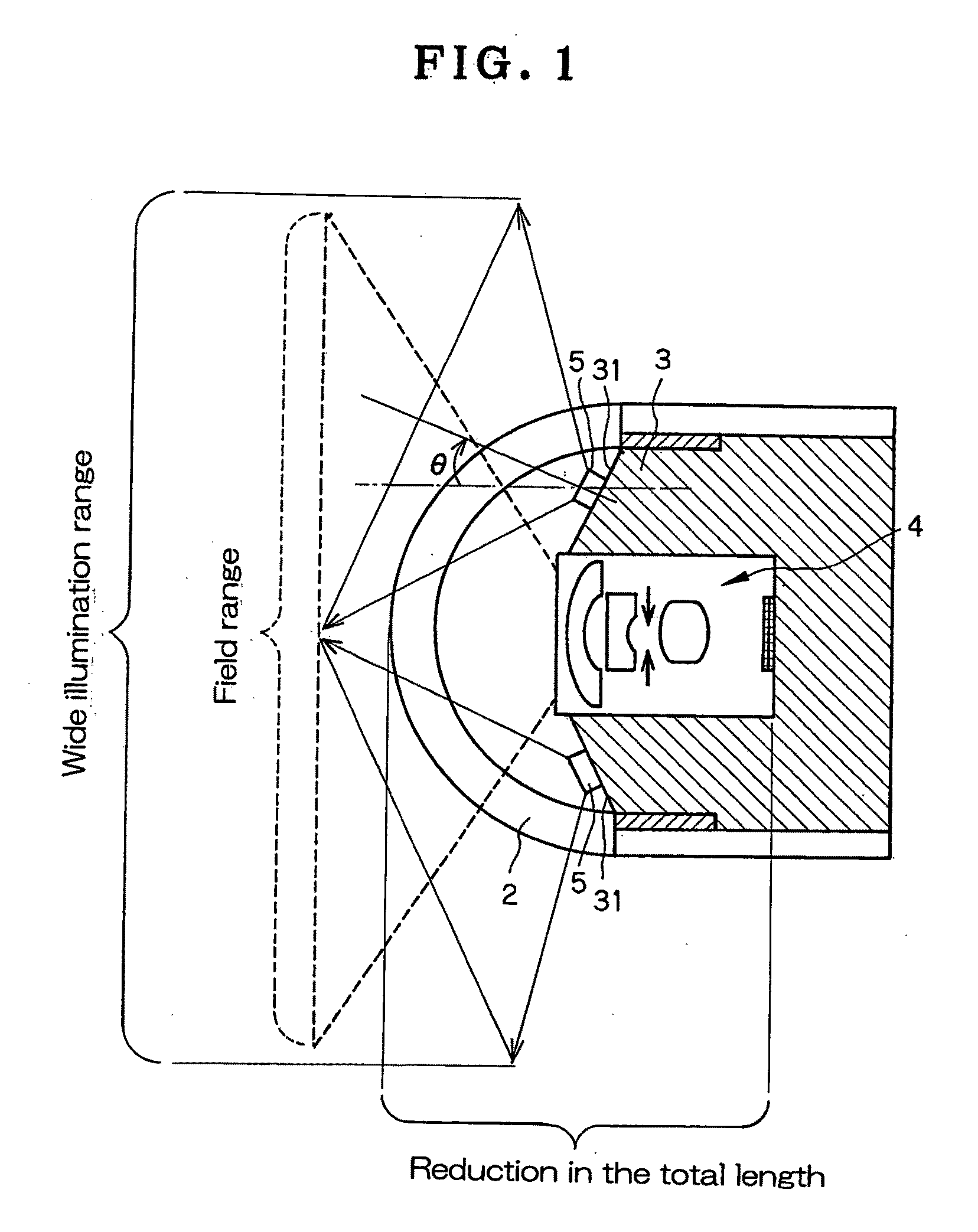

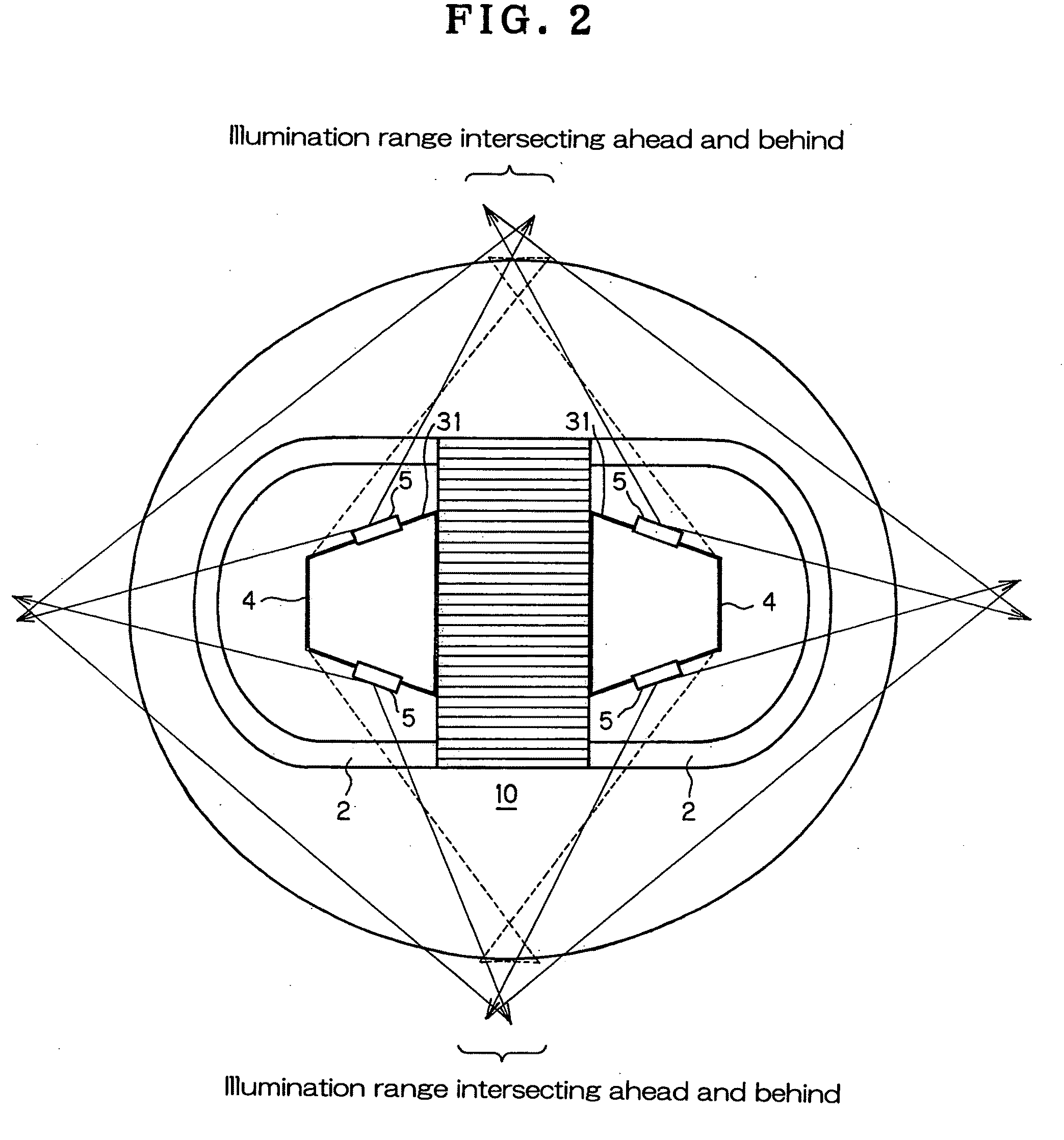

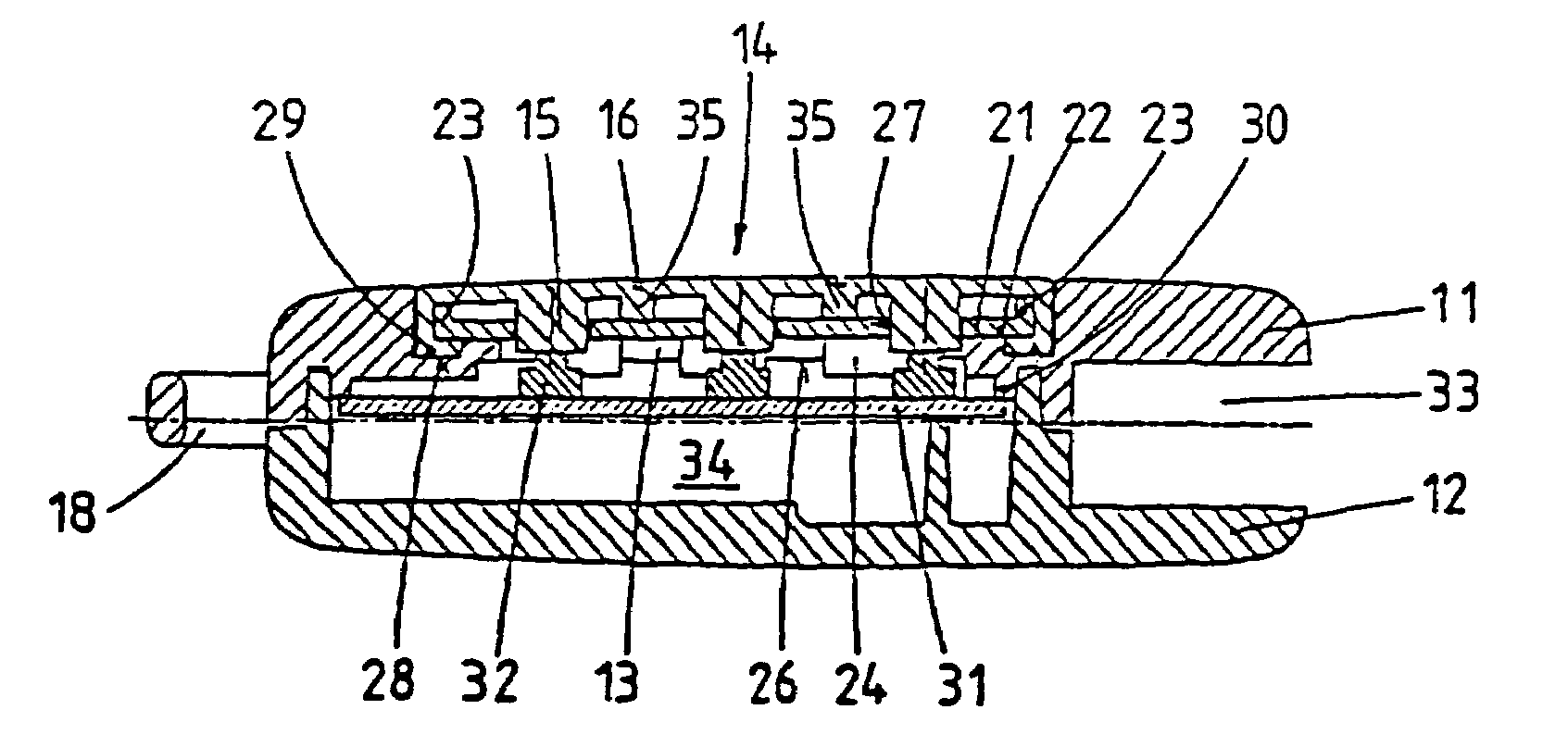

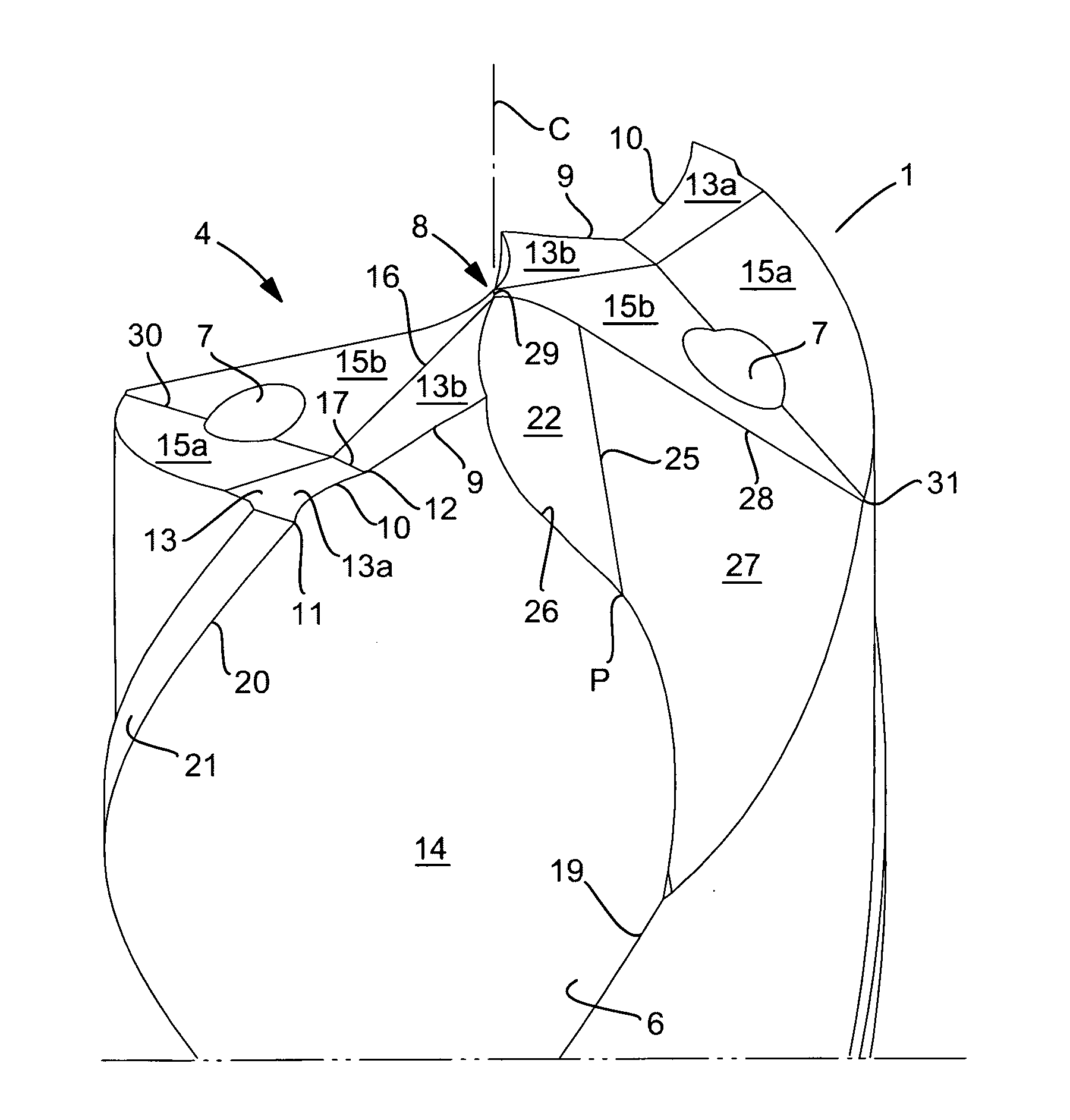

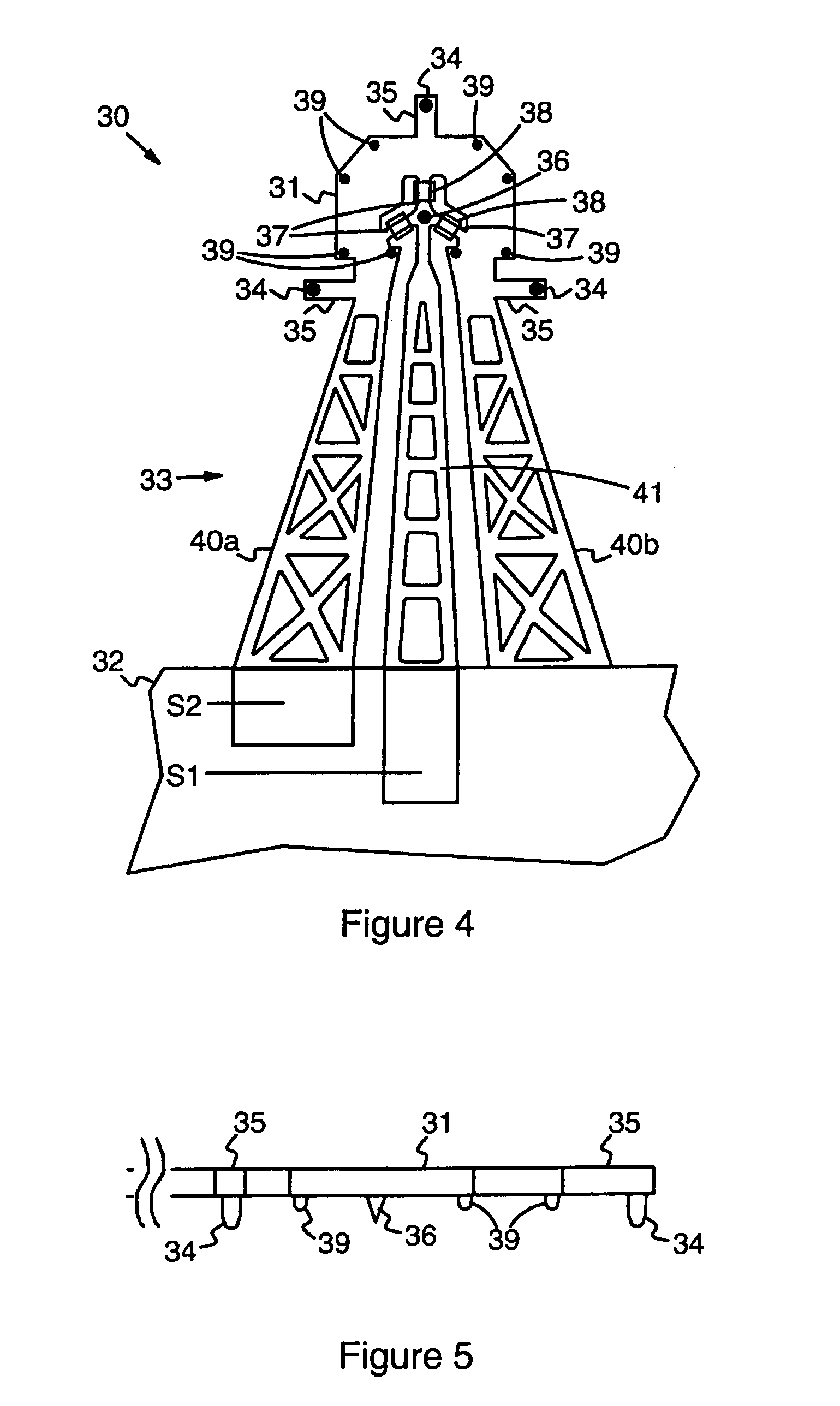

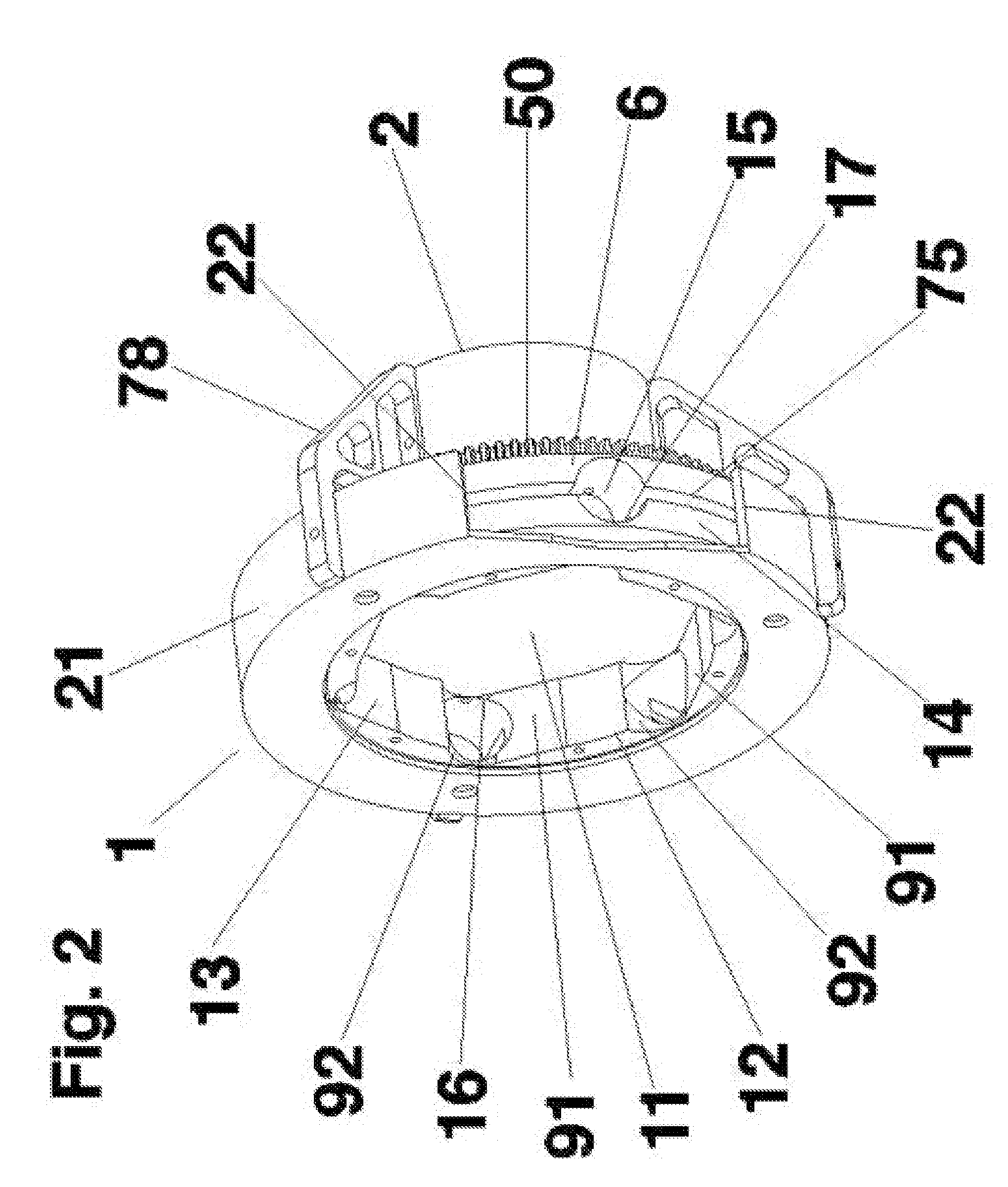

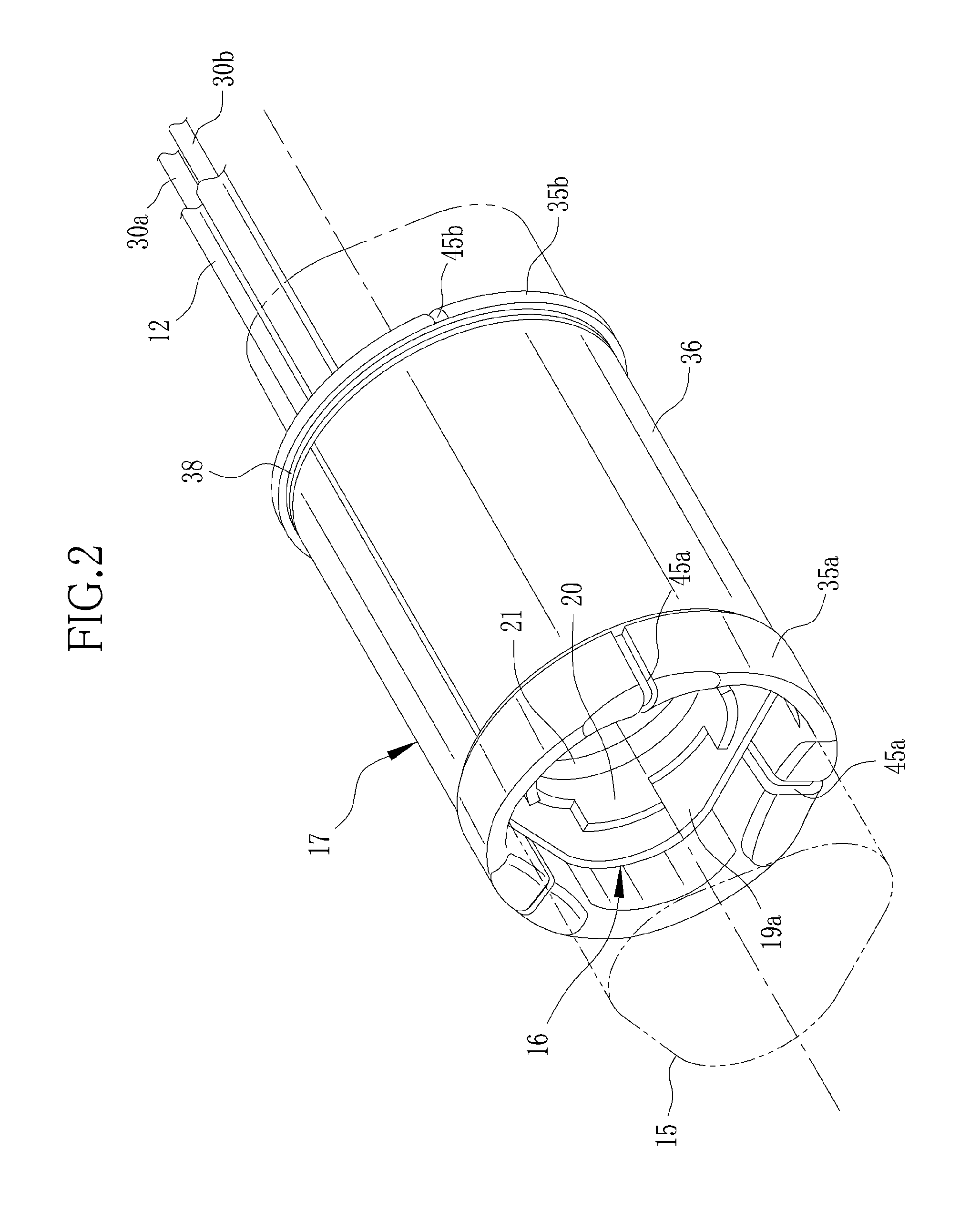

Capsule endoscope

InactiveUS20090069633A1Improve filtering effectEliminate the problemSurgeryEndoscopesCapsule EndoscopesMedicine

The invention relates to a capsule endoscope layout capable of achieving a small-format, wide-angle, wide light-distribution arrangement with limited variations. A capsule endoscope 1 comprises an objective lens 4, a transparent dome 2 to cover the object side of the objective lens, and light emitter devices located around the outer periphery of the objective lens. The endoscope 1 further comprises an integral-piece holder member 30 adapted to hold the objective lens 4 in place and hold the light emitter devices 5 at a position set back from an end of, and around, the objective lens 4 while the light emitter devices 5 are inclined outward at an angle with a center axis of said objective lens 4.

Owner:OLYMPUS MEDICAL SYST CORP

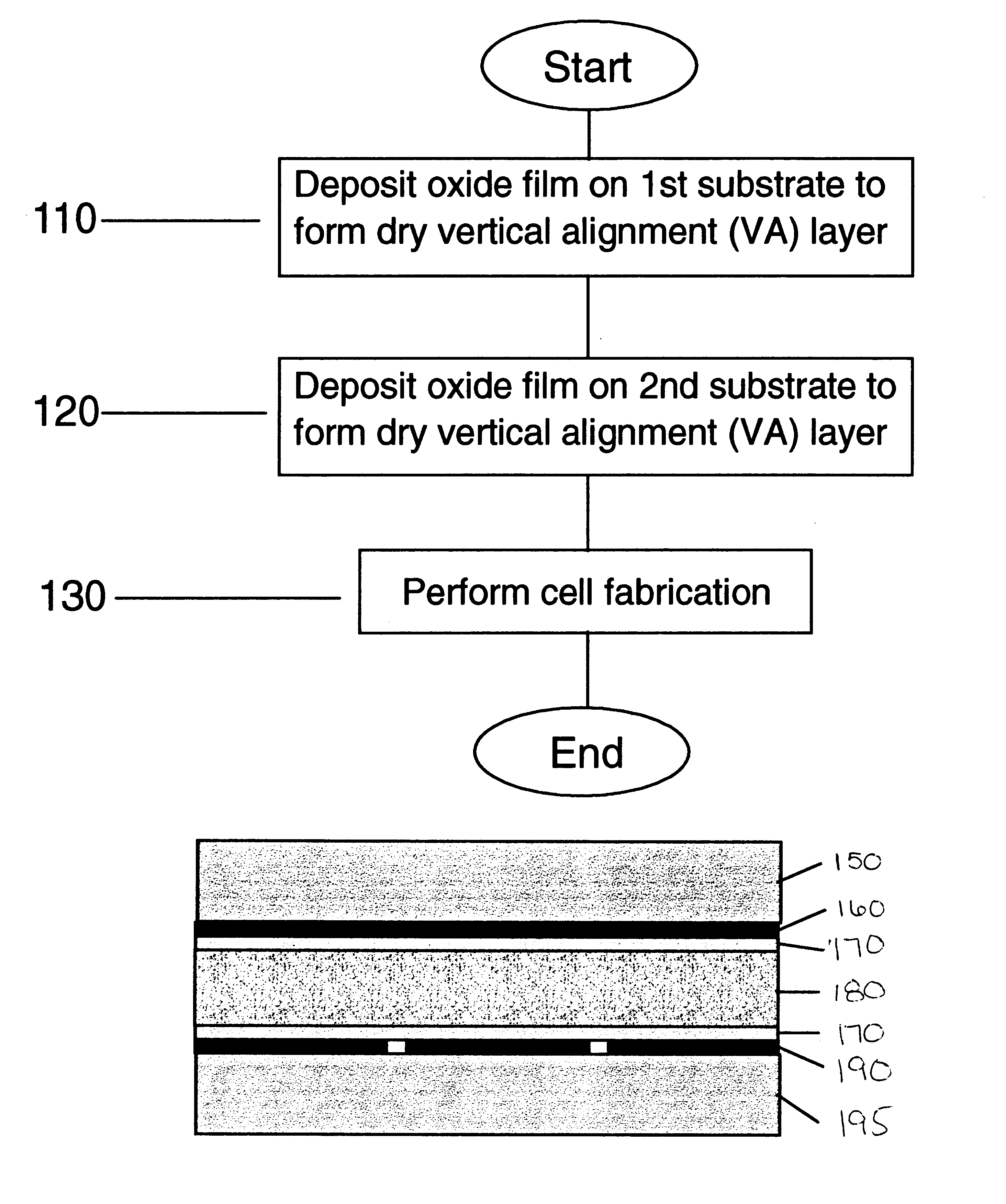

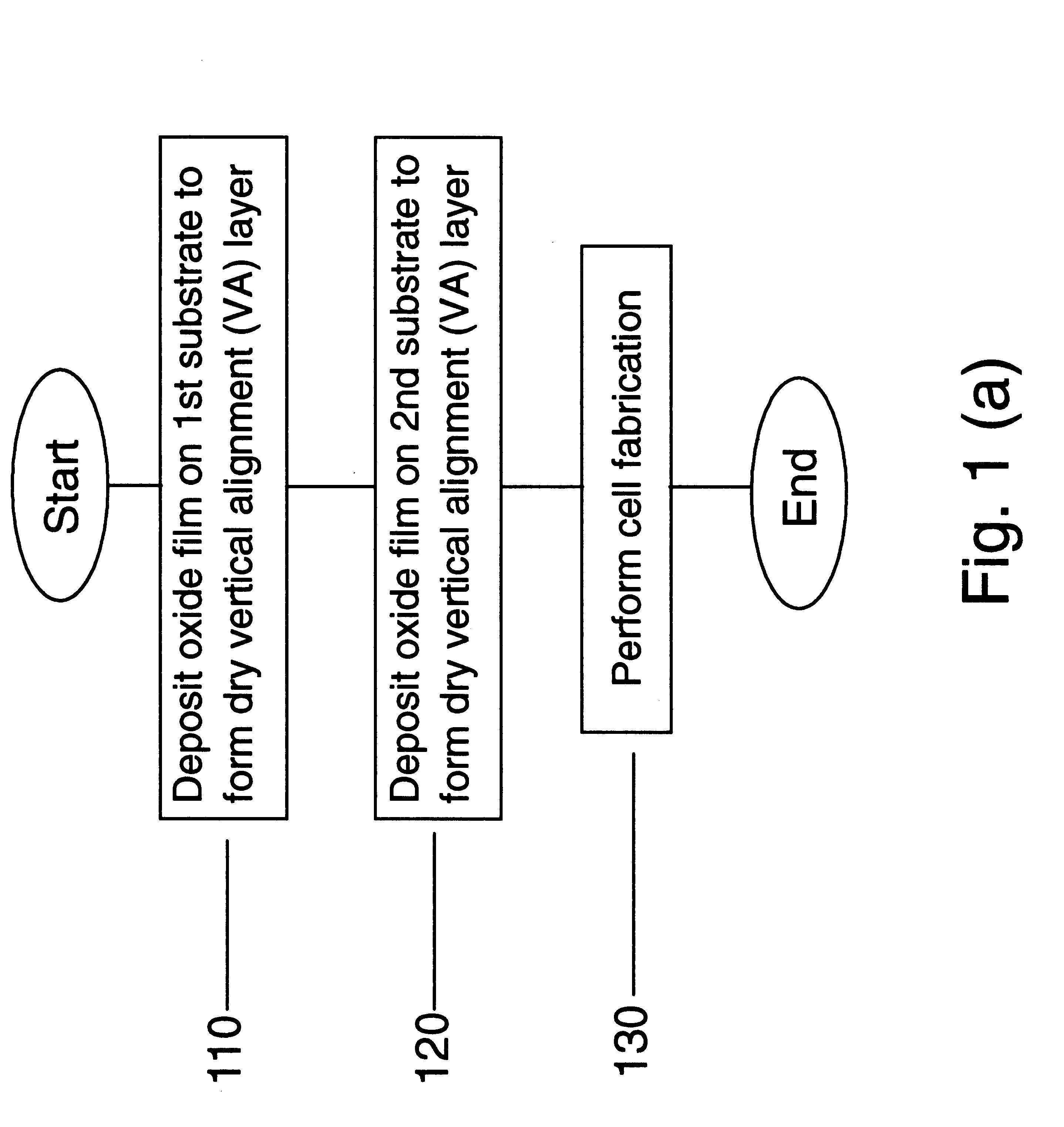

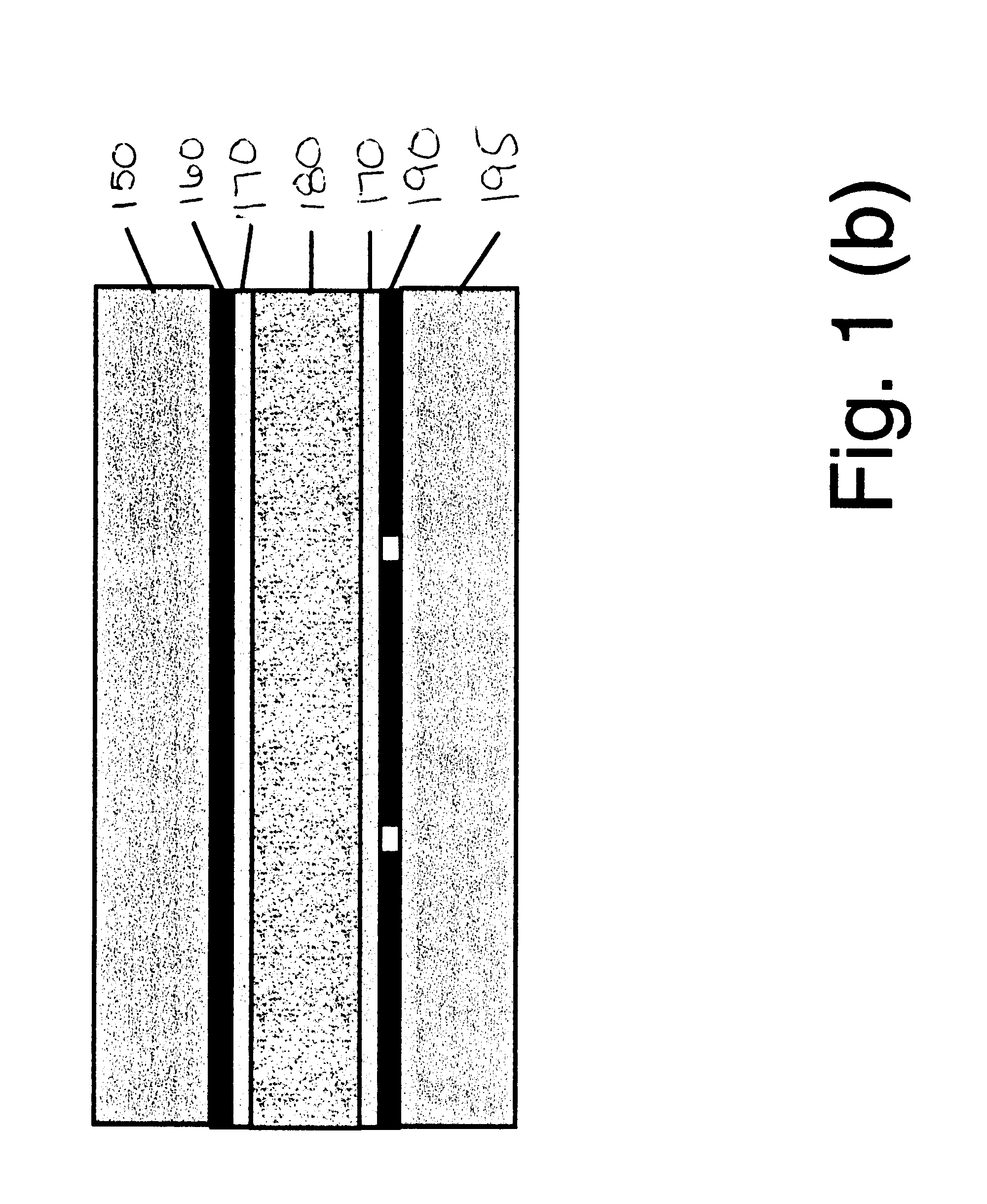

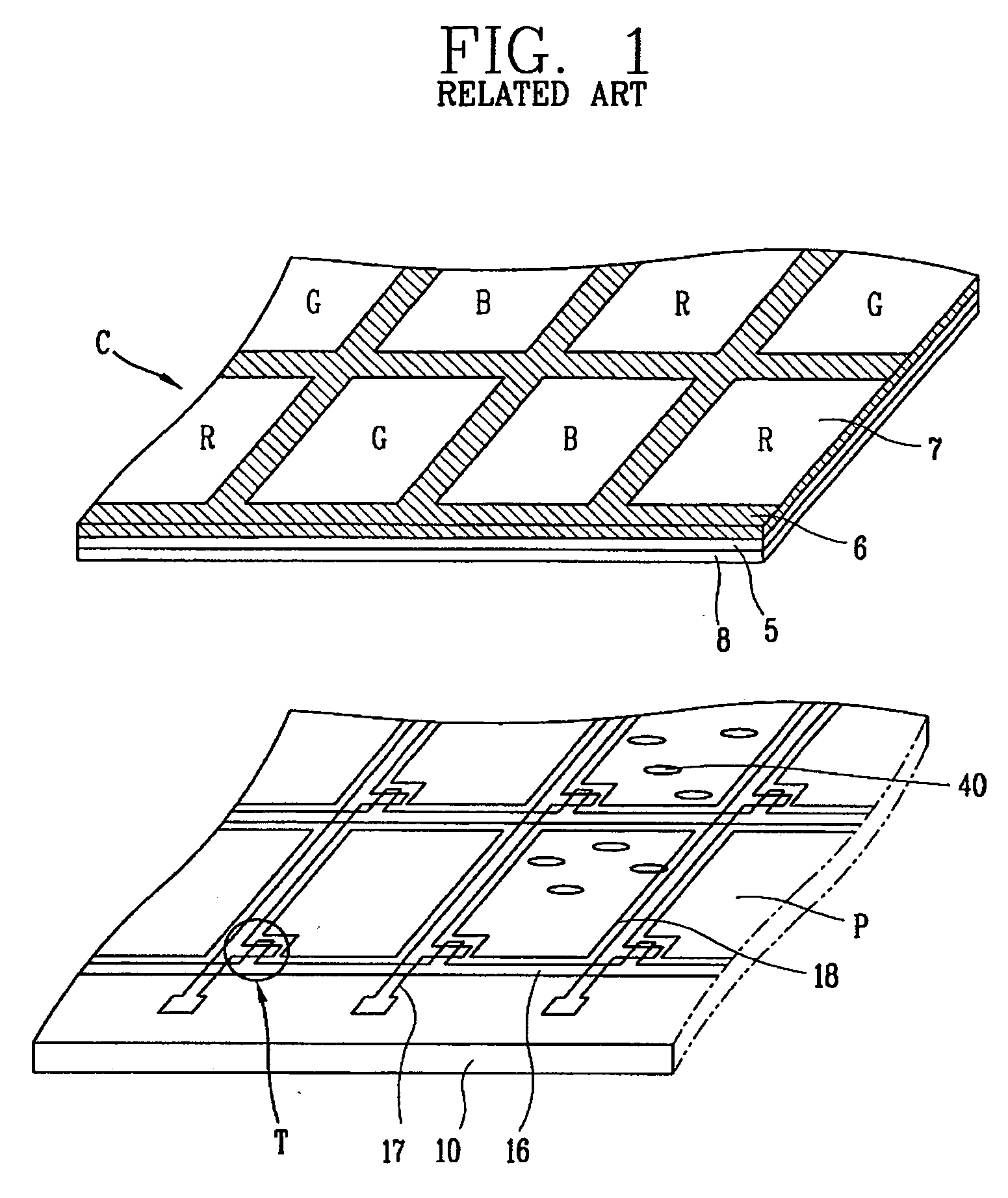

Vertical aligned liquid crystal display and method using dry deposited alignment layer films

InactiveUS6724449B1Reliable alignmentImprove charge retentionStatic indicating devicesNon-linear opticsVertical alignmentEngineering

A liquid crystal display device includes a first substrate, a dry alignment film deposited over the substrate, a second substrate coupled to the first substrate with the dry alignment film deposited over the second substrate therebetween and forming a cell gap, and a liquid crystal material formed in the cell gap. The dry alignment film allows for a truly vertical alignment of molecules of the liquid crystal material such that the molecules form an angle of substantially 90° relative to the substrate. The dry alignment film can be an oxide layer, a nitride layer, an oxynitride layer or a silicon layer. This dry alignment layer can be treated to form a tilted homeotropic alignment, such that the liquid crystal molecules have a pretilt angle of 0.5 to 10 degrees from a substrate normal direction. The truly vertical alignment process can be incorporated with a ridge and fringe field process method to form a multidomain Vertical Alignment (VA) Liquid Crystal Display's (LCDs) which have wide viewing angles.

Owner:INFOVISION OPTOELECTRONICS HLDG LTD +1

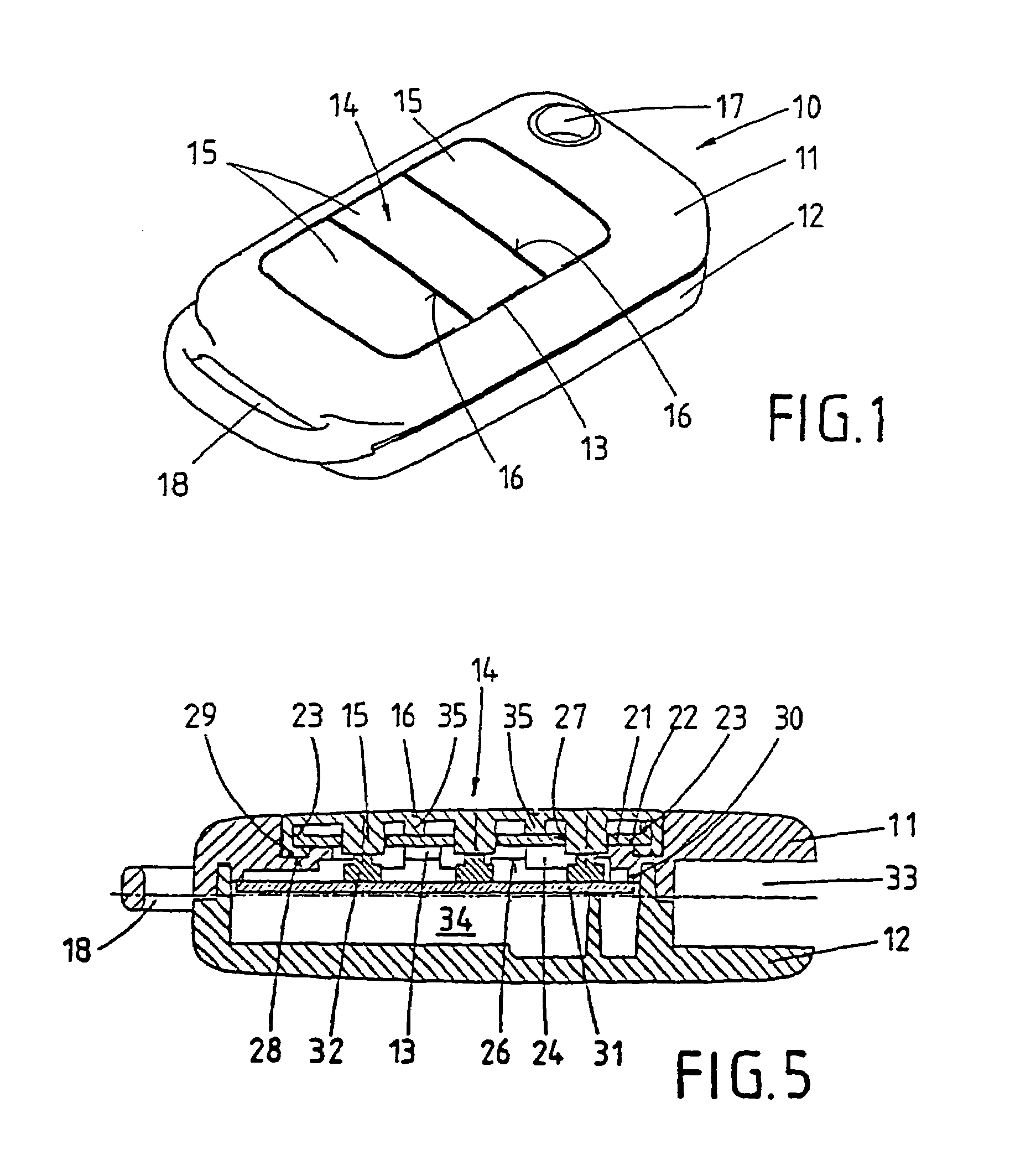

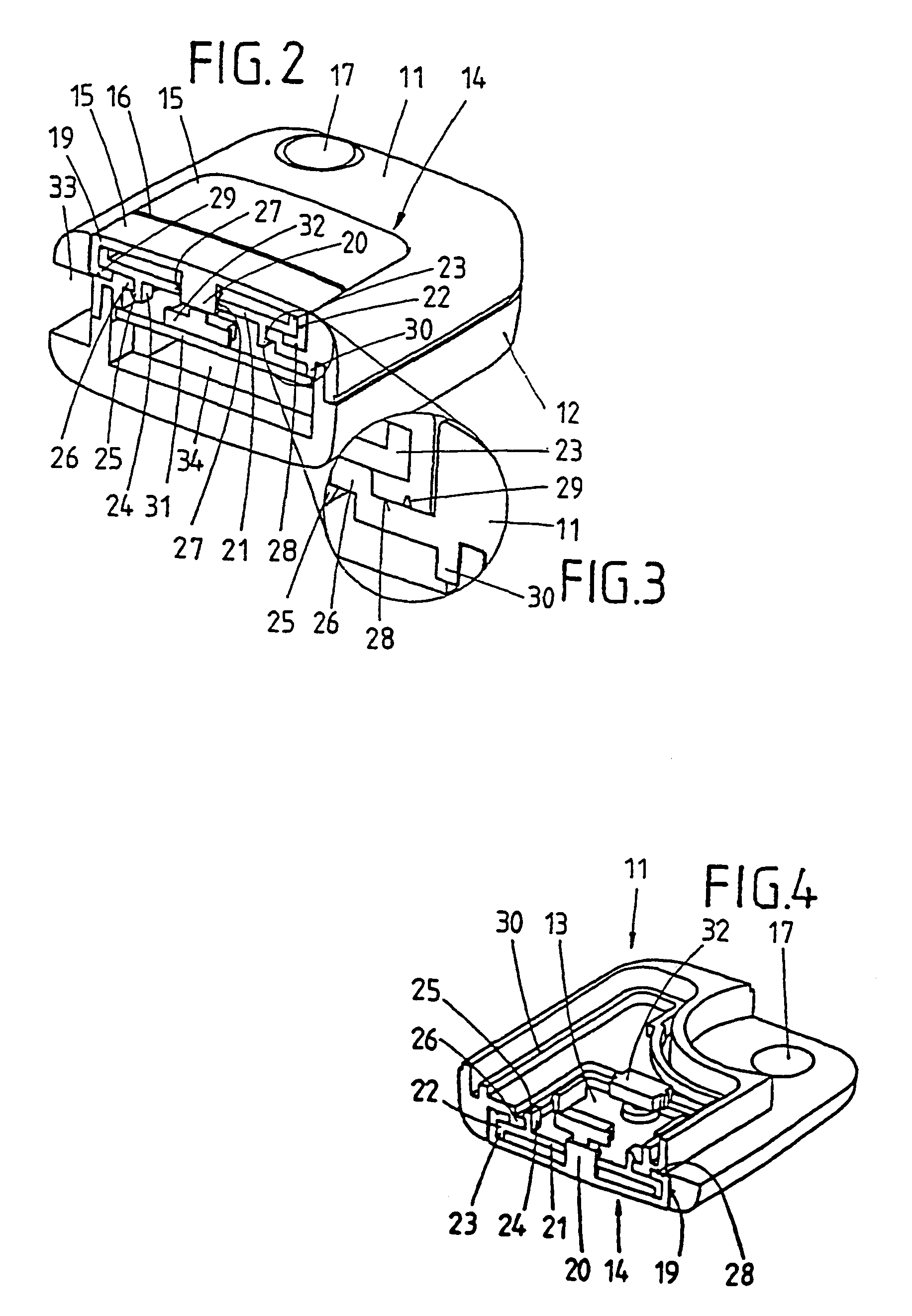

Housing for an electronic key

InactiveUS7041924B2Feel goodImprove lookTelemetry/telecontrol selection arrangementsContact surface shape/structureEngineeringElectronic component

The invention relates to a housing (10) for a key, especially for use in motor vehicles. Said housing consists of electric and electronic components (32) disposed therein and arranged at least partially on a plate (31); a recess which can be covered by an elastic keypad (14) comprising at least one key (15). According to the invention, a support (21) is associated with the keypad (14) for retention on said housing (10). The keypad (14) surrounds the support (21) which is disposed beneath the keypad with a peripheral edge (19), whereby the elastic edge (19) is supported on a shoulder (28) of the housing (10) and the edge (19) is pressed against the shoulder (28) of said housing in a sealing manner by retaining means (24, 25).

Owner:AUDI AG

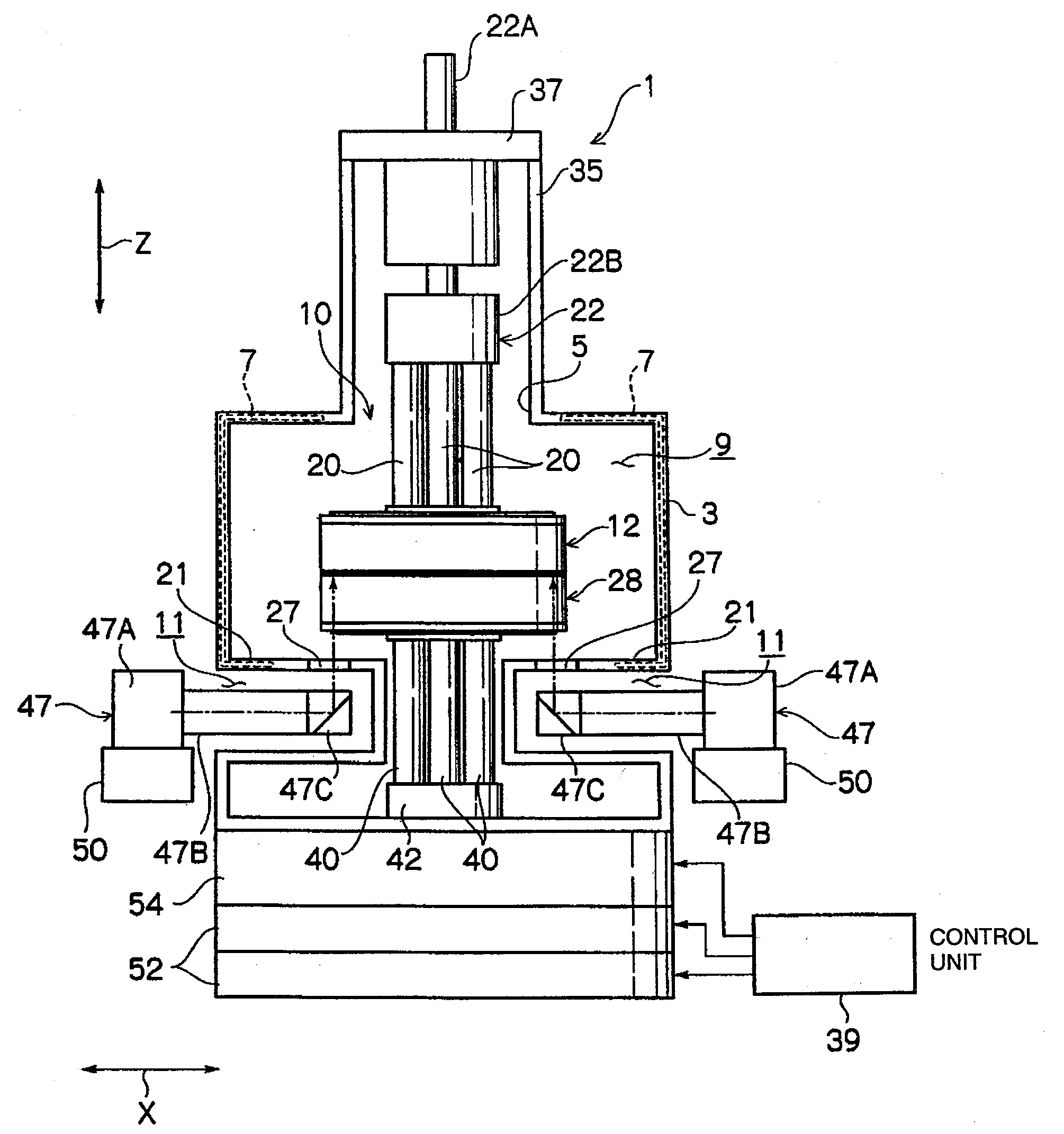

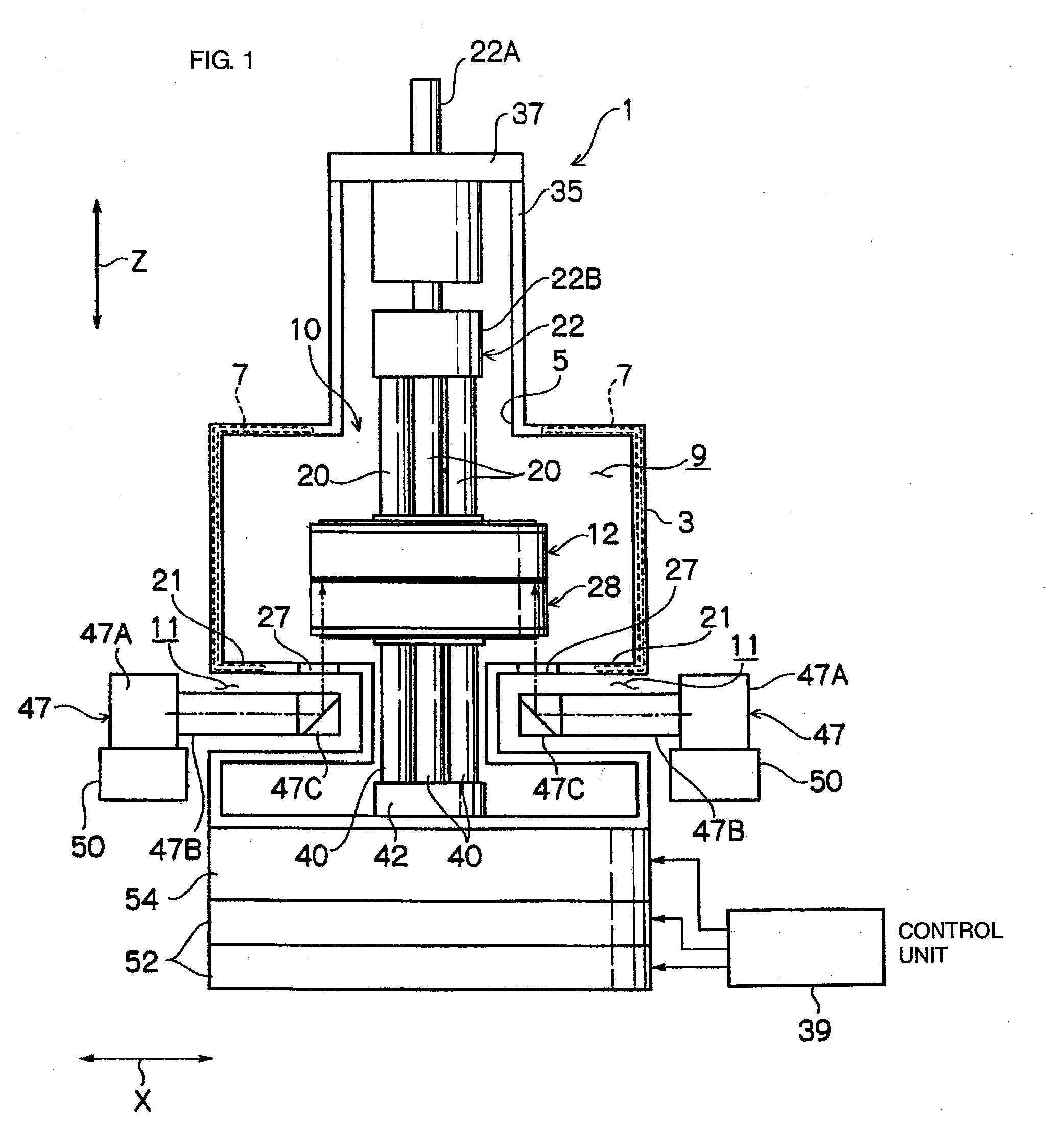

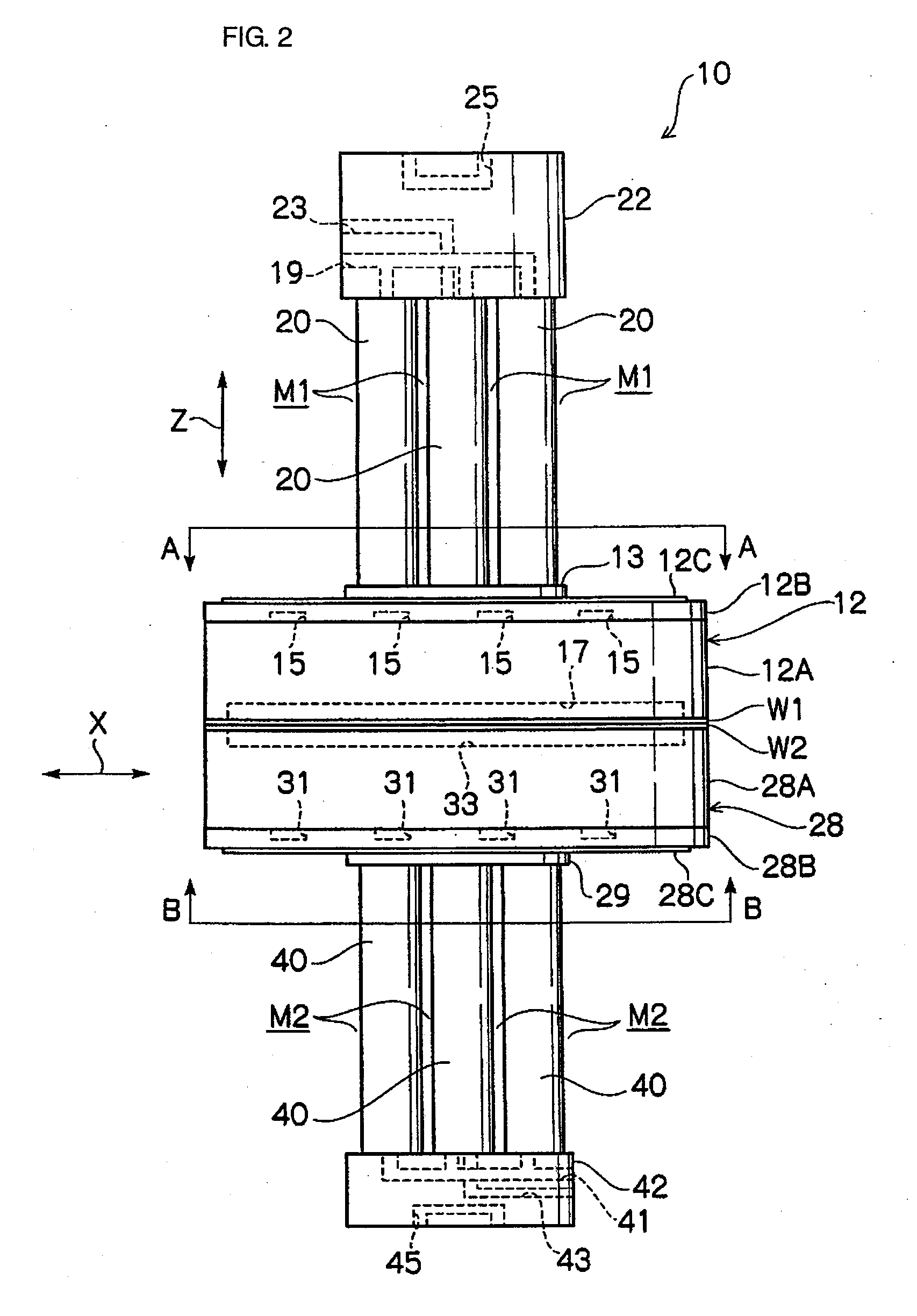

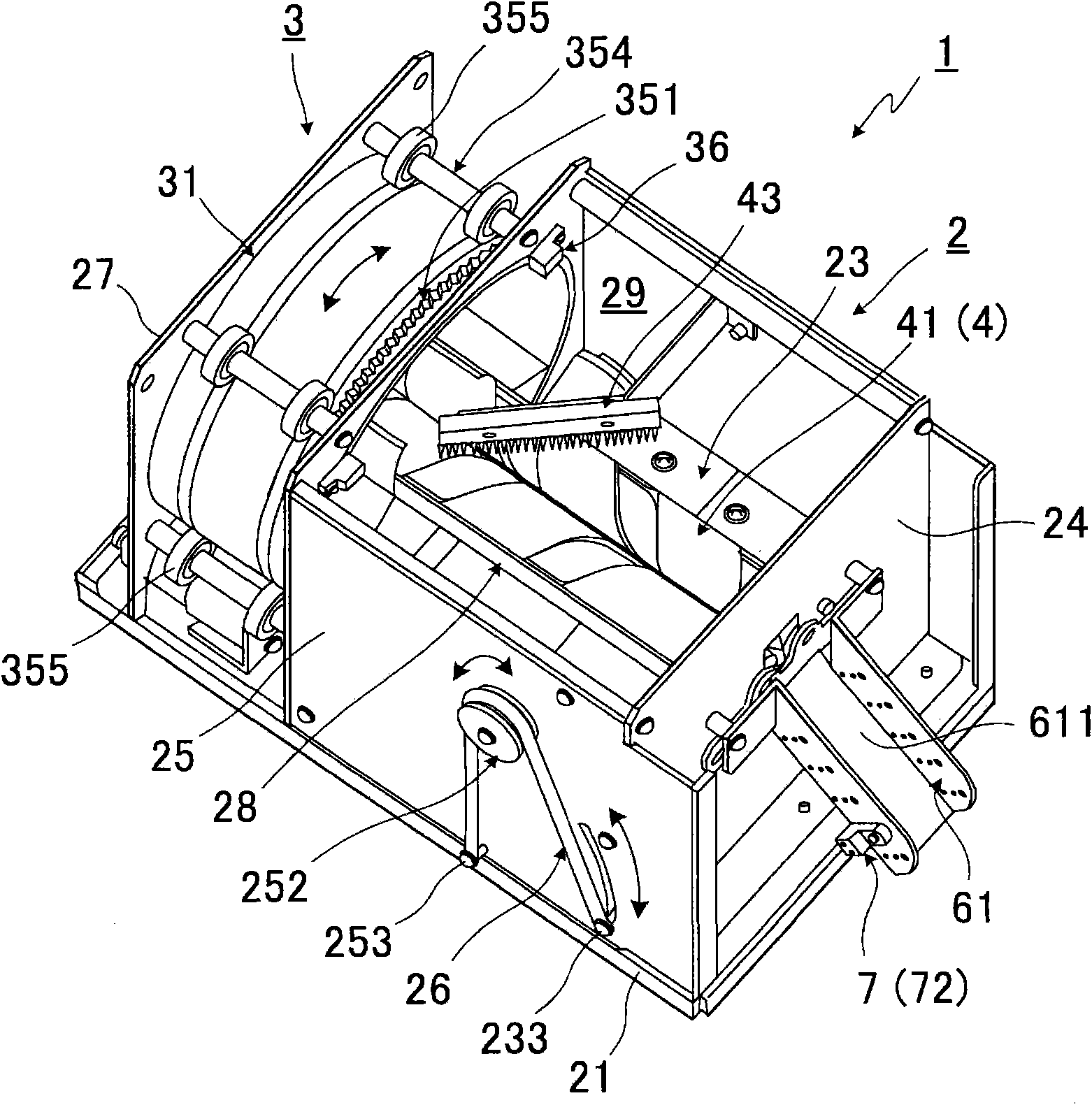

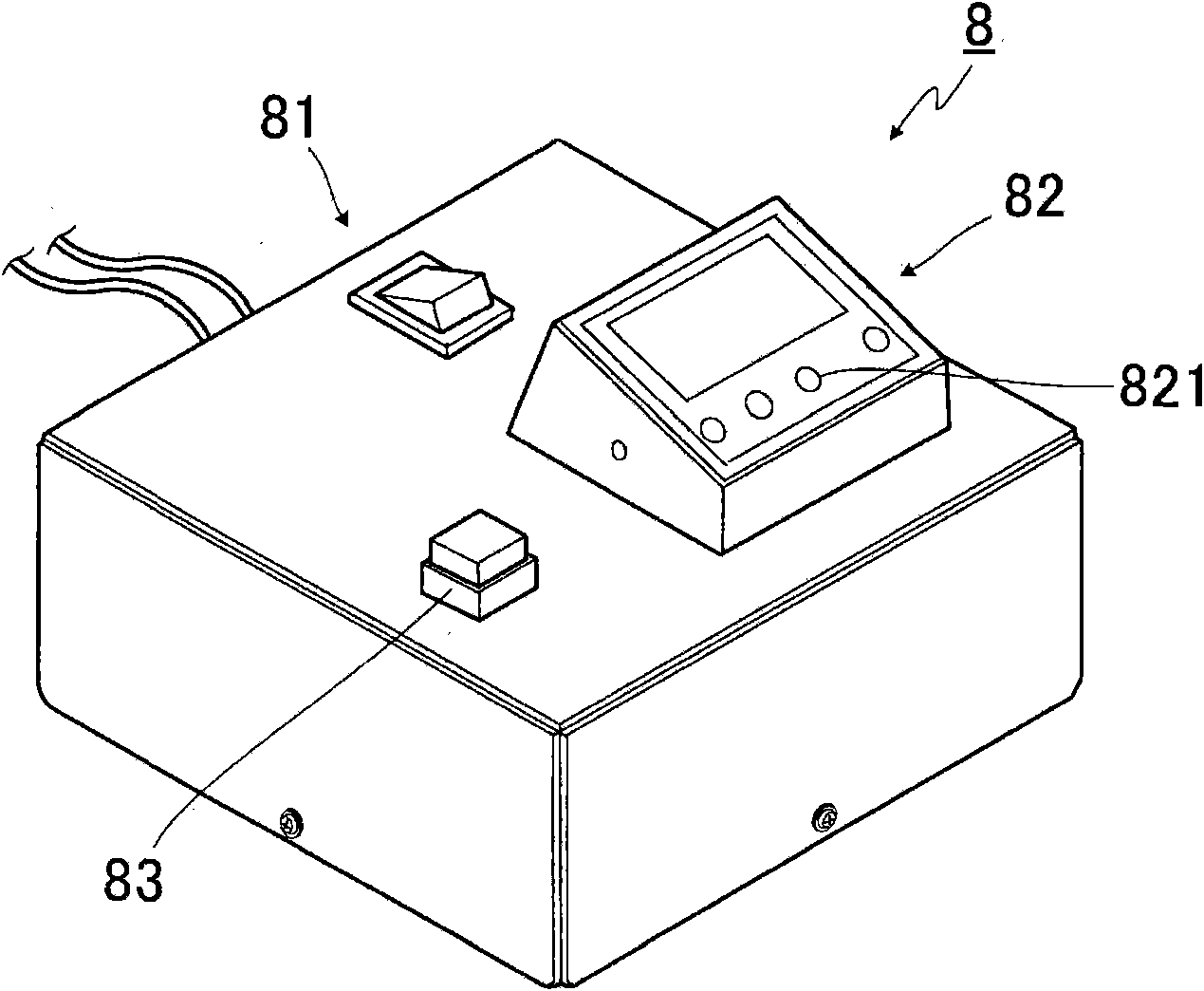

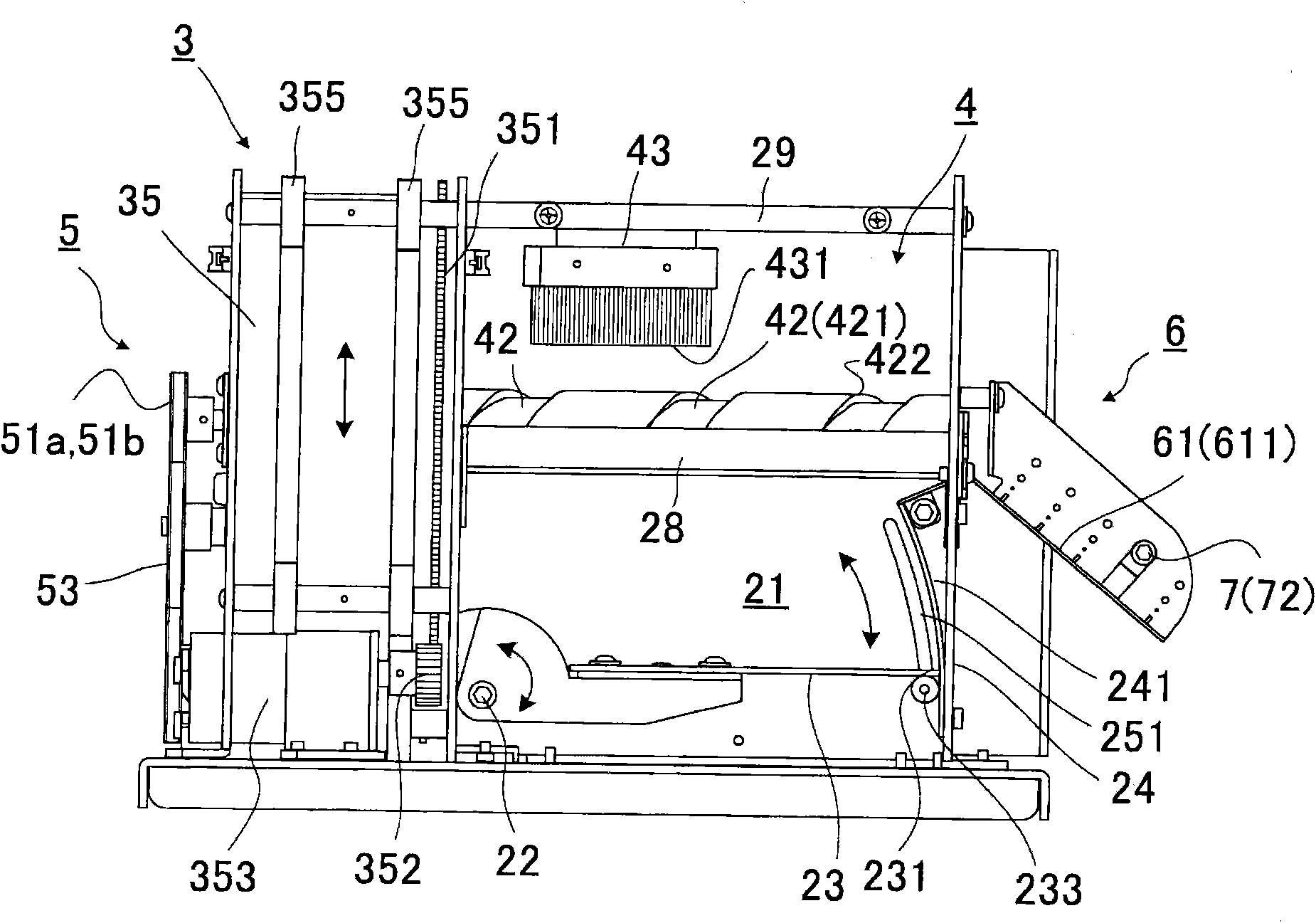

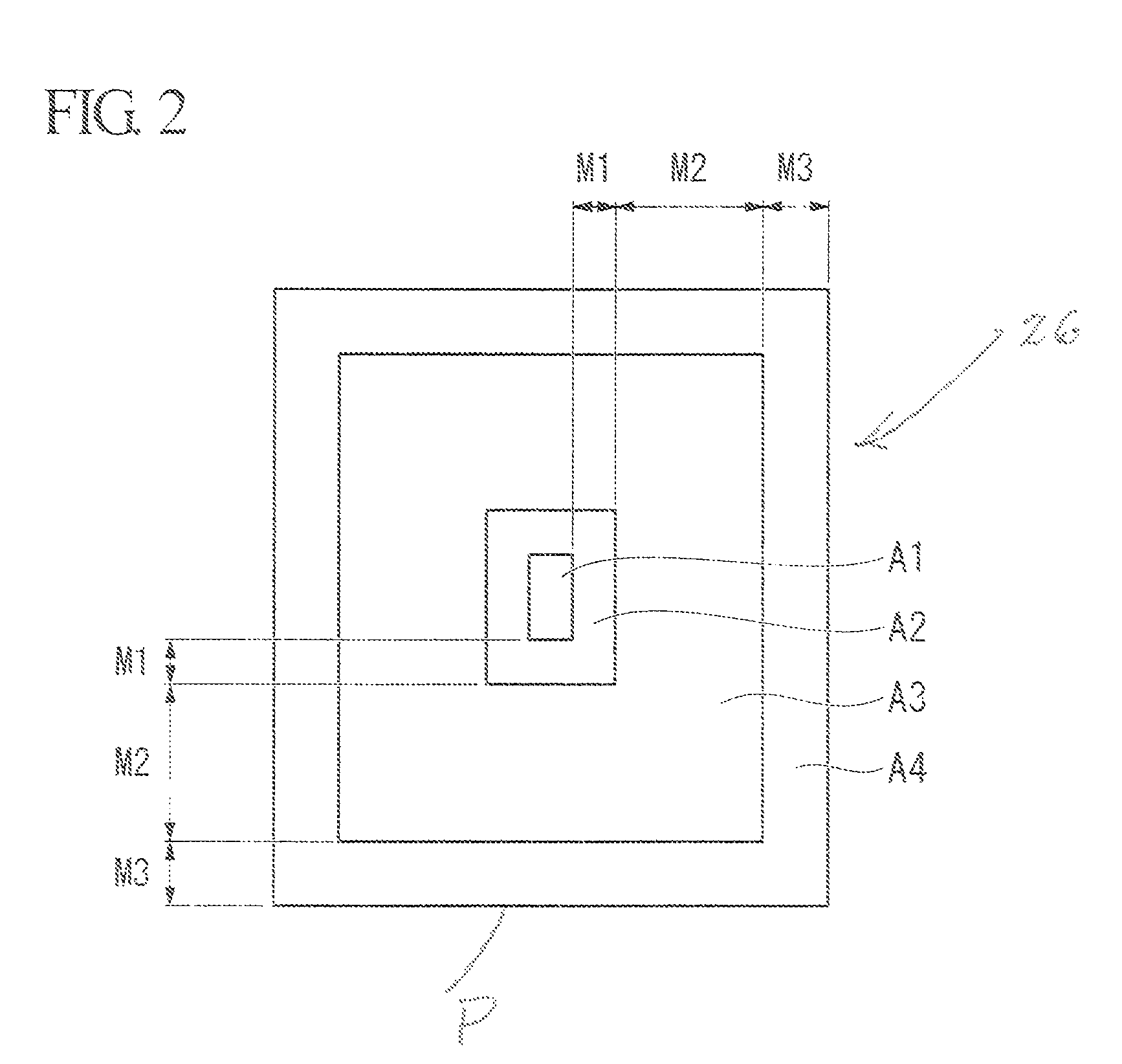

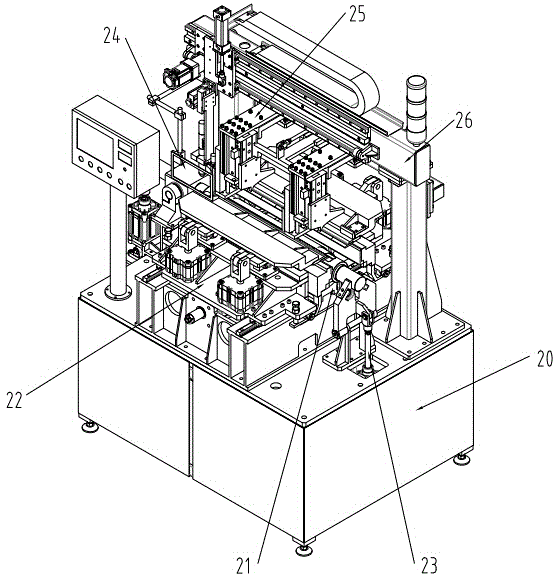

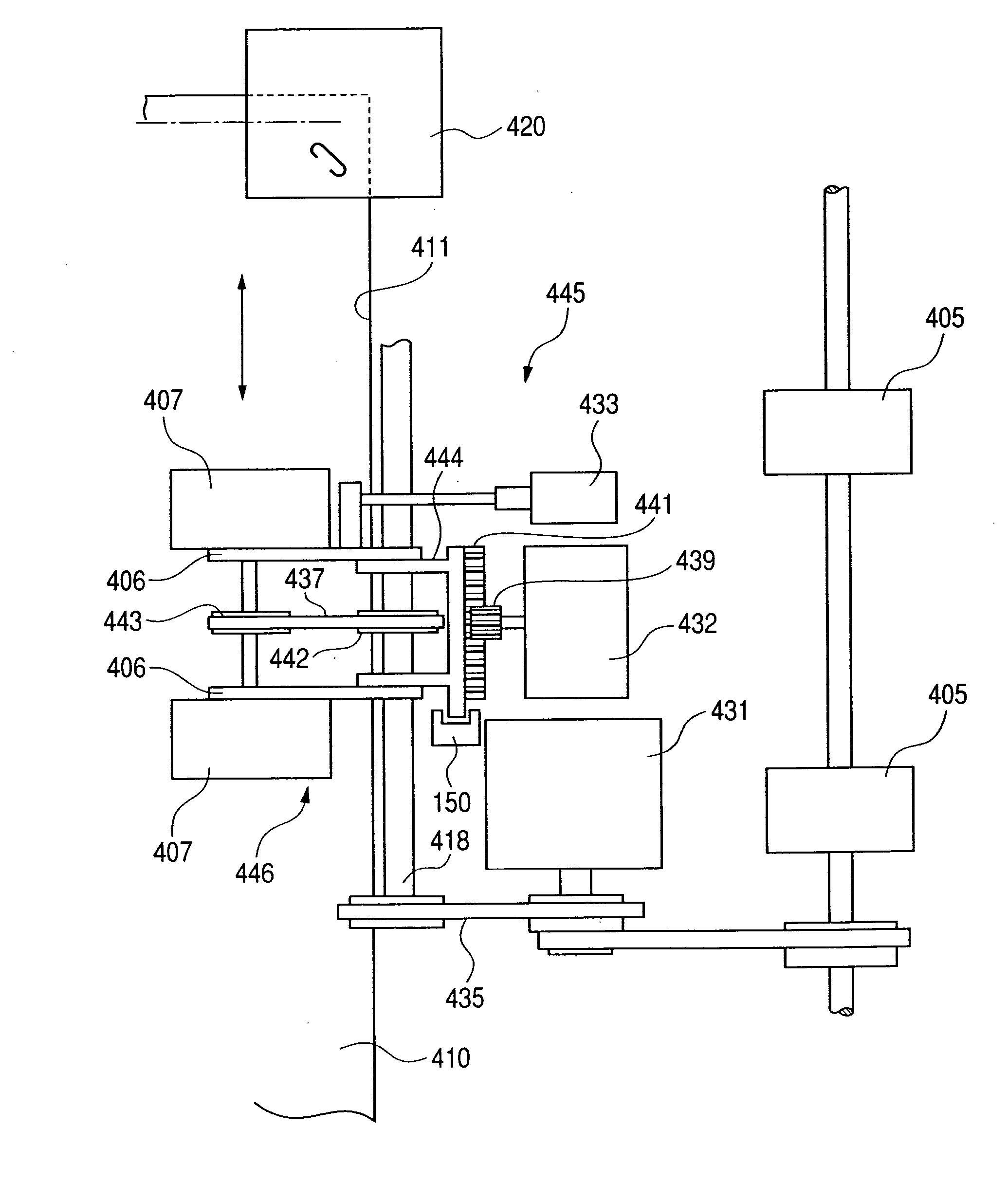

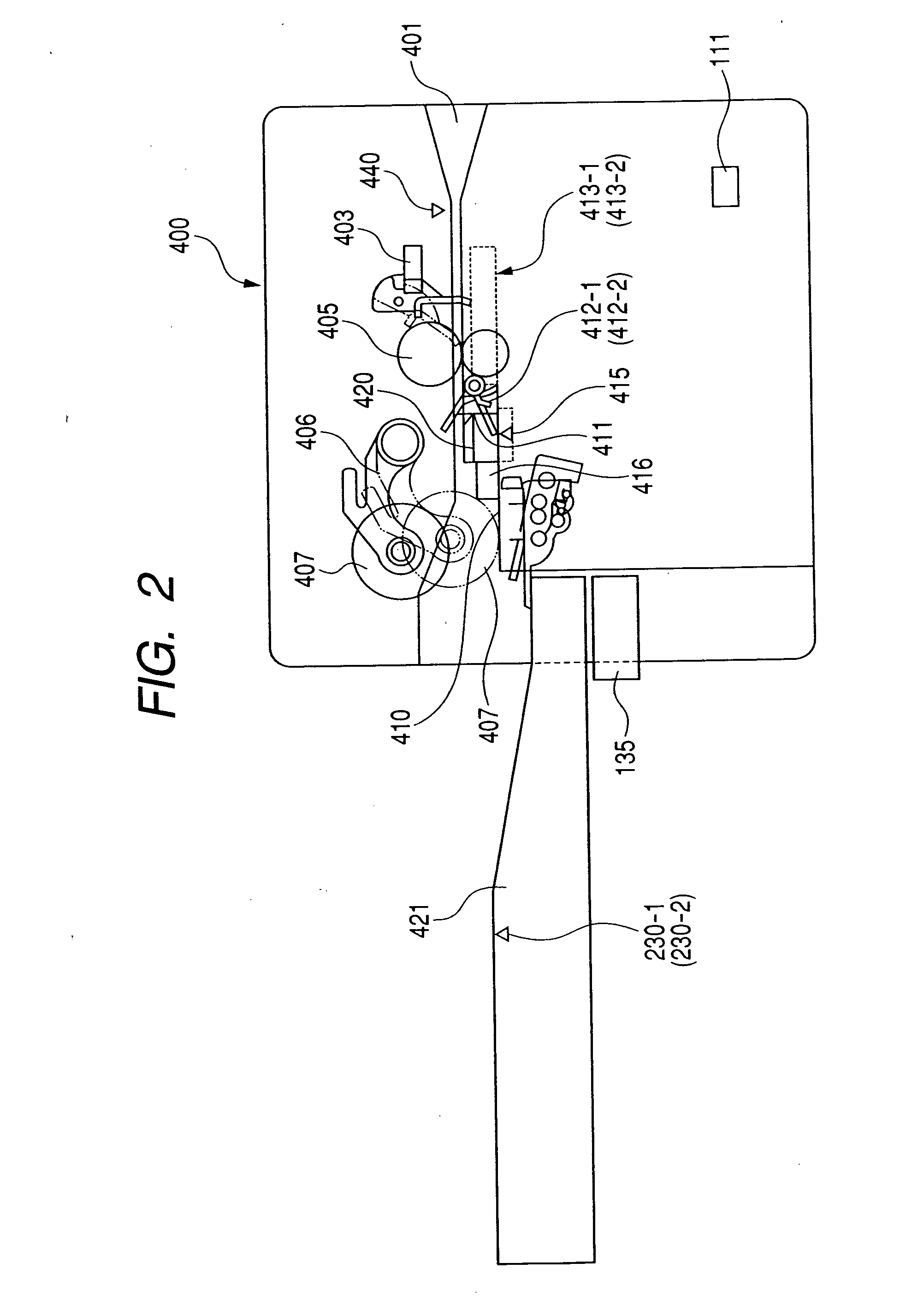

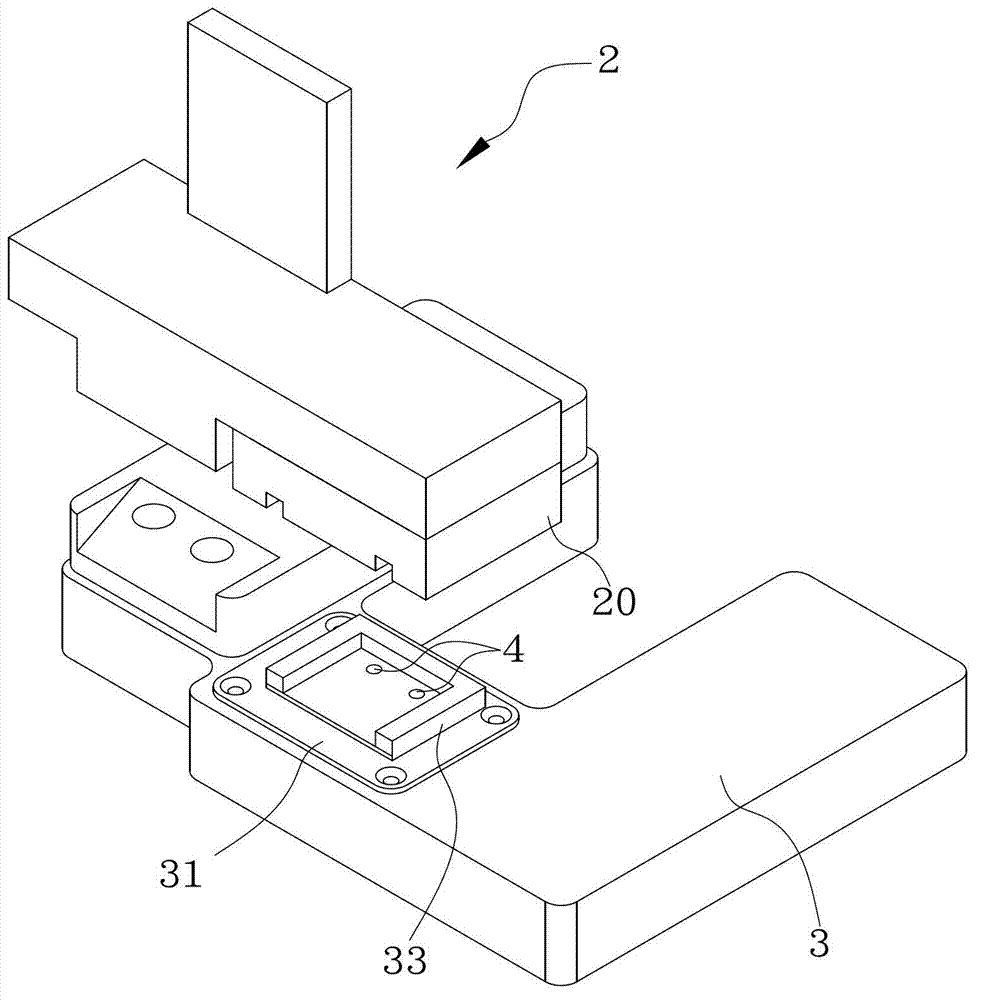

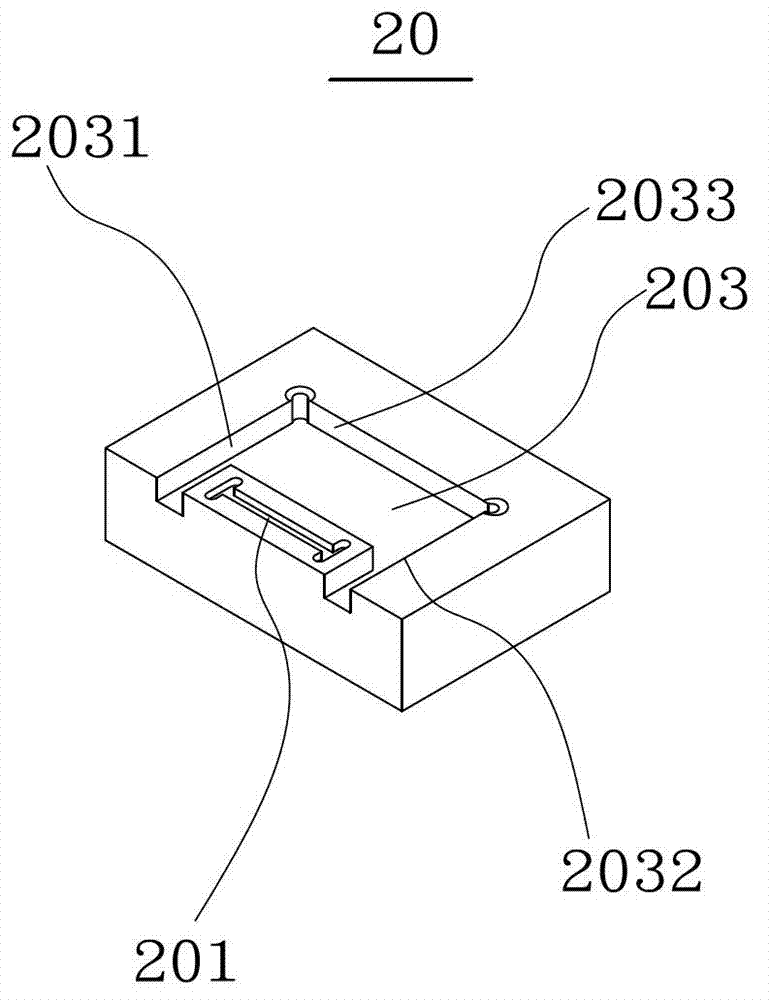

Aligning device, bonding apparatus, and aligning method

InactiveUS20080245472A1Reliable alignmentFreedom of movementWelding/cutting auxillary devicesSemiconductor/solid-state device manufacturingEngineeringElectronic component

An aligning device that can reliably correct misalignment between electronic components for increasing the accuracy in aligning the electronic components, a bonding apparatus equipped with the aligning device, and an aligning method. The aligning device comprises a chamber; a flexible bellows configured to define an airtight chamber therein with the chamber; a driving unit configured to move one of a first block member and a second block member relative to the other, the first block member being for holding a first electronic component and being provided in the airtight chamber, and the second block member being for holding a second electronic component and being provided in the airtight chamber; and an image-taking port protruding inward from an outer surface of the chamber so as to define a space, the image-taking port having an observation window through which at least one of the first electronic component and the second electronic component is observed. In an embodiment, an image-taking port 21 protrudes inward from an outer surface of a chamber 3 so as to define a space 11. Thus, even when the chamber 3 moves together with a second block-member 28, an image recognizing device 47 can be provided in the space 11 so as to be prevented from interfering with the motion of the chamber 3. This allows the chamber 3 to freely move without any restriction. As a result, one of a first block member 12 and the second block member 28 can be freely moved relative to the other without being restricted by the placement of the image recognizing device 47, and a first wafer W1 and a second wafer W2 can be aligned reliably.

Owner:MURATA MFG CO LTD

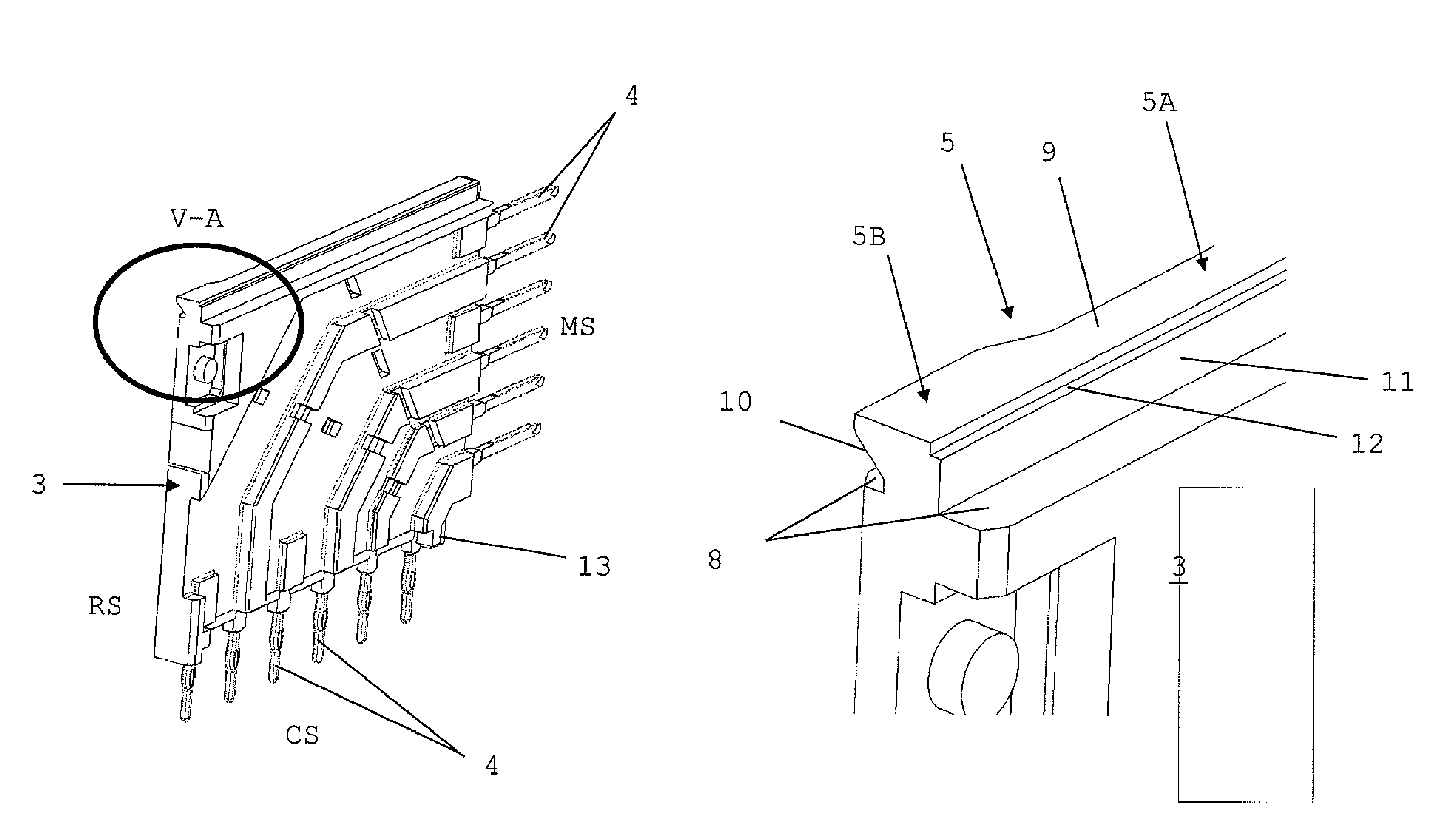

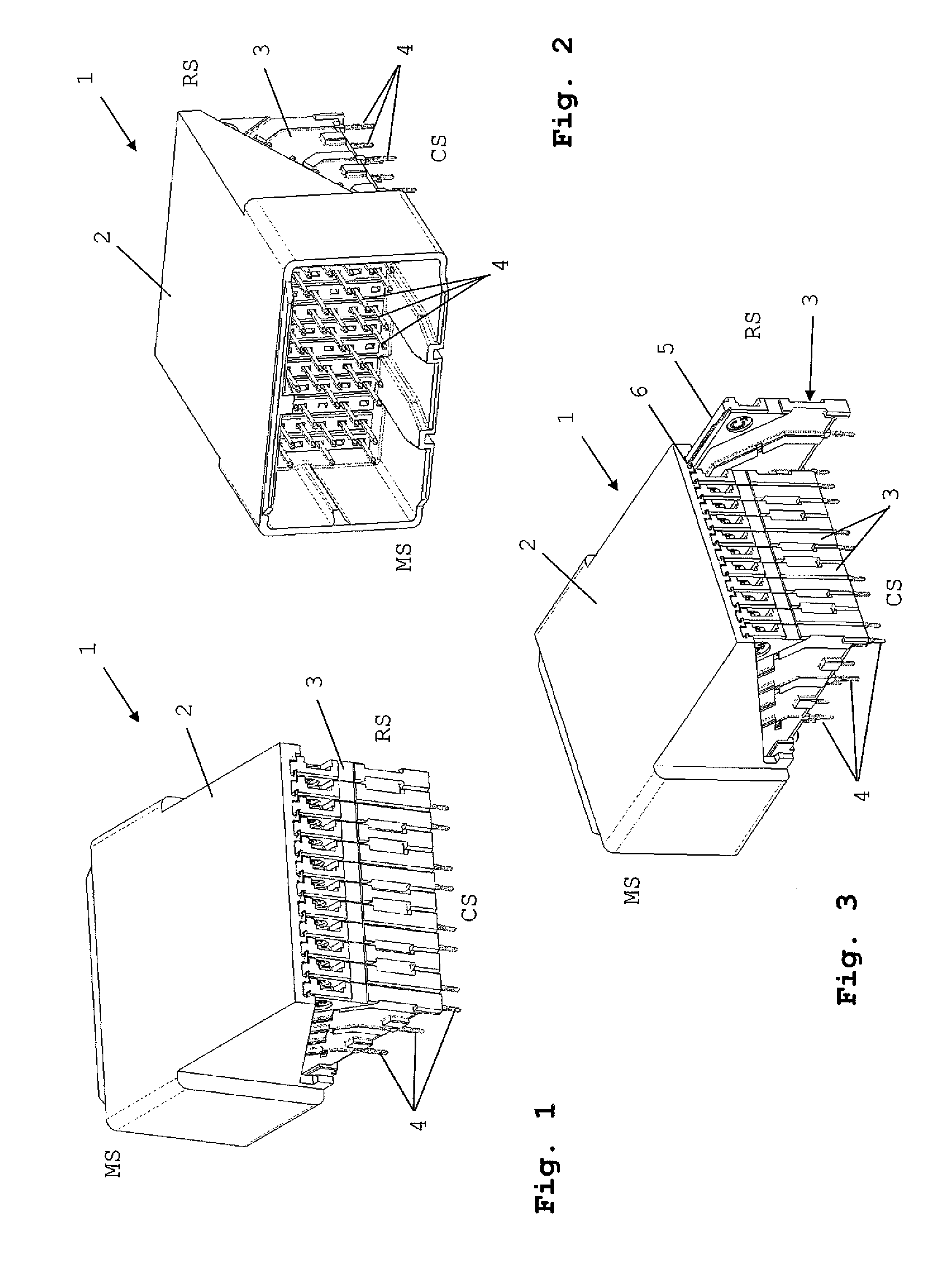

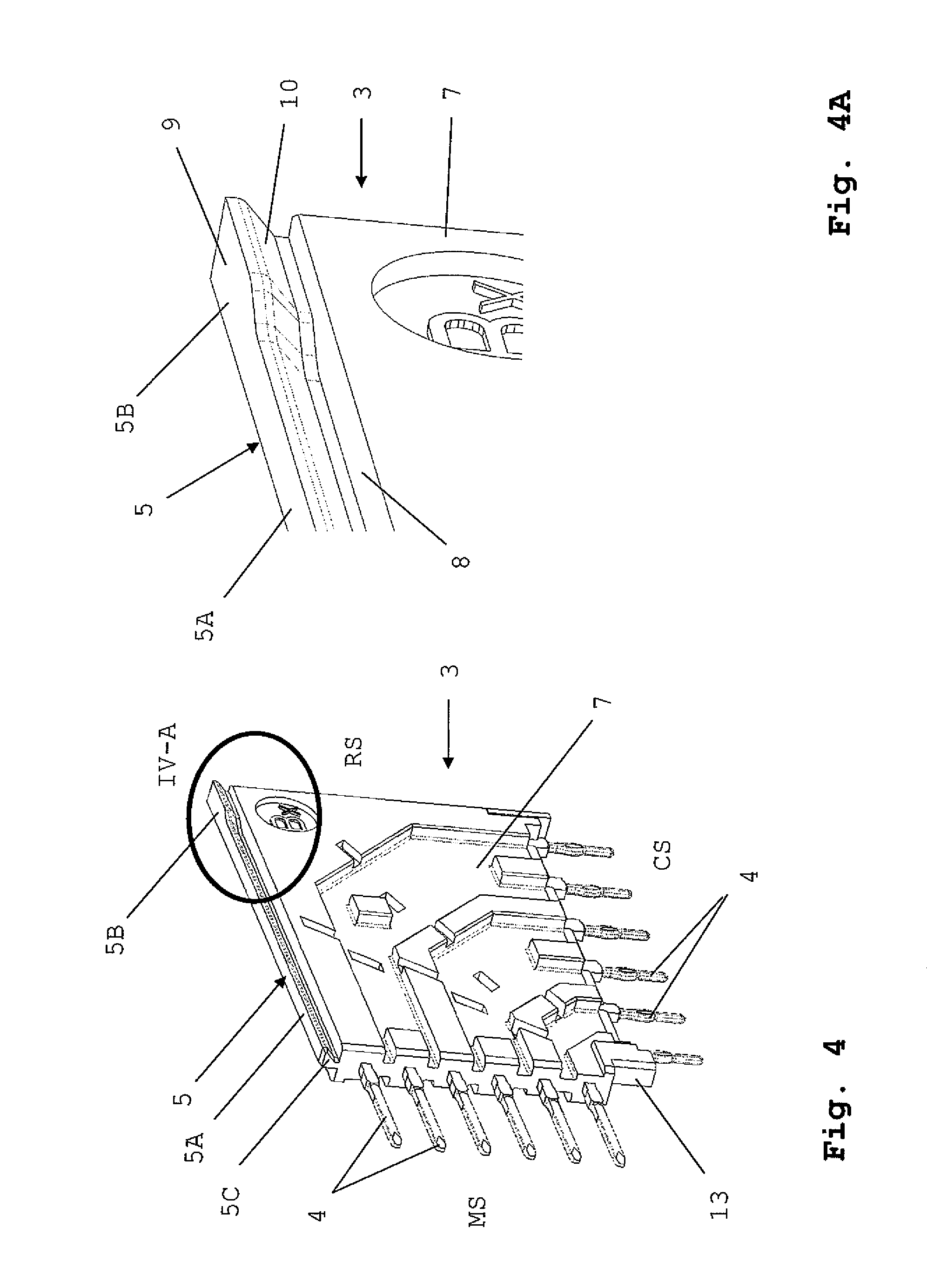

Modular connector

ActiveUS8210877B2Improves localisation and mounting accuracy of partReliable manufacturingIncorrect coupling preventionCoupling protective earth/shielding arrangementsModularityElectrical connector

An electrical connector includes at least two parts: a housing having a mating side (MS) and a rear side (RS) and a terminal module having a mating side and a rear side. One part includes a mounting structure and the other part includes a corresponding receiving structure for receiving the mounting structure of the other part. The mounting structure extends in a direction from the mating side to the rear side of the part and includes a cross-section perpendicular to that direction, which cross-section has an asymmetric profile.

Owner:FCI ASIA PTE LTD

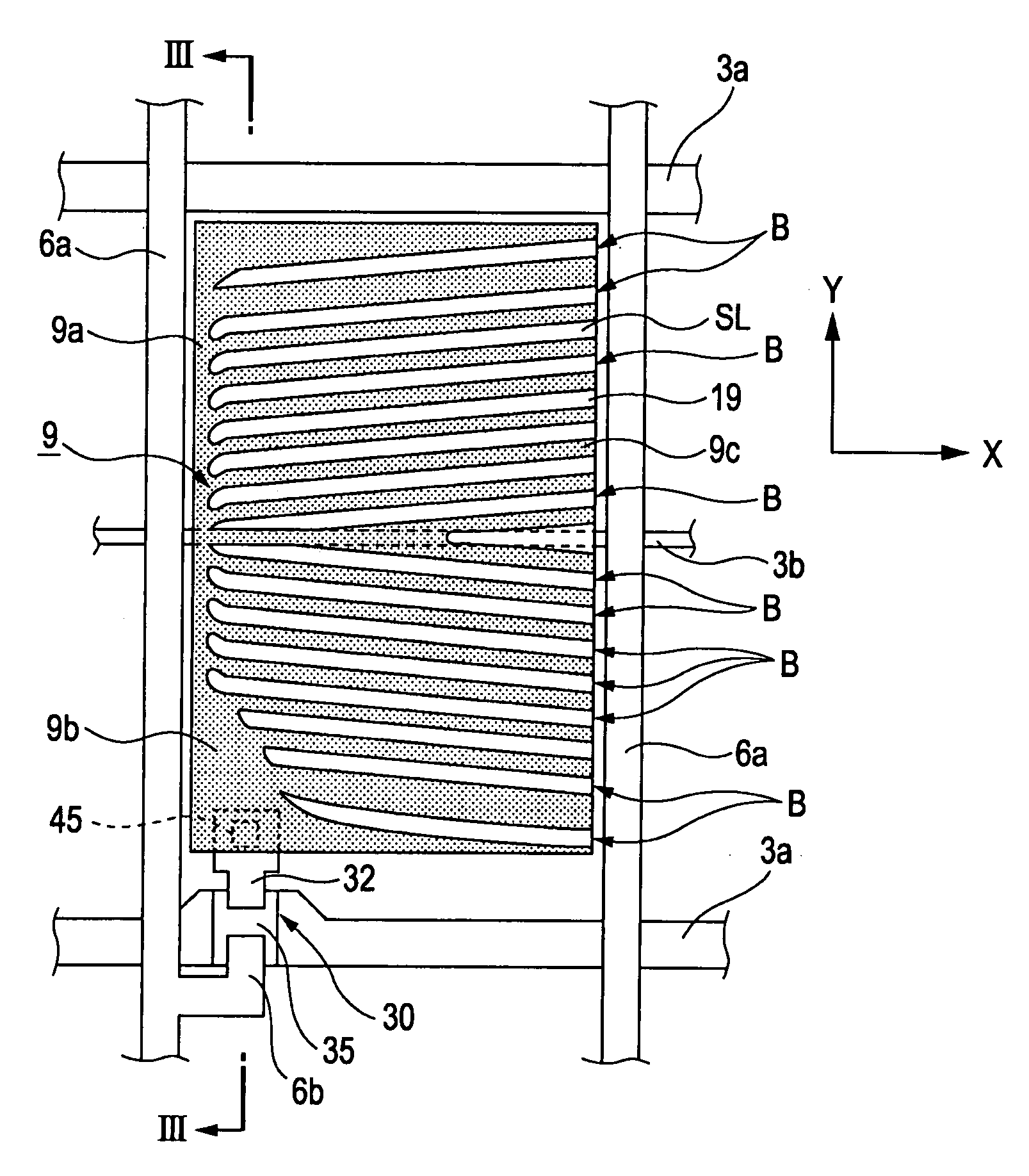

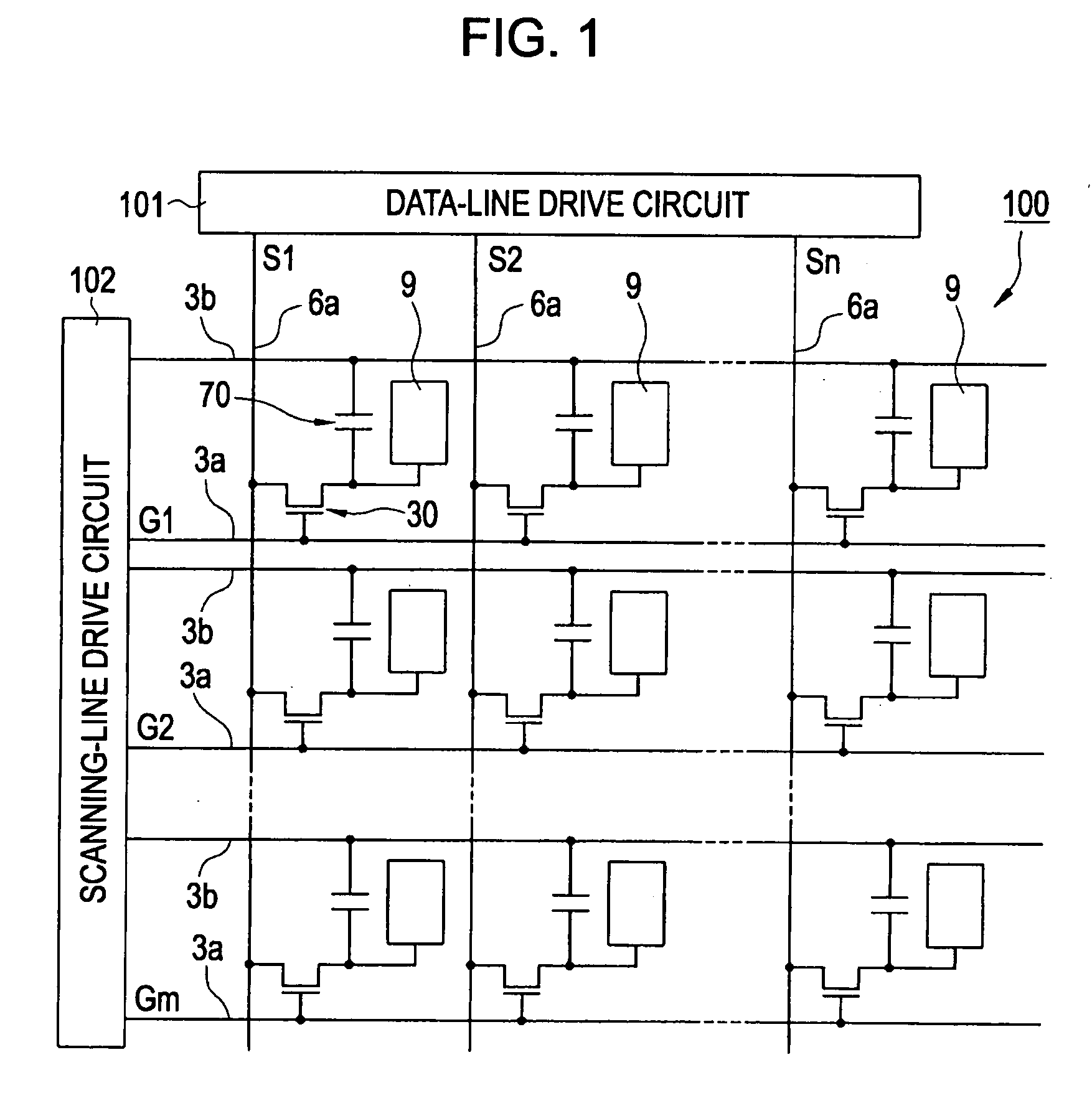

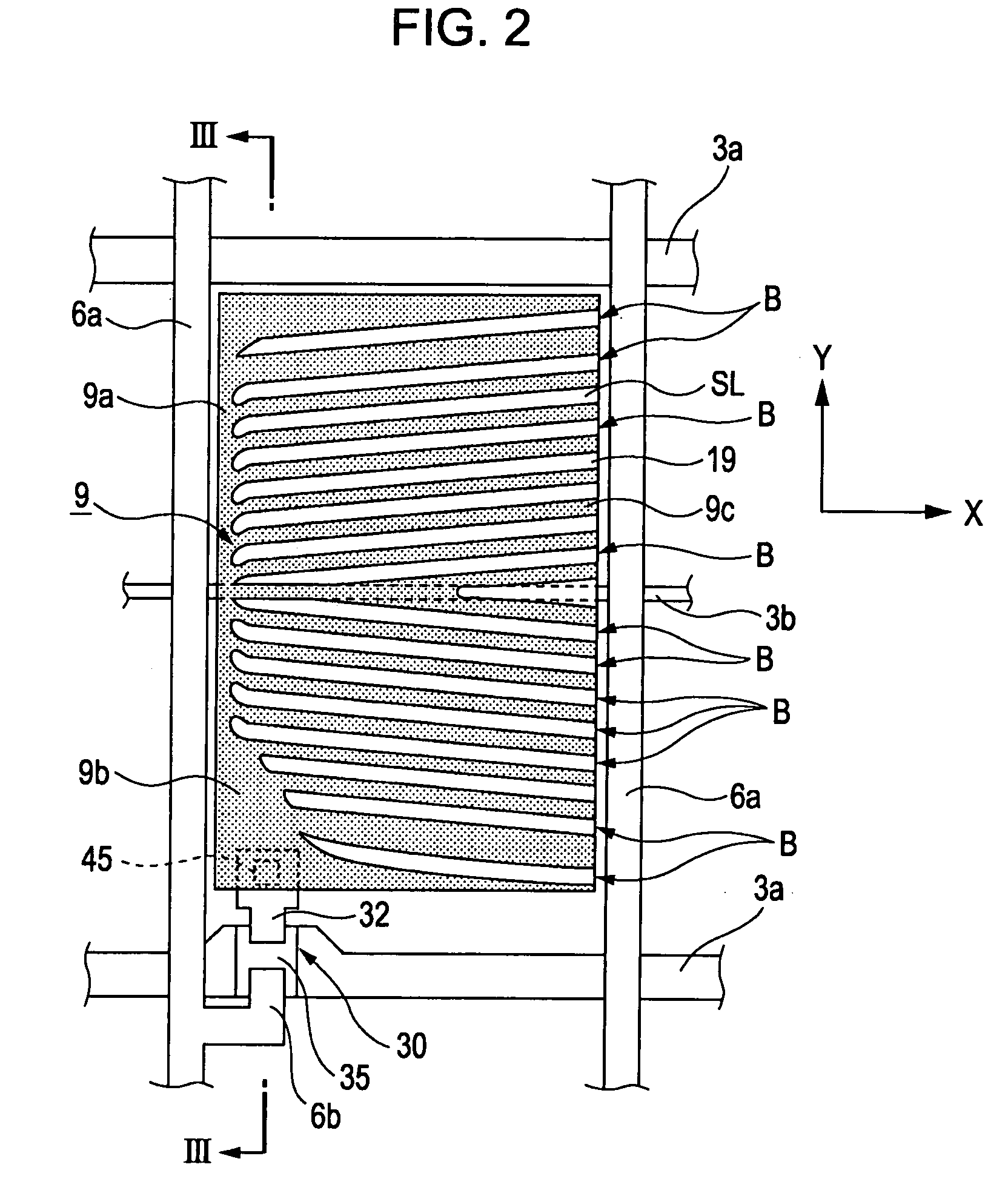

Liquid crystal device and electronic apparatus

A liquid crystal device includes a first substrate and a second substrate facing each other with a liquid crystal layer held therebetween; first electrodes and second electrodes provided on a surface of the first substrate, the surface facing toward the liquid crystal layer; data lines and scanning lines provided on the surface of the first substrate, the surface facing toward the liquid crystal layer, the data lines and the scanning lines intersecting one another; and switching elements connected to the corresponding data lines and the corresponding scanning lines. The alignment of liquid crystal molecules of the liquid crystal layer is controlled by an electric field induced between the first and second electrodes. The first electrodes are arranged in corresponding pixel regions enclosed by the data lines and the scanning lines. Each of the second electrodes has a plurality of branch electrodes extending in a direction intersecting a corresponding one of the data lines and a connecting portion electrically connecting the branch electrodes with one another such that at least one of first and second ends of the adjacent branch electrodes is open. The second electrodes are arranged such that each of the second electrodes partially overlaps a corresponding one of the first electrodes in a corresponding one of the pixel regions when viewed in plan.

Owner:EPSON IMAGING DEVICES CORP

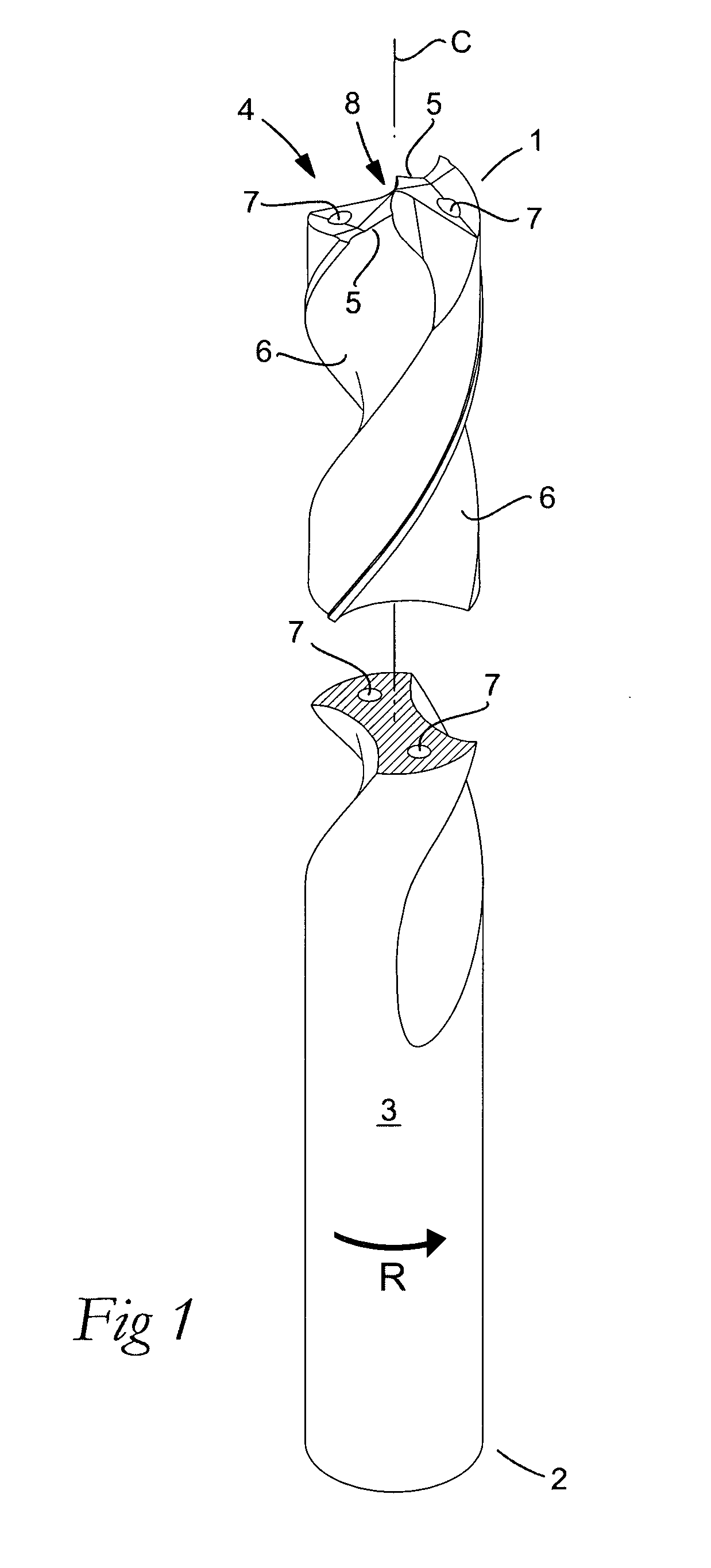

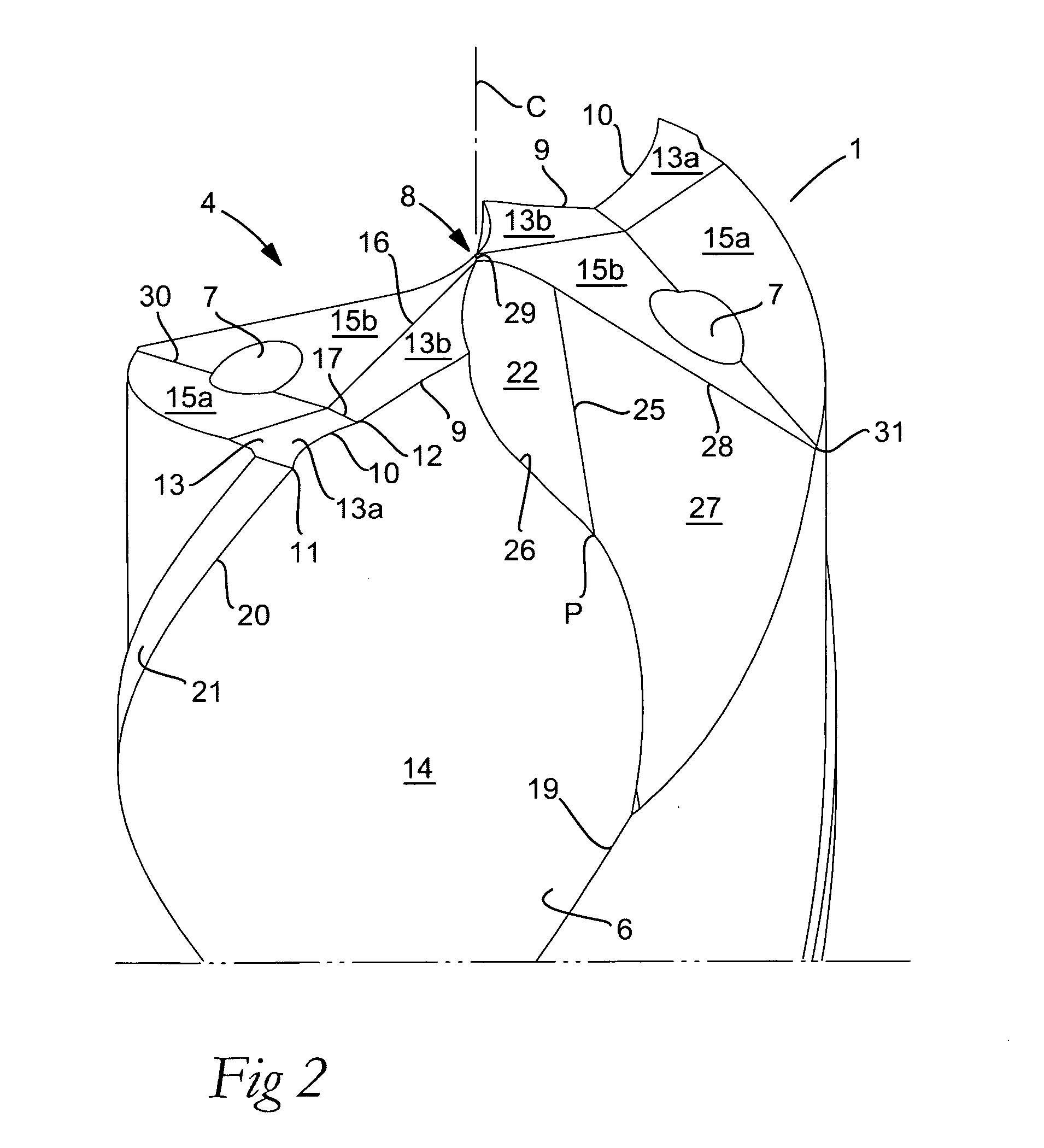

Drill body

ActiveUS20090279965A1Moderate cutting forceReliable alignmentWood turning toolsTransportation and packagingEngineeringDrill

Owner:SANDVIK INTELLECTUAL PROPERTY AB

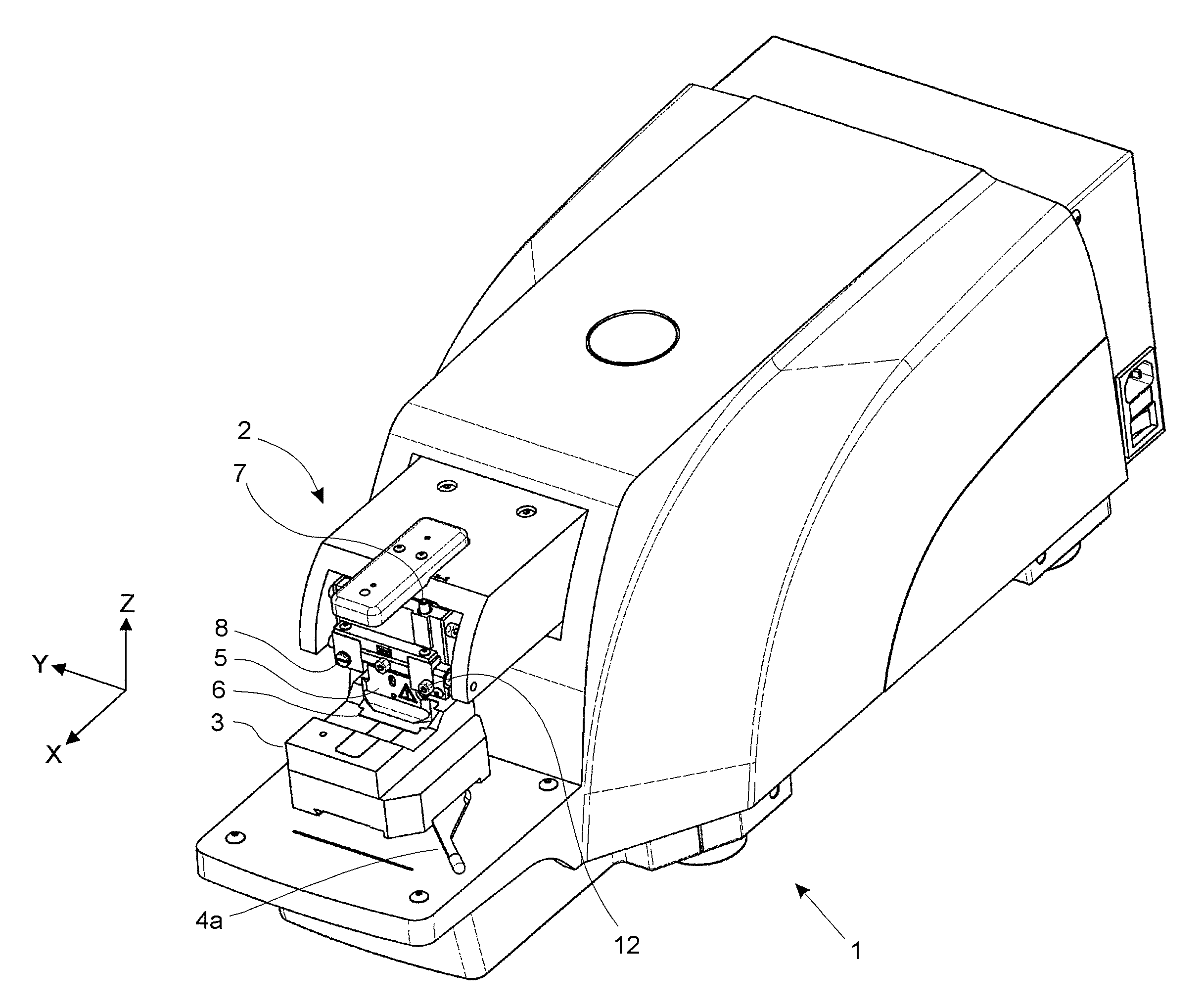

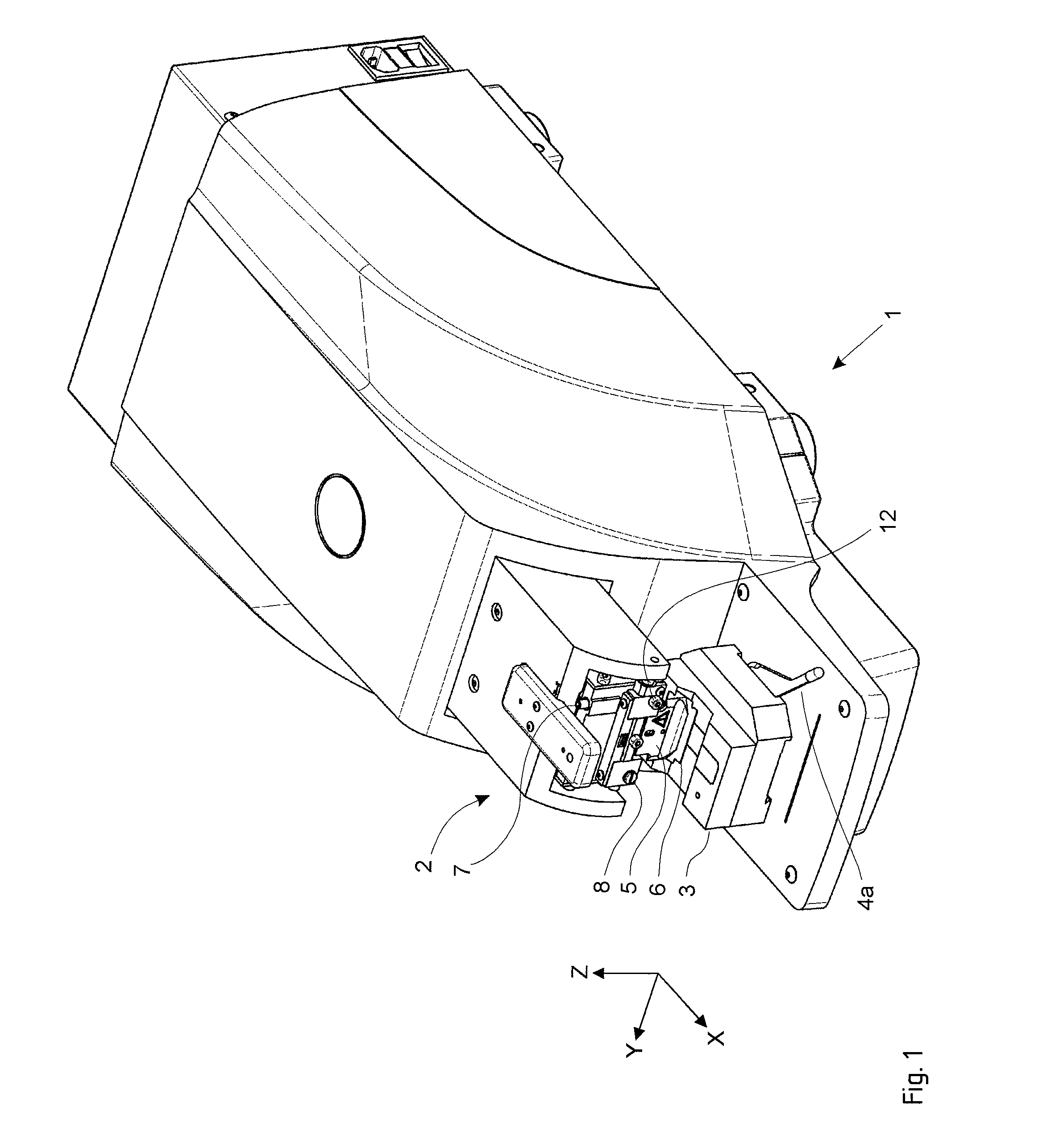

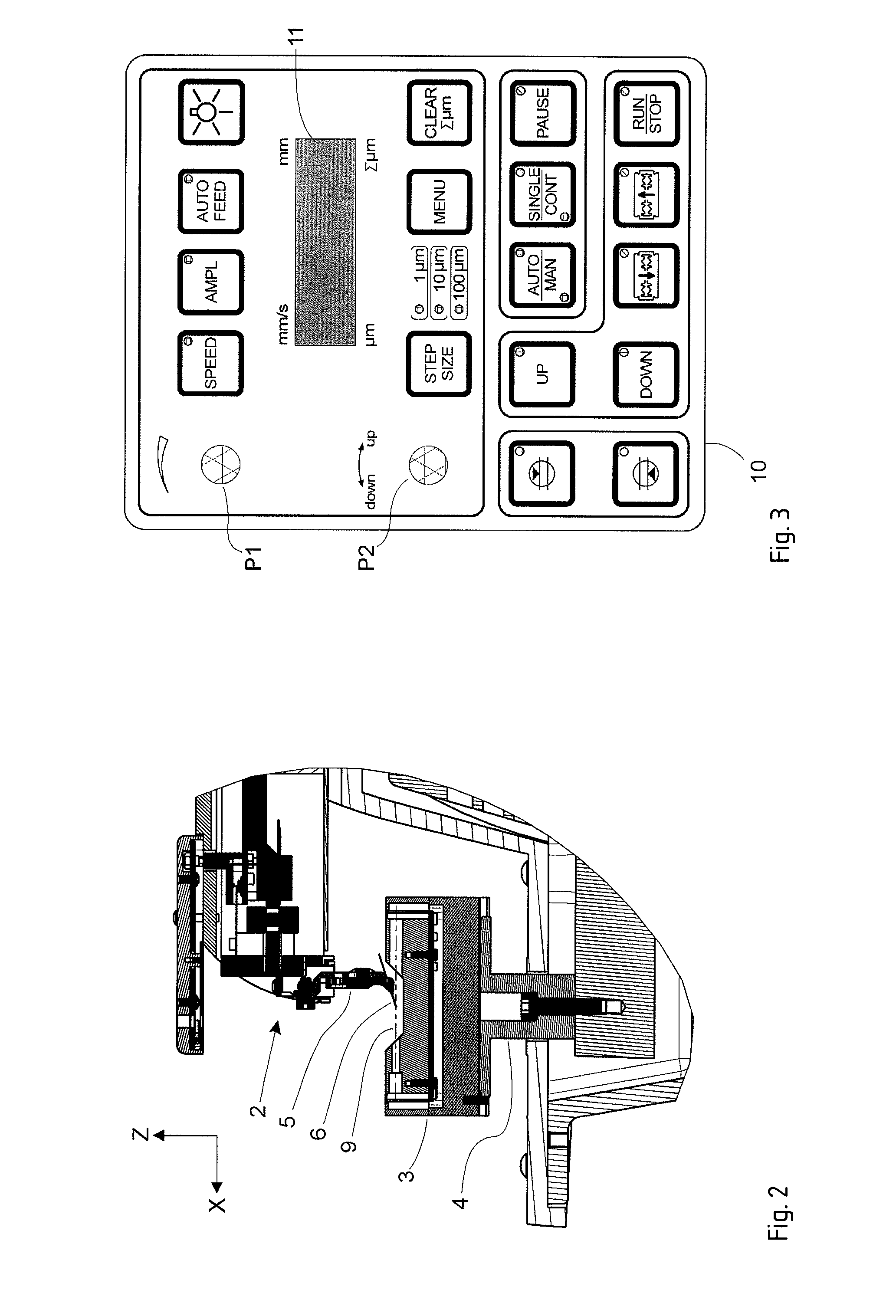

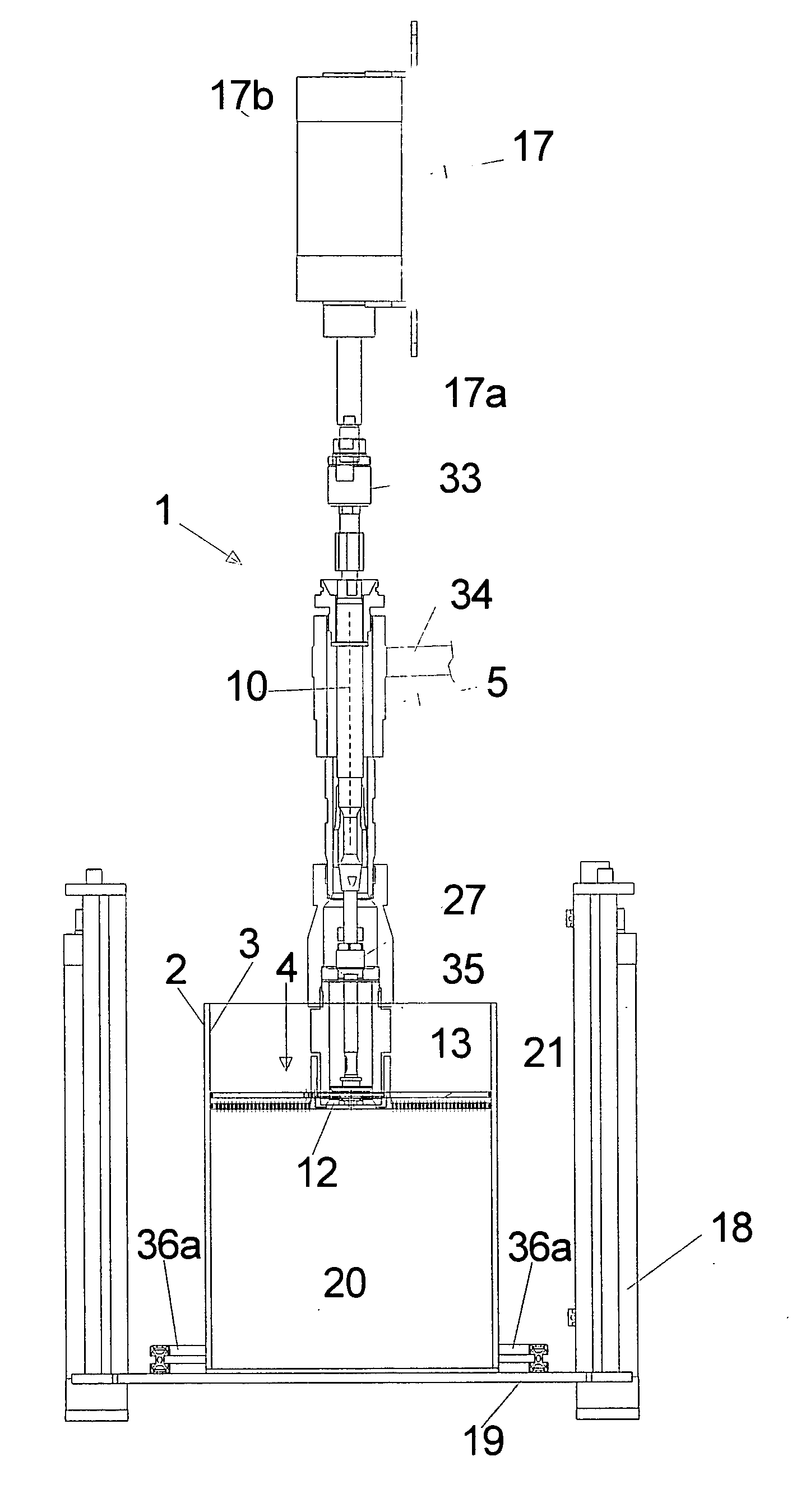

Vibrating Microtome With Automated Measurement Of Vertical Runout

ActiveUS20080072722A1Simplify and speed up alignmentReliable alignmentAutomatic control devicesWithdrawing sample devicesTime courseSection plane

In a vibrating microtome (1), a knife (6) is caused to vibrate during a sectioning operation in a direction parallel to a section plane and substantially parallel to the knife's edge, during which a transverse offset can occur as a consequence of a potentially present inclination of the cutting edge with respect to the section plane. A measuring device (3) for measuring the transverse offset comprises a light barrier (9) into which the cutting edge is placeable so as to partially cover the light of the light barrier. The vibrating microtome (1) generates, from the motion of the knife, a control application signal (pklo, pkhi) that describes the time course of the vibration of the knife (6), and the electronic measurement system of the measuring device (3) measures the coverage of the light barrier as a consequence of the vibration of the knife as an oscillating signal (tpm), and determines the transverse offset from the signal values at points in time that are defined by the control application signal.

Owner:LEICA BIOSYST NUSSLOCH

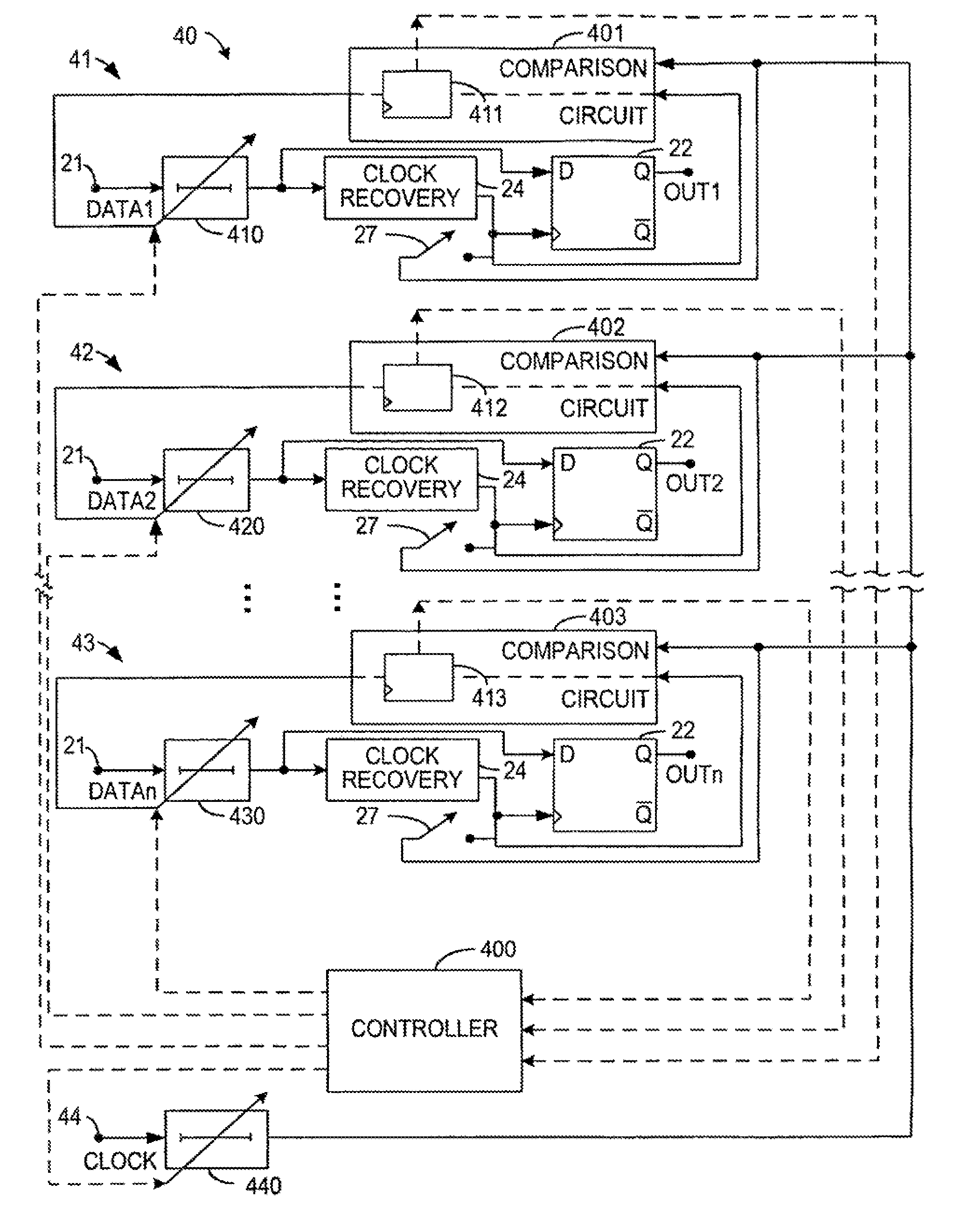

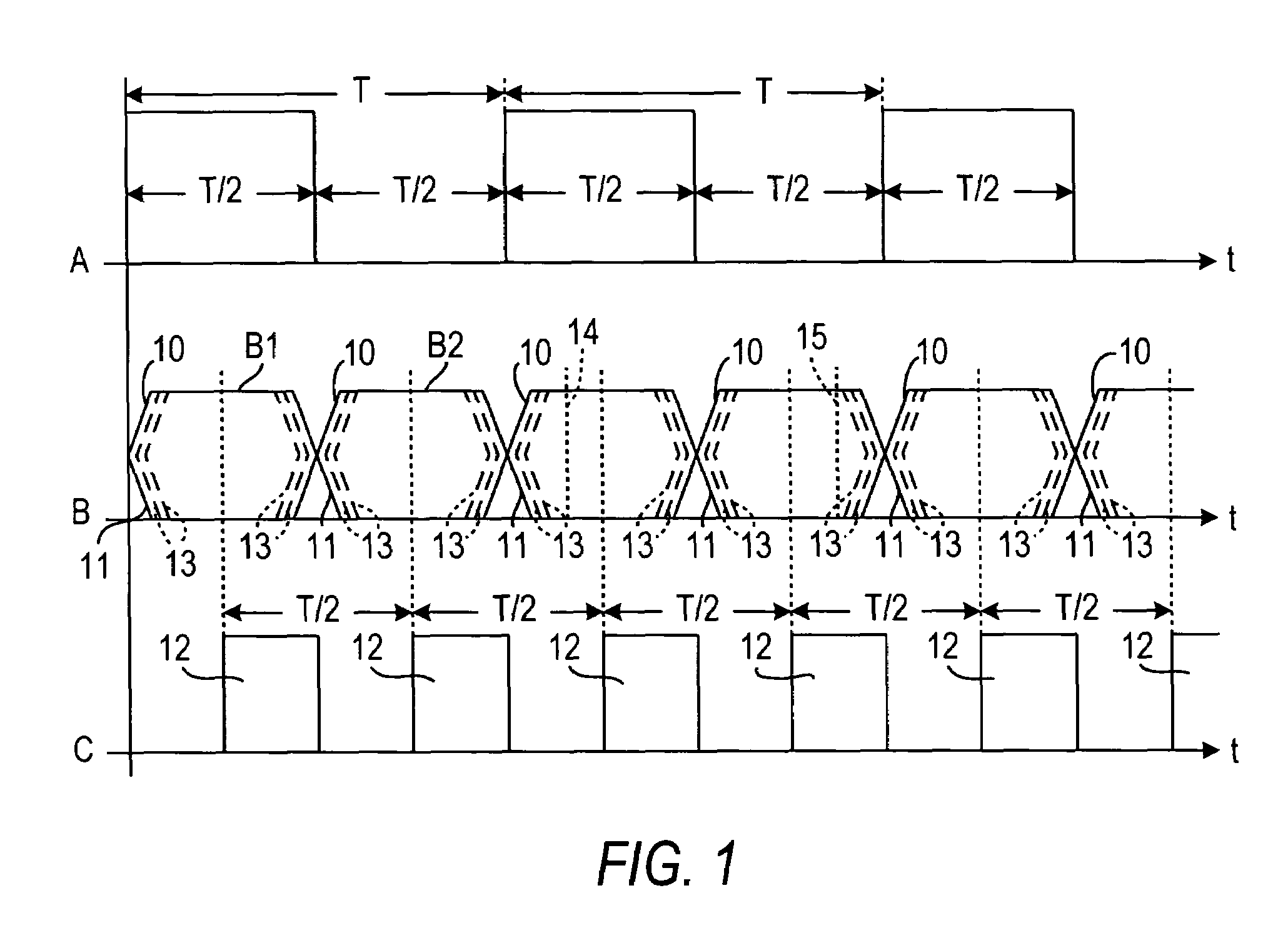

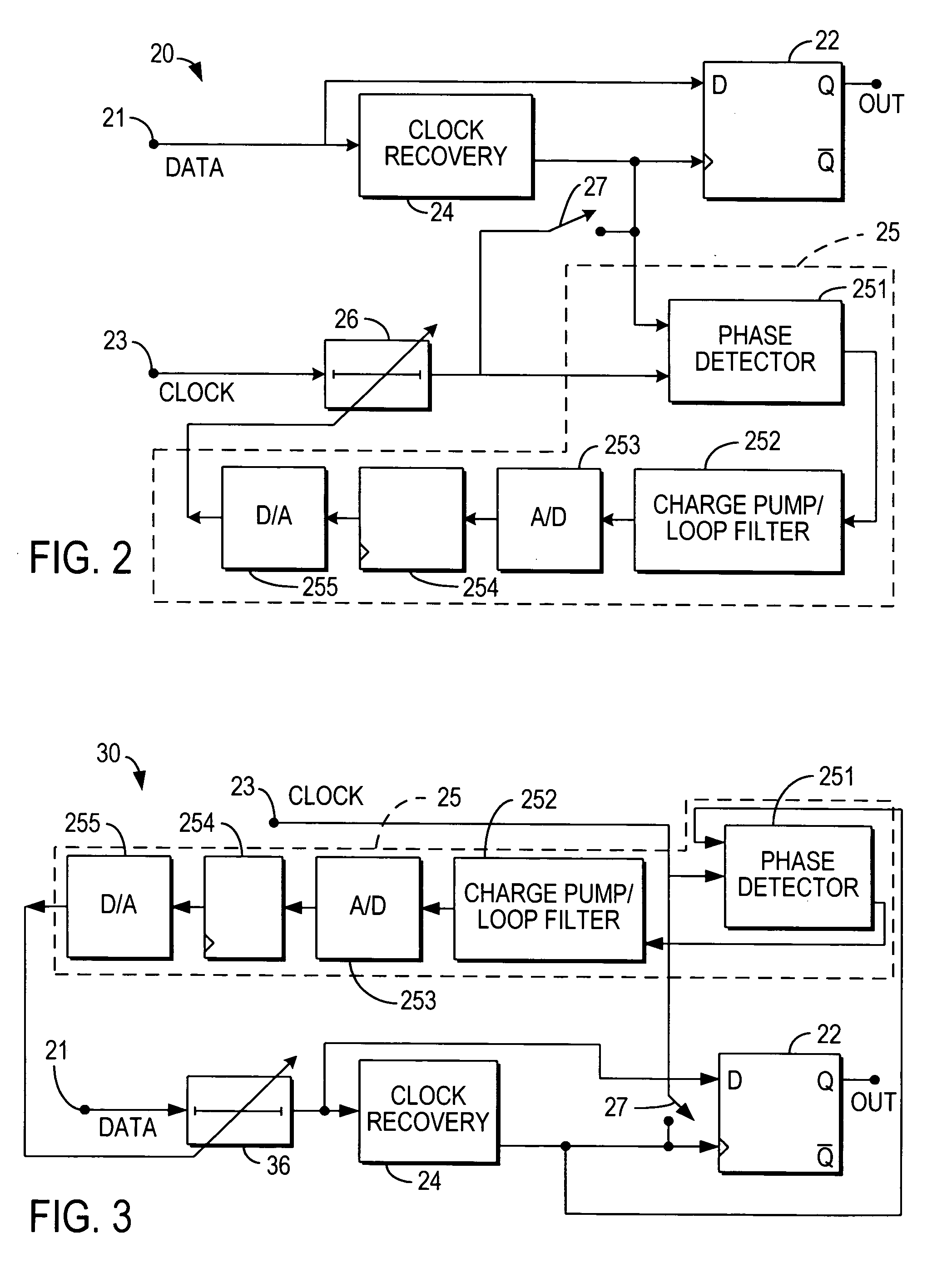

Alignment of clock signal with data signal

InactiveUS7486752B1Reliable alignmentReduce power consumptionChannel dividing arrangementsAngle demodulation by phase difference detectionData signalTime alignment

A received clock signal is aligned (“eye centered”) with a received data signal by recovering a separate clock from the data signal and comparing and aligning the received clock with the recovered clock by delaying one or both of the received clock and the received data as necessary. After the necessary delays are set, the comparison / alignment circuitry can be turned off, until the next time alignment is necessary, to conserve power. In a multiple channel system, any combination of each received data channel, the received clock, or individual branches of the received clock in each channel can be delayed as necessary. Each channel can have its own comparison / alignment circuitry so that all channels can be aligned simultaneously, or re-usable circuitry can be provided for connection sequentially to each channel where sequential alignment of the channels is fast enough.

Owner:ALTERA CORP

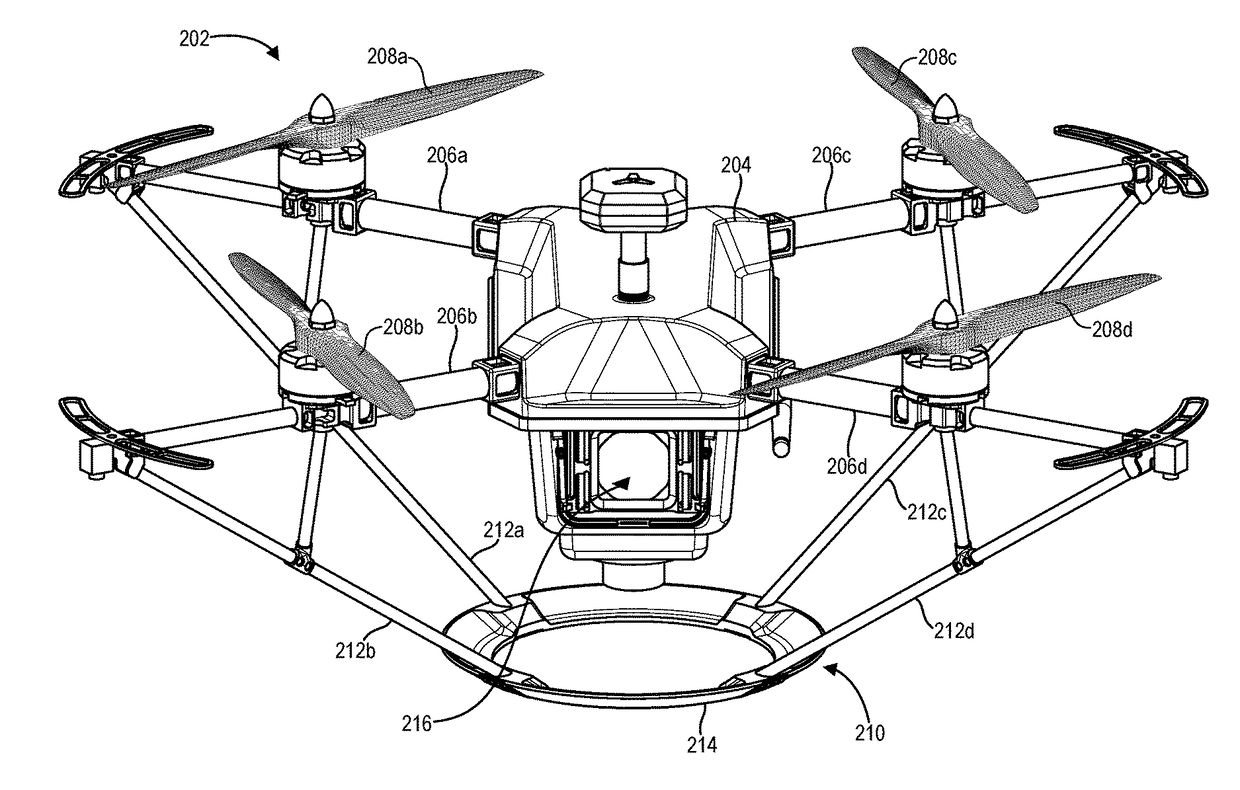

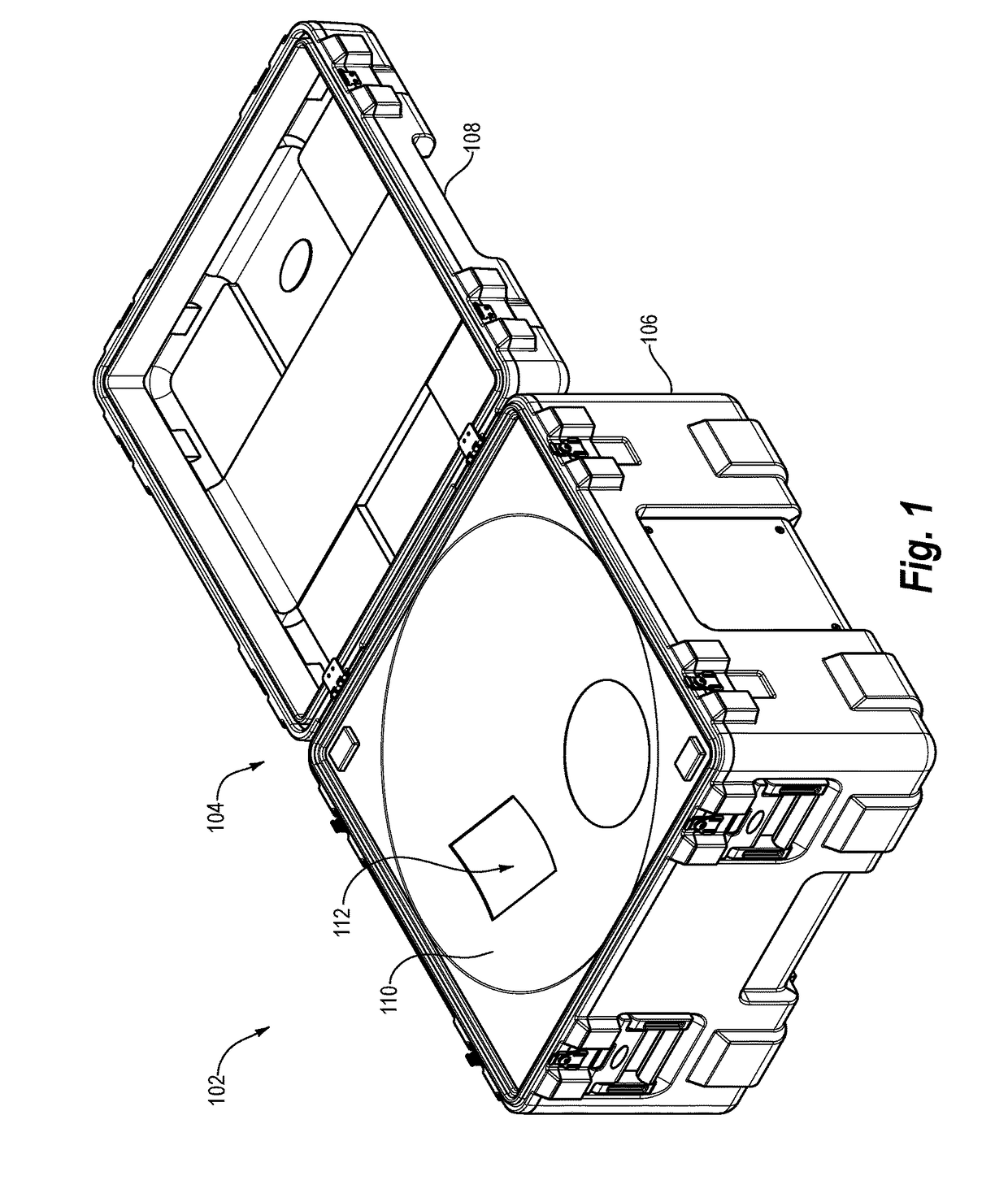

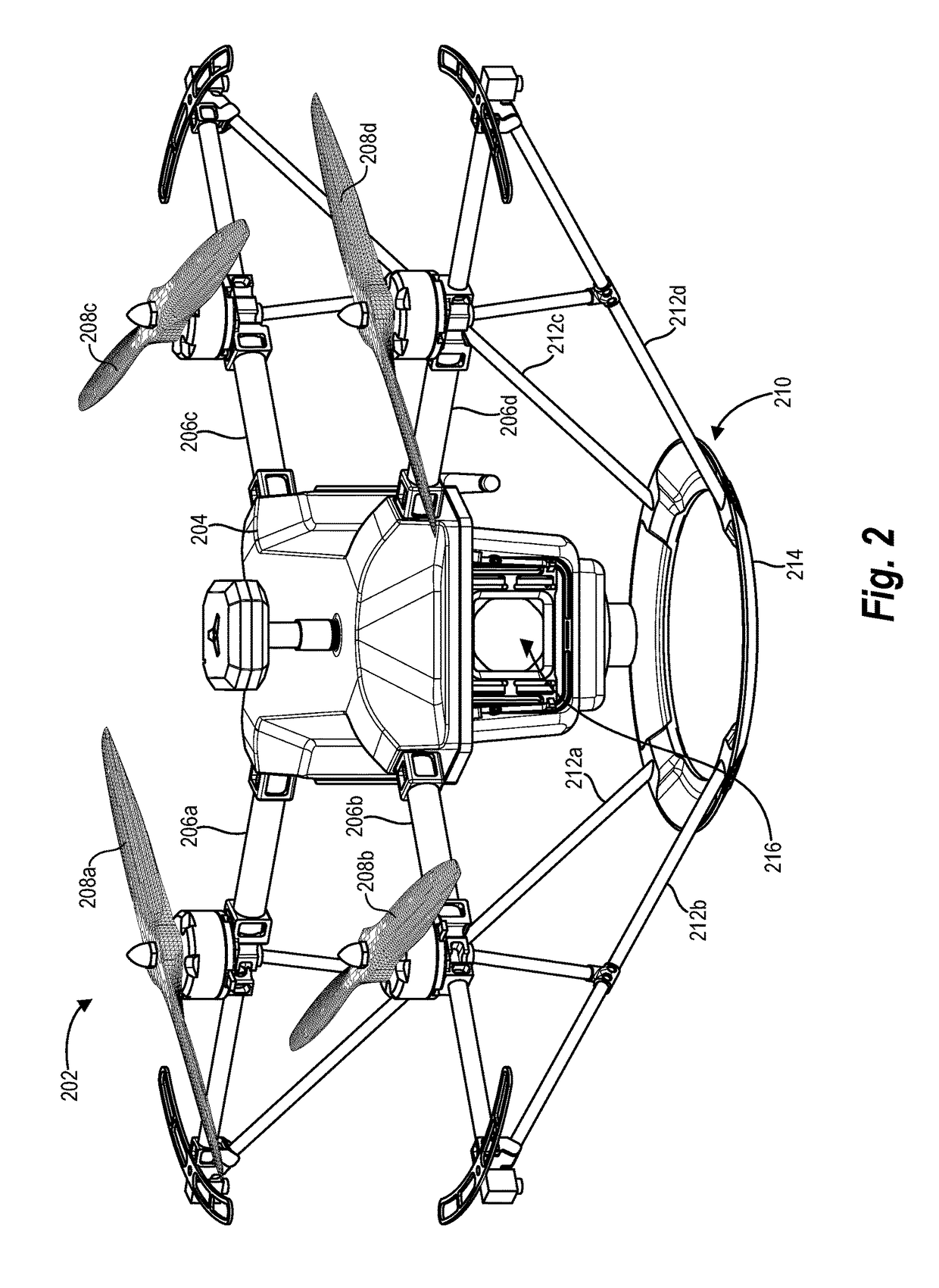

Battery arm sensor assembly

InactiveUS20170247120A1Conveniently removedEasy to assembleUnmanned aerial vehiclesRemote controlled aircraftFlight vehicleBattery cell

The present disclosure is directed toward a system for autonomously landing an unmanned aerial vehicle (UAV) within an unmanned aerial vehicle ground station (UAVGS) and removing a battery assembly from within the UAV while landed. In particular, systems described herein enable a battery arm to engage a battery assembly and remove the battery assembly from within the UAV. Additionally, the battery arm can include one or more sensors that detect a pattern of sensor contacts arranged on an end of the battery assembly. In particular, the sensors on the battery arm can detect and identify the battery assembly based on the particular pattern of sensor contacts on the end of the battery assembly.

Owner:SKYCATCH

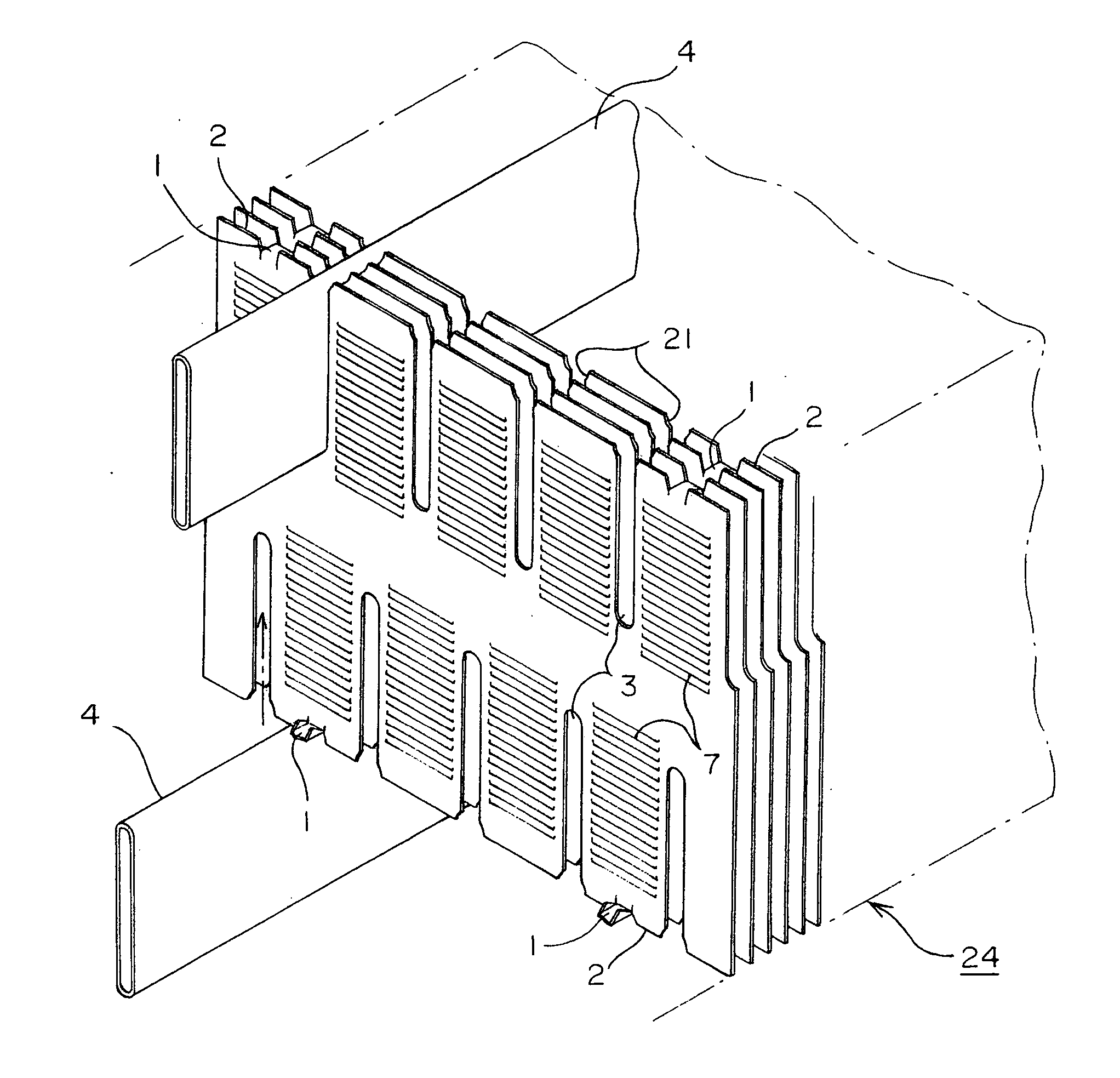

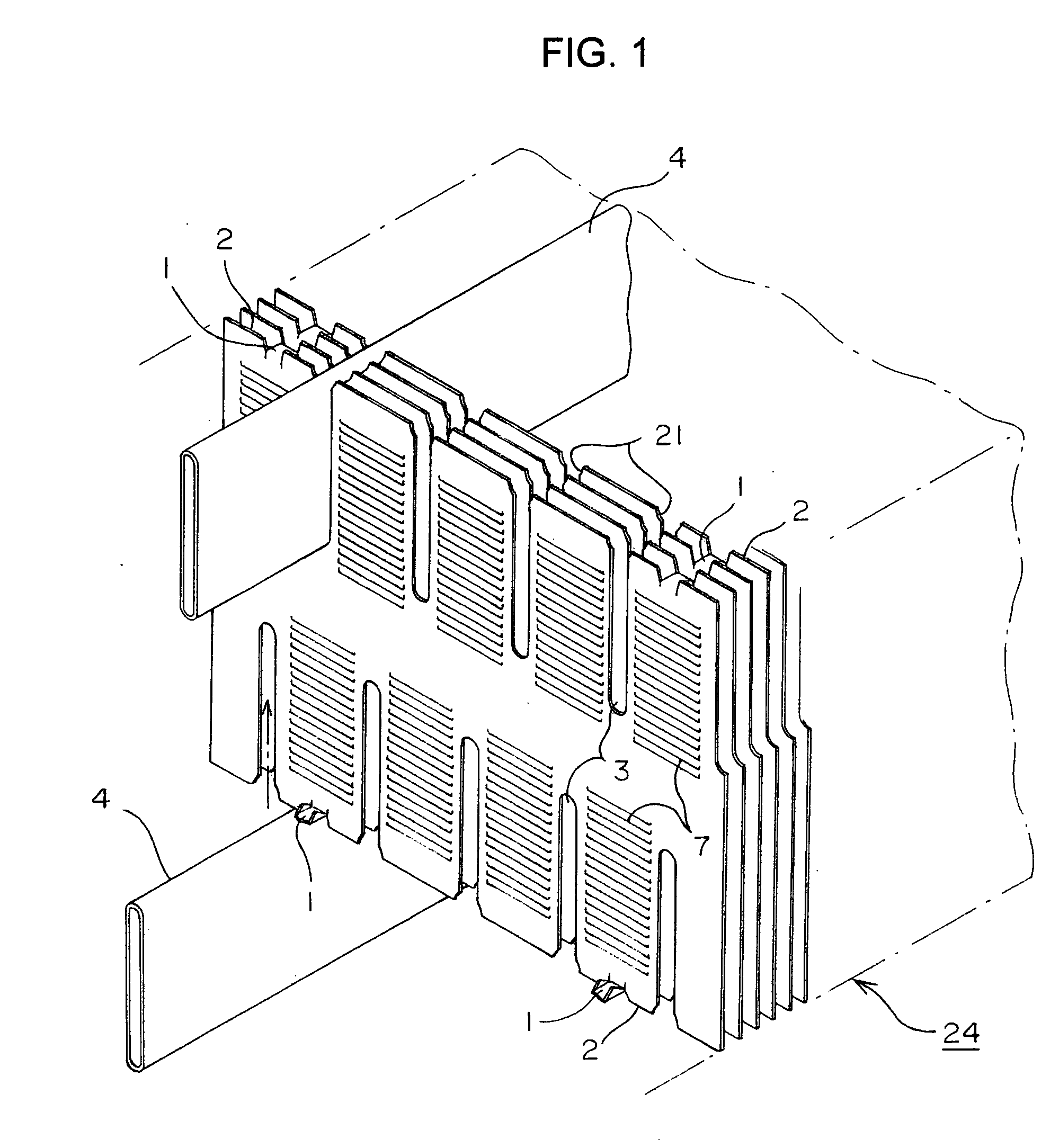

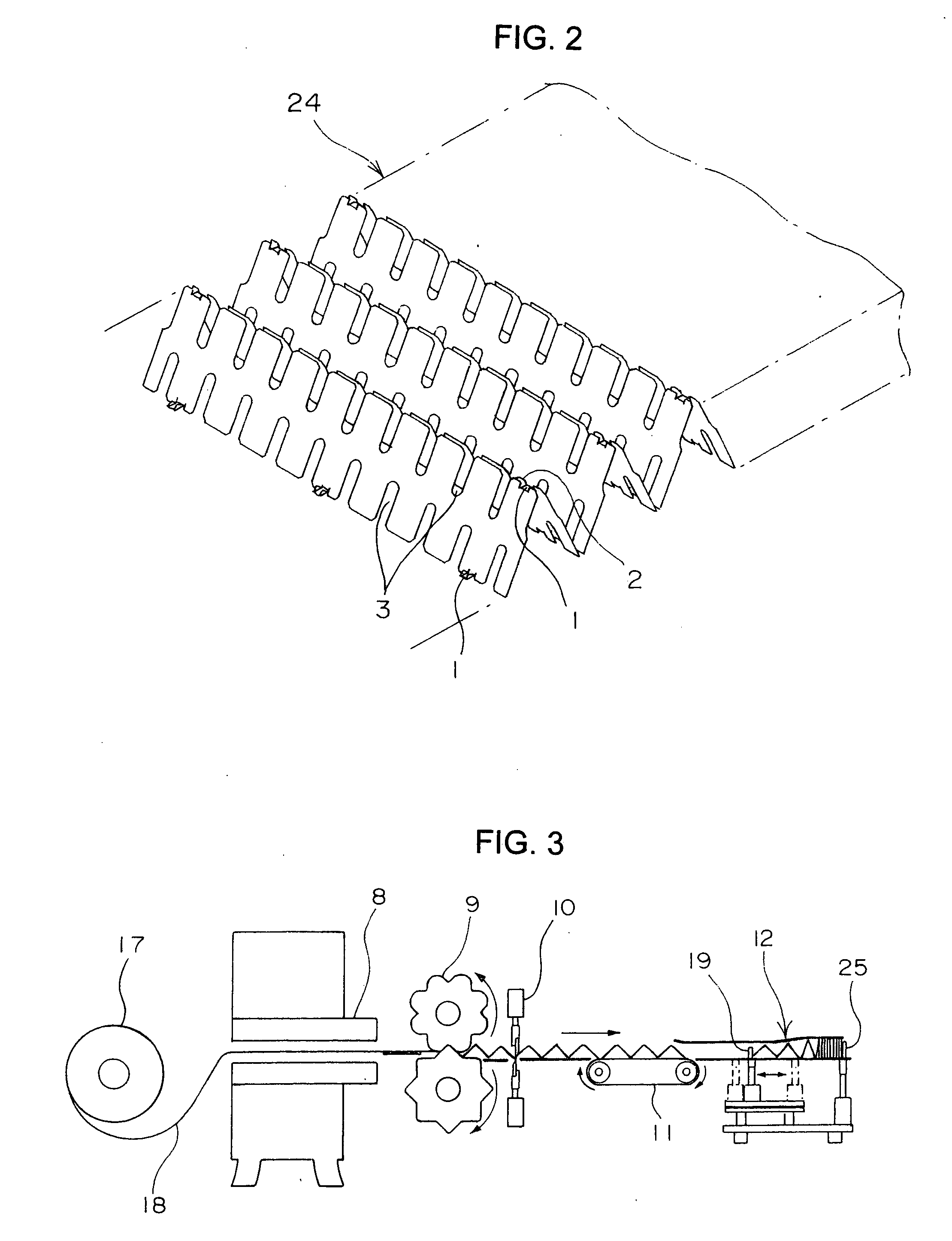

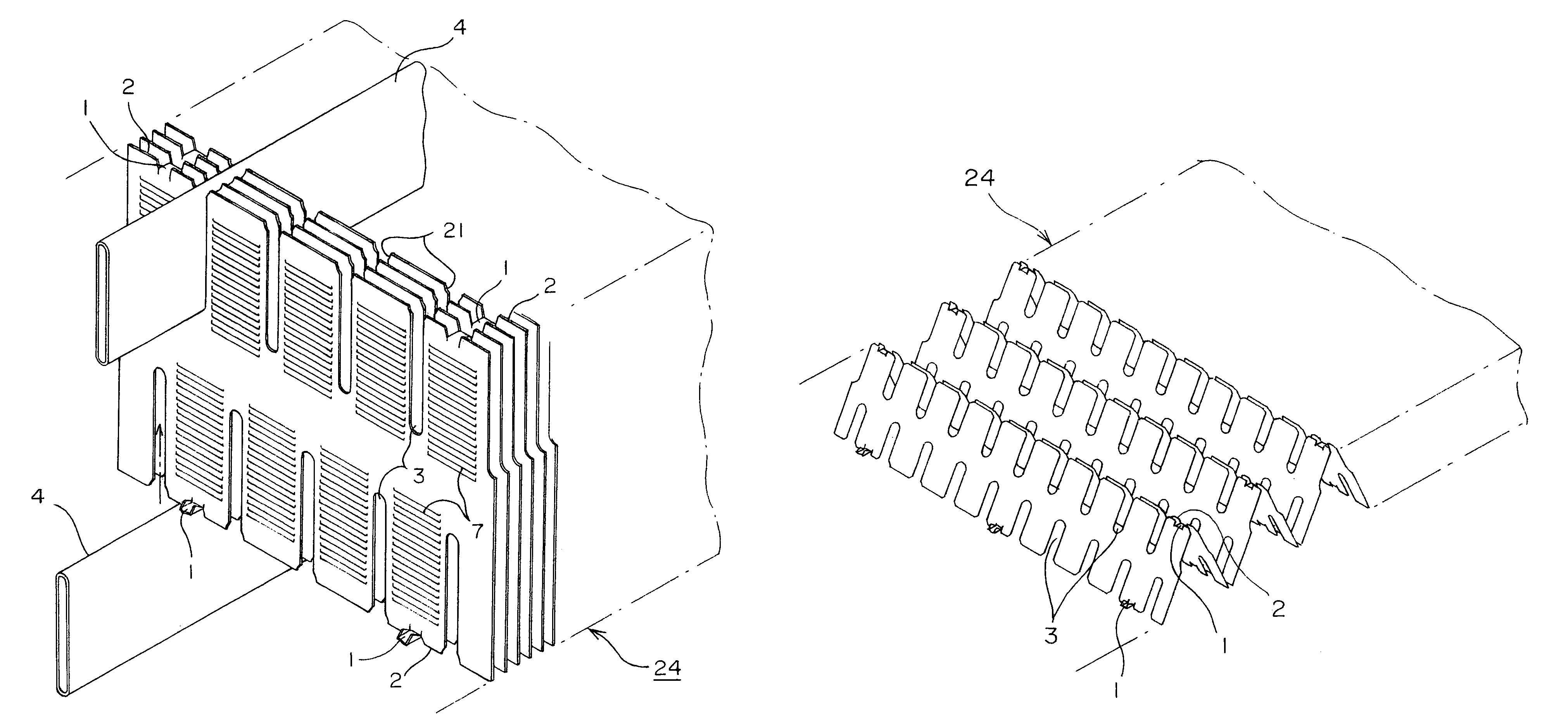

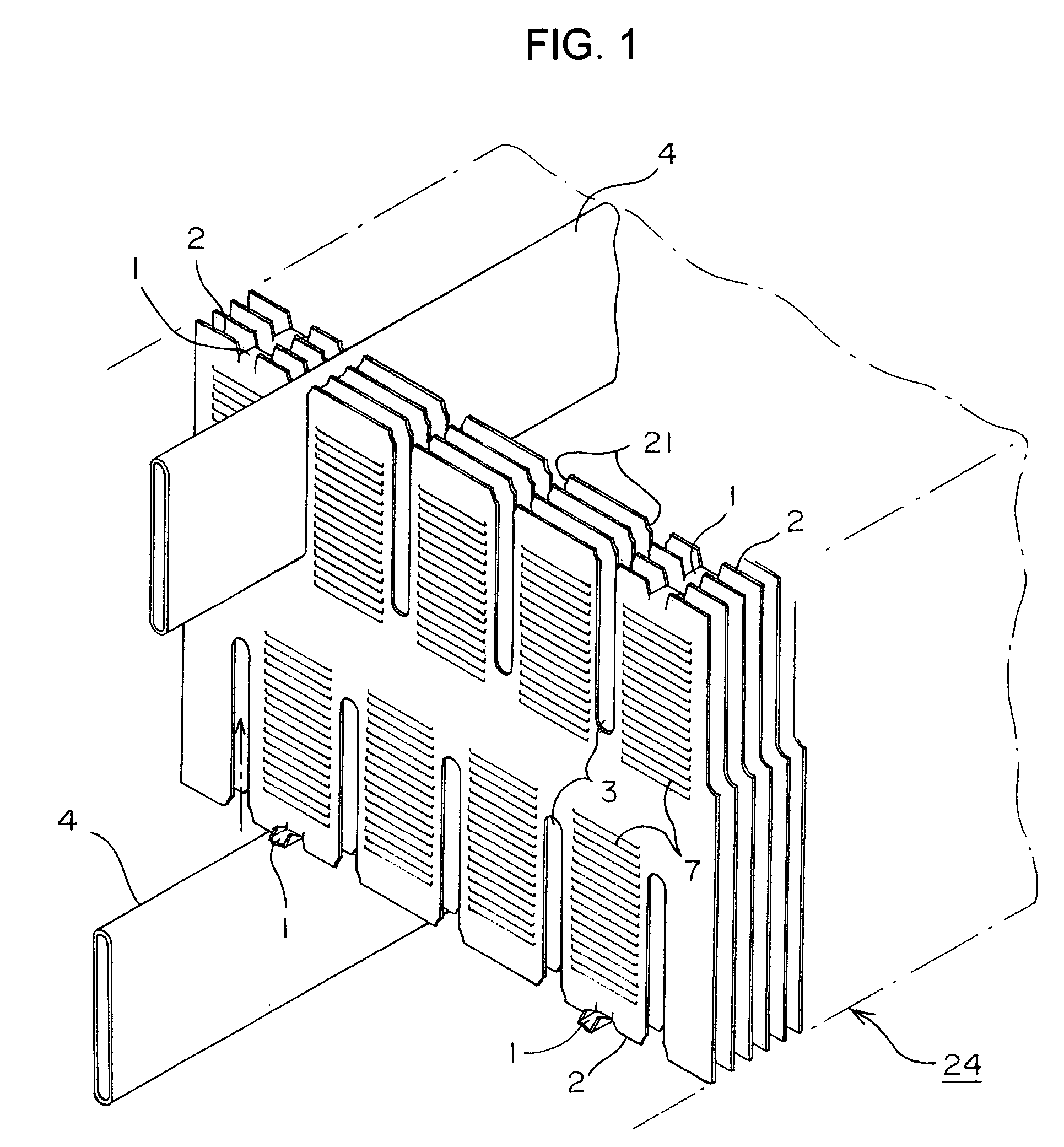

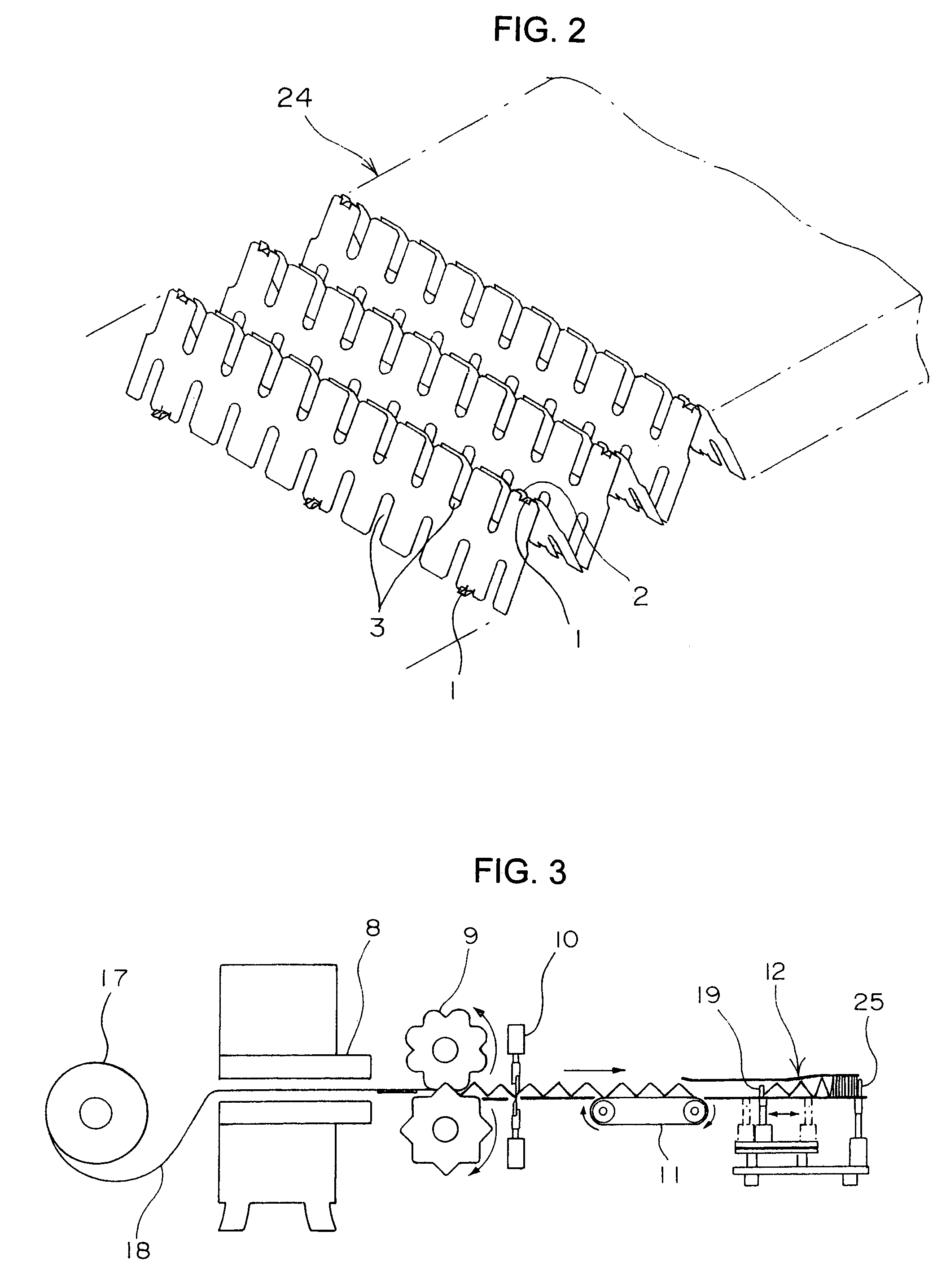

Plate fin for heat exchanger and heat exchanger core

InactiveUS20060070726A1Reliable alignmentImprove reliabilityHeat exhanger finsStationary conduit assembliesEngineeringBand shape

A plate type heat exchanger employing flat tubes, which can be manufactured easily and which have a high heat exchange performance includes a thin strip-shaped metal plate cut in the width direction and having remaining small connected portions and many cut portions disposed at fixed intervals in the longitudinal direction slits are formed in both sides of the cut portions having the same center. The strip-shaped metal plate is bent at the connected portions in a zigzag manner to form an aggregation of fin elements, and the flat tubes are engaged with the front and rear sides of the aggregation of the fin elements.

Owner:T RAD CO LTD

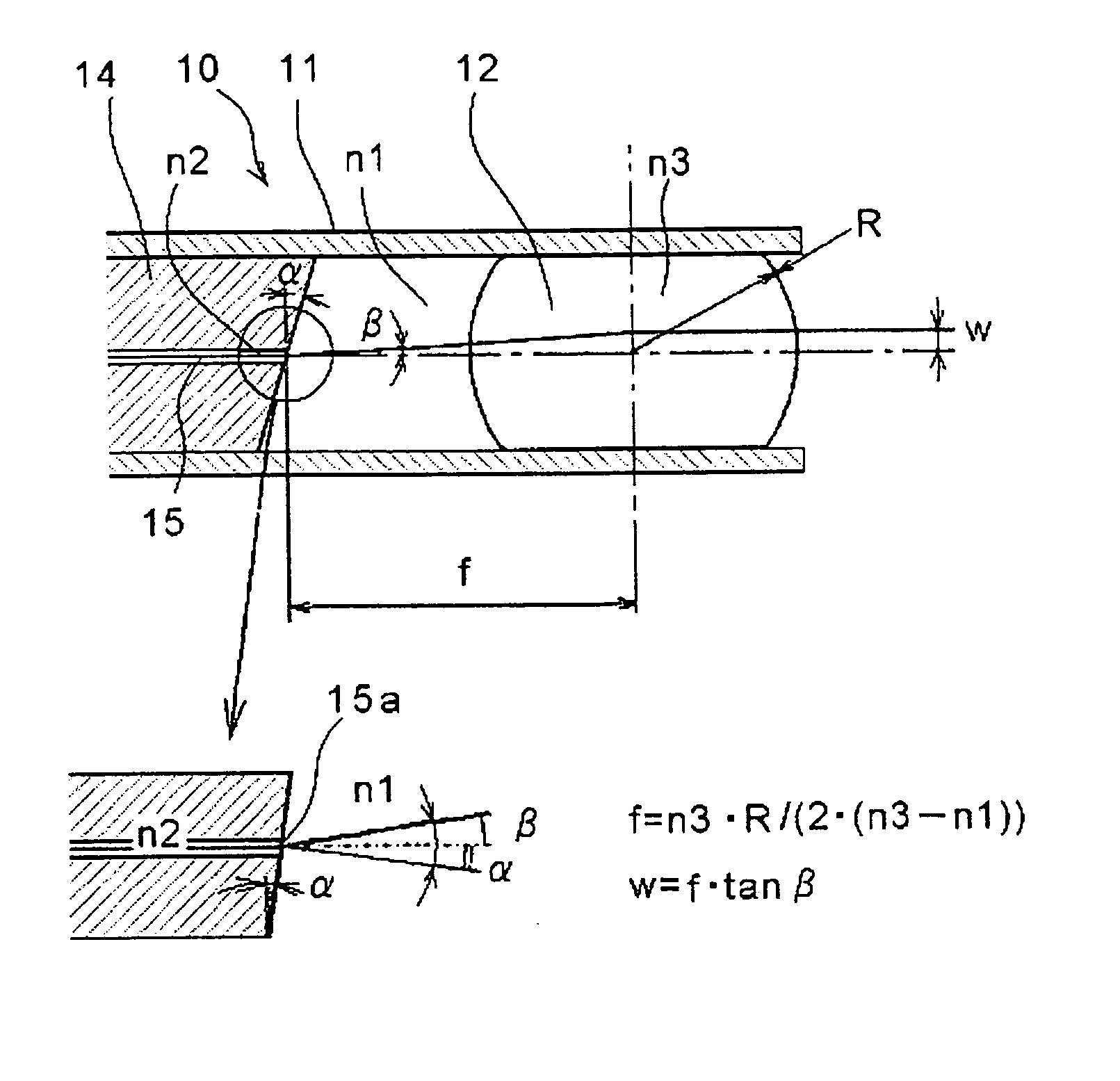

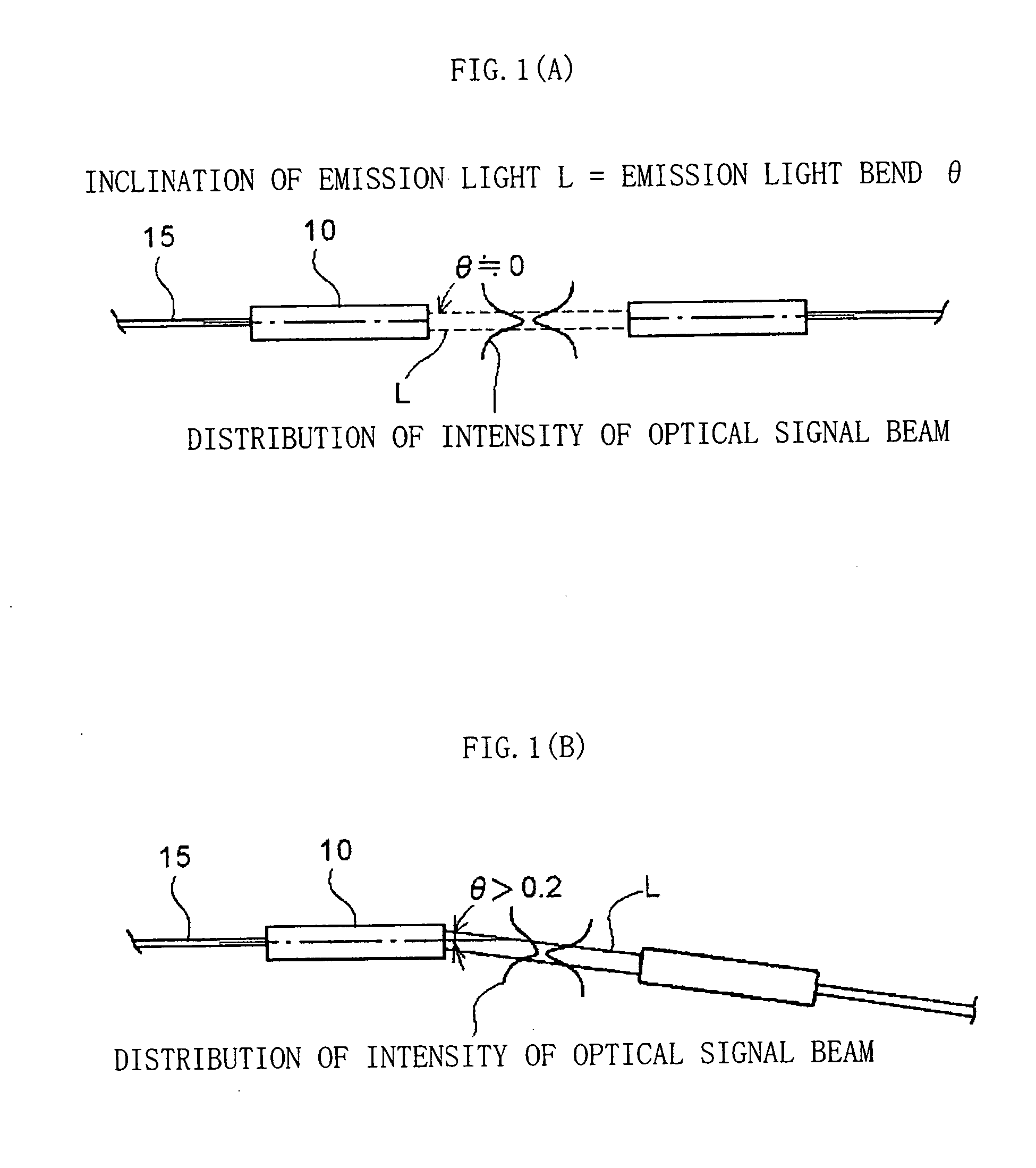

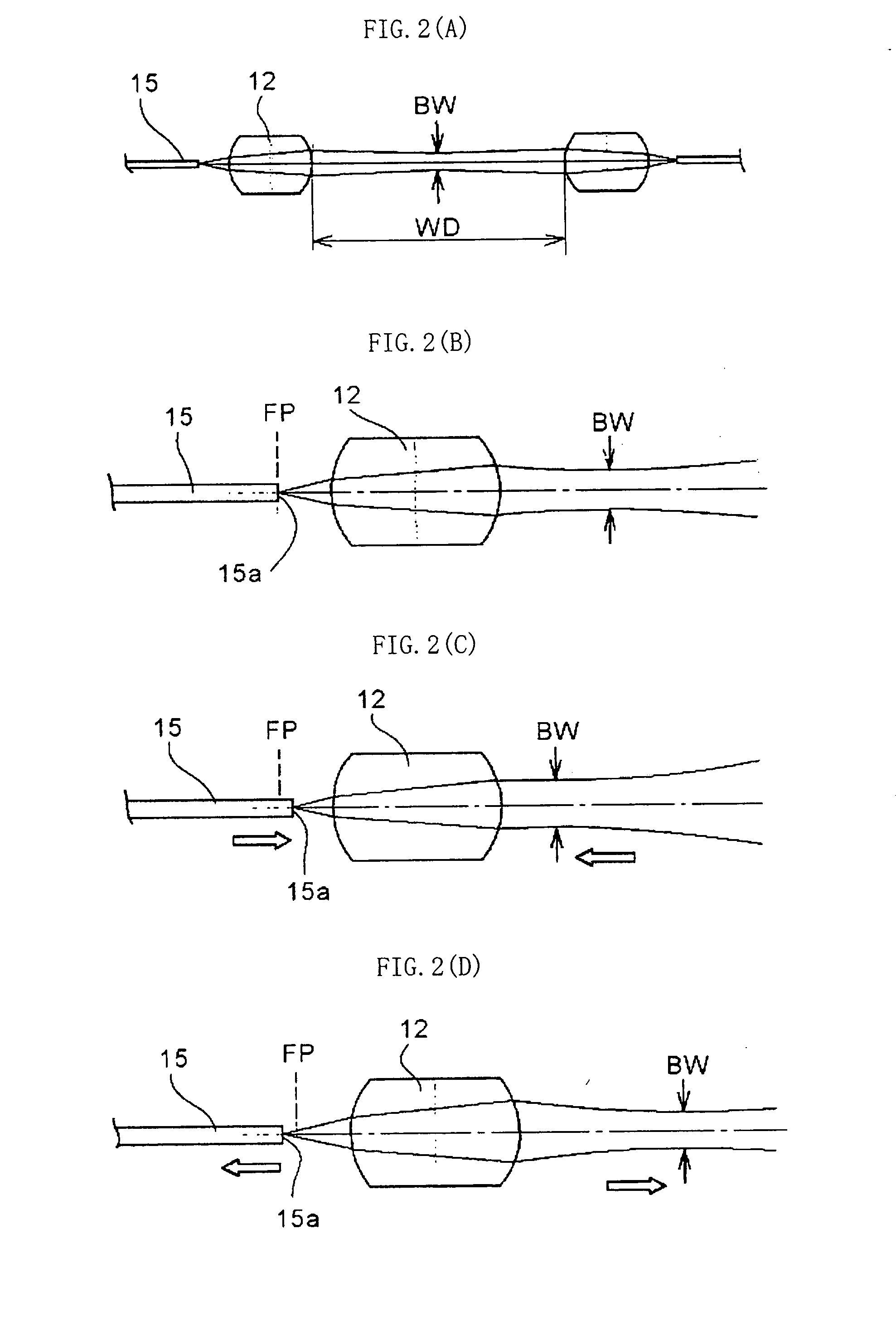

Optical collimator-use lens component, optical collimator, and method of assembling these

InactiveUS20050123240A1Coupling efficiency is highHigh-quality communication performanceCoupling light guidesOptical axisAdhesive

Disclosed is an optical collimator-use lens component including: a thin tube; a partially spherical lens that has been fixed in an inner hole of the thin tube so that an insertion portion having a predetermined length is left, is made of glass whose refractive index is approximately uniform, and has translucent spherical surfaces, whose centers of curvature are approximately the same, at both ends of a cylindrical portion of the partially spherical lens; and an adhesive that bonds the partially spherical lens to the thin tube. An axial deviation amount between a center axis of the thin tube and an optical axis of the partially spherical lens is 5 μm or less. When a capillary tube, in whose inner hole an optical fiber has been fixed and whose axial deviation amount between an outer peripheral surface of the capillary tube and a core center of an end surface of the optical fiber is 1.5 μm or less, is inserted into the insertion portion of the thin tube and the end surface of the optical fiber is fixed at a position at which a distance of the end surface to a focal point position of the partially spherical lens becomes ±40 μm or less, emission light has an emission light bend of 0.2° or less with respect to the center axis of the thin tube.

Owner:NIPPON ELECTRIC GLASS CO LTD

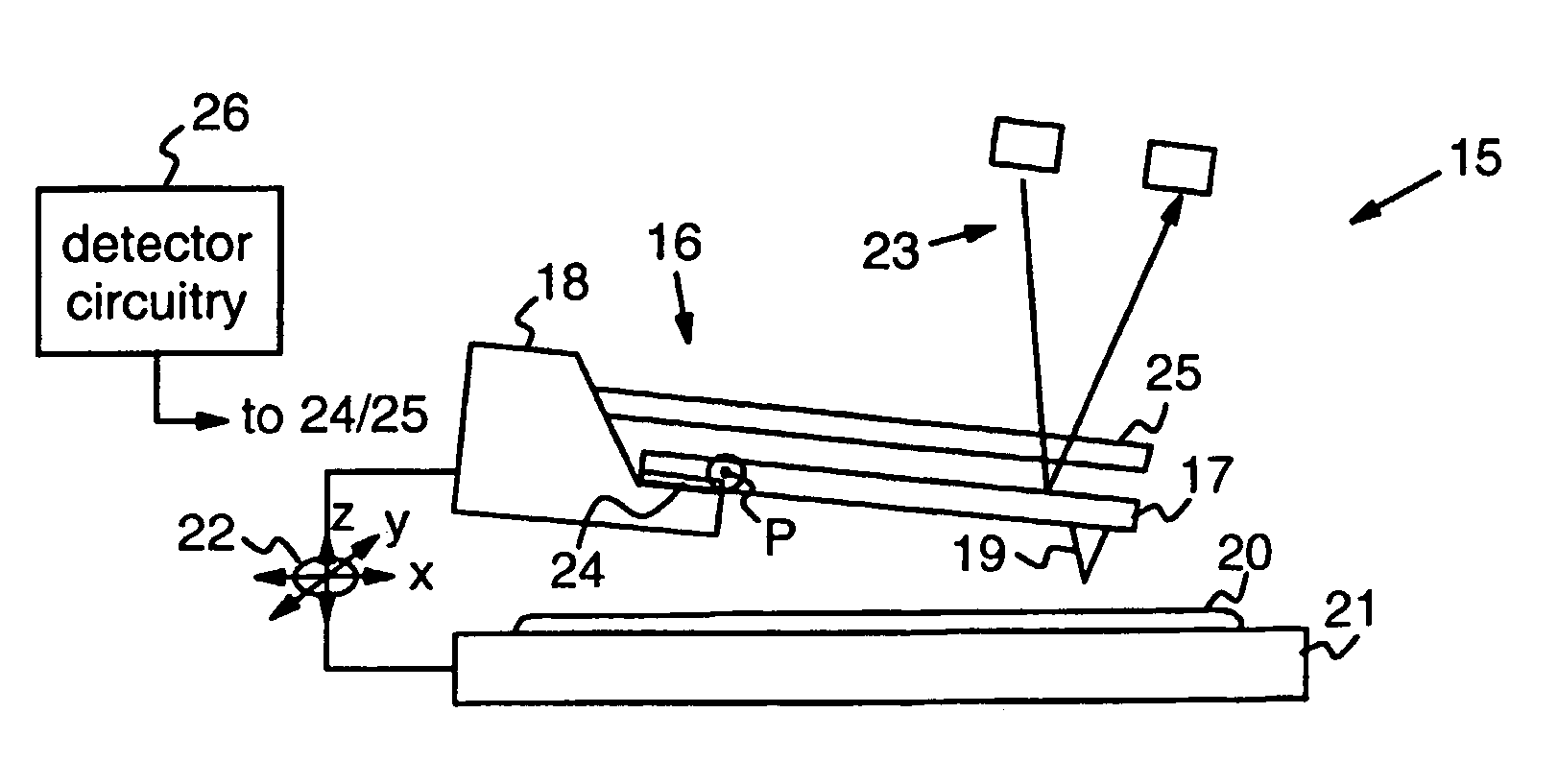

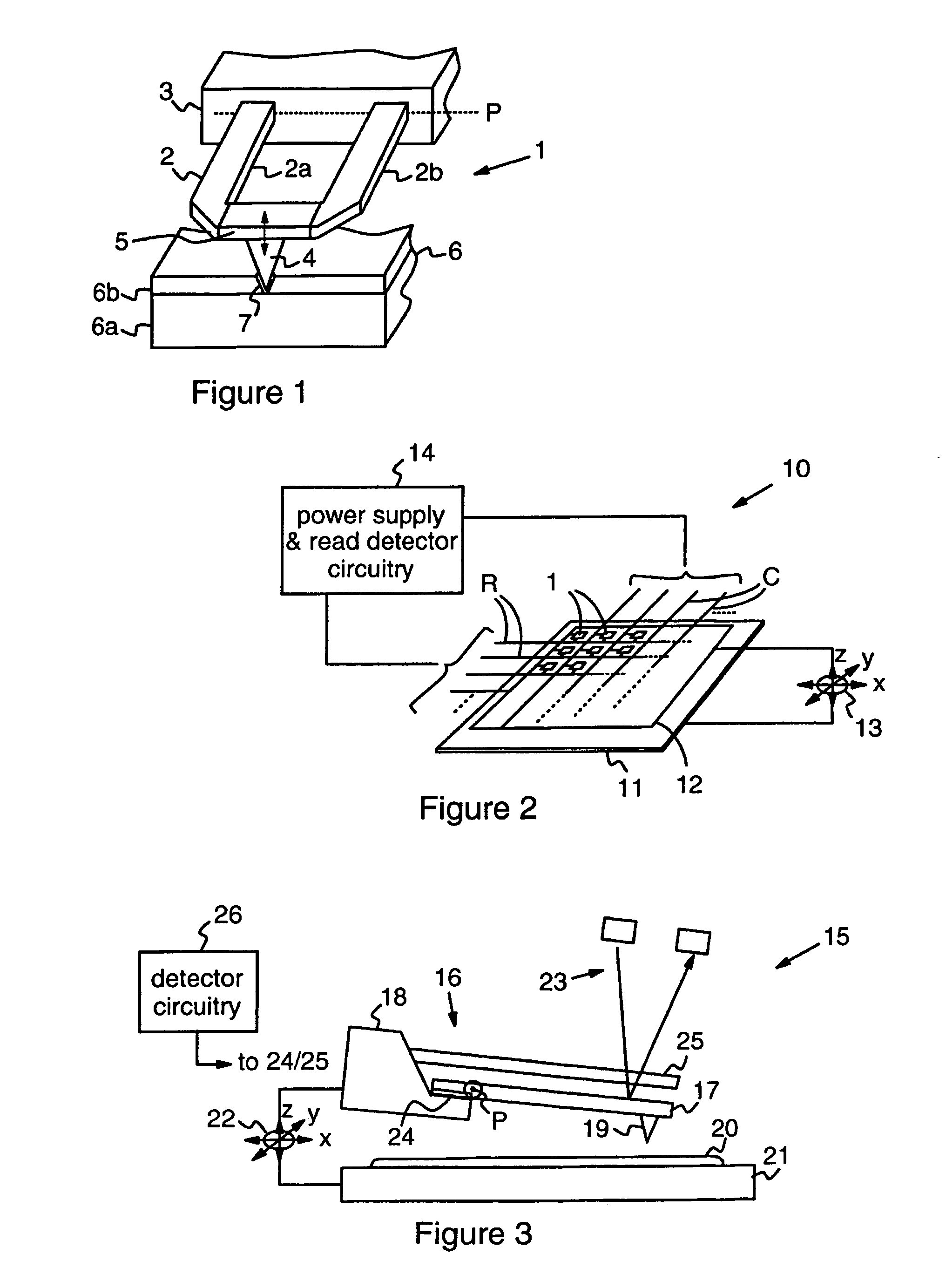

Scanning probe for data storage and microscopy

InactiveUS7268348B2Reduced Alignment DifficultyGood precisionMaterial analysis using wave/particle radiationNanoinformaticsScanning probe microscopyCantilever

A cantilever device for scanning a surface comprises a support, a tip platform and a flexible arm arrangement. The tip platform has a plurality of tips. These comprise at least two contact tips providing points of contact with a surface to be scanned, and a scanning tip for scanning the surface, where the scanning tip may be one of the two or more contact tips provided on the platform. The flexible arm arrangement connects the tip platform to the support and allows orientation of the platform, via flexing of the arm arrangement, to bring the contact tips into contact with a surface to be scanned. The platform is then at a well-defined orientation relative to the scan surface, and the scanning tip is appropriately positioned for the scanning operation. Scanning probe microscopes and data storage devices incorporating such cantilever devices are also provided.

Owner:IBM CORP

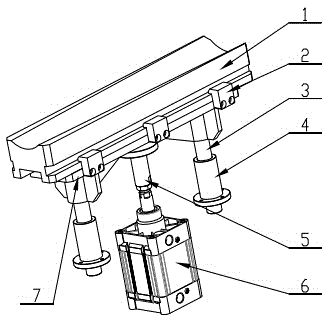

Screw supplier

The invention provides a screw supplier, which can be used in large-scale screws with various sizes and shapes, has universality, can form a firm structure by a comparatively simple composition, and has easy maintenance. The screw supplier parallelly and horizontally arrange a pair of arrangement rollers on the upper part of the storage part for storing screws, wherein opposite spiral helical flutes are provided on the external circumstance surface of the pair of arrangement rollers, the helical flutes are in U shape with wide width, less depth and square edges, the total width of the opposite helical flutes is lower than the diameter of the bar shape screw thread part of the supplied screws. In addition, brush components are provided at the upside of the storage part upstream side of the arrangement rollers, the brush components span nearly total width of a pair of arrangement rollers in the horizontal direction, and the lower front end of the brushes configured into brush components is located at vicinity of the height of the couched screws.

Owner:OHTAKE ROOT IND

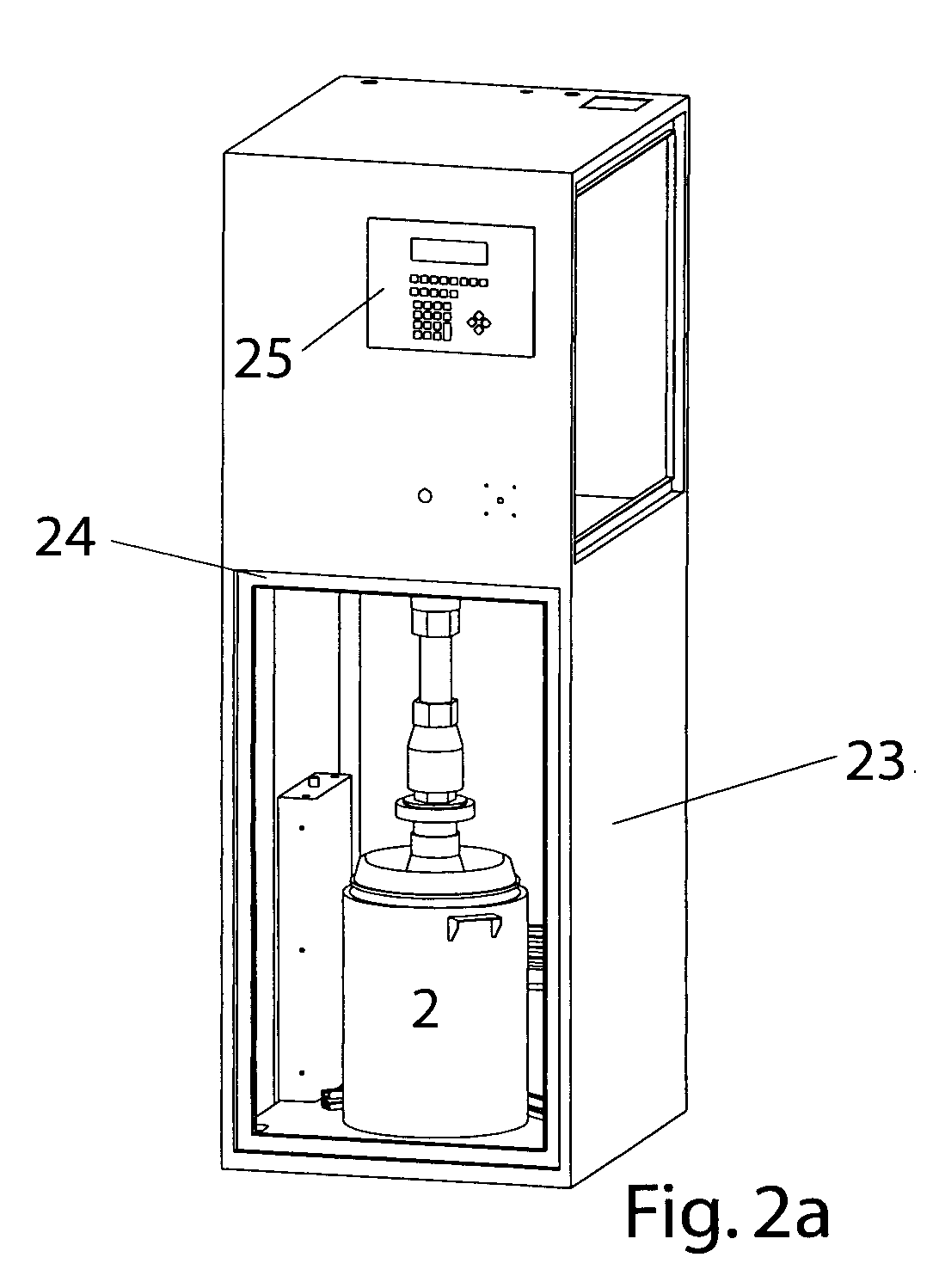

Emptying device

ActiveUS20070039978A1Inexpensive mannerAvoid Sealing ProblemsLiquid surface applicatorsVolume measurement and fluid deliveryEngineeringMechanical engineering

Owner:SCHEUGENPFLUG

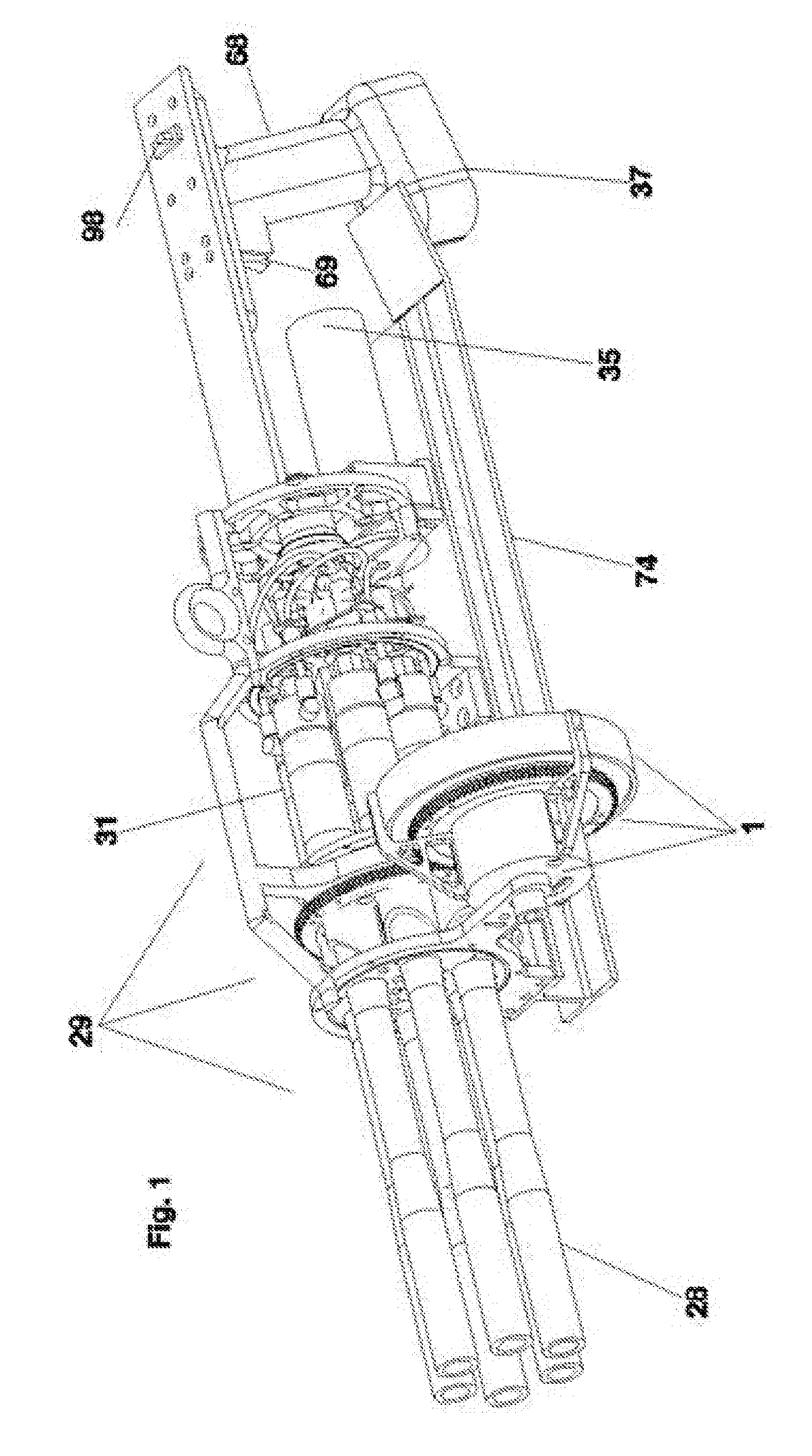

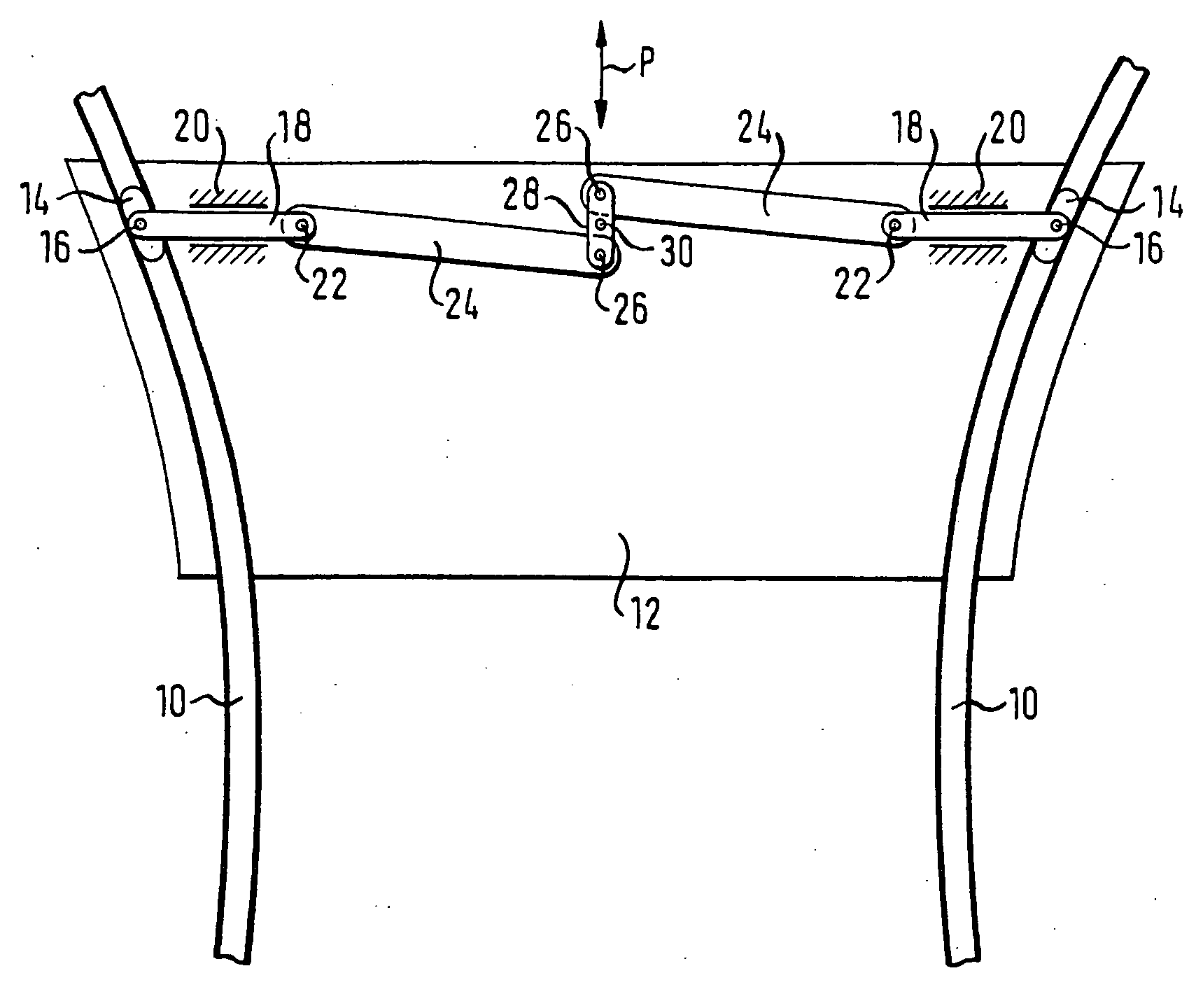

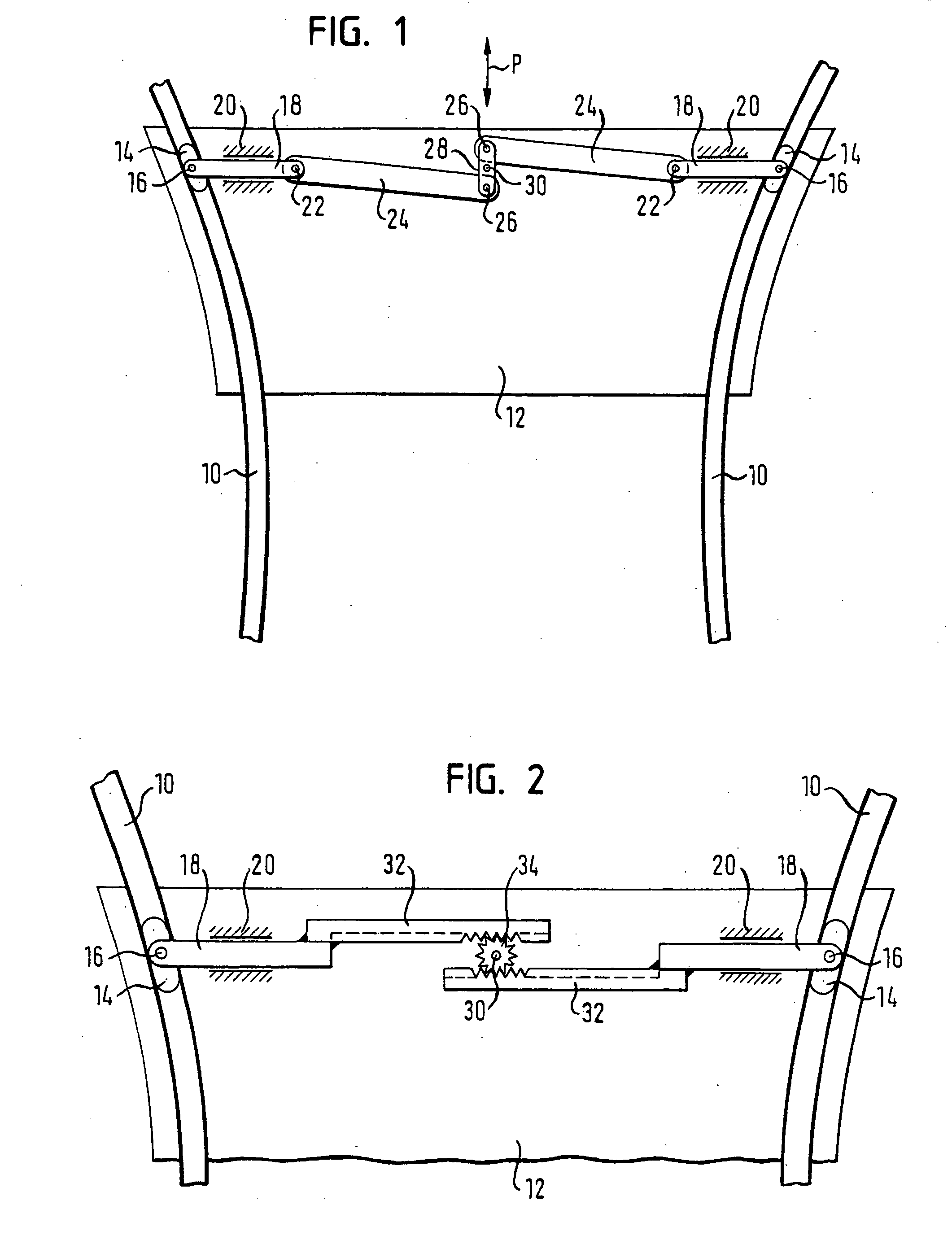

Double clutch assembly

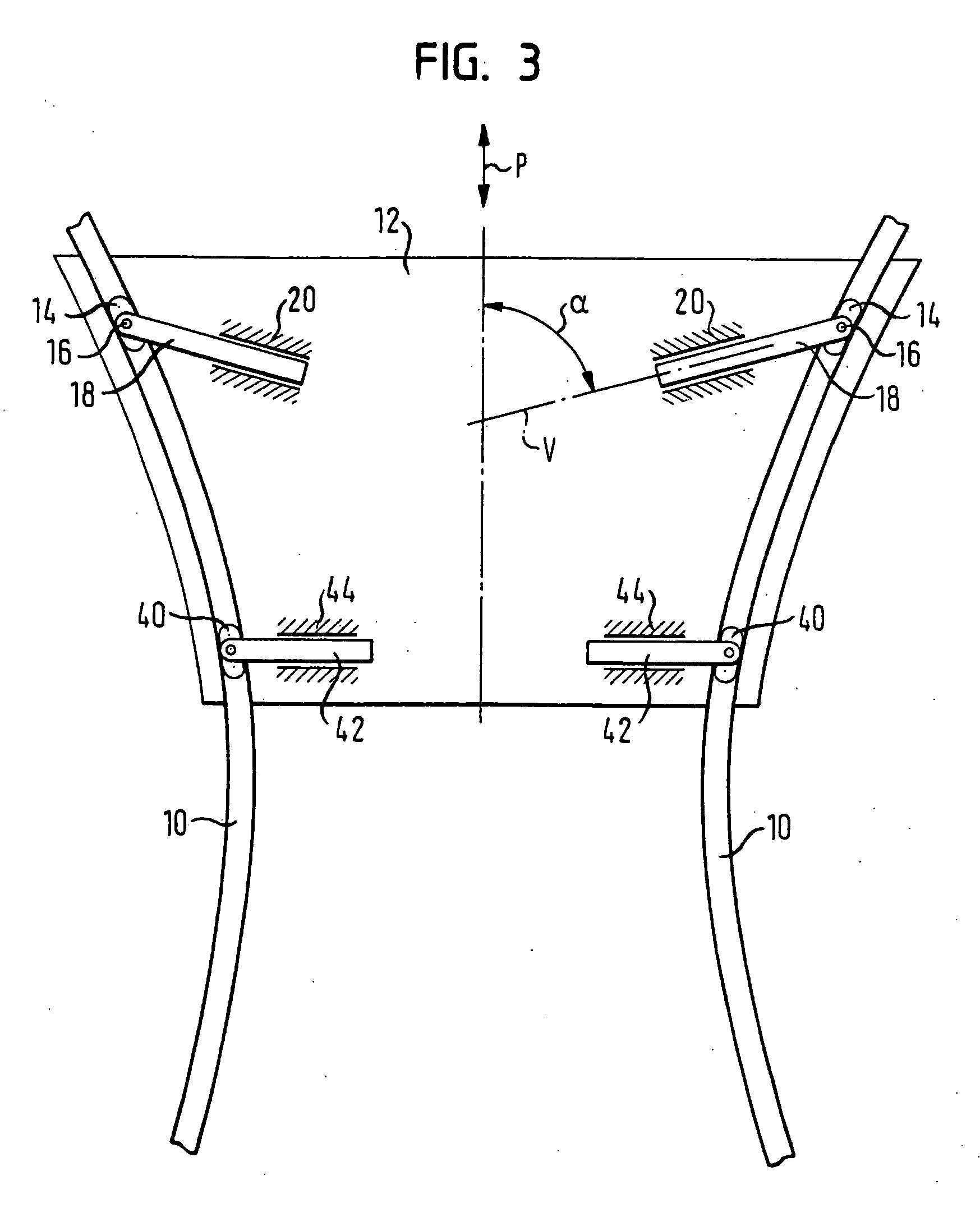

InactiveUS20040079606A1Easy accessReliable alignmentRoad transportFriction clutchesAbutmentDriven element

A double clutch assembly includes a first clutch area with a first pressure plate, which can be moved by a first force-exerting assembly toward an abutment assembly; a second clutch area with a second pressure plate, which can be moved by a second force-exerting assembly toward an abutment assembly; and a connecting assembly for connecting the abutment assembly to a drive element. The connecting assembly includes a connecting plate assembly with a first, radially outer connecting section, which extends over an outer circumferential surface of the abutment assembly and is attached thereto by a plurality of connecting elements.

Owner:ZF SACHS AG

Semiconductor device having an increased area of one of the opposing electrode parts for preventing generation of unconnected positions the electrodes on the bonded wafers

InactiveUS7986045B2High reliability in electrical connectionIncrease the areaSemiconductor/solid-state device detailsSolid-state devicesEngineeringFace shape

In this semiconductor device, connection parts between wafers are electrically insulated from each other, and a junction face shape of second electrical signal connection parts is larger than the shape of a positioning margin face that is formed by an outer shape when the periphery of a minimum junction face, which has half the area of a junction area of the first electrical signal connection part, is enclosed by a same width dimension as a positioning margin dimension between the first wafer and the second wafer.

Owner:HONDA MOTOR CO LTD

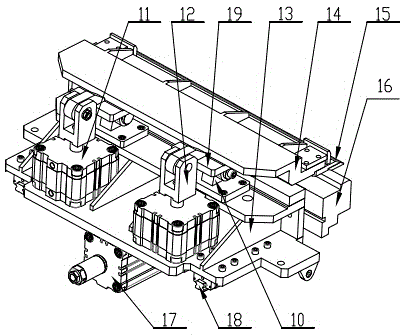

Longitudinal seam welding machine suitable for thin-wall small-diameter suspended single-face welding and double-face forming

ActiveCN104128736AGuaranteed straightnessAvoid positionWelding/cutting auxillary devicesAuxillary welding devicesEngineeringSeam welding

The invention relates to welding equipment, in particular to a longitudinal seam welding machine suitable for thin-wall small-diameter suspended single-face welding and double-face forming. The longitudinal seam welding machine comprises a rack. The rack is provided with a work-piece locating device, folding and pressing devices, a central spindle supporting device, a central spindle device, a centering device and a walking gantry welding device. The first folding and pressing device and the second folding and pressing device are located on a sliding rail and connected with a horizontal air cylinder. The central spindle device is located above the locating device. According to the technical scheme, acting force is exerted on a longitudinal seam of a rolling pipe from left and right, under the effect of the misalignment-preventing centering device, seam alignment of a work-piece can be finished without manual adjustment, the straightness of butt seams can be ensured, and the phenomena that positions of the butt seams need to be manually adjusted many times and misalignment is corrected in the past production process can be avoided.

Owner:CHENGDU AIGRE TECH

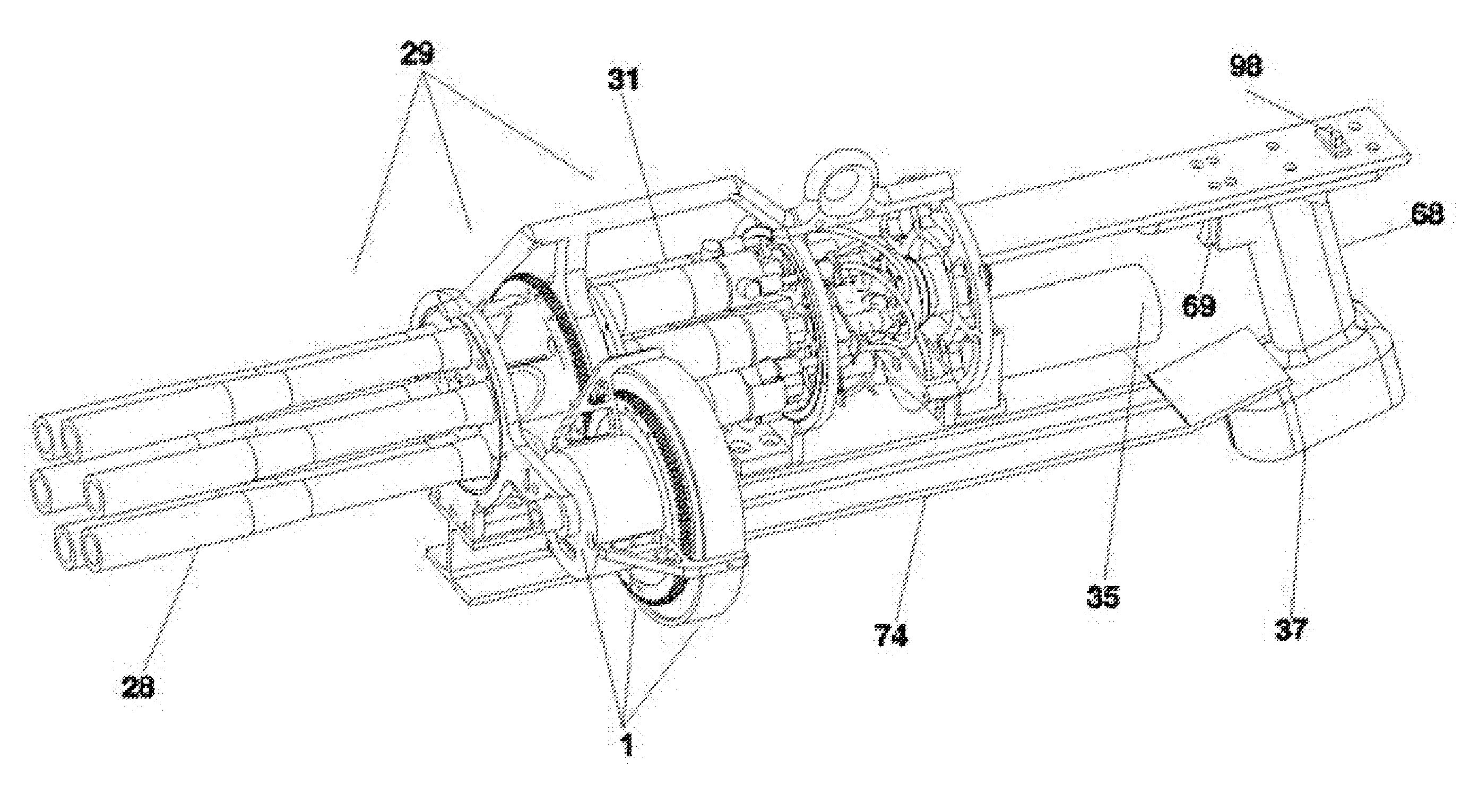

Paintball loader and paintball Galting gun

InactiveUS20110083654A1Prevent paintball breakageImprove reliabilityAmmunition loadingCompressed gas gunsCentrifugal forceProjectile

A gatling gun style projectile launcher comprising an assembly of rotating, pressurized-air driven guns. A loader assembly mounted on the gun assembly rotates synchronously through mating of drive gears with the assembly of guns. The loader applies centrifugal force to the paintballs within, urging them into loader tubes positioned in the wall of the loader. Synchronous timing gears align the rotating loader tubes with cognate breech openings in the guns, thereby transferring paintballs into the firing positions from which the paintballs are launched.

Owner:GALINSON RICHARD

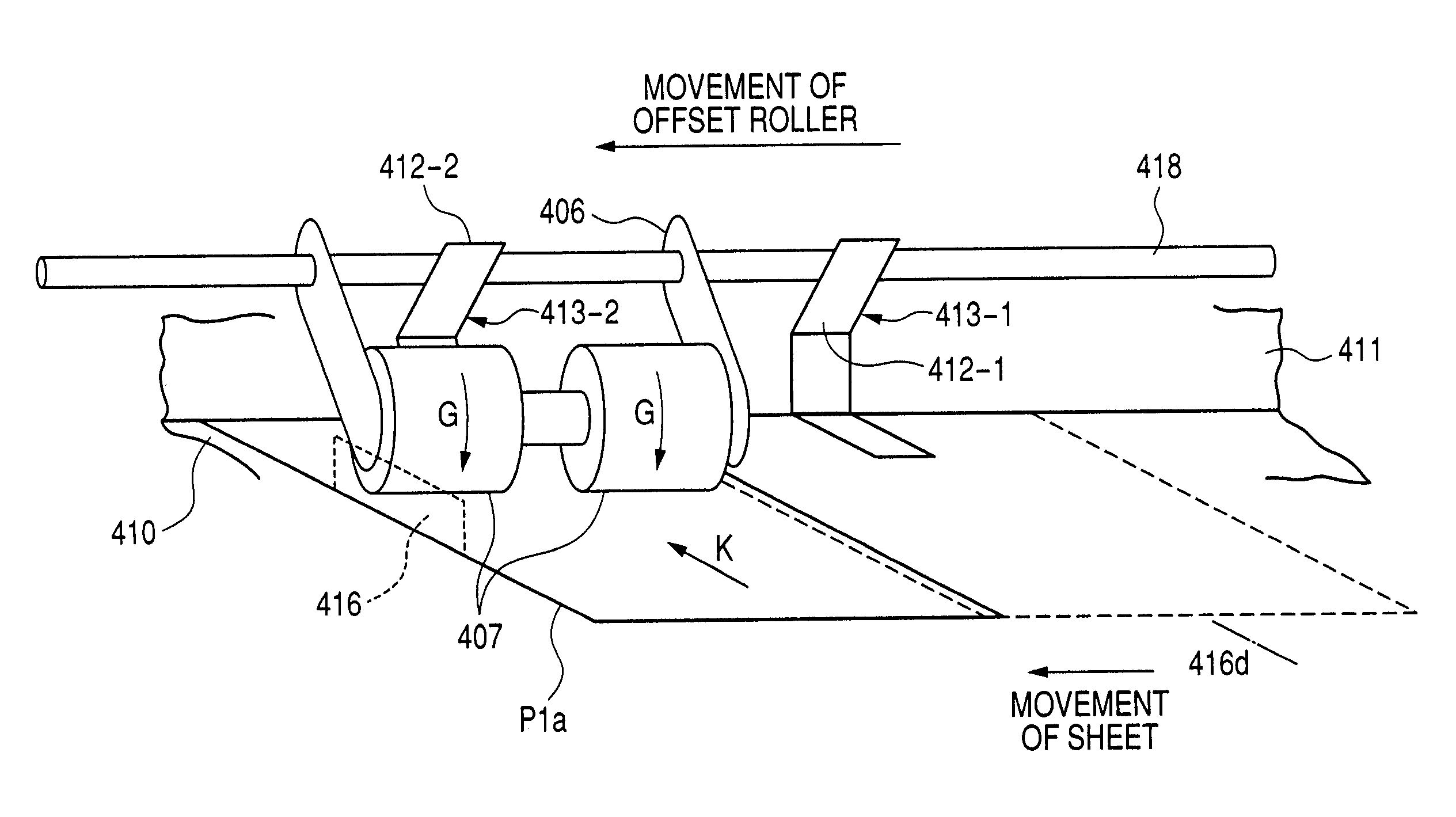

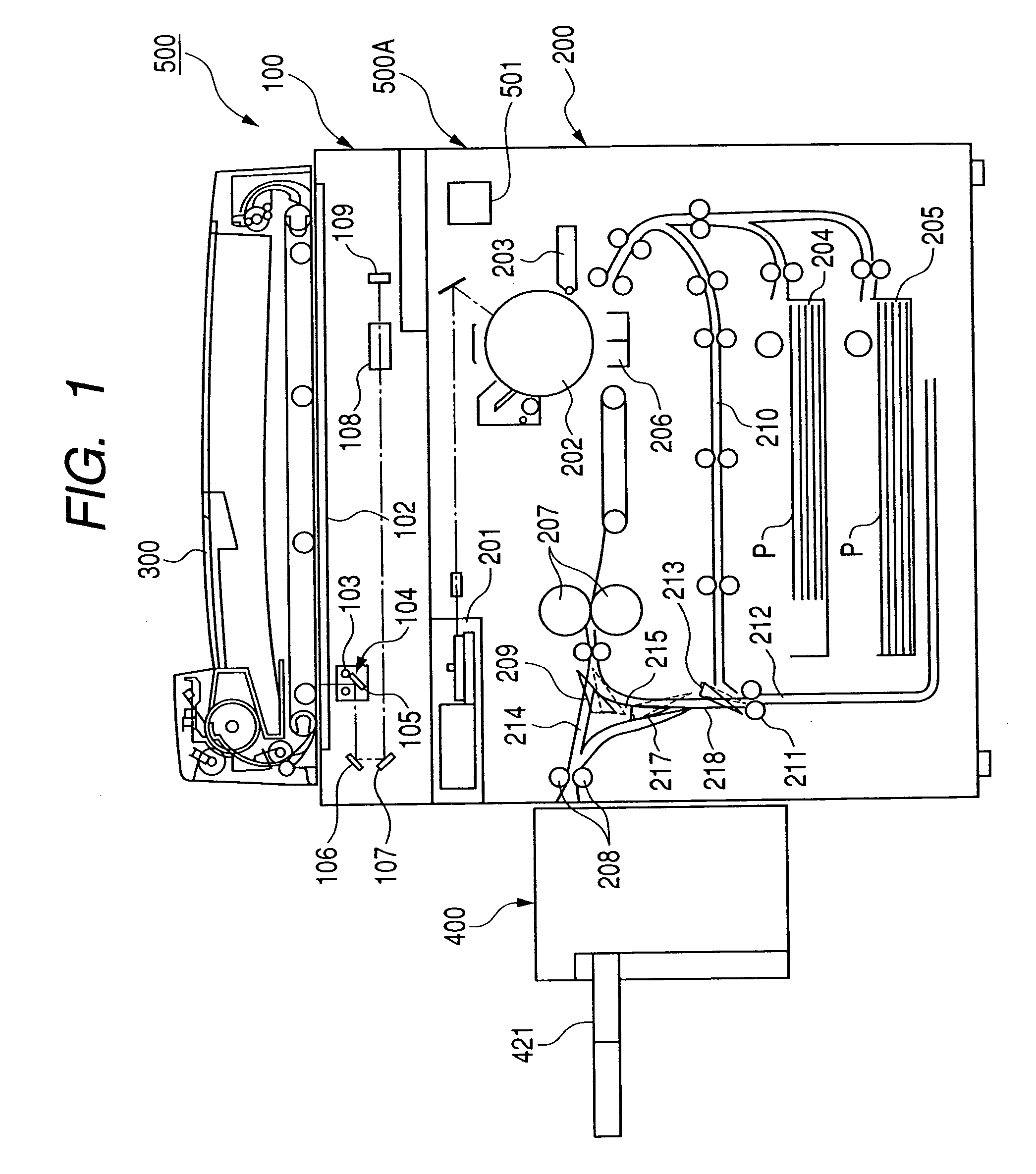

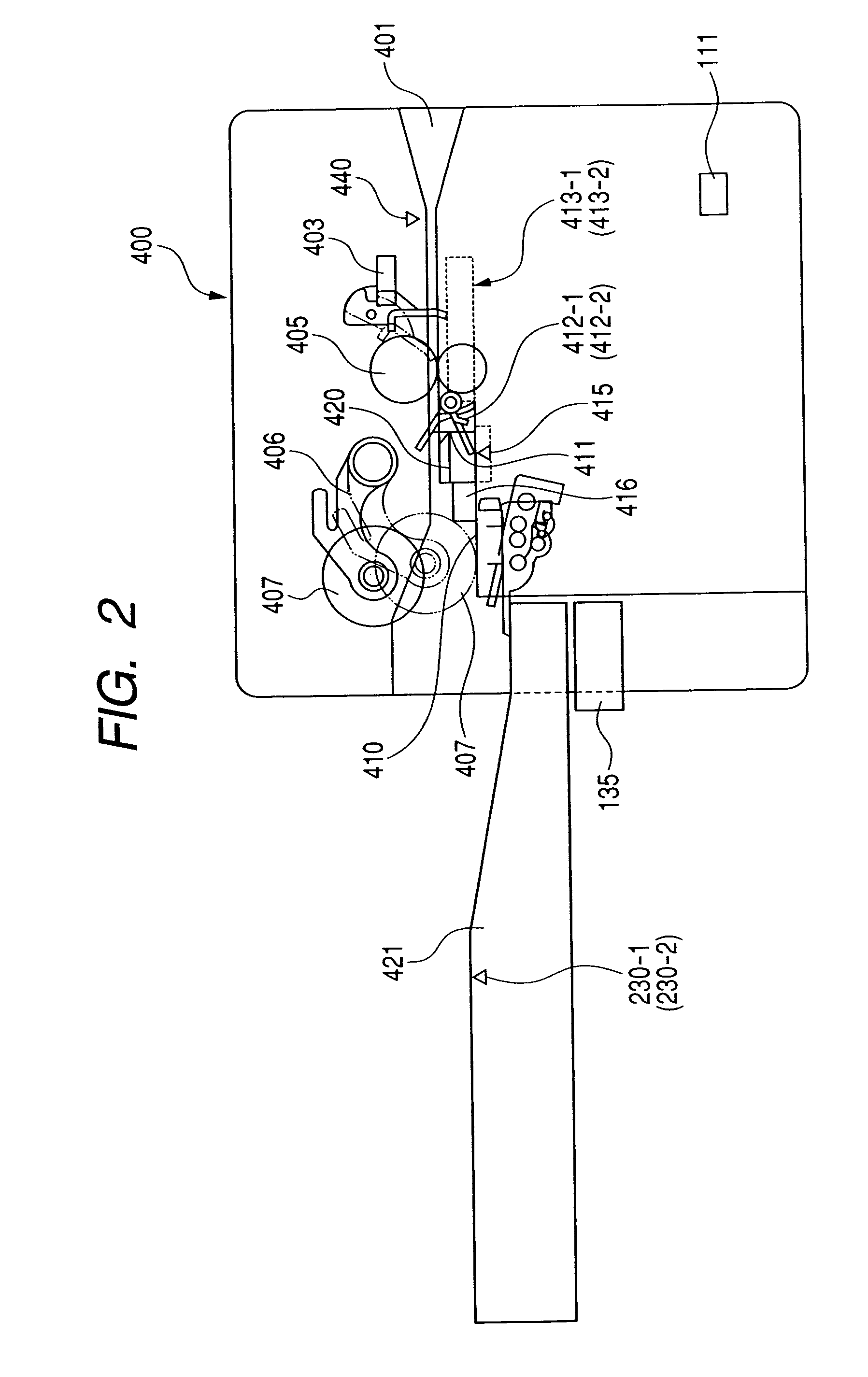

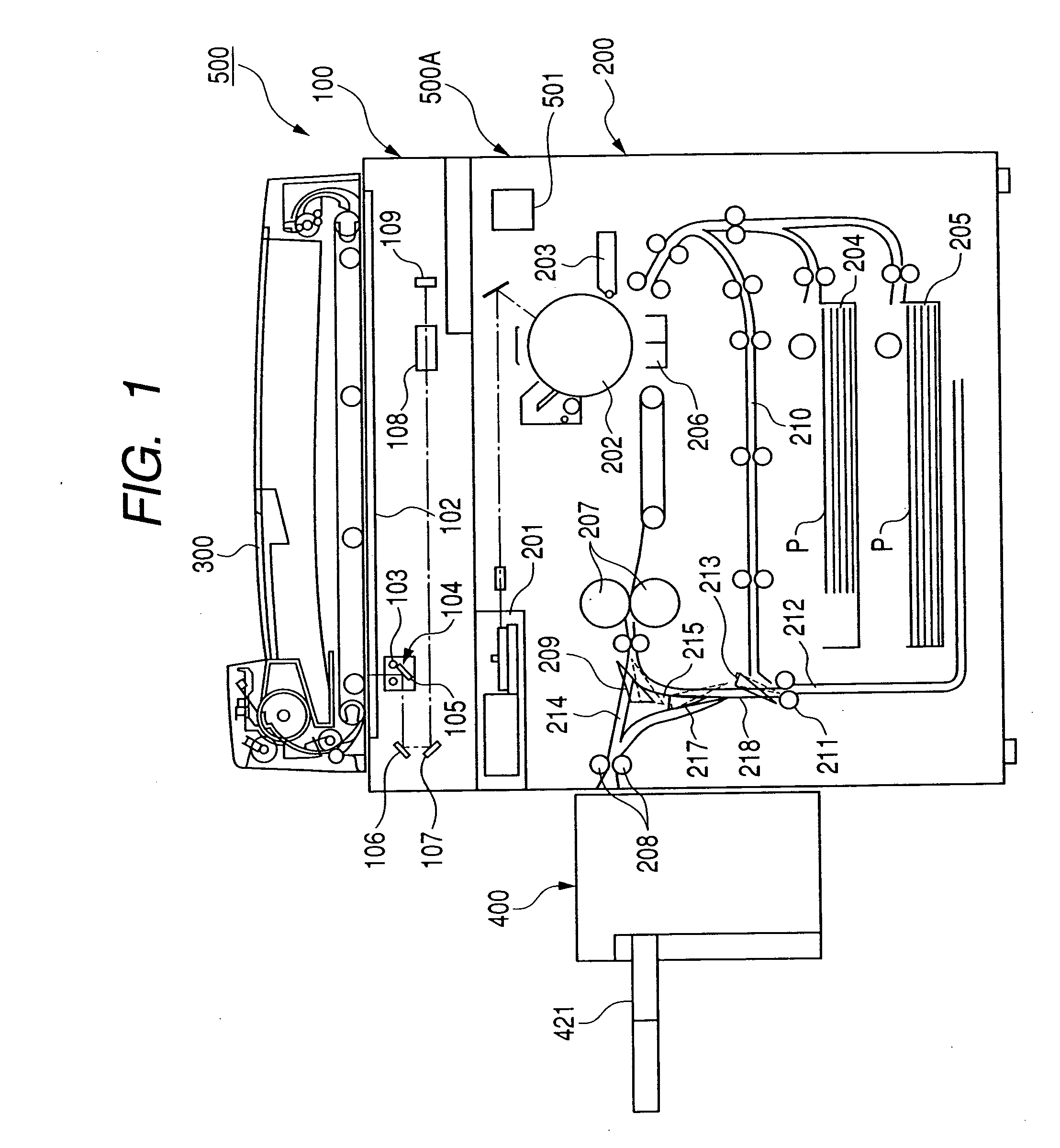

Sheet processing apparatus and image forming apparatus having the same

A sheet processing apparatus including a cross-directionally moving device for moving a sheet in a direction crossing a sheet discharging direction, and a cross-side restricting member for receiving one side edge of the sheet moved in the crossing direction by the cross-directionally moving device, and restricting the movement of the sheet, wherein the cross-directionally moving device moves the next sheet from a position between the other side edge of the sheet received by the cross-side restricting member and the cross-side restricting member to the cross-side restricting member.

Owner:COPYER

Sheet processing apparatus and image forming apparatus having the same

ActiveUS20060181006A1Reliable alignmentRegistering devicesFunction indicatorsImage formationSheet material

A sheet processing apparatus including a cross-directionally moving device for moving a sheet in a direction crossing a sheet discharging direction, and a cross-side restricting member for receiving one side edge of the sheet moved in the crossing direction by the cross-directionally moving device, and restricting the movement of the sheet, wherein the cross-directionally moving device moves the next sheet from a position between the other side edge of the sheet received by the cross-side restricting member and the cross-side restricting member to the cross-side restricting member.

Owner:COPYER

Fixture pressing mechanism for flexible circuit board

InactiveCN102879614ANot crushedAvoid breakingMeasurement instrument housingFlexible circuitsEngineering

Owner:AU OPTRONICS (SUZHOU) CORP LTD +1

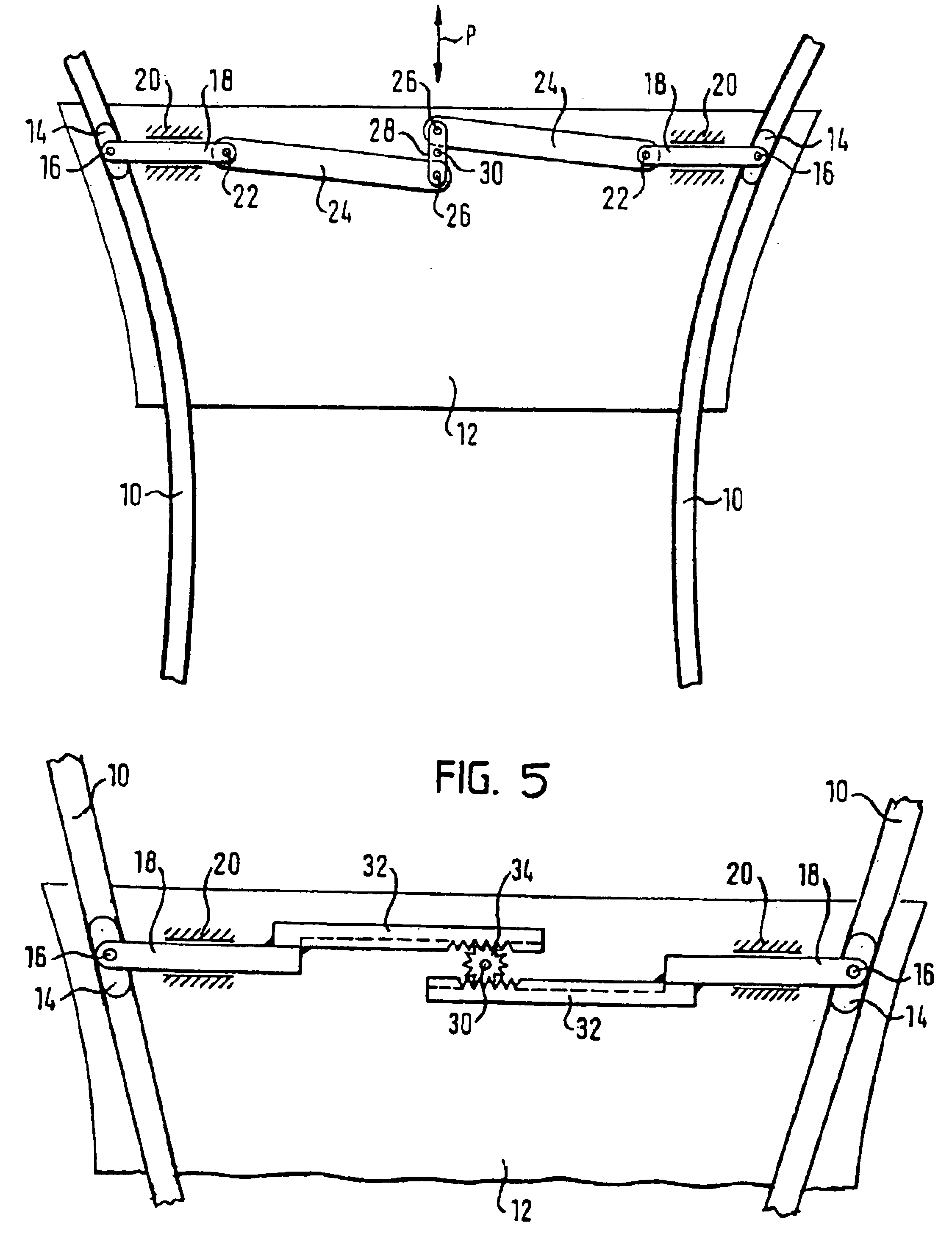

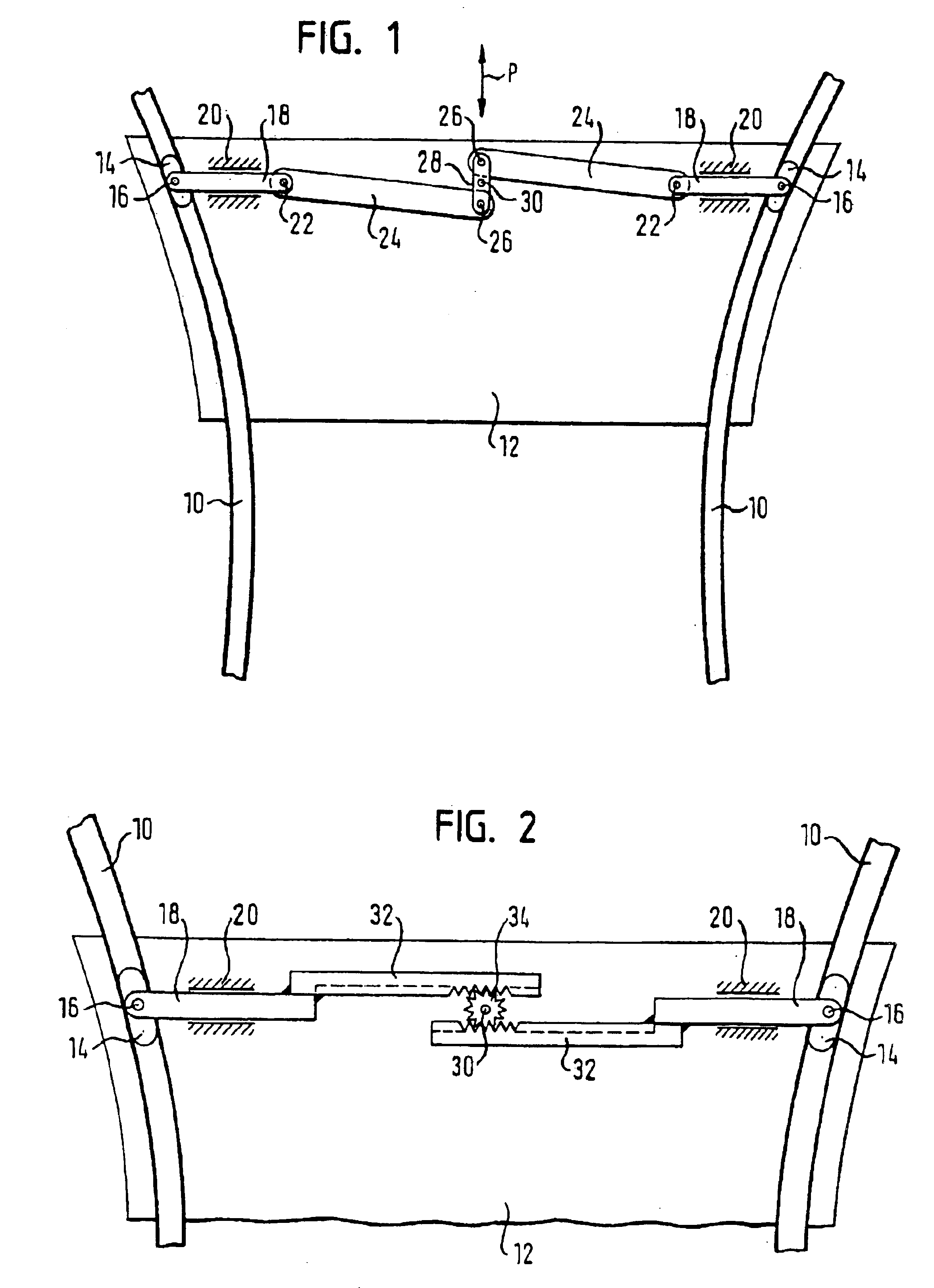

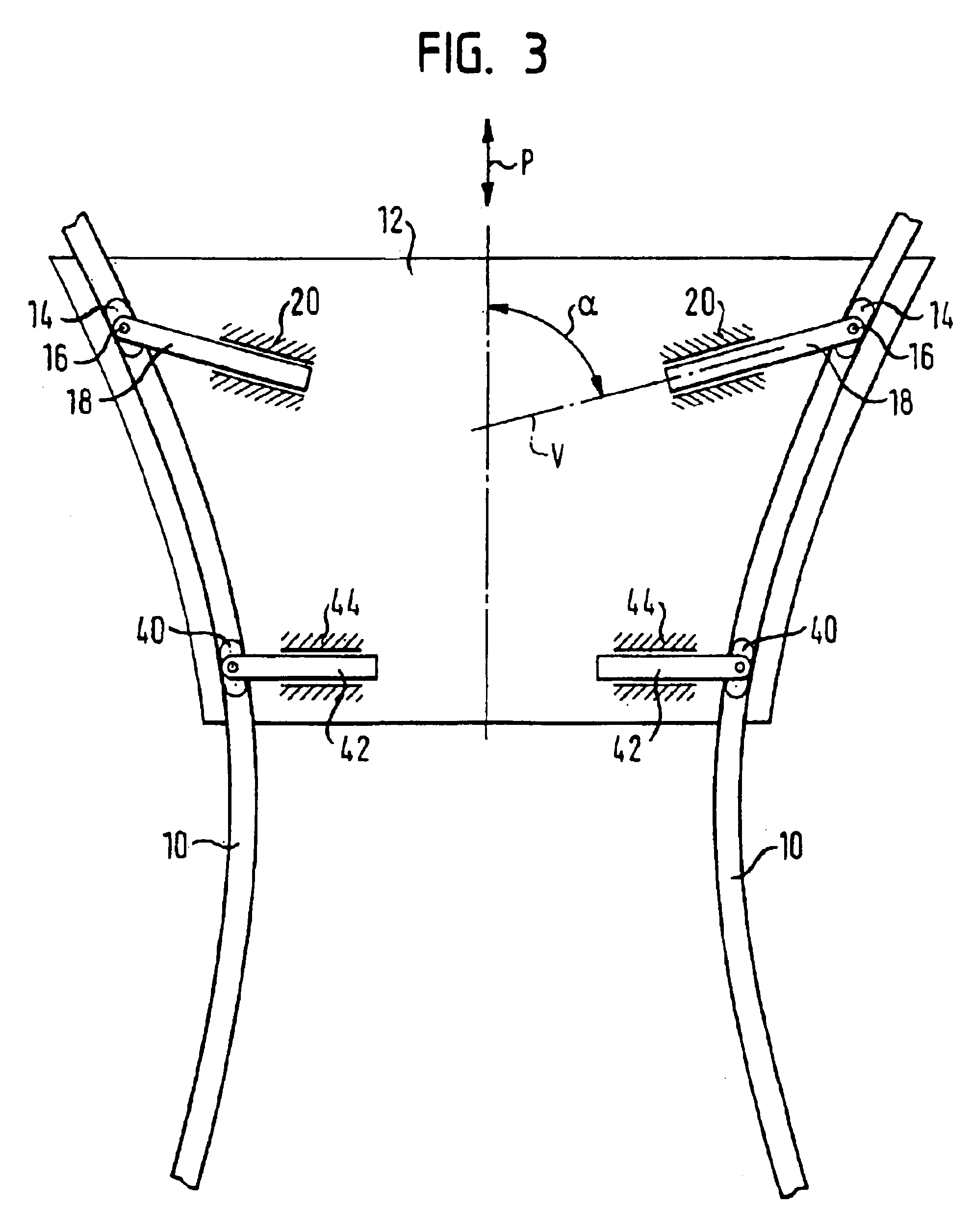

Sliding roof system for a motor vehicle

InactiveUS20050001457A1Reduce riskSlow motionEngine sealsSuperstructure subunitsMotorized vehicleMechanical engineering

The present invention relates to a cover for a sliding roof system having at least two guide elements, which are movably arranged on two opposite sides of the cover such that the distance between them is variable. The two guide elements are each attached in a sliding guide, which predefines a displacement direction for the guide elements that differs from the displacement direction of the cover, such that the cover is centered with regard to the two guide elements. The invention also relates to a sliding roof system having two guide tracks, which extend along a roof of a motor vehicle at a changing distance, and a cover.

Owner:ROOF SYST GERMANY

Plate fin for heat exchanger and heat exchanger core

InactiveUS7111670B2Improve reliabilityReliable alignmentHeat exhanger finsStationary conduit assembliesPlate heat exchangerEngineering

A plate type heat exchanger employing flat tubes, which can be manufactured easily and which have a high heat exchange performance includes a thin strip-shaped metal plate cut in the width direction and having remaining small connected portions and many cut portions disposed at fixed intervals in the longitudinal direction slits are formed in both sides of the cut potions having the same center. The strip-shaped metal plate is bent at the connected portions in a zigzag manner to form an aggregation of fin elements, and the flat tubes are engaged with the front and rear sides of the aggregation of the fin elements.

Owner:T RAD CO LTD

Sliding roof system for a motor vehicle

InactiveUS6916064B2Reduce riskSlow motionEngine sealsSuperstructure subunitsMobile vehicleMotor vehicle part

Owner:ROOF SYST GERMANY

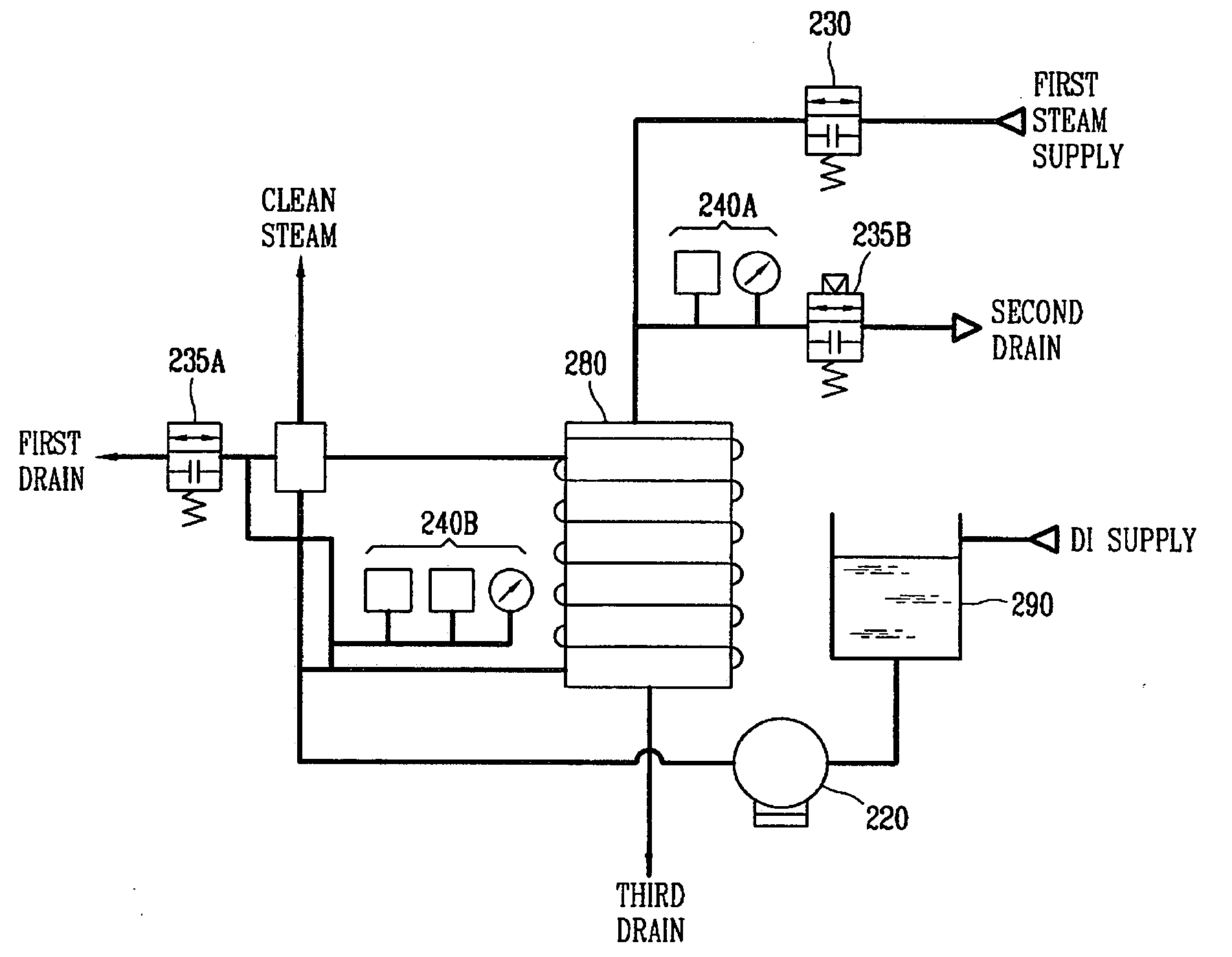

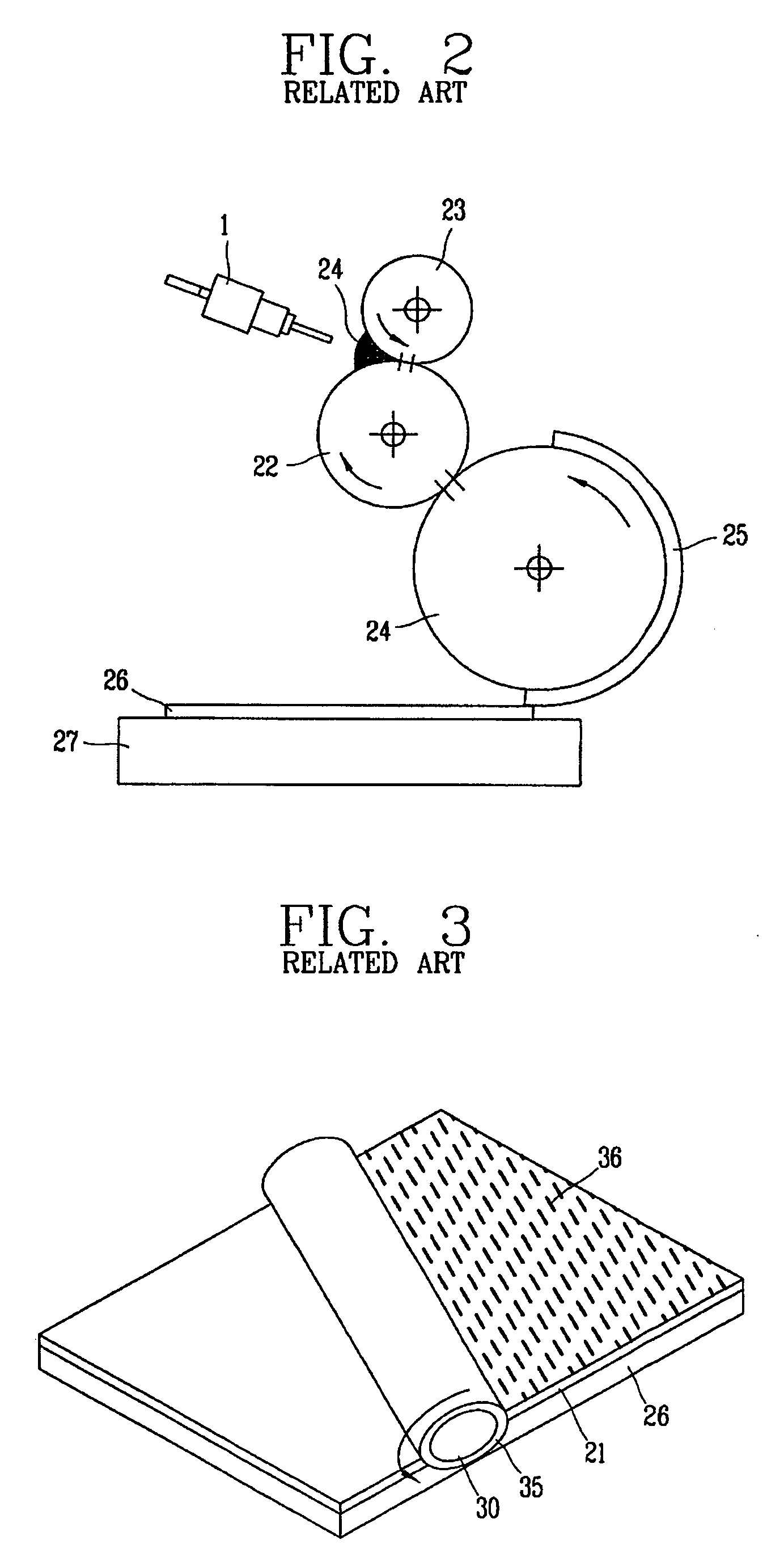

Apparatus for inspecting alignment film and method for fabricating liquid crystal display device using the same

ActiveUS20060286701A1Reliable alignmentImprove processing yieldSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsLiquid-crystal displayEngineering

An apparatus for inspecting an alignment film and a method for fabricating a liquid crystal display device using the same are disclosed. By changing a spraying structure of a steam inspecting unit to check whether an alignment film is defective or not, a water splash phenomenon can be prevented and spraying can be performed uniformly on a large-scale glass. The apparatus for inspecting an alignment film comprises a first steam generating unit for generating first steam; a second steam generating unit for generating second steam by using the first steam as a heat source; and a steam spraying unit for spraying the second steam onto a substrate of a substrate to inspect an alignment film formed on the substrate.

Owner:LG DISPLAY CO LTD

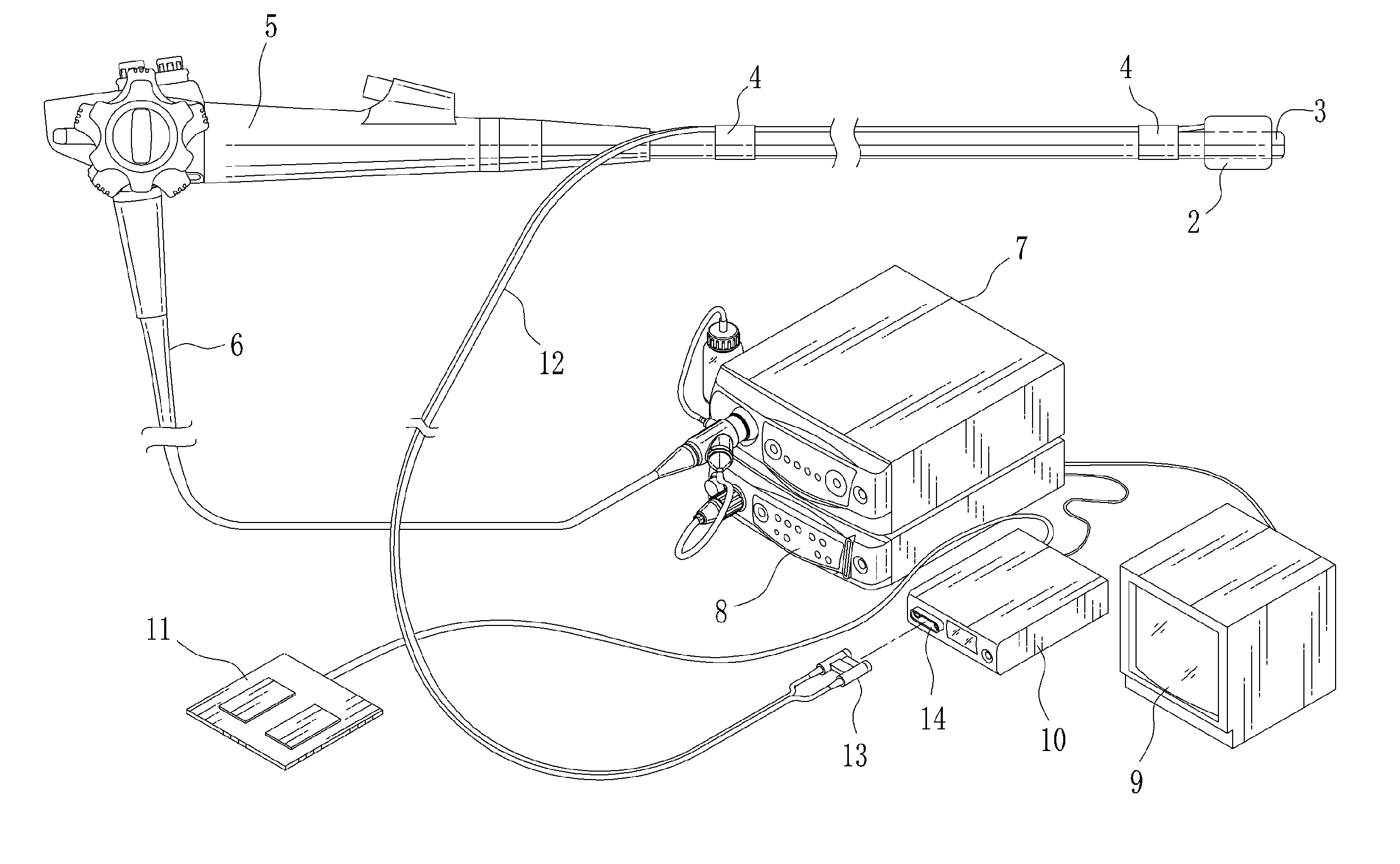

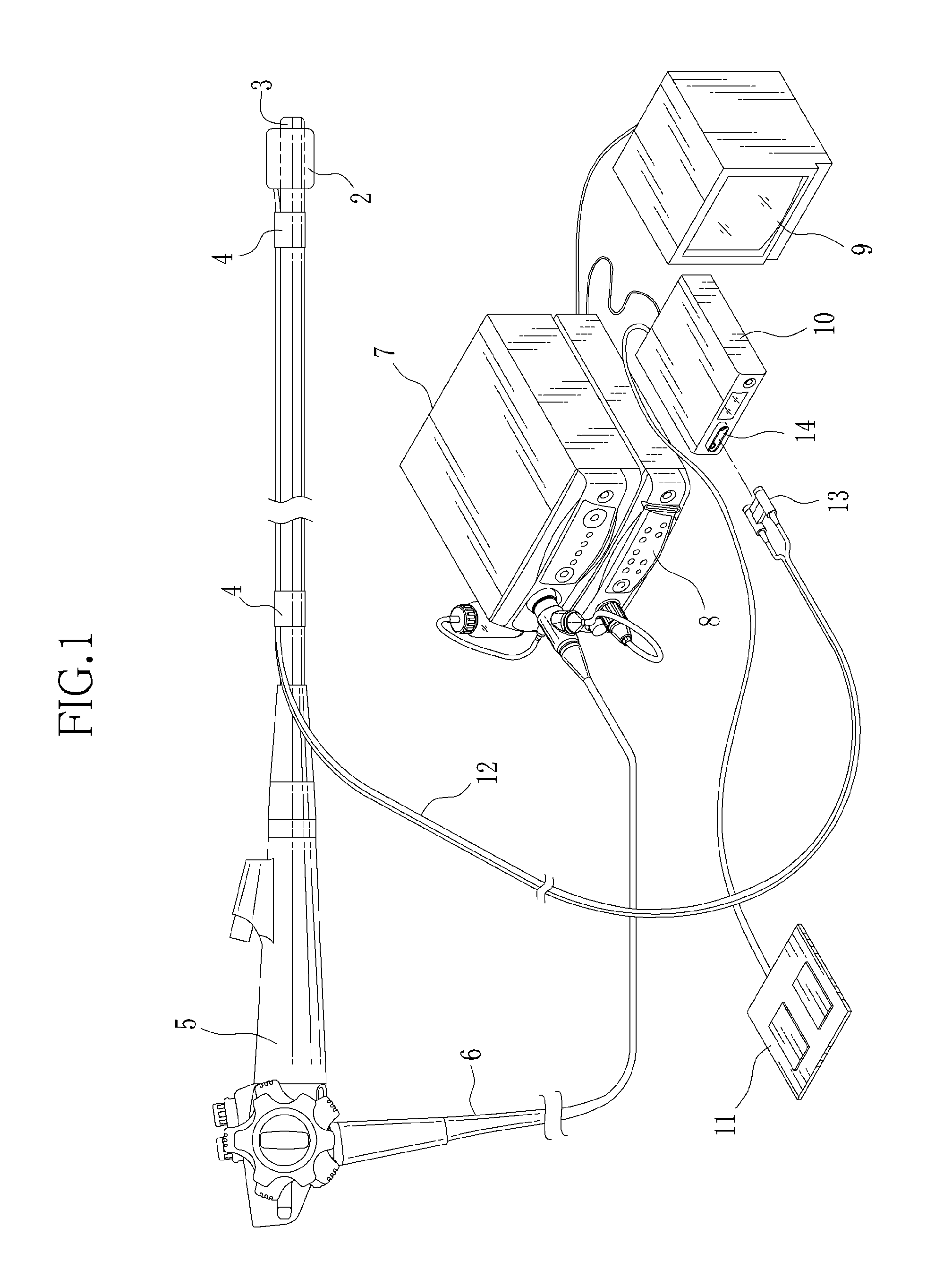

Propulsion assembly for endoscope

InactiveUS20130158353A1Reduce frictionAvoid damageGastroscopesOesophagoscopesEngineeringMechanical engineering

A propulsion assembly for an endoscope includes a support sleeve and a barrel unit. An endless track device is disposed to extend along inner and outer surfaces of the barrel unit, for endlessly moving in an axial direction of an elongated tube of the endoscope, and contacting a wall of a body cavity, for propulsion of the elongated tube. Worm wheels are disposed on the support sleeve, for driving the endless track device by engagement therewith. Plural idler rollers are disposed on the inner surface of the barrel unit in a rotatable manner, for keeping the endless track device movable in driving of the worm wheels. An guide projection is formed on the endless track device. A guide groove is formed in the barrel unit, for receiving the guide projection, to guide the endless track device on the barrel unit in the axial direction.

Owner:FUJIFILM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com