Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

262results about How to "Improve charge retention" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

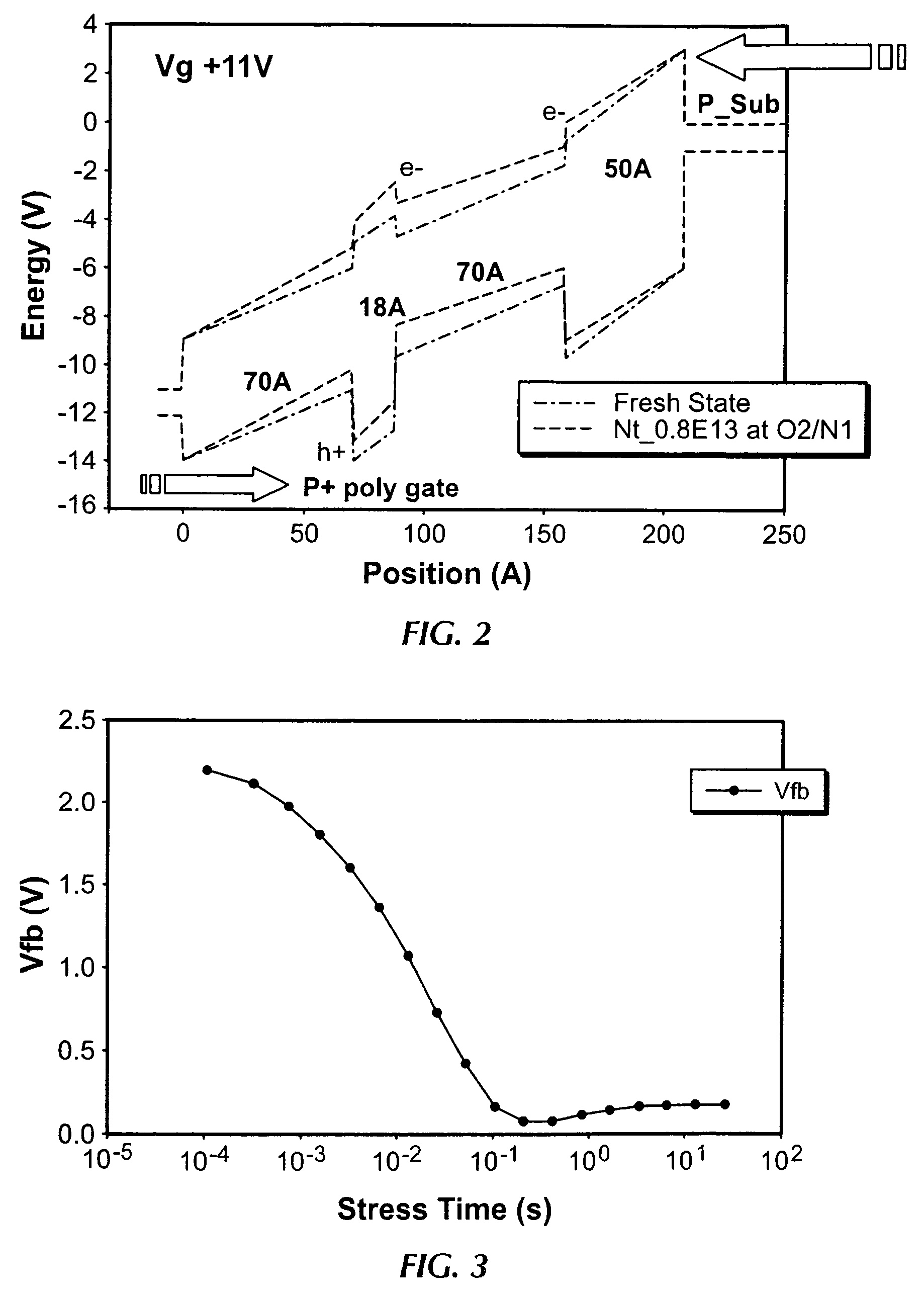

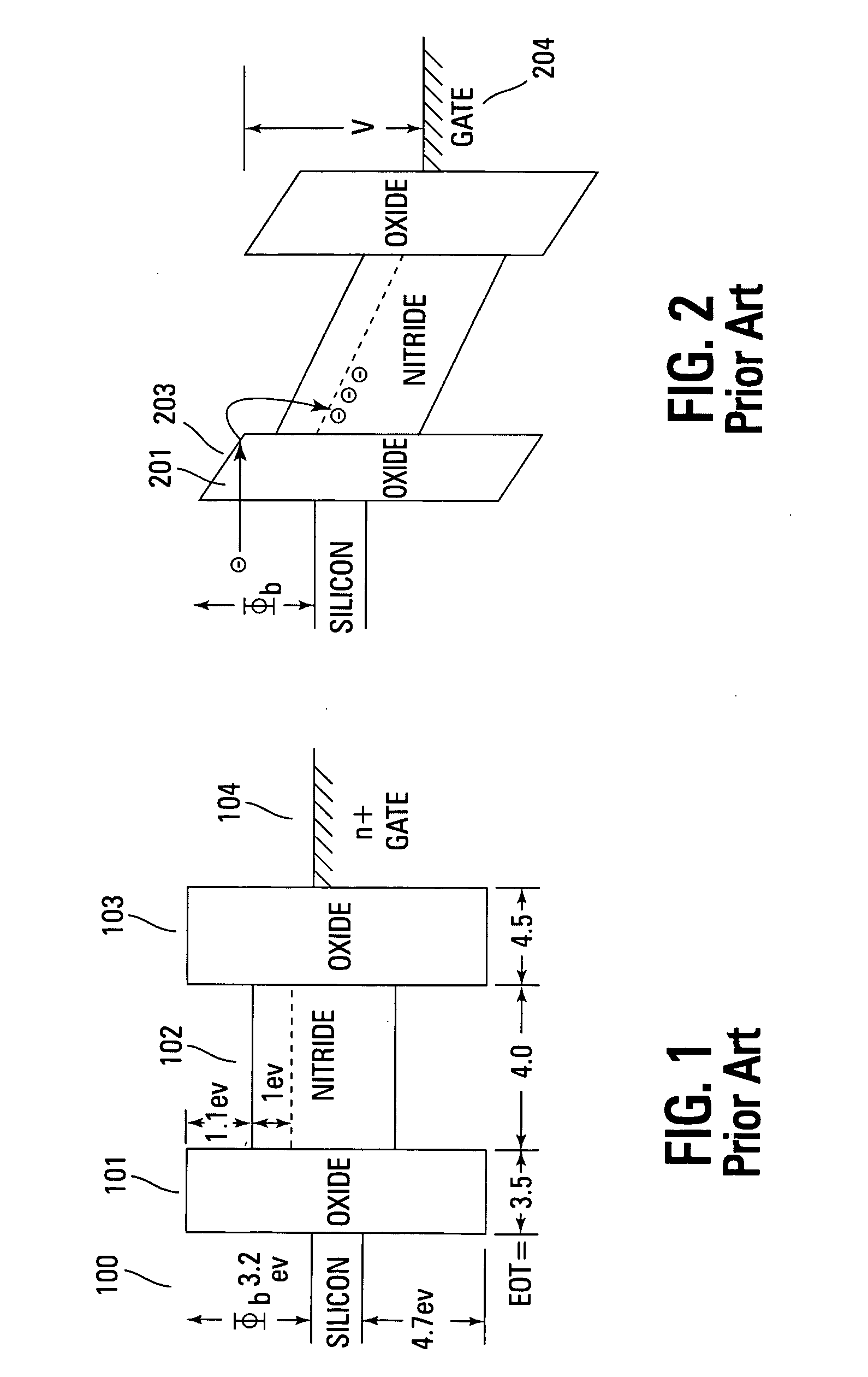

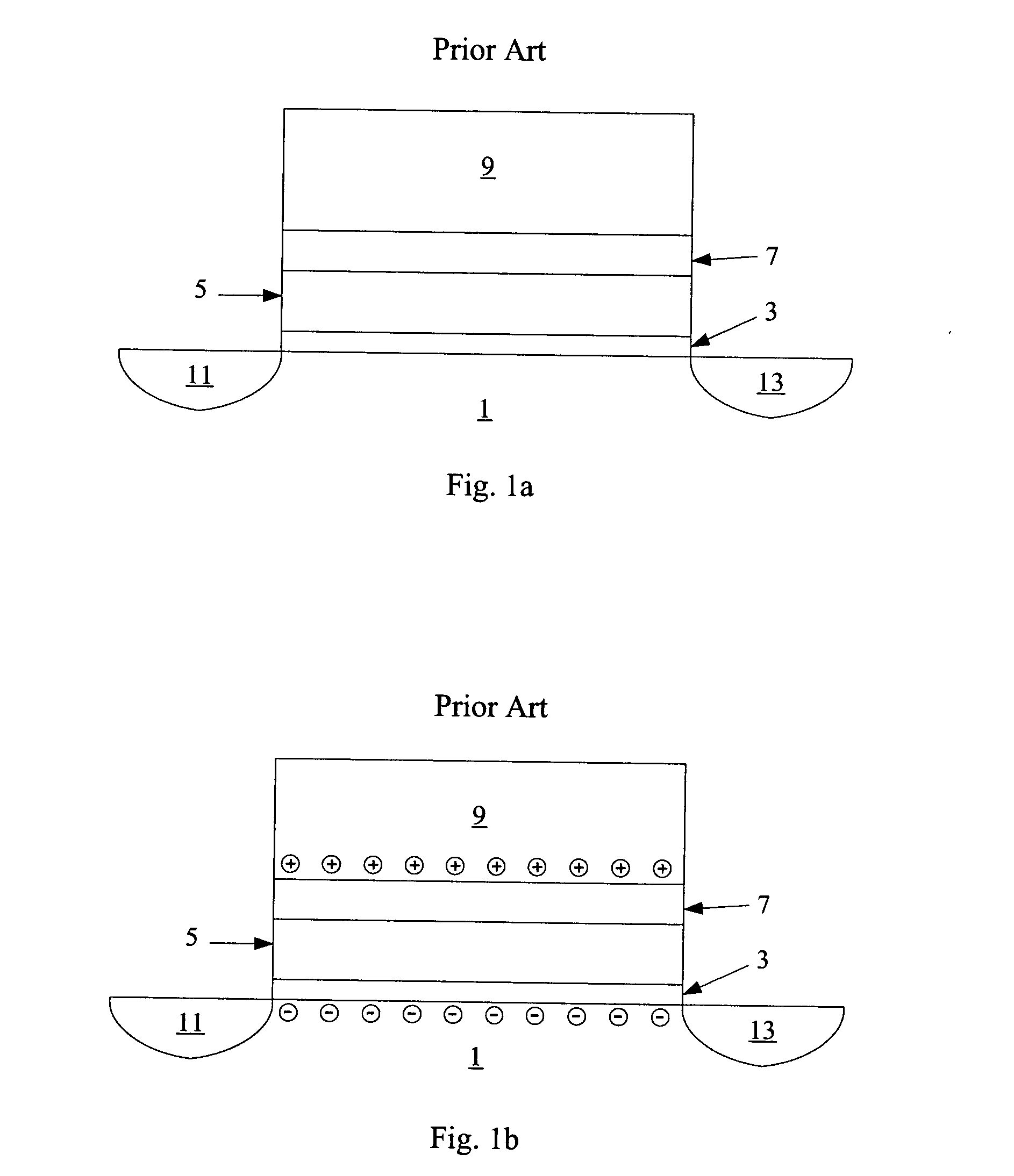

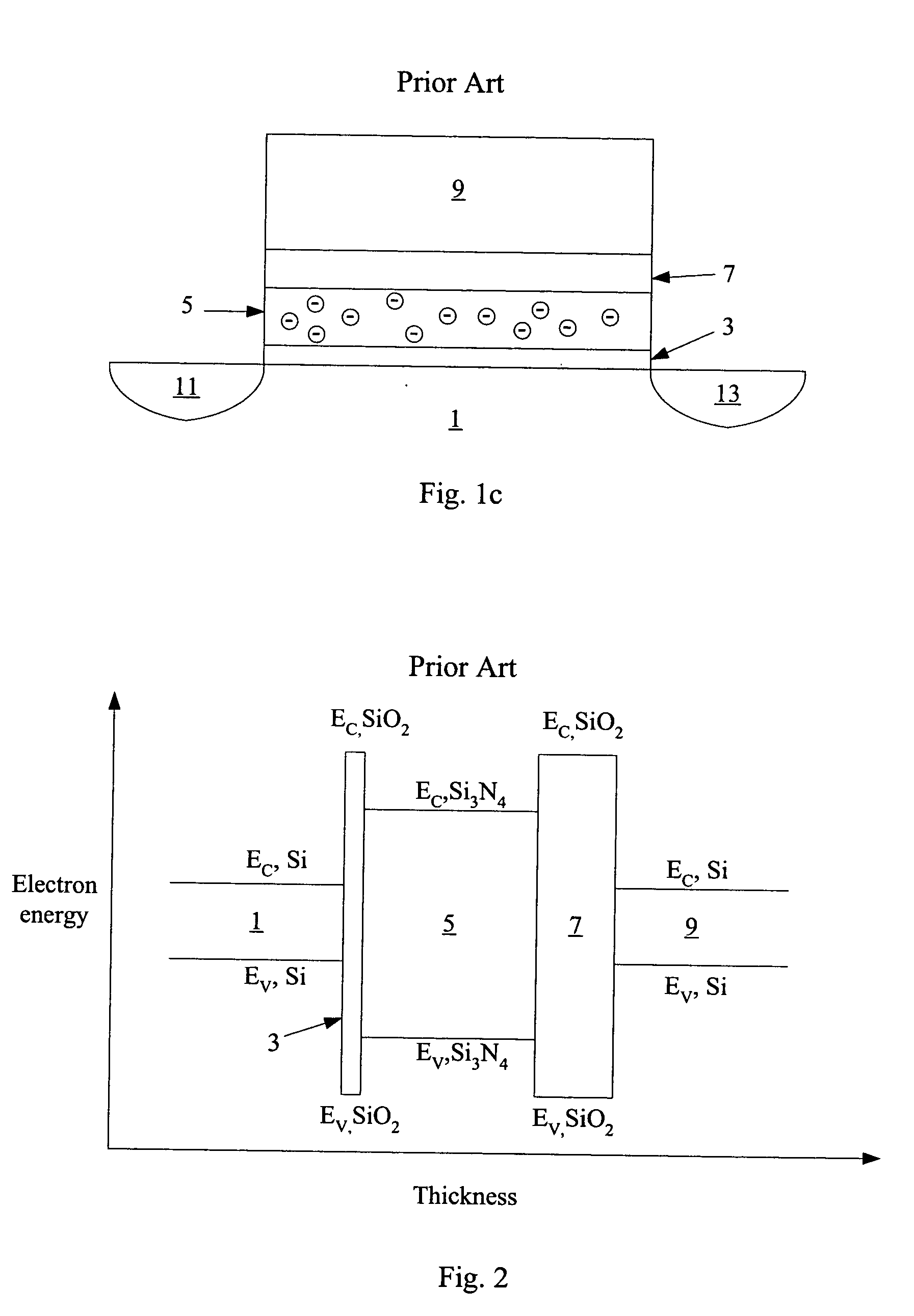

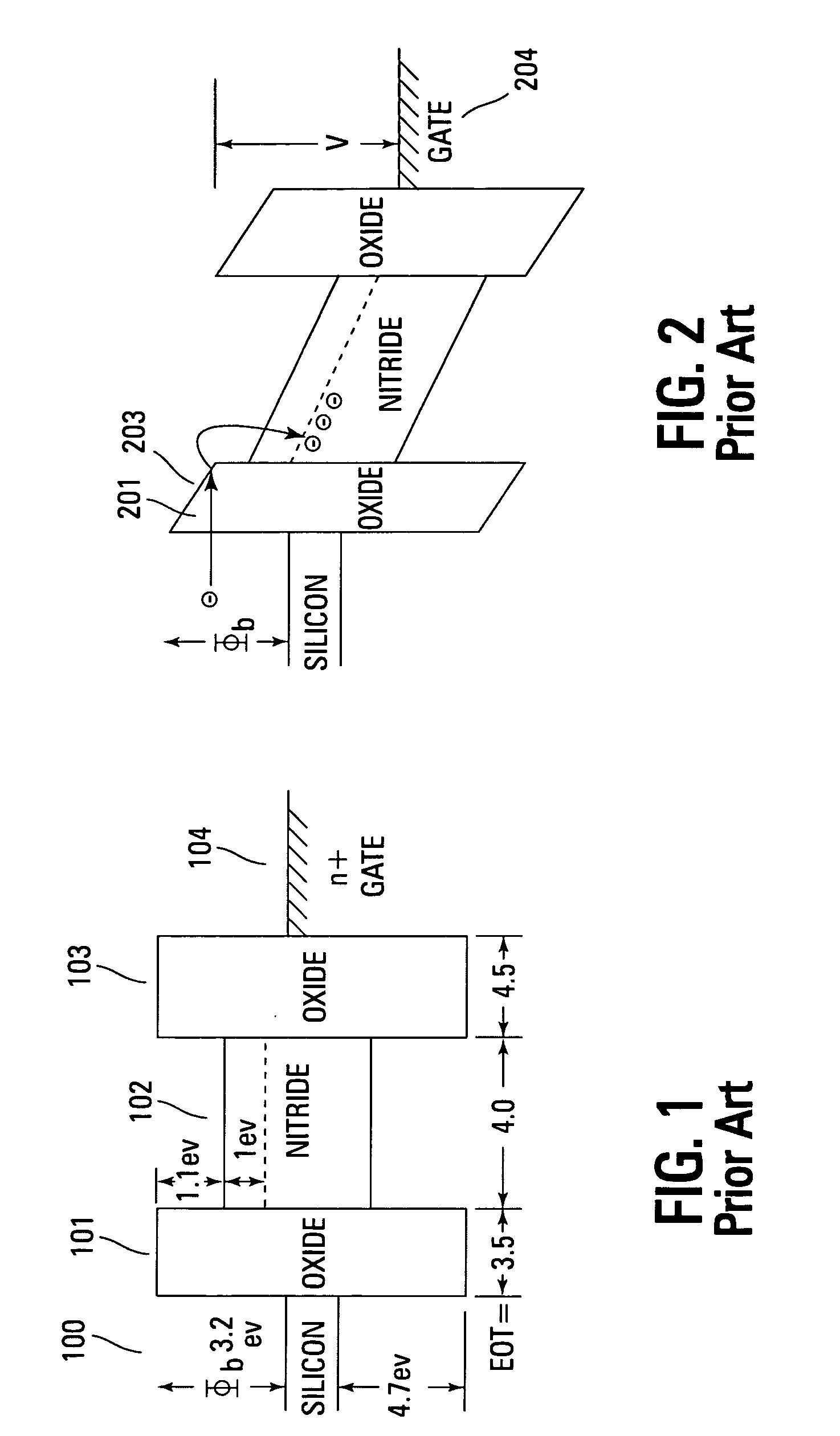

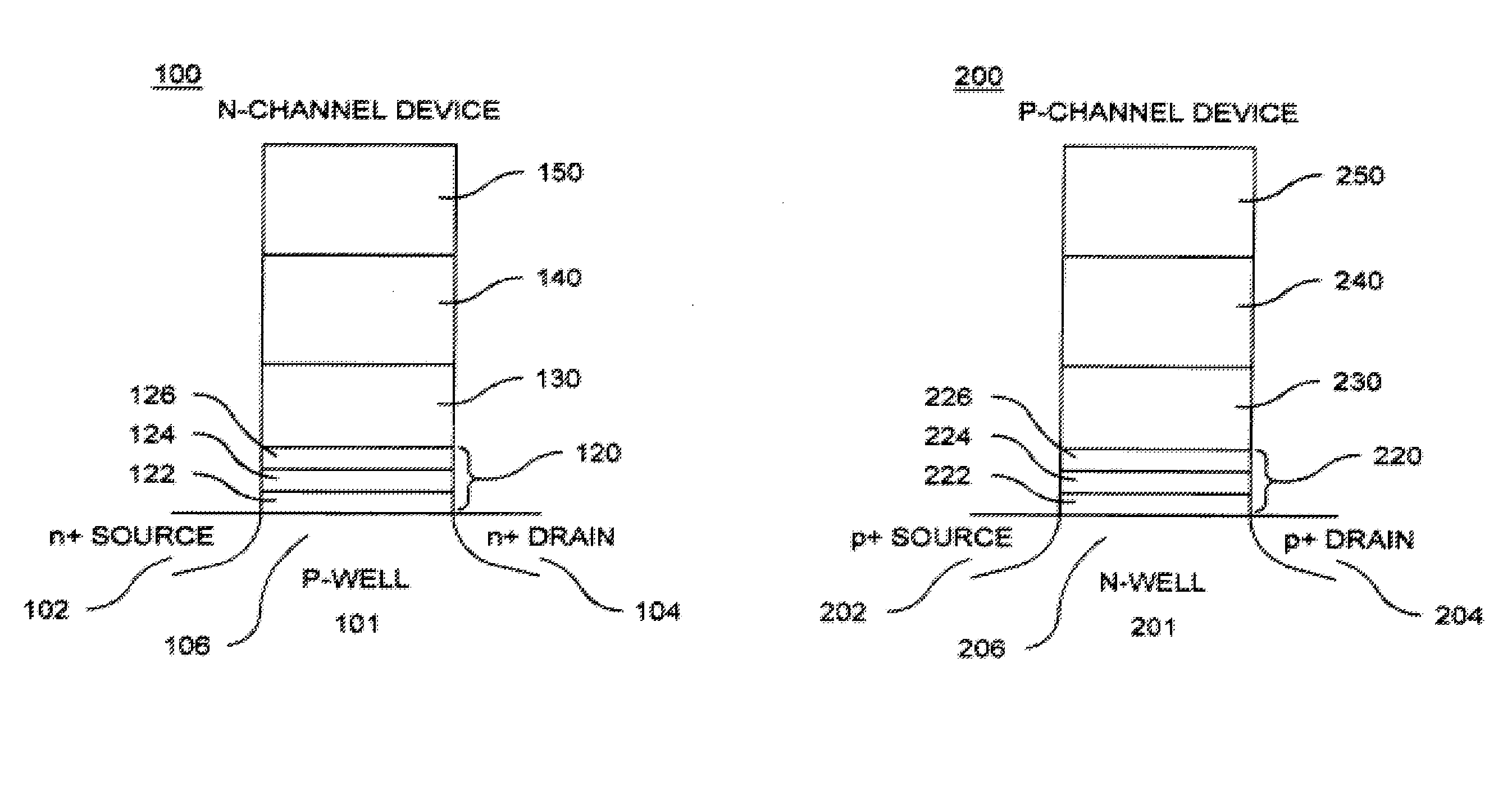

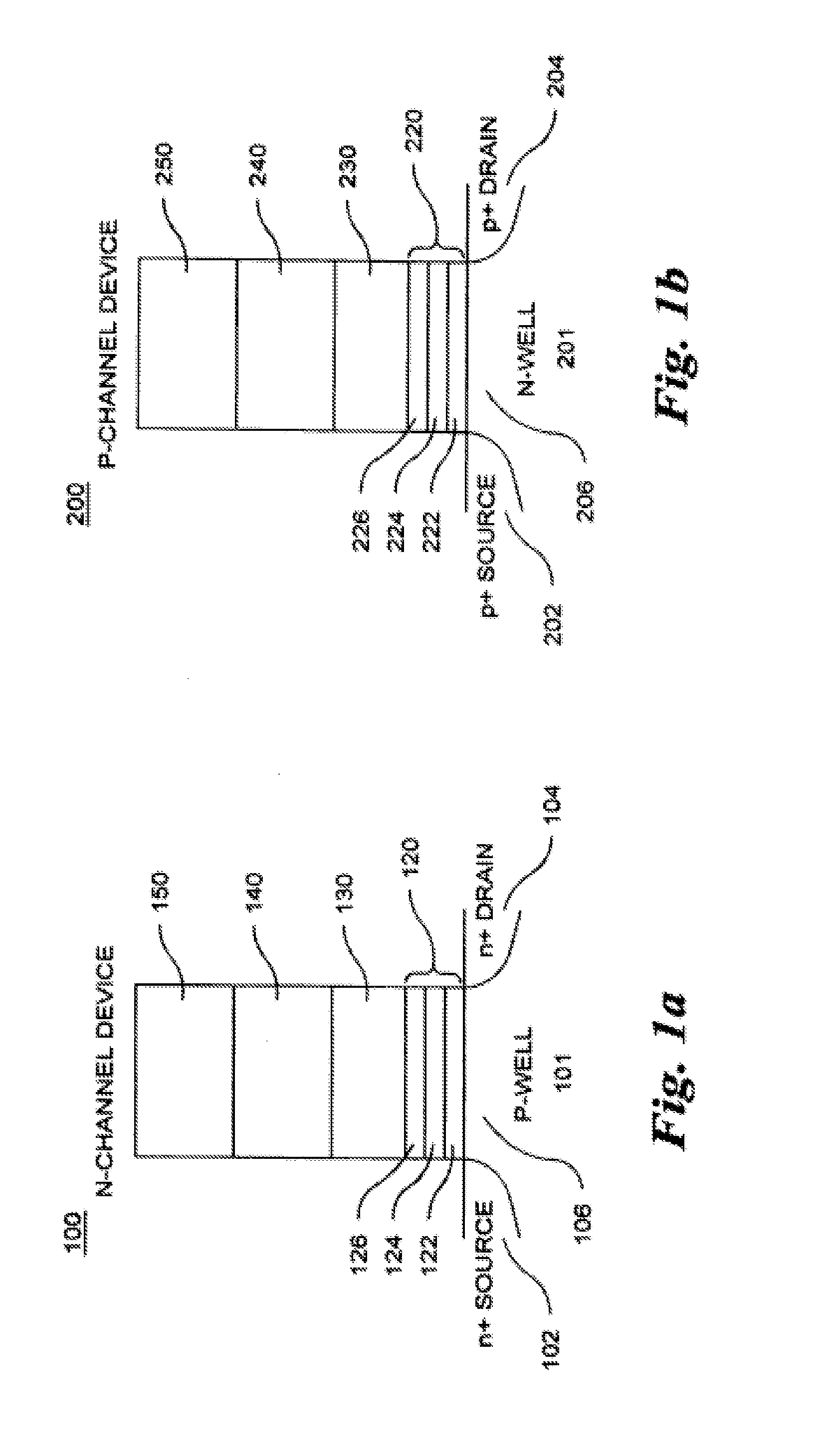

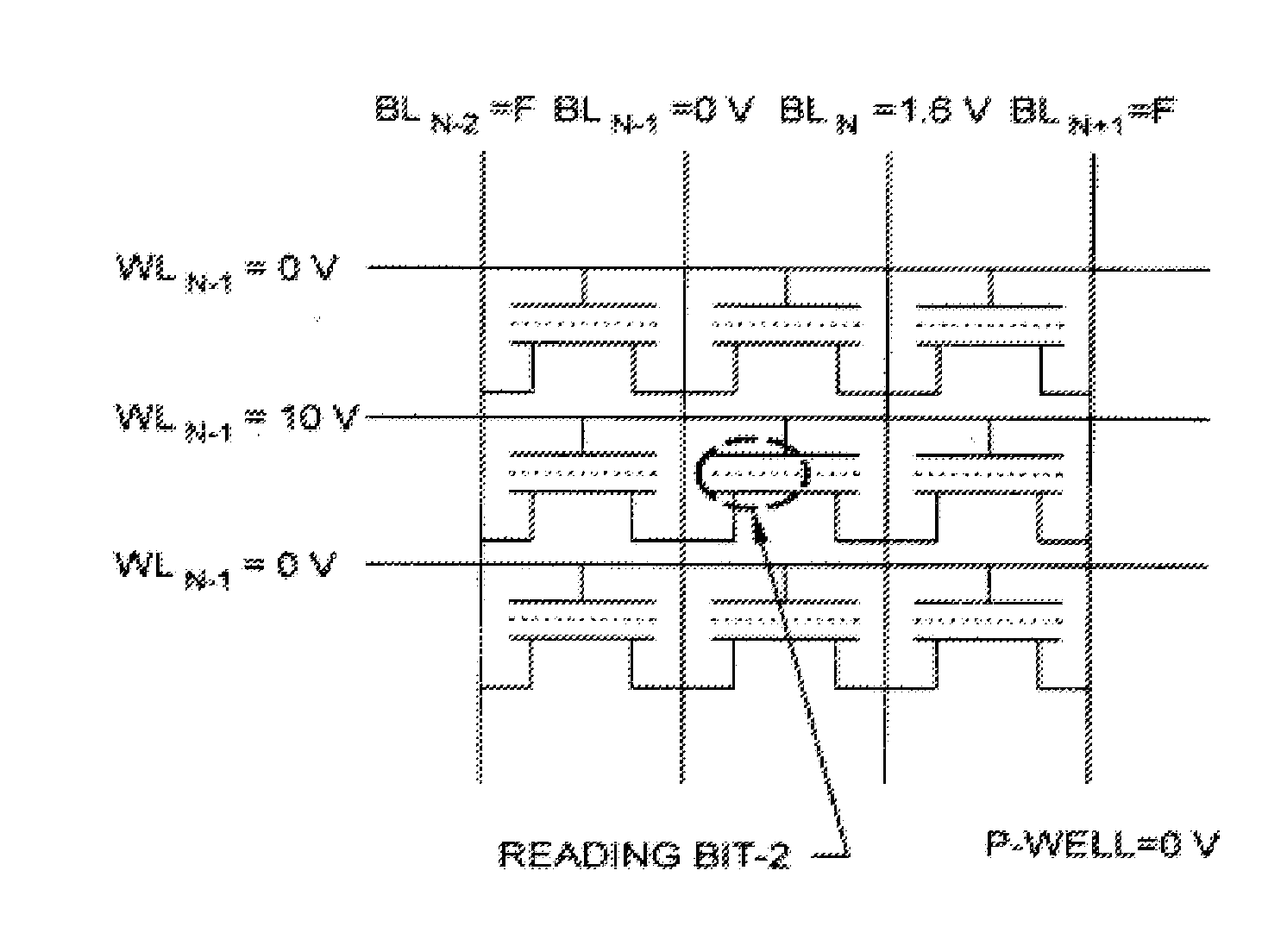

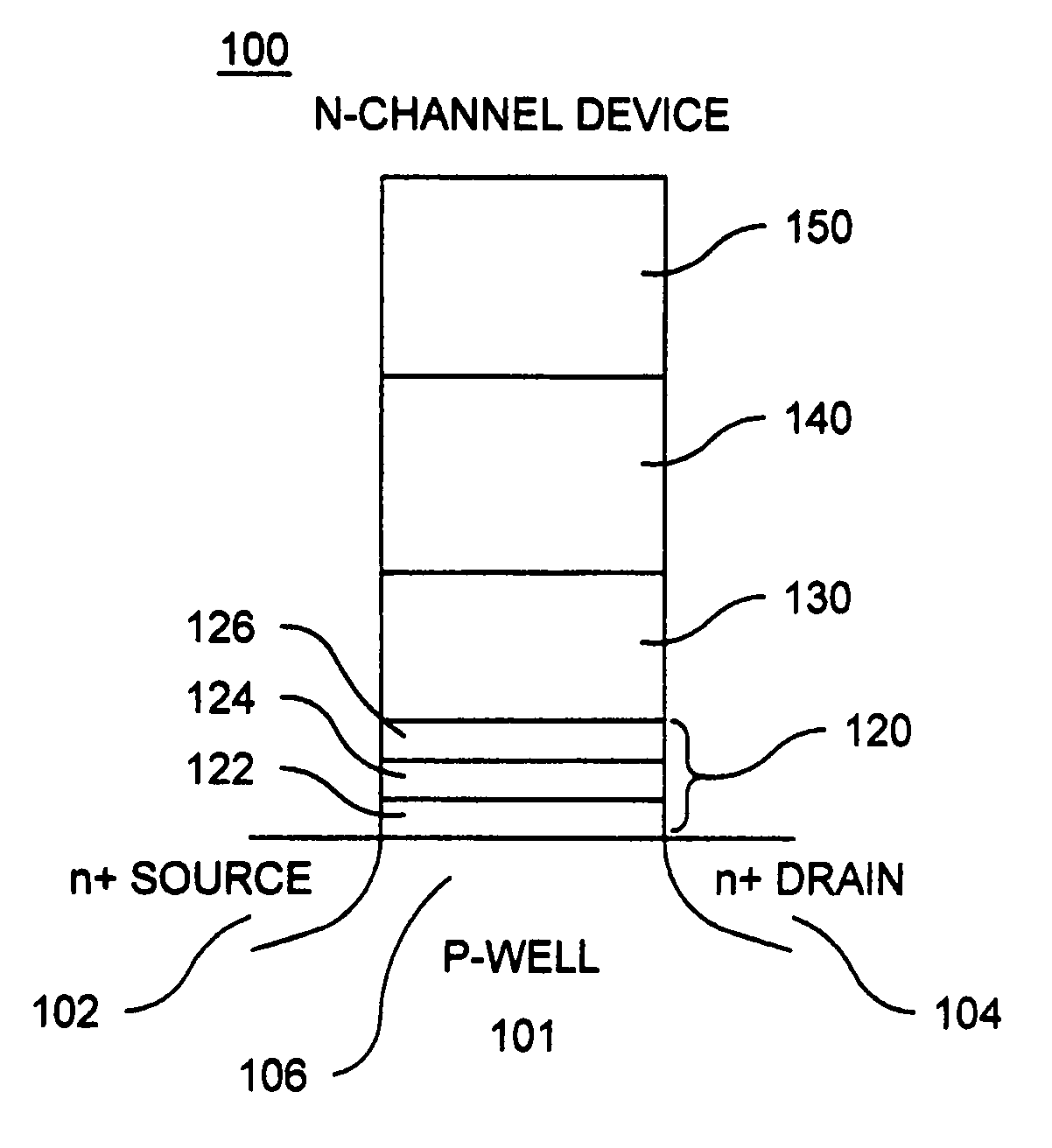

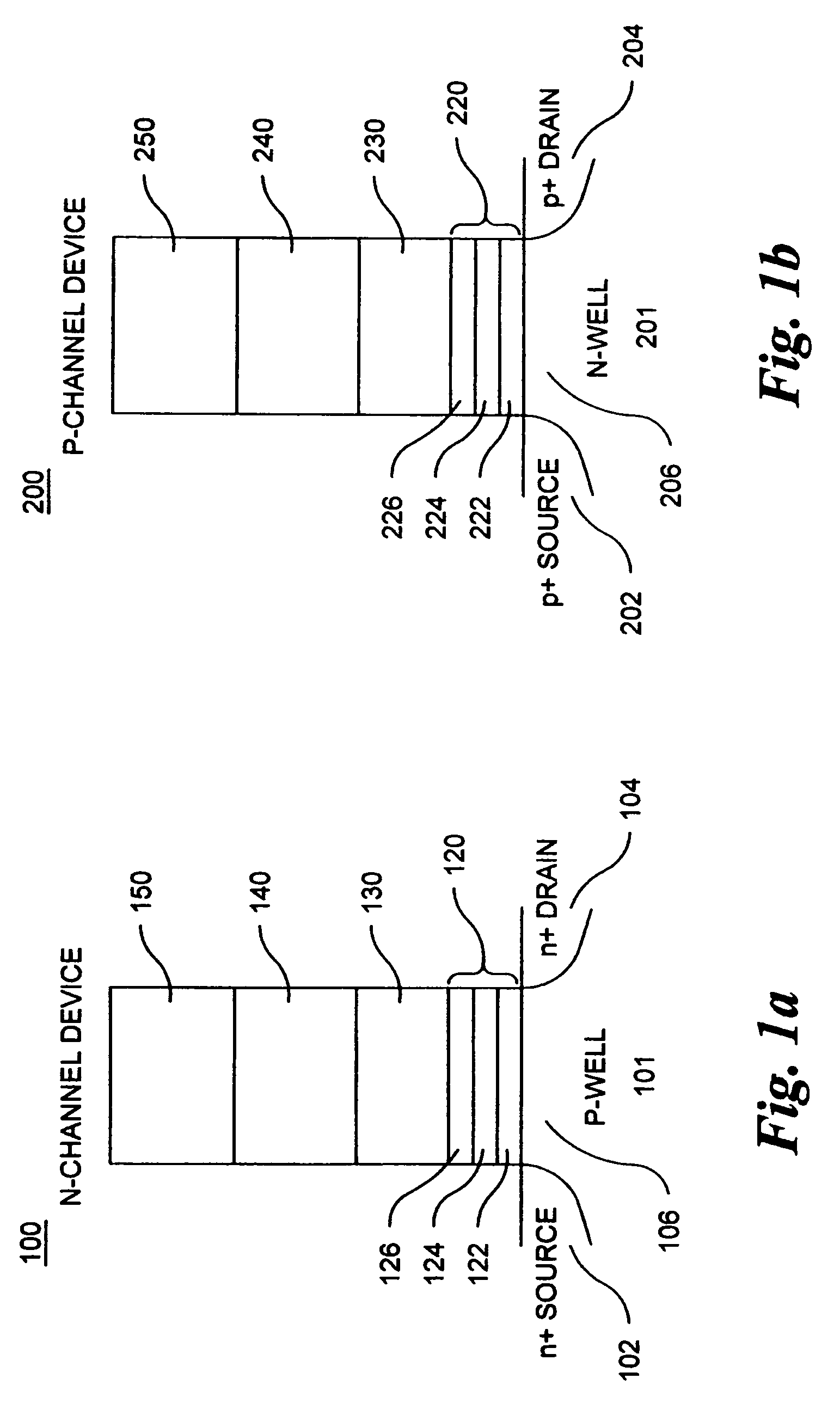

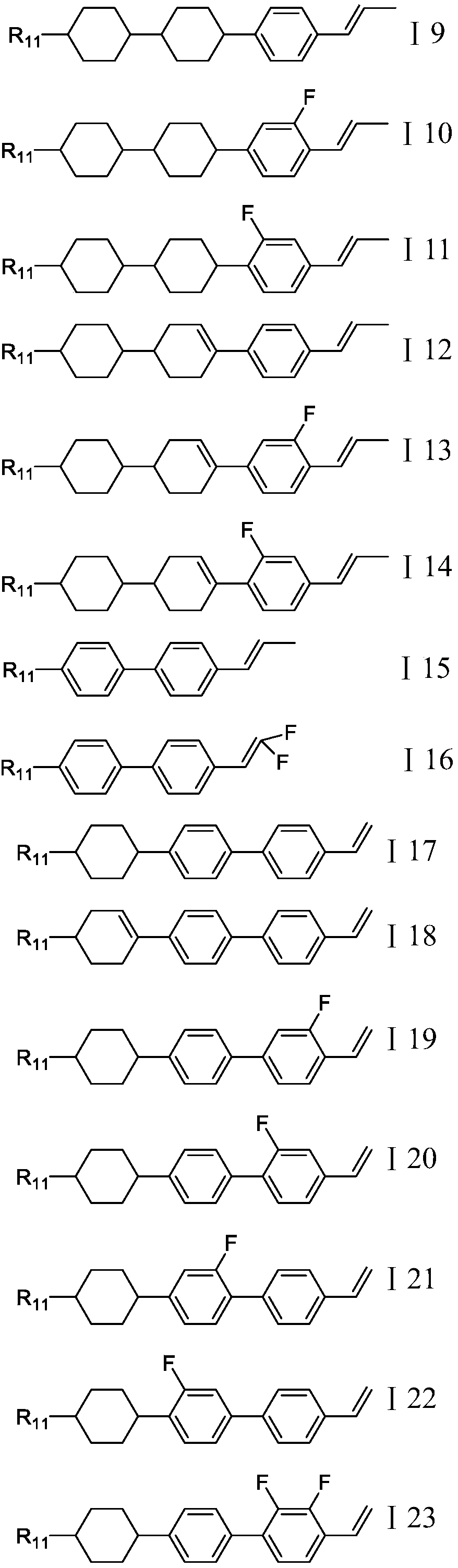

Methods of operating non-volatile memory cells having an oxide/nitride multilayer insulating structure

ActiveUS7450423B2Easy to eraseReduce interface damageTransistorRead-only memoriesNitrideDielectric layer

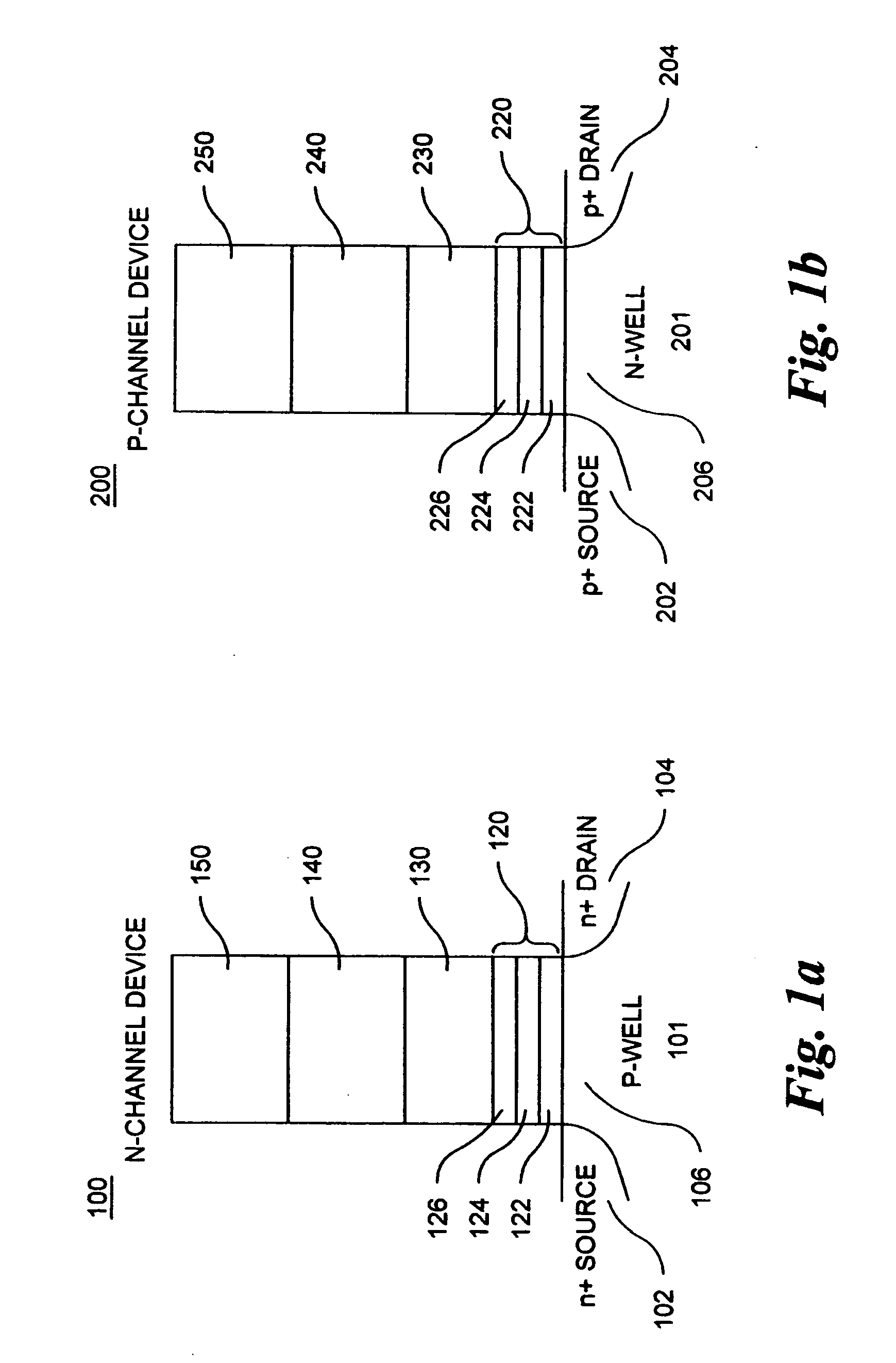

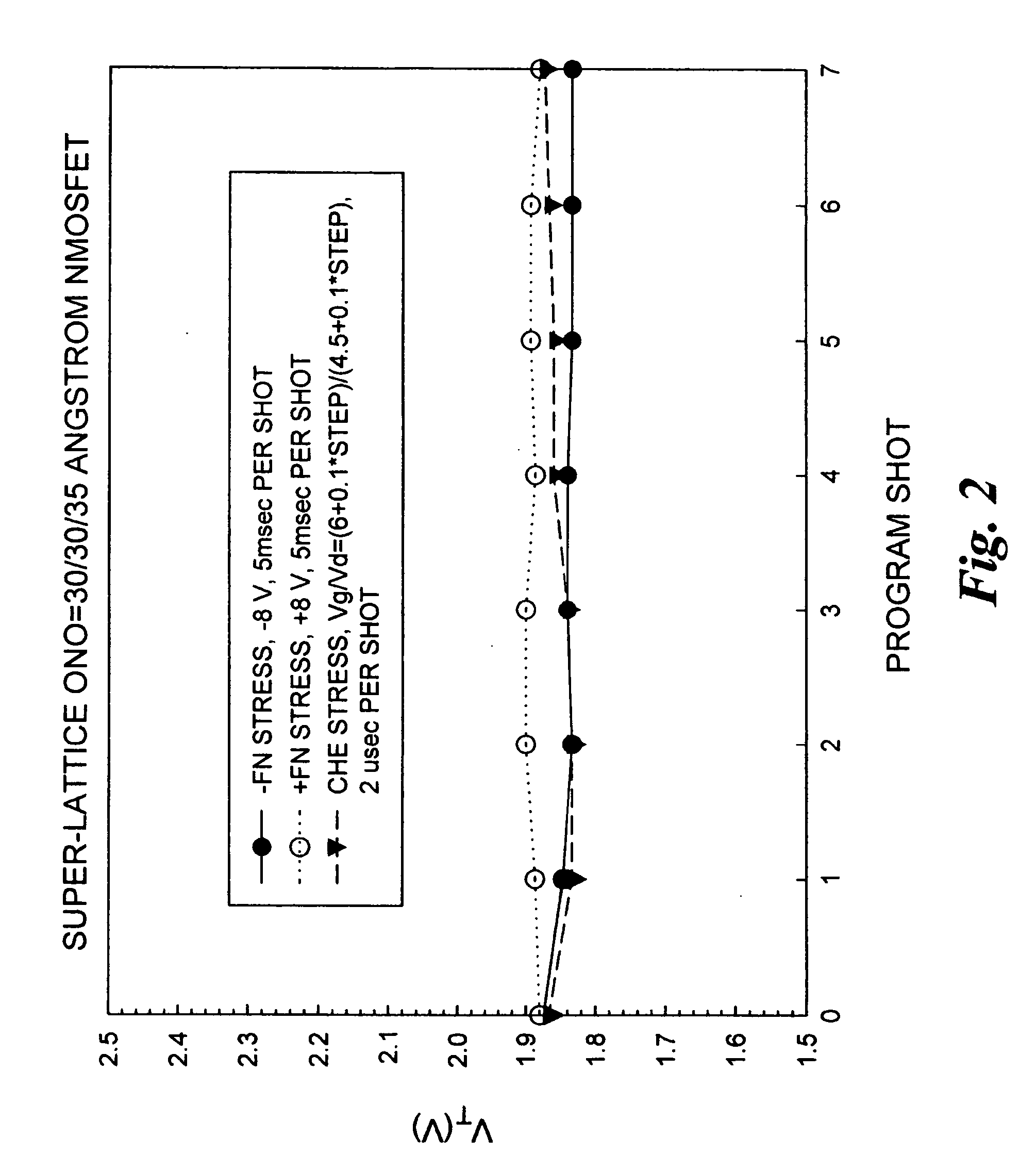

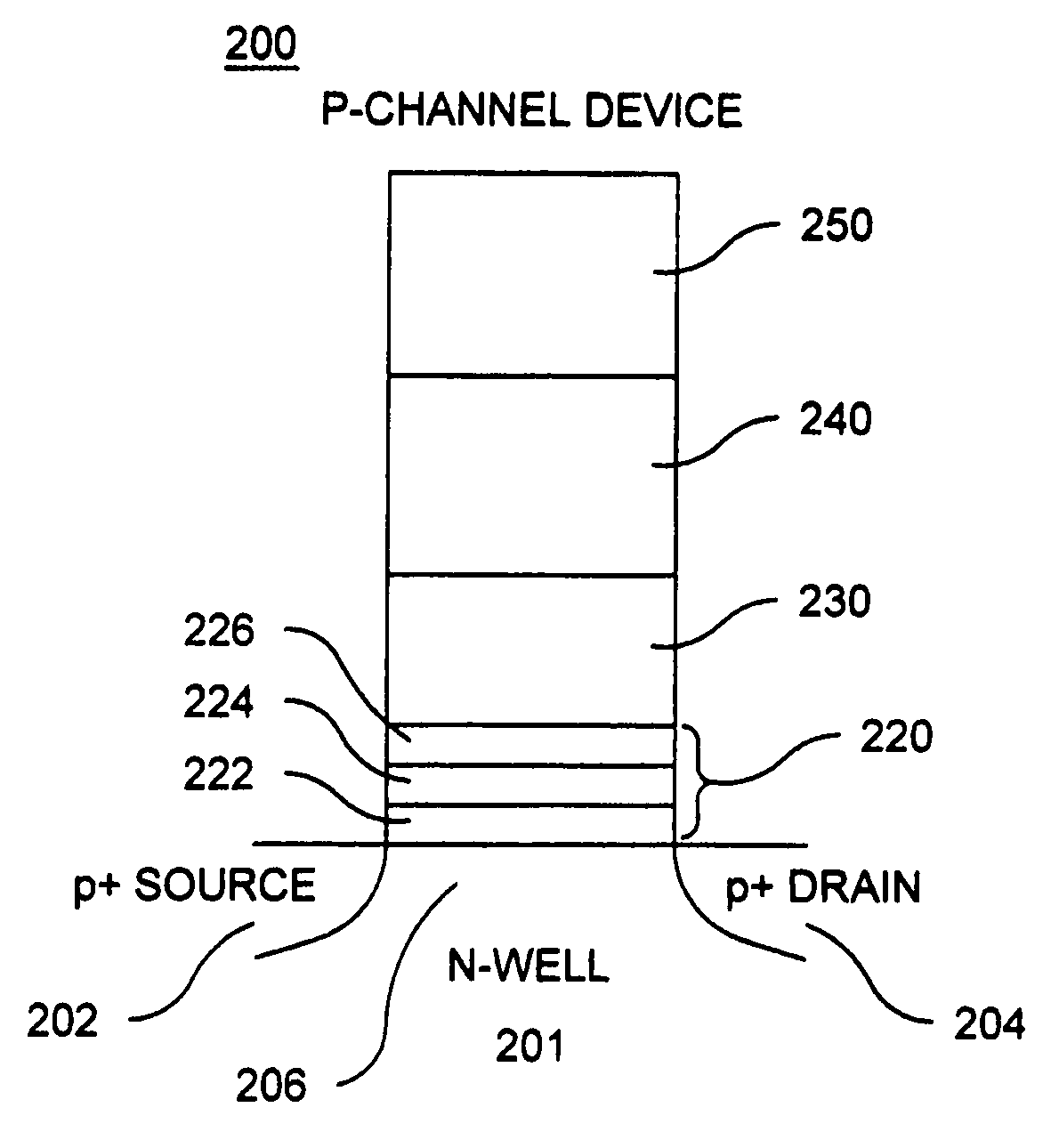

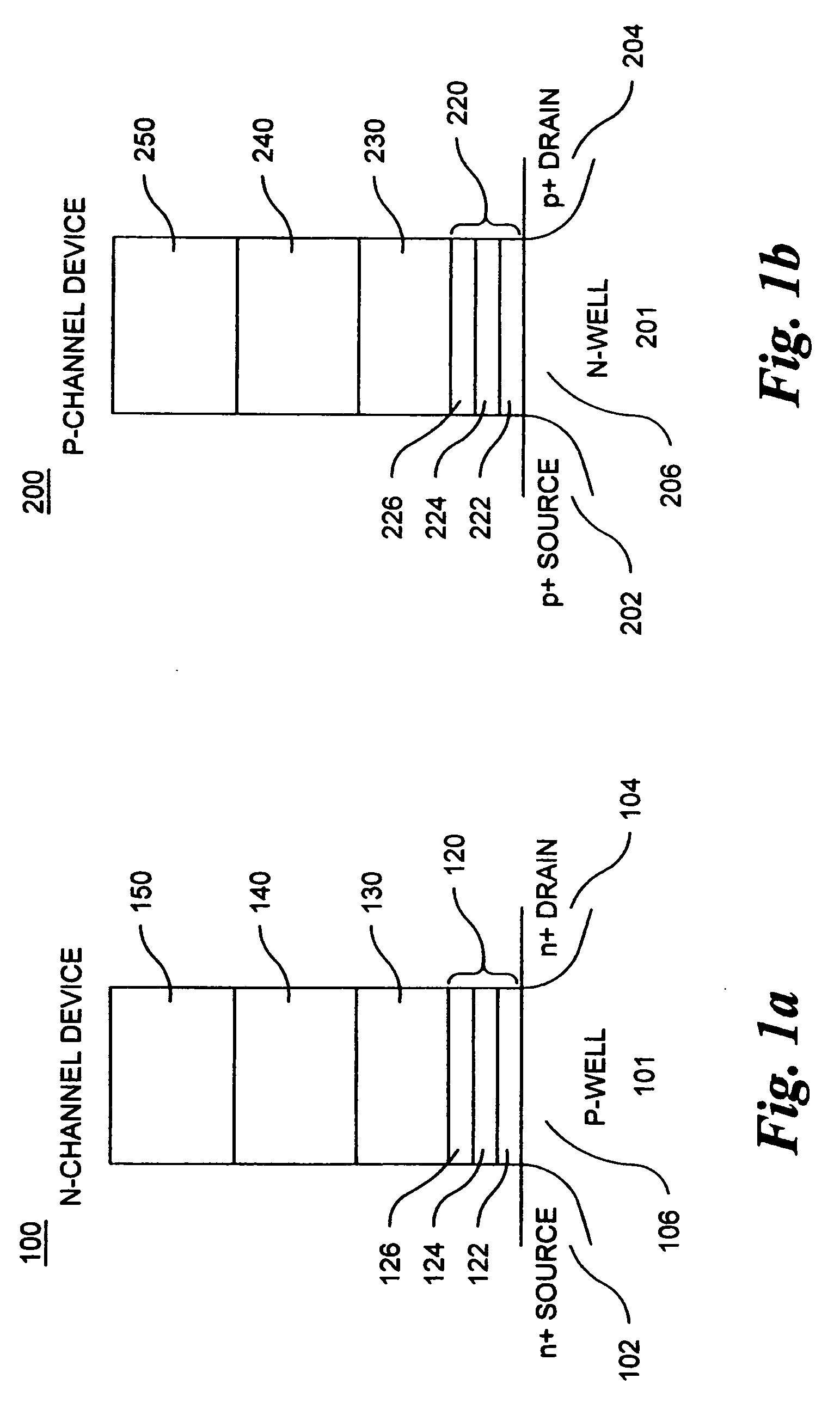

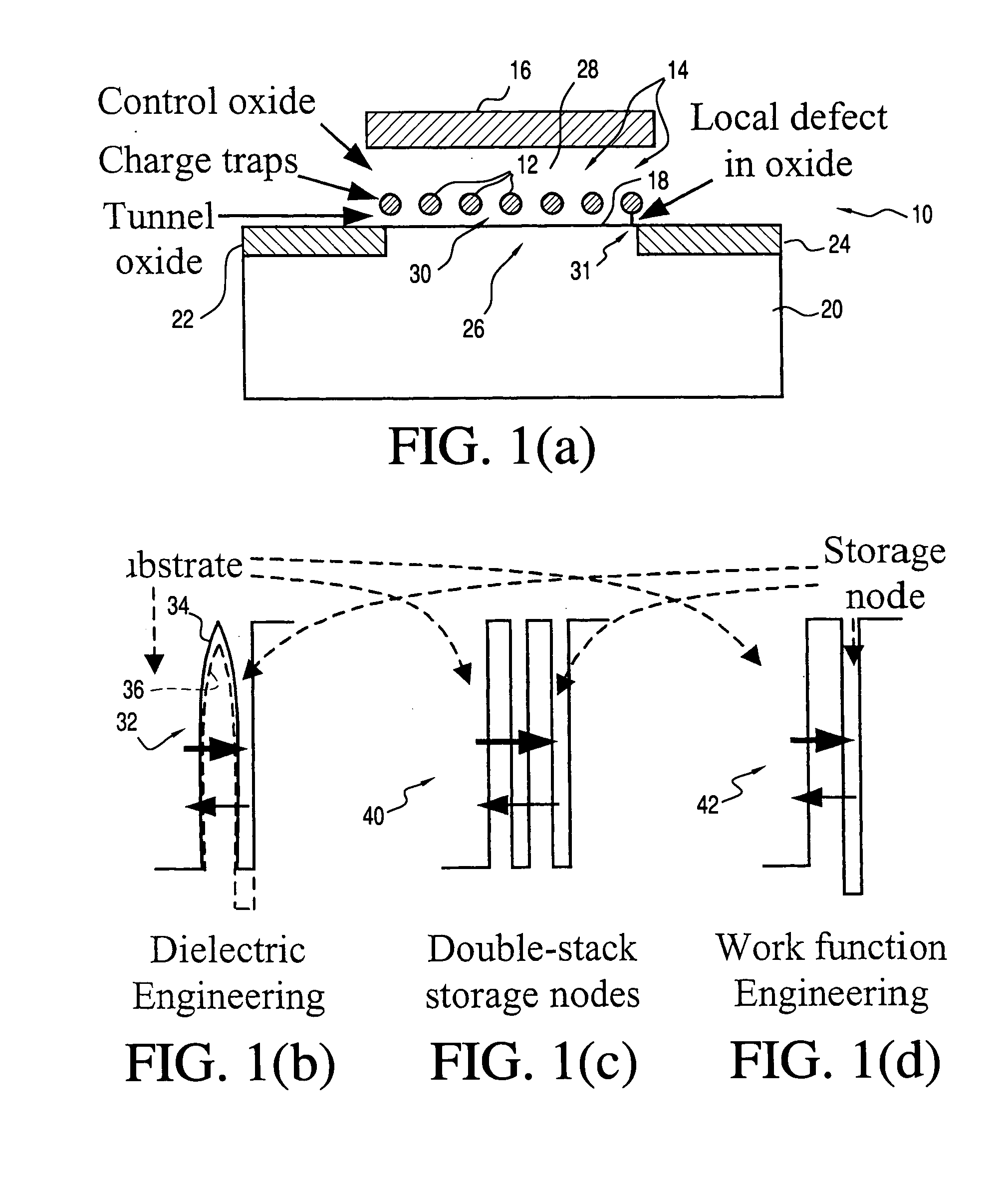

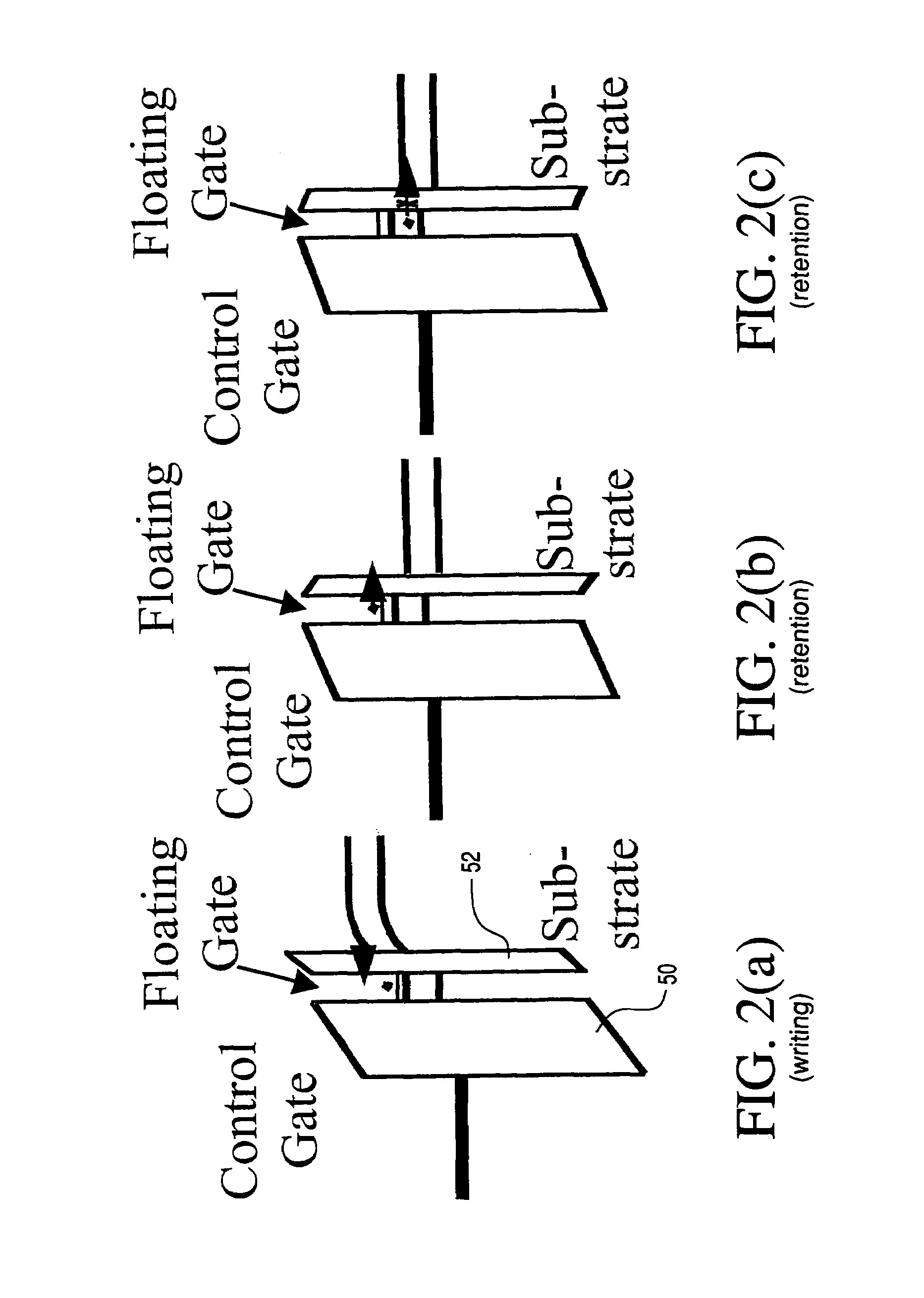

A method of operating a memory cell by applying a positive voltage to the gate sufficient to cause hole tunneling from the gate toward the charge storage layer is disclosed. The method is applied to a memory cell including a semiconductor layer having at least two source / drain regions disposed below a surface of the semiconductor layer and separated by a channel region. The memory cell also has a lower insulating layer disposed above the channel region; a charge storage layer disposed above the lower insulating layer; an upper insulating multi-layer structure disposed above the charge storage layer. The upper insulating multi-layer structure comprises a lower dielectric layer and an upper nitride layer disposed above the lower dielectric layer and the memory cell has a gate disposed above the upper insulating multi-layer structure.

Owner:MACRONIX INT CO LTD

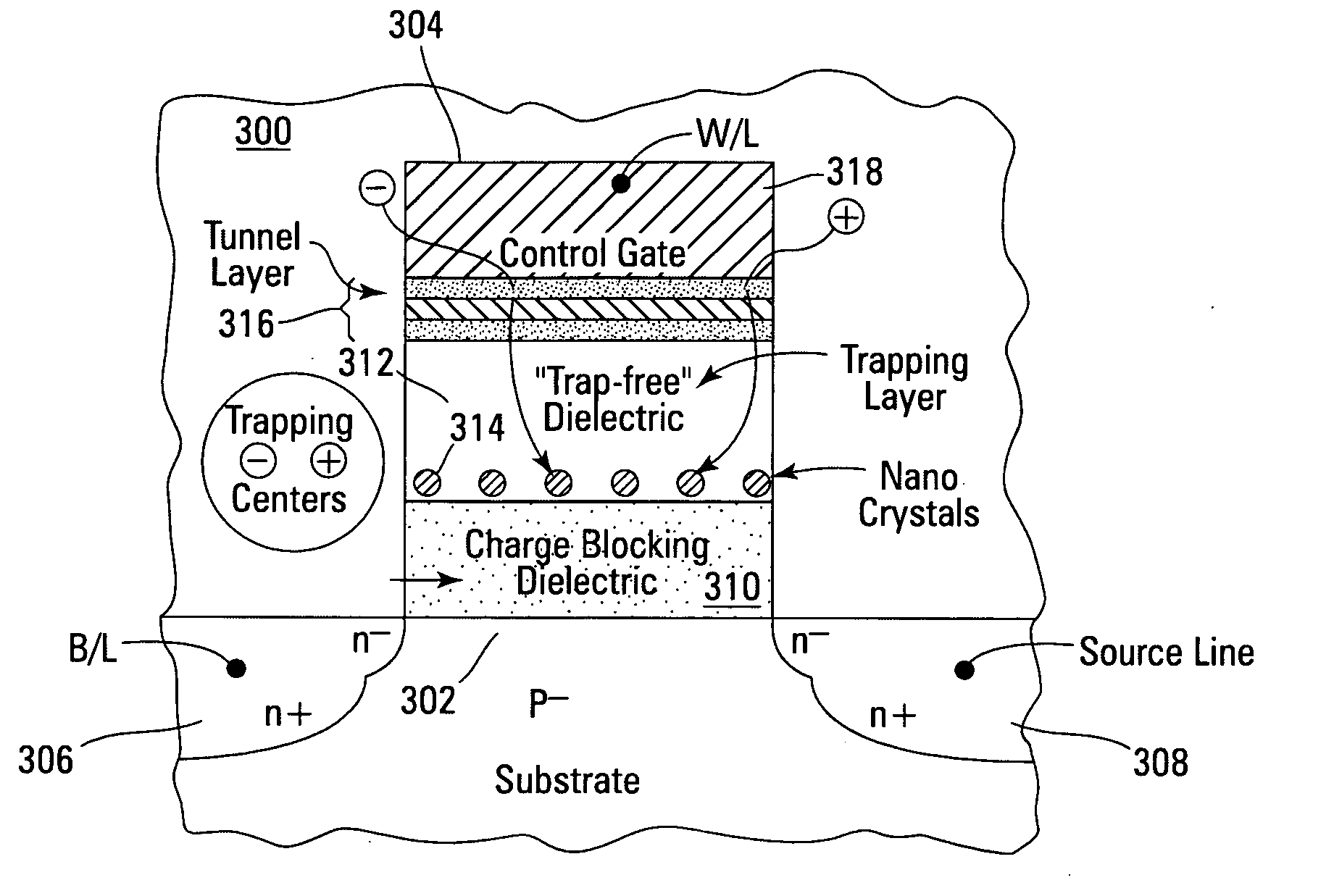

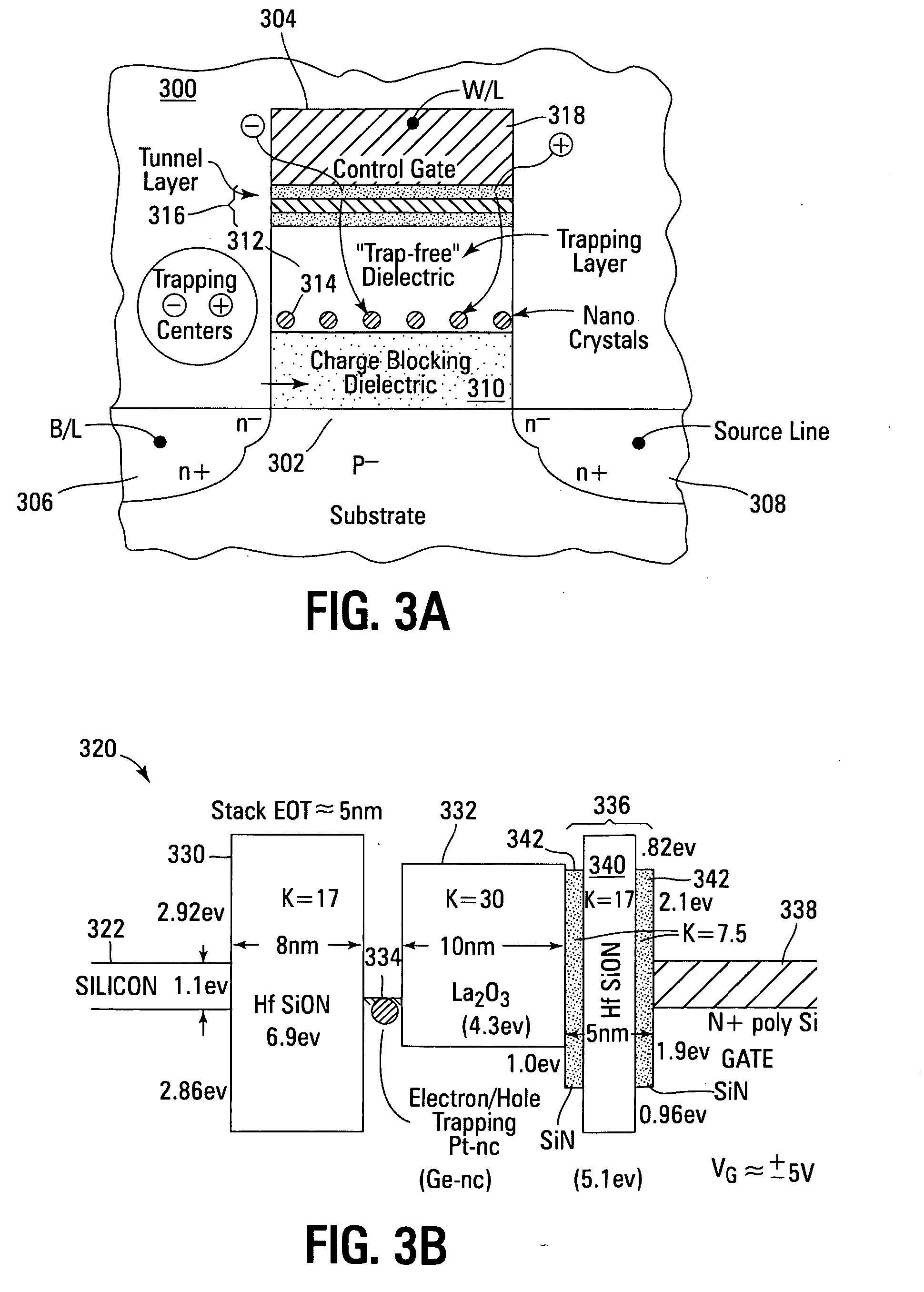

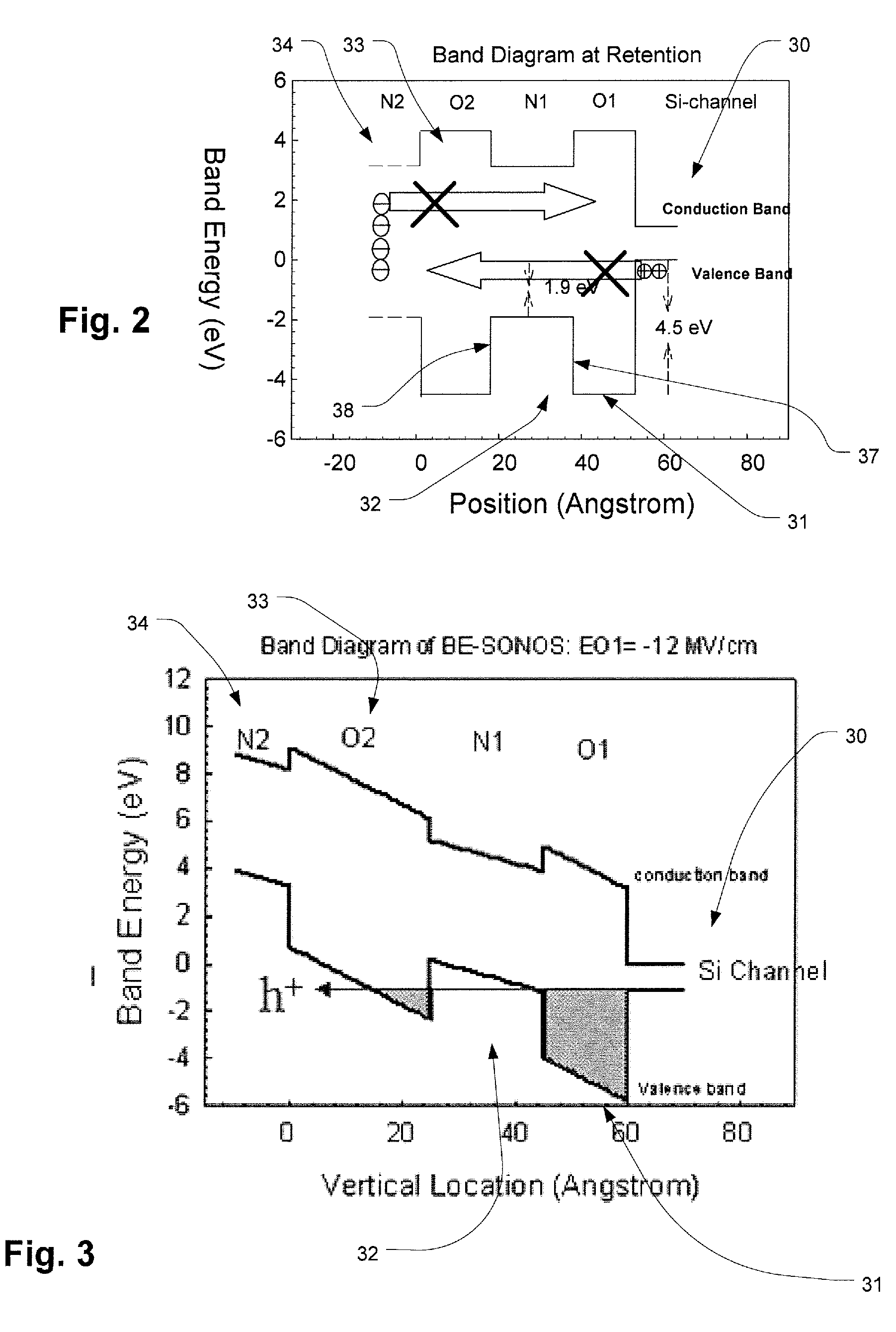

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

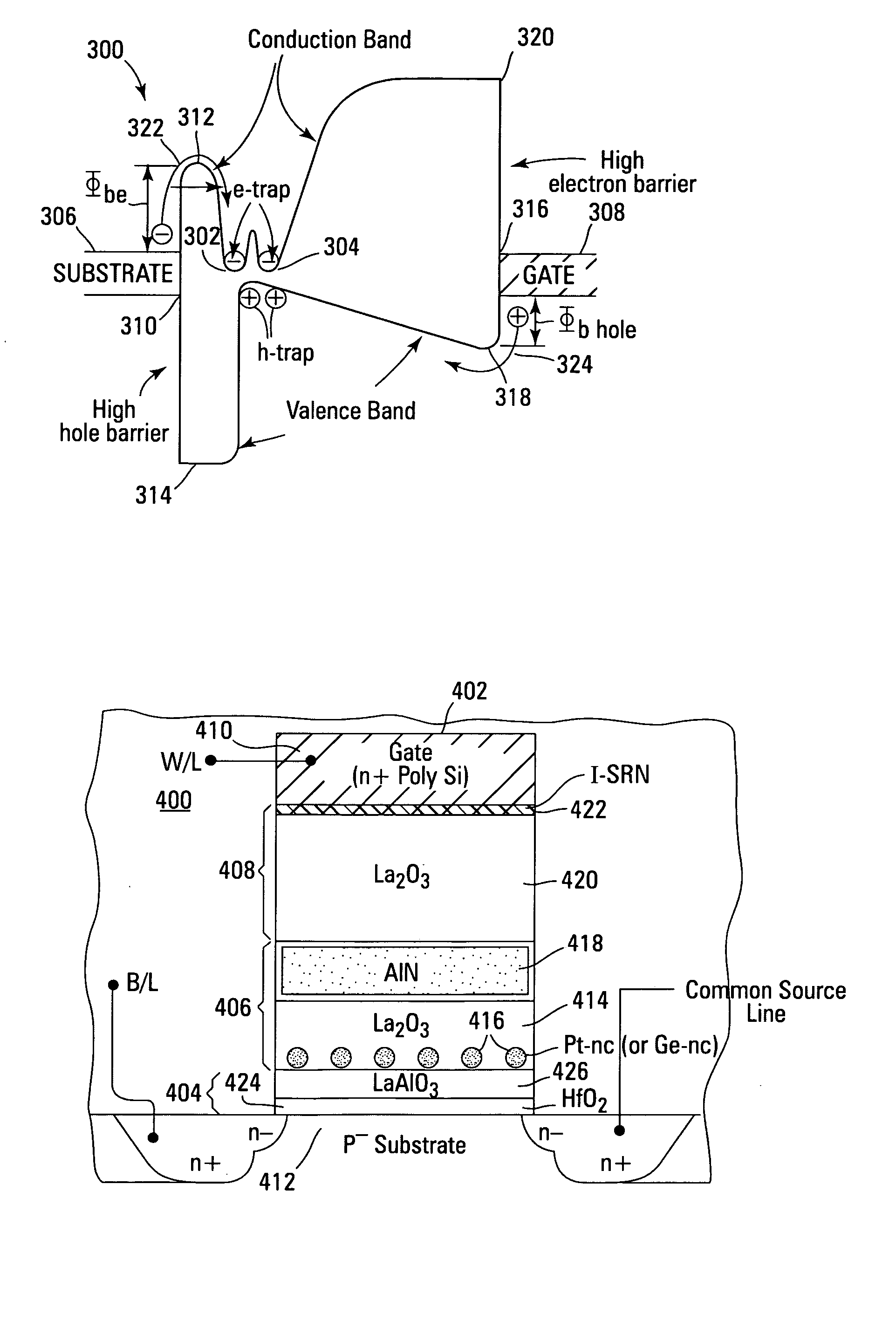

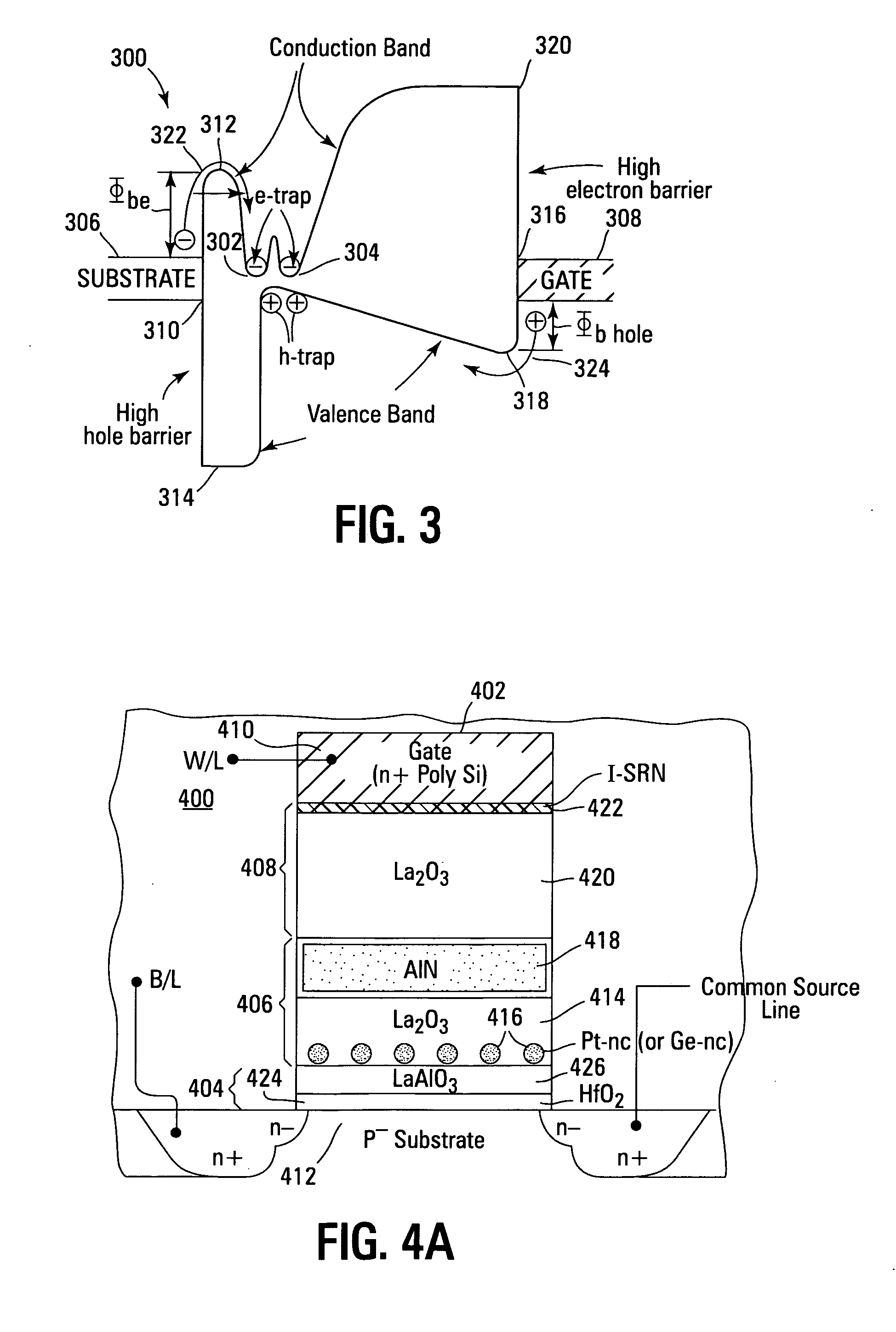

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

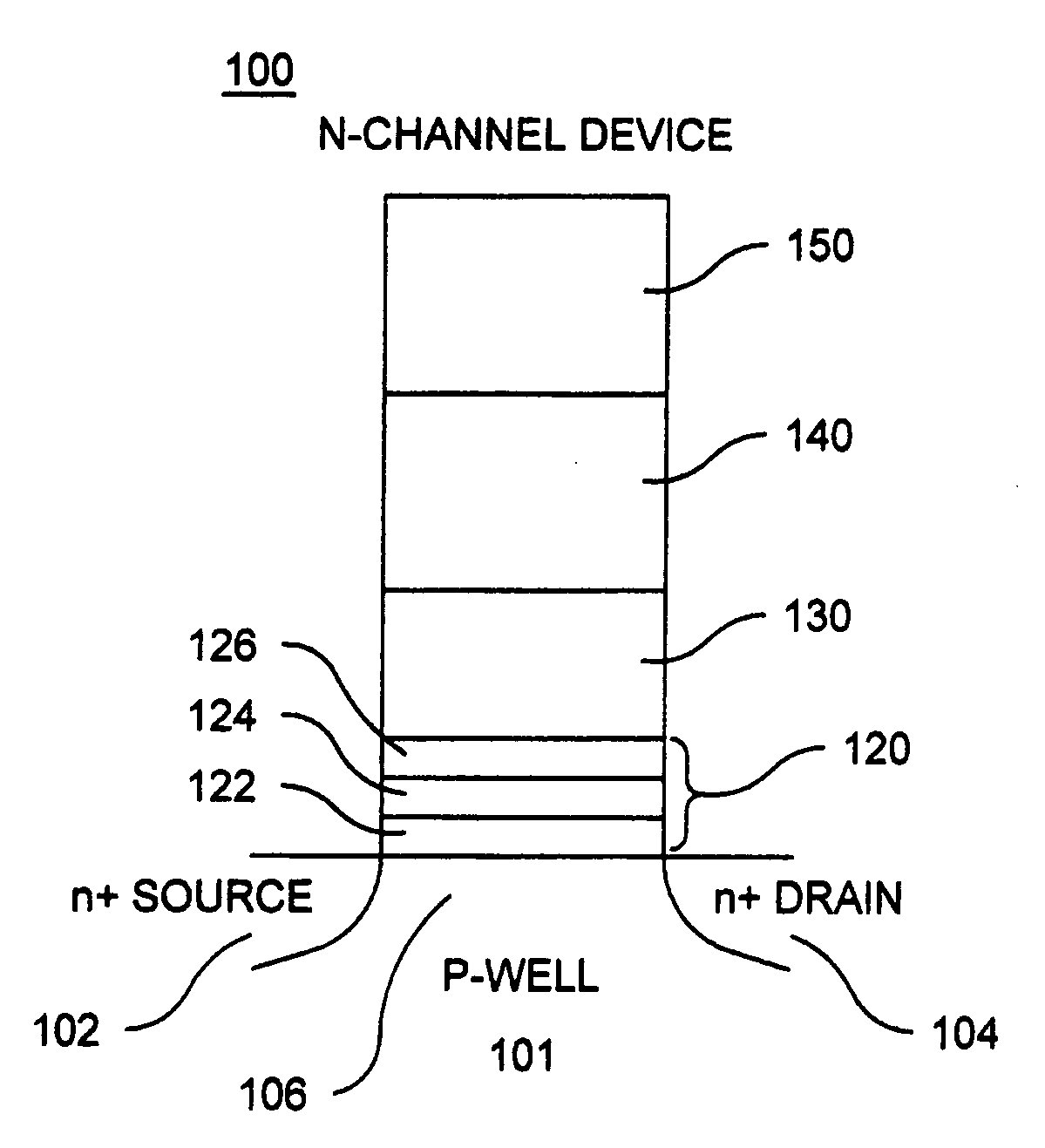

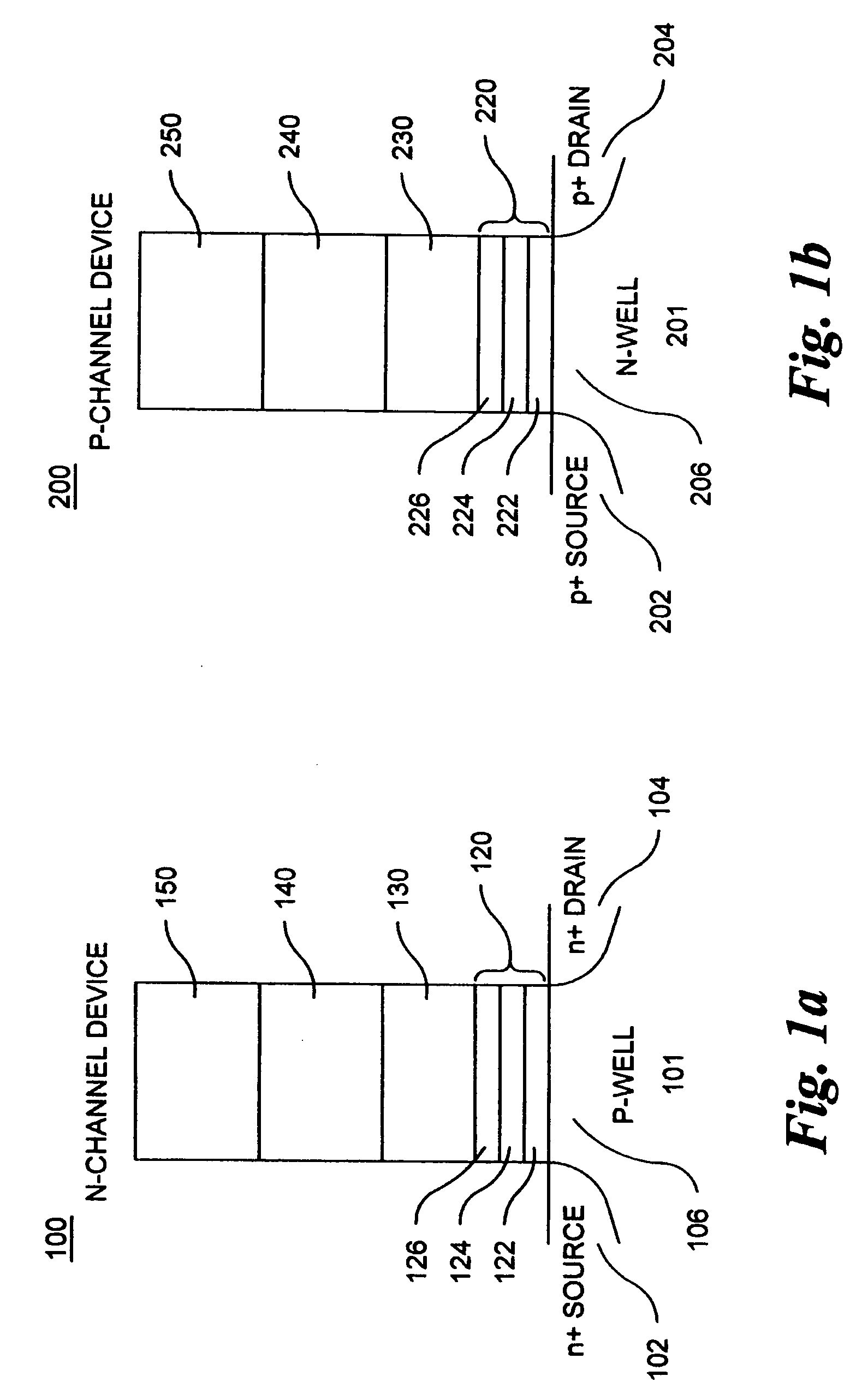

Non-volatile memory cells, memory arrays including the same and methods of operating cells and arrays

ActiveUS20060202261A1Easy to eraseLarge operating windowSolid-state devicesRead-only memoriesEngineeringDielectric structure

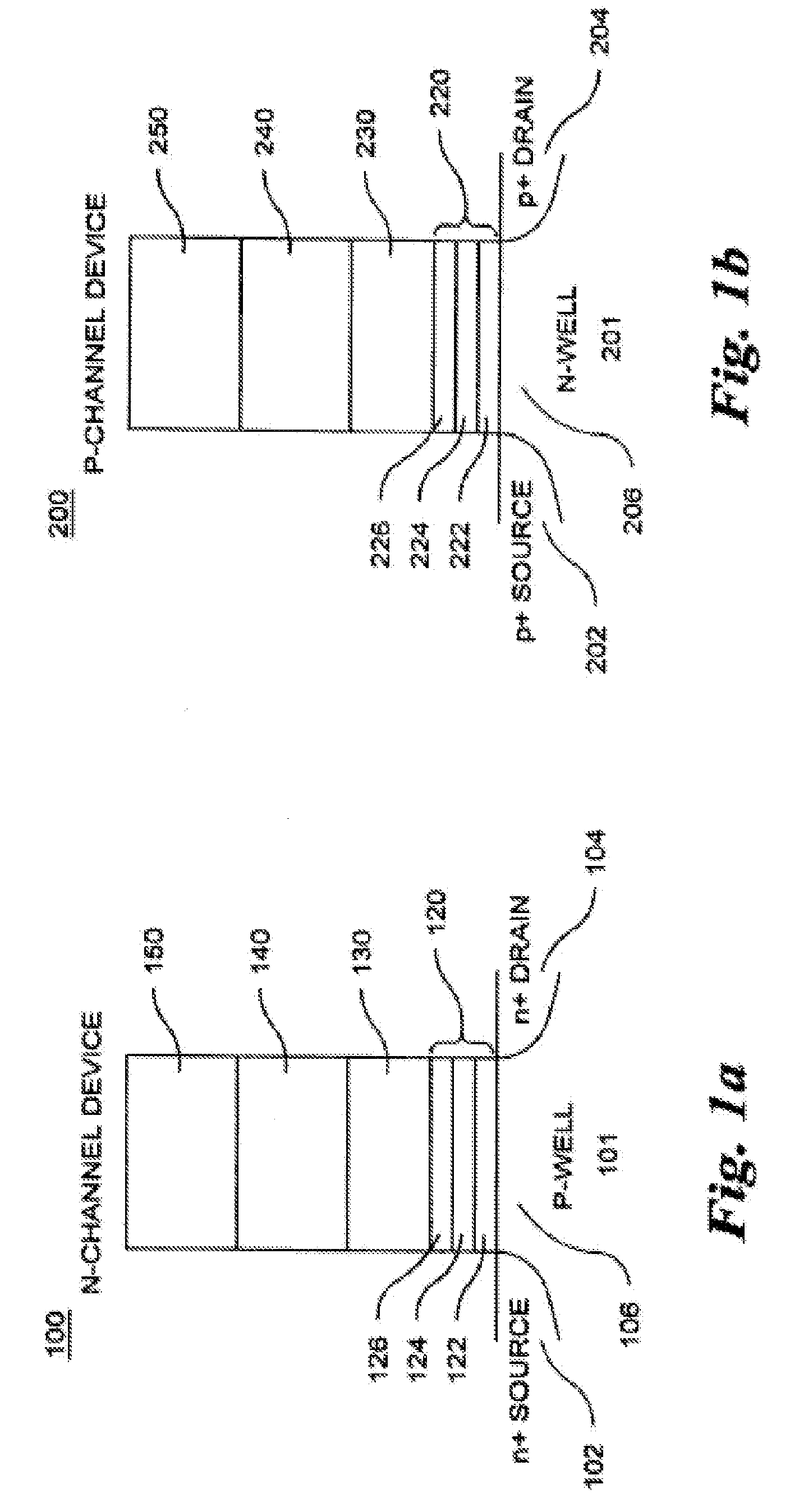

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a small hole-tunneling-barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD

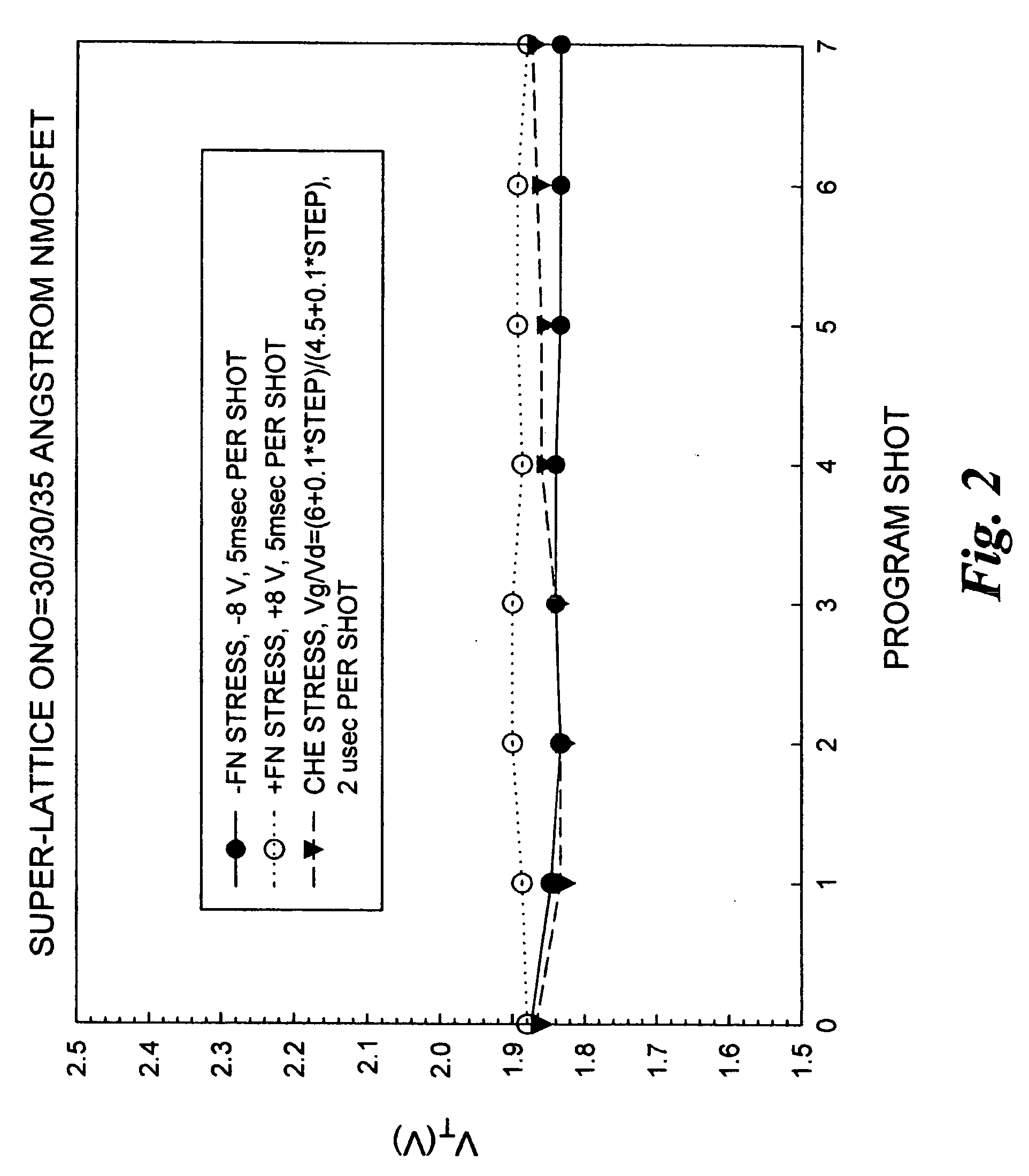

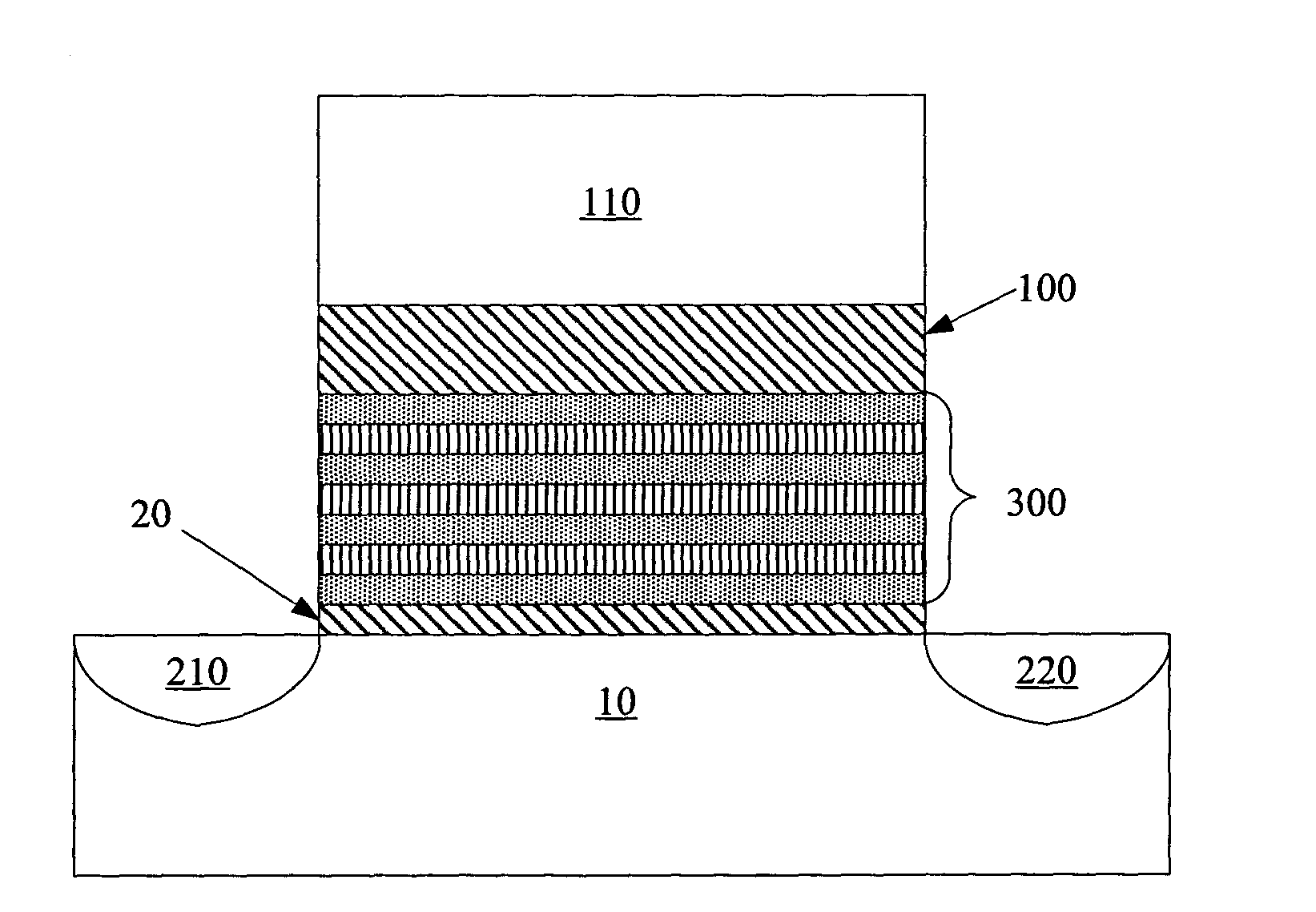

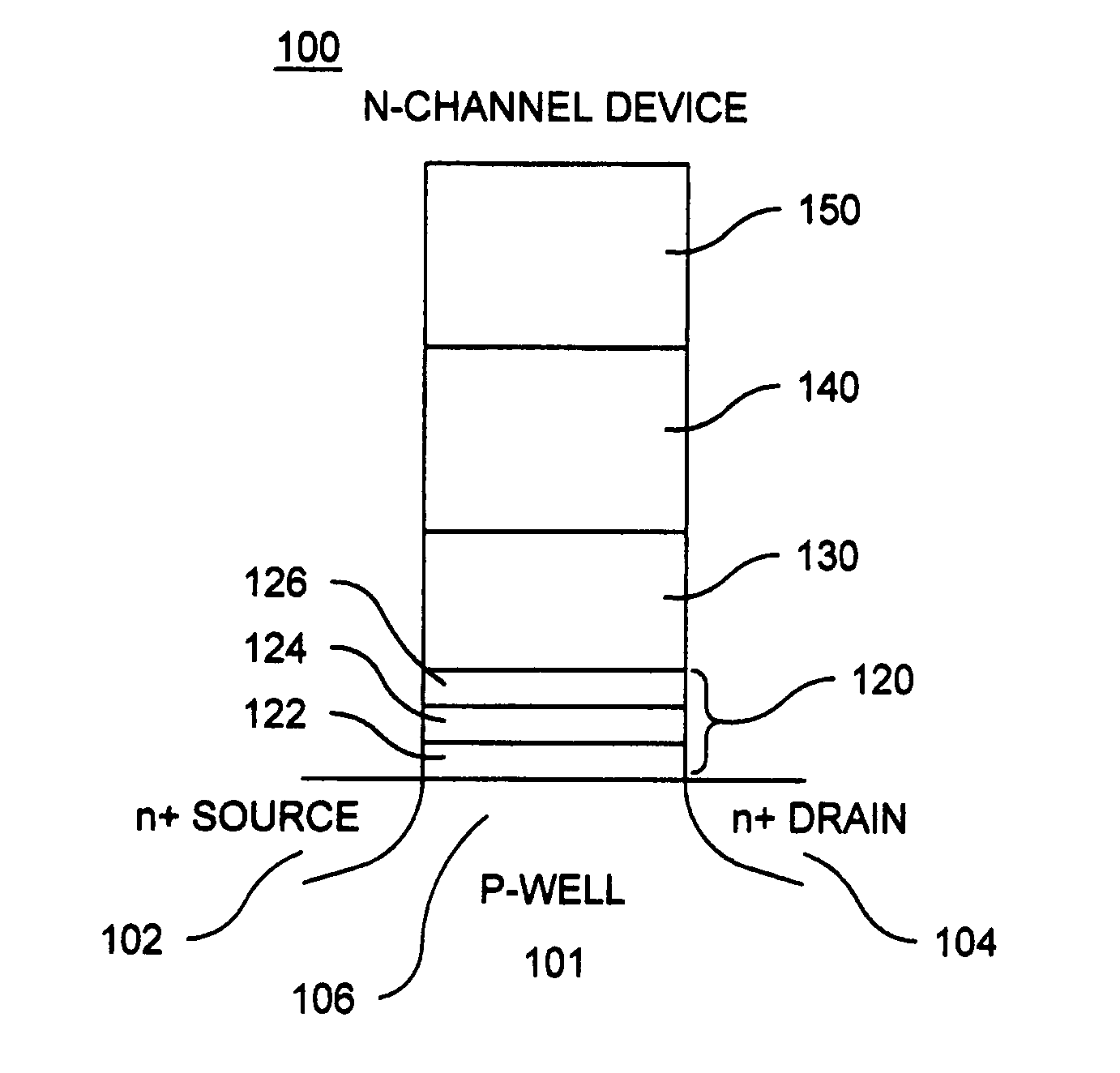

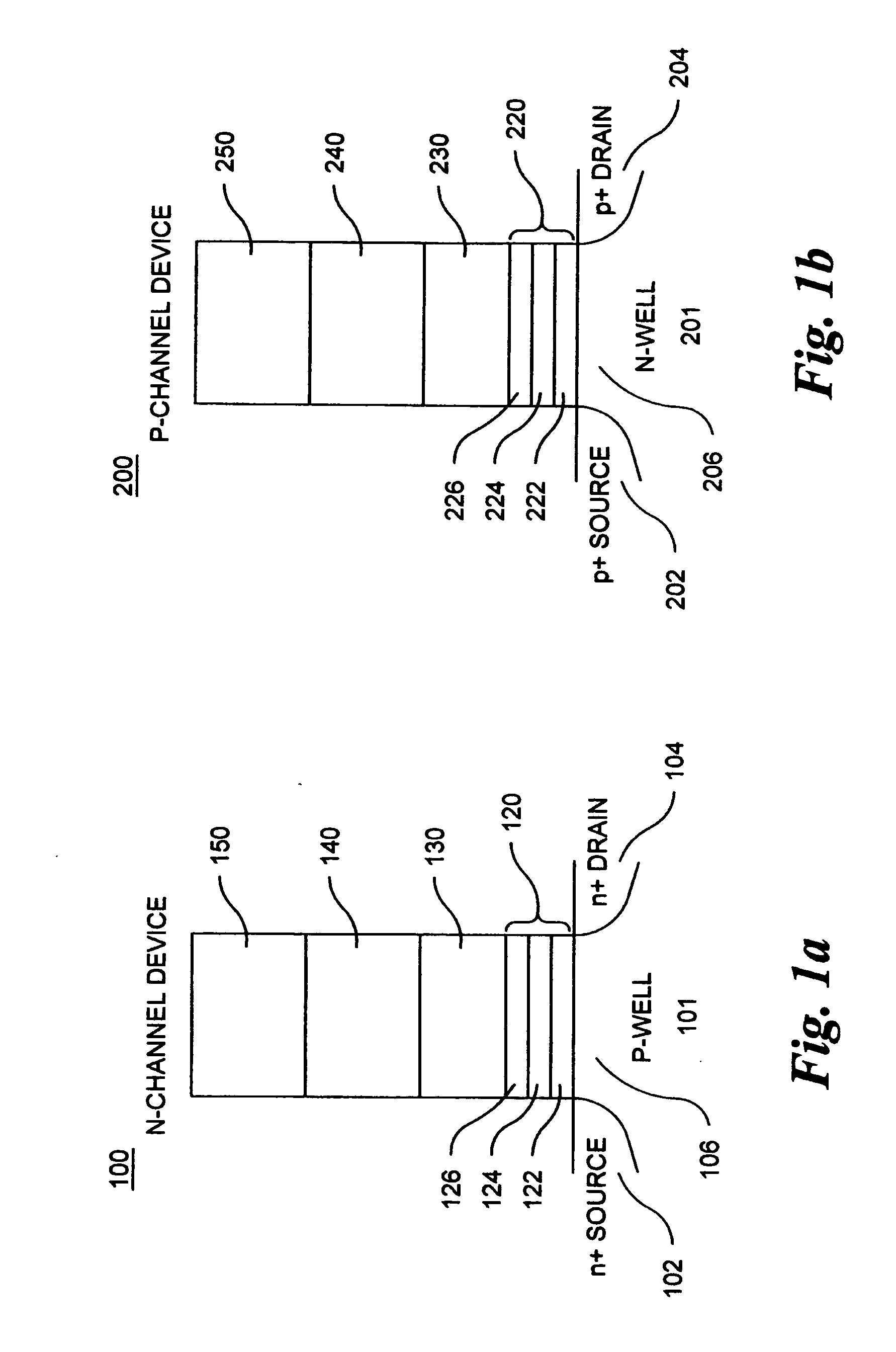

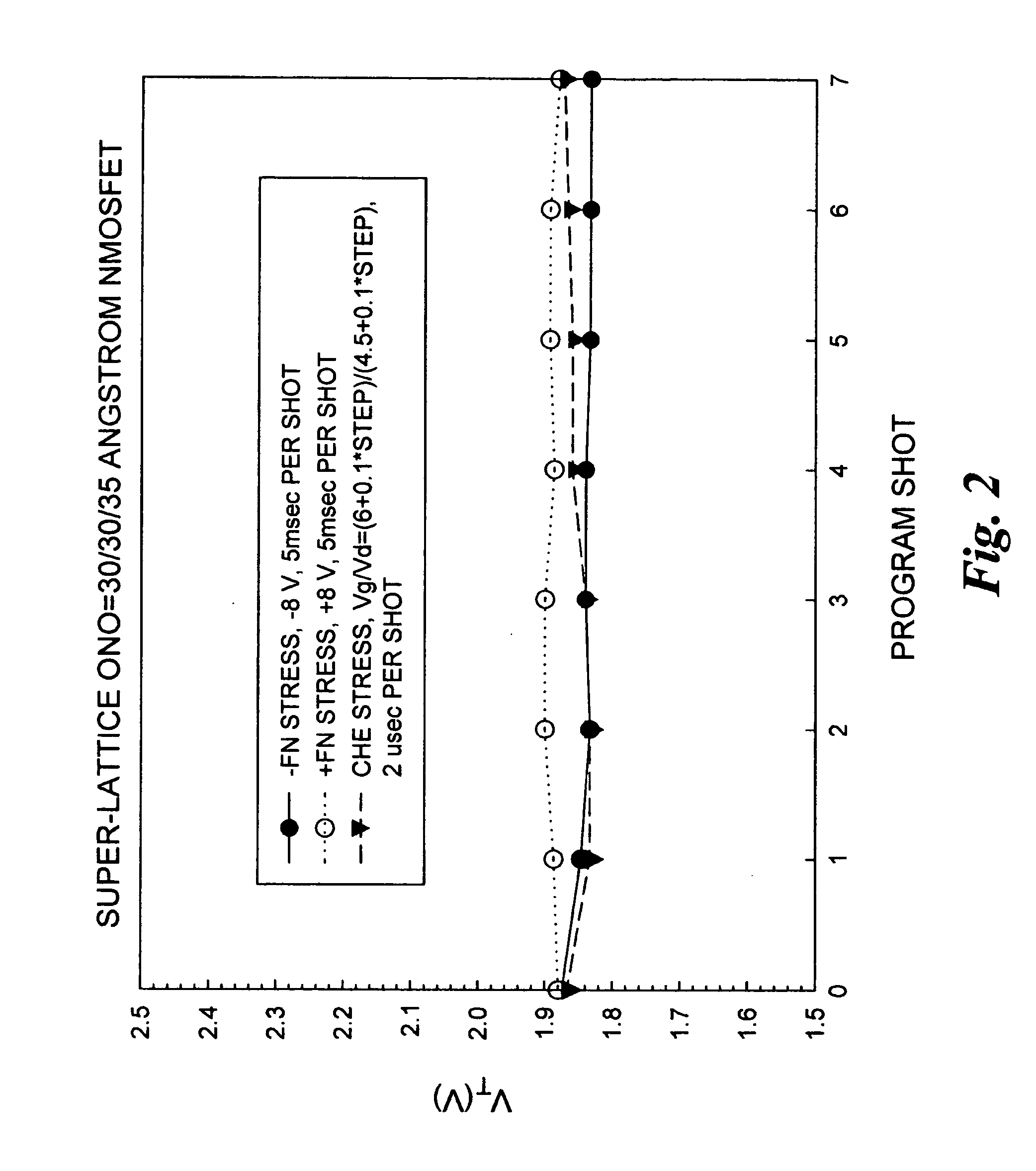

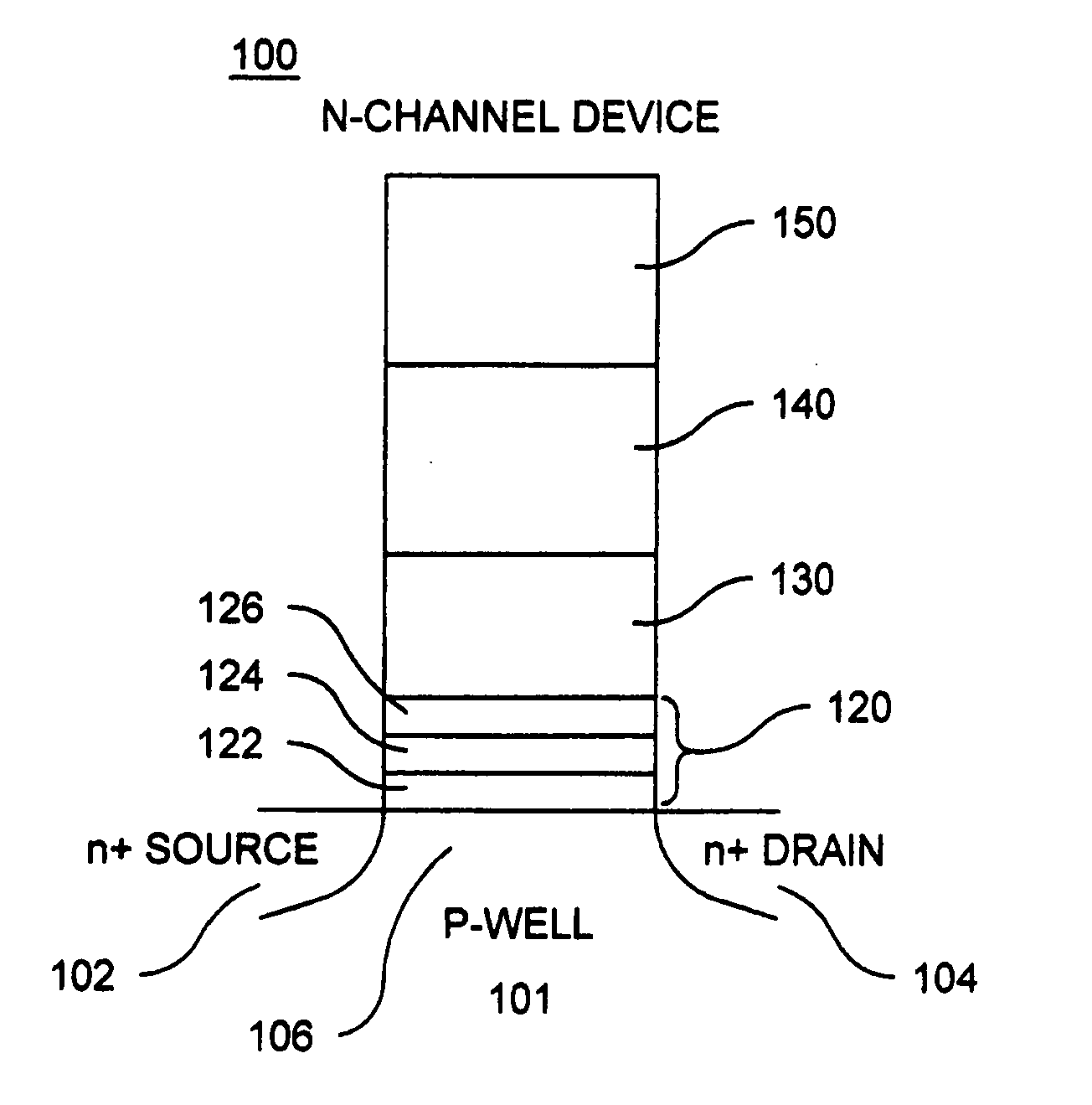

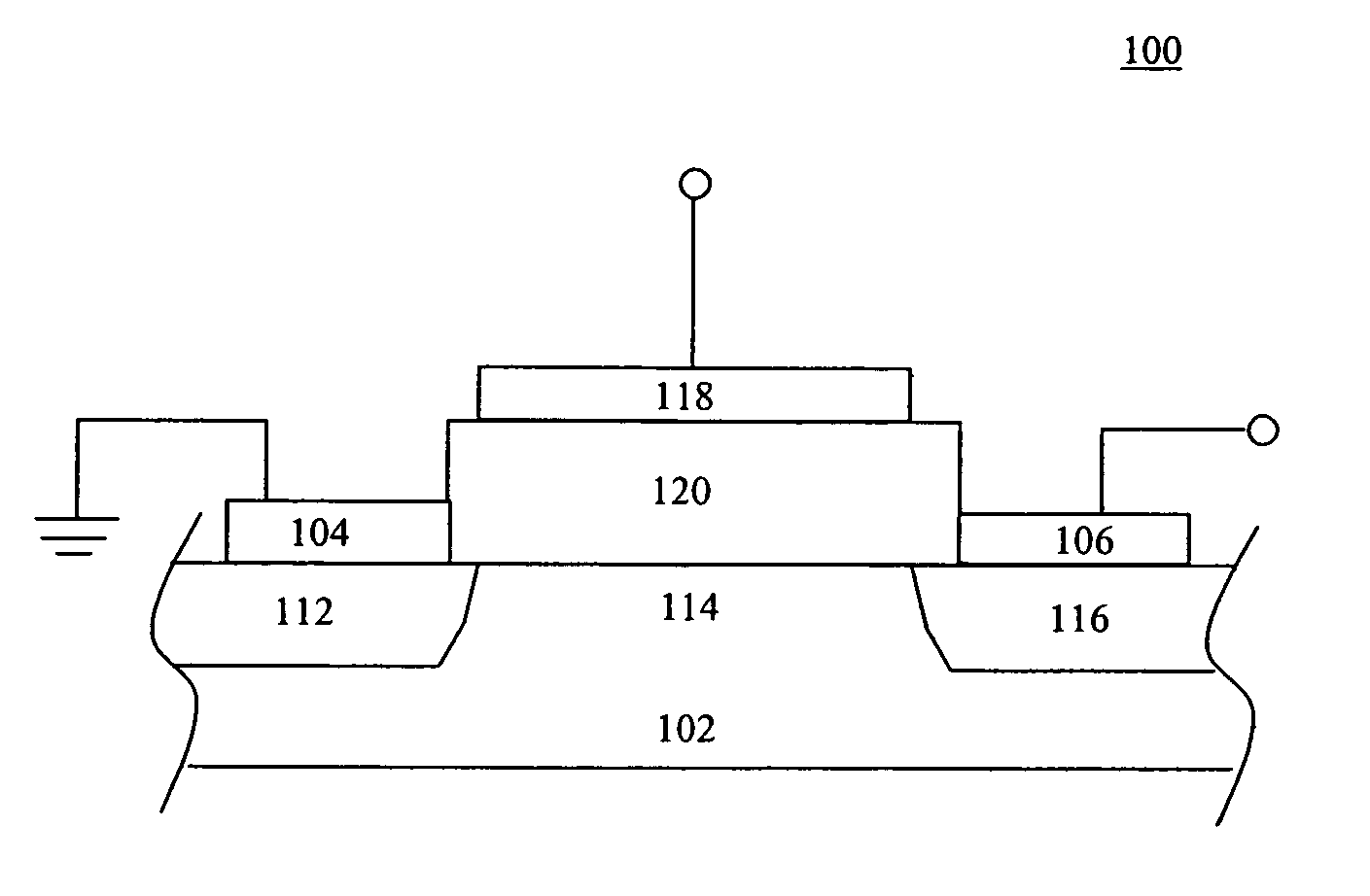

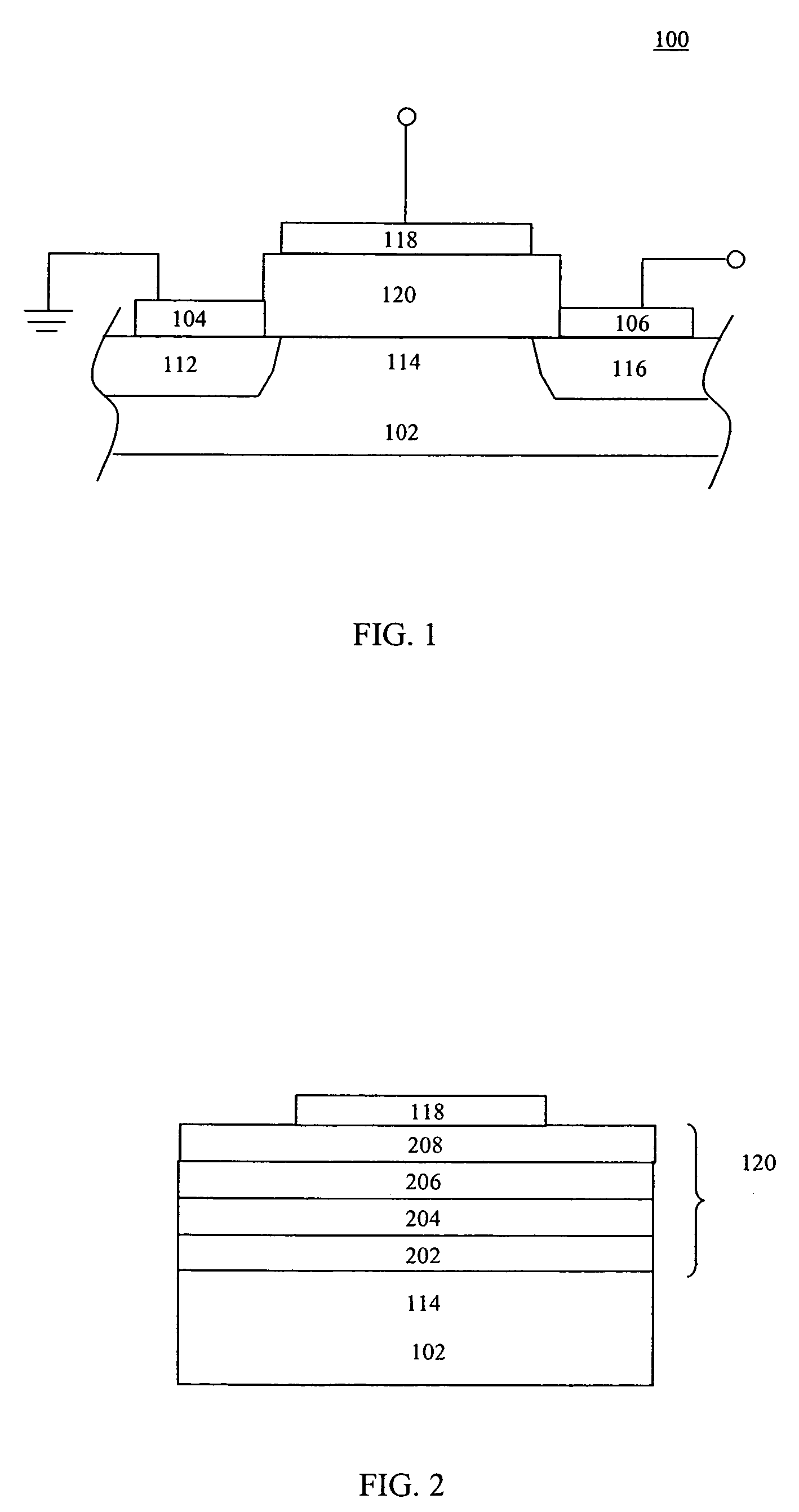

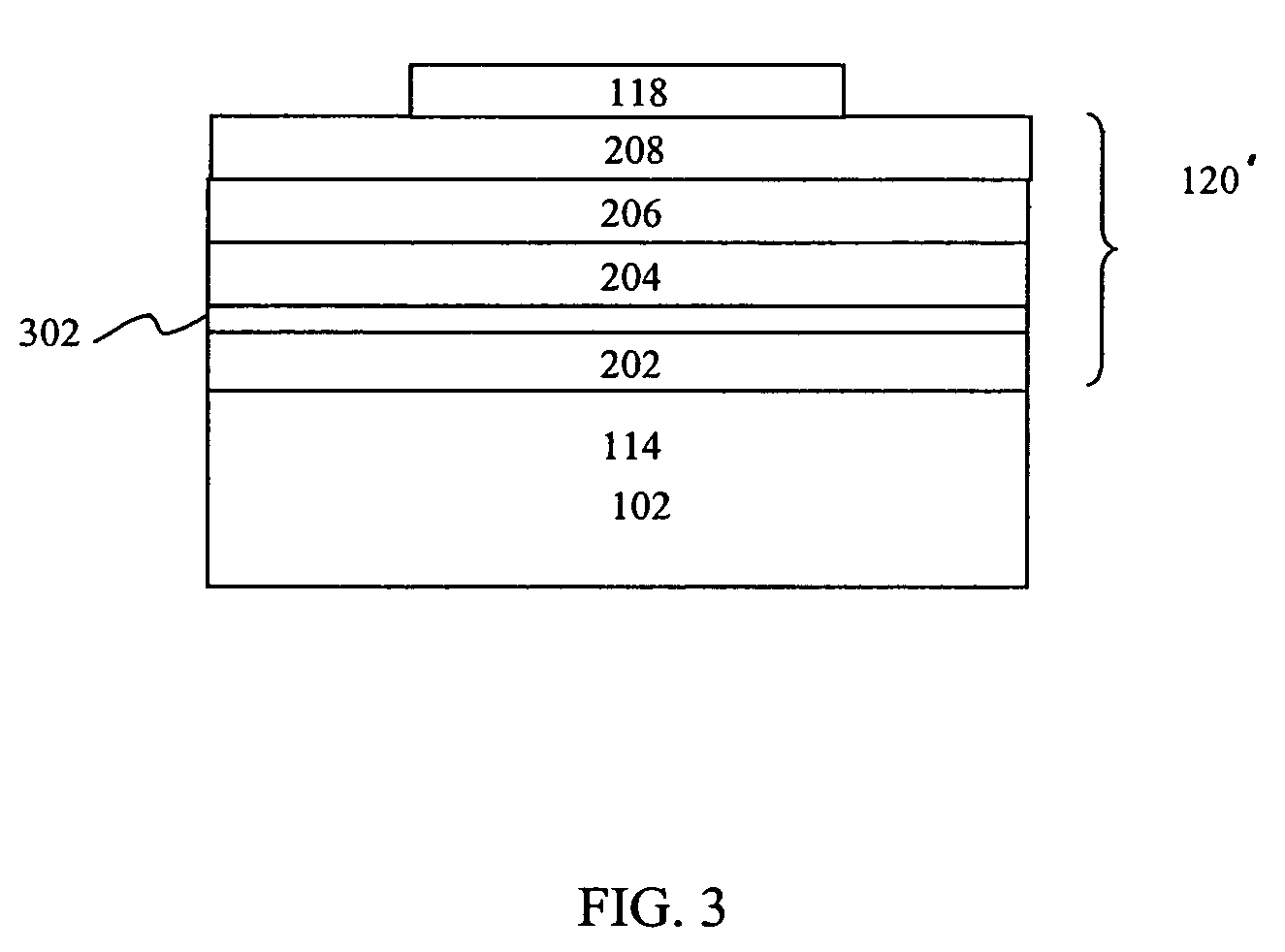

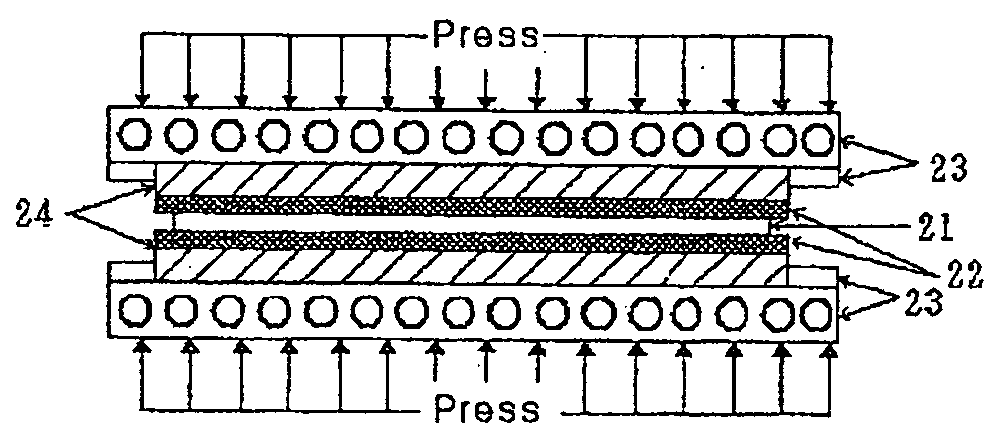

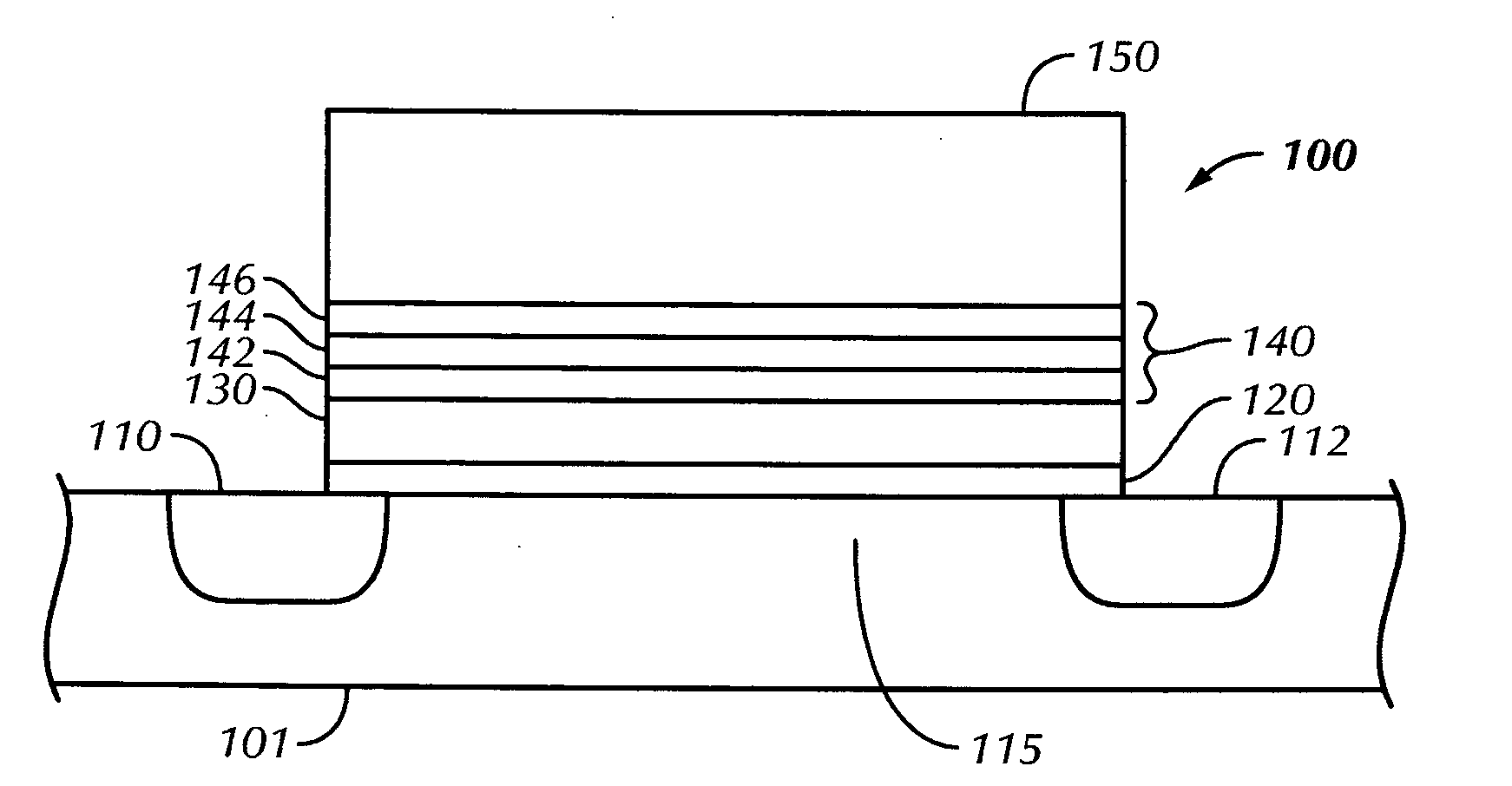

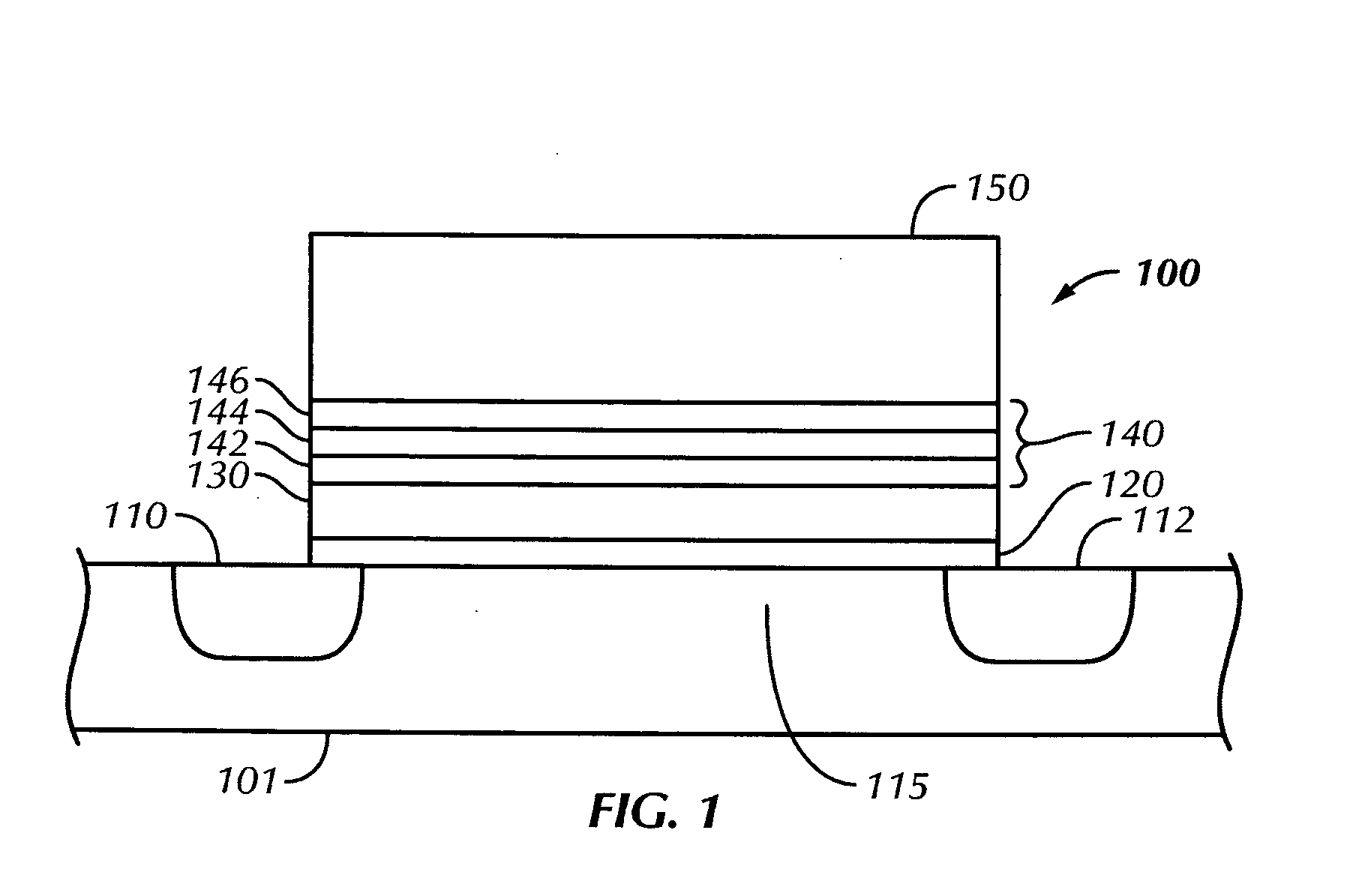

Storage layer optimization of a nonvolatile memory device

ActiveUS20050062098A1Improve charge retentionSemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierSilicon dioxide

The traditional nitride-only charge storage layer of a SONOS device is replaced by a multifilm charge storage layer comprising more than one dielectric material. Examples of such a multifilm charge storage layer are alternating layers of silicon nitride and silicon dioxide, or alternating layers of silicon nitride and aluminum oxide. The use of more than one material introduces additional barriers to migration of charge carriers within the charge storage layer, and improves both endurance and retention of a SONOS-type memory cell comprising such a charge storage layer.

Owner:SANDISK TECH LLC

Non-volatile memory cells, memory arrays including the same and methods of operating cells and arrays

ActiveUS20060198190A1Easy to optimizeEasy to eraseSolid-state devicesRead-only memoriesDielectric structureCondensed matter physics

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a small hole-tunneling-barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD

Non-volatile memory cells, memory arrays including the same and methods of operating cells and arrays

InactiveUS20060198189A1Easy to eraseLarge operating windowRead-only memoriesDigital storageDielectric structureCondensed matter physics

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a small hole-tunneling-barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD

Non-volatile memory cells, memory arrays including the same and methods of operating cells and arrays

ActiveUS20060202252A1Easy to optimizeEasy to eraseSolid-state devicesRead-only memoriesTunnel barrierEngineering

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a small hole-tunneling-barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD +1

Electron blocking layers for electronic devices

InactiveUS20080150003A1Improve performanceEnhancement of charge retention propertySemiconductor/solid-state device manufacturingSemiconductor devicesCharge retentionHafnium

Methods and apparatuses for electronic devices such as non-volatile memory devices are described. The memory devices include a multi-layer control dielectric, such as a double or triple layer. The multi-layer control dielectric includes a combination of high-k dielectric materials such as aluminum oxide (Al2O3), hafnium oxide (HfO2), and / or hybrid films of hafnium aluminum oxide. The multi-layer control dielectric provides enhanced characteristics, including increased charge retention, enhanced memory program / erase window, improved reliability and stability, with feasibility for single or multistate (e.g., two, three or four bit) operation.

Owner:SANDISK TECH LLC

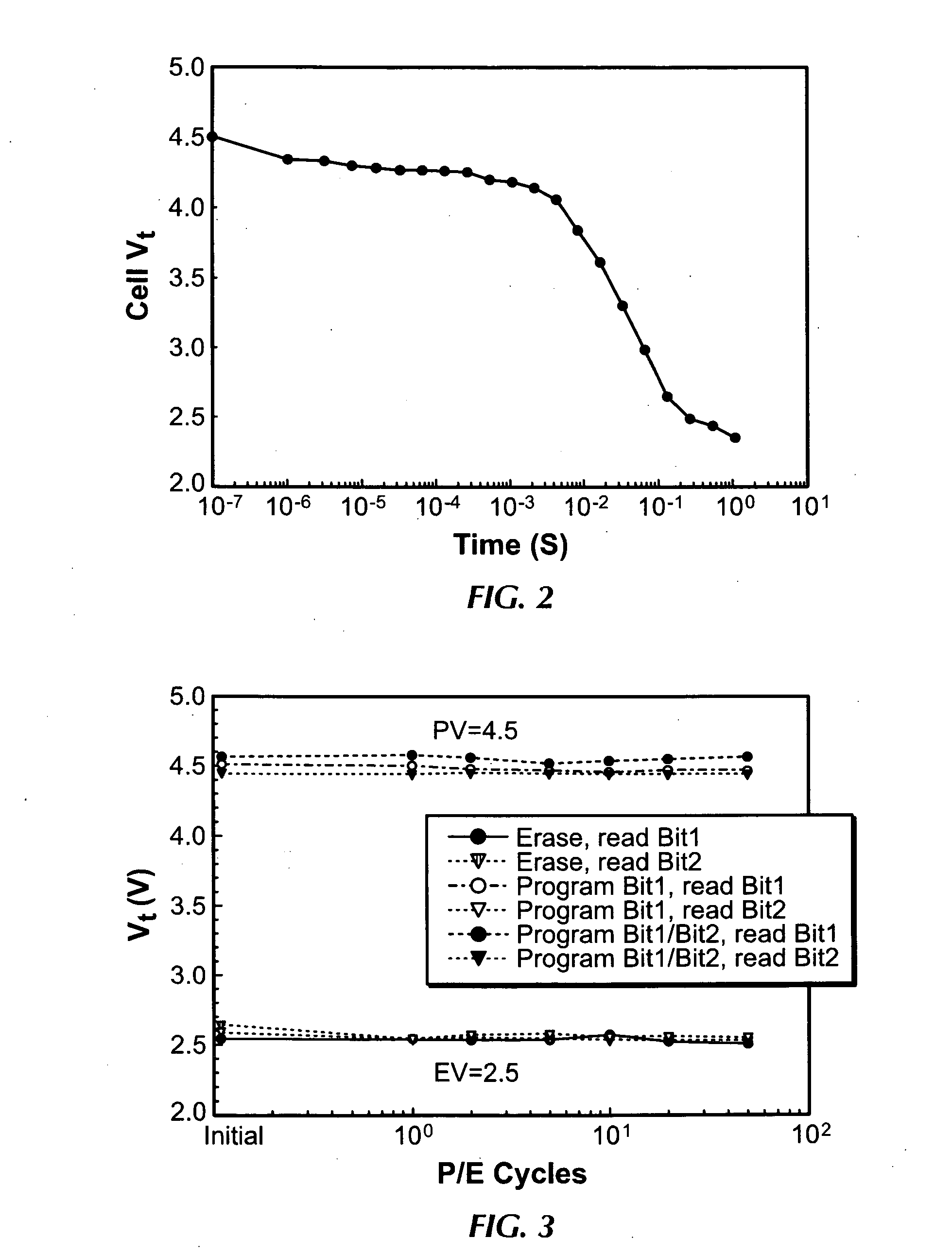

High performance multi-level non-volatile memory

ActiveUS20070045711A1Increased device feature scalingEfficient erasureTransistorSemiconductor/solid-state device manufacturingCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize band engineered gate-stacks and multiple charge trapping layers allowing a multiple trapping site gate-insulator stack memory cell that utilizes a band engineered direct tunneling or crested barrier tunnel layer and charge blocking layer for high speed programming / erasure. Charge retention is enhanced by utilization of nano-crystals and / or bulk trapping materials in a composite non-conductive trapping layer and a high K dielectric insulating layers. The band-gap engineered gate-stack with asymmetric direct tunneling or crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage high speed tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. Memory cell embodiments of the present invention allow multiple levels of bit storage in a memory cell through multiple charge centroids and / or multiple threshold voltage levels.

Owner:MICRON TECH INC

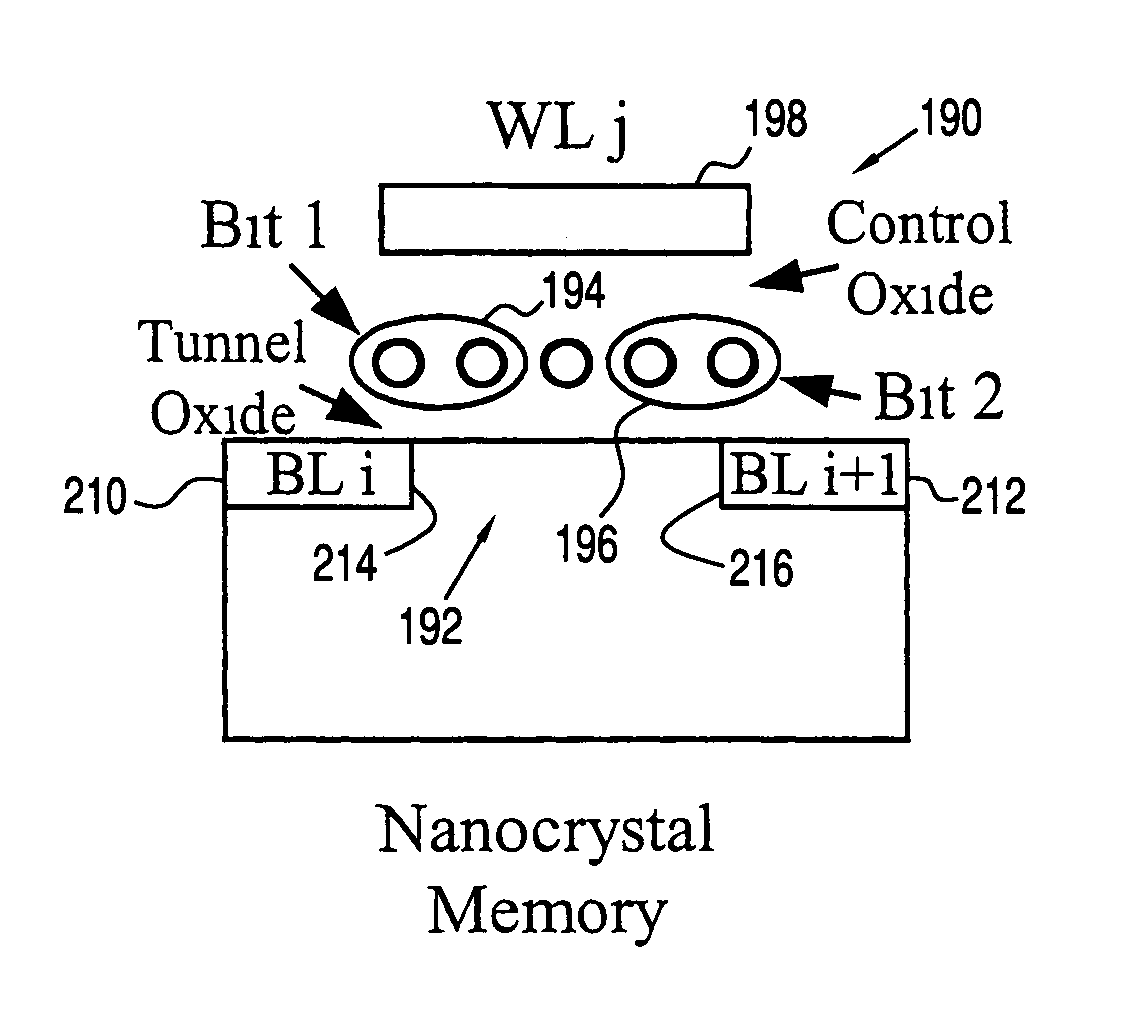

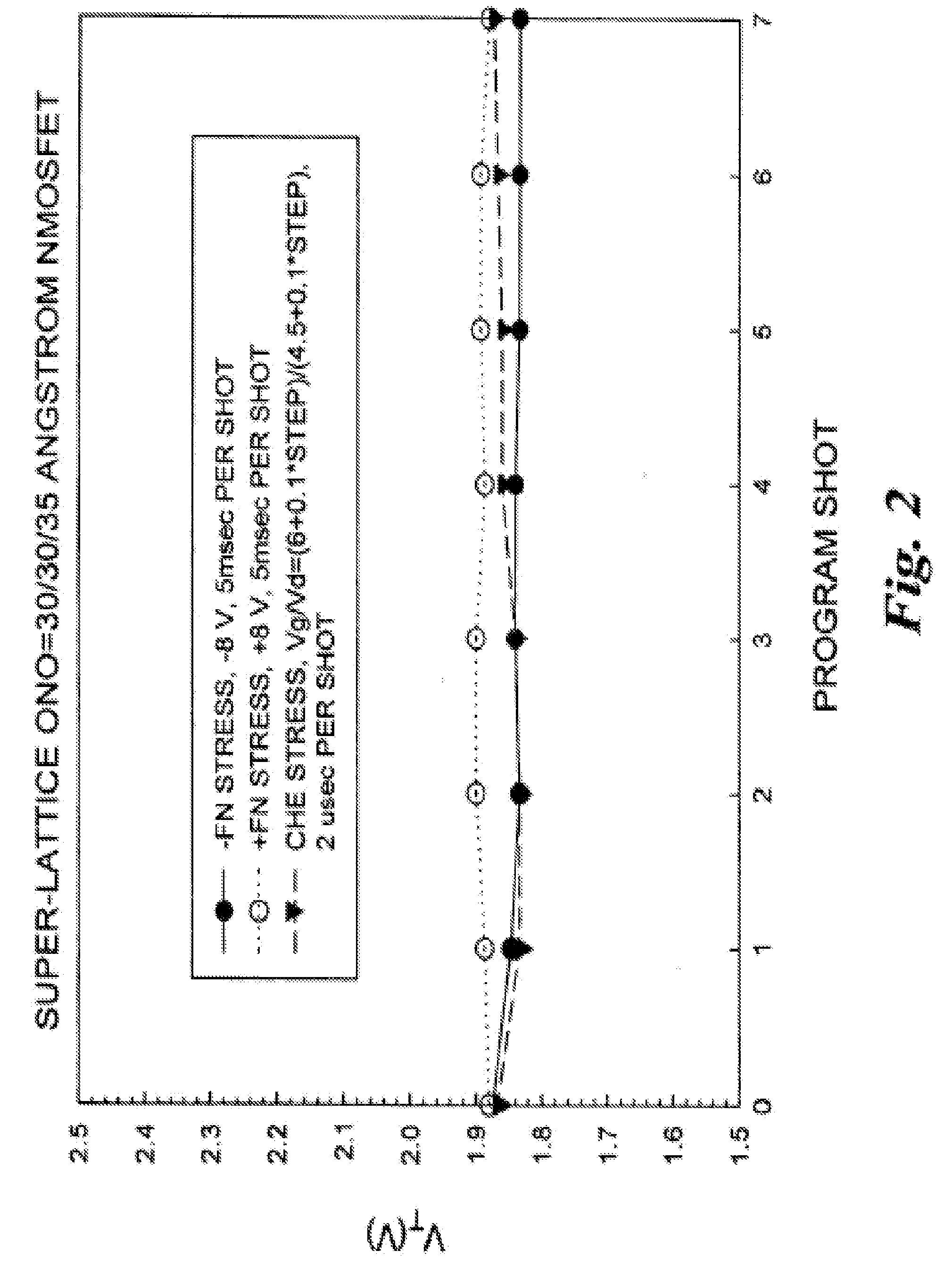

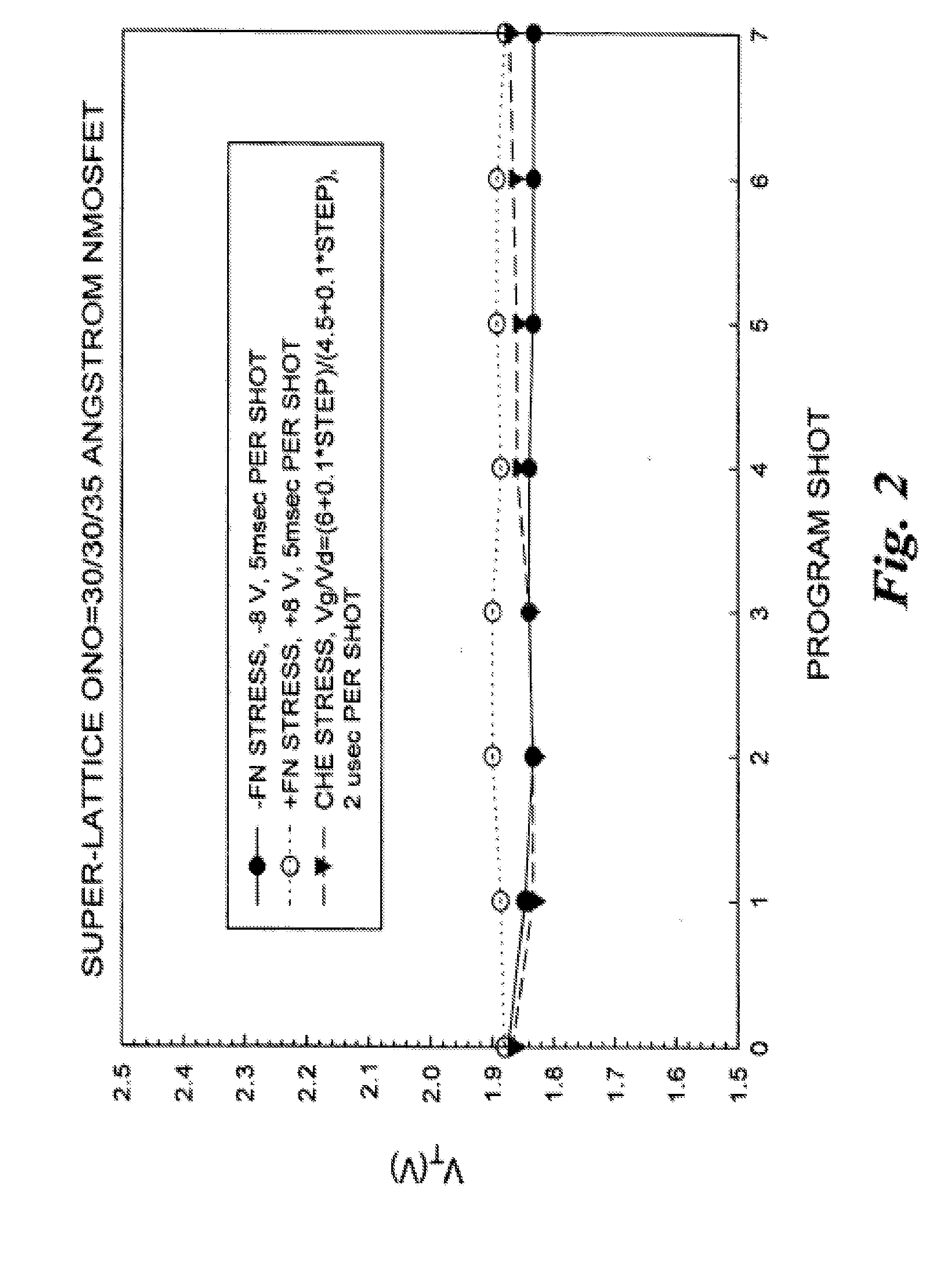

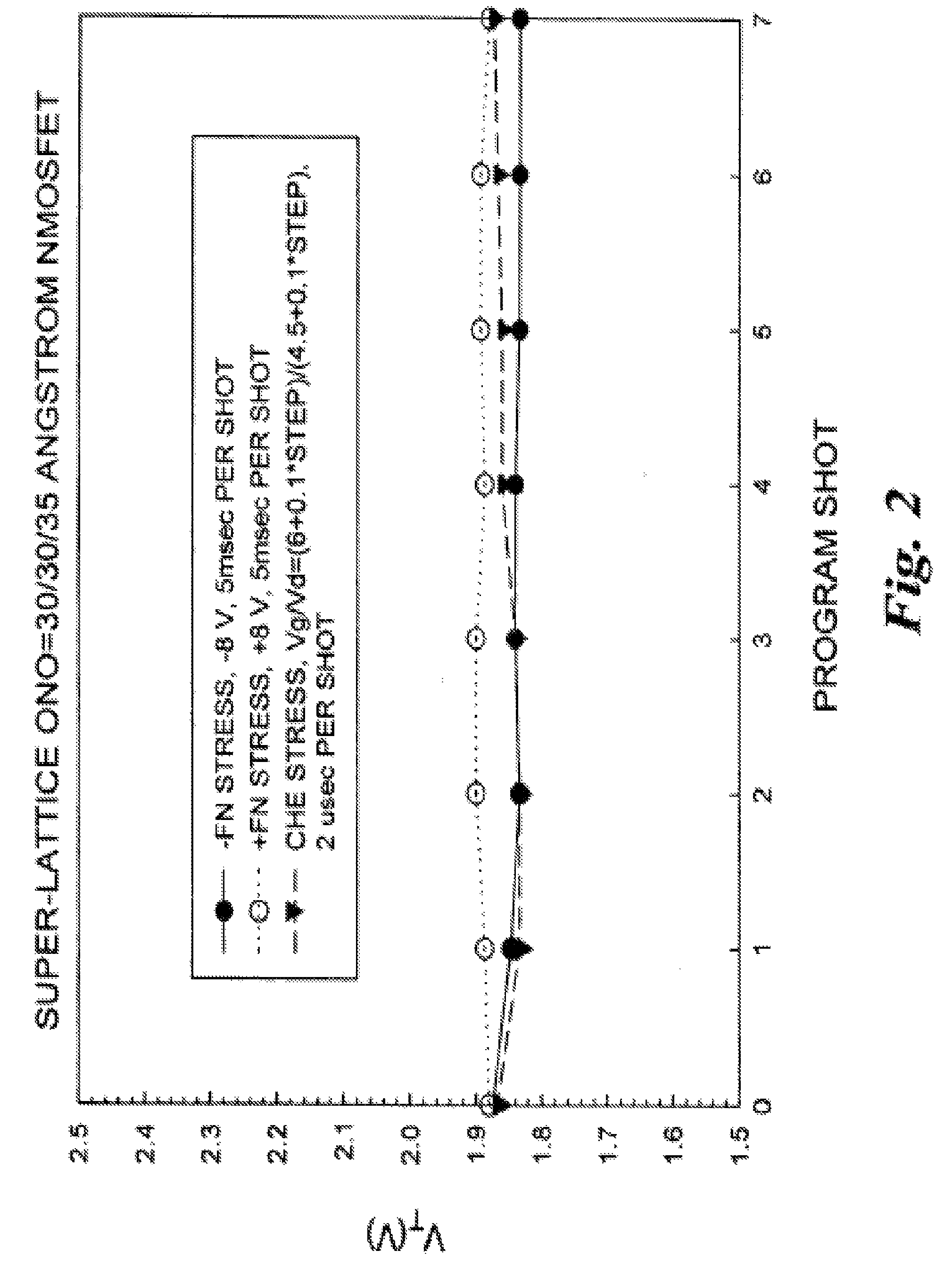

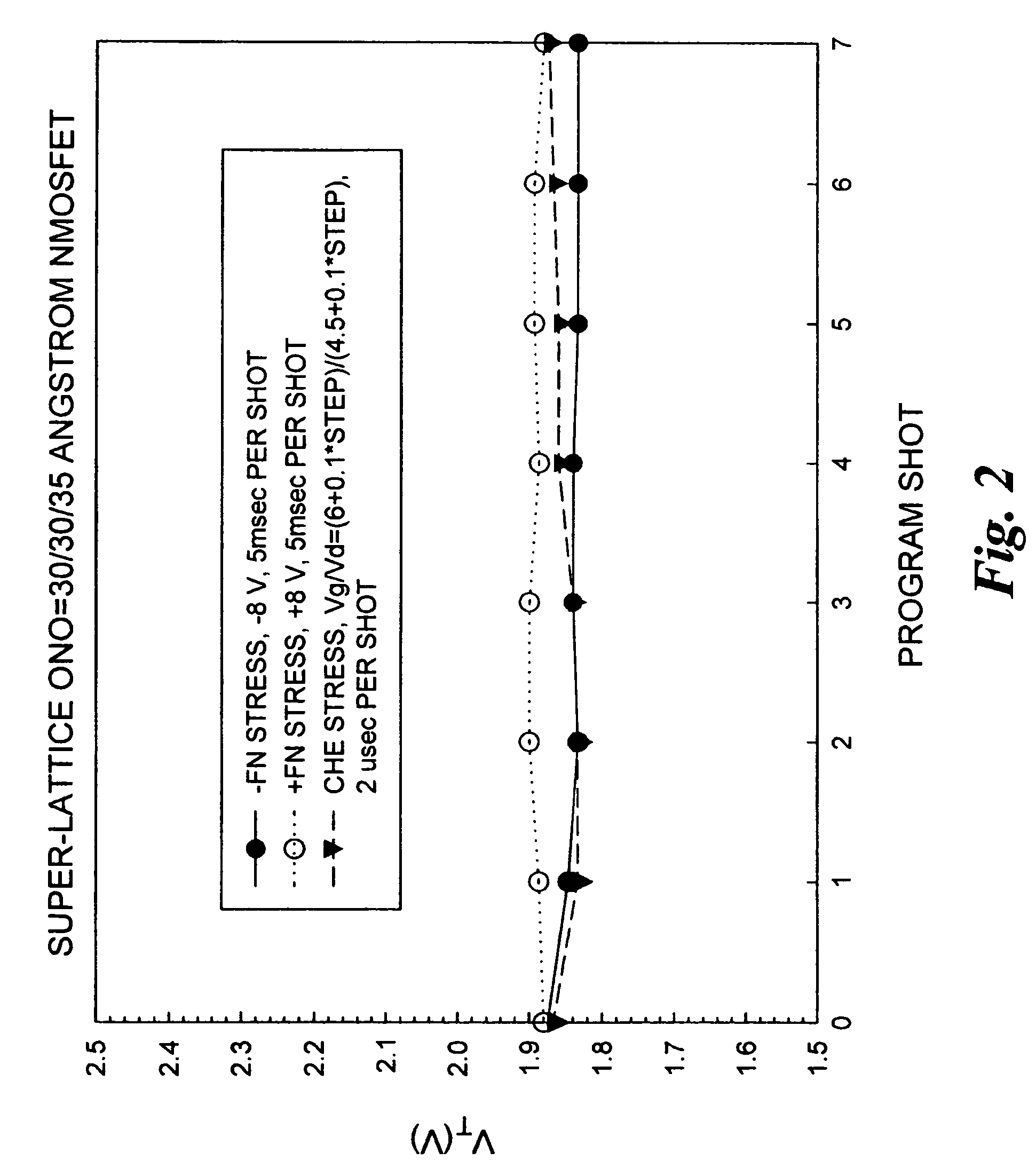

Multibit metal nanocrystal memories and fabrication

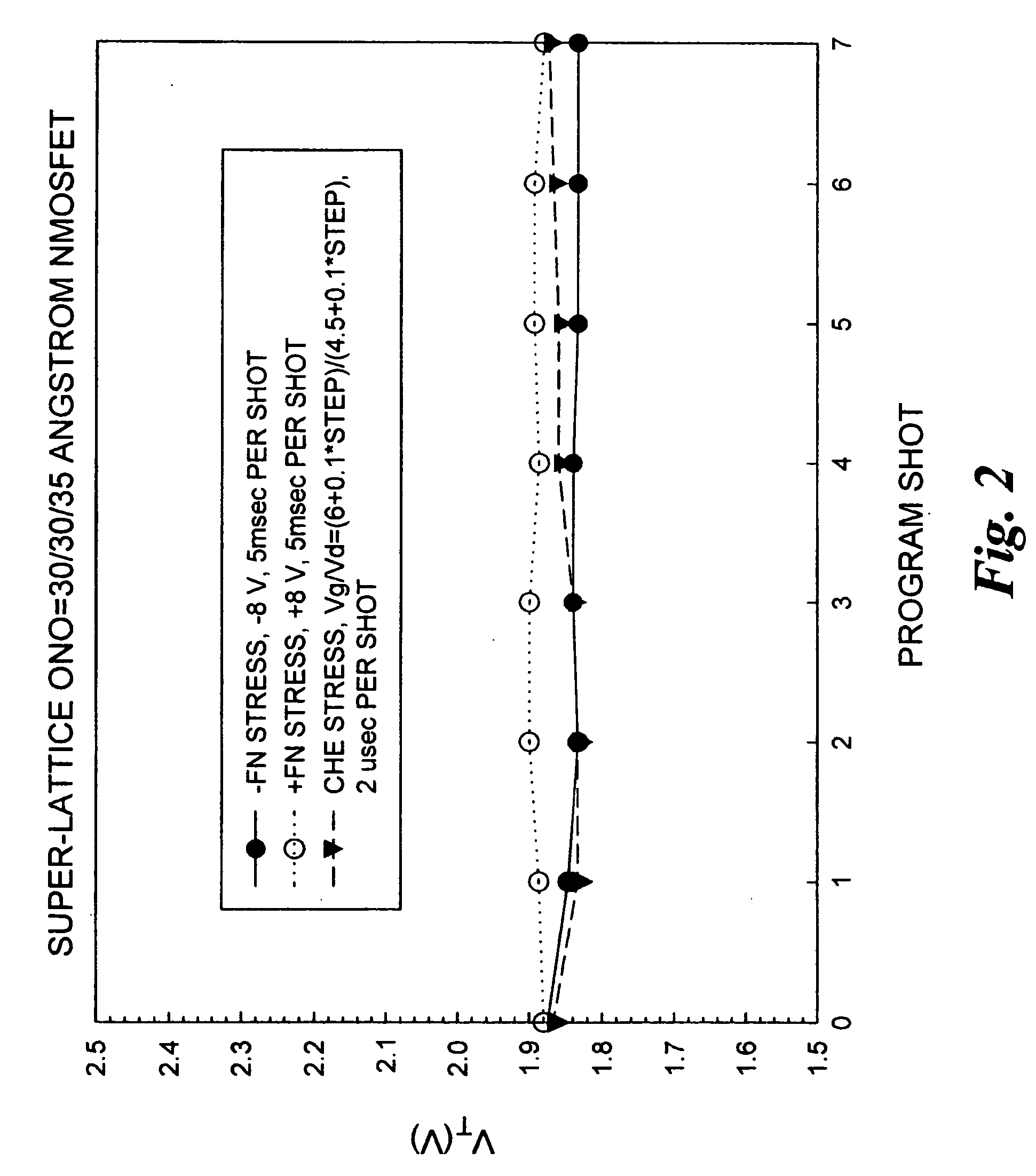

ActiveUS7259984B2Improve performanceImprove charge retentionNanoinformaticsRead-only memoriesRetention timeSemiconductor nanocrystals

Metal nanocrystal memories are fabricated to include higher density states, stronger coupling with the channel, and better size scalability, than has been available with semiconductor nanocrystal devices. A self-assembled nanocrystal formation process by rapid thermal annealing of ultra thin metal film deposited on top of gate oxide is integrated with NMOSFET to fabricate such devices. Devices with Au, Ag, and Pt nanocrystals working in the F-N tunneling regime, with hot-carrier injection as the programming mechanism, demonstrate retention times up to 106s, and provide 2-bit-per-cell storage capability.

Owner:CORNELL RES FOUNDATION INC

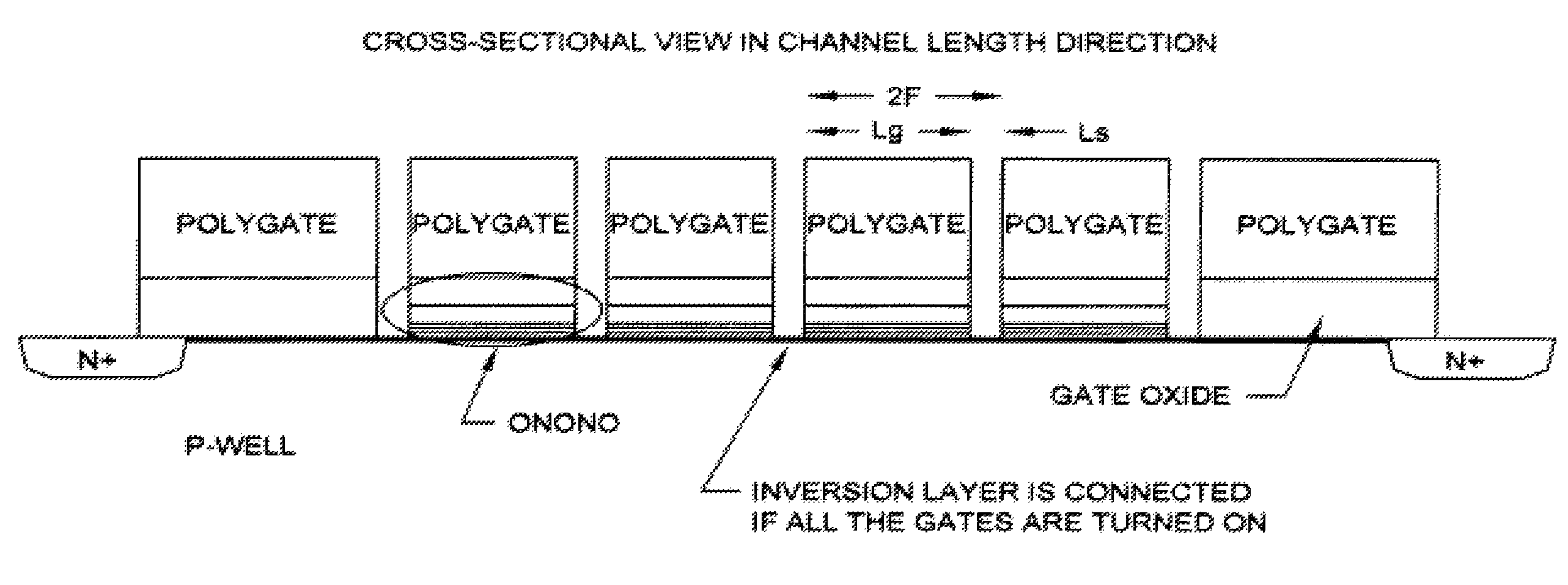

Silicon on insulator and thin film transistor bandgap engineered split gate memory

ActiveUS20080175053A1Large thermal budgetLarge lateral diffusionSolid-state devicesRead-only memoriesDielectric structureBand-gap engineering

Memory cells comprising thin film transistor, stacked arrays, employing bandgap engineered tunneling layers in a junction free, NAND configuration. The cells comprise a channel region in a semiconductor strip formed on an insulating layer; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising a multilayer structure including at least one layer having a hole-tunneling barrier height lower than that at the interface with the channel region; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer Arrays and methods of operation are described.

Owner:MACRONIX INT CO LTD

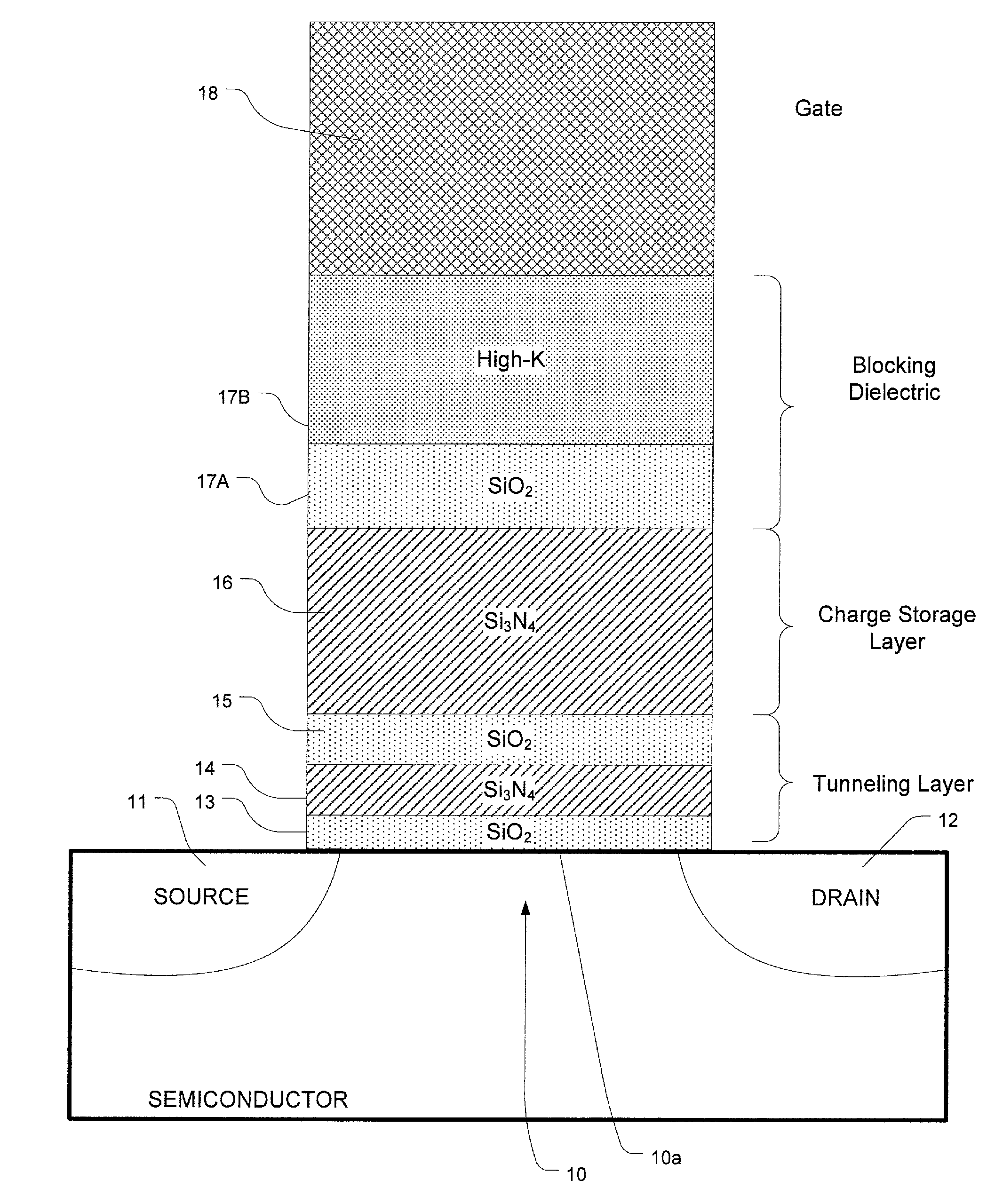

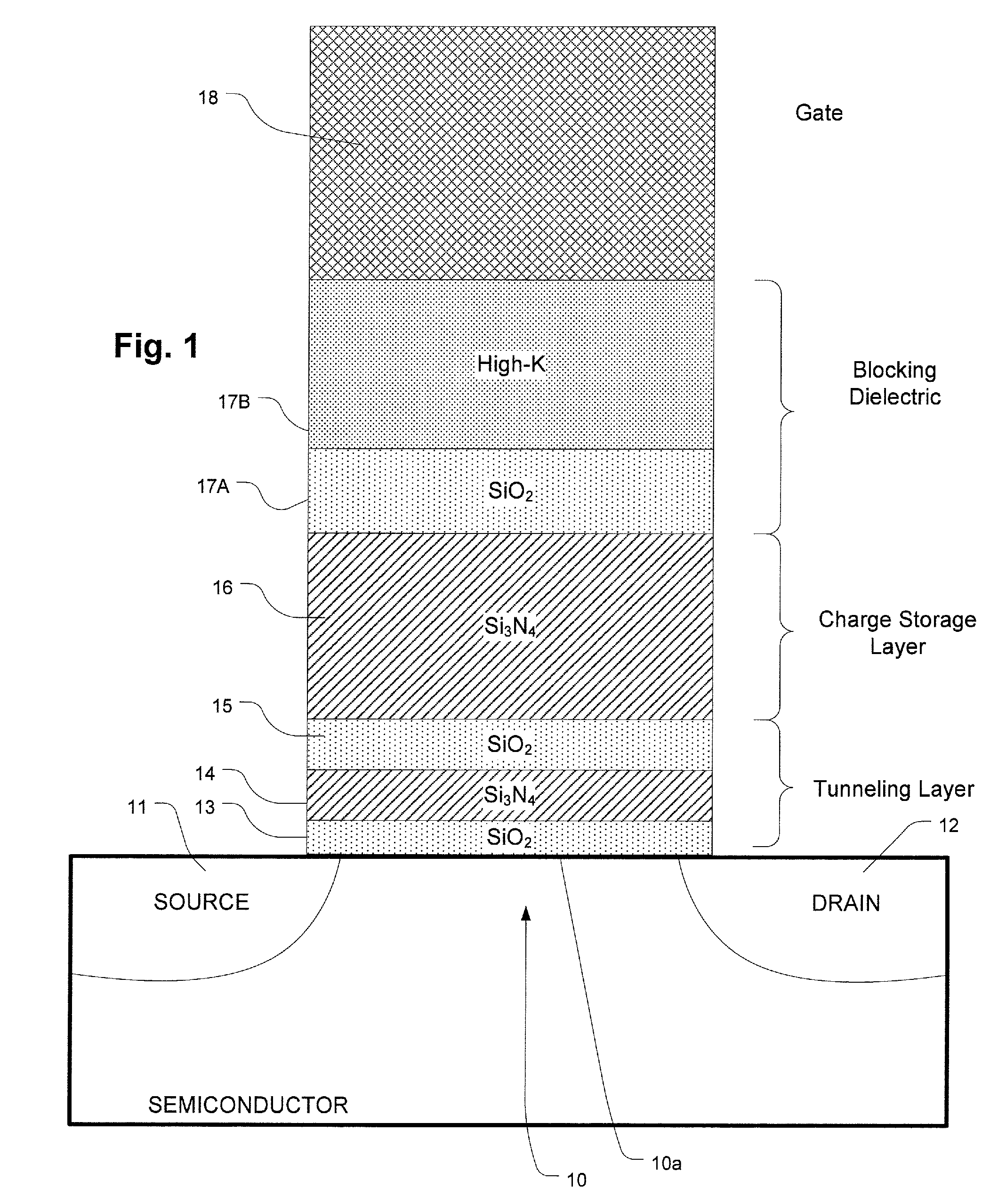

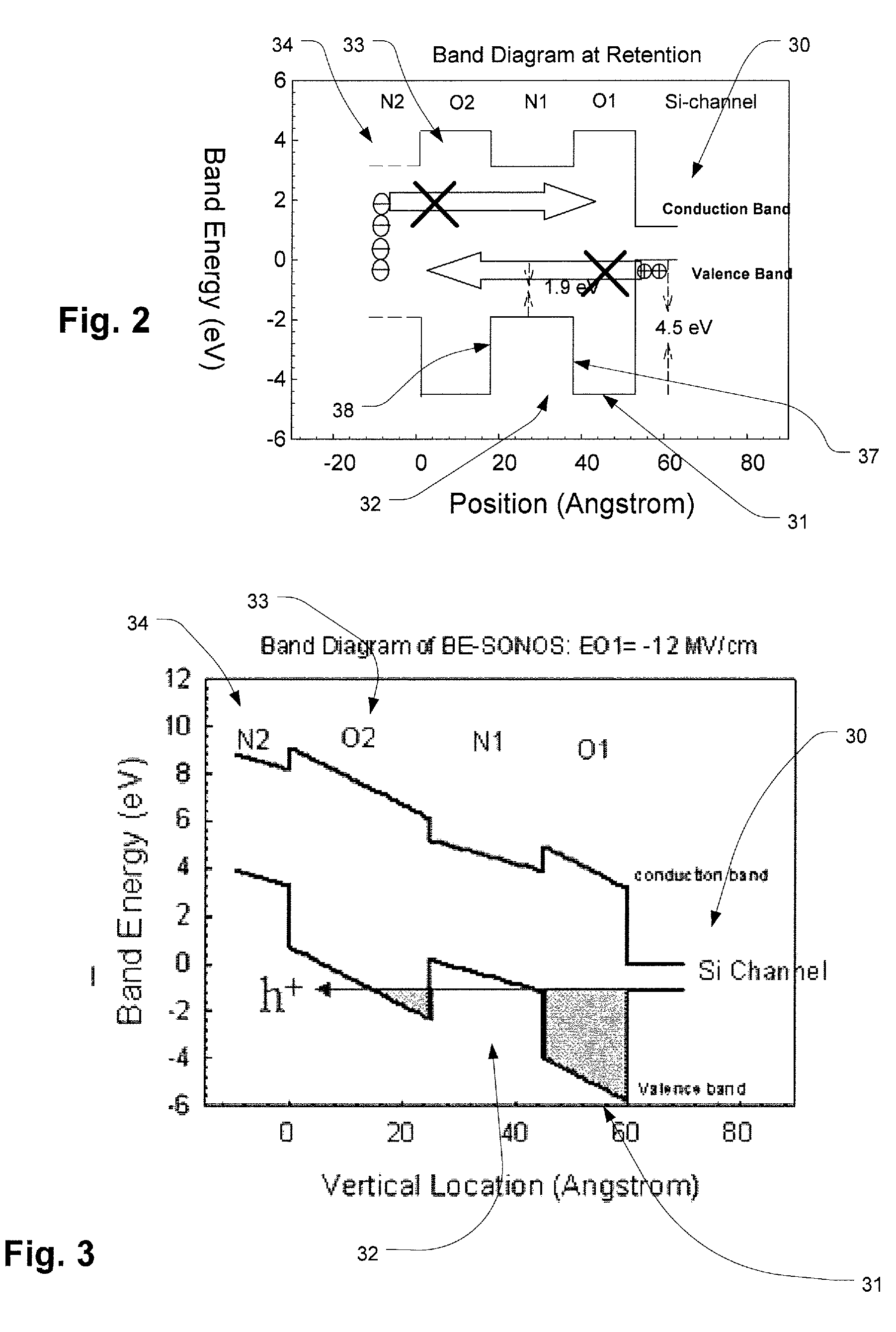

High-κ capped blocking dielectric bandgap engineered SONOS and MONOS

ActiveUS7816727B2Excellent characteristicsImprove reliabilitySolid-state devicesRead-only memoriesDielectricTrapping

A blocking dielectric engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking dielectric including a buffer layer in contact with the charge trapping element, such as silicon dioxide which can be made with high-quality, and a second capping layer in contact with said one of the gate and the channel. The capping layer has a dielectric constant that is higher than that of the first layer, and preferably includes a high-κ material. The second layer also has a conduction band offset that is relatively high. A bandgap engineered tunneling layer between the channel and the charge trapping element is provided which, in combination with the multilayer blocking dielectric described herein, provides for high-speed erase operations by hole tunneling. In an alternative, a single layer tunneling layer is used.

Owner:MACRONIX INT CO LTD

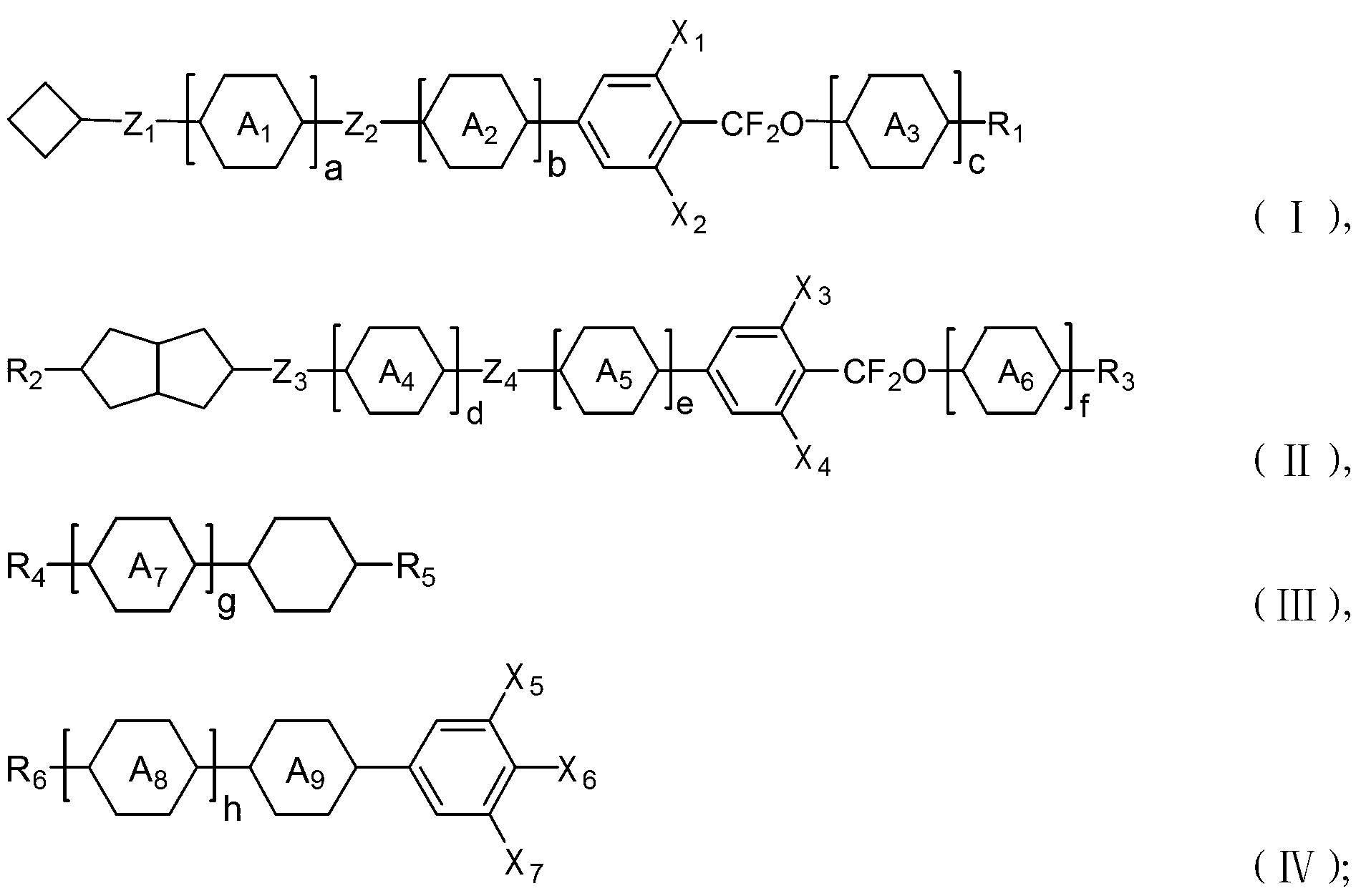

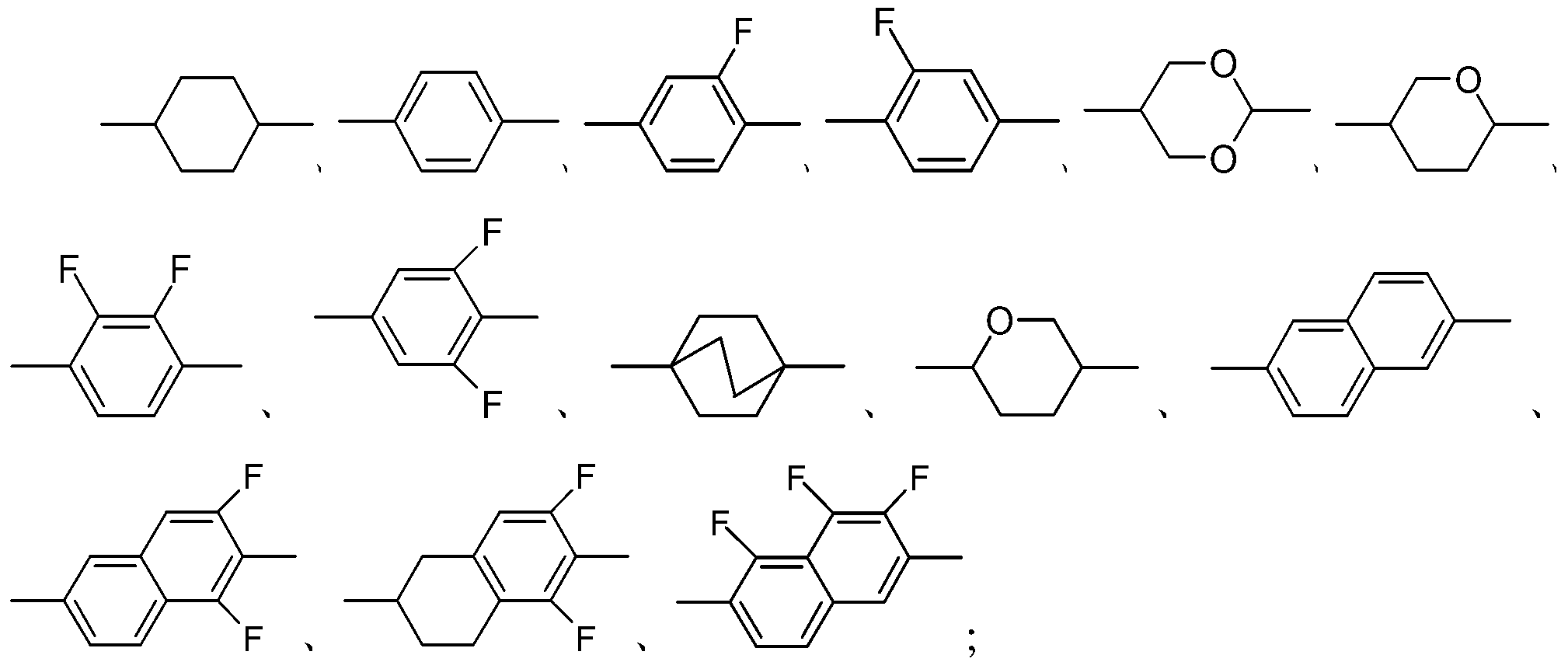

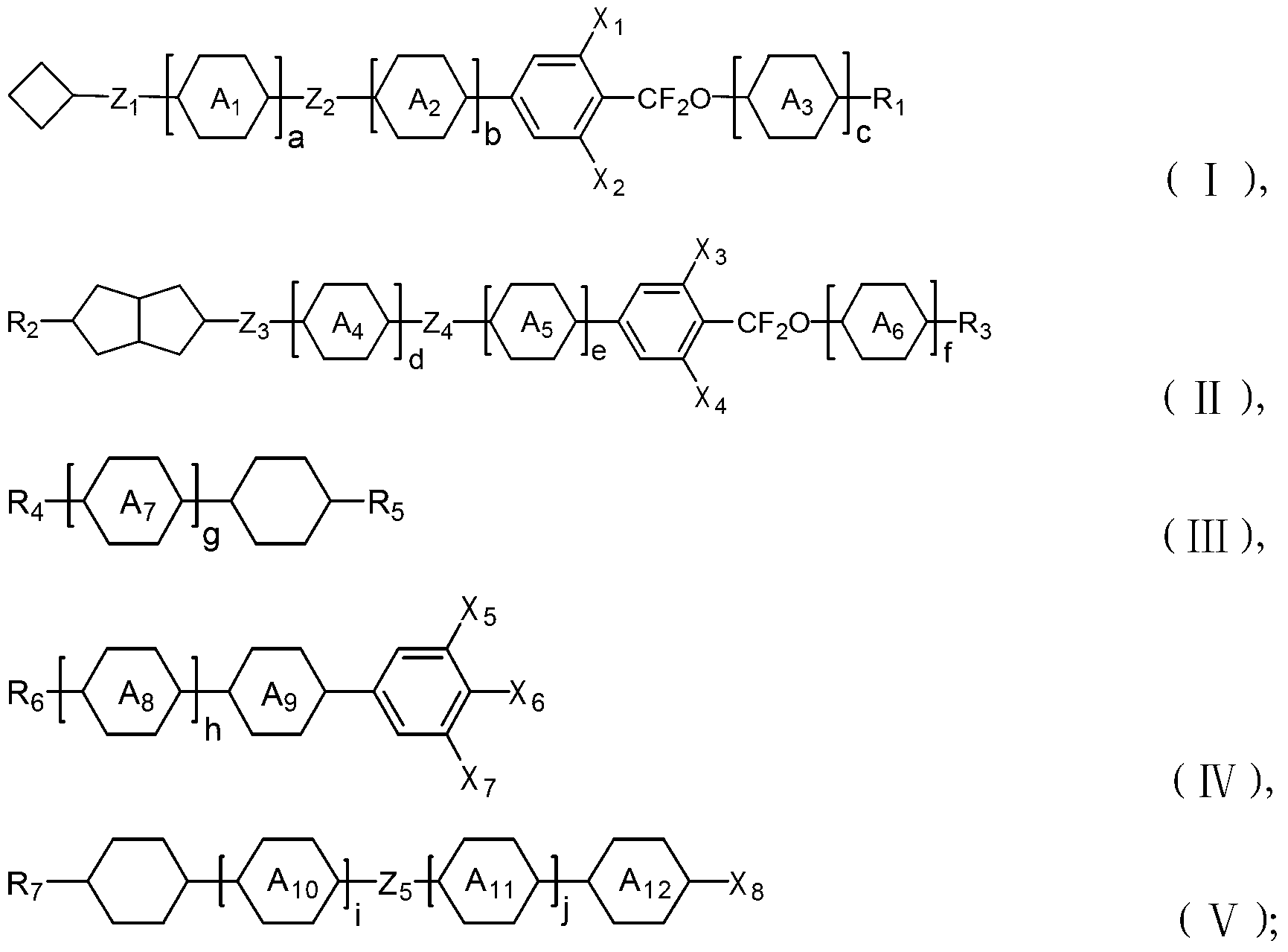

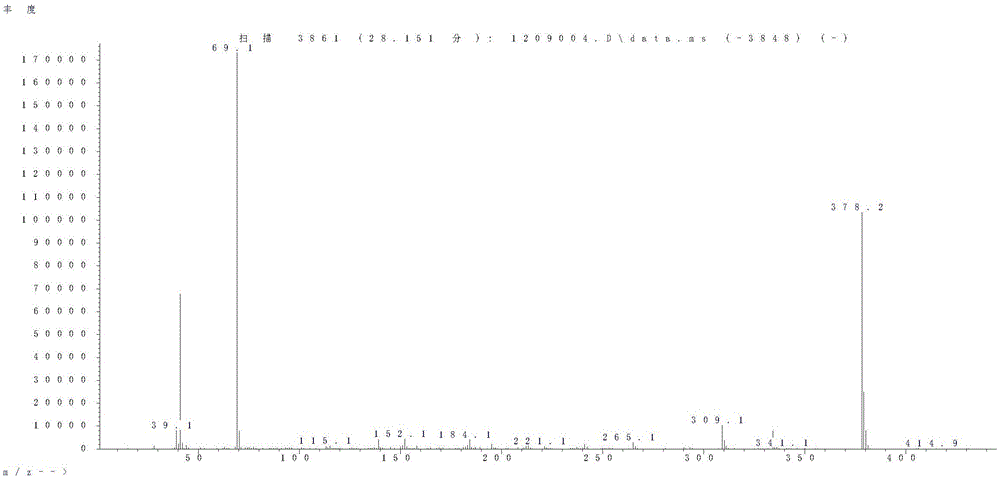

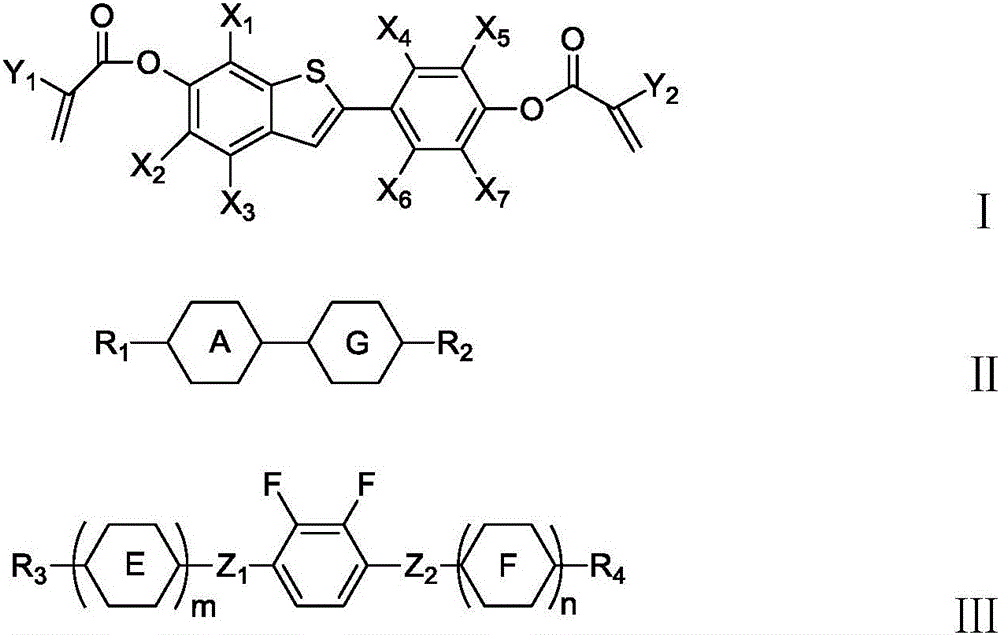

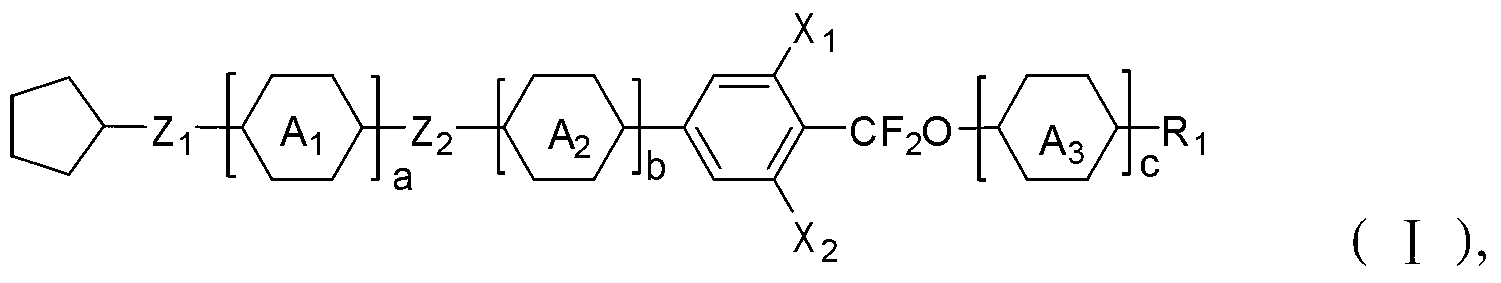

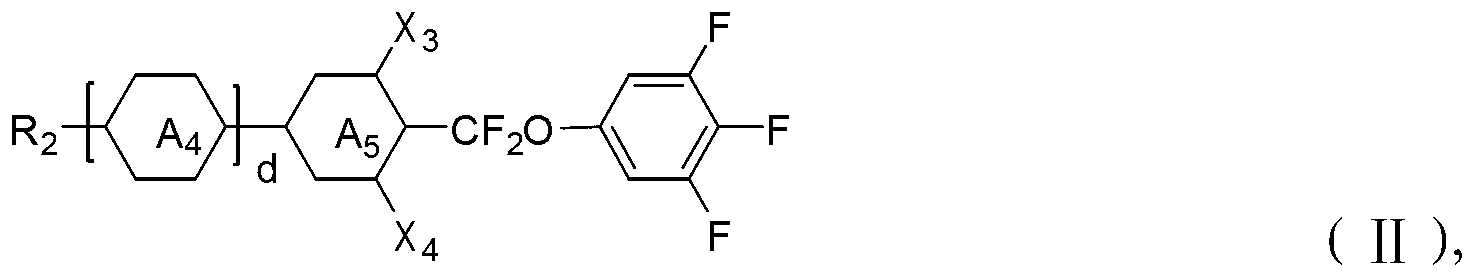

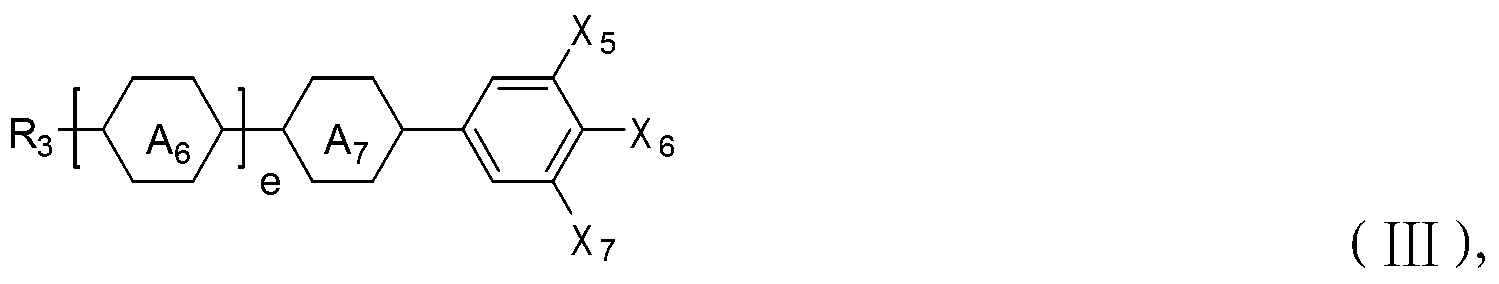

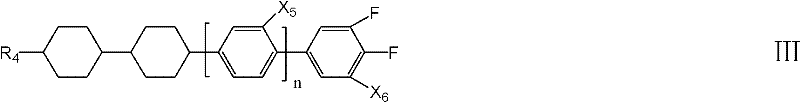

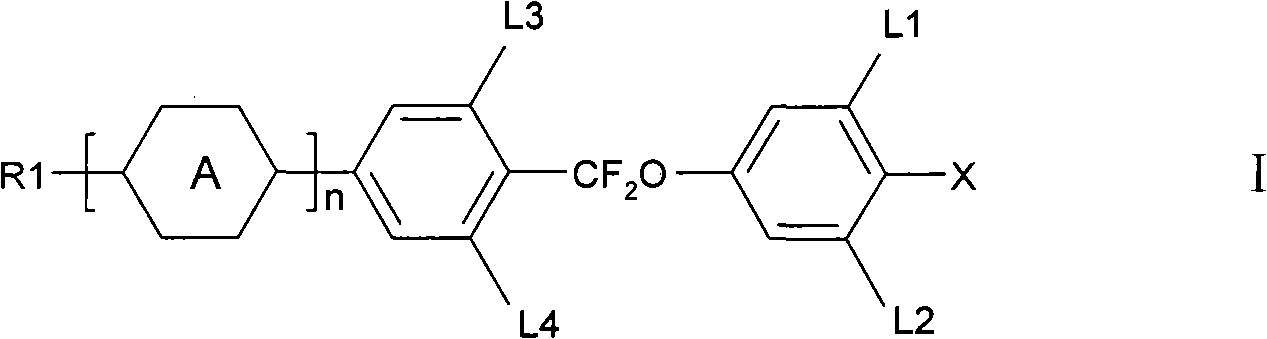

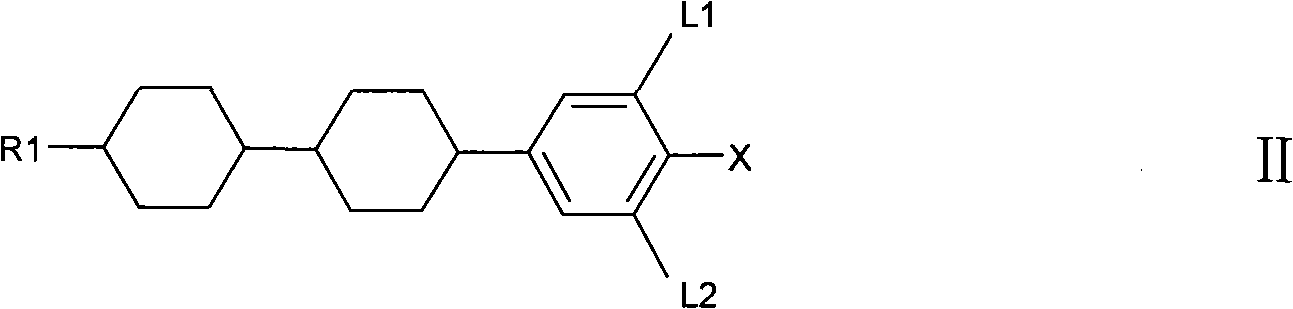

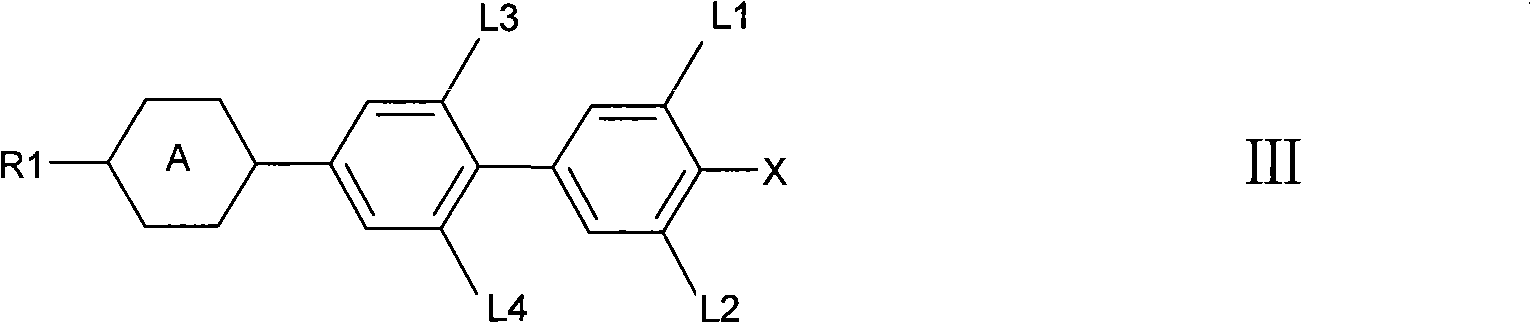

Positive dielectric anisotropy liquid crystal combination with rapid response

ActiveCN103254911AImprove high temperature stabilityLow viscosityLiquid crystal compositionsNon-linear opticsIn planeCharge retention

The invention discloses a positive dielectric anisotropy liquid crystal combination with rapid response. The positive dielectric anisotropy liquid crystal combination comprises 5-60 percent of first component, 1-50 percent of second component, 1-40 percent of third component, 0-40 percent of fourth component and an optically active compound, wherein the first component is formed from compounds with a structural formula I and a structural formula II, a compound with a structural formula III is used as the second component, a compound with a structural formula VI is used as the third component, a compound with a structural formula V is used as the fourth component, and the mass of the optically active compound is 0-0.2 percent of the mass sum of the liquid crystal combination. The liquid crystal combination has high charge retention, larger positive dielectric anisotropy, higher clearing point, good low-temperature stability, lower rotary viscometer and higher response speed and is particularly suitable for manufacturing active matrixes TN-TFT(Twisted Nematic-Thin Film Transistor), IPS (In-Plane Switching)-TFT liquid crystal display elements and liquid crystal displays.

Owner:BEIJING CHENGZHI YONGHUA DISPLAY TECHNOLOGY CO LTD

Methods of operating bandgap engineered memory

ActiveUS20070268753A1Easy to eraseLarge operating windowSolid-state devicesRead-only memoriesDielectric structureCondensed matter physics

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a hole-tunneling barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays and methods of operation.

Owner:MACRONIX INT CO LTD

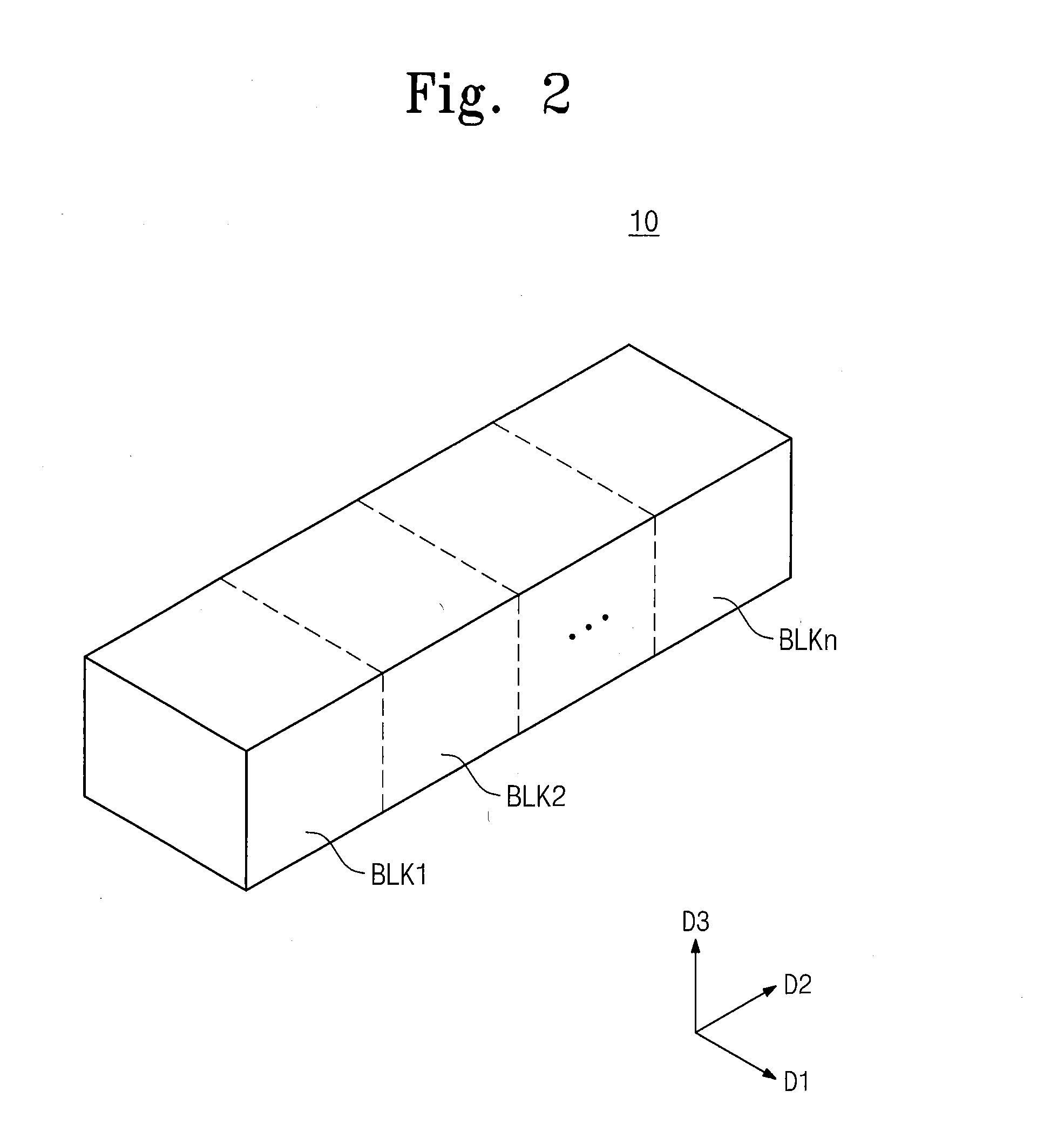

Silicon on insulator and thin film transistor bandgap engineered split gate memory

ActiveUS8482052B2Large operating windowEasy to operateTransistorSolid-state devicesDielectric structureSemiconductor

Thin film transistor memory cells are stackable, and employ bandgap engineered tunneling layers in a junction free, NAND configuration, that can be arranged in 3D arrays. The memory cells have a channel region in a semiconductor strip formed on an insulating layer, a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure having a multilayer structure including at least one layer having a hole-tunneling barrier height lower than that at the interface with the channel region, a charge storage layer disposed above the tunnel dielectric structure, an insulating layer disposed above the charge storage layer, and a gate electrode disposed above the insulating layer.

Owner:MACRONIX INT CO LTD

Self-rechargeable alkaline battery

InactiveUS20060257734A1Improve charge retentionIncrease surface areaNon-aqueous electrolyte cellsElectrolyte/reactants regenerationManganese oxidePotassium hydroxide

Disclosed herein is a self-rechargeable alkaline battery. The battery comprises a cathode and an anode, at least one of which is constructed of a metallic plate, an electrode receptor equipped to the cathode, an electrode donor equipped to the anode, a separator provided between the electrode donor and the electrode receptor, an electrolyte comprising an aqueous potassium hydroxide solution and an aqueous sodium hydroxide solution and having at least one powdered material selected from the group consisting of aluminum oxide, manganese oxide, and silicon oxide. The battery has a self-rechargeable ability, stable output characteristics, and a remarkably increased life span.

Owner:PICO SCI CORP

Bandgap engineered split gate memory

ActiveUS20070267687A1Easy to eraseLarge operating windowTransistorSolid-state devicesDielectric structureCondensed matter physics

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a hole-tunneling barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays and methods of operation.

Owner:MACRONIX INT CO LTD

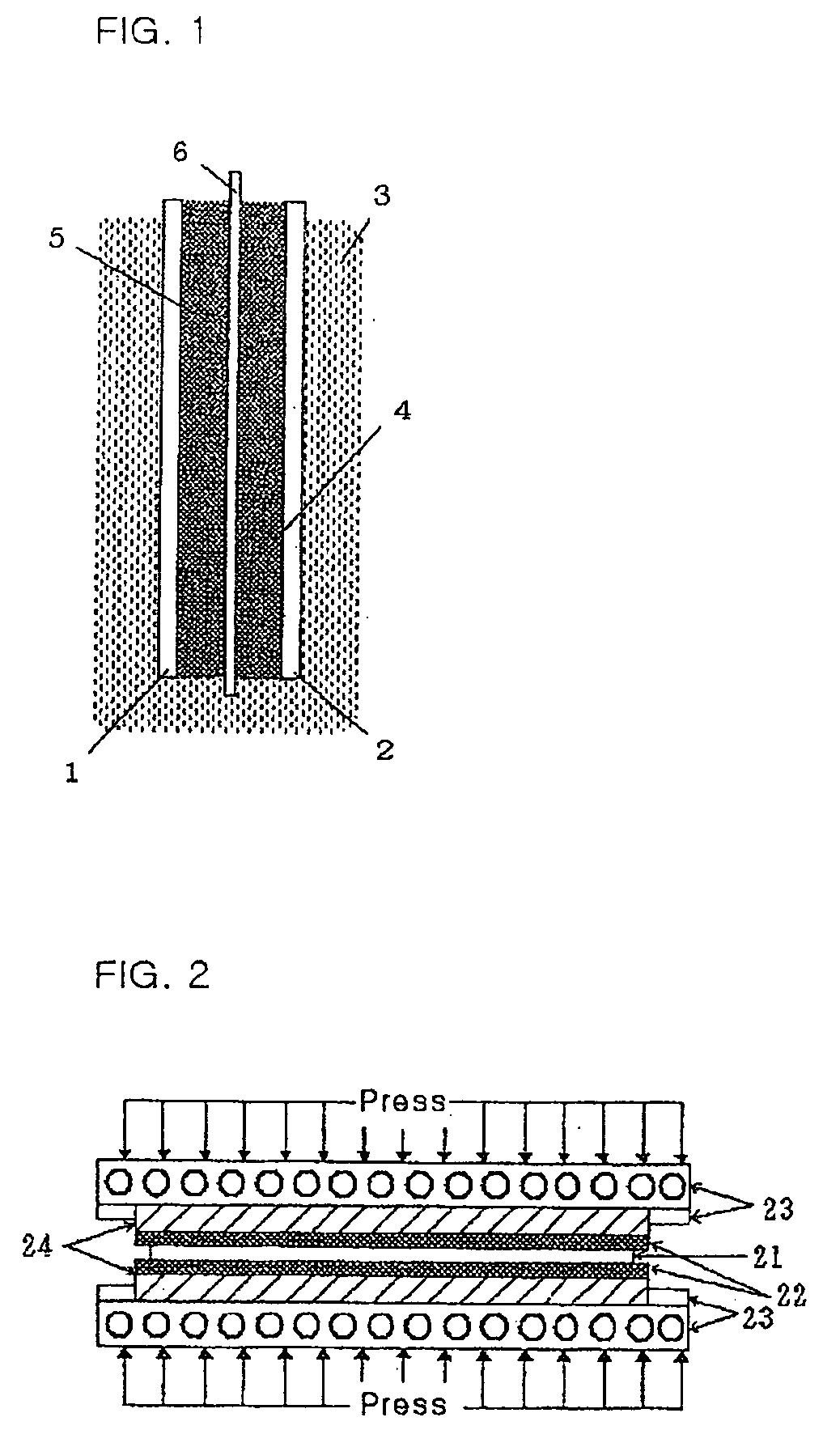

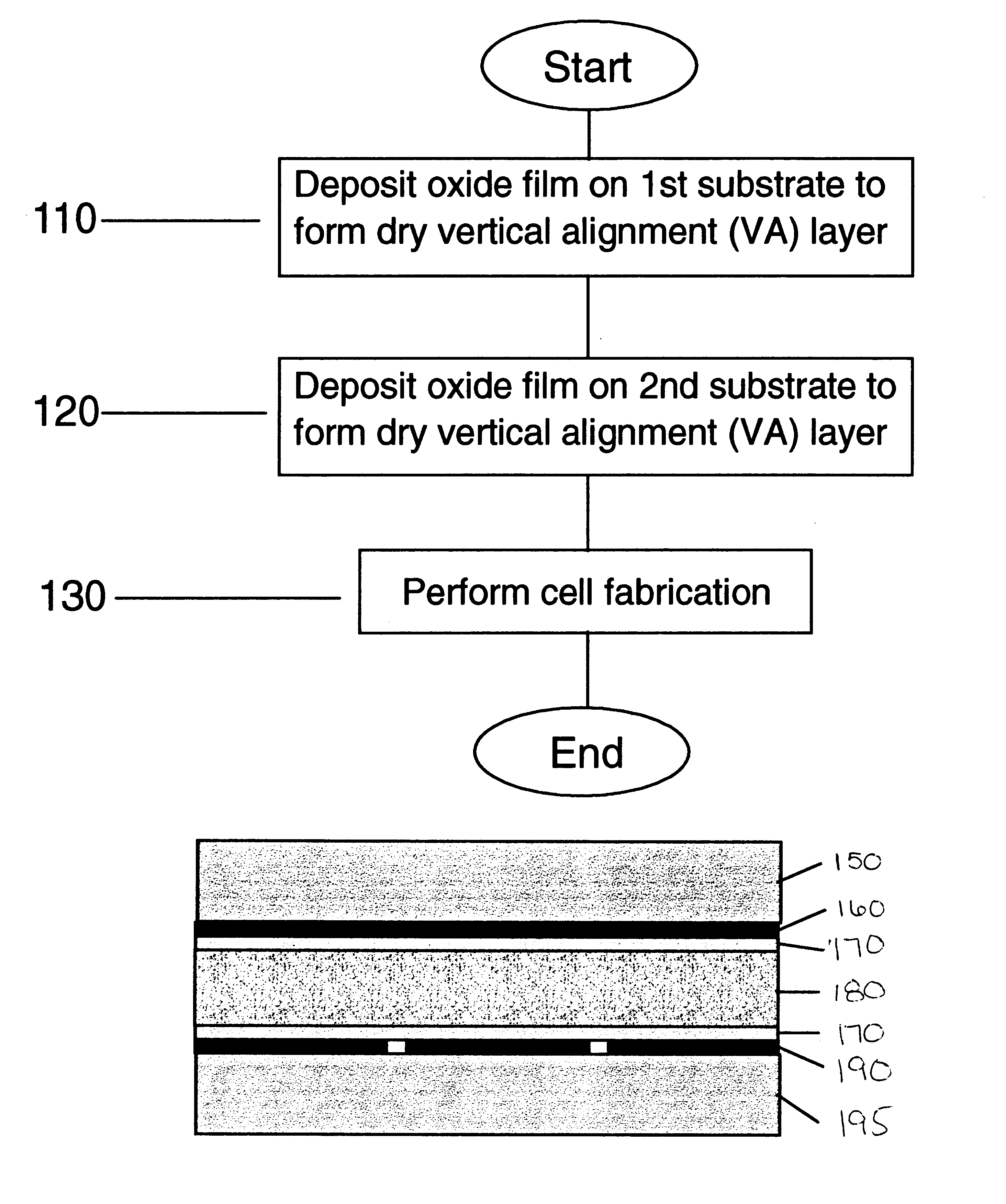

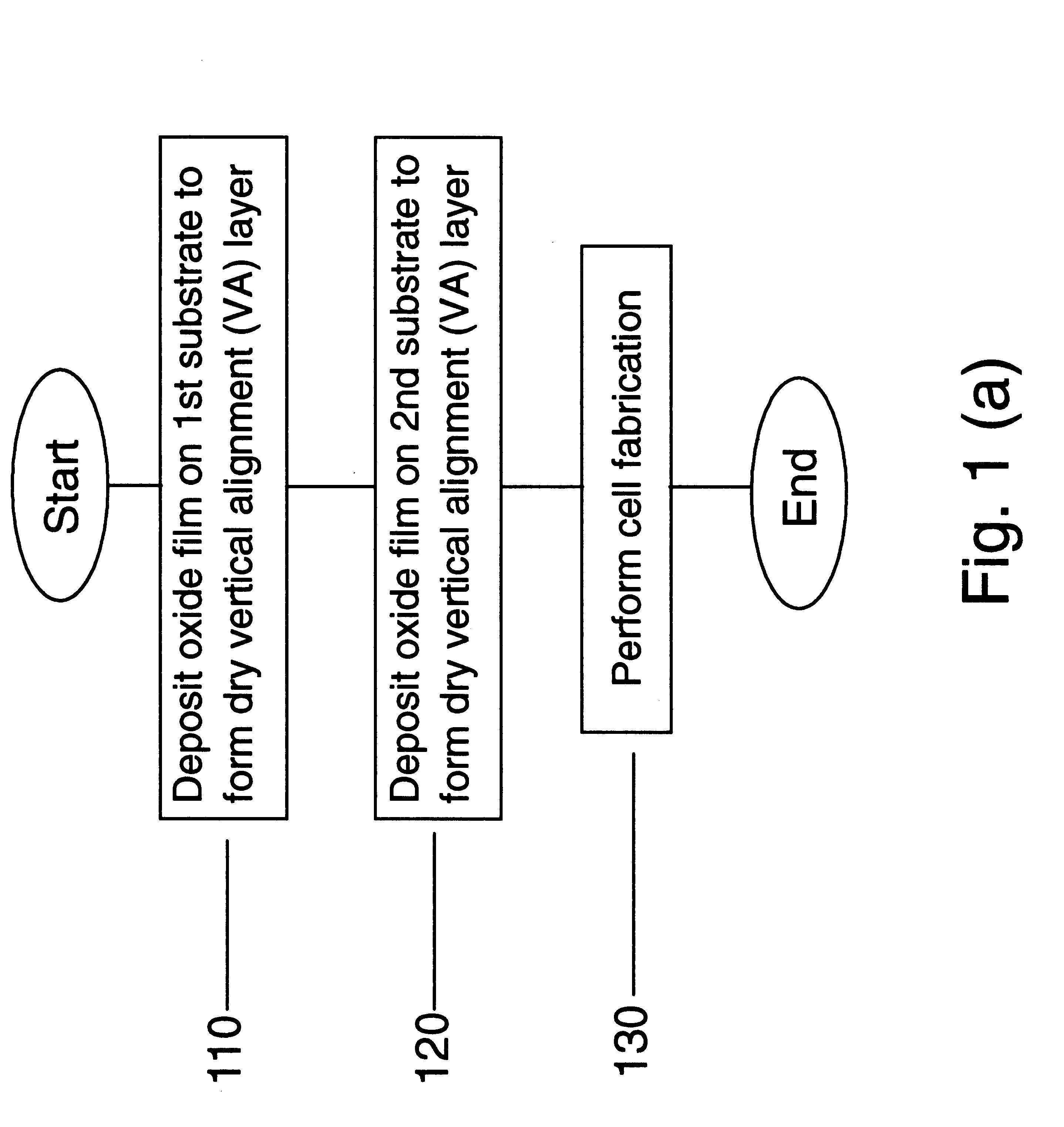

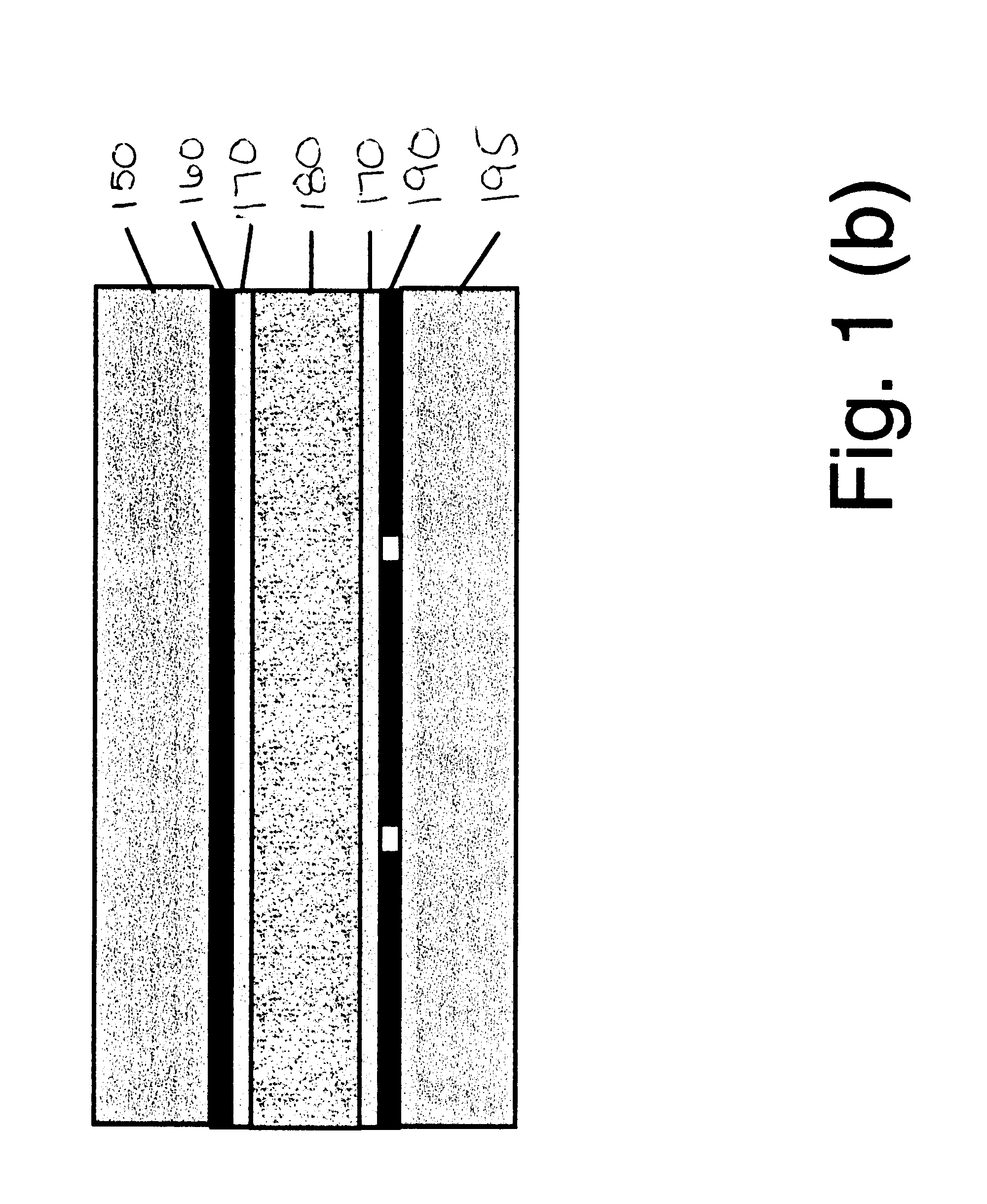

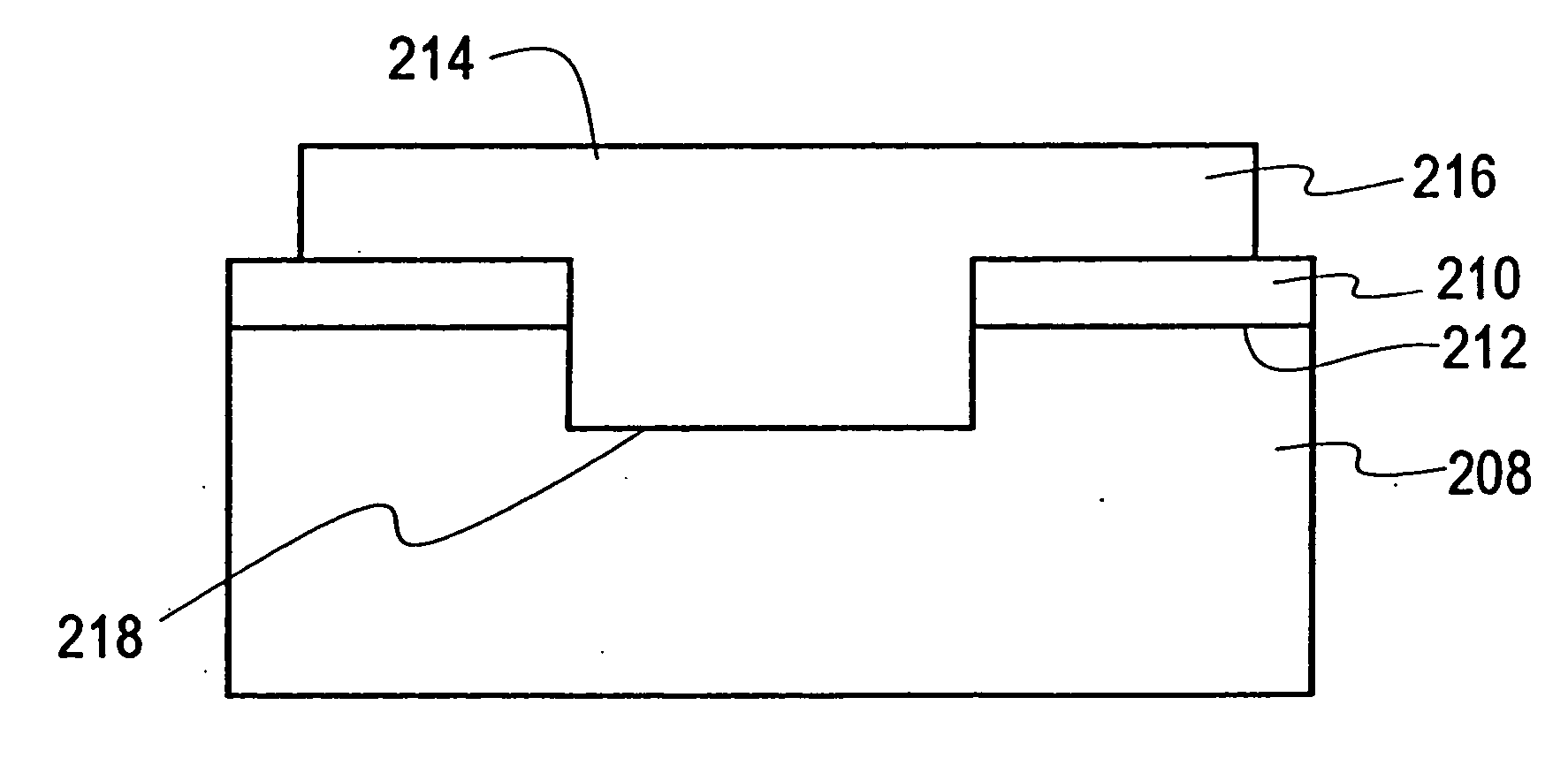

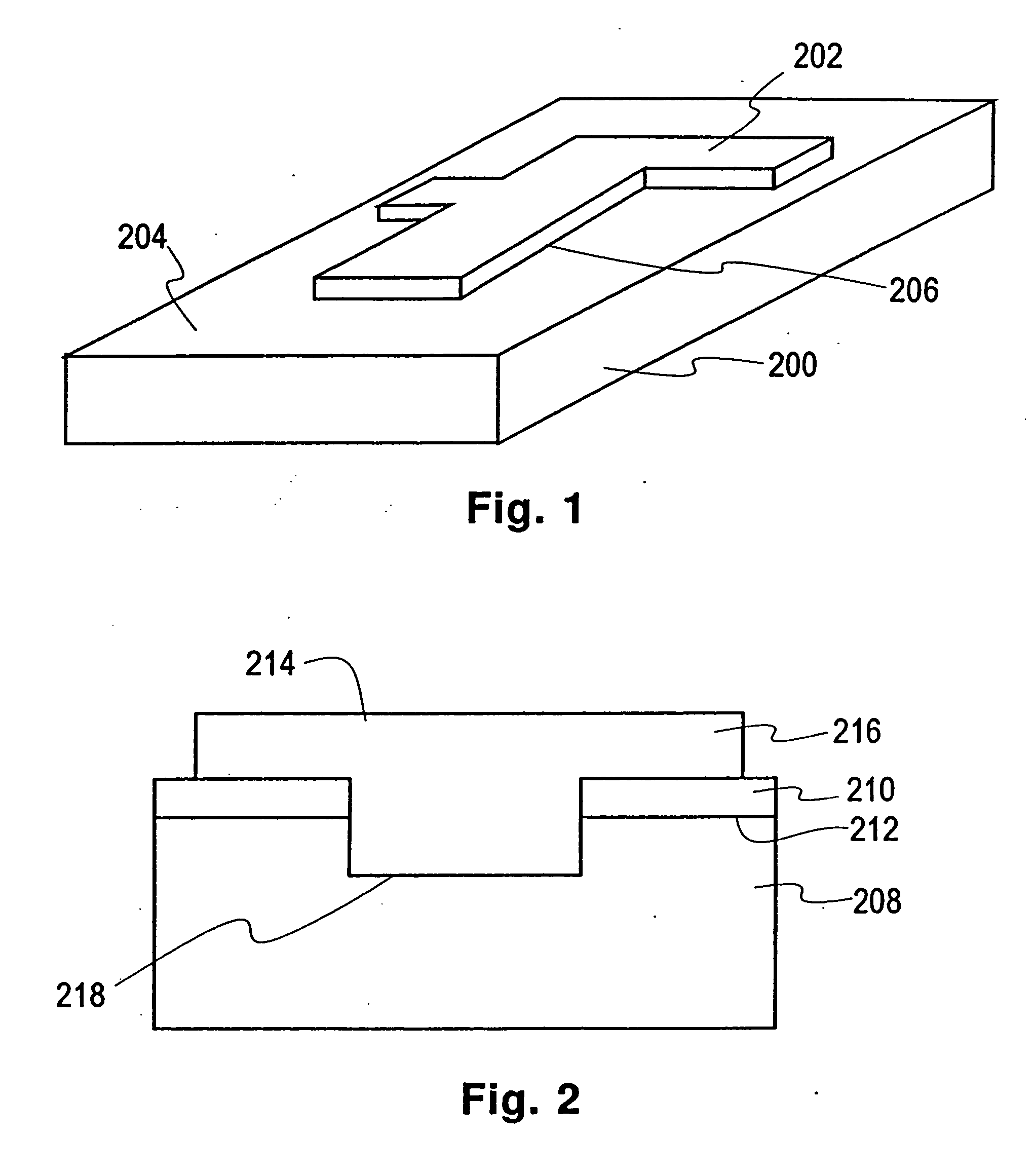

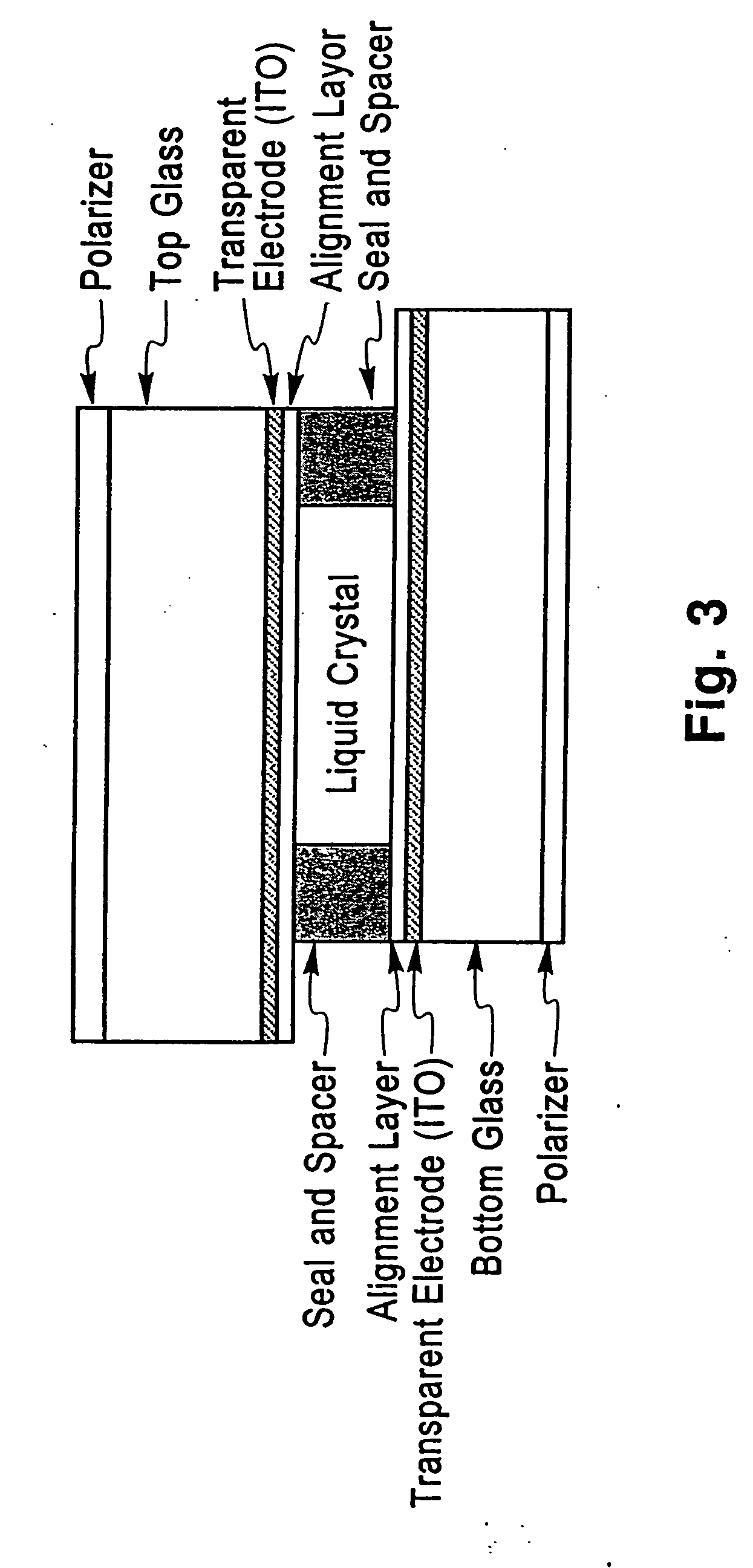

Vertical aligned liquid crystal display and method using dry deposited alignment layer films

InactiveUS6724449B1Reliable alignmentImprove charge retentionStatic indicating devicesNon-linear opticsVertical alignmentEngineering

A liquid crystal display device includes a first substrate, a dry alignment film deposited over the substrate, a second substrate coupled to the first substrate with the dry alignment film deposited over the second substrate therebetween and forming a cell gap, and a liquid crystal material formed in the cell gap. The dry alignment film allows for a truly vertical alignment of molecules of the liquid crystal material such that the molecules form an angle of substantially 90° relative to the substrate. The dry alignment film can be an oxide layer, a nitride layer, an oxynitride layer or a silicon layer. This dry alignment layer can be treated to form a tilted homeotropic alignment, such that the liquid crystal molecules have a pretilt angle of 0.5 to 10 degrees from a substrate normal direction. The truly vertical alignment process can be incorporated with a ridge and fringe field process method to form a multidomain Vertical Alignment (VA) Liquid Crystal Display's (LCDs) which have wide viewing angles.

Owner:INFOVISION OPTOELECTRONICS HLDG LTD +1

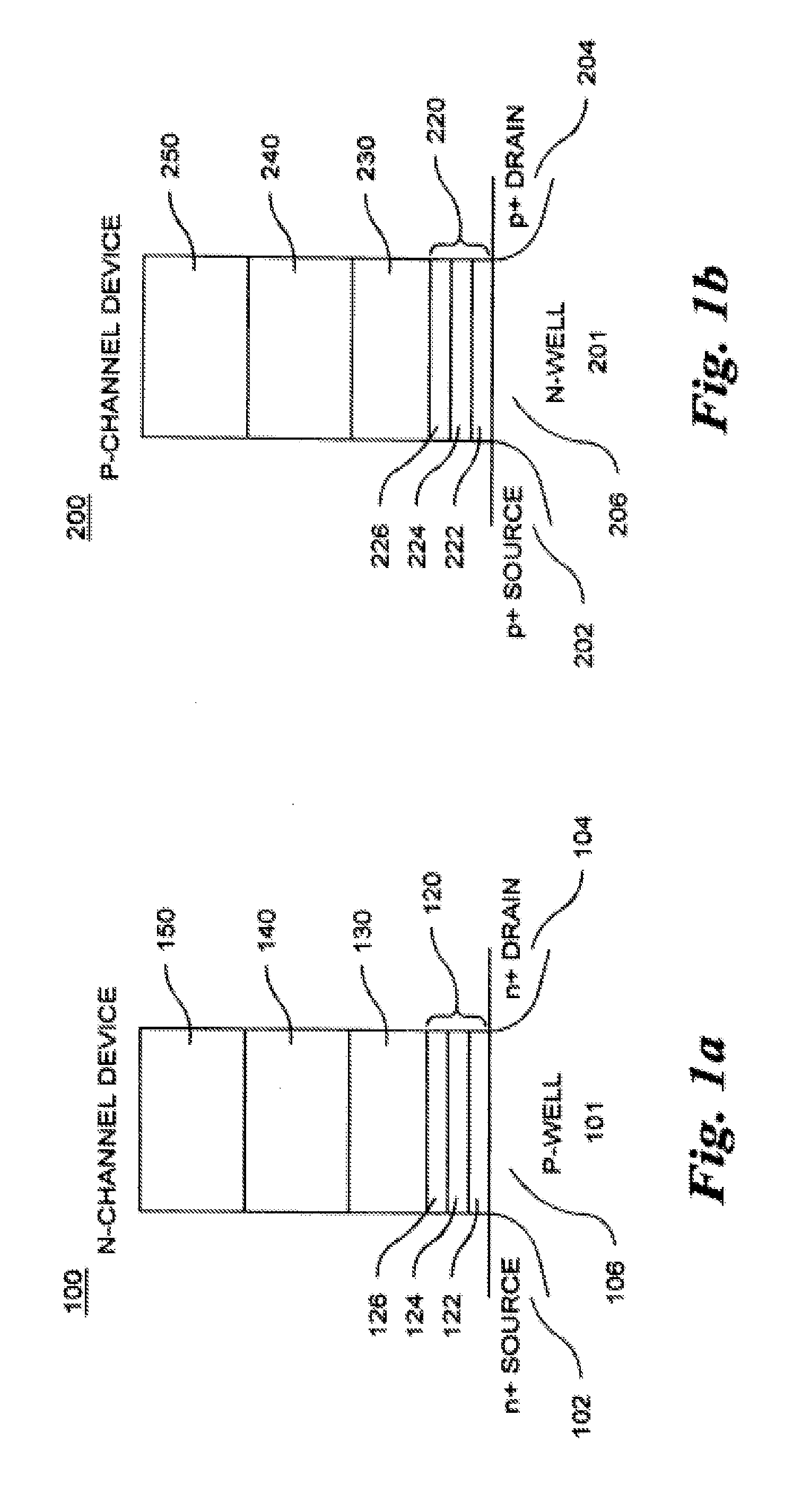

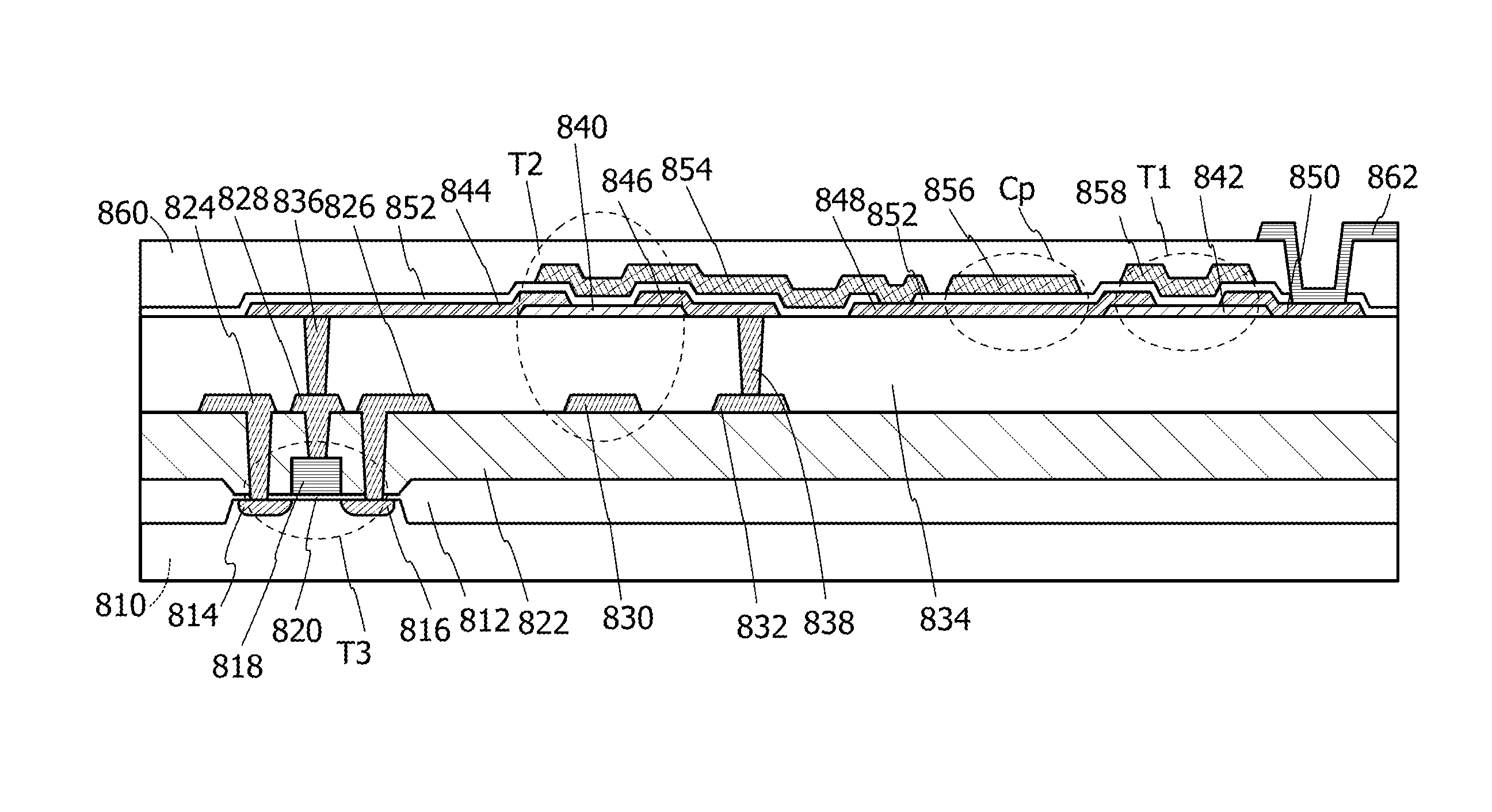

Semiconductor device

InactiveUS20140374747A1Small sizeImprove charge retention characteristicsTransistorSolid-state devicesGate leakage currentCharge retention

To provide a semiconductor device with excellent charge retention characteristics, a transistor including a thick gate insulating film to achieve low leakage current is additionally provided such that its gate is connected to a node for holding charge. The node is composed of this additional transistor and a transistor using an oxide semiconductor in its semiconductor layer including a channel formation region. Charge corresponding to data is held at the node.

Owner:SEMICON ENERGY LAB CO LTD

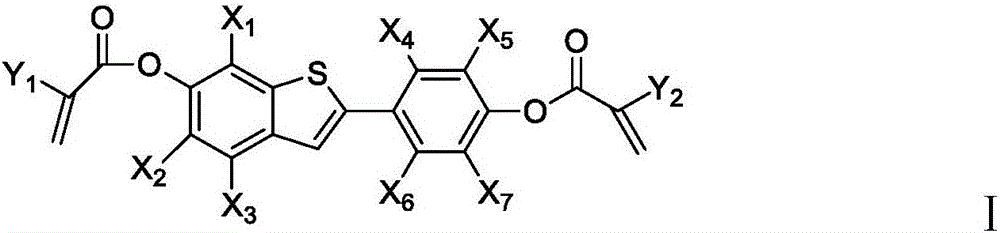

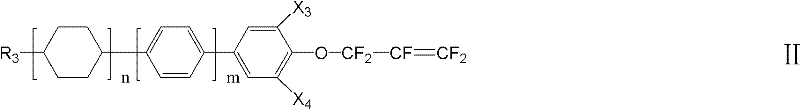

Polymerizable compound containing benzothiophene

ActiveCN105753837AGood miscibilityImproves UV resistanceLiquid crystal compositionsOrganic chemistryLiquid-crystal displayBenzothiophene

The invention discloses a polymerizable compound represented in a formula I, liquid crystal composition containing the polymerizable compound represented in the formula I as well as a liquid crystal display device. In the formula I, X1-X7 represent H, F or CH3 independently, and Y1 and Y2 represent CH3, CH2F, CHF2 or CF3 independently. The polymerizable compound is particularly suitable for PSVA liquid crystal composition applied to a display or TV, and has no or obviously reduced image sticking after long-term operation.

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

Non-volatile memory cells, memory arrays including the same and methods of operating cells and arrays

ActiveUS7642585B2Easy to eraseLarge operating windowTransistorSemiconductor/solid-state device detailsMemory cellDielectric structure

Memory cells comprising: a semiconductor substrate having a source region and a drain region disposed below a surface of the substrate and separated by a channel region; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising at least one layer having a small hole-tunneling-barrier height; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD +1

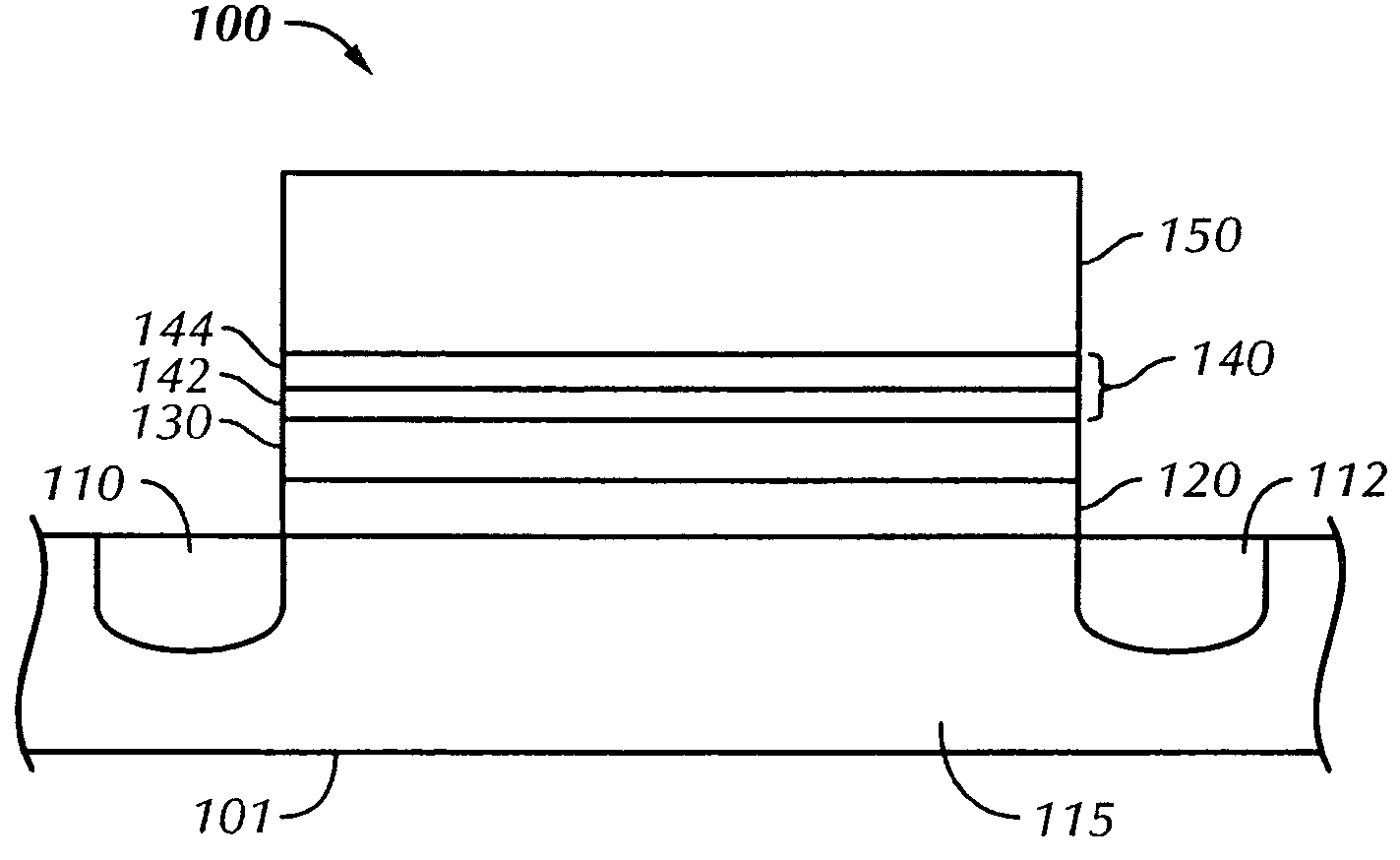

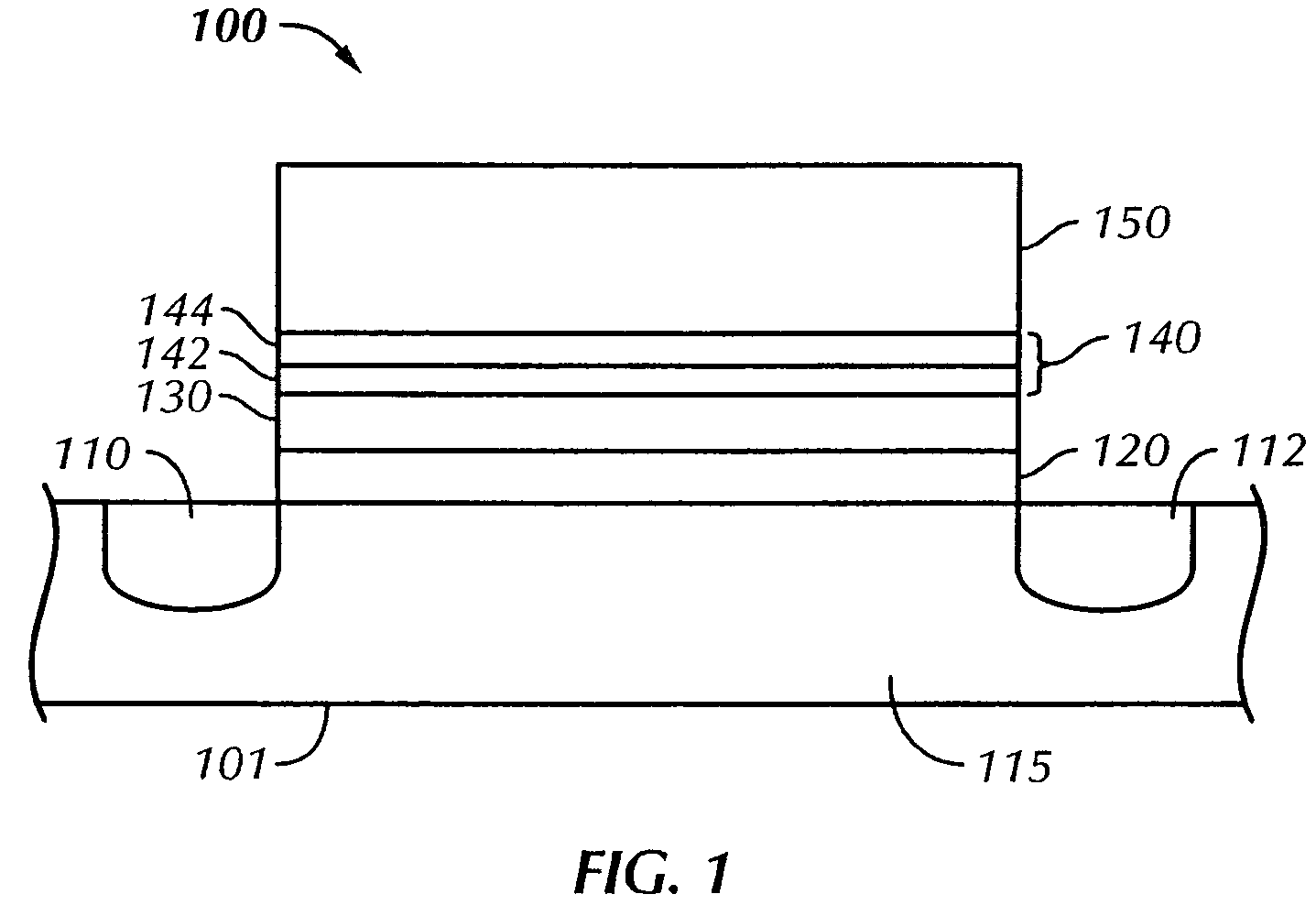

Non-volatile memory cells having a polysilicon-containing, multi-layer insulating structure, memory arrays including the same and methods of operating the same

ActiveUS20080099826A1Facilitates positive voltage erase operationReduce semiconductor layer/oxide interface damageTransistorRead-only memoriesPolycrystalline siliconSemiconductor

Memory cells including a semiconductor layer having at least two source / drain regions disposed below a surface of the semiconductor layer and separated by a channel region; a lower insulating layer disposed above the channel region; a charge storage layer disposed above the lower insulating layer; an upper insulating multi-layer structure disposed above the charge storage layer, wherein the upper insulating multi-layer structure comprises a polysilicon material layer interposed between a first dielectric layer and a second dielectric layer; and a gate disposed above the upper insulating multi-layer structure are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD

Positive dielectric anisotropic liquid crystal composition

ActiveCN103289708AProperly positive dielectric anisotropyAppropriate optical anisotropyLiquid crystal compositionsDielectric anisotropyTotal response

The invention discloses a positive dielectric anisotropic liquid crystal composition. The positive dielectric anisotropic liquid crystal composition comprises 1%-40% by weight of compound with a structural formula I, 1%-50% by weight of compound with a structural formula II, 1%-60% by weight of compound with a structural formula III and 1%-80% by weight of compound with a structural formula IV, and an optically active compound accounting for 0-0.5% of the total weight of the liquid crystal composition can be additionally added. The liquid crystal composition has the advantages of suitable positive dielectric anisotropy, lower rotary viscosity, very low total response time, lower voltage and higher resistivity and voltage holding ratio, and further has broad application prospects and application values in liquid crystal display.

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

Liquid crystal composition

ActiveCN102643653AImprove performanceImproves UV resistanceLiquid crystal compositionsNon-linear opticsLiquid-crystal displayLiquid composition

The invention provides a liquid crystal composition, containing the following components in percentage by weight: (1) 1-60wt% of one or more compounds with a type-I structure, and (2) 1-60wt% of one or more compounds with a type-II structure. The composition provided by the invention may further contain (3) 0-40wt% of one or more compounds with a type-III structure, (4) 0-40wt% of one or more compounds with a type-IV structure, (5) 0-40wt% of one or more compounds with a type-V structure, (6) 1-40wt% of one or more compounds with a type-VI structure, (7) 1-40wt% of one or more compounds with a type-VII structure, and other optically active components accounting for 0.05-0.5% of the total weight of the other components. The composition provided by the invention has an excellent performanceof applying to a TFT (thin film transistor) liquid crystal display screen of the modes such as TN (twisted nematic), IPS (in-plane switching), FFS (fringe field switching), ADS (advanced super dimension switching) or OCB (optically compensated birefringence); and the preparation method is simple and easy in operation.

Owner:BEIJING BAYI SPACE LCD MATERIALS TECH

Liquid crystal composition and liquid crystal display element or liquid crystal display device

ActiveCN107674687AOvercoming the defect of low reliabilityQuick responseLiquid crystal compositionsCrystallographyCharge retention

The invention disclosed a liquid crystal composition, which contains one or a plurality of compounds represented by a formula I-a and / or I-b, one or a plurality of compounds represented by a formula II, and one or a plurality of compounds represented by a formula III, wherein the formulas I-a, I-b, II and III are defined in the specification. A purpose of the present invention is to provide a liquid crystal composition and a liquid crystal display element or a liquid crystal display device containing the liquid crystal composition. According to the present invention, the liquid crystal composition has low viscosity, can achieve fast response, and further has moderate dielectric anisotropy delta[epsilon], moderate optical anisotropy delta[n], high thermal stability and high light stability;and the liquid crystal display element or the liquid crystal display device containing the liquid crystal composition has advantages of wide nematic phase temperature range, suitable birefringence anisotropy, high resistivity, good ultraviolet resistance, high charge retention, low vapor pressure and the like.

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

HIGH-k CAPPED BLOCKING DIELECTRIC BANDGAP ENGINEERED SONOS AND MONOS

ActiveUS20090059676A1Excellent characteristicsImprove reliabilitySolid-state devicesRead-only memoriesDielectricTrapping

A blocking dielectric engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking dielectric comprising a buffer layer in contact with the charge trapping element, such as silicon dioxide which can be made with high-quality, and a second capping layer in contact with said one of the gate and the channel. The capping layer has a dielectric constant that is higher than that of the first layer, and preferably comprises a high-κ material. The second layer also has a conduction band offset that is relatively high. A bandgap engineered tunneling layer between the channel and the charge trapping element is provided which, in combination with the multilayer blocking dielectric described herein, provides for high-speed erase operations by hole tunneling. In an alternative, a single layer tunneling layer is used.

Owner:MACRONIX INT CO LTD

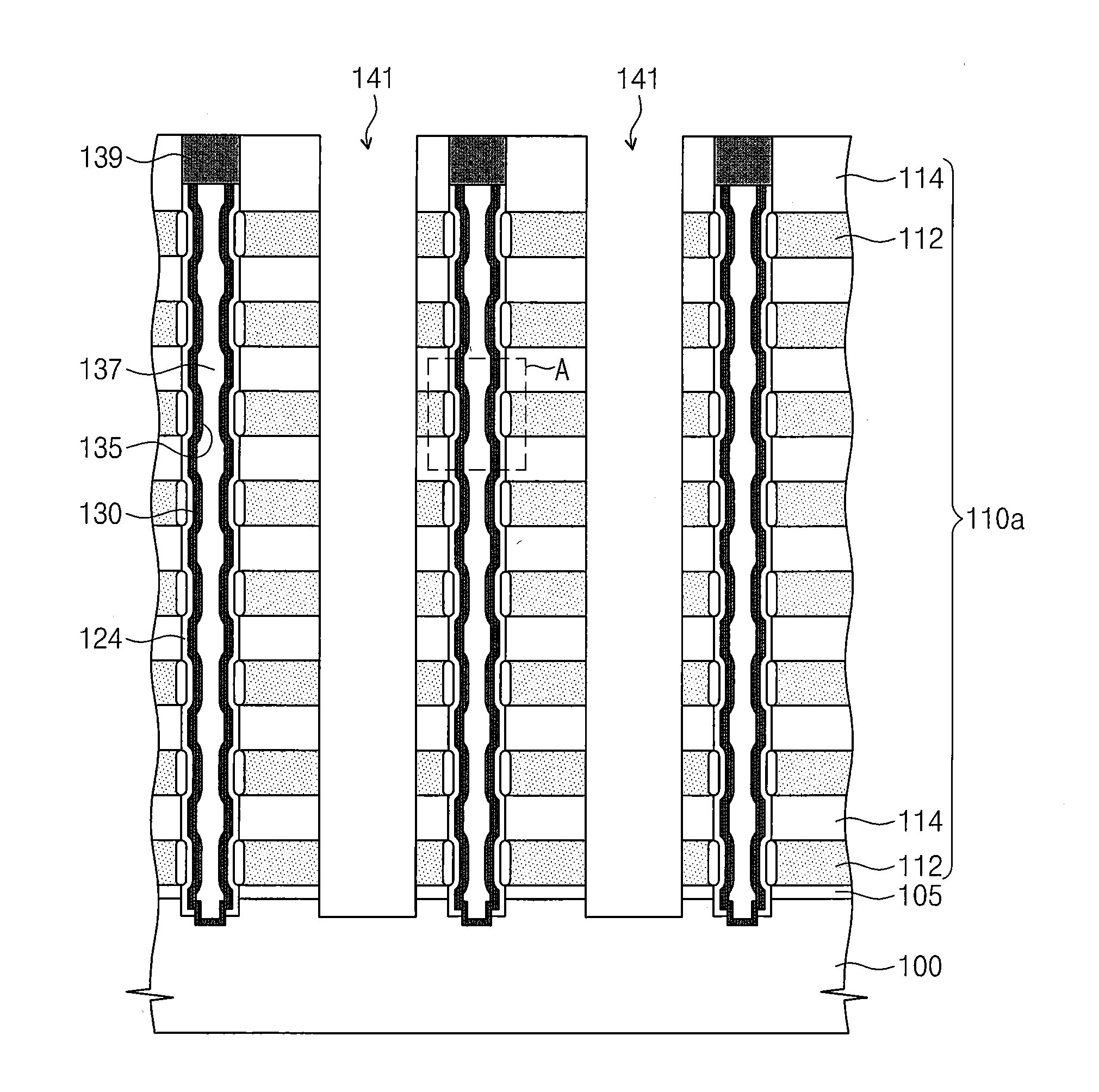

Vertical memory devices having charge storage layers with thinned portions

ActiveUS20160225786A1High dielectric constantReduce lossesSolid-state devicesSemiconductor devicesSemiconductorDevice material

A semiconductor device includes a stack comprising insulating patterns vertically stacked on a substrate and gate patterns interposed between the insulating patterns, an active pillar passing through the stack and electrically connected to the substrate and a charge storing layer interposed between the stack and the active pillar. The charge storing layer includes a first portion between the active pillar and one of the gate patterns, a second portion between the active pillar and one of the insulating patterns, and a third portion joining the first portion to the second portion and having a thickness less than that of the first portion.

Owner:SAMSUNG ELECTRONICS CO LTD

Patterns of electrically conducting polymers and their application as electrodes or electrical contacts

InactiveUS20060238690A1High light transmittanceImprove charge retentionLaser detailsCathode-ray/electron-beam tube vessels/containersResistConductive polymer

Electronic devices having patterned electrically conductive polymers providing electrical connection thereto and methods of fabrication thereof are described. Liquid crystal display cells are described having at least one of the electrodes providing a bias across the liquid crystal material formed from a patterned electrically conductive polymer. Thin film transistors having patterned electrically conductive polymers as source drain and gate electrodes are described. Light emitting diodes having anode and coated regions formed from patterned electrically conductive polymers are described. Methods of patterning using a resist mask; patterning using a patterned metal layer, patterning the metal layer using a resist; and patterning the electrically conductive polymer directly to form electrodes and anode and cathode regions are described.

Owner:GLOBALFOUNDRIES INC

Liquid crystal composition for TFT (Thin-Film Transistor) display

ActiveCN101831307AImprove performanceLower average response timeLiquid crystal compositionsHigh resistanceLiquid-crystal display

The invention provides a liquid crystal composition for TFT (Thin-Film Transistor) display. The liquid crystal composition is prepared from the following components in percentage by weight: 1-40 percent of I-type compound, 1-70 percent of II-type compound, 1-40 percent of III-type compound, 0-45 percent of IV-type compound and 0-20 percent of V-type compound. The liquid crystal composition has excellent performance, extremely low total response time (ttot=ton+toff), lower voltage, high resistance ratio and voltage retention ratio, and can also have different threshold voltages, clearing points and delta n characteristics by adjusting the contents of the components, thereby being particularly suitable for manufacturing rapid-response TN-TFT liquid crystal displays.

Owner:BEIJING BAYI SPACE LCD MATERIALS TECH

Method for fabricating self-aligned double layered silicon-metal nanocrystal memory element

InactiveUS7393745B2Improve charge retentionHigher data storing density of a metal nanocrystalTransistorNanoinformaticsEngineeringNanometre

Owner:IND TECH RES INST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com