Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

43 results about "Band-gap engineering" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Band-gap engineering is the process of controlling or altering the band gap of a material. This is typically done to semiconductors by controlling the composition of alloys or constructing layered materials with alternating compositions. A band gap is the range in a solid where no electron state can exist. The band gap of insulators is much larger than in semiconductors. Conductors or metals have a much smaller or nonexistent band gap than semiconductors since the valence and conduction bands overlap. Controlling the band gap allows for the creation of desirable electrical properties.

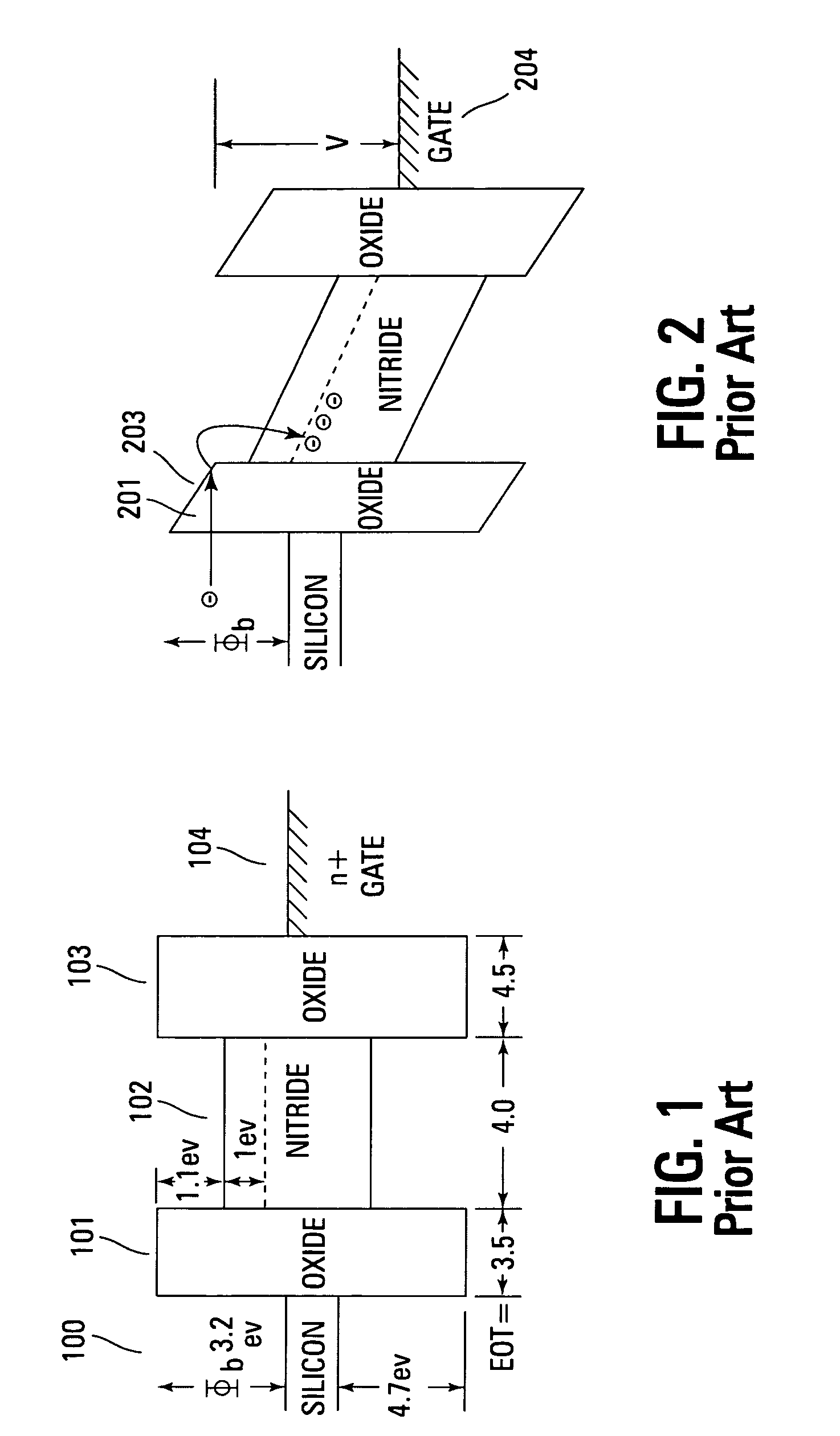

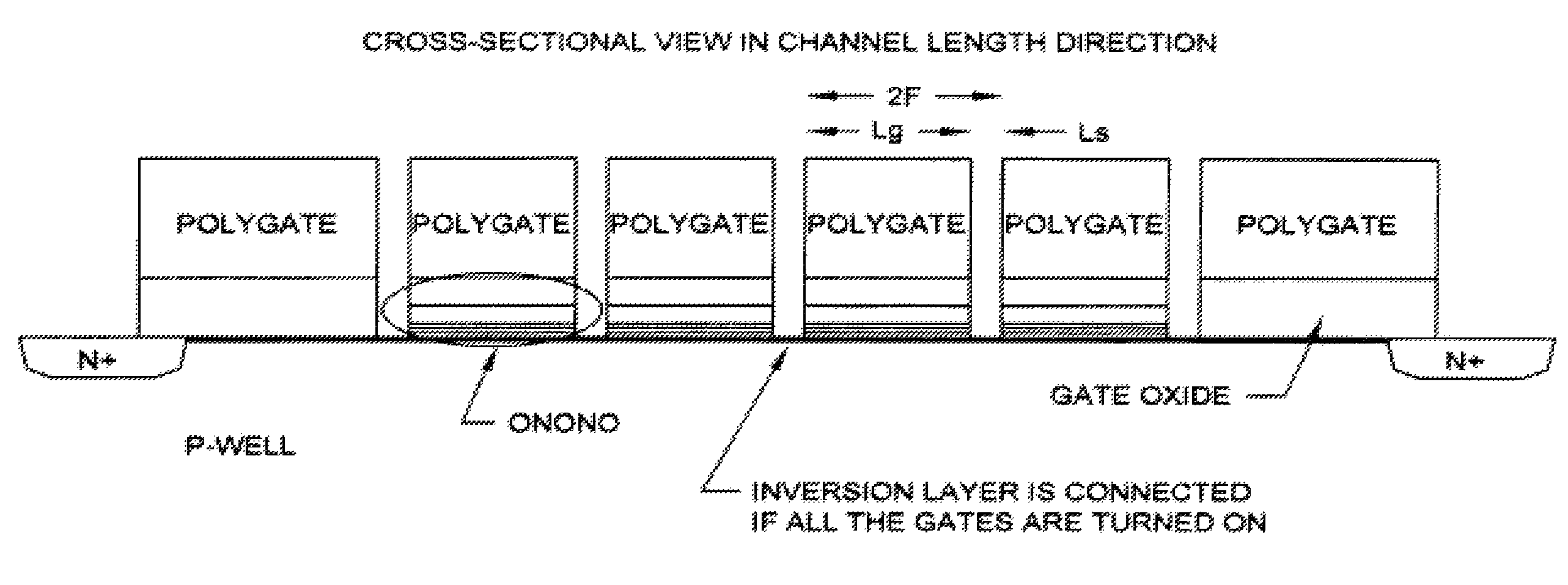

High density NAND non-volatile memory device

ActiveUS20070012988A1Efficient eraseReduce harmSolid-state devicesRead-only memoriesCharge retentionLow voltage

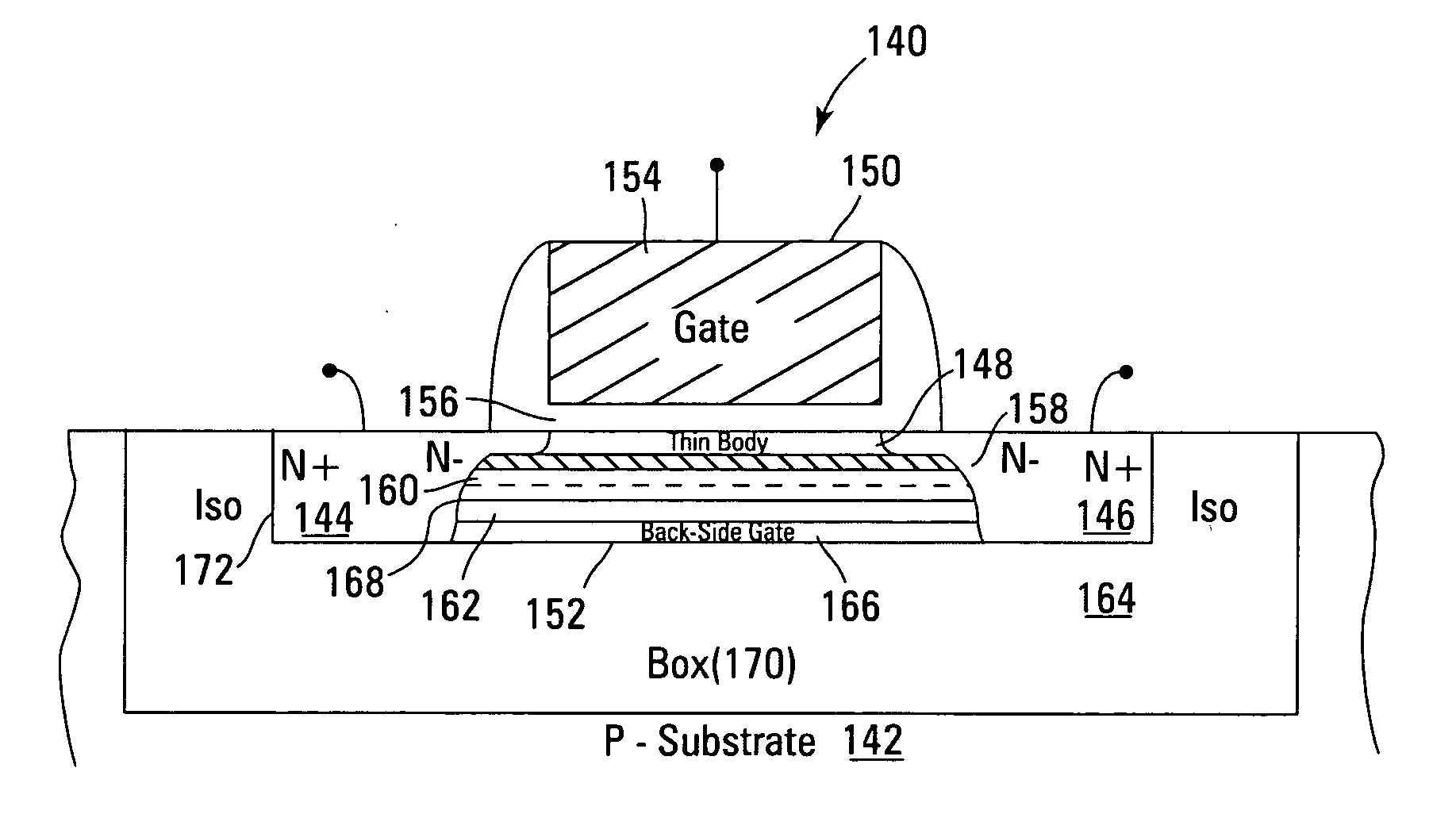

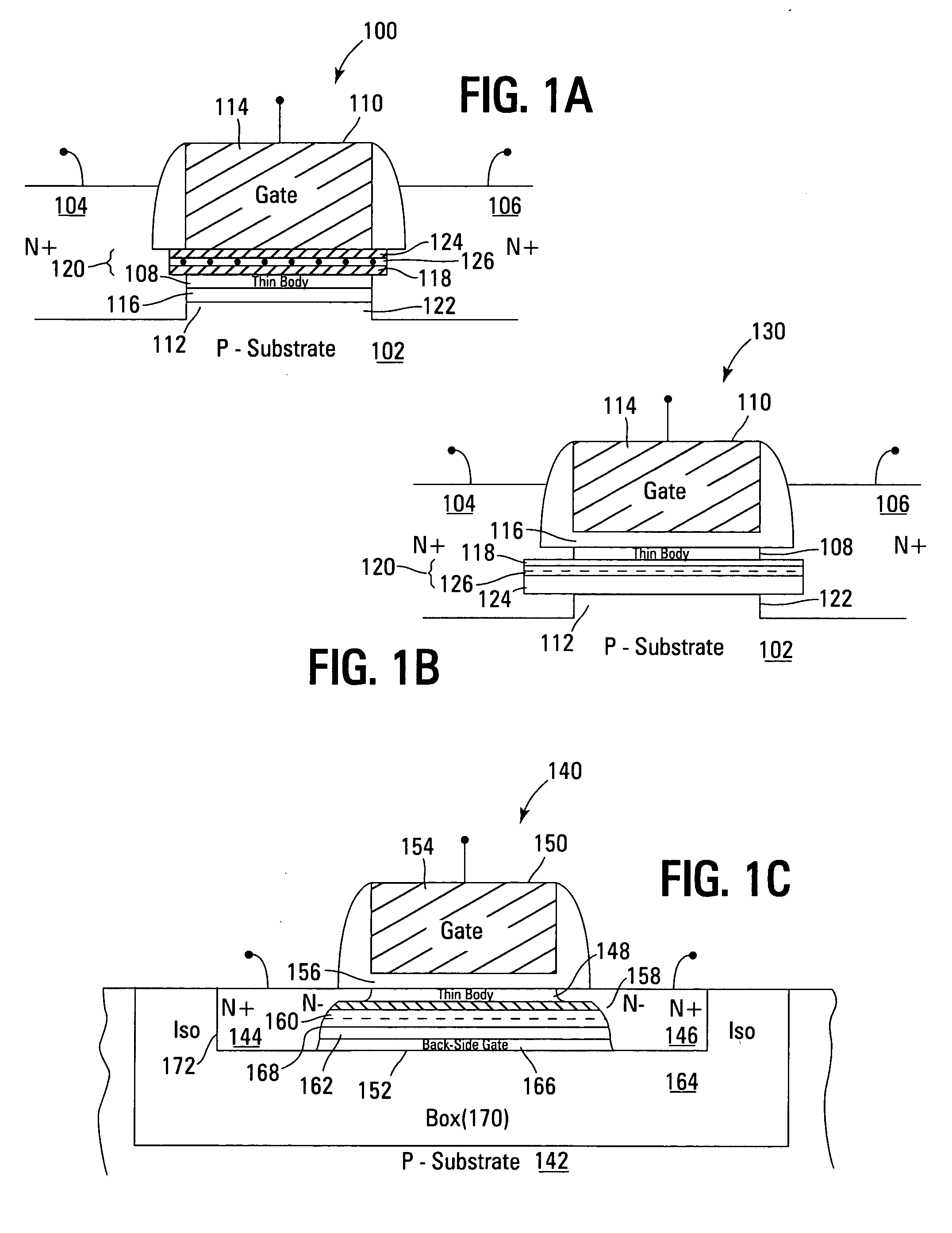

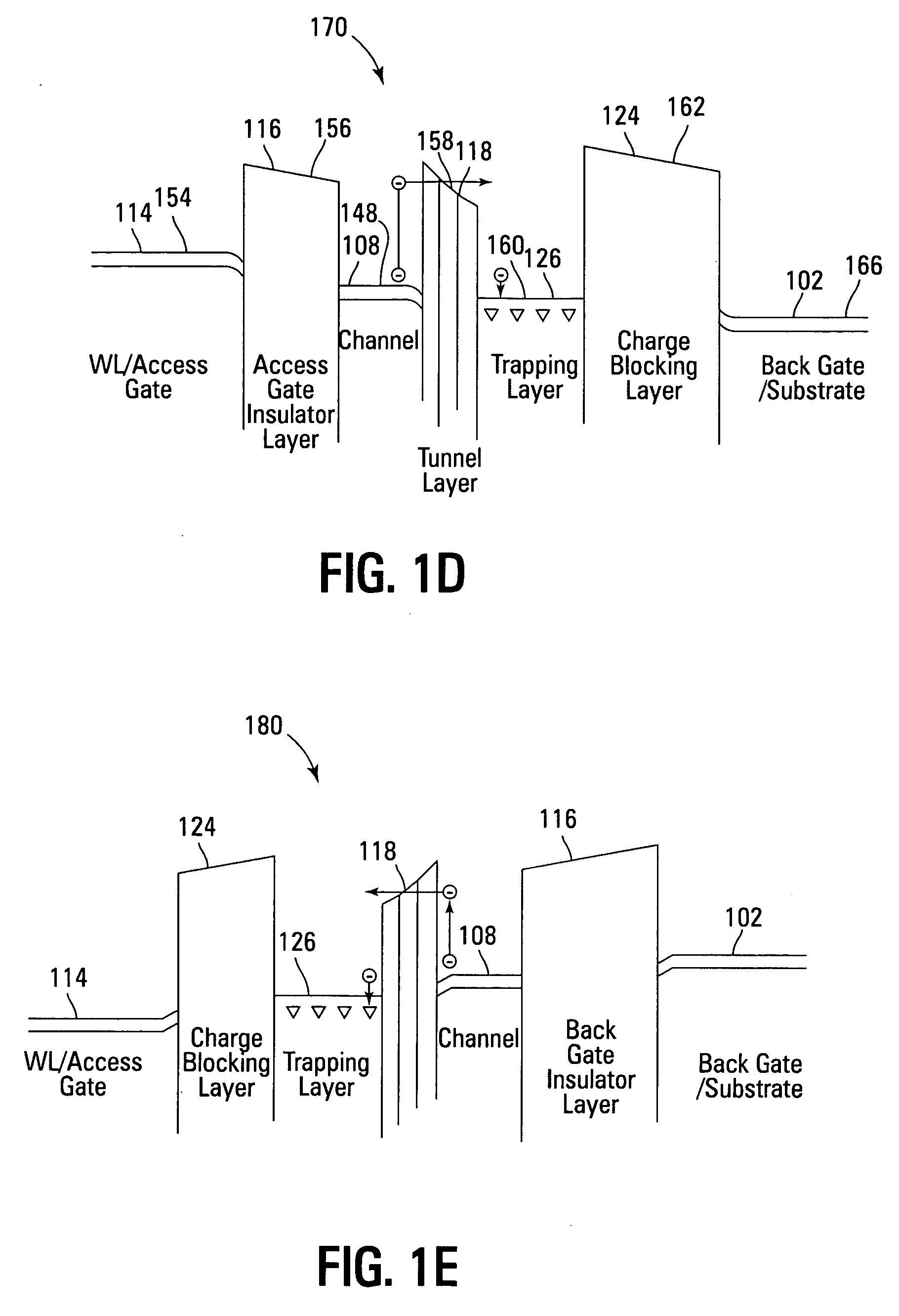

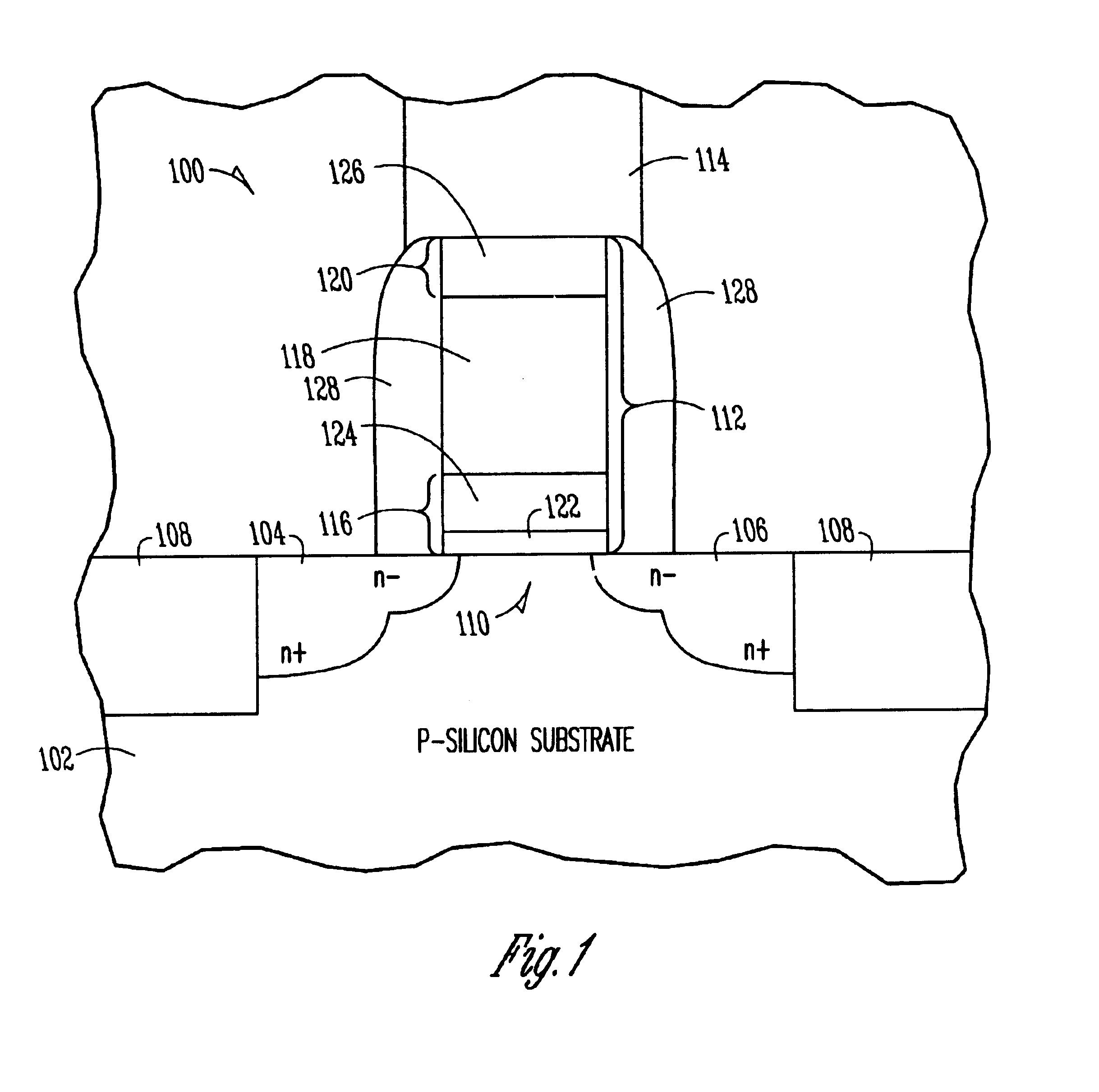

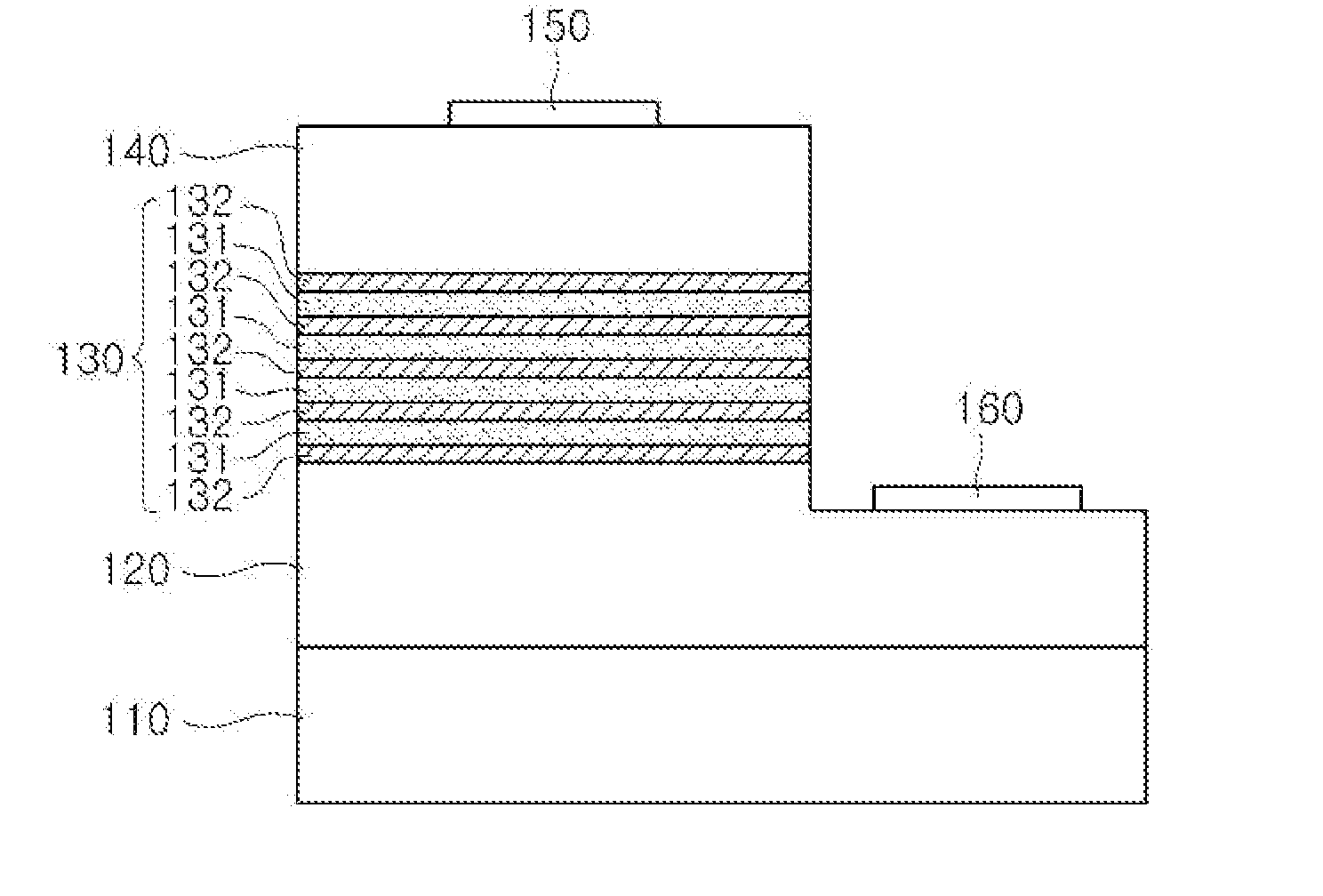

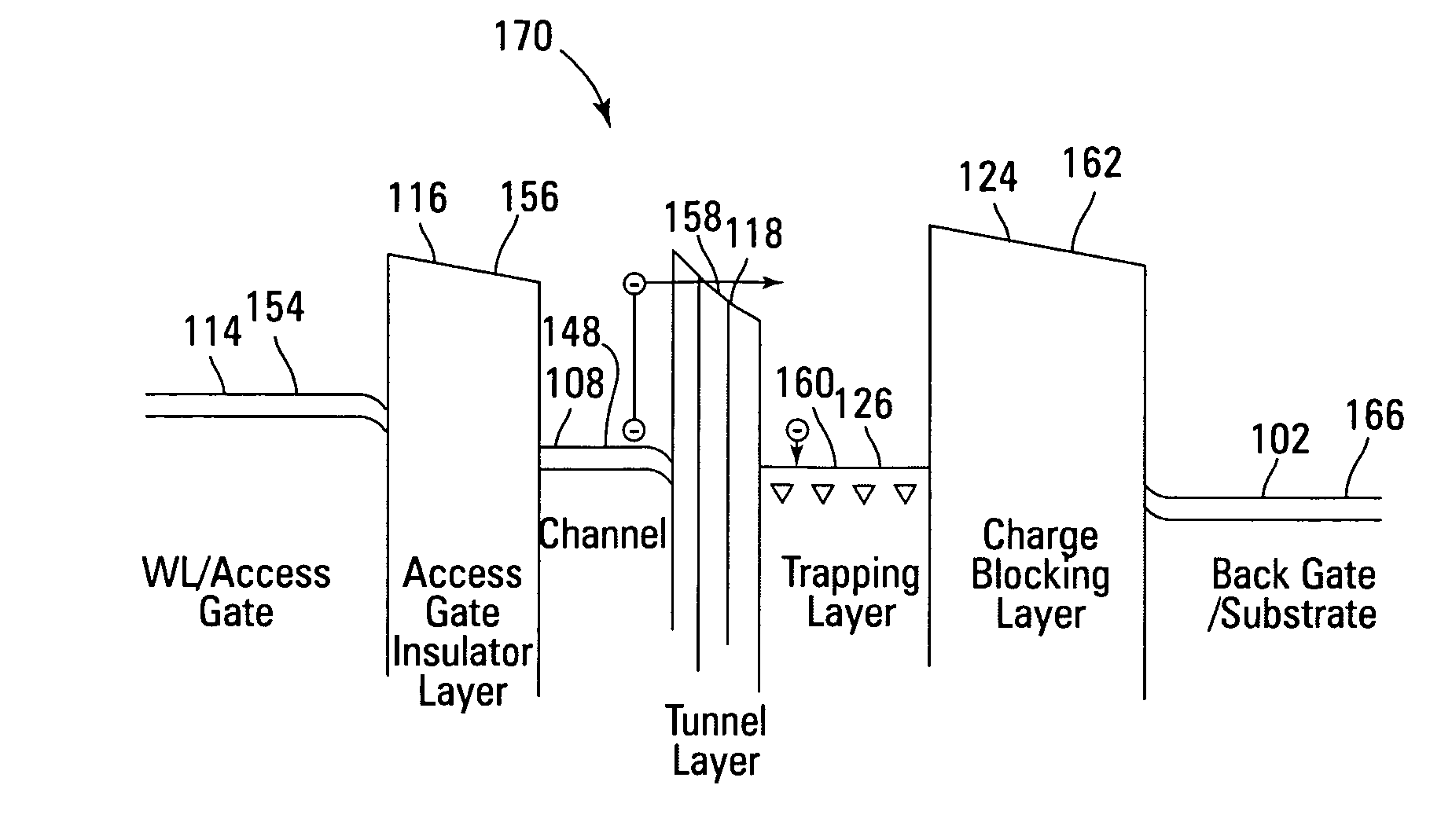

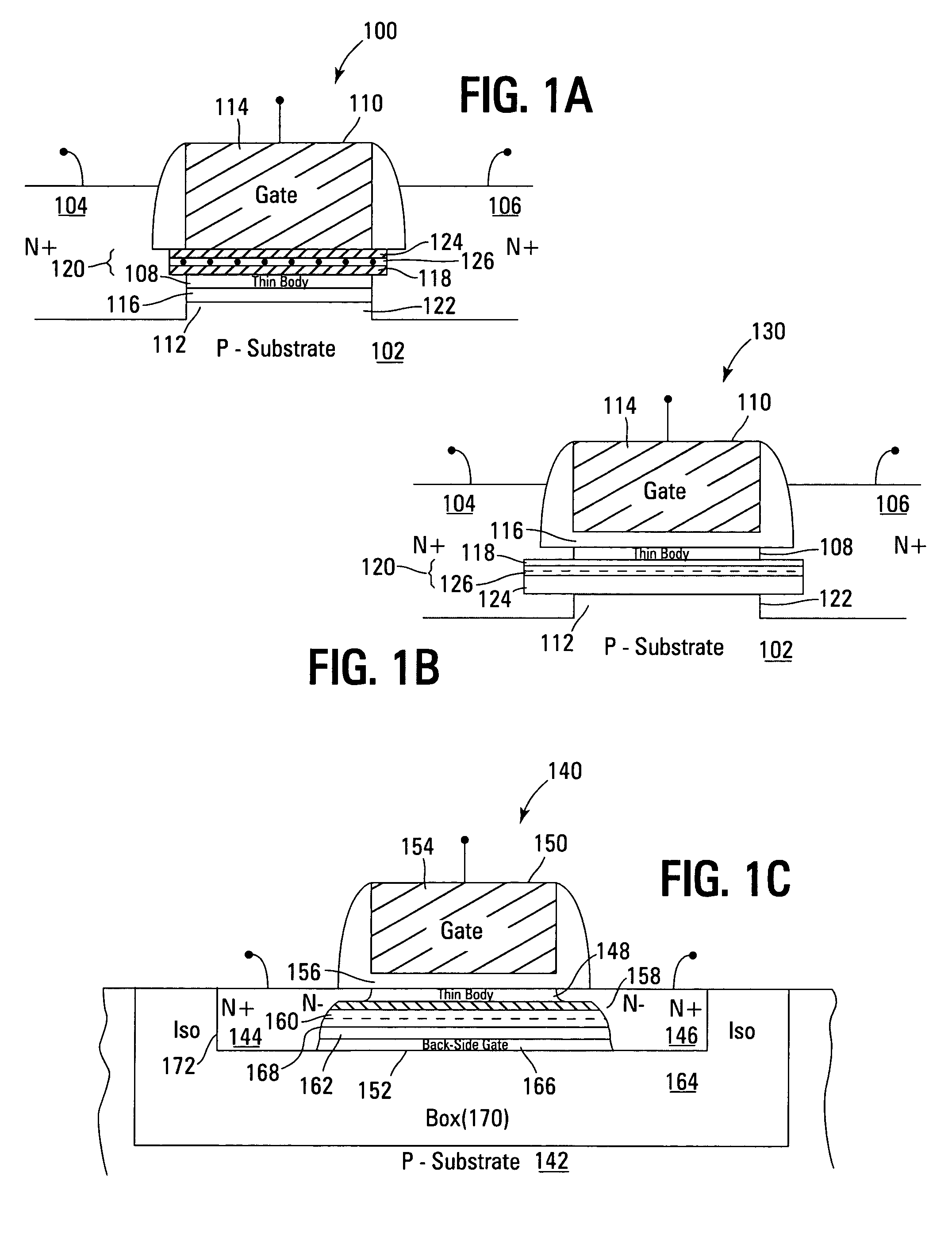

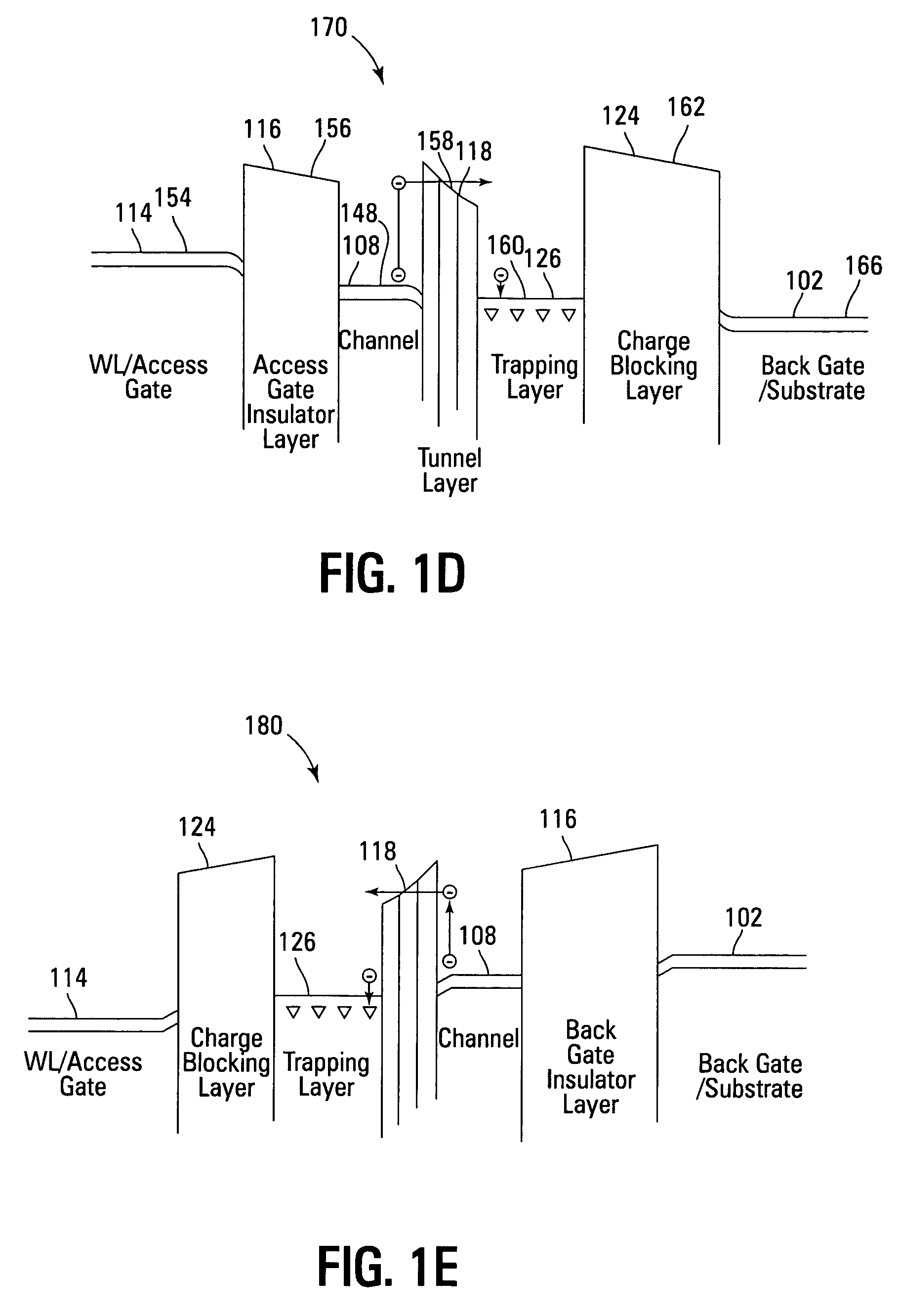

Non-volatile memory devices and arrays are described that utilize dual gate (or back-side gate) non-volatile memory cells with band engineered gate-stacks that are placed above or below the channel region in front-side or back-side charge trapping gate-stack configurations in NAND memory array architectures. The band-gap engineered gate-stacks with asymmetric or direct tunnel barriers of the floating node memory cells of embodiments of the present invention allow for low voltage tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The memory cell architecture also allows for improved high density memory devices or arrays with the utilization of reduced feature word lines and vertical select gates.

Owner:MICRON TECH INC

Asymmetric band-gap engineered nonvolatile memory device

Owner:MICRON TECH INC

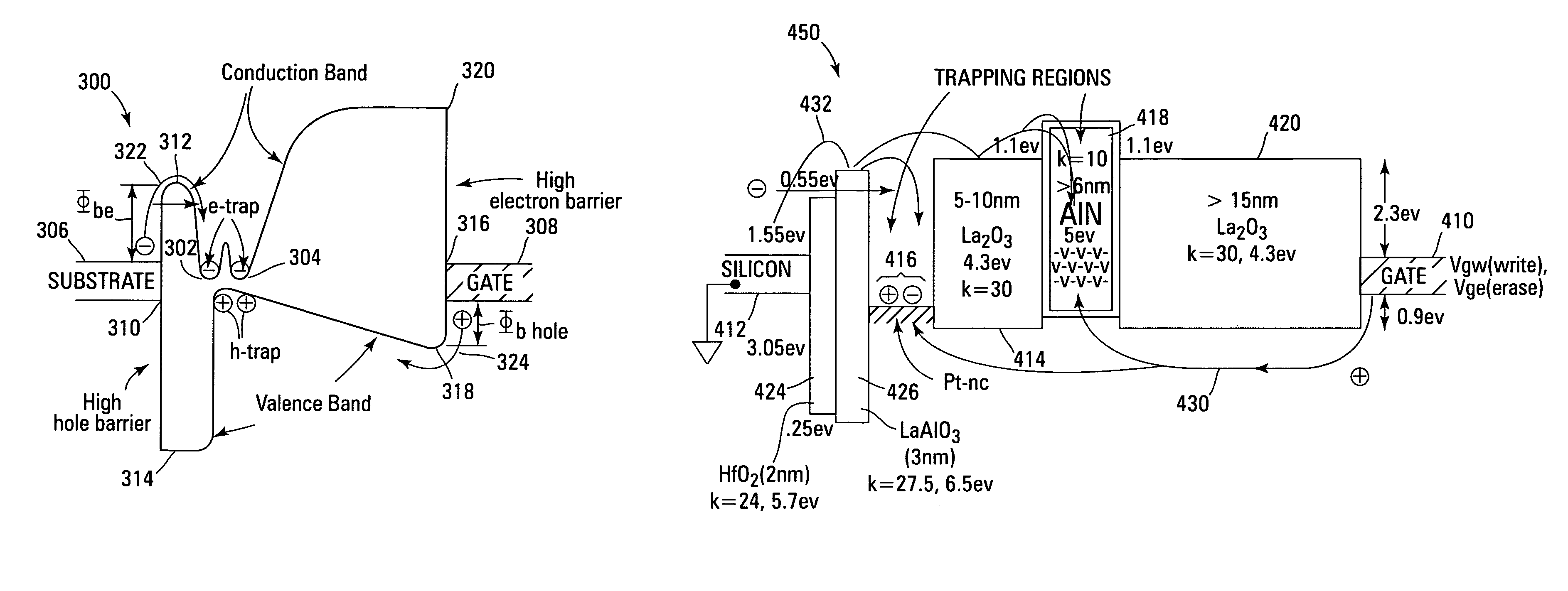

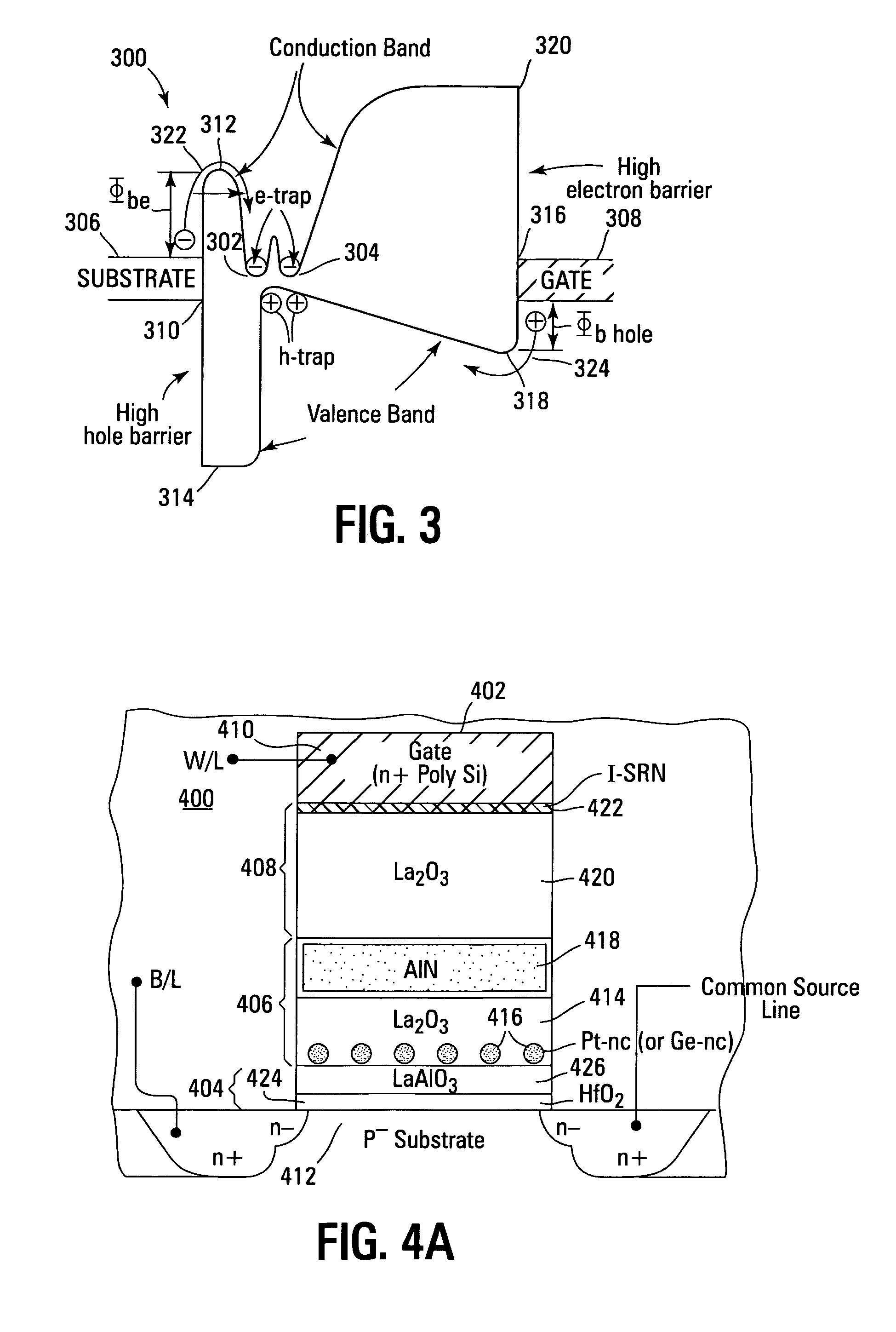

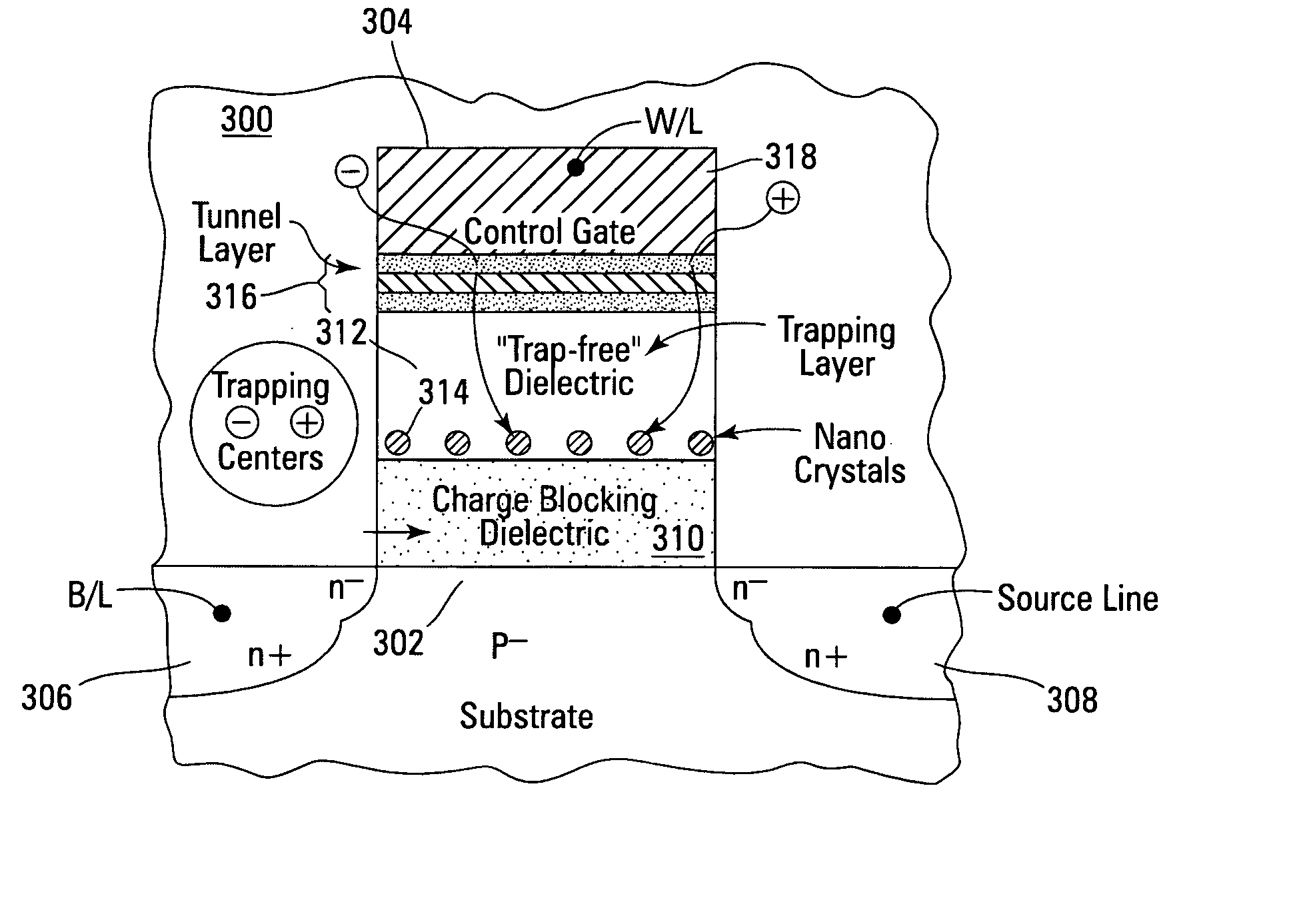

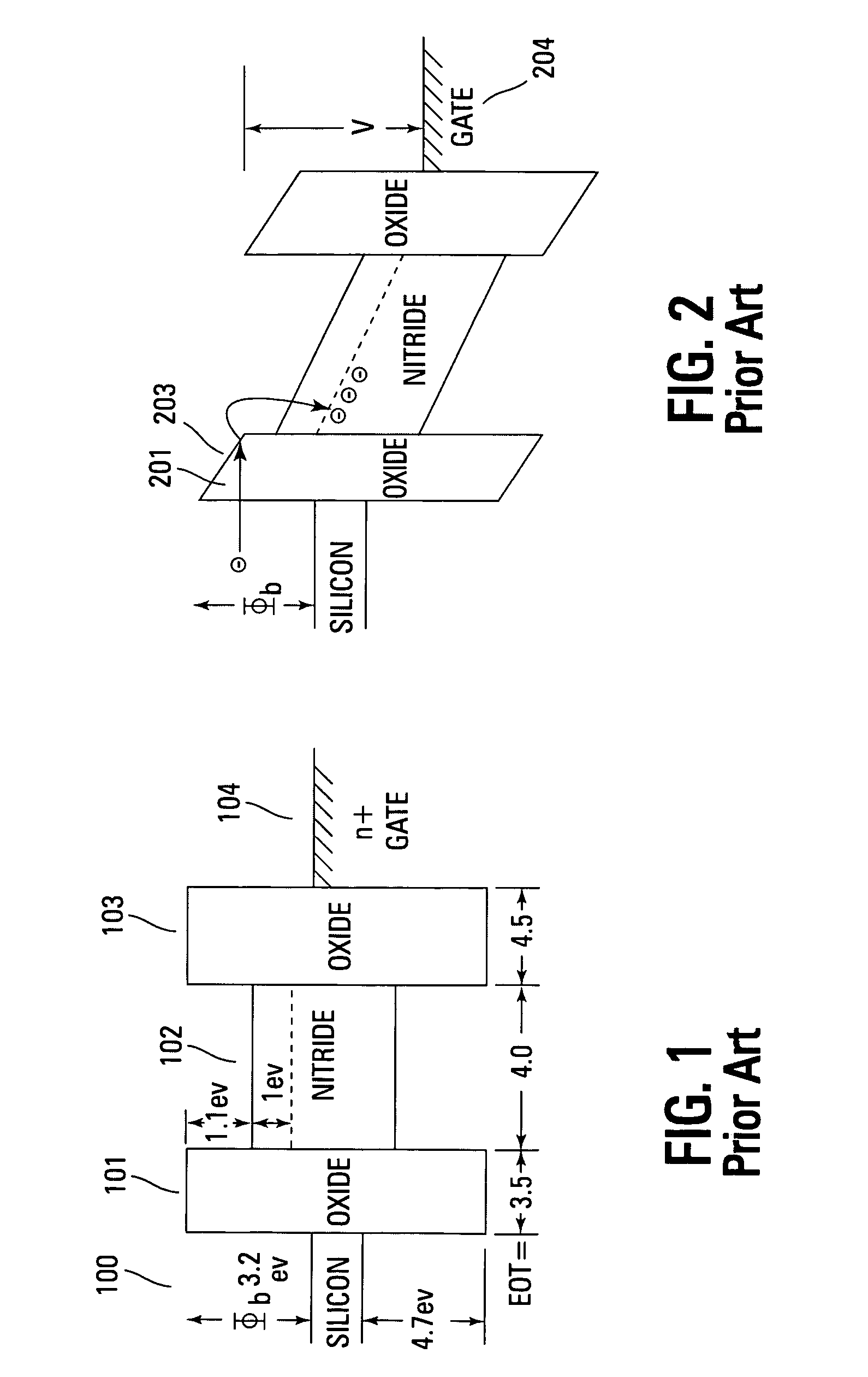

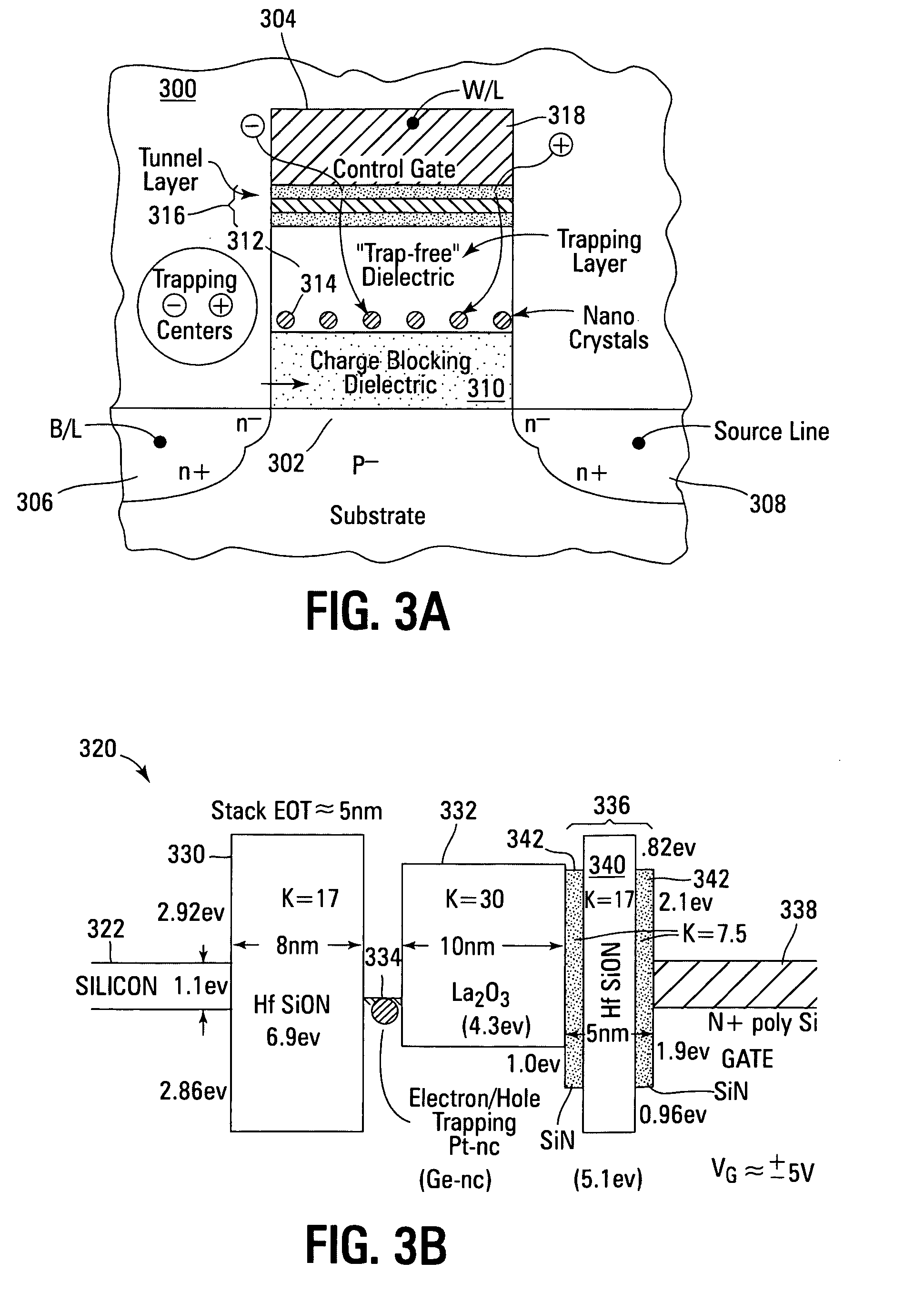

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

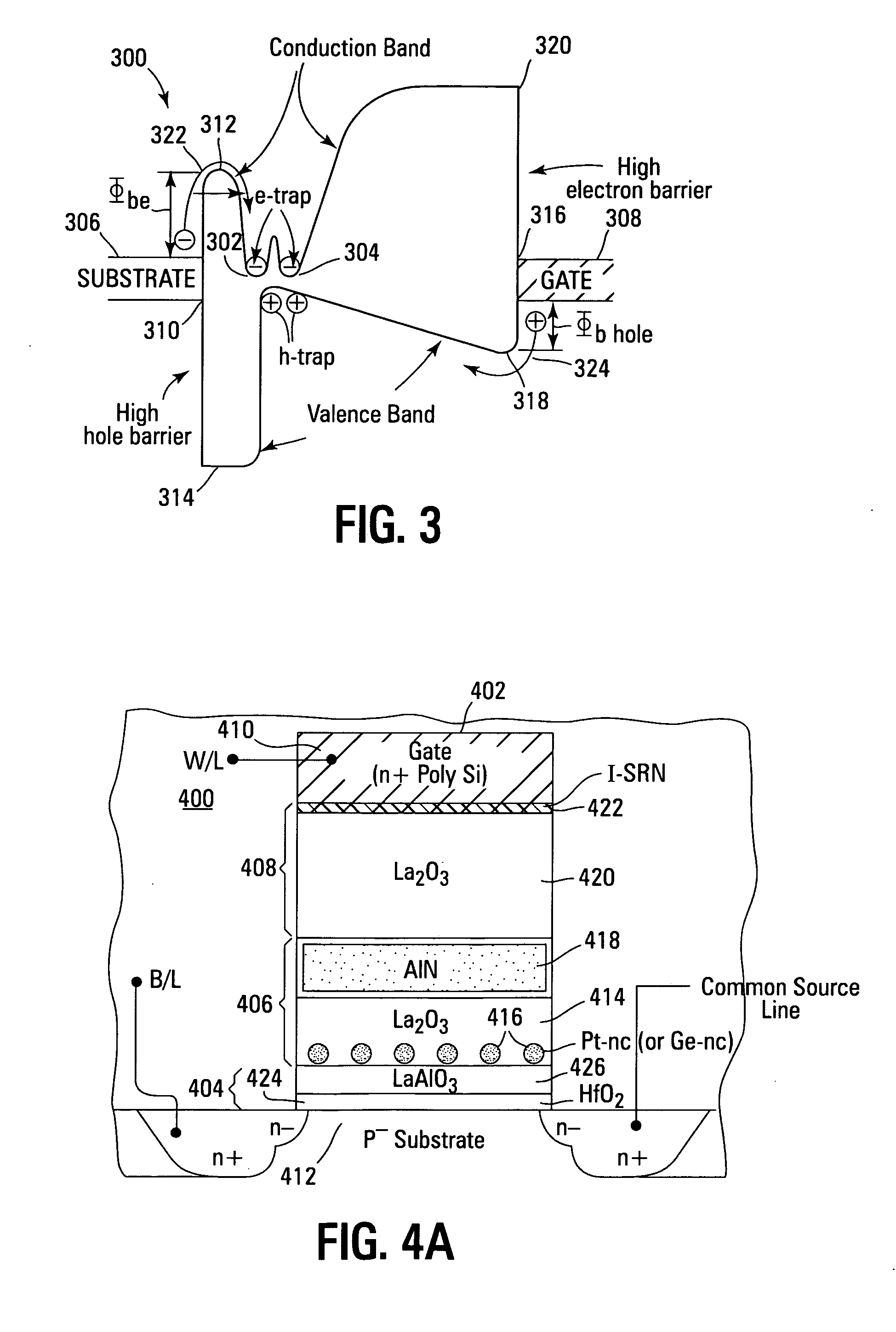

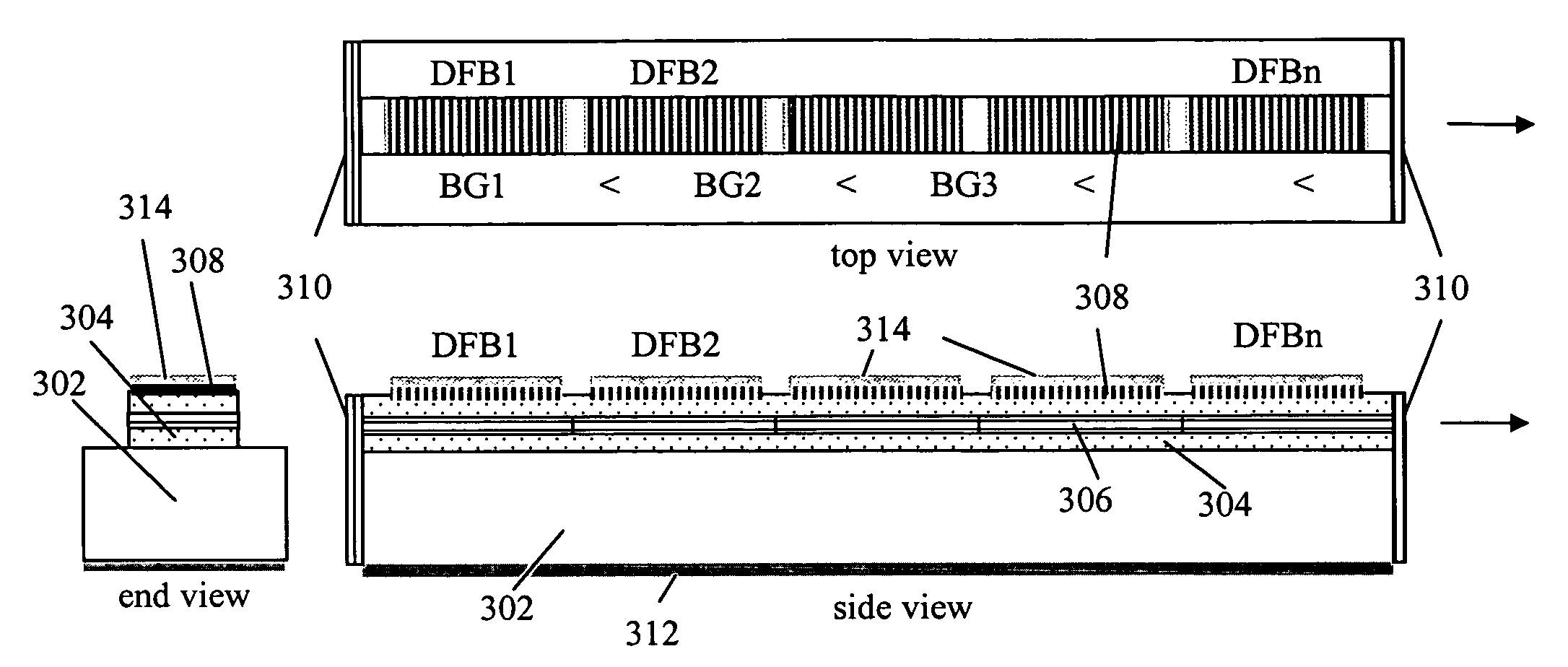

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

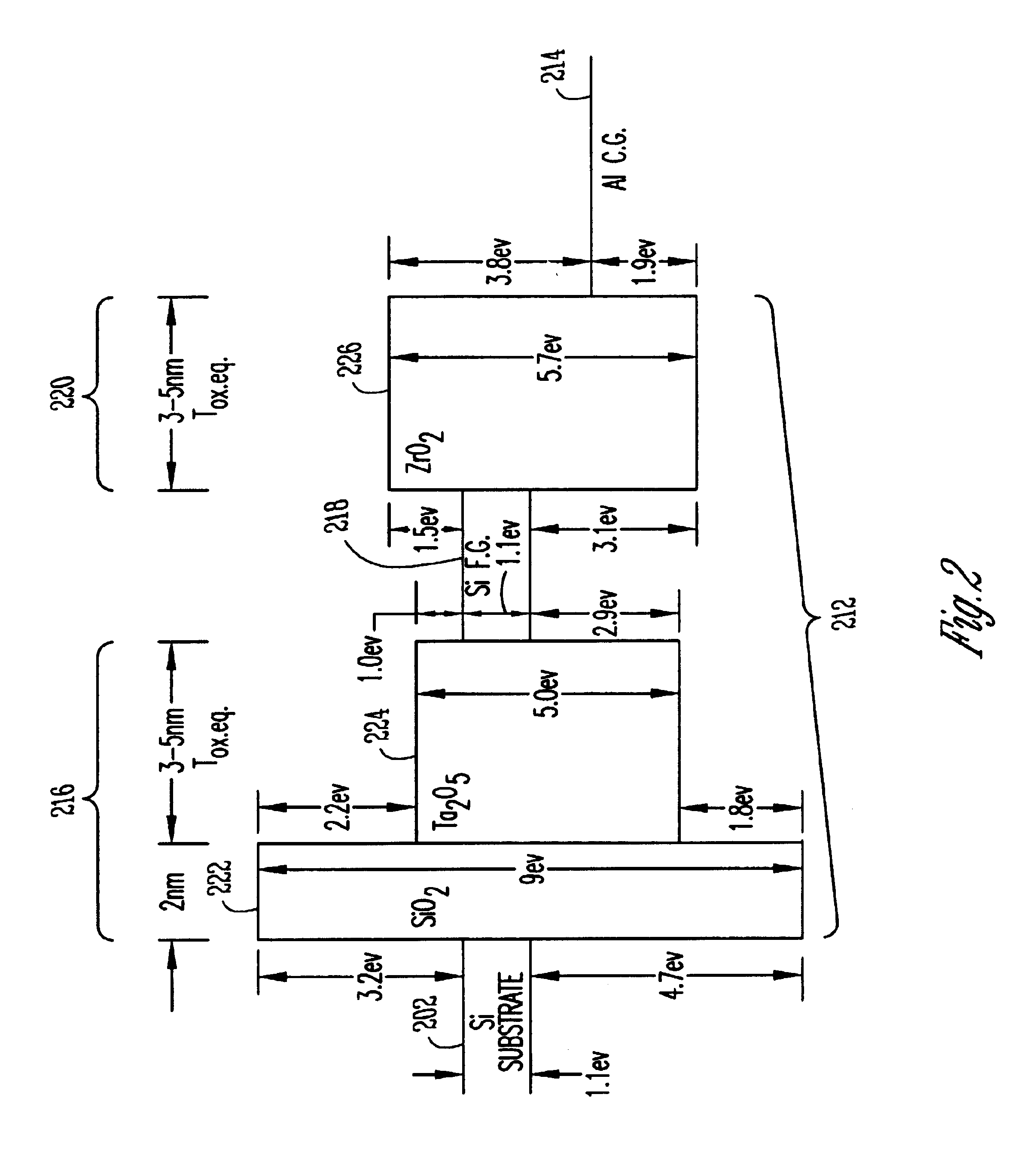

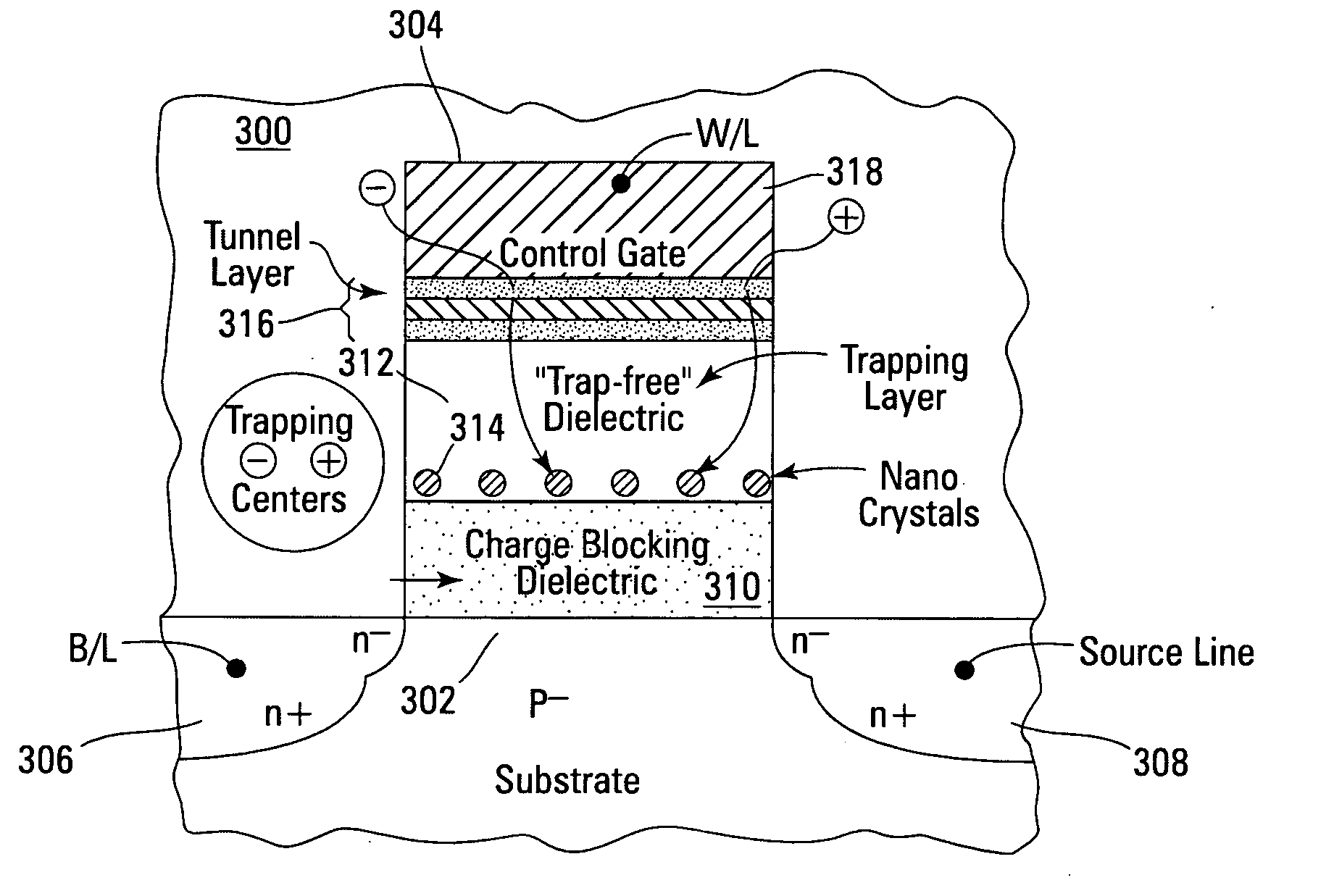

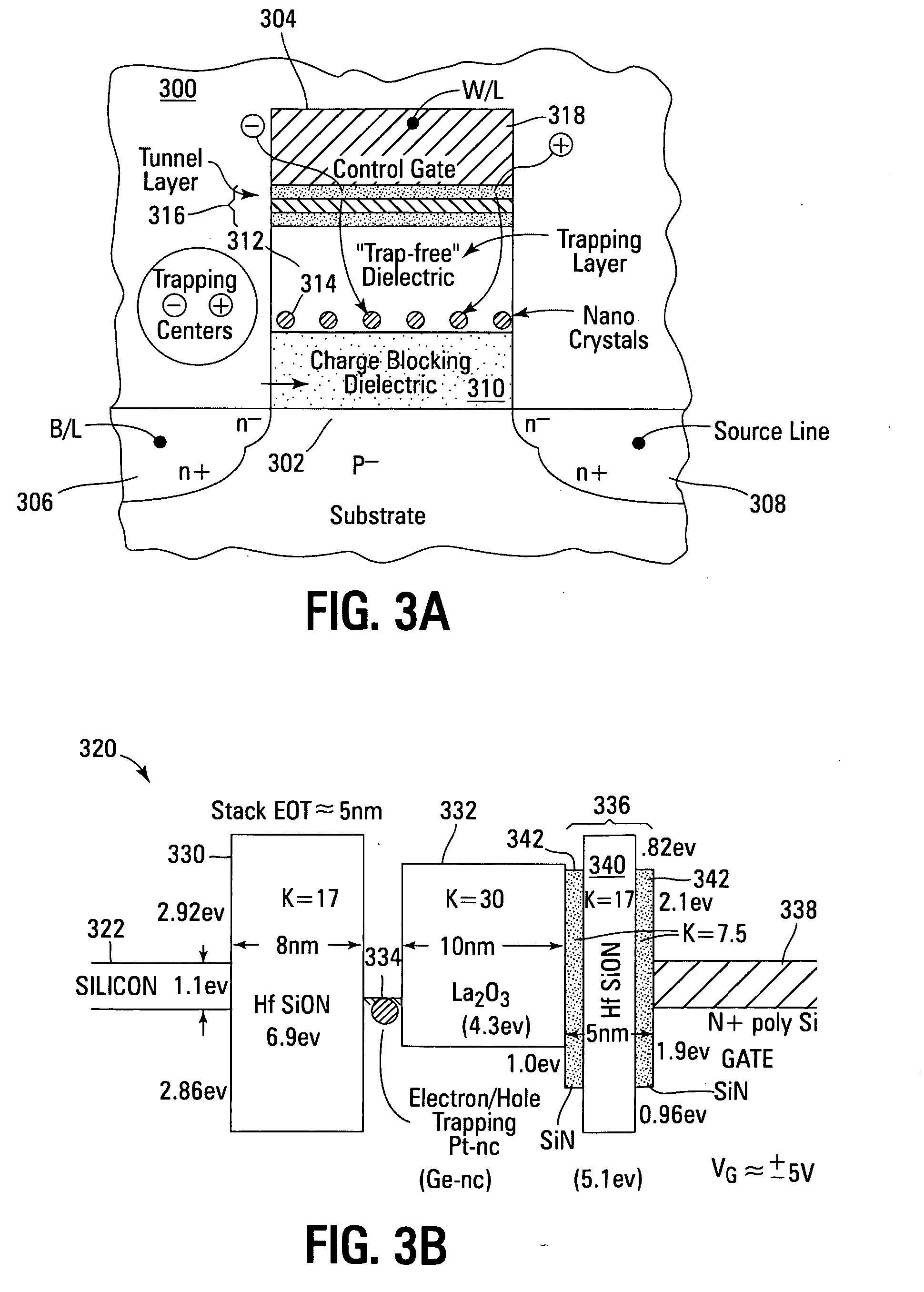

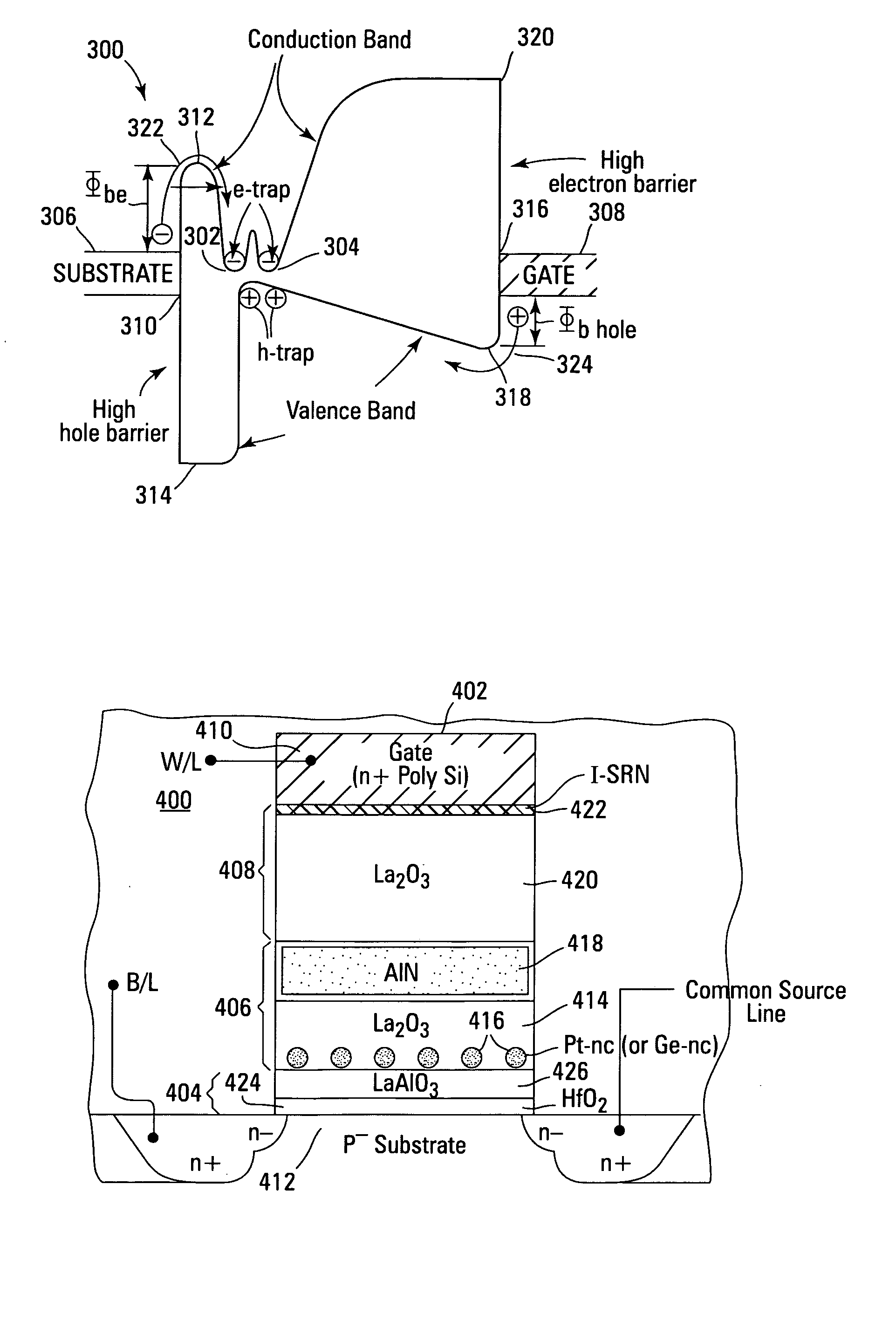

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

Charge trapping memory cell with high speed erase

InactiveUS20090039414A1Eliminates hole tunneling barrierEffectively preventing charge leakageSolid-state devicesRead-only memoriesDielectricTrapping

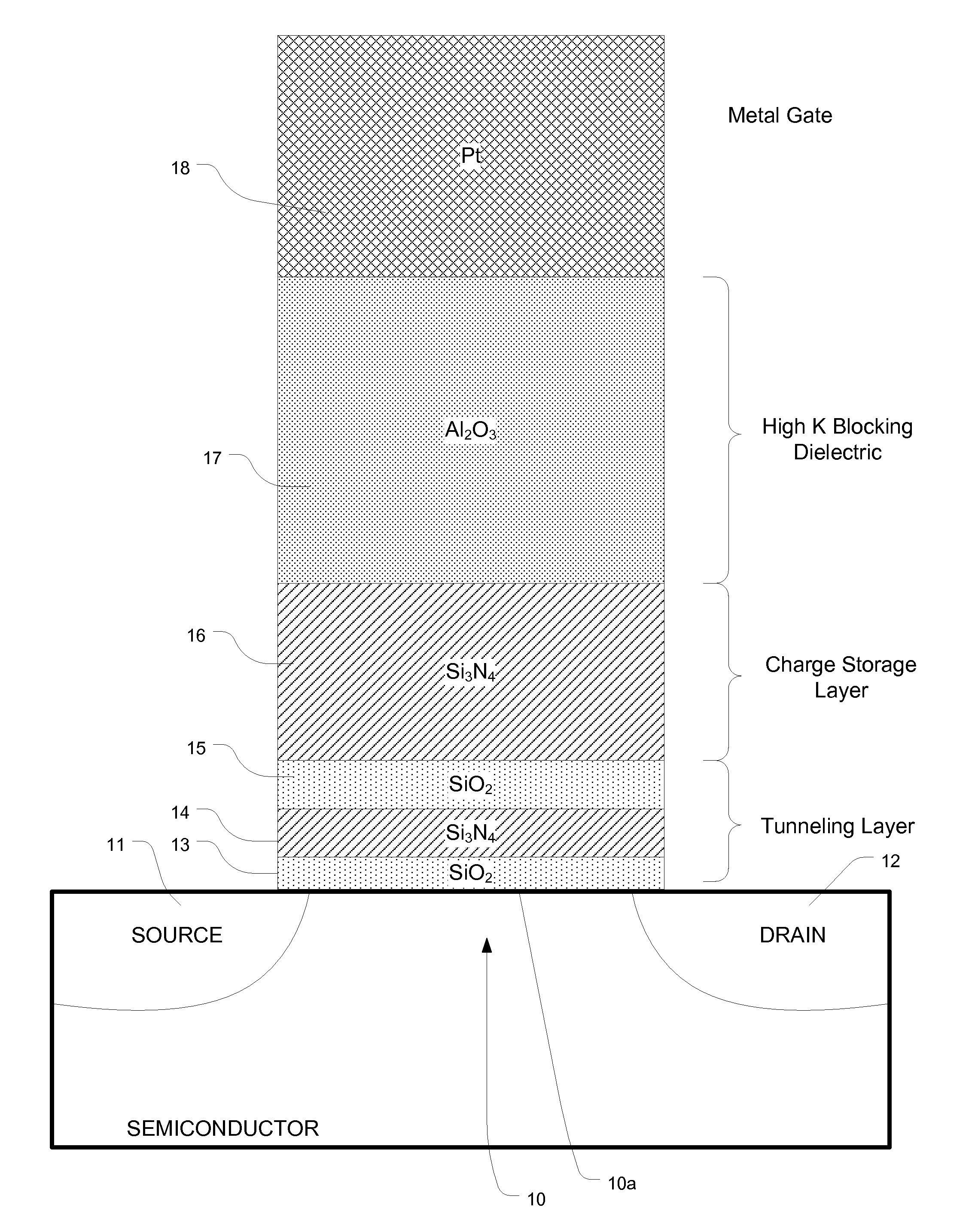

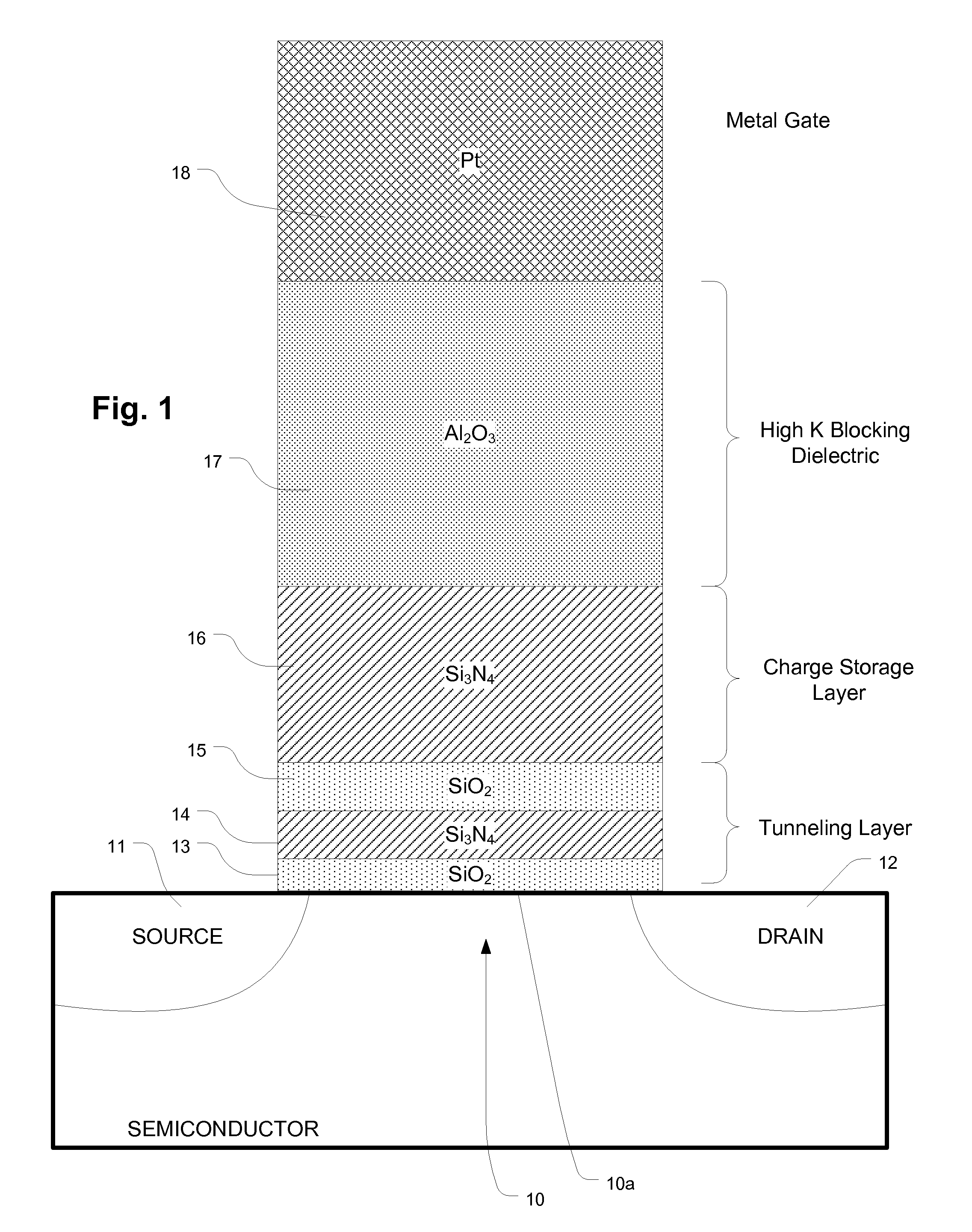

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a metal or metal compound gate, such as a platinum gate, by a blocking layer of material having a high dielectric constant, such as aluminum oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric. Fast program and erase speeds with memory window as great as 7 V are achieved.

Owner:MACRONIX INT CO LTD

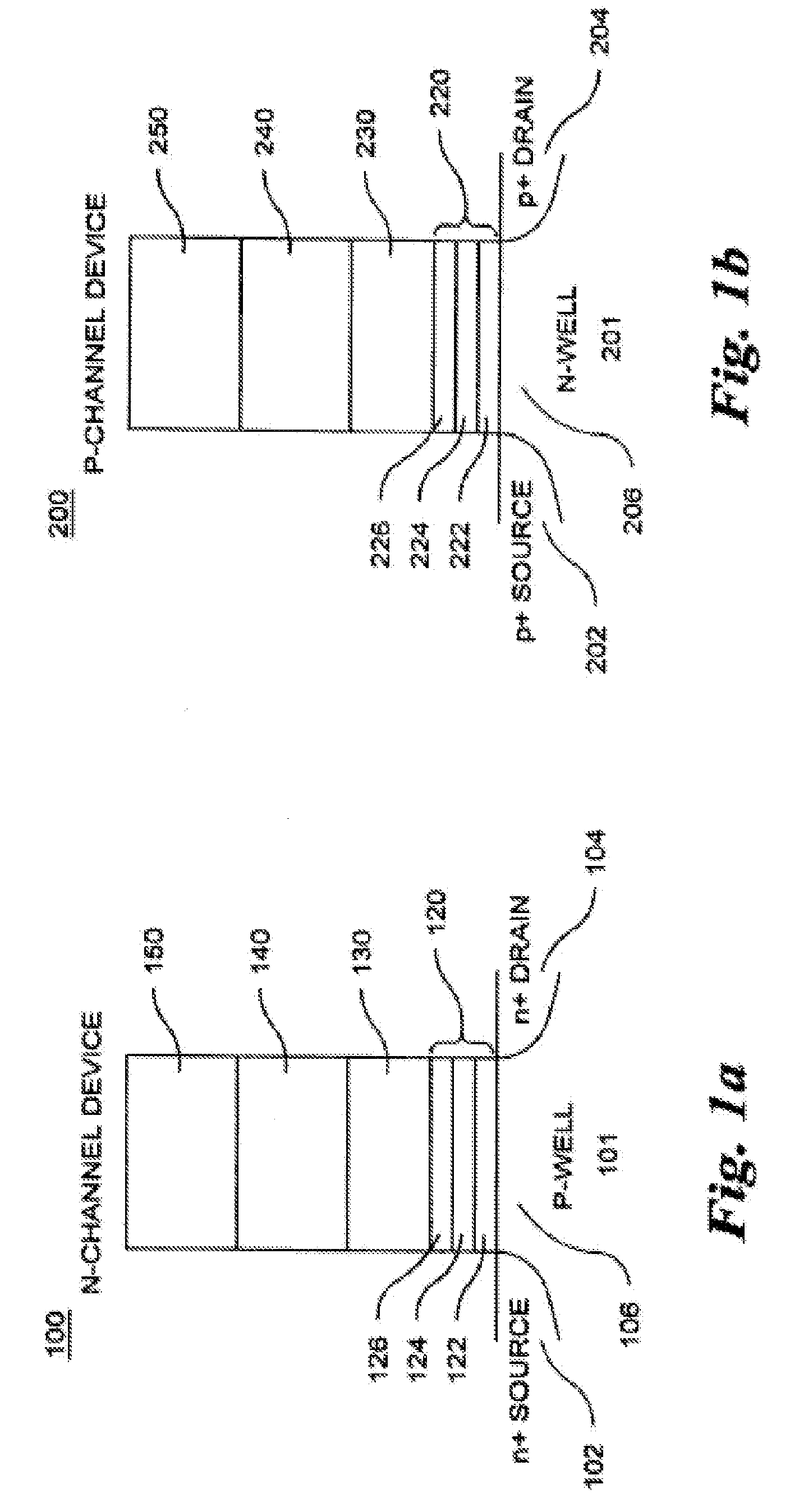

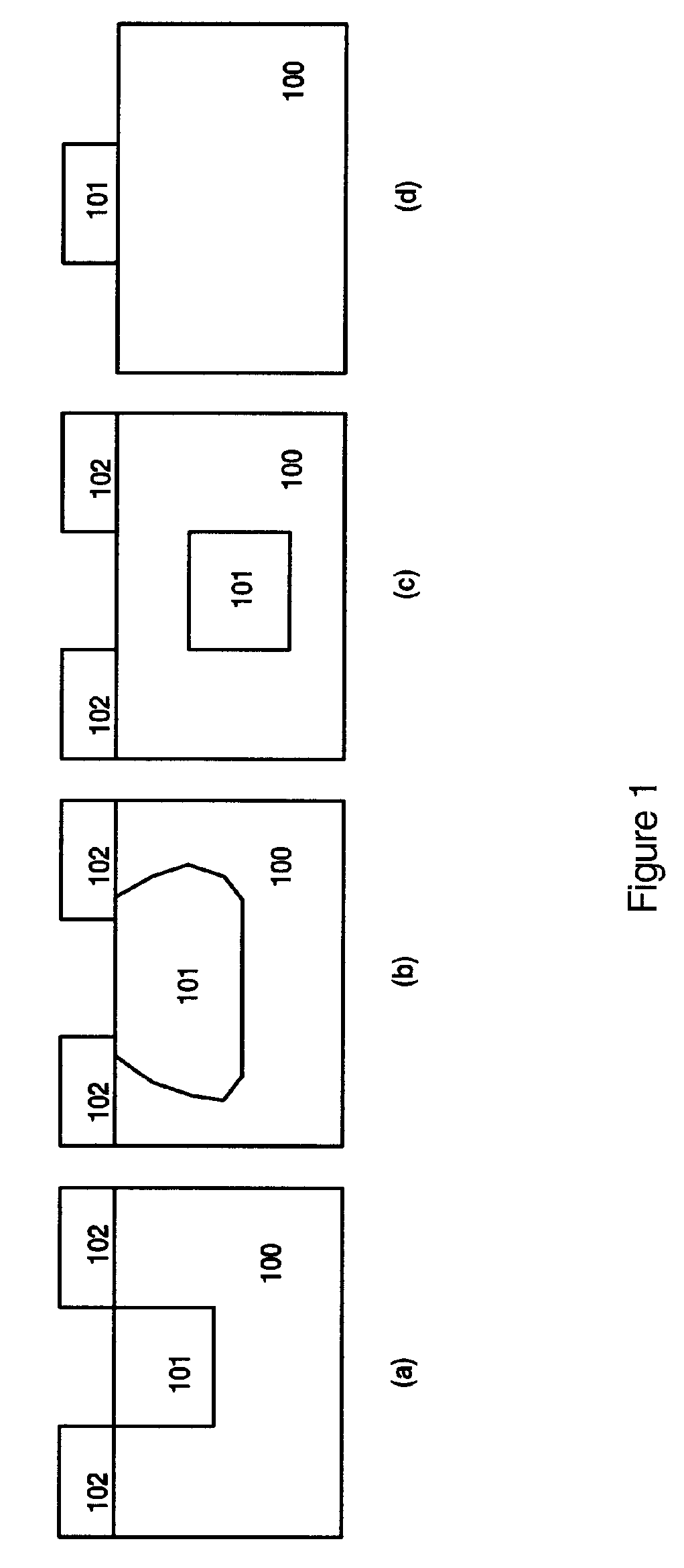

Method of fabricating CMOS devices having a single work function gate electrode by band gap engineering and article made thereby

InactiveUS20070069302A1Lower threshold voltageEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingCMOSWork function

A method utilizing a common gate electrode material with a single work function for both the pMOS and nMOS transistors where the magnitude of the transistor threshold voltages is modified by semiconductor band engineering and article made thereby.

Owner:INTEL CORP

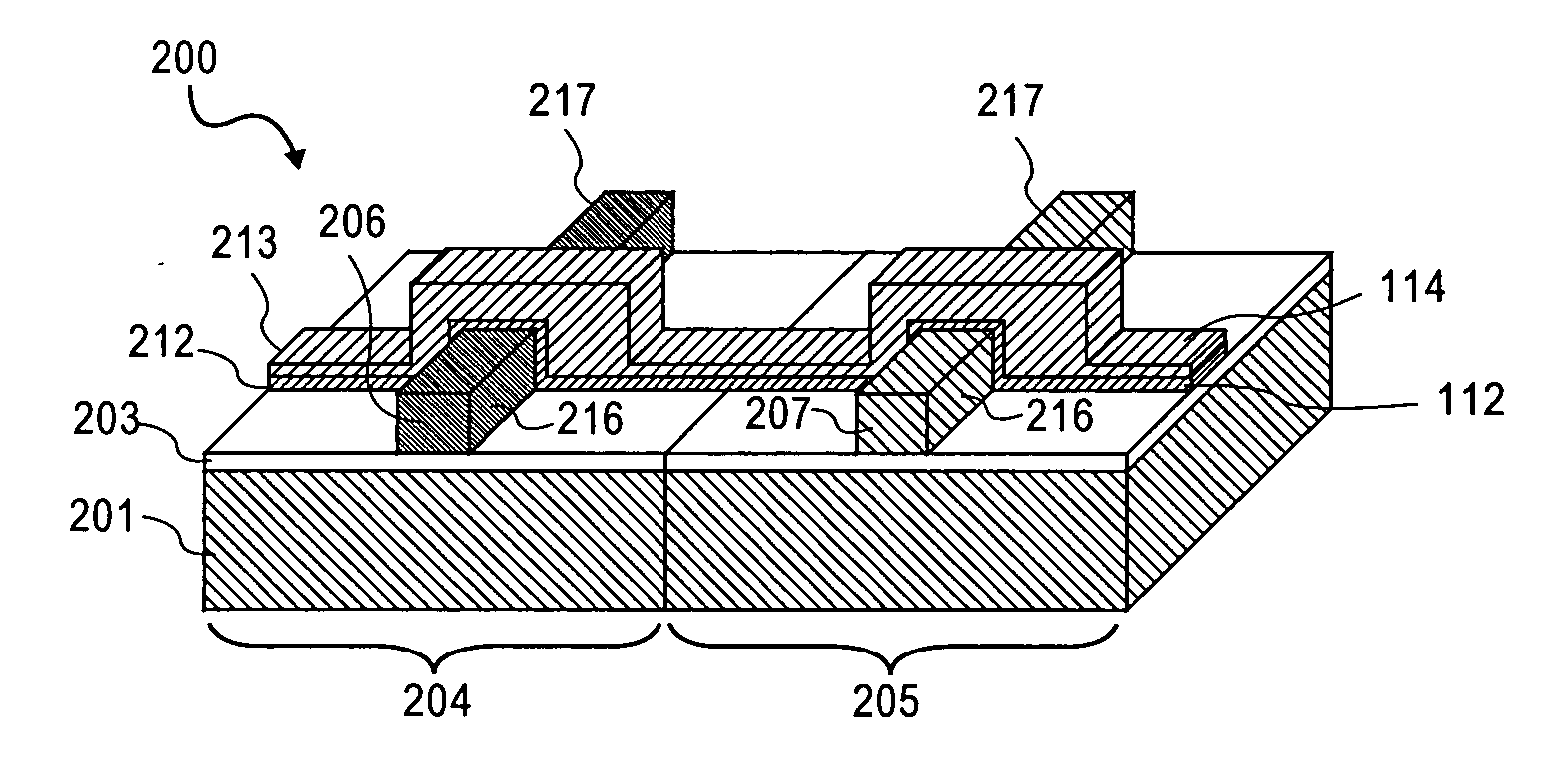

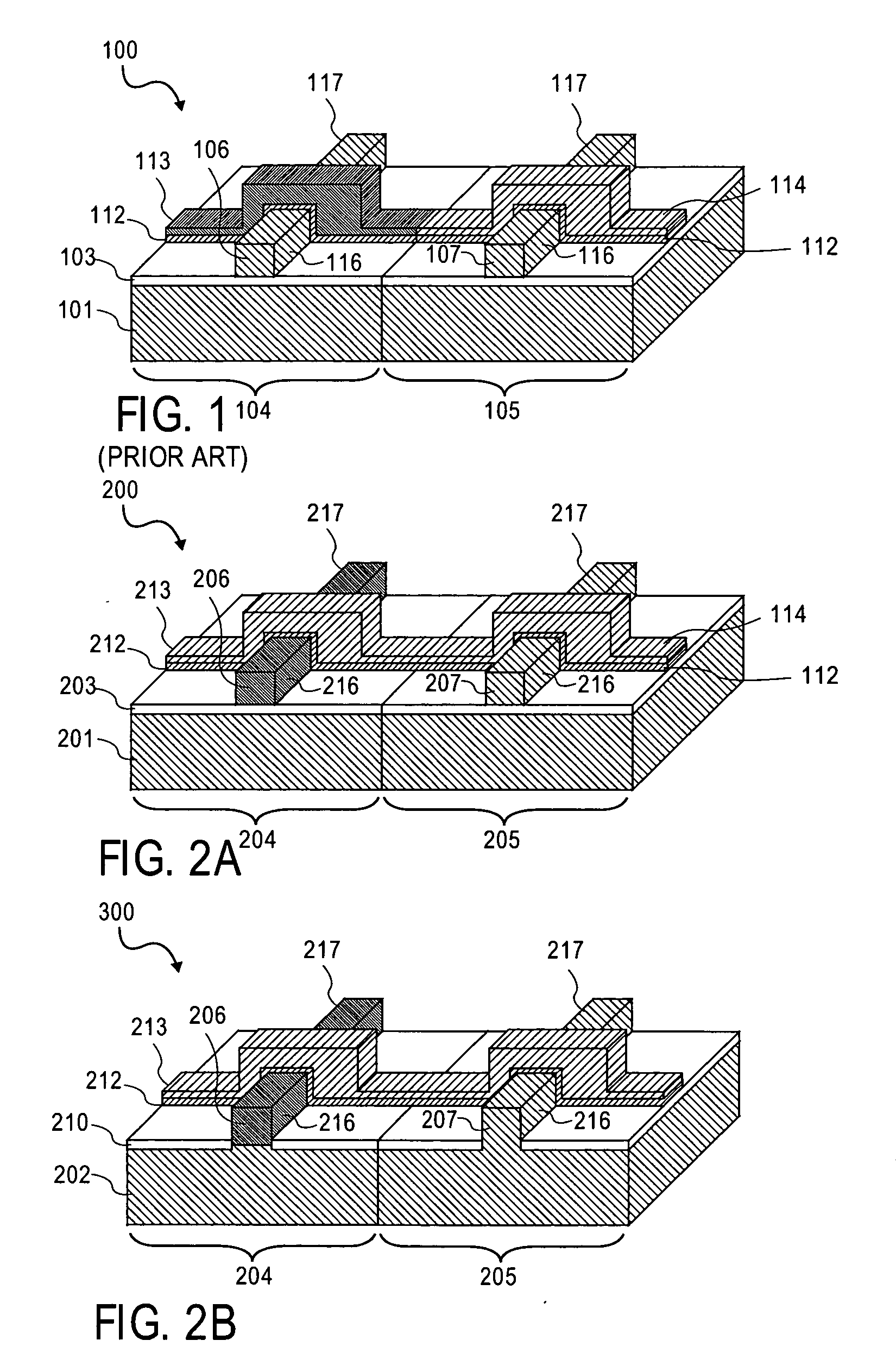

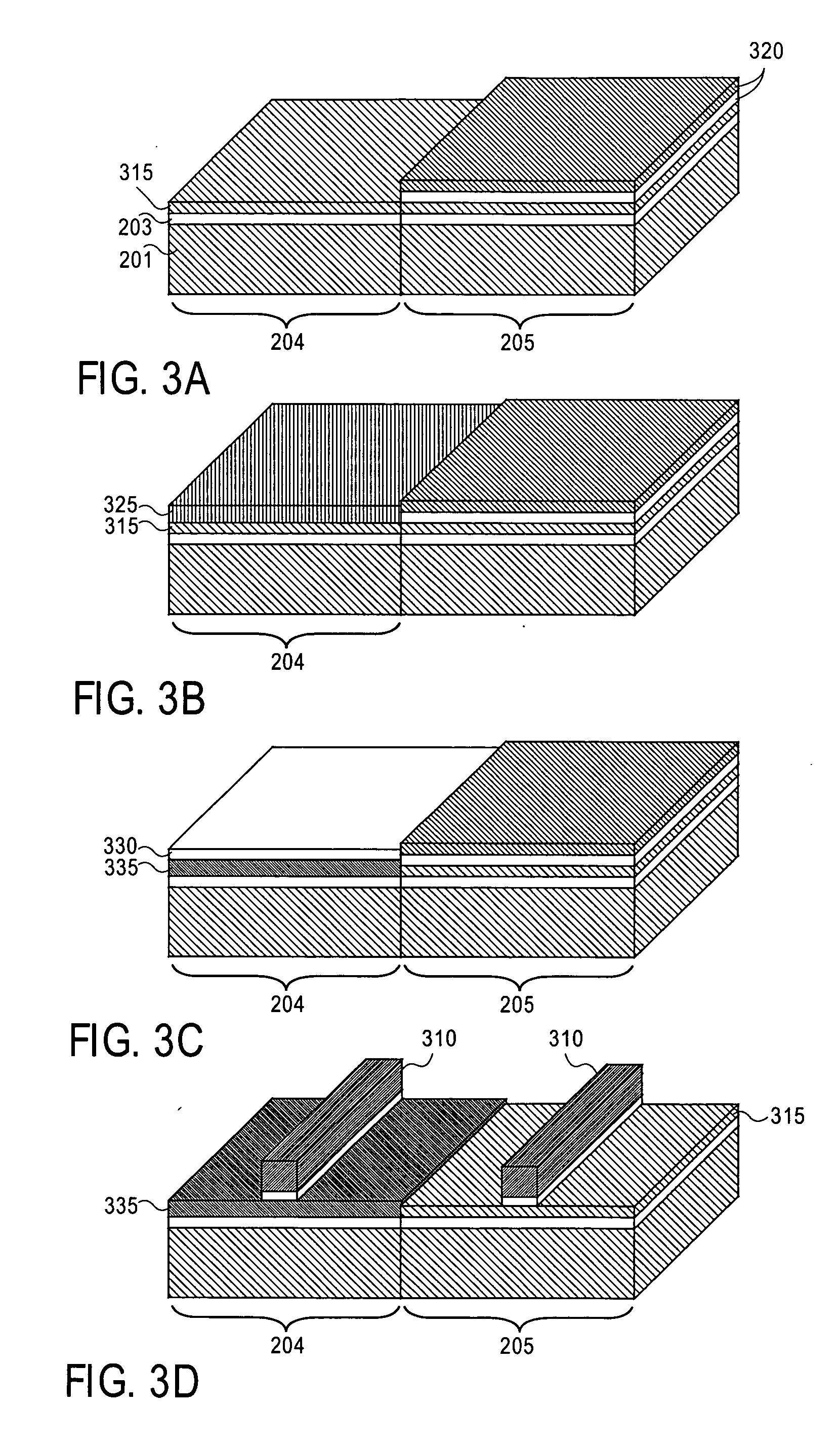

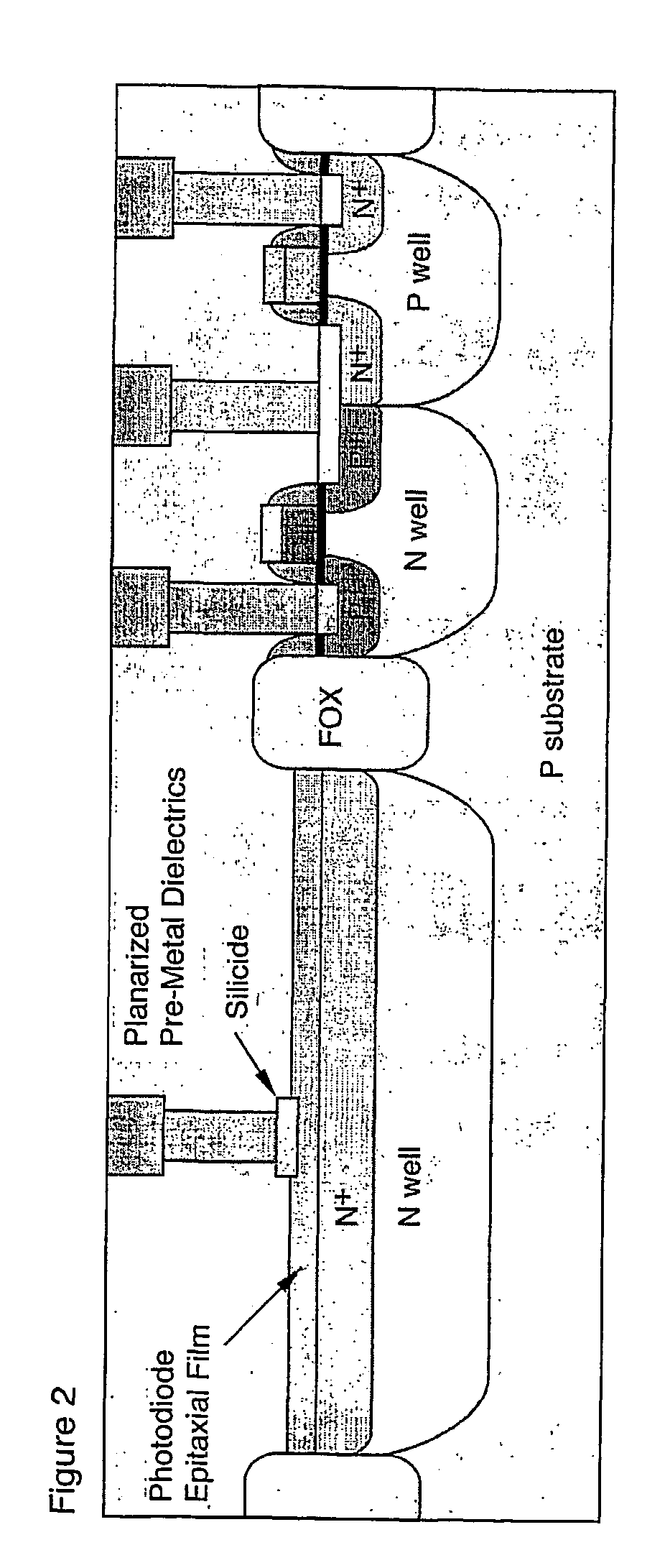

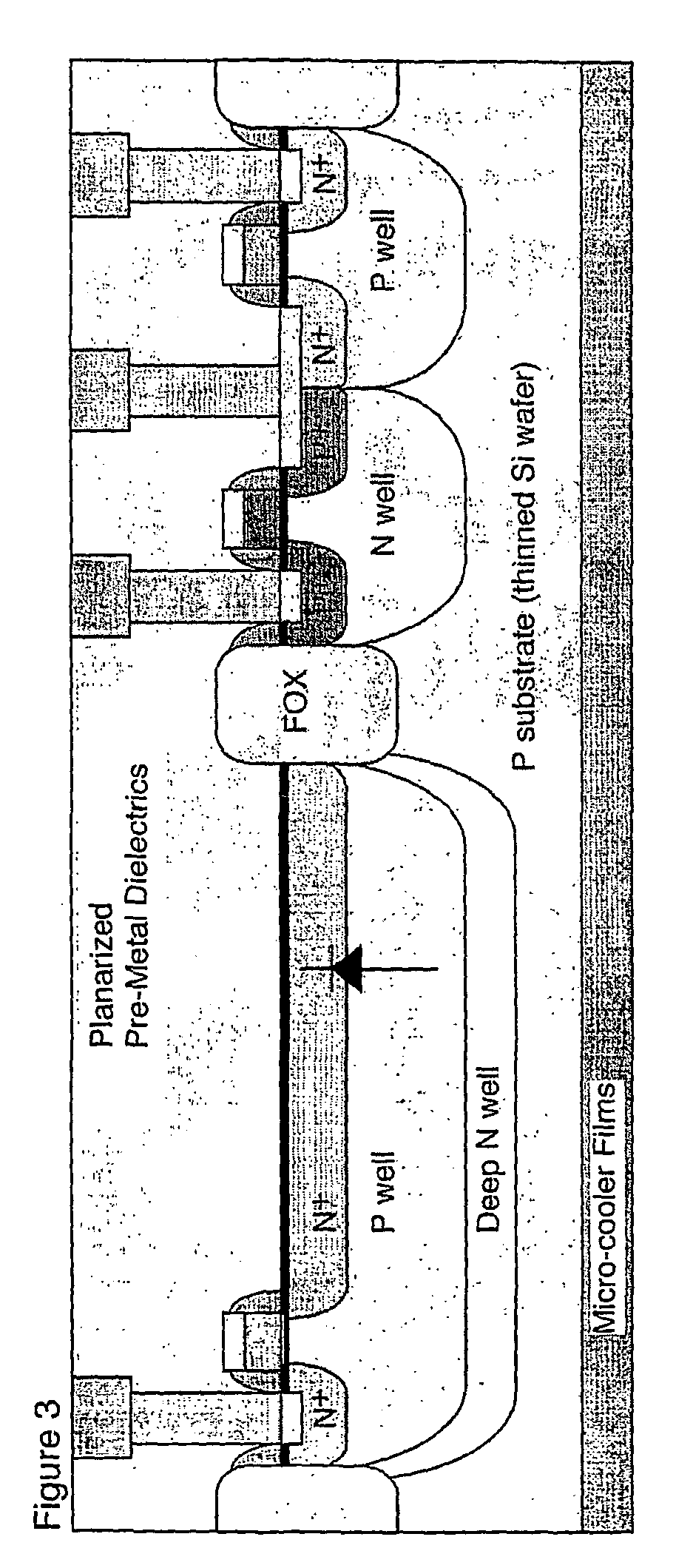

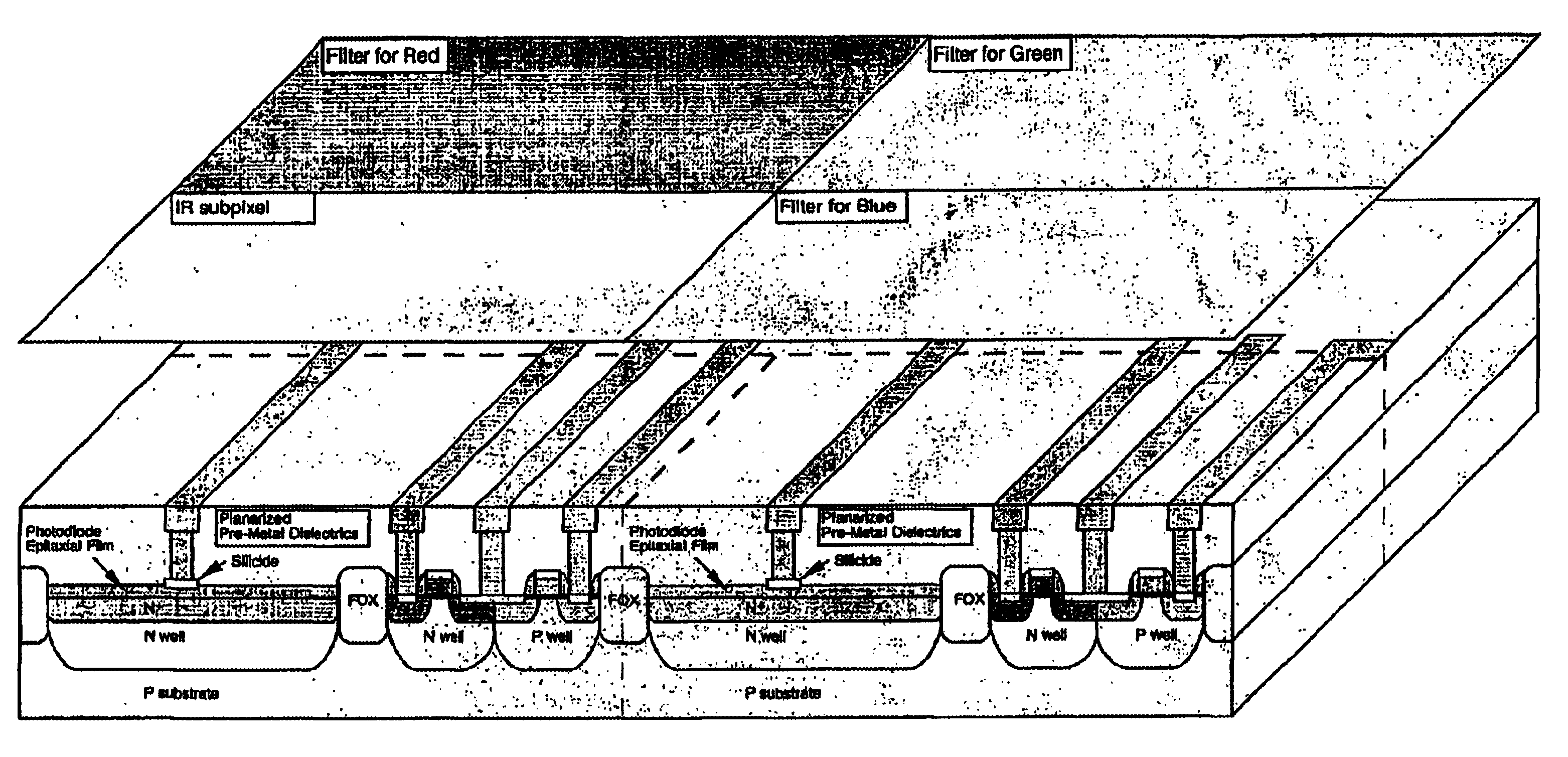

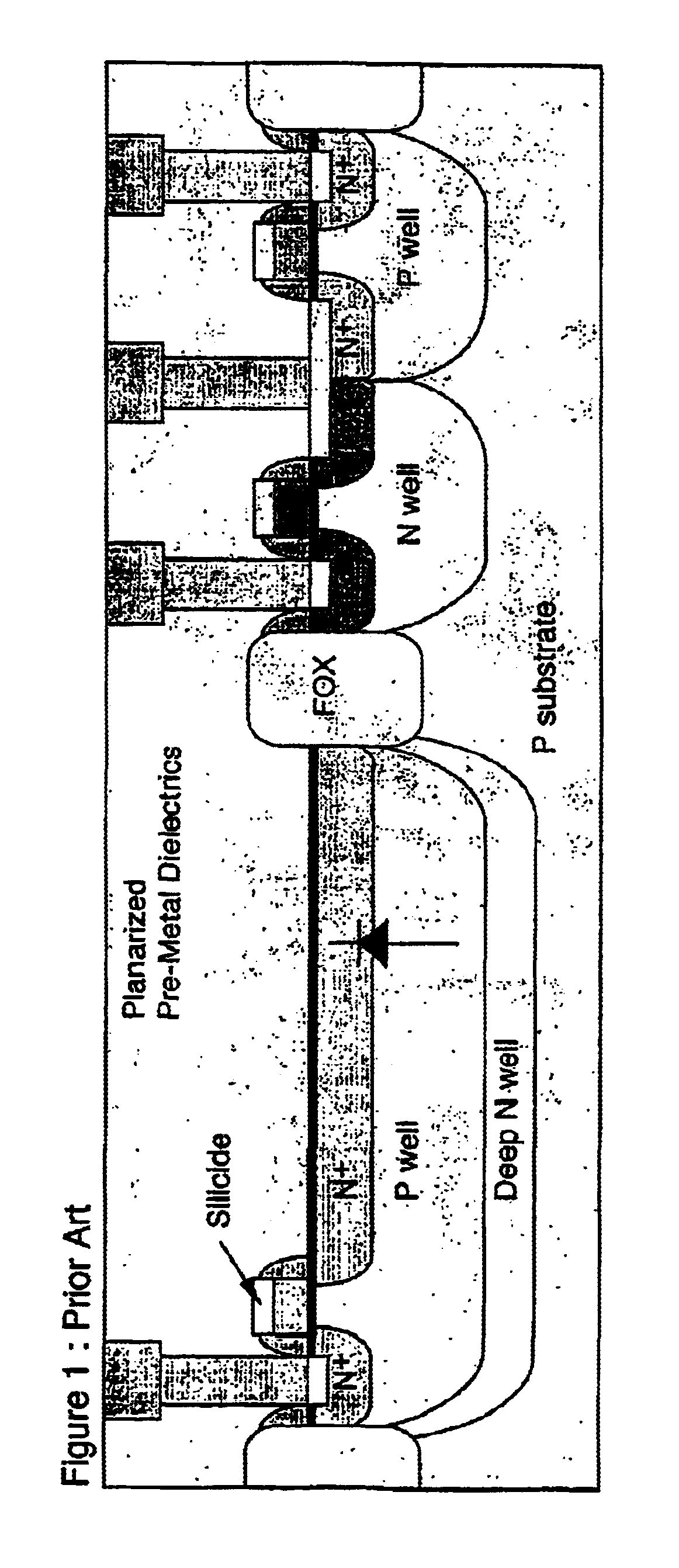

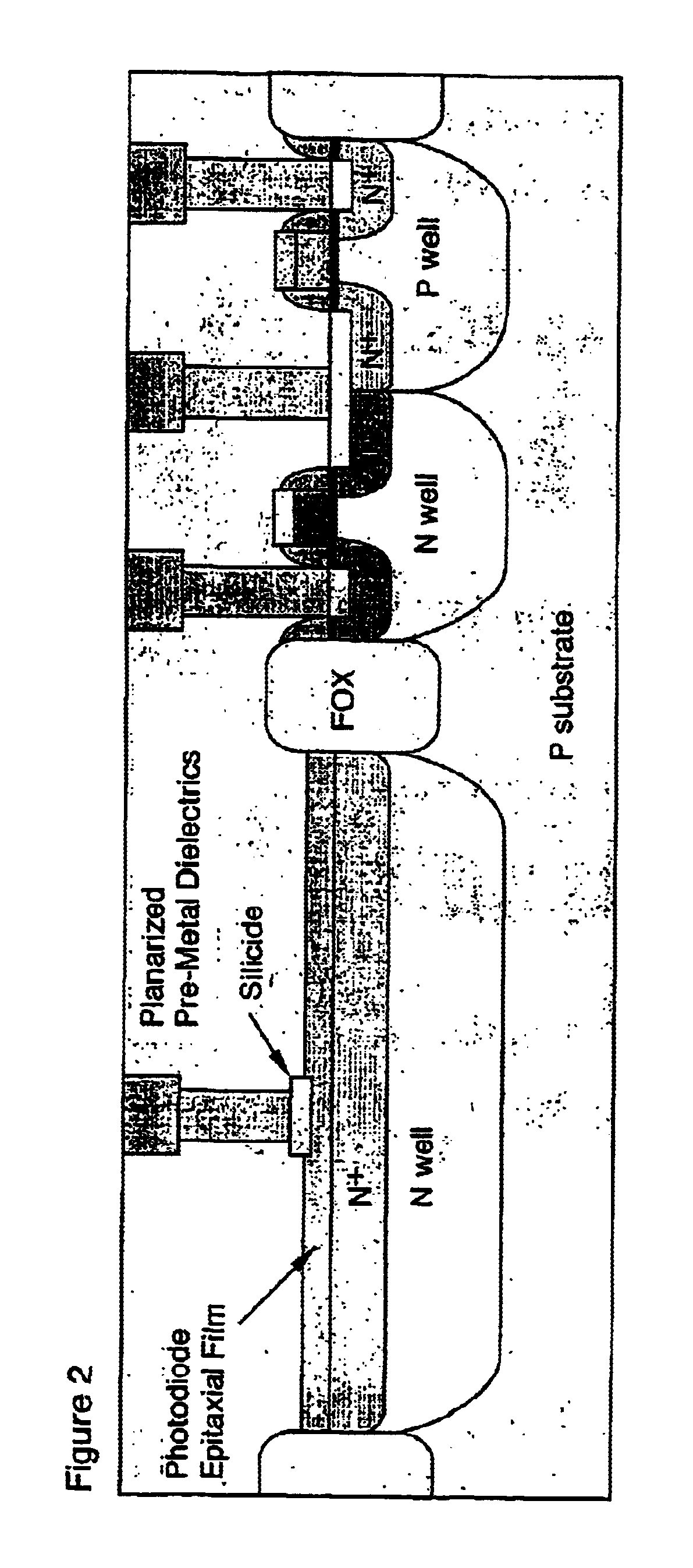

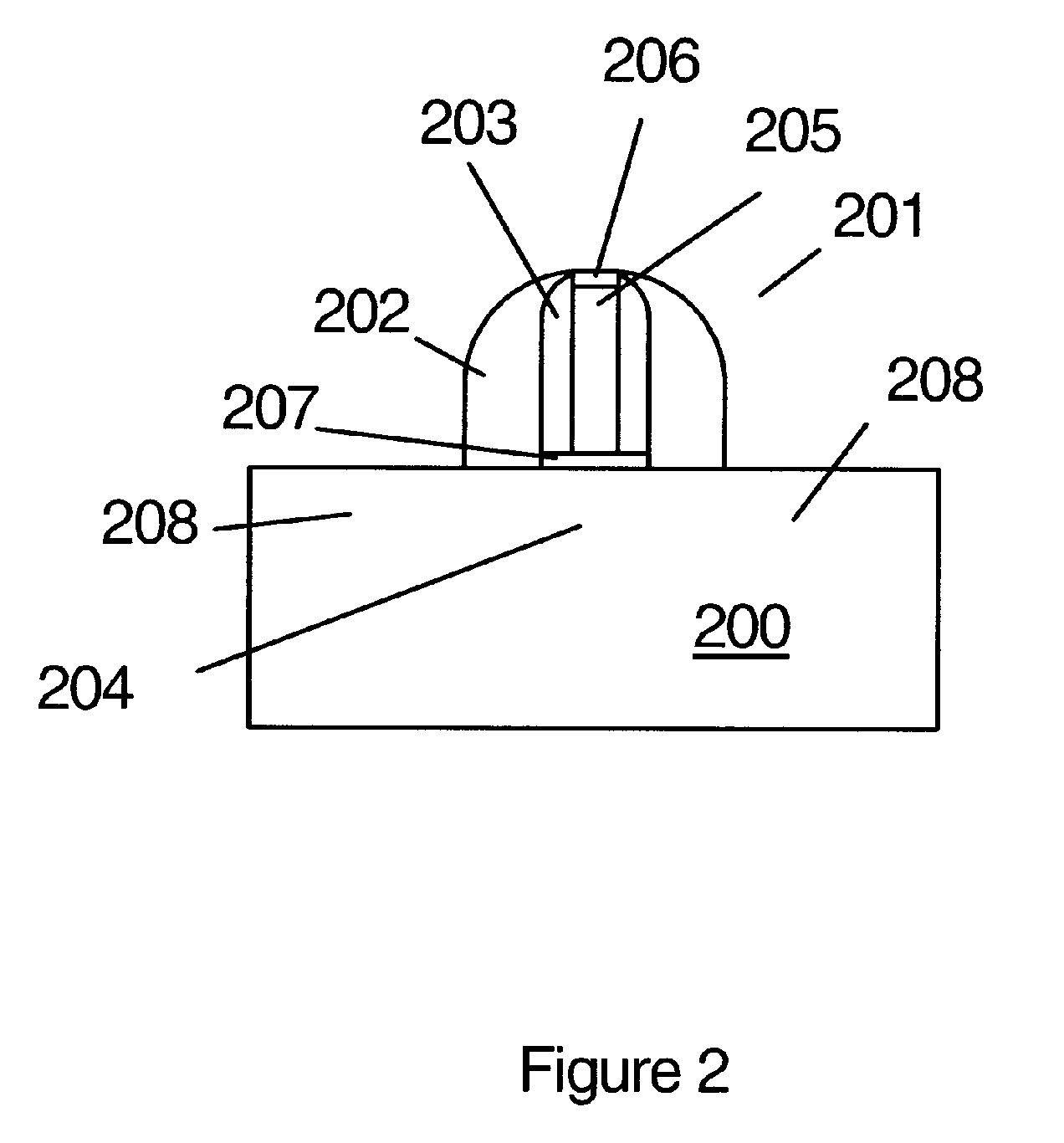

Method of fabricating heterojunction photodiodes integrated with cmos

A method in which thin-film p-i-n heterojunction photodiodes are formed by selective epitaxial growth / deposition on pre-designated active-area regions of standard CMOS devices. The thin-film p-i-n photodiodes are formed on active areas (for example n<+>-doped), and these are contacted at the bottom (substrate) side by the "well contact" corresponding to that particular active area. There is no actual potential well since that particular active area has only one type of doping. The top of each photodiode has a separate contact formed thereon. The selective epitaxial growth of the p-i-n photodiodes is modular, in the sense that there is no need to change any of the steps developed for the "pure" CMOS process flow. Since the active region is epitaxially deposited, there is the possibility of forming sharp doping profiles and band-gap engineering during the epitaxial process, thereby optimizing several device parameters for higher performance. This new type of light sensor architecture, monolithically integrated with CMOS, decouples the photo-absorption active region from the MOSFETs, hence the bias applied to the photodiode can be independent from the bias between the source, drain, gate and substrate (well) of the MOSFETs.

Owner:QUANTUM SEMICON

High performance multi-level non-volatile memory

ActiveUS20070045711A1Increased device feature scalingEfficient erasureTransistorSemiconductor/solid-state device manufacturingCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize band engineered gate-stacks and multiple charge trapping layers allowing a multiple trapping site gate-insulator stack memory cell that utilizes a band engineered direct tunneling or crested barrier tunnel layer and charge blocking layer for high speed programming / erasure. Charge retention is enhanced by utilization of nano-crystals and / or bulk trapping materials in a composite non-conductive trapping layer and a high K dielectric insulating layers. The band-gap engineered gate-stack with asymmetric direct tunneling or crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage high speed tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. Memory cell embodiments of the present invention allow multiple levels of bit storage in a memory cell through multiple charge centroids and / or multiple threshold voltage levels.

Owner:MICRON TECH INC

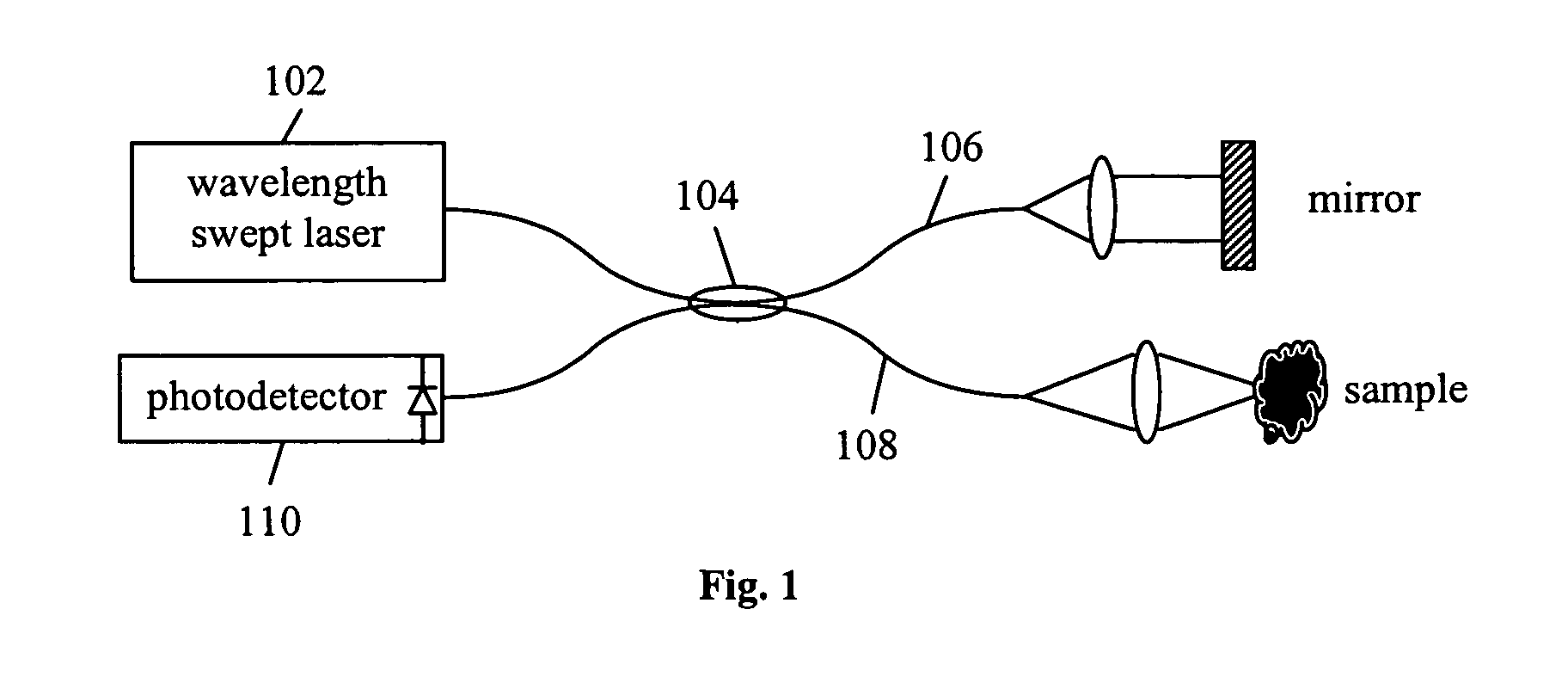

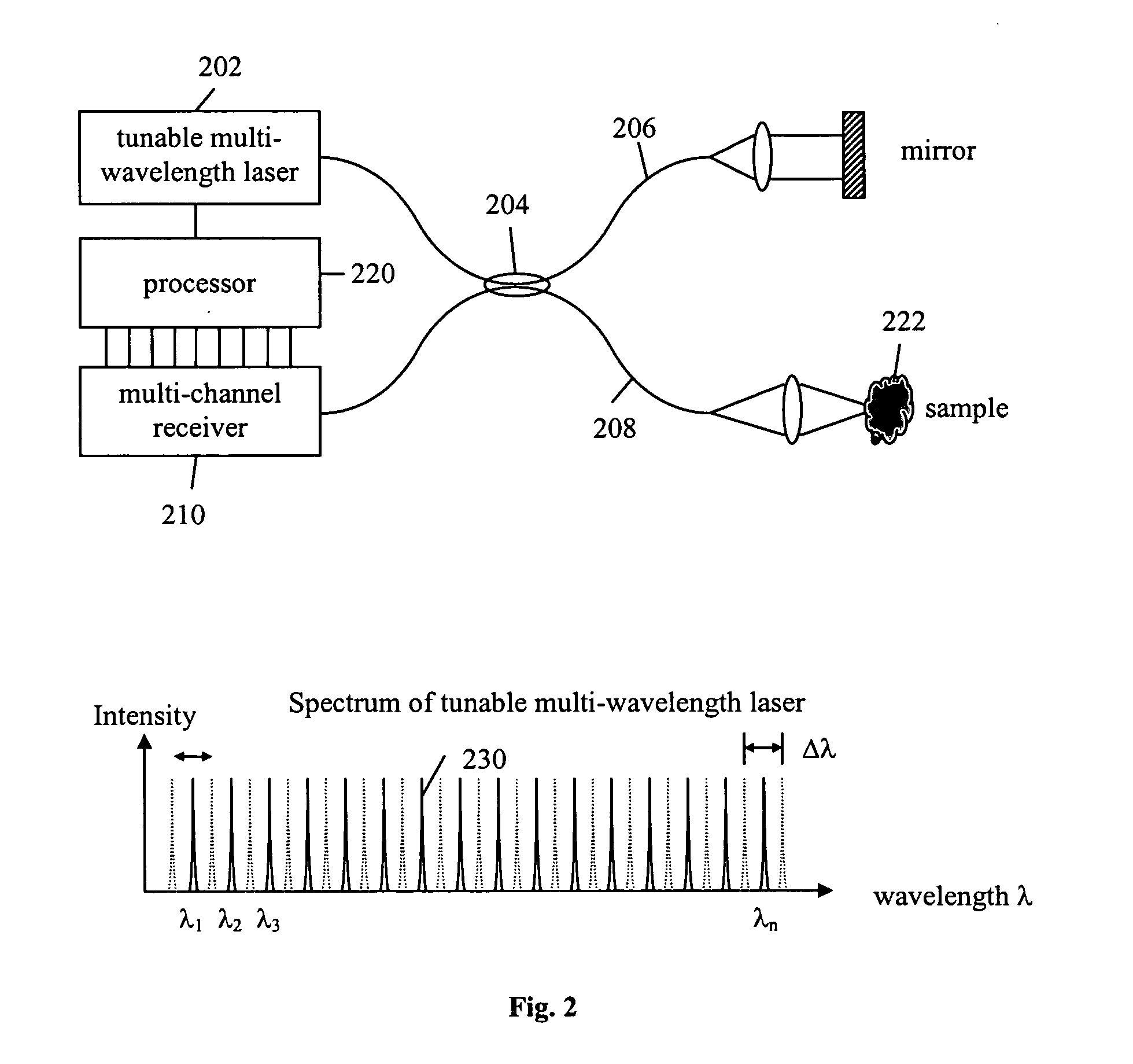

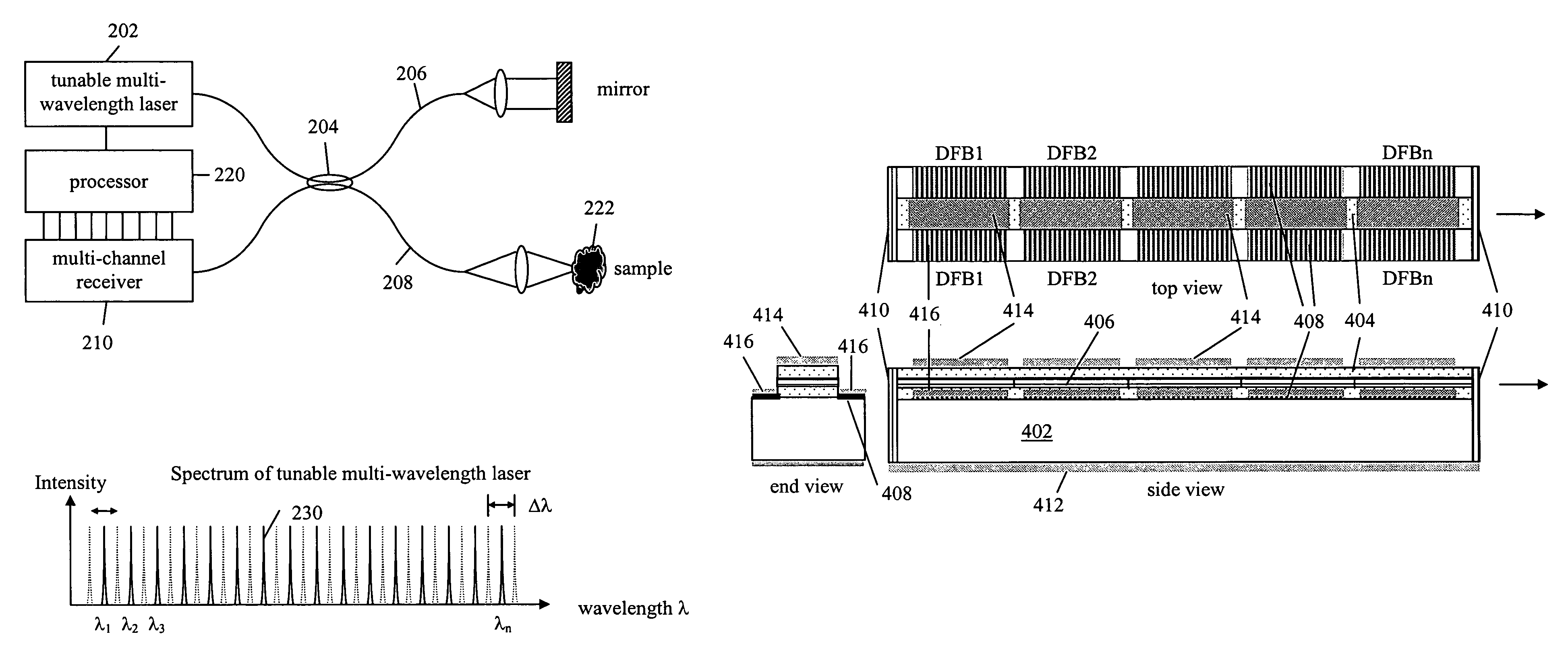

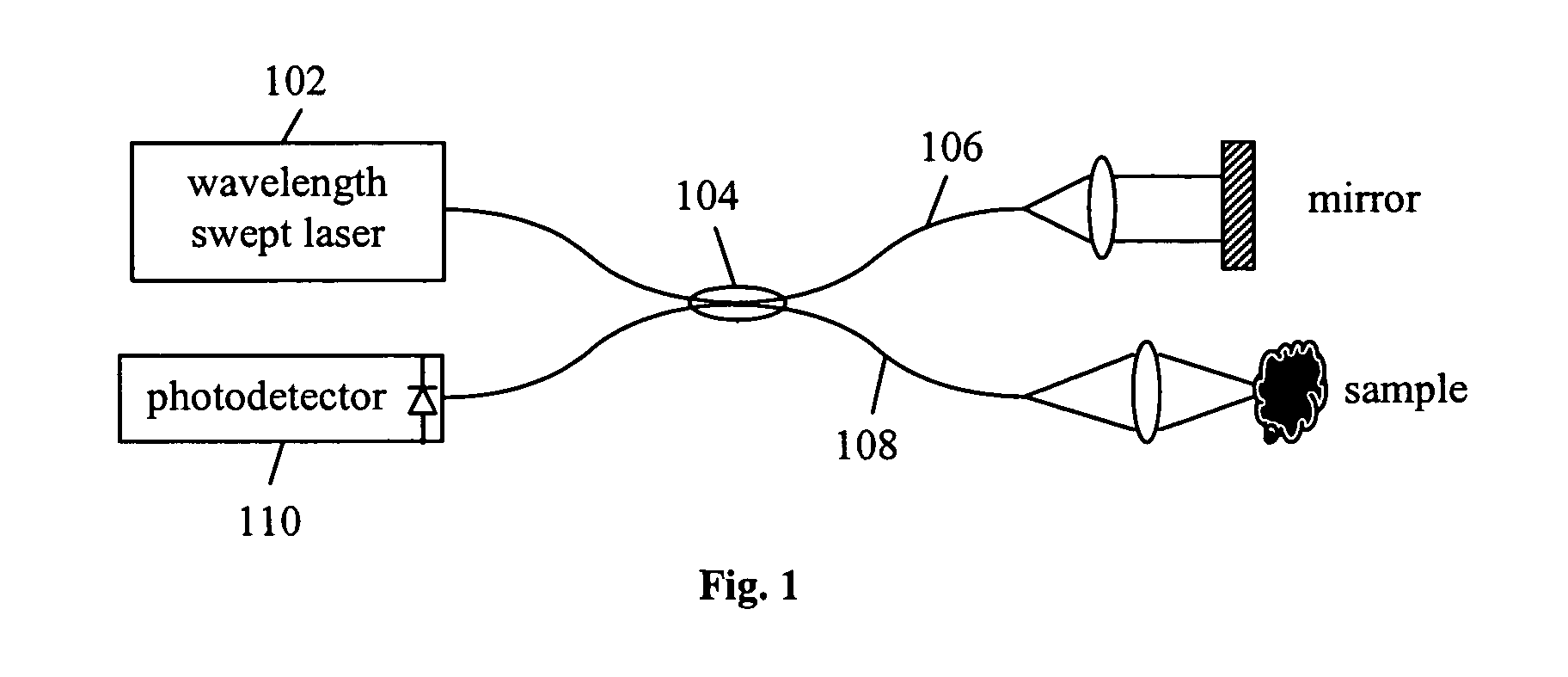

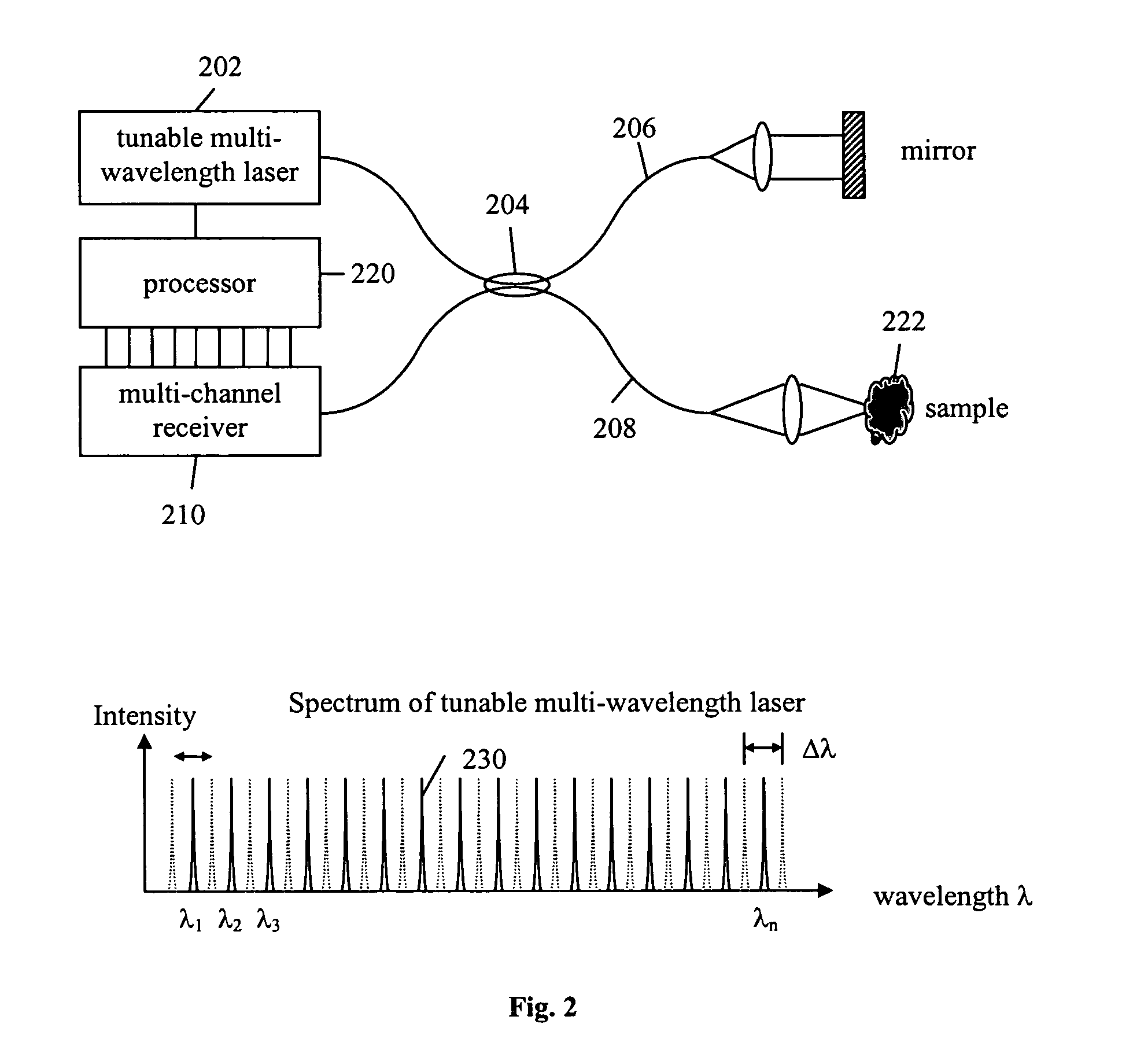

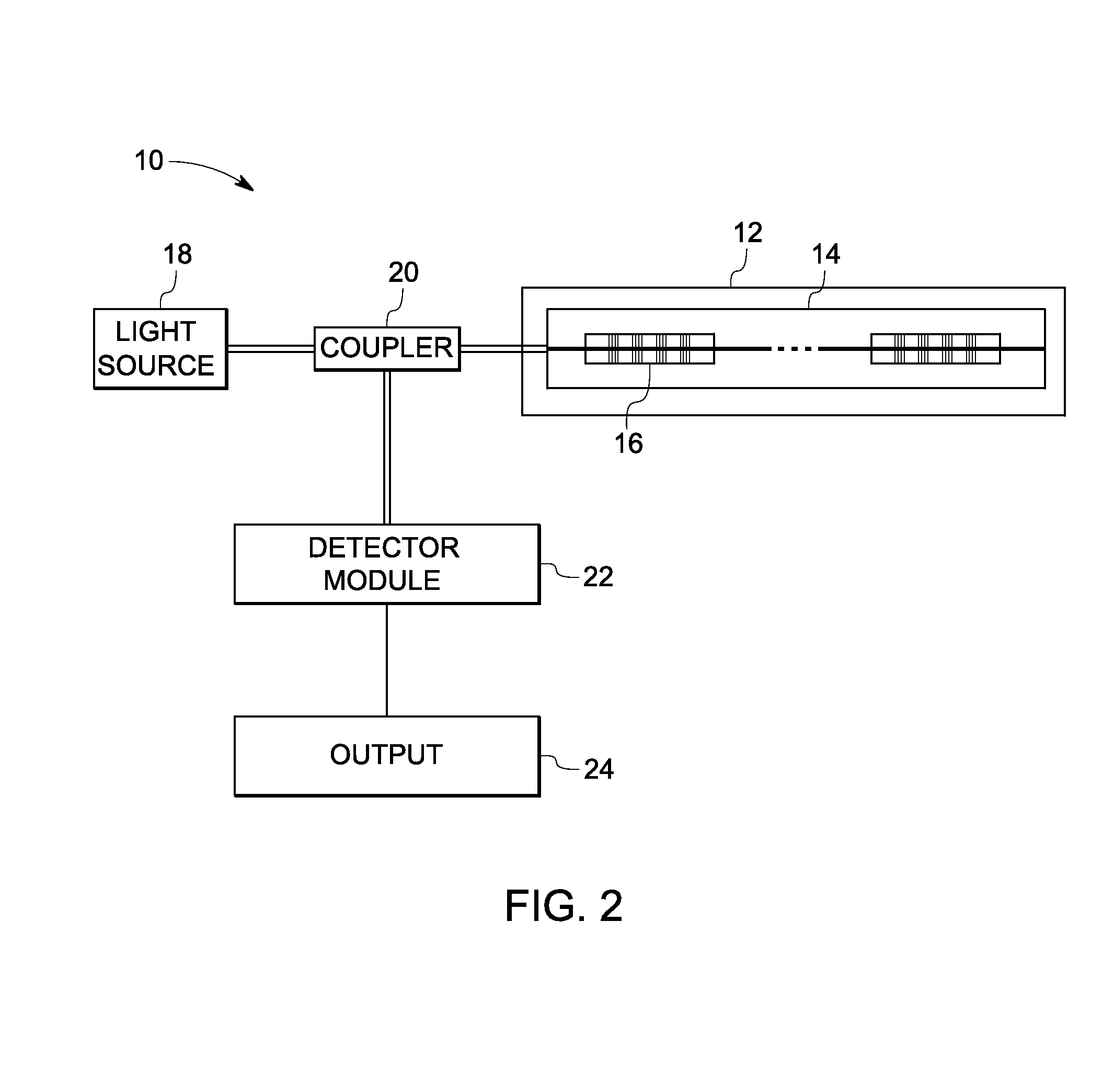

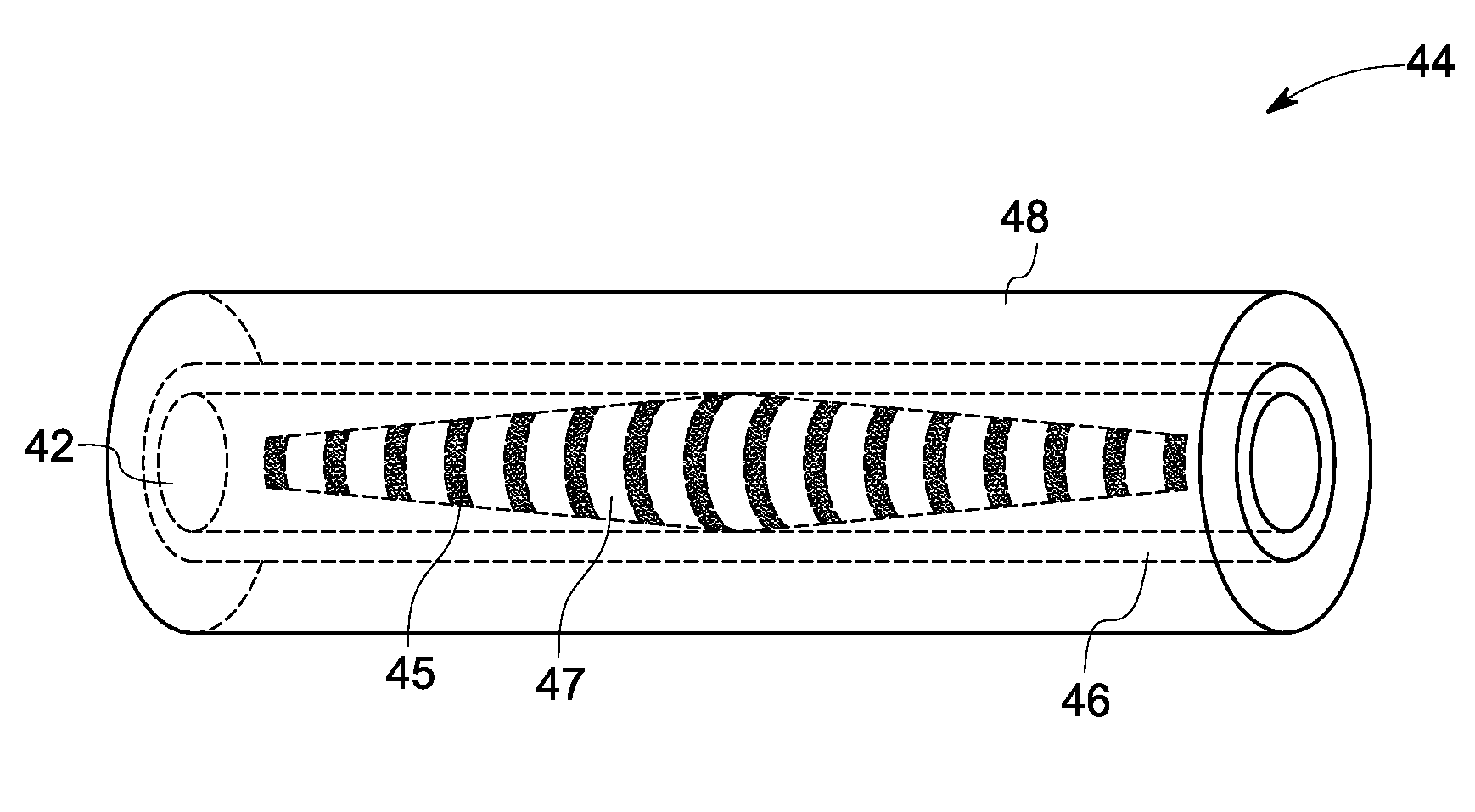

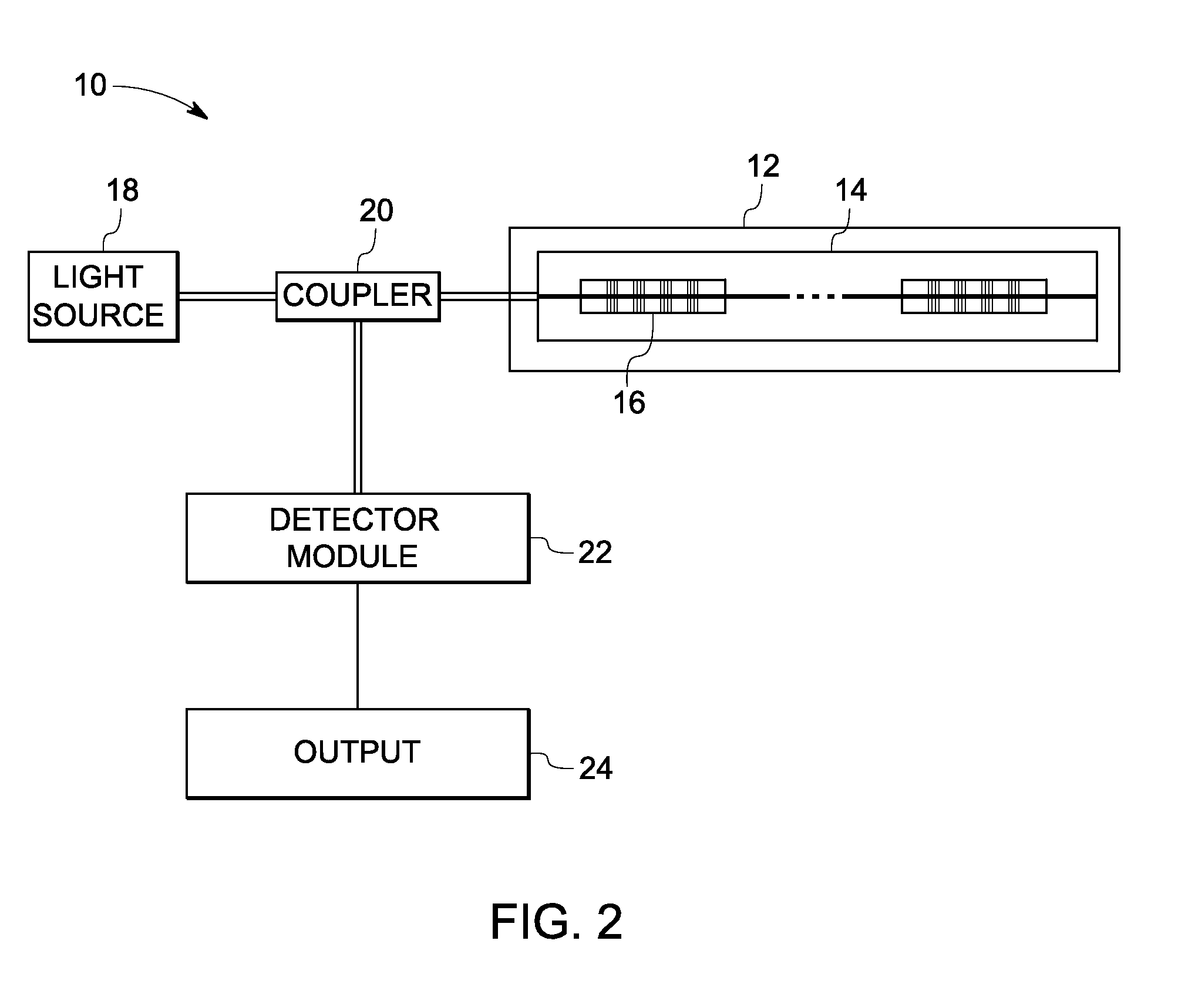

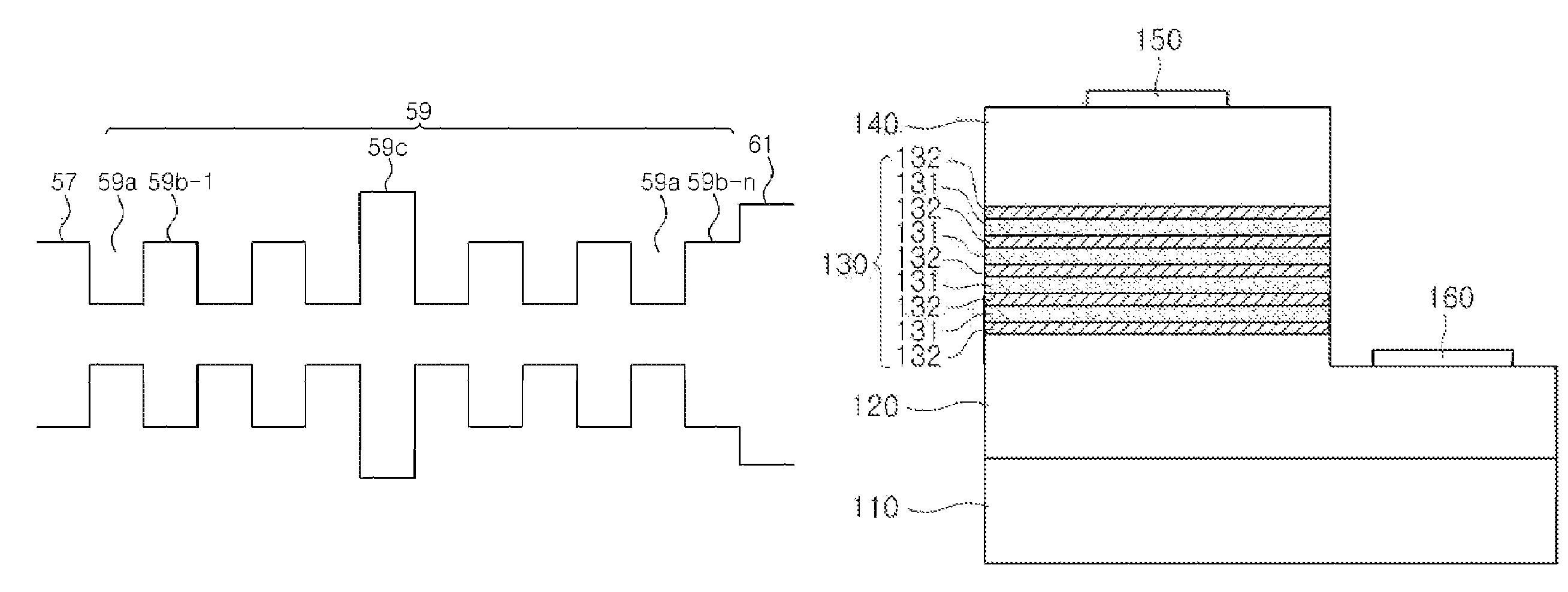

Light source for swept source optical coherence tomography based on cascaded distributed feedback lasers with engineered band gaps

ActiveUS20080037608A1Laser detailsLaser optical resonator constructionDistributed feedback laserGrating

The present invention is a tunable semiconductor laser for swept source optical coherence tomography, comprising a semiconductor substrate; a waveguide on top of said substrate with multiple sections of different band gap engineered multiple quantum wells (MQWs); a multiple of distributed feedback (DFB) gratings corresponding to each said band gap engineered MWQs, each DFB having a different Bragg grating period; and anti-reflection (AR) coating deposited on at least the laser emission facet of the laser to suppress the resonance of Fabry-Perot cavity modes. Each DFB MQWs section can be activated and tuned to lase across a fraction of the overall bandwidth as is achievable for a single DFB laser and all sections can be sequentially activated and tuned so as to collectively cover a broad bandwidth, or simultaneously activated and tuned to enable a tunable multi-wavelength laser. The laser hence can emit either a single lasing wavelength or a multiple of lasing wavelengths and is very suitable for swept-source OCT applications.

Owner:CARL ZEISS MEDITEC INC

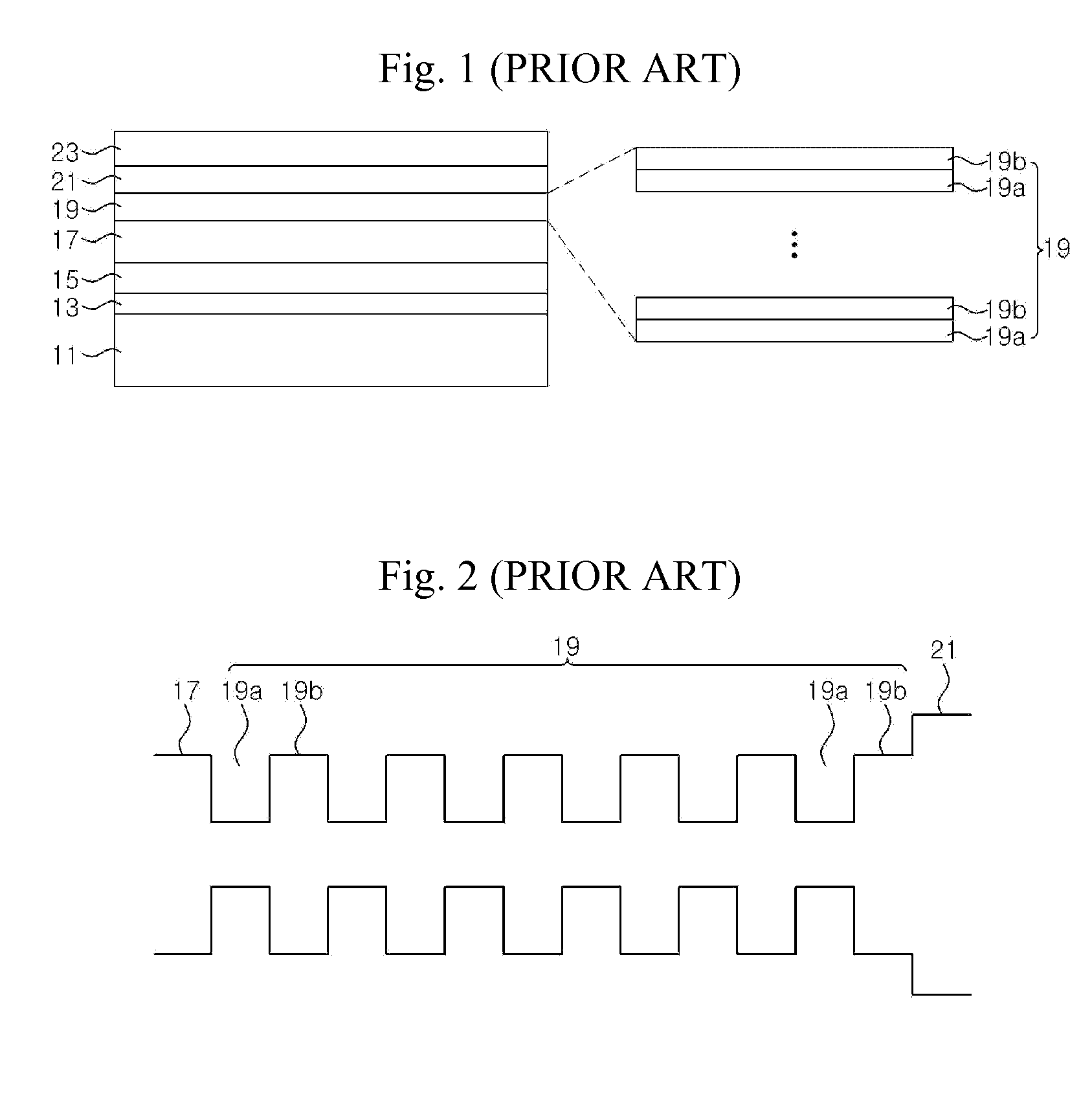

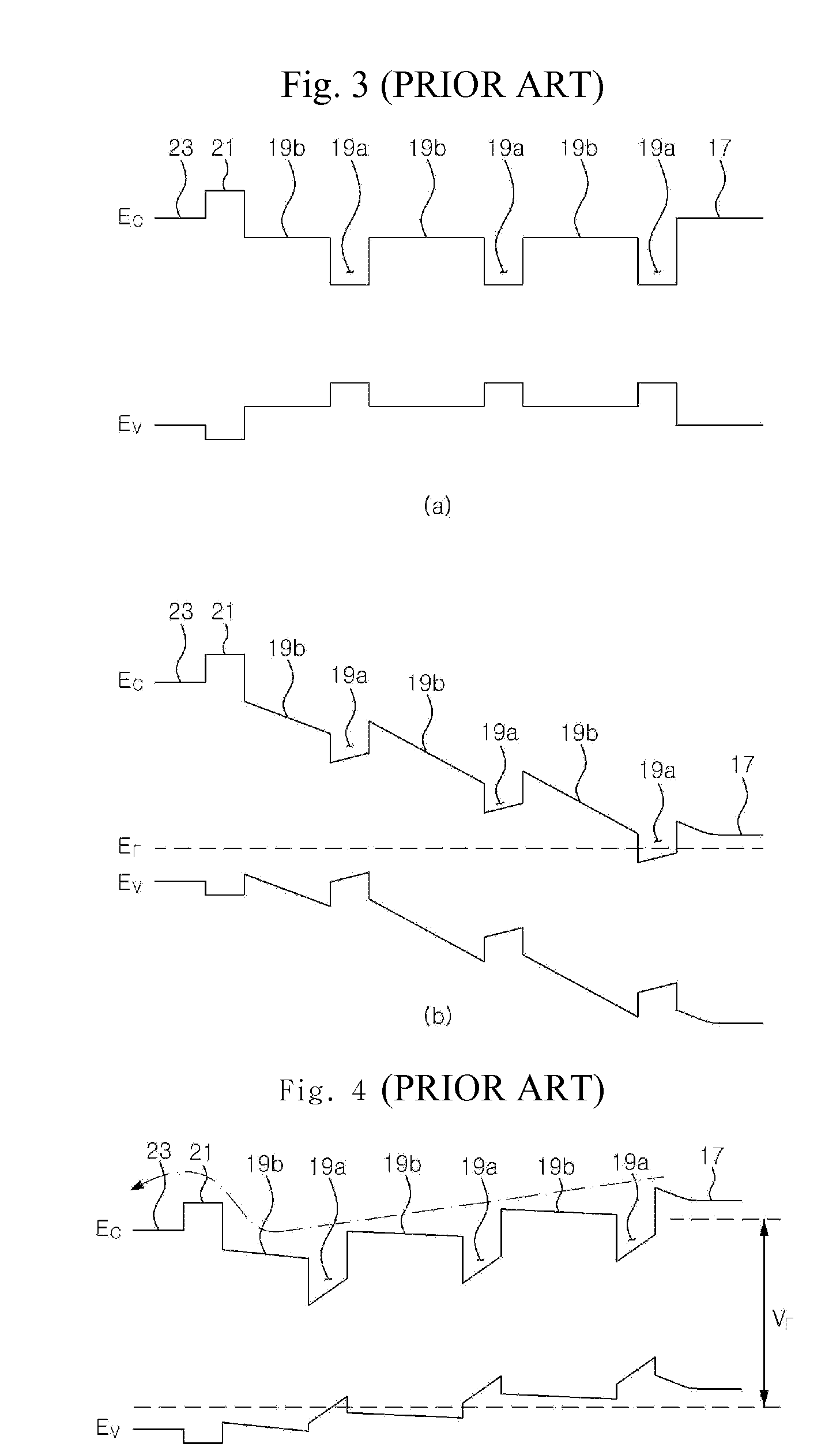

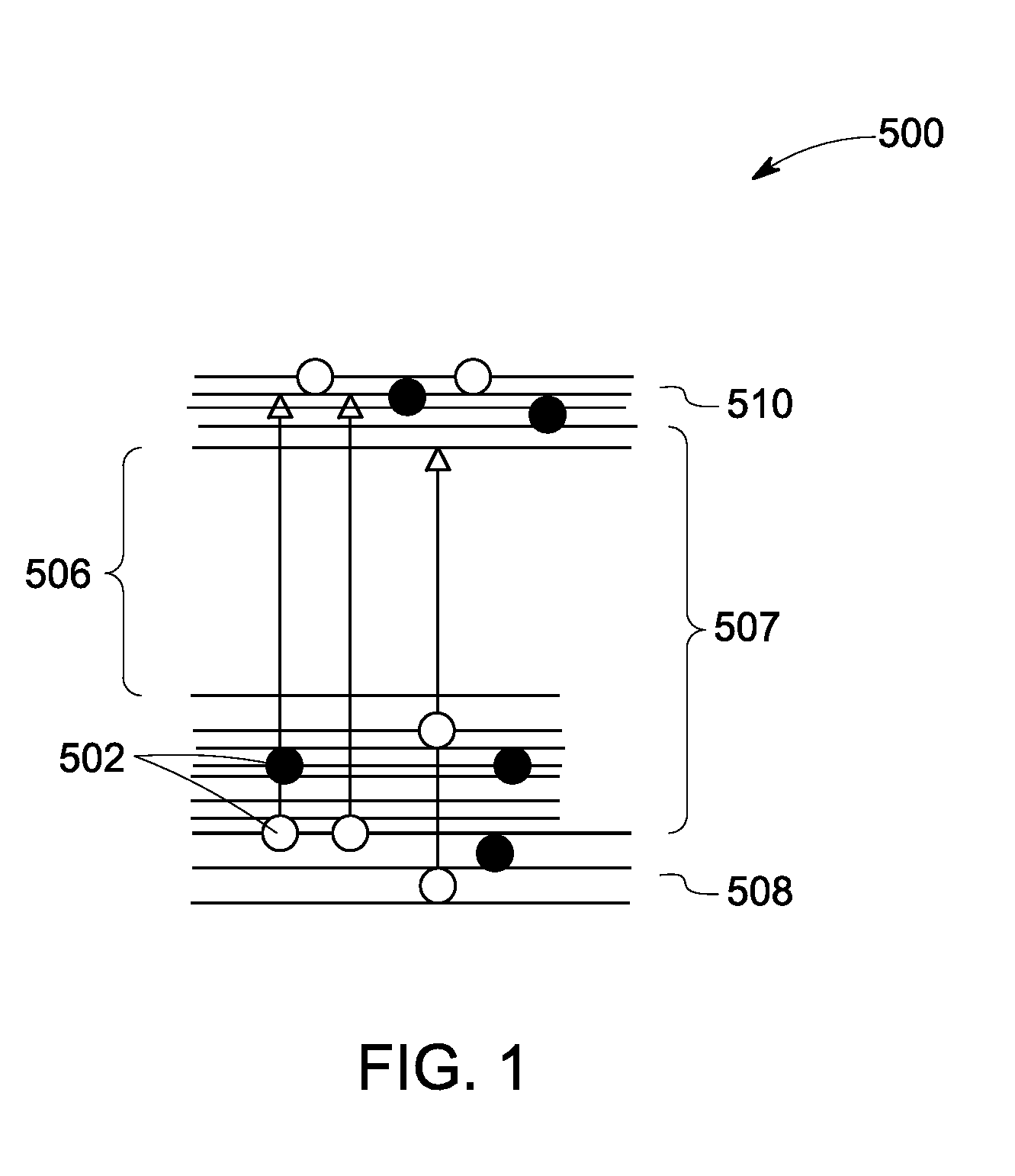

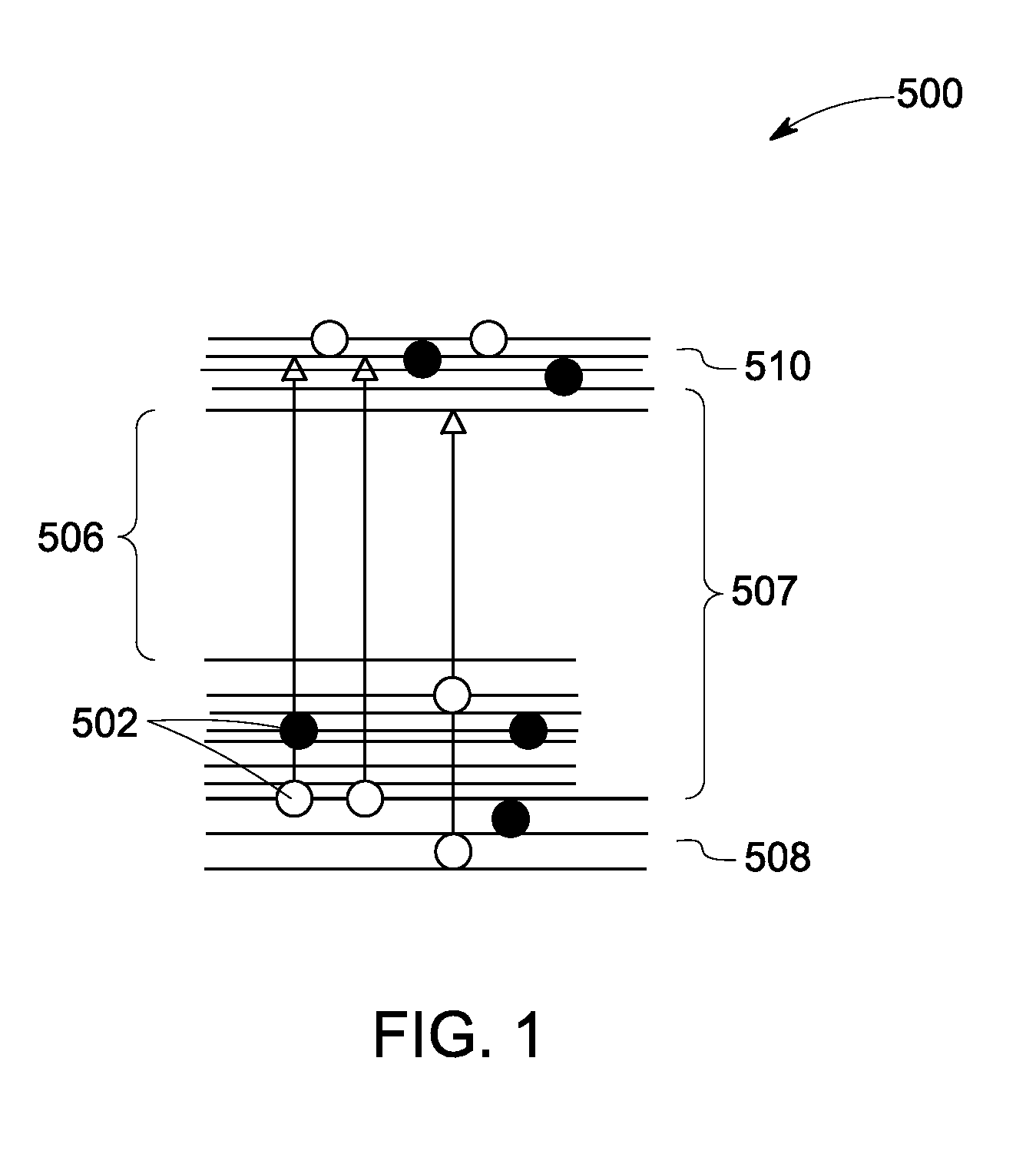

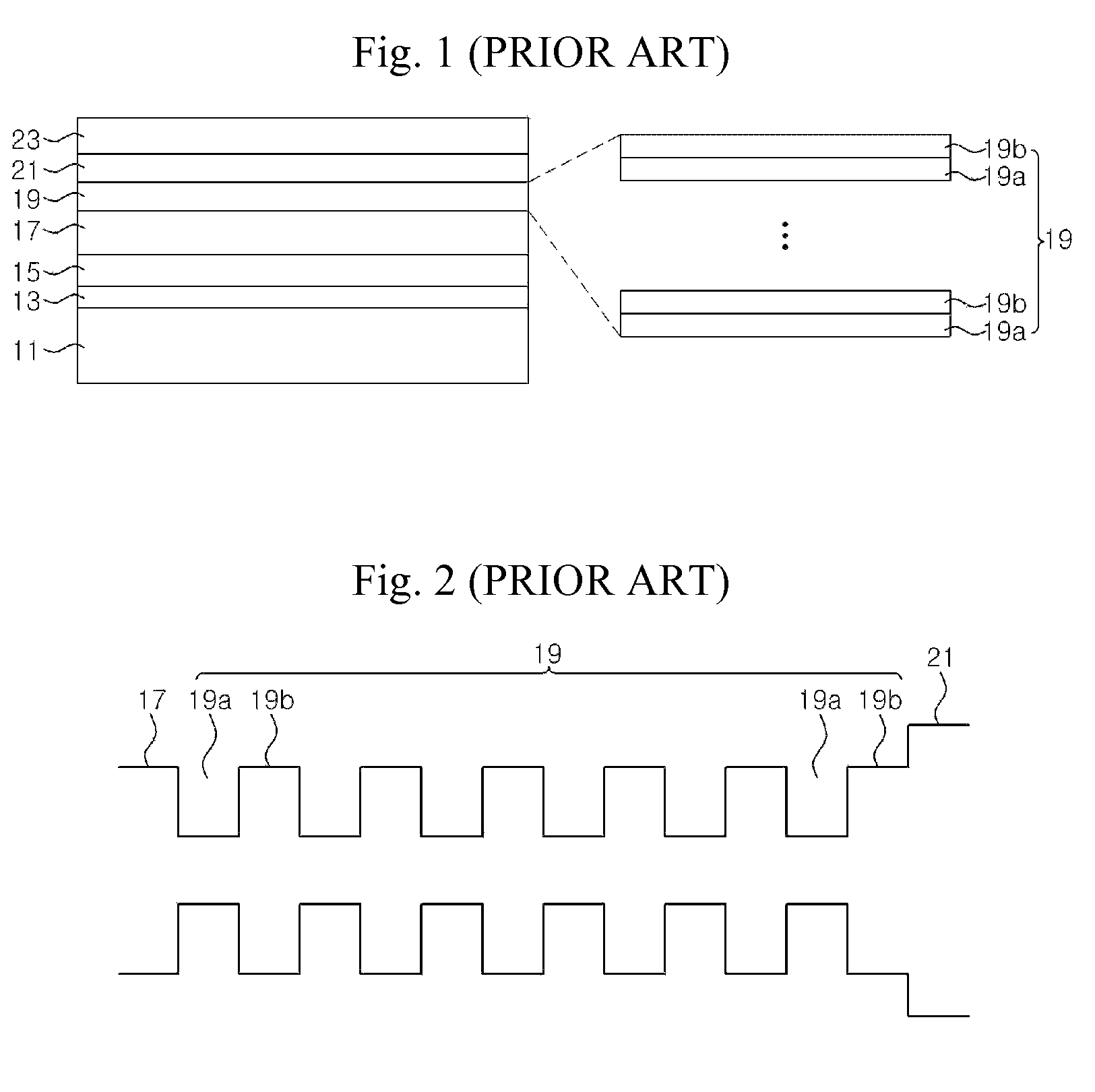

Light emitting diode having active region of multi quantum well structure

ActiveUS20080308787A1Improve luminous efficiencyEnhance rate of recombinationSemiconductor devicesImpurity dopingLight-emitting diode

Disclosed is a light emitting diode (LED) having an active region of a multiple quantum well structure in which well layers and barrier layers are alternately laminated between a GaN-based N-type compound semiconductor layer and a GaN-based P-type compound semiconductor layer. The LED includes a middle barrier layer having a bandgap relatively wider than the first barrier layer adjacent to the N-type compound semiconductor layer and the n-th barrier layer adjacent to the P-type compound semiconductor layer. The middle barrier layer is positioned between the first and n-th barrier layers. Accordingly, positions at which electrons and holes are combined in the multiple quantum well structure to emit light can be controlled, and luminous efficiency can be enhanced. Furthermore, an LED is provided with enhanced luminous efficiency using a bandgap engineering or impurity doping technique.

Owner:SEOUL VIOSYS CO LTD

High density NAND non-volatile memory device

ActiveUS7829938B2Reduce harmImproved high density memory device and arraySolid-state devicesRead-only memoriesCharge retentionTrapping

Non-volatile memory devices and arrays are described that utilize dual gate (or back-side gate) non-volatile memory cells with band engineered gate-stacks that are placed above or below the channel region in front-side or back-side charge trapping gate-stack configurations in NAND memory array architectures. The band-gap engineered gate-stacks with asymmetric or direct tunnel barriers of the floating node memory cells of embodiments of the present invention allow for low voltage tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The memory cell architecture also allows for improved high density memory devices or arrays with the utilization of reduced feature word lines and vertical select gates.

Owner:MICRON TECH INC

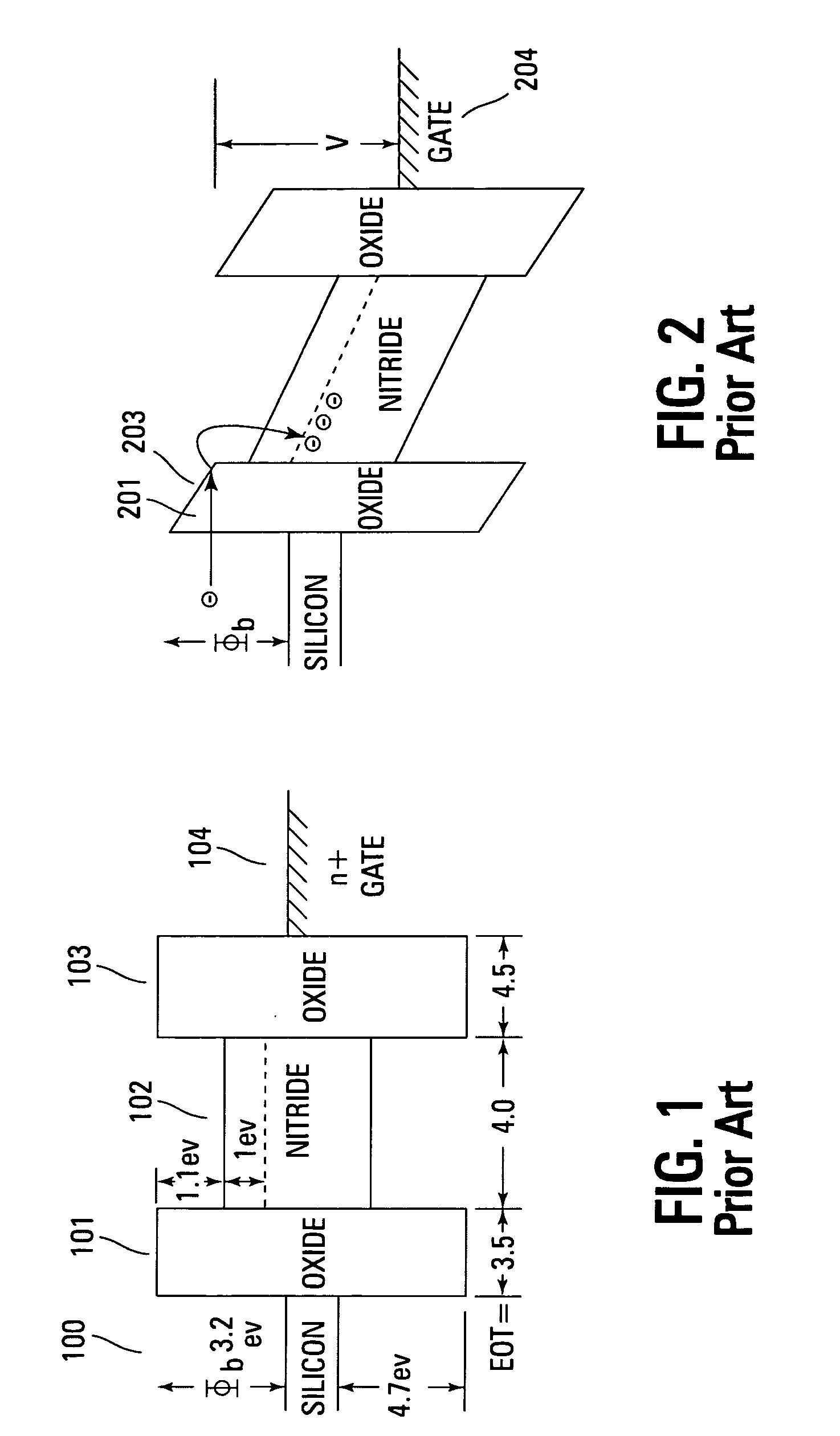

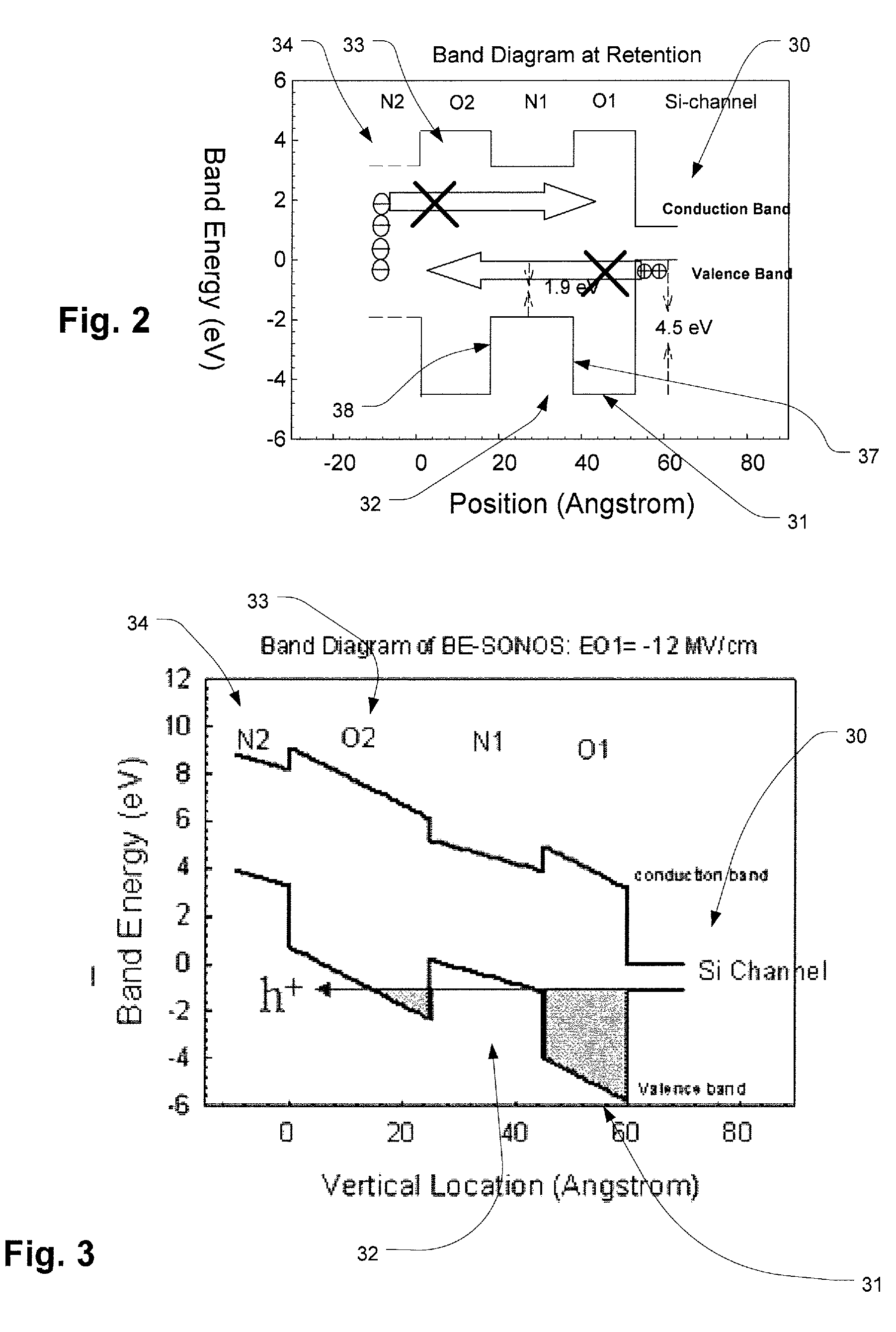

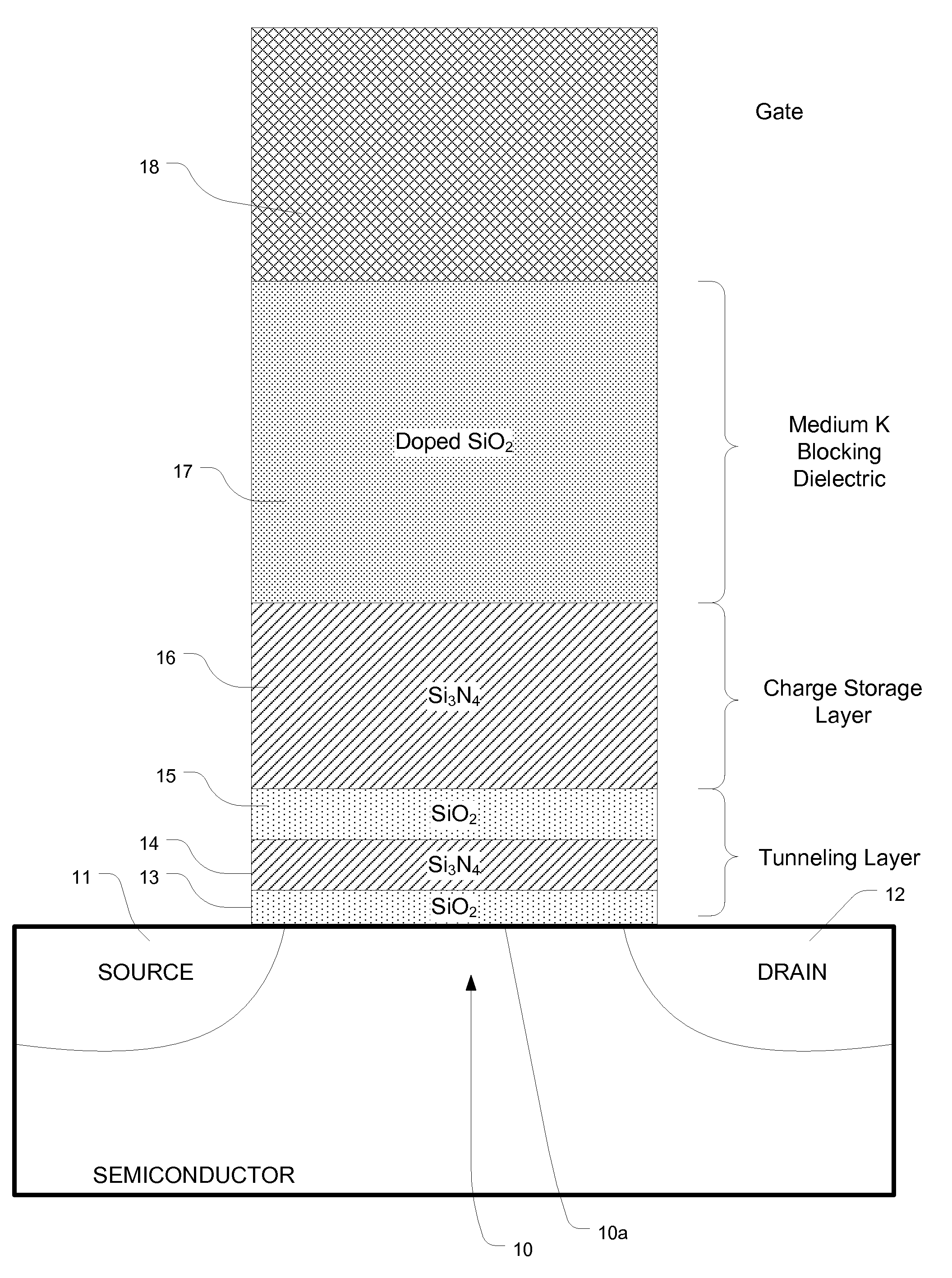

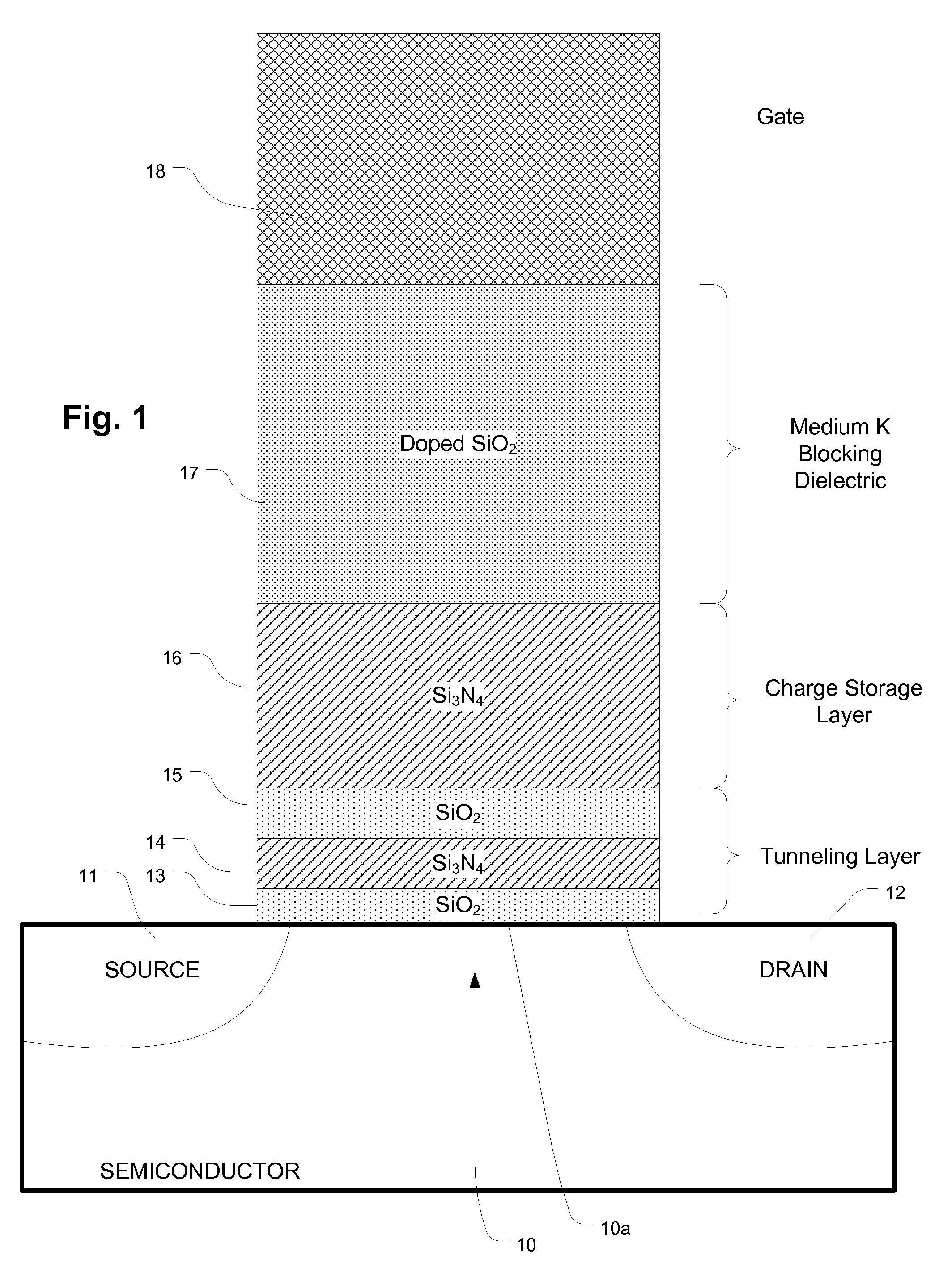

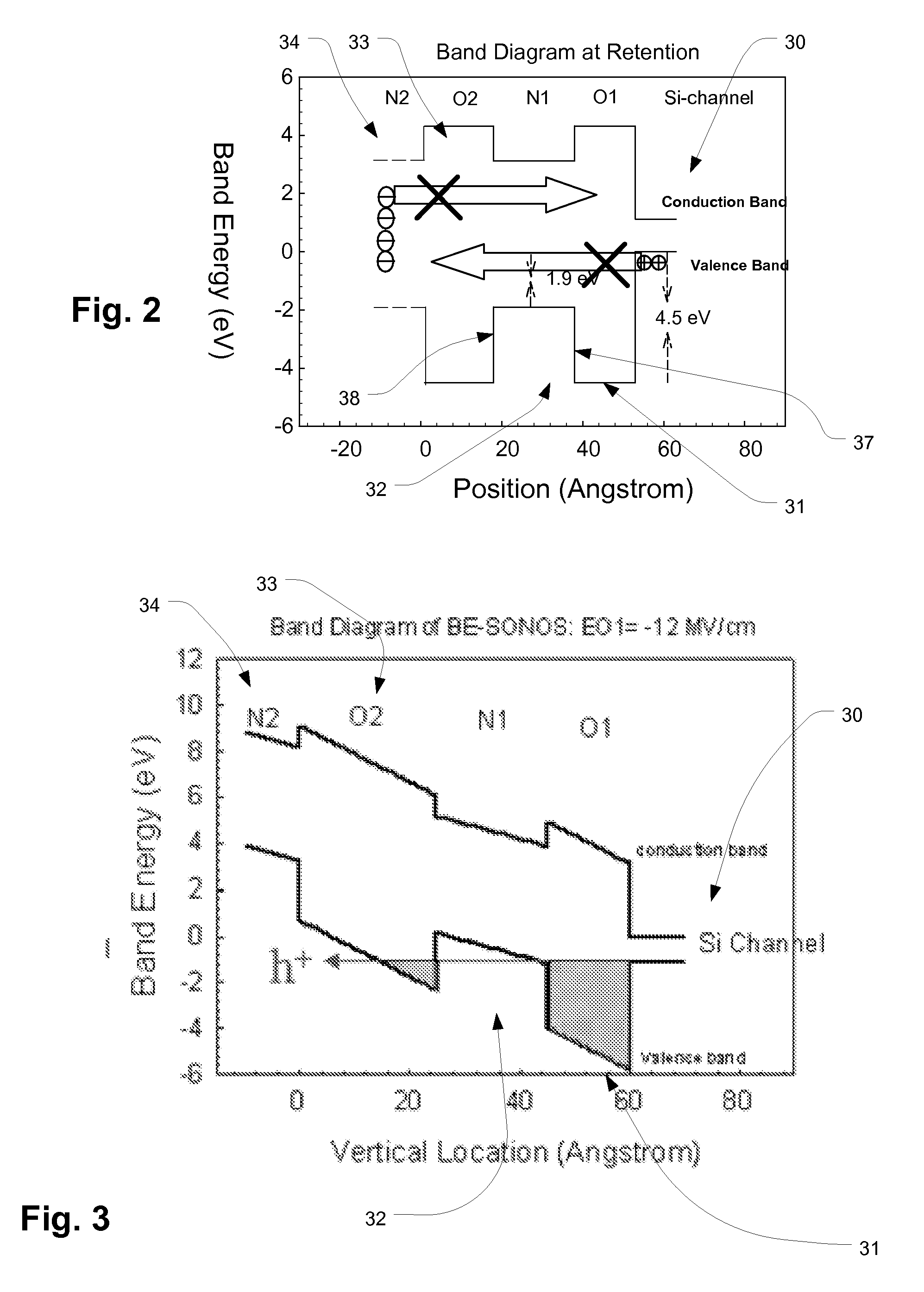

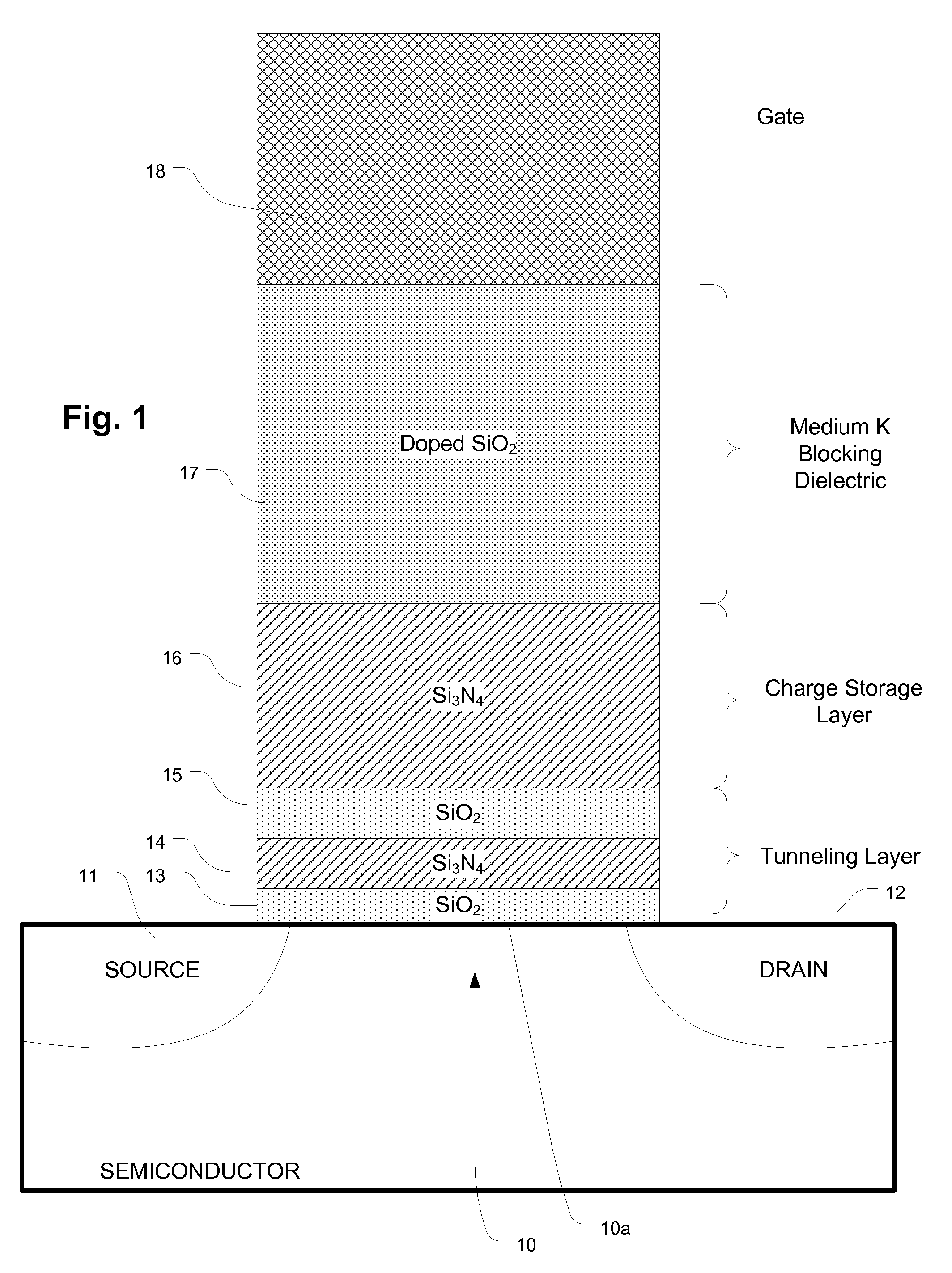

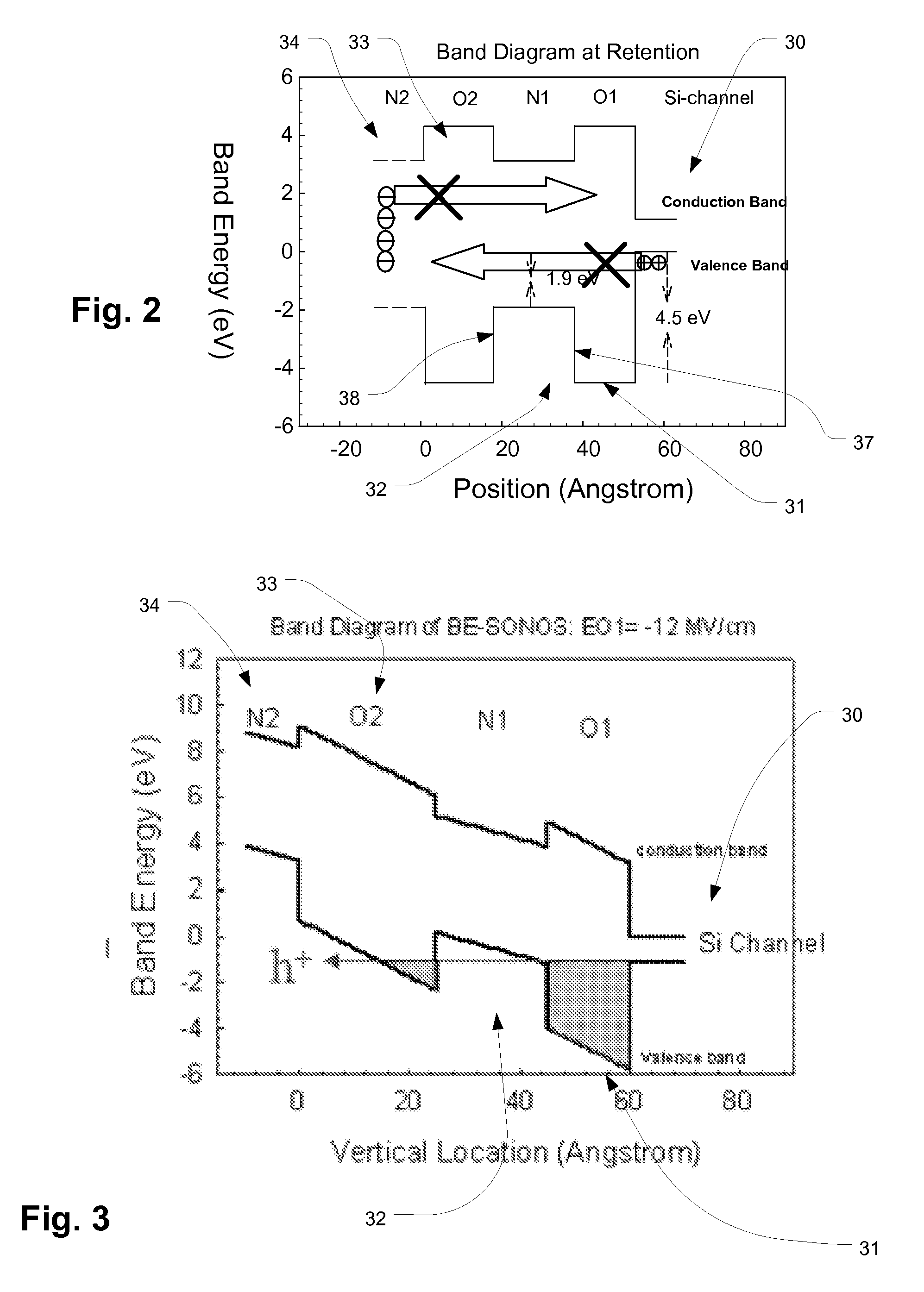

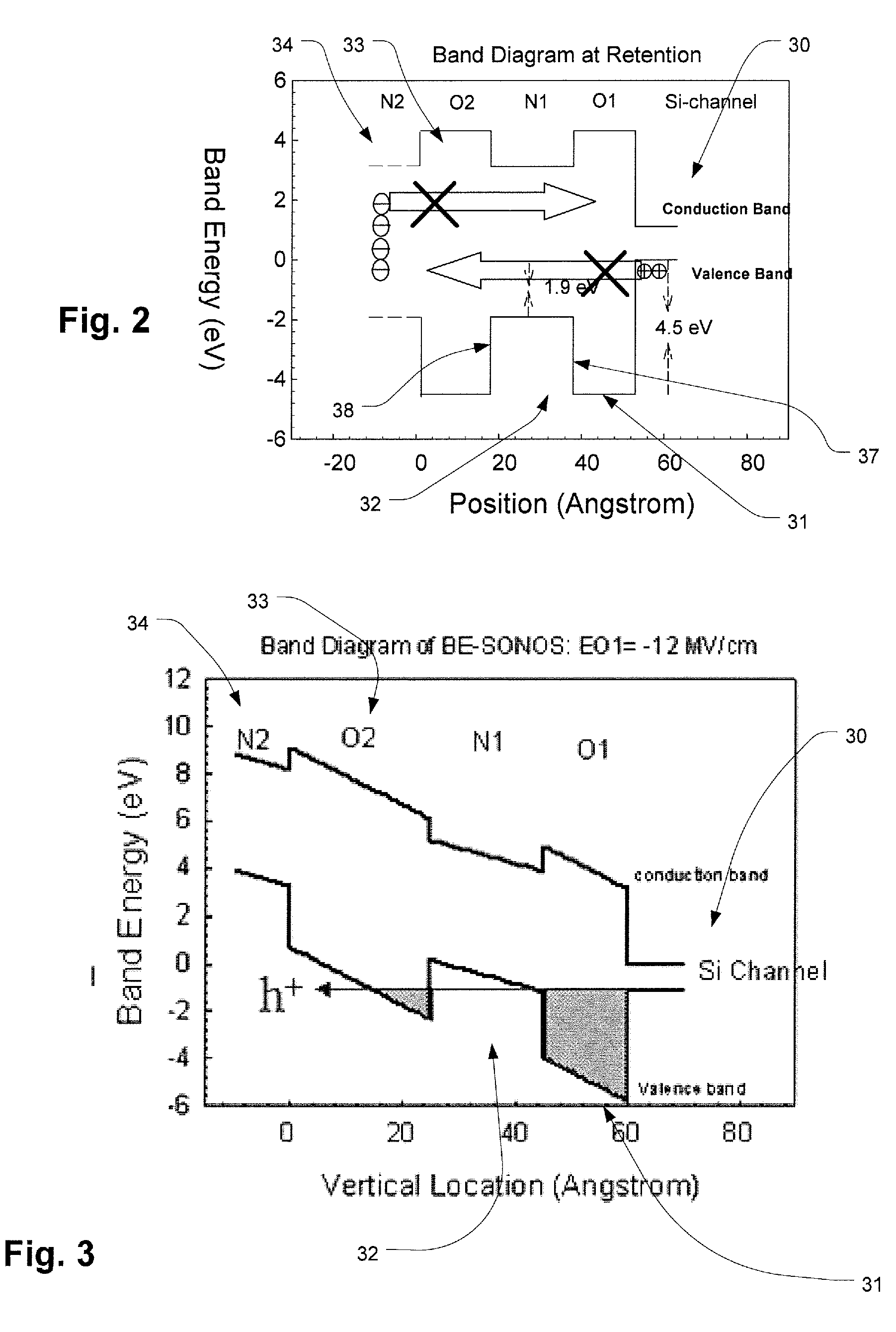

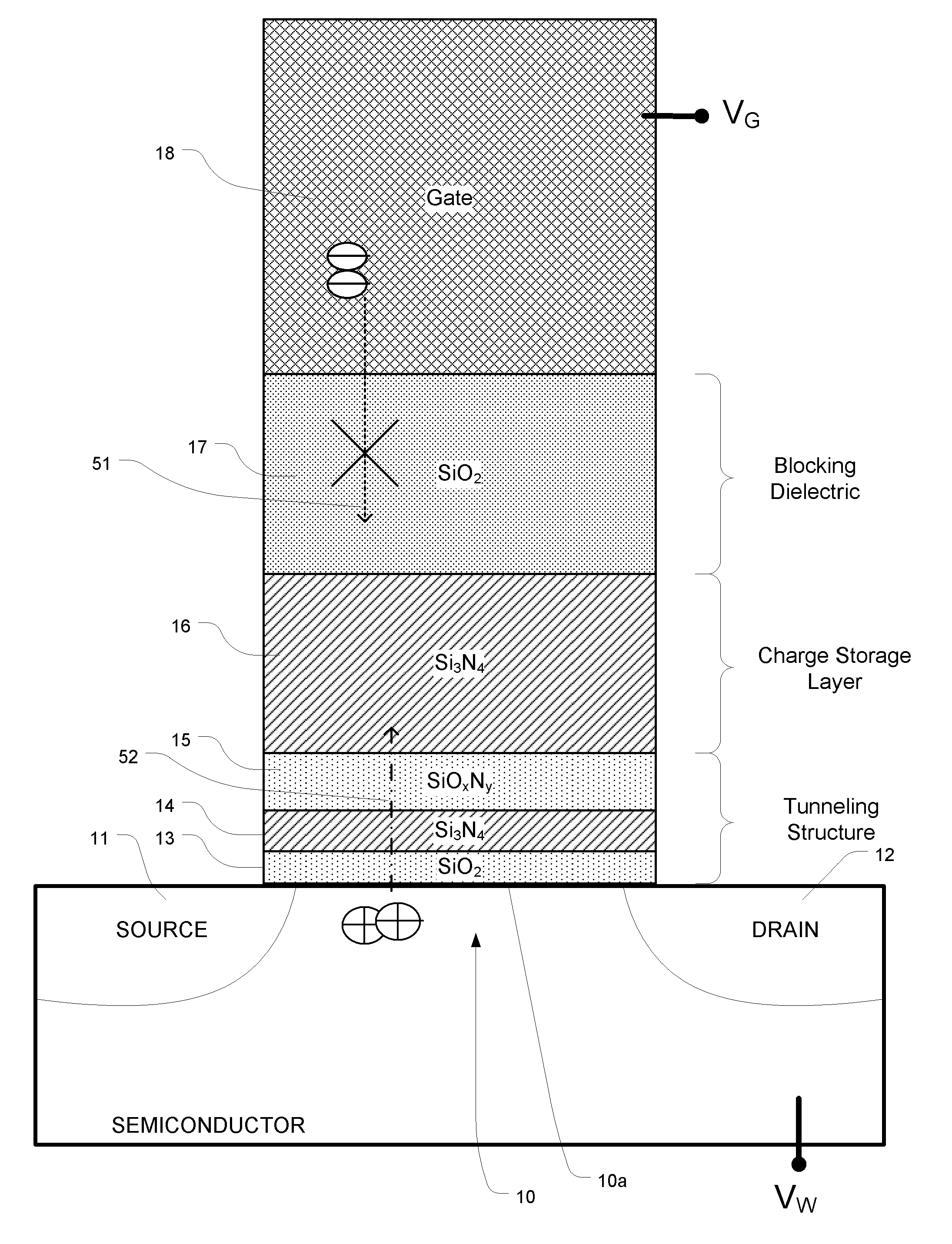

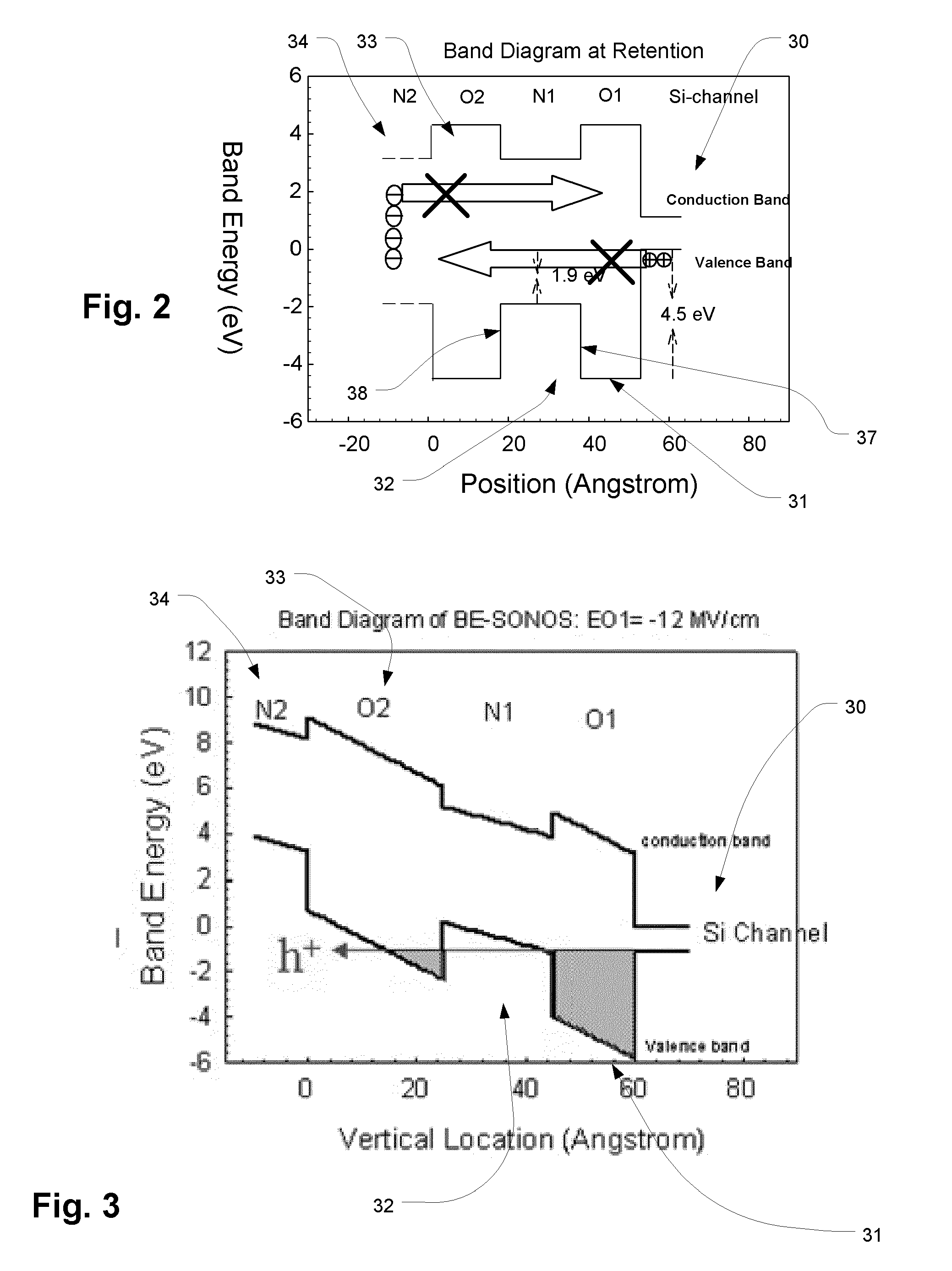

High-κ capped blocking dielectric bandgap engineered SONOS and MONOS

ActiveUS7816727B2Excellent characteristicsImprove reliabilitySolid-state devicesRead-only memoriesDielectricTrapping

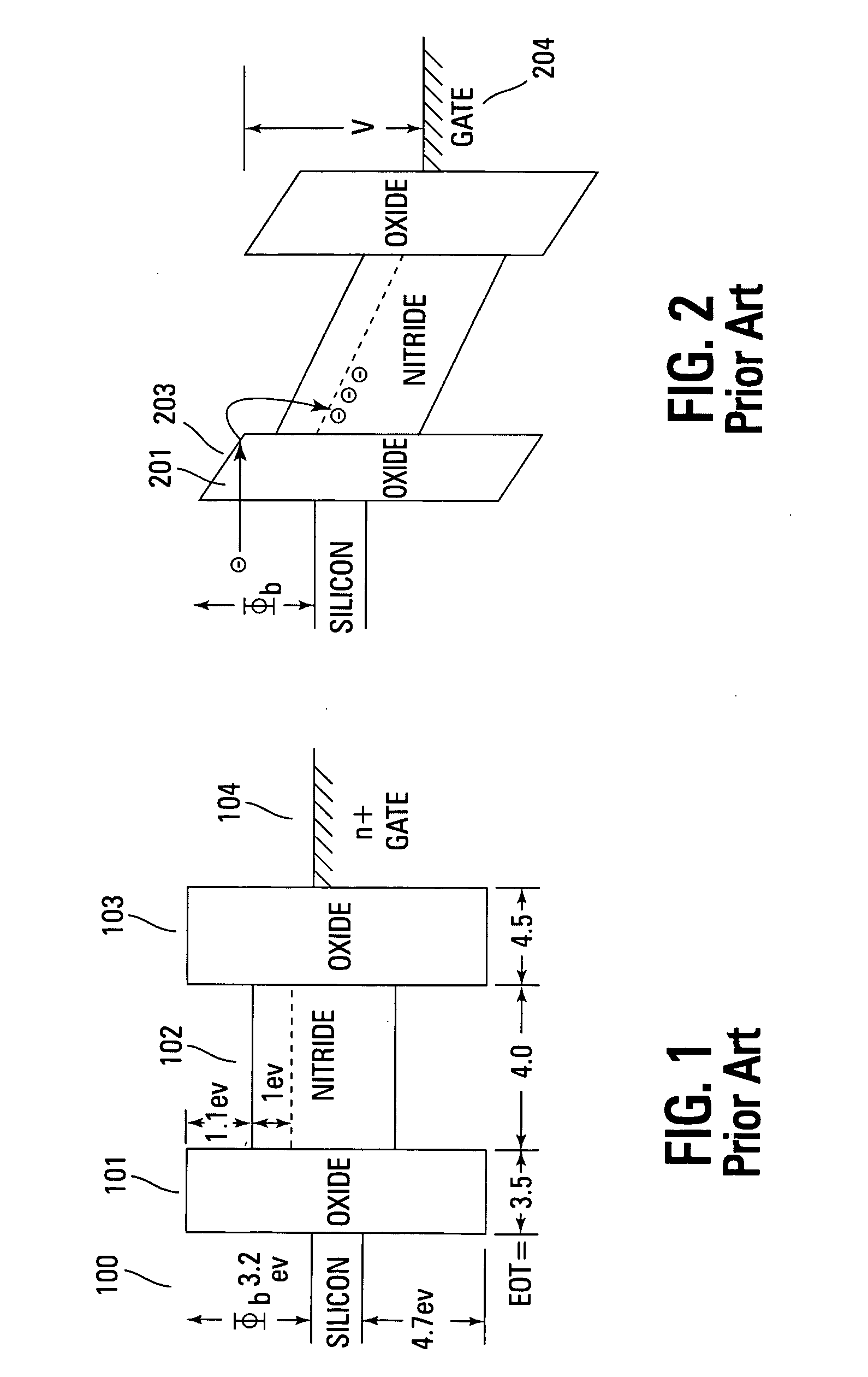

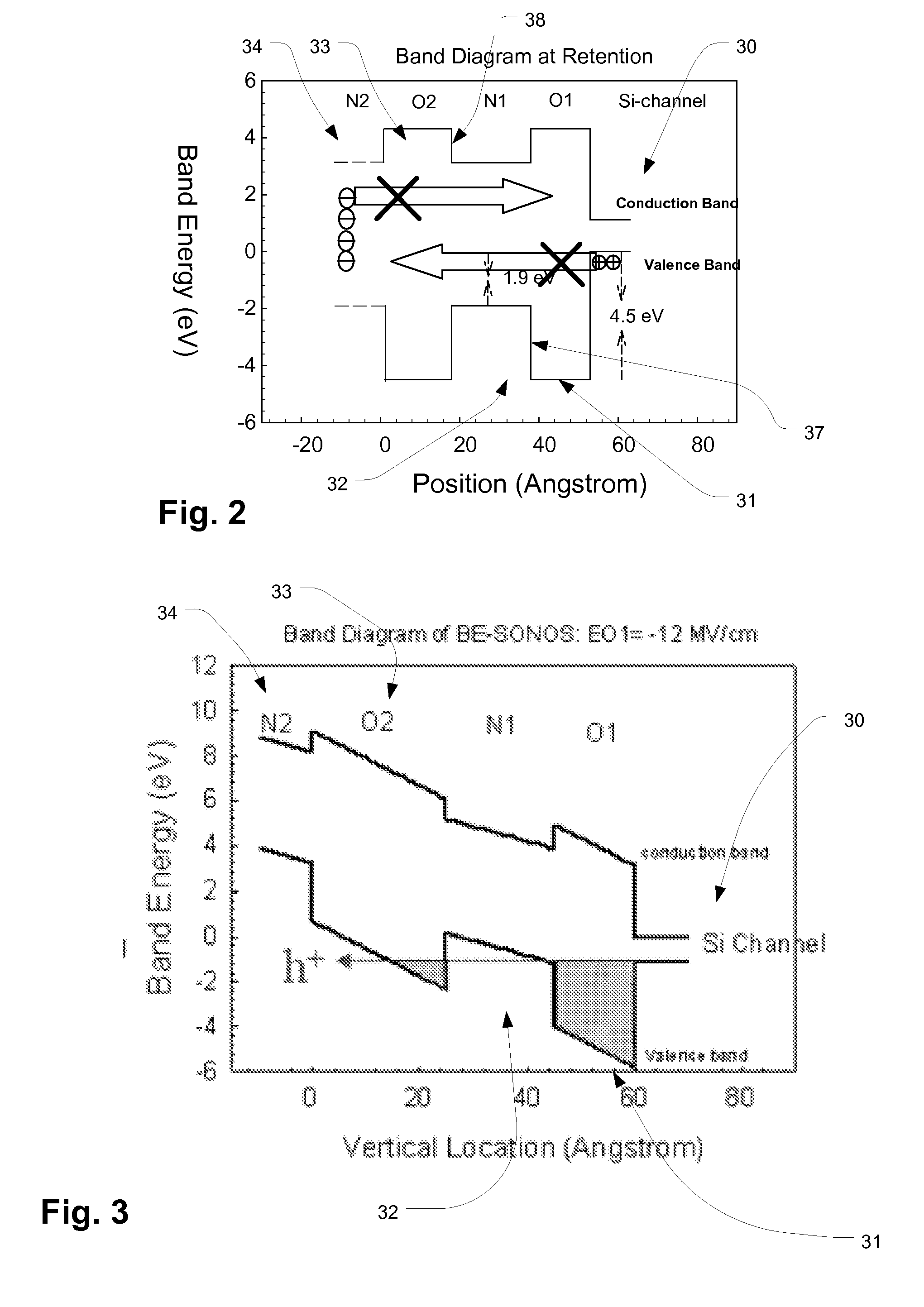

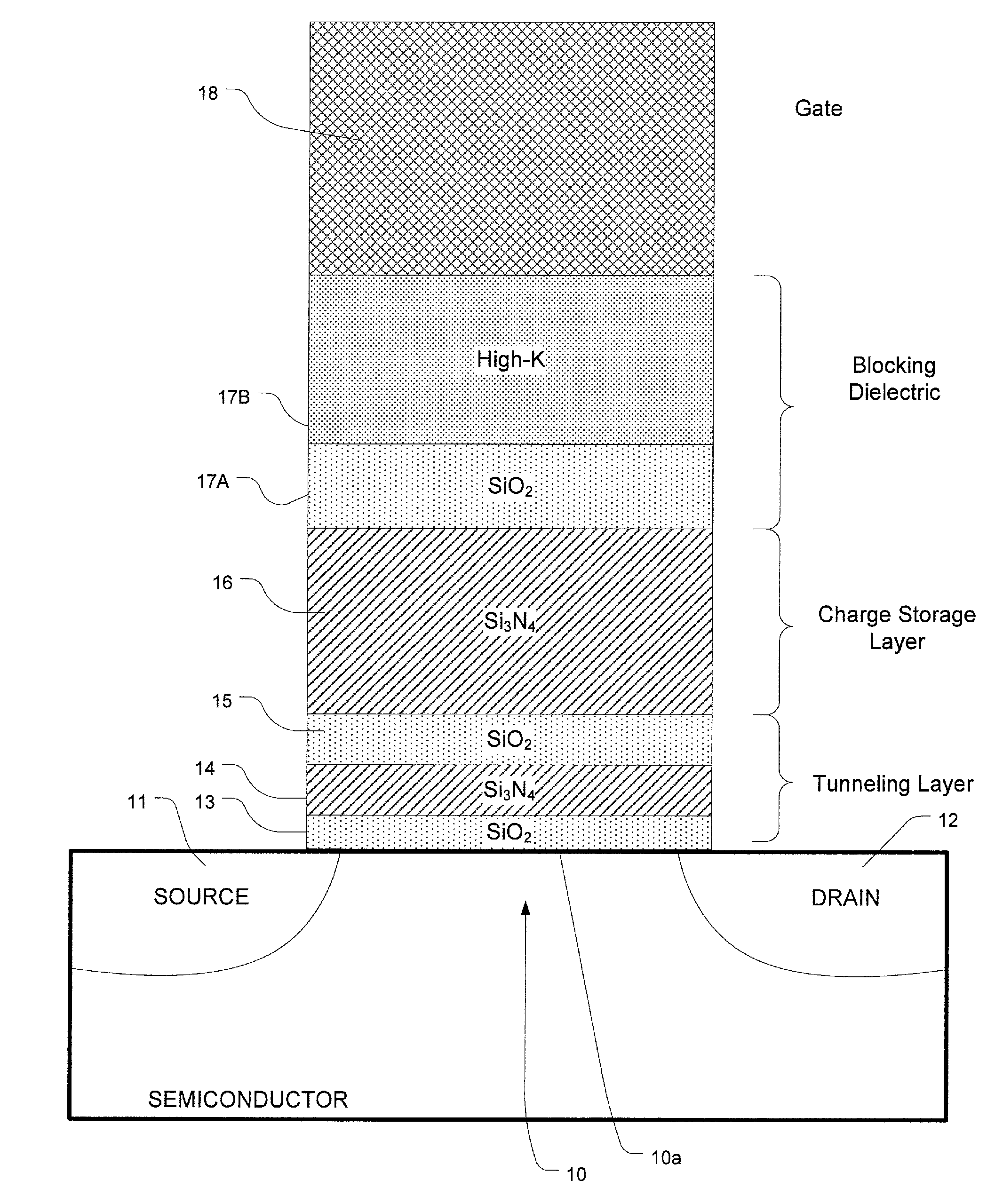

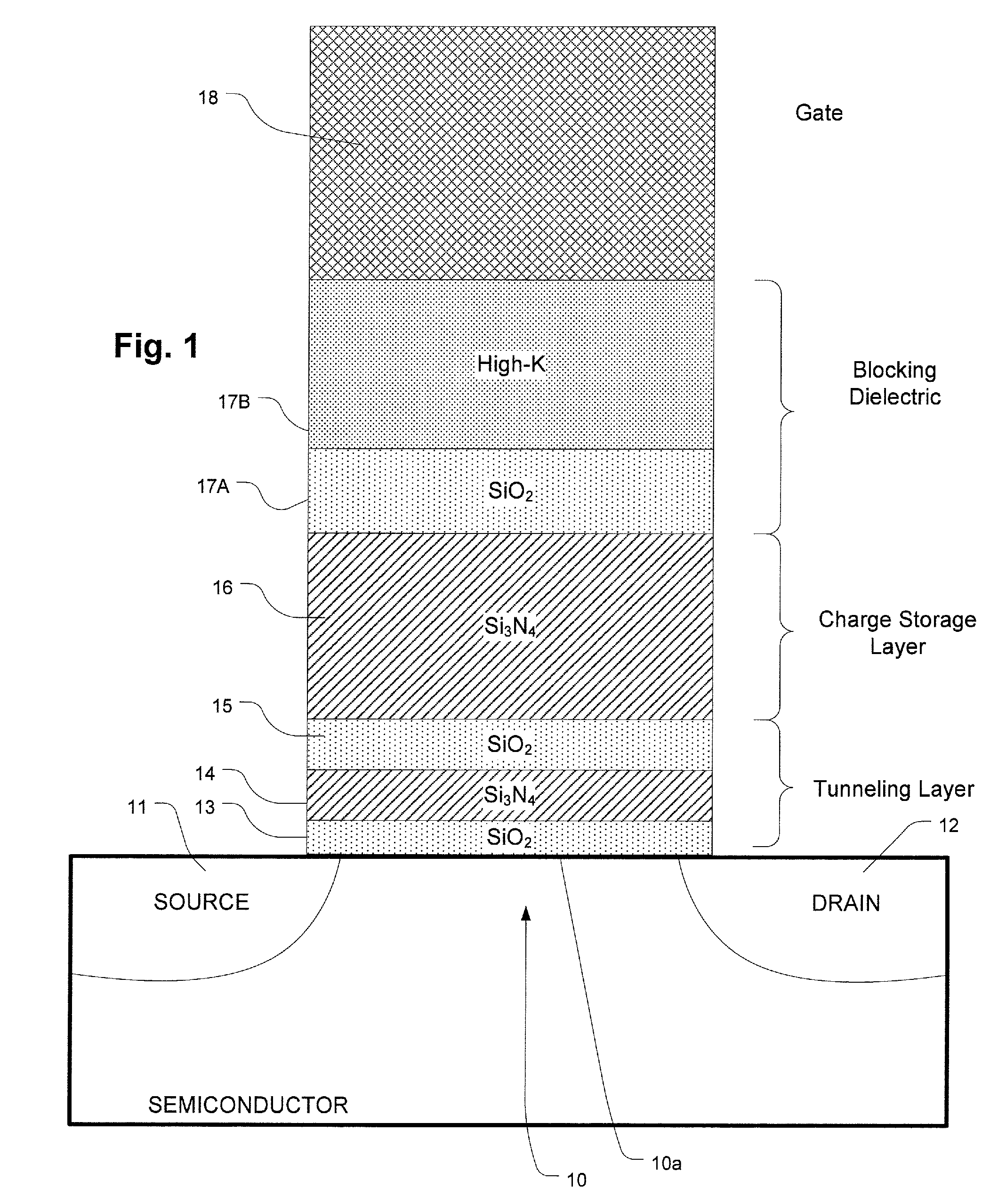

A blocking dielectric engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking dielectric including a buffer layer in contact with the charge trapping element, such as silicon dioxide which can be made with high-quality, and a second capping layer in contact with said one of the gate and the channel. The capping layer has a dielectric constant that is higher than that of the first layer, and preferably includes a high-κ material. The second layer also has a conduction band offset that is relatively high. A bandgap engineered tunneling layer between the channel and the charge trapping element is provided which, in combination with the multilayer blocking dielectric described herein, provides for high-speed erase operations by hole tunneling. In an alternative, a single layer tunneling layer is used.

Owner:MACRONIX INT CO LTD

High performance multi-level non-volatile memory device

Non-volatile memory devices and arrays are described that utilize band engineered gate-stacks and multiple charge trapping layers allowing a multiple trapping site gate-insulator stack memory cell that utilizes a band engineered direct tunneling or crested barrier tunnel layer and charge blocking layer for high speed programming / erasure. Charge retention is enhanced by utilization of nano-crystals and / or bulk trapping materials in a composite non-conductive trapping layer and a high K dielectric insulating layers. The band-gap engineered gate-stack with asymmetric direct tunneling or crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage high speed tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. Memory cell embodiments of the present invention allow multiple levels of bit storage in a memory cell through multiple charge centroids and / or multiple threshold voltage levels.

Owner:MICRON TECH INC

Method of fabricating heterojunction photodiodes integrated with CMOS

Owner:QUANTUM SEMICON

Silicon on insulator and thin film transistor bandgap engineered split gate memory

ActiveUS20080175053A1Large thermal budgetLarge lateral diffusionSolid-state devicesRead-only memoriesDielectric structureBand-gap engineering

Memory cells comprising thin film transistor, stacked arrays, employing bandgap engineered tunneling layers in a junction free, NAND configuration. The cells comprise a channel region in a semiconductor strip formed on an insulating layer; a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure comprising a multilayer structure including at least one layer having a hole-tunneling barrier height lower than that at the interface with the channel region; a charge storage layer disposed above the tunnel dielectric structure; an insulating layer disposed above the charge storage layer; and a gate electrode disposed above the insulating layer Arrays and methods of operation are described.

Owner:MACRONIX INT CO LTD

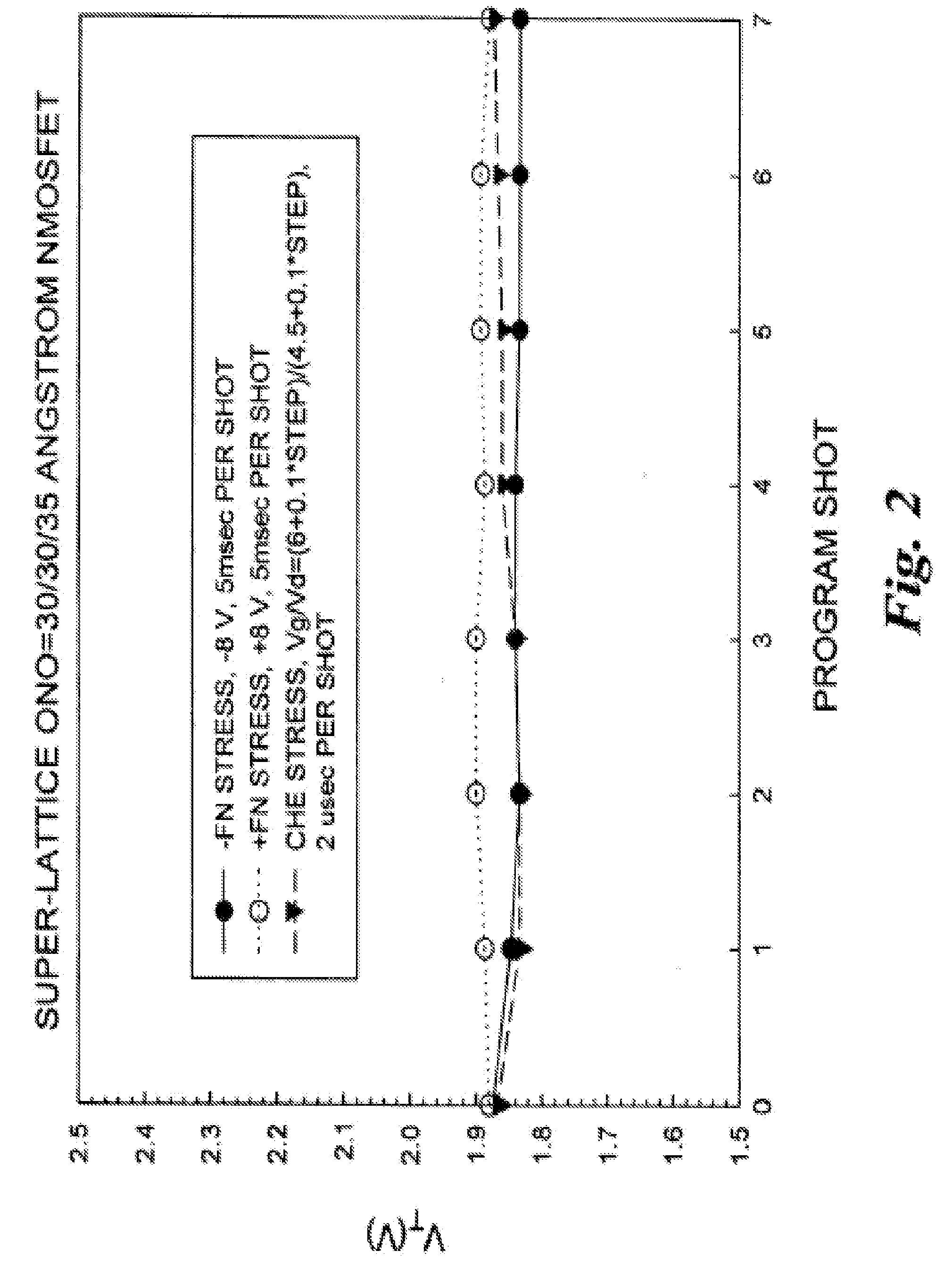

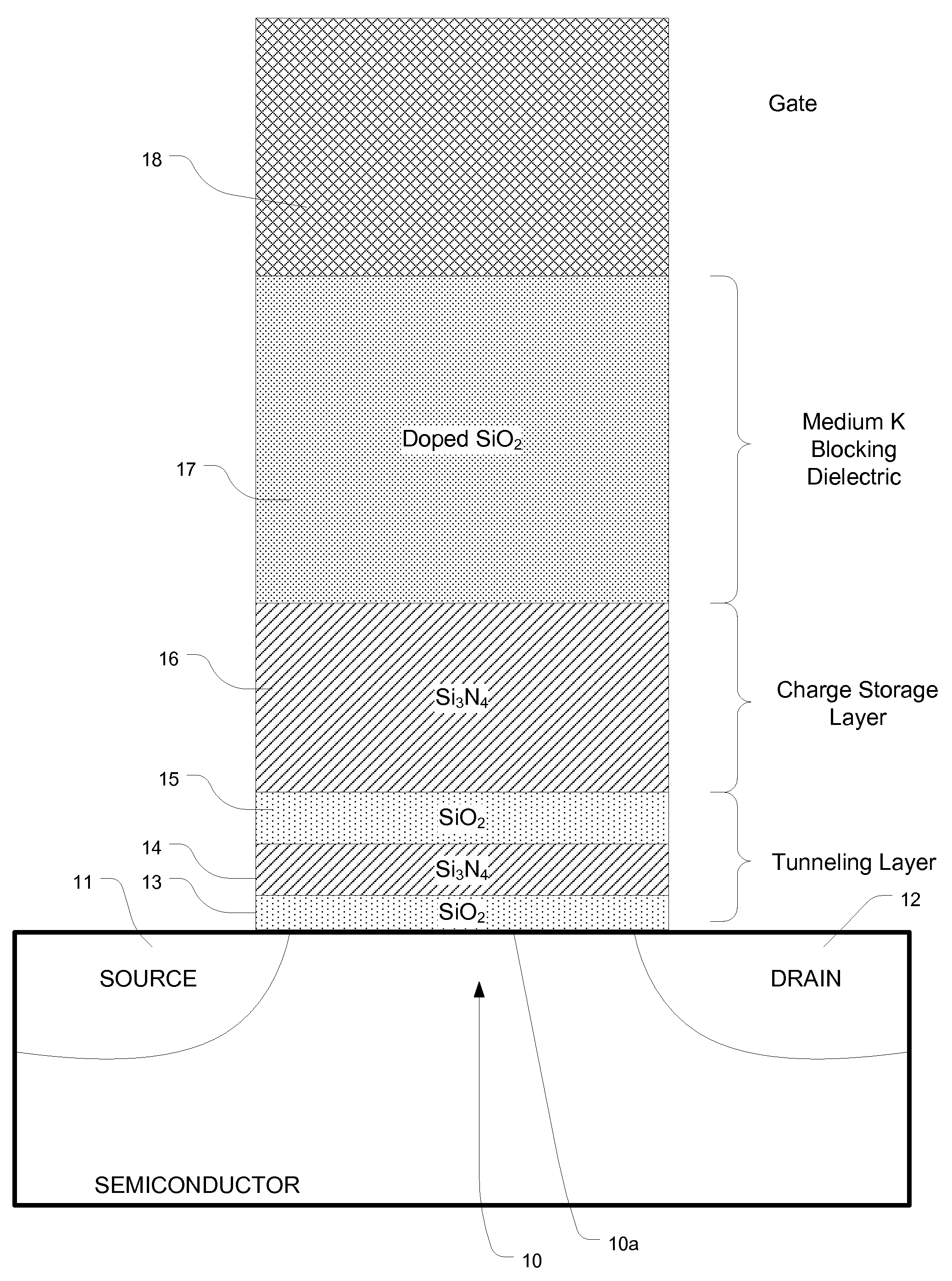

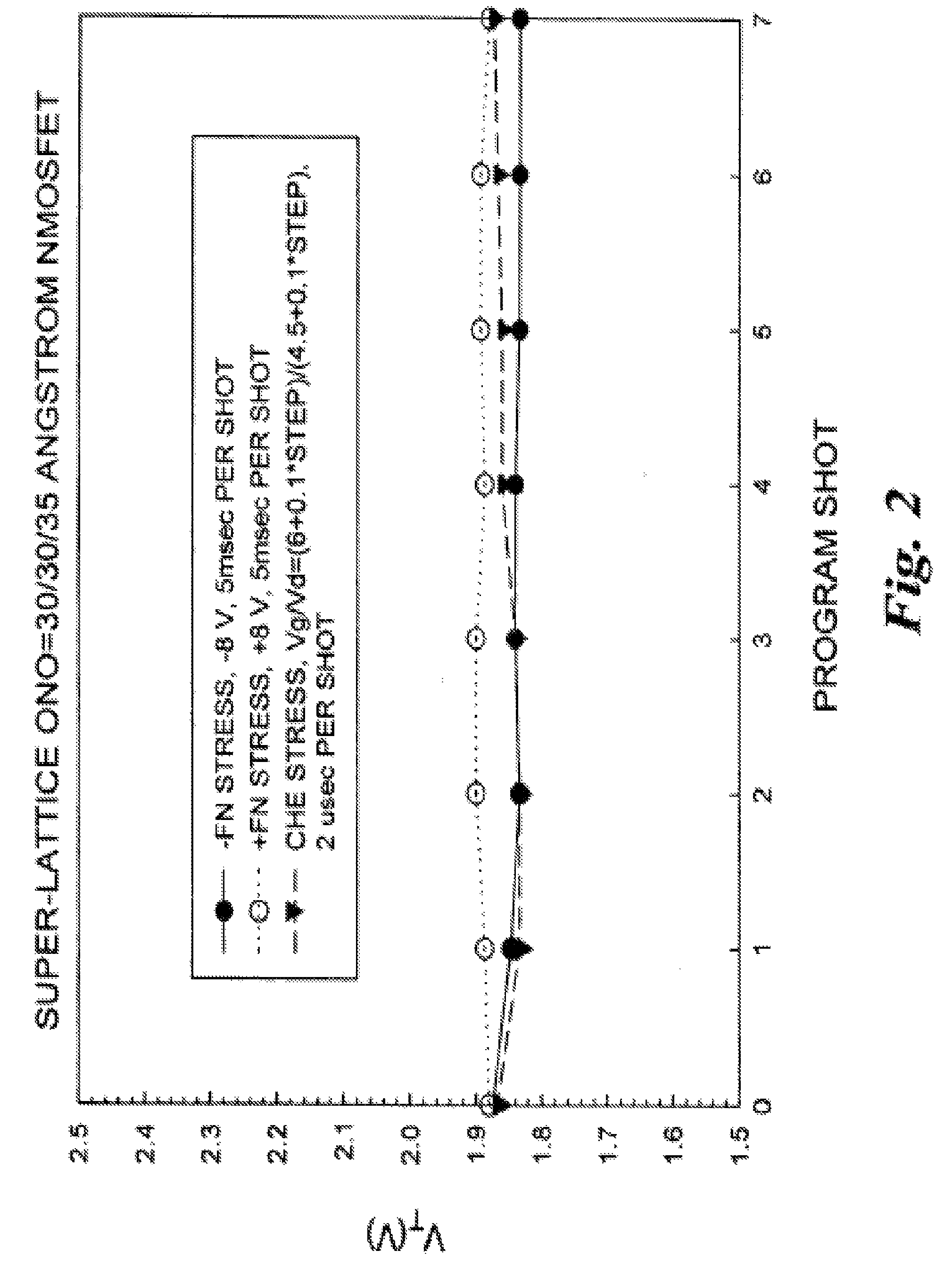

Blocking dielectric engineered charge trapping memory cell with high speed erase

ActiveUS7737488B2High barrier heightFast programmingSolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking layer of metal doped silicon oxide material having a medium dielectric constant, such as aluminum doped silicon oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric.

Owner:MACRONIX INT CO LTD

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

Blocking dielectric engineered charge trapping memory cell with high speed erase

ActiveUS20090039416A1Fast programmingImprove reliabilitySolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking layer of metal doped silicon oxide material having a medium dielectric constant, such as aluminum doped silicon oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric.

Owner:MACRONIX INT CO LTD

Silicon on insulator and thin film transistor bandgap engineered split gate memory

ActiveUS8482052B2Large operating windowEasy to operateTransistorSolid-state devicesDielectric structureSemiconductor

Thin film transistor memory cells are stackable, and employ bandgap engineered tunneling layers in a junction free, NAND configuration, that can be arranged in 3D arrays. The memory cells have a channel region in a semiconductor strip formed on an insulating layer, a tunnel dielectric structure disposed above the channel region, the tunnel dielectric structure having a multilayer structure including at least one layer having a hole-tunneling barrier height lower than that at the interface with the channel region, a charge storage layer disposed above the tunnel dielectric structure, an insulating layer disposed above the charge storage layer, and a gate electrode disposed above the insulating layer.

Owner:MACRONIX INT CO LTD

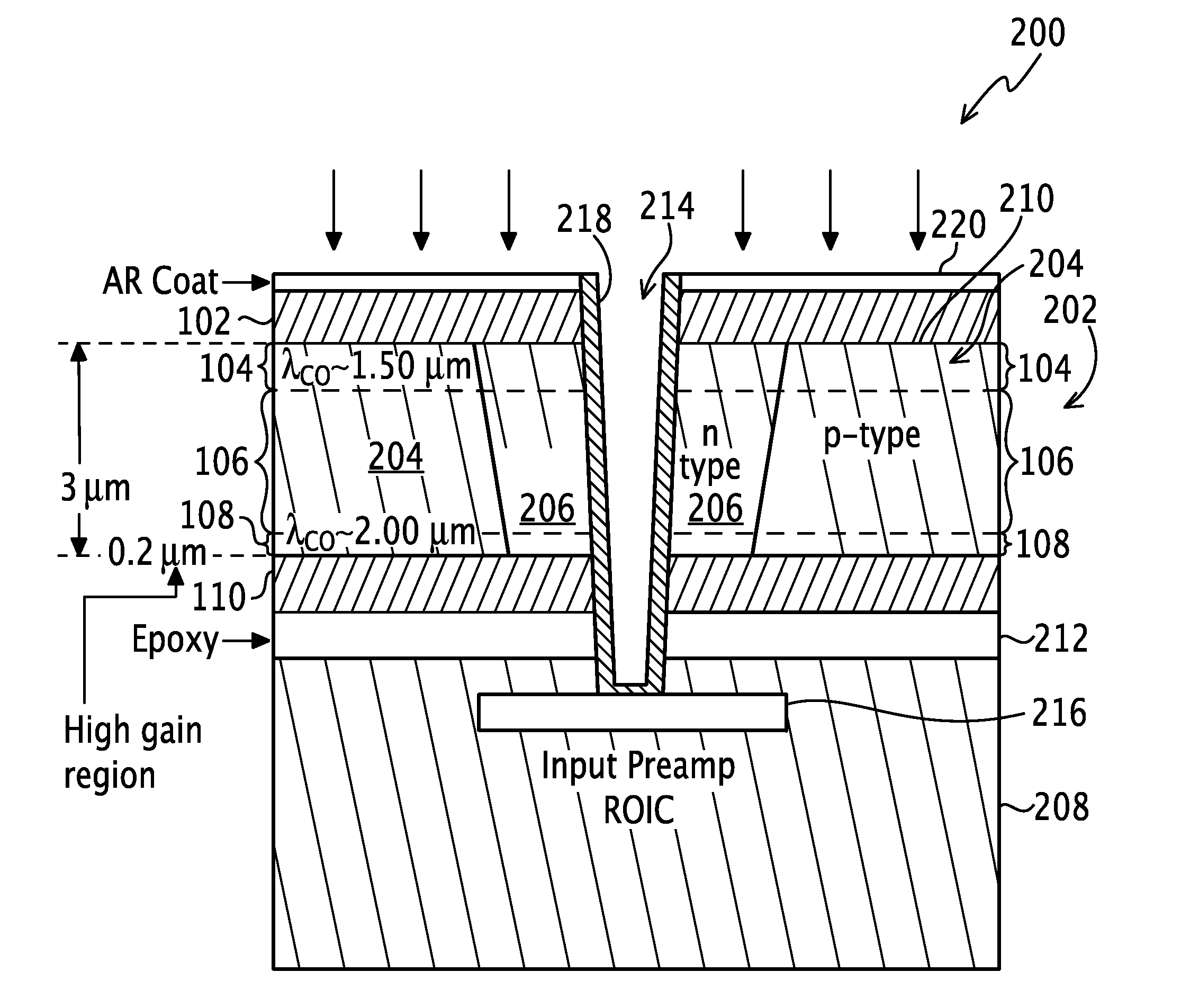

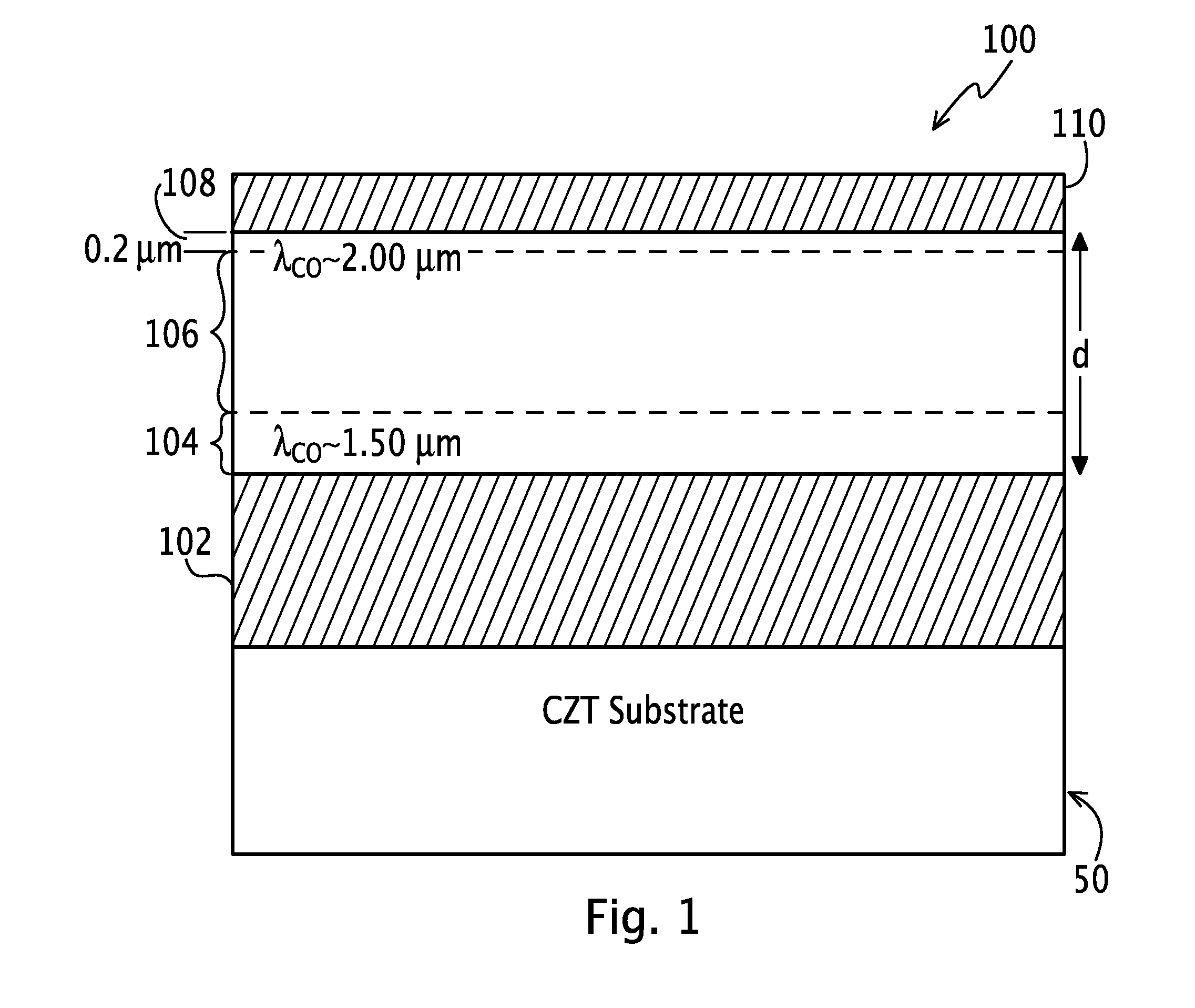

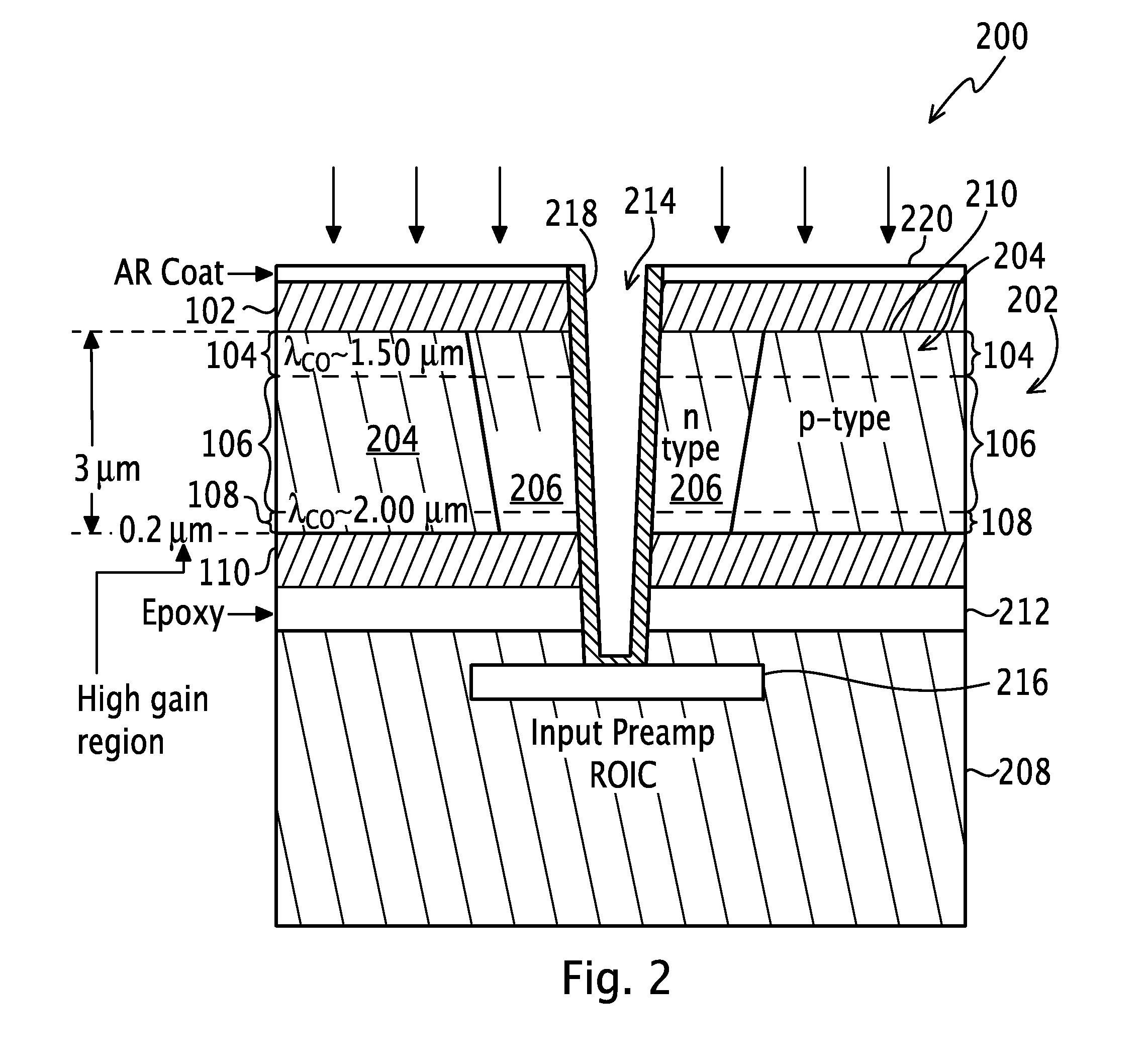

Radiation detector having a bandgap engineered absorber

ActiveUS20110031401A1Photometry using reference valueSolid-state devicesElectrical conductorSemiconductor materials

A radiation detector is provided that includes a photodiode having a radiation absorber with a graded multilayer structure. Each layer of the absorber is formed from a semiconductor material, such as HgCdTe. A first of the layers is formed to have a first predetermined wavelength cutoff. A second of the layers is disposed over the first layer and beneath the first surface of the absorber through which radiation is received. The second layer has a graded composition structure of the semiconductor material such that the wavelength cutoff of the second layer varies from a second predetermined wavelength cutoff to the first predetermined wavelength cutoff such that the second layer has a progressively smaller bandgap than the first bandgap of the first layer. The graded multilayer radiation absorber structure enables carriers to flow toward a conductor that is used for measuring the radiation being sensed by the radiation absorber.

Owner:DRS NETWORK & IMAGING SYST

Light source for swept source optical coherence tomography based on cascaded distributed feedback lasers with engineered band gaps

ActiveUS7554668B2Laser optical resonator constructionMaterial analysis by optical meansDistributed feedback laserGrating

The present invention is a tunable semiconductor laser for swept source optical coherence tomography, comprising a semiconductor substrate; a waveguide on top of said substrate with multiple sections of different band gap engineered multiple quantum wells (MQWs); a multiple of distributed feedback (DFB) gratings corresponding to each said band gap engineered MWQs, each DFB having a different Bragg grating period; and anti-reflection (AR) coating deposited on at least the laser emission facet of the laser to suppress the resonance of Fabry-Perot cavity modes. Each DFB MQWs section can be activated and tuned to lase across a fraction of the overall bandwidth as is achievable for a single DFB laser and all sections can be sequentially activated and tuned so as to collectively cover a broad bandwidth, or simultaneously activated and tuned to enable a tunable multi-wavelength laser. The laser hence can emit either a single lasing wavelength or a multiple of lasing wavelengths and is very suitable for swept-source OCT applications.

Owner:CARL ZEISS MEDITEC INC

HIGH-k CAPPED BLOCKING DIELECTRIC BANDGAP ENGINEERED SONOS AND MONOS

ActiveUS20090059676A1Excellent characteristicsImprove reliabilitySolid-state devicesRead-only memoriesDielectricTrapping

A blocking dielectric engineered, charge trapping memory cell includes a charge trapping element that is separated from a gate by a blocking dielectric comprising a buffer layer in contact with the charge trapping element, such as silicon dioxide which can be made with high-quality, and a second capping layer in contact with said one of the gate and the channel. The capping layer has a dielectric constant that is higher than that of the first layer, and preferably comprises a high-κ material. The second layer also has a conduction band offset that is relatively high. A bandgap engineered tunneling layer between the channel and the charge trapping element is provided which, in combination with the multilayer blocking dielectric described herein, provides for high-speed erase operations by hole tunneling. In an alternative, a single layer tunneling layer is used.

Owner:MACRONIX INT CO LTD

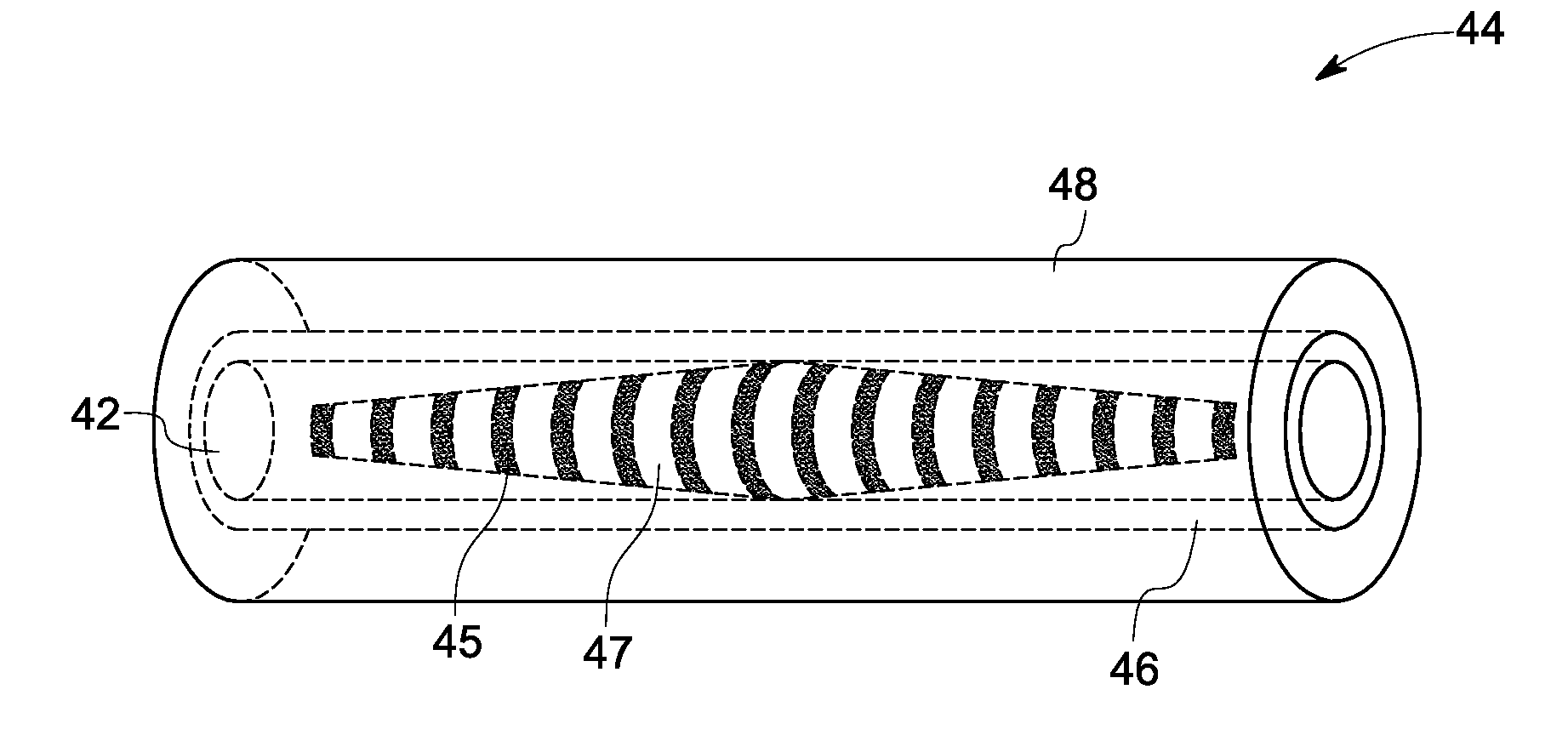

Fiber bragg grating for high temperature sensing

ActiveUS20090074347A1Increase photosensitivityIncrease the number ofGlass making apparatusOptical fibre with multilayer core/claddingFiberGrating

A method of fiber core material band gap engineering for artificially modifying fiber material properties is provided. The method includes doping the fiber core material with one or more atoms for enhancing photosensitivity to the fiber material. The method also includes co-doping the fiber core material with one or more ions for enhancing an amorphous network crosslink mean coordination number. The method further includes thermally annealing the fiber core material for widening the band gap of the fiber core material.

Owner:AIR PROD & CHEM INC

Fiber Bragg grating for high temperature sensing

ActiveUS7499605B1Increase photosensitivityIncreased band gapGlass making apparatusOptical fibre with multilayer core/claddingFiberGrating

A method of fiber core material band gap engineering for artificially modifying fiber material properties is provided. The method includes doping the fiber core material with one or more atoms for enhancing photosensitivity to the fiber material. The method also includes co-doping the fiber core material with one or more ions for enhancing an amorphous network crosslink mean coordination number. The method further includes thermally annealing the fiber core material for widening the band gap of the fiber core material.

Owner:AIR PROD & CHEM INC

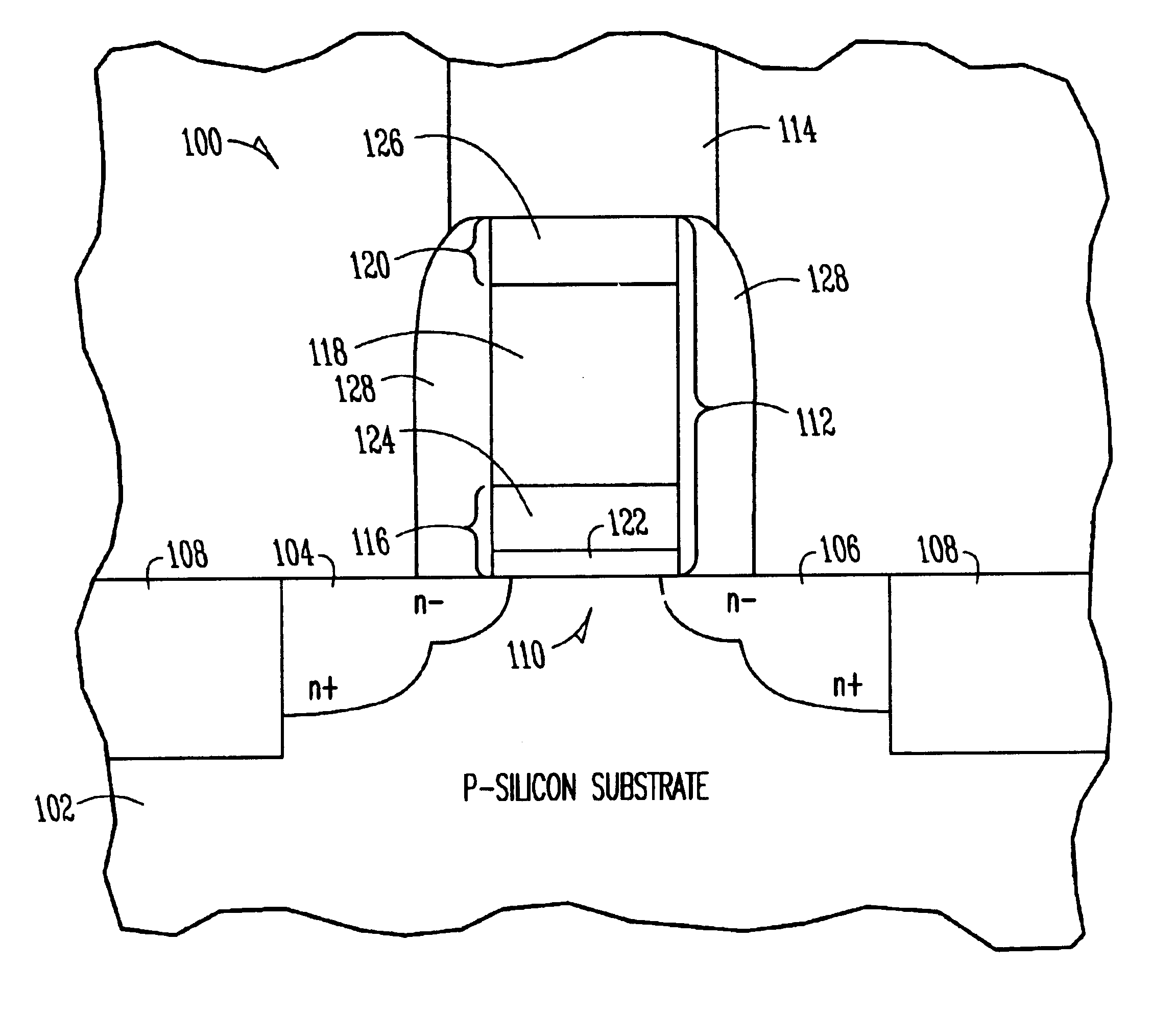

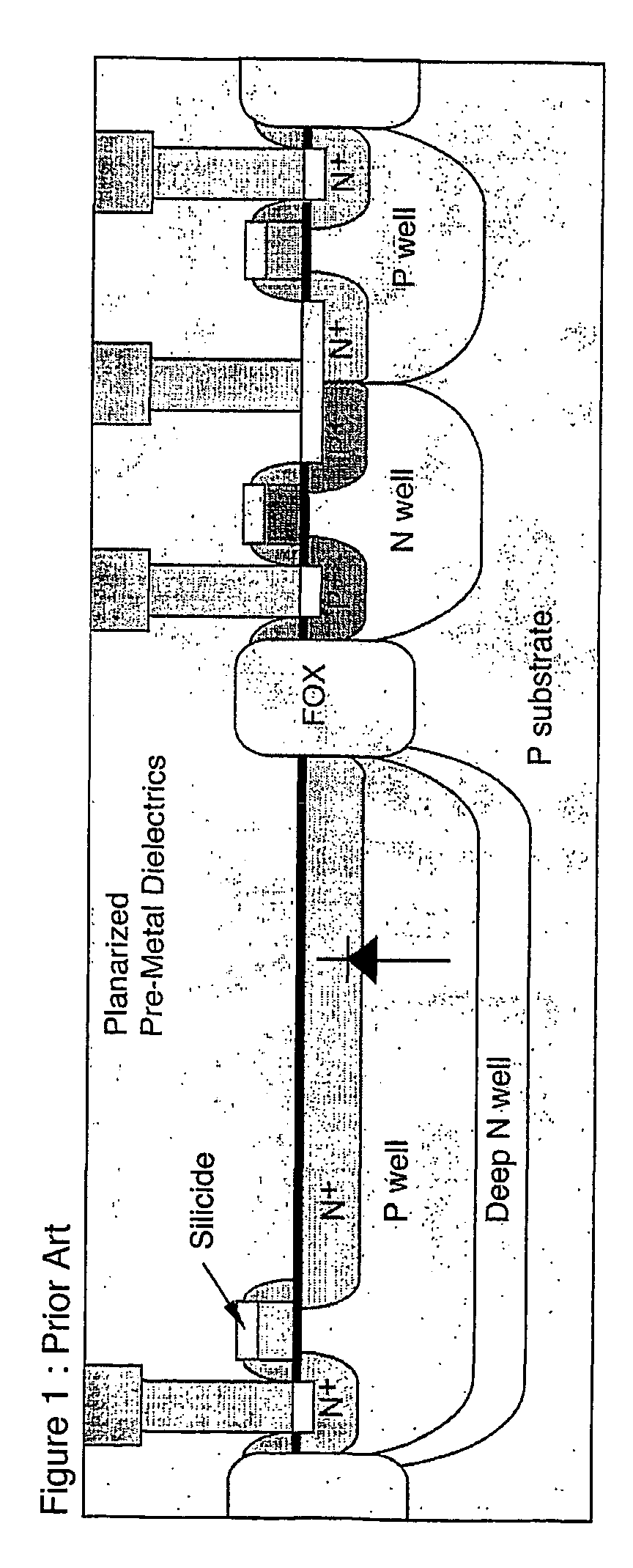

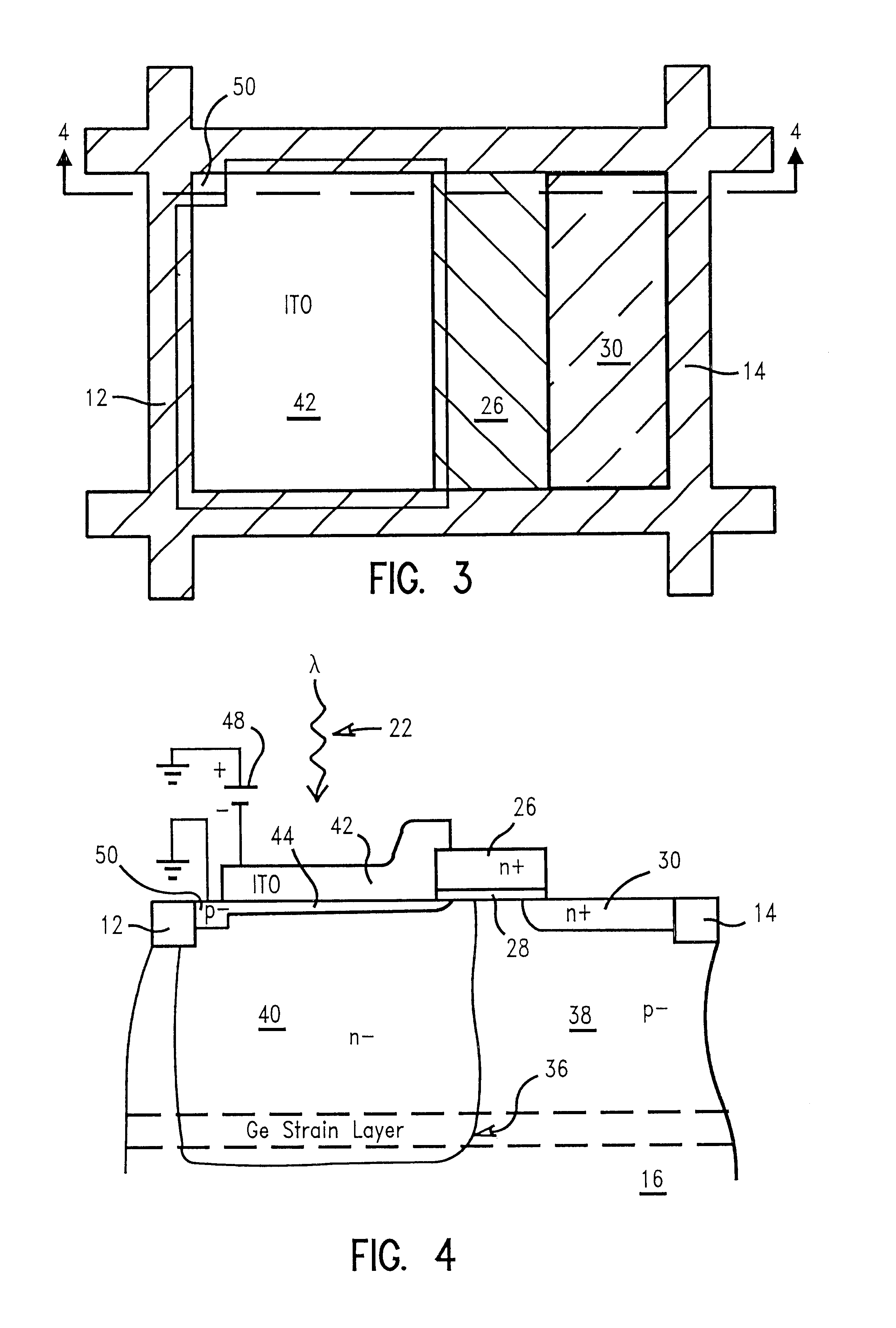

Method of detecting electromagnetic radiation with bandgap engineered active pixel cell design

InactiveUS6278102B1High light sensitivityReduce thicknessSolid-state devicesMaterial analysis by optical meansCMOS sensorSemiconductor materials

A method of detecting electromagnetic radiation with an active pixel sensor photosensitive device having an extremely thin virtual pinning layer formed by inverting semiconductor material at the surface of a photosensitive region. The thin pinning layer improves blue light response. The inverted pinning layer is produced by connecting a negative potential source to a transparent conductive layer, preferably made of indium-tin-oxide positioned over most of the photosensitive region. The conductive layer is insulated from the photosensitive region by a thin insulating layer. Connection to the pinning layer is through a coupling region formed in an area not covered by the conductive and insulating layers. Red light response is improved and the depth of the photosensitive region reduced by creating a strained layer, preferably of germanium silicon, deep within the photosensitive region. The strained layer has a modified bandgap which increases the absorption rate of red light.

Owner:GLOBALFOUNDRIES INC

Charge trapping memory cell having bandgap engineered tunneling structure with oxynitride isolation layer

ActiveUS20110075486A1Increase erasing speedSolve the lack of heightSolid-state devicesRead-only memoriesTrappingIsolation layer

A band gap engineered, charge trapping memory cell includes a charge storage structure including a trapping layer. a blocking layer, and a dielectric tunneling structure including a thin tunneling layer, a thin bandgap offset layer and a thin isolation layer comprising silicon oxynitride. The memory cell is manufactured using low thermal budget processes.

Owner:MACRONIX INT CO LTD

Epitaxy of Silicon-Carbon Substitutional Solid Solutions by Ultra-Fast Annealing of Amorphous Material

InactiveUS20070238267A1Semiconductor/solid-state device manufacturingSemiconductor devicesElectronCmos process

Expitaxial substitutional solid solutions of silicon carbon can be obtained by an ultrafast anneal of an amorphous carbon-containing silicon material. The anneal is performed at a temperature above the recrystallization point, but below the melting point of the material and preferably lasts for less than 100 milliseconds in this temperature regime. The anneal is preferably a flash anneal or laser anneal. This approach is able to produce epitaxial silicon and carbon-containing materials with a substantial portion of the carbon atoms at substitutional lattice positions. The approach is especially useful in CMOS processes and other electronic device manufacture where the presence of epitaxial Si1−yCy, y<0.1 is desired for strain engineering or bandgap engineering.

Owner:GLOBALFOUNDRIES INC

Light emitting diode having active region of multi quantum well structure

ActiveUS7649195B2Improve luminous efficiencyEnhance rate of recombinationSemiconductor devicesImpurity dopingControl electronics

Disclosed is a light emitting diode (LED) having an active region of a multiple quantum well structure in which well layers and barrier layers are alternately laminated between a GaN-based N-type compound semiconductor layer and a GaN-based P-type compound semiconductor layer. The LED includes a middle barrier layer having a bandgap relatively wider than the first barrier layer adjacent to the N-type compound semiconductor layer and the n-th barrier layer adjacent to the P-type compound semiconductor layer. The middle barrier layer is positioned between the first and n-th barrier layers. Accordingly, positions at which electrons and holes are combined in the multiple quantum well structure to emit light can be controlled, and luminous efficiency can be enhanced. Furthermore, an LED is provided with enhanced luminous efficiency using a bandgap engineering or impurity doping technique.

Owner:SEOUL VIOSYS CO LTD

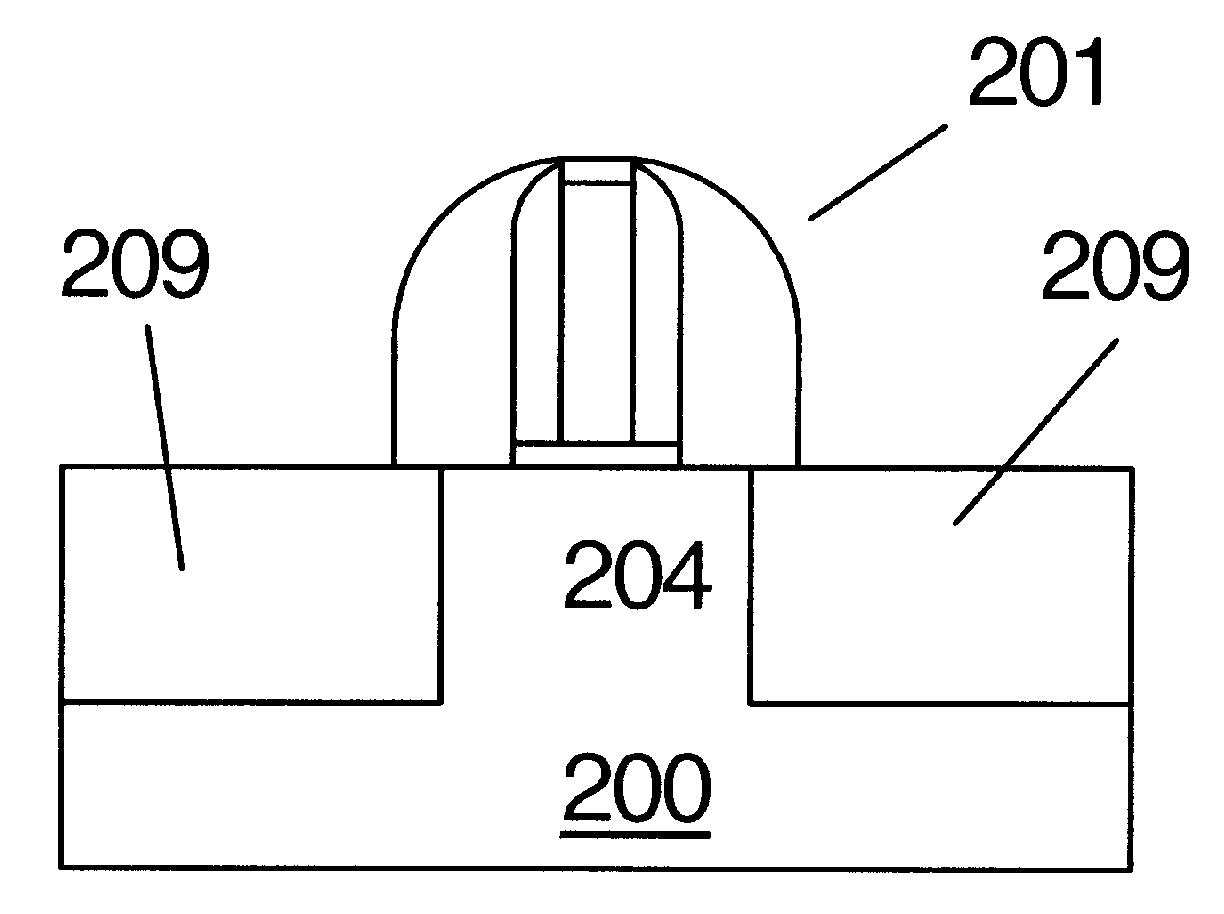

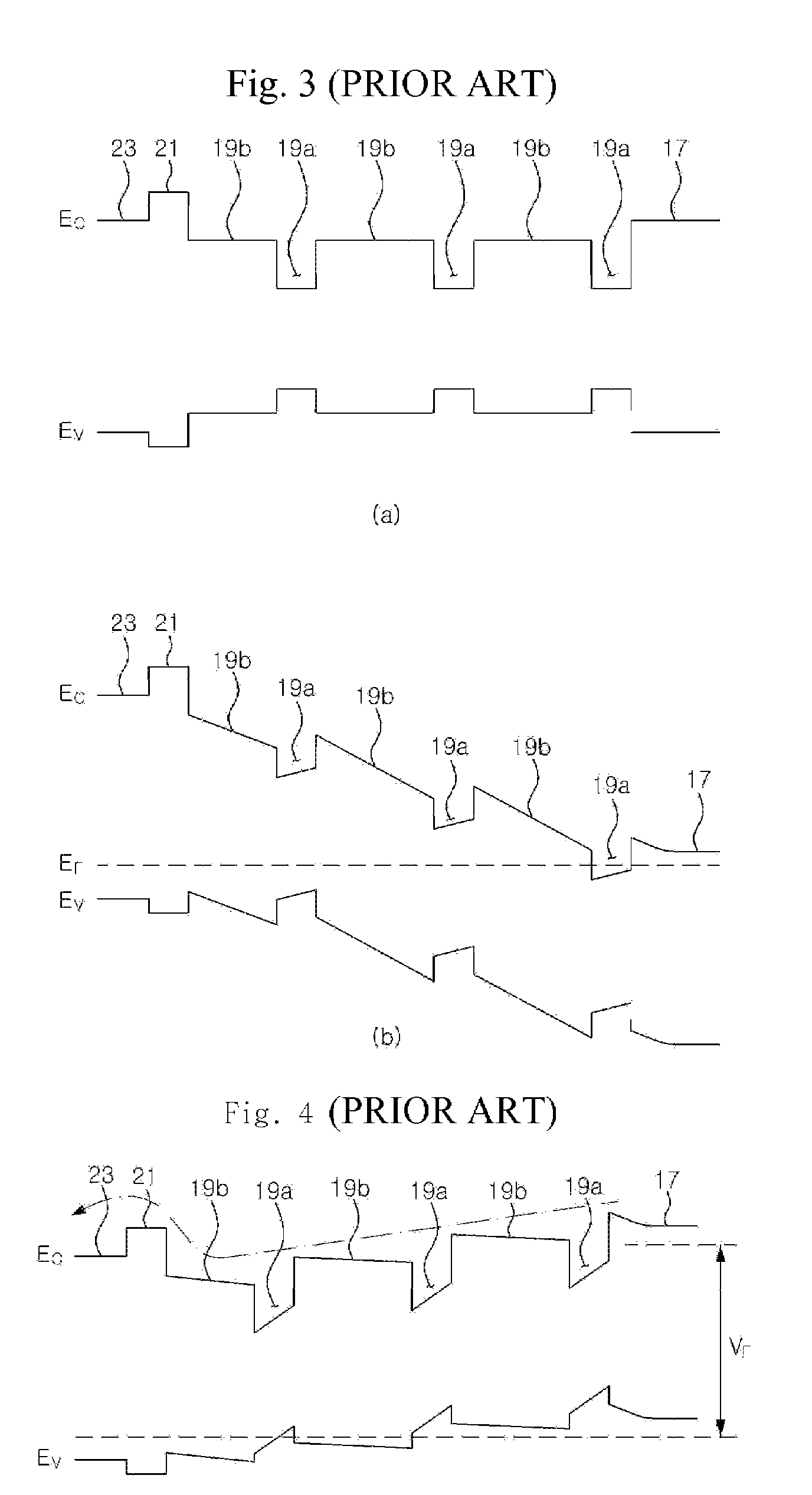

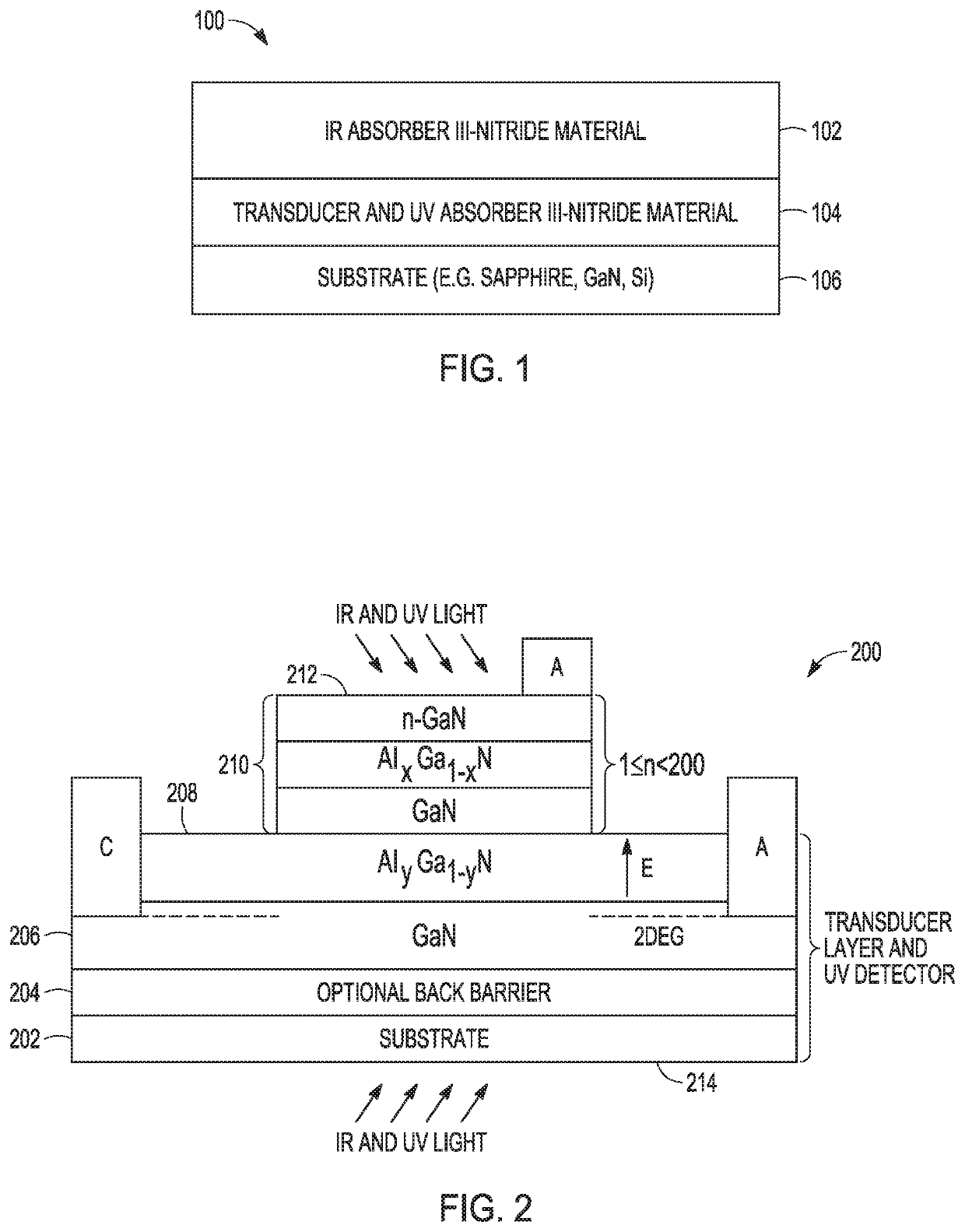

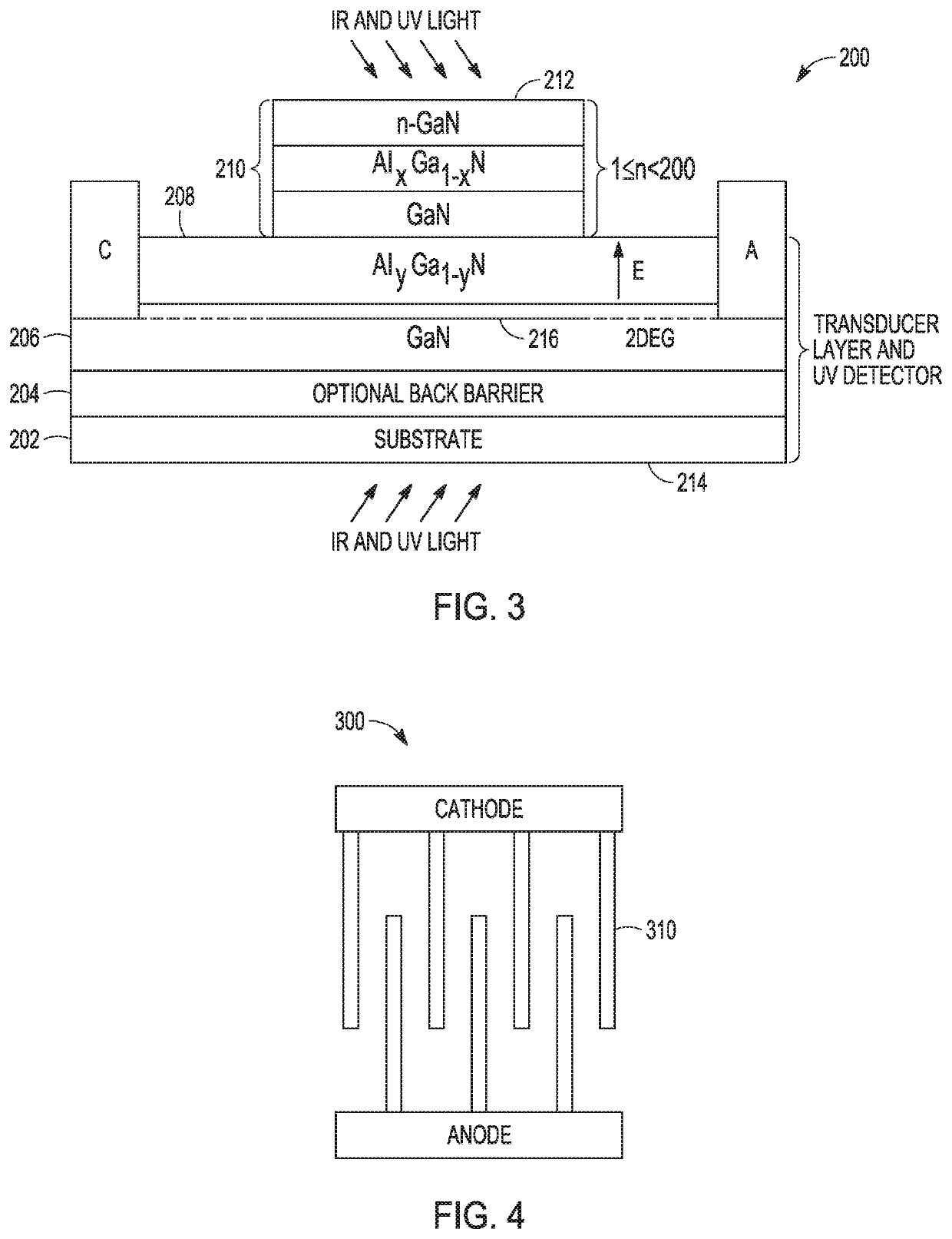

Semiconductor photodetector assembly

ActiveUS20200220036A1Reduce cost factorImprove performanceSemiconductor devicesPhotodetectorUltraviolet

Techniques to use energy band gap engineering (or band offset engineering) to produce a photodetector semiconductor assembly that can be tuned to absorb light in one or more wavelengths. For example, the assembly can be tuned to receive infrared (IR) and / or ultraviolet (UV) light. The photodetector assembly can operate as a photodiode, a phototransistor, or can include both a photodiode and a phototransistor.

Owner:ANALOG DEVICES INC

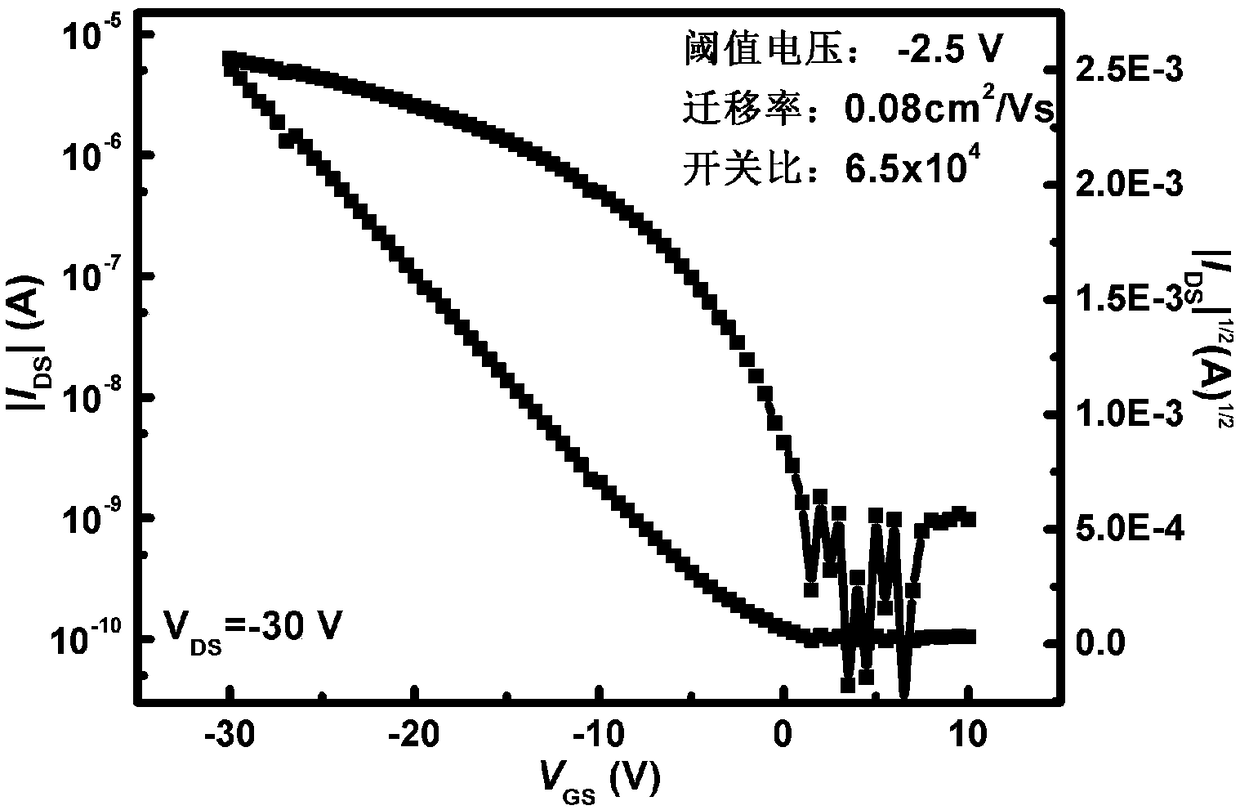

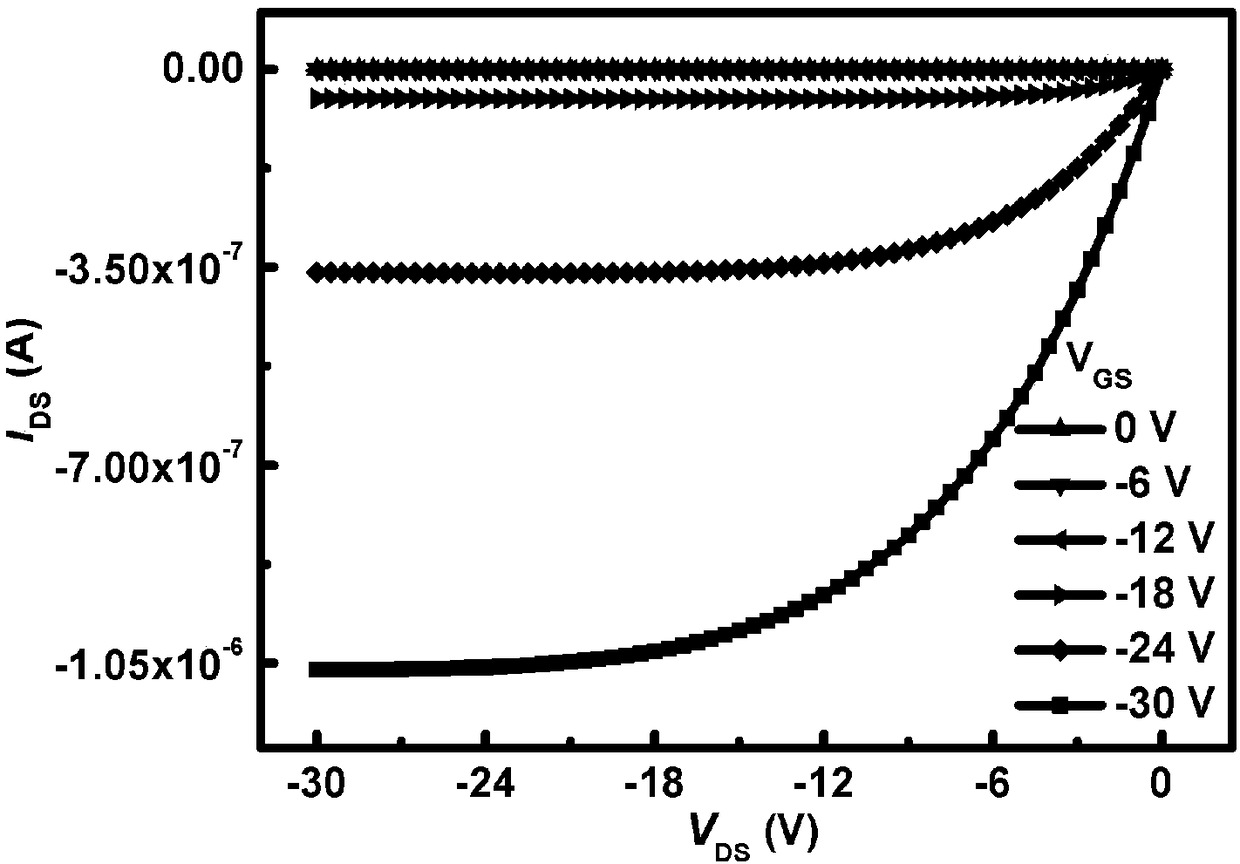

Bipolar high-capacity organic field effect transistor memory and preparation method thereof

InactiveCN108155291AEnabling high-capacity bipolar storageLong-lasting propertiesSolid-state devicesSemiconductor/solid-state device manufacturingOrganic field-effect transistorP–n junction

The invention discloses a bipolar high-capacity organic field effect transistor memory and a preparation method thereof. A series of P type and N type organic semiconductor materials are designed through band-gap engineering, a structure similar to an inorganic P-N junction is constructed through a solution spin-coating technology, and the problem of electron hole annihilation on the same wafer issolved, so that bipolar information storage of an electron hole is achieved. Meanwhile, due to a low threshold voltage, when the integrity is improved in the future, the power consumption and heatingare reduced, and information storage stability is achieved. The method aims to prepare a mixed nano-film with bipolar capture sites through simple solution spin-coating and achieve large-capacity bipolar storage. The preparation method of a film is beneficial to reduction of the production cost and large-area preparation in the low-temperature air environment.

Owner:NANJING UNIV OF POSTS & TELECOMM

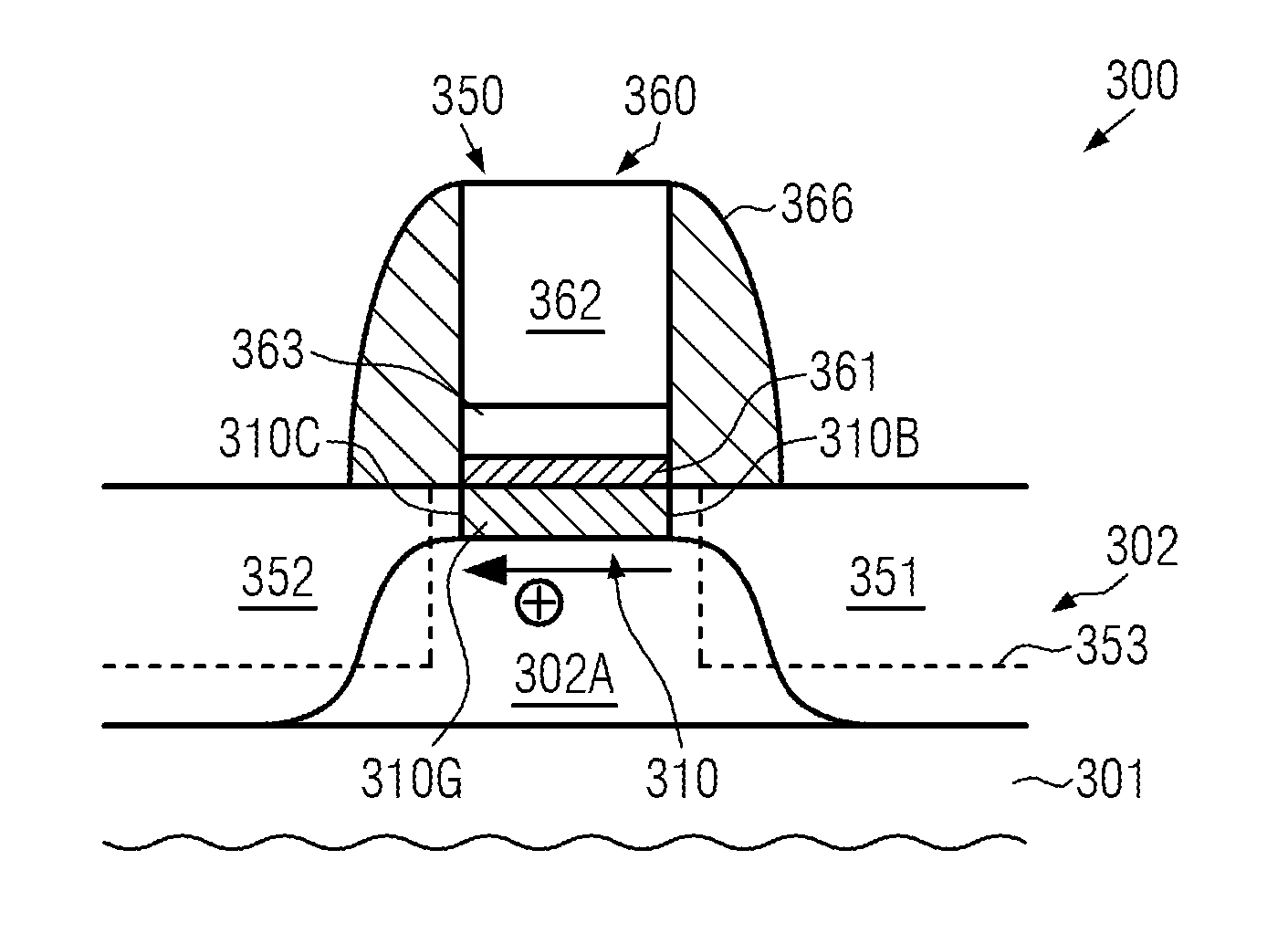

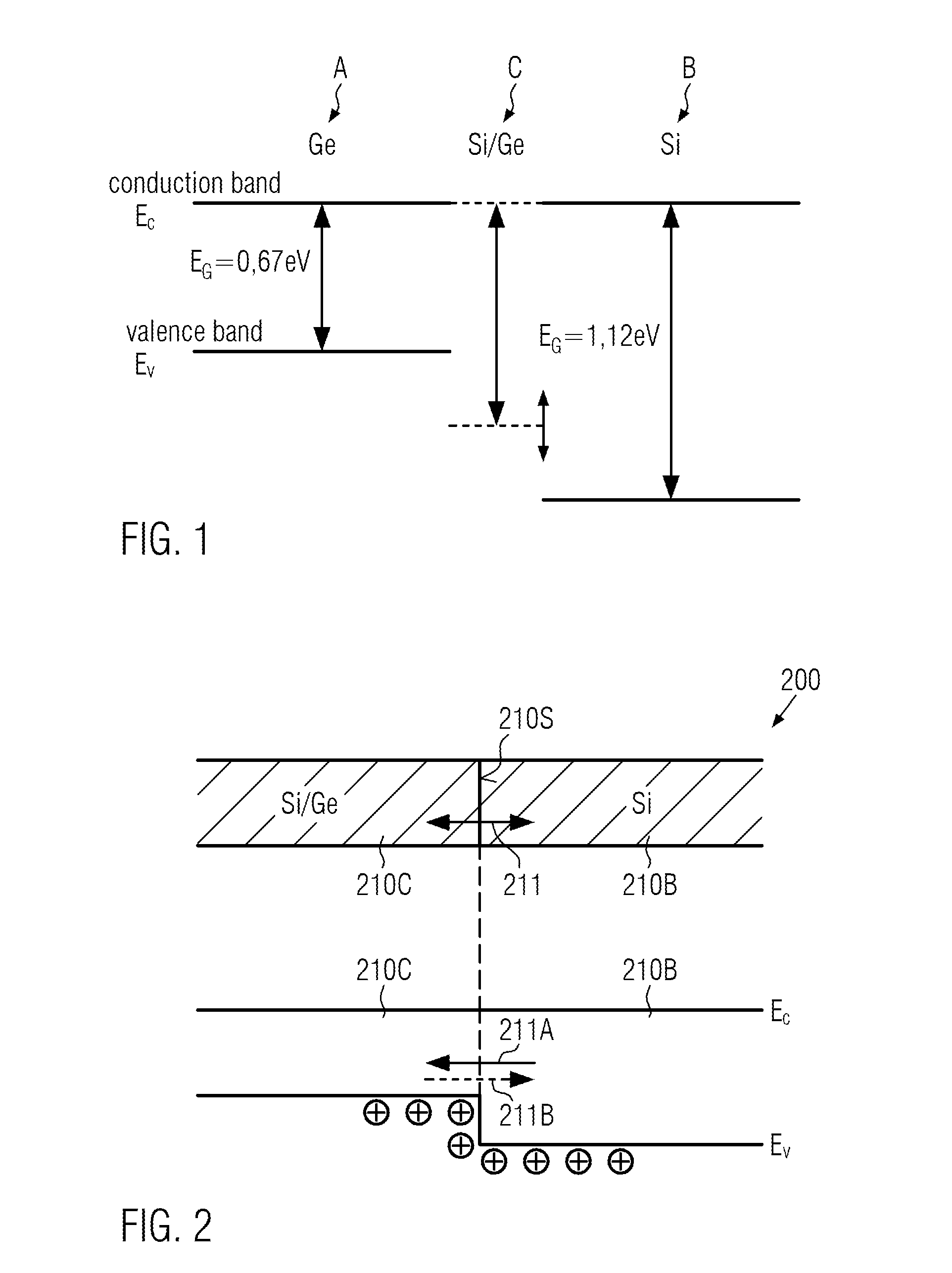

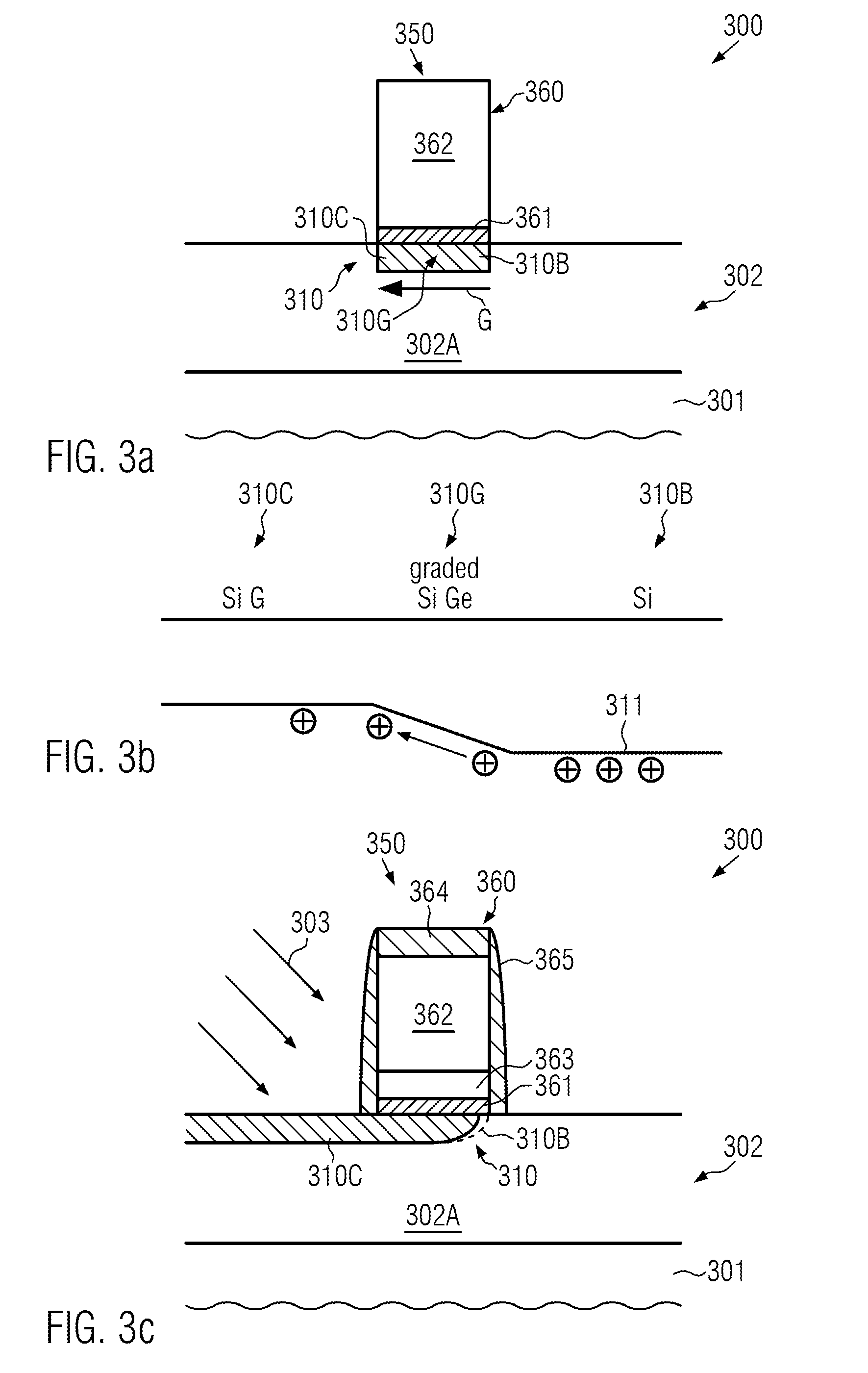

Drive current increase in field effect transistors by asymmetric concentration profile of alloy species of a channel semiconductor alloy

ActiveUS8501601B2Increased charge carrier velocityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentSemiconductor alloys

When forming sophisticated transistors, the channel region may be provided such that the gradient of the band gap energy of the channel material may result in superior charge carrier velocity. For example, a gradient in concentration of germanium, carbon and the like may be implemented along the channel length direction, thereby obtaining higher transistor performance.

Owner:GLOBALFOUNDRIES U S INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com