Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

49results about How to "Reduce antenna effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Receiver

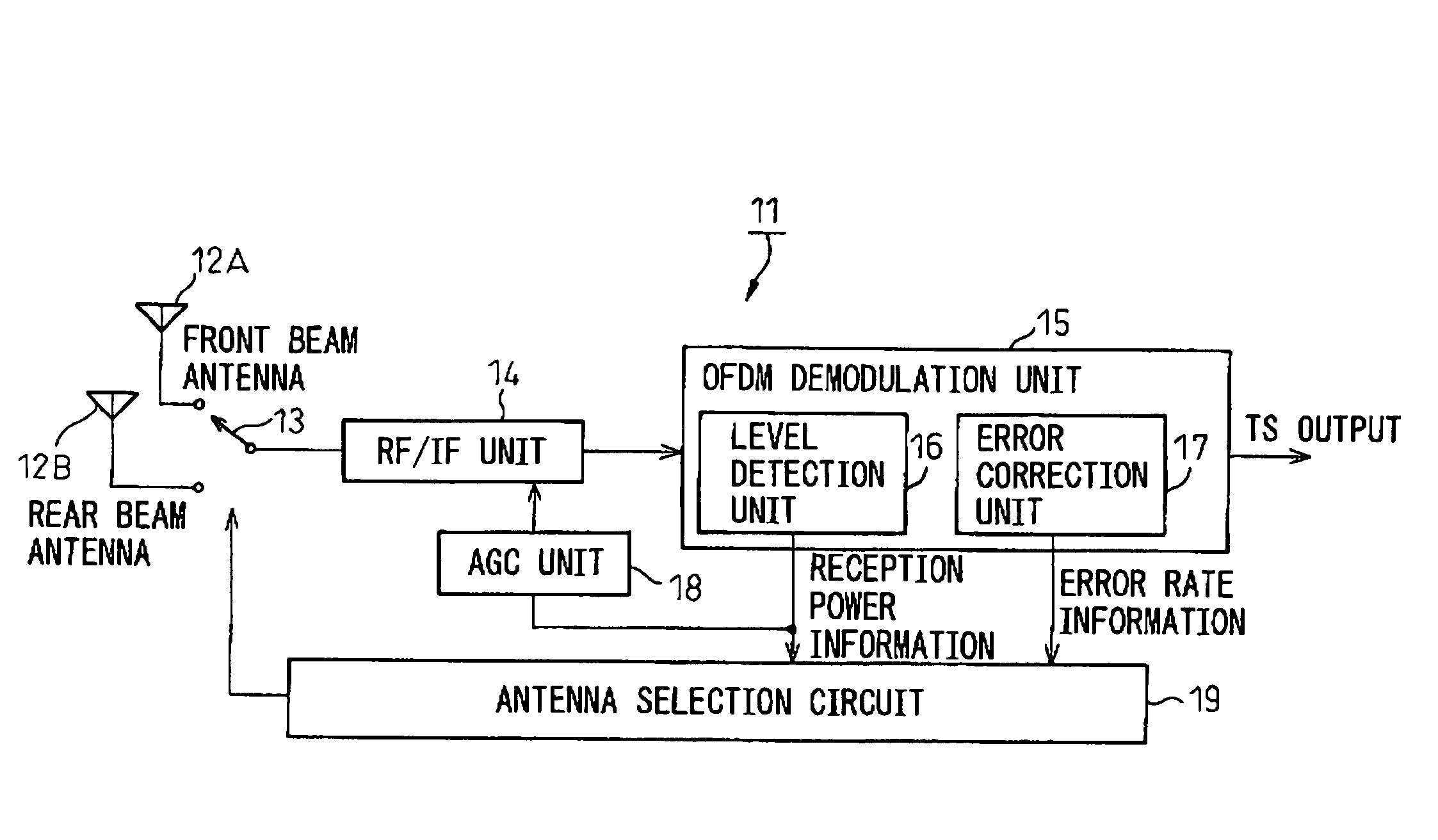

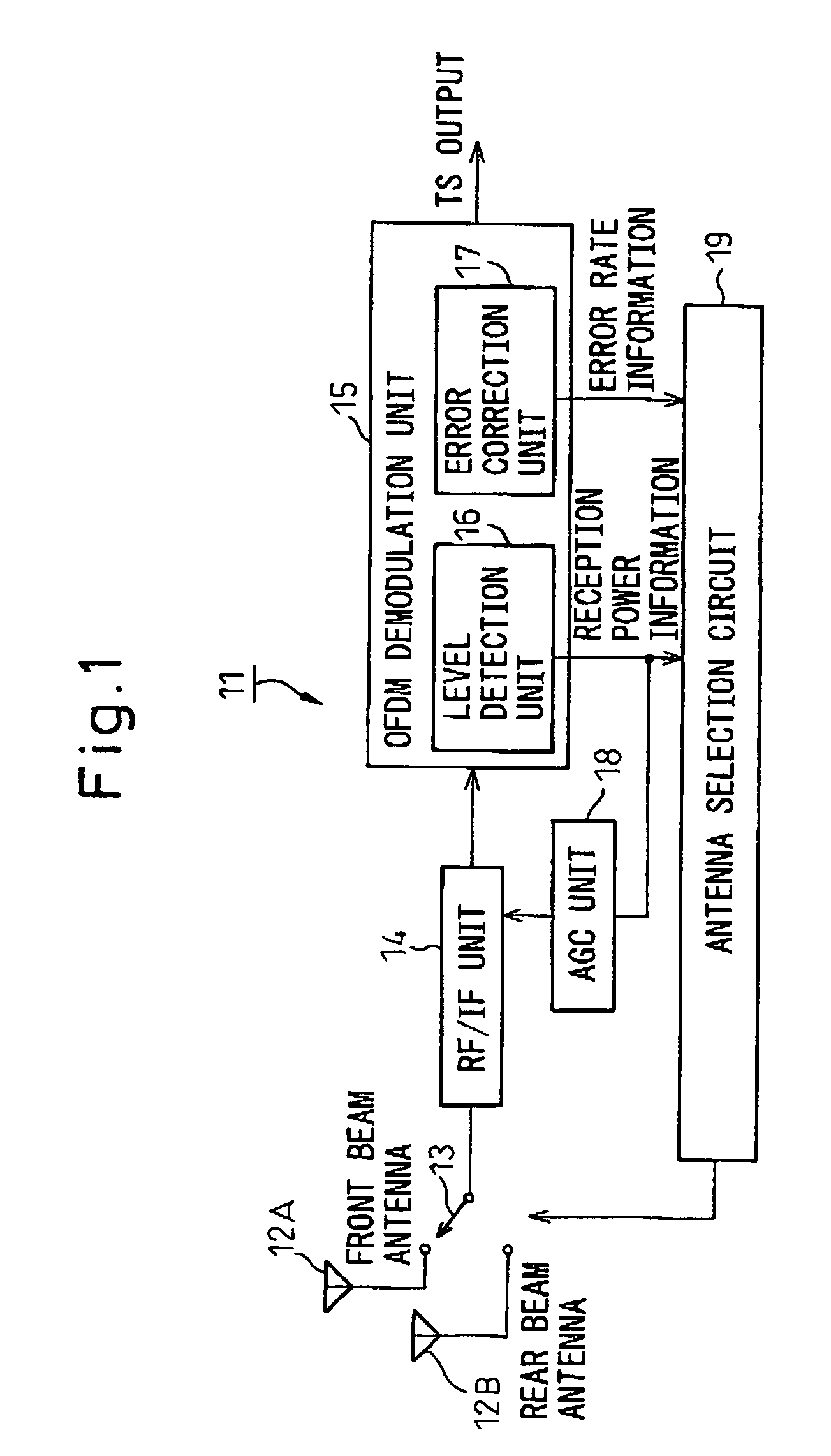

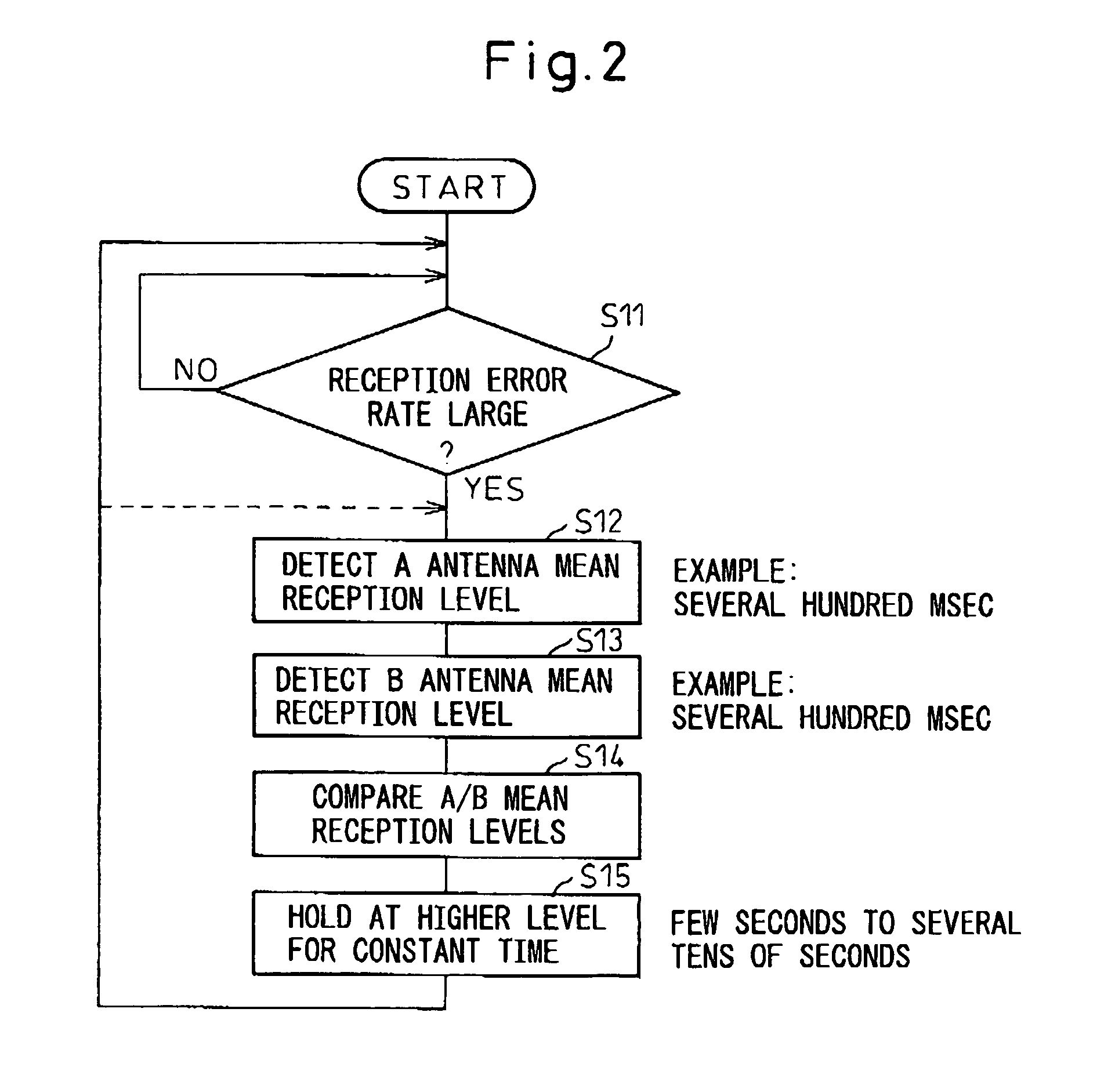

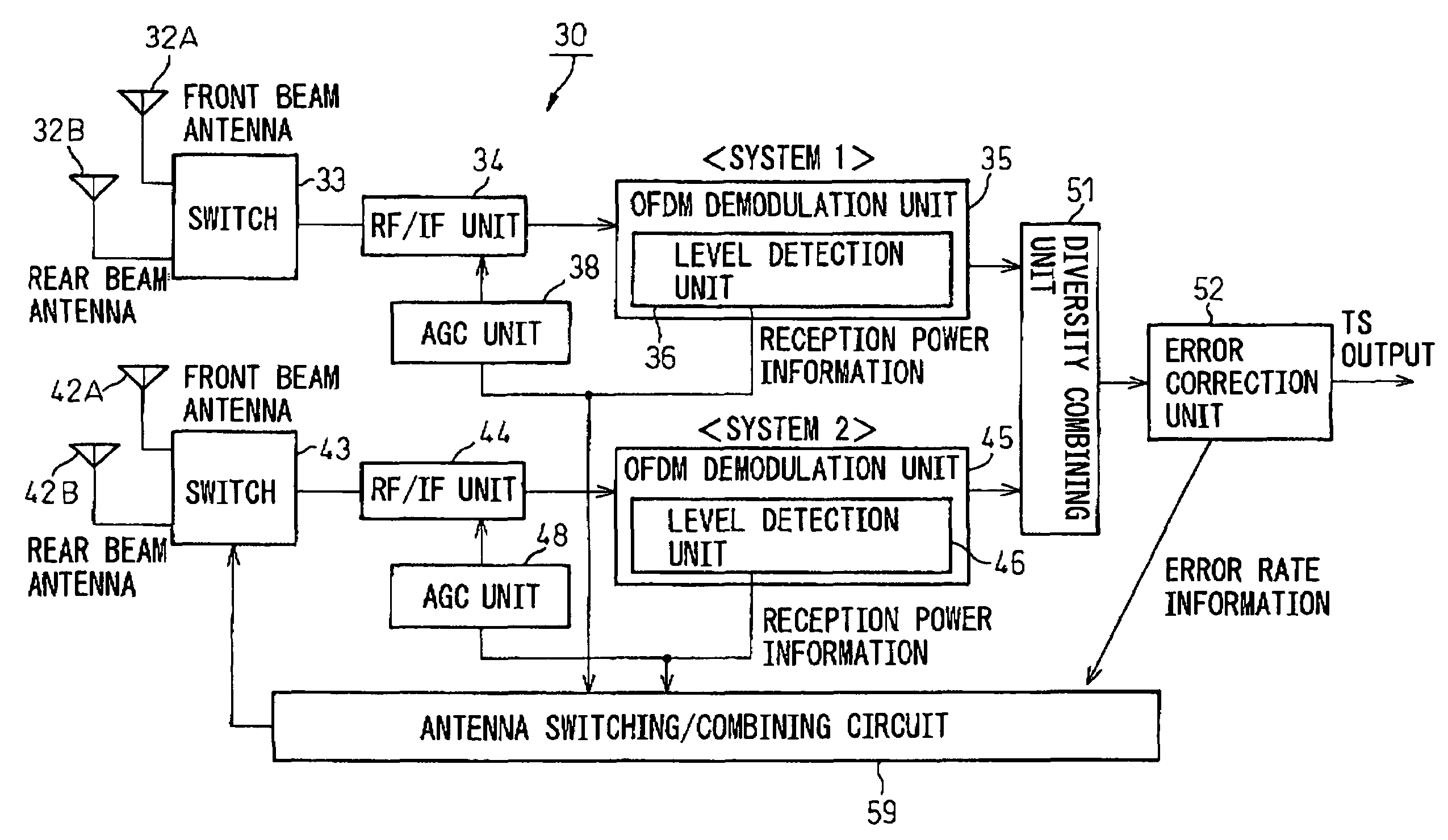

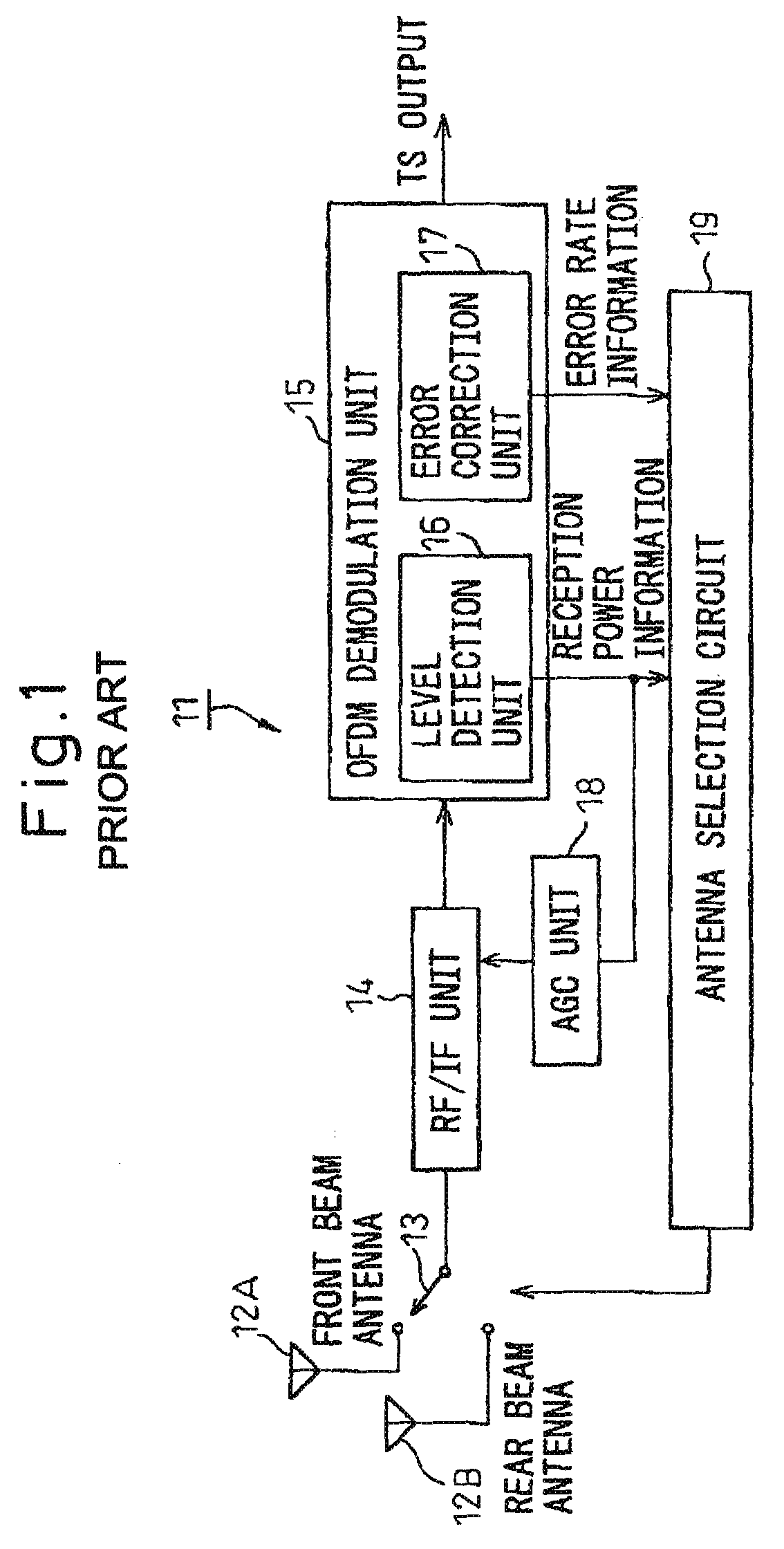

InactiveUS20050245224A1Small reception levelSuppressing fluctuation of reception levelSpatial transmit diversityModulated-carrier systemsDirectional antennaEngineering

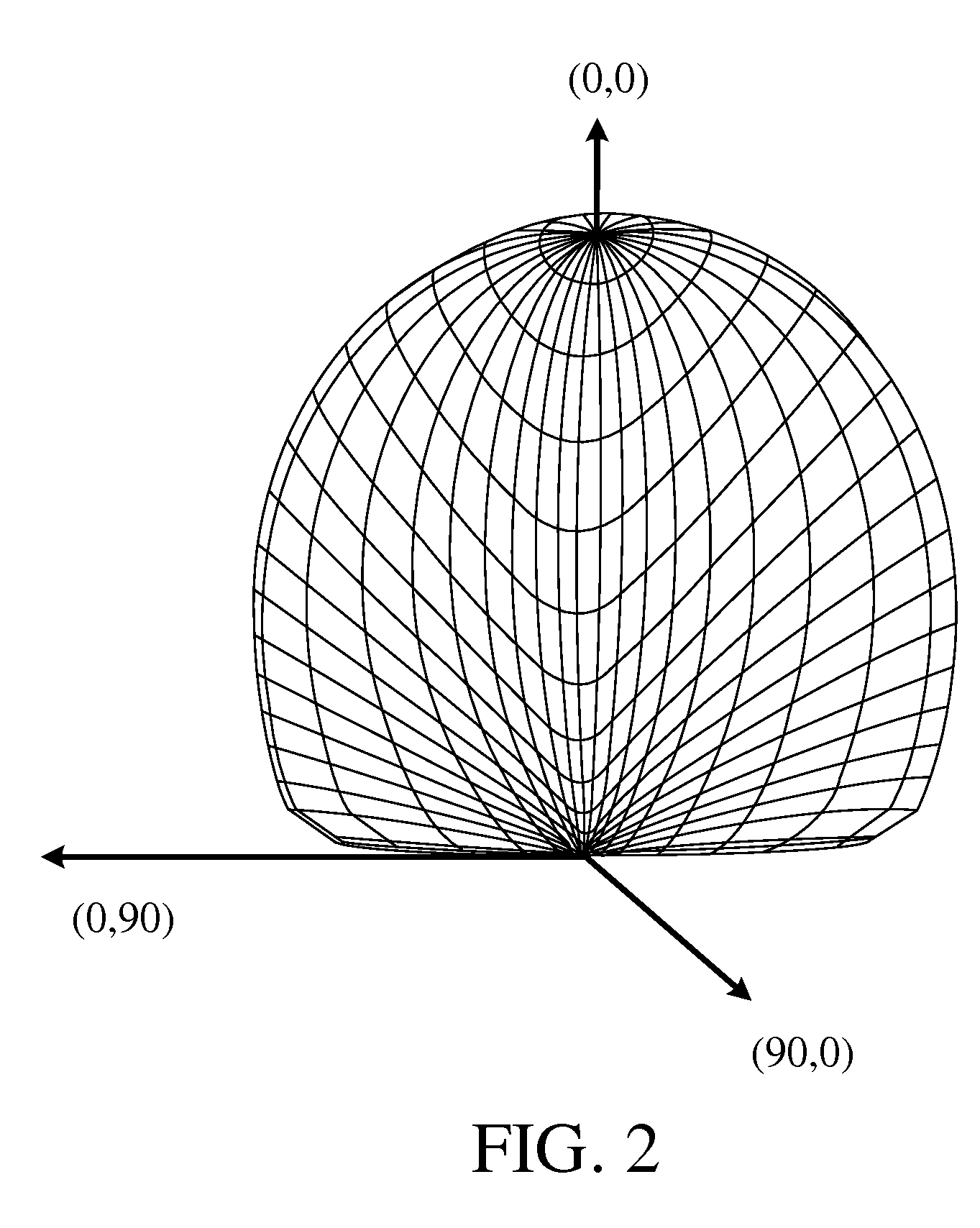

A receiver for receiving a digital signal of a radio wave etc. modulated by the OFDM scheme, provided with a first reception unit having a first antenna set comprising a plurality of directional antennas, a first switching / combining unit for outputting a signal received at one directional antenna of said first antenna set or a combined signal of signals received by at least two directional antennas in the first antenna set; a second reception unit having a second antenna set comprising a plurality of directional antennas, a second switching / combining unit for outputting a signal received at one directional antenna of the second antenna set or a combined signal of signals received by at least two directional antennas in the second antenna set; and a switching / combining control unit for controlling the switching / combining operation of the reception signals of the first switching / combining unit and / or the second switching / combining unit based on the states of reception in the first reception unit and the second reception unit.

Owner:FUJITSU GENERAL LTD

Capacitive distance sensor

ActiveCN102954753ASimple measurement circuitReduce thermal noiseUsing electrical meansElectric/magnetic depth measurementCapacitive couplingPhysics

The invention provides a capacitive distance sensor. The capacitive distance sensor is on the basis of the physical principle that the value of a capacitor is inversely proportional to the distance between capacitor plates; and once a coupling capacitor is generated between the surface of a detected conductor and a capacitance measuring plate on the single side of the surface of a sensor, the distance from the capacitance measuring plate to the surface of the detected conductor can be calculated by measuring the value of the coupling capacitor. The capacitive distance sensor provided by the invention has a circuit structure, and comprises the capacitance measuring plate, a reference capacitor, a capacitor coupling plate, a reference capacitor charging circuit, a capacitance measuring plate discharging circuit, a charge neutralization circuit, a programmable level generator 1, a programmable level generator 2 and a voltage comparator. The capacitive distance sensor has the characteristics of linearization, resistance to shifting, and low noise.

Owner:MICROARRAY MICROELECTRONICS CORP LTD

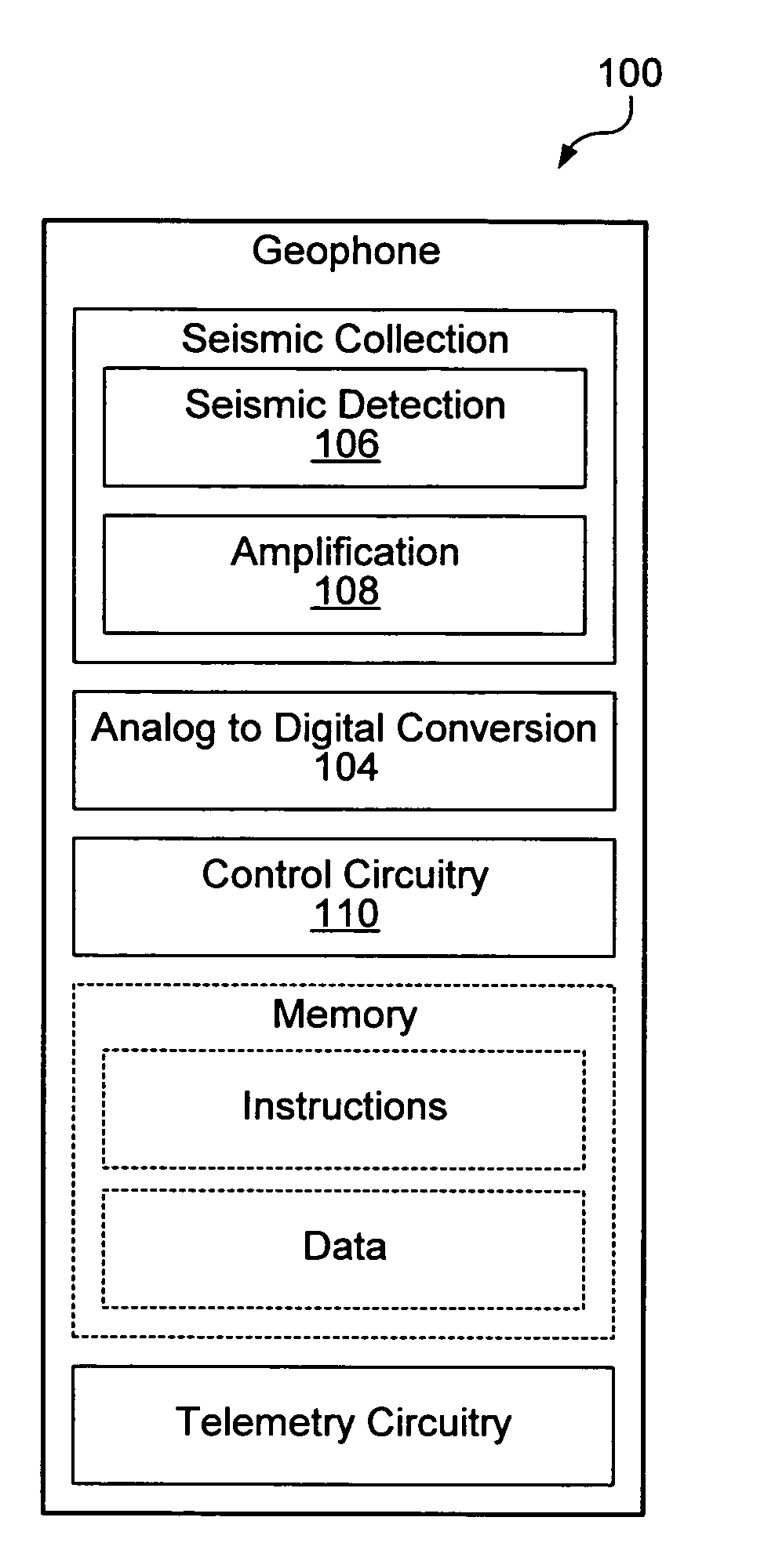

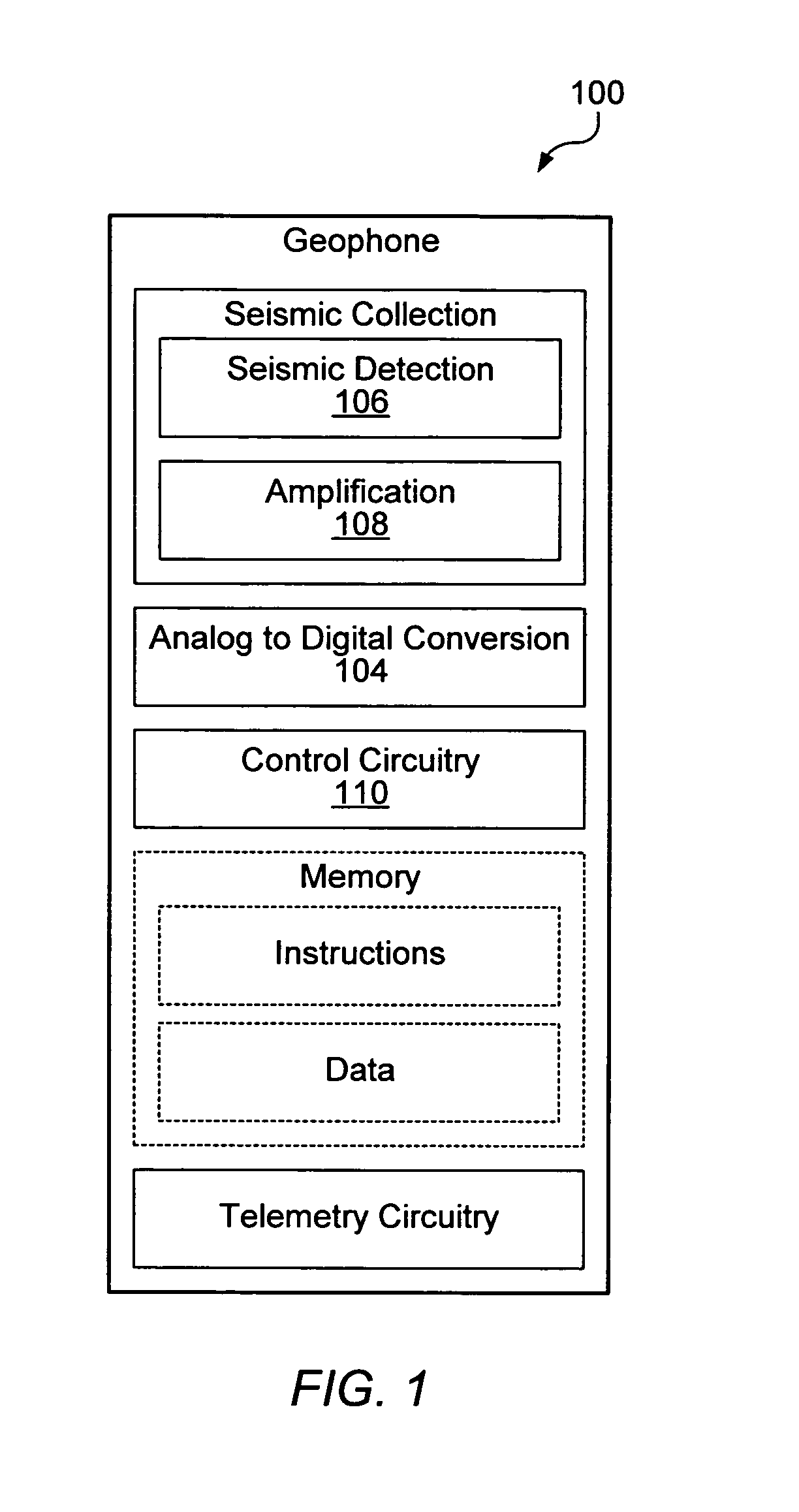

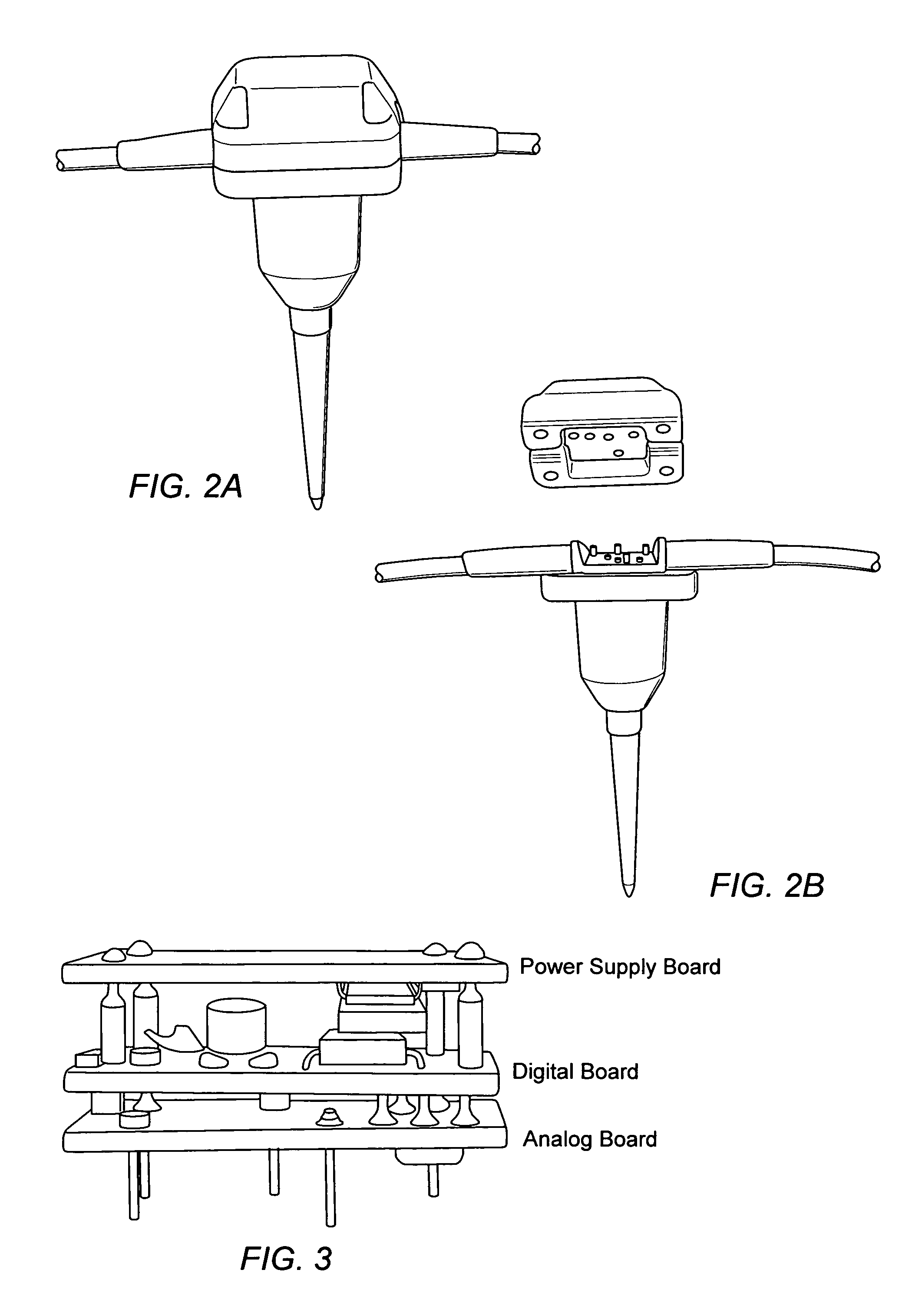

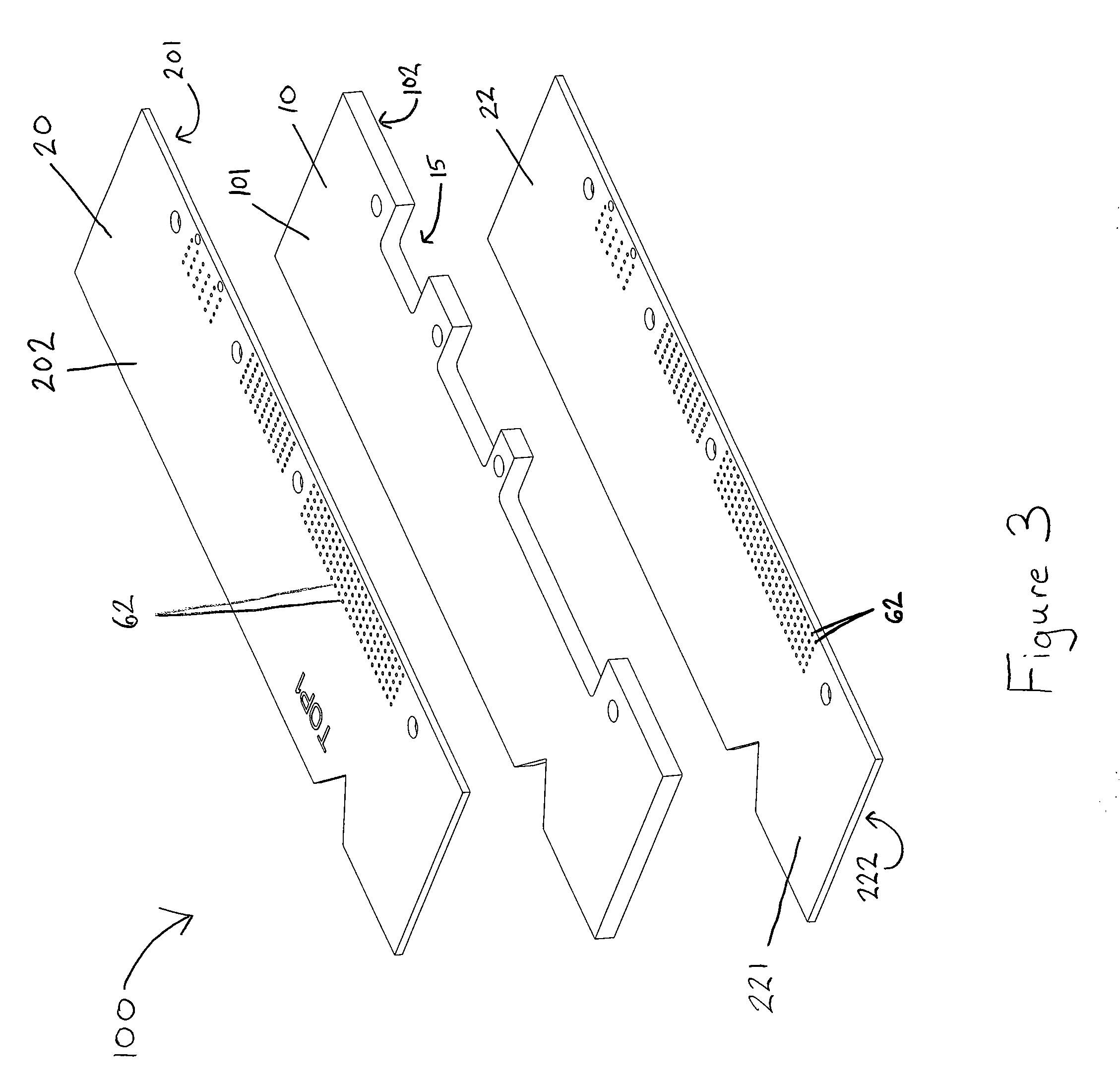

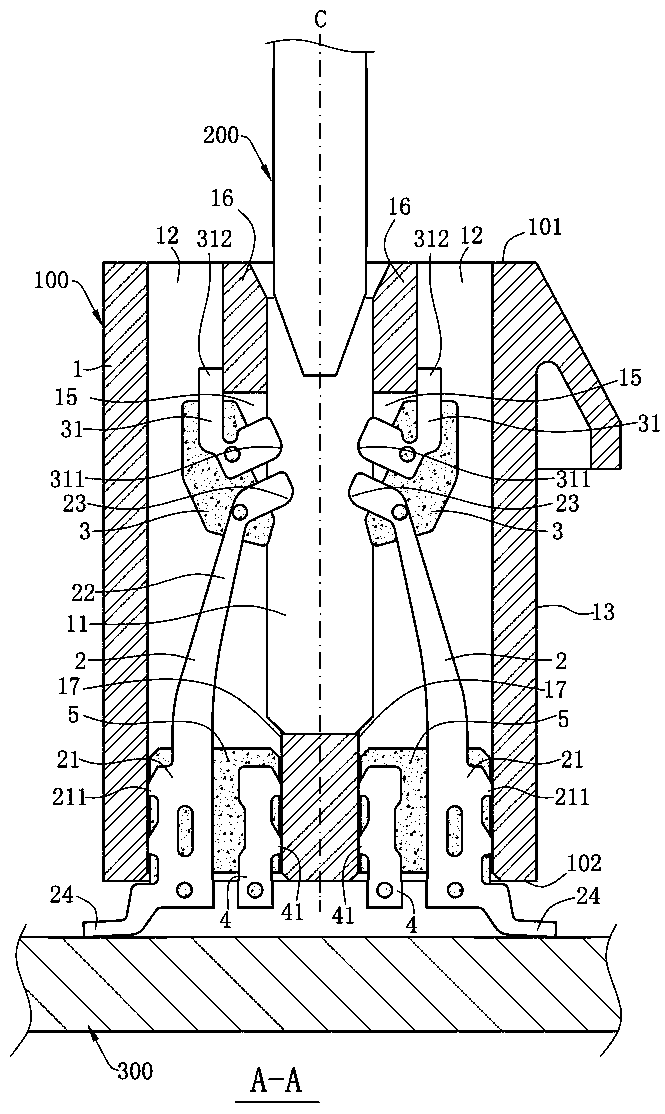

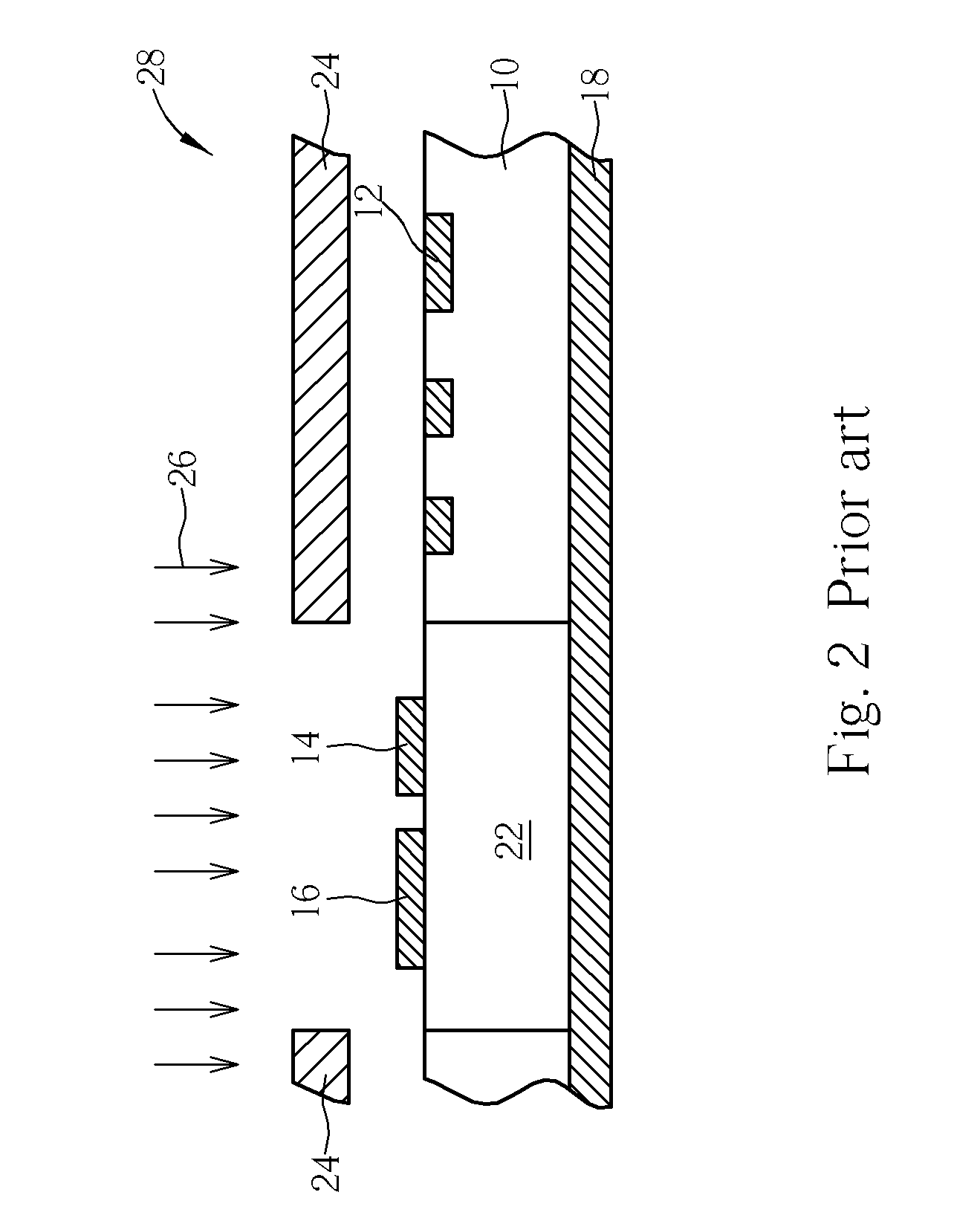

Method and apparatus for gathering seismic data

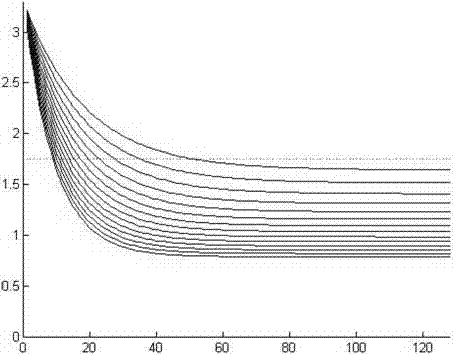

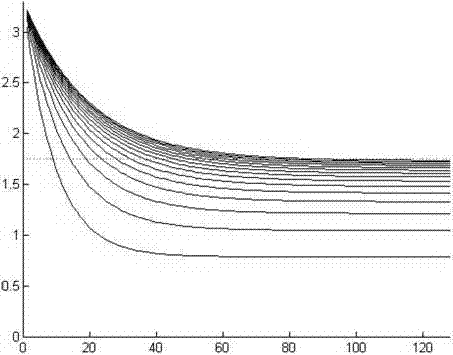

InactiveUS7085196B2Eliminate problemReduce antenna effectSeismic signal receiversSeismic signal transmissionData loggerEngineering

In the present invention, a seismic receiver contains an onboard digitizer that samples and converts a signal from detected seismic energy into the digital domain. The receiver contains an analog to digital converter, a transmission circuitry, and a link to the seismic detection circuitry. The signal from the seismic detection circuitry is converted into a digital signal, which is then relayed to the data recorder. These components are all resident to the receiver itself. Additional control circuitry is employed to provide clocking and testing functions. These receivers communicate with one another, and provide sampled seismic data on an individual basis. The components may be prepared on a PCB and put inside the receiver cap. The PCB may be flexible in nature, as to provide a maximum of surface mounted components in the smallest amount of space.

Owner:NEMETH GEZA

Receiver

InactiveUS7636593B2Small reception levelSuppressing fluctuation of reception levelSpatial transmit diversityModulated-carrier systemsDirectional antennaEngineering

Owner:FUJITSU GENERAL LTD

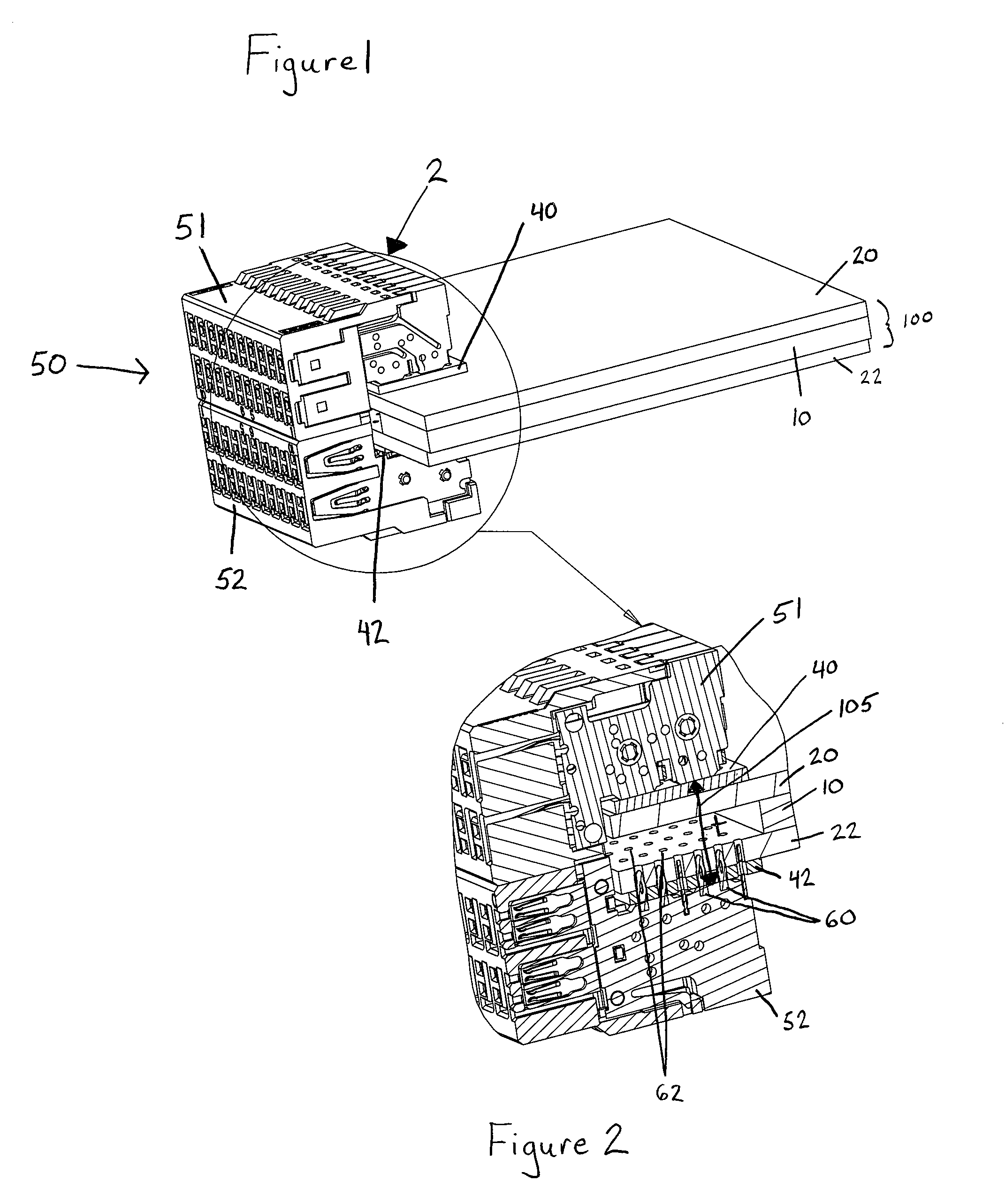

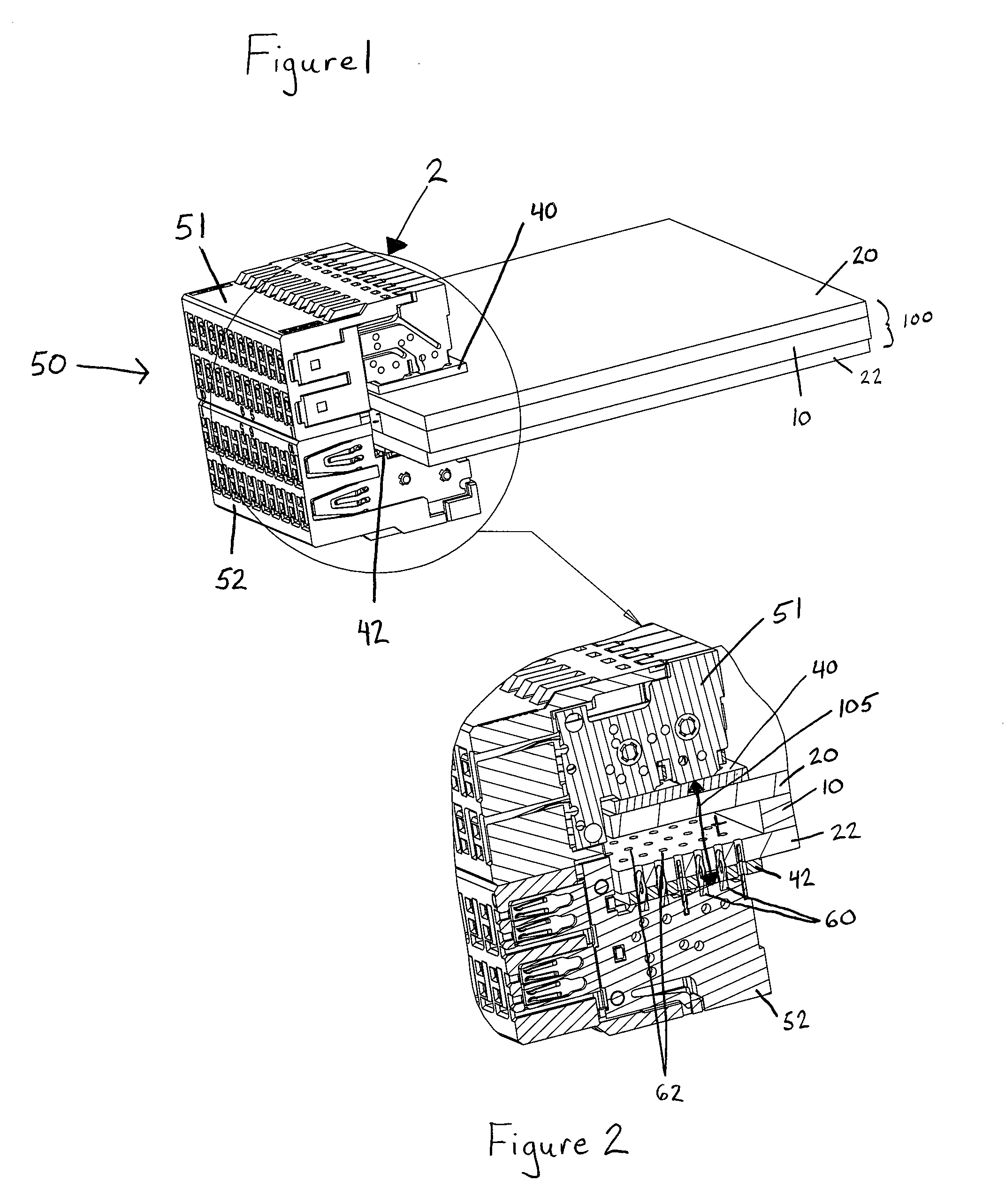

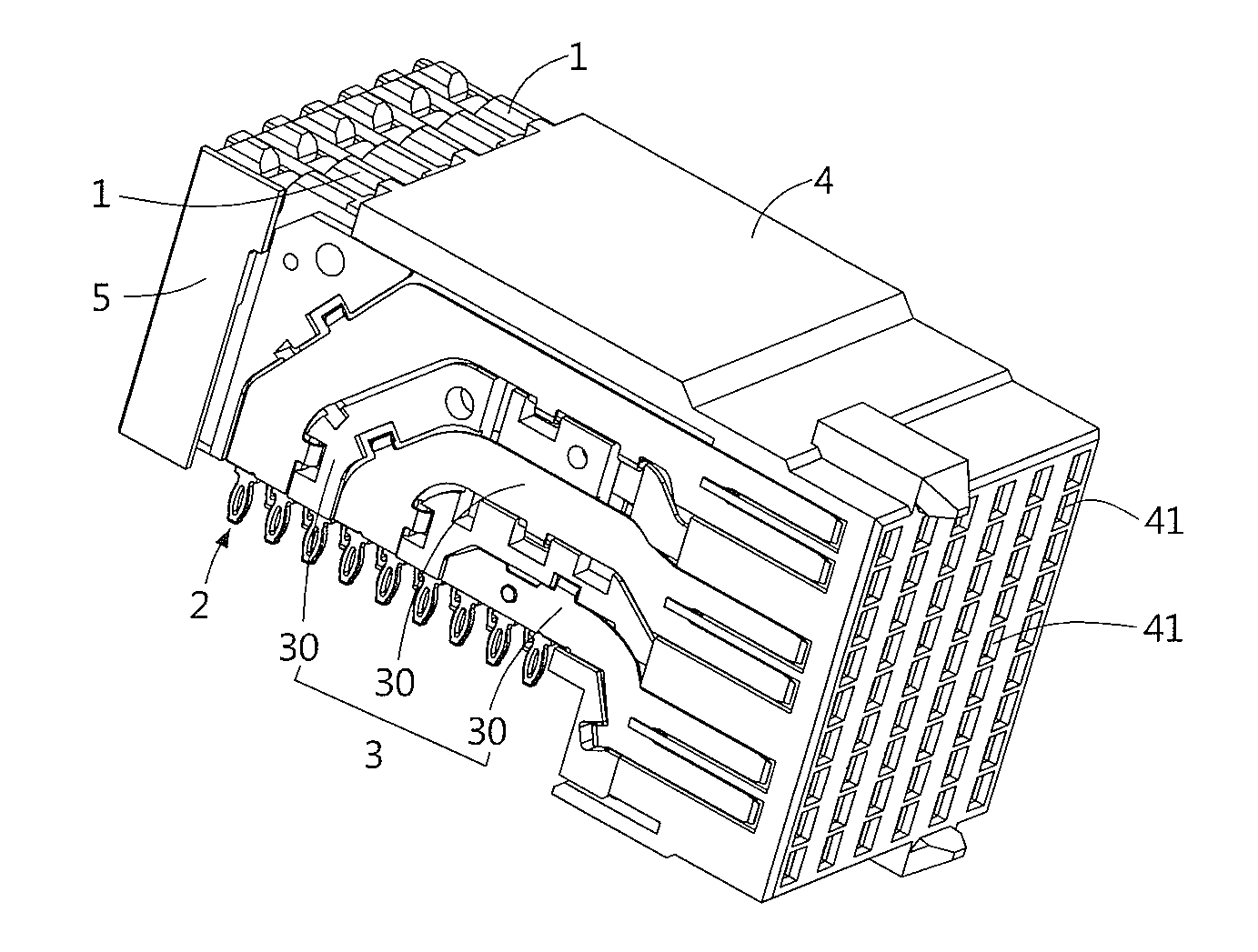

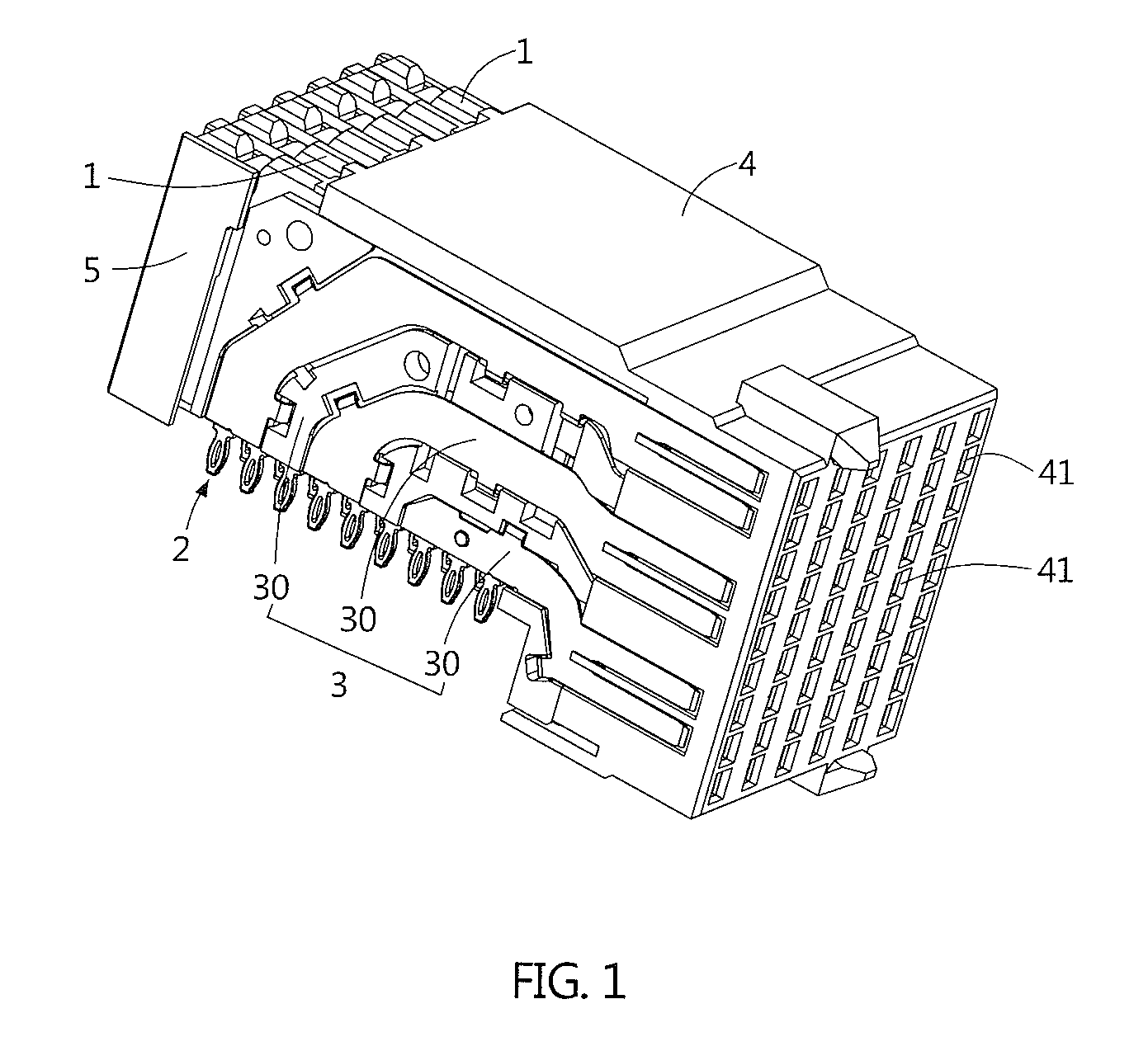

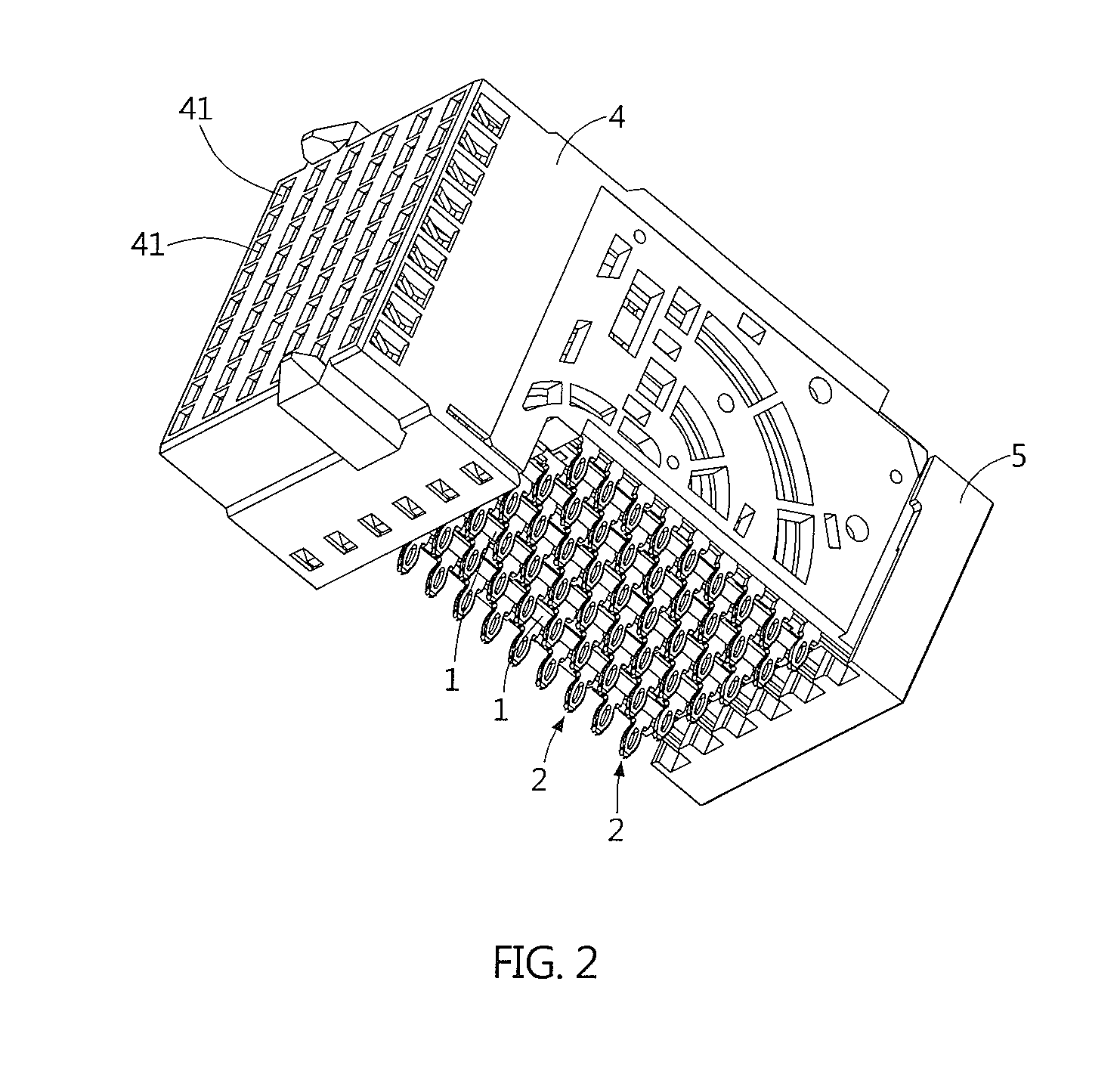

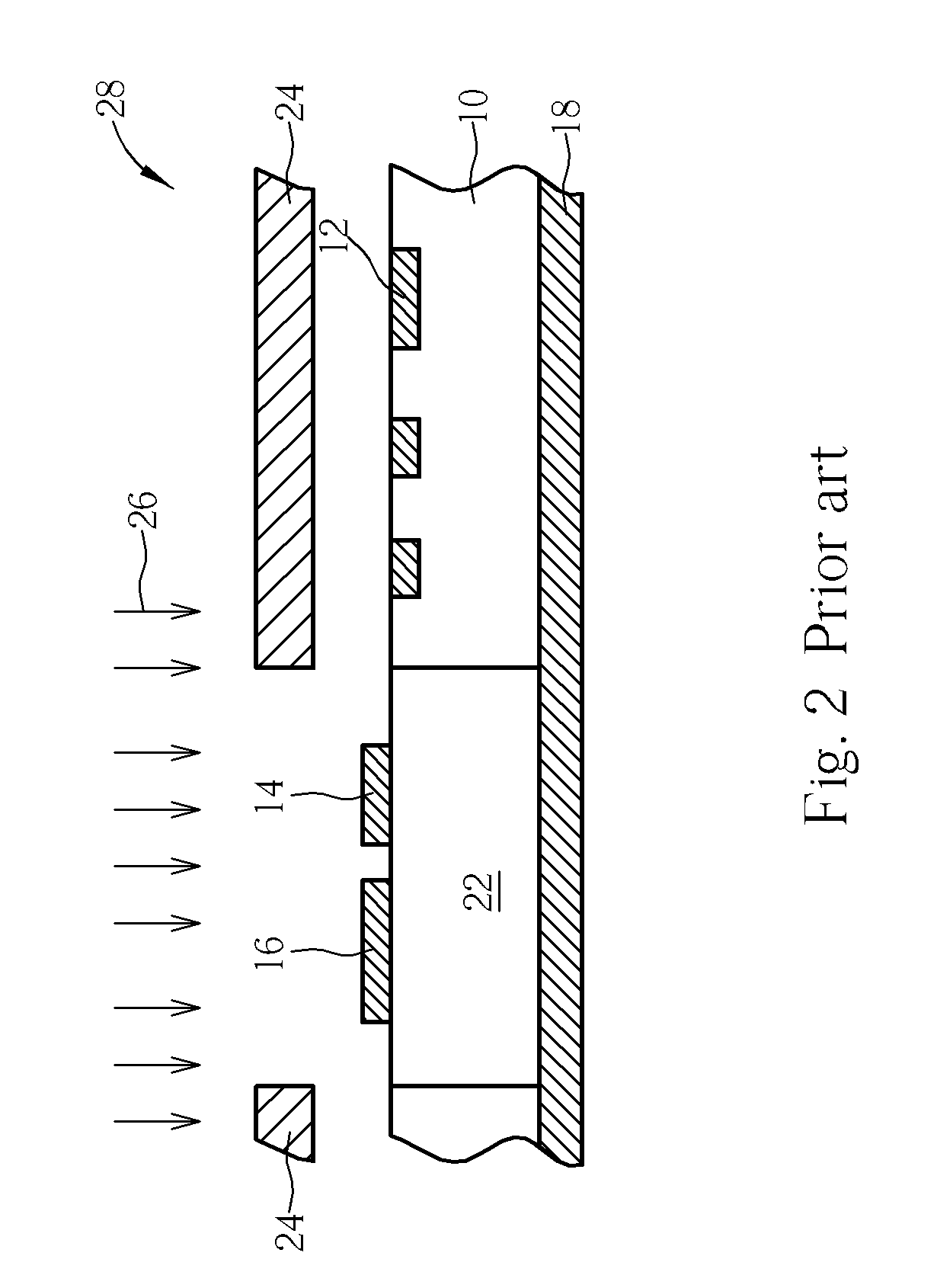

Straddle mount connector

ActiveUS7442055B2Reduce antenna effectReduce eliminateCoupling device detailsPrinted circuitsEngineeringStraddle

A straddle mount connector for use with a computer card having multiple circuit boards on opposing sides of a heat sink is disclosed. The straddle mount connector includes a pair of connector portions on opposing sides of the computer card. A first surface of the first connector portion is in electrical and physical contact with a board on one side of the heat sink while a first surface of the second connector portion is in electrical and physical contact with the board on the other side of the surface. The first surface of the first connector portion and the first surface of the second connector portion are separated by a fixed, predetermined distance.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

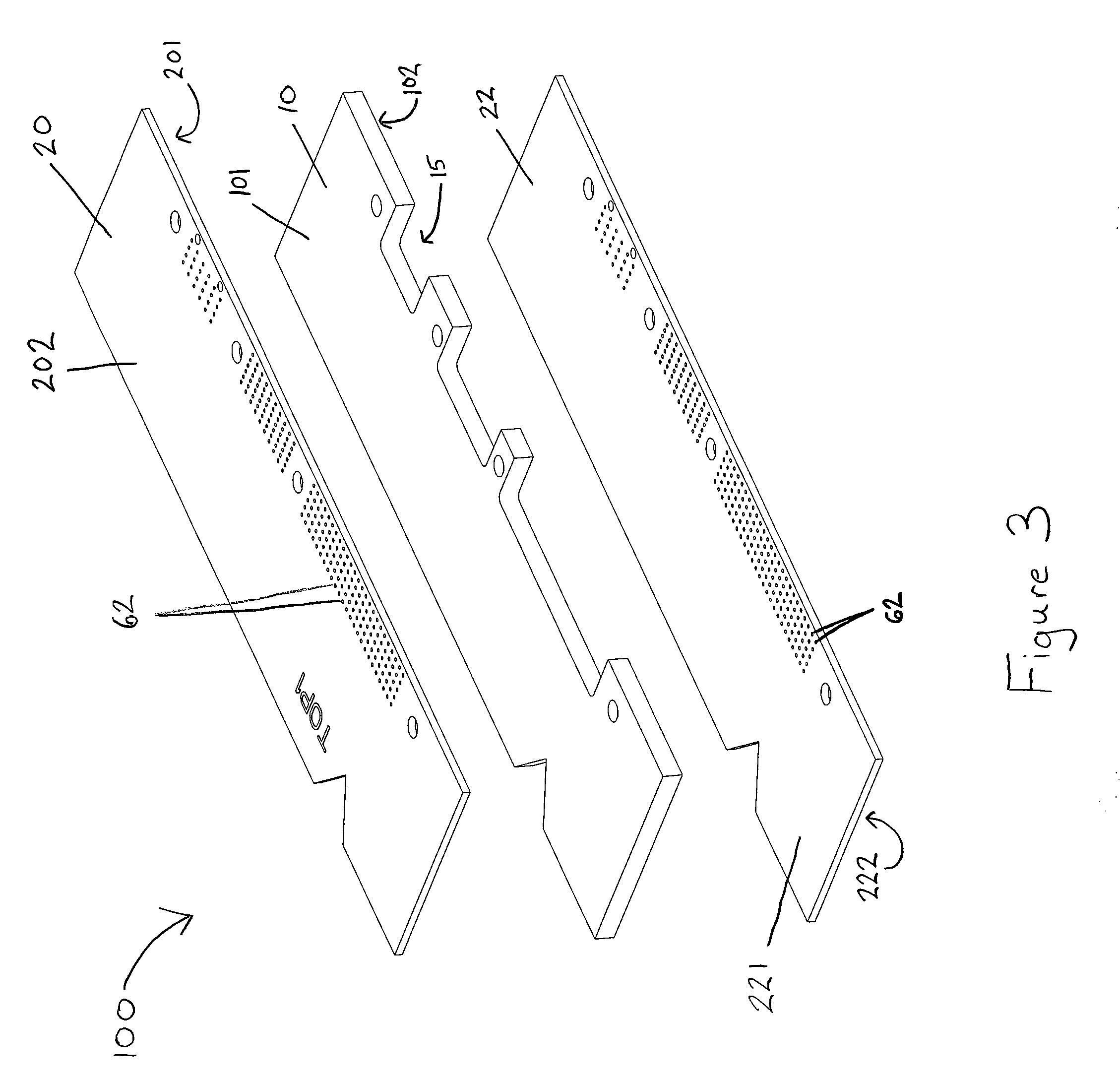

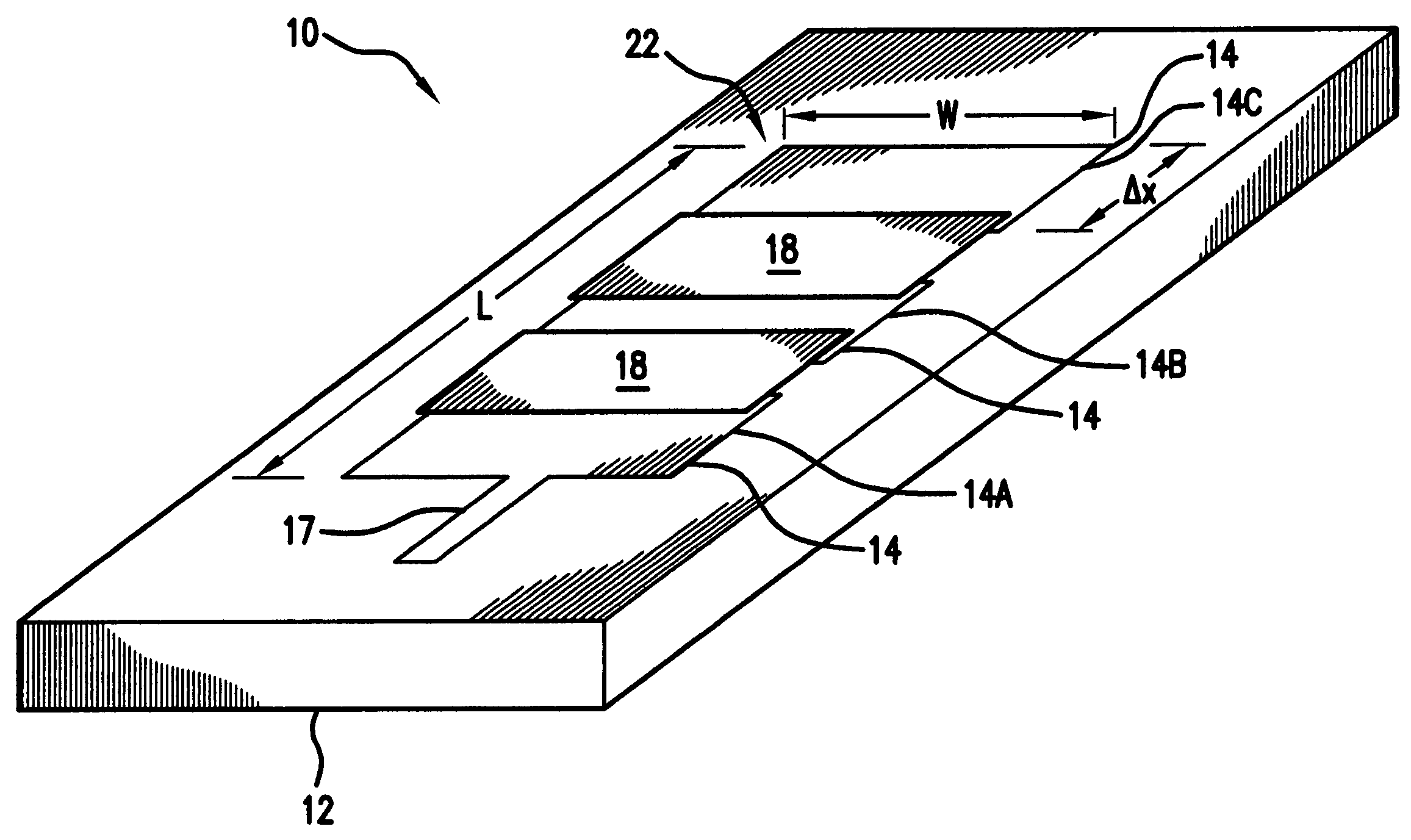

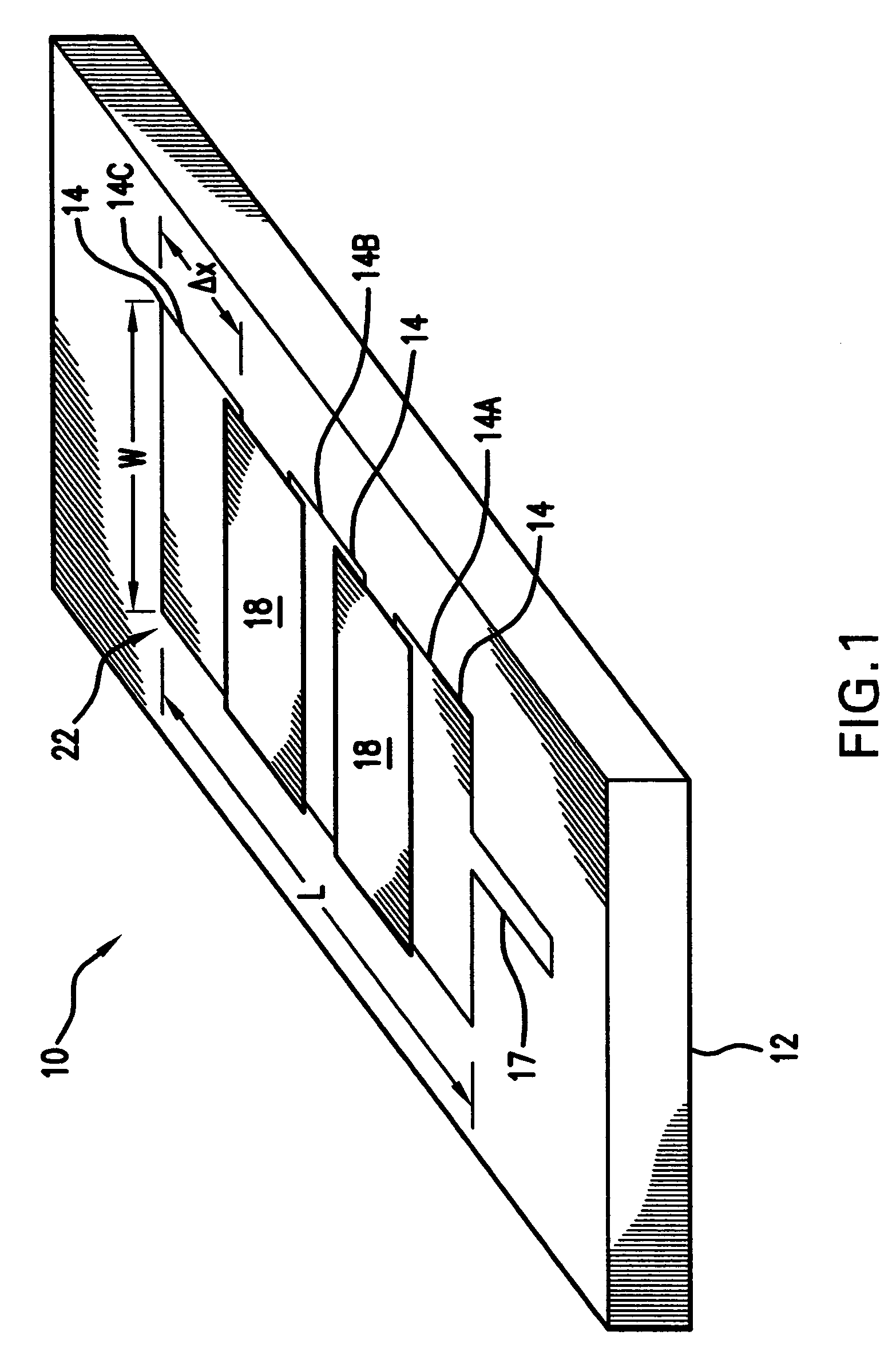

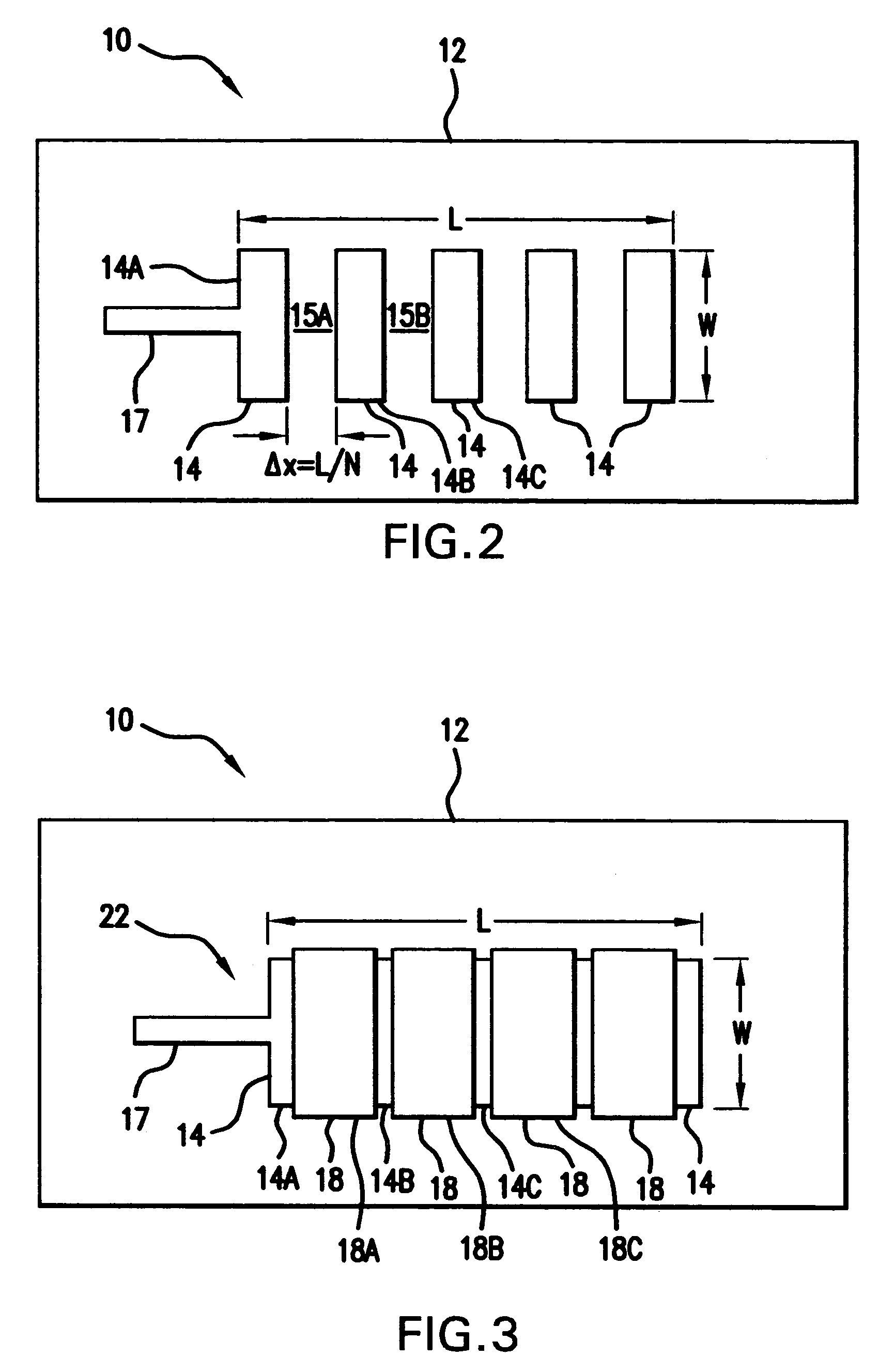

Segmented microstrip patch antenna with exponential capacitive loading

InactiveUS7061431B1Improve bandwidth characteristicsHigh bandwidthSimultaneous aerial operationsRadiating elements structural formsCapacitanceMicrostrip patch antenna

A segmented patch antenna has a dielectric material substrate, a plurality of primary electrically conductive segments consecutively disposed on the dielectric material substrate and spaced apart so that a portion of the substrate is exposed between any pair of adjacent primary segments, and a layer of dielectric material disposed over the primary segments. Secondary electrically conductive segments are disposed over the layer of dielectric material wherein each secondary segment corresponds to a pair of adjacent primary segments. Each secondary segment overlaps a portion of each primary segment of the corresponding pair of adjacent primary segments to which that secondary segments corresponds. The overlap of each secondary segment with a portion of each primary segment in a pair of adjacent primary segments produces a plurality of capacitive gaps that capacitively couple the primary and secondary segments together to define a single antenna.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

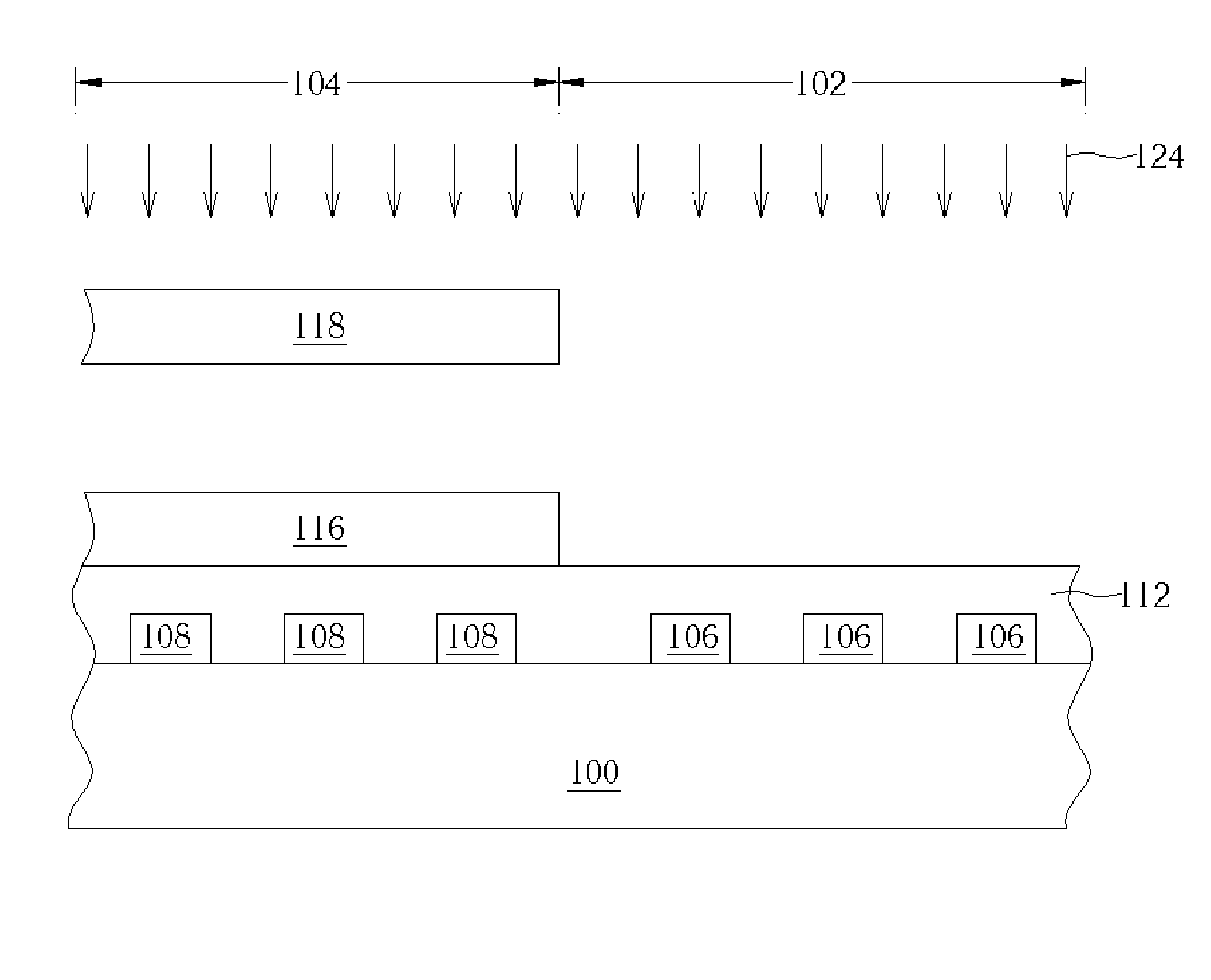

Method of forming a semi-insulating region

InactiveUS20050085004A1Enhanced couplingLarge scaleSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor

A semiconductor substrate is provided, and at least one first mask is formed above the semiconductor substrate. The first mask blocks at least one semi-insulating region. A second mask is thereafter formed on a surface of the semiconductor substrate. The second mask covers the semi-insulating region. The semi-insulating region is implanted with a high energy beam of particles by utilizing the second mask and the first mask as particle hindering masks. Finally, the second mask is removed.

Owner:UNITED MICROELECTRONICS CORP

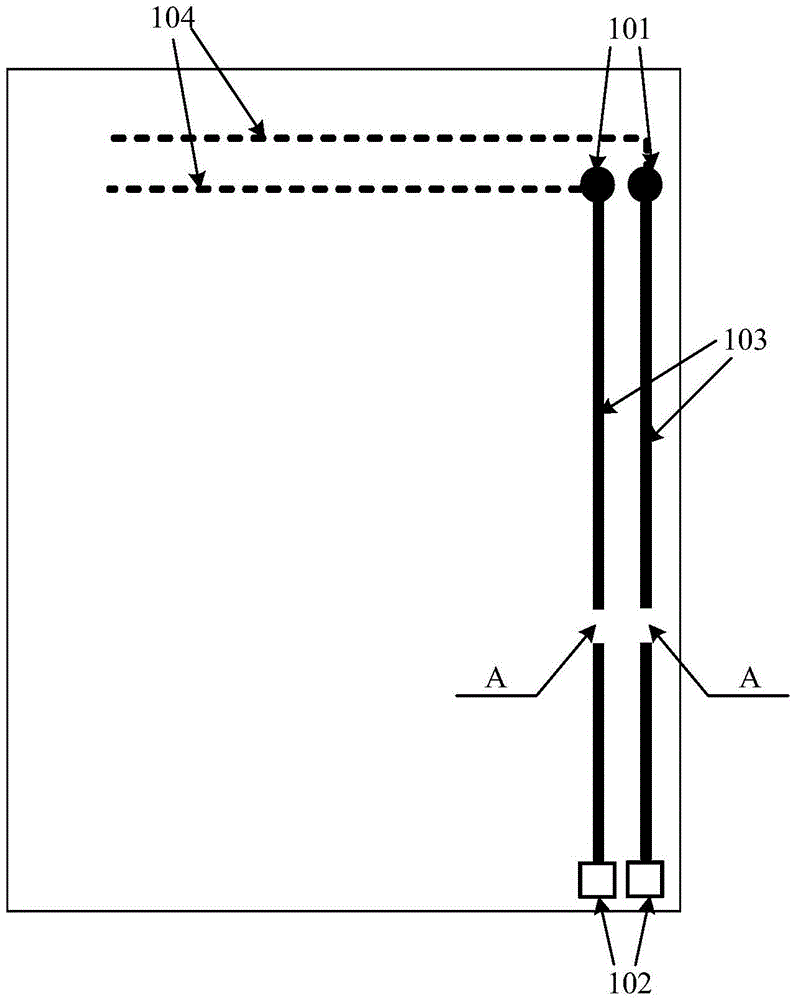

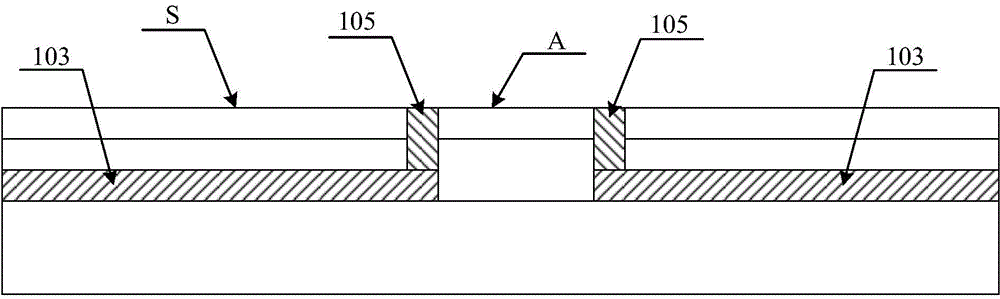

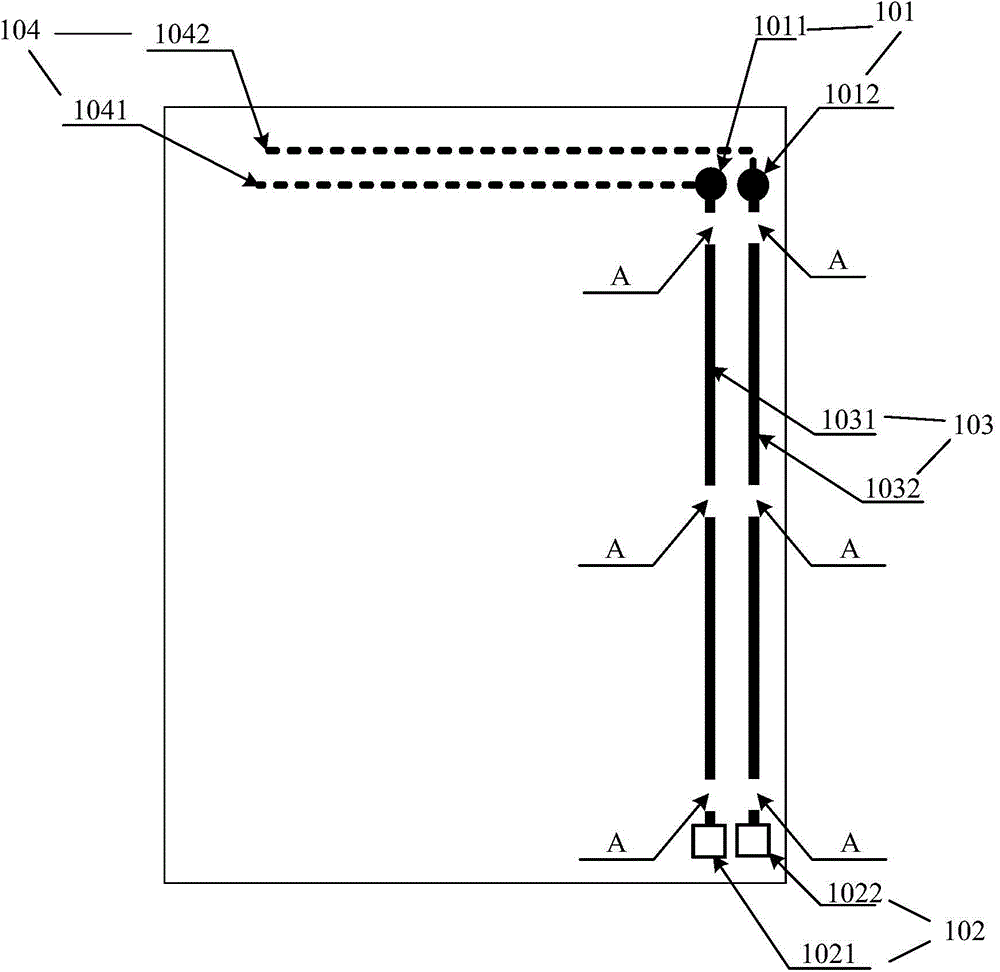

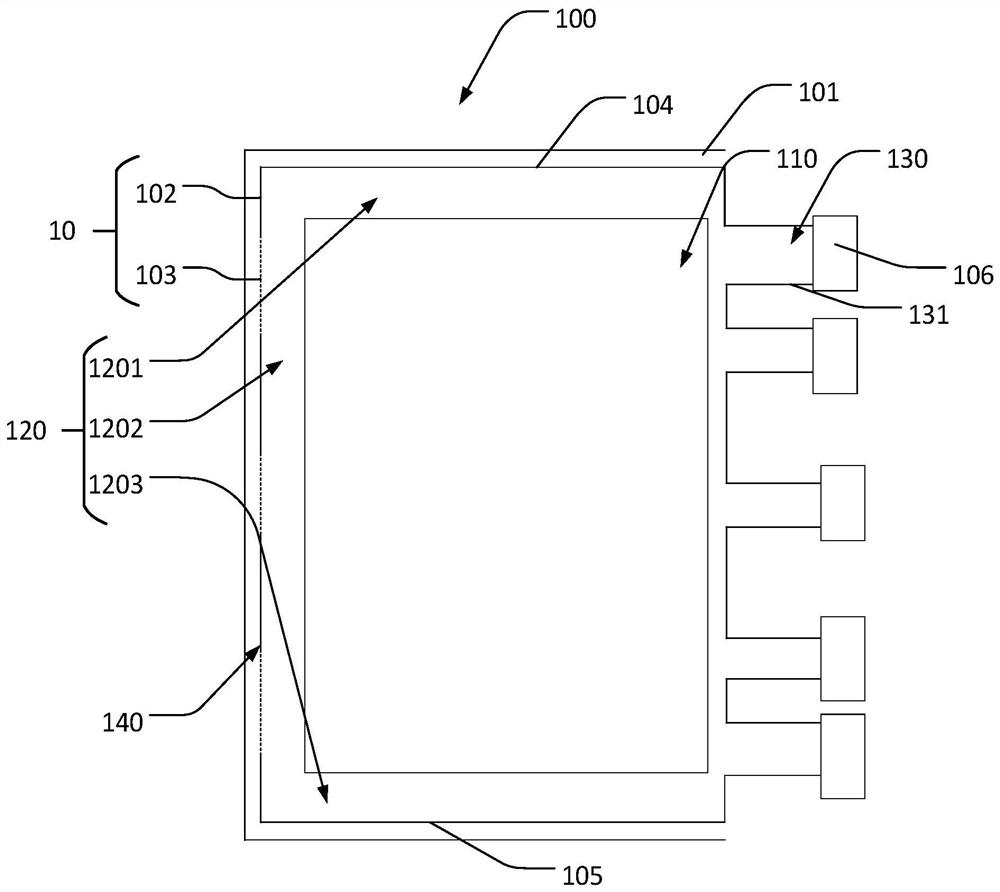

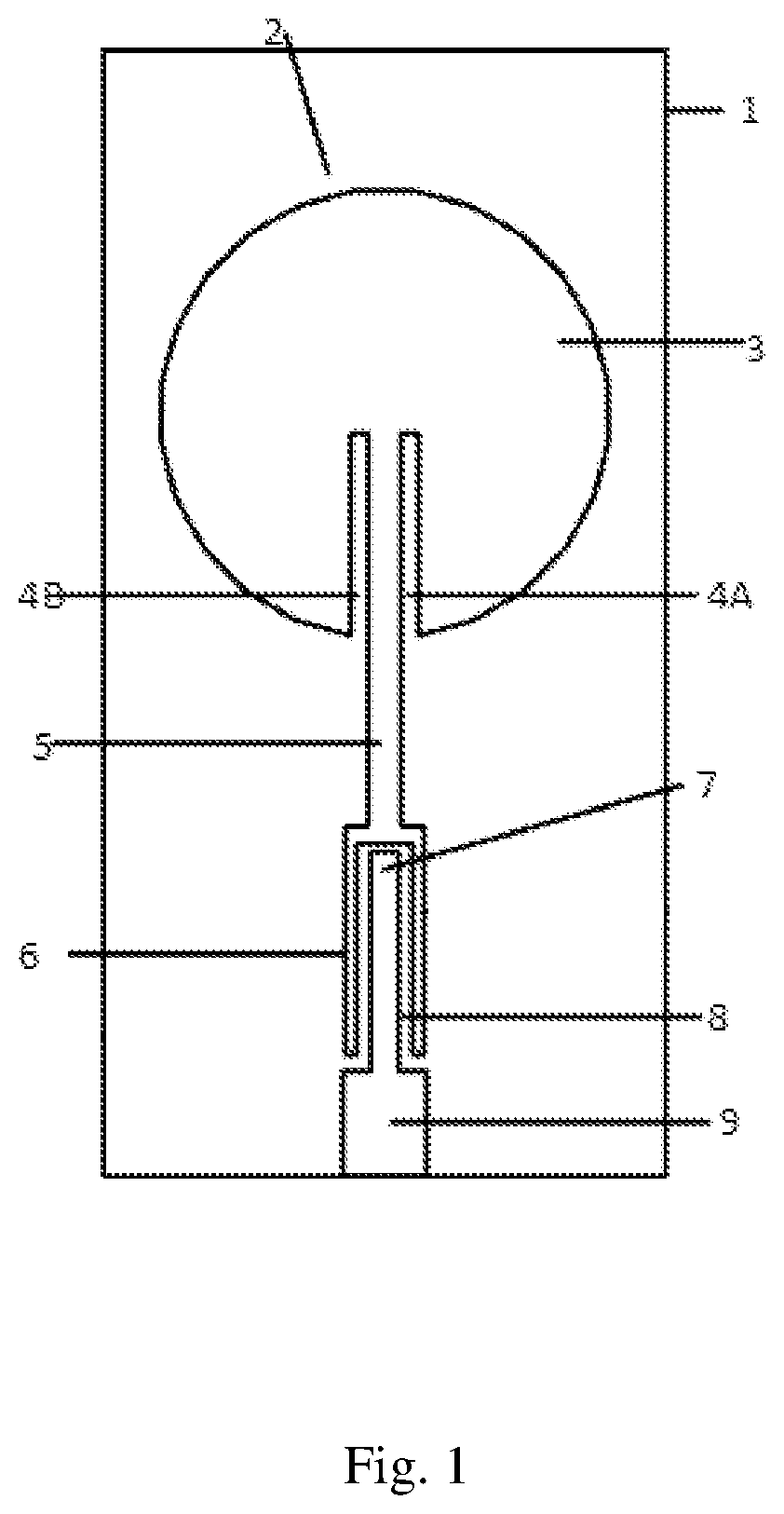

Array substrate, manufacture method for array substrate and display device

ActiveCN104701327AReduce antenna effectSolve problems that damage working circuitsSemiconductor/solid-state device testing/measurementSolid-state devicesAntenna effectDisplay device

The invention discloses an array substrate, a manufacture method for an array substrate and a display device and relates to the display technical field. The array substrate comprises a test circuit connected with a work circuit interface and a test interface; the test circuit comprises at least one cut-off point, two ends of each cut-off point on the test circuit are respectively provided with a conductive contact running through the upper surface of the array substrate; while performing the test to the work circuit, the conductive contacts at two ends of all cut-off points are switched on for having breakover for the test circuit. At least one cut-off point is formed on the test circuit during the forming process of the test circuit, and the sub test circuit cut from the cut-off point is not long, so that the antenna effect caused by longer test circuit is reduced, and the problem that the work circuit is damaged by the charge collected by the slender test circuit for the antenna effect of the related technology can be solved; the work circuit is not damaged by the test circuit due to the antenna effect.

Owner:BOE TECH GRP CO LTD +1

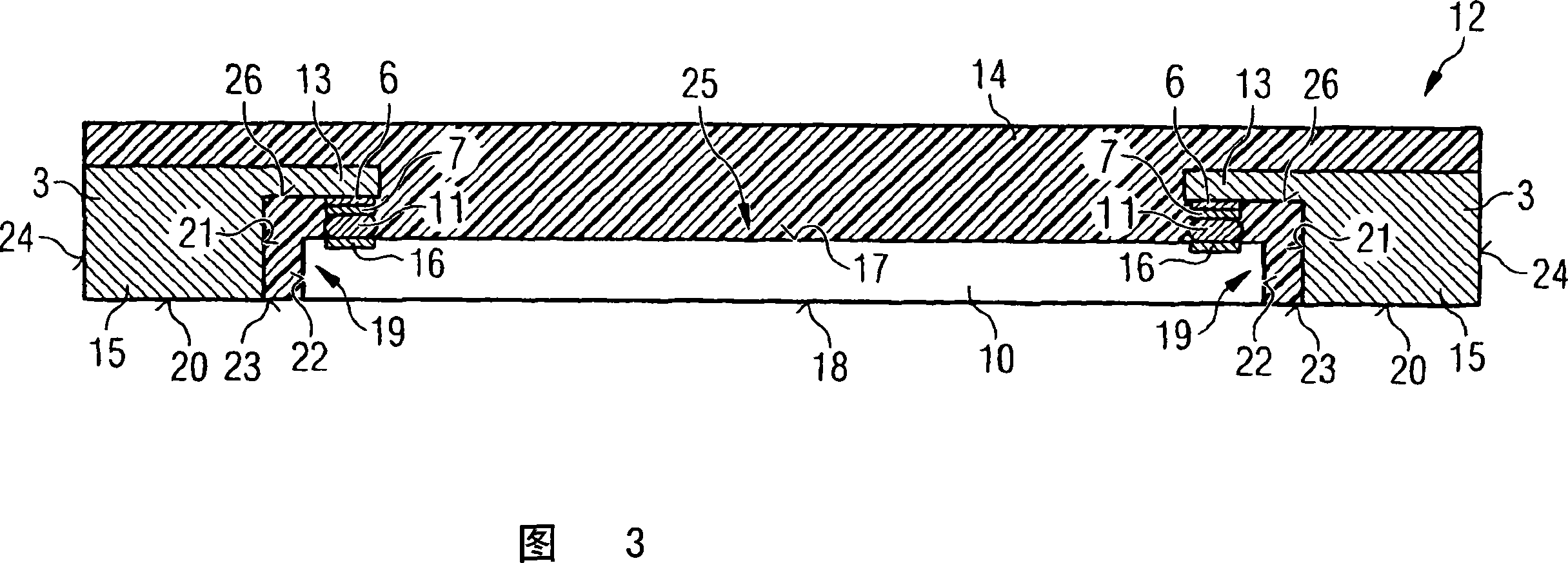

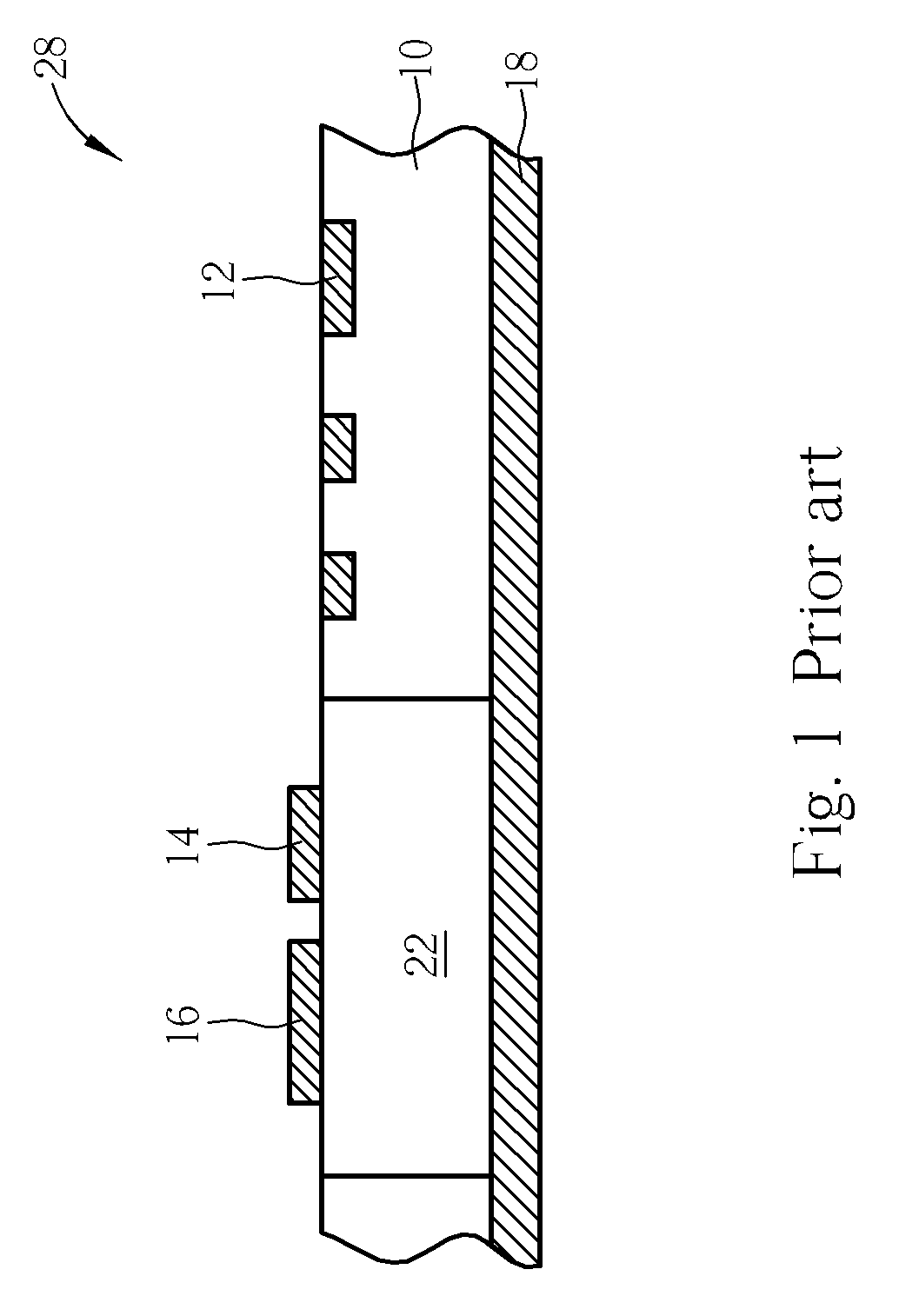

Leadframe, semiconductor package and method for producing the same

InactiveCN101103460AReduce distanceThin packageSemiconductor/solid-state device detailsSolid-state devicesContact padSemiconductor chip

A semiconductor package includes a lead frame (2) comprising a chip position (4) and a plurality of lead fingers (3). Each lead finger (3) includes a incision (19) in an inner edge providing a chip recess (25). The semiconductor package (12) further includes a semiconductor chip (10) locating in the chip recess (25). The semiconductor chip (10) is arranged with an active surface (17) with a plurality of chip contact pads (16) on each of which an electrically conductive bump (11) is disposed. The inner portions (13) of the lead fingers (3) protrude into the chip position (4) and are electrically connected to the chip contact pads (16) by electrically conductive bumps (11).

Owner:INFINEON TECH AG

Semiconductor integrated circuit device, design method, design apparatus, and program

InactiveUS8484595B2Eliminate the effects ofReduce antenna effectSemiconductor/solid-state device detailsSolid-state devicesDesign standardEngineering

Owner:RENESAS ELECTRONICS CORP

Method and apparatus for gathering seismic data

InactiveUS20060233051A1Reduce antenna effectEasy to containSeismic signal receiversSeismic signal transmissionSurface mountingEngineering

Owner:AMFIT INCORPORATED

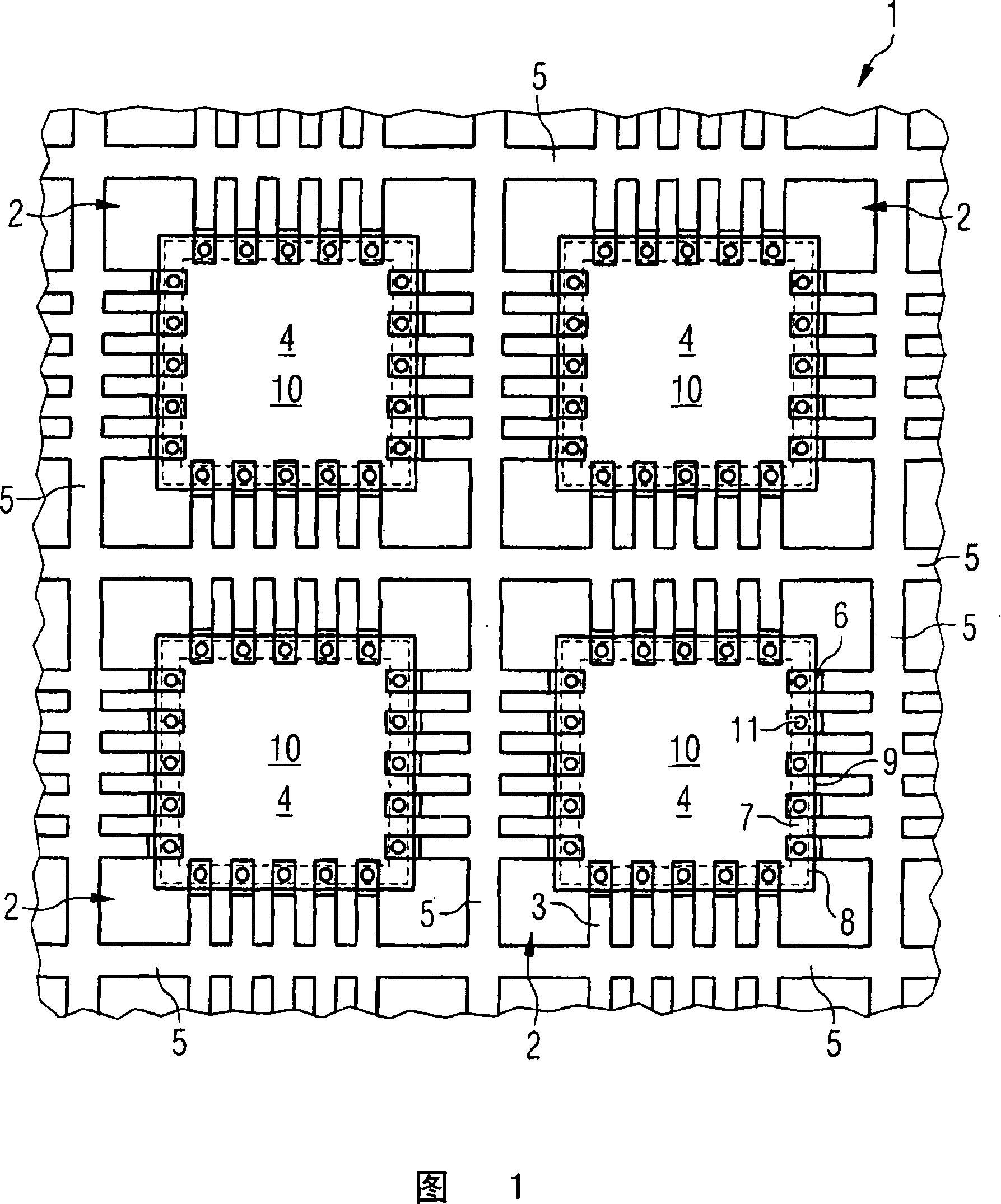

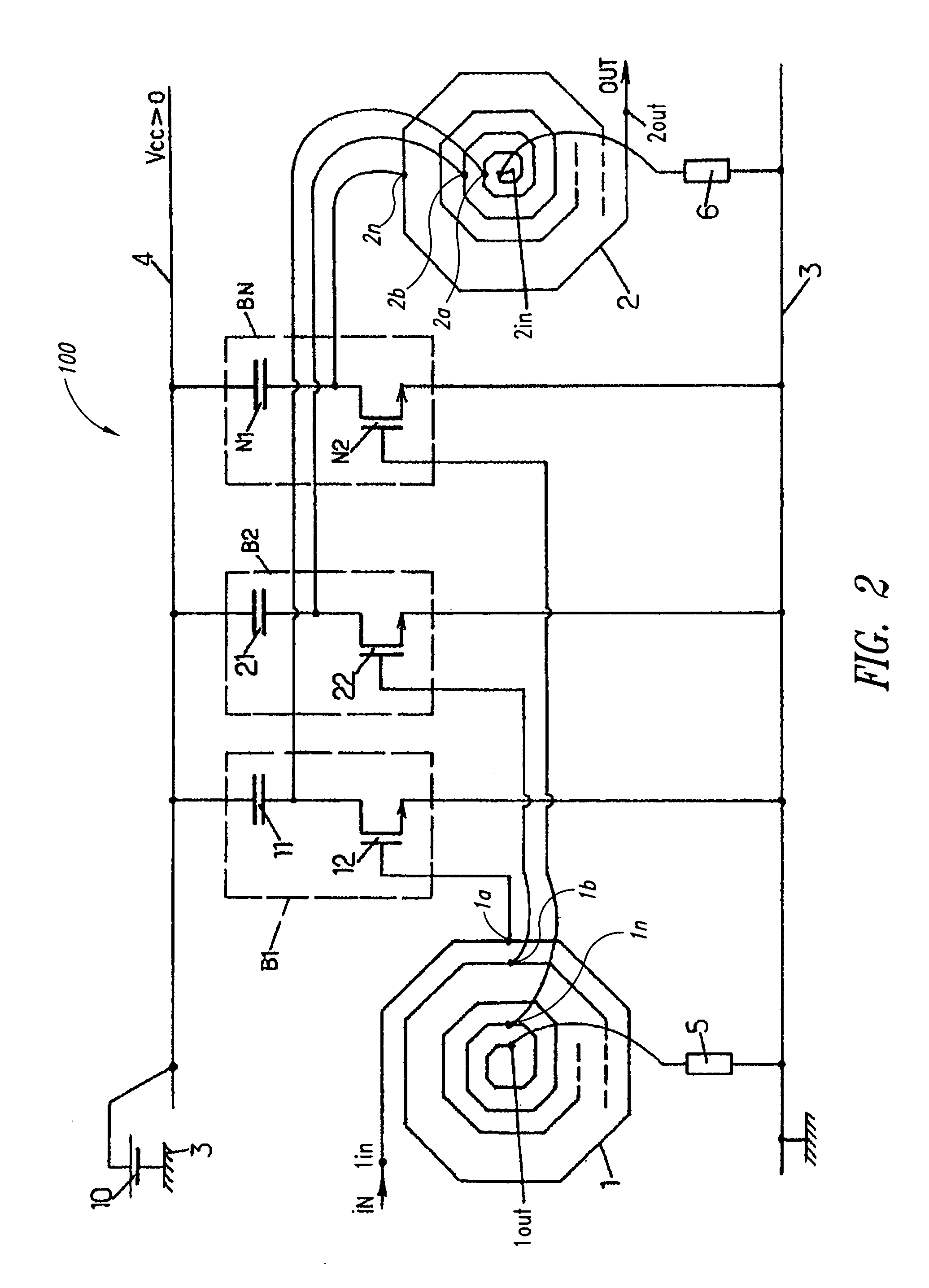

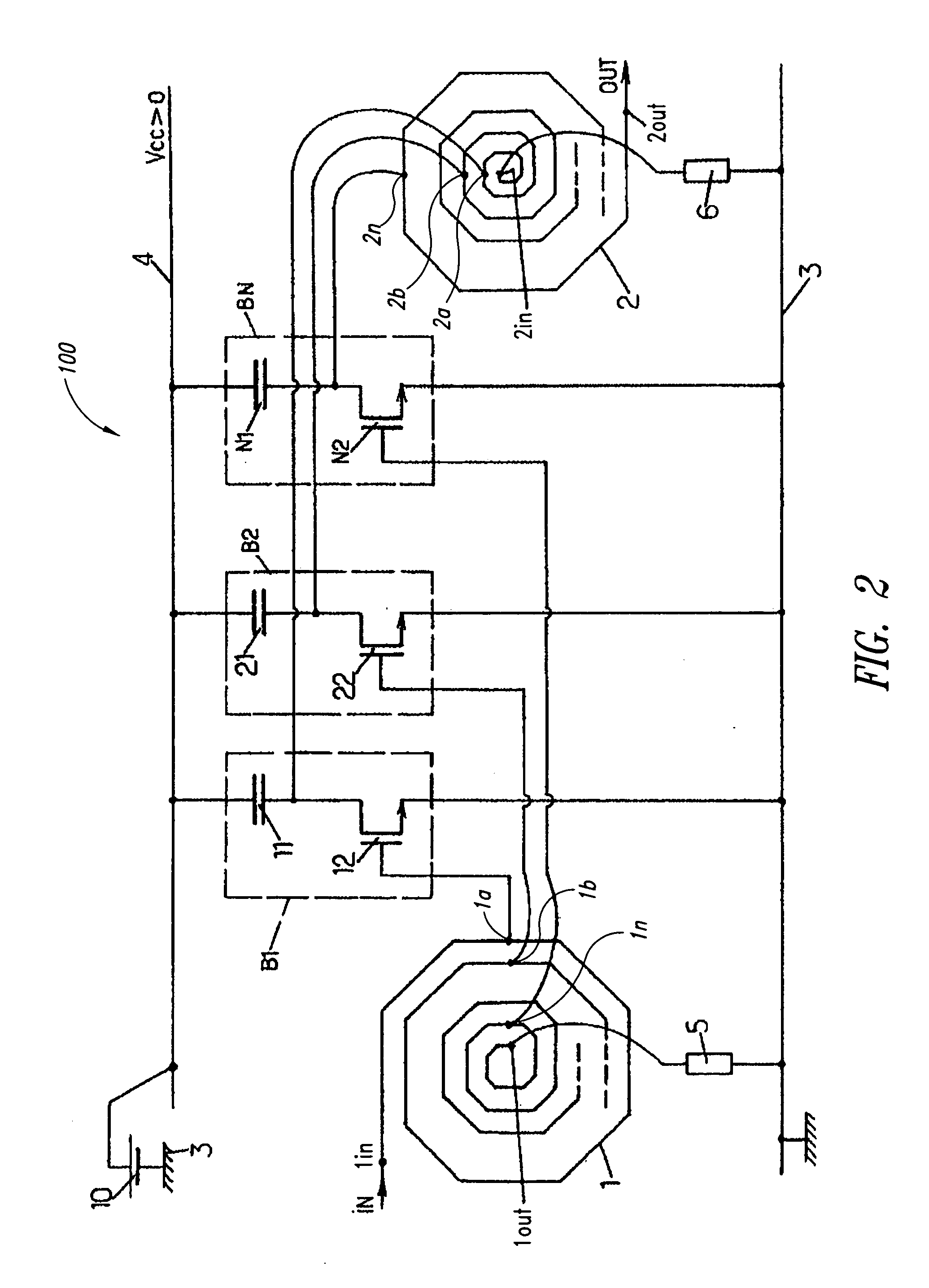

Electronic signal amplifier and method and article for determining the gain of such an amplifier

ActiveUS7224229B2Low production costLow costAmplifier combinationsAmplifiers wit coupling networksAudio power amplifierInductor

An embodiment of an electronic signal amplifier comprises a power source, an input inductor, an output inductor and one or more branches connected in parallel between the terminals of the power source. Each branch comprises a transistor having a control electrode connected to an intermediate terminal of the input inductor, a first main electrode connected to a first terminal of the power source, and a second main electrode connected to a second terminal of the power source via a capacitor. The second main electrode of each transistor of a branch is also connected to an intermediate terminal of the output inductor.

Owner:STMICROELECTRONICS SRL

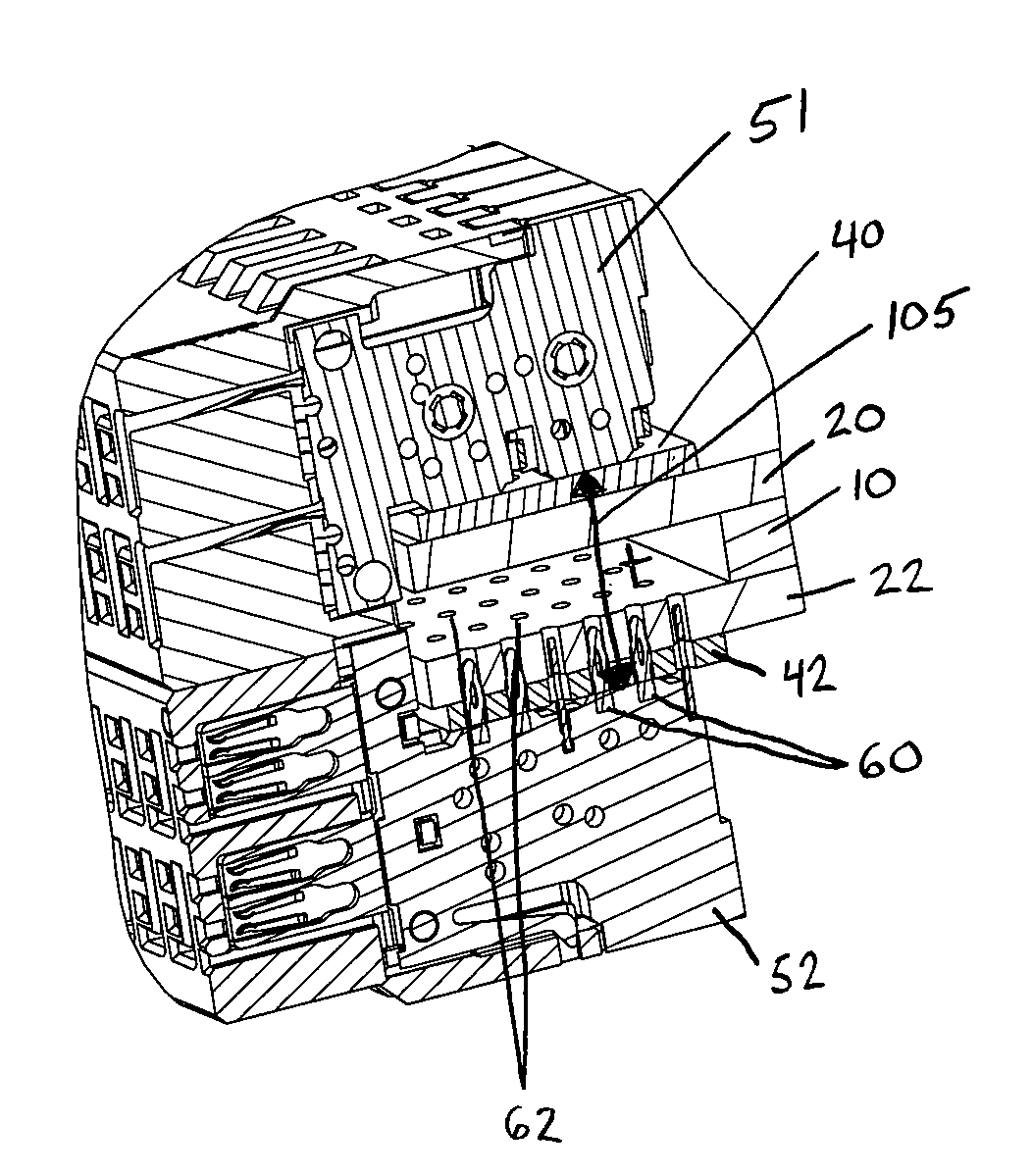

Straddle Mount Connector

ActiveUS20080020609A1Reduce antenna effectReduce eliminateCoupling device detailsPrinted circuitsStraddleEngineering

A straddle mount connector for use with a computer card having multiple circuit boards on opposing sides of a heat sink is disclosed. The straddle mount connector includes a pair of connector portions on opposing sides of the computer card. A first surface of the first connector portion is in electrical and physical contact with a board on one side of the heat sink while a first surface of the second connector portion is in electrical and physical contact with the board on the other side of the surface. The first surface of the first connector portion and the first surface of the second connector portion are separated by a fixed, predetermined distance.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

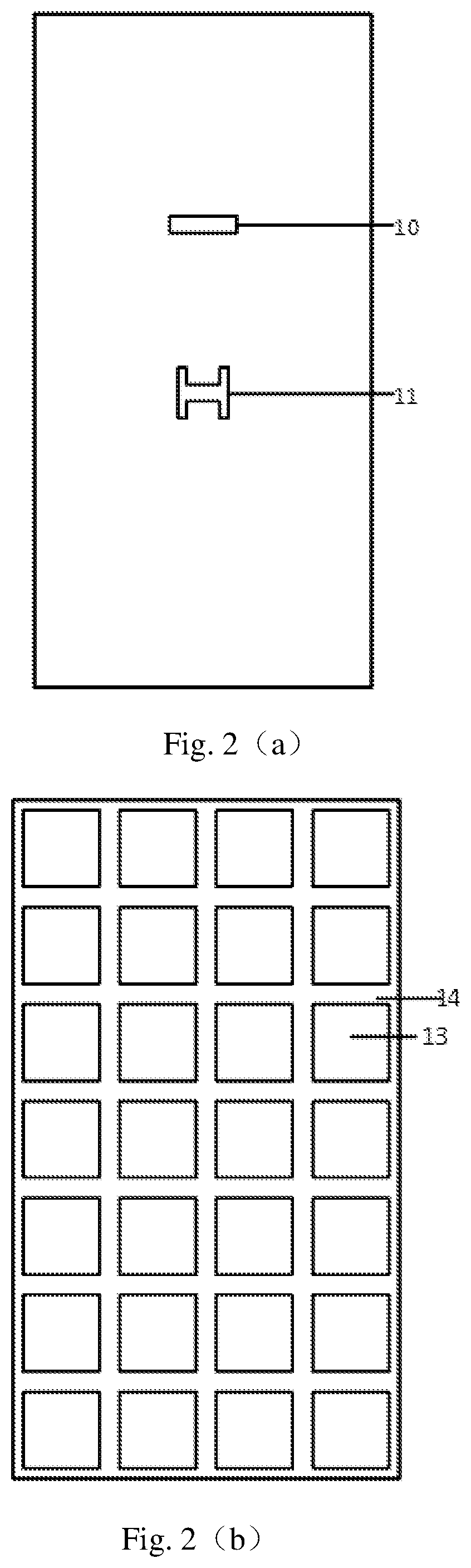

Leaky-wave dual-antenna system

ActiveUS20100156740A1Reduce maximum coupling factorHigh gainAntenna arraysSimultaneous aerial operationsAntenna arrayMicrostrip

The invention discloses a leaky-wave dual-antenna system comprising a transmitting antenna array and a receiving antenna array. The transmitting antenna array comprises plural first microstrips and plural corresponding first differential circuits, and each of the first differential circuit matches the corresponding first microstrip by a L-type matching network; the receiving antenna array comprises plural second microstrips and plural corresponding second differential circuits, and each of the second differential circuit matches the corresponding second microstrip by a L-type matching network. A first end and a second end of each of the first differential circuits are respectively connected to the corresponding first microstrip; a third end and a fourth end of each of the second differential circuits are respectively connected to the corresponding second microstrip.

Owner:NAT CHUNG SHAN INST SCI & TECH

Chip bonding pad of integrated circuit, manufacture method thereof and integrated circuit comprising bonding pad

ActiveCN101615606AReduce antenna effectSemiconductor/solid-state device detailsSolid-state devicesAntenna effectEngineering

The invention provides an integrated circuit, a chip bonding pad structure and a manufacture method. The chip bonding pad comprises a main bonding pad and a ring bonding pad. In a process of fabricating charges comprising formation of the chip bonding pad, a grid of a metal oxide semiconductor transistor in a substrate of the integrated circuit is electrically connected with the ring bonding pad,therefore area ratio from an antenna to the grid is less than a proportion of a given antenna, thus effectively reducing or avoiding antenna effect. The main bonding pad is electrically coupled with the ring bonding pad through a metal bridge formed in an upper inside cable metal layer or an uppermost conductive bonding pad layer. The chip bonding pad provided by the invention is a probe bonding pad on a parameter testing line or a bonding pad on the integrated circuit.

Owner:TSMC CHINA COMPANY

Semiconductor integrated circuit device, design method, design apparatus, and program

InactiveUS20110204358A1Eliminate the effects ofReduce antenna effectSemiconductor/solid-state device detailsSolid-state devicesDesign standardEngineering

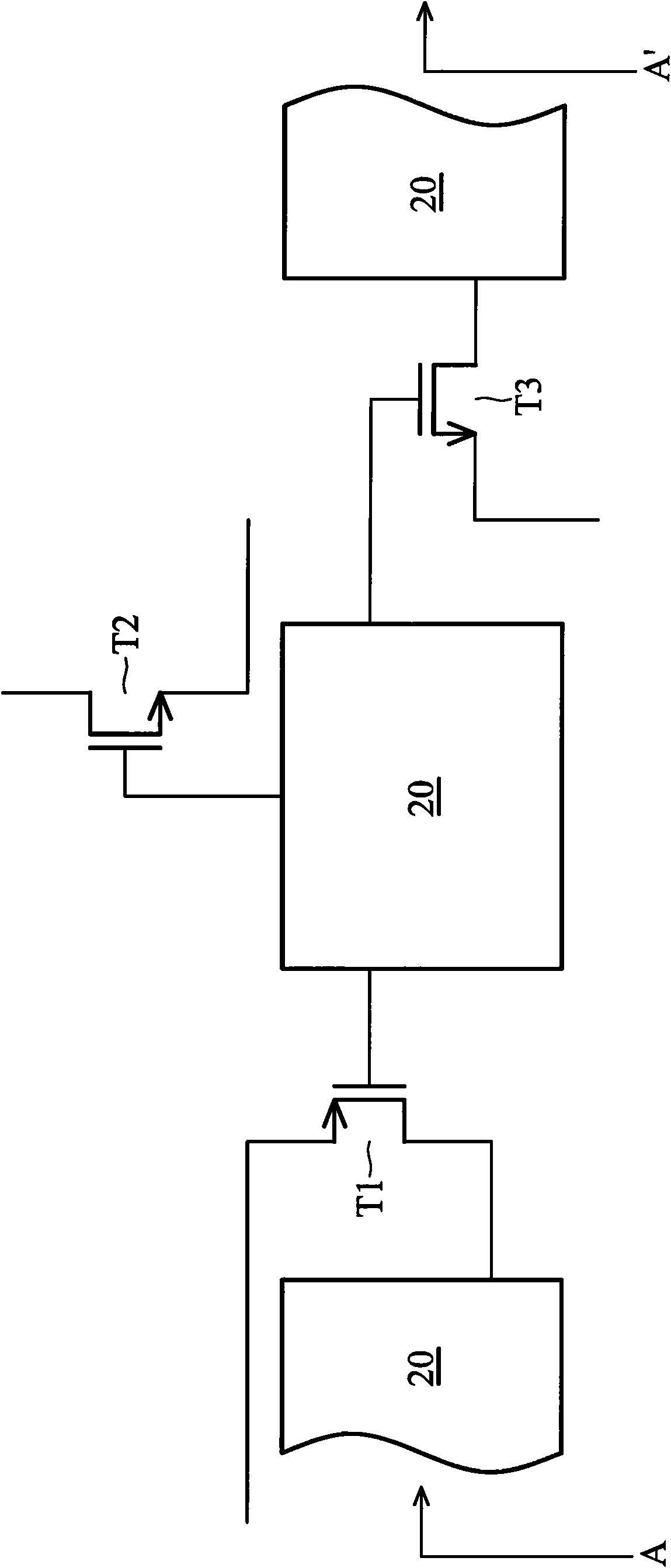

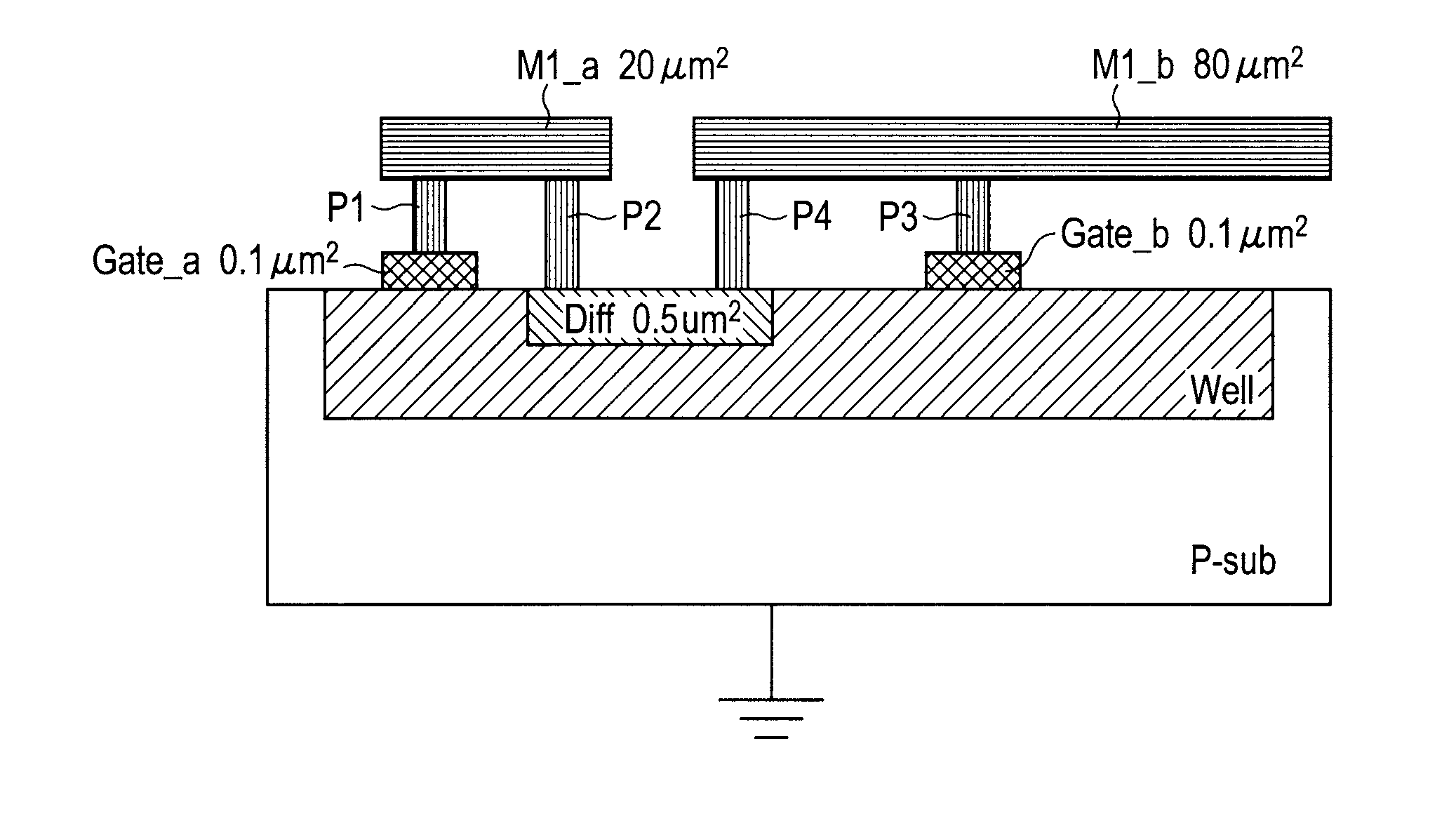

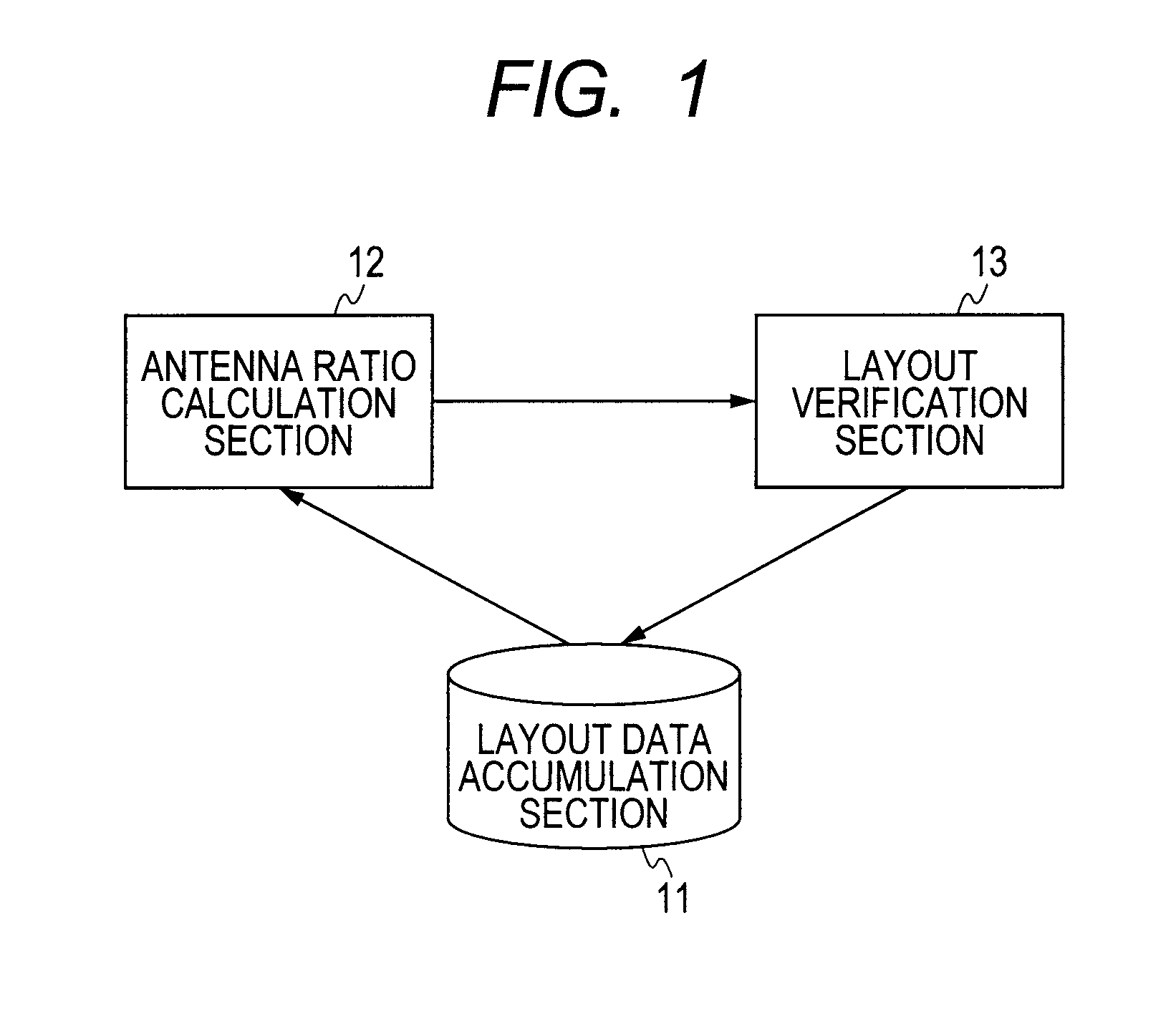

An antenna ratio calculation section extracts components from which two or more independent metal wires are coupled to one of diffusion layer regions based on layout data read from a layout data accumulation section, determines, for each of the components, the area of each of the two or more independent metal wires and electrodes coupled to the respective metal wires, determines an antenna ratio between the area of each of the metal wires and the area of the electrode coupled to the metal wire, and determines a moderation value for moderating a design standard associated with plasma charge damage related to one of the metal wires based on the ratio of the total area of all the metal wires coupled to the one of the diffusion layer regions to the area of the one of the metal wires.

Owner:RENESAS ELECTRONICS CORP

Electronic signal amplifier and method and article for determining the gain of such an amplifier

ActiveUS20050189994A1Low production costLow costAmplifier combinationsAmplifiers wit coupling networksAudio power amplifierInductor

An embodiment of an electronic signal amplifier comprises a power source, an input inductor, an output inductor and one or more branches connected in parallel between the terminals of the power source. Each branch comprises a transistor having a control electrode connected to an intermediate terminal of the input inductor, a first main electrode connected to a first terminal of the power source, and a second main electrode connected to a second terminal of the power source via a capacitor. The second main electrode of each transistor of a branch is also connected to an intermediate terminal of the output inductor.

Owner:STMICROELECTRONICS SRL

Mask plate, display panel and preparation method thereof

ActiveCN111857446AReduce antenna effectInput/output processes for data processingAntenna effectMetal membrane

The invention provides a mask plate, a display panel and a preparation method thereof, the display panel comprises a display area and a peripheral area surrounding the display area, and the peripheralarea comprises a wiring area and a binding area. The wiring area is provided with a first grounding wire. According to the invention, the first grounding wire is wired through double-layer or multi-layer metal, and an ESD protection effect can be achieved in use of a finished product. Specifically, an original grounding wire of a single metal film layer is replaced with a mode of jumper wire in adouble-layer or multi-layer metal film layer to serve as a first grounding wire, and the antenna effect generated in the single-film-layer metal wire manufacturing process is weakened.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Electrical connector

ActiveCN107800007APrevent kneelingEffect of electrical connectionCoupling device detailsTwo-part coupling devicesElectrical connectorElectrical contacts

The invention discloses an electrical connector. The electrical connector is used for a plug component to insert and comprises an insulation body and a plurality of terminals, wherein the insulation body is provided with an abutting surface and a plurality of terminal grooves, the abutting surface is provided with a plug space in a sunken way, the plurality of terminal grooves are arranged at oneside of the plug space, the plurality of terminals are respectively accommodated in the plurality of terminal grooves, each terminal is provided with a main body part, a connection part and a contactpart, the connection part sequentially extends towards the abutting surface from the main body part, the contact part is exposed out of the plug space, an insulator piece is arranged on the connectionpart and is provided with a guide part, the guide part is exposed out of the plug space and is near to the abutting surface relative to the contact part, and when the plug component enters the plug space, the plug component is in contact with the guide part to drive the terminal to deviate from the plug space and then is in electrical contact with the contact part, thus, an enough space can be enabled to be provided for the plug component to insert, the terminal can be effectively prevented from touching a pin, and the terminal is prevented from being damaged to cause influence on electricalconnection between the plug component and a circuit board.

Owner:DEYI PRECISION ELECTRONIC IND CO LTD PANYU

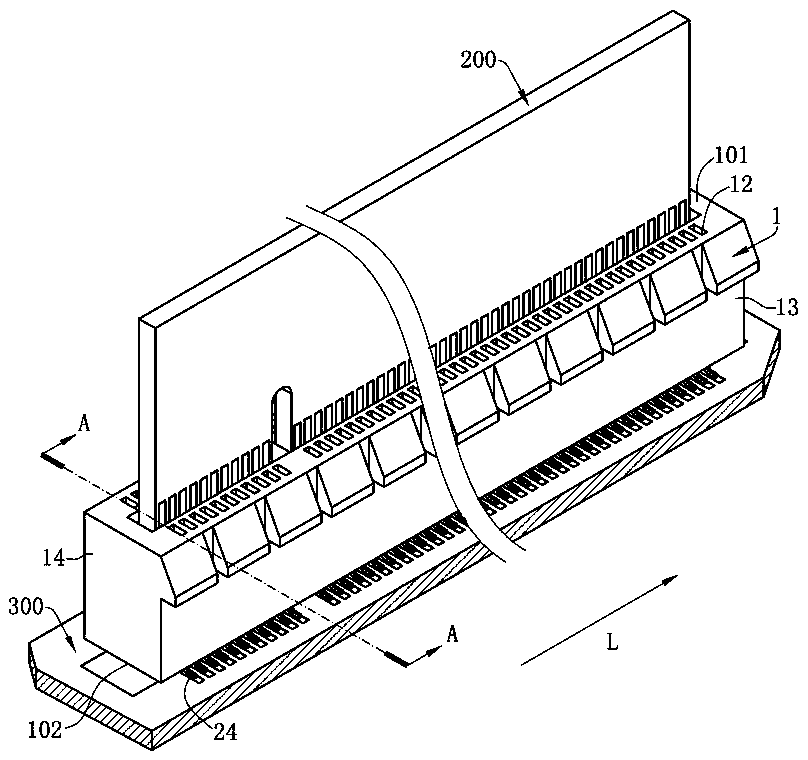

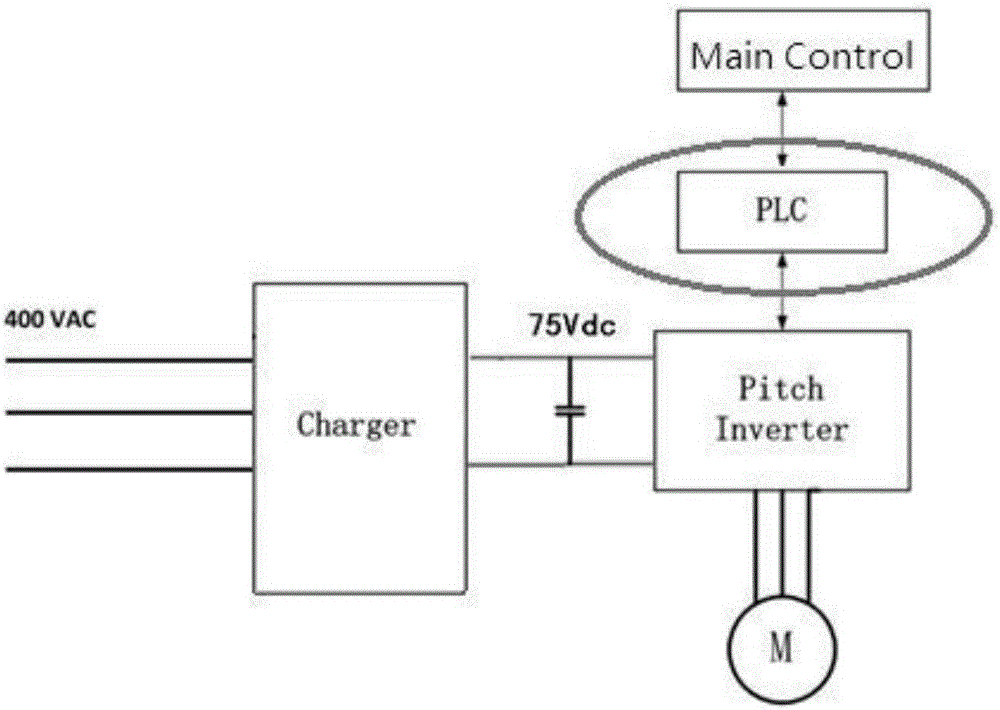

Low-pressure variable pitch system with variable pitch servo driver with integrated PLC function

ActiveCN106762411ASave internal spaceSimple designWind motor controlMachines/enginesInterior spaceEngineering

The invention relates to the technical field of wind-power electromechanical control equipment, in particular to a low-pressure variable pitch system with a variable pitch servo driver with the integrated PLC function. The low-pressure variable pitch system comprises the variable pitch servo driver with the PLC control function. The variable pitch servo driver comprises four circuit boards, a heat-dissipation cold plate, a conductive copper column terminal and a plastic shell, wherein the four circuit boards are a power board, a power driving board, a servo control board and a PLC control board; the power board is fixed on the heat-dissipation cold plate, and the power driving board is fixed above the power board through a board to board terminal and a copper column; the servo control board and the PLC control board are connected with the power driving board through signal cables and are fixed on the plastic shell. The low-pressure variable pitch system greatly saves the inner space of a variable pitch cabinet and is convenient to design a variable pitch cabinet body.

Owner:DALIAN SHINERGY SCI & TECH DEV

Electrical Connector Capable of Suppressing Crosstalk

ActiveUS20150079844A1Effectively suppressing crosstalkReduce antenna effectCoupling protective earth/shielding arrangementsElectrical connectorCrosstalk

An electrical connector includes insulating portions arranged side by side, terminal sets, shield sets, and a casing. Each terminal set includes signal terminals and ground terminals. Each signal / ground terminal includes a fixing section disposed in the insulating portion, an assembling section downwardly stretching from the fixing section to protrude from the insulating portion, and a contacting section forwardly stretching from the fixing section to protrude from the insulating portion. Each shield set including shields is disposed on a lateral surface of the insulating portion. Each shield is spacedly arranged and connected to the ground terminal. Each shield includes a body section having at least one bending section, and a protrusion section protruding from the body section. The body section and the protrusion section shield the assembling section and the contacting section of the signal terminal respectively. It can effectively suppress crosstalk between the signal terminals by the shield sets.

Owner:ADVANCED CONNECTEK INC

Method of forming a semi-insulating region

InactiveUS20050148207A1Enhanced couplingLarge scaleSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor

A semiconductor substrate is provided, and at least one first mask is formed above the semiconductor substrate. The first mask has a plurality of thicknesses and blocks at least one semi-insulating region. A second mask is thereafter formed on a surface of the semiconductor substrate. The second mask covers the semi-insulating region. The semi-insulating region is implanted with a high energy beam of particles by utilizing the second mask and the first mask as particle hindering masks. Finally, the second mask is removed.

Owner:UNITED MICROELECTRONICS CORP

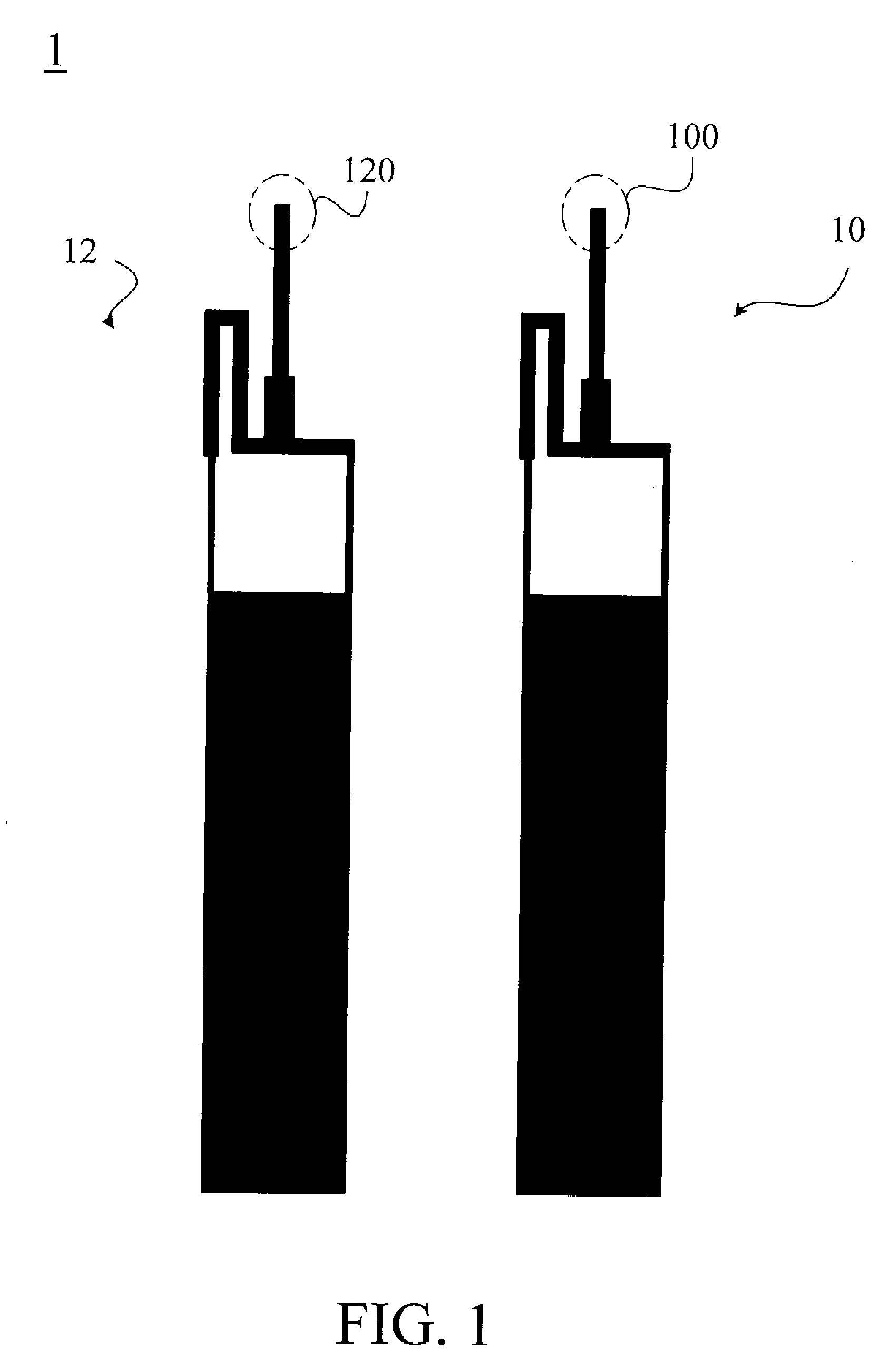

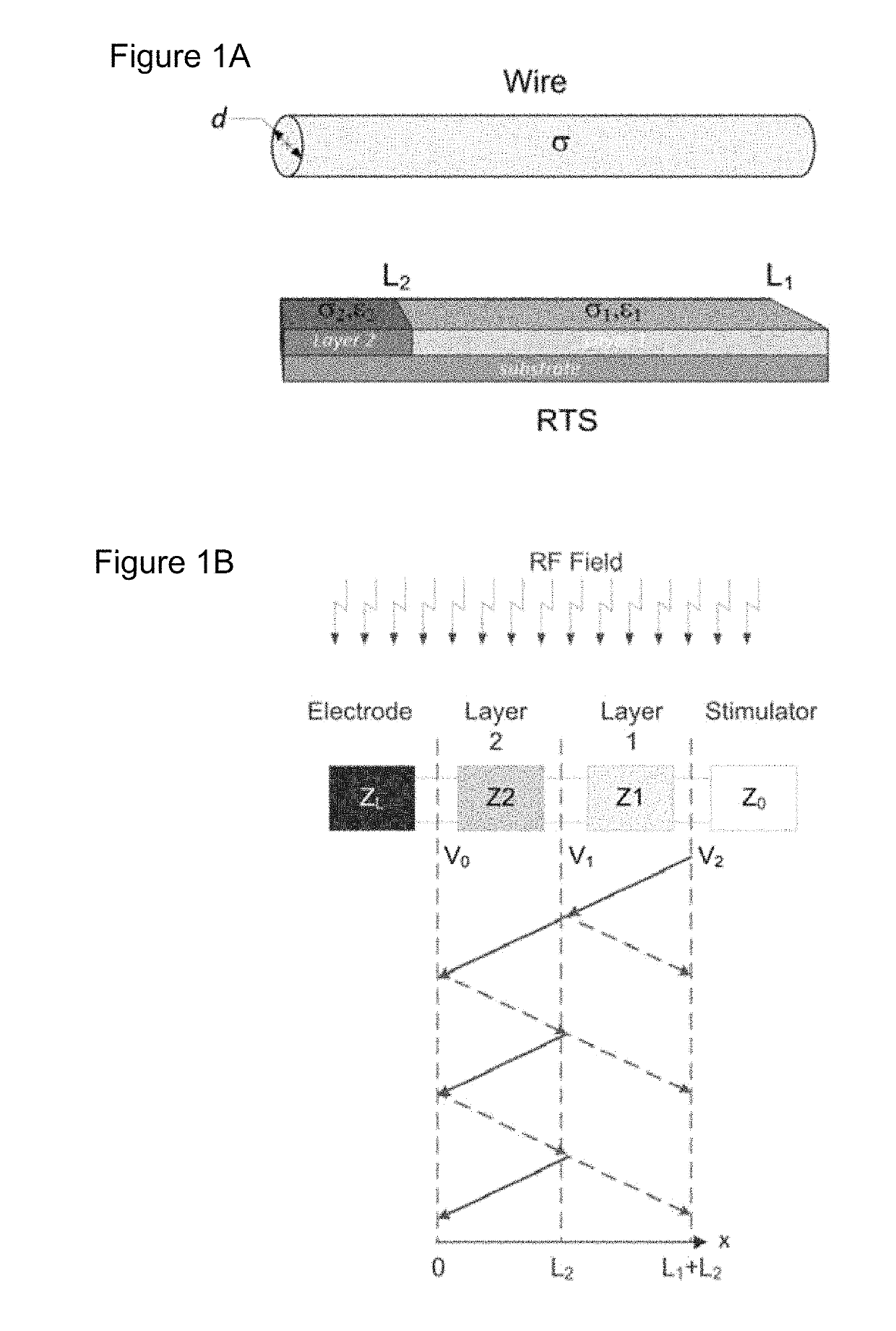

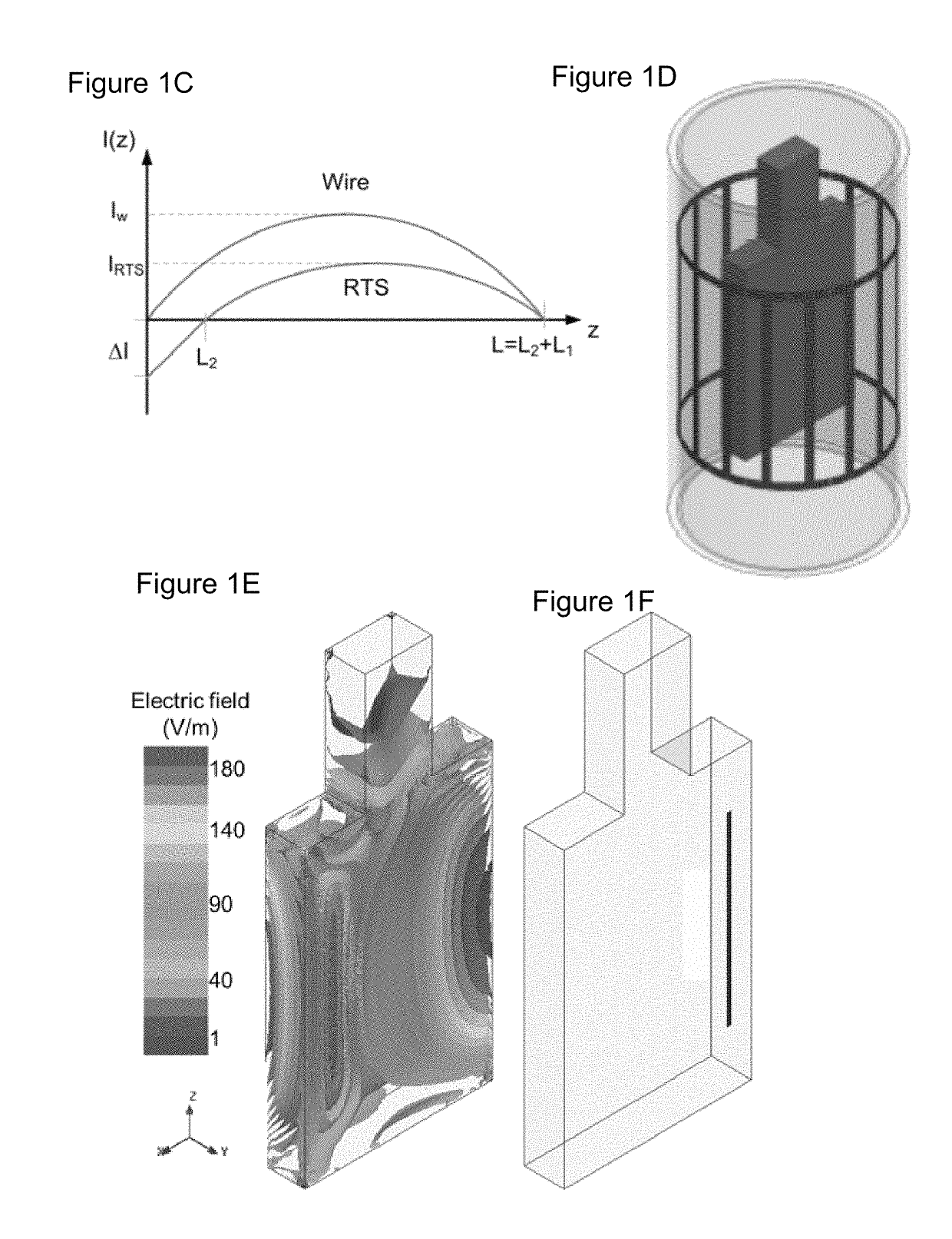

MRI compatible leads for a deep brain stimulation system

ActiveUS10335590B2Limited compatibilityReduce antenna effectSpinal electrodesHead electrodesRadio frequencyMri compatible

A lead for an implanted medical device is disclosed in which the lead is adapted for electrical communication with an electrical signal source and has a distal tip with an electrode. The lead comprises a wire adapted to be placed in electrical communication with electrode. The wire includes: (i) a core comprising a polymeric material, and (ii) a metallic layer surrounding an outer surface of the core. The metallic layer includes a first section having a first thickness and a second section having a second thickness, wherein the first thickness is greater than the second thickness. The lead is substantially transparent to radio frequency waves in clinically-applicable magnetic resonance environments to reduce radio frequency absorption and avoid substantial heating effects.

Owner:THE GENERAL HOSPITAL CORP

Method of forming a semi-insulating region

InactiveUS20050170619A1Enhanced couplingLarge scaleSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor

A semiconductor substrate is provided, and at least one first mask is formed above the semiconductor substrate. The first mask has a plurality of thicknesses and blocks at least one semi-insulating region. A second mask is thereafter formed on a surface of the semiconductor substrate. The second mask covers the semi-insulating region. The semi-insulating region is implanted with a high energy beam of particles by utilizing the second mask and the first mask as particle hindering masks. Finally, the second mask is removed.

Owner:UNITED MICROELECTRONICS CORP

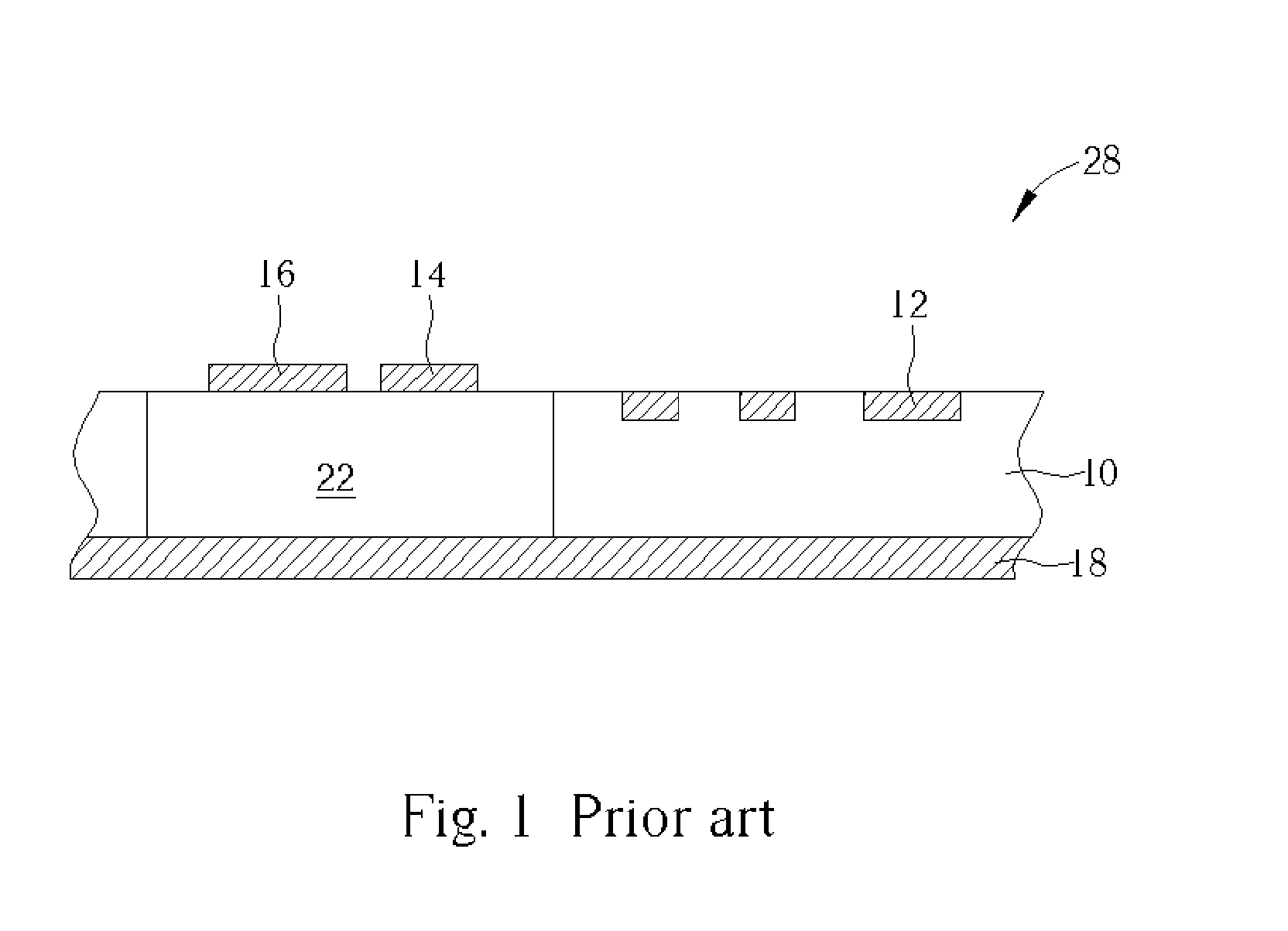

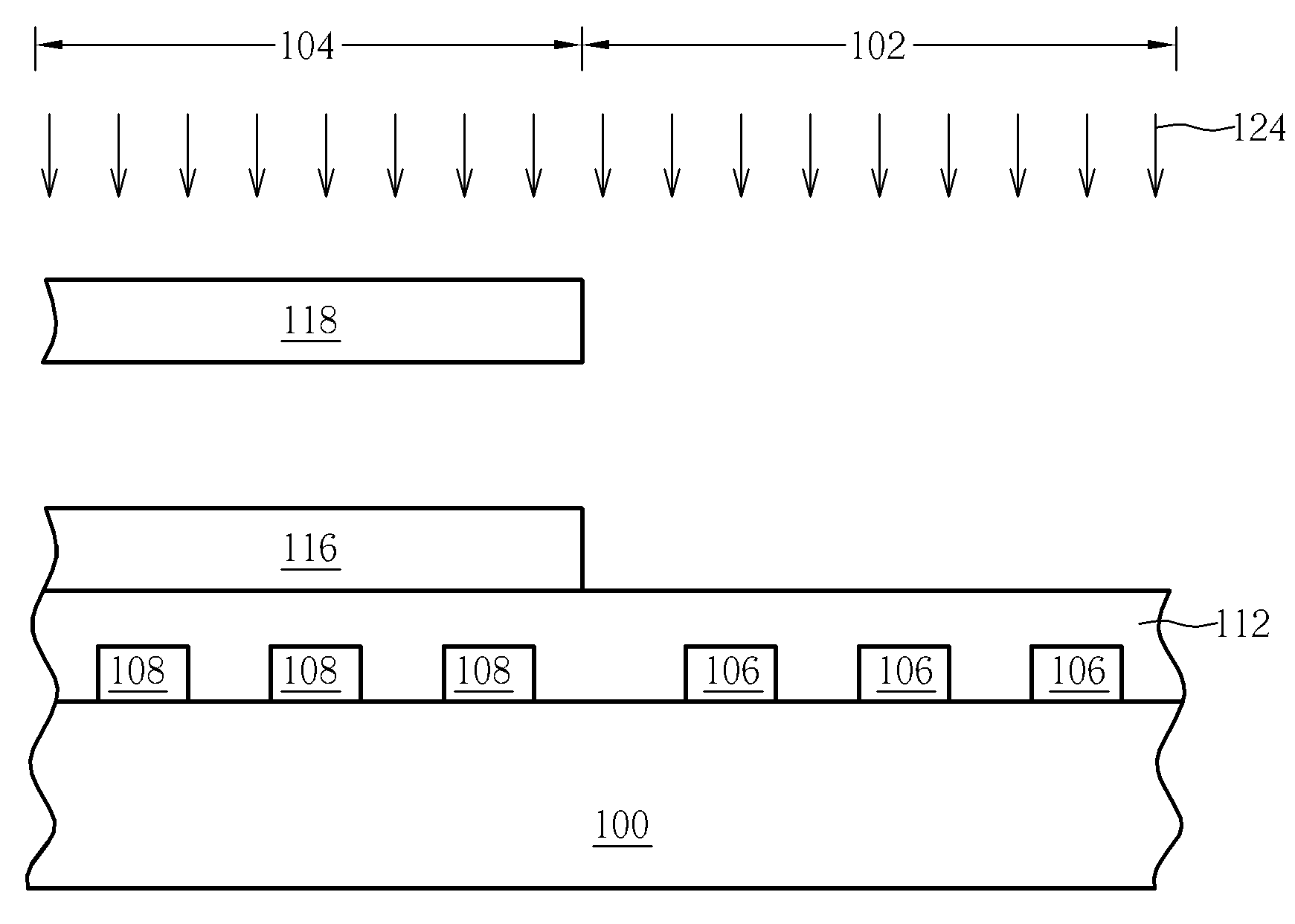

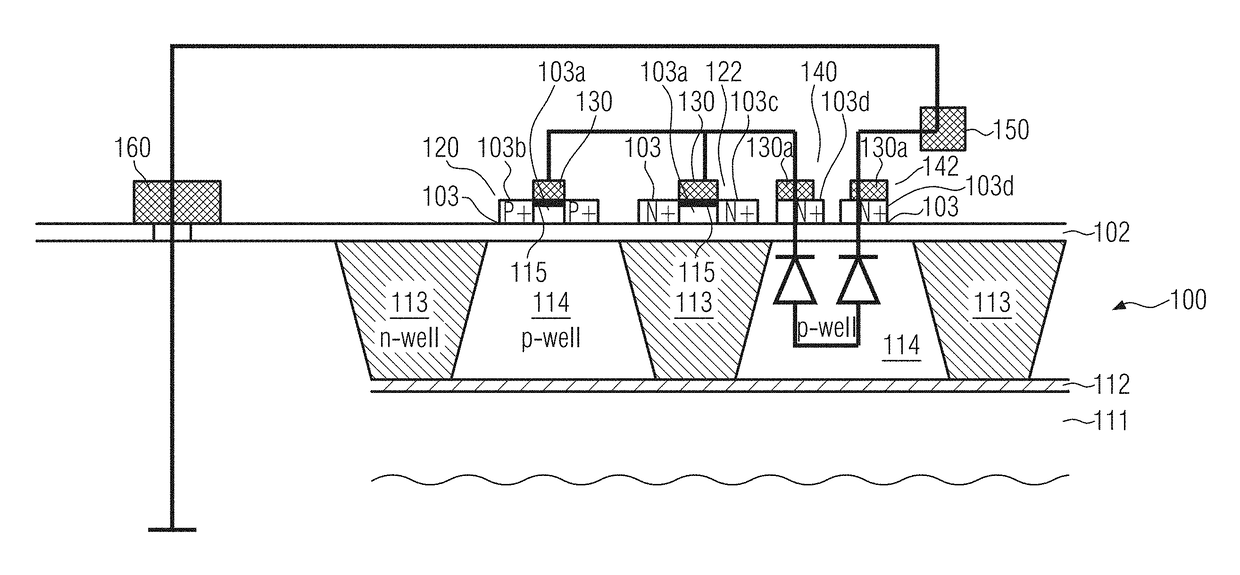

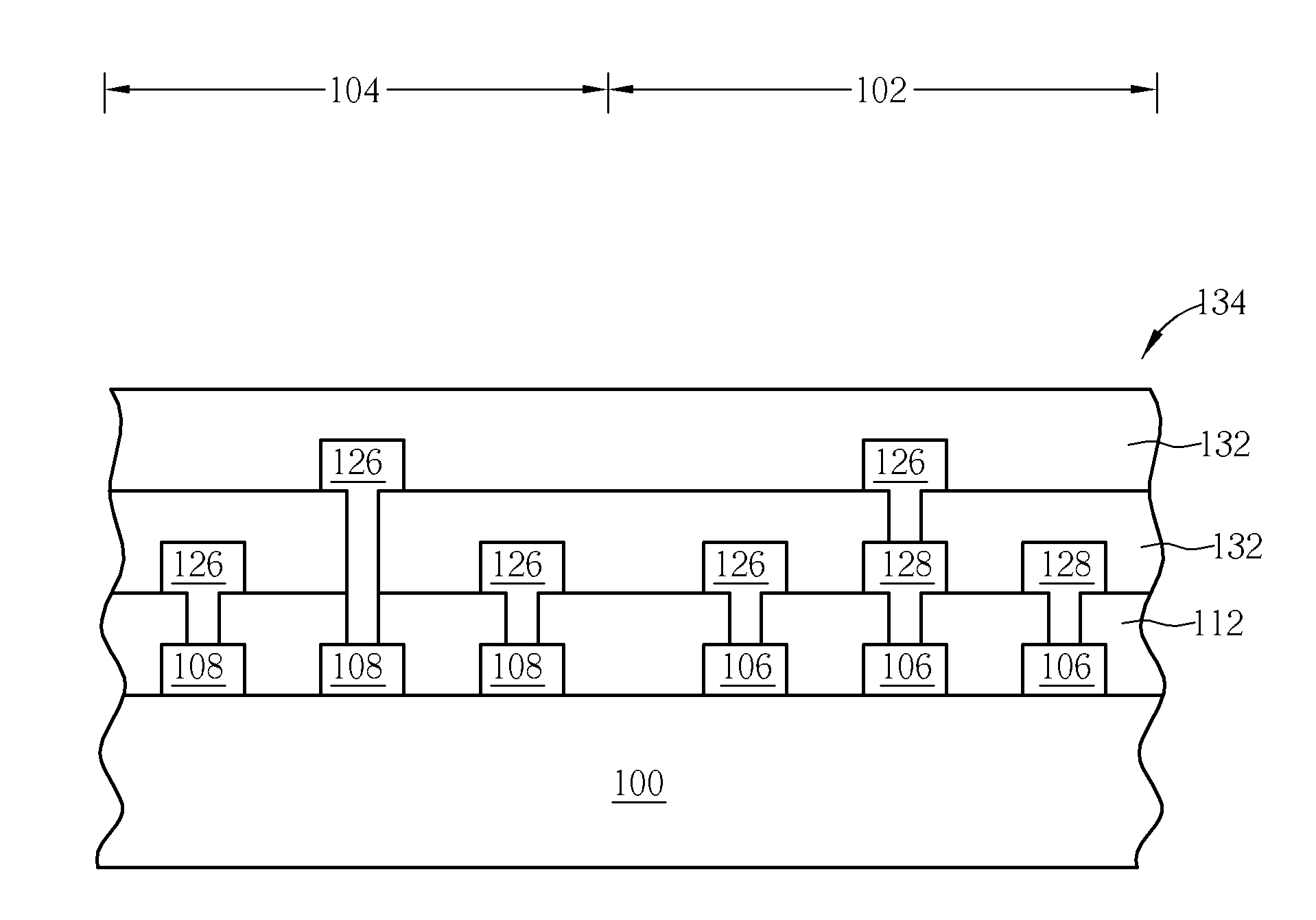

Reducing antenna effects in SOI devices

ActiveUS9773811B2Reduce antenna effectTransistorSemiconductor/solid-state device detailsAntenna effectGate dielectric

It is provided a semiconductor device comprising a power line, a Silicon-on-Insulator, SOI, substrate comprising a semiconductor layer and a semiconductor bulk substrate comprising a first doped region, a first transistor device formed in and above the SOI substrate and comprising a first gate dielectric formed over the semiconductor layer and a first gate electrode formed over the gate dielectric, a first diode electrically connected to the first gate electrode and a second diode electrically connected to the first diode and the power line; and wherein the first and second diodes are partially formed in the first doped region.

Owner:GLOBALFOUNDRIES U S INC

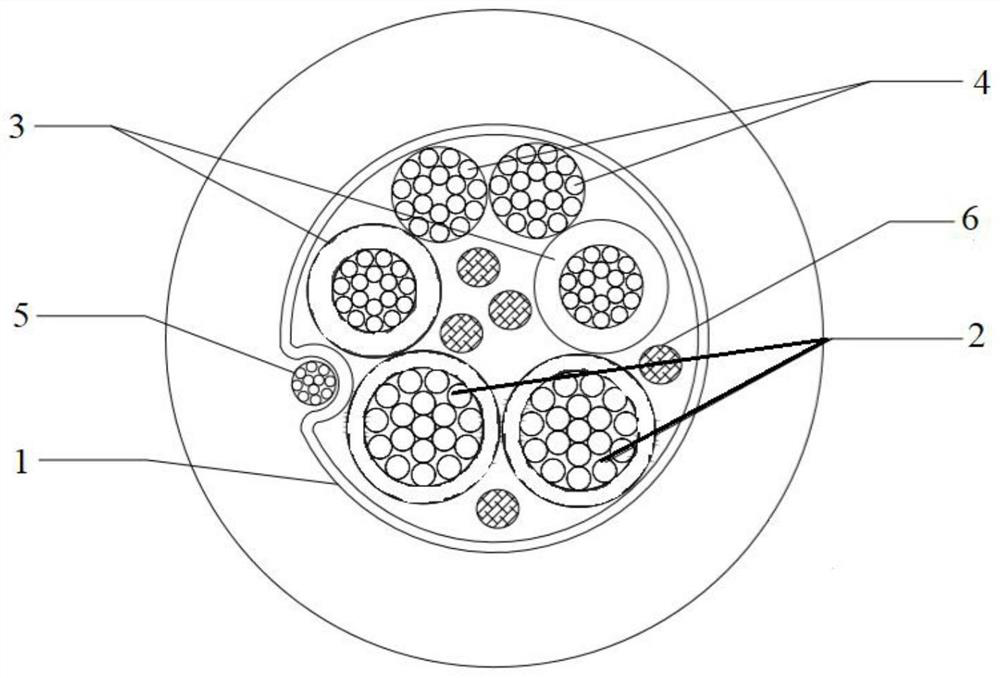

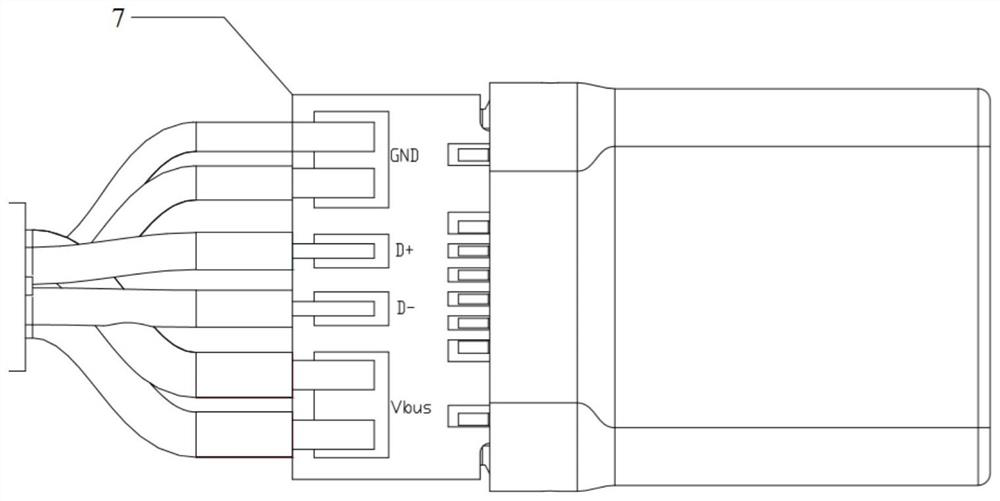

Data line and electronic equipment

ActiveCN113067212AGood groundingSimple manufacturing processFlexible cablesCoupling protective earth/shielding arrangementsCapacitanceAluminum foil

The invention discloses a data line and electronic equipment. The data line comprises an AM connector, a Type C connector, a connecting line and at least one capacitor, the two ends of the connecting line are electrically connected with the AM connector and the TypeC connector respectively, the connecting line comprises an aluminum foil used for shielding electromagnetic waves, and a containing space is formed in the inner side of the aluminum foil; the two power lines, the two signal lines and the two inner ground lines are arranged in the accommodating space on the inner side of the aluminum foil; the outer ground wire is arranged on the outer side of the aluminum foil; the power line is used for providing power, and the signal line is used for transmitting USB signals; the inner ground wire is arranged between the two signal wires and connected with the two signal wires and the inner side of the aluminum foil, and the inner ground wire is used for providing backflow for the power supply and providing reference ground for the signal wires; the outer ground wire is connected with the outer side of the aluminum foil and the metal shell of the AM connector; and the at least one capacitor is used for introducing electromagnetic waves coupled to a metal shell of the Type C connector to a ground wire.

Owner:VIVO MOBILE COMM CO LTD

BSI process deep trench isolation manufacturing method

PendingCN112038359AKey Dimension AdjustmentImprove uniformitySolid-state devicesDiodeAntenna effectEngineering physics

The invention discloses a BSI process deep trench isolation manufacturing method. The method comprises the following steps: conducting etching to form deep trench isolation, then depositing metal witha first preset thickness, fully filling the deep trench isolation, and forming covering layers on the surface and two sides of the deep trench isolation; removing a part of the covering layers with asecond preset thickness by grinding; and conducting etching to remove the residual covering layers by adopting an etching process with an adjustable wafer in-plane etching rate, and only reserving metal filling in the deep trench isolation. According to the invention, the in-plane uniformity of the wafer can be improved, and the problem of insufficient wafer edge windows is solved; and the metalon the surface of the deep trench isolation is removed in two steps, and the size of the metal on the top of the deep trench isolation can be adjusted, so antenna effect is reduced, and RTS is reduced.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Method for solving antenna effect of cooling fin

ActiveCN109872976AReduce antenna effectSemiconductor/solid-state device detailsSolid-state devicesAntenna effectElectromagnetic interference

The invention relates to the technical field of electronics and particularly relates to a method for solving antenna effect of a cooling fin. The method comprises the steps of S1, providing an integrated chip and setting a heat conduction layer and a metal cooling fin on the integrated chip in sequence; and S2, adjusting thickness of the heat conduction layer to be unequal to a preset value, thereby reducing the antenna effect of the metal cooling fin. The technical scheme provided by the invention has the beneficial effects that an electromagnet interference method for solving the antenna effect is disclosed; the thickness of the heat conduction layer is adjusted to be unequal to the preset value, so the antenna effect of the metal cooling fin is reduced; a designer is assisted to designan H-shaped heat sink with low radiation; and an engineer is assisted to analyze an EMI (Electromagnet Interference) radiation problem of an electronic product.

Owner:JINGCHEN SEMICON SHENZHEN CO LTD

Filtering antenna for wearable apparatus

PendingUS20210273319A1Small sizeEasy to integrateAntenna adaptation in movable bodiesRadiating elements structural formsInterference (communication)Electrical conductor

The invention discloses a filtering antenna for wearable devices, which includes a top dielectric substrate, a bottom dielectric substrate, an antenna radiation unit, a top metal ground, a bottom metal ground, and an artificial magnetic conductor structure. The antenna radiation unit is printed on an upper surface of the top dielectric substrate, the top metal ground is printed on a lower surface of the top dielectric substrate, the artificial magnetic conductor structure is etched on an upper surface of the bottom dielectric substrate, and the bottom metal ground is printed on a lower surface of the bottom dielectric substrate. The antenna radiation unit is formed by a circular patch and a microstrip coupling feed stub structure. The invention has the advantages of miniaturization, easy integration, low profile, high gain, anti-interference, may work in the 5.8-GHz ISM frequency band, may be used in wearable devices, has filtering effect etc., and is suitable in the field of human body wireless local area network communications.

Owner:SOUTH CHINA UNIV OF TECH

Method of forming a semi-insulating region

InactiveUS20060180832A1Reduce antenna effectImprove RF performanceSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor

A semiconductor substrate is provided, and at least one first mask is formed above the semiconductor substrate. The first mask has a plurality of thicknesses and blocks at least one semi-insulating region. A second mask is thereafter formed on a surface of the semiconductor substrate. The second mask covers the semi-insulating region. The semi-insulating region is implanted with a high energy beam of particles by utilizing the second mask and the first mask as particle hindering masks. Finally, the second mask is removed.

Owner:UNITED MICROELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com