Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

131results about How to "Less susceptible to noise" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

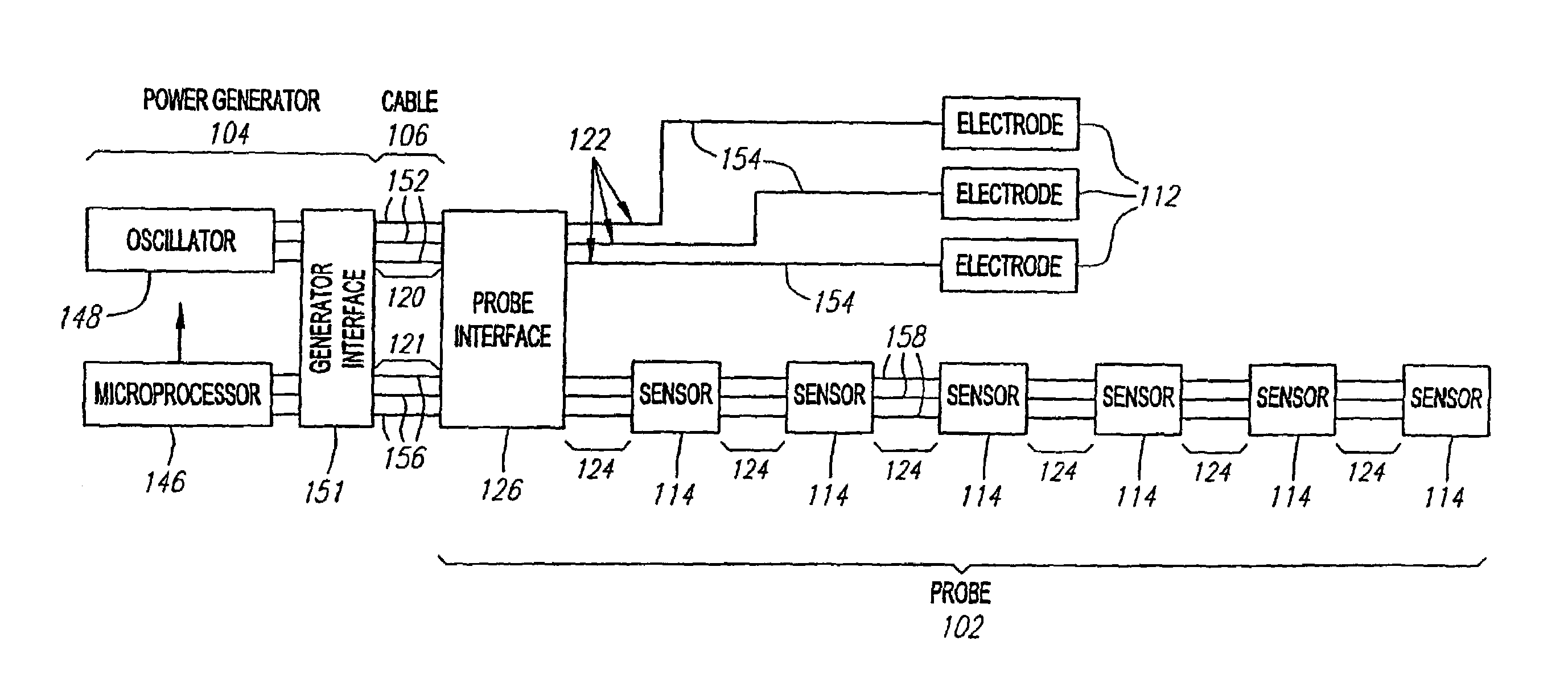

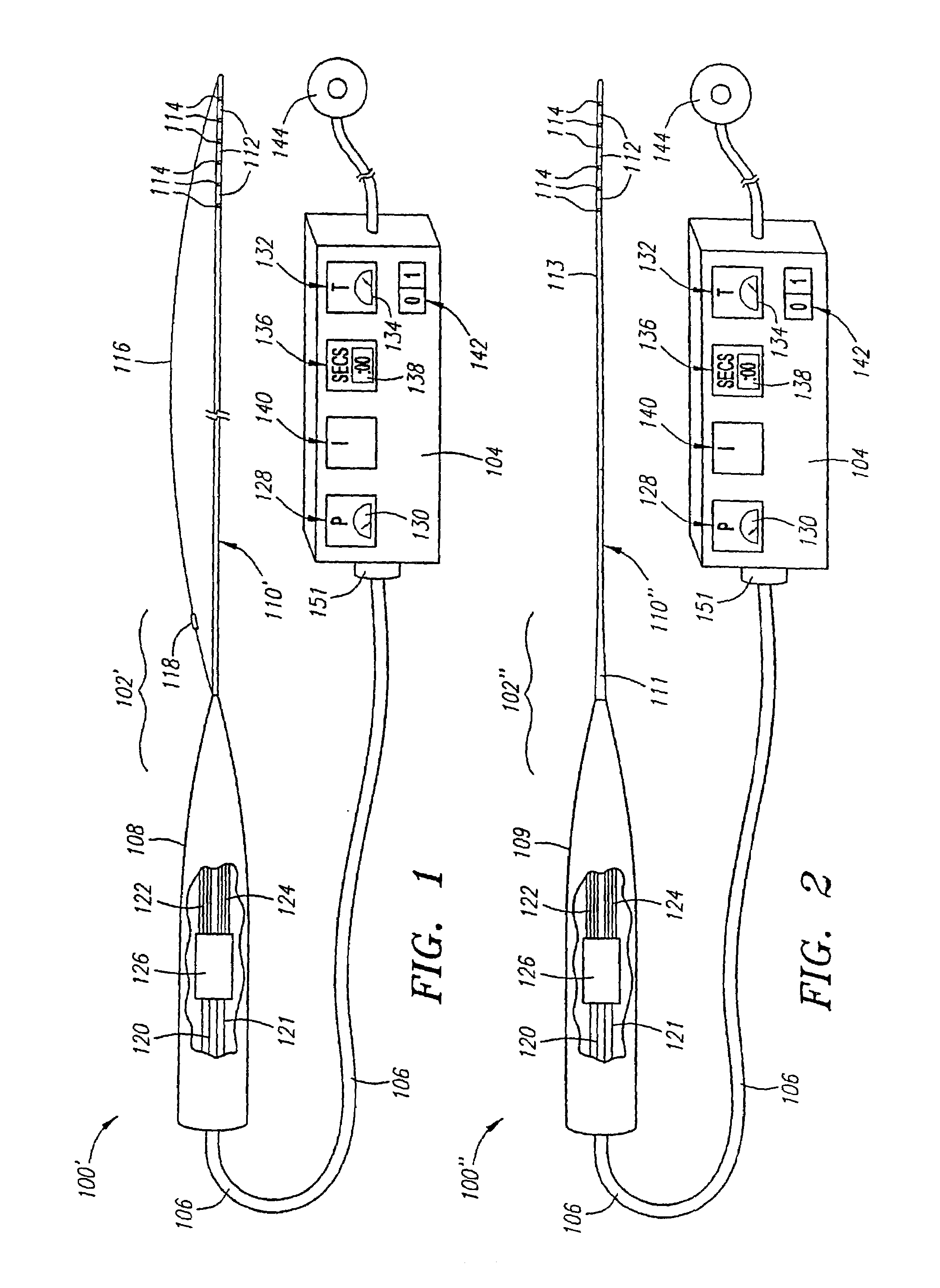

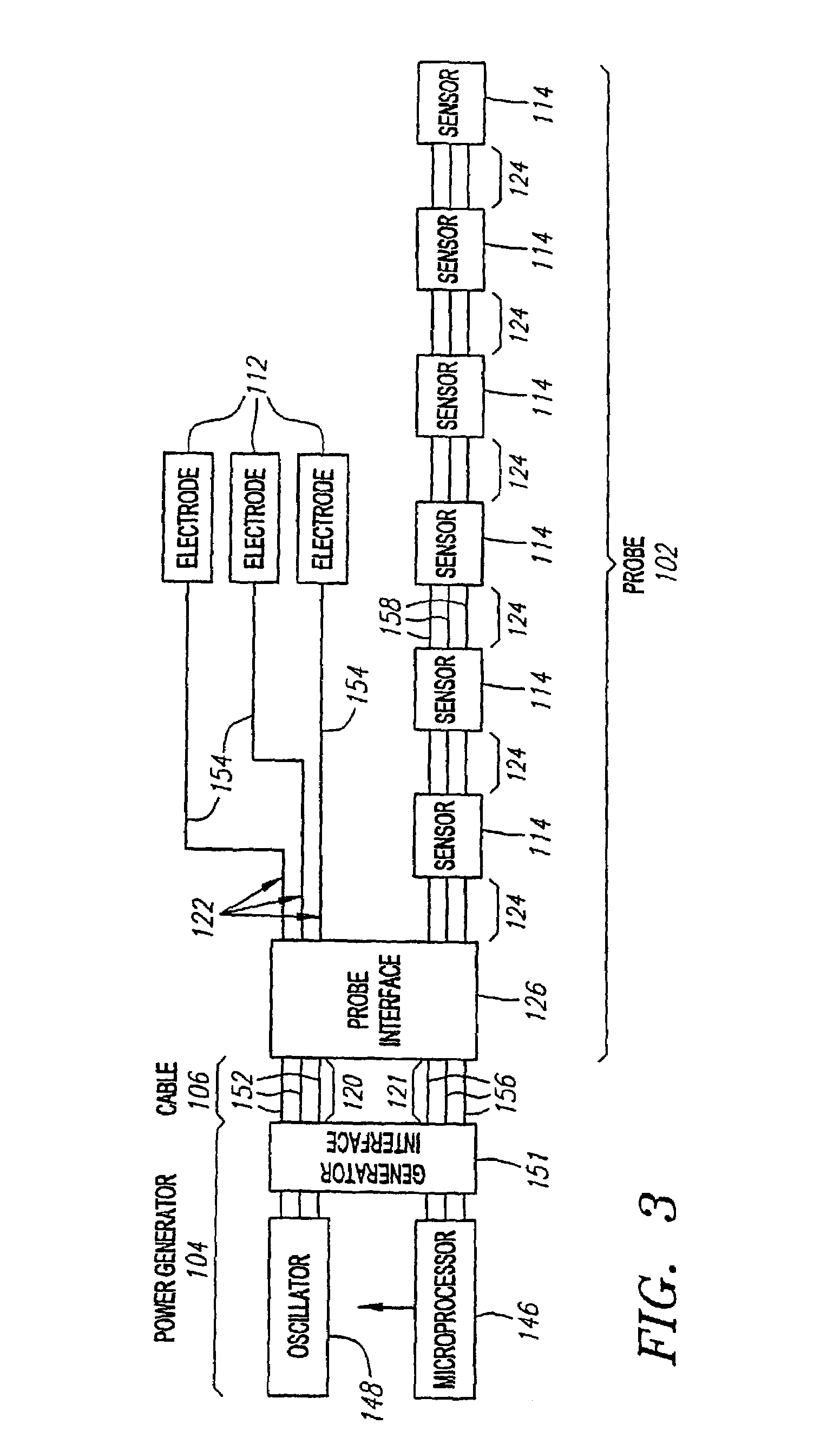

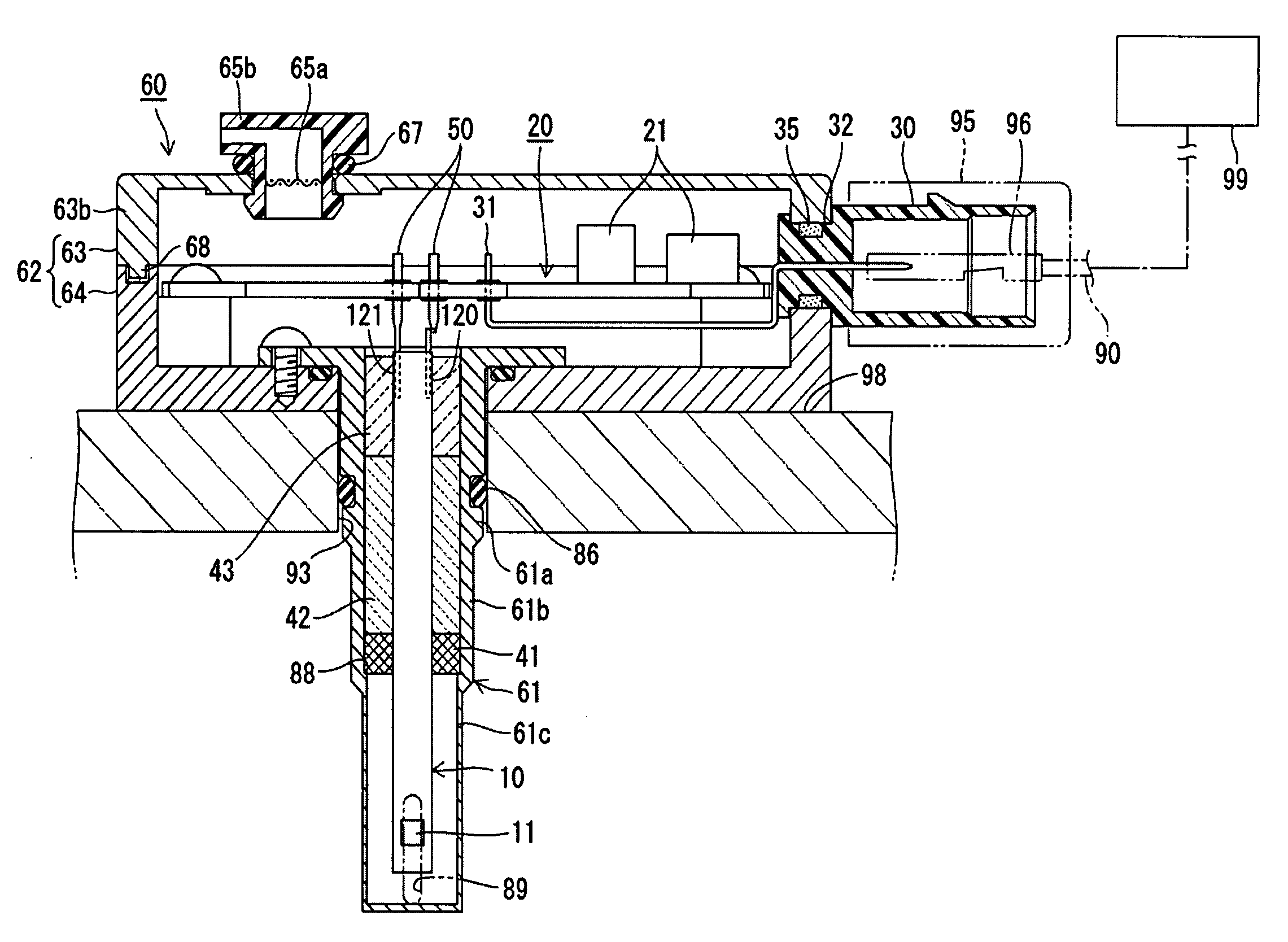

Medical probe with reduced number of temperature sensor wires

InactiveUS6979329B2Little and no noiseReduce in quantityThermometers using electric/magnetic elementsCatheterBody tissueDigital switching

Systems and methods for reducing the number of temperature measurement wires in multiple temperature sensor ablation systems are described. In a preferred embodiment, temperature sensors capable of measuring the temperature of body tissue and transmitting the temperature data digitally are incorporated in a catheter or probe ablation system that also includes electrodes in operative contact with the sensors. The sensors are connected in parallel to a common electrical bus, thereby allowing the system to operate using a reduced number of electrical paths as compared to conventional ablation systems. The present invention is also directed to ablation systems that incorporate analog sensors rather than digital sensors. In this embodiment, the system utilizes digital switching, filtering circuits, or oscillators to reduce the number of wires required to operate the sensors.

Owner:BOSTON SCI SCIMED INC

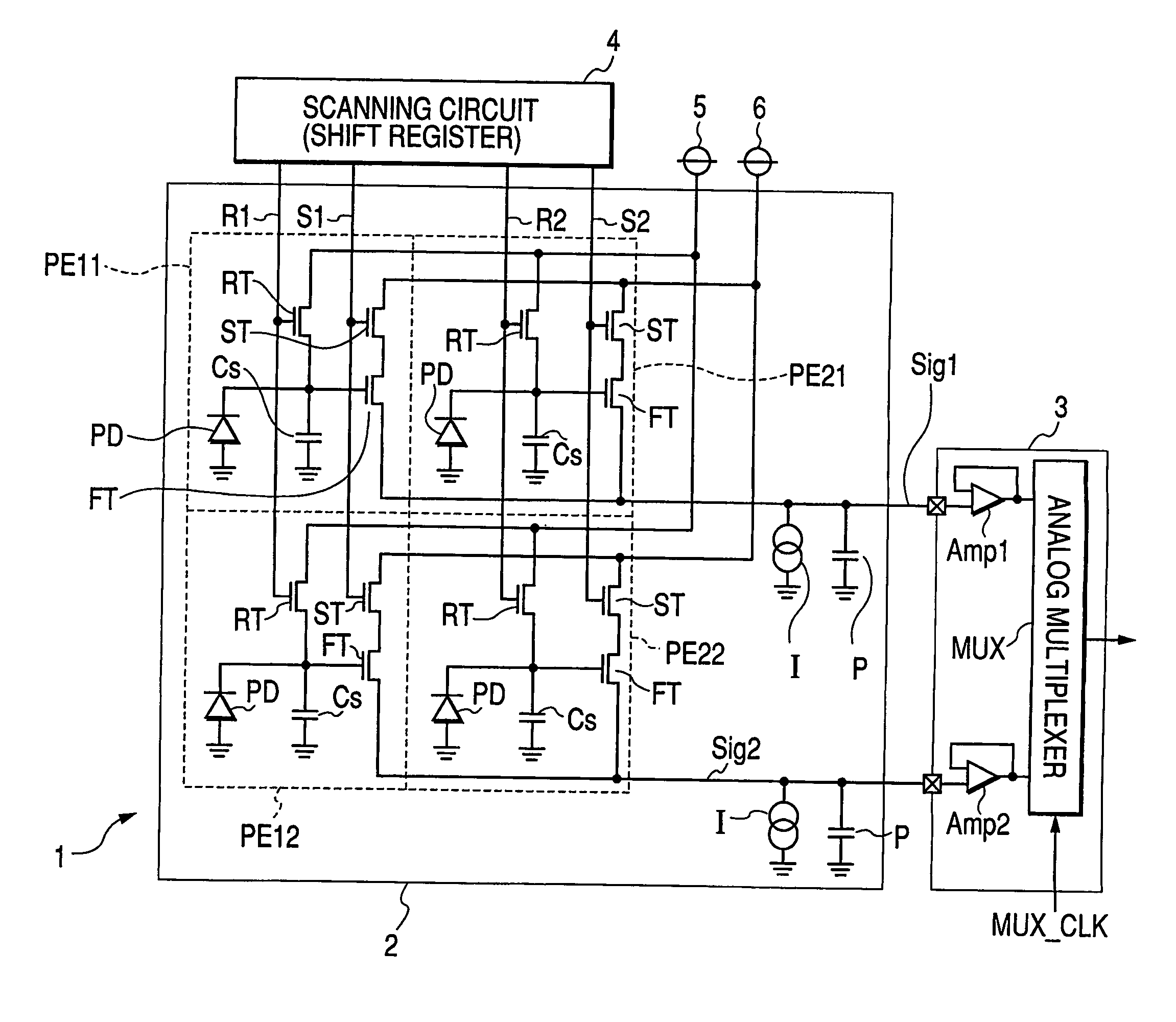

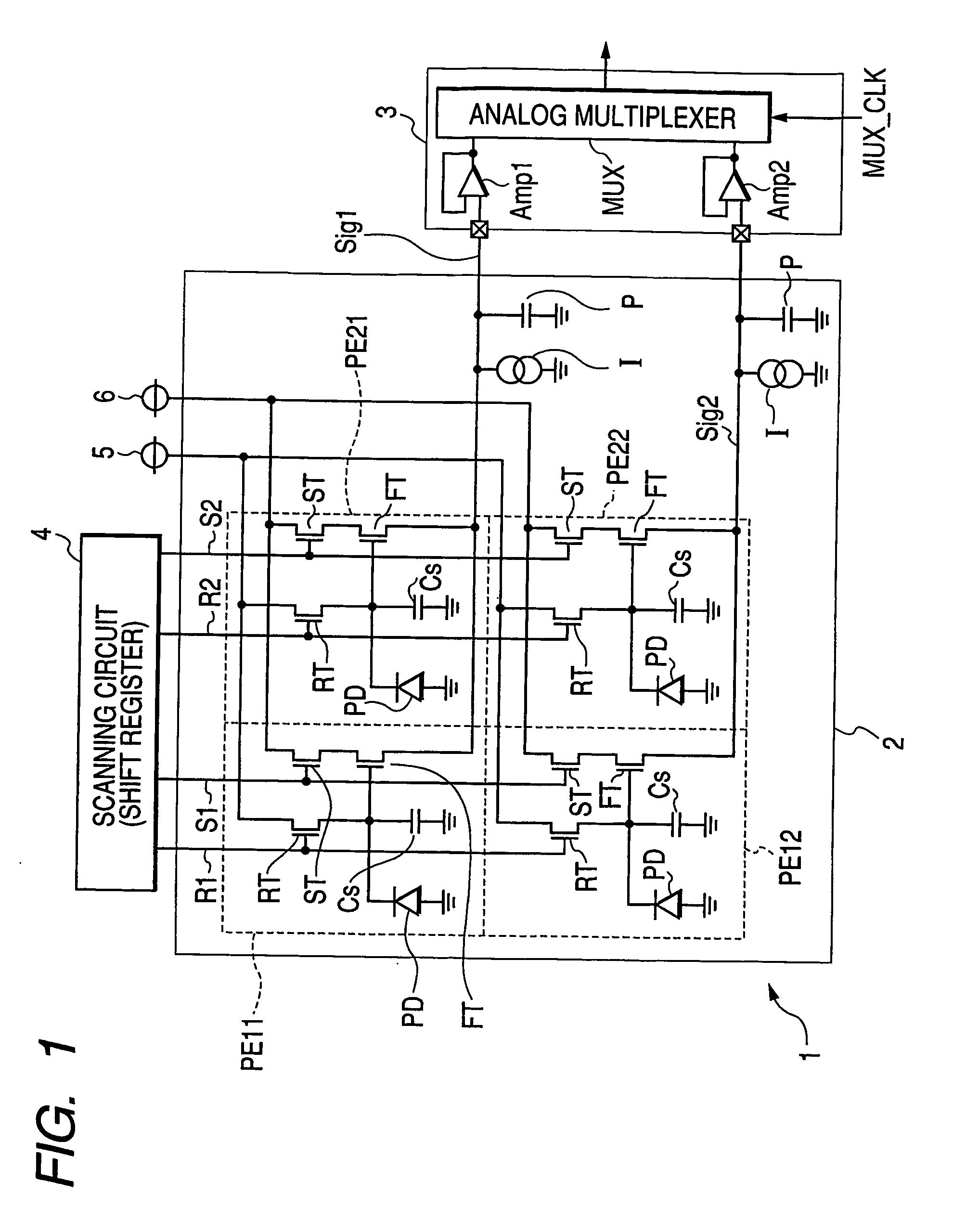

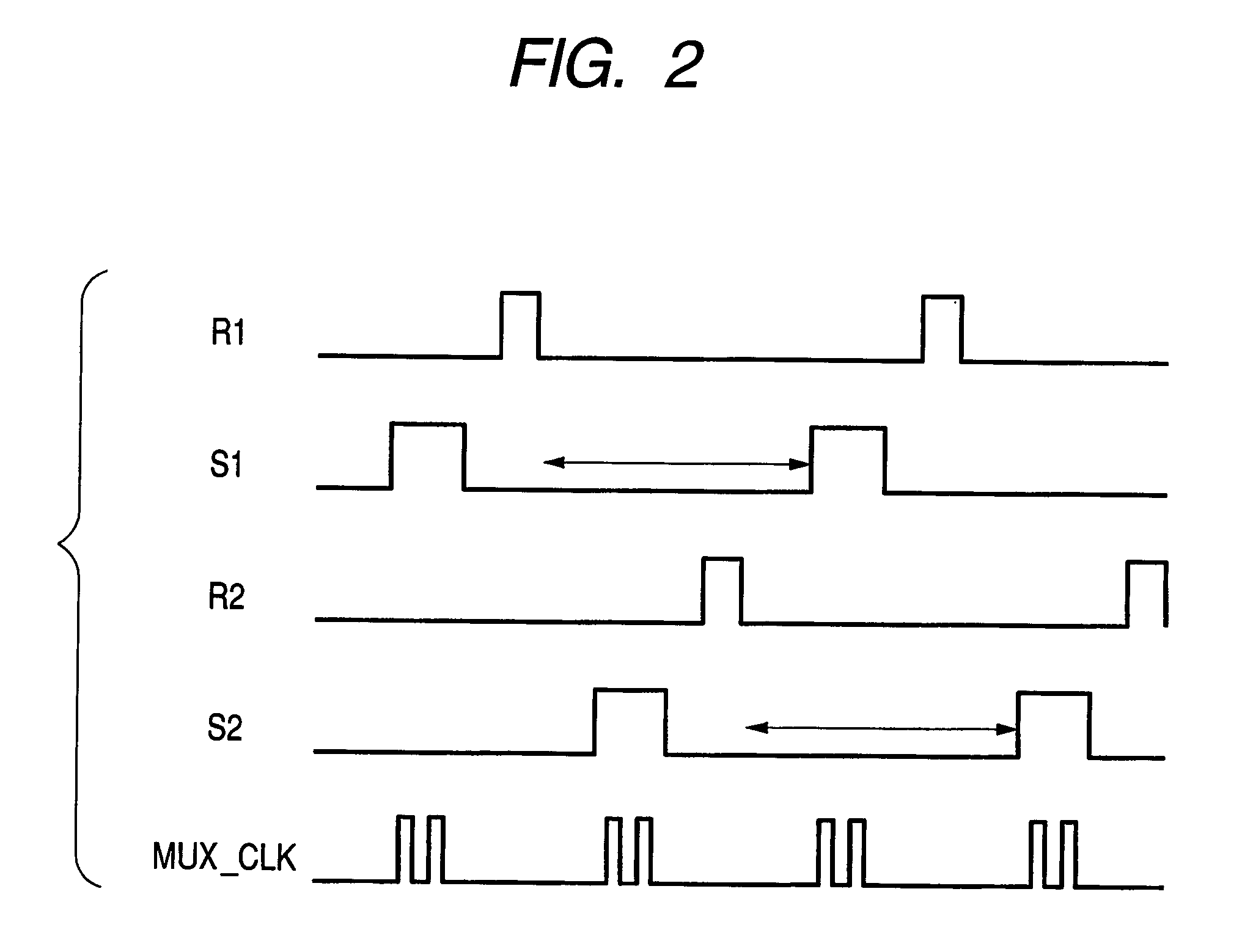

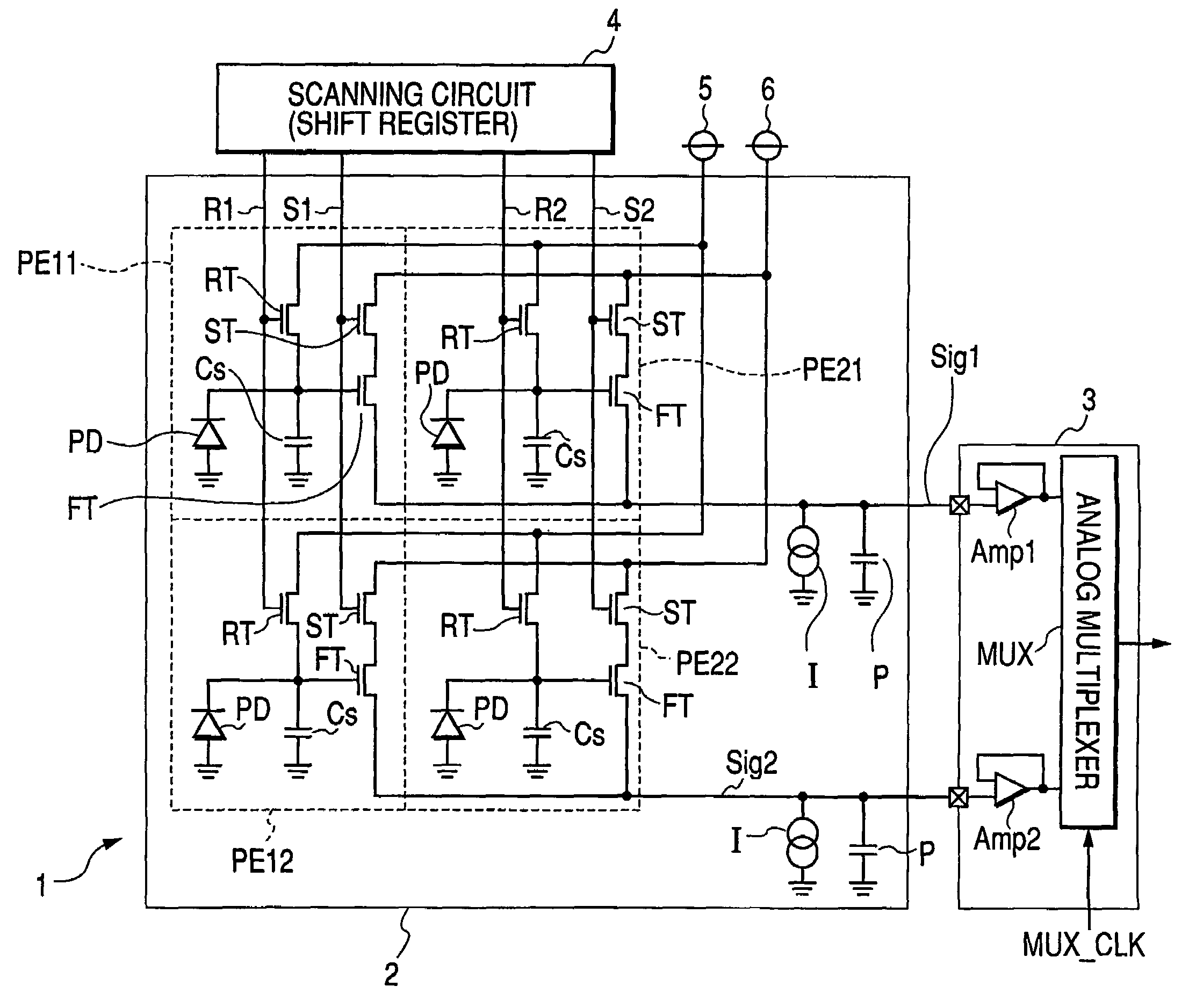

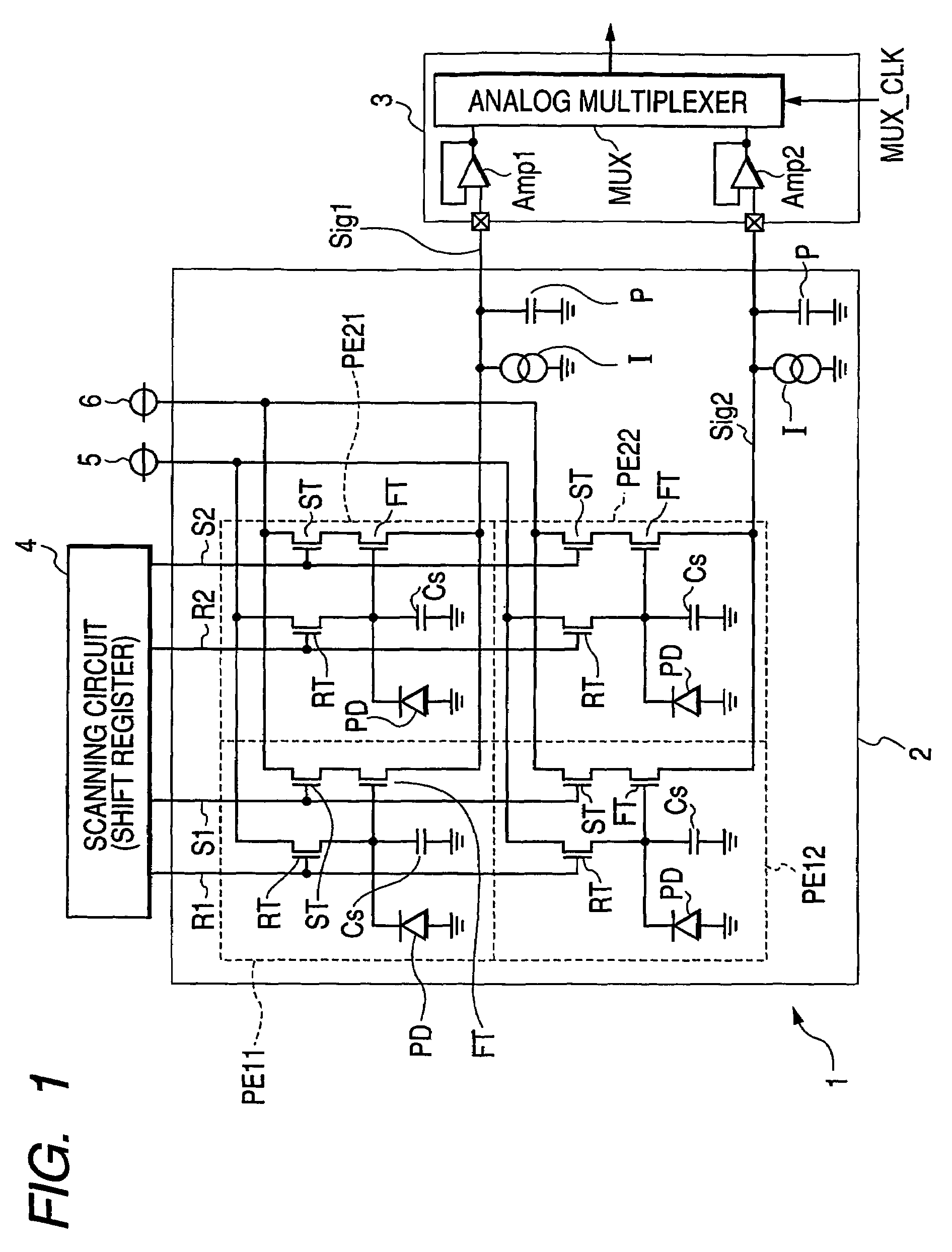

Photoelectric converting apparatus

InactiveUS20060119719A1Reduce impactSimple configurationTelevision system detailsTelevision system scanning detailsEngineeringPhotoelectric conversion

A photoelectric converting apparatus of the present invention includes a photoelectric converting element, a resetting transistor in which a source is connected to the photoelectric converting element and a drain is connected to a resetting power source, a readout transistor in which a gate is connected to the photoelectric converting element and a drain is connected to a readout power source, a signal line connected to a source of the readout transistor, a selecting transistor connected between the readout power source or the signal line and the readout transistor, and a constant current source connected to the signal line.

Owner:CANON KK

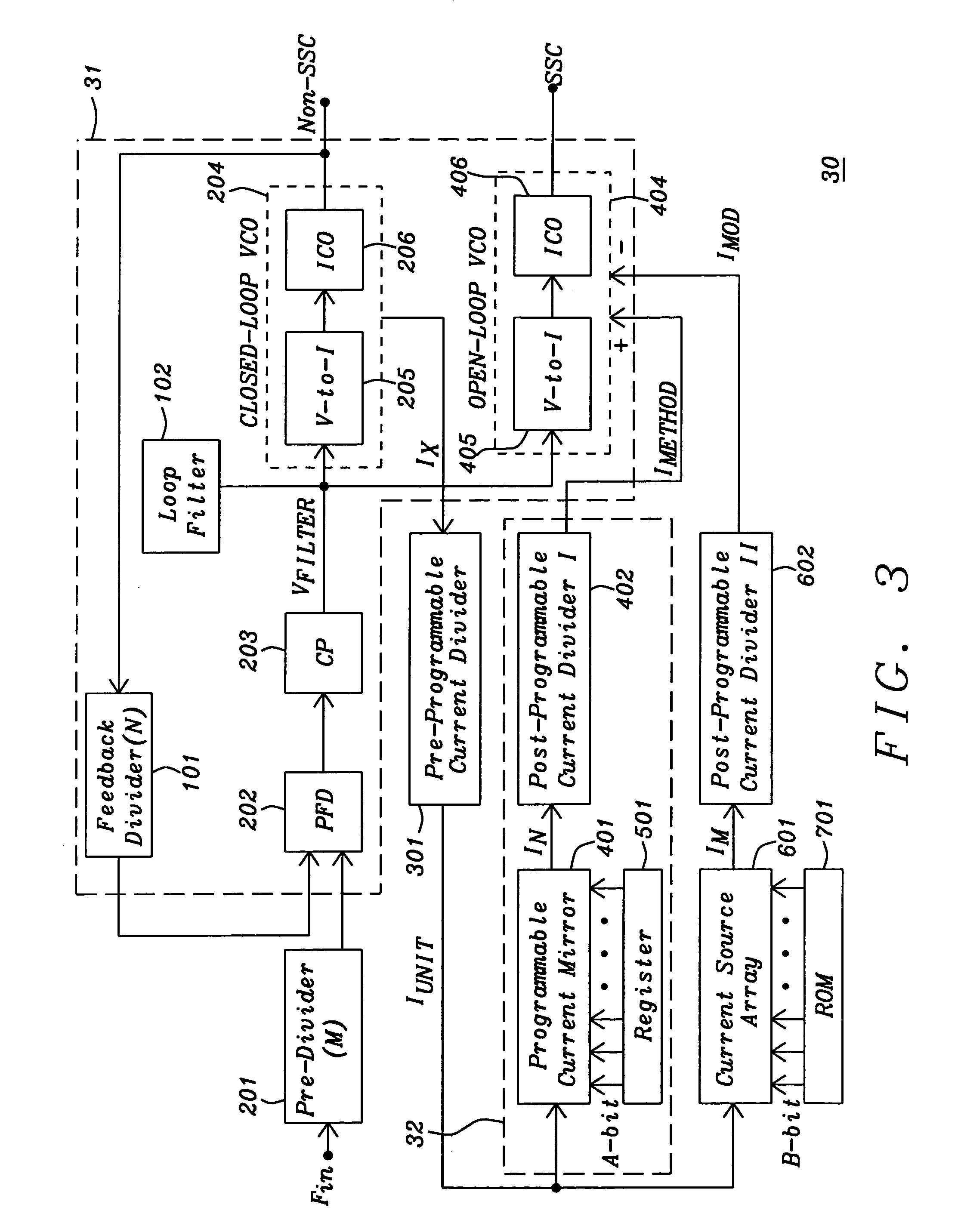

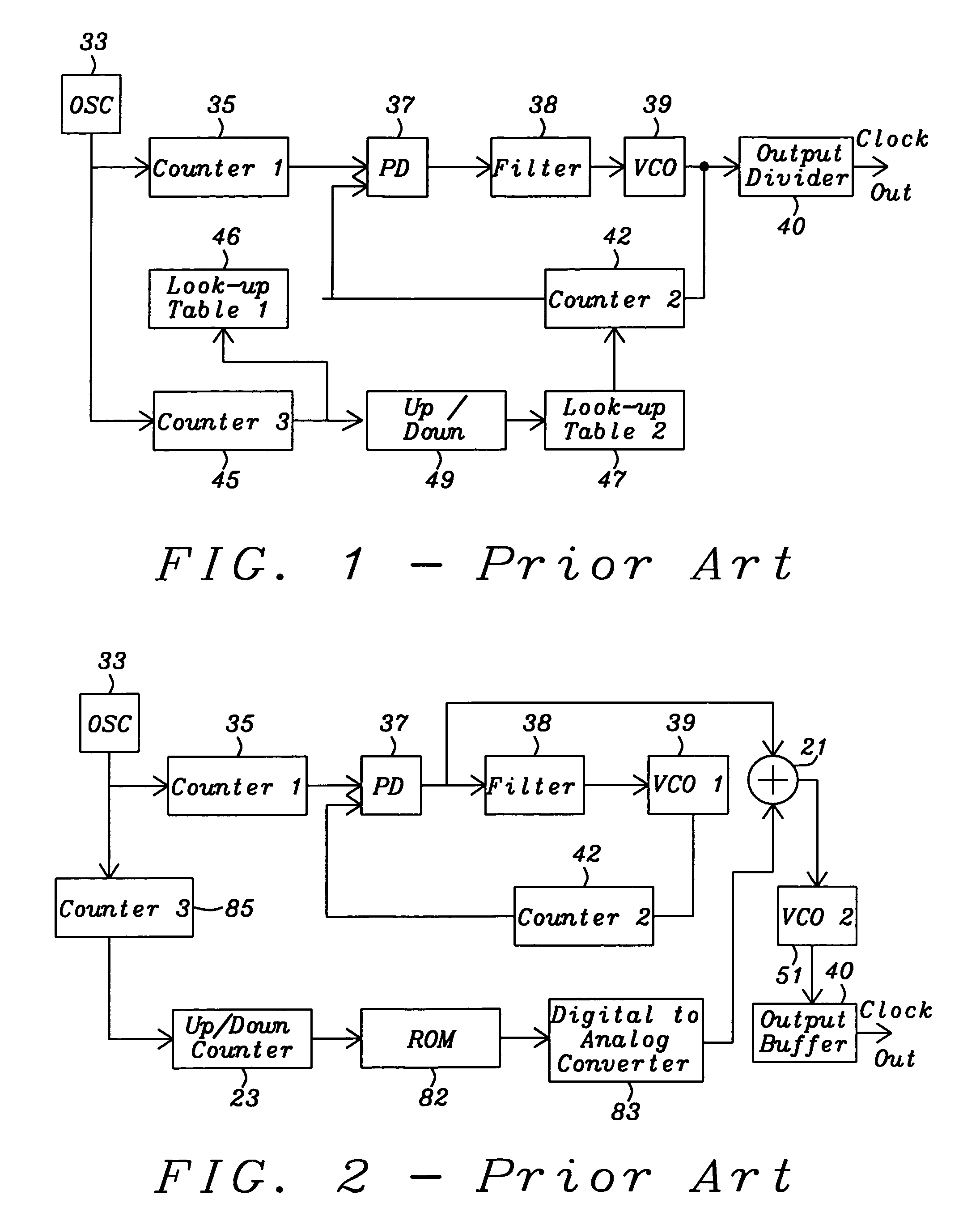

Spread spectrum clock generator

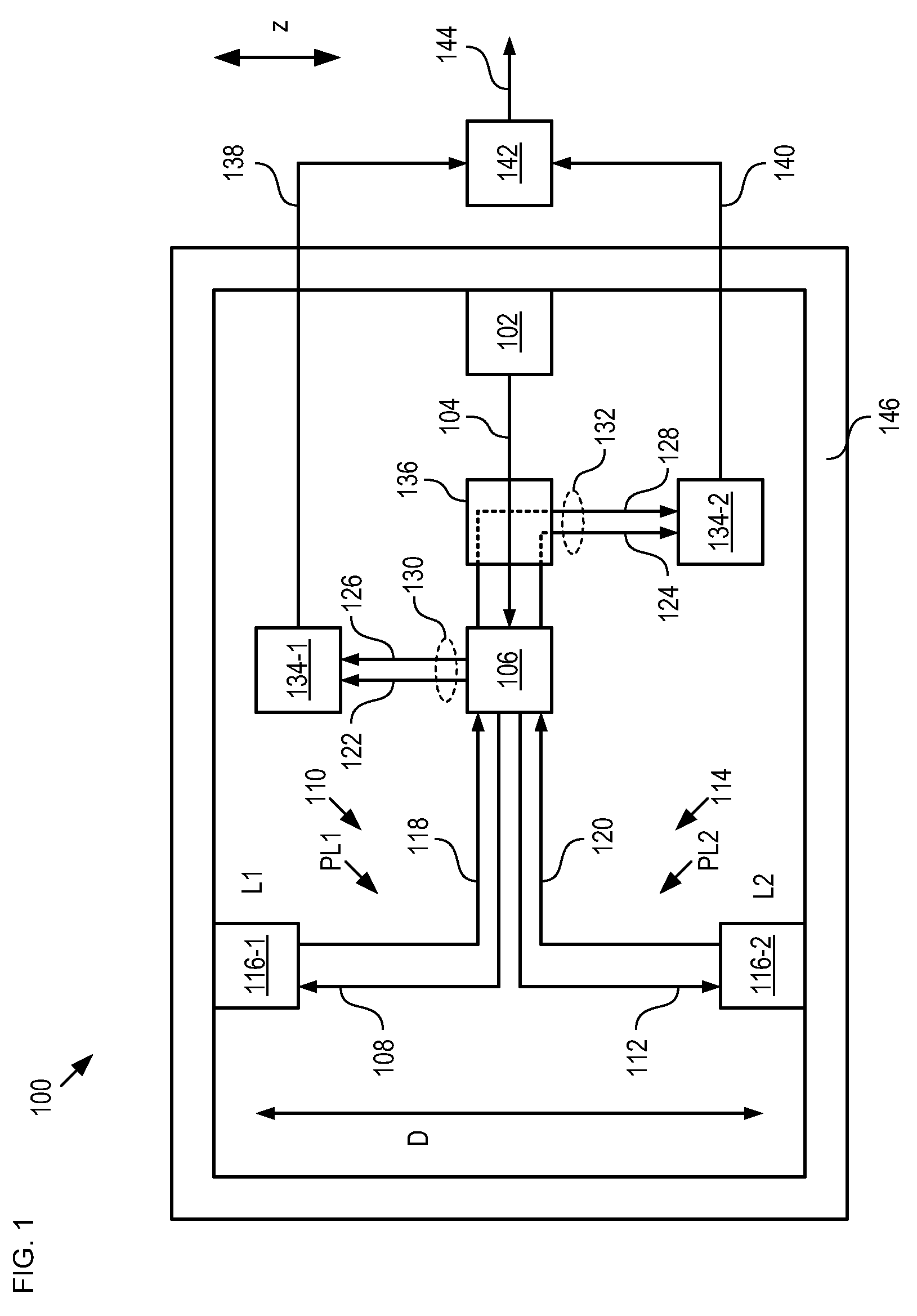

InactiveUS20060056491A1Robust architectureLess susceptible to noisePulse automatic controlElectrical apparatus interference reductionClosed loopCurrent controlled oscillator

A spread spectrum clock generator comprises a conventional closed-loop VCO and an open-loop VCO where both are coupled to the same point of the PLL. Both VCOs comprise a V-to-I converter followed by a current-controlled oscillator and are identical in design but only the open-loop VCO receives the modulation current to generate the spread spectrum clock signal. The open-loop ICO is part of the spread spectrum generator and in one embodiment of the invention receives feedback current signals representing the modulation method and modulation ratio. This ensures that the modulated clock output tracks the PLL output frequency. In a second embodiment the closed-loop VCO receives from the spread spectrum generator the feedback current signal representing the modulation method (center / down spread) while the open-loop VCO receives the feedback signal representing the modulation ratio.

Owner:KARMIC DESIGN USA

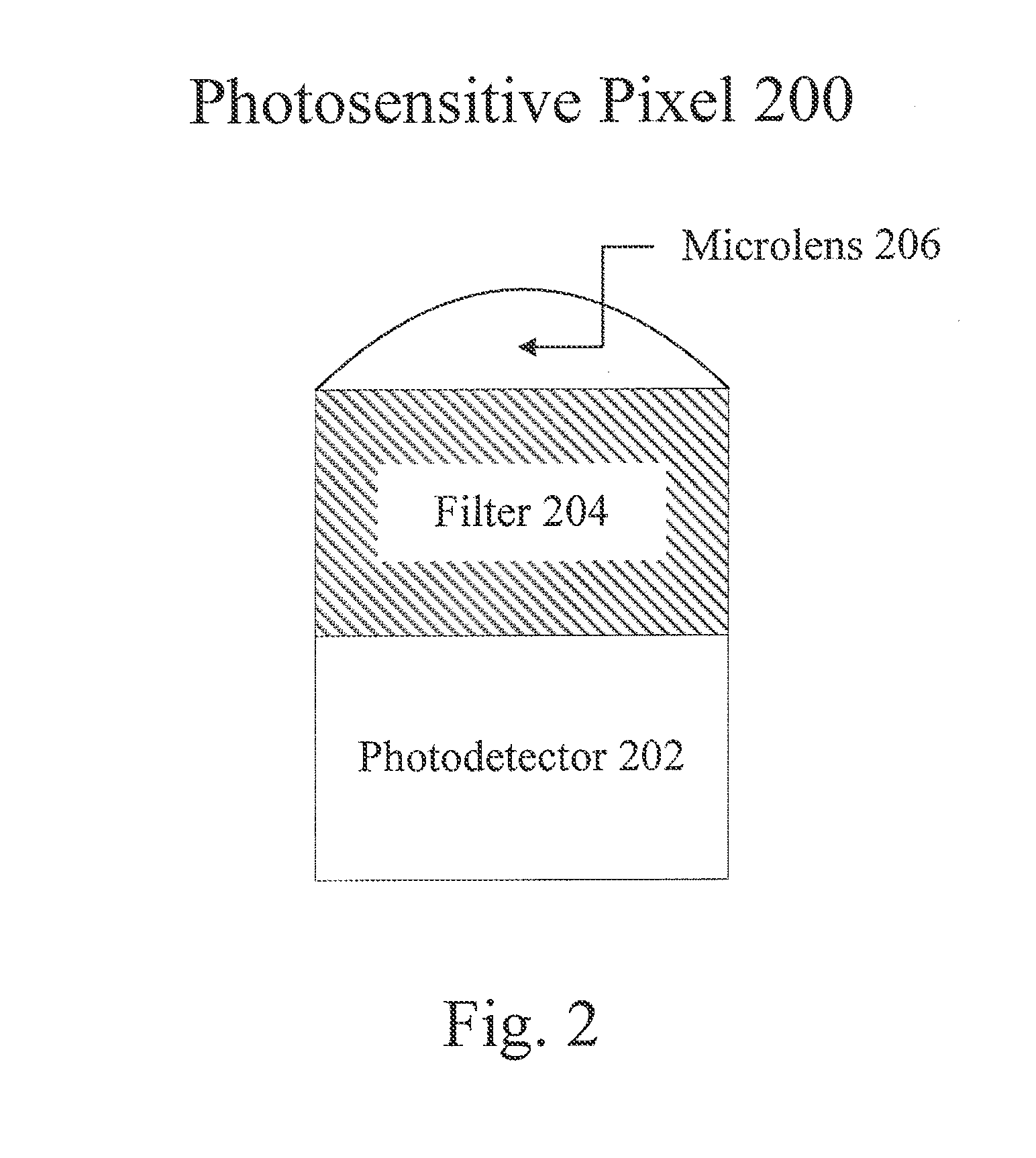

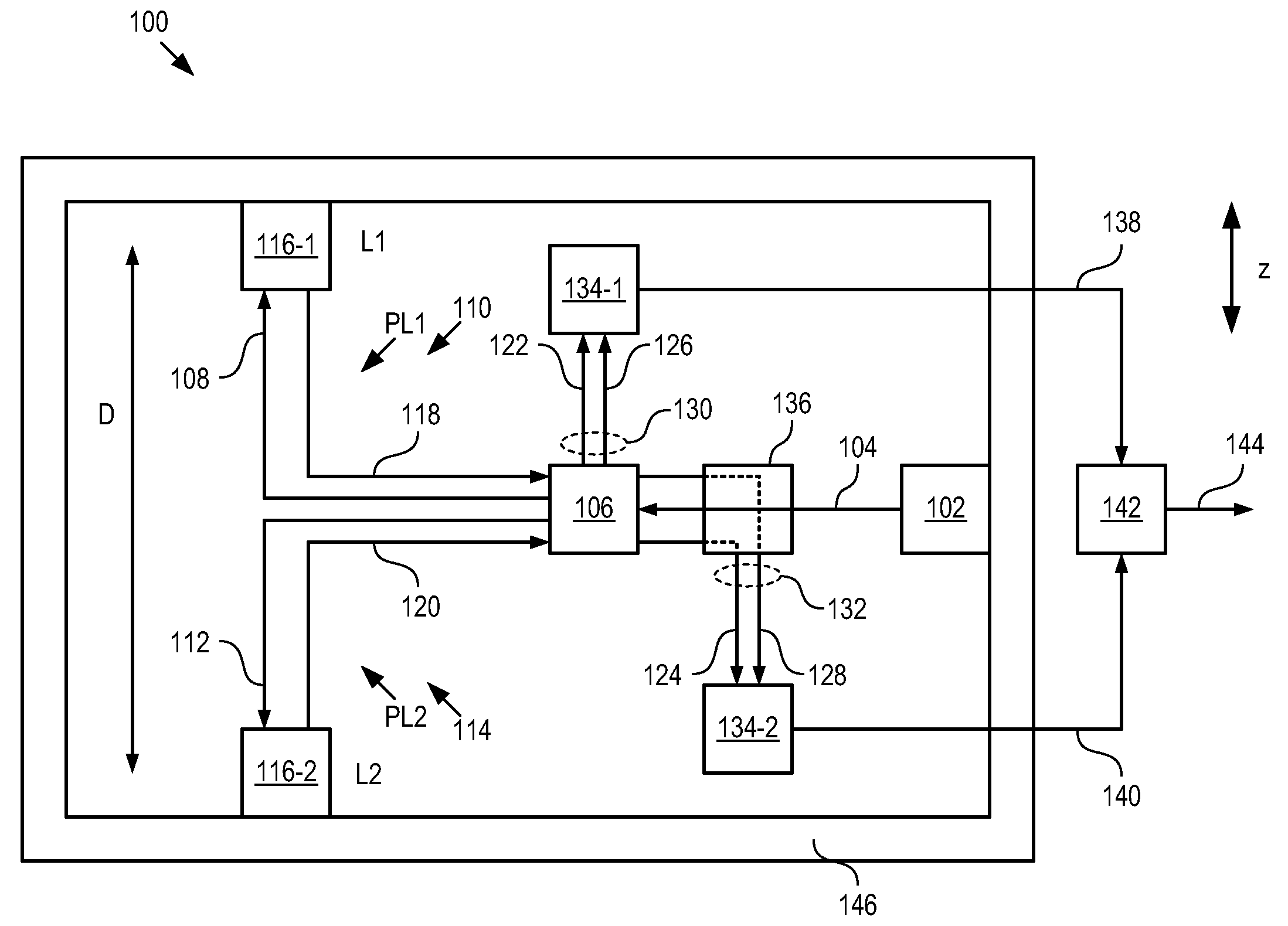

Systems and methods for creating full-color image in low light

ActiveUS20130329053A1Good color reproductionSusceptible to noiseTelevision system detailsImage analysisElectric signalImage processor

Full-color images of low-light scenes are generated by the systems and methods described herein using only two light channels. An array of photosensitive pixels includes two sets of pixels, the first sensitive only to light associated with a first light channel, the second only to light associated with a second light channel. Thus the first set of pixels generate a first set of electrical signals in response to incident light within the first light channel, and the second set of pixels generate a second set of electrical signals in response to incident light within the second light channel. An image processor receives the first and second sets of electrical signals and generates a full-color image of the scene by processing only signals generated by the first and second sets of pixels.

Owner:CHROMATRA

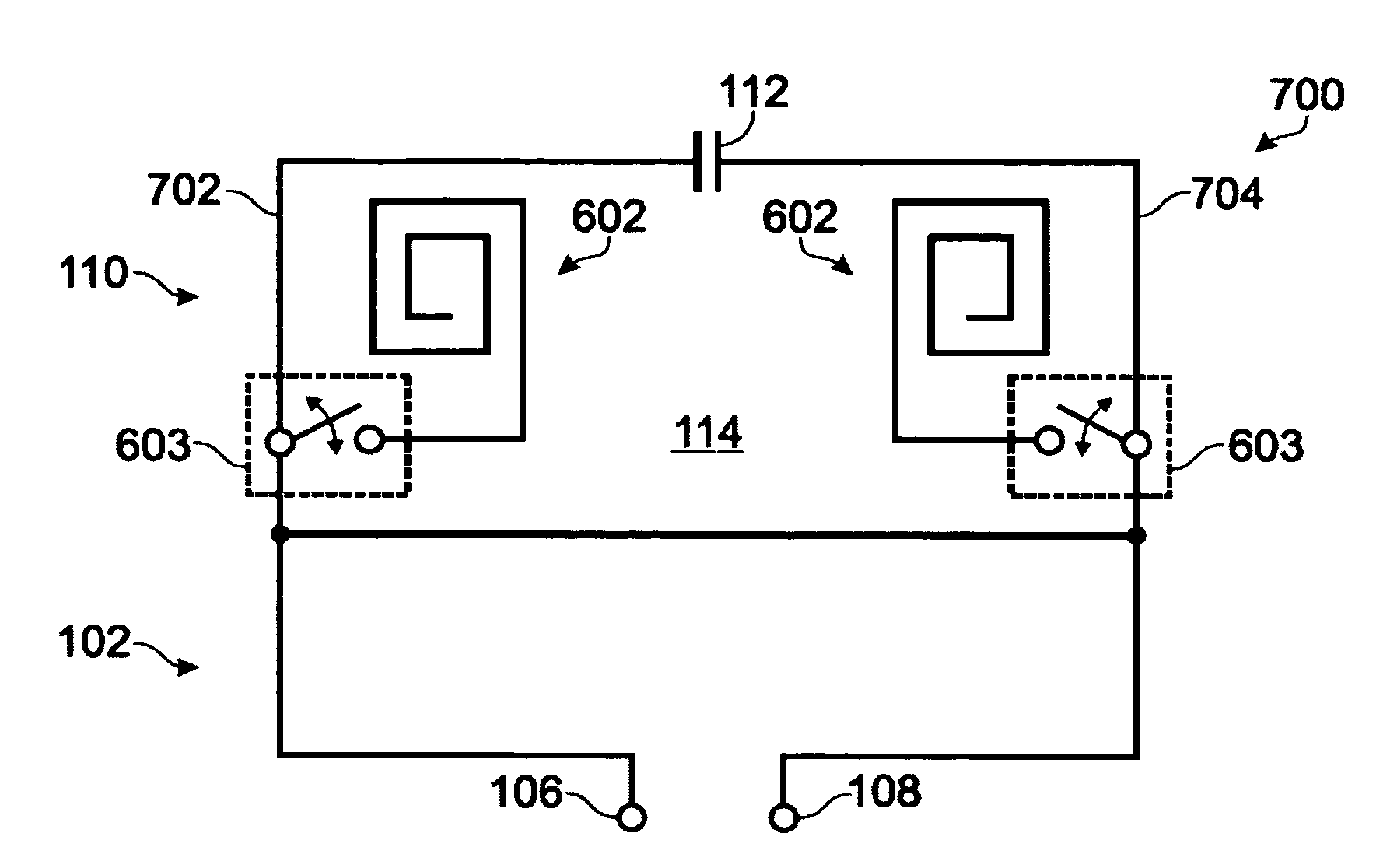

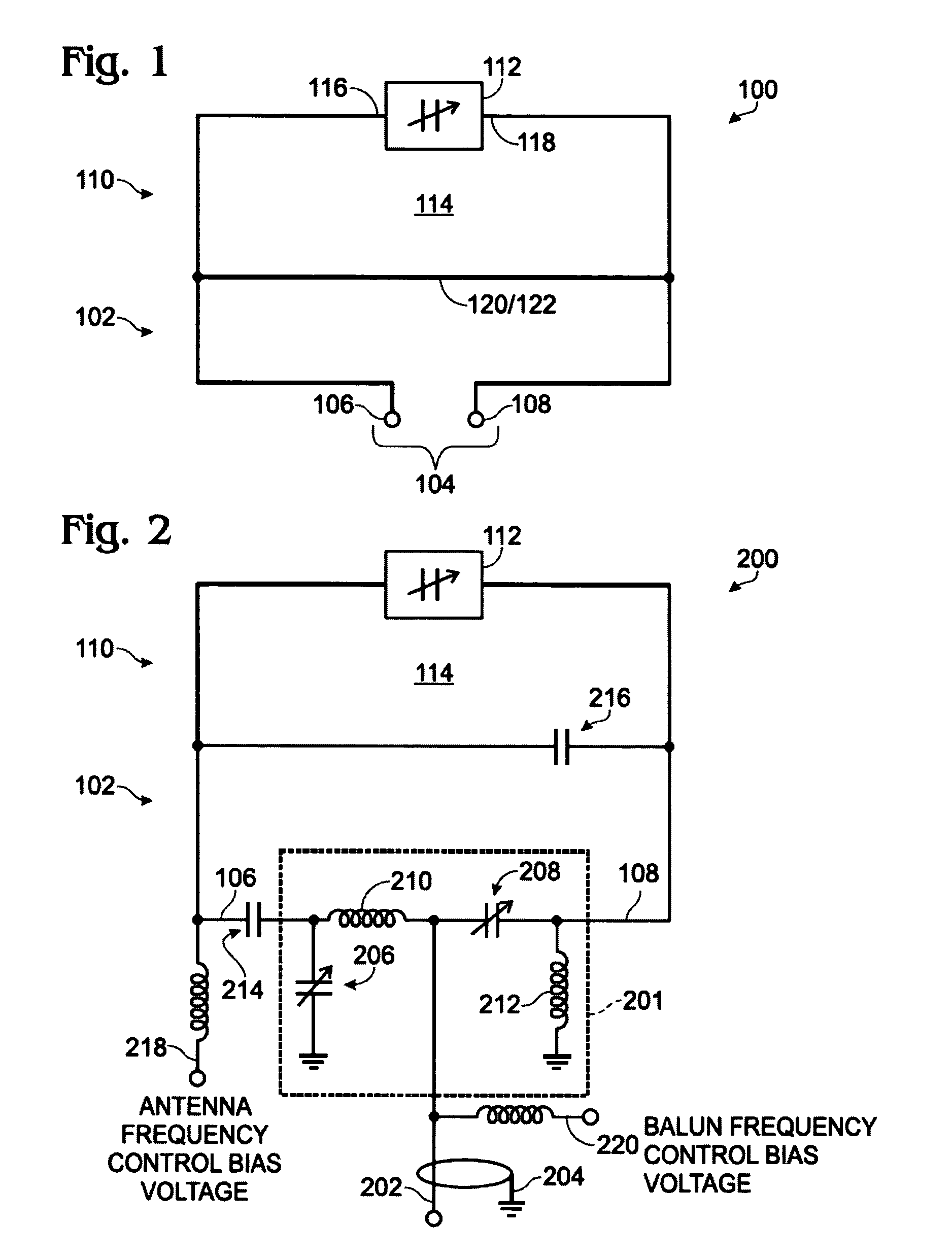

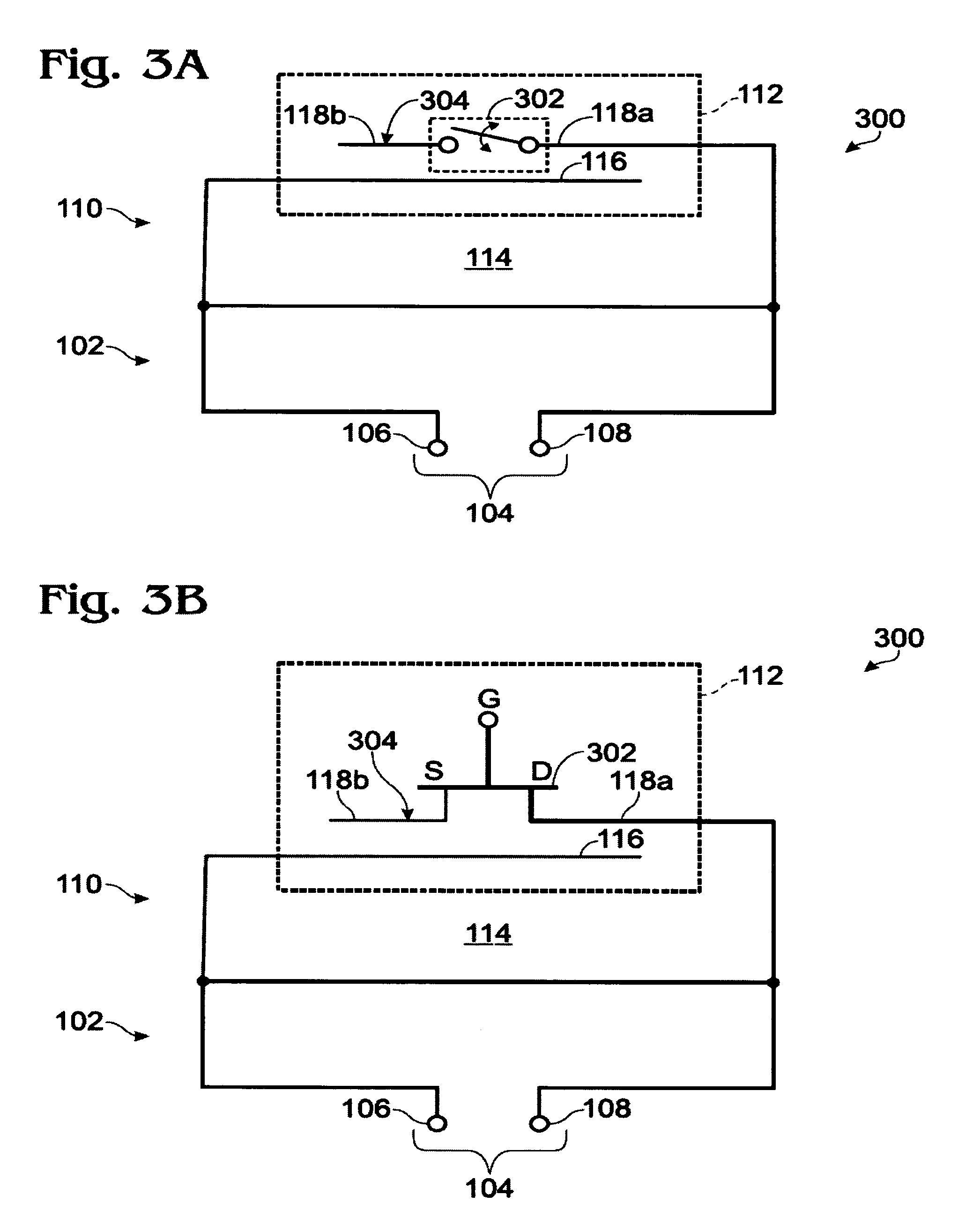

Tunable capacitively-loaded magnetic dipole antenna

InactiveUS7408517B1Minimize susceptibilityLess susceptible to RF noiseResonant long antennasAntenna arraysCapacitanceTransformer

A frequency-tunable capacitively-loaded magnetic dipole antenna includes a transformer loop having a balanced feed interface, and a capacitively-loaded magnetic dipole radiator with a tunable effective electrical length. In one embodiment, the capacitively-loaded magnetic dipole radiator includes a tunable electric field bridge. For example, the capacitively-loaded magnetic dipole radiator may comprise a quasi loop with a tunable electric field bridge interposed between the quasi loop first and second ends. The electric field bridge may be an element such as a ferroelectric (FE) tunable capacitor or a microelectromechanical system (MEMS) capacitor, to name a couple of examples. In certain embodiments, the capacitively-loaded magnetic dipole radiator includes a quasi loop with a loop perimeter. The effective electrical length of the radiator is changed by adjusting the perimeter using an element such as a MEMS switch, or a semiconductor switch.

Owner:KYOCERA CORP

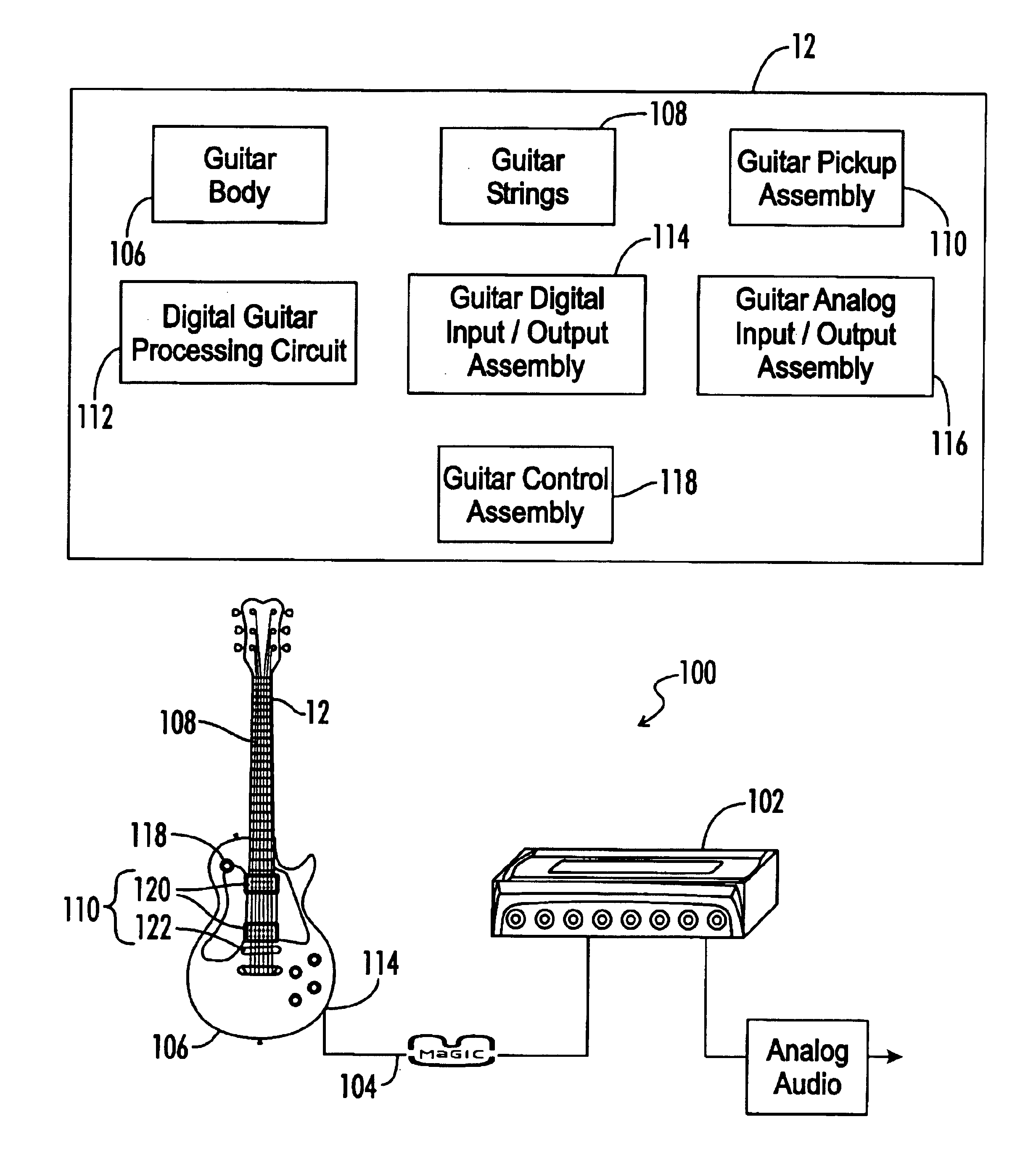

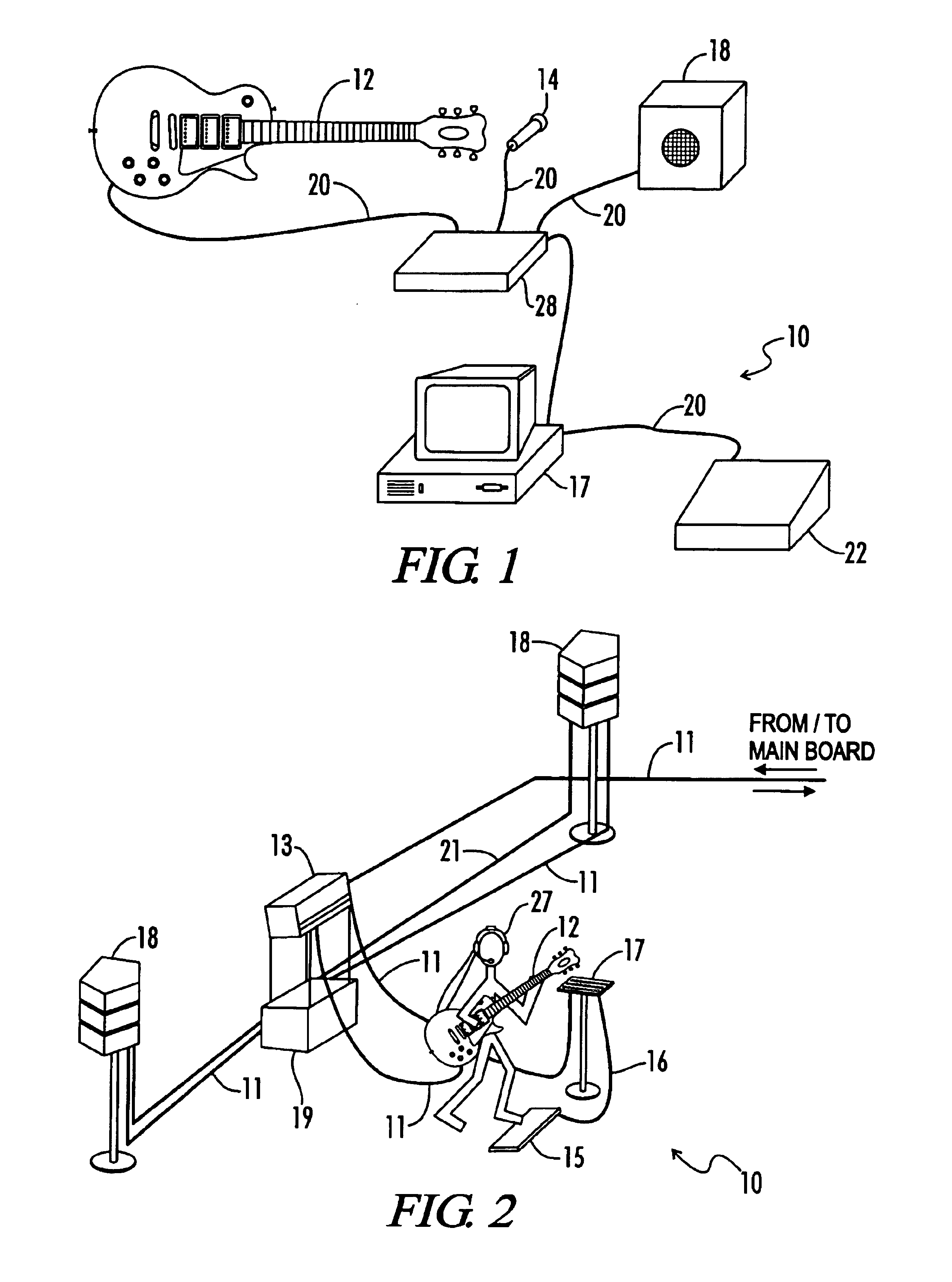

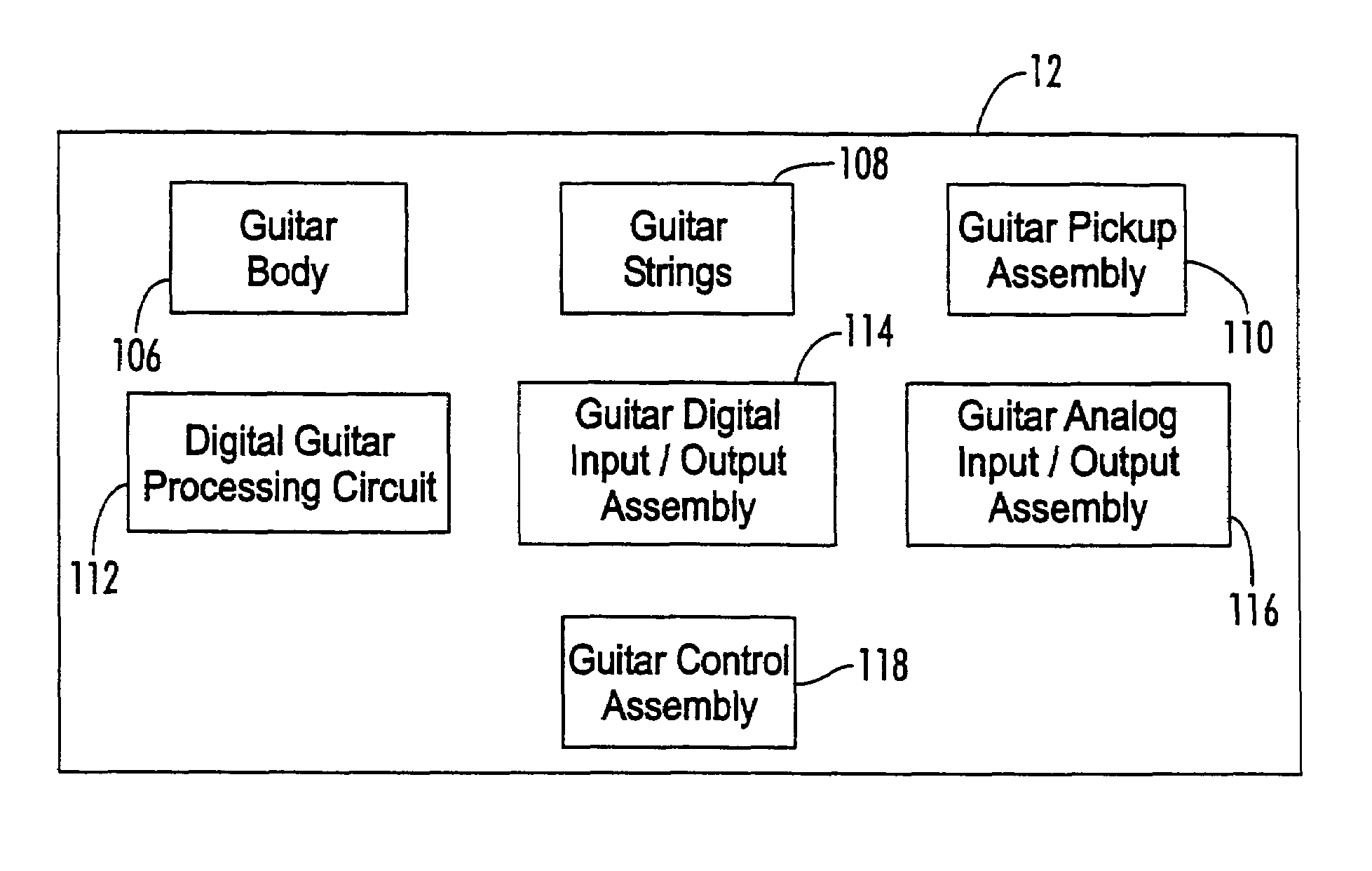

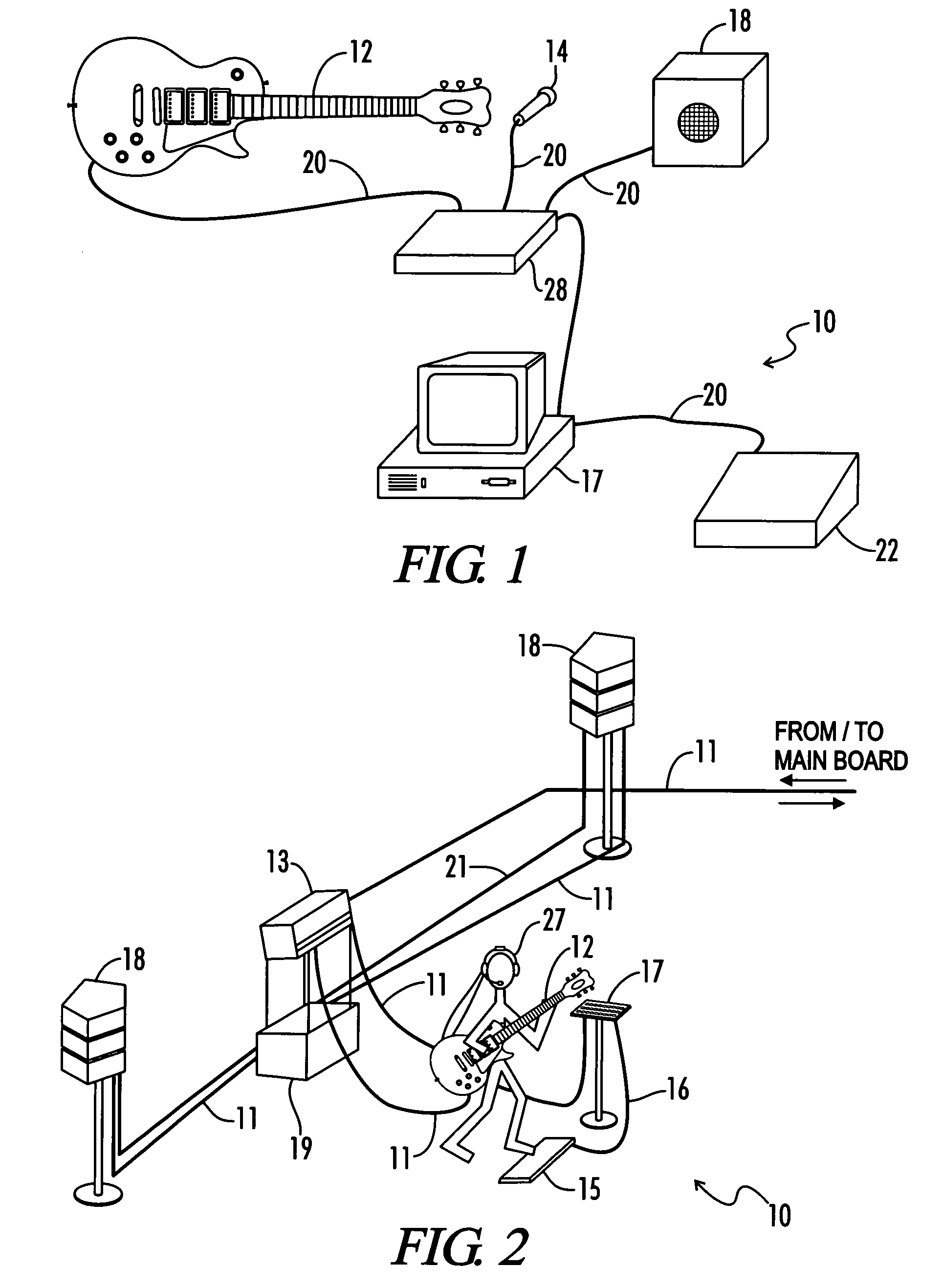

Digital guitar processing circuit

InactiveUS6888057B2Reduce and eliminate noise signalIncreased complexityElectrophonic musical instrumentsVibrating stringDigital signal

A digital guitar processing circuit includes a guitar converter circuit and a guitar formatting circuit. The guitar converter circuit receives one or more analog string signals representative of the string vibrations of a guitar and generates one or more digital string signals based upon the analog string signals. The guitar formatting circuit formats the digital string signals to be compatible with a digital communication protocol, and outputs the formatted digital string signals.

Owner:GIBSON BRANDS

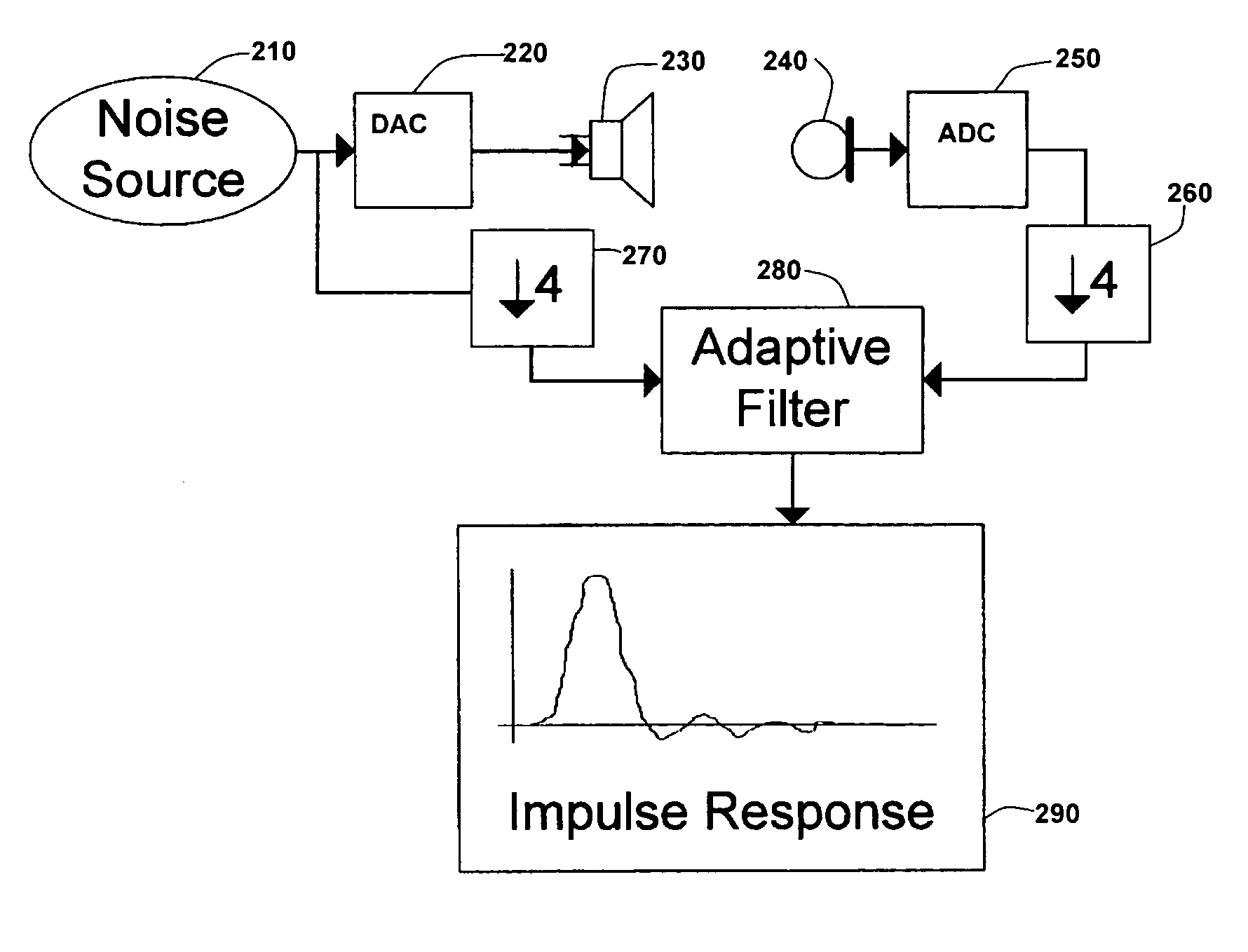

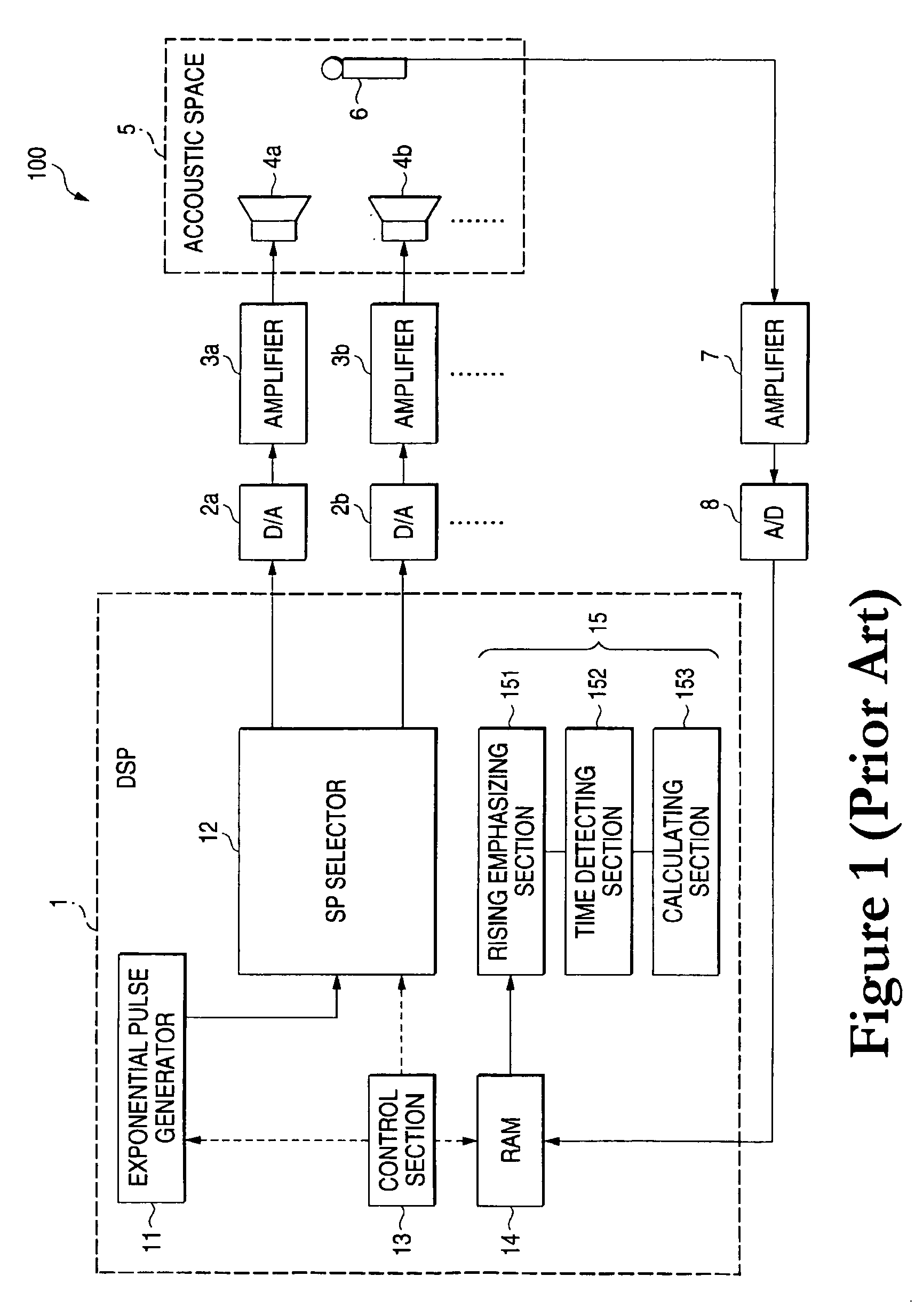

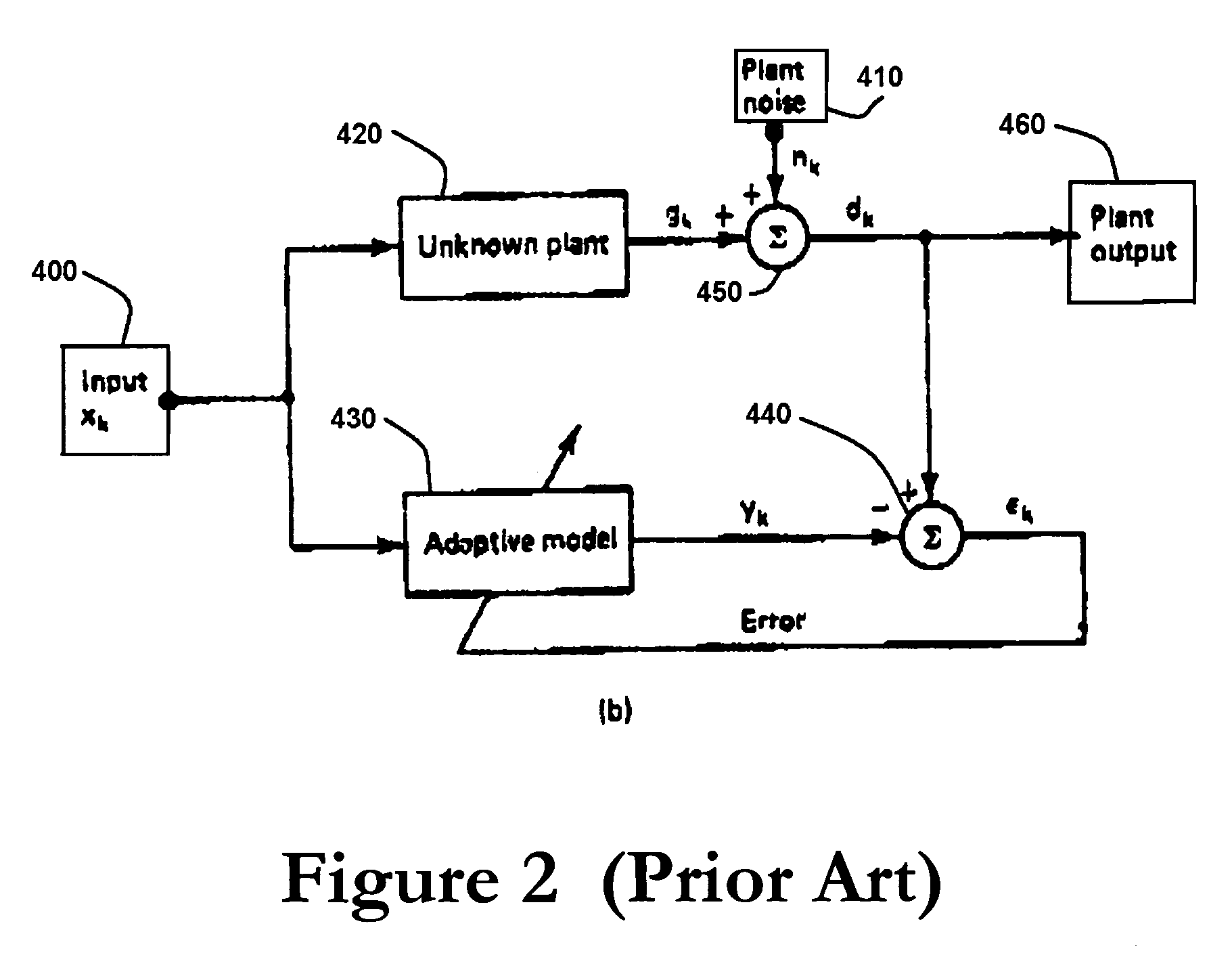

Speaker distance measurement using downsampled adaptive filter

InactiveUS20060062398A1Easy to measureLess susceptible to noiseStereophonic circuit arrangementsUsing reradiationMean squareImage resolution

A downsampled adaptive filter is used to find the impulse response of a home theater system. Downsampling yields higher maximum measurable distance for given filter length. By using a Least-Mean-Square (LMS) adaptive filter, almost anything can be used as the source noise. While downsampling may decrease the resolution of the distance measurement, Adaptive Filtering allows a much broader range of test signals, as opposed to MLS (Maximum Length Sequence) in which the test signal defines the technique (a pseudo-random Maximum Length Sequence.)

Owner:CIRRUS LOGIC INC

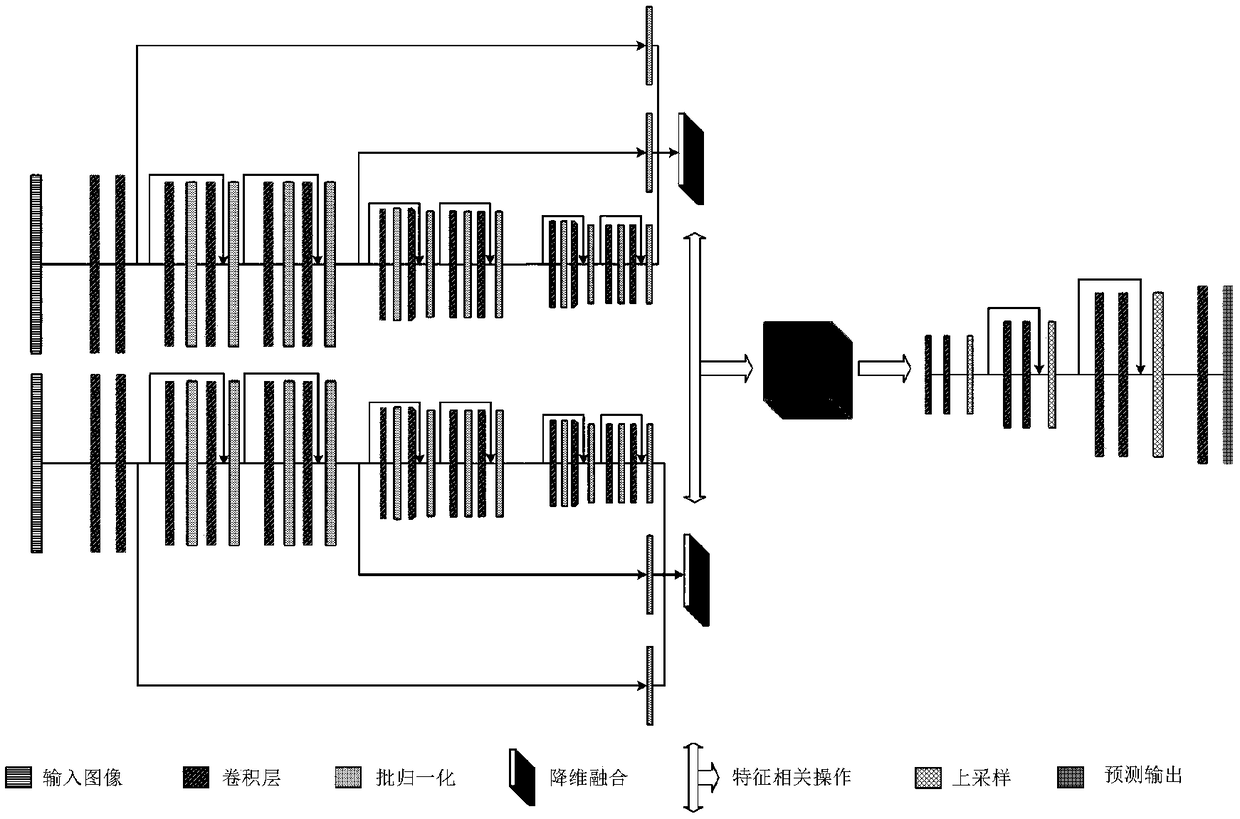

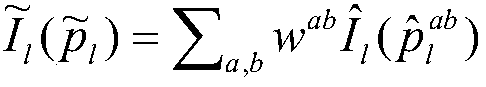

A binocular depth estimation method based on depth neural network

ActiveCN109377530AImprove generalization abilityGood for training optimizationImage analysisGeometric image transformationViewpointsNetwork model

The invention relates to a binocular depth estimation method based on a depth neural network, which comprises the following steps: 1) preprocessing the input left and right viewpoint images to enhancedata; 2) constructing a multi-scale network model for binocular depth estimation, wherein the model comprises a plurality of convolution layers, an activation layer, a residual connection, a multi-scale pooling connection and a linear upsampling layer; 3) Designing the loss function to minimize the results in the continuous training process, so as to obtain the optimal network weights; 4) inputting the image to be processed into the network model to obtain the corresponding depth map, and repeatedly repeating the above steps until the network converges or reaches the training times. The invention adopts the idea of unsupervised learning, and only the left and right viewpoint images obtained by the binocular camera are used as network input. The adaptive design of the network sets the internal and external parameters of the camera as a single model parameter, so it can be applied to multiple camera systems without modifying the network.

Owner:浙江七巧连云生物传感技术股份有限公司

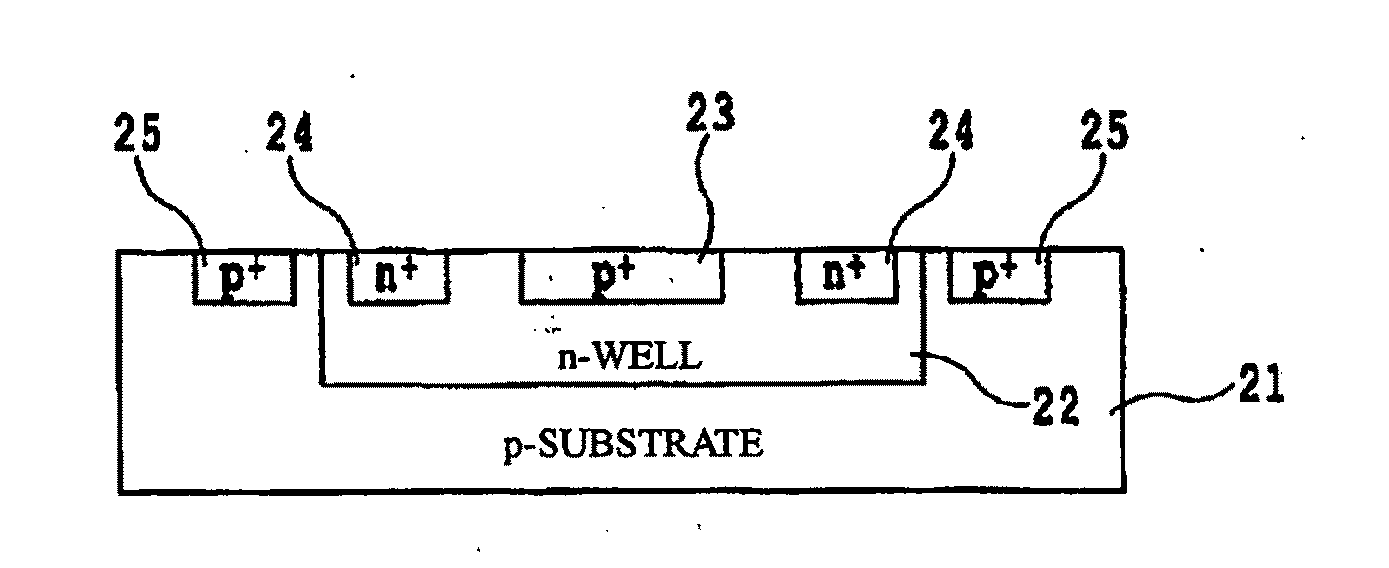

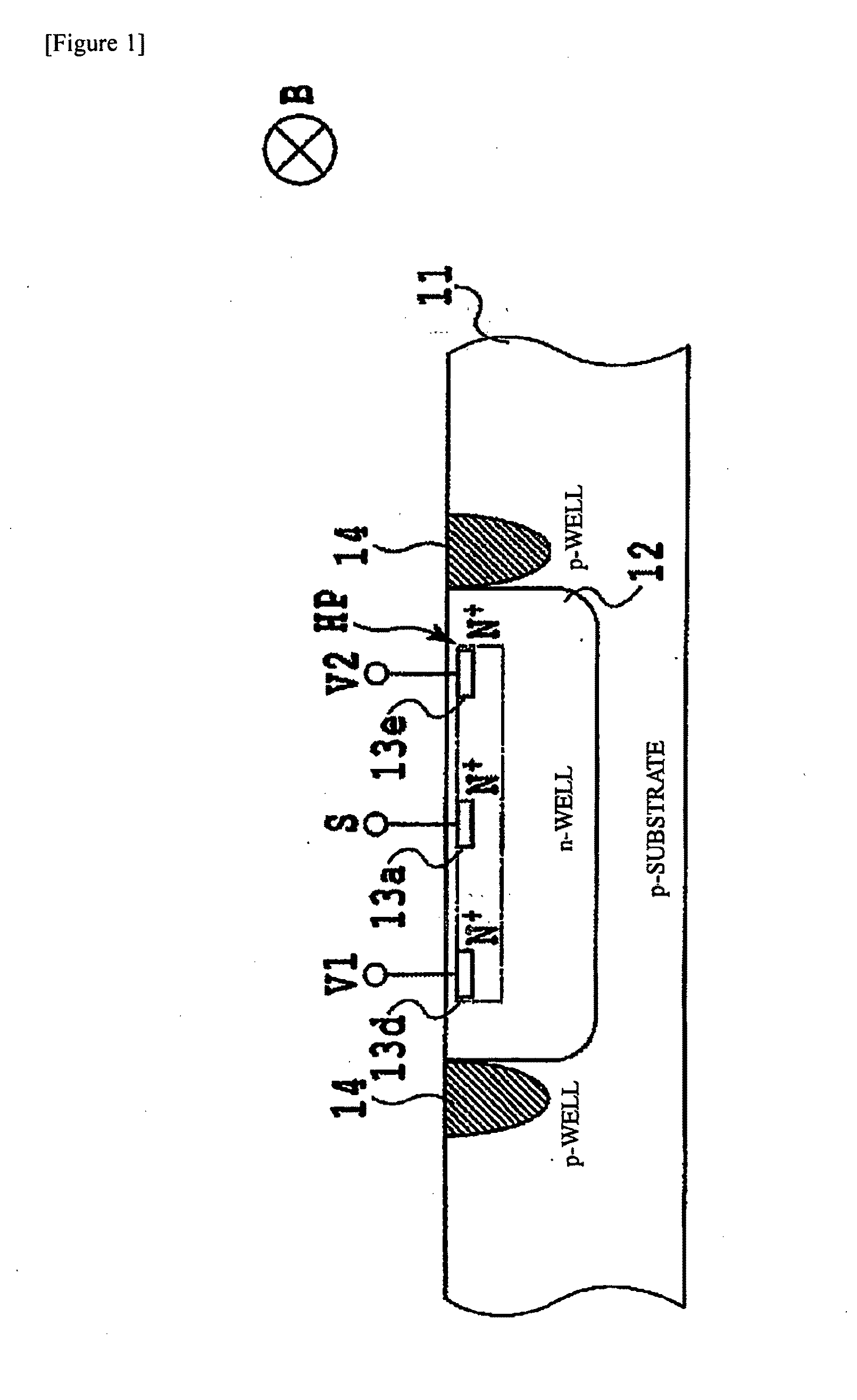

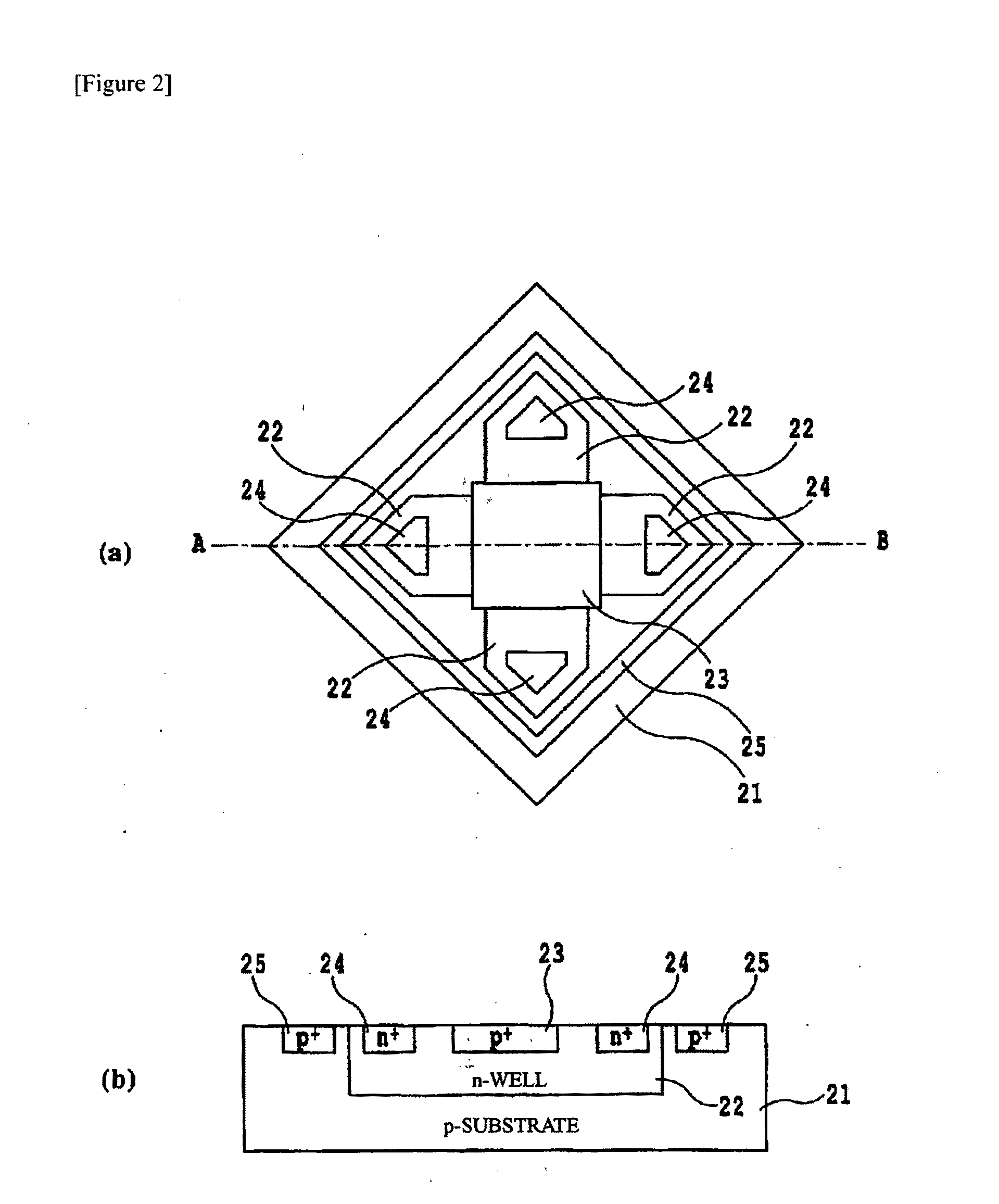

Hall Element and Magnetic Sensor

ActiveUS20100164483A1High sensitivityImprovement in S/N ratio per currentSolid-state devicesMagnetic field measurement using galvano-magnetic devicesHall elementOptoelectronics

A Hall element is provided which has a high sensitivity and contributes to an improvement in S / N ratio per current by using a low-concentration n-well within a suitable range. The Hall element includes a p-type semiconductor substrate layer 21 of p-type silicon, and an n-type impurity region 22 located in a surface of the p-type semiconductor substrate layer 21, the n-type impurity region 22 functioning as a magnetic sensing part 26. A p-type impurity region 23 is located in a surface of the n-type impurity region 22, and n-type regions 24 are located laterally of the p-type impurity region 23. A p-type substrate region 21a having a resistivity equal to that of the p-type semiconductor substrate layer 21 is located to extend around the n-type impurity region 22. An impurity concentration N in the n-type impurity region 22 functioning as the magnetic sensing part 26 is preferably from 1×1016 to 3×1016 (atoms / cm3), and a distribution depth D of the impurity concentration is preferably from 3.0 μm to 5.0 μm.

Owner:ASAHI KASEI ELECTRONICS CO LTD

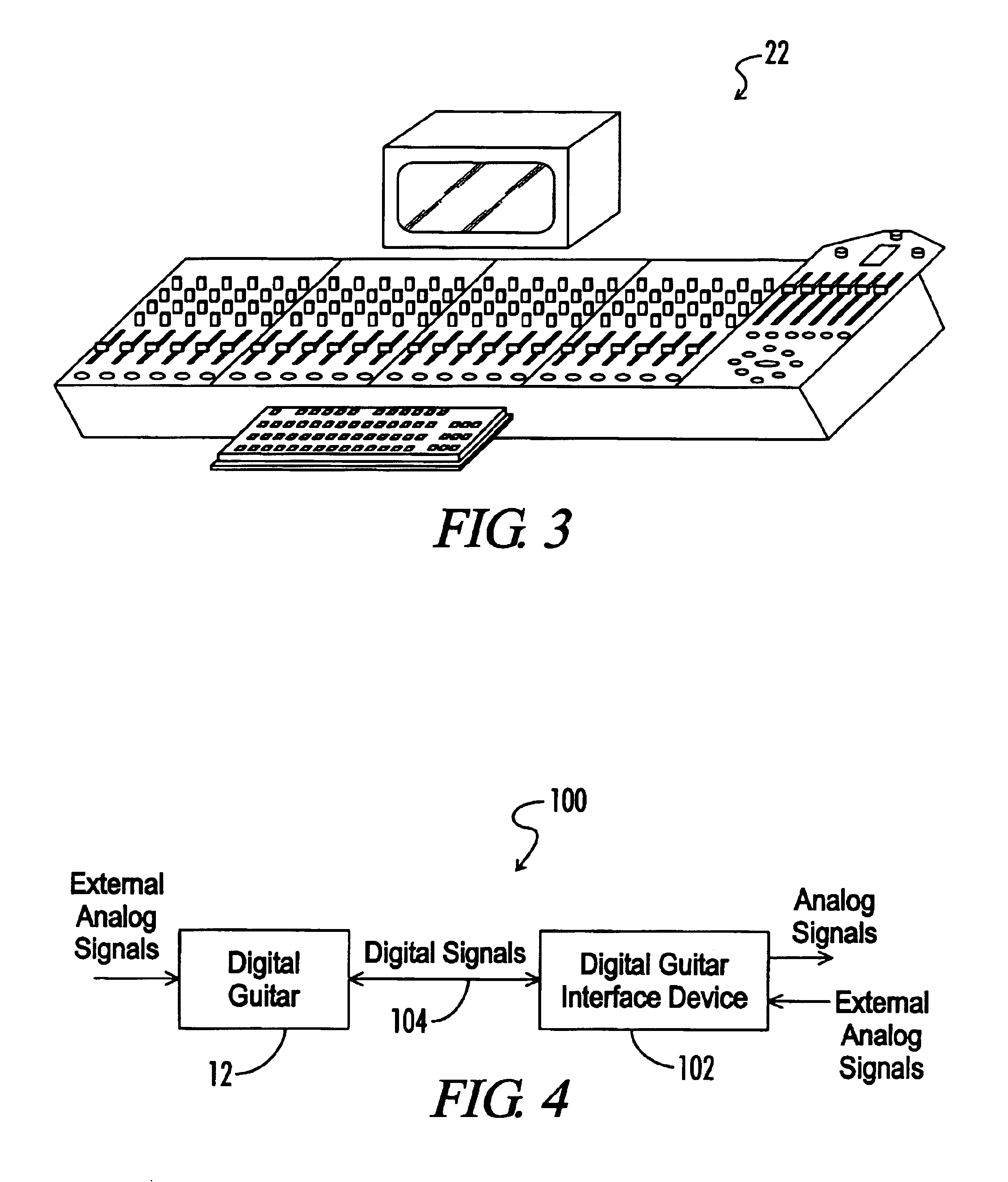

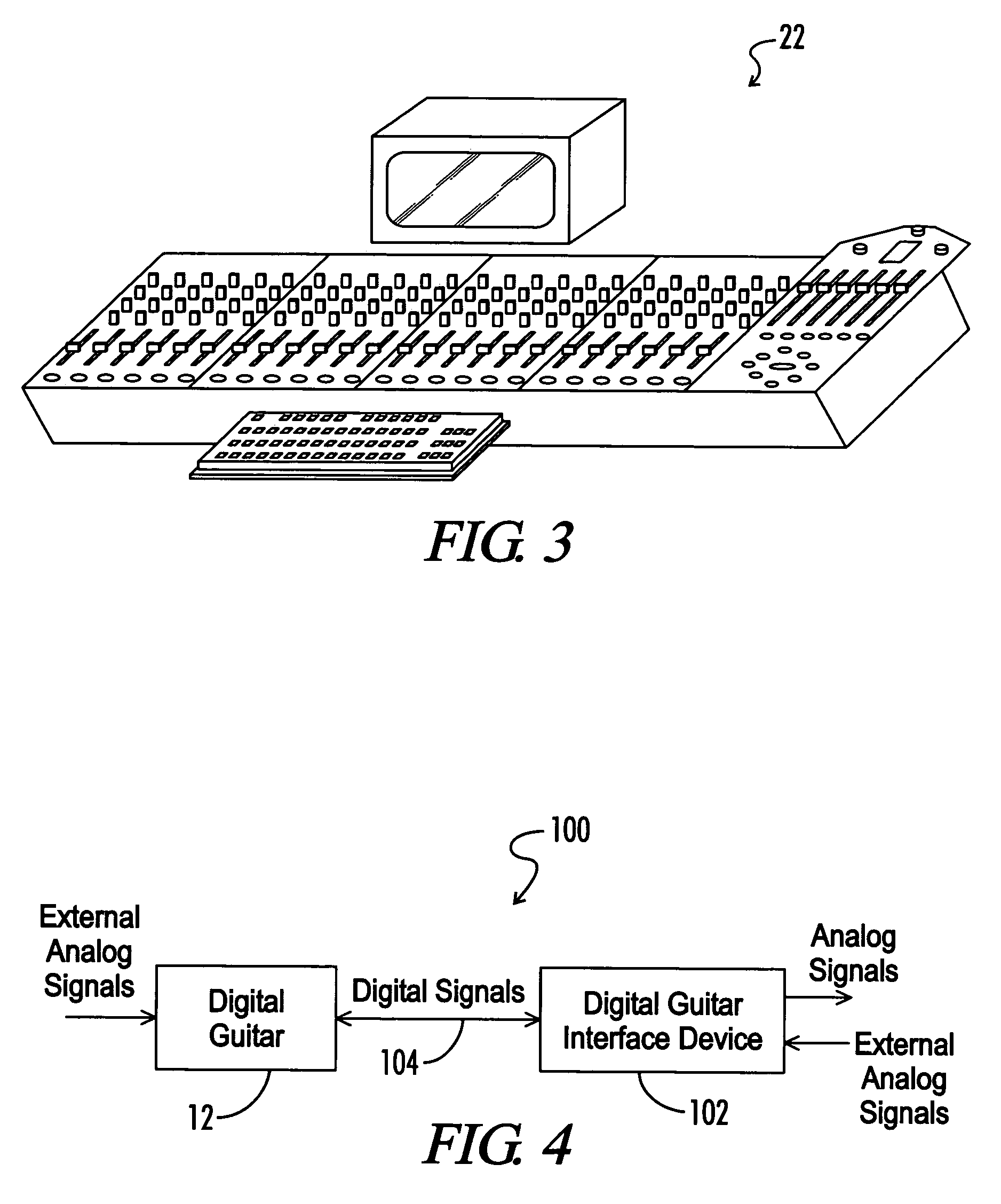

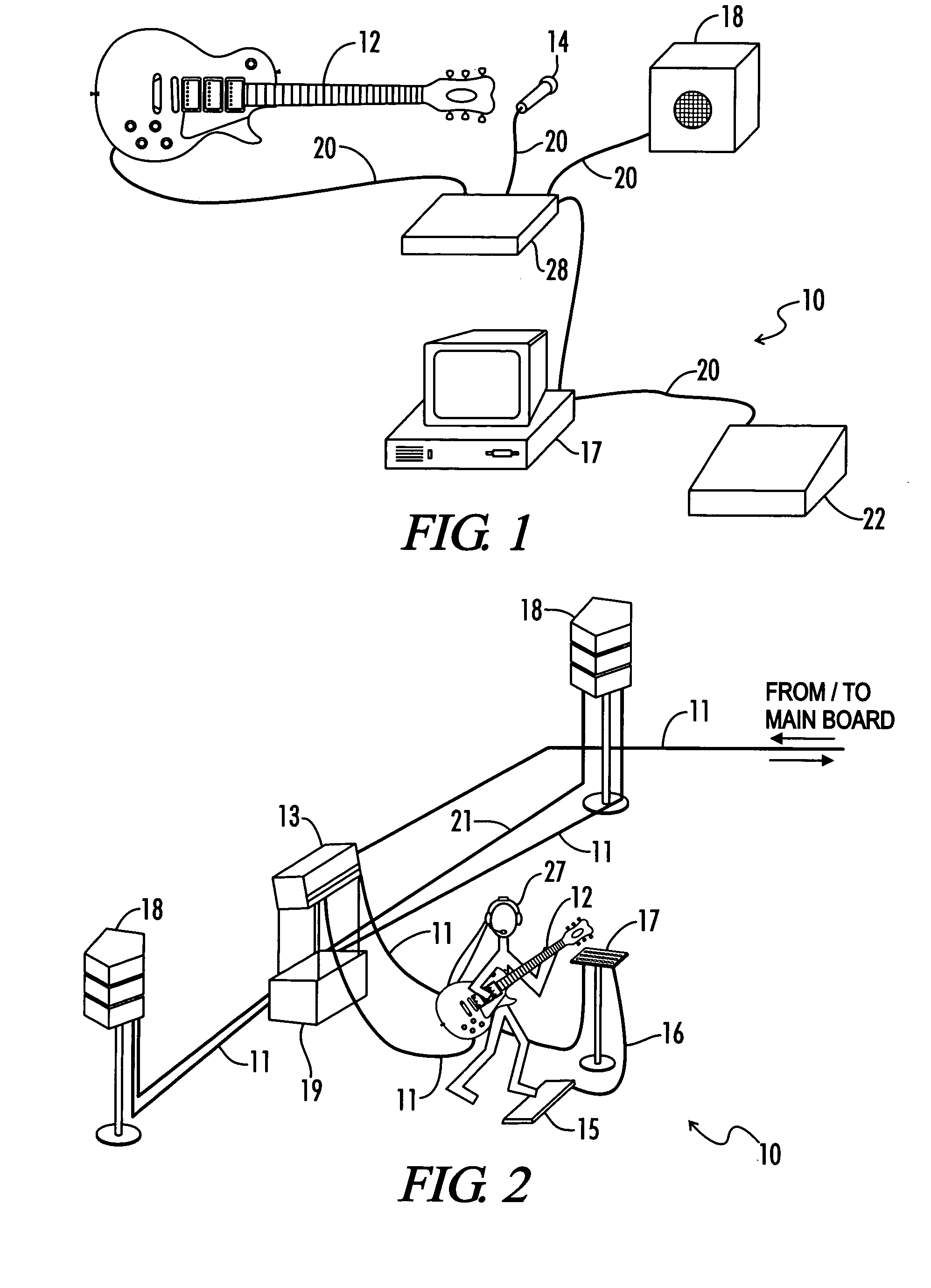

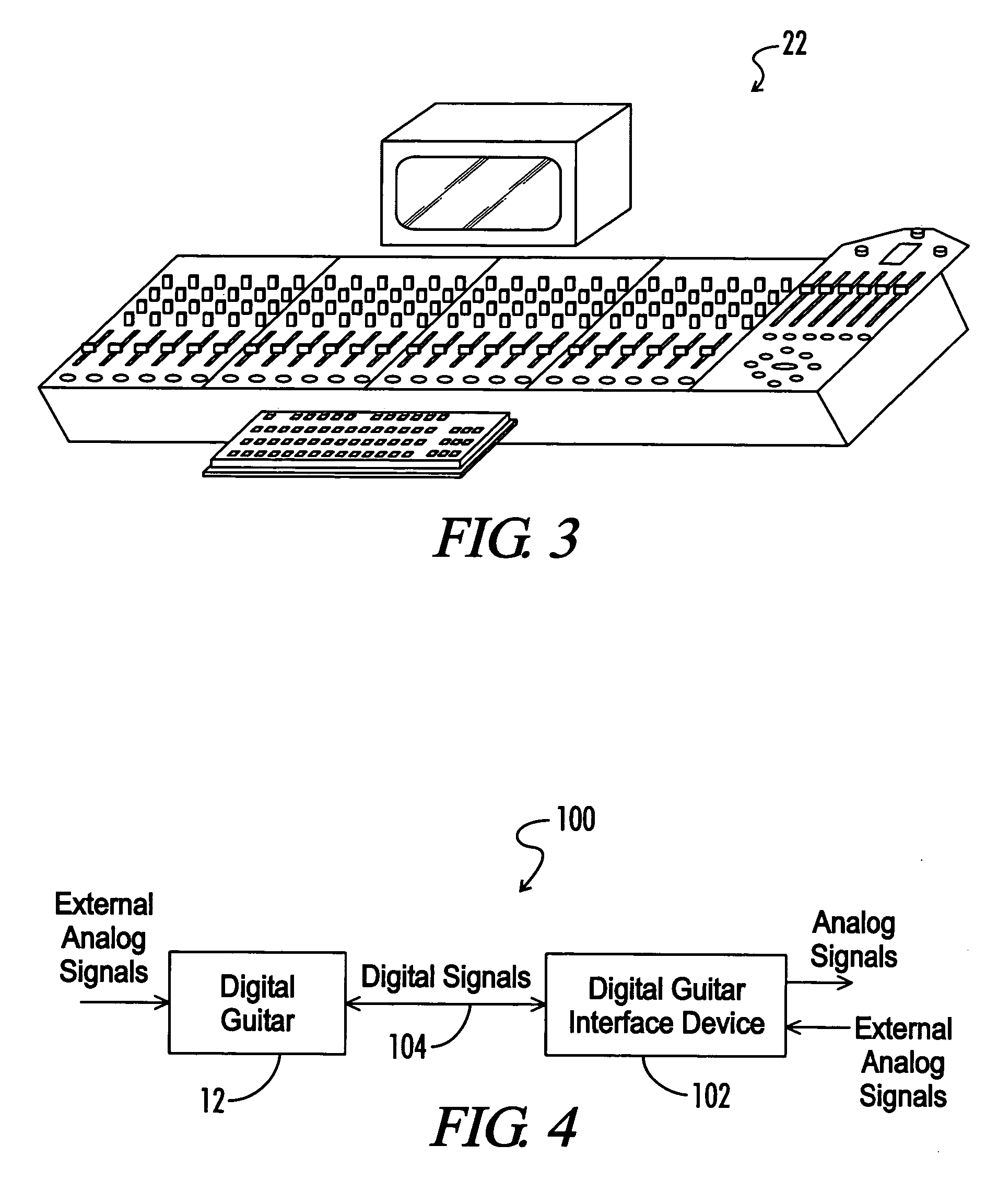

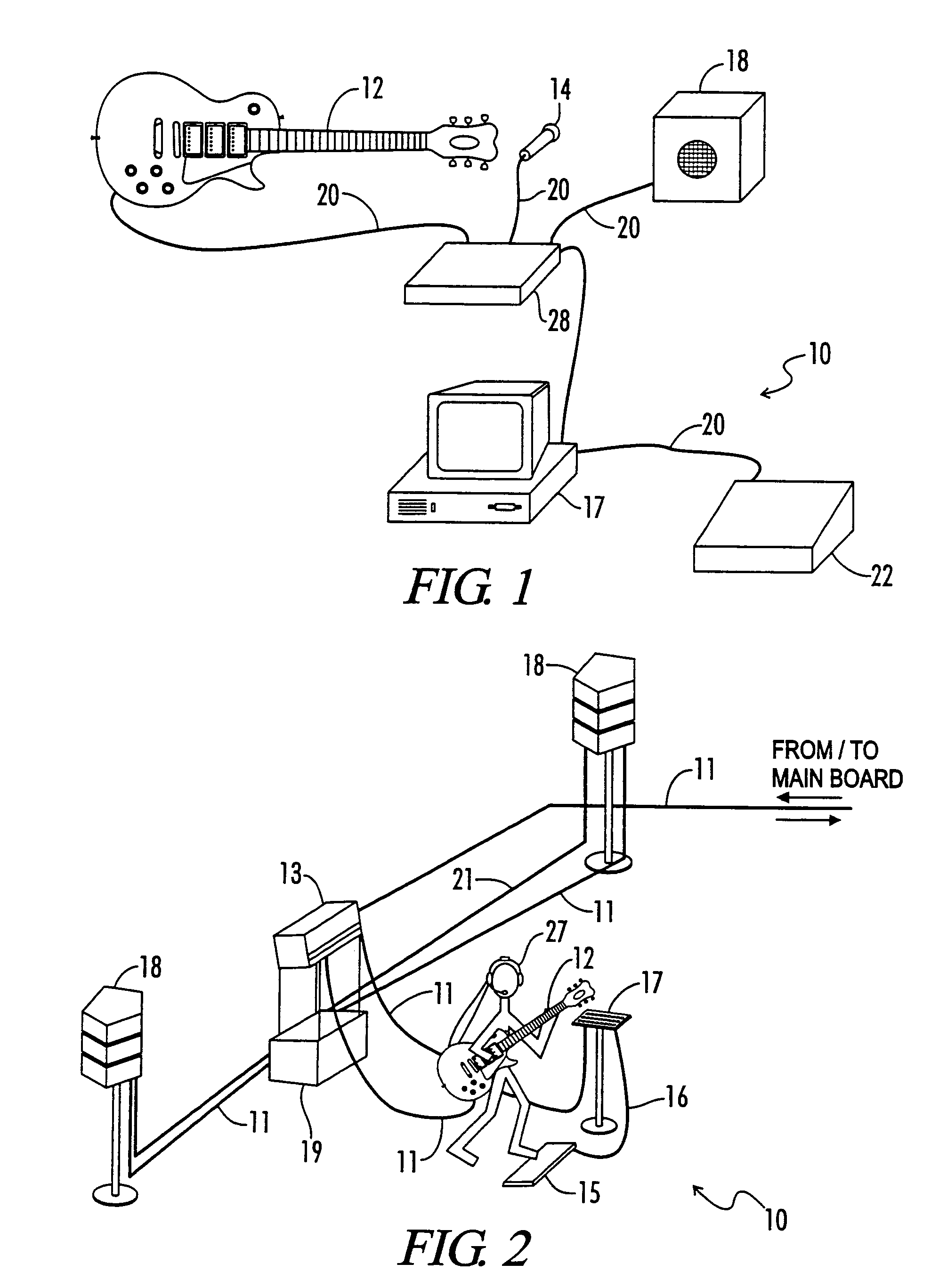

Digital guitar system

InactiveUS7220912B2Increased complexityLess susceptible to noiseElectrophonic musical instrumentsAnalog signalEngineering

A digital guitar system and method includes a digital guitar and a digital guitar interface device, and a method of converting a conventional guitar into a digital guitar. The guitar is adapted to generate analog audio signals, convert those signals into digital signals, format the digital signals according to a digital communication protocol, and to output the formatted signals. The guitar may include a novel multi-signal guitar pickup that generates some of the analog audio signals. The guitar is further adapted to receive digital signals, convert those signals into analog signals, and output the analog signals. The interface device is adapted to receive digital signals, convert those signals into analog signals, and output the analog signals.

Owner:GIBSON BRANDS

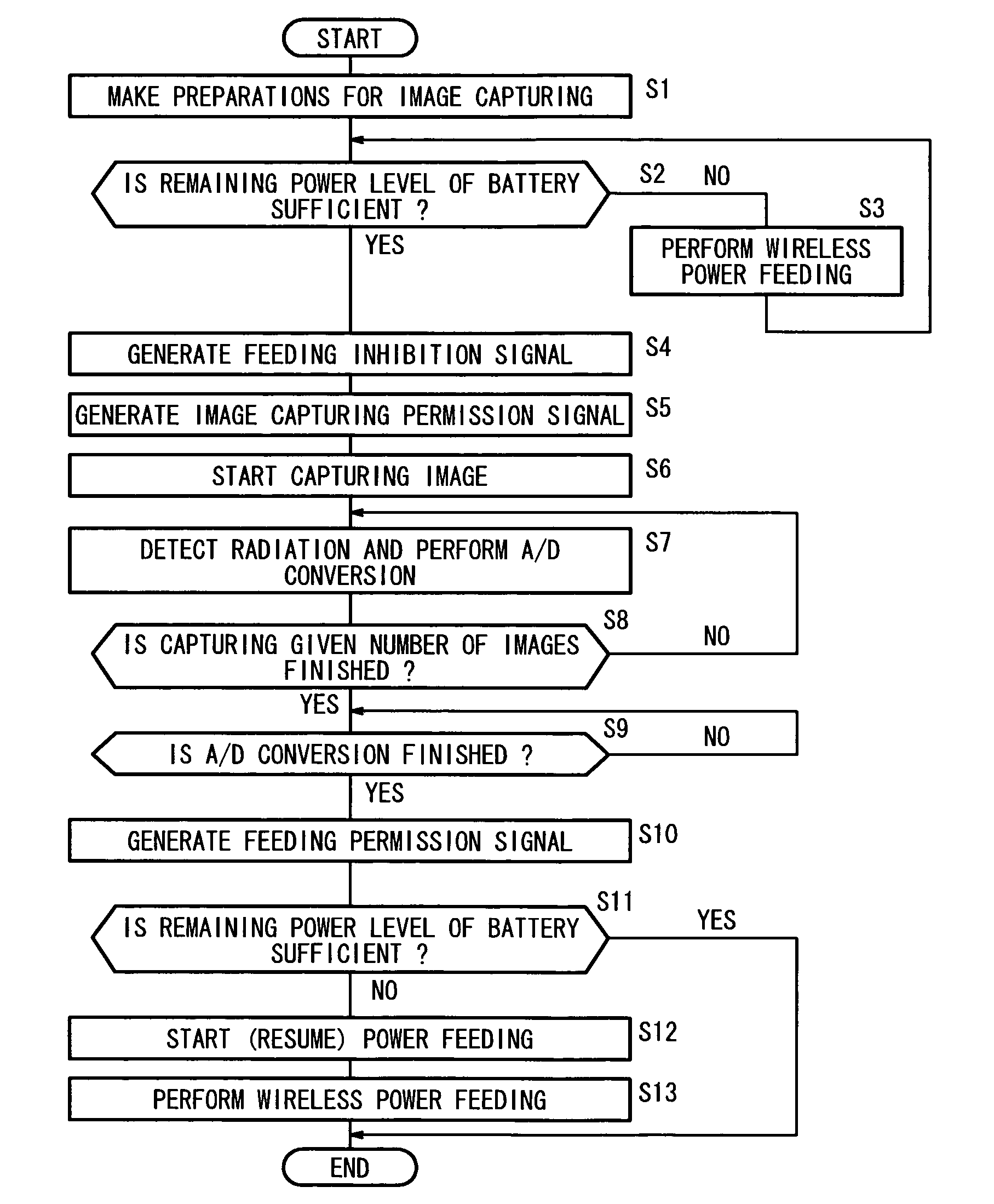

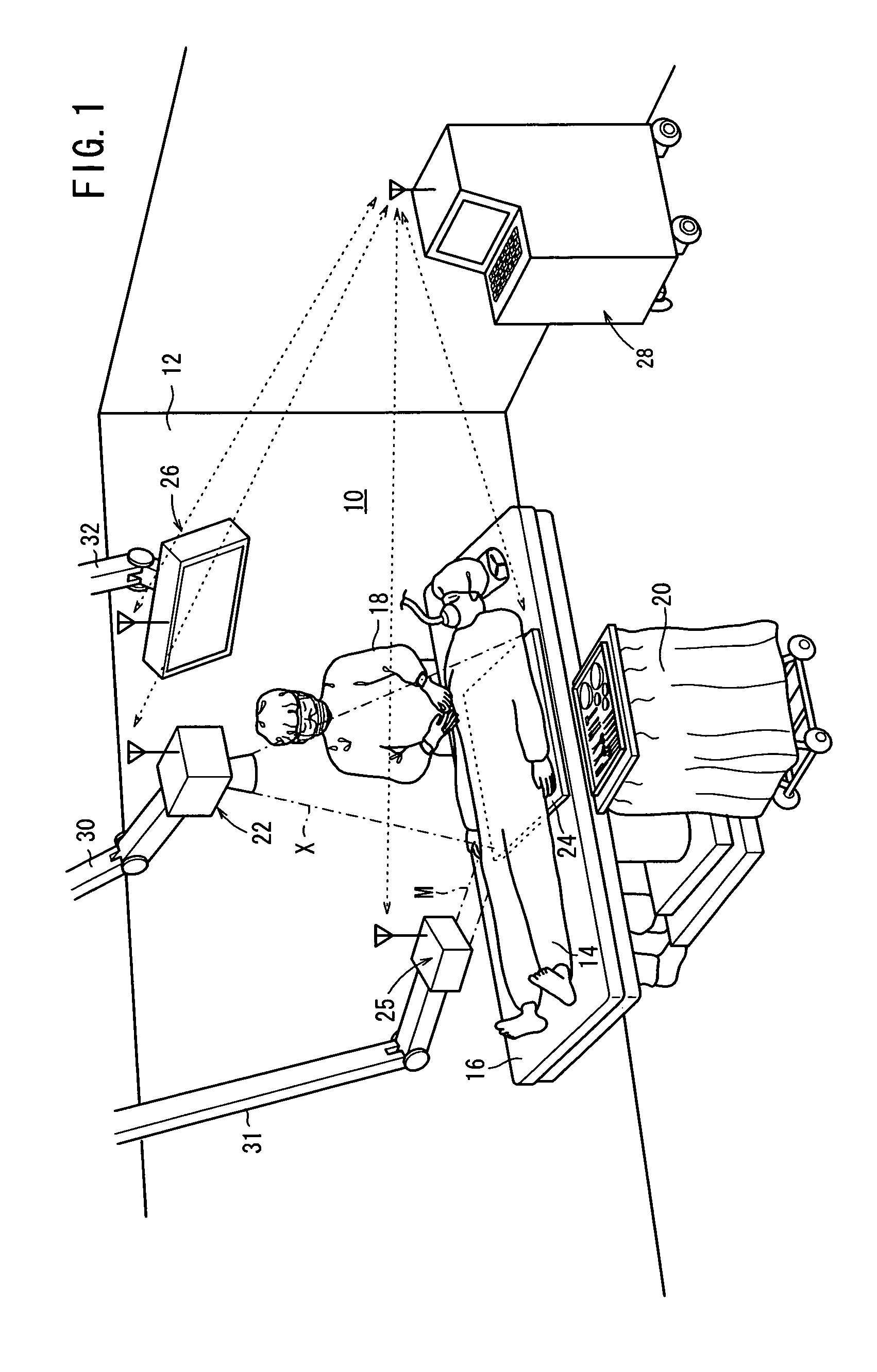

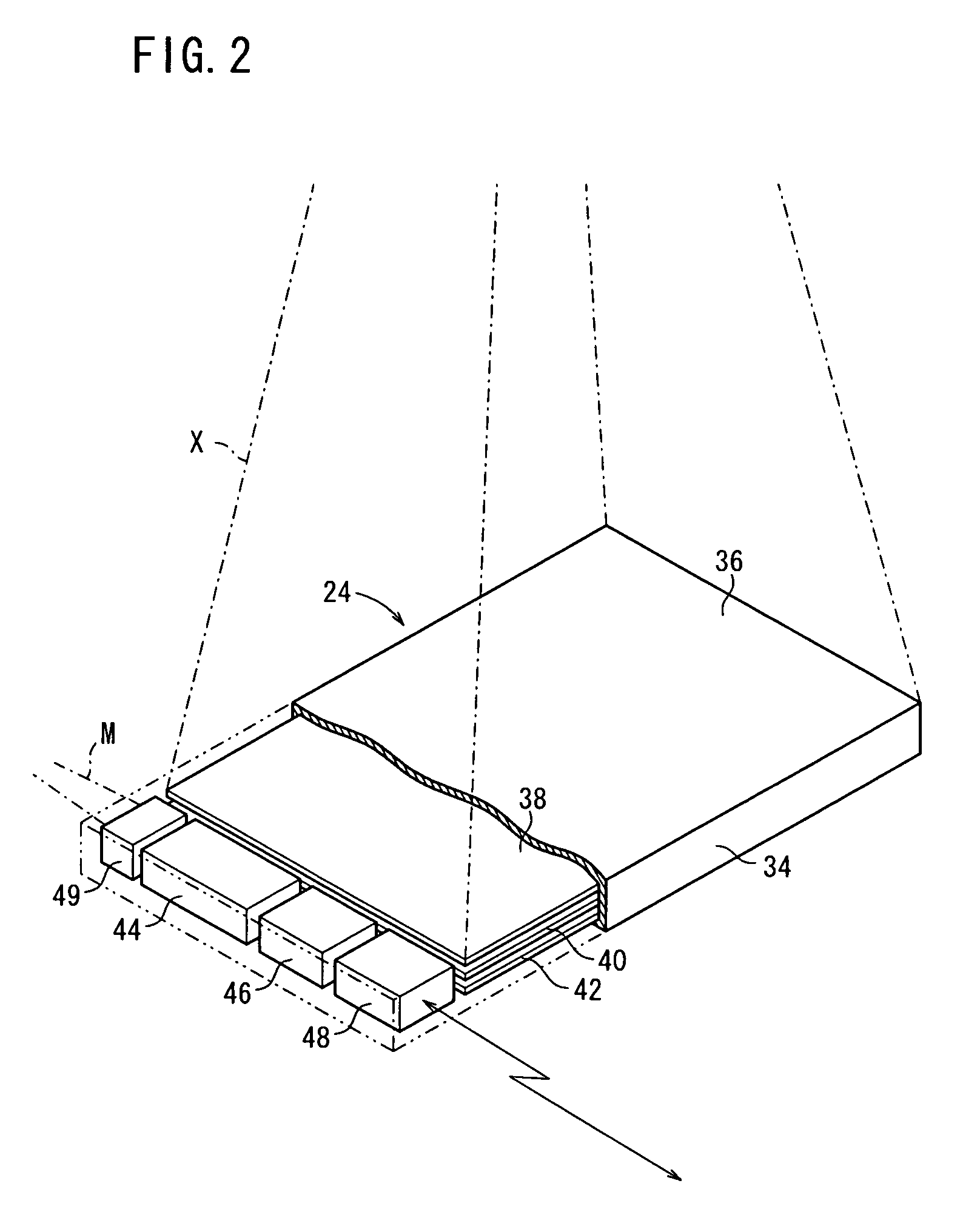

Radiation detecting apparatus, radiographic image capturing system, and radiographic image capturing method

ActiveUS7991119B2Delay in supplyHigh quality imagingMaterial analysis by optical meansPhotometry using electric radiation detectorsImage captureElectric power

An electronic cassette in a radiographic image capturing system includes a radiation detector for detecting radiation applied from an image capturing apparatus and transmitted through a patient, a contactless power receiver for receiving electric power supplied contactlessly from a power feeder and supplying the electric power to a battery, an A / D converter for performing an A / D conversion to convert analog radiographic image information generated based on the radiation applied to the radiation detector into digital radiographic image information, an end-of-A / D-conversion determining unit for determining whether the A / D conversion is finished or not, and a charging controller for stopping the power feeder from supplying electric power contactlessly after the image capturing apparatus has started capturing images until the end-of-A / D-conversion determining unit judges that the A / D conversion is finished.

Owner:FUJIFILM CORP

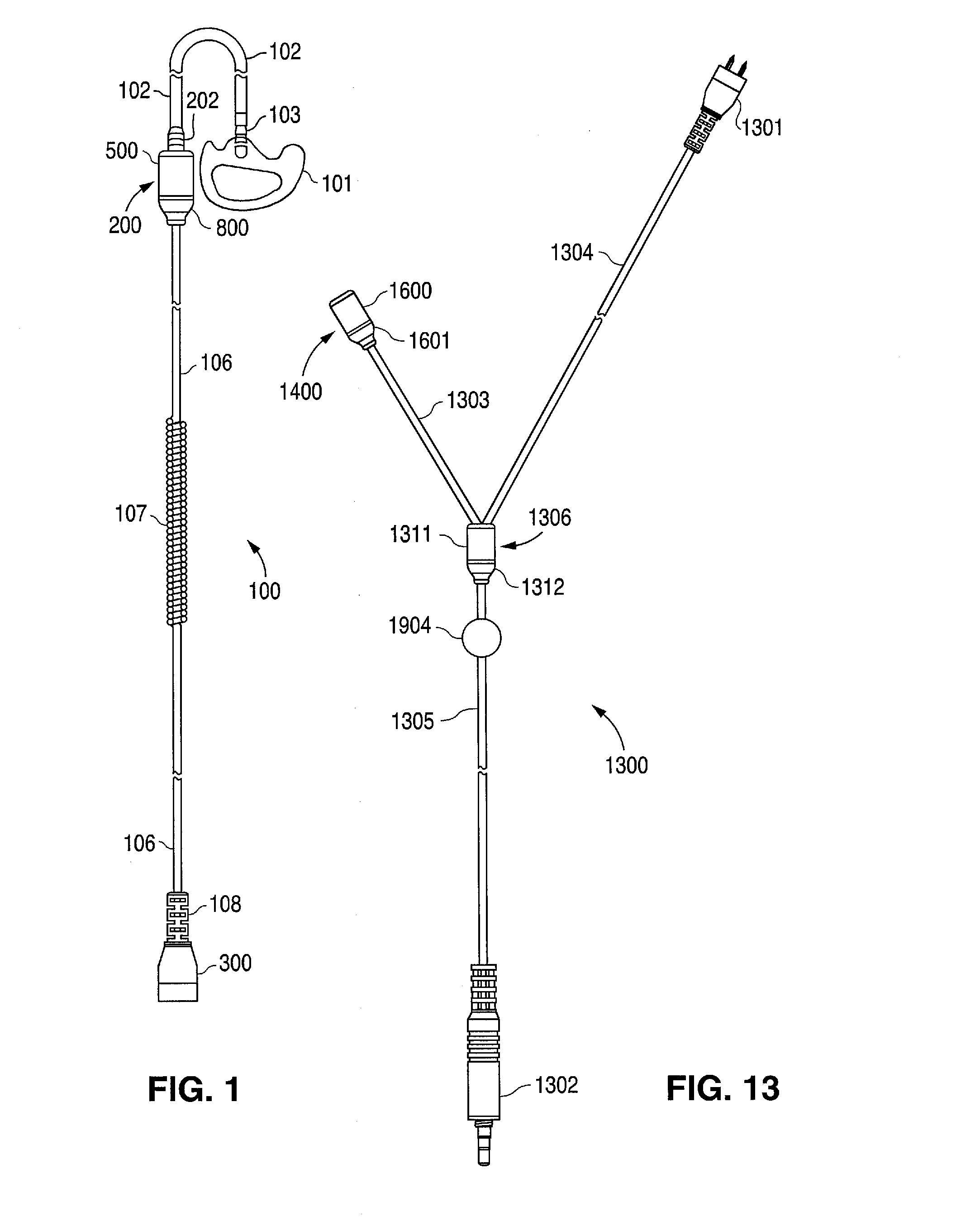

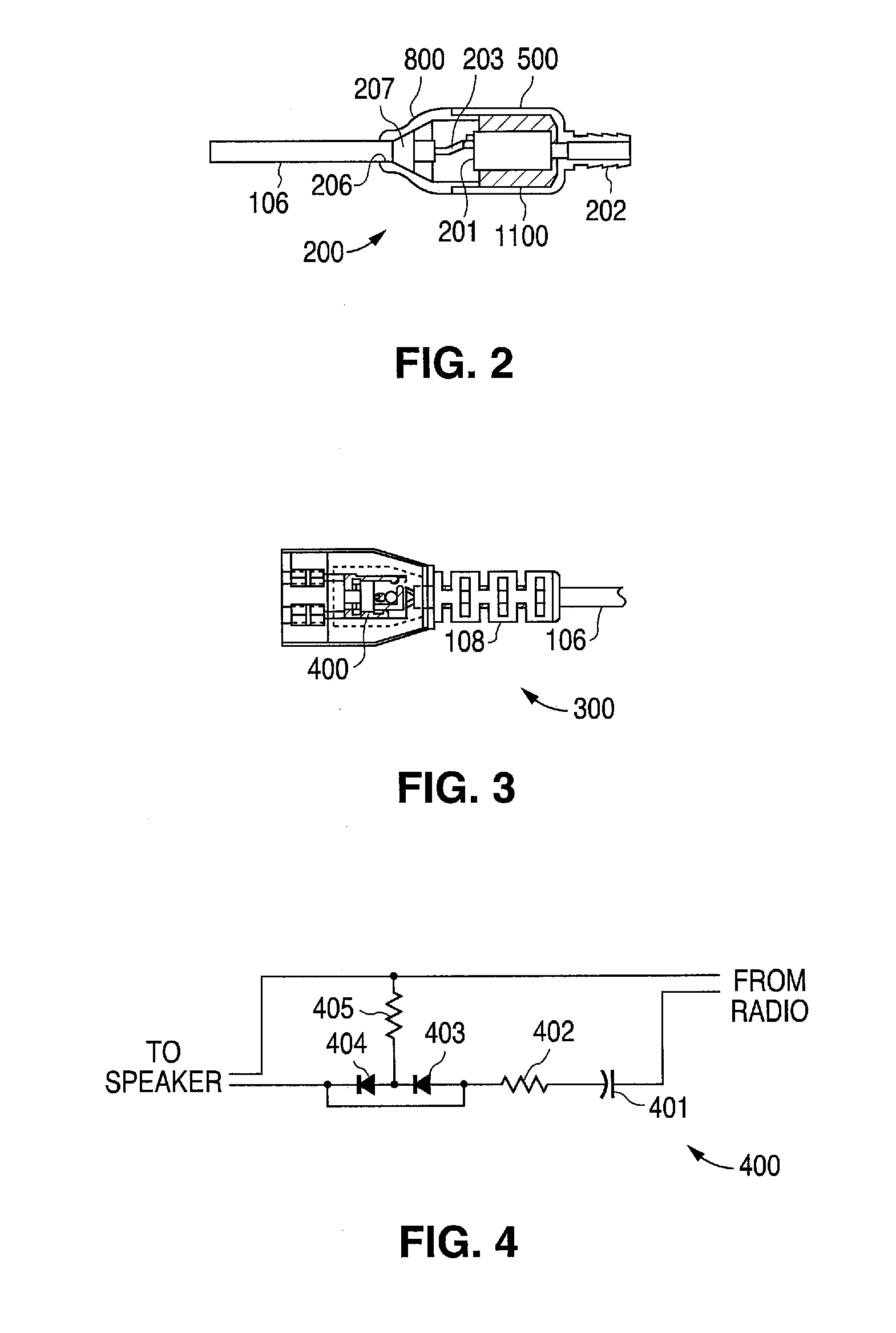

Radio Cable Assembly

InactiveUS20080159577A1Increased durabilityLess susceptible to ambient noisePiezoelectric/electrostrictive microphonesMicrophonesTransducerEngineering

A radio system for use by police officers, firemen, soldiers and the like is disclosed. The radio system has a portable two-way radio, a microphone, a speaker, and a cable. The microphone can have a housing, a microphone transducer disposed within the housing, and a buffer disposed intermediate the microphone transducer and the housing. The speaker can have a housing formed of a substantially rigid material and a speaker transducer disposed within the housing. The cable can facilitate electrical communication between the portable two-way radio and the microphone and between the portable two-way radio and the speaker. The speaker and the microphone are configured so as to provide better and more reliable performance.

Owner:SUREFIRE LLC

Breakout box for digital guitar

ActiveUS7220913B2Increased complexityLess susceptible to noiseElectrophonic musical instrumentsEngineeringAnalog device

A guitar interface device for a digital guitar system is adapted to receive digital signals, convert those signals into analog signals, and output the analog signals, so that the digital guitar system may be utilized with conventional analog equipment. The interface device includes an input assembly to receive the digital signals, a processing circuit to generate the analog signals, and an output assembly to output the analog signals.

Owner:GIBSON BRANDS

Digital guitar system

InactiveUS7399918B2Increased complexityLess susceptible to noiseElectrophonic musical instrumentsAnalog signalAudio frequency

A digital guitar system and method includes a digital guitar and a digital guitar interface device, and a method of converting a conventional guitar into a digital guitar. The guitar is adapted to generate analog audio signals, convert those signals into digital signals, format the digital signals according to a digital communication protocol, and to output the formatted signals. The guitar may include a novel multi-signal guitar pickup that generates some of the analog audio signals. The guitar is further adapted to receive digital signals, convert those signals into analog signals, and output the analog signals. The interface device is adapted to receive digital signals, convert those signals into analog signals, and output the analog signals.

Owner:GIBSON BRAND INC

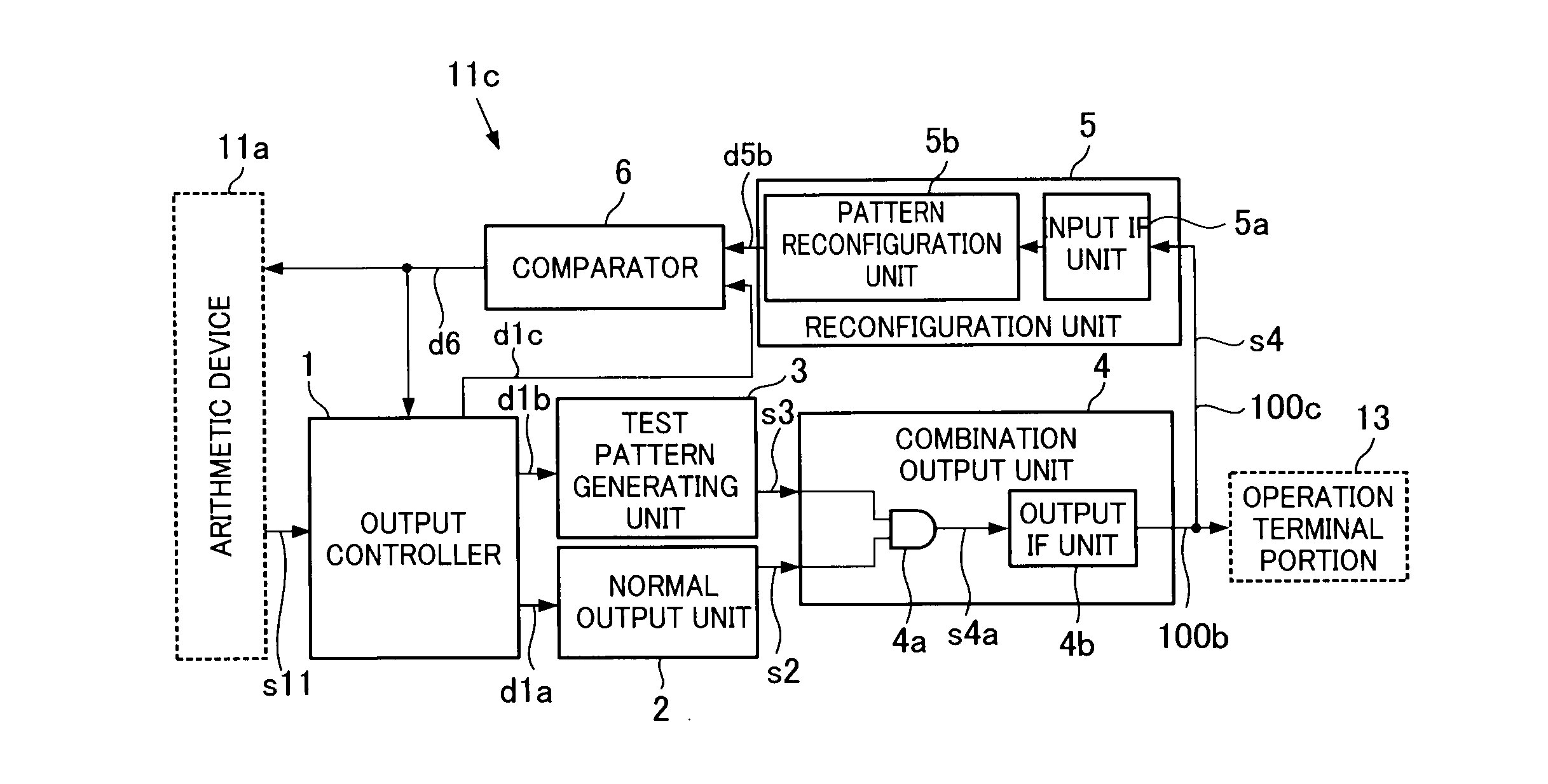

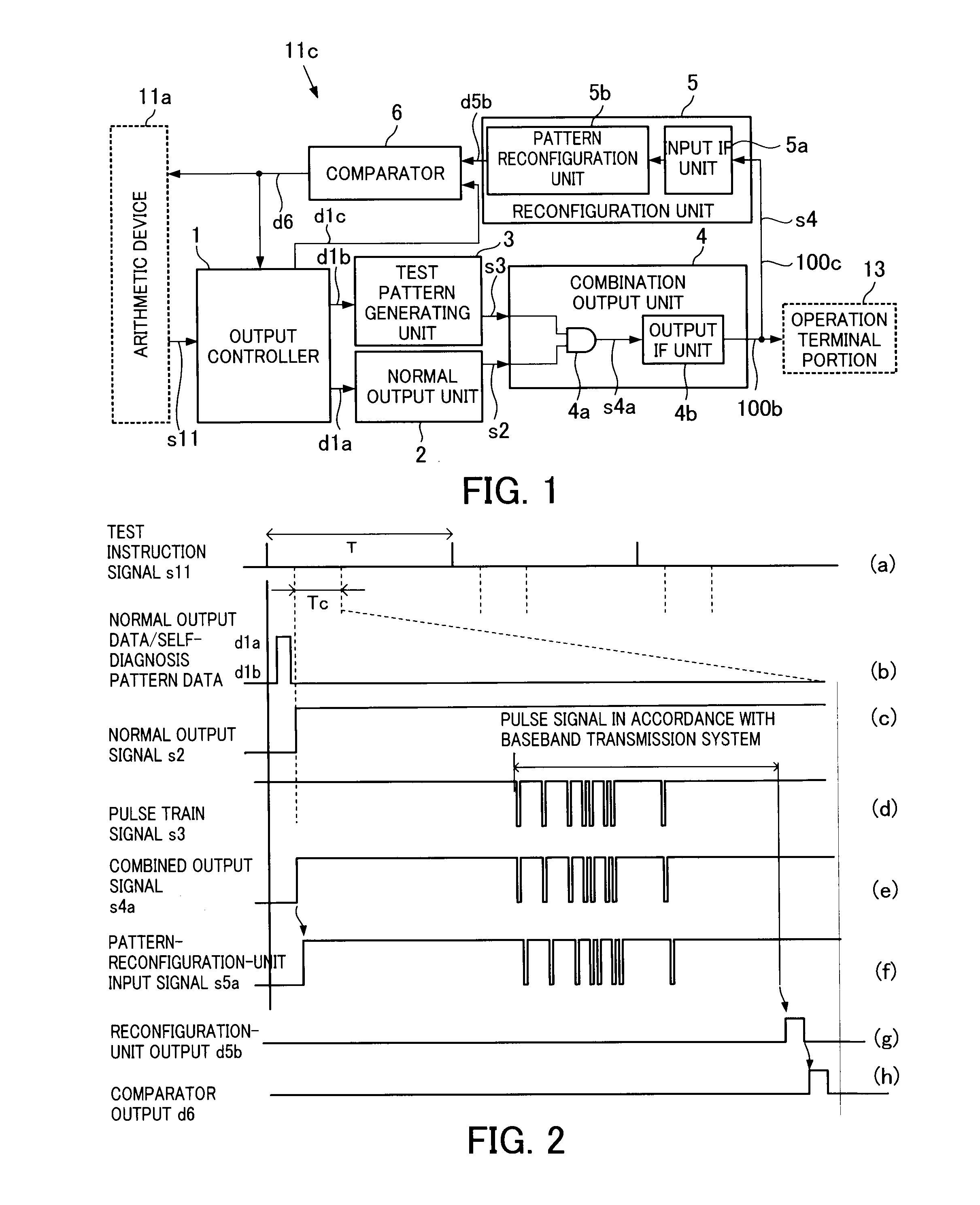

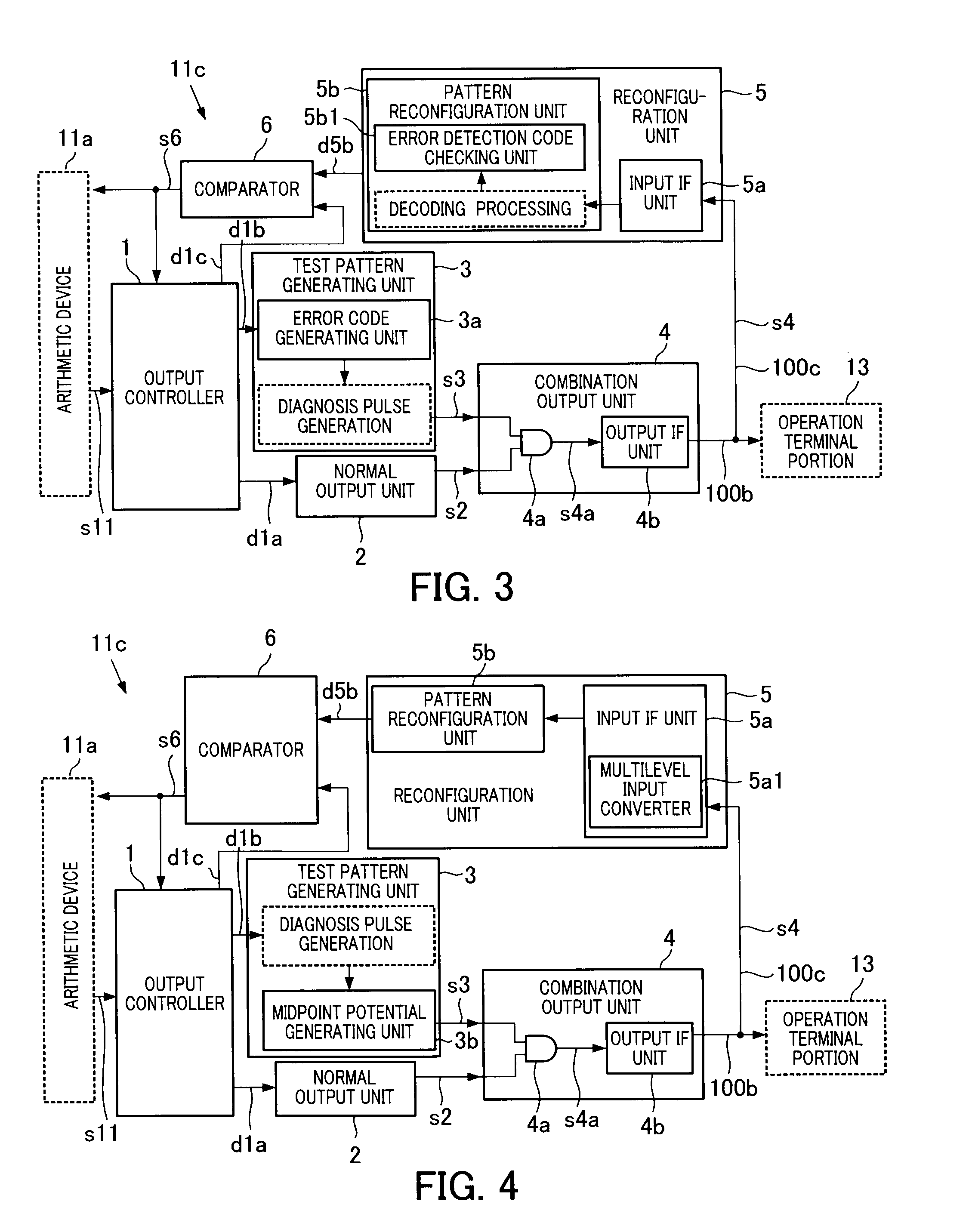

Safety output device

InactiveUS20110173497A1Less susceptible to noiseAvoid signalingProgramme controlError detection/correctionOutput devicePattern generation

A safety output includes an output controller to make an instruction to output normal output data and first self-diagnosis pattern data synchronously with a control cycle, a normal output unit to output the normal output data synchronously with the control cycle, a test pattern generating unit to encode the self-diagnosis pattern data into a pulse train signal having a pulse width not larger than a preset value and output the pulse train signal in accordance with a baseband transmission system, a combination output unit to combine the pulse train signal with the normal output signal and output the resultant signal, a reconfiguration unit to decode the inputted operation-terminal-portion output signal to reconfigure the operation-terminal-portion output signal as second self-diagnosis pattern data, and a comparator to compare the first self-diagnosis pattern data with the second self-diagnosis pattern data to judge the presence or absence of a difference.

Owner:KK TOSHIBA

Hexaphonic pickup for digital guitar system

ActiveUS7166794B2Reduce and eliminate noise signalImproved pickup constructionElectrophonic musical instrumentsEngineeringDigital signal

A novel multi-signal guitar pickup is provided. The pickup includes a coil assembly for each string that is capable of generating two signals which can be combined together in a predetermined manner to generate an x-plane and a y-plane signal. The pickup is particularly useful in a digital guitar system which generates multiple digital signals representative of the vibrations of each string.

Owner:GIBSON BRANDS

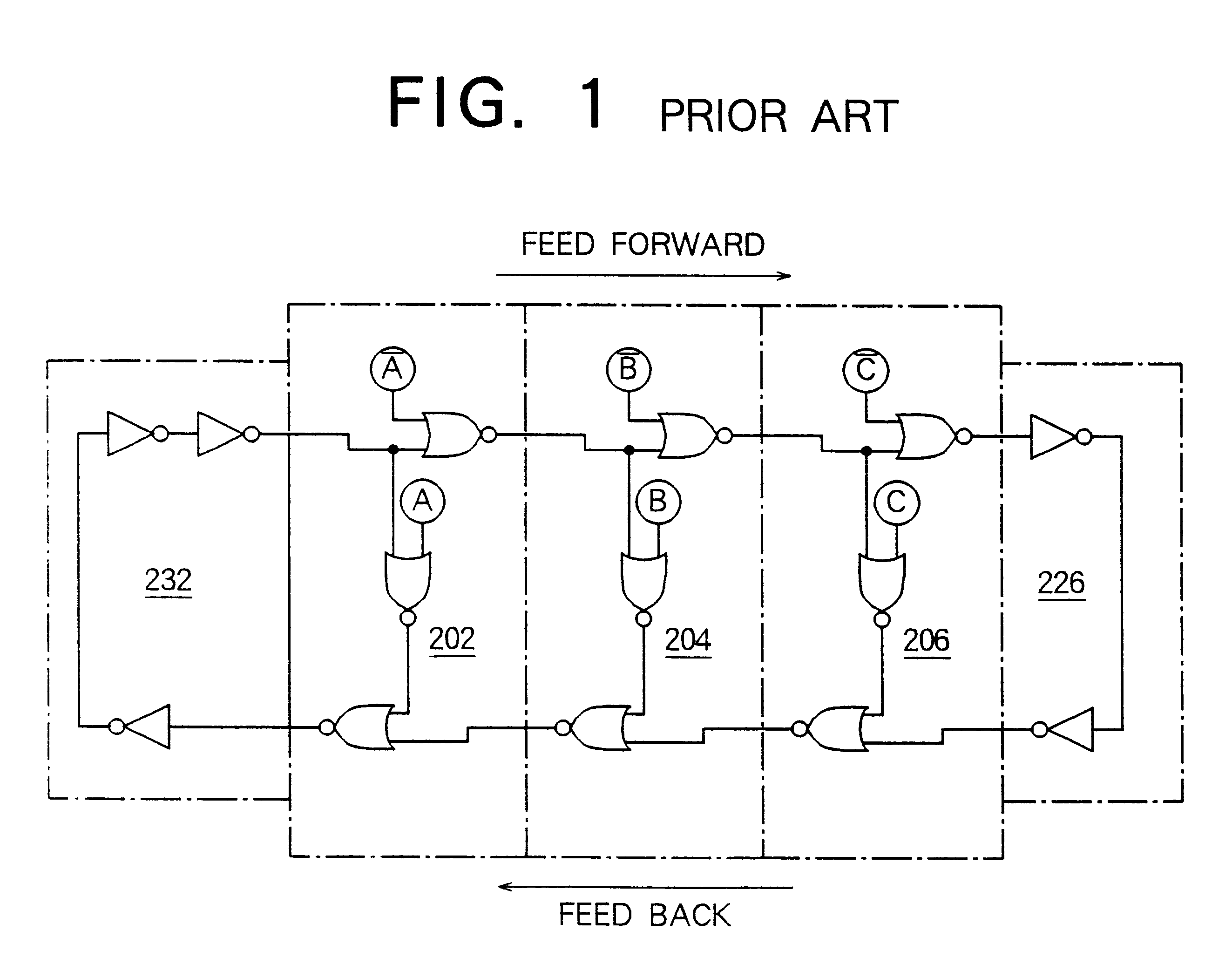

Variable delay circuit

InactiveUS6304124B1High gain accuracyLess susceptible to noiseSingle output arrangementsPulse generation by logic circuitsFrequency multiplierSignal variation

A variable delay section comprises a gate element and a plurality of (N) delay elements for delaying the signal change on the output of the gate element. A difference between a first delay provided by n-th delay section and a second delay provided by (n+1)th delay section is constant for any of n's between 1 and N-1. A plurality of variable delay sections are cascaded to form a frequency multiplier, with the output of the last stage variable delay section being fed-back to the input of the first stage variable delay section through a selector. The other input of the selector is connected to the input of the variable delay circuit to allow the internal signal to pass the variable delay sections for K times.

Owner:NEC CORP

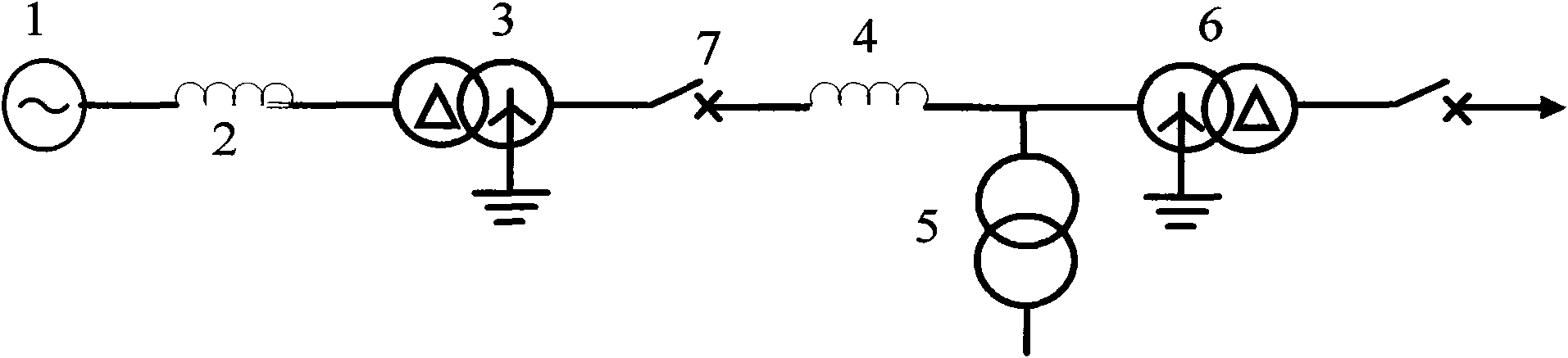

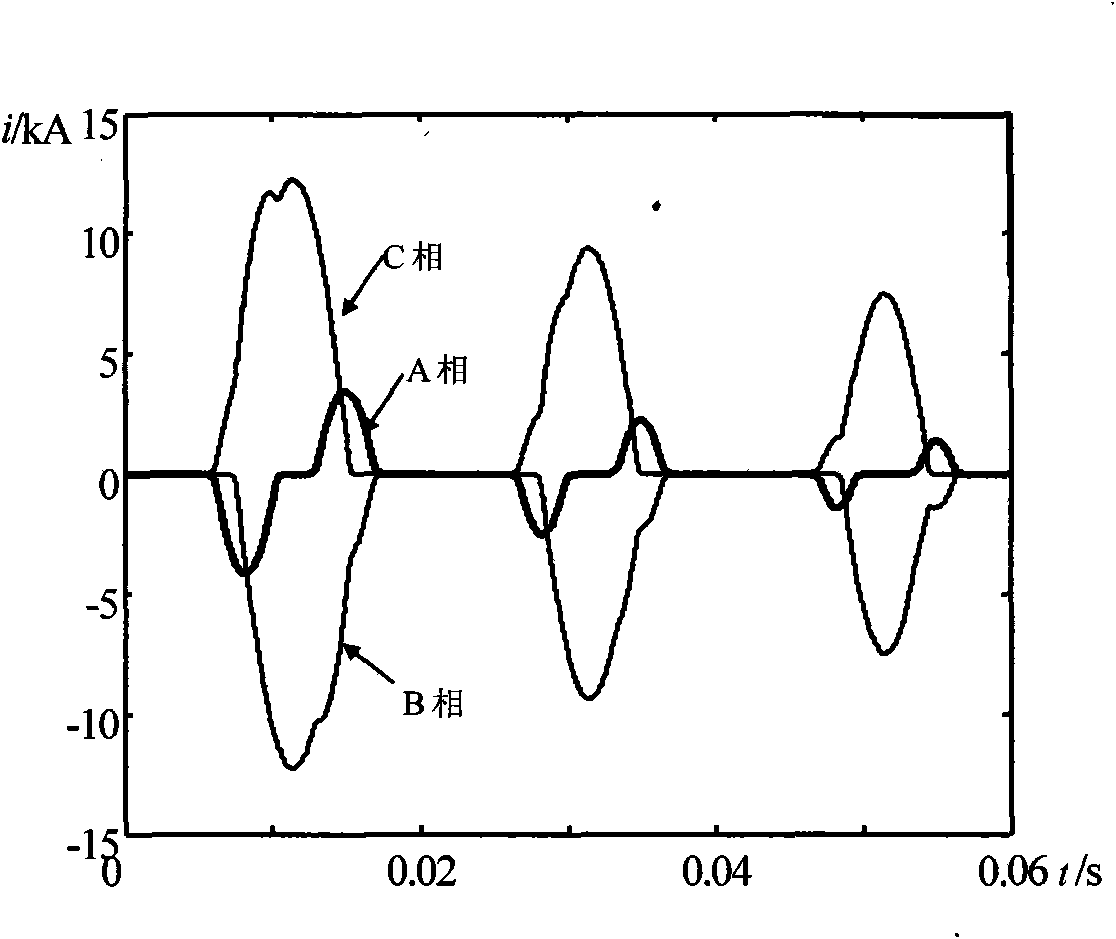

Recognition method of magnetizing inrush current and internal short circuit of power transformer by utilizing morphological structure

ActiveCN101567552ALess susceptible to noiseImprove reliabilityEmergency protective circuit arrangementsWave shapeEngineering

The invention relates to a recognition method of magnetizing inrush current and internal short circuit of a power transformer by utilizing a morphological structure. The method comprises the following steps of: constructing a sine half-sinusoid discrete series with the amplitude of A and the frequency of 50Hz by utilizing the maximum value and the minimum value of sample data of a power frequency cycle, and reducing the series by 10 percent so as to be used as a structural element; carrying out morphological analysis to three-phase differential currents respectively by utilizing a sine half-sinusoid structural element; obtaining a waveform consistency coefficient of an original signal and a morphological analysis result so as to reflect the similarity degree of the comparison between the original signal and a sine wave; and realizing the recognition of the magnetizing inrush current and the internal short circuit of the power transformer by comparing the size of the waveform consistency coefficient. By theoretical analysis and stimulation verification, the method is proved to be effective.

Owner:KUNMING UNIV OF SCI & TECH

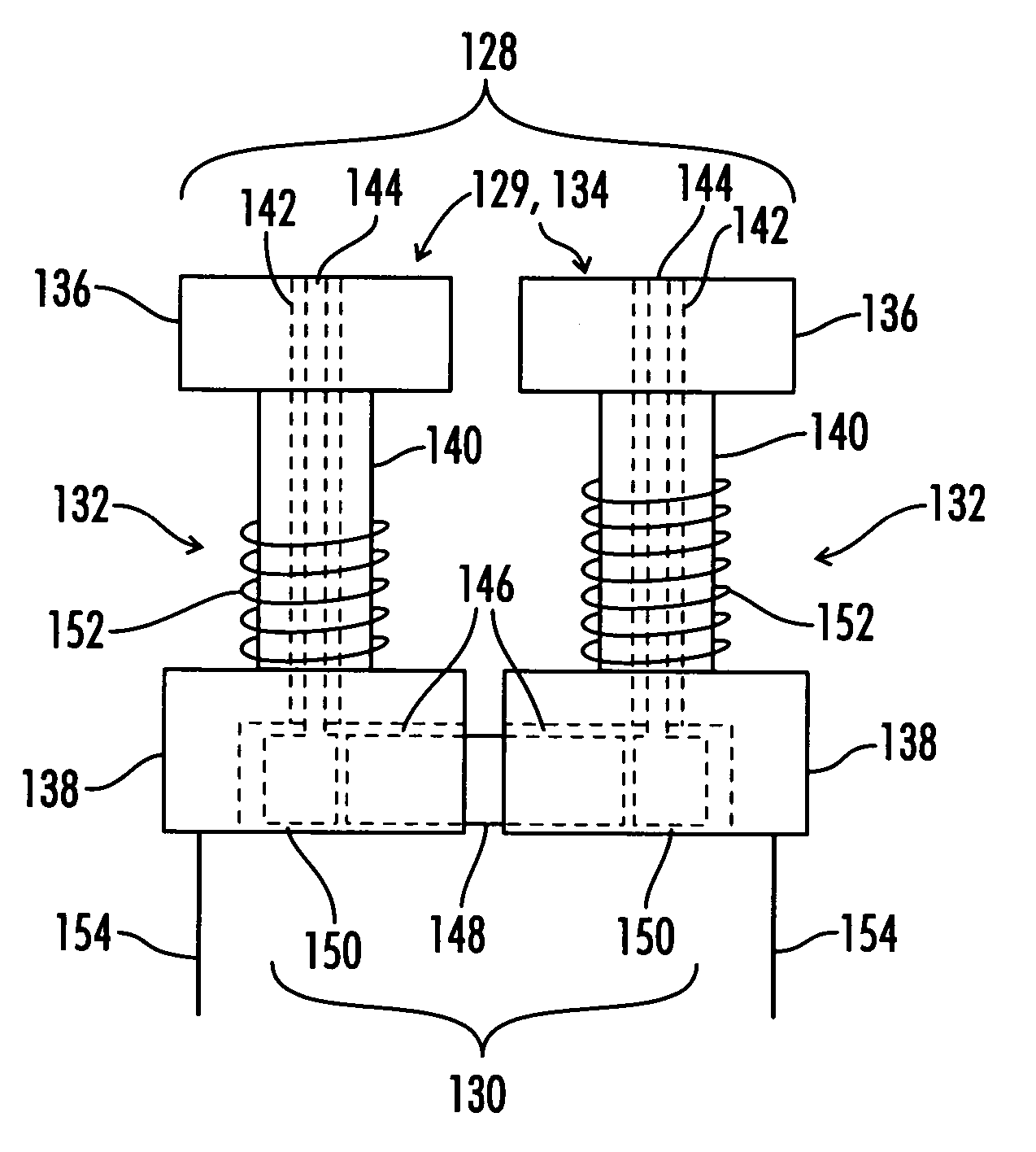

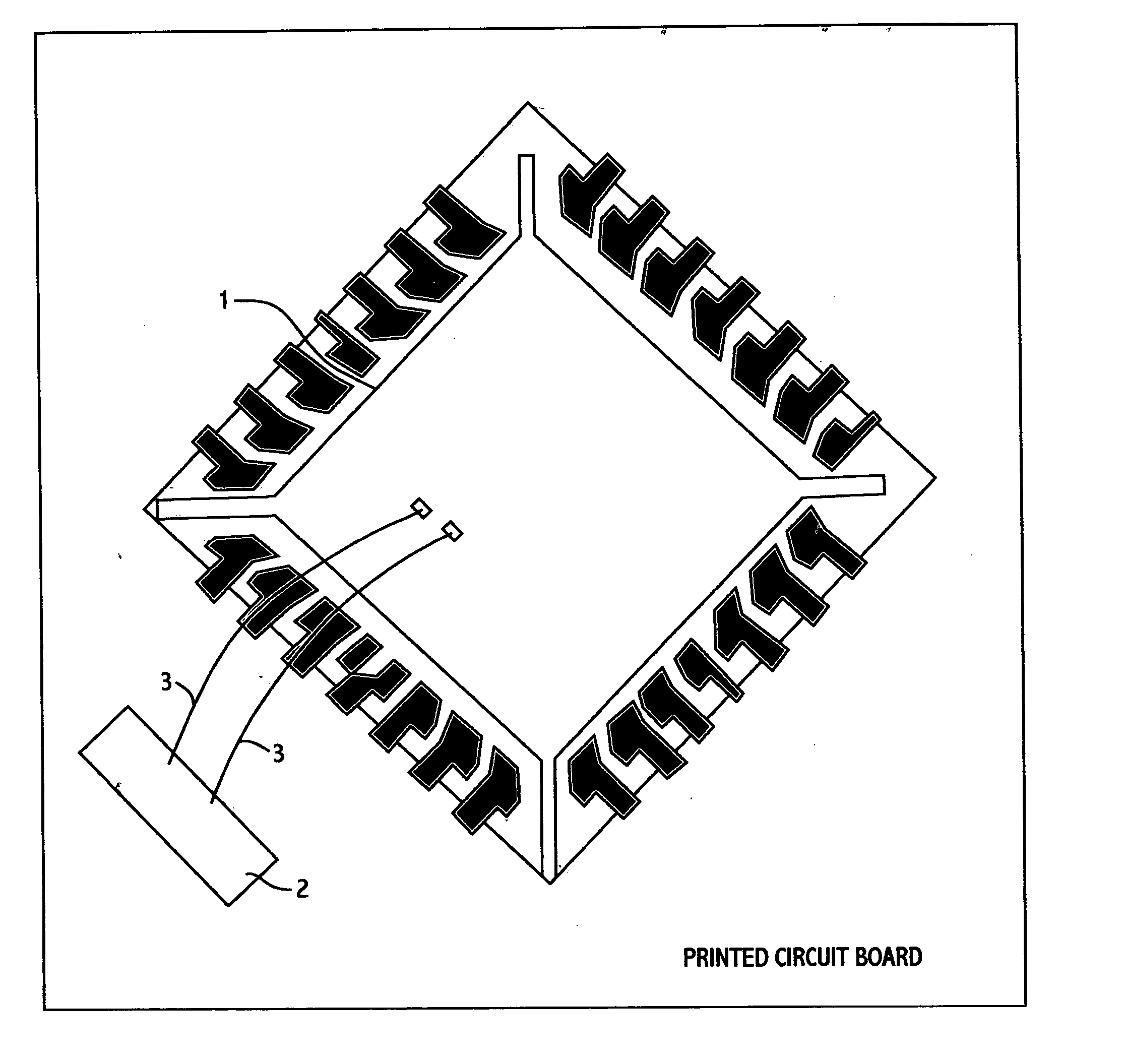

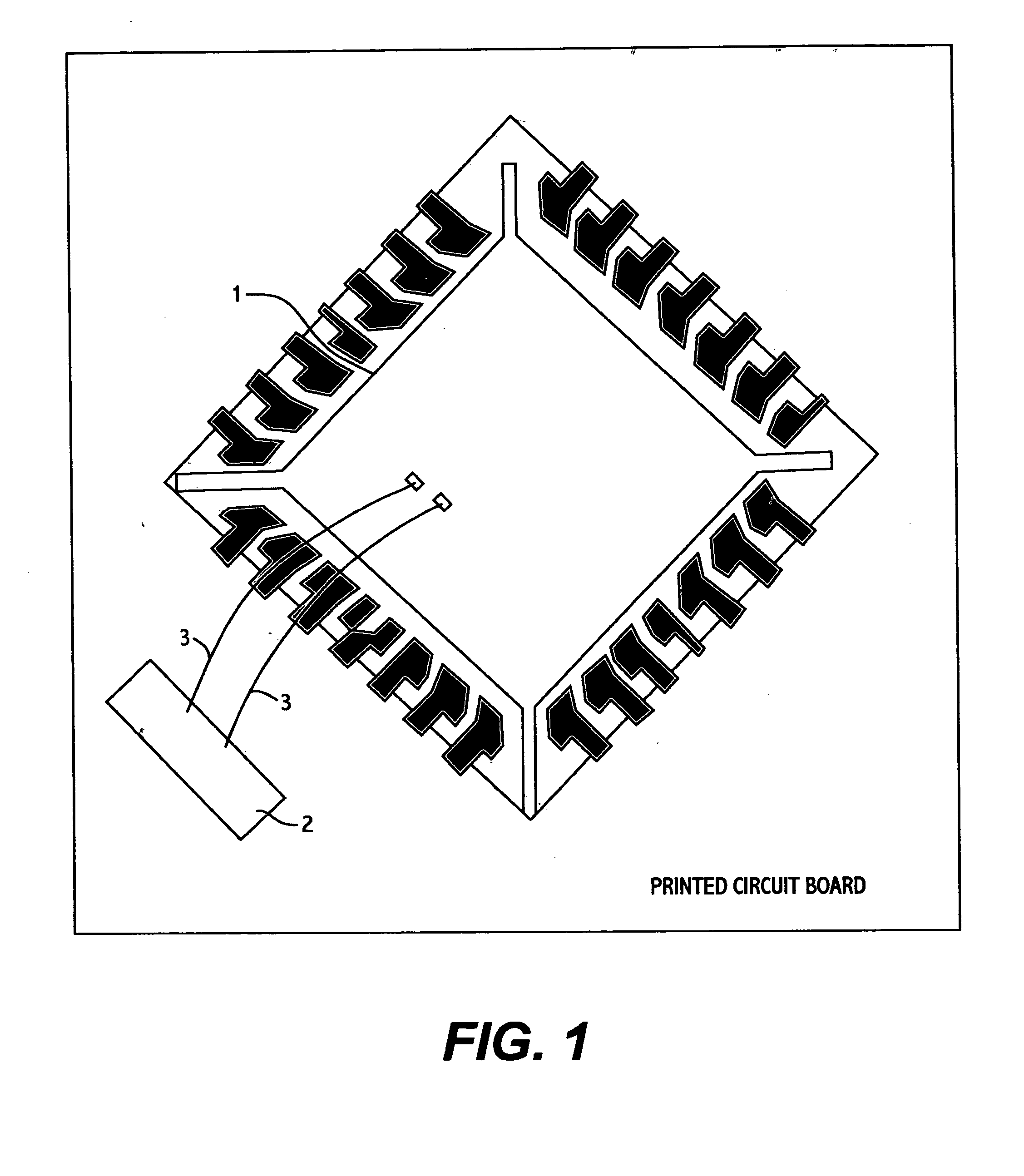

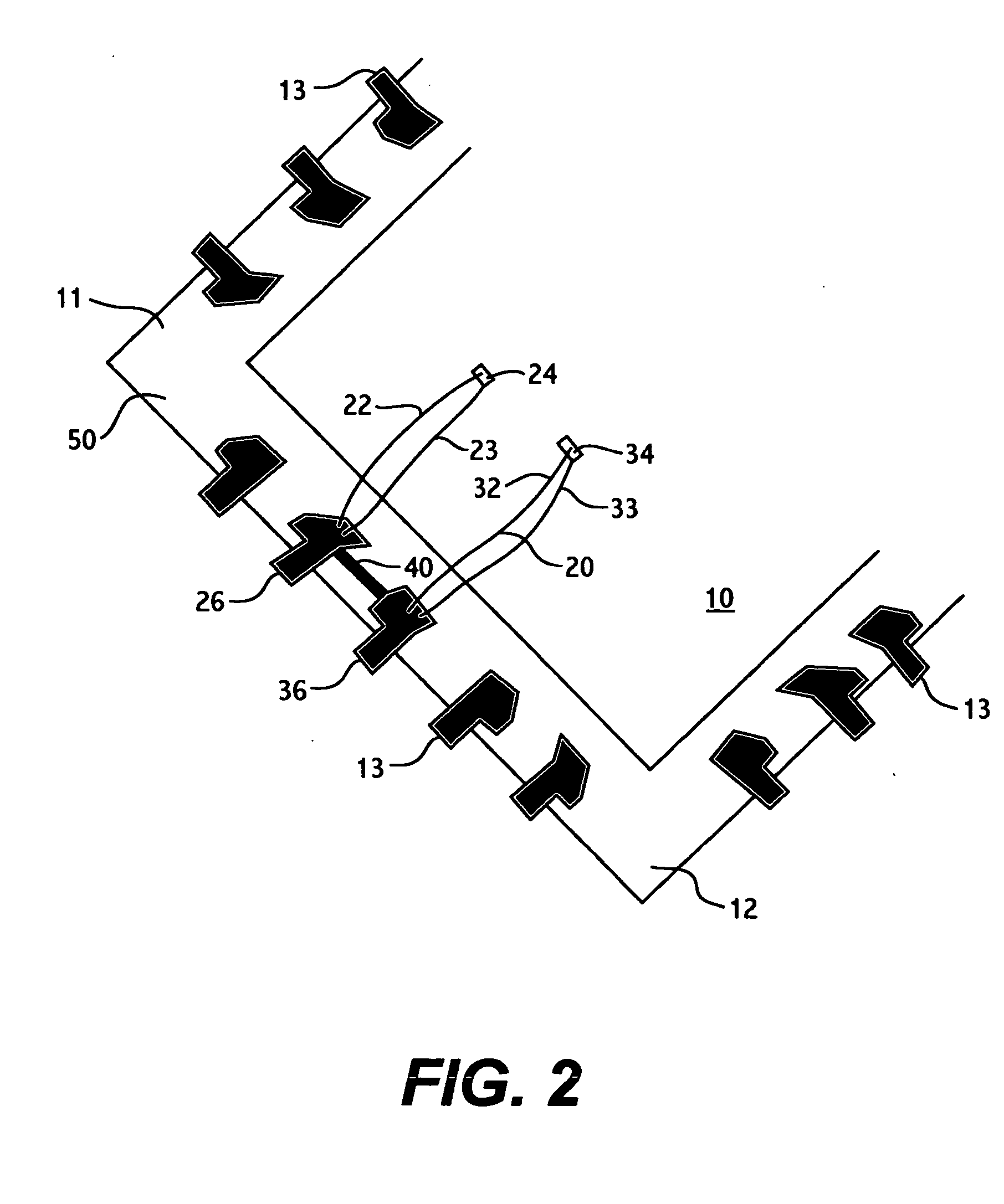

Integrated circuit package having an inductance loop formed from a multi-loop configuration

InactiveUS20050045986A1Process economyFew process stepsSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorLoop length

An integrated circuit package includes an inductance loop formed from a connection of lead wires and one or more input / output (I / O) package pins. In one embodiment, the inductance loop is formed from first and second wires which connect a first bonding pad on the integrated circuit chip to a first I / O pin of the package and a third and fourth wires which connect a second bonding pad on the chip to a second I / O pin of the package. To complete the inductor loop, the first and second I / O pins are connected by a third conductor between the pins. The third conductor may include one or more bonding wires and the I / O pins are preferably ones which are adjacent one another. However, the loop may be formed from non-adjacent connections of I / O pins based, for example, on loop-length requirements, space considerations, and / or other design or functional factors. In another embodiment, connection between the first and second I / O pins is established by making the I / O pins have a unitary construction. In another embodiment, connection between the first and second I / O pins is established by a metallization layer located either on the surface of the package substrate or within this substrate. By forming the inductor loop within the limits of the integrated circuit package, a substantial reduction in space requirements is realized, which, in turn, promotes miniaturization. Also, the integrated circuit may be implemented in any one of a variety of systems, at least one parameter of which is controlled by the length of the inductor loop of the package.

Owner:GCT SEMICONDUCTOR INC

Gravity Gradient Sensor

InactiveUS20090235740A1Less susceptible to noiseLess sensitive to noiseUsing optical meansGravitational wave measurementPhotovoltaic detectorsAccelerometer

A gravimeter for detecting a gravity difference between two points is disclosed. The gravimeter comprises an interferometric arrangement wherein the length of a reference arm is dependent upon the gravity local to a first accelerometer and the length of a sample arm is dependent upon the gravity local to a second accelerometer. A pair of photodetectors that operate in complimentary fashion provide electrical signals based on a first signal conveyed by the reference arm and a second signal conveyed by the sample arm. A change in the differential gravity between the two points induces equal and opposite changes to the magnitudes of the two electrical signals.

Owner:SYMPHONY ACOUSTICS

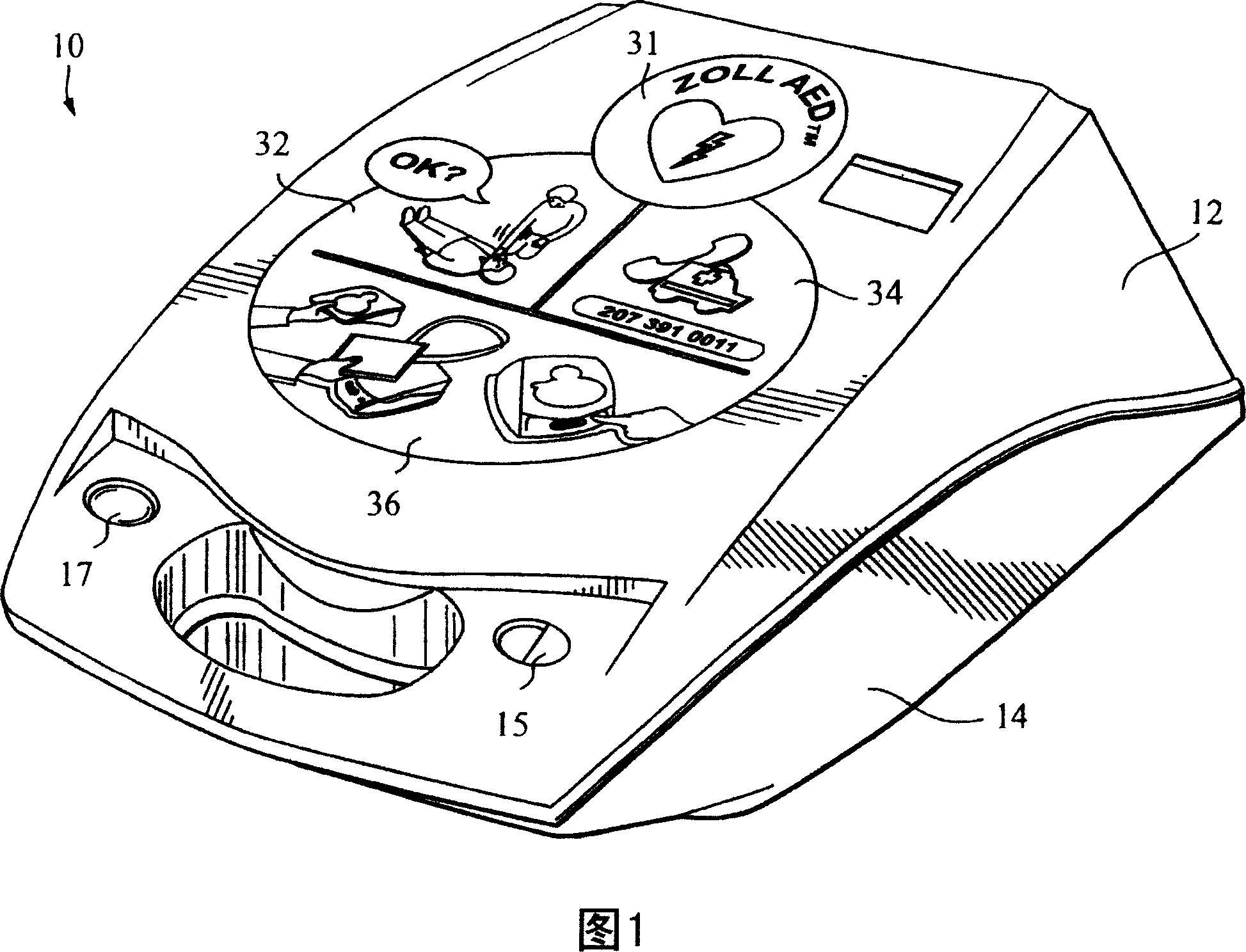

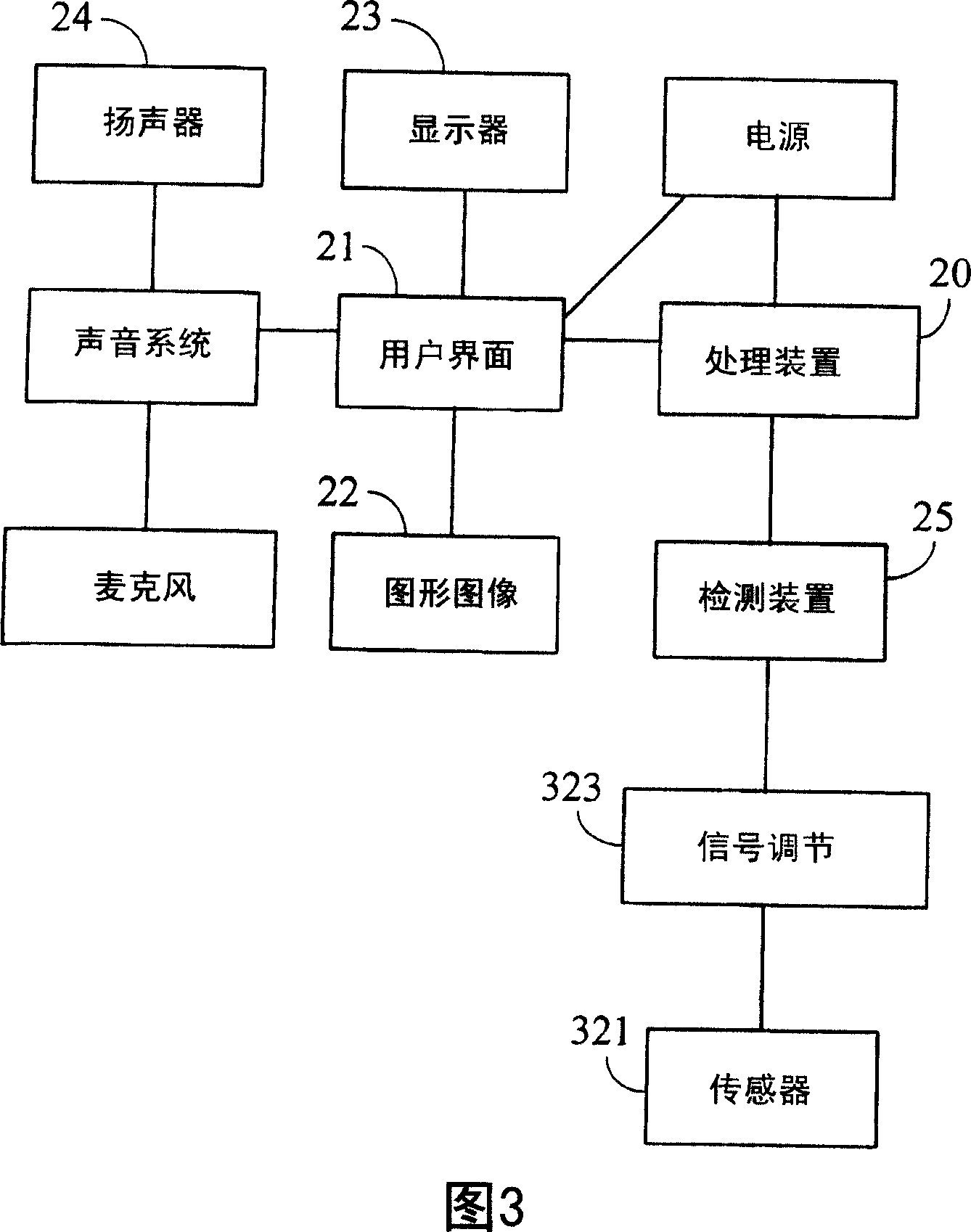

Automated resuscitation device sensing and promoting artificial respiration

InactiveCN101061985AEfficient measurementEasy to measureTracheal tubesDiagnosticsTidal volumeCardiac resuscitation

A device for assisting a caregiver in delivering cardiac resuscitation to a patient, the device comprising a user interface configured to deliver prompts to a caregiver to assist the caregiver in delivering cardiac resuscitation to a patient; at least one sensor configured to detect the caregiver's progress in delivering the cardiac resuscitation, wherein the sensor is configured to provide a signal containing information indicative of ventilation; a memory in which a plurality of different prompts are stored, including at least one ventilation progress prompt to guide the rescuer's performance of ventilation; a processor configured to process the output of the sensor to determine a parameter descriptive of ventilation progress and to determine whether the ventilation progress prompt should be selected for delivery. Possible parameters descriptive of ventilation progress include ventilation rate, delivered tidal volume, and flow rate.

Owner:ZOLL MEDICAL CORPORATION

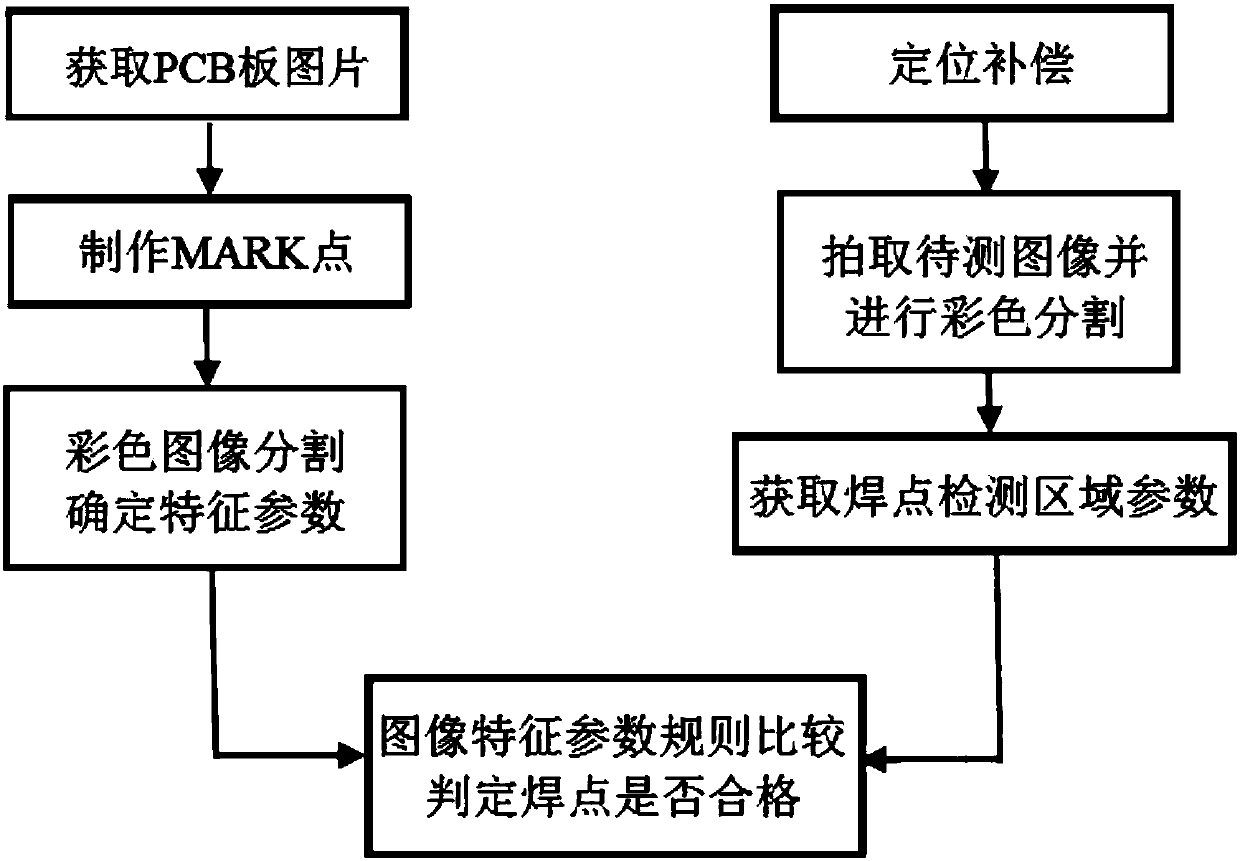

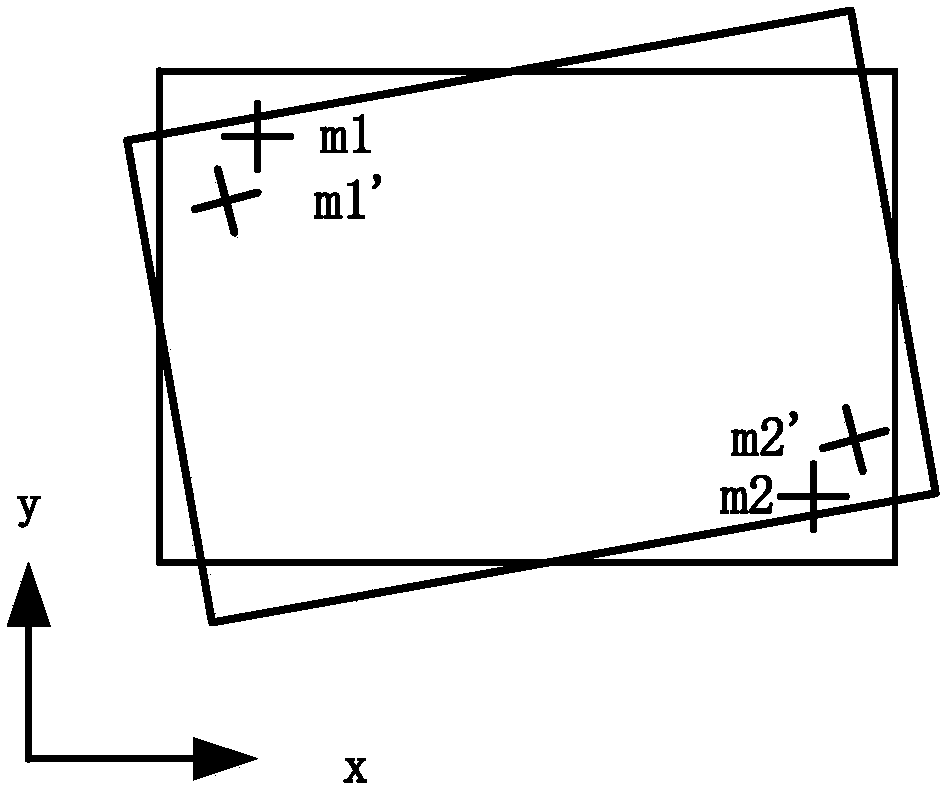

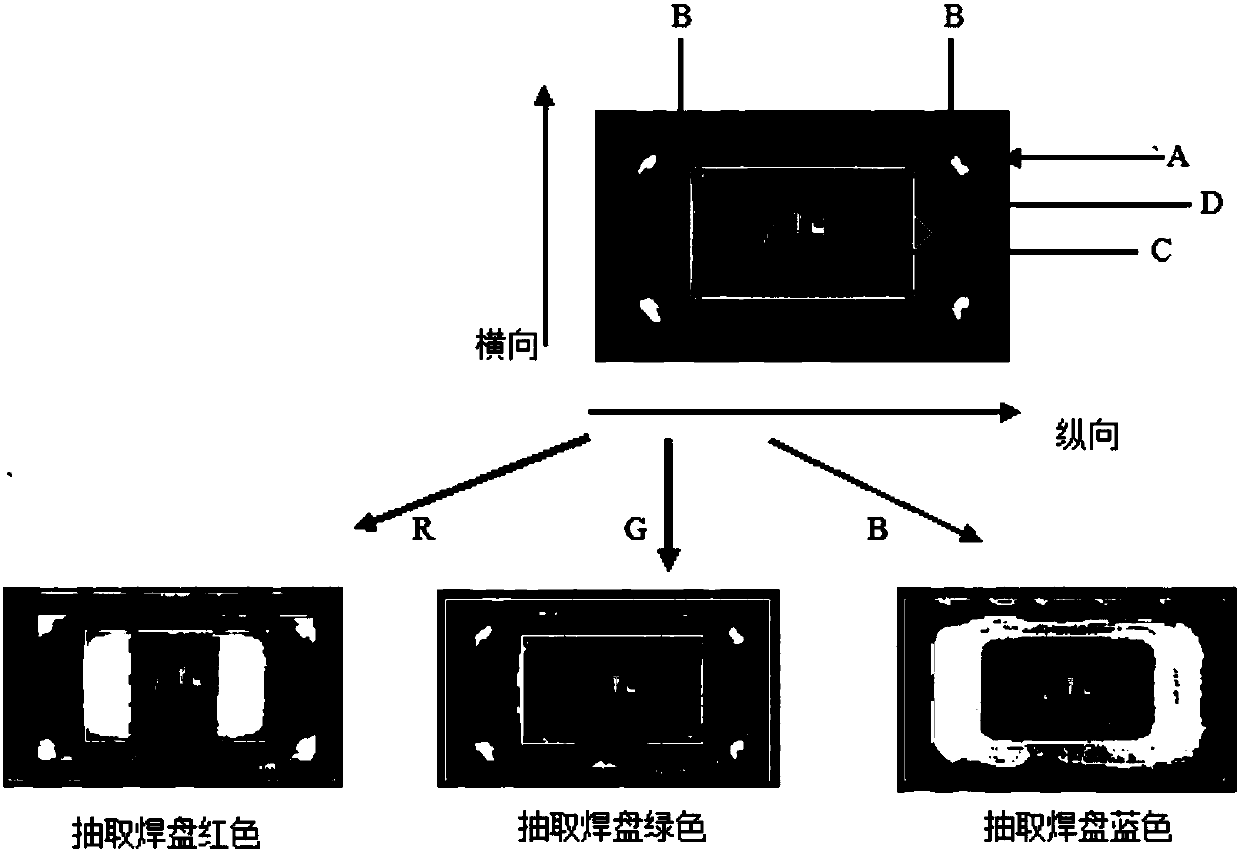

Mount element detection method based on color image segmentation and gradient projection positioning

ActiveCN107945184ALess susceptible to noiseGood robustnessImage enhancementImage analysisImage segmentationColor model

The invention discloses a mount element detection method based on color image segmentation and gradient projection positioning, and belongs to the technical field of automatic optical detection of mount elements. The mount element detection method based on color image segmentation and gradient projection positioning is characterized in that a designed image acquisition system is used to acquire color images; three-color (red, green and blue) images are converted into an HSI color model which is formed by three parameters (H (Hue), S (saturation) and I (Intensity)); as the HSI model directly uses the hue and the saturation having no relation with brightness when the HSI color model extracts the color information, the mount element detection method based on color image segmentation and gradient projection positioning is accurate and highly efficient in segmentation; one the above basis, positioning and detection of elements are carried out; positioning mainly uses the color and geometrical characteristics, and a positioning method based on gradient projection and a principal component characteristic value detection method are proposed; and the mount element detection method based oncolor image segmentation and gradient projection positioning has the advantages of high positioning accuracy and efficiency and accurate detection.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY

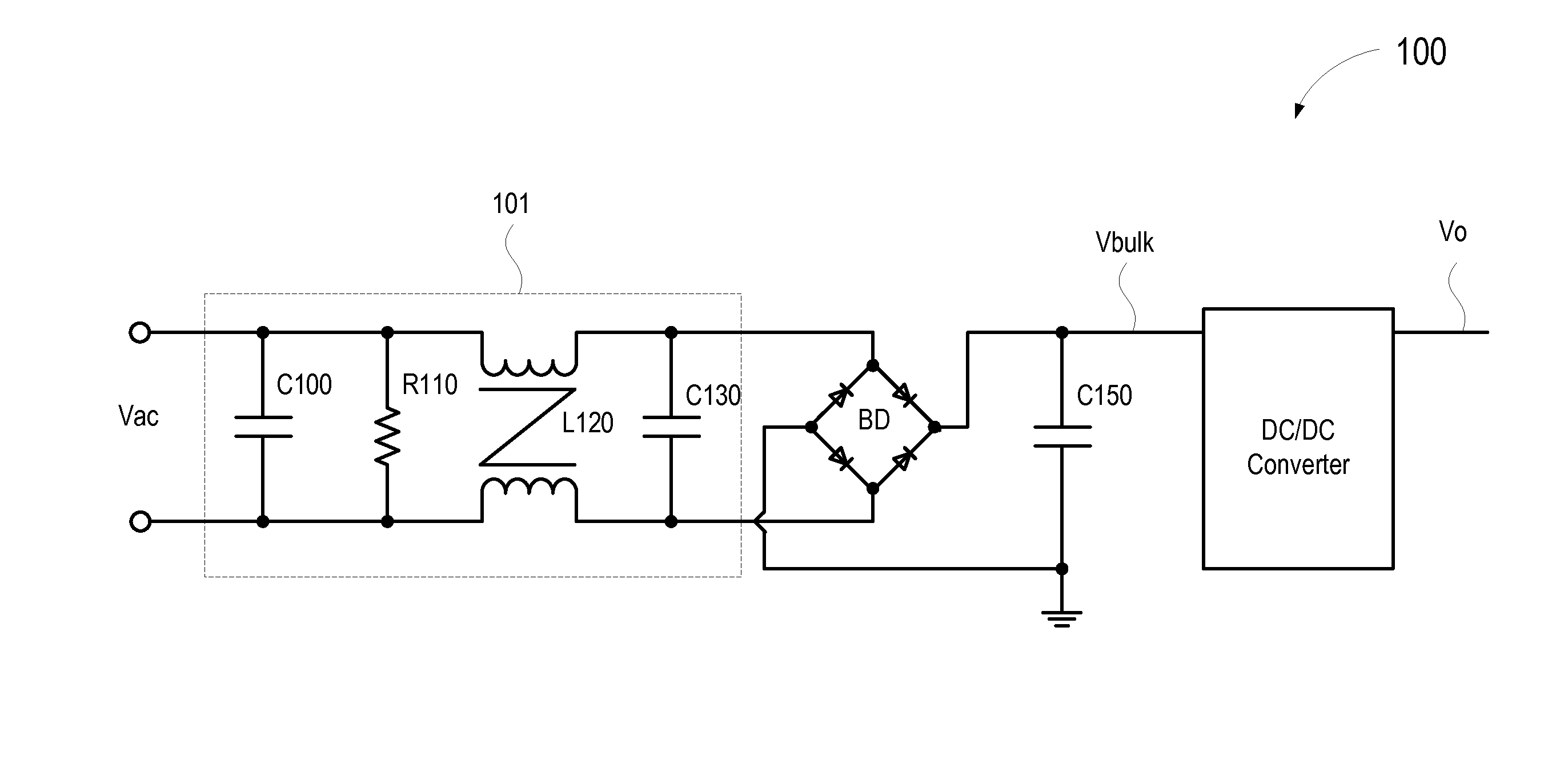

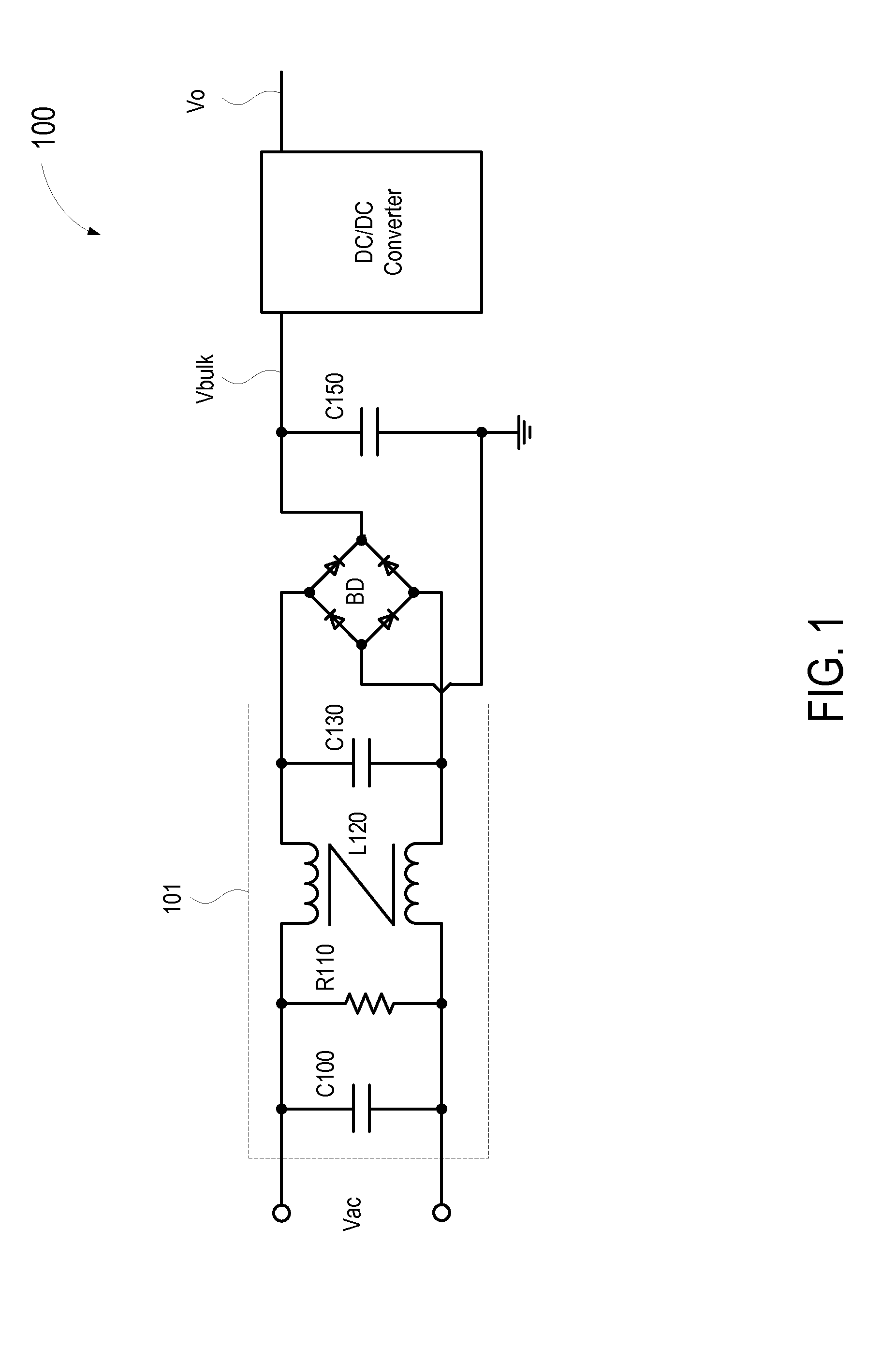

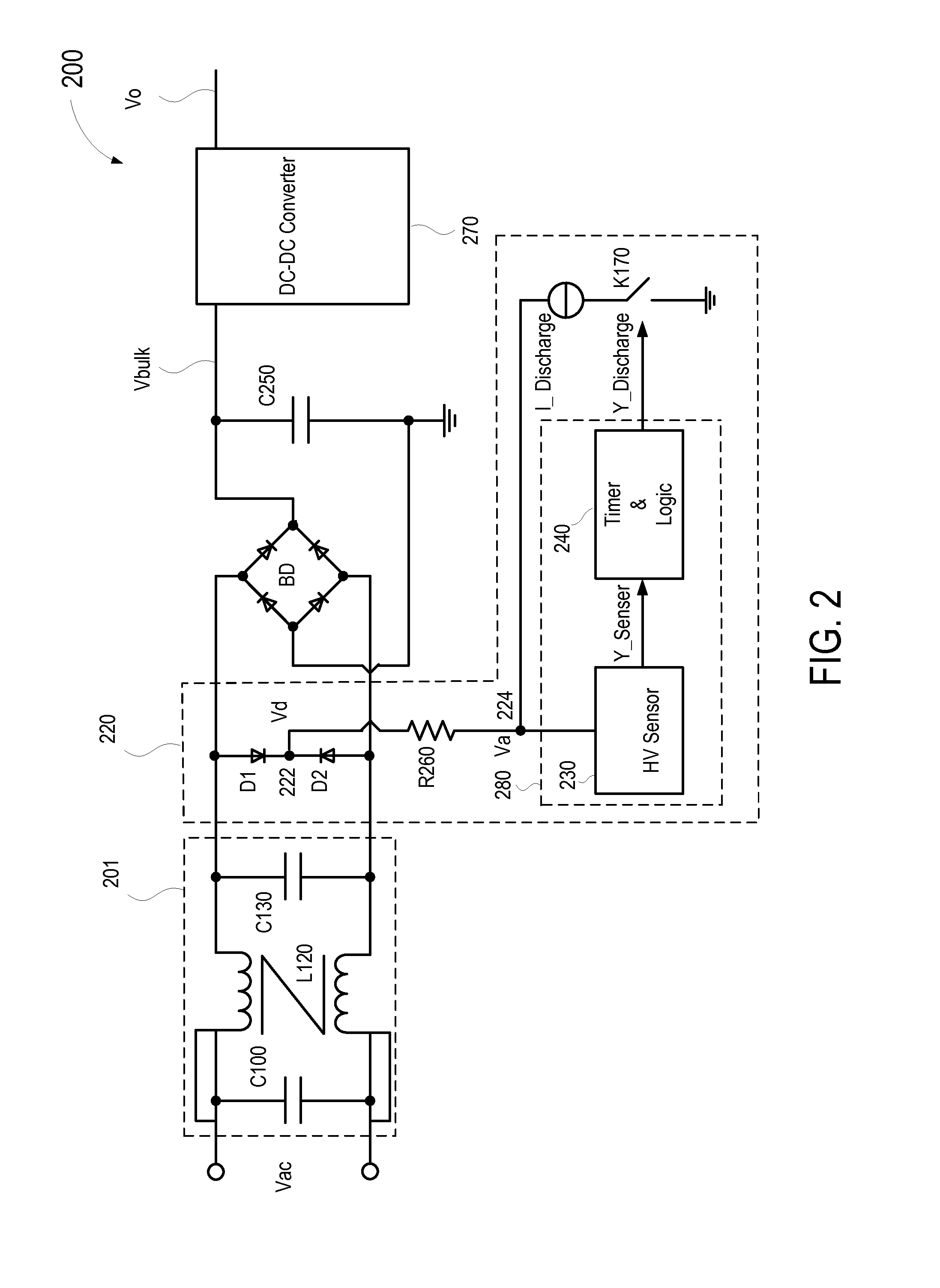

Capacitor discharge circuit for power supply EMI filters

ActiveUS20160241135A1Less susceptible to noiseLess susceptible to instabilityPower conversion systemsCapacitanceComparators circuits

A discharging circuit for a power supply includes a rectifying circuit for coupling to an input filter capacitor coupled to an AC input voltage for providing a rectified AC voltage. A discharge resistor is coupled to the rectifying circuit, and a power switch and a discharging current source are coupled in series with the discharging resistor. A discharge control circuit is coupled to the discharge resistor for providing a discharge signal to cause the power switch to turn on for discharging the capacitor using the discharging current source. The discharging control circuit includes an AC voltage sampling circuit for providing a sampled rectified voltage, a signal-shaping circuit for providing a time-varying signal derived from the sampled rectified voltage, a comparator circuit for comparing the sampled rectified voltage and the time-varying signal, and a counter circuit for providing the discharge signal in response to an output of the comparator circuit.

Owner:BCD SHANGHAI MICRO ELECTRONICS CO LTD

Gas sensor

InactiveUS20090200164A1Improve versatilityLess susceptible to electric noiseMaterial electrochemical variablesElectricityCylinder head

A gas sensor includes a plate-like sensor element having solid electrolyte layers; a circuit board having a processing circuit for processing an output signal from the sensor element; terminals connected to the sensor element and to the circuit board and serving as electric junctions therebetween; and a metallic casing which encloses the sensor element, the circuit board, and the terminals and has attachment portions for attachment to an external object. The attachment portions are attached to an inlet pipe at a position located downstream of an EGR gas inlet or to a cylinder head.

Owner:NGK SPARK PLUG CO LTD

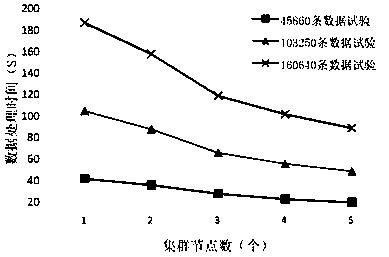

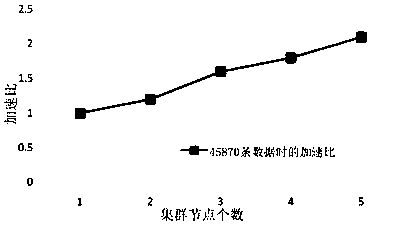

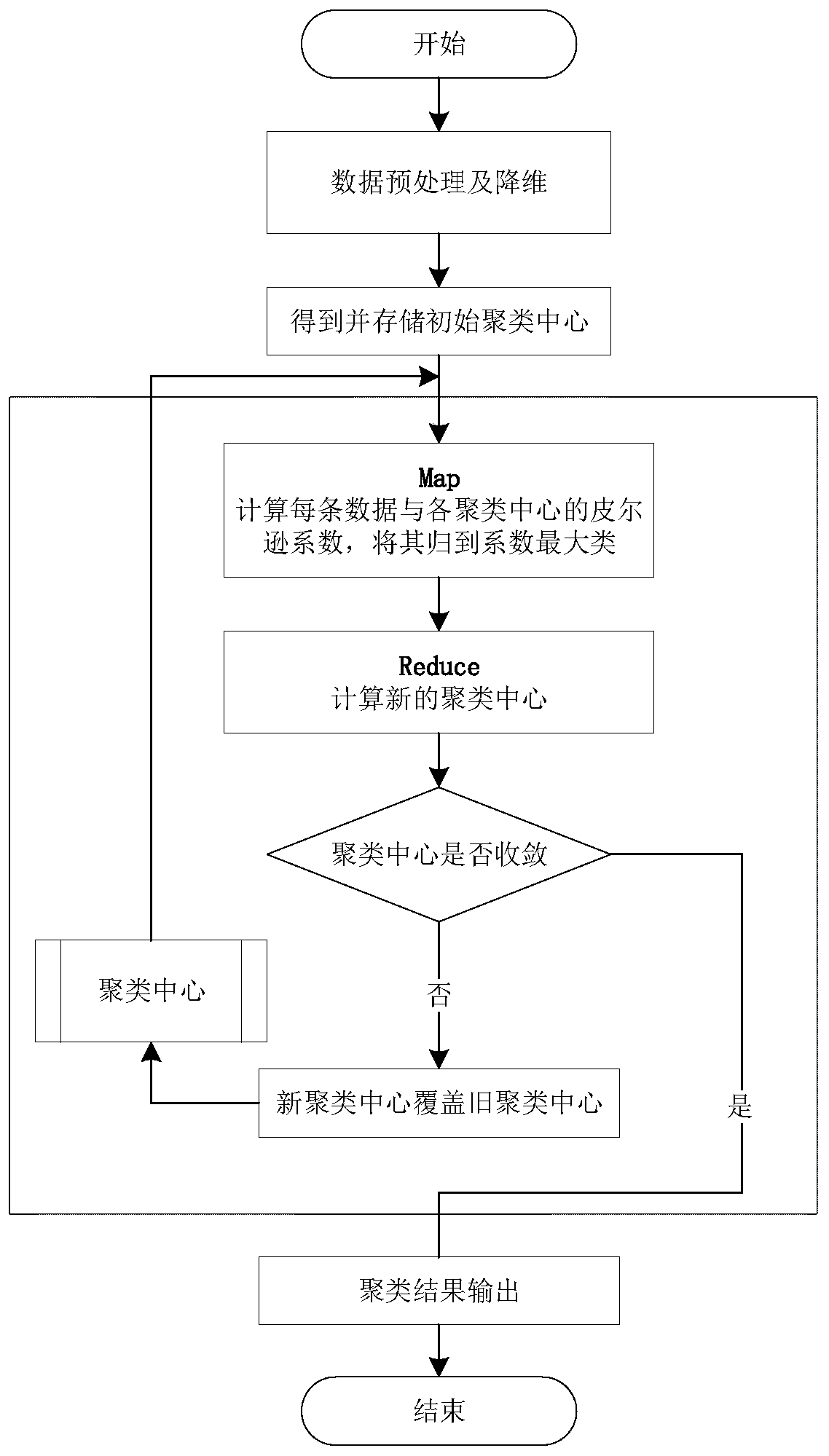

Power grid peak load clustering extraction method based on Pearson coefficient and MapReduce parallel computing

PendingCN110069467AEliminate the difference in sizeEliminate differencesDigital data information retrievalCharacter and pattern recognitionSpearman's rank correlation coefficientNODAL

A power grid peak load clustering extraction method based on Pearson coefficient and MapReduce parallel computing comprises the following steps: 1, conducting data cleaning and abnormal data restoration on a load data set, and then conducting dimensionality reduction on the load data set; 2, storing the data set subjected to dimension reduction in a Hadoop distributed file system line by line, anddividing the data set into slices to form sub-data sets; 3, reading each slice sub-data set in the step 2 by using a MapReduce computing architecture, and selecting an initial clustering center by using a Pearson correlation coefficient as a similarity criterion through a parallel model; and 4, allocating the clustering calculation task to the Map task node in the MapReduce, and combining the initial clustering center in the step 3 to complete parallel clustering of the data set. The method is more suitable for power load big data processing derived from more and more vigorous development information times.

Owner:SHENYANG POLYTECHNIC UNIV

Photoelectric converting apparatus

InactiveUS7592599B2Reduce the impact of noiseSimple configurationTelevision system detailsTelevision system scanning detailsPhotoelectric conversionConstant current source

A photoelectric converting apparatus of the present invention includes, in one embodiment, a photoelectric converting element, a resetting transistor in which a source is connected to the photoelectric converting element and a drain is connected to a resetting power source, a readout transistor in which a gate is connected to the photoelectric converting element and a drain is connected to a readout power source, a signal line connected to a source of the readout transistor, a selecting transistor connected between the readout power source or the signal line and the readout transistor, and a constant current source connected to the signal line.

Owner:CANON KK

Spread spectrum clock generator

InactiveUS7161970B2Robust architectureLess susceptible to noisePulse automatic controlElectrical apparatus interference reductionClosed loopEngineering

A spread spectrum clock generator comprises a conventional closed-loop VCO and an open-loop VCO where both are coupled to the same point of the PLL. Both VCOs comprise a V-to-I converter followed by a current-controlled oscillator and are identical in design but only the open-loop VCO receives the modulation current to generate the spread spectrum clock signal. The open-loop ICO is part of the spread spectrum generator and in one embodiment of the invention receives feedback current signals representing the modulation method and modulation ratio. This ensures that the modulated clock output tracks the PLL output frequency. In a second embodiment the closed-loop VCO receives from the spread spectrum generator the feedback current signal representing the modulation method (center / down spread) while the open-loop VCO receives the feedback signal representing the modulation ratio.

Owner:KARMIC DESIGN USA

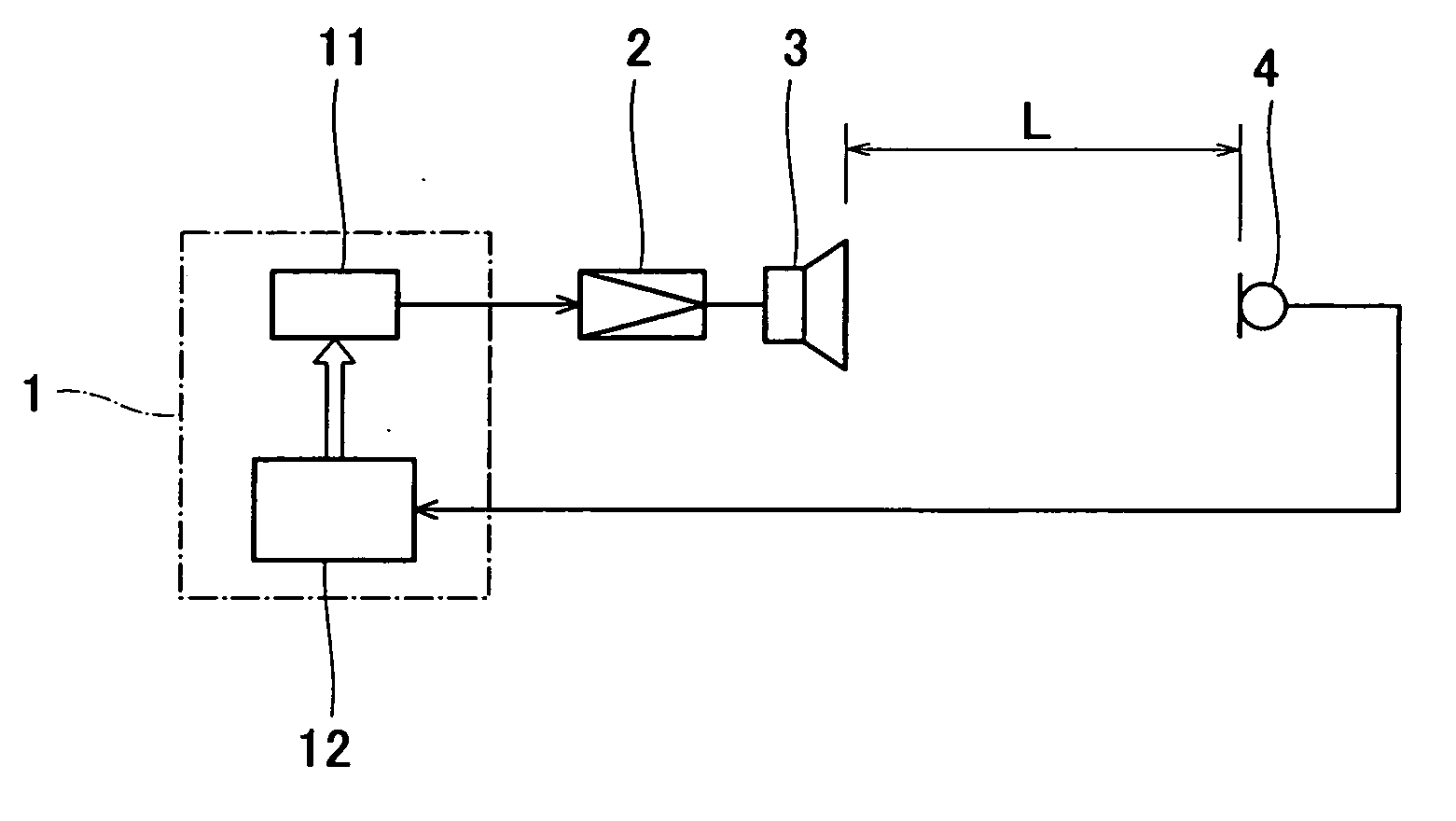

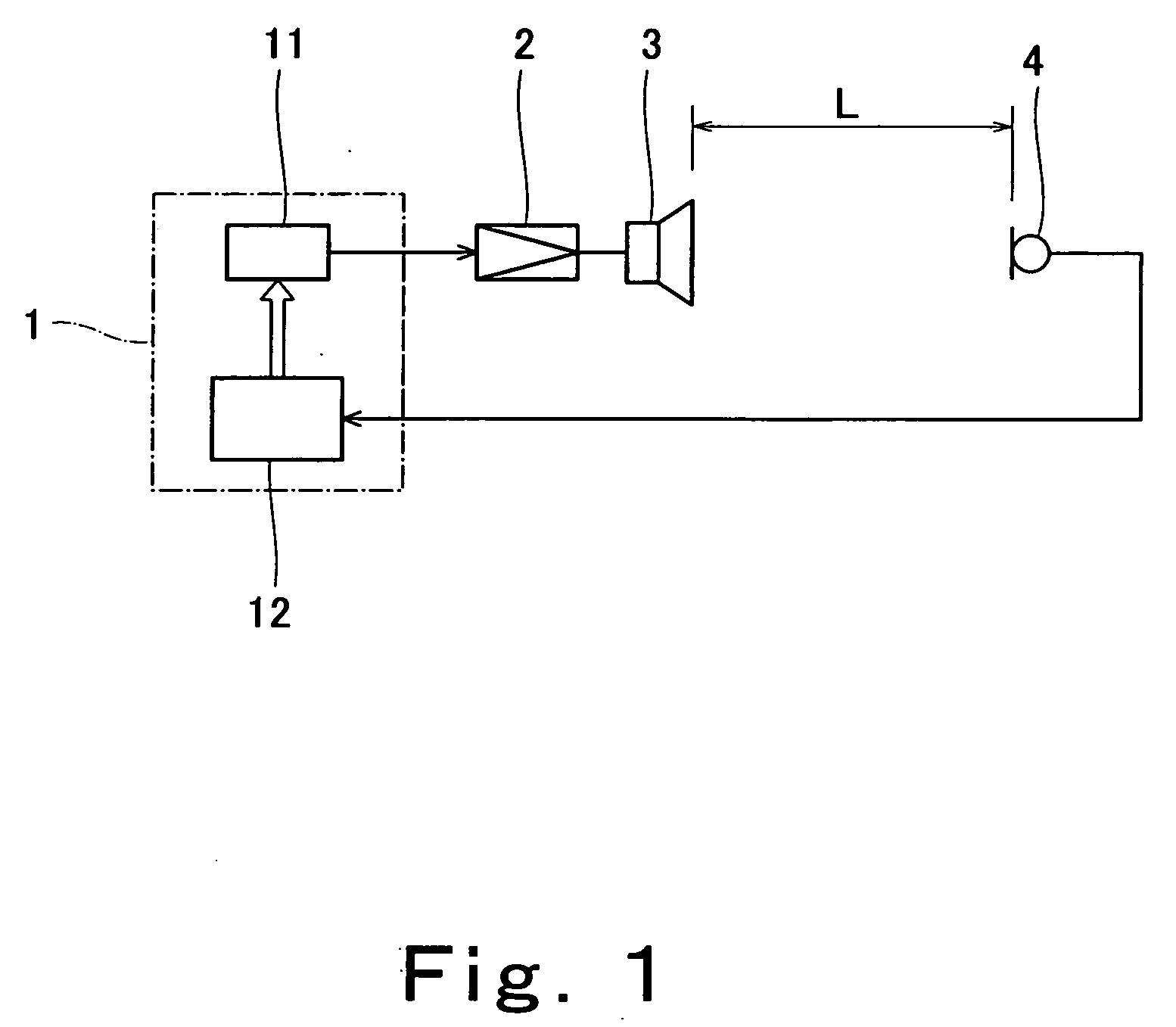

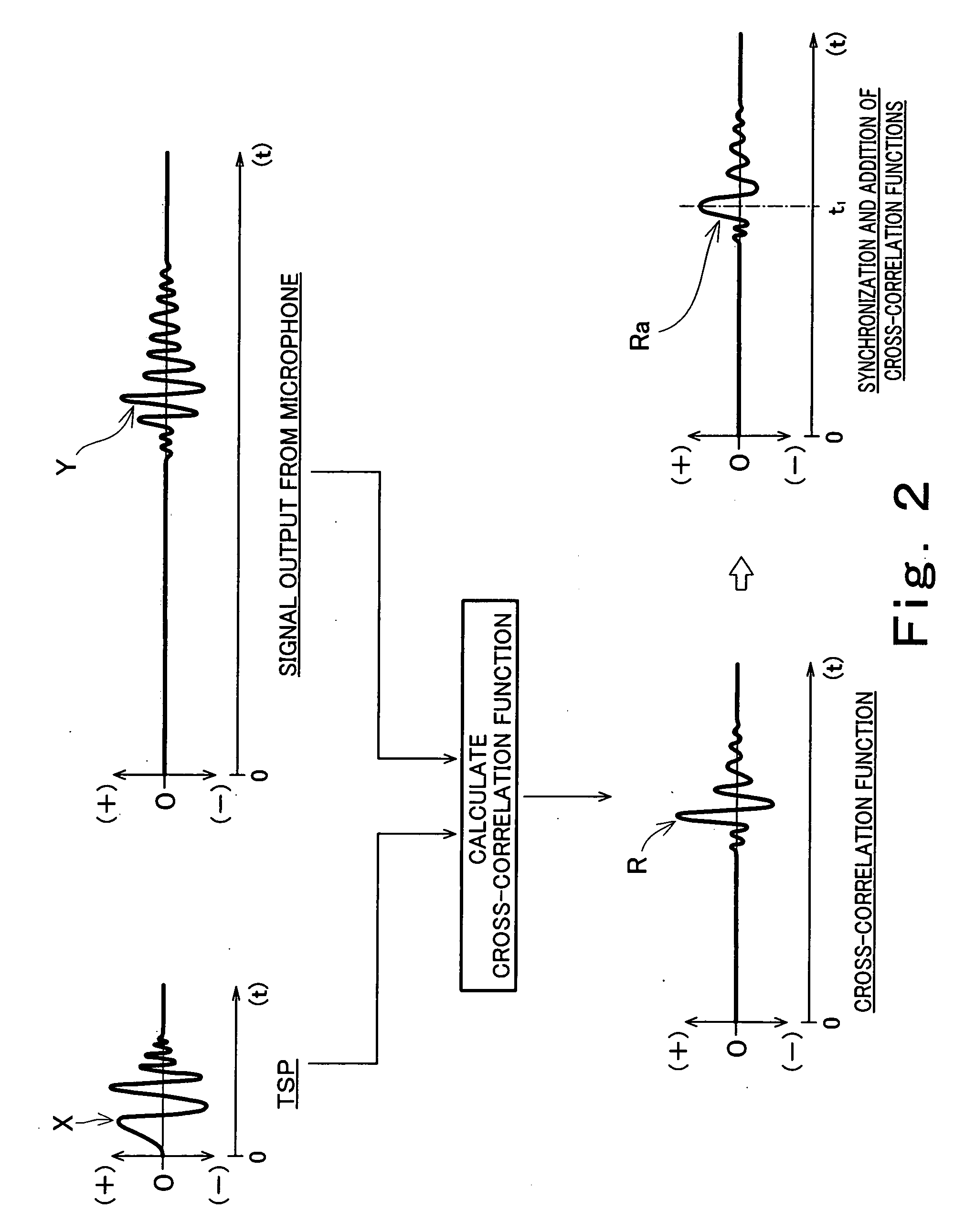

Method and device for measuring sound wave propagation time between loudspeaker and microphone

ActiveUS20060140414A1Less susceptible to noiseLess susceptible to timeUsing reradiationStereophonic systemsSound sourcesPropagation time

A device 1 for measuring a propagation time of a sound wave comprises a sound source means 11 and a calculation means 12. The sound source means 11 outputs a time stretched pulse as a sound source signal input to a speaker 3. The calculation means 12 calculates a cross-correlation function of the time stretched pulse and the sound signal which is output from the speaker 3 and is received in a microphone 4. Based on the cross-correlation function, the propagation time of the sound wave between the speaker 3 and the microphone 4 is found.

Owner:TOA CORP +1

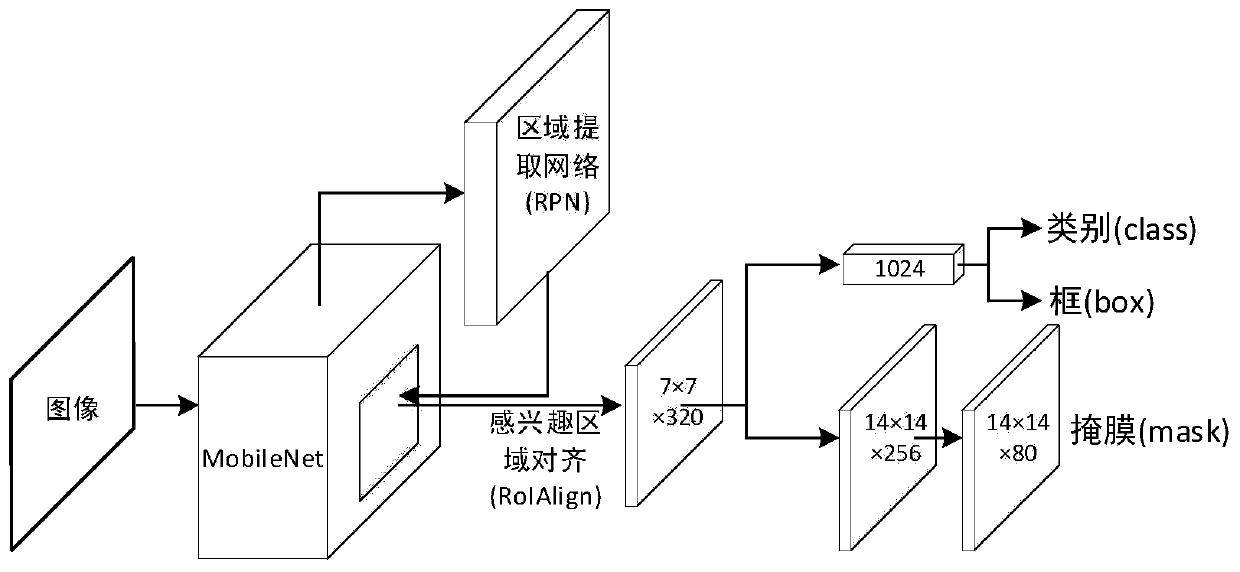

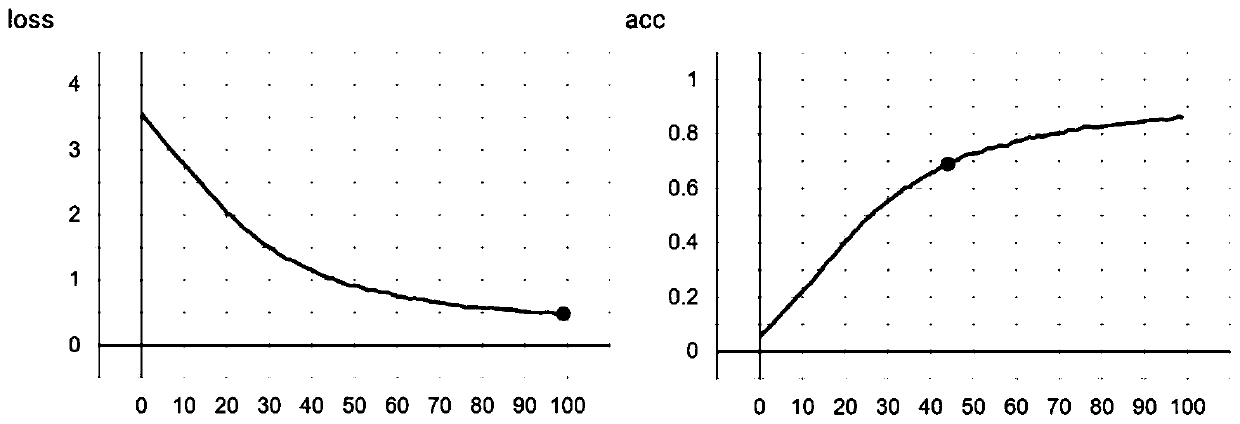

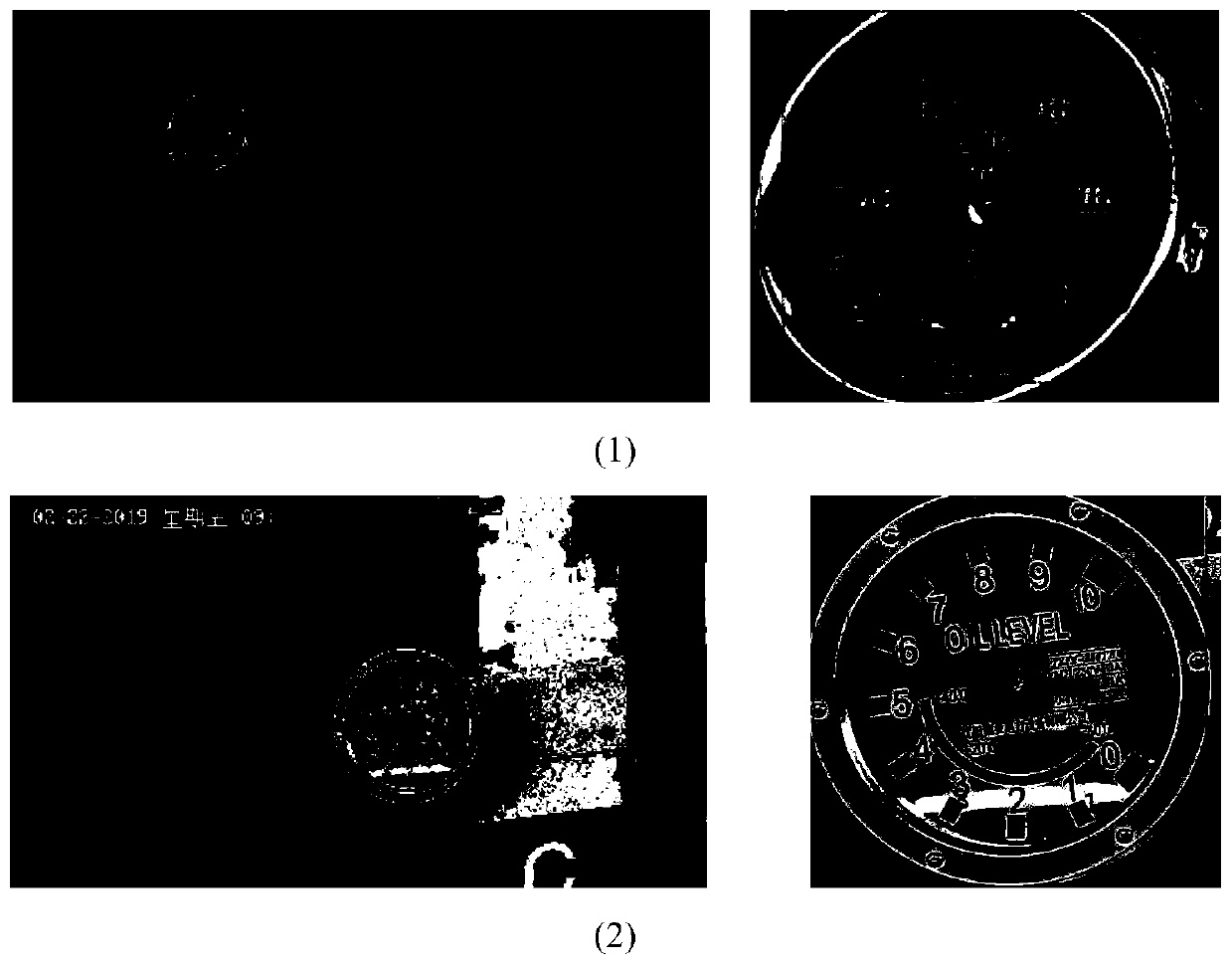

Pointer instrument automatic reading method based on key point detection

InactiveCN110909738ASolve the problem of low accuracyVersatilityCharacter and pattern recognitionRgb imageEngineering

The invention discloses a pointer instrument automatic reading method based on key point detection. The pointer instrument automatic reading method includes the steps: collecting a front RGB image ofthe pointer instrument, and constructing a key point detection network based on an improved mask region convolutional neural network; inputting the front RGB image of the pointer instrument with knowninstrument readings and the readings thereof into a key point detection network for training, and predicting a to-be-detected object to obtain a positioning position and key points of scale lines andpointers on a dial plate; fitting an arc formed by the scale lines and a straight line where the pointer is located based on the detected key points; and finally, automatically calculating the reading of the pointer type instrument according to the relative angle between the straight line where the pointer is located and the arc formed by the scale lines. The pointer instrument automatic readingmethod can achieve the automatic reading of the pointer instrument, is good in precision and robustness, can be suitable for various types of pointer instruments, and is important in engineering valueand significance.

Owner:杭州远鉴信息科技有限公司

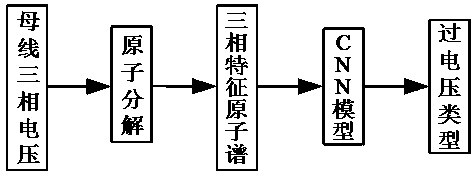

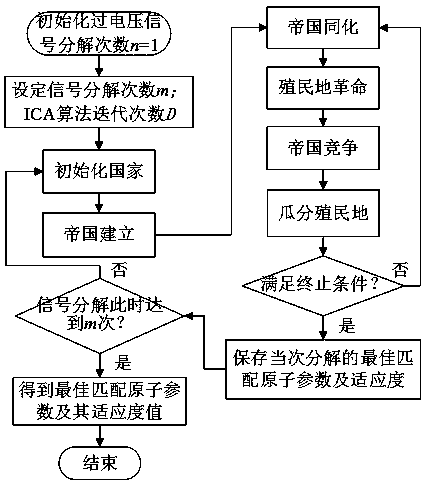

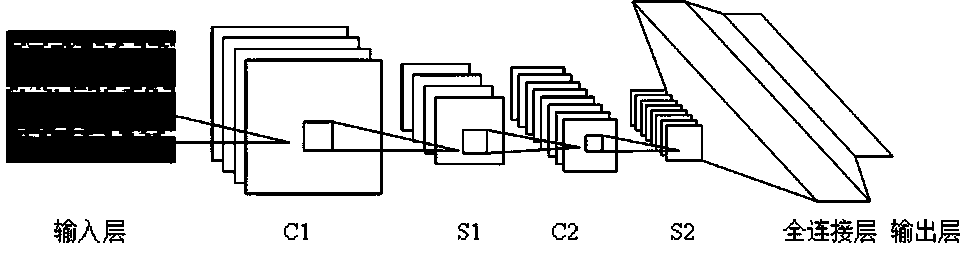

Novel method for identifying overvoltage inside distribution network

ActiveCN109142851AImprove speed and precisionNot easily affected by noiseCurrent/voltage measurementNeural architecturesPhysical modelThree-phase

The invention relates to a novel method for identifying overvoltage inside a distribution network. An atomic decomposition algorithm optimized based on an imperial colonial competition algorithm is applied to the analysis of over-voltage signals, and the optimized algorithm can be used to extract the internal characteristics of signals quickly and effectively without being disturbed by noise. A three-phase characteristic atomic spectrum is constructed based on the atomic decomposition algorithm, waveform signals only containing time-domain information are converted into high-dimensional characteristics containing time-frequency information, and the time-frequency characteristics of overvoltage signals are described completely. The three-phase characteristic atomic spectrum is recognized directly by using a convolution neural network, the shortcomings of a shallow learning identification algorithm for the identification of high-dimensional characteristics are overcome, and the subjectivity and complexity in the process of characteristic reduction are avoided. Simulation waveforms and physical models verify that the distribution network overvoltage type identification method of the invention has high identification accuracy and strong adaptability.

Owner:FUZHOU UNIVERSITY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com