Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

245results about How to "Good coplanarity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

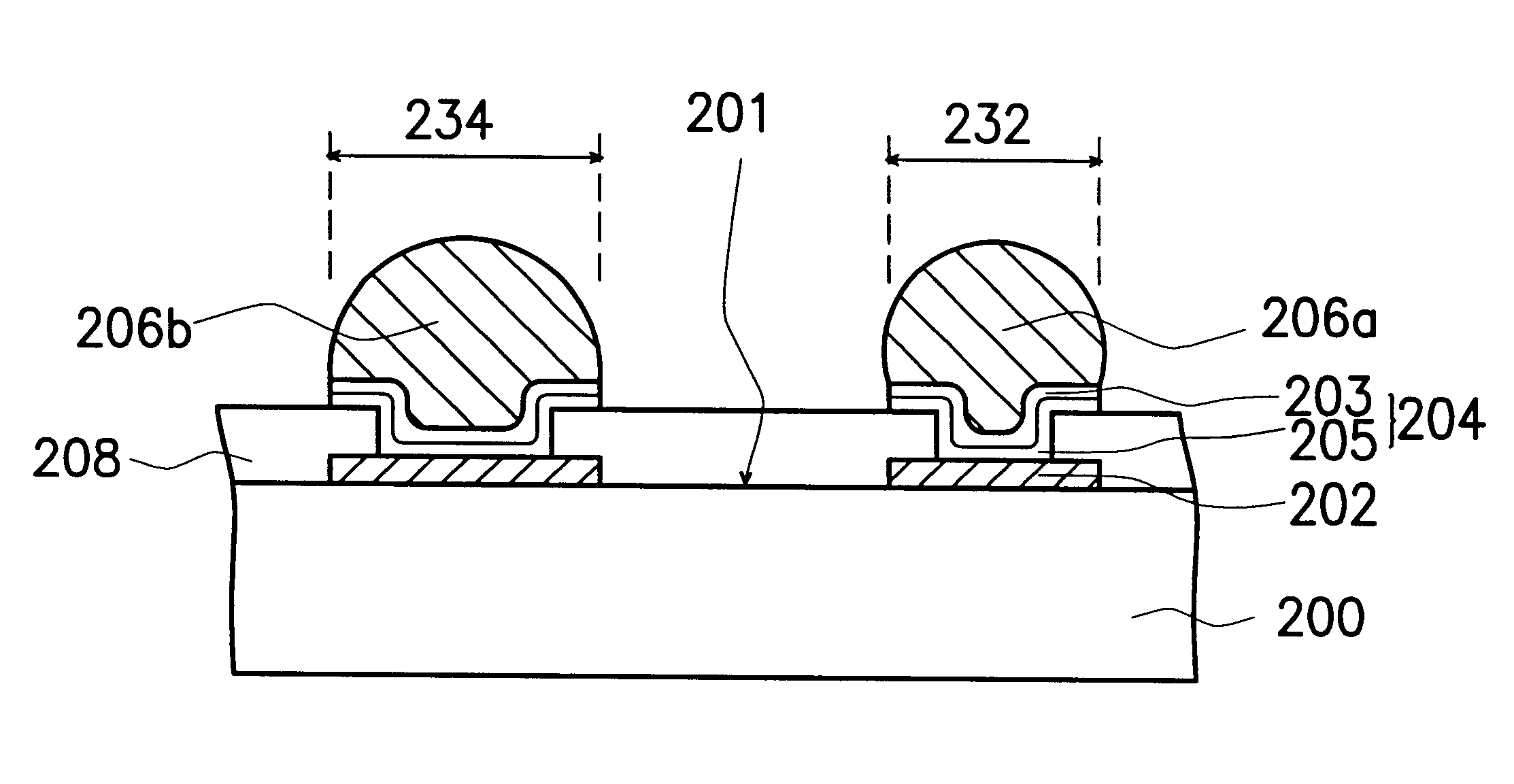

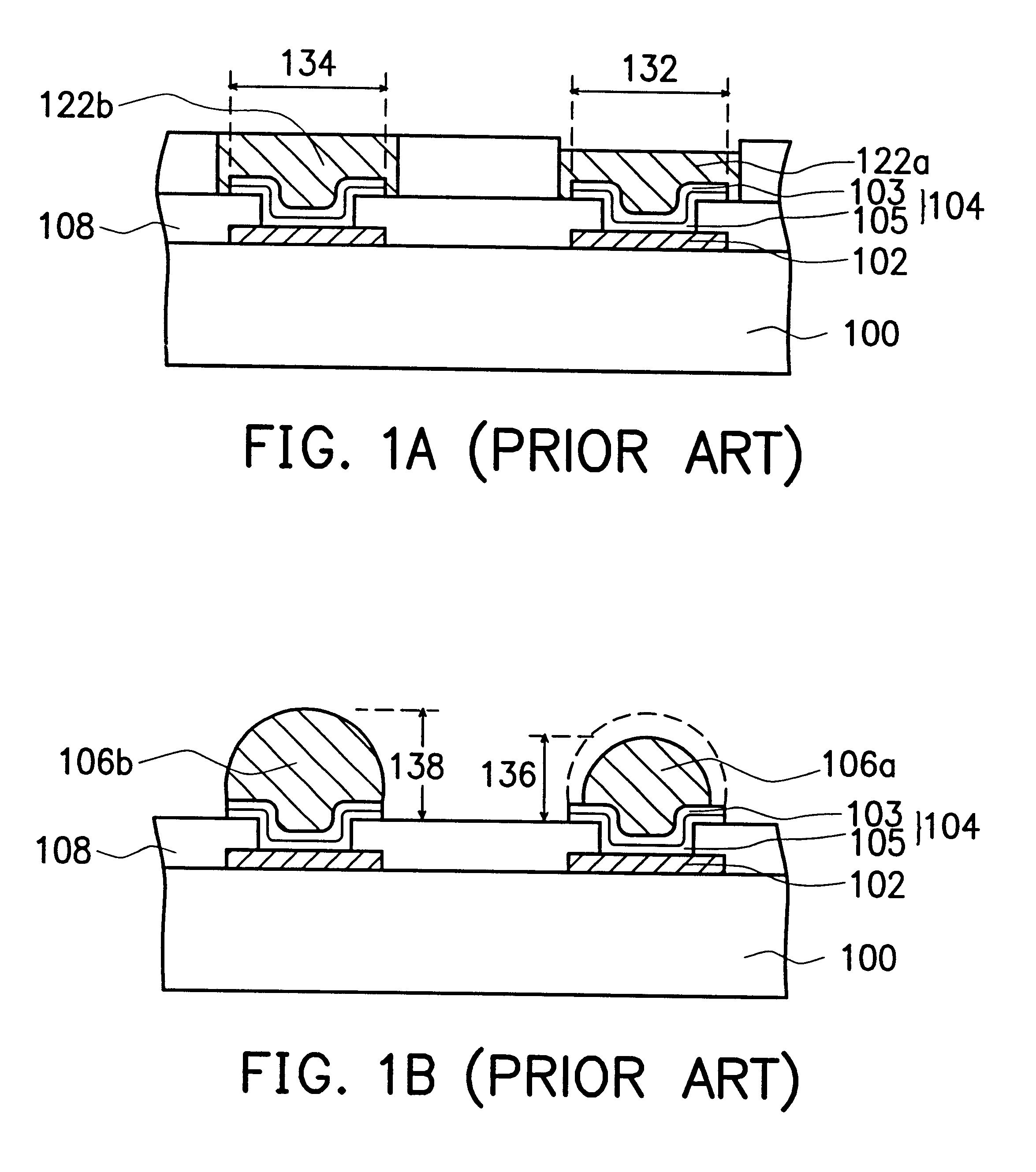

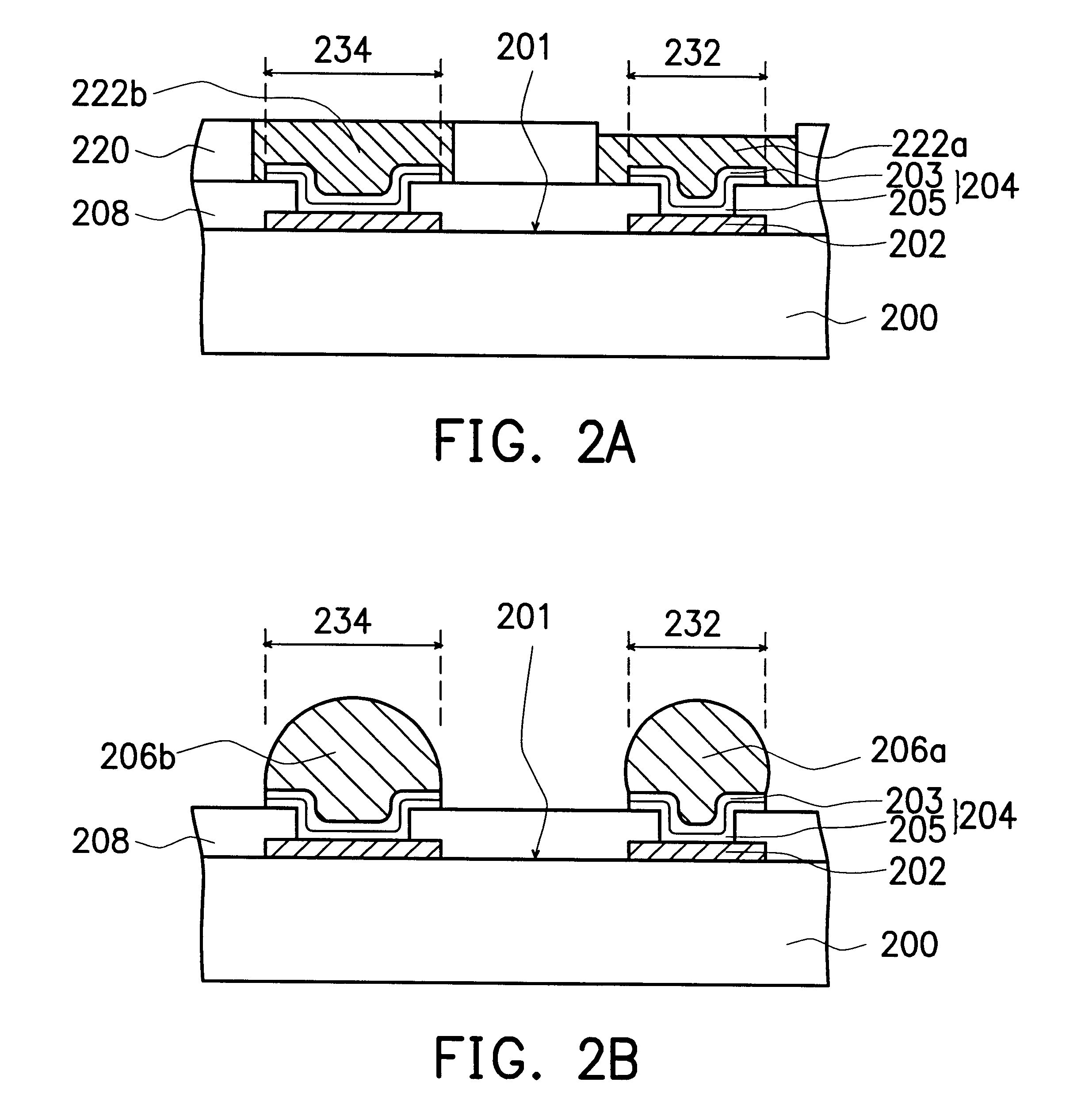

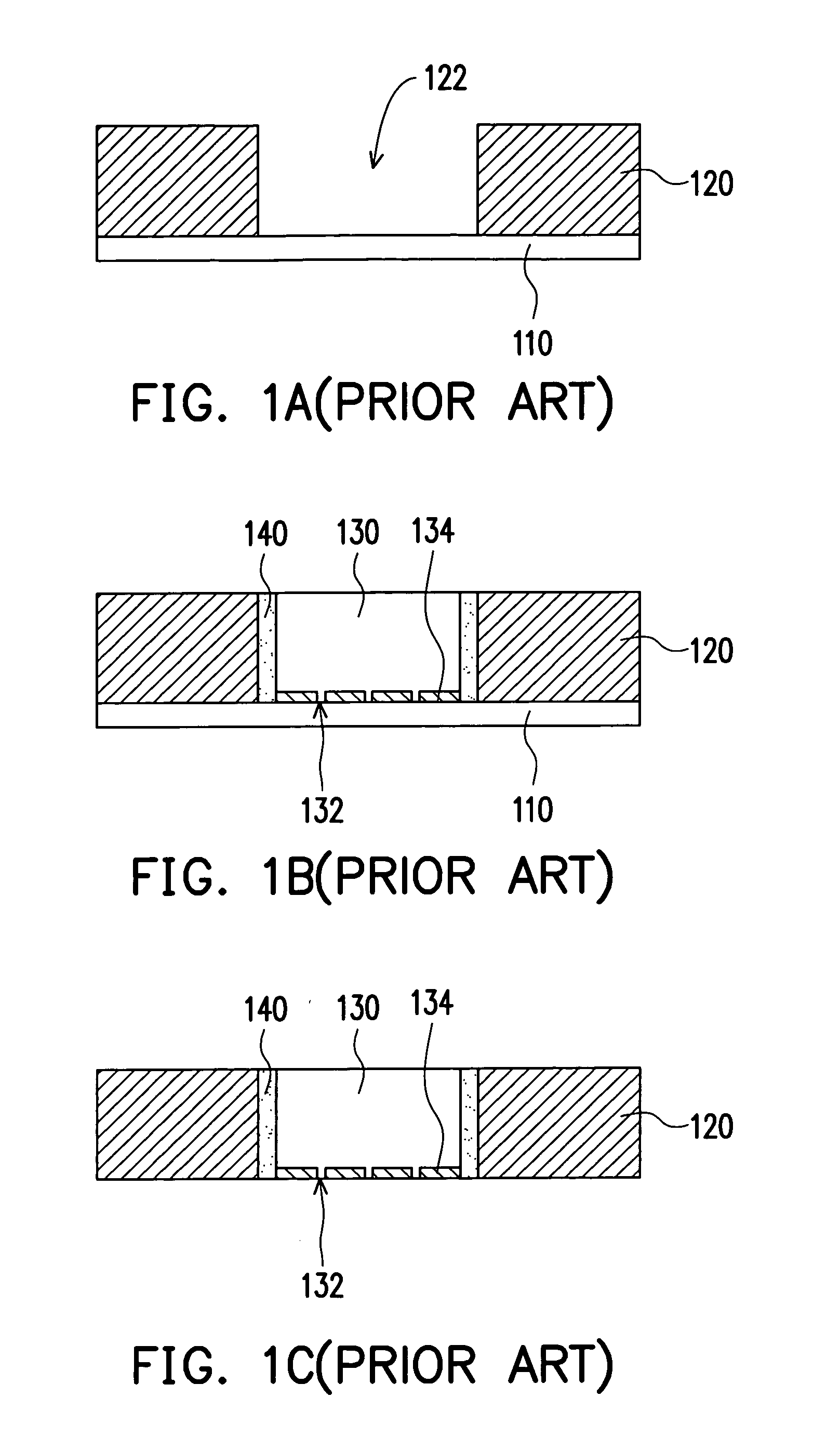

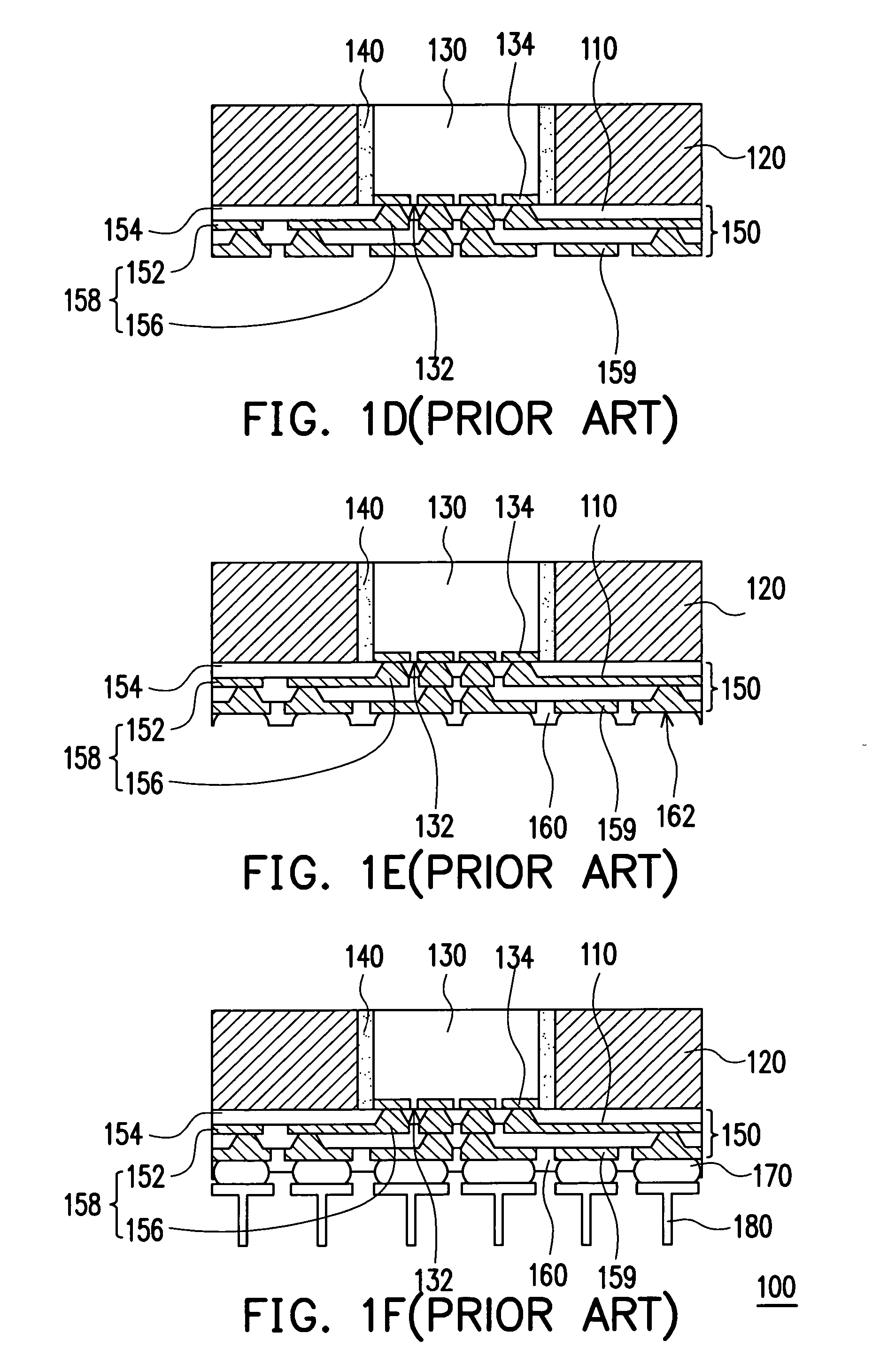

Structure of solder bumps with improved coplanarity and method of forming solder bumps with improved coplanarity

InactiveUS6415974B2Good coplanarityPrinted circuit assemblingSemiconductor/solid-state device detailsMetallurgyCurrent distribution

A structure of solder bumps with improved coplanarility, comprising a substrate, a passivation layer, a plurality of Under Ball Metallurgy (UBM) layers and a plurality of solder bumps. The substrate has at least an active surface, and a plurality of bonding pads are provided thereon. The UBM layers with various areas are electrically connected to the bonding pads. Finally, the solder bumps are formed with uniform-height on the UBM layers. A method of forming solder bumps with improved coplanarity. A UBM structure with various sizes of openings is provided to control the volume of the solder, wherein the various sizes of openings are corresponding to the current distribution across the wafer. The purpose of the various openings is to control the volume of the solder in order to form uniform-heights of solder bumps, the coplanarity of the solder bumps can thus be improved.

Owner:SILICONWARE PRECISION IND CO LTD

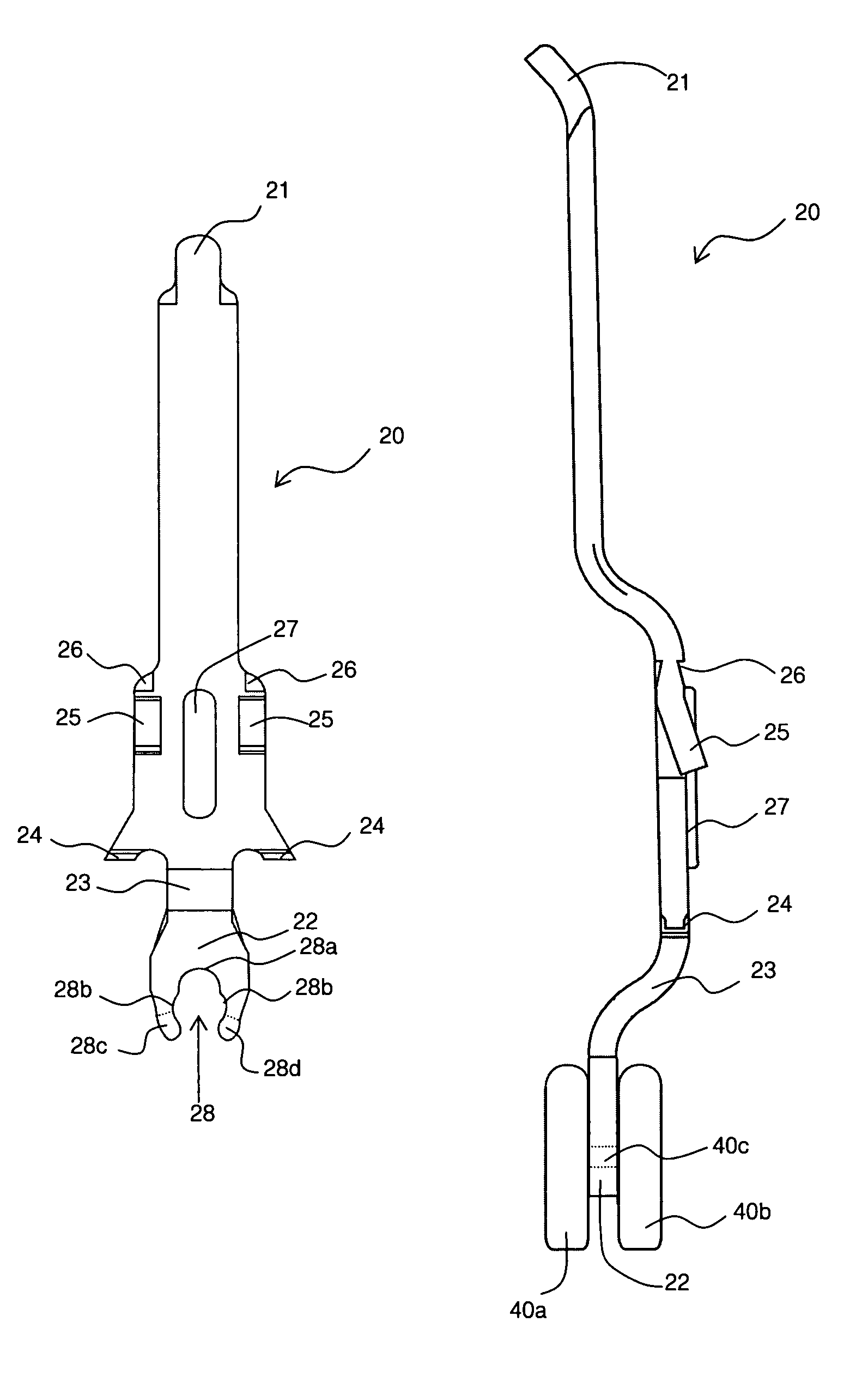

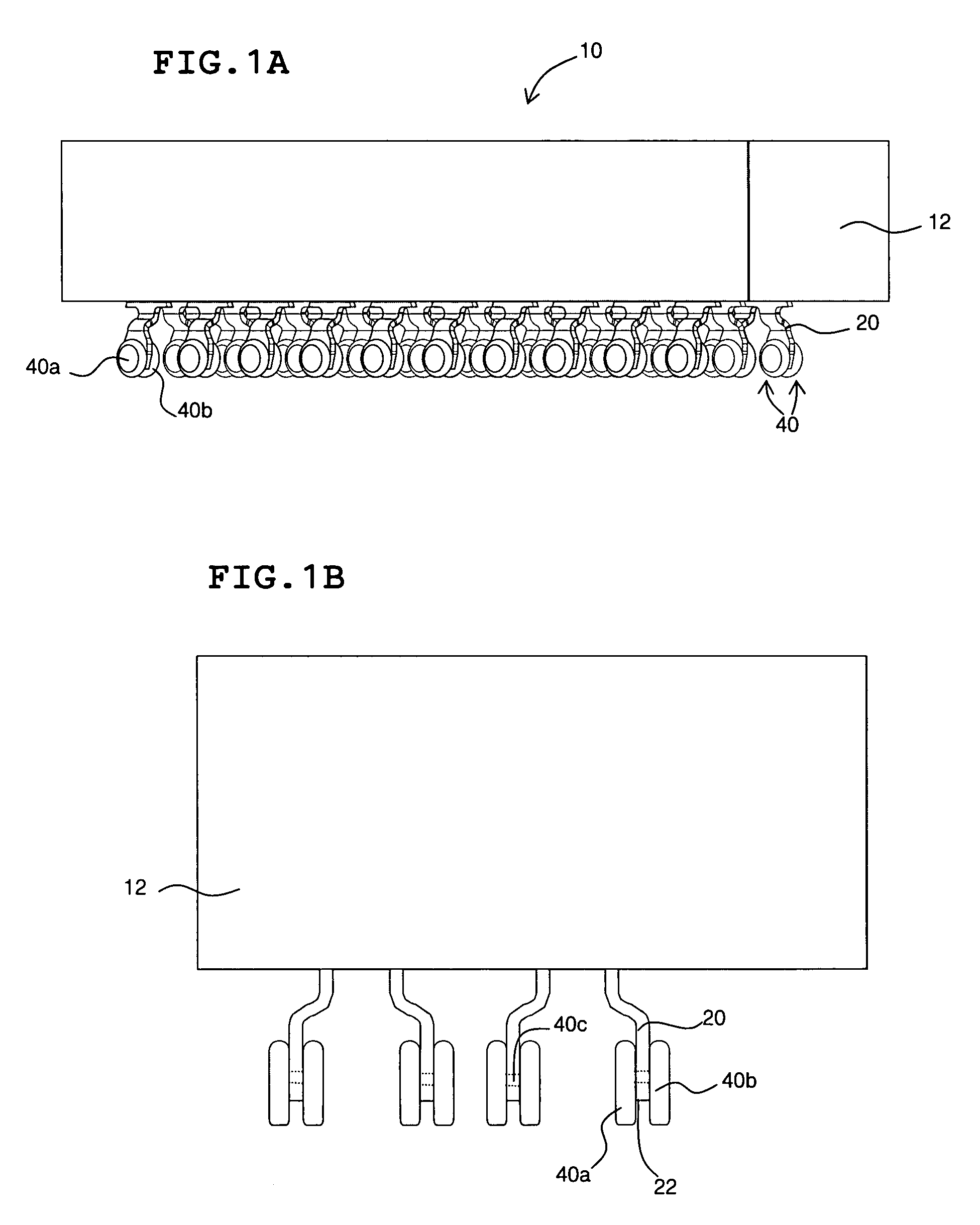

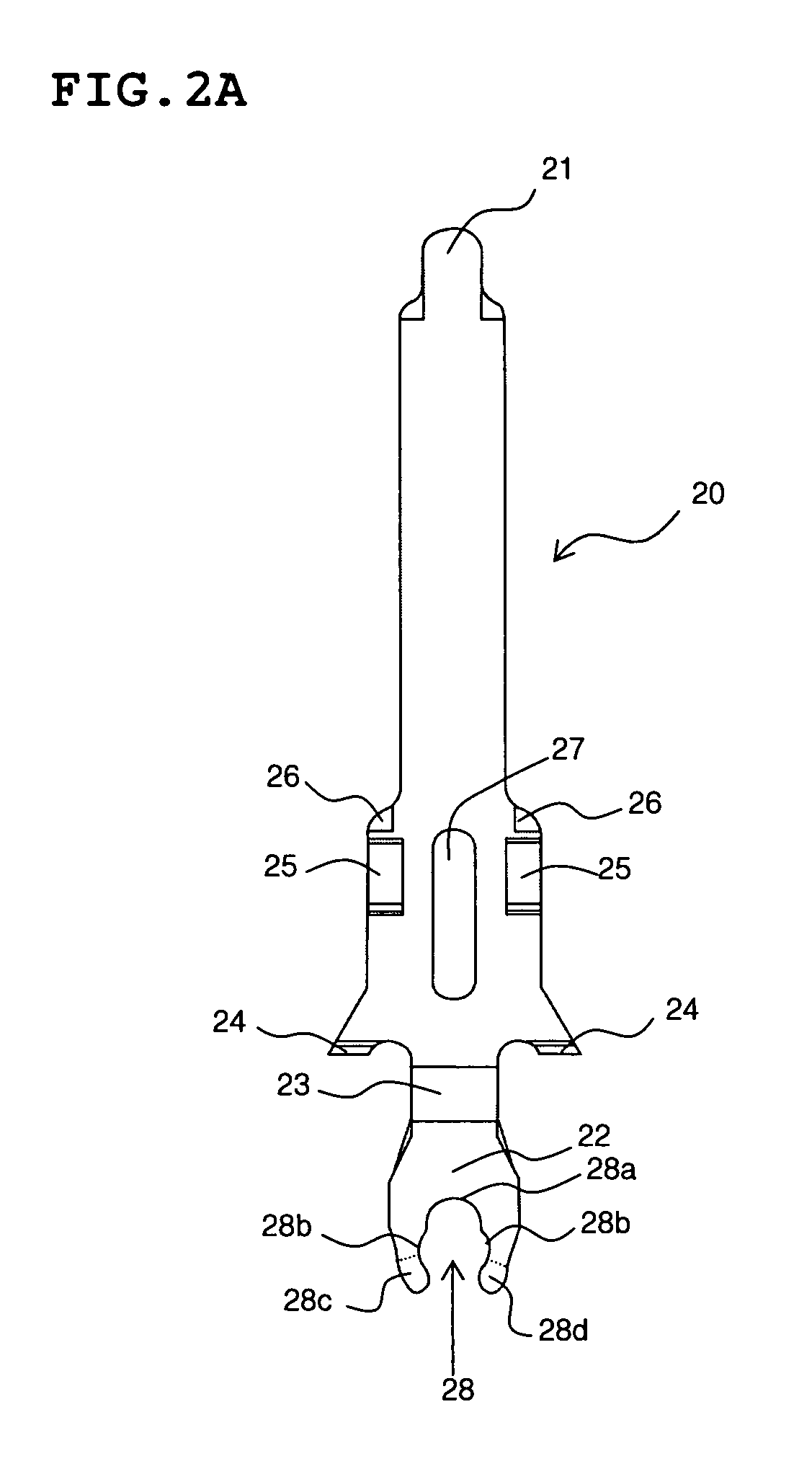

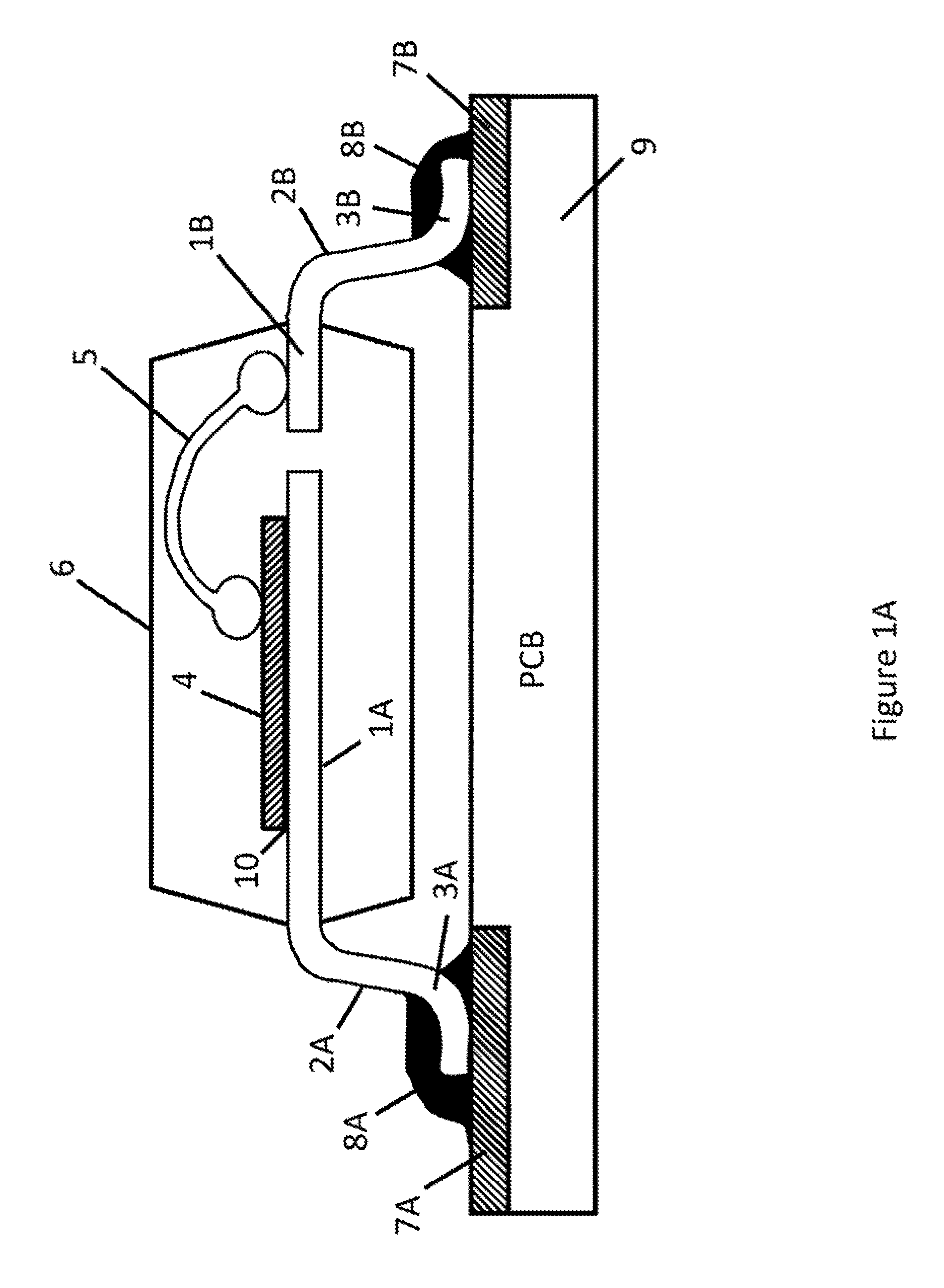

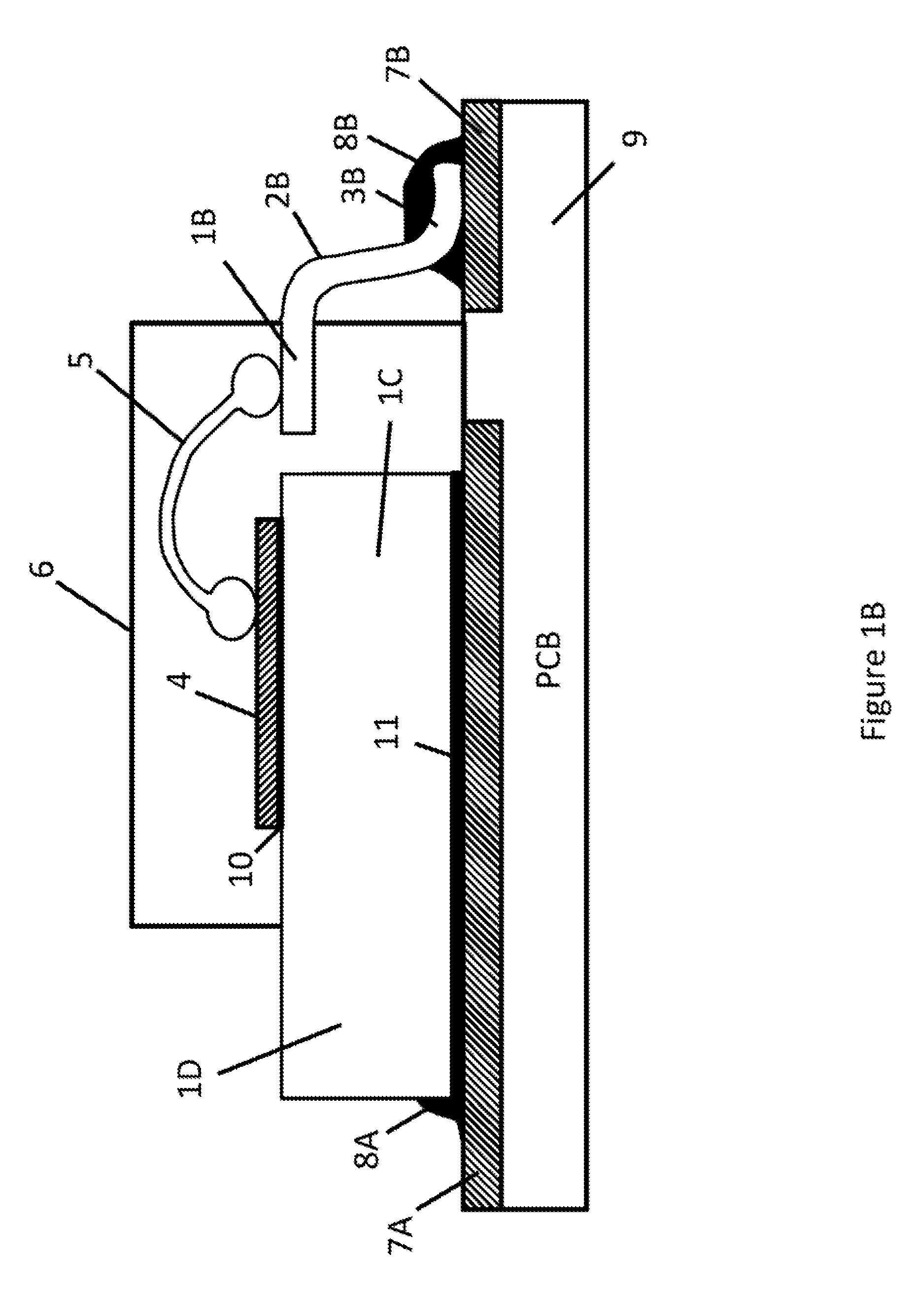

Electric contact and an electric connector both using resin solder and a method of connecting them to a printed circuit board

InactiveUS6717065B2Increase the cross-sectional areaGreat freedomTwo pole connectionsContact member assembly/disassemblyElectrical conductorEngineering

An electric contact using resin solder is connected to a printed circuit board, which has a conductor provided on a surface thereof. This electric contact comprises a leg, which contacts the conductor of the printed circuit board, and a connecting part, which is connected to the conductor of the counterpart member. At least a part of the leg, which contacts the conductor of the printed circuit board, is made of a lead-free ultrahigh-conductive plastic being a conductive resin composite. An electric connector includes the electric contact and an insulating housing, which holds the electric contact so that the part of the leg, which contacts the conductor of the printed circuit board, is exposed.

Owner:JST MFG CO LTD

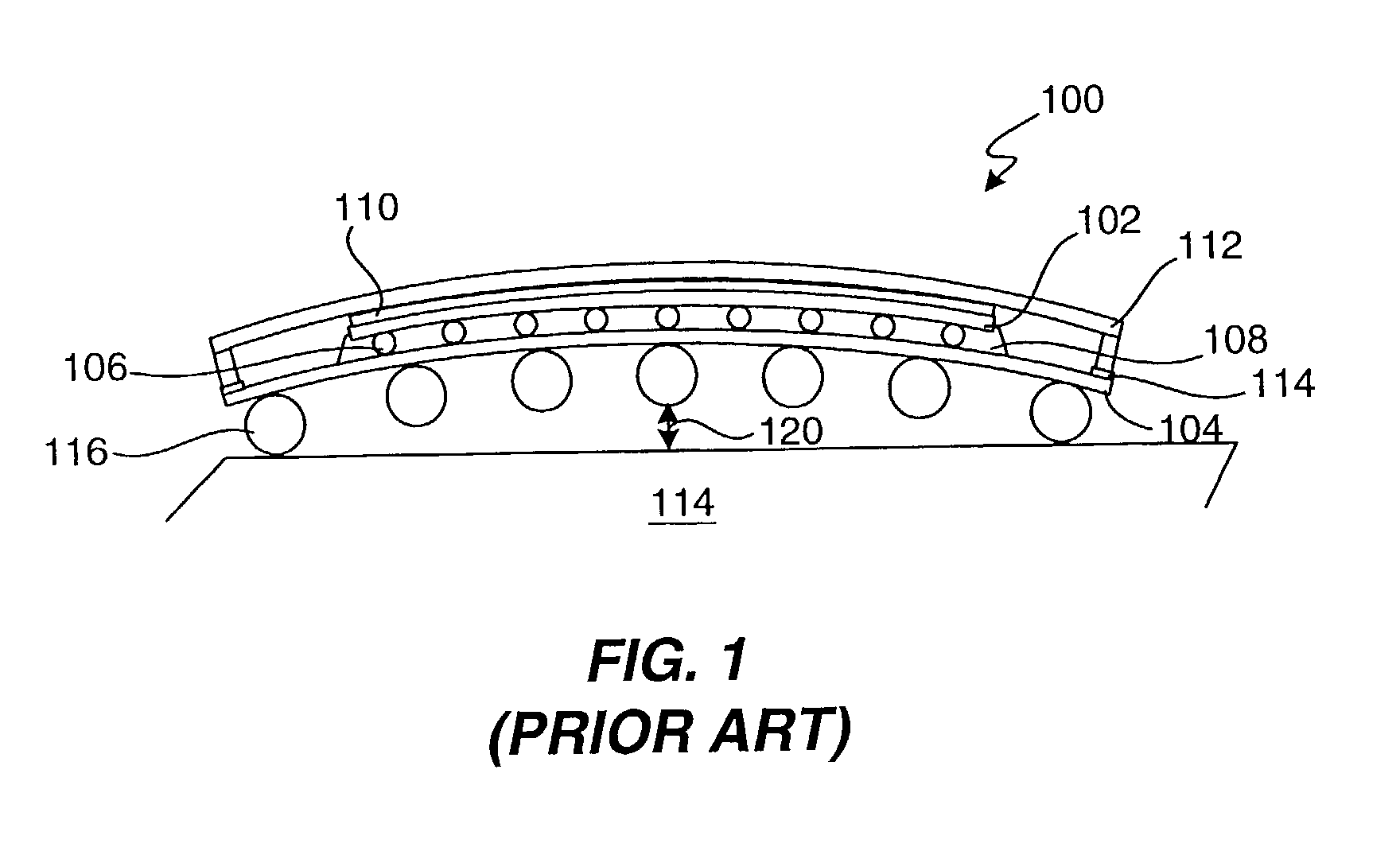

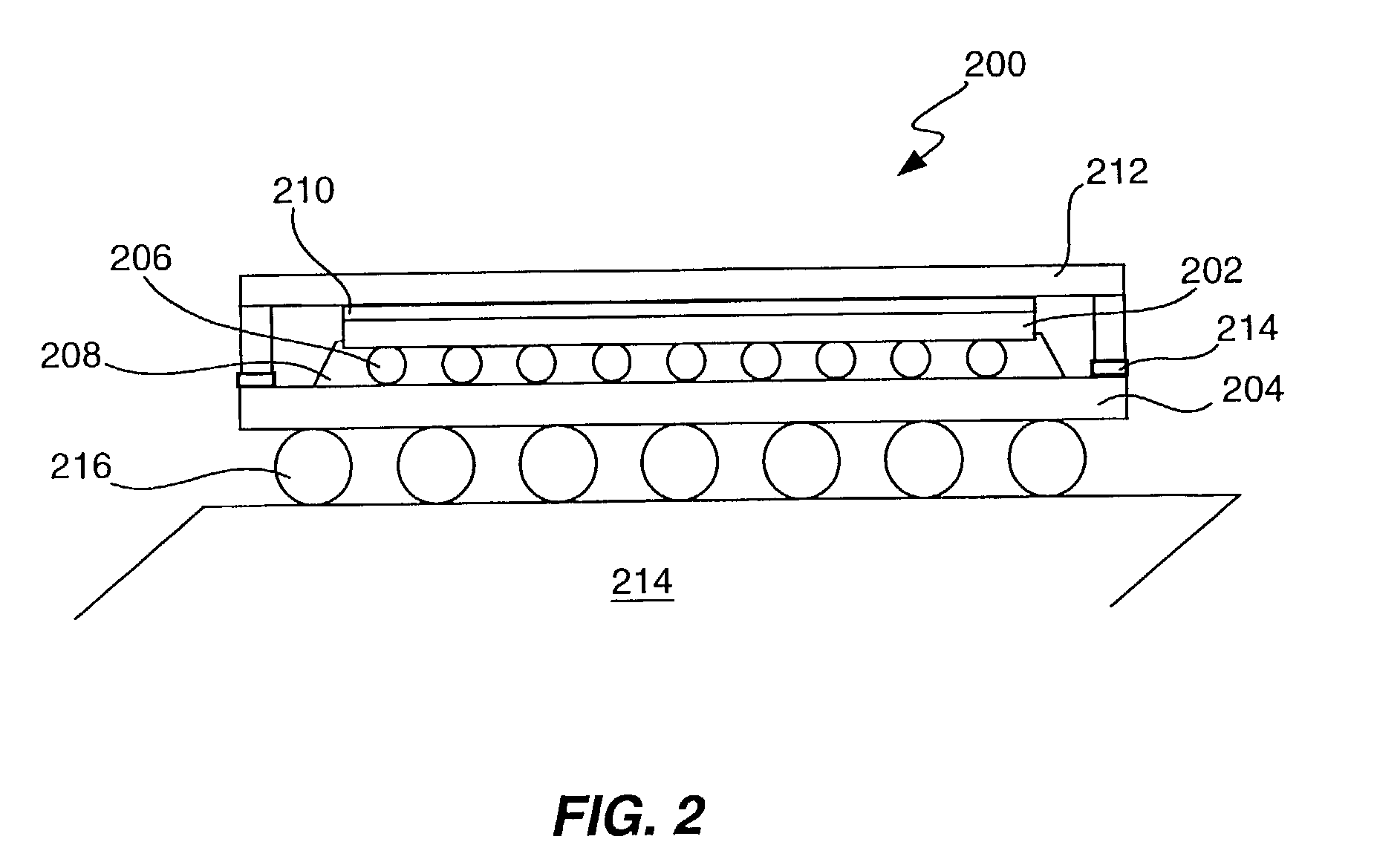

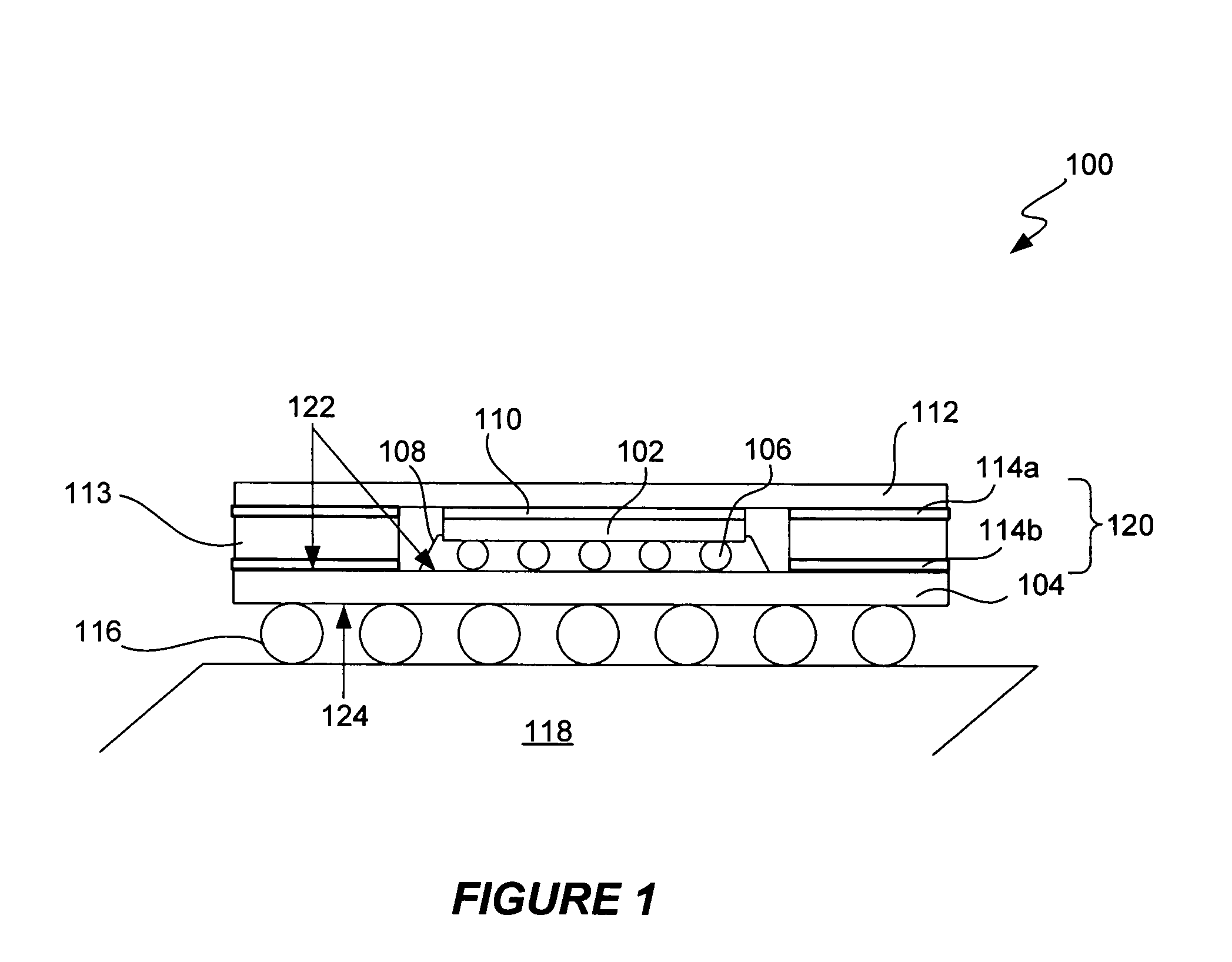

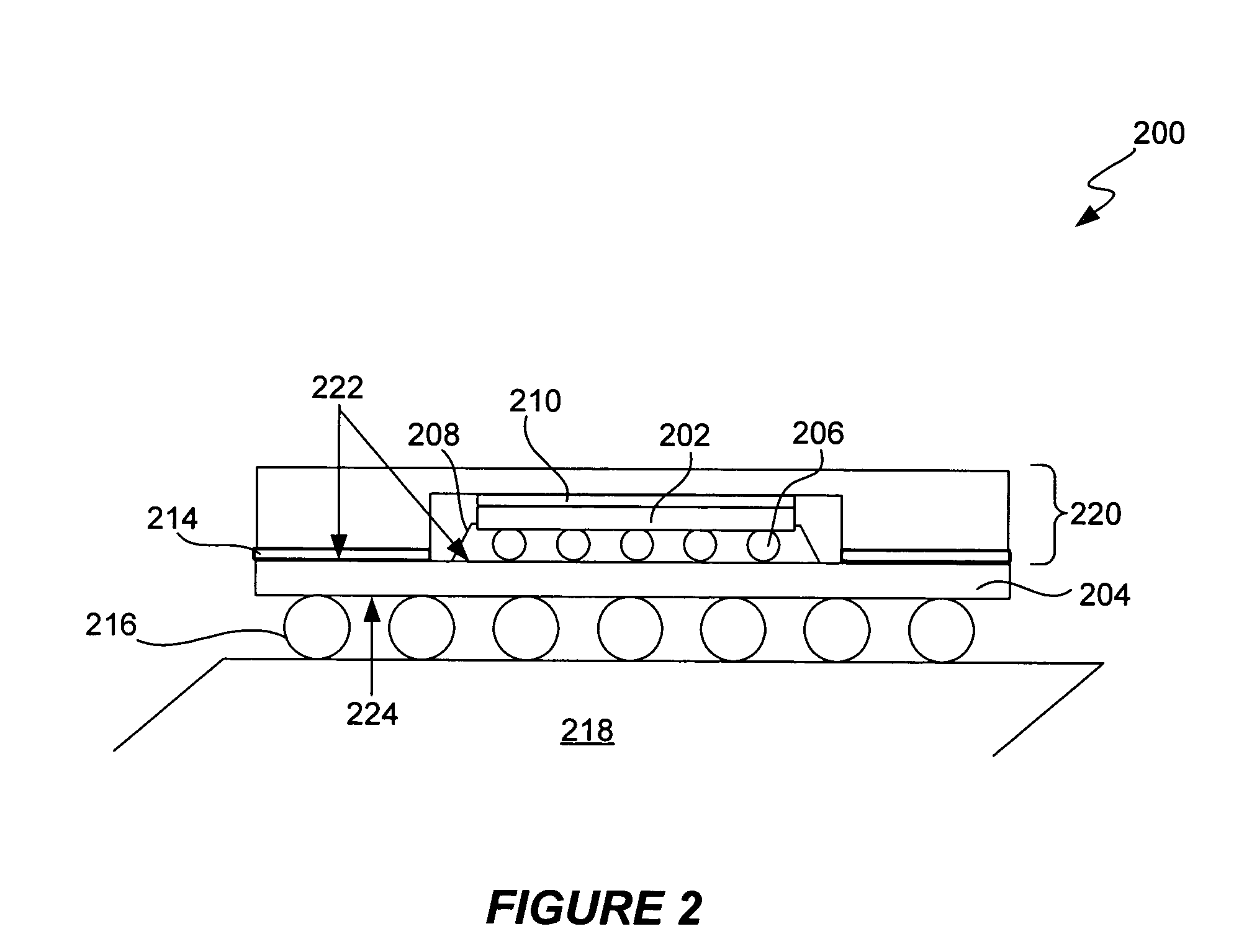

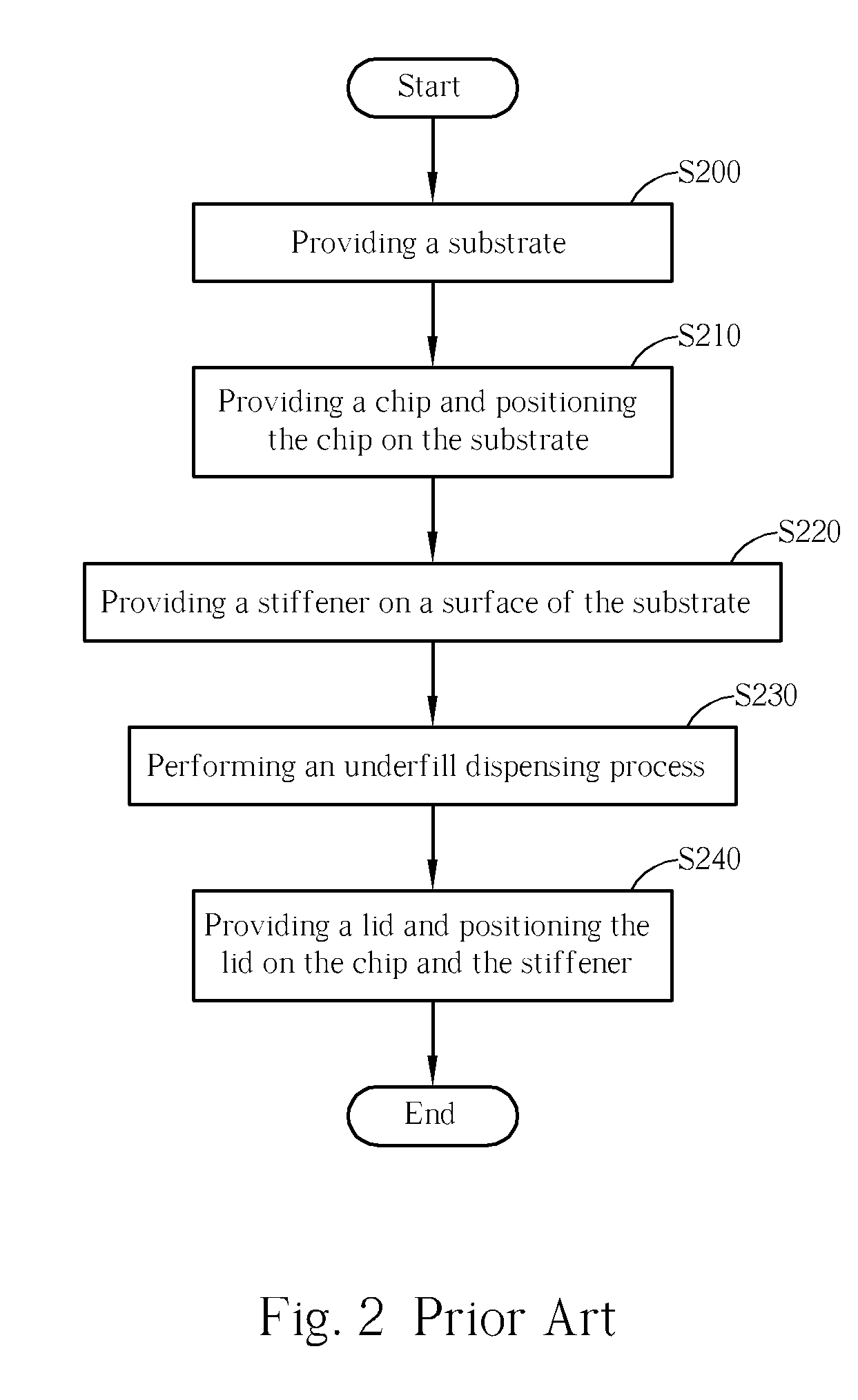

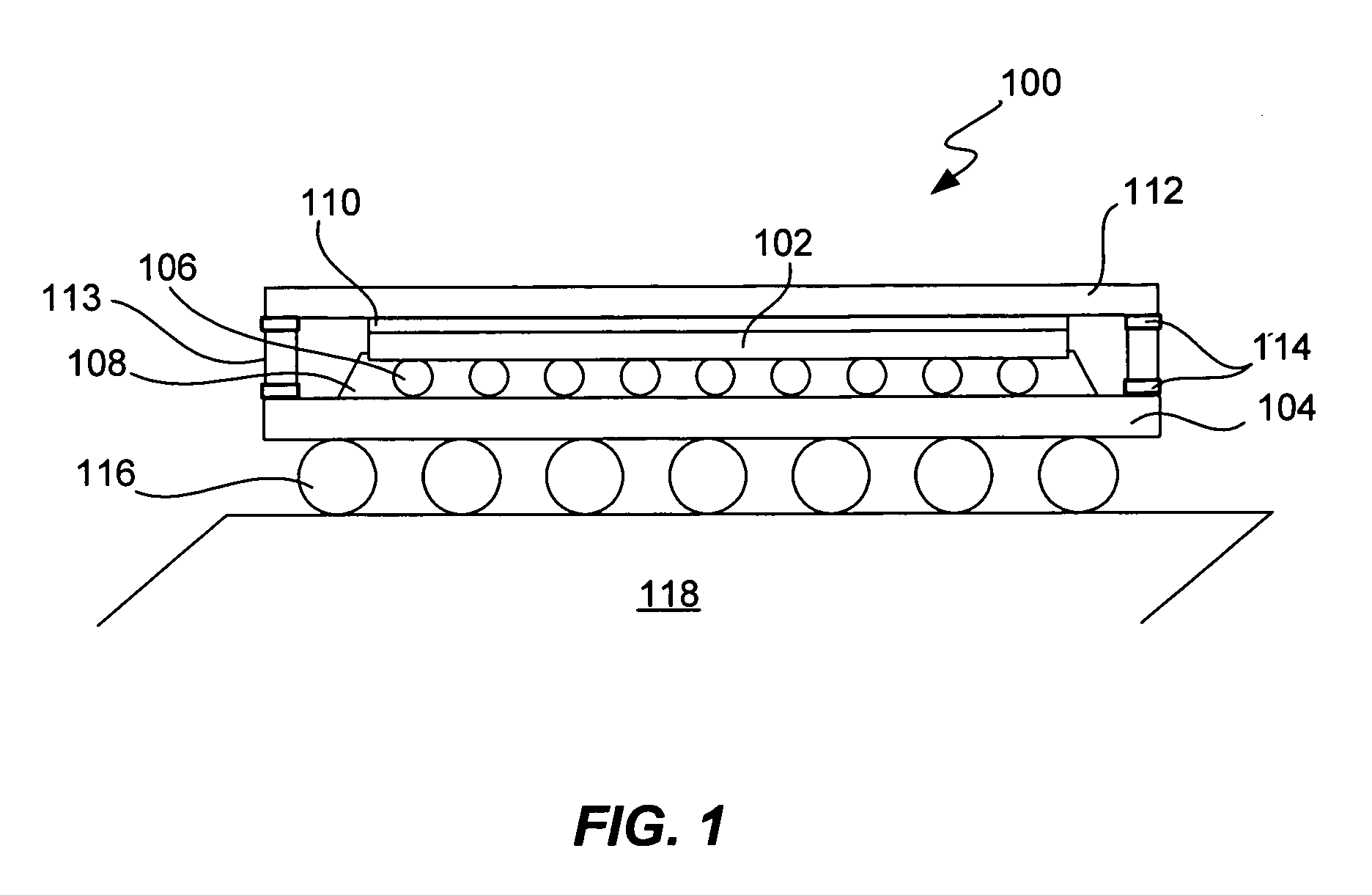

Flip chip package with warpage control

ActiveUS6949404B1Less bowEnhance reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringHeat spreader

Provided are a semiconductor flip chip package with warpage control and fabrication methods for such packages. The packages of the present invention include heat spreader lids that are rigidly attached to the die or packaging substrate with a bond that can withstand the considerable bowing pressures caused by the CTE mismatch between the die and substrate. The result is a package with less bowing and so improved co-planarity (in compliance with industry specifications) with the PCB board to which it is ultimately bound. Package reliability is thereby also enhanced, particularly for large die sizes.

Owner:ALTERA CORP

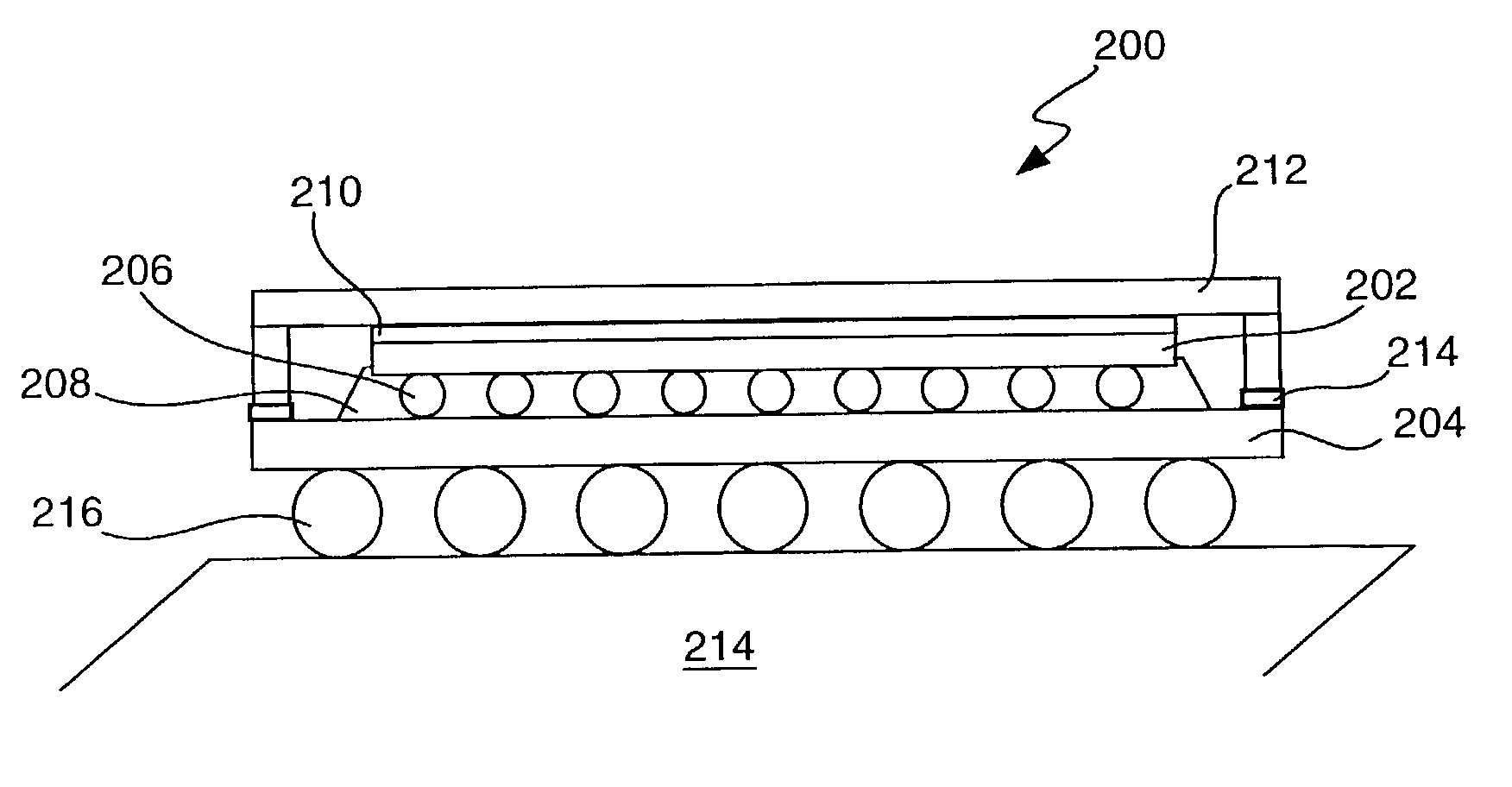

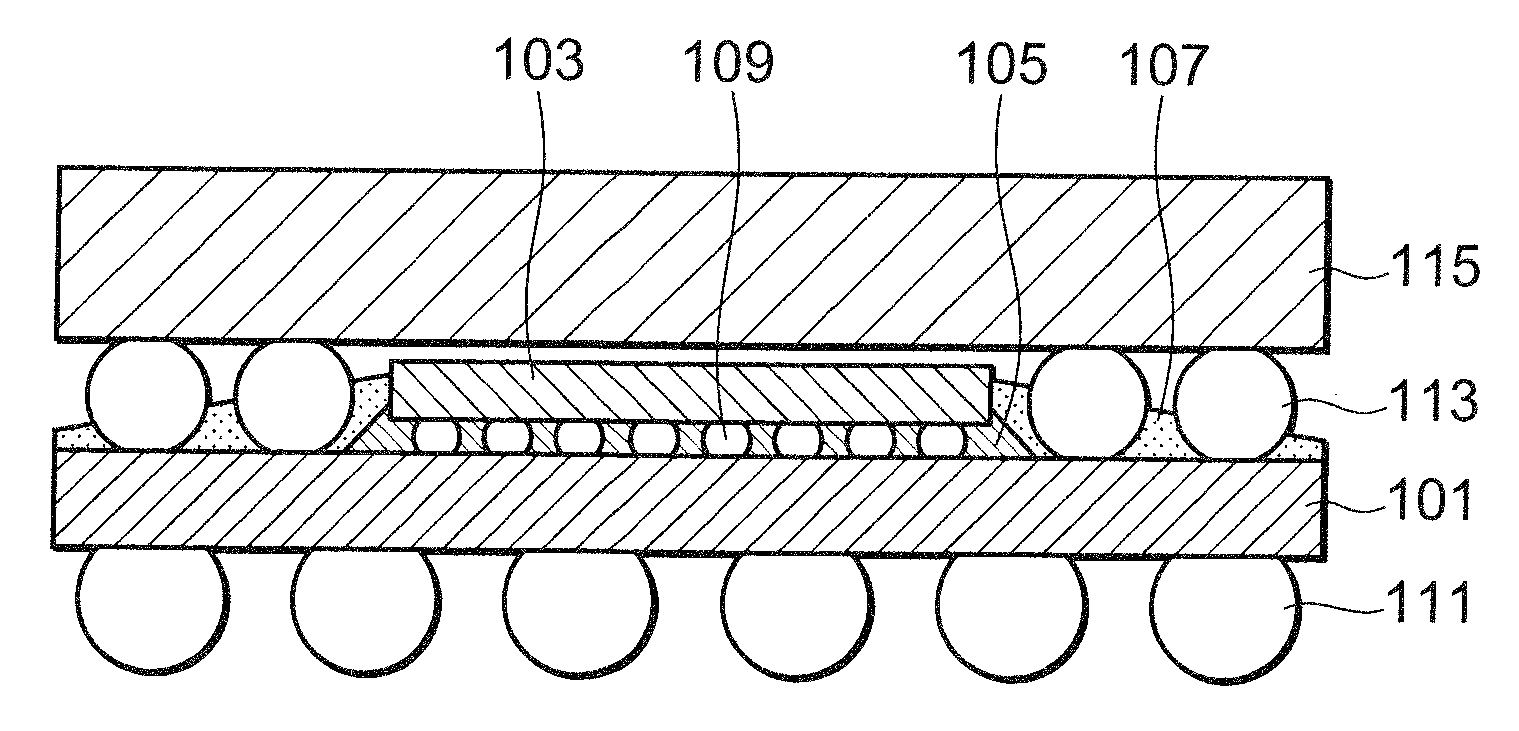

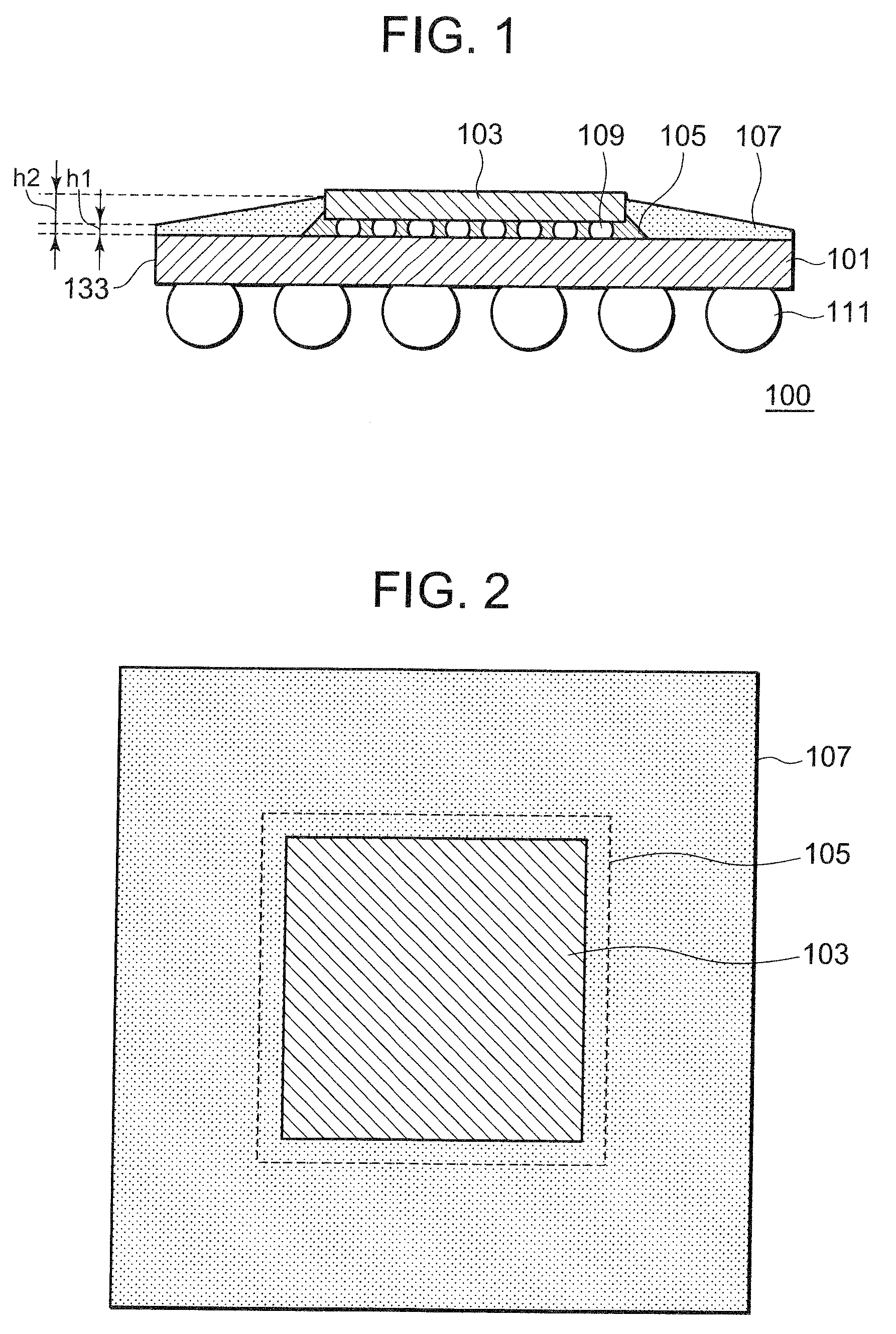

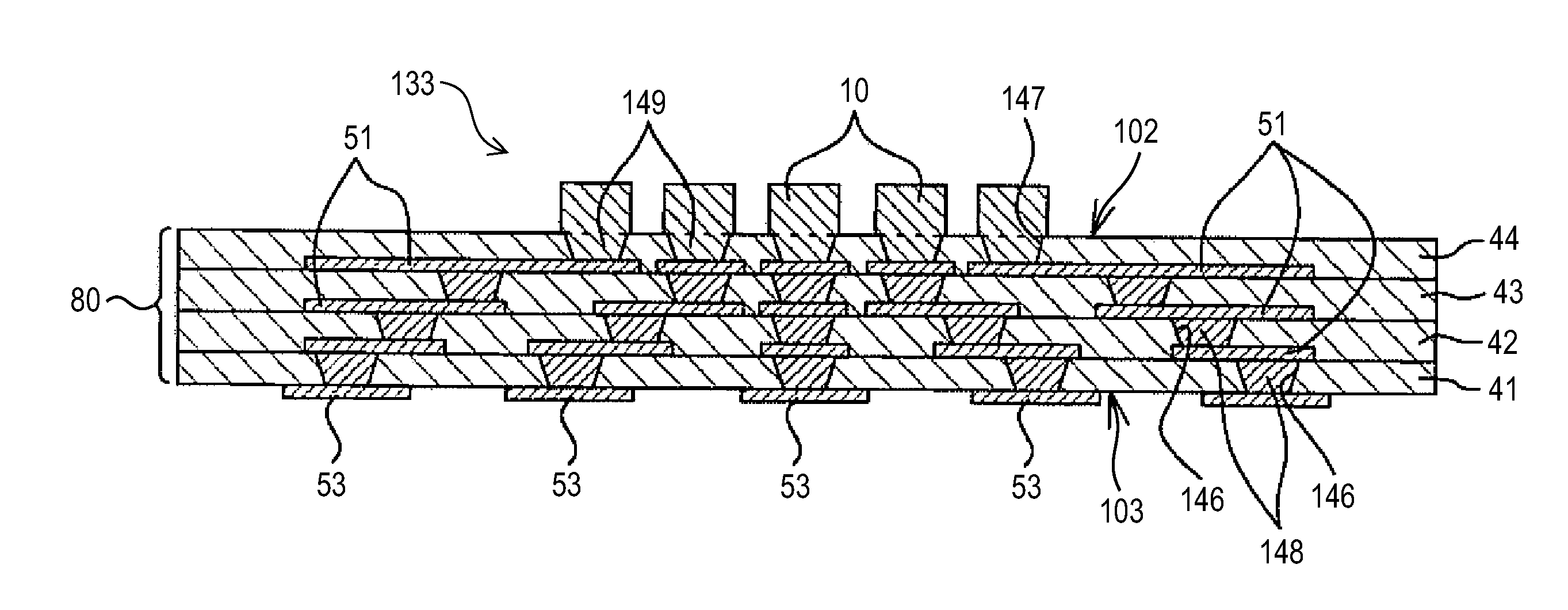

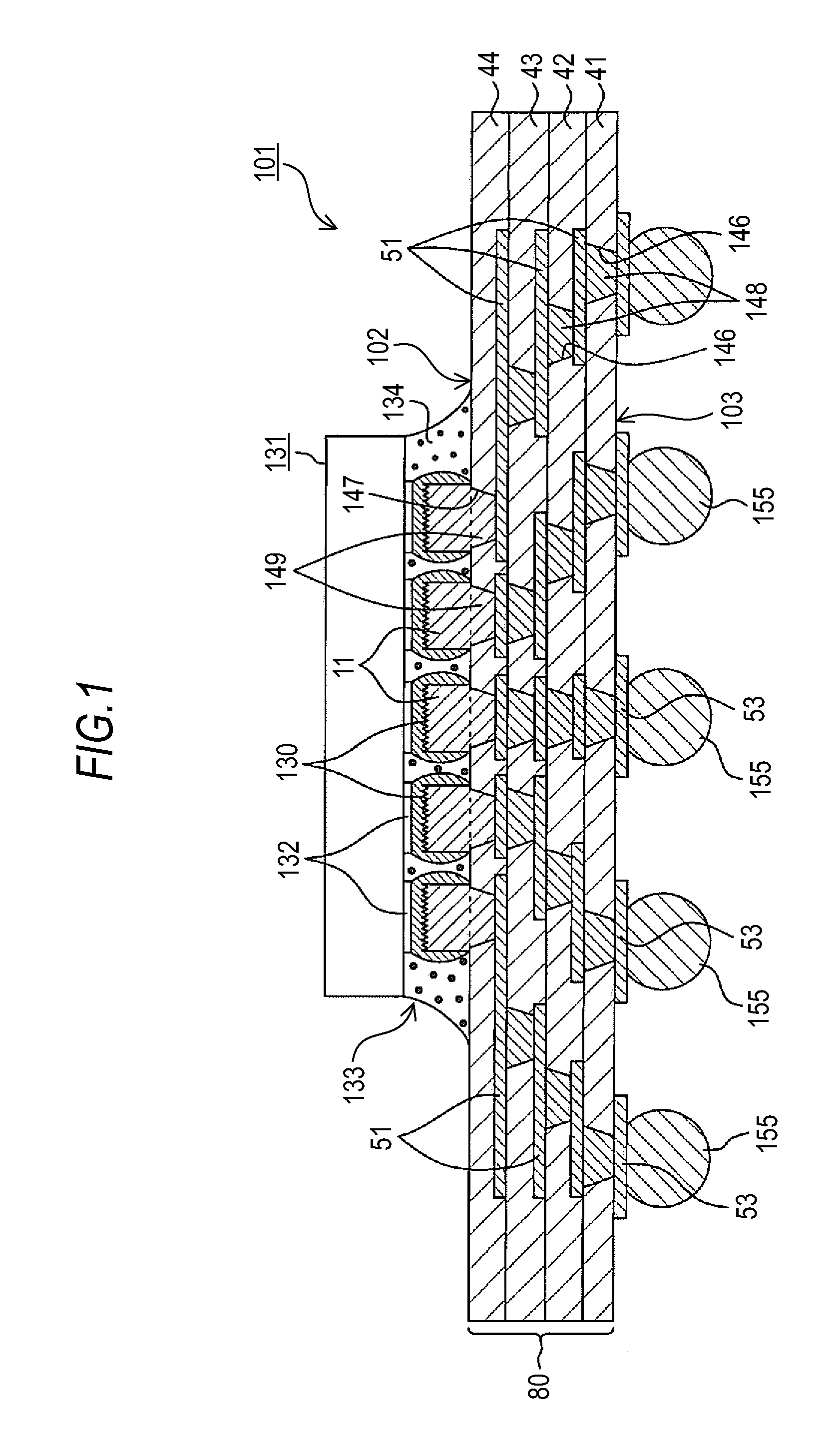

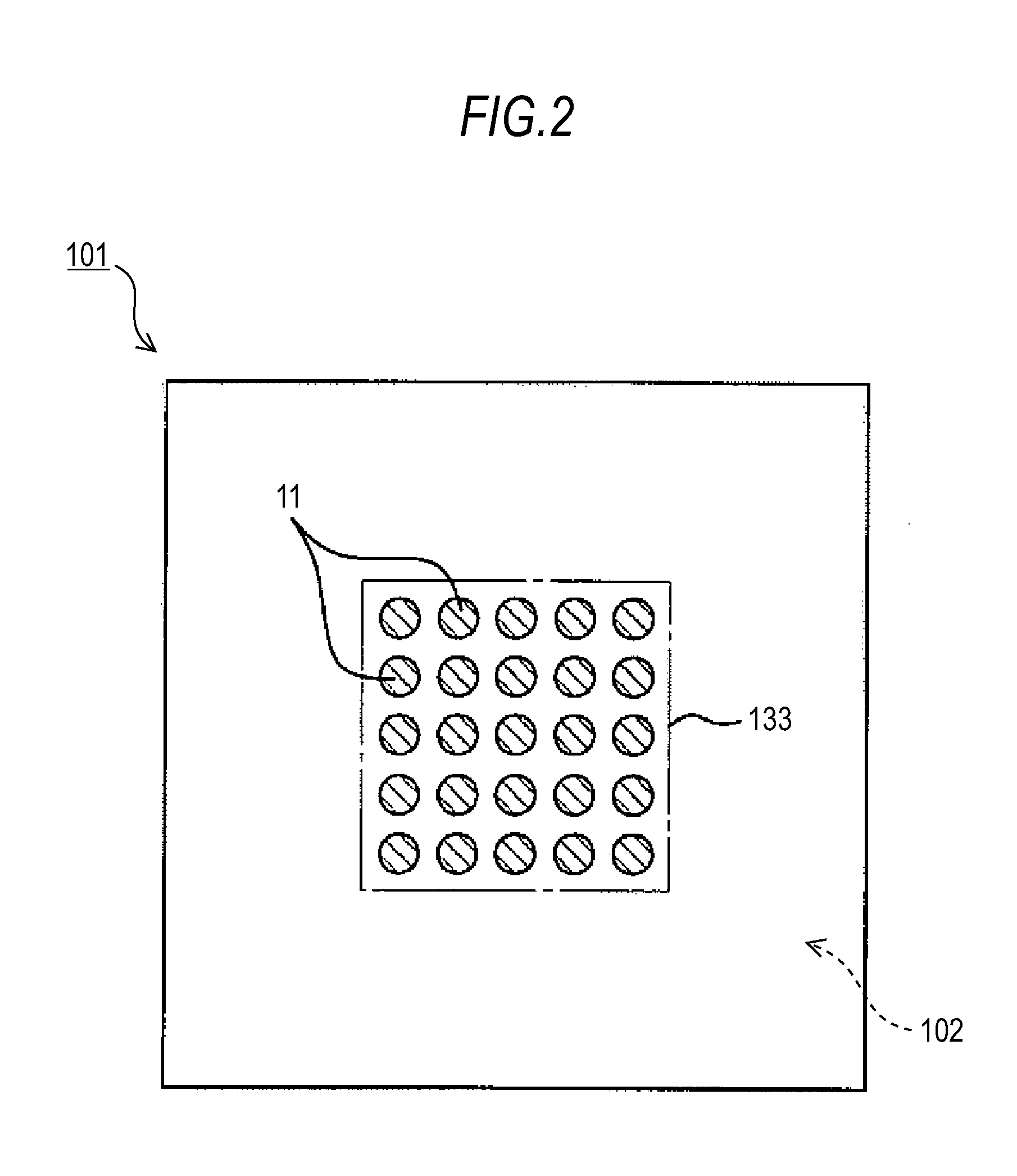

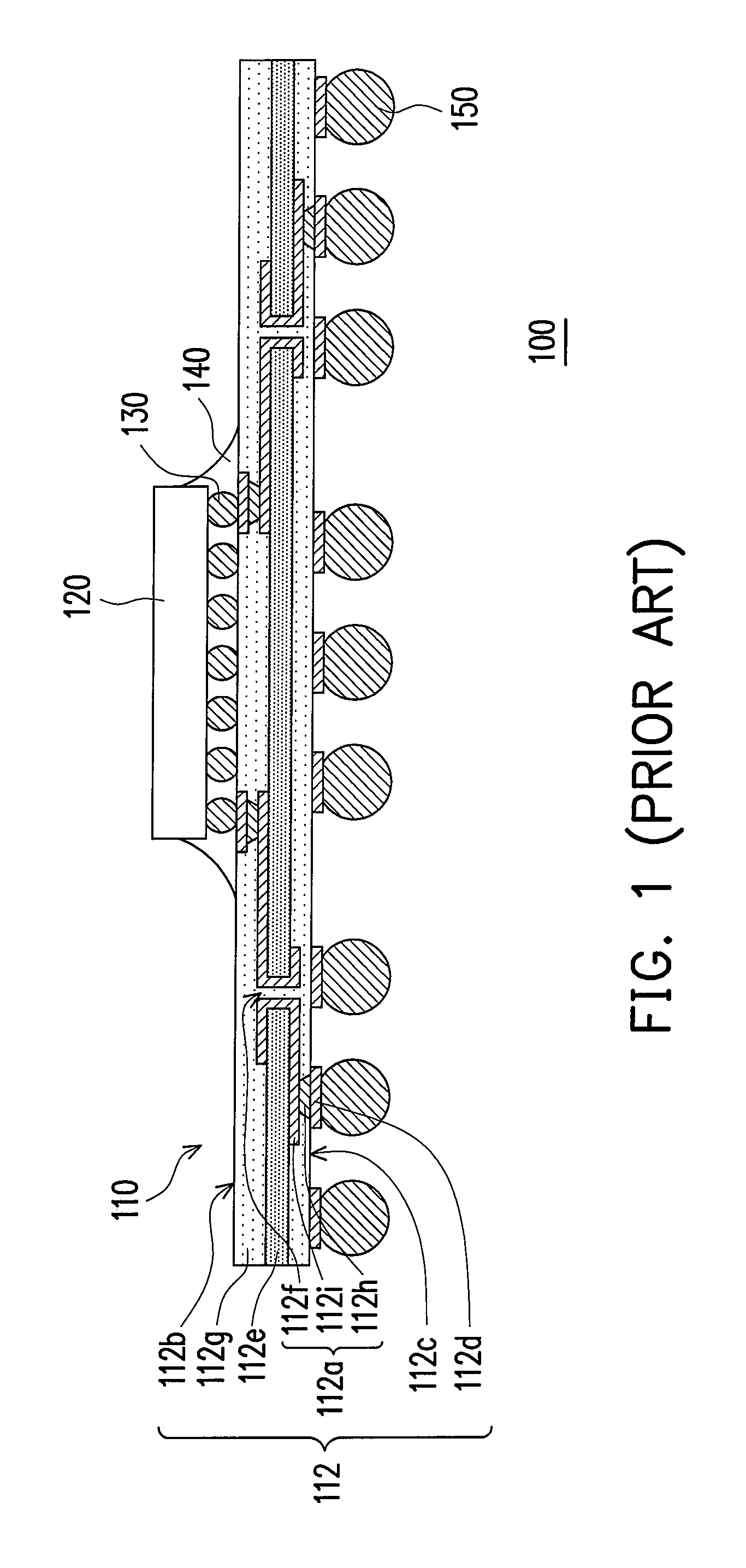

Semiconductor device including wiring substrate having element mounting surface coated by resin layer

InactiveUS20080251913A1Thin structureSuppression of decline in manufacturing yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor device

In one embodiment of the present invention, there is provided a semiconductor device including a first semiconductor element mounted, through flip-chip bonding, on the element mounting surface of a first wiring substrate, and a resin layer that coats substantially the entire element mounting surface of the first wiring substrate. The first semiconductor element has two opposite surfaces. One surface faces the element mounting surface of the first wiring substrate, and the other surface is not coated by the resin layer.

Owner:NEC ELECTRONICS CORP

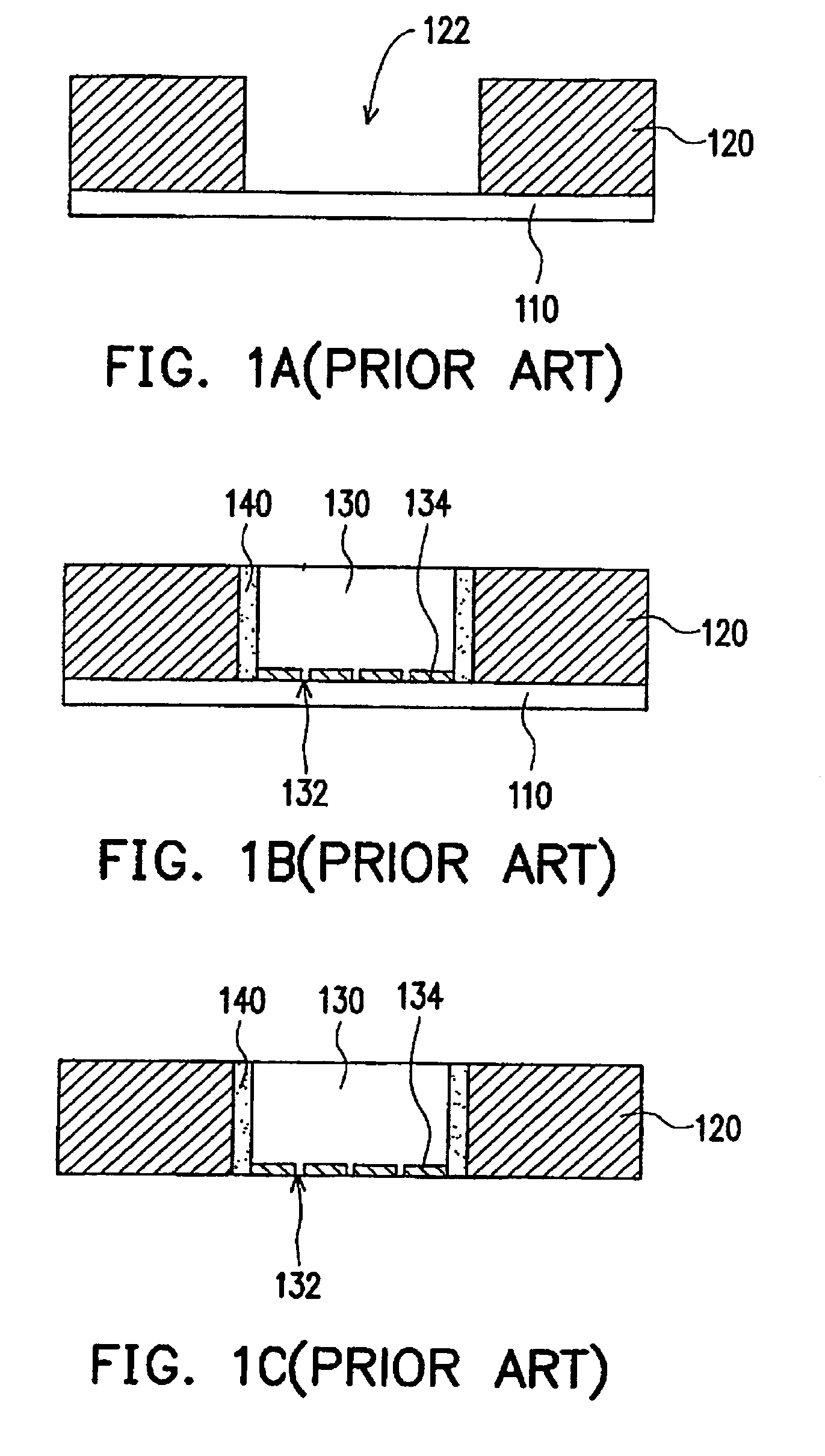

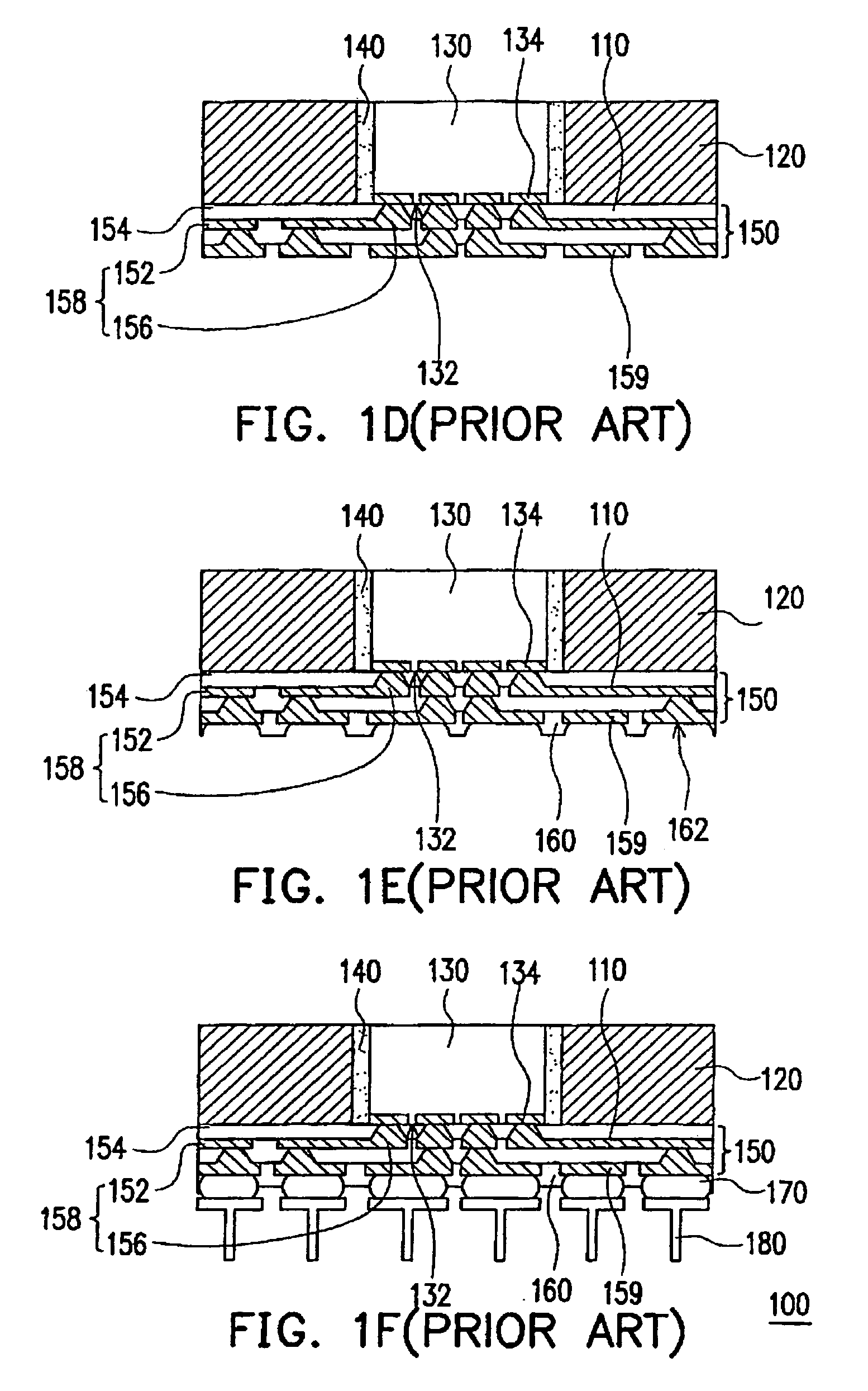

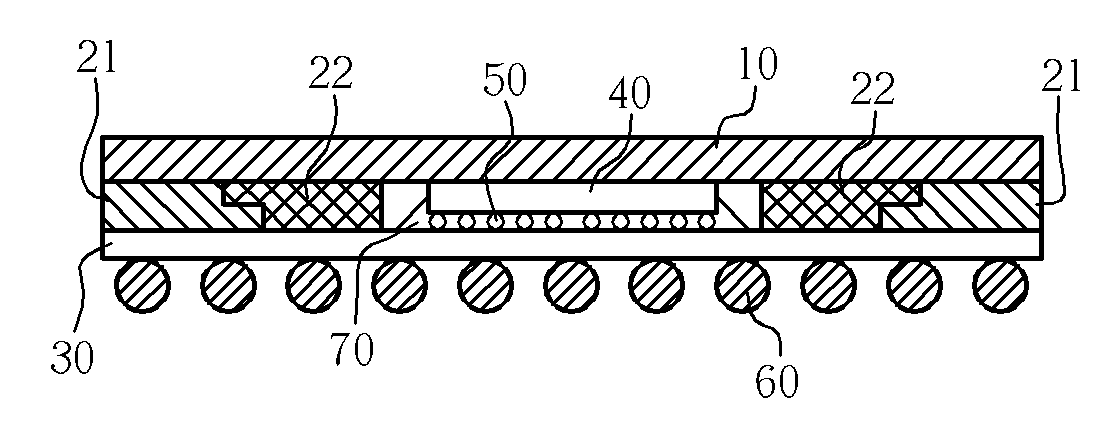

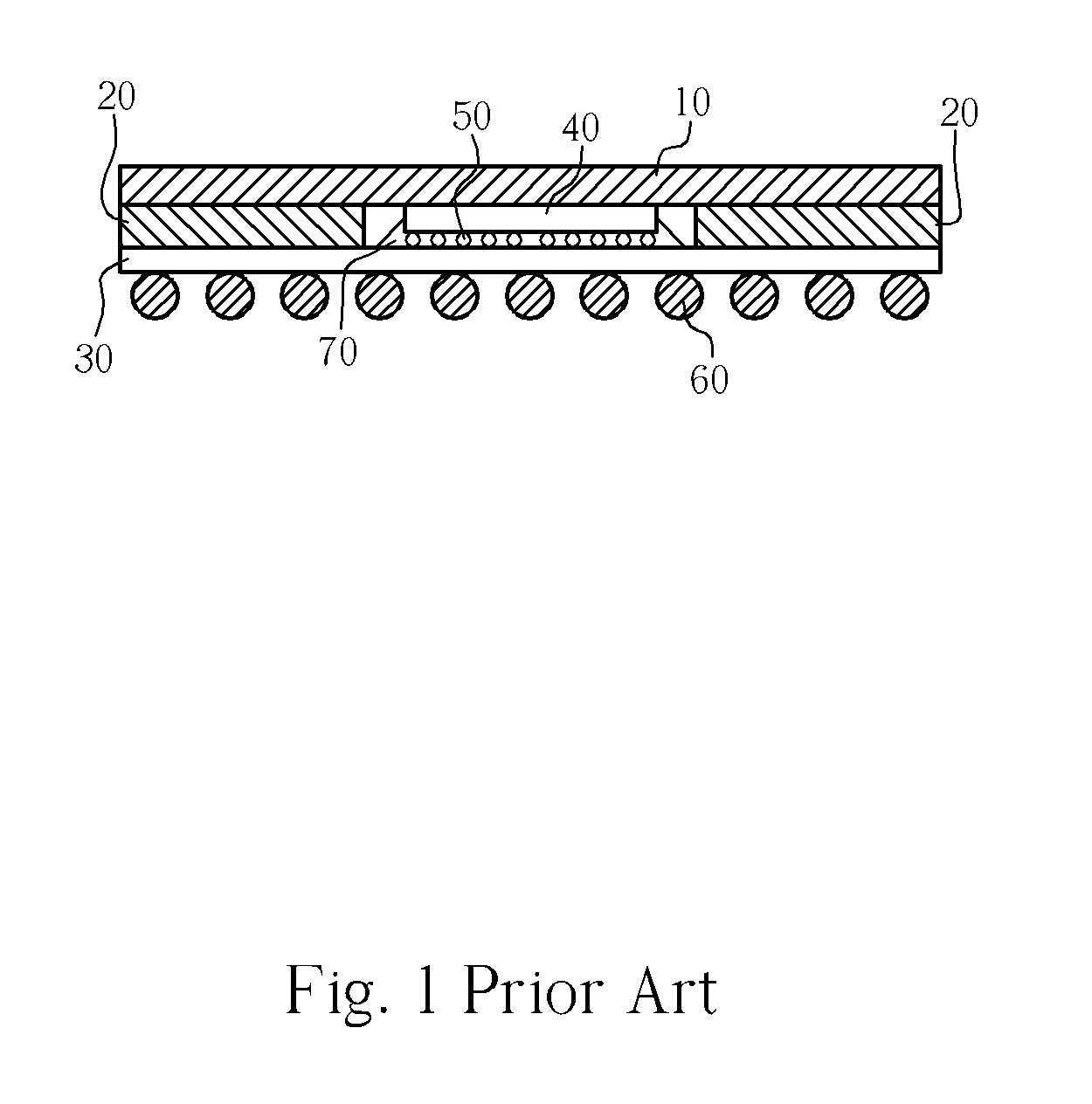

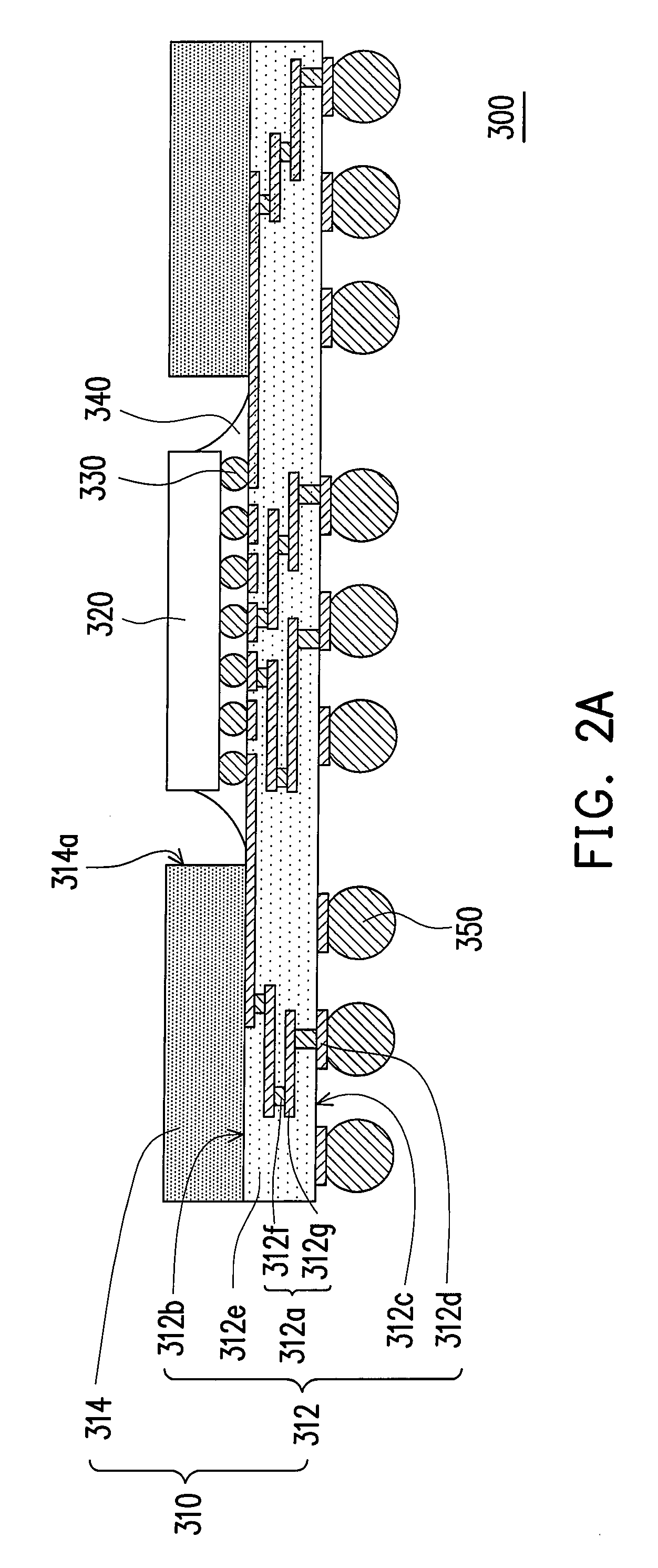

Chip embedded package structure

ActiveUS20050253244A1Processing time be shortenIncrease positioning accuracySemiconductor/solid-state device detailsSolid-state devicesElectrically conductiveElectrical and Electronics engineering

A chip embedded package structure is provided. A stiffener is disposed on a tape. The tape has at least an alignment mark and the stiffener has at least a chip opening. A chip having a plurality of bonding pads thereon is disposed on the tape within the chip opening such that the bonding pads face the tape. A plurality of through holes is formed in the tape to expose the bonding pads respectively. After that, an electrically conductive material is deposited to fill the through holes and form a plurality of conductive vias that connects with the bonding pads respectively. A multi-layered interconnection structure is formed on the surface of the tape away from the chip. The multi-layered interconnection structure has an inner circuit that connects to the conductive vias. The inner circuit has a plurality of metallic pads disposed on the outer surface of the multi-layered interconnection structure.

Owner:VIA TECH INC

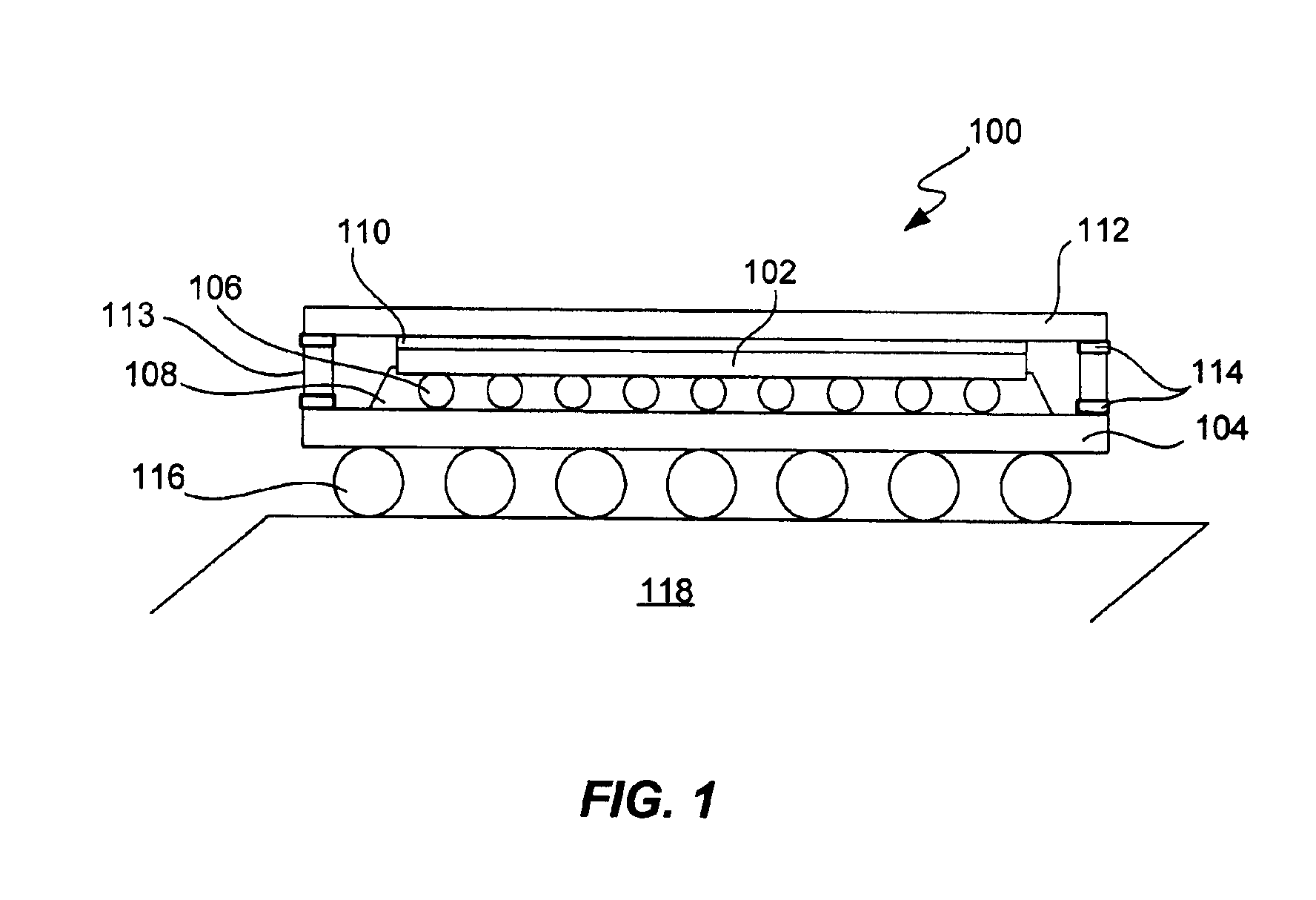

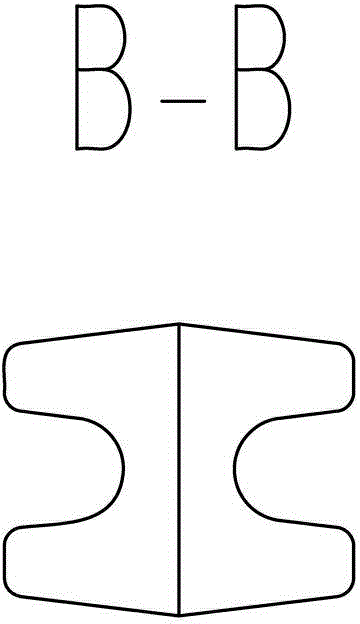

Stiffener for flip chip BGA package

ActiveUS7459782B1Improve package reliabilityLess bowingSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

Provided are semiconductor die flip chip packages with warpage control and fabrication methods for such packages. A package includes a heat spreader that is attached to a die and a stiffener, which are in turn attached to a package substrate. In general, the stiffener is made of a material that has a relatively low CTE value. For example, the stiffener material may have a CTE value less than 12 ppm / ° C. The material may also have a relatively low mass density value of less than 8.9 g / cm3. Such a material may include natural graphite or some composite form of it. The result is a package with less bowing and so improved co-planarity (e.g., in compliance with industry specifications) with the surface to which it is ultimately bound; thereby, improving the reliability of the package. Moreover, a package that is relatively lighter and more robust than conventional semiconductor die flip chip packages can be realized.

Owner:ALTERA CORP

Method for forming a raised source and drain without using selective epitaxial growth

InactiveUS6090691AEasily controllable depthGood coplanaritySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

A method for forming a raised source and drain structure without using selective epitaxial silicon growth. A semiconductor substrate is provided having one or more gate areas covered by dielectric structures. Doped polysilicon structures are adjacent to the dielectric structures on each side and are co-planar with the dielectric structures from a CMP process. The first dielectric structures are removed to form gate openings and a liner oxide layer is formed on the bottom and sidewalls of the gate openings. Dielectric spacers are formed on the liner oxide layer over the sidewalls of the gate openings, and the liner oxide layer is removed from the bottom of the gate openings and from over the doped polysilicon structures. Source and drain regions are formed in the semiconductor substrate by diffusing impurity ions from the doped polysilicon layer. A gate oxide layer and a gate polysilicon layer are formed over the semiconductor structure and the gate polysilicon layer is planarized to form a gate electrode. In a key step, the dielectric spacers are removed to form spacer openings, and impurity ions are implanted through the spacer openings and annealed to form source and drain extensions. The dielectric spacers are reformed and a self-aligned silicide layer is formed on the doped polysilicon structure and the gate electrode. Alternatively, the self-aligned silicide layer can be formed prior to removing the dielectric spacers and implanting ions to form source and drain extensions.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

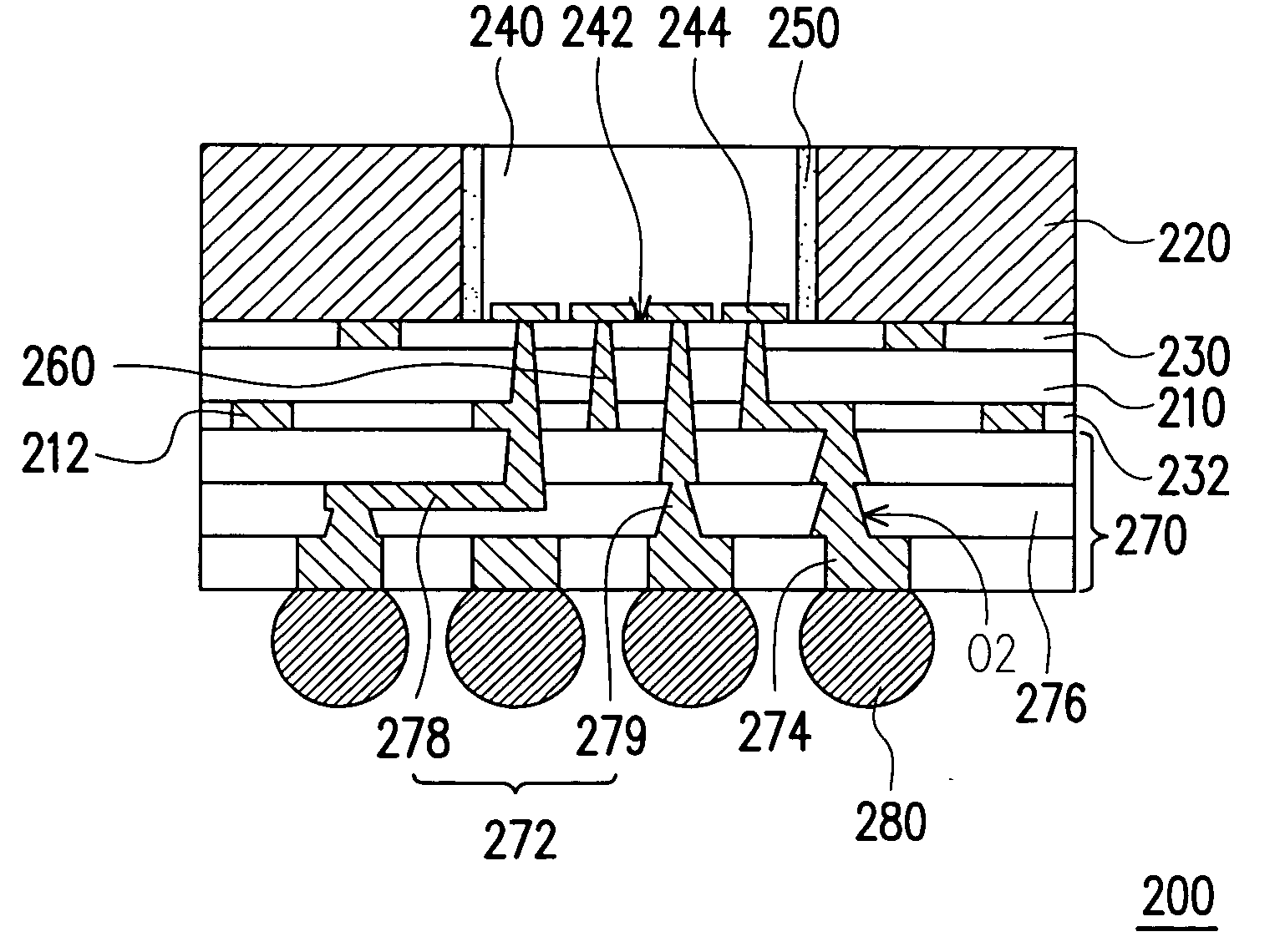

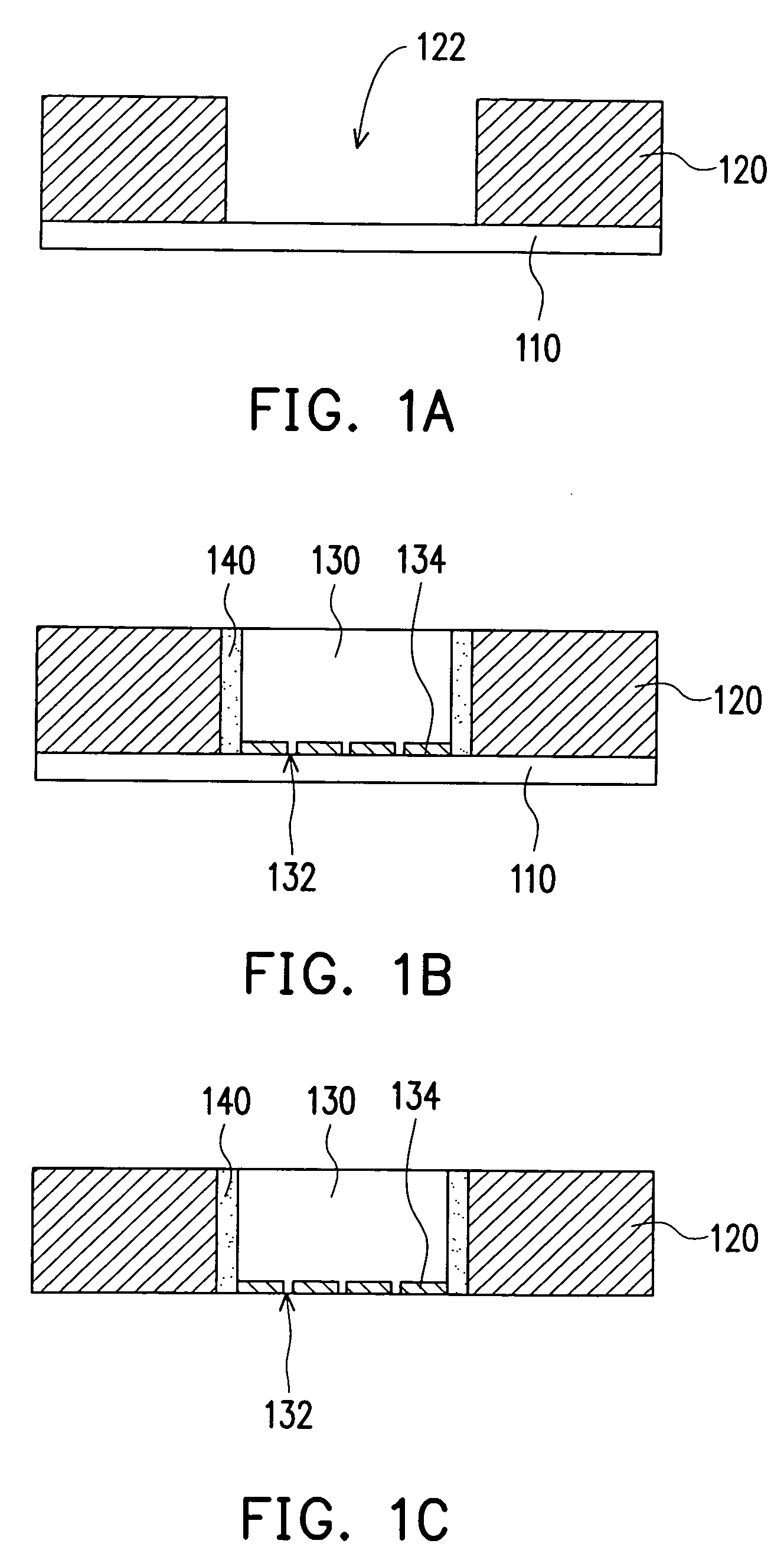

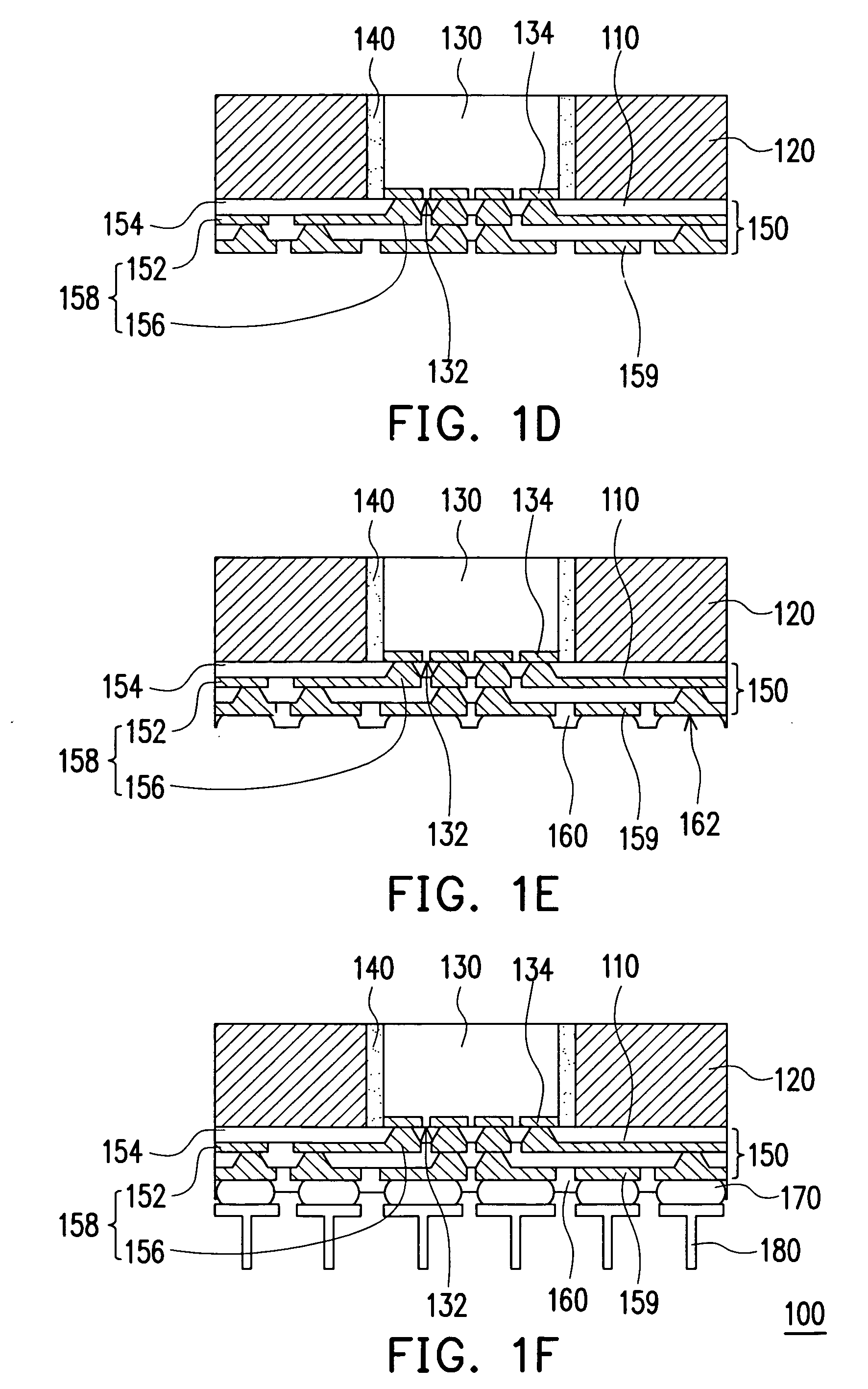

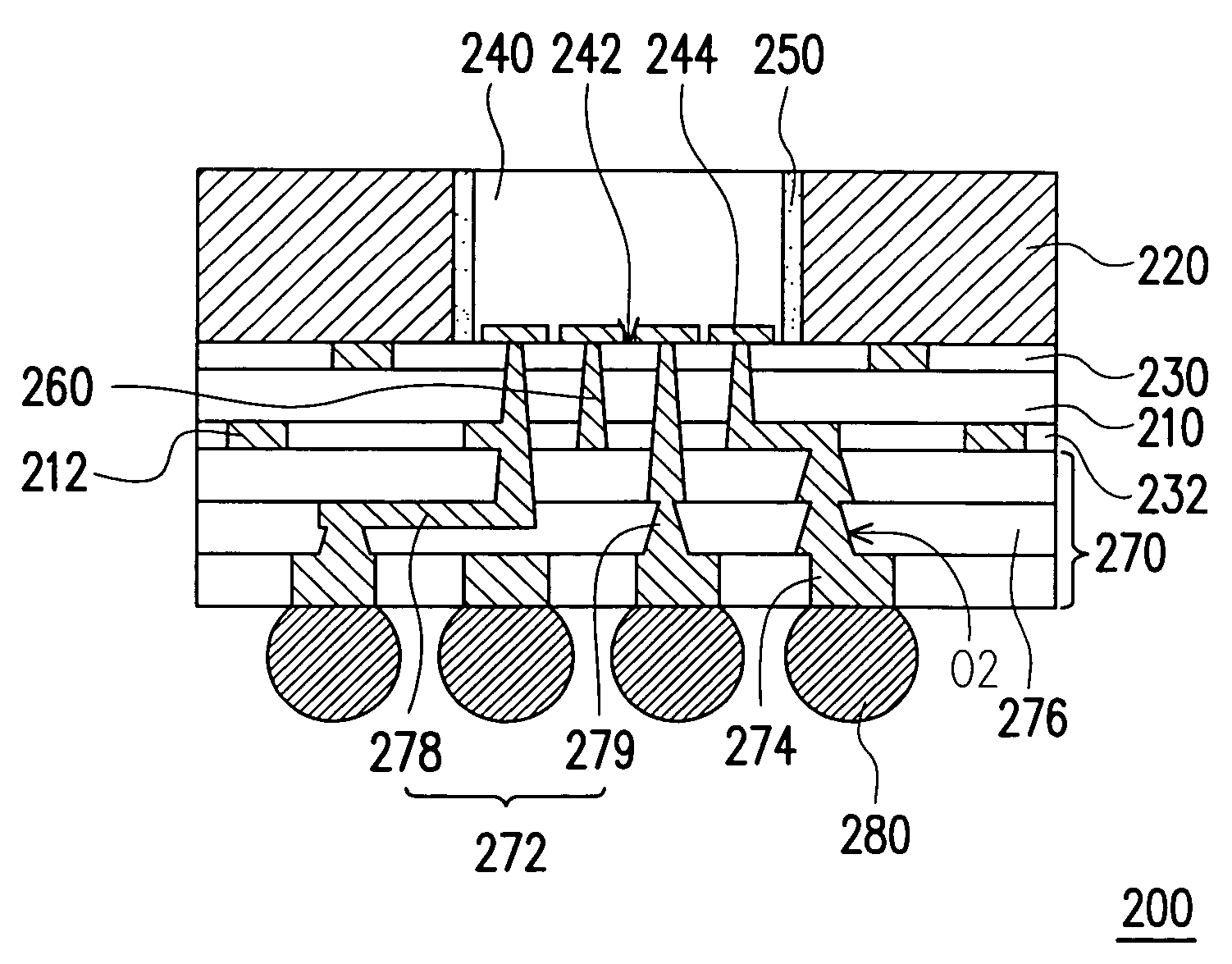

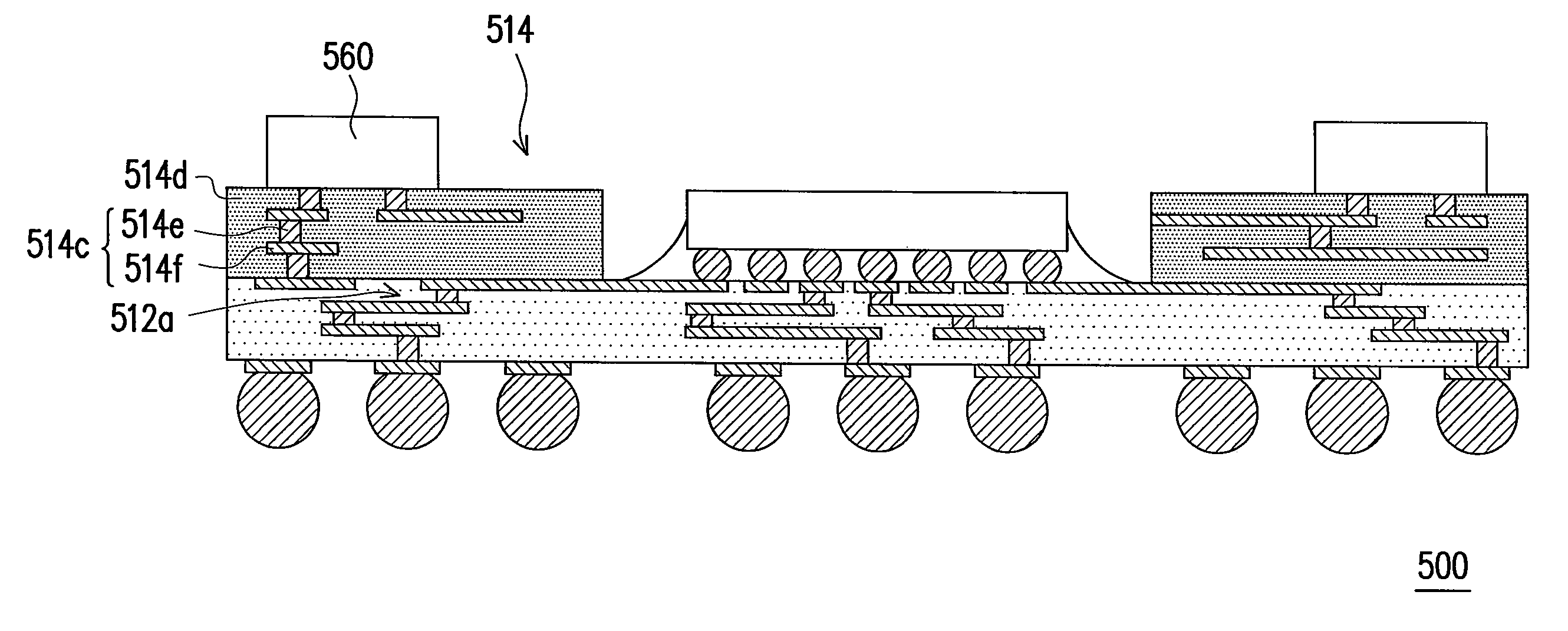

Chip embedded package structure

ActiveUS7170162B2Improving structural coplanarity and package reliabilityReduce processing timeSemiconductor/solid-state device detailsSolid-state devicesInterconnectionElectrical and Electronics engineering

A chip embedded package structure is provided. A stiffener is disposed on a tape. The tape has at least an alignment mark and the stiffener has at least a chip opening. A chip having a plurality of bonding pads thereon is disposed on the tape within the chip opening such that the bonding pads face the tape. A plurality of through holes is formed in the tape to expose the bonding pads respectively. After that, an electrically conductive material is deposited to fill the through holes and form a plurality of conductive vias that connects with the bonding pads respectively. A multi-layered interconnection structure is formed on the surface of the tape away from the chip. The multi-layered interconnection structure has an inner circuit that connects to the conductive vias. The inner circuit has a plurality of metallic pads disposed on the outer surface of the multi-layered interconnection structure.

Owner:VIA TECH INC

Structure and material for assembling a low-K Si die to achieve a low warpage and industrial grade reliability flip chip package with organic substrate

ActiveUS6909176B1Less bowingConsiderable pressureSemiconductor/solid-state device detailsSolid-state devicesAdhesiveEngineering

Provided are a semiconductor low-K Si die flip chip package with warpage control and fabrication methods for such packages. The packages include heat spreaders that are attached to the low-K Si die and packaging substrate. In general, the modulus of the thermal interface material, which is used to attach the heat spreader to the low-K Si die, is selected as high as possible relative to other commercially available thermal interface materials. On the other hand, the modulus of the adhesive, which is used to attach the heat spreader via an optional stiffener to the substrate, is selected as low as possible relative to other commercially available adhesives. The result is a package with less bowing and so improved co-planarity (in compliance with industry specifications) with the surface to which it is ultimately bound. Moreover, the low-K Si die and package reliabilities are thereby enhanced.

Owner:ALTERA CORP

Process for fabricating chip embedded package structure

ActiveUS20060105500A1Good coplanarityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesMagnetic tapeEngineering

A process for fabricating a chip embedded package structure is provided. A stiffener is disposed on a tape. A chip is disposed on the tape inside a chip opening of the stiffener such that an active surface of the chip faces the tape. Through holes are formed passing the tape and exposing bonding pads of the chip on the active surface respectively. Conductive material is deposited into the though holes to form a plurality of conductive vias which are connected to the bonding pads respectively. A multi-layered interconnection structure is formed on the tape on the opposite of the chip, wherein the multi-layered interconnection structure comprises an inner circuit which is connected to the conductive vias, and the inner circuit has a plurality of metallic pads on a surface of the multi-layered interconnection structure away from the tape.

Owner:VIA TECH INC

Wiring substrate and manufacturing method of the same

InactiveUS20130098670A1Reliably and easily obtainGood coplanaritySemiconductor/solid-state device detailsSolid-state devicesBiomedical engineeringElectrical conductor

Embodiments of the present invention provide a wiring substrate that includes a structure where a plurality of projection electrodes are arranged within an electrode formation region on a substrate main surface. At least one among the plurality of projection electrodes has a larger outer diameter than an outer diameter of a via conductor and is a variant projection electrode which has a roughened upper surface. Embodiments of the present invention also provide methods for manufacturing wiring substrates having one or more of said variant projection electrode.

Owner:NGK SPARK PLUG CO LTD

Low stress and warpage laminate flip chip BGA package

InactiveUS7009307B1Less bowingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesAdhesiveEngineering

Owner:ALTERA CORP

Flip-chip package structure with stiffener

ActiveUS20080001308A1Good coplanarityPackage structure is simpleSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A flip-chip package structure with stiffener includes a substrate, a first stiffener positioned on a surface of the substrate, a chip having a plurality of bumps adopted to electrically connect the substrate and the chip, and a second stiffener positioned on the surface of the substrate and connected with the first stiffener. The first stiffener is positioned outside of the second stiffener.

Owner:ADVANCED SEMICON ENG INC

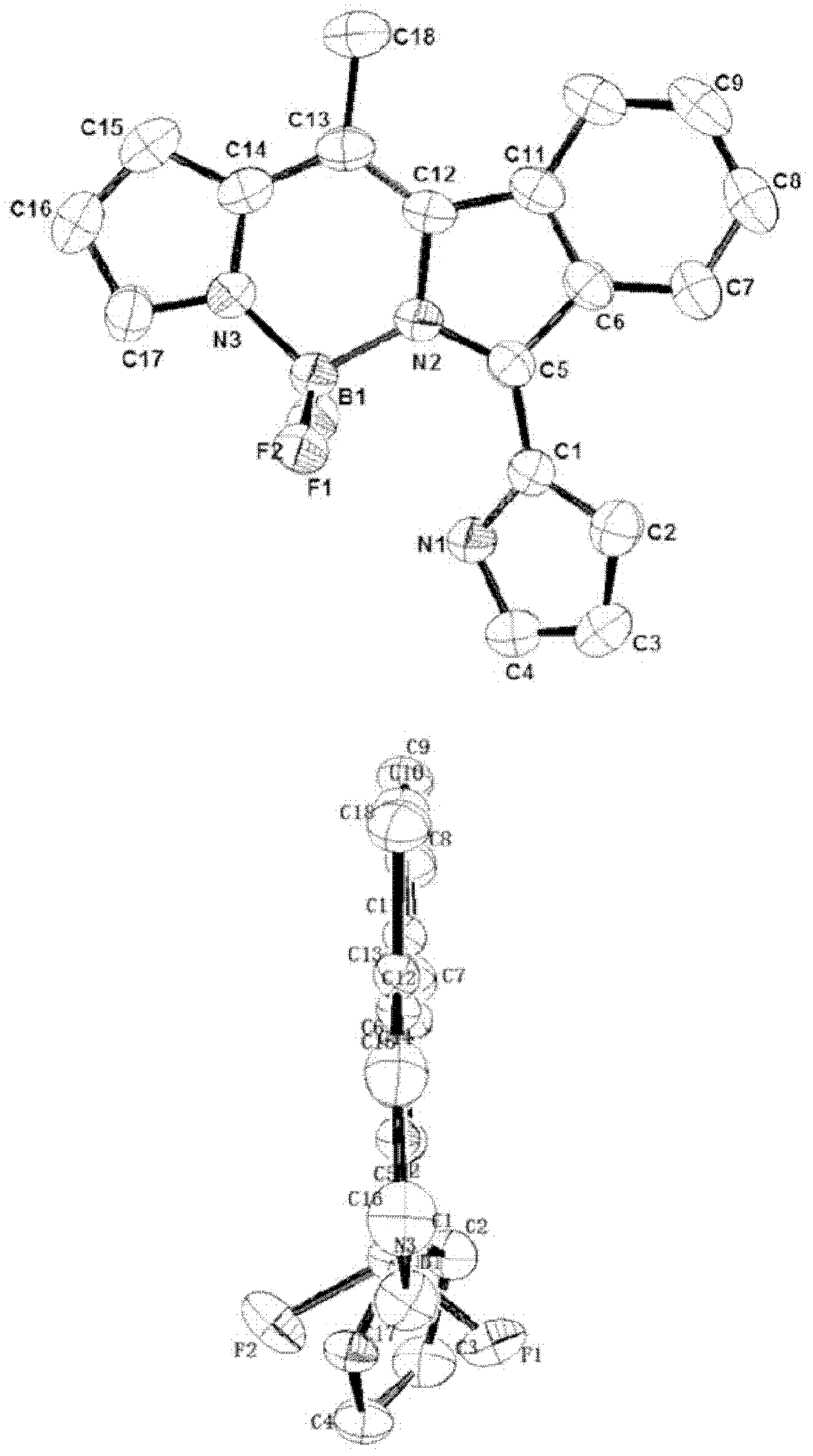

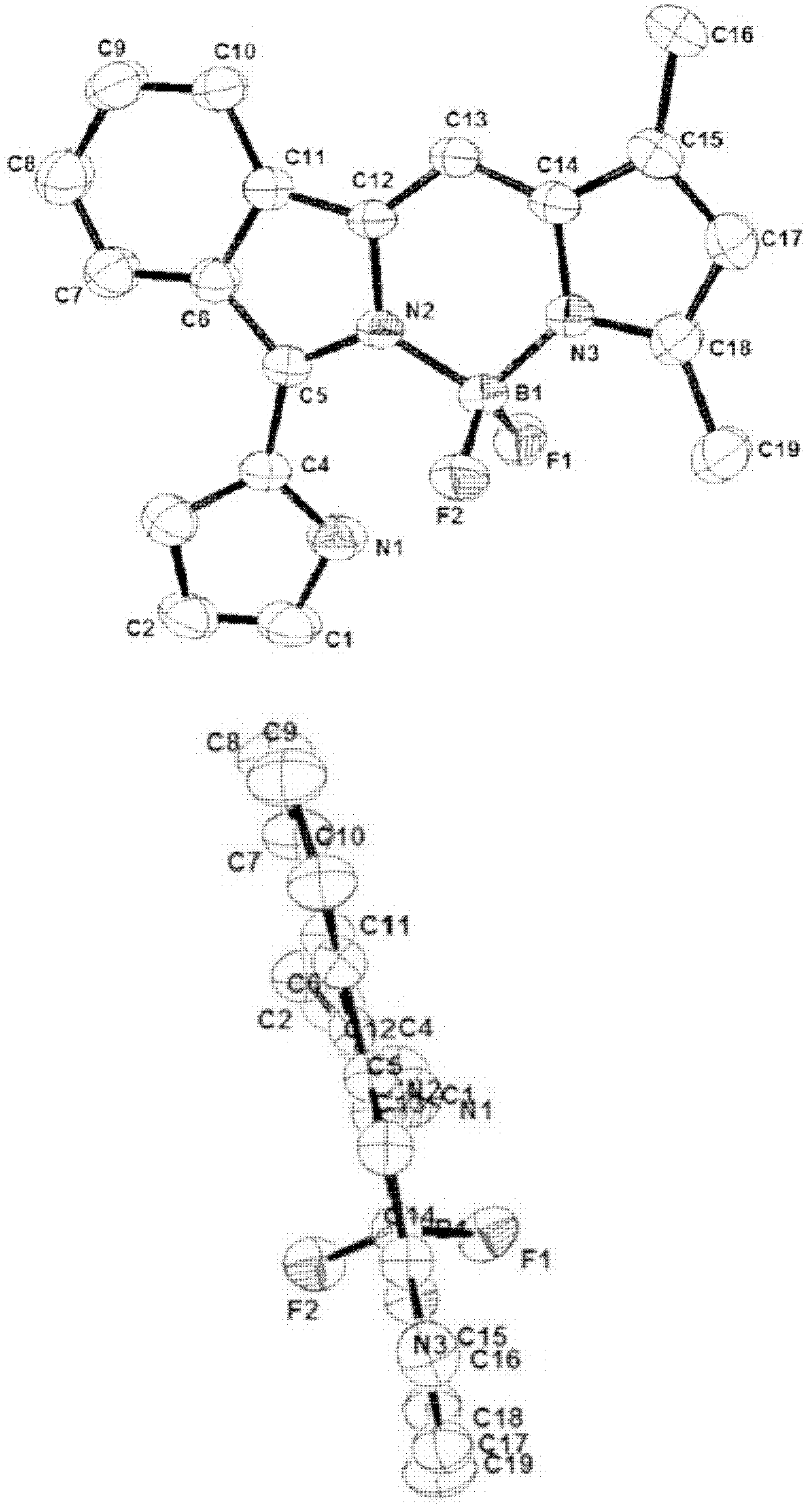

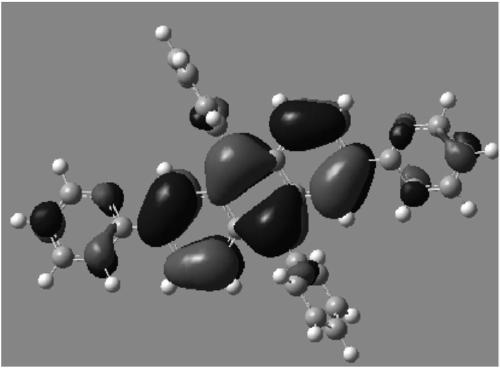

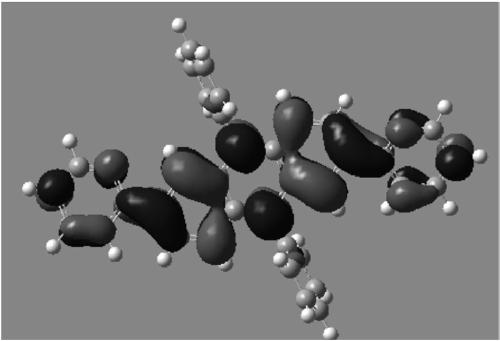

Near infrared fluoro-boron dipyrrole fluorescent dyes and synthesis method thereof

InactiveCN102702774AGood photochemical propertiesGood coplanarityMethine/polymethine dyesAzo dyesQuantum yieldInfrared

The invention relates to near infrared fluoro-boron dipyrrole fluorescent dyes and a synthesis method of the fluorescent dyes. The dyes have the general formula shown in the specification. The fluorescent dyes are synthesized from aldehyde or imine compounds of halogenated pyrrole or isoindazole and pyrrole derivatives by a one-pot method. The emission wavelength of the fluorescent dyes is more than 600nm, and the emission spectra of the monostyryl-substituted dyes and derivatives thereof can be up to 714nm. The fluorescent dyes have excellent light, physical and chemical performances of higher fluorescent quantum yield (0.61-0.91) and better light stability and the like, and has excellent application prospects in fluorescence labeling, biological imaging and other bioanalysis fields.

Owner:ANHUI NORMAL UNIV

Structure and material for assembling a low-K Si die to achieve a low warpage and industrial grade reliability flip chip package with organic substrate

InactiveUS7144756B1Less bowingConsiderable pressureSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor

Provided are a semiconductor low-K Si die flip chip package with warpage control and fabrication methods for such packages. The packages include heat spreaders that are attached to the low-K Si die and packaging substrate. In general, the modulus of the thermal interface material, which is used to attach the heat spreader to the low-K Si die, is selected as high as possible relative to other commercially available thermal interface materials. On the other hand, the modulus of the adhesive, which is used to attach the heat spreader via an optional stiffener to the substrate, is selected as low as possible relative to other commercially available adhesives. The result is a package with less bowing and so improved co-planarity (in compliance with industry specifications) with the surface to which it is ultimately bound. Moreover, the low-K Si die and package reliabilities are thereby enhanced.

Owner:ALTERA CORP

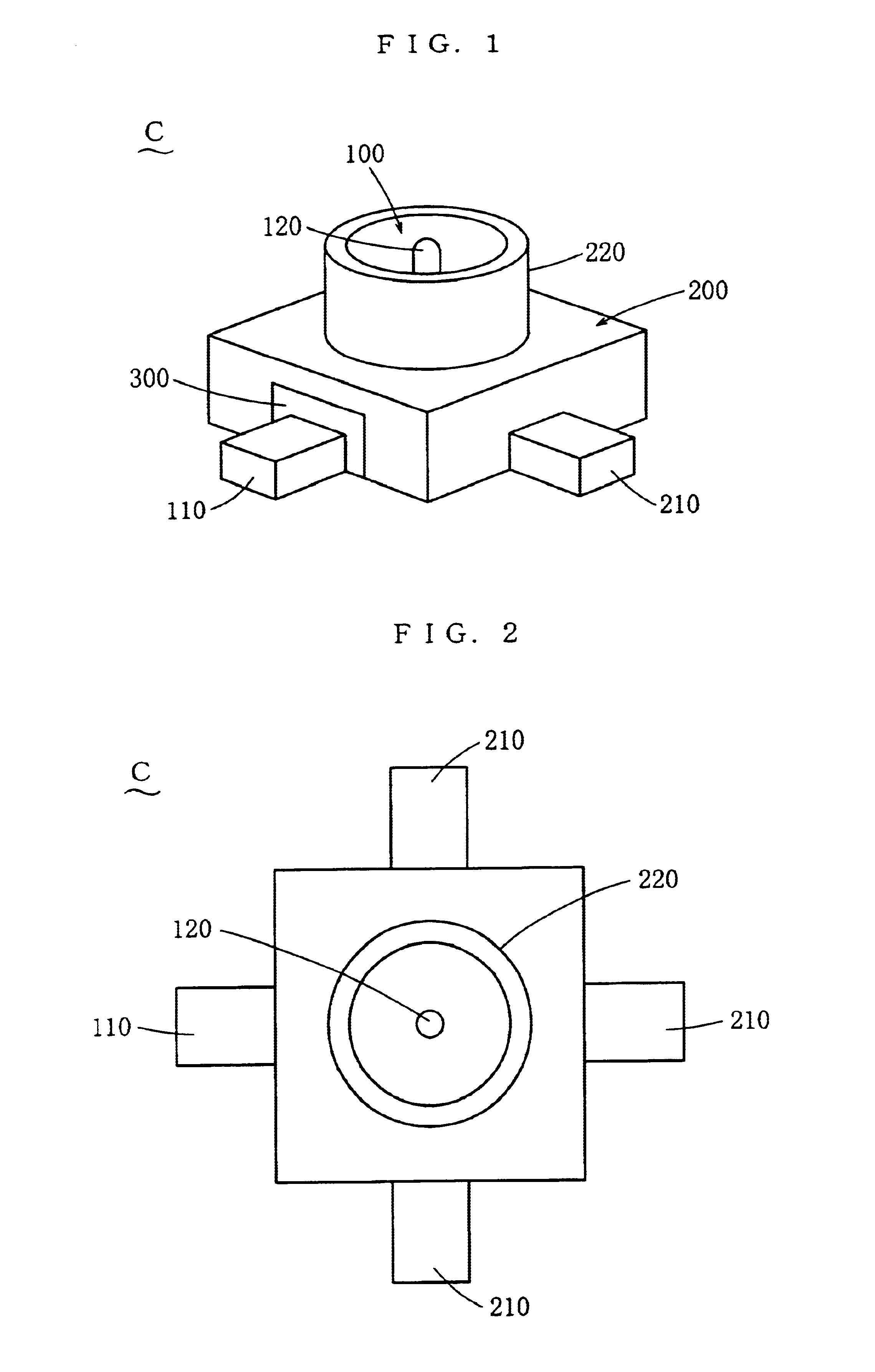

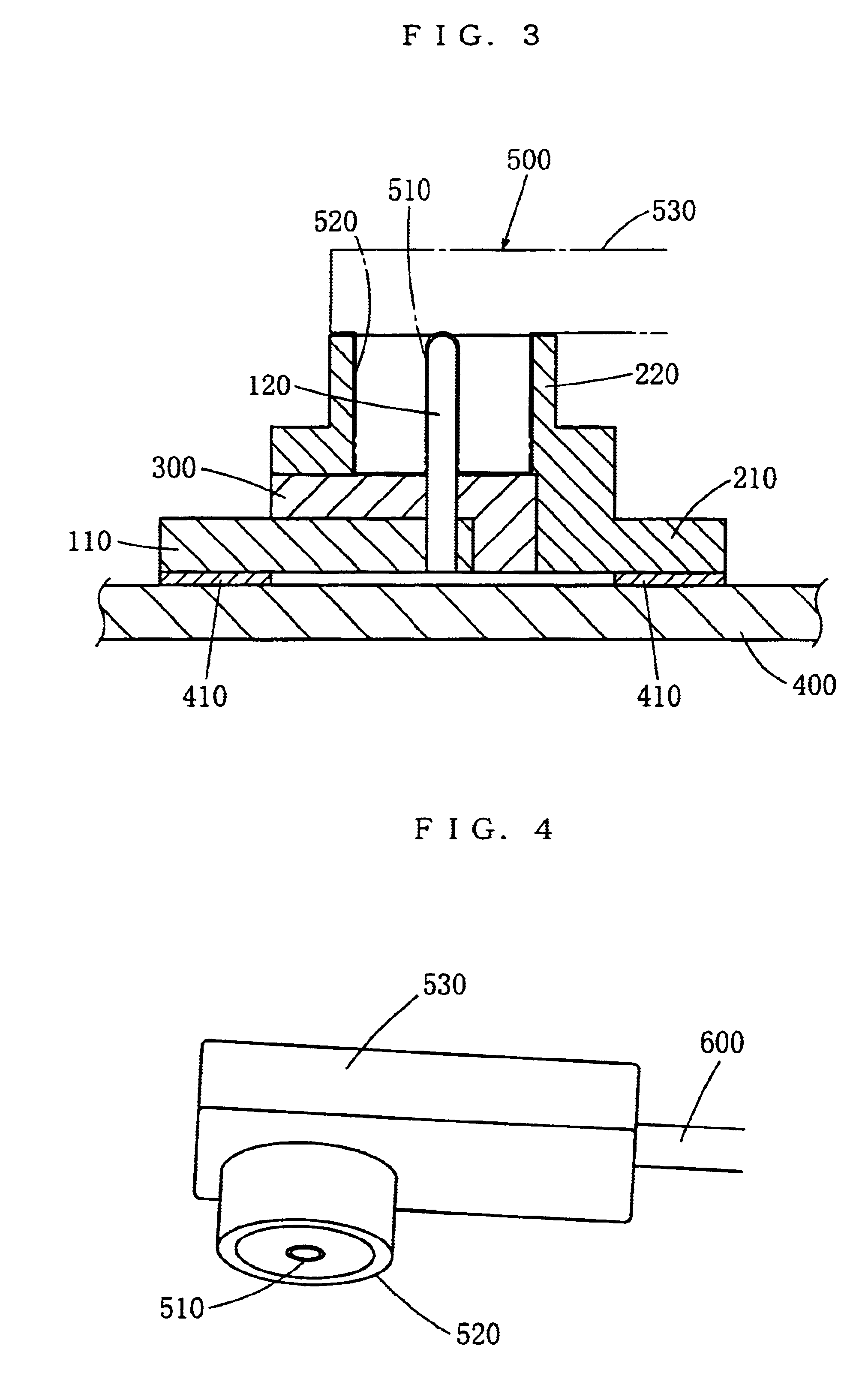

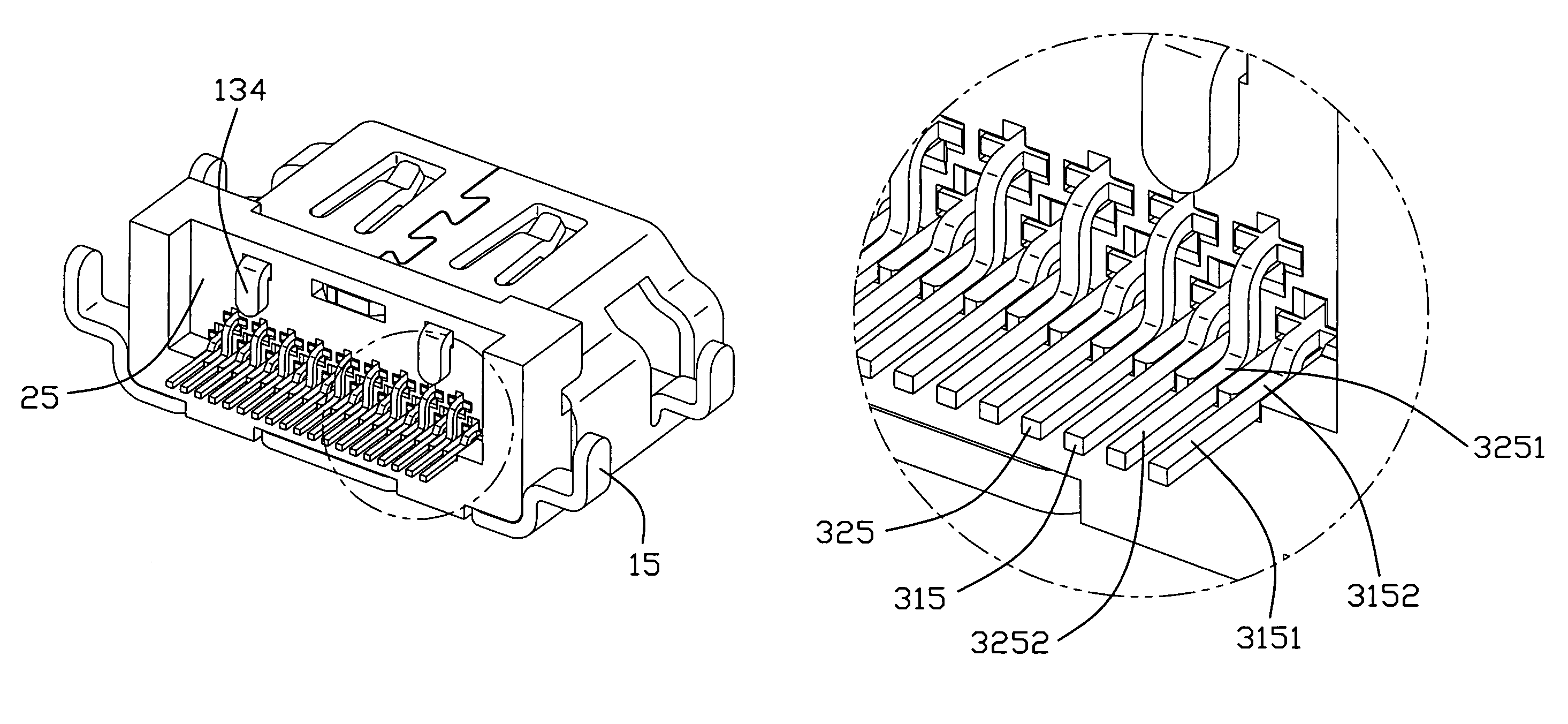

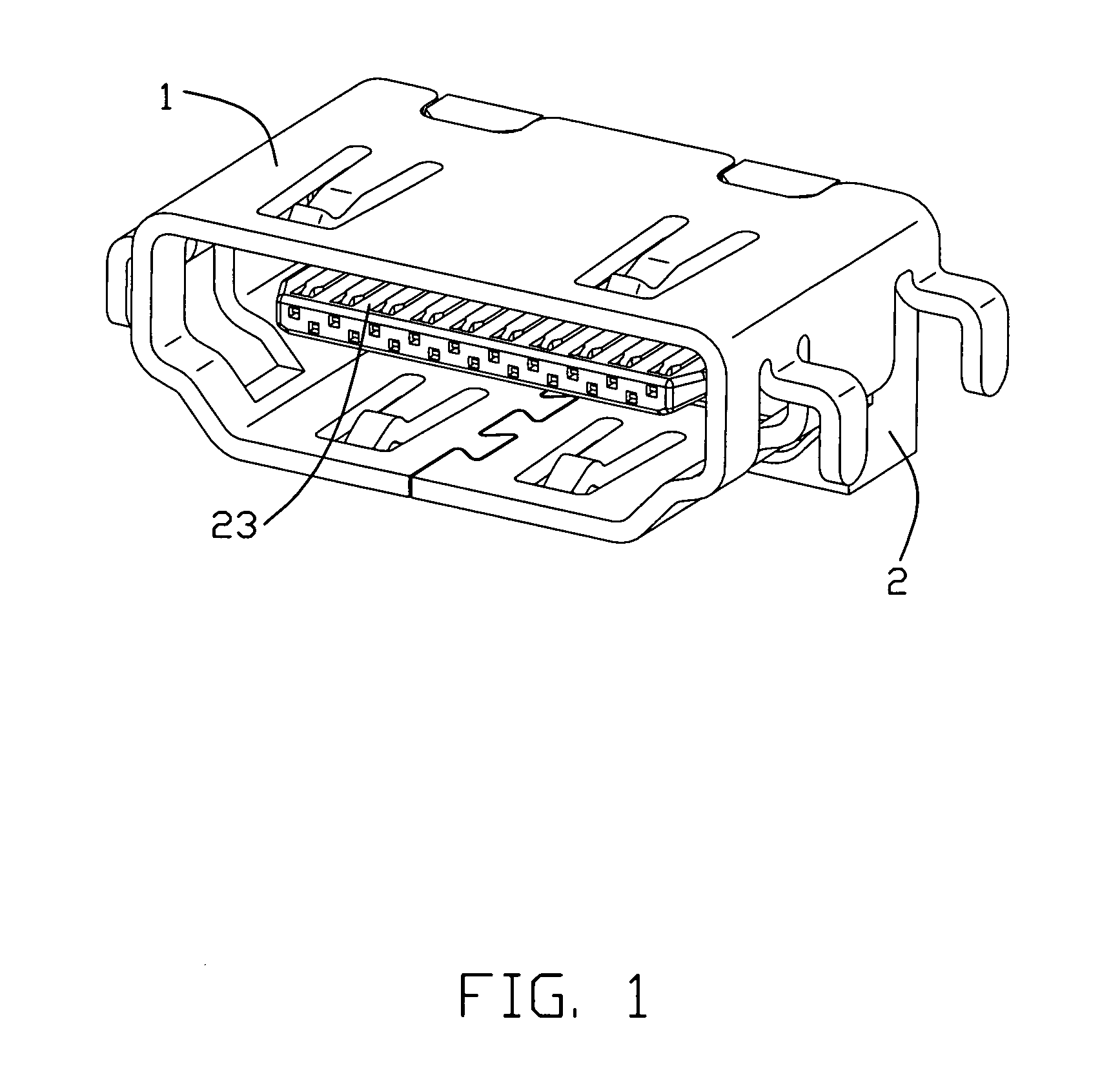

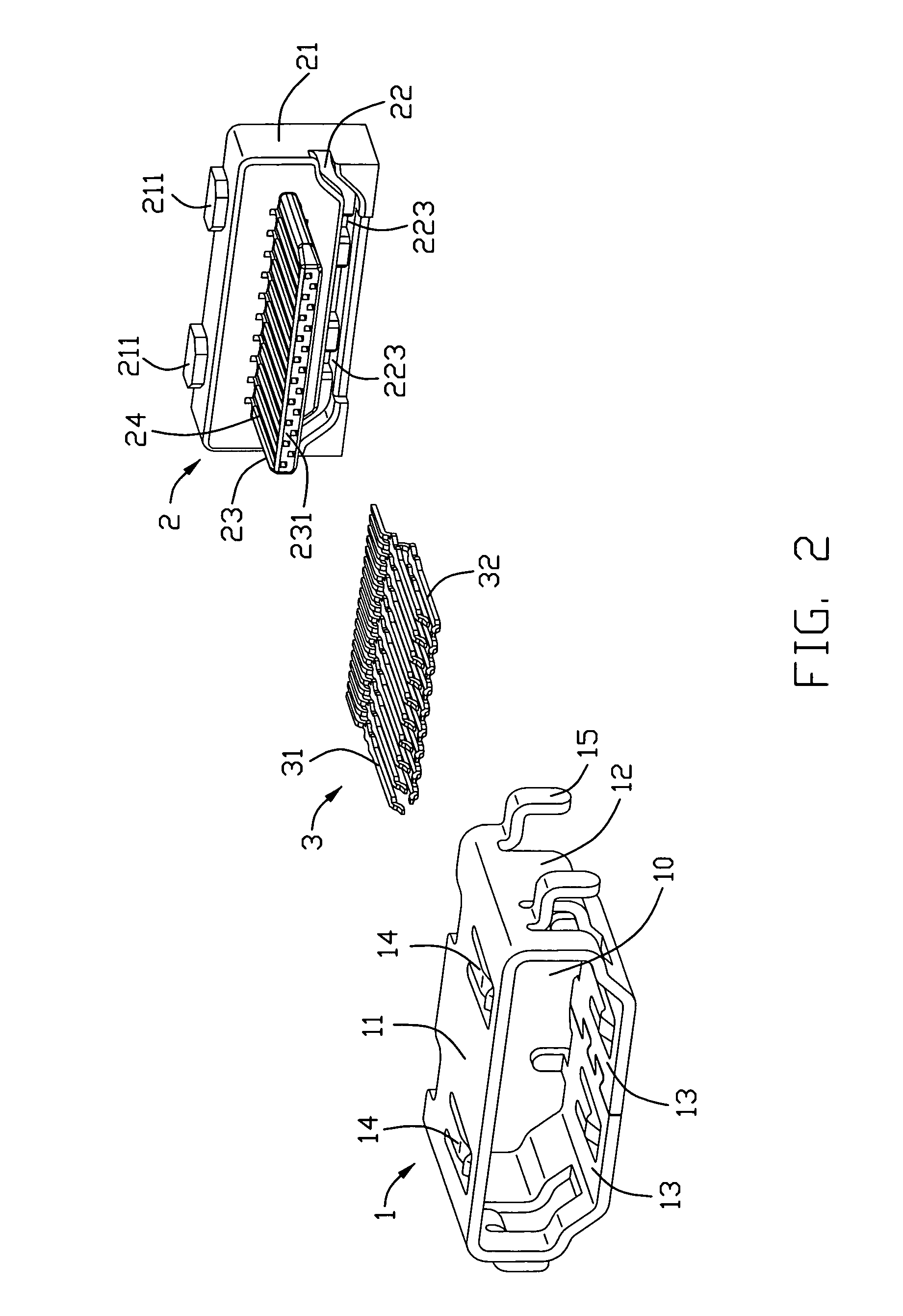

Electrical connector providing a better coplanarity for terminal solders

ActiveUS7445469B2Good coplanaritySecuring/insulating coupling contact membersTwo-part coupling devicesEngineeringElectrical connector

An electrical connector of the present invention includes an insulating housing (2) mounting a plurality of terminals (3) and a metallic shell (1) surrounding the insulating housing (2). The insulating housing (2) defines a plurality of terminal grooves (24) therein. A plurality of terminals (3) mounted on the insulating housing (2), each comprises a mating portion (312,322) received in the terminal groove (24) and a solder portion (315,325) extending out of the terminal groove. A terminal solder coplanarity means is provided at a rear portion of the housing.

Owner:HON HAI PRECISION IND CO LTD

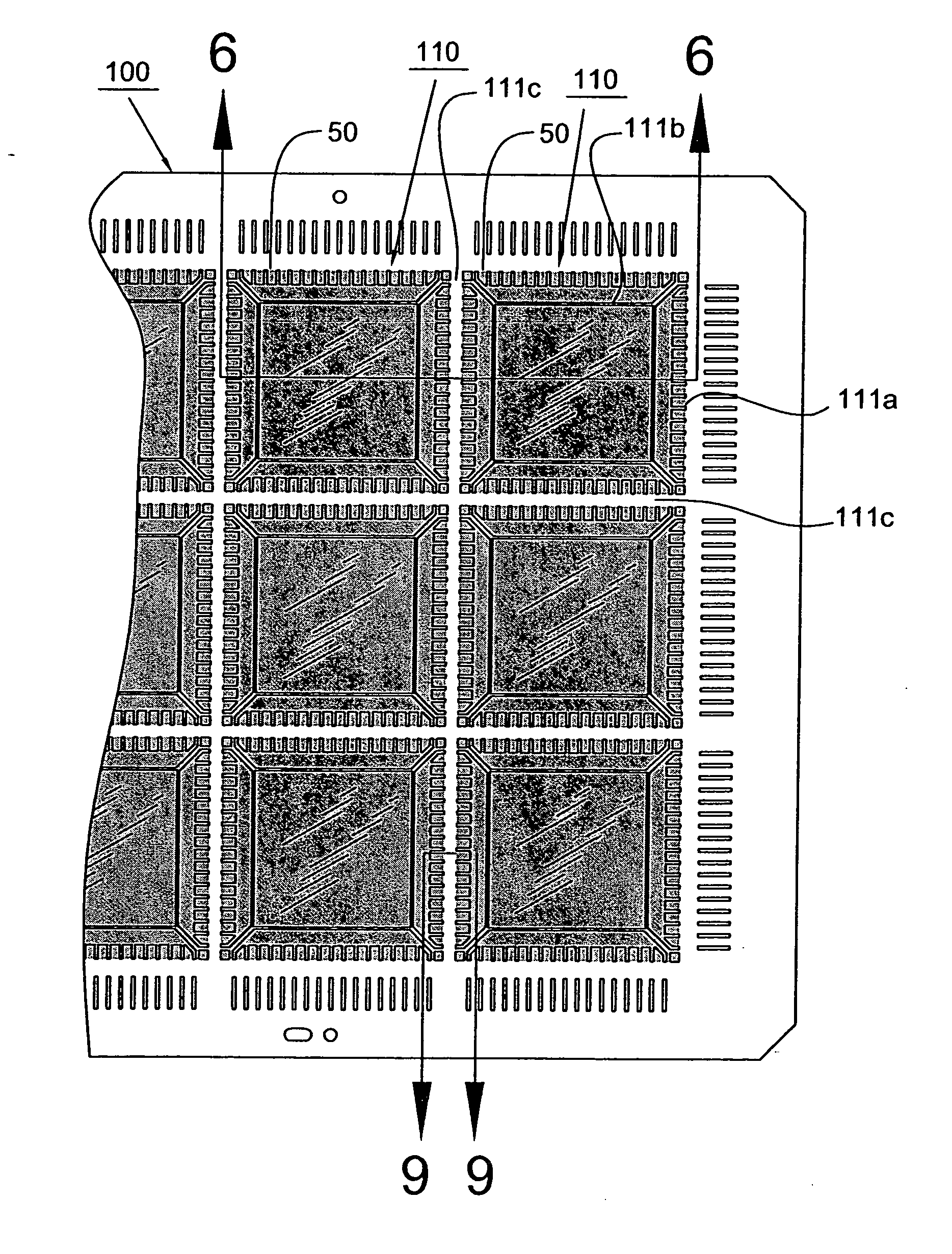

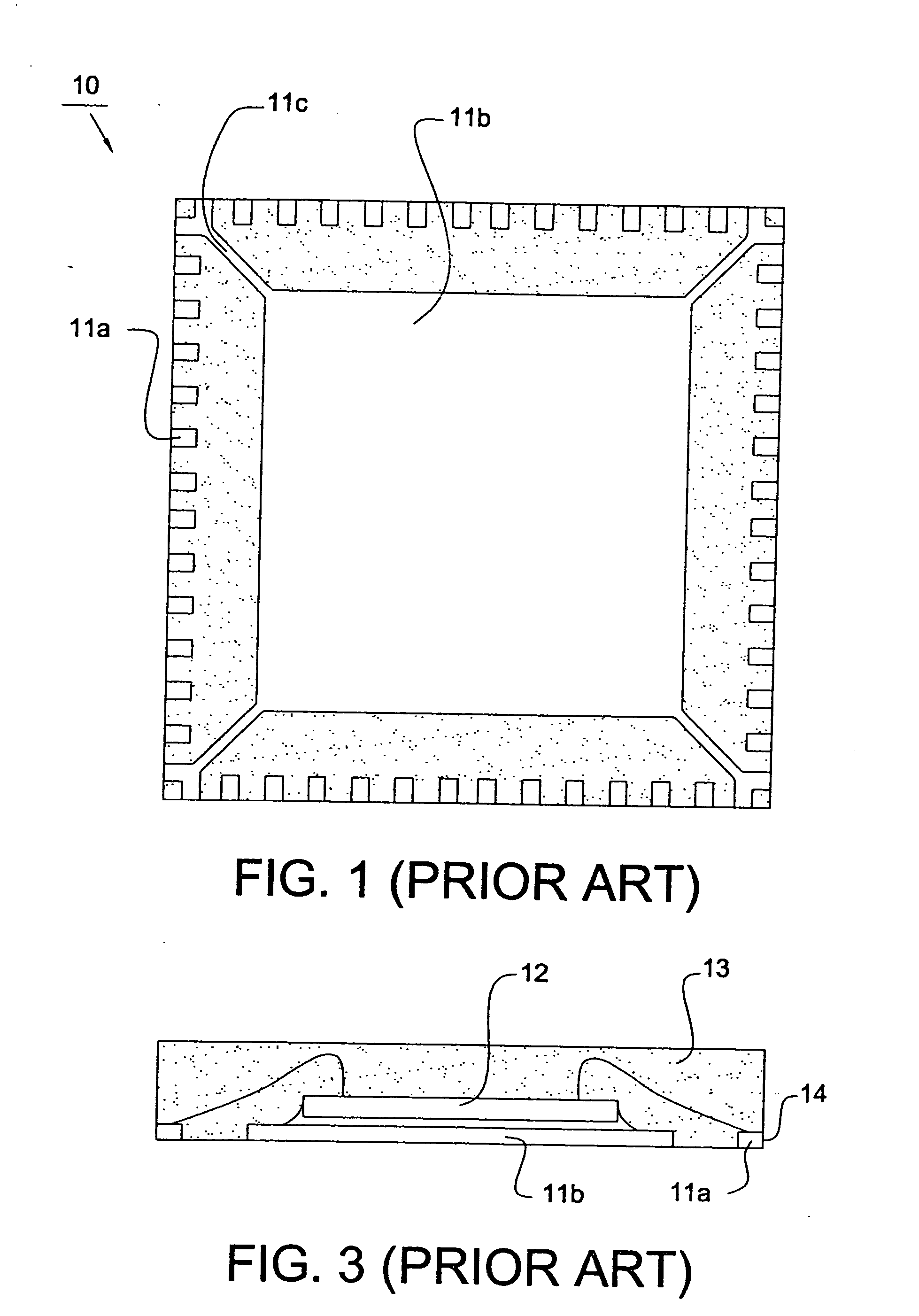

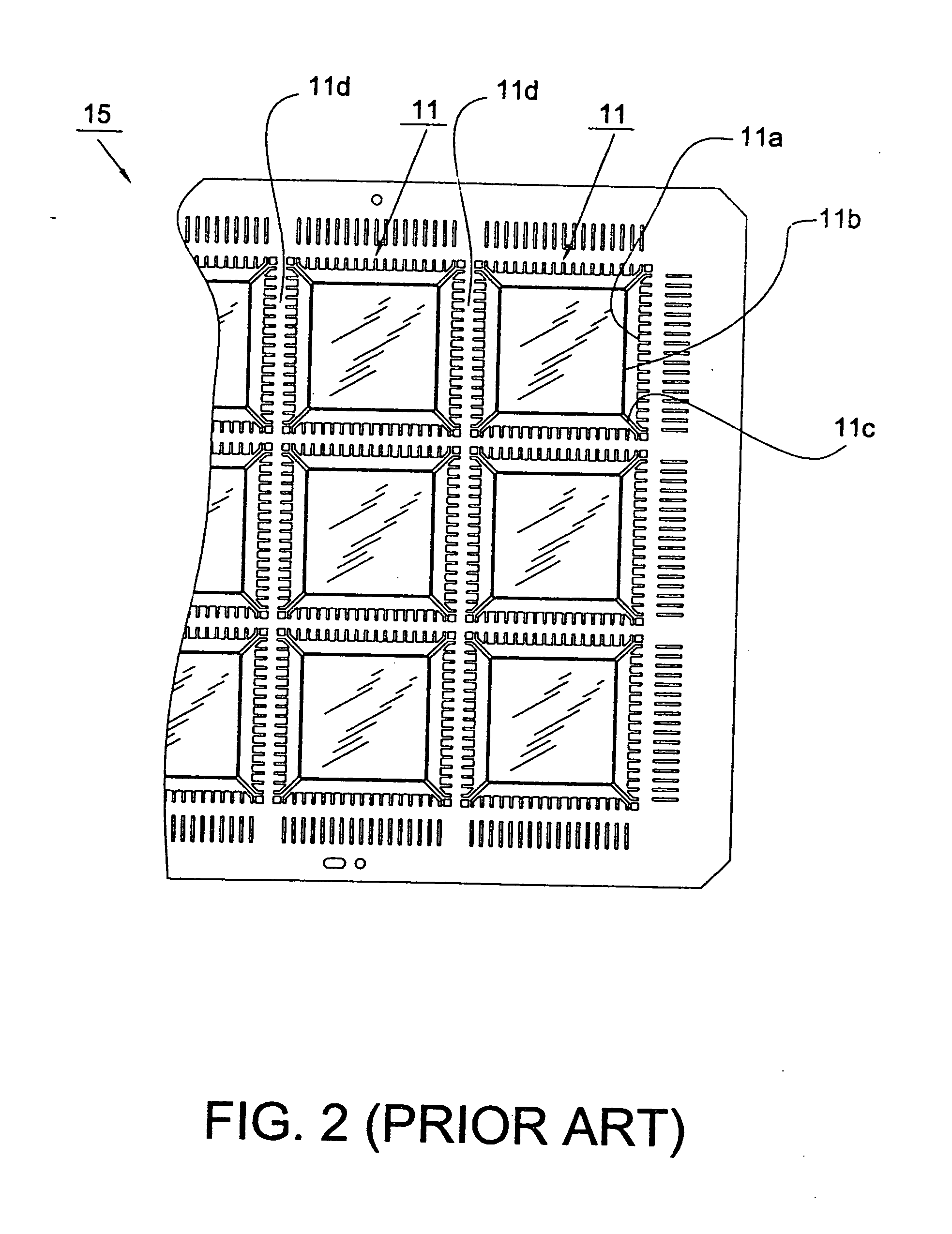

Singulation method used in leadless packaging process

InactiveUS20050037618A1Reduce decreaseGood coplanaritySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipLead frame

A singulation method used in leadless packaging process is disclosed. An array of molded products on an upper surface of a lead frame is utilized in the singulation method. The lead frame has a plurality of dambars between the molded products. The lower surface of the lead frame is attached with a tape. Each of the molded products includes a semiconductor chip encapsulated in a package body and electrically coupled to the upper surface of the lead frame. The singulation method is accomplished by etching the upper surface of the lead frame with the package bodies as mask until each dambar is etched away.

Owner:ADVANCED SEMICON ENG INC

Connector having improved contacts with fusible members

ActiveUS6979238B1Reliable reflowGood coplanarityPrinted circuit assemblingLine/current collector detailsEngineeringElectrical connector

Owner:SAMTEC

Organic electroluminescent device

ActiveCN109251176ALow working voltageImprove luminous efficiencyOrganic chemistrySolid-state devicesChemical LinkageElectronic transmission

The invention discloses an organic electroluminescent device comprising a first electrode, a second electrode and a layer of or a plurality of layers of organic layers located between the first electrode and the second electrode. The organic layer at least comprises a luminescent layer and an electronic transmission layer; the electronic transmission layer is 5-100 nm in thickness, and the electronic transmission layer contains at least one compound represented by the formula (I), wherein L1 and L2 are independently selected from chemical bonds, C6-C12 arylene or sub-polycyclic aromatic groups, and C3-C12 heteroarylene or sub-polyheterocyclic aromatic groups respectively; R1, R2, R3, R4 and R5 are independently selected from hydrogen, halogen, cyano groups, nitro groups, C1-C10 alkylene, C6-C30 substituted or non-substituted aryl or polycyclic aromatic groups, and C3-C30 substituted or non-substituted heteroaryl or polyheterocyclic aromatic groups respectively, and R2 and R5 can be connected with each other to form a ring structure; Ar1 and Ar2 are independently selected from C6-C30 substituted or non-substituted aryl or polycyclic aromatic groups, and C3-C30 substituted or non-substituted heteroaryl or polyheterocyclic aromatic groups respectively. The organic electroluminescent device has the advantages of low working voltage and high luminescent efficiency.

Owner:BEIJING ETERNAL MATERIAL TECH +1

Chip package and coreless package substrate thereof

ActiveUS7586188B2Reduce residual stressGood coplanaritySemiconductor/solid-state device detailsSolid-state devicesContact padEngineering

Owner:VIA TECH INC

Novel organic electroluminescence device

ActiveCN107833974ALow working voltageImprove luminous efficiencyOrganic chemistrySolid-state devicesElectronic transmissionOrganic layer

The invention discloses a novel organic electroluminescence device. The device comprises a first electrode, a second electrode and one or more layers of organic layers between the first electrode andthe second electrode. Each organic layer at least comprises a light emitting layer and an electronic transmission layer. The device is characterized in that the thickness of each electronic transmission layer is 5-100nm; each electronic transmission layer comprises at least one kind of compound shown by the formula (I) shown in the description, wherein L is selected from a chemical bond, an arylidene or sub-polycyclic aromatic hydrocarbon group of C6-C12, and a sub-heteroaryl or sub-polycyclic heteroaryl aromatic hydrocarbon group of C3-C12; the Ar1, the Ar2 and the Ar3 are respectively selected from the substituted or non-substituted aryl or polycyclic aromatic hydrocarbon group of C6-C30, and the substituted or non-substituted heteroaryl group or polycyclic heteroaryl aromatic hydrocarbon group of C3-C30; the R1, the R2, the R3 and the R4 are selected from hydrogen, the alkylene of C1-C10, the halogen, the cyan, the nitryl, the substituted or non-substituted aryl or polycyclic aromatic hydrocarbon group of C6-C30, and the substituted or non-substituted heteroaryl group or polycyclic heteroaryl aromatic hydrocarbon group of C3-C30; and the R3 can be connected with the R4, so an annular structure can be formed. According to the invention, the device is advantaged by low working voltage and high light emitting efficiency.

Owner:BEIJING ETERNAL MATERIAL TECH +1

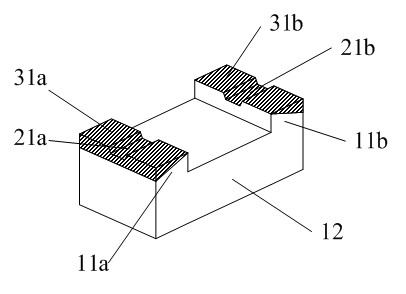

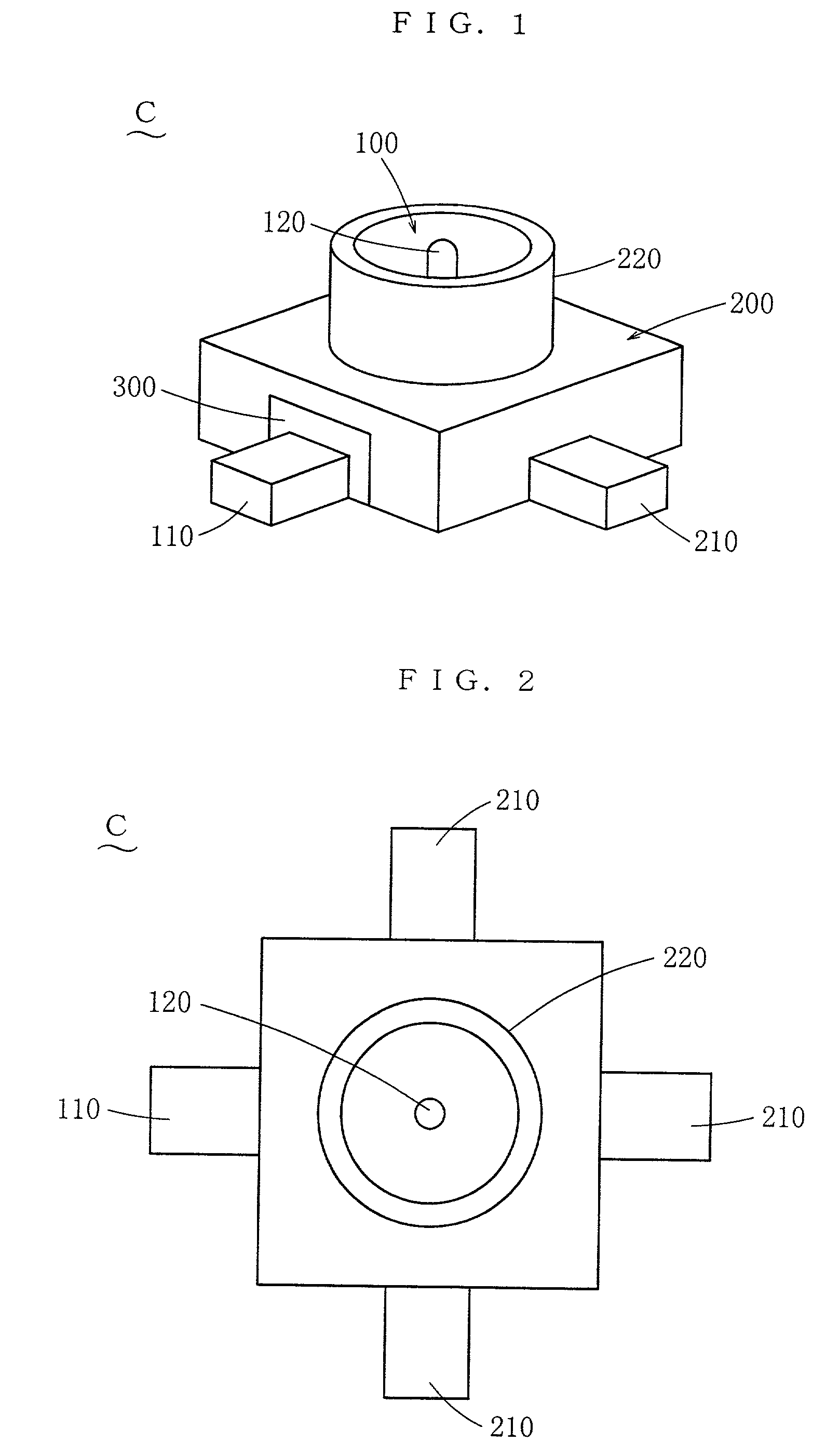

Core column component of winding type pasted electronic element and manufacturing method thereof

ActiveCN102097200AEasy to weldGood coplanarityInorganic material magnetismTransformers/inductances magnetic coresElectronic componentElectrode

The invention discloses a core column component of a winding type pasted electronic element and a manufacturing method of the core column component. The core column component comprises a core column and an external electrode, wherein the core column comprises a left-end convex part, a right-end convex part and a core column body which is connected with the left-end and right-end convex parts, grooves are arranged on both the left-end and right-end convex parts, and the external electrode continuously covers the upper surfaces of the left-end and right-end convex parts and the surface of the groove. The method of the invention is used for manufacturing the core column component. By means of the core column component of the invention, coil ends with various wire diameters can be conveniently welded without increasing the overall height of the product.

Owner:SHENZHEN SUNLORD ELECTRONICS

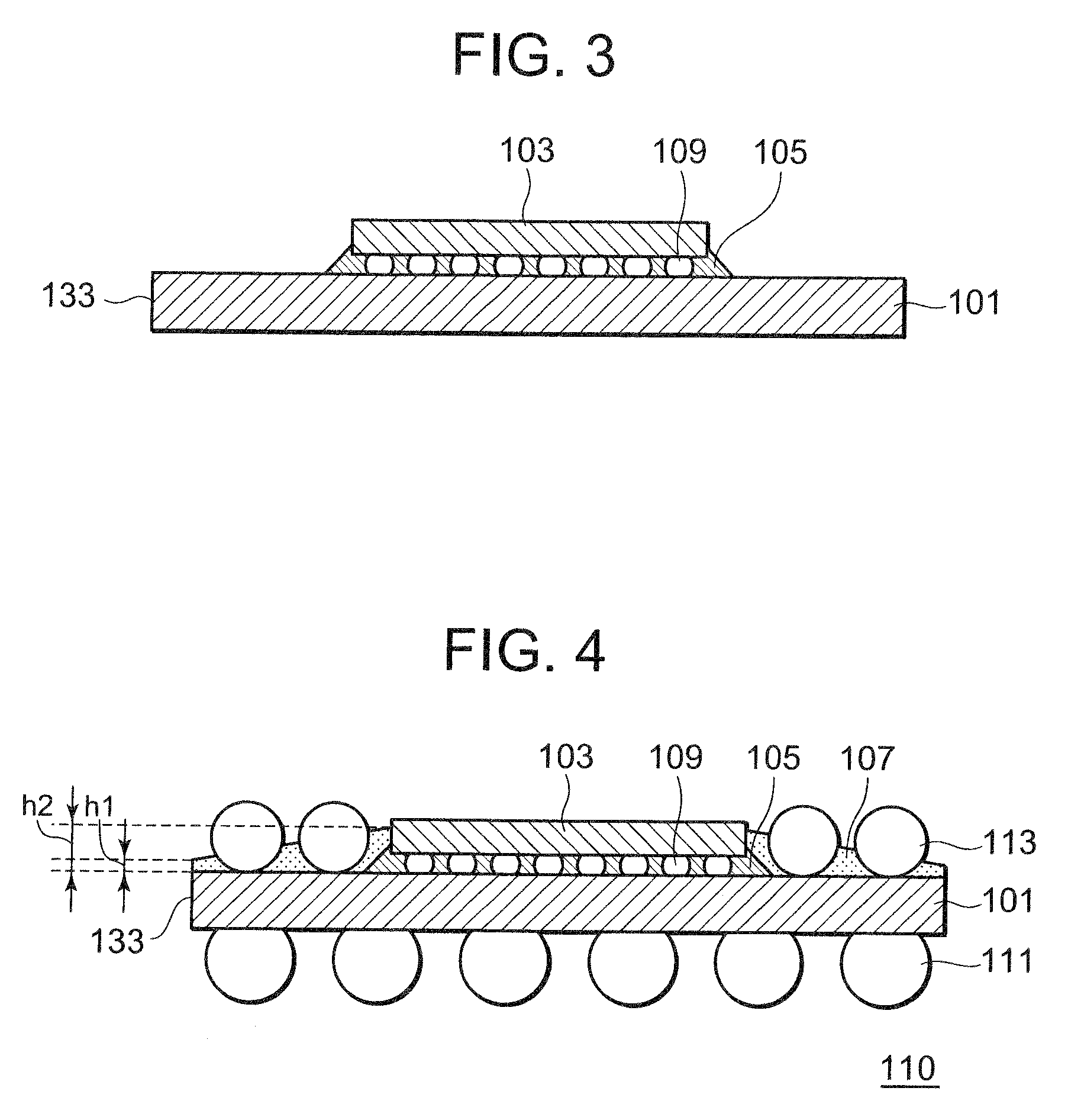

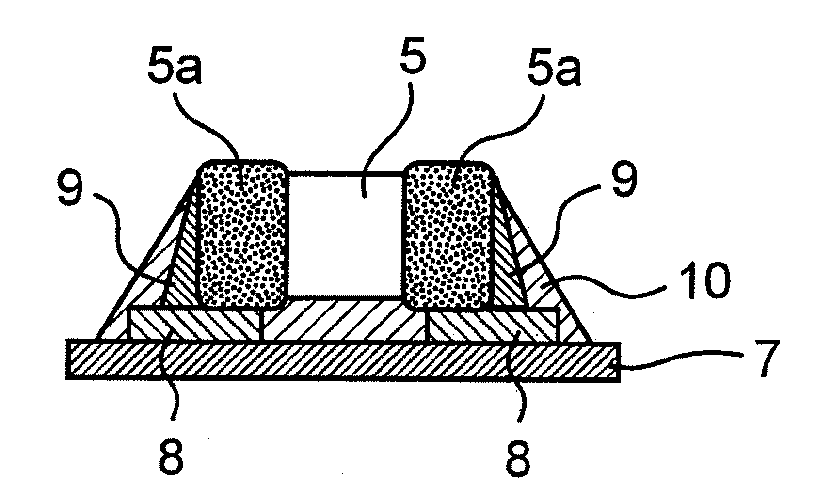

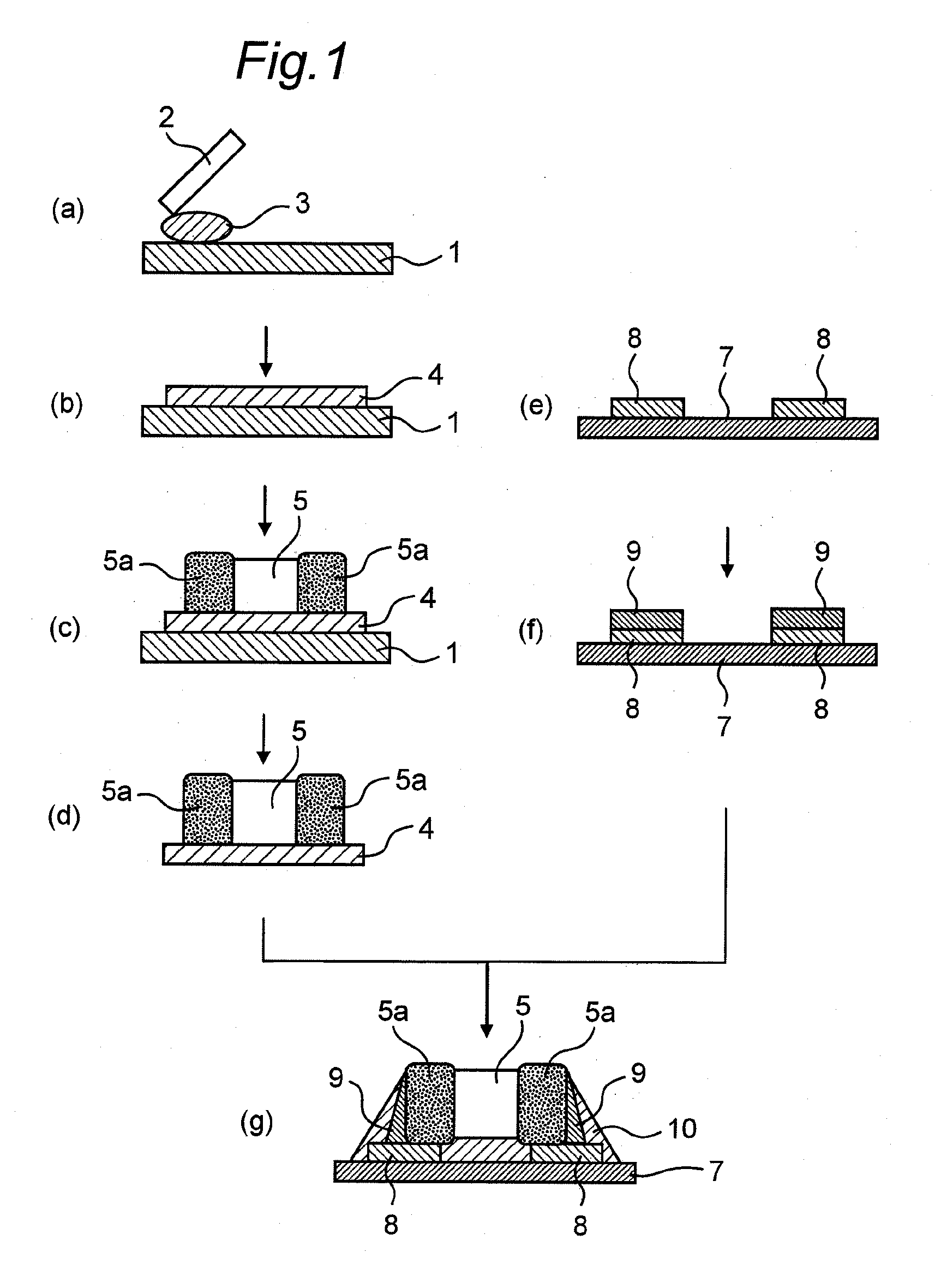

Electronic Device and Manufacturing Method for Electronic Device

InactiveUS20100101845A1Secured stablyImproved junction reliabilityPrinted circuit detailsFinal product manufactureThermal energyEngineering

An electronic device manufacturing method includes: setting a solder material on electrodes of a first circuit assembly; setting a resin having a flux action on one surface of a second circuit assembly so as to entirely cover solder bumps formed on the one surface of the second circuit assembly; setting the second circuit assembly on the first circuit assembly via the resin so that the solder material set on the electrodes of the first circuit assembly and the solder bumps of the second circuit assembly are put into contact with each other; and applying thermal energy to connecting portions between the solder material and the solder bumps and to the resin. By carrying out these processes, an electronic device in which the first circuit assembly and the second circuit assembly are joined together and in which their junction portions are sealed by the resin is manufactured. As a result, in the electronic device, junction reliability can be improved.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Electroplating solution composition capable of being used for improving salient point coplanarity

ActiveCN105441994AGood coating coplanaritySmooth coatingSemiconductor devicesSolution compositionElectricity

The invention discloses an electroplating solution composition capable of being used for improving salient point coplanarity. The electroplating solution composition comprises a leveling agent which is polymer with positive electricity, wherein a polymeric monomer of the polymer comprises the following monomer structure: FORMULA as shown in the specification, wherein R1 on N is selected from alkyls of C1-4, and R2 on the N is selected from the alkyls of C1-4. During high-speed electroplating (2.5 mu m / min), the electroplating solution composition provided by the invention still can keep relatively good plating coplanarity which is much smaller than an industrial required value by 3%; the plating is flat in feature, can be used for copper pillar salient point electroplating of a 3D interconnecting and packaging process, and has a good market prospect.

Owner:SHANGHAI SINYANG SEMICON MATERIALS

Electric contact and an electric connector both using resin solder and a method of connecting them to a printed circuit board

InactiveUS20020139574A1Increase the cross-sectional areaGreat freedomTwo pole connectionsContact member assembly/disassemblyElectricityElectrical conductor

The objectives of the present invention include to mount an electric contact or an electric connector on a printed circuit board without conducting the soldering work, and to make mounting the electric contact on a printed circuit board by an automatic machine even when the electric contact is microminiaturized. The electric contact using resin solder according to the present invention is connected to a printed circuit board, which has a conductor being provided on a surface thereof. This electric contact comprises a leg, which contacts the conductor of the printed circuit board, and a connecting part, which is connected to the conductor of the counterpart member. At least a part of the leg, which contacts the conductor of the printed circuit board, is made of a lead-free ultrahigh-conductive plastic being a conductive resin composite. The electric connector comprises the electric contact and an insulating housing, which holds the electric contact so that the part of the leg, which contacts the conductor of the printed circuit board, is exposed.

Owner:JST MFG CO LTD

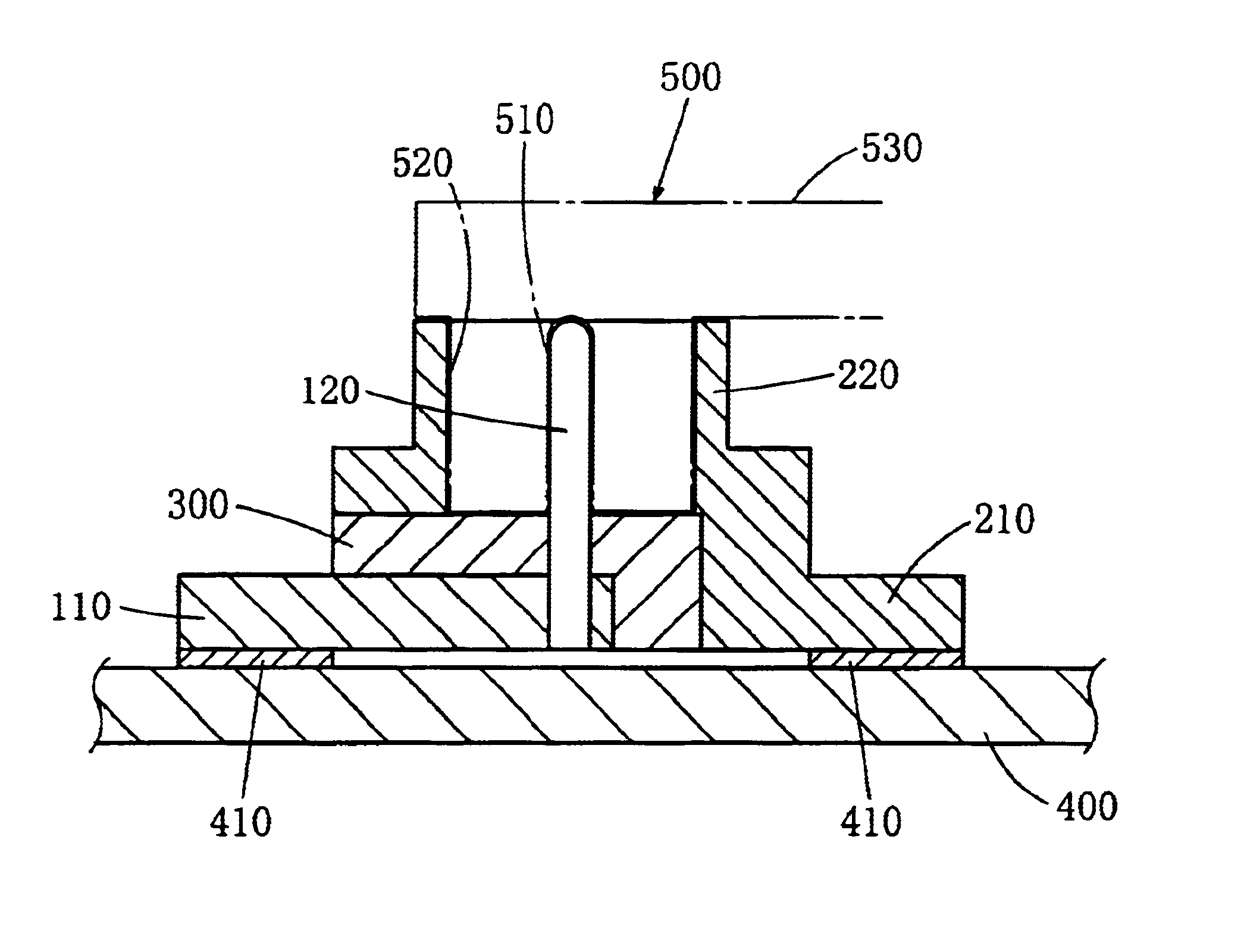

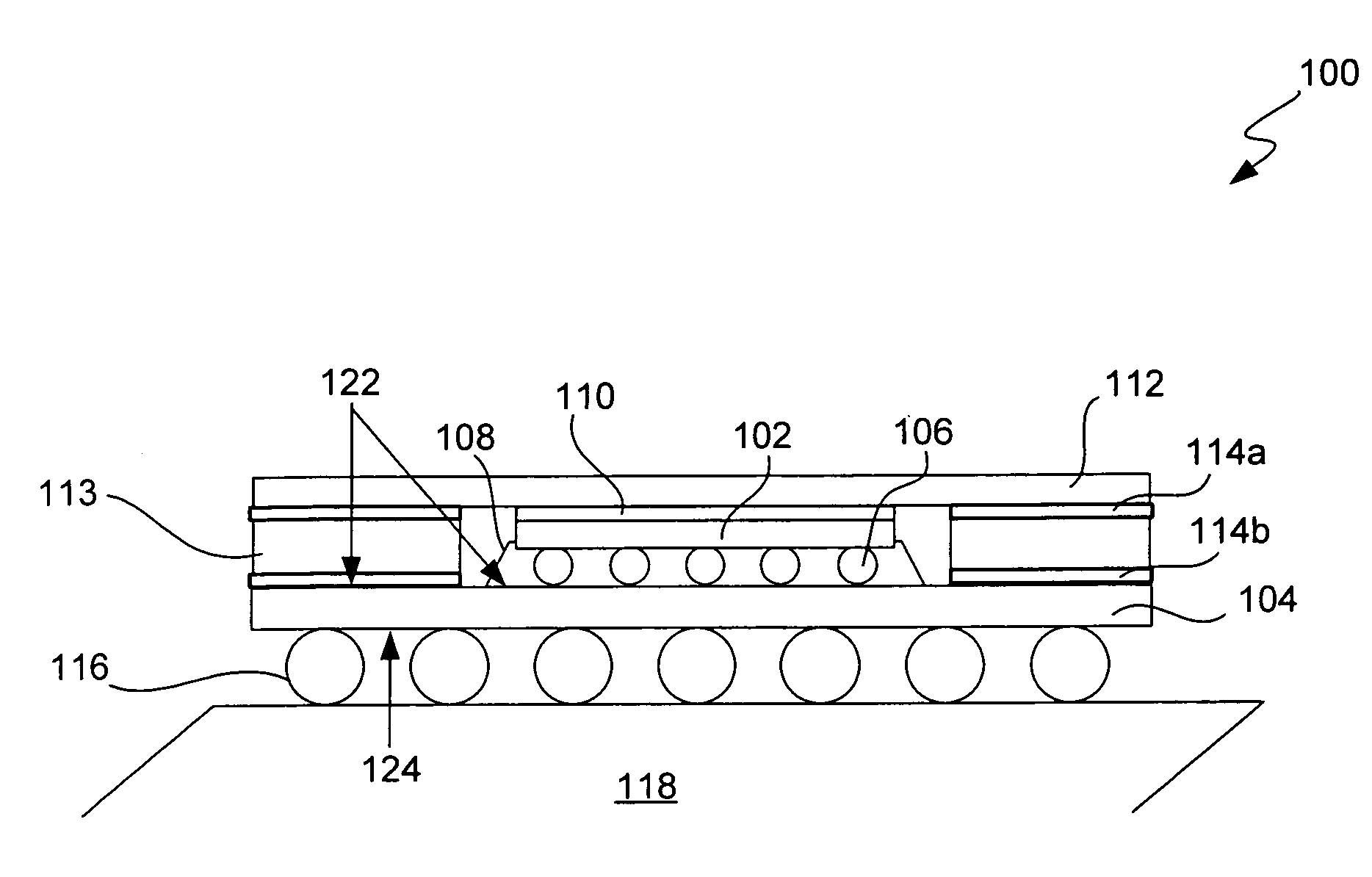

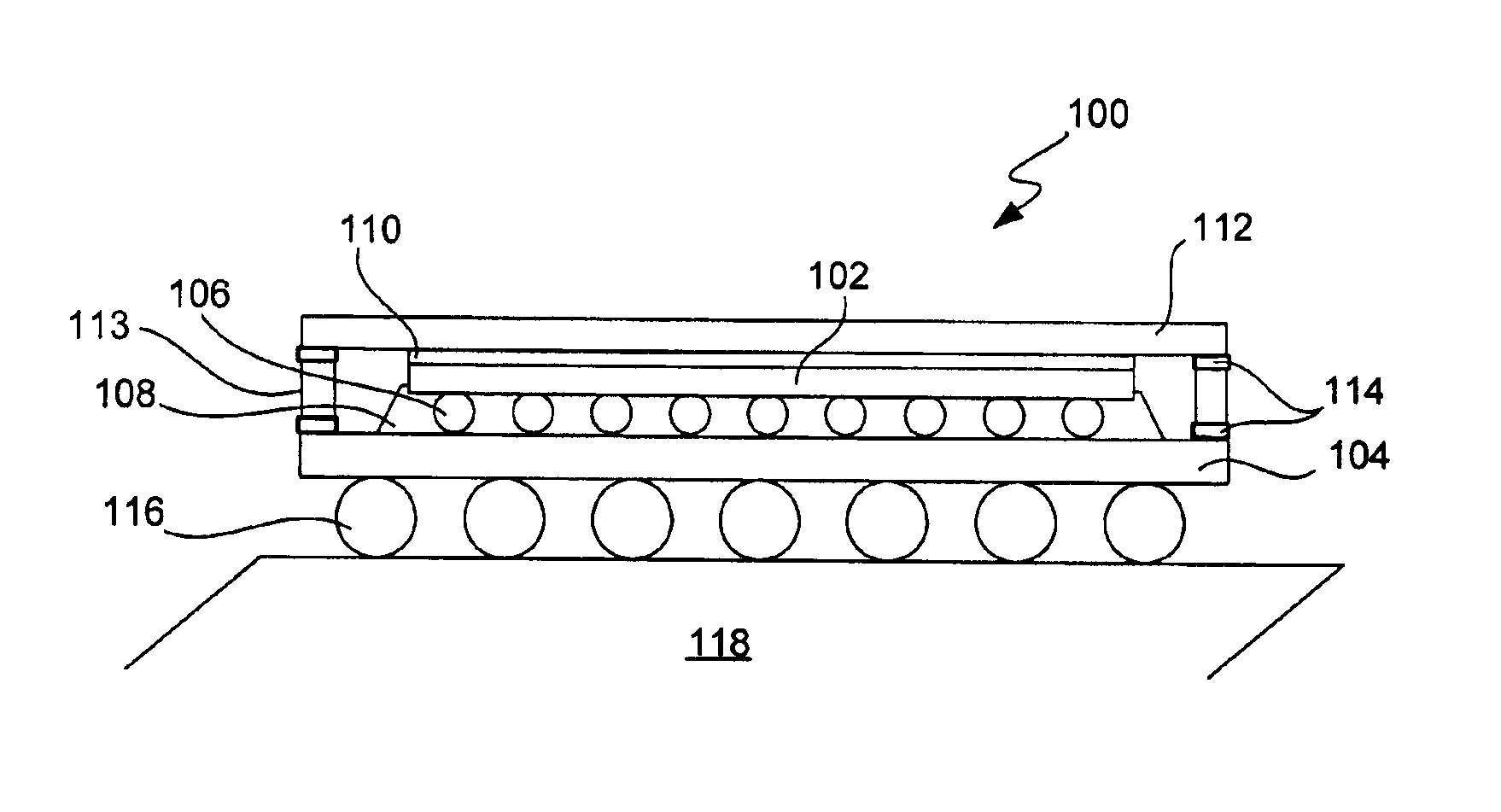

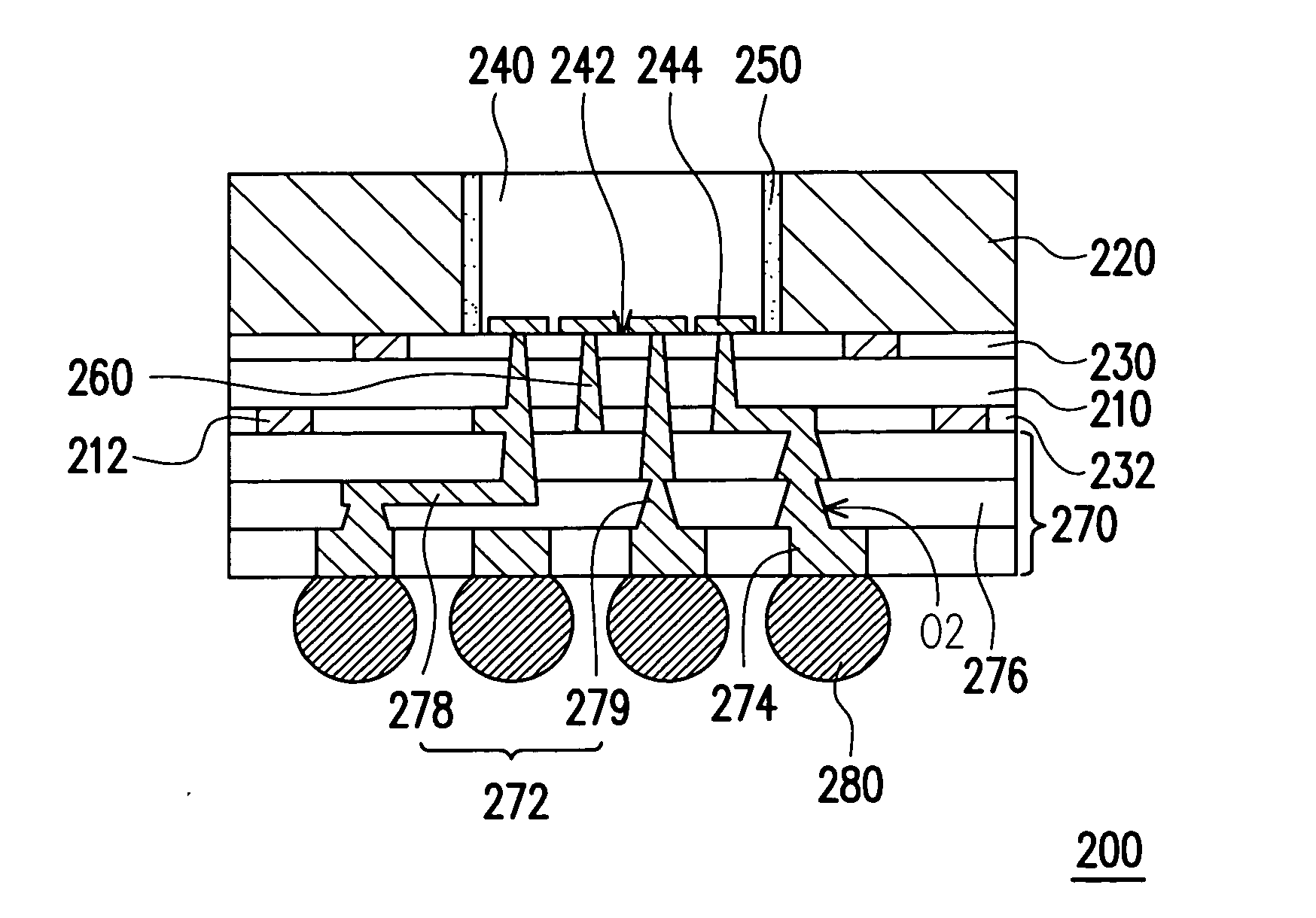

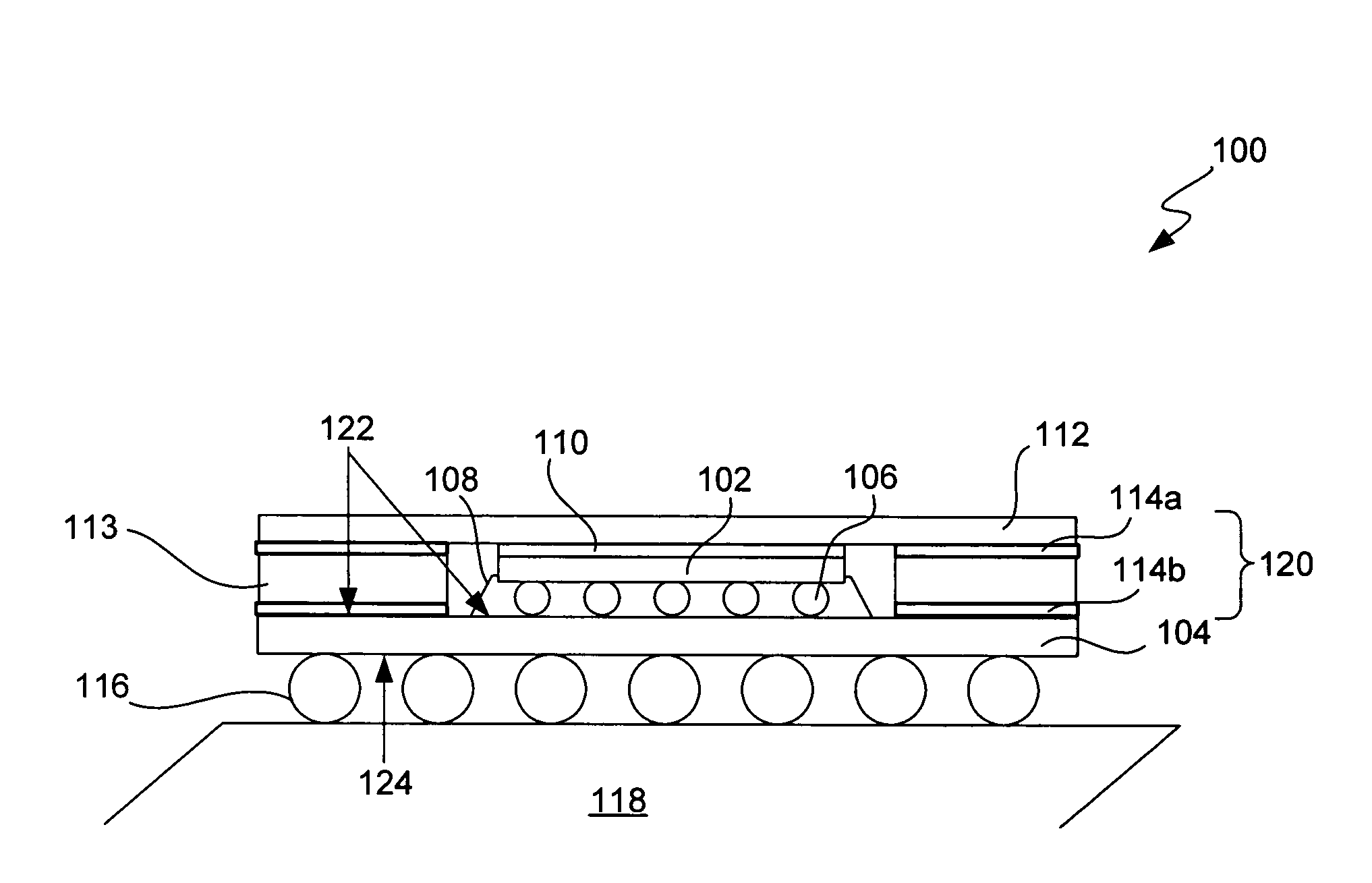

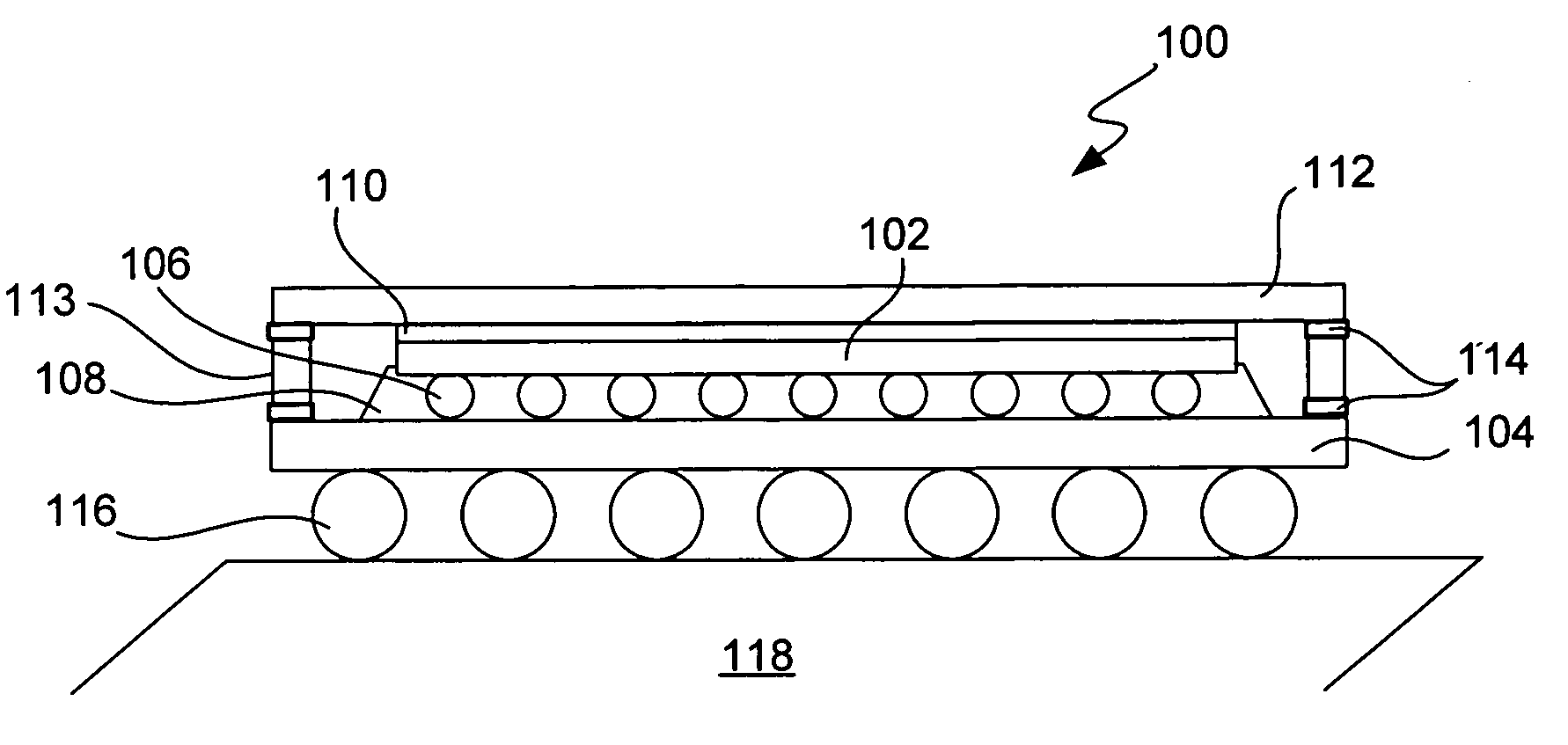

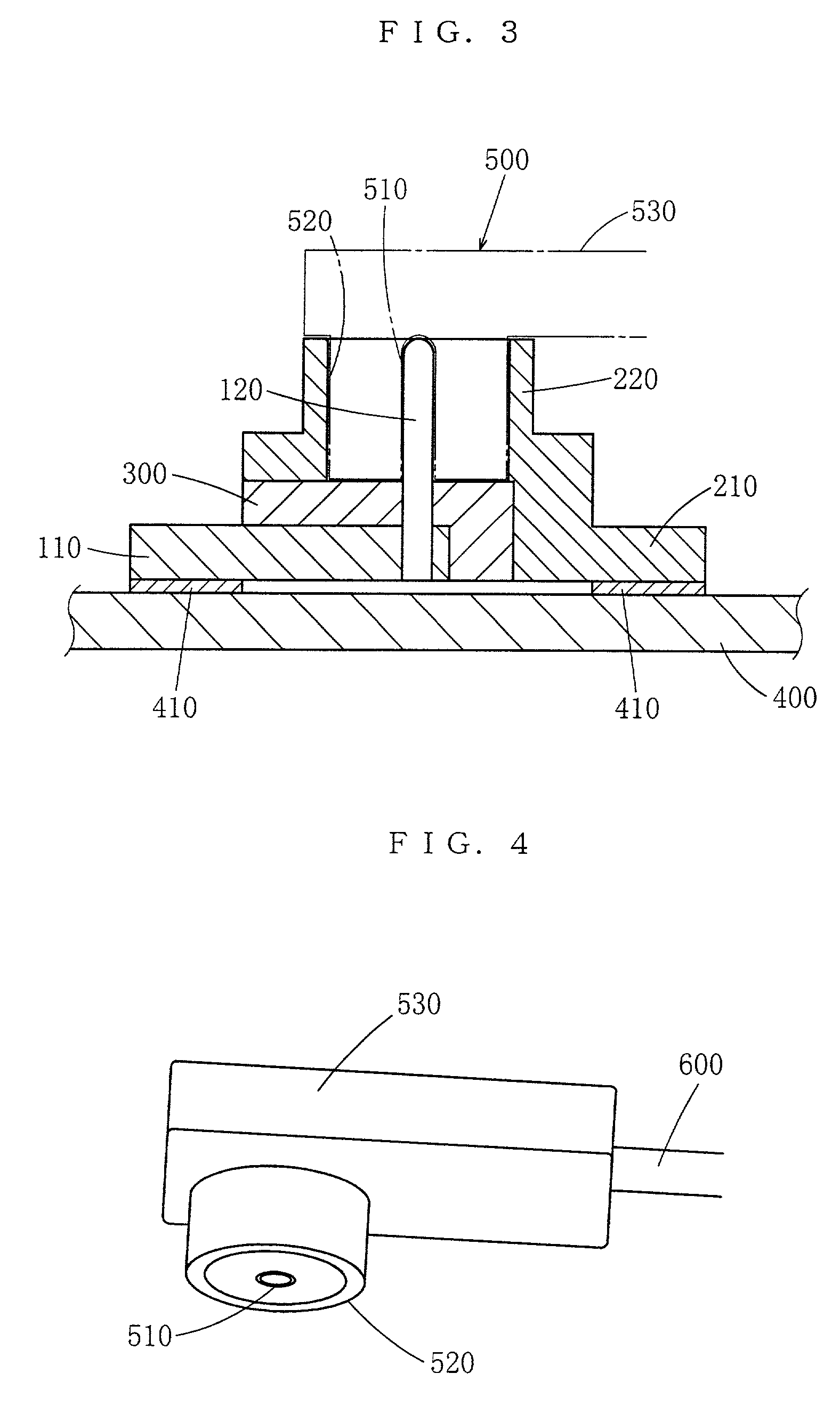

Electronic device carrier adapted for transmitting high frequency signals

InactiveUS7015574B2Reliable contactGood coplanarityCross-talk/noise/interference reductionSemiconductor/solid-state device detailsGround trackVoltage reference

An electronic device carrier (110) adapted for transmitting high-frequency signals, including a circuitized substrate with a plurality of conductive layers (240a to 240g) insulated from each other, the conductive layers being arranged in a sequence from a first one of the conductive layers (240a) wherein a plurality of signal tracks (200) each one ending with a contact area (205) for transmitting a high-frequency signal are formed, and a reference structure (215a, 215b, 230) connectable to a reference voltage or ground for shielding the signal tracks the reference structure includes at least one reference track (230) formed in a second one of the conductive layers (240b) adjacent to the first conductive layer and at least one further reference track formed in one of the conductive layers (240d) different from the first and second conductive layer, a portion of each signal track excluding at least the area corresponding to the orthographic projection of associated contact area being superimposed in plan view to a corresponding reference track and at least a part of the area corresponding to the orthographic projection of the contact area associated to each signal track being superimposed in plan view to a corresponding further reference track with interposition of a floating conductive track, i.e. a track not connected to any signal, reference voltage or ground track.

Owner:IBM CORP

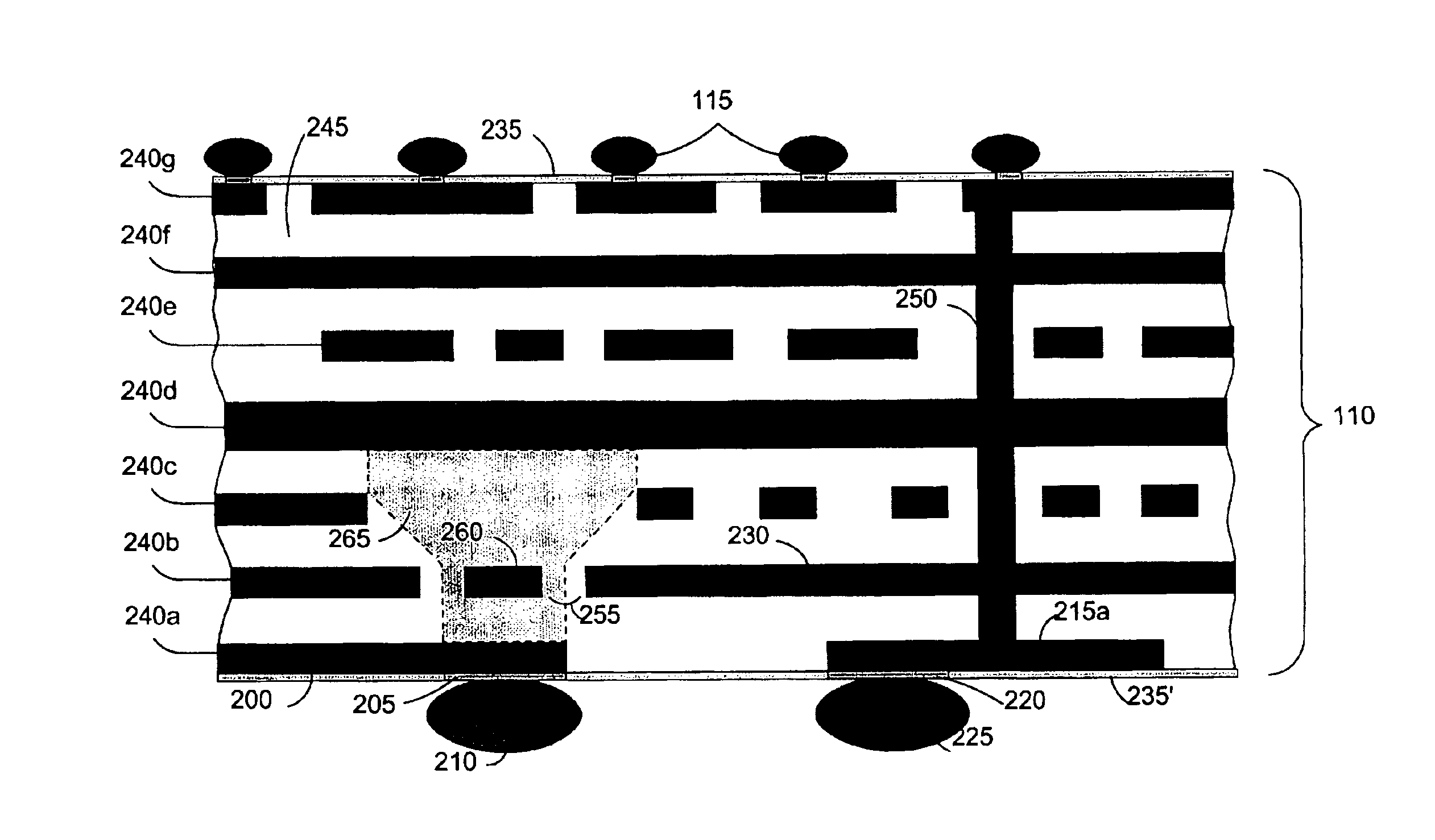

Universal surface-mount semiconductor package

ActiveUS9576932B2Flexible package manufacturing, coplanarity, low-profile capabilityEliminate needSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSurface mounting

In the fabrication of semiconductor packages, a leadframe is formed by masking and etching a metal sheet from both sides, and a plastic block is formed over a plurality of dice attached to die pads in the leadframe. A laser beam is used to form individual plastic capsules for each package, and a second laser beam is used to singulate the packages by severing the metal conductors, tie bars and rails between the packages. A wide variety of different types of packages, from gull-wing footed packages to leadless packages, with either exposed or isolated die pads, may be fabricated merely by varying the patterns of the openings in the mask layers and the width of the plastic trenches created by the first laser beam.

Owner:ADVENTIVE INT LTD

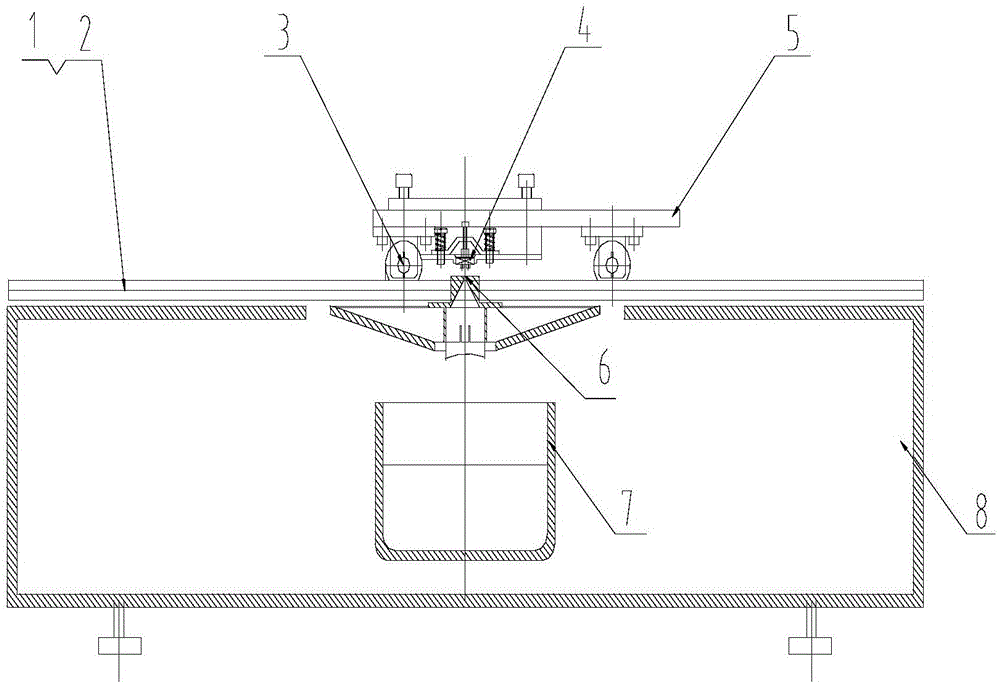

Special fixture for gold removal and tin coating for QFN encapsulated components, and method for gold removal and tin coating

ActiveCN106312233AAvoid difficultiesShort heating timeWelding/soldering/cutting articlesMetal working apparatusEngineeringTin

The invention discloses a special fixture for gold removal and tin coating for QFN encapsulated components, and a method for gold removal and tin coating. The special fixture is composed of a cross brace, a rail seat, a bottom frame, an upper supporting plate, a component supporting plate, a fastener, a press sheet, a long screw rod, a short screw rod, a component screw rod, a bearing seat, a cotter pin and a wheel shaft, wherein the cross brace and the rail seat form a guide rail; the wheel shaft, the bearing seat and the bottom frame are assembled into a lower supporting mechanism capable of moving on the guide rail; the upper supporting plate is fixed on the bottom frame, the component supporting plate is placed in a groove of the upper supporting plate, and the components are placed in installation hole positions of the component supporting plate; and the guide rail of the special fixture is horizontally placed on the table surface of a repair workbench for through-hole components, and the lower supporting mechanism is moved to enable bonding pads of the QFN components to complete gold removal and tin coating through the wave crests of a spewing molten tin-lead alloy. The method disclosed by the invention is high in applicability, and can be used for gold removal and tin coating for all the QFN components on the repair workbench for through-hole components.

Owner:BEIJING RES INST OF SPATIAL MECHANICAL & ELECTRICAL TECH

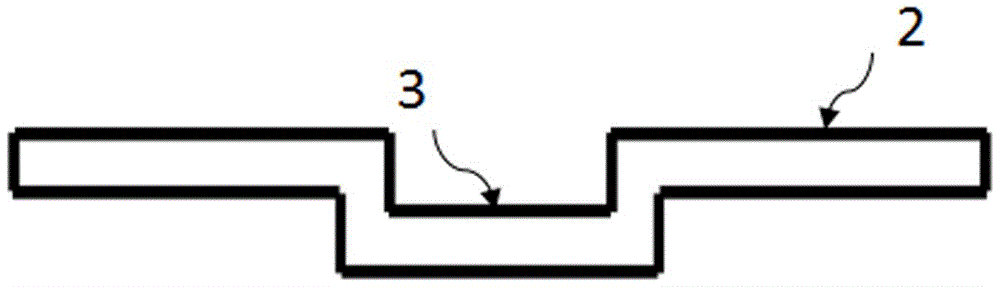

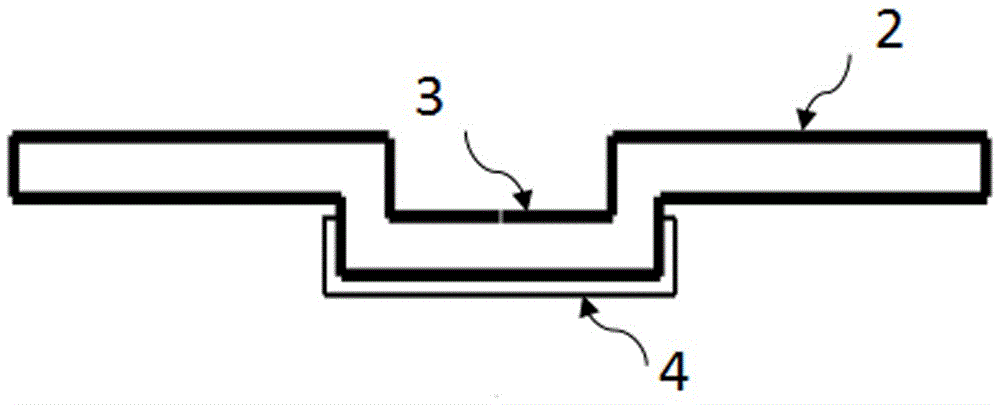

Weld-leg internally-installed surface-mounted elastic key and manufacturing method thereof

The invention discloses a weld-leg internally-installed surface-mounted elastic key and a manufacturing method thereof. The key comprises a base and a key soft body. The key soft body comprises a key convex body, an elastic soft main body and a conductive contact. The elastic soft main body is in a conical cylinder shape, the small-opening inner edge of the elastic soft main body is connected with the key convex body, the large opening end of the elastic soft main body is connected with the upper surface of the base, and a through hole corresponding to the large opening end of the elastic soft main body in size is formed in the middle of the base; the conductive contact is arranged on the lower end face of the key convex body; protruding-downwards weld legs are arranged on the bottom end face of the base and are not exposed out of the outer side of the base, and the lower end faces and the periphery faces of the weld legs are the weld faces. A key lead is good in coplanarity, and the requirements of the size, the shape and the number of the different key leads can be met; the weld-leg internally-installed surface-mounted elastic key is applied to surface mounting application, and has the advantages of being low in manufacturing cost and good in practicability; by means of the key, gapless arrangement can be achieved, and particularly, the key has the prominent advantages in high-density product application occasions and high-integration-density product application occasions.

Owner:GUILIN XUYAN ELECTROMECHANICAL TECH CO LTD

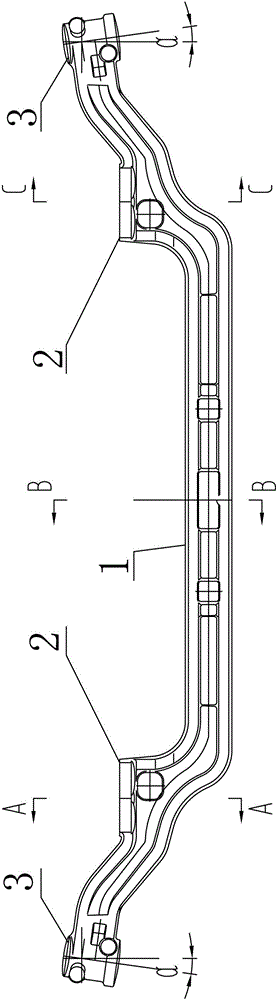

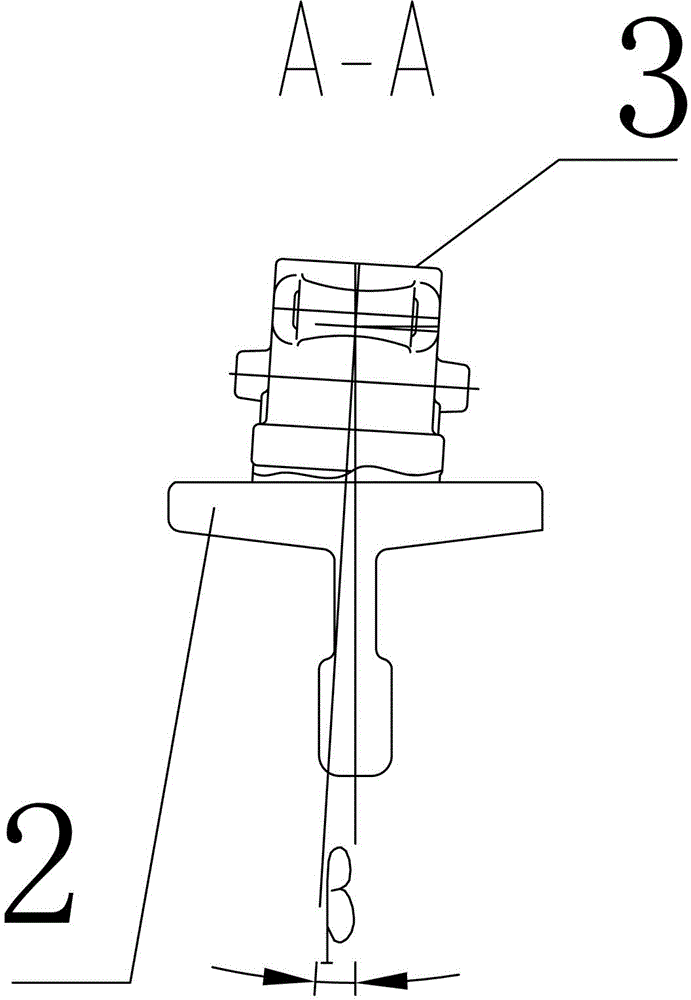

Special front shaft machining clamp capable of automatically aligning caster angle and inward camber

InactiveCN104924123ASuperiorReduce distortionAutomatic control devicesFeeding apparatusFistCaster angle

The invention provides a special front shaft machining clamp capable of automatically aligning a caster angle and an inward camber. The caster angle and the inward camber of a workblank are automatically aligned within a certain amount of deformation of the workblank of a front shaft, a front shaft leaf spring face is directly milled after alignment is performed, and a coordinated system using the aligned front shaft leaf spring face as the positioning basis is built and used as the basis during subsequent machining. According to the scheme, the clamp comprises a front shaft H-shaped beam portion auxiliary supporting structure, an H-shaped beam portion auxiliary clamping structure, a clamping H-shaped beam portion, a wedge iron self-locking clamping unit, a manual thread clamping unit, a floating supporting device and an inward camber correcting unit, wherein the front shaft H-shaped beam portion auxiliary supporting structure can abut against the front shaft H-shaped beam portion so as to play a supporting role, the H-shaped beam portion auxiliary clamping structure can compress the portion above the front shaft H-shaped beam portion, the clamping H-shaped beam portion is matched with the H-shaped beam portion auxiliary supporting structure, the wedge iron self-locking clamping unit is arranged at the rear portion of the front shaft leaf spring face, the manual thread clamping unit is arranged at the front portion of the front shaft leaf spring face and used in cooperation with the wedge iron self-locking clamping unit to clamp the front shaft leaf spring face portion, the floating supporting device is arranged at the lower portion of the front shaft leaf spring face, and the inward camber correcting unit is arranged at the position of a front shaft left fist face and used for correcting the front shaft inward camber.

Owner:ANYANG INST OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com