Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1147results about How to "Finish quickly" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

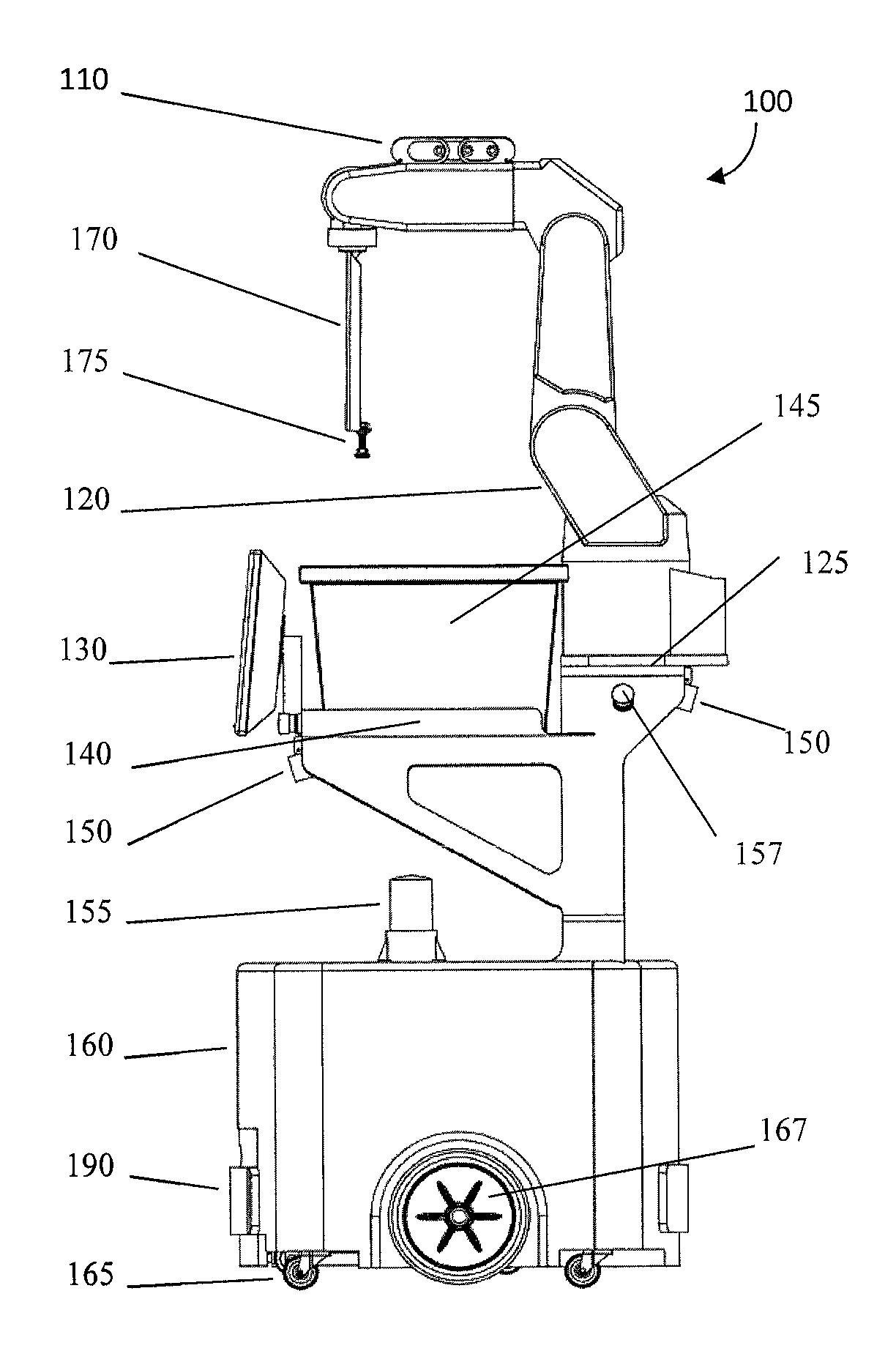

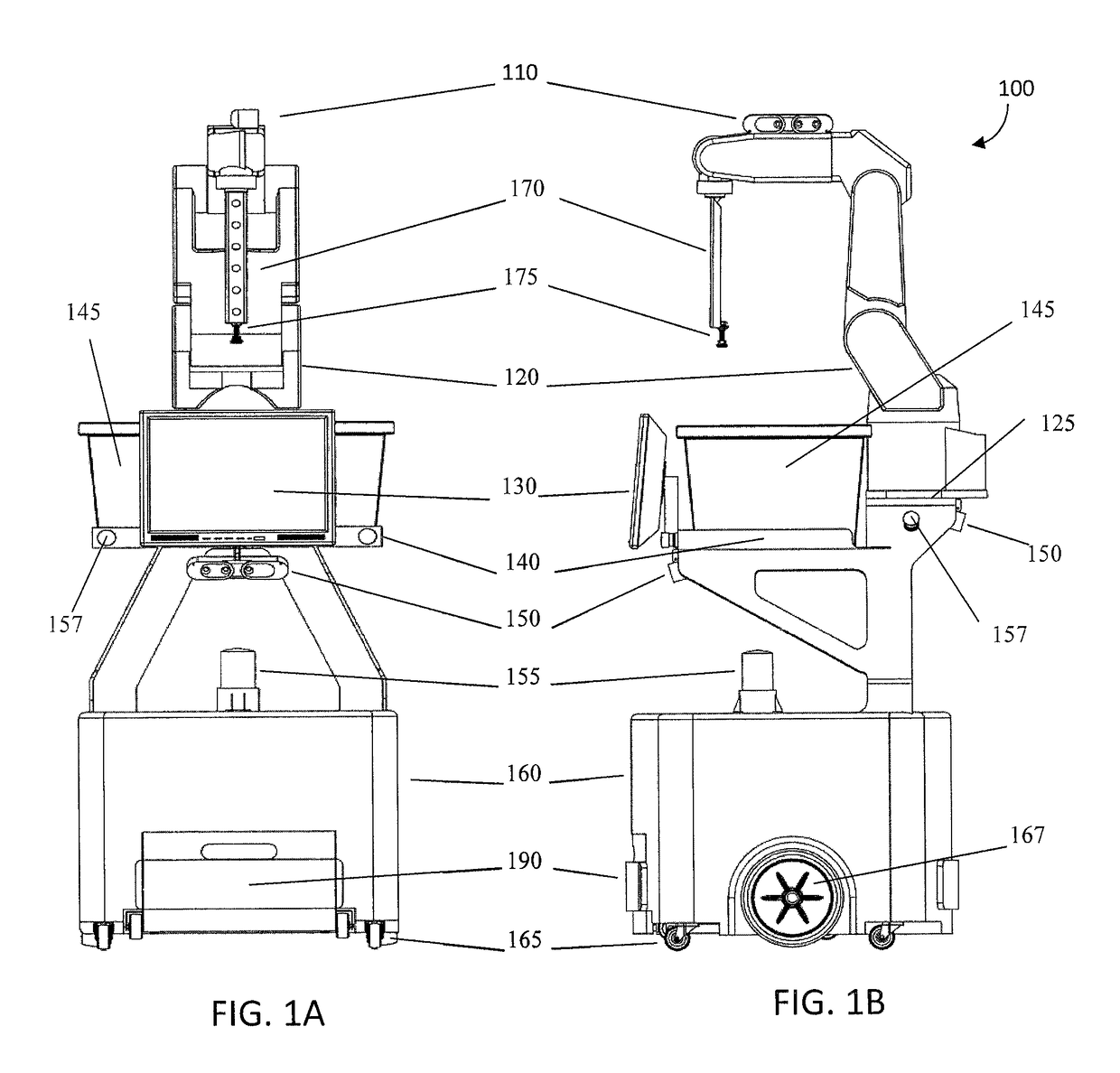

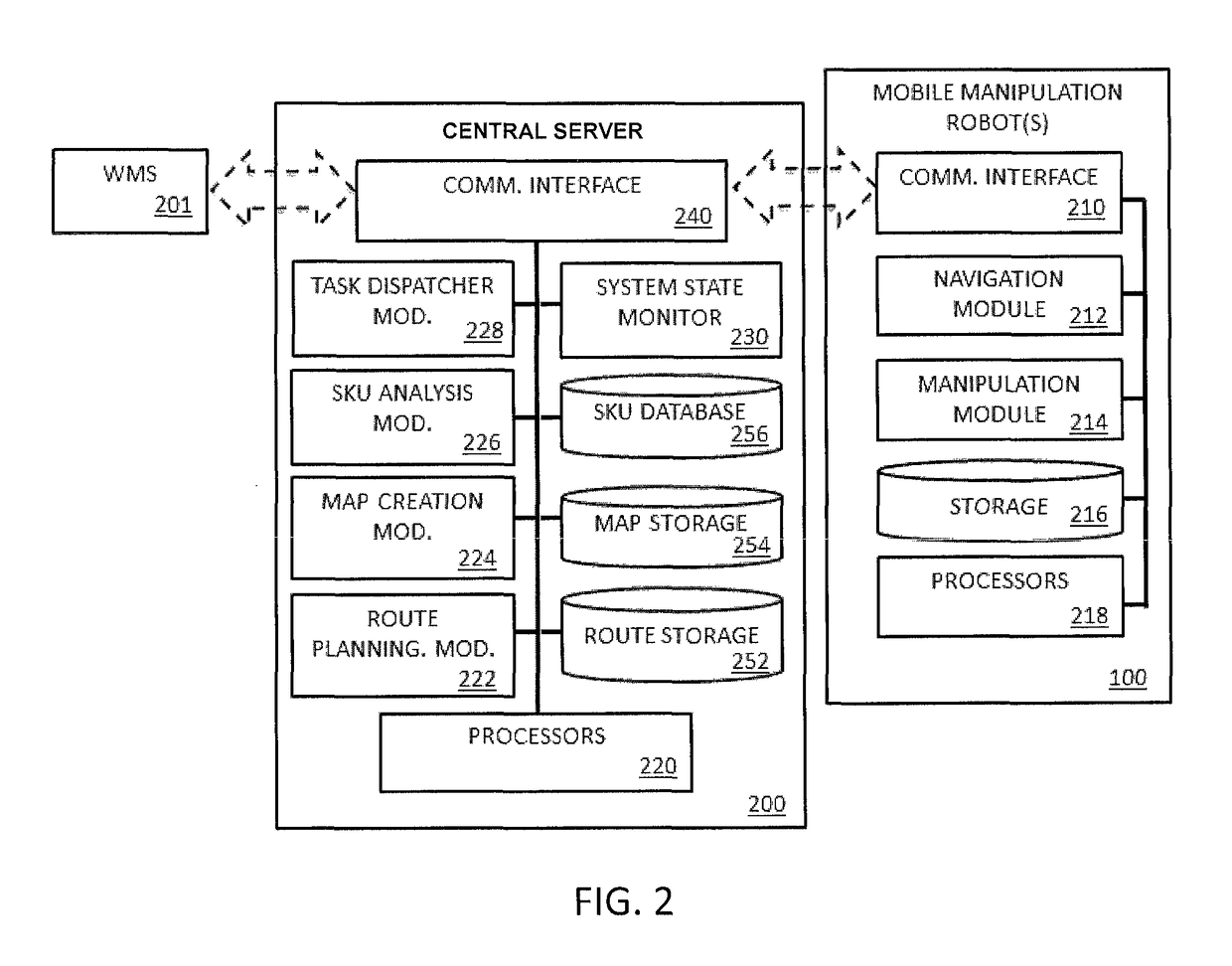

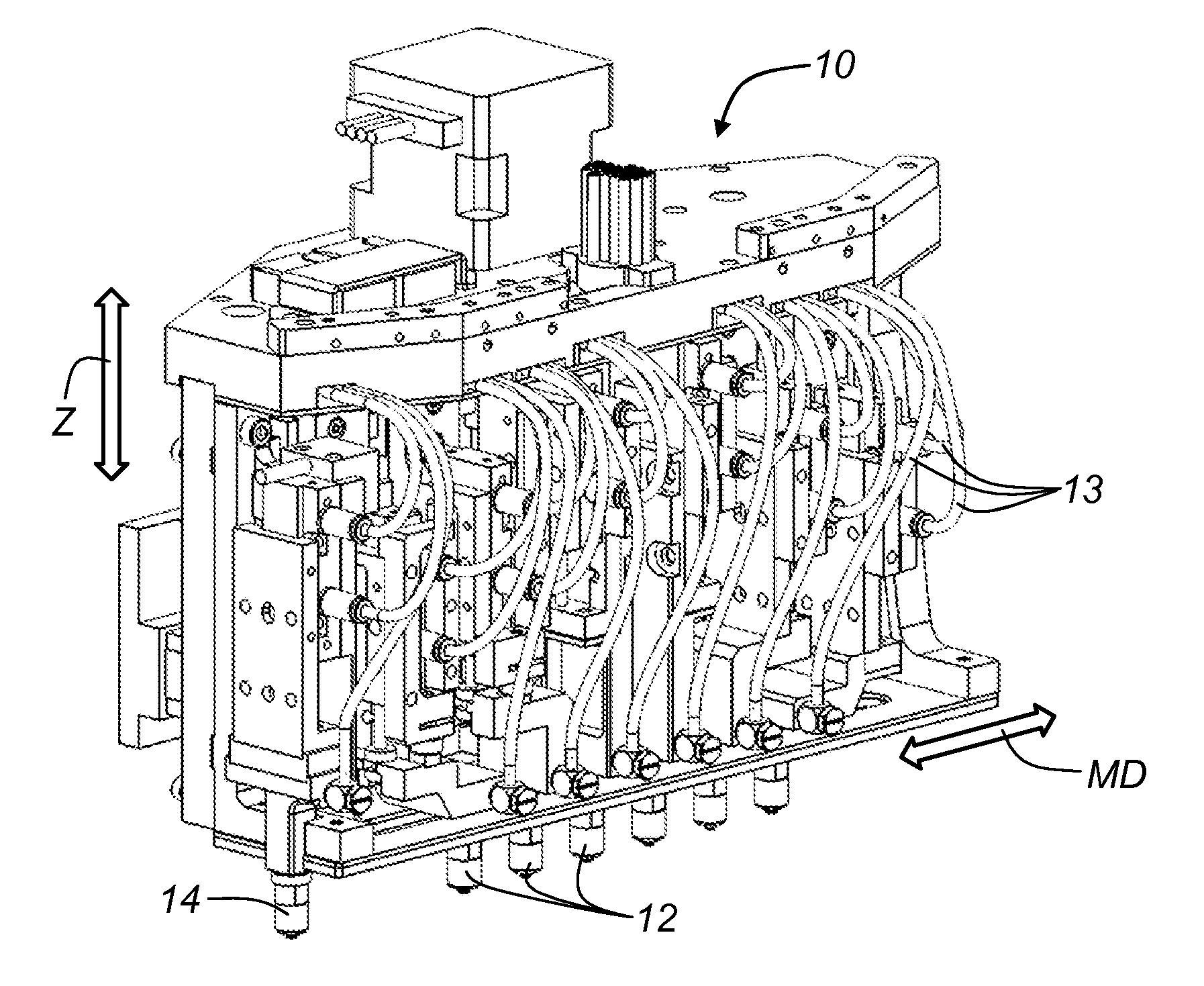

System and method for piece-picking or put-away with a mobile manipulation robot

ActiveUS20150032252A1Overcomes shortcomingReduce complexity and costProgramme-controlled manipulatorAutonomous decision making processLogistics managementPosition dependent

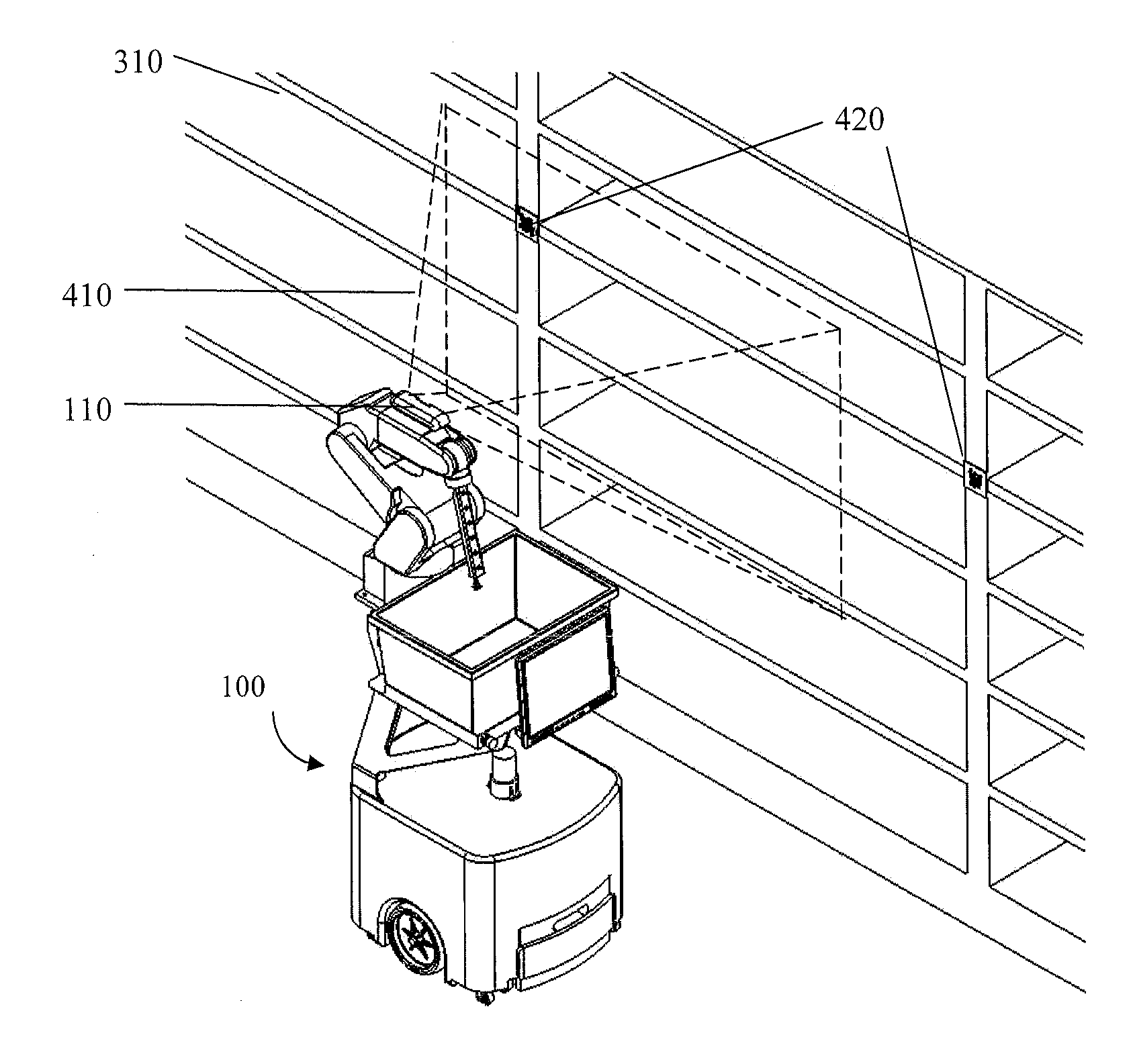

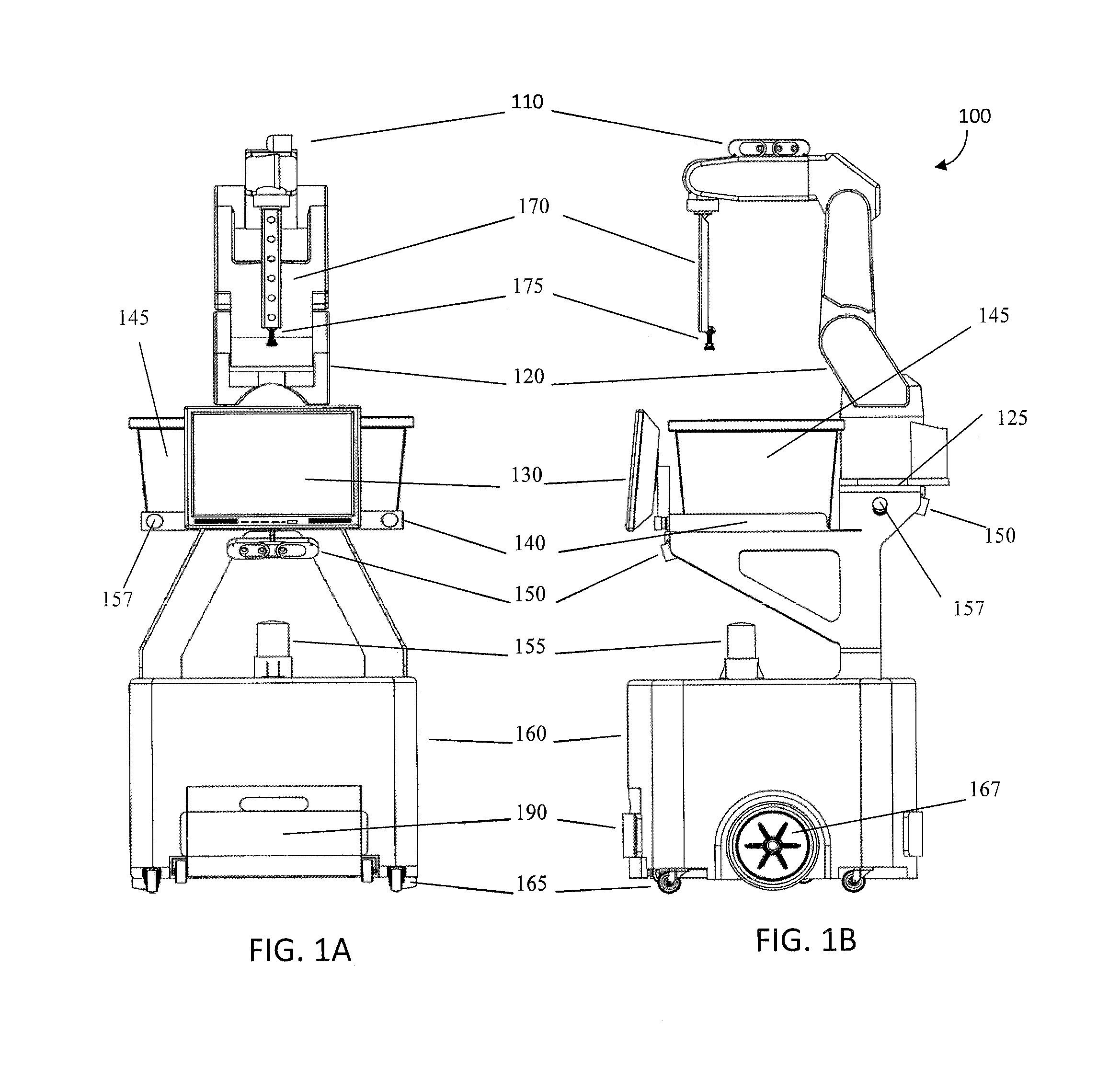

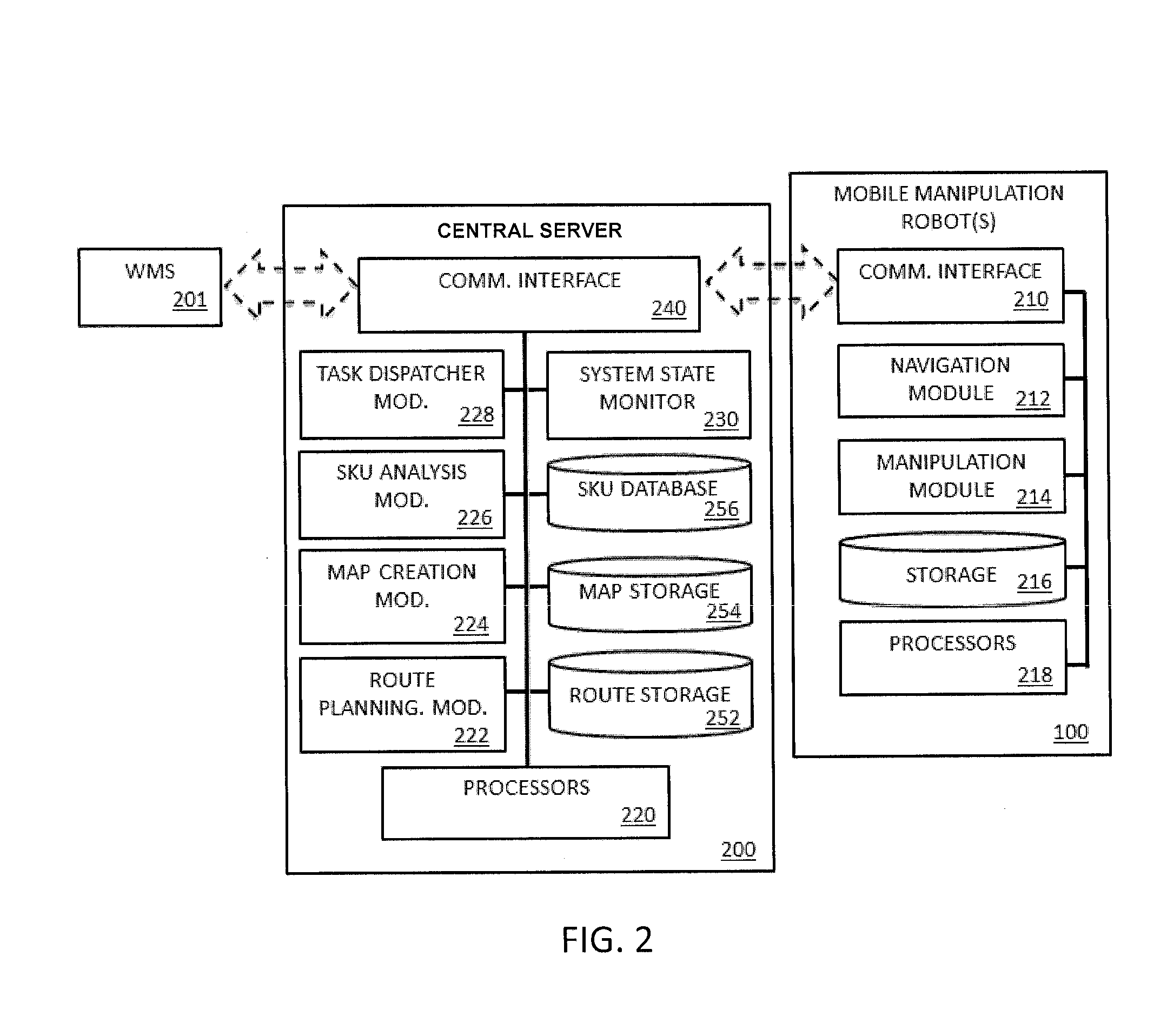

A method and system for piece-picking or piece put-away within a logistics facility. The system includes a central server and at least one mobile manipulation robot. The central server is configured to communicate with the robots to send and receive piece-picking data which includes a unique identification for each piece to be picked, a location within the logistics facility of the pieces to be picked, and a route for the robot to take within the logistics facility. The robots can then autonomously navigate and position themselves within the logistics facility by recognition of landmarks by at least one of a plurality of sensors. The sensors also provide signals related to detection, identification, and location of a piece to be picked or put-away, and processors on the robots analyze the sensor information to generate movements of a unique articulated arm and end effector on the robot to pick or put-away the piece.

Owner:IAM ROBOTICS

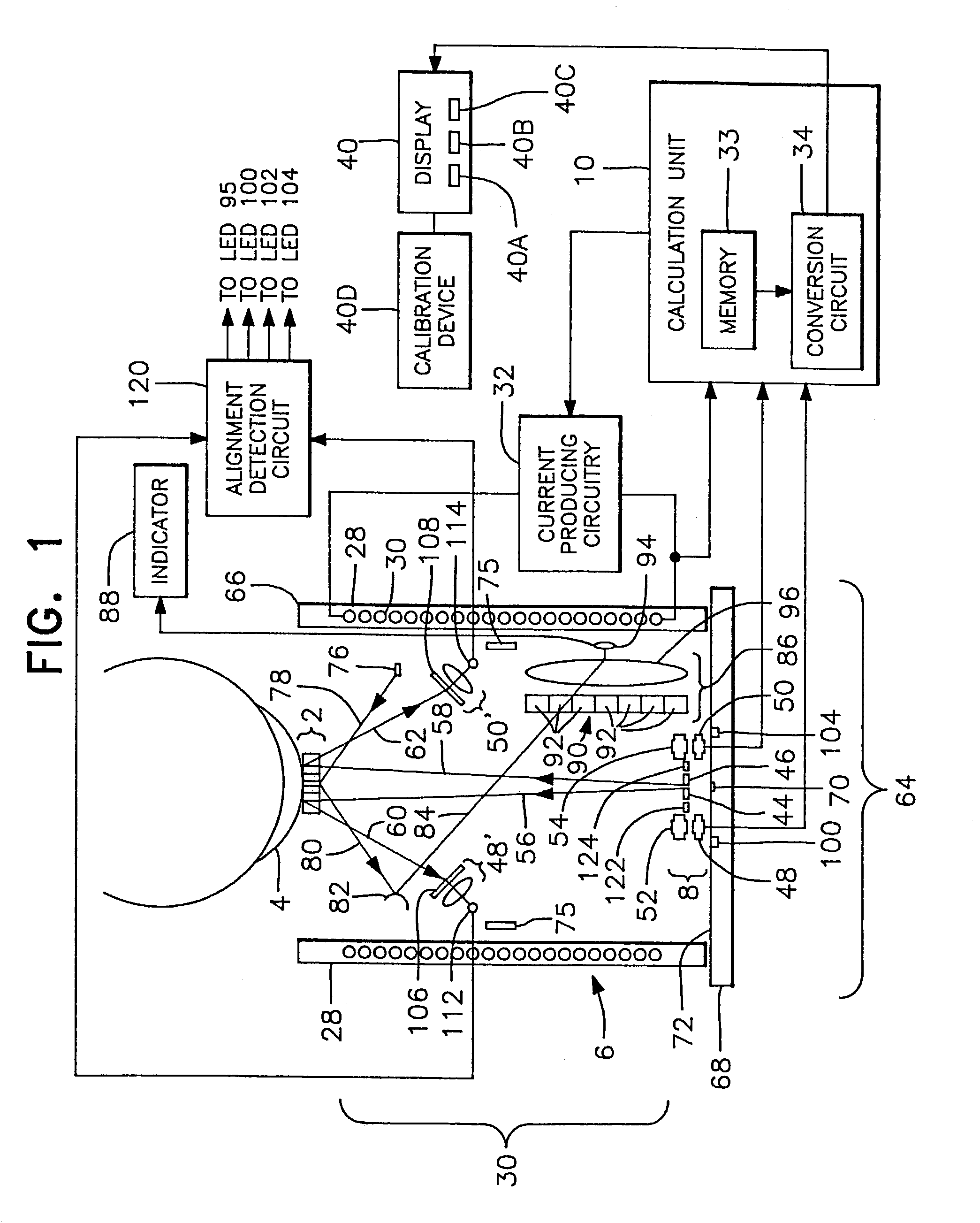

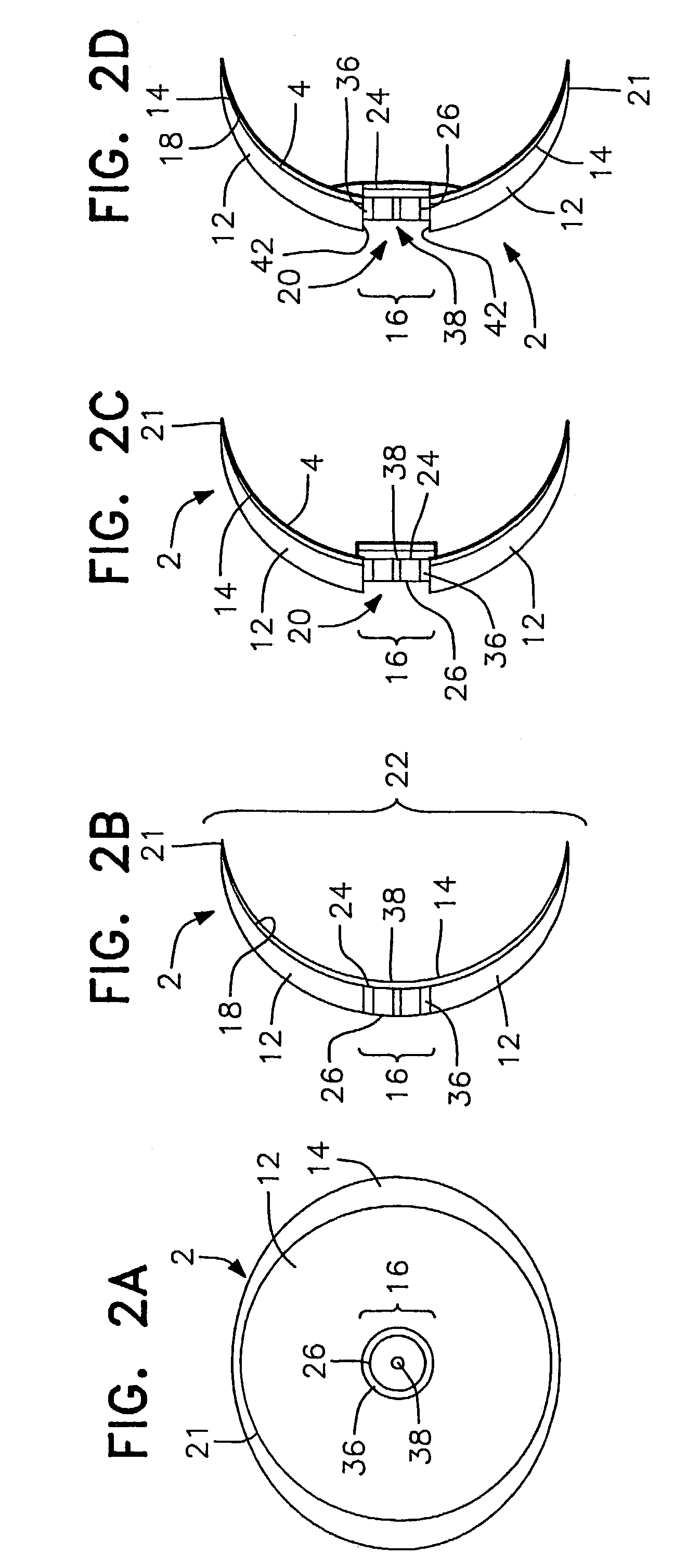

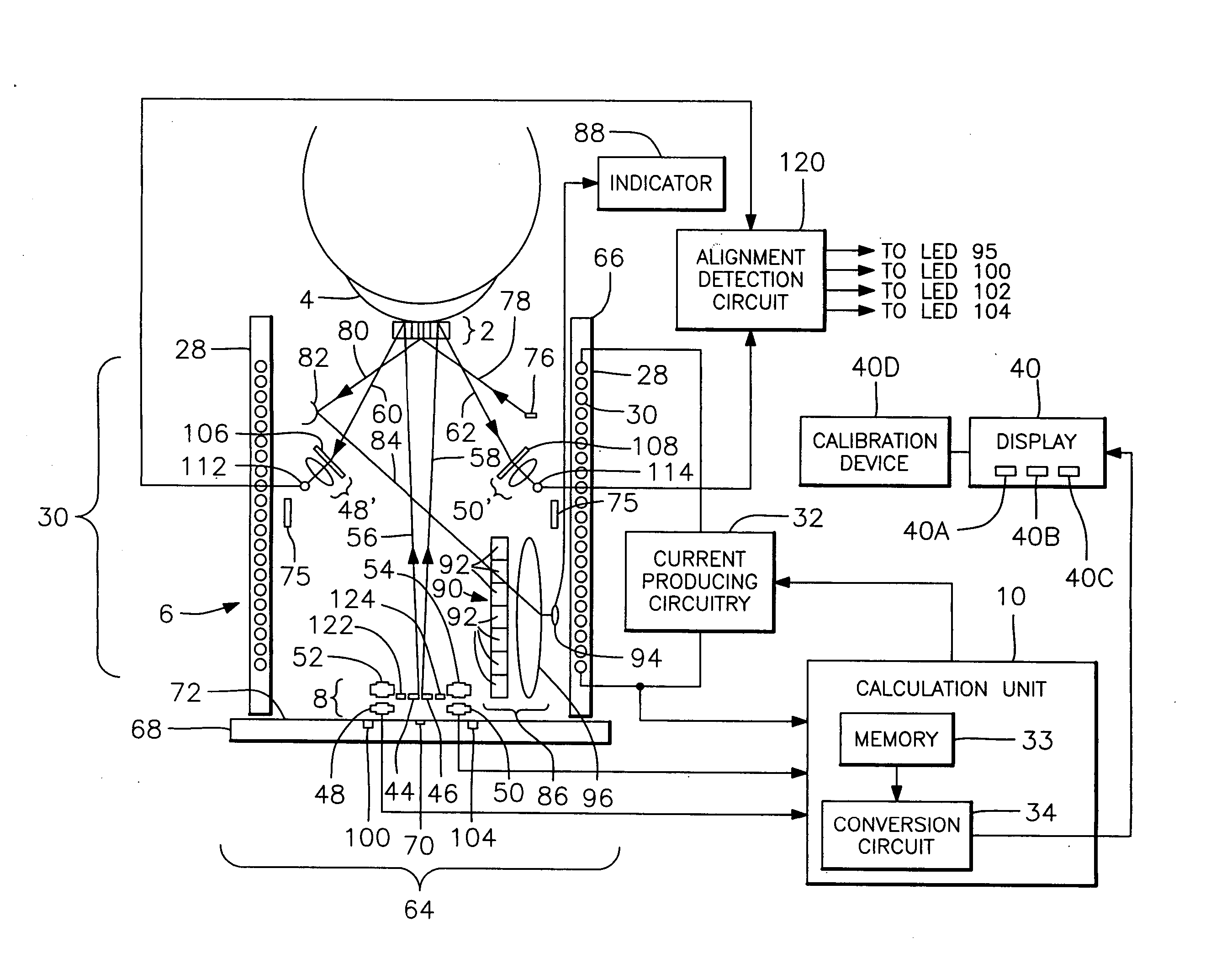

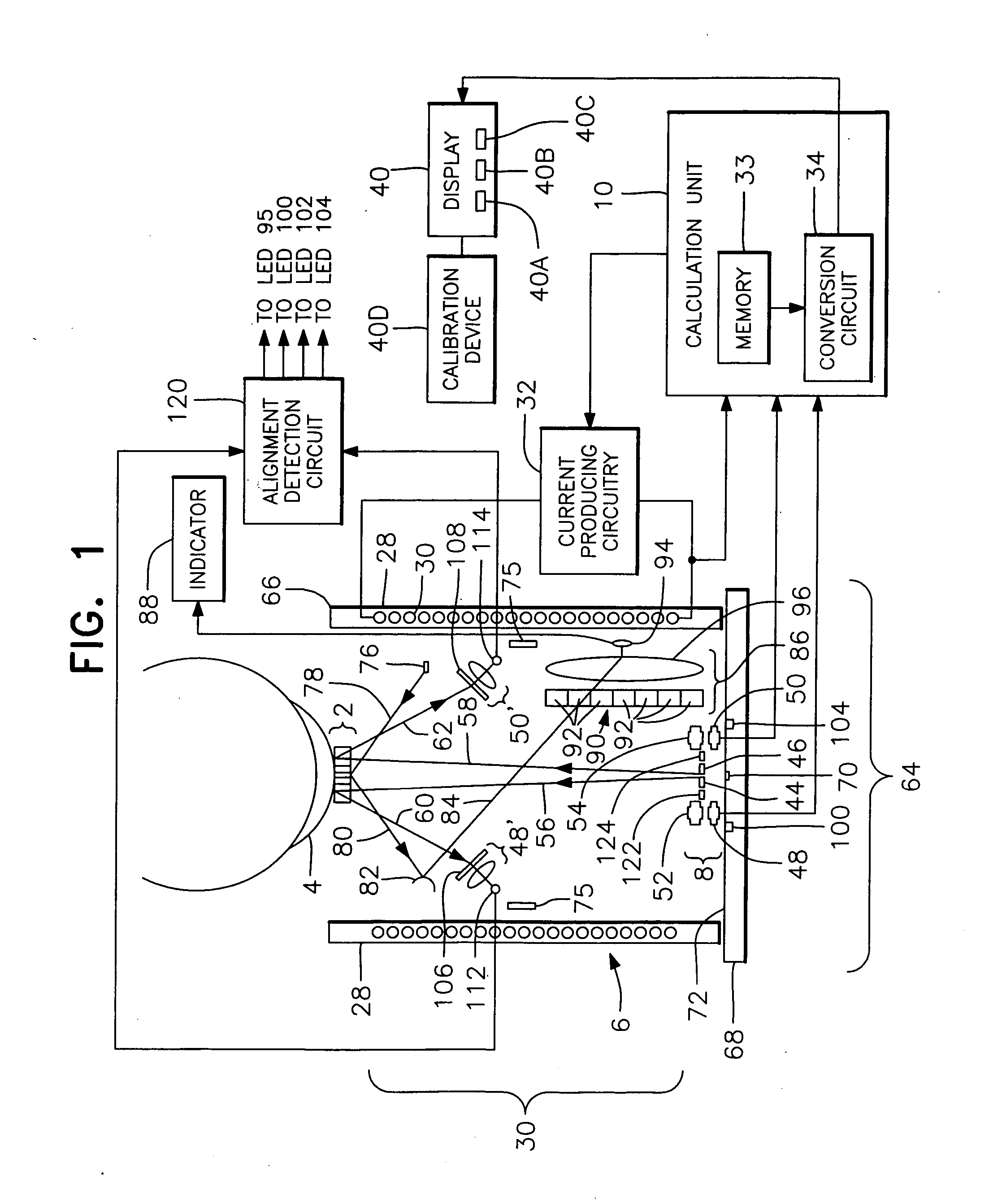

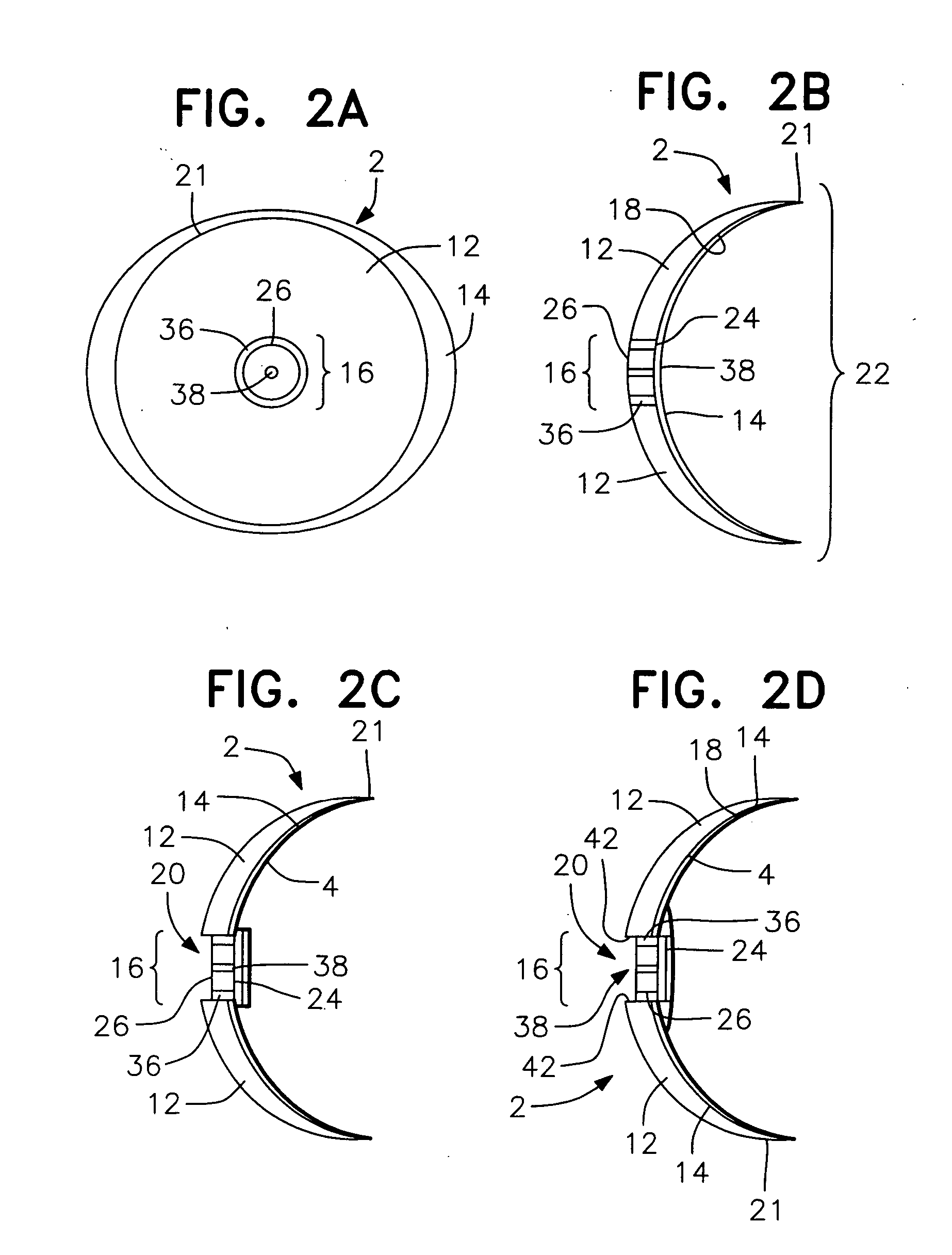

Noninvasive measurement of chemical substances

InactiveUS7041063B2High densityEarly diagnosisOrganic active ingredientsHeart defibrillatorsConjunctivaInfrared

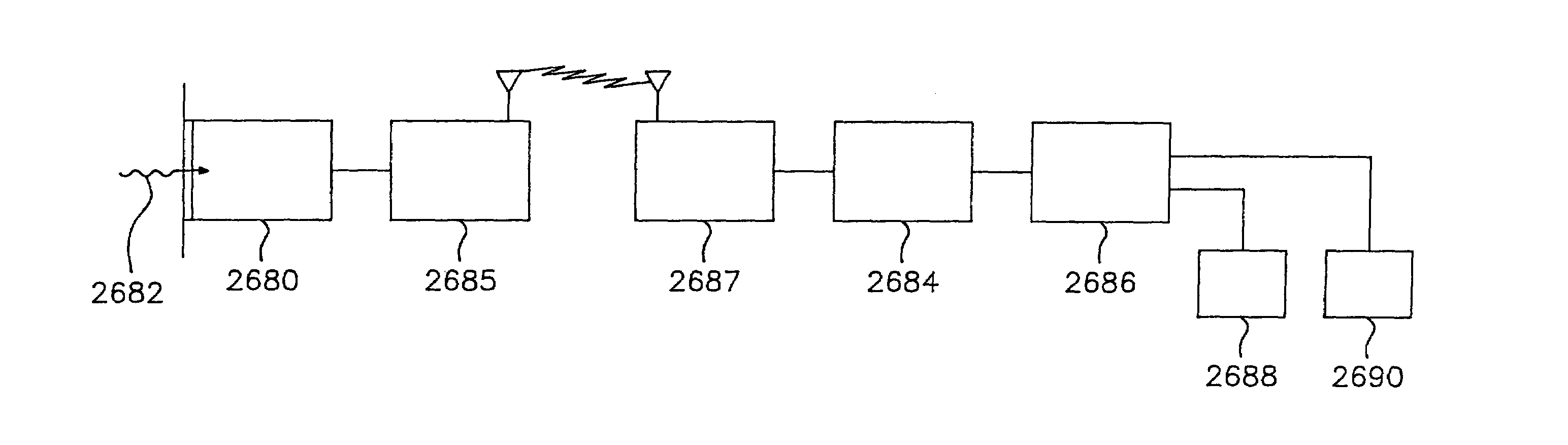

Utilization of a contact device placed on the eye in order to detect physical and chemical parameters of the body as well as the non-invasive delivery of compounds according to these physical and chemical parameters, with signals being transmitted continuously as electromagnetic waves, radio waves, infrared and the like. One of the parameters to be detected includes non-invasive blood analysis utilizing chemical changes and chemical products that are found in the conjunctiva and in the tear film. A transensor mounted in the contact device laying on the cornea or the surface of the eye is capable of evaluating and measuring physical and chemical parameters in the eye including non-invasive blood analysis. The system utilizes eye lid motion and / or closure of the eye lid to activate a microminiature radio frequency sensitive transensor mounted in the contact device. The signal can be communicated by wires or radio telemetered to an externally placed receiver. The signal can then be processed, analyzed and stored. Several parameters can be detected including a complete non-invasive analysis of blood components, measurement of systemic and ocular blood flow, measurement of heart rate and respiratory rate, tracking operations, detection of ovulation, detection of radiation and drug effects, diagnosis of ocular and systemic disorders and the like.

Owner:GEELUX HLDG LTD

Contact lens for collecting tears and detecting analytes for determining health status, ovulation detection, and diabetes screening

InactiveUS20070016074A1Increase oxygenationIncreased riskOrganic active ingredientsHeart defibrillatorsConfocalChemical products

Owner:GEELUX HLDG LTD

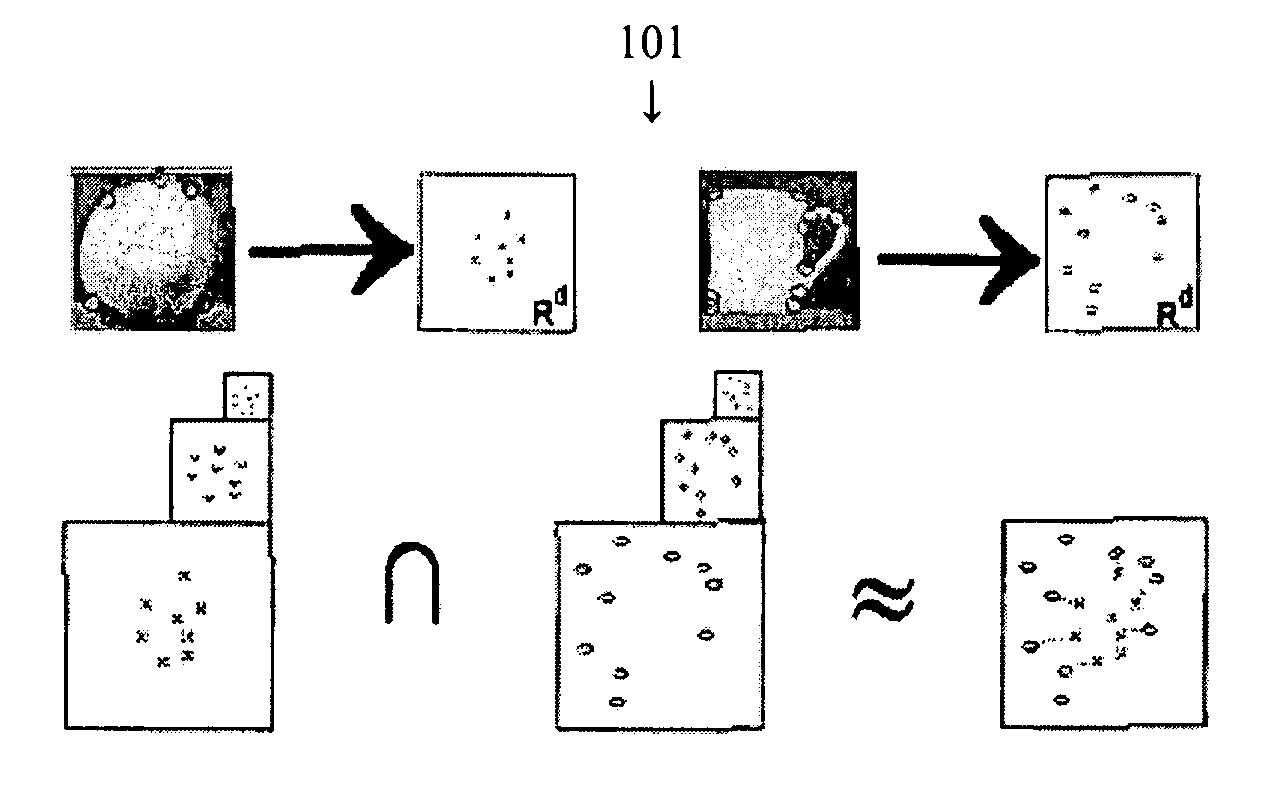

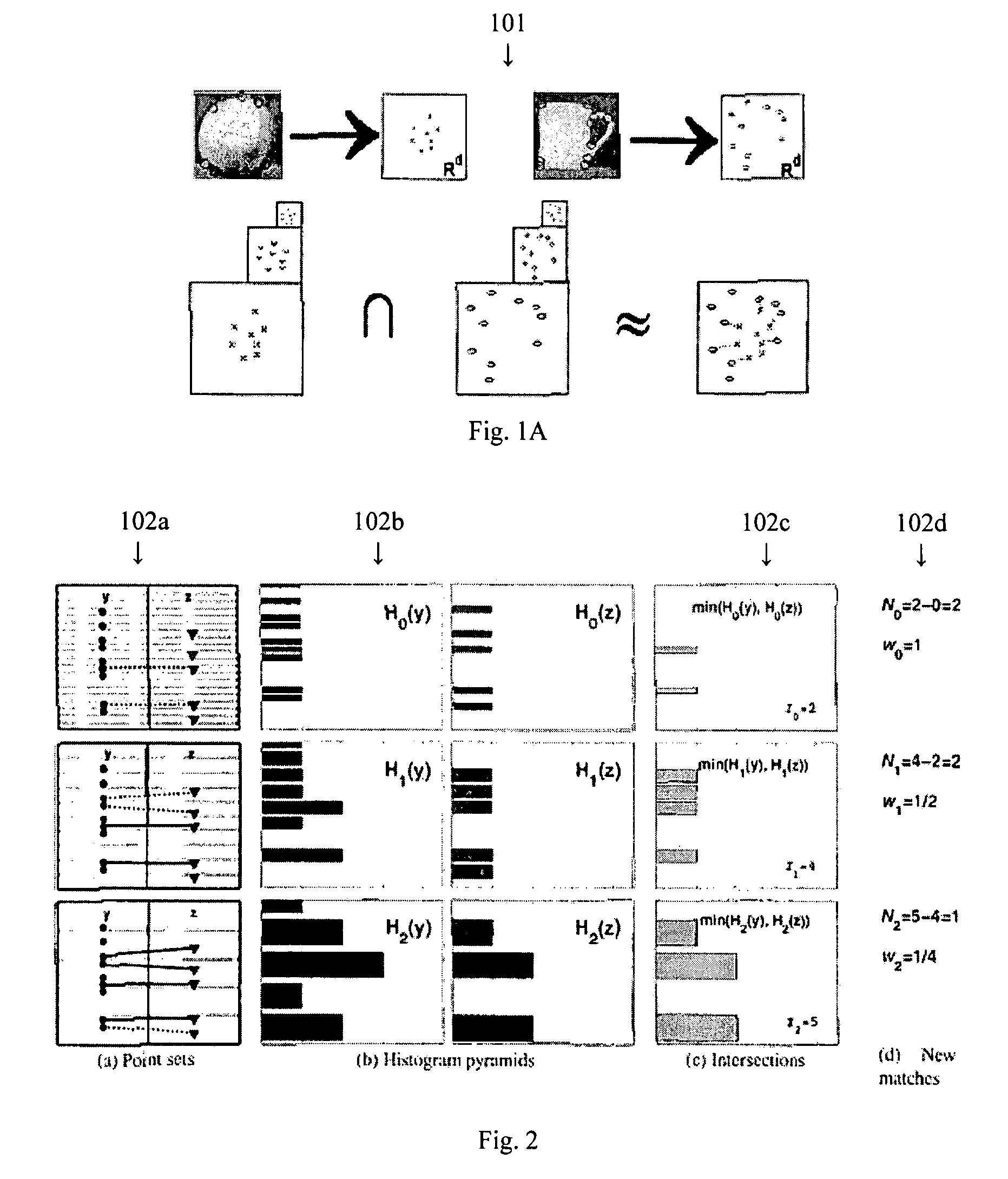

Pyramid match kernel and related techniques

InactiveUS7949186B2Search can be accomplished more quicklyFinish quicklyCharacter and pattern recognitionFeature vectorCluster group

Owner:MASSACHUSETTS INST OF TECH

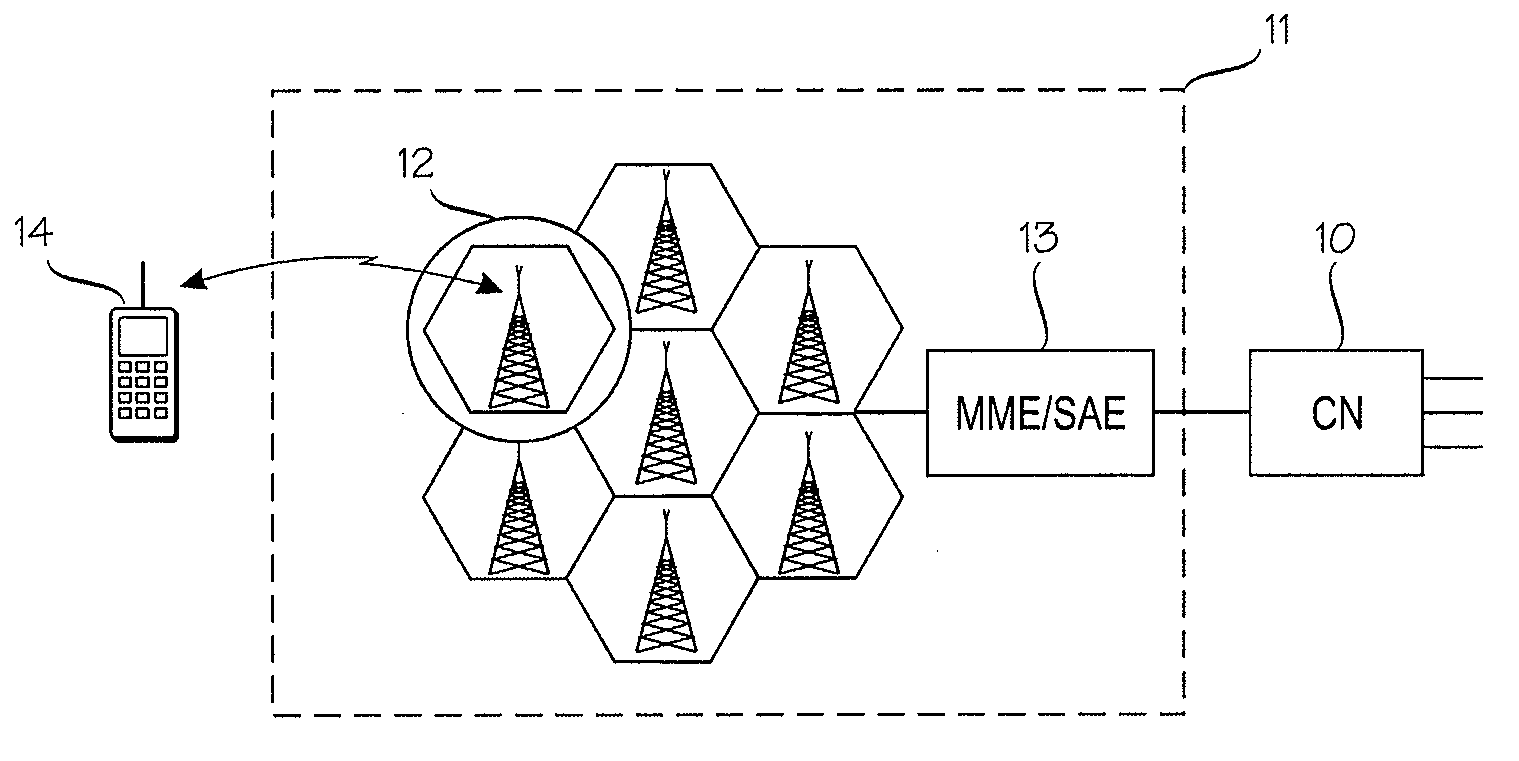

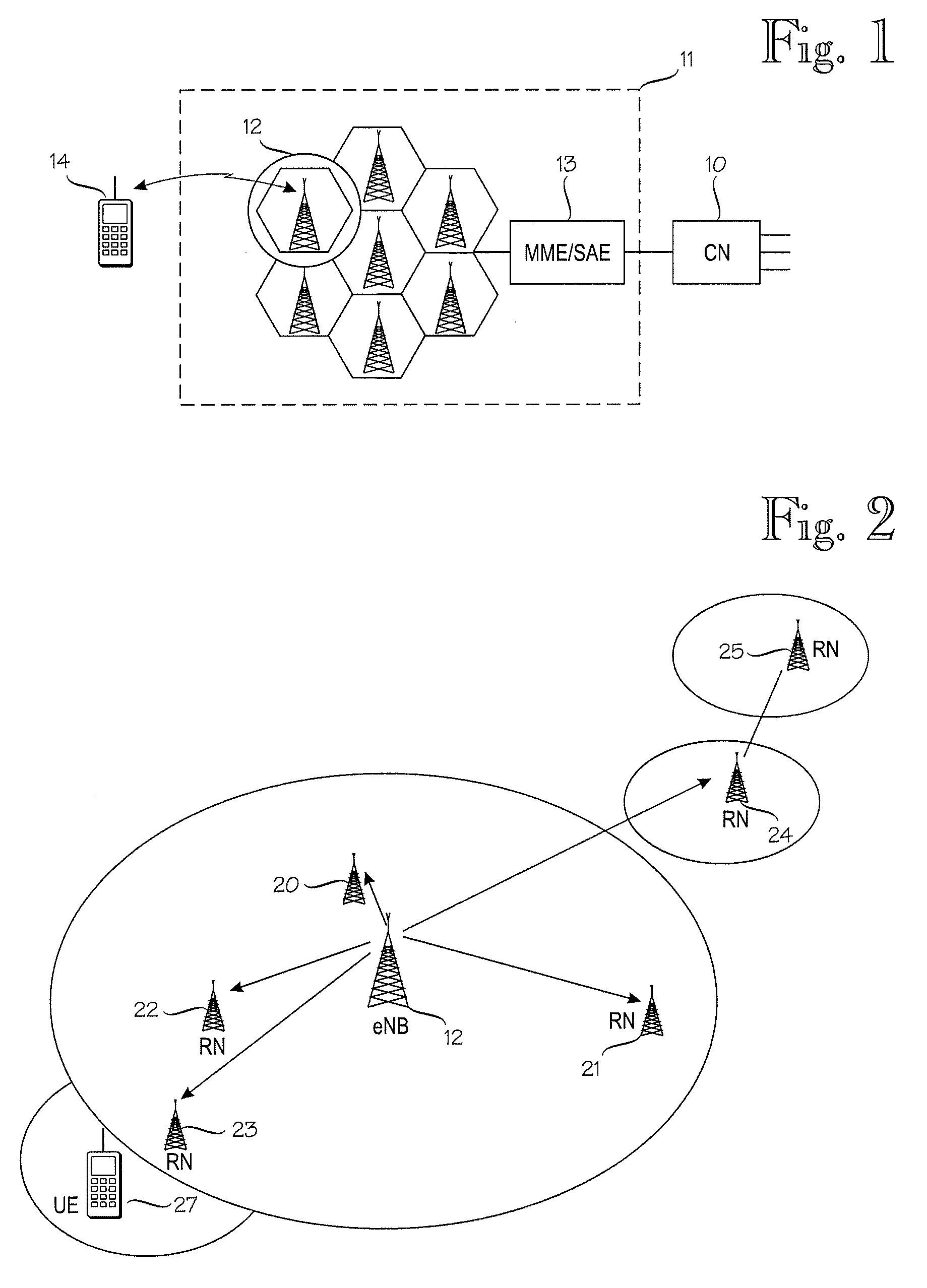

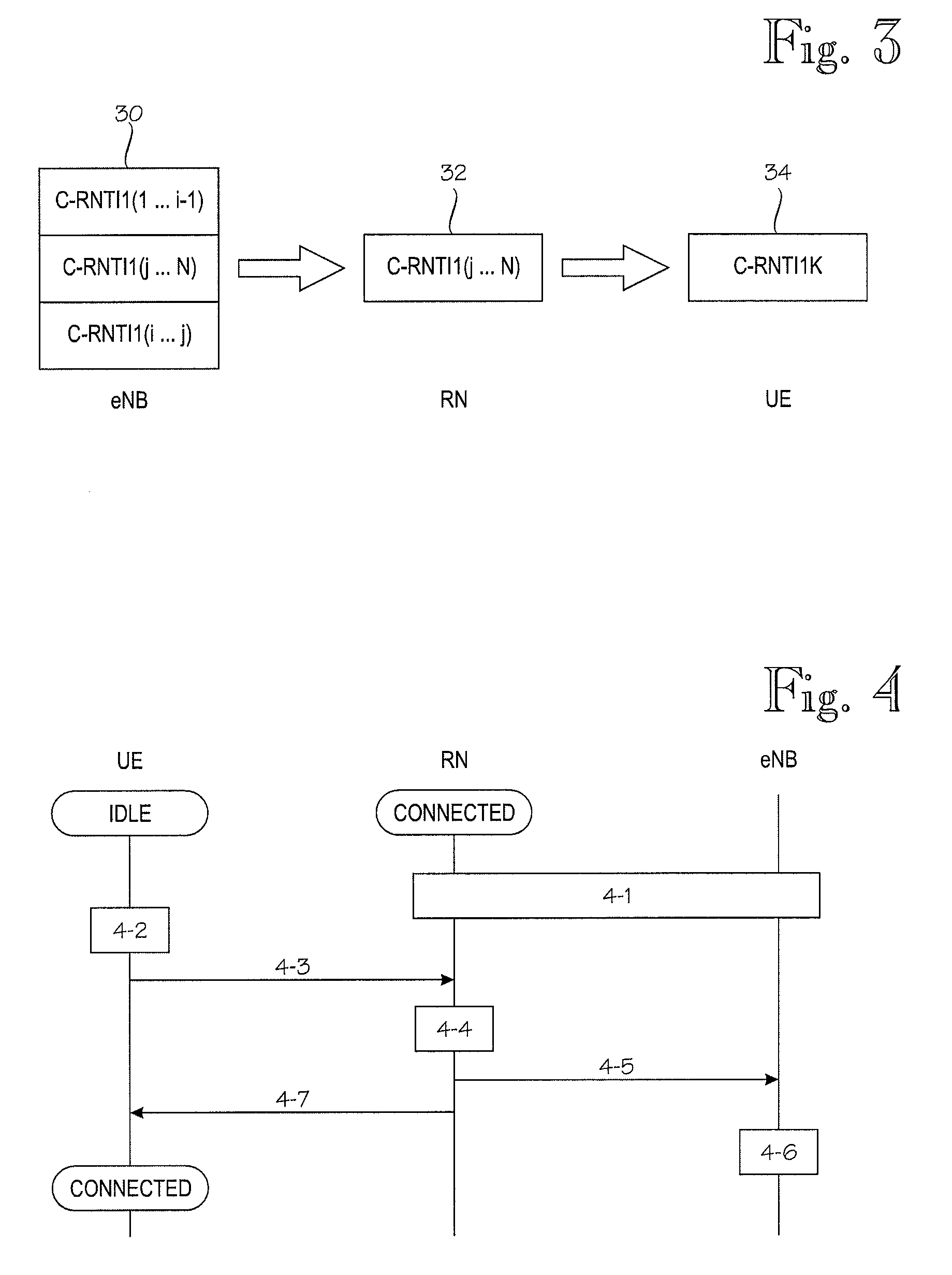

Allocation of user equipment identifier

ActiveUS20090111476A1Finish quicklyError preventionTransmission systemsCommunications systemUser equipment

A communication system that comprises a base station and a substation connected to the base station. The base station maintains a set of identifiers, each identifier of the set being at least temporarily allocatable to a user equipment for identifying the user equipment when it resides in a cell of the base station. From the set of identifiers of the base station at least one subset of identifiers is extracted, and assigned to the substation. The substation may then respond to a connection establishment request of user equipment by providing it with an identifier from the subset of identifiers assigned to it. The substation also transmits to the base station information on the connection establishment request and on the identifier provided to the user equipment.

Owner:WSOU INVESTMENTS LLC

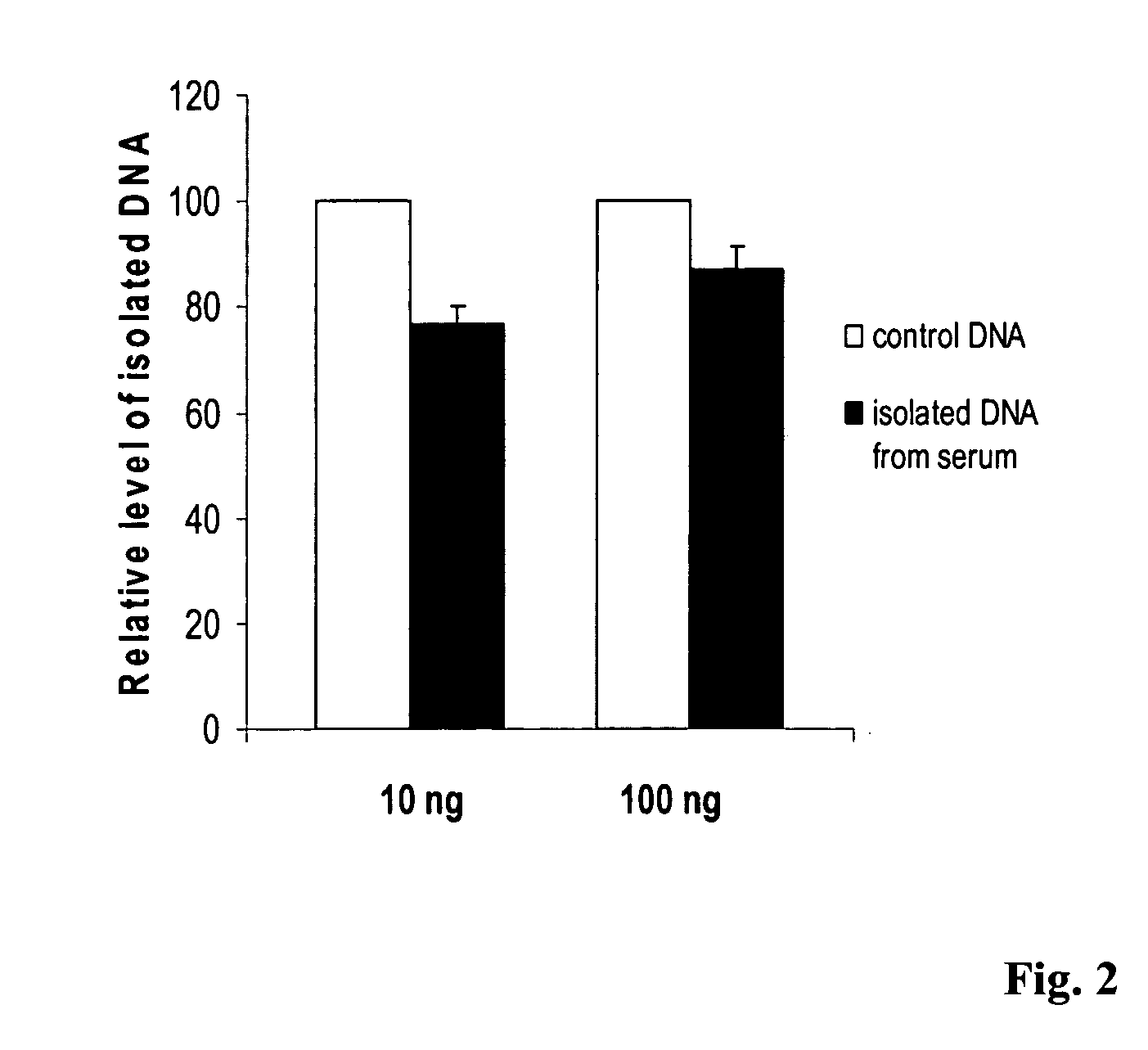

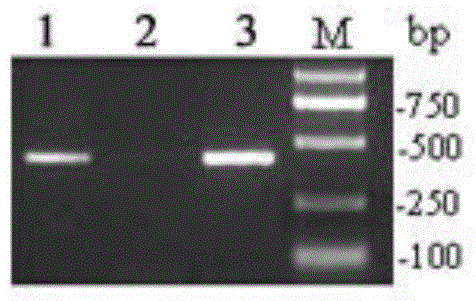

Method for isolating and modifying DNA from blood and body fluids

InactiveUS20070042384A1Highly efficient and fast isolation and modificationEasily and quickly isolatedSugar derivativesMicrobiological testing/measurementModified dnaPcr assay

This invention is related a method for rapidly isolating and modifying DNA from plasma / serum and body fluids. This invention provides a procedure and composition to obtain a high yield of modified DNA for methylation-specific PCR assay by coupling DNA isolation and modification courses.

Owner:LI WEIWEI +1

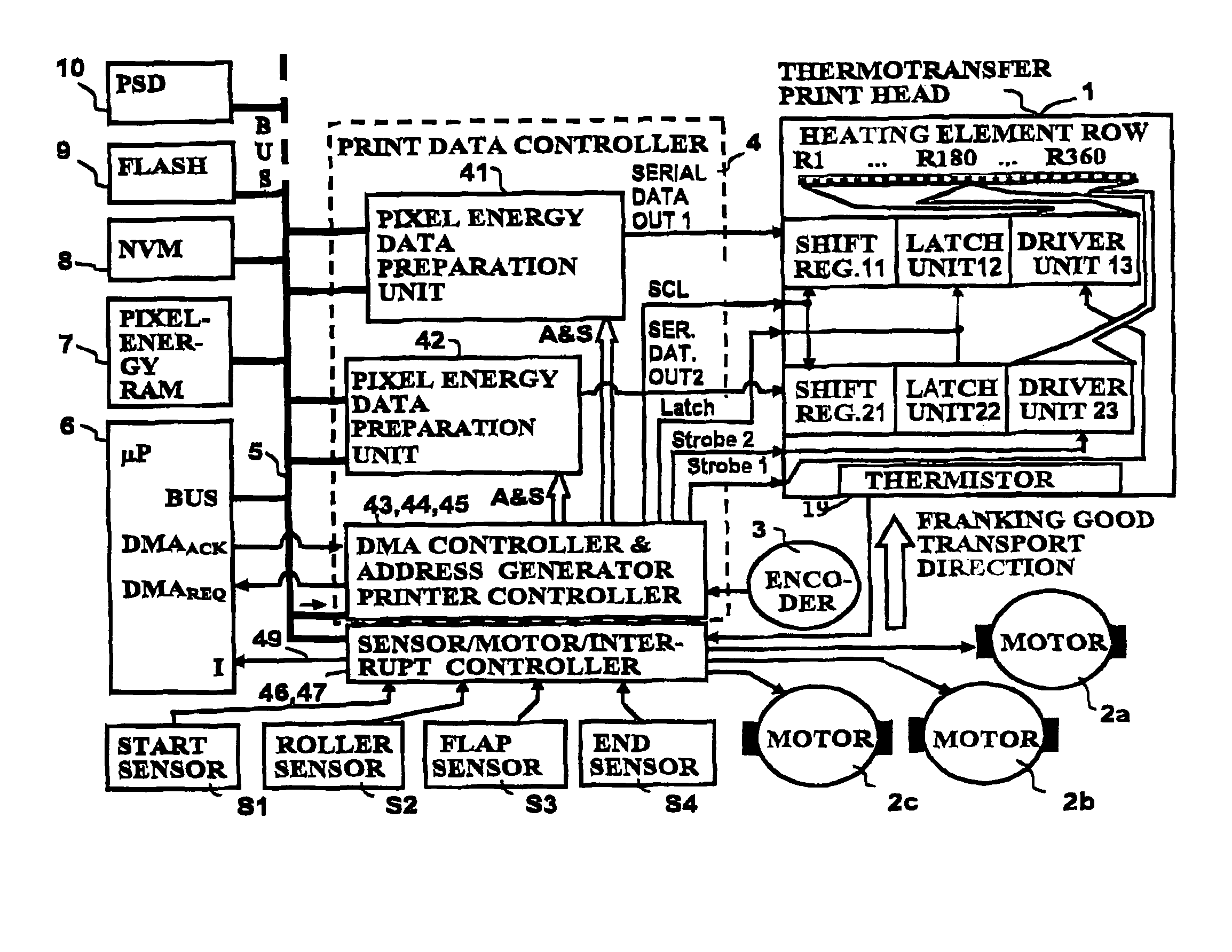

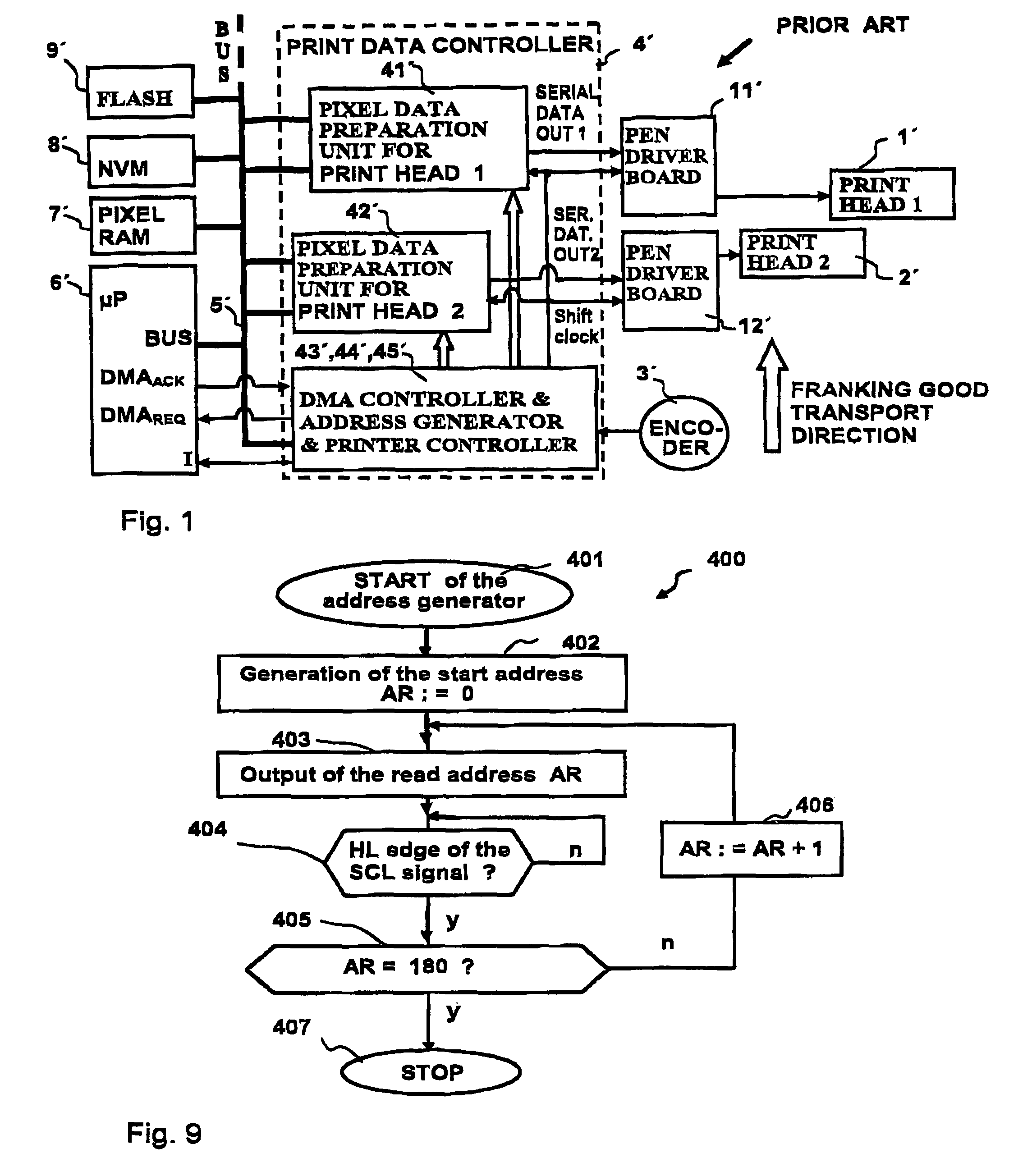

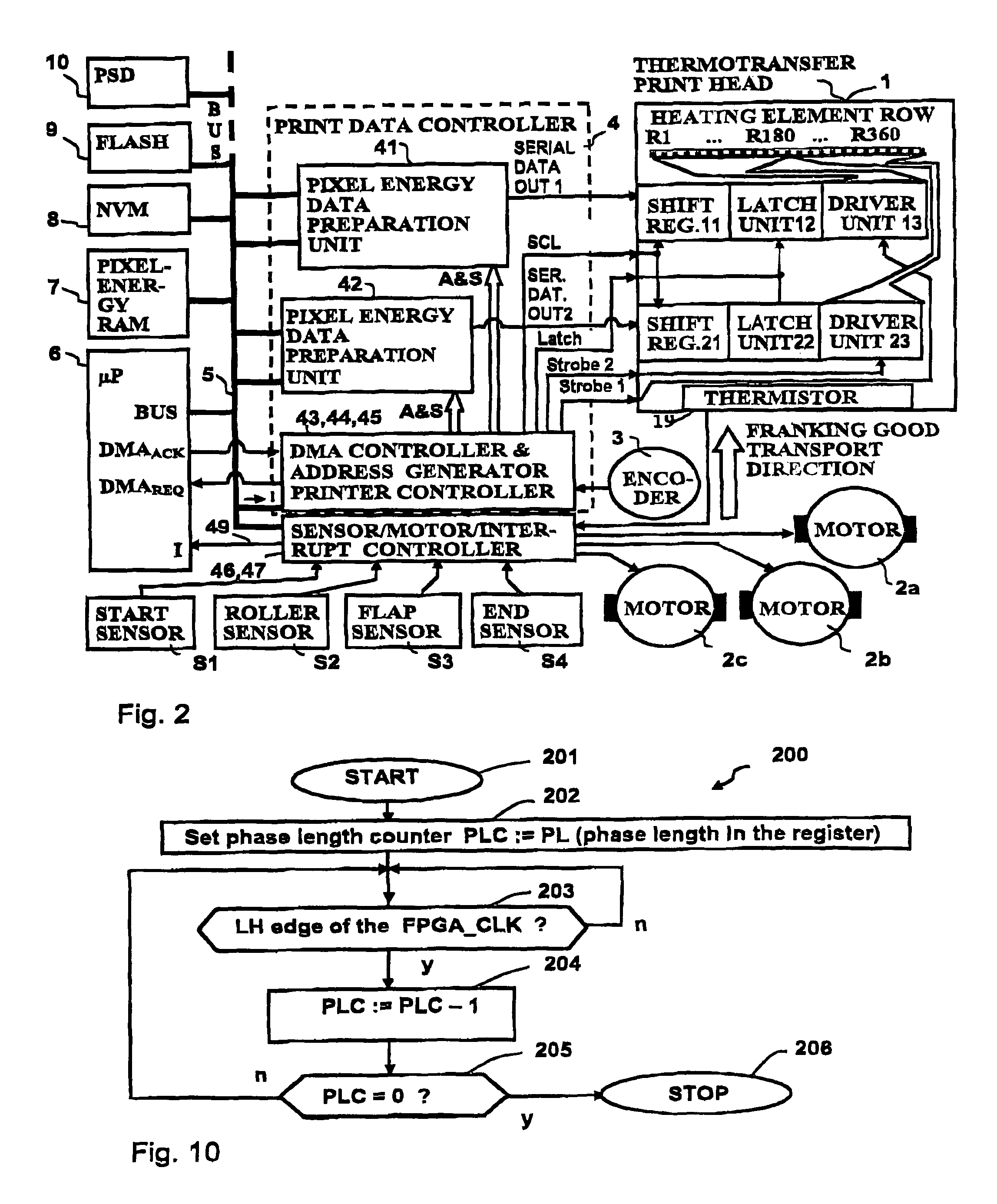

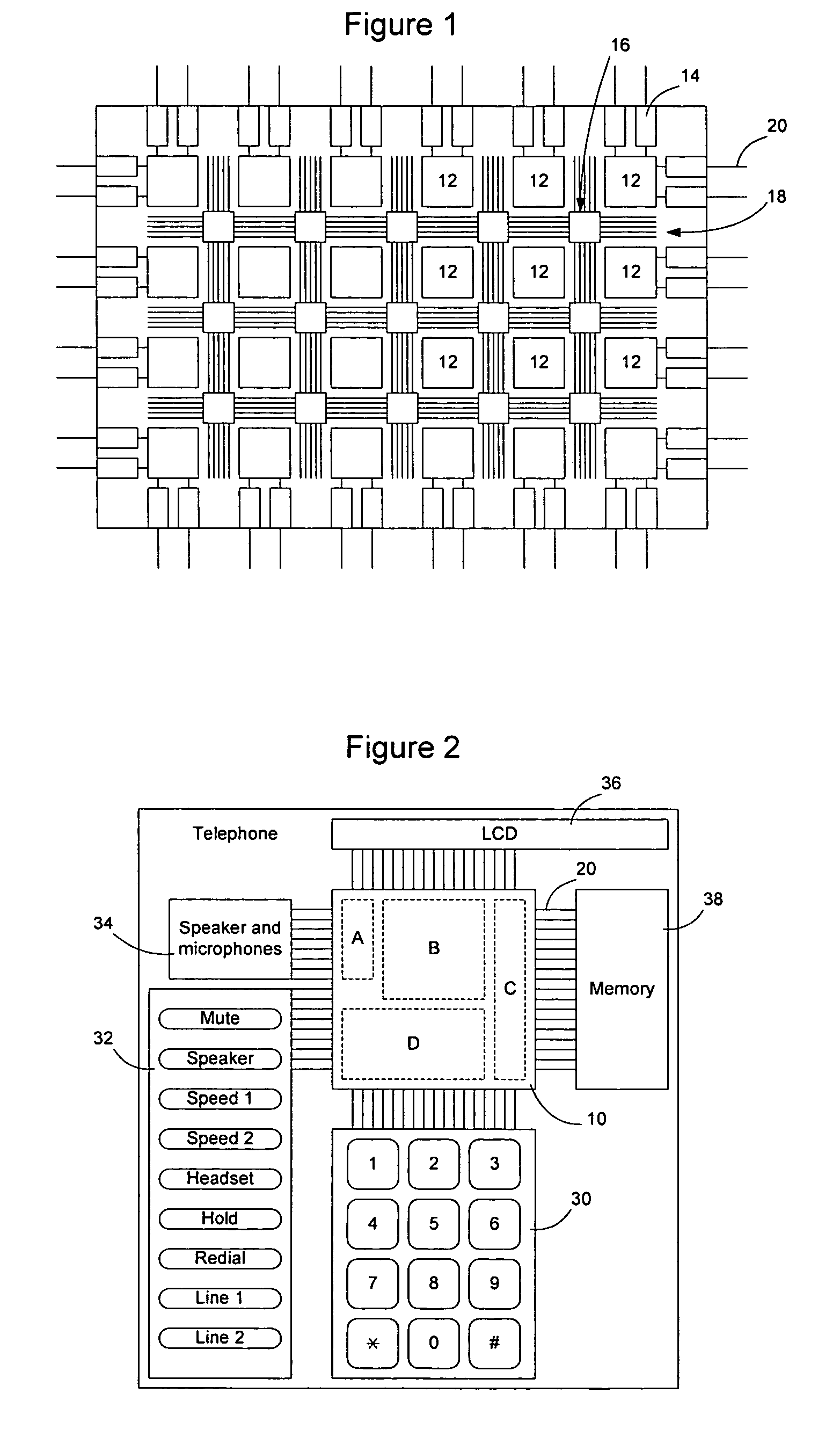

Method and arrangement for control of the printing of a thermotransfer printing device

InactiveUS7965308B2Improve throughputHigh resolutionRecording apparatusFranking apparatusShift registerData control

In a method and an arrangement for controlling printing by a thermotransfer printing apparatus with relative movement between a thermotransfer print head and a print medium, a microprocessor that provides pixel energy data to a pixel energy memory by making an energy value calculation and by coding, and a print data controller prepares the pixel energy data by decoding during the printing in a number (corresponding to the pixel energy value) of binary pixel data each with the same binary value. The print data controller includes at least one pixel energy data preparation unit, a DMA controller, an address generator, a printer controller and a phase counter. The DMA controller allows an access to the pixel energy data stored in the pixel energy memory as code in order to provide the pixel energy data in print columns to the at least one pixel energy data preparation unit. The address generator generates addresses for selection of the buffered code during each phase of a number of phases. The phase counter supplies a phase count value to a phase data preparation unit in which the code value A and phase count value B are compared in order to generated binary pixel data, which are serially supplied from the output D to at least one shift register of the thermotransfer print head.

Owner:FRANCOTYP POSTALIA

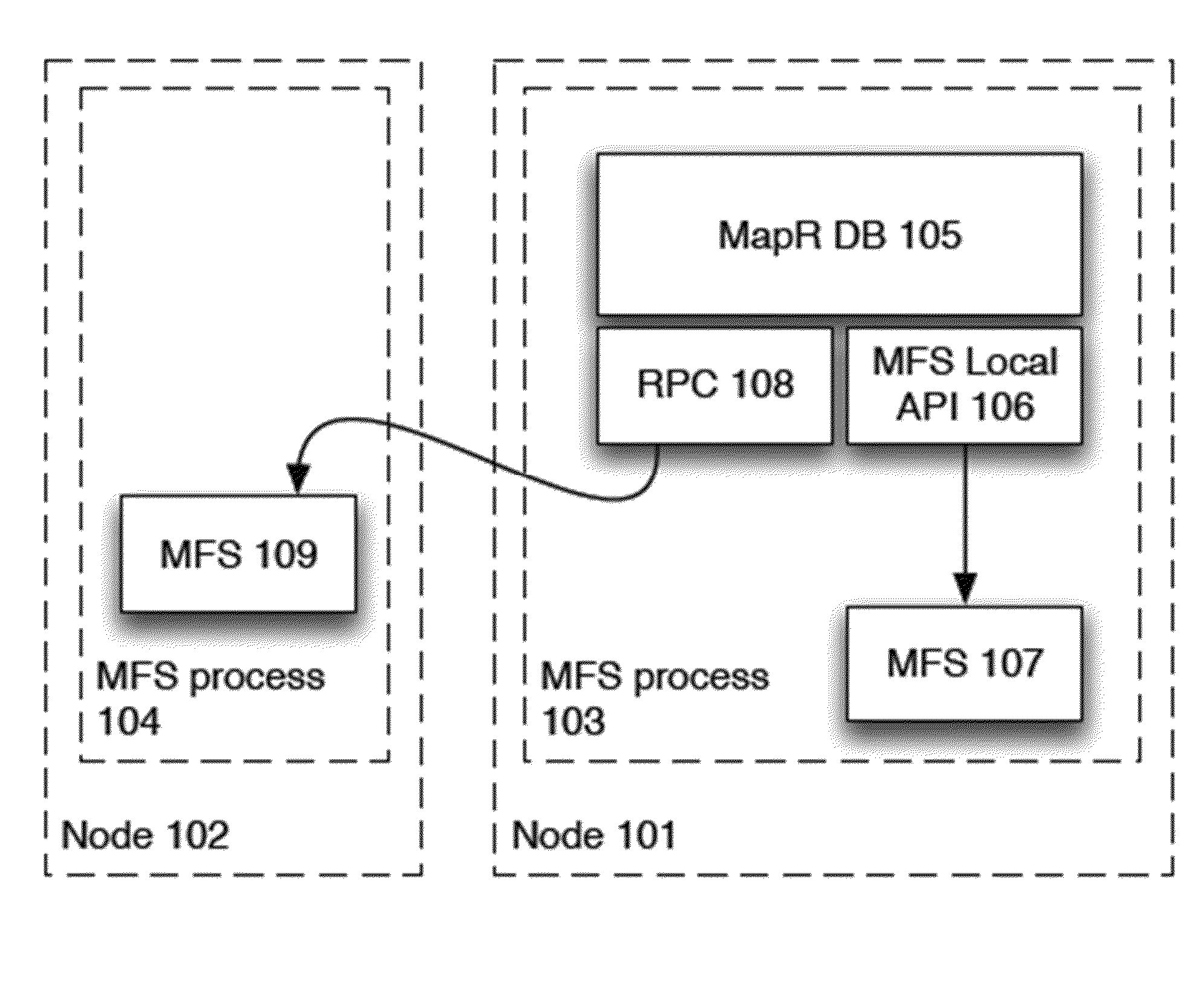

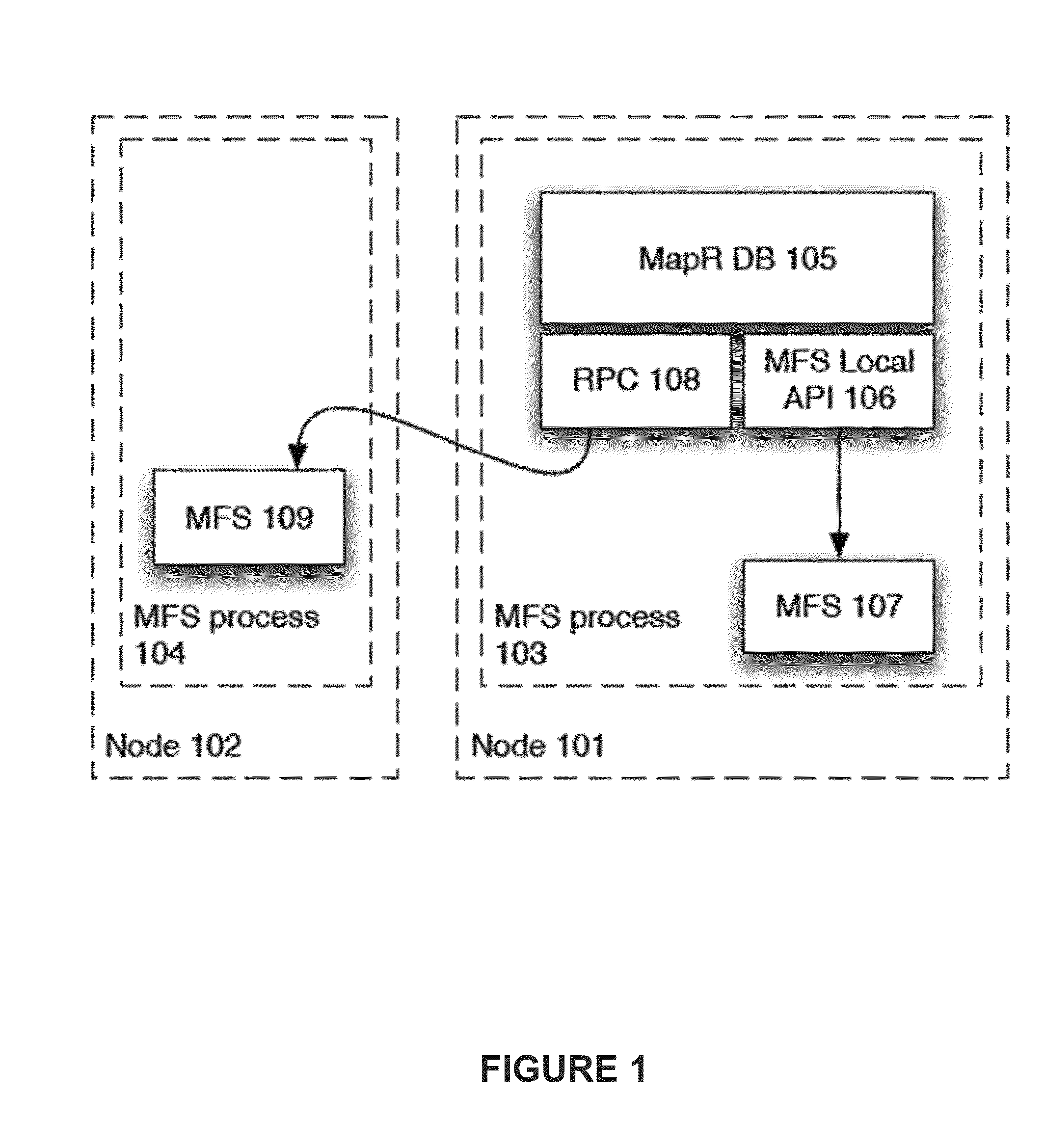

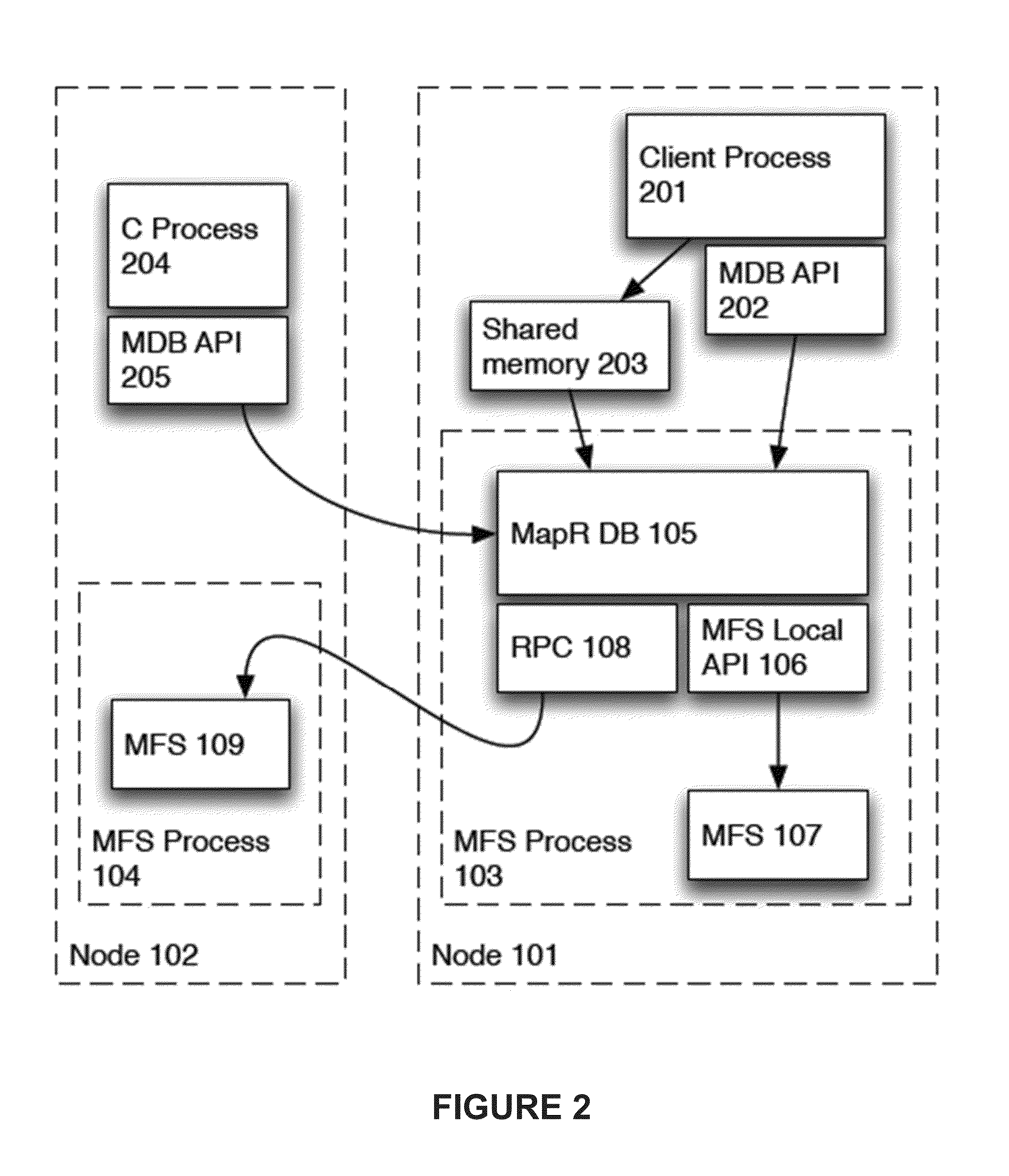

Table format for map reduce system

ActiveUS20140081918A1Small sizeEasy to operateDigital data processing detailsFile system administrationHigh rateMap reduce

A key-value store provides column-oriented access to data in a distributed and fault tolerant manner. Data can be inserted into the data store and data can be retrieved either randomly or sequentially from the data store at high rates. Keys for a table are ordered and the entire table is divided into key ranges. Each key range is handled by a table which itself is divided into key ranges called a partition. Partitions are also divided into segments. Such recursive division into smaller and smaller key ranges provides parallelism. At the highest level, operations on tablets can be distributed to different nodes. At lower levels, different threads can handle operations on individual segments. Large-scale restructuring operations can be decomposed into operations on individual segments so that a global lock on larger objects does not need to be kept across the entire operation.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

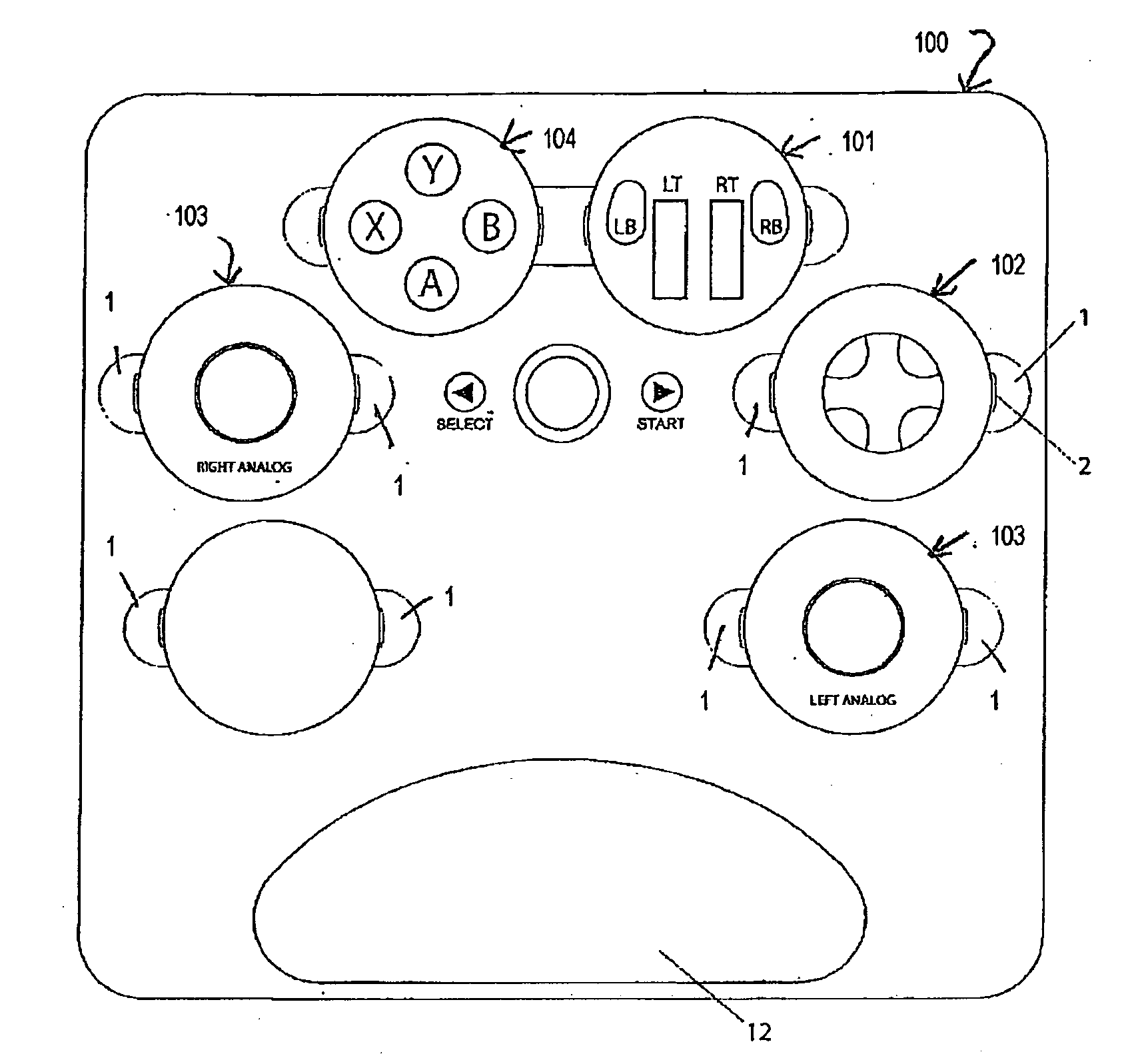

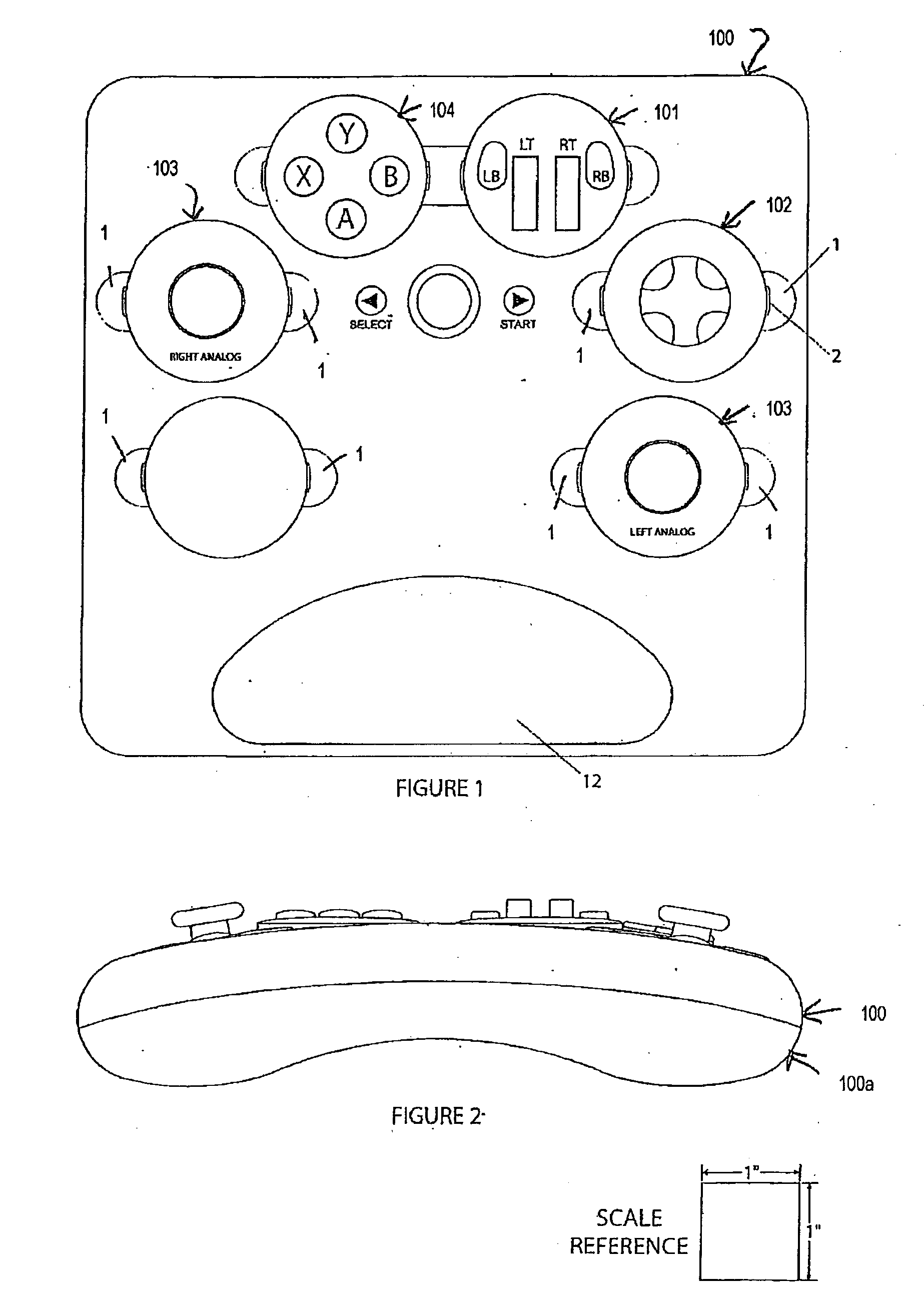

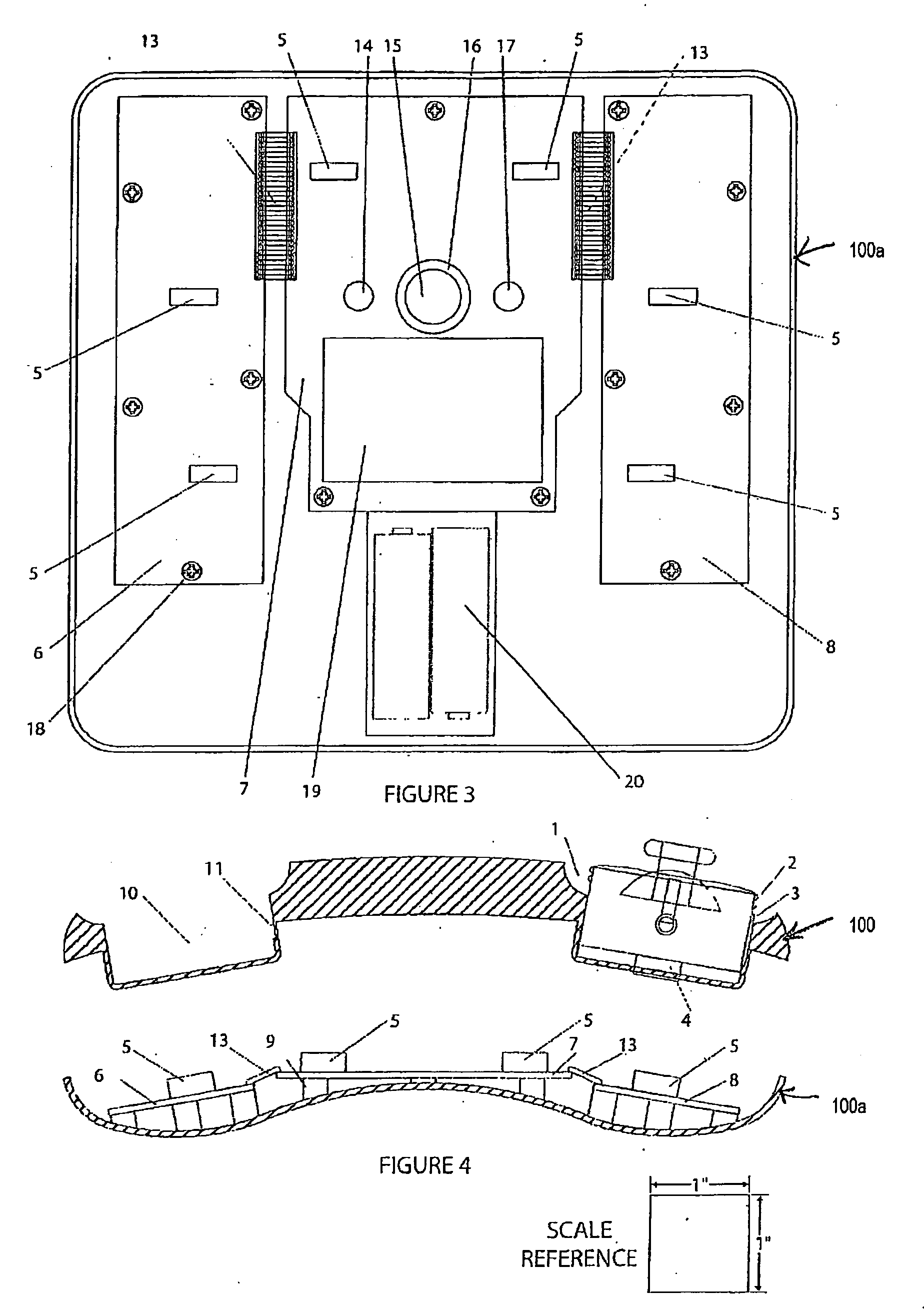

Configurable single handed video game controller

InactiveUS20090054146A1Reduce needFinish quicklyVideo gamesSpecial data processing applicationsJoystickGame player

A video game controller that can be configured using a set of video game control switch modules for single hand usage (left or right). The controller is comprised of a controller housing having a base receptacle containing circuitry and a top enclosure which contains several module slots in which removable video game control switch modules can to be inserted and connected to the game controller circuitry via a parallel bus. The removable video game control switch modules which contain the game controls themselves, such as analog joysticks and triggers, can be inserted into any module slot allowing a game player to arrange the controller as desired and have a high level of customization on a per-game or per-user basis.

Owner:EPSTEIN MICHAEL +1

System and method for piece-picking or put-away with a mobile manipulation robot

ActiveUS9785911B2Overcomes shortcomingReduce complexity and costProgramme-controlled manipulatorAutonomous decision making processLogistics managementActuator

A method and system for piece-picking or piece put-away within a logistics facility. The system includes a central server and at least one mobile manipulation robot. The central server is configured to communicate with the robots to send and receive piece-picking data which includes a unique identification for each piece to be picked, a location within the logistics facility of the pieces to be picked, and a route for the robot to take within the logistics facility. The robots can then autonomously navigate and position themselves within the logistics facility by recognition of landmarks by at least one of a plurality of sensors. The sensors also provide signals related to detection, identification, and location of a piece to be picked or put-away, and processors on the robots analyze the sensor information to generate movements of a unique articulated arm and end effector on the robot to pick or put-away the piece.

Owner:IAM ROBOTICS

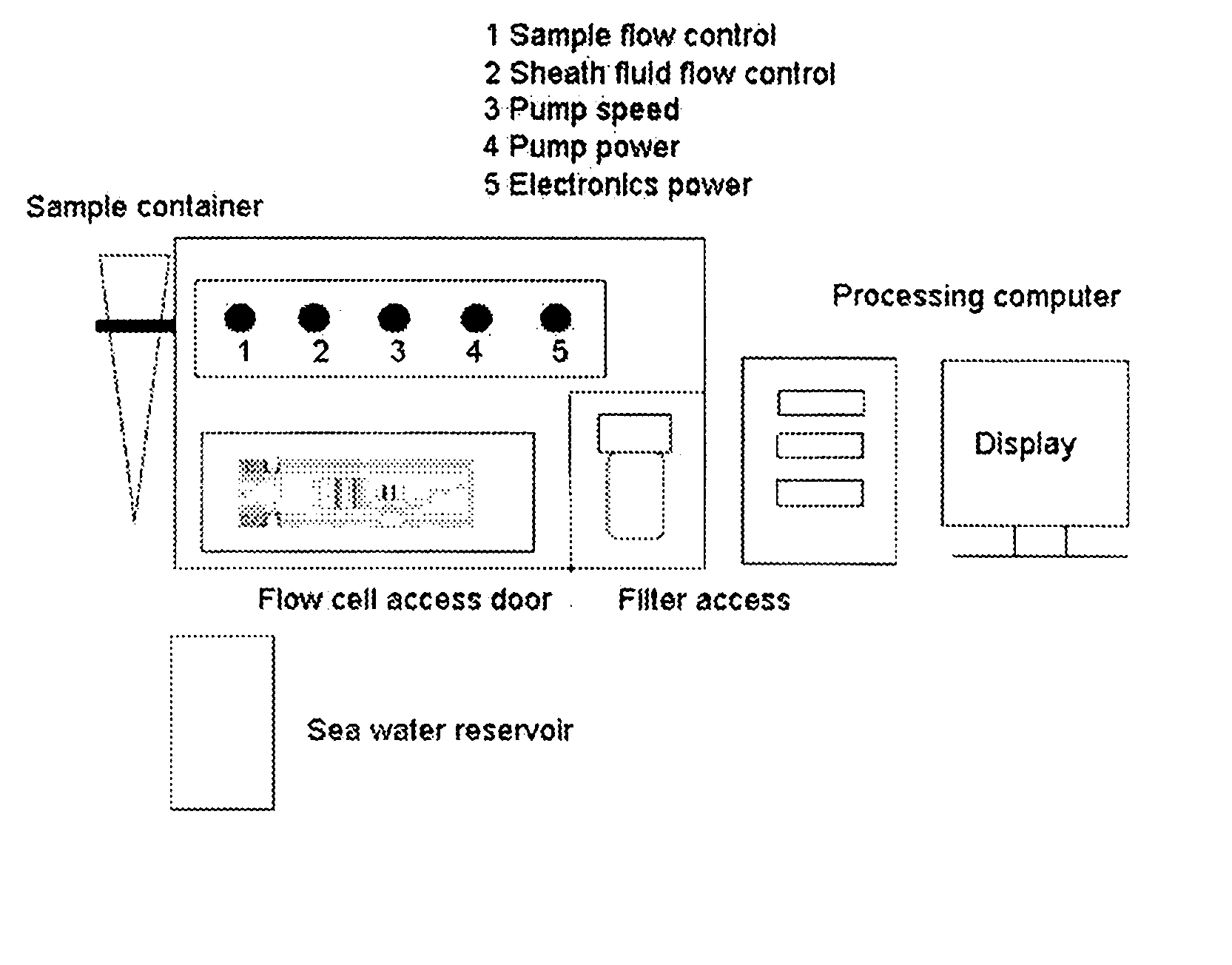

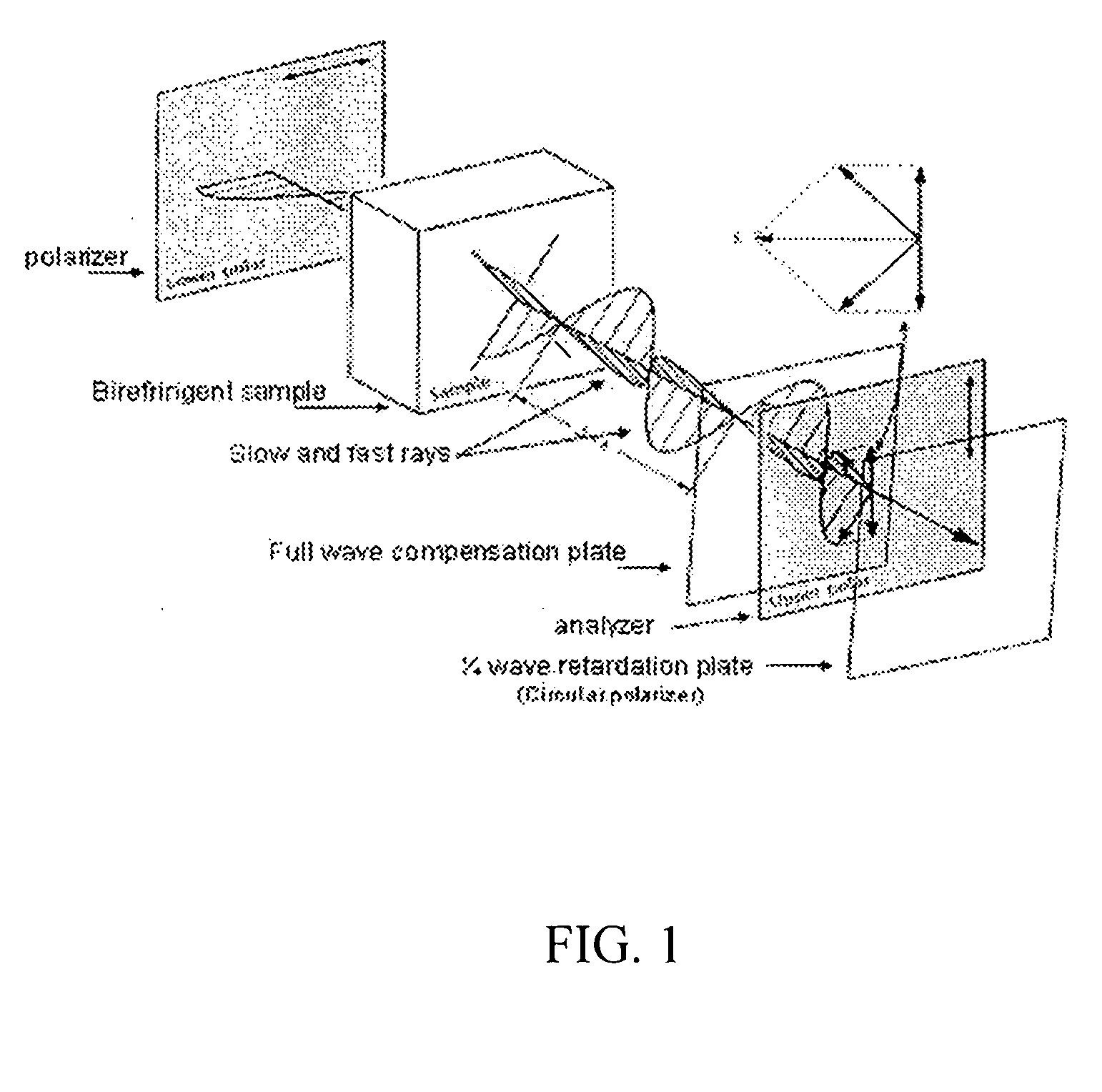

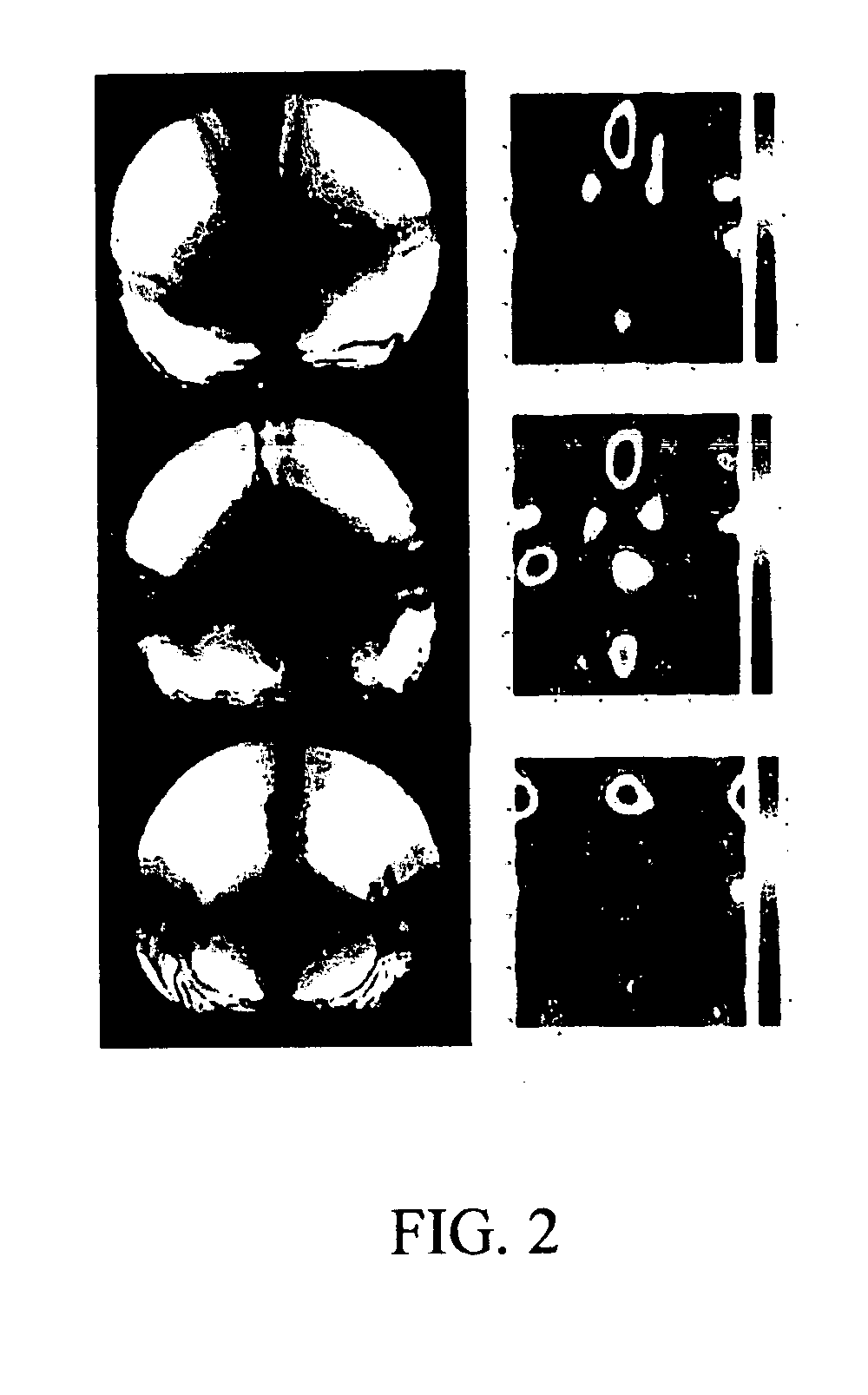

Optical method and system for rapid identification of multiple refractive index materials using multiscale texture and color invariants

ActiveUS20050126505A1Rapid and accurate identificationRapid and accurate and classificationClimate change adaptationCharacter and pattern recognitionGabor wavelet transformFeature set

An innovative optical system and method is disclosed for analyzing and uniquely identifying high-order refractive indices samples in a diverse population of nearly identical samples. The system and method are particularly suitable for ultra-fine materials having similar color, shape and features which are difficult to identify through conventional chemical, physical, electrical or optical methods due to a lack of distinguishing features. The invention discloses a uniquely configured optical system which employs polarized sample light passing through a full wave compensation plate, a linear polarizer analyzer and a quarter wave retardation plate for producing vivid color bi-refringence pattern images which uniquely identify high-order refractive indices samples in a diverse population of nearly visually identical samples. The resultant patterns display very subtle differences between species which are frequently indiscernable by conventional microscopy methods. When these images are analyzed with a trainable with a statistical learning model, such as a soft-margin support vector machine with a Gaussian RBF kernel, good discrimination is obtained on a feature set extracted from Gabor wavelet transforms and color distribution angles of each image. By constraining the Gabor center frequencies to be low, the resulting system can attain classification accuracy in excess of 90% for vertically oriented images, and in excess of 80% for randomly oriented images.

Owner:WOODS HOLE OCEANOGRAPHIC INSTITUTION

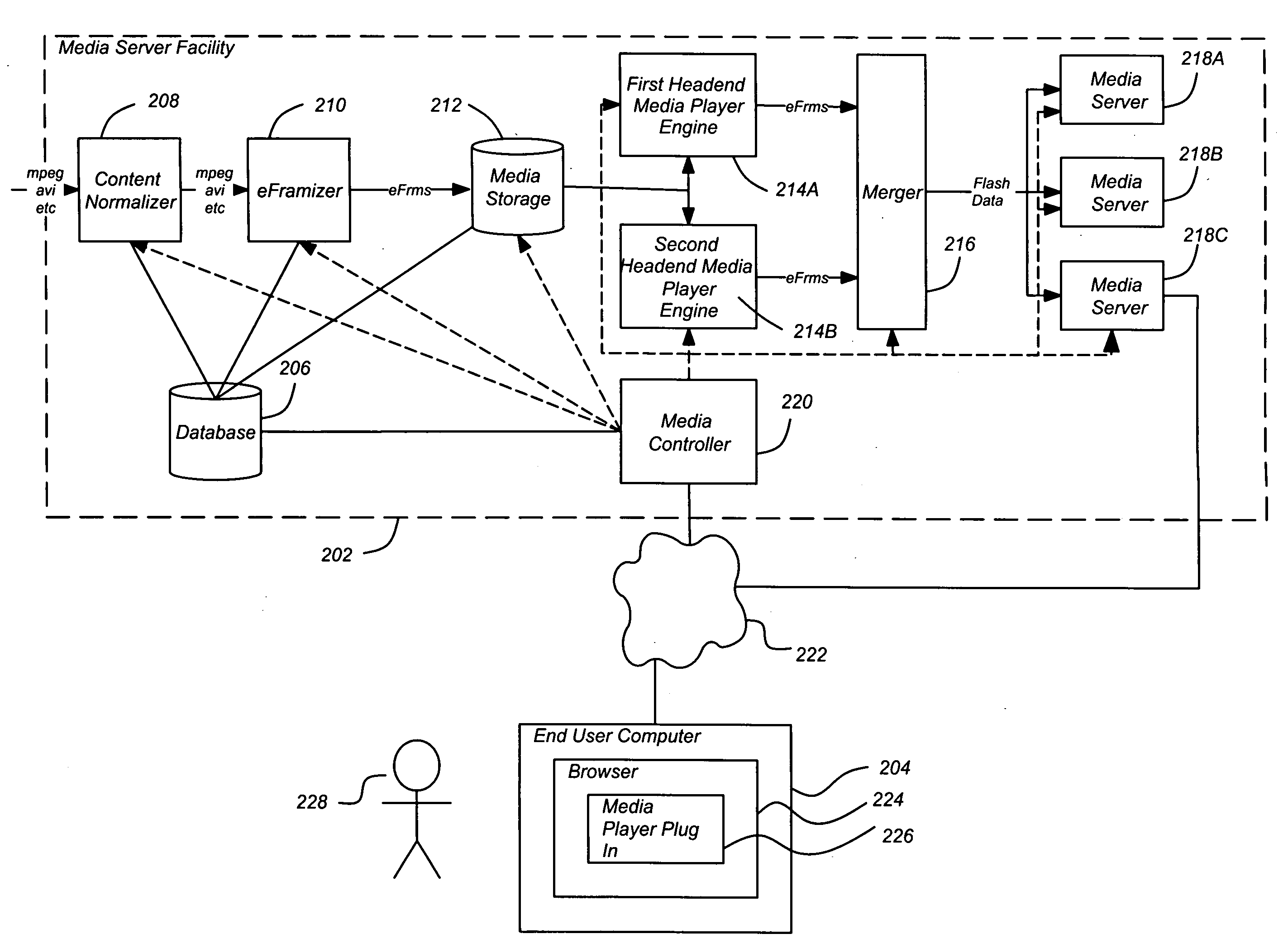

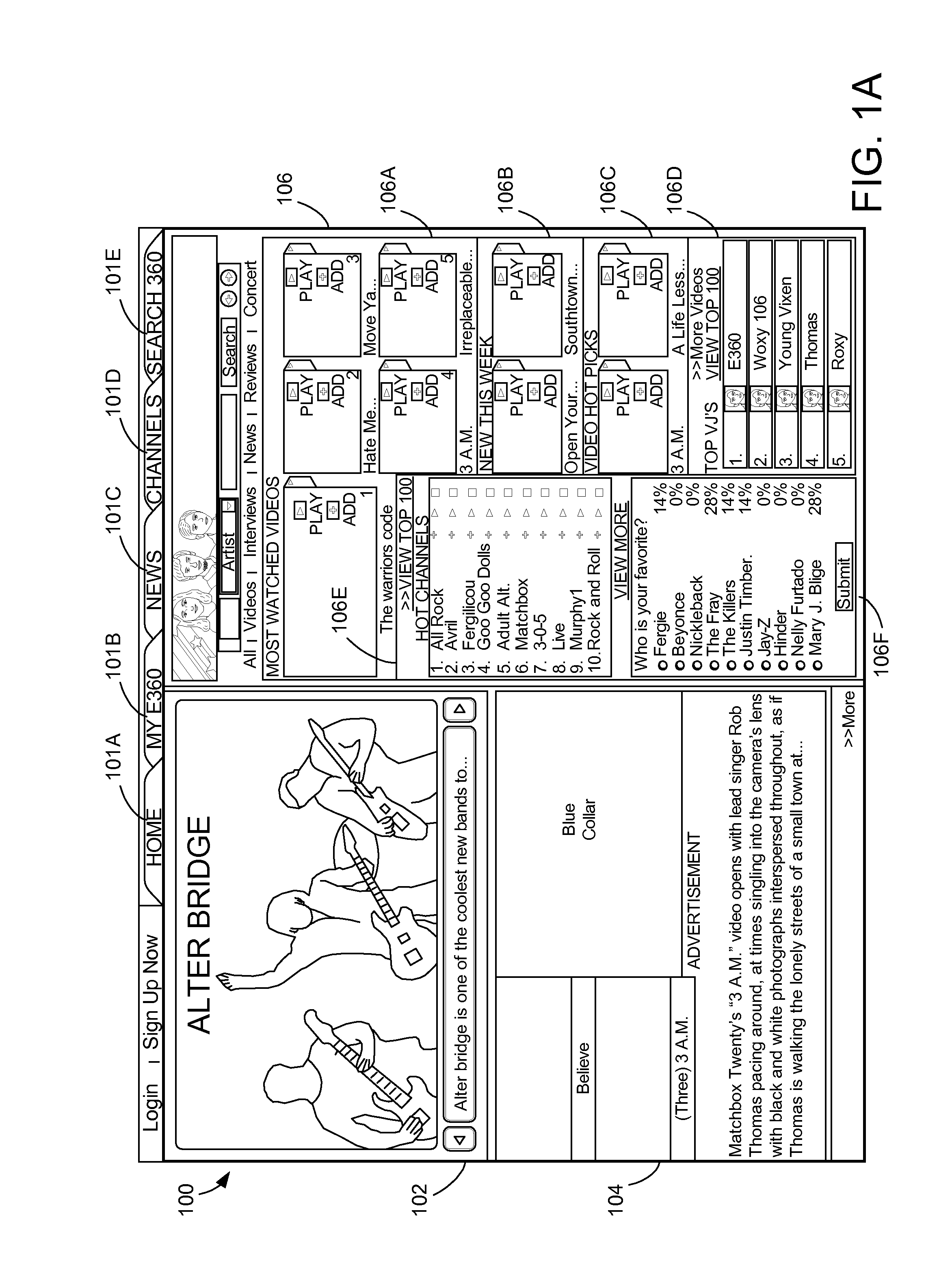

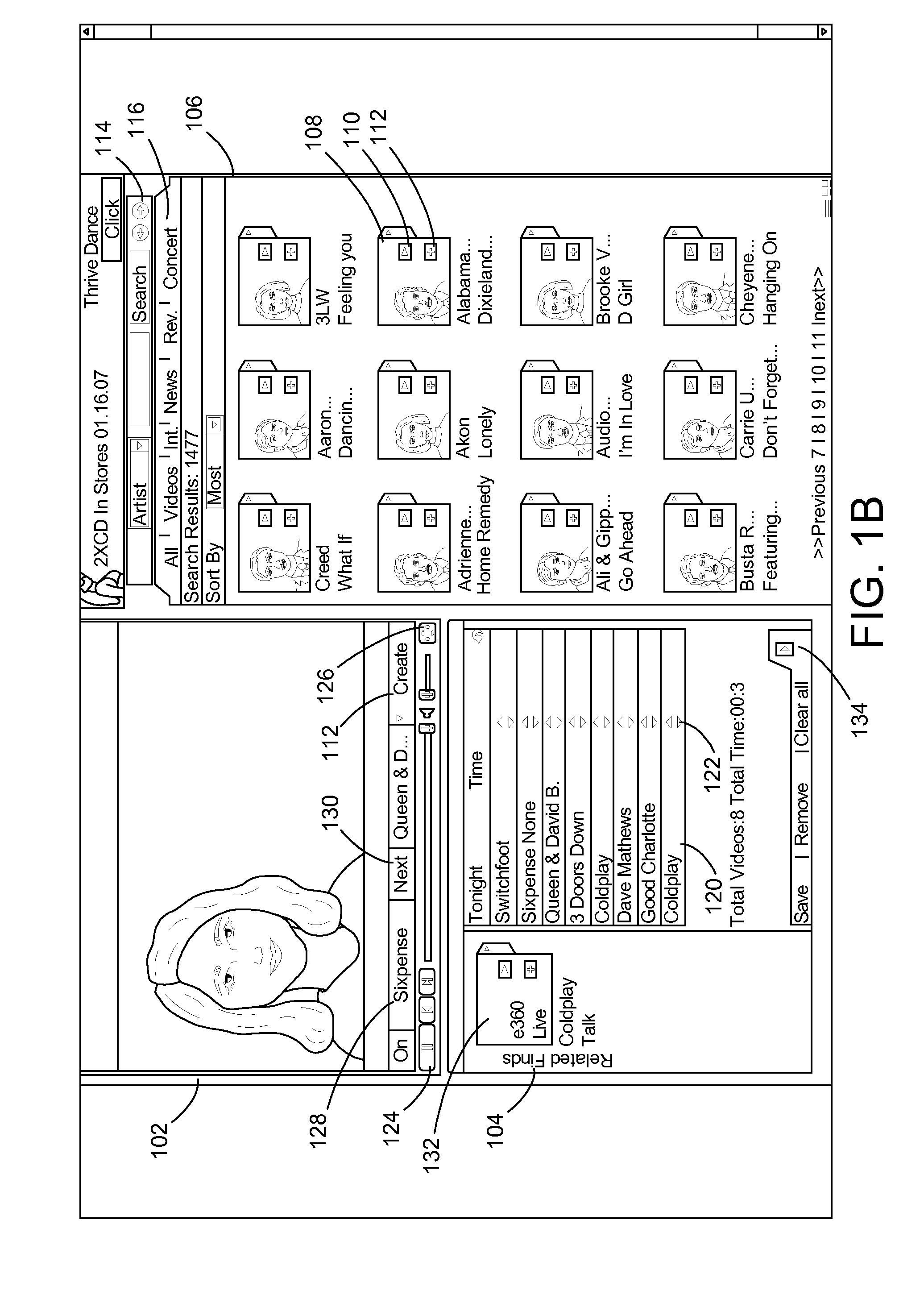

Method and apparatus for providing continuous playback of media programs at a remote end user computer

InactiveUS20080209066A1Less stressful on throughput requirementThroughput requirementMultiple digital computer combinationsTransmissionThe InternetMedia server

A method and apparatus of providing programmably seamless continuous playback of a plurality of media programs at an end-user remote from a media server facility is disclosed. The method permits playing a first media program via a first video reproduction engine disposed at the media server facility and transmitting the played first media program to the first user via the Internet, before completing playing the first media program and merging the closing of the first media program and the initiated second media program at the media server facility.

Owner:SPIO MARY A +2

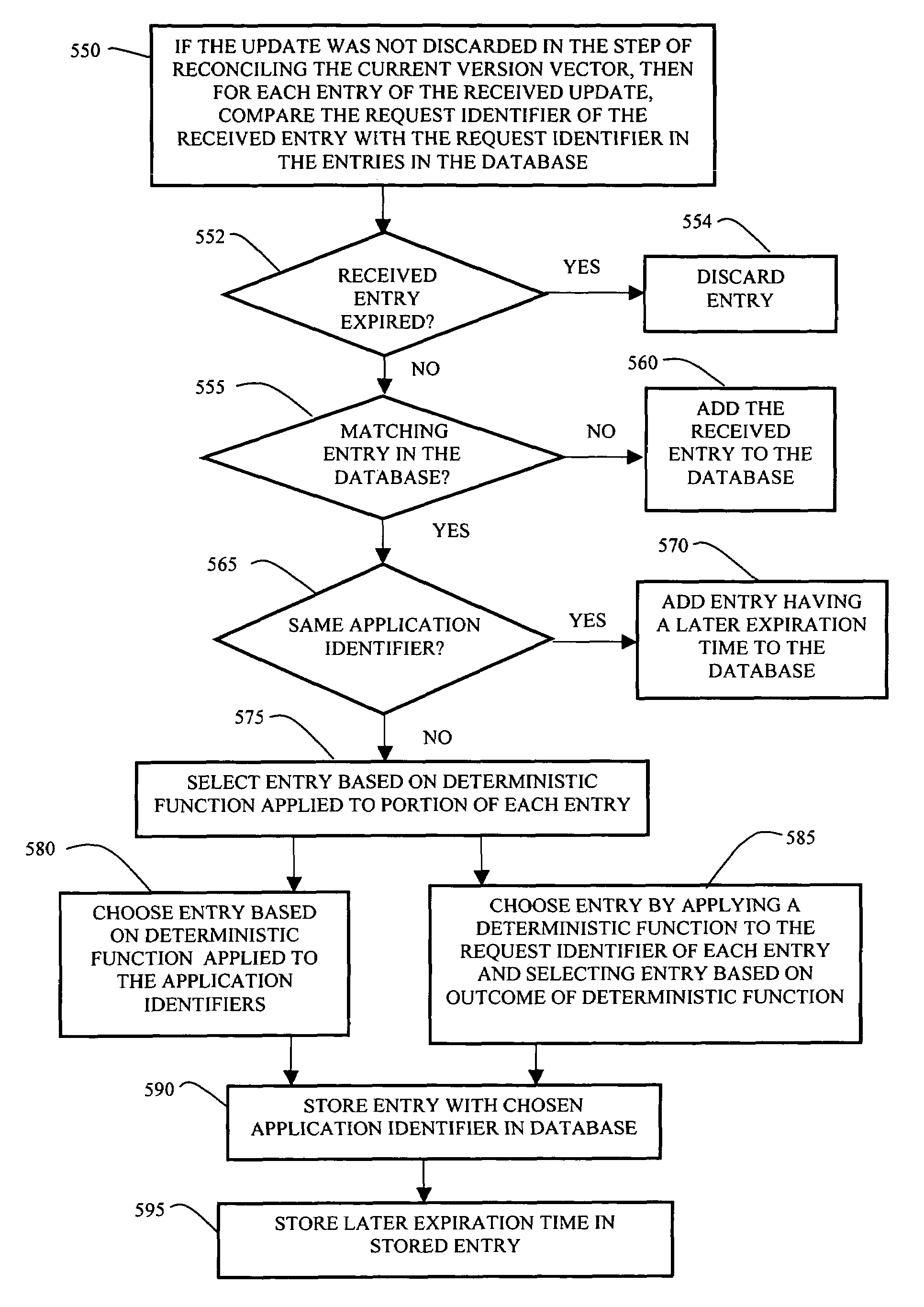

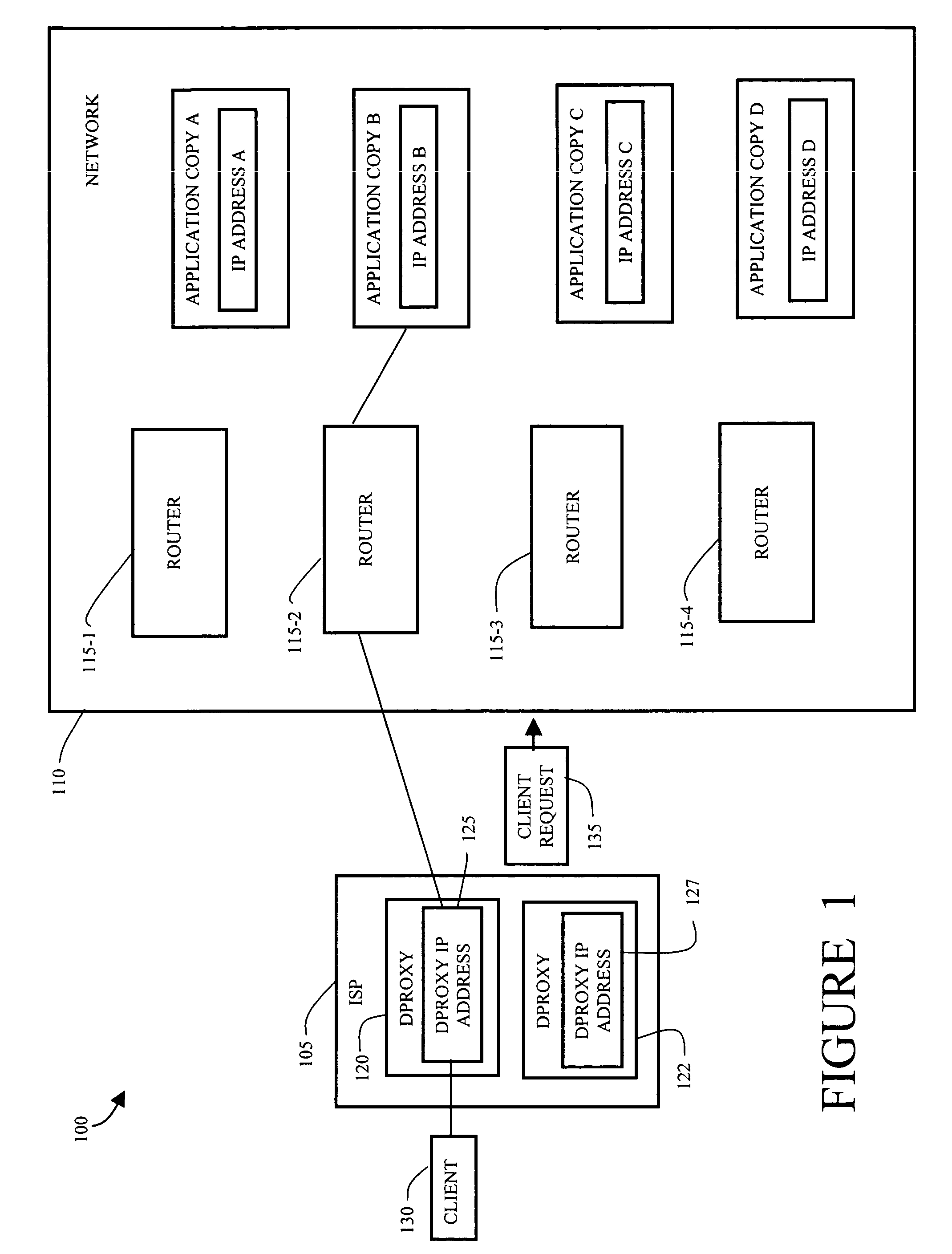

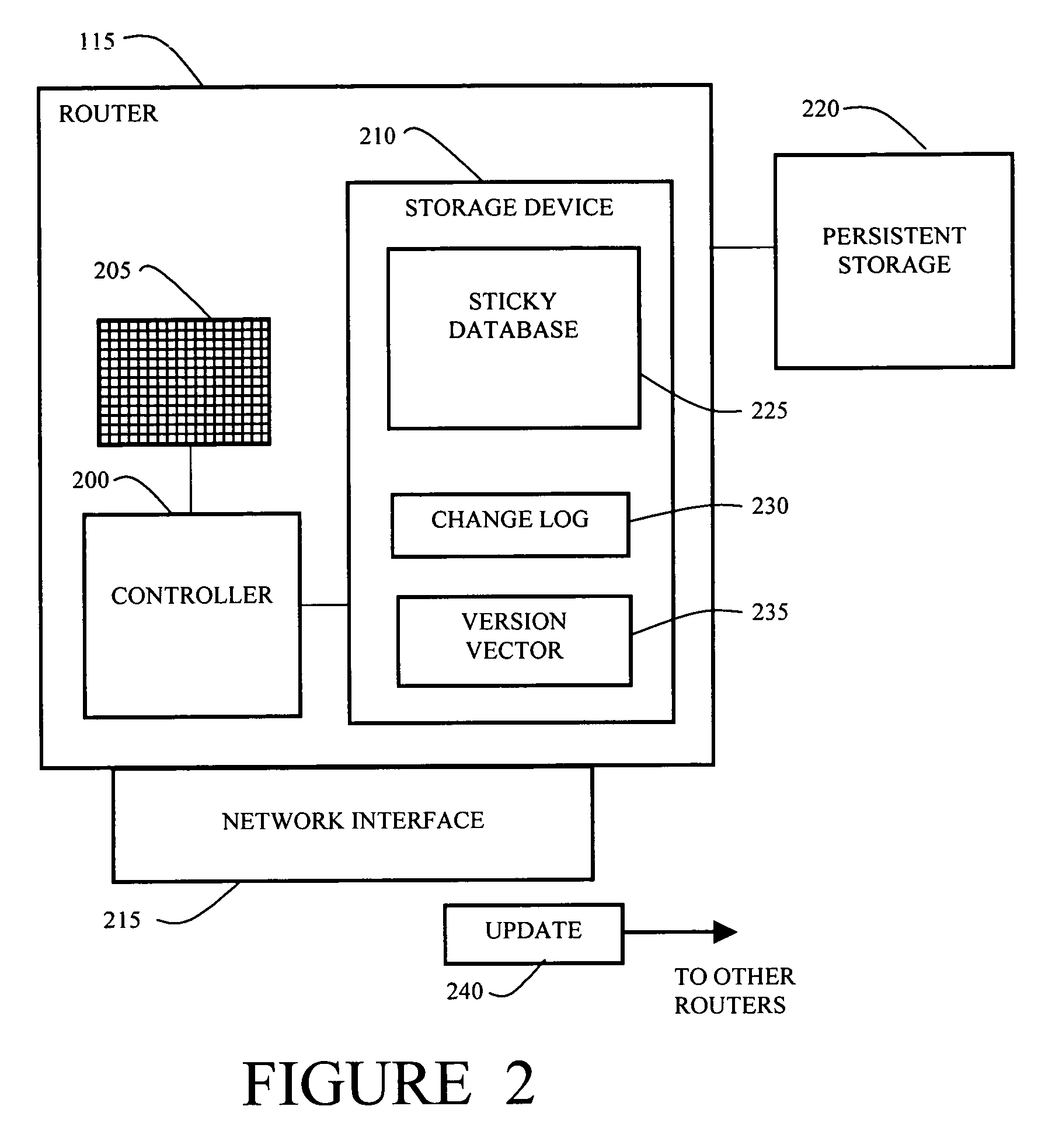

Method and apparatus for providing sticky bindings using version vectors

InactiveUS7610387B1Promote recoveryImprove performanceDatabase queryingTime-division multiplexClient-sideComputer science

In a network having a plurality of routers and also an application running at a plurality of replicas, a system for maintaining a client session between a client and a particular replica includes providing a database of bindings of client request identifiers to replicas. The system further includes a change log of changes made to the database where each entry has an event number. A version vector associated with the database and the change log holds a most recent event number for each router in the network. The system receives updates of change events made at the routers in the network and reconciles the updates with the database and current version vector. The system has data to maintain a client session between the client and the particular replica through repeated requests. Also the system and routers share data so that the client session can be maintained no matter which router handles subsequent client requests.

Owner:CISCO TECH INC

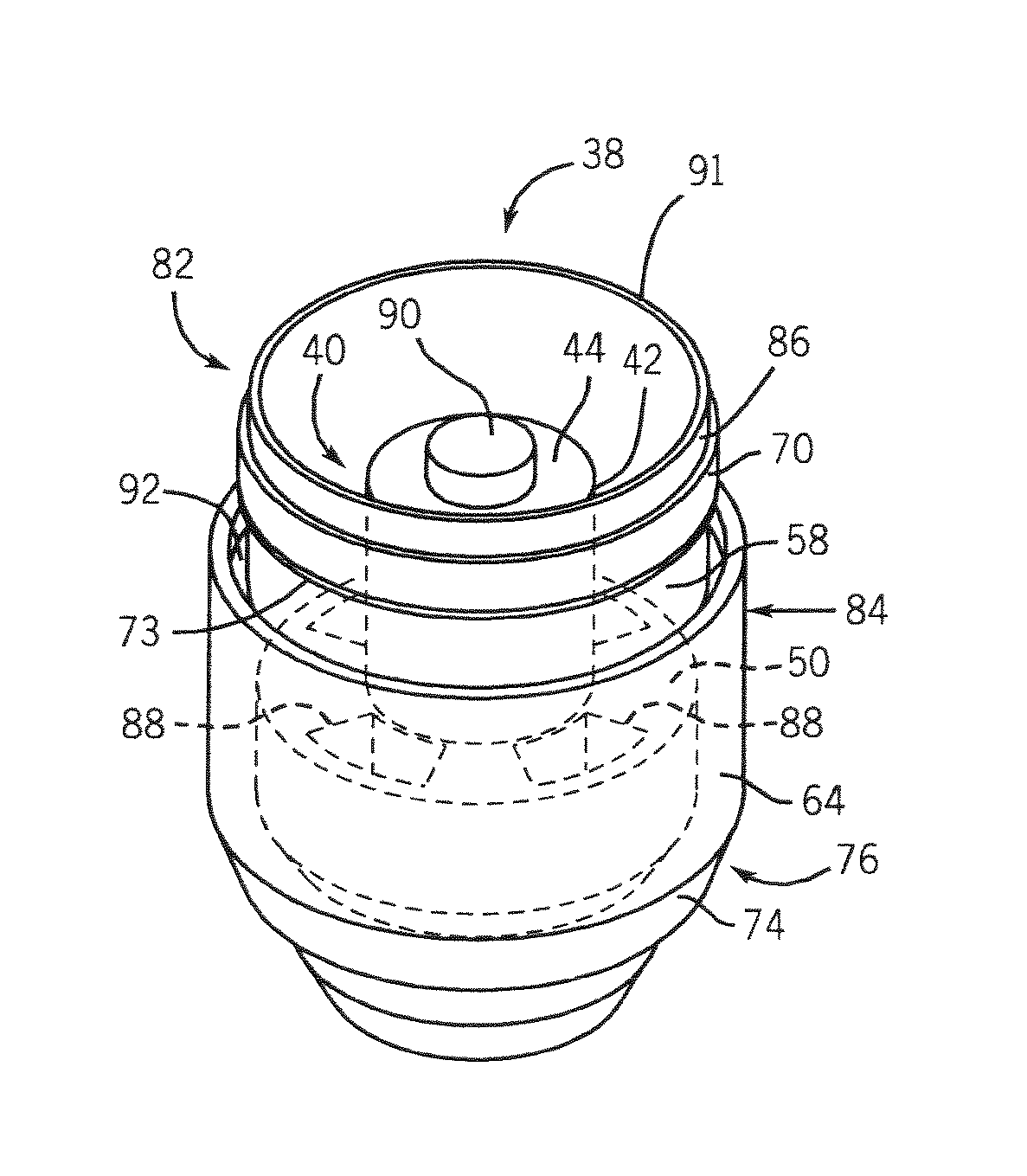

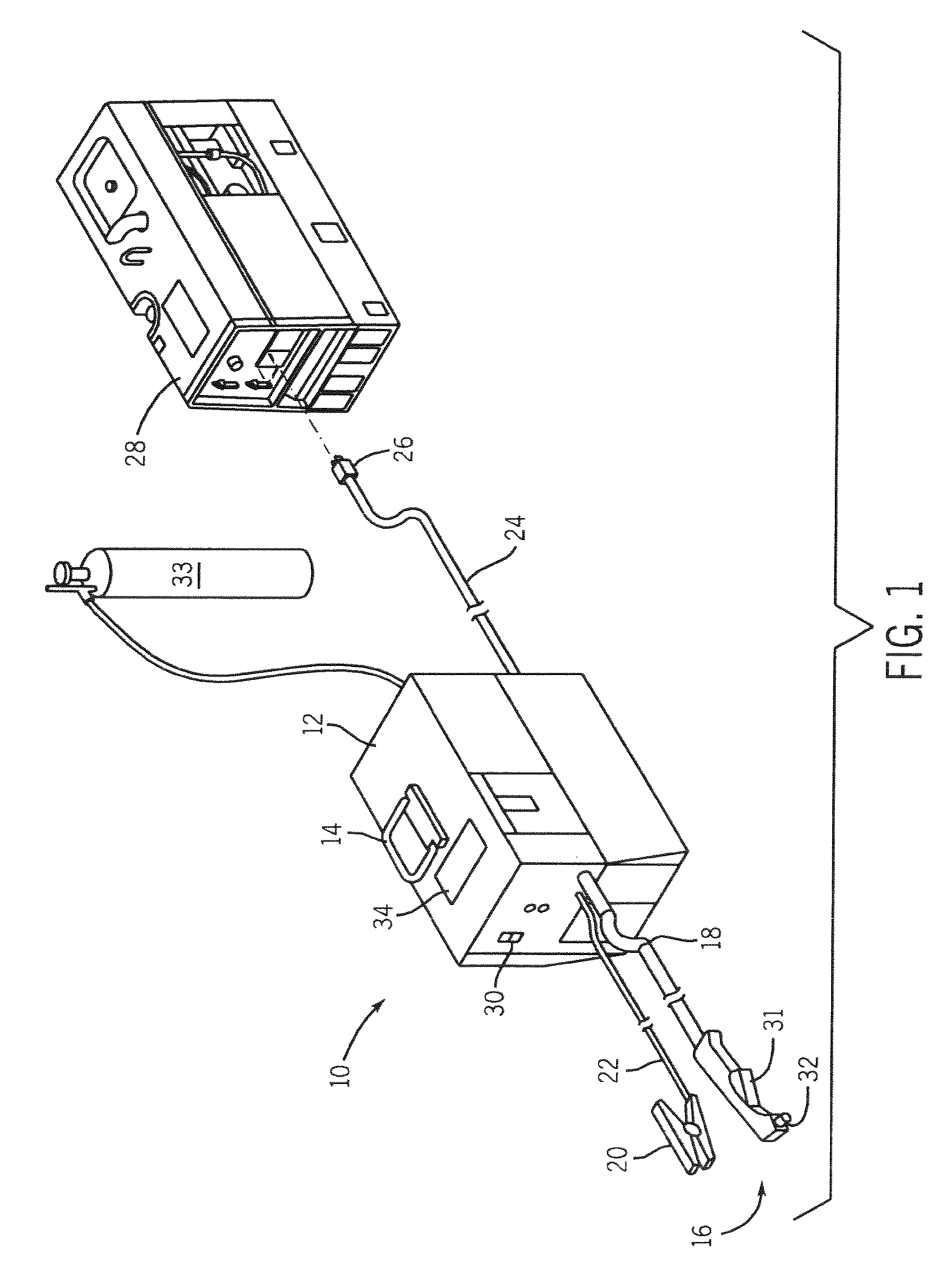

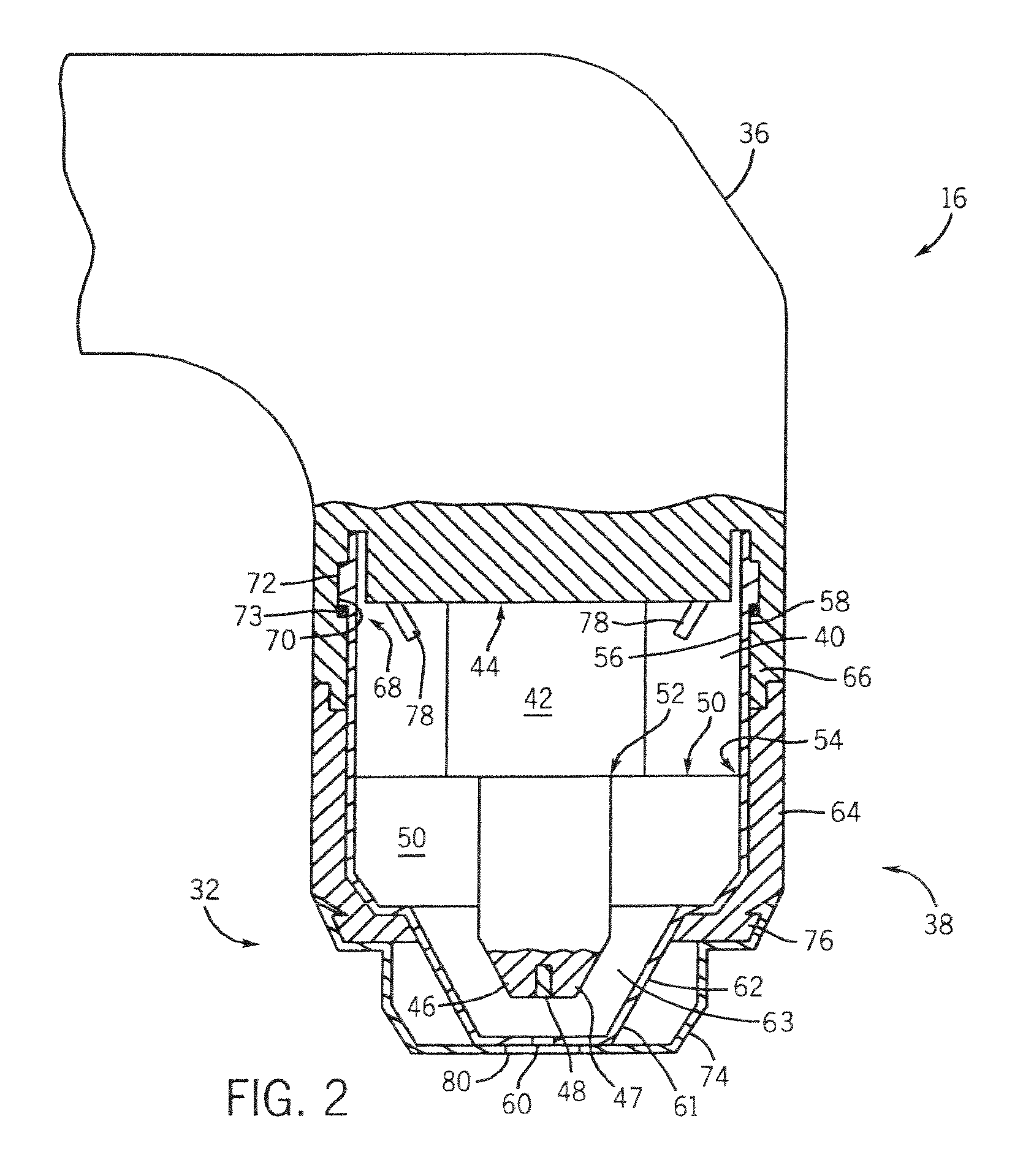

One-piece consumable assembly

InactiveUS8395076B2Minimizes numberFinish quicklyPlasma welding apparatusWelding/cutting media/materialsEngineeringTorch

An apparatus and method of manufacturing a plasma torch consumable is disclosed. The invention includes at least two of a tip, a shielding cup, an electrode, and a swirl ring being integral to form a unitary one-piece assembly prior to being attached to the torch. Such a construction minimizes the number of parts that must be handled and orientated when connecting the consumable assembly to a plasma torch.

Owner:ILLINOIS TOOL WORKS INC

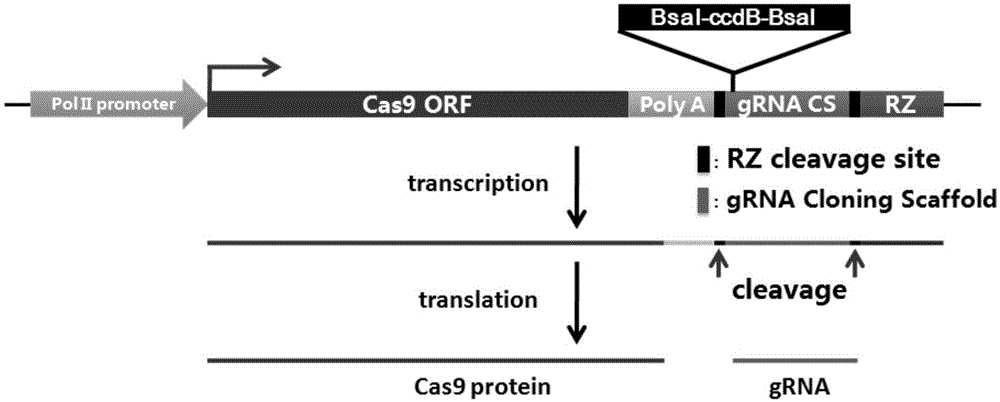

CRISPR/Cas9 single transcription unit directionally modified backbone vector and application thereof

ActiveCN105132451AComplete efficientlyCo-transcriptionVector-based foreign material introductionGenome editingGene engineering

The invention belongs to the technical field of gene engineering, and concretely relates to a CRISPR / Cas9 single transcription unit directionally modified backbone vector and an application thereof. Technical problems to be solved in the invention comprise low species versatility and difficult realization of Cas9 protein expression and gRNA transcription cooperation of present CRISPR / Cas9 genome editing systems. A technical scheme in the invention is characterized in that a CRISPR / Cas9 single transcription unit backbone vector is constructed, and transcription of Cas9 and a guide RNA core unit are regulated by a promoter. The invention also provides a method for constructing a target site specifically modified Cas9-gRNA recombinant vector by adopting the CRISPR / Cas9 single transcription unit backbone vector. The efficient CRISPR / Cas9 single transcription unit backbone vector can effectively realize Pol II promoter driving-based Cas9 and gRNA unit cooperative transcription, and also can realize simple, fast and efficient genome directional heredity modification of various eukaryotes.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

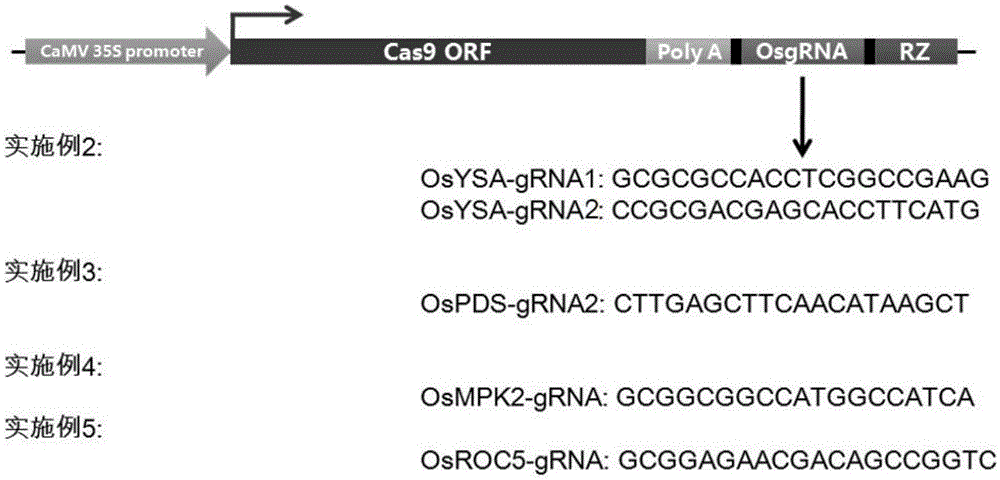

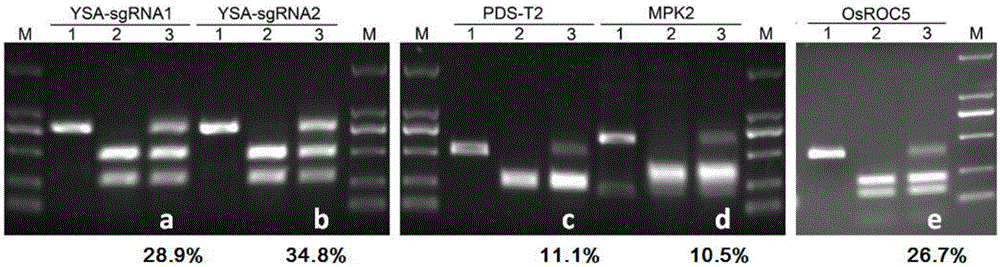

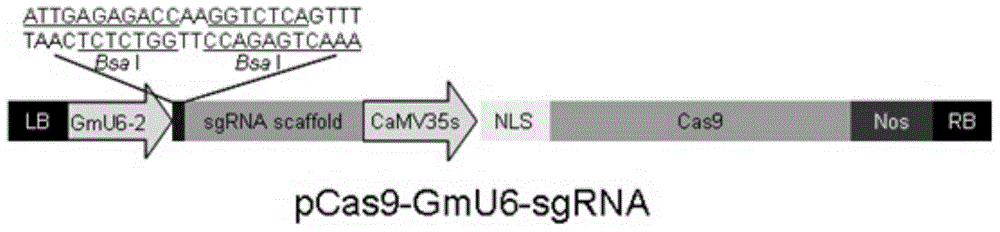

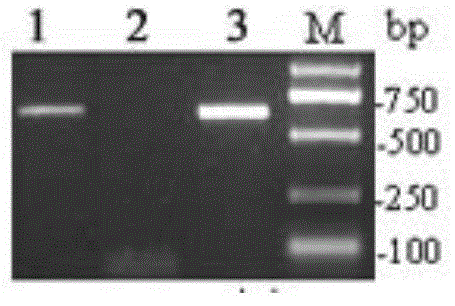

Construction of soybean CRISPR/Cas9 system and application of soybean CRISPR/Cas9 system in soybean gene modification

InactiveCN104450774AFinish quicklyHigh mutation rateVector-based foreign material introductionAngiosperms/flowering plantsGene ModificationBiology

The invention relates to construction of a soybean CRISPR / Cas9 system. The construction disclosed by the invention is mainly characterized in that a core sequence is designed according to a target gene, and the core sequence is constructed into an expression carrier with cas9. The soybean CRISPR / Cas9 system utilizes the core sequence to identify the target gene, the cas9 shears the target gene, and various mutations can be generated in the process of repairing a broken chain by an organism. The invention also provides application of the soybean CRISPR / Cas9 system in soybean gene modification. With the adoption of the construction and the application provided by the invention, the constructed soybean CRISPR / Cas9 system is simple, the soybean gene can be rapidly and efficiently modified, and the problems of the traditional ZFNs system is too complex, wastes time and is low in efficiency are overcome.

Owner:INST OF CROP SCI CHINESE ACAD OF AGRI SCI

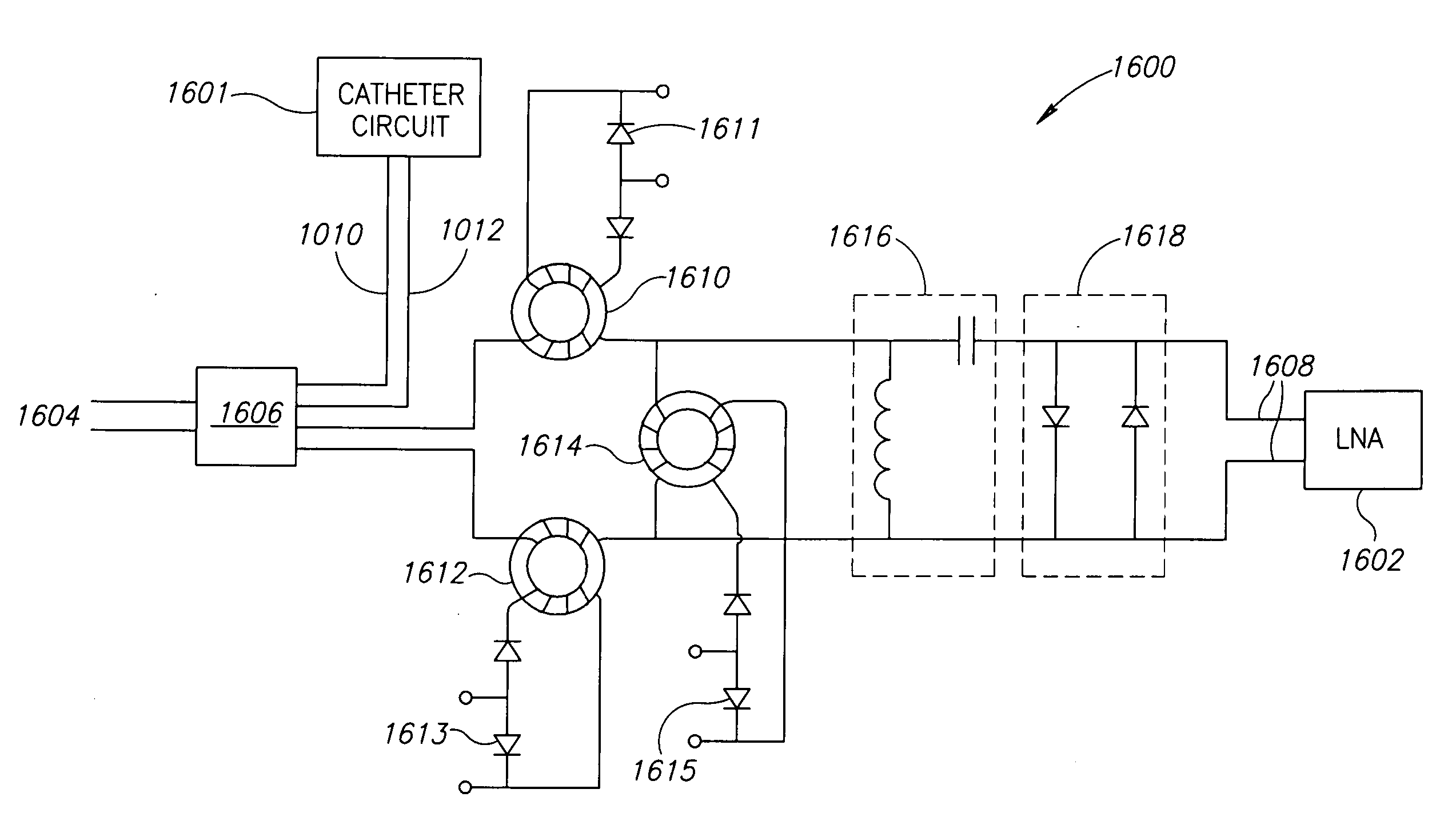

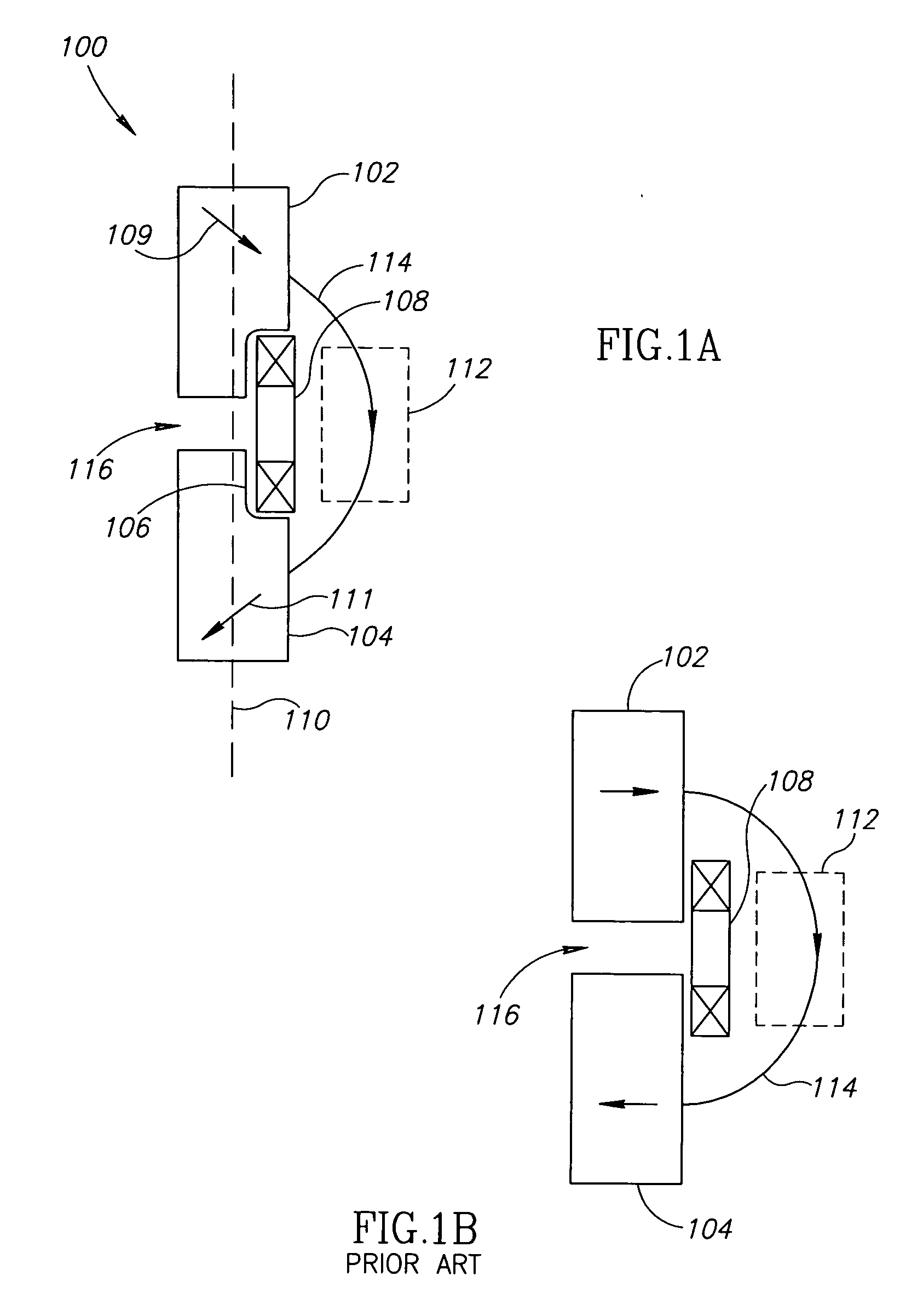

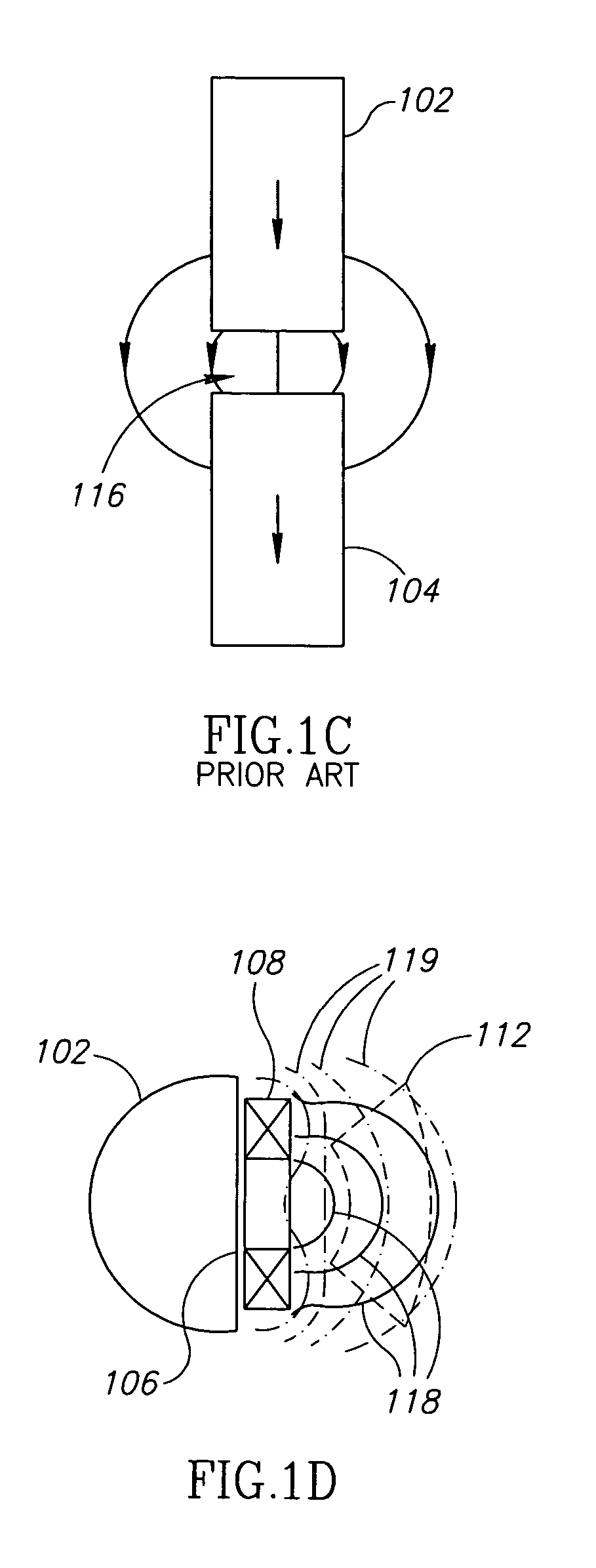

Magnet and coil configurations for MRI probes

InactiveUS20060084861A1High enough saturation flux densityImprove signal-to-noise ratioMagnetic measurementsCatheterElectric signalExcited nucleus

A probe, with a longitudinal axis, for use in an NMR system, the probe comprising: (a) a plurality of static magnetic field sources which create a static magnetic field that is non-axisymmetric about the longitudinal axis, in a region outside the probe; and (b) at least one antenna, compromising one or more antennas together capable of creating a time-varying magnetic field which is capable of exciting nuclei in a sub-region of the region, and capable of receiving NMR signals from said excited nuclei and generating NMR electrical signals therefrom; wherein the plurality of magnetic field sources comprise adjacent static magnetic field sources that are magnetized in directions that differ by more than 10 degrees and less than 170 degrees.

Owner:TOPSPIN MEDICAL ISRAEL

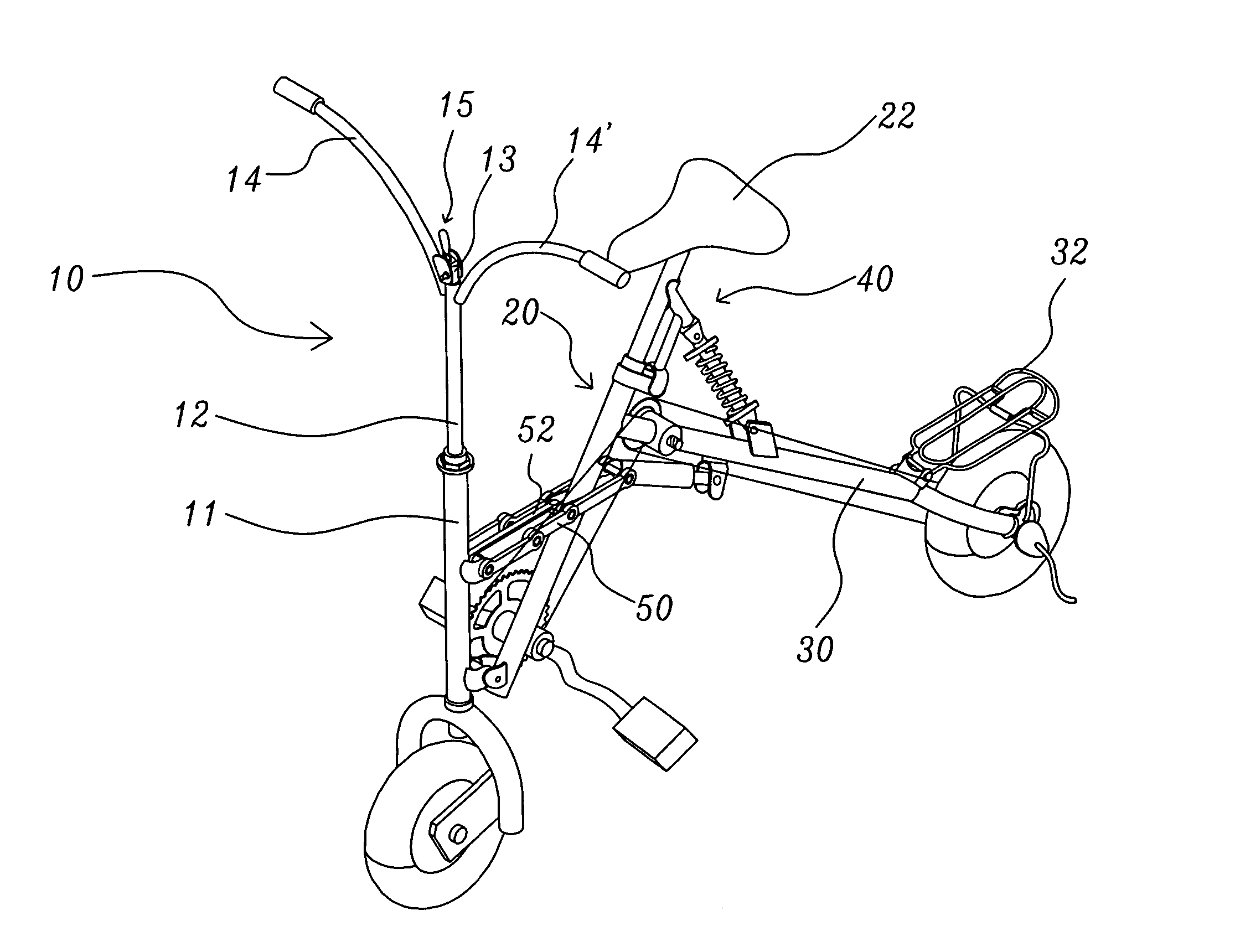

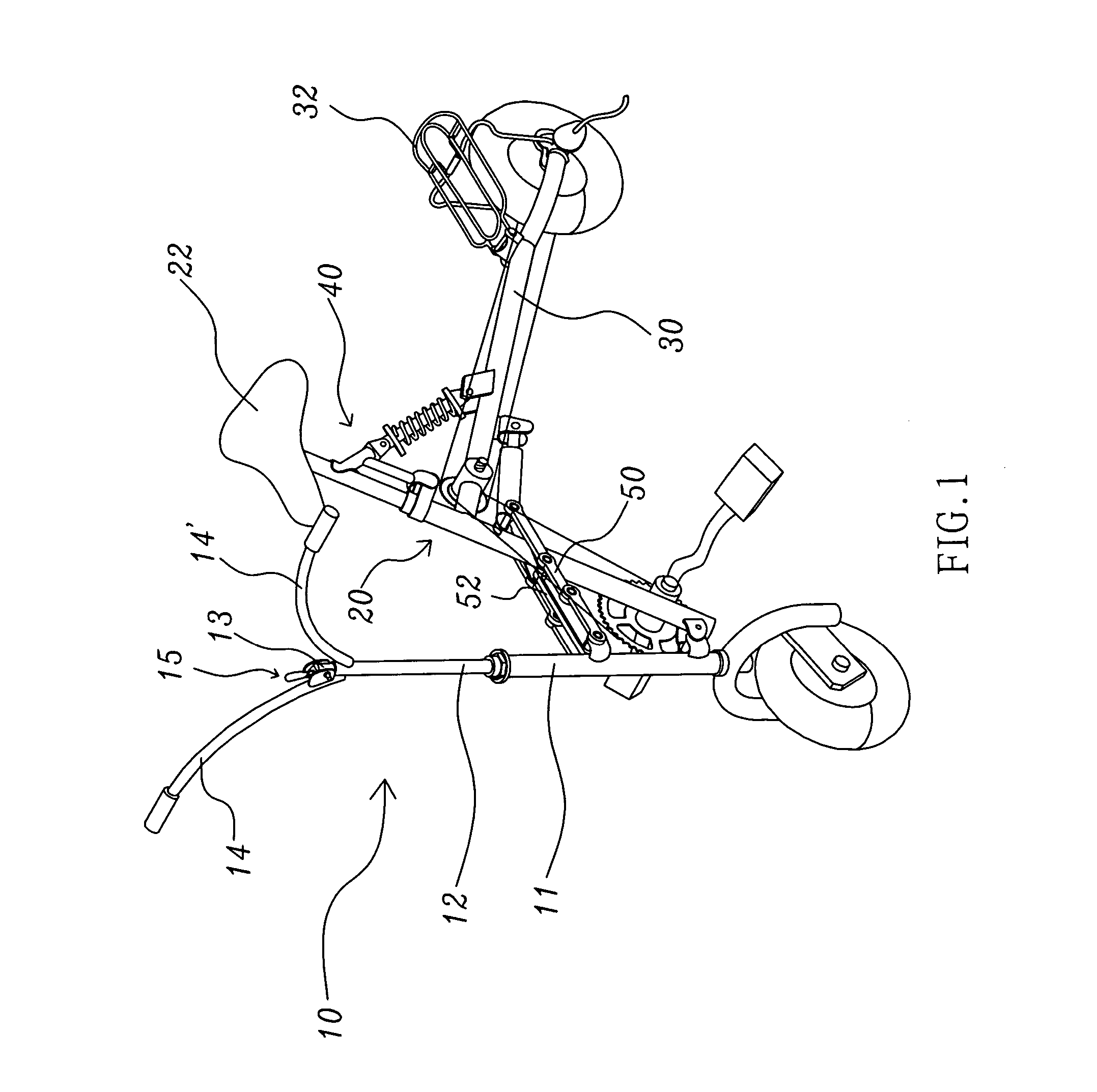

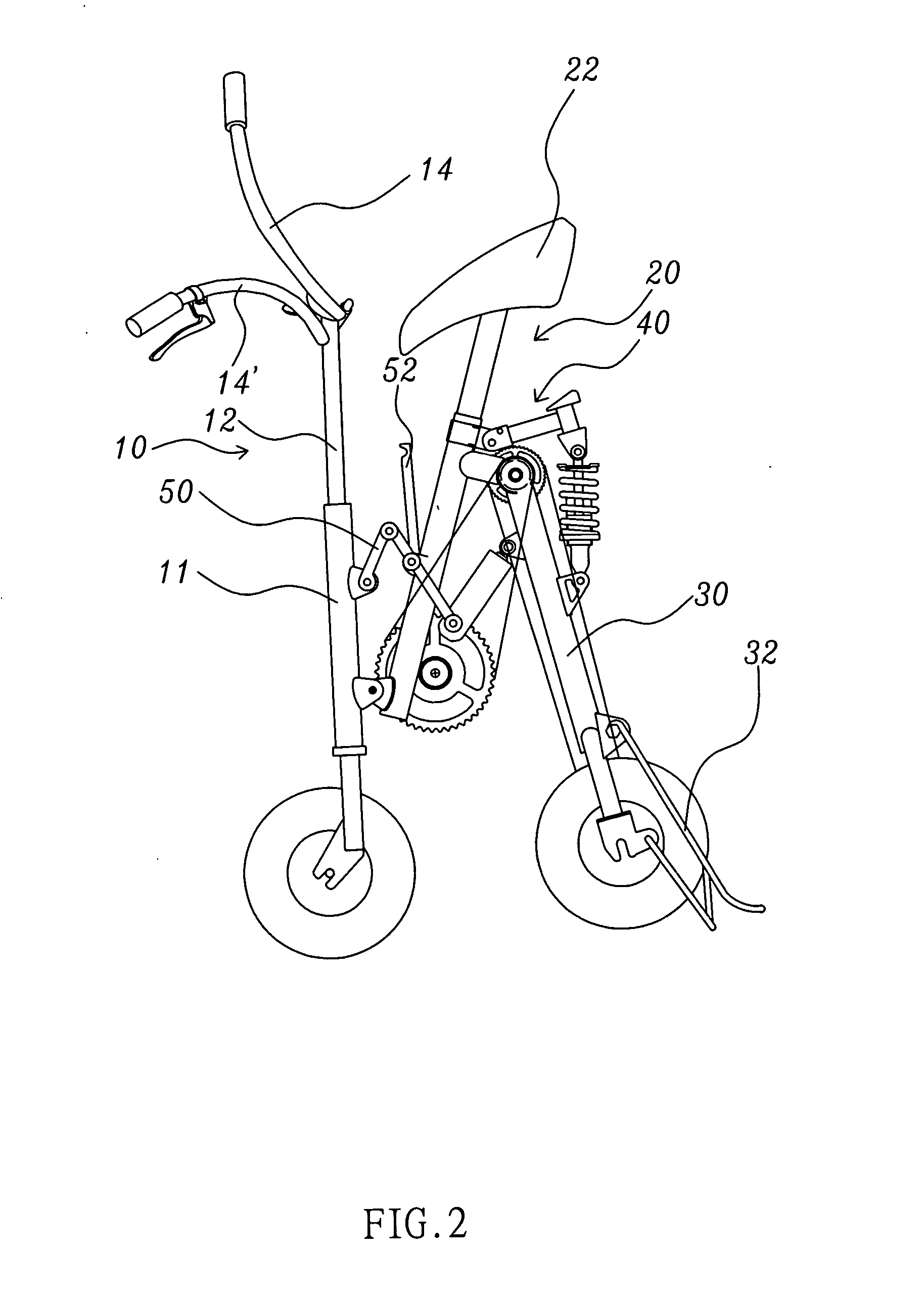

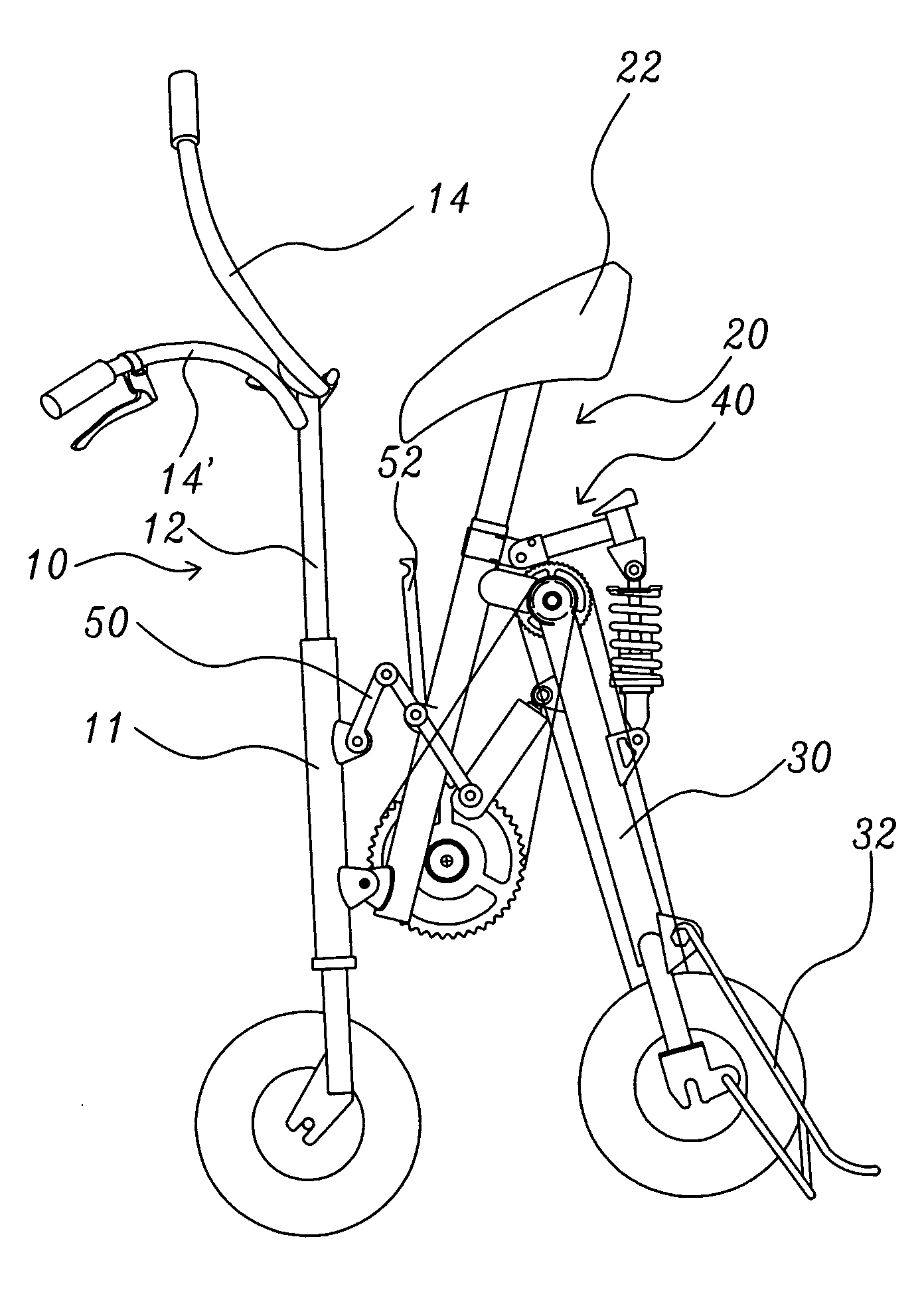

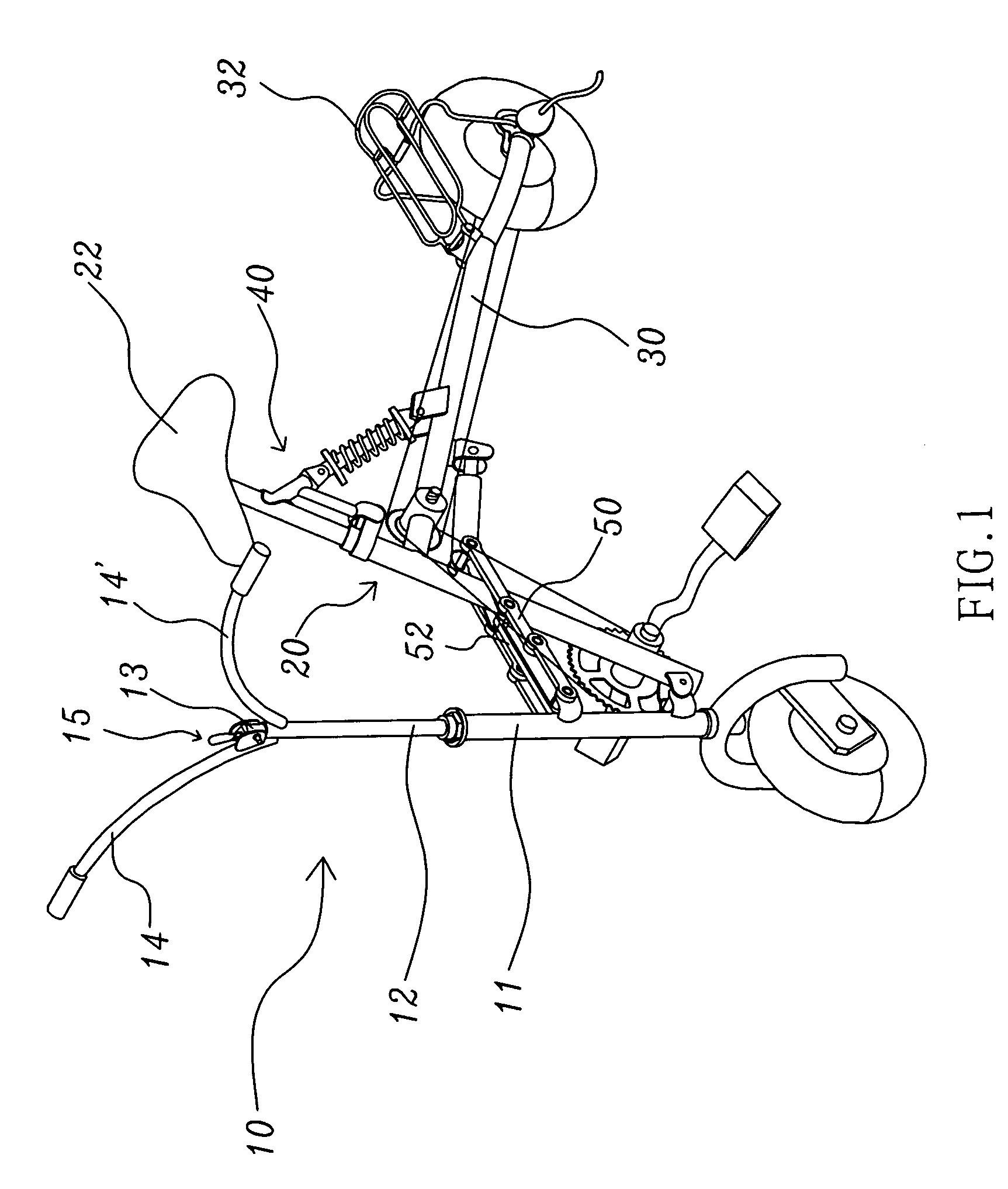

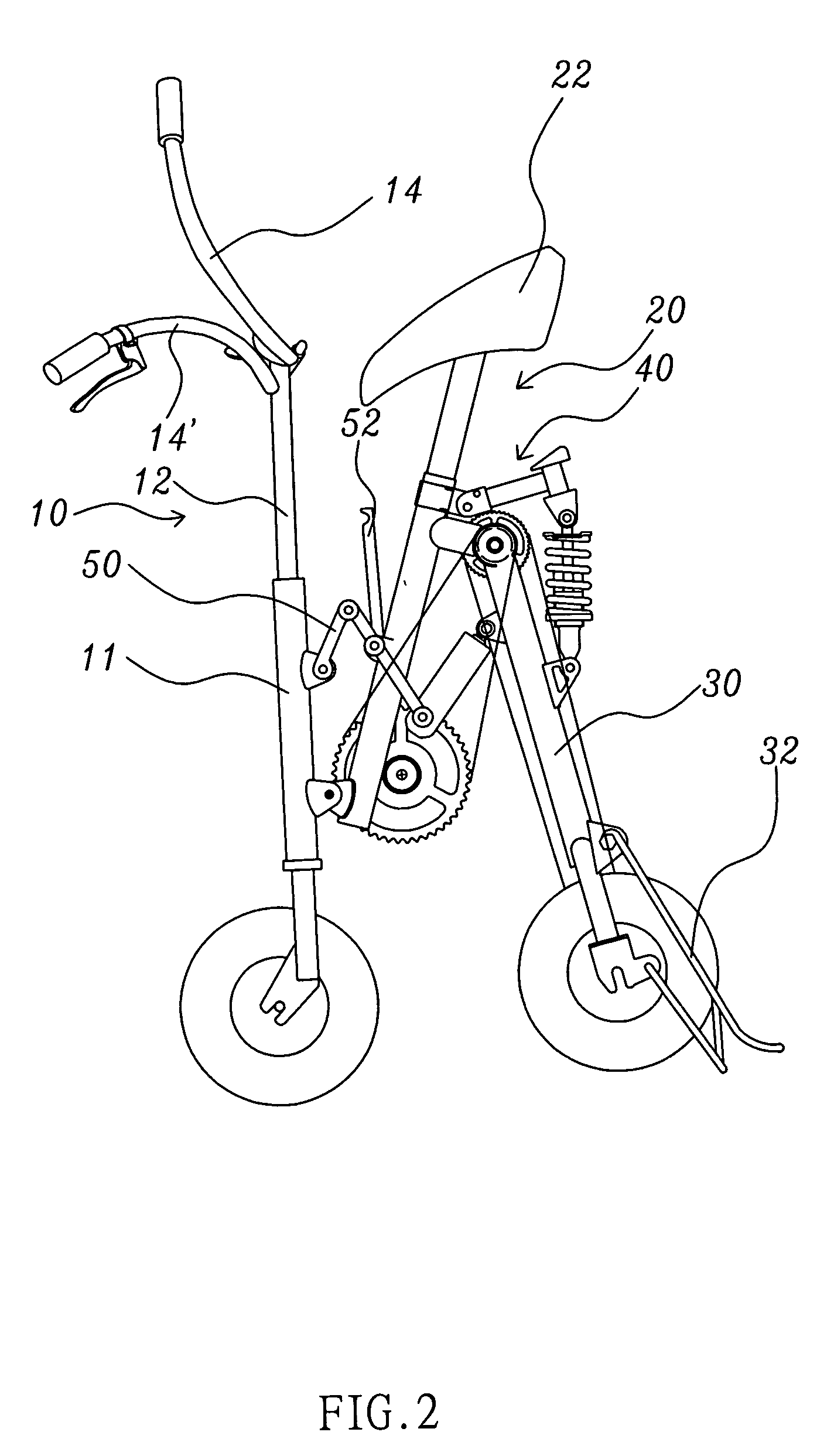

Folding bicycle structure

InactiveUS20050035570A1Fast to accomplishConvenient to usePassenger cyclesWheel based transmissionTubing setEngineering

A folding bicycle comprises a retractable front tube set. Handles at two sides of the top of the front tube set can be folded to the same side. An eccentric rotation device is pivotally provided at the top of the front tube set to drive an internal tube to retract in an outer tube for positioning. A seat tube is pivotally connected with the front tube set. A saddle is provided at the top of the seat tube. A rear tube is pivotally connected with the seat tube. A fastening device is provided between the rear tube and the seat tube to fix the seat tube. The front tube set, the seat tube and the rear tube are connected together by a joint link, which provides the function of a joint to let the front tube set, the seat tube and the rear tube unfold or fold with one another.

Owner:CHU ARTHUR

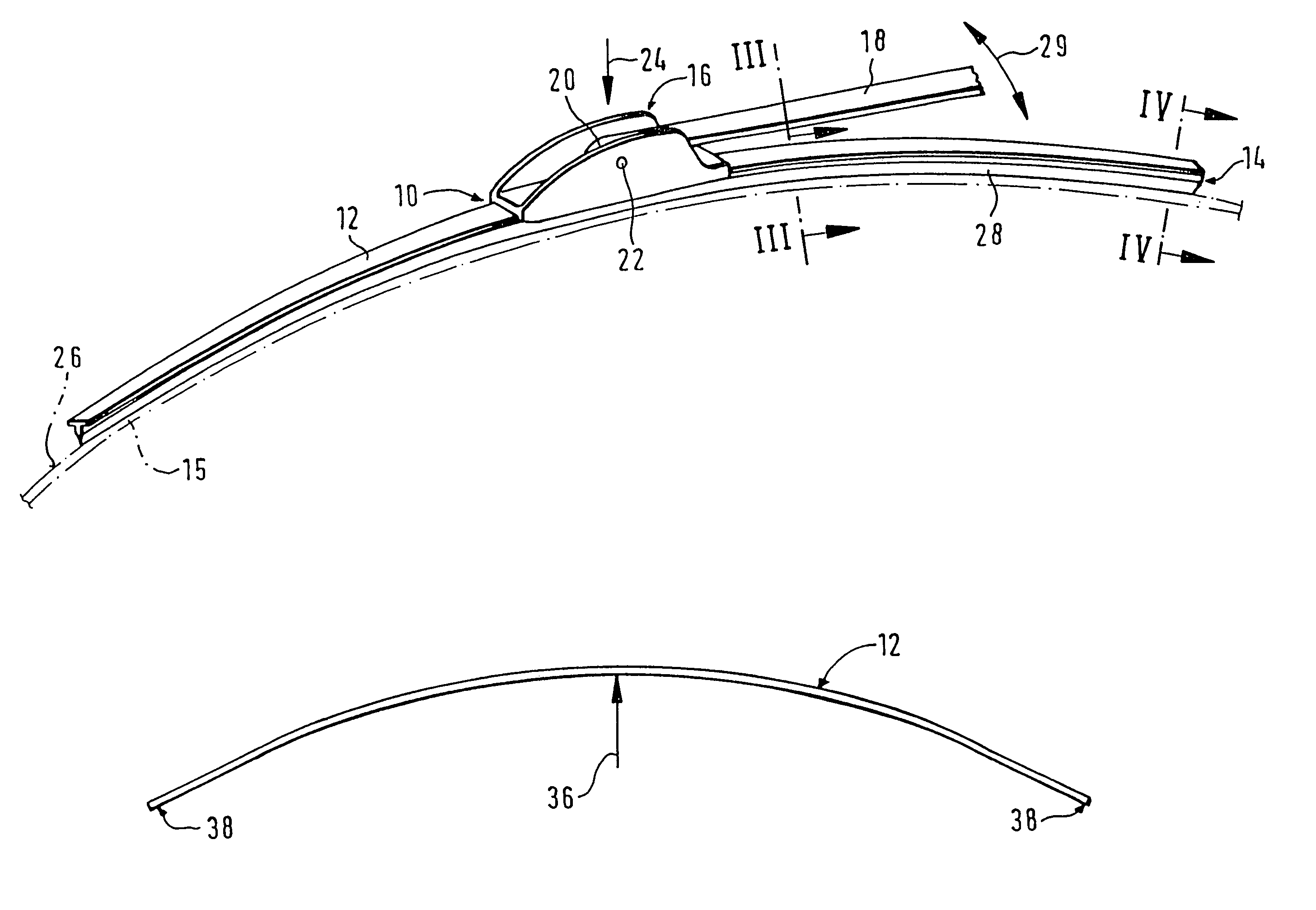

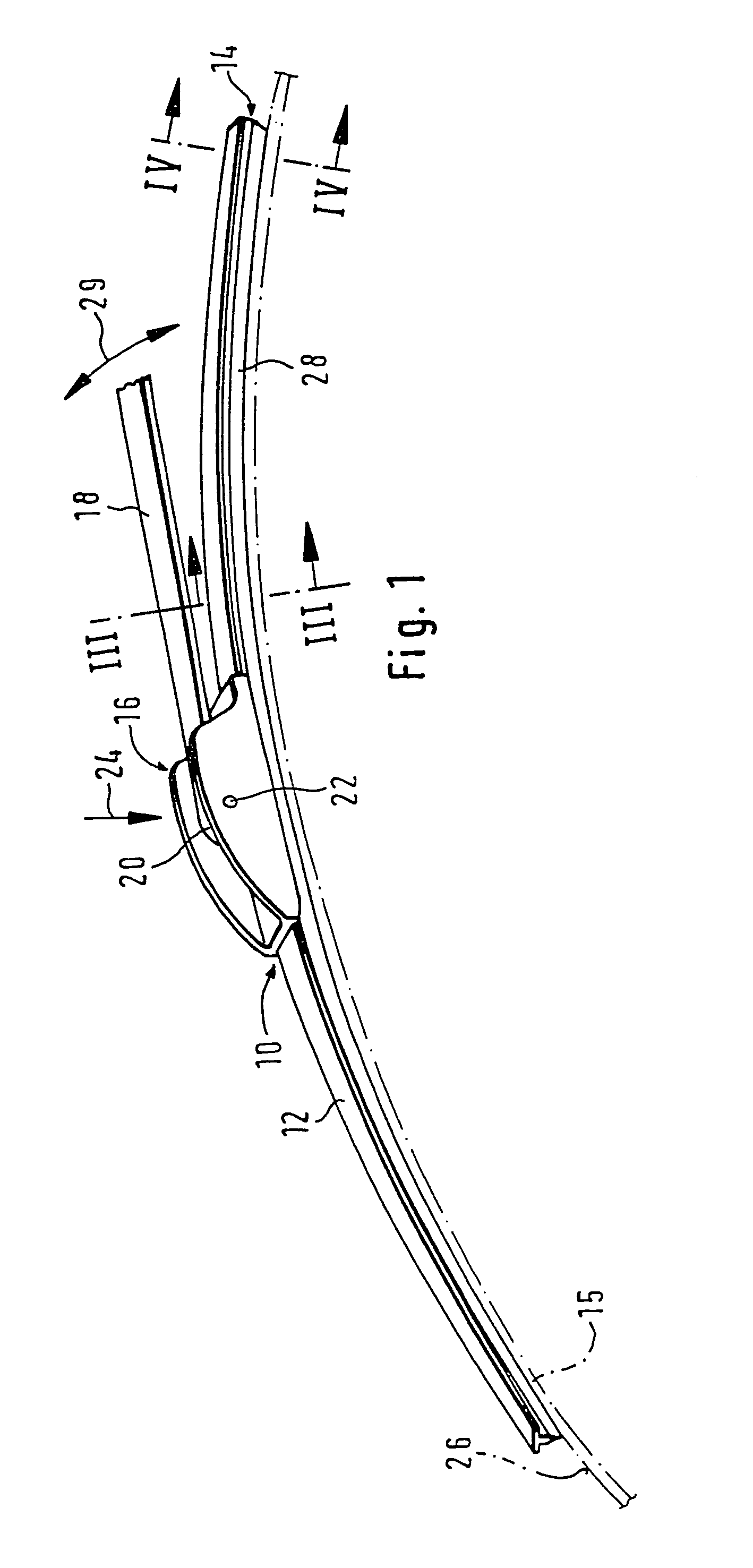

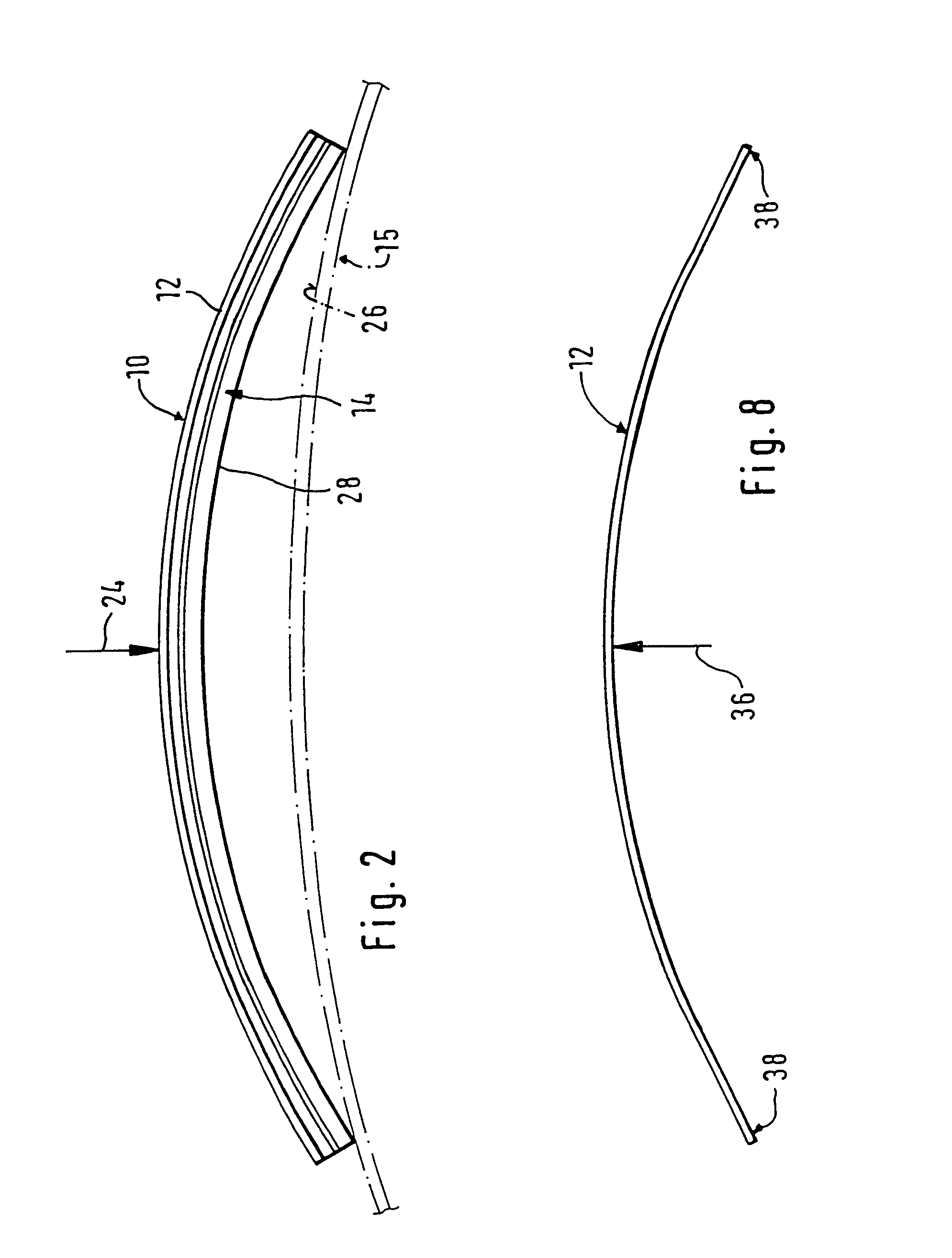

Wiper blade for motor vehicle windows

InactiveUS6973698B1Reduce contact pressureFinished more quicklyWindow cleanersVehicle cleaningMobile vehicleContact force

A wiper device with a wiper blade for cleaning windows of motor vehicles, in which the wiper blade can be moved back and forth laterally to its longitudinal span by a driven wipe arm which can be connected to the wiper blade and loads the same against the window. The wiper blade has an elongated wiper strip that can be placed against the window and an elongated spring-elastic carrying element, which has a connecting unit for the wiper arm and is disposed parallel to the longitudinal axis of the wiper strip to distribute a contact force over the entire wiper strip length. A particularly effective and low-noise operation of the wiper system is achieved because the contact force of the wiper strip against the window is greater in its center section than in at least one of two end sections of the wiper strip.

Owner:ROBERT BOSCH CORP

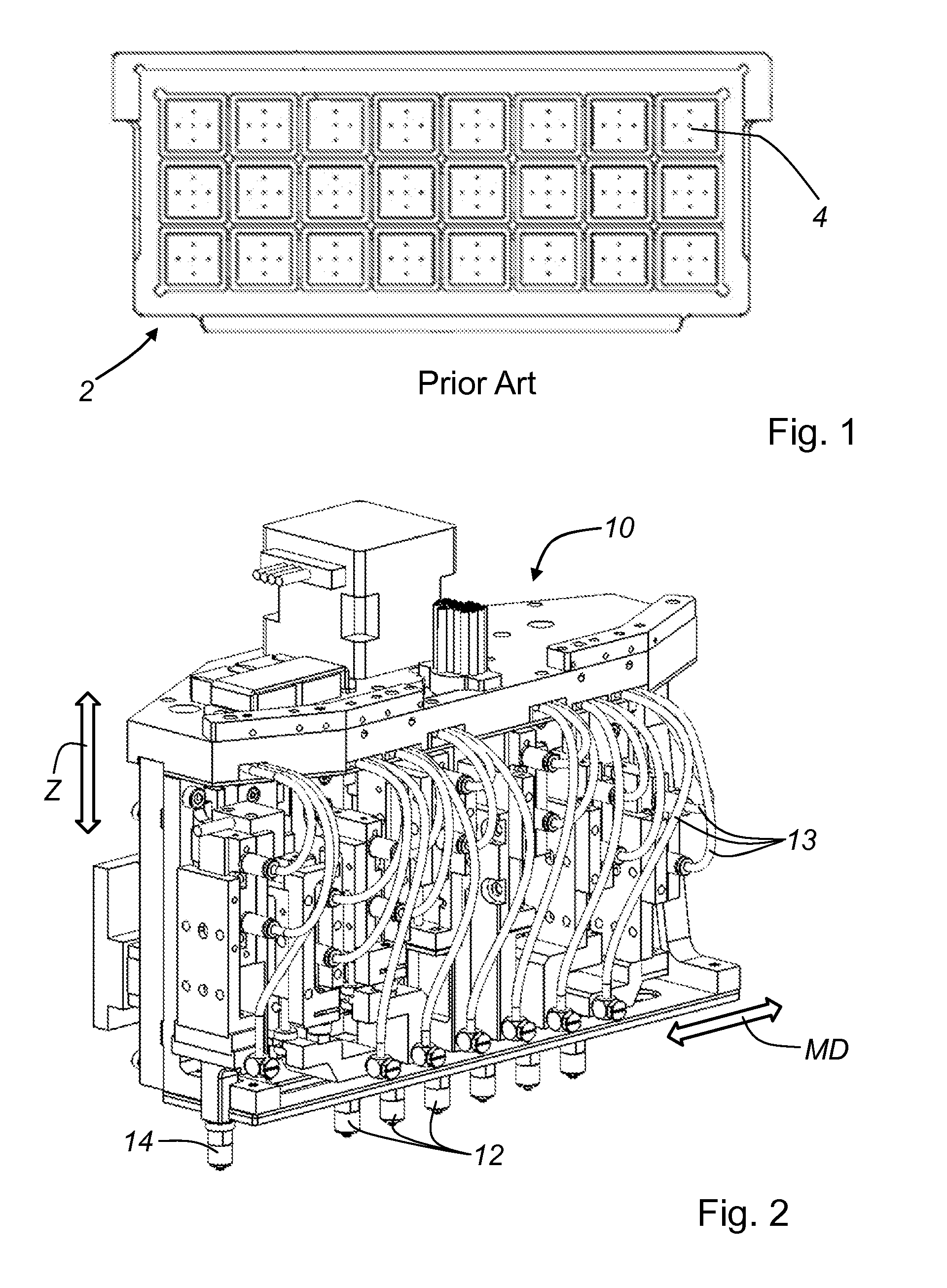

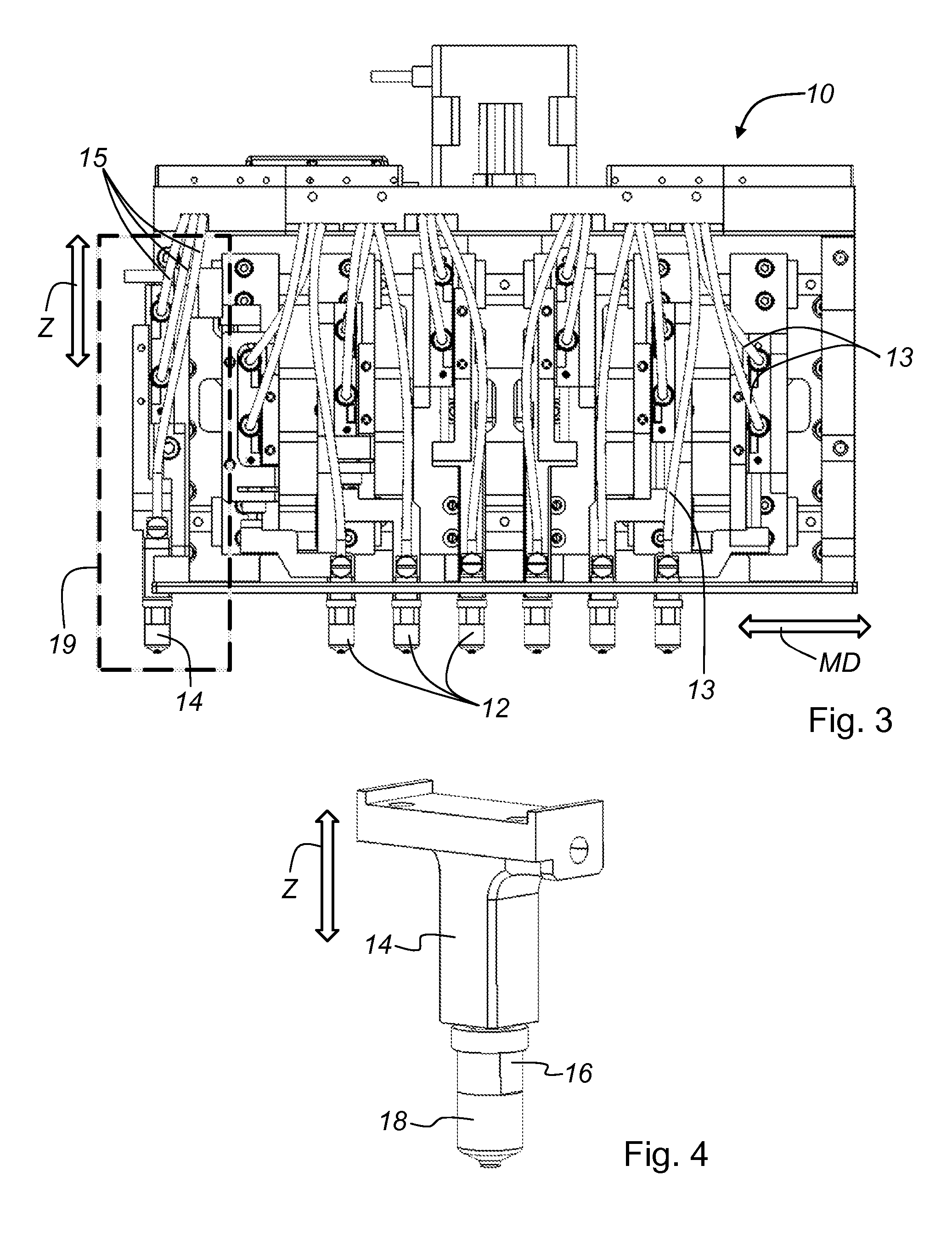

Pick and place device with automatic pick-up-height adjustment and a method and a computer program product to automatically adjust the pick-up-height of a pick and place device

ActiveUS20150298316A1Finish quicklyAvoid damageProgramme-controlled manipulatorDigital data processing detailsFlow transducerInlet valve

A pick and place device, a method and a computer program product for automatic pick- up-height adjustment. A first pneumatic system has a first and second controllable valves. The second controllable valve is connected with its input port to a vacuum source. An output port of the first controllable valve and an output port of the second controllable valve are connected to a common tube in fluid communication with at least one vacuum nozzle of the pick and place device. A second pneumatic system, with an inlet valve and an outlet valve are in fluid communication via a connecting tube. An open air exhaust and a flow controller are arranged in the connecting tube between the inlet valve and the outlet valve. A flow sensor detects the changes of the small air flow. The flow sensor is via a tube in fluid communication with the at least one vacuum nozzle.

Owner:KLA TENCOR TECH CORP

Folding bicycle structure

InactiveUS6883817B2Finish quicklyEasy to usePassenger cyclesWheel based transmissionEngineeringMechanical engineering

A folding bicycle comprises a retractable front tube set. Handles at two sides of the top of the front tube set can be folded to the same side. An eccentric rotation device is pivotally provided at the top of the front tube set to drive an internal tube to retract in an outer tube for positioning. A seat tube is pivotally connected with the front tube set. A saddle is provided at the top of the seat tube. A rear tube is pivotally connected with the seat tube. A fastening device is provided between the rear tube and the seat tube to fix the seat tube. The front tube set, the seat tube and the rear tube are connected together by a joint link, which provides the function of a joint to let the front tube set, the seat tube and the rear tube unfold or fold with one another.

Owner:CHU ARTHUR

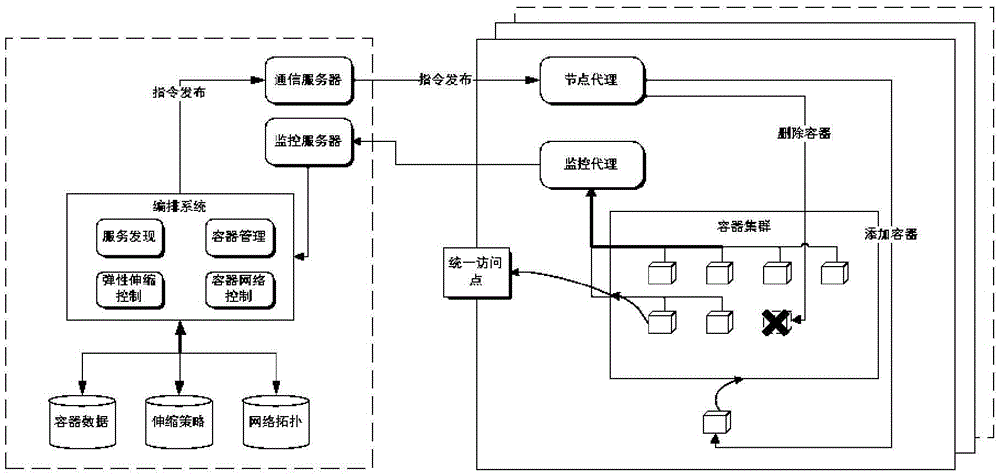

Elastic expansion method based on container cluster and application system thereof

InactiveCN105554102AAvoid wastingImprove resource utilizationTransmissionIdle timeResource utilization

The present invention provides an elastic expansion method based on a container cluster and an application system thereof. The method comprises the steps of (1) creating a container cluster, and setting the threshold of elastic expansion, (2) judging whether a container in the container cluster is started or not, and executing a corresponding operation according to a judgment result, (3) setting a unified access point when all containers are started, (4) triggering elastic expansion when the indicator of the container in the container cluster reaches the set threshold, and adding or deleting the container, (5) in the elastic expansion process, adjusting the unified access point as a load balance strategy, which means that an access flow is always oriented to a viable container, (6) adding a new container into the range managed by the unified access point if the new container exists after the elastic expansion is completed. According to the method and the system, the number of the container cluster can be dynamically adjusted according to a monitoring data result, thus online application access in not influenced by application traffic, the maximization of resource utilization is realized, and the waste of resources in an idle time is avoided.

Owner:CETC CHINACLOUD INFORMATION TECH CO LTD

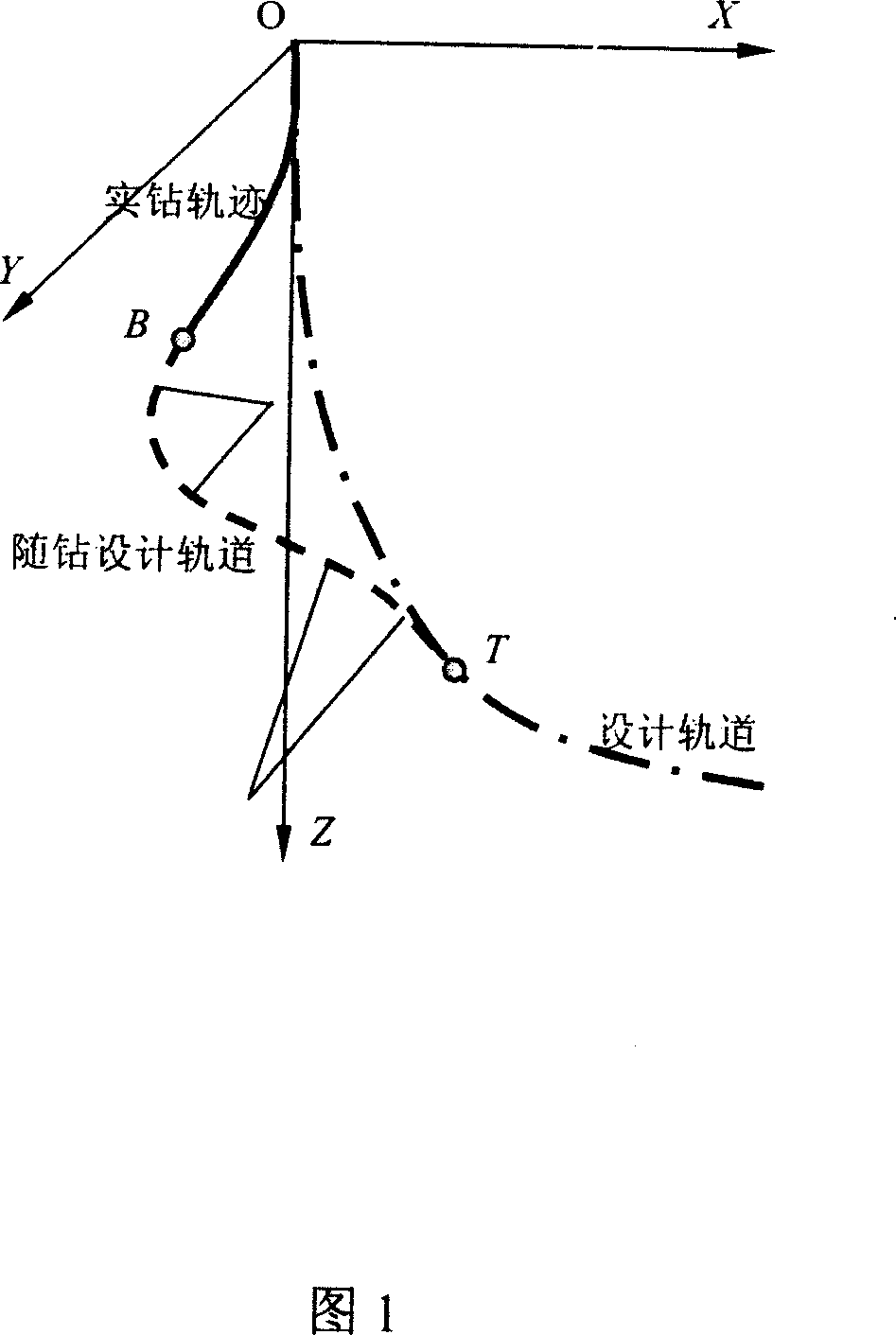

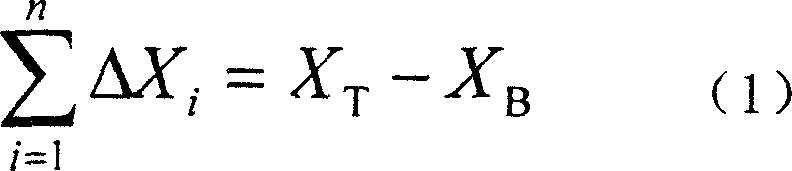

Design-while-drilling method for controlling borehole track while drilling well

InactiveCN1936263AIdeal control targetSafe completionSurveyDirectional drillingSection planePetroleum

The invention relates to well bore rail control and design that includes the process of determining well bore section shape, building equation set, expanding equation set, giving known parameters, and solving the equation set. It could meet the request of target intake direction and coordinate location, and could select 4 random feature parameters as the indeterminate parameters. The invention could improve drilling speed and wellbore quality, lower drilling cost.

Owner:CHINA PETROLEUM & CHEM CORP +1

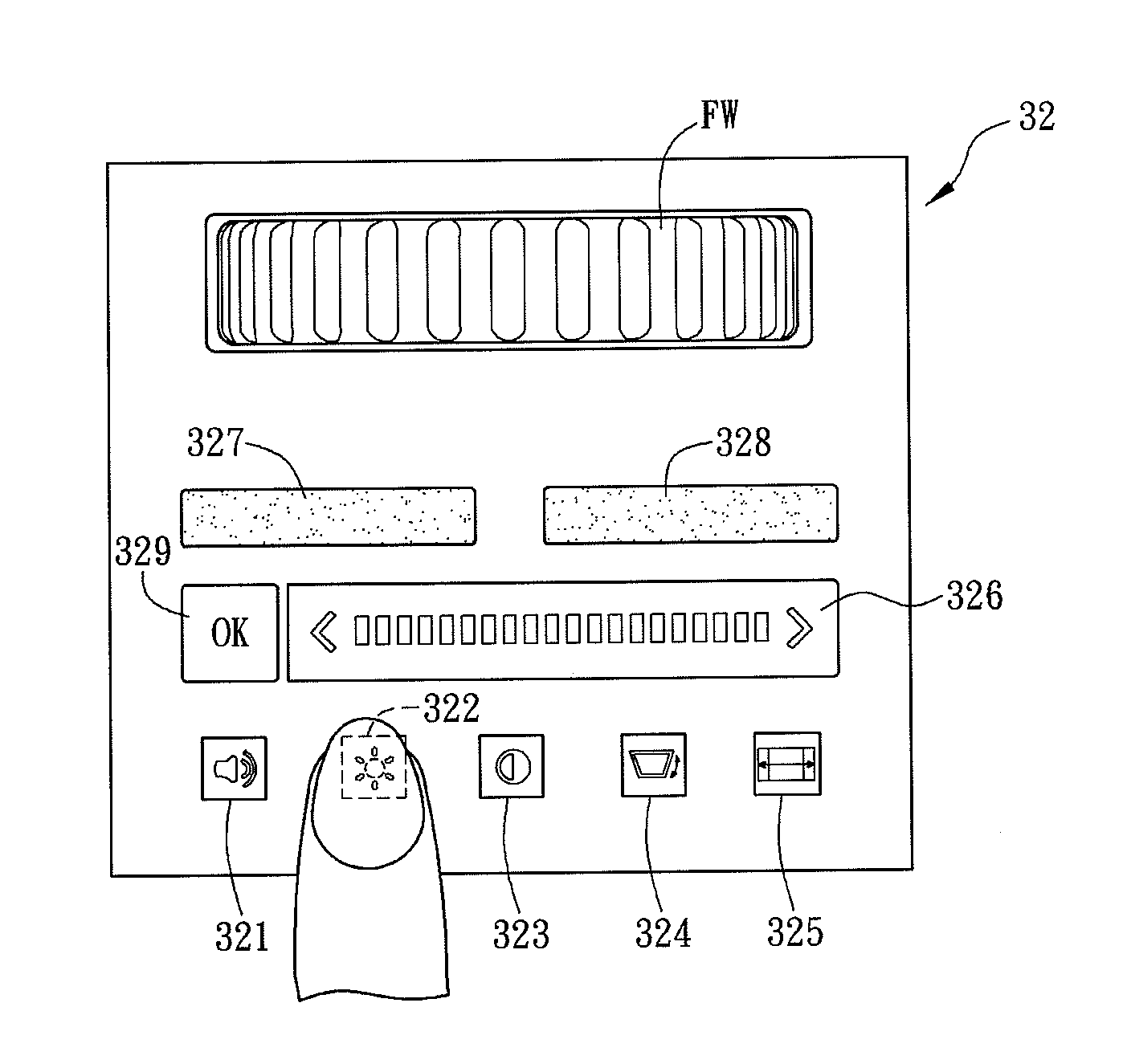

Electronic device and method for adjusting settings thereof

InactiveUS20120110510A1Low costLabor savingInput/output processes for data processingTime efficientTime cost

A method for adjusting settings of an electronic device is disclosed. The method includes the steps as follows: providing a user interface including a plurality of main setting menu keys and a control unit; selecting one of the main setting menu keys to call a main setting value corresponding to the main setting menu key; outputting a corresponding main setting option image at least including a main setting value display area according to the main setting value; and providing a touch control event to operate the control unit for adjusting the main setting value and then display the adjusted main setting value on the main setting value display area. The touch control event includes a touch displacement event and a touch event. The method for adjusting the settings is contemplated for user's intuitive operation to save the time cost.

Owner:ASUSTEK COMPUTER INC

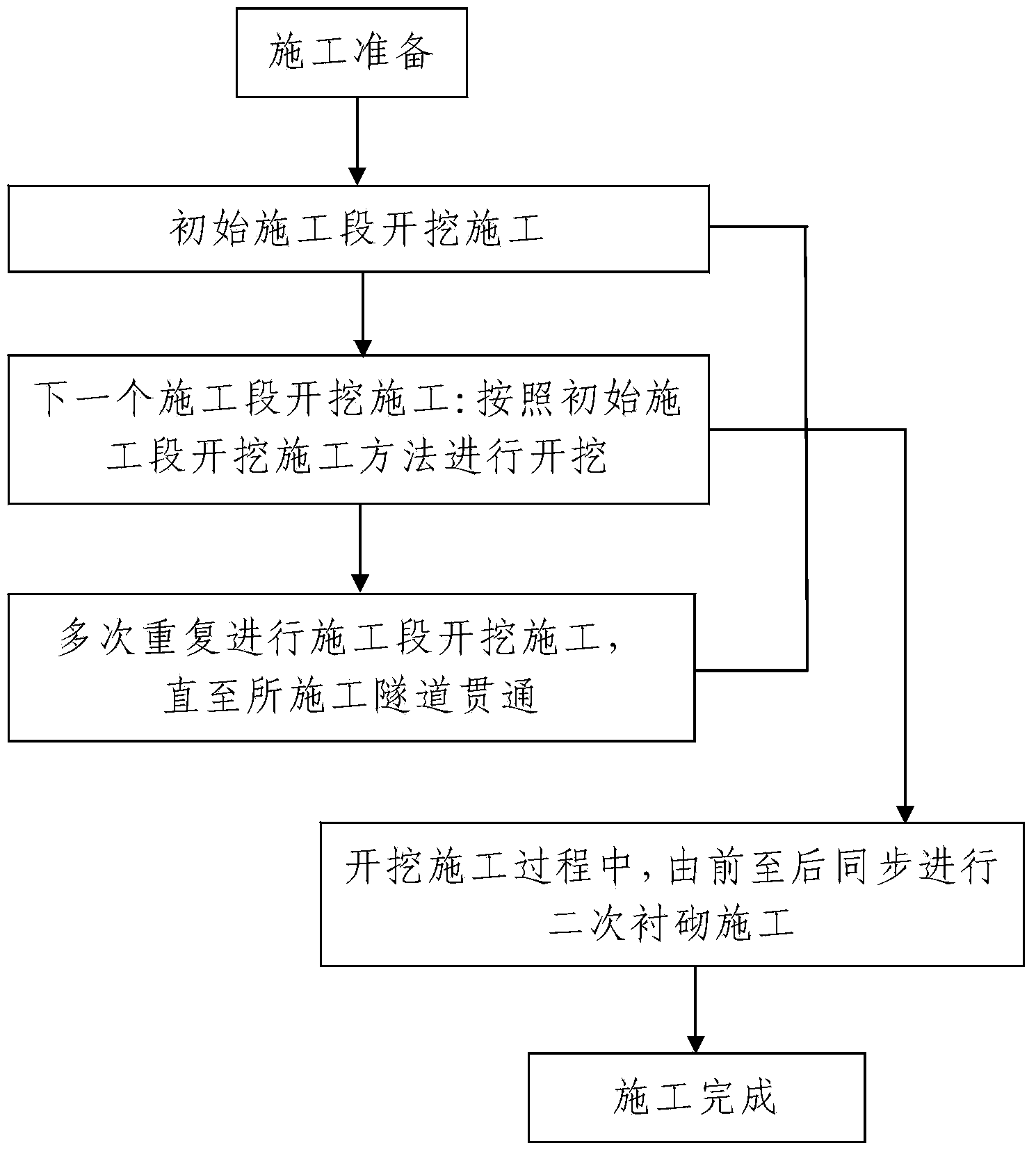

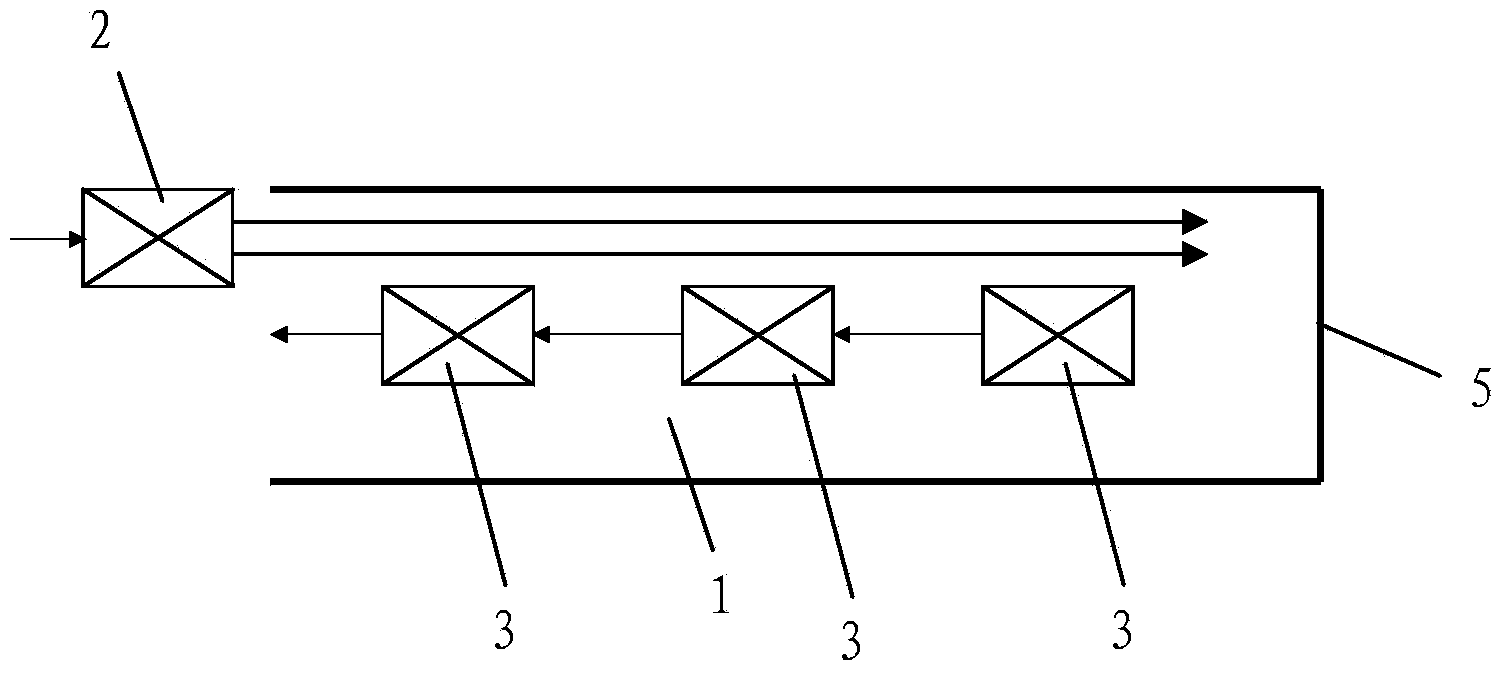

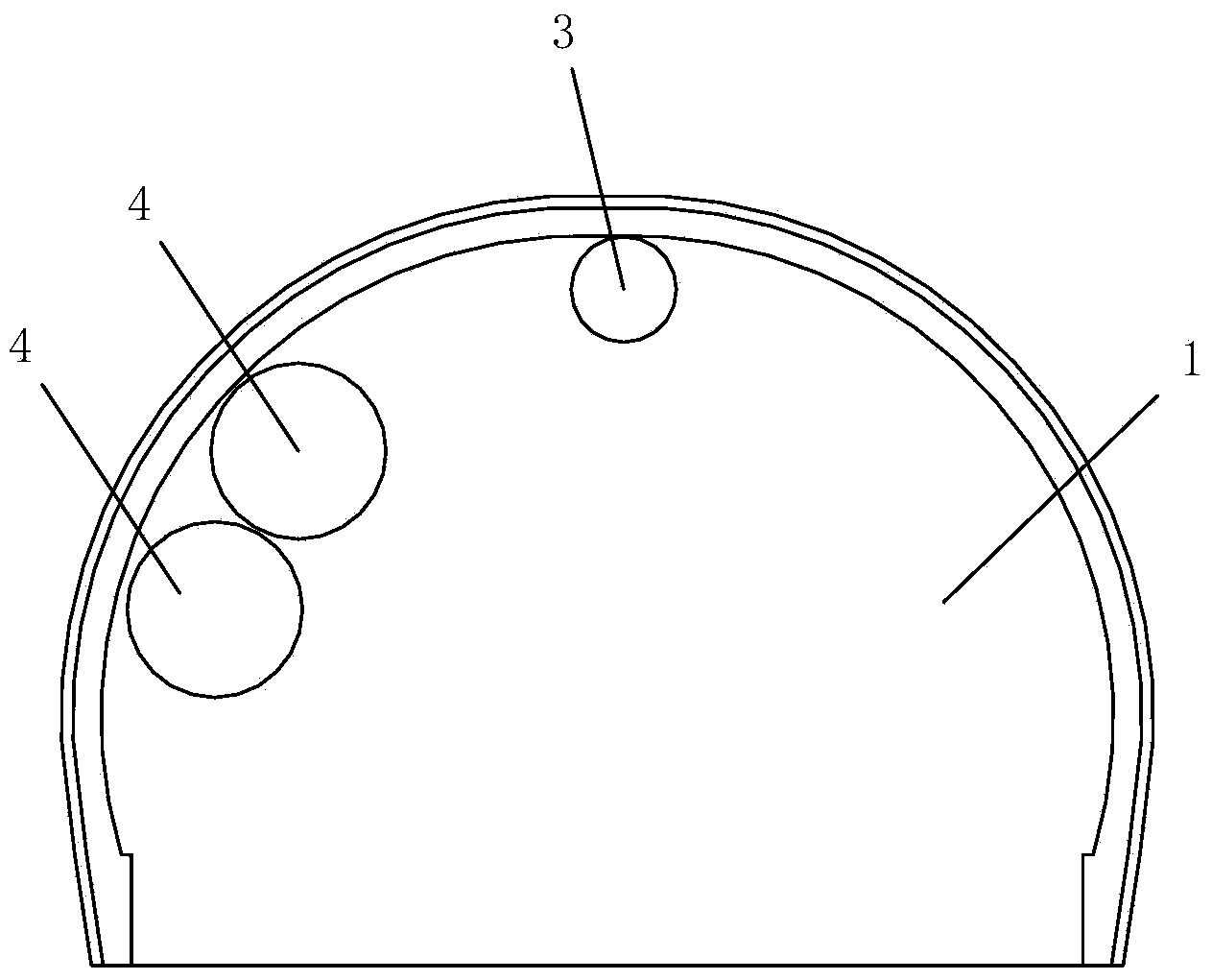

Long tunnel fast construction process

ActiveCN103470267AReasonable designSimplify construction stepsUnderground chambersTunnel/mines ventillationTunnel constructionWater seepage

The invention discloses a long tunnel fast construction process. The tunnel construction method in the direction from the entrance to the exit and the tunnel construction method in the direction from the exit to the entrance are the same and each construction section is respectively constructed from back to front. The construction process is as follows: 1, excavating construction at an initial construction section, the process is as follows: performing advance geology forecast, determining the excavating construction method for the current construction section, excavating and primary supporting; 2, excavating construction at the next construction section; 3, repeating the step 2 for multiple times until the construction tunnel is through, wherein in the tunnel construction process, found water seepage areas are timely subjected to draining treatment, and the secondary lining construction is synchronously performed on the tunnel holes formed by excavating from front to back. The long tunnel fast construction method is reasonable in design, simple and convenient in construction, safe in the construction process, short in construction process and fast in construction progress, thus effectively solving the defects and shortcomings such as large equipment investment, long construction period and slow construction progress of the existing long tunnel construction.

Owner:中铁二十局集团第二工程有限公司

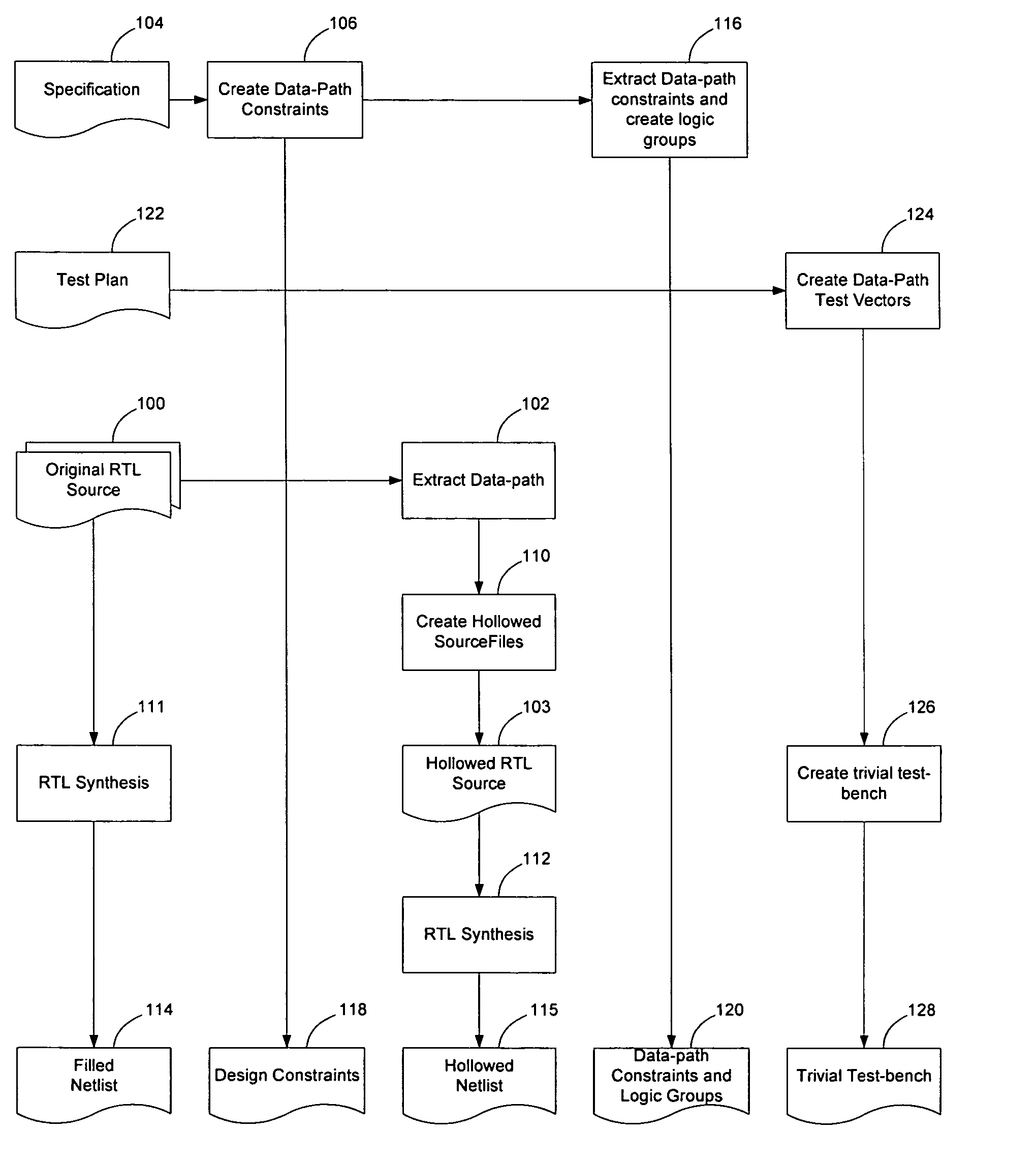

Method and apparatus for automating the design of programmable logic devices

InactiveUS20050183055A1Cost-effectiveFinish quicklyCAD circuit designSoftware simulation/interpretation/emulationTest designDesign review

The design of programmable logic devices, such as FPGAs, may be automated to allow scripts, setup files, and other tool files to be created directly from hollowed and filled netlist, and data-path and design constraint files without extensive human intervention. This allows an FPGA design to be created directly from a logic file to accelerate the FPGA design process. Once hollowed and filled netlists, and data-path and design constraint files have been generated from a design in a standard fashion, the implementation of that design onto an FPGA in an optimized fashion is automated by providing a computer program that is capable of implementing the design, testing the design, evaluating the test results, and altering the design to arrive at a more optimal design. The process may include several steps, such as initial placement of logic groups, sizing of logic groups and FPGA selection, timing analysis, and filled netlist complete design review. The steps may be iterative.

Owner:NORTEL NETWORKS LTD

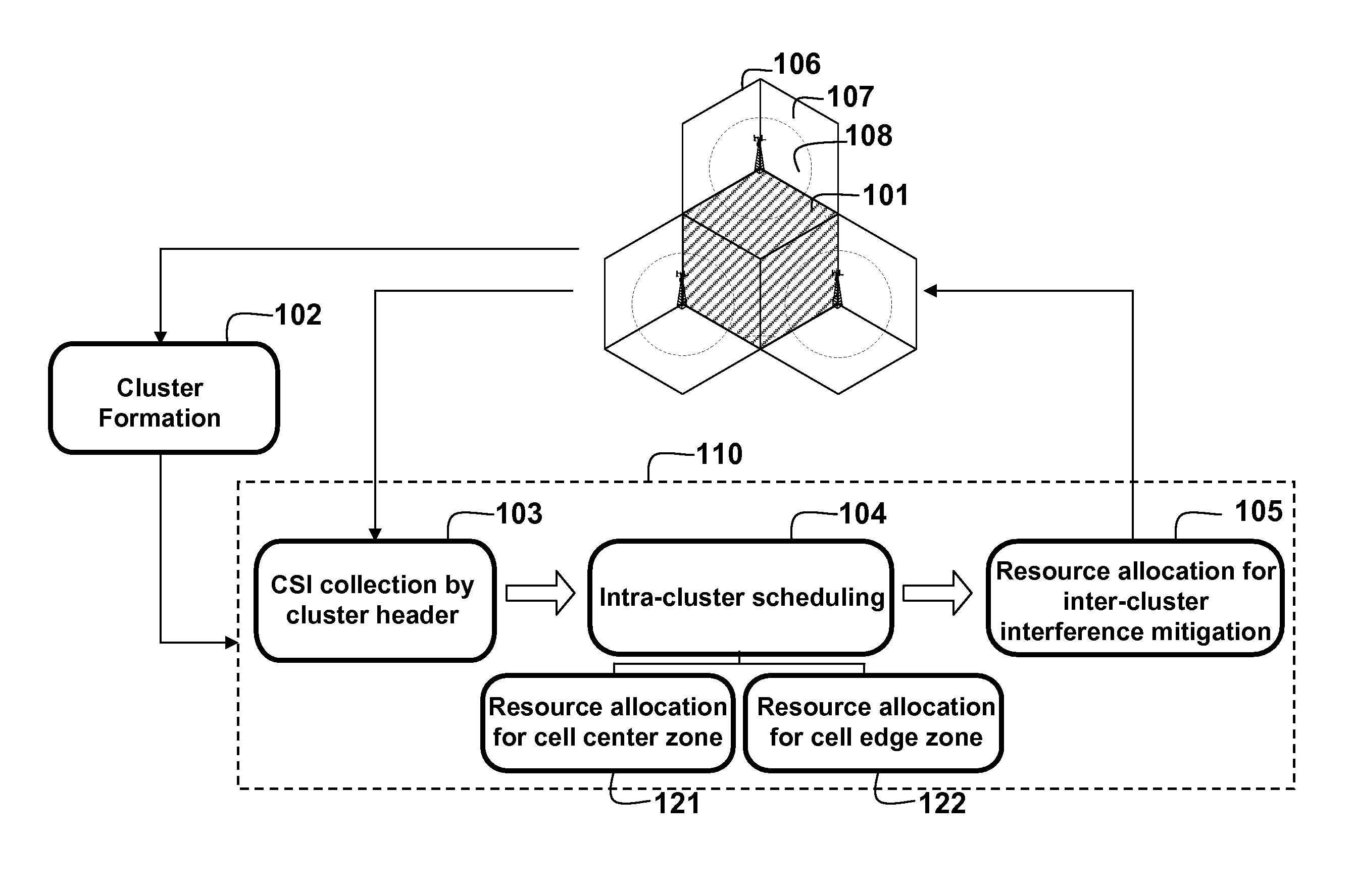

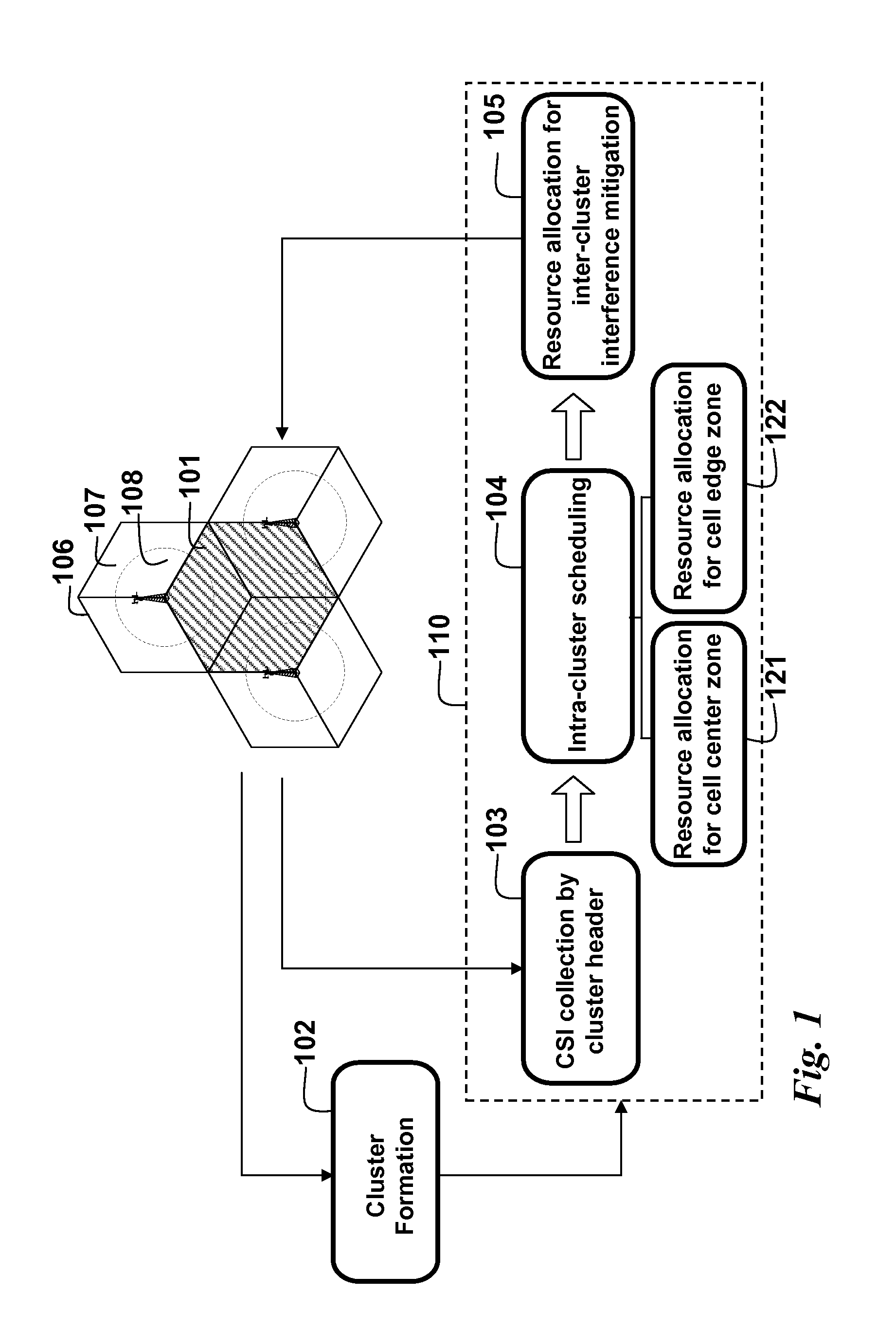

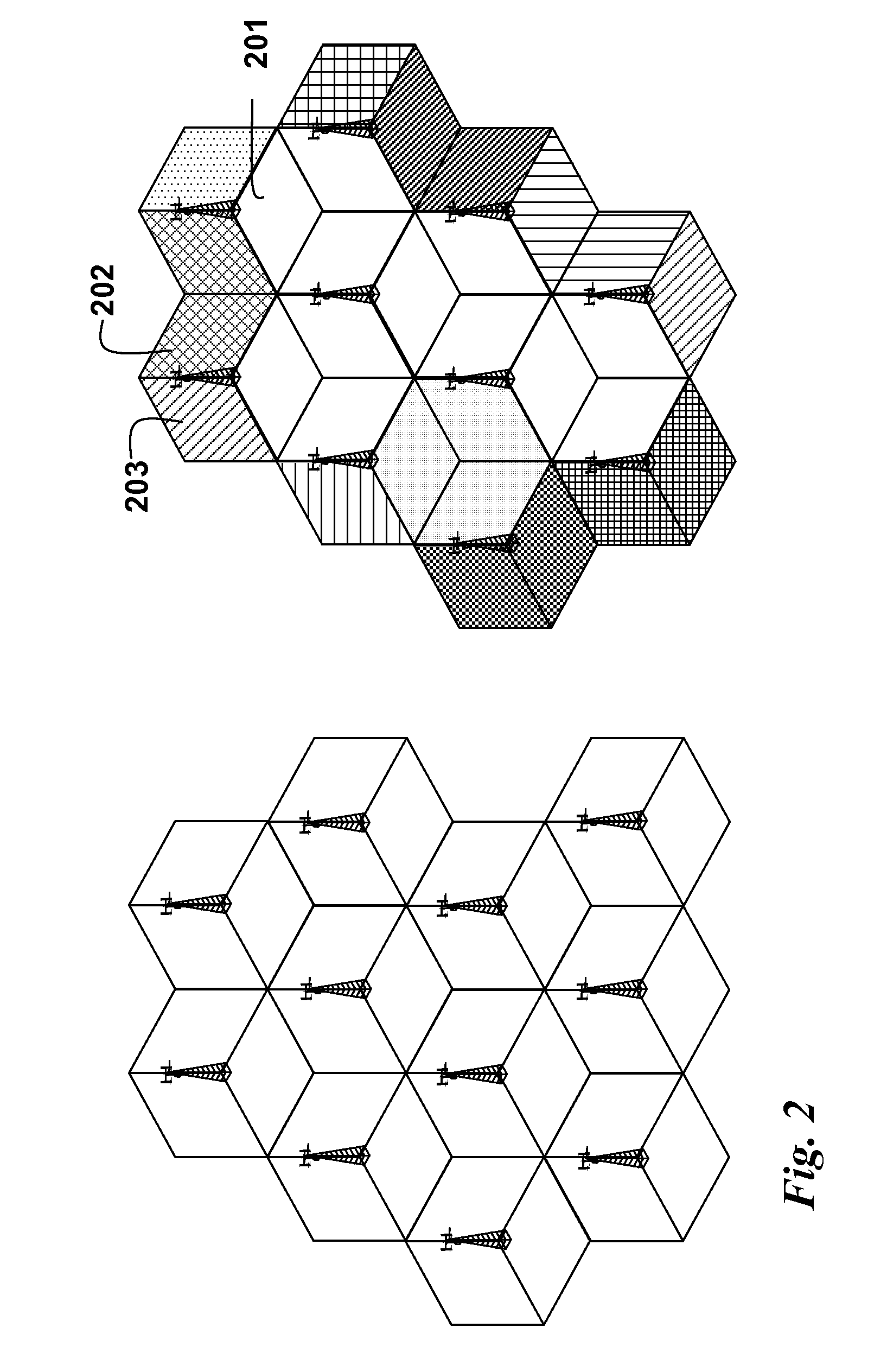

Clustering Based Resource Allocation in Multi-Cell OFDMA Networks

InactiveUS20100214997A1Interference can be avoided and reducedImprove performanceWireless commuication servicesNetwork planningOverlap zoneResource block

A method allocates resource in an Orthogonal Frequency-Division Multiple Access (OFDMA) network, including a set of Base Stations (BSs) and a set of Mobile Stations (MSs) for each BS. OFDMA frame are constructed as multiple resource blocks, and each resource block contains symbols transmitted on different subcarriers. A cluster is formed from adjacent sectors of different neighboring cells to jointly optimize the resource allocation in multiple frames, and three non-overlap zones are sequentially identified in cluster: cell center zone, cell edge zone, and cluster corner zone. Resource allocation includes intra-cluster proportional fair scheduling and inter-cluster interference mitigation. Intra-cluster scheduling further includes resource allocation for cell center zone and resource allocation for cell edge zone.

Owner:MITSUBISHI ELECTRIC RES LAB INC

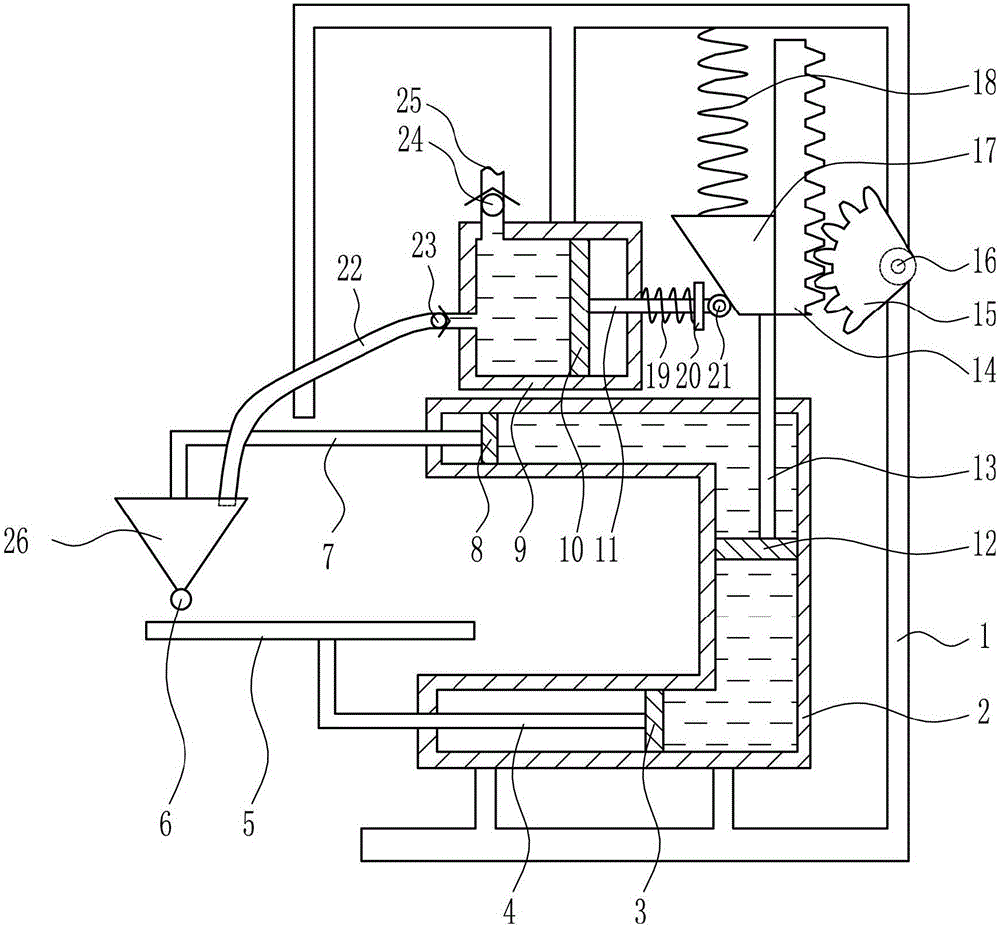

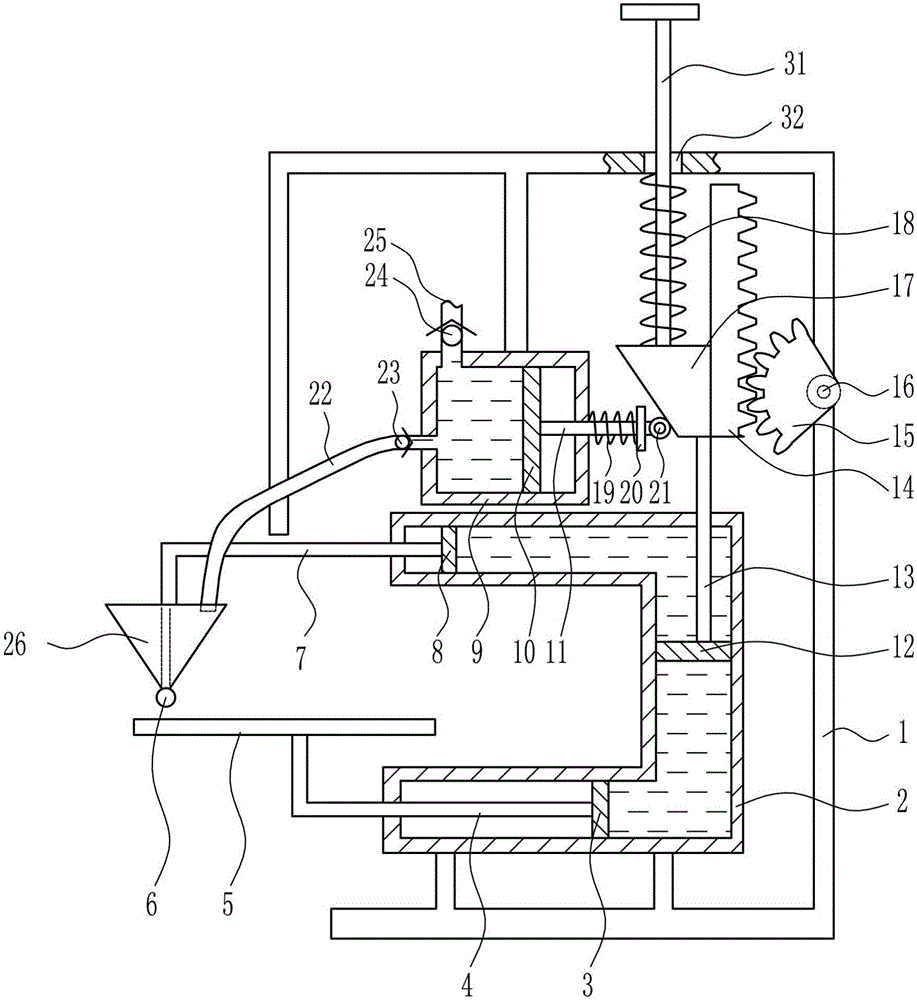

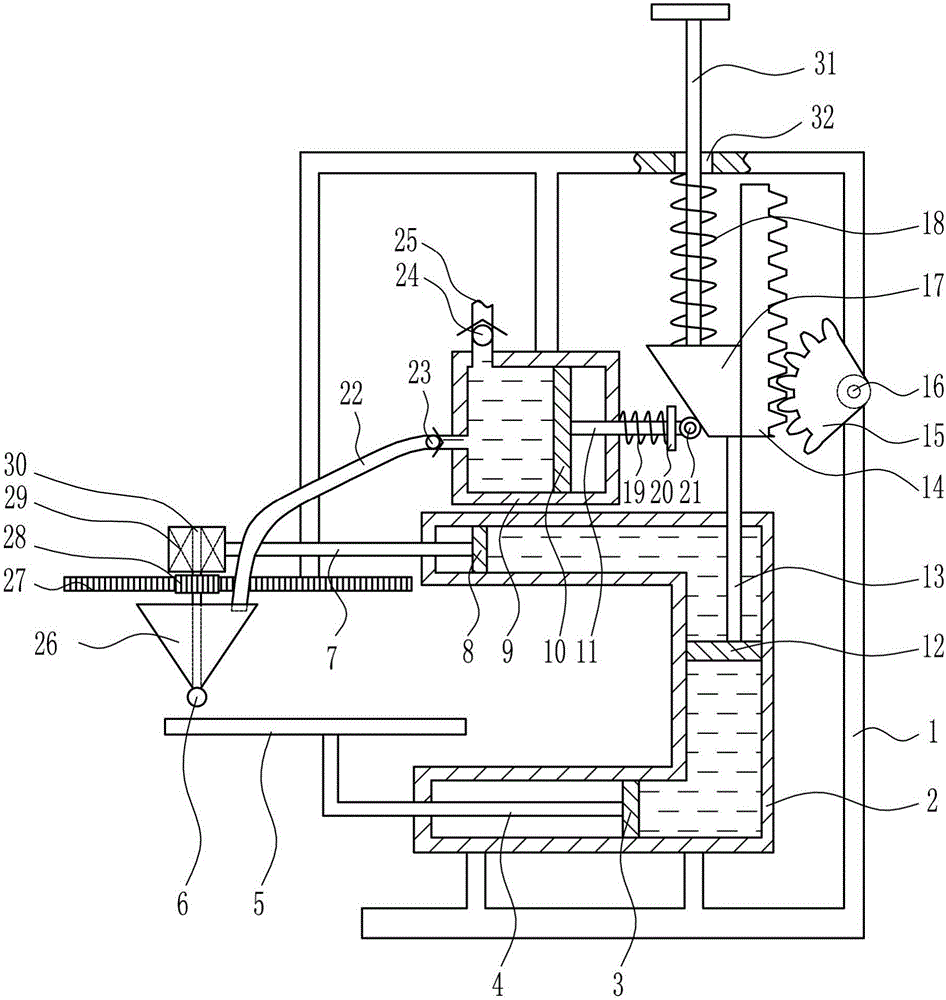

Efficient gluing equipment for shoemaking in shoe factories

InactiveCN106670056AApply glue evenlyDevice stableLiquid surface applicatorsCoatingsPistonFixed frame

The invention relates to gluing equipment, in particular to efficient gluing equipment for shoemaking in shoe factories. According to the efficient gluing equipment for shoemaking in the shoe factories, rapid gluing can be conducted, the gluing effect is good, and the gluing efficiency is high. The efficient gluing equipment for shoemaking in the shoe factories comprises a fixed frame, a U-shaped cylinder body, a first piston, a first left-right movement rod, a placing plate, a gluing head, a second left-right movement rod, a second piston, a small cylinder body and the like. The small cylinder body, a motor and the U-shaped cylinder body are arranged on the fixed frame in sequence from top to bottom. The motor is provided with a fan-shaped gear. The first piston is arranged in the lower portion of the U-shaped cylinder body in a matched mode. The first left-right movement rod is arranged on the left portion of the first piston. The efficient gluing equipment for shoemaking in the shoe factories achieves the effects of being good in gluing effect and high in gluing efficiency; a large number of gluing tasks can be rapidly completed through the efficient gluing equipment; in addition, a large amount of labor force is not needed; and a glued finished product is beautiful.

Owner:林永远

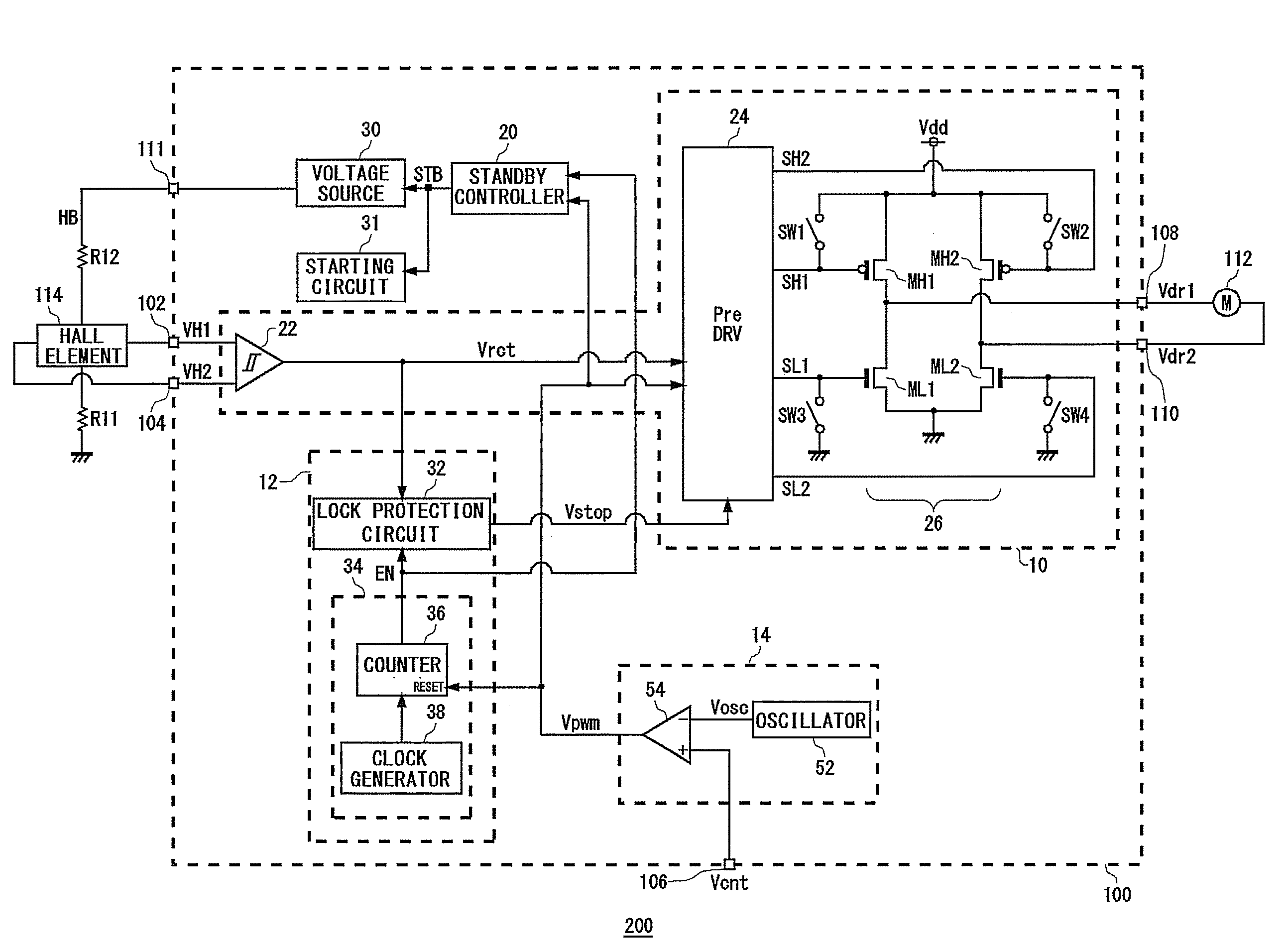

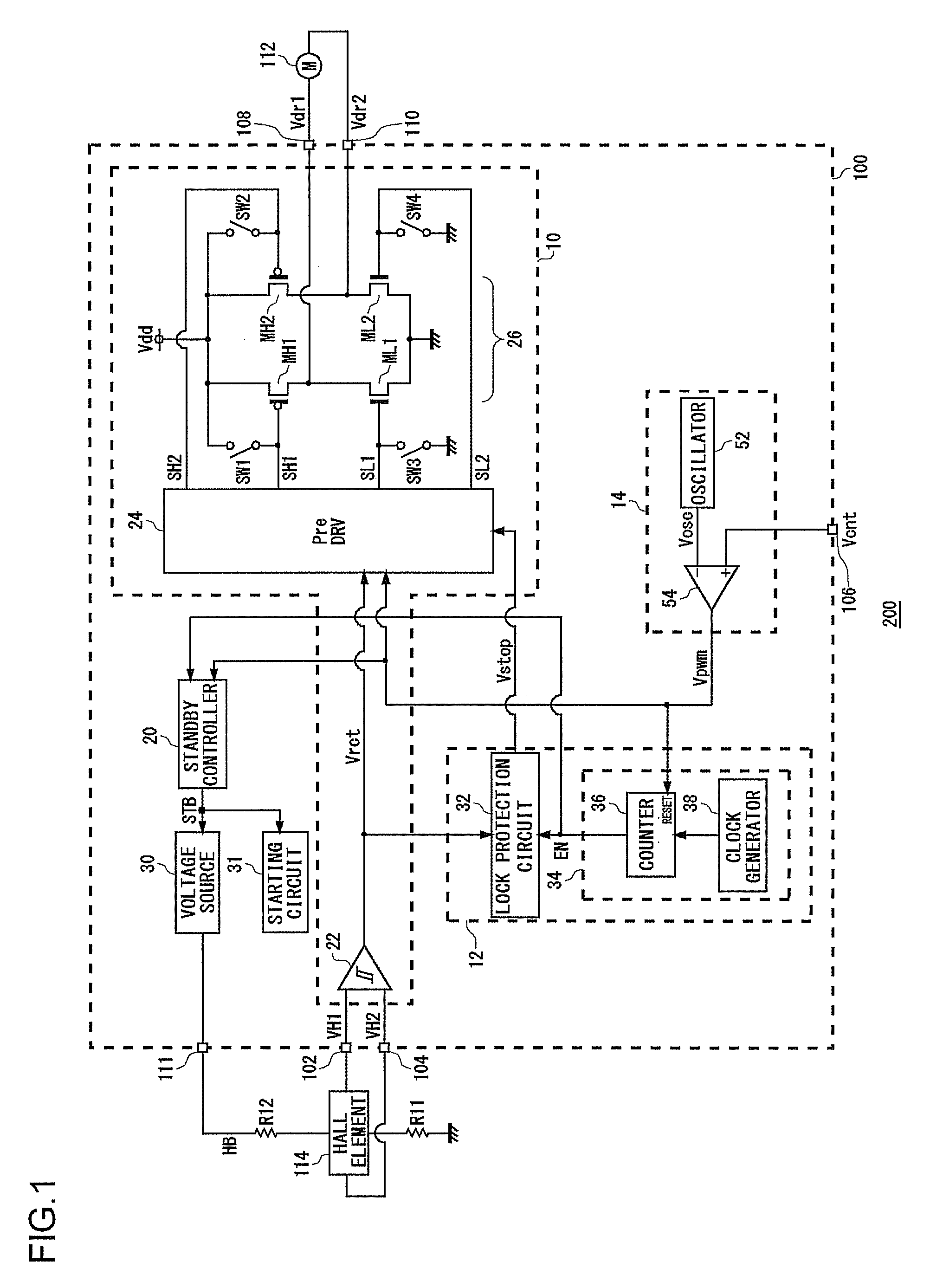

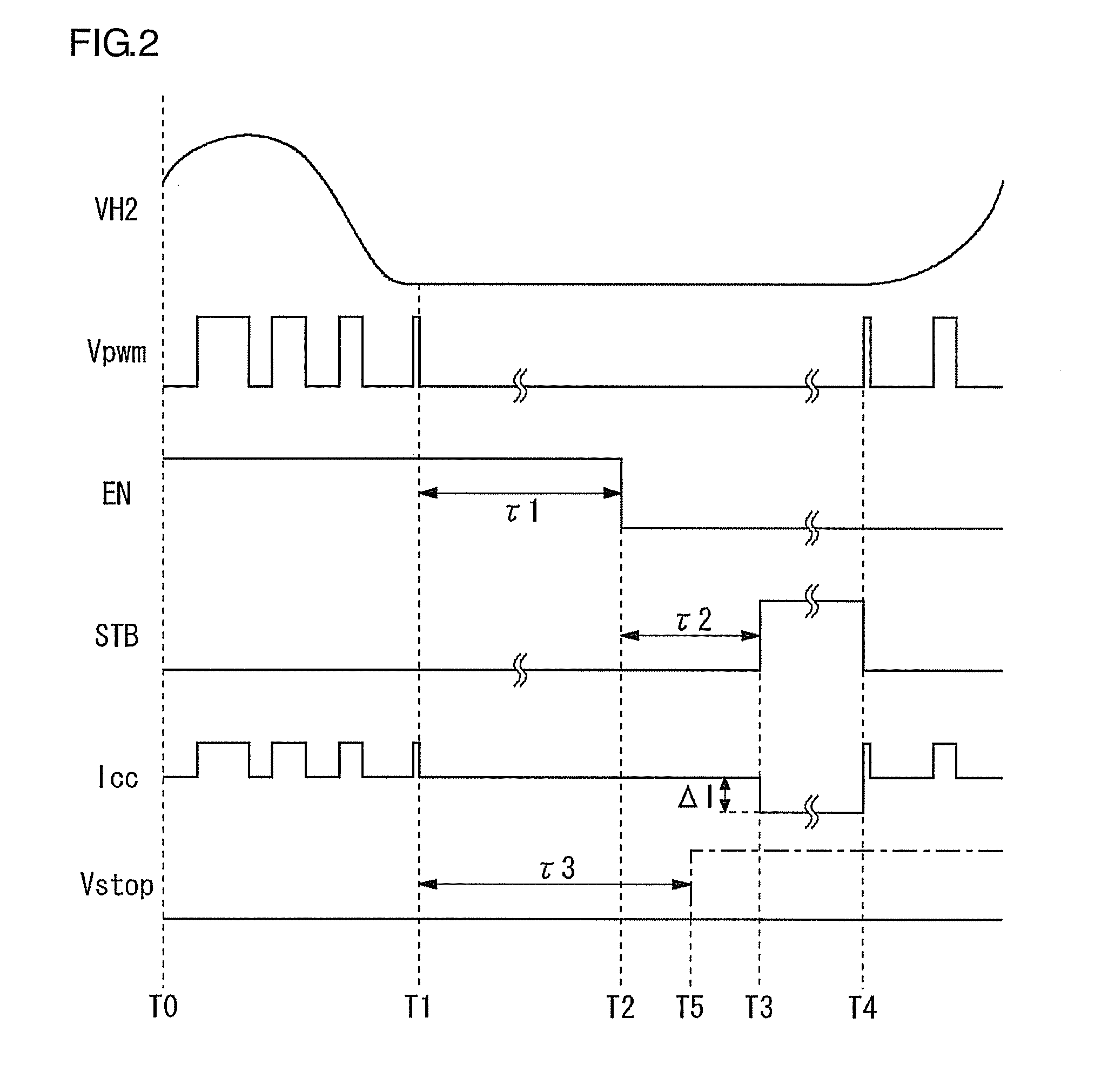

Motor drive device with lock protection function

ActiveUS20080315808A1SpeedReduce power consumptionCommutation monitoringSynchronous motors startersStart timeMotor drive

A cooling system is provided with a motor drive device, a fan motor, and a Hall element. The motor drive device includes a lock protection circuit and a lock controller. When a control signal instructing rotation of the fan motor that is to be driven instructs stoppage of the motor for a predetermined time-period or longer, the lock controller has the lock protection circuit inactive. At an occasion when the control signal has continued to instruct stoppage of the fan motor for a first time-period or longer, a standby controller starts time measurement, and after a further predetermined second time-period has elapsed, makes at least a part of the motor drive device transition to a standby mode.

Owner:ROHM CO LTD

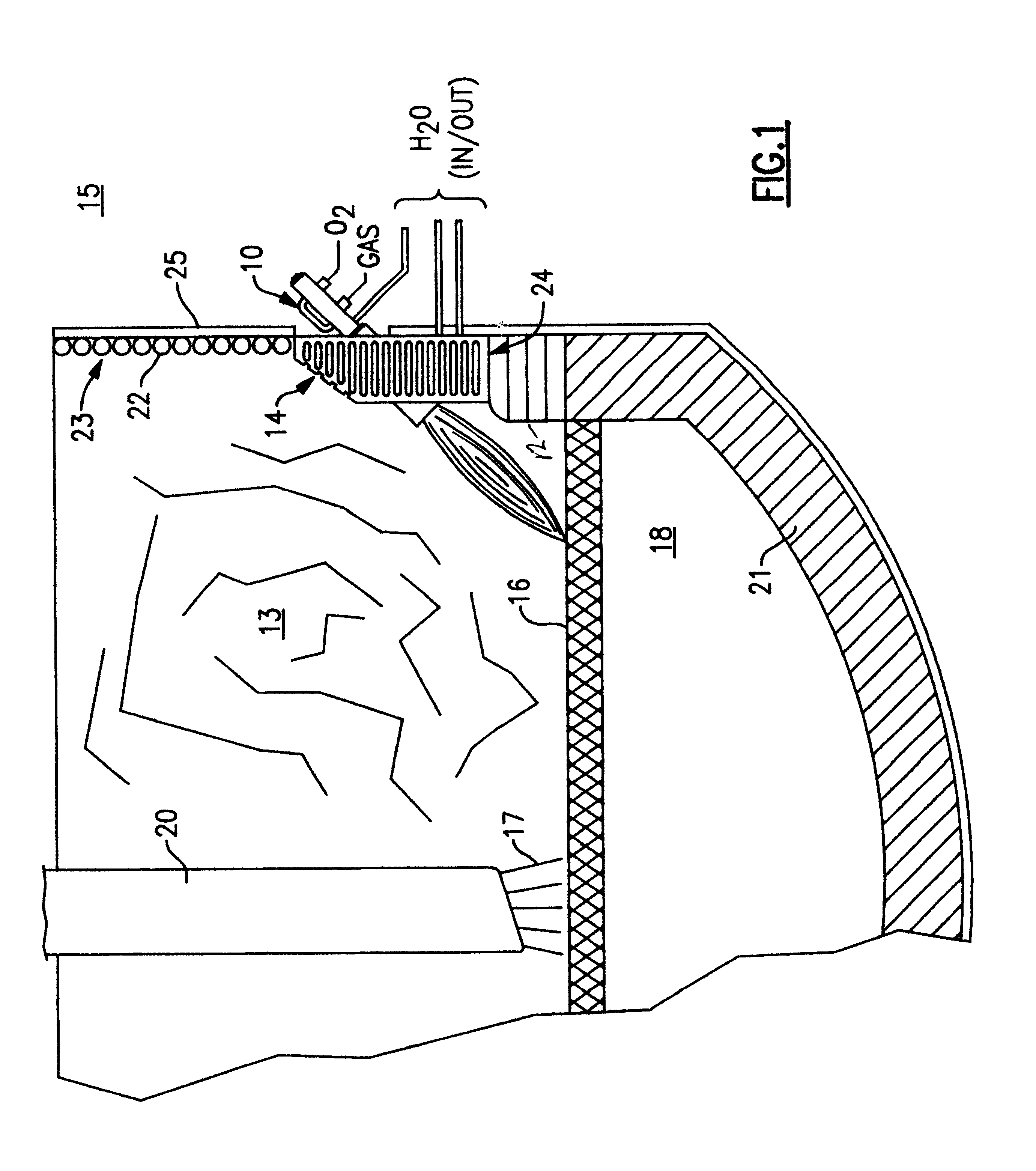

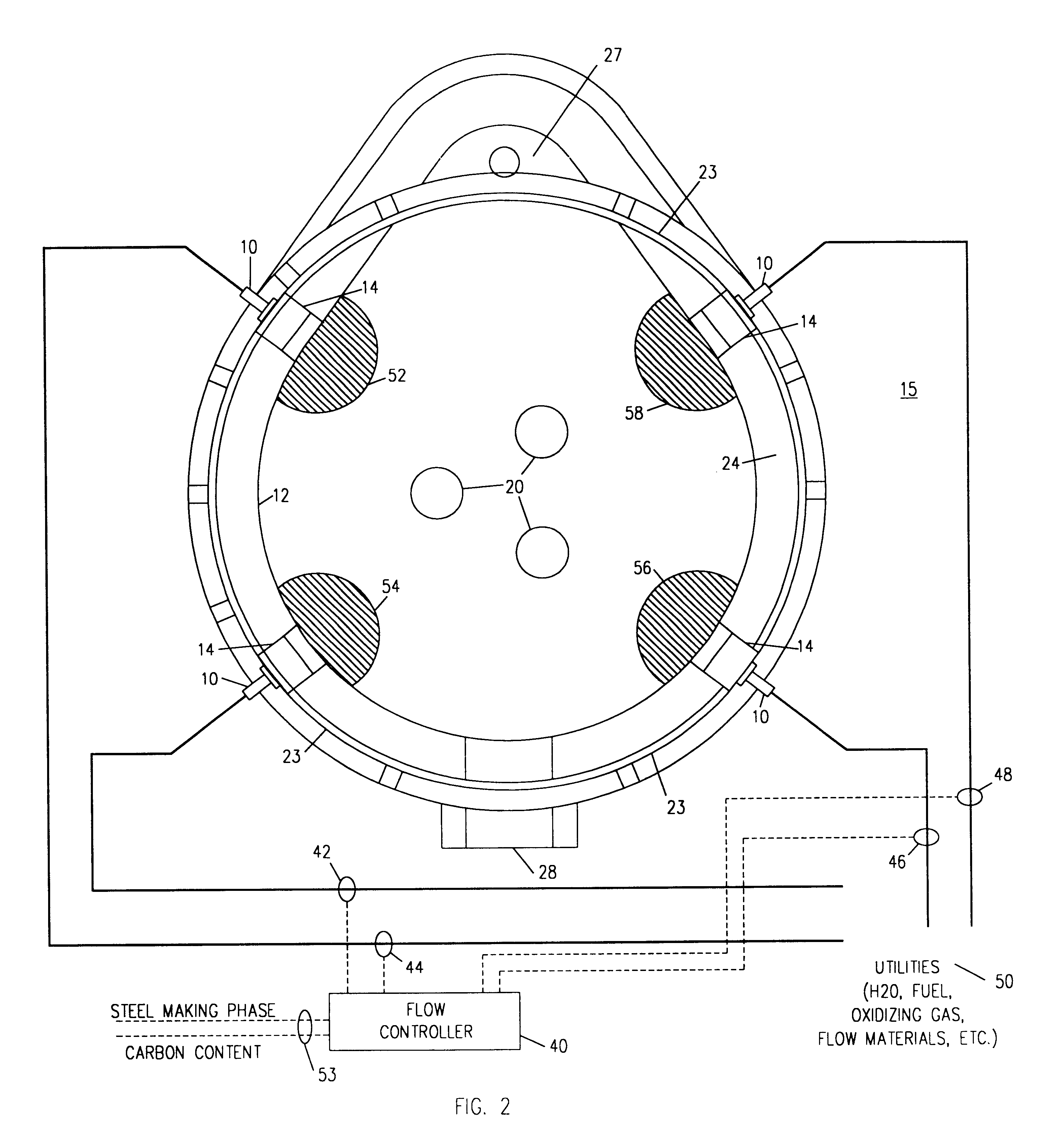

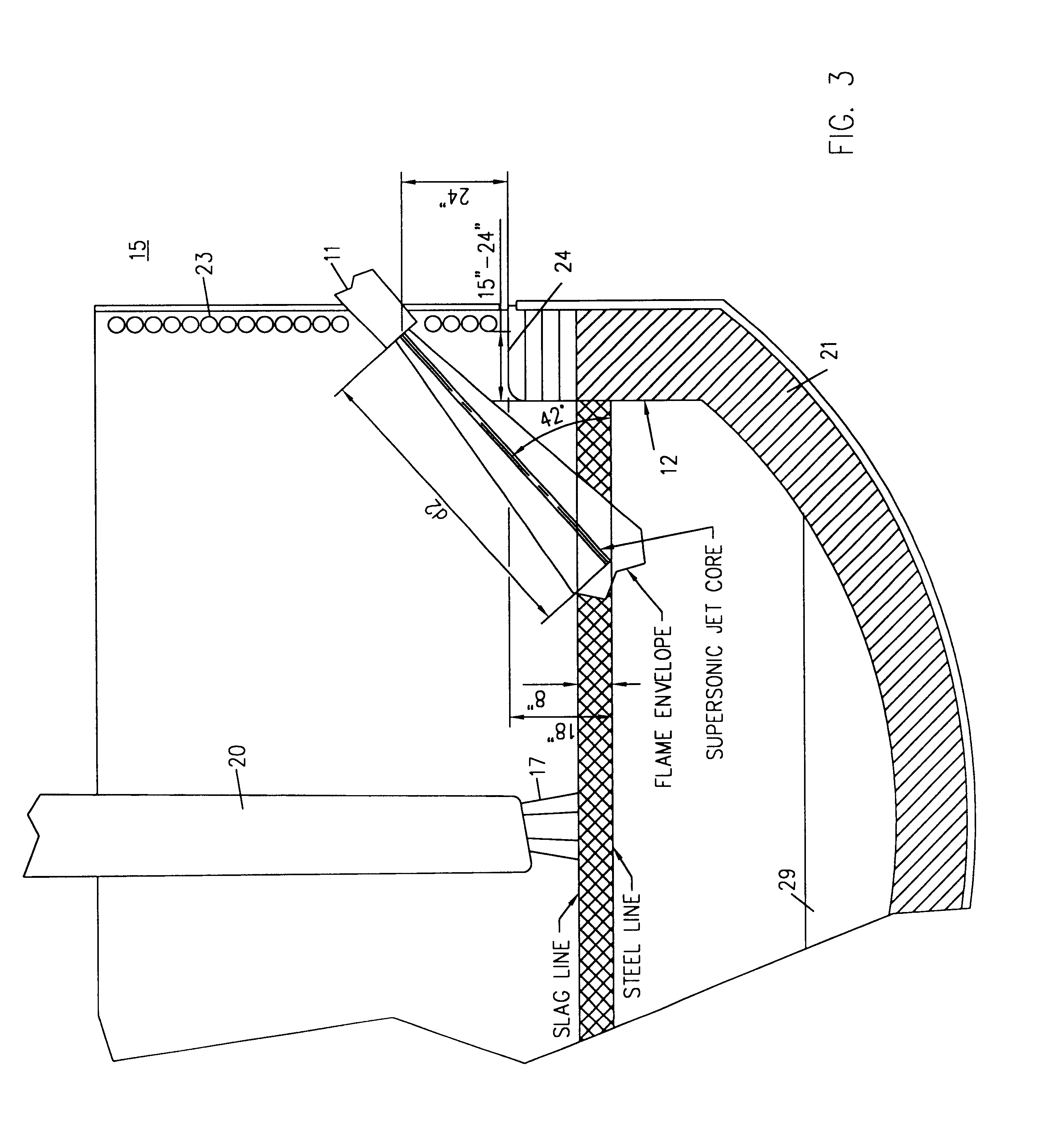

Method for melting and decarburization of iron carbon melts

InactiveUS6749661B2Shorten the construction periodHigh energyElectric discharge heatingStirring devicesElectric arc furnaceSlag

A method and an apparatus for advantageously introducing a flame and a high velocity oxidizing gas into a furnace for metal melting, refining and processing, particularly steel making in an electric arc furnace. The steel making process of an electric arc furnace is made more efficient by shortening the time of the scrap melting phase and introducing an effective high velocity oxidizing gas stream into the process sooner to decarburize the melted metal. In one implementation of an apparatus, improved efficiency is obtained by mounting a fixed burner / lance closer to the hot face of the furnace refractory at an effective injection angle. This mounting technique shortens the distance that the flame of the burner has to melt through the scrap to clear a path to the molten metal and shortens the distance the high velocity oxygen from the lance travels to the slag-metal interface thereby increasing its penetrating power. The method additionally includes supplying a plurality of reaction zones with the high velocity oxidizing gas to decarburize the melted metal. The plurality of reaction zones increases the surface area available for the reaction thereby allowing a more rapid rate of decarburization and a more homogenous metal bath. The reaction zones are supplied with the high velocity oxidizing gas according to an oxygen supply profile which is related to the carbon content of the metal bath. In this manner an optimal amount of oxygen can be introduced into the metal bath to shorten the decarburization process without producing excessive oxidation of the metal bath and excessive free oxygen in the furnace.

Owner:PROCESS TECH INT

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com