Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

53 results about "Solder interconnect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

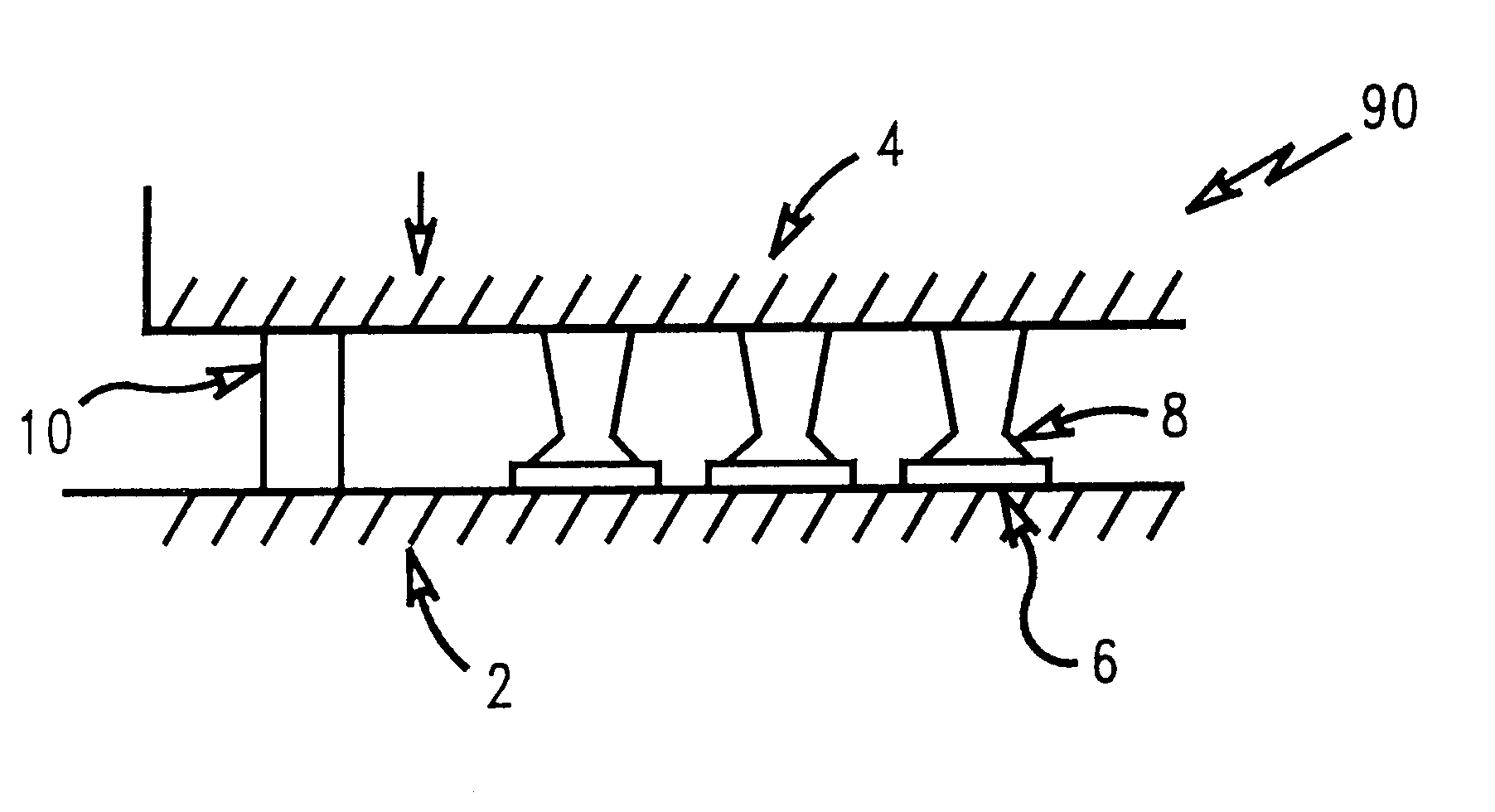

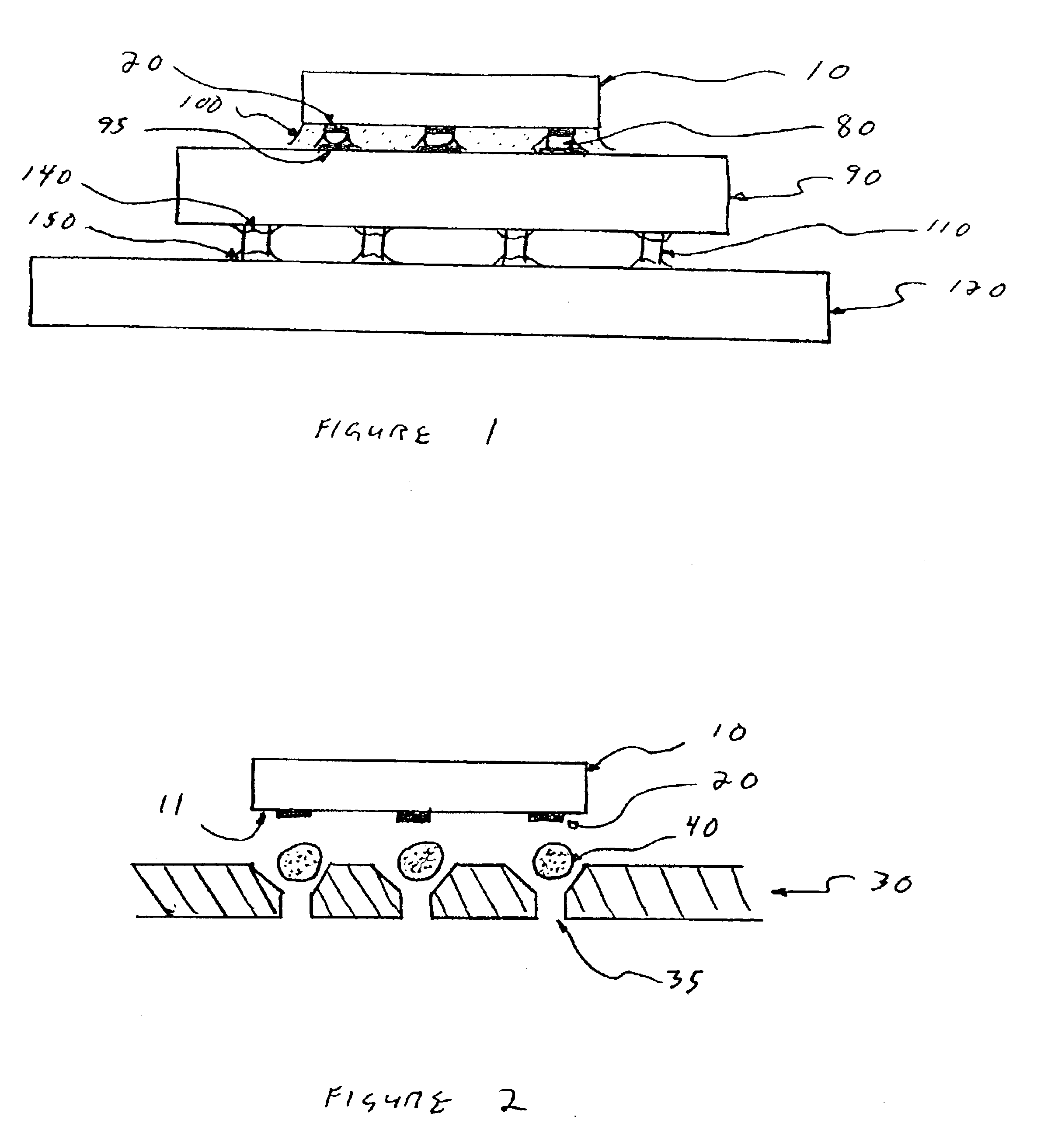

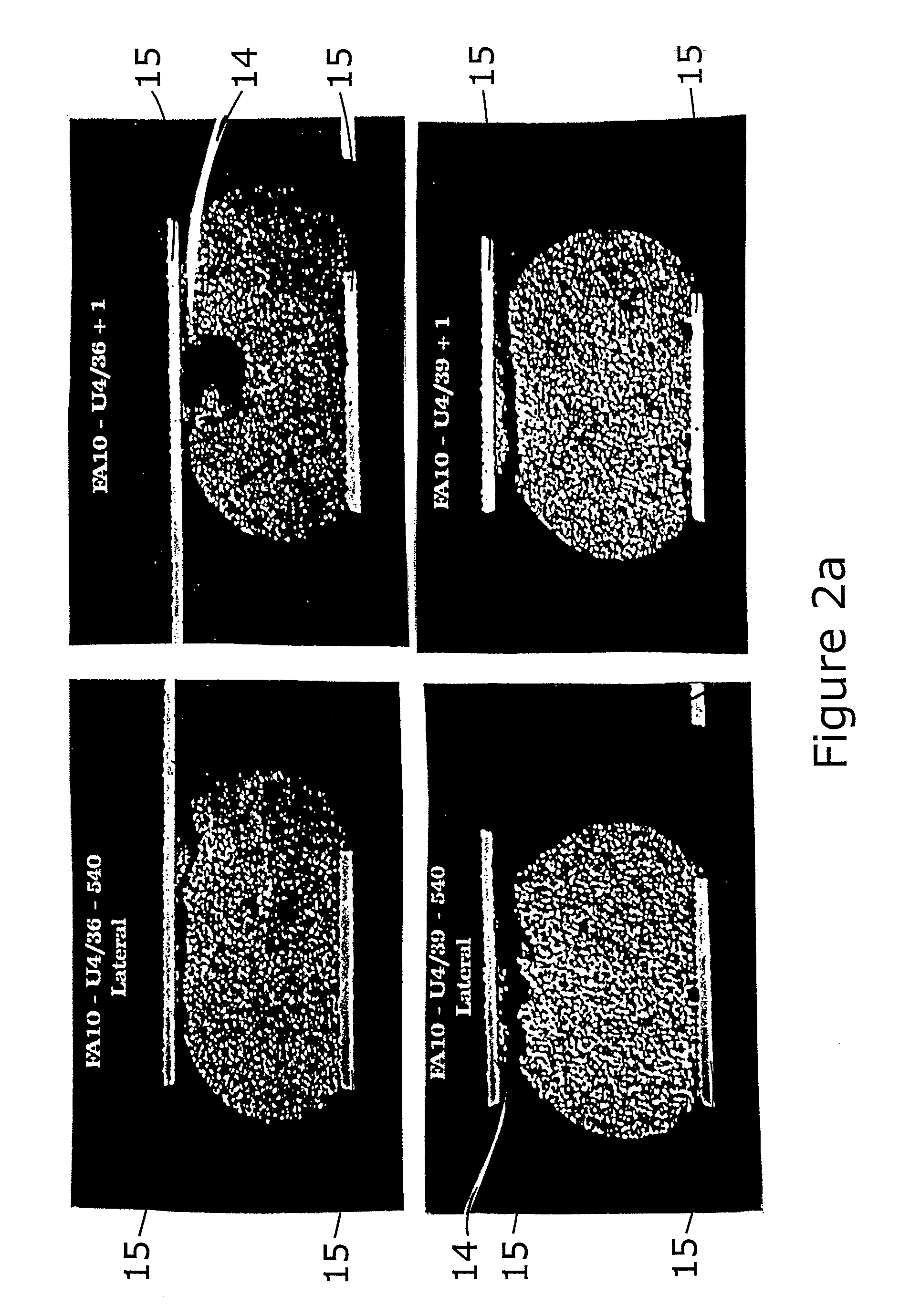

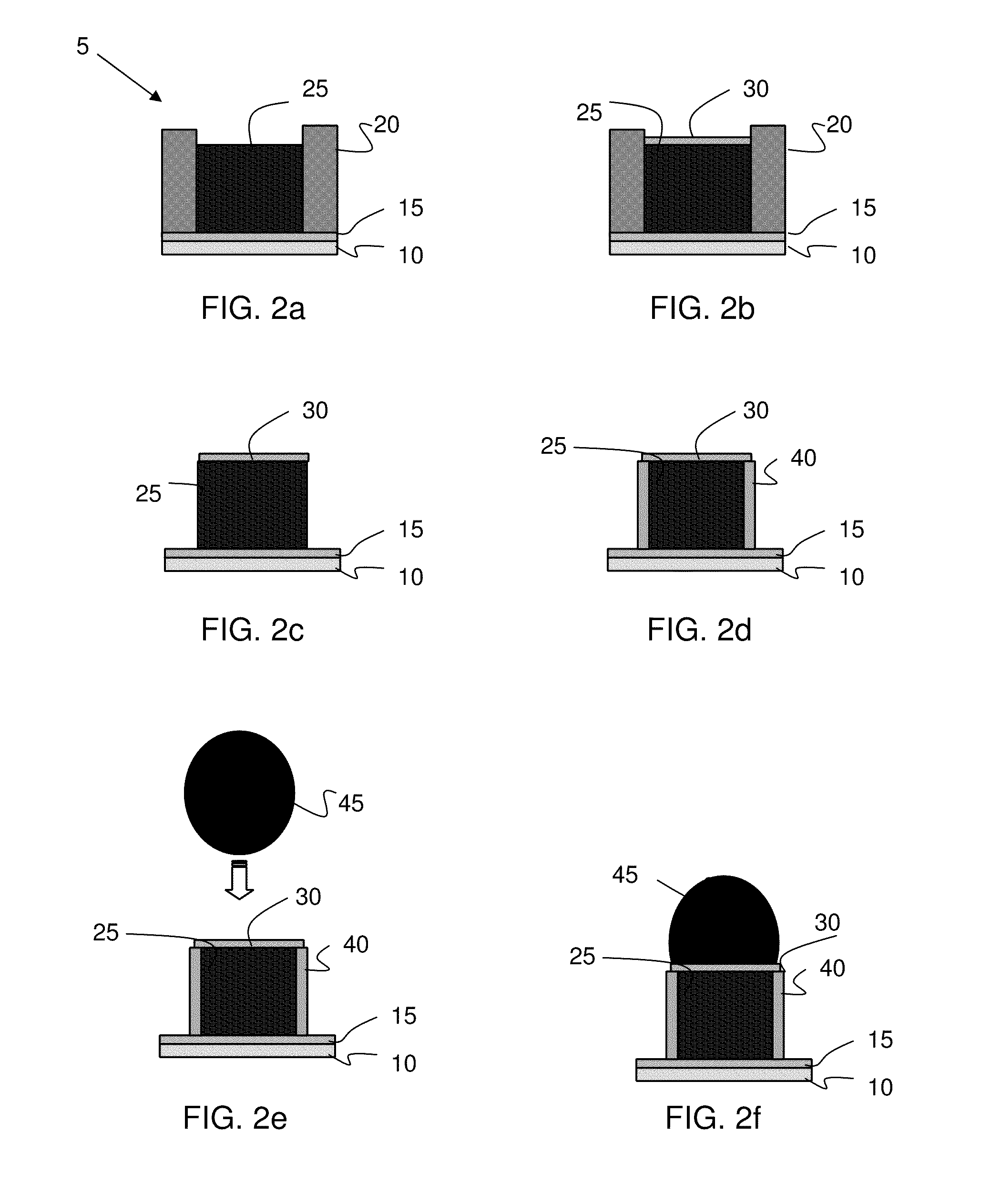

Process for forming cone shaped solder for chip interconnection

InactiveUS6184062B1Improve reliabilityAvoid more failuresPrinted circuit assemblingFinal product manufactureRoom temperatureSemiconductor chip

A method of forming non-spherically shaped solder interconnects, preferably conical, for attachment of electronic components in an electronic module. Preferably, the solder interconnects of the present invention are cone shaped and comprise of depositing a first solder followed by a second solder having a lower reflow temperature than the first solder. Warm placement of the electronic component at a somewhat elevated temperature than room temperature but less than the solder reflow temperature reduces the force required during placement of a semiconductor chip to a substrate. After warm placement, reflow of the module occurs at the lower reflow temperature of the second solder. The conical shape of the solder interconnects are formed by a heated coining die which may also coin a portion of the interconnects with flat surfaces for stand-offs. The ability of the cone shaped solder interconnects to meet the opposing surface of a chip or substrate at different heights accommodates the camber typically associated with chip and substrate surfaces.

Owner:IBM CORP

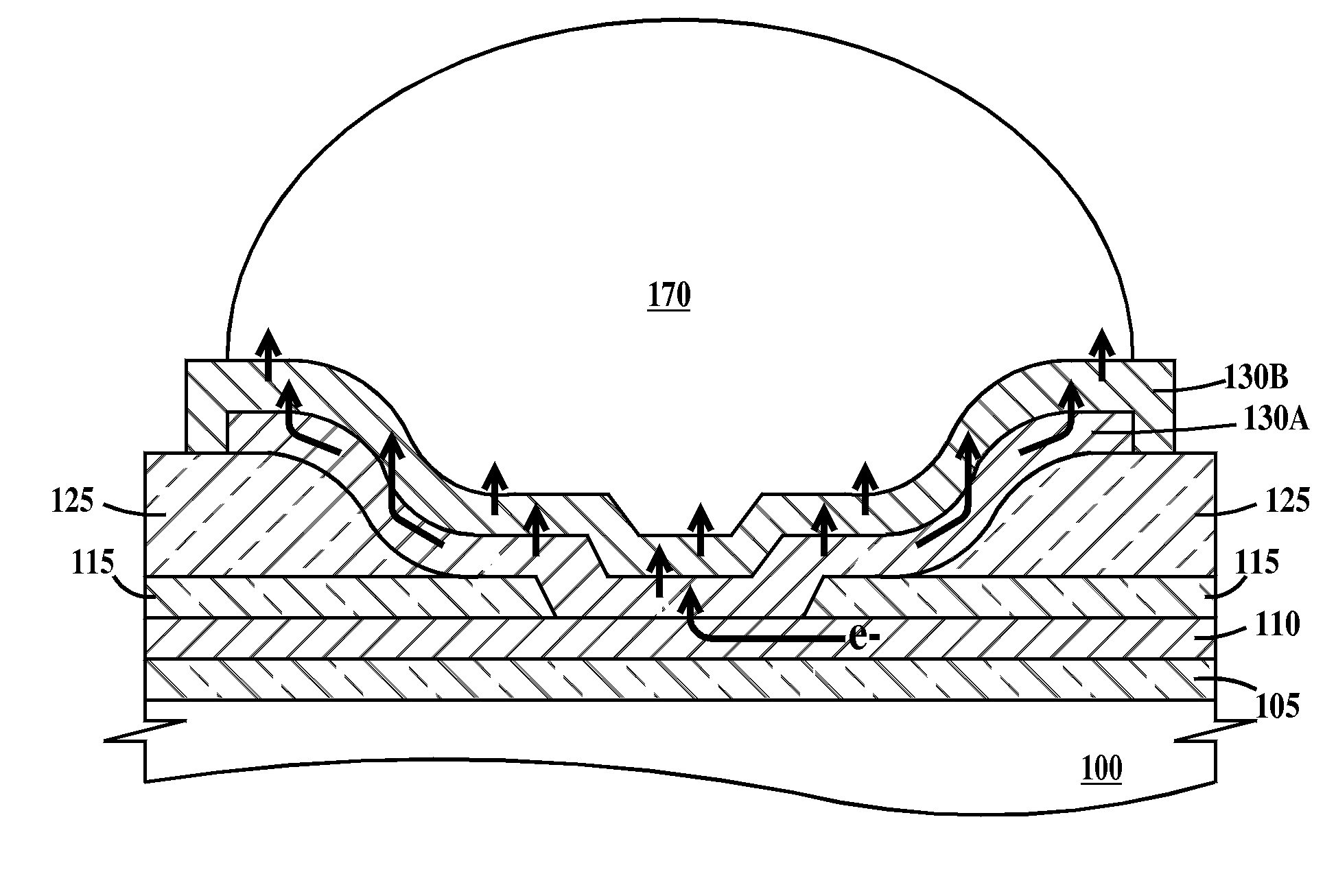

Solder interconnect pads with current spreading layers

InactiveUS20090206479A1Semiconductor/solid-state device detailsSolid-state devicesElectrically conductiveSolder interconnect

Structure and methods of making the structures. The structures include a structure, comprising: an organic dielectric passivation layer extending over a substrate; an electrically conductive current spreading pad on a top surface of the organic dielectric passivation layer; an electrically conductive solder bump pad comprising one or more layers on a top surface of the current spreading pad; and an electrically conductive solder bump containing tin, the solder bump on a top surface of the solder bump pad, the current spreading pad comprising one or more layers, at least one of the one or more layers consisting of a material that will not form an intermetallic with tin or at least one of the one or more layers is a material that is a diffusion barrier to tin and adjacent to the solder bump pad.

Owner:ULTRATECH INT INC

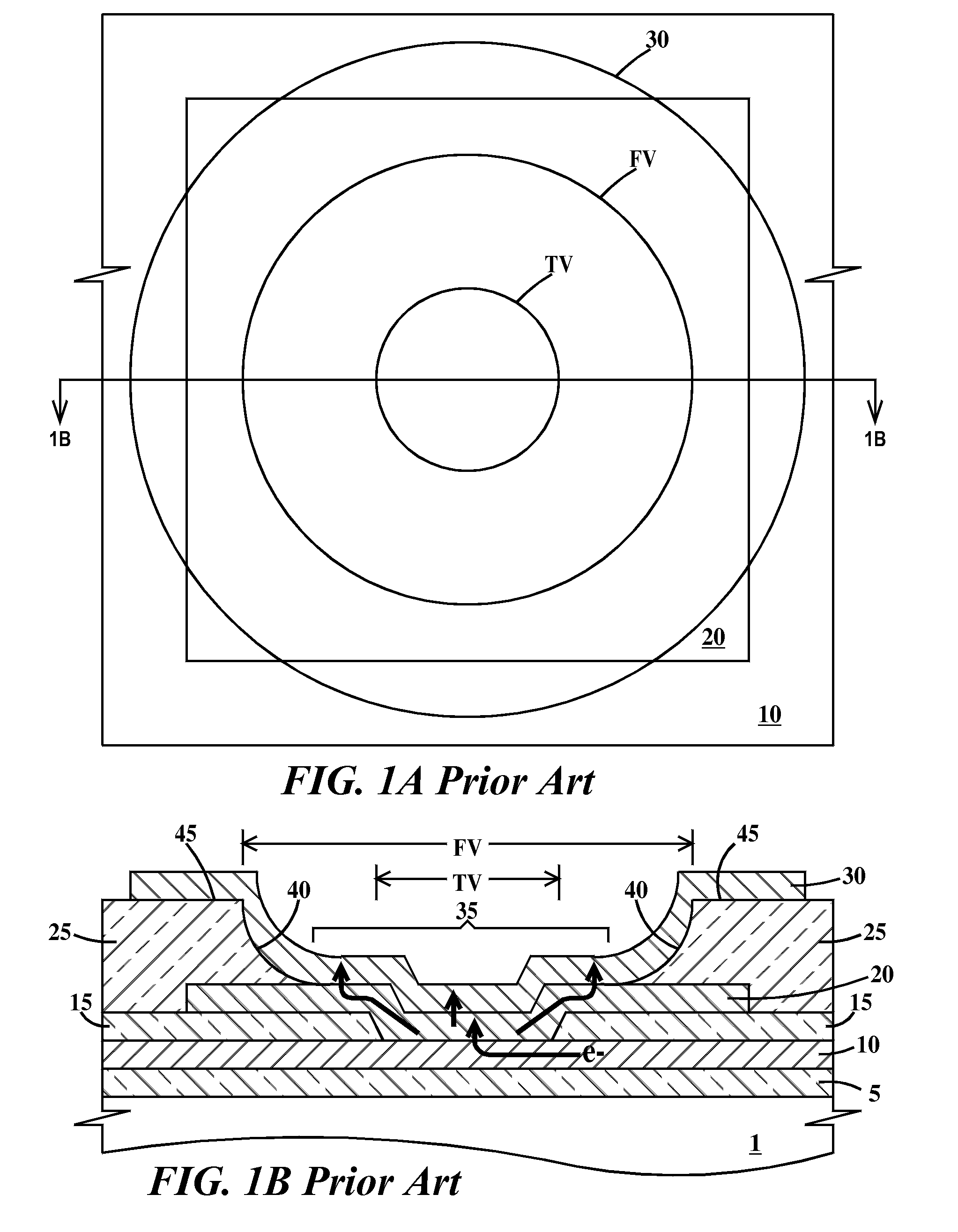

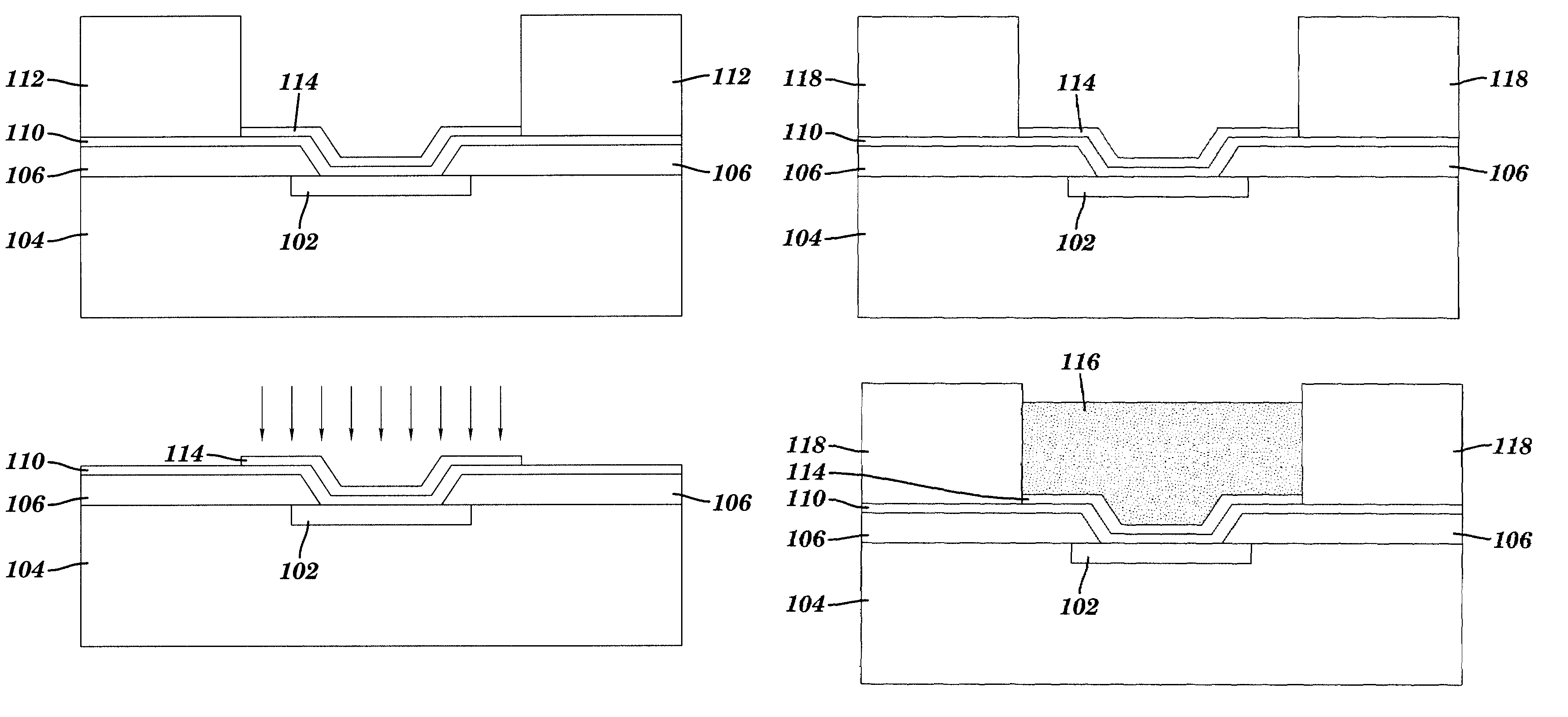

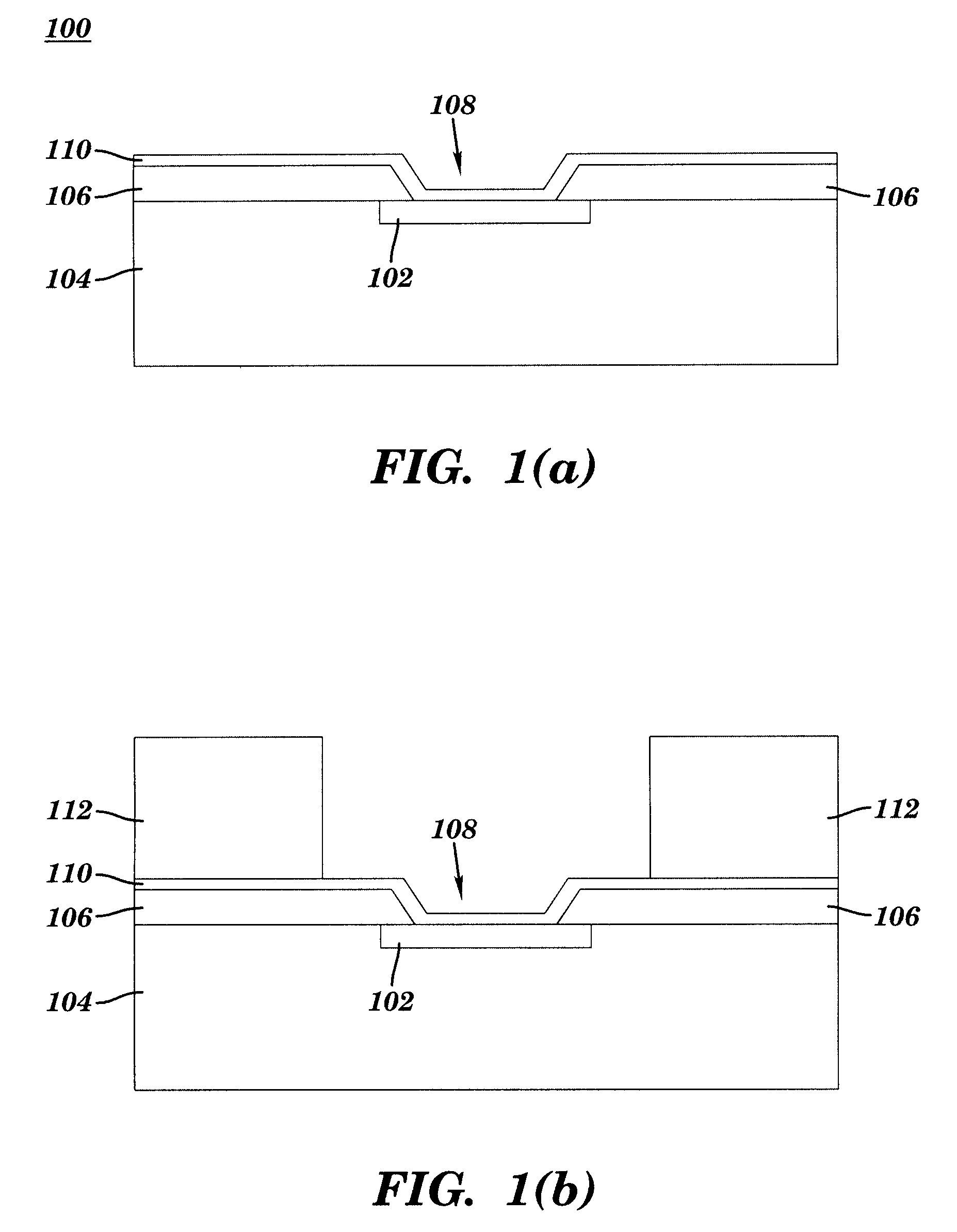

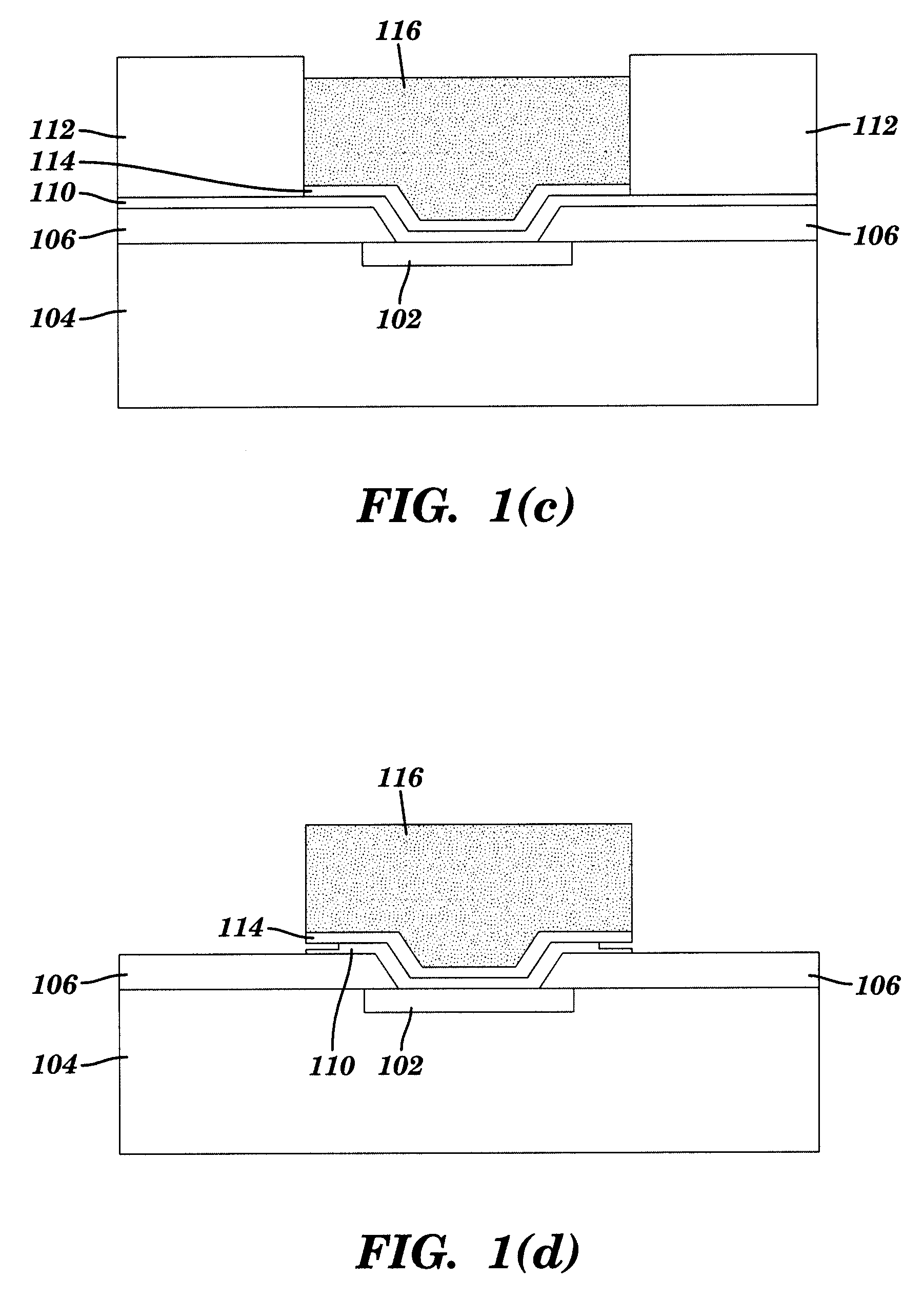

Structure and method for lead free solder electronic package interconnections

InactiveUS20050106059A1Printed circuit assemblingSemiconductor/solid-state device detailsSolder interconnectionChip carrier

An electronic package having a solder interconnect liquidus temperature hierarchy to limit the extent of the melting of the C4 solder interconnect during subsequent second level join / assembly and rework operations. The solder hierarchy employs the use of off-eutectic solder alloys of Sn / Ag and Sn / Cu with a higher liquidus temperature for the C4 first level solder interconnections, and a lower liquidus temperature alloy for the second level interconnections. When the second level chip carrier to PCB join / assembly operations occur, the chip to chip carrier C4 interconnections do not melt completely. They continue to have a certain fraction of solids, and a lower fraction of liquids, than a fully molten alloy. This provides reduced expansion of the solder join and consequently lower stresses on the C4 interconnect.

Owner:FAROOQ MUKTA G +2

Solder interconnect on IC chip

ActiveUS20060125094A1Improve electrical performanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipActive surface

A semiconductor chip suited for being electrically connected to a circuit element includes a line and a bump. The bump is connected to the line and is adapted to be electrically connected to the line. A plane that is horizontal to an active surface of the semiconductor chip is defined. The area that the connection region of the line and the bump is projected on the plane is larger than 30,000 square microns or has an extension distance larger than 500 microns.

Owner:QUALCOMM INC

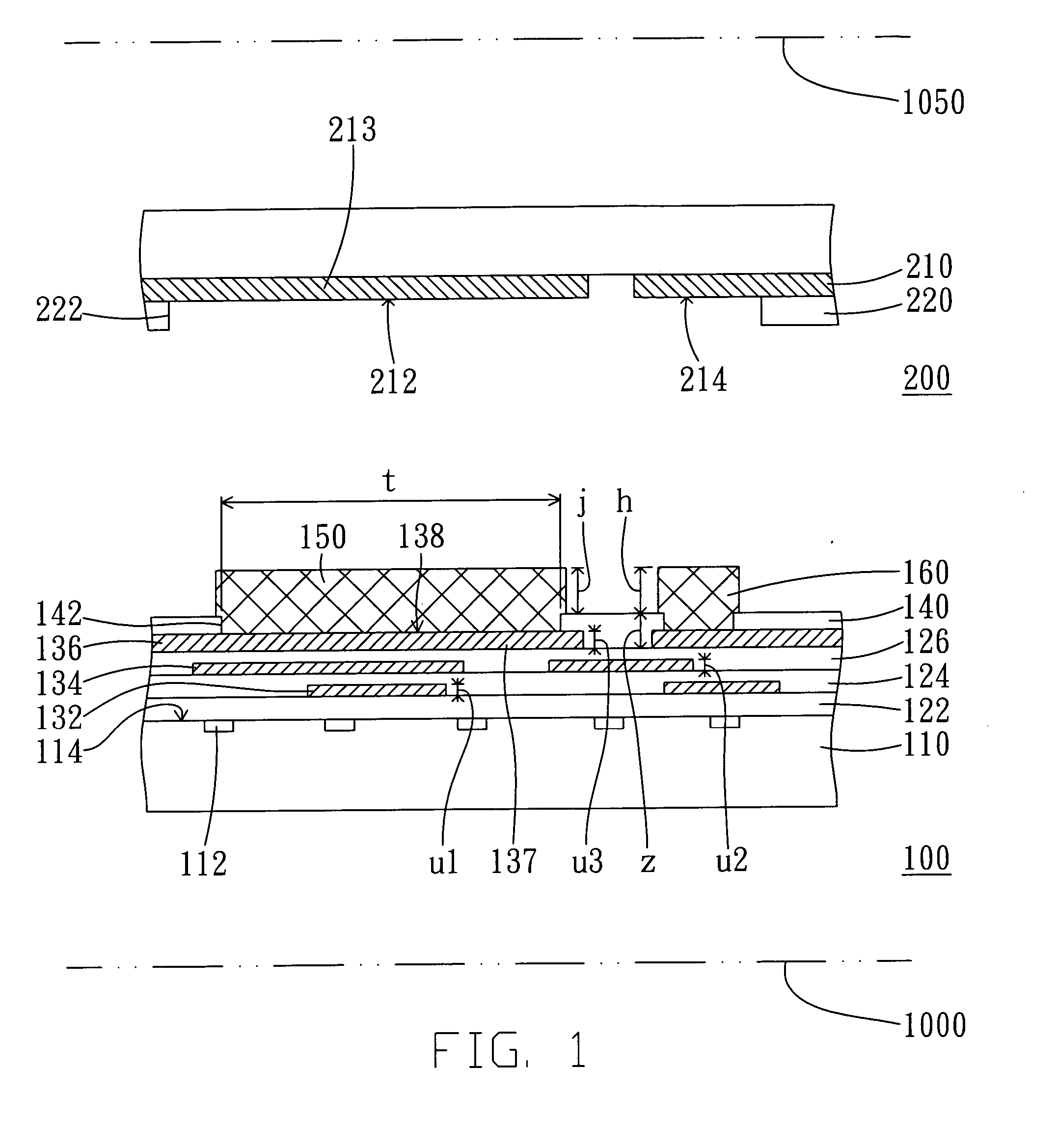

Etched leadframe flipchip package system

ActiveUS7250685B2Semiconductor/solid-state device detailsSolid-state devicesLead frameIntegrated circuit

The present invention provides an etched leadframe flipchip package system comprising forming a leadframe comprises forming contact leads and etching a plurality of multiple dotted grooves on the contact leads, and attaching a flipchip integrated circuit having solder interconnects on the contact leads between each of the plurality of the multiple dotted grooves.

Owner:STATS CHIPPAC LTD

Method for forming robust solder interconnect structures by reducing effects of seed layer underetching

ActiveUS20050208748A1Semiconductor/solid-state device detailsSolid-state devicesElectrode potentialDevice material

A method for forming an interconnect structure for a semiconductor device includes defining a via in a passivation layer so as expose a top metal layer in the semiconductor device. A seed layer is formed over the passivation layer, sidewalls of the via, and the top metal layer. A barrier layer is formed over an exposed portion of the seed layer, the exposed portion defined by a first patterned opening. The semiconductor device is annealed so as to cause atoms from the barrier layer to diffuse into the seed layer thereunderneath, wherein the annealing causes diffused regions of the seed layer to have an altered electrical resistivity and electrode potential with respect to undiffused regions of the seed layer.

Owner:INVENSAS CORP

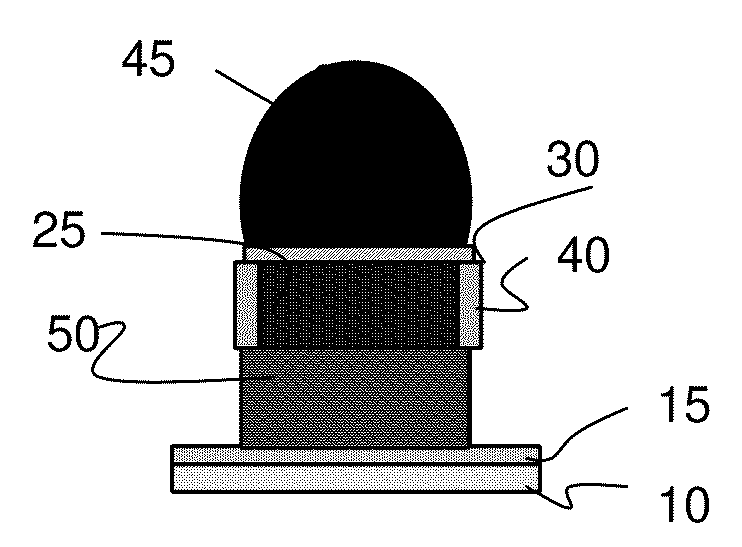

Solder Interconnect with Non-Wettable Sidewall Pillars and Methods of Manufacture

ActiveUS20110193218A1Semiconductor/solid-state device detailsSolid-state devicesSolder wettingNickel alloy

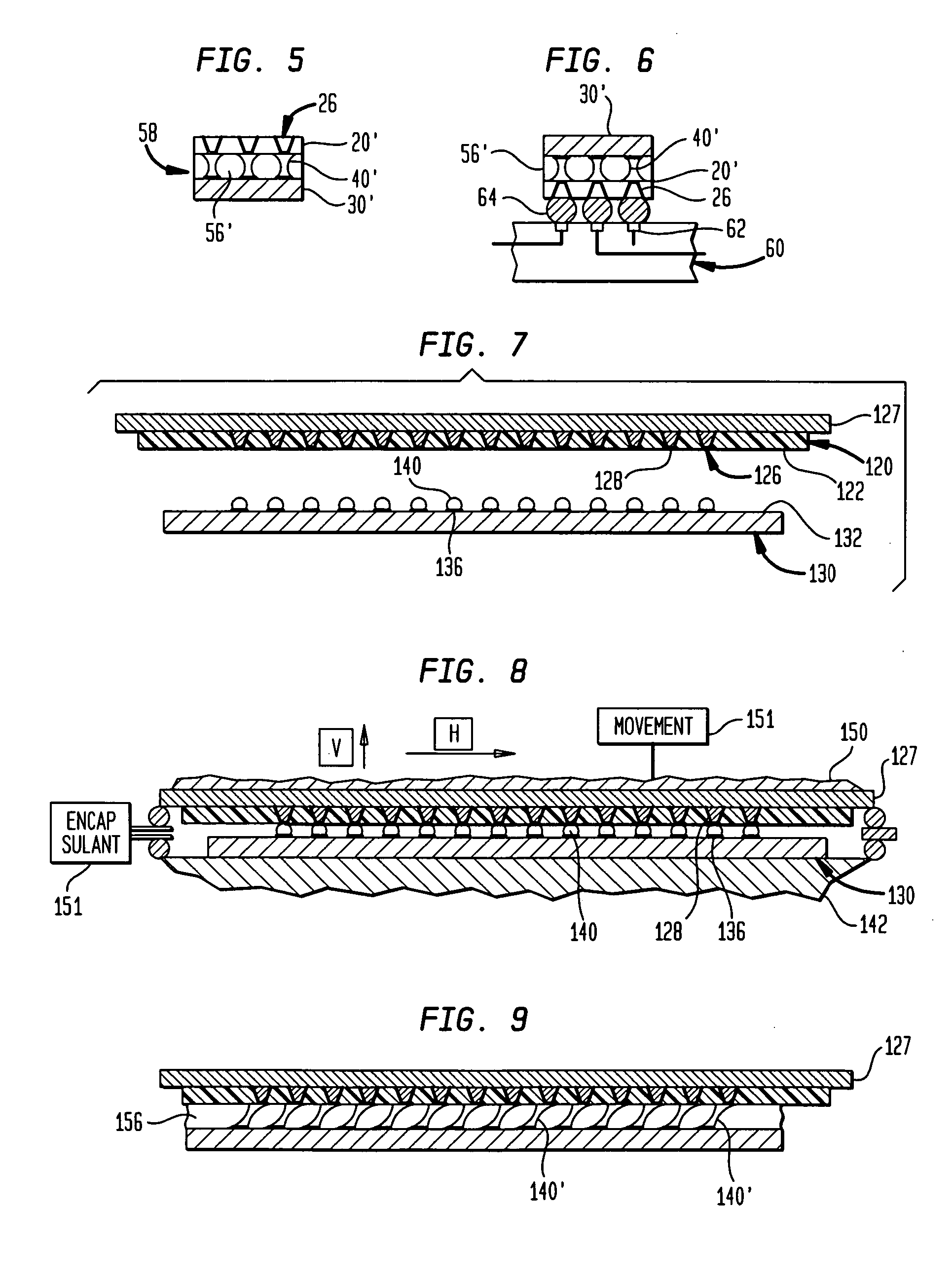

A solder interconnect structure is provided with non-wettable sidewalls and methods of manufacturing the same. The method includes forming a nickel or nickel alloy pillar on an underlying surface. The method further includes modifying the sidewall of the nickel or nickel alloy pillar to prevent solder wetting on the sidewall.

Owner:GLOBALFOUNDRIES US INC

Structure and method for lead free solder electronic package interconnections

InactiveUS6854636B2Printed circuit assemblingSemiconductor/solid-state device detailsSolder interconnectionChip carrier

An electronic package having a solder interconnect liquidus temperature hierarchy to limit the extent of the melting of the C4 solder interconnect during subsequent second level join / assembly and rework operations. The solder hierarchy employs the use of off-eutectic solder alloys of Sn / Ag and Sn / Cu with a higher liquidus temperature for the C4 first level solder interconnections, and a lower liquidus temperature alloy for the second level interconnections. When the second level chip carrier to PCB join / assembly operations occur, the chip to chip carrier C4 interconnections do not melt completely. They continue to have a certain fraction of solids, and a lower fraction of liquids, than a fully molten alloy. This provides reduced expansion of the solder join and consequently lower stresses on the C4 interconnect.

Owner:INVENSAS CORP

Etched leadframe flipchip package system

ActiveUS20070108565A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

The present invention provides an etched leadframe flipchip package system comprising forming a leadframe comprises forming contact leads and etching a plurality of multiple dotted grooves on the contact leads, and attaching a flipchip integrated circuit having solder interconnects on the contact leads between each of the plurality of the multiple dotted grooves.

Owner:STATS CHIPPAC LTD

Circuit Board with Variable Topography Solder Interconnects

InactiveUS20110100692A1Final product manufacturePrinted electric component incorporationElectrical conductorSolder mask

Various circuit boards and methods of making the same are disclosed. In one aspect, a method of manufacturing is provided that includes applying a solder mask to a first side of a first circuit board. The first side of the first circuit board includes a first conductor structure and a second conductor structure. A first opening is formed in the solder mask that extends to the first conductor structure. The first opening has a first area. A second opening is formed in the solder mask that extends to the second conductor structure and has a second area larger than the first area.

Owner:ATI TECH INC

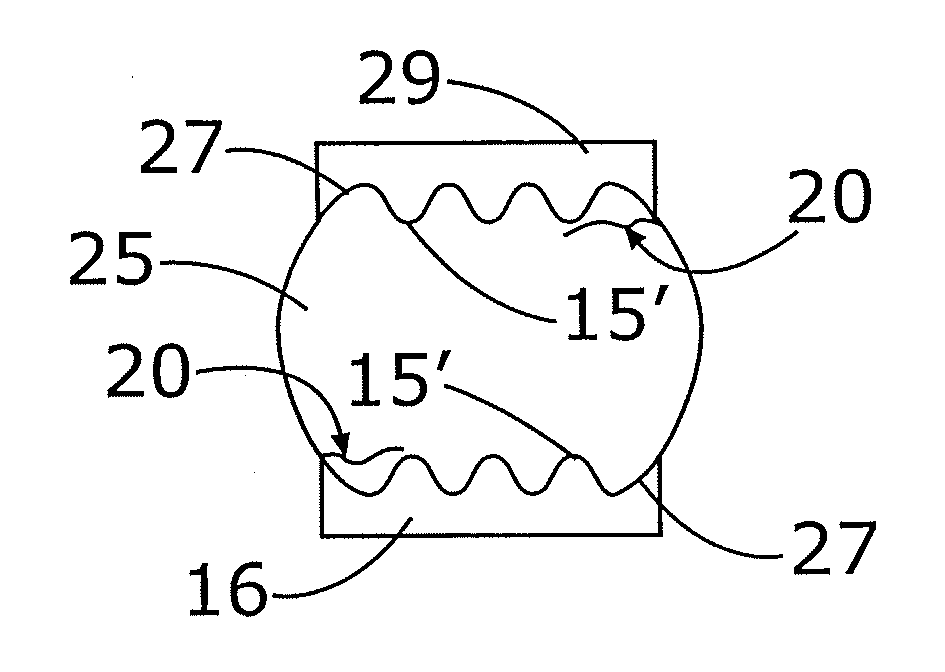

Solder Interconnect Joints For A Semiconductor Package

InactiveUS20080029888A1Improve fatigue lifeControl damagePrinted circuit assemblingFinal product manufactureCrazingMetallurgy

A method and article of fabrication is described featuring a solder layer having a serpentine, interrupted, or interdigitated boundary. The non-planar design of the boundary layer increases the fatigue life of the solder joint by limiting the damage caused by micro-cracking. This irregularity of the solder boundary constrains the propagation of cracks by creating obstacles along the crack path, redirecting the crack away from the intermetallic layer, or by increasing the path along which the crack propagates.

Owner:IBM CORP

Process for forming cone shaped solder for chip interconnection

InactiveUS20010015495A1Easy to joinPrinted circuit assemblingFinal product manufactureRoom temperatureSemiconductor chip

Owner:INT BUSINESS MASCH CORP

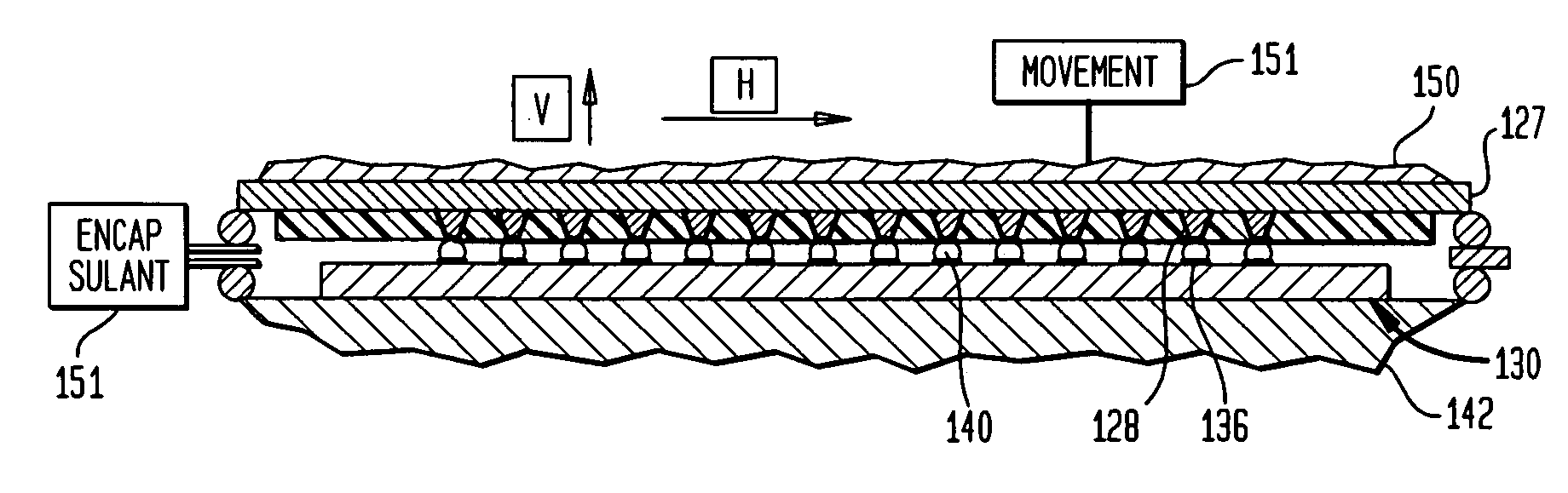

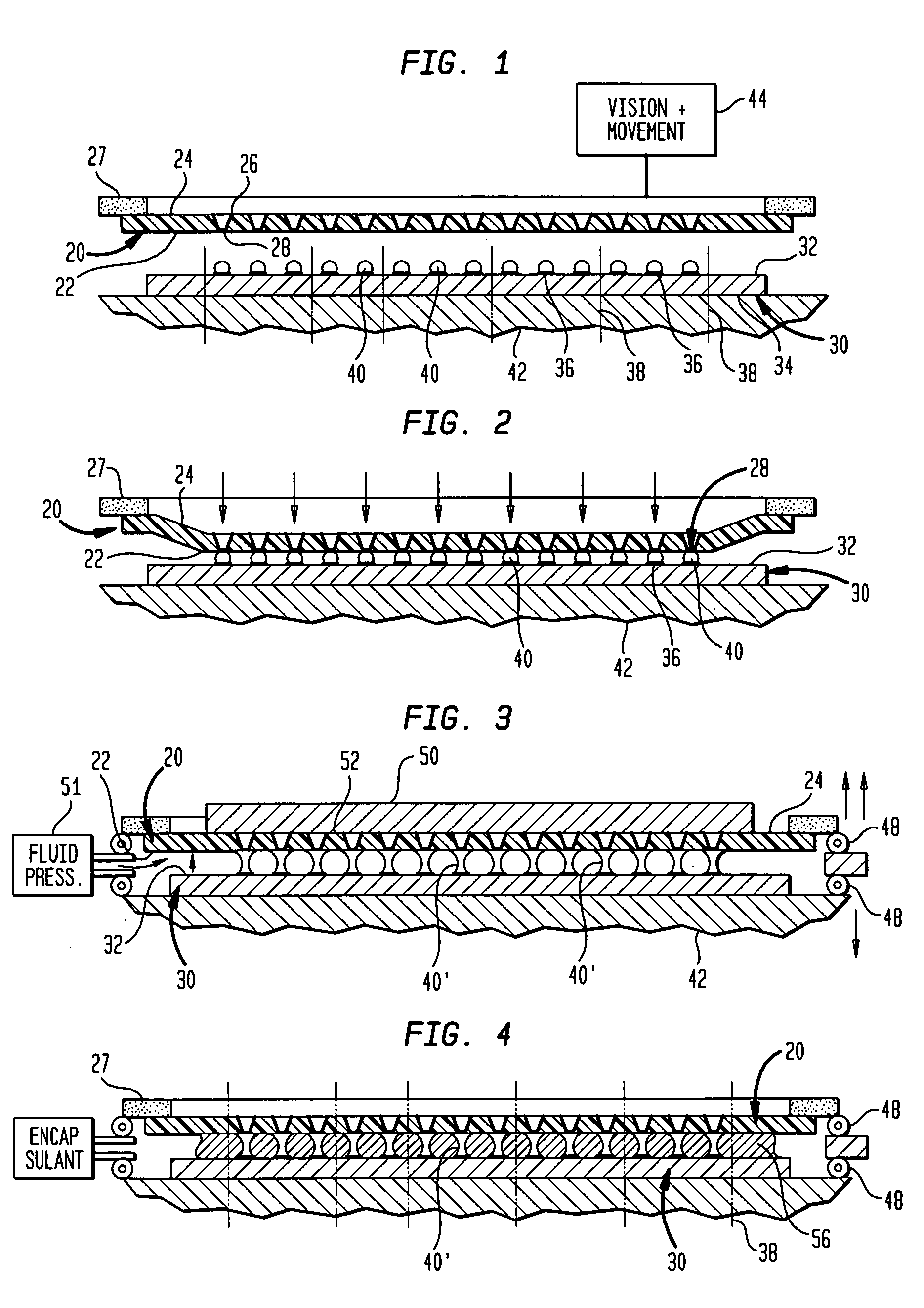

Solder interconnect structure and method using injection molded solder

InactiveCN1817538AEasy interconnectionImprove carrying capacityPrinted circuit assemblingFinal product manufactureElectrical conductorOptoelectronics

Improved interconnects are produced by injection molded solder which fills mold arrays with molten solder so that columns that have much greater height to width aspect ratios greater than one are formed, rather than conventional flip chip bumps. The columns may have filler particles or reinforcing conductors therein. In the interconnect structures produced, the cost and time of a subsequent underfill step is reduced or avoided. The problem of incompatibility with optical interconnects between chips because underfills require high loading of silica fillers which scatter light, is solved, thus allowing flip chips to incorporate optical interconnects.

Owner:INT BUSINESS MASCH CORP

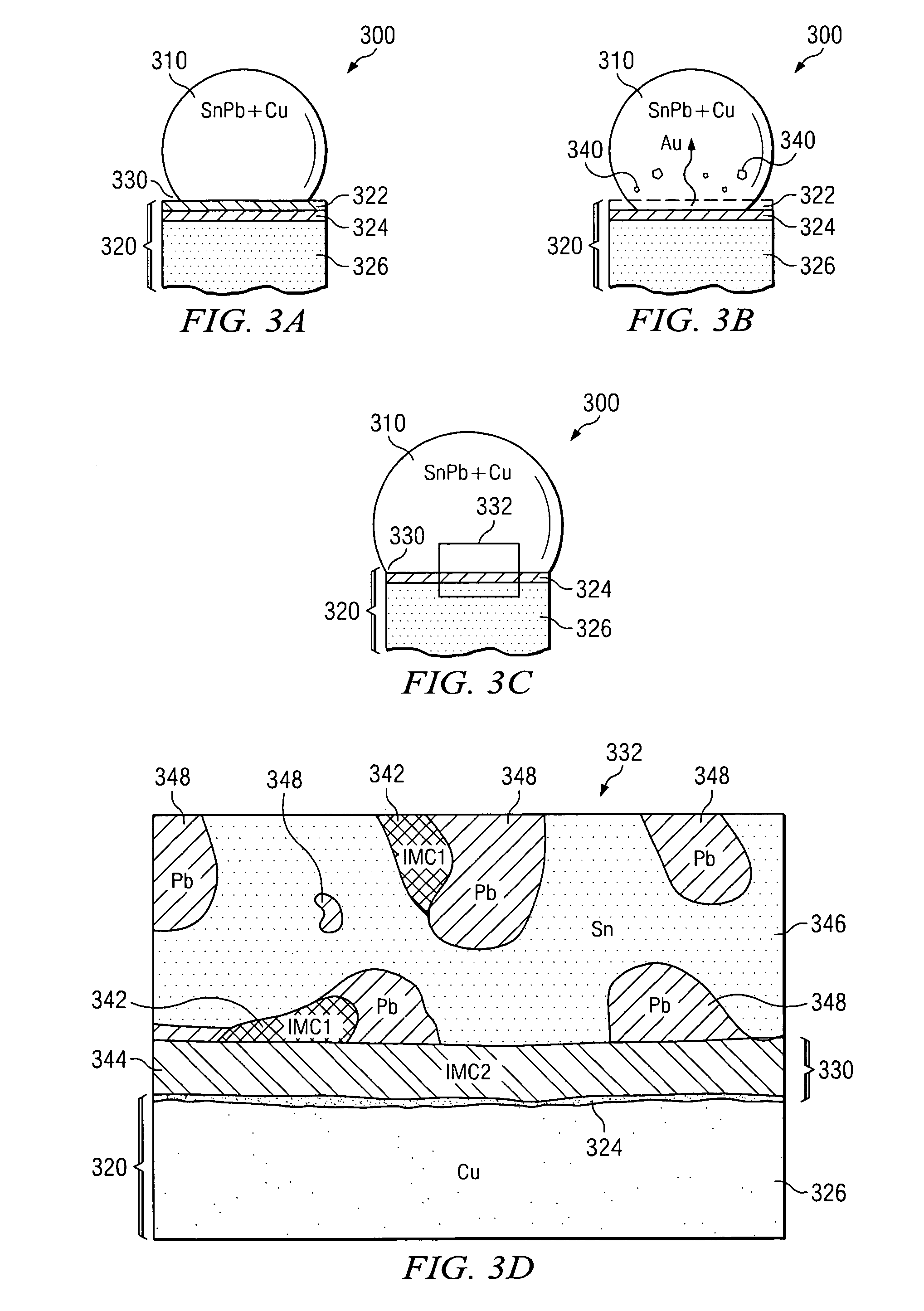

Method and structure to reduce risk of gold embritlement in solder joints

ActiveUS20050161829A1Reducing gold embrittlementPrinted circuit assemblingSemiconductor/solid-state device detailsCopperTin

A method for reducing gold embrittlement in solder joints, and a copper-bearing solder according to the method, are disclosed. Embodiments of the invention comprise adding copper to non-copper based solder, such as tin-lead solder. The embodiments may further comprise using the copper-bearing solder as a solder interconnect on a gold-nickel pad.

Owner:TEXAS INSTR INC

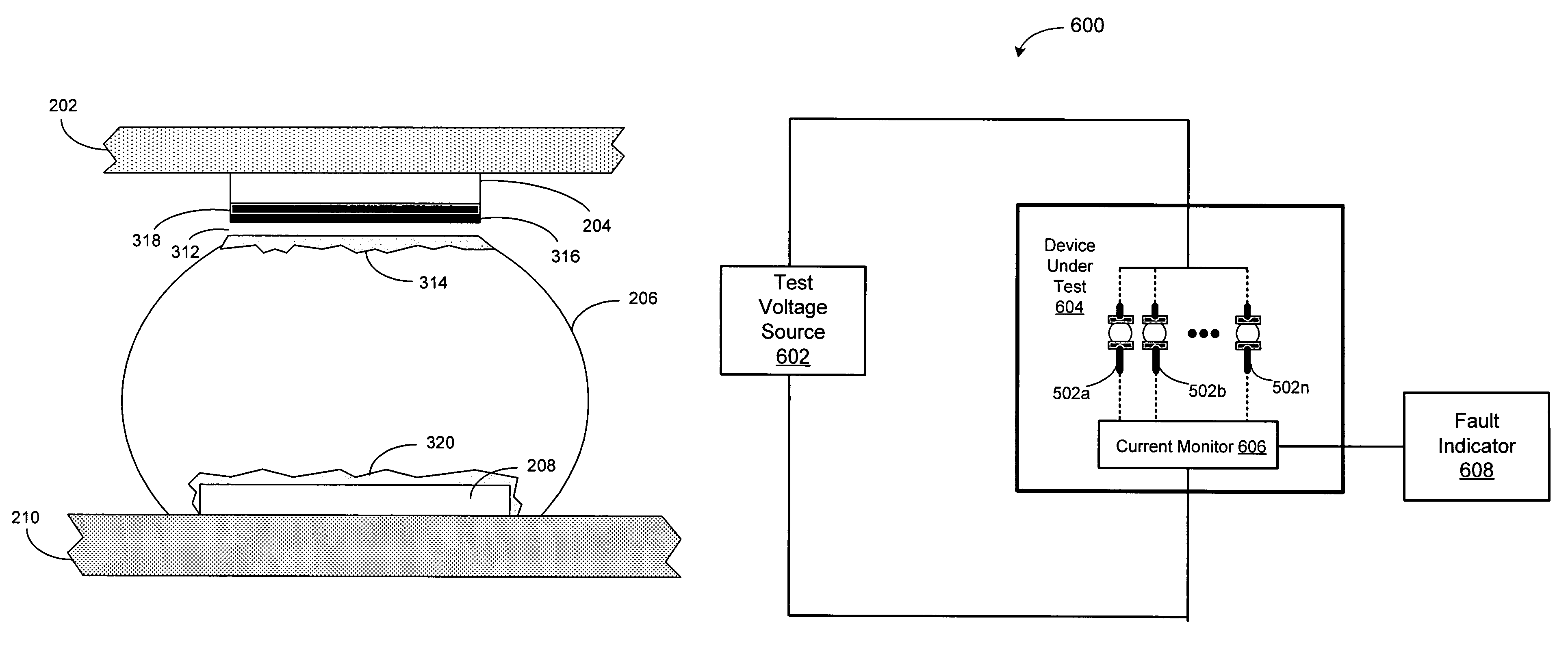

Solder interconnect integrity monitor

ActiveUS7478741B1More levelMore sensitivitySemiconductor/solid-state device testing/measurementFinal product manufactureNon destructiveElectrical and Electronics engineering

An apparatus and method for non-destructive solder interconnect integrity monitoring that can detect existing fracture damage, identify new or incipient fractures, and be implemented across multiple component configurations. Said components can be implemented to detect, on a continuous basis, solder interconnect fractures as they occur during actual end-use, throughout the lifecycle of monitored components, rather than relying on a one-time electrical check prior to shipment.

Owner:ORACLE INT CORP

Solder interconnect pads with current spreading layers

Structure and methods of making the structures. The structures include a structure, comprising: an organic dielectric passivation layer extending over a substrate; an electrically conductive current spreading pad on a top surface of the organic dielectric passivation layer; an electrically conductive solder bump pad comprising one or more layers on a top surface of the current spreading pad; and an electrically conductive solder bump containing tin, the solder bump on a top surface of the solder bump pad, the current spreading pad comprising one or more layers, at least one of the one or more layers consisting of a material that will not form an intermetallic with tin or at least one of the one or more layers is a material that is a diffusion barrier to tin and adjacent to the solder bump pad.

Owner:ULTRATECH INT INC

Solder interconnect structure and method using injection molded solder

InactiveUS20060118604A1Facilitate underfill reinforcementGreat standoffFinal product manufacturePrinted circuit aspectsElectrical conductorOptoelectronics

Improved interconnects are produced by injection molded solder which fills mold arrays with molten solder so that columns that have much greater height to width aspect ratios greater than one are formed, rather than conventional flip chip bumps. The columns may have filler particles or reinforcing conductors therein. In the interconnect structures produced, the cost and time of a subsequent underfill step is reduced or avoided. The problem of incompatibility with optical interconnects between chips because underfills require high loading of silica fillers which scatter light, is solved, thus allowing flip chips to incorporate optical interconnects.

Owner:IBM CORP

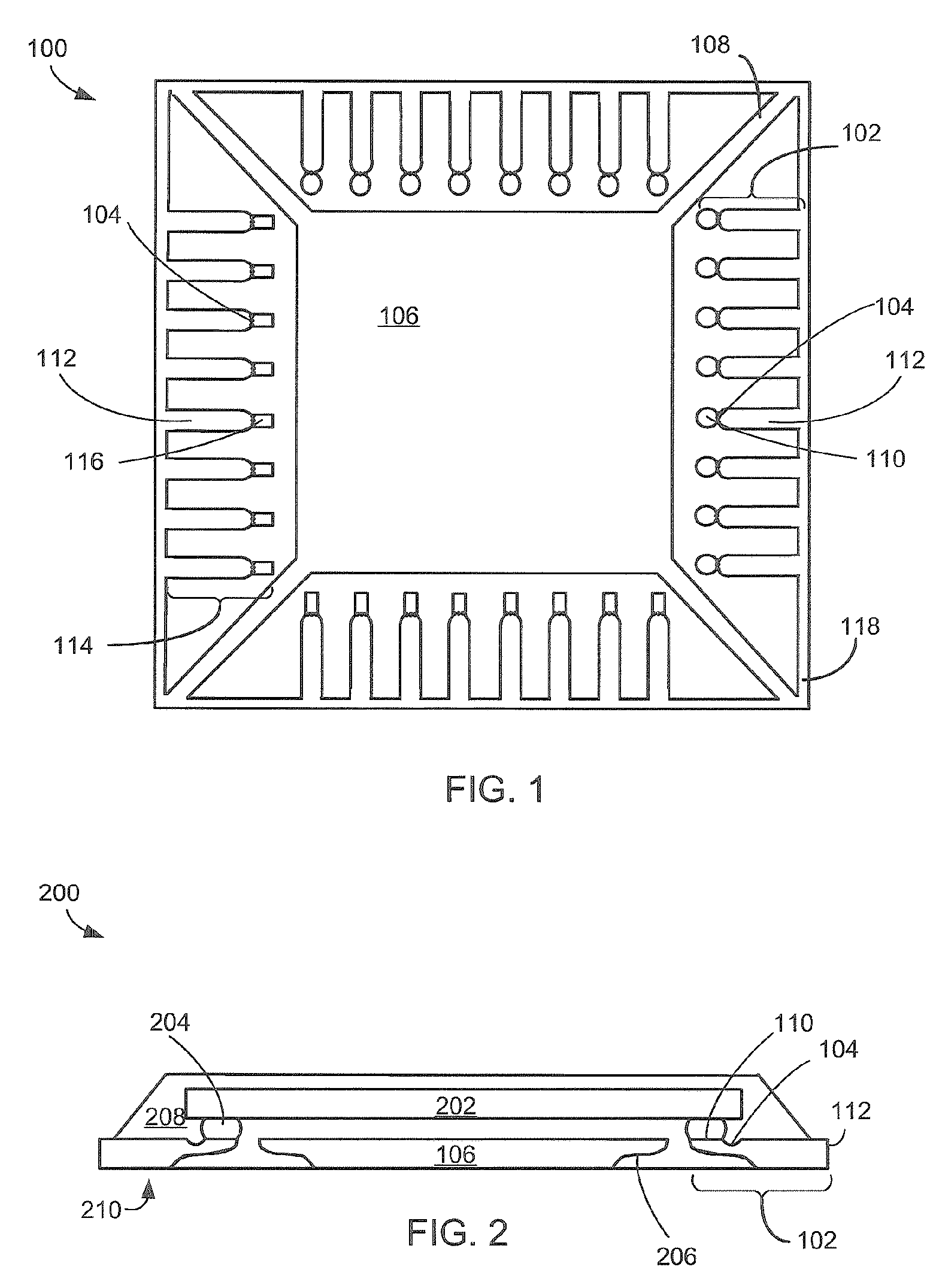

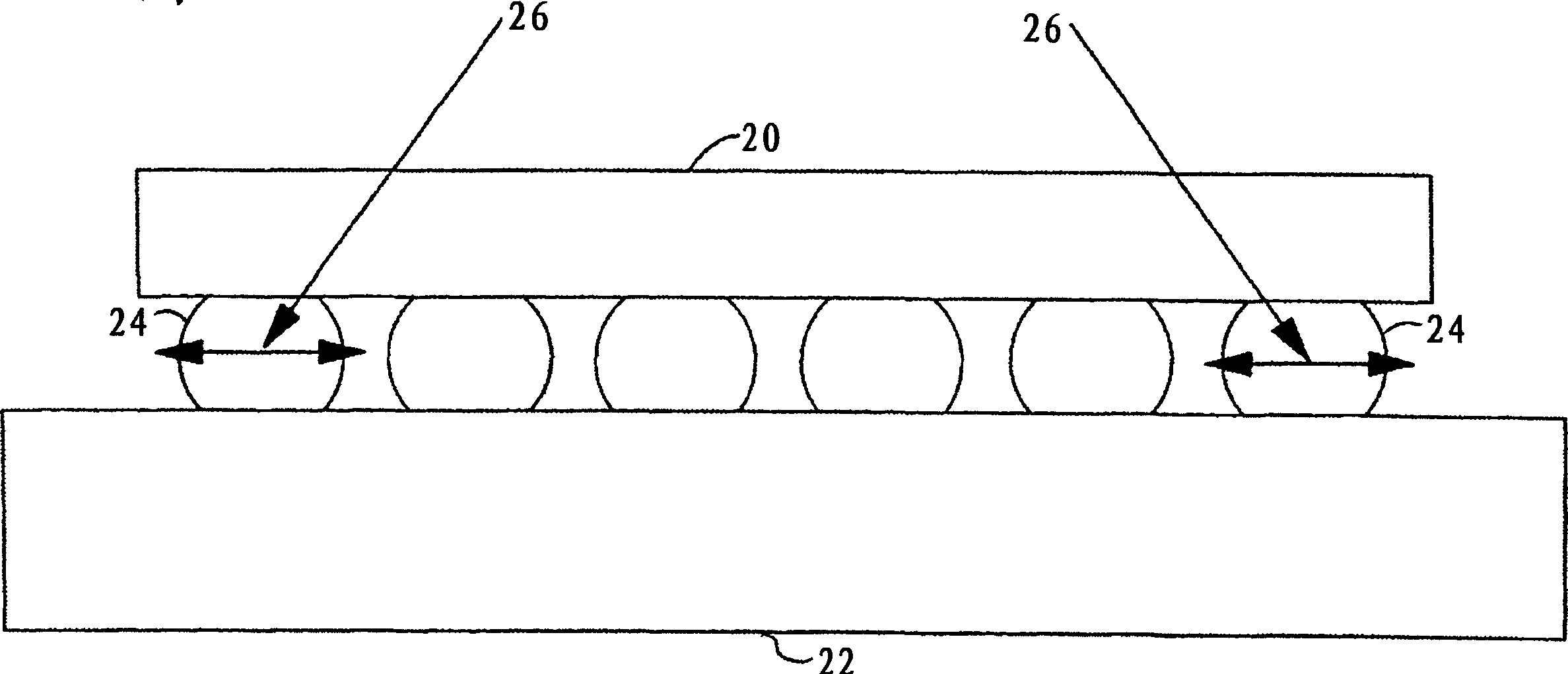

Variable temperature solders for multi-chip module packaging and repackaging

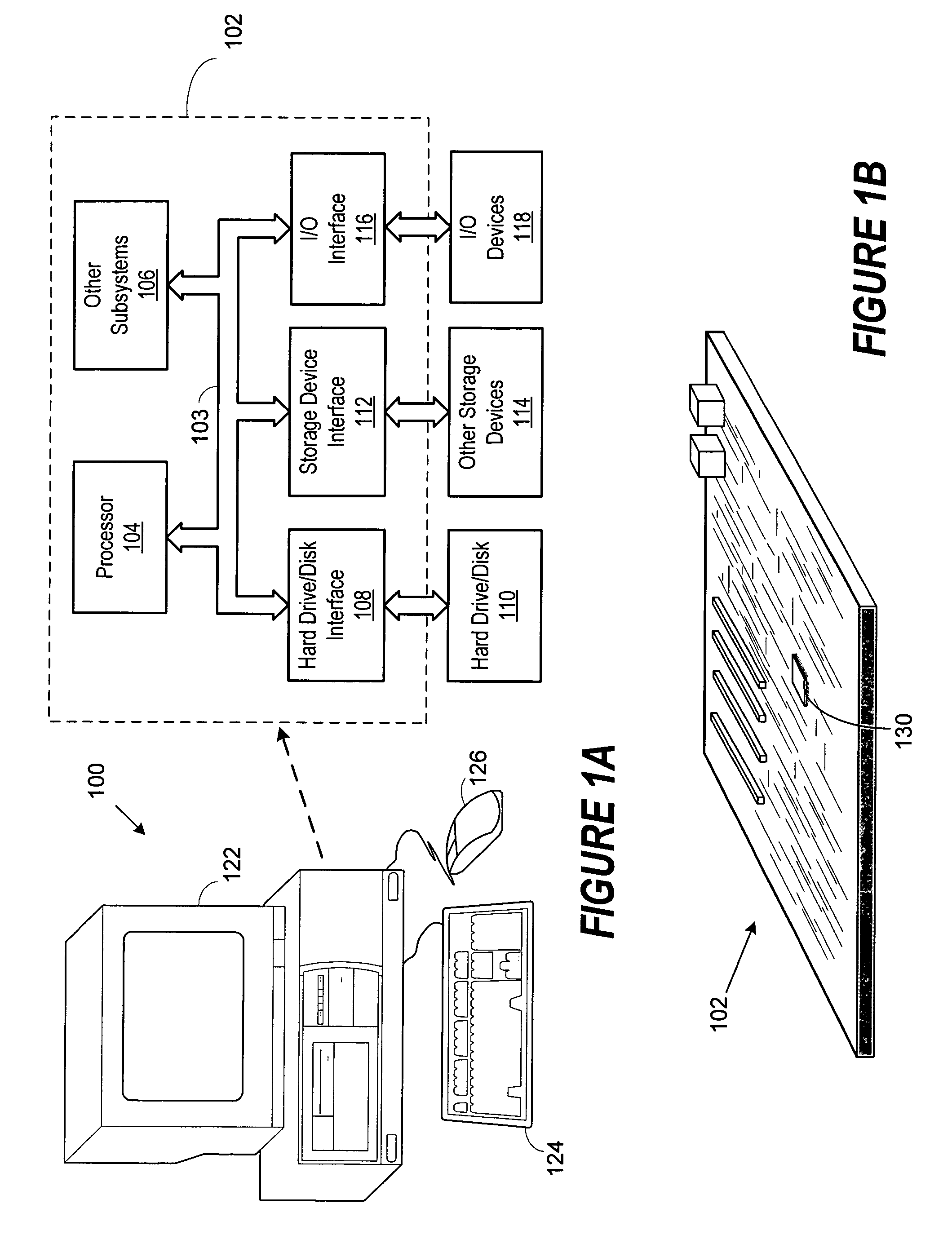

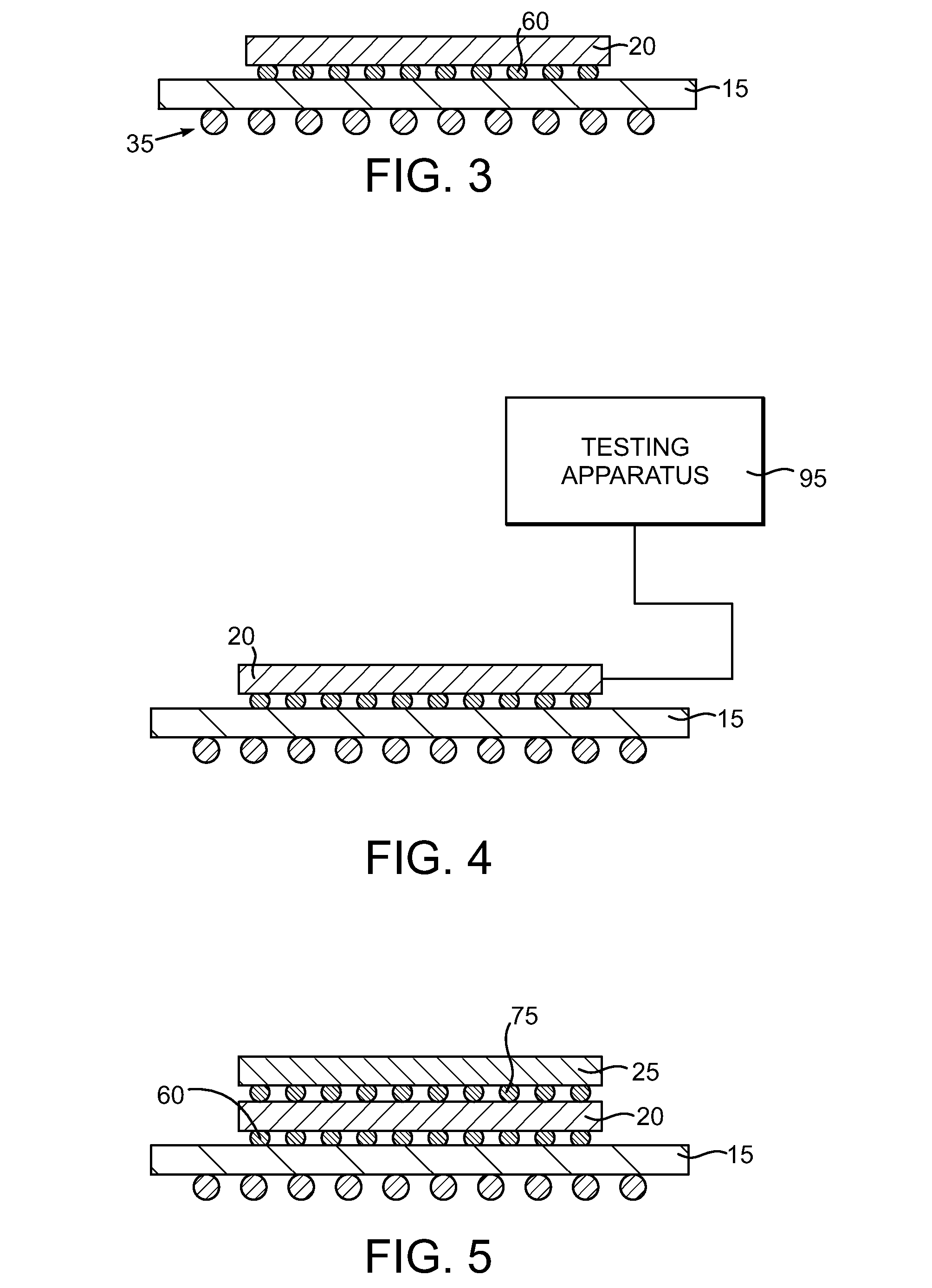

ActiveUS20140346664A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor chipComputer module

Various methods of mounting semiconductor chips on a substrate are disclosed. In one aspect, a method of manufacturing is provided that includes coupling a first plurality of solder interconnect structures to a first semiconductor chip. The first solder interconnect structures have a first melting point. The first semiconductor chip may be tested. If the first semiconductor chip passes the testing, then a second semiconductor chip is coupled to the first semiconductor chip using a second plurality of solder interconnect structures that have a second melting point lower than the first melting point.

Owner:ADVANCED MICRO DEVICES INC

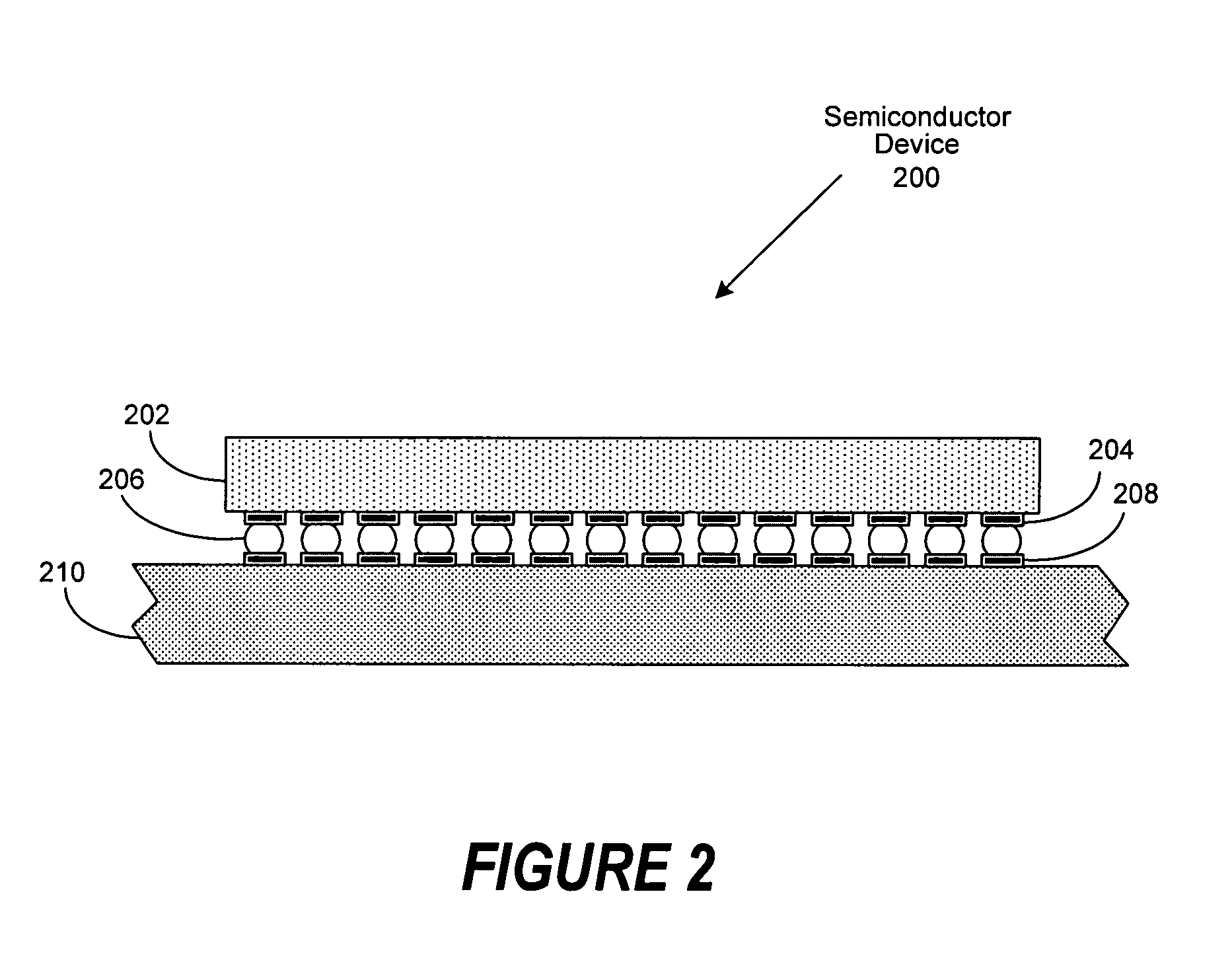

Microelectronic packages with solder interconnections

InactiveUS20060113680A1Relieve pressureImprove fatigue resistancePrinted circuit assemblingFinal product manufactureThermal fatigueSurface mounting

A soldered assembly for a microelectronic element includes a microelectronic element, solder columns extending from a surface of the microelectronic element and terminals connected to distal ends of the columns. The assembly can be handled and mounted using conventional surface-mount techniques, but provides thermal fatigue resistance. The solder columns may be inclined relative to the chip surface, and may contain long, columnar inclusions preferentially oriented along the lengthwise axes of the columns.

Owner:TESSERA INC

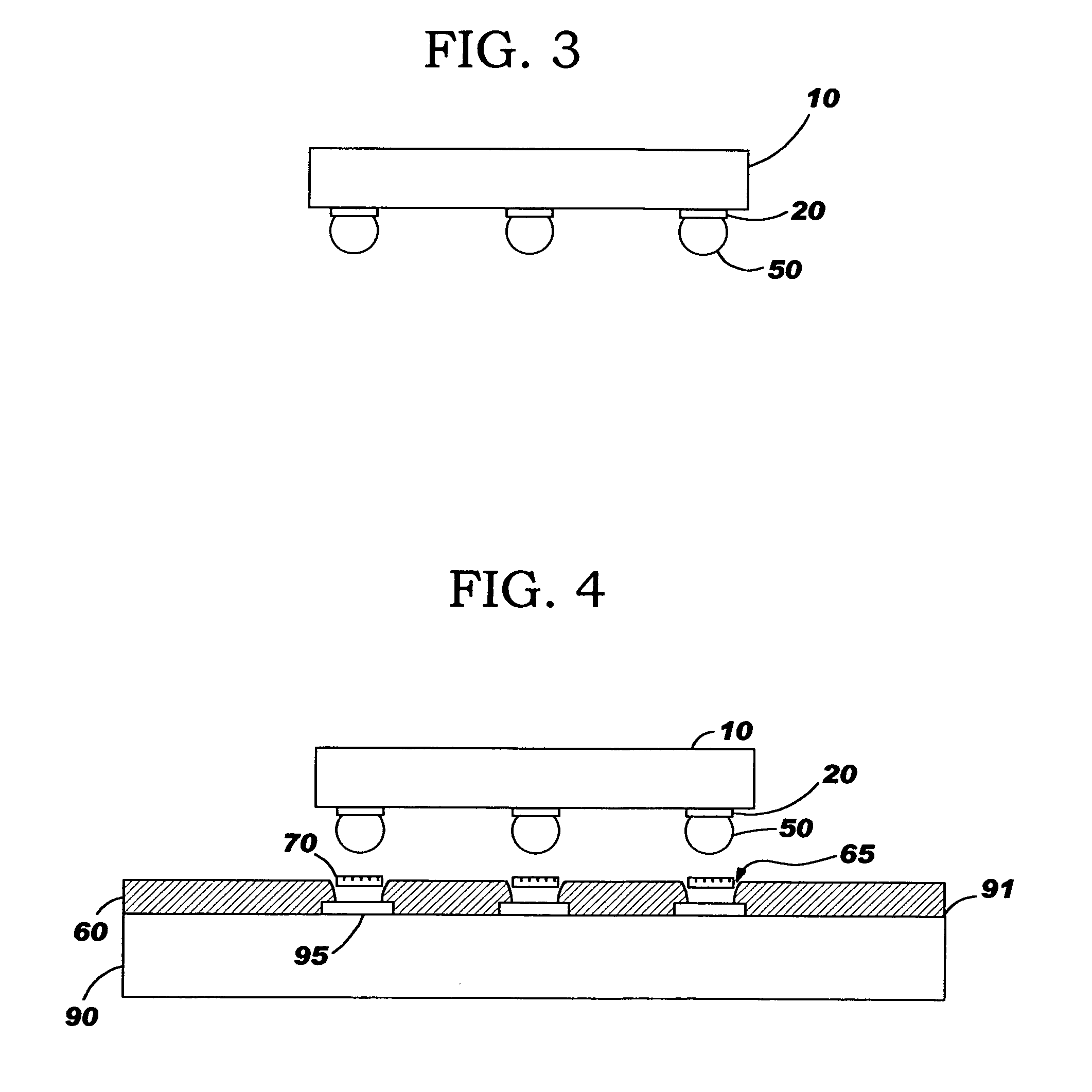

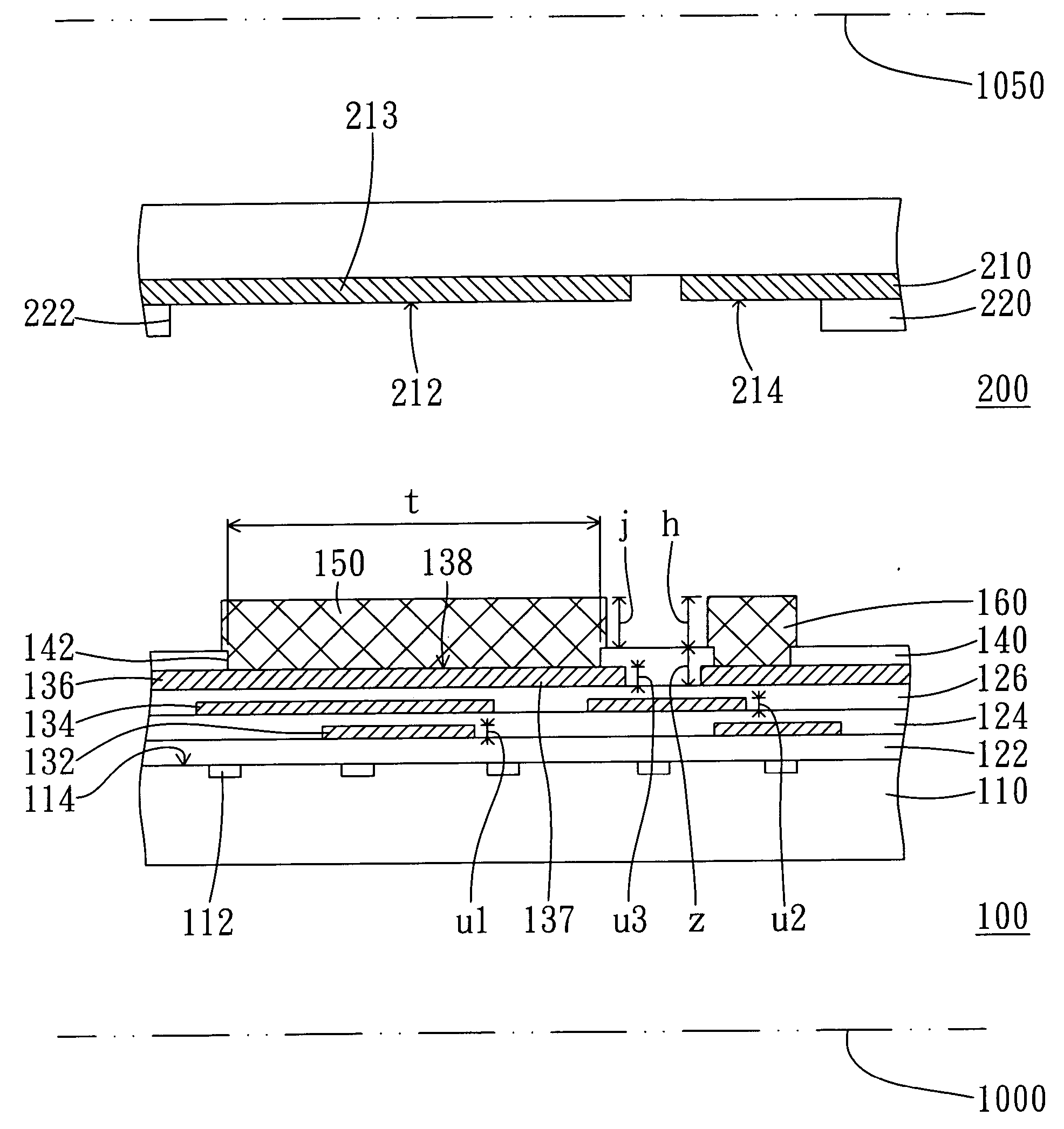

Partially underfilled solder grid arrays

InactiveUS20090256268A1Final product manufactureSemiconductor/solid-state device detailsEngineeringMesh grid

An electronic device and a method of forming the device. The device including a module having opposite top surface and bottom surfaces; a first set of pads on the top surface of the module and a second set of pads on the bottom surface of the module substrate, wires within the module electrically connecting the first set of pads to the second set of pads; a set of solder interconnects in electrical and physical contact with a the second set of module pads; and a dielectric underfill layer formed on the bottom surface of the module, the underfill layer filling the space between lower regions of the solder interconnects of the set of solder interconnects, upper regions of the solder interconnects of the set of solder interconnects extending past a top surface of the underfill layer.

Owner:GLOBALFOUNDRIES INC

Solder interconnect structure and method using injection molded solder

InactiveUS7523852B2Facilitate underfill reinforcementGreat standoffFinal product manufacturePrinted circuit aspectsElectrical conductorOptoelectronics

Improved interconnects are produced by injection molded solder which fills mold arrays with molten solder so that columns that have much greater height to width aspect ratios greater than one are formed, rather than conventional flip chip bumps. The columns may have filler particles or reinforcing conductors therein. In the interconnect structures produced, the cost and time of a subsequent underfill step is reduced or avoided. The problem of incompatibility with optical interconnects between chips because underfills require high loading of silica fillers which scatter light, is solved, thus allowing flip chips to incorporate optical interconnects.

Owner:INT BUSINESS MASCH CORP

Solder interconnect with non-wettable sidewall pillars and methods of manufacture

ActiveUS8637392B2Semiconductor/solid-state device detailsSolid-state devicesSolder wettingNickel alloy

A solder interconnect structure is provided with non-wettable sidewalls and methods of manufacturing the same. The method includes forming a nickel or nickel alloy pillar on an underlying surface. The method further includes modifying the sidewall of the nickel or nickel alloy pillar to prevent solder wetting on the sidewall.

Owner:GLOBALFOUNDRIES US INC

Method for forming robust solder interconnect structures by reducing effects of seed layer underetching

InactiveUS6995084B2Semiconductor/solid-state device detailsSolid-state devicesElectrode potentialSemiconductor

A method for forming an interconnect structure for a semiconductor device includes defining a via in a passivation layer so as expose a top metal layer in the semiconductor device. A seed layer is formed over the passivation layer, sidewalls of the via, and the top metal layer. A barrier layer is formed over an exposed portion of the seed layer, the exposed portion defined by a first patterned opening. The semiconductor device is annealed so as to cause atoms from the barrier layer to diffuse into the seed layer thereunderneath, wherein the annealing causes diffused regions of the seed layer to have an altered electrical resistivity and electrode potential with respect to undiffused regions of the seed layer.

Owner:INVENSAS CORP

Chip package solder interconnect formed by surface tension

InactiveUS8138099B1Facilitating chip joiningSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSelf-assembly

Disclosed herein is a solder self-assembly structure, an IC chip including a solder self-assembly structure, and a method of making the same. The structure includes a release layer disposed on a portion of an upper surface of the substrate, laterally spaced from a via in the substrate. A barrier layer metallization (BLM) is disposed in a first part over a portion of the substrate including a via, and in a second part over the release layer, leaving a surface of the substrate exposed between the first portion and the second portion of the BLM. A solder structure is disposed over the first and second portions of the BLM and the exposed surface of the substrate disposed there between. When the solder structure is reflowed and annealed, surface tension in the solder causes self-assembly of a three-dimensional, compliant solder structure.

Owner:GLOBALFOUNDRIES INC

Method for forming robust solder interconnect structures by reducing effects of seed layer underetching

InactiveUS20060009022A1Semiconductor/solid-state device detailsSolid-state devicesElectrode potentialDevice material

A method for forming an interconnect structure for a semiconductor device includes defining a via in a passivation layer so as expose a top metal layer in the semiconductor device. A seed layer is formed over the passivation layer, sidewalls of the via, and the top metal layer. A barrier layer is formed over an exposed portion of the seed layer, the exposed portion defined by a first patterned opening. The semiconductor device is annealed so as to cause atoms from the barrier layer to diffuse into the seed layer thereunderneath, wherein the annealing causes diffused regions of the seed layer to have an altered electrical resistivity and electrode potential with respect to undiffused regions of the seed layer.

Owner:INVENSAS CORP

Solder Interconnect

InactiveUS20100015762A1Small grain sizeReduce grain sizeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipCrystallite

Various solder interconnect methods and apparatus are disclosed. In aspect, a method of manufacturing is provided that includes coupling a semiconductor chip to a circuit board with plural solder joints whereby an interstitial space is left between the semiconductor chip and the circuit board. The semiconductor chip and the circuit board are heated at a first temperature lower than a melting point of constituents of the plural solder joints to liberate contaminants from the interstitial space. The semiconductor chip and the circuit board are heated again at a second temperature higher than a melting point of at least one the constituents but not all of the constituents of the plural solder joints to shrink grain sizes of the at least one constituent. An underfill is placed in the interstitial space.

Owner:GLOBALFOUNDRIES INC

Method and structure to reduce risk of gold embrittlement in solder joints

A method for reducing gold embrittlement in solder joints, and a copper-bearing solder according to the method, are disclosed. Embodiments of the invention comprise adding copper to non-copper based solder, such as tin-lead solder. The embodiments may further comprise using the copper-bearing solder as a solder interconnect on a gold-nickel pad.

Owner:TEXAS INSTR INC

Reduction of solder interconnect stress

ActiveUS20180061799A1Semiconductor/solid-state device detailsSolid-state devicesInterposerMinor axis

A first electrical contact and second contact is upon an interposer and / or upon a processing device. The first contact includes a minor axis and a major axis. The second contact includes diameter axes. The first contact is positioned such that the major axis is generally aligned with the direction of expansion of the interposer and / or the processing device. The first electrical contact may further be positioned within a power / ground or input / output (I / O) region of the interposer and / or processing device. The first electrical contact may further be positioned within a center region that is surrounded by a perimeter region of the interposer and / or the processing device. The dimensions or aspect ratios of major and minor axes of neighboring first electrical contacts within an electrical contact grid may differ relative thereto. Further, the angle of respective major and minor axes of neighboring first electrical contacts within the electrical contact grid may differ relative thereto.

Owner:INT BUSINESS MASCH CORP

System and method for creating orthogonal solder interconnects

PendingUS20210076505A1Printed circuit assemblingWelding/cutting auxillary devicesEngineeringSolder interconnection

An apparatus and method for soldering an electrical component to a circuit board includes a stage positioning the circuit board and electrical component in alignment with a solder tip along an axis. A first spring-loaded compression mechanism maintains contact between the circuit board and the electrical component, and a second spring-loaded compression mechanism brings the soldering tip into thermal contact with the circuit board and the electrical component such that solder disposed adjacent to the circuit board and the electrical component melts. When the second spring-loaded compression mechanism removes its applied force such that the soldering tip comes out of contact with the circuit board, the first spring-loaded compression mechanism maintains the contact between the circuit board and the electrical component while the solder cools and solidifies.

Owner:RAYTHEON CO

Laser ablation tape for solder interconnect formation

ActiveUS20140335686A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringSolder paste

A tape capable of laser ablation may be used in the formation of microelectronic interconnects, wherein the tape may be attached to bond pads on a microelectronic device and vias may be formed by laser ablation through the tape to expose at least a portion of corresponding bond pads. The microelectronic interconnects may be formed on the bond pads within the vias, such as by solder paste printing and solder reflow. The laser ablation tape can be removed after the formation of the microelectronic interconnects.

Owner:INTEL CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com