Microelectronic packages with solder interconnections

a micro-electronic and interconnection technology, applied in the direction of printed circuit aspects, sustainable manufacturing/processing, final product manufacturing, etc., can solve the problems of thermal fatigue stress on the solder bond in such assemblies temperature rise and fall of the assembly, etc., to achieve enhanced flexibility and fatigue resistance, the effect of relieving the stress on the bond

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

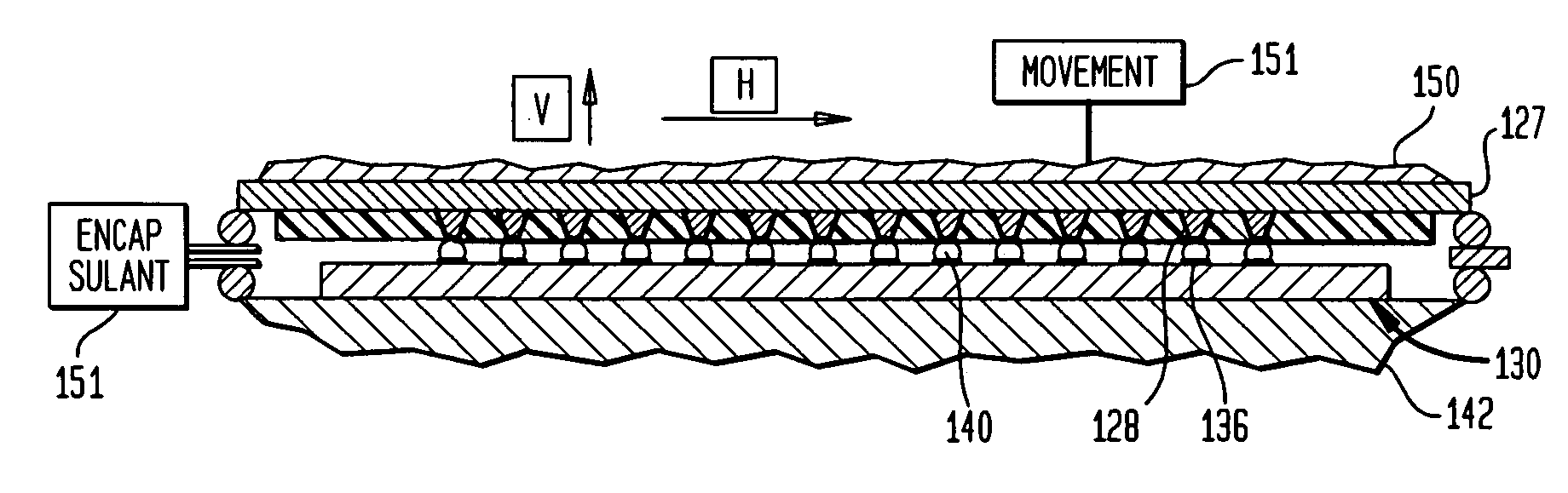

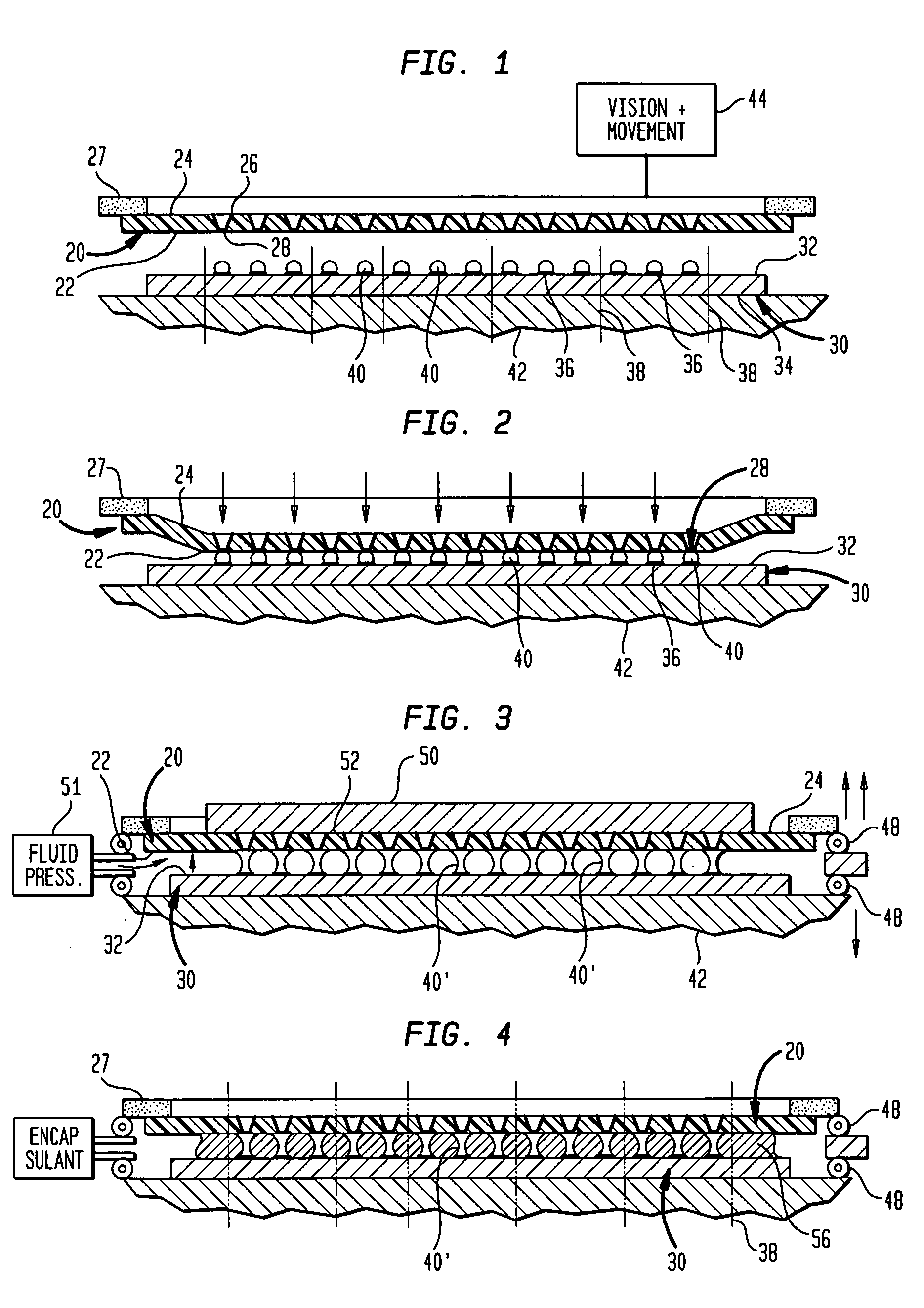

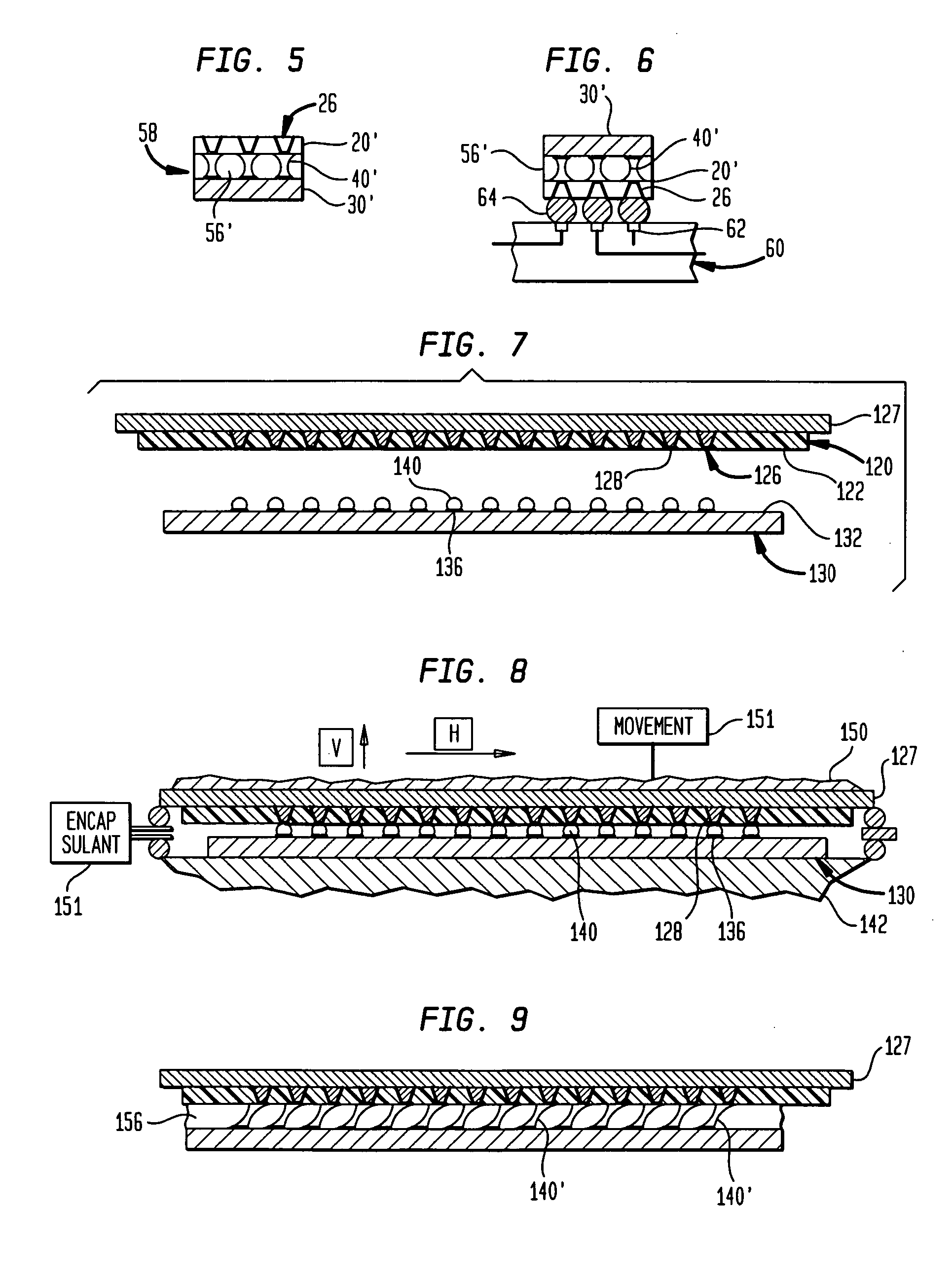

[0026] A process in accordance with one embodiment of the invention utilizes a flexible dielectric sheet 20 having oppositely facing inner surface 22 and outer surface 24. Sheet 20 may be formed from the polymeric materials such as a polyimide. The thickness of sheet 20 is greatly exaggerated in FIG. 1 for clarity of illustration. Typically, sheet 20 is about 25-100 μm thick. Sheet 20 has numerous holes extending through it. These holes are provided with metallic via liners 26. Each via liner defines a pad 28 on the inner surface 22 of the sheet. Each via liner is also exposed at the outer surface 24 of the sheet. Sheet 20 is attached to a ring-like frame 27 formed from a rigid material. The sheet may be stretched on the frame in the manner disclosed in U.S. Pat. No. 5,518,964, the disclosure of which is hereby incorporated by reference herein and in the manner discussed in U.S. Pat. No. 6,217,972, the disclosure of which is also incorporated by reference herein. As described in suc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com