Solder interconnect structure and method using injection molded solder

一种焊料、电连接的技术,应用在焊接/切割介质/材料、焊接设备、制造工具等方向,能够解决硅器件功率增加、机械应力增加、不允许芯片和衬底充分隔离等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

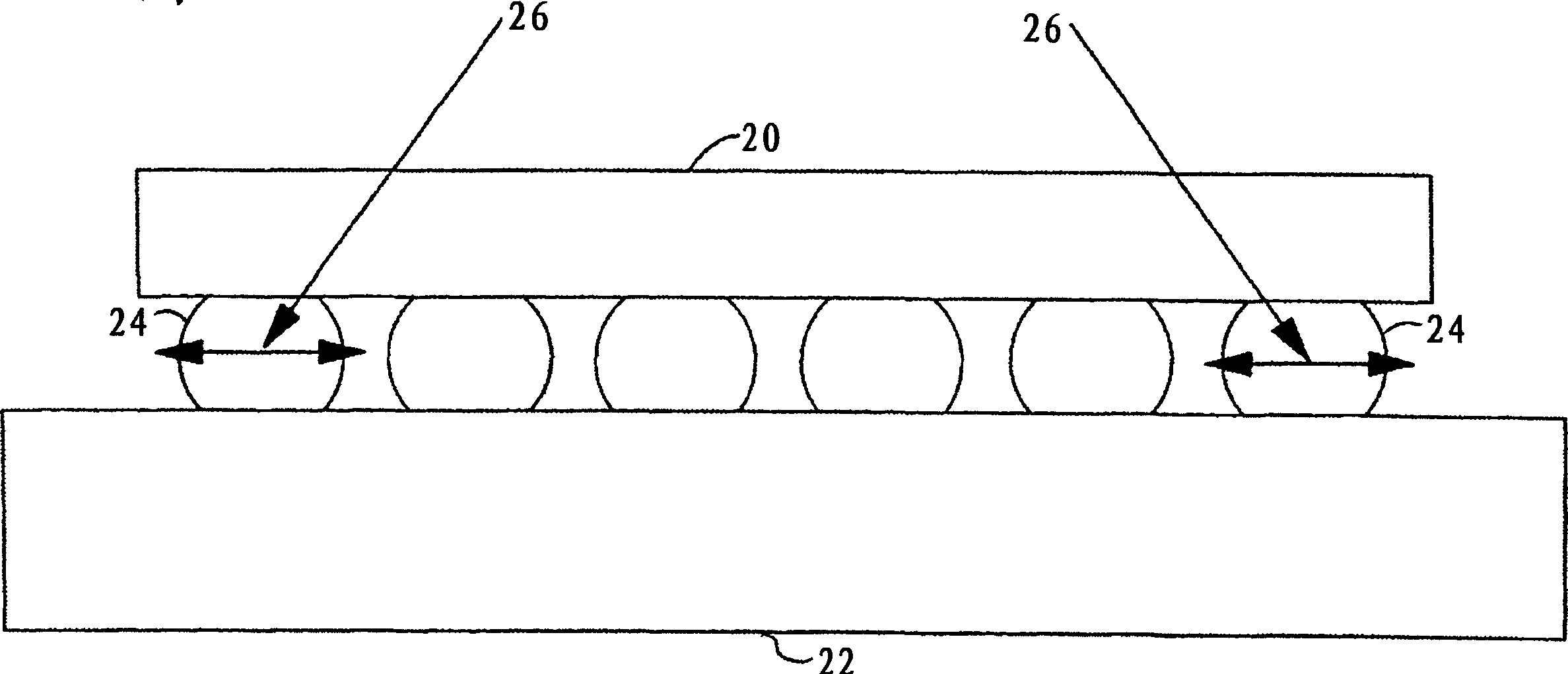

[0058] A preferred structure for improved flip chip interconnection may have cylindrical solder pillars with a diameter of 25-150 microns, preferably 50-100 microns. The interconnection may be 100-600 microns long, with an aspect ratio of length to diameter of 1.5:1-10:1, preferably in the range of 2:1 to 4:1. The manufacturing method of the interconnection will be described below.

[0059] The rectangular or square mold plates are patterned into an array with preferably cylindrical cavities. The mold plate can be a combination of borosilicate glass or a laser-processed polymer layer and glass. For example, in the United States Patent Application Serial No. 10 / XXXXXX, the name is: Combination Solder Transfer Mold Plate Structure and Its Manufacturing Method, Attorney Docket No . YOR920030189 US1, this document is granted the same assignee as the present invention and is incorporated in this application for reference. In addition, the size of the die plate may include 200mm or 300m...

example 2

[0063] Another preferred structure for improving flip-chip interconnection is that copper wires with a diameter of 25-100 microns are buried in solder pillars with a diameter of 50-150 microns. The interconnection can be 100-600 microns long with an aspect ratio of length to diameter of 1.5:1-10:1, preferably in the range of 2:1 to 4:1. The manufacturing method of the interconnection will be described below.

[0064] The rectangular or square mold plates are patterned into an array with preferably cylindrical cavities. The mold plate can be a combination of borosilicate glass or a laser-processed polymer layer and glass. For example, in the United States Patent Application Serial No. 10 / XXXXXX, the name is: Combination Solder Transfer Mold Plate Structure and Its Manufacturing Method, Attorney Docket No . YOR920030189 US1, this document is granted the same assignee as the present invention and is incorporated in this application for reference. In addition, the size of the die plat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| melting point | aaaaa | aaaaa |

| melting point | aaaaa | aaaaa |

| melting point | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com