Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

87 results about "Semiconductor nanostructures" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

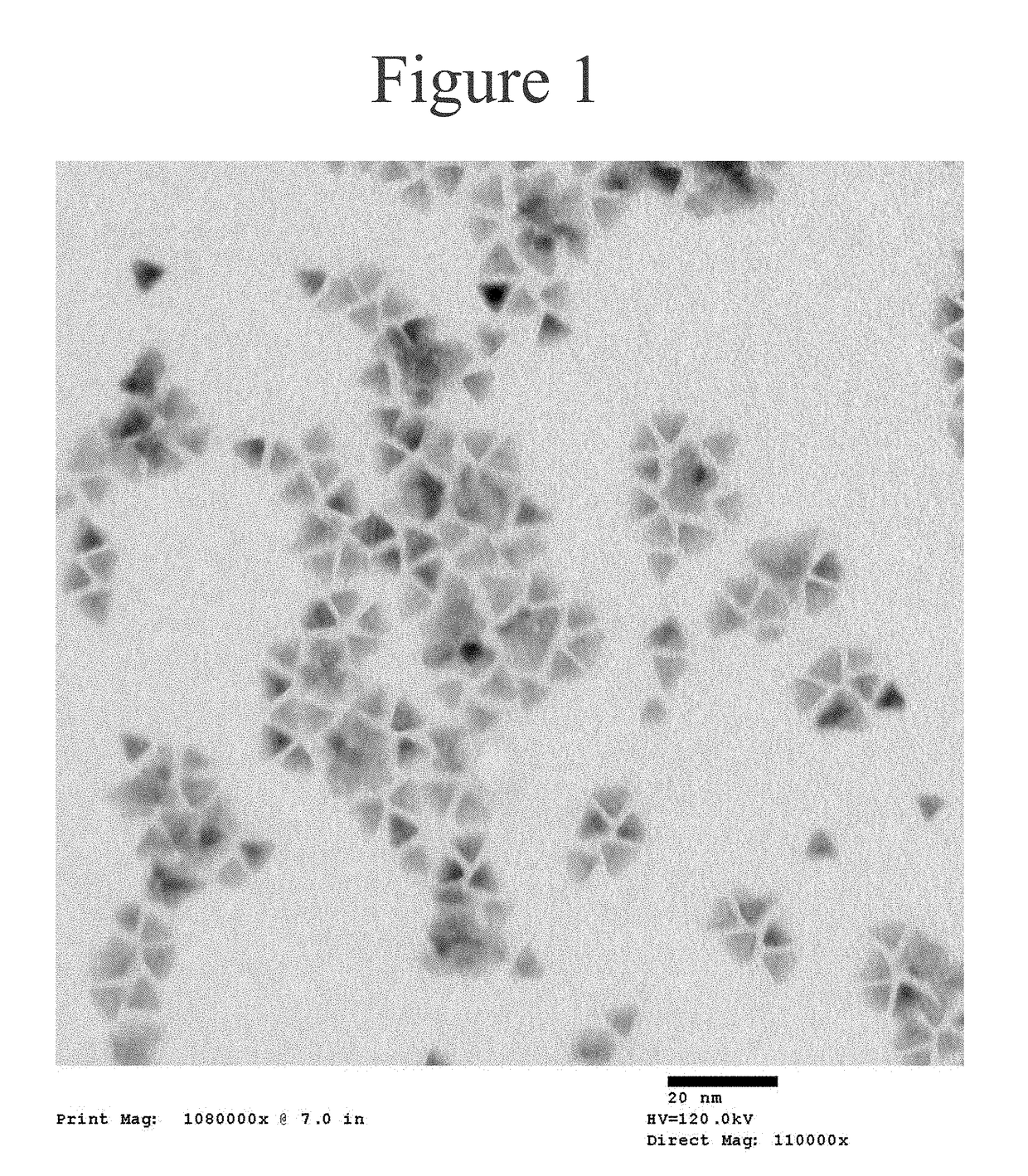

Monodisperse core/shell and other complex structured nanocrystals and methods of preparing the same

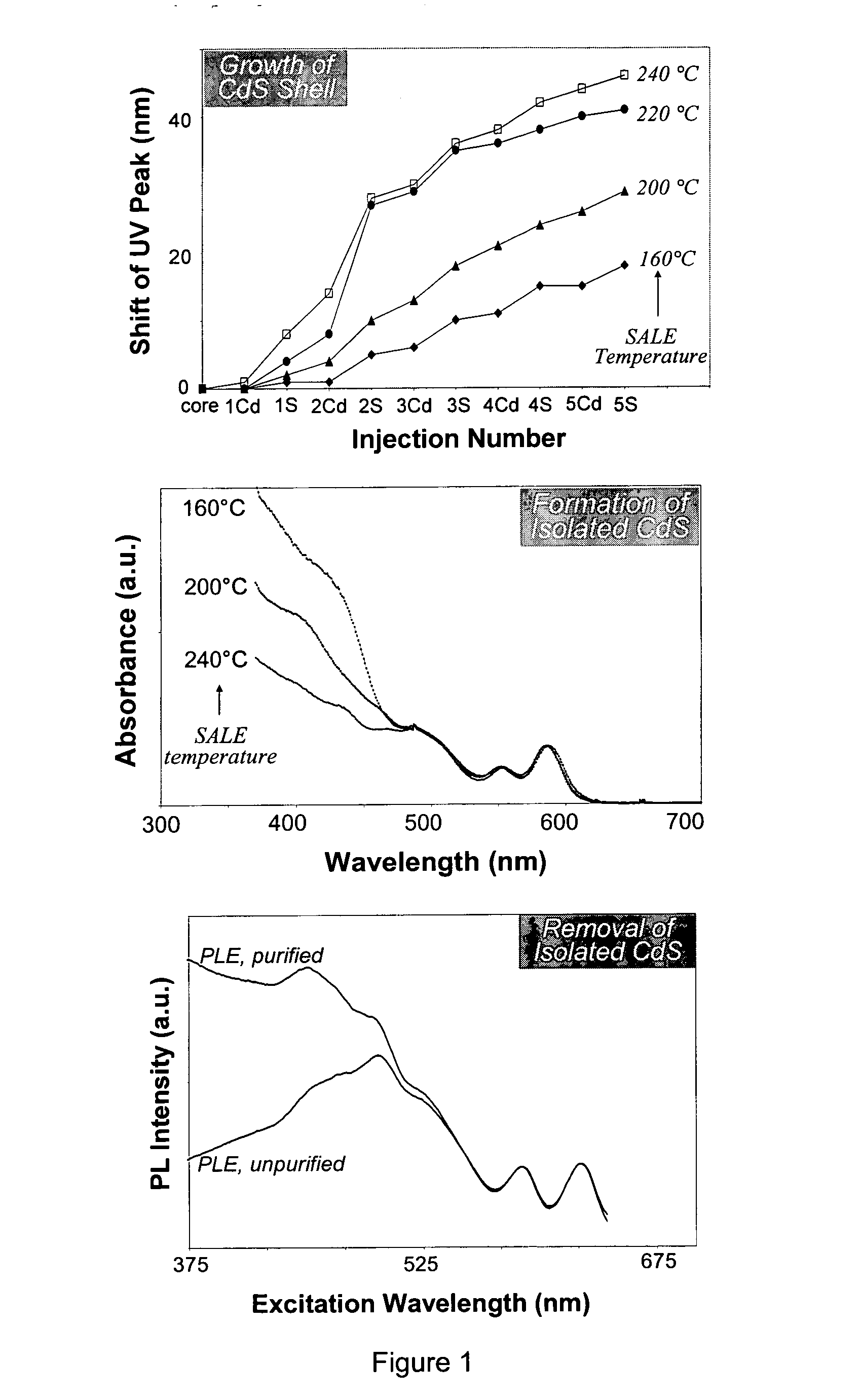

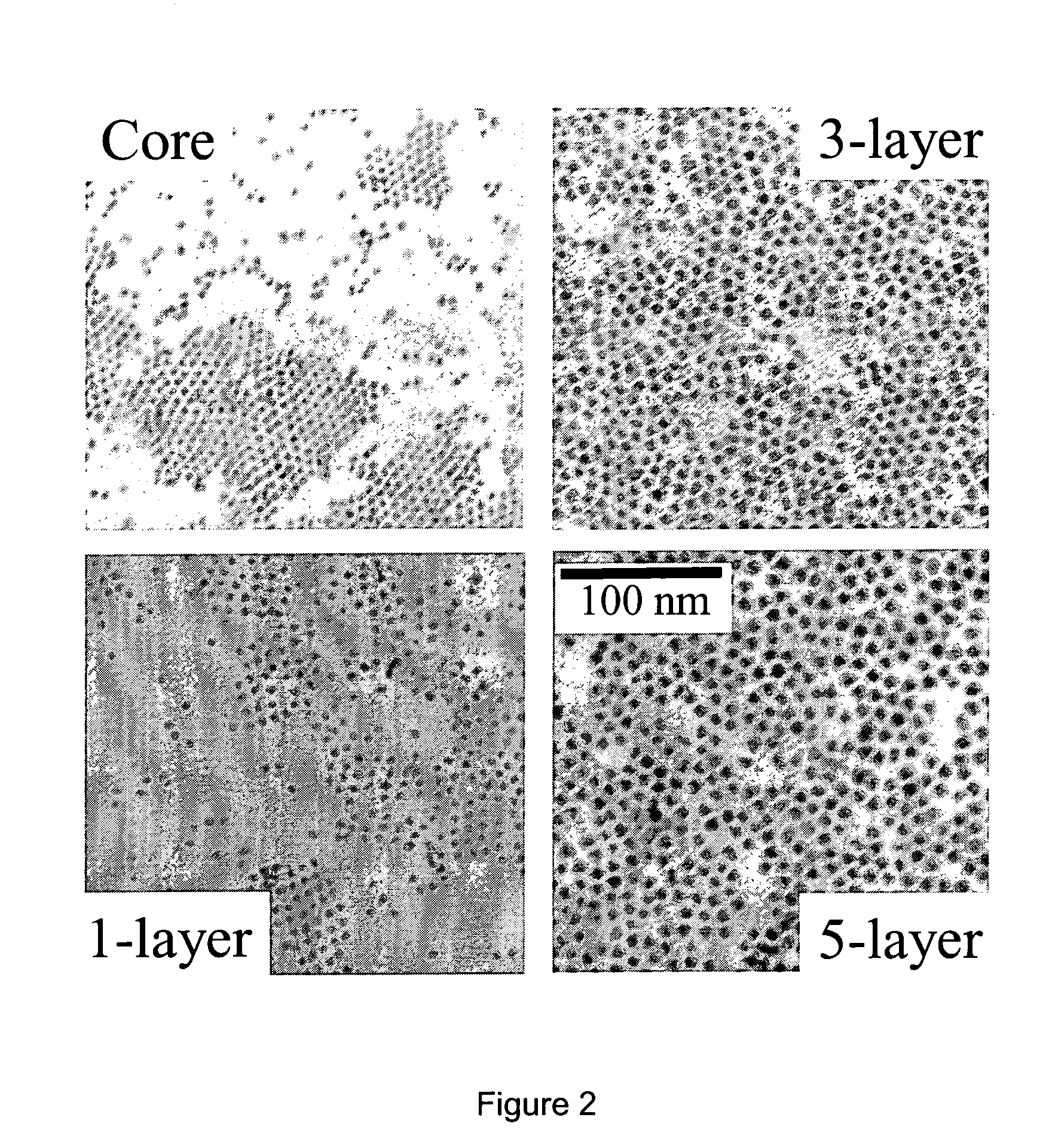

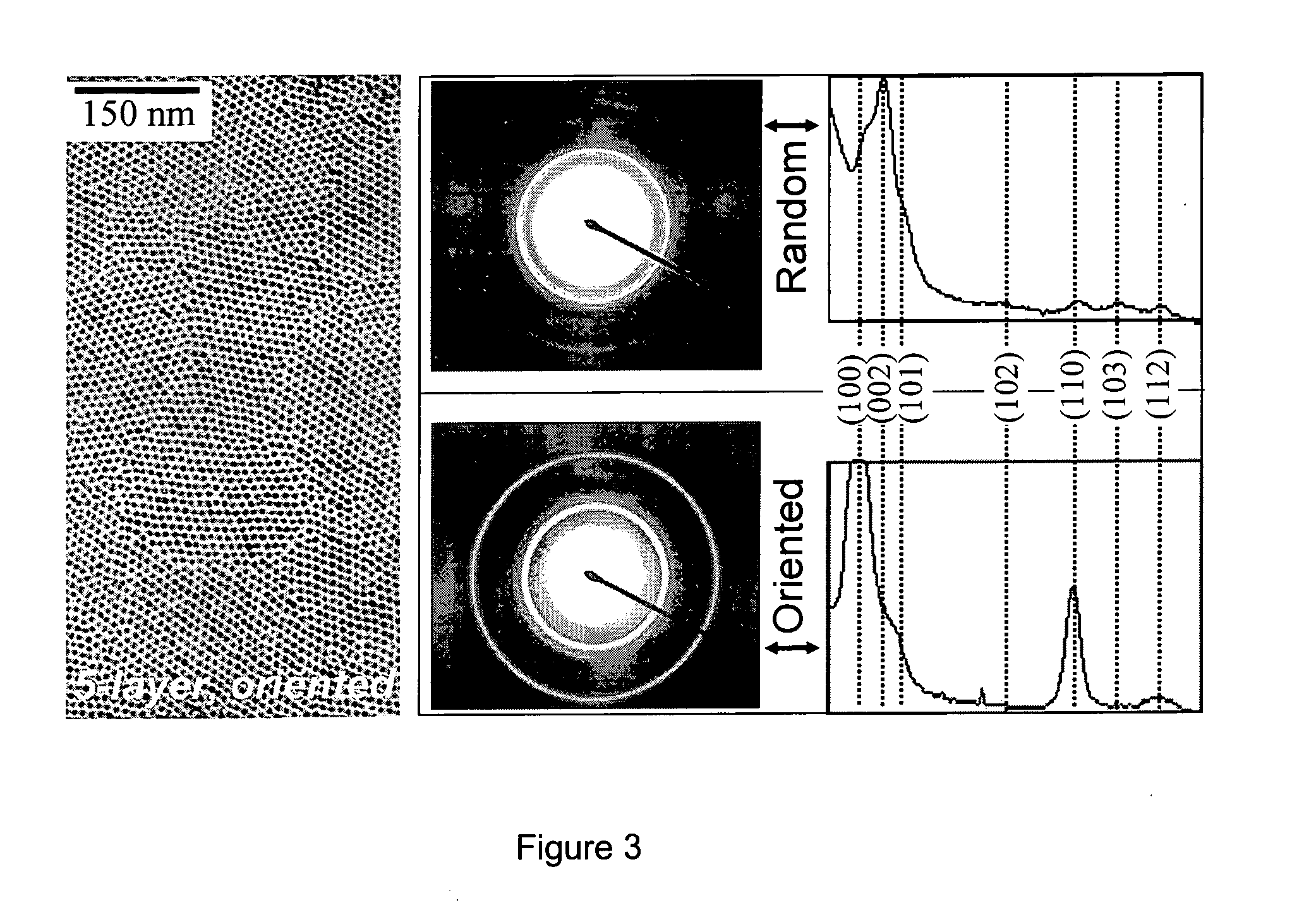

ActiveUS20050129947A1Narrow size distributionQuality improvementMaterial nanotechnologyFrom normal temperature solutionsChemistrySemiconductor nanostructures

The present invention provides new compositions containing naearly monodisperse colloidal core / shell semiconductor nanocrystals with high photoluminescence quantum yields (PL QY), as well as other complex structured semiconductor nanocrystals. This invention also provides new synthetic methods for preparing these nanocrystals, and new devices comprising these compositions. In addition to core / shell semiconductor nanocrystals, this patent application also provides complex semiconductor nanostructures, quantum shells, quantum wells, doped nanocrystals, and other multiple-shelled semiconductor nanocrystals.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ARKANSAS

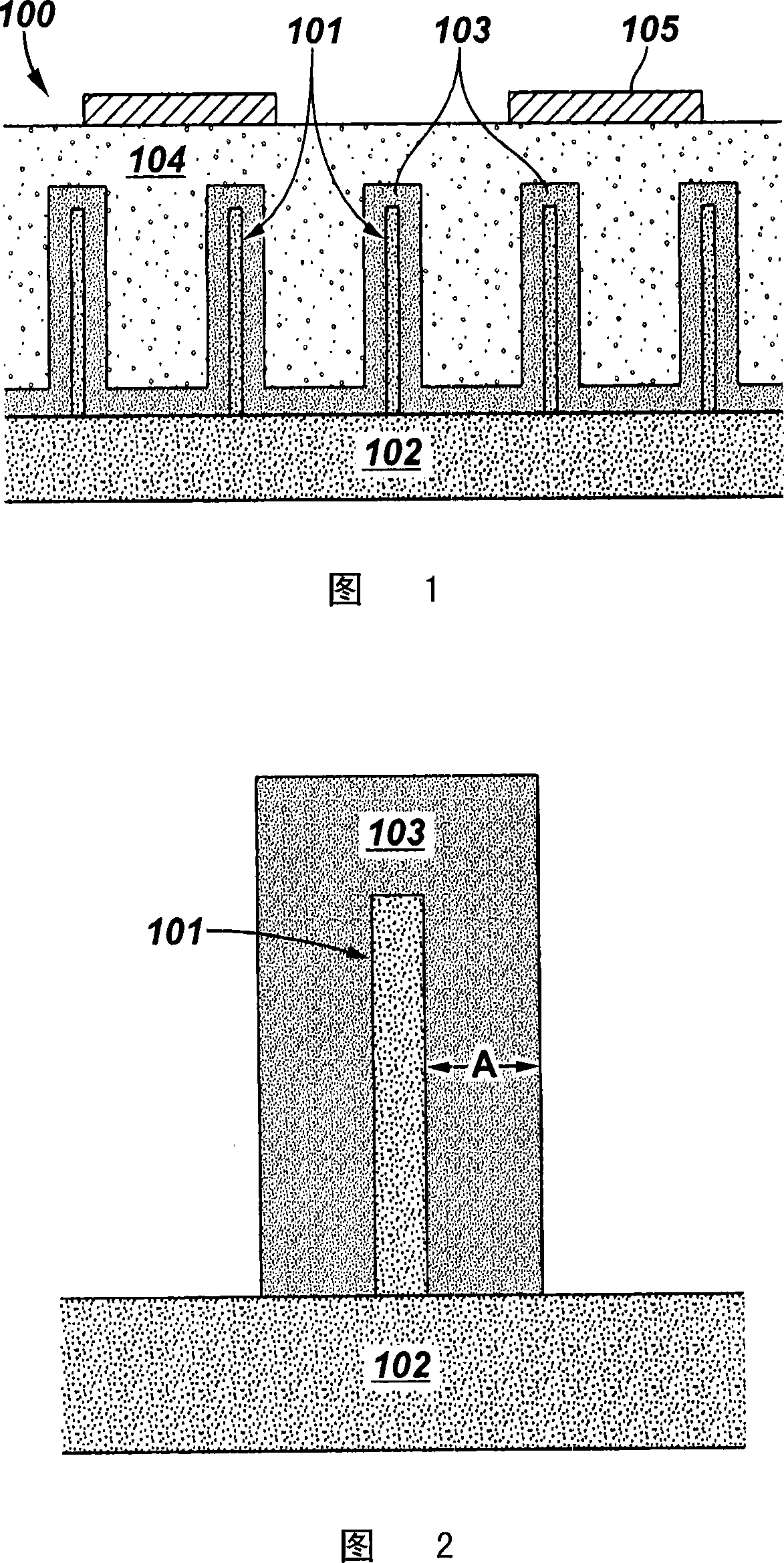

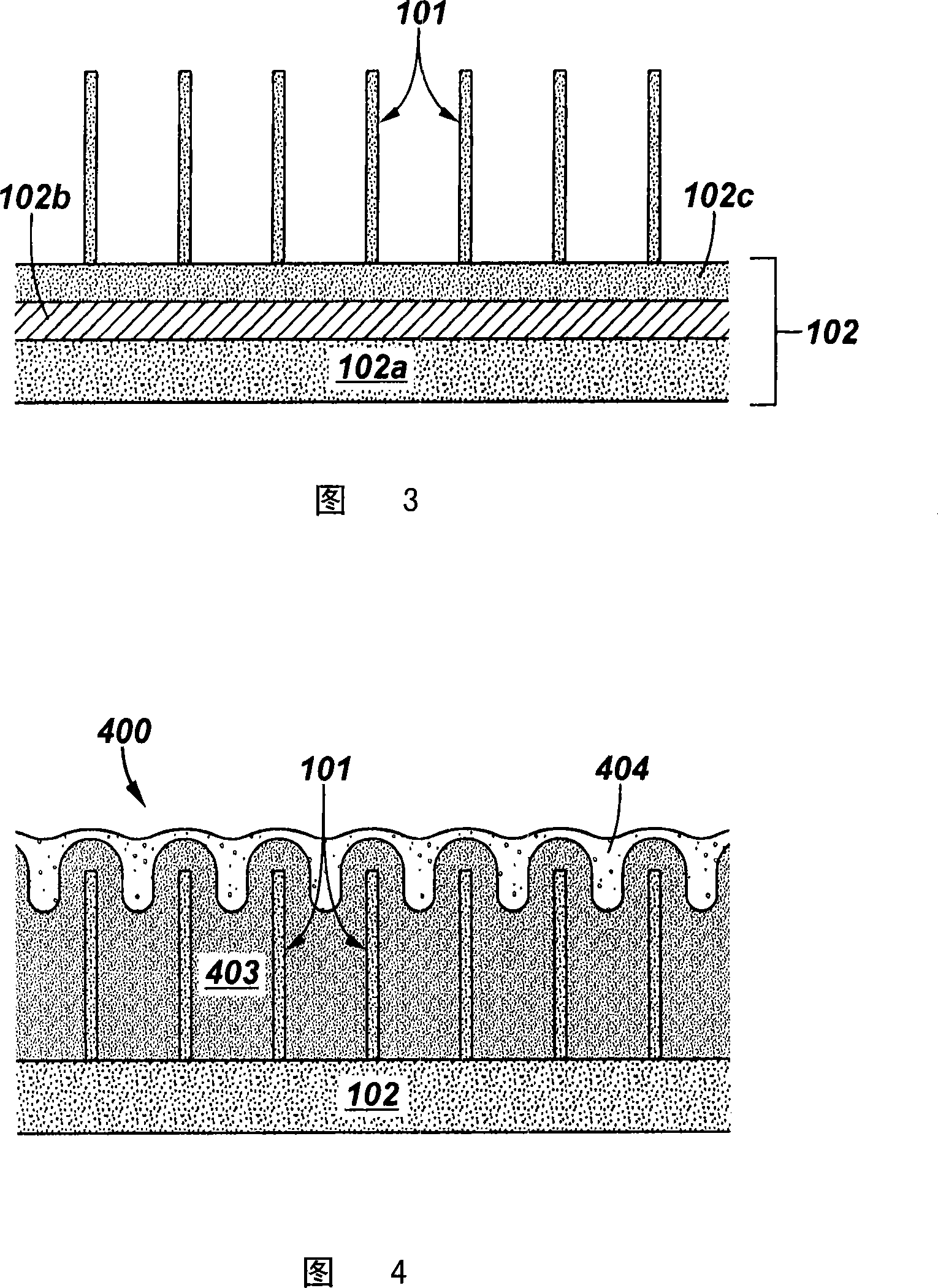

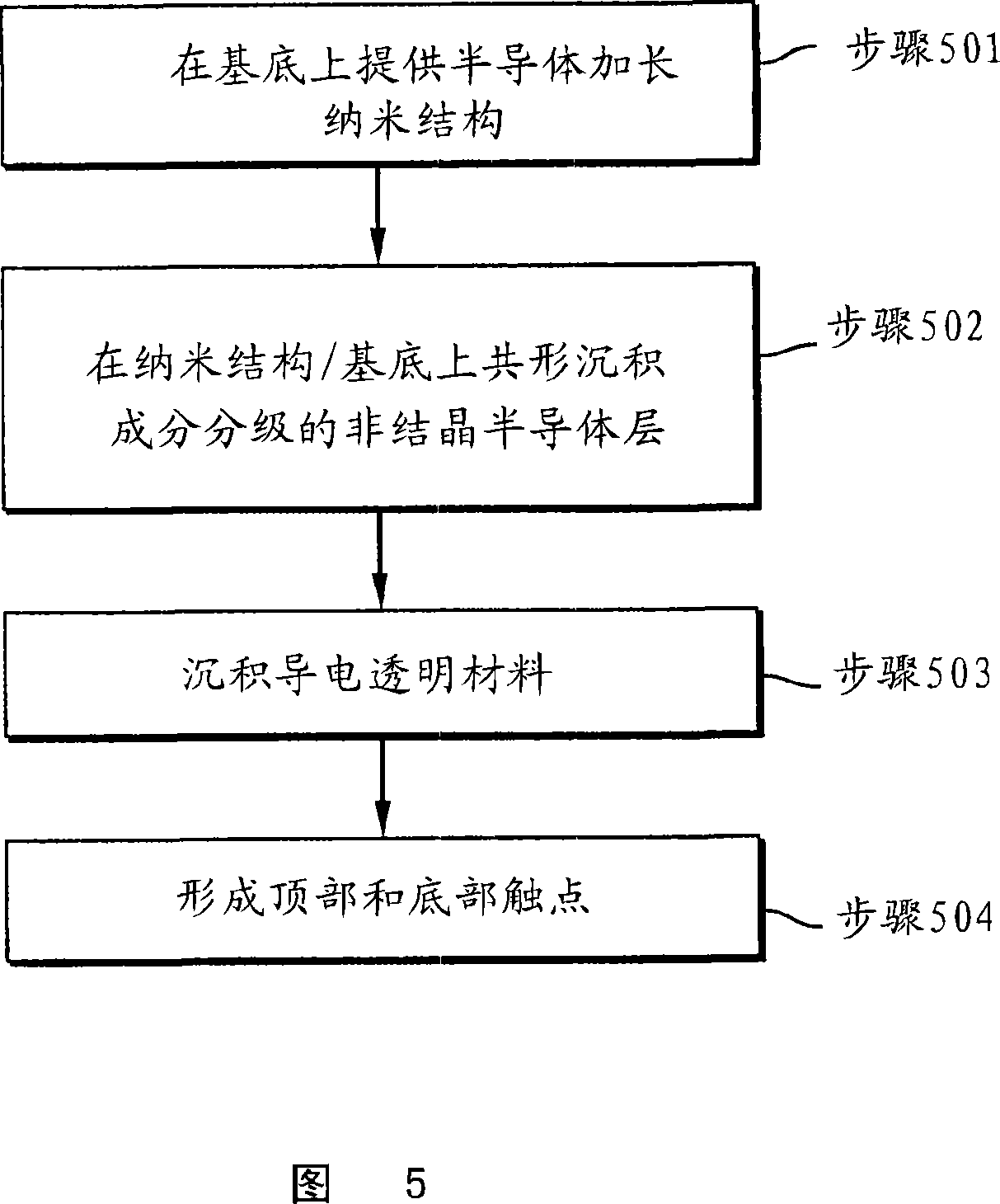

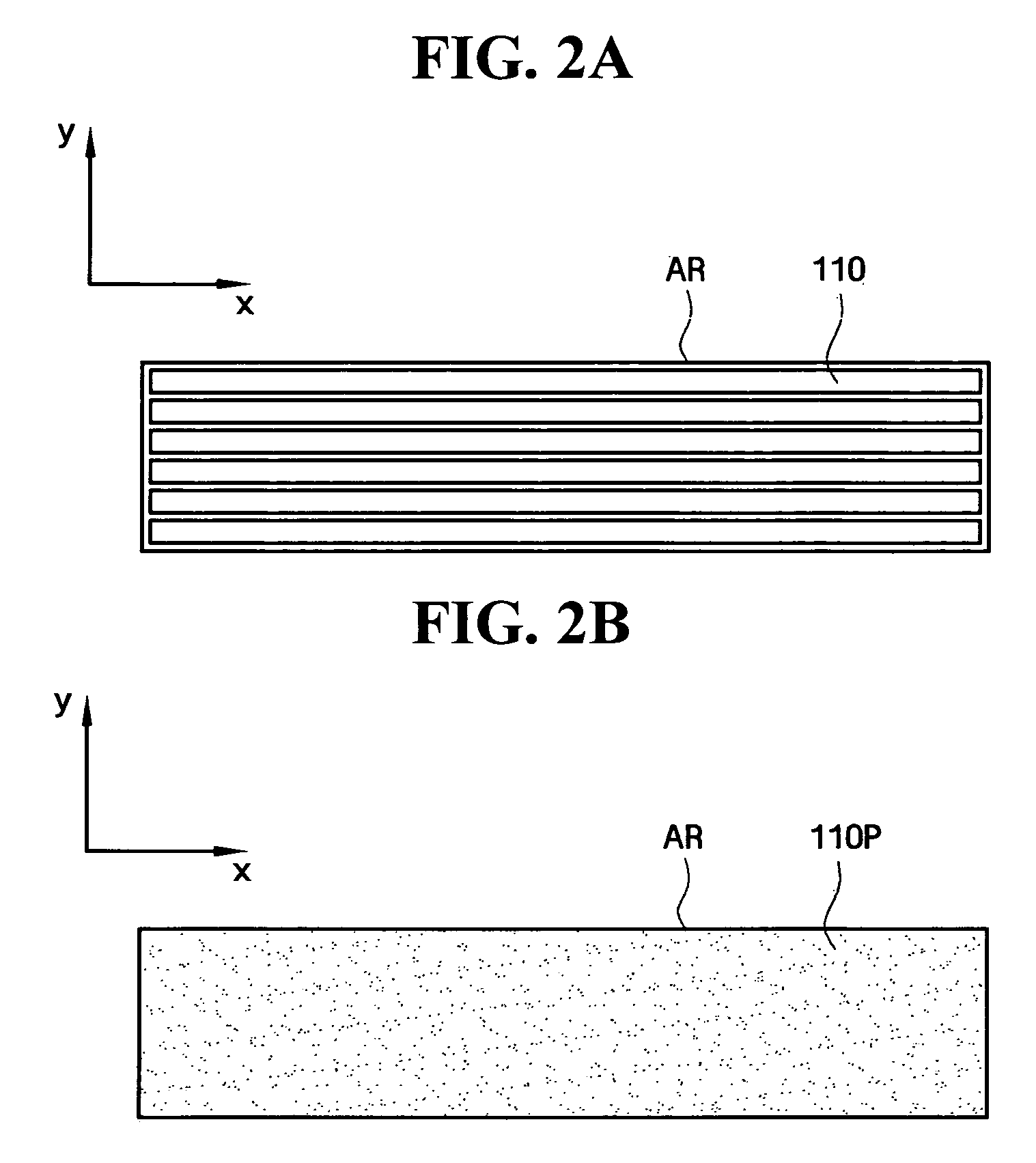

Graded hybrid amorphous silicon nanowire solar cells

InactiveUS20080135089A1Raise VocIncrease IscPV power plantsSemiconductor/solid-state device manufacturingAmorphous siliconSilicon nanowires

In some embodiments, the present invention is directed to compositionally-graded hybrid nanostructure-based photovoltaic devices comprising elongated semiconductor nanostructures and an amorphous semiconductor single layer with continuous gradation of doping concentration across its thickness from substantially intrinsic to substantially conductive. In other embodiments, the present invention is directed to methods of making such photovoltaic devices, as well as to applications which utilize such devices (e.g., solar cell modules).

Owner:GENERAL ELECTRIC CO

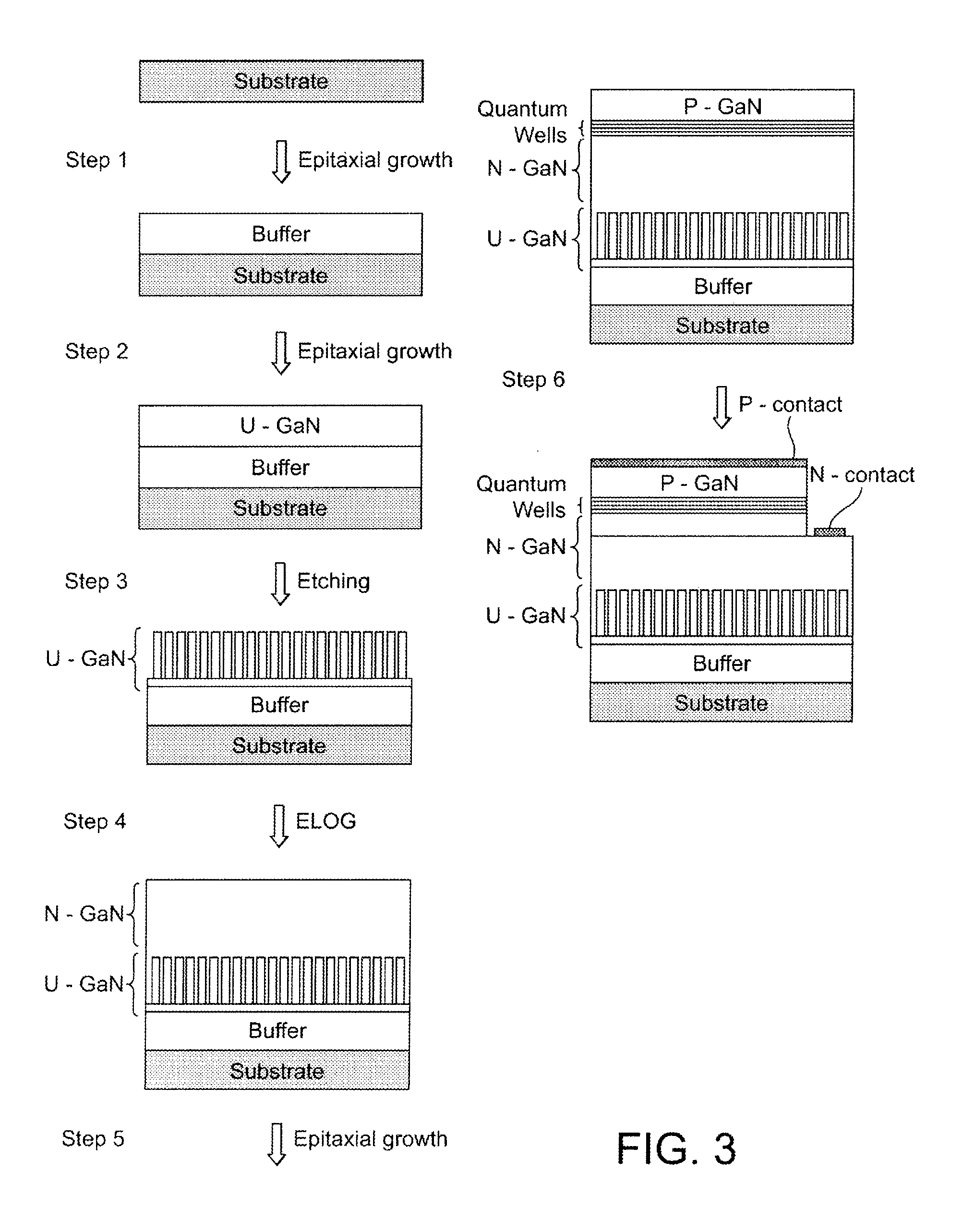

Production of semiconductor devices

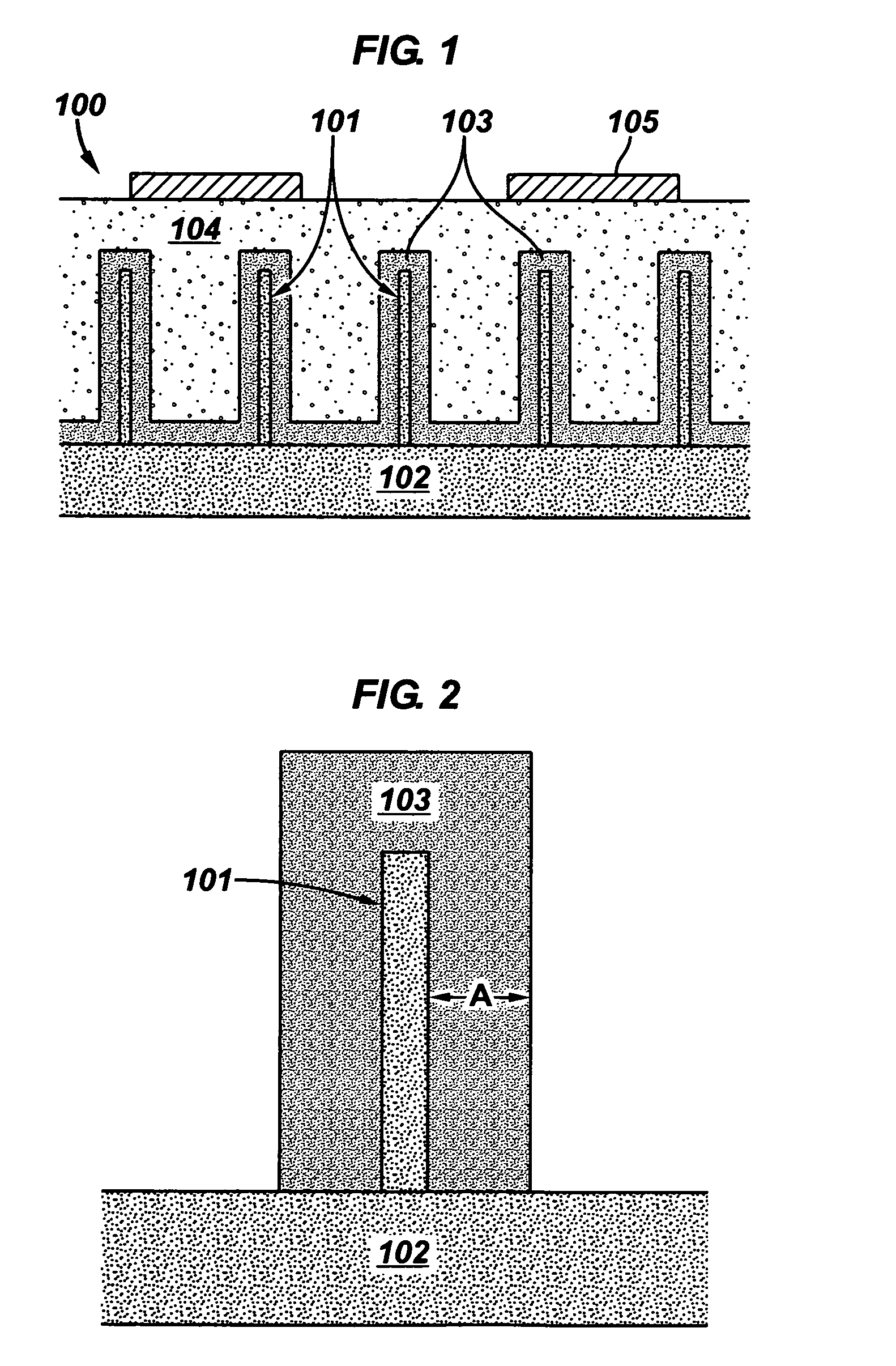

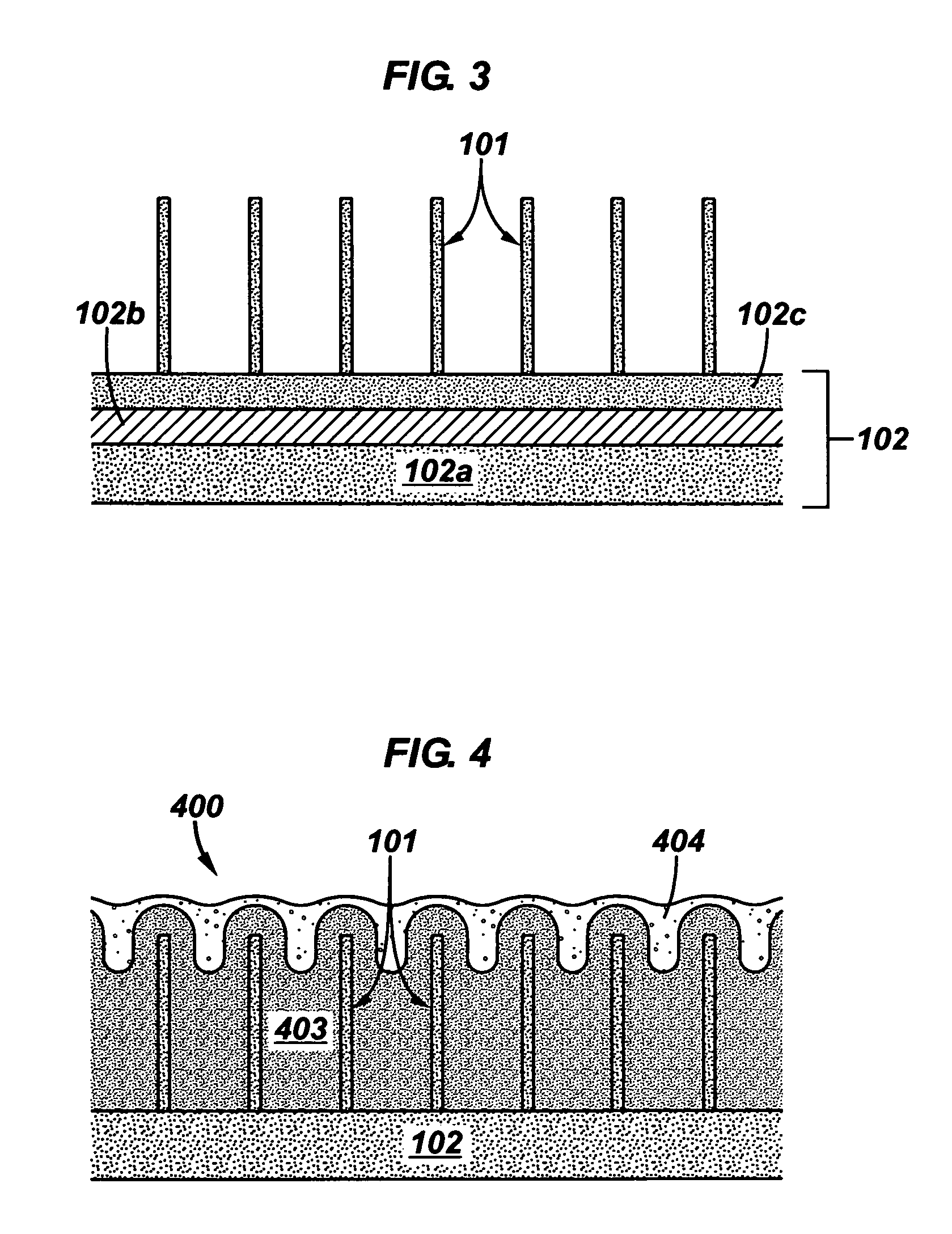

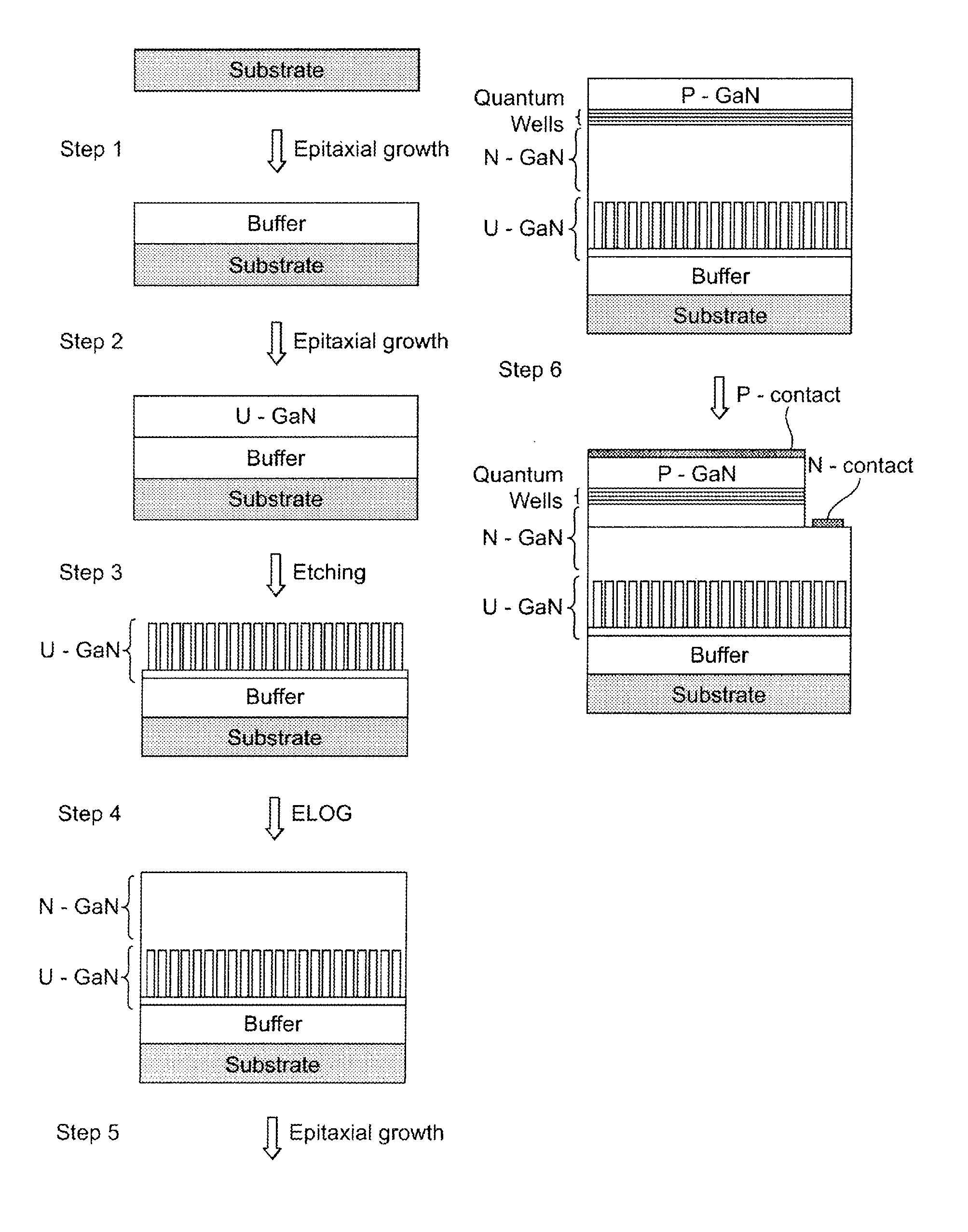

ActiveUS20100276665A1Large growth rateReduce defect densityNanostructure manufactureSemiconductor/solid-state device manufacturingNanometreNano structuring

A method of producing a layered semiconductor device comprises the steps of: (a) providing a base comprising a plurality of semiconductor nano-structures, (b) growing a semiconductor material onto the nano-structures using an epitaxial 5 growth process, and (c) growing a layer of the semiconductor material using an epitaxial growth process.

Owner:QUANTUM NIL LTD +1

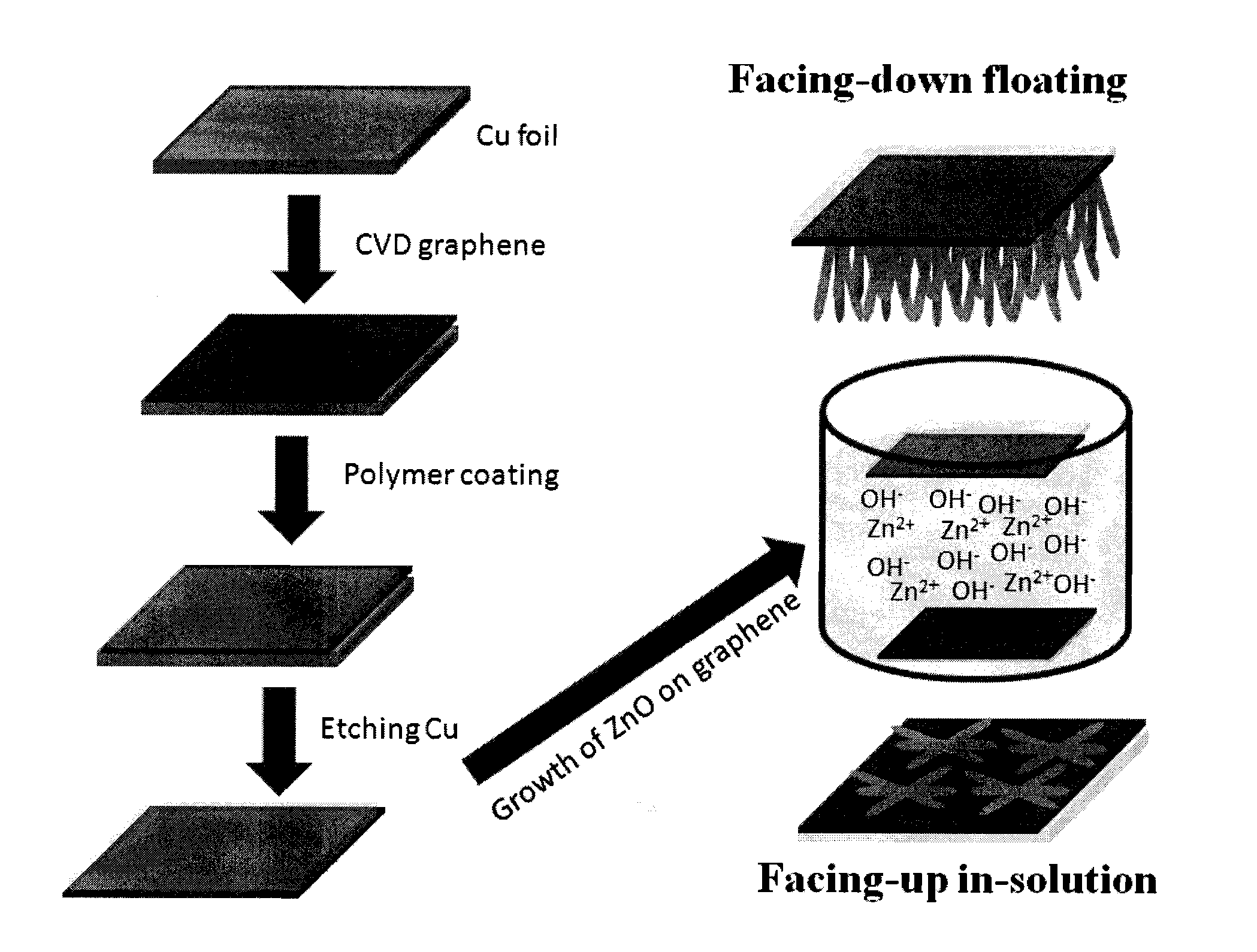

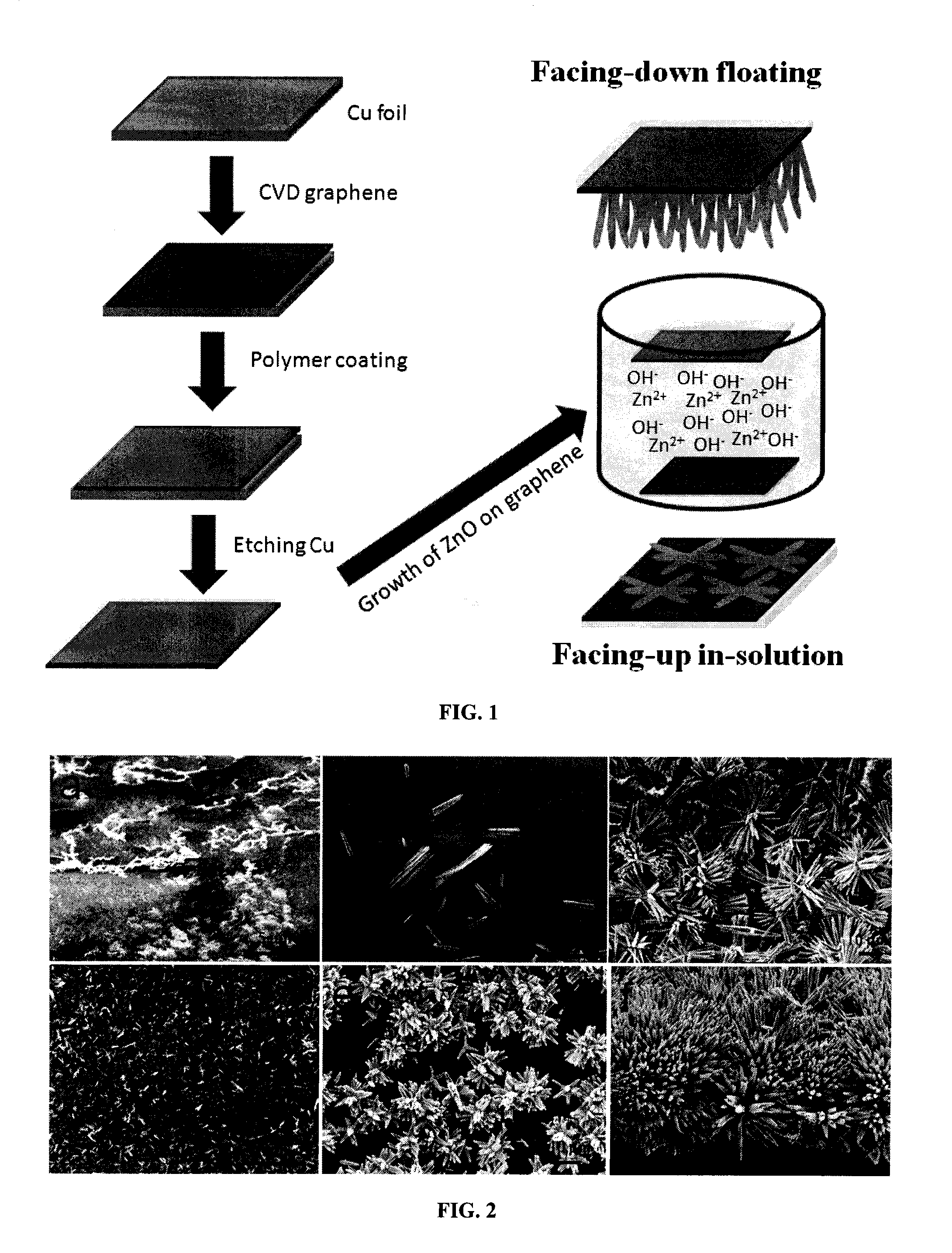

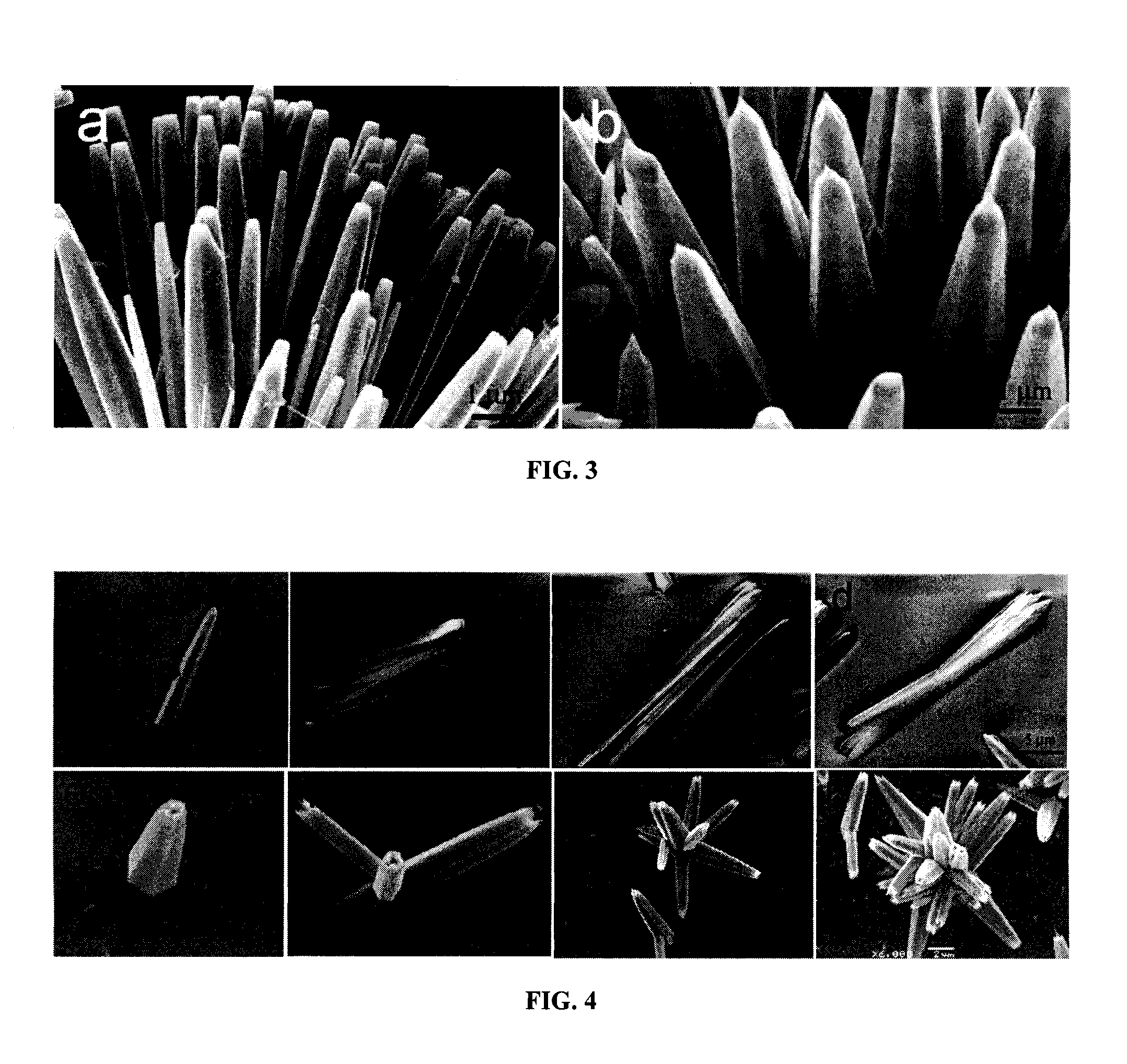

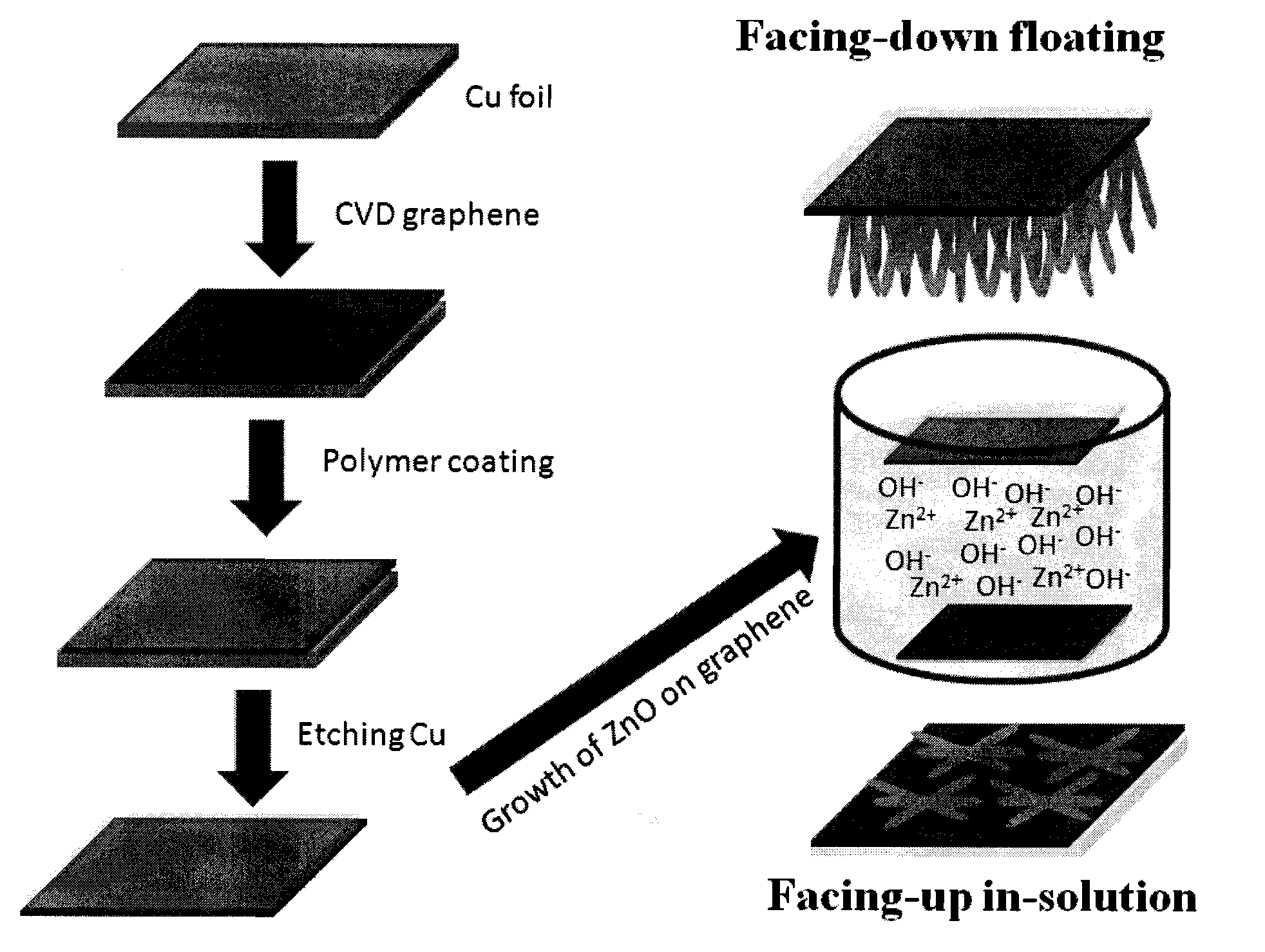

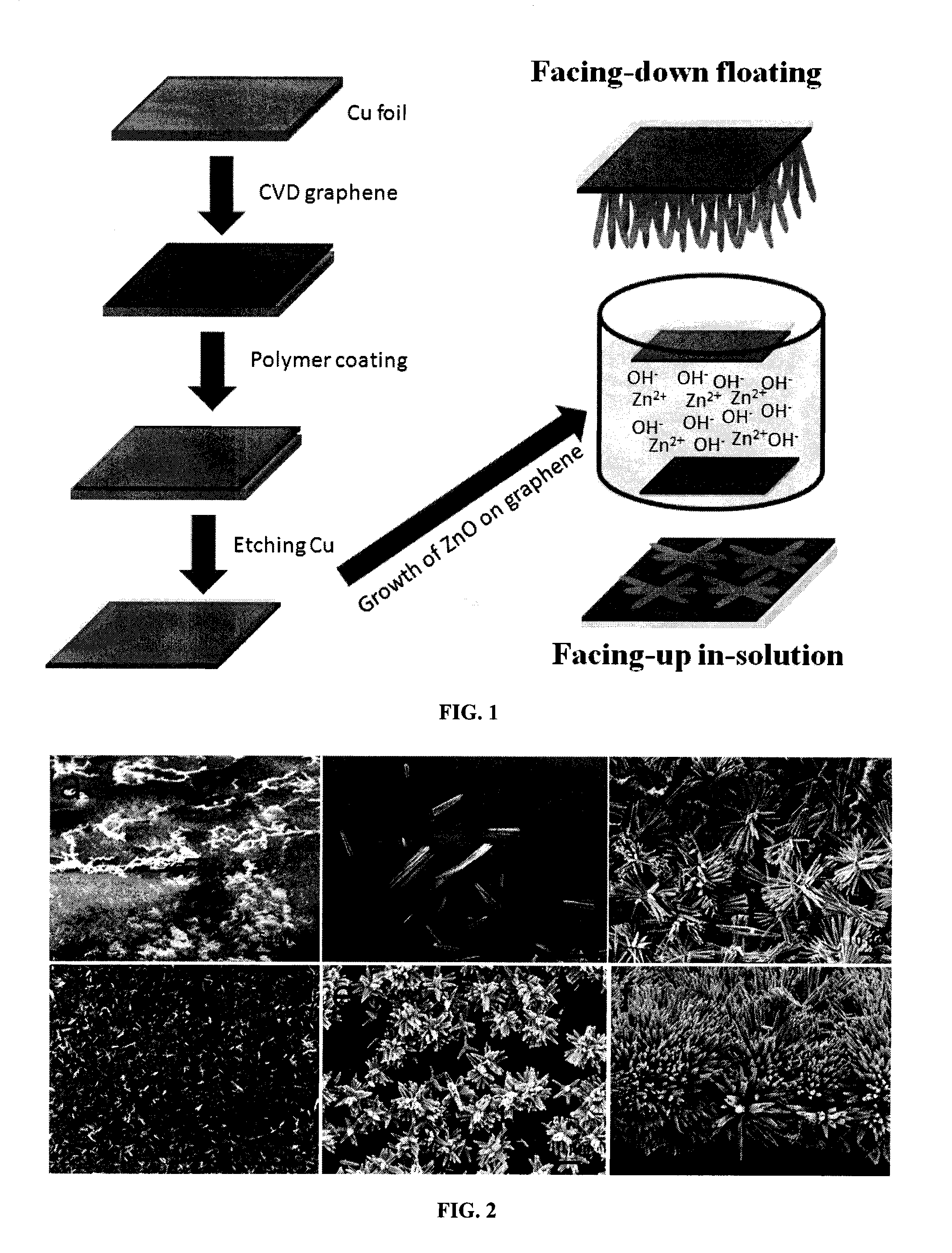

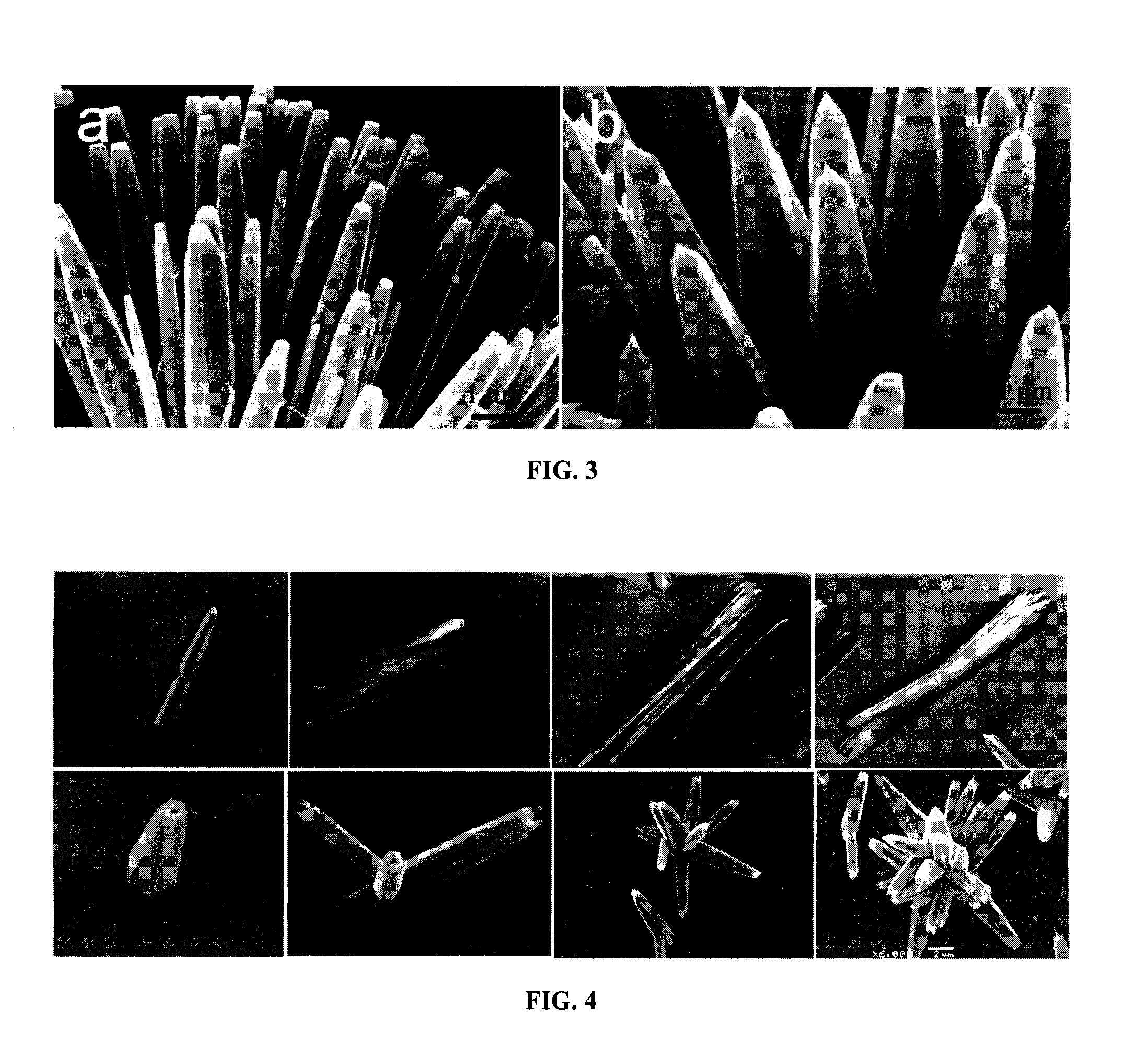

Semiconductor-Graphene Hybrids Formed Using Solution Growth

InactiveUS20130099196A1Improve mobilitySolve the thickerMaterial nanotechnologyPretreated surfacesNano structuringGas phase

A novel method for fabrication of hybrid semiconductor-graphene nanostructures in large scale by floating graphene sheets on the surface of a solution is provided. Using this approach, crystalline ZnO nano / micro-rod bundles on graphene fabricated using chemical vapor deposition were prepared. UV detectors fabricated using the as-prepared hybrid ZnO-graphene nano-structure with graphene being one of the two electrodes show high sensitivity to ultraviolet light, suggesting the graphene remained intact during the ZnO growth. This growth process provides a low-cost and robust scheme for large-scale fabrication of semiconductor nanostructures on graphene and may be applied for synthesis of a variety of hybrid semiconductor-graphene nano-structures demanded for optoelectronic applications including photovoltaics, photodetection, and photocatalysis.

Owner:UNIVERSITY OF KANSAS

Nanostructures having high performance thermoelectric properties

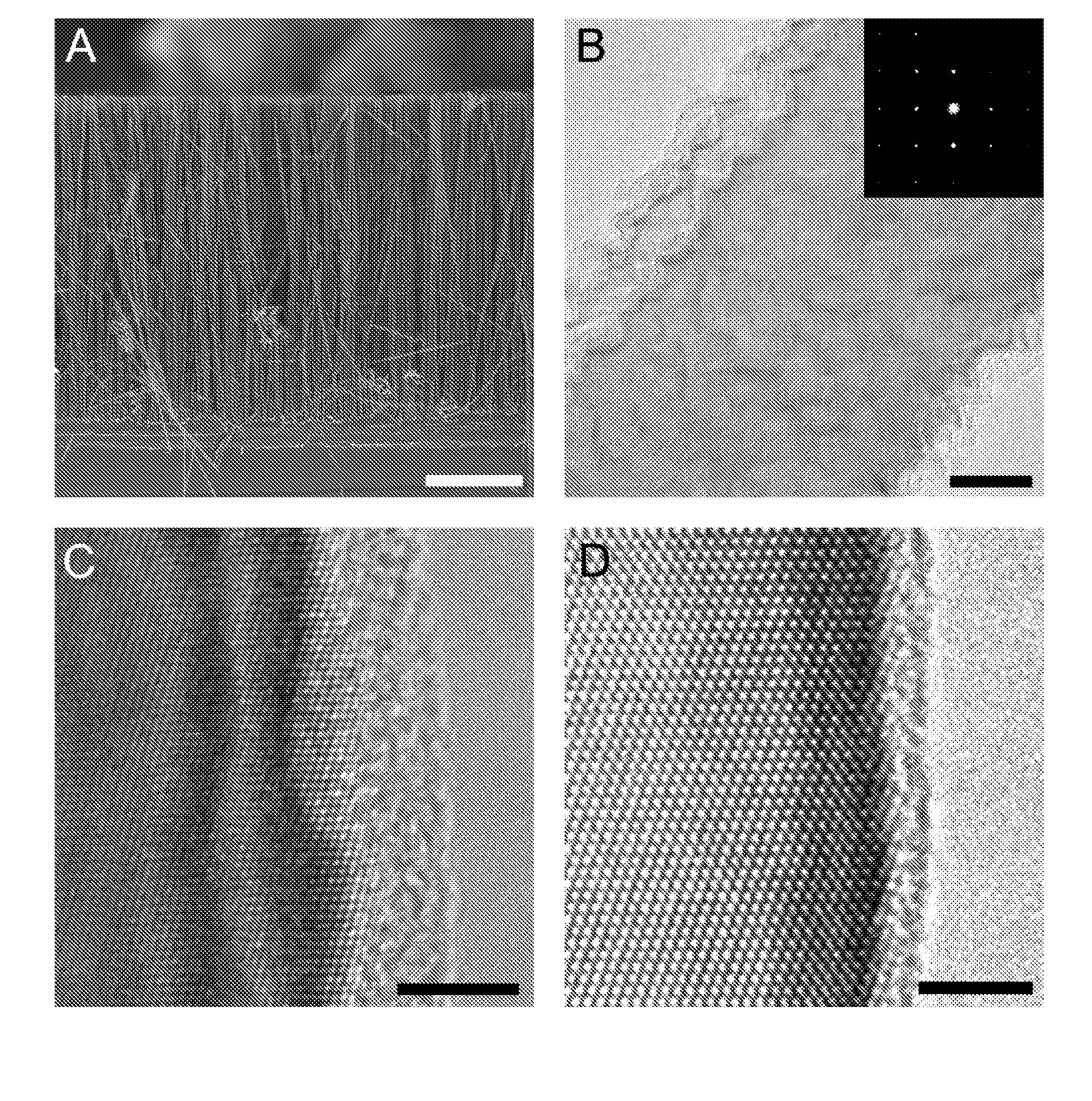

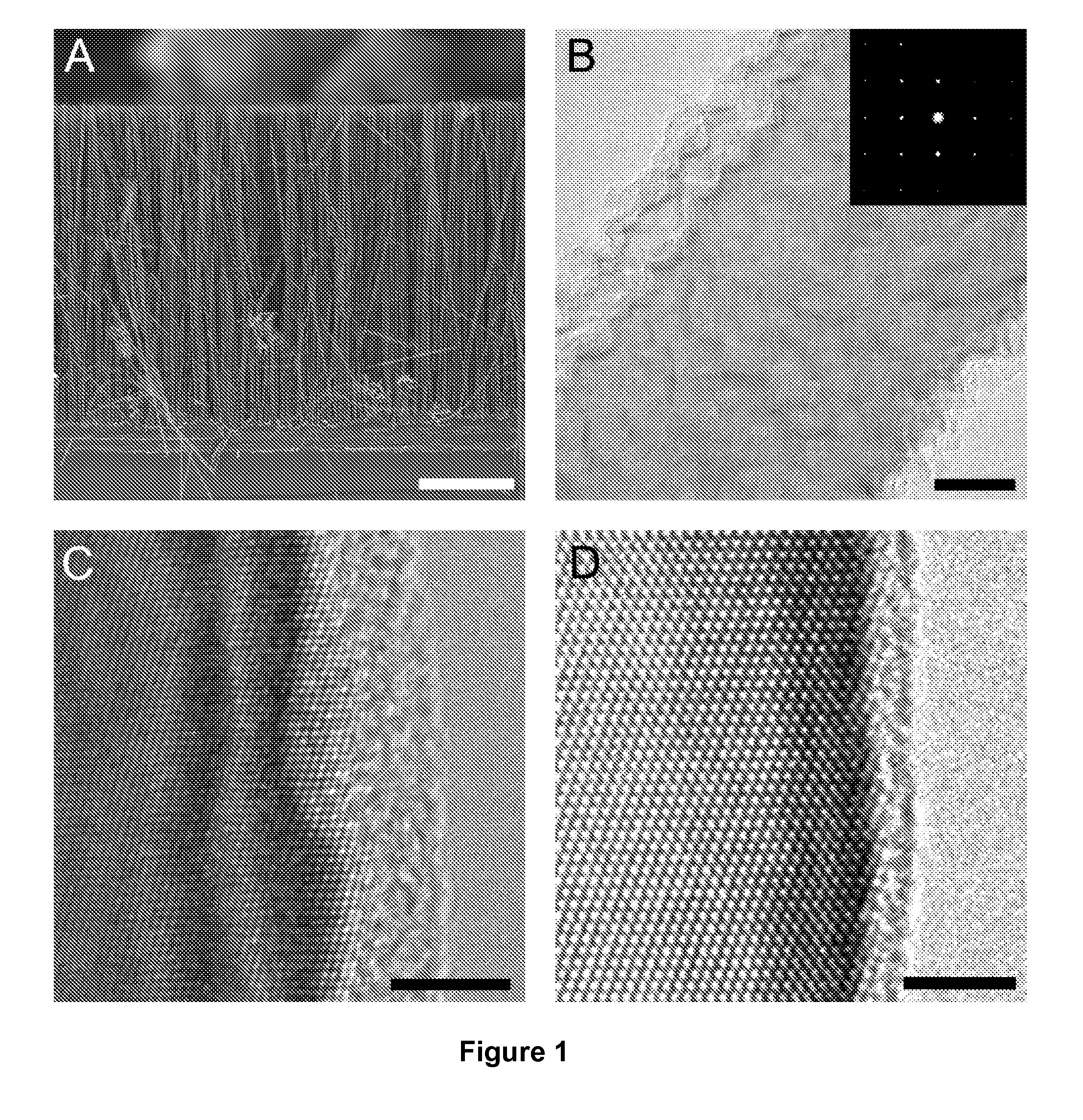

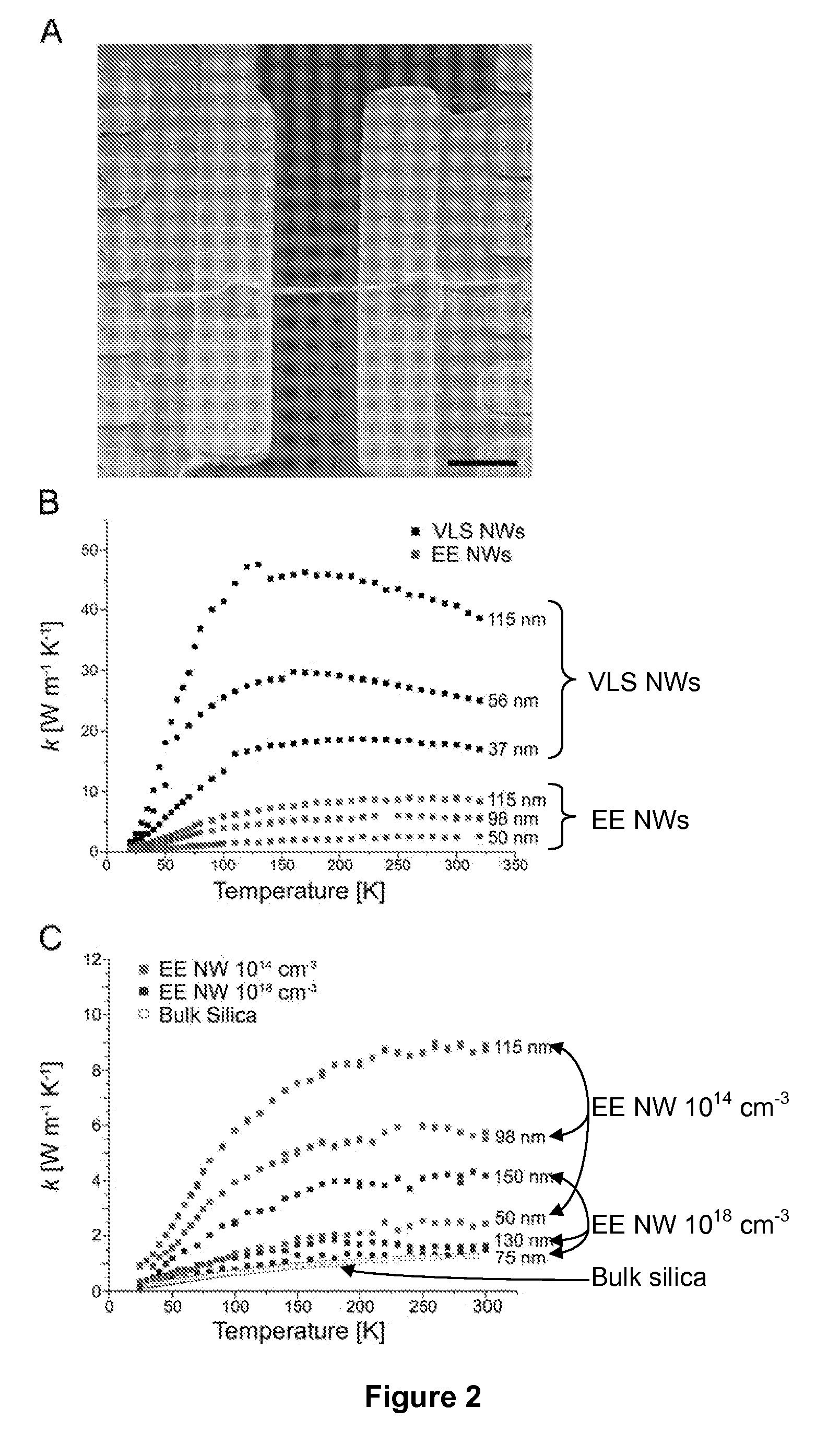

InactiveUS20110114145A1Reduce the temperatureIncrease temperatureThermoelectric device with peltier/seeback effectIndividual molecule manipulationThermoelectric coolingNanowire

The invention provides for a nanostructure, or an array of such nanostructures, each comprising a rough surface, and a doped or undoped semiconductor. The nanostructure is an one-dimensional (1-D) nanostructure, such a nanowire, or a two-dimensional (2-D) nanostructure. The nanostructure can be placed between two electrodes and used for thermoelectric power generation or thermoelectric cooling.

Owner:RGT UNIV OF CALIFORNIA

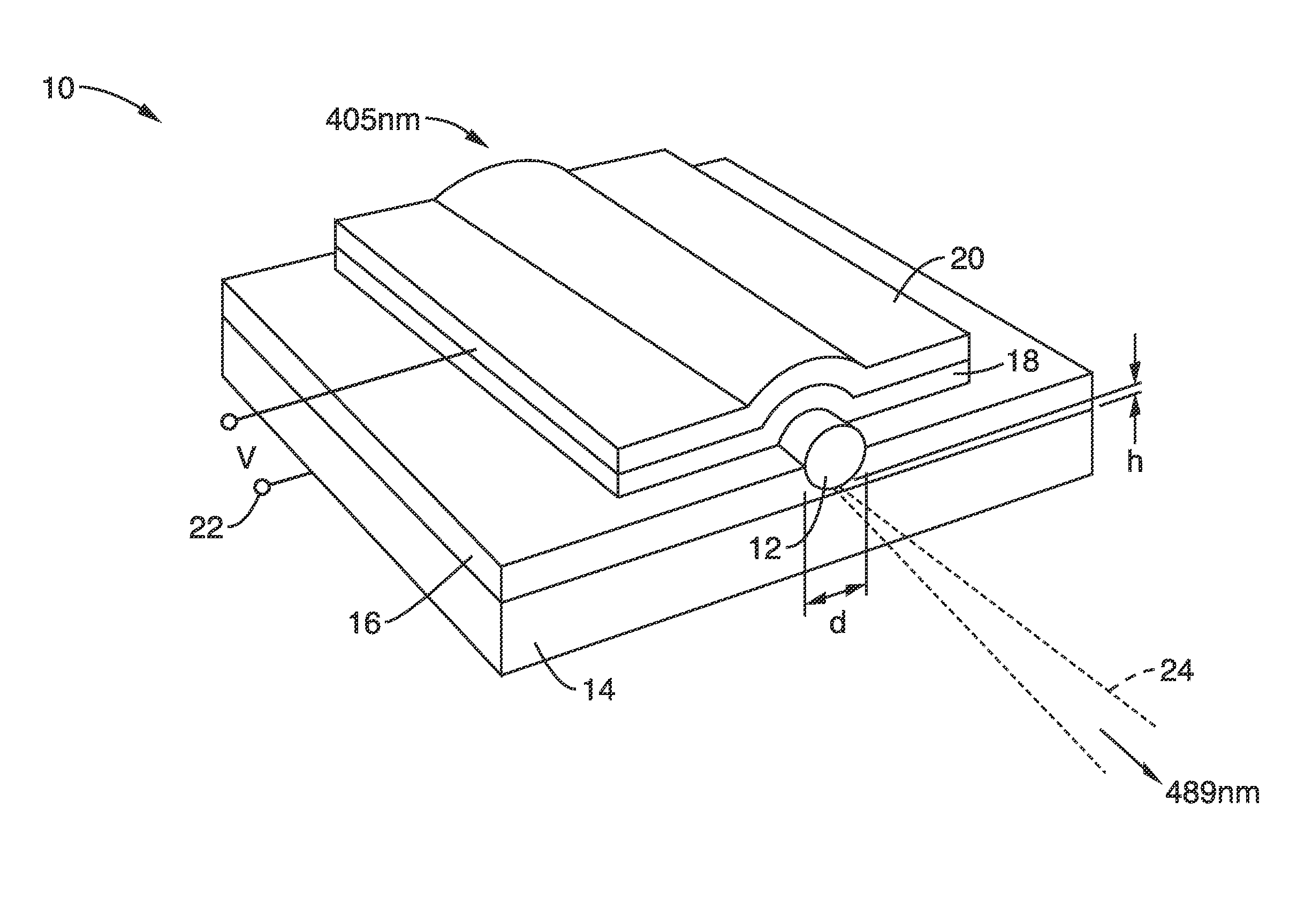

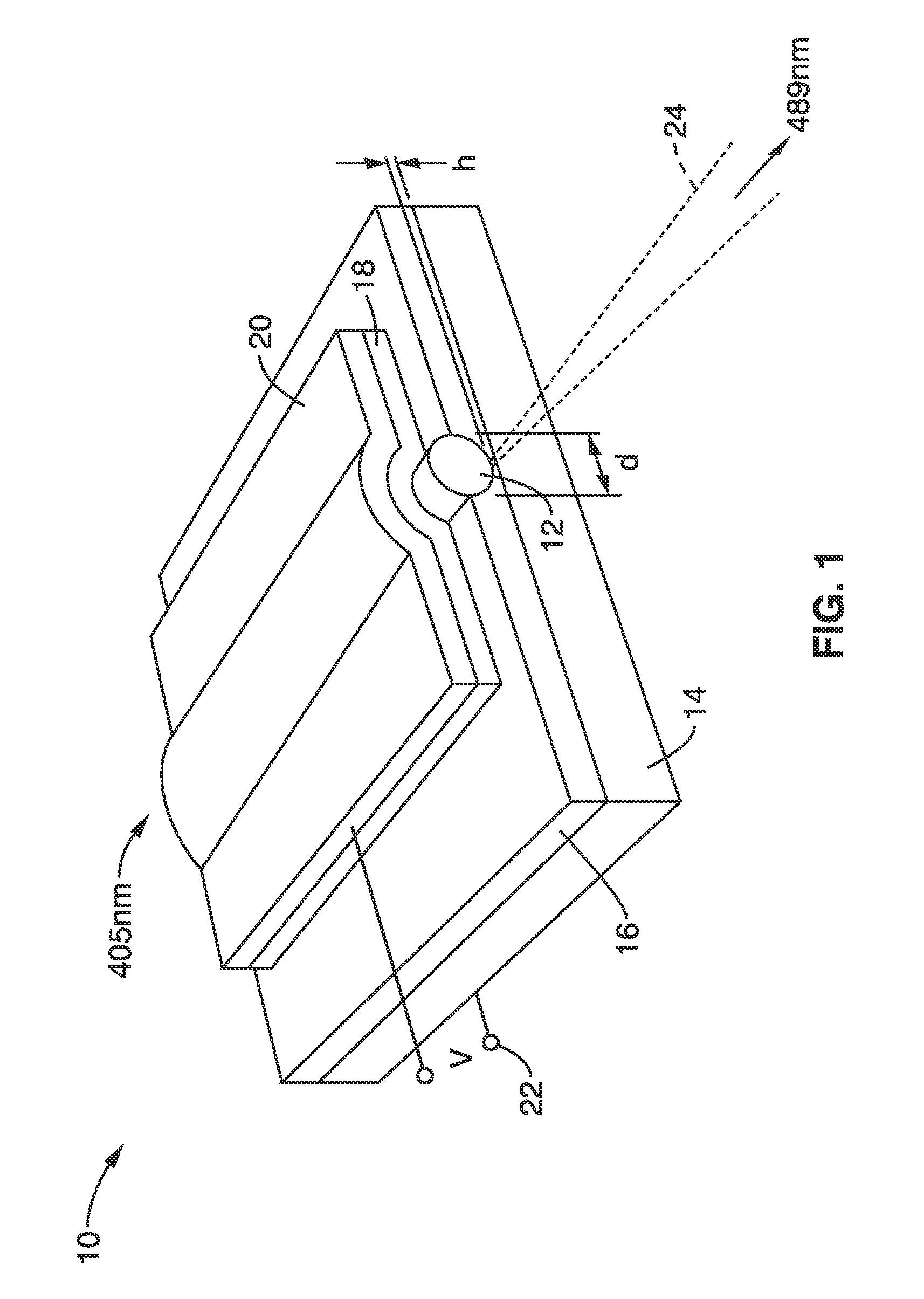

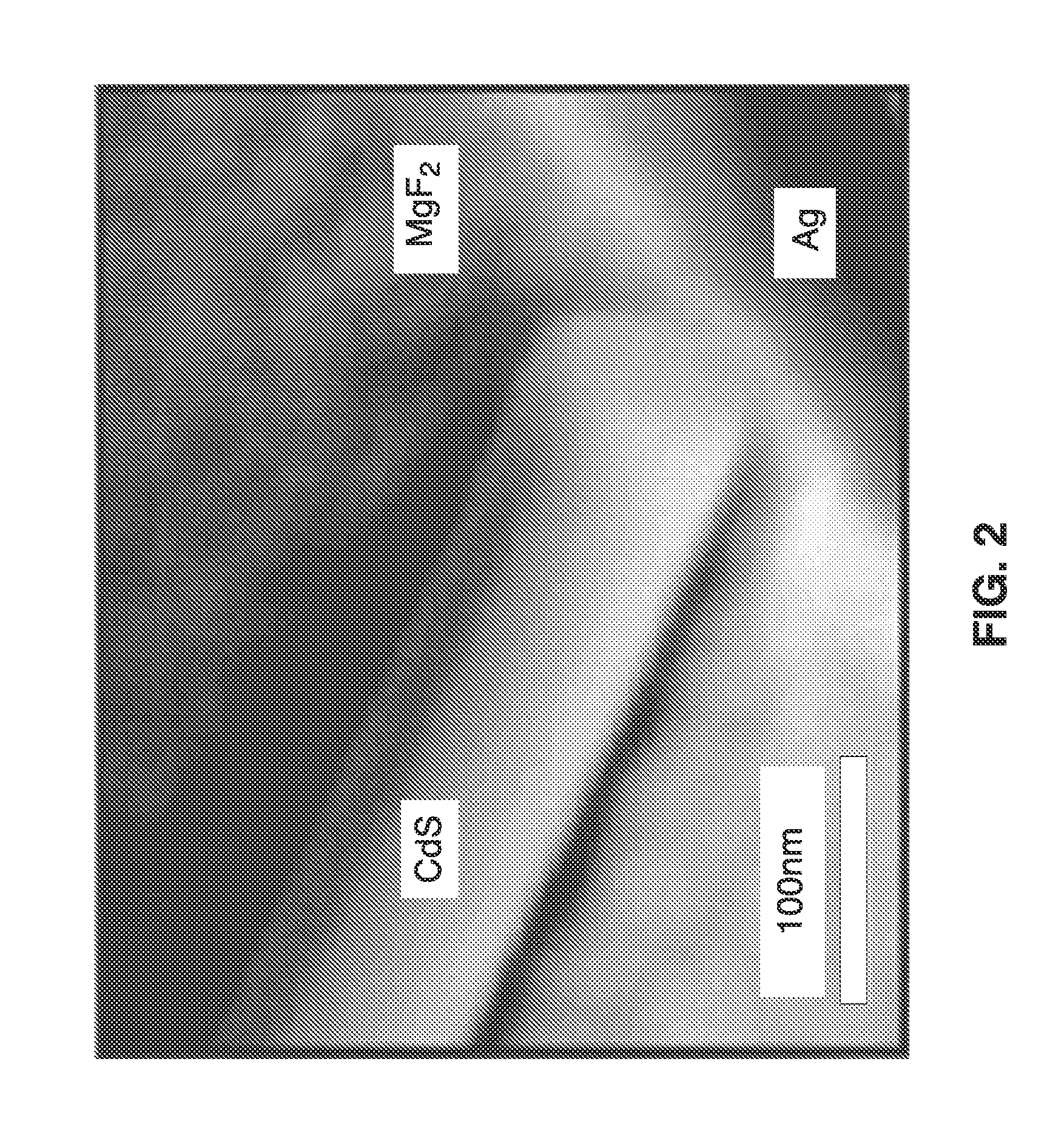

Plasmon lasers at deep subwavelength scale

ActiveUS20130148682A1Efficient generation of sub-wavelength high intensity lightWide modulation bandwidthOptical wave guidanceLaser detailsModulation bandwidthPlasmonic waveguide

Hybrid plasmonic waveguides are described that employ a high-gain semiconductor nanostructure functioning as a gain medium that is separated from a metal substrate surface by a nanoscale thickness thick low-index gap. The waveguides are capable of efficient generation of sub-wavelength high intensity light and have the potential for large modulation bandwidth >1 THz.

Owner:RGT UNIV OF CALIFORNIA

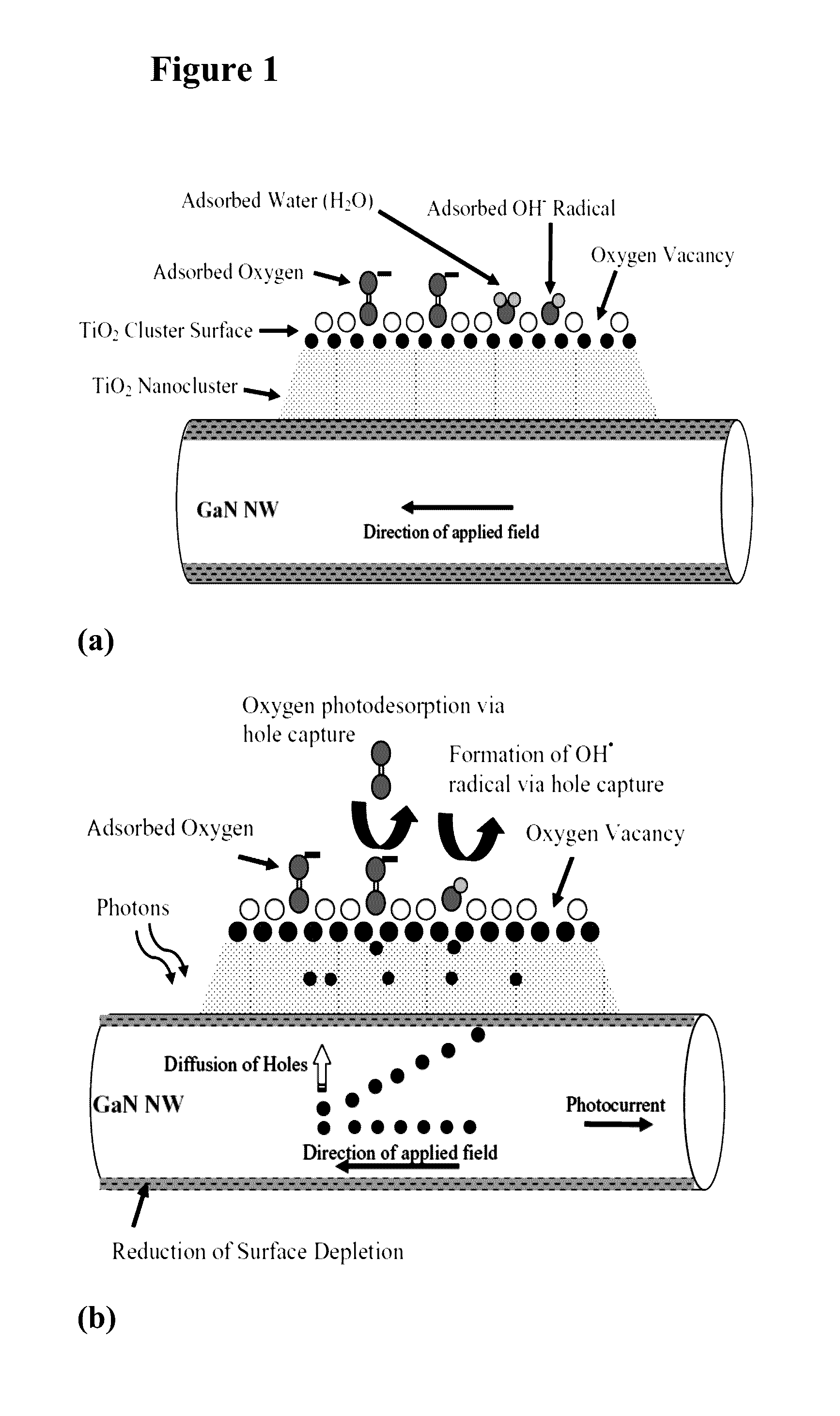

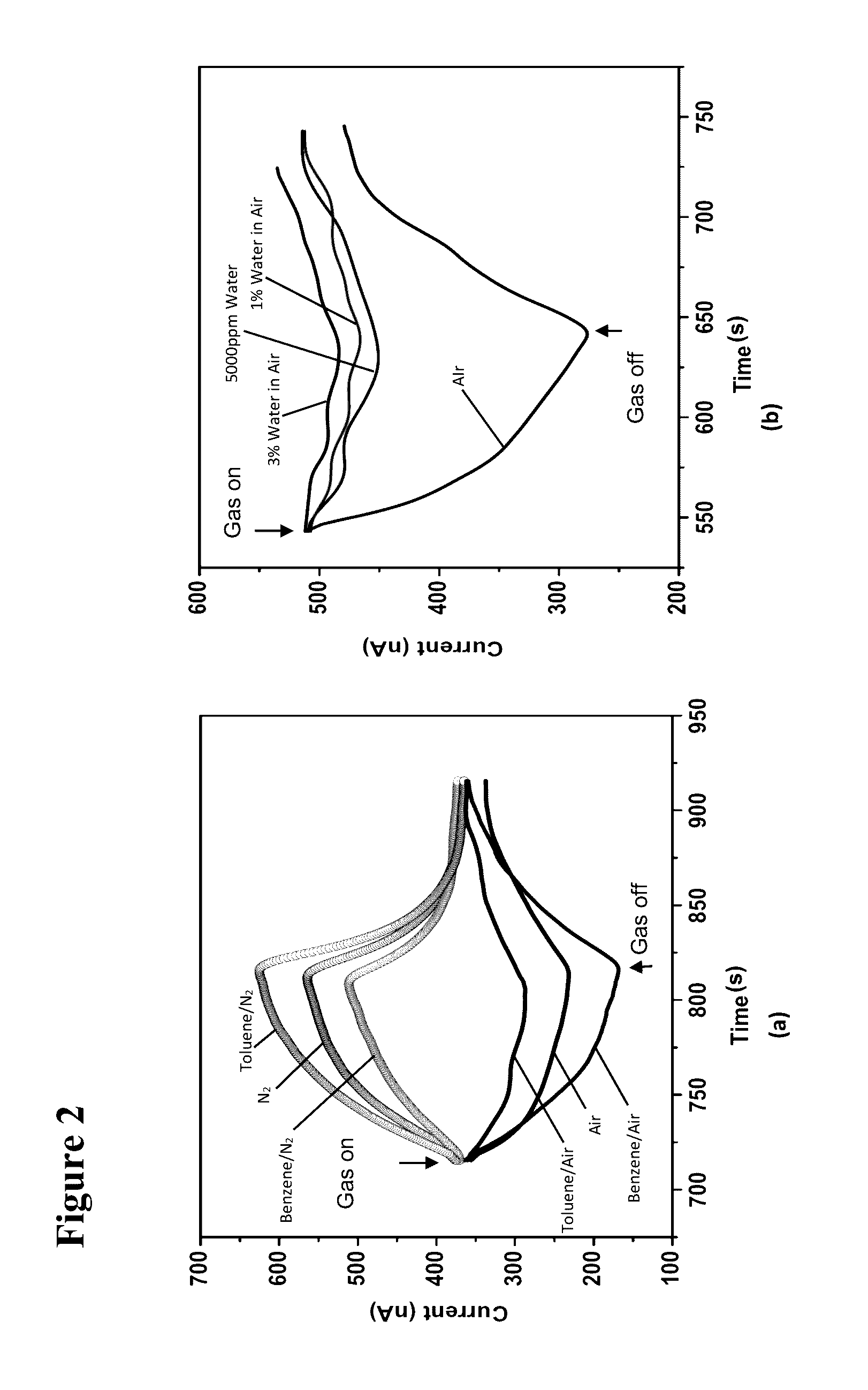

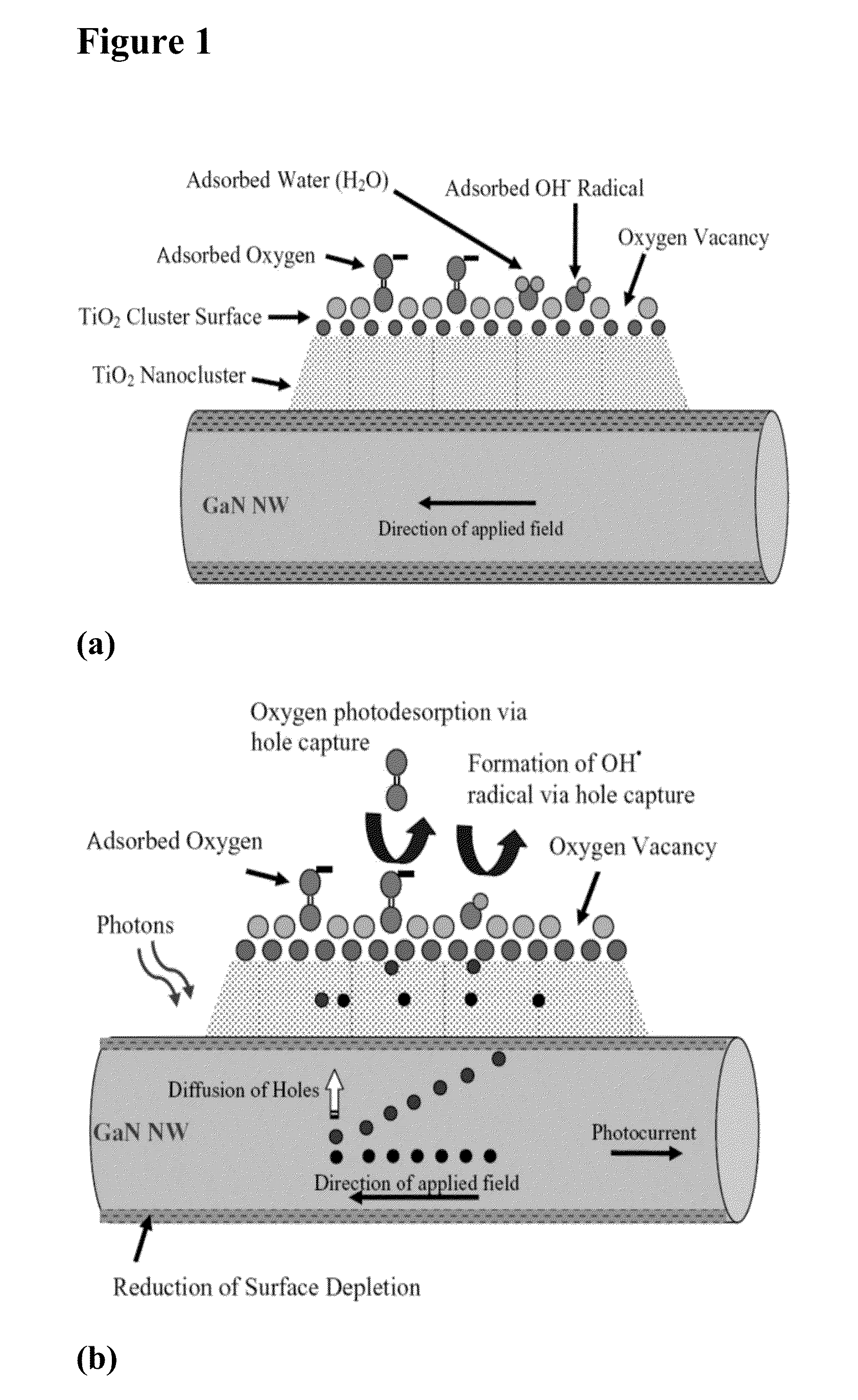

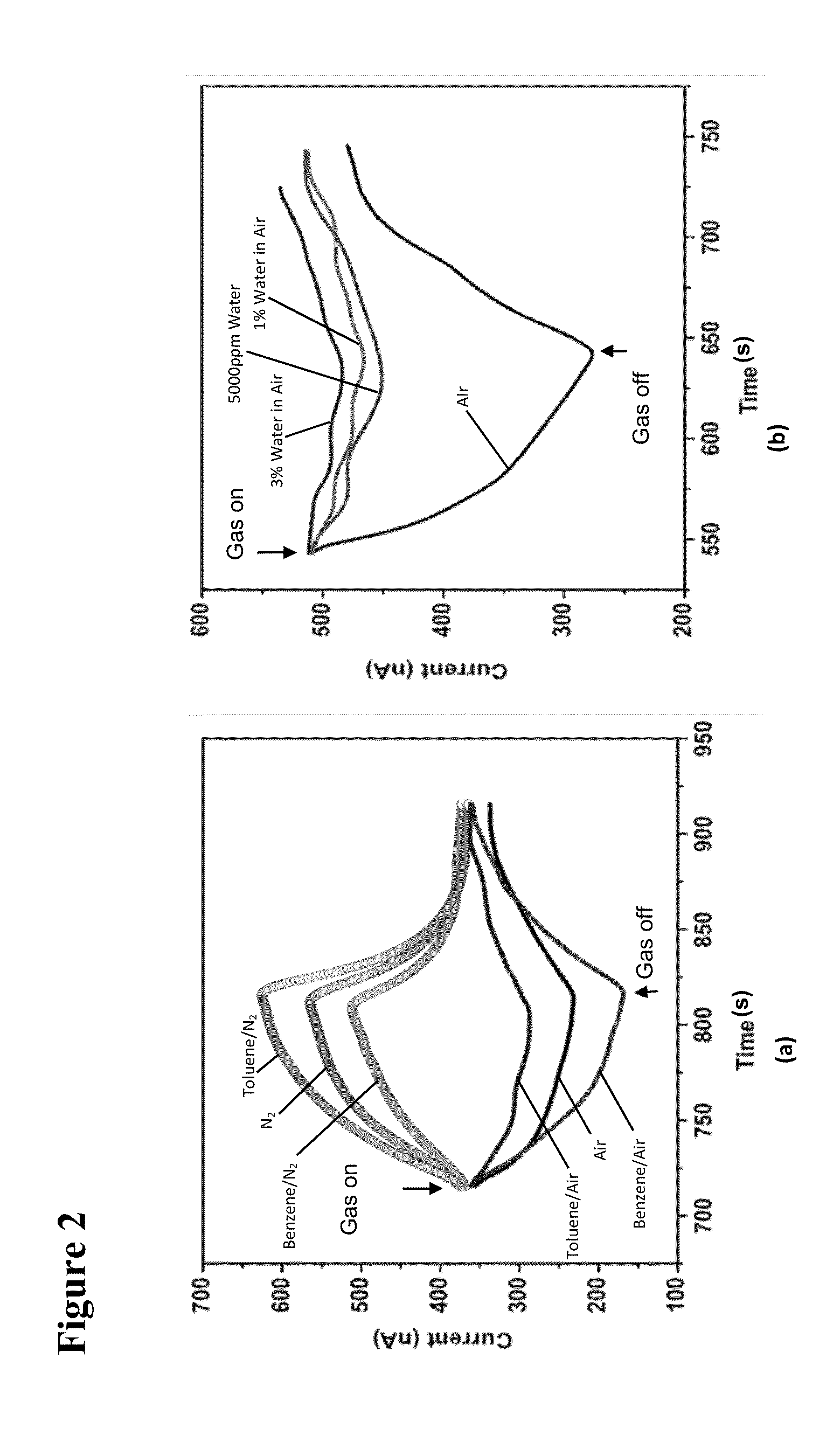

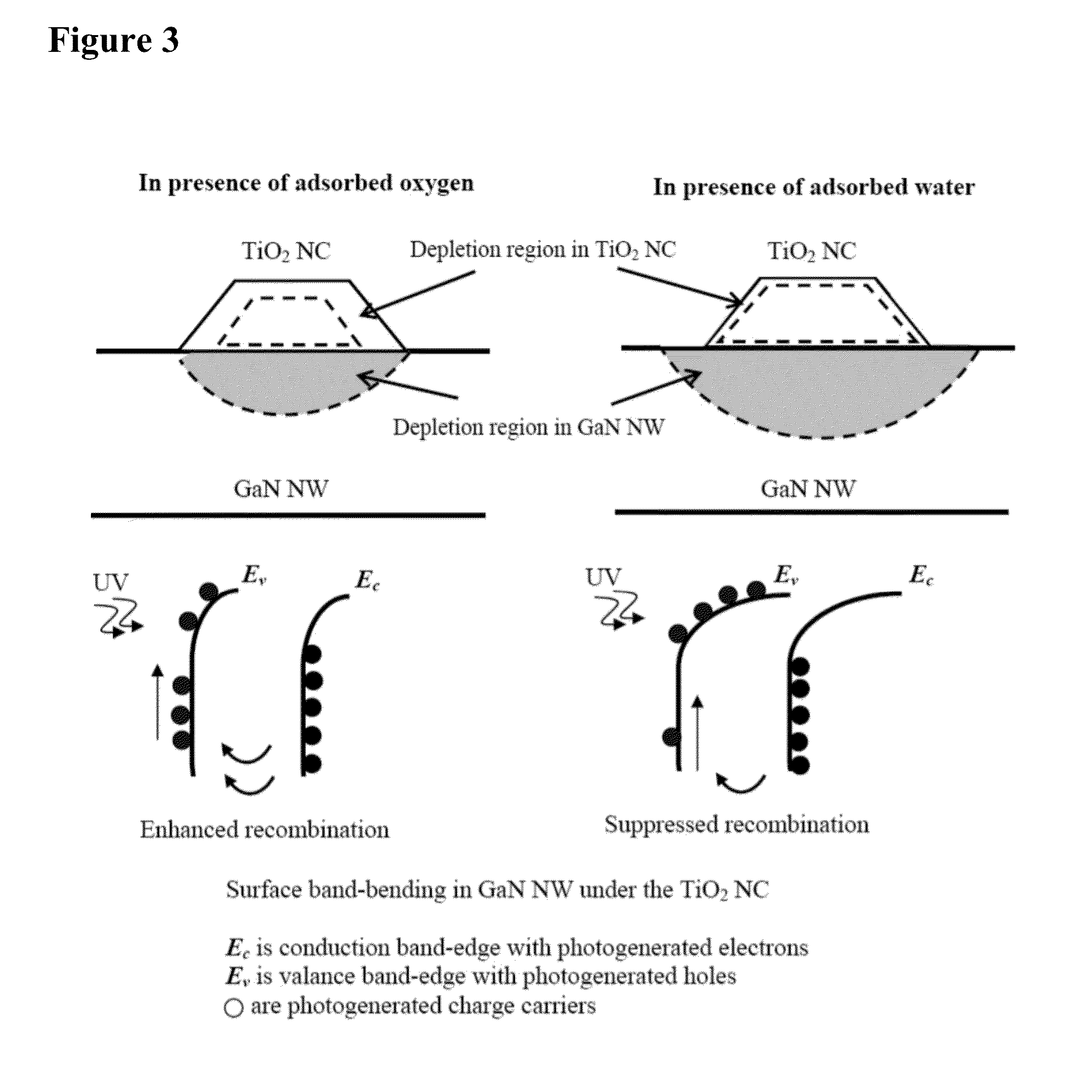

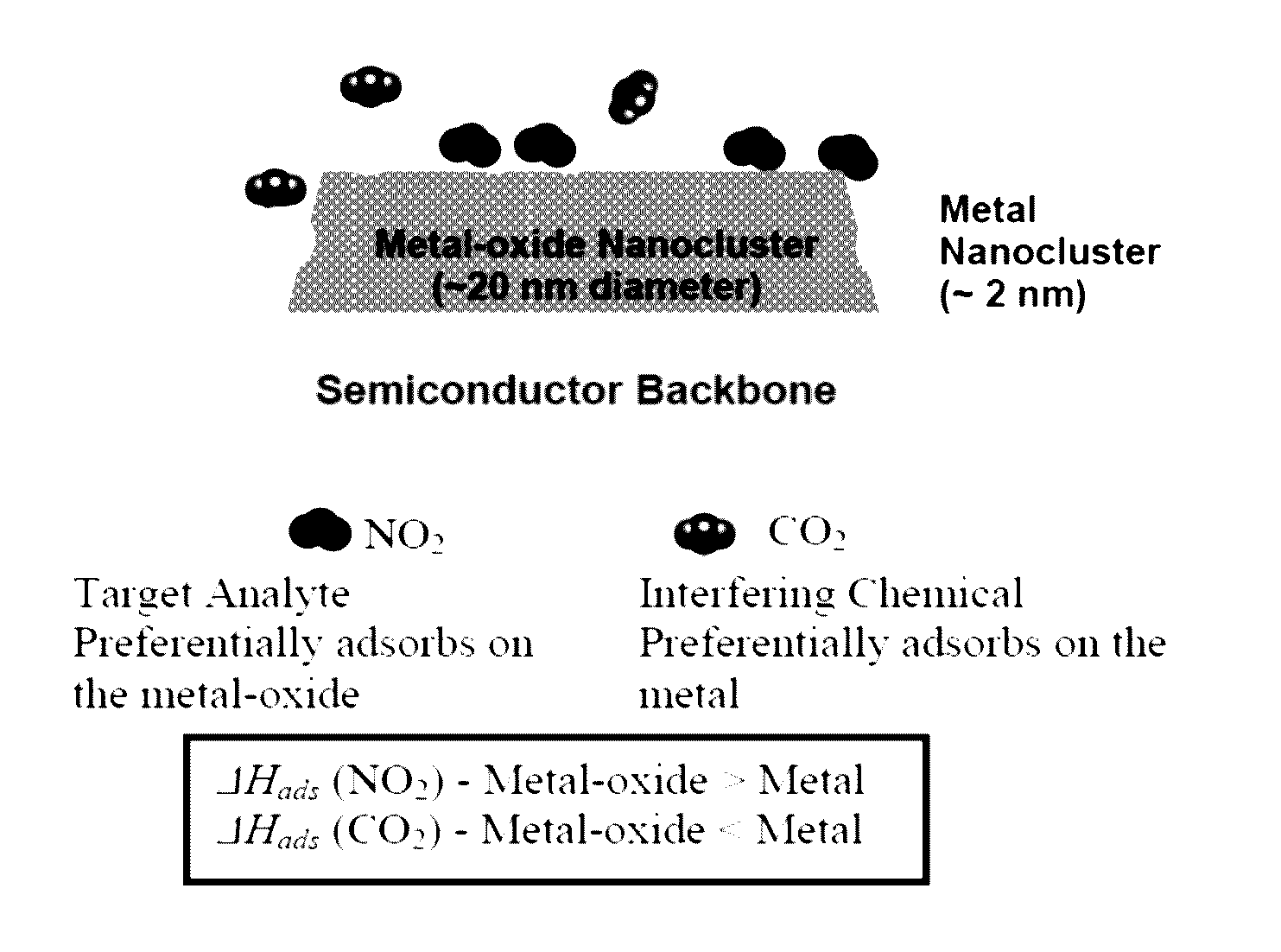

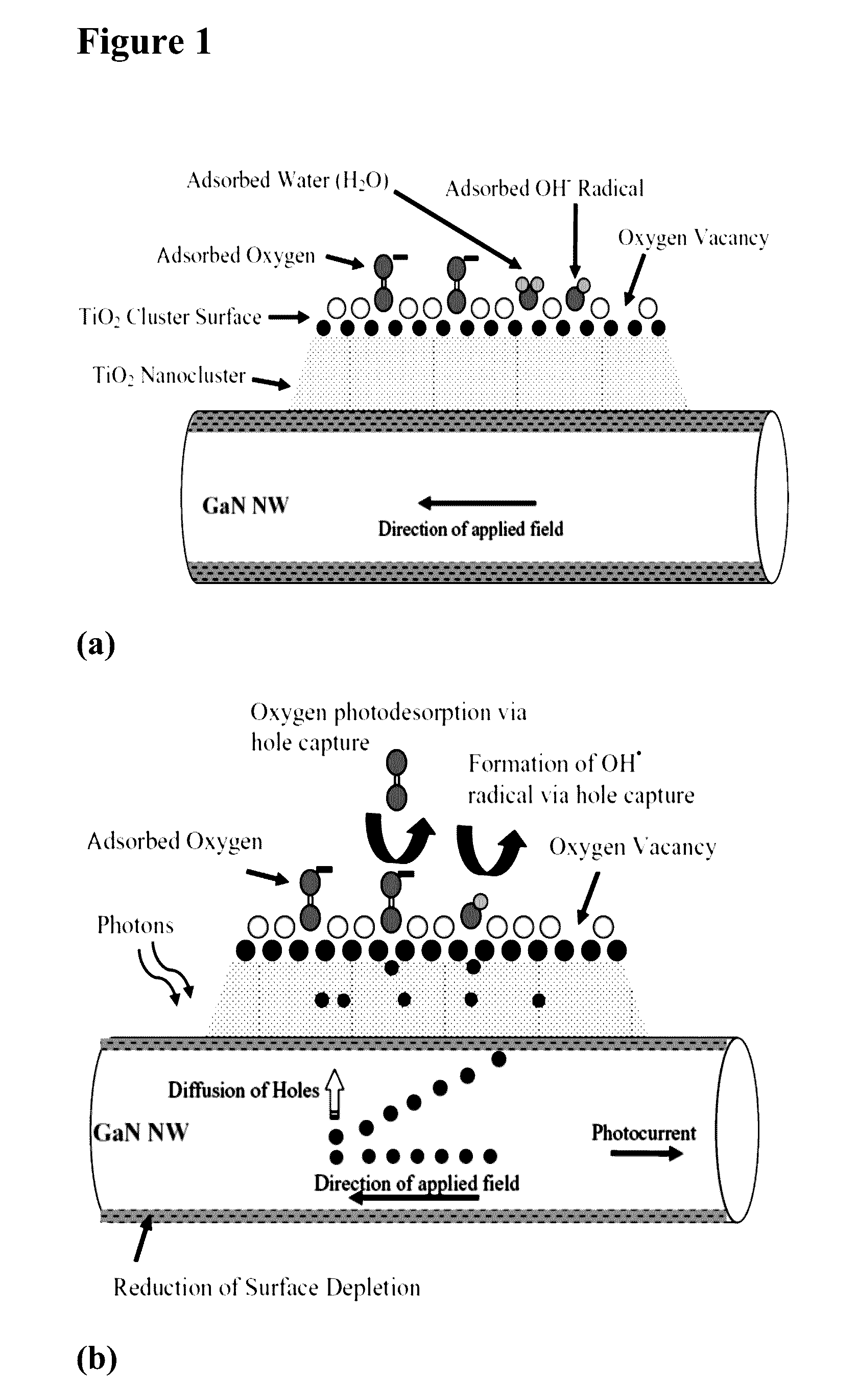

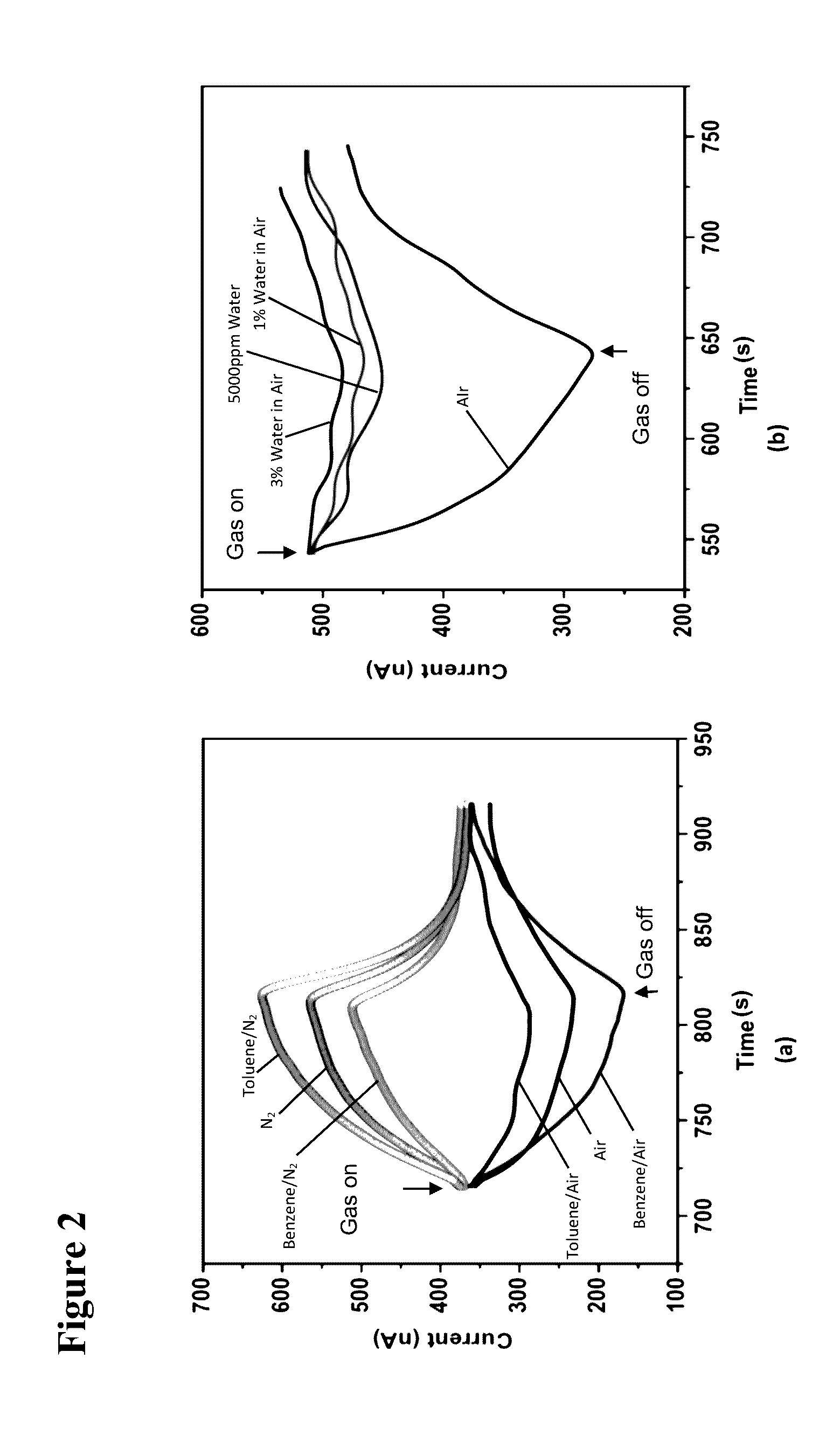

Highly Selective Nanostructure Sensors and Methods of Detecting Target Analytes

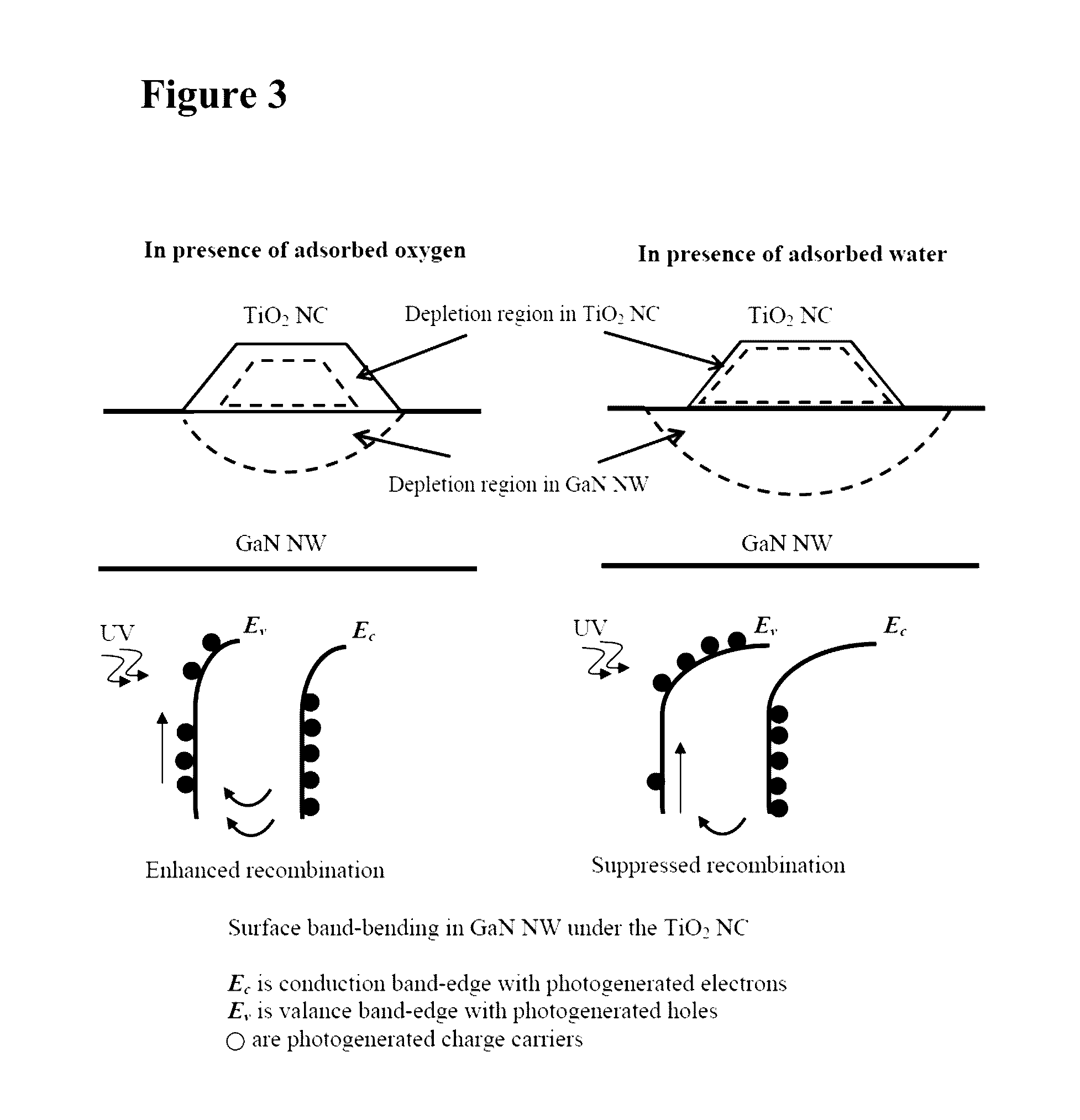

ActiveUS20170038326A1Improve conductivityHigh selectivityGas analyser construction detailsMaterial resistanceMetal oxide nanoparticlesAnalyte

A nanostructure sensing device comprises a semiconductor nanostructure having an outer surface, and at least one of metal or metal-oxide nanoparticle clusters functionalizing the outer surface of the nanostructure and forming a photoconductive nanostructure / nanocluster hybrid sensor enabling light-assisted sensing of a target analyte.

Owner:UNIV OF MARYLAND +1

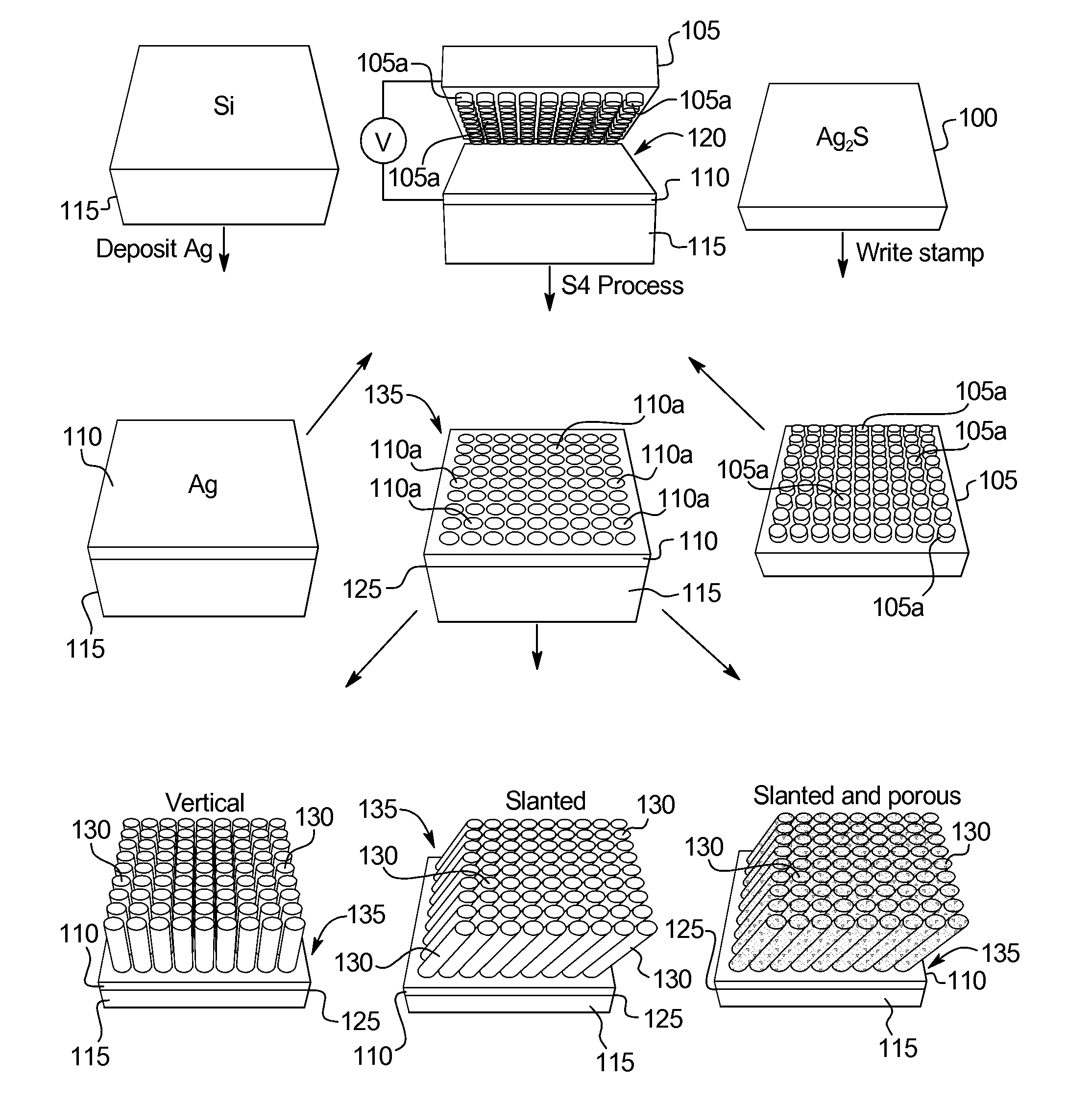

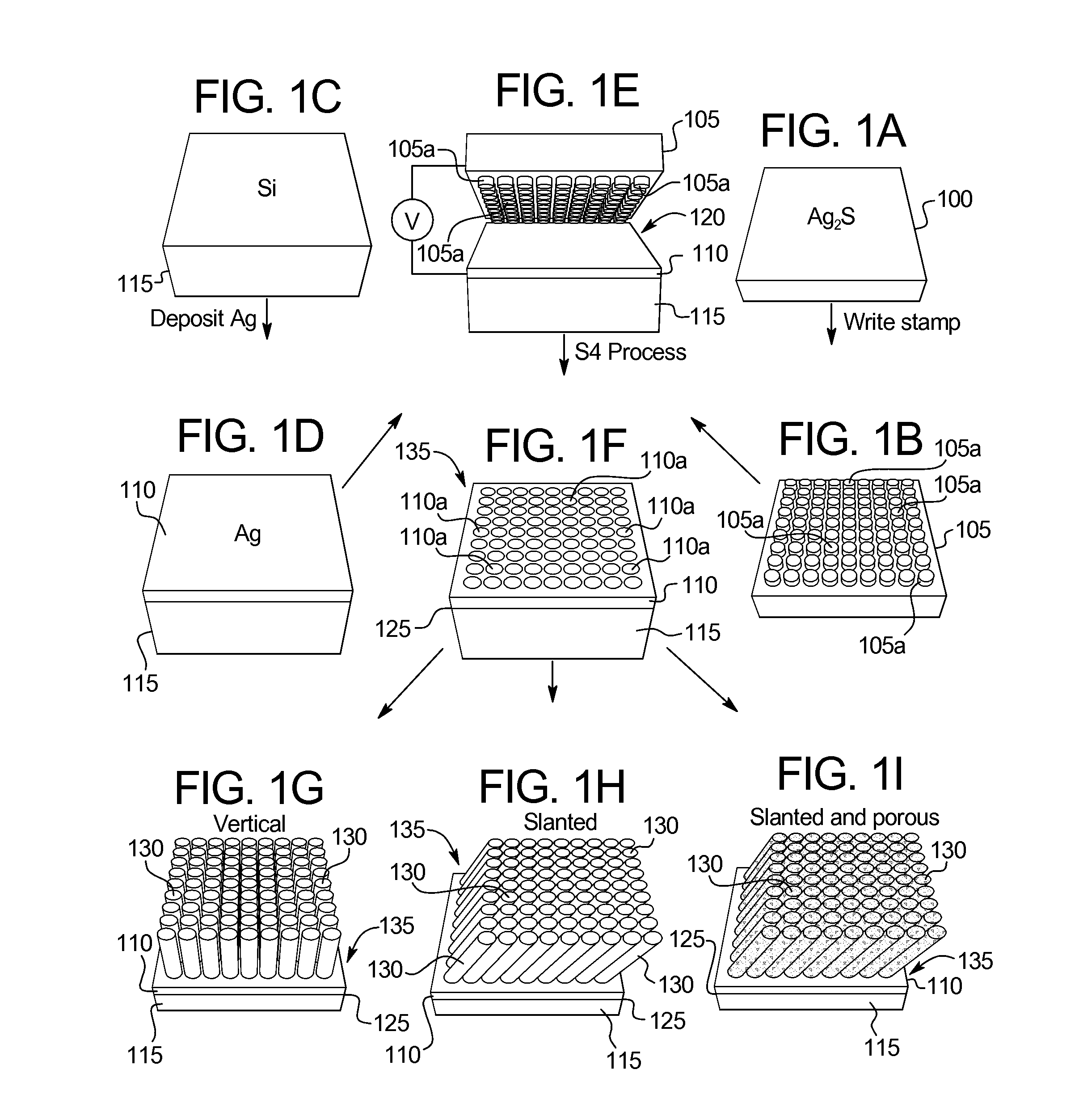

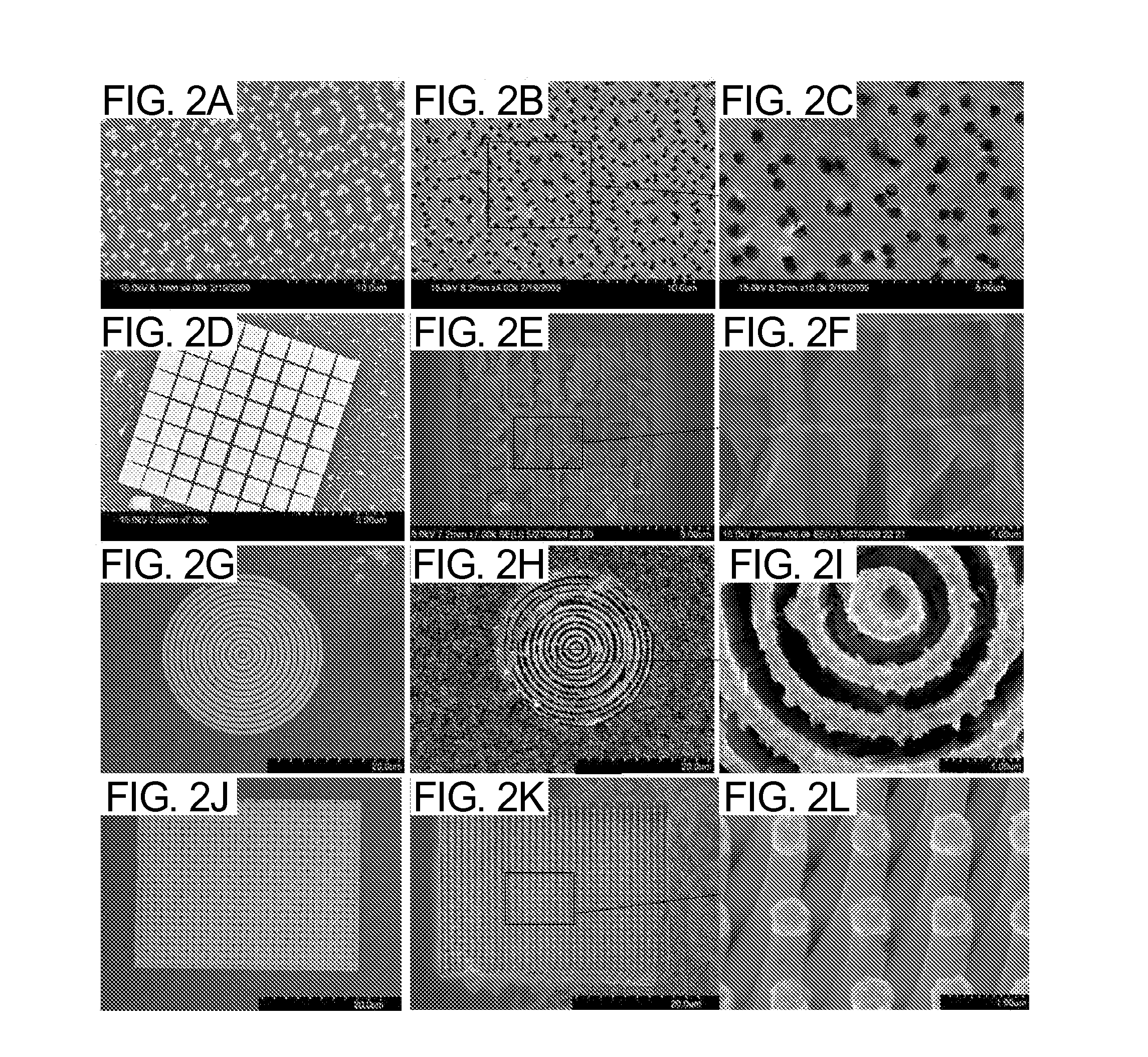

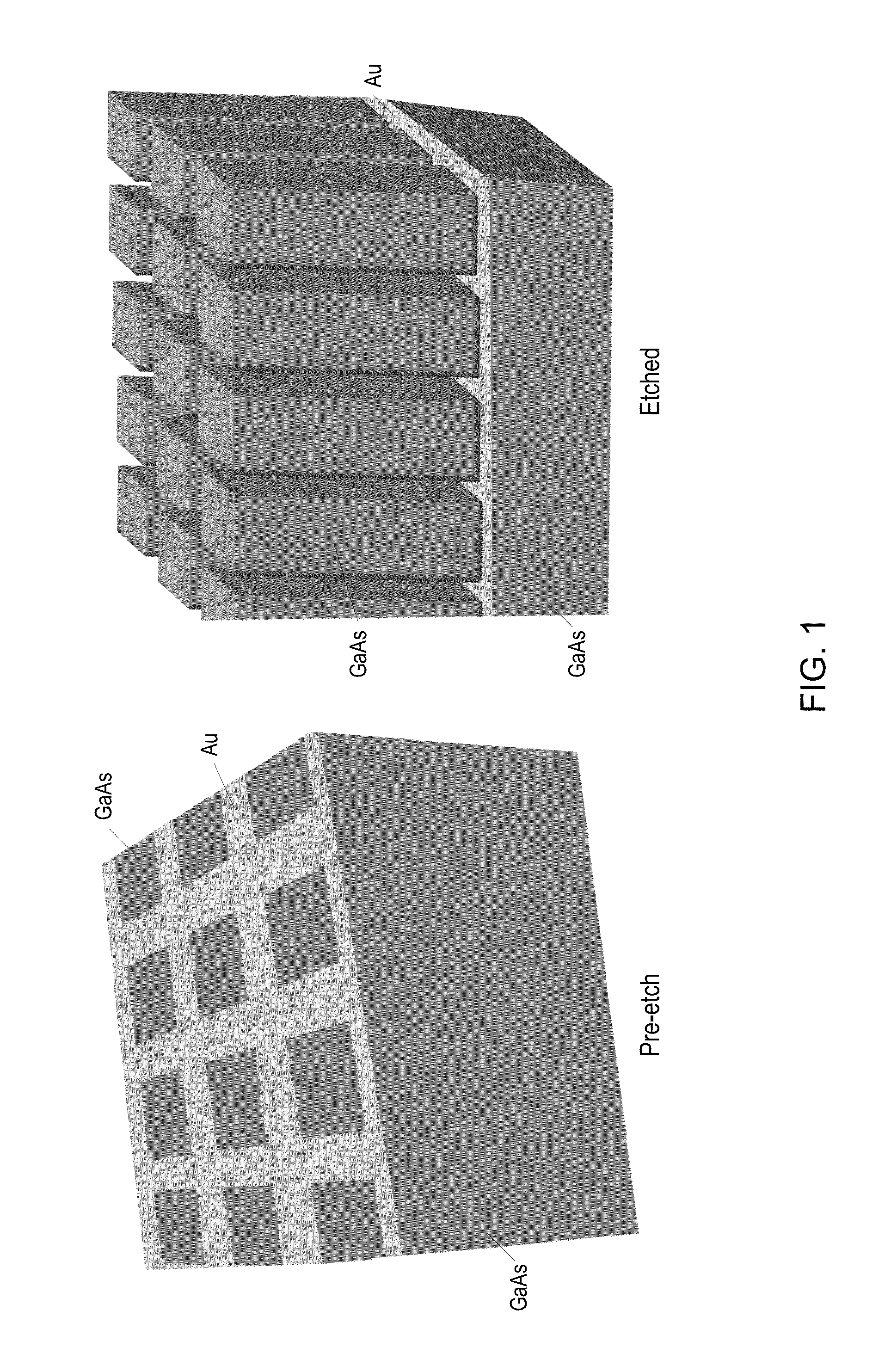

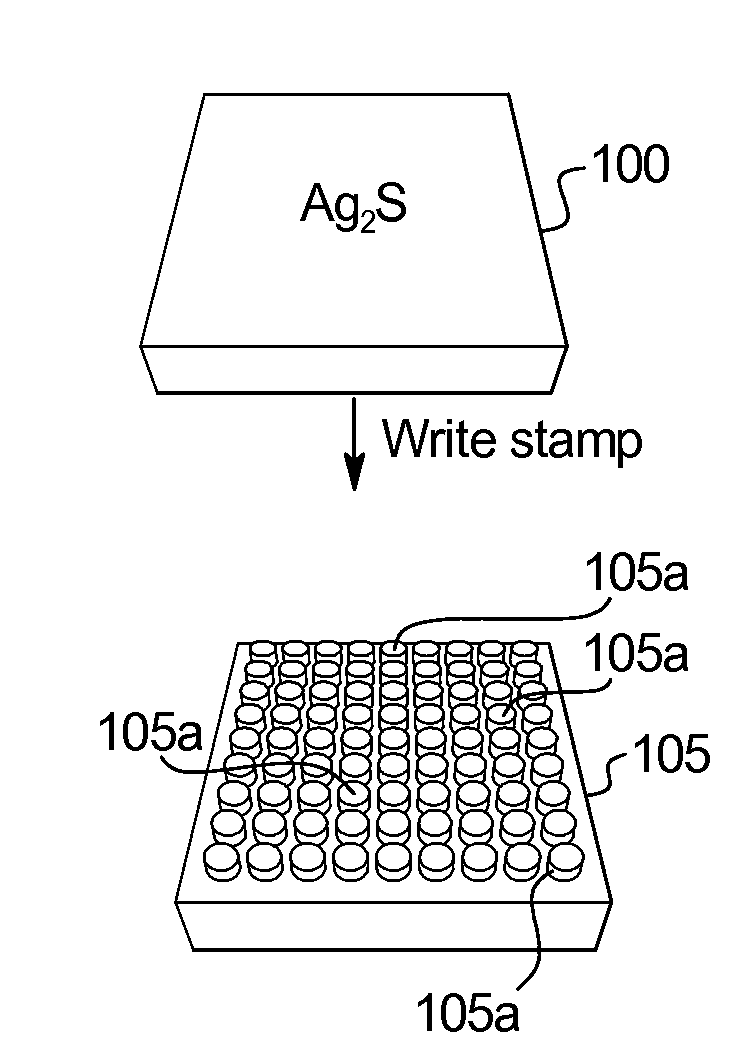

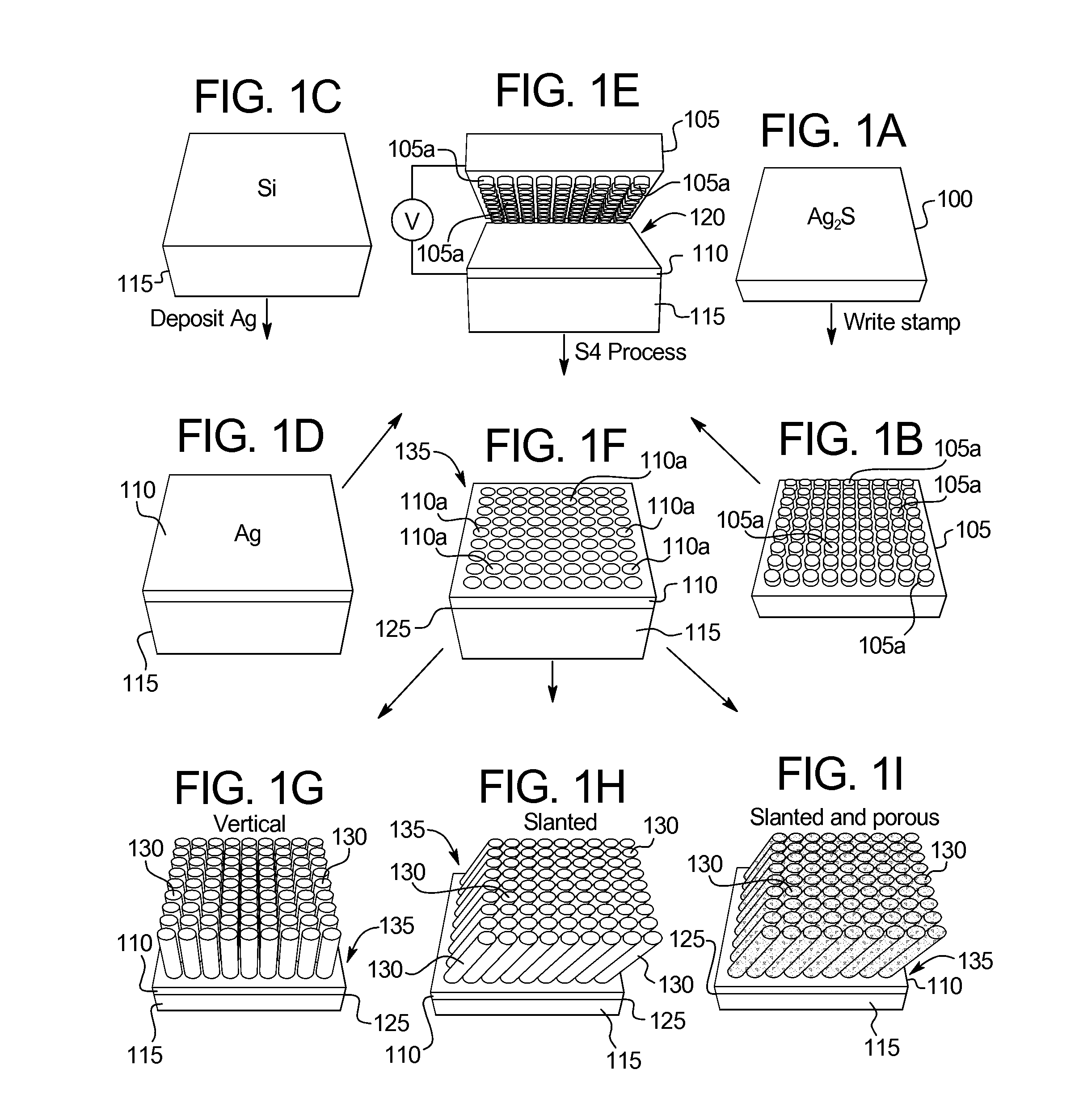

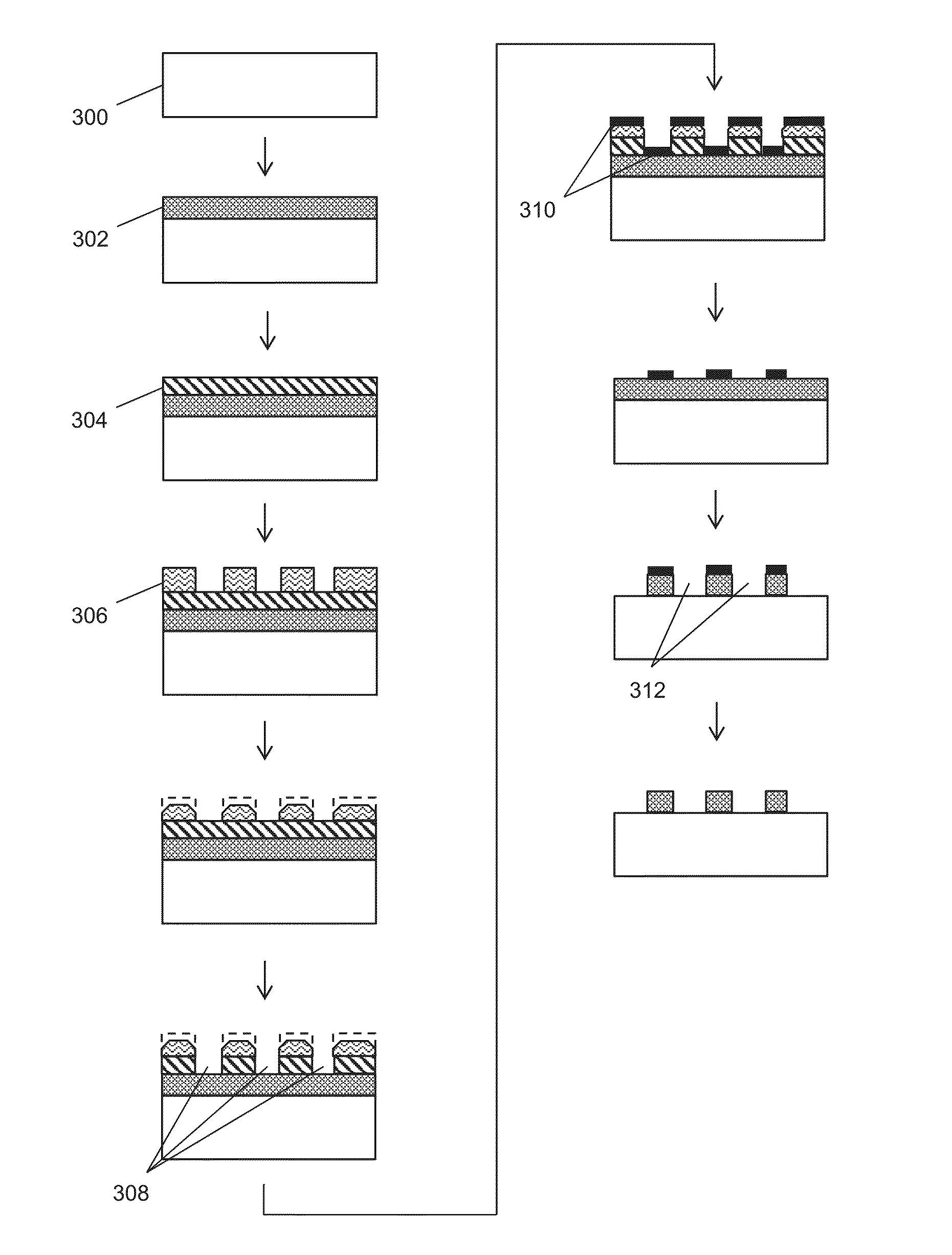

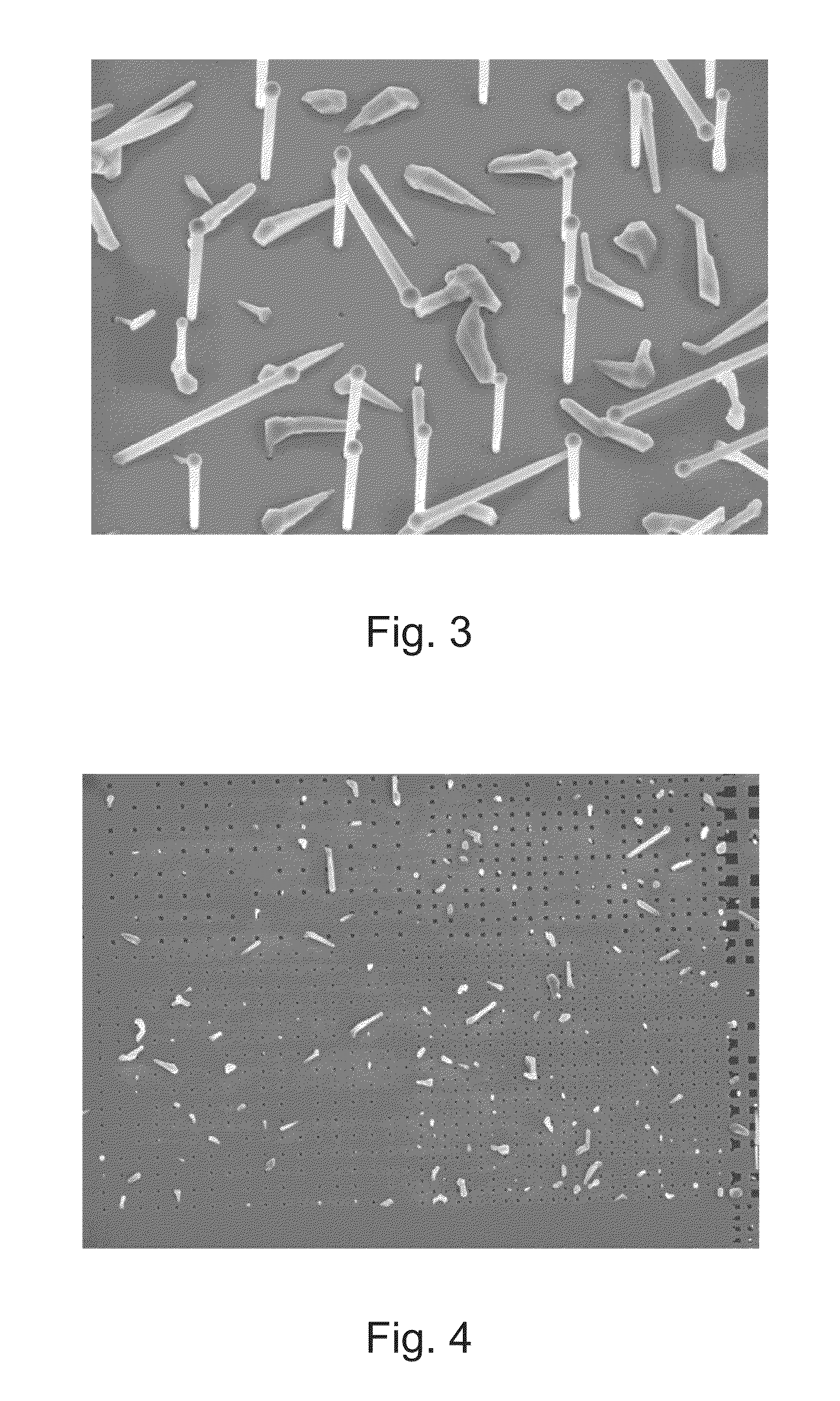

Method of forming an array of high aspect ratio semiconductor nanostructures

ActiveUS20130052762A1High aspect ratioNanoinformaticsSemiconductor/solid-state device manufacturingNanometreMaterials science

A new method for forming an array of high aspect ratio semiconductor nanostructures entails positioning a surface of a stamp comprising a solid electrolyte in opposition to a conductive film disposed on a semiconductor substrate. The surface of the stamp includes a pattern of relief features in contact with the conductive film so as to define a film-stamp interface. A flux of metal ions is generated across the film-stamp interface, and a pattern of recessed features complementary to the pattern of relief features is created in the conductive film. The recessed features extend through an entire thickness of the conductive film to expose the underlying semiconductor substrate and define a conductive pattern on the substrate. The stamp is removed, and material immediately below the conductive pattern is selectively removed from the substrate. Features are formed in the semiconductor substrate having a length-to-width aspect ratio of at least about 5:1.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

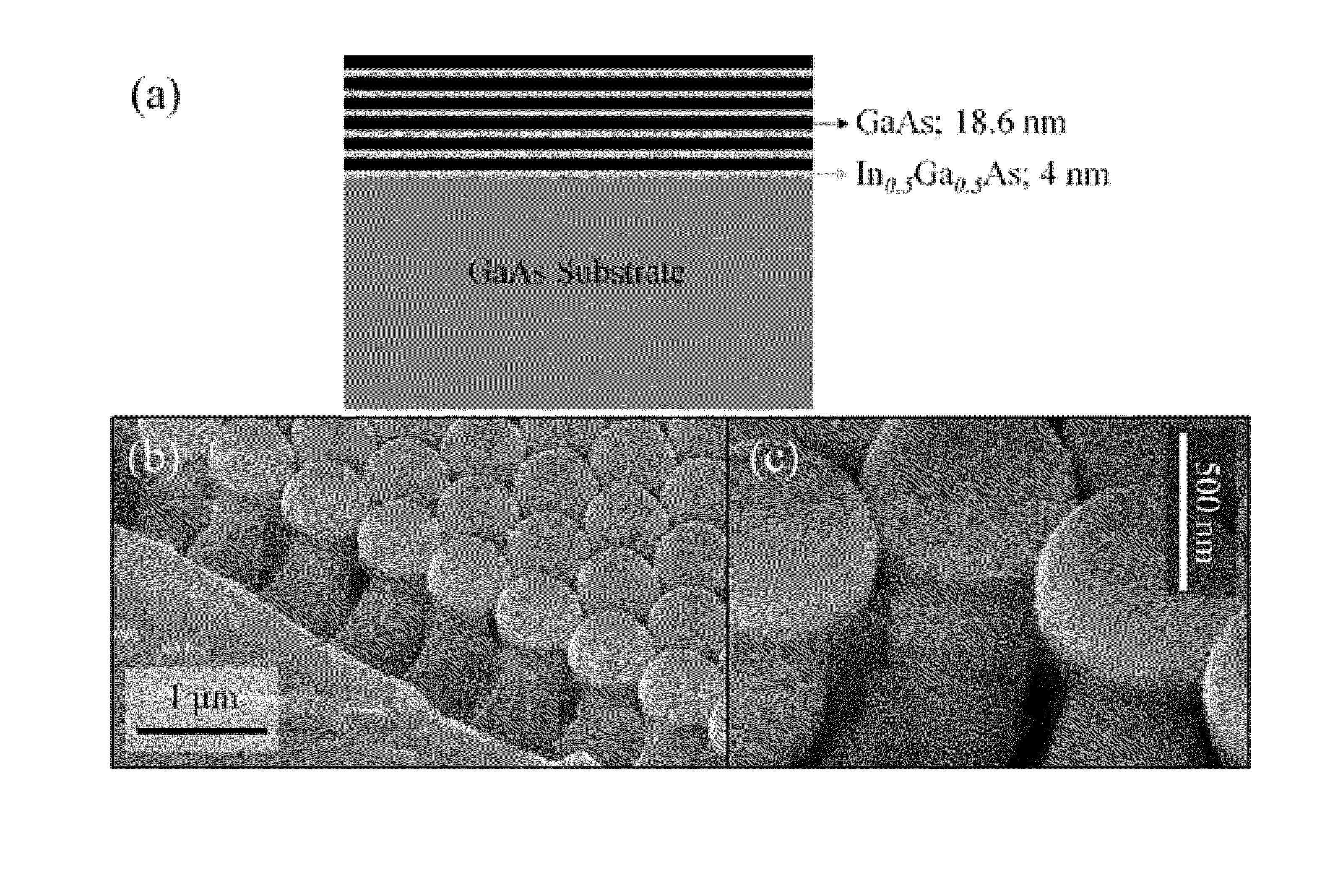

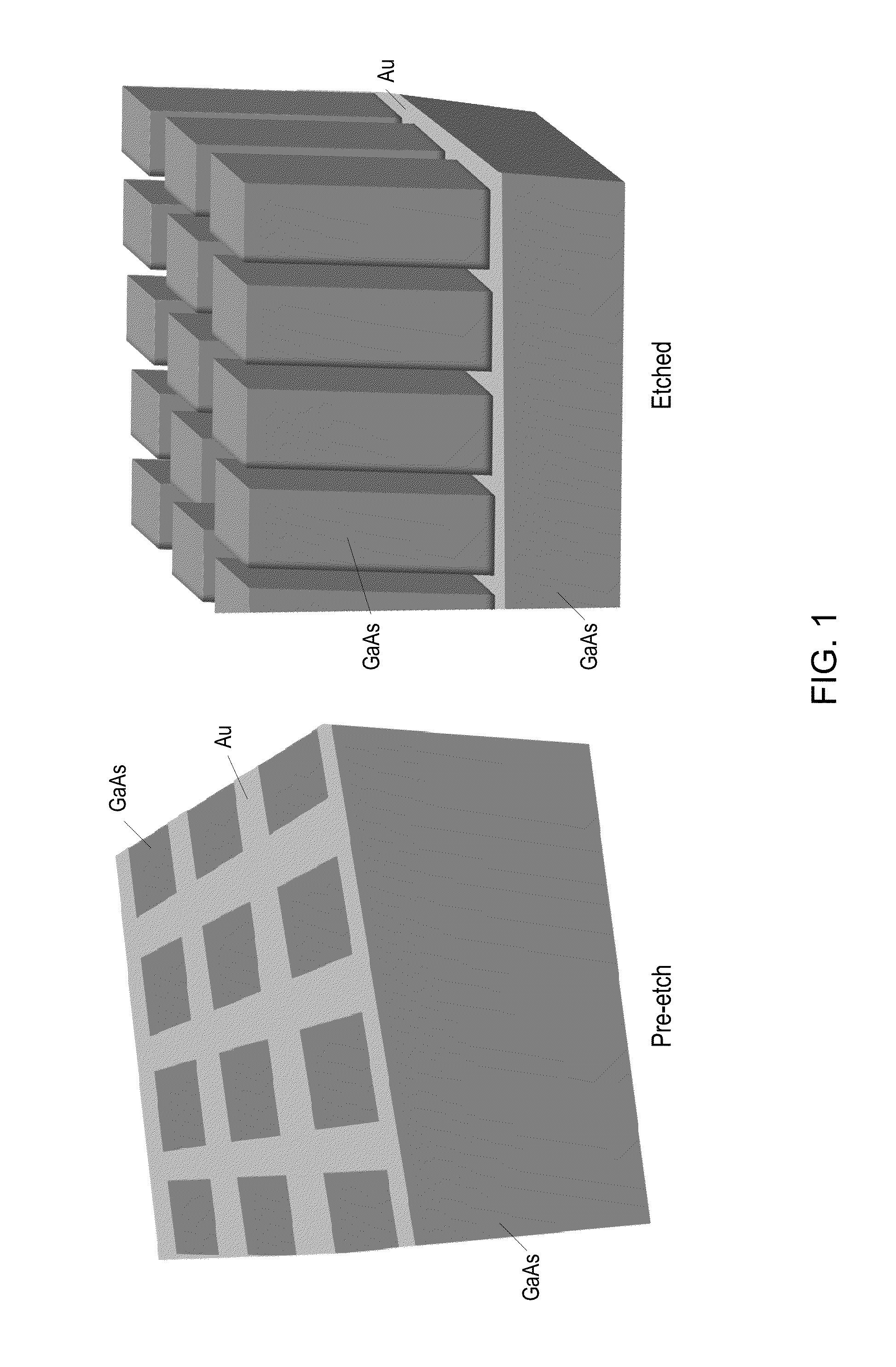

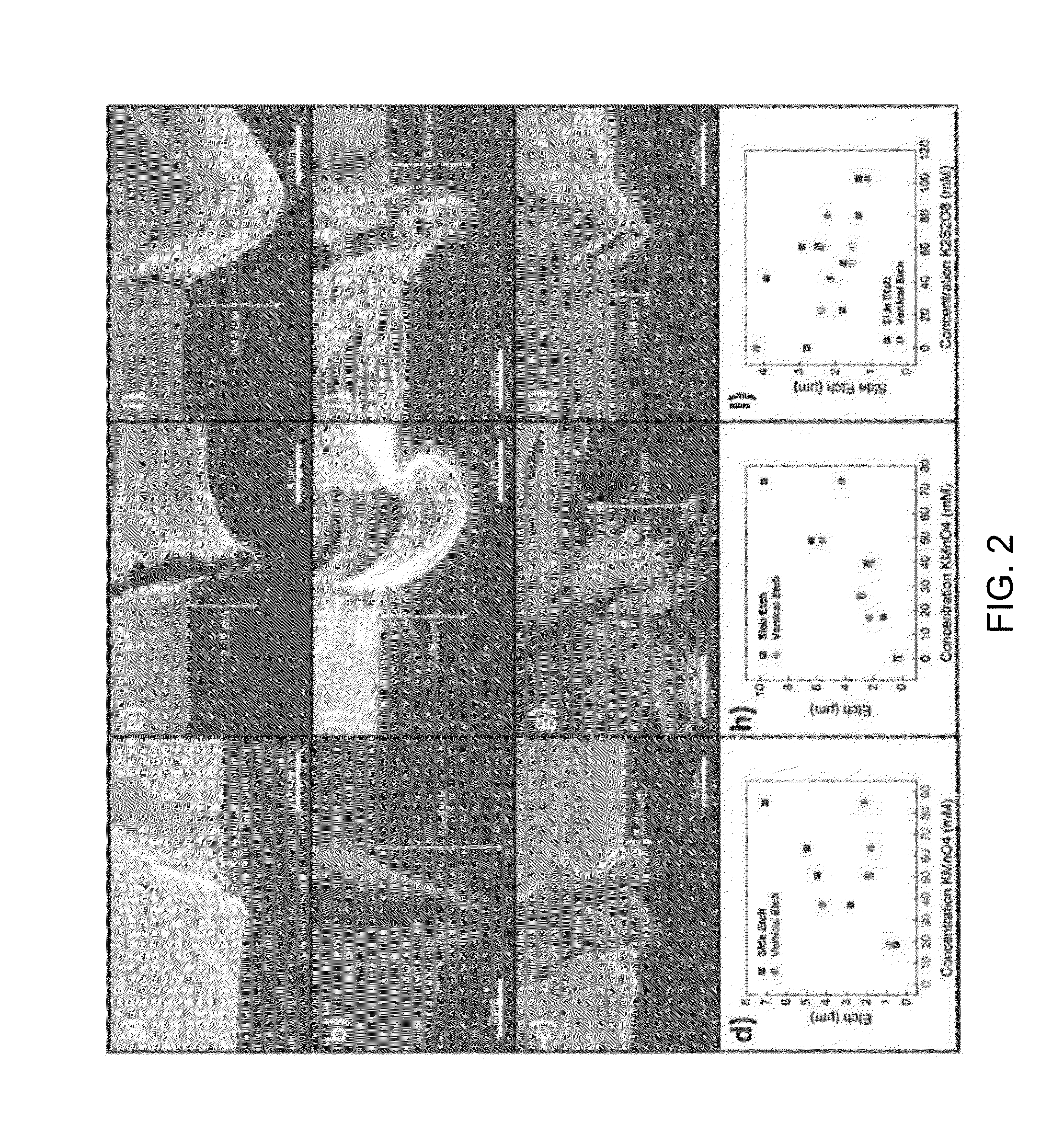

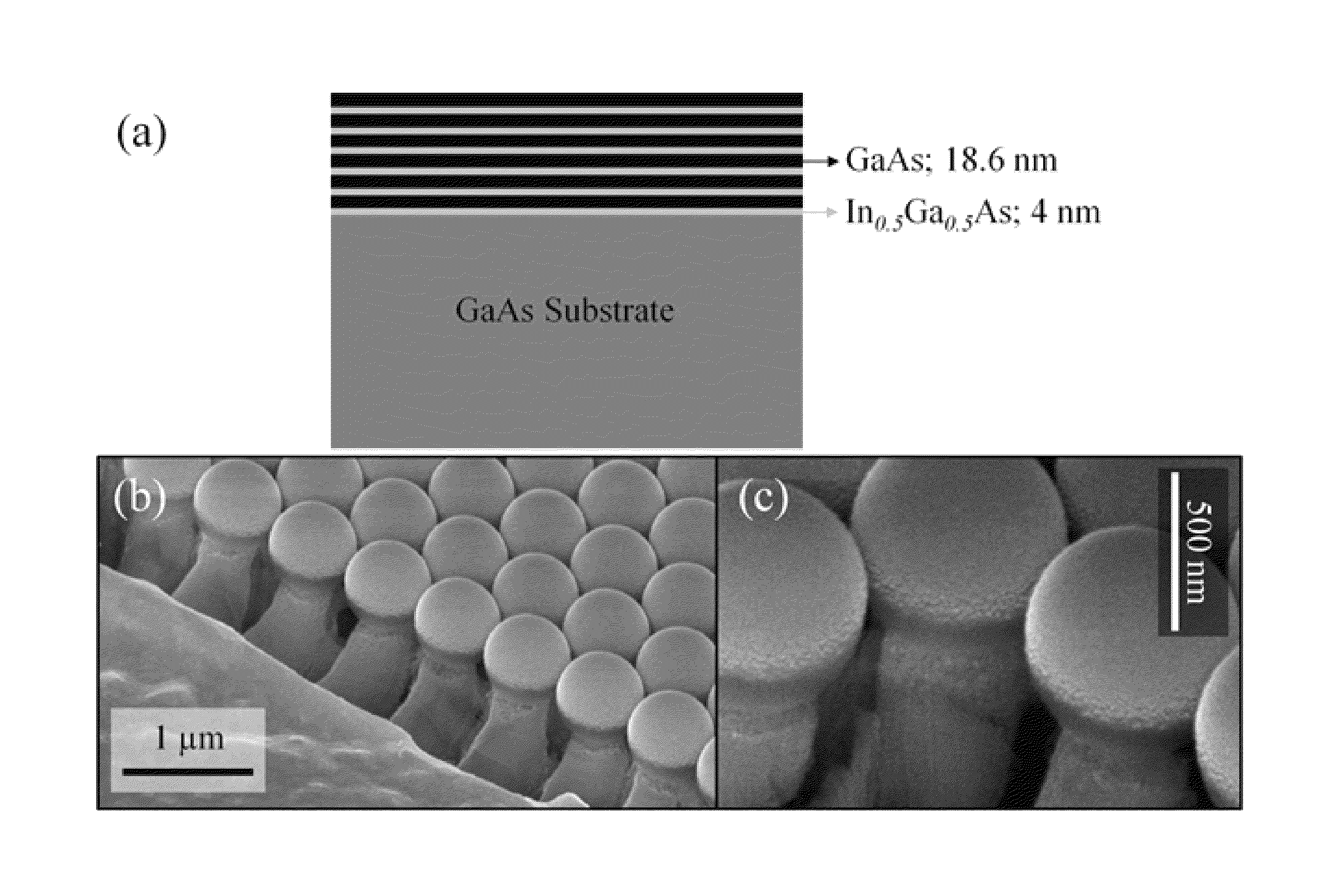

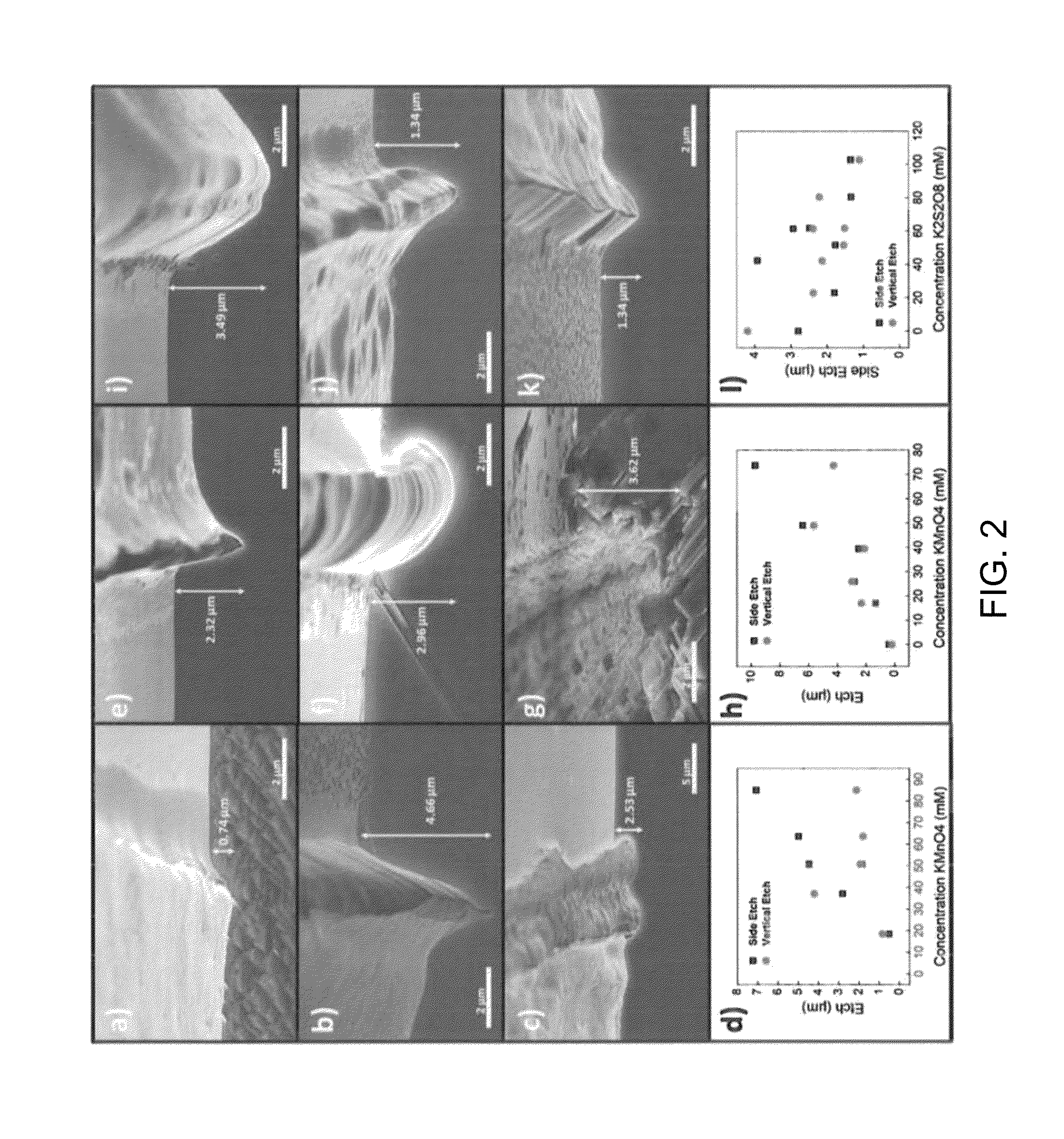

Metal assisted chemical etching to produce iii-v semiconductor nanostructures

Methods of metal assisted chemical etching III-V semiconductors are provided. The methods can include providing an electrically conductive film pattern disposed on a semiconductor substrate comprising a III-V semiconductor. At least a portion of the III-V semiconductor immediately below the conductive film pattern may be selectively removed by immersing the electrically conductive film pattern and the semiconductor substrate into an etchant solution comprising an acid and an oxidizing agent having an oxidation potential less than an oxidation potential of hydrogen peroxide. Such methods can form high aspect ratio semiconductor nanostructures.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

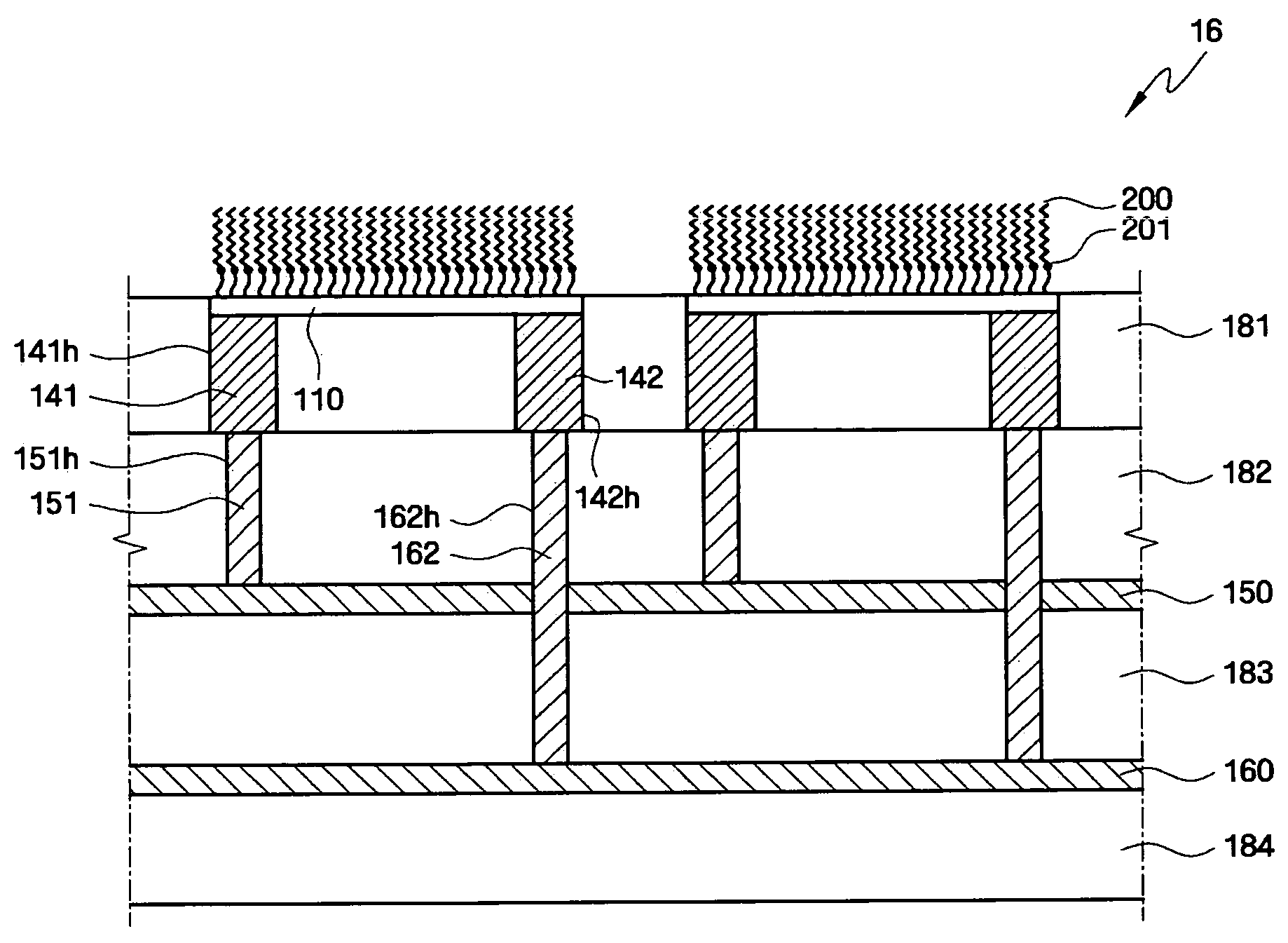

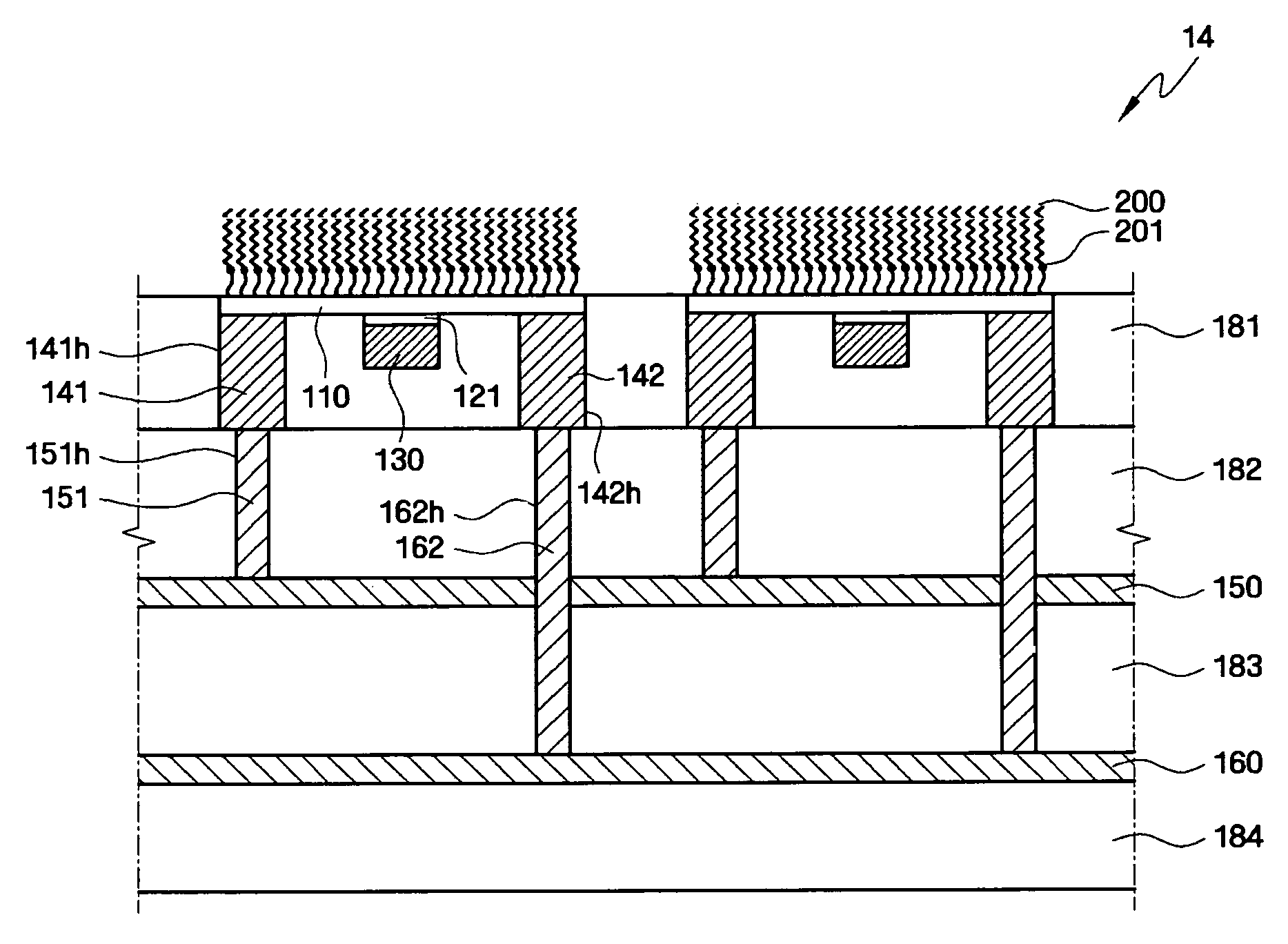

Biosensor using nanoscale material as transistor channel and method of fabricating the same

InactiveUS20090085072A1Semiconductor/solid-state device detailsIndividual molecule manipulationEngineeringNanometre

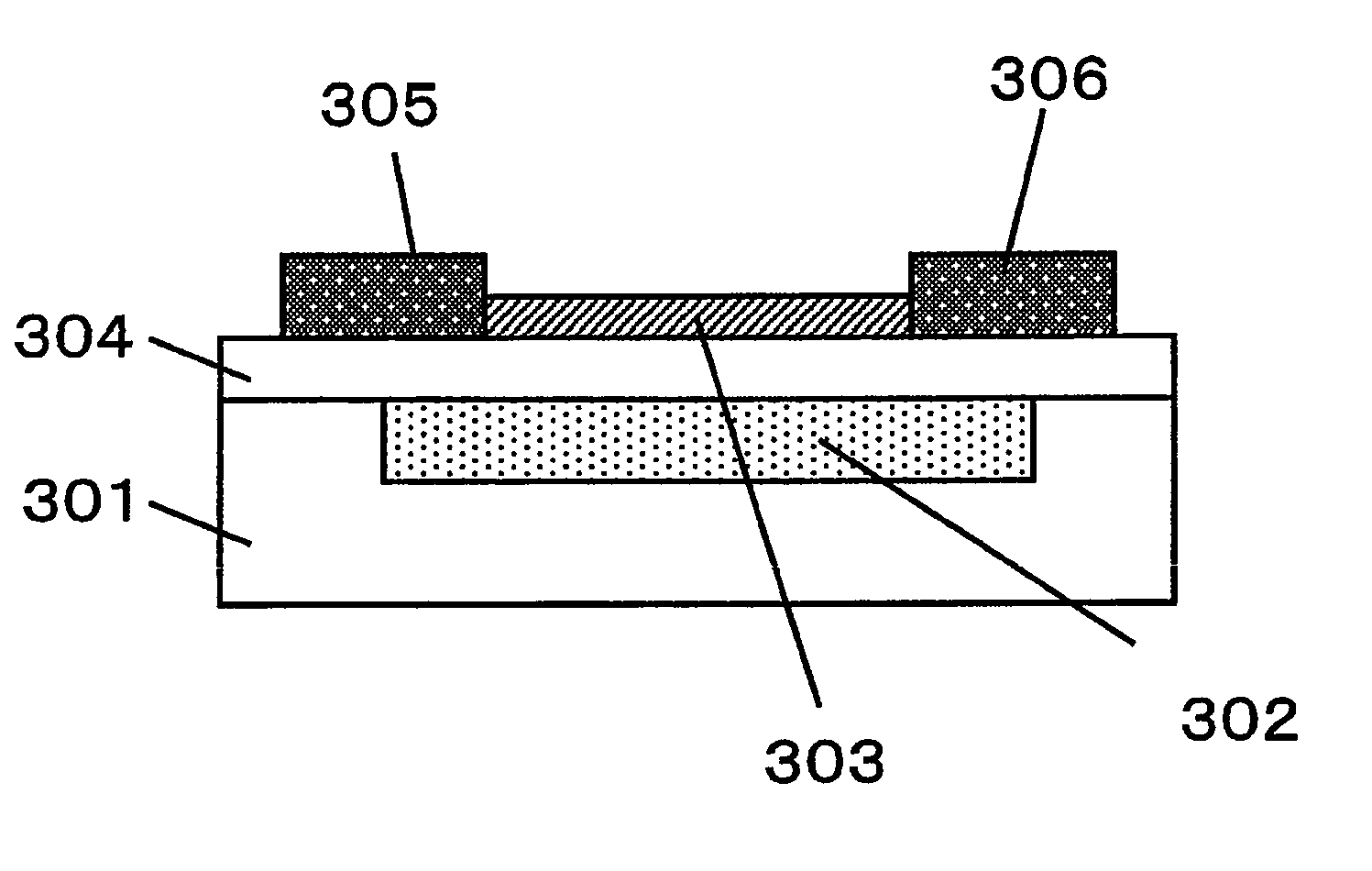

Example embodiments relate to a biosensor using a nanoscale material as a channel of a transistor and a method of fabricating the same. A biosensor according to example embodiments may include a plurality of insulating films. A first signal line and a second signal line may be interposed between the plurality of insulating films. A semiconductor nanostructure may be disposed on the plurality of insulating films, the semiconductor nanostructure having a first side electrically connected to the first signal line and a second side electrically connected to the second signal line. A plurality of probes may be coupled to the semiconductor nanostructure. A biosensor according to example embodiments may have a reduced analysis time.

Owner:SAMSUNG ELECTRONICS CO LTD

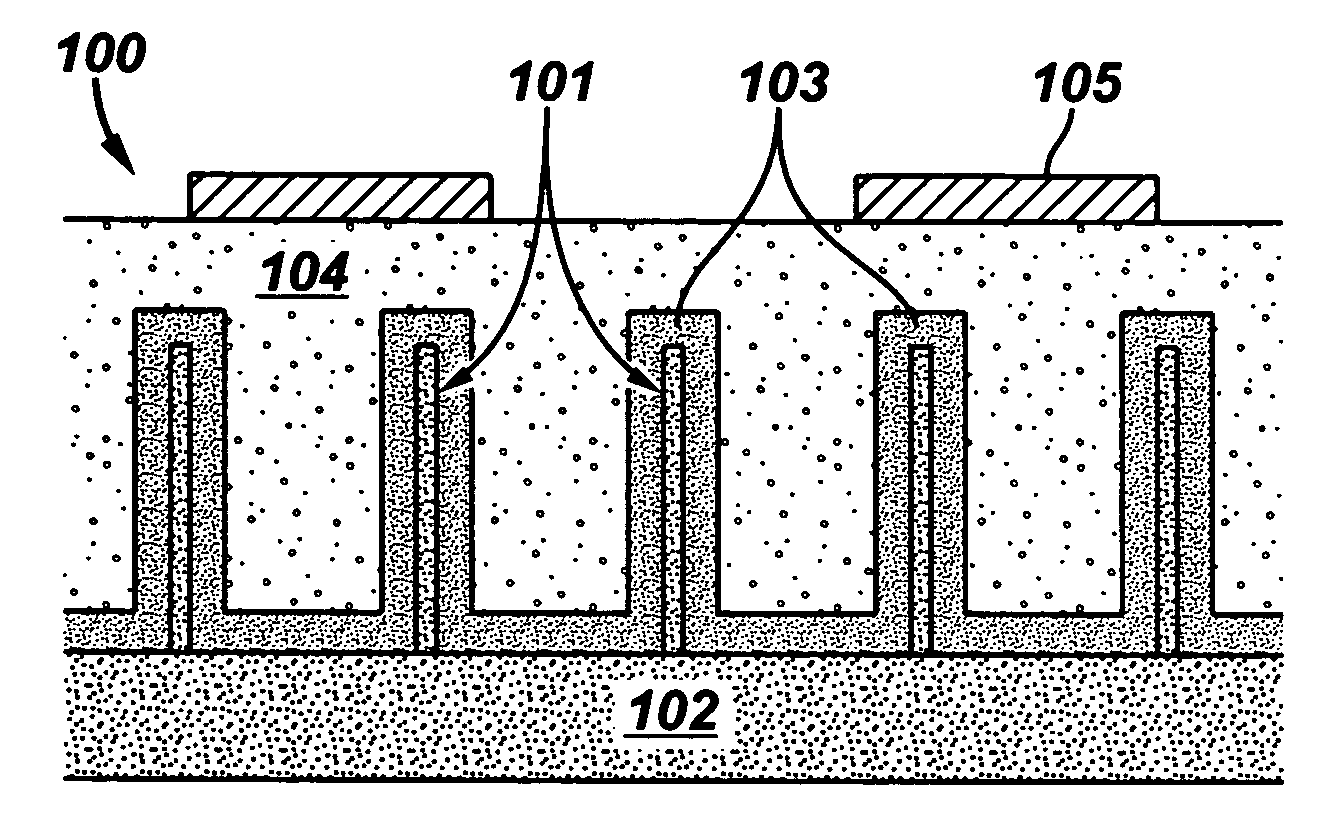

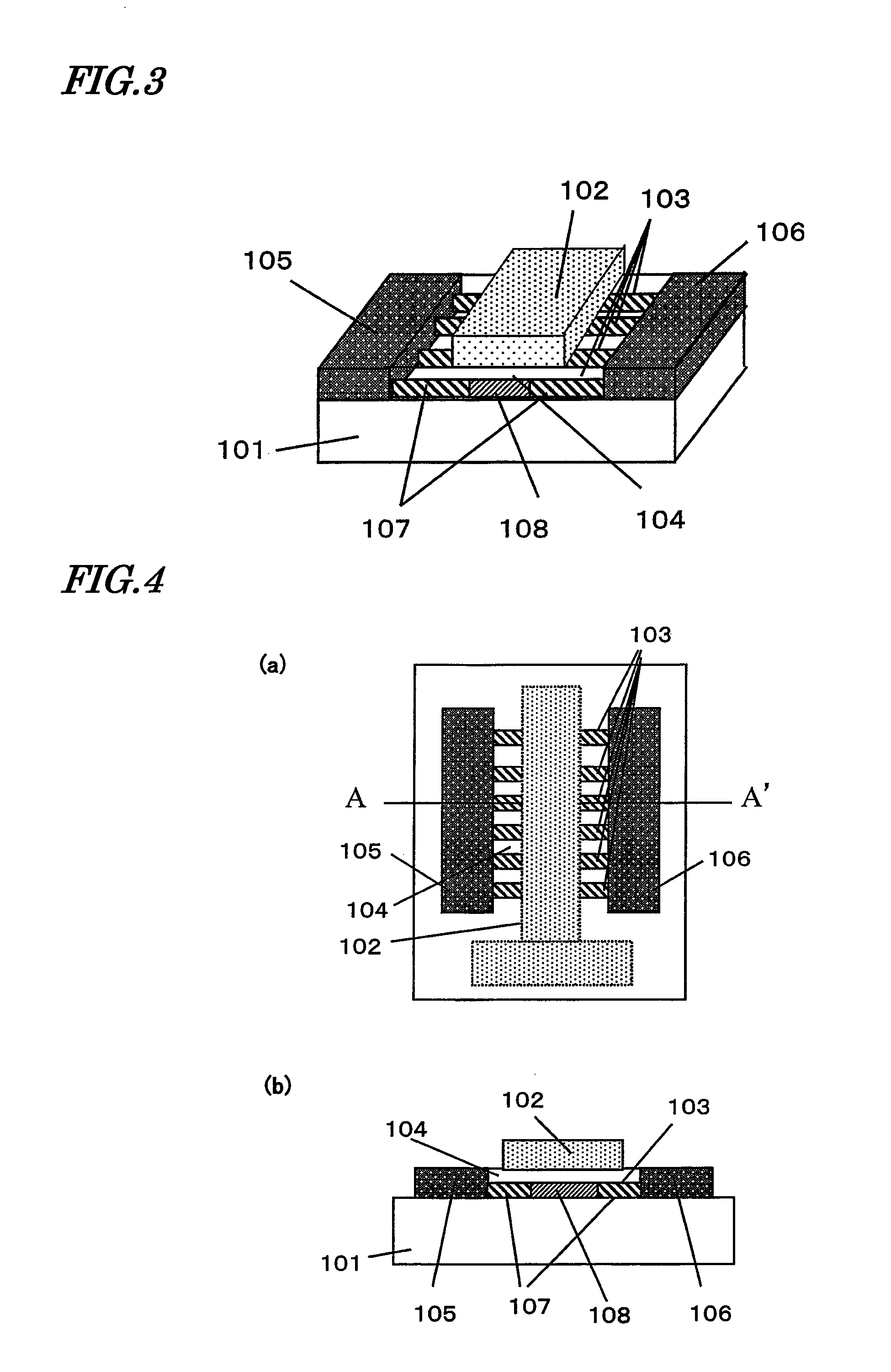

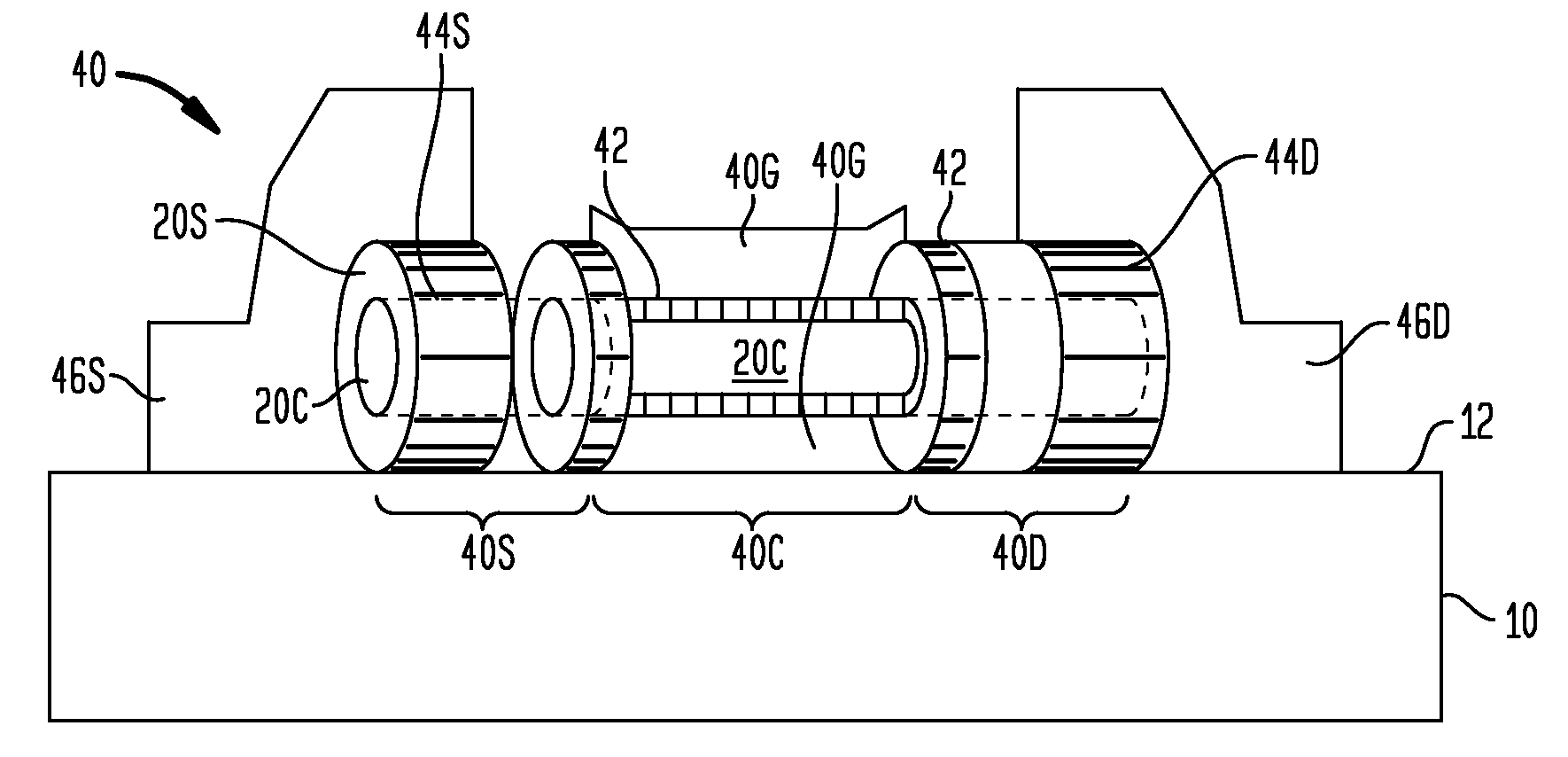

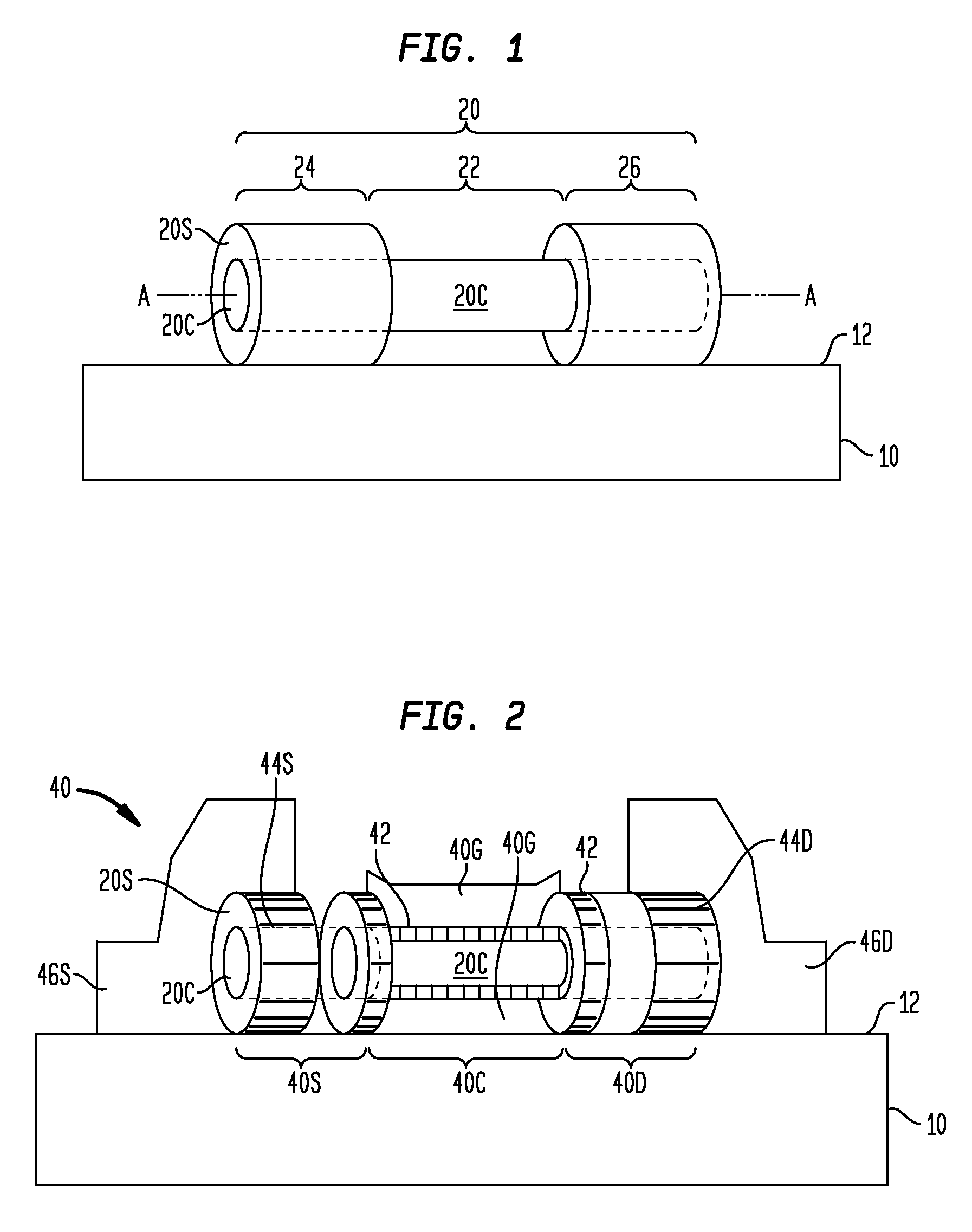

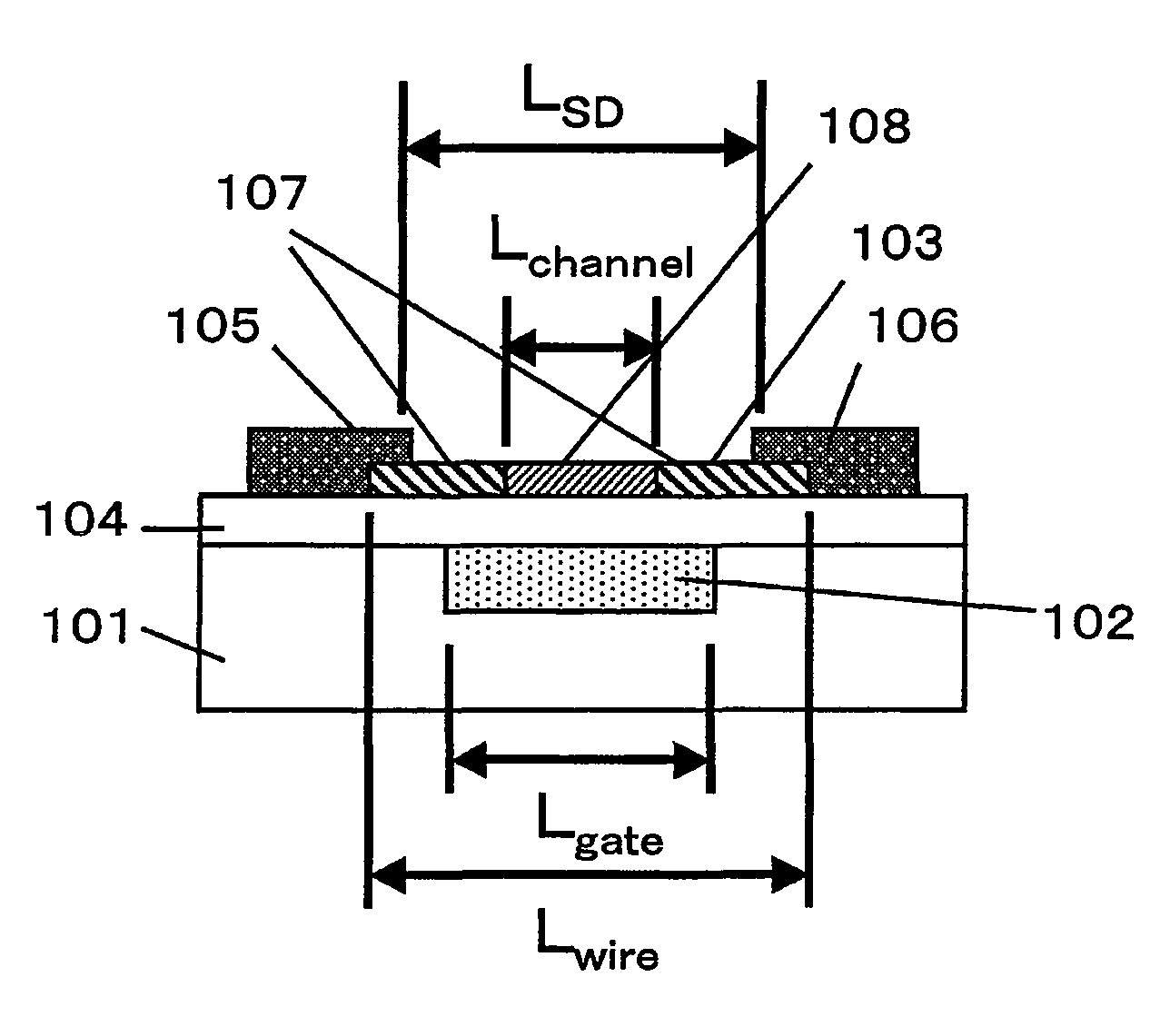

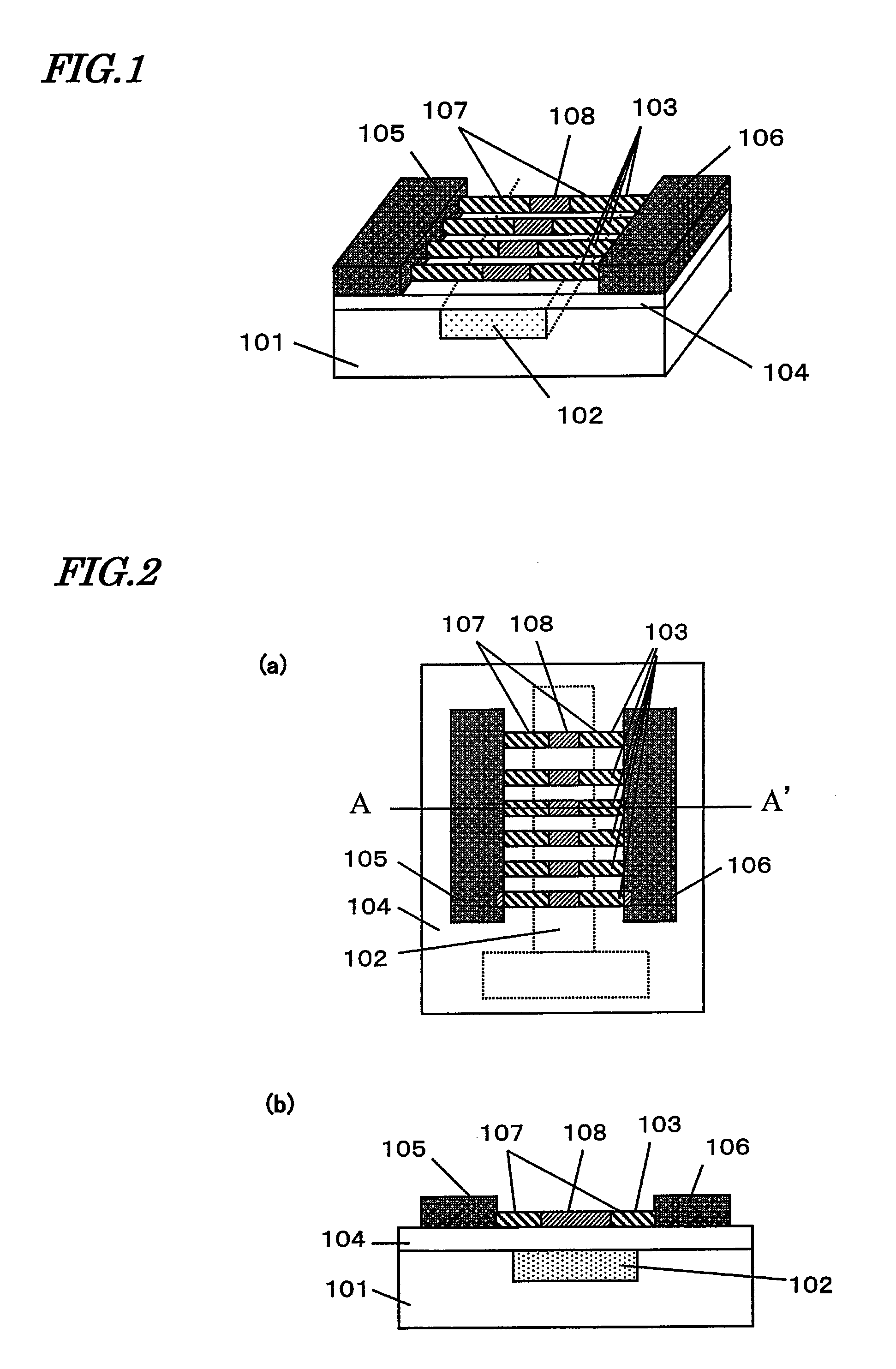

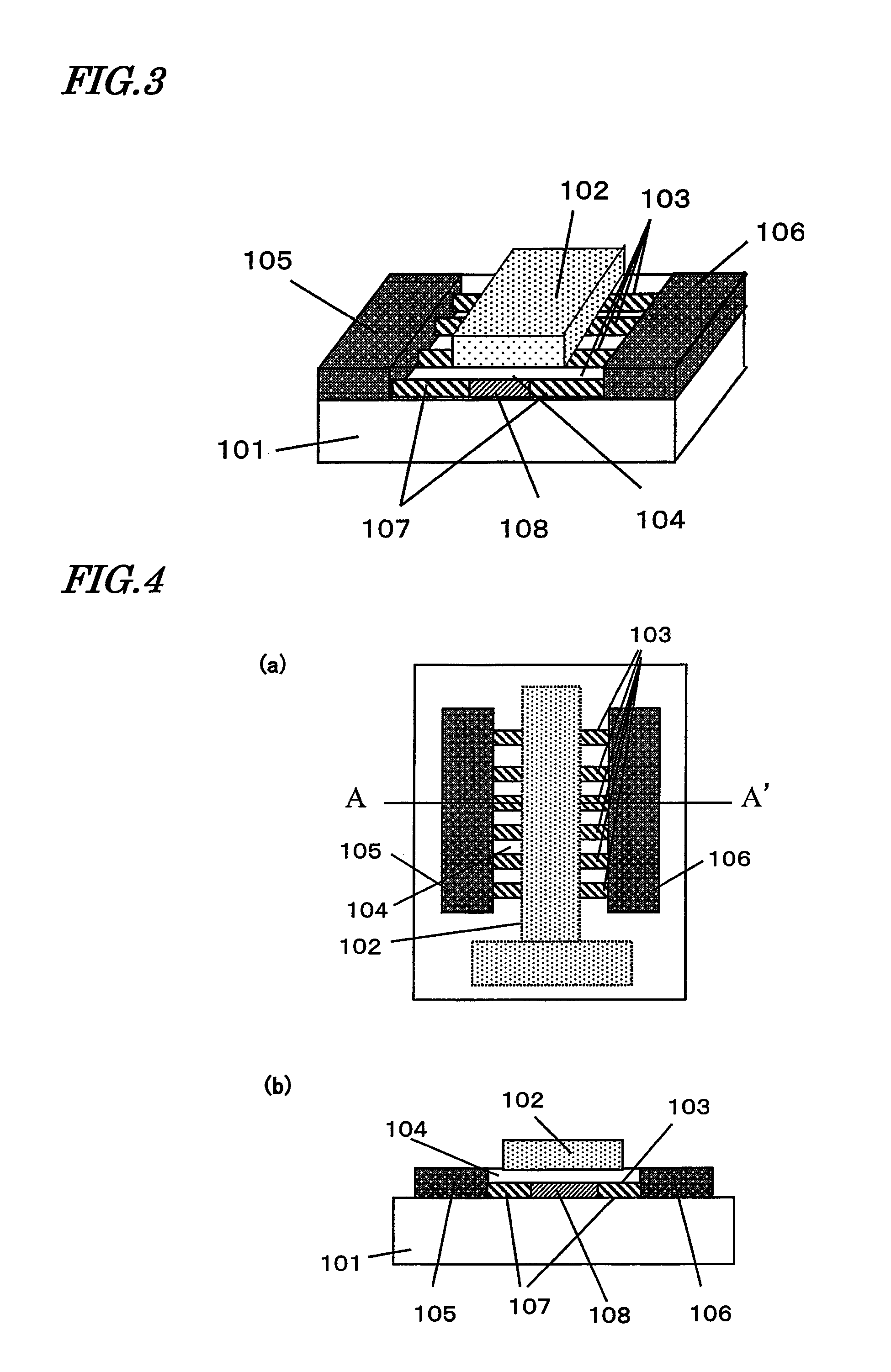

Field effect transistor

ActiveUS20100001259A1Increase resistanceSuppress mutationNanoinformaticsSemiconductor/solid-state device manufacturingHigh concentrationField-effect transistor

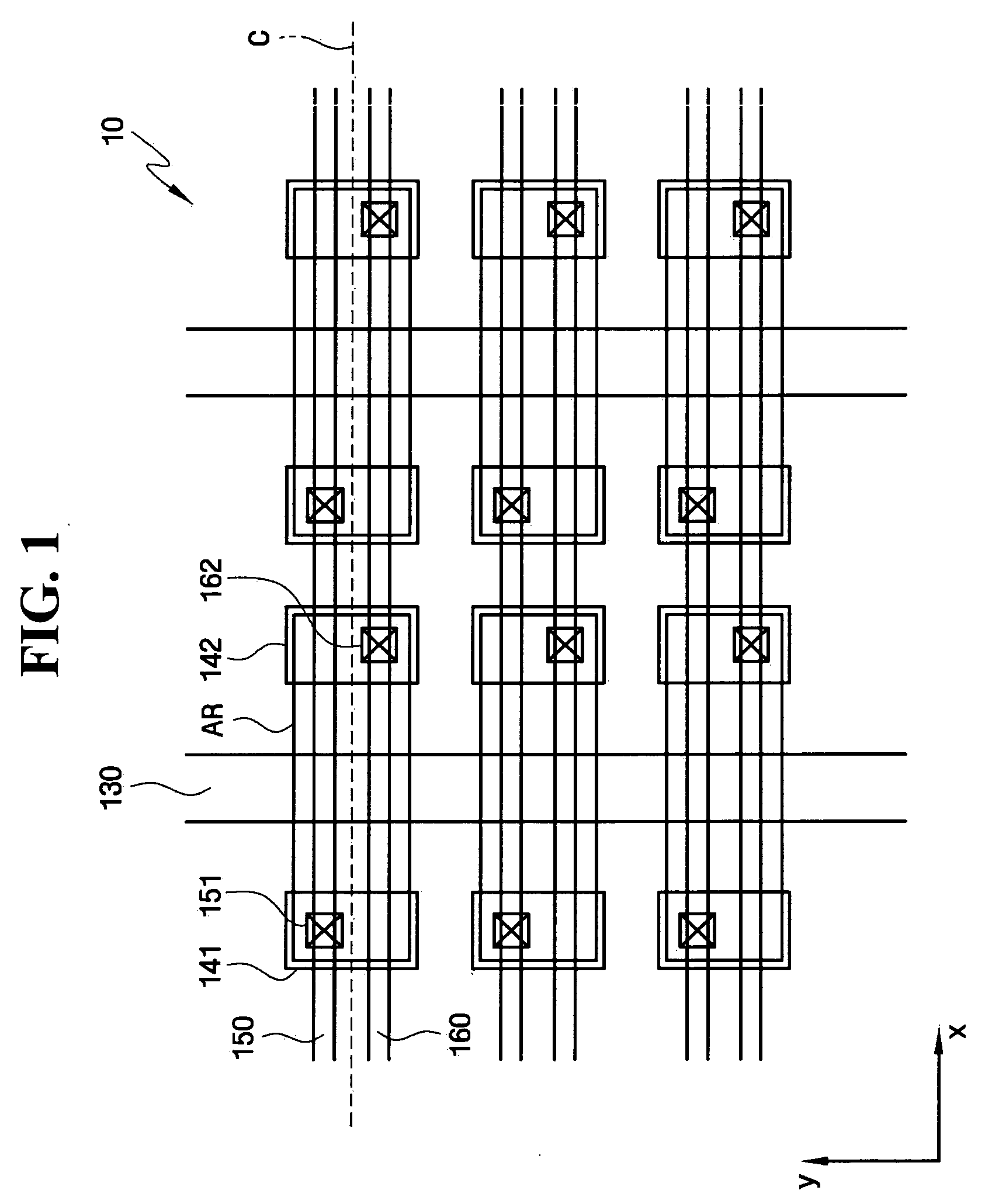

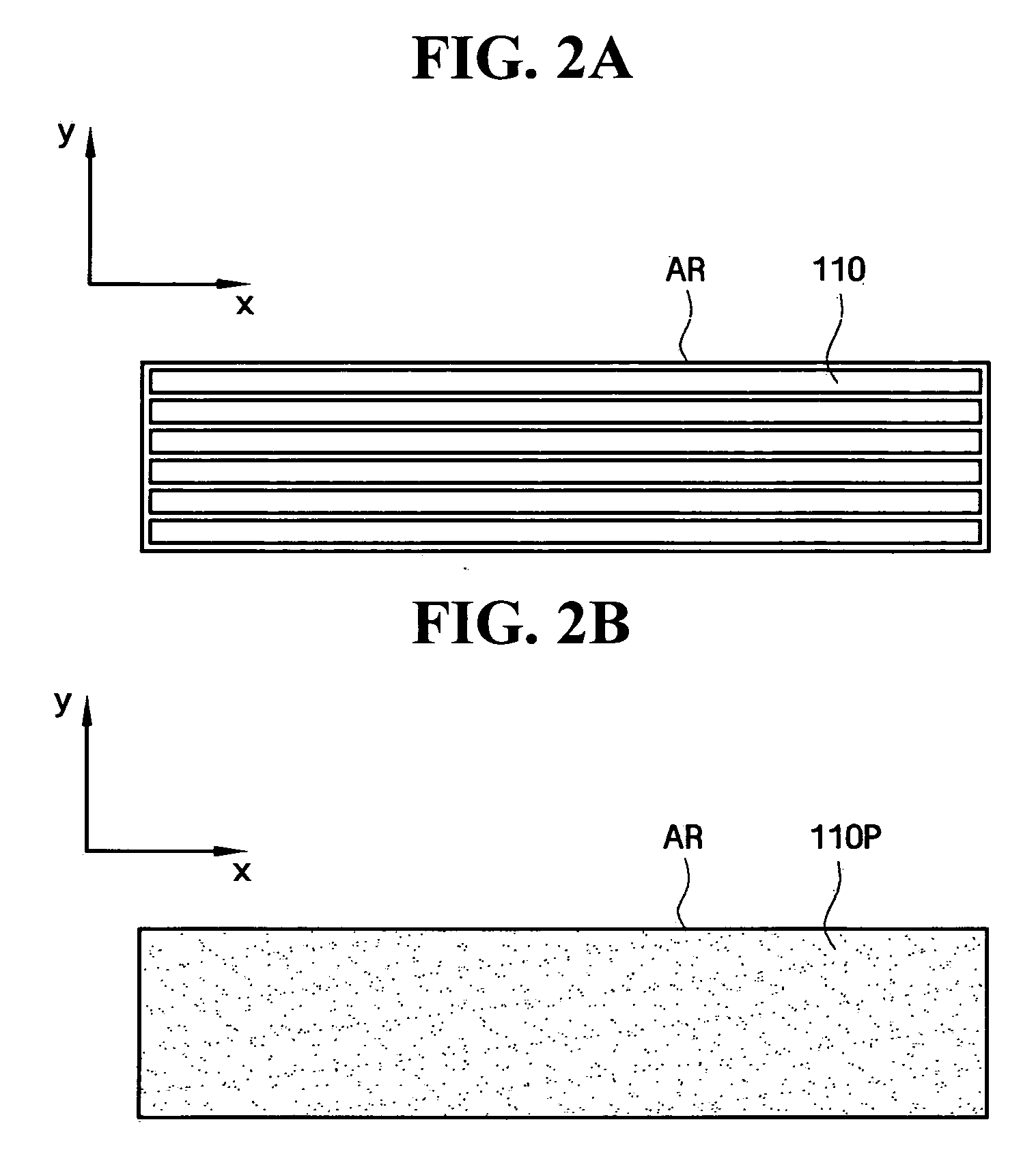

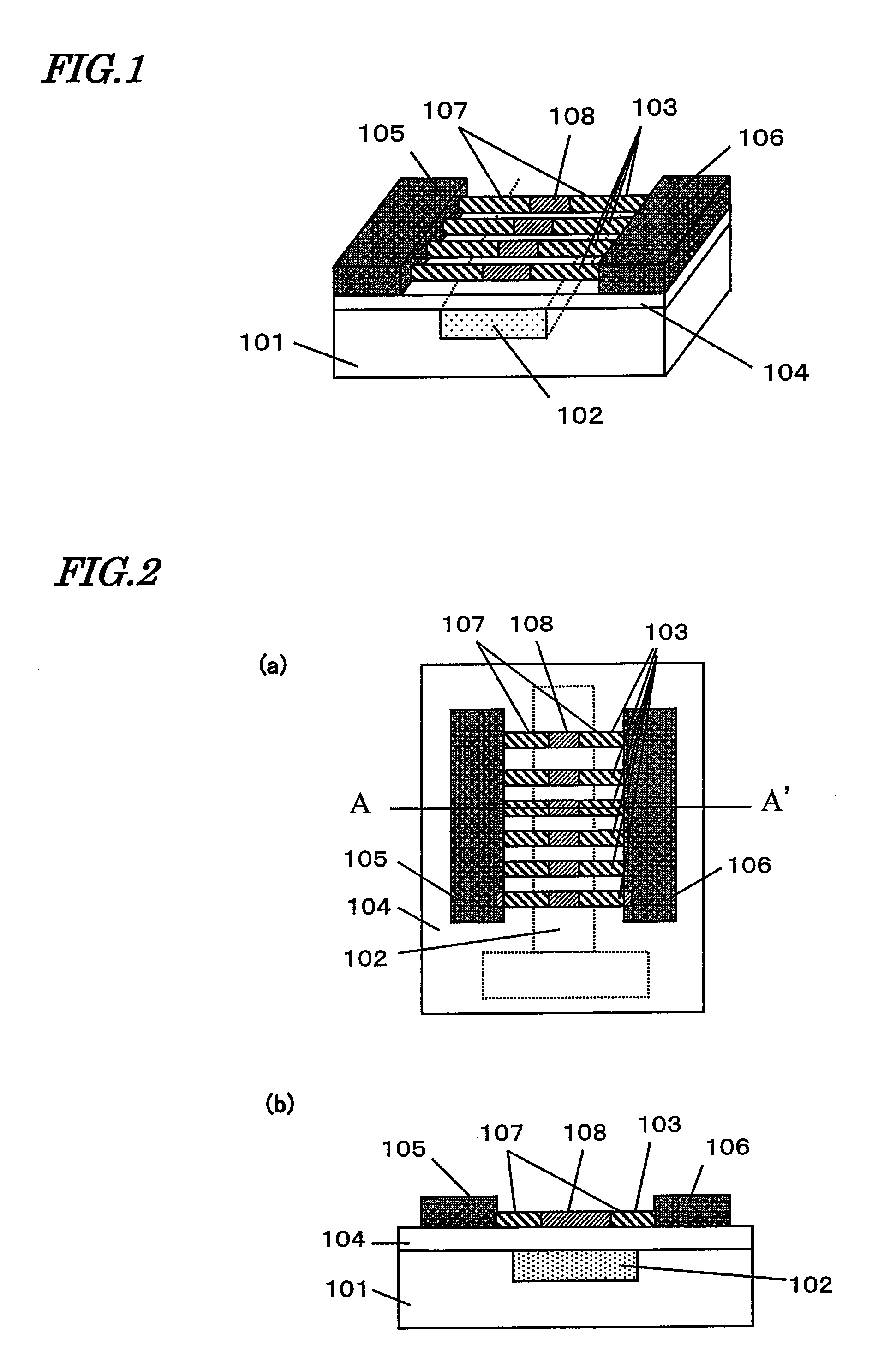

A source electrode 105 which is connected to a portion of at least one semiconductor nanostructure 103 among a plurality of semiconductor nanostructures, a drain electrode 106 connected to another portion of the semiconductor nanostructure 103, and a gate electrode 102 capable of controlling electrical conduction of the semiconductor nanostructure 103 are included. The semiconductor nanostructures 103 include a low concentration region 108 having a relatively low doping concentration and a pair of high concentration regions 107 having a higher doping concentration than that of the low concentration region 108 and being connected to both ends of the low concentration region 108. The doping concentration of the high concentration regions 107 is 1×1019 cm−3 or more; the length of the low concentration region 108 is shorter than a length of the gate electrode 102 along a direction from the source electrode 105 to the drain electrode 106; and the length of the gate electrode 102 is shorter than the interspace between the source electrode 105 and the drain electrode 106.

Owner:JOLED INC

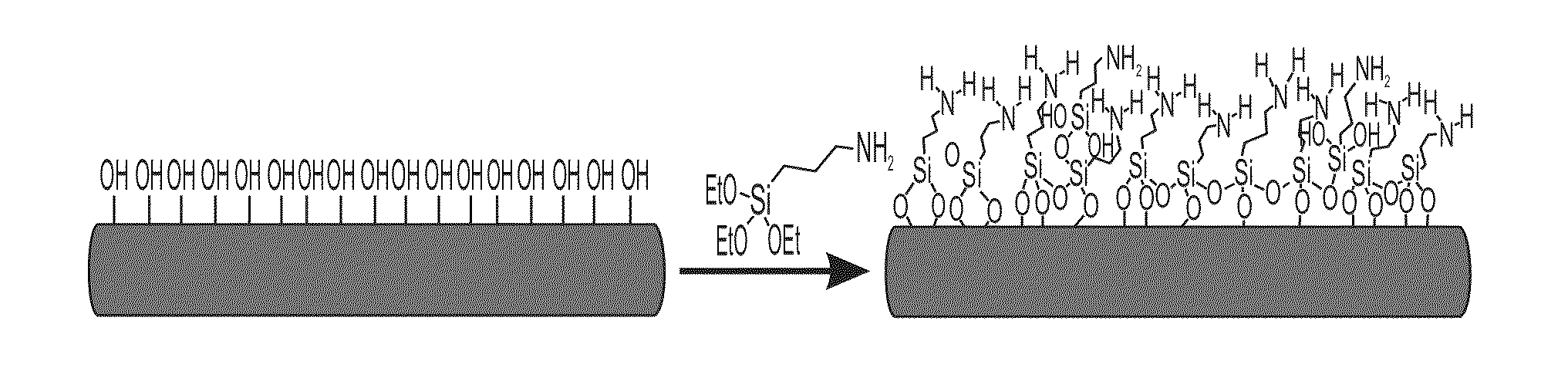

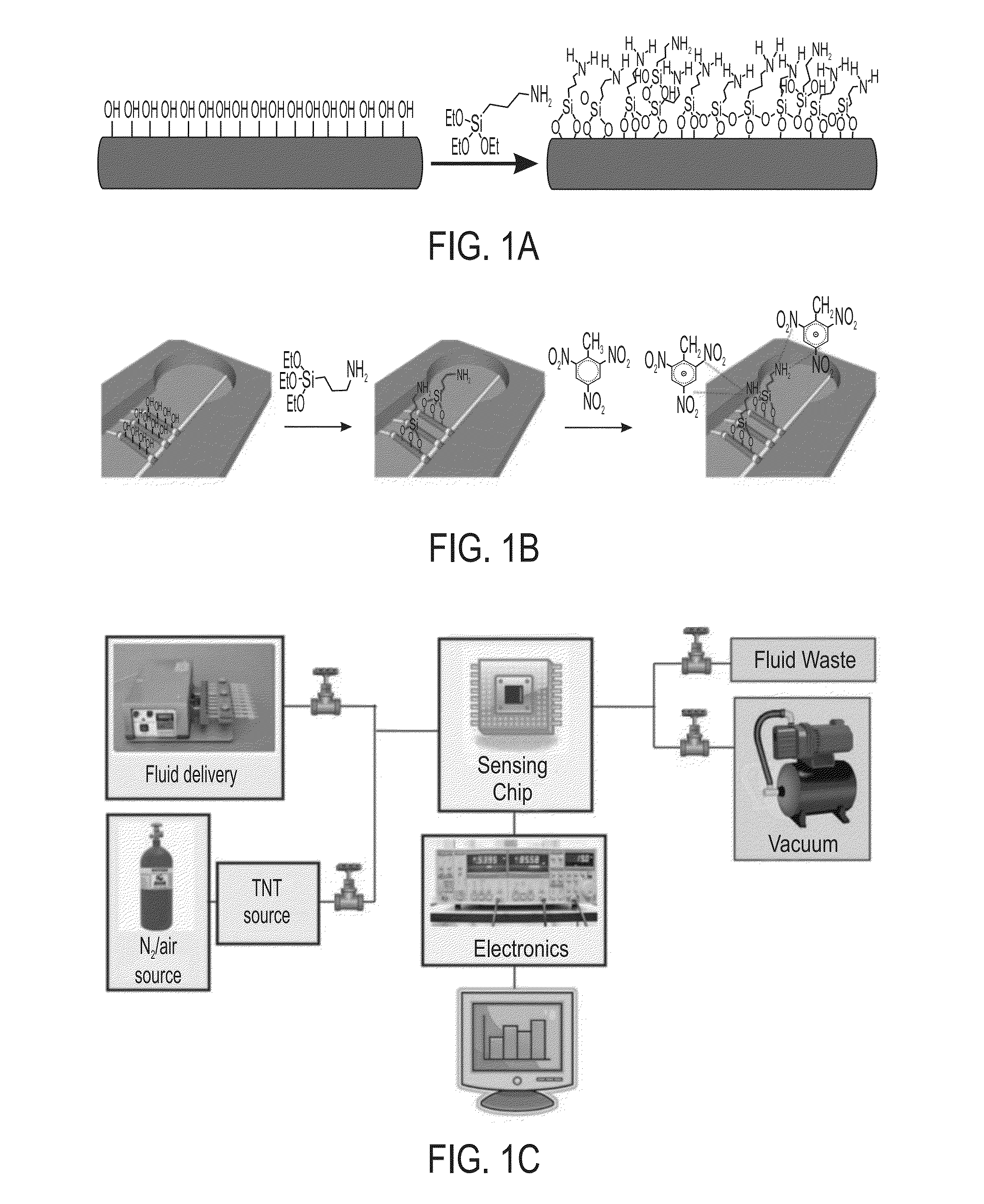

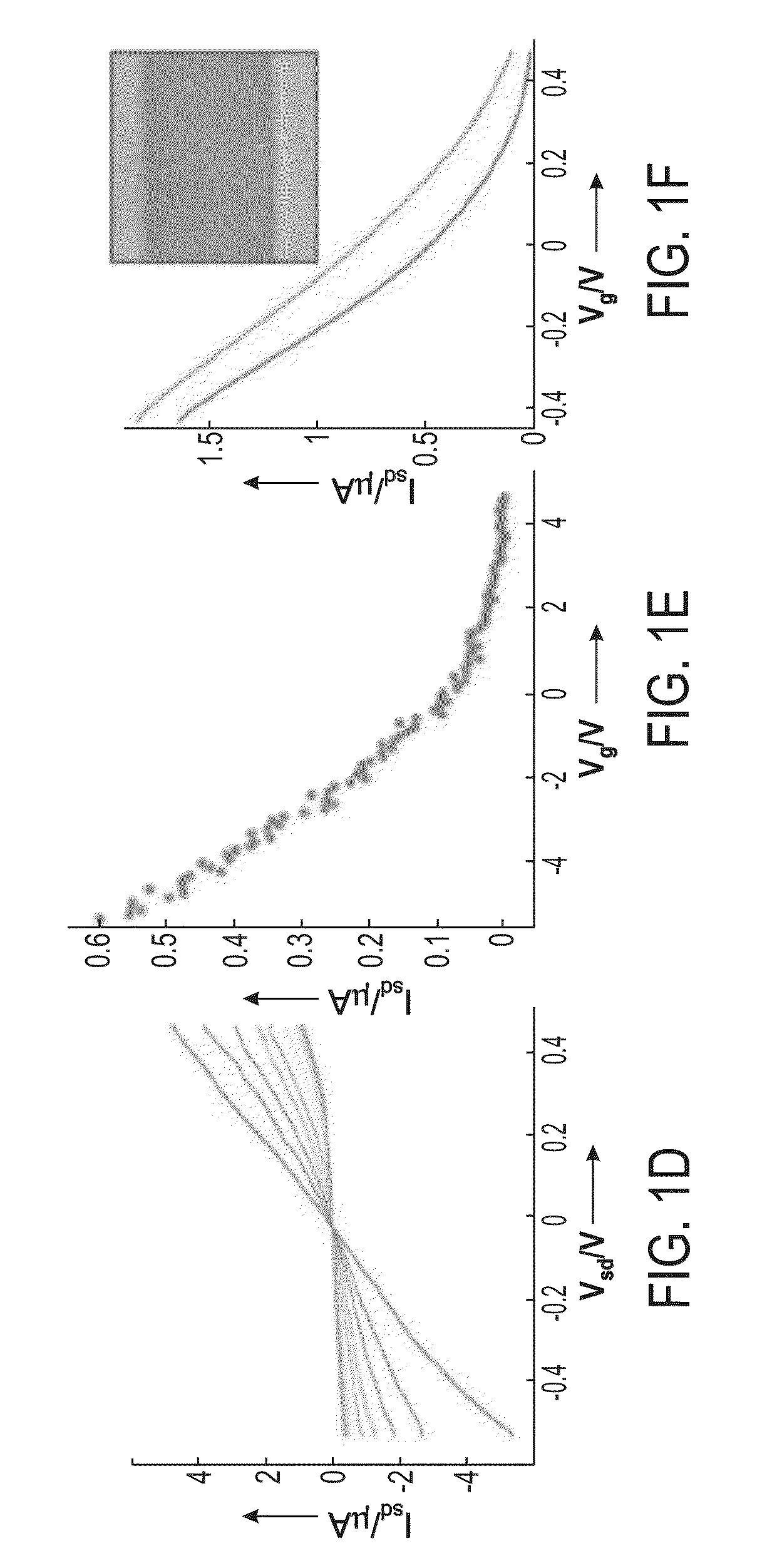

Functionalized nanostructures for detecting nitro-containing compounds

InactiveUS20130115705A1Improve abilitiesUnprecedented sensitivityFuel testingMaterial analysis by electric/magnetic meansNitro compoundLiquid state

Devices, methods and systems for detecting nitro-containing compounds such as TNT, which utilize semiconductor nanostructures modified by a functional moiety that interacts with the nitro-containing compound, are disclosed. The functional moiety is attached to the nanostructures and is being such that upon contacting a sample that contains the nitro-containing compound, the nanostructure exhibits a detectable change in an electrical property, which is indicative of the presence and / or amount of the nitro-containing compound in the sample. Electronic noses for generating recognition patterns of various nitro-containing compounds, comprising a plurality of nanostructures modified by versatile functional moieties are also disclosed. The devices, methods and systems are suitable for detecting nitro-containing compounds in both liquid and gaseous states and for detecting a concentration of a nitro-containing compound such as TNT as low as attomolar concentrations.

Owner:RAMOT AT TEL AVIV UNIV LTD

Metal assisted chemical etching to produce III-V semiconductor nanostructures

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

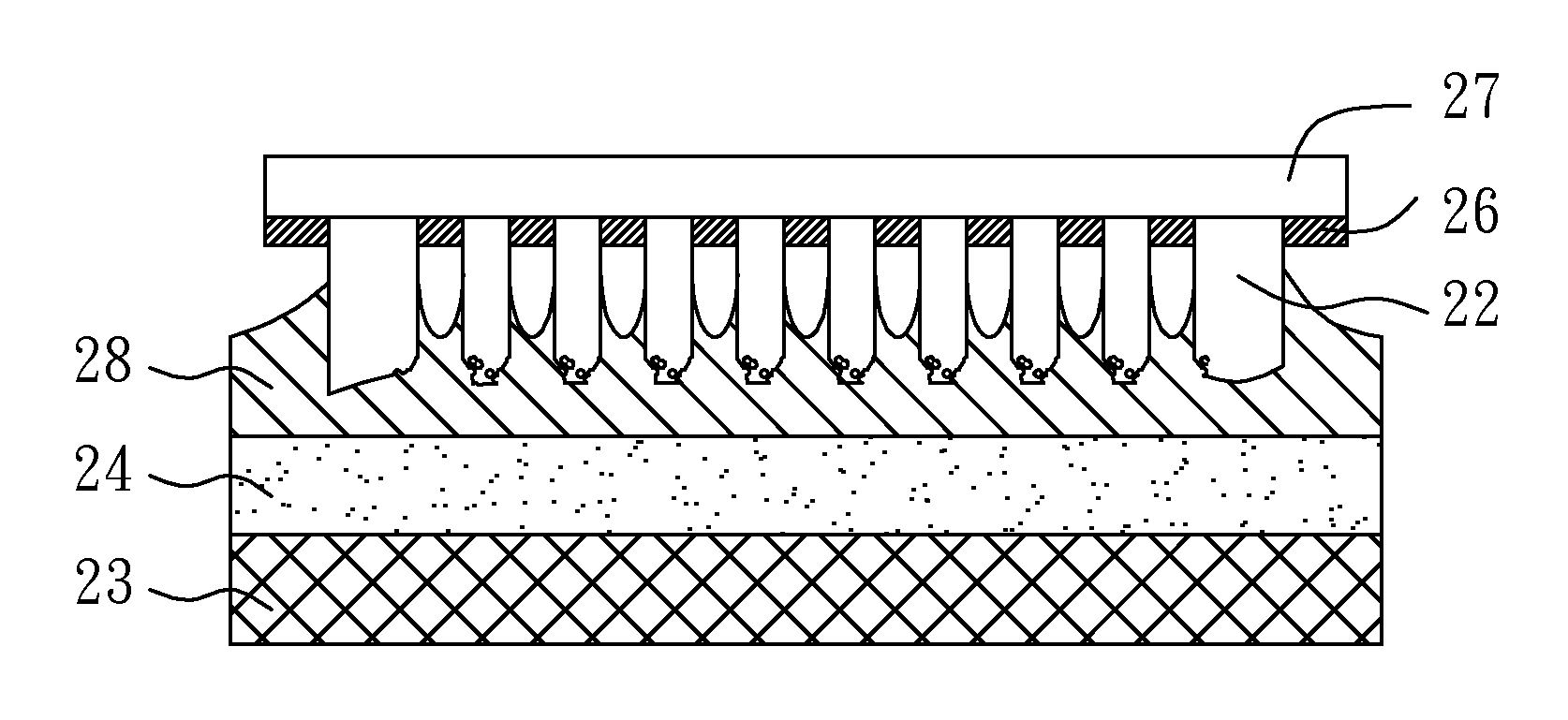

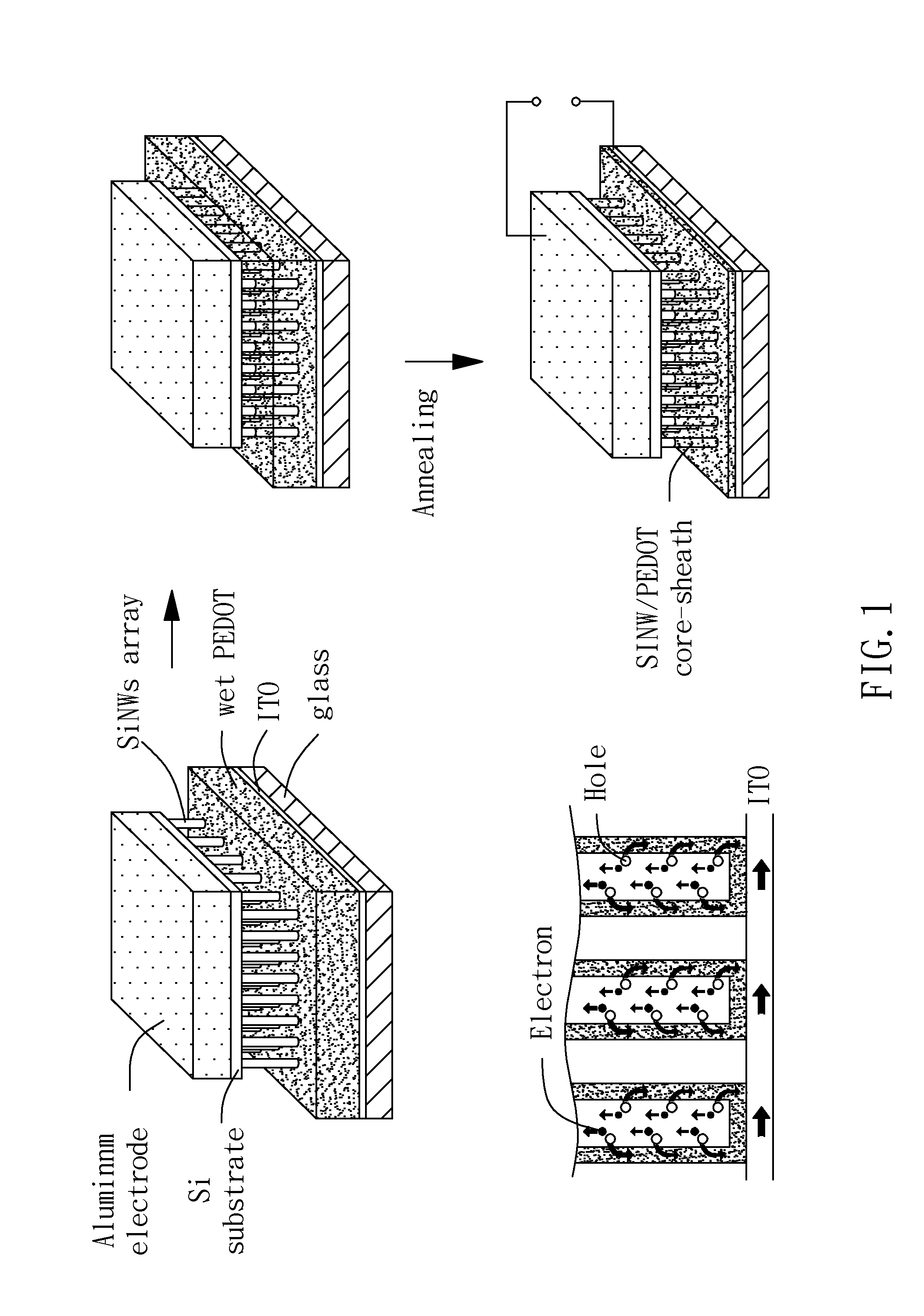

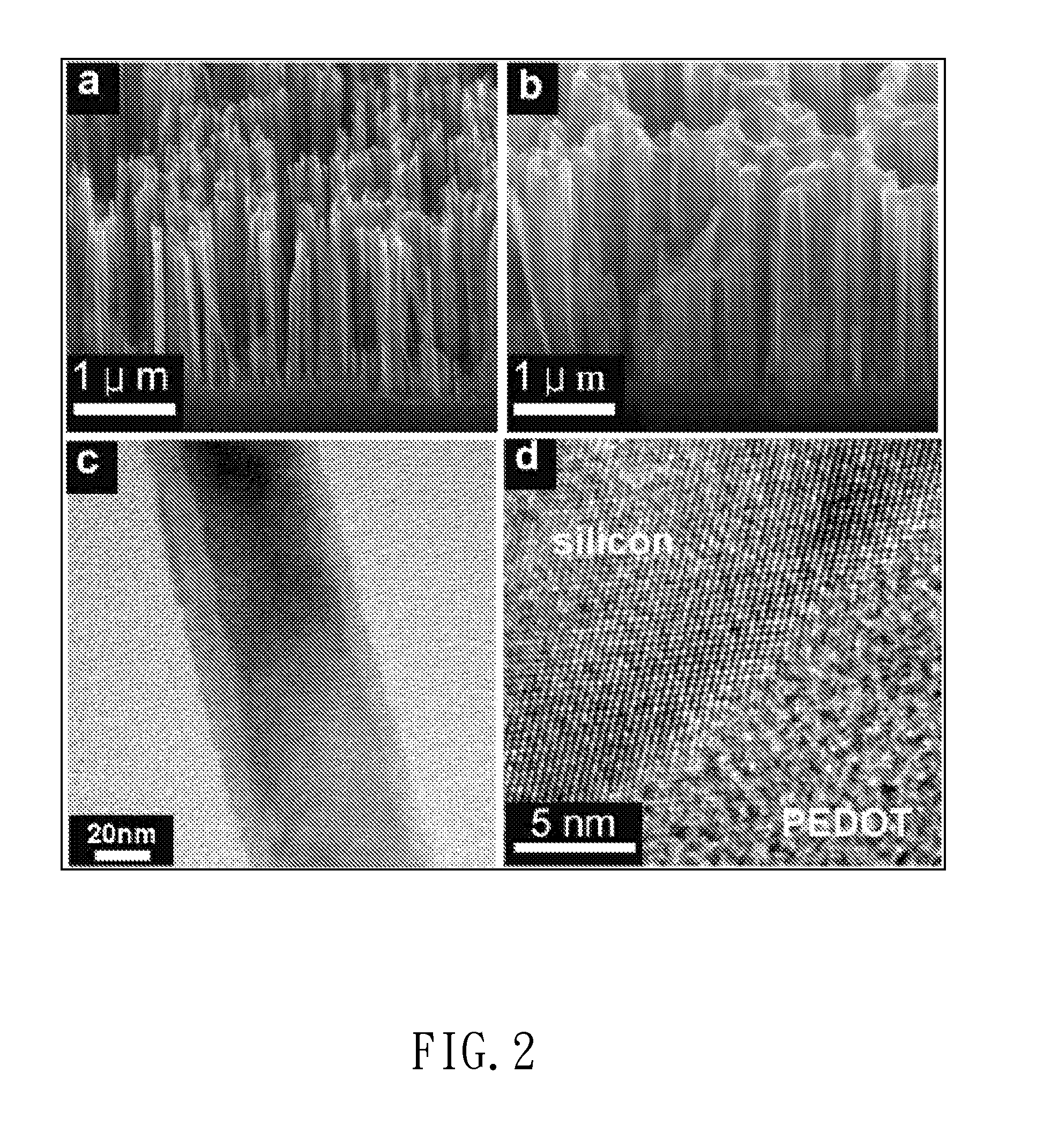

Solar cell and method for fabricating the heterojunction thereof

InactiveUS20110315201A1Improve conversion efficiencyLow costSolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionConductive polymer

Embodiments of the present invention provide methods to fabricate semiconductor nanostructure / polymer heterojunctions of solar cells. The methods comprise that a conductive polymer is adhered on the surface of semiconductor nanostructures by capillary effect and core-sheath shaped heterojunctions are formed. The incident photo-to-current conversion efficiency (IPCE) of the solar cells having core-sheath heterojunctions can reach 30% or more.

Owner:NAT TAIWAN UNIV

Highly Selective Nanostructure Sensors and Methods of Detecting Target Analytes

ActiveUS20150268207A1Improve conductivityHigh selectivityMaterial analysis by electric/magnetic meansTarget analysisMetal oxide nanoparticles

A nanostructure sensing device comprises a semiconductor nanostructure having an outer surface, and at least one of metal or metal-oxide nanoparticle clusters functionalizing the outer surface of the nanostructure and forming a photoconductive nanostructure / nanocluster hybrid sensor enabling light-assisted sensing of a target analyte.

Owner:GEORGE MASON UNIVERSITY +3

Graded hybrid amorphous silicon nanowire solar cells

The present invention is directed to compositionally-graded hybrid nanostructure-based photovoltaic devices comprising elongated semiconductor nanostructures and an amorphous semiconductor single layer with continuous gradation of doping concentration across its thickness from substantially intrinsic to substantially conductive. In other embodiments, the present invention is directed to methods of making such photovoltaic devices, as well as to applications which utilize such devices (e.g., solar cell modules).

Owner:GENERAL ELECTRIC CO

Semiconductor-graphene hybrids formed using solution growth

InactiveUS8878157B2Prevent orImprove mobilityMaterial nanotechnologySolid-state devicesNano structuringGas phase

Owner:UNIVERSITY OF KANSAS

Method for synthesizing core shell nanocrystals at high temperatures

ActiveUS20170349824A1Polycrystalline material growthFrom normal temperature solutionsCore shellMaterials science

The invention is in the field of nanostructure synthesis. The invention relates to methods for producing nanostructures, particularly Group III-V and Group II-VI semiconductor nanostructures. The invention also relates to high temperature methods of synthesizing nanostructures comprising simultaneous injection of cores and shell precursors.

Owner:SHOEI CHEM IND CO LTD

Biosensor using nanoscale material as transistor channel and method of fabricating the same

InactiveUS8013366B2Individual molecule manipulationSemiconductor/solid-state device detailsElectricityNanometre

Owner:SAMSUNG ELECTRONICS CO LTD

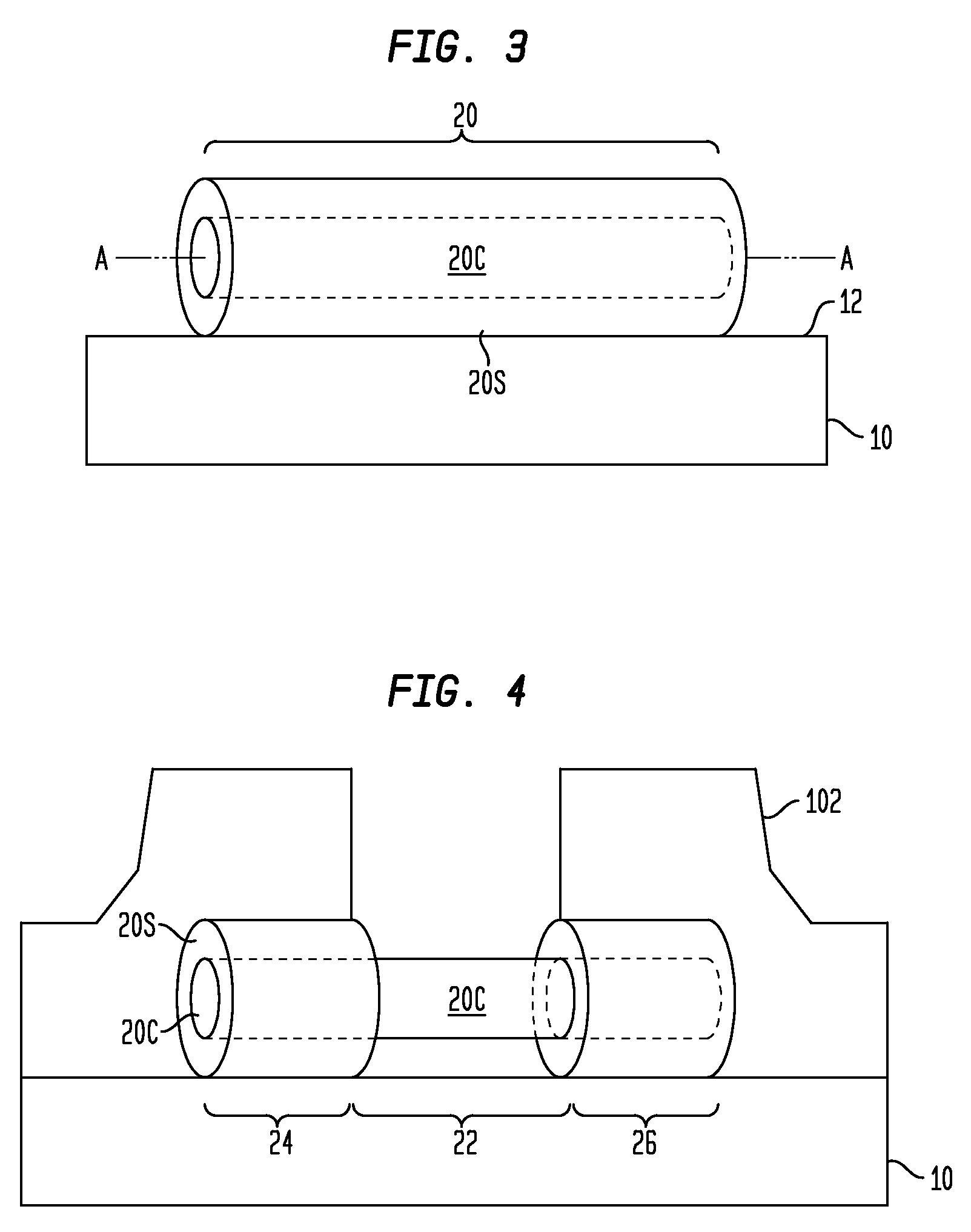

Semiconductor nanostructures, semiconductor devices, and methods of making same

A semiconductor structure is provided, which includes multiple sections arranged along a longitudinal axis. Preferably, the semiconductor structure comprises a middle section and two terminal sections located at opposite ends of the middle section. A semiconductor core having a first dopant concentration preferably extends along the longitudinal axis through the middle section and the two terminal sections. A semiconductor shell having a second, higher dopant concentration preferably encircles a portion of the terminal sections, but not at the middle section, of the semiconductor structure. It is particularly preferred that the semiconductor structure is a nanostructure having a cross-sectional dimension of not more than 100 nm.

Owner:GLOBALFOUNDRIES INC

Field effect transistor

ActiveUS8106382B2Increase resistanceSuppress mutationNanoinformaticsSemiconductor/solid-state device manufacturingHigh concentrationField-effect transistor

A source electrode 105 which is connected to a portion of at least one semiconductor nanostructure103 among a plurality of semiconductor nanostructures, a drain electrode 106 connected to another portion of the semiconductor nanostructure 103, and a gate electrode 102 capable of controlling electrical conduction of the semiconductor nanostructure 103 are included. The semiconductor nanostructures 103 include a low concentration region 108 having a relatively low doping concentration and a pair of high concentration regions 107 having a higher doping concentration than that of the low concentration region 108 and being connected to both ends of the low concentration region 108. The doping concentration of the high concentration regions 107 is 1×1019 cm−3 or more; the length of the low concentration region 108 is shorter than a length of the gate electrode 102 along a direction from the source electrode 105 to the drain electrode 106; and the length of the gate electrode 102 is shorter than the interspace between the source electrode 105 and the drain electrode 106.

Owner:JOLED INC

Method of forming an array of high aspect ratio semiconductor nanostructures

A new method for forming an array of high aspect ratio semiconductor nanostructures entails positioning a surface of a stamp comprising a solid electrolyte in opposition to a conductive film disposed on a semiconductor substrate. The surface of the stamp includes a pattern of relief features in contact with the conductive film so as to define a film-stamp interface. A flux of metal ions is generated across the film-stamp interface, and a pattern of recessed features complementary to the pattern of relief features is created in the conductive film. The recessed features extend through an entire thickness of the conductive film to expose the underlying semiconductor substrate and define a conductive pattern on the substrate. The stamp is removed, and material immediately below the conductive pattern is selectively removed from the substrate. Features are formed in the semiconductor substrate having a length-to-width aspect ratio of at least about 5:1.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

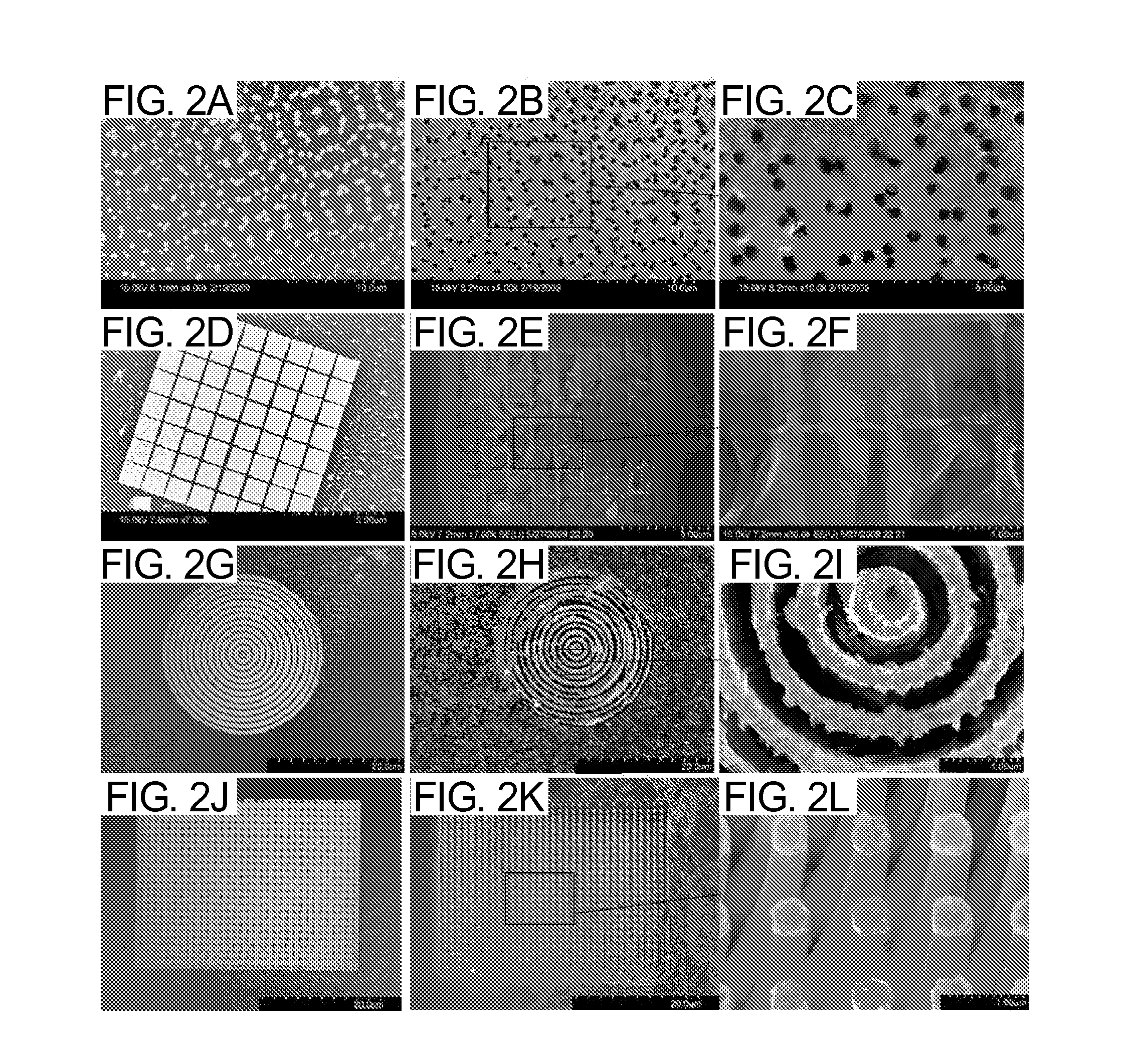

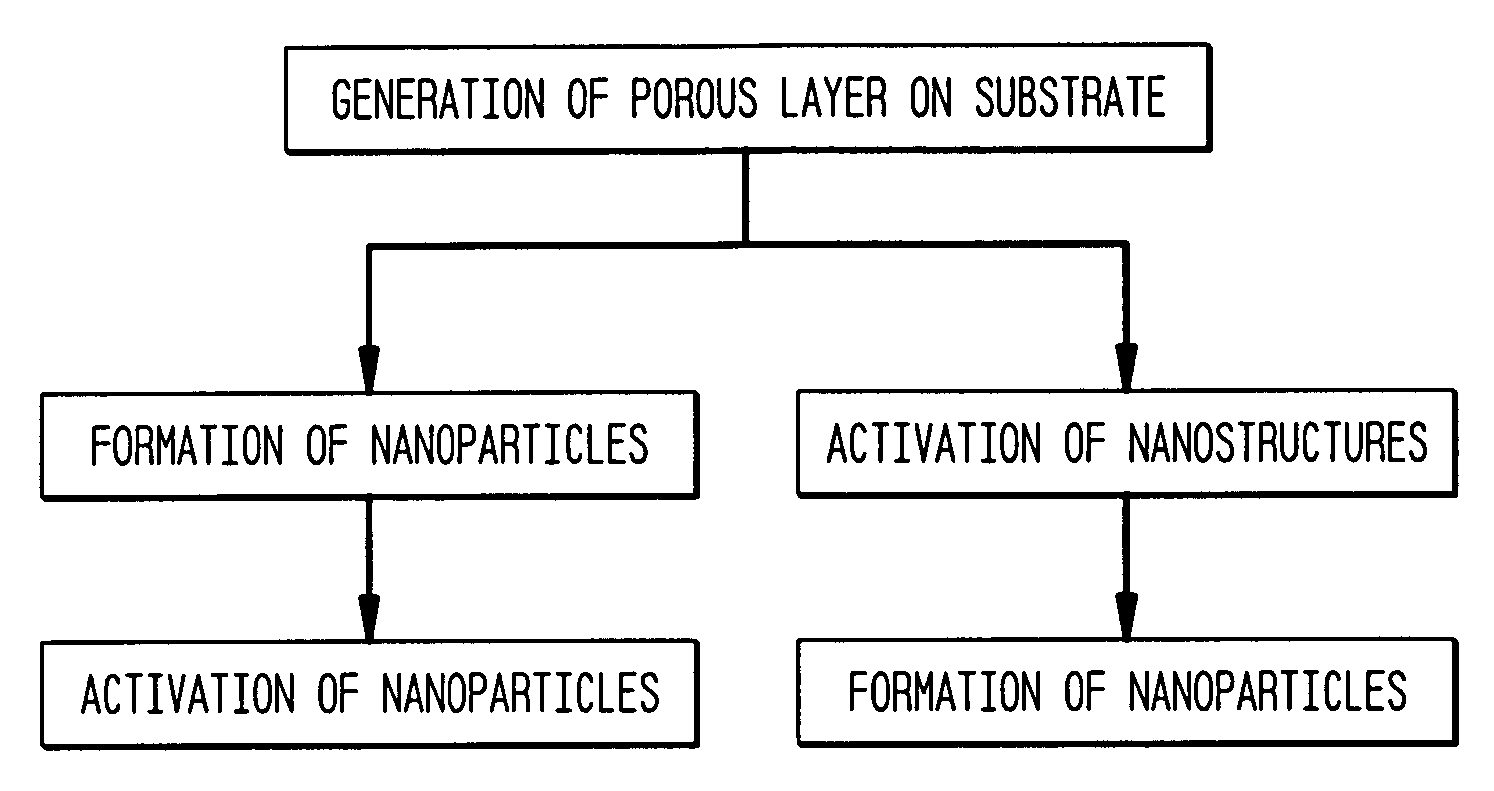

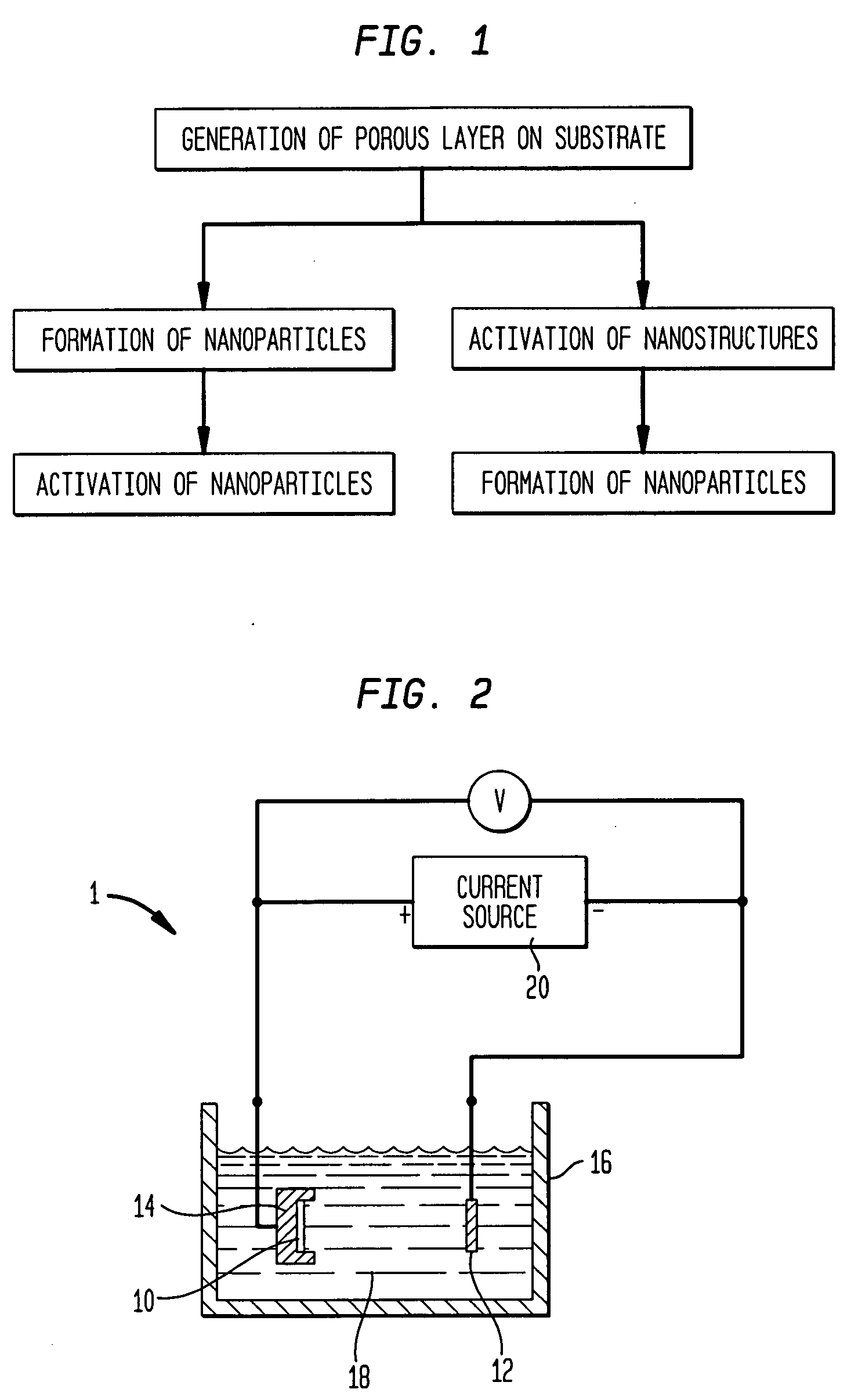

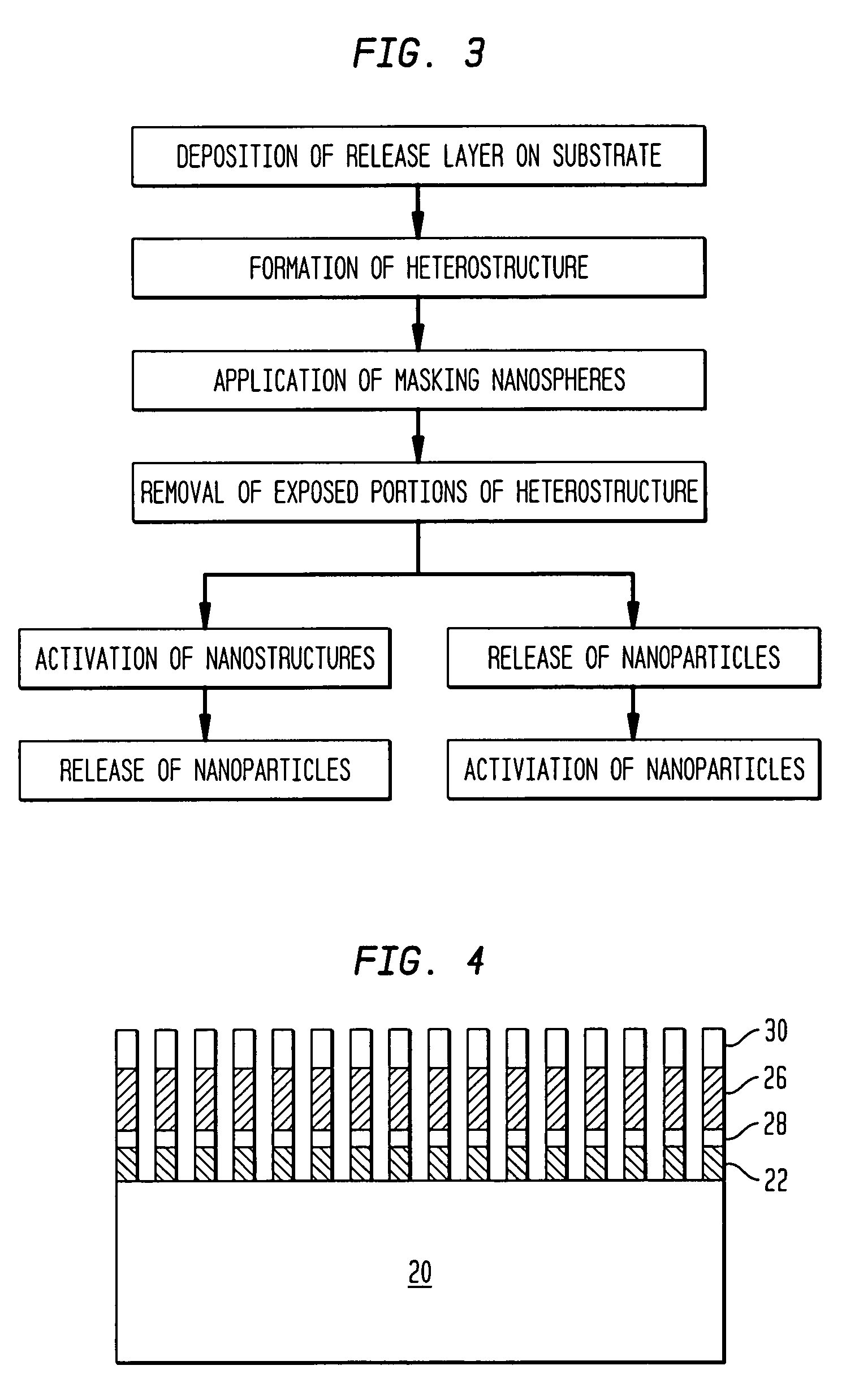

Surface-activation of semiconductor nanostructures for biological applications

InactiveUS20060116002A1Improve hydrophilicityNanoinformaticsMaterial analysis by optical meansFluorescencePorous layer

The present invention provides means and methods for producing surface-activated semiconductor nanoparticles suitable for in vitro and in vivo applications that can fluoresce in response to light excitation. Semiconductor nanostructures can be produced by generating a porous layer in semiconductor substrate comprising a network of nanostructures. Prior or subsequent to cleavage from the substrate, the nanostructures can be activated by an activation means such as exposing their surfaces to a plasma, oxidation or ion implantation. In some embodiments, the surface activation renders the nanostructures more hydrophilic, thereby facilitating functionalization of the nanoparticles for either in vitro or in vivo use.

Owner:SPIRE

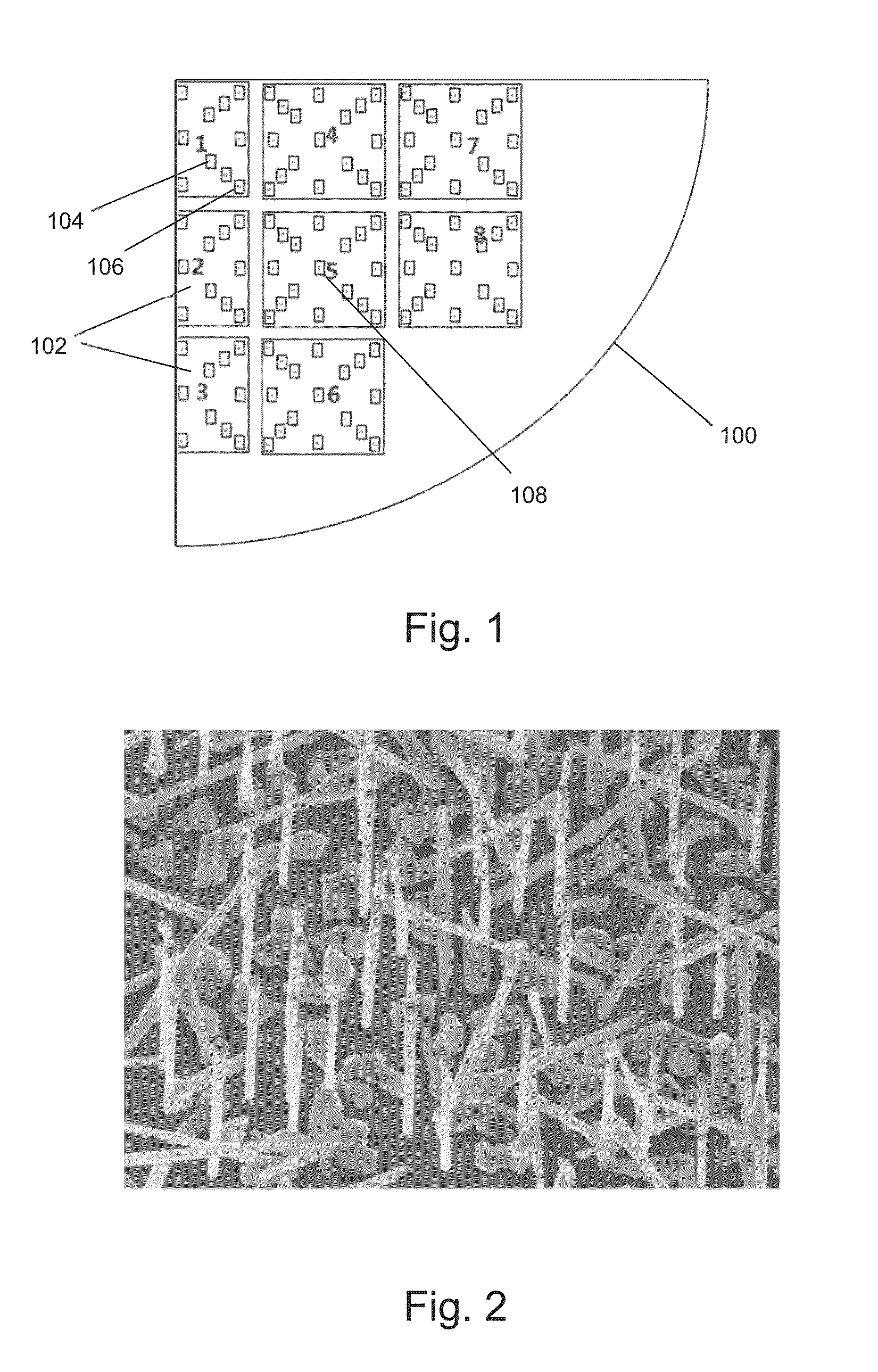

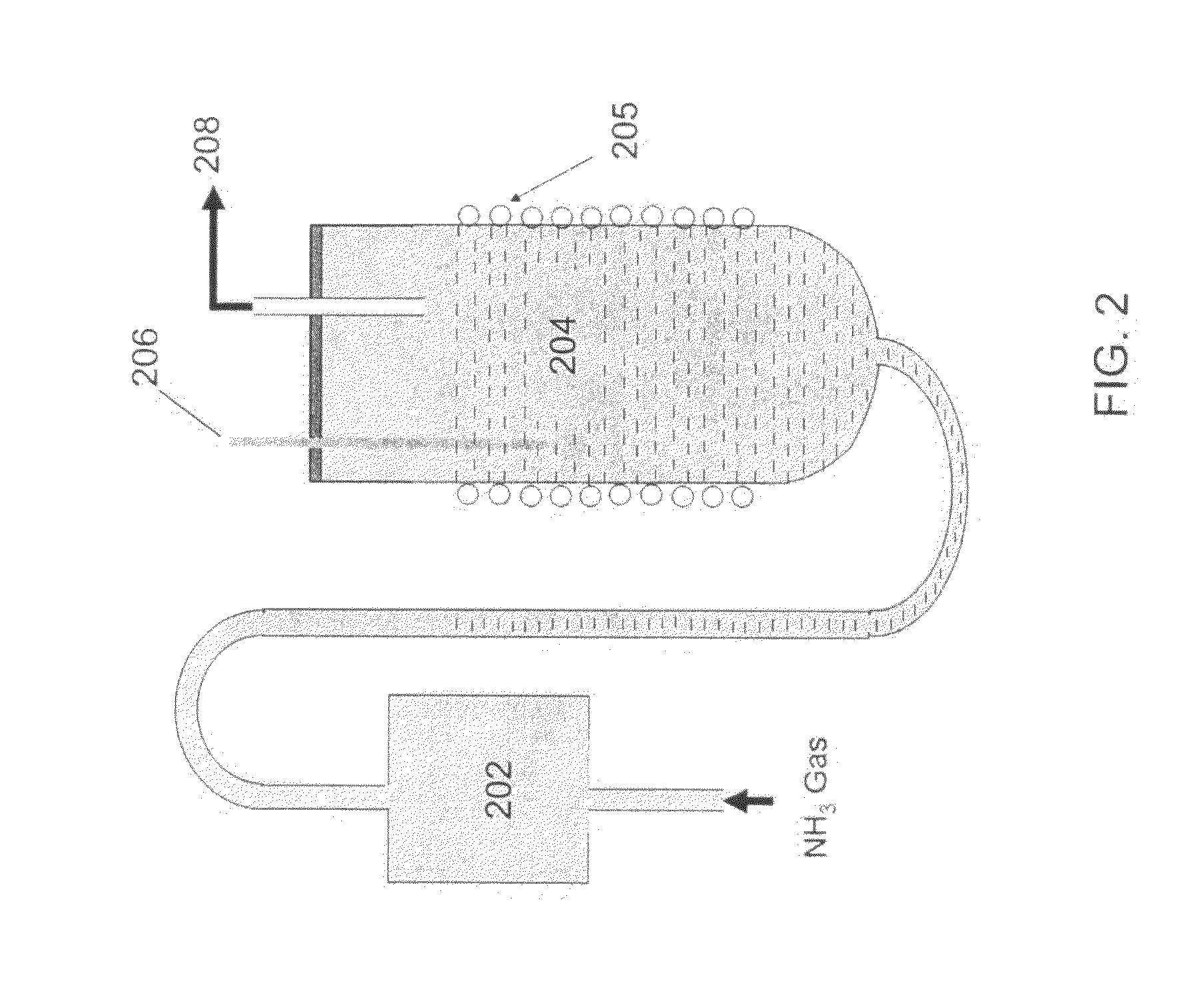

Method of preparing a substrate for nanowire growth, and a method of fabricating an array of semiconductor nanostructures

InactiveUS20150311072A1Ensure growthInhibition formationSemiconductor/solid-state device manufacturingNanotechnologyThin oxideNanowire

The present invention provides a reproducible preliminary in-situ oxide removal step for patterned self-assisted III-V semiconductor nanowire growth. Here “in-situ” means located within the same treatment environment or apparatus as the nanowire growth process, e.g. with a molecular beam epitaxy (MBE) apparatus or the like. Providing an in-situ process may prevent the formation of a thin oxide layer during transfer of the substrate into the nanowire growth apparatus.

Owner:GASP SOLAR APS +1

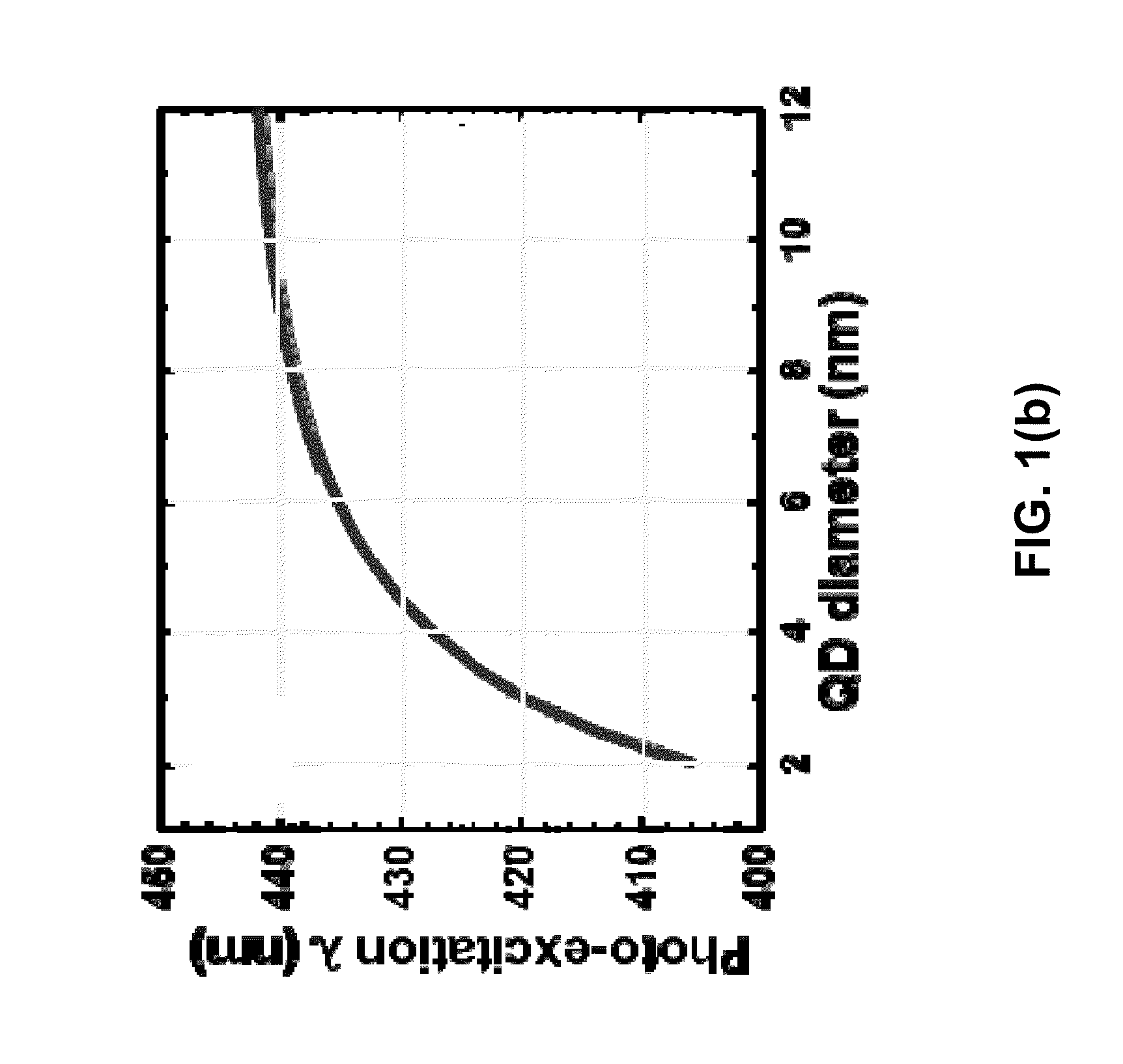

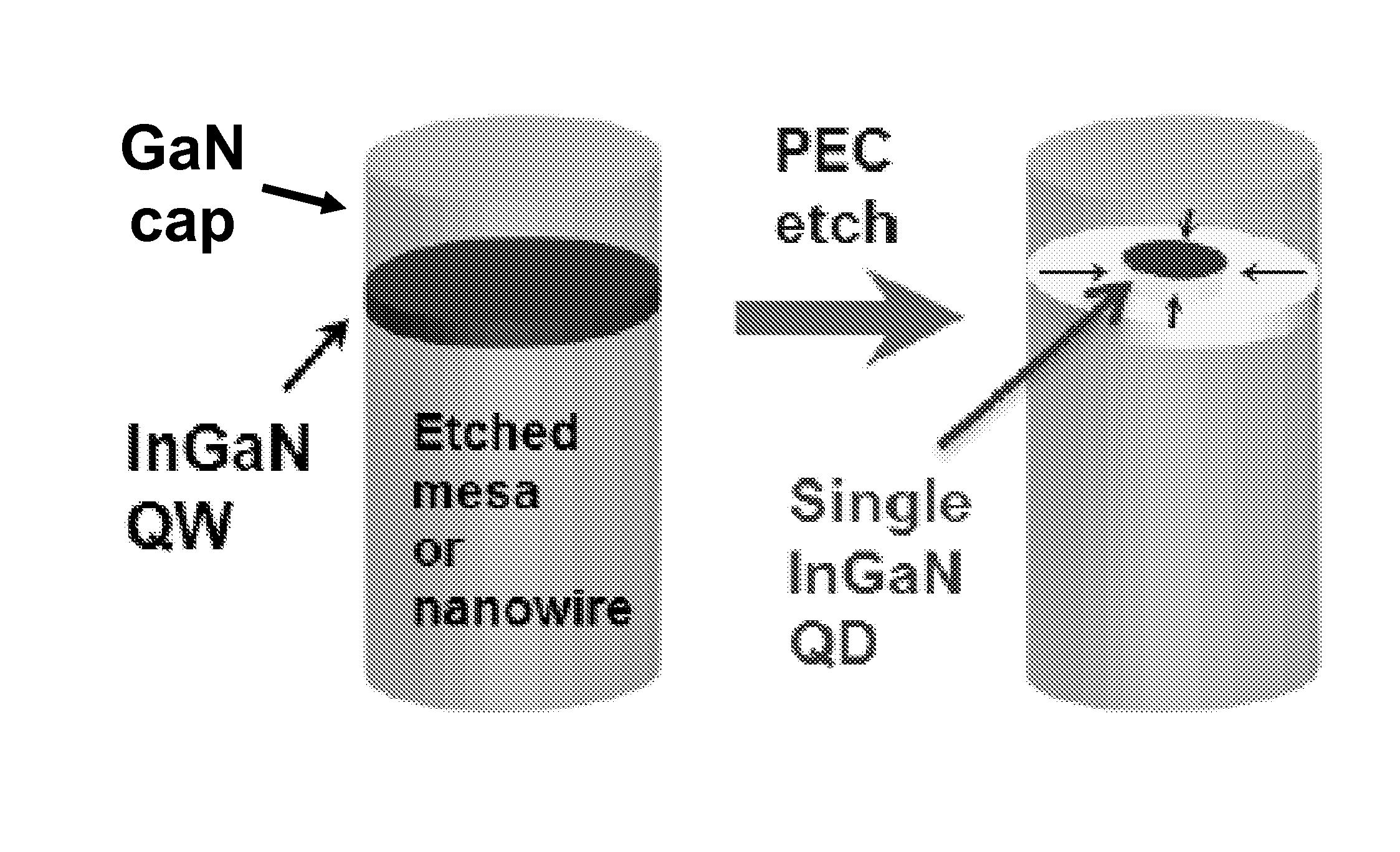

Quantum-size-controlled photoelectrochemical etching of semiconductor nanostructures

ActiveUS9276382B2Increase etch rateIncrease of bandgapsLaser detailsIndividual molecule manipulationPhotoelectrochemical etchingPhotoluminescence

Quantum-size-controlled photoelectrochemical (QSC-PEC) etching provides a new route to the precision fabrication of epitaxial semiconductor nanostructures in the sub-10-nm size regime. For example, quantum dots (QDs) can be QSC-PEC-etched from epitaxial InGaN thin films using narrowband laser photoexcitation, and the QD sizes (and hence bandgaps and photoluminescence wavelengths) are determined by the photoexcitation wavelength.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

Highly selective nanostructure sensors and methods of detecting target analytes

ActiveUS9476862B2High selectivityLow power operationMaterial analysis by electric/magnetic meansAnalysis by subjecting material to chemical reactionMetal oxide nanoparticlesAnalyte

A nanostructure sensing device comprises a semiconductor nanostructure having an outer surface, and at least one of metal or metal-oxide nanoparticle clusters functionalizing the outer surface of the nanostructure and forming a photoconductive nanostructure / nanocluster hybrid sensor enabling light-assisted sensing of a target analyte.

Owner:GEORGE MASON UNIVERSITY +3

Plasmon lasers at deep subwavelength scale

ActiveUS8509276B2Efficient generation of sub-wavelength high intensity lightPotentialOptical wave guidanceLaser active region structureModulation bandwidthPlasmonic waveguide

Hybrid plasmonic waveguides are described that employ a high-gain semiconductor nanostructure functioning as a gain medium that is separated from a metal substrate surface by a nanoscale thickness thick low-index gap. The waveguides are capable of efficient generation of sub-wavelength high intensity light and have the potential for large modulation bandwidth >1 THz.

Owner:RGT UNIV OF CALIFORNIA

Quantum-Size-Controlled Photoelectrochemical Etching of Semiconductor Nanostructures

ActiveUS20150270136A1Increase etch rateLower the volumeLaser detailsIndividual molecule manipulationPhotoelectrochemical etchingPhotoluminescence

Quantum-size-controlled photoelectrochemical (QSC-PEC) etching provides a new route to the precision fabrication of epitaxial semiconductor nanostructures in the sub-10-nm size regime. For example, quantum dots (QDs) can be QSC-PEC-etched from epitaxial InGaN thin films using narrowband laser photoexcitation, and the QD sizes (and hence bandgaps and photoluminescence wavelengths) are determined by the photoexcitation wavelength.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

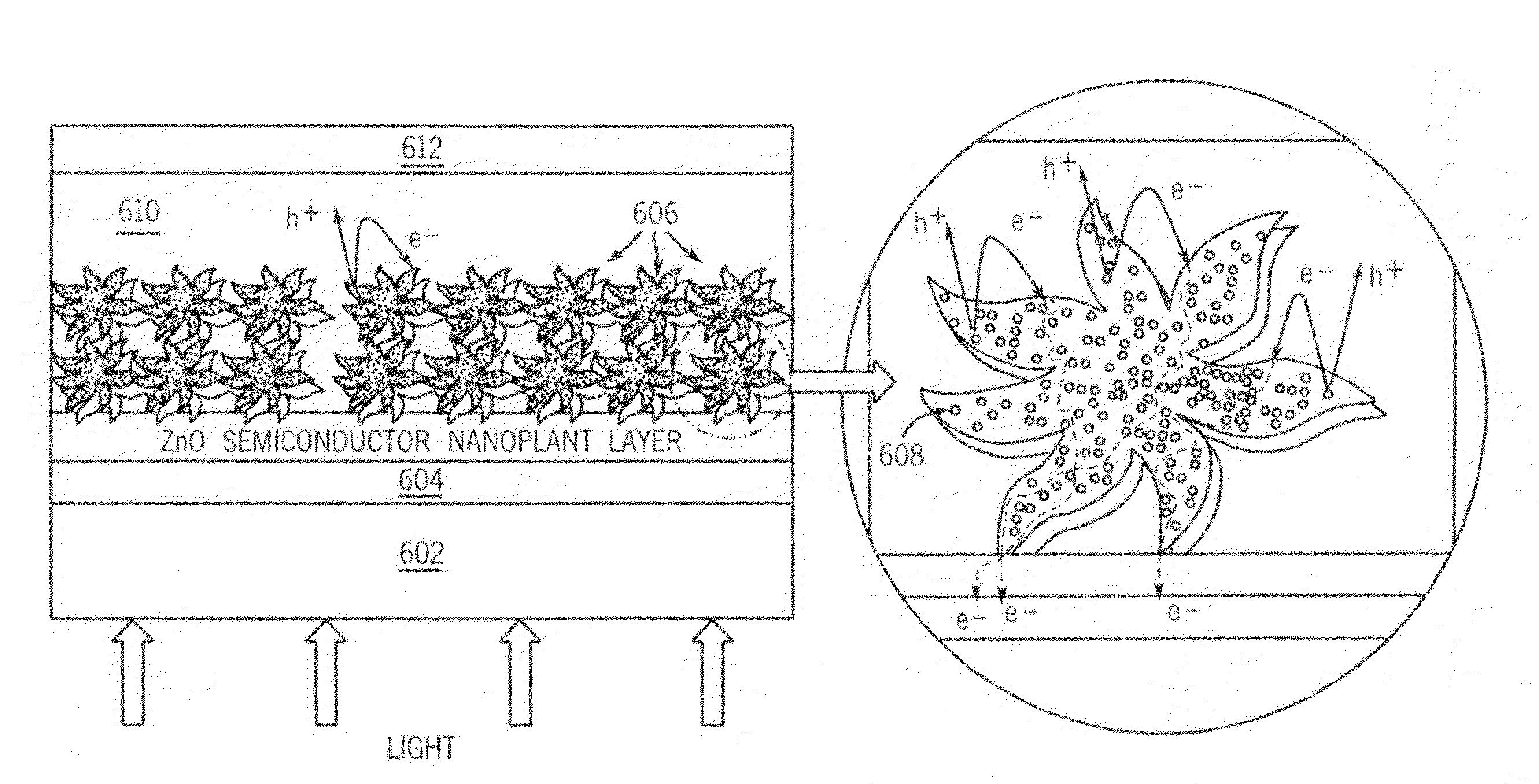

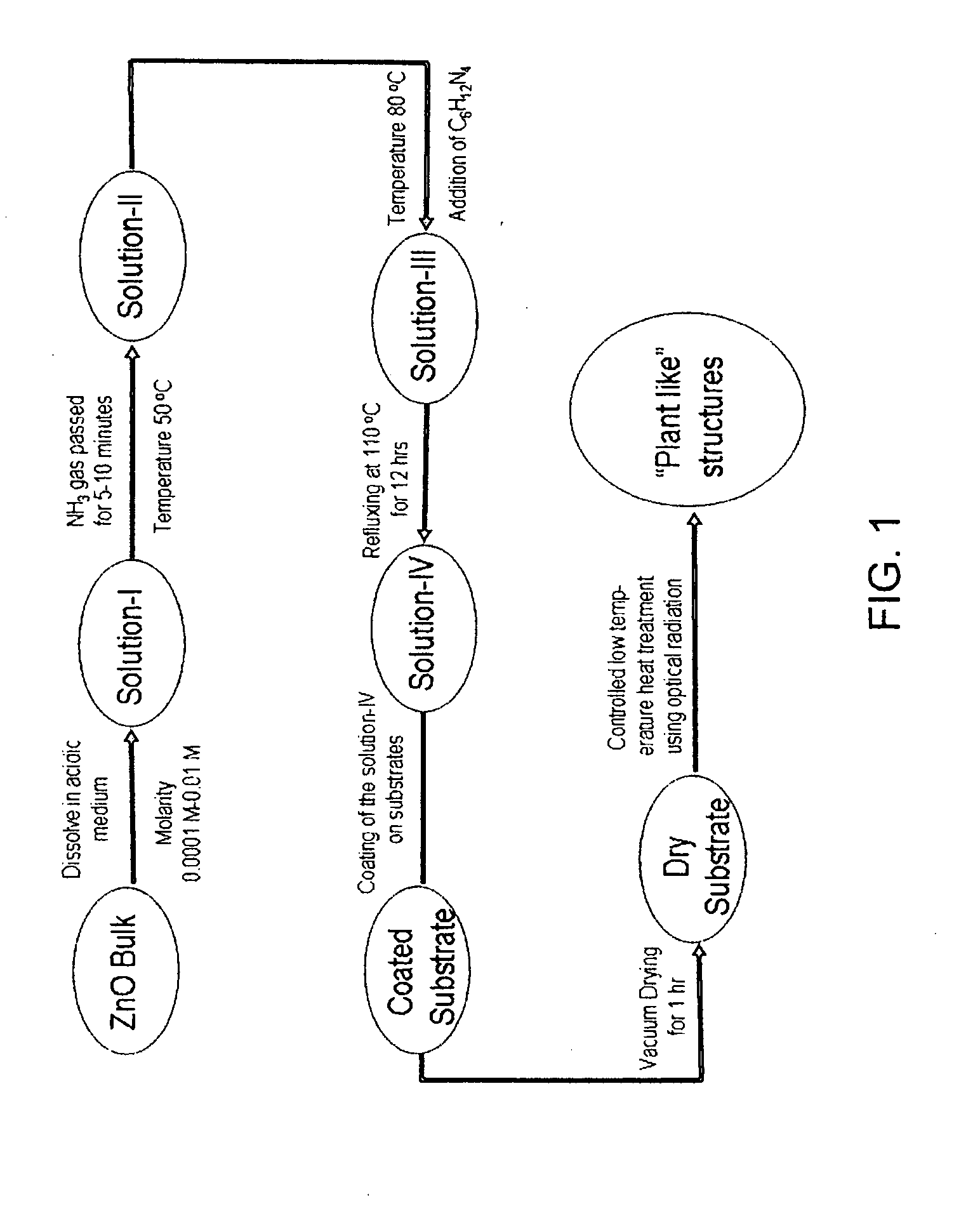

METHODS OF FABRICATING NANOSTRUCTURED ZnO ELECTRODES FOR EFFICIENT DYE SENSITIZED SOLAR CELLS

InactiveUS20090008637A1Large specific surface areaQuick collectionMaterial nanotechnologyPolycrystalline material growthZincNanometre

The present invention provides methods of forming metal oxide semiconductor nanostructures and, in particular, zinc oxide (ZnO) semiconductor nanostructures, possessing high surface area, plant-like morphologies on a variety of substrates. Optoelectronic devices, such as photovoltaic cells, incorporating the nanostructures are also provided.

Owner:UNIV OF UTAH RES FOUND

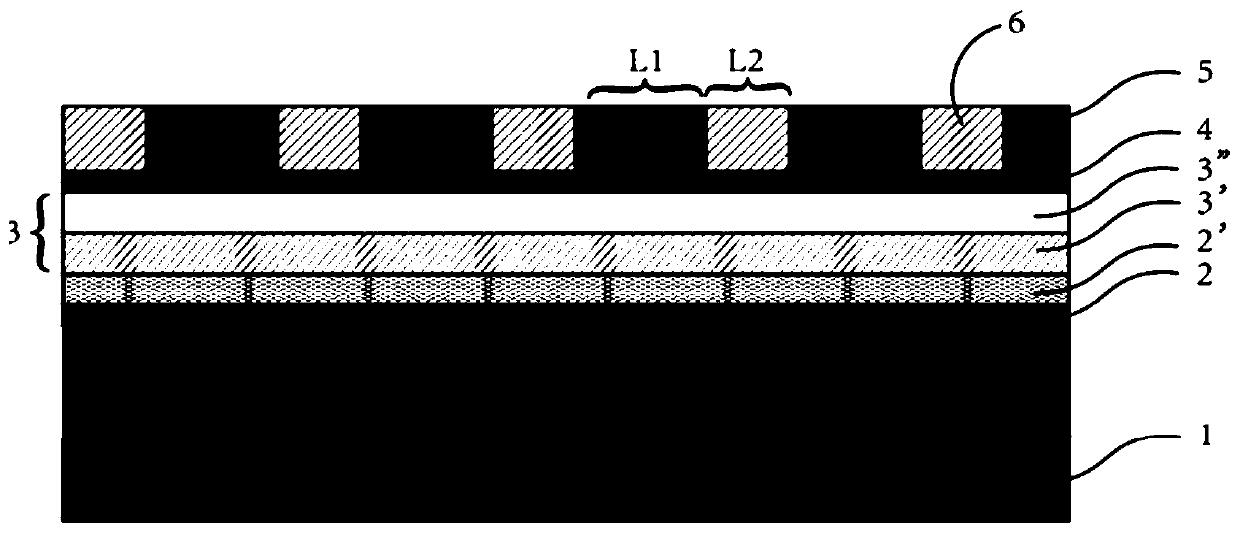

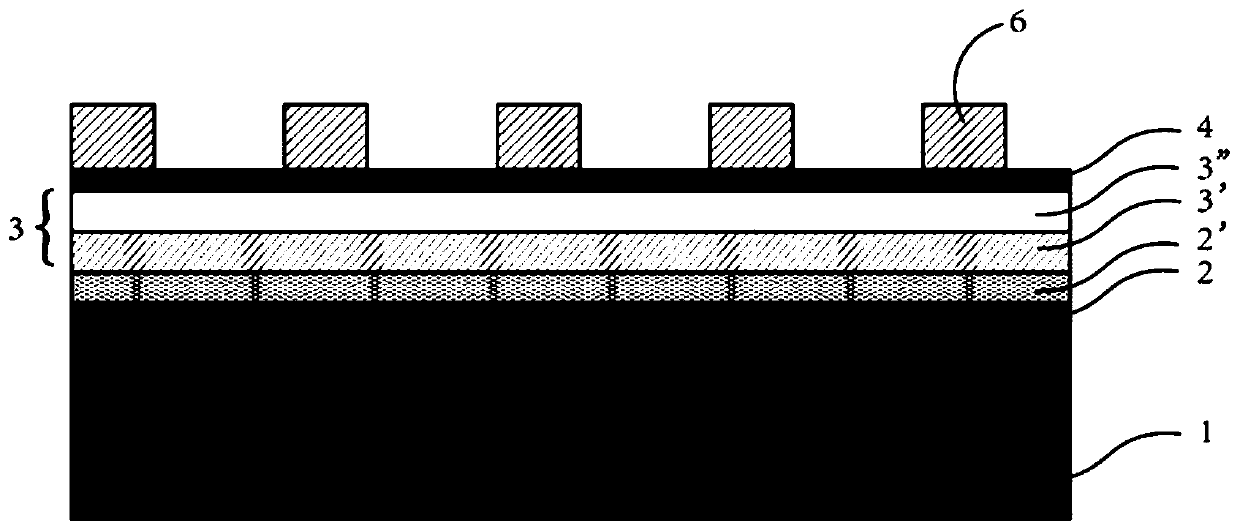

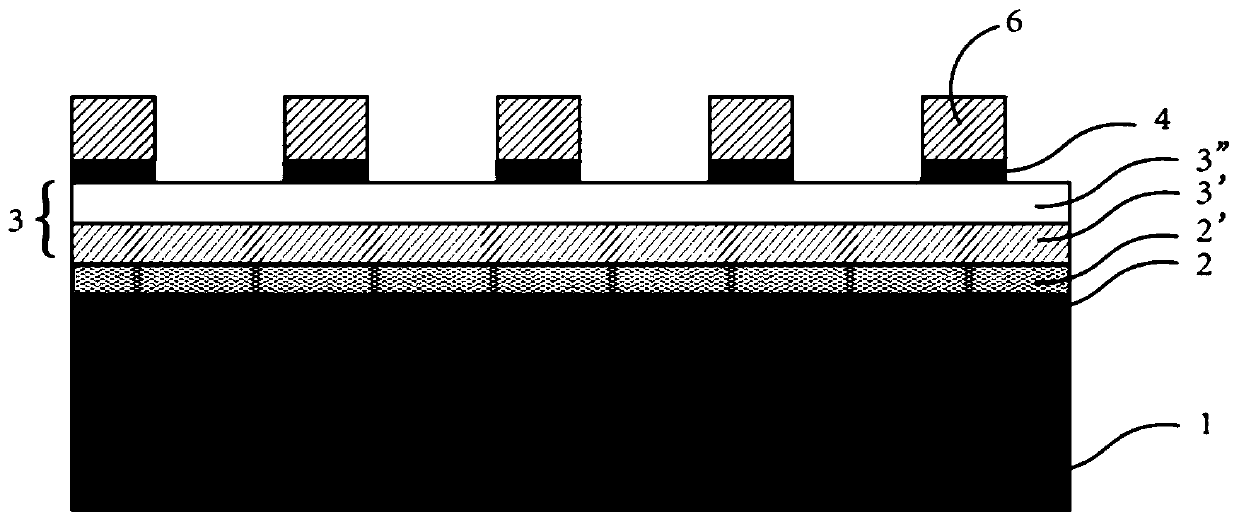

Method for preparing semiconductor nanostructure through directional self-assembly and mask regulation and control

PendingCN110993566ASolving Process Control IssuesReduce heavy dependenceSemiconductor/solid-state device manufacturingEngineeringDielectric layer

The invention discloses a method for preparing a semiconductor nanostructure through directional self-assembly and mask regulation and control. The method comprises: forming a double-layer hard mask layer, a photoetching stacking layer and a buffer layer on a semiconductor substrate, spin-coating a block copolymer (BCP) layer on the buffer layer, and annealing to form a self-assembly template pattern; removing a certain block then to form a photoetching pattern, sequentially transferring the pattern to a buffer layer, a photoetching stacking layer and a second hard mask layer, depositing a dielectric layer on the patterned second hard mask layer, flattening, removing the second hard mask layer then, and transferring the pattern to a first mask layer and a semiconductor substrate by takingthe patterned dielectric layer as a mask. According to the method, the problem of directional self-assembly caused by the thickness of the block copolymer and low etching selectivity among different block molecules in the existing pattern transfer process can be greatly solved.

Owner:CHENGDU TECHCAL UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com