Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

134 results about "Read-modify-write" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, read–modify–write is a class of atomic operations (such as test-and-set, fetch-and-add, and compare-and-swap) that both read a memory location and write a new value into it simultaneously, either with a completely new value or some function of the previous value. These operations prevent race conditions in multi-threaded applications. Typically they are used to implement mutexes or semaphores. These atomic operations are also heavily used in non-blocking synchronization.

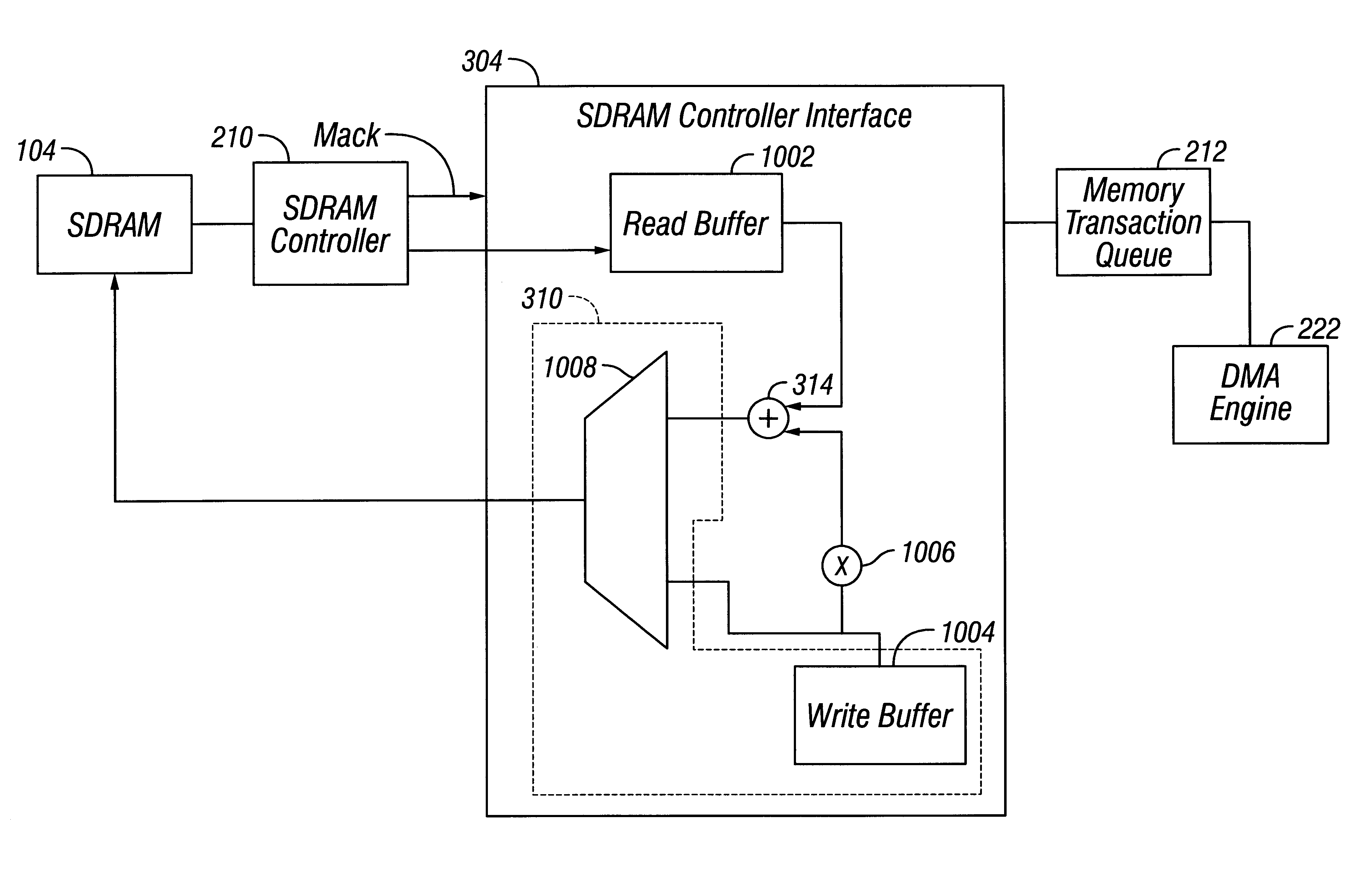

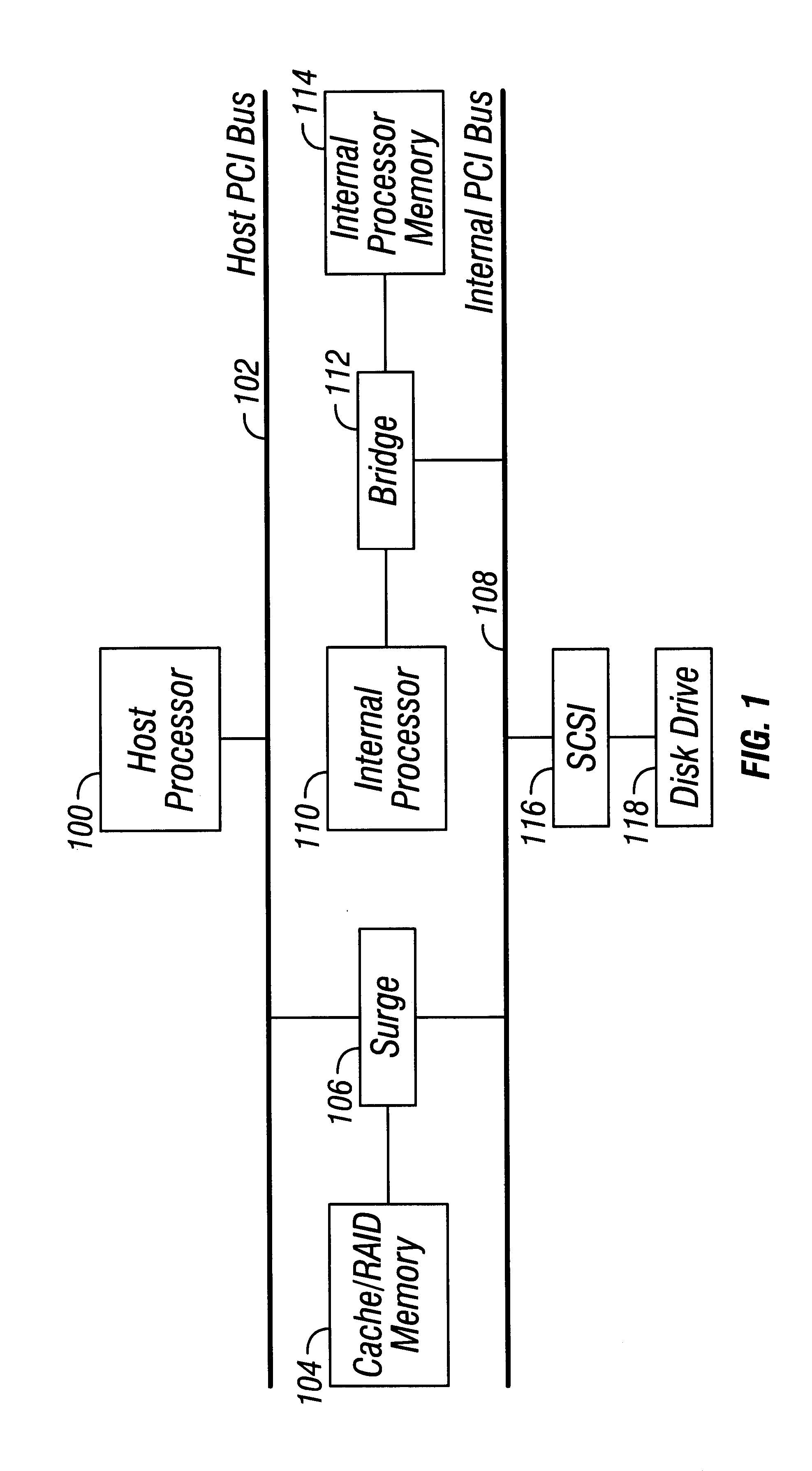

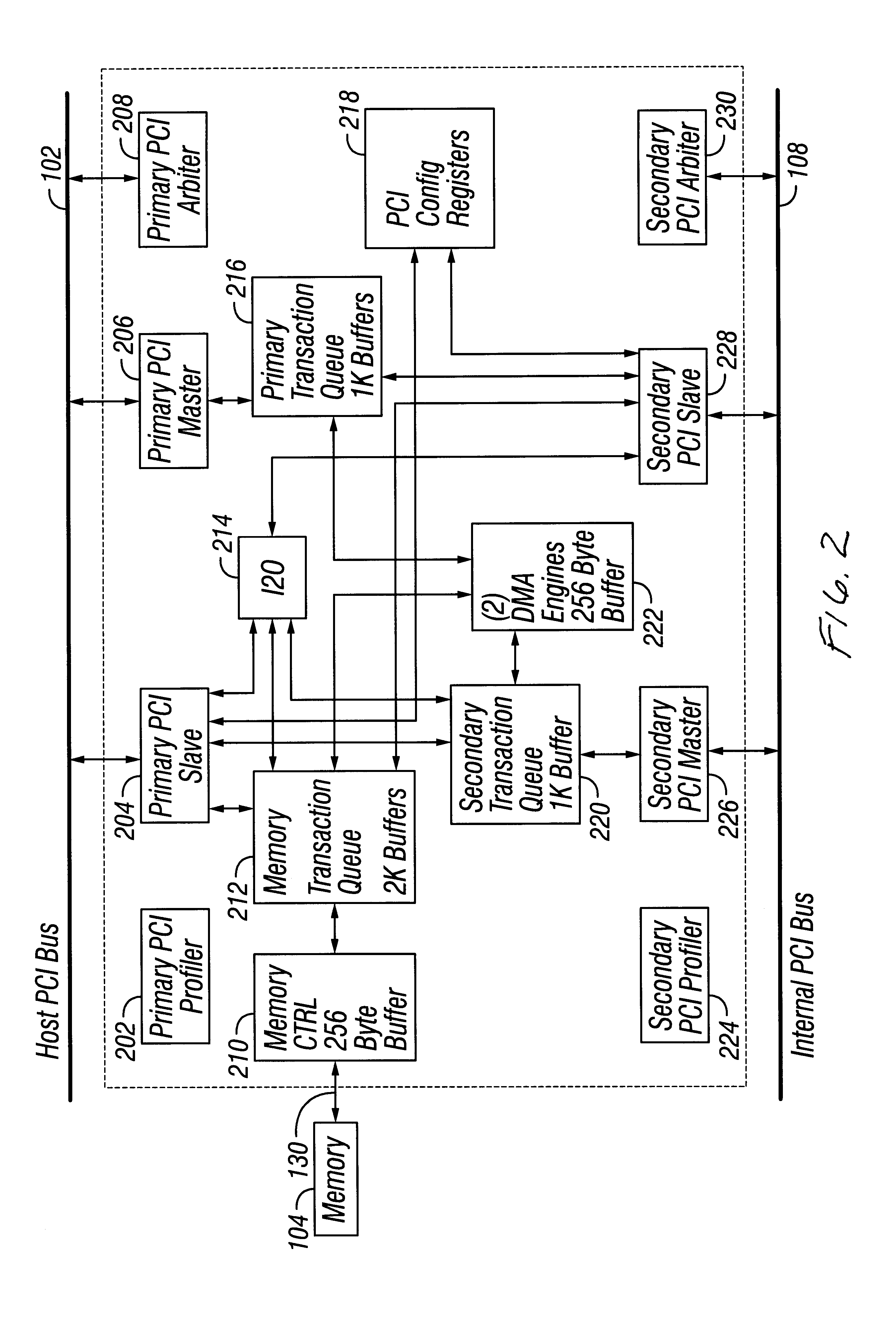

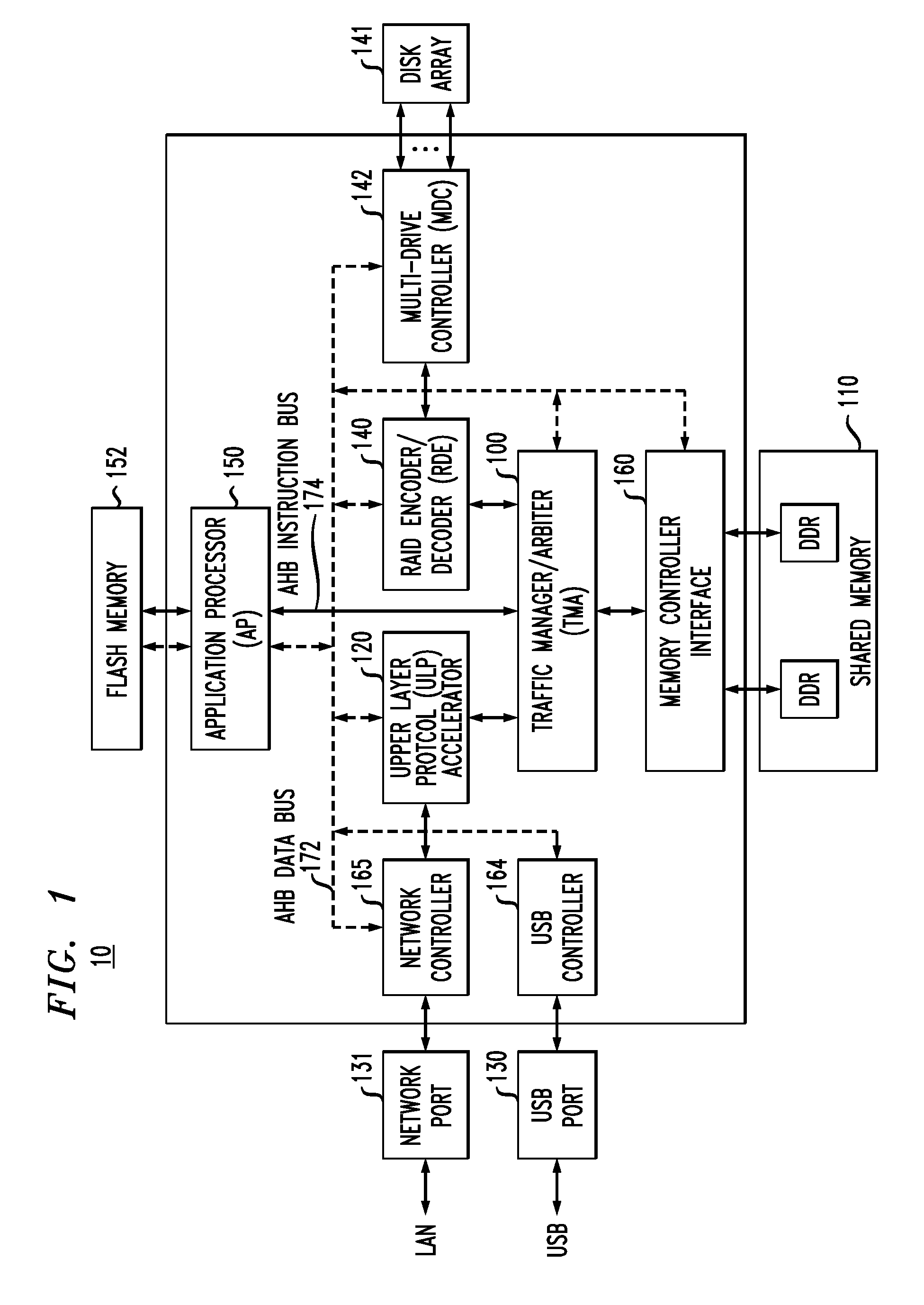

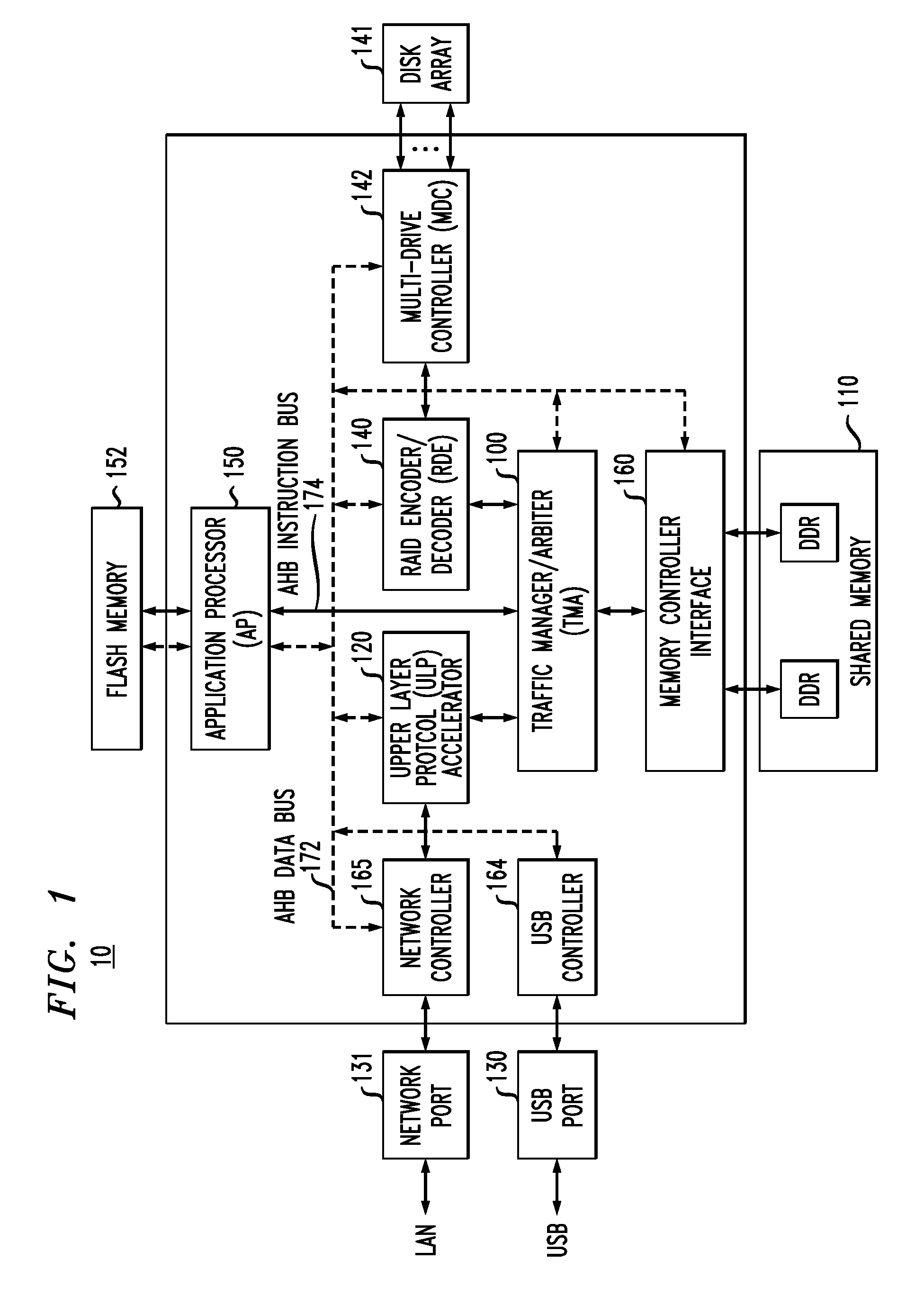

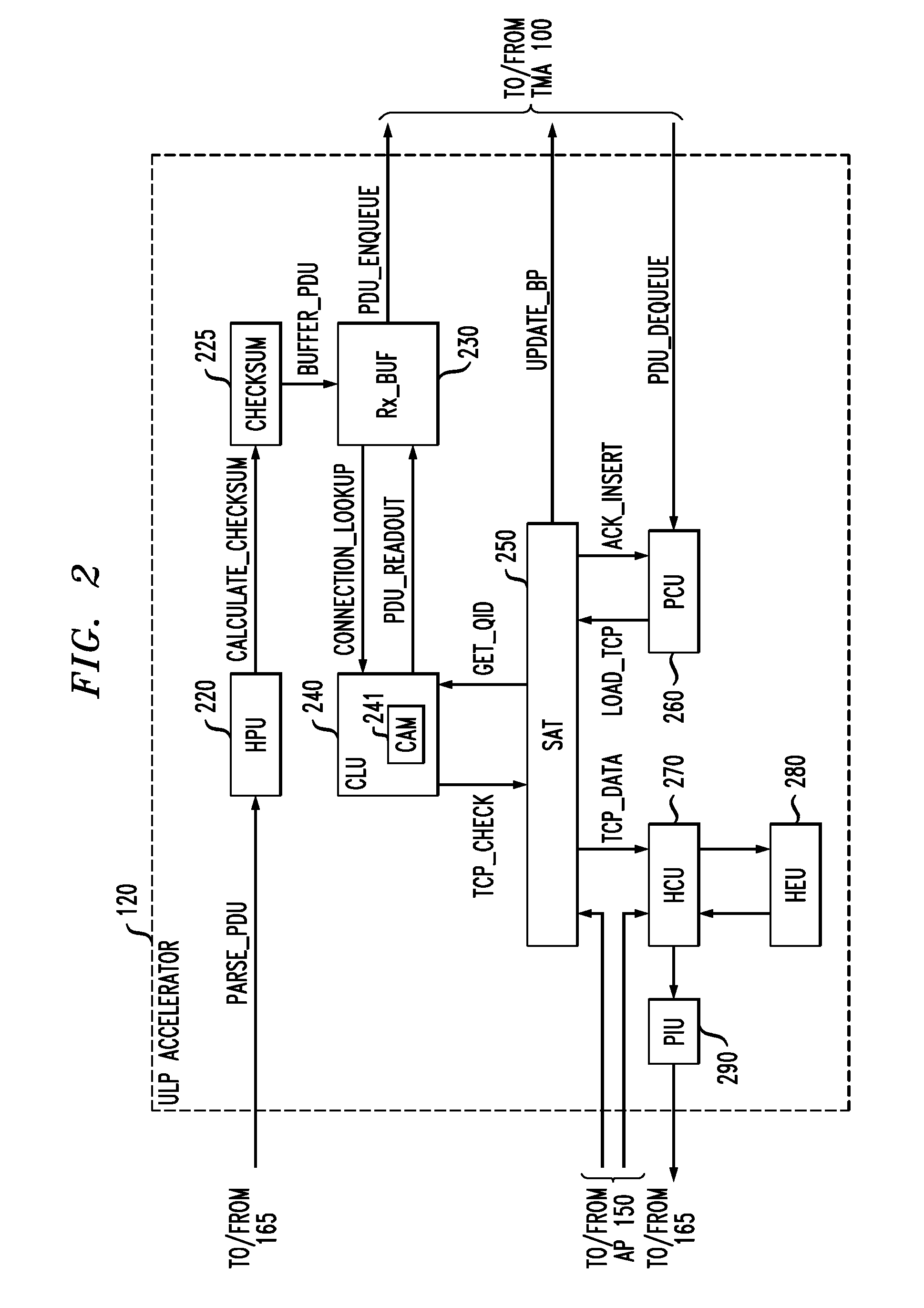

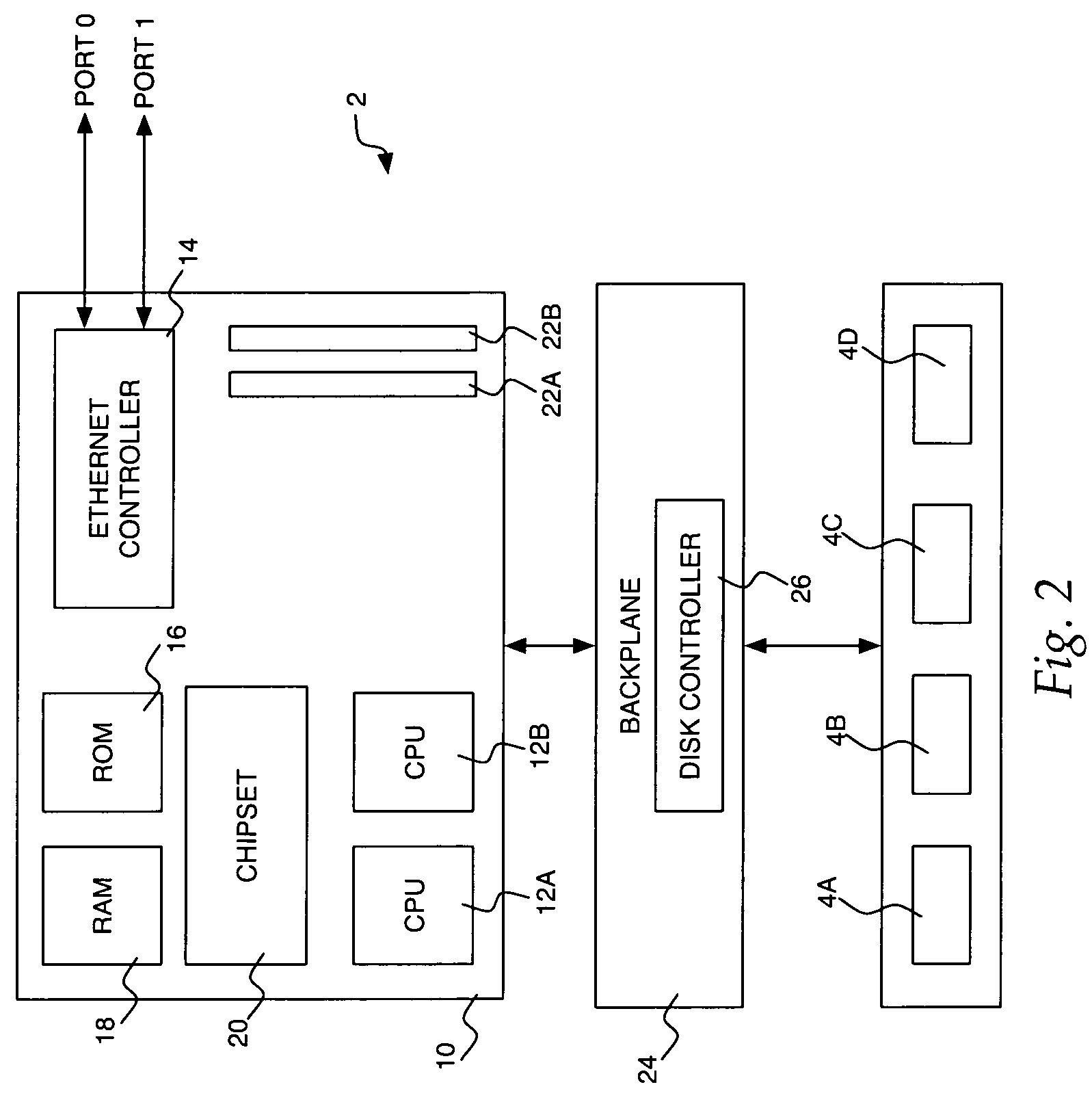

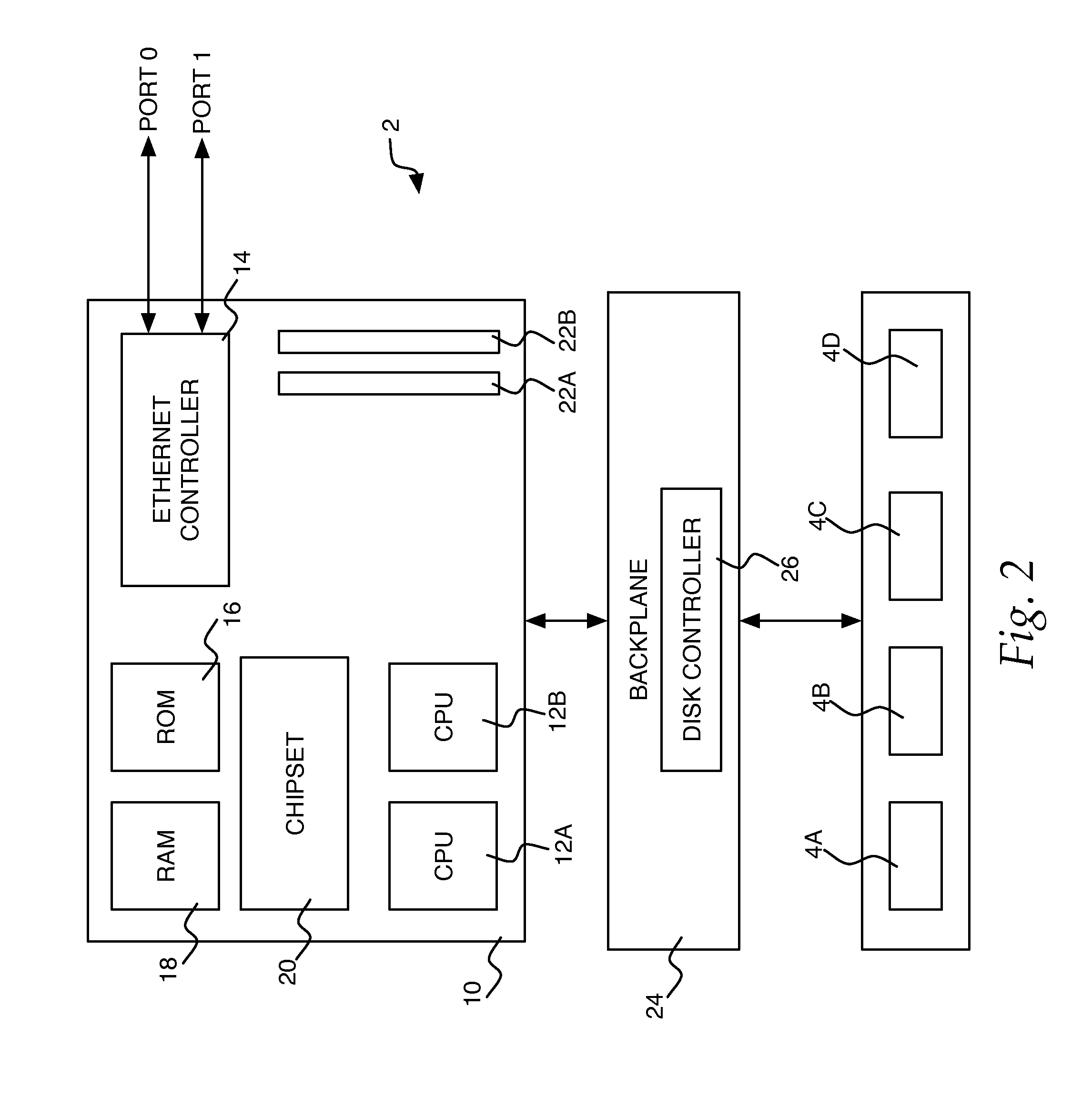

Raid XOR operations to synchronous DRAM using a read buffer and pipelining of synchronous DRAM burst read data

A memory interface controller includes a read buffer to pipeline data from a synchronous dynamic random access memory (DRAM) in response to a plurality of consecutive SDRAM burst read requests, a write buffer to store write data, an exclusive or (XOR) engine to XOR the write data with the data from the read buffer, and a write interface to write resulting data from XORing the write data and the data from the read buffer to the synchronous DRAM. Data is pipelined in the read buffer by repeatedly issuing an SDRAM burst read request before data is transferred out of the synchronous DRAM in response to a previous SDRAM burst read request until a desired amount of data is stored in the read buffer. The memory interface controller thus can perform an external read-modify-write cycle for the synchronous DRAM. The synchronous DRAM can serve as a RAID (Redundant Array s of Inexpensive Disks) memory.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

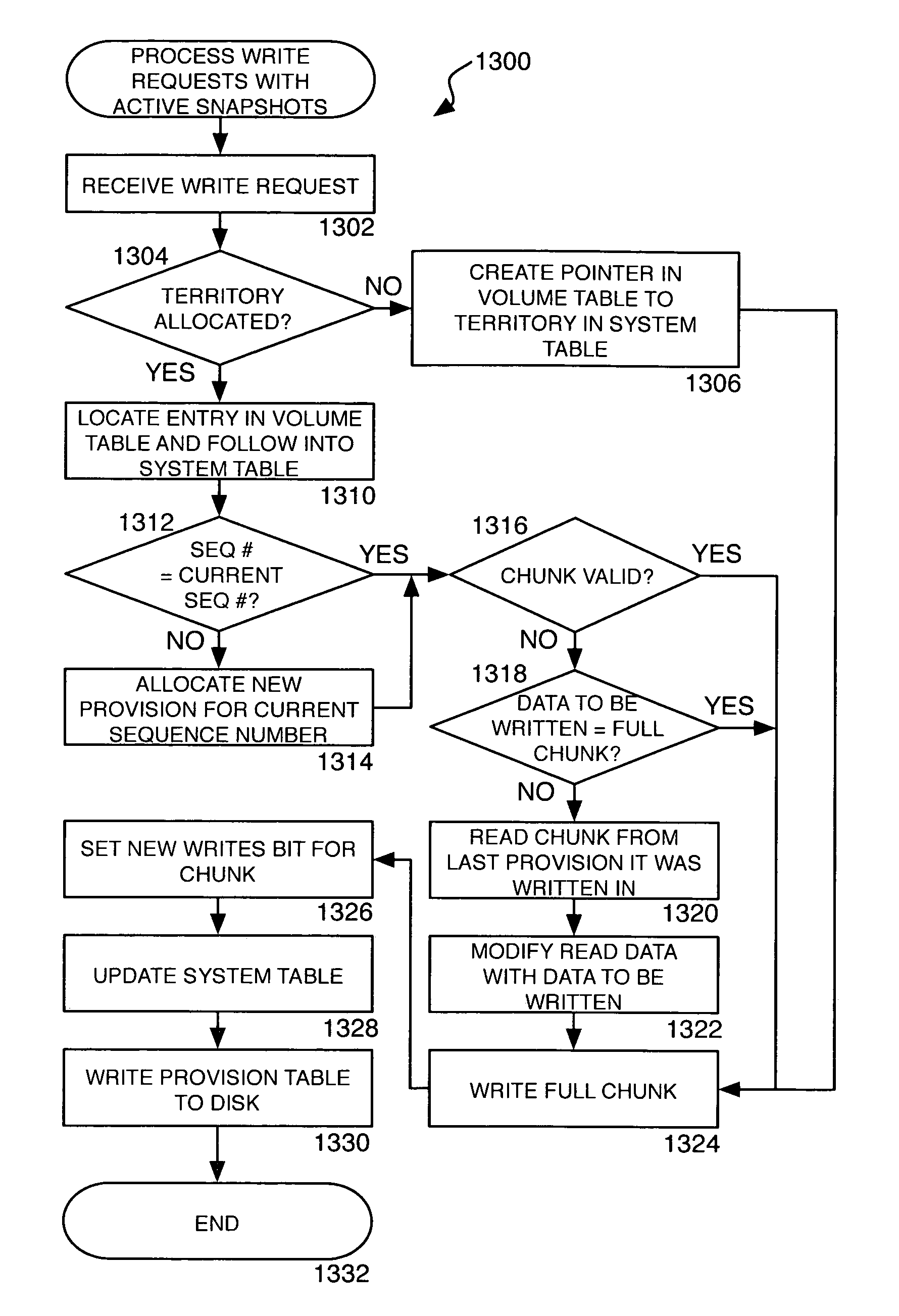

Method, system, apparatus, and computer-readable medium for taking and managing snapshots of a storage volume

ActiveUS7373366B1No performance lossScroll fastError detection/correctionSpecial data processing applicationsGranularityInvalid Data

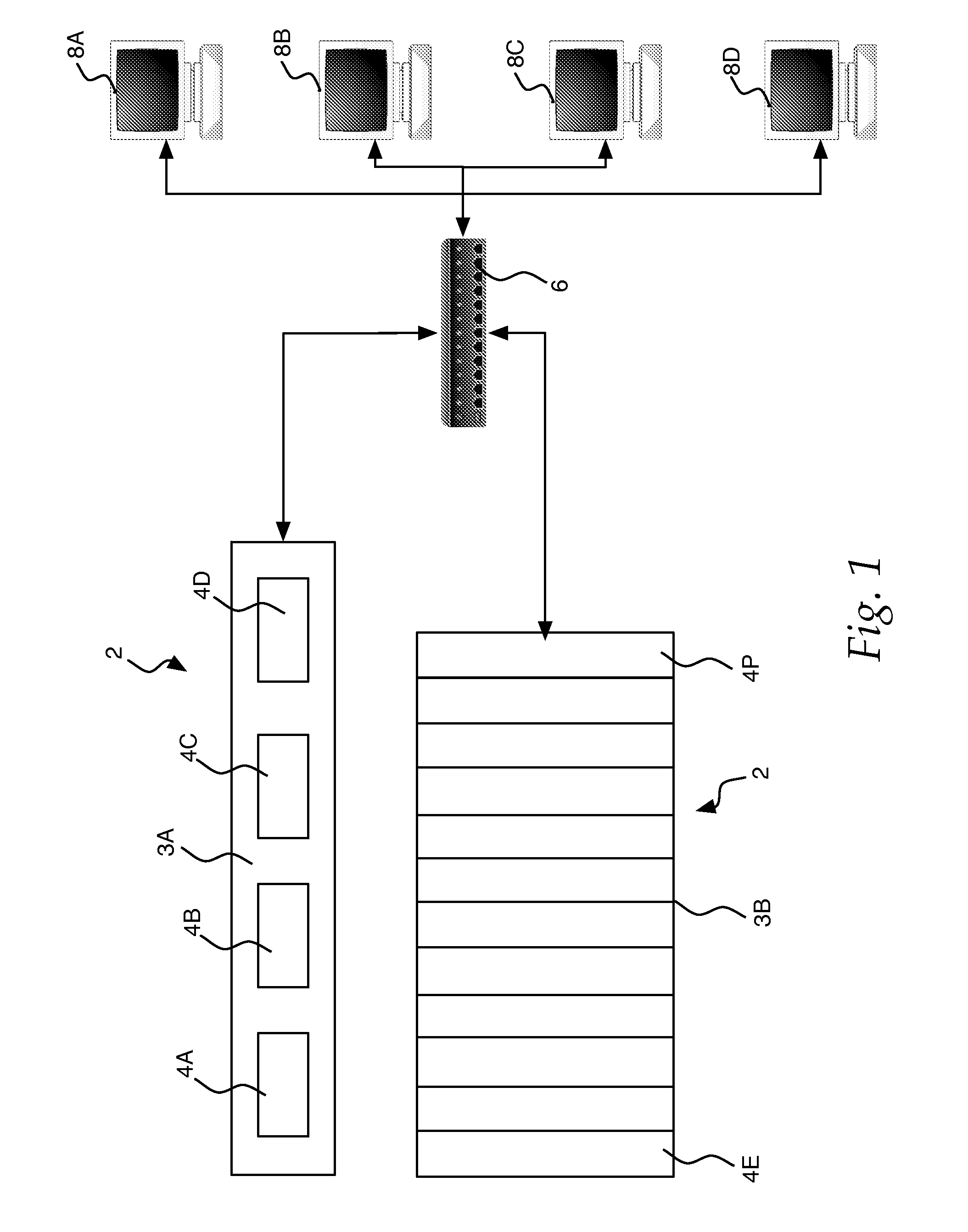

A method, system, apparatus, and computer-readable medium are provided for taking snapshots of a storage volume. According to aspects of one method, each snapshot is represented as a unique sequence number. Every fresh write access to a volume in a new snapshot lifetime is allocated a new section in the disk, called a provision, which is labeled with the sequence number. Read-modify-write operations are performed on a sub-provision level at the granularity of a chunk. Because each provision contains chunks with valid data and chunks with invalid data, a bitmap is utilized to identify the valid and invalid chunks with each provision. Provisions corresponding to different snapshots are arranged in a linked list. Branches from the linked list can be created for storing writable snapshots. Provisions may also be deleted and rolled back by manipulating the contents of the linked lists.

Owner:AMZETTA TECH LLC

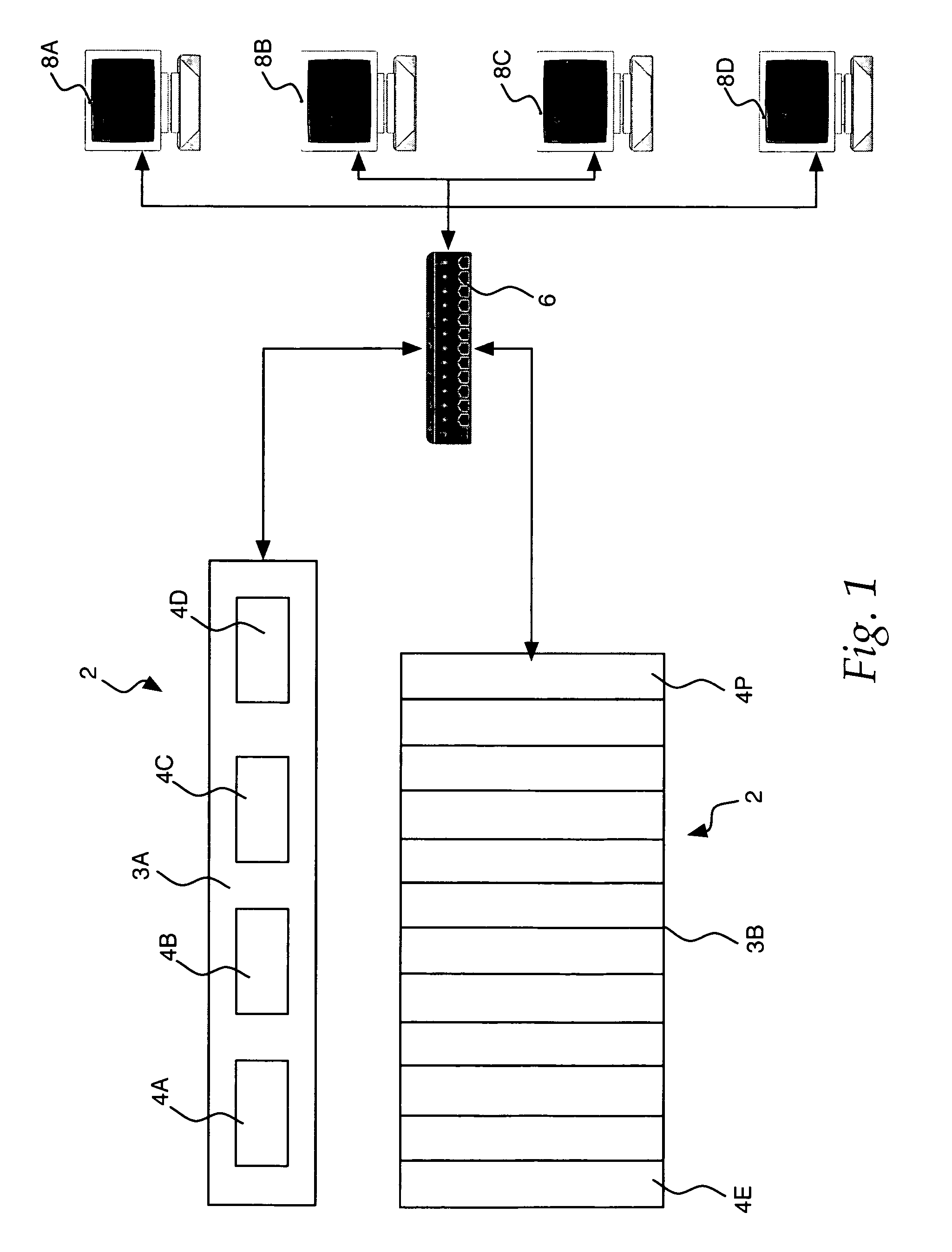

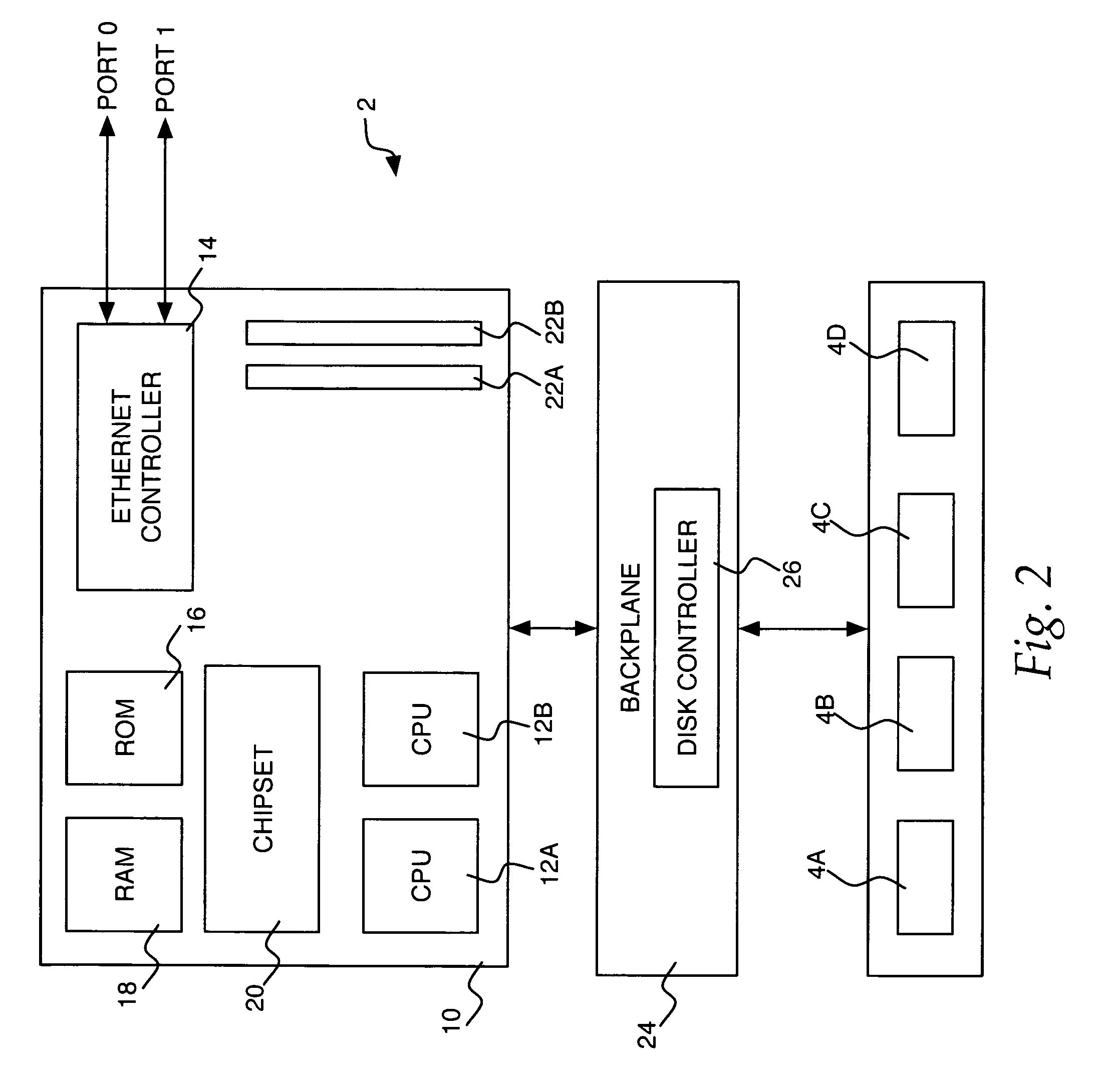

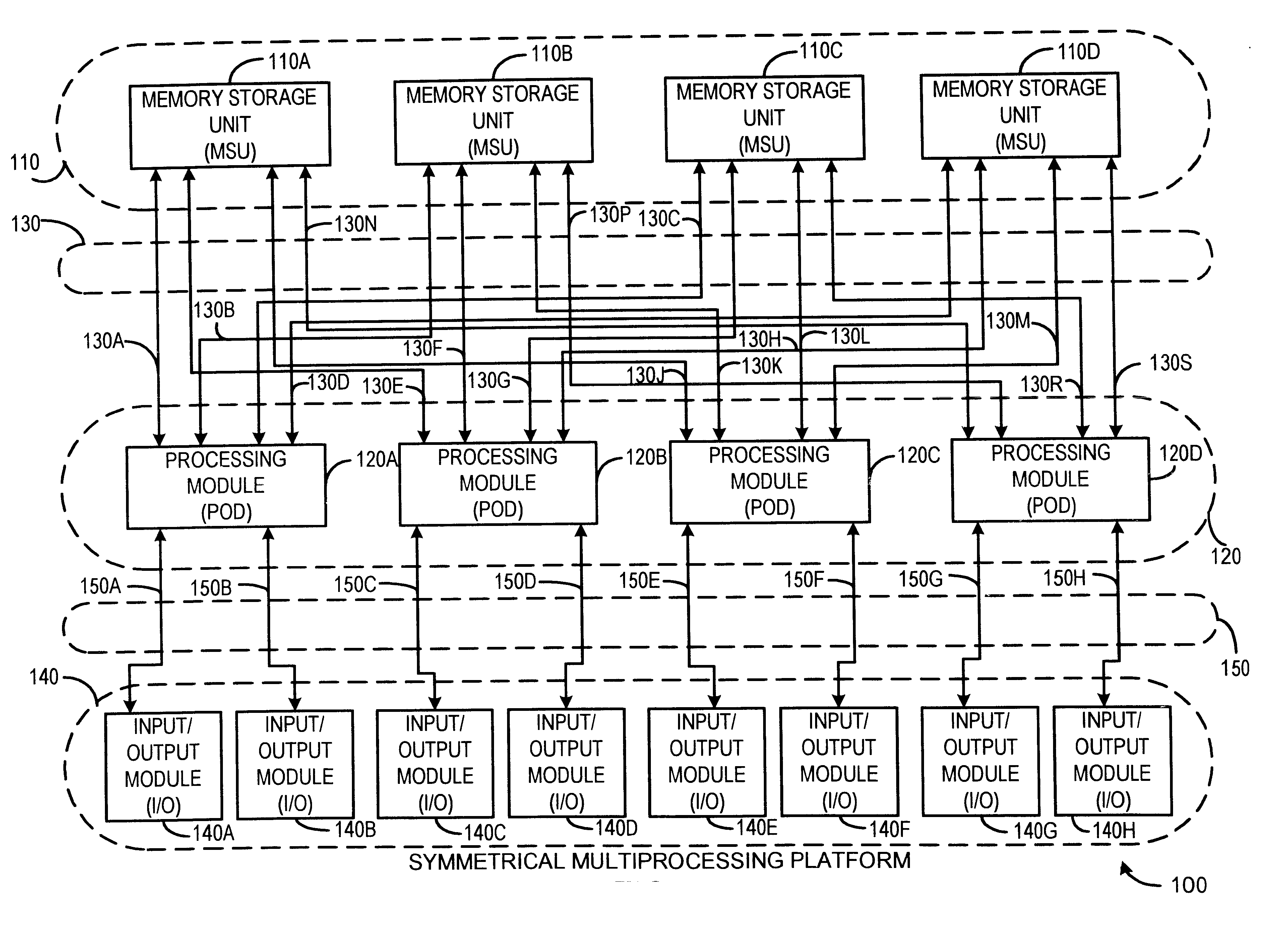

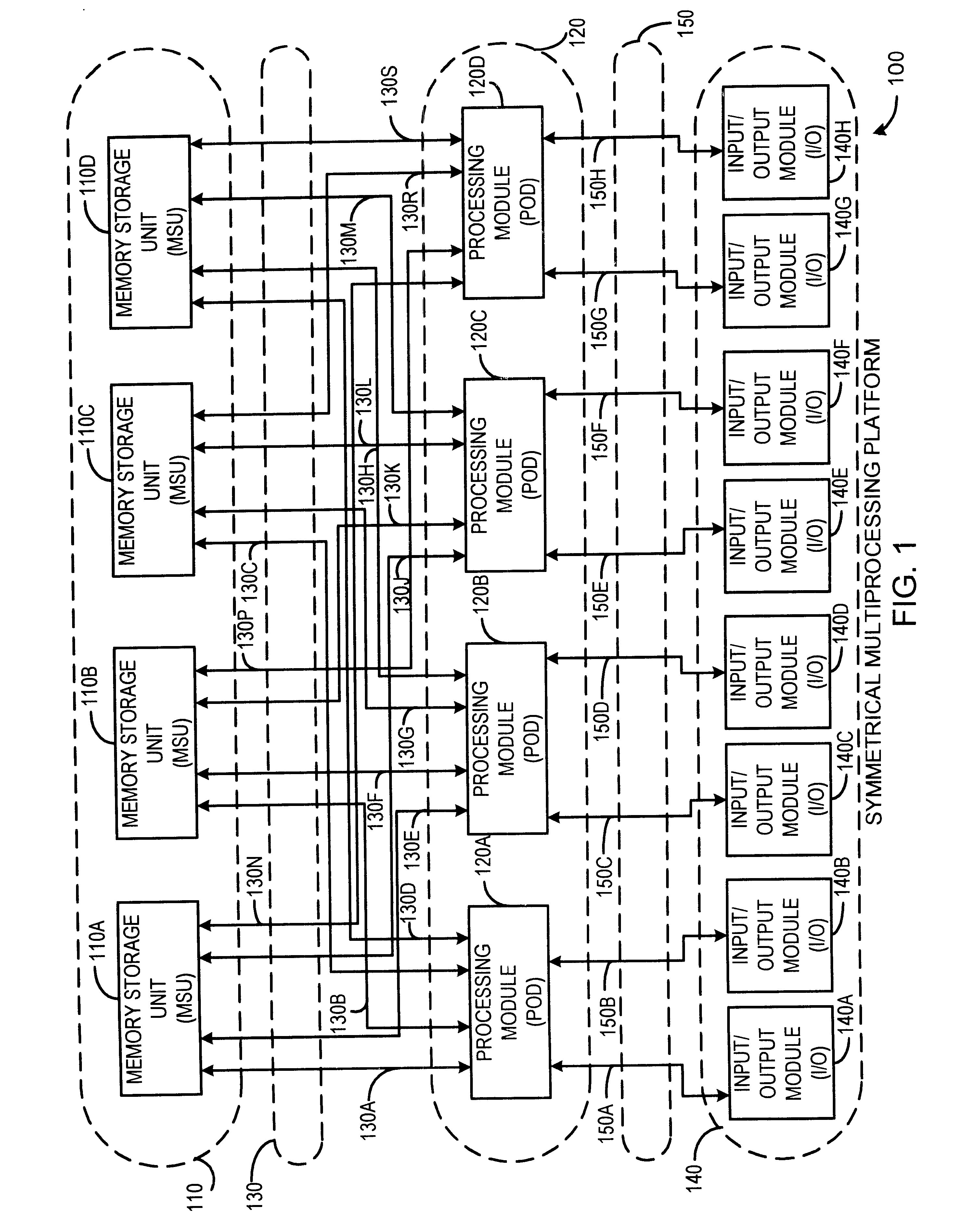

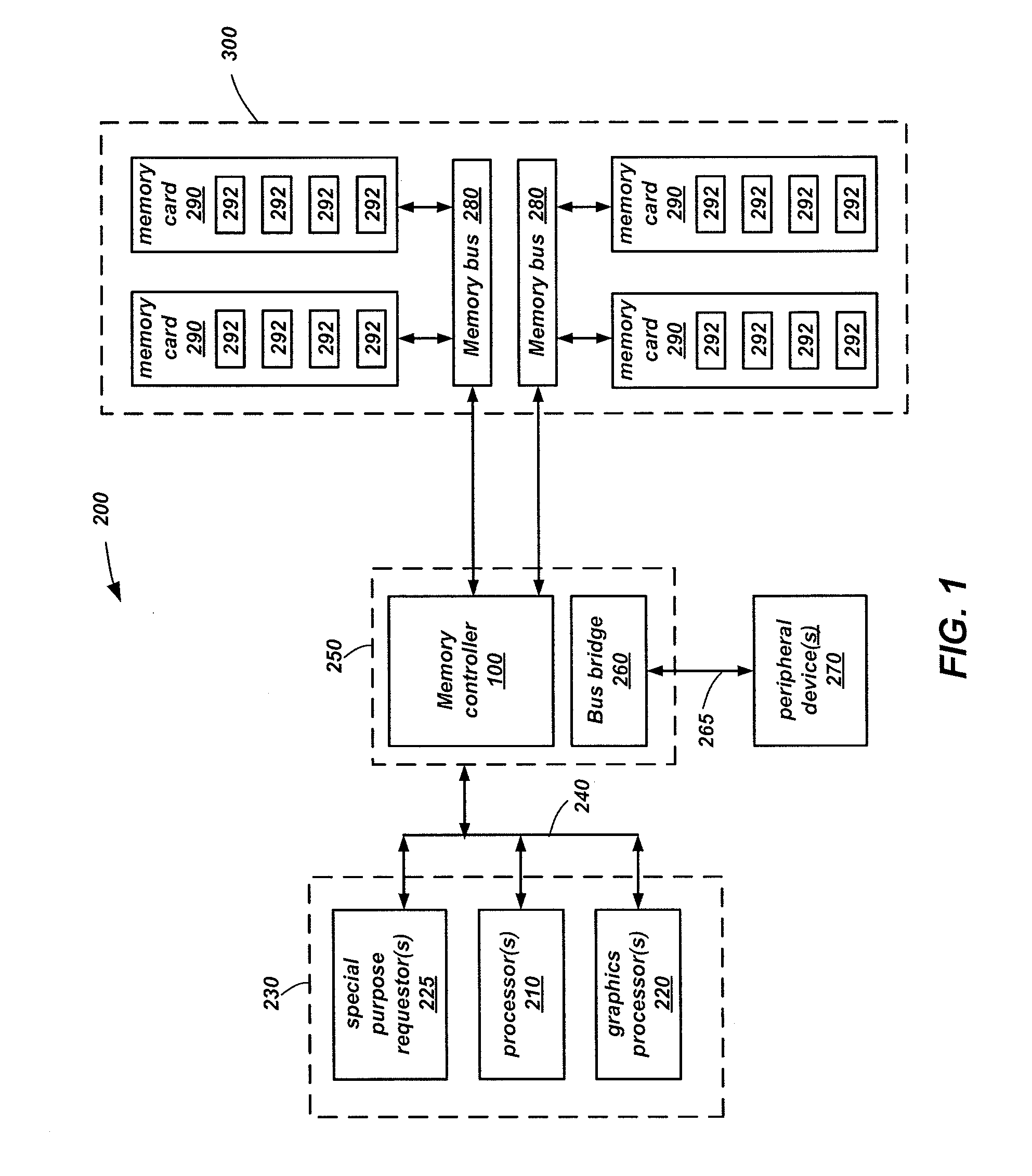

High-speed memory storage unit for a multiprocessor system having integrated directory and data storage subsystems

InactiveUS6415364B1Easy to manageImprove system throughputMemory adressing/allocation/relocationInput/output processes for data processingHigh speed memoryImpact system

A high-speed memory system is disclosed for use in supporting a directory-based cache coherency protocol. The memory system includes at least one data system for storing data, and a corresponding directory system for storing the corresponding cache coherency information. Each data storage operation involves a block transfer operation performed to multiple sequential addresses within the data system. Each data storage operation occurs in conjunction with an associated read-modify-write operation performed on cache coherency information stored within the corresponding directory system. Multiple ones of the data storage operations may be occurring within one or more of the data systems in parallel. Likewise, multiple ones of the read-modify-write operations may be performed to one or more of the directory systems in parallel. The transfer of address, control, and data signals for these concurrently performed operations occurs in an interleaved manner. The use of block transfer operations in combination with the interleaved transfer of signals to memory systems prevents the overhead associated with the read-modify-write operations from substantially impacting system performance. This is true even when data and directory systems are implemented using the same memory technology.

Owner:UNISYS CORP

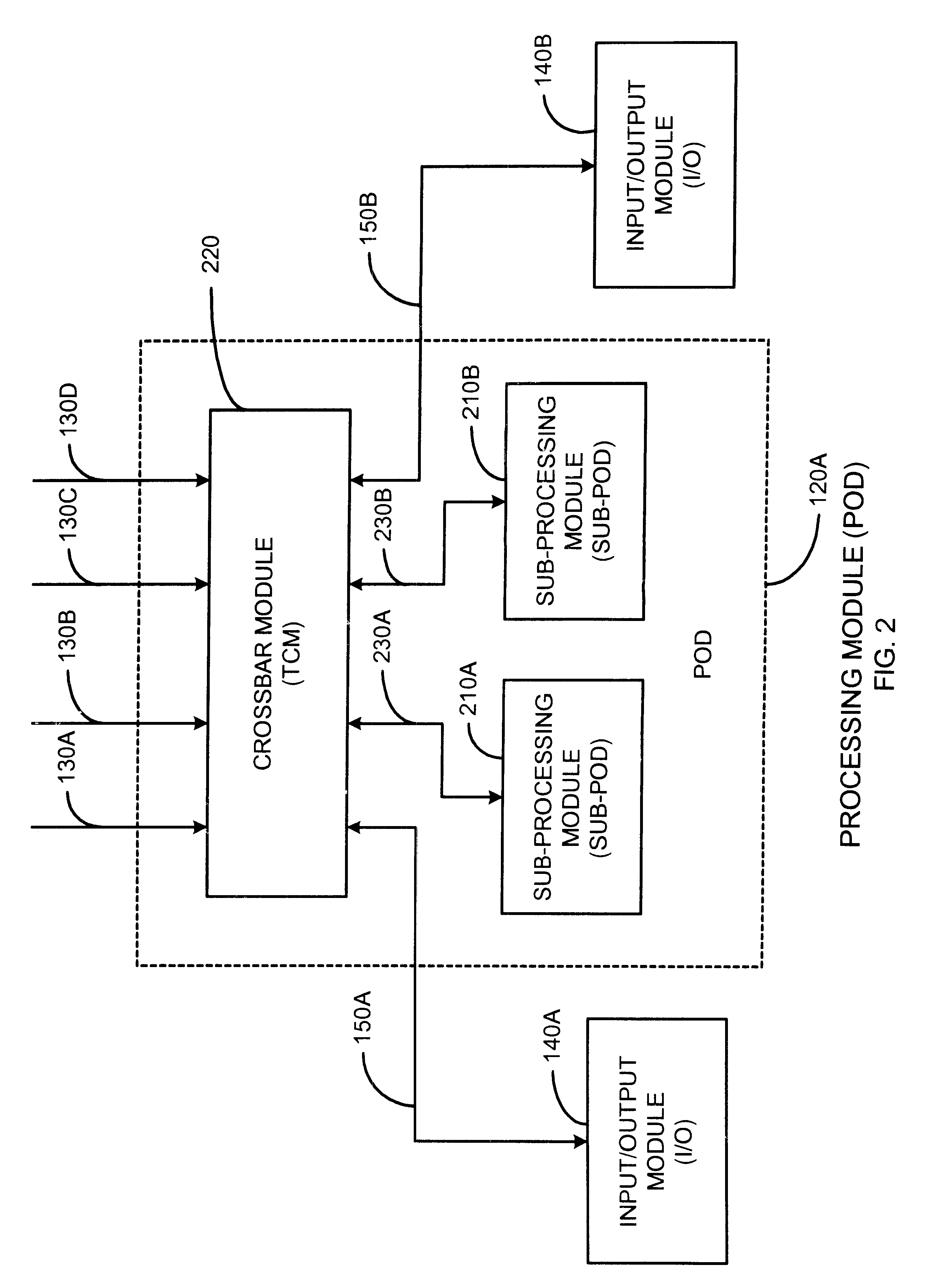

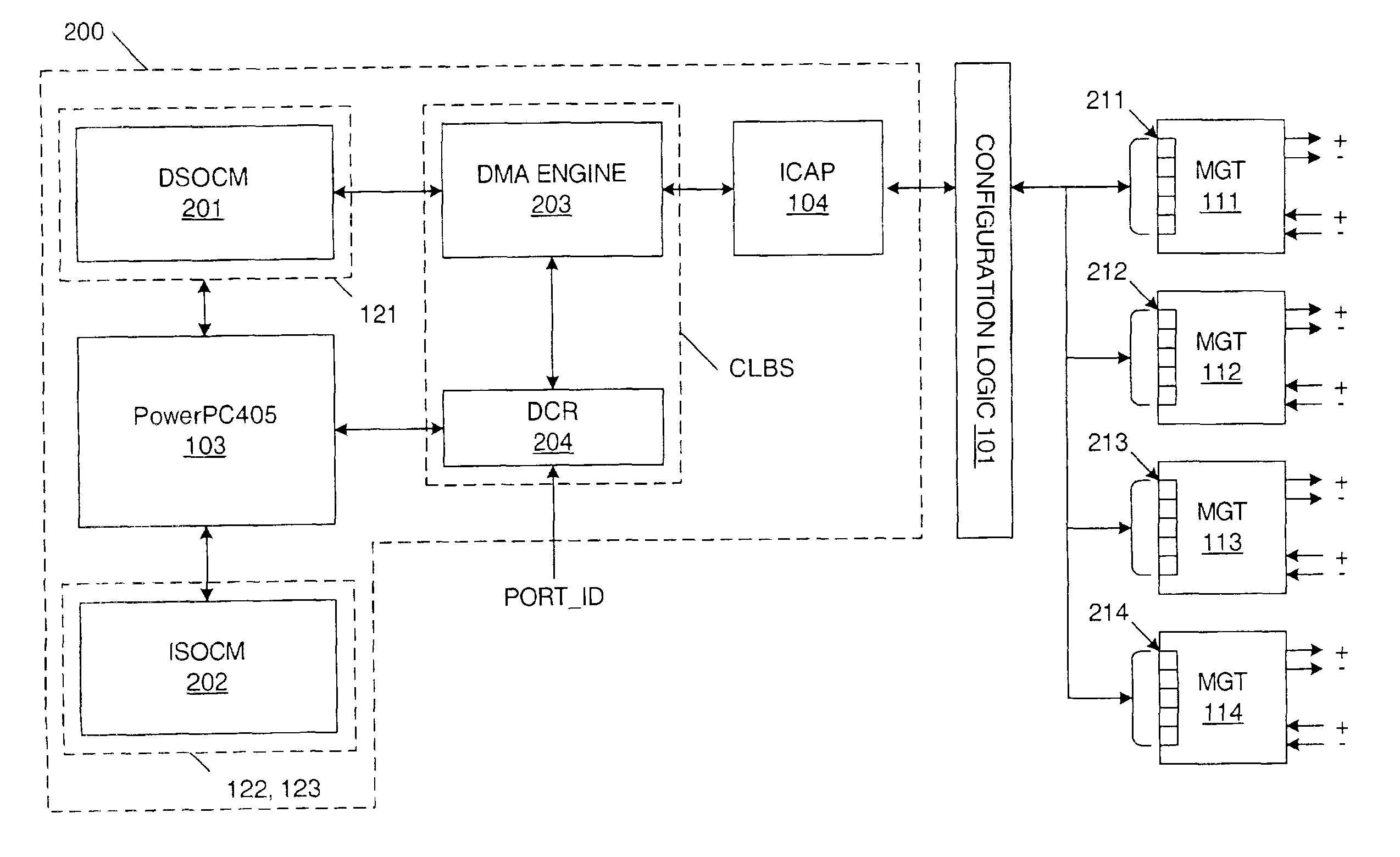

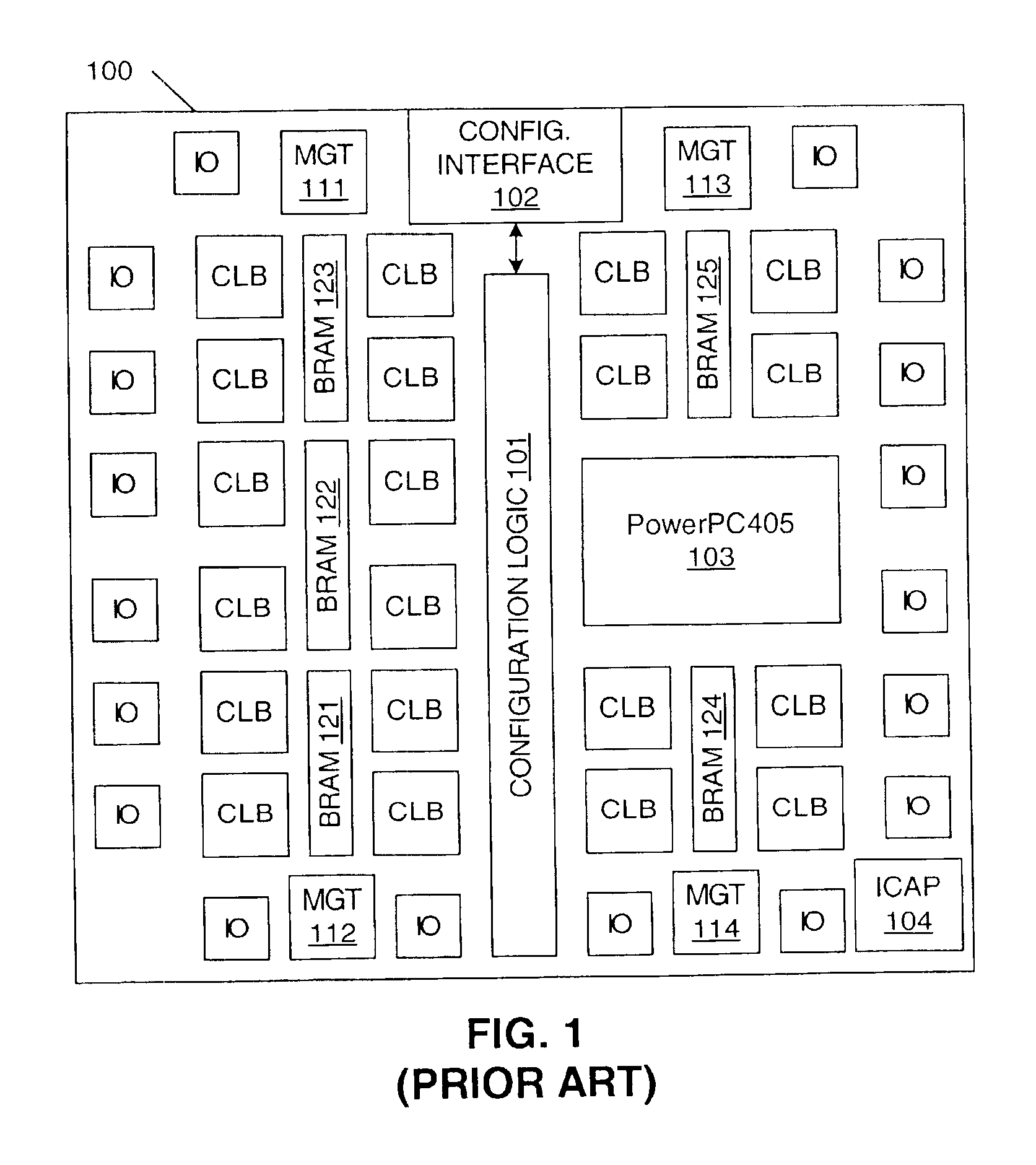

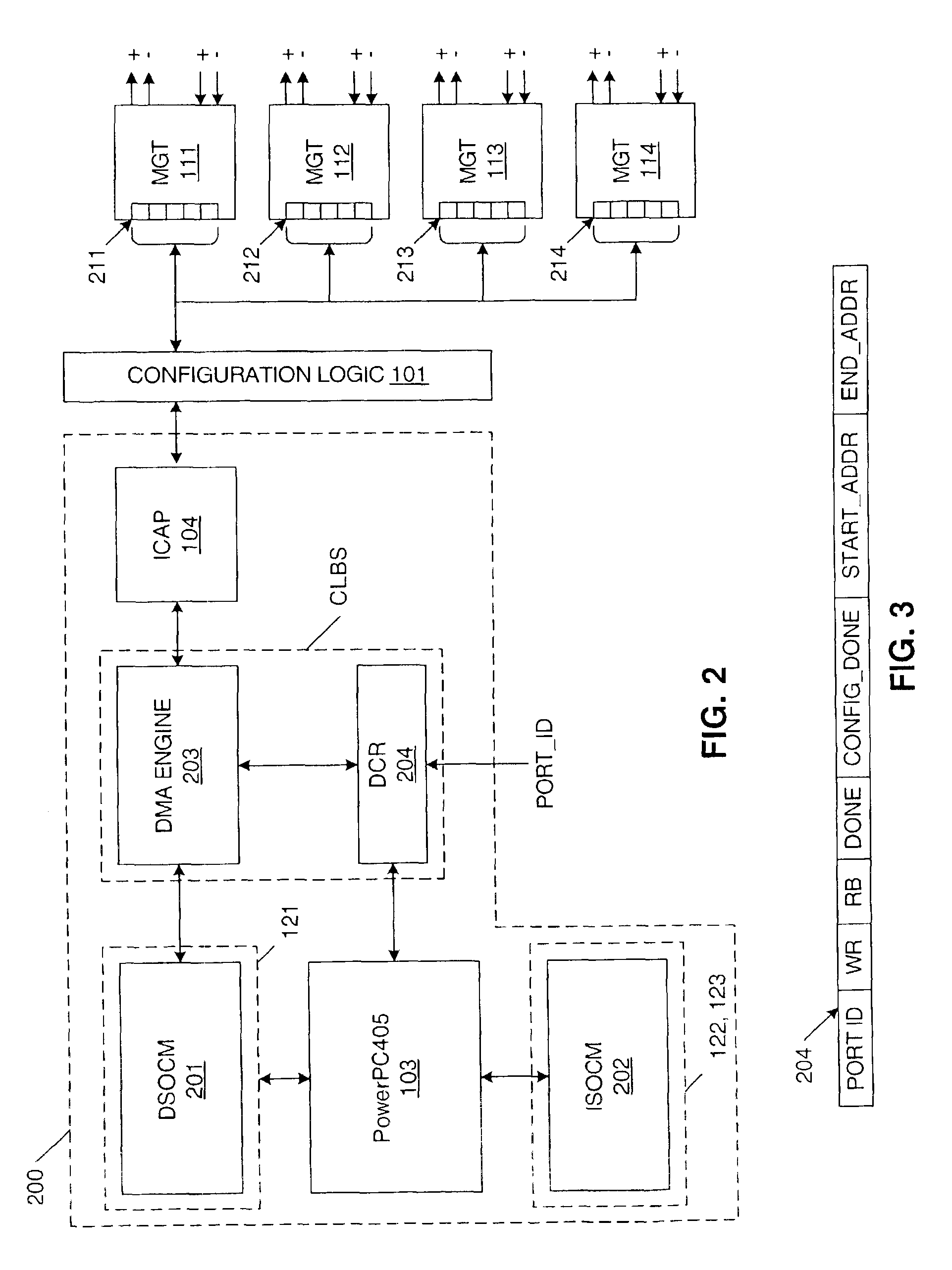

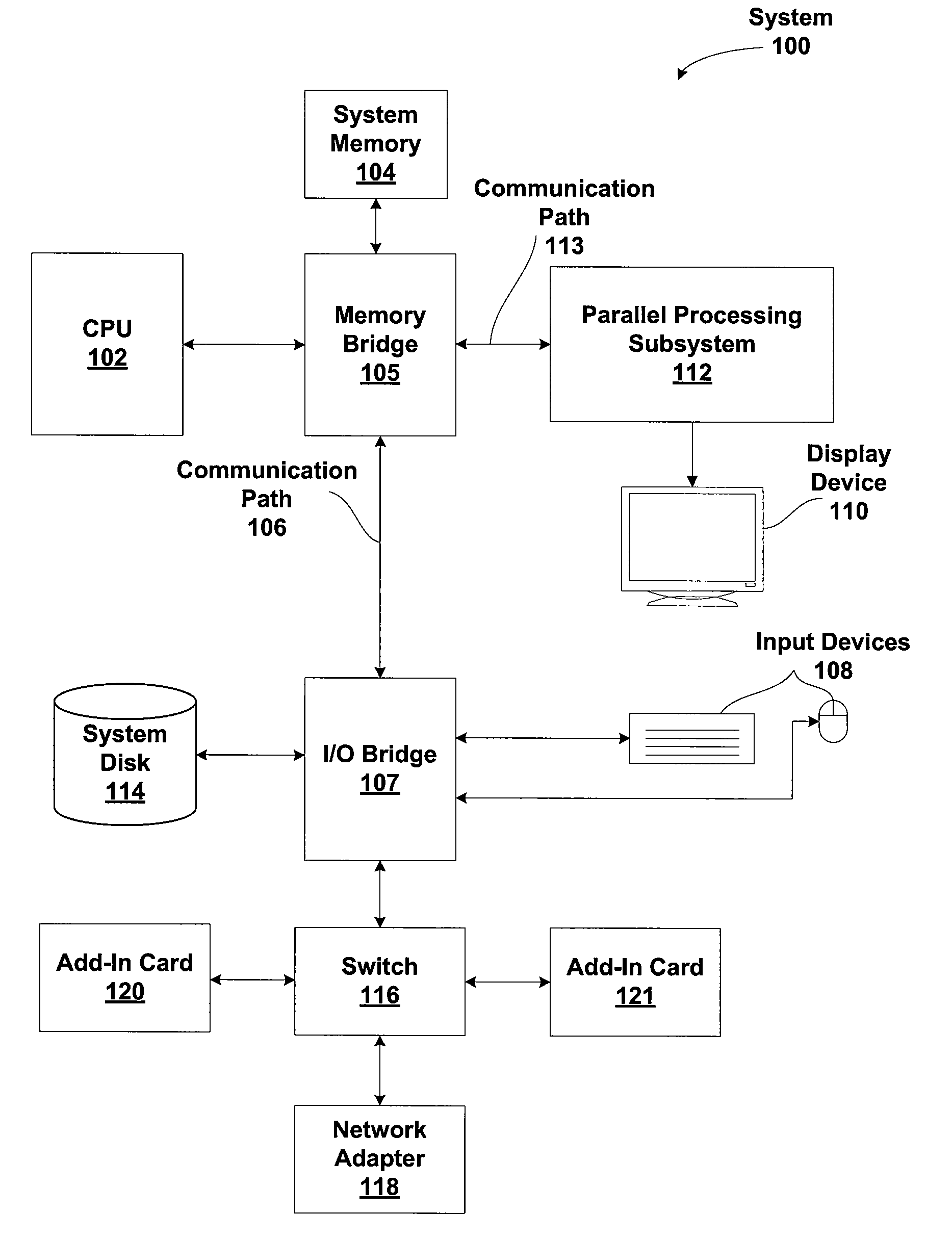

Partial reconfiguration of a programmable logic device using an on-chip processor

InactiveUS6907595B2Fully understandSolid-state devicesArchitecture with single central processing unitProgrammable logic deviceRead-modify-write

A programmable logic device, such as a field programmable gate array, is partially reconfigured using a read-modify-write scheme that is controlled by a processor. The partial reconfiguration includes (1) loading a base set of configuration data values into a configuration memory array of the programmable logic device, thereby configuring the programmable logic device; (2) reading a first frame of configuration data values from the configuration memory array; (3) modifying a subset of the configuration data values in the first frame of configuration data values, thereby creating a first modified frame of configuration data values; and (4) overwriting the first frame of configuration data values in the configuration memory array with the first modified frame of configuration data values, thereby partially reconfiguring the programmable logic device. The steps of reading, modifying and overwriting are performed under the control of a processor.

Owner:XILINX INC

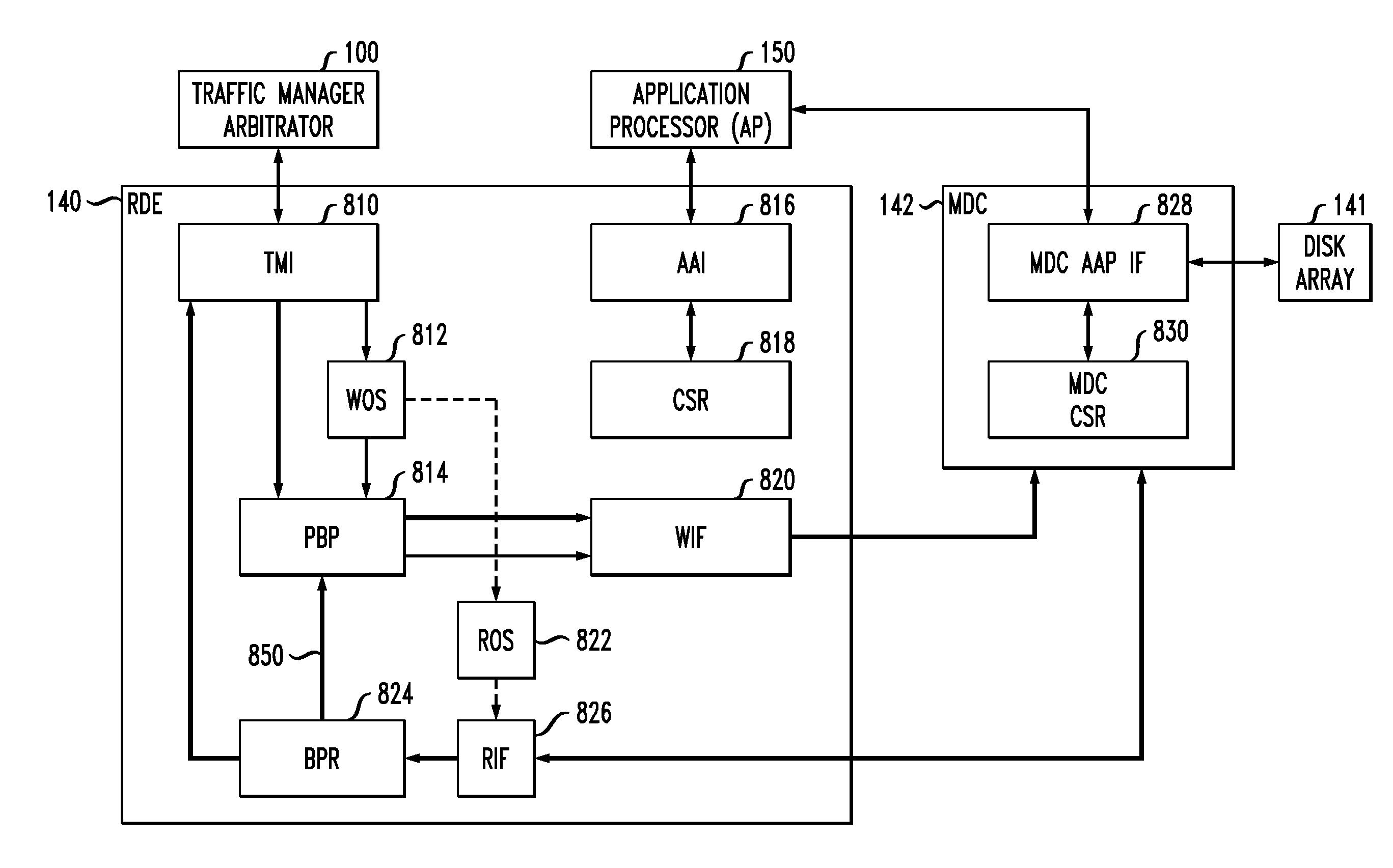

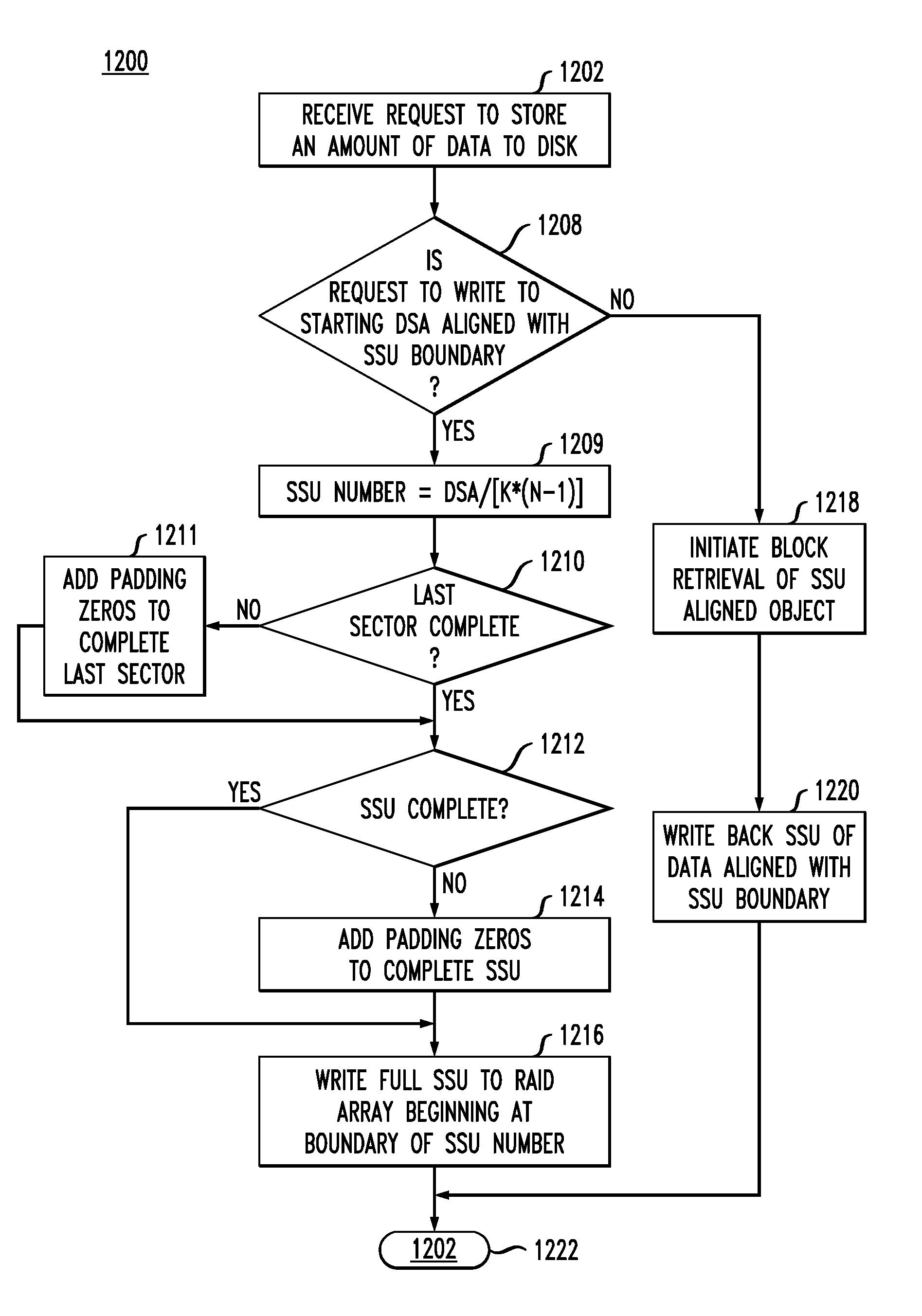

Aligned Data Storage for Network Attached Media Streaming Systems

InactiveUS20130091237A1Redundant array of inexpensive disk systemsDigital computer detailsRAIDNetwork connection

Described embodiments provide a server for transferring data packets of streaming data sessions between devices. A redundant array of inexpensive disks (RAID) array having one or more stripe sector units (SSU) stores media files corresponding to the one or more data sessions. The RAID control module receives a request to perform the write operation to the RAID array beginning at a starting data storage address (DSA) and pads the data of the write operation if the amount of data is less than a full SSU of data, such that the padded data of the write operation is a full SSU of data. The RAID control module stores the full SSU of data beginning at a starting data storage address (DSA) that is aligned with a second SSU boundary, without performing a read-modify-write operation.

Owner:BROADCOM INT PTE LTD

Memory device with multiple processors having parallel access to the same memory area

InactiveUS6279088B1Energy efficient ICTOperational speed enhancementArithmetic logic unitRead-modify-write

A digital computer performs read-modify-write (RMW) processing on each bit of a row of memory in parallel, in one operation cycle, comprising: (a) addressing a memory, (b) reading each bit of a row of data from the memory in parallel, (c) performing the same computational operation on each bit of the data in parallel, using an arithmetic logic unit (ALU) in a dedicated processing element, and (d) writing the result of the operation back into the original memory location for each bit in the row.

Owner:SATECH GRP A B LLC

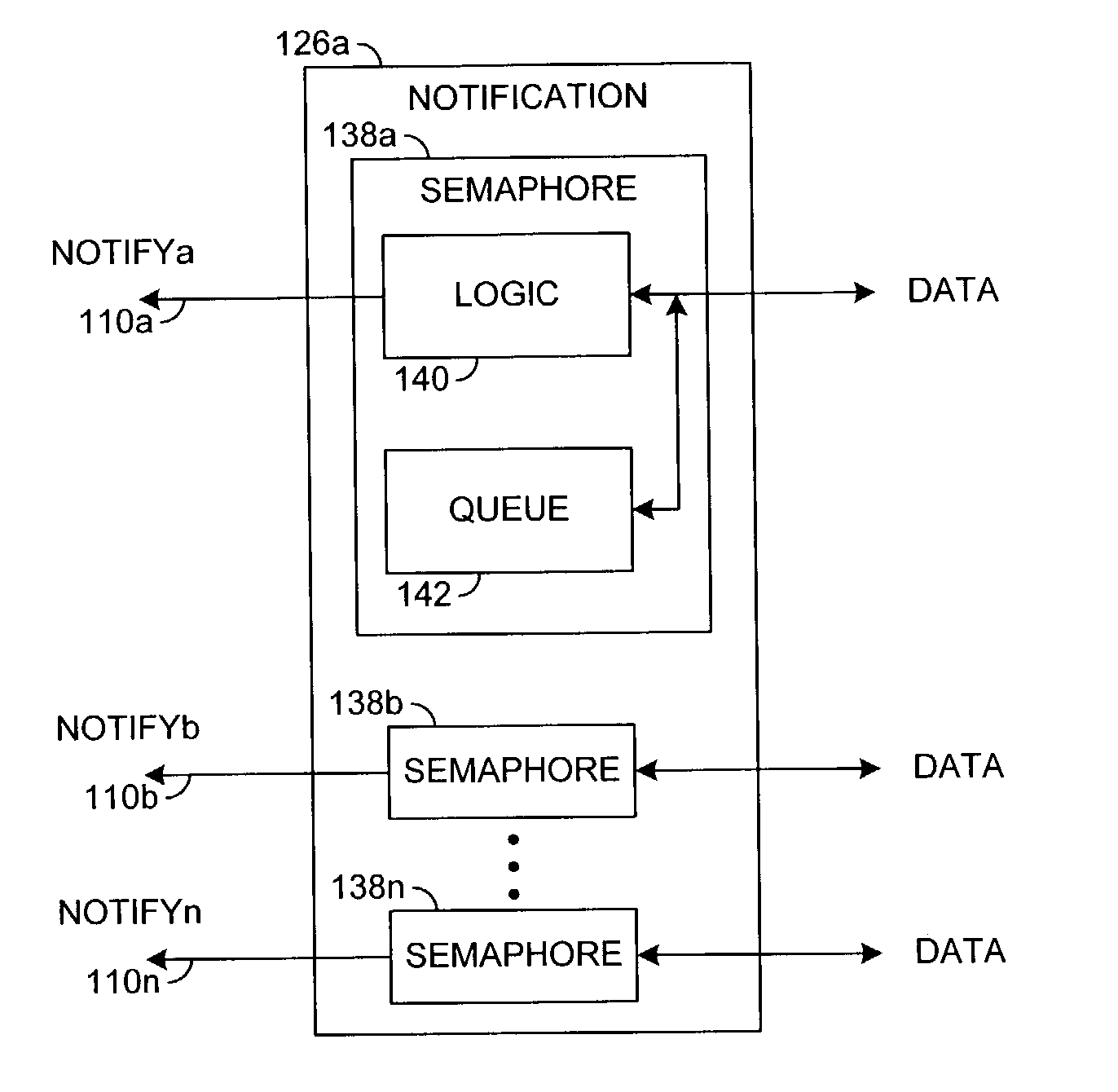

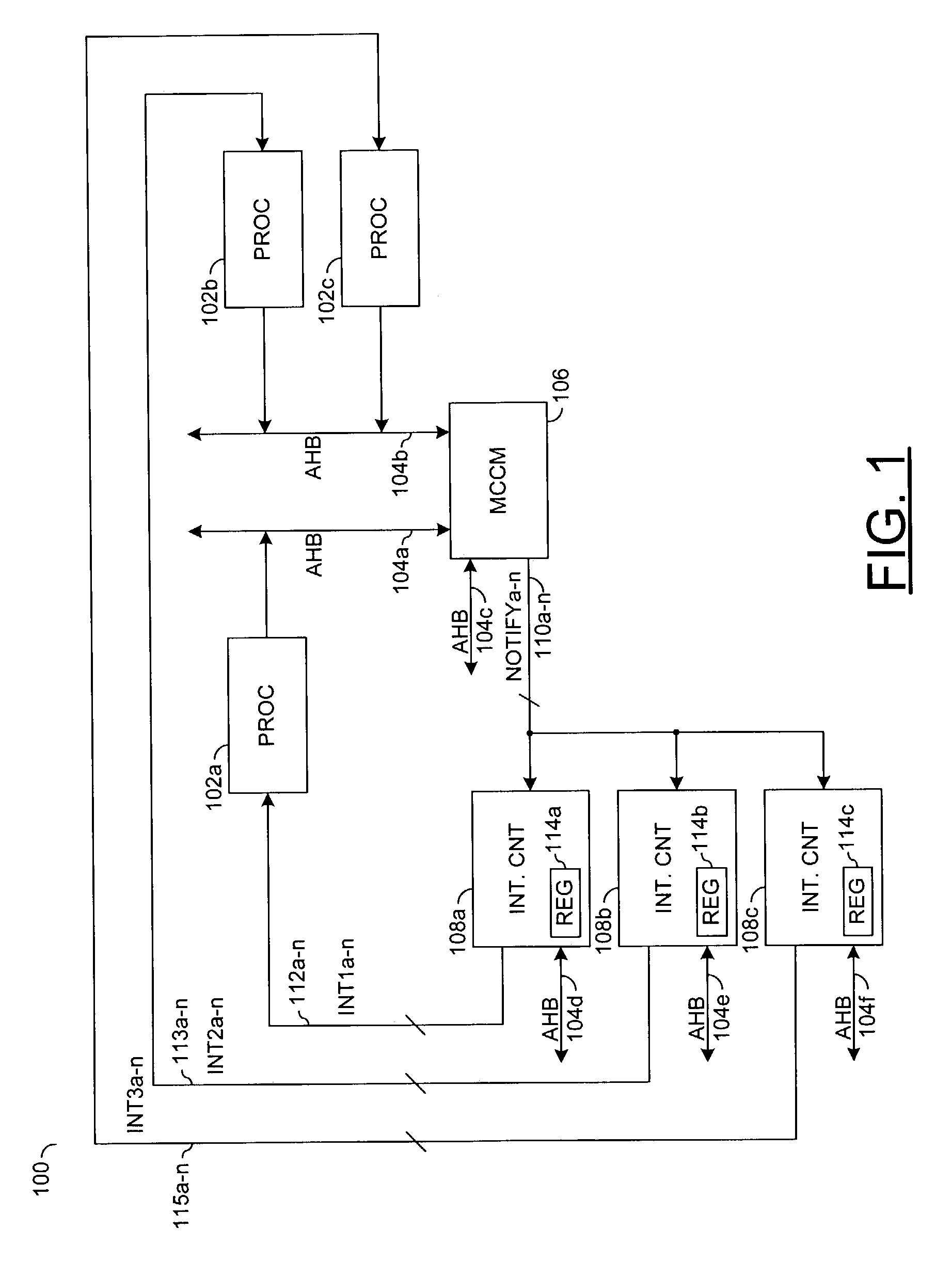

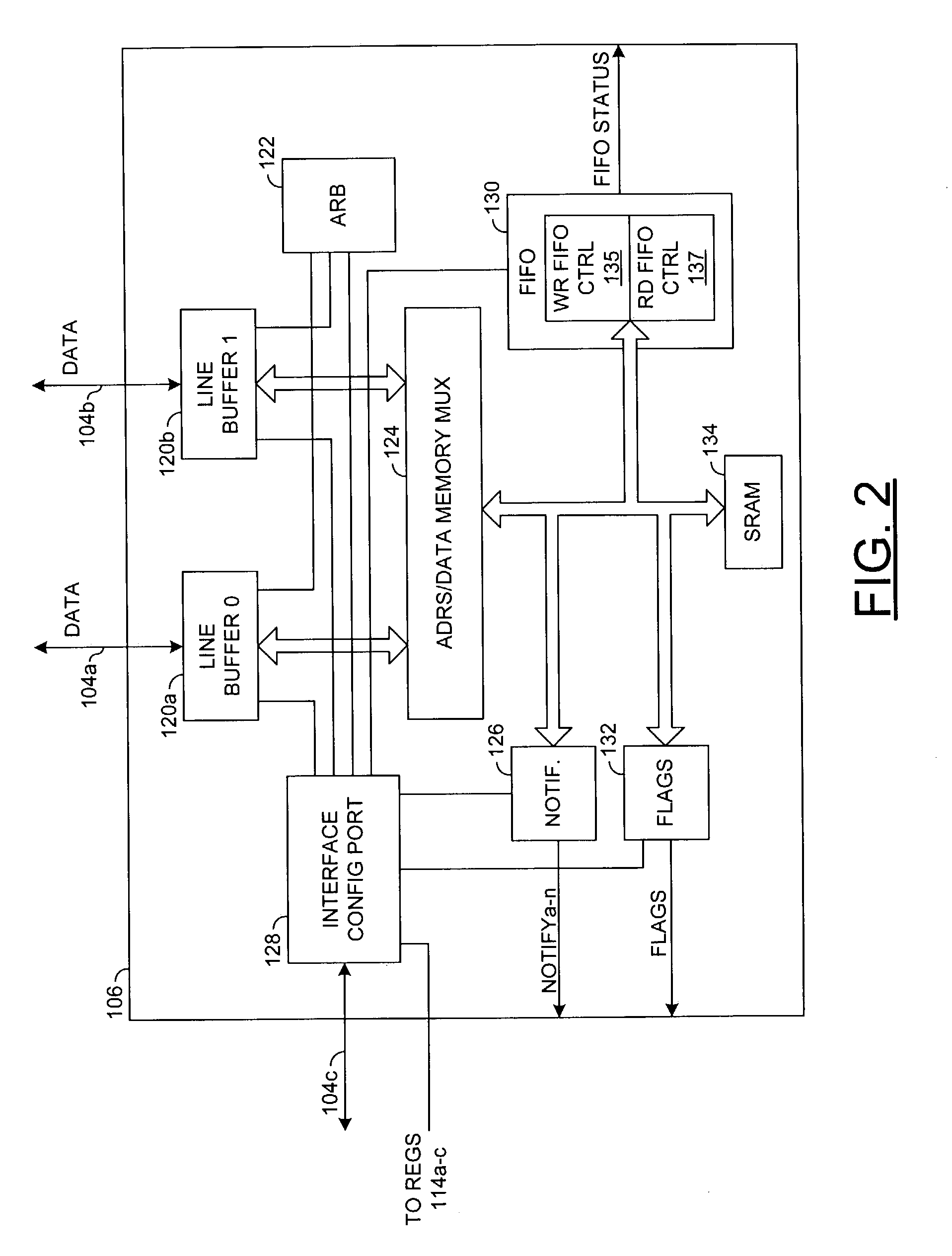

System method for use of hardware semaphores for resource release notification wherein messages comprises read-modify-write operation and address

InactiveUS7007108B2Firmly connectedLower latencyProgram synchronisationMultiple digital computer combinationsSignal onRead-modify-write

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

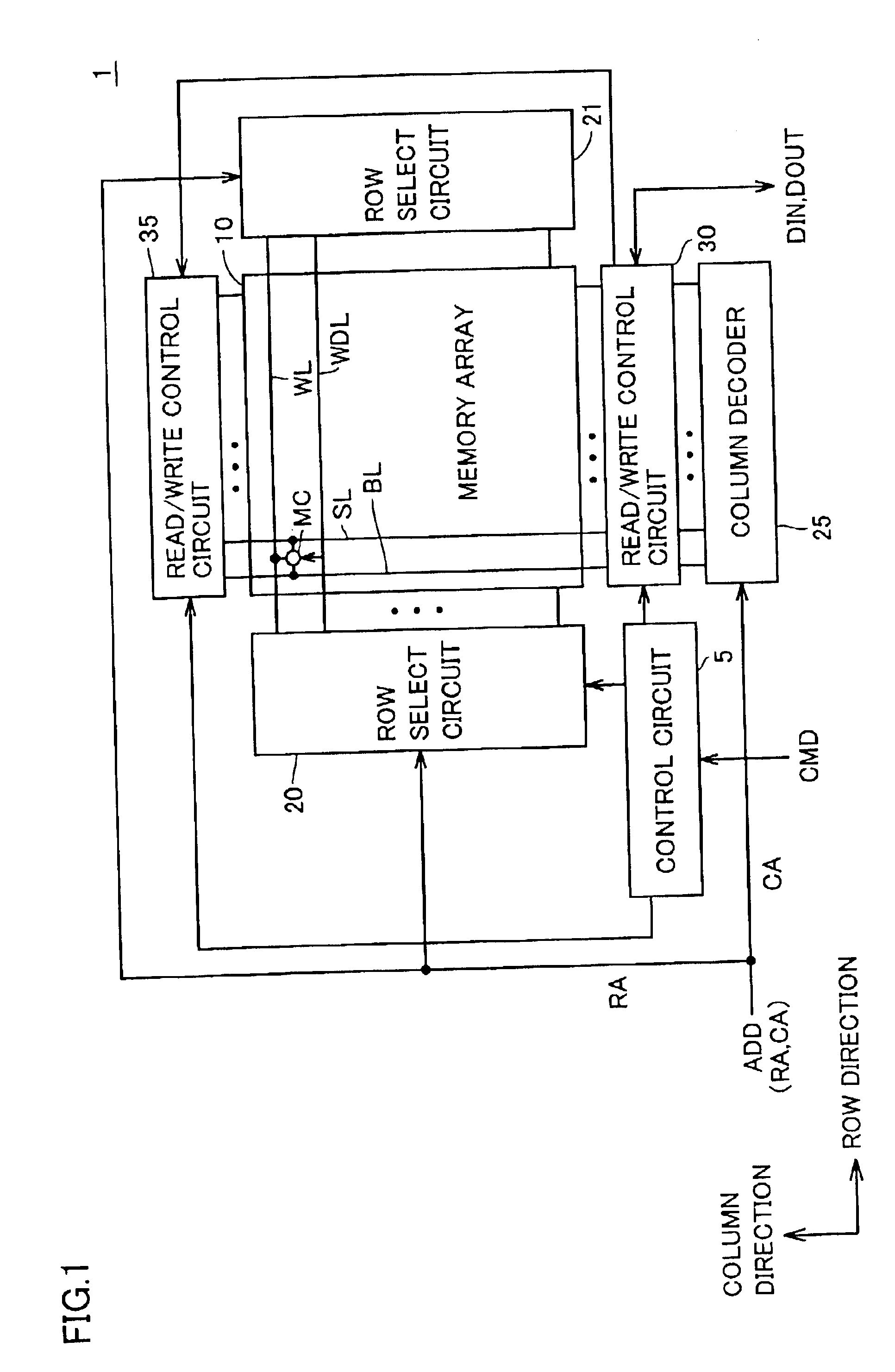

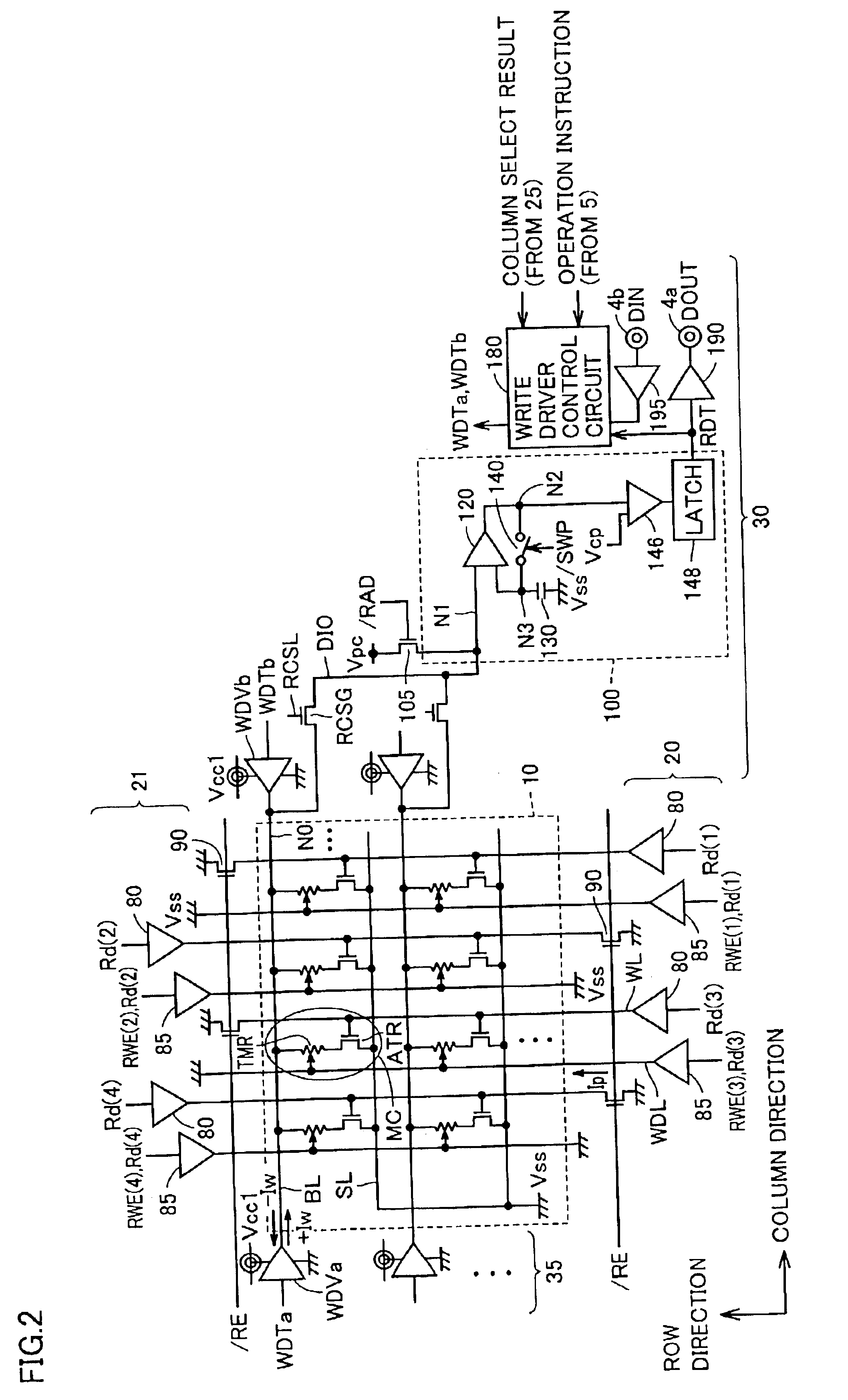

Thin film magnetic memory device executing self-reference type data read

InactiveUS6842366B2High operating requirementsSimple structureMagnetic-field-controlled resistorsSolid-state devicesHigh rateReference type

In one data read operation, data read for reading stored data before and after a predetermined data write magnetic field is applied to a selected memory cell, respectively, is executed, and the data read is executed in accordance with comparison of voltage levels corresponding to the data read operations before and after application of the predetermined data write magnetic field. In addition, data read operations before and after the application of a data write magnetic field are executed using read modify write. It is thereby possible to avoid an influence of an offset or the like resulting from manufacturing irregularities in respective circuits forming a data read path, to improve efficiency of the data read operation with accuracy and to execute a high rate data read operation.

Owner:RENESAS ELECTRONICS CORP

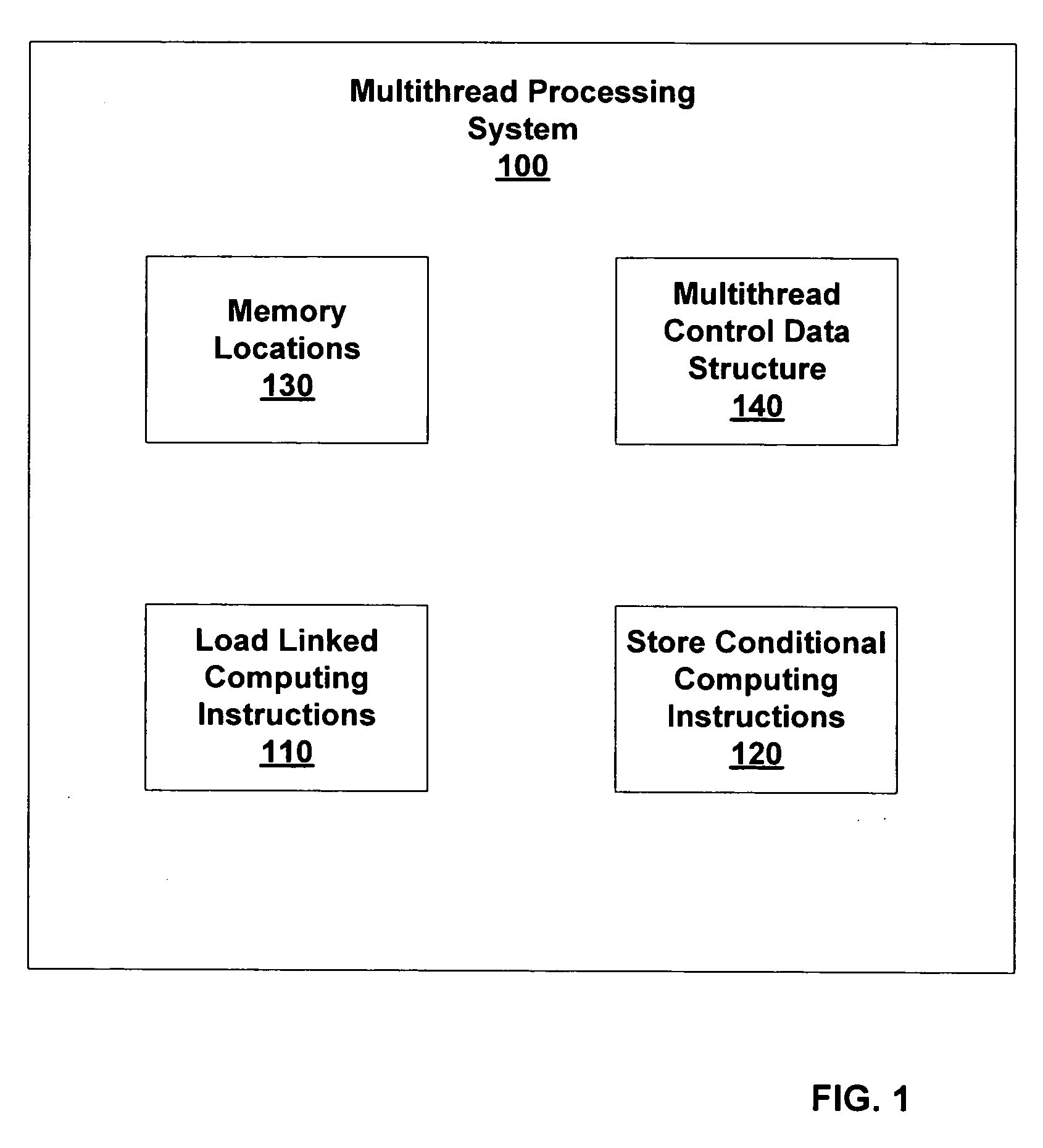

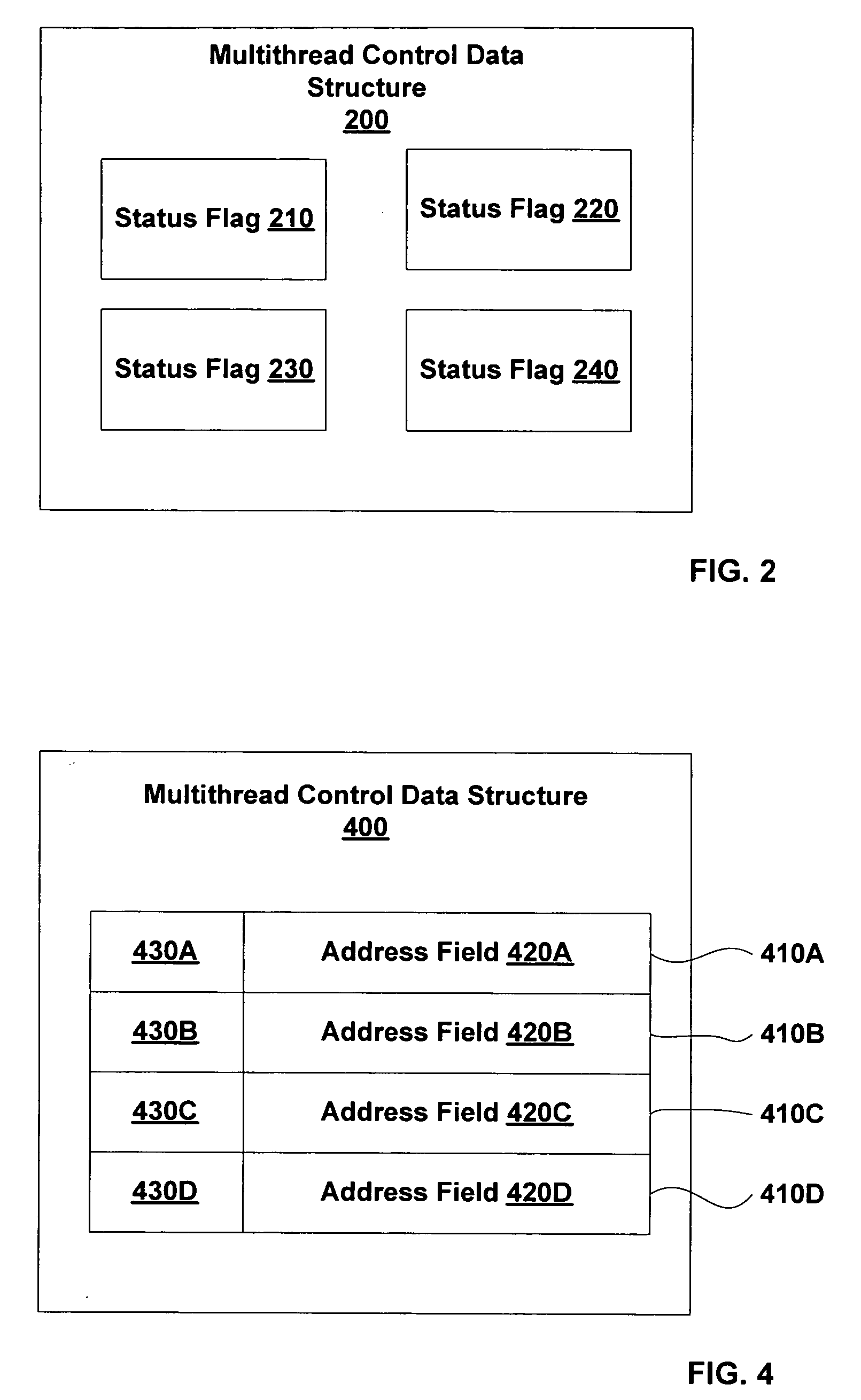

Implementation of load linked and store conditional operations

InactiveUS20060161919A1Improve system throughputReduce needMultiprogramming arrangementsMemory systemsParallel computingControl data

Systems and methods of managing Load Linked and Store Conditional operations in a multithread processing environment are disclosed. These systems and methods utilize a multithread control data structure to assure the atomicity of multiple read-modify-write sequences executed by concurrent processing threads while avoiding live-lock and without halting a concurrent processing thread to wait for the conclusion of a Store Conditional operation executed by another concurrent processing thread. Three different multithread control data structures and associated methods are disclosed. The multithread control data structure is optionally implemented in hardware.

Owner:INTEGRATED DEVICE TECH INC

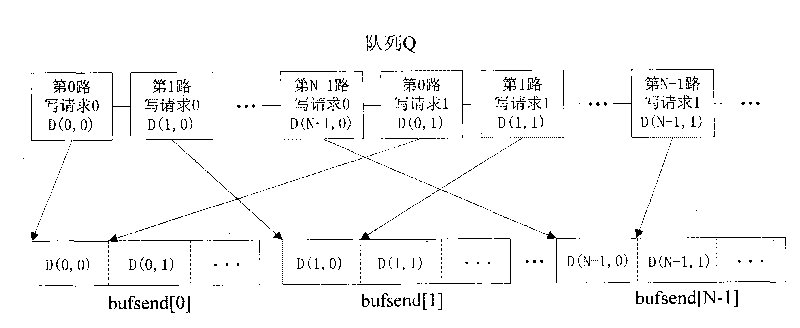

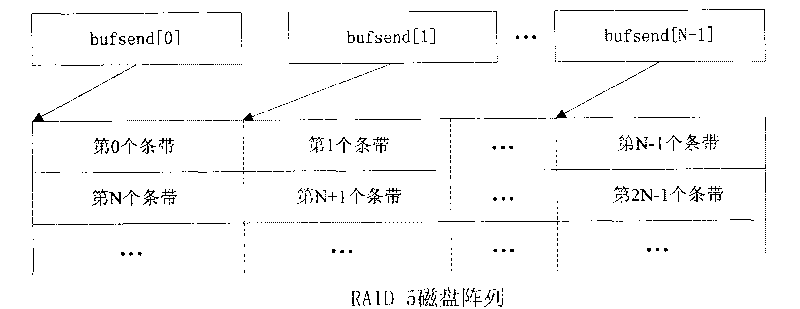

RAID5-orientated optimal design method for writing operation in continuous data storage

ActiveCN101727299AAvoid overheadRealize continuous writingInput/output to record carriersRAIDComputer architecture

The invention discloses an RAID (redundant array of independent disc) 5-orientated optical design method for a writing operation in continuous data storage. The method comprises the steps of: in continuous data storage application, saving writing data blocks, transmitted by an application program, in a memory buffer area; constructing an alignment data block of which the length is the same as that of a complete strip of an RAID5; then enabling the alignment data block to fill the overall strip opportunely on the RAID5; and then transmitting the alignment data block to the RAID5 so as to write the overall strip of the RAID5. Therefore, the written data blocks fill the overall strip of the RAID5 opportunely to avoid the expense for generating the verification of reconstruction, read-modify-write and the like; and the continuity of the data blocks avoids the expense of track seeking of a magnetic head, and improves the throughput capacity of a storage system. Simultaneously, the data blocks written into the RAID5 are sequenced and are written into adjacent strips continuously so as to realize the continuous I / O transmission of the RAID5. The invention is also suitable for an RAID6.

Owner:TOYOU FEIJI ELECTRONICS

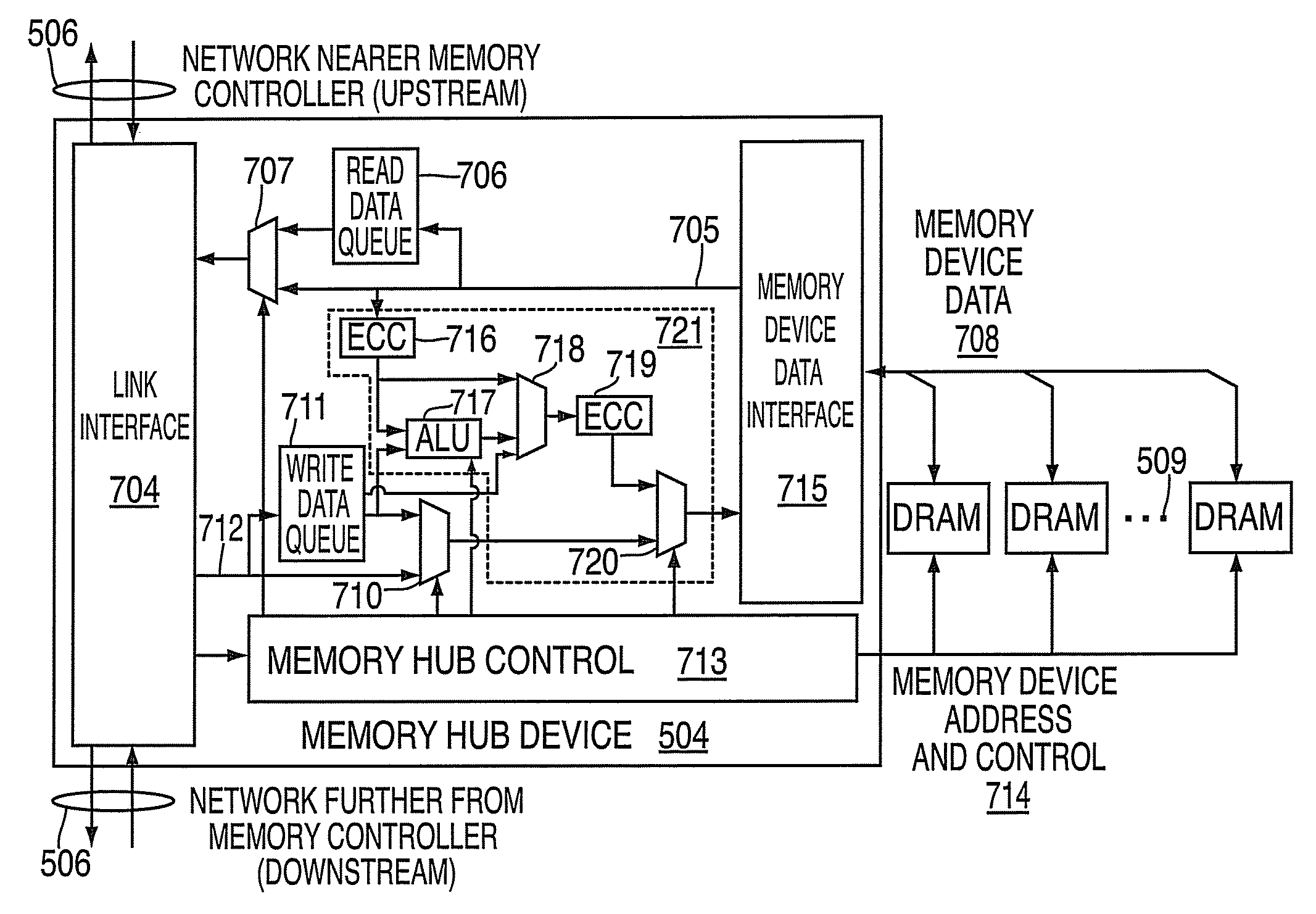

Systems and methods for providing data modification operations in memory subsystems

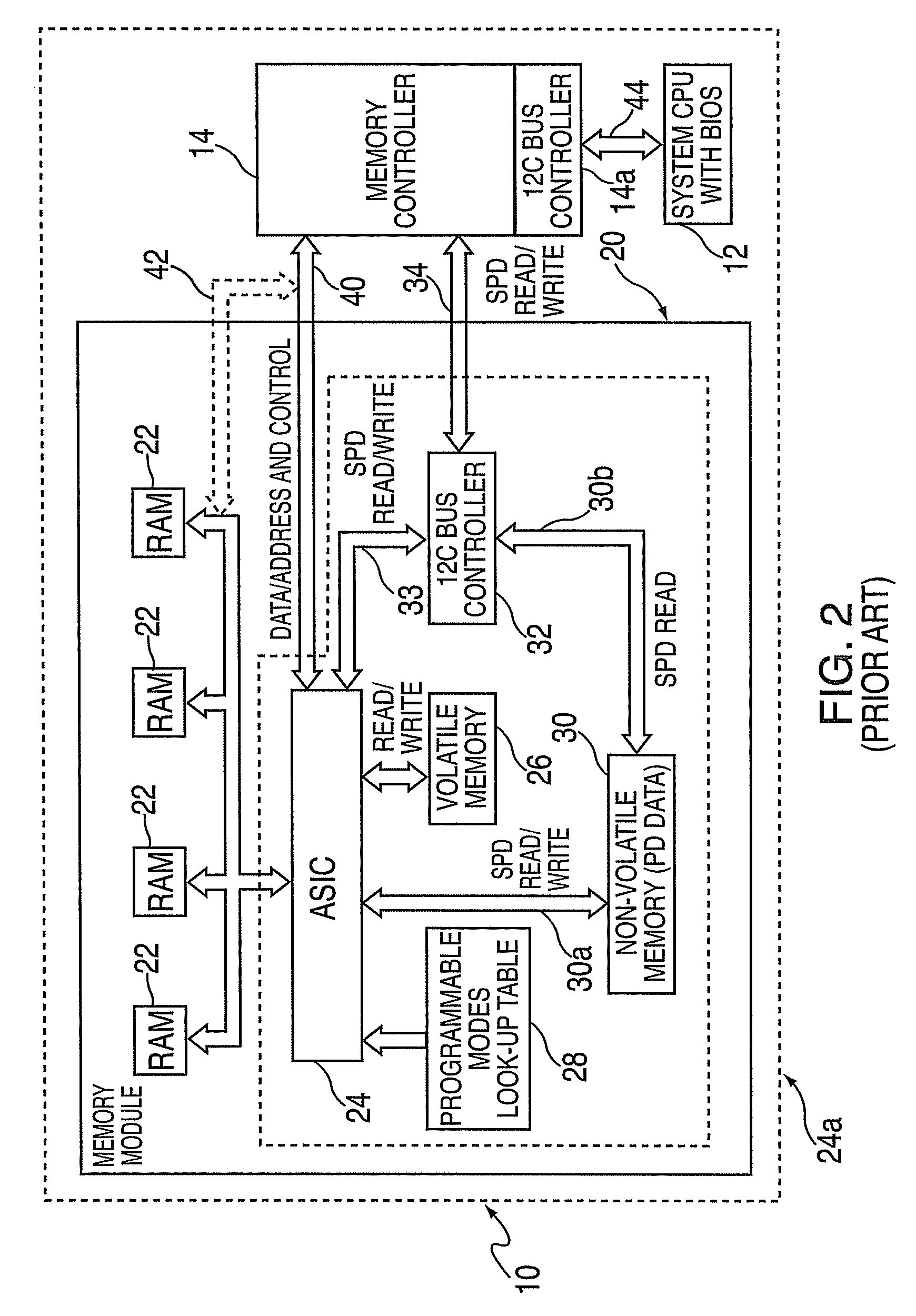

InactiveUS7584336B2Memory architecture accessing/allocationMemory adressing/allocation/relocationMemory busRead-modify-write

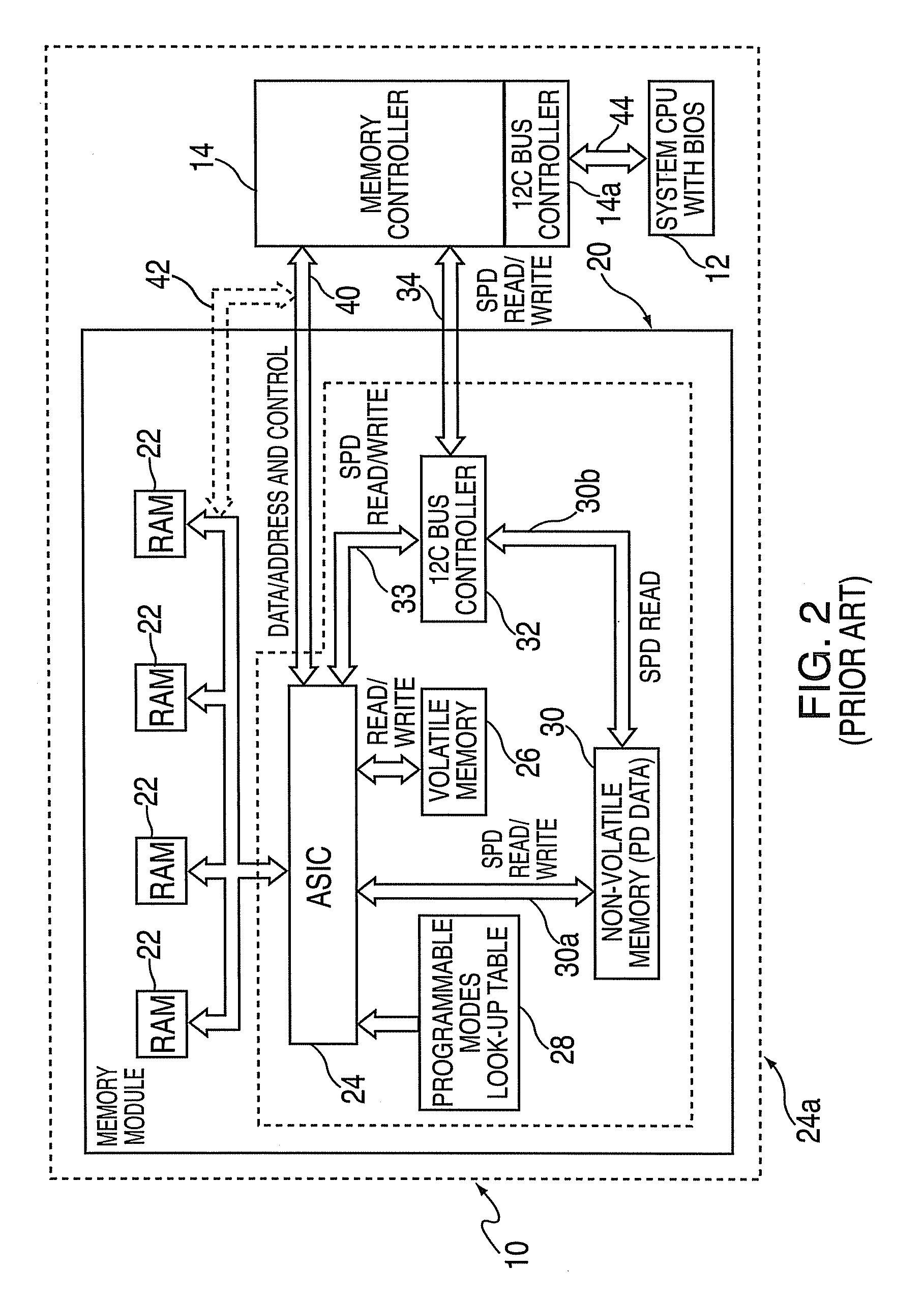

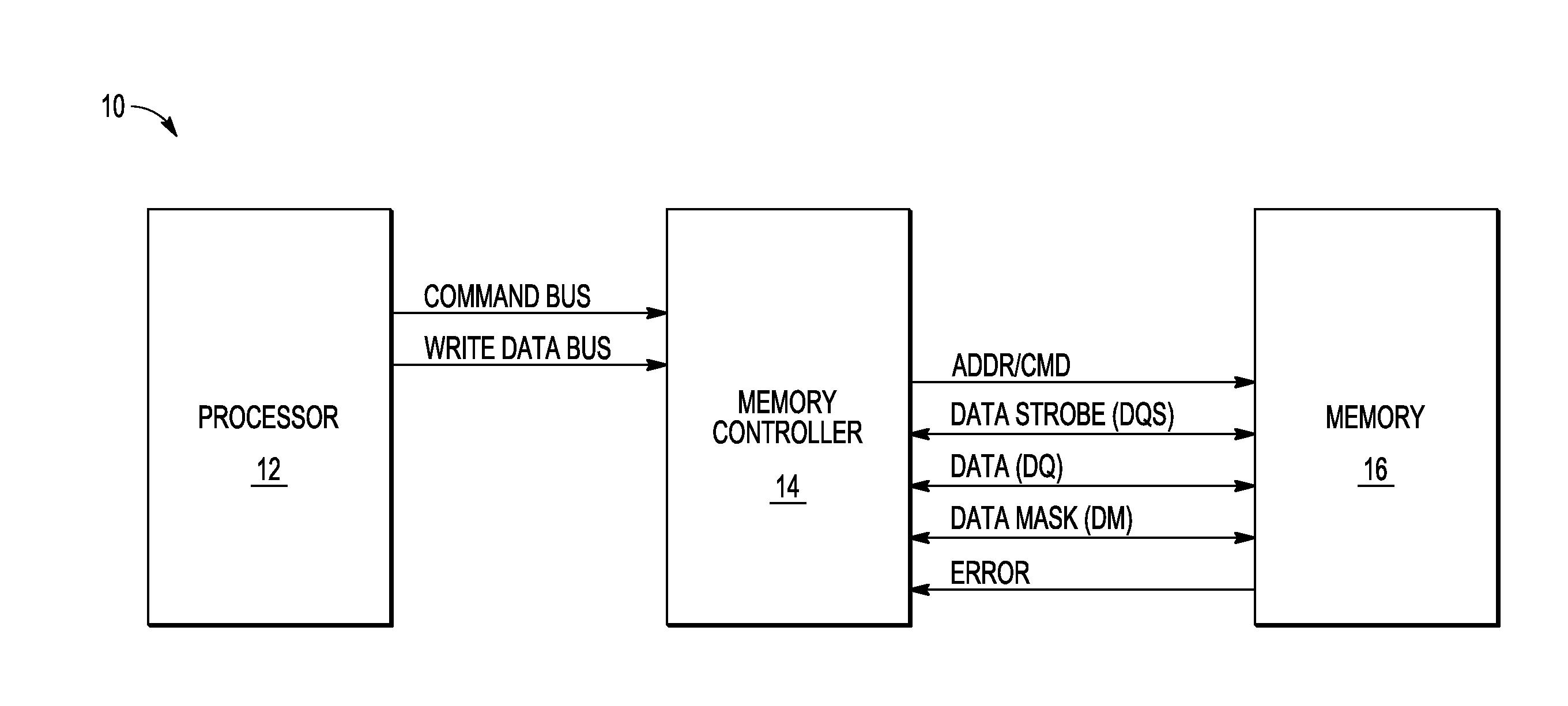

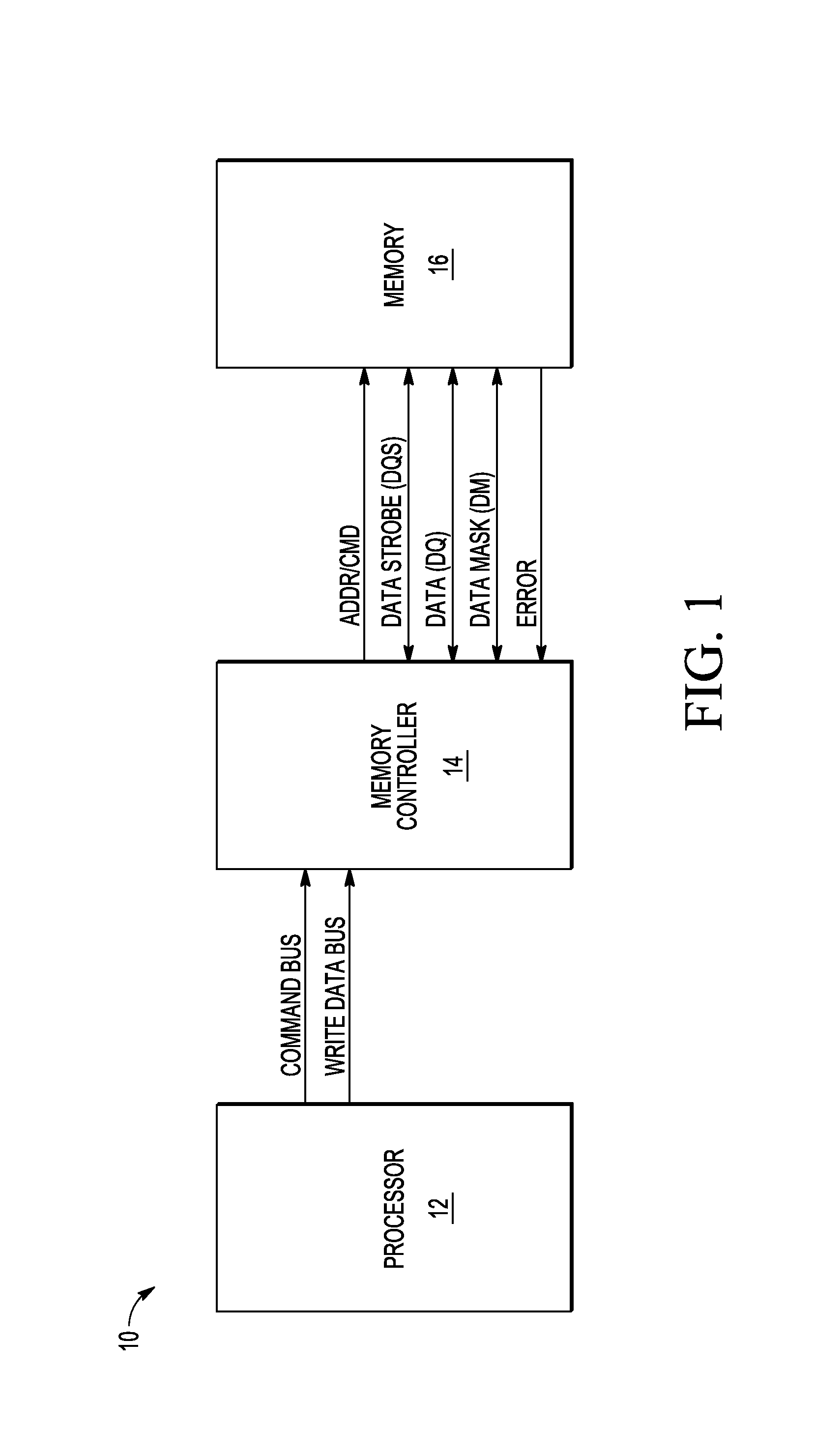

Systems and methods for providing data modification operations in memory subsystems. Systems include a plurality of memory devices, a memory controller, one or more memory busses connected to the memory controller and a memory hub device. The memory controller receives and responds to memory access requests including memory update requests from a processor. The memory controller also generates a memory update command in response to receiving a memory update request. The memory hub device includes a first port, a second port and a control unit. The first port is in communication with the memory controller via one or more of the memory busses for transferring data and control information between the memory hub device and the memory controller. The second port is in communication with one or more of the memory devices. The control unit decodes the memory update command from the data and control information and accesses the memory devices via the second port to perform the memory update command local to the memory hub devices as a logical read-modify-write sequence.

Owner:INT BUSINESS MASCH CORP

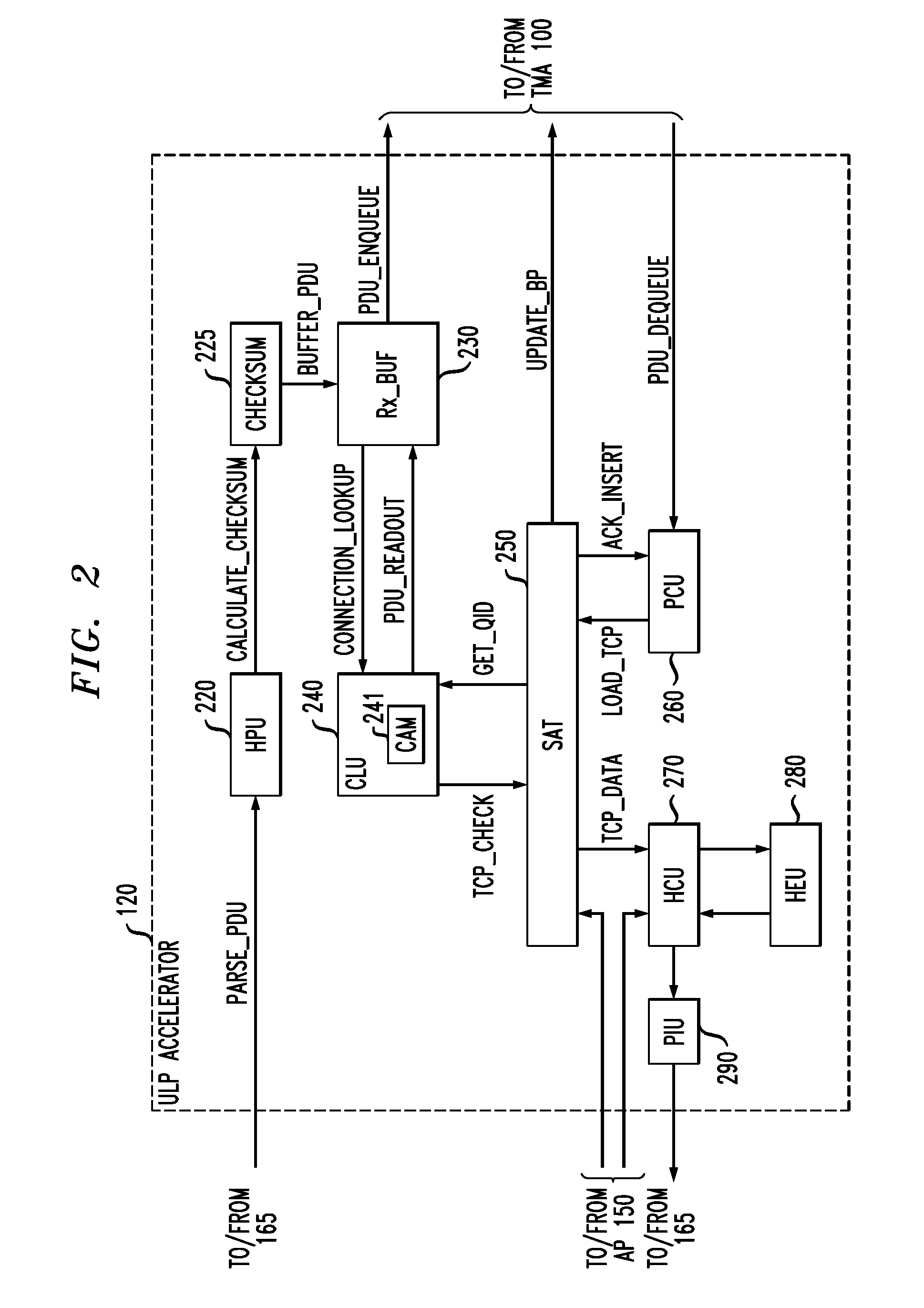

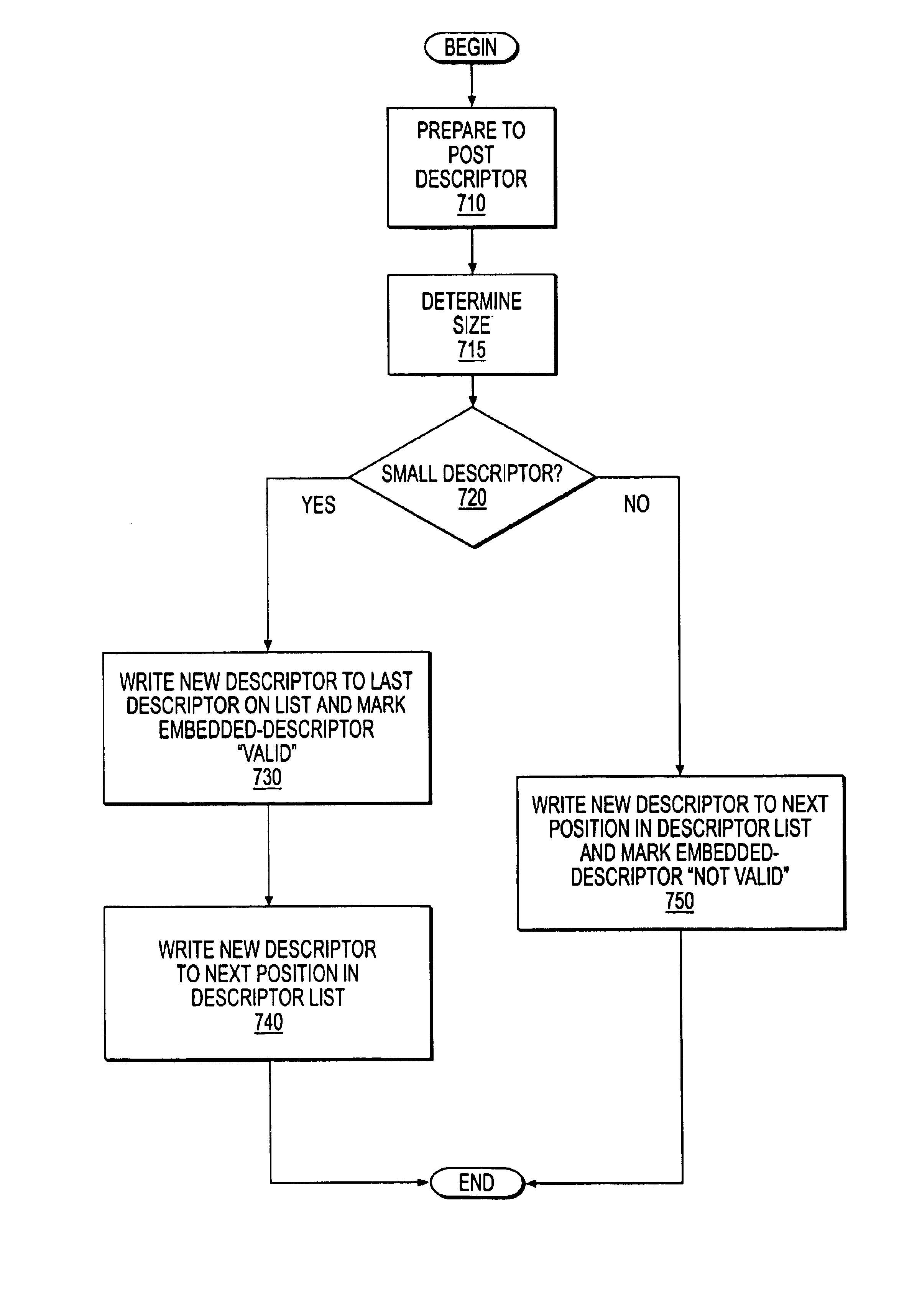

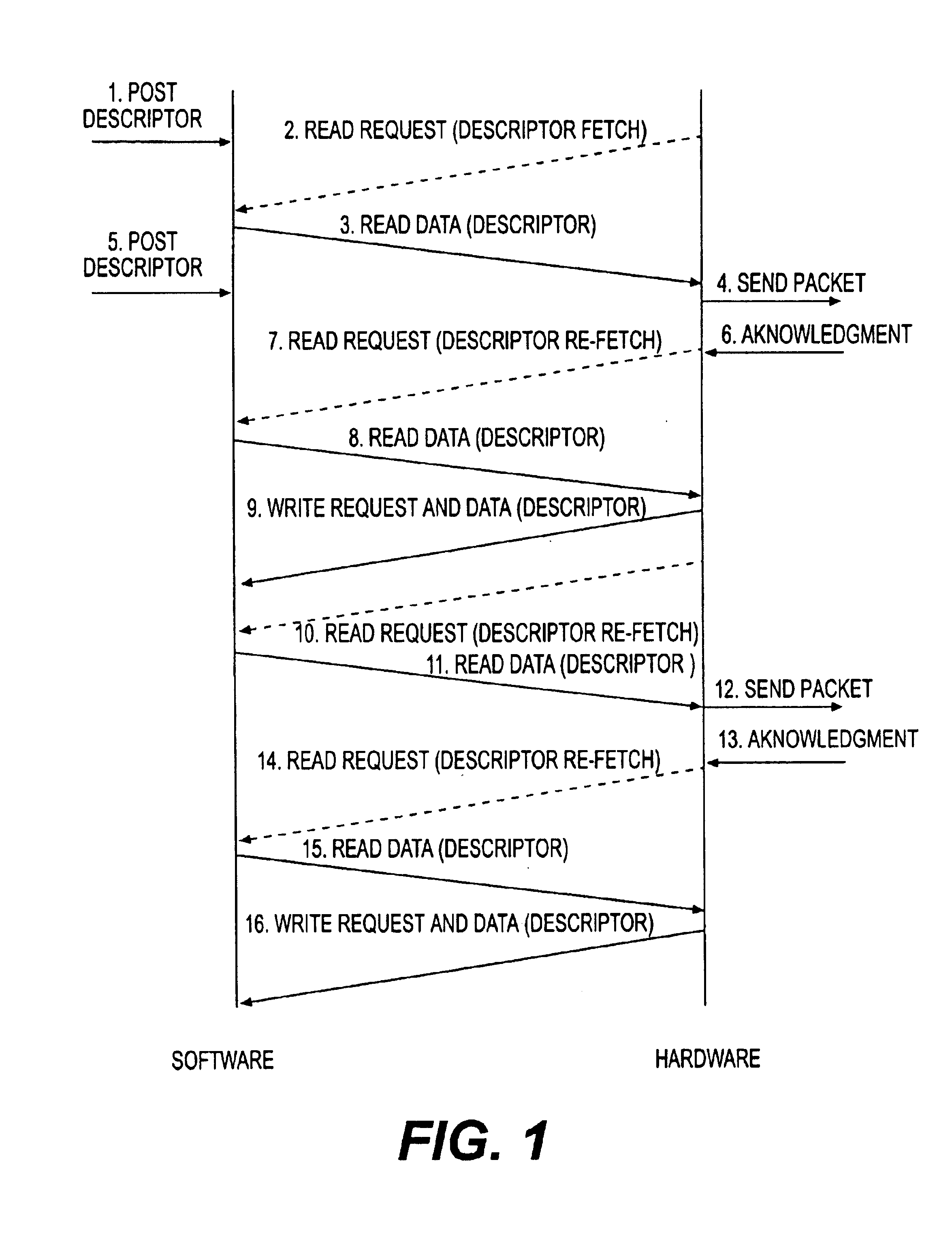

Methods, system and article of manufacture for pre-fetching descriptors

InactiveUS6857030B2Network connectionsInput/output processes for data processingEmbedded systemRead-modify-write

A system and method for reducing the number of memory accesses by a hardware device to a descriptor memory is disclosed. Methods, systems and articles of manufacture consistent with the present invention enable software to embed a subsequent descriptor it is posting in the descriptor memory into a current descriptor listed in the descriptor memory. Additionally, hardware is configured to transmit a data packet associated with the current descriptor to a recipient device. When hardware receives an acknowledgment message from the recipient device associated with the transmitted data packet, it fetches the current descriptor to update a completion code within the current descriptor using a Read-Modify-Write (RMW) transfer sequence. As part of the RMW memory operation, hardware may use the embedded copy of the subsequent descriptor within the current descriptor to transmit the next data packet associated with the subsequent descriptor. This process avoids hardware from having to fetch the embedded descriptor from the descriptor memory before transmitting the next data packet.

Owner:ORACLE INT CORP

Aligned data storage for network attached media streaming systems

InactiveUS8521955B2Redundant array of inexpensive disk systemsDigital computer detailsStreaming dataRAID

Owner:BROADCOM INT PTE LTD

Lock Mechanism to Enable Atomic Updates to Shared Memory

ActiveUS20090240860A1Reduce in quantityUnauthorized memory use protectionProgram controlLocking mechanismRead-modify-write

A system and method for locking and unlocking access to a shared memory for atomic operations provides immediate feedback indicating whether or not the lock was successful. Read data is returned to the requestor with the lock status. The lock status may be changed concurrently when locking during a read or unlocking during a write. Therefore, it is not necessary to check the lock status as a separate transaction prior to or during a read-modify-write operation. Additionally, a lock or unlock may be explicitly specified for each atomic memory operation. Therefore, lock operations are not performed for operations that do not modify the contents of a memory location.

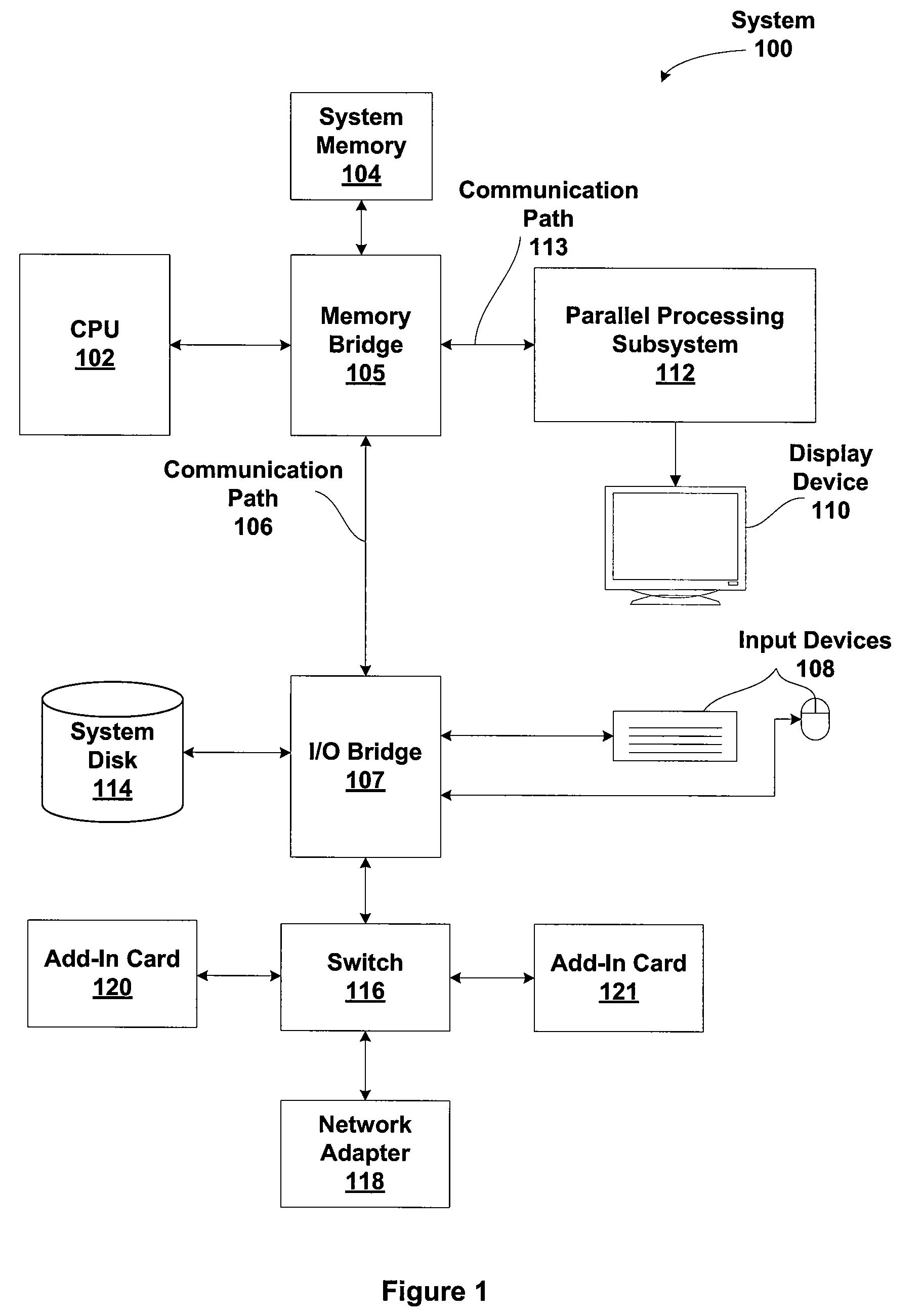

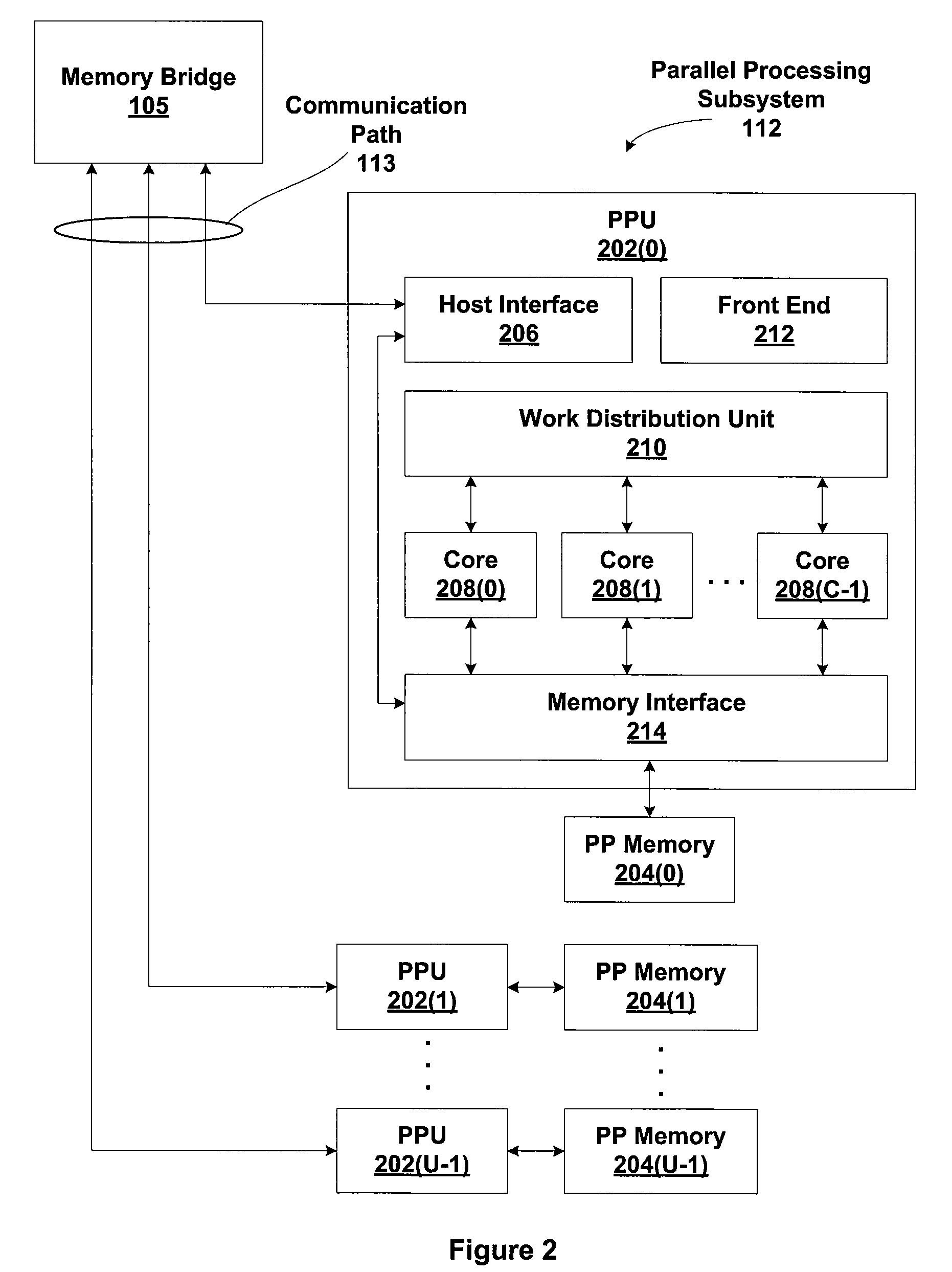

Owner:NVIDIA CORP

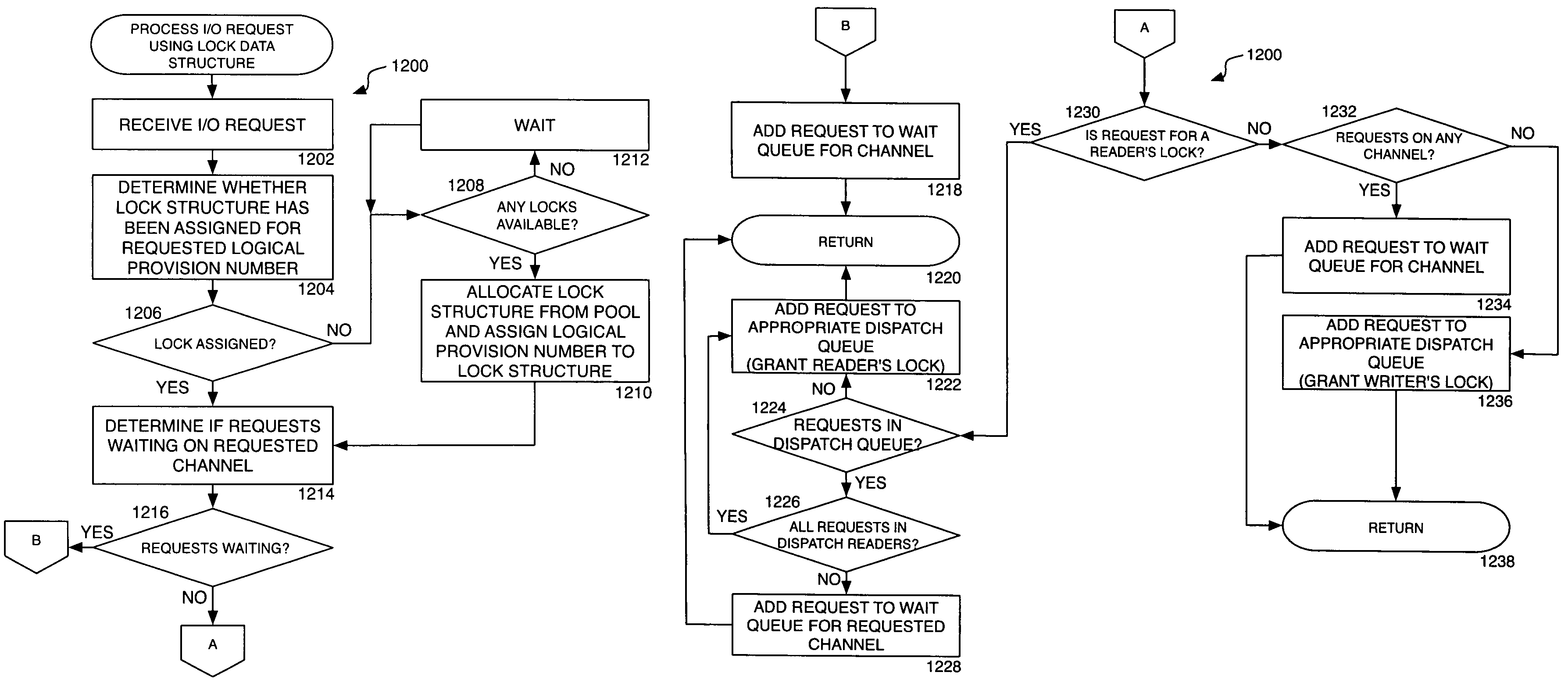

Method, system, apparatus, and computer-readable medium for locking and synchronizing input/output operations in a data storage system

ActiveUS7562200B1Reduce the possibilityData processing applicationsMemory loss protectionGranularityRead-modify-write

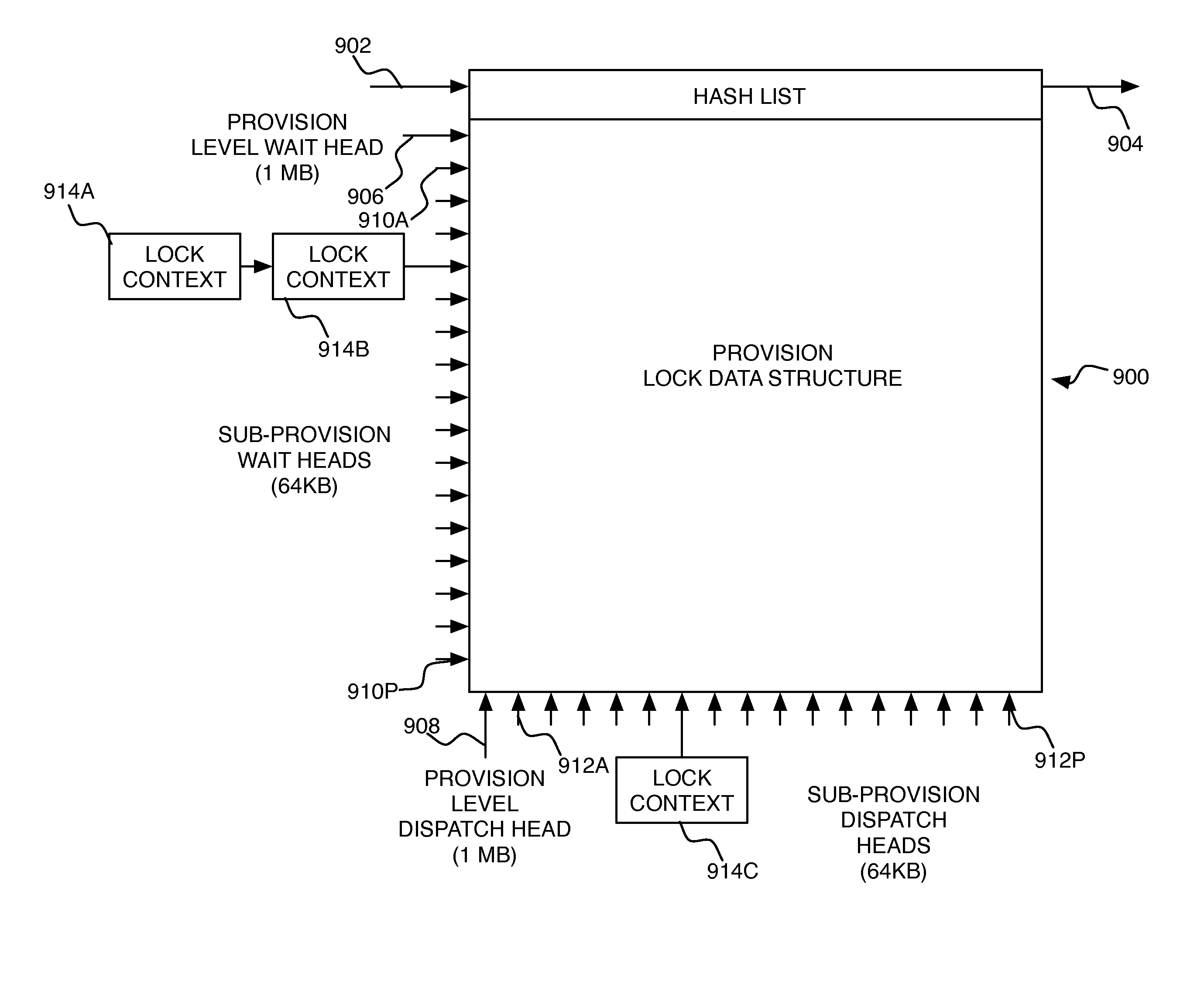

A method, system, apparatus, and computer-readable medium are provided for synchronizing I / O operations in a computer system. According to aspects of the invention, multiple reader and writer locks are provided that may be acquired by calling processes at two different granularities. Locks may be acquired for an area of storage equivalent to the logical unit of allocation or for a sub-provision area equivalent to a unit of snapshot read-modify-write. Each lock is represented by a lock data structure that represents the same amount of logical address space as the logical unit of allocation. A request that arrives to the lock data structure is made to wait in a lock wait queue until the request can be honored. Requests that have been honored but that have not yet released the lock are maintained in a dispatch queue. When a writer lock is assigned to a lock request, no other readers or writers may be allocated to it. When a reader lock is assigned to a lock request, the lock may also be given to other readers, but not to a writer. A round robin technique is utilized to respond to requests for locks so that one lock does not starve the other locks.

Owner:AMZETTA TECH LLC

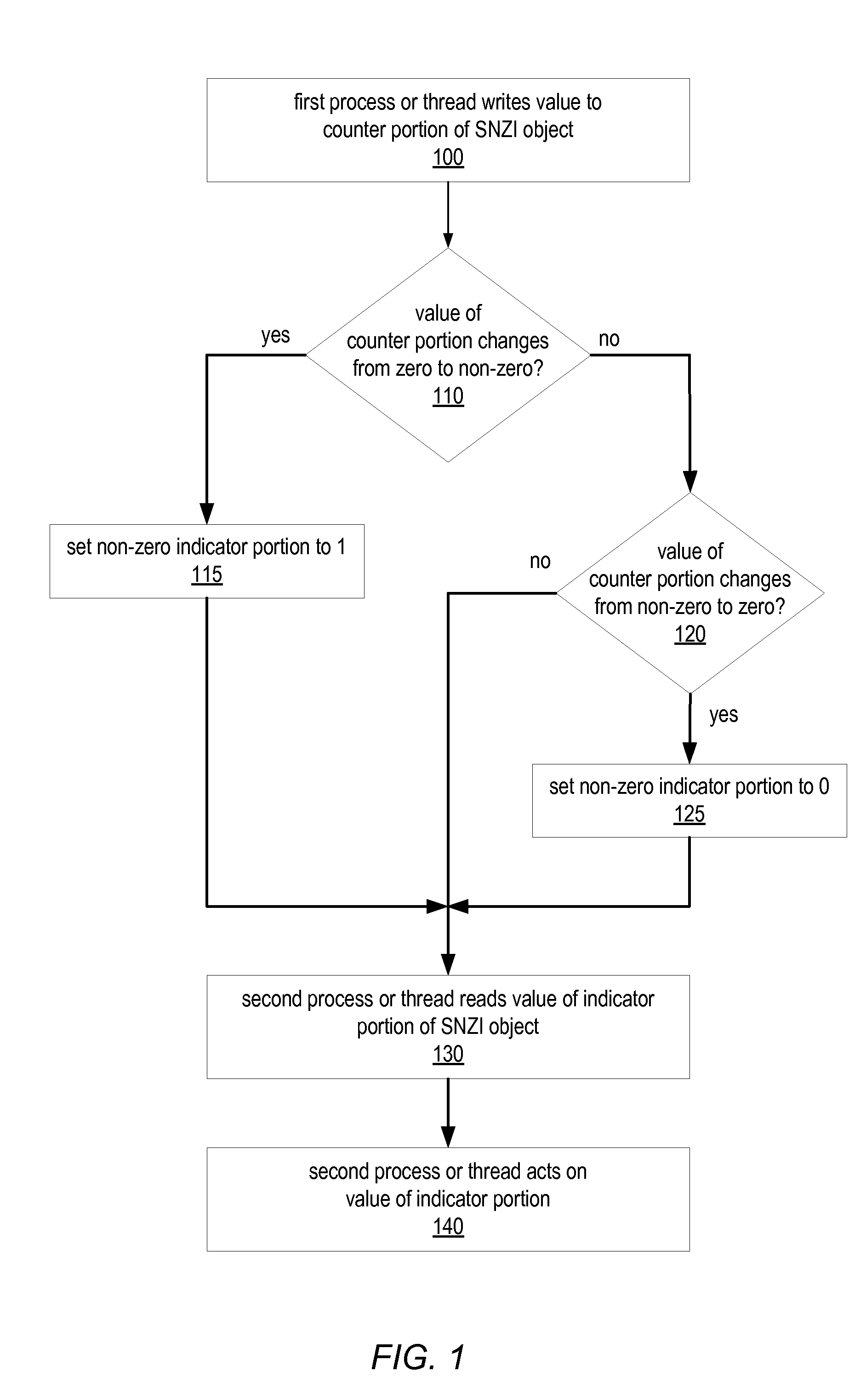

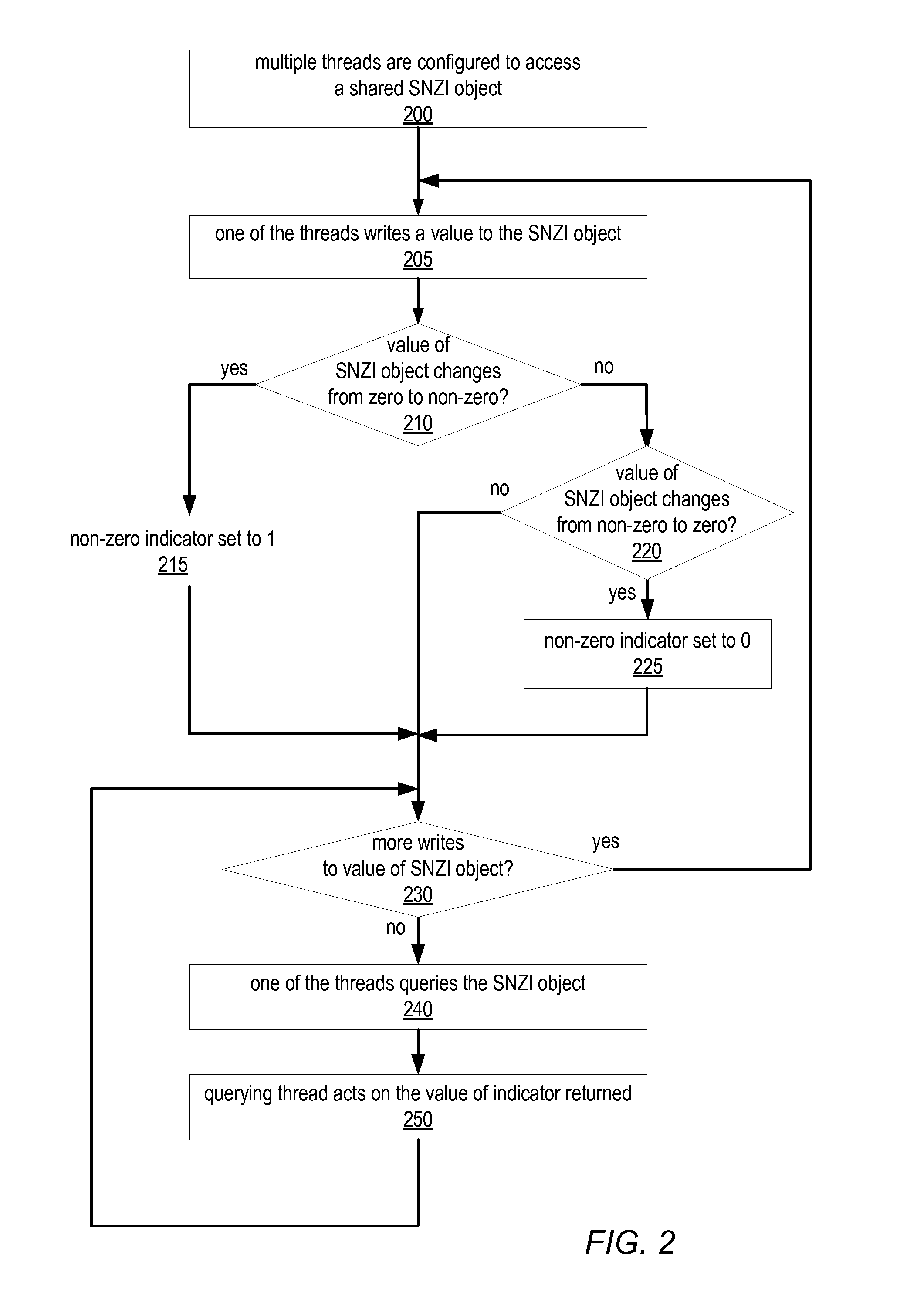

System and Method for Implementing Shared Scalable Nonzero Indicators

ActiveUS20090125548A1Program synchronisationSpecial data processing applicationsConcurrent computingConcurrent computation

A Scalable NonZero Indicator (SNZI) object in a concurrent computing application may include a shared data portion (e.g., a counter portion) and a shared nonzero indicator portion, and / or may be an element in a hierarchy of SNZI objects that filters changes in non-root nodes to a root node. SNZI objects may be accessed by software applications through an API that includes a query operation to return the value of the nonzero indicator, and arrive (increment) and depart (decrement) operations. Modifications of the data portion and / or the indicator portion may be performed using atomic read-modify-write type operations. Some SNZI objects may support a reset operation. A shared data object may be set to an intermediate value, or an announce bit may be set, to indicate that a modification is in progress that affects its corresponding indicator value. Another process or thread seeing this indication may “help” complete the modification before proceeding.

Owner:SUN MICROSYSTEMS INC

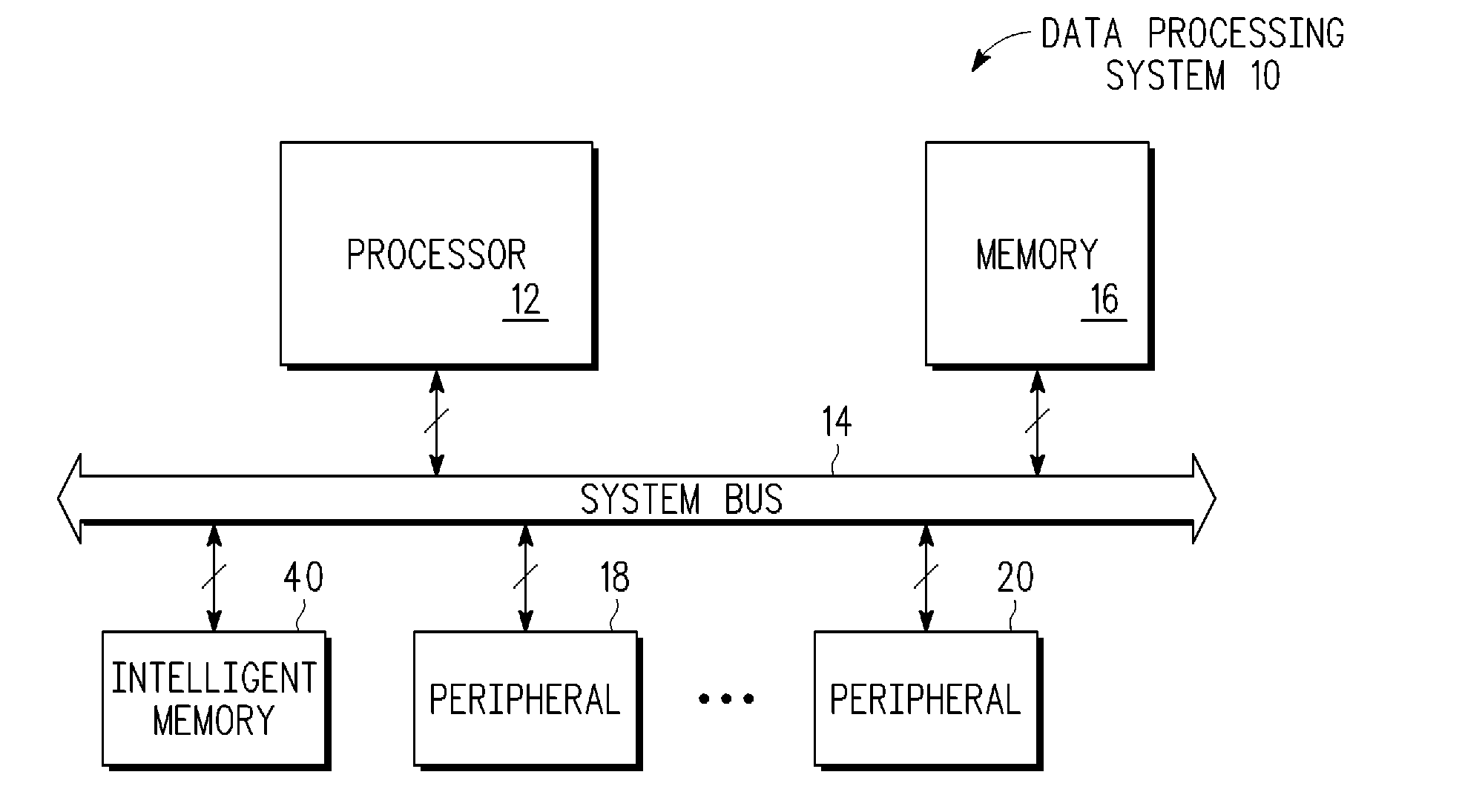

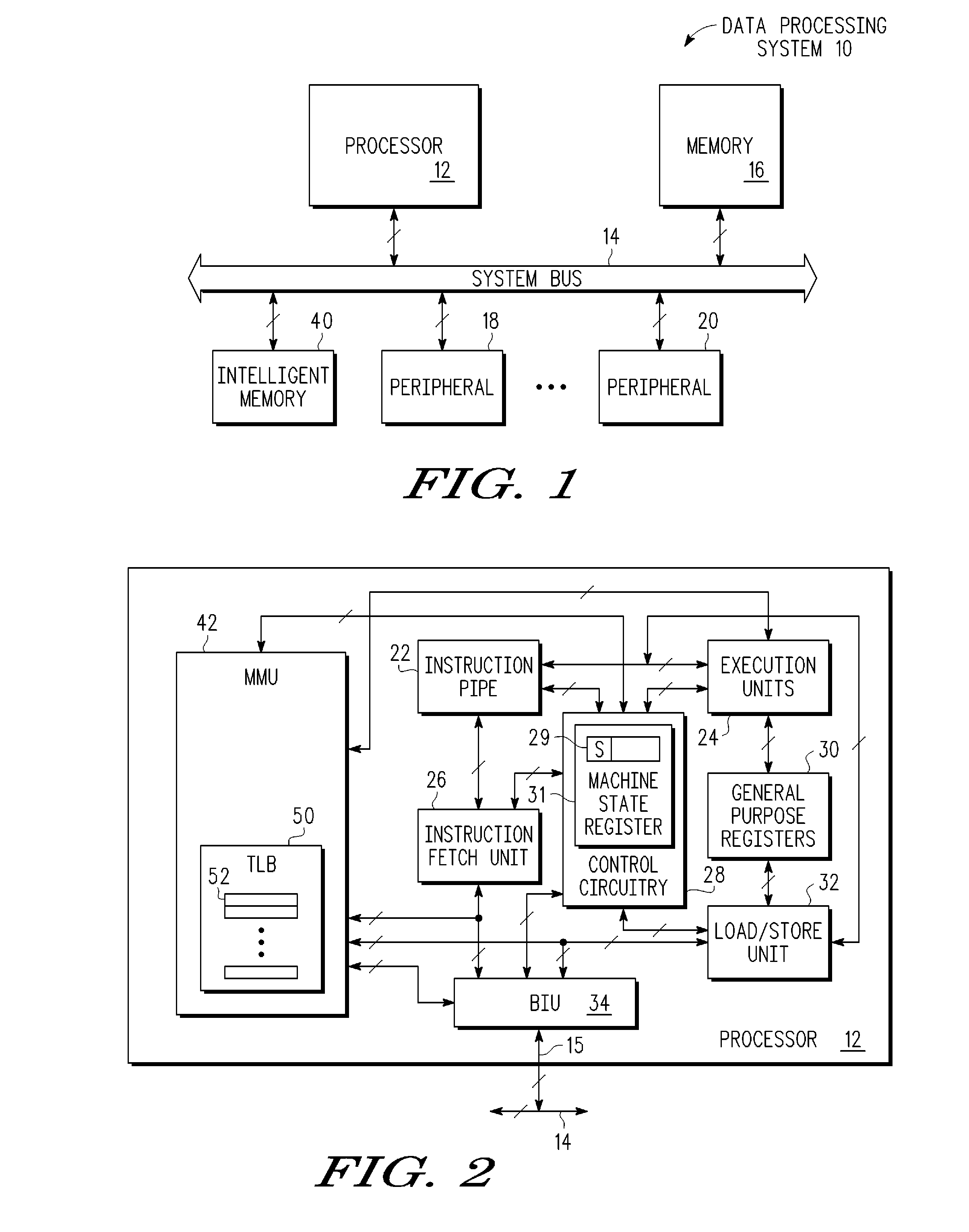

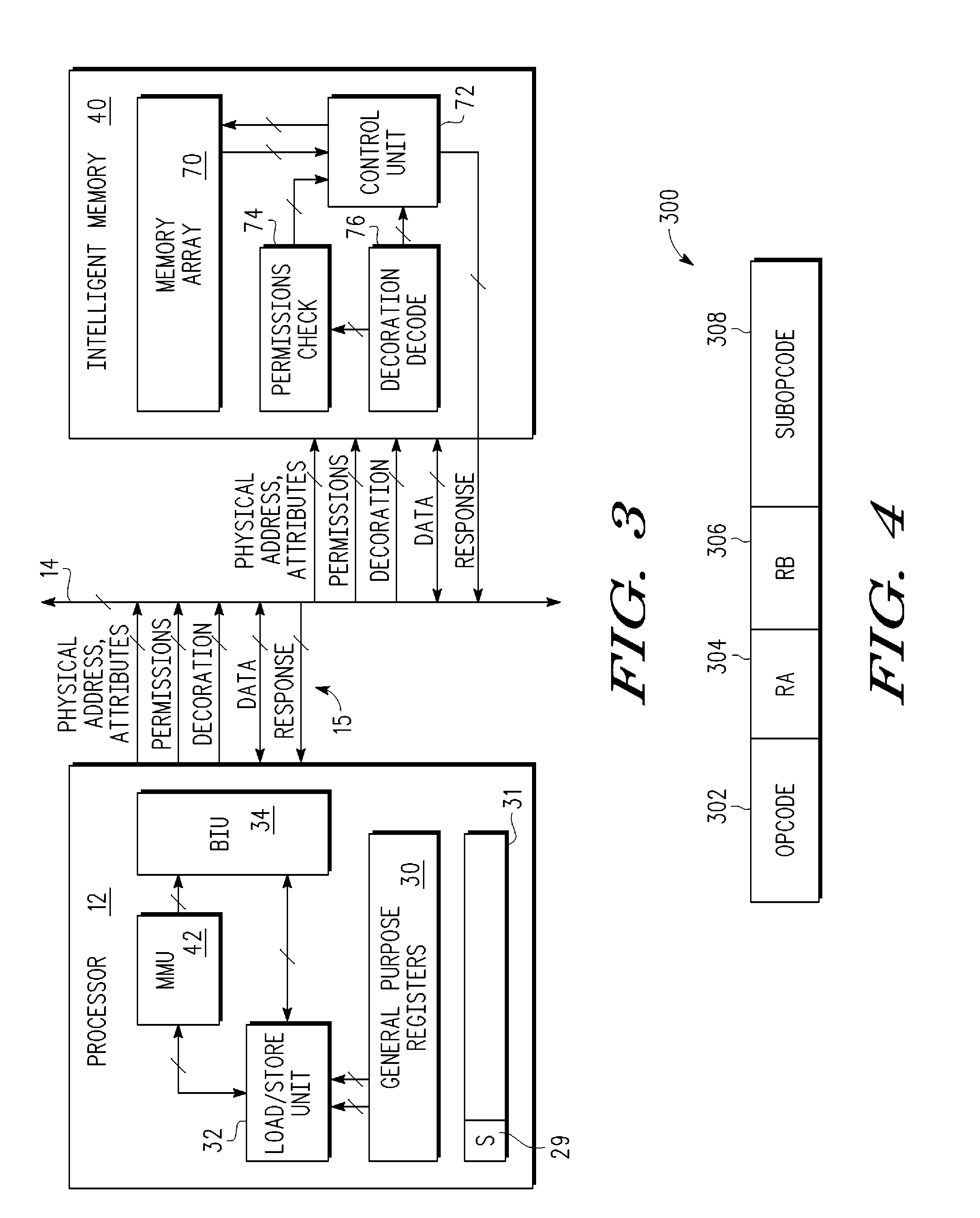

Data processor for processing a decorated storage notify

A data processing system having a processor and a target device processes decorated instructions (i.e. an instruction having a decoration value). A device of the data processing system such as the processor sends transactions to the target device over a system interconnect. A decorated storage notify (DSN) transaction includes an indication of an instruction operation, an address associated with the instruction operation, and a decoration value (i.e. a command to the target device to perform a function in addition to a store or a load). The transaction on the system interconnect includes an address phase and no data phase, thereby improving system bandwidth. In one form the target device (e.g. a memory with functionality in addition to storage functionality) performs a read-modify-write operation using information at a storage location of the target device.

Owner:NXP USA INC

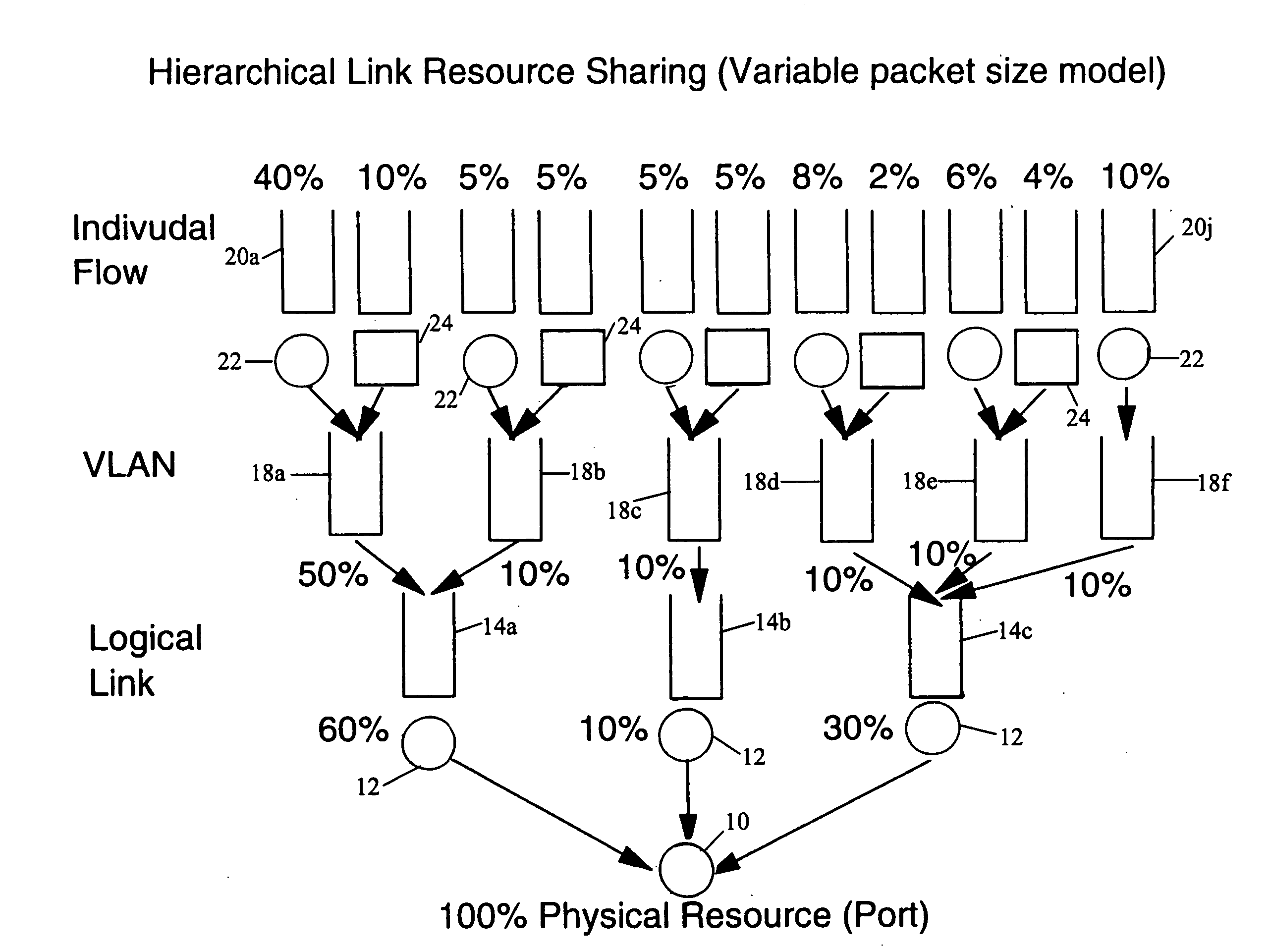

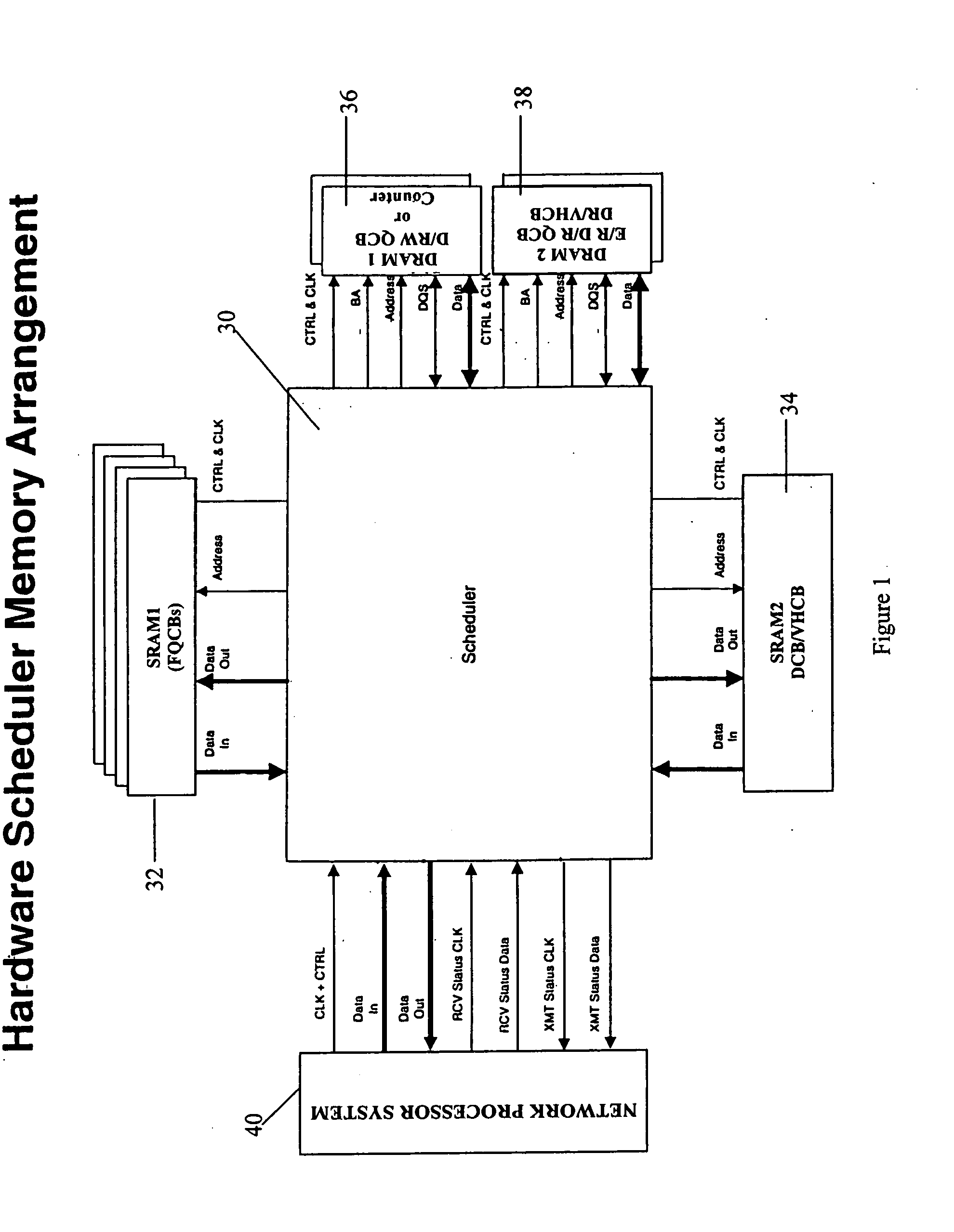

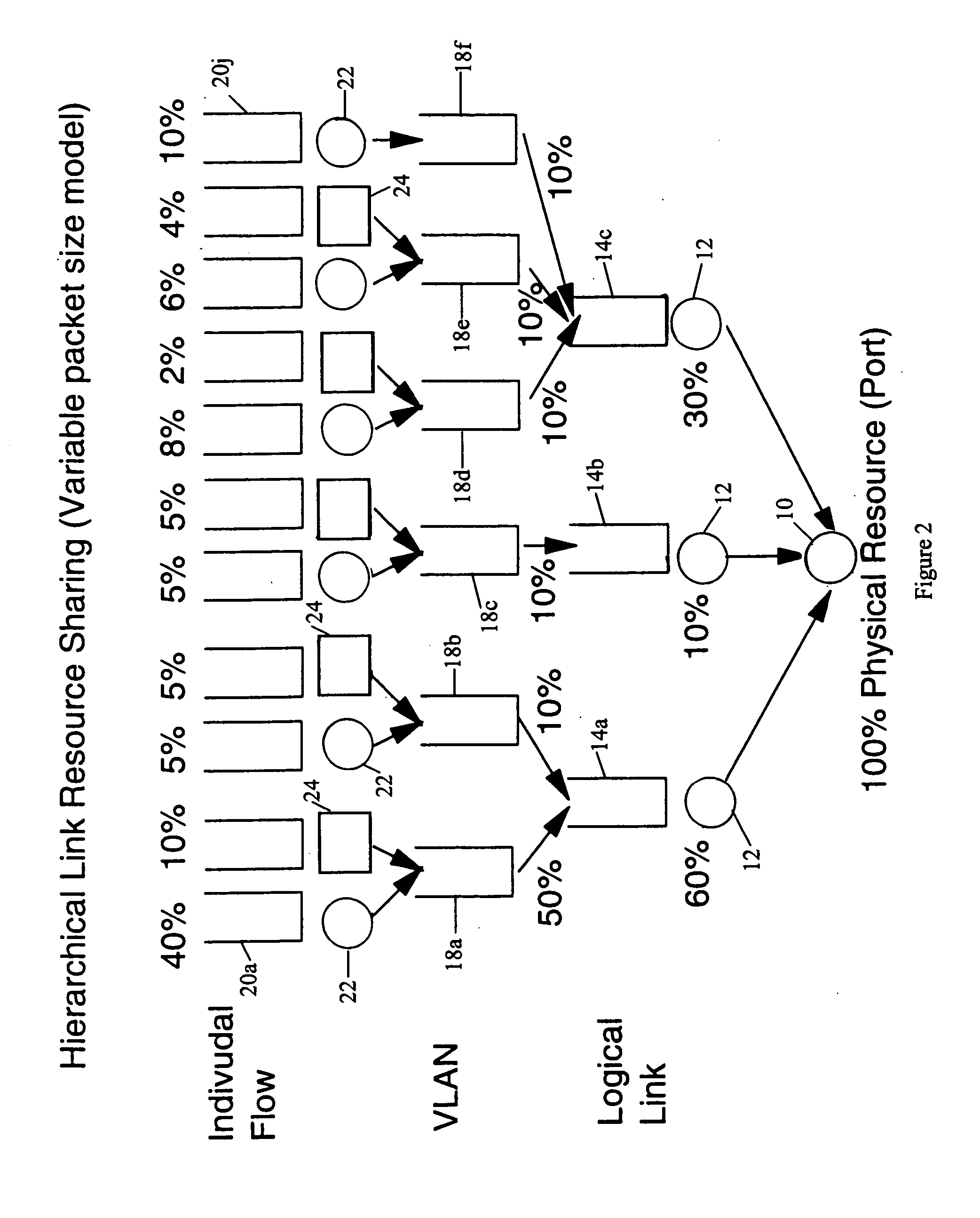

Structure and method for scheduler pipeline design for hierarchical link sharing

InactiveUS20050177644A1Reduce in quantityMultiple digital computer combinationsData switching networksTraffic capacityExternal storage

A pipeline configuration is described for use in network traffic management for the hardware scheduling of events arranged in a hierarchical linkage. The configuration reduces costs by minimizing the use of external SRAM memory devices. This results in some external memory devices being shared by different types of control blocks, such as flow queue control blocks, frame control blocks and hierarchy control blocks. Both SRAM and DRAM memory devices are used, depending on the content of the control block (Read-Modify-Write or ‘read’ only) at enqueue and dequeue, or Read-Modify-Write solely at dequeue. The scheduler utilizes time-based calendars and weighted fair queueing calendars in the egress calendar design. Control blocks that are accessed infrequently are stored in DRAM memory while those accessed frequently are stored in SRAM.

Owner:IBM CORP

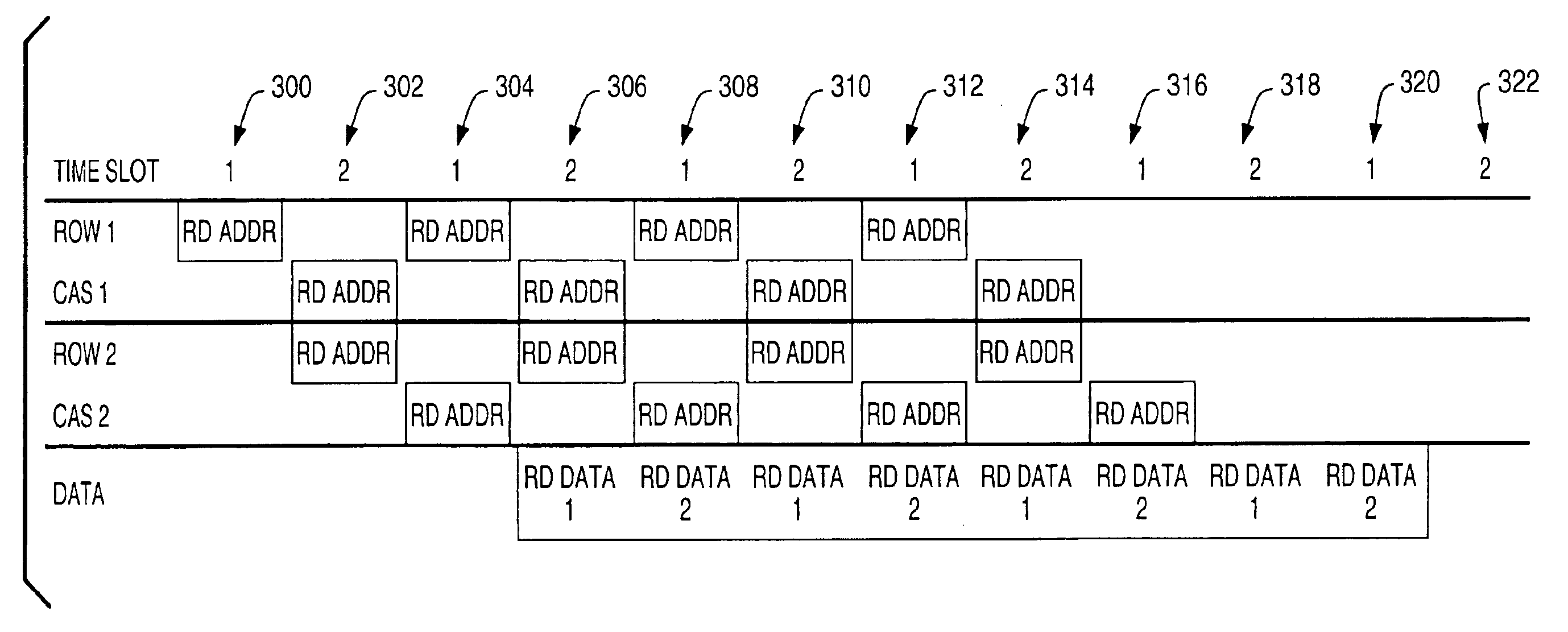

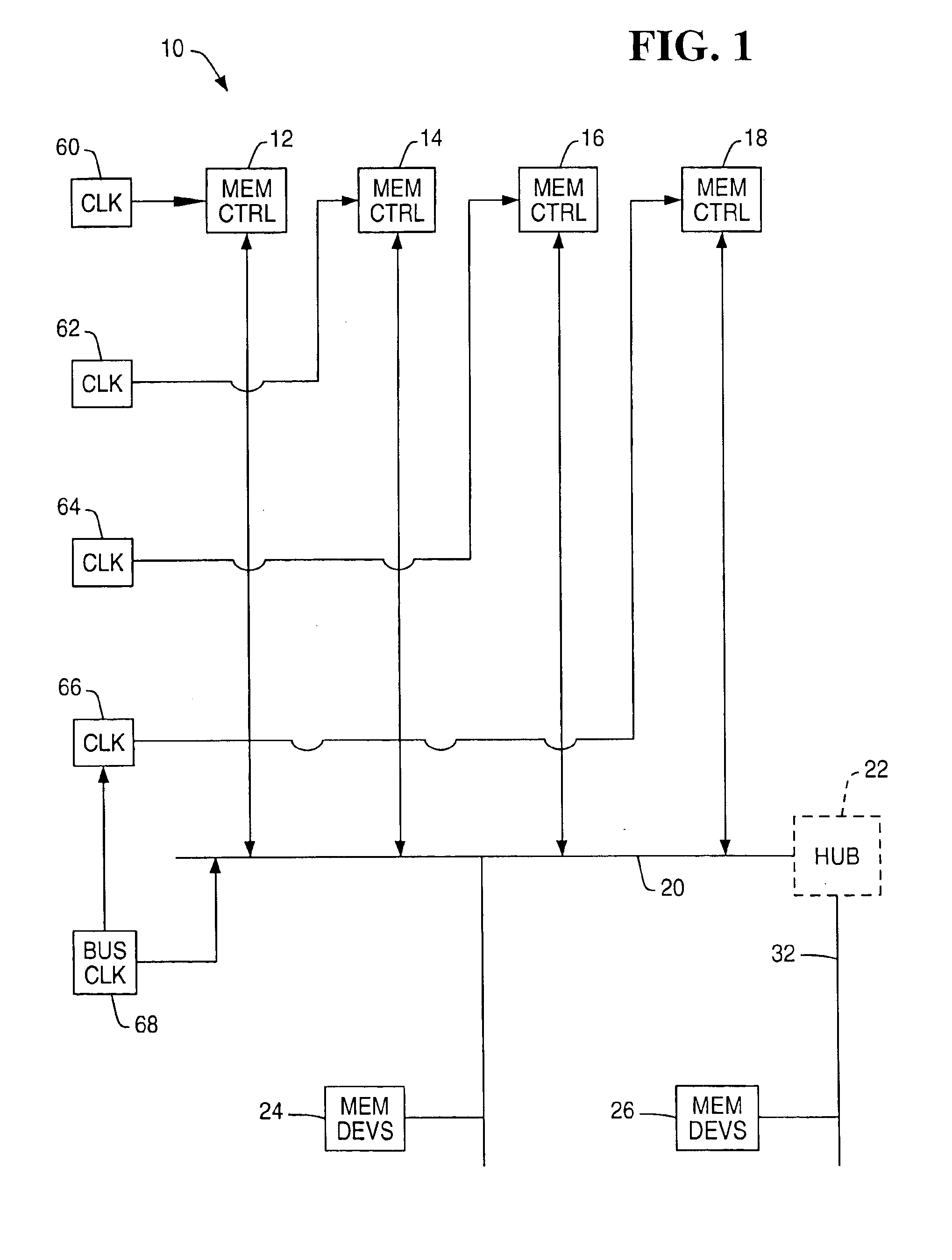

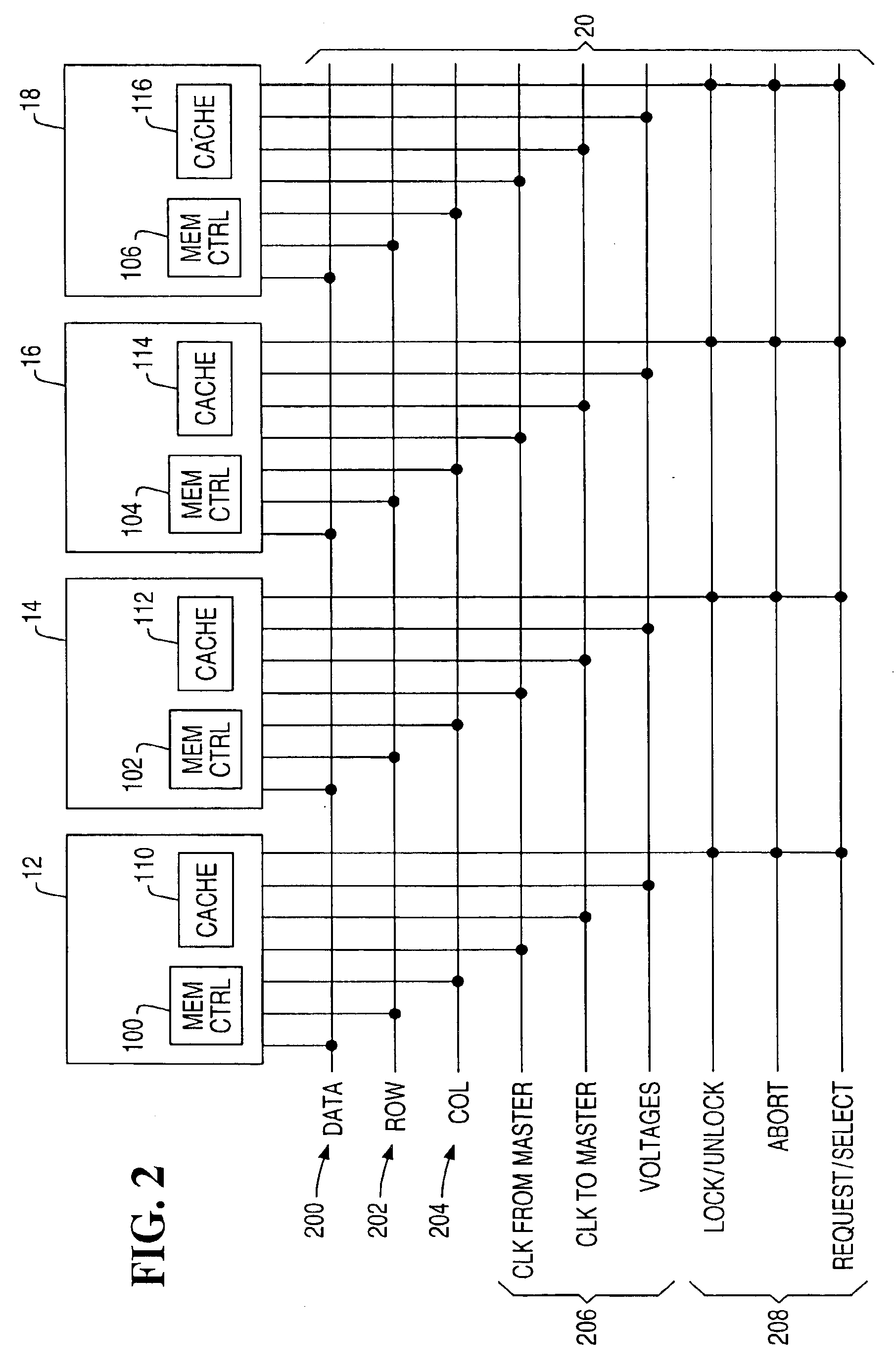

Providing multiple memory controllers on a memory bus

InactiveUS6868486B1Memory adressing/allocation/relocationInput/output processes for data processingParallel computingMemory bus

A system comprises a plurality of memory controllers connected to a memory bus. Each memory controller is able to generate memory requests on the memory bus according to a predetermined priority scheme. One priority scheme is a time slot priority scheme, and another priority scheme is a request-select priority scheme. The plurality of memory controllers are able to monitor memory requests generated by another memory controller in performing memory-related actions, such as memory requests (read or write), read-modify-write transaction, and cache coherency actions. In one arrangement, the memory bus is a Rambus channel.

Owner:TERADATA US

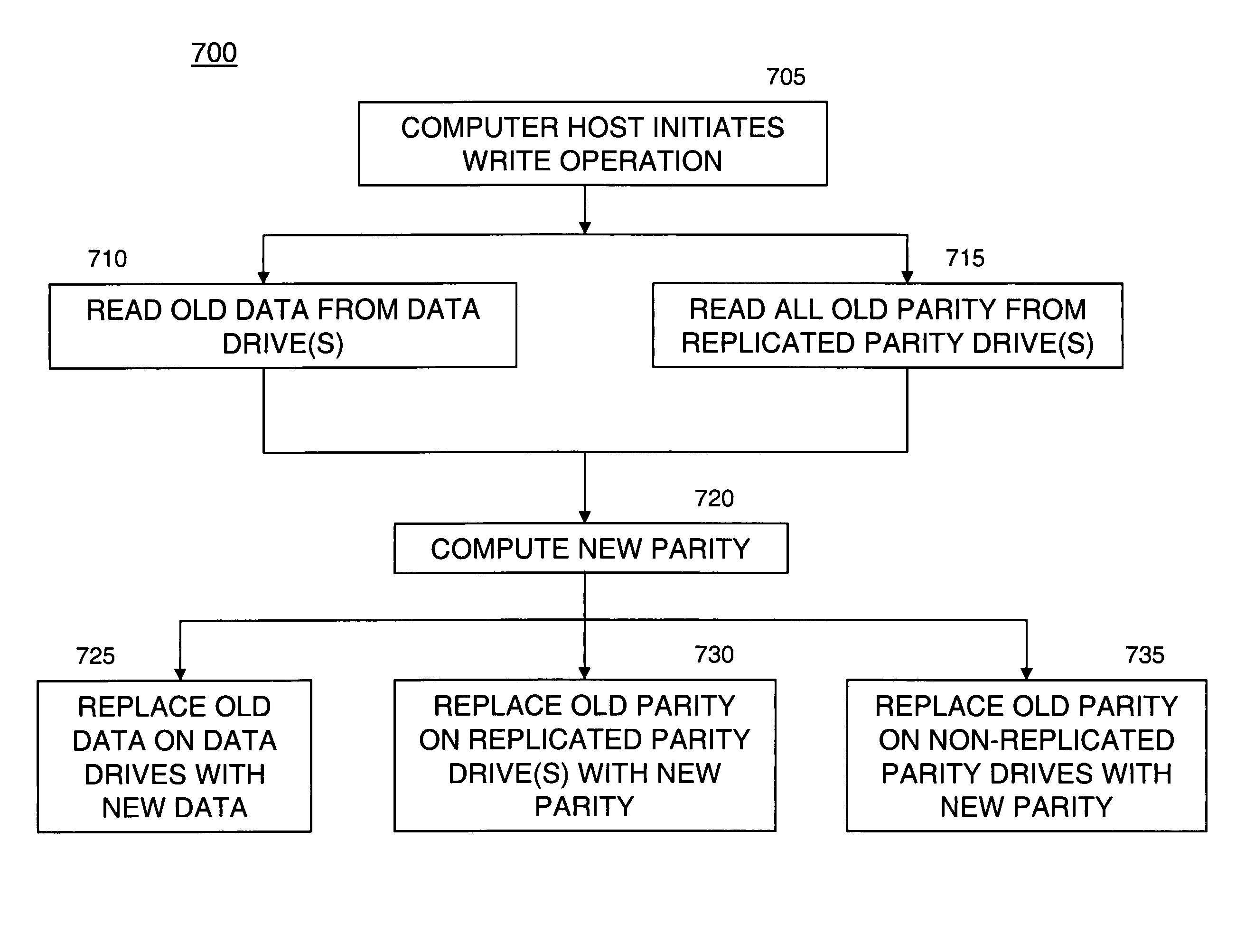

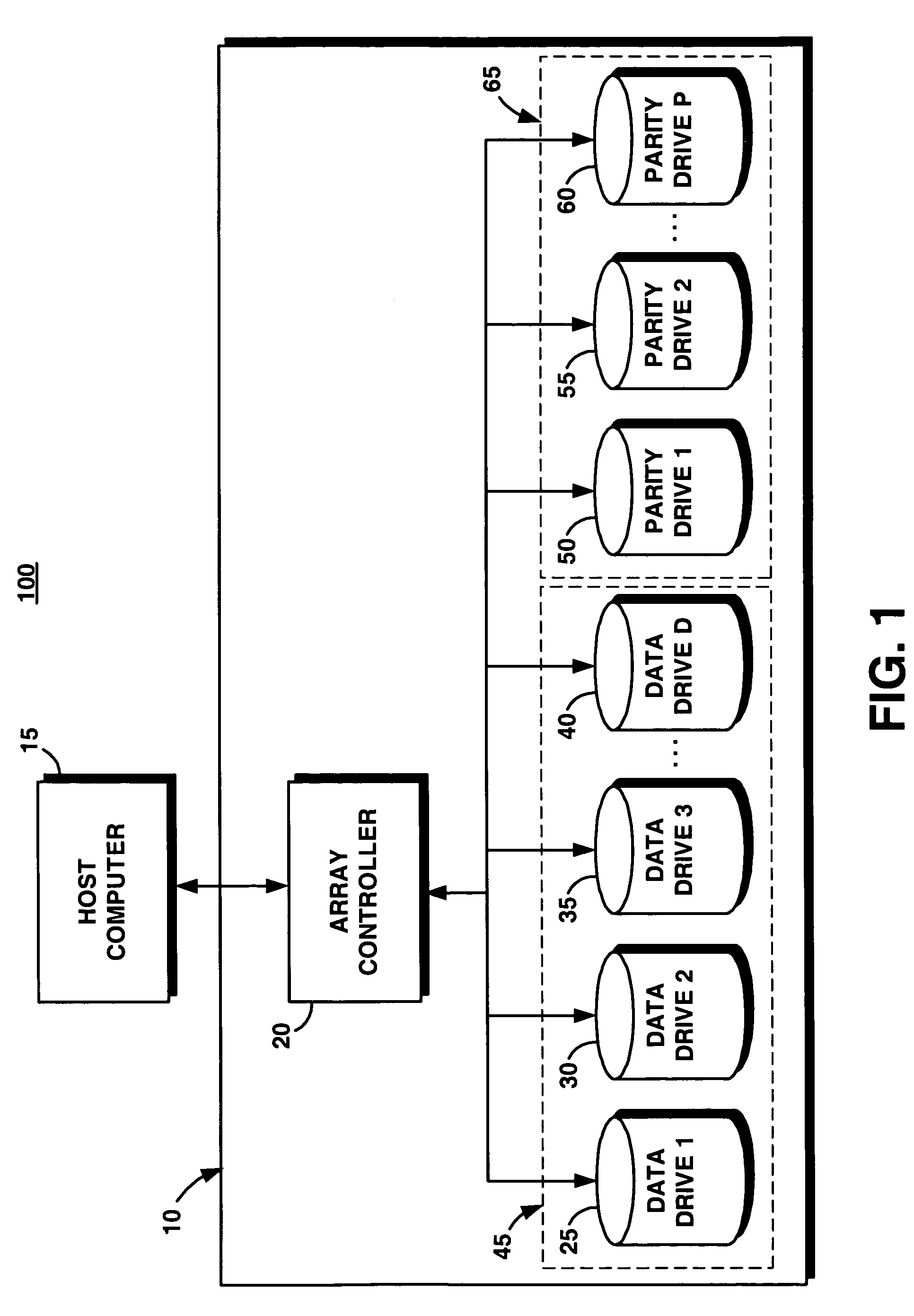

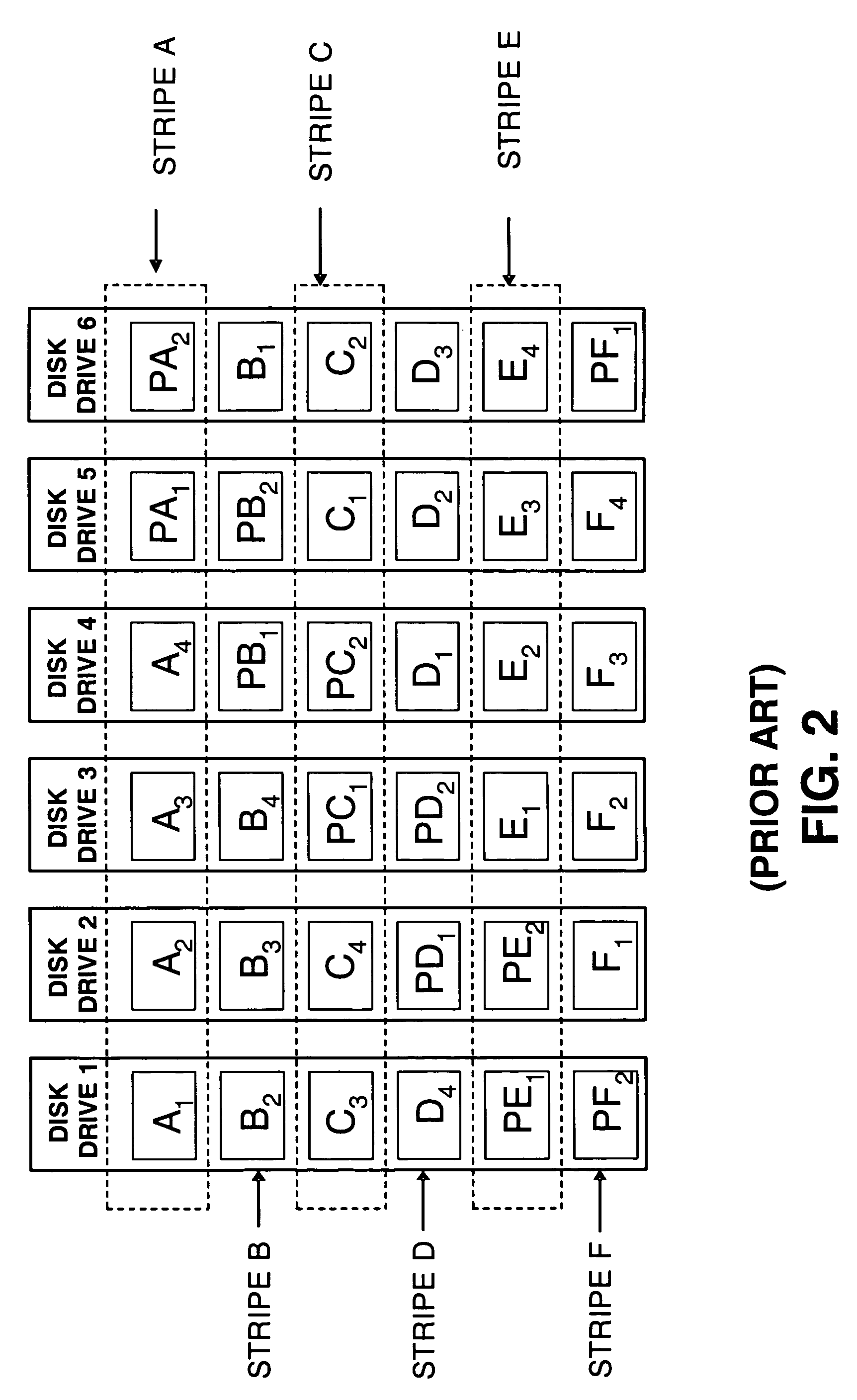

System and method for improving the performance of operations requiring parity reads in a storage array system

InactiveUS7353423B2Improve read performanceImprove performanceError detection/correctionMemory systemsRAIDParity drive

Owner:INT BUSINESS MASCH CORP

System, apparatus, and method for modifying the order of memory accesses

ActiveUS20110099341A1Memory adressing/allocation/relocationProgram controlMemory interfaceParallel computing

Systems and methods for controlling memory access operations are disclosed. The system may include one or more requestors performing requests to memory devices. Within a memory controller, a request queue receives requests from a requestor, a bank decoder determines a destination bank, and the request is placed in an appropriate bank queue. An ordering unit determines if the current request can be reordered relative to the received order and generates a new memory cycle order based on the reordering determination. The reordering may be based on whether there are multiple requests to the same memory page, multiple reads, or multiple writes. A memory interface executes each memory request in the memory cycle order. A data buffer holds write data until it is written to the memory and read data until it is returned to the requestor. The data buffer also may hold memory words used in read-modify-write operations.

Owner:MICRON TECH INC

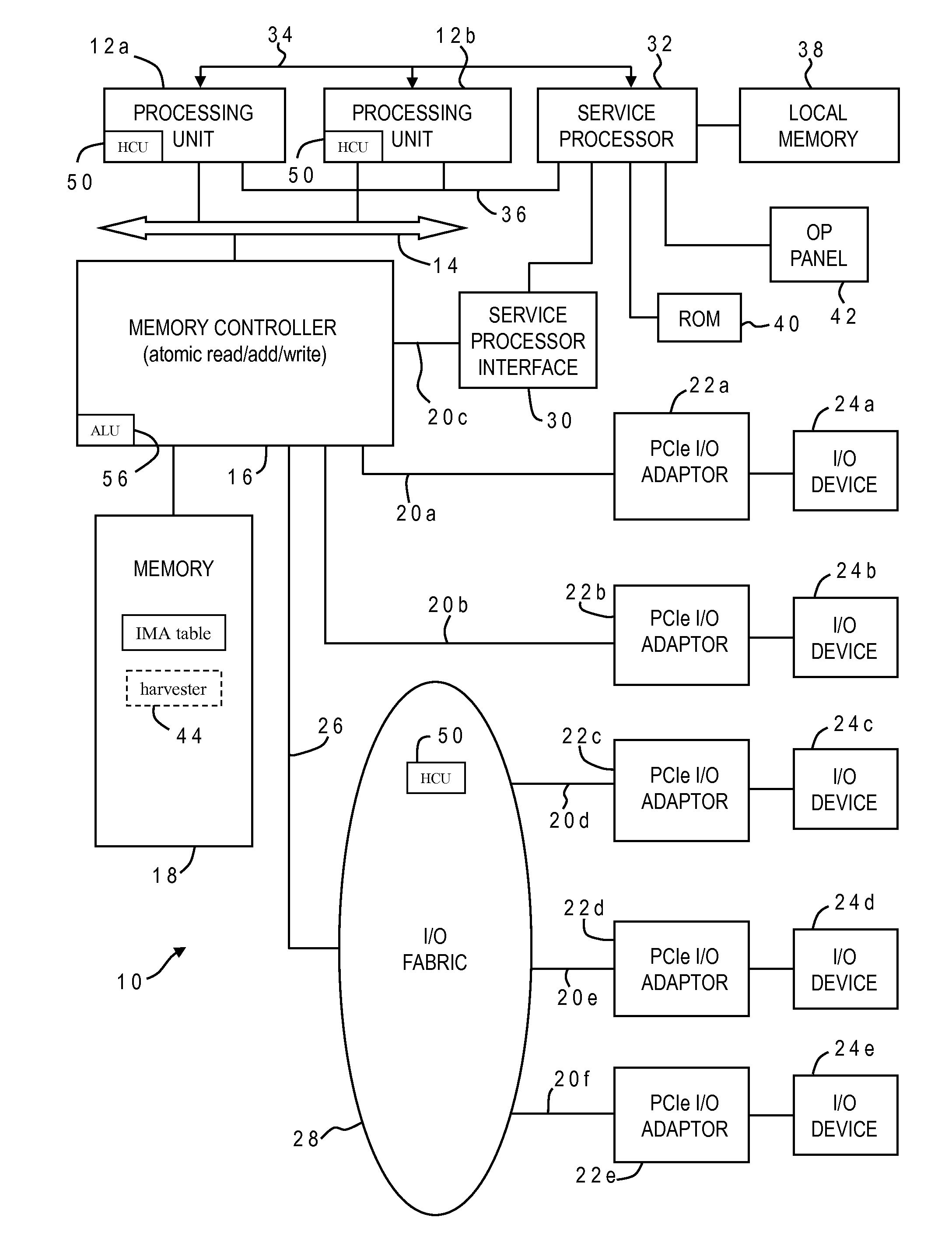

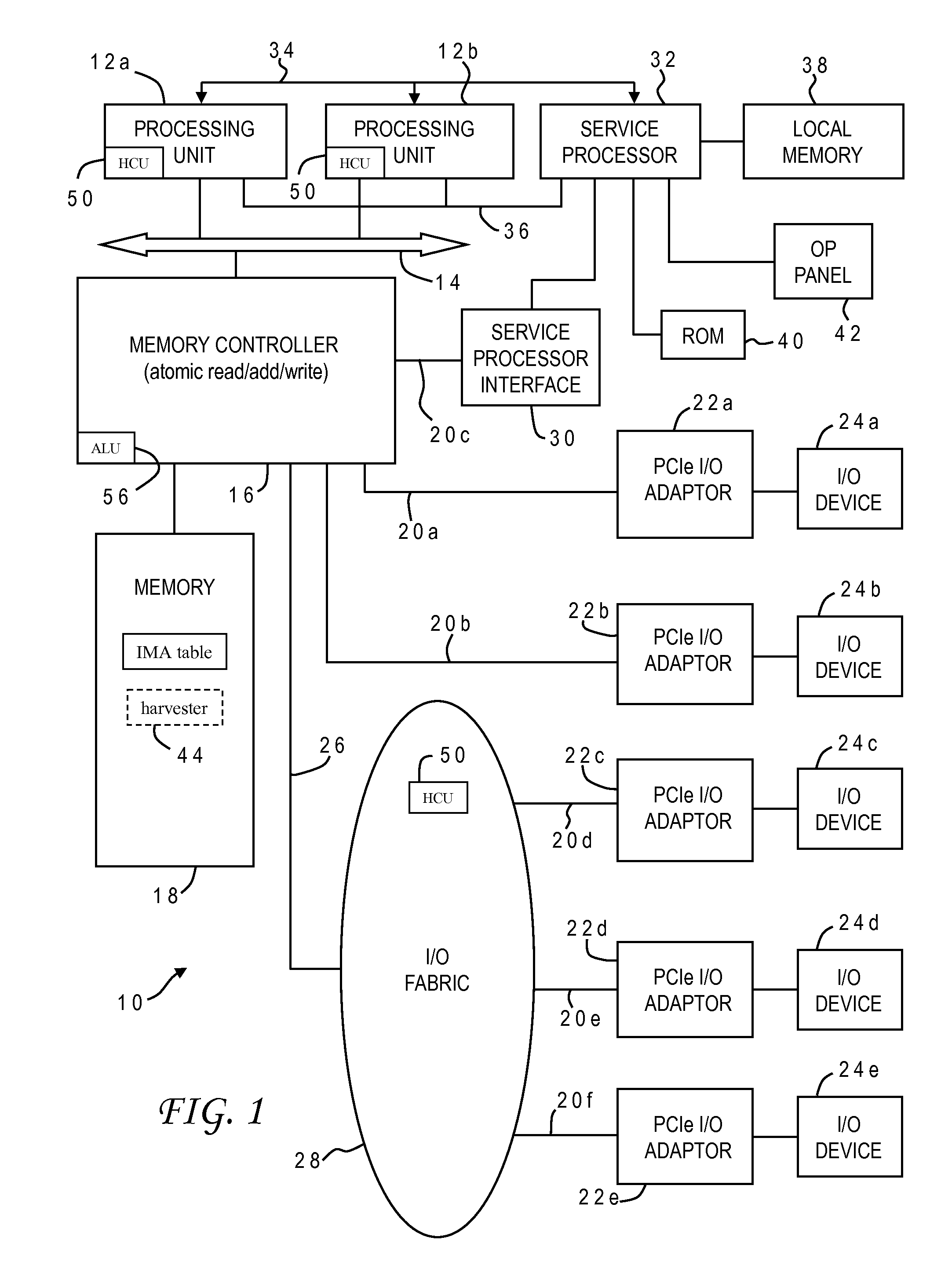

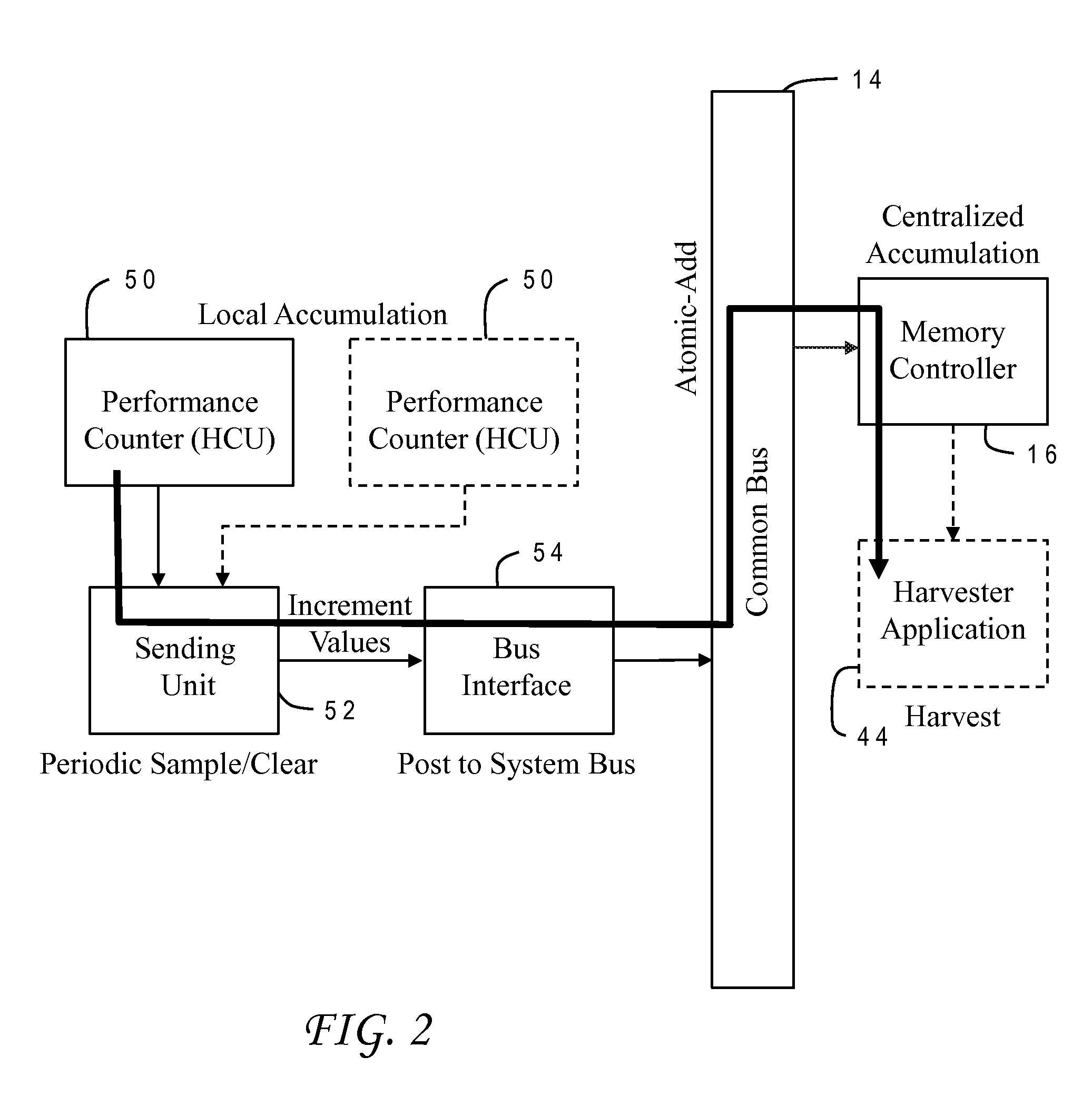

Continuous in-memory accumulation of hardware performance counter data

ActiveUS20140379953A1Error detection/correctionMemory systemsArithmetic logic unitComputerized system

In-memory accumulation of hardware counts in a computer system is carried out by continuously sending count values from full-speed hardware counter units to a memory controller. A sending unit periodically samples performance data from the hardware counter units, and transmits count values to a bus interface for an interconnection bus which communicates with the memory controller. The memory controller responsively updates an accumulated count value stored in system memory using the current count value, e.g., incrementing the accumulated count value. A count value can be sent with a pointer to a memory location and an instruction on how the location is to be updated. The instruction may be an atomic read-modify-write operation, and the memory controller can include a dedicated arithmetic logic unit to carry out that operation. A data harvester can then be used to harvest accumulated count values by reading them from a table in system memory.

Owner:IBM CORP

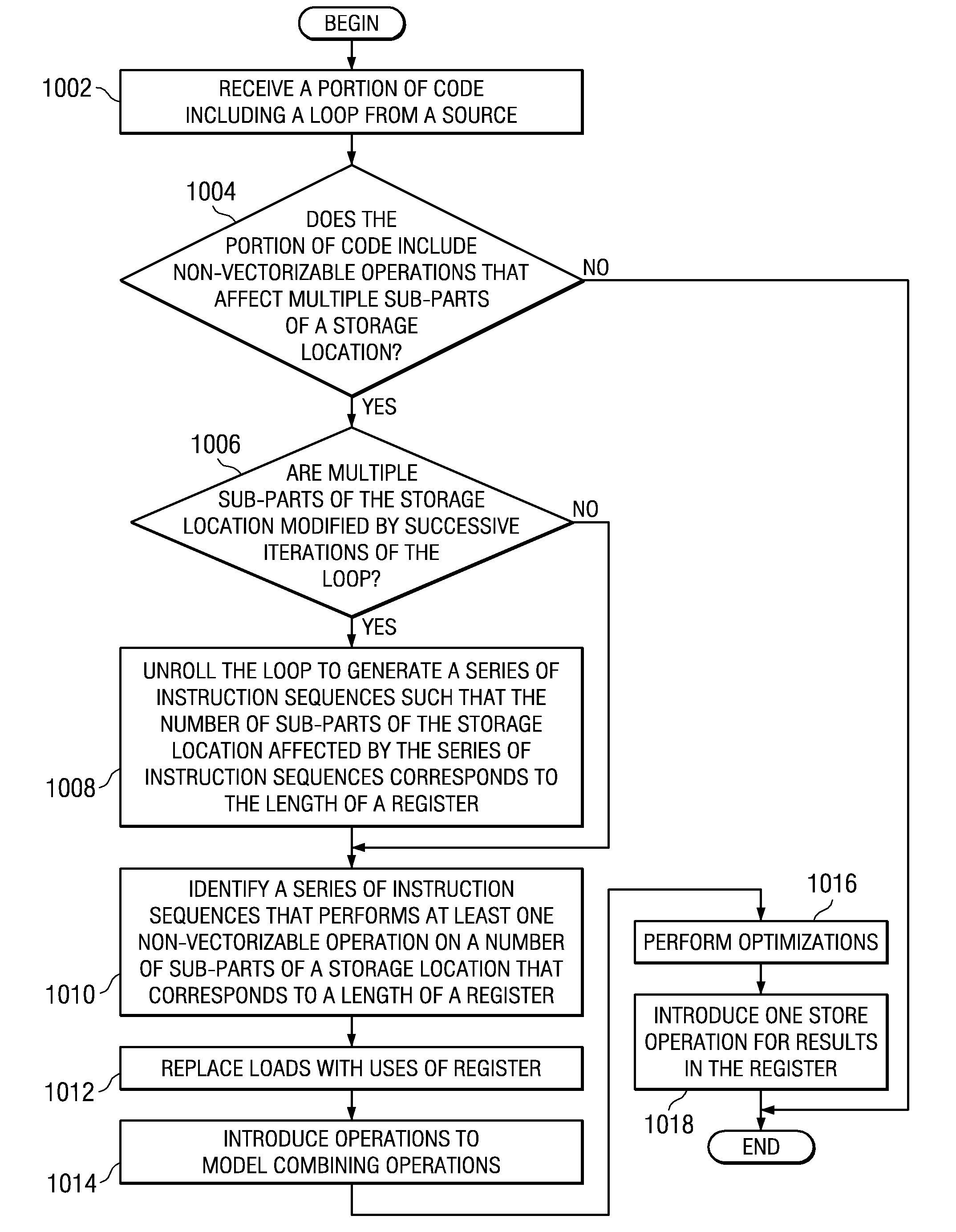

Compiler Method for Eliminating Redundant Read-Modify-Write Code Sequences in Non-Vectorizable Code

A computer implemented method, apparatus, and computer usable program code for eliminating redundant read-modify-write code sequences in non-vectorizable code. Code is received comprising a sequence of operations. The sequence of operations includes a loop. Non-vectorizable operations are identified within the loop that modifies at least one sub-part of a storage location. The non-vectorizable operations are modified to include a single store operation for the number of sub-parts of the storage location.

Owner:IBM CORP

Systems and methods for providing data modification operations in memory subsystems

InactiveUS20070288707A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMemory busRead-modify-write

Systems and methods for providing data modification operations in memory subsystems. Systems include a plurality of memory devices, a memory controller, one or more memory busses connected to the memory controller and a memory hub device. The memory controller receives and responds to memory access requests including memory update requests from a processor. The memory controller also generates a memory update command in response to receiving a memory update request. The memory hub device includes a first port, a second port and a control unit. The first port is in communication with the memory controller via one or more of the memory busses for transferring data and control information between the memory hub device and the memory controller. The second port is in communication with one or more of the memory devices. The control unit decodes the memory update command from the data and control information and accesses the memory devices via the second port to perform the memory update command local to the memory hub devices as a logical read-modify-write sequence.

Owner:IBM CORP

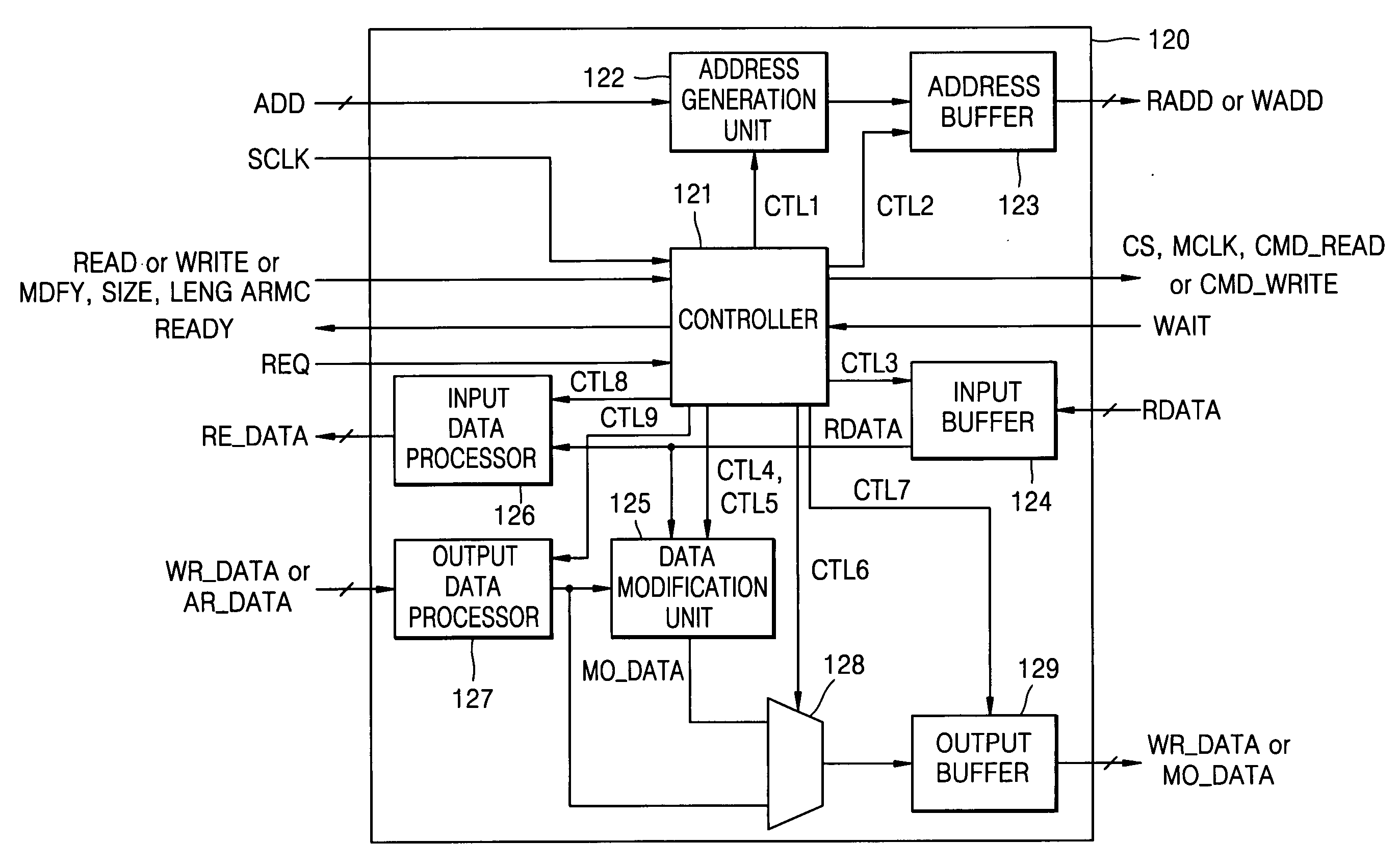

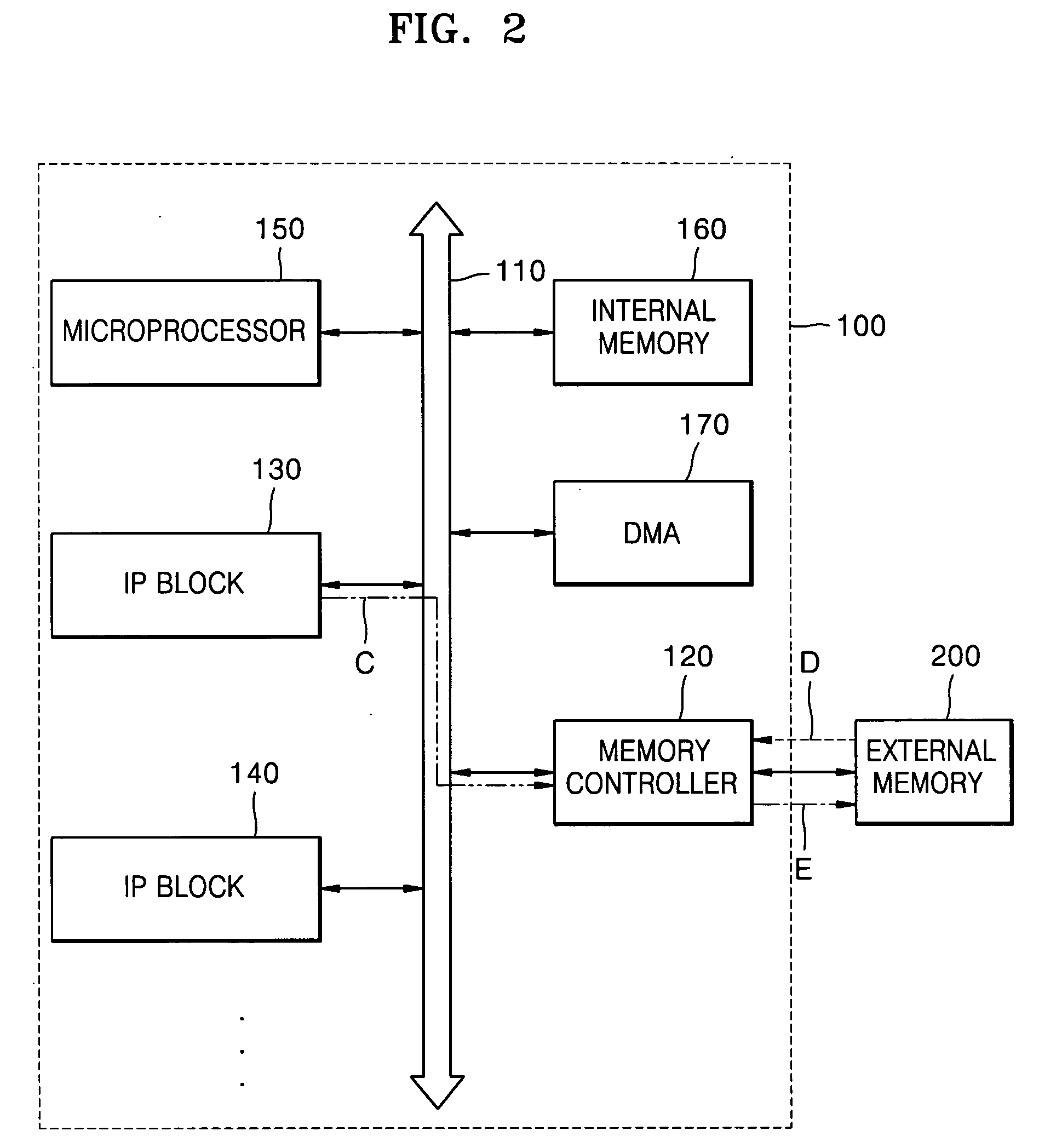

Memory controller having a read-modify-write function

ActiveUS20050198458A1Shorten the timeEnergy efficient ICTMechanical apparatusIntellectual propertyAccess time

Provided are a memory controller with data read-modify-write function, and a system-on-chip (SOC) having such a memory controller, where the memory controller is connected to a memory, the memory controller is connected to IP (intellectual property) blocks and a microprocessor via a system bus, and, in response to one of read, write, and modify request signals received from the one of the IP blocks or the microprocessor and an address signal, the memory controller reads a data signal from the memory, writes a write data signal to the memory, or modifies the data signal read from the memory and writes the modified data signal to the memory such that the memory controller and the SOC can reduce occupation time for the system bus and access time for the memory and additionally reduce unnecessary power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

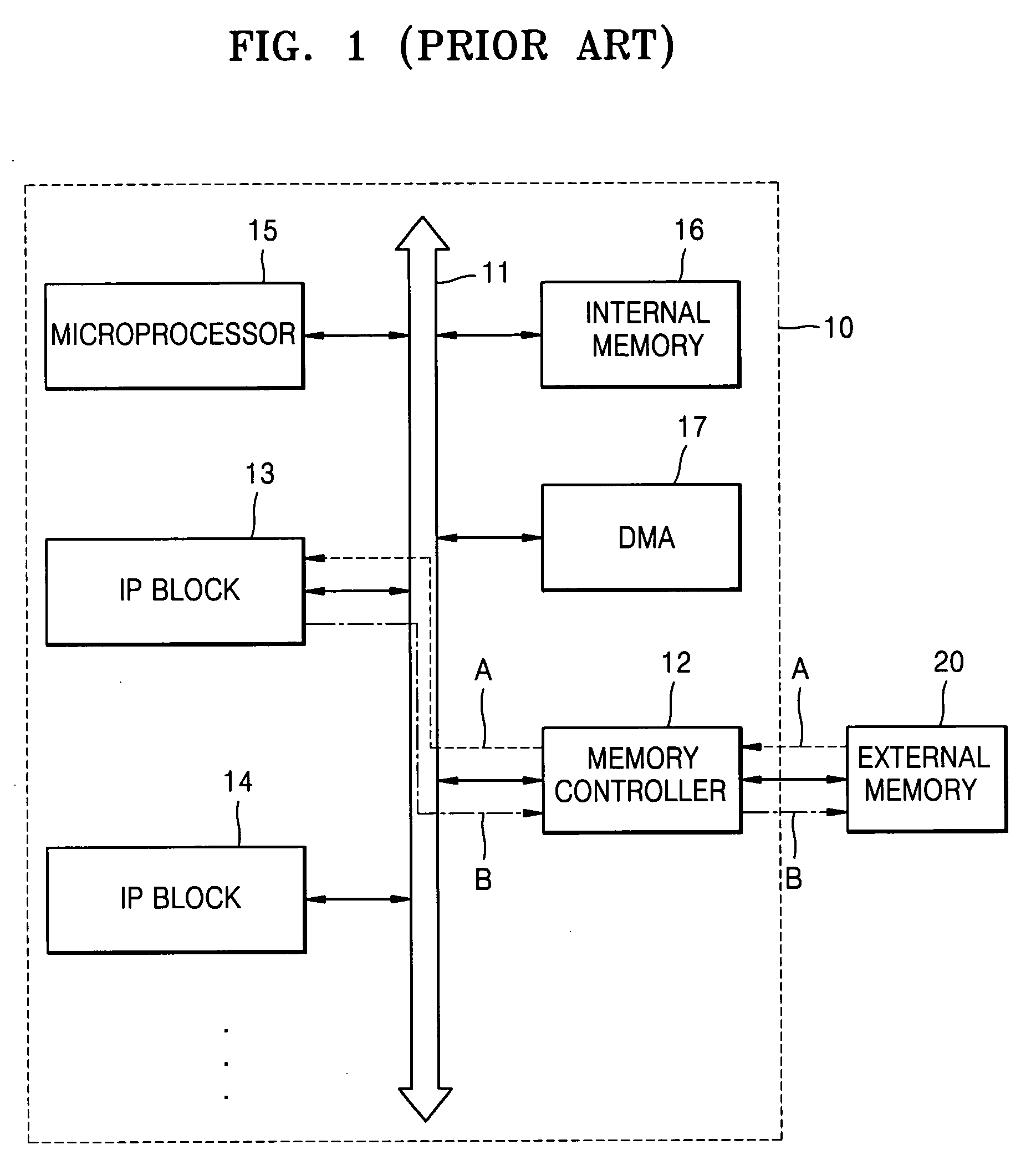

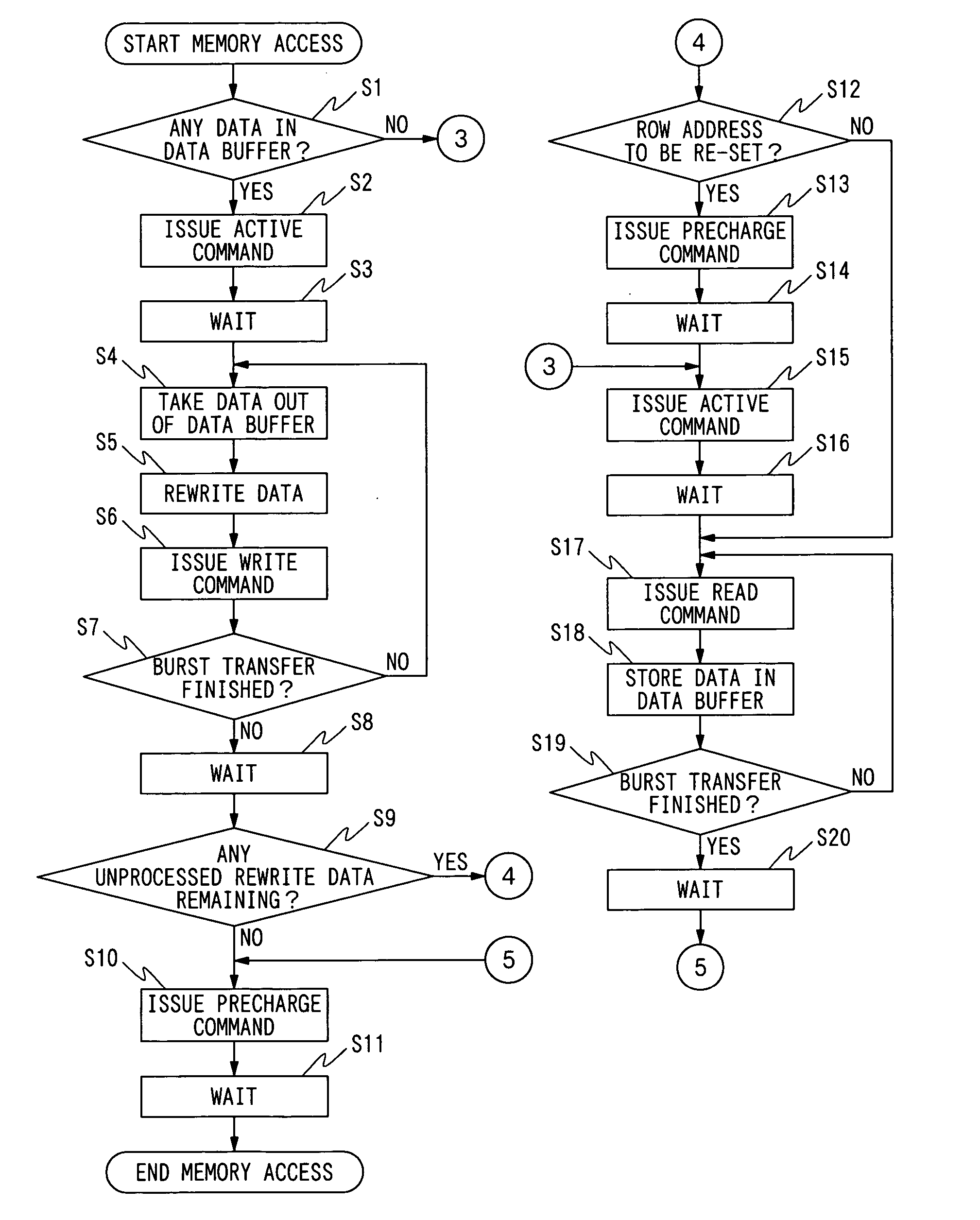

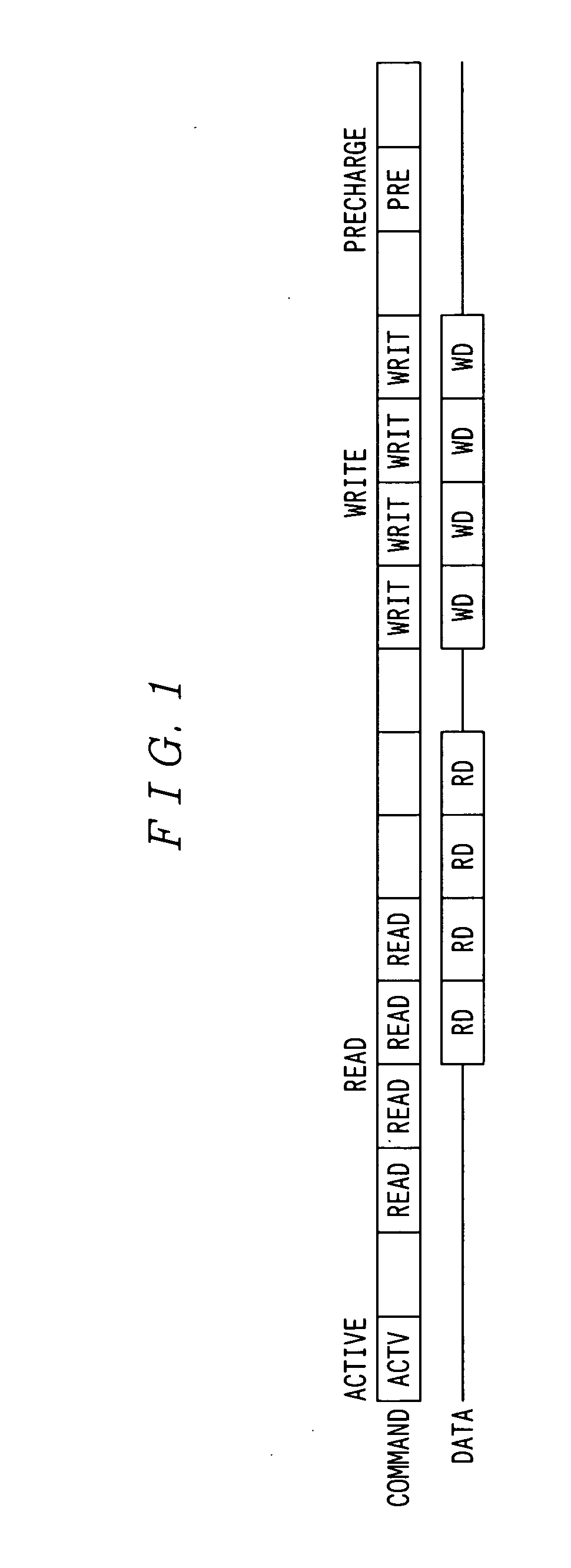

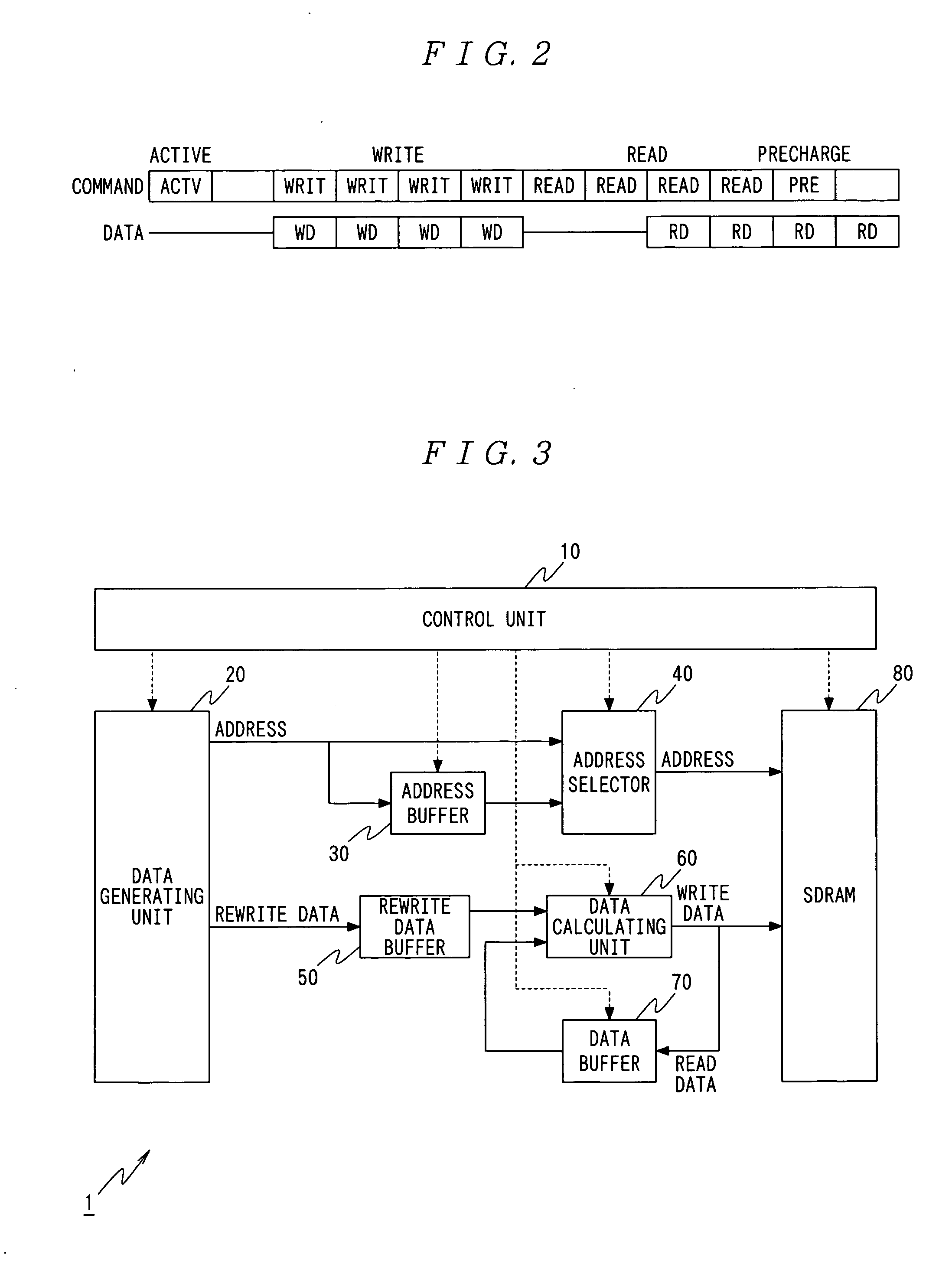

Information processing apparatus and method of accessing memory

InactiveUS20050166007A1Improve processing speedReduce adverse effectsEnergy efficient ICTMemory adressing/allocation/relocationInformation processingRead-modify-write

The present invention makes it possible to inexpensively and quickly execute a process of rewriting data stored in a memory, thus reducing the power consumption of an information processing apparatus. In connection with a conventional Read-Modify-Write function, an information processing apparatus 1 first issues a write instruction, and after all the write commands in the write instruction have been issued, issues read commands from the read instruction. That is, the read commands are issued immediately after the write commands without issuing a precharge command from the write instruction or an active command from the read instruction. This serves to avoid executing the precharge and active commands between instructions which commands are unwanted for accesses to the same row address. The adverse effect of a CAS latency can also be avoided. Therefore, it is possible to inexpensively and quickly execute the process of rewriting data stored in the memory.

Owner:SEIKO EPSON CORP

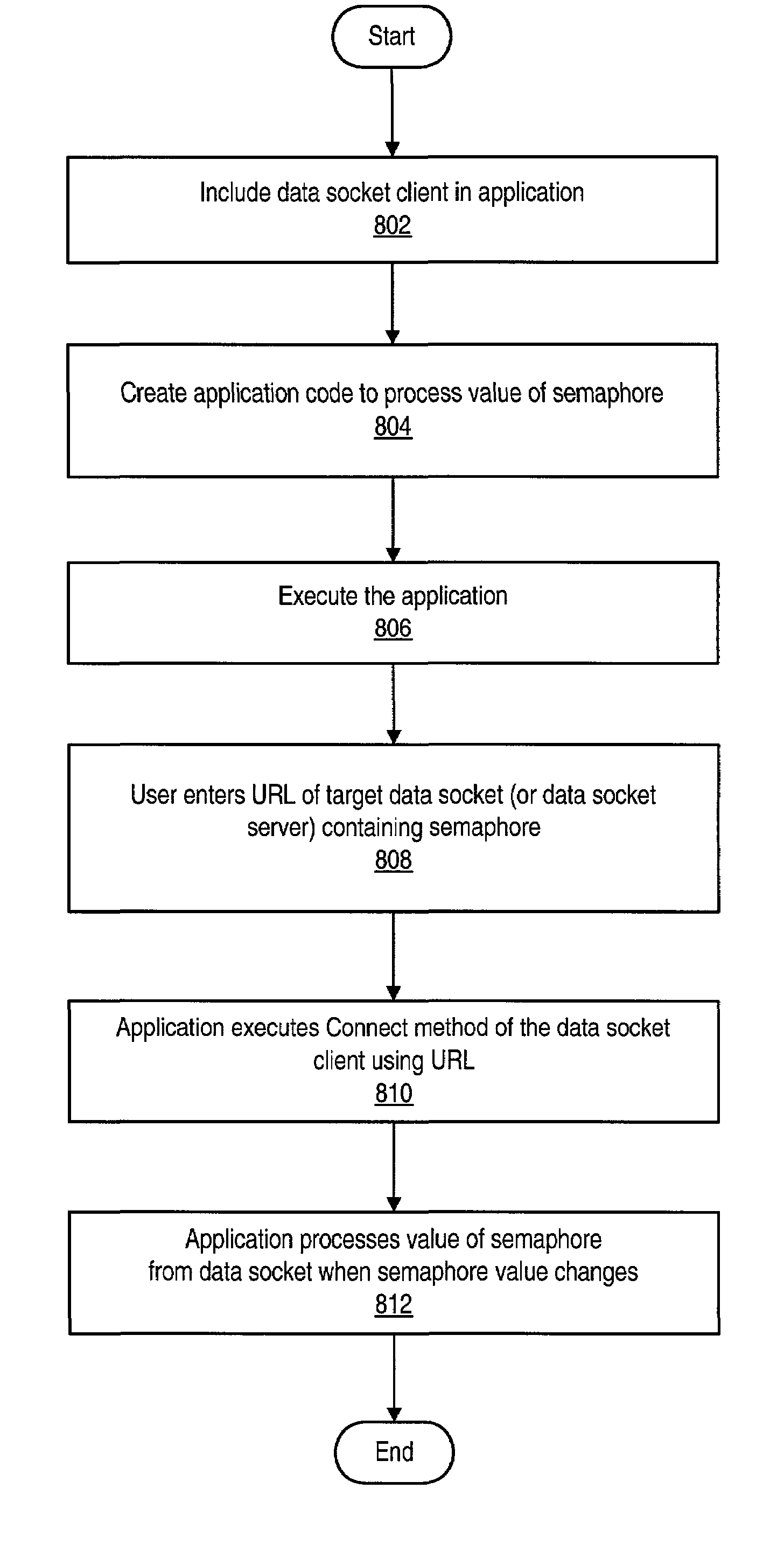

Network system including data socket components for accessing internet semaphores

InactiveUS7237013B2Data processing applicationsMultiprogramming arrangementsThe InternetComputerized system

An improved method and system for accessing data from a semaphore in a computer system, through the use of a software component in an application. The method may involve multiple software components in a corresponding multiple of applications in a corresponding multiple of computer systems. In that case, one or more requests to perform a locked read-modify-write operation on the data comprised in the semaphore may be received from one or more of the multiple software components. When multiple requests are received, the multiple requests may be stored in a queue, and processed sequentially. The corresponding multiple of applications may use the semaphore to synchronize operation of the applications. The multiple of computer systems and the computer memory may be connected through a network (e.g., the Internet). Accessing data from a semaphore in a computer system may include publishing or writing data to the semaphore.

Owner:NATIONAL INSTRUMENTS

Error recovery in a data processing system which implements partial writes

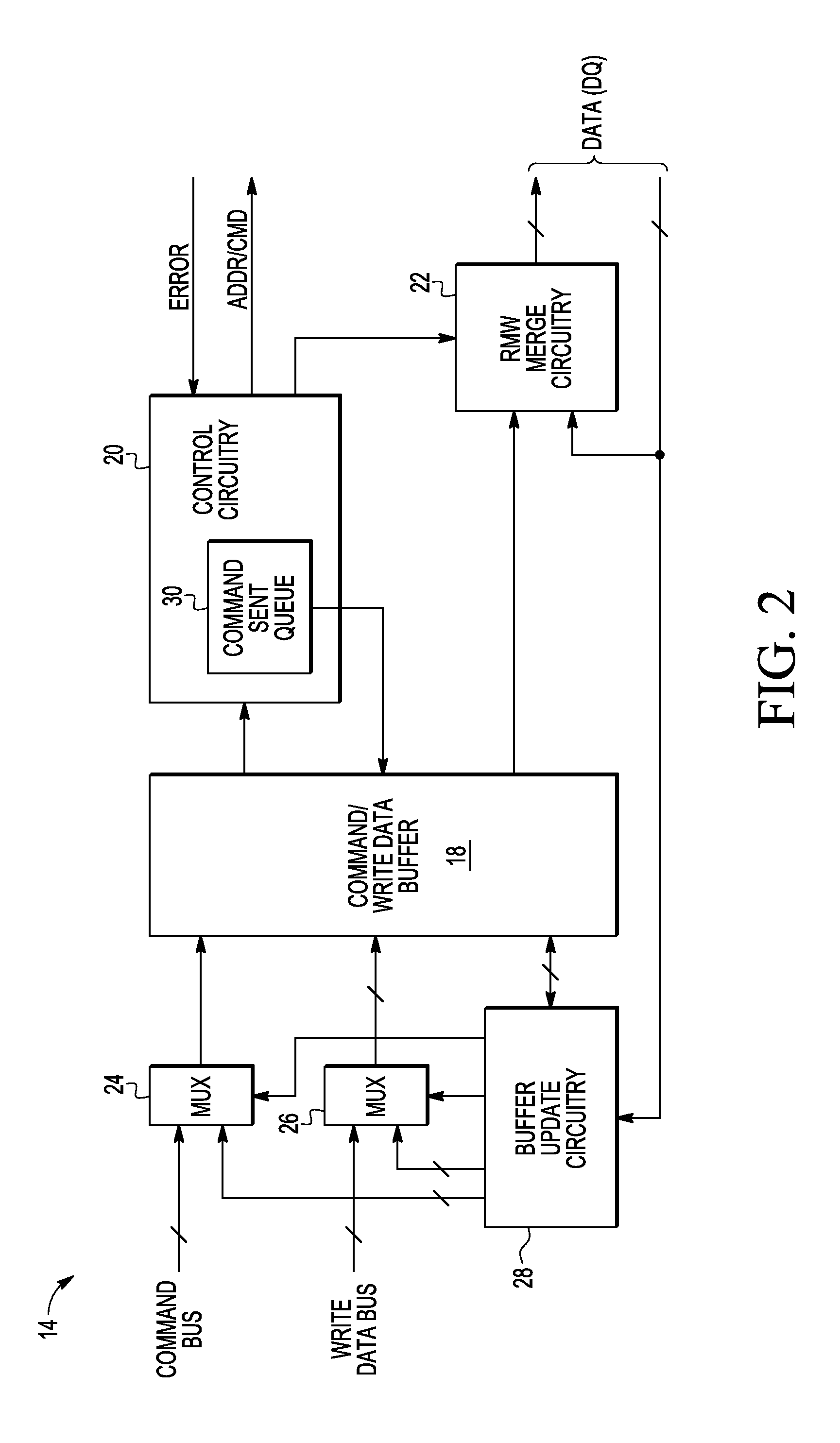

ActiveUS20160139837A1Input/output to record carriersMemory systemsData processing systemRead-modify-write

A data processing system includes a command buffer and control circuitry. The command buffer is configured to store pending write requests to a memory in which each pending write request has corresponding write data. The control circuitry is configured to select a pending write request from an entry of the command buffer and send the selected write request to the memory. The selected write request is a partial write request having first write data stored in the entry. Sending the selected write request includes performing a read-modify-write (RMW), wherein the control circuitry is configured to, after a read operation of the RMW, update the pending write request in the entry from a partial write request to a full write request.

Owner:NXP USA INC

Locking and synchronizing input/output operations in a data storage system

ActiveUS7774569B1Reduce the possibilityData processing applicationsMemory loss protectionGranularityRead-modify-write

Owner:AMZETTA TECH LLC

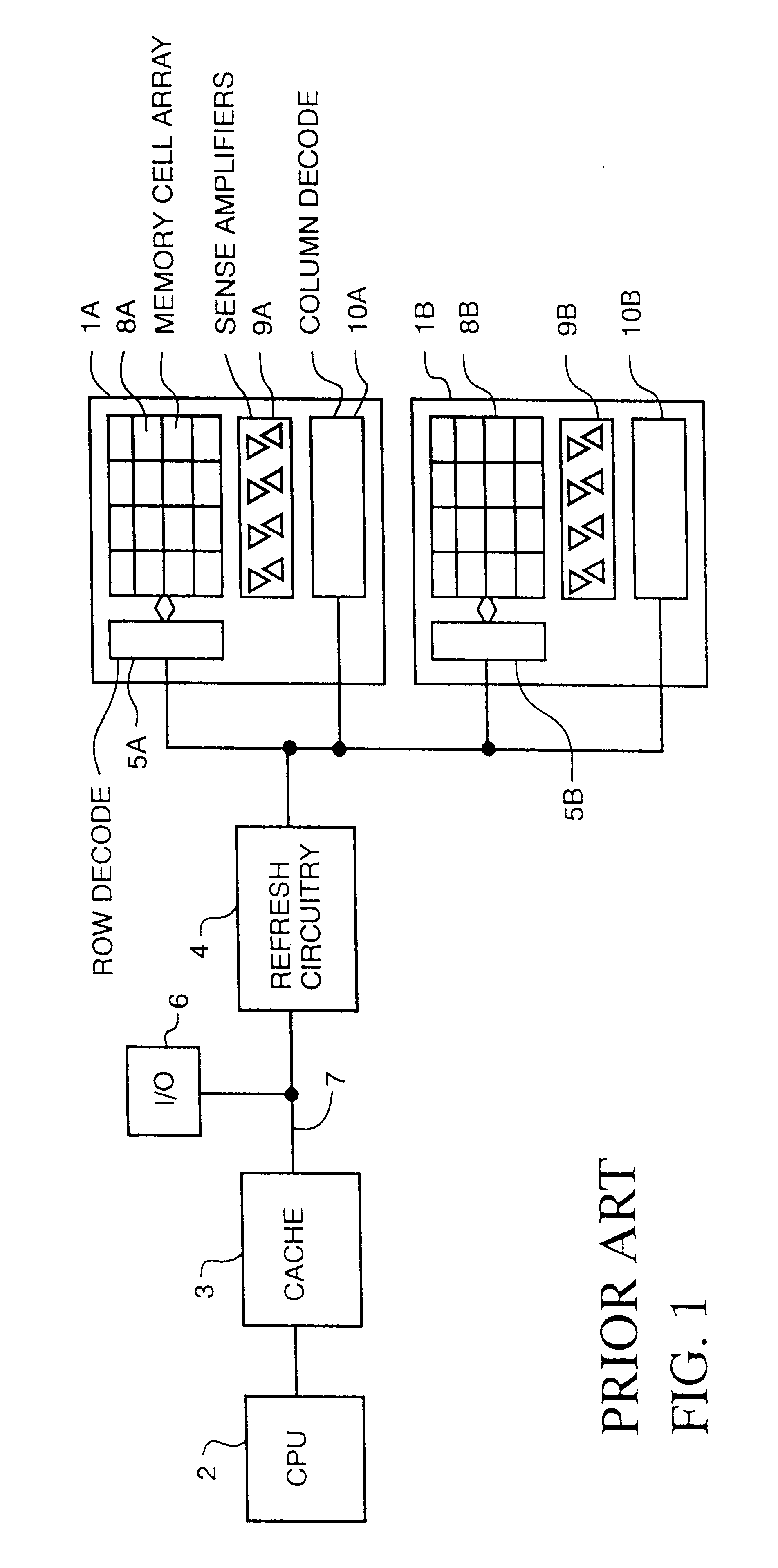

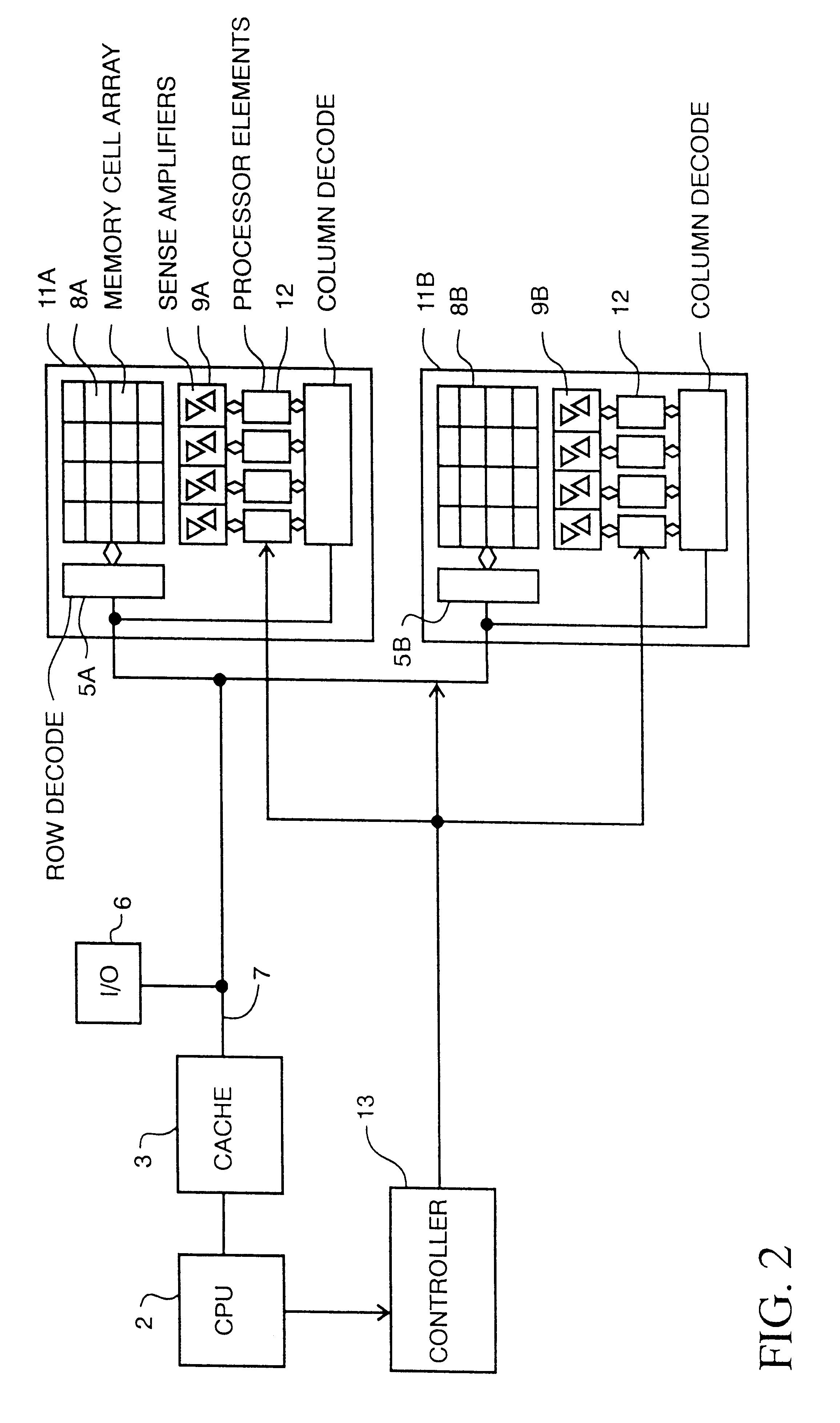

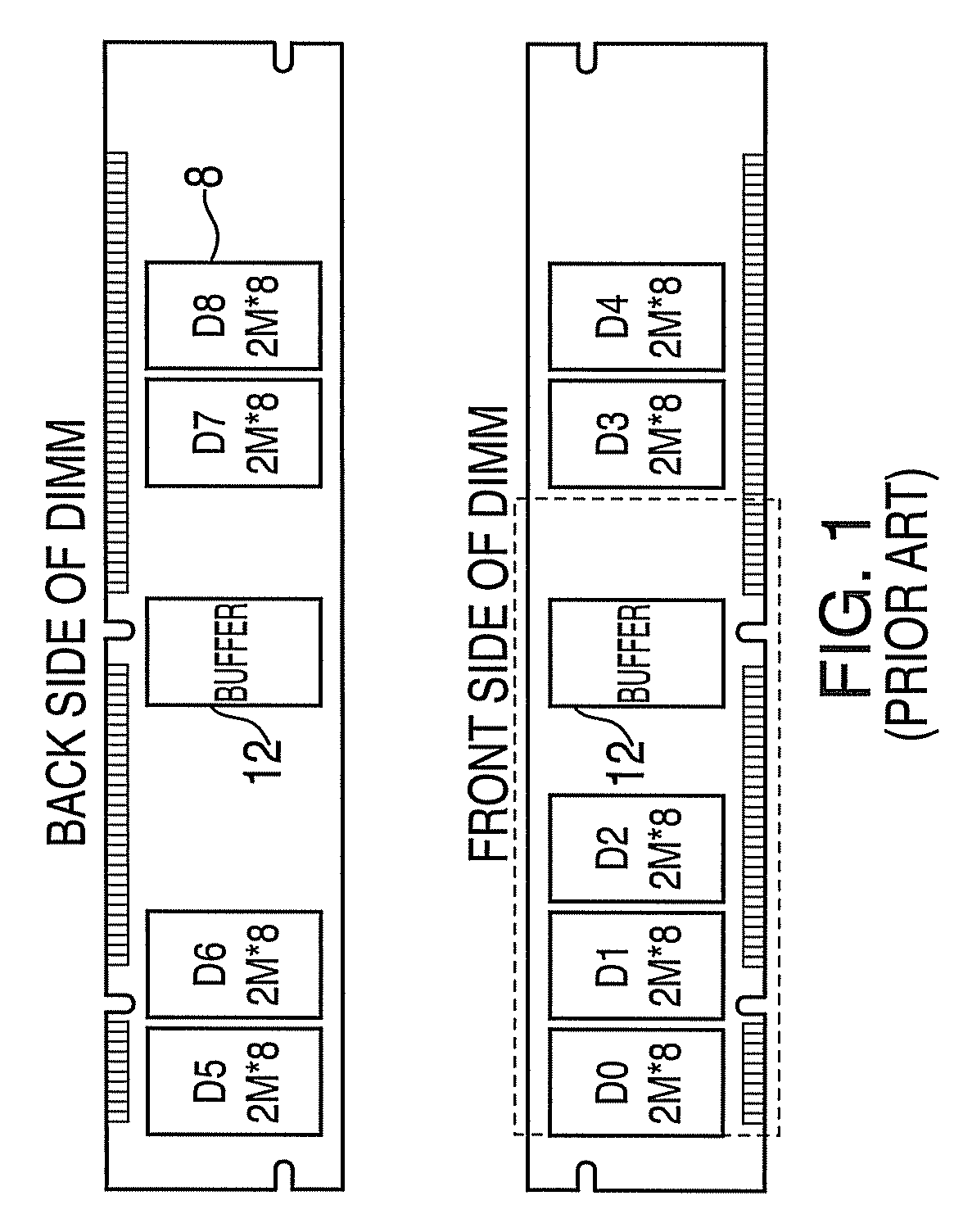

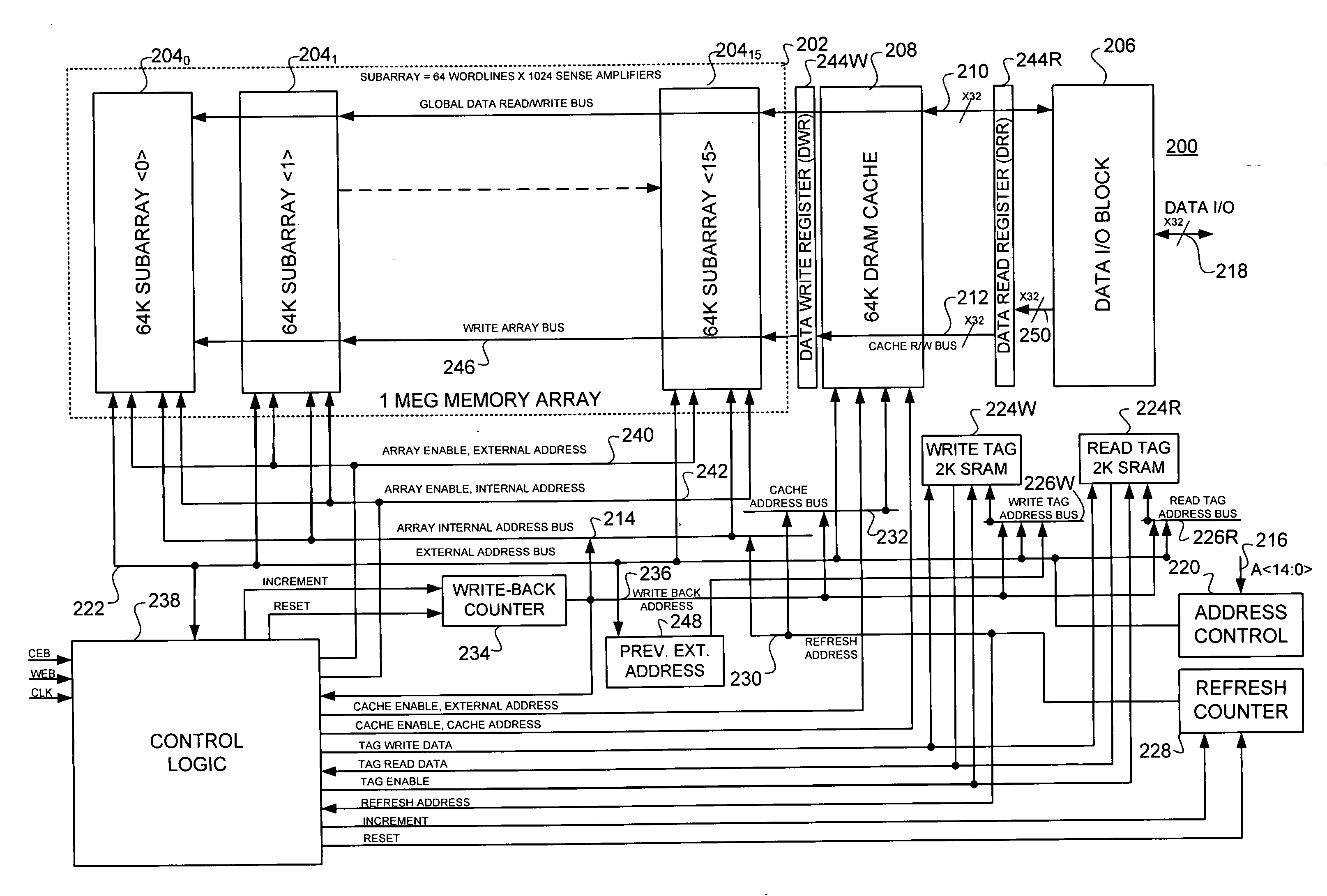

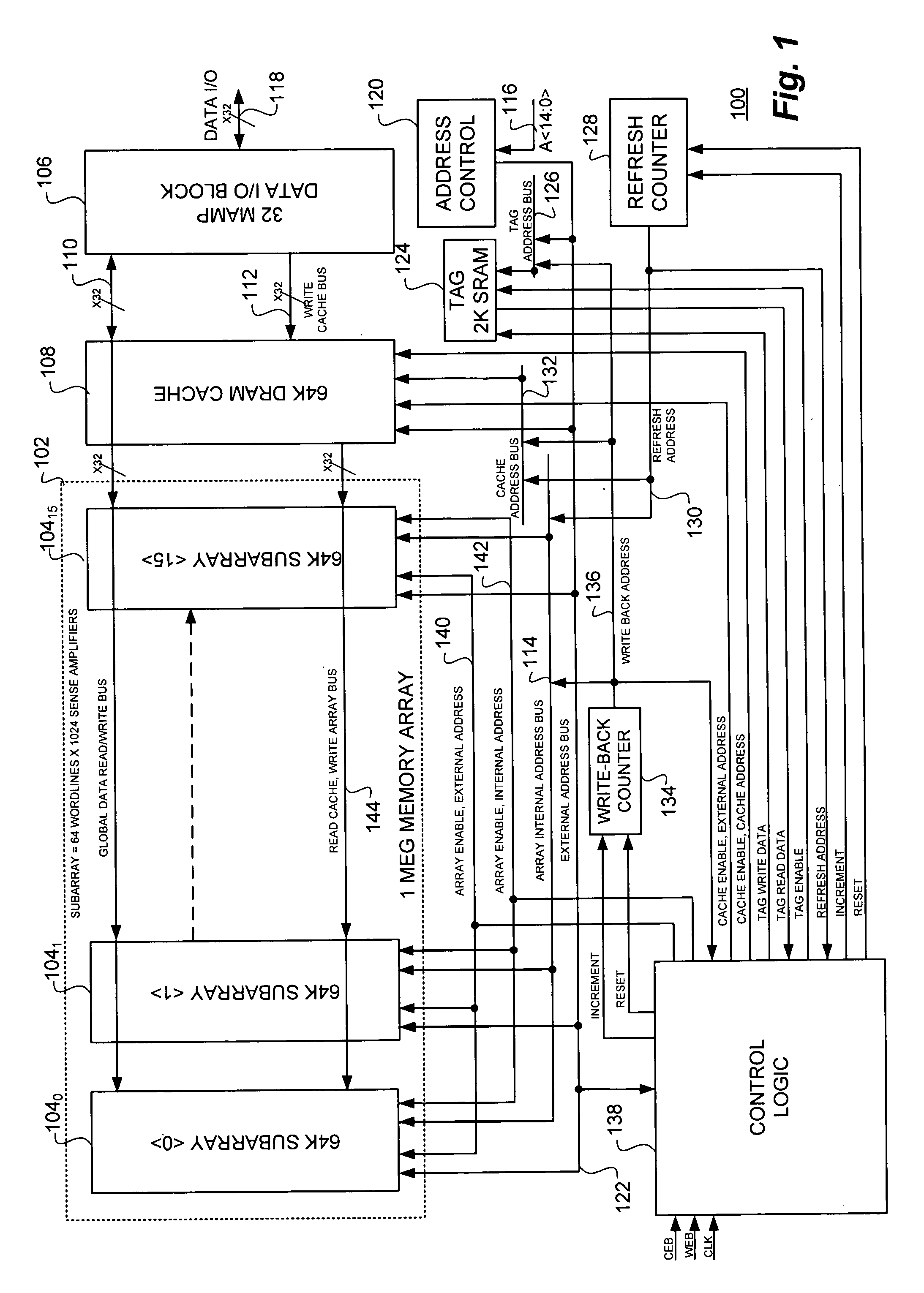

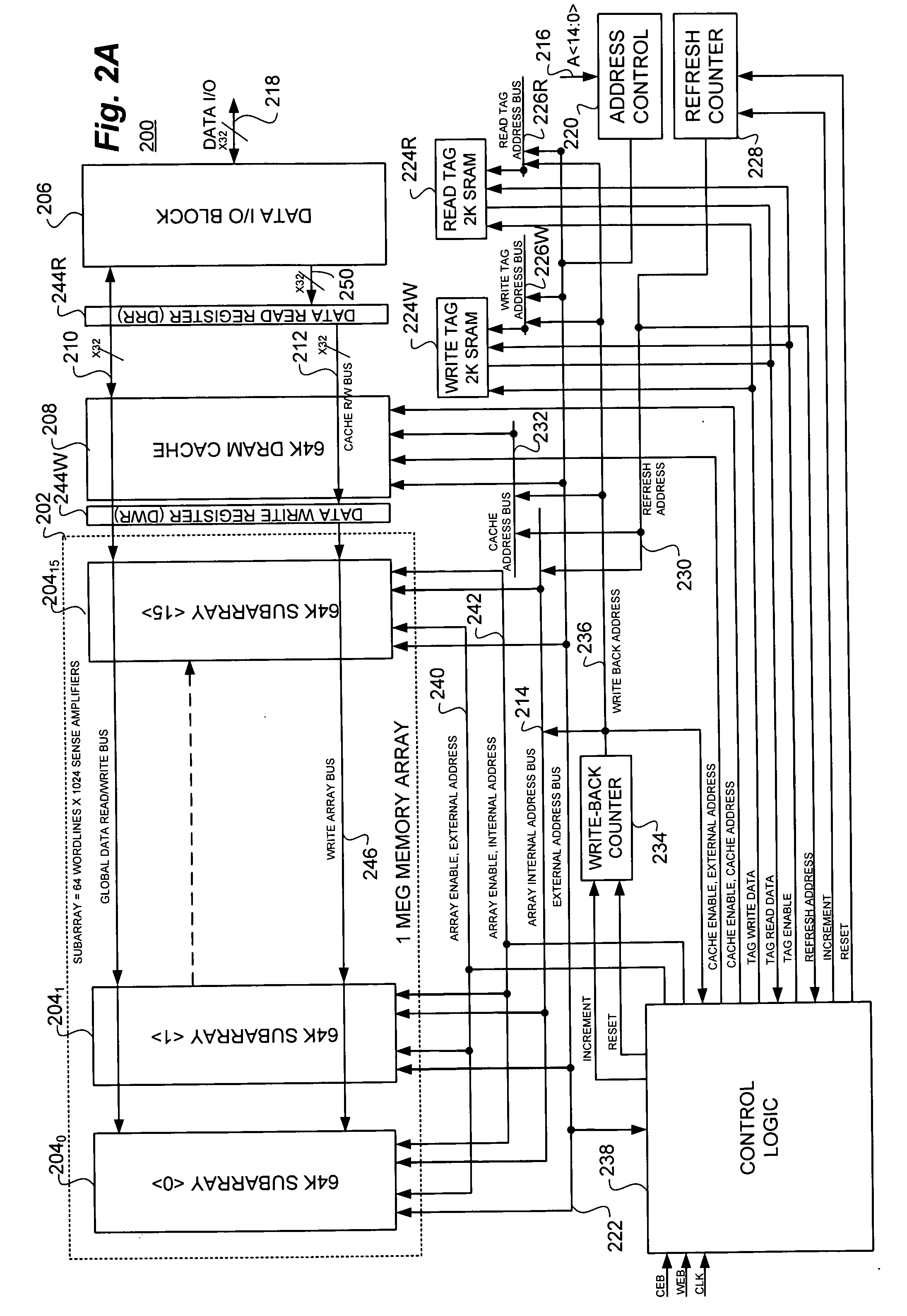

Static random access memory (SRAM) compatible, high availability memory array and method employing synchronous dynamic random access memory (DRAM) in conjunction with a data cache and separate read and write registers and tag blocks

InactiveUS20060190676A1Eliminate requirementsShorten the timeDigital storageMemory systemsStatic random-access memoryRandom access memory

A high-speed, static random access memory (SRAM) compatible, high availability memory array and method employing synchronous dynamic random access memory (DRAM) in conjunction with a data cache and separate data read and write registers and tag blocks. The inclusion of separate data read and write registers allows the device to effectively operate at a cycle time limited only by the DRAM subarray cycle time. Further, the inclusion of two tag blocks allows one to be accessed with an externally supplied address and the other to be accessed with a write-back address, thus eliminating the requirement for a single tag to execute two read-modify write cycles in one DRAM cycle time.

Owner:INVENSAS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com