Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

77 results about "Nonlinear capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

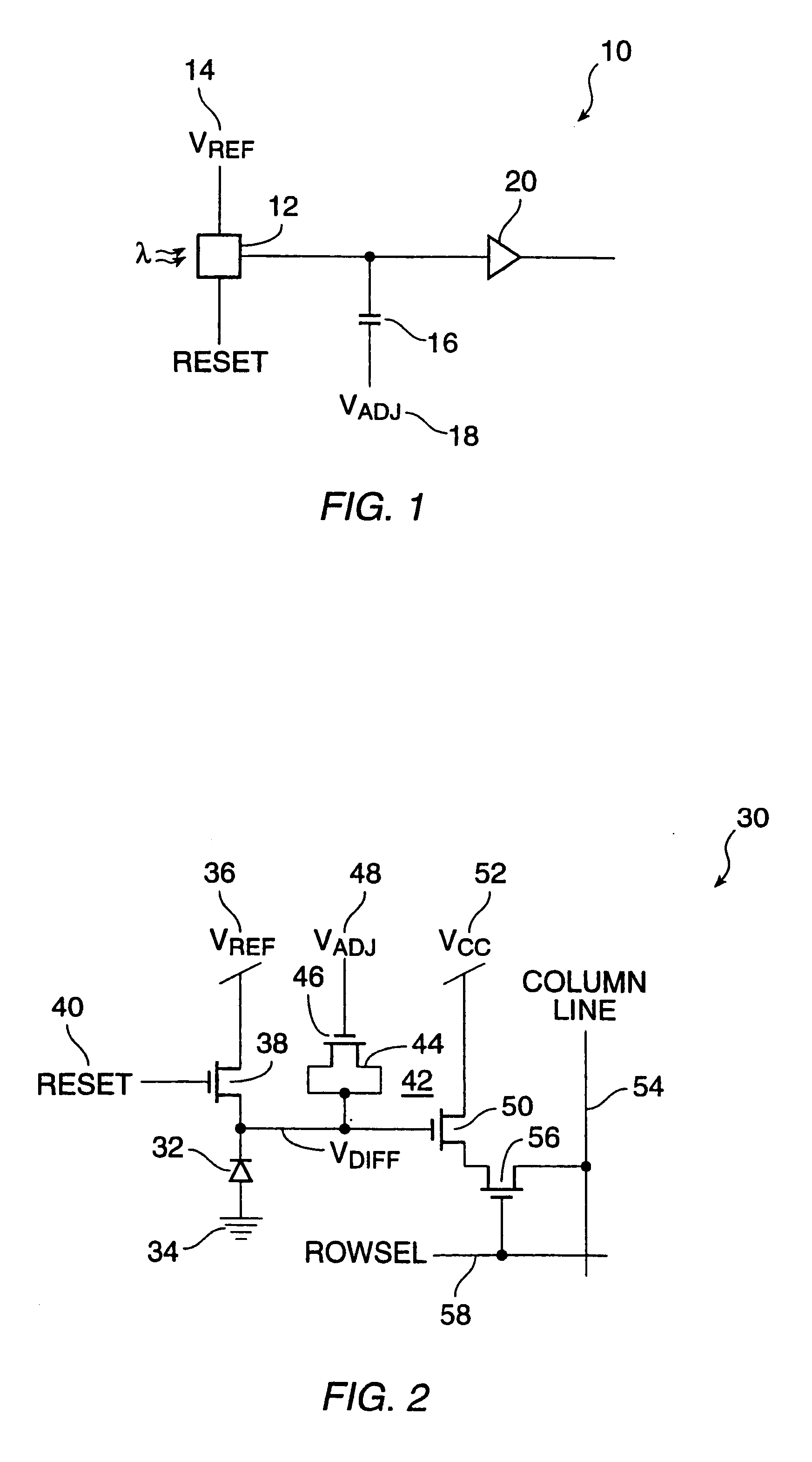

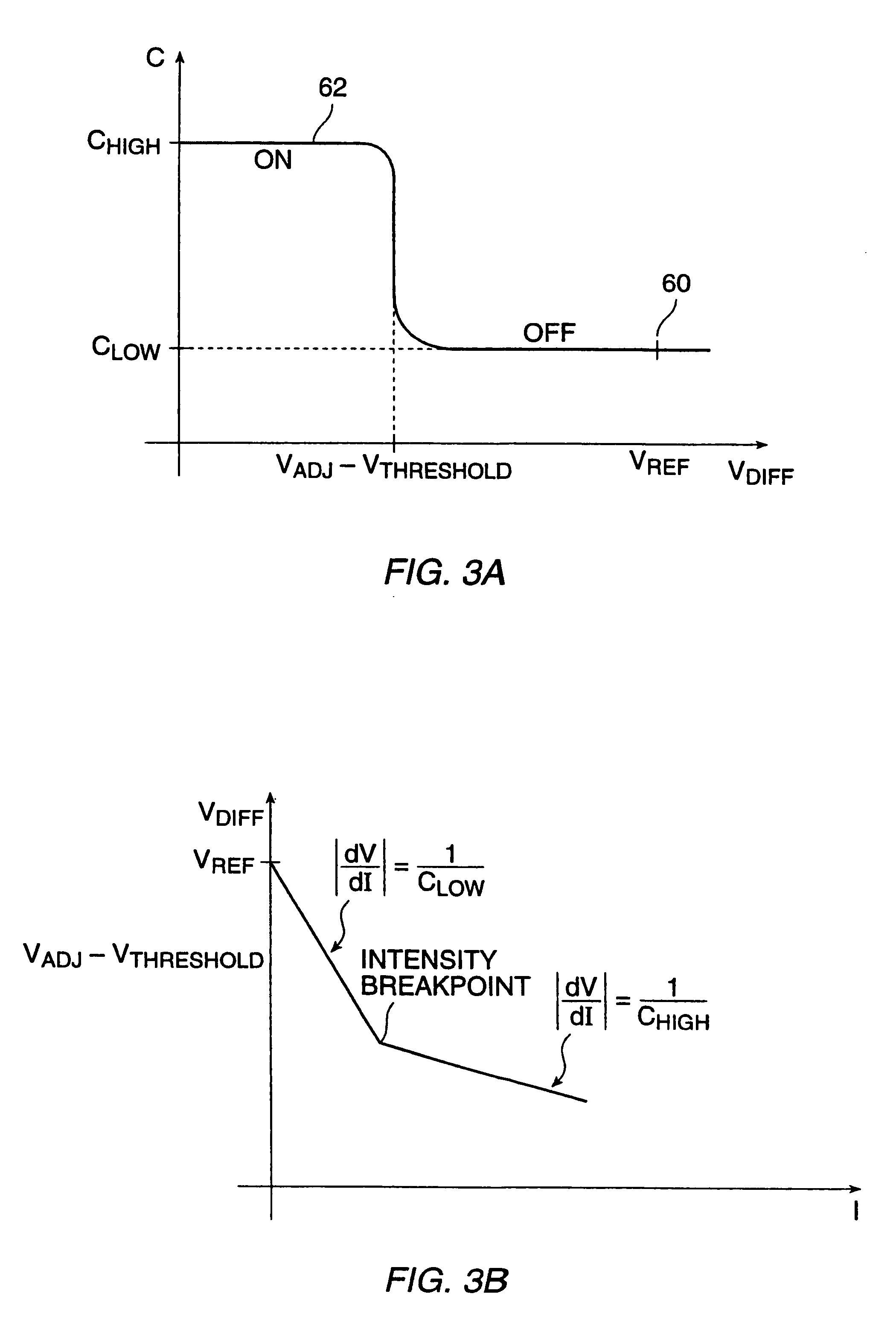

Storage pixel sensor and array with compression

InactiveUS6512544B1Television system detailsTelevision system scanning detailsCapacitanceSemiconductor

A storage pixel sensor disposed on a semiconductor substrate comprises a photosensor. At least one nonlinear capacitive element is coupled to the photosensor. At least one nonlinear capacitive element is arranged to have a compressive photocharge-to-voltage gain function. An amplifier has an input coupled to the nonlinear capacitor and an output. Other, non-capacitive elements may be employed to produce a compressive photo-charge-to-voltage gain having at least one breakpoint.

Owner:FOVEON

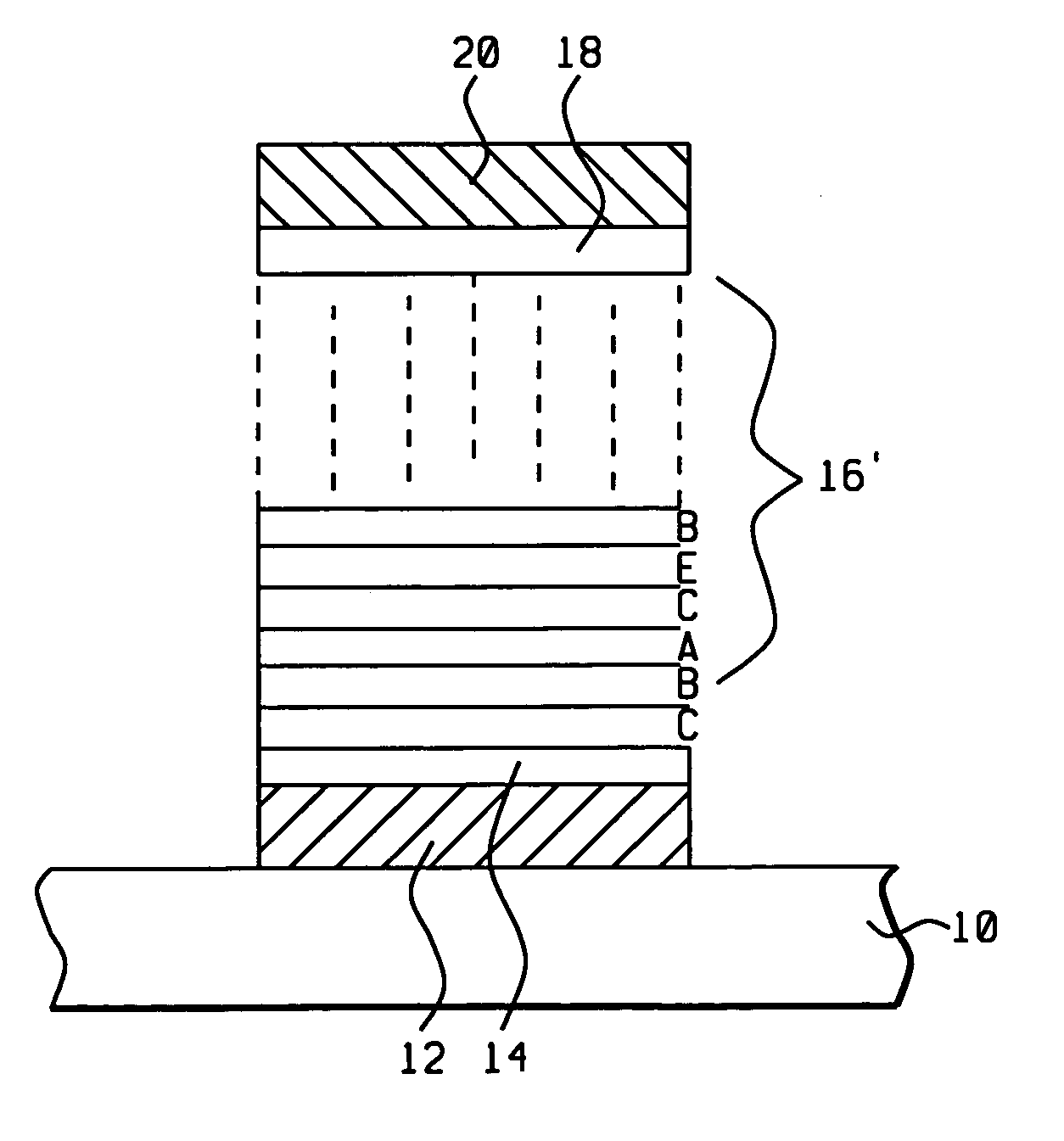

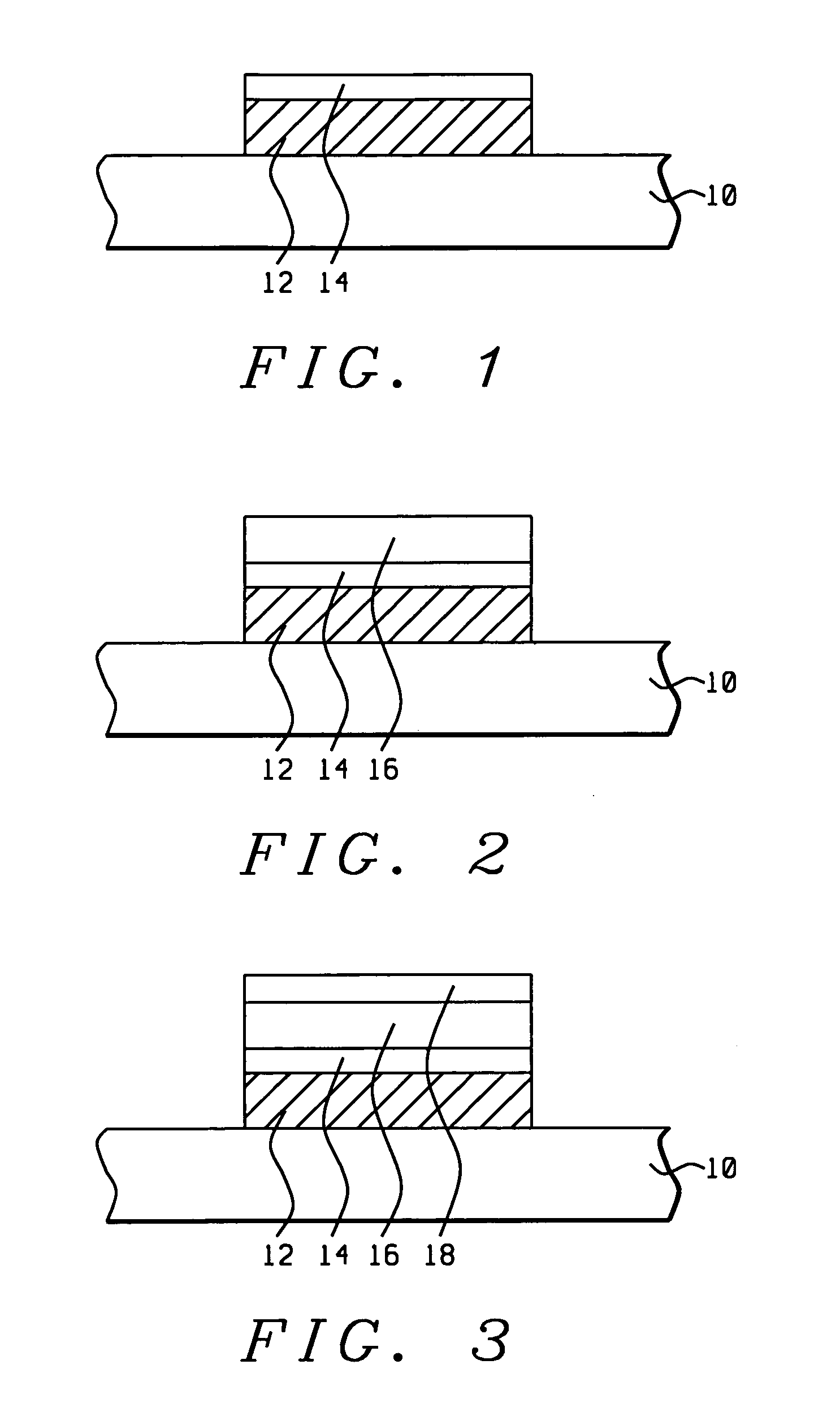

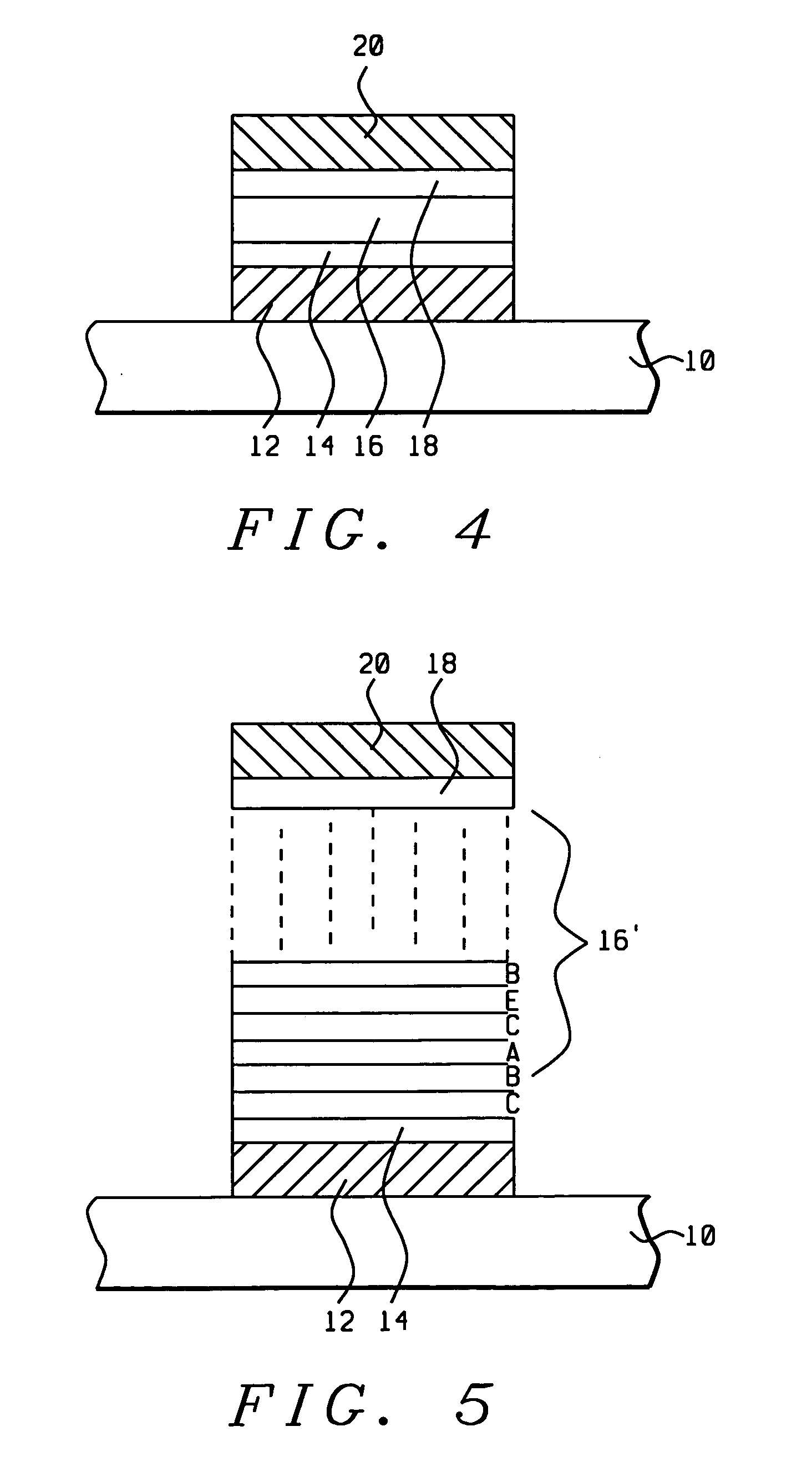

Method for making metal capacitors with low leakage currents for mixed-signal devices

InactiveUS20050132549A1Reduce leakage currentHigh capacitance per unit areaElectrolytic capacitorsSemiconductor/solid-state device manufacturingCapacitanceMetal-insulator-metal

A method for making metal-insulator-metal (MIM) capacitors having insulators with high-dielectric-constant and sandwiched between wide-band-gap insulators resulting in low leakage currents and high capacitance per unit area is achieved. The high-k layer increases the capacitance per unit area for next generation mixed-signal devices while the wide-band-gap insulators reduce leakage currents. In a second embodiment, a multilayer of different high-k materials is formed between the wide-band-gap insulators to substantially increase the capacitance per unit area. The layer materials and thicknesses are optimized to reduce the nonlinear capacitance dependence on voltage.

Owner:TAIWAN SEMICON MFG CO LTD

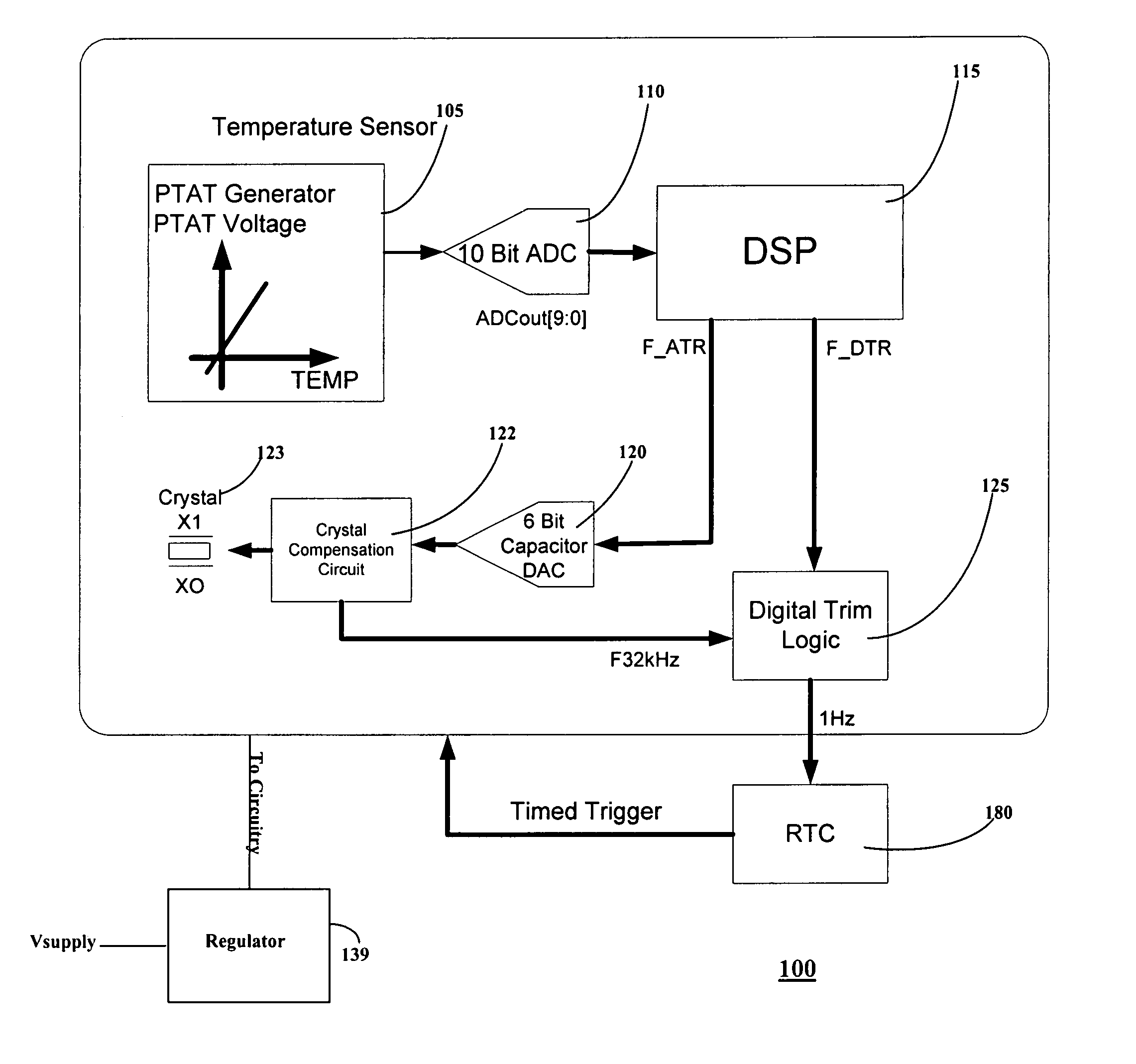

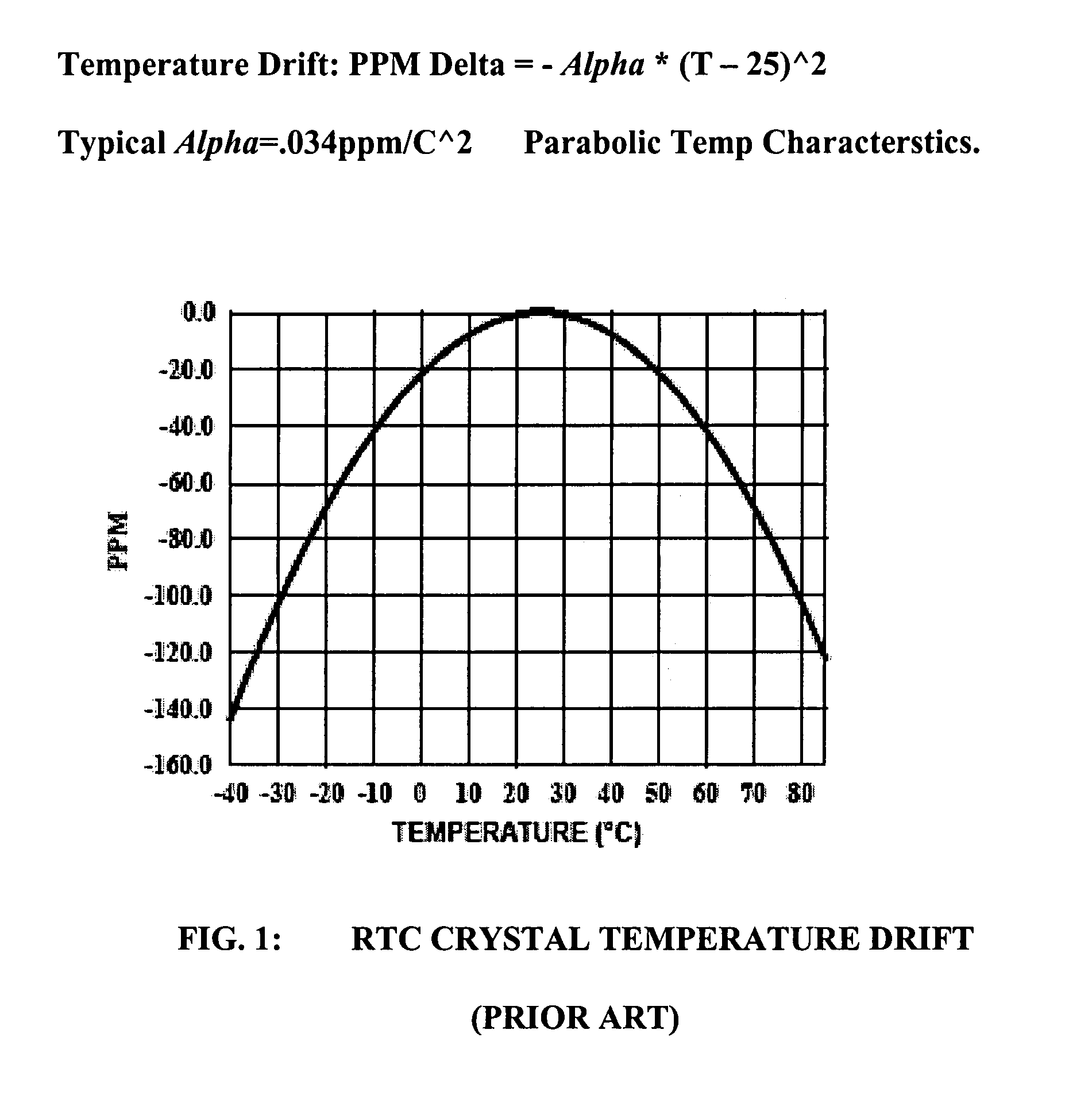

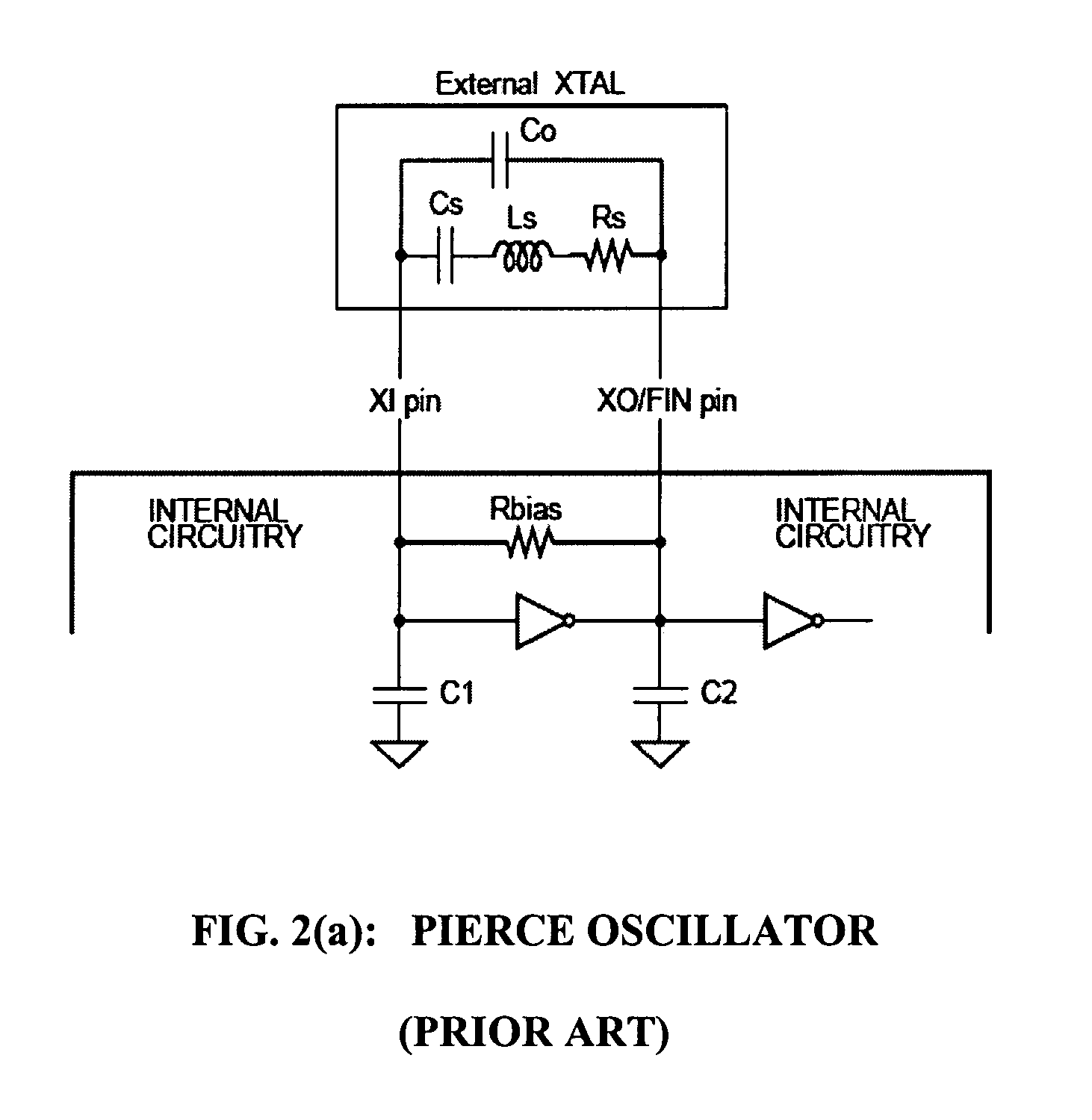

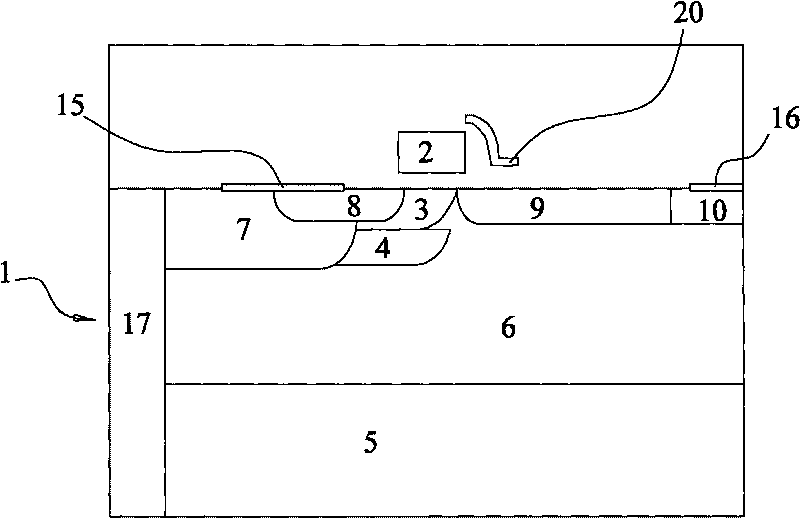

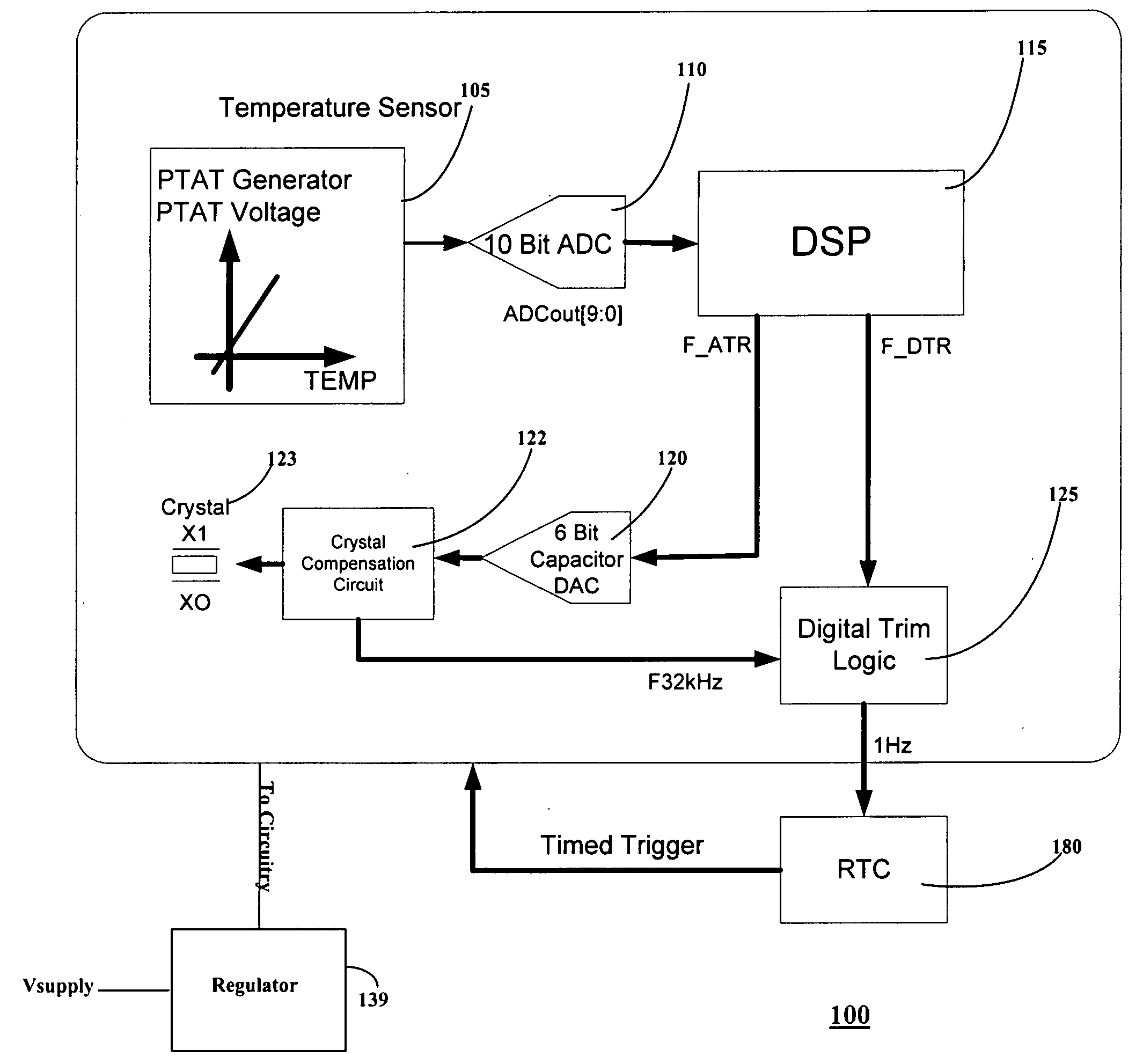

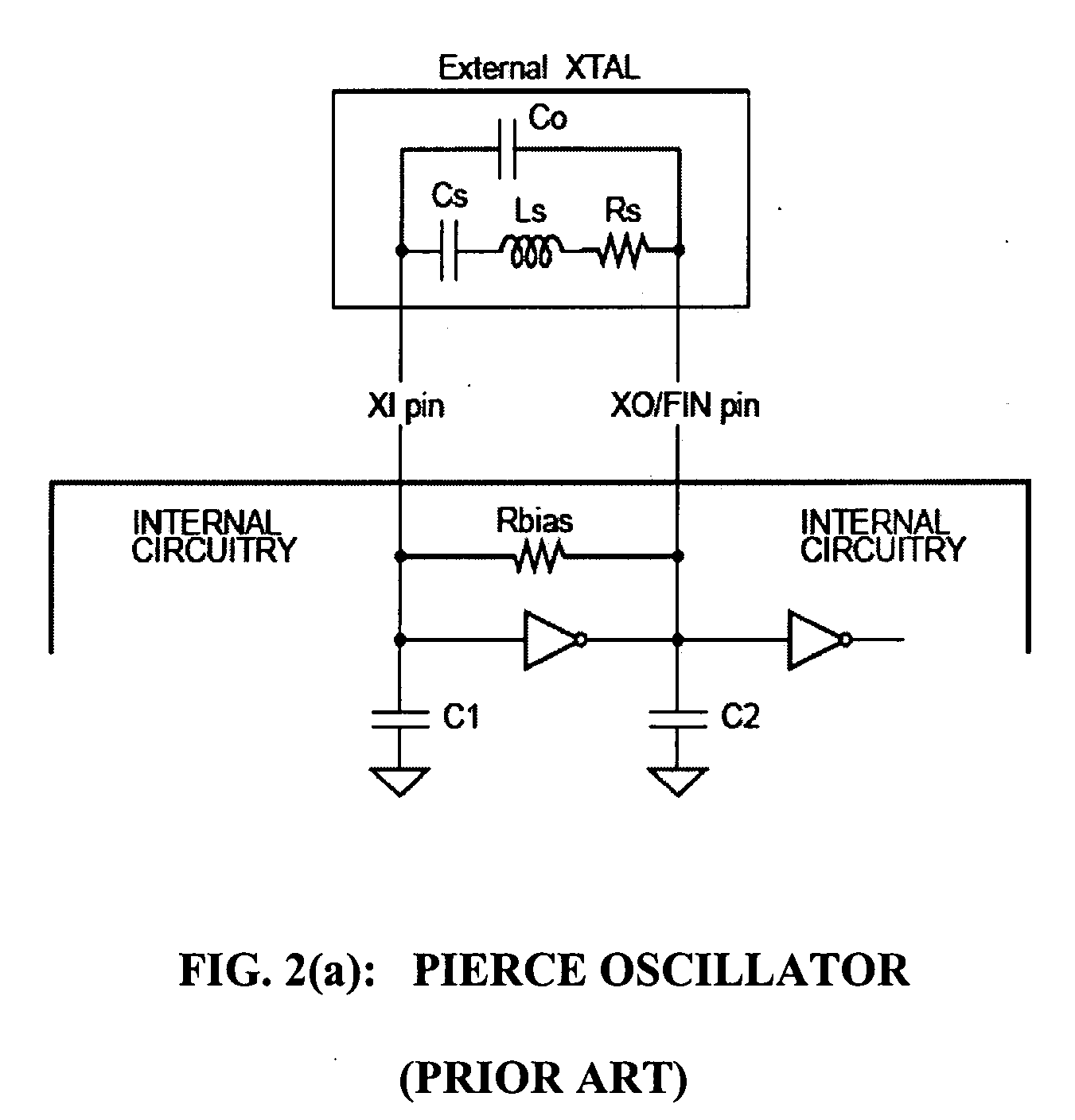

Automatic circuit and method for temperature compensation of oscillator frequency variation over temperature for a real time clock chip

ActiveUS7371005B1Low power operationFrequency stabilisation mechanismGenerator stabilizationCapacitanceReal-time clock

An automatic temperature compensated real-time clock (RTC) chip includes a clock portion having a crystal oscillator block including crystal compensation circuitry adapted to be coupled to a crystal. The crystal compensation circuitry includes a non-linear capacitor DAC including a plurality of load capacitors, wherein the load capacitors have respective switches which switch respective ones of the load capacitors to change a parallel resonance frequency (fp) generated by the oscillator block. The capacitor DAC is arranged so that Analog Trimming (ATR) bits received cause an arrangement of the switches to provide a non-linear change in overall load capacitance to result in a linear relationship between fp and the ATR bits. A temperature sensor block is coupled to the crystal for measuring a temperature of at least the crystal. An A / D converter is coupled to the temperature sensor for outputting a digital temperature signal representative of the temperature of the crystal. A DSP engine receives the digital temperature signal and calculates frequency correction needed to correct for frequency inaccuracy and determines a bit sequence including the ATR bits appropriate to achieve the frequency correction.

Owner:INTERSIL INC

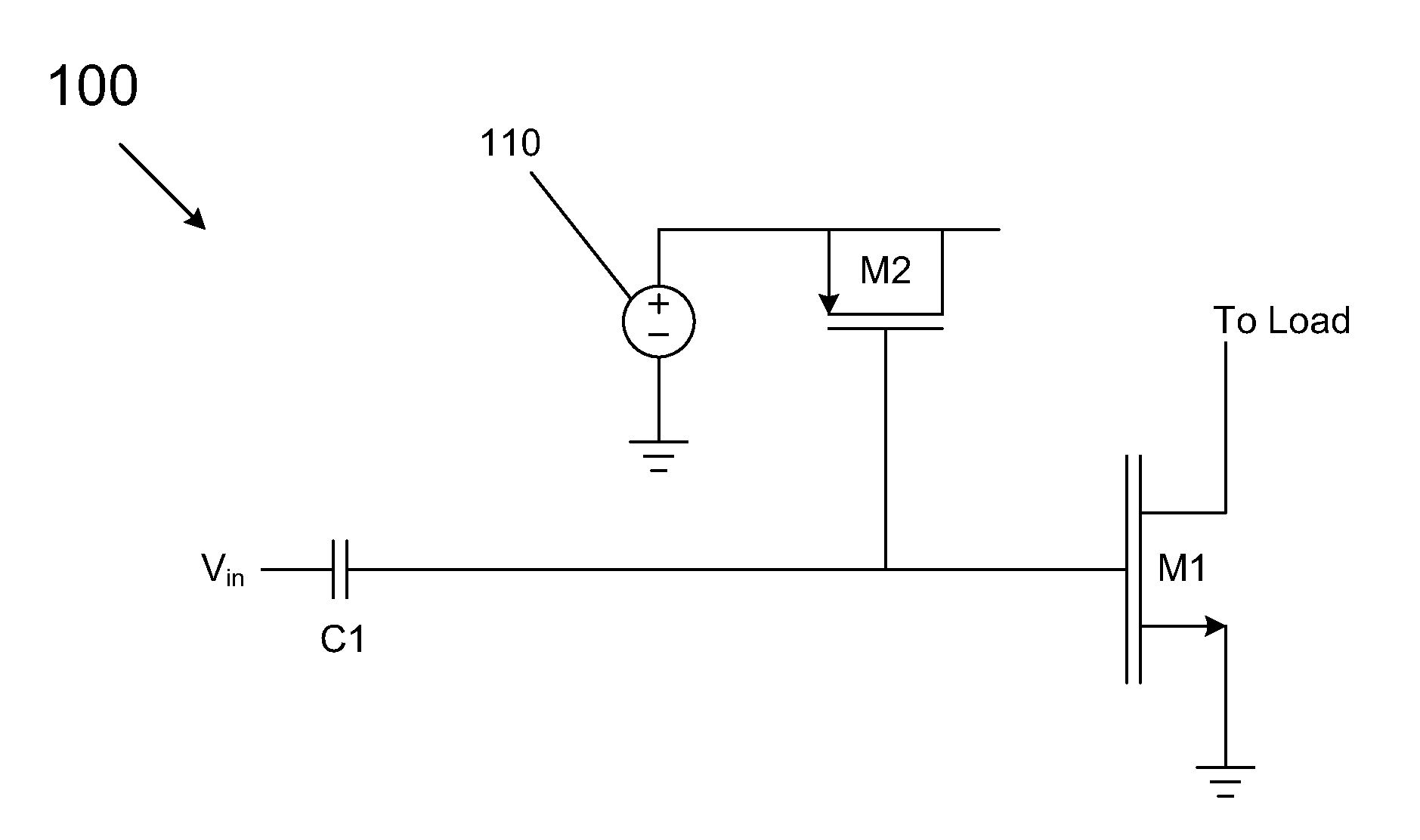

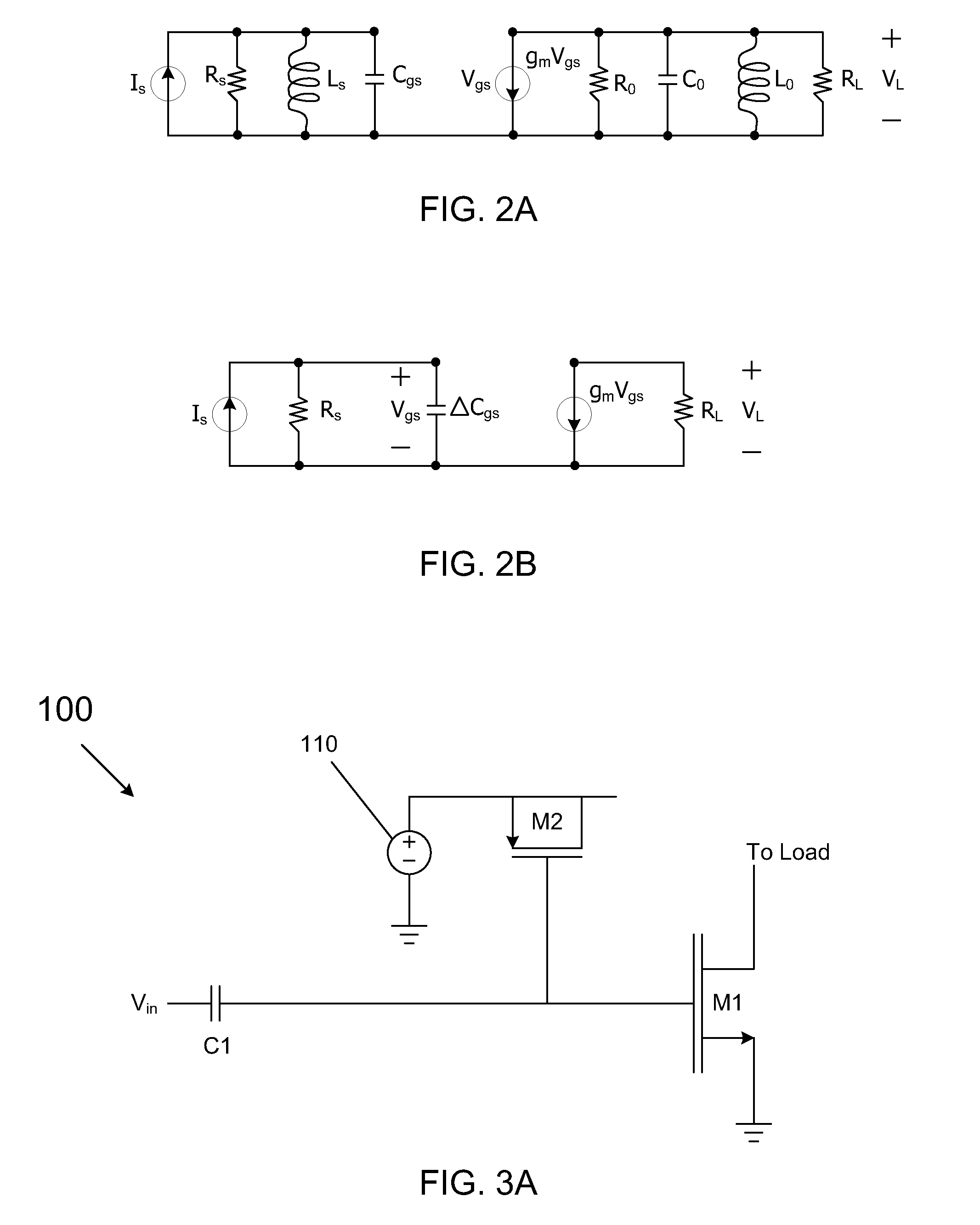

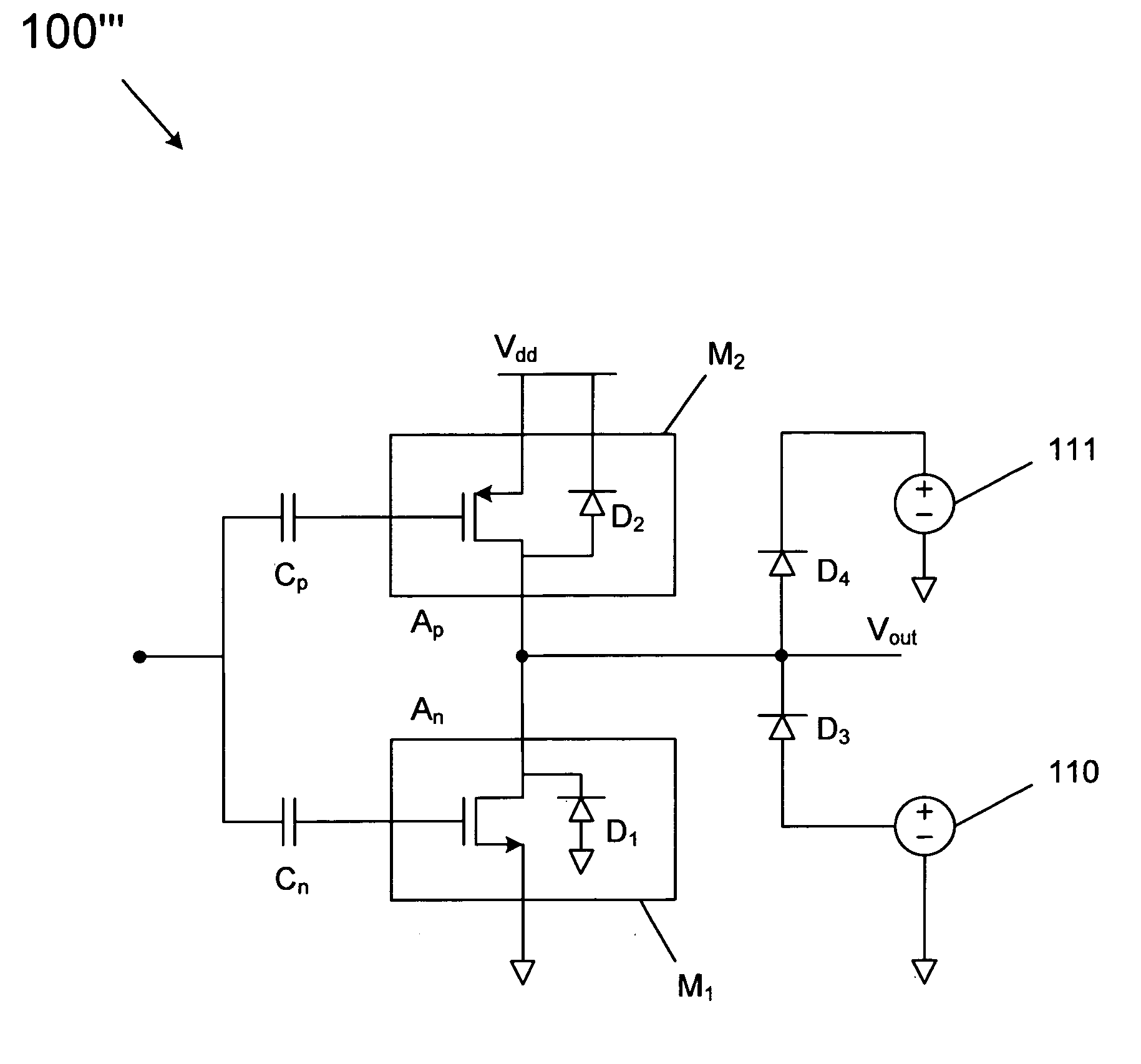

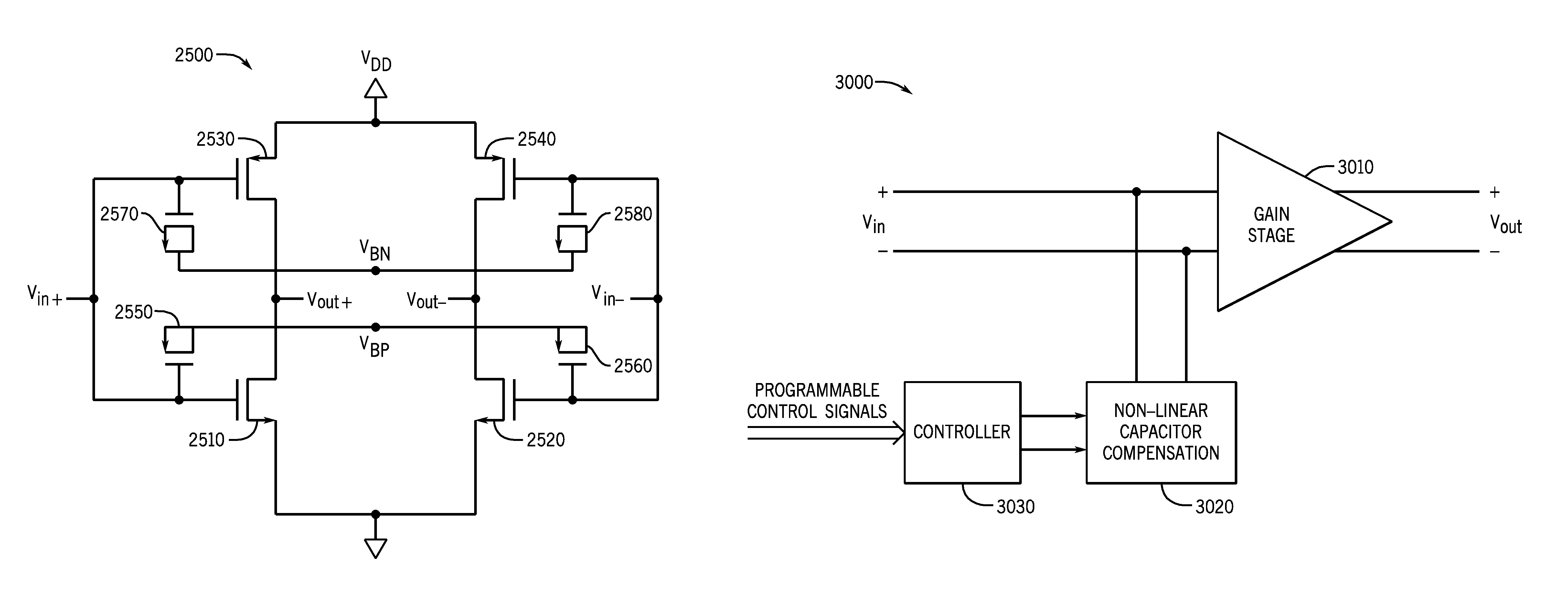

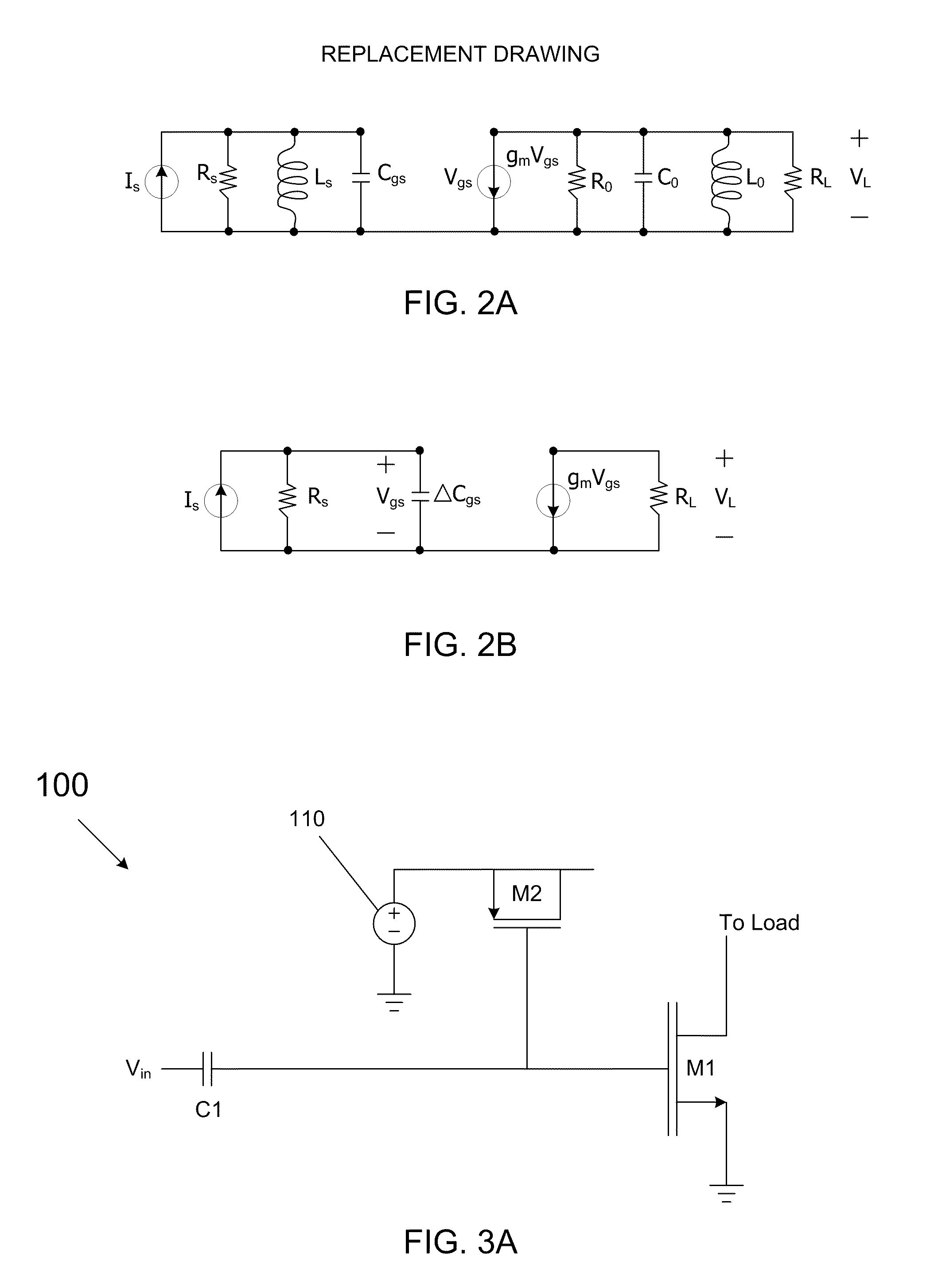

Non-linear capacitance compensation

Embodiments are directed to capacitance compensation via a compensation device coupled to a gain device to compensate for a capacitance change occurring due to an input signal change, along with a controller coupled to the compensation device to receive the input signal and to control an amount of compensation based on the input signal. In some embodiments, banks may be formed of multiple compensation devices, where each of the banks has a different size and is coupled to receive a different set of bias voltages.

Owner:AVAGO TECH INT SALES PTE LTD

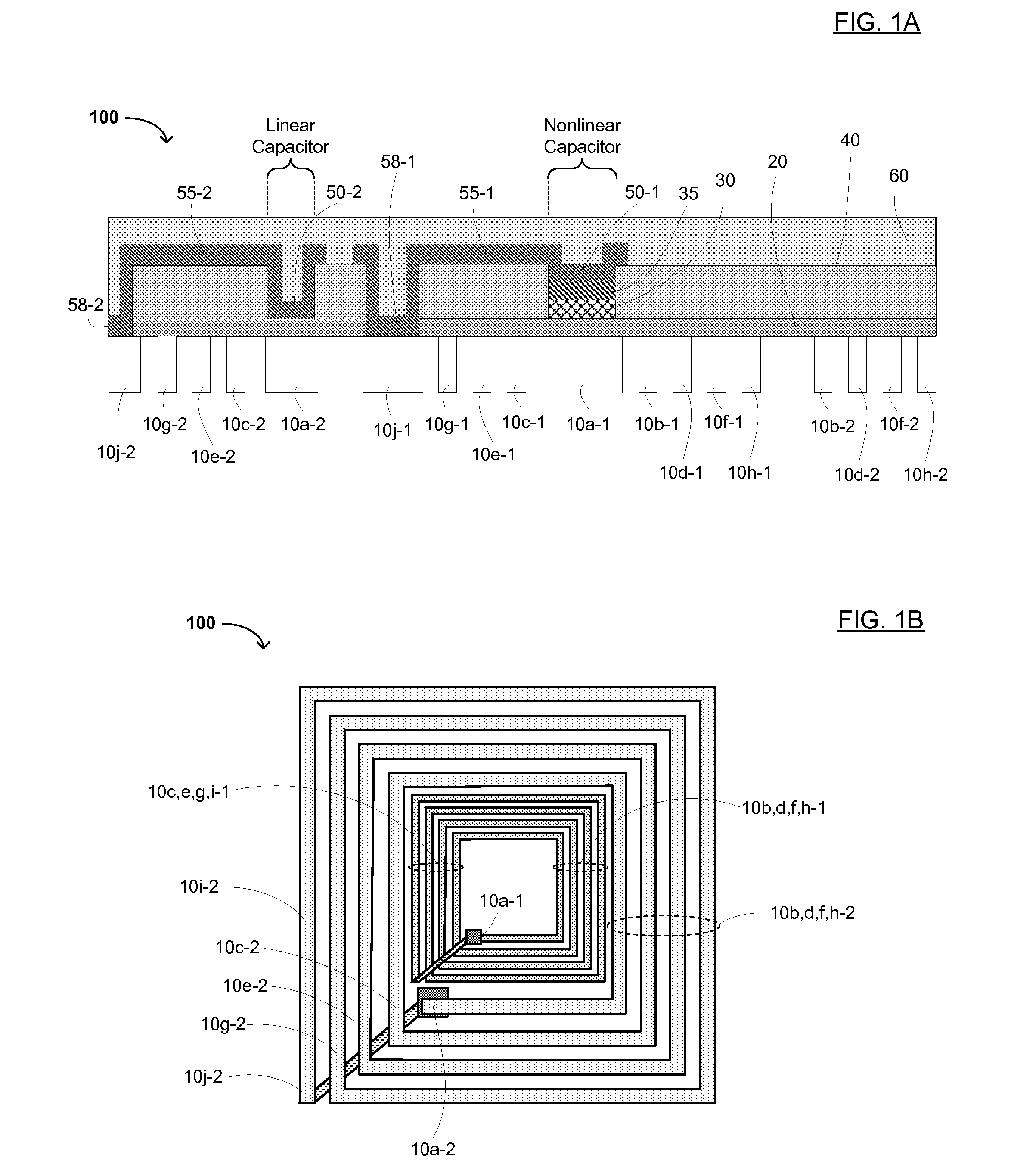

Electronic article surveillance (EAS) tag/device with coplanar and/or multiple coil circuits, an EAS tag/device with two or more memory bits, and methods for tuning the resonant frequency of an RLC EAS tag/device

ActiveUS7498948B1Low costExpand the scope of detectionBurglar alarm by hand-portable articles removalElectricityInductor

An EAS device, and methods for making the device for tuning the resonant frequency of the same is disclosed. The EAS device includes: an outer inductor having one end coupled to a linear or nonlinear capacitor plate; an inner inductor having one end coupled to the other type of capacitor; a first dielectric film on the outer and inner inductors and the capacitor plates coupled thereto, having openings exposing other ends of the outer and inner inductors; a second linear capacitor plate on the dielectric film; a second nonlinear capacitor plate on the dielectric film; a second dielectric film containing holes for the second linear and nonlinear capacitor plates, and exposing the other ends of the first and second inductors; and first and second conducting straps on the second dielectric film, configured to electrically connect one of the exposed inductor ends to a corresponding second capacitor plate.

Owner:ENSURGE MICROPOWER ASA

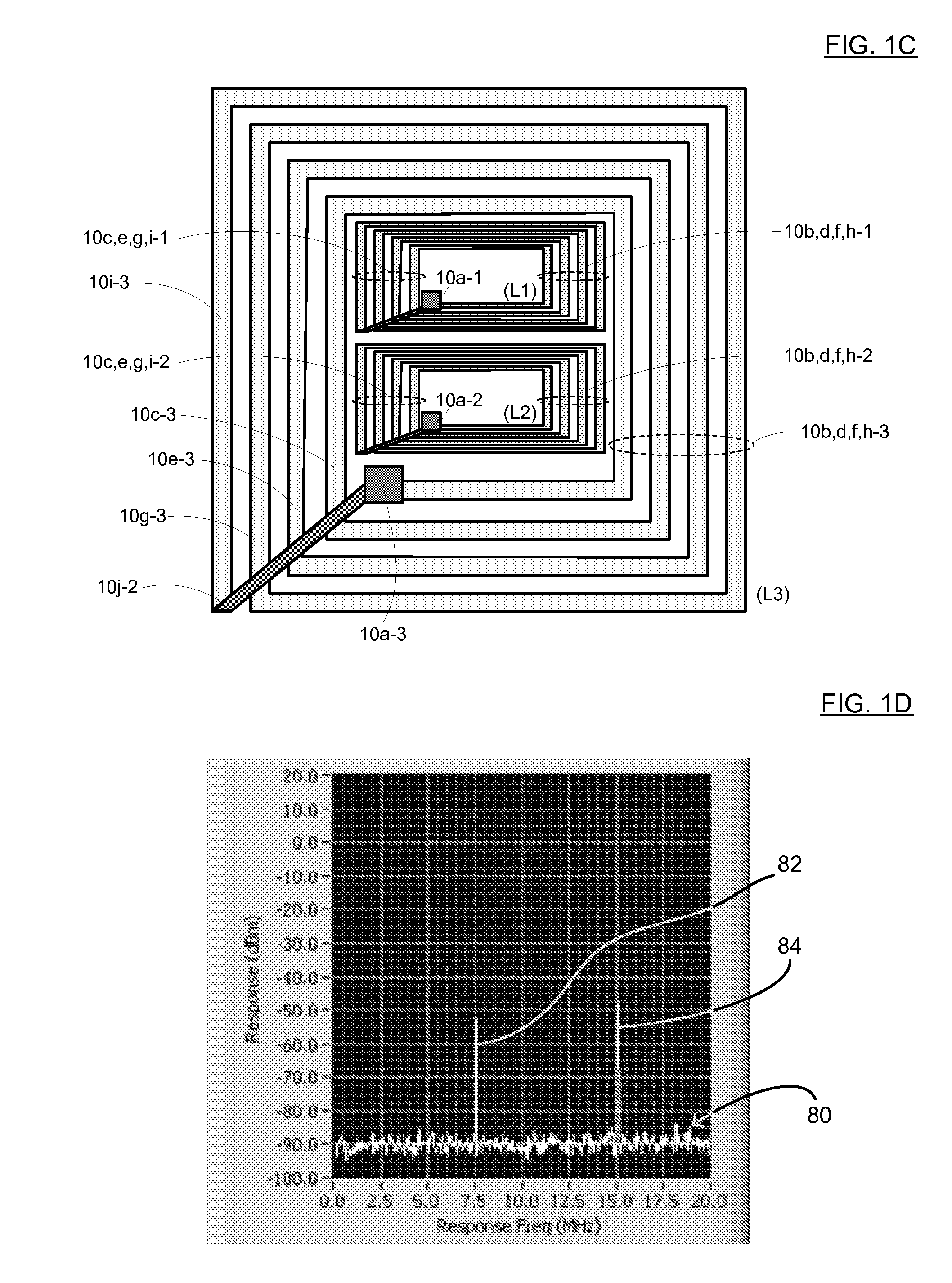

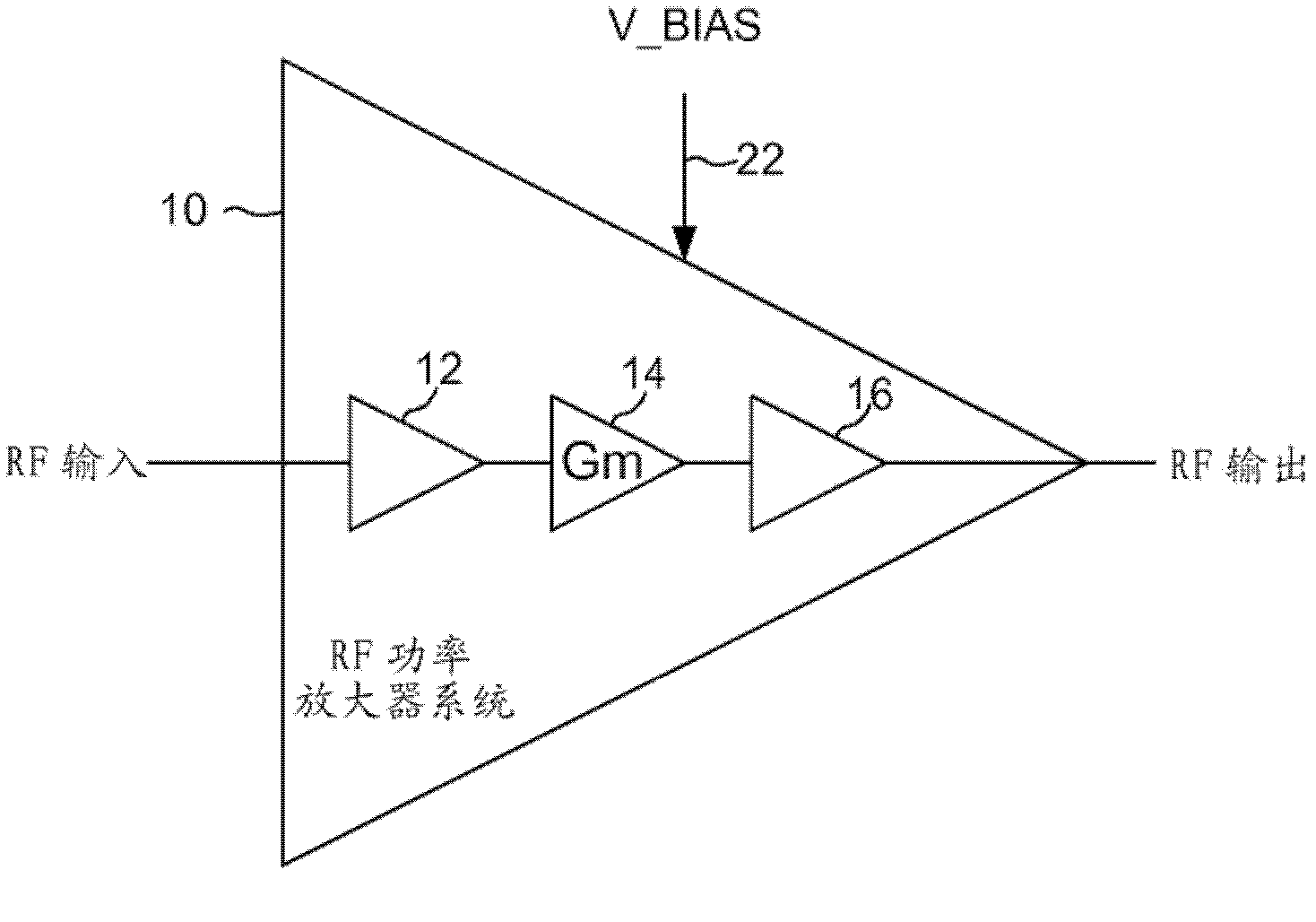

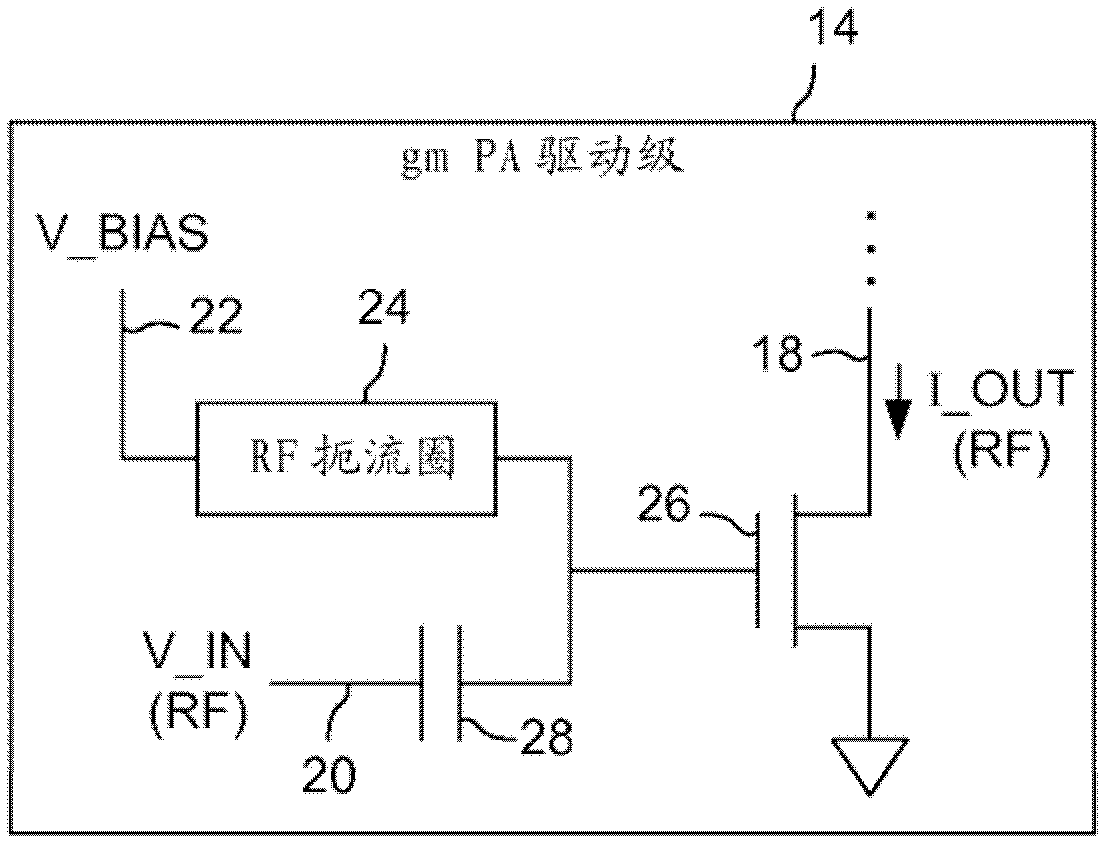

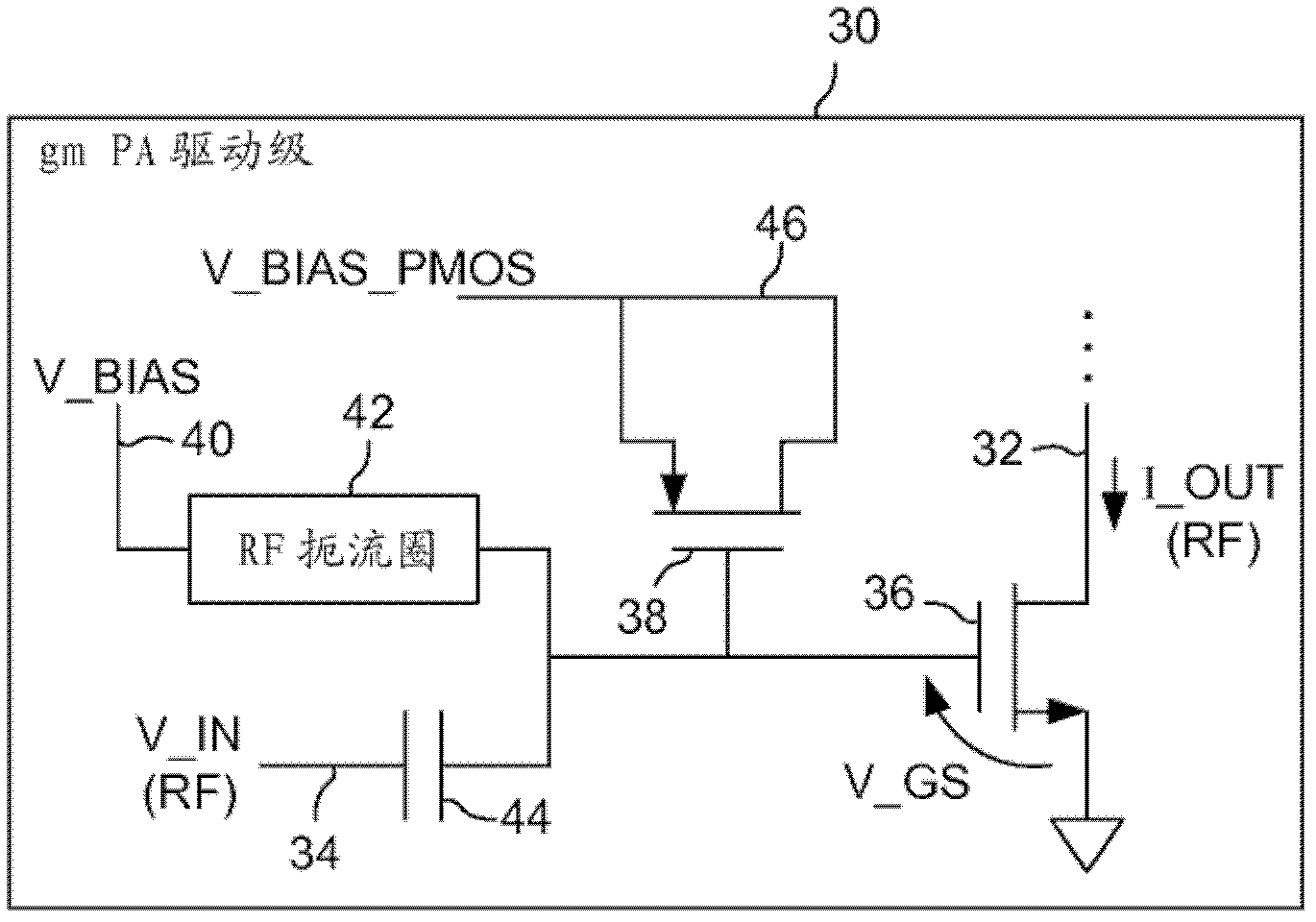

Adaptive biasing radio frequency power amplifier

ActiveCN106571780ALower on-resistanceReduce conduction voltage dropAmplifier modifications to reduce temperature/voltage variationPower amplifiersCapacitanceGain compression

The application discloses an adaptive biasing radio frequency power amplifier comprising a biasing circuit and a power level amplifying circuit. The biasing circuit is used for providing dynamic bias voltage for a transistor II in the power level amplifying circuit; the work voltage I is connected to one end of a resistor I; the other end of the resistor I is used as an output end of the biasing circuit; the work voltage II is connected to the anode of a diode I; the cathode of the diode I is connected to the output end of the biasing circuit; the value of the work voltage II makes the diode I in a default critical conduction status. the power level amplifying circuit comprises a transistor I and the transistor II, which adopt common source and common gate structures; the transistor I adopts common source connection and the grid of the transistor I receives radio frequency input signals; the transistor II adopts common grade connection and the drain electrode of the transistor II outputs drain voltage II. The application provides adaptive biasing voltage postponing gain compression and reducing phase distortion caused by non-linear capacity.

Owner:RDA MICROELECTRONICS SHANGHAICO LTD

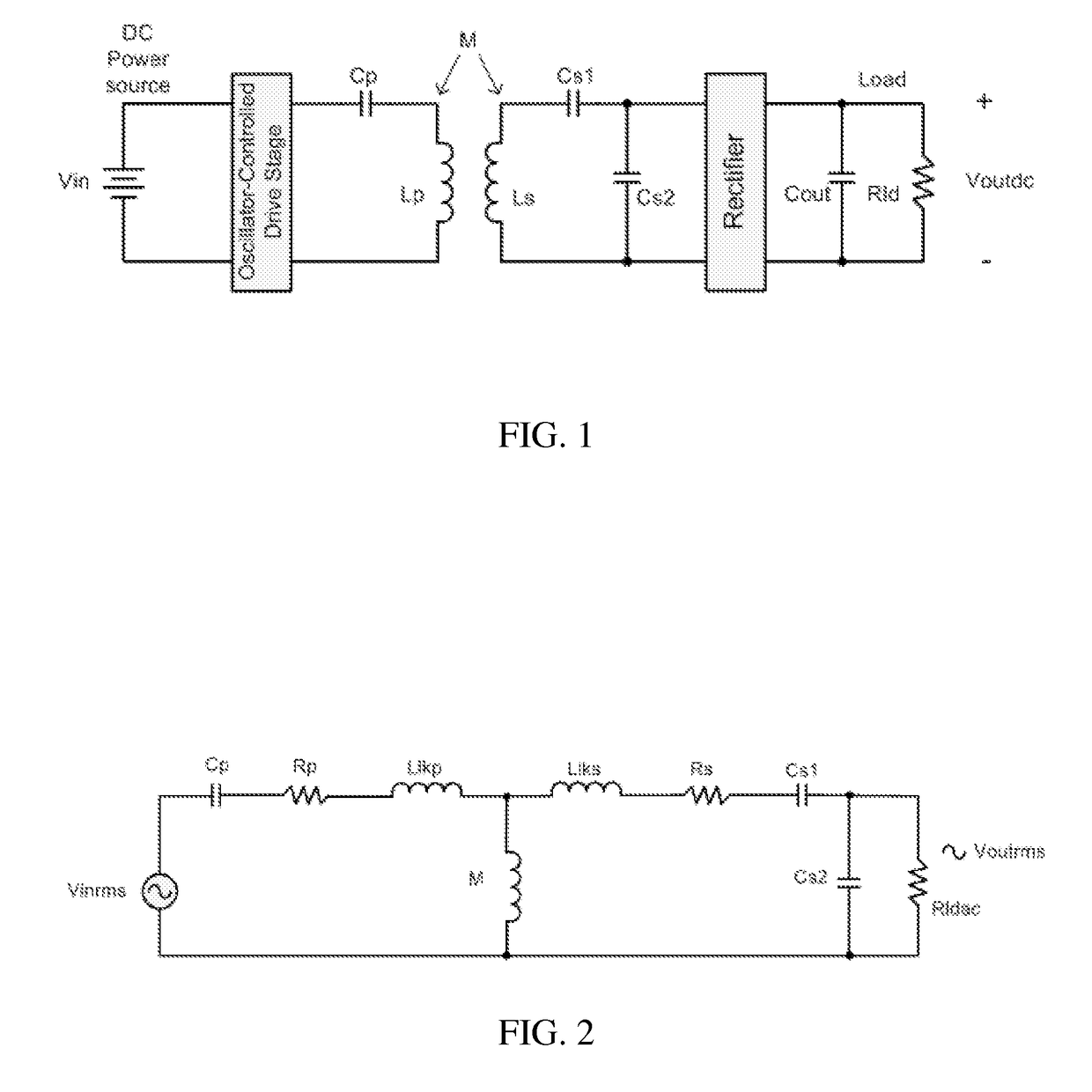

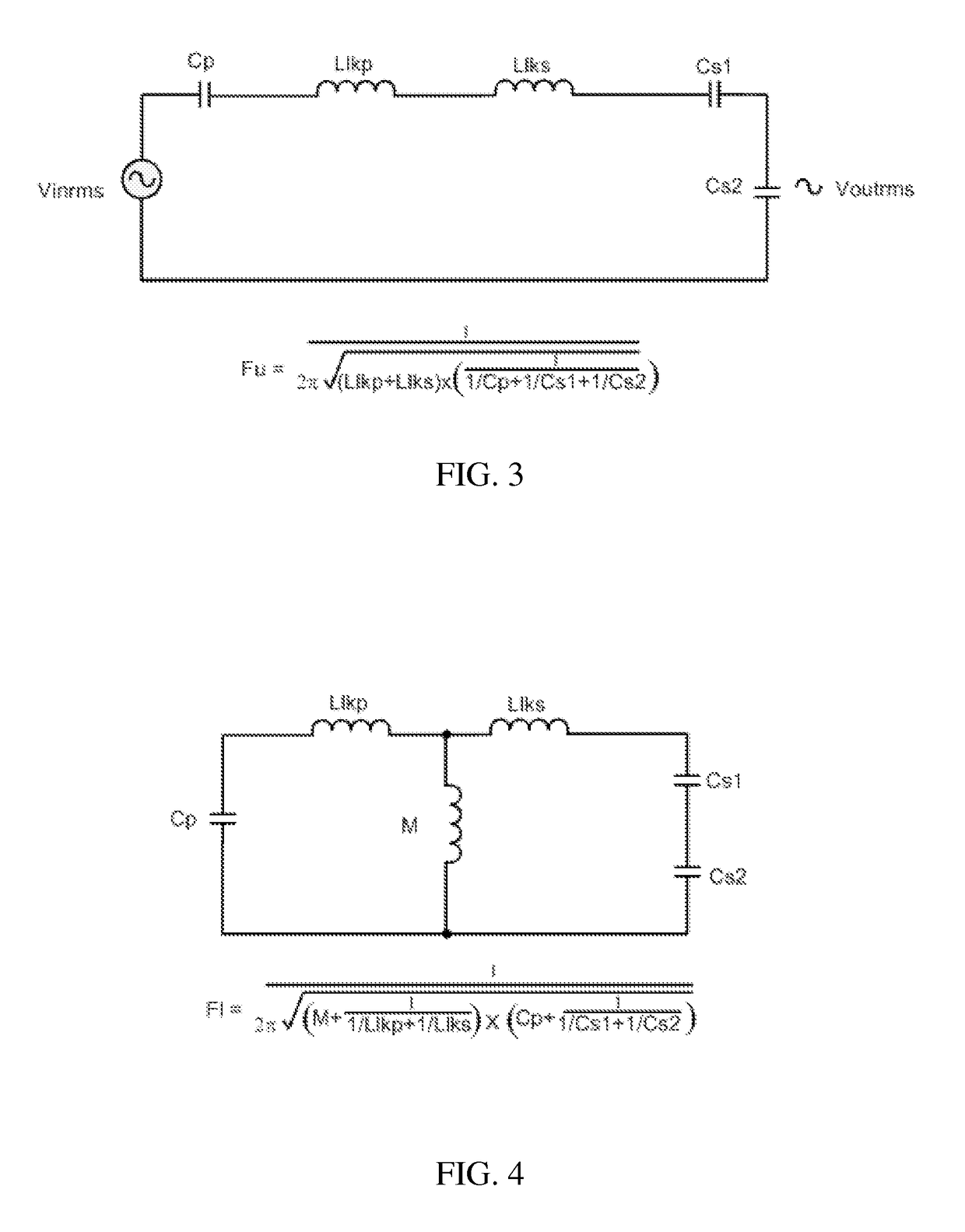

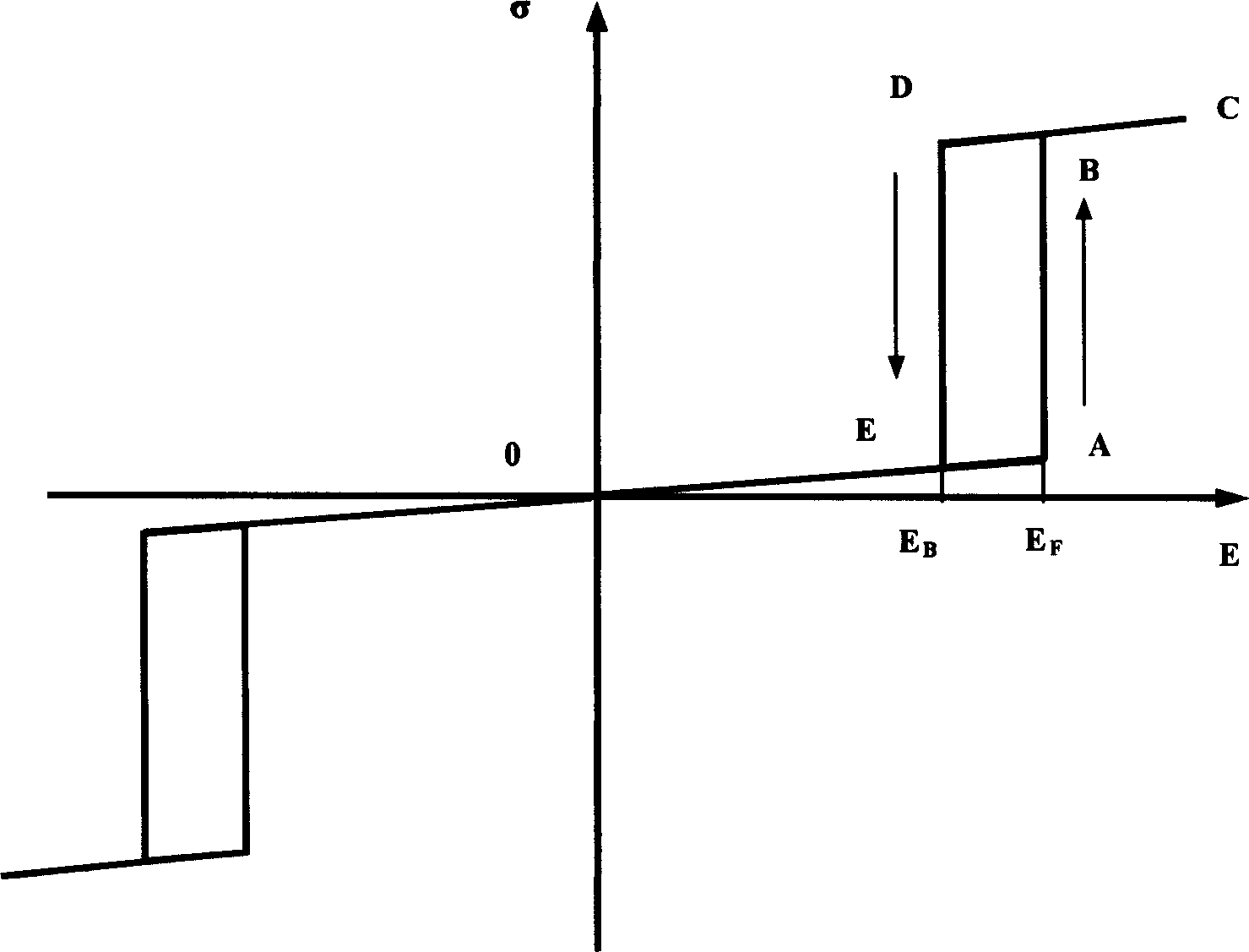

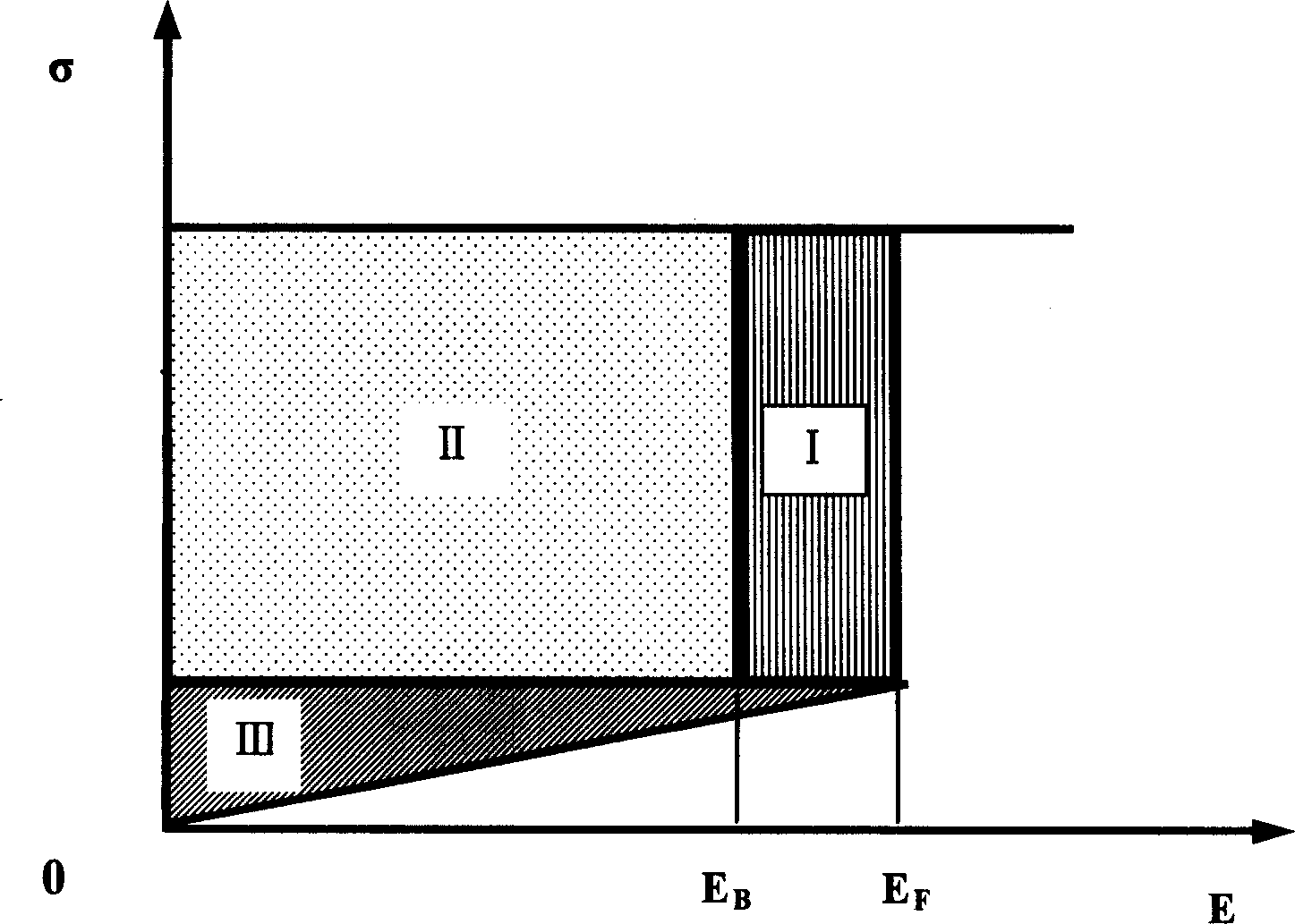

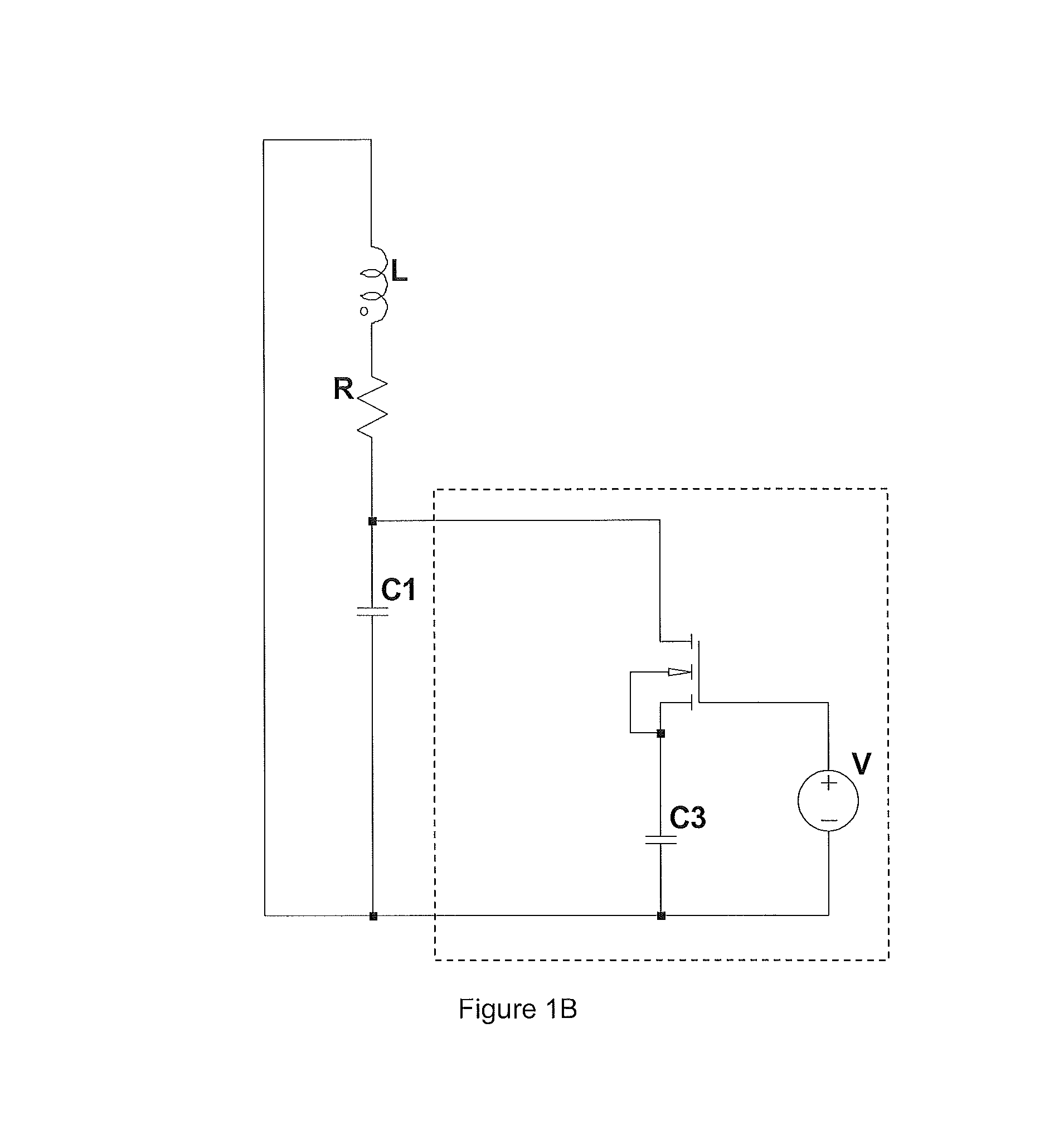

Variable-distance wireless-power-transfer system with fixed tuning and power limiting

ActiveUS20170237302A1Low efficiencyHigh voltageNear-field transmissionBatteries circuit arrangementsElectric power transmissionCapacitance

A wireless-power-transfer system includes a transmitter circuit and a receiver circuit. The transmitter circuit includes a primary series-resonant capacitor connected to an oscillator-controlled drive stage that provides fixed-frequency output and a transmitting coil connected to the primary series-resonant capacitor. The transmitting resonant frequency is below the fixed frequency of the oscillator-controlled drive stage. The receiver circuit includes a receiving coil, a secondary series-resonant capacitor connected in series with the receiving coil, and a secondary parallel-resonant capacitor connected in parallel with the receiving coil. The receiving resonant frequency increases as a nonlinear capacitance of the at least one rectifier decreases when the rectifier-circuit DC output increases.

Owner:MURATA MFG CO LTD

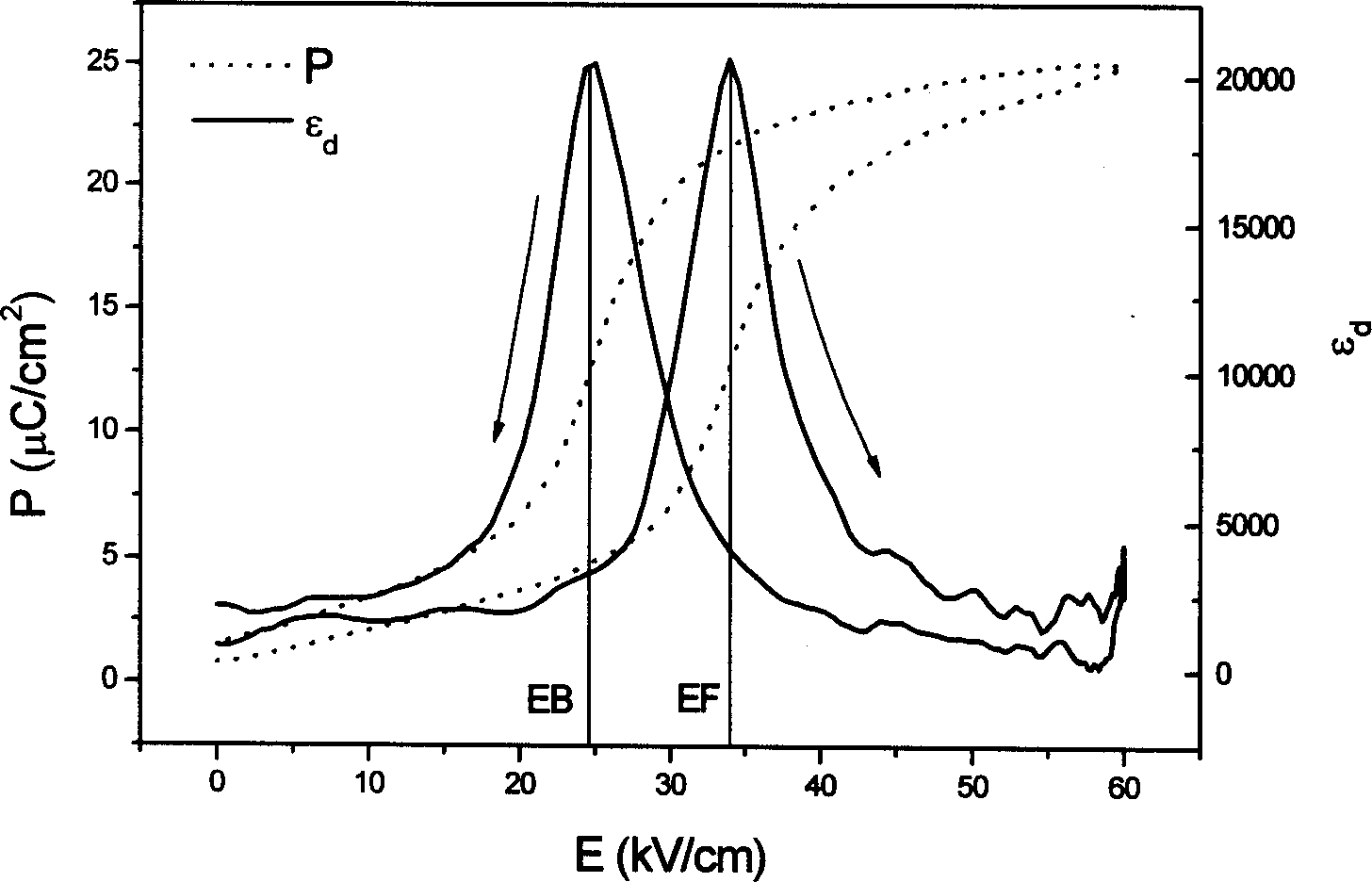

Dielectric nonlinear capacitor ceramic material and its making technique

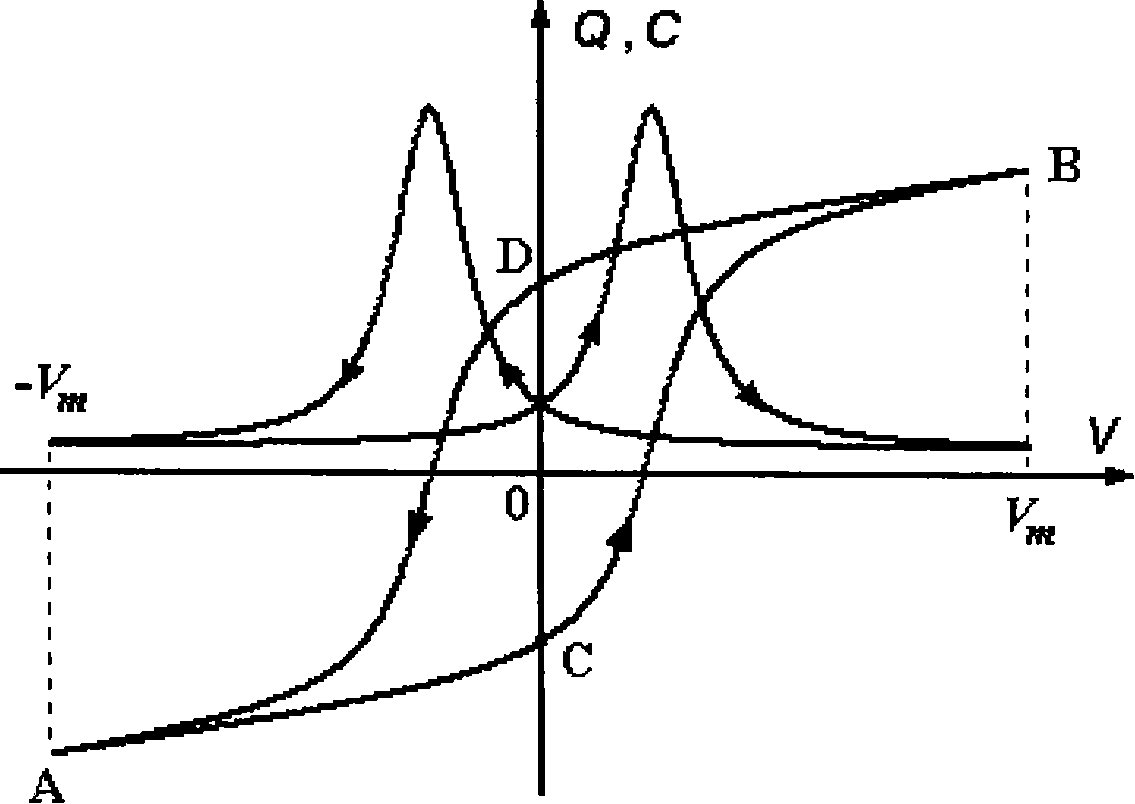

InactiveCN1688004AHigh energy storage densityIncrease the number of cyclesFixed capacitor dielectricCeramicsLead zirconate titanateStrontium

This invention discloses an anti-ferroelectric ceramic capacitor material and its preparation technology, which applies Sn of positive four valency to replace Zr of positive 4 valency, applies the positive 3 valency La to replace 2 valency Pb in the compound of Pb(Zr, Ti) O3 to form a multi-component solid solution with Pb vacancy. The balanced formula of the charge and the valency is: (Pb1-3 2 / 2Laz)[(Zri-ysny)1-Tix]O3, in which, x varies between 0.06`0.20, y: 0.2010.40, z varies between 0.02-0.08, or positive 2 valency Sr or Ba is added to replace 2 valency Pb in Pb(zr, Ti) O3, the formula is [(Pb1-wBw)1-3z / 2Laz][Zr1-ySny]1-xTix ]O3, B expresses Sr or Ba of 2 valency, w varies between 0.02-0.12. A conventional electronic ceramic preparation method is applied in the method.

Owner:XI AN JIAOTONG UNIV

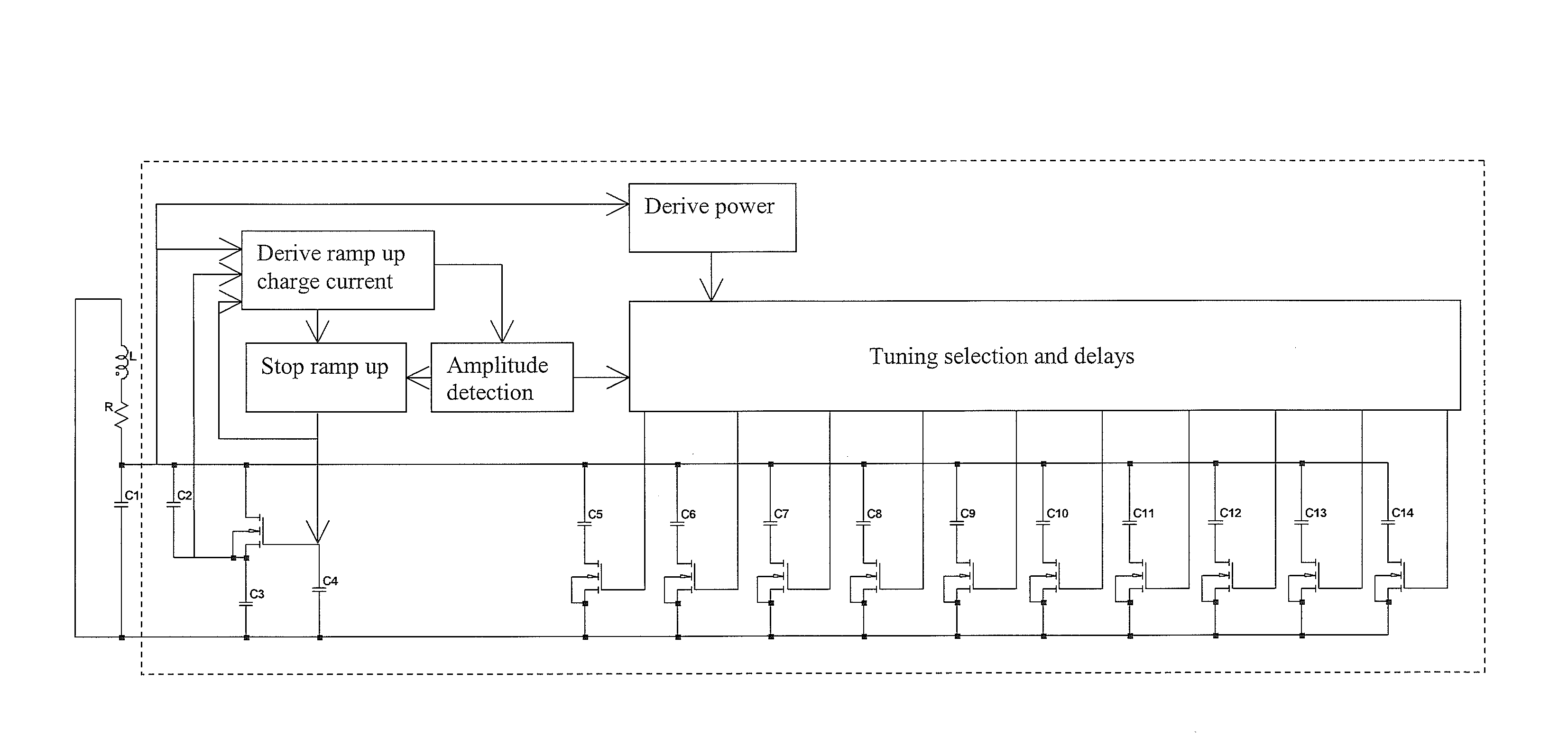

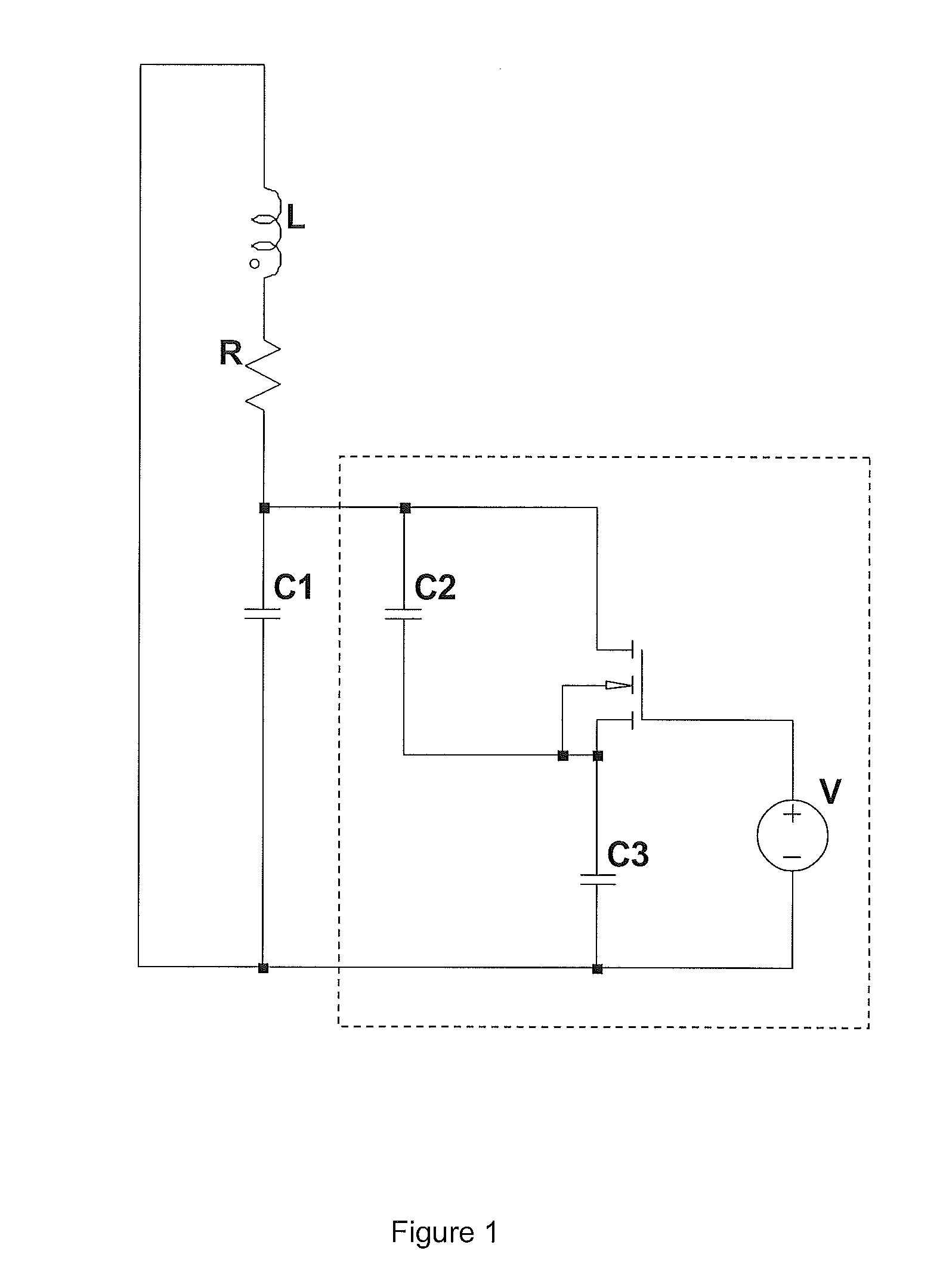

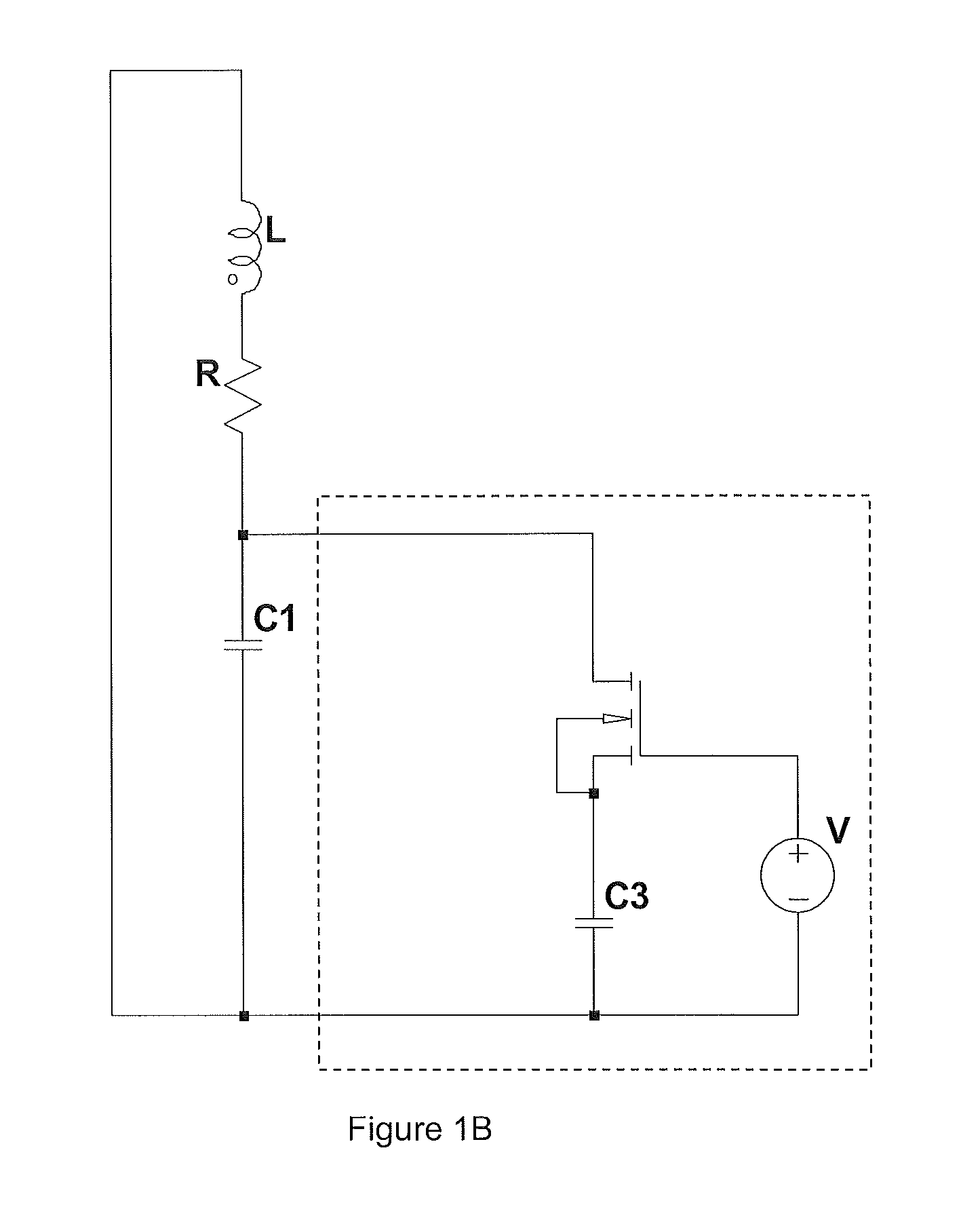

Tuned resonant circuits

ActiveUS20110241750A1Easy to tuneReducing and eliminating needPulse automatic controlGenerator stabilizationCapacitanceSignal on

A circuit block which comprises a non-linear capacitor with two different values of capacitance dependent on a value of a voltage of a resonant signal on the capacitor; a plurality of second capacitors each coupled to a respective switch to enable a said second capacitor to be switched in or out of parallel connection with the nonlinear capacitor; and a tuning control, coupled to the second capacitor switches, and sensing an amplitude of the resonant signal. The tuning control circuit is configured to control the second capacitor switches to successively switch the second capacitors in / out of parallel connection with the non-linear capacitor dependent on the amplitude of the resonant signal until the non-linear capacitor has substantially a single one of two different values, such that in a resonant circuit the circuit block then behaves as a fixed value capacitor.

Owner:SUREFLAP

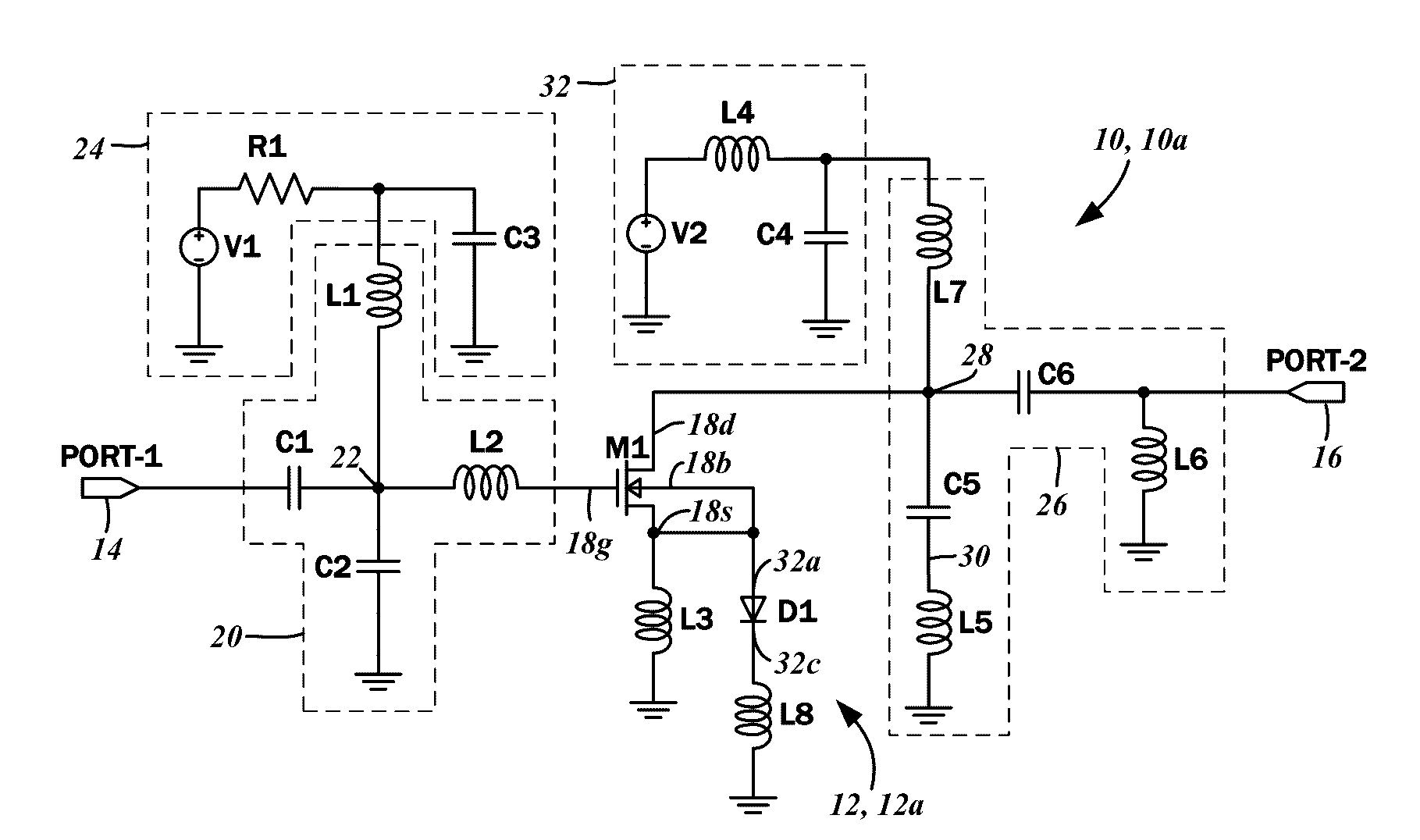

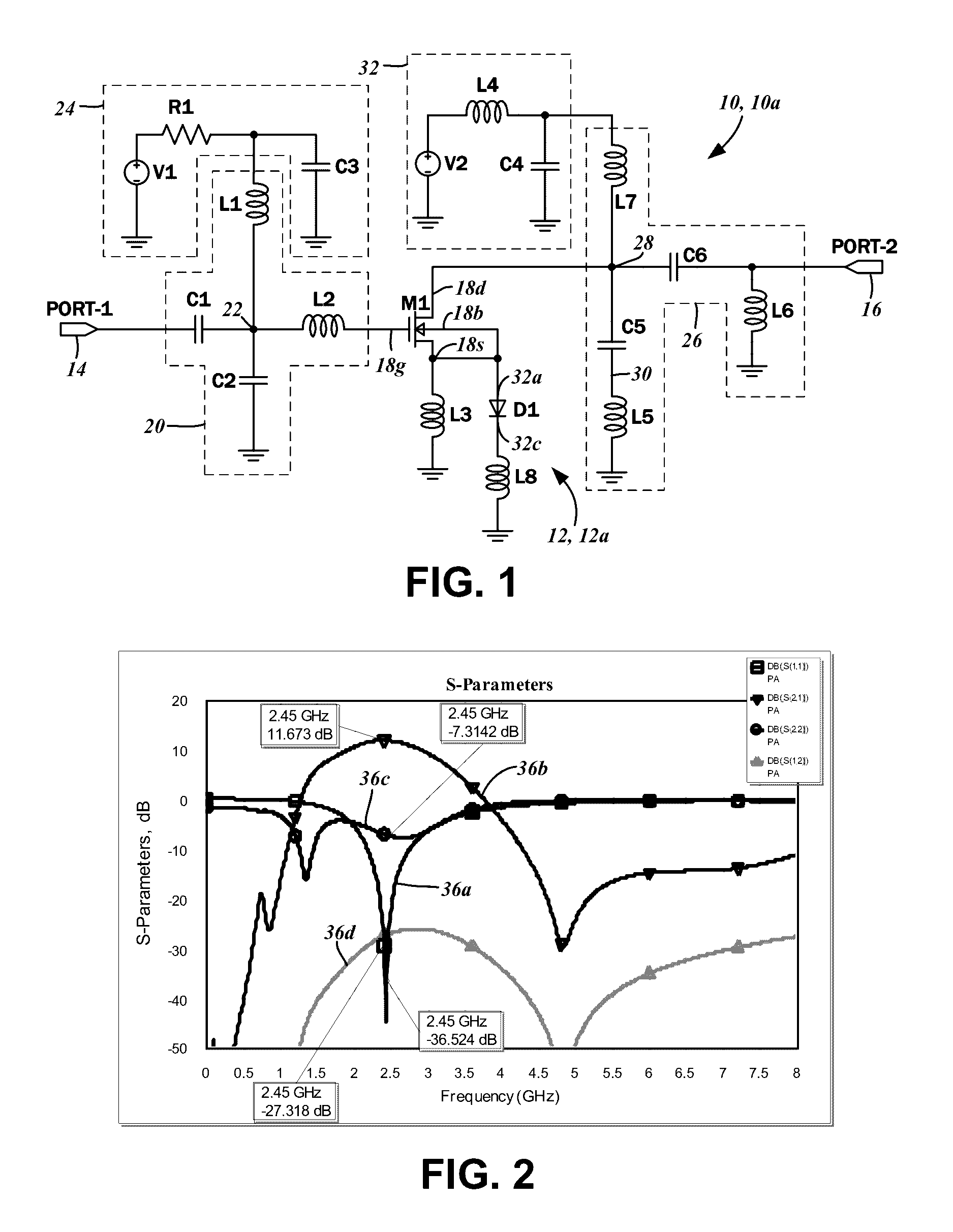

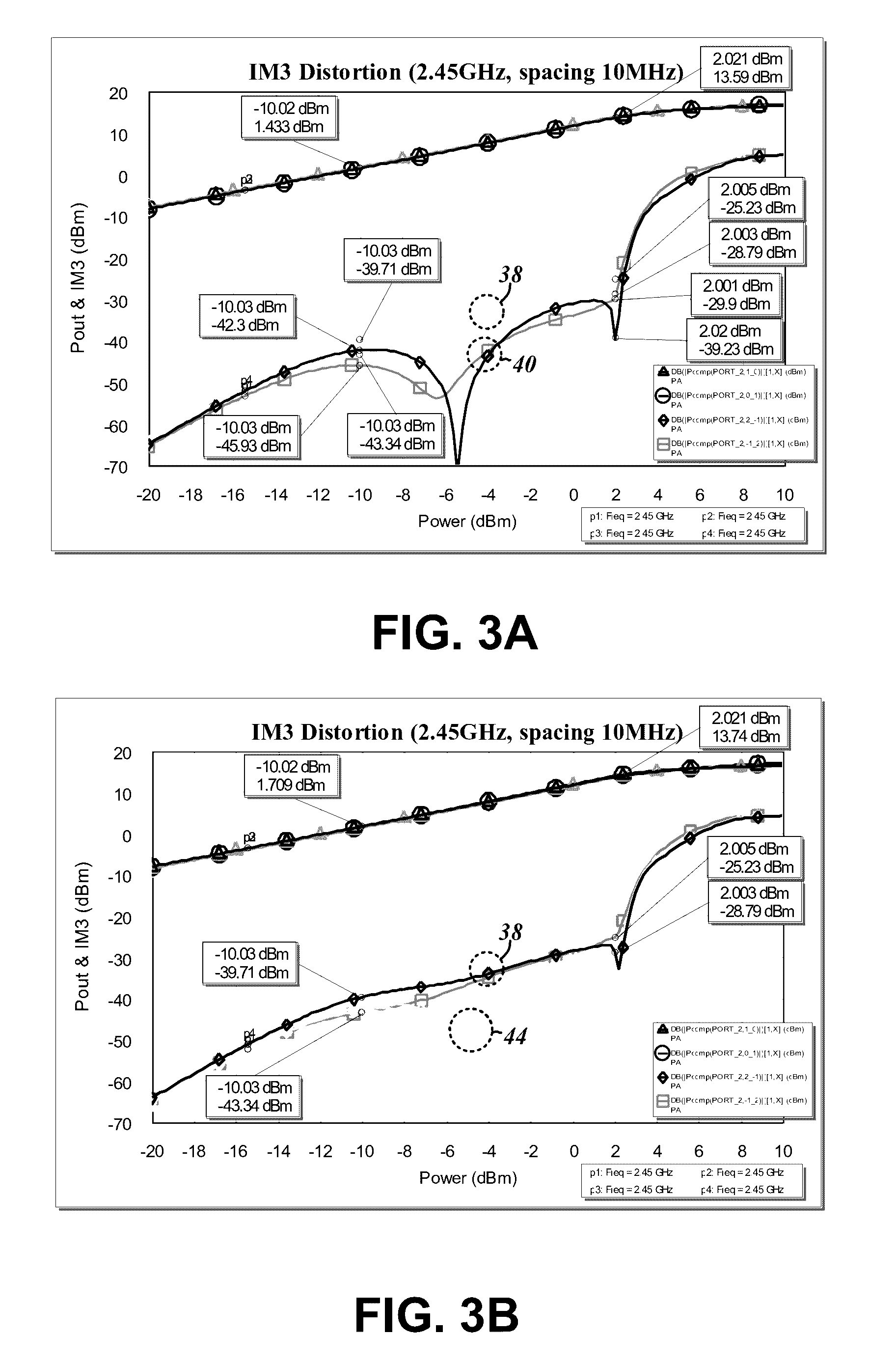

Compensating for non-linear capacitance effects in a power amplifier

In one implementation, a power amplifier may include a gain device to receive an input signal and to output an amplified signal, and a compensation device coupled to the gain device to compensate for a change in a capacitance of the gain device occurring due to a change in the input signal. The power amplifier may be formed using a complementary metal oxide semiconductor (CMOS) process.

Owner:AVAGO TECH INT SALES PTE LTD

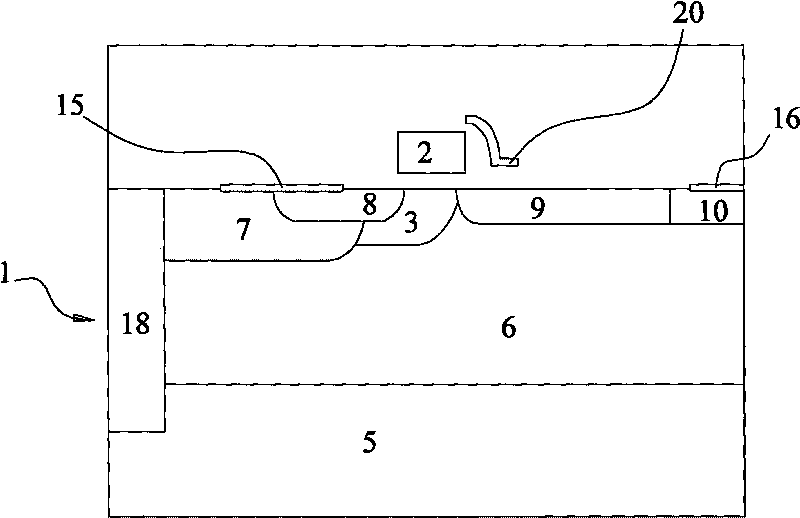

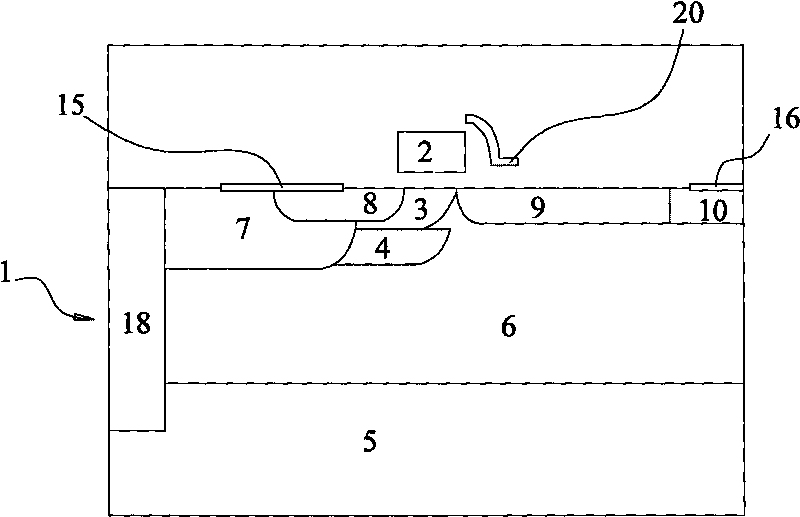

LDMOS device with transverse diffusing buried layer below grid

ActiveCN101719515ASuppression of short channel effectsReduce nonlinear capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSRadio frequency

The invention discloses an LDMOS device with a transverse diffusing buried layer below a grid, comprising a semiconductor body and the grid positioned on the semiconductor body. A first conduction type doping channel region is arranged on the semiconductor body and below the grid; and a first conduction type transverse diffusing buried layer is arranged below the first conduction type doping channel region. The invention can properly reduce the use level of doping ions injected to the first conduction type doping channel region under the precondition of effectively inhibiting the short channel effect of the LDMOS device, thereby reducing the nonlinear capacitors of the LDMOS device so that the radio frequency power and the performance of the LDMOS device are further improved.

Owner:INNOGRATION SUZHOU +2

Automatic circuit and method for temperature compensation of oscillator frequency variation over temperature for a real time clock chip

ActiveUS20080117722A1Frequency stabilisation mechanismGenerator stabilizationCapacitanceReal-time clock

An automatic temperature compensated real-time clock (RTC) chip includes a clock portion having a crystal oscillator block including crystal compensation circuitry adapted to be coupled to a crystal. The crystal compensation circuitry includes a non-linear capacitor DAC including a plurality of load capacitors, wherein the load capacitors have respective switches which switch respective ones of the load capacitors to change a parallel resonance frequency (fp) generated by the oscillator block. The capacitor DAC is arranged so that Analog Trimming (ATR) bits received cause an arrangement of the switches to provide a non-linear change in overall load capacitance to result in a linear relationship between fp and the ATR bits. A temperature sensor block is coupled to the crystal for measuring a temperature of at least the crystal. An A / D converter is coupled to the temperature sensor for outputting a digital temperature signal representative of the temperature of the crystal. A DSP engine receives the digital temperature signal and calculates frequency correction needed to correct for frequency inaccuracy and determines a bit sequence including the ATR bits appropriate to achieve the frequency correction.

Owner:INTERSIL INC

RF power amplifiers with diode linearizer

ActiveUS20160329866A1Reduces inter-modulation productAmplifier modifications to reduce non-linear distortionNegative-feedback-circuit arrangementsCapacitanceAudio power amplifier

A radio frequency (RF) power amplifier circuit with a diode linearizer circuit. The power amplifier circuit has an input and an output, as well as a power amplifier transistor with a first terminal connected to the input, a second terminal connected to the output, and a third terminal. The linearizer circuit is connected to the third terminal and to ground, and has a non-linear current-voltage curve as well as a non-linear capacitance. The linearizer circuit reduces inter-modulation products in a current through the power amplifier transistor from the second terminal to the third terminal that corresponds to an input signal applied to the input.

Owner:SKYWORKS SOLUTIONS INC

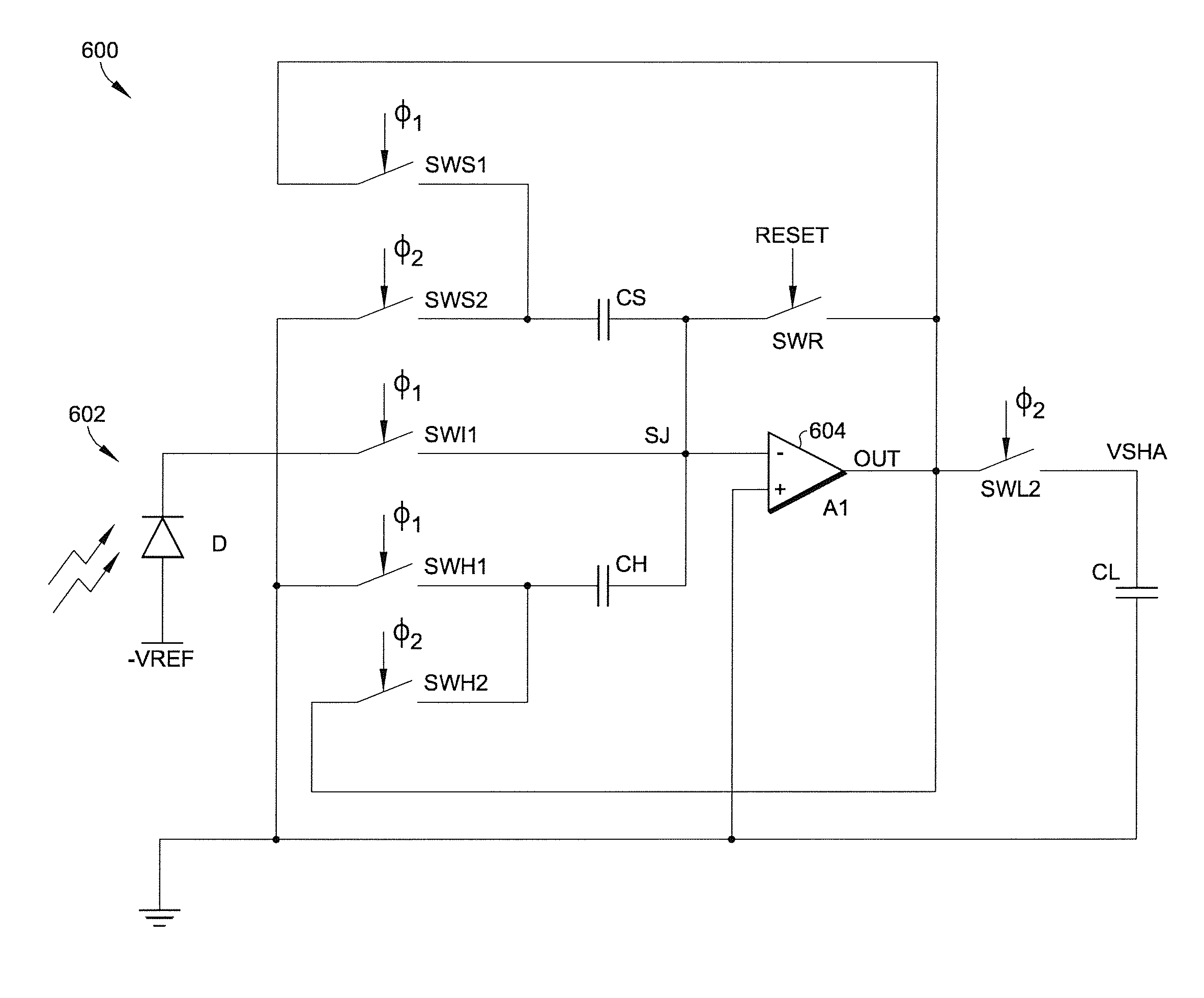

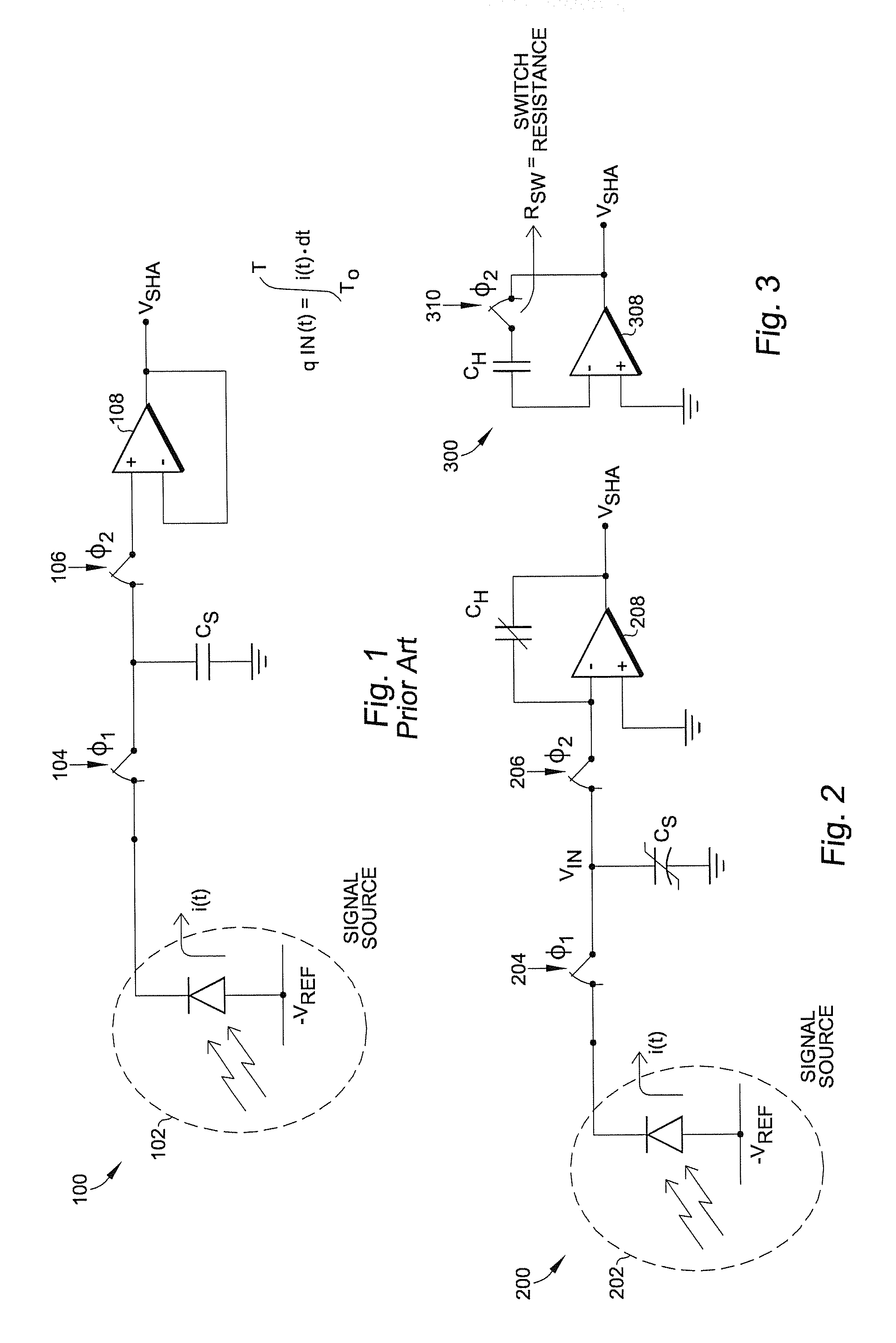

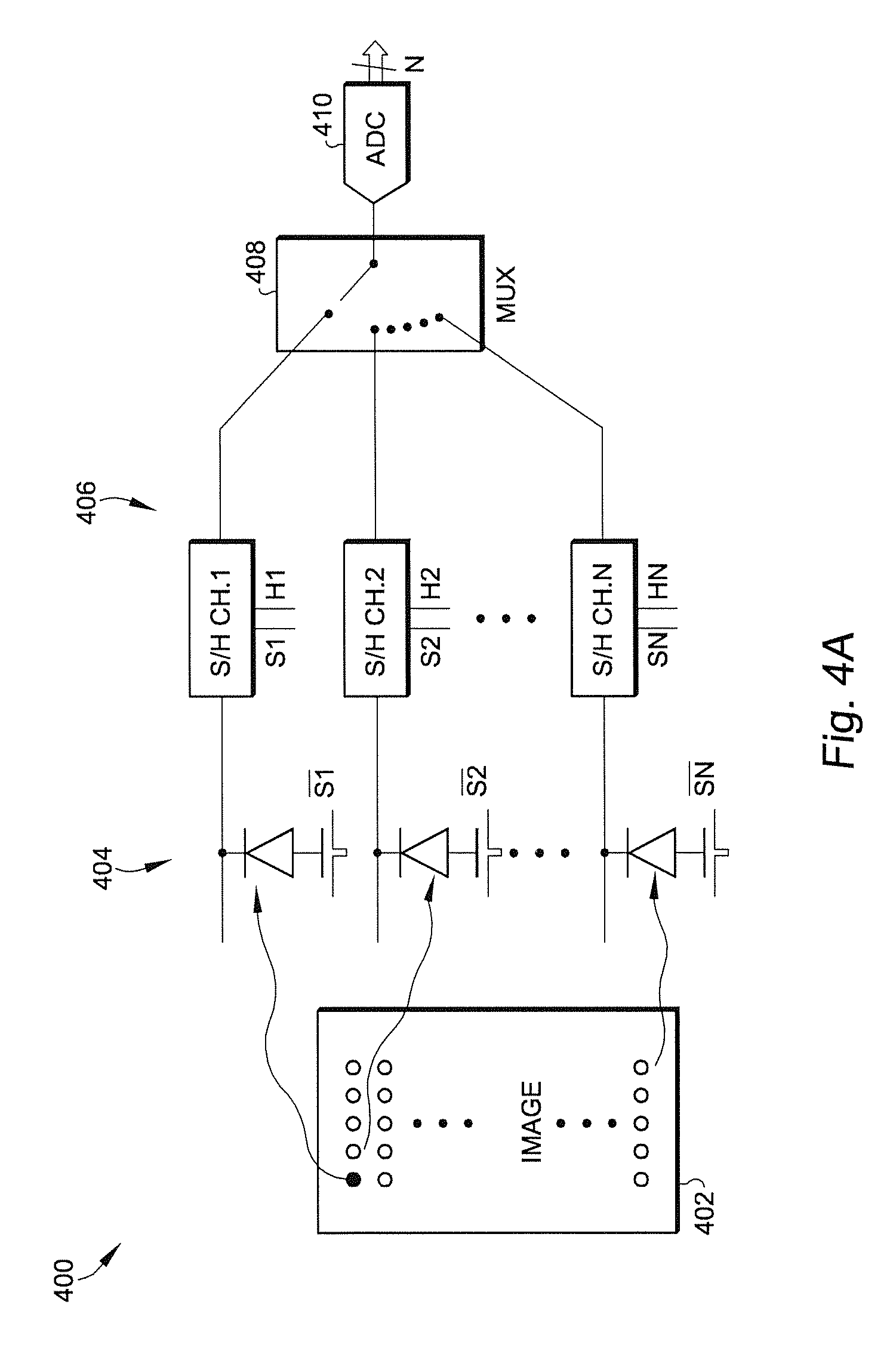

Low-noise low-distortion signal acquisition circuit and method with reduced area utilization

ActiveUS9076554B1Analogue/digital conversionElectric signal transmission systemsLow noiseLow distortion

A sample and hold amplifier includes an input node for receiving an input current signal, a non-linear sampling capacitor circuit having an input coupled to the input node, an operational amplifier having a negative input coupled to an output of the non-linear sampling capacitor circuit, a positive input coupled to ground, and an output for providing a sample and hold voltage signal, and a linear capacitor coupled between the negative input and the output of the operational amplifier. The non-linear sampling capacitor includes a non-linear capacitor coupled between an intermediate node and ground, a first switch coupled between the input and the intermediate node configured to switch according to a first phase signal, and a second switch coupled between the output and the intermediate node configured to switch according to a second phase signal.

Owner:CAES COLORADO SPRINGS LLC

Non-linear capacitance compensation

Owner:AVAGO TECH INT SALES PTE LTD

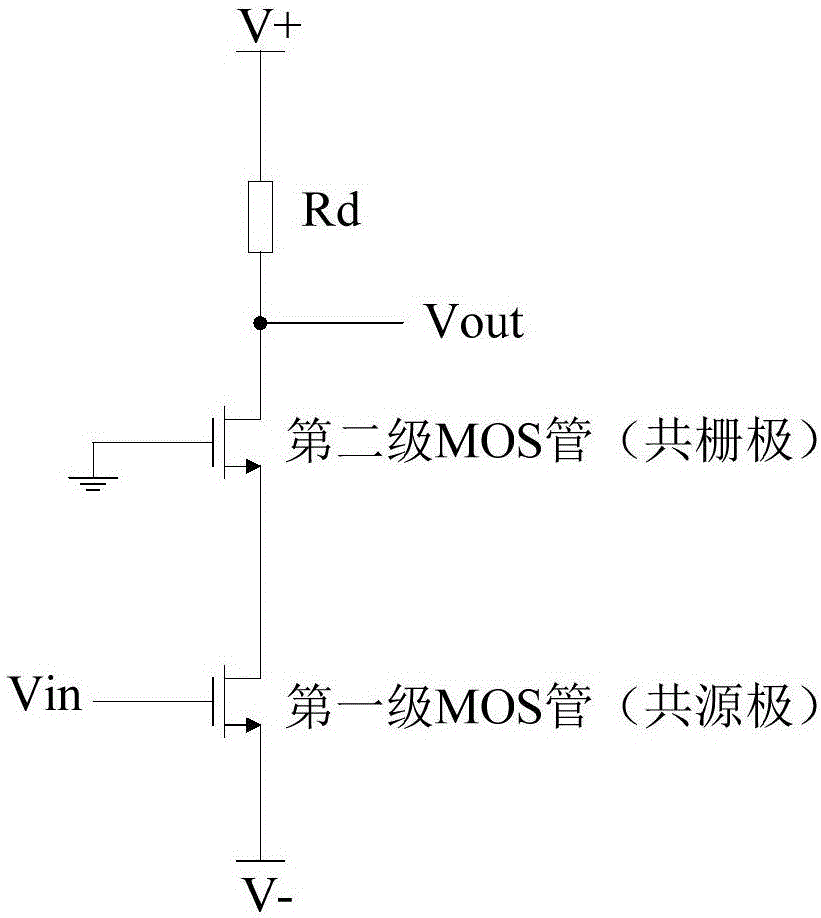

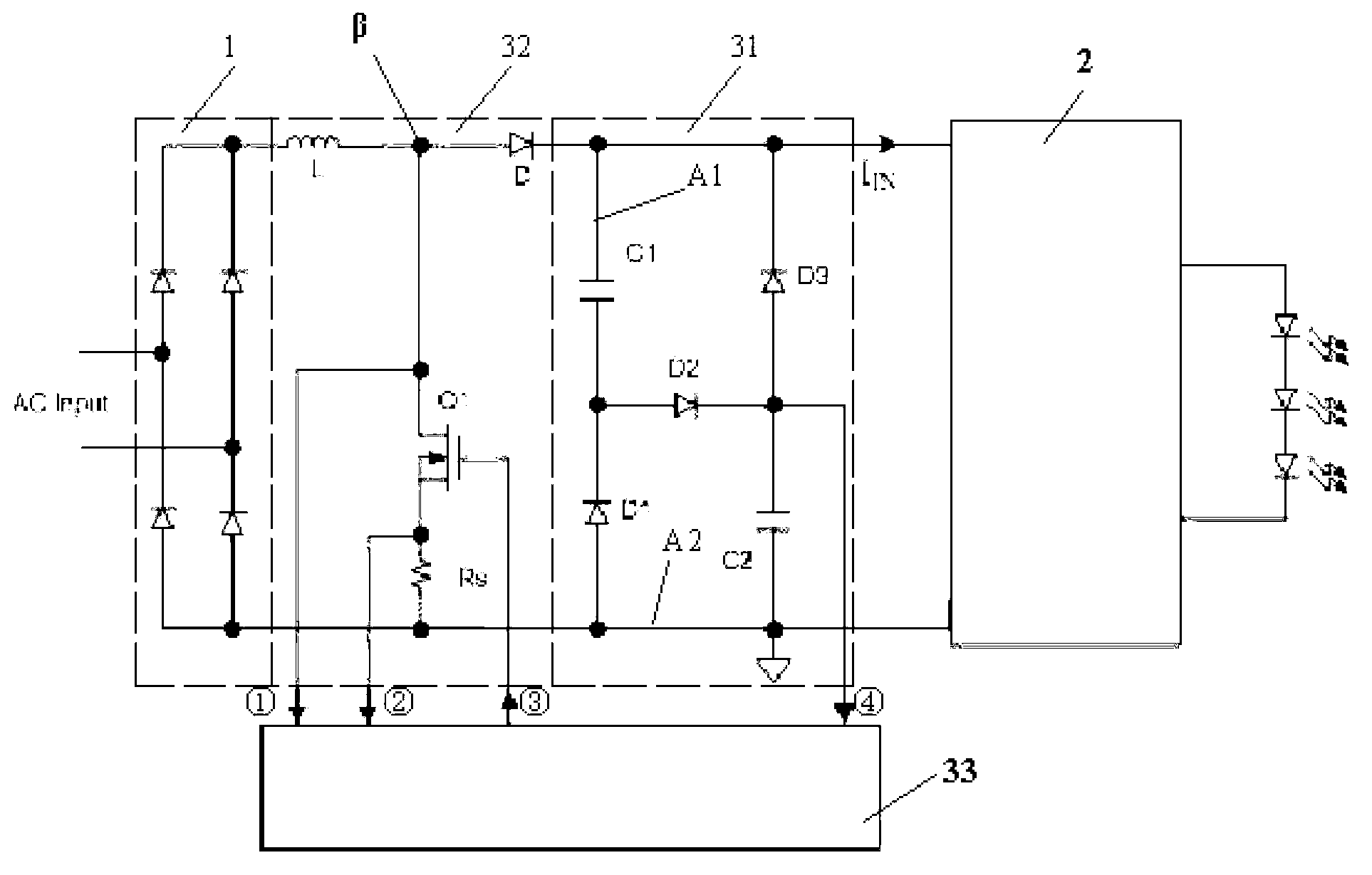

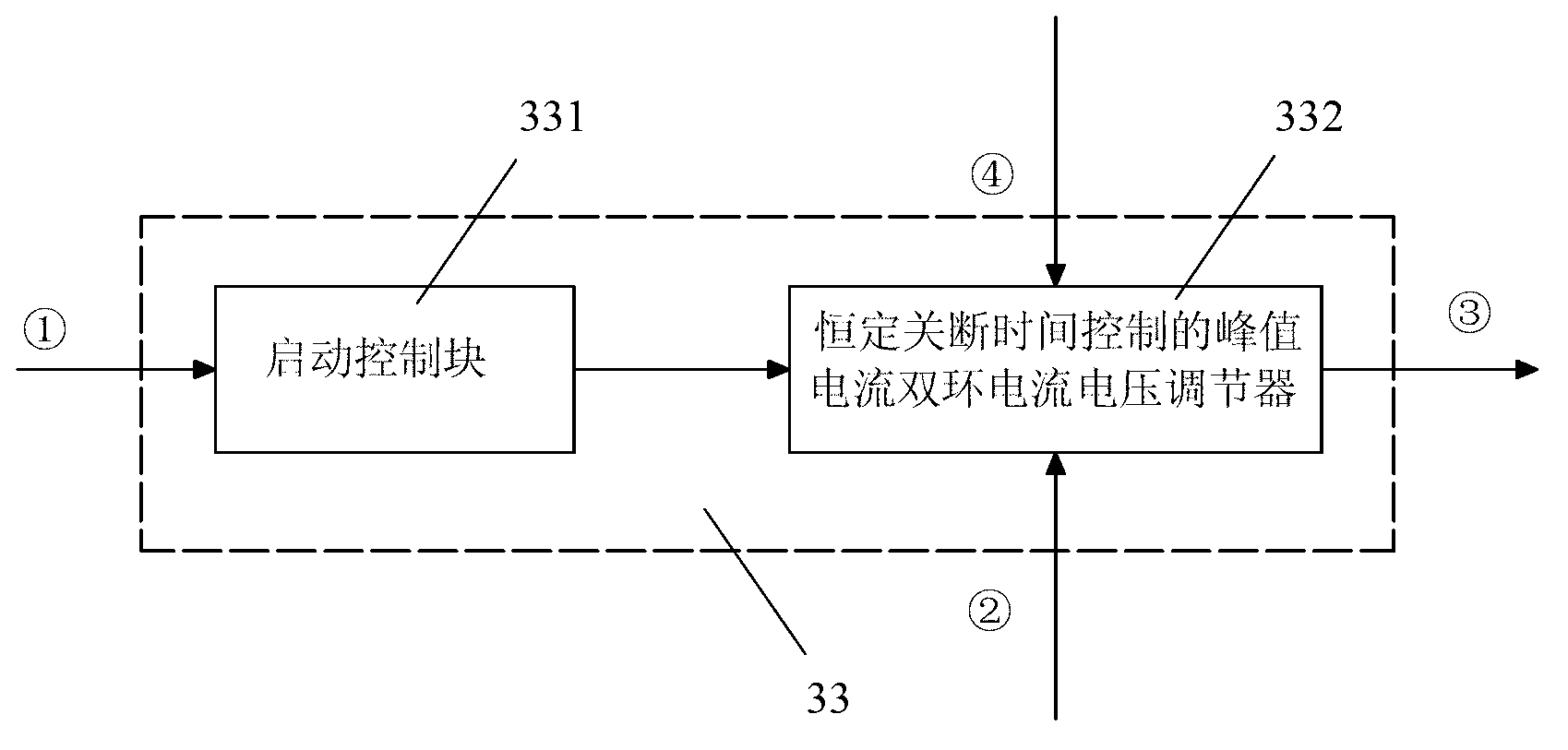

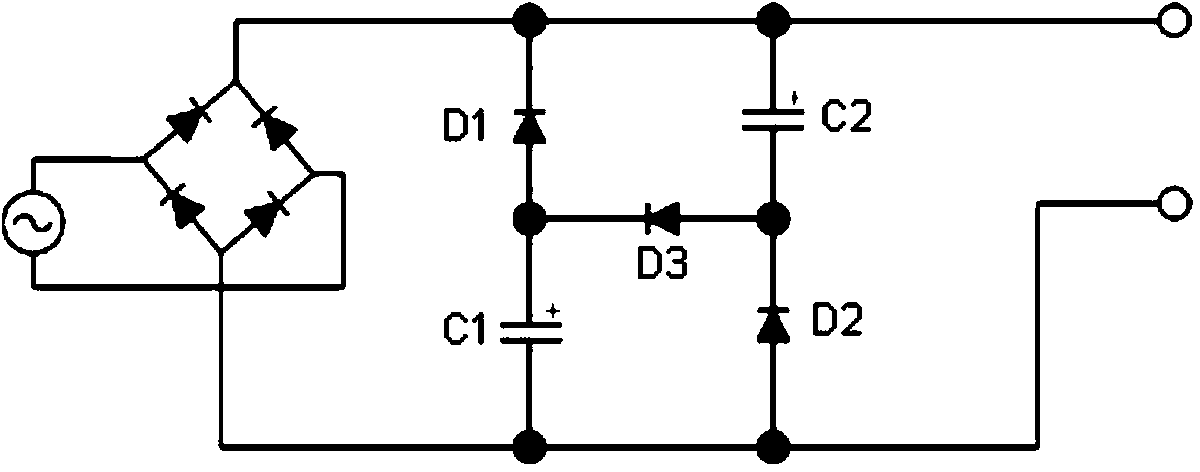

High-power-factor direct-current current output light-emitting diode (LED) driving circuit with low-energy-storage capacitor

ActiveCN102858071AGood Input Voltage RegulationHigh input power factorElectric light circuit arrangementCapacitancePower factor

The invention discloses a high-power-factor direct-current current output light-emitting diode (LED) driving circuit with a low-energy-storage capacitor. The LED driving circuit is composed of a diode rectifying bridge (1), an active non-linear capacitor network (3) and a follow-up switch power converter (2). The output end of the diode rectifying bridge (1) supplies power to the active non-linear capacitor network (3). Output voltage of the active non-linear capacitor network (3) is formed by overlapping direct current voltage with alternating current voltage with twice of electric supply frequency. The output voltage of the active non-linear capacitor network (3) supplies power to the follow-up switch power converter (2). The active non-linear capacitor network (3) is composed of a lower-energy-storage capacitor and an active switch network. By means of the LED driving circuit, the low-capacitance capacitor (such as a thin film capacitor and a ceramic medium capacitor) can be utilized to finish the energy storage function.

Owner:邳州市景鹏创业投资有限公司

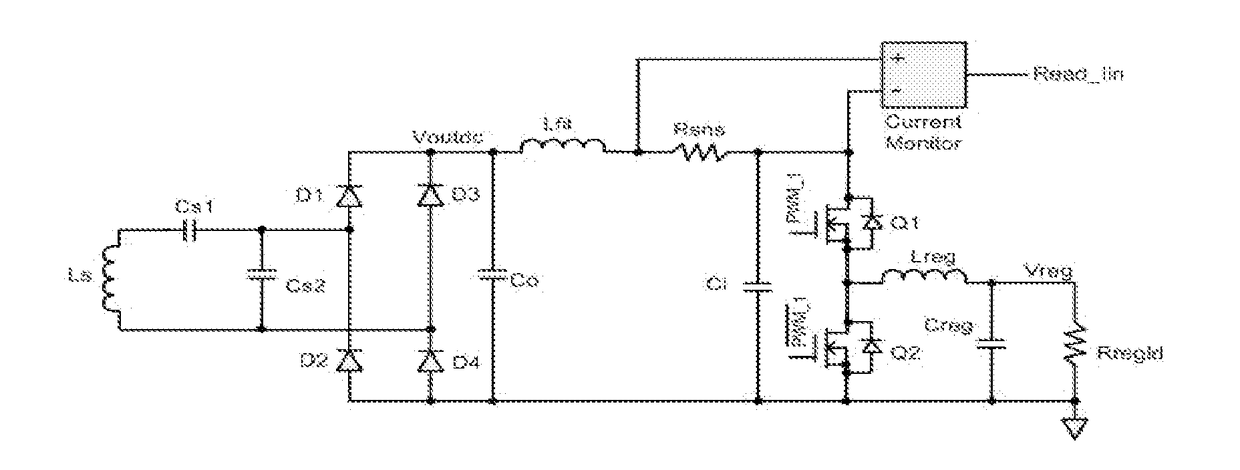

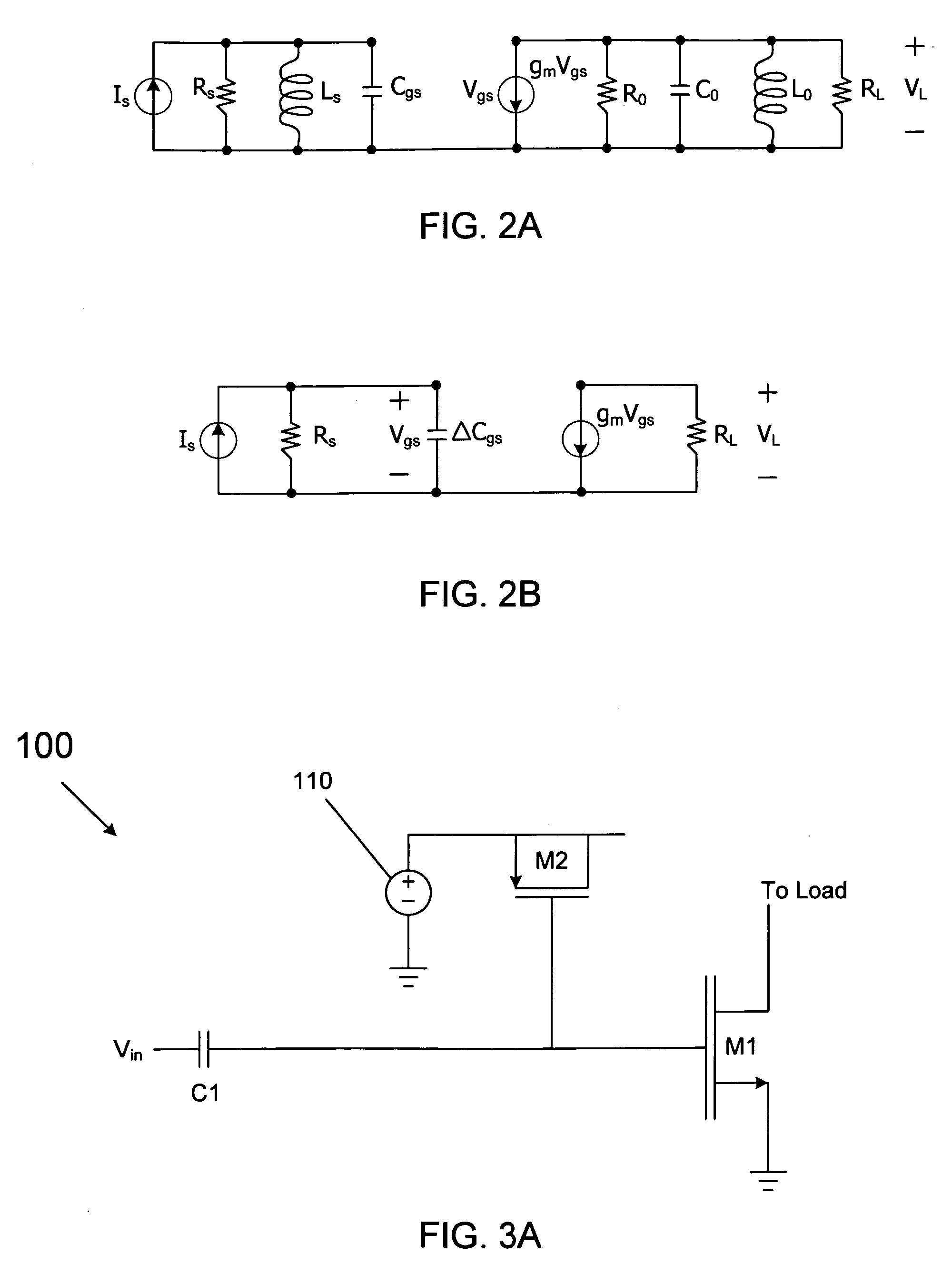

Radio frequency power amplifier with linearizing predistorter

ActiveCN102577136AAmplifier modifications to reduce non-linear distortionHigh frequency amplifiersMOSFETCapacitance

A power amplifier circuit includes an amplifier MOSFET and a predistorter MOSFET. The predistorter MOSFET source and drain are connected together, and the predistorter MOSFET is connected between the gate of the amplifier MOSFET and a second bias voltage signal. This biasing of the predistorter MOSFET causes it to provide a nonlinear capacitance at the gate of the amplifier MOSFET. The combined non-linear capacitances of the amplifier MOSFET and predistorter MOSFET provide predistortion that promotes cancellation of the distortion or nonlinearity contributed by the amplifier MOSFET alone.

Owner:SKYWORKS SOLUTIONS INC

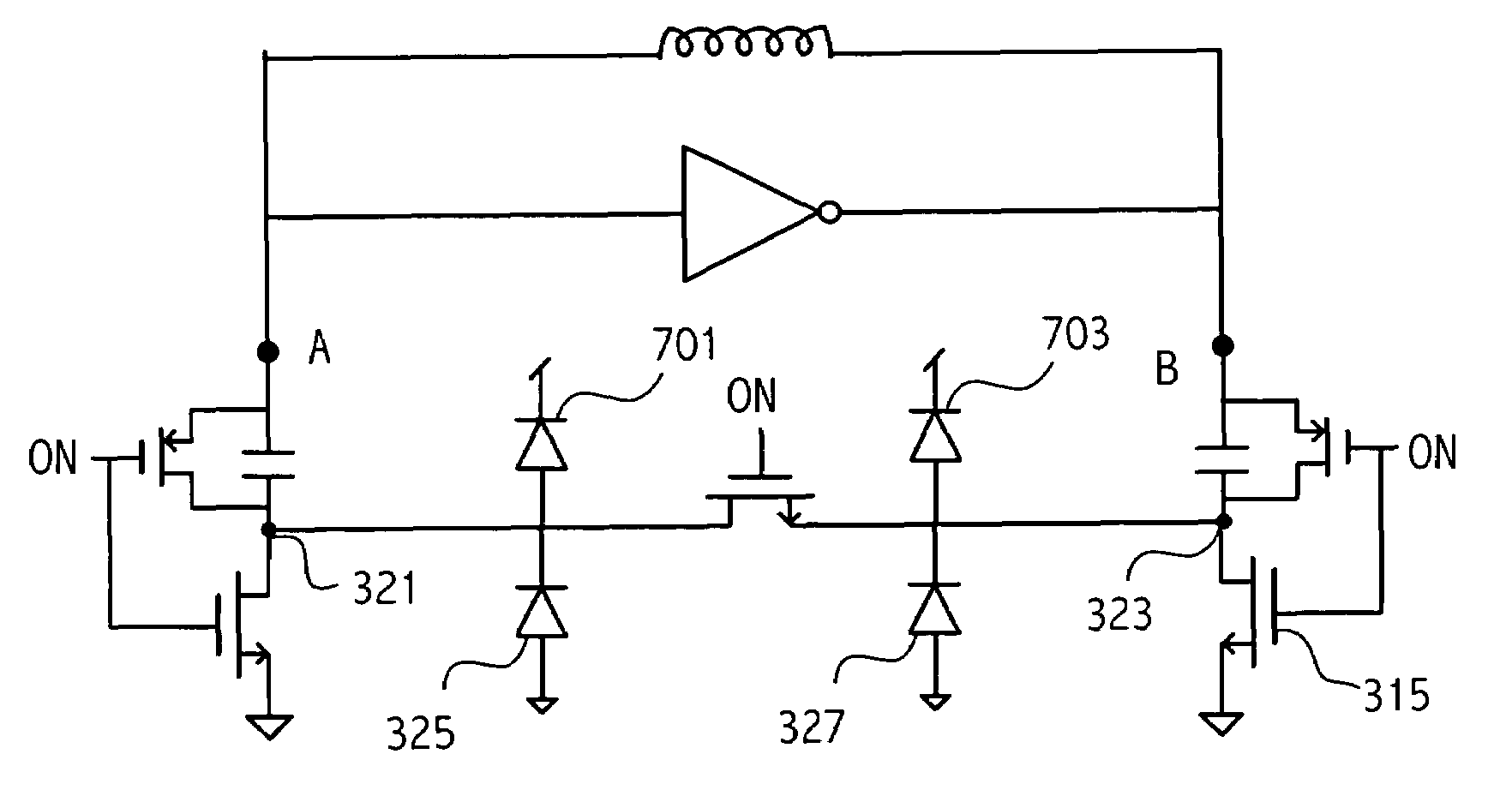

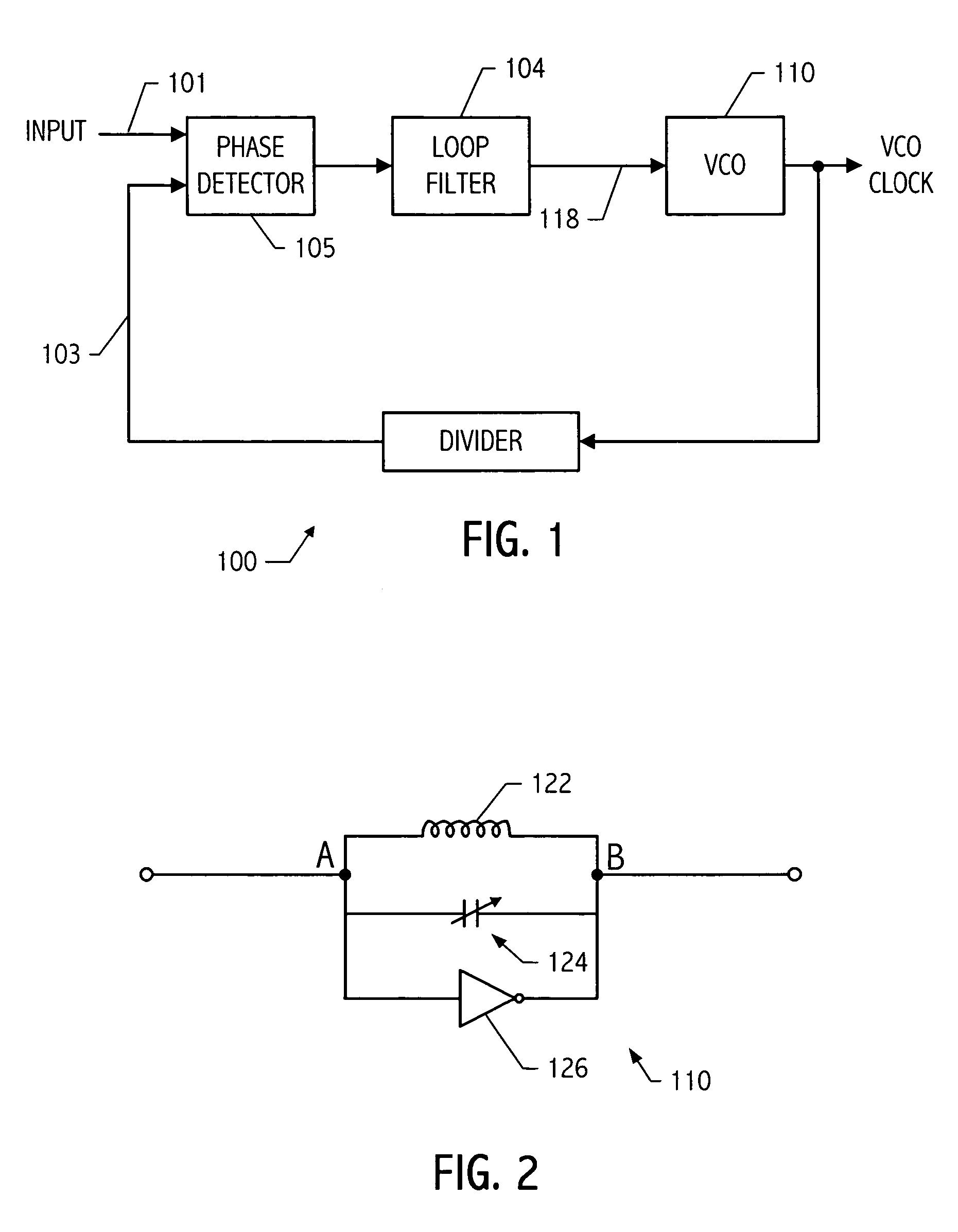

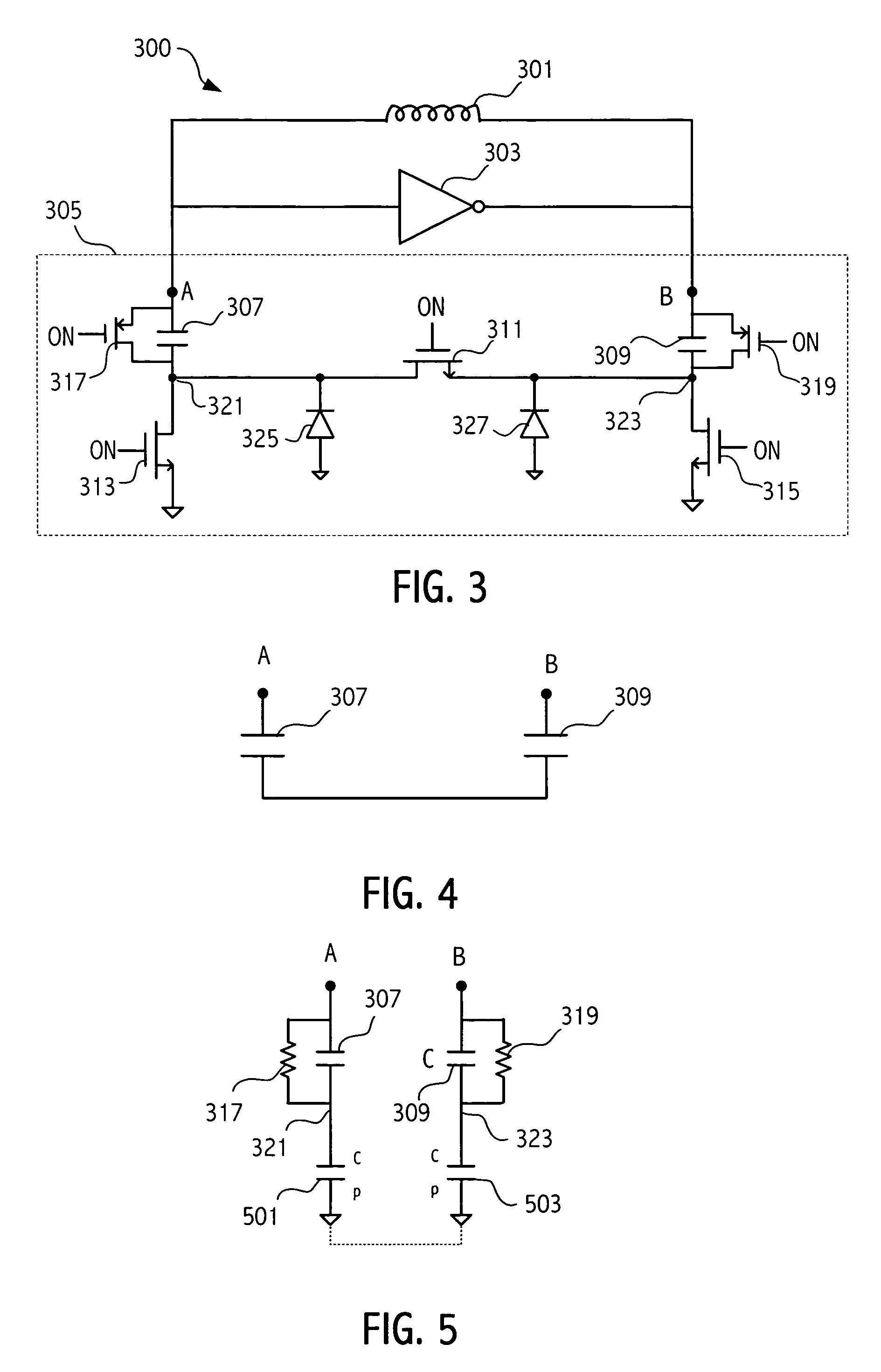

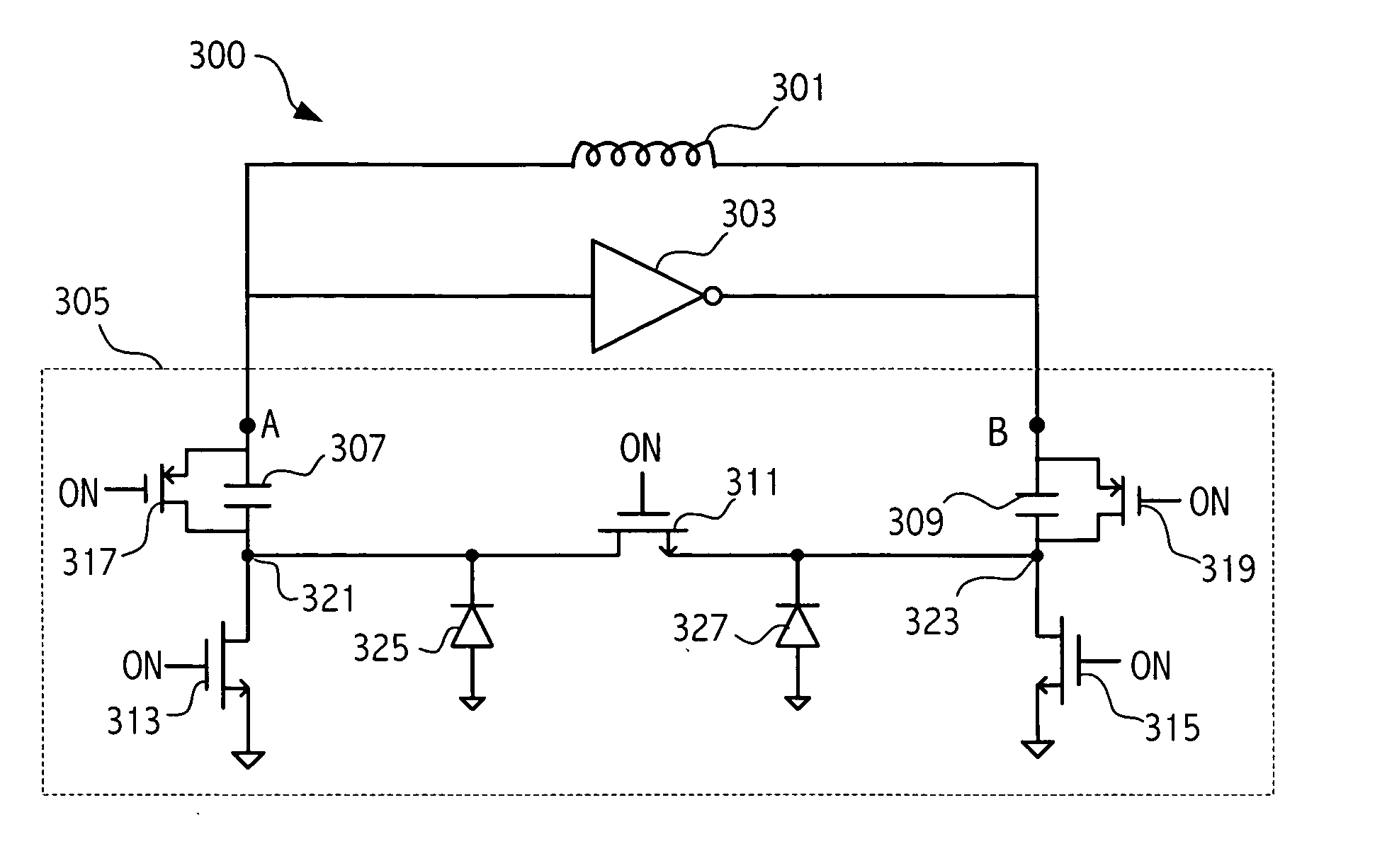

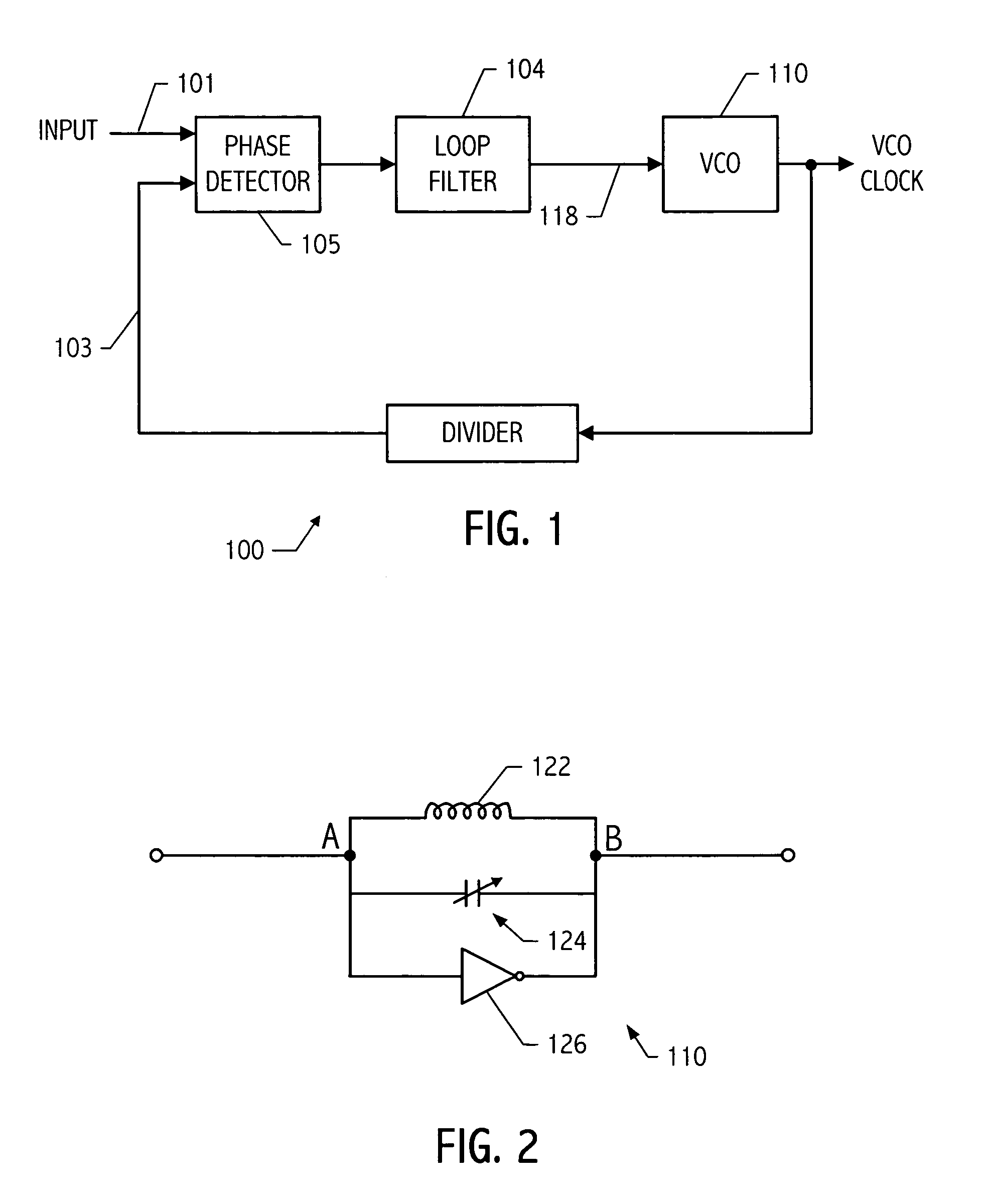

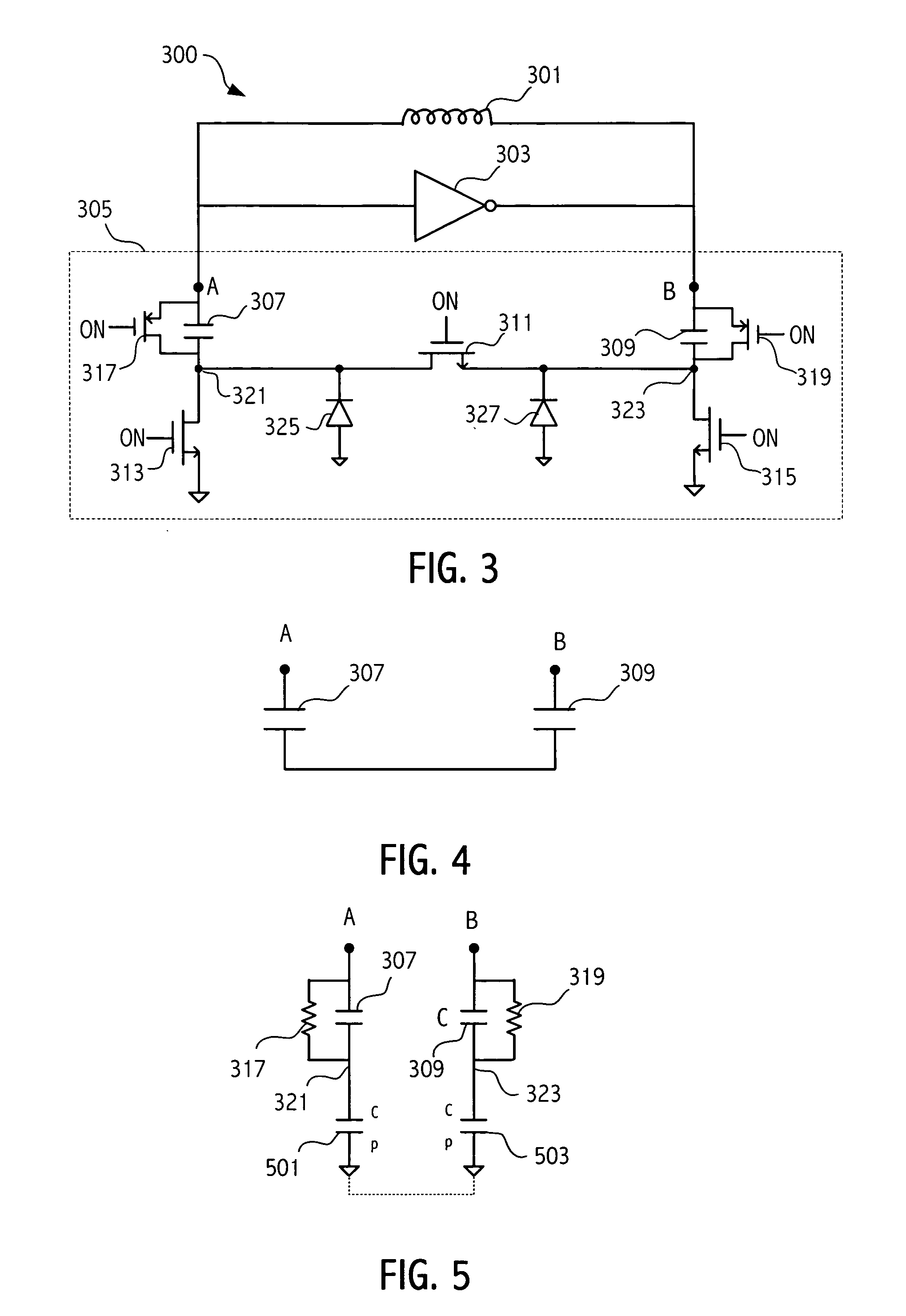

Method and apparatus for noise compensation in an oscillator circuit

ActiveUS7253693B2Angle modulation by variable impedencePulse automatic controlCapacitanceVoltage variation

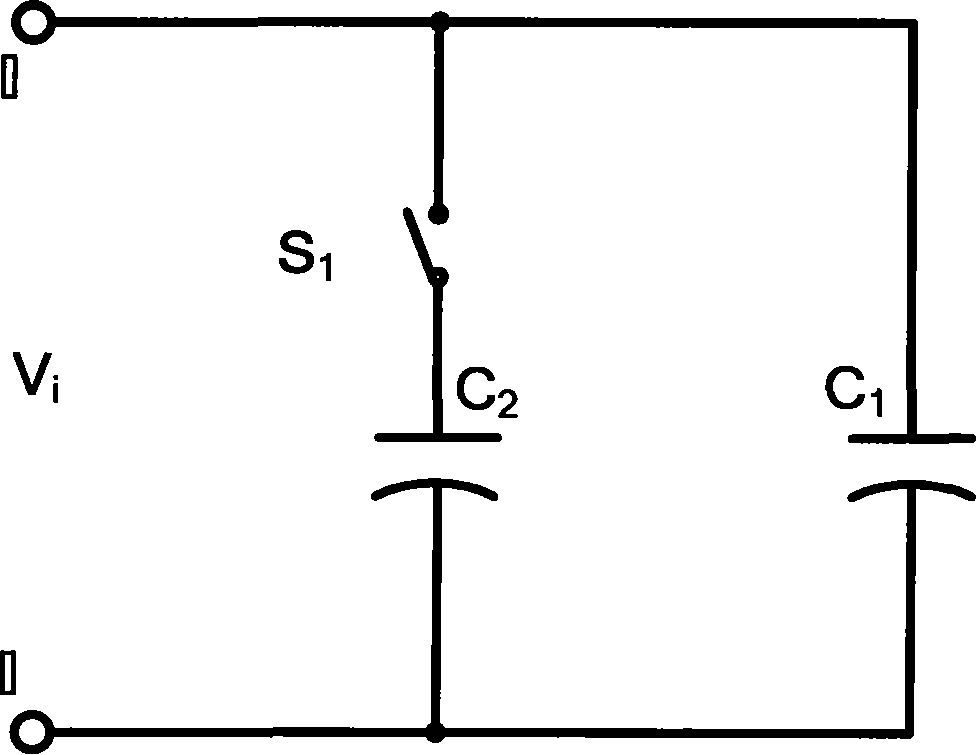

A variable capacitance circuit includes a first and a second capacitor. A switch having an associated first nonlinear capacitance, selectively couples the first and second capacitors. To compensate for the first nonlinear capacitance, a second nonlinear capacitance is coupled to the switch that has a capacitance value responsive to a change in voltage that moves in a direction of change opposite to a direction of change of the first nonlinear capacitance.

Owner:SKYWORKS SOLUTIONS INC

Method and apparatus for noise compensation in an oscillator circuit

A variable capacitance circuit includes a first and a second capacitor. A switch having an associated first nonlinear capacitance, selectively couples the first and second capacitors. To compensate for the first nonlinear capacitance, a second nonlinear capacitance is coupled to the switch that has a capacitance value responsive to a change in voltage that moves in a direction of change opposite to a direction of change of the first nonlinear capacitance.

Owner:SKYWORKS SOLUTIONS INC

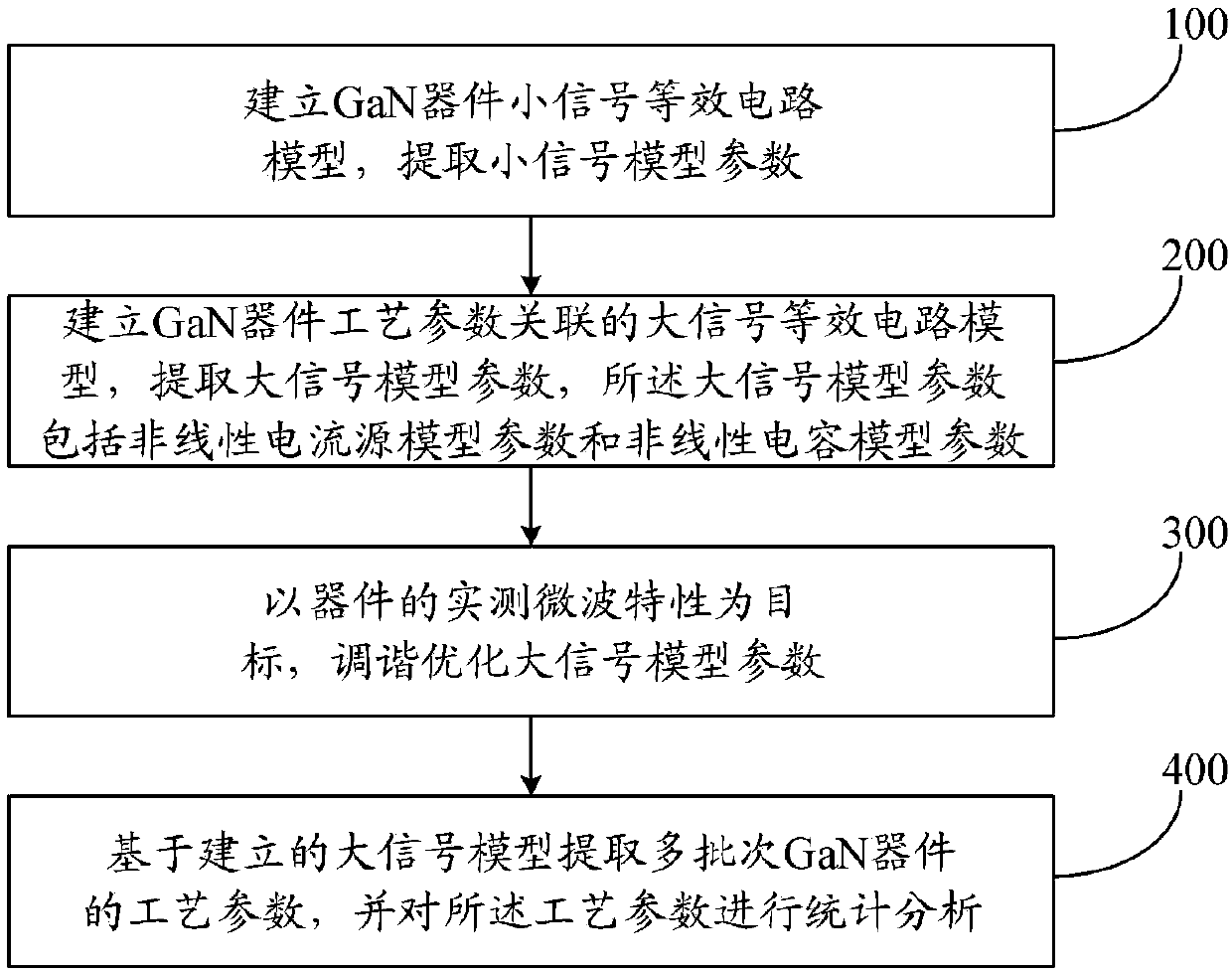

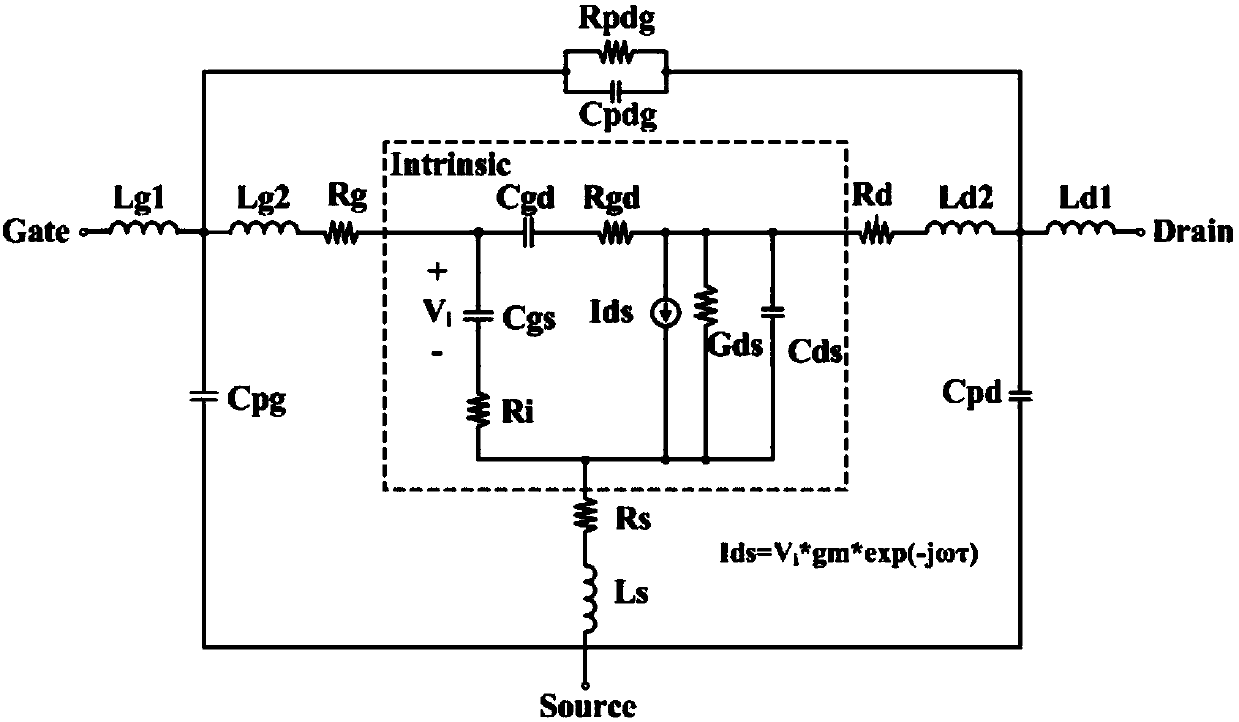

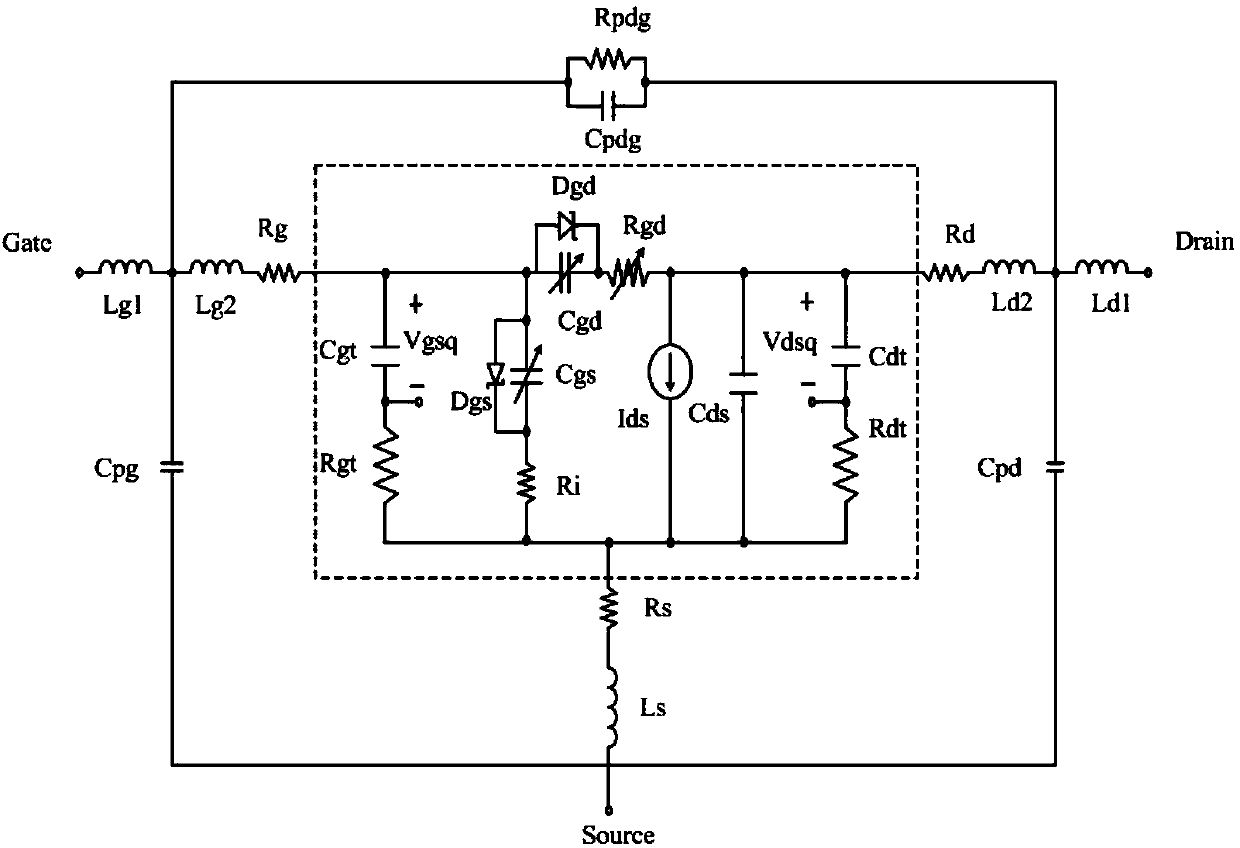

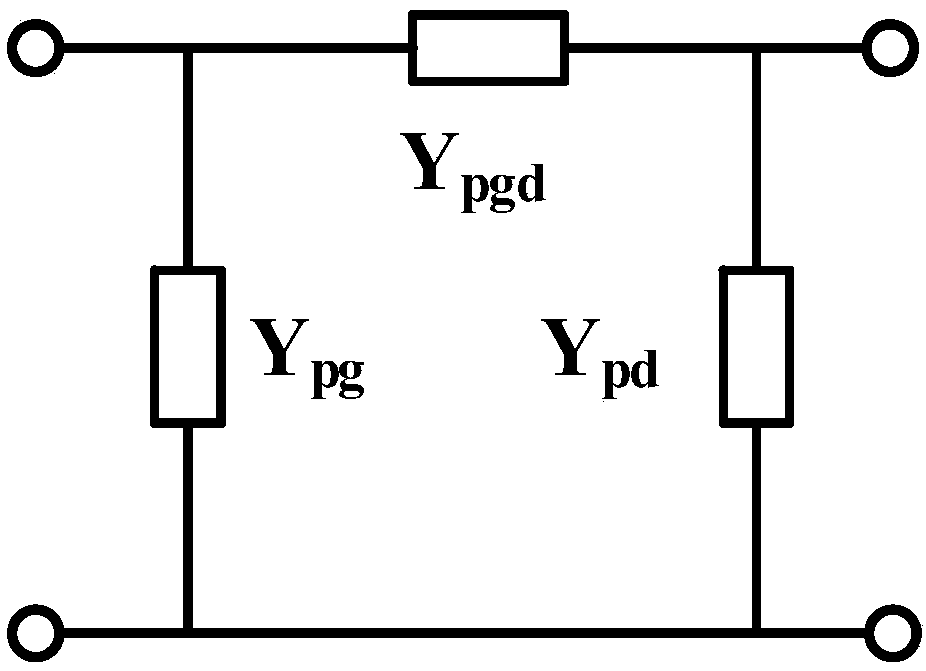

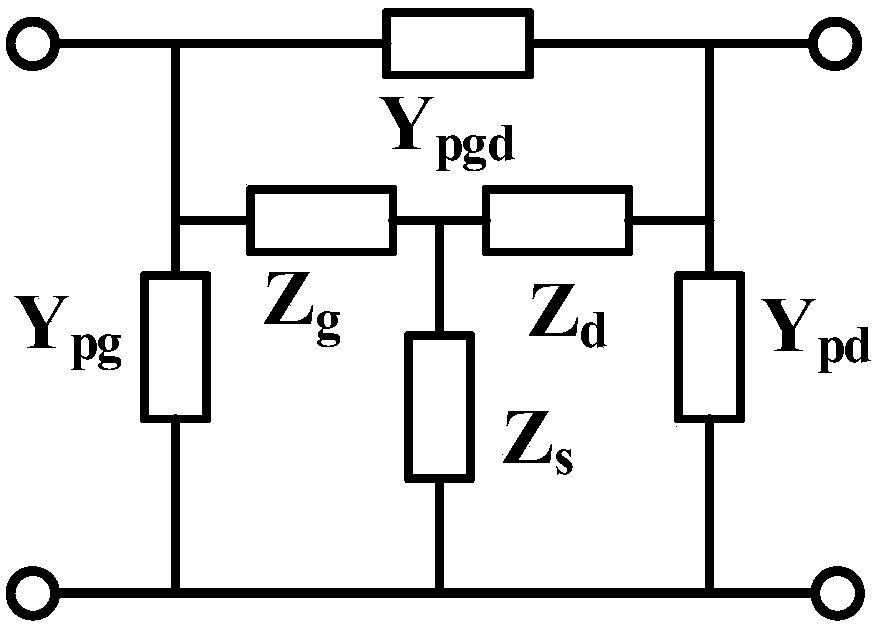

GaN technological parameter statistical analysis method based on large signal equivalent circuit model

ActiveCN107636656AHigh precisionProbabilistic CADSpecial data processing applicationsCapacitanceMicrowave

The invention provides a GaN technological parameter statistical analysis method based on large signal equivalent circuit model. The analysis method comprises the following steps: a step 1: establishing a GaN device small signal equivalent circuit model, and extracting small signal model parameters; a step 2: establishing a GaN device large signal equivalent circuit model, and extracting large signal model parameters, that is non-linear current source model parameter and non-linear capacitance model parameter; a step 3: actually measured microwave characteristics of the device are used as objects in order to tune and optimize large signal model parameters; a step 4: extracting multiple-batch GaN device technological parameters based on established large signal model, and carrying out statistical analysis of the technological parameters. The GaN device model technological parameter statistical analysis method firstly establishes the GaN device small signal equivalent circuit model, andthen establishes GaN device large signal equivalent circuit model related to technological parameters, finally technological parameter statistical distribution is obtained by multiple-bath device modeling, and the method is good for device yield analysis and technological parameter optimization.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

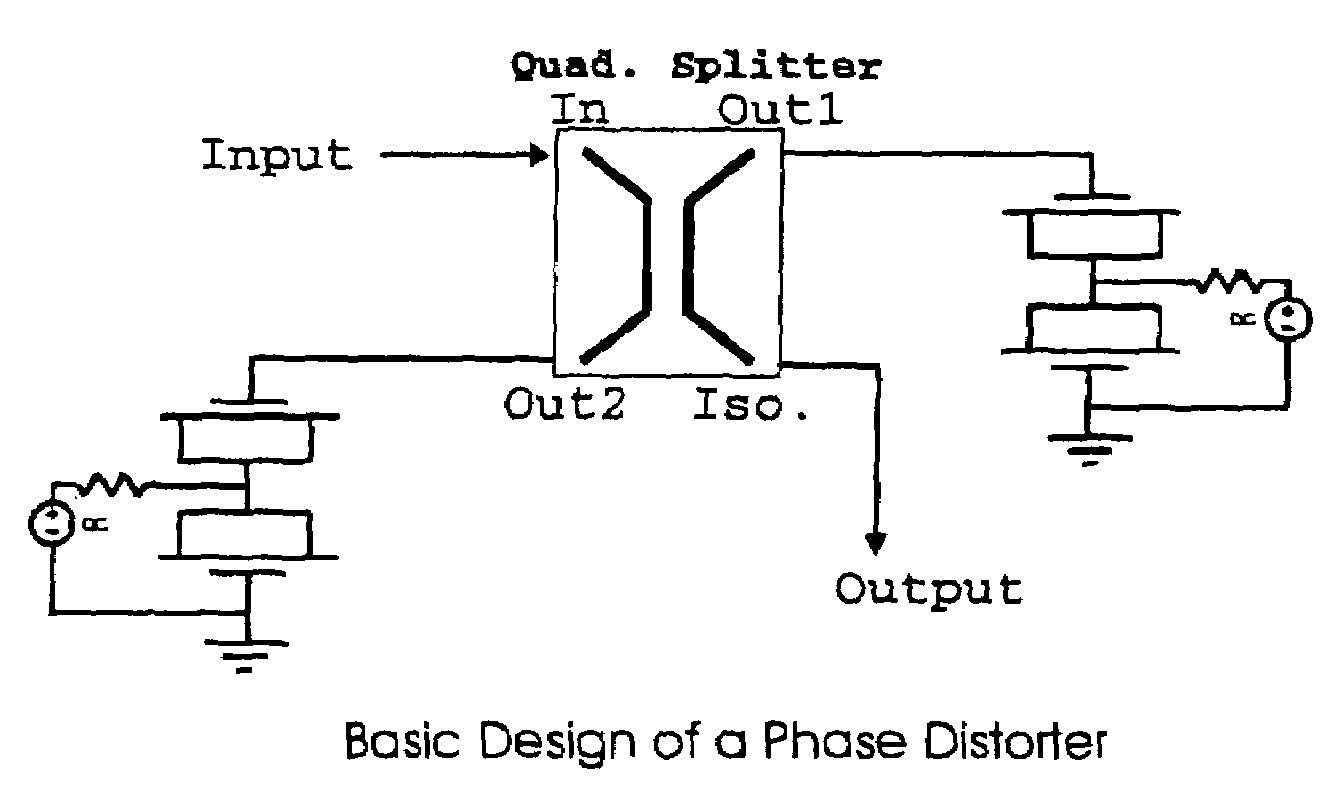

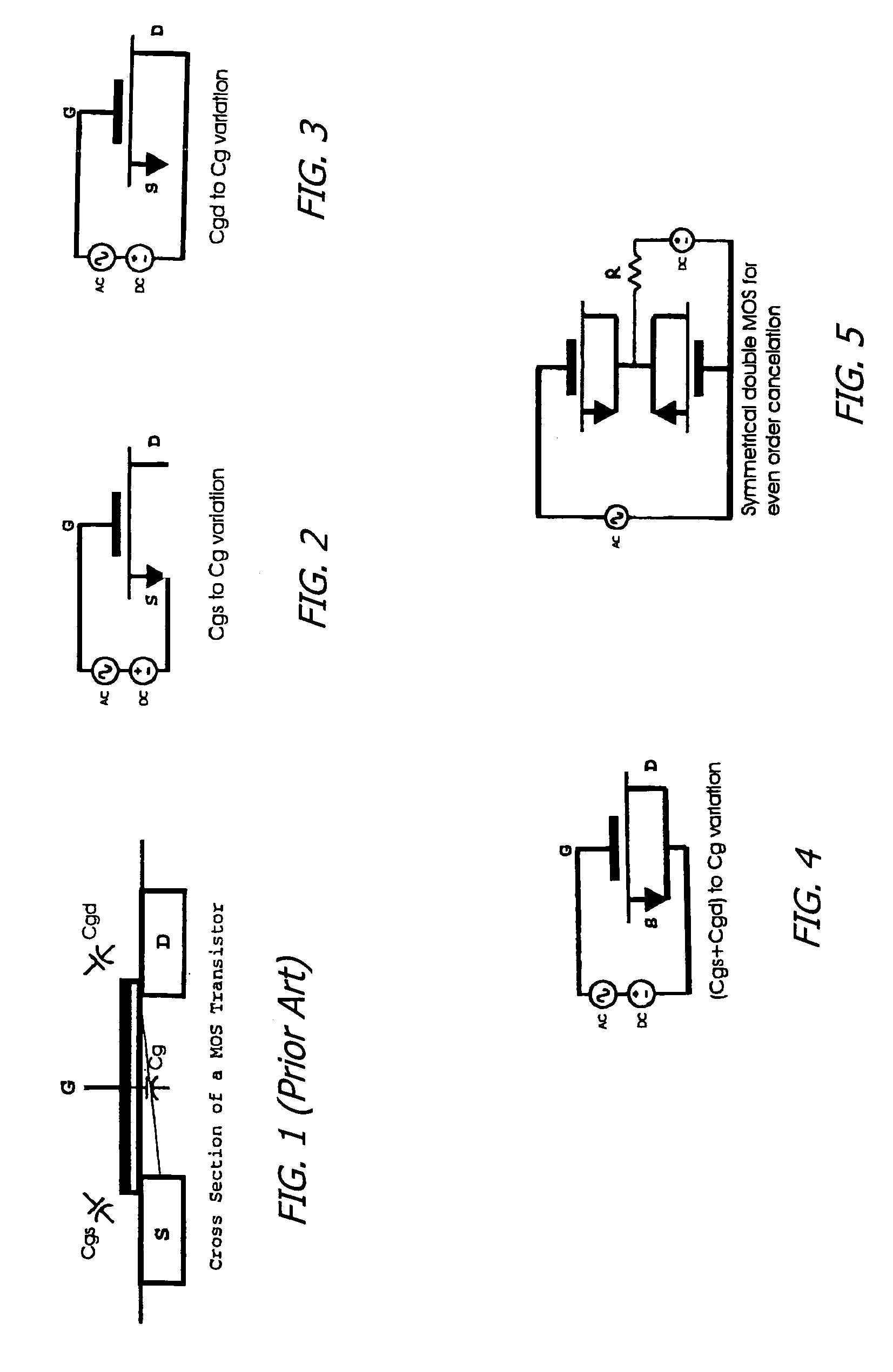

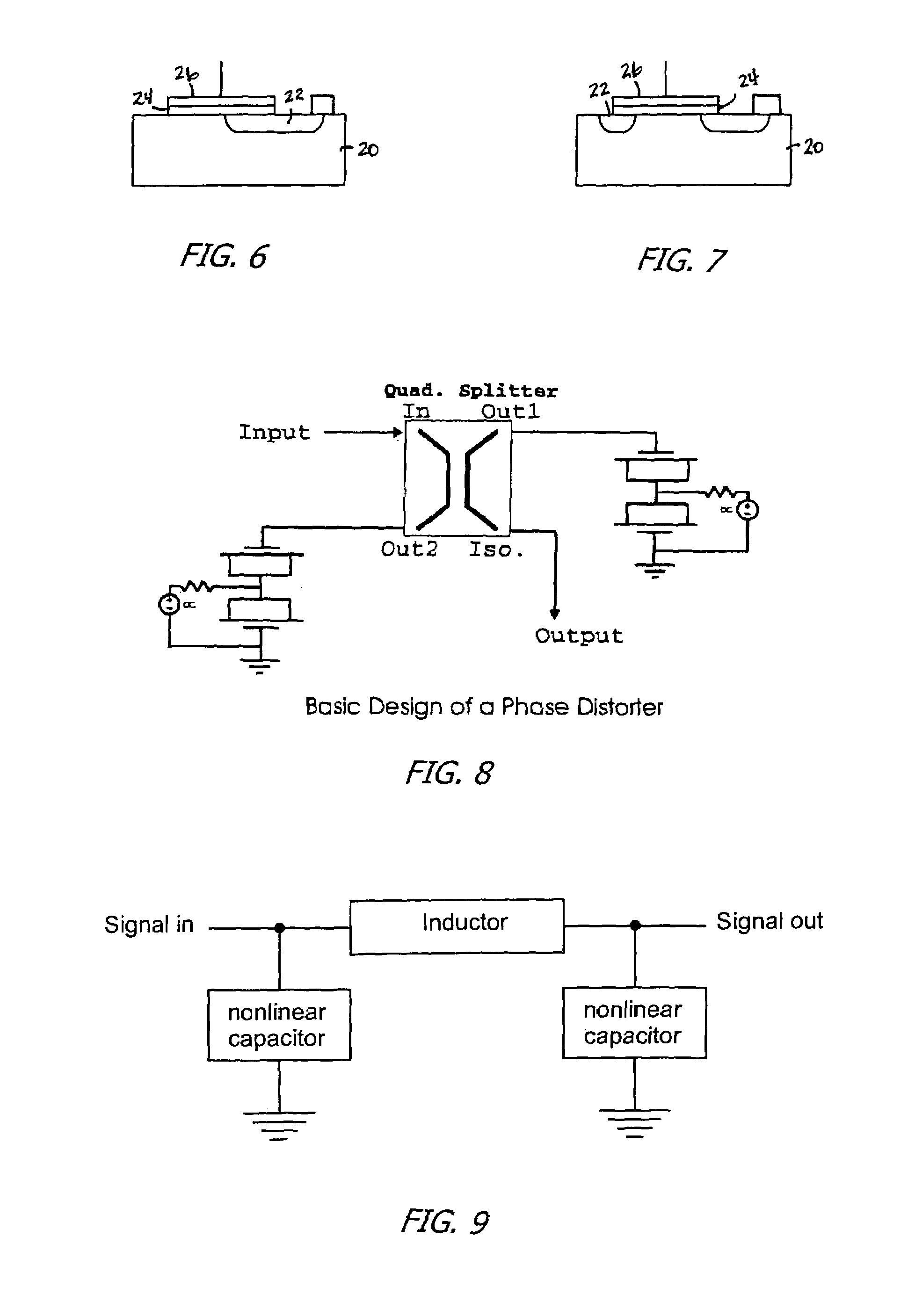

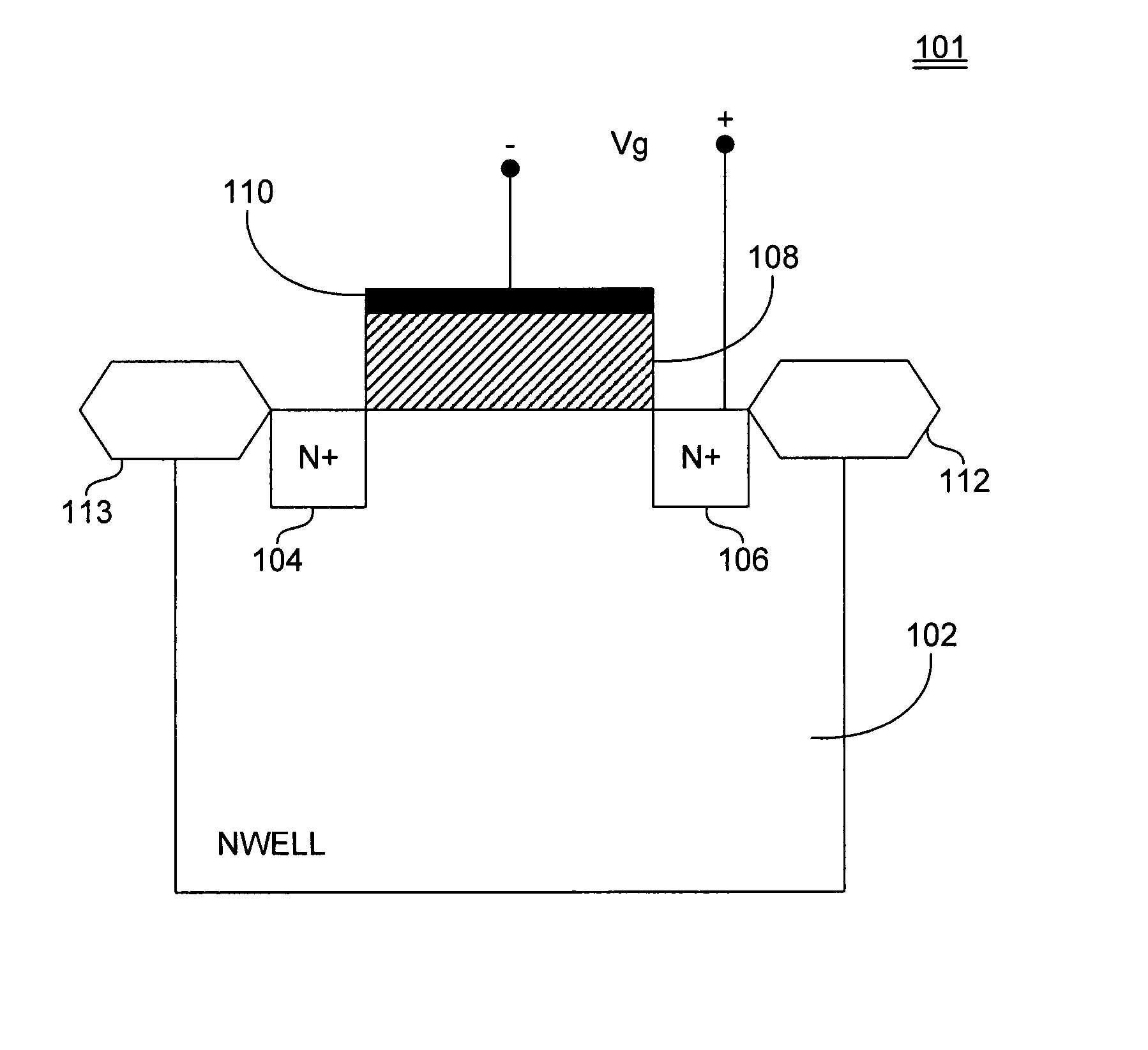

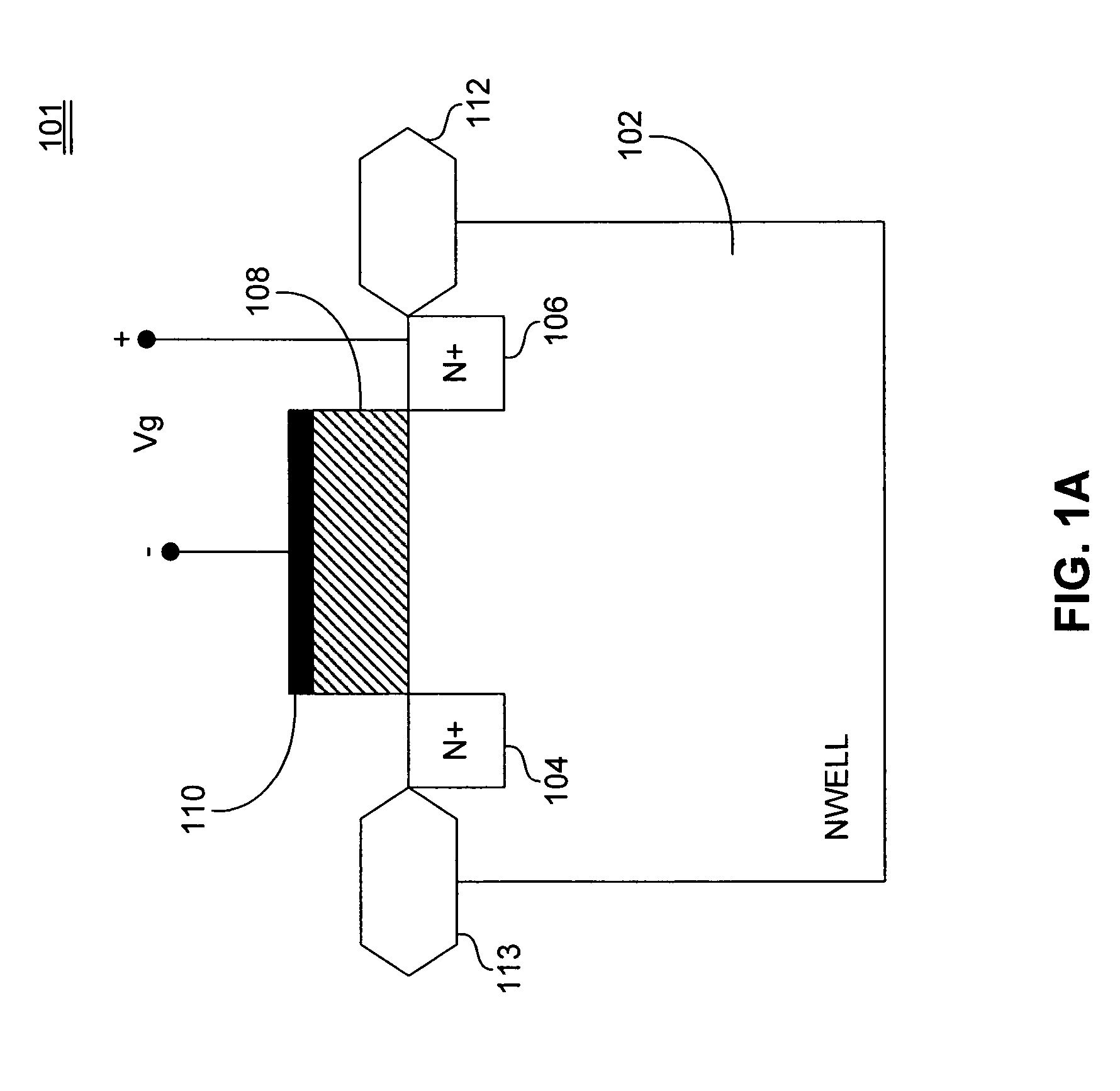

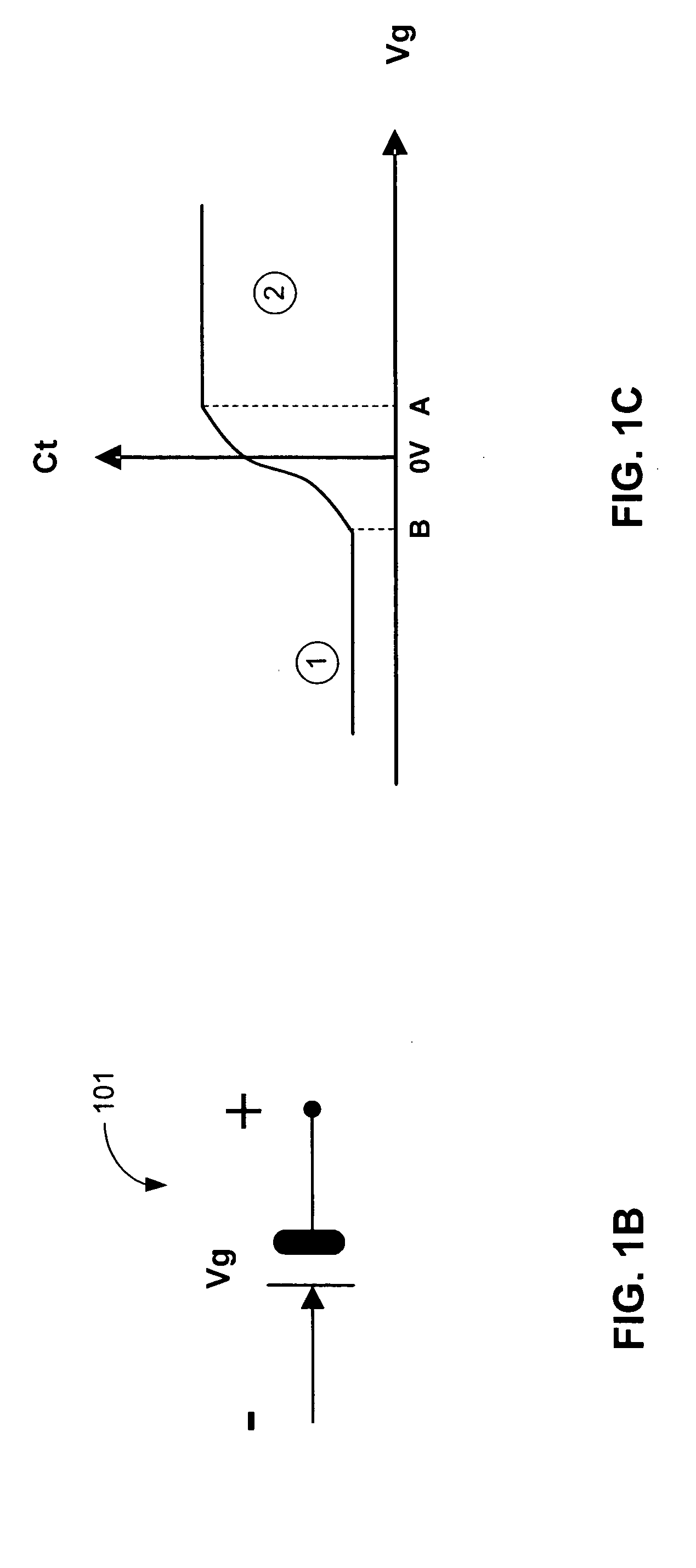

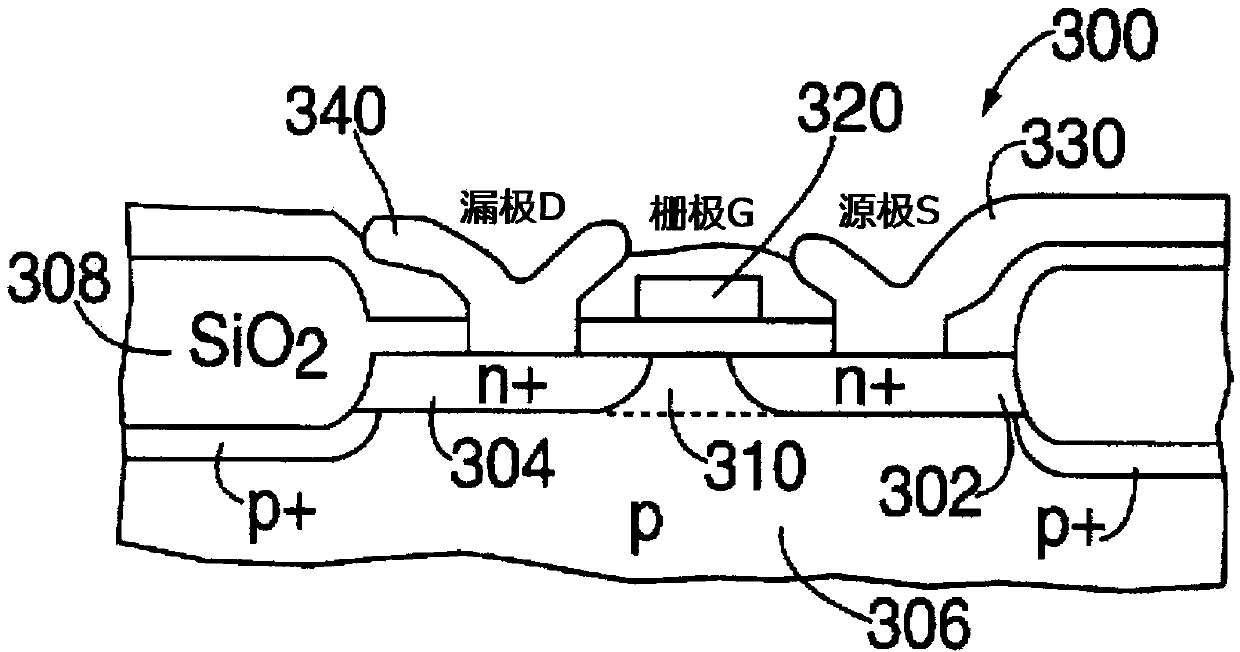

Phase distortion using MOS nonlinear capacitance

ActiveUS7110718B1Resonant long antennasNegative-feedback-circuit arrangementsCapacitancePhase distortion

RF phase distortion circuits and methods for controllably phase distorting an RF signal based on amplitude of the RF signal. An MOS device is provided having a body of a first conductivity type and at least one region of a second conductivity type in the body, with a conductive layer over at least part of the body and the region of the second conductivity type and insulated therefrom. The MOS device may be coupled into a phase distortion circuit individually or in back-to-back pairs and biased to invert the body under the conductive layer for small signal amplitudes and not for large signal amplitudes, or to not invert the body under the conductive layer for small signal amplitudes and to invert the body under the conductive layer for large signal amplitudes. Various embodiments are disclosed.

Owner:MAXIM INTEGRATED PROD INC

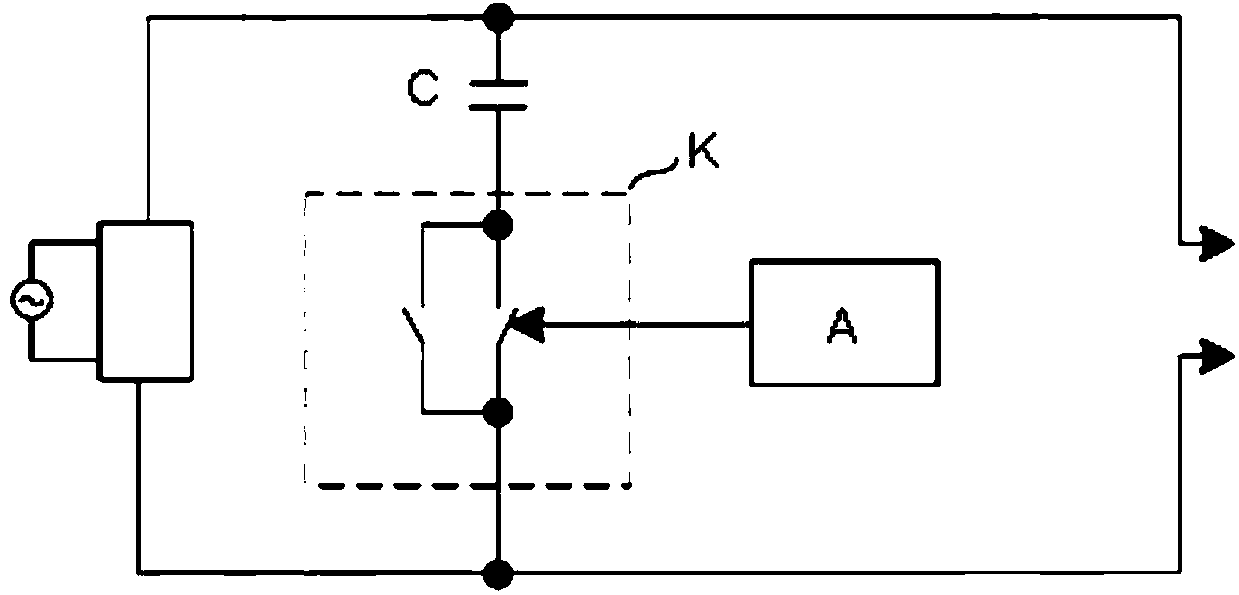

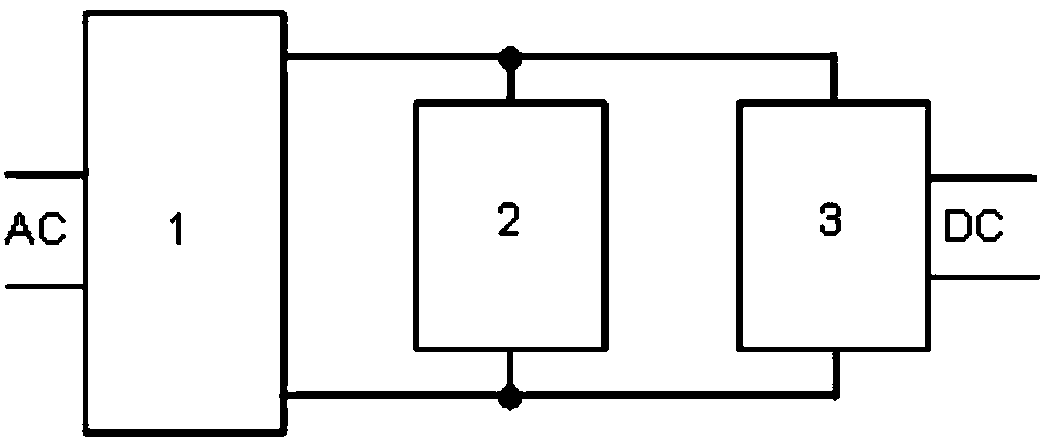

High-power factor active valley-fill type alternating current and direct current converter

ActiveCN103762868AIncrease powerImprove efficiencyEfficient power electronics conversionAc-dc conversionCapacitancePower factor

The invention belongs to the technical field of electronics, and relates to alternating current and direct current conversion and power control, in particular to a high-power factor active valley-fill type alternating current and direct current converter. The high-power factor active valley-fill type alternating current and direct current converter is composed of a diode rectifier bridge (1), an active nonlinear capacitance network (2) and a subsequent switch power converter (3), wherein the output of the diode rectifier bridge (1) supplies the active nonlinear capacitance network (2) and the subsequent switch power converter (3) with power; the output of the active nonlinear capacitance network (2) is controlled to supply the subsequent switch power converter (3) with power.

Owner:江苏鑫昊空调设备有限公司

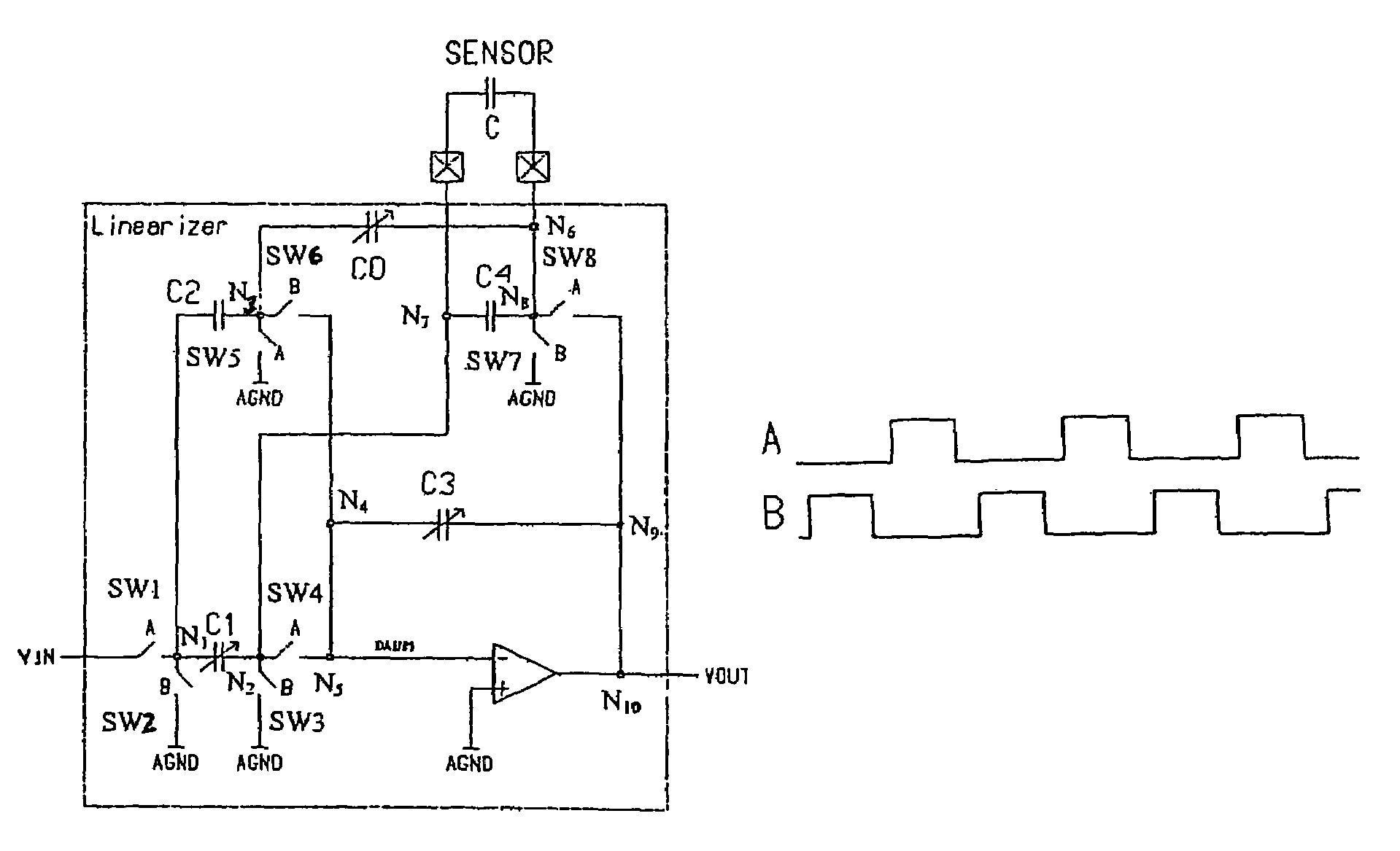

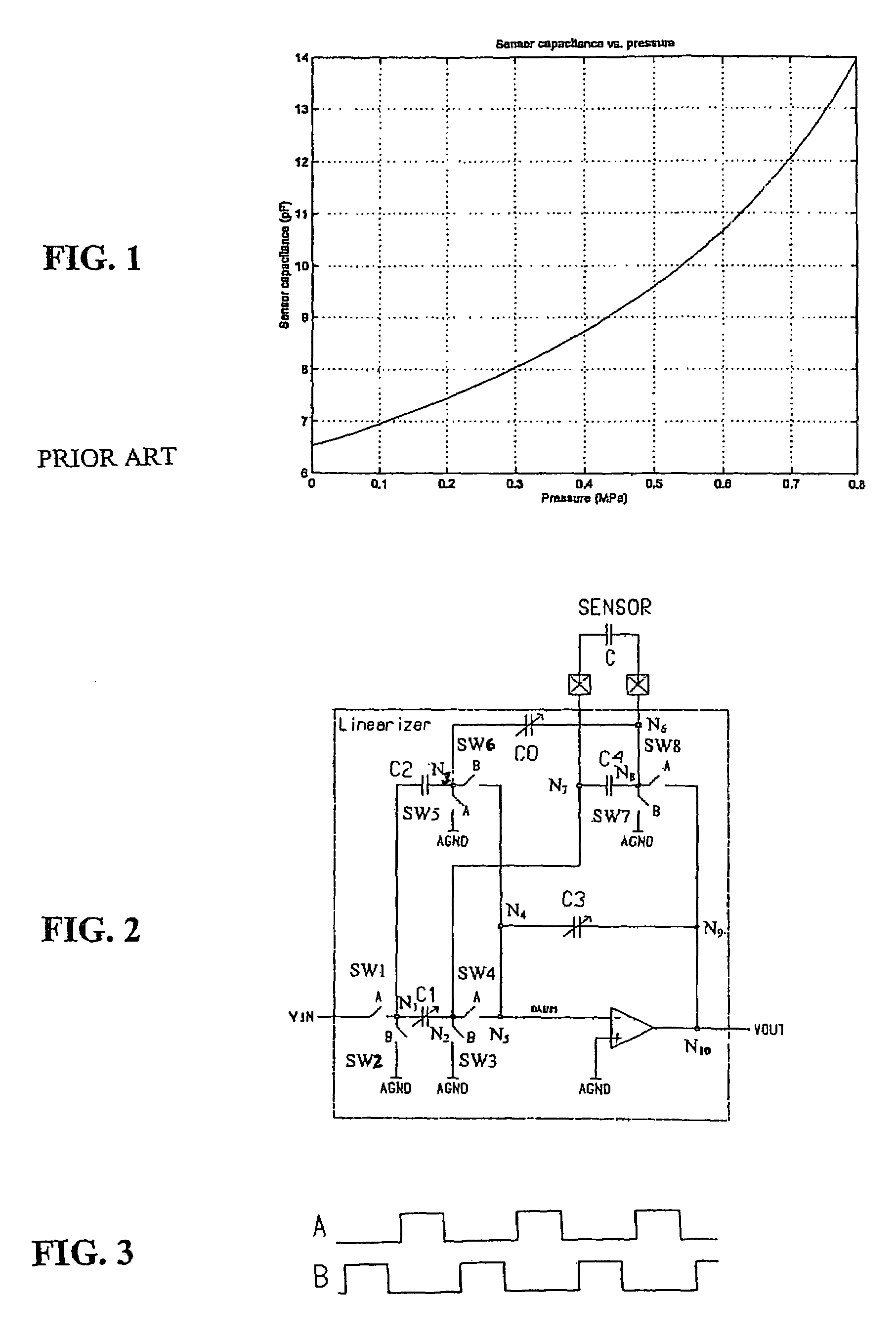

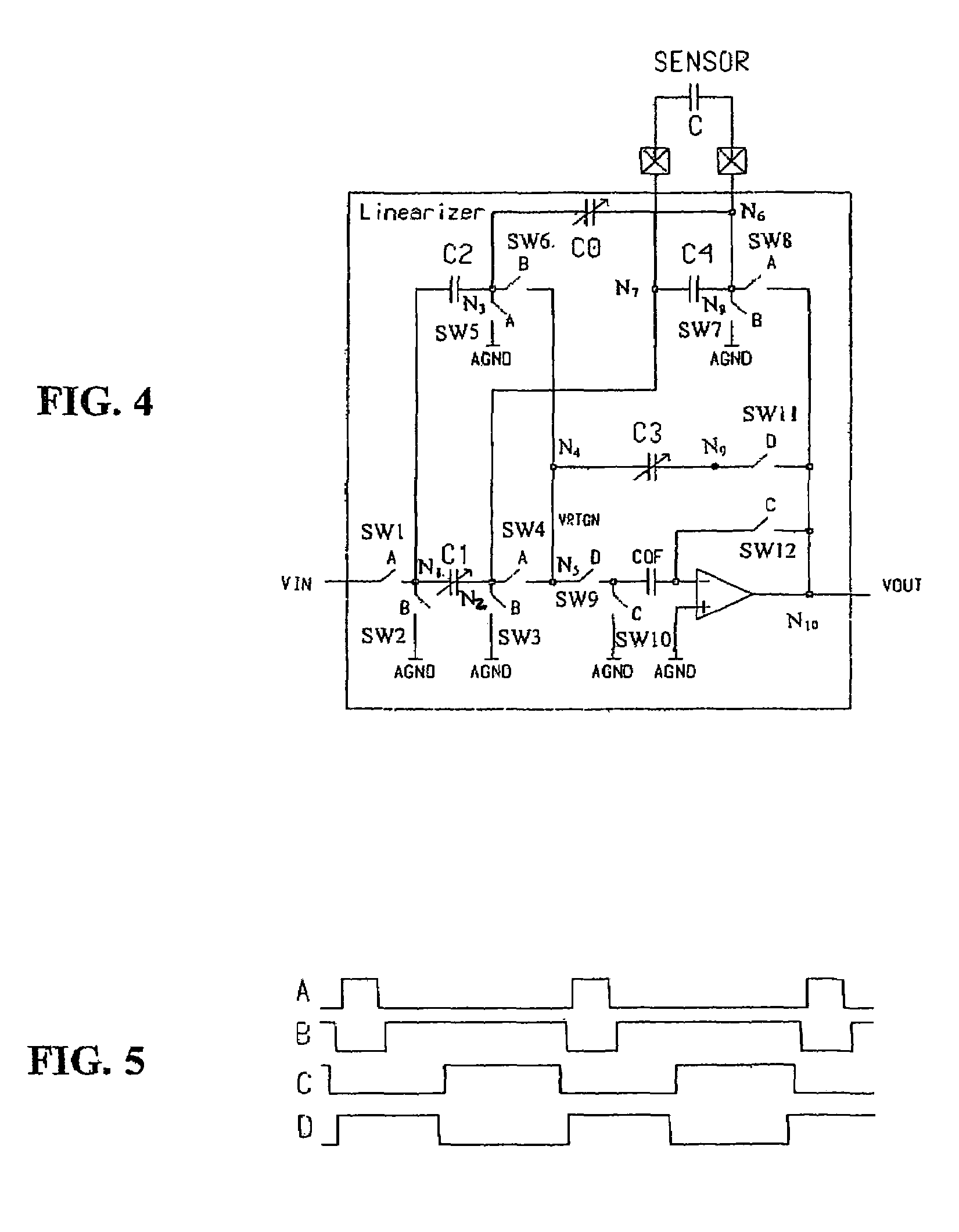

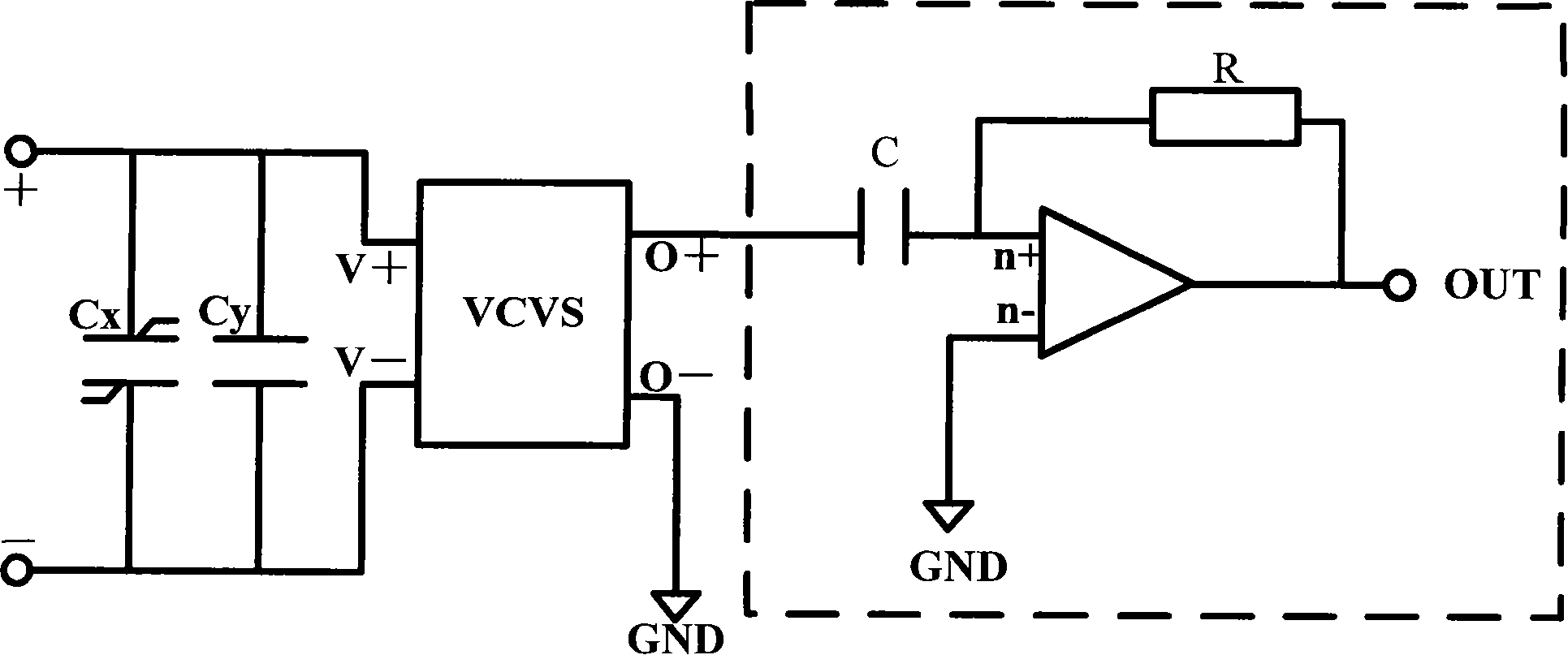

Linearizer circuit

InactiveUS7444252B2Correct nonlinearitySimple circuitResistance/reactance/impedenceTesting/calibration of speed/acceleration/shock measurement devicesCapacitive pressure sensorOperational amplifier applications

A linearizer circuit which corrects inherent nonlinearity of a capacitive pressure sensor is provided. The linearizer is based on an operational amplifier configuration including a feedback network of switched capacitor type that is switched between a first switching phase and a second switching phase .In this switched capacitor configuration, DC gain of the operational amplifier configuration in the second switching phase can be adapted to realize a linearization function required to substantially linearize a non-linear capacitance-pressure characteristic of a capacitive pressure sensor when the capacitive pressure sensor is connected to be part of the feedback network.

Owner:MICRO ANALOG SYST

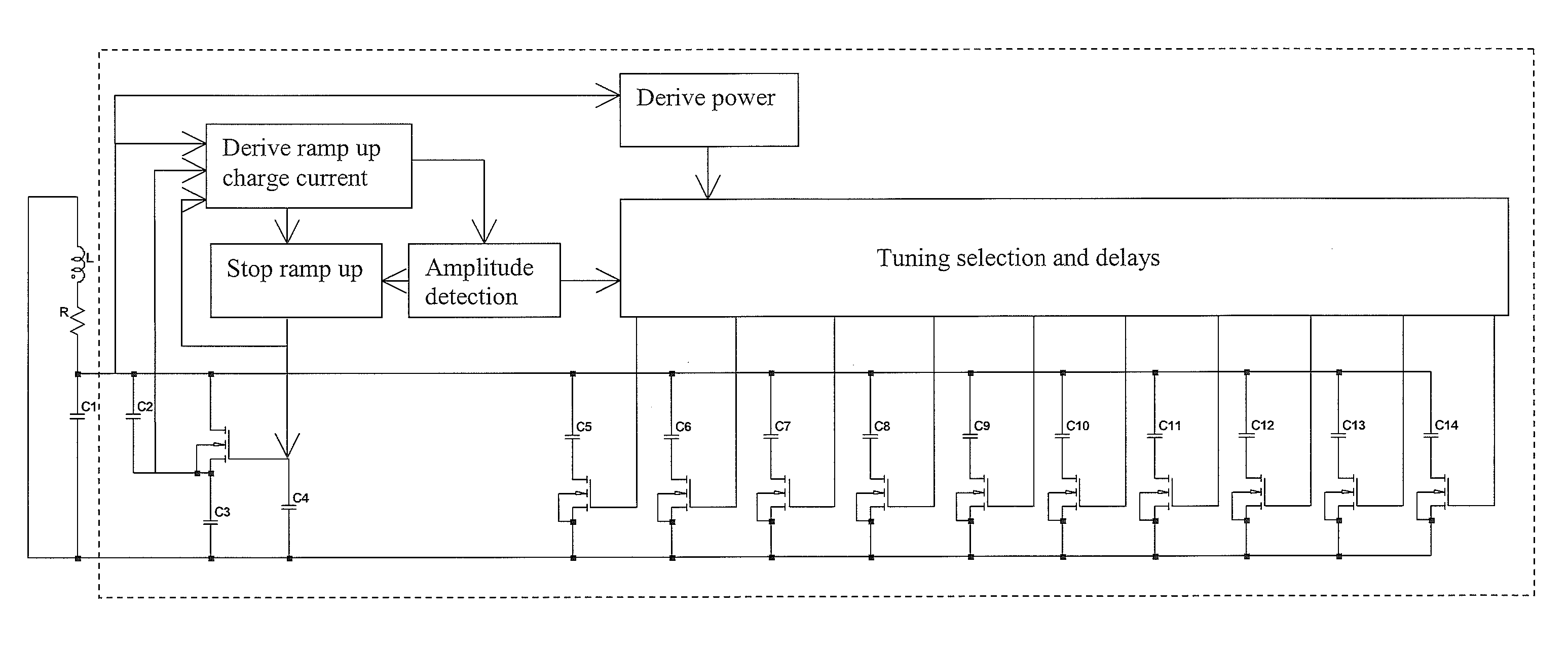

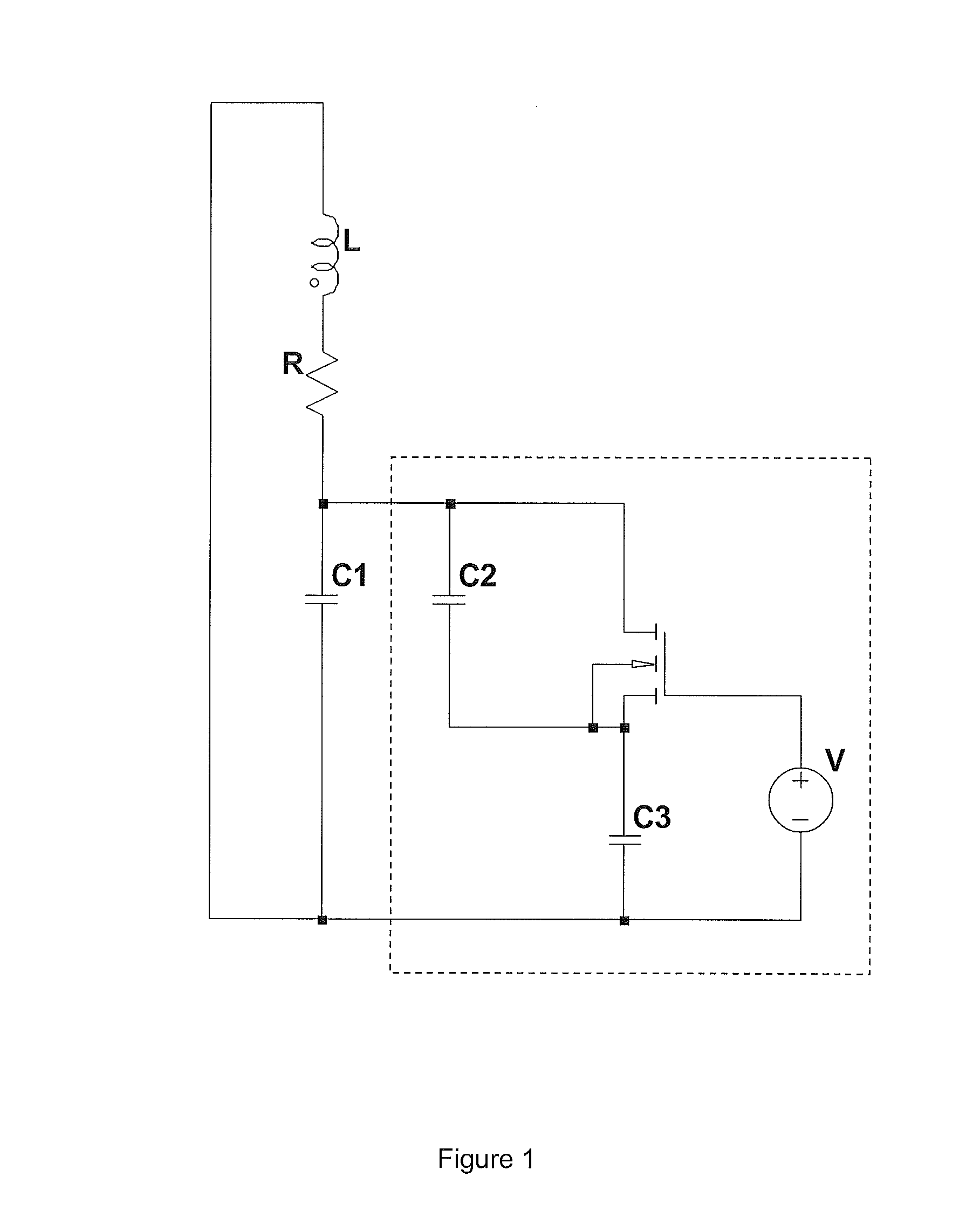

Tuned resonant circuits

ActiveUS8576021B2Reducing and eliminating needImprove toleranceAngle modulation by variable impedencePulse automatic controlCapacitanceSignal on

A circuit block which comprises a non-linear capacitor with two different values of capacitance dependent on a value of a voltage of a resonant signal on the capacitor; a plurality of second capacitors each coupled to a respective switch to enable a said second capacitor to be switched in or out of parallel connection with the nonlinear capacitor; and a tuning control, coupled to the second capacitor switches, and sensing an amplitude of the resonant signal. The tuning control circuit is configured to control the second capacitor switches to successively switch the second capacitors in / out of parallel connection with the non-linear capacitor dependent on the amplitude of the resonant signal until the non-linear capacitor has substantially a single one of two different values, such that in a resonant circuit the circuit block then behaves as a fixed value capacitor.

Owner:SUREFLAP

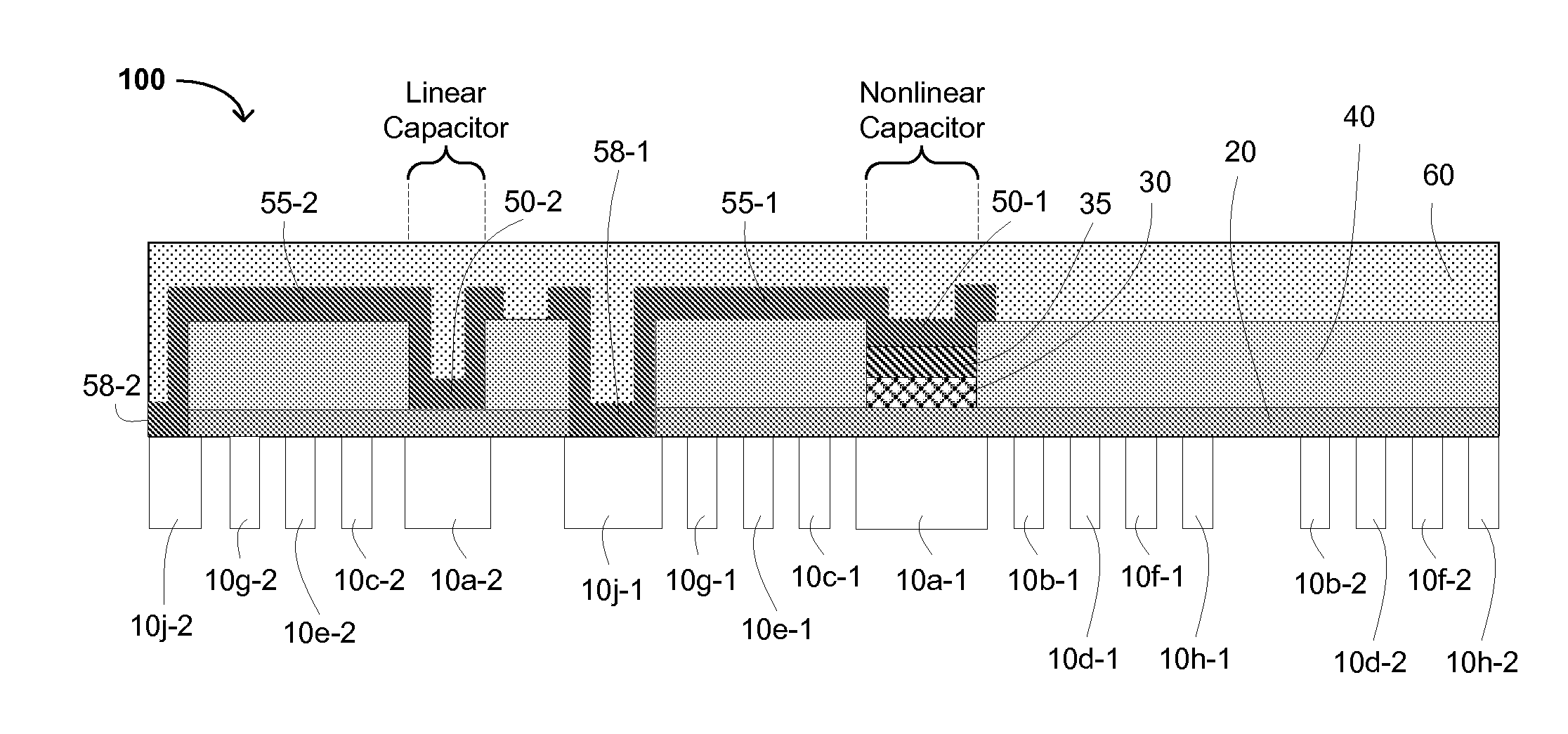

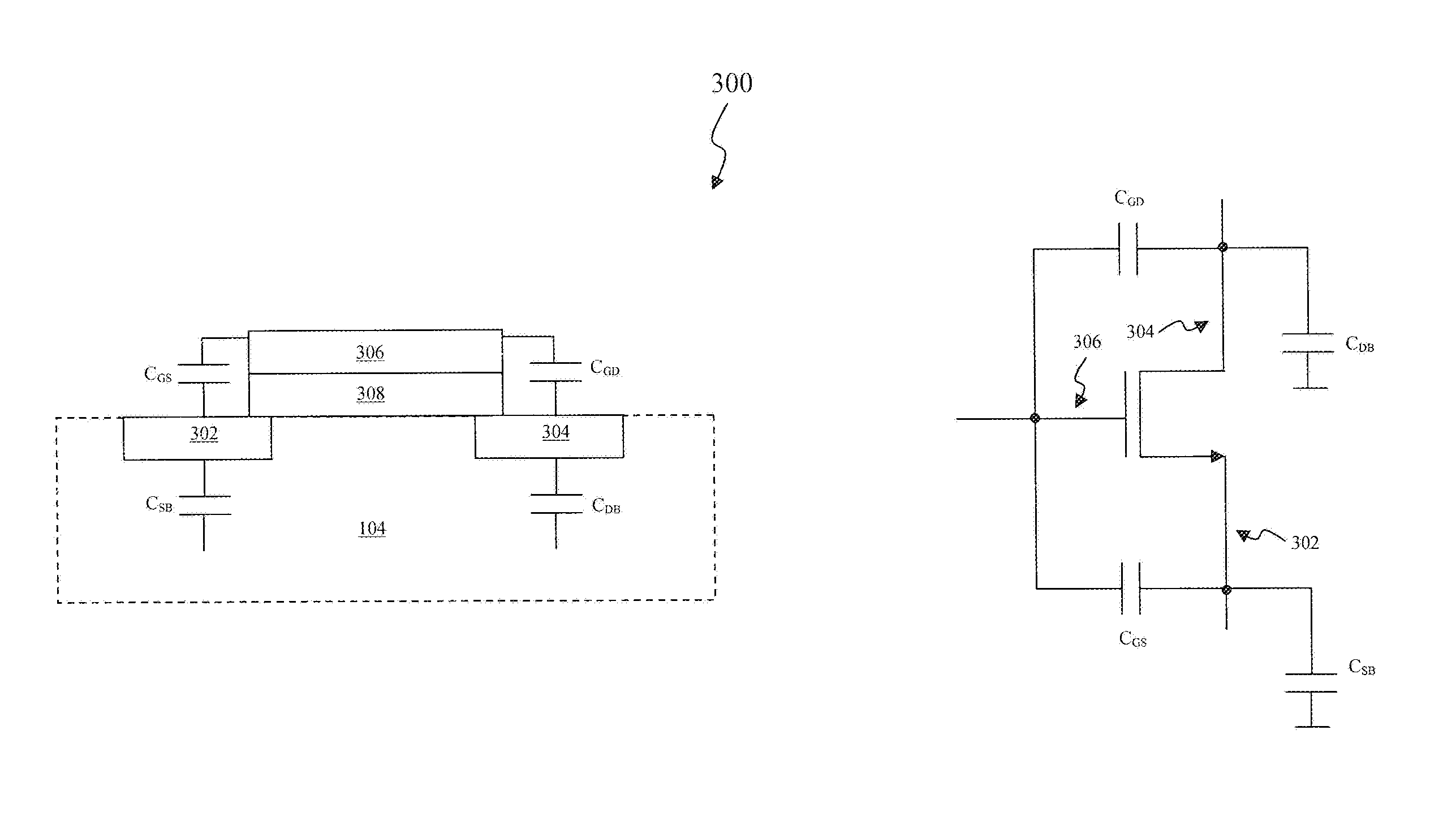

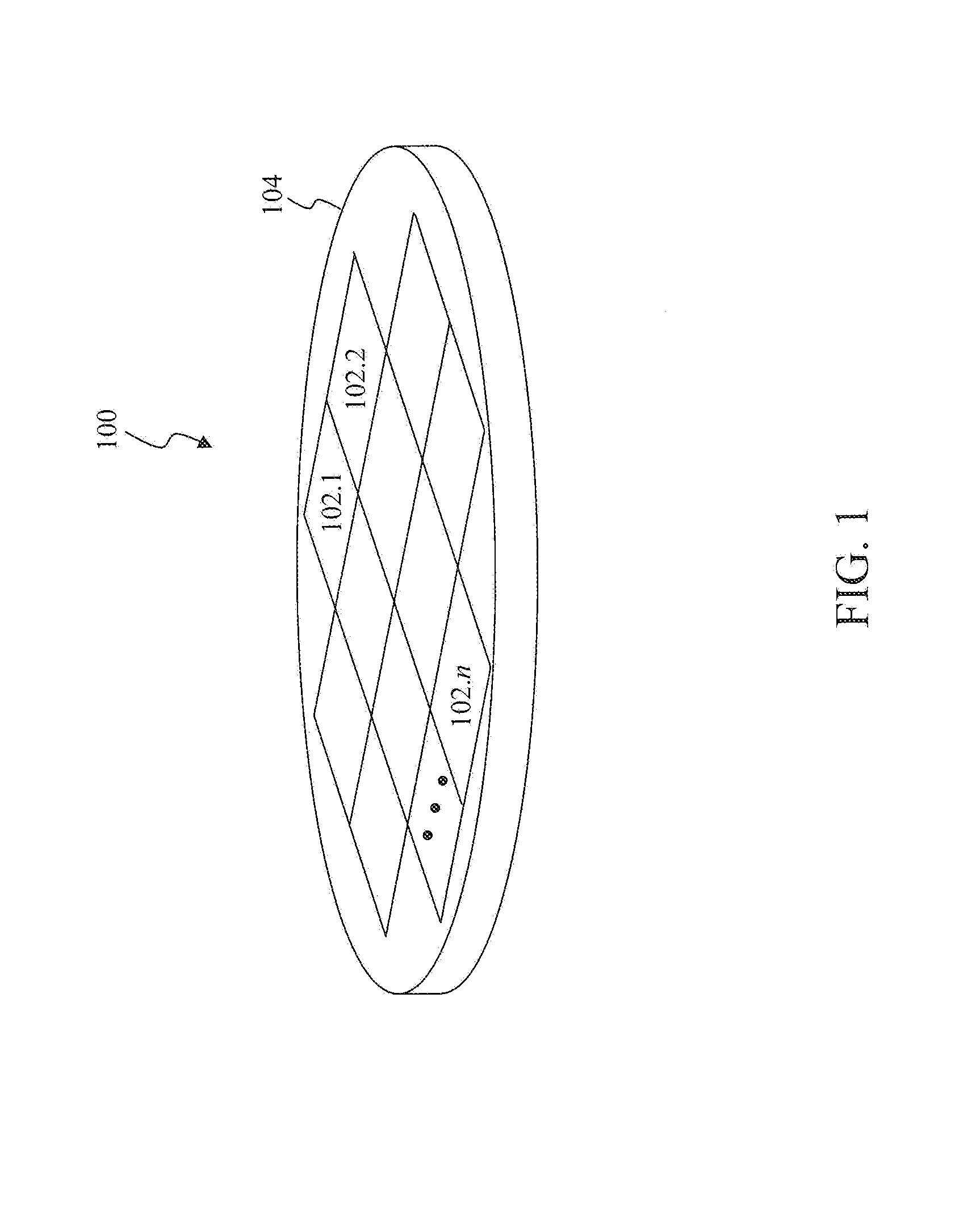

Digital-To-Analog Converter Using Nonlinear Capacitance Compensation

ActiveUS20160254820A1Electronic switchingDigital-analogue convertorsComputer moduleParasitic capacitance

A semiconductor device fabrication operation is commonly used to manufacture one or more integrated circuits onto a semiconductor substrate. The semiconductor device fabrication operation forms one or more transistors onto an arrangement of fabrication layers to form the one or more integrated circuits which introduces unwanted capacitances, often referred to as parasitic capacitances, into the one or more transistors. The one or more integrated circuits include one or more compensation modules that, when combined with the parasitic capacitances of the one or more transistors, ideally linearizes the non-linearity caused by the parasitic capacitances of the one or more transistors. For example, the one or more compensation modules incorporate a non-linear or a piecewise linear transfer function that is inversely related to the parasitic capacitances of the one or more transistors.

Owner:AVAGO TECH INT SALES PTE LTD

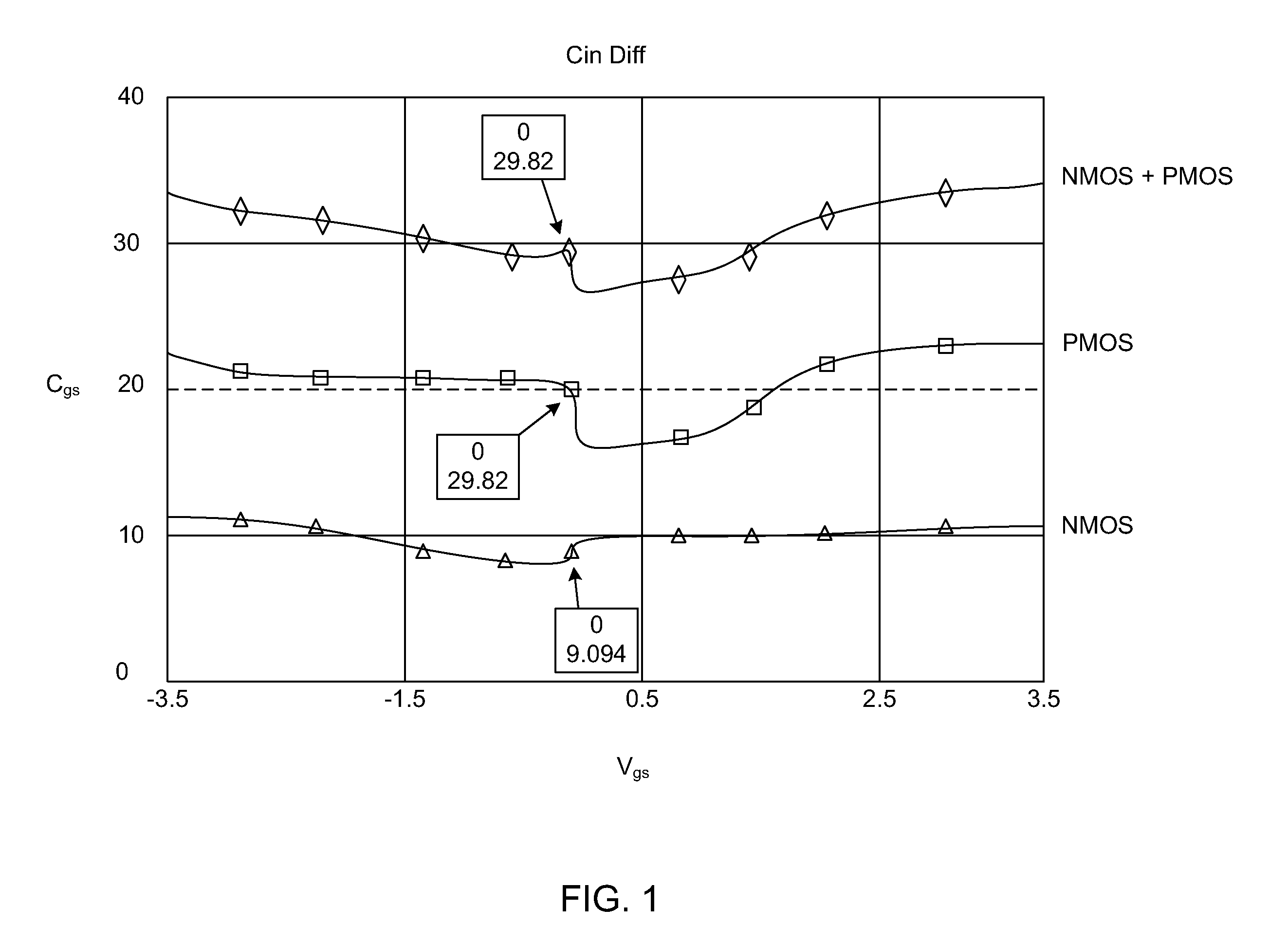

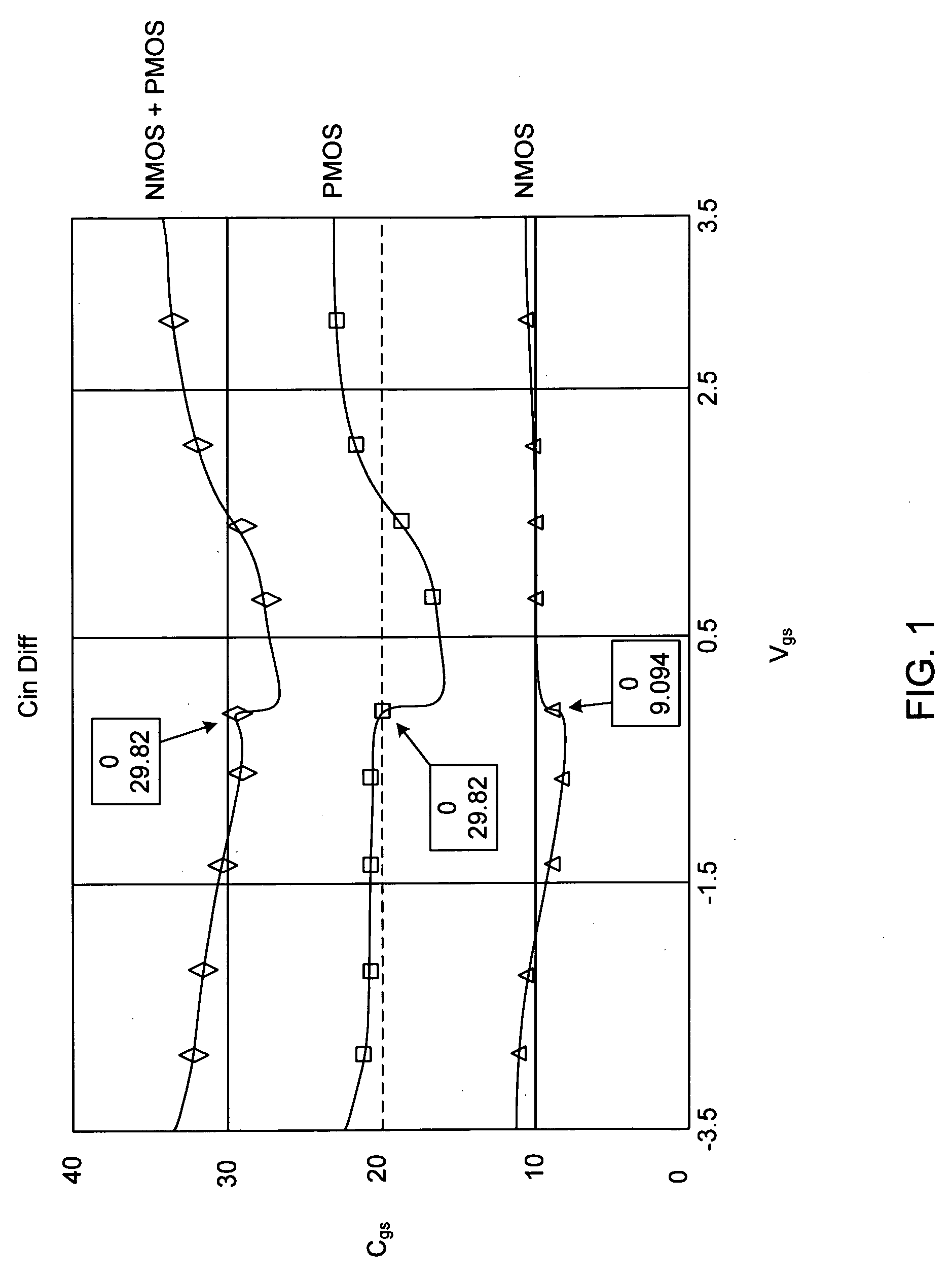

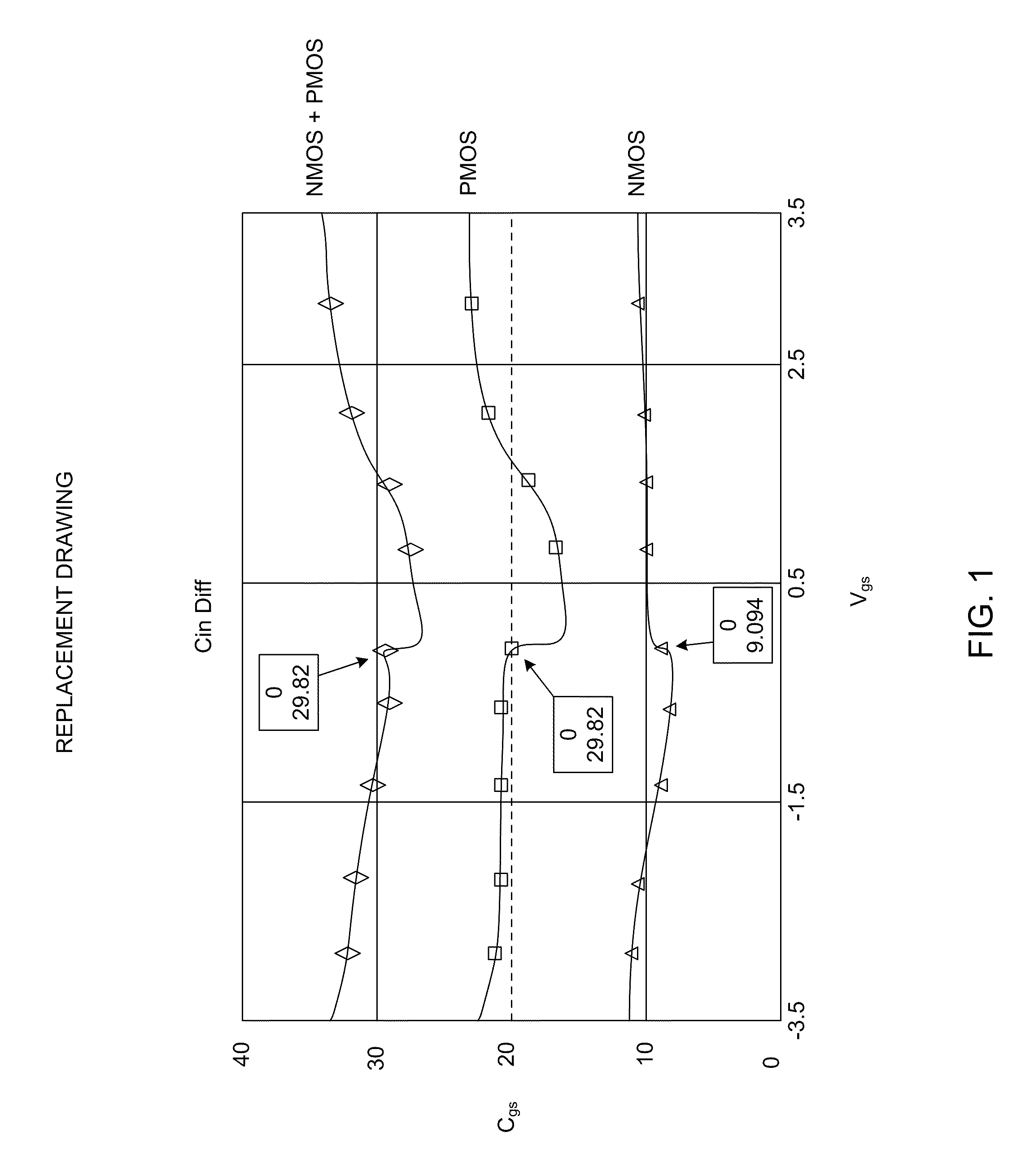

Bias-independent capacitor based on superposition of nonlinear capacitors for analog/RF circuit applications

A first MOS-on-NWELL device is formed on a substrate and has its pickup terminals optionally connected together. A second MOS-on-NWELL device is formed on the substrate and has its pickup terminals optionally connected together. A gate of the first MOS-on-NWELL device is connected to the pickup terminals of the second MOS-on-NWELL device. A gate of the second MOS-on-NWELL device is connected to the pickup terminals of the first MOS-on-NWELL device. A first PMOS transistor is formed on a substrate and has its source and drain terminals connected together. A second PMOS transistor is formed on a substrate and has its source and drain terminals connected together. A gate of the first PMOS transistor is connected to the source and drain terminals of the second PMOS transistor. A gate of the second PMOS transistor is connected to the source and drain terminals of the first PMOS transistor. A combination of the first and second PMOS transistors are connected in parallel with the first and second MOS-on-NWELL devices.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Ferro-electricity capacitance behavior model for SPICE circuit simulation procedure

InactiveCN101251871AImprove simulation speedFast simulationSpecial data processing applicationsCapacitanceControl signal

The invention belongs to the integrated circuit design technical field which relates to an integrated circuit design which applies a ferroelectric condenser, in particular to a ferroelectric condenser behavioral model which is applied in an SPICE circuit simulation program. The model utilizes the expression function in the SPICE program to establish a master copy of a non-linear condenser, and the master copy of the non-linear condenser is matched with a differential circuit to be a control circuit and simulates physical behaviors of the ferroelectric condenser. The model comprises a linear condenser, the non-linear condenser, a voltage control voltage source and the differential circuit, wherein, a parallel circuit which consists of the linear condenser and the non-linear condenser is connected in series with the voltage control voltage source and the differential circuit in turn. Compared with the prior art, electric behaviors of the ferroelectric condenser in the model are completely represented by the non-linear condenser and can be precisely evaluated by utilization of an expression. The operation control of the model is completely completed by the differential circuit and the control process is simple, thereby being favorable for improving the simulation speed. Moreover, control signals are differential of input voltage to time, thereby the model is more suitable for simulation of transient states.

Owner:TSINGHUA UNIV

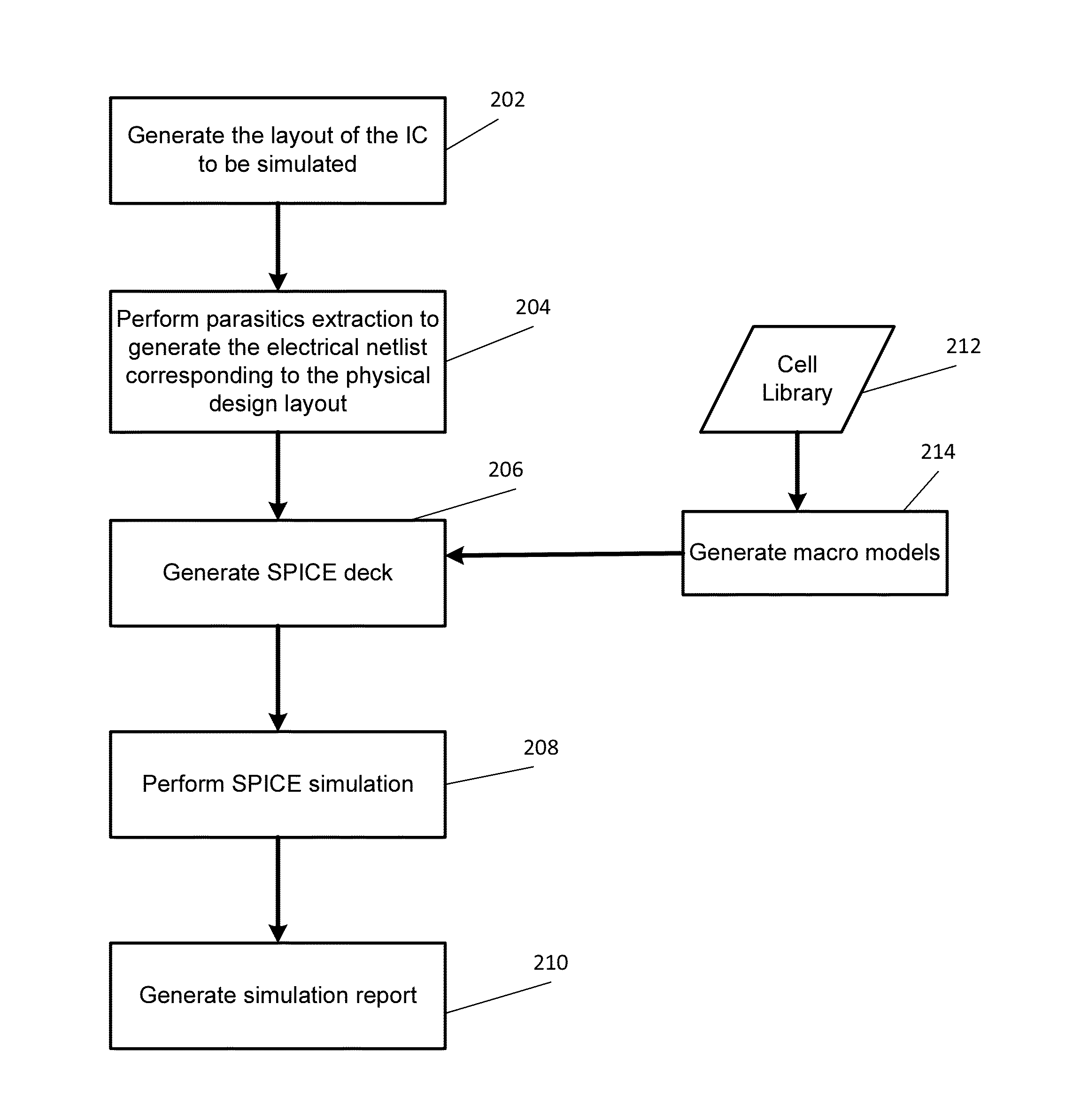

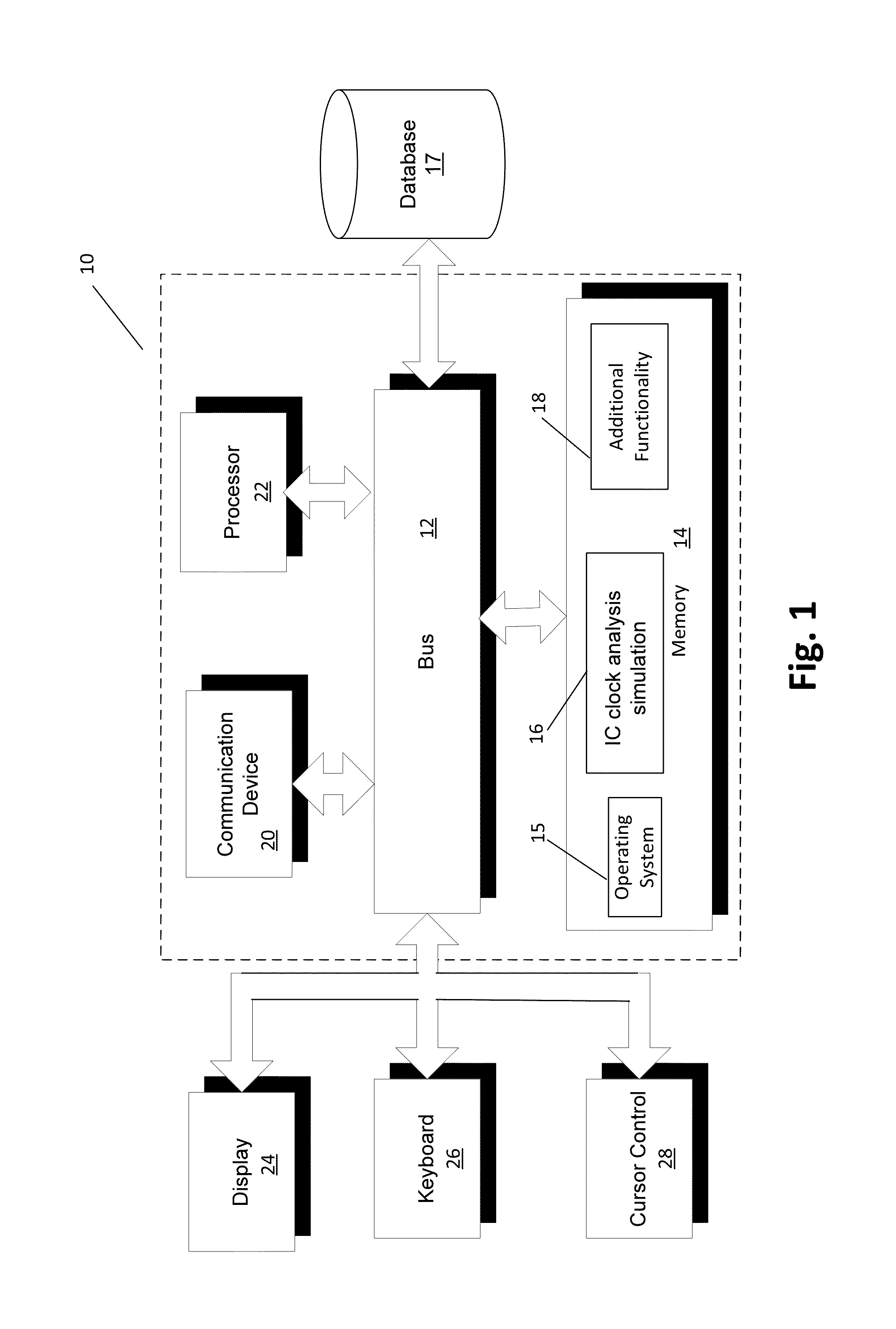

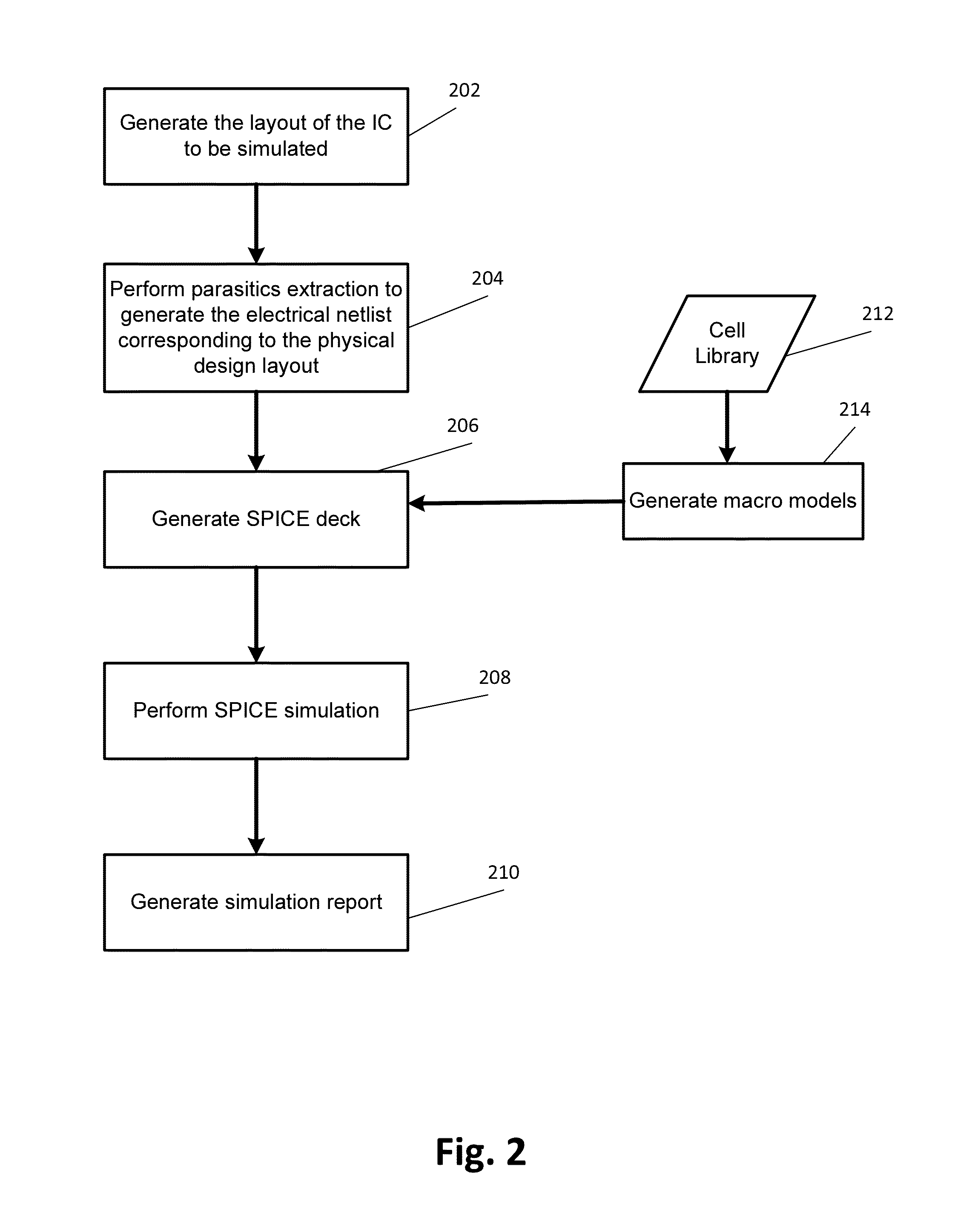

Integrated circuit clock analysis with macro models

ActiveUS8464195B1Computer aided designSoftware simulation/interpretation/emulationSimulation basedNetlist

An integrated circuit clock analysis system receives a cell library of gates of the integrated circuit and generates a macro model for each of the gates, where each macro model includes at least one of a nonlinear current source model, an input parasitics model or a nonlinear capacitors model. The system then tunes the macro models and generates a simulation deck from an electrical netlist of a layout of the integrated circuit and the tuned macro models. The system then performs clock analysis simulation based on the simulation deck.

Owner:ORACLE INT CORP

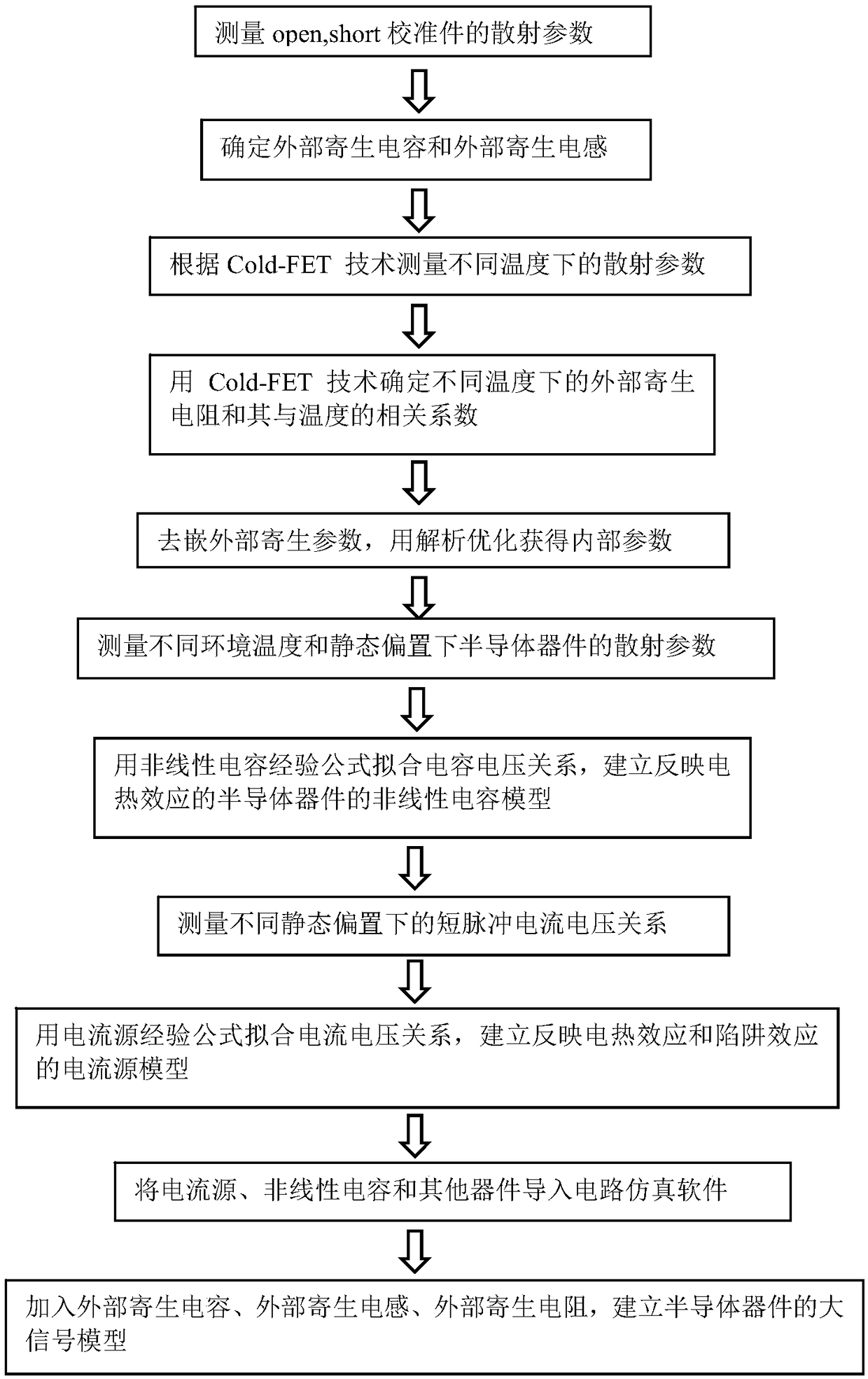

Method for building analytical model of semiconductor device based on empirical formulas

ActiveCN108153926ACAD circuit designSpecial data processing applicationsCapacitanceEmpirical formula

The embodiment of the invention includes a method for building an analytical model of a semiconductor device based on the empirical formula of nonlinear capacitance and the empirical formula of a current source. The method includes the following steps of measuring a group of scattering parameters of the semiconductor device under combinations of different environment temperatures and different static biases; determining a group of external parasitic parameters; building a small-signal equivalent circuit model of the semiconductor device; based on the determined external parasitic parameters, removing the external parasitic parameters in the scattering parameters to obtain a group of intrinsic parameters of the small-signal equivalent circuit model of the semiconductor device; using the empirical formula of the nonlinear capacitance to build a nonlinear capacitance model; using the empirical formula of the current source to build a current source model; using the intrinsic parameters, the nonlinear capacitance model and the current source model to build a large-signal equivalent model of the semiconductor device.

Owner:NAT UNIV OF SINGAPORE +1

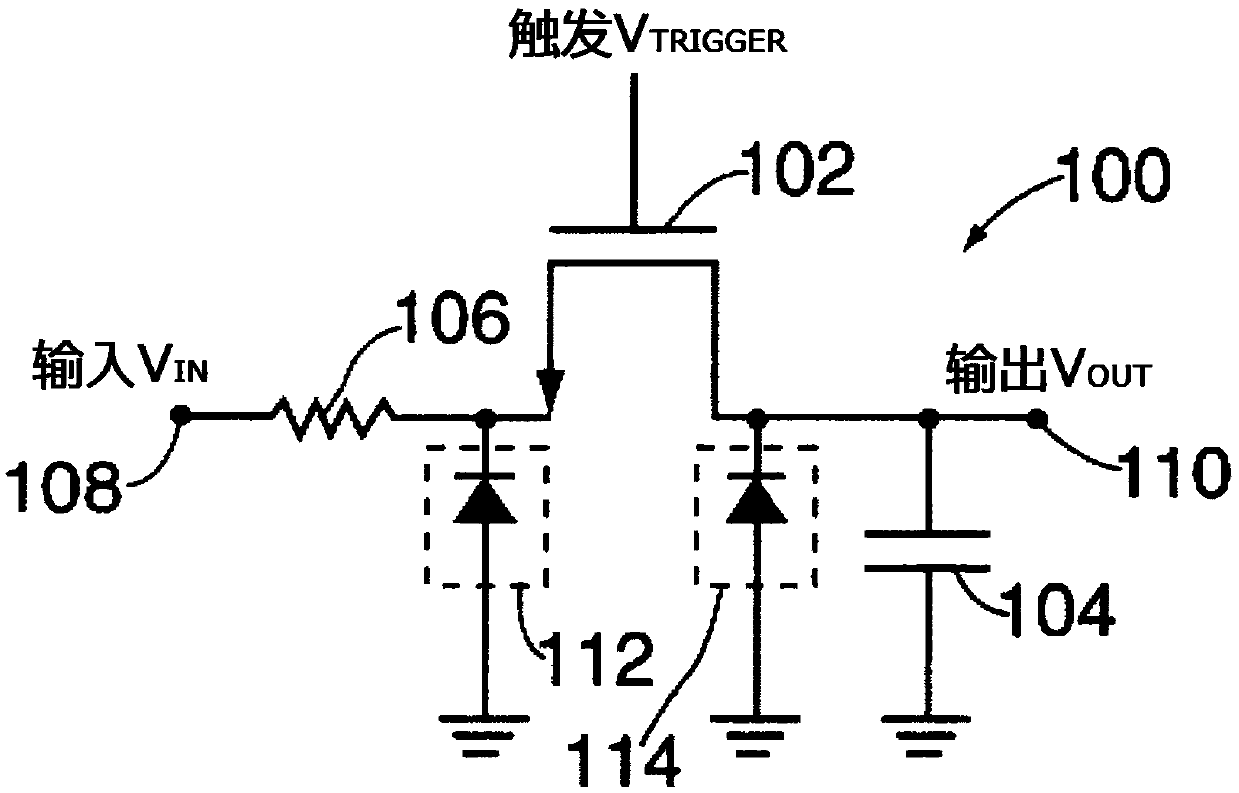

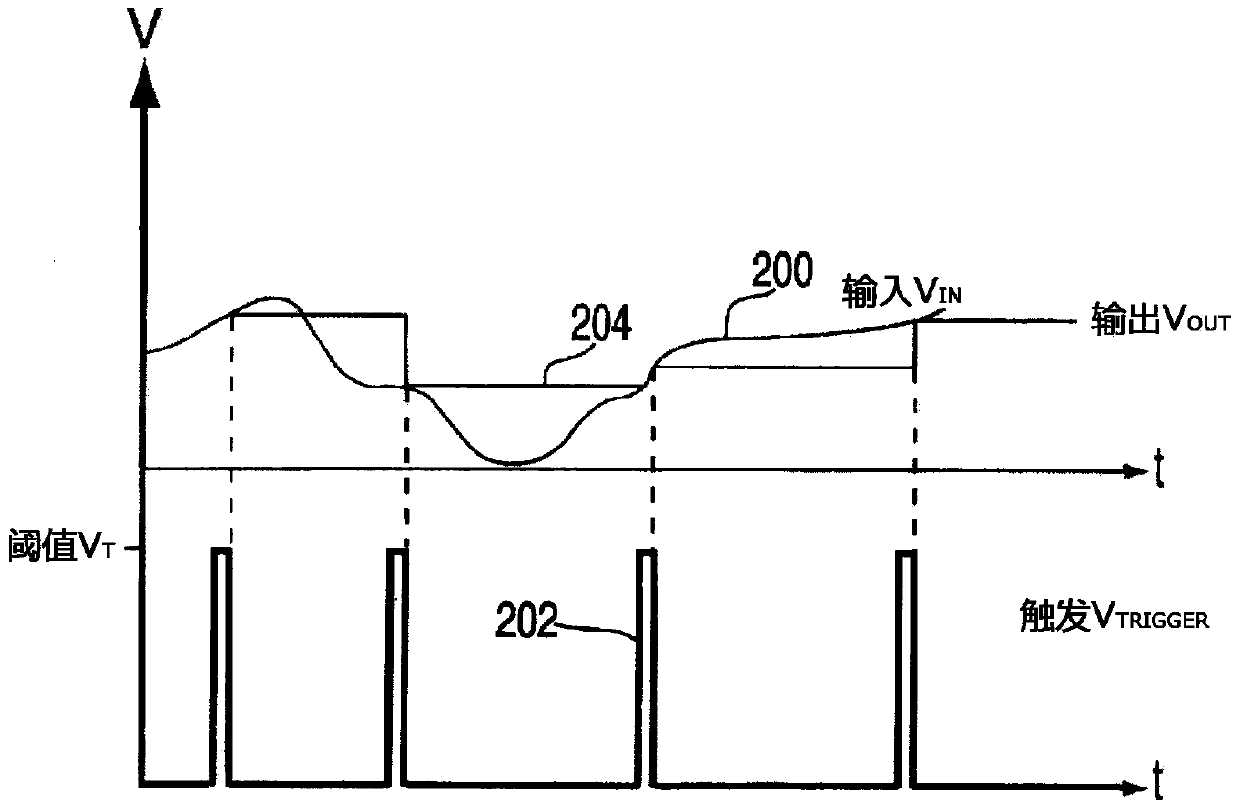

Circuit for compensating nonlinear capacitance to reduce harmonic distortion to greatest extent

InactiveCN103633948AAmplifier modifications to reduce non-linear distortionLogic circuit coupling/interface arrangementsTotal harmonic distortionParasitic capacitance

Provided is a circuit for compensating nonlinear capacitance to reduce harmonic distortion to the greatest extent. The circuit can improve stray capacitance between transistors and is independent of the adopted process technology. In a preferential instance, a pair of diodes with inversely proportional actions is provided for a parasitic diode in an integrated circuit during operation, so stray capacitance of the transistors in the circuit is linearized. If the diodes do not exist in the circuit, different input signals can give rise to changes of the stray capacitance, and therefore harmonic distortion of the circuit is caused. Another embodiment of the invention further provides a complementary transistor. The complementary transistor forms another stray capacitance which is basically opposite to the stray capacitance in the transistors. In addition, according to proportions of different elements, the two methods can be combined, for instance, the diodes can be added while the complementary transistor is used.

Owner:SUZHOU BATELAB MICROELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com