Circuit for compensating nonlinear capacitance to reduce harmonic distortion to greatest extent

A technology of nonlinear capacitance and harmonic distortion, which is applied in improving amplifiers to reduce nonlinear distortion, logic circuit connection/interface layout, etc., and can solve the problems of circuit limitation, high cost, and multi-space.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

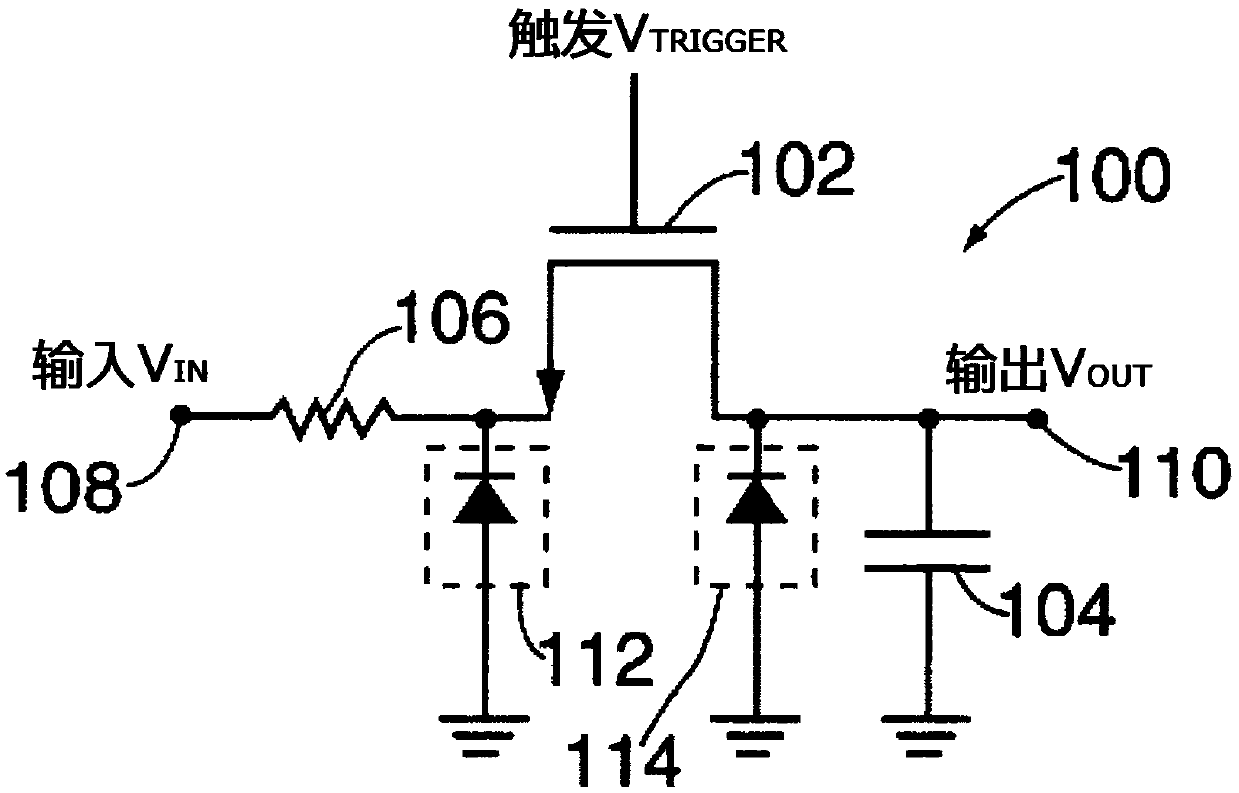

[0023] figure 1 is a simplified schematic of a typical track and hold circuit. Such as figure 1 As shown, the T / H circuit 100 employs a metal oxide semiconductor (MOS) transistor 102 and a capacitor 104 . Resistor 106 represents the input source impedance. MOS transistor 102 also includes parasitic junction capacitances at the drain and source, represented by PJC diodes 112 and 114, respectively. In the figure, PJC diodes 112 and 114 are shown by dashed boxes, which represent the pn junction of MOS transistor 102 .

[0024] Ideally, an input signal V IN resulting in a voltage change at the input node 108 . When the gate of MOS transistor 102 is coupled to a voltage greater than the voltage at input node 108, MOS transistor 102 acts like a resistor—allowing capacitor 104 to charge and discharge such that the output V at output node 110 OUT With the input signal V IN change (i.e. tracking mode). When the gate of the MOS transistor 102 is coupled to a voltage less than th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com