Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

197 results about "Manycore processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Manycore processors are specialist multi-core processors designed for a high degree of parallel processing, containing numerous simpler, independent processor cores (from a few tens of cores to thousands or more). Manycore processors are used extensively in embedded computers and high-performance computing.

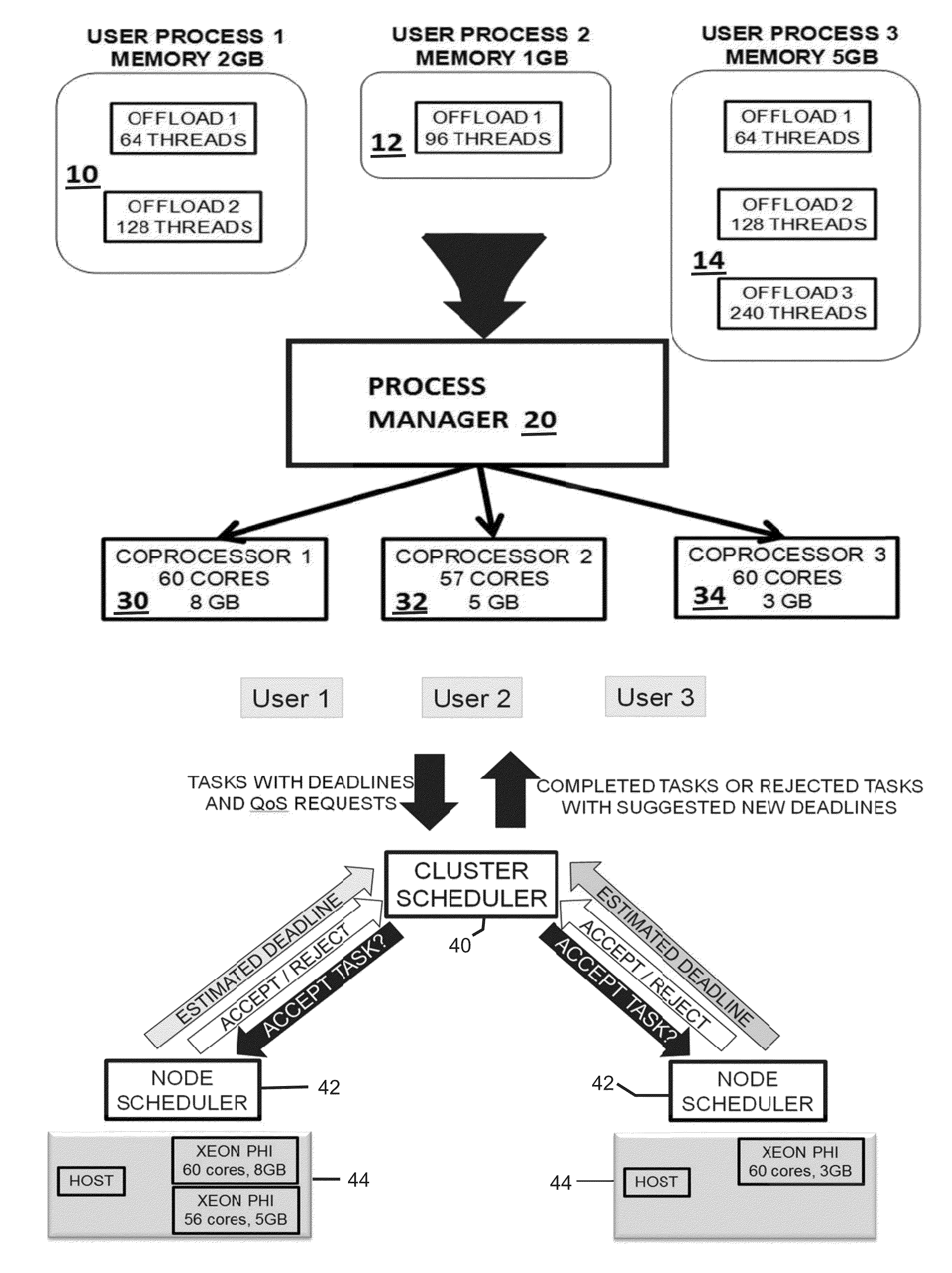

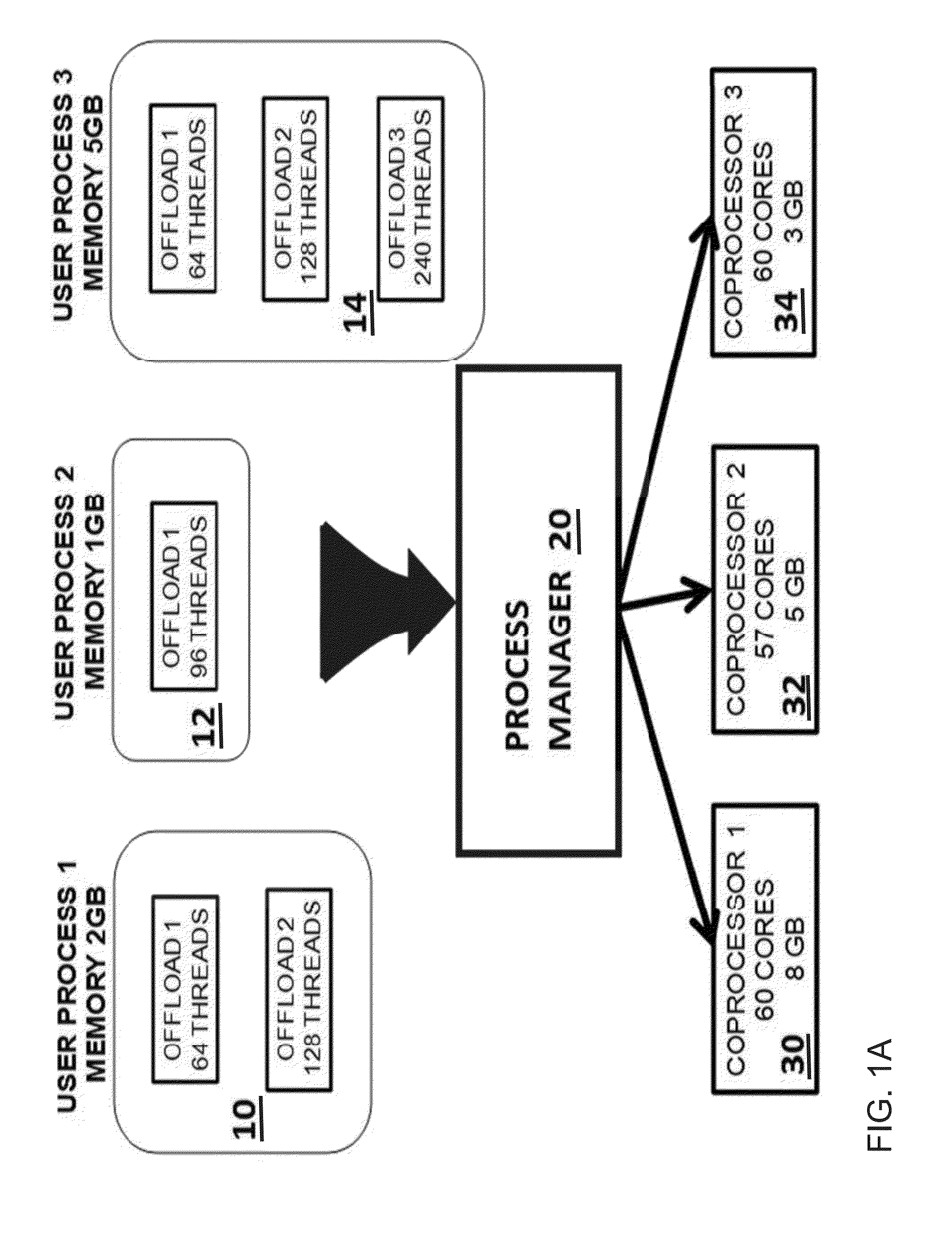

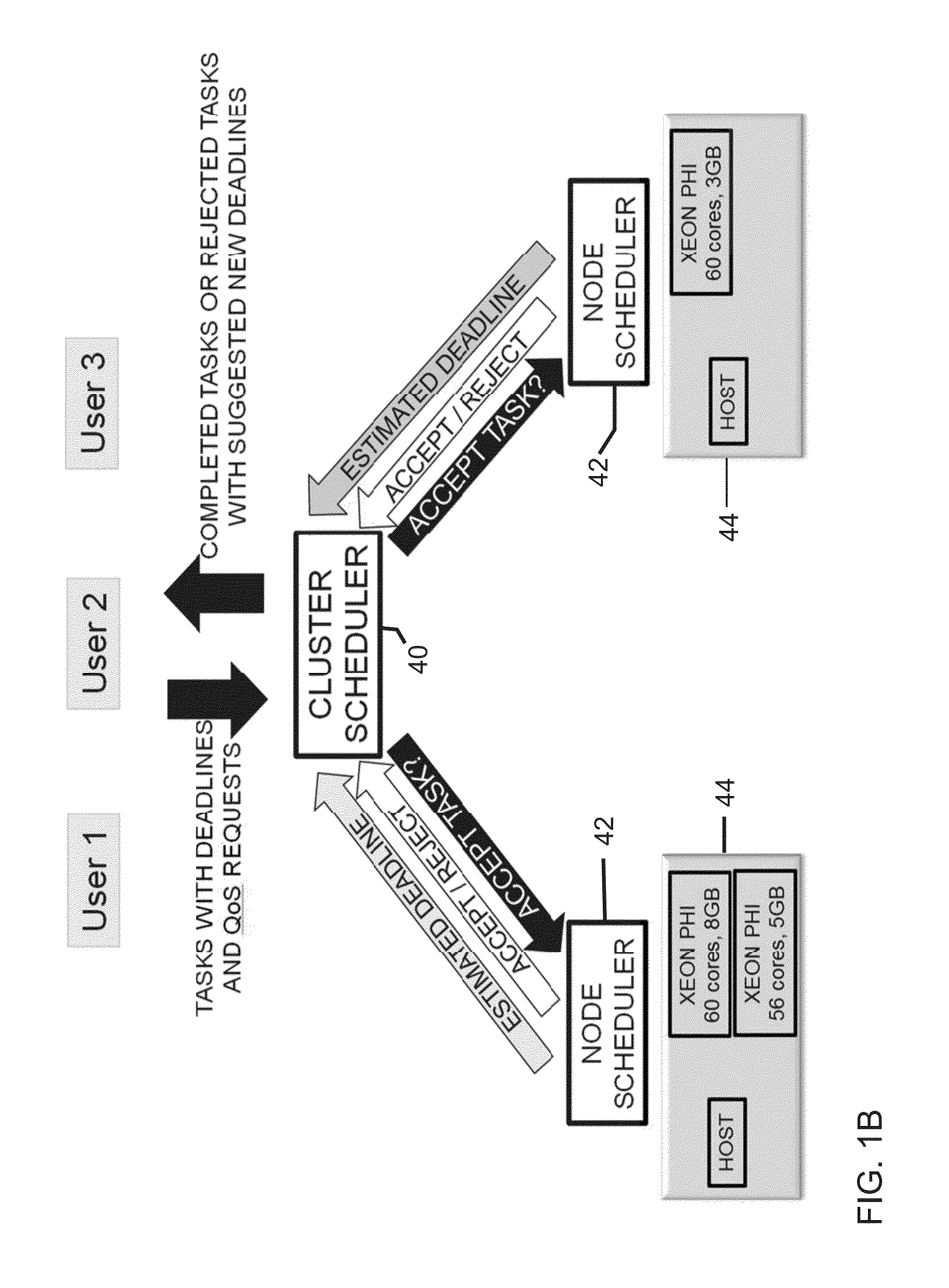

Simultaneous scheduling of processes and offloading computation on many-core coprocessors

Methods and systems for scheduling jobs to manycore nodes in a cluster include selecting a job to run according to the job's wait time and the job's expected execution time; sending job requirements to all nodes in a cluster, where each node includes a manycore processor; determining at each node whether said node has sufficient resources to ever satisfy the job requirements and, if no node has sufficient resources, deleting the job; creating a list of nodes that have sufficient free resources at a present time to satisfy the job requirements; and assigning the job to a node, based on a difference between an expected execution time and associated confidence value for each node and a hypothetical fastest execution time and associated hypothetical maximum confidence value.

Owner:NEC CORP

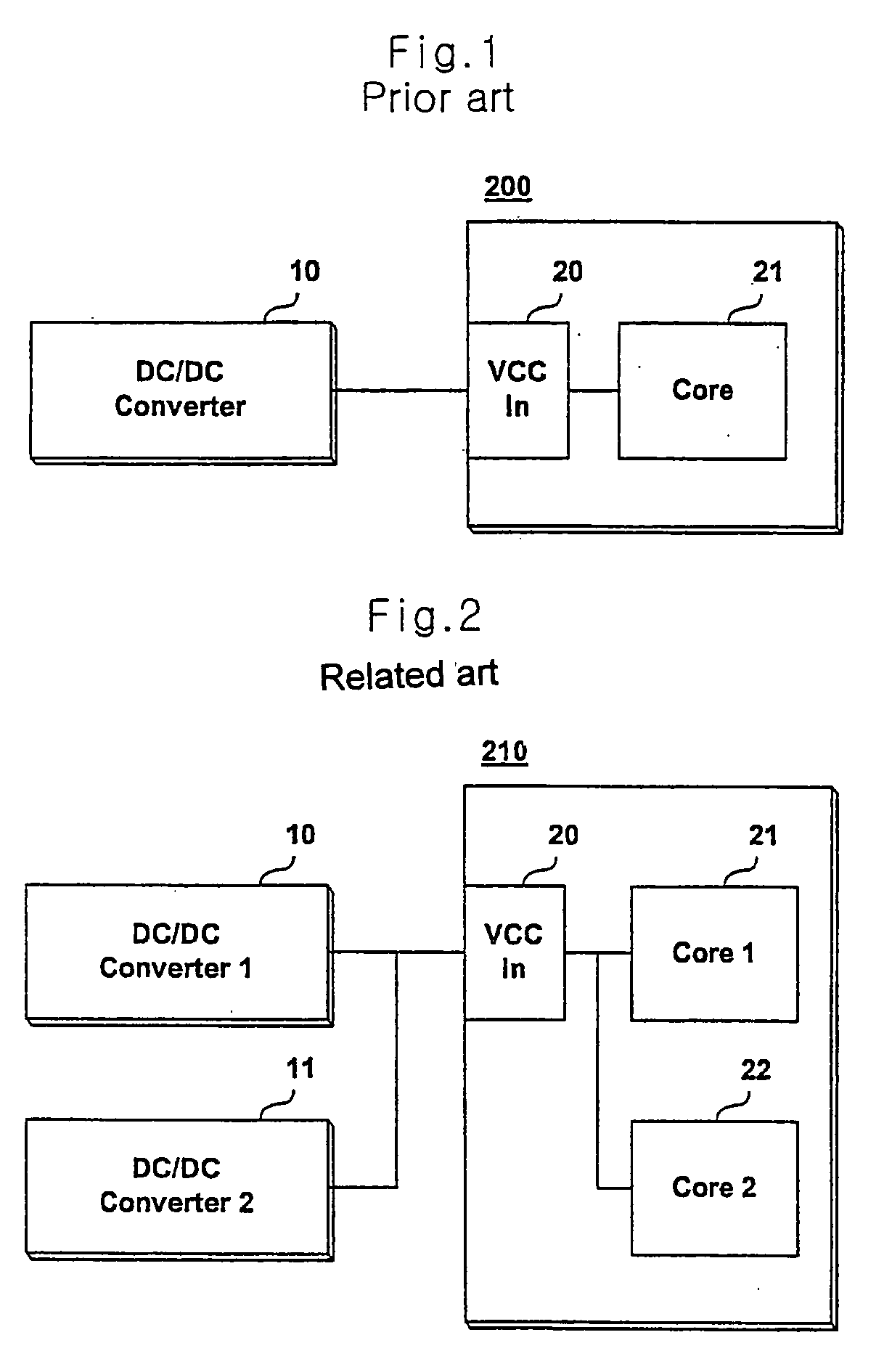

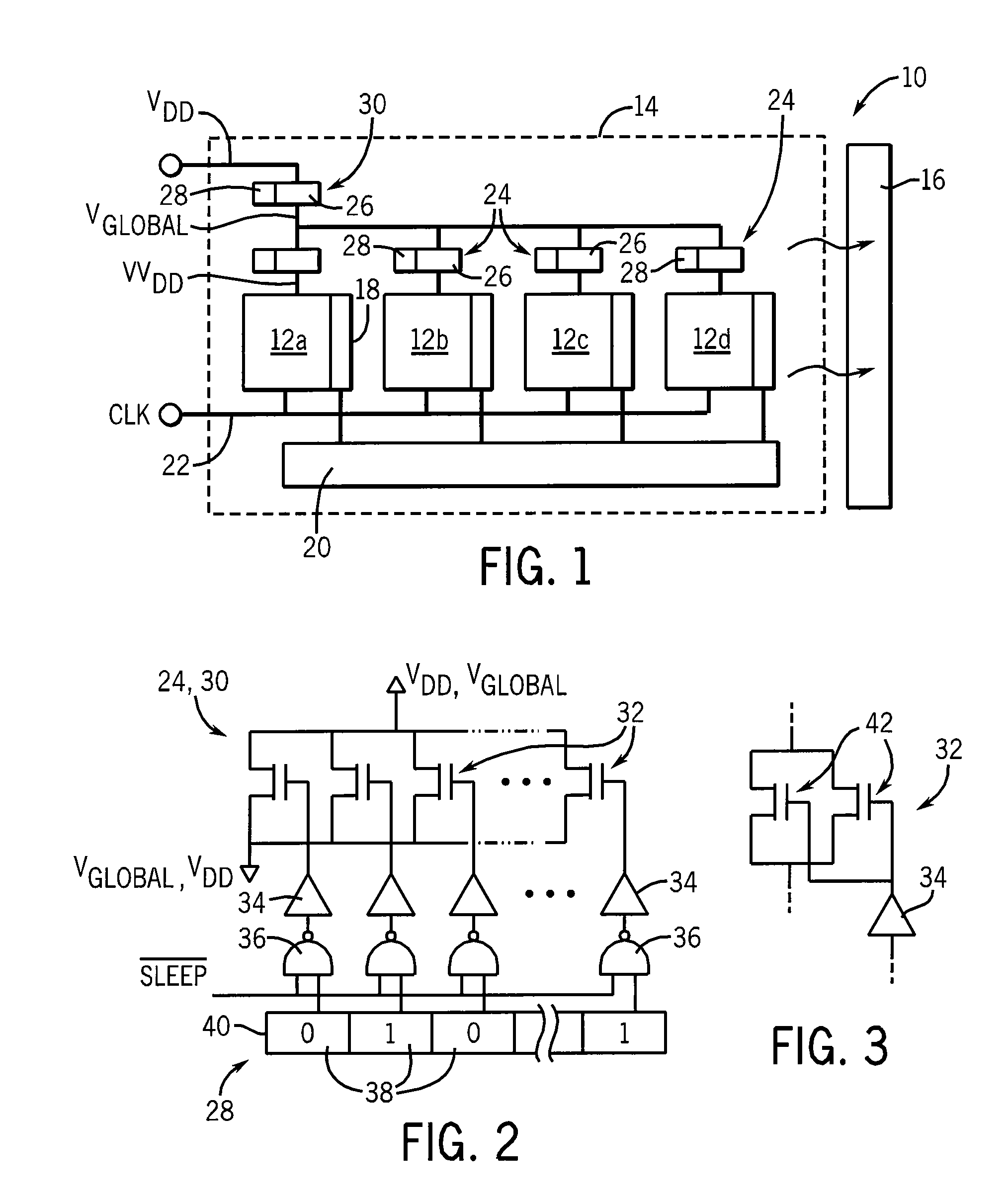

Apparatus for controlling power of processor having a plurality of cores and control method of the same

Embodiments of an apparatus and methods for controlling power of a processor having a plurality of cores can independently control individual or selected cores and power supply circuits corresponding to the cores based on, for example, an operation state of the processor or a power mode. Embodiments of an apparatus for controlling power of a processor having a plurality of cores can include a plurality of power supply units each capable of independently supplying a supply power to a plurality of cores provided in one processor, a unit for checking at least one among a use state, a use amount and a power mode of each core and for turning on / off each checked core, and a unit that contacts with the unit for checking for controlling the power supply units in response to an on / off operation of each core.

Owner:LG ELECTRONICS INC

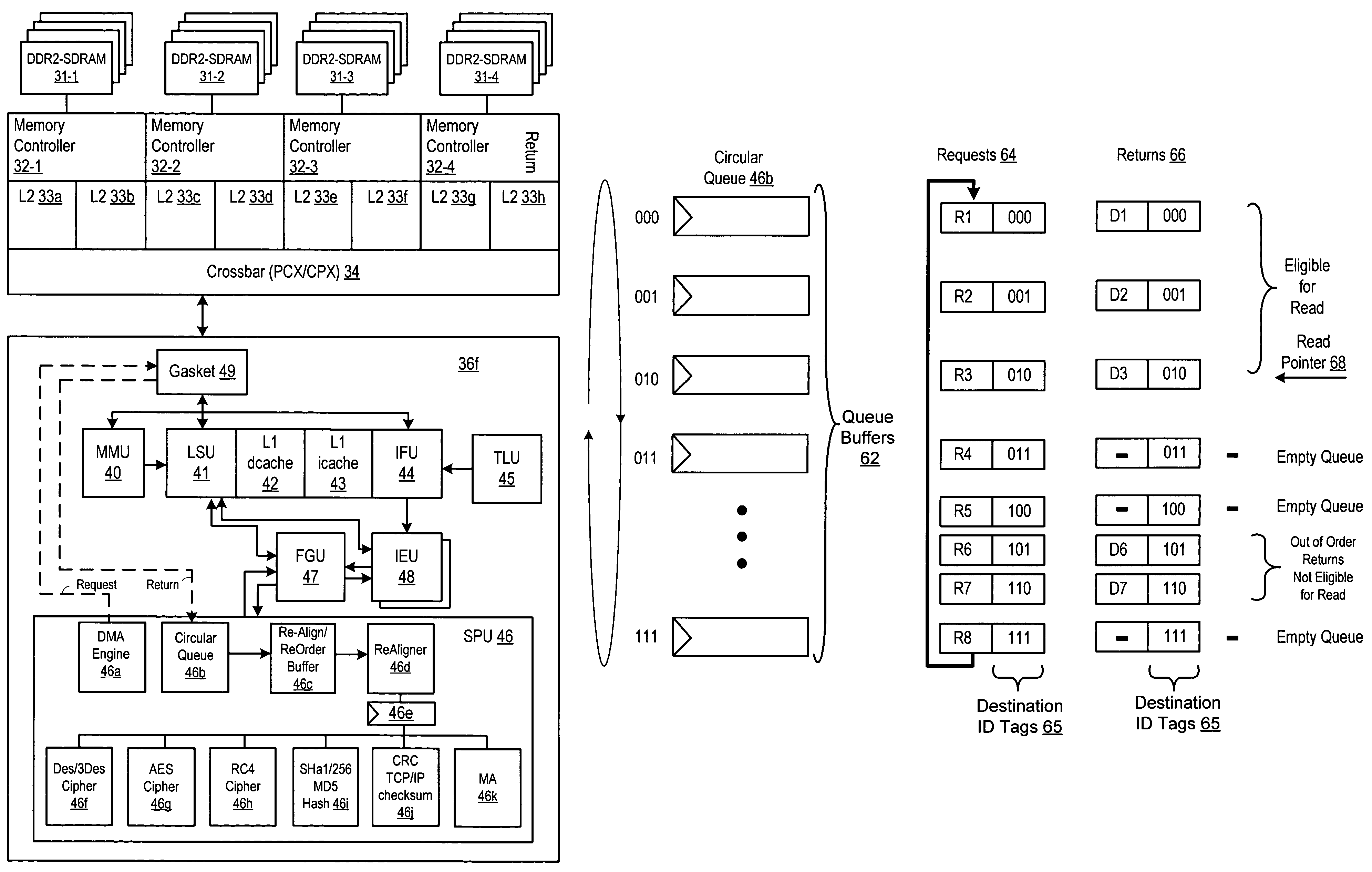

Out-of-order memory transactions in a fine-grain multithreaded/multi-core processor

ActiveUS7571284B1Improve performanceEfficient processingGeneral purpose stored program computerMultiprogramming arrangementsProcessing coreMulti-core processor

A method and apparatus for implementing out-of-order memory transactions in a multithreaded, multicore processor. In the present invention, circular queue comprising a plurality of queue buffers is used to store load data returned by a memory unit in response to a request issued by a processing module, such as a stream processing unit, in a processing core. As requests are issued, a destination queue buffer ID tag is transmitted as part of the request. When the request is returned, that destination number is reflected back and is used to control which queue within the circular queue will be used to store the retuned load data. Separate pointers are used to indicate the order of the queues to be read and the order of the queues to be written. The method and apparatus implemented by the present invention allows out-of-order data to be processed efficiently, thereby improving the performance of a fine grain multithreaded, multi-core processor.

Owner:ORACLE INT CORP

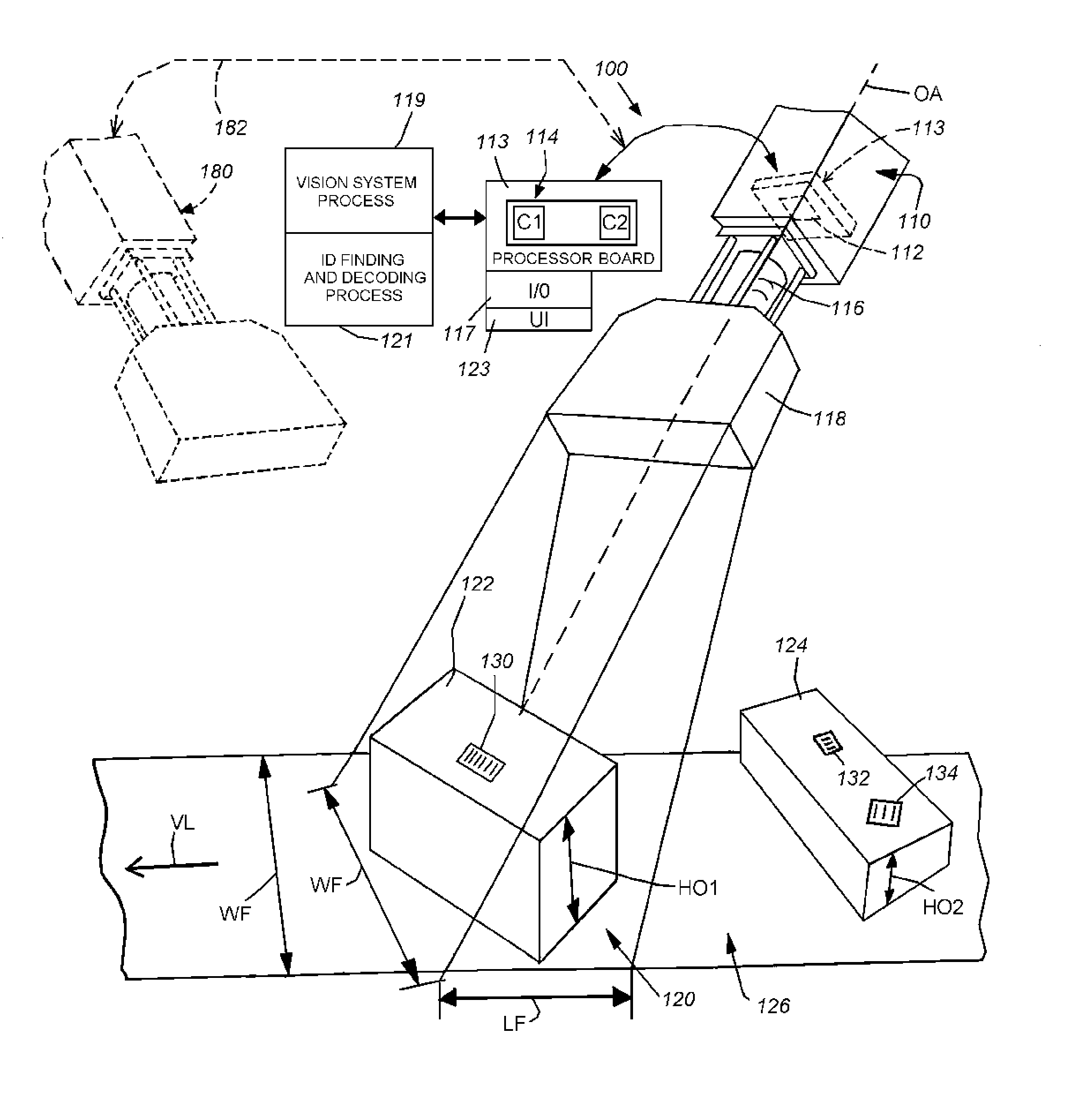

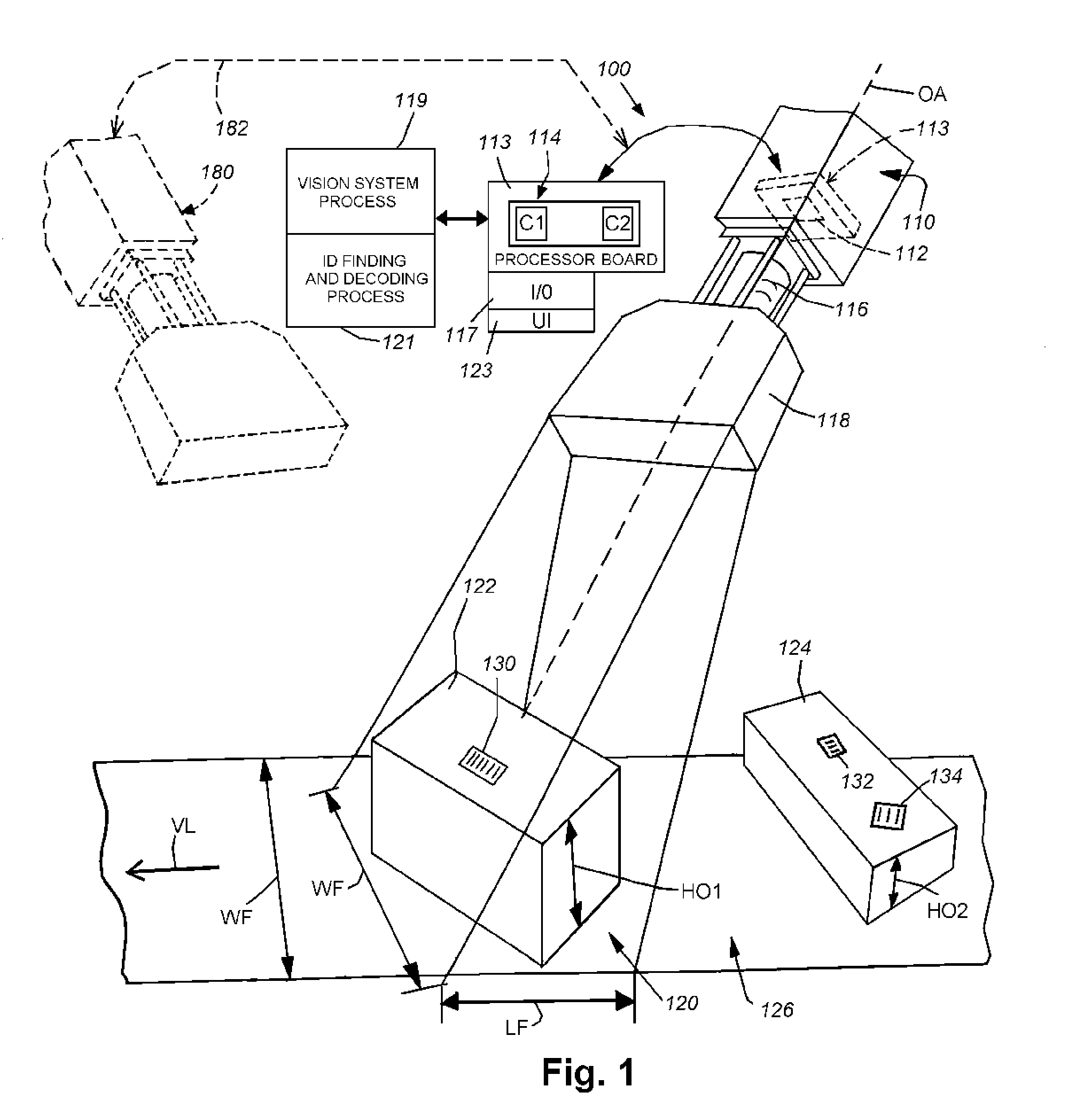

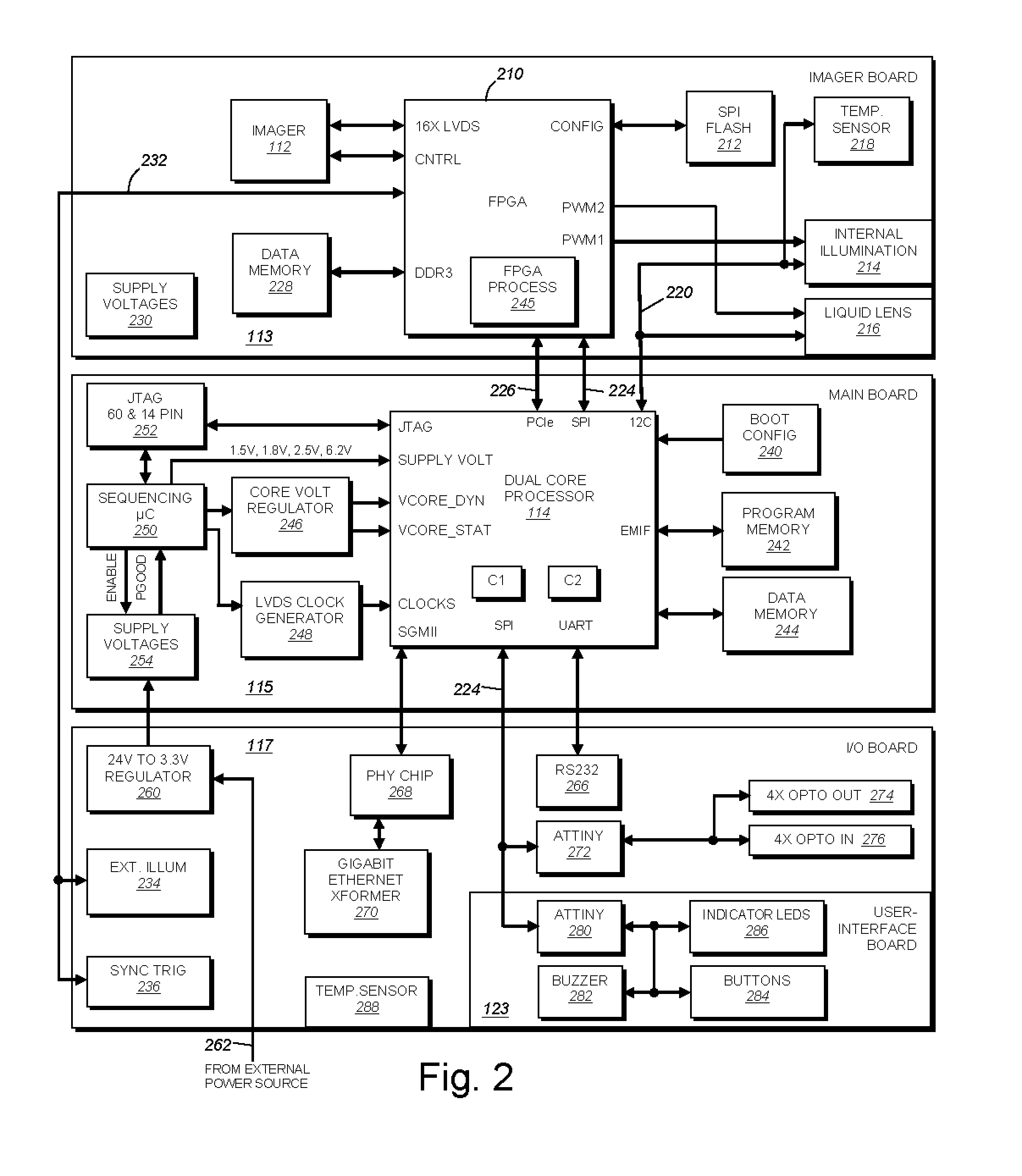

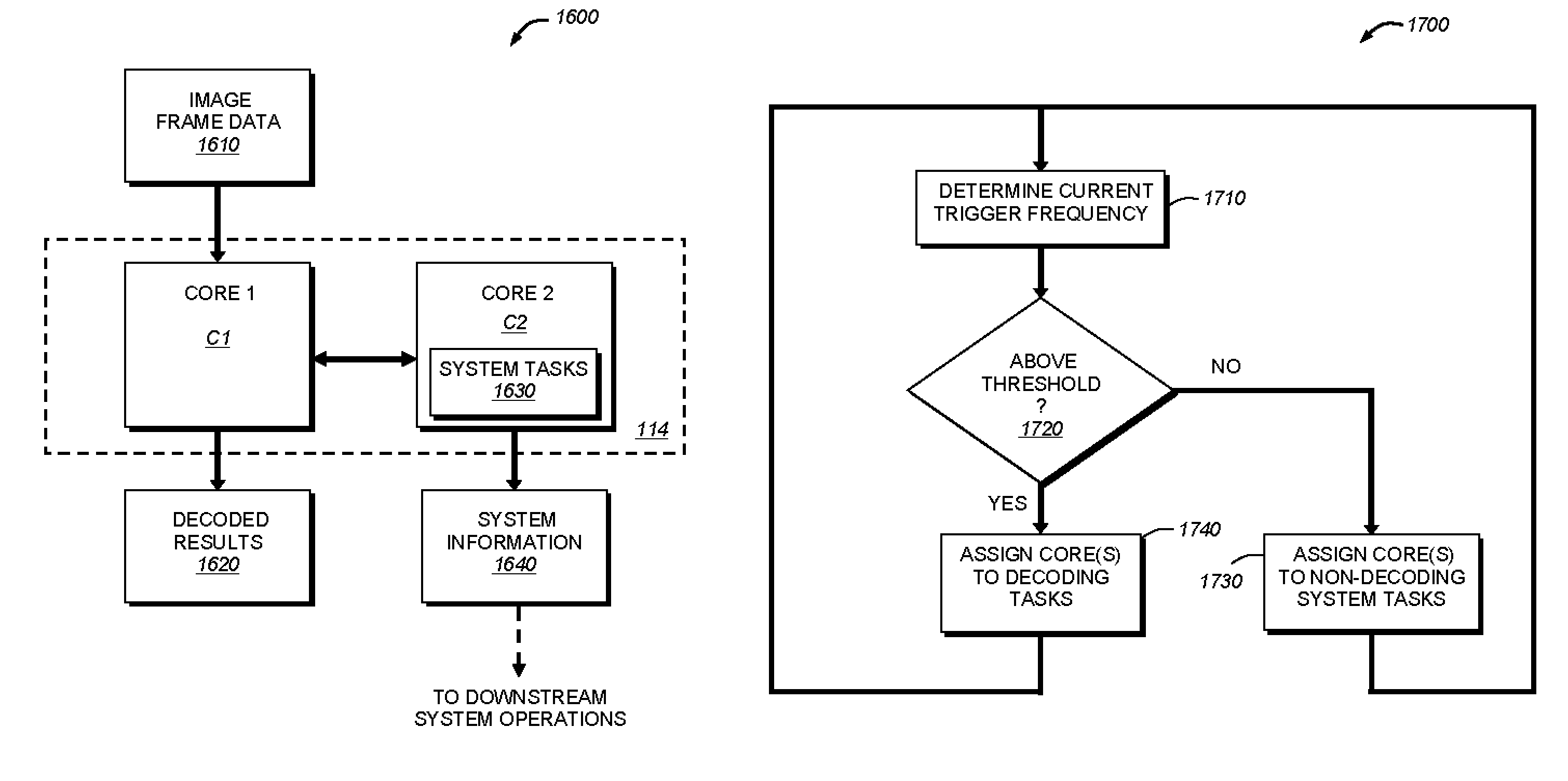

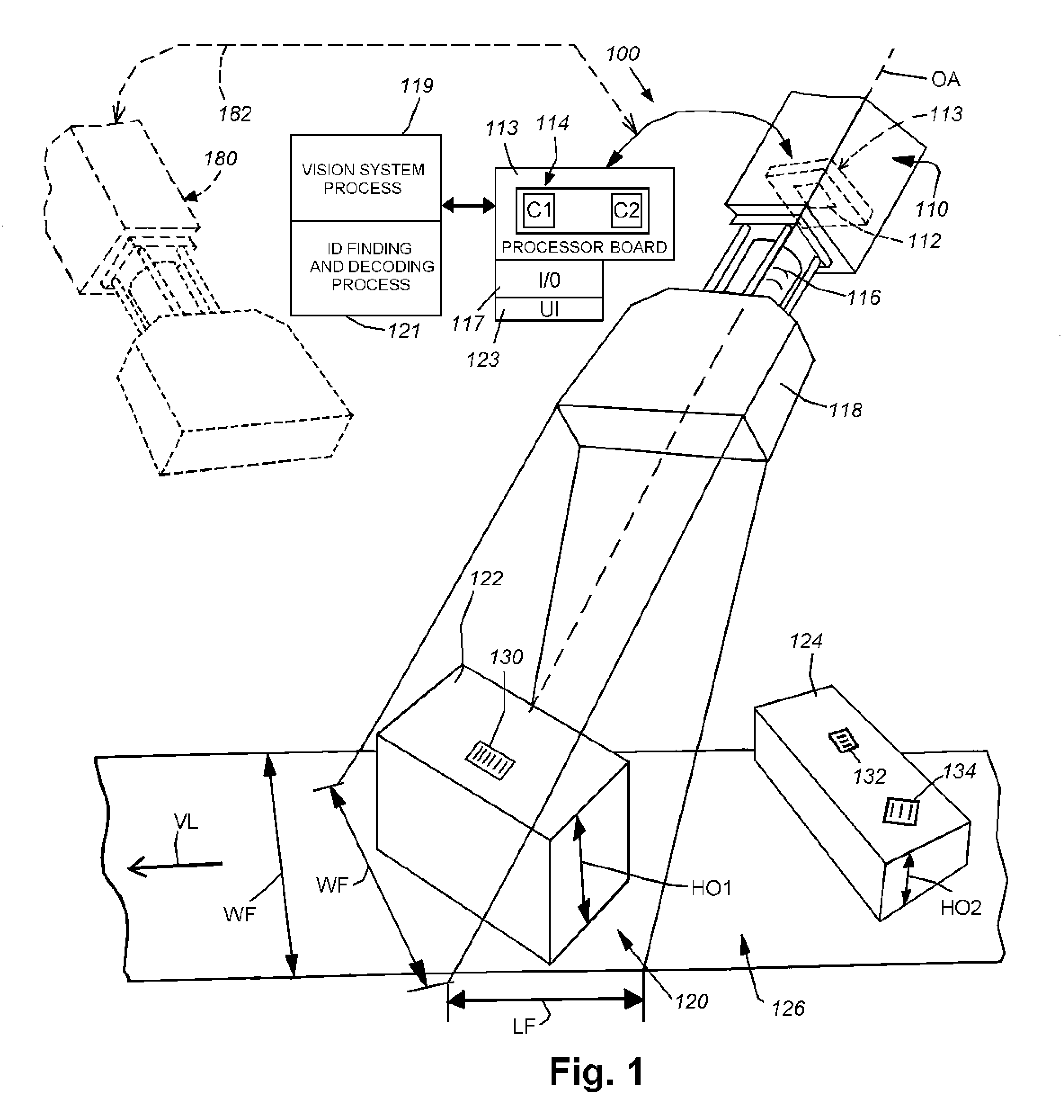

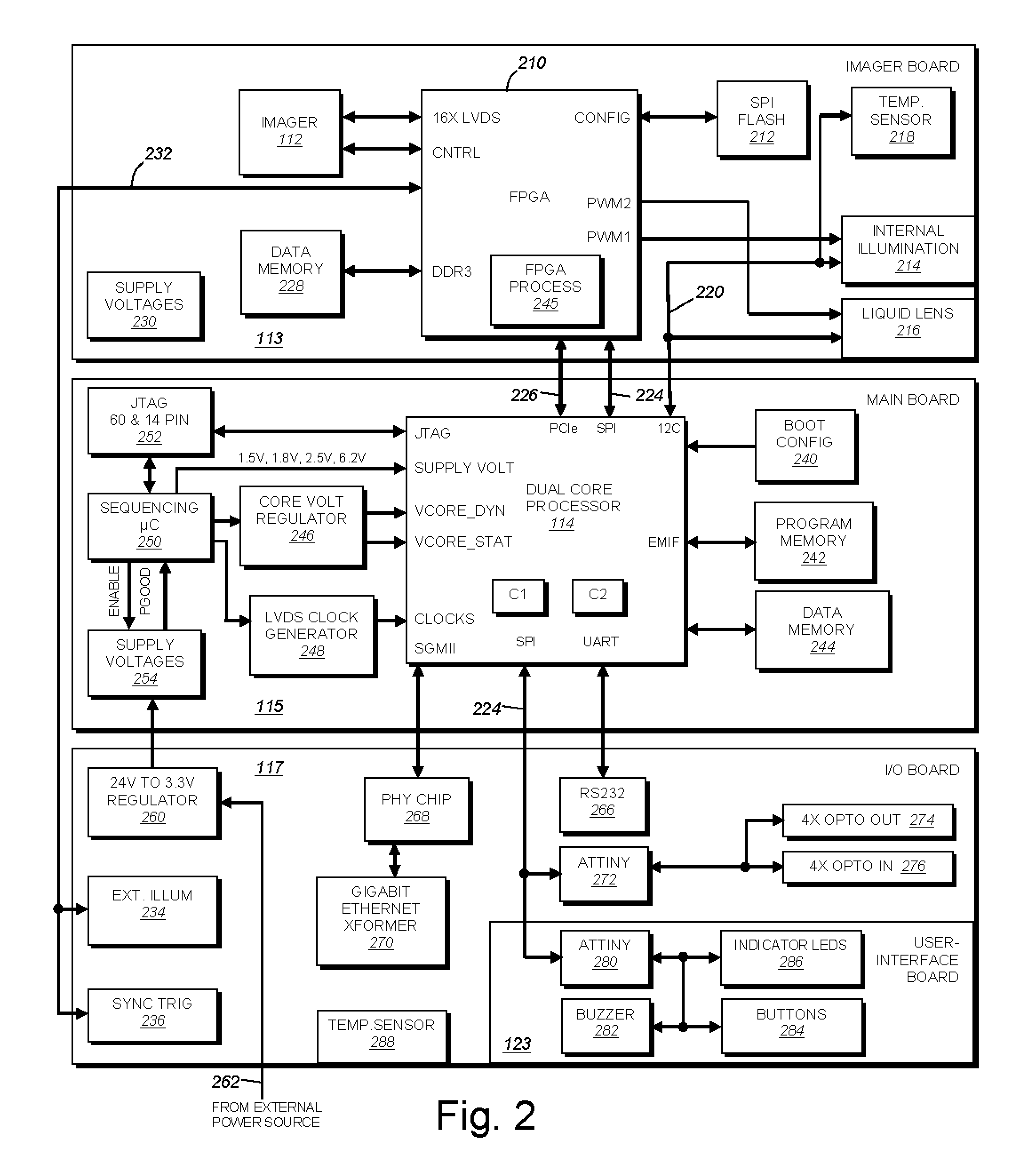

Systems and methods for operating symbology reader with multi-core processor

ActiveUS20140097251A1Efficiently dissipatedHighly effectiveTransmission systemsSensing by electromagnetic radiationCamera lensHigh resolution imaging

This invention provides a vision system camera, and associated methods of operation, having a multi-core processor, high-speed, high-resolution imager, FOVE, auto-focus lens and imager-connected pre-processor to pre-process image data provides the acquisition and processing speed, as well as the image resolution that are highly desirable in a wide range of applications. This arrangement effectively scans objects that require a wide field of view, vary in size and move relatively quickly with respect to the system field of view. This vision system provides a physical package with a wide variety of physical interconnections to support various options and control functions. The package effectively dissipates internally generated heat by arranging components to optimize heat transfer to the ambient environment and includes dissipating structure (e.g. fins) to facilitate such transfer. The system also enables a wide range of multi-core processes to optimize and load-balance both image processing and system operation (i.e. auto-regulation tasks).

Owner:COGNEX CORP

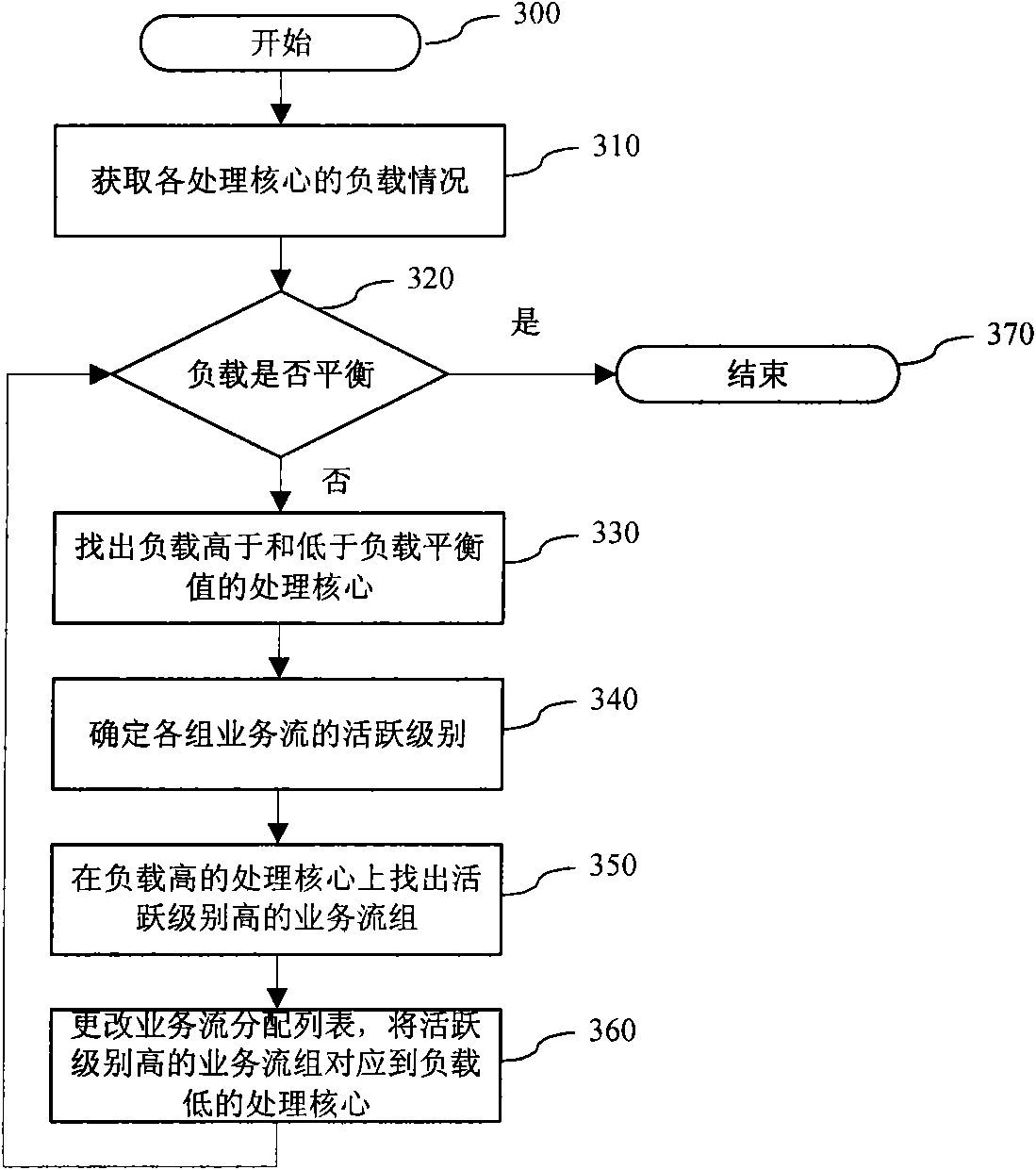

Method and device for multi-core parallel concurrent processing of network traffic flows

ActiveCN101610209ARegulating loadTake advantage of processingData switching networksProcessing coreTraffic flow

The invention relates to a method and a device for the multi-core parallel concurrent processing of network traffic flows. The method comprises the following steps: capturing a data pocket from a network; and unpacking the data pocket into a plurality of traffic flows and generating a traffic flow distribution list so that a multi-core processor processes the traffic flows according to the traffic flow distribution list. The method is characterized by also comprising following steps: acquiring the load condition of each processing core; and confirming the active level of each traffic flow after generating the traffic flow distribution list which is changed according to the load conditions and the active levels so as to dynamically distribute the traffic flows. The invention effectively adjusts the load of each processing core and fully utilizes the processing performance of the multi-core processor by dynamically distributing the network traffic flows into a plurality of processing cores.

Owner:BEIJINGNETENTSEC

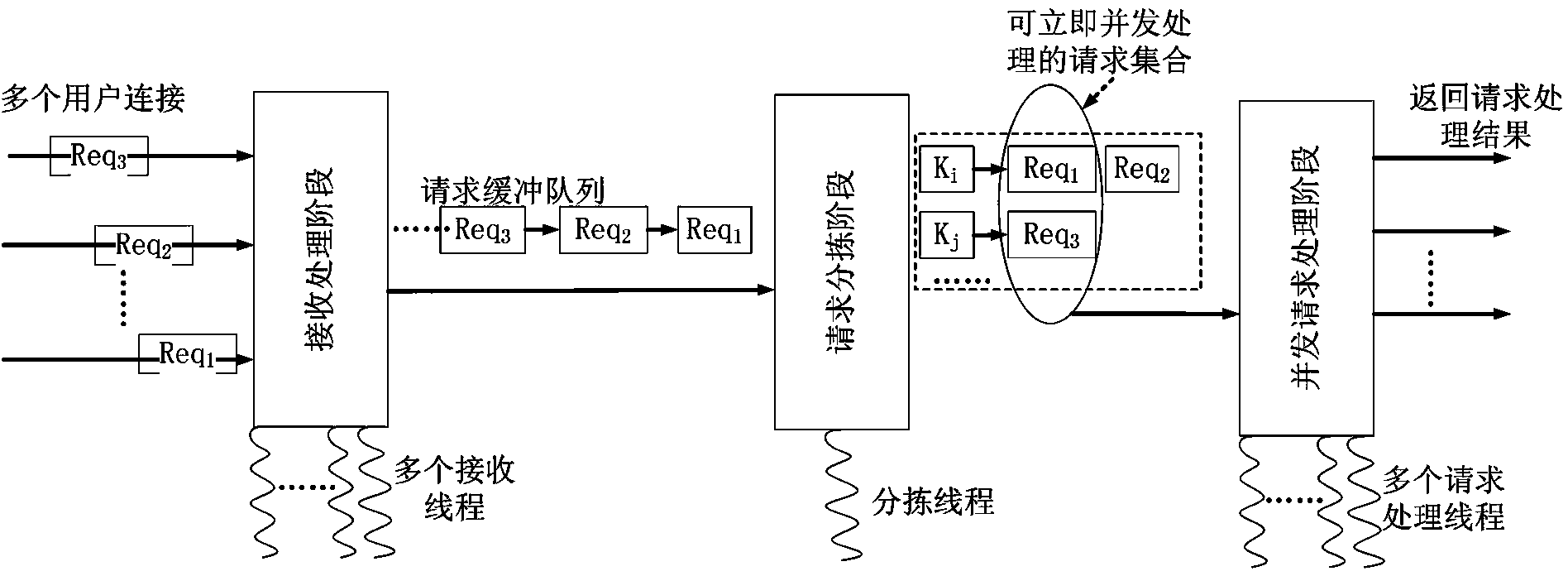

Method of high-speed concurrent processing of user requests of Key-Value database

ActiveCN103218455AImprove granularityStrong concurrent processing abilityConcurrent instruction executionSpecial data processing applicationsKey-value databaseMulti-core processor

The invention discloses a method of high-speed concurrent processing of user requests of a Key-Value database. The method of the high-speed concurrent processing of the user requests of the Key-Value database comprises the steps of (1) receiving the user requests, and sequentially adding the user requests into a request buffering queue; (2) initializing a key code classification queuing list, continuously popping the user requests out from the request buffering queue according to a first-in first-out order, sorting the user requests to different pending processing queues according to different key codes of the user requests, and adding a mapping relation between the key codes and the pending processing queues into the key code classification queuing list; and (3) initializing a request assembly, continuously popping the user requests out on the head portion of the pending processing queues to the request assembly, using worker threads with a preset number to carry out concurrent processing on the user requests in the request assembly, and returning processing results to users. The method of the high-speed concurrent processing of the user requests of the Key-Value database has the advantages of being high in concurrent processing fine grit, good in concurrent processing capacity, high in use ratio of hardware resources, balanced in load of all processor cores in a multi-core processor, and capable of ensuring sequence among read-write dependent requests.

Owner:NAT UNIV OF DEFENSE TECH

Device and method for correcting errors in a system having at least two execution units having registers

InactiveUS20090044044A1The process is convenient and fastEasy to operateRedundant operation error correctionRedundant hardware error correctionProcessor registerExecution unit

A device for correcting errors in a system having at least two execution units having registers is presented, the registers being designed for recording data. The device has comparison device(s) that are set up such that through a comparison of data that are provided for storage in the registers, a deviation and thus an error may be ascertained. Furthermore, at least one shadow register that is set up such that data concerning the data of the registers may be stored therein, and device(s) are provided for restoring error-free data in at least one register on the basis of the data in the at least one shadow register when an error is detected. This device may be used to improve the safety of a multicore processor.

Owner:ROBERT BOSCH GMBH

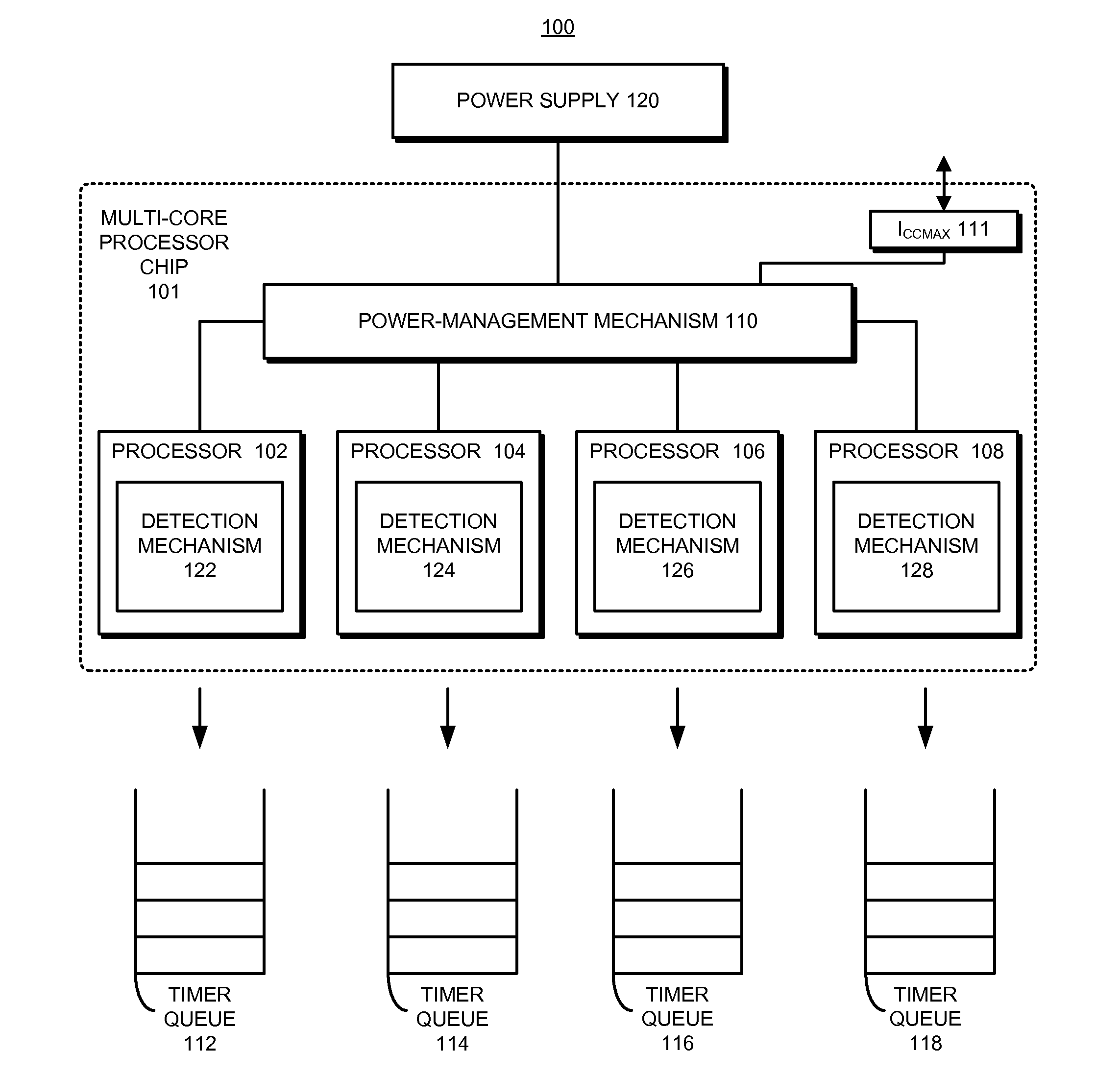

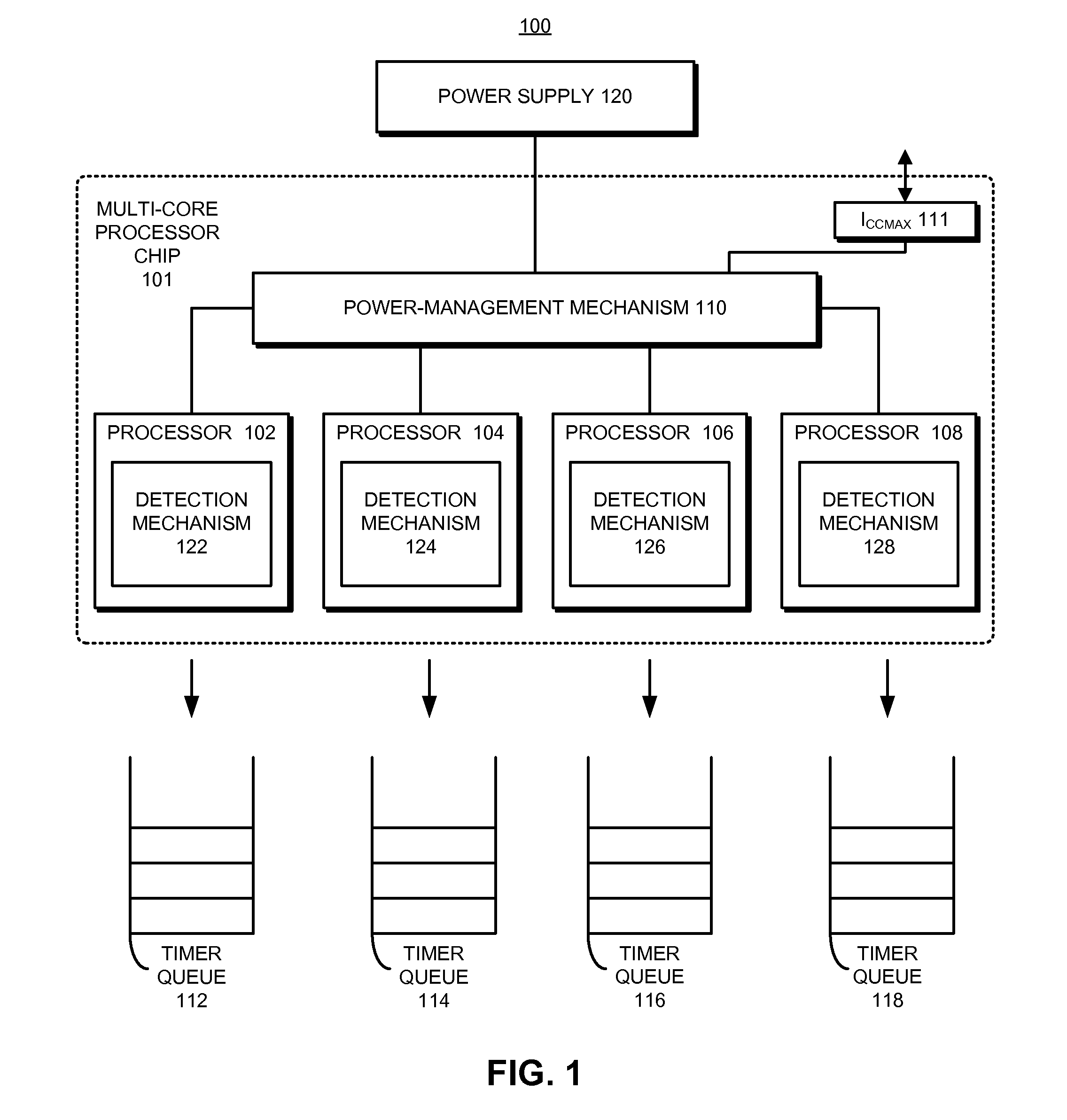

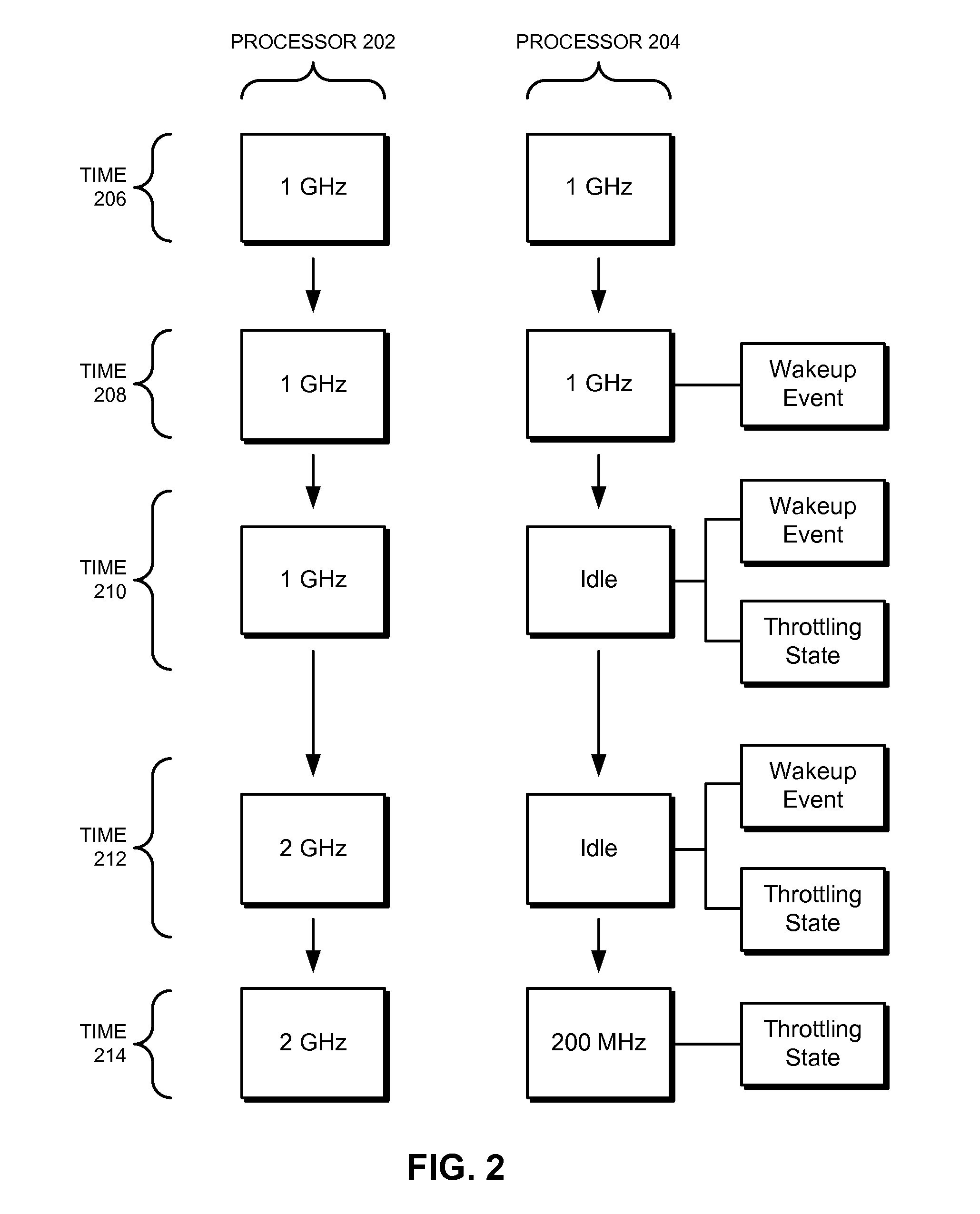

Facilitating power management in a multi-core processor

ActiveUS20120072746A1Convenient power managementSave powerEnergy efficient ICTVolume/mass flow measurementEffective powerActive state

The disclosed embodiments provide a system that facilitates power management in a multi-core processor. During operation, the system detects a change related to a number of active processor cores in the multi-core processor. (Within this system, a given processor core can reside in an active state, wherein the given processor core can draw an active power, or alternatively in a constrained state, wherein the given processor core can draw a constrained power, which is less than the active power.) In response to detecting the change, the system computes a new current limit ICCMAX for the multi-core processor based on the number of active and constrained processor cores. Finally, the system communicates ICCMAX to a power-management mechanism within the multi-core processor. This enables the power-management mechanism to use ICCMAX to account for power saved by the constrained processor cores when the multi-core system is subsequently determining whether to change its operating frequency.

Owner:APPLE INC

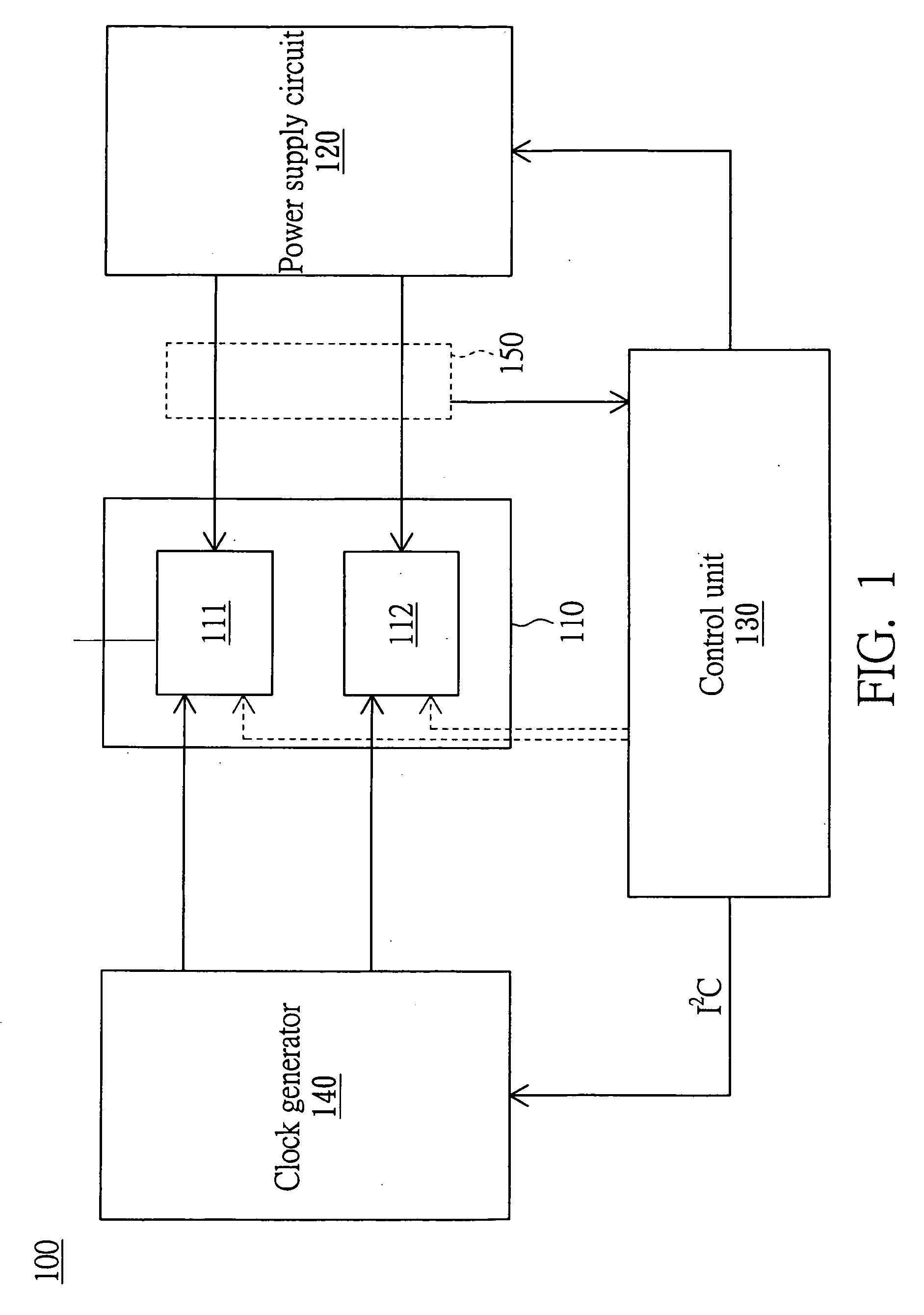

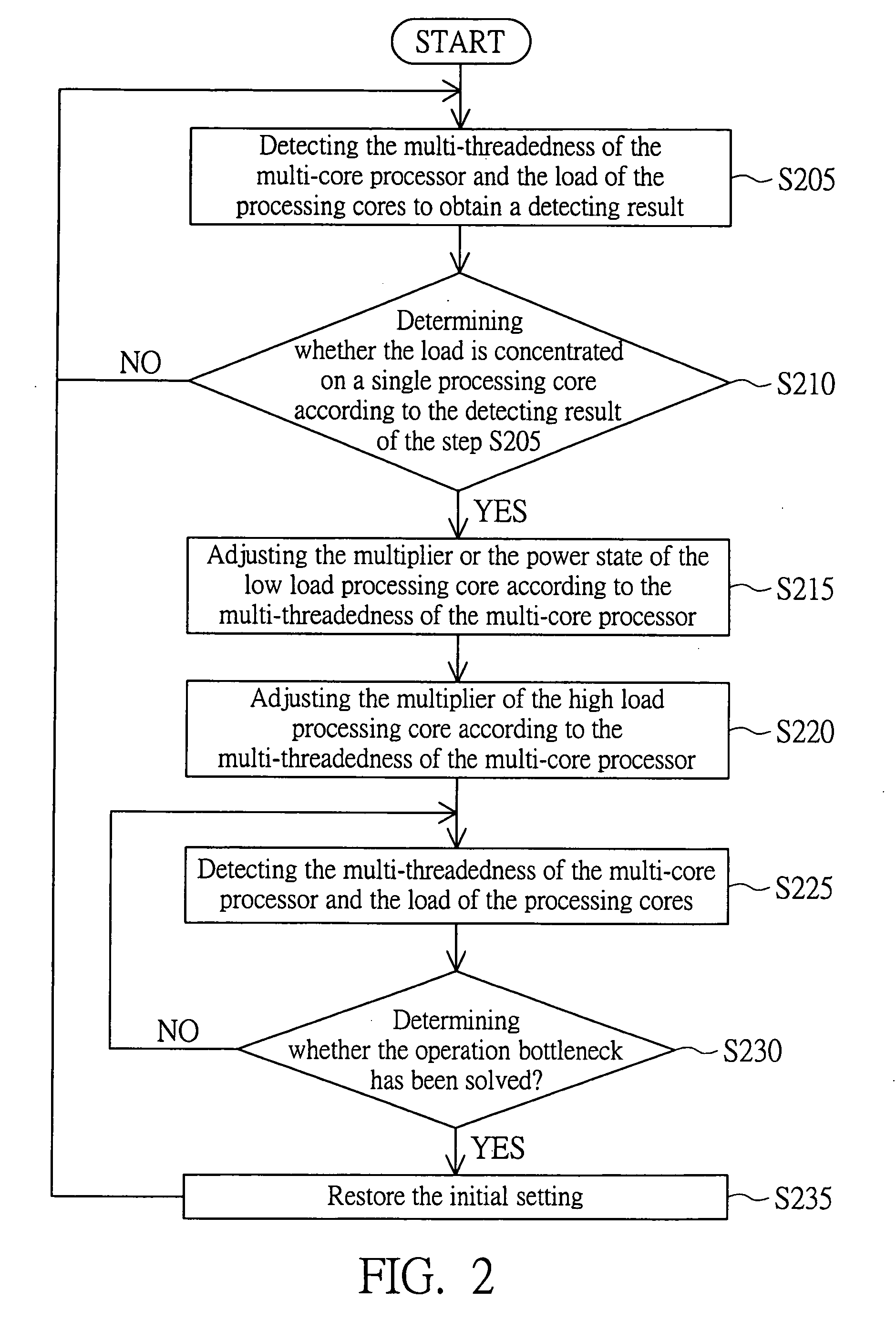

Adjusting performance method for multi-core processor

InactiveUS20080189569A1Decrease operation bottleneckImprove throughputMultiprogramming arrangementsGenerating/distributing signalsProcessing coreMulti-core processor

An adjusting performance method for a multi-core processor is provided. A plurality of processing cores of the multi-core processor at least includes a first processing core and a second processing core. The adjusting performance method includes the steps of detecting the multi-threadedness of the multi-core processor and the load of the processing cores to obtain a detecting result in the step (a), determining whether the operation bottleneck is concentrated on one processing core of the processing cores according to the detecting result in the step (b), and adjusting the operating frequency of the first processing core according to the multi-threadedness of the multi-core processor if the operation bottleneck occurs at the first processing core in the step (c).

Owner:ASUSTEK COMPUTER INC

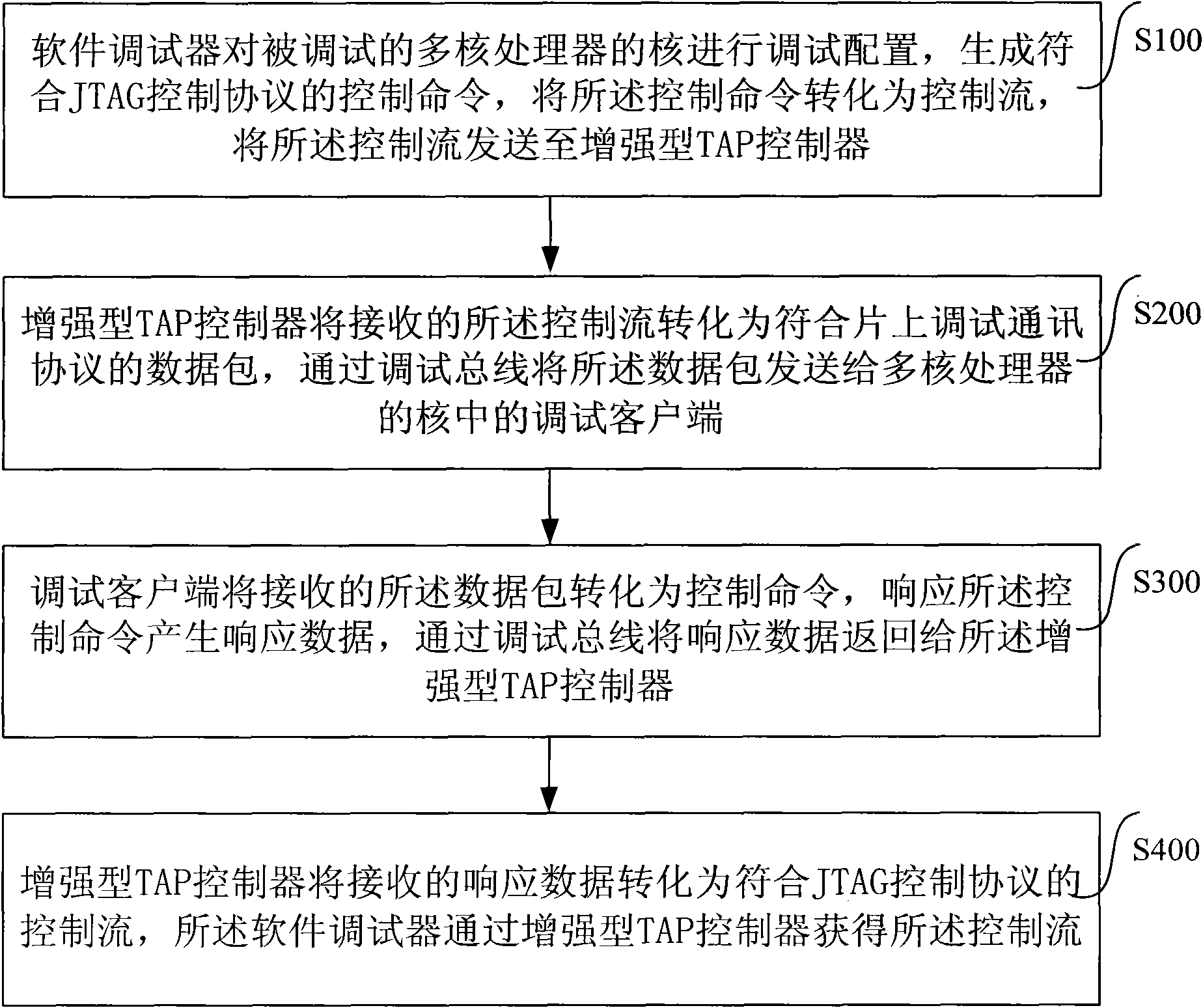

Multicore processor, and system and method for debugging multicore processor

InactiveCN102103535ANo need to change the interface designWithout changing the designDetecting faulty computer hardwareJoint Test Action GroupAccess port

The invention discloses a multicore processor. The multicore processor comprises a test access port controller and a debugging connector; the test access port controller is provided with an interface connected with a joint test action group (JTAG) simulator; the debugging connector is connected with test access ports of all the cores of the processor; all the test access ports are connected with the debugging connector in parallel; and the test access port controller is used for controlling the debugging connector to connect the cores of the processor to be tested to the simulator. In the processor with the structure, the designs of the standard JTAG port and the test access ports are not needed to be changed. The invention also discloses a system and a method for debugging the multicore processor.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

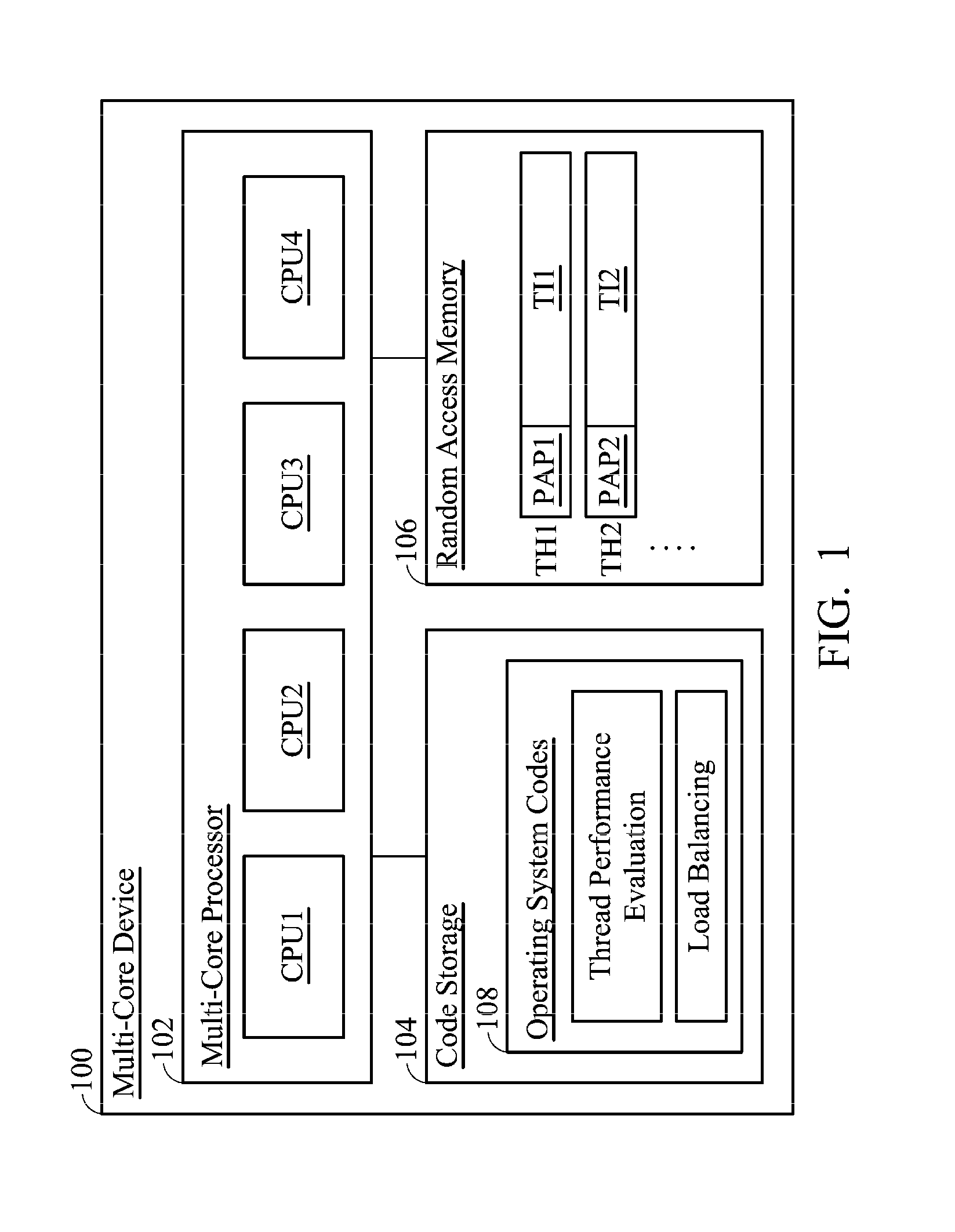

Multi-core device and multi-thread scheduling method thereof

InactiveUS20140089936A1Program initiation/switchingResource allocationThread schedulingParallel computing

A multi-core device and a multi-thread scheduling method thereof are disclosed. The multi-thread scheduling method includes the following steps: recording thread performance-associated parameters for a thread; and performing a thread load balancing between multiple central processing units of a multi-core processor of the multi-core device. The thread load balancing is performed according to a thread critical performance condition of the thread and the thread critical performance condition is determined based on the thread performance-associated parameters.

Owner:HTC CORP

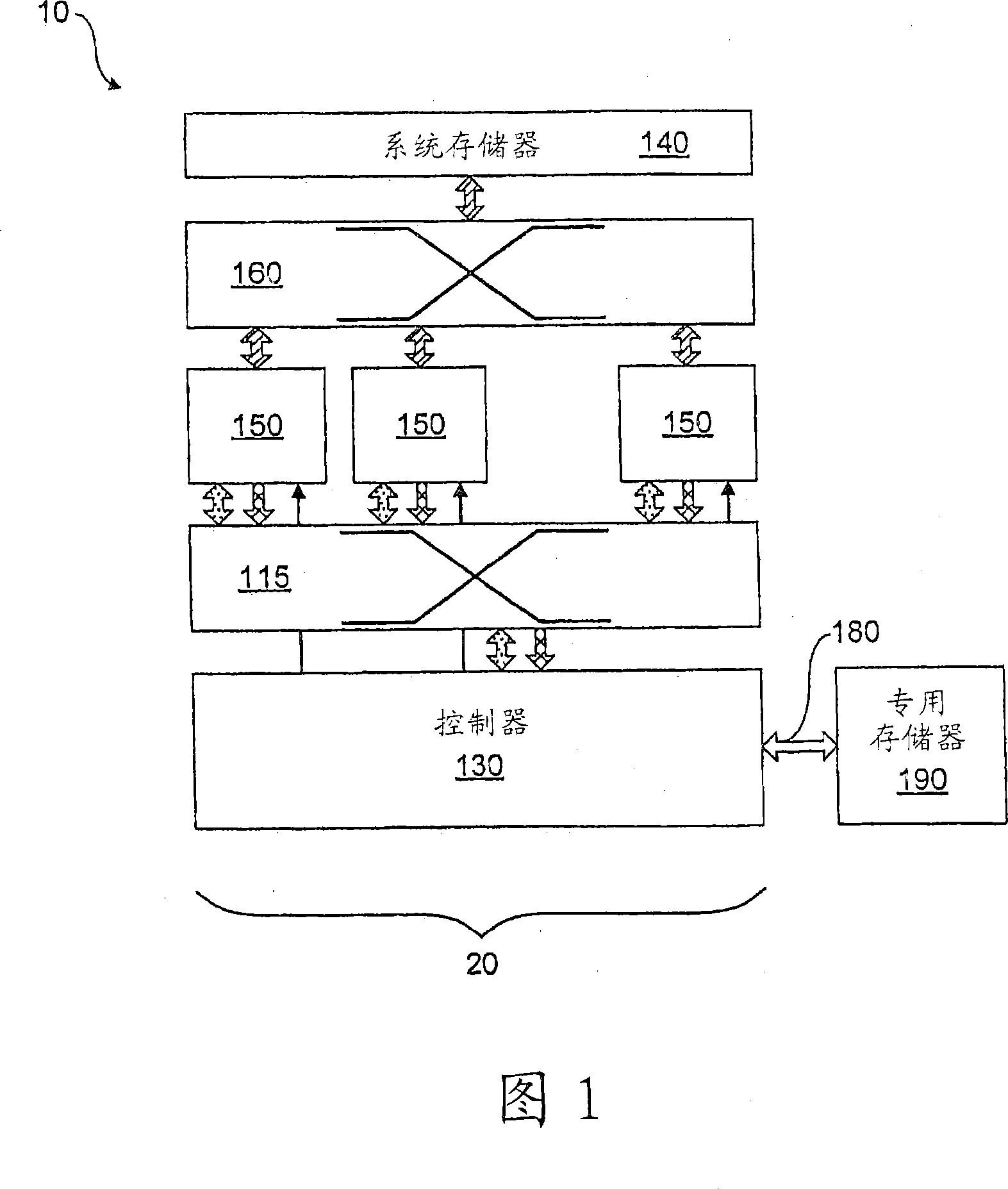

System and method for distributed multi-processing security gateway

ActiveUS8079077B2Digital data processing detailsUnauthorized memory use protectionData packNetwork addressing

A system and method for a distributed multi-processing security gateway establishes a host side session, selects a proxy network address for a server, uses the proxy network address to establish a server side session, receives a data packet, assigns a central processing unit core from a plurality of central processing unit cores in a multi-core processor of the security gateway to process the data packet, processes the data packet according to security policies, and sends the processed data packet. The proxy network address is selected such that a same central processing unit core is assigned to process data packets from the server side session and the host side session. By assigning central processing unit cores in this manner, higher capable security gateways are provided.

Owner:A10 NETWORKS

Systems and methods for operating symbology reader with multi-core processor

ActiveUS8794521B2Efficiently dissipatedHighly effectiveSensing by electromagnetic radiationComputer hardwareHigh resolution imaging

This invention provides a vision system camera, and associated methods of operation, having a multi-core processor, high-speed, high-resolution imager, FOVE, auto-focus lens and imager-connected pre-processor to pre-process image data provides the acquisition and processing speed, as well as the image resolution that are highly desirable in a wide range of applications. This arrangement effectively scans objects that require a wide field of view, vary in size and move relatively quickly with respect to the system field of view. This vision system provides a physical package with a wide variety of physical interconnections to support various options and control functions. The package effectively dissipates internally generated heat by arranging components to optimize heat transfer to the ambient environment and includes dissipating structure (e.g. fins) to facilitate such transfer. The system also enables a wide range of multi-core processes to optimize and load-balance both image processing and system operation (i.e. auto-regulation tasks).

Owner:COGNEX CORP

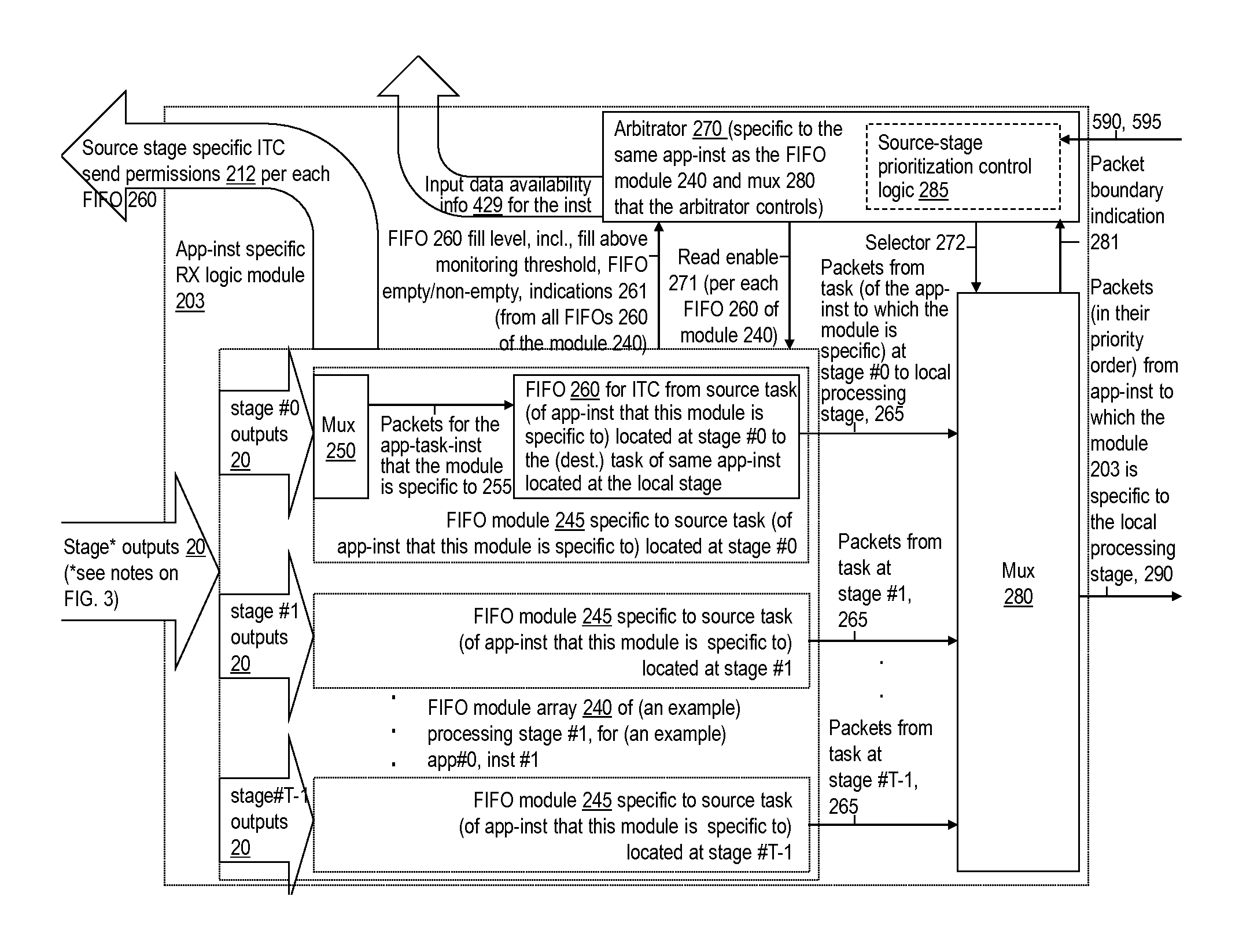

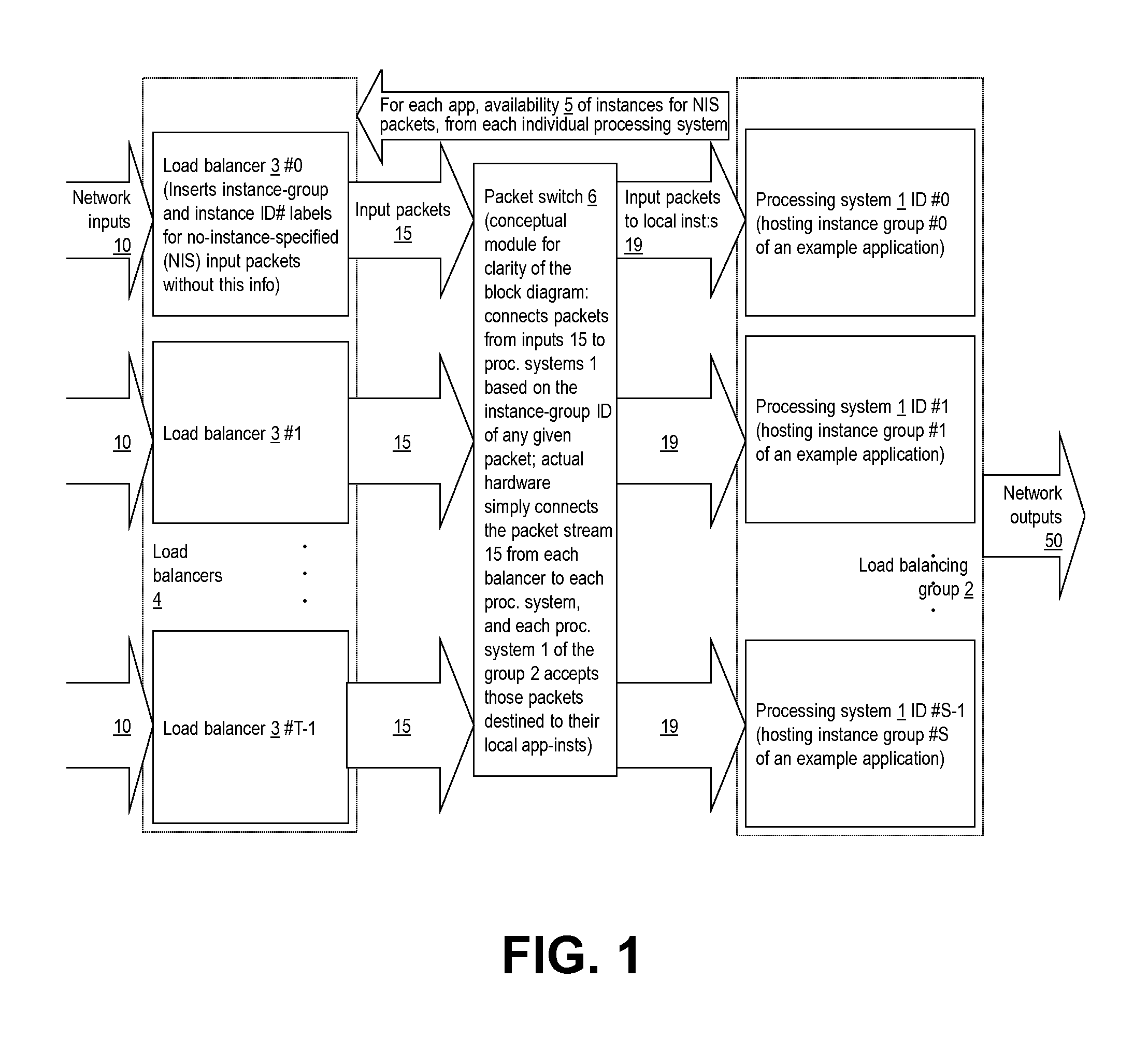

Concurrent program execution optimization

InactiveUS9448847B2Effective inter-application isolationAvoid accessResource allocationSoftware engineeringParallel computingManycore processor

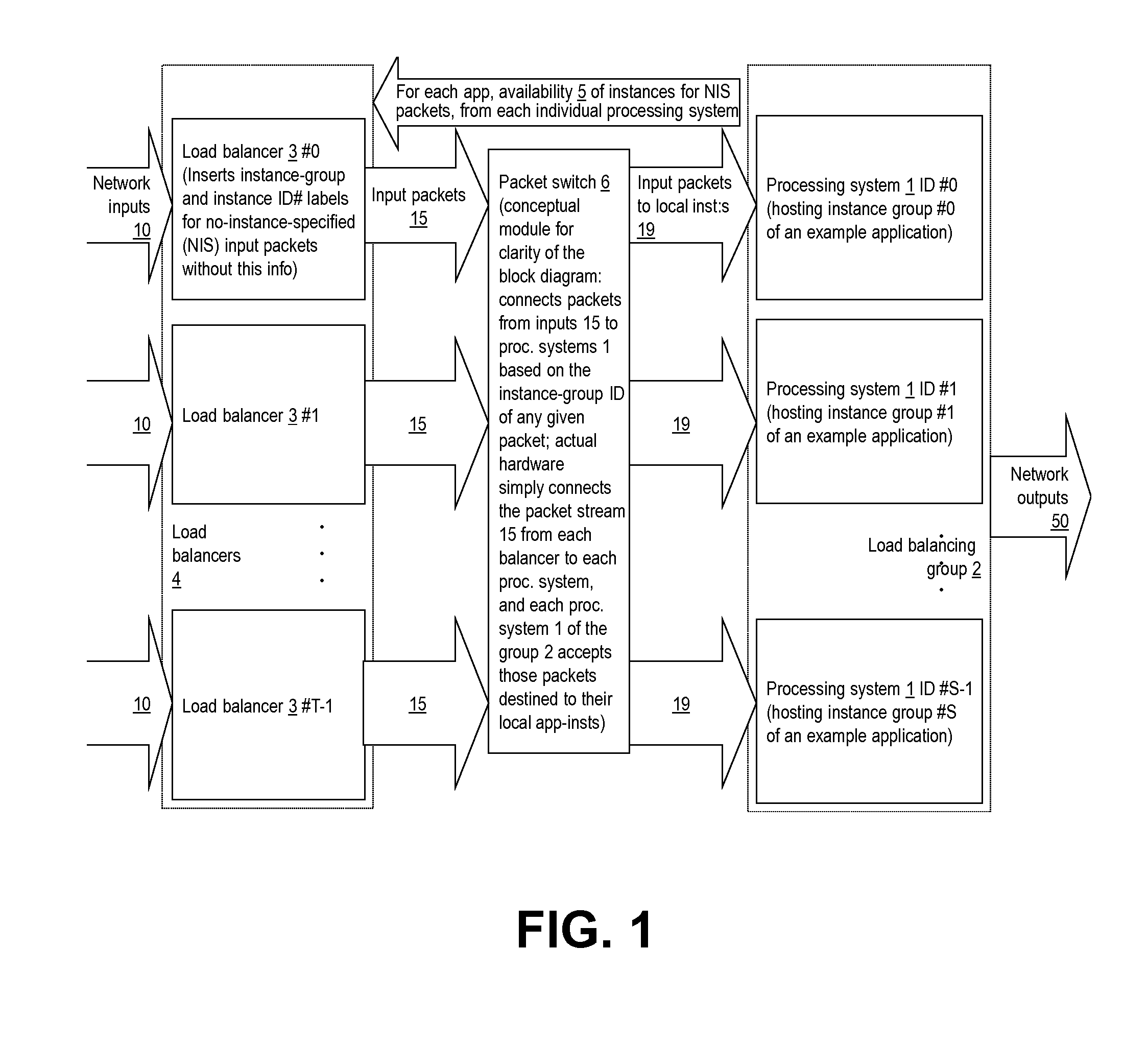

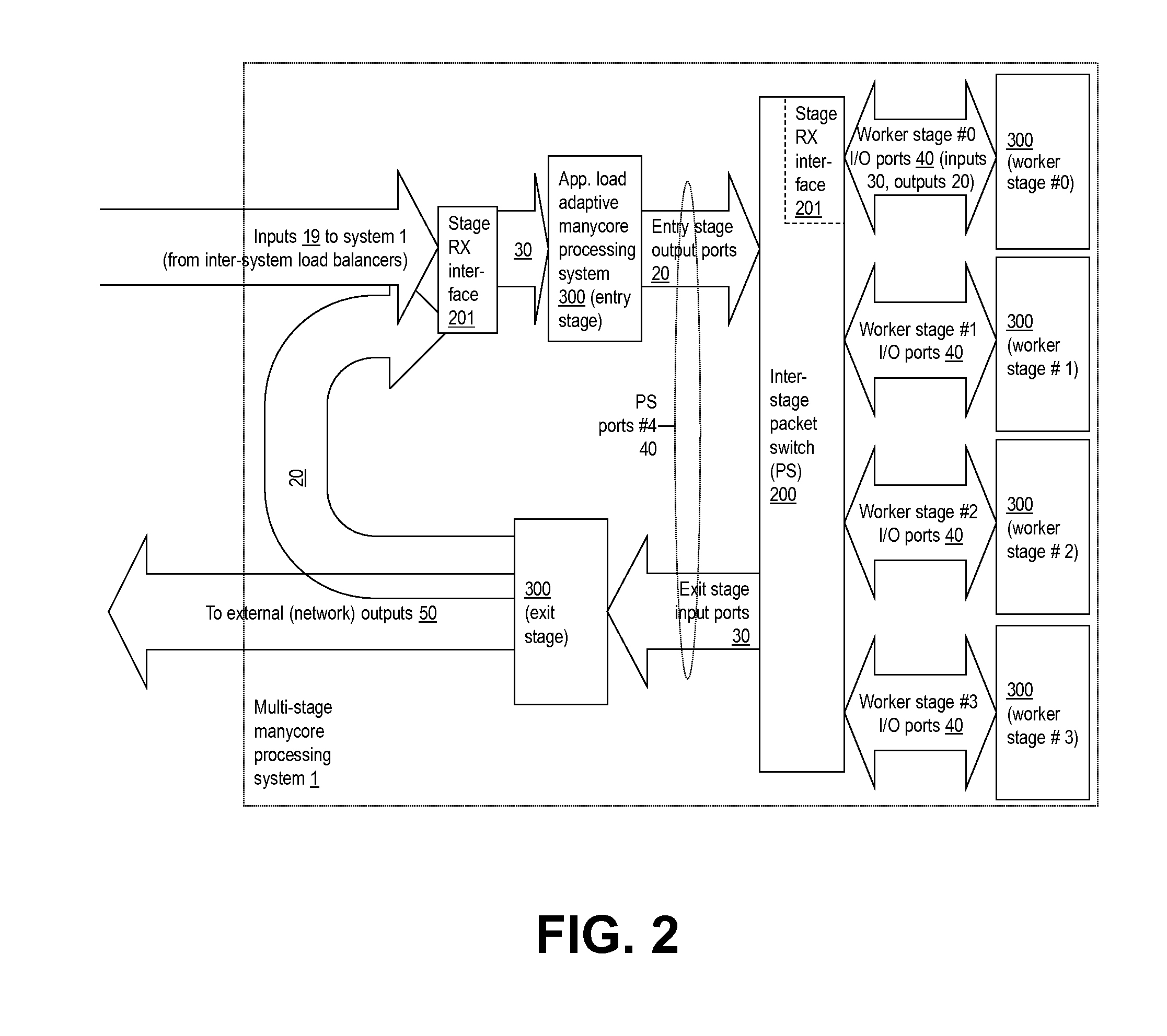

An architecture for a load-balanced groups of multi-stage manycore processors shared dynamically among a set of software applications, with capabilities for destination task defined intra-application prioritization of inter-task communications (ITC), for architecture-based ITC performance isolation between the applications, as well as for prioritizing application task instances for execution on cores of manycore processors based at least in part on which of the task instances have available for them the input data, such as ITC data, that they need for executing.

Owner:THROUGHPUTER

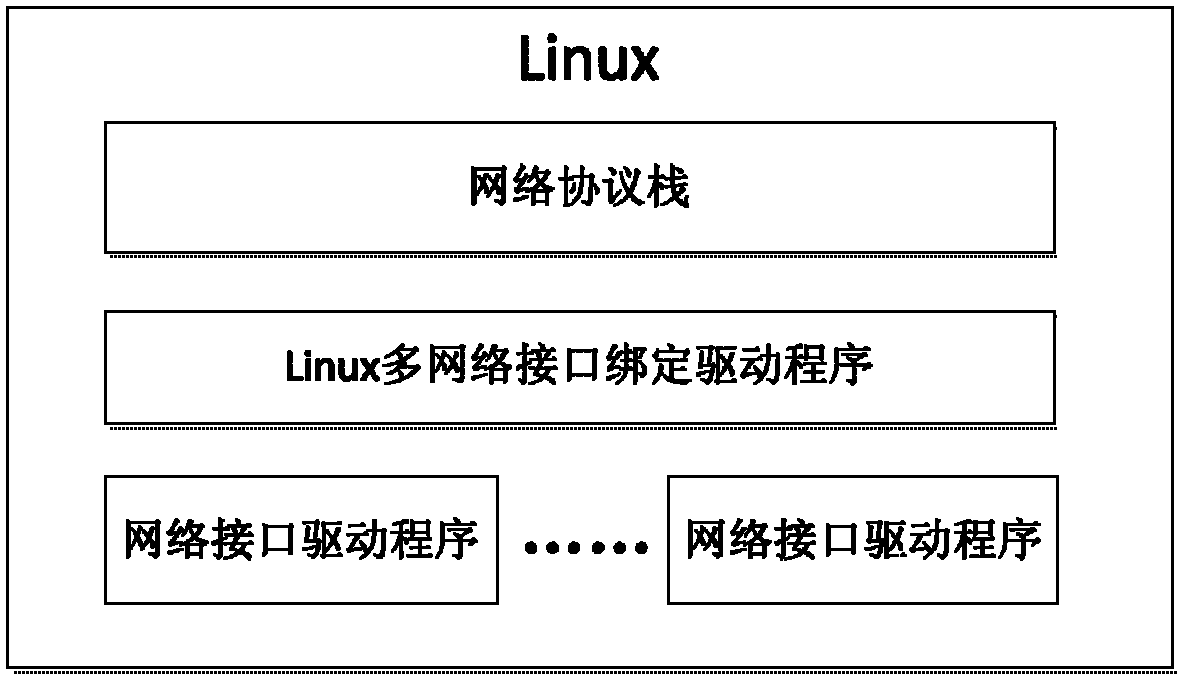

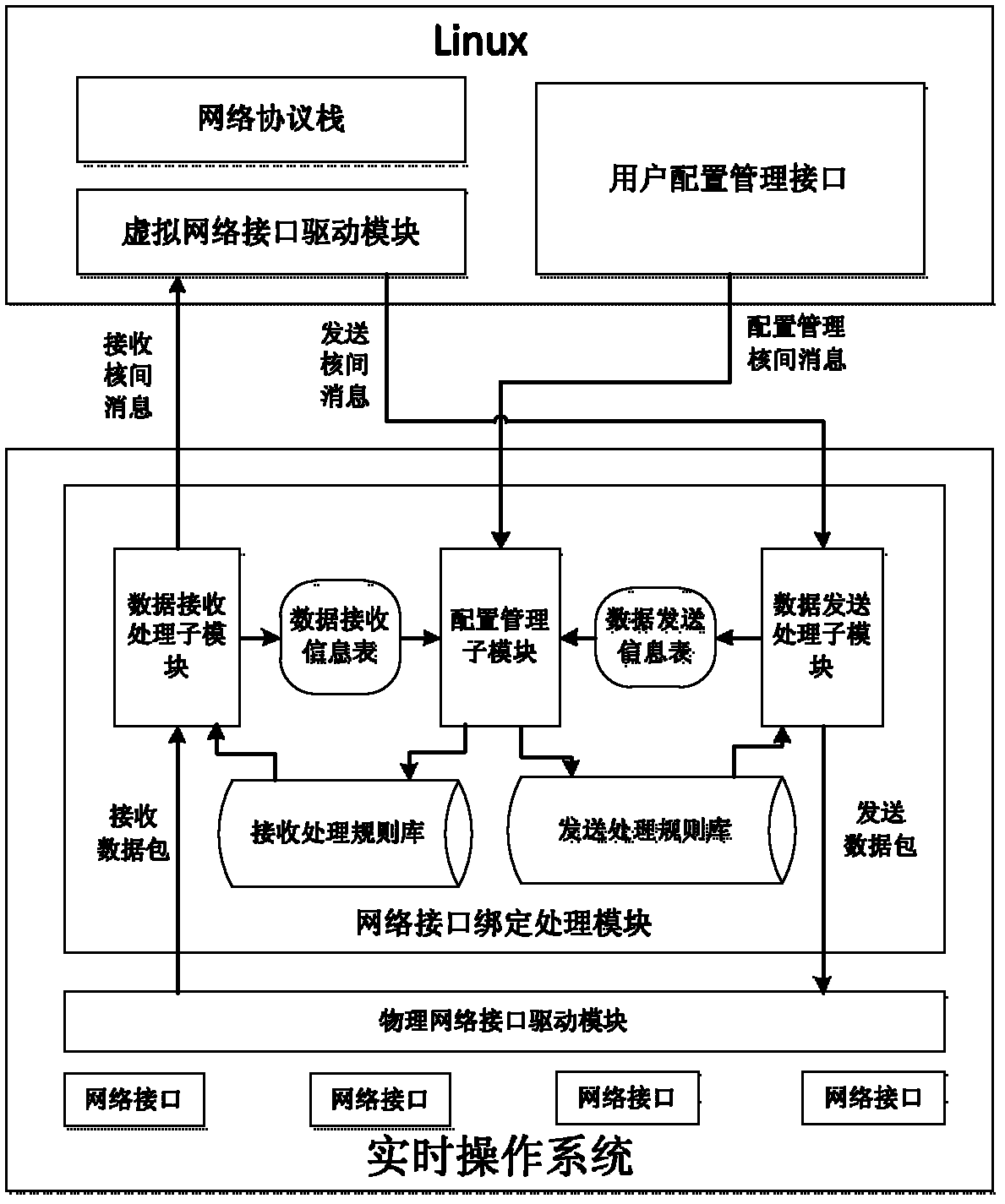

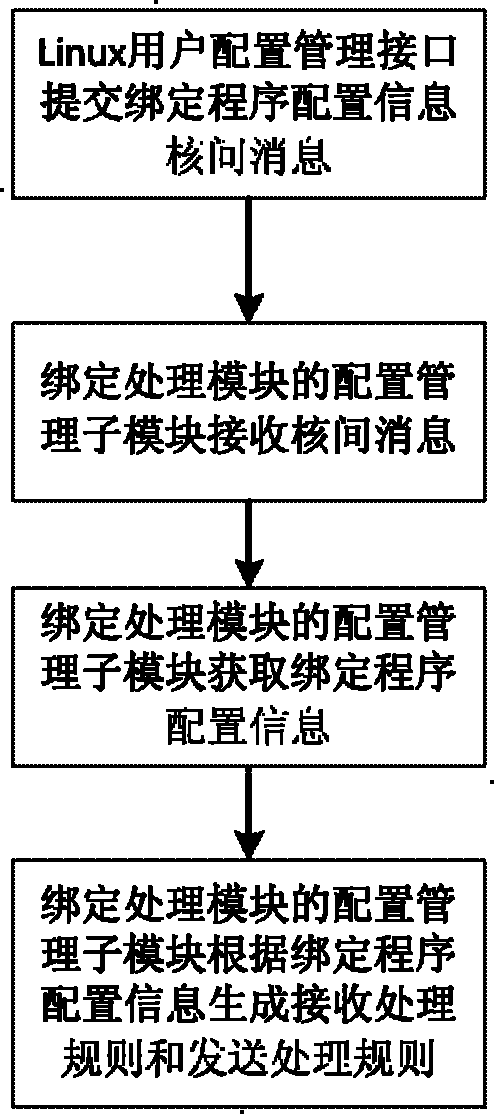

Binding system and method of multiple network interfaces

ActiveCN103176780AIncrease flexibilityEfficient data processingSoftware simulation/interpretation/emulationOperational systemGNU/Linux

The invention discloses a binding system and method of multiple network interfaces. A Linux operating system and a real-time operating system simultaneously operate based on a multi-core processor. The real-time operating system comprises a physical network interface drive module and a network interface binding processing module aiming at the plurality of network interfaces. The Linux operating system comprises a virtual network interface drive module and a user configuration management interface. The physical network interface drive module is responsible for managing and controlling the network interfaces and receiving and dispatching physical network data. The network interface binding processing module is responsible for obtaining a data package from the physical network interface drive module, processing the received data package according to rules in a data receiving and processing rule base and submitting the processed data package to the virtual network interface drive module at a receiving side. The network interface binding processing module is responsible for receiving data from the virtual network interface drive module, processing the received data package according to a data dispatching rule base and submitting the processed data package to the physical network interface drive module to conduct dispatch at a dispatch side.

Owner:ZHENGZHOU SEANET TECH CO LTD

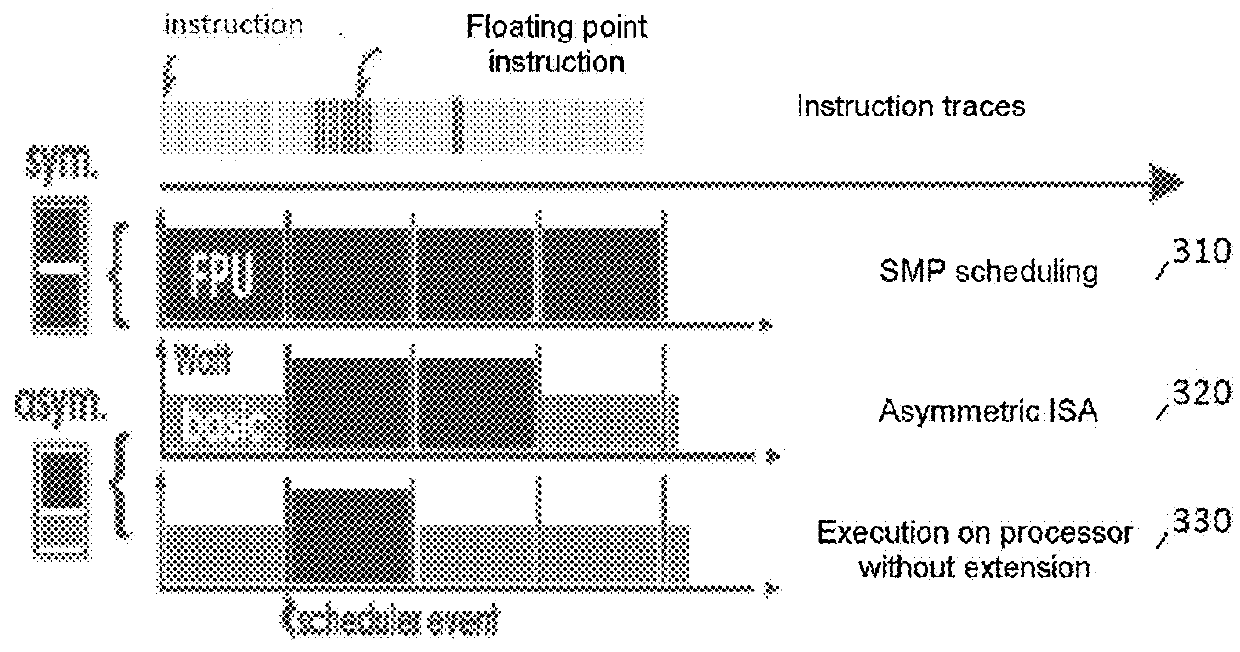

Placement of a calculation task on a functionally asymmetric processor

InactiveUS20180095751A1Task placement is flexible and transparent for the userReduced flexibilityProgram initiation/switchingRuntime instruction translationParallel computingFunctional asymmetry

A method for managing a calculation task on a functionally asymmetric multicore processor, at least one core of the processor associated with one or more hardware extensions, comprises the steps of receiving a calculation task associated with instructions that can be executed by a hardware extension; receiving calibration data associated with the hardware extension; and determining an opportunity cost of execution of the calculation task as a function of the calibration data. Developments describe the determination of the calibration data in particular by counting or by computation (on line and / or off line) of the classes of the instructions executed, the execution of a predefined set of instructions representative of the execution room of the extension, the inclusion of energy and temperature aspects, the translation or the emulation of instructions or the placement of calculation tasks on the different cores. System and software aspects are described.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

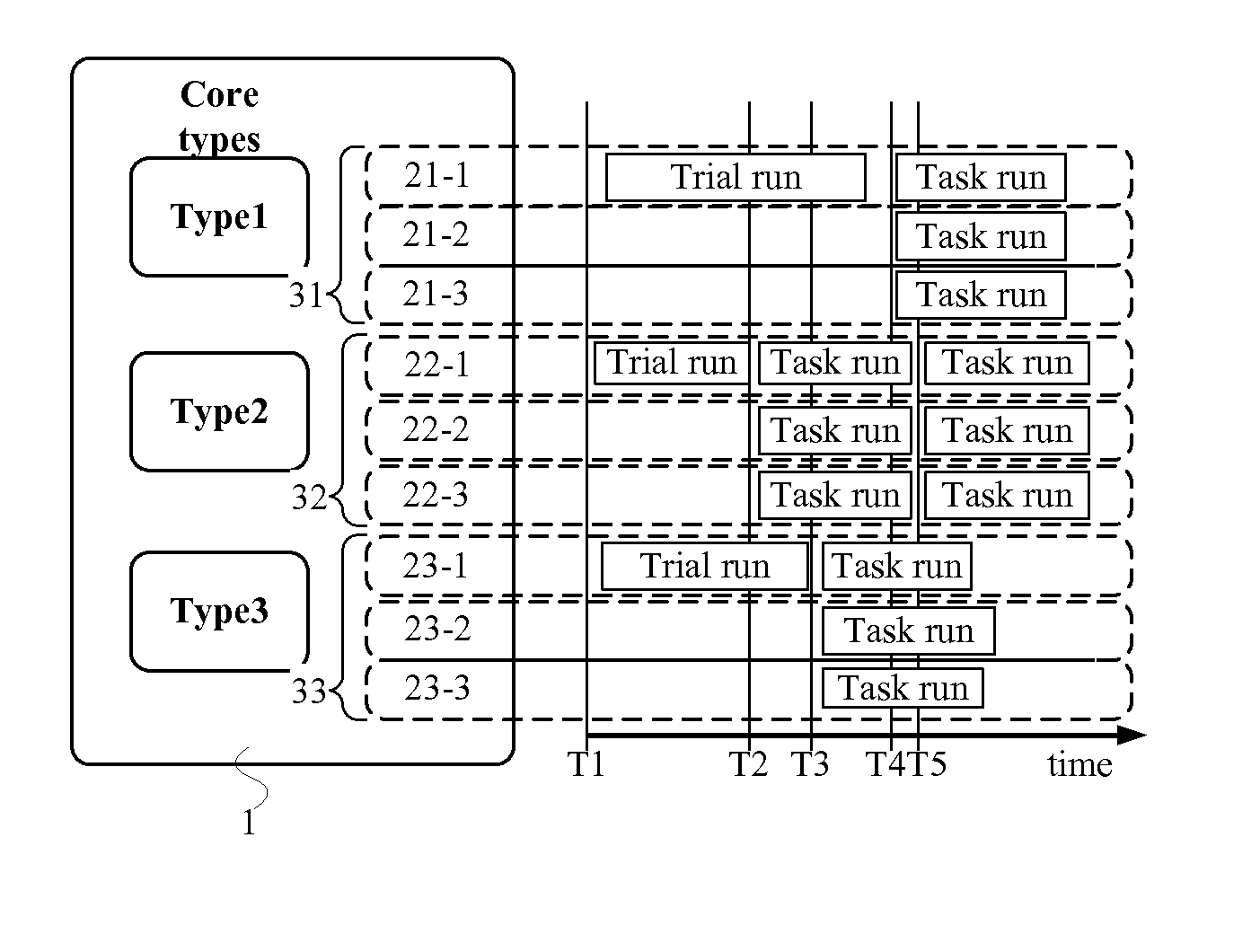

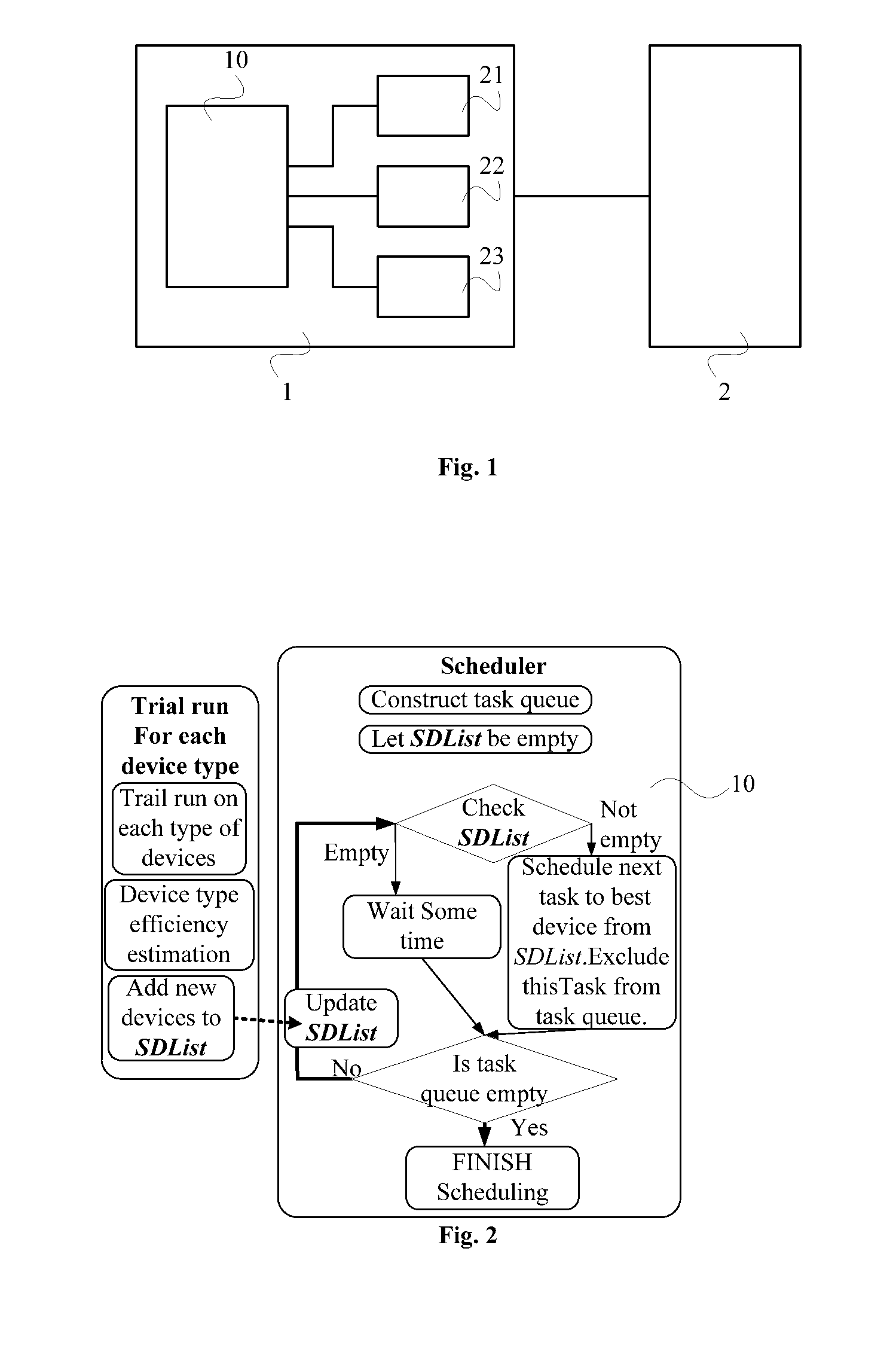

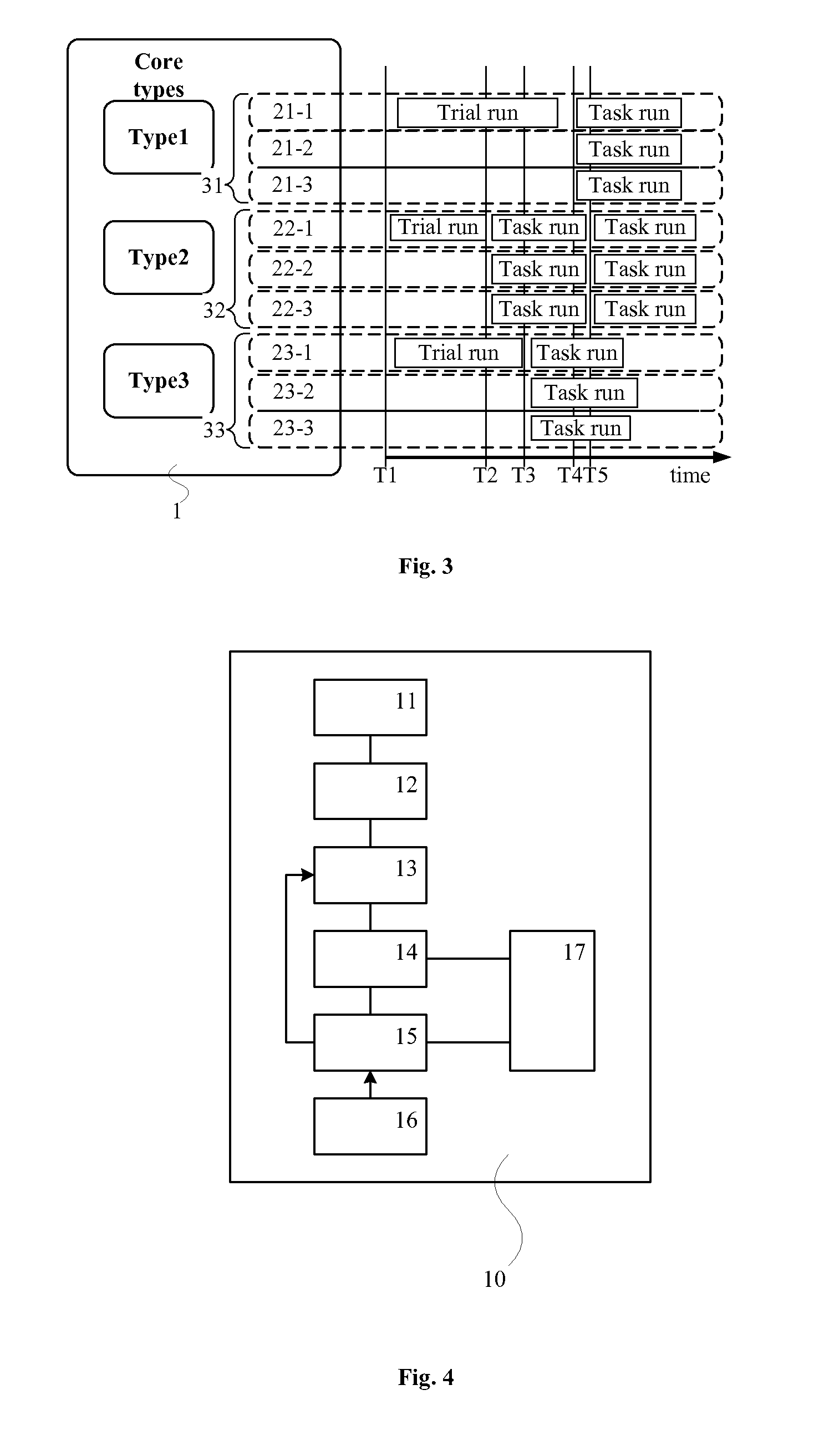

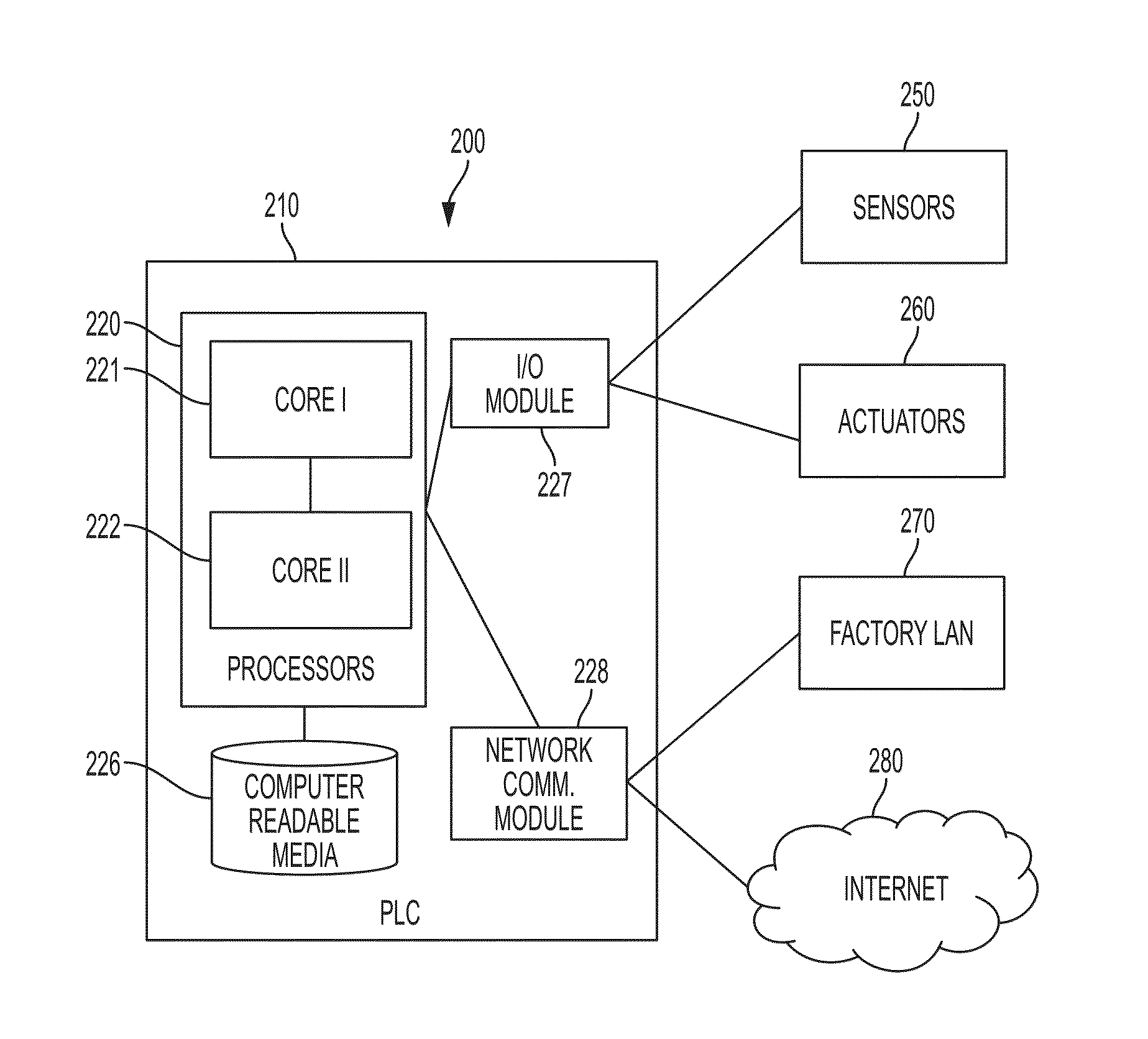

Processing method for a multicore processor and multicore processor

The present invention relates to a multicore processor 1. In order to select one of the multiple cores 21, 22, 23 in such a processor, an execution time of tasks which are performed multiple times is determined Based on the determined execution time on the individual cores 21, 22, 23, an appropriate core 21, 22, 23 for further executions of a task is selected. Additionally, the present invention further provides a code generator and code generating method for providing appropriate machine code for a multicore processor 1.

Owner:HUAWEI TECH CO LTD

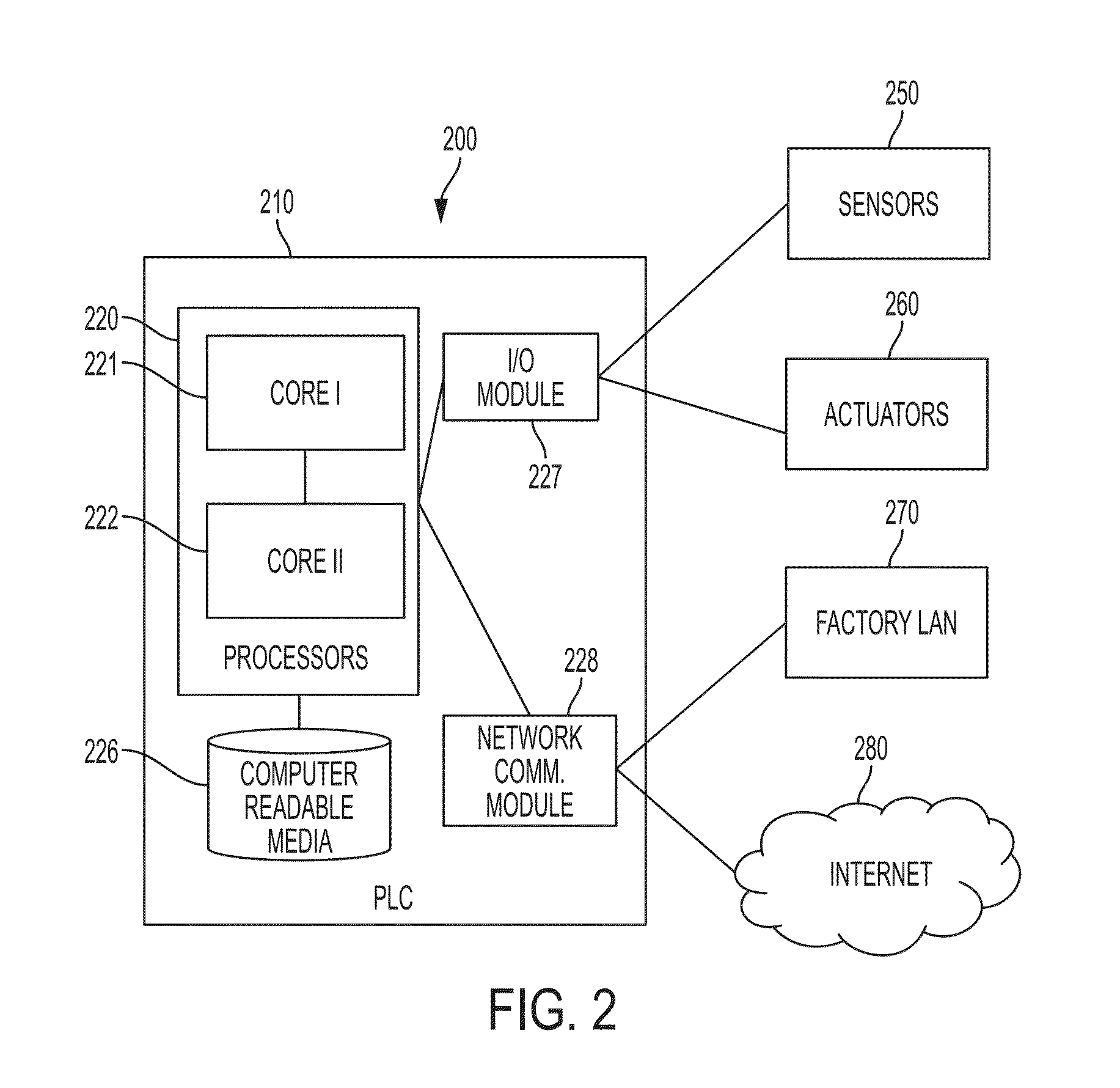

System and method of multi-core based software execution for programmable logic controllers

InactiveUS20160091882A1Computer controlSimulator controlProgrammable logic controllerProgrammable Interrupt Controller

Real-time programmable logic controller software is executed on a multicore processor system. An organizational block executer is executed on a first core, and system service functions associated with the programmable logic controller software are executed on the second core. The organizational block executer includes I / O scanning and logic solving in a single-threaded execution. Core-switch operations may be cyclically performed to move execution of the organizational block executer from the first core to the second core and back to the first core.

Owner:SIEMENS CORP

Concurrent Program Execution Optimization

InactiveUS20150058857A1Avoid conflicting resource access decisionEffective inter-application isolationSoftware engineeringInterprogram communicationComputer architectureEngineering

An architecture for a load-balanced groups of multi-stage manycore processors shared dynamically among a set of software applications, with capabilities for destination task defined intra-application prioritization of inter-task communications (ITC), for architecture-based ITC performance isolation between the applications, as well as for prioritizing application task instances for execution on cores of manycore processors based at least in part on which of the task instances have available for them the input data, such as ITC data, that they need for executing.

Owner:THROUGHPUTER

JTAG (Joint Test Action Group) real-time on-chip debug method and system of multicore processor

ActiveCN101840368AGood versatilityOvercome the problem of uncertain delayError detection/correctionClient-sideComputer hardware

The invention relates to JTAG (Joint Test Action Group) real-time on-chip debug method and system of a multicore processor. In the method, a software debugger generates a control command in accordance with a JTAG control protocol to cores of a debugged multicore processor, converts the control command to a control flow, and then sends the control flow to an enhanced TAP controller; the enhanced TAP controller converts the received control flow into a data packet in accordance with an on-chip debug communication protocol and sends the data packet to a debug user terminal through a debug bus; the debug user terminal converts the received data packet into a control command, and a response control command generates response data returned to the enhanced TAP controller through the debug bus; the enhanced TAP controller converts the received response data into a control flow in accordance with the JTAG control protocol, and the software debugger obtains the control flow through the enhancedTAP controller. The invention can debug the multicore processor, but is not limited by the quantity of cores of the multicore processor.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

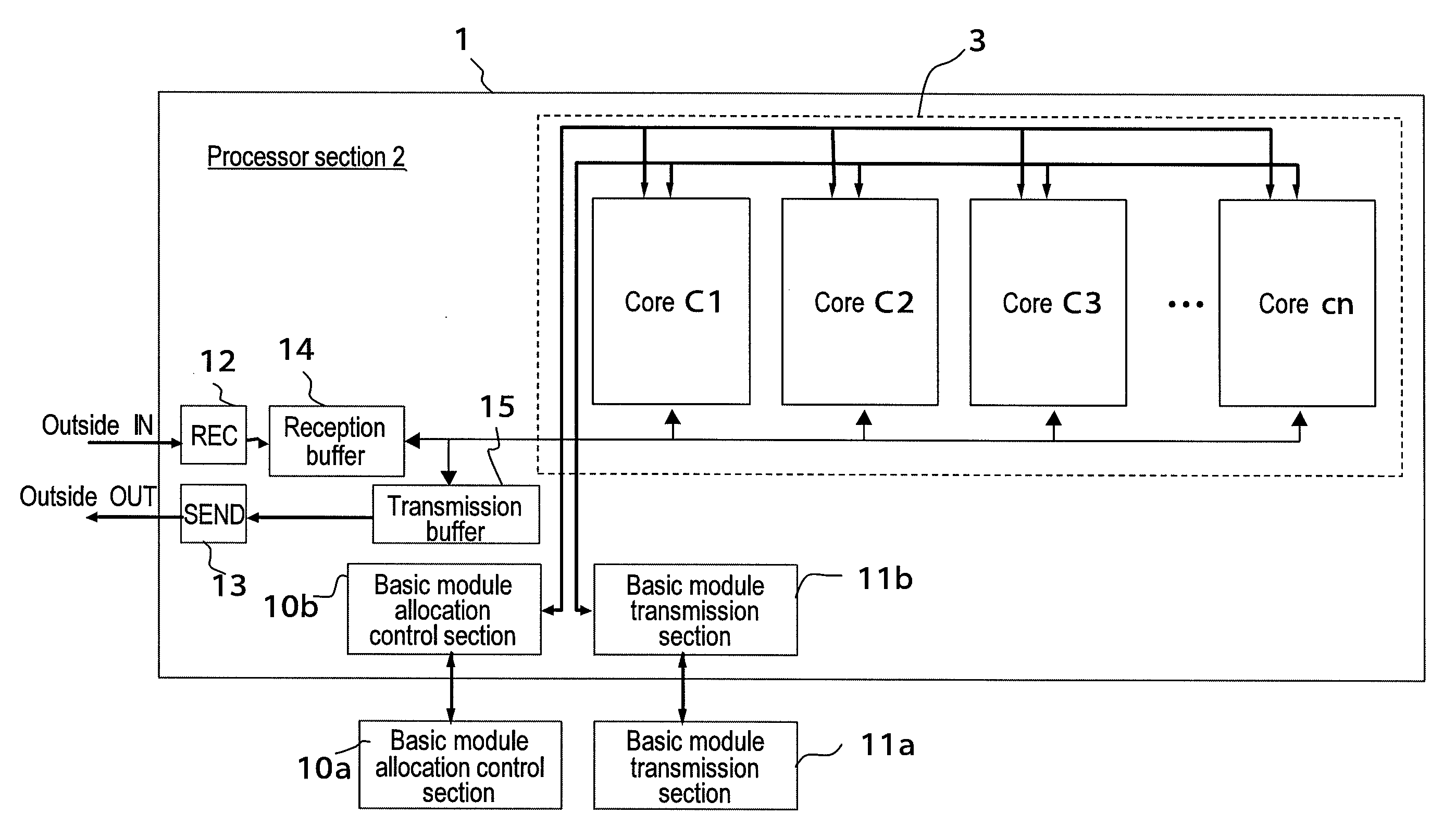

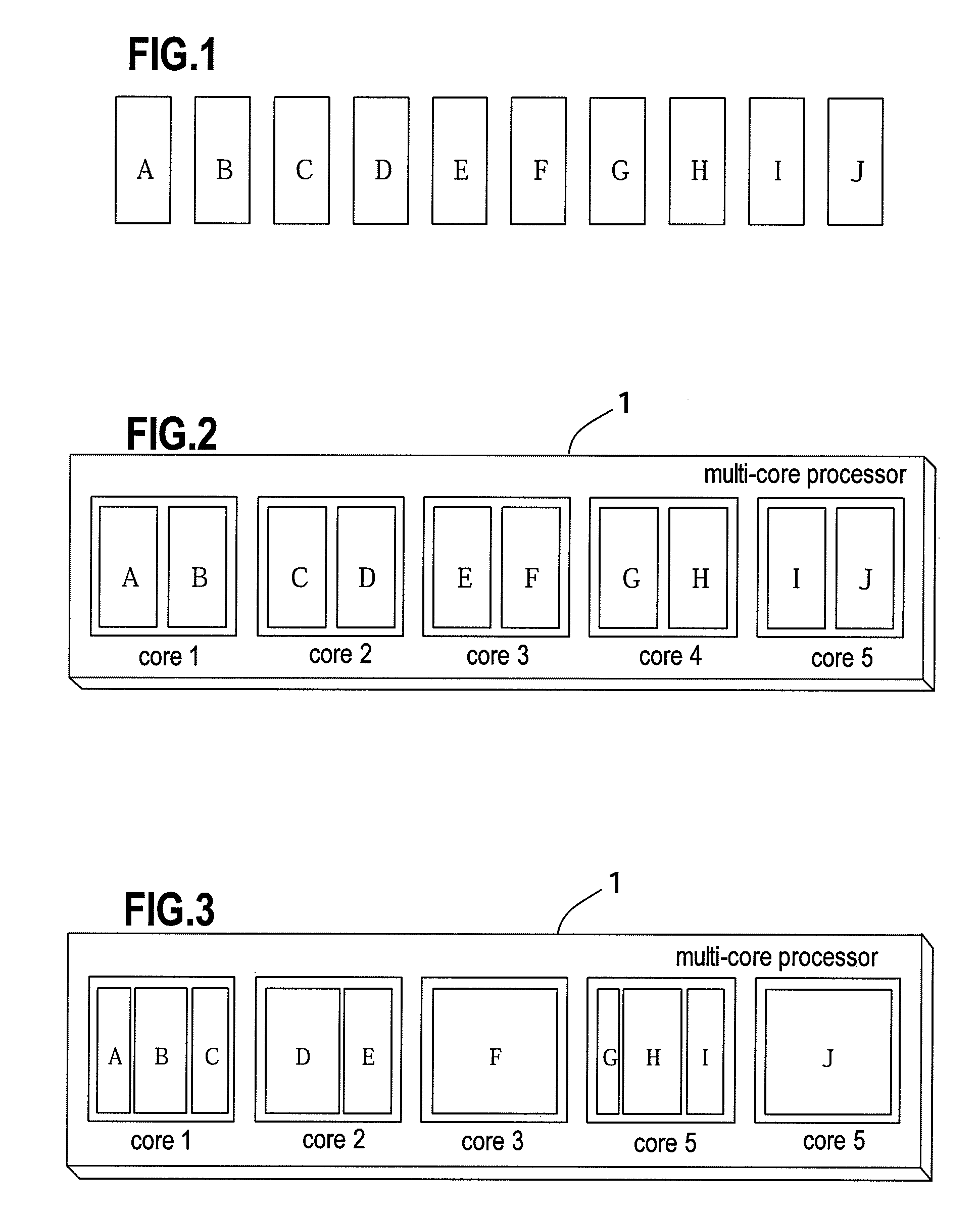

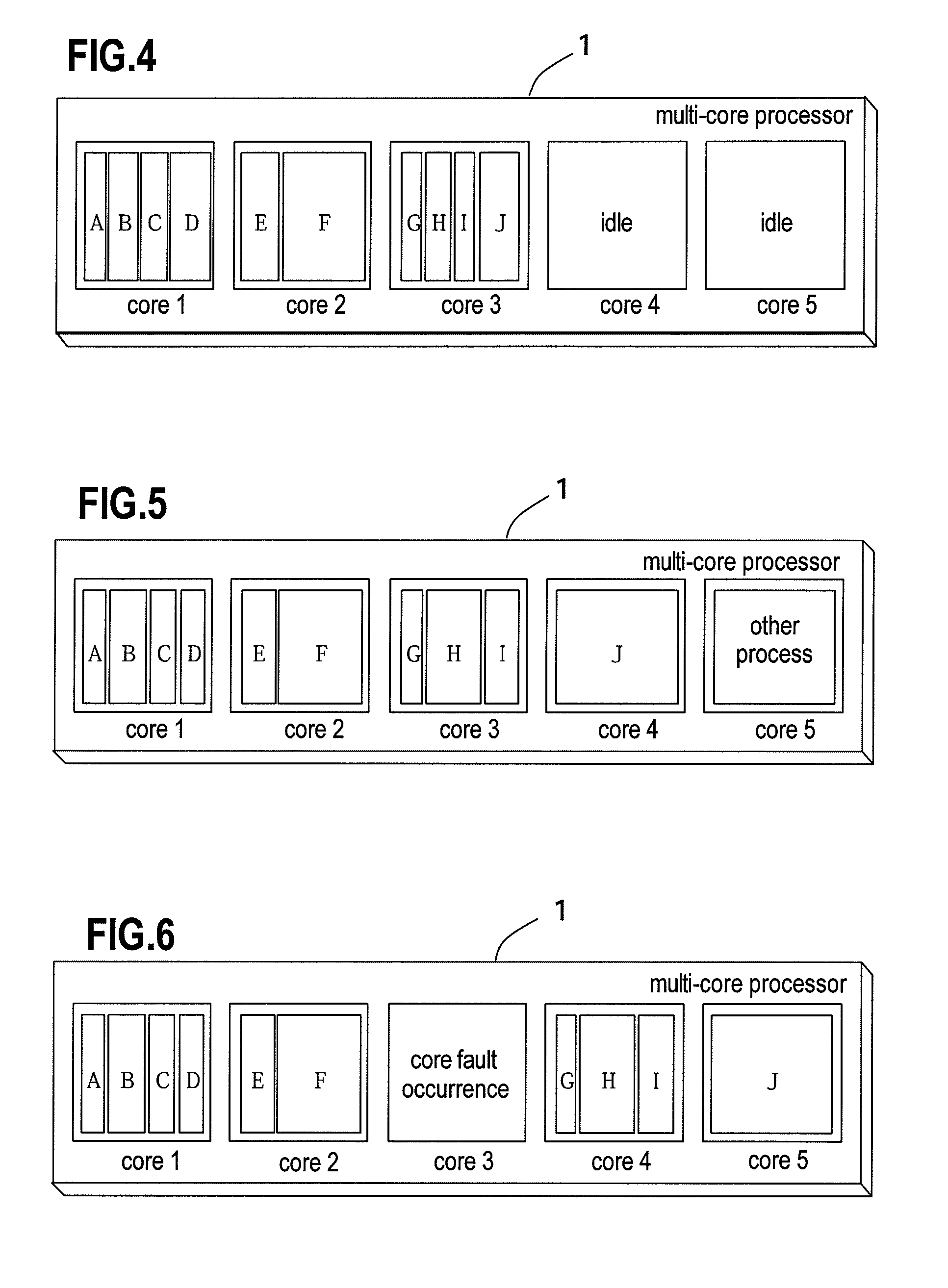

Multi-core processor

InactiveUS20080168466A1Simple and efficient processAutomated methodMultiprogramming arrangementsMemory systemsMulti-core processorInput/output

An algorithm in a multi-core processor having a plurality of cores for deciding processing allocation to each core to distribute the processing load thereof, and an efficient processing allocation algorithm simplified for software engineers are established. In order to achieve the above processing load distribution, the multi-core processor includes a plurality of basic modules divided into minimum configuration units, each having a uniform input / output format interface, so as to perform required processing contents in the overall processor. As an initial allocation, the above plurality of basic modules are allocated in distribution to the above plurality of cores, and subsequently, based on functional information of each core, the above plurality of initially allocated basic modules are relocated either periodically or at appropriate timing.

Owner:FUJITSU LTD

Web browsing apparatus and method through storing and optimizing javascript® code

ActiveUS20120185822A1Software engineeringSpecific program execution arrangementsWeb applicationWeb page

A web browsing method and apparatus for enhancing a user's convenience in web browsing is provided in a system that uses a multi-core processor. The web browsing method and apparatus is applicable in a system, such as a smart phone that has a low computing power or that has a storage device like a flash memory operating in a rapid manner. Optimized machine codes are stored in files and incremental optimization is achieved, so the JAVASCRIPT® program of the web application has a small compilation overhead and achieves fast execution.

Owner:SAMSUNG ELECTRONICS CO LTD +1

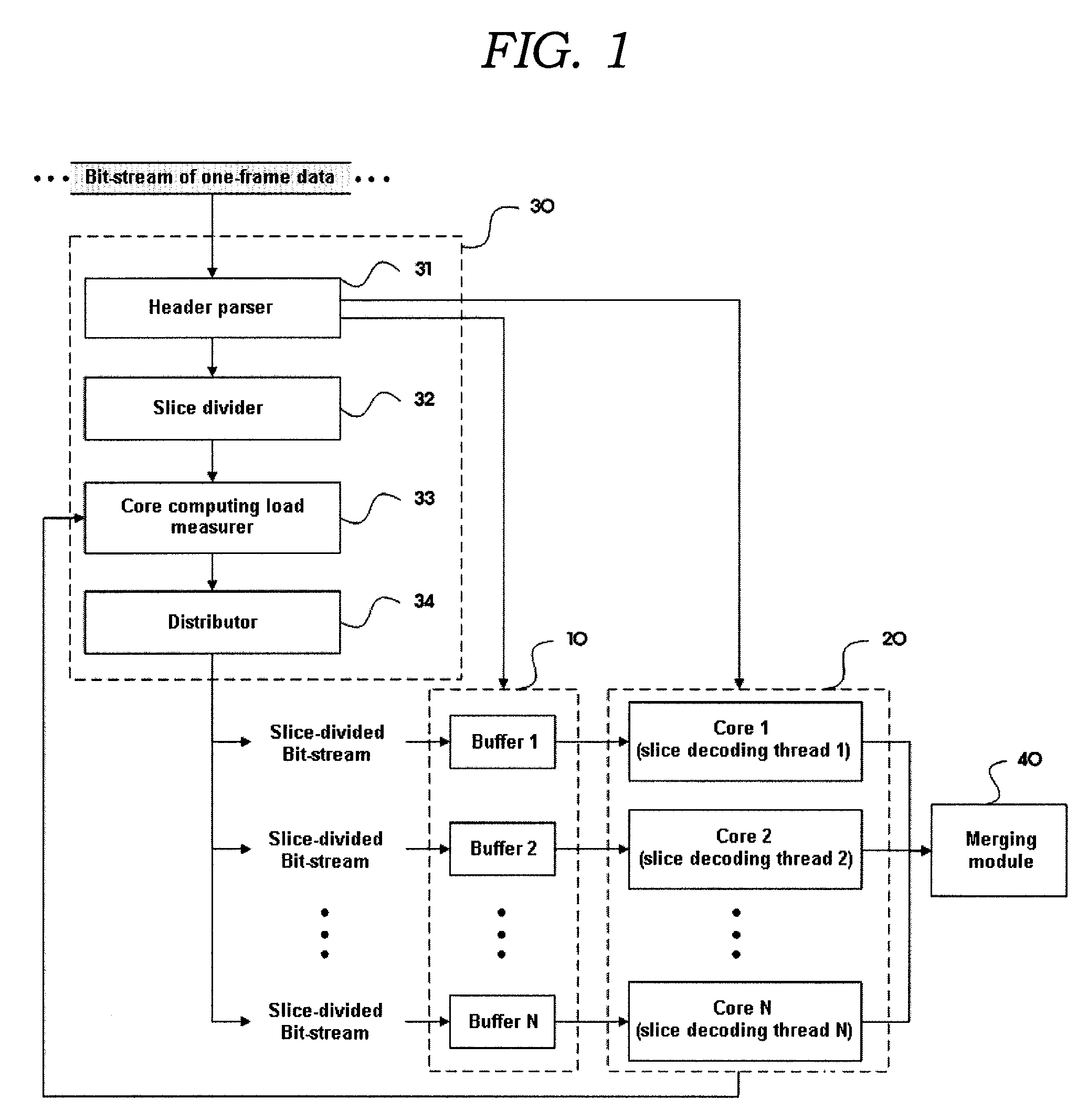

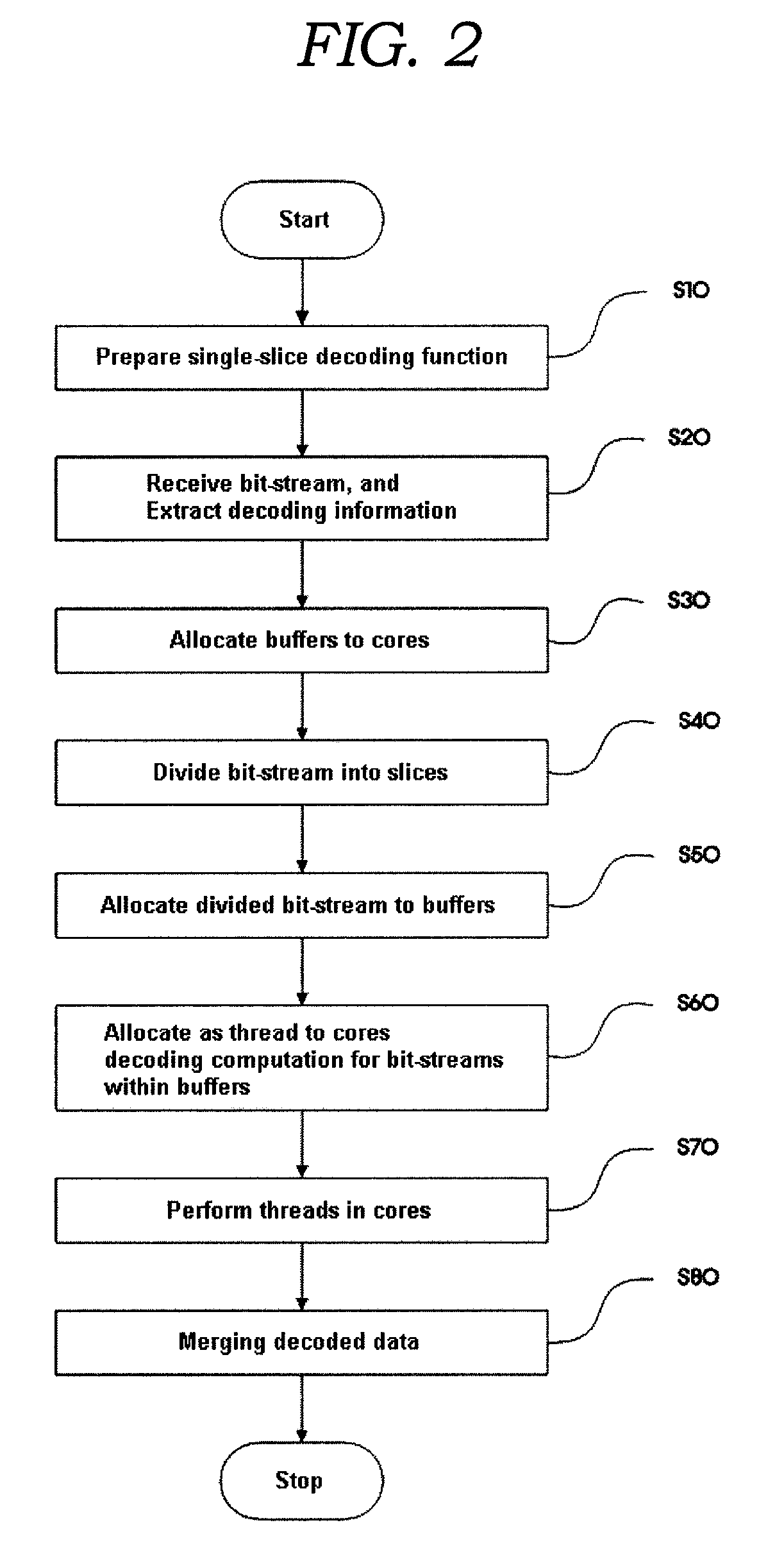

Distributed decoding device using multi-core processor and method for the same

InactiveUS7796061B2Computing power of each core can be effectively utilizedEffective divisionProgram control using stored programsPicture reproducers using cathode ray tubesMulti-core processorData buffer

Provided is a distributed decoding device using a multi-core processor, including a multi-core processor that includes a plurality of cores which process data as threads; an MPEG division module that receives MPEG data, extracts decoding information from the MPEG data, divides the MPEG data into individual slices, and generates and provides a single-slice decoding function, which separately decodes one slice, such that threads which decode the divided slices allocated thereto are distributed to the cores within the multi-core processor; a memory that includes a plurality of buffers which receive the slices from the MPEG data division module to store therein and provide the stored slices to the cores of the multi-core processor; and a merging module that merges the data decoded through the cores of the multi-core processor.

Owner:DVICO +1

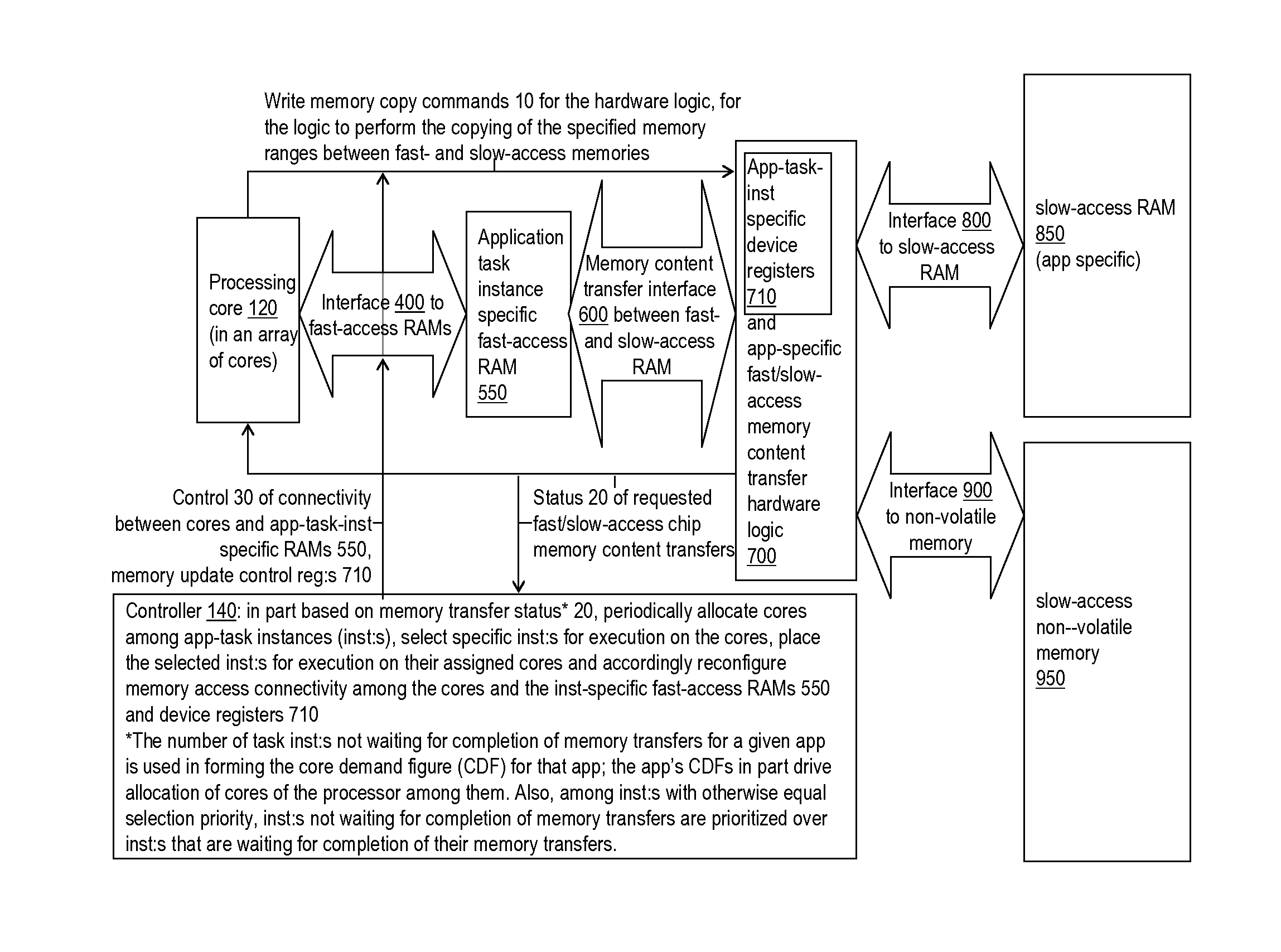

Memory Architecture For Dynamically Allocated Manycore Processor

ActiveUS20140229669A1Input/output to record carriersResource allocationDevice registerProcessing core

Invented hardware logic based methods and systems enable dynamically allocating and assigning an array of processing cores among instances of software programs, based on at least in part on indications of which instances of the programs are ready-to-execute, wherein such an indication for any given program instance is based at least in part on whether its fast-access memory contents are ready for it to execute without it needing at that time access to memories other than its fast-access memory. The invention also provides hardware logic based mechanisms for automating the updating of the fast-access memories for instances of the programs dynamically sharing the array of cores according to control by the program instances via their associated hardware device registers, including while a given program instance whose fast-access memory contents are being updated is not assigned for execution on any of the cores.

Owner:THROUGHPUTER

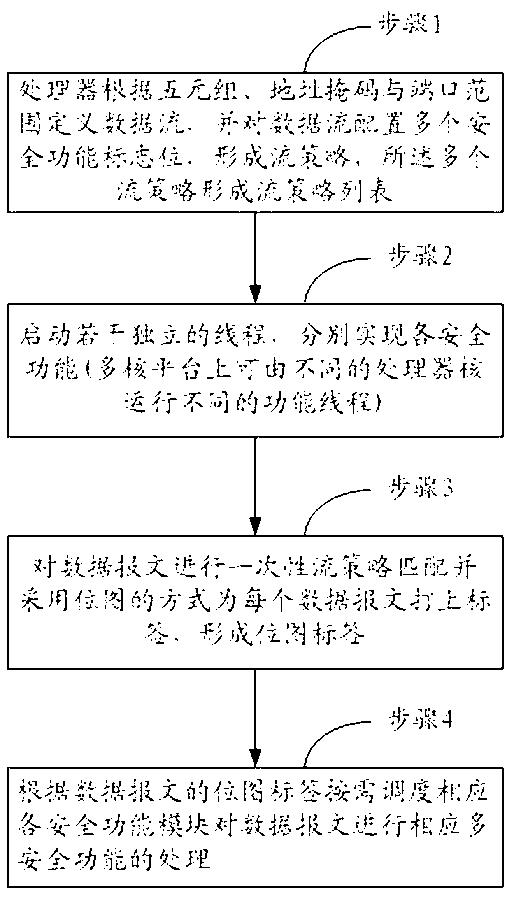

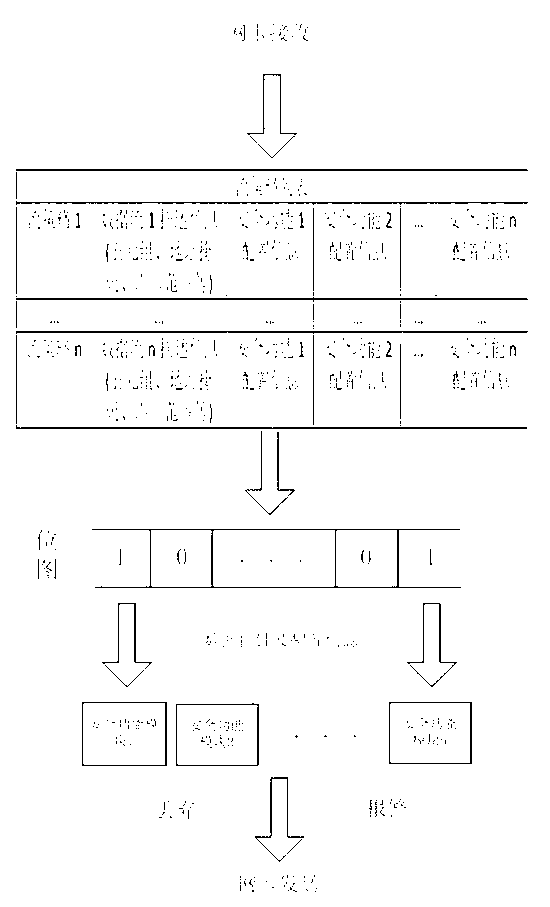

Implementation method and device for security gateway based on stream strategy

InactiveCN102801659AImprove processing efficiencyImprove parallelismNetwork connectionsEngineeringManycore processor

The invention relates to the field of data communication, in particular to an implementation method and device for a security gateway based on a stream strategy. The implementation method for the security gateway based on the stream strategy provided aims to solve the problem that in the prior art, the processing efficiency of data messages and the utilization ratio of the processor, in particular the multi-core processor are very low. The strategy is uniformly set for the data stream by combining address mask and port range according to quintuple. One-step stream strategy match is carried for a data message and associated security function module is invoked on demand according to the match result, therefore, the inquiry efficiency of the stream strategy is enhanced when multiple security function modules coexist. The invention is mainly applied to the field of data communication.

Owner:成都卫士通信息产业股份有限公司

Debug in a multicore architecture

ActiveCN101084488AHardware monitoringSoftware testing/debuggingMulticore architectureParallel computing

The present invention provides debugging in a multi-core architecture. A method of monitoring thread execution within a multi-core processor architecture comprising a plurality of interconnected processor units for processing threads, the method comprising: receiving a plurality of thread parameter indicators, the thread The parameter indicator represents one or more parameters related to the function and / or identity and / or execution location of one or more threads; comparing at least one of these thread parameter indicators with a first plurality of predetermined criteria, Each of the first plurality of predetermined criteria represents an indicator of interest; and generating an output based on thread parameter indicators identified as being of interest as a result of said comparing.

Owner:斯诺普西斯公司

Test method and tool for master-slave systems on multicore processors

A test method for a master-slave concurrent system running on a multicore processor includes the steps of establishing a PFA, otherwise called probabilistic finite automata, or probabilistic finite state machine, for a given regular expression; generating test patterns by running the PFA; splitting and merging the test patterns to generate an interleaved test pattern; and performing test on the master-slave system according to the interleaved test pattern. In an embodiment, the method further includes a step of debugging failures of the multicore processor during testing.

Owner:NATIONAL TSING HUA UNIVERSITY

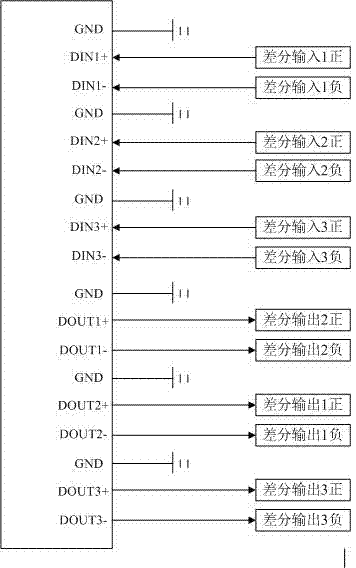

FPGA-based scalable multi-core processor verification platform

InactiveCN102289541AScale upLarger FPGA applications with largeSpecial data processing applicationsManycore processorBackplane

The invention relates to an FPGA-based scalable multi-core processor verification platform. It is a hardware platform for verifying a large-scale multi-core processor architecture. It is composed of several self-made FPGA development boards. Each development board is composed of a core board and a base board. The core board is embedded with cycloneIIIFPGA. The base board Equipped with 4 LVDS interfaces, it can communicate with other development boards through this interface. The connected development board array is rich in resources and can carry out large-scale FPGA prototype verification.

Owner:SHANGHAI UNIV

Reordering buffer for memory access locality

ActiveUS20140164743A1Keep localInstruction analysisDigital computer detailsBatch processingScheduling instructions

Systems and methods for scheduling instructions for execution on a multi-core processor reorder the execution of different threads to ensure that instructions specified as having localized memory access behavior are executed over one or more sequential clock cycles to benefit from memory access locality. At compile time, code sequences including memory access instructions that may be localized are delineated into separate batches. A scheduling unit ensures that multiple parallel threads are processed over one or more sequential scheduling cycles to execute the batched instructions. The scheduling unit waits to schedule execution of instructions that are not included in the particular batch until execution of the batched instructions is done so that memory access locality is maintained for the particular batch. In between the separate batches, instructions that are not included in a batch are scheduled so that threads executing non-batched instructions are also processed and not starved.

Owner:NVIDIA CORP

Method and apparatus for optimizing clock speed and power dissipation in multicore architectures

ActiveUS8281164B2Reduce voltageHigh voltageEnergy efficient ICTVolume/mass flow measurementMulticore architectureEngineering

A multicore processor provides for local power control at each of the cores which is used to lower the maximum operating frequency of cores by any amount above of the maximum operating frequency of the slowest core. This power savings is then used to increase the maximum operating frequency of the frequency balanced cores within a power constraint.

Owner:WISCONSIN ALUMNI RES FOUND

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com