Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

148 results about "Fft processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

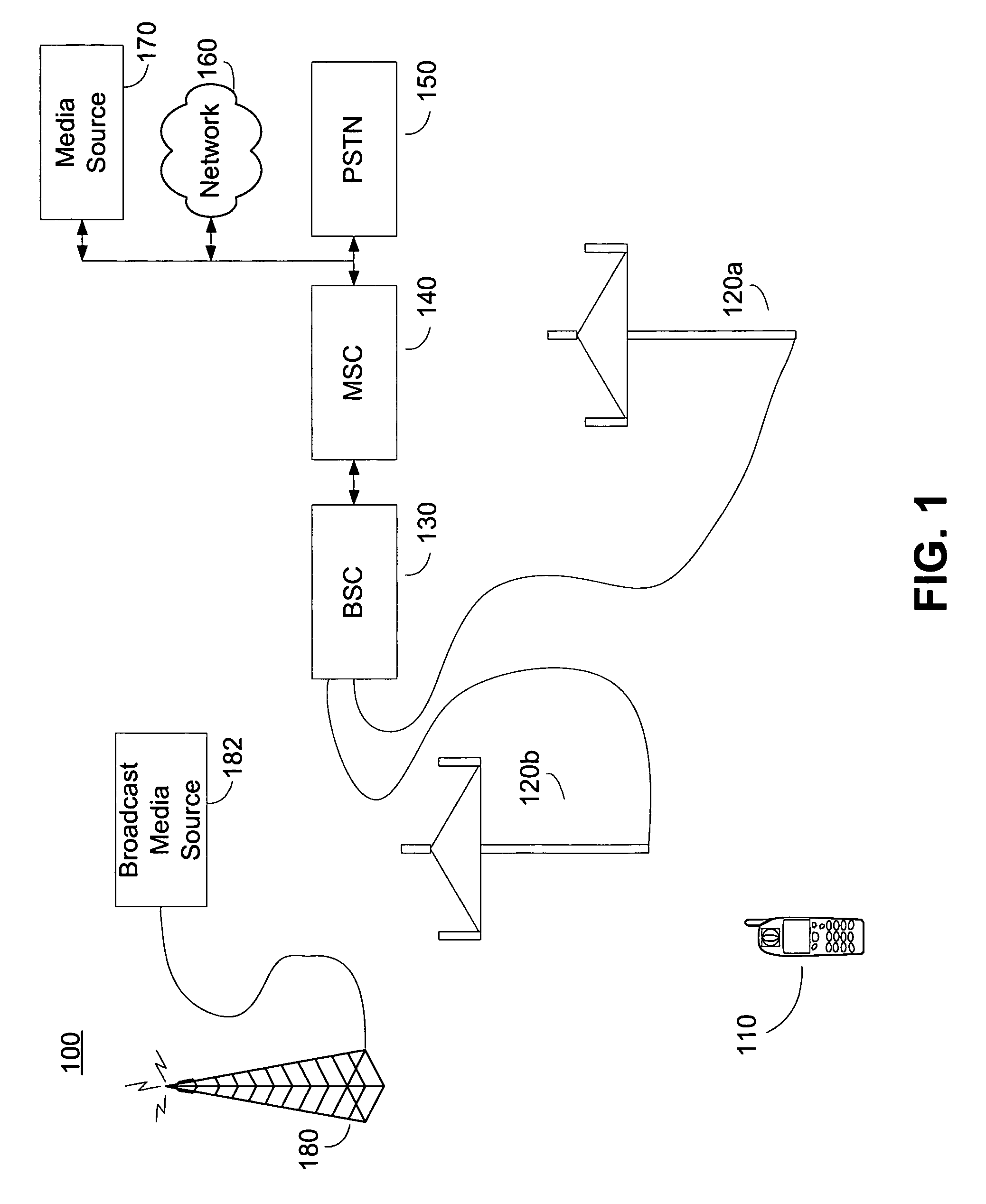

Multi-carrier communication systems employing variable symbol rates and number of carriers

ActiveUS20020006167A1Error detection/prevention using signal quality detectorTransmission path divisionCommunications systemClock rate

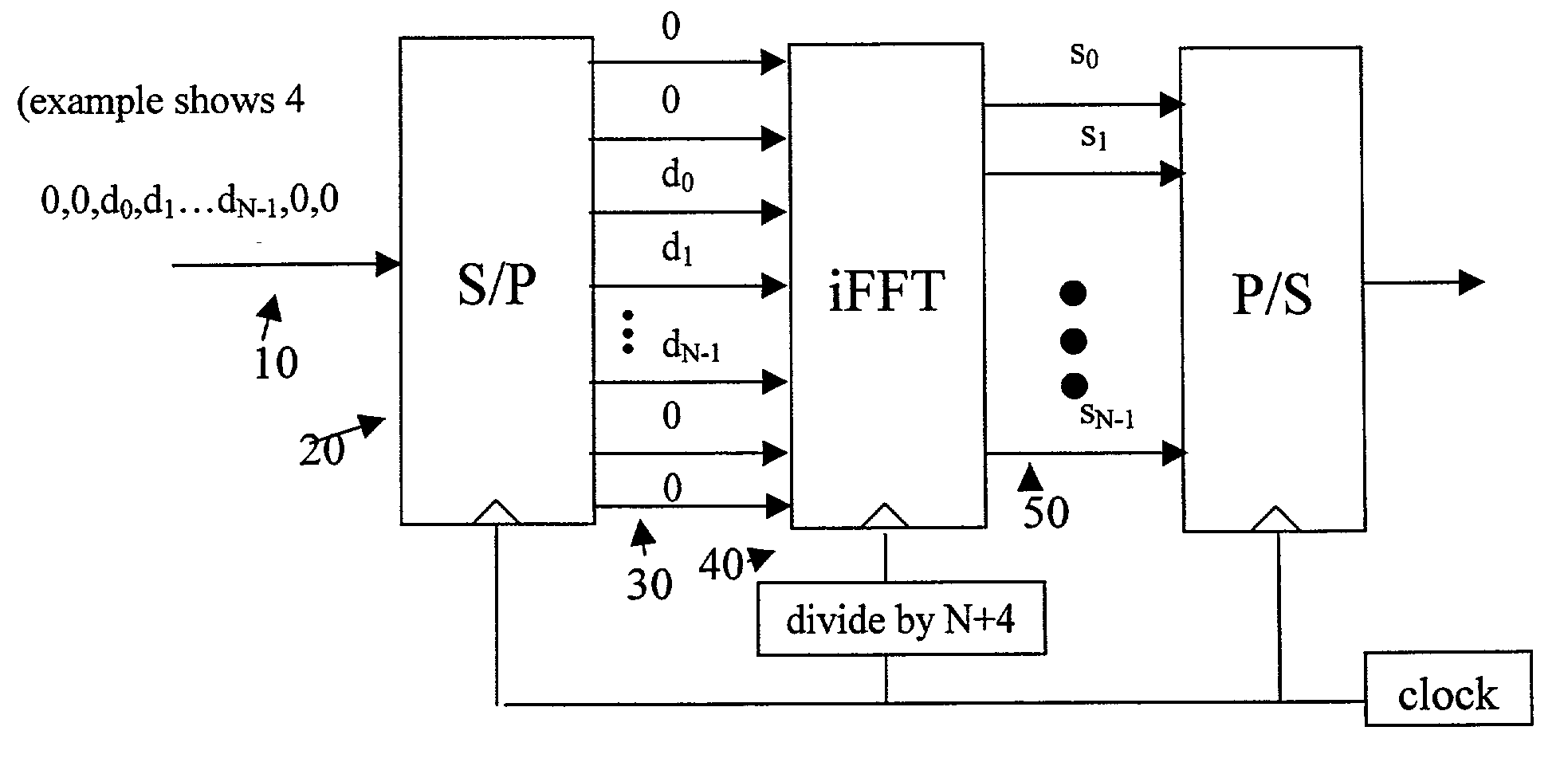

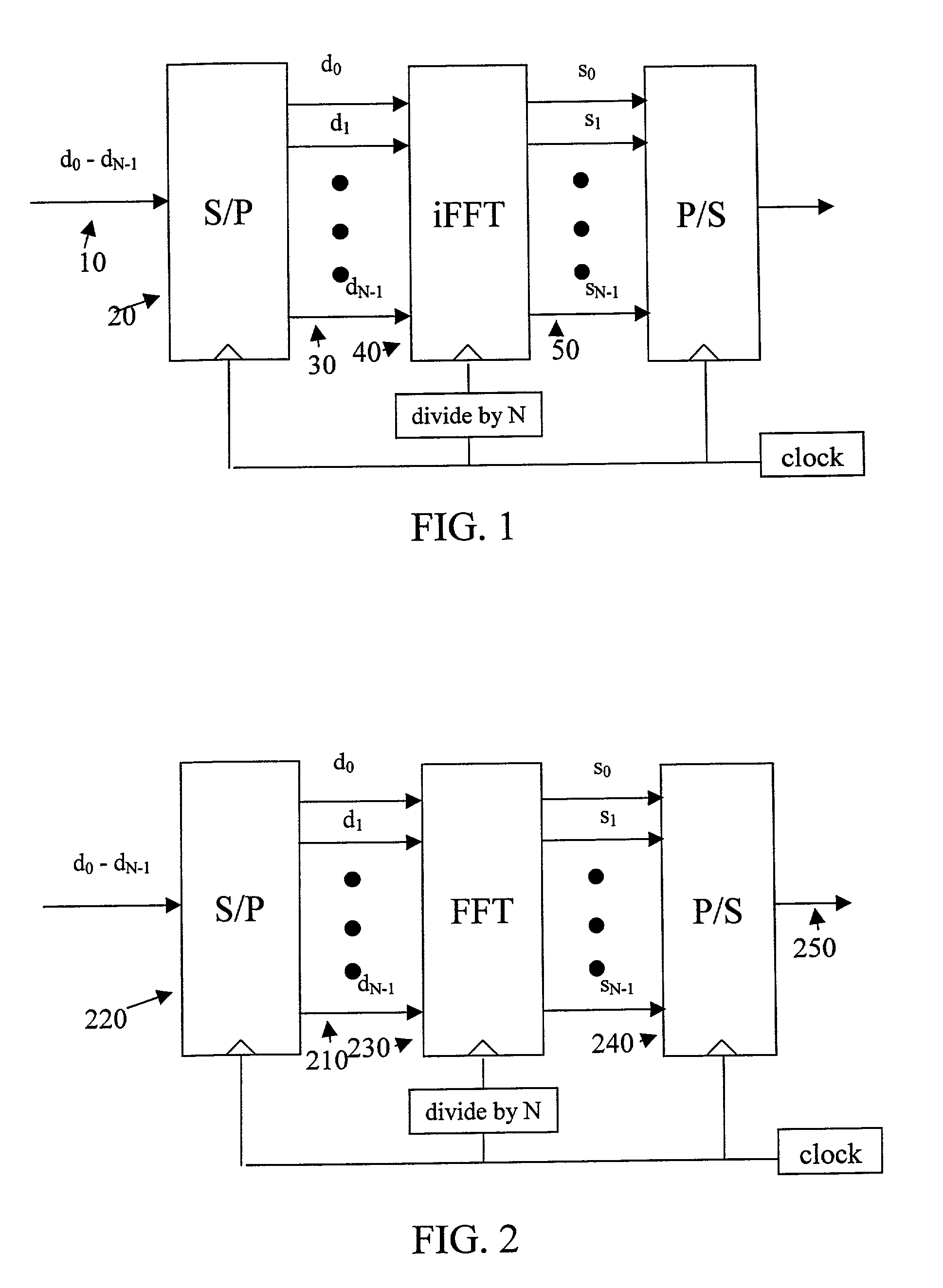

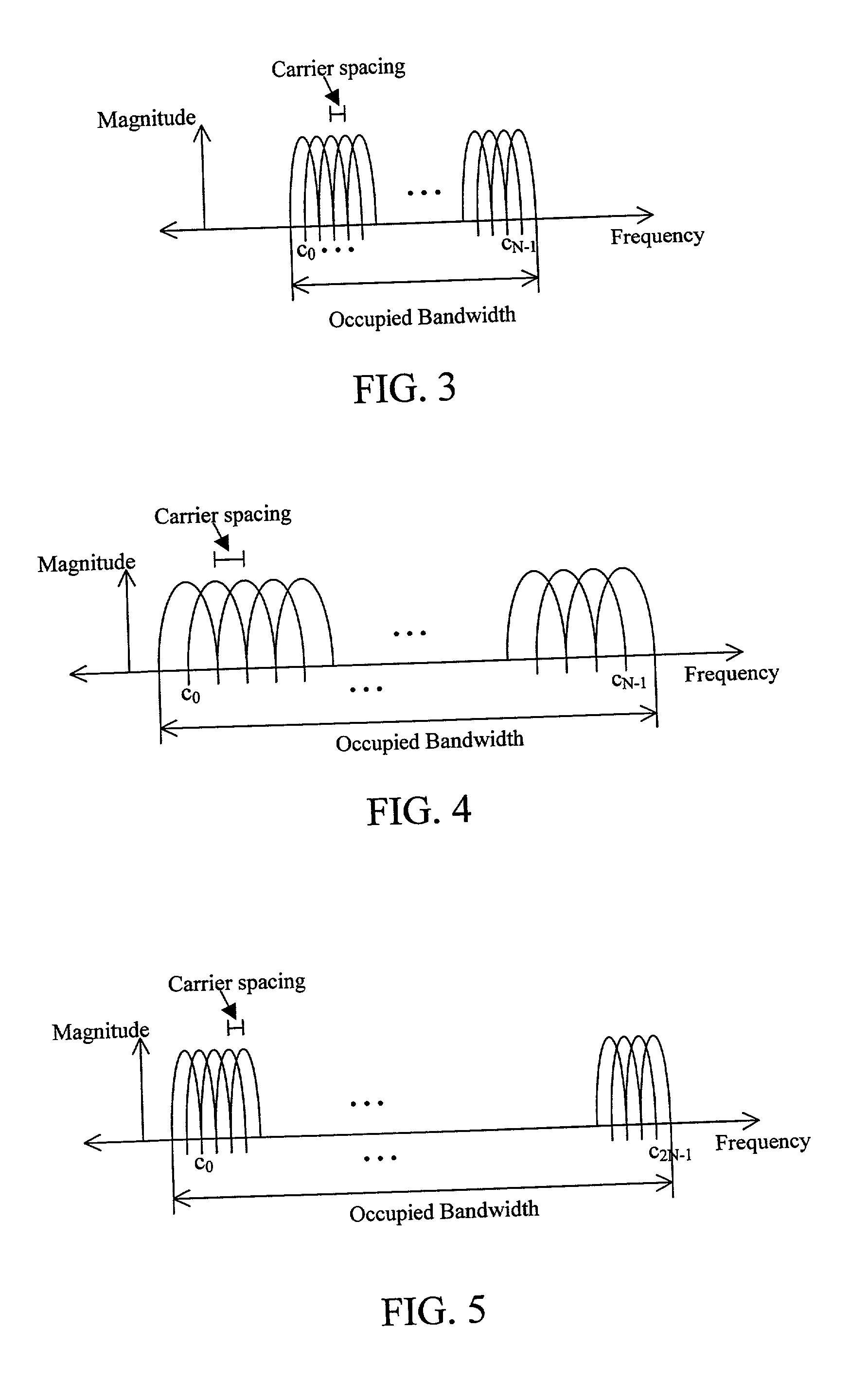

A multi-carrier communication system such as an OFDM or DMT system has nodes which are allowed to dynamically change their receive and transmit symbol rates, and the number of carriers within their signals. Changing of the symbol rate is done by changing the clocking frequency of the nodes' iFFT and FFT processors, as well as their serializers and deserializers. The nodes have several ways of dynamically changing the number of carriers used. The selection of symbol rate and number of carriers can be optimized for a given channel based on explicit channel measurements, a priori knowledge of the channel, or past experience. Provision is made for accommodating legacy nodes that may have constraints in symbol rate or the number of carriers they can support. The receiver can determine the correct symbol rate and number of carriers through a priori knowledge, a first exchange of packets in a base mode that all nodes can understand, or an indication in the header of the data packet which is transmitted in a base mode of operation that all nodes can understand.

Owner:THE CONNECTIVITY PATENT TRUST

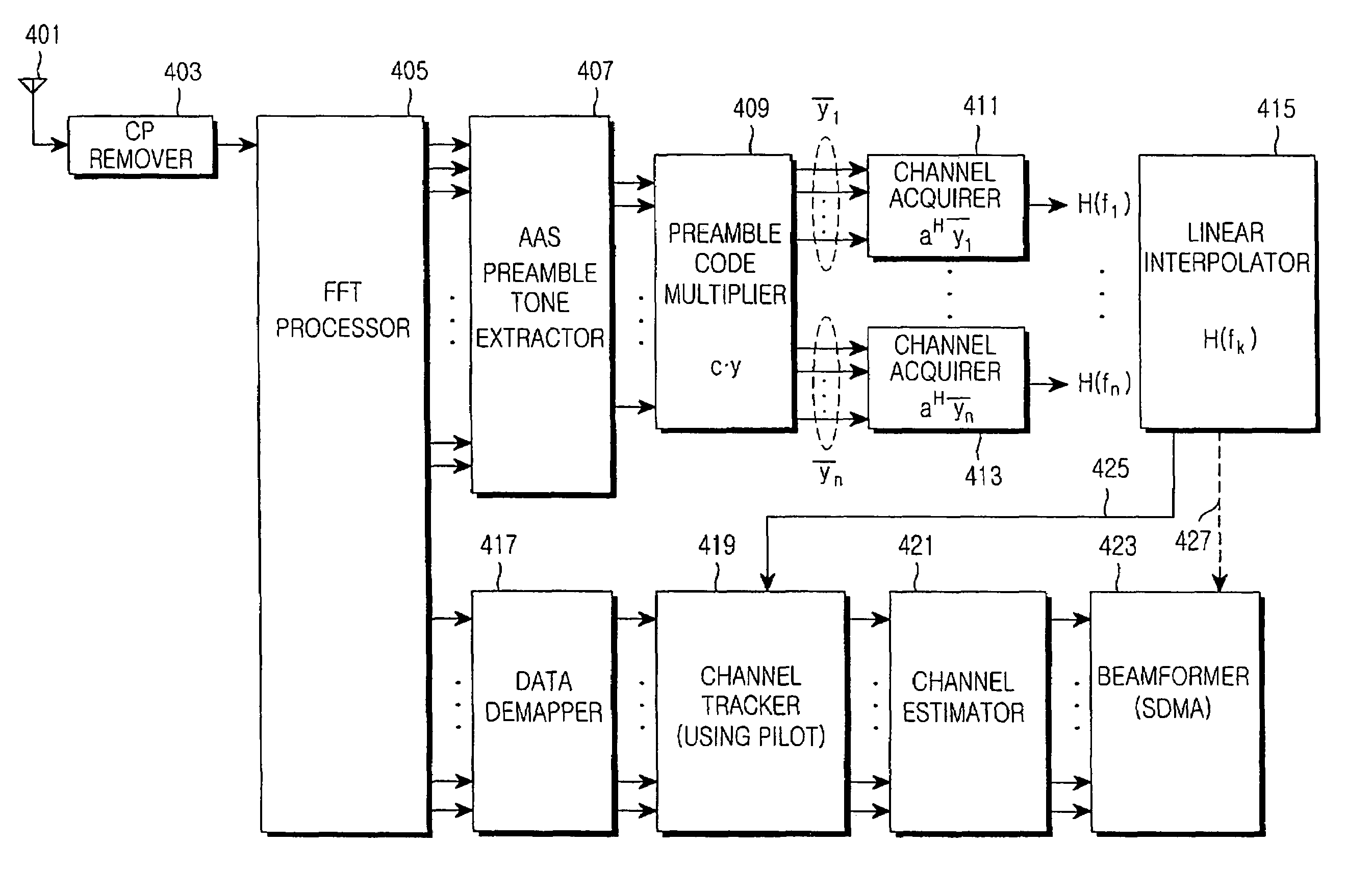

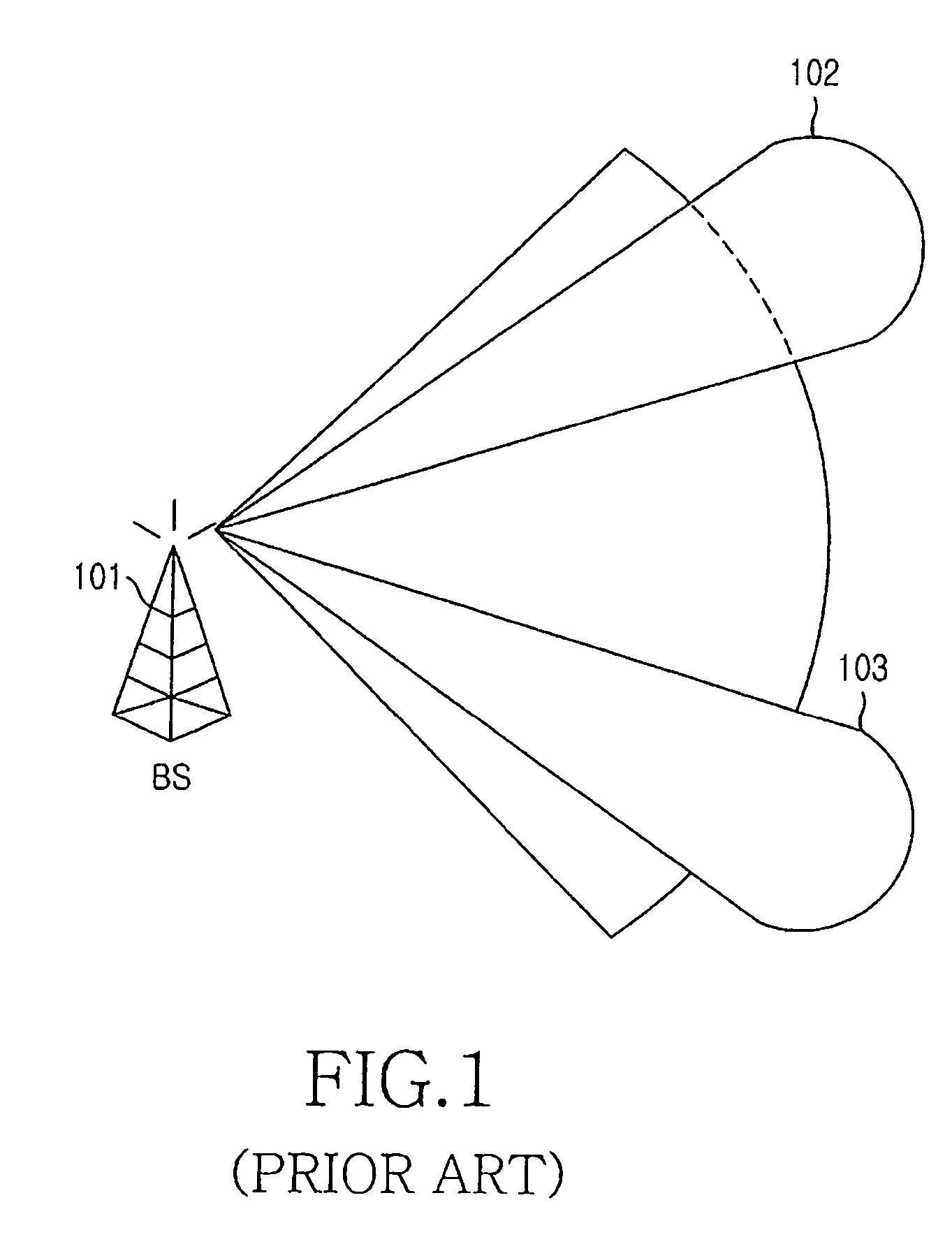

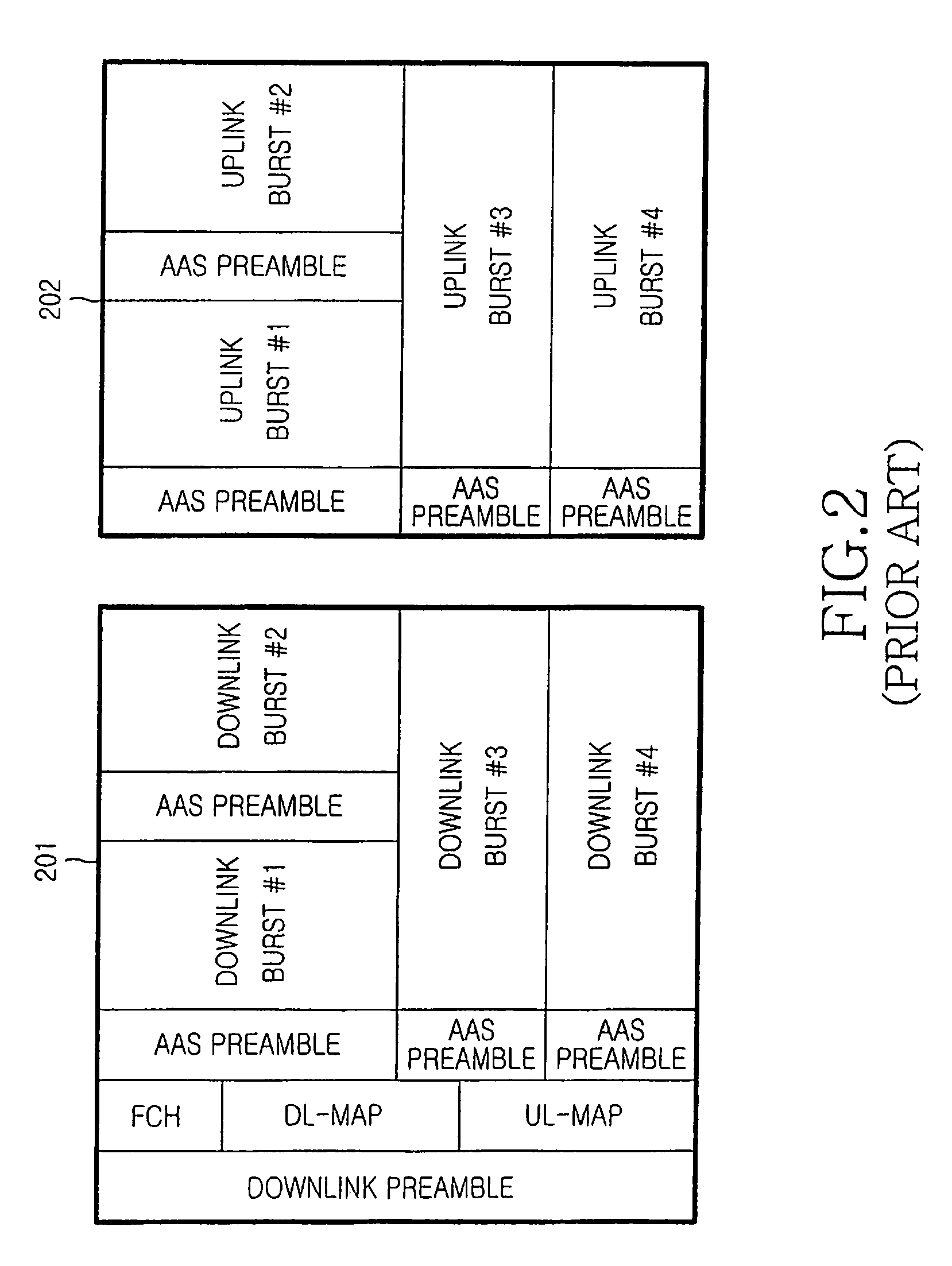

Apparatus and method for channel estimation in an SDMA-OFDM system

ActiveUS20060205437A1Increase data rateAccurate channel estimationModulated-carrier systemsTime-division multiplexTime domainSmart antenna

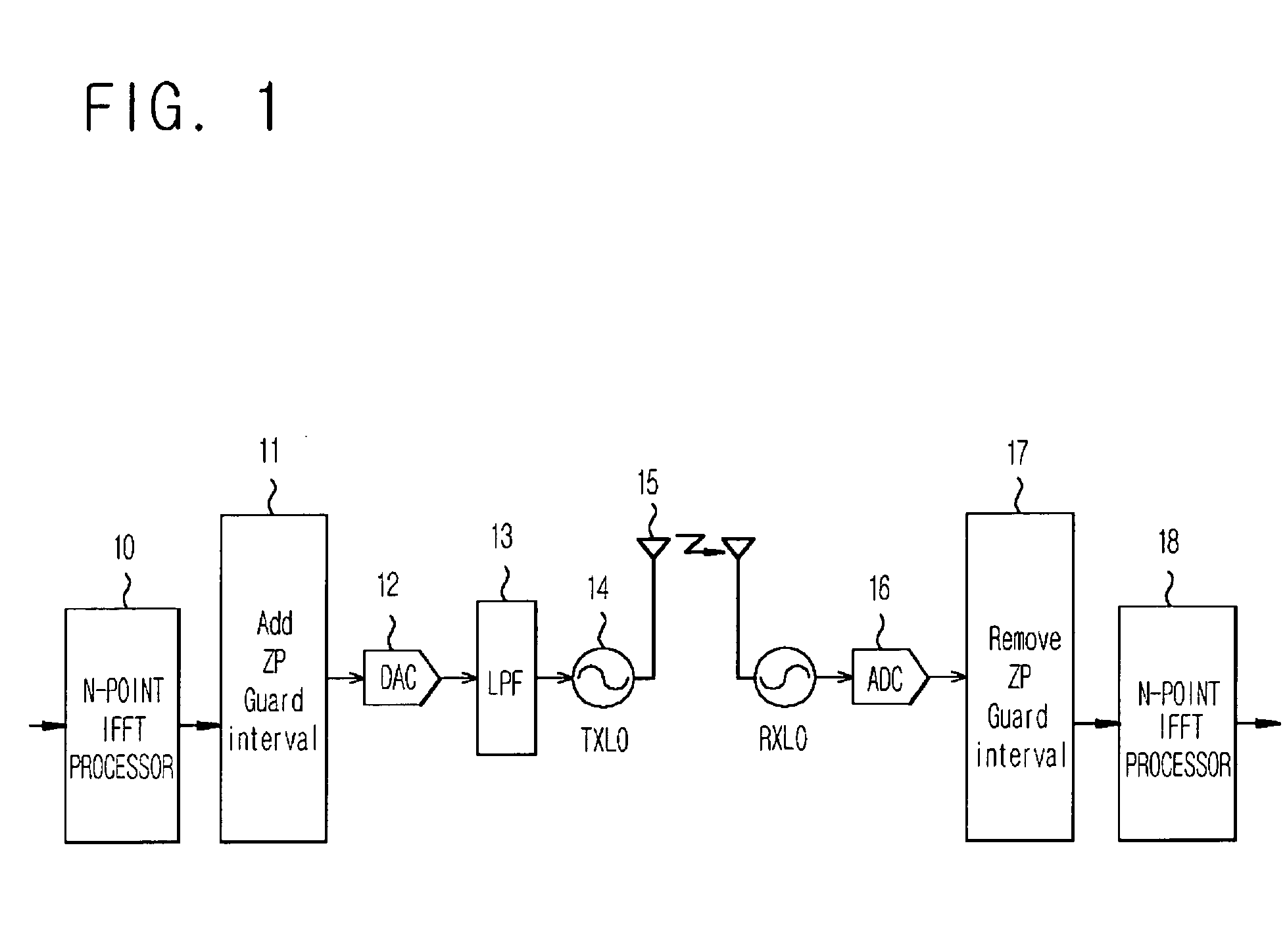

Provided is a channel estimation apparatus and method in a broadband wireless communications system using a smart antenna are provided. In the channel estimation apparatus, an FFT processor converts a received time-domain signal into a frequency-domain signal by FFT-processing the received time-domain signal. A channel acquirer estimates a first channel information for an SDMA user using a preamble signal allocated to the SDMA user in the frequency-domain signal. A channel tracker estimates a second channel information for the SDMA user using pilots in a data area allocated to the SDMA user in the frequency-domain signal. A channel estimator estimates a final channel information by weighting the first channel information and the second channel information according to a channel change rate.

Owner:SAMSUNG ELECTRONICS CO LTD

Residue division multiplexing system and apparatus for discrete-time signals

InactiveUS6317409B1Easy to useSimple structureFrequency-division multiplexAmplitude-modulated carrier systemsDiscrete-time signalEngineering

A multiplexing system utilizes the whole transmission bandwidth without inducing interchannel interference for a linear channel with additive noise. Using the multiplexing system, the linear distortion channel is decomposed into independent linear distortion subchannels. Treating z-transforms as polynomials, a multiplexer at a receiver utilizes the Chinese remainder procedure to combine subchannel signals into a multiplexed signal to be transmitted through a single transmission channel. A demultiplexer at a receiver recovers the transmitted subchannel signals by taking residue polynomials on the factor polynomials used in the Chinese remainder procedure. The multiplexer that combines M subchannel signals of length K may be implemented by K M-point IFFT processors using 1-ej2pim / Mz-K (m=0 to M-1) as relatively prime polynomials required in the Chinese remainder procedure. Samples from the subchannel signals are arranged in K groups of M samples such that each group contains samples at the same position in the subchannel signals, M-point inverse DFTs of the arranged samples are computed for all of the groups, and finally the multiplexed signal is obtained by performing polyphase composition of the inverse DFT outputs. Reversing the process of multiplexing, the demultiplexer is implemented by K M-point FFT processors. Another class of the system is a multiplexing system using (1-ej2pim / Mr0z-1) (1-ej2pim / Mr1z-1) . . . (1-ej2pim / MrK-1z-1) (m=0 to M-1) as relatively prime polynomials, wherein ri is a non-zero complex number (i=0 to K-1). The multiplexer obtains the multiplexed signal by applying the Chinese remainder procedure recursively, starting with the subchannel signals Xm(z) regarding them as residue polynomials on mod((1-ej2pim / Mr0z-1) (1-ej2pim / Mr1z-1) . . . (1-ej2pim / MrK-1z-1)) (m=0 to M-1).

Owner:MURAKAMI HIDEO

GPS receiver and method for detecting a jammer signal using fast fourier transform

InactiveUS20050285781A1Sufficient energyImprove receiver sensitivityPosition fixationBeacon systemsPeak valueFrequency offset

A global positioning system (GPS) receiver and method are provided for detecting a jammer signal using fast Fourier transform (FFT). A correlator correlates GPS signals received from GPS satellites with codes based on a plurality of carrier frequency signals having predetermined frequency offsets therebetween, and computes n correlated samples associated with each of the GPS satellites. A memory stores the n correlated samples associated with each of the GPS satellites and n FFT bins corresponding thereto. A FFT processor transforms the n correlated samples read from the memory using n-point FFT to obtain the n FFT bins, and transfers the n FFT bins to the memory. A peak detector detects largest peaks exceeding a lowered detection threshold from the FFT bins associated with each of the GPS satellites. A jammer detection unit makes a determination as to whether a peak relatively far away from other peaks is present among the largest peaks, and detects a signal of a peak far away from other peaks.

Owner:SAMSUNG ELECTRONICS CO LTD

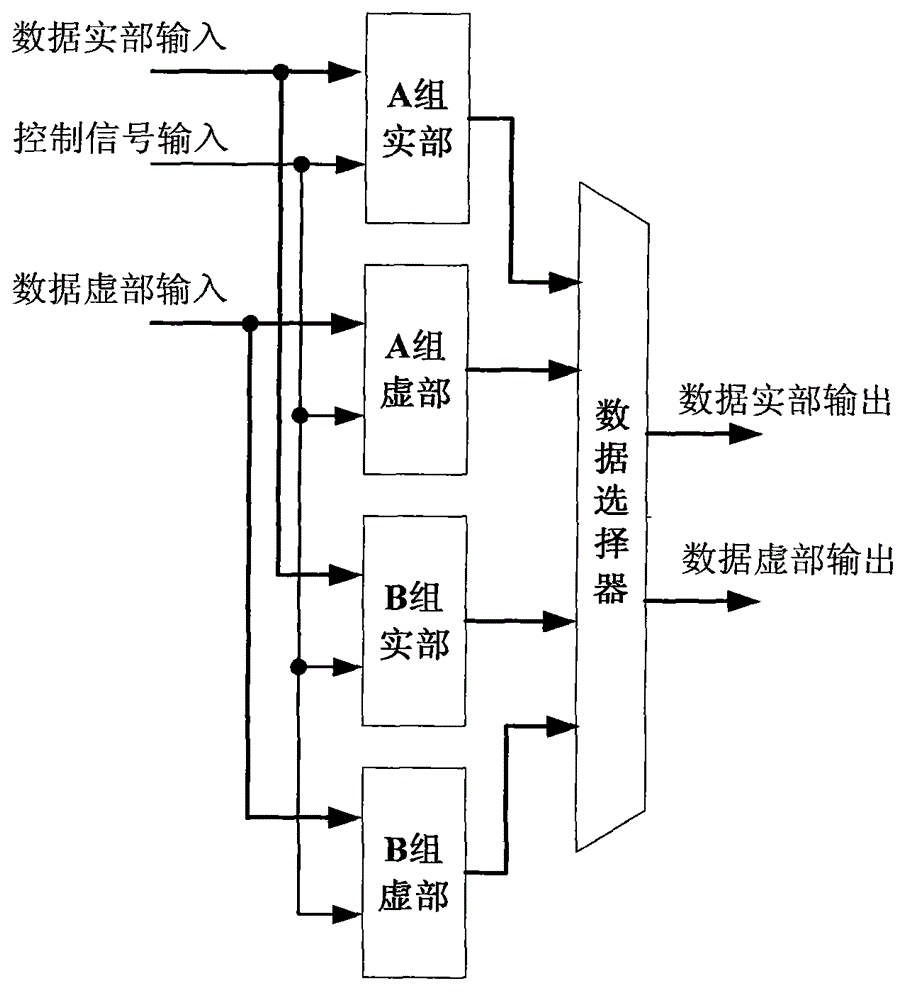

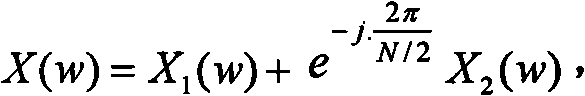

2N-point and N-point FFT/IFFT dual mode processor

InactiveUS20060093052A1Easy to useImprove receiver performanceDigital computer detailsSecret communicationDual modeControl signal

A 2N-point and N-point FFT / IFFT dual mode processor is provided. The processor includes a butterfly operator, the first and second MUXs, and the first and second N-point FFT processors. The butterfly operator receives 2N data and butterfly-operates on the received 2N data when receiving a control signal ‘0’ from the controller. The first and second MUXs respectively receive results from the butterfly operator to output the results in an increment of N when receiving a control signal ‘0’ from the controller, and respectively outputs different N data when receiving a control signal ‘1’ from the controller. The first and second N-point FFT processors N-point FFT operate on the results from the first and second MUXs and respectively output the same under control of the controller. Since the N-point FFT operation can be simultaneously performed two times at a receiver, the performance of the receiver can be enhanced.

Owner:ELECTRONICS & TELECOMM RES INST

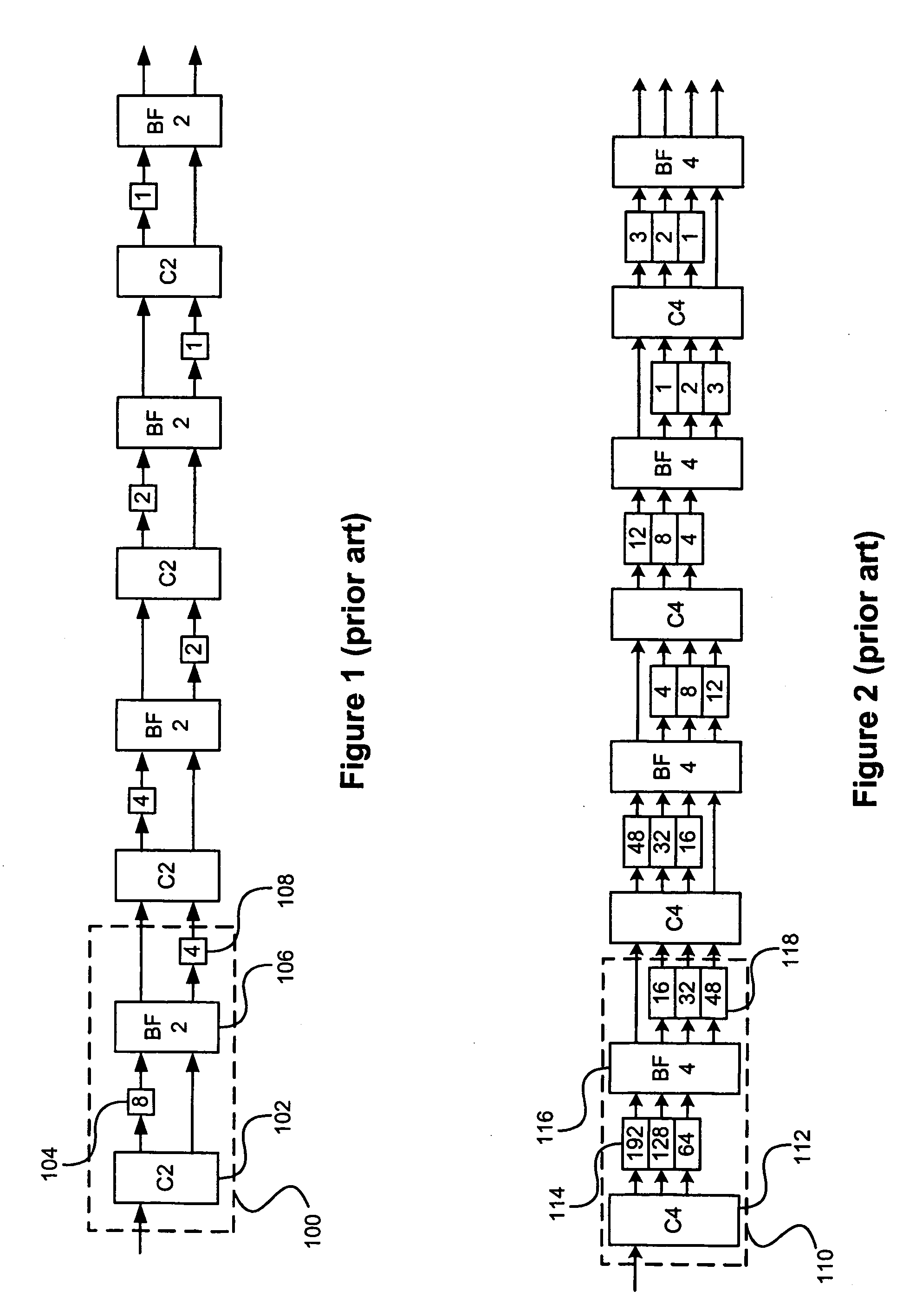

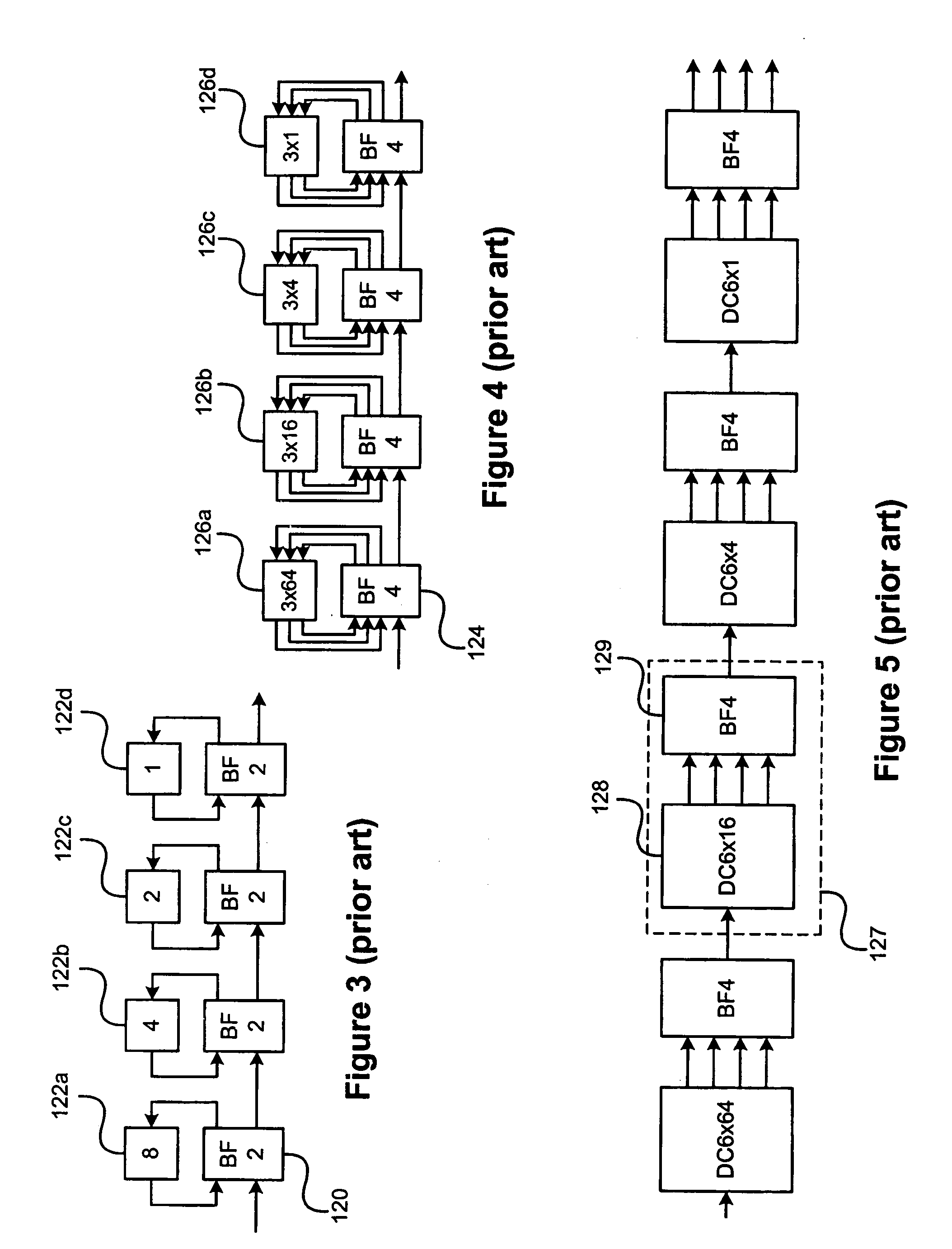

FFT processor suited for a DMT engine for multichannel CO ADSL application

ActiveUS6917955B1Economical with resourceLower latencyDigital computer detailsMulti-frequency code systemsMultiplexingFft processor

A real-valued FFT processor implements Bergland's real-valued FFT and uses unique interstage switching / delay modules to reduce pipeline latency. Modified hybrid floating point arithmetic is also employed to provide maximum SNR. The real-valued FFT processor is particularly suited for a DMT engine and, in a multichannel CO ADSL application, the DMT engine can be multiplexed between the channels to provide an economic, low cost CO solution.

Owner:ANALOG DEVICES INC

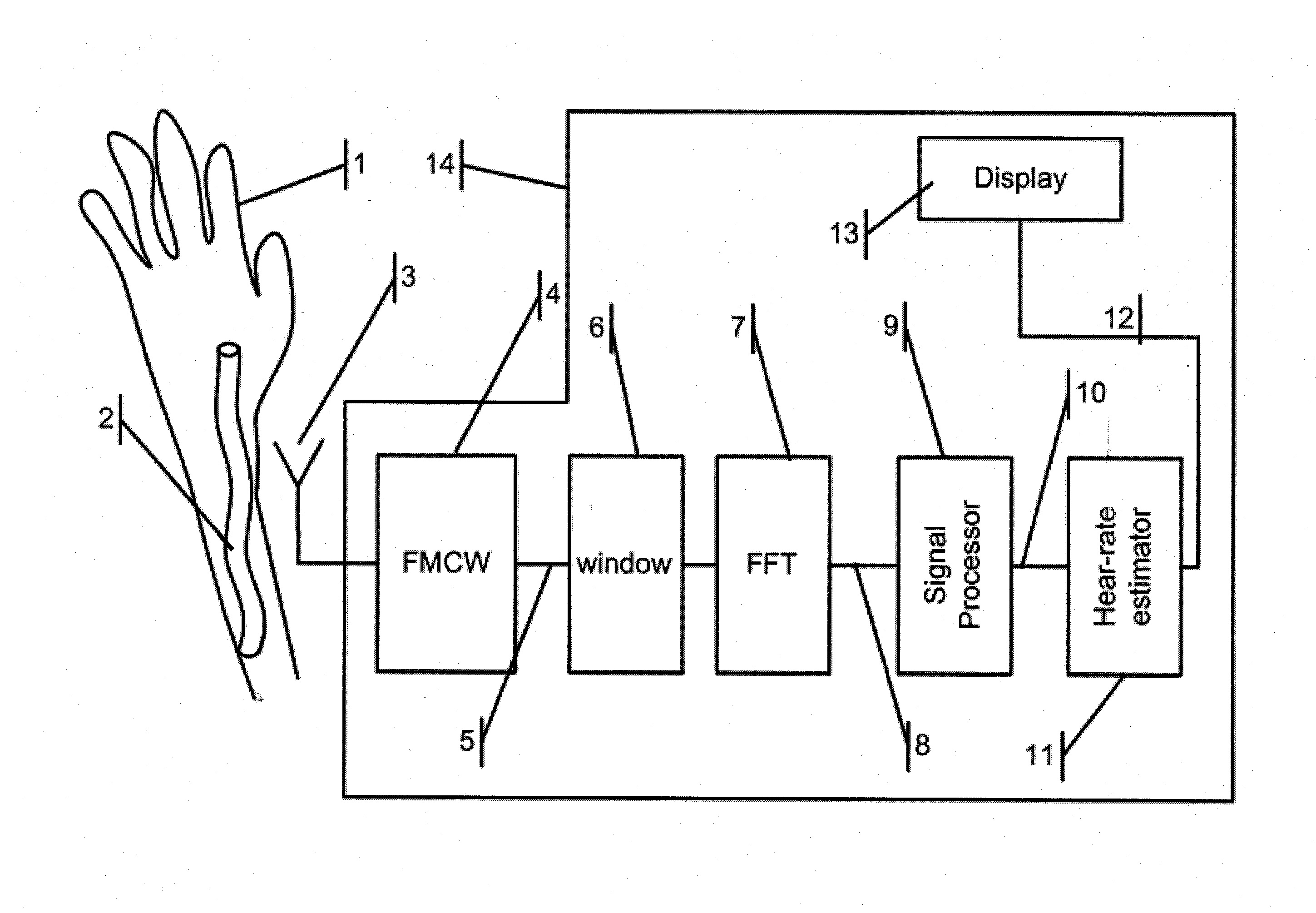

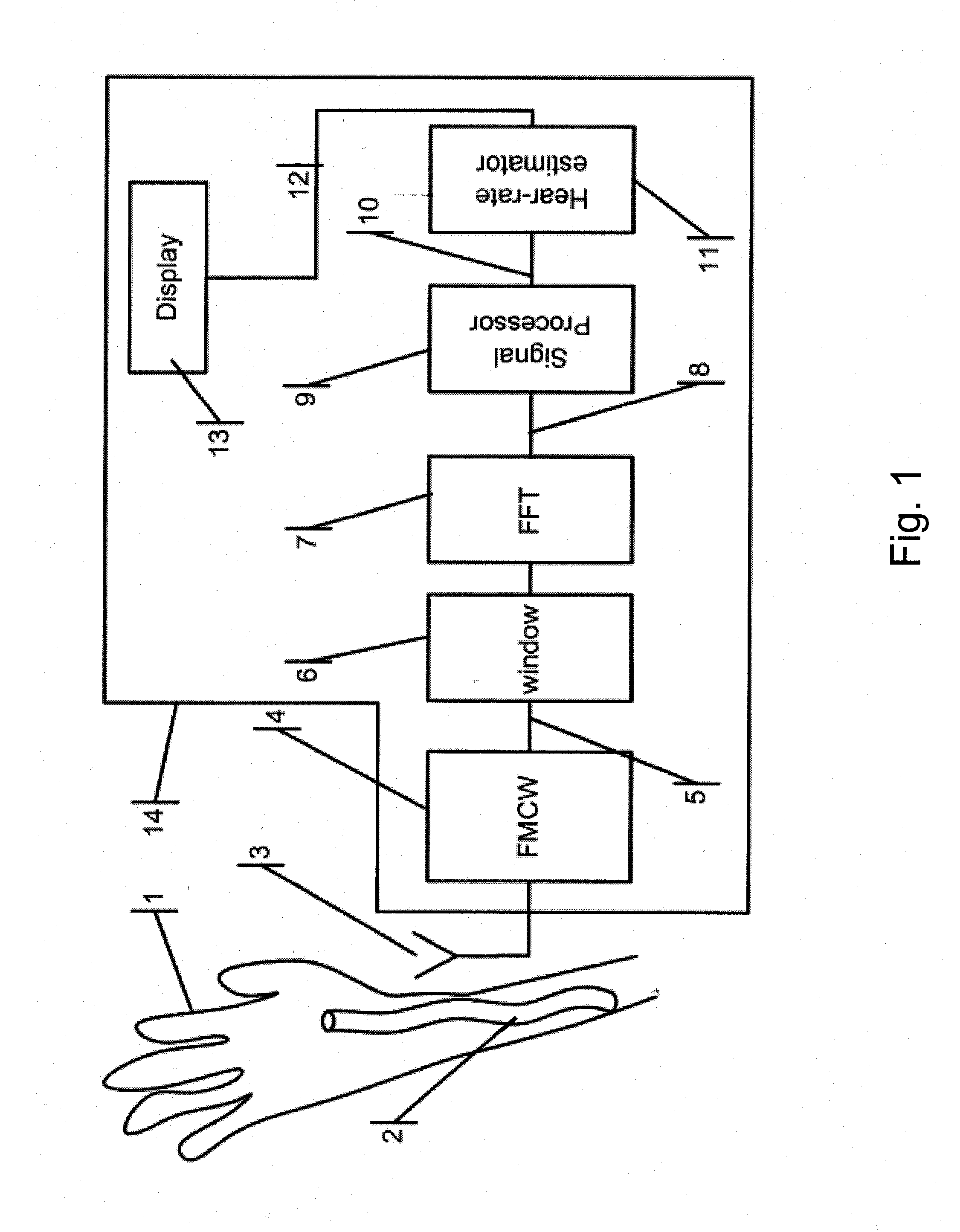

Microwave contactless heart rate sensor

ActiveUS20150018676A1SensorsMeasuring/recording heart/pulse rateFrequency spectrumReflection Magnitude

A heart-rate sensor for detecting artery blood-flow volume per unit length change in a human or animal subject, which comprises an antenna for sensing the instantaneous volume of blood in the artery of the subject, to be measured; a RADAR unit for transmitting microwave signals into a subject's body part or limb representing tissue targets. The output of the RADAR unit includes a superposition of signals each of which corresponding to a different tissue target with amplitudes that relate to the target's reflection strength; a sampling circuitry for converting reflected signals to digital; a window function circuitry for suppressing unwanted spectral sidebands originating from the subsequent processor operating on time truncated data; an FFT processor following the window function circuitry, for splitting the superposition according to its relative frequency into a multiplicity of bins, each of which with an amplitude that represents the reflection magnitude of a target at a specific distance from the antenna; a signal processor for filtering out the effect of the sensor movement with respect to the subject body part, or the movement of the body part, and for generating a signal, the amplitude of which is proportional to the artery varying dilatation representing the heart-rate; a heart-rate estimator for measuring the frequency of the artery dilatation variations and for canceling the interference of the amplitude of any signal that does not originate from the artery; a battery for powering the sensor.

Owner:SENSIFREE

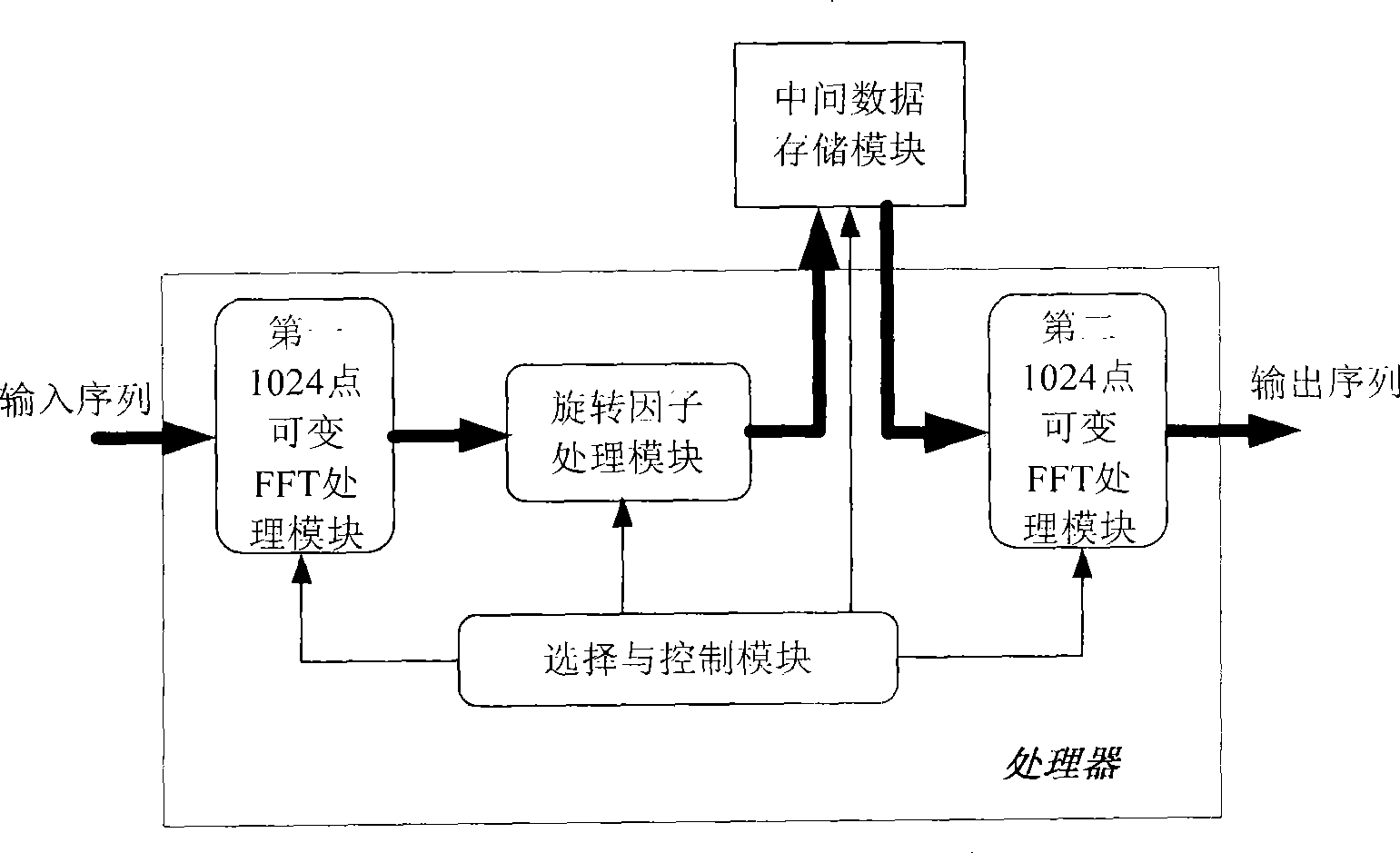

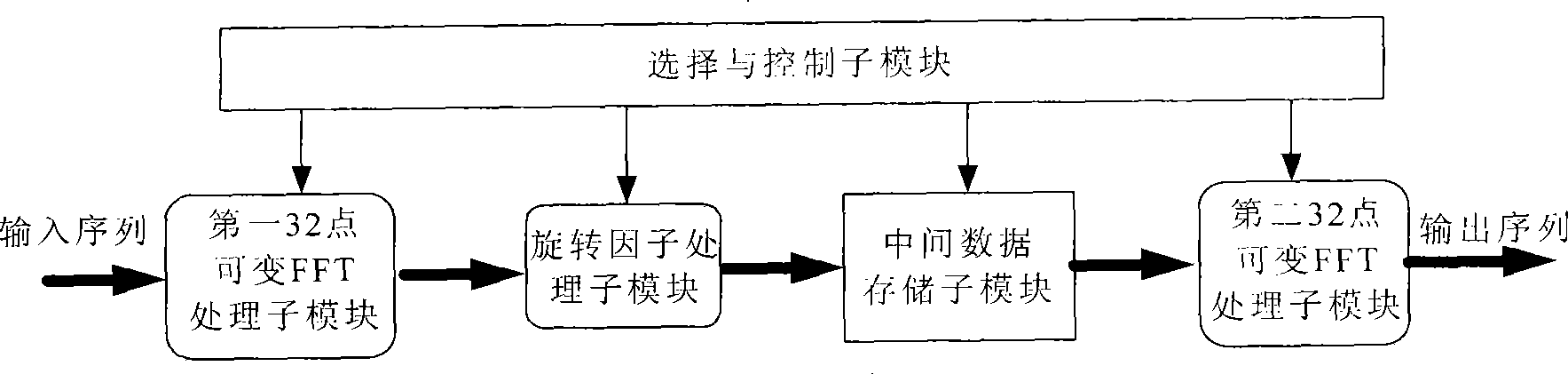

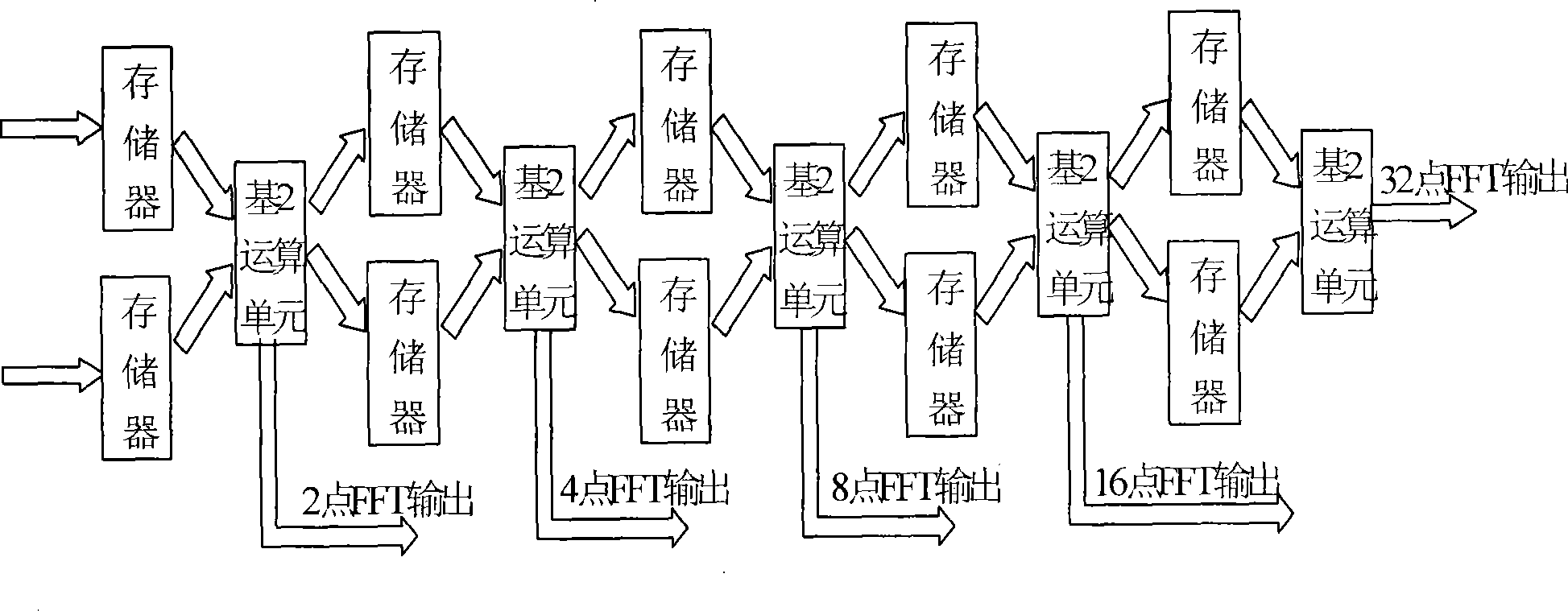

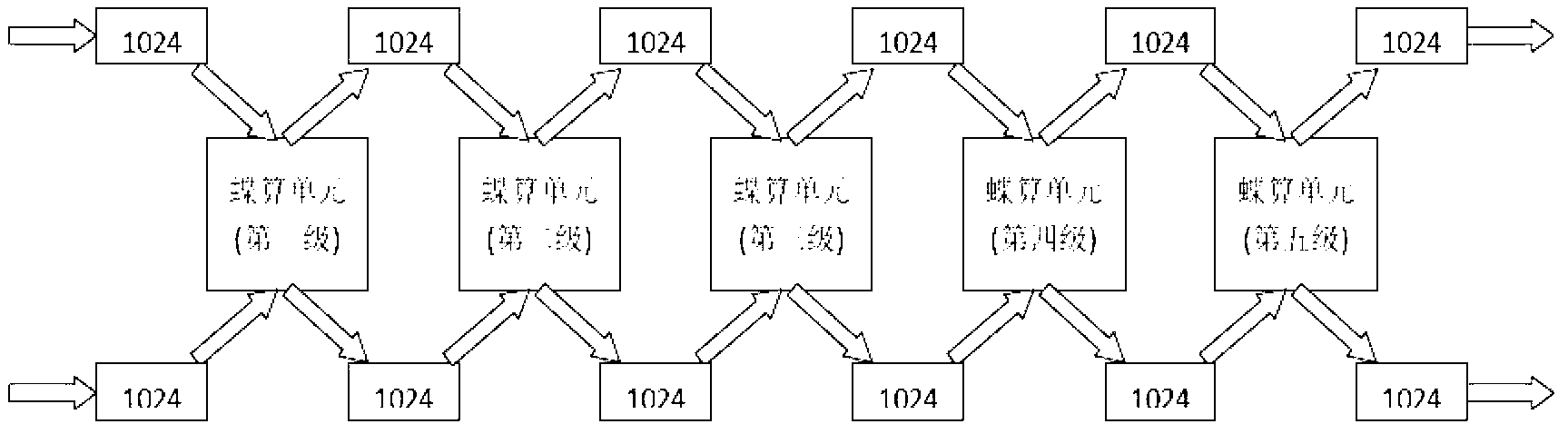

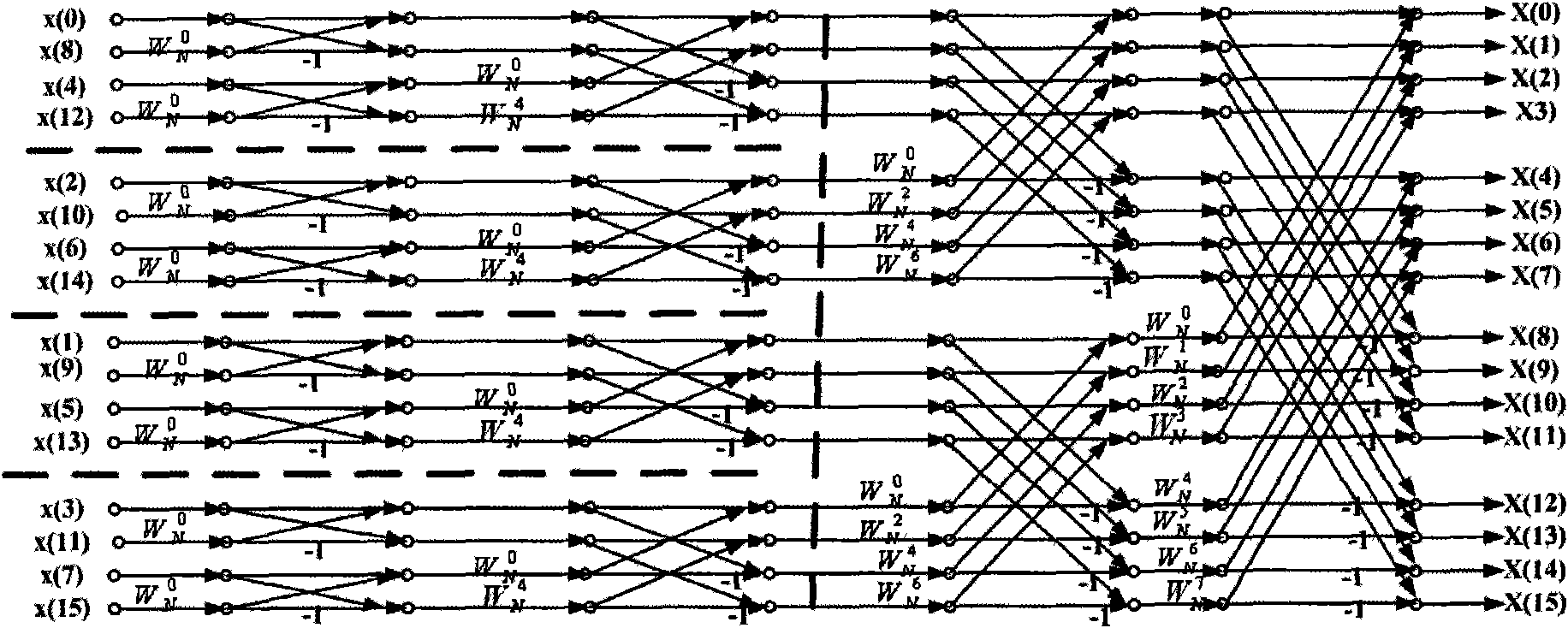

Point-variable assembly line FFT processor

InactiveCN101504638AReal-time processingUpdate output data in real timeComplex mathematical operationsFft processorParallel computing

The invention provides a pipeline FFT processor variable in the number of points, which comprises a first 1024-point variable FFT processing module, a twiddle-factor processing module, a second 1024-point variable FFT processing module and a selection-control module, wherein the four modules and an intermediate data storage module outside the processor jointly complete FFT two-dimensional processing large in the number of points; each 1024-point variable FFT processing module comprises a first 32-point variable FFT processing sub-module, a second 32-point variable FFT processing sub-module, a twiddle-factor processing sub-module, an intermediate data storage sub-module and a selection-control sub-module; variable-point FFT operation is implemented through the 32-point variable FFT processing sub-modules; the twiddle-factor processing module generates and multiplies intermediate twiddle factors by the result of FFT operation; and the selection-control module realizes control over a whole chip. The processor is suitable to be realized in single-chip FPGA or ASIC, and can simultaneously obtain high speed, low power consumption, high precision and other characteristics.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

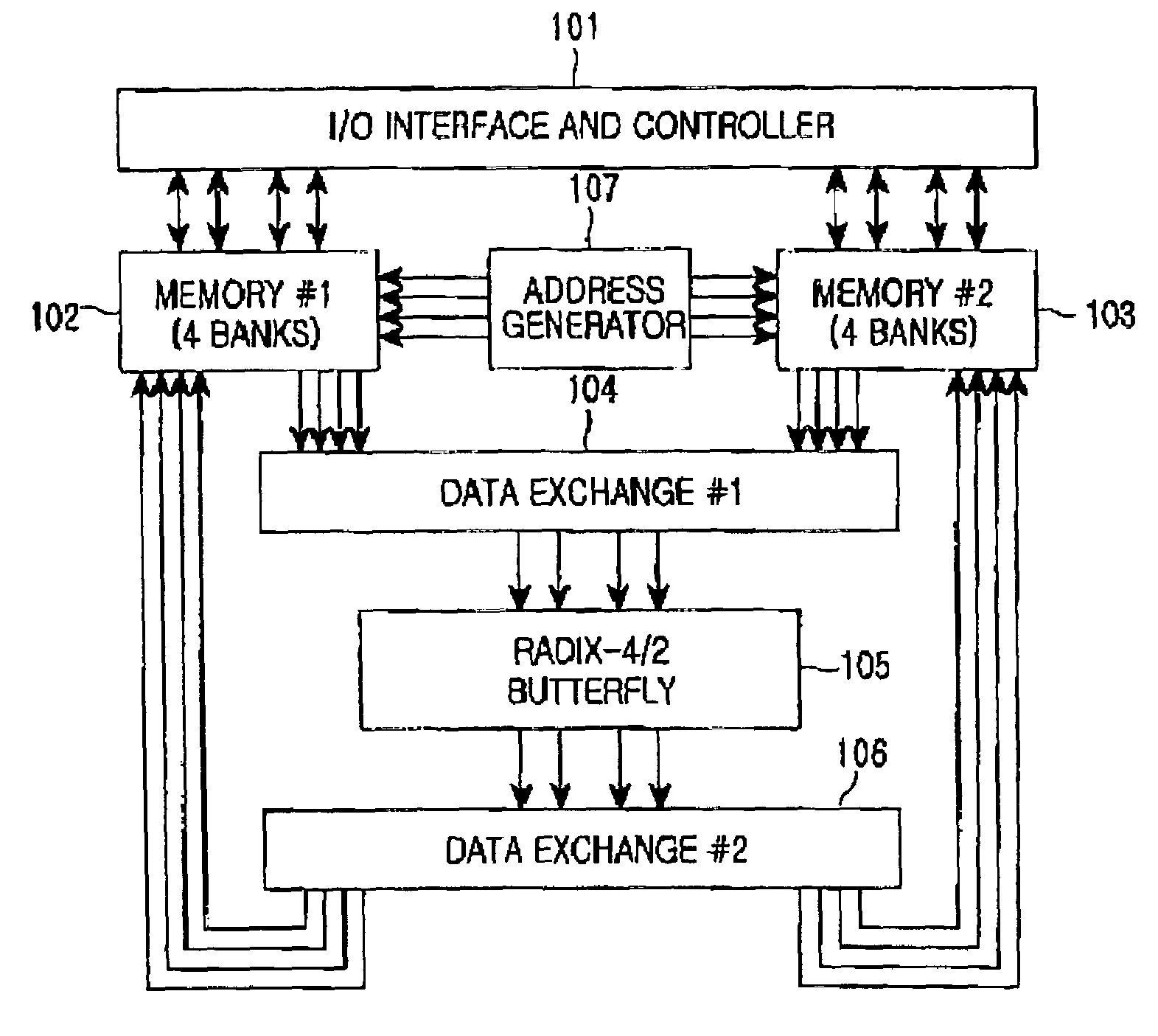

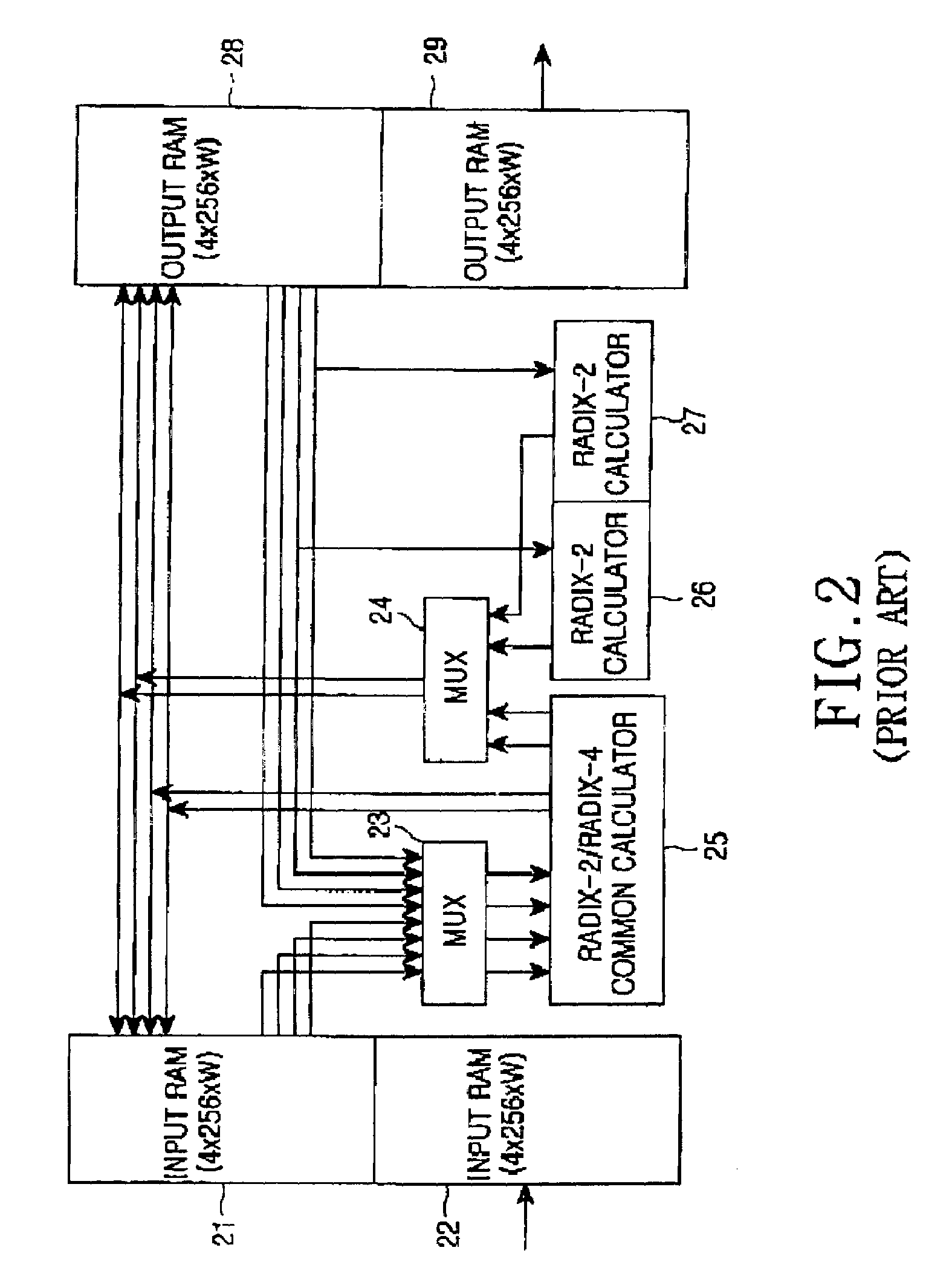

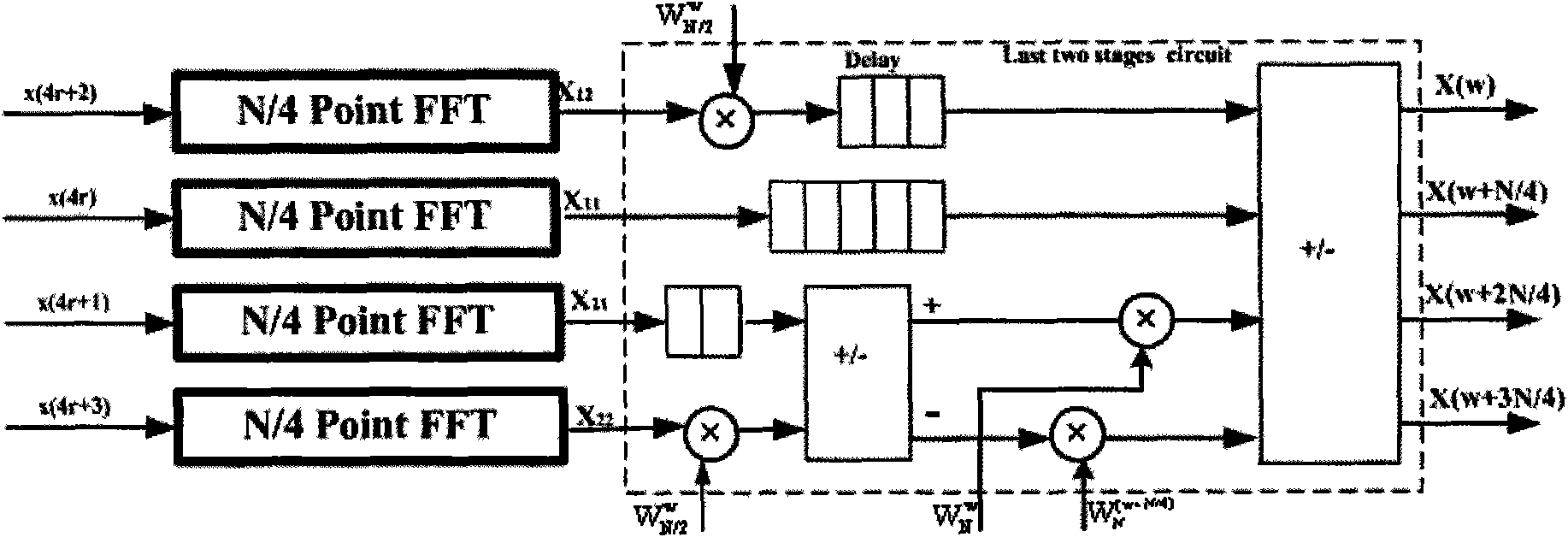

Modulation apparatus using mixed-radix fast fourier transform

ActiveUS7164723B2Minimized in sizeMinimize complexityCode conversionDigital computer detailsModem deviceParallel computing

An FFT (Fast Fourier Transform) processor is disclosed which is a core block of an OFDM (Orthogonal Frequency Division Multiplexing) or DMT (Discrete Multi-tone) MODEM. The FFT processor simultaneously performs sequential input and output by applying an in-place algorithm for a mixed-radix multi-bank memory, thereby realizing continuous processing with only a 2N-word memory having 4 banks. The FFT processor minimizes its complexity while satisfying a high-speed calculation requirement.

Owner:AJOU UNIV IND ACADEMIC COOP FOUND +1

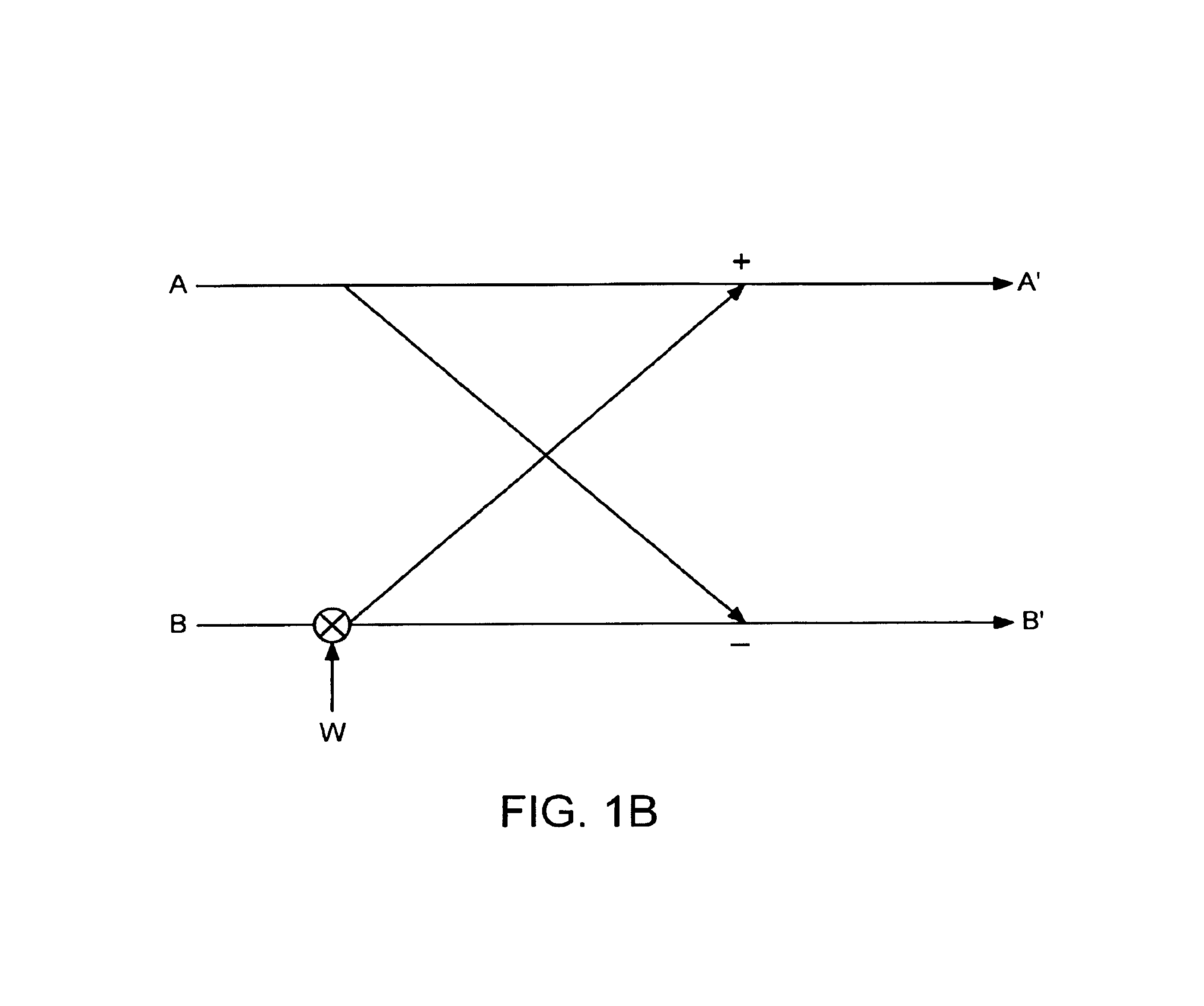

Recoded radix-2 pipeline FFT processor

InactiveUS20050015420A1Digital computer detailsComplex mathematical operationsComputational scienceRotation factor

A single-path delay feedback pipelined fast Fourier transform processor comprising at least one set of triplet FFT stage means: a first FFT stage means comprising a radix-2 butterfly, a feedback memory, and a multiplication by unity; a second FFT stage means comprising a trivial coefficient pre-multiplication, a radix-2 butterfly, a feedback memory, and a multiplication by selectable unity or WNN / 8; and a third FFT stage means comprising a trivial coefficient pre-multiplication, a butterfly, a feedback memory, and a complex twiddle coefficient multiplication with coefficients determined using a twiddle factor decomposition technique.

Owner:CYGNUS COMM CANADA CO

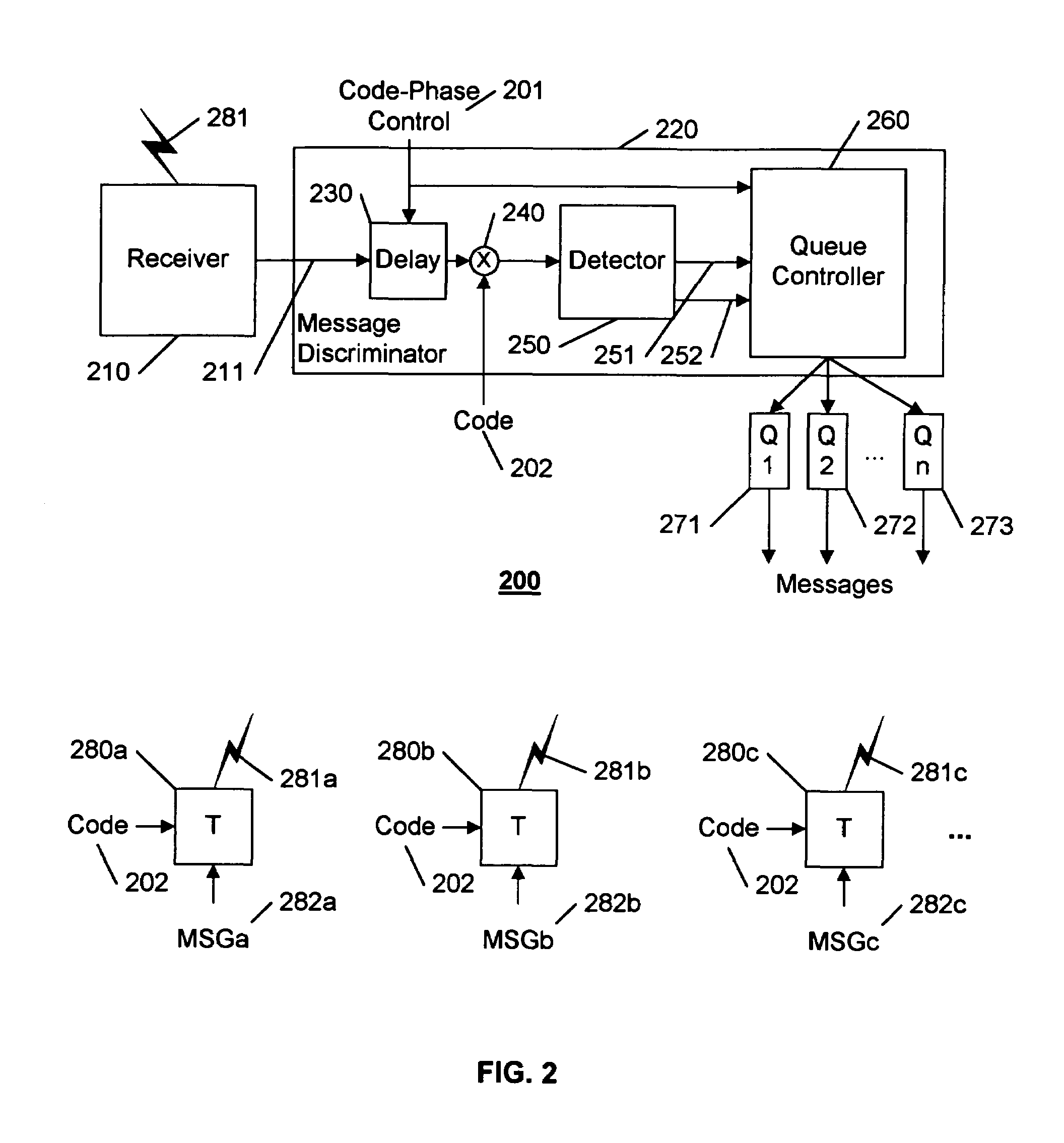

Asynchronous spread-spectrum communications

Communications from autonomous spread-spectrum transmitters are received by dynamically searching the communications band for messages having the same communications parameters, including the use of the same spreading code, but having potentially different code-phases. A receiver that is independent of the transmitters samples the communications band at each code-phase of the spreading code. When a message element is detected at a particular code-phase, the message element is appended to a queue associated with this code-phase. Message elements detected at other code-phases are appended to queues associated with the corresponding code-phases. Gaps between message elements at each code-phase define the beginning and end of each message. In a preferred embodiment of this invention, the processing of the samples occurs at a frequency above the baseband of the encoded message. An FFT processor provides a magnitude and phase associated with each detected message. The magnitude distinguishes message elements from noise elements, and changes in phase determine the bit value associated with each message elements.

Owner:COMTECH MOBILE DATACOM CORP

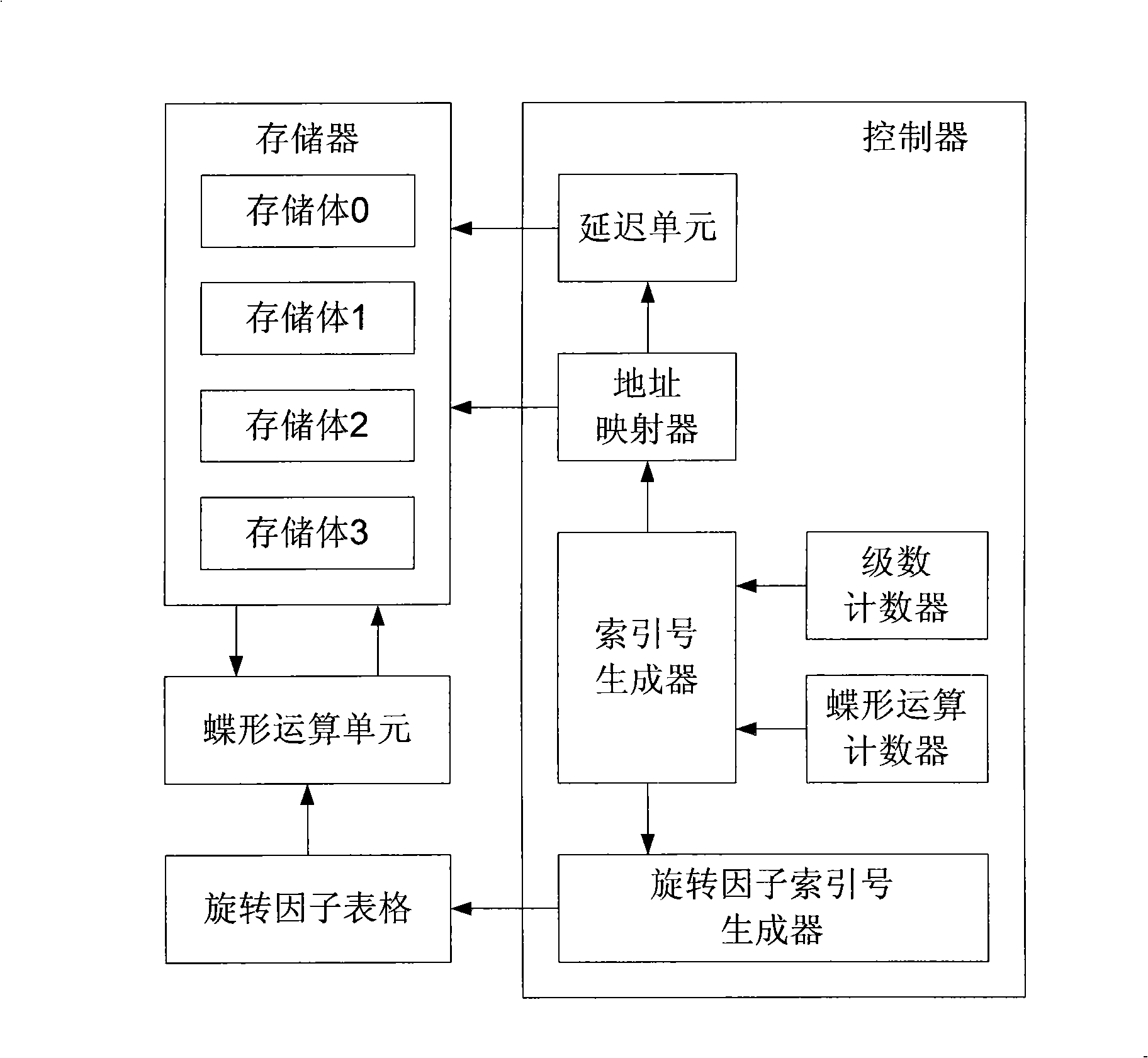

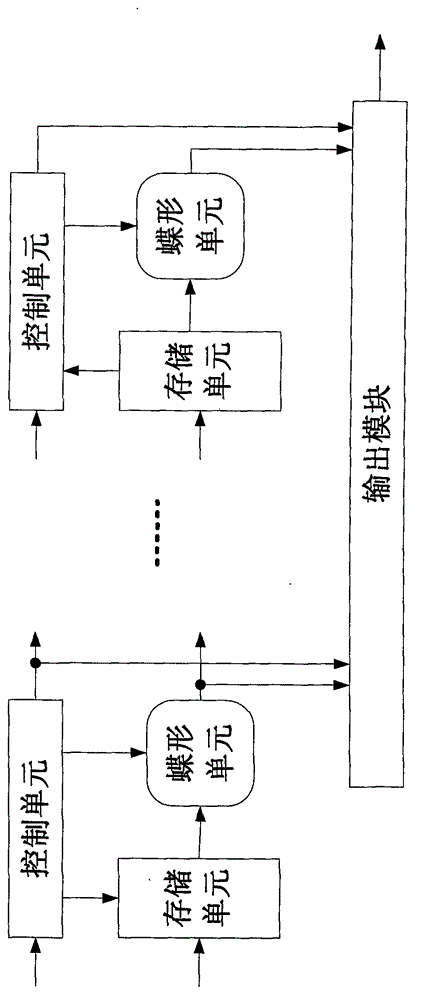

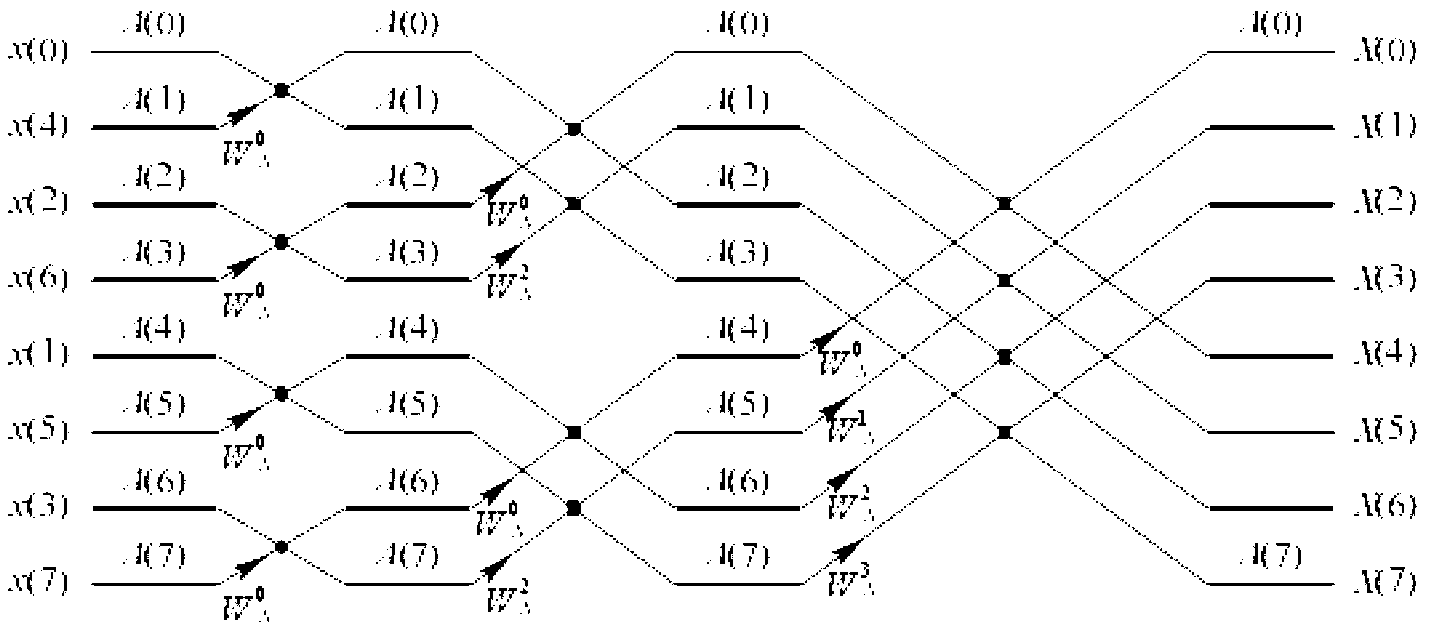

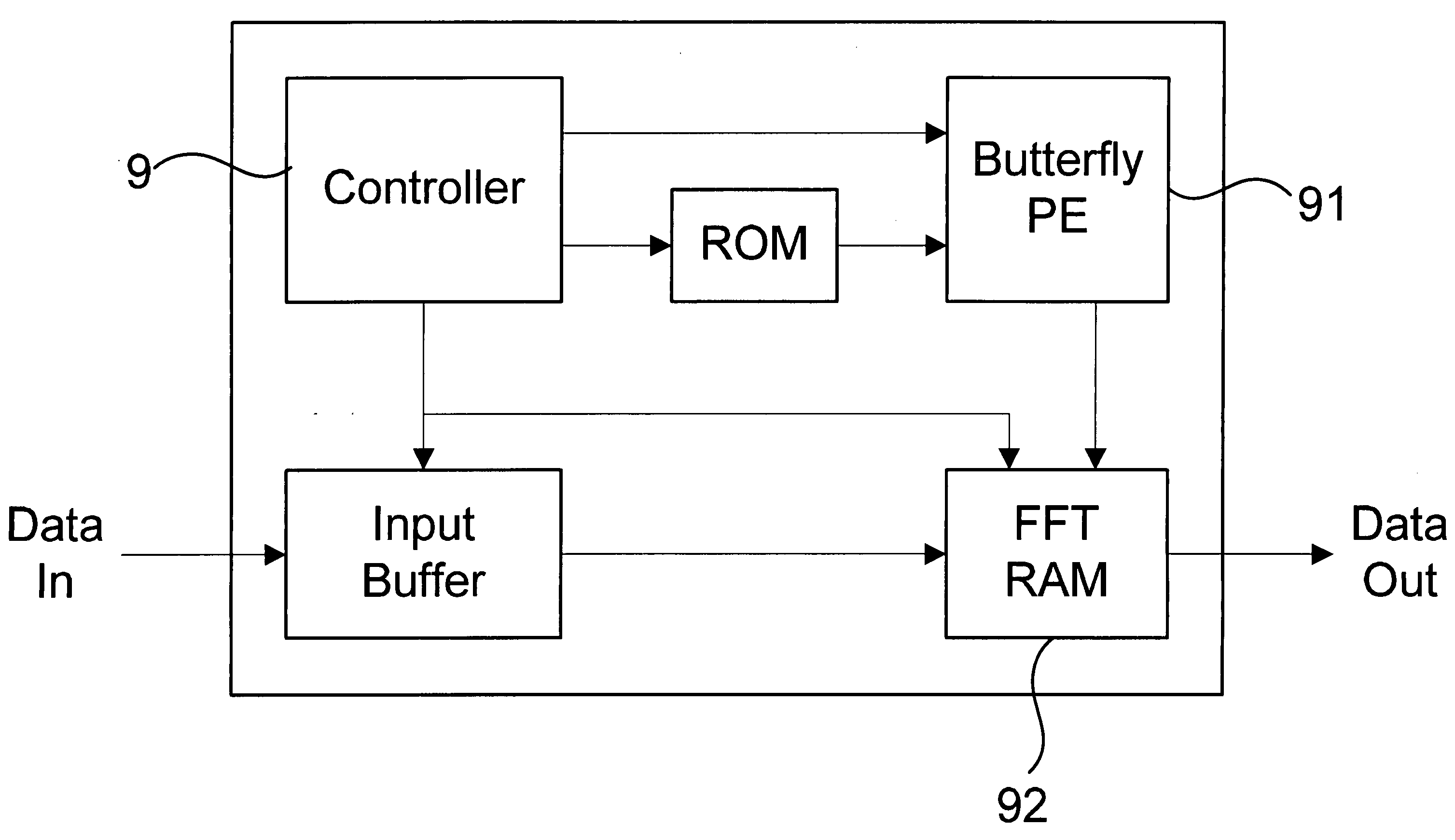

FFT processor data storage system and method

ActiveCN101290613AIncrease profitReduce areaComplex mathematical operationsFft processorTwiddle factor

The invention discloses a system and a method for data storage of an FFT processor. The data storage system comprises a controller, a storage, a papilionaceous operation unit and a twiddle factor form; the storage is used for storing data; the twiddle factor form stores a twiddle factor needed for each papilionaceous operation according to the sequence; the papilionaceous operation unit is used for the papilionaceous operation; the controller comprises a papilionaceous operation counter, a series counter, an index number generator, an address mapping device, a delay unit and a twiddle factor serial number generator; the data storage method comprises the following steps that: according to the input sequence, input data is recorded as dindex, wherein, the index is equal to 0, 1, ..., N-1; the index is represented by a binary digit and needs m bits, wherein, the m is equal to log 2N, that is, recorded as index[m-1:0]; and the input data is stored in the storage. The system and the method for data storage of the FFT processor use a single-port storage to realize the conflict-free read-write access; and the utilization rate of the papilionaceous operation unit is nearly 100 percent, thereby effectively improving the utilization efficiency of hardware resource.

Owner:MAXSCEND MICROELECTRONICS CO LTD

Multi-fpga tree-based fft processor

InactiveUS20100030831A1Well formedDigital computer detailsComplex mathematical operationsFourier transform on finite groupsFft processor

A fast Fourier transform (FFT) computation system comprises a plurality of field programmable gate arrays (FPGAs), a plurality of initial calculations modules, a plurality of butterfly modules, a plurality of external interfaces, and a plurality of FPGA interfaces. The FPGAs may include a plurality of configurable logic elements that may be configured to perform mathematical calculations for the FFT. The initial calculations modules may be formed from the configurable logic elements and may be implemented according to a split-radix tree architecture that includes a plurality of interconnected nodes. The initial calculations modules may perform the initial split-radix calculations of the FFT. The butterfly modules may be formed from the configurable logic elements and may be implemented according to the split-radix tree architecture to perform at least a portion of the FFT computation in an order that corresponds to the connection of the nodes of the split-radix tree architecture. The FPGA interfaces are included in each FPGA and allow communication between the FPGAs. The external interfaces are also included in each FPGA and allow communication with one or more external devices in order to receive data which requires an FFT computation and to transmit the FFT computation results.

Owner:L 3 COMM INTEGRATED SYST

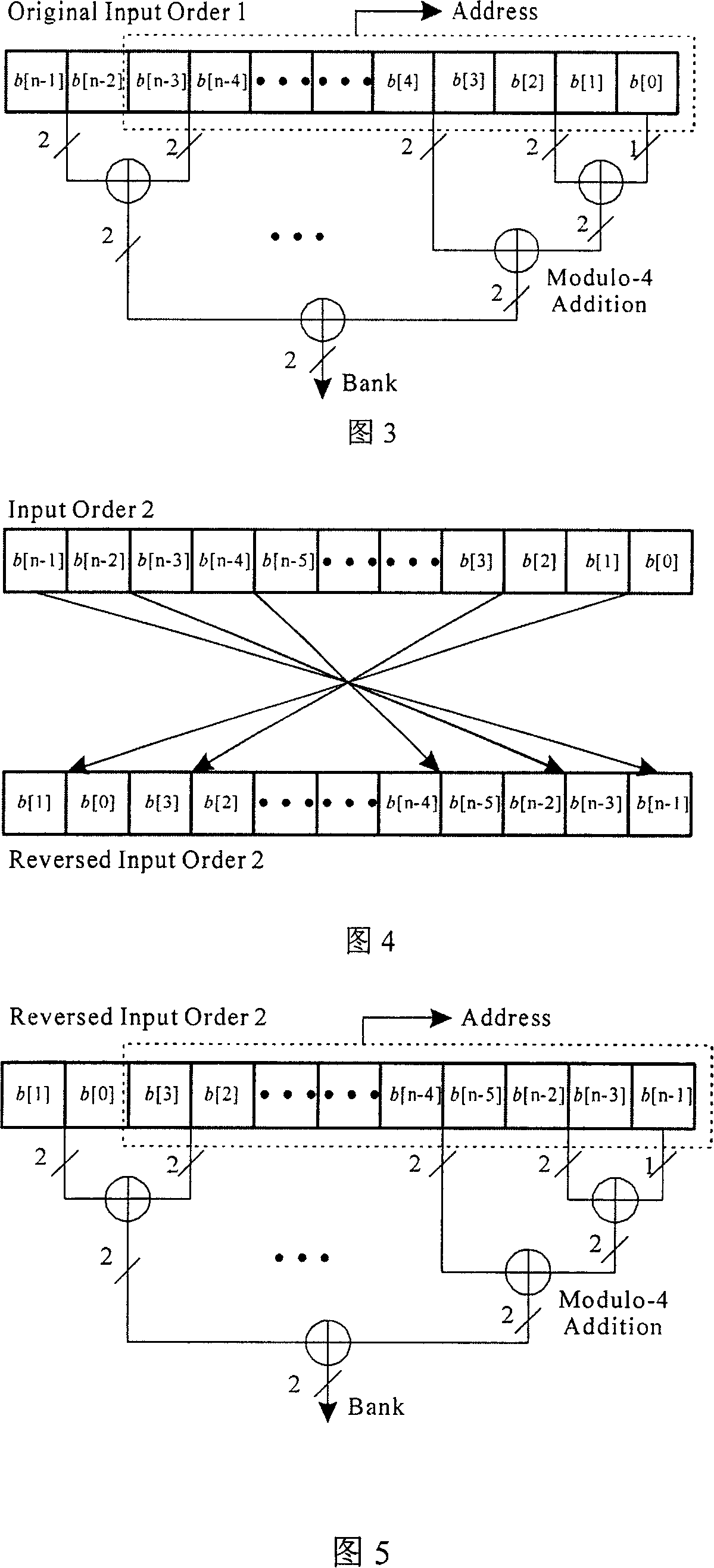

Address mapping method and system for FFT processor with completely parallel data

InactiveCN1504890AImprove parallelismImprove efficiencyDigital data processing detailsMemory adressing/allocation/relocationRotation factorParallel computing

The invention is a full-parallel FFT-processor address mapping method, storing operation number in dual-port memory and rotation factor in ROM; determining R / W addresses for operation number and rotation factor. It fully uses common address operation character of FFT algorithm itself, uses 4 data memory bodies and 3 rotation-factor ones, performs data input and output in the same location, is able to provide an operation number for a butterfly operation in each period and has maximum parallelity. During processor working, the rotation factor only demands simple one-increased mode addressing. It is applied to N point (N is the power of 2) FFT calculation, having high efficiency of base-4 operation and calculation range of base-2 operation.

Owner:宁波高新区中科芯元集成电路技术有限公司

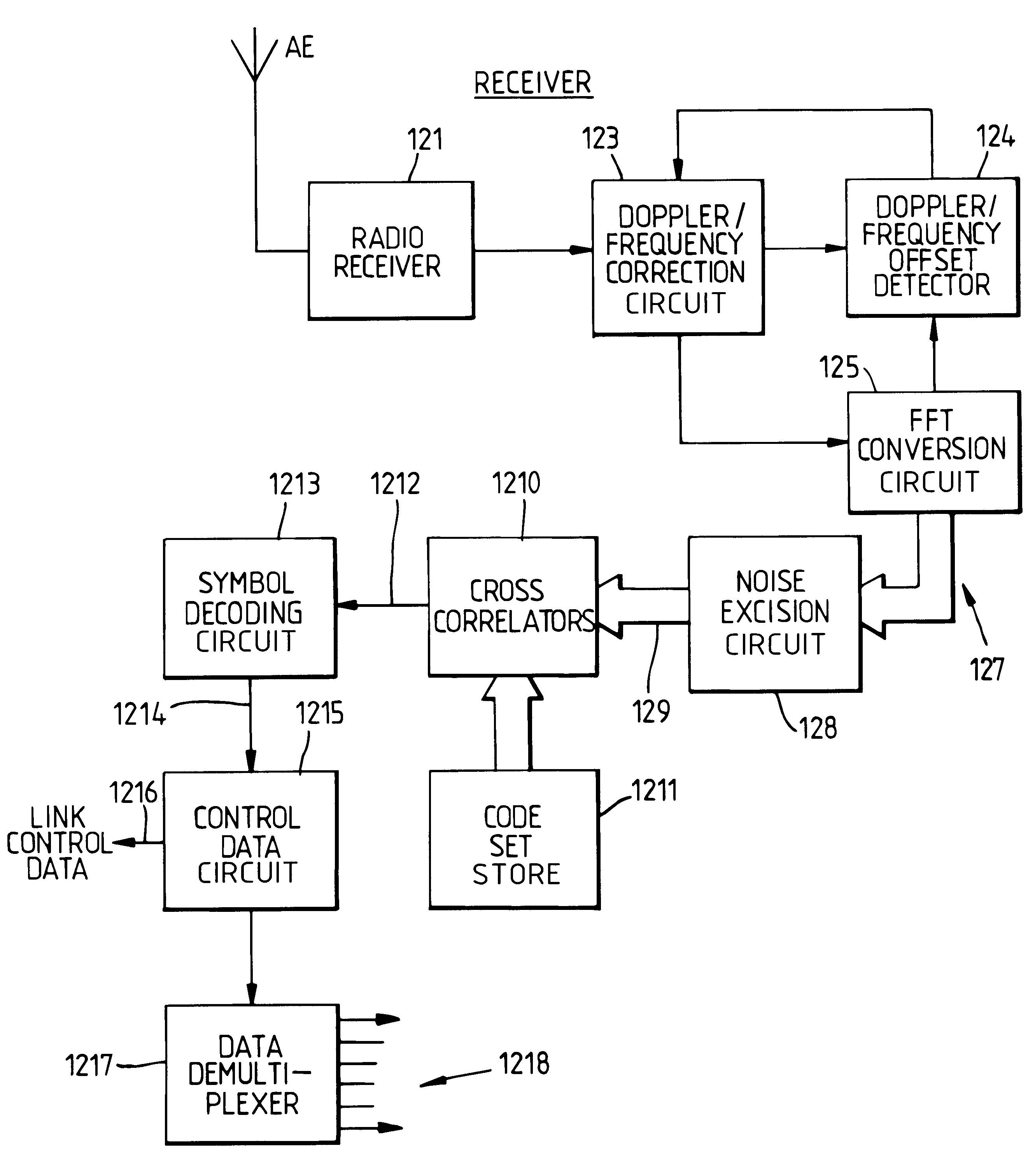

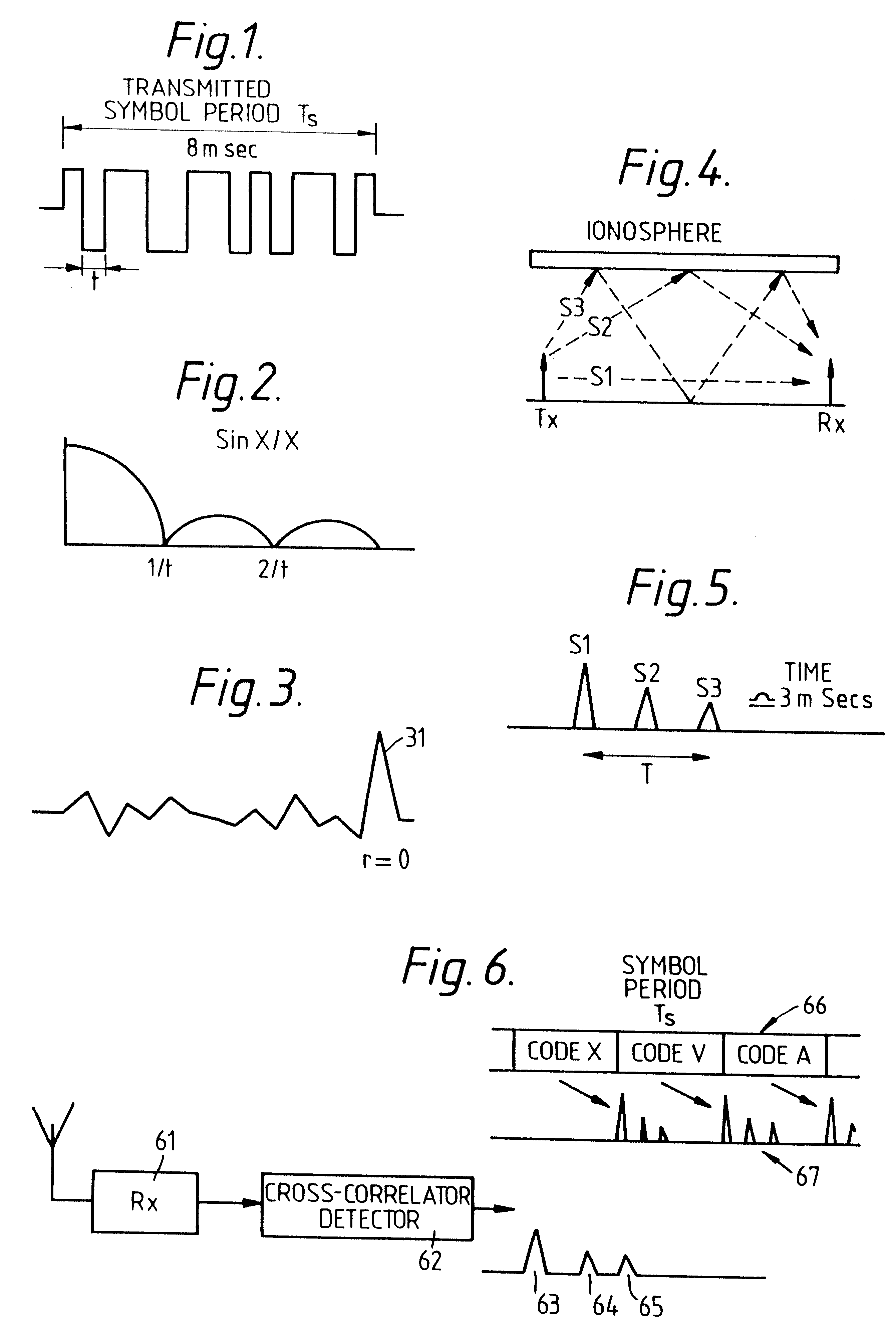

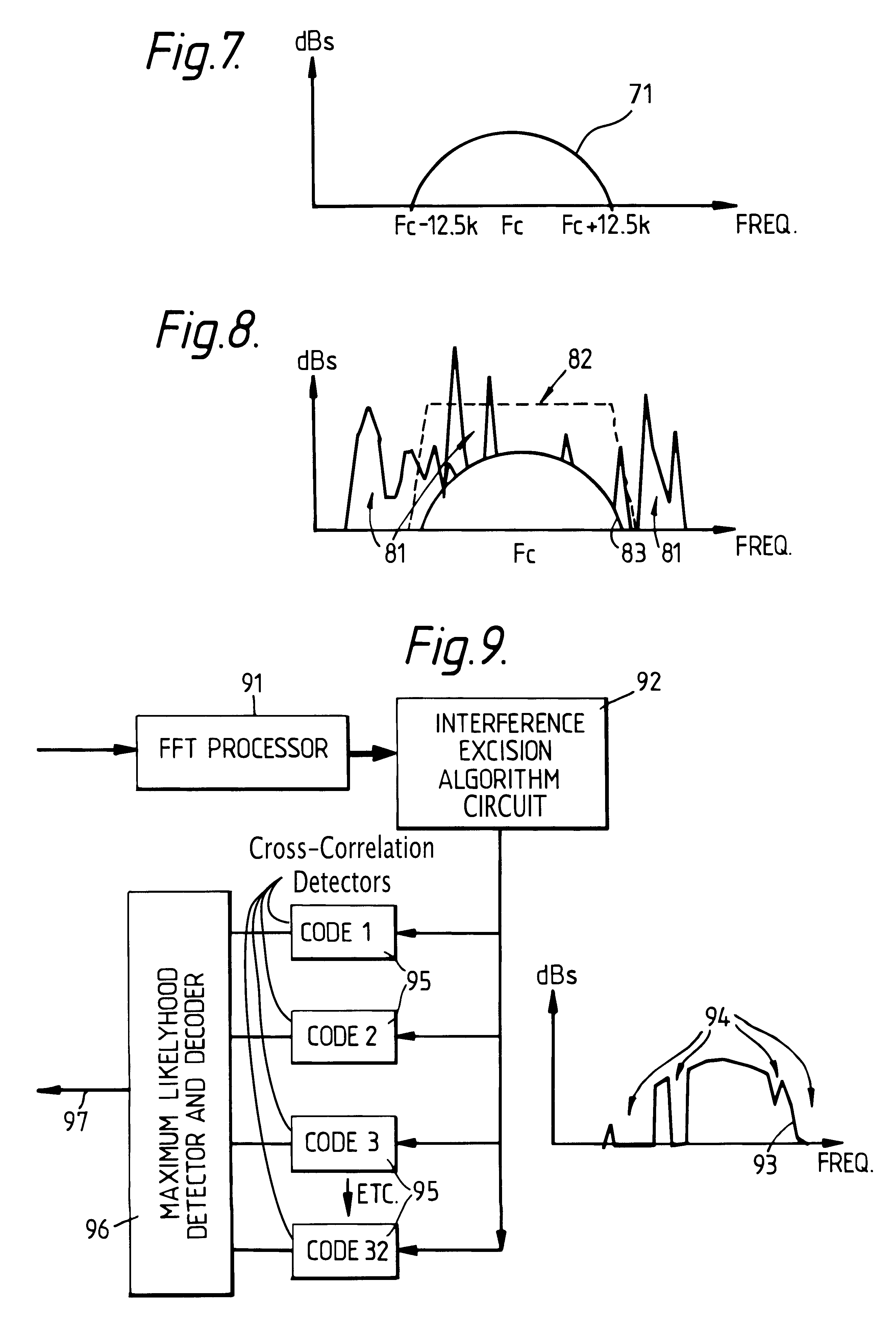

High data rate multiplexed multichannel high frequency broadcast system

InactiveUS6473453B1FunctionalLow cross correlation functionCode division multiplexTransmissionFrequency spectrumInterference canceller

A high frequency communications system comprises eight multiplexed (112) spread spectrum channels with data in each channel transmitted using, for example, 32 semi-orthogonal codes to enable 5 bits of data to be sent for every coded symbol transmitted. The multiplexed data is connected to a phase shift key (PSK) modulator (117) to modulate an hf carrier. At the receiver, inband interference is removed by frequency excision (92, 128) or weighting, making use of the facts that the interference is generally narrow-band and the spectrum of the frequency components of the received signal should be symmetrical about the carrier frequency. The detected signal is Fourier transformed by an FFT processor (91) and then connected to an interference exciser (92, 128) where signal samples symmetrical about the carrier frequency are compared and any sample which exceeds the respective symmetrical sample by more than a predetermined threshold is excised or given a low weighting. After interference excision the remaining signal is connected to a bank (1210) of 32 cross-correlation detectors before connection to a maximum likelihood detector and decoder (1213).

Owner:XYLON LLC

Apparatus and method for channel estimation in an SDMA-OFDM system

Provided is a channel estimation apparatus and method in a broadband wireless communications system using a smart antenna are provided. In the channel estimation apparatus, an FFT processor converts a received time-domain signal into a frequency-domain signal by FFT-processing the received time-domain signal. A channel acquirer estimates a first channel information for an SDMA user using a preamble signal allocated to the SDMA user in the frequency-domain signal. A channel tracker estimates a second channel information for the SDMA user using pilots in a data area allocated to the SDMA user in the frequency-domain signal. A channel estimator estimates a final channel information by weighting the first channel information and the second channel information according to a channel change rate.

Owner:SAMSUNG ELECTRONICS CO LTD

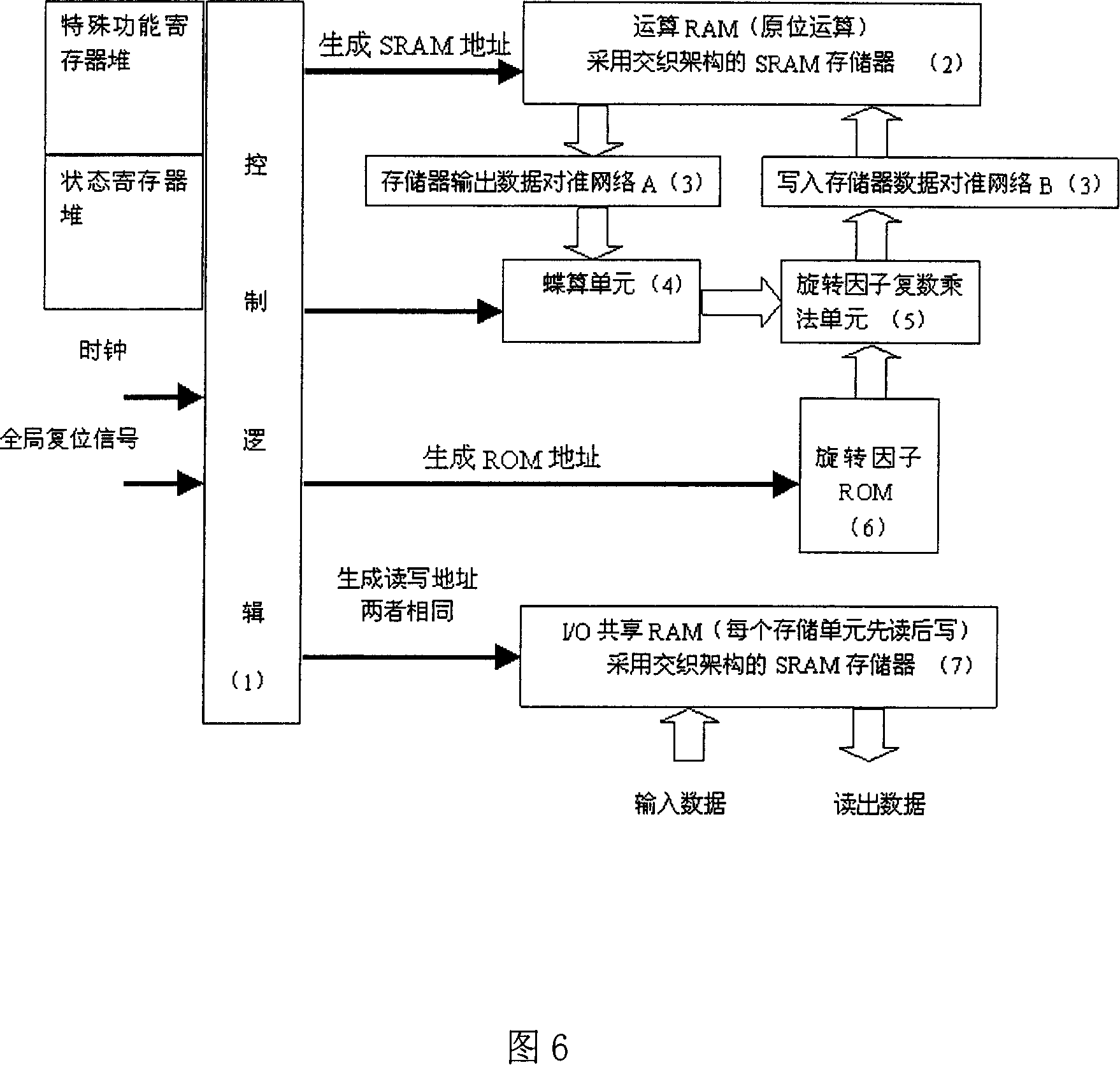

Low memory spending hybrid base FFT processor and its method

InactiveCN101083643AMulti-frequency code systemsComplex mathematical operationsComputer architectureFft processor

Being related to area of wireless communication technique, especially the invention is related to general operand conflict free created mixed base FFT processor with low spending memory. The FFT processor is composed of control logic unit, operation RAM, network, butterfly operation unit, complex multiplication unit of twiddle factor (CMUTF), twiddle factor ROM, and I / O shared RAM. The control logic unit controls the operation RAM, the butterfly operation unit, twiddle factor ROM, and I / O shared RAM. Through network, the operation RAM is connected to the butterfly operation unit, and CMUTF. CMUTF is connected to the twiddle factor ROM.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

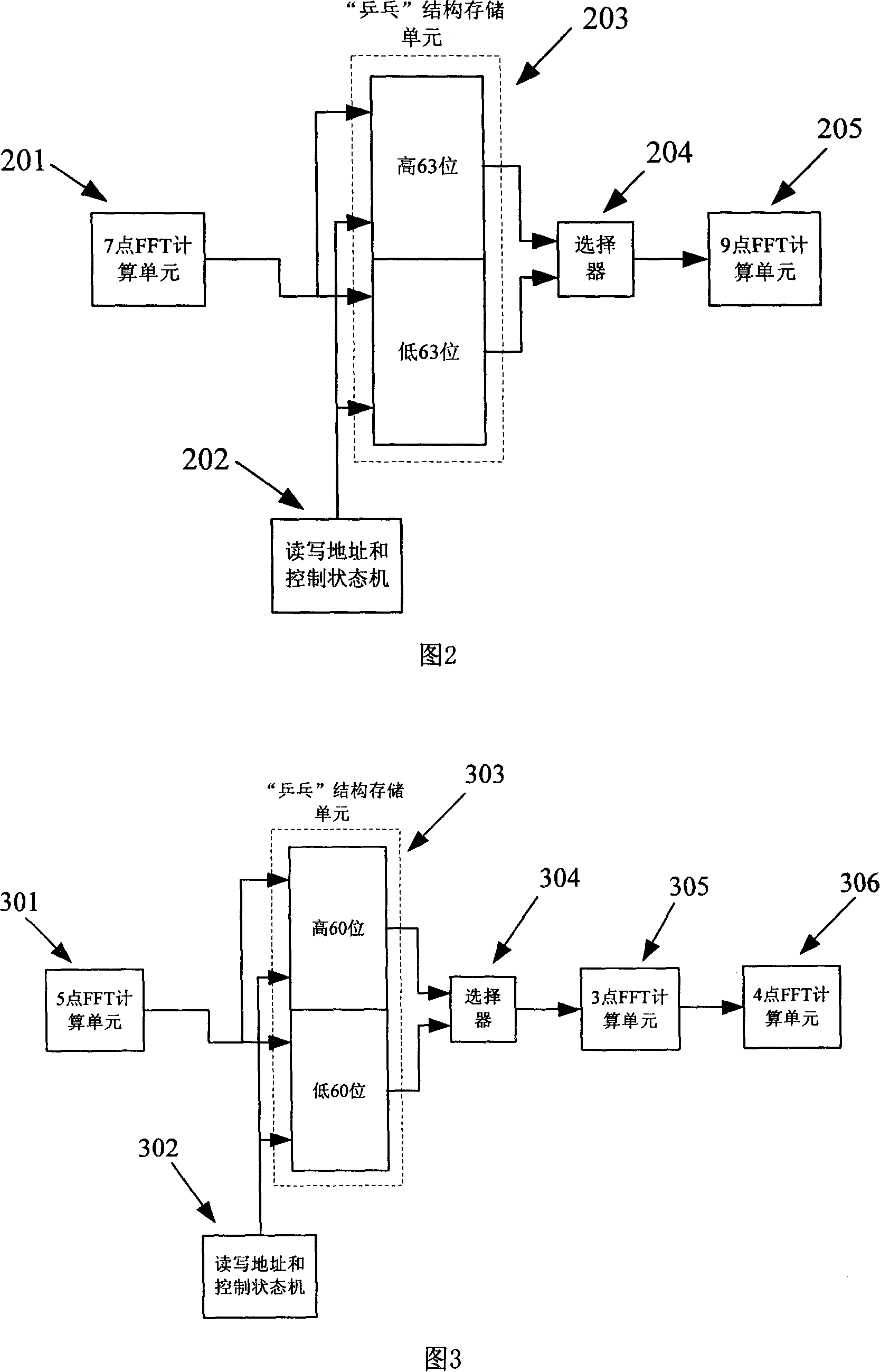

3780-point quick fourier transformation processor of pipelining structure

InactiveCN101136891AImprove data throughputGuaranteed calculation accuracyMulti-frequency code systemsComplex mathematical operationsDigital signal processingFast Fourier transform

3780 points Fast Fourier Transform (FFT) processor is based on pipeline architecture. Based on mixed base algorithm, the invention decomposes 3780 points FFT into 63X60. Based on prime factor algorithm, 63 points FFT and 60 points FFT are decomposed to 7X9 and 5X3X4 respectively. Characters are that the state design based on pipeline is adopted by each FFT arithmetic unit, and memory unit of using 'ping-pong' structure is in use for storing arithmetic data so as to constitute 3780 points FFT processor in complete pipeline architecture. Thus, the input data can be carried out FFT operation uninterruptedly, and operational result can be output uninterruptedly. The invention raises data throughput of processor, and reduces complexity for controlling address of reading and writing memory.

Owner:FUDAN UNIV +1

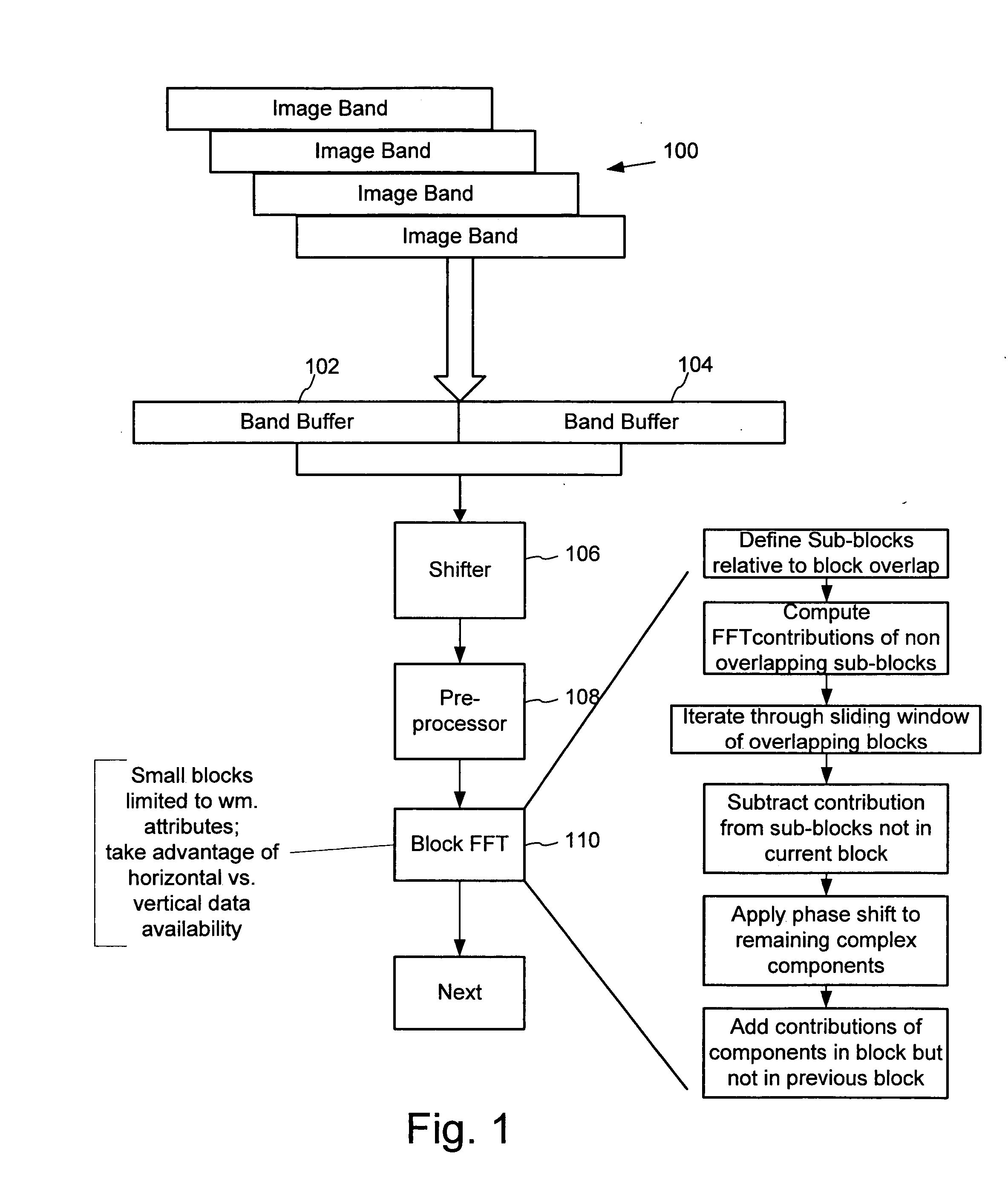

Optimized digital watermarking functions for streaming data

ActiveUS20050169497A1Limit digital watermark processingAvoid redundant calculationsUser identity/authority verificationCharacter and pattern recognitionStreaming dataData stream

In one aspect of the invention, a digital watermark detector comprises a memory buffer for managing an incoming stream of data. The detector includes logic for transferring overlapping data blocks from the memory buffer to a frequency domain transform processor, such as an FFT processor. The frequency domain transform processor including logic to re-use frequency domain transform operation results for overlapping portions of the data blocks. In another aspect of the invention, a digital watermark detector comprises a memory buffer for a block of data, and pipelined watermark processor segments. The segments each perform different watermark detector operations in series. These segments concurrently operate on different data segments of the block of data in a processing pipeline. One embodiment employs pipelined processors for setting up data for subsequent detecting stages, such as pipelined data conversion, re-sampling, pre-filtering and frequency domain transforms. Alternative embodiments pipeline data transformations, correlation operations (e.g., matched filter operations) etc. Data flows through the processing pipeline until it reaches a critical point. At stages before the critical point, data may be dropped as not likely to include digital watermark data. This pruning of data helps reduce un-needed processing and / or false positives of watermark detection.

Owner:DIGIMARC CORP

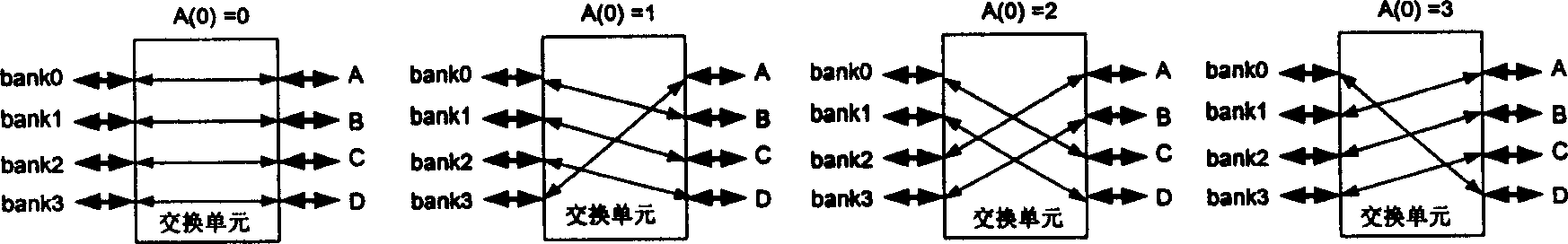

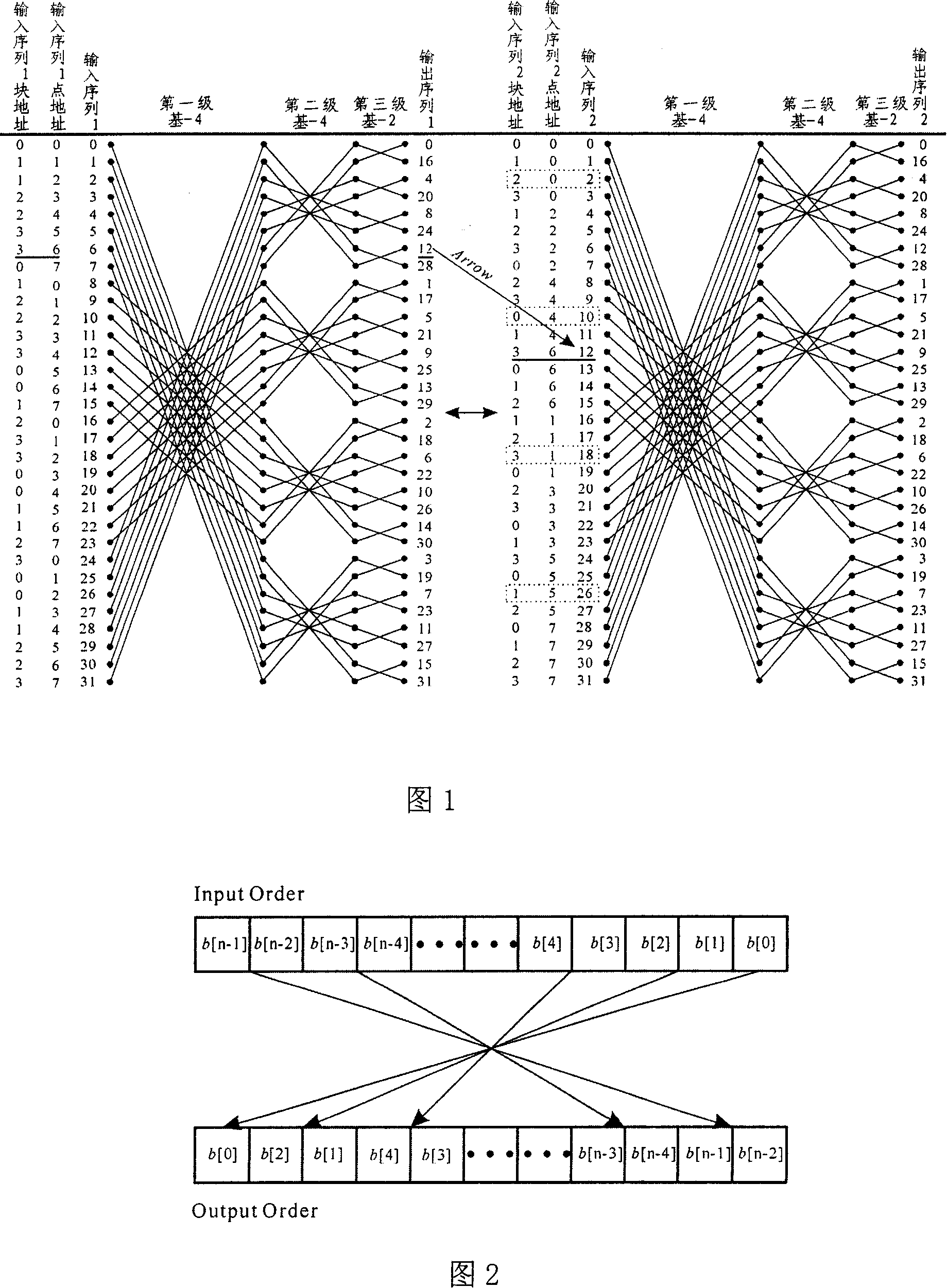

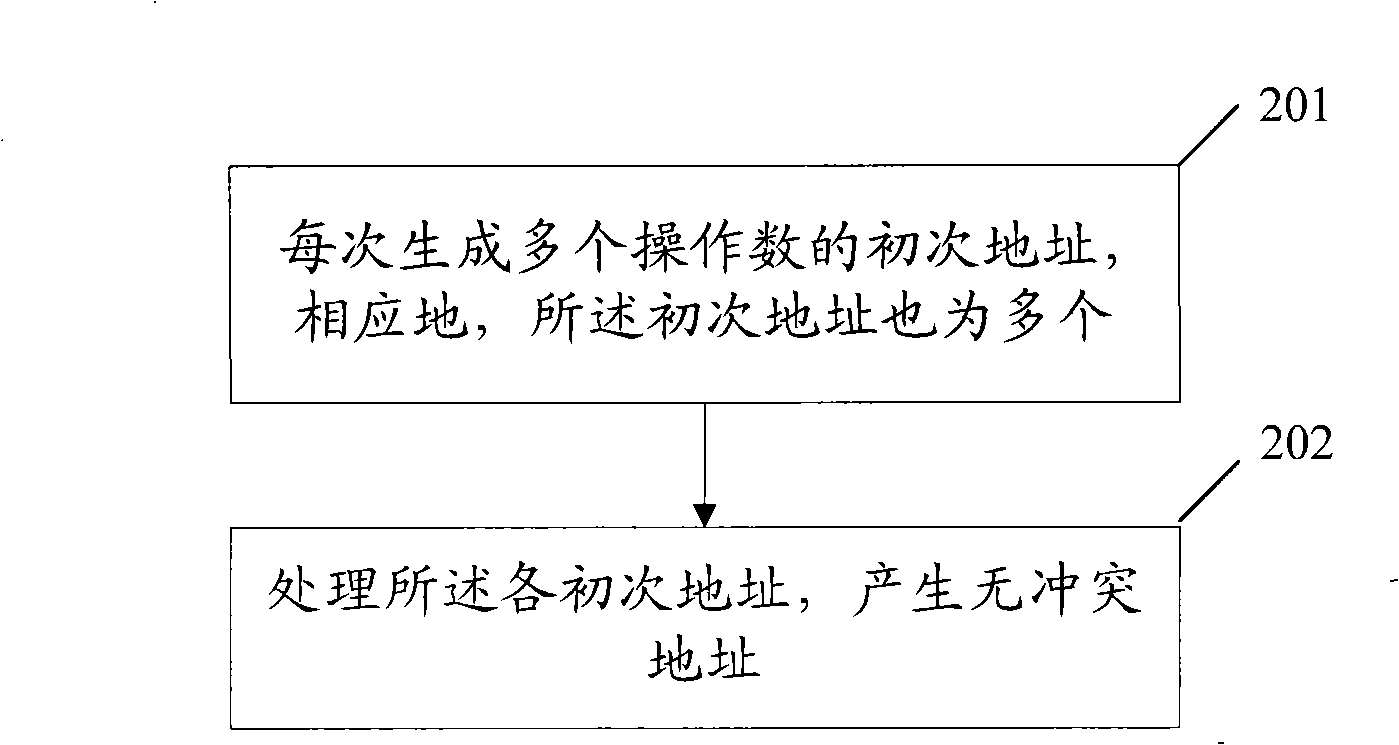

Address mappings method and operand parallel FFT processing system

The invention relates to an address mapping method and an FFT processing system with parallel operands. A primary address with a plurality of operands is generated at each time by the method, then the primary address is processed to generate a stack address and an inner address, wherein, the stack address is an address of a memory stack contained by a memory for storing the operands and the inner address is an address of all operands in all memory stacks; by adopting the address mapping method, the operands can be stored in different memory stacks, thereby ensuring that the operands can be in parallel in the butterfly-shaped operation. A collision removal mapper of the FFT processing system with the parallel operands is used for converting the primary address of the operands into a non-collision address, thereby ensuring that the operands can be stored in different memory stacks, and an FFT processor can access the operands in parallel so as to accelerate the operation speed.

Owner:RDA MICROELECTRONICS SHANGHAICO LTD

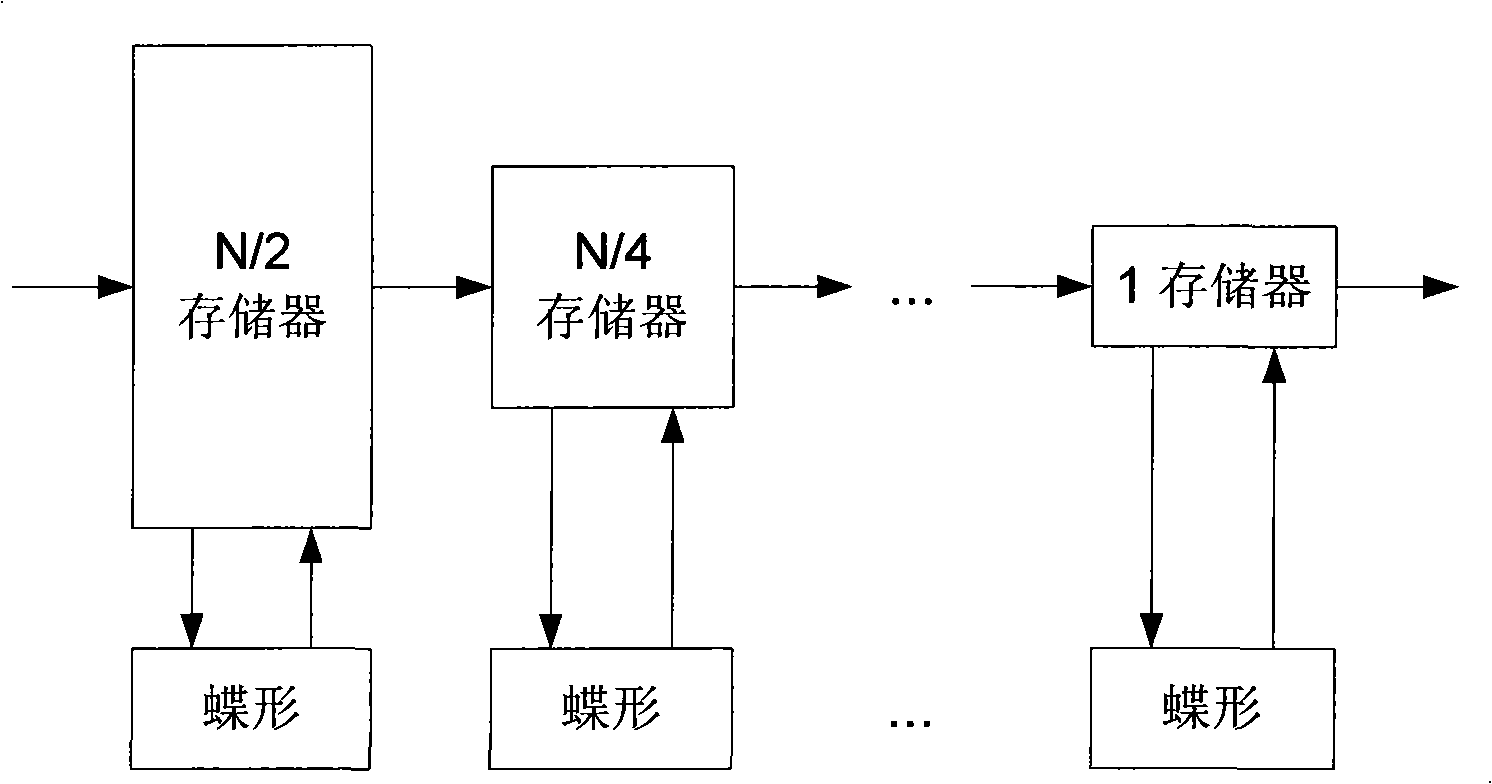

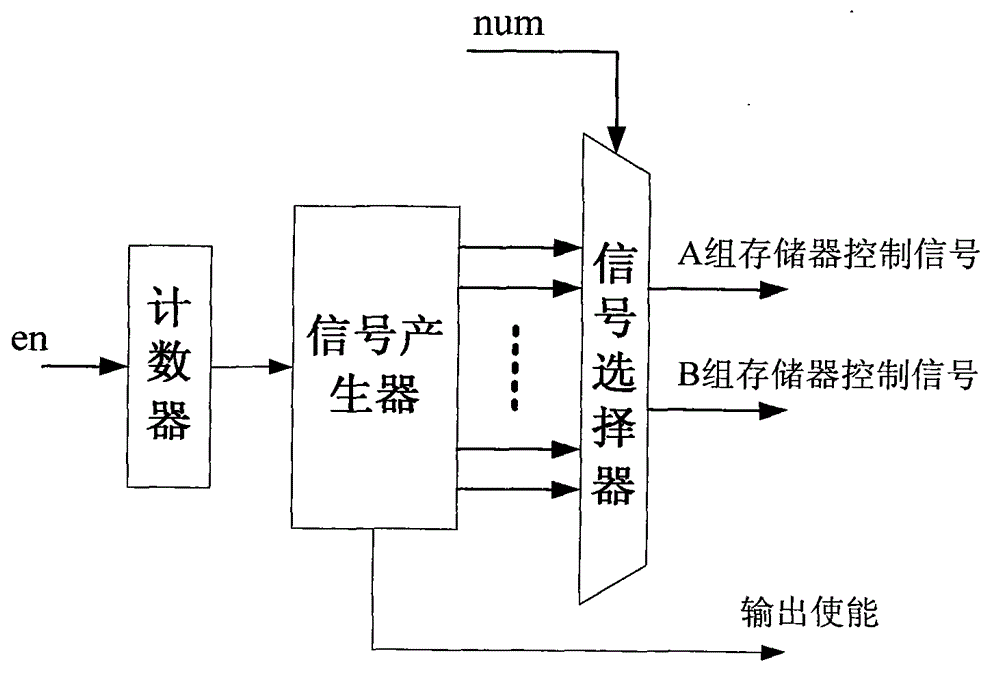

High-speed variable point FFT (Fast Fourier Transform) processor based on FPGA (Field-Programmable Gate Array) and processing method of high-speed variable point FFT processor

InactiveCN102945224AOvercoming complexityOvercoming the problem of poor module portabilityComplex mathematical operationsFast Fourier transformComputer architecture

The invention discloses a high-speed variable point FFT (Fast Fourier Transform) processor based on FPGA (Field-Programmable Gate Array) and a processing method of the high-speed variable point FFT processor. The FFT processor disclosed by the invention comprises a multi-stage processing module and a first-stage output module; the multi-stage processing module and the output module are cascaded together in pipeline manner. The processing method disclosed by the invention comprises the following steps: 1, initially configuring; 2, receiving data; 3, saving data; 4, carrying out butterfly processing; 5, judging whether the FFT operation is finished or not; and 6, outputting result. The invention mainly solves the problems that the conventional FFT processor is complicated to control, the module is poor in transportability, and the hardware is hard to realize. Through the adoption of radix-2 algorithm with an improved structure, the structures of all stages of the FFT processor of the invention are firm, the control logic is simple, the module is high in transportability, and the high-speed variable point FFT processor is very suitable to realize in one-chip FPGA, and can obtain characteristics of high speed and high precision at the same time.

Owner:XIDIAN UNIV

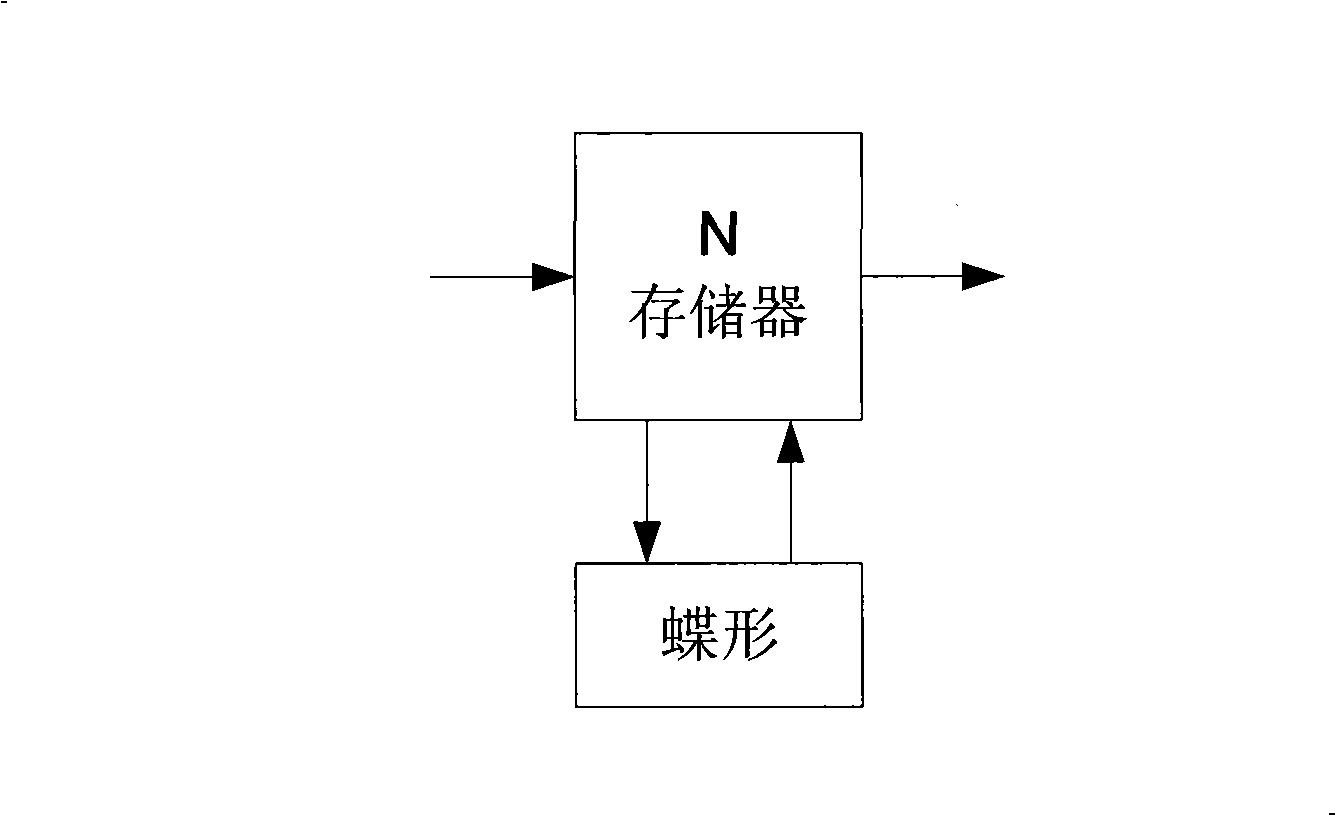

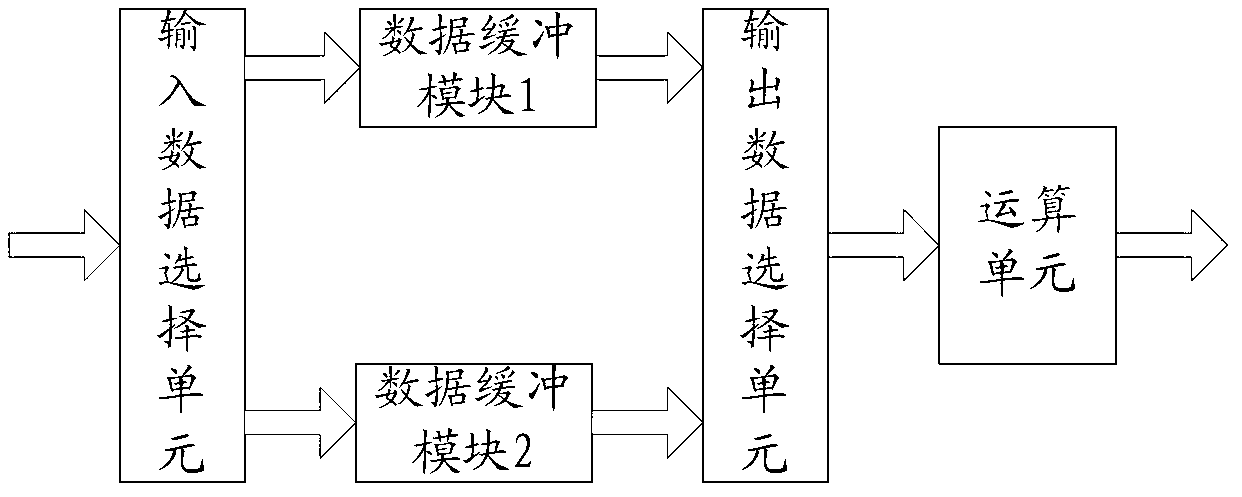

Point-changeable floating point FFT (fast Fourier transform) processor

ActiveCN104268122AShorten operation timeConsume less resourcesProgram controlMemory systemsFast Fourier transformTime domain

The invention relates to a point-changeable floating point FFT processor. The point-changeable floating point FFT processor comprises a data selection and storage module, butterfly calculation units and a rotating factor storage, wherein the data selection and storage module is used for storing input data and outputting data required by the butterfly calculation unit according to the time domain radix-2 algorithm; when FFT points are selected to be 1024, externally input data are placed in order inside the RAM (random access memory) of the data selection and storage module, and when the FFT points are selected to be the others, the data are placed at intervals; the butterfly calculation units are used for completing the butterfly calculation of the FFT algorithm, and the number of the butterfly calculation units is four; the rotating factor storage is used for storing rotating factors required by the butterfly calculation units, and the address of the rotating factor storage is controlled by the data selection and storage module. The point-changeable floating point FFT processor comprises the four butterfly calculation units, thereby reducing the original calculation time by three quarters and achieving a calculation speed four times as high as that of IP (intellectual property) cores of the ALTERA corporation, and meanwhile due to the fact that the points can be selected to be 32, 64, 128, 256,612 or 1024, achieves point configurability and use flexibility.

Owner:ANHUI SUN CREATE ELECTRONICS

Pilot transmitting apparatus and method for sc-fdma system

ActiveUS20100039927A1Without usingMultiple modulation transmitter/receiver arrangementsTransmission path divisionCyclic prefixFft processor

Provided are a pilot transmitting apparatus and method capable of selectively using an OFDMA scheme and an SC-FDMA scheme. The pilot transmitting apparatus includes a pilot inserter for inserting a pilot signal in a modulated symbol and inserting a cyclic prefix code for the inserted pilot signal, an FFT processor for receiving symbols with a pilot inserted thereto from the pilot inserter and performing an FFT process on the received symbols, an IFFT processor for receiving the transformed data from the FFT processor and performing an IFFT process on the transformed data, a mapping processor for mapping the output of the FFT processor to input positions of the IFFT processor to load the frequency domain transformed data on predetermined sub-carriers, and a cyclic prefix inserter for inserting a cyclic prefix code for the output of the IFFT processor.

Owner:ELECTRONICS & TELECOMM RES INST

Butterfly-shaped operation FFT processor

InactiveCN101354700AReduce complexityReduce computational complexityComplex mathematical operationsBroadcast system receivingRotation factorComputation complexity

The invention discloses a butterfly computation FFT processor, wherein a complex multiplier used for realizing multiplication of data and a rotation factor is a CORDIC rotation operator, and the rotation angle corresponding to the rotation factor is stored into a rotation factor memory. The butterfly computation FFT processor adopts the CORDIC rotation algorithm to realize multiplication operation of the data and the rotation factor and then uses data shift to replace complex multiplication operation, thereby reducing the computation complexity. Simultaneously, due to adoption of the CORDIC rotation algorithm to realize complex multiplication, only the rotation angle corresponding to the rotation factor is required to be stored into the rotation factor memory without the necessity of storing the sine value and the cosine value of a corresponding angle of the rotation factor, thereby a rotation factor memory unit can be saved and the reading complexity of the rotation factor is reduced.

Owner:SICHUAN PANOVASIC TECH

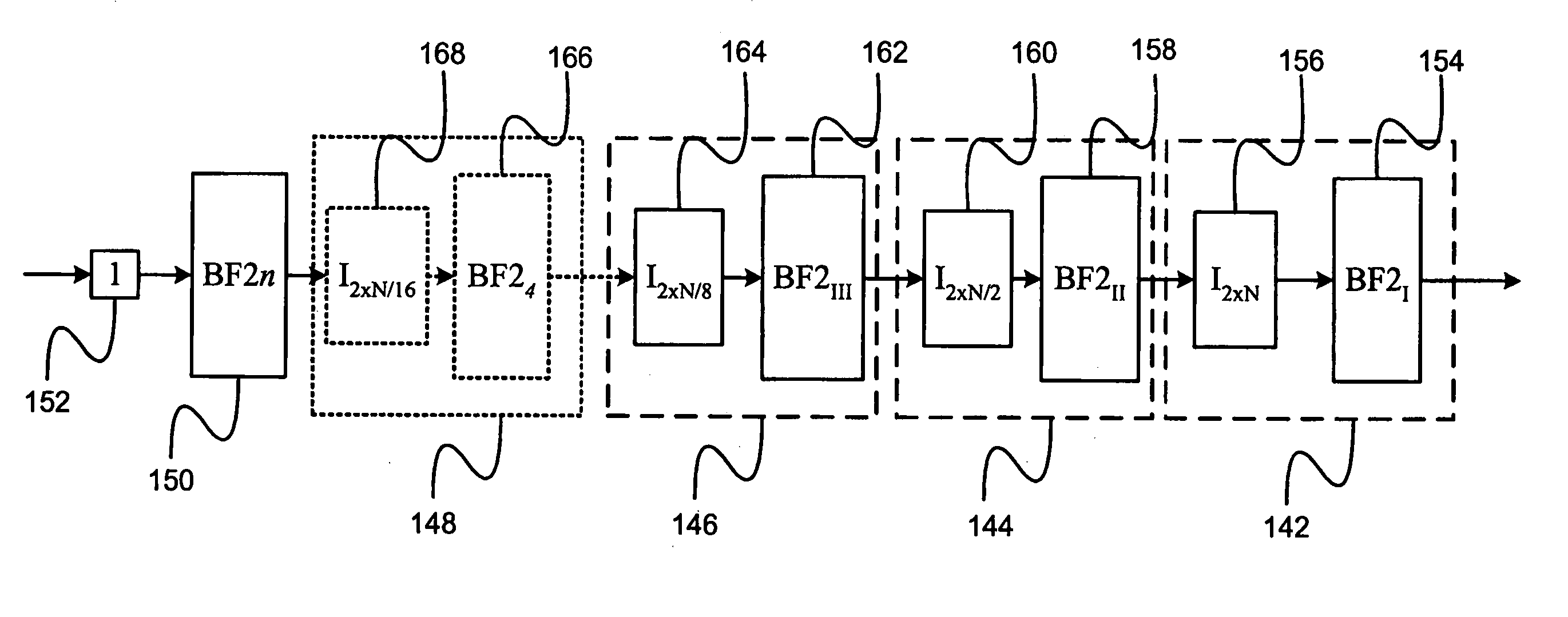

Pipelined FFT processor with memory address interleaving

InactiveUS20050114420A1Avoid overwritingReduce areaDigital computer detailsComplex mathematical operationsMemory addressParallel computing

An FFT processor using a single delay path and a permuter provides a reduction in the implementation area and a related reduction in power consumption through efficiencies obtained by the modification of a butterfly unit and the use of a novel interleaver. The modified butterfly unit is obtained by removal of complex variable multipliers, which is possible due to the simplification of twiddle factors in the stages that correspond to the modified butterfly unit.

Owner:MICROSEMI SOLUTIONS (US) INC

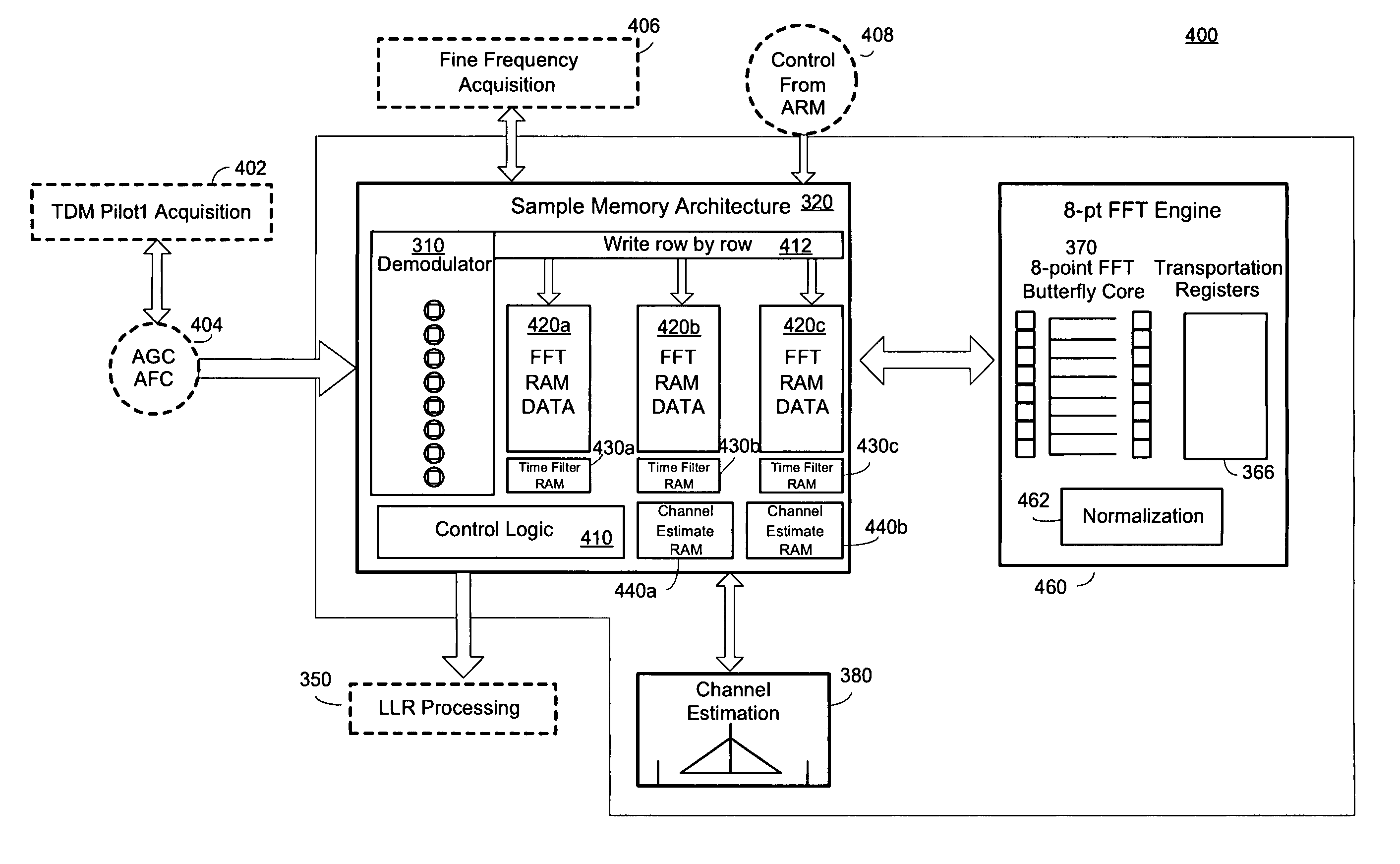

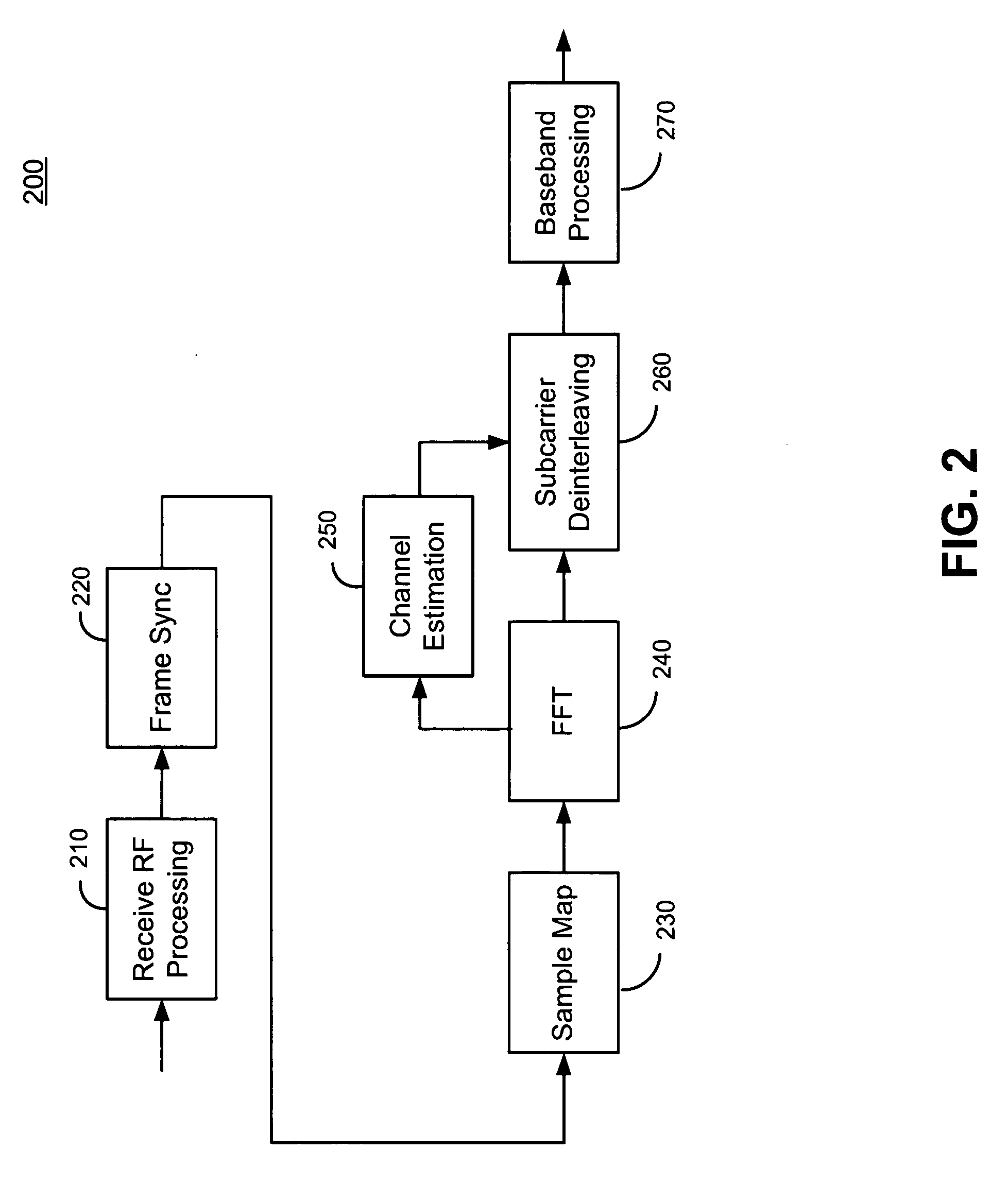

Fast fourier transform processing in an OFDM system

InactiveUS20060224650A1Effectively pipelinedError detection/correctionAmplitude-modulated carrier systemsFast Fourier transformFft processor

An FFT processor for an OFDM receiver includes multiple interrelated operational blocks. The FFT processor is configured to perform data demodulation, channel estimation, and fine timing acquisition on received OFDM symbols. The FFT processor incorporates a pipelined FFT engine using a memory architecture shared with channel estimation and demodulation blocks. The combination of the shared memory structure and the pipelined FFT operation enable the channel estimation and demodulation processing to be completed during the time used to capture the next received symbol.

Owner:QUALCOMM INC

FFT processor with pipeline structure

ActiveCN103226543ASave storage spaceReduce areaComplex mathematical operationsFast Fourier transformParallel computing

The invention discloses an FFT (Fast Fourier Transform) processor with a pipeline structure, which is used for processing an N-point r-DIT-FFT calculation, wherein the N equals to 2 <M>, and the M is a positive integer. The processor comprises L-level butterfly calculate units, a plurality of input storage units, and two output storage units, wherein the L equals to log r <N>; each level of butterfly calculate unit is connected with two input storage units; each level of the butterfly calculate unit is connected with the two input storage units of a next level of butterfly calculate unit except the Lth-level butterfly calculate unit; the Lth level butterfly calculate unit is connected with the two output storage units; storage spaces of two input storage units of a first-level butterfly calculate unit, and two input storage units and the two output storage units of the Lth level butterfly calculate unit are N point; and storage spaces of two input storage units of a Kth level butterfly calculate unit are r <K> point, wherein the K is a positive integer larger than one and less than L.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

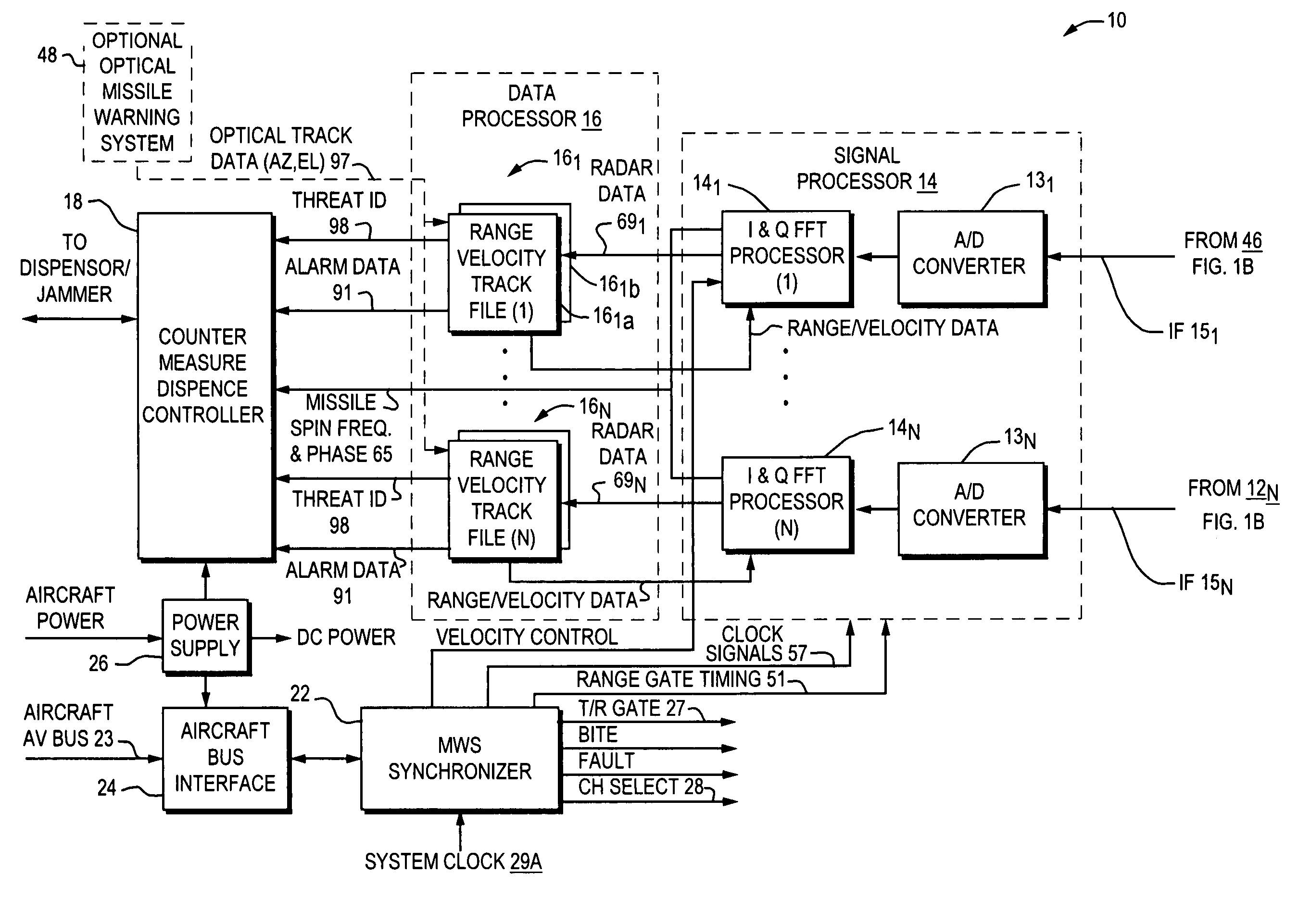

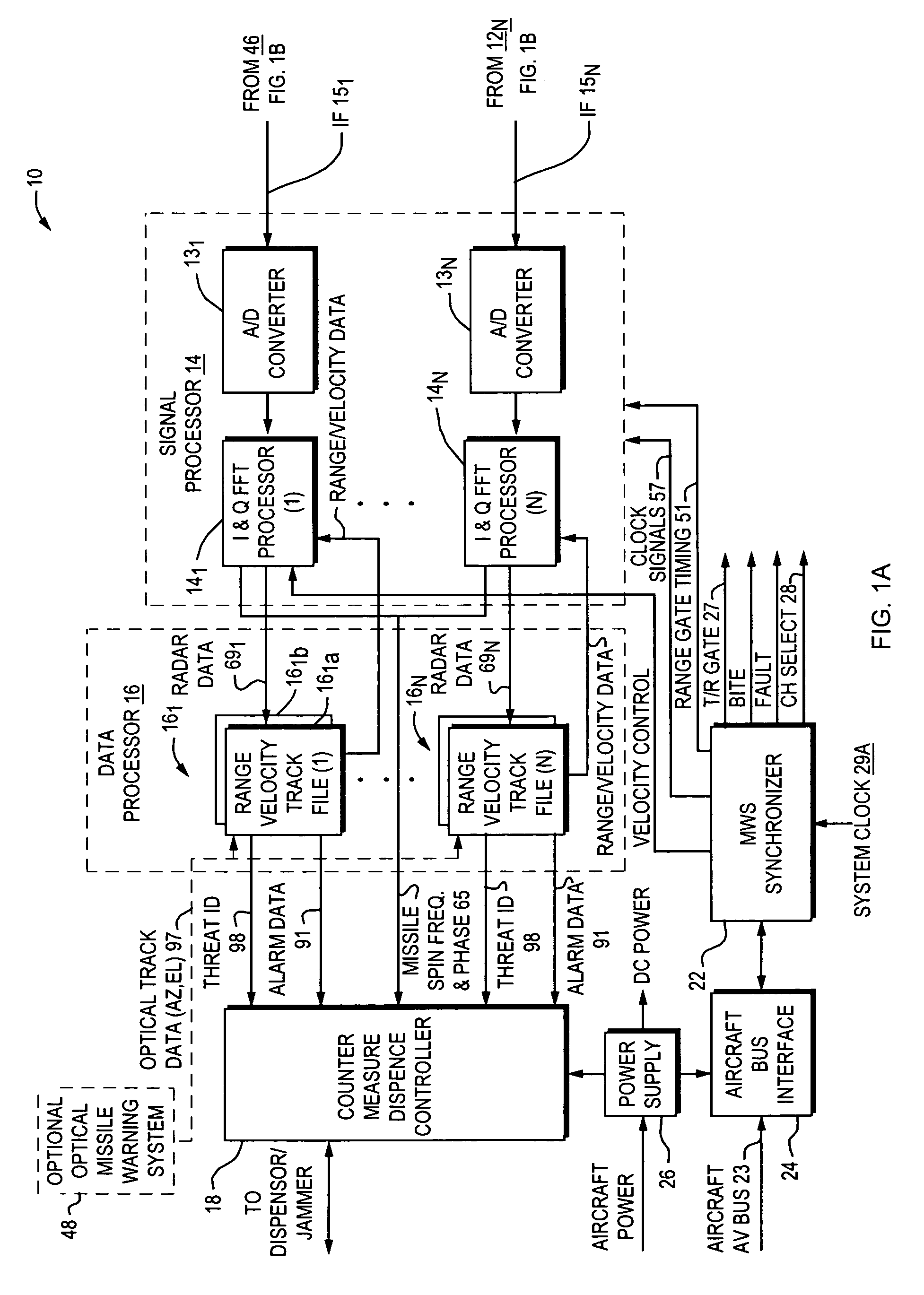

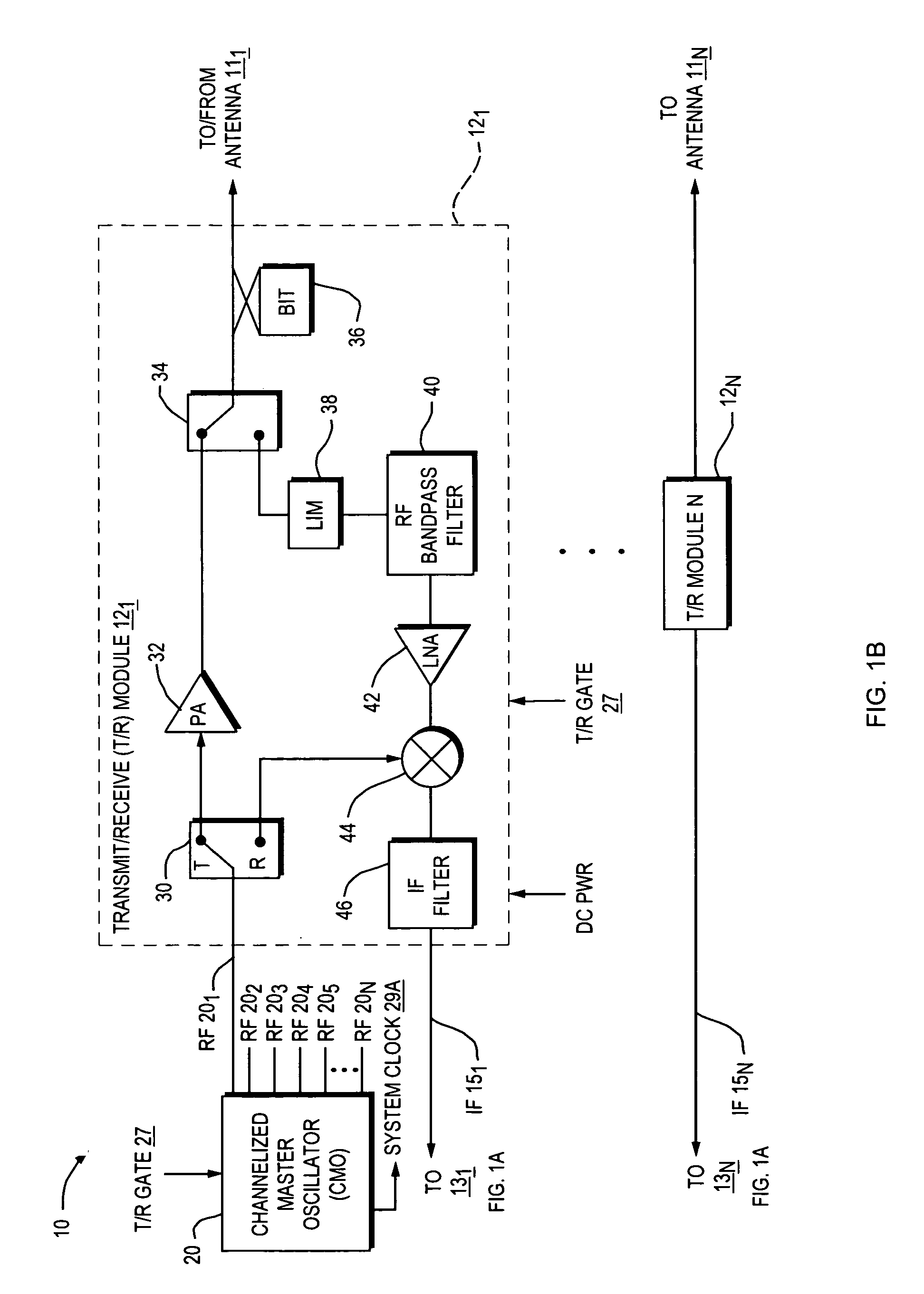

Airborne distributed pulse doppler radar missile warning system

InactiveUS7425916B2Reduce lossesExpand the scope of detectionDefence devicesWave based measurement systemsPulsed dopplerFalse alarm

A digital missile warning system comprising a distributed pulse doppler radar having a plurality of antennas, each being coupled to a transmit / receive (T / R) module located adjacent to the antenna, and parallel signal processing channels including an A / D converter, FFT processor and a range / velocity track file processor in each channel for each antenna resulting in enhanced detection range, reduced False Alarm Rate (FAR), faster response time, reduced size, weight and installation requirements, improved reliability and reduced acquisition and life cycle costs. An optional optical missile warning system can provide azimuth and elevation data to the track file processors which enables a three (3) dimensional track of a missile, with azimuth and elevation angles provided by the optical system and range, velocity and acceleration data provided by the pulse doppler radar. The combination of Pulse Doppler Radar MWS and the Optical MWS produces close to a zero False Alarm Rate (FAR). Further, means to extract a threat IR missiles' roll rate and its seeker spin rate and phase angle are provided.

Owner:STEVENS JR ROBERT R

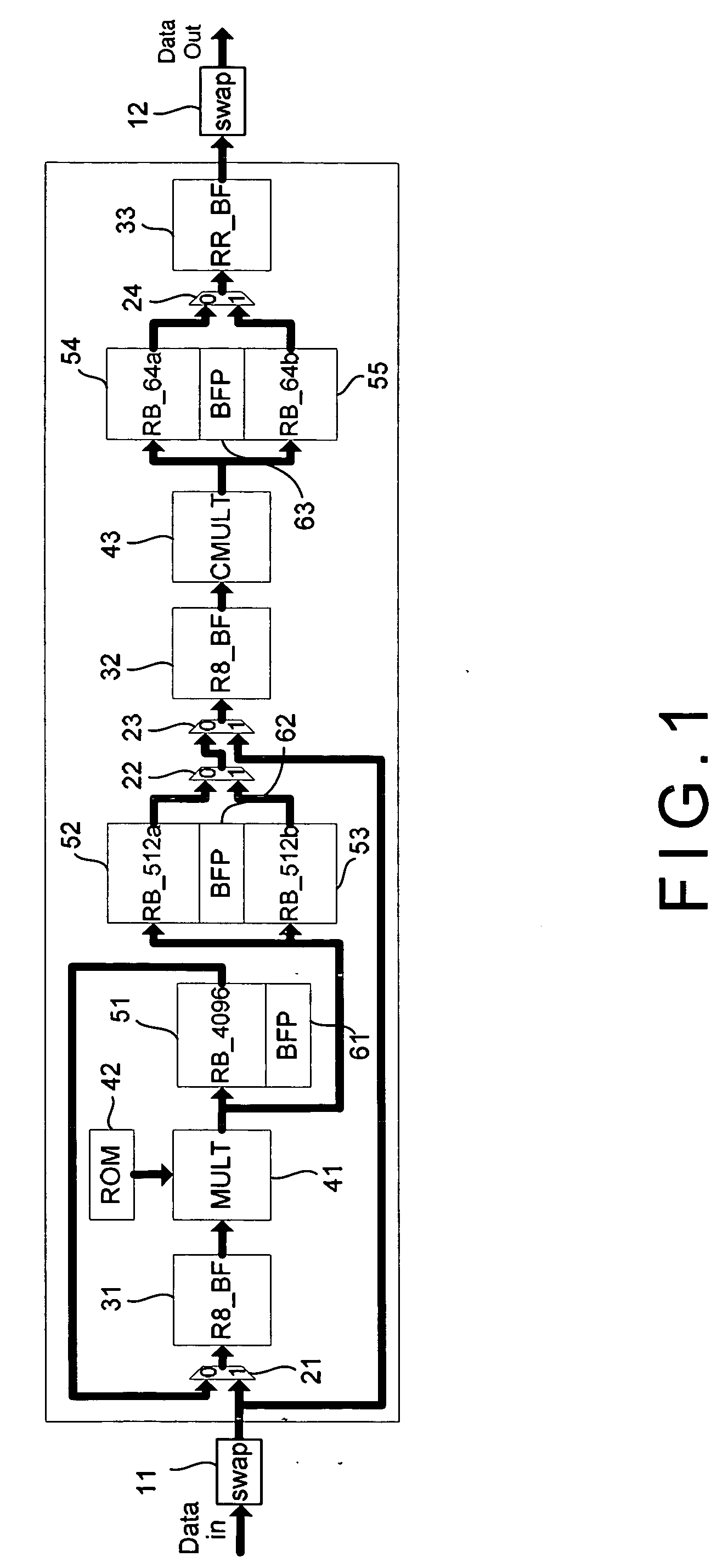

Pipeline-based reconfigurable mixed-radix FFT processor

ActiveUS20080155003A1Reduce computing time costsReduce hardware costsDigital computer detailsComplex mathematical operationsSignal-to-noise ratio (imaging)Block floating-point

The present invention discloses a fast Fourier transform (FFT) processor based on multiple-path delay commutator architecture. A pipelined architecture is used and is divided into 4 stages with 8 parallel data path. Yet, only three physical computation stages are implemented. The process or uses the block floating point method to maintain the signal-to-noise ratio. Internal storage elements are required in the method to hold and switch intermediate data. With good circuit partition, the storage elements can adjust their capacity for different modes, from 16-point to 4096-point FFTs, by turning on or turning off the storage elements.

Owner:NAT CHIAO TUNG UNIV

Method of realizing parallel structure for FFT processor based on FPGA

InactiveCN101582059AImprove processing speedImprove system throughputComplex mathematical operationsBinary multiplierFpga implementations

The invention discloses a method of realizing parallel structure for FFT processor based on FPGA, which is used for FFT operation on N point. The FPGA comprises a plurality of special multipliers, a plurality of mass RAM and a plurality of logic gates. The method comprises the following steps: (1) dividing N point into M segments equally with N / M point on each segment; (2) translating FFT operation of N point into an expression of the FFT operation of the M segments (with N / M point on each segment); (3) extracting the coefficients of the expressions of FFT operation of M segment obtained in step (2), multiplying the coefficients with FFT operation results in corresponding M segment through FPGA inner circuit by using special multipliers, mass RAM and logic gates, and summing the product results of all segments to obtain FFT operation result of N point. By splitting a longer sequence into shorter sequences, the method in the invention effectively improves the processing speed of the long sequence FFT and system throughput.

Owner:SHANGHAI BOOM FIBER SENSING TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com