Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

98 results about "Rotation factor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Recoded radix-2 pipeline FFT processor

InactiveUS20050015420A1Digital computer detailsComplex mathematical operationsComputational scienceRotation factor

A single-path delay feedback pipelined fast Fourier transform processor comprising at least one set of triplet FFT stage means: a first FFT stage means comprising a radix-2 butterfly, a feedback memory, and a multiplication by unity; a second FFT stage means comprising a trivial coefficient pre-multiplication, a radix-2 butterfly, a feedback memory, and a multiplication by selectable unity or WNN / 8; and a third FFT stage means comprising a trivial coefficient pre-multiplication, a butterfly, a feedback memory, and a complex twiddle coefficient multiplication with coefficients determined using a twiddle factor decomposition technique.

Owner:CYGNUS COMM CANADA CO

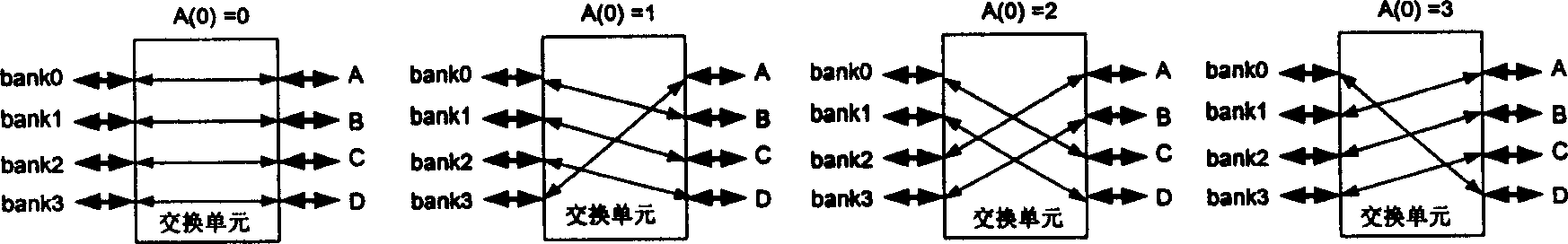

Address mapping method and system for FFT processor with completely parallel data

InactiveCN1504890AImprove parallelismImprove efficiencyDigital data processing detailsMemory adressing/allocation/relocationRotation factorParallel computing

The invention is a full-parallel FFT-processor address mapping method, storing operation number in dual-port memory and rotation factor in ROM; determining R / W addresses for operation number and rotation factor. It fully uses common address operation character of FFT algorithm itself, uses 4 data memory bodies and 3 rotation-factor ones, performs data input and output in the same location, is able to provide an operation number for a butterfly operation in each period and has maximum parallelity. During processor working, the rotation factor only demands simple one-increased mode addressing. It is applied to N point (N is the power of 2) FFT calculation, having high efficiency of base-4 operation and calculation range of base-2 operation.

Owner:宁波高新区中科芯元集成电路技术有限公司

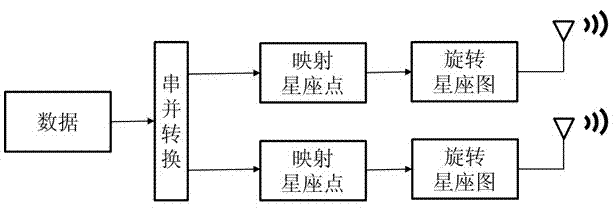

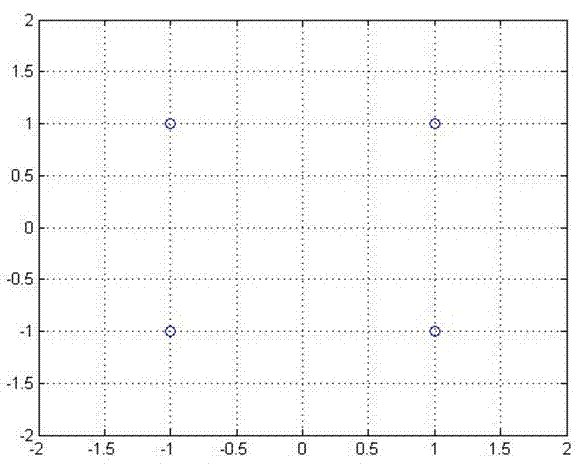

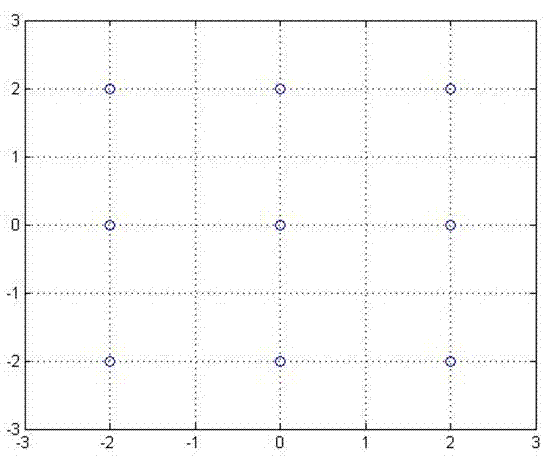

Rotation constellation diagram based coding and decoding method for spatial multiplex multi-aerial system

InactiveCN102833043ASolve the problem of sharp drop in bit error performanceImprove bit error performanceError prevention/detection by diversity receptionRotation factorDecoding methods

The invention discloses a rotation constellation diagram based coding and decoding method for a spatial multiplex multi-aerial system. According to the method, the rotation constellation diagram based coding and decoding method and the spatial multiplex multi-aerial system are combined, a transmission signal is subjected to serial and parallel conversion at a transmitting end and a mapped onto a modulation constellation diagram, all constellation points rotate by using origin points as circle centers at set angles and reversely rotate at the same set angles after signs are detected at a receiving end, a signal sequence is modulated through the constellation diagram and is subjected to parallel and serial conversion, and the signal is output. By the method, the problem of error rate increase caused by constellation point overlap in a related channel is solved, and the error rate of the spatial multiplex multi-aerial system in the related channel is reduced better on the premise of not increasing system bandwidth resources and unnecessarily reducing transmission rate. Compared with the traditional spatial multiplex multi-aerial system, only a rotation factor is multiplied at the transmitting end and the receiving end, and the coding method is low in hardware cost and excellent in error code performance.

Owner:SOUTH CHINA UNIV OF TECH

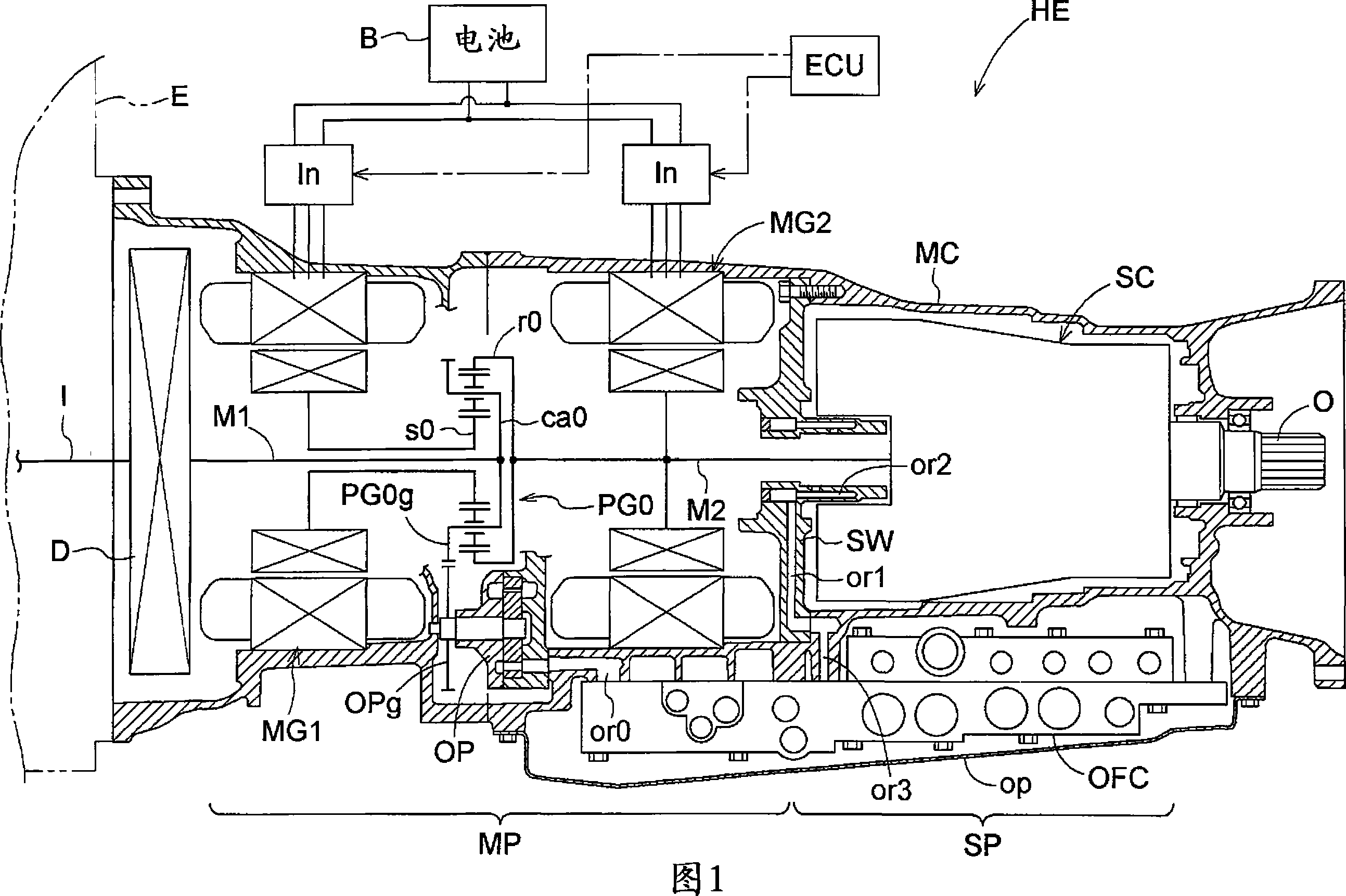

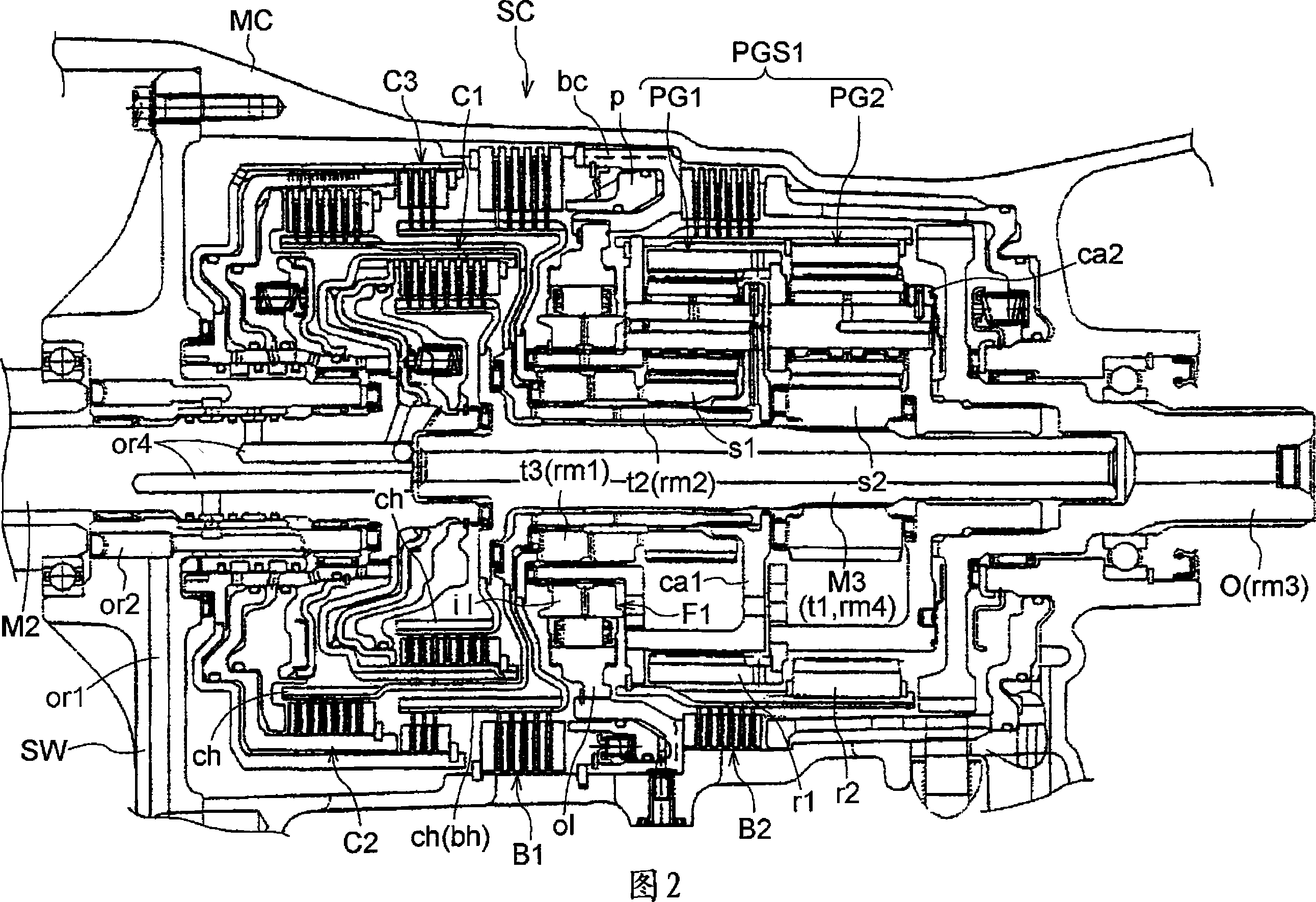

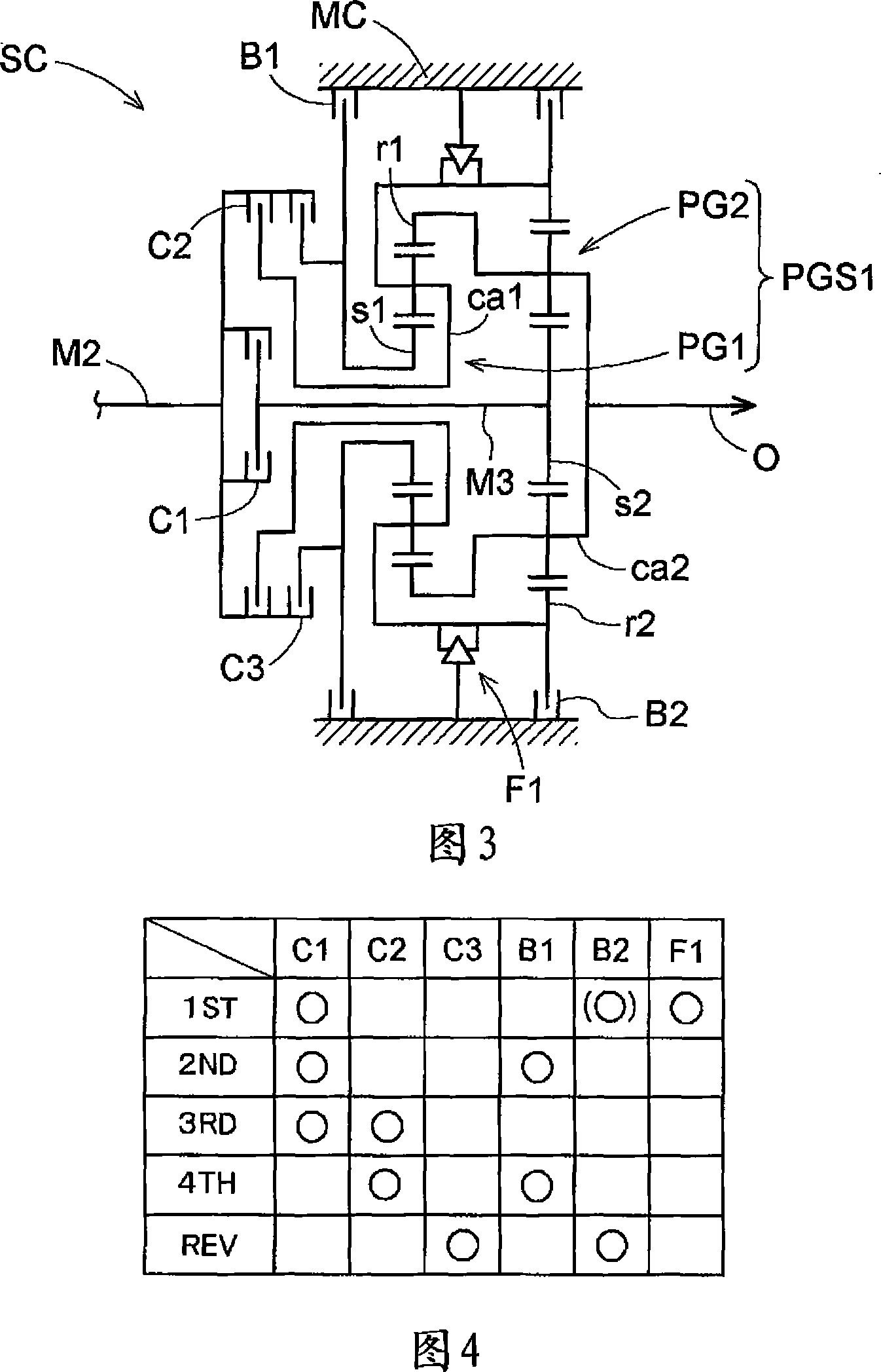

Hybrid drive device

ActiveCN101233005AEffective gear stageSmooth backHybrid vehiclesGearing controlRotation factorLow speed

The present invention provides a hybrid driving device adopting a dual-motor separation method, which can ensure acceleration performance in a low-speed range and has high fuel efficiency in a high-speed range. An input shaft drivingly connected to the engine, an output shaft drivingly connected to the wheels, a first electric motor and a second electric motor are provided, and planetary gears for power distribution constituting the first, second, and third rotation elements in the order of rotation speed are provided, wherein The first electric motor is connected to the first rotating element, the input shaft is connected to the second rotating element, the intermediate transmission shaft and the second electric motor are connected to the third rotating element, and a transmission is provided, which has a plurality of shifting stages and will be transmitted from the intermediate transmission shaft The power from the transmission is output to the output shaft. The multiple shift stages of the transmission include at least an increase shift stage and a deceleration shift stage. , there is a partition through which the intermediate drive shaft passes.

Owner:AISIN AW CO LTD +1

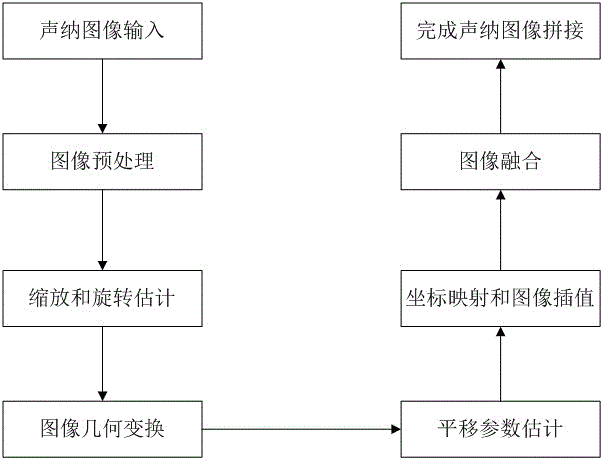

Sonar image splicing method

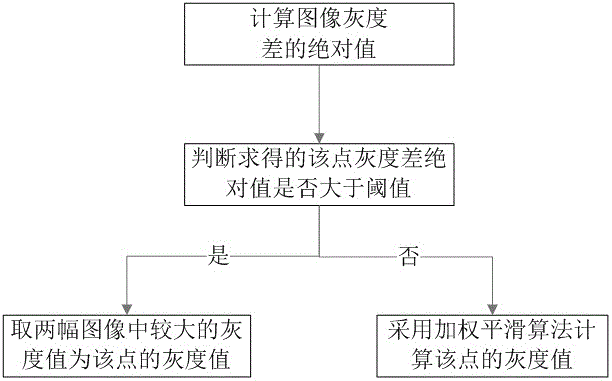

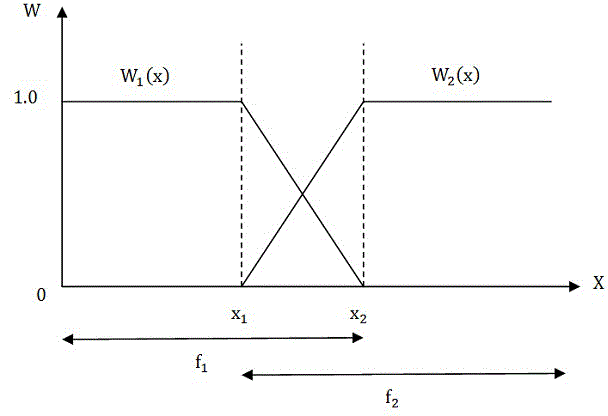

InactiveCN103606139AIncrease contrastSolve the problem of small detection range viewing angleImage enhancementPhase correlationFrequency spectrum

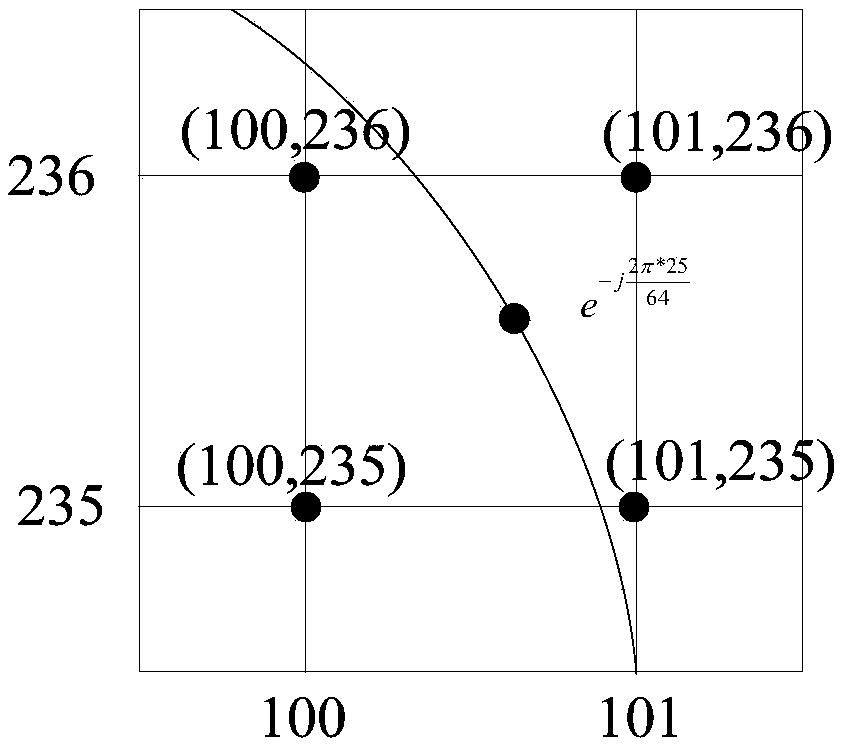

The invention relates to a sonar image splicing method. The method comprises the steps of removing noise in order to increase the contrast ratio through image preprocessing; transforming a scaling parameter and a rotation parameter into translation parameters through carrying out log-polar transformation to an image amplitude frequency spectrum, and carrying out algorithm analysis based on phase correlation; filtering scale and rotation factors through image geometric transformation; working out the translation parameters through an algorithm based on the phase correlation; and carry out coordinate mapping through the scaling parameter, the rotation parameter and the translation parameters which are worked out, and carrying out image interpolation through a bilinear interpolation algorithm. The registration of all sonar images is achieved by continuously repeating the above steps, then the splicing of the sonar images is achieved through brightness adjustment and image superposed area fusion. According to the invention, the problem that the detection scope visual angle of sonar is narrow in an underwater monitoring process is solved, through sonar image splicing, a series of sonar images are spliced to a large-scale sonar image, and therefore the sonar can simultaneously monitor a large-scale underwater environment.

Owner:SHANGHAI UNIV

Butterfly-shaped operation FFT processor

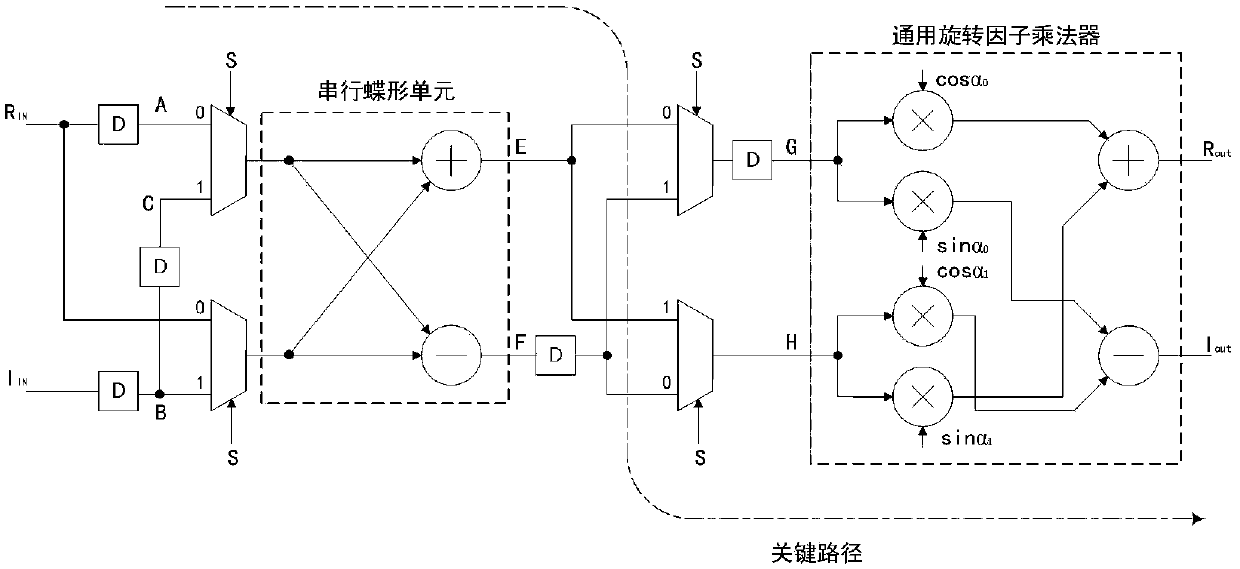

InactiveCN101354700AReduce complexityReduce computational complexityComplex mathematical operationsBroadcast system receivingRotation factorComputation complexity

The invention discloses a butterfly computation FFT processor, wherein a complex multiplier used for realizing multiplication of data and a rotation factor is a CORDIC rotation operator, and the rotation angle corresponding to the rotation factor is stored into a rotation factor memory. The butterfly computation FFT processor adopts the CORDIC rotation algorithm to realize multiplication operation of the data and the rotation factor and then uses data shift to replace complex multiplication operation, thereby reducing the computation complexity. Simultaneously, due to adoption of the CORDIC rotation algorithm to realize complex multiplication, only the rotation angle corresponding to the rotation factor is required to be stored into the rotation factor memory without the necessity of storing the sine value and the cosine value of a corresponding angle of the rotation factor, thereby a rotation factor memory unit can be saved and the reading complexity of the rotation factor is reduced.

Owner:SICHUAN PANOVASIC TECH

Scene scan

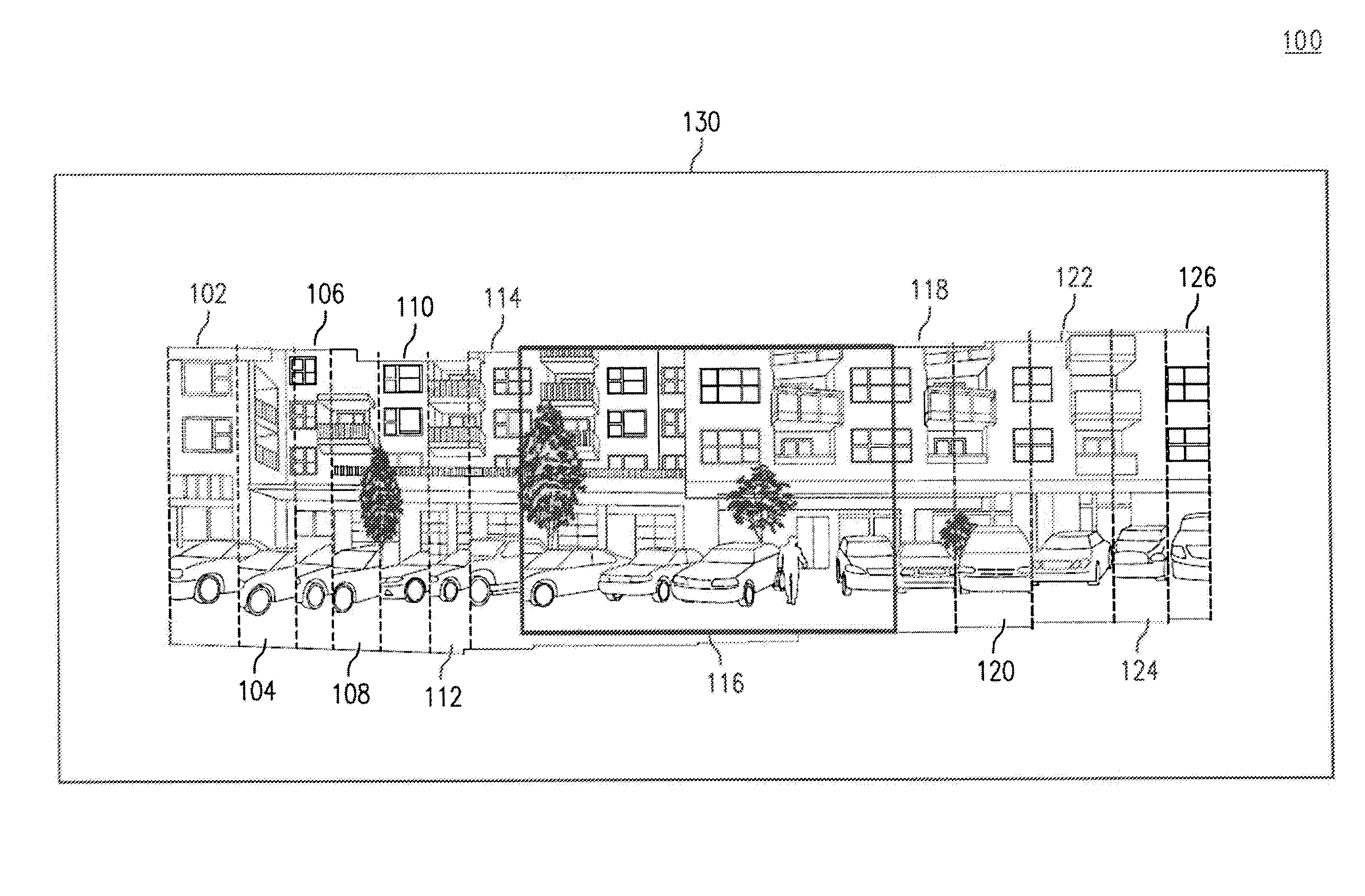

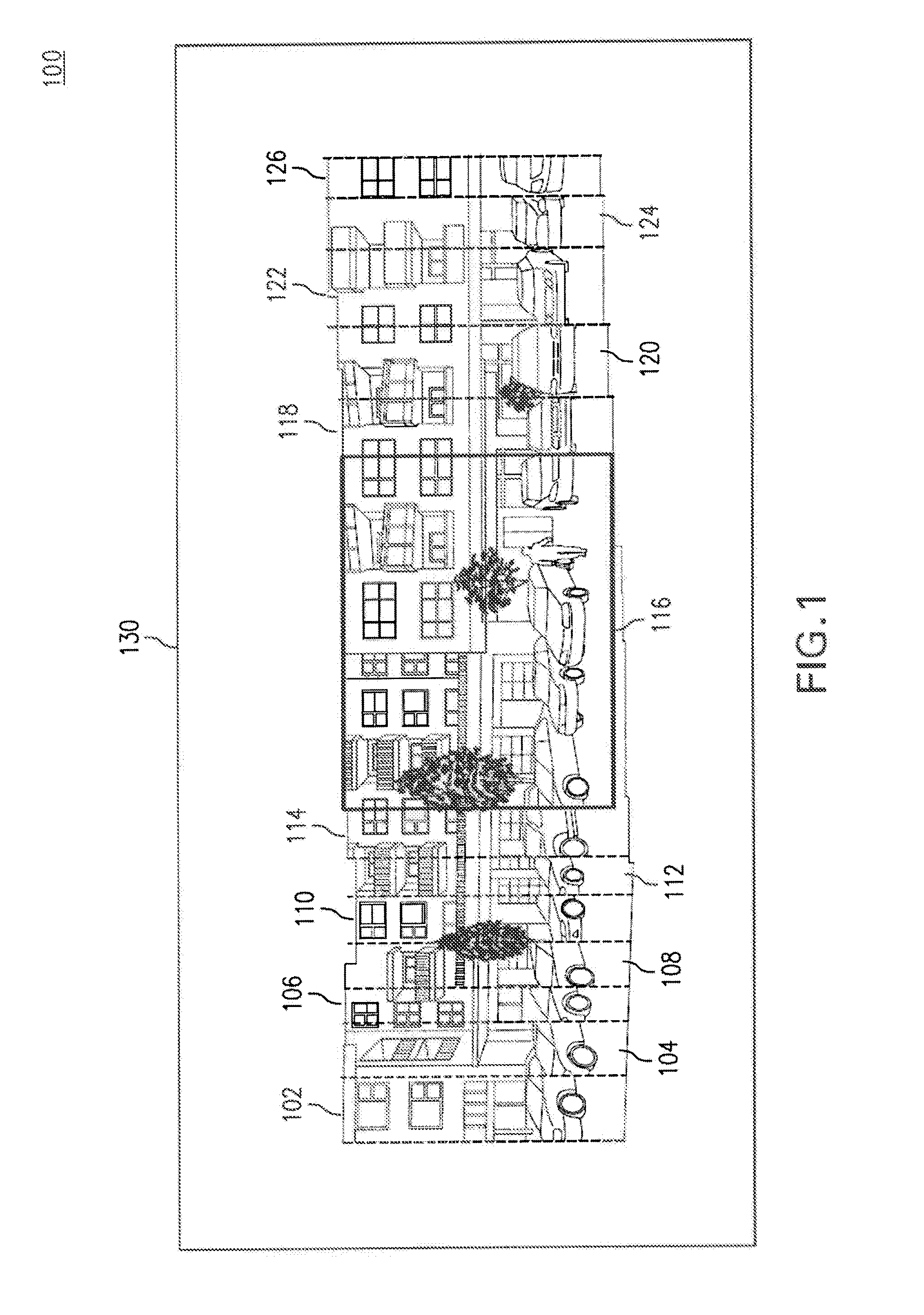

ActiveUS9047692B1Geometric image transformation2D-image generationRotation factorPattern recognition

Systems, methods, and computer storage mediums are provided for creating a scene scan from a group of photographic images. An exemplary method includes determining a set of common features for at least one pair of photographic images. The features include a portion of an object captured in each of a first and a second photographic image included in the pair. The first and second photographic images may be captured from different optical centers. A similarity transform for the at least one pair of photographic images is the determined. The similarity transform is provided in order to render the scene scan from each pair of photographic images. At least one of the rotation factor, the scaling factor, or the translation factor associated with the similarity transform is used to position each pair of photographic images such that the set of common features between a pair of, at least in part, align.

Owner:GOOGLE LLC

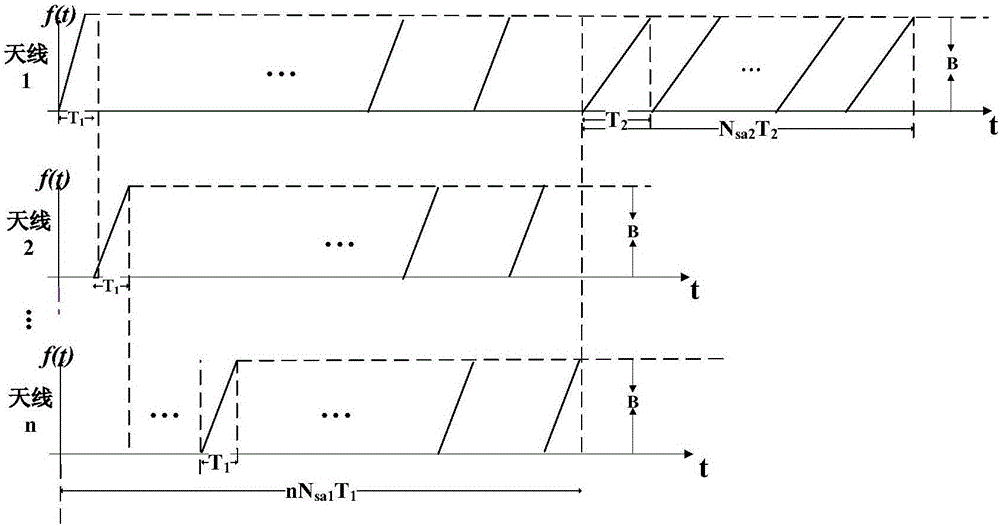

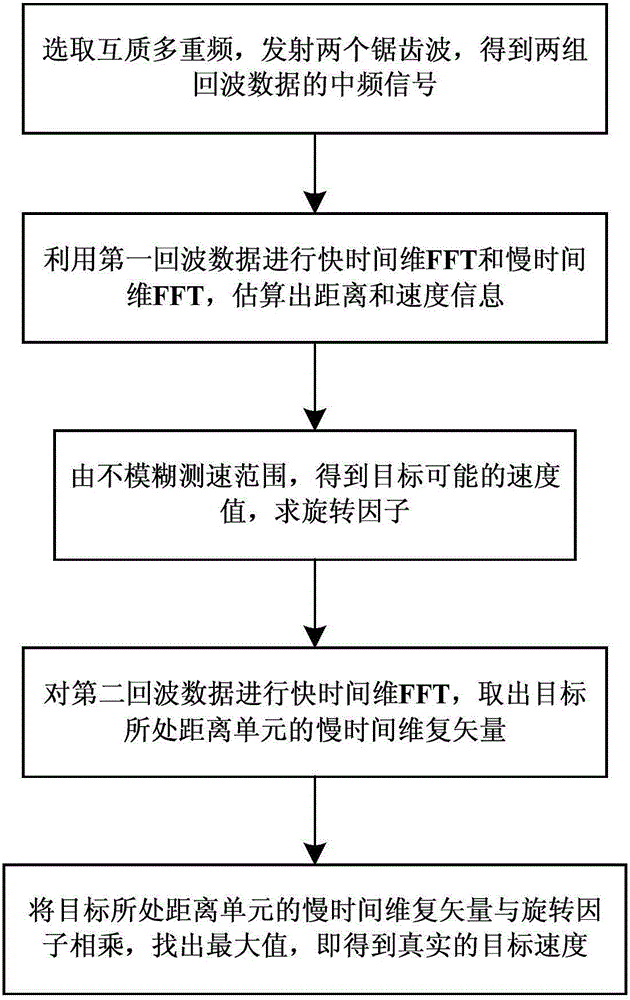

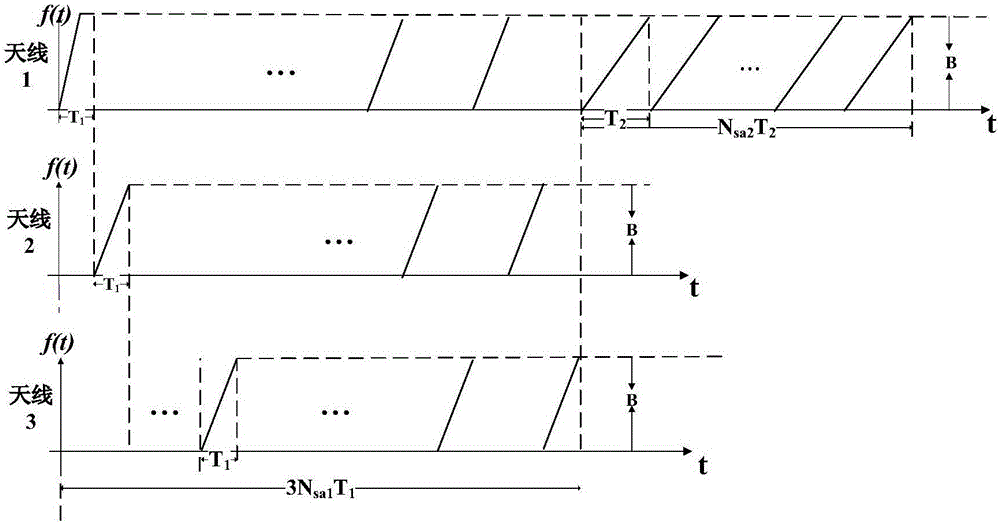

Velocity ambiguity resolving method suitable for linear frequency-modulation continuous wave radar system

ActiveCN106842166AReduce complexityRadio wave reradiation/reflectionRotation factorFast Fourier transform

The invention discloses a velocity ambiguity resolving method suitable for a linear frequency-modulation continuous wave radar system. The method comprises the steps of firstly obtaining first echo data and second echo data according to an originally received intermediate-frequency signal; secondly, estimating a target distance and an ambiguous velocity and then determining a discrete Fourier transform rotation factor according to the target distance and the ambiguous velocity; thirdly, carrying out fast Fourier transform of a fast time dimension by using a reference signal and obtaining a slow time dimension complex vector of a distance unit at which the target is located according to the distance unit, at which the target is located, obtained in the first step; and finally multiplying the slow time dimension complex vector by the discrete Fourier transform rotation factor to find out a real unambiguous velocity corresponding to the maximum value. By creatively utilizing the concept of the least common multiple, a simple and effective velocity ambiguity resolving scheme is provided; the hardware implementation complexity is reduced; and a supportable guarantee is provided for parameter estimation and further operation of the whole system.

Owner:SOUTHEAST UNIV

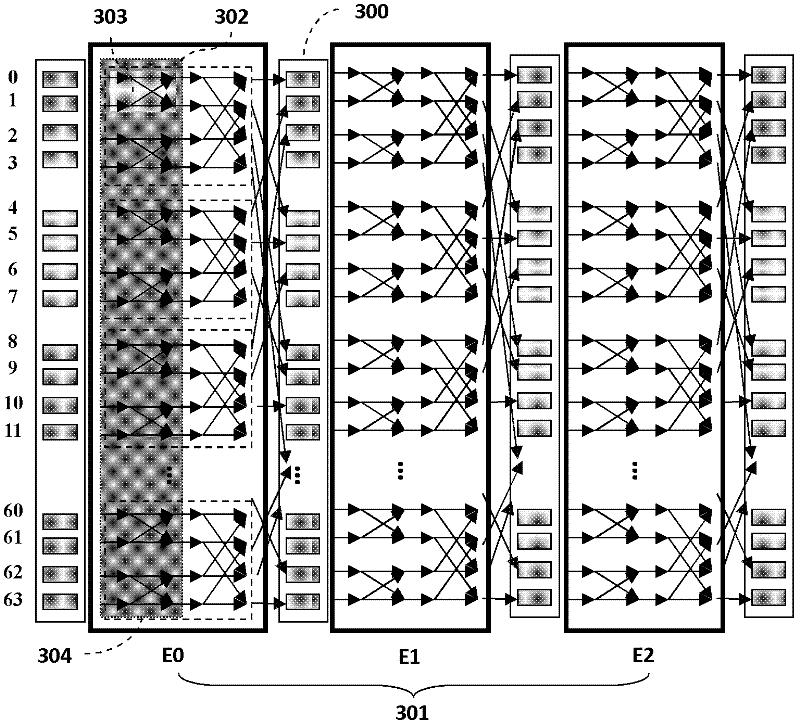

Device and method for realizing pulse compression of 65536 points on basis of FPGA (Field Programmable Gate Array)

ActiveCN106484658AImprove parallelismProcessing speedComplex mathematical operationsTriangular functionRotation factor

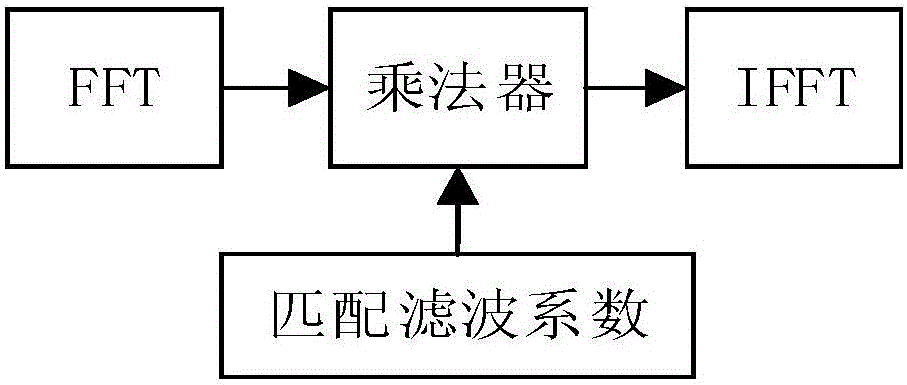

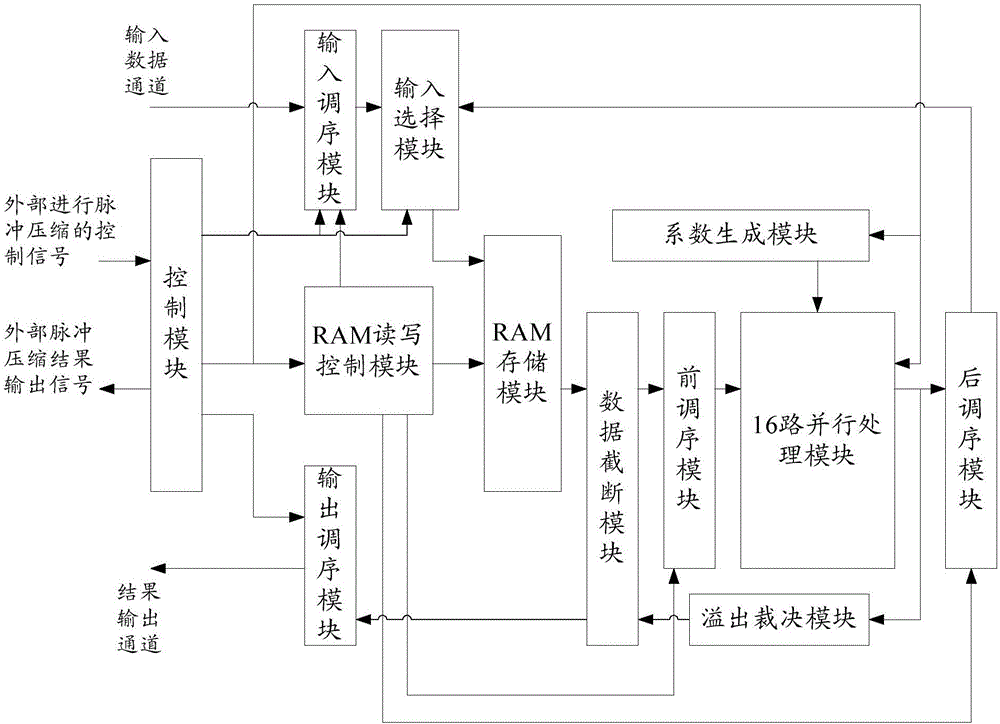

The invention belongs to the technical field of radar signal processing and discloses a device and method for realizing pulse compression of 65536 points on the basis of an FPGA (Field Programmable Gate Array). The implementation process comprises the following steps of: firstly receiving data from 16 paths in parallel, and storing the data into 16 block RAMs by adopting the principle of parallel reading and no conflict; then reading 16 numbers once by a production line mode, carrying out 4 stages of radix-16 butterfly computation and in-situ storage and finishing FFT (Fast Fourier Transform) processing; carrying out parallel and matched filtering processing on 16 paths and in-situ storage; then realizing IFFT processing by 4 stages of butterfly computation; and finally outputting for 16 paths in parallel, wherein rotation factors and matched filtering coefficients are generated in real time by using sectional linear triangular function tables and a mode of checking table differences. The device and method disclosed by the invention have the advantages that the use of RAM resources in the FPGA is greatly saved, the processing speed is obviously increased, and the data throughput is increased.

Owner:XIDIAN UNIV

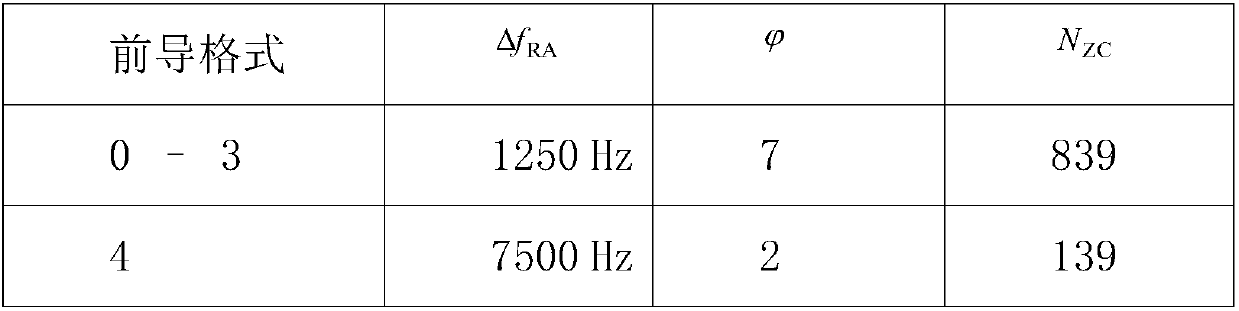

DFT algorithm for ZC sequence in PRACH channel of LTE system

ActiveCN107222282AReduce storageThe modulo process is simpleCode division multiplexWireless communicationRotation factorControl signal

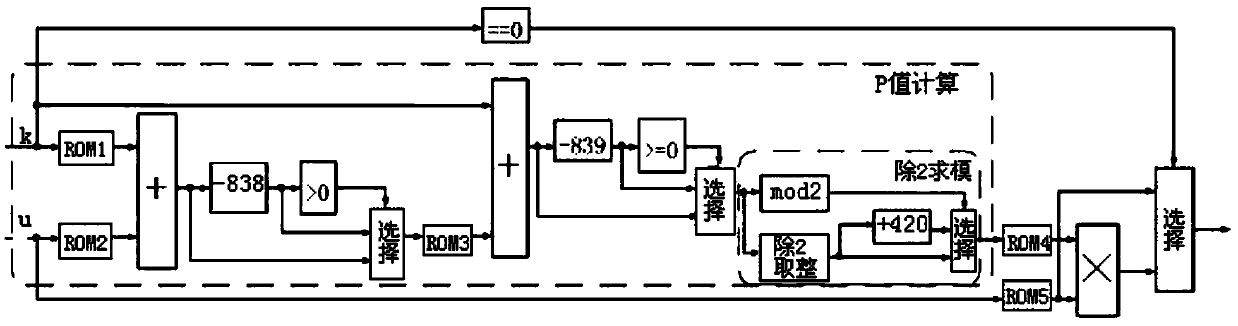

The invention relates to the technical field of mobile communication, and discloses a DFT algorithm for a ZC sequence in a PRACH channel of a LTE system. The DFT algorithm comprises the following process of: inputting a parameter k into an ROM1, and reading an output parameter k' of the ROM1; inputting a parameter u into an ROM2, and reading an output parameter u' of the ROM2; subtracting Nzc-1 from a value A obtained by adding k' with u' to obtain a parameter B; inputting A and B into a first selector, outputting a result according to a control signal, and inputting the result into an ROM3; reading output data of the ROM3, adding the output data with k to obtain a value C, and subtracting Nzc from the value C to obtain a parameter D; inputting C and D into a second selector, and according to a control signal, obtaining an output result of the second selector; adding a value E obtained after dividing the output result of the second selector by 2 and carrying out rounding with (with reference to the specification) to obtain a parameter F, inputting E and F into a third selector, taking a result G obtained by carrying out mod2 processing on the output result of the second selector as a control signal, and outputting a p value of a rotation factor index; and according to the p value, obtaining a DFT algorithm result of the ZC sequence. According to the scheme, the solving process of the p value is low in storage capacity, and the algorithm is simple.

Owner:电信科学技术第五研究所有限公司

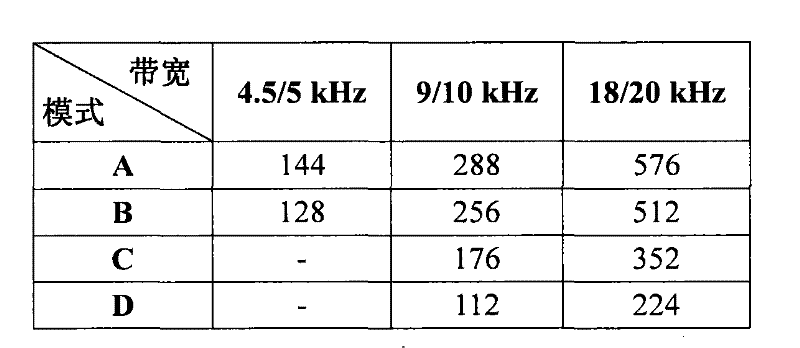

Discrete Fourier transform processing device and method in data rights management (DRM) system

InactiveCN102609396AEasy to implementReduce demandComplex mathematical operationsRotation factorFast Fourier transform

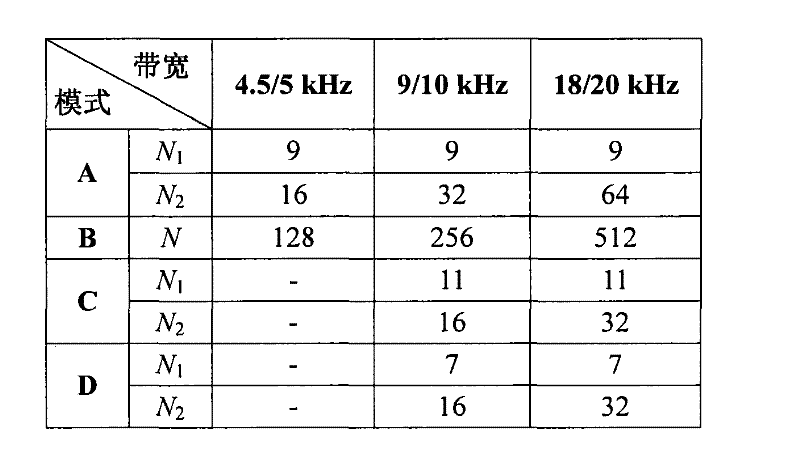

The invention provides a solution for solving ten DFTs (discrete Fourier transform) with different points in a DRM system, wherein the DFT processor is composed of a controller, an address generator, a first memory, a second memory, a re-ordering unit, a small point WFTA (Winograd Fourier transform algorithm) unit and a variable point base 2FFT (fast Fourier transform algorithm) unit; the DFT operation with points N of 112, 128, 144, 176, 224, 256, 288, 352, 512 and 576 can be finished. The DFT processor repeatedly adopts the small point WFTA unit and base 2FFT unit, reduces re-ordering process, adopts memory resource share mechanism, and does not need rotation factor multiplying, so that the processor is easy to achieve FPGA (field programmable gate array). The requirement of the memory and the logical resource can be reduced effectively when the processing speed is ensured, thus, the aim for reducing hardware cost and power consumption can be achieved.

Owner:COMMUNICATION UNIVERSITY OF CHINA +2

Method for realizing 3780-point fast Fourier transform/inverse fast Fourier transform (FFT/IFFT) and processor thereof

InactiveCN102214159AGuaranteed real-timeSave storage resourcesComplex mathematical operationsRotation factorFast Fourier transform

The invention relates to a method for realizing 3780-point fast Fourier transform / inverse fast Fourier transform (FFT / IFFT) and a processor thereof. The processor consists of a top layer, an intermediate layer and a bottom layer, wherein the top layer resolves 3780-point by using a mixed based number algorithm, the intermediate layer resolves 63-point and 60-point FFT by using a prime factor algorithm, and the bottom layer complete 7-point, 9-point, 3-point, 4-point and 5-point FFT calculation by using a winograd fourier transform algorithm (WFTA) algorithm. The method realizes 3780-point FFT by combining the mixed base number algorithm, the prime factor algorithm and the WFTA algorithm, avoids errors caused by calculating 4096-point by using an interpolation method, and reduces rotation factors and a chaotic unit in the mixed base number algorithm. Furthermore, an index structure completed by a multiplex memory in the design has a simple circuit, is easy to realize, and can save chip resources.

Owner:FUZHOU UNIV

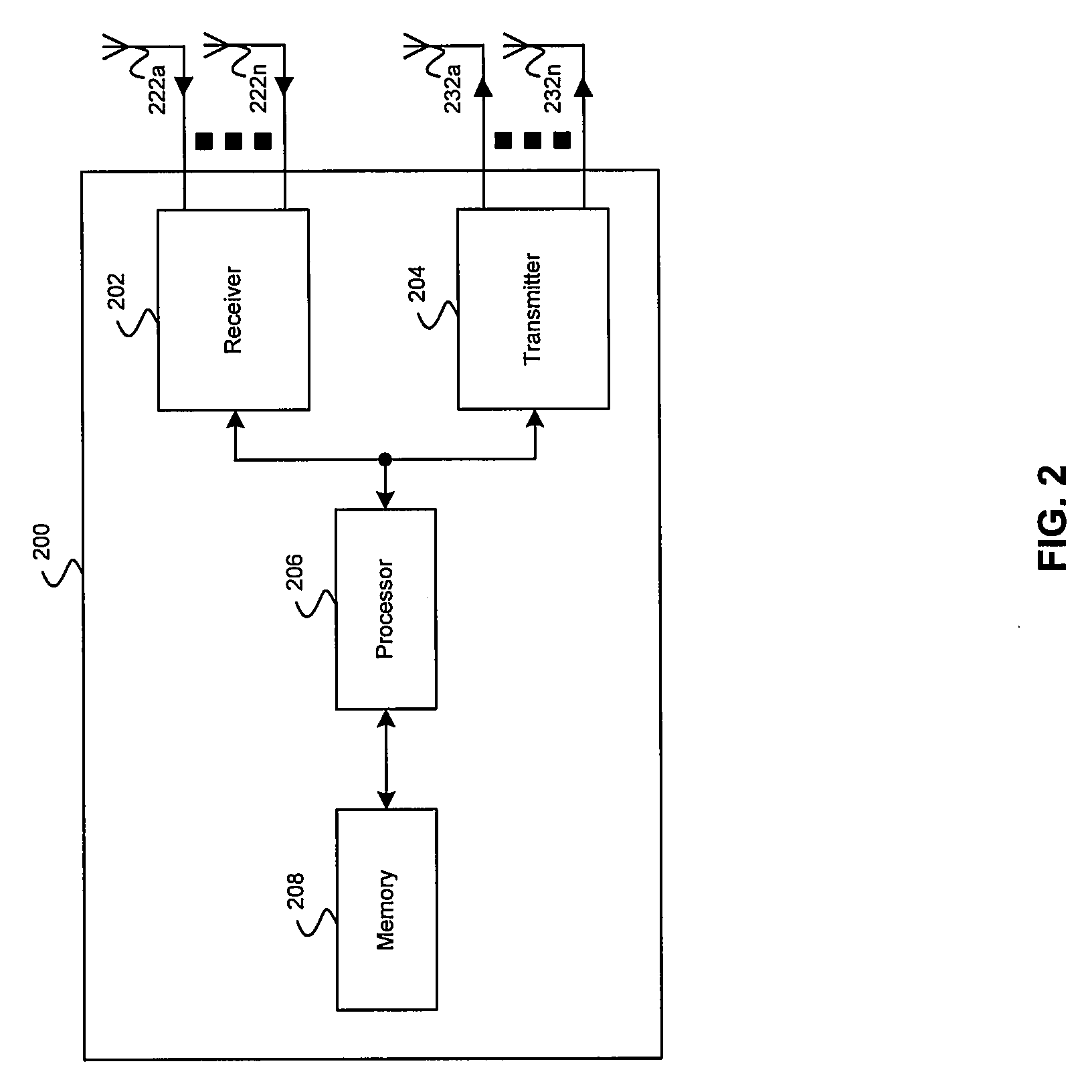

Method and system for sfbc/stbc in a communication diversity system using angle feedback

InactiveUS20080311873A1Modulated-carrier systemsPolarisation/directional diversityRotation factorCommunications system

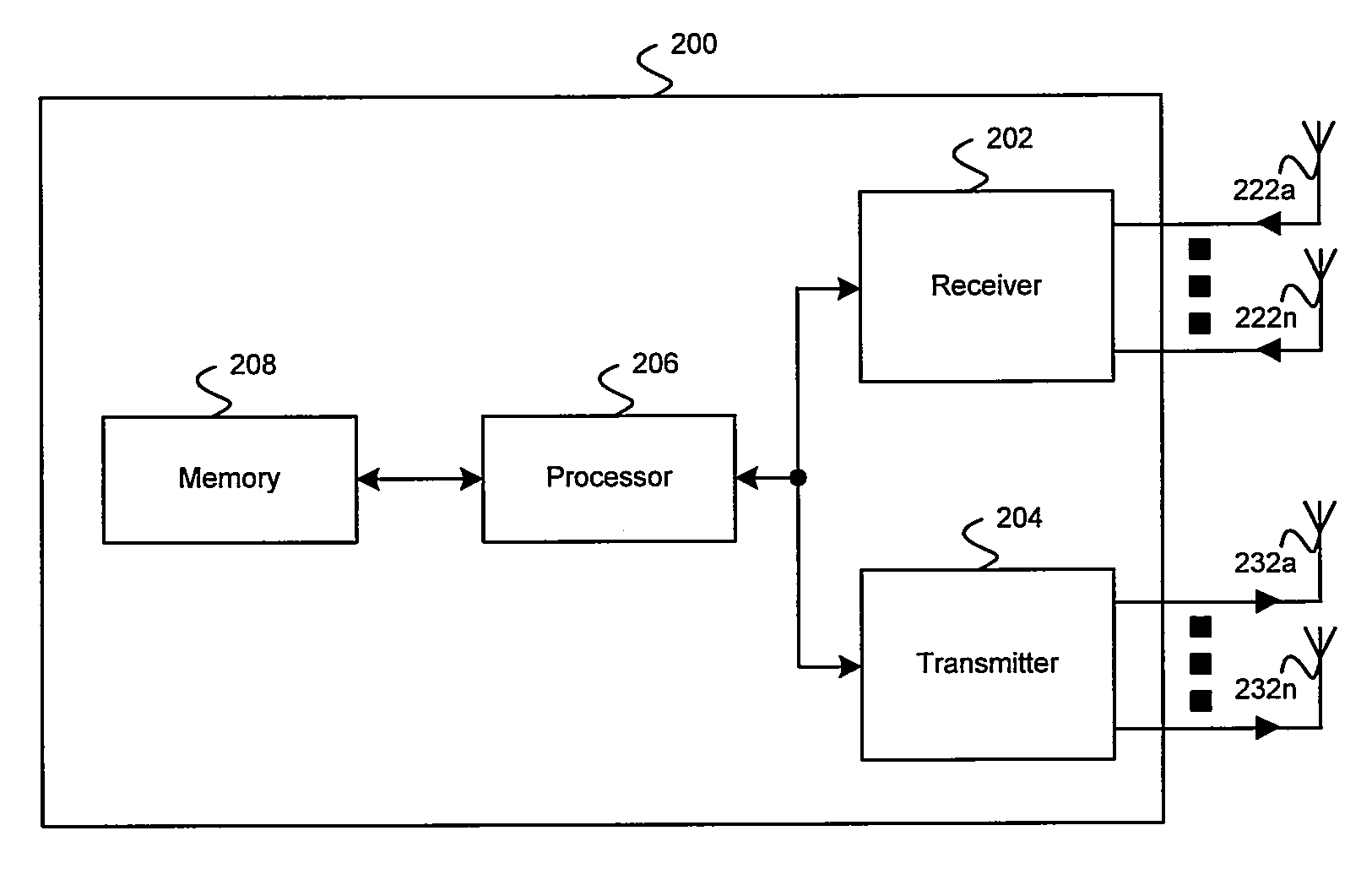

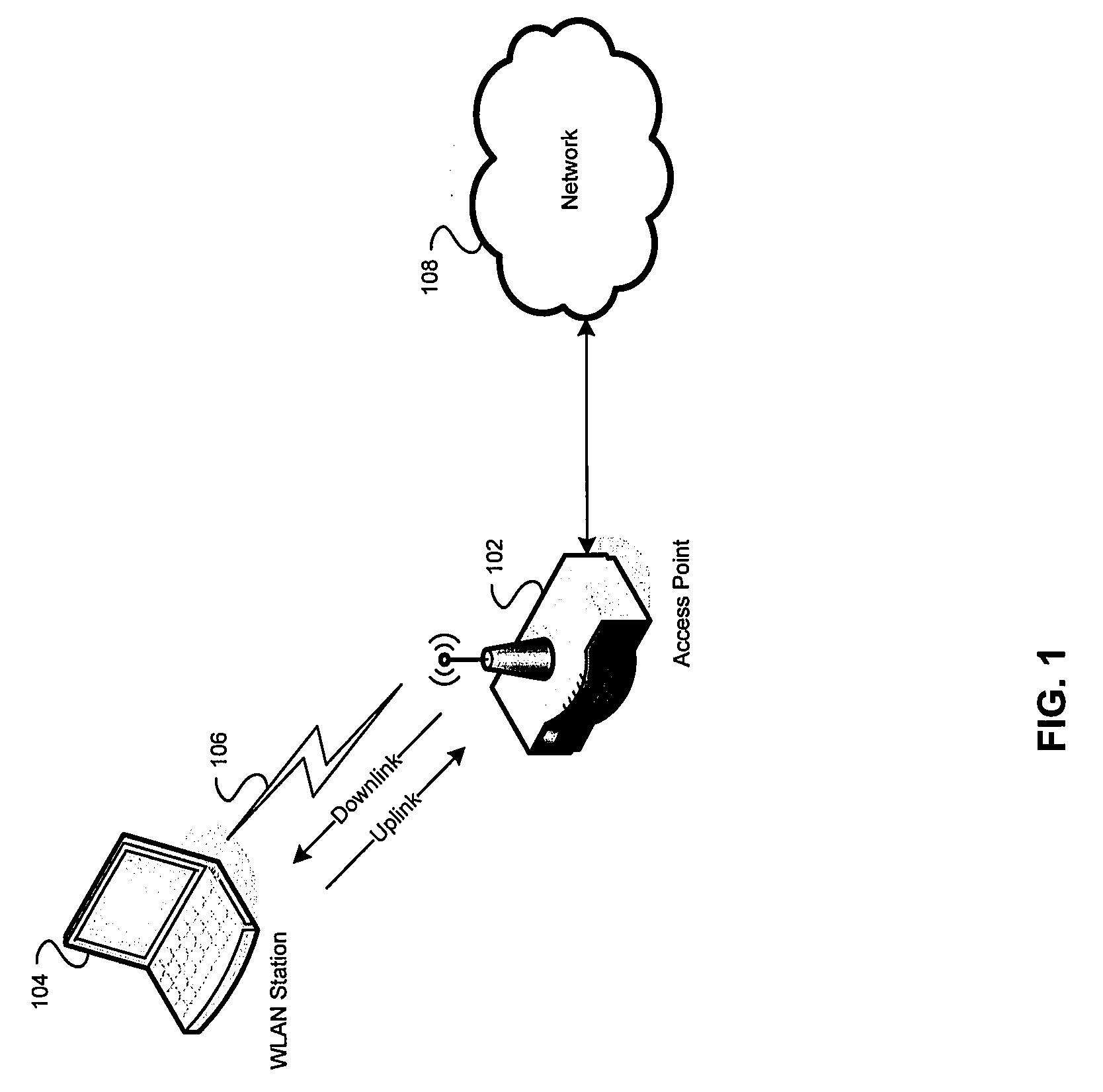

Aspects of a system for STBC / SFBC in a communication system using angle feedback may include a receiver, which enables reception of signals via a plurality of receiving antennas. The receiver may enable computation of a rotation factor value based on the received signals and utilization of the computed rotation factor value to receive subsequent signals via the plurality of receiving antennas. The received signals may comprise preamble data. The receiver may enable computation of channel estimate values based on the received preamble data. A rotation angle value may be computed based on the computed channel estimate values. The rotation factor value may be computed based on the computed rotation angle value. The receiver may enable transmission of feedback information comprising the computed rotation factor and / or the computed rotation angle.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

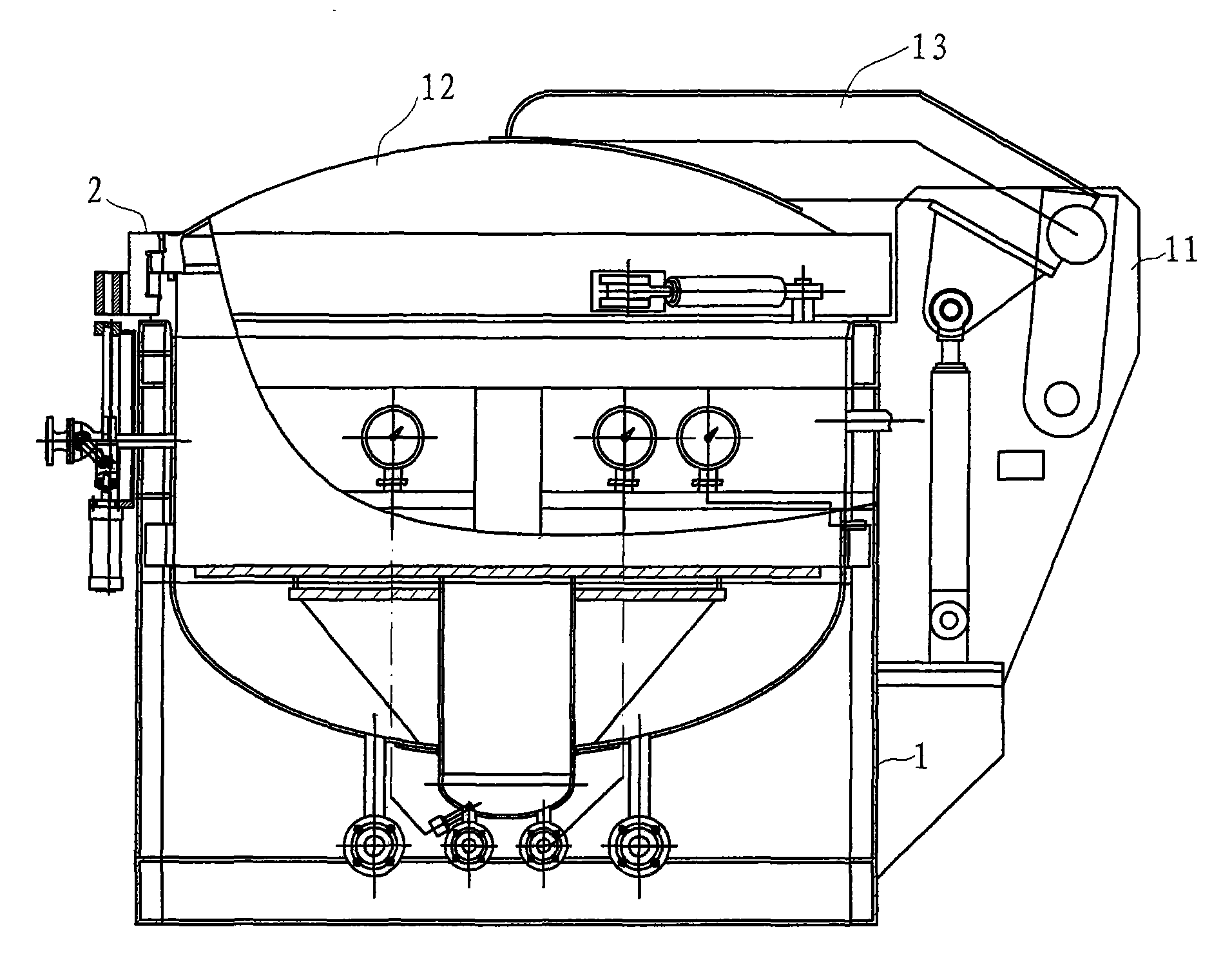

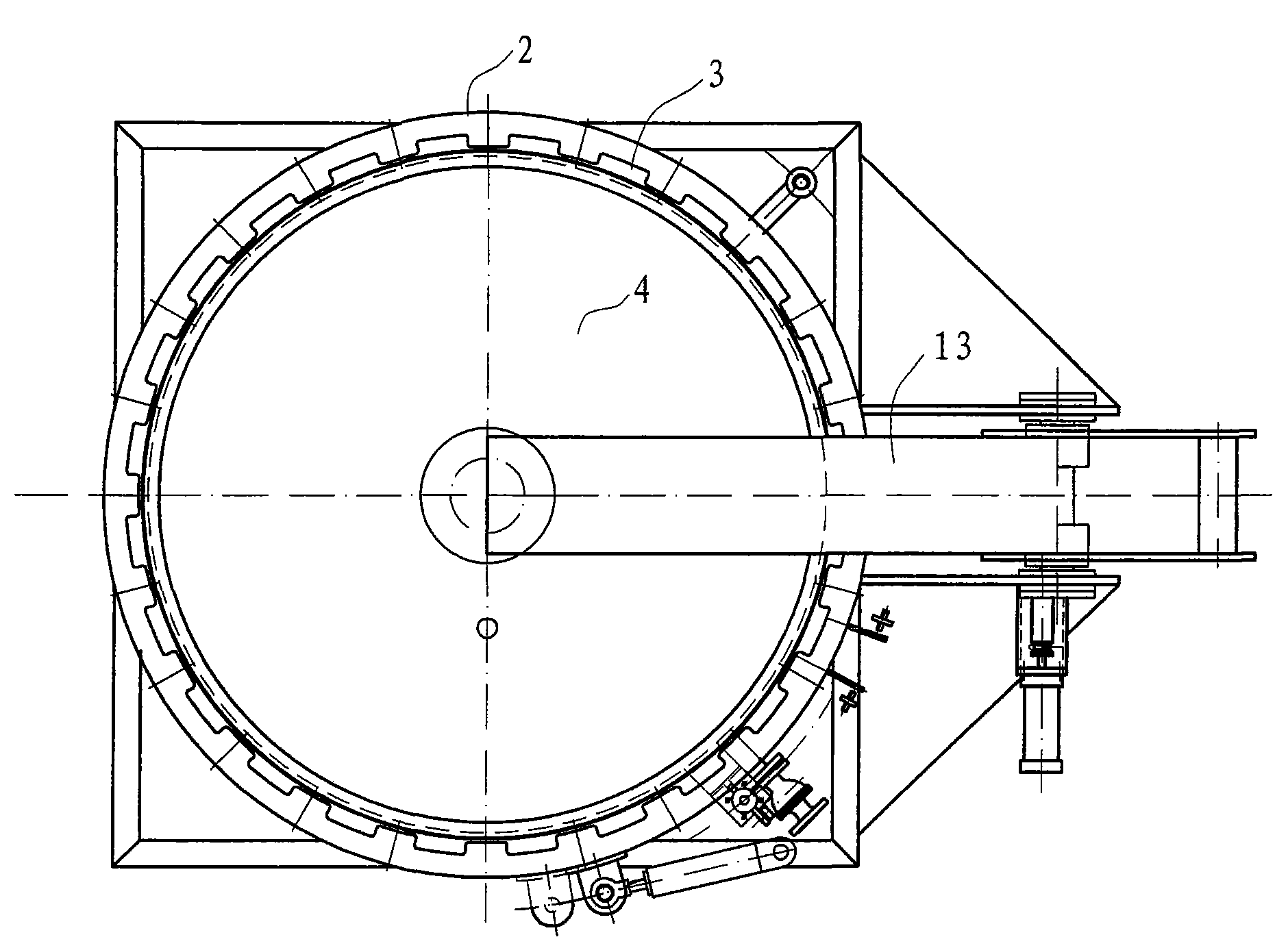

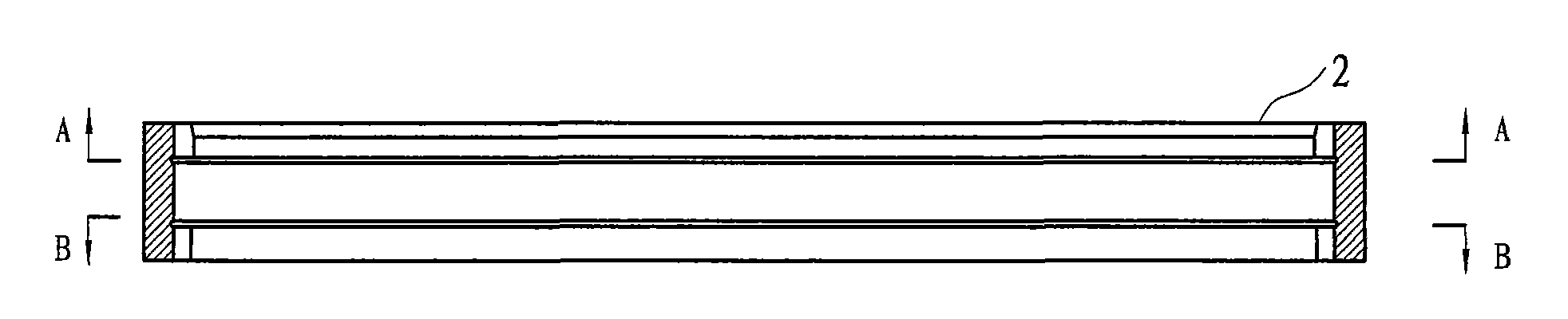

Circle quick door-opening device of pressure container

InactiveCN101592224ALess fixed structure requirementsReduce wearPressure vesselsRotation factorEngineering

The invention discloses a circle quick door-opening device of a pressure container, which comprises an end enclosure, an upper flange and a lower flange which is connected with a tank body. The upper flange is arranged at a port of the end enclosure, the upper flange is evenly distributed with upper flange teeth along the circumferential direction, and the lower flange is evenly distributed with lower flange teeth along the circumferential direction. The device is characterized in that the device also comprises a circle which is arranged at the circumferential outsides of the upper flange and the lower flange, the upper end part of the circle is provided with upper teeth matched with the upper flange teeth to be locked, and the lower end part of the circle is provided with lower teeth matched with the lower flange teeth to be locked. Compared with the prior art, the device has the advantages that the locking and loosing of the circle are adopted for replacing the rotation of a quick opening cover, then relative rotation is not needed between the upper flange and the lower flange, and a sealing ring is abraded little; in addition, only the rising and falling of the quick opening cover are considered, the rotation factor does not need to be considered, so the requirement for the fixed structure of the quick opening cover is relatively less, and the manufacturing cost can be reduced.

Owner:余姚市舜江机械实业有限公司

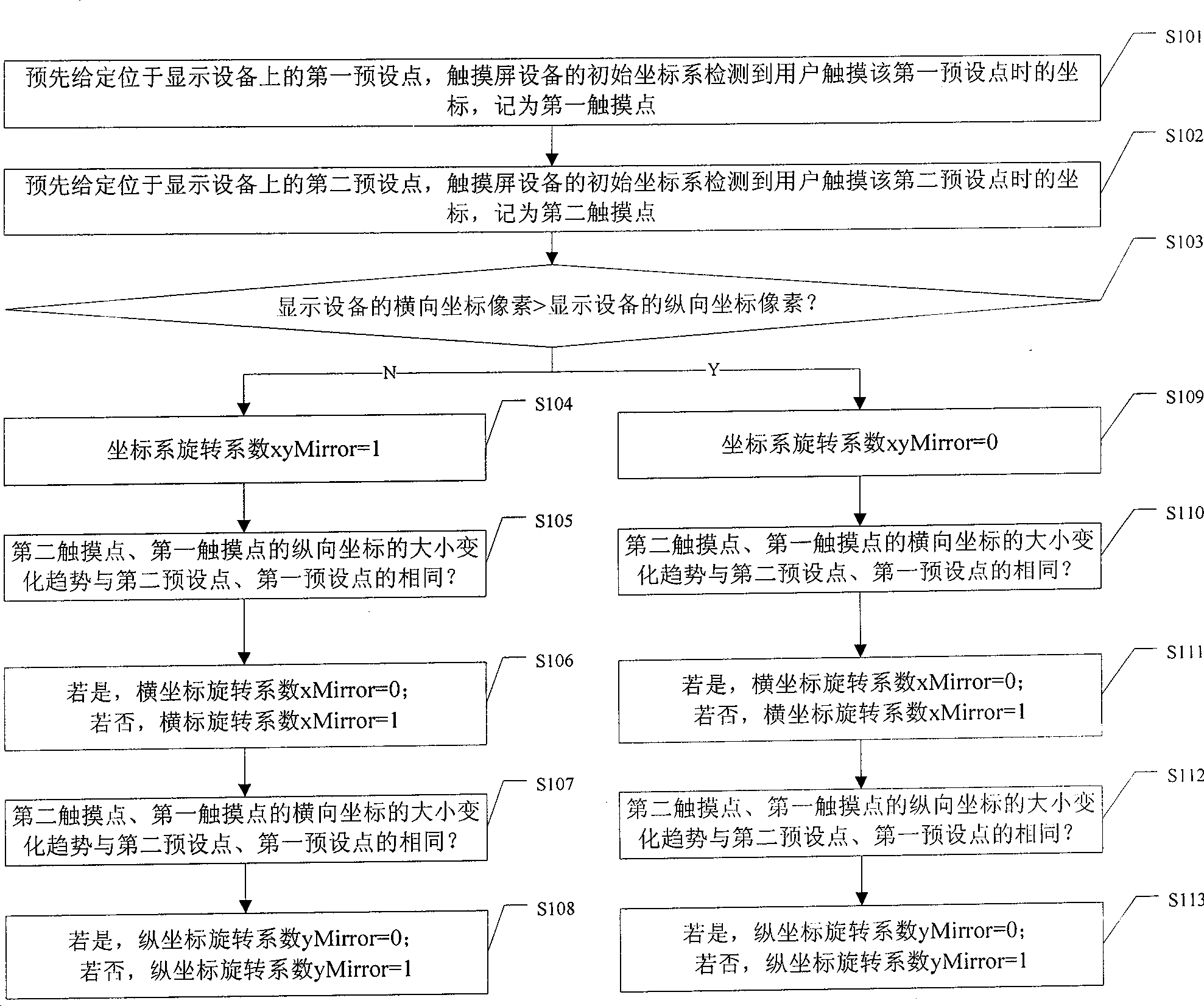

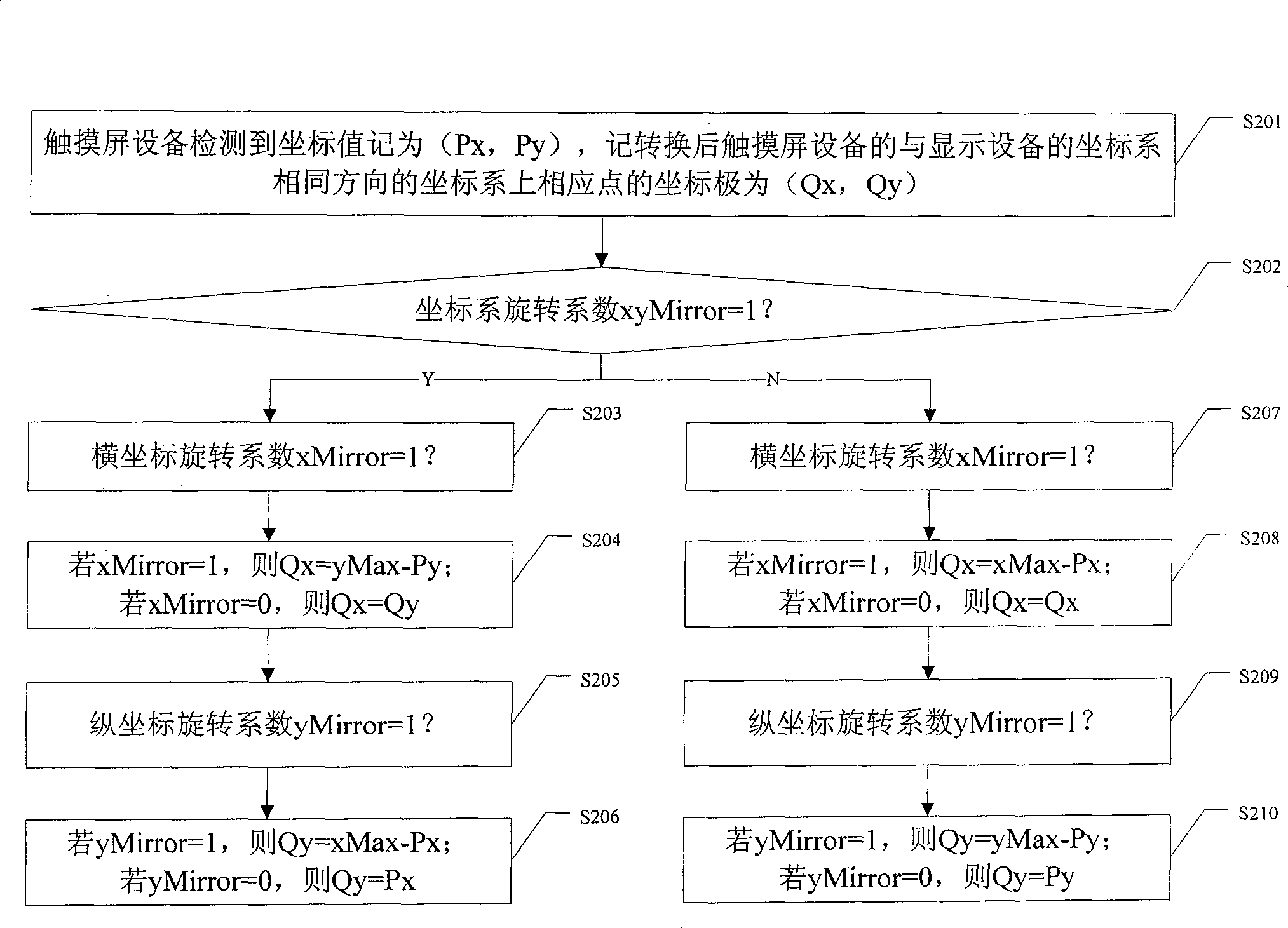

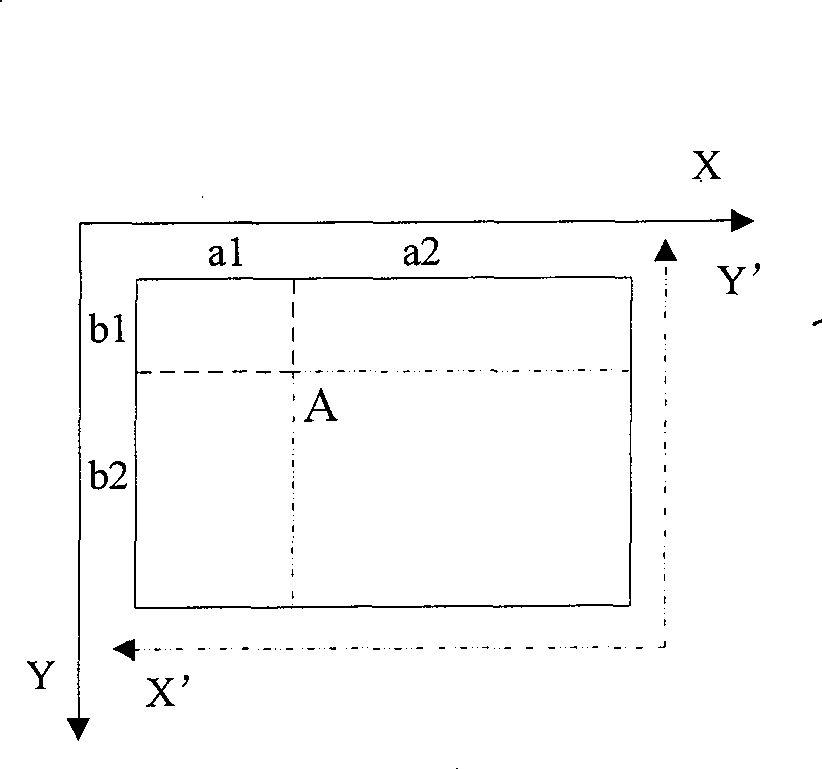

Calibrating method and apparatus for touch screen equipment

InactiveCN101382858AEasy to convertInput/output processes for data processingRotation factorSimulation

The invention relates to a calibration method and a calibration device for touch screen equipment. A coordinate system rotation coefficient is determined according to the maximum pixel values of a first coordinate and a second coordinate of display equipment; according to the coordinate system rotation coefficient, a first preset point and a second preset point located at the display equipment, and a first touch point and a second touch point which are detected by the touch screen equipment when the first and the second preset points are touched, a first coordinate rotation coefficient and a second coordinate rotation coefficient are determined and a transforming relationship which transforms an initial coordinate system of the touch screen equipment into the transformed coordinate system of the touch screen equipment, with a coordinate system direction the same as that of the display equipment; according to the transforming relationship, the touch screen equipment can output the position coordinate of the transformed coordinate system, which has the same coordinate system direction as the display equipment, thus being convenient for transforming the position coordinate into the coordinate located at the display equipment and preventing the circumstance that the real touch position is different from the display position of the display equipment, which is caused by that when the touch screen equipment is installed on the display equipment, the direction is different.

Owner:GUANGDONG VTRON TECH CO LTD

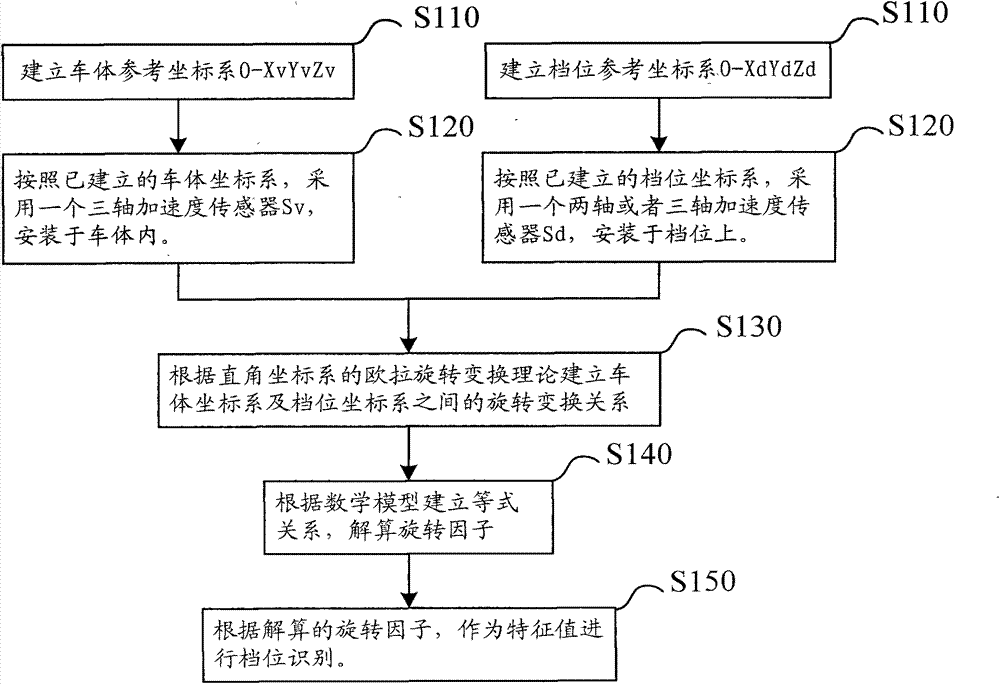

Vehicle gear recognition method and device

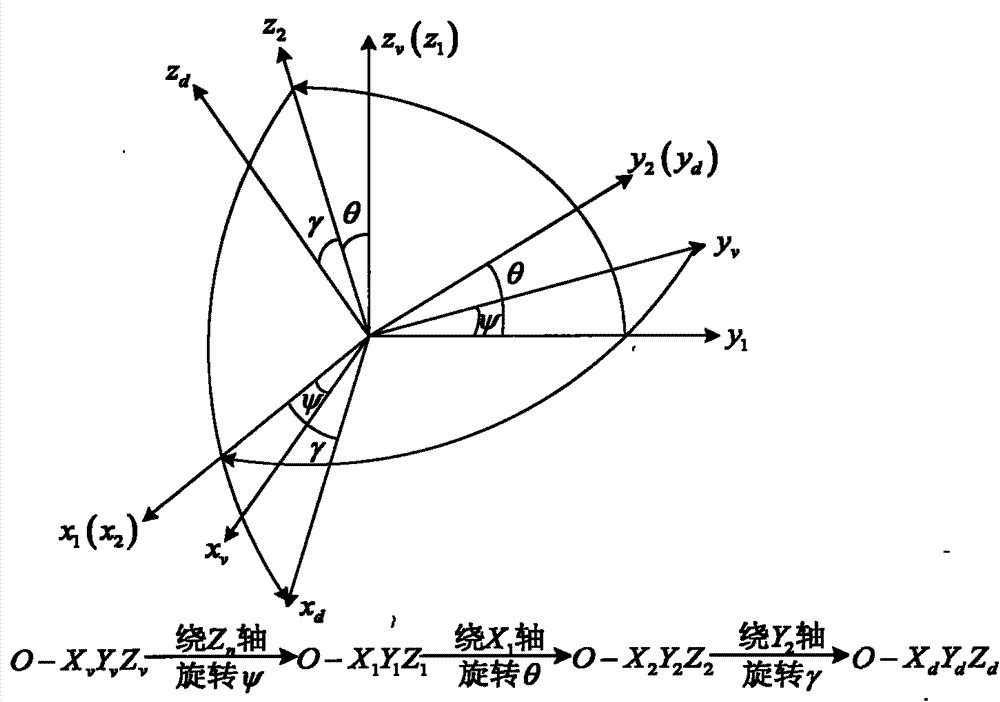

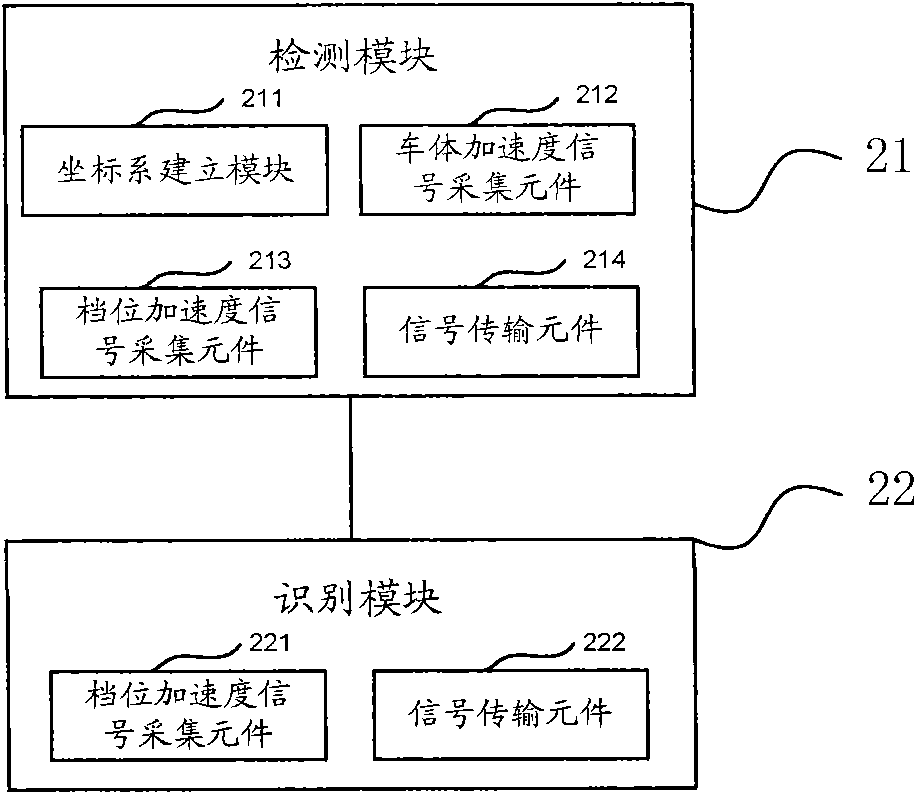

ActiveCN103640480ASimple structureOptimize layoutGearing controlElectric/fluid circuitRotation factorEngineering

The invention discloses a vehicle gear recognition method and device. The method includes the steps of building a vehicle body reference coordinate system and a gear reference coordinate system, collecting a vehicle body acceleration signal according to a built vehicle body coordinate system, and collecting a gear acceleration signal according to a built gear coordinate system. According to an Euler rotation transformation theory of a right-angle coordinate system, a rotation transformation relationship between the vehicle body coordinate system and the gear coordinate system is built, an equation relationship between a vehicle body acceleration vector and a gear acceleration vector is built according to the rotation transformation relationship between the vehicle body coordinate system and the gear coordinate system, a rotation factor between the gear reference coordinate system and the vehicle body reference coordinate system is solved according to the built equation relationship, and the rotation factor serves as a feature value for gear recognition. The method has the advantages of being simple in structure, easy to arrange and easy to achieve in a project. The state of a gear can be recognized when a vehicle runs under actual road conditions and a gear shifting motion is finished.

Owner:ATSUMITEC AUTO PARTS (FOSHAN) CO LTD

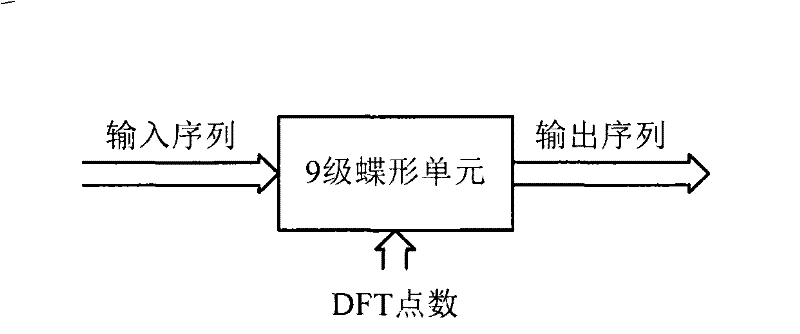

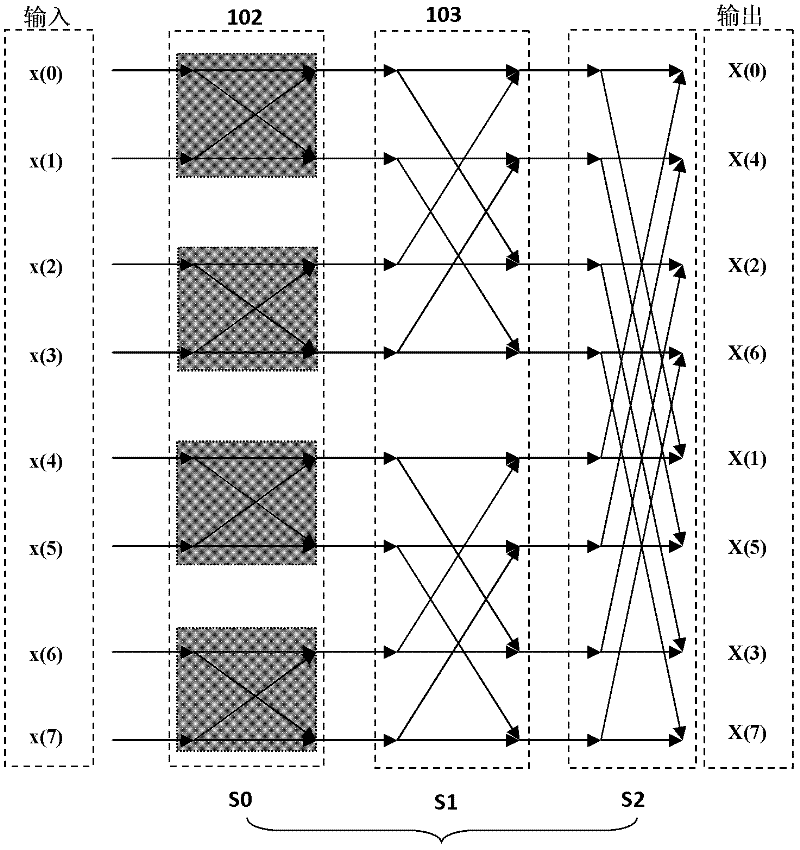

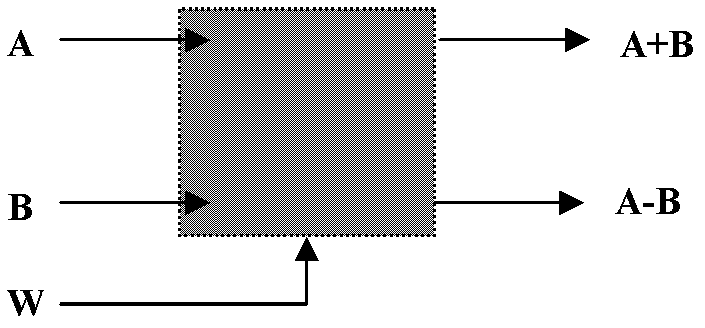

Fast Fourier transform hardware design method based on base 2-2 algorithm

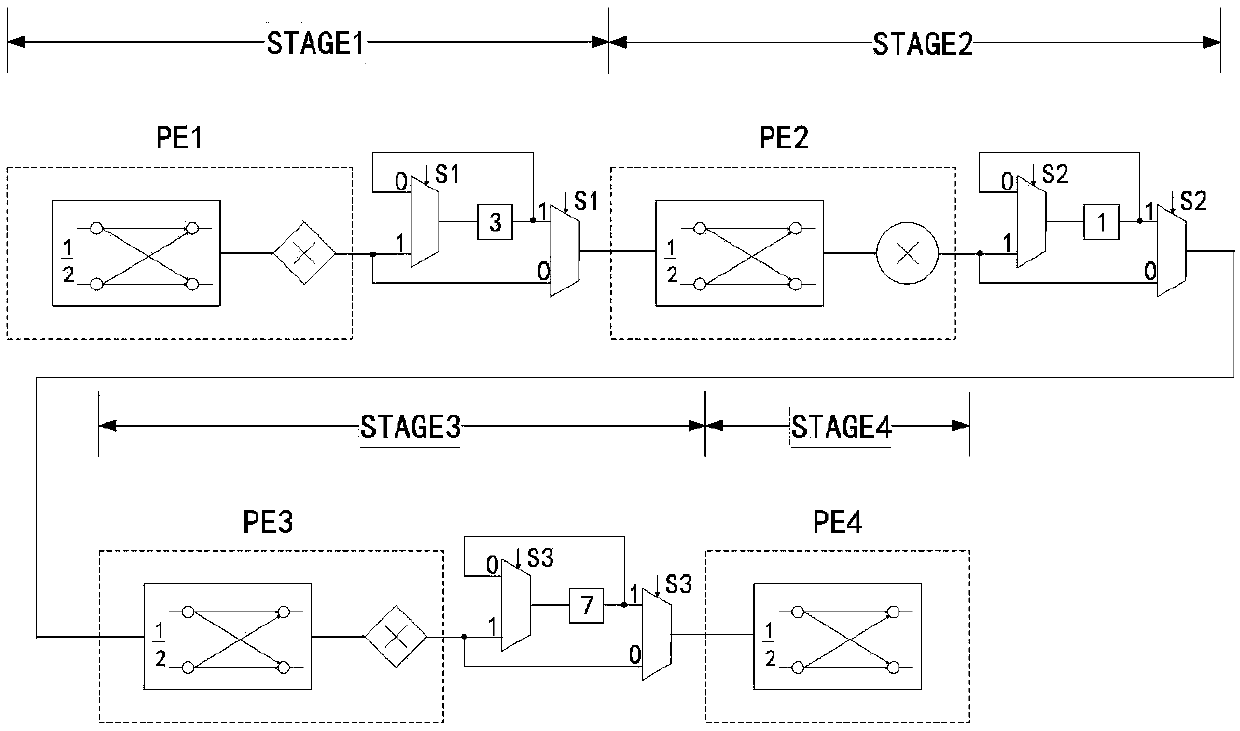

PendingCN109522674AReduce overheadImprove hardware efficiencyCAD circuit designComplex mathematical operationsFast Fourier transformRotation factor

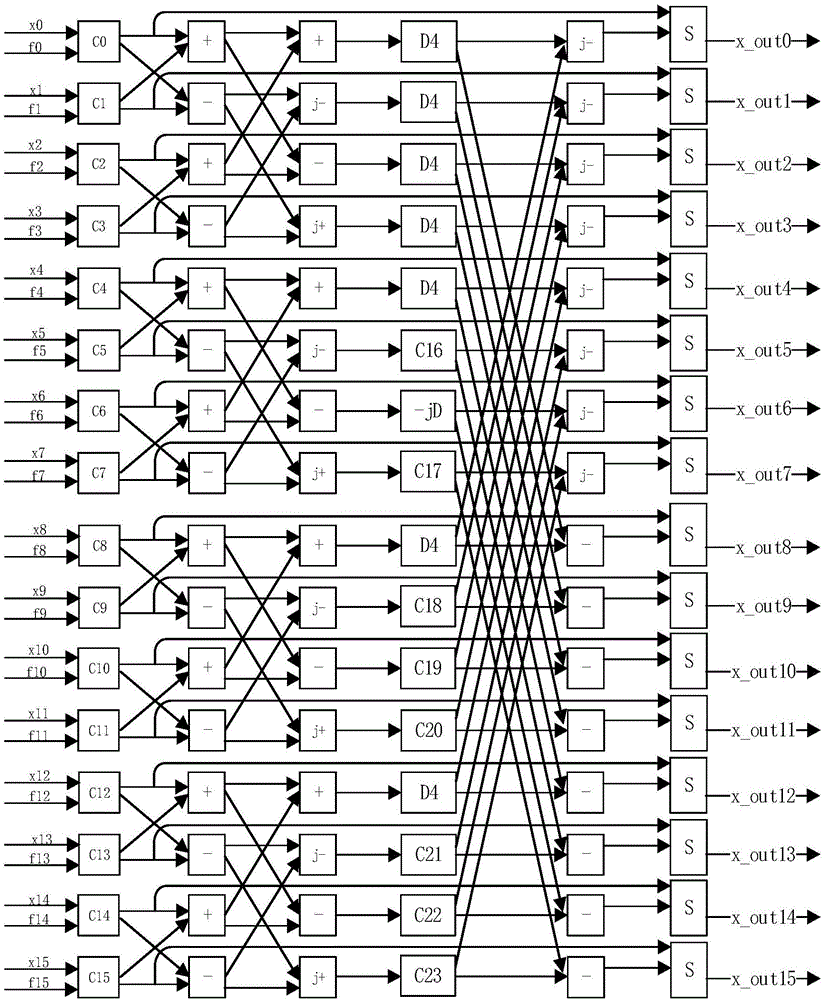

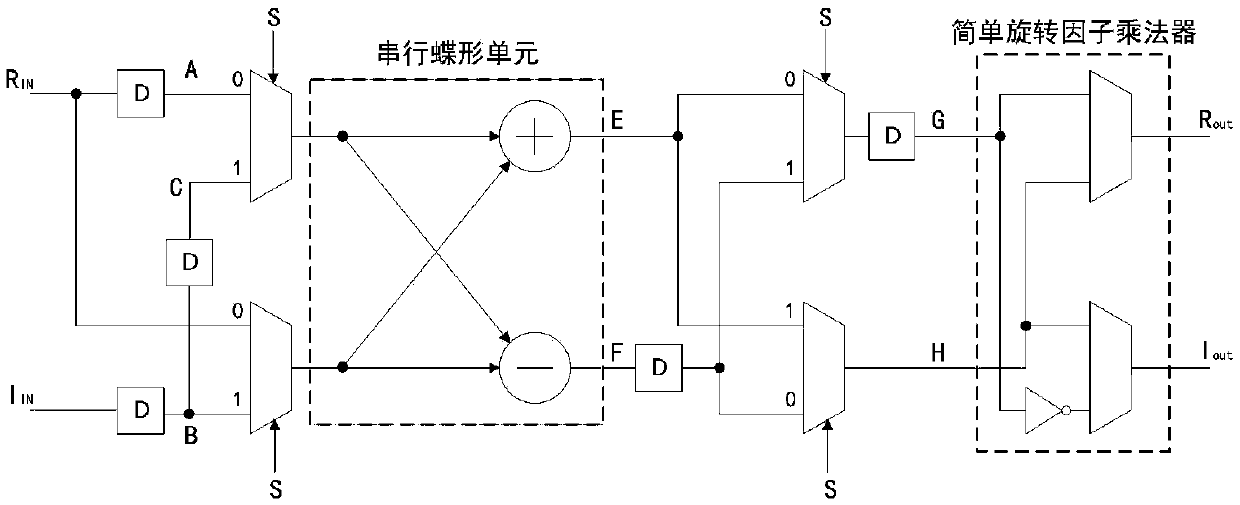

The invention relates to a base 2-. According to the fast Fourier transform hardware design method of the 2 algorithm, a frequency domain extraction mode is adopted, 16-point FFT of a base 22 algorithm of frequency domain extraction is obtained, a 16-point data flow diagram is obtained, and an overall structure of the base 22 FFT of 16 points based on a serial butterfly unit is designed; The structure comprises four processing stages, and each stage comprises a processing unit and an inverted sequence unit; Wherein the processing unit comprises a butterfly unit and a rotation factor multiplierunit. Each butterfly unit only comprises two adders, a serial butterfly unit of a real number adder and a subtracter is adopted, calculation is completed through two clock periods, addition and subtraction of a real part and an imaginary part are completed respectively, and a simple rotation factor multiplier and a complex rotation factor multiplier unit are designed for an odd number processingstage and an even number processing stage respectively.

Owner:TIANJIN UNIV

Method and device for processing data to be transmitted by adopting space-time coding by combining with precoding

InactiveCN101789814AProcessing speedReduce complexitySpatial transmit diversityTransmitter/receiver shaping networksRotation factorPrecoding

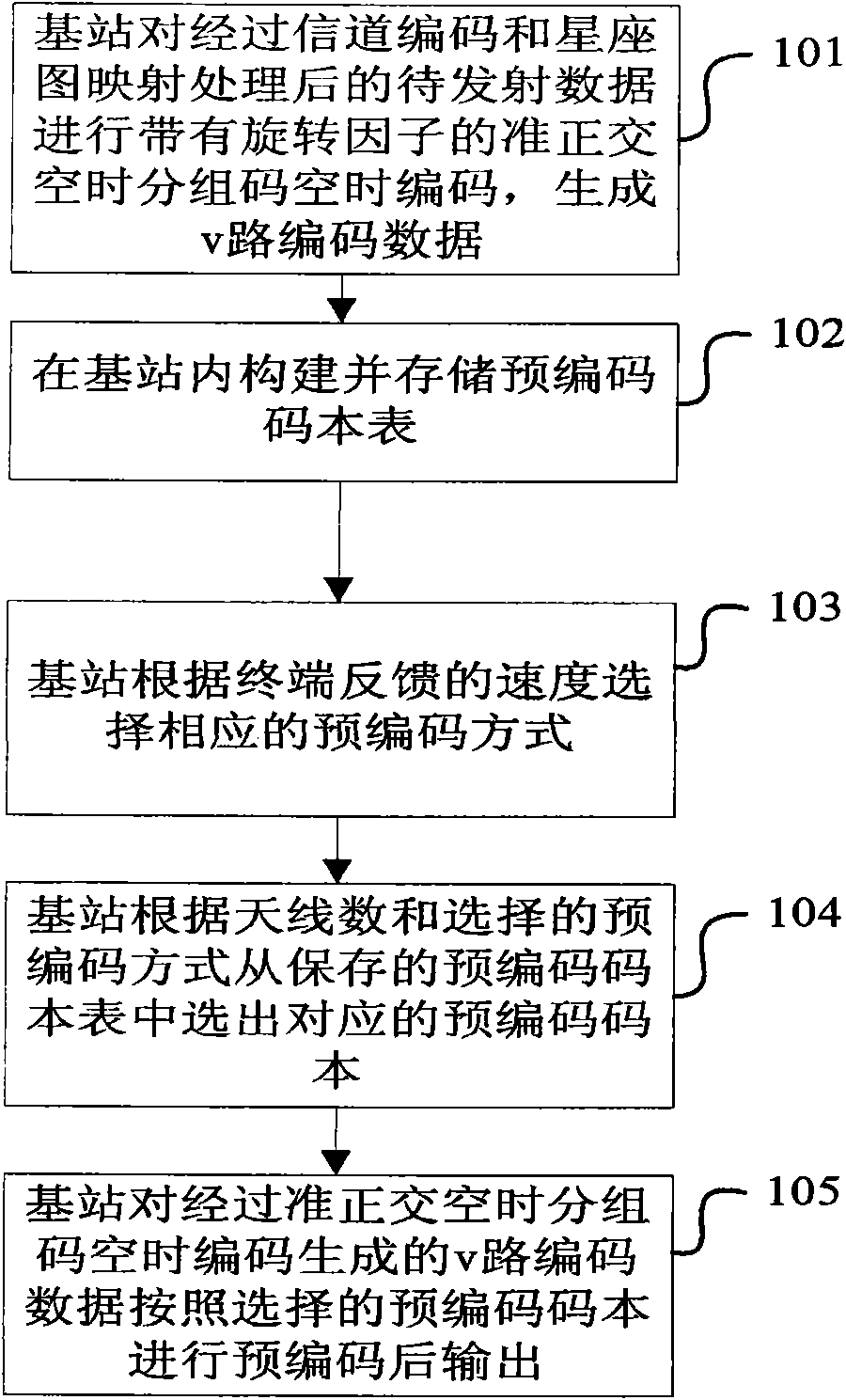

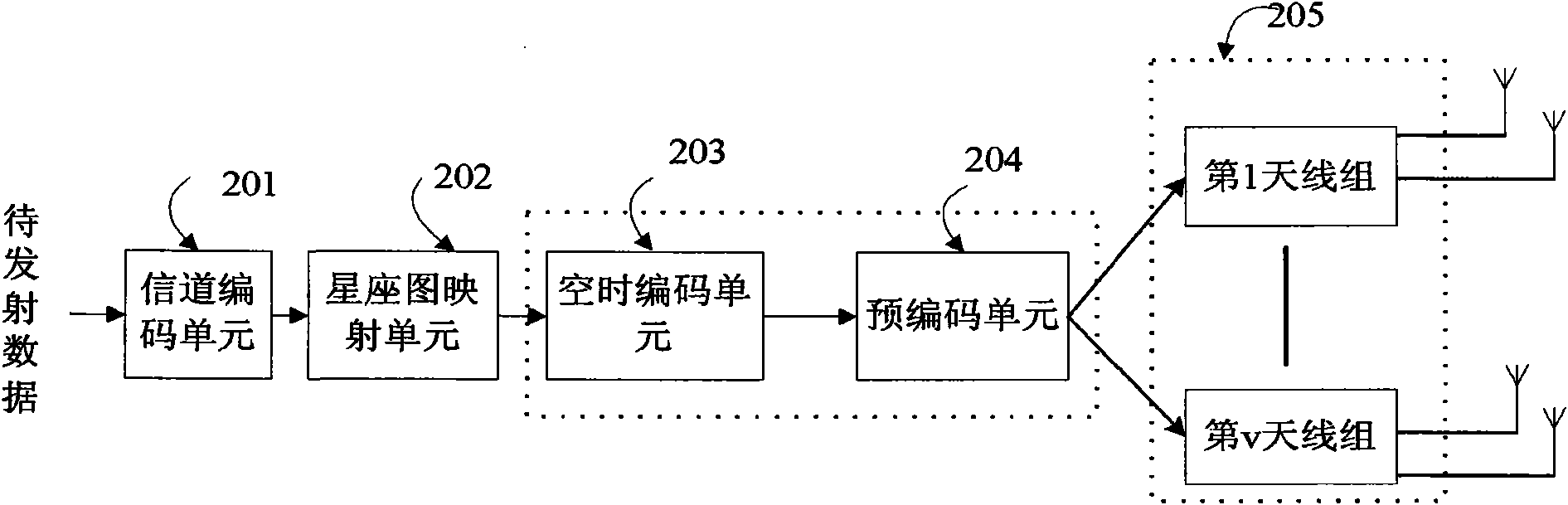

The invention discloses method and device for processing data to be transmitted by adopting space-time coding by combining with precoding, which are applied to a base station with multiple transmitting antennas. The method comprises the following steps of: carrying out quasi-orthogonal space-time block code space-time coding with rotation factors on the data to be transmitted by the base station to generate multi-path coded data corresponding to the antennas in number; meanwhile, selecting a corresponding precoding mode by the base station according to speed fed back by a terminal and selecting a corresponding precoding codebook from a precoding codebook list stored in the base station by combining with the number of the antennas; precoding the multi-path coded data by the base station according to the selected precoding codebook and then outputting the coded data. The invention overcomes the constellation extension brought during carrying out the quasi-orthogonal space-time block code space-time coding so as to ensure that the data transmitted by the base station from the transmitting antennas can be self-adaptive to the conditions of channels.

Owner:ZTE CORP

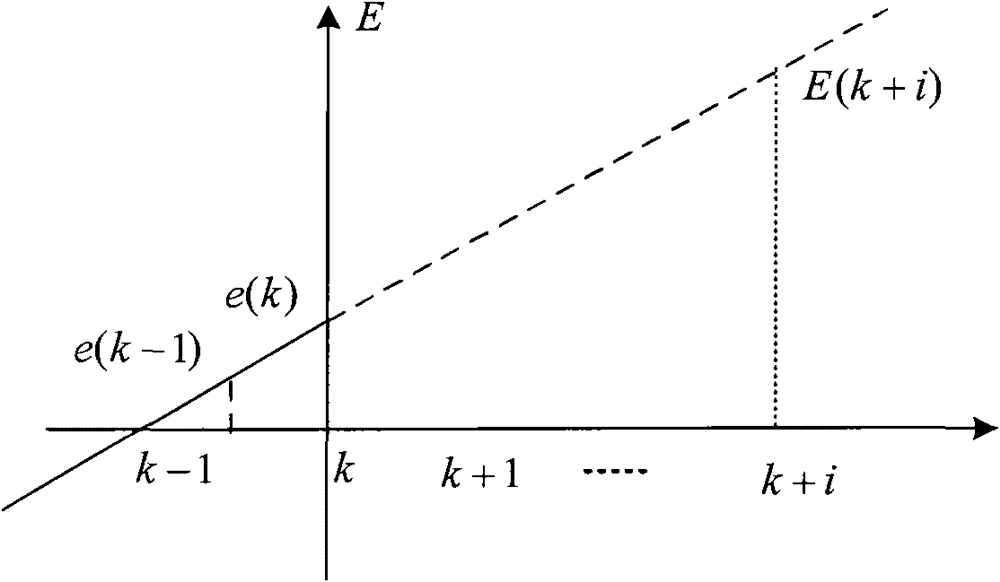

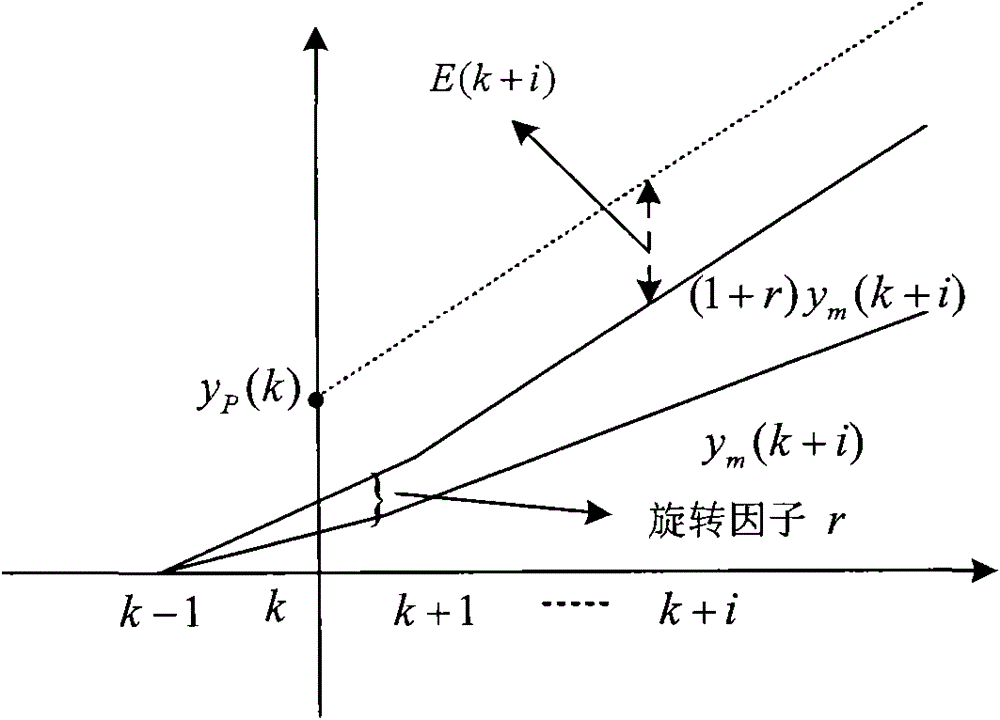

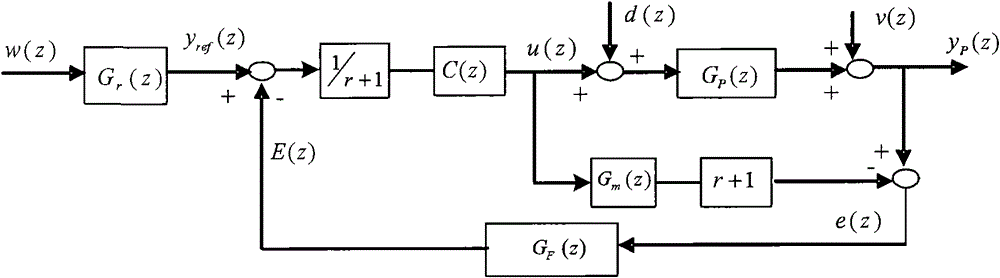

Prediction control method for non-self-balancing system

InactiveCN102749844AEliminates bias in tracking given valuesImprove robustnessAdaptive controlRotation factorControl system

The invention relate to the design of a prediction control method for a non-self-balancing system and mainly aims to solve the problems of difficult control on the non-self-balancing system, difficult modeling for the non-self-balancing system, difficult guarantee for the stability of a control system and irregular adjustment on parameters of a controller in the prior art. A single controller is adopted to only perform a step response test on a controlled target to obtain a prediction model of the target, and a prediction control algorithm is built by constructing control input of single freedom degree and introducing the concept of a rotation factor into a performance index by using a special error feedback correction method. The prediction control algorithm comprises the following steps of (1) building control input of single freedom degree: selecting future system control input which consists of one primary function weighing; (2) performing step signal excitation on the controlled target to obtain a process model; (3) building a future system expected performance index, and introducing the concept of the rotation factor into a performance index function; (4) deducing future prediction output; (5) building the special error feedback correction; and (6) ensuring the stability of the control system and tracing set value. Due to the adoption of the technical scheme, the problems are better solved, and the method can be used for operation control of the non-self-balancing system.

Owner:CHINA PETROLEUM & CHEM CORP +1

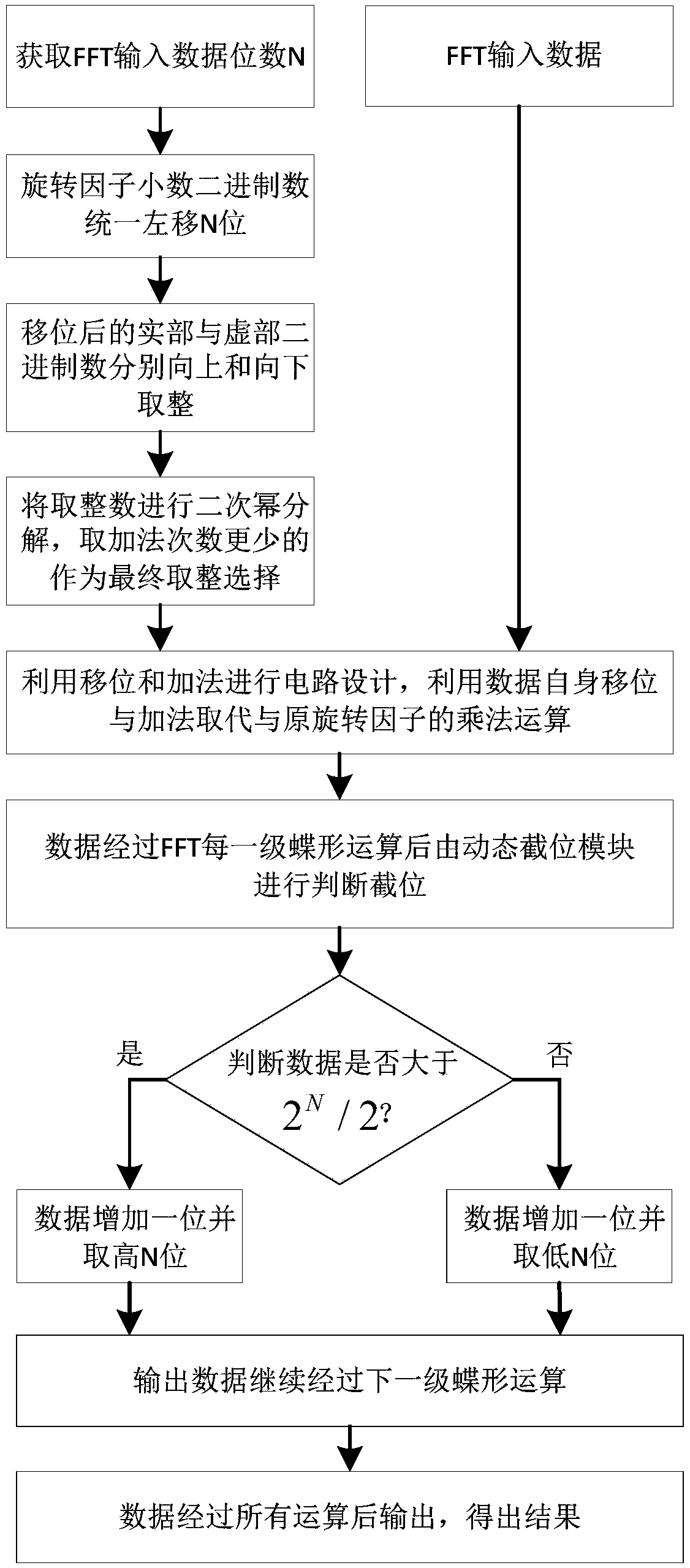

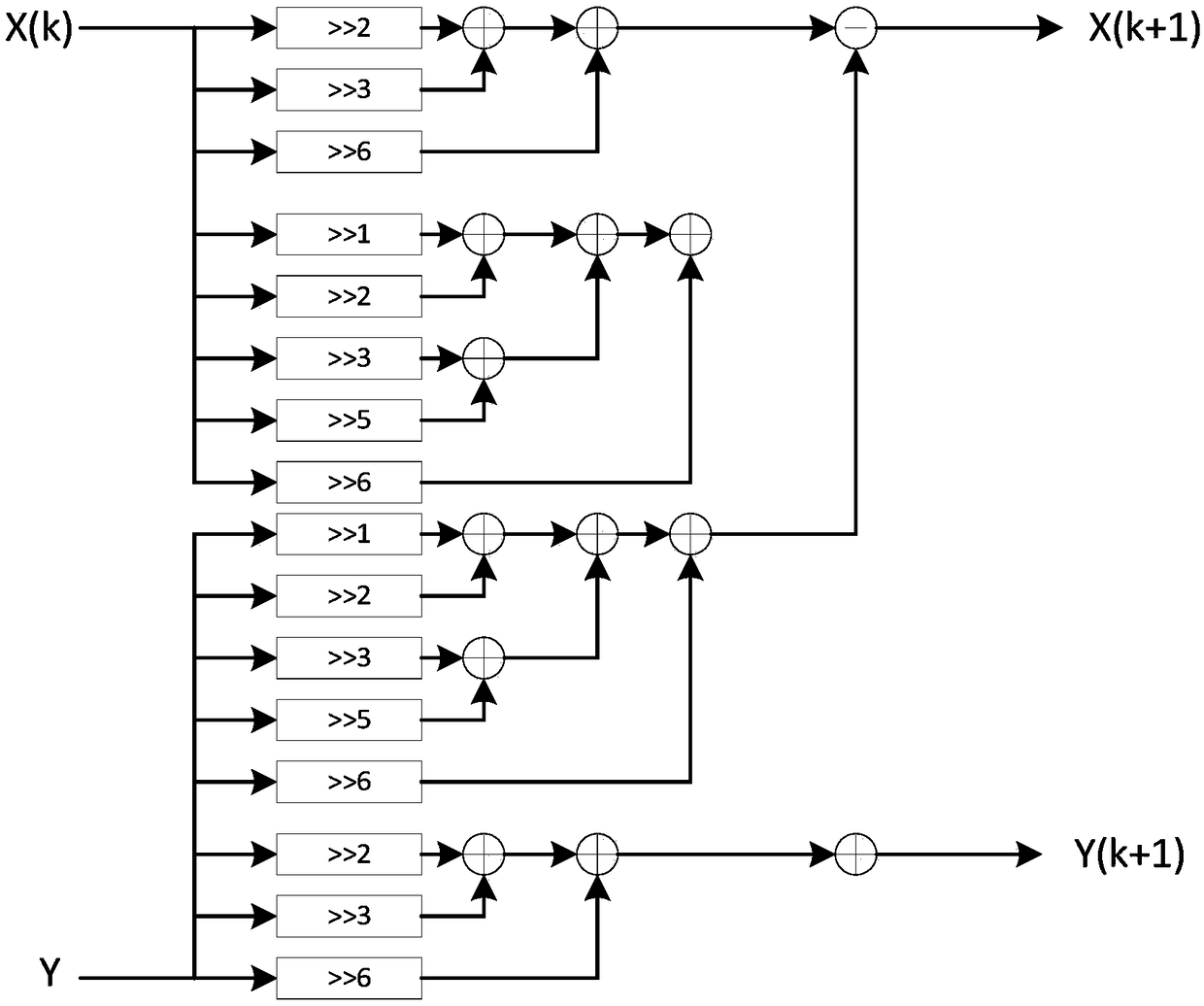

A low-complexity multiplier-free fixed-point FFT optimization method based on dynamic truncation

ActiveCN109359267AReduce in quantityImprove performanceComplex mathematical operationsRotation factorDigital signal processing

The invention belongs to the application field of software radio and digital signal processing thereof, in particular to a low-complexity multiplier-free fixed-point FFT optimization method based on dynamic truncation. The method includes obtaining FFT input data bits N and input data; shifting the decimal fraction of each rotation factor by N bits to the left, and dividing the data into a real part and an imaginary part, wherein N is the number of bits of the input data; rounding up the real part and the imaginary part up and down respectively, so that they are approximated to integers; All integers are factorized to the second power, and the integer with the least number of additions is selected; The circuit is designed by using shift and addition, and the multiplication of the originalrotation factor is replaced by the shift and addition of the data itself. The present invention further reduces the number of adders while replacing conventional complex multipliers with shift and add-subtract. At the same time, the dynamic bit-truncation module is added to restrain the growth of data bits, reduce the consumption of hardware resources, improve the computing speed and improve the performance of the circuit.

Owner:HARBIN ENG UNIV

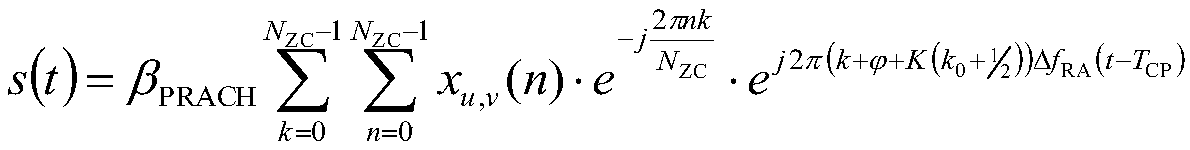

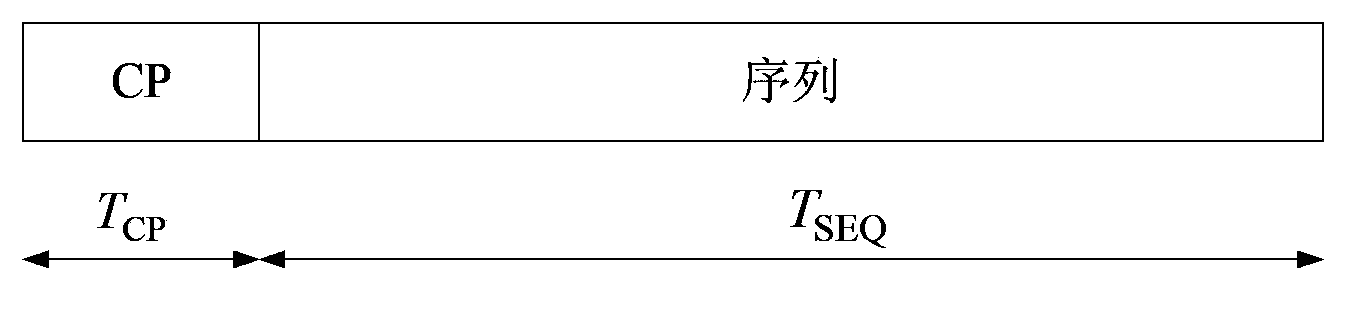

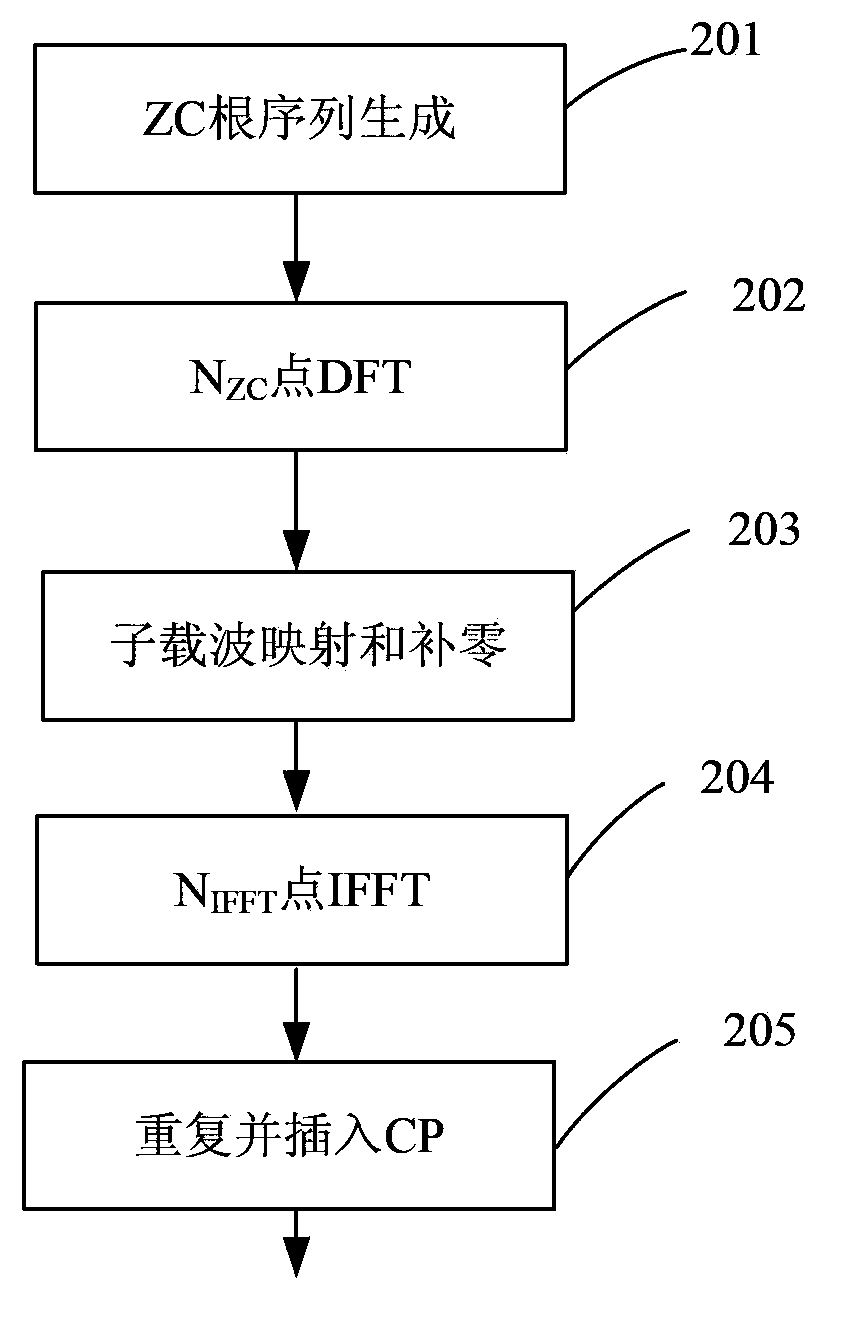

Generation method and device for physical random accessing channel baseband signal

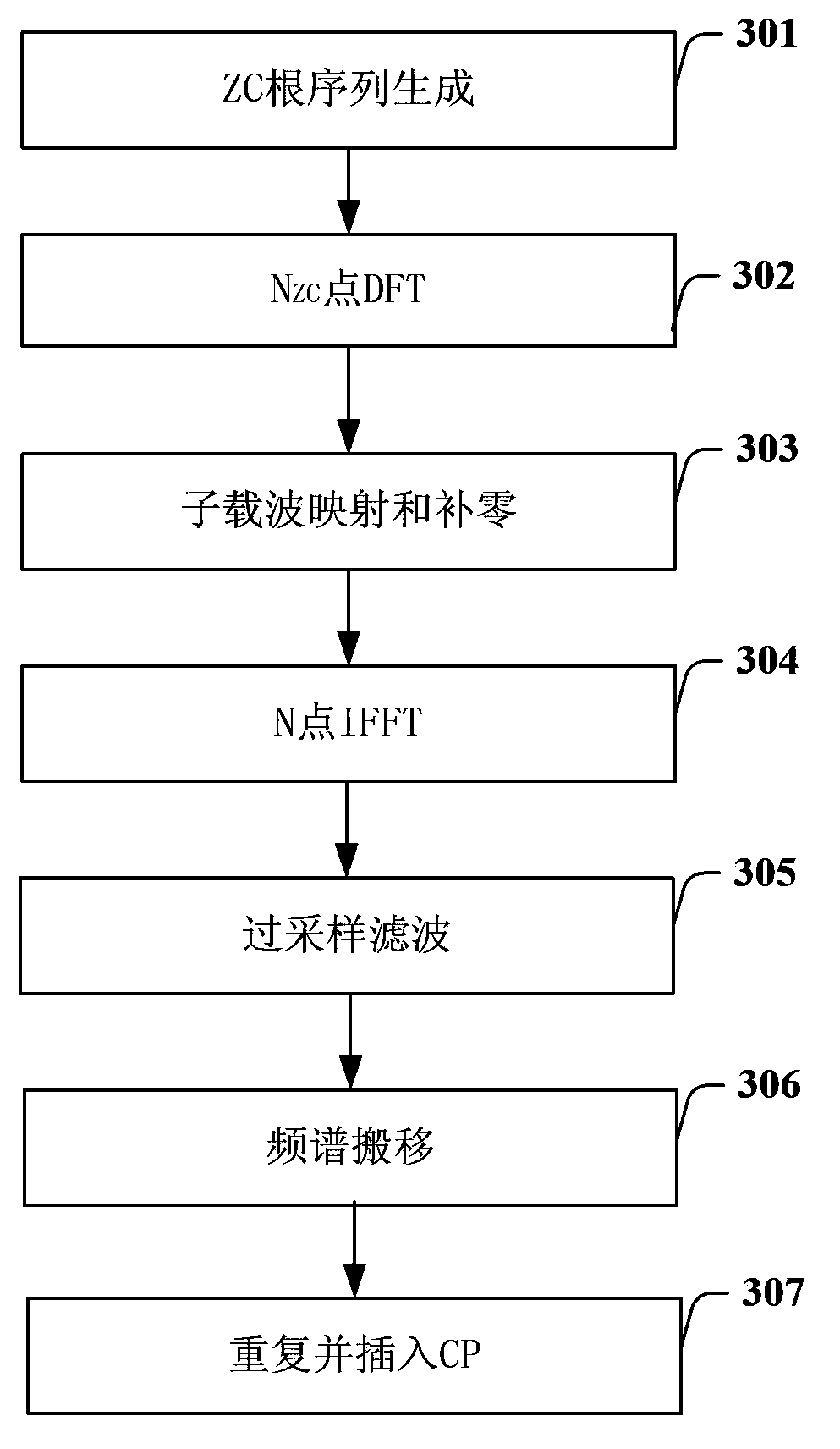

ActiveCN103516500ASmall amount of calculationTransmitter/receiver shaping networksTransmission path multiple useRotation factorFrequency spectrum

The invention relates to a generation method and device for a physical random accessing channel baseband signal. The generation method and device for the physical random accessing channel baseband signal can significantly reduce computation complexity and memory space. The method comprises the steps that a ZC root sequence corresponding to a physical random access channel is generated; the discrete Fourier transform is conducted on the ZC root sequence; subcarrier mapping and zero-filling are conducted on the output sequence of the discrete Fourier transform; the rapid inverse Fourier transform is conducted on the sequence after the mapping and zero-filling; first frequency spectrum shift is conducted on the sequence after the rapid inverse Fourier transform; sampling and filtering are conducted on the data after the conduction of the first frequency spectrum shift; second frequency spectrum shift is conducted on the data after sampling and filtering, wherein the rotation factor of the second frequency spectrum shift is the same as the rotation factor of the rapid Fourier transform with the length being Nsys.

Owner:LEADCORE TECH

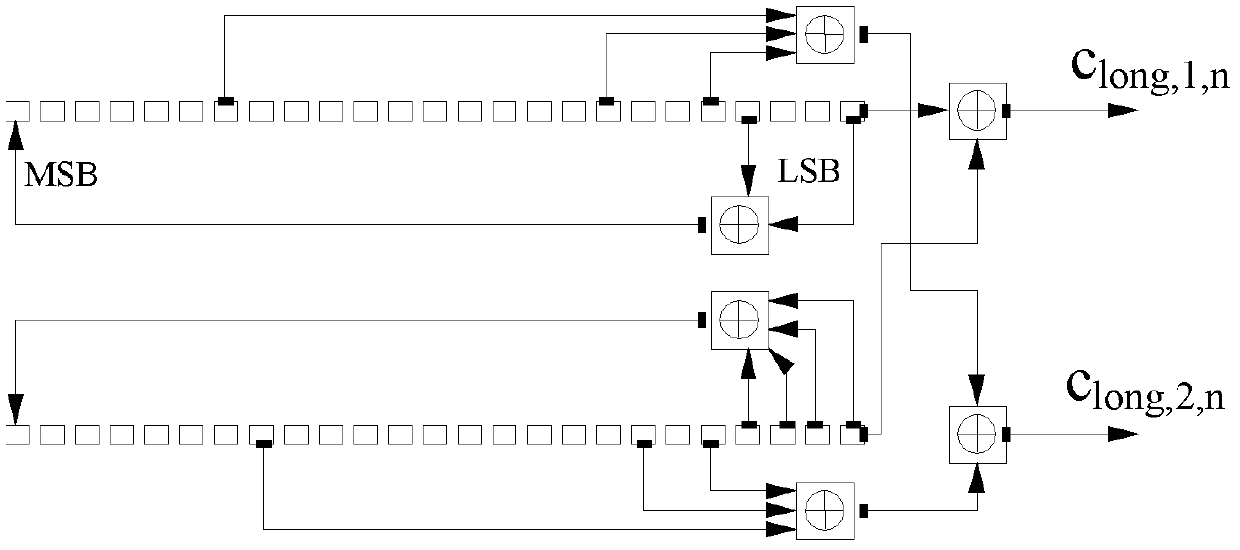

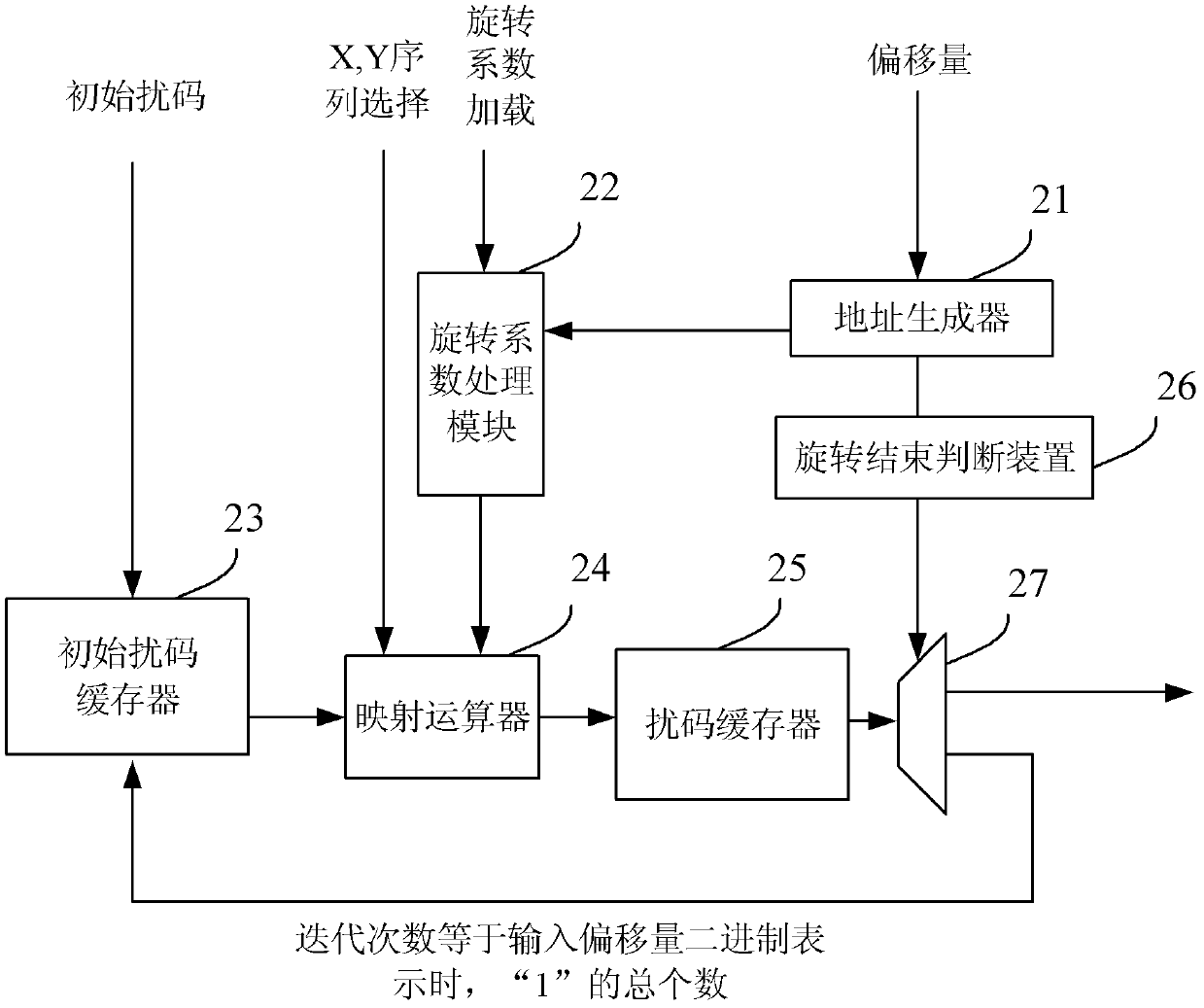

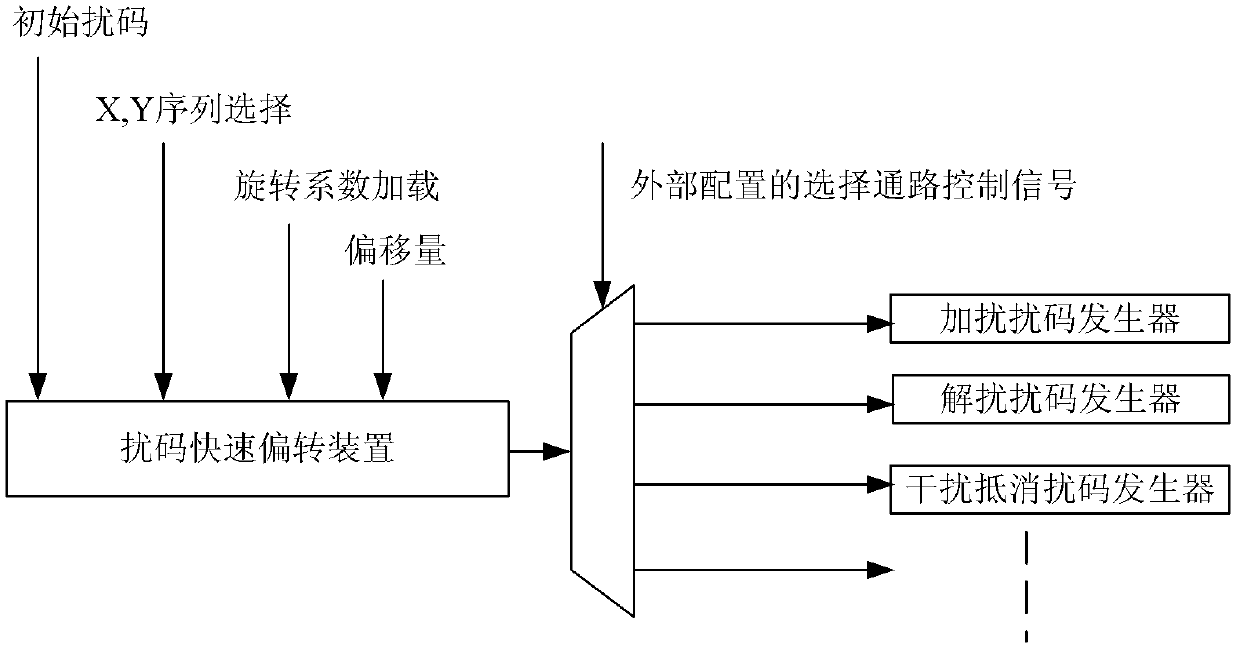

Generation method and generation apparatus of scrambling code, and processing apparatus of scrambling code

ActiveCN103378917AImprove performanceIncrease flexibilityMultiplex code generationTransmissionRotation factorCode generation

Provided are a scrambling code generation method, apparatus and a scrambling code processing apparatus, the method comprising the steps of converting the inputted phase shift into a binary number, according to the position of the effective bit with the highest weight in the binary number to generate an access address of a rotation factor, according to the access address to select a corresponding rotation factor from a rotation factor table; mapping a K bits original scrambling code sequence to a 2K bits scrambling code sequence, and calculating the mapped scrambling code sequence with the rotation factor to obtain the rotated scrambling code sequence; updating the effective bit with the highest weight to zero; if the updated phase shift is zero, outputting the rotated scrambling code sequence, and if the updated phase shift is not zero, regarding the updated phase shift as the present inputted phase shift and the rotated scrambling code sequence as the original scrambling code sequence, and repeating the above processes. The solution improves the performance and the flexibility, furthermore has a lower cost.

Owner:SANECHIPS TECH CO LTD

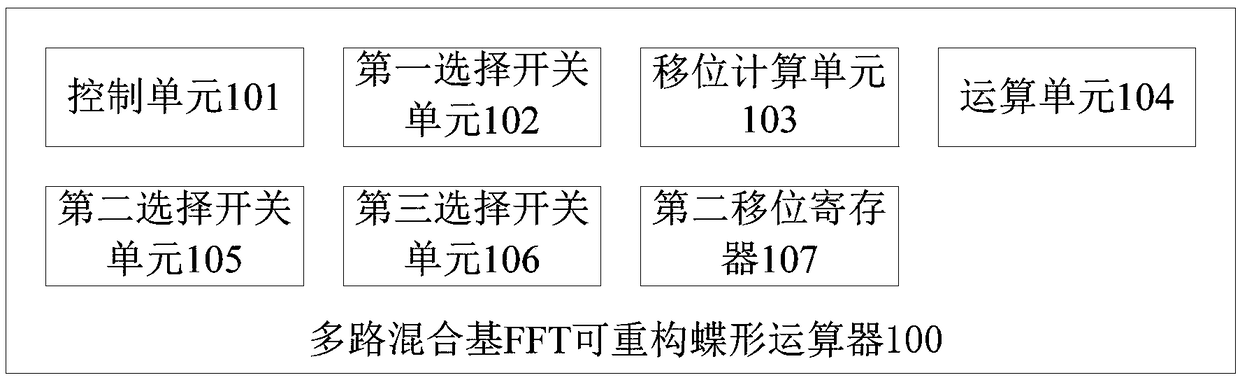

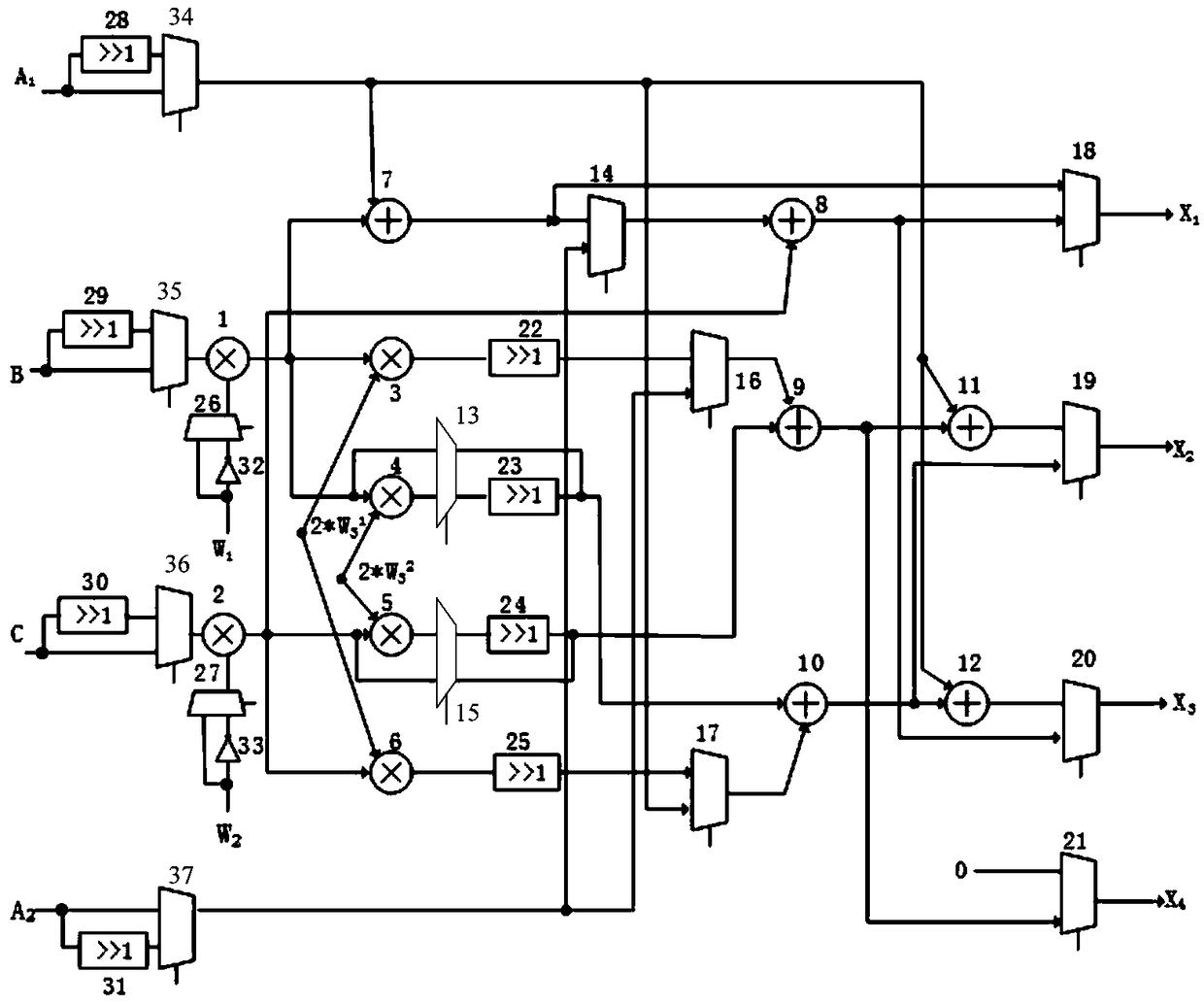

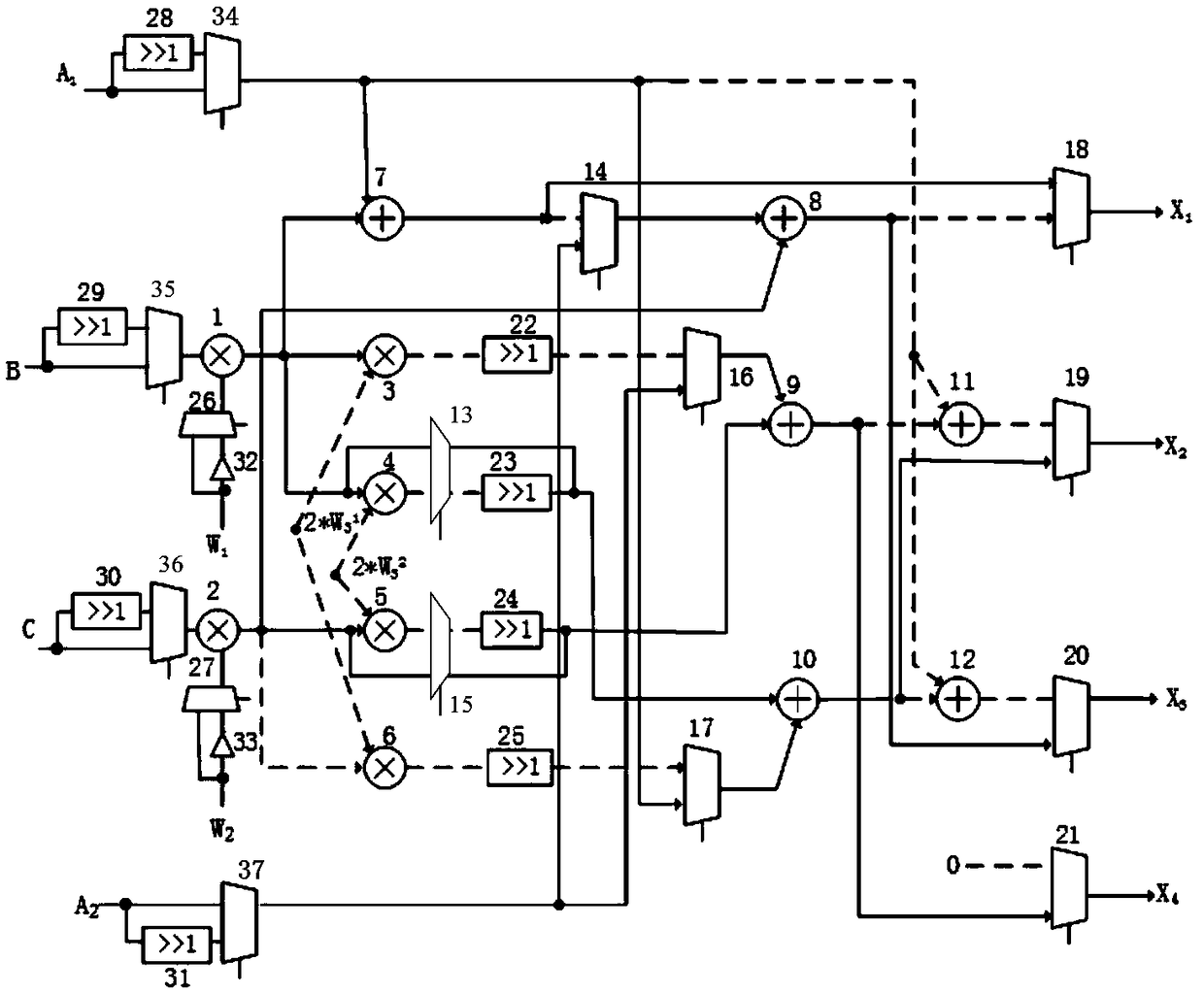

Multipath hybrid-based FFT reconfigurable butterfly arithmetic unit

ActiveCN109117188AImprove calculation accuracyImprove utilization efficiencyEnergy efficient computingMemory systemsRotation factorElectronic component

A FFT reconfigurable butterfly-shaped arithmetic unit with multiple mix bases is composed of a control unit, a first selection switch unit and an arithmetic unit. The control unit is used for generating an operation instruction according to the received data to be operated, wherein, the data to be operated comprises a digital signal to be processed, a rotation factor and a preset rotation factor coefficient; the first selection switch unit is configured to select a corresponding conduction mode according to an operation instruction. The operation unit is configured to perform butterfly operation on the data to be operated according to the conduction mode. By adopting the technical proposal of the invention, the utilization efficiency of the electronic components in the butterfly-shaped arithmetic unit is improved, the circuit hardware resources and power consumption are reduced, and the accuracy and real-time performance of the calculation data are improved.

Owner:HEFEI UNIV OF TECH

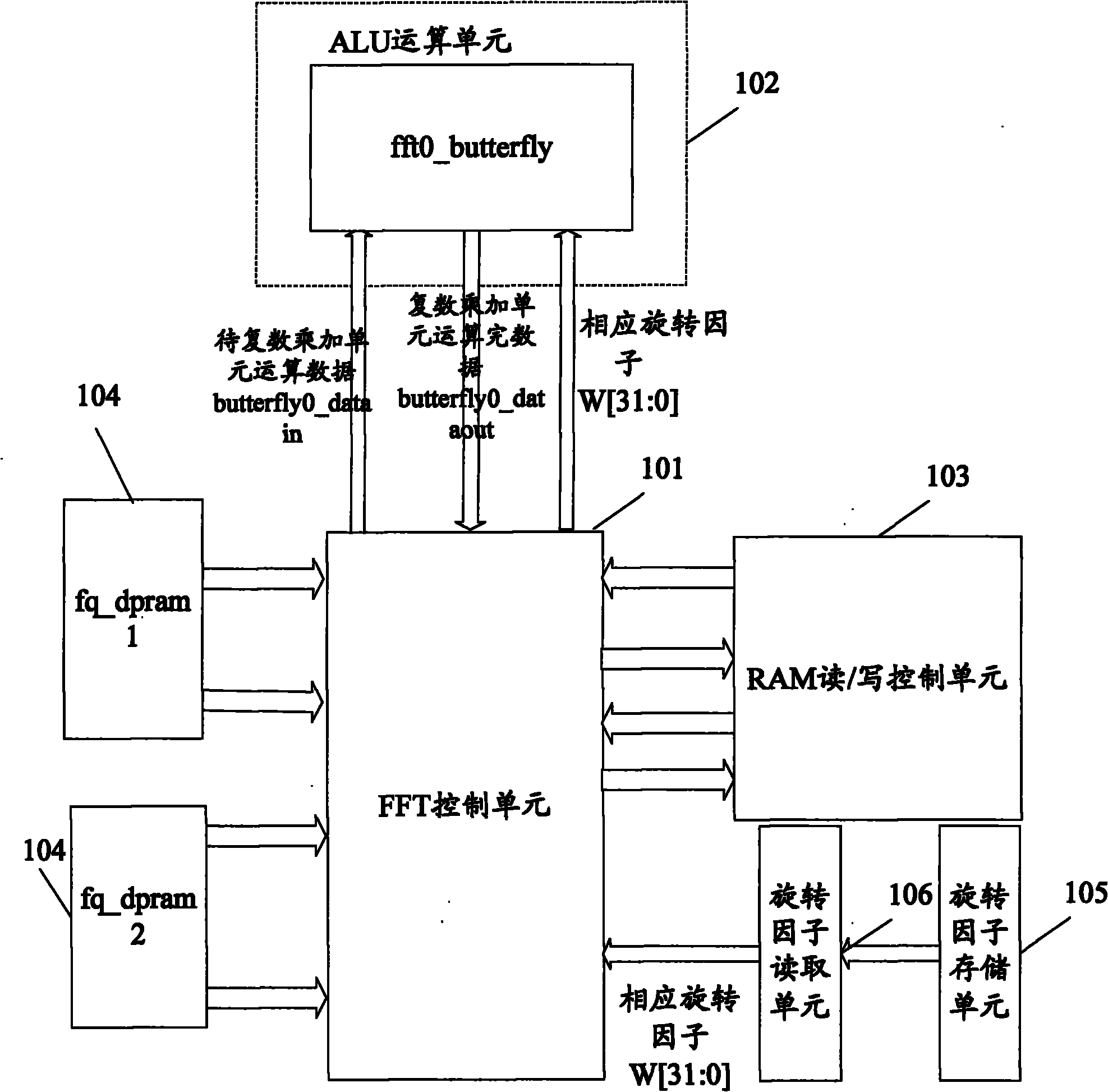

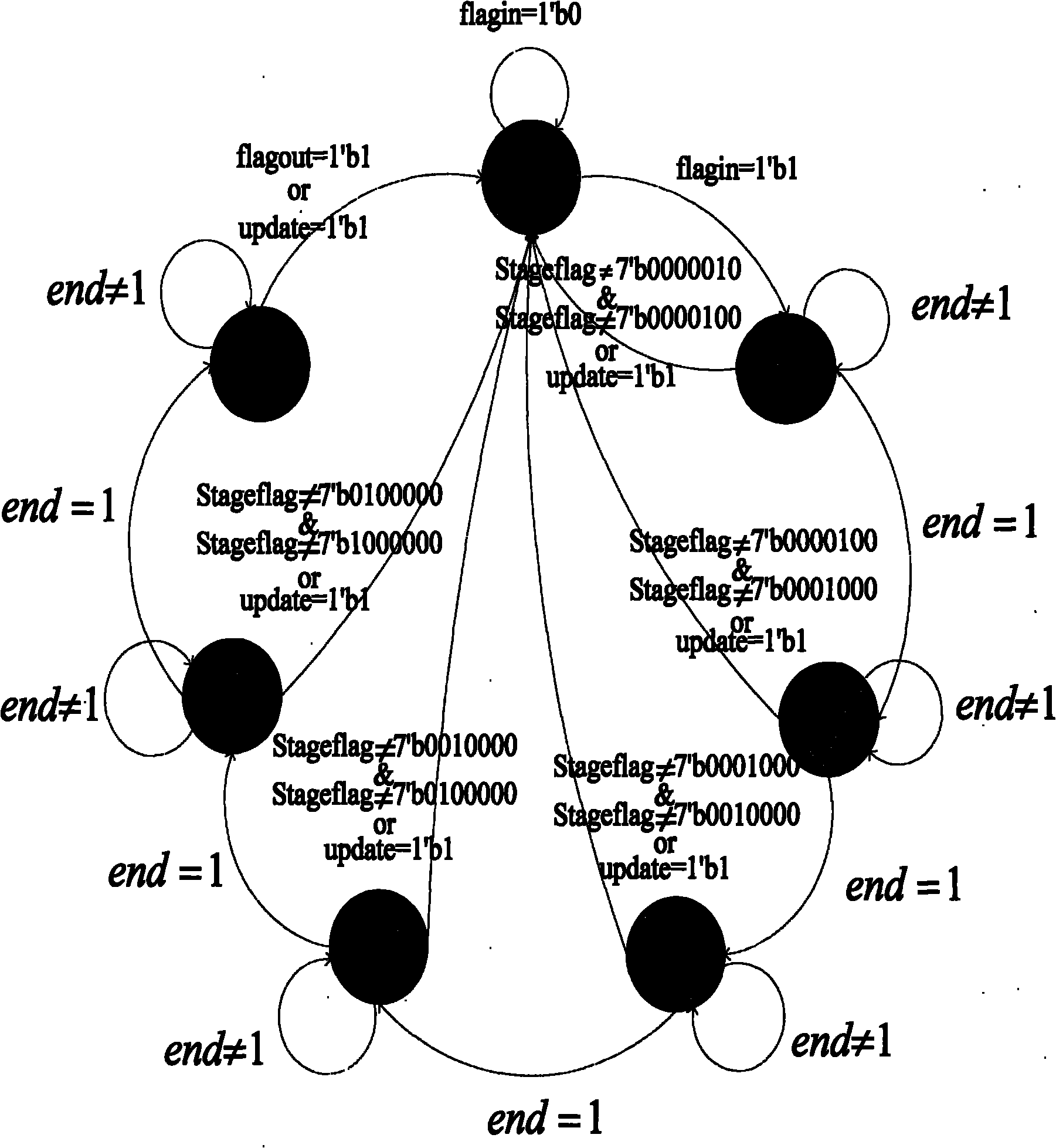

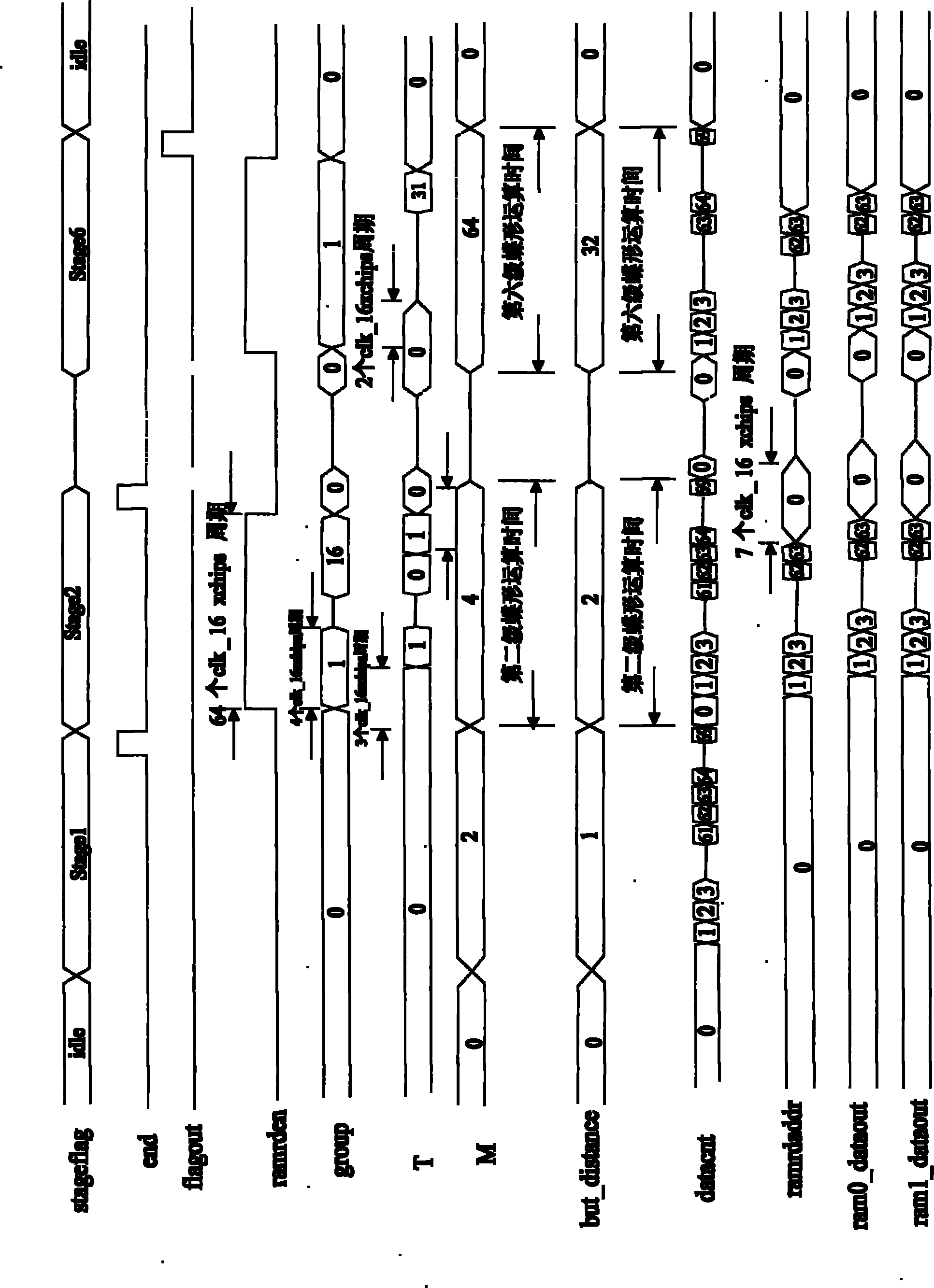

Device and method for implementing FFT and IFFT operation

InactiveCN102033852AFast operationComplex mathematical operationsRotation factorFast Fourier transform

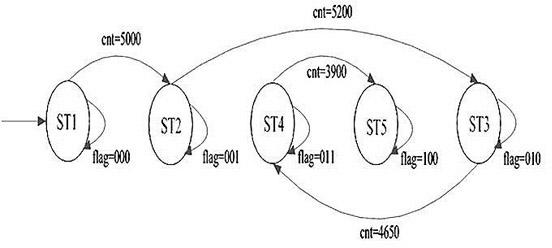

The invention discloses a device and a method for implementing fast Fourier transform (FFT) and inverse fast Fourier transform (IFFT) operation. The device comprises an FFT / IFFT control unit, an arithmetic logical unit (ALU) operation unit, a random access memory (RAM) read / write control unit and a rotation factor reading unit, wherein the FFT / IFFT control unit is used for inputting two paths of data and rotation factors to be operated into the ALU operation unit, storing the ALU output calculation results into corresponding RAMs respectively and controlling the switching of butterfly operation of each stage of FFT / IFFT by using a state machine; the ALU operation unit is used for performing FFT / IFFT butterfly operation on the two paths of data to be operated respectively; the RAM read / write control unit is used for performing read and write control on a plurality of RAMs, wherein the plurality of RAMs store the FFT / IFFT butterfly operation results of each stage; and the rotation factor reading unit is used for calculating the storage address of the rotation factor required for calculating the butterfly operation of each stage in a rotation factor storage unit. The device improves the speed of FFT and IFFT in the prior art.

Owner:SANECHIPS TECH CO LTD

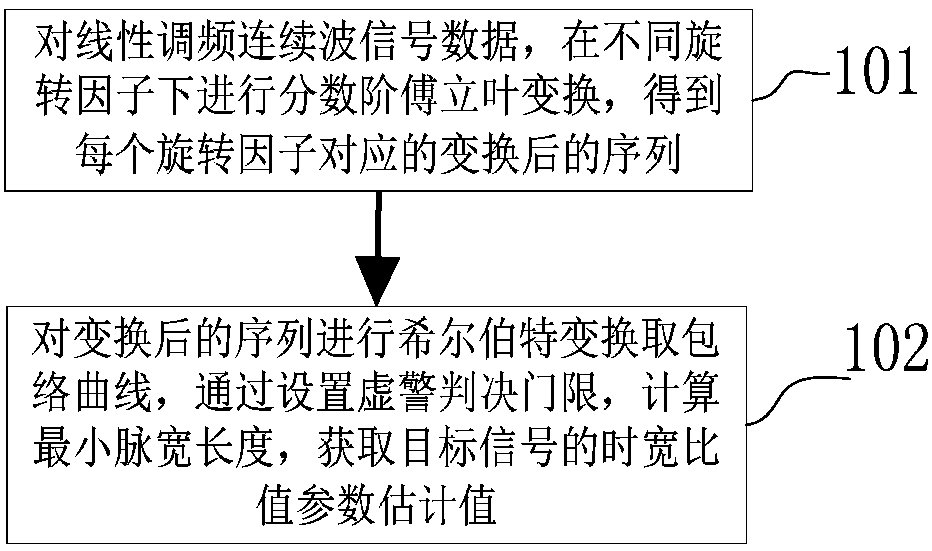

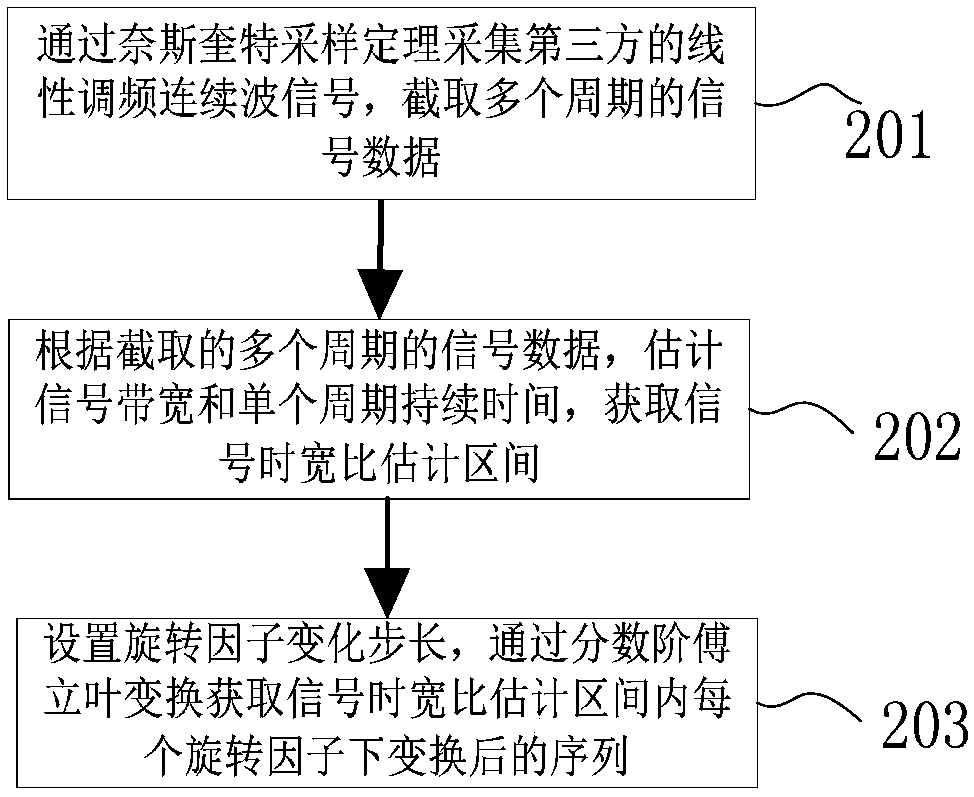

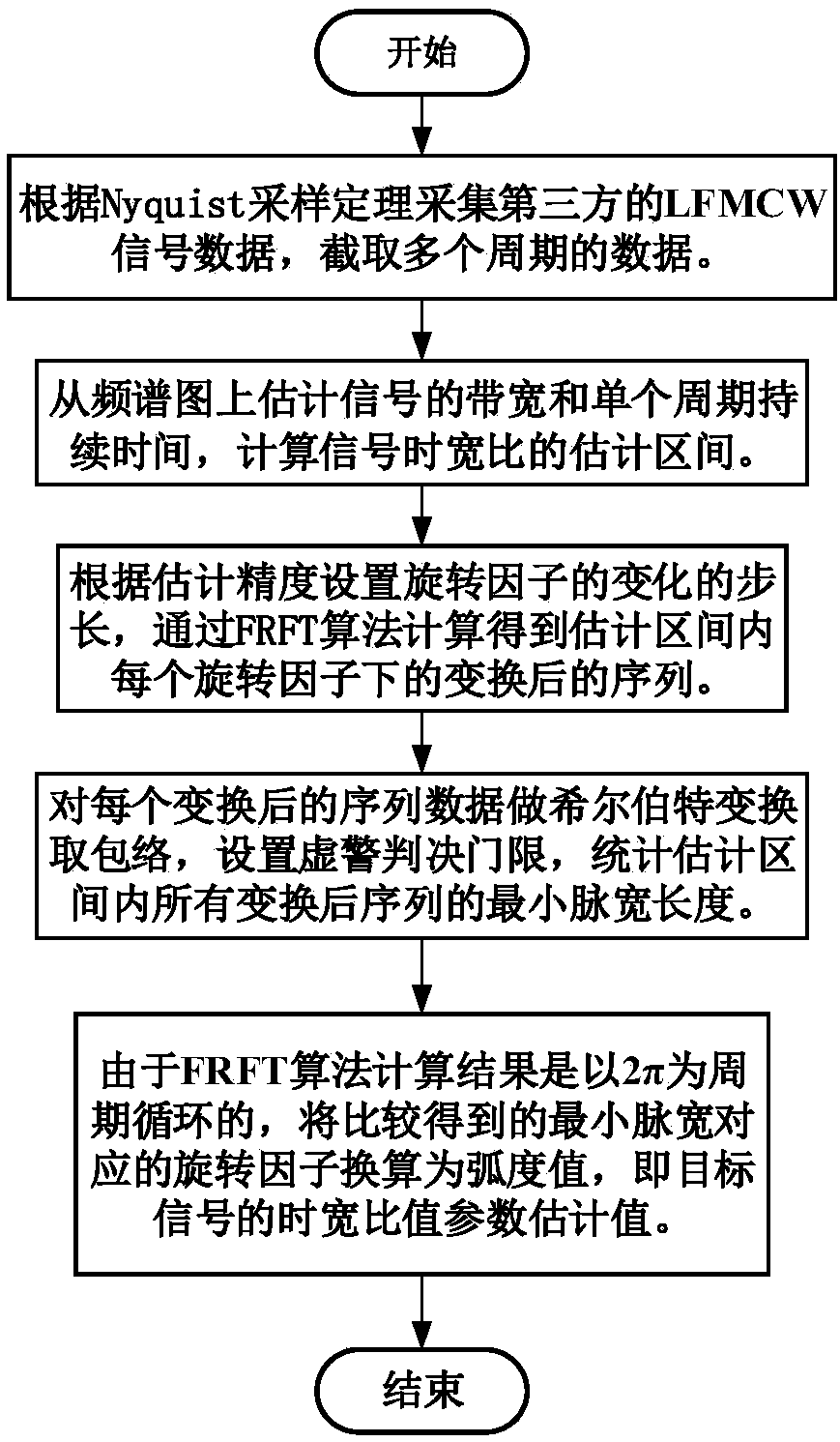

Linear frequency modulation continuous wave time-width ratio estimation method based on fractional Fourier transform and minimum pulse width detection

ActiveCN108169739AOvercoming delayOvercoming scalabilityRadio wave reradiation/reflectionFrequency spectrumTarget signal

The invention relates to a linear frequency modulation continuous wave time-width ratio estimation method based on fractional Fourier transform and minimum pulse width detection. The method comprises:fractional Fourier transform is carried out on linear frequency modulation continuous wave signal data at different rotation factors to obtain a transformed sequence corresponding to each rotation factor; and Hilbert transform is carried out on the transformed sequence to obtain an envelope curve, a false alarm decision threshold is set and a minimum pulse width length is calculated, and a time-width ratio parameter estimation value of a target signal is obtained. According to the invention, high-dimensional complex calculation is not needed; the method is simple and is easy to realize; problems of multi-path delay and spectrum expansion caused by mutual interference between a direct wave and an indirect wave are solved effectively; a multi-path delay problem caused by multi-times reflection of the radar signal is solved; the operation load is reduced effectively and the estimation precision is improved; and the method has advantages of great practical application value, stable performance, and high reliability and efficiency.

Owner:PLA STRATEGIC SUPPORT FORCE INFORMATION ENG UNIV PLA SSF IEU

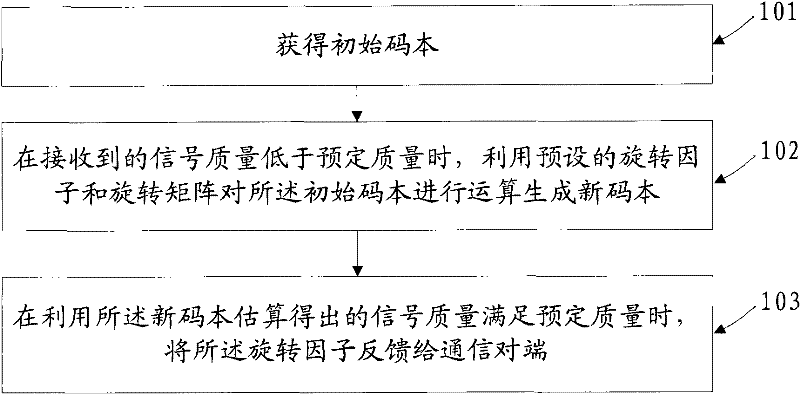

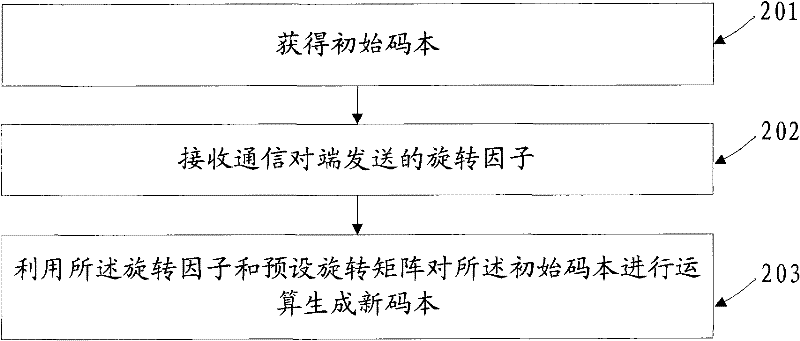

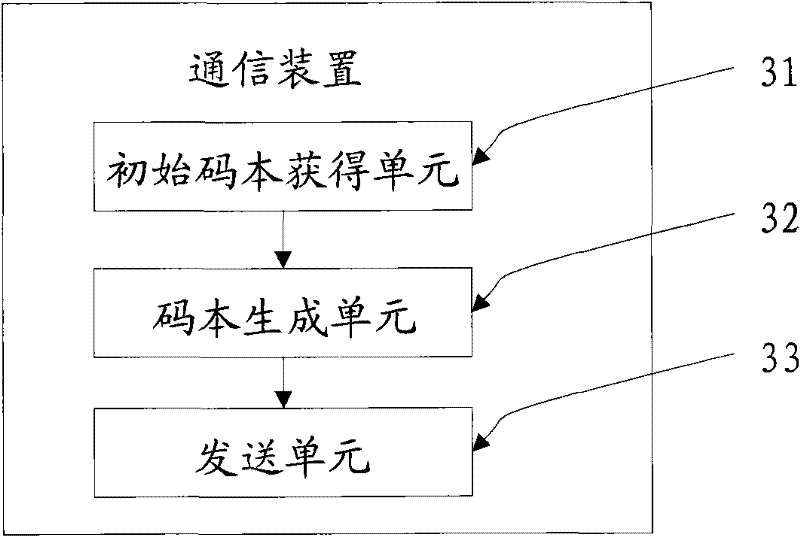

Codebook generation method, device and system for multiple-input multiple-output system

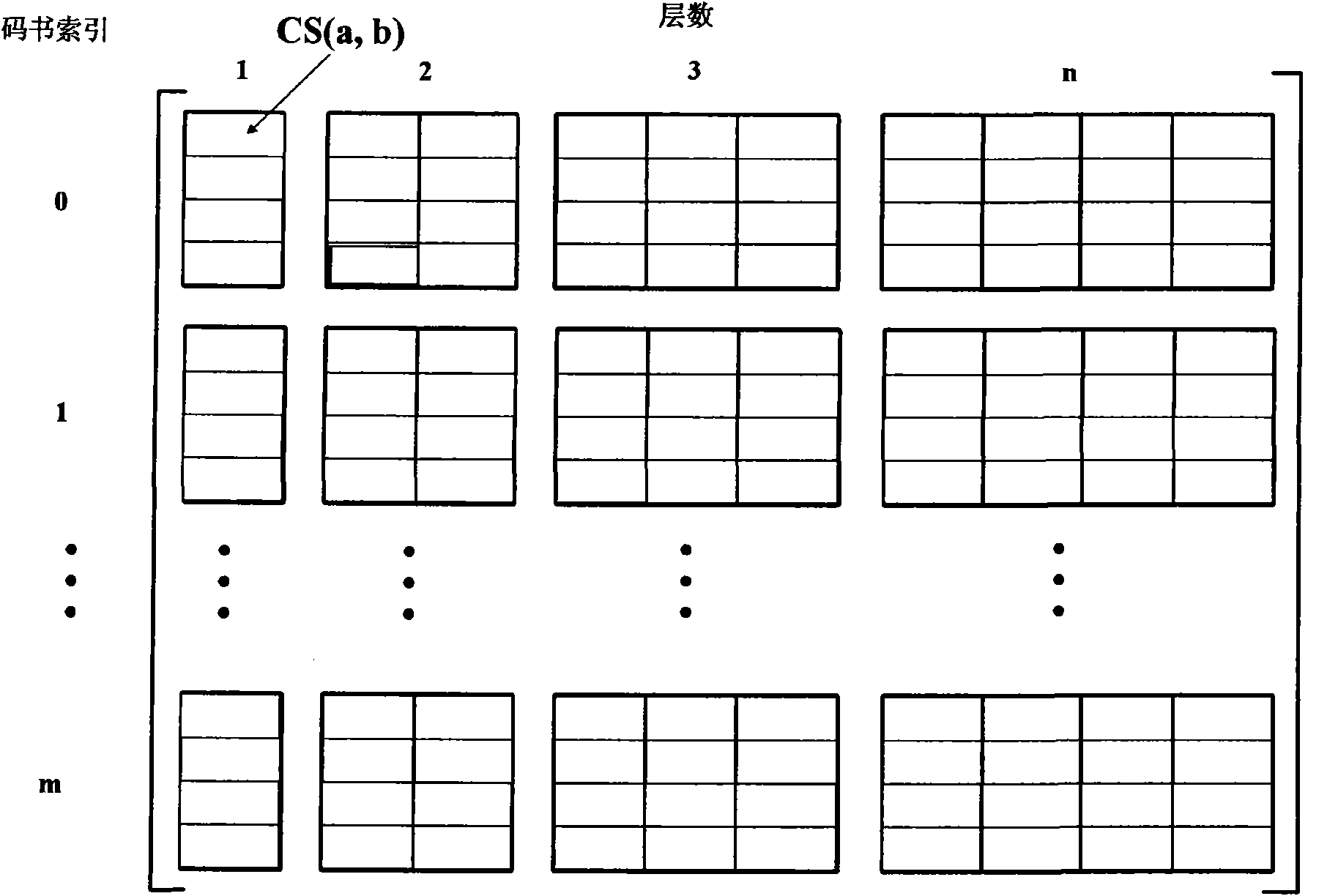

ActiveCN102195691AHigh precisionDoes not increase storage spaceSpatial transmit diversityError prevention/detection by diversity receptionRotation factorPrecoding

The invention discloses a codebook generation method, a codebook generation device and a codebook generation system for a multiple-input multiple-output system, which relate to the technical field of wireless communication. The accuracy of a codebook and precoding performance are improved on the basis of not increasing a conventional codebook memory space of a receiver. The same preset codebook set is configured in two ends communicating with each other in the system. The method comprises the following steps of: obtaining an initial codebook; and when the quality of received signals is lower than preset quality, operating the initial codebook by utilizing a rotation factor and a rotation matrix to generate a new codebook, precoding a data stream by using the new codebook, and when the quality, estimated by utilizing the new codebook, of the signals meets the preset quality, transmitting the rotation factor to communication opposite-ends. The embodiment of the invention is mainly applied in the field of precoding codebook designing.

Owner:HUAWEI TECH CO LTD +1

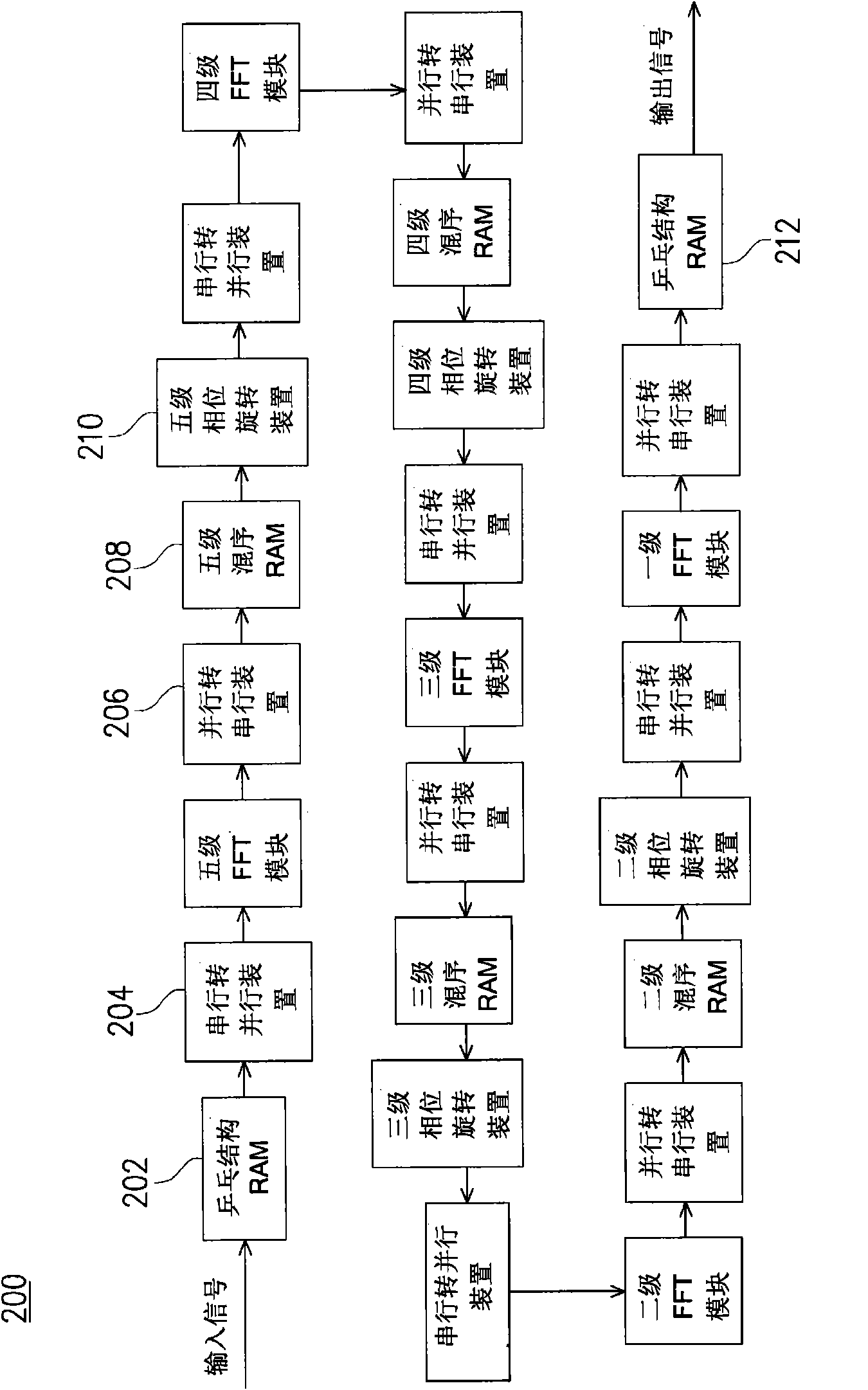

Multi-granularity parallel FFT (Fast Fourier Transform) computing device

ActiveCN102411557AReduce visitsReduce power consumptionComplex mathematical operationsFast Fourier transformRotation factor

The invention discloses a multi-granularity parallel FFT (Fast Fourier Transform) computing device which comprises three memorizers, a butterfly computation device, a state control unit, a data inverted sequence network and a first selector, wherein the three memorizers are multi-granularity parallel memorizers and used for storing butterfly group data and rotation factors corresponding to the butterfly group data, and the butterfly computation device is used for completing the computation of one butterfly group according to the butterfly group data output from the first selector and the rotation factors corresponding to the butterfly group data and being output from one memorizer and writing a computation result to other two memorizers. By using specific read-write granularity, the multi-granularity parallel FFT computing device can be used for reading the butterfly group data and the rotation factors corresponding to the butterfly group data in parallel from the multi-granularity parallel memorizers without generating memorizer conflict and needing additional steps for sequencing read-write data.

Owner:BEIJING SMART LOGIC TECH CO LTD

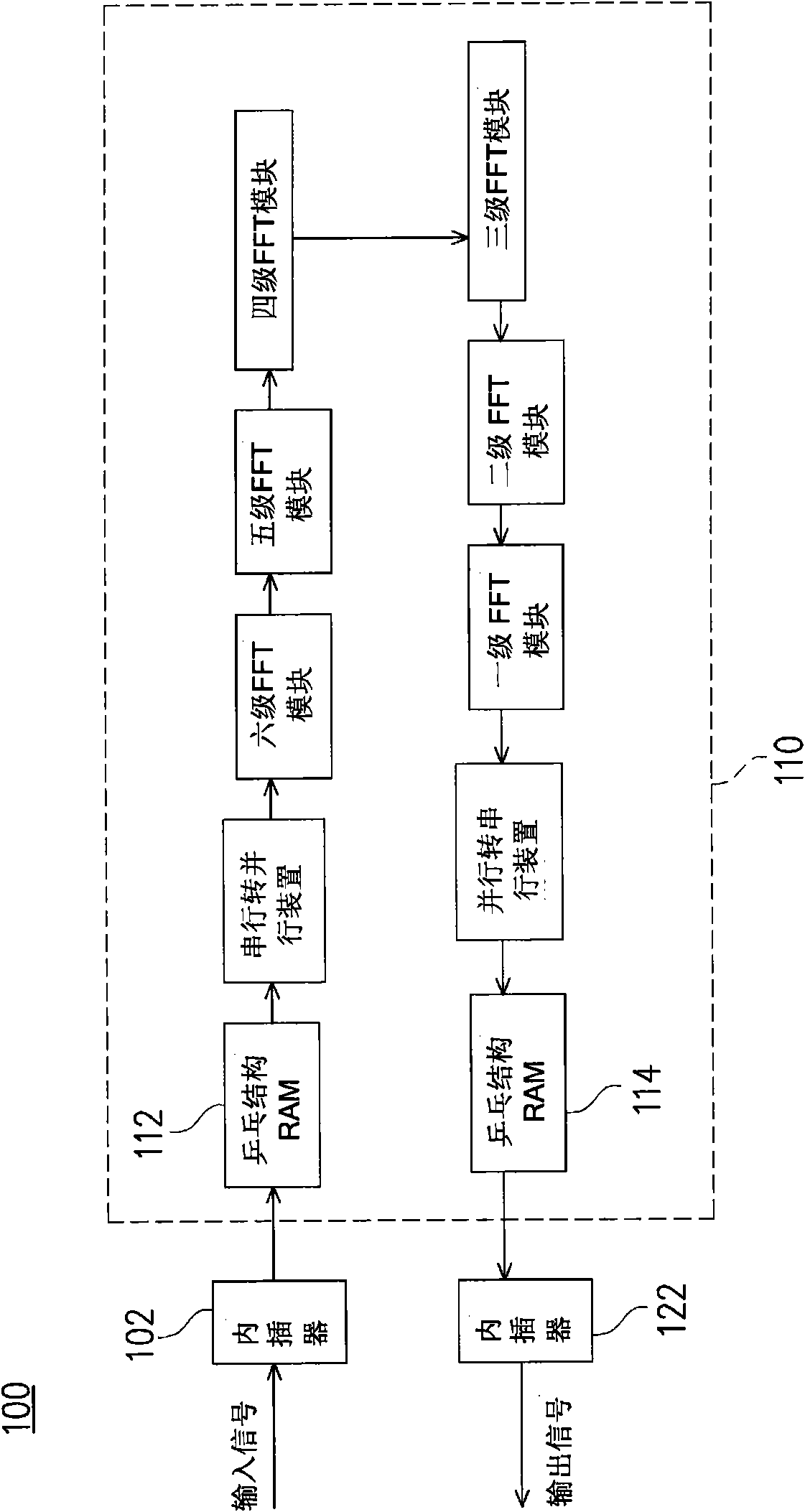

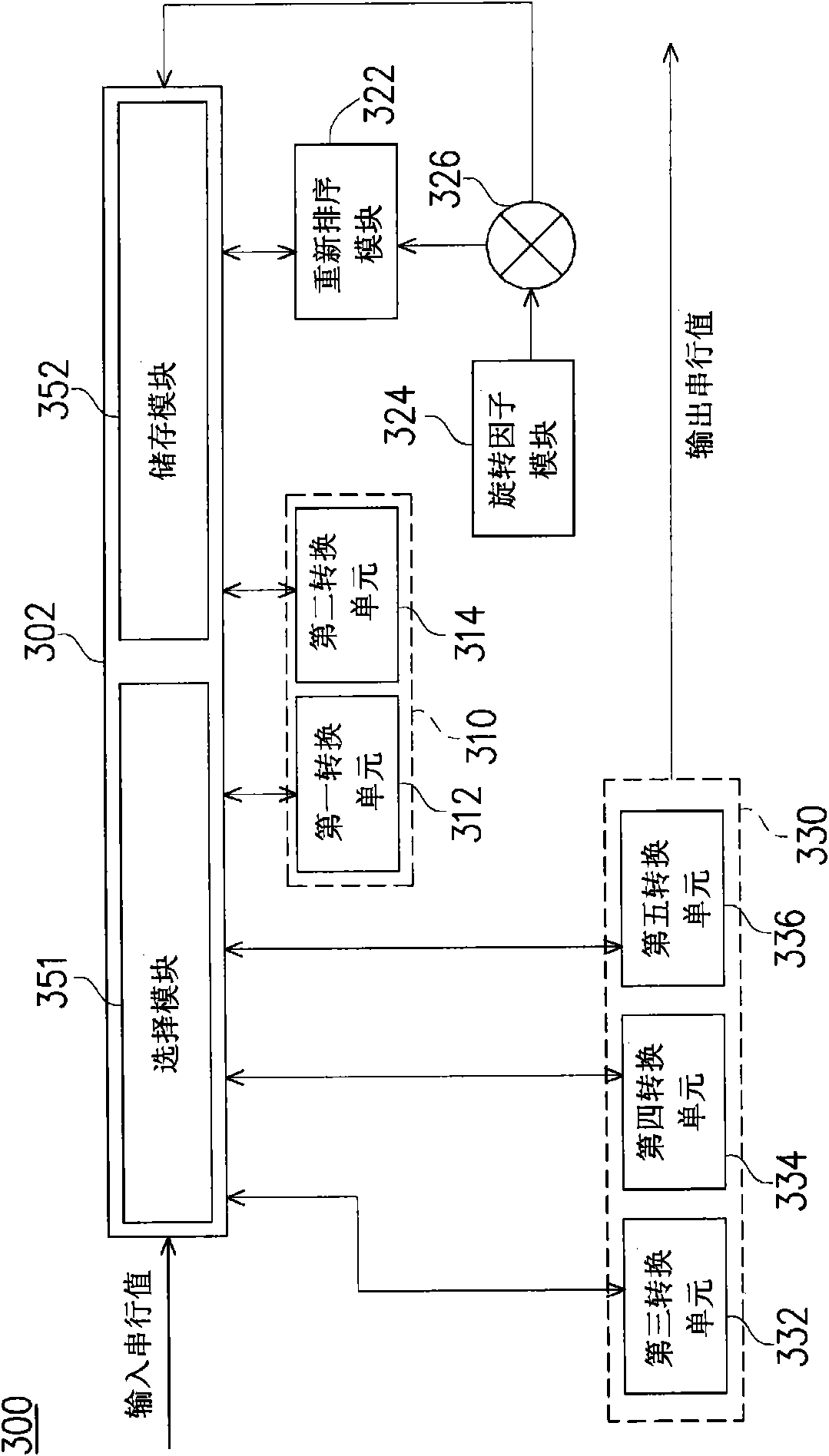

Fast Fourier converter, reverse fast Fourier converter and reverse fast method thereof

ActiveCN102073620ALess processing time delayRealize fully pipelined Fourier transform operationComplex mathematical operationsRotation factorFast methods

The invention discloses a fast Fourier converter, a reverse fast Fourier converter and a reverse fast method thereof. The fast Fourier converter is applied to Fourier conversion operation at the 3,780 point and comprises a sequence inserting device, a first conversion module, a rearranging module, a multiplying unit and a second conversion module, wherein the sequence inserting device receives aninput serial value and provides a plurality of point values to the first conversion module and the second conversion module, according to the requirements of the fast Fourier conversion operation; the first conversion module carries out the fast Fourier conversion operation at the 63 point and outputs the operation result to the sequence inserting device for temporarily storing the result; the rearranging module rearranges the result temporarily stored by the sequence inserting device; the multiplying unit multiplies each rearranged point value by a proper rotation factor; and the second conversion module performs the fast Fourier conversion operation at the 60 point on the multiplying result and generates an output serial value.

Owner:扬智电子科技(中国)有限公司

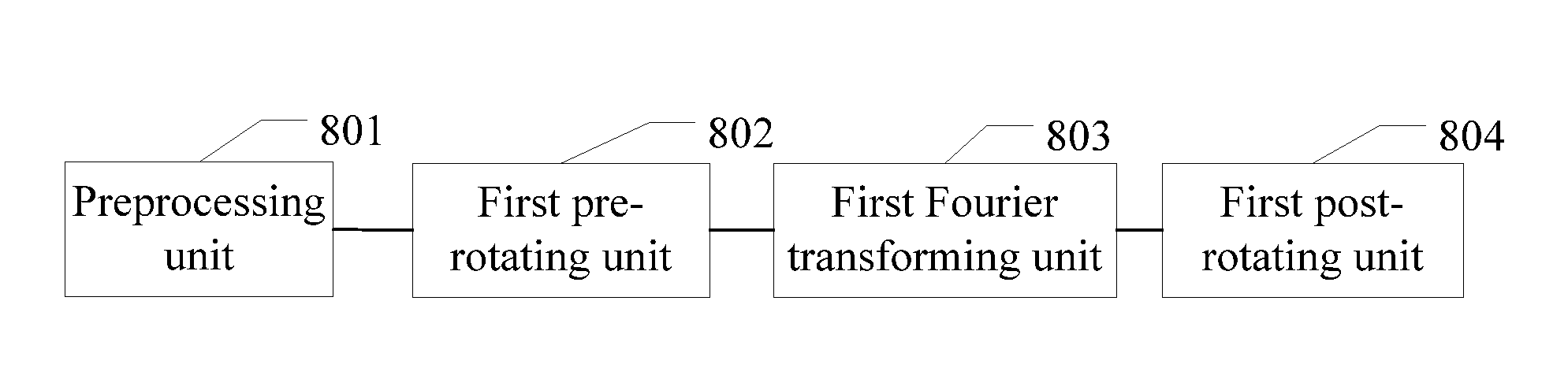

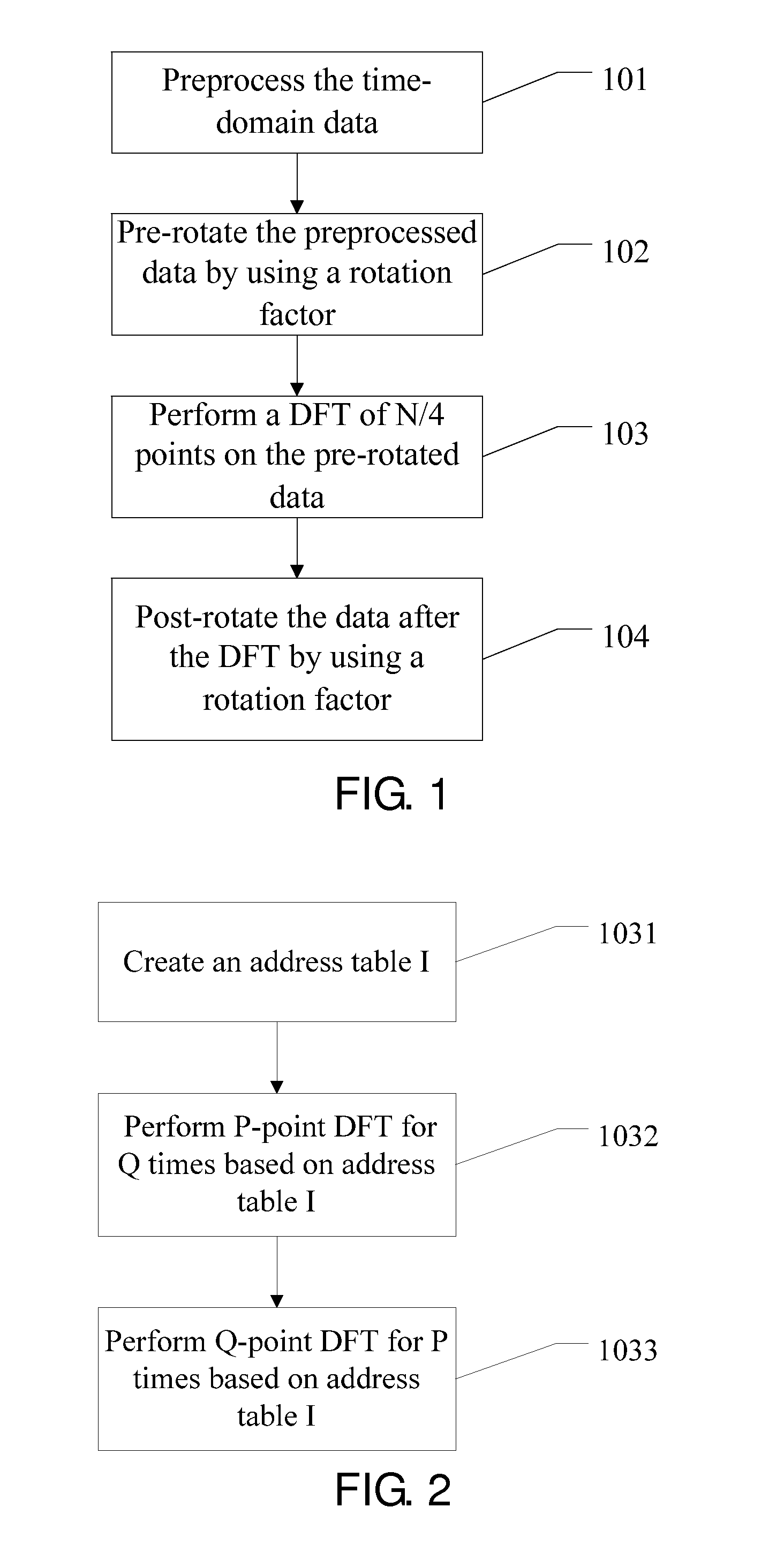

Signal Processing Method and Data Processing Method and Apparatus

ActiveUS20110185001A1Improve efficiencyReduce storageSpeech analysisCode conversionPattern recognitionRotation factor

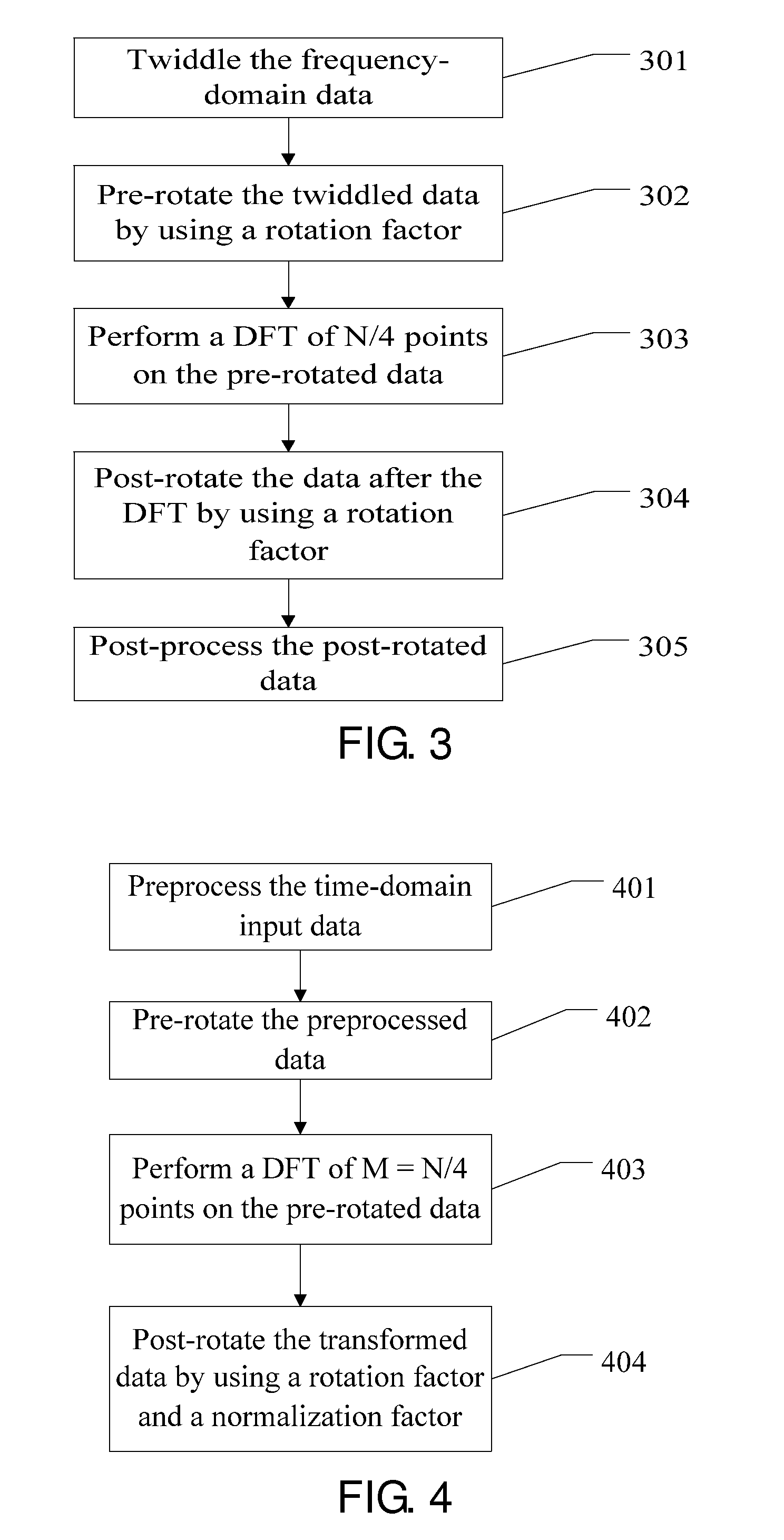

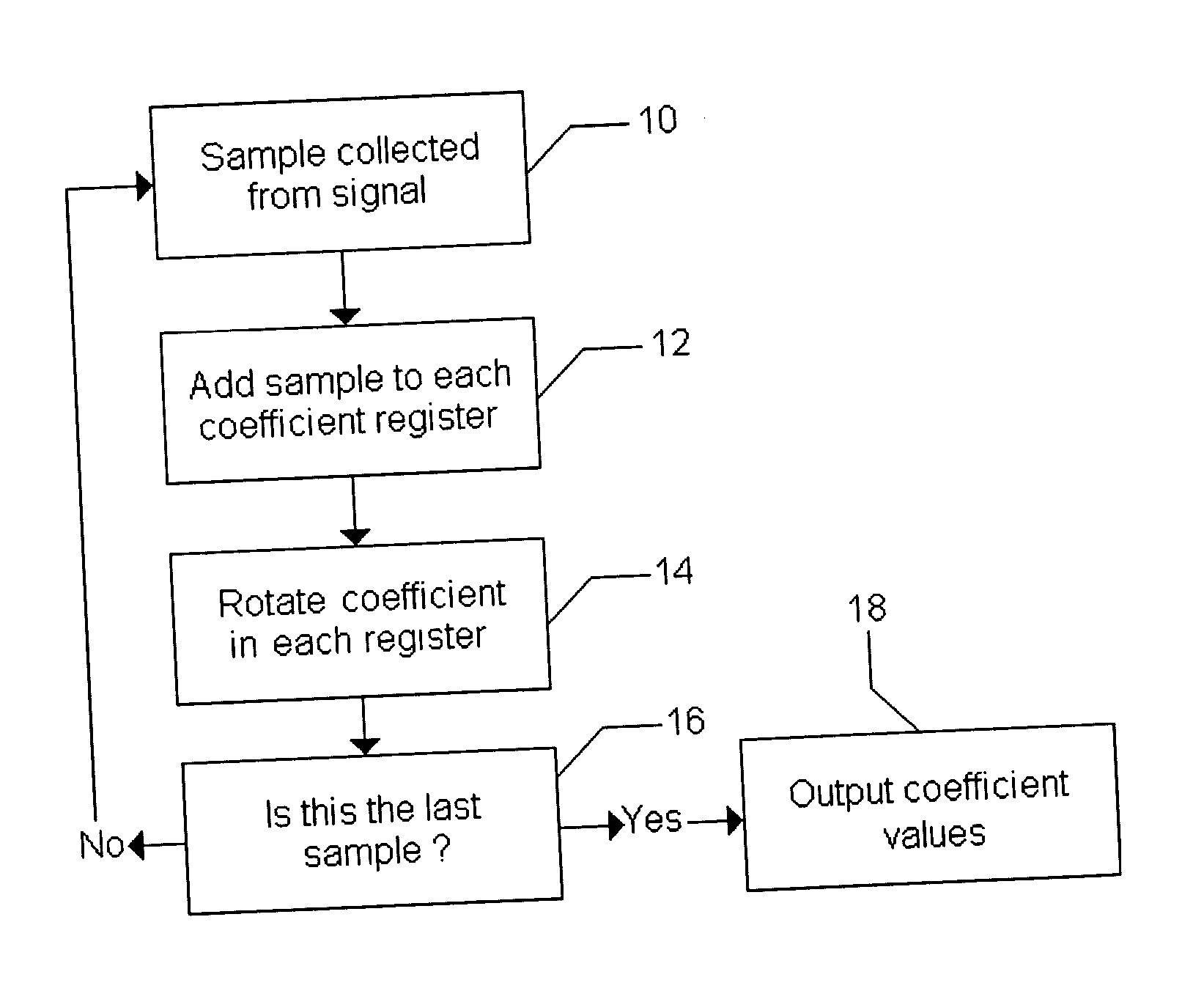

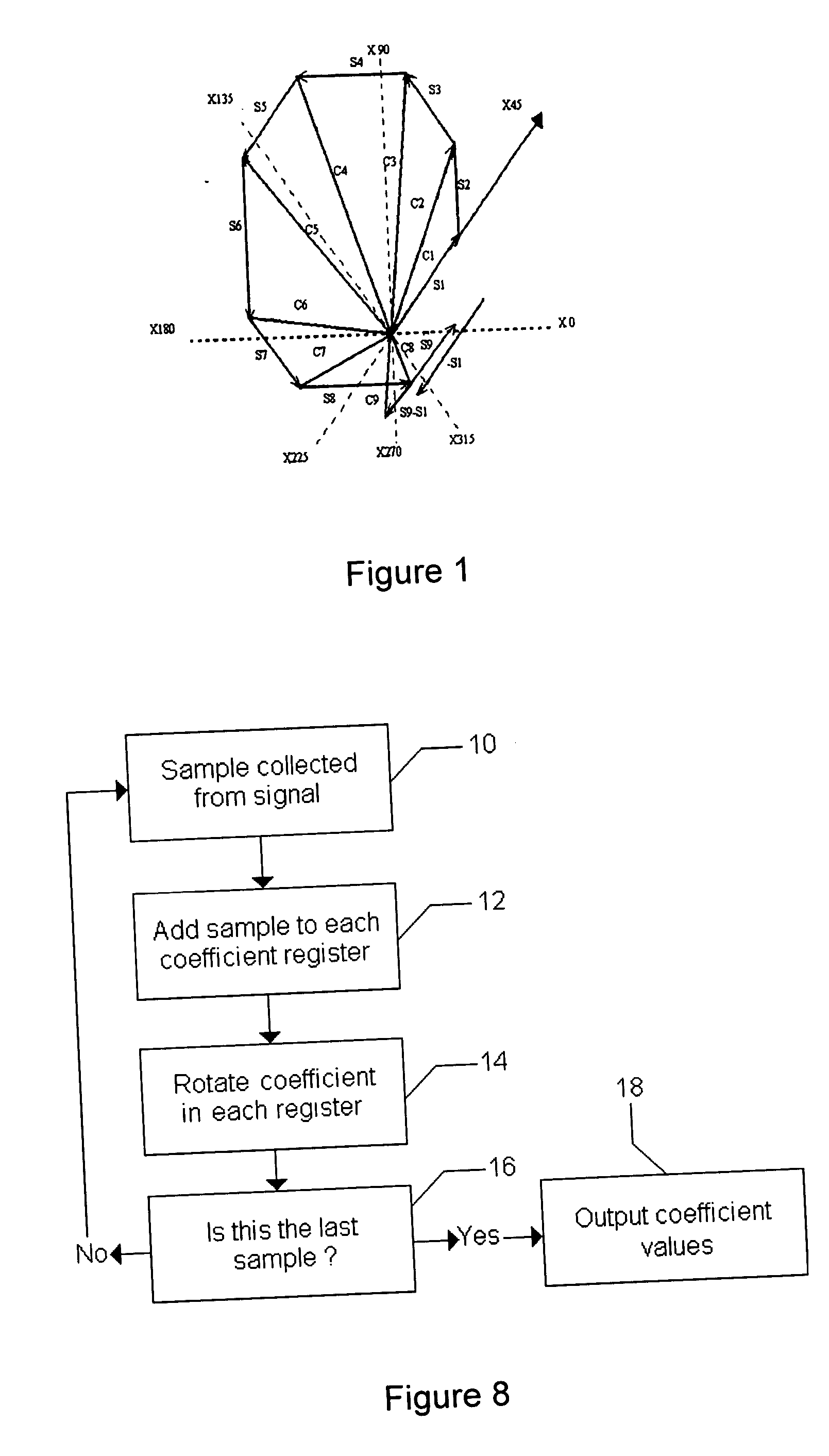

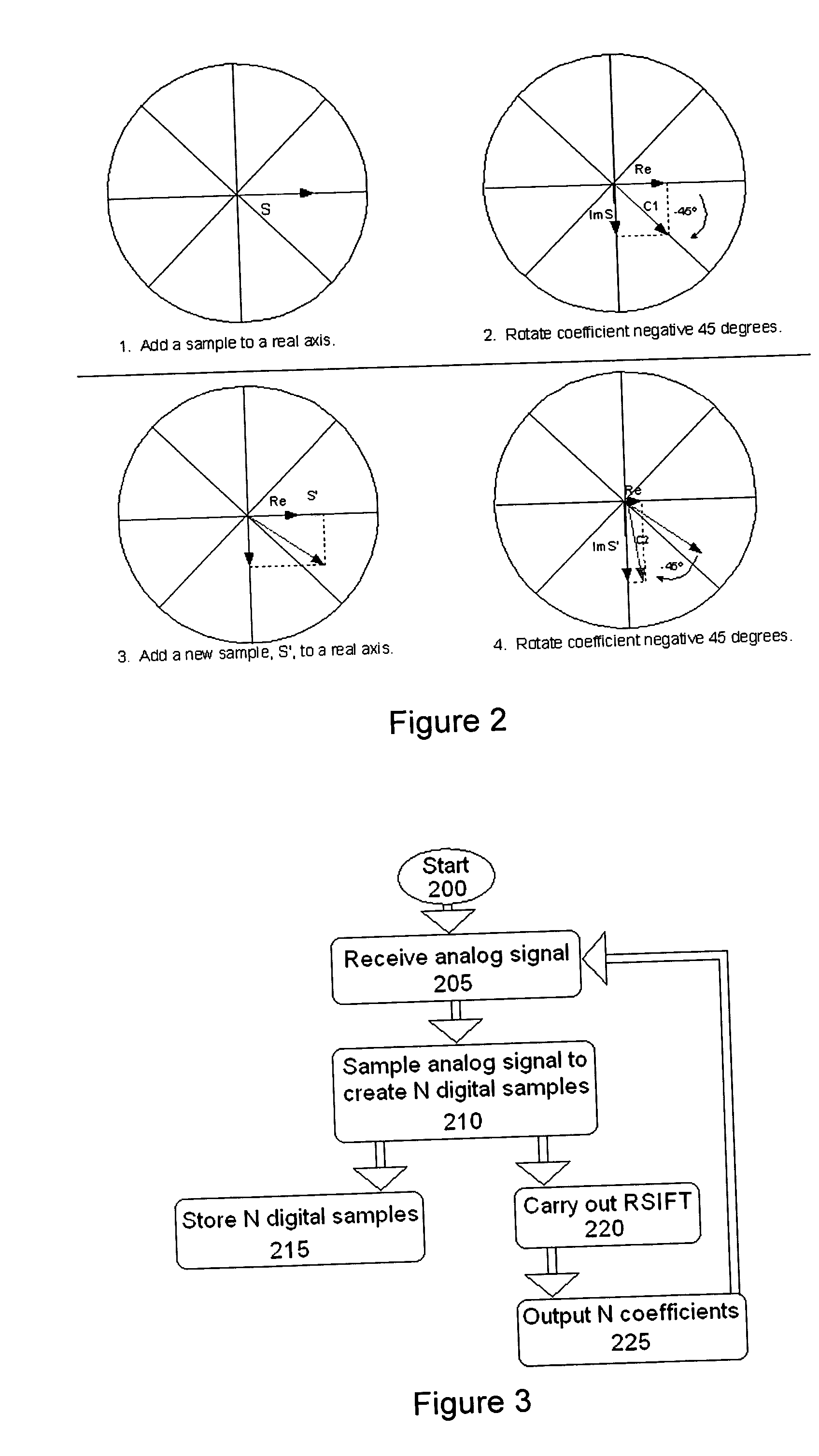

The present invention discloses a signal processing method and a data processing method and apparatus. A time-domain to frequency-domain signal processing method includes: pre-processing time-domain data; pre-rotating the pre-processed data by using a rotation factor a·WNn+0.5; performing a discrete Fourier transform (DFT) of N / 4 points on the pre-rotated data; and post-rotating the data transformed by the DFT by using a rotation factor b·WNn+0.5 to obtain frequency-domain data. A frequency-domain to time-domain signal processing method includes: twiddling frequency-domain data; pre-rotating the twiddled data by using a rotation factor c·WNn+0.5; performing a DFT of N / 4 points on the pre-rotated data; and post-rotating the data transformed by the DFT by using a rotation factor d·WNn+0.5; and post-processing the post-rotated data to obtain time-domain data. The present invention increases the efficiency of signal processing.

Owner:HUAWEI TECH CO LTD

Rotational sliding aperture fourier transform

InactiveUS20050256918A1Digital computer detailsComplex mathematical operationsRotation factorComputer science

Owner:PELTON WALTER E

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com