Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

36results about How to "Thin Package Thickness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

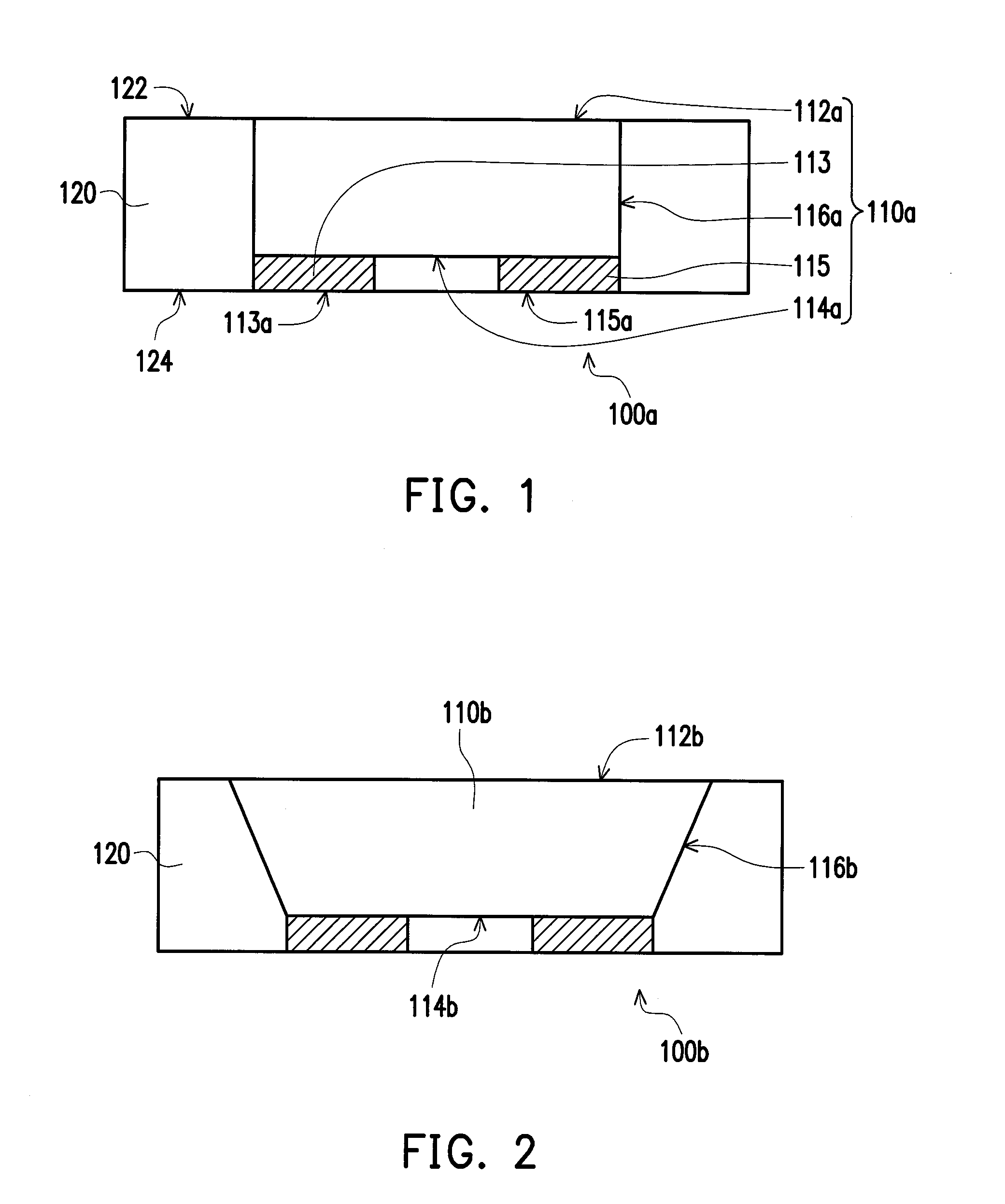

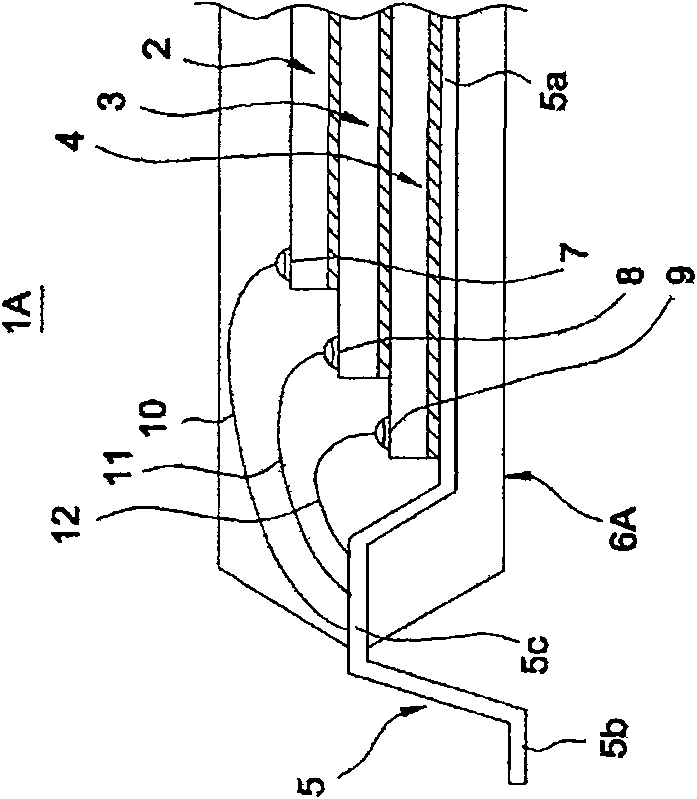

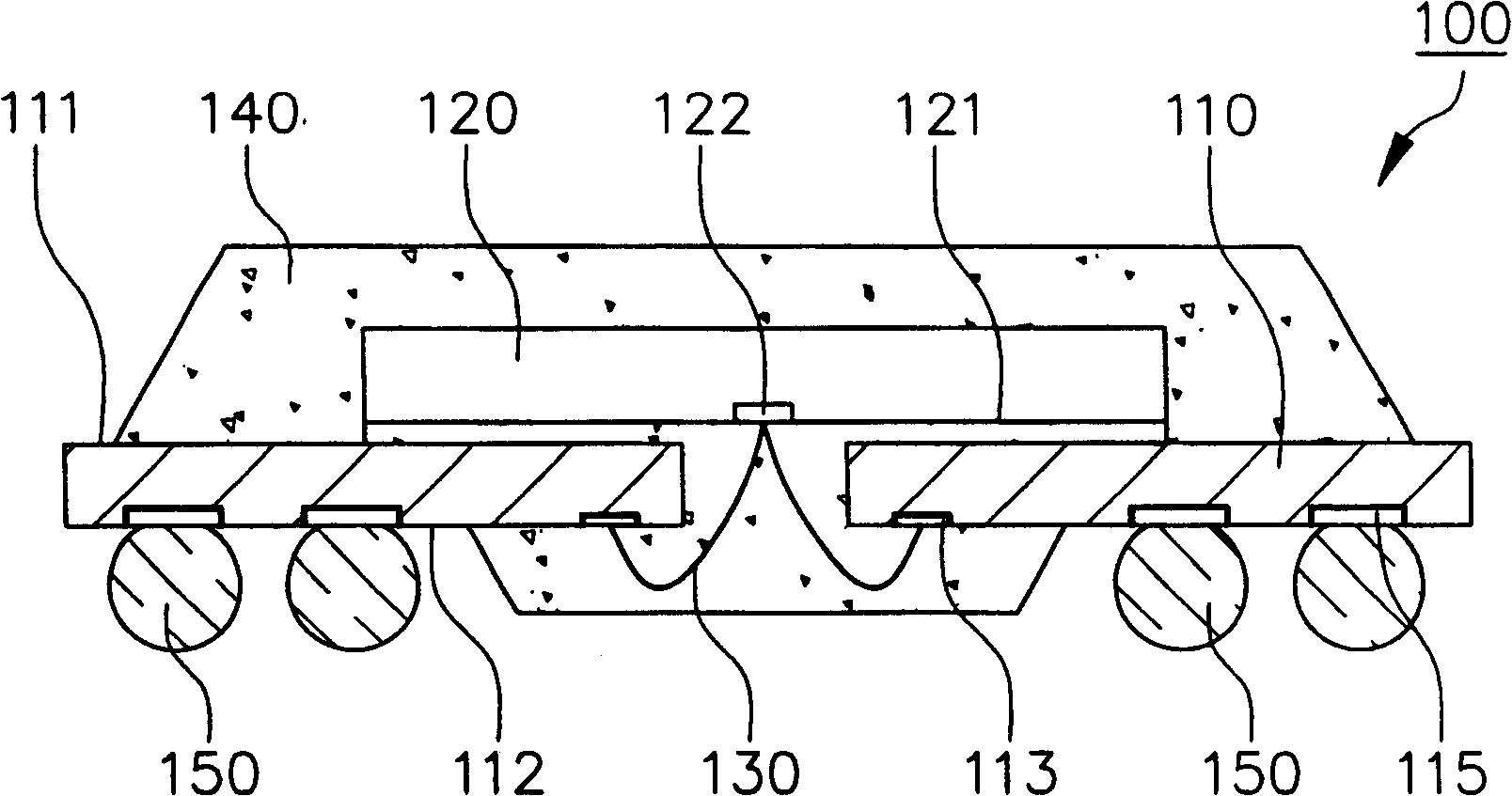

Package process and package structure

InactiveUS20100327465A1Reduce package thicknessAvoid fracturesFinal product manufactureSemiconductor/solid-state device detailsEngineeringSemiconductor

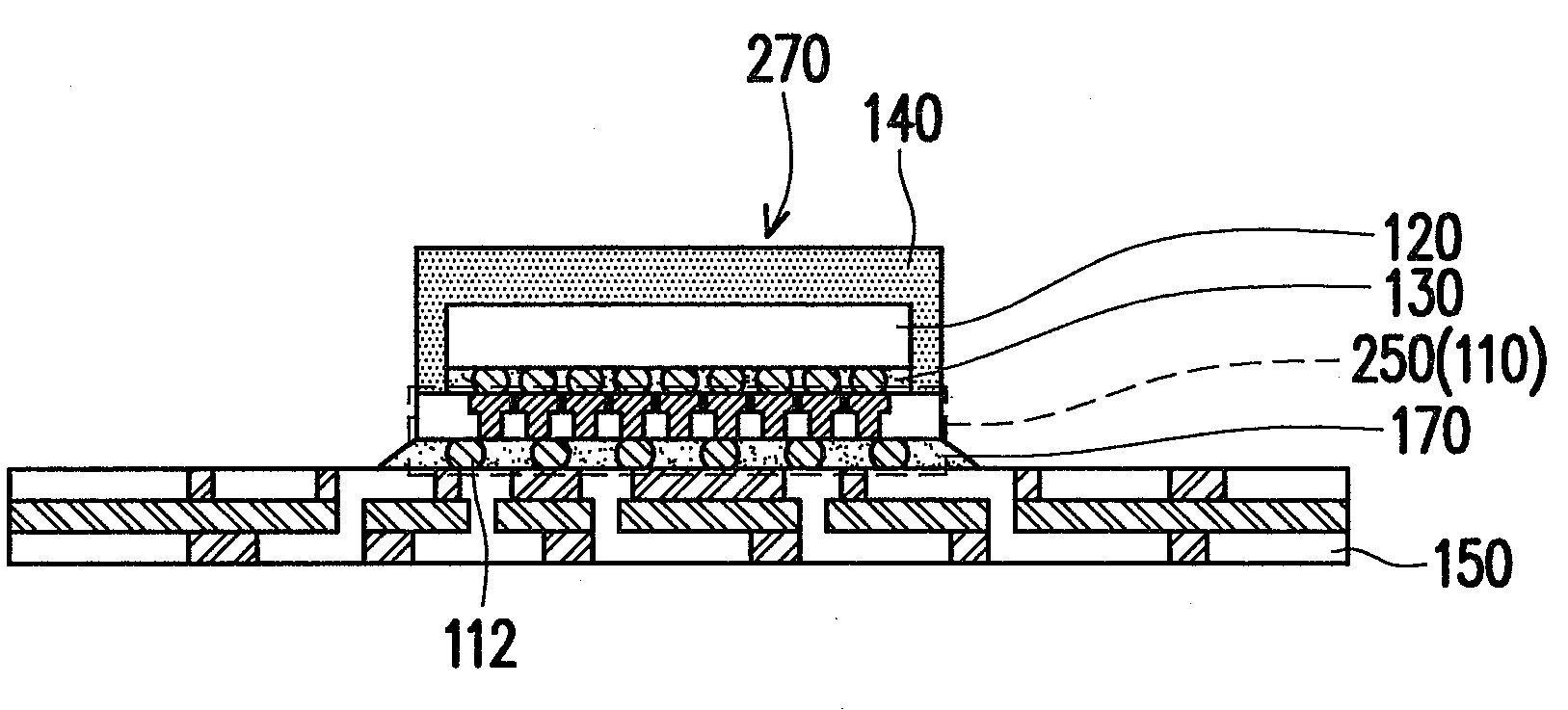

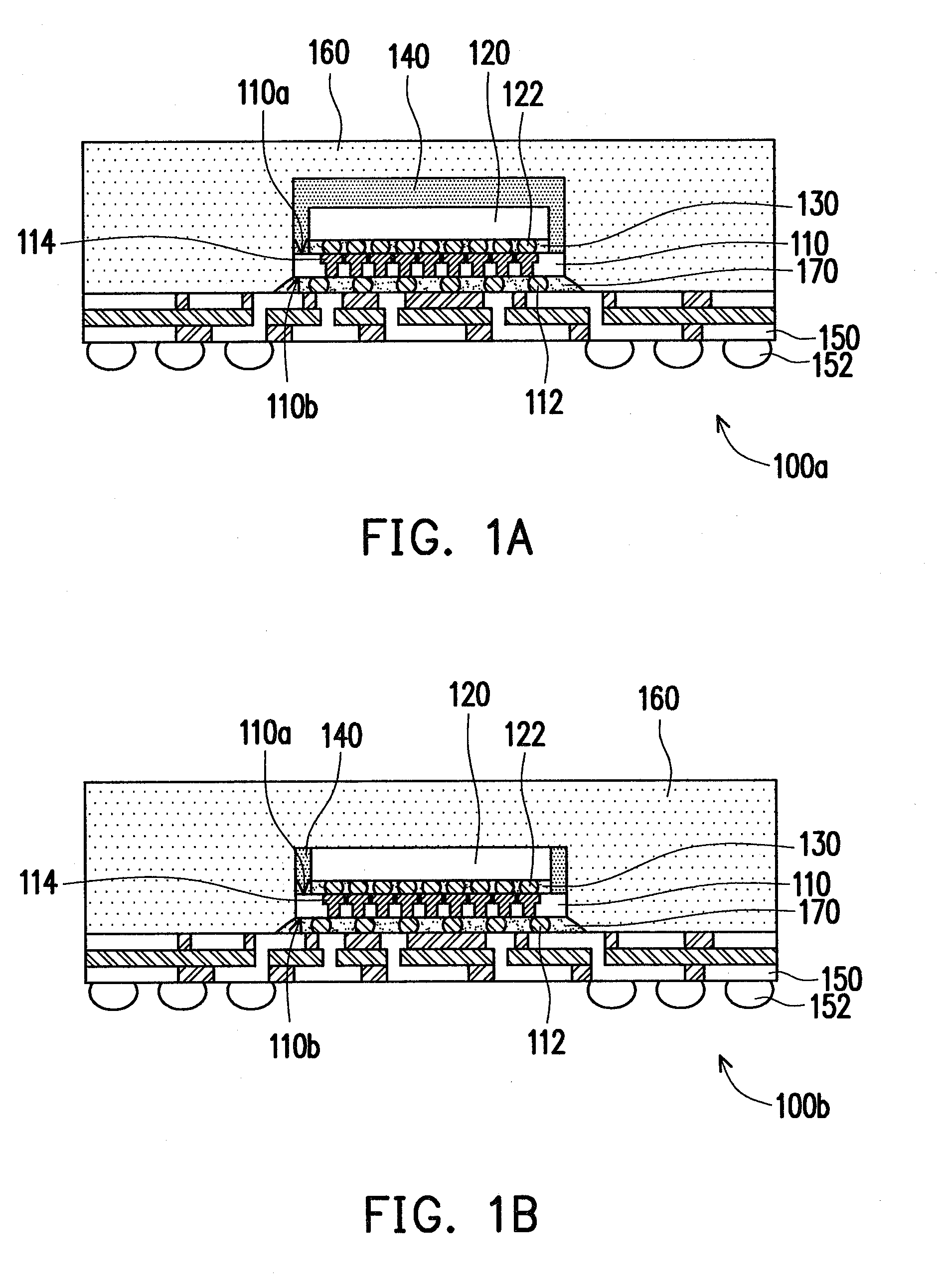

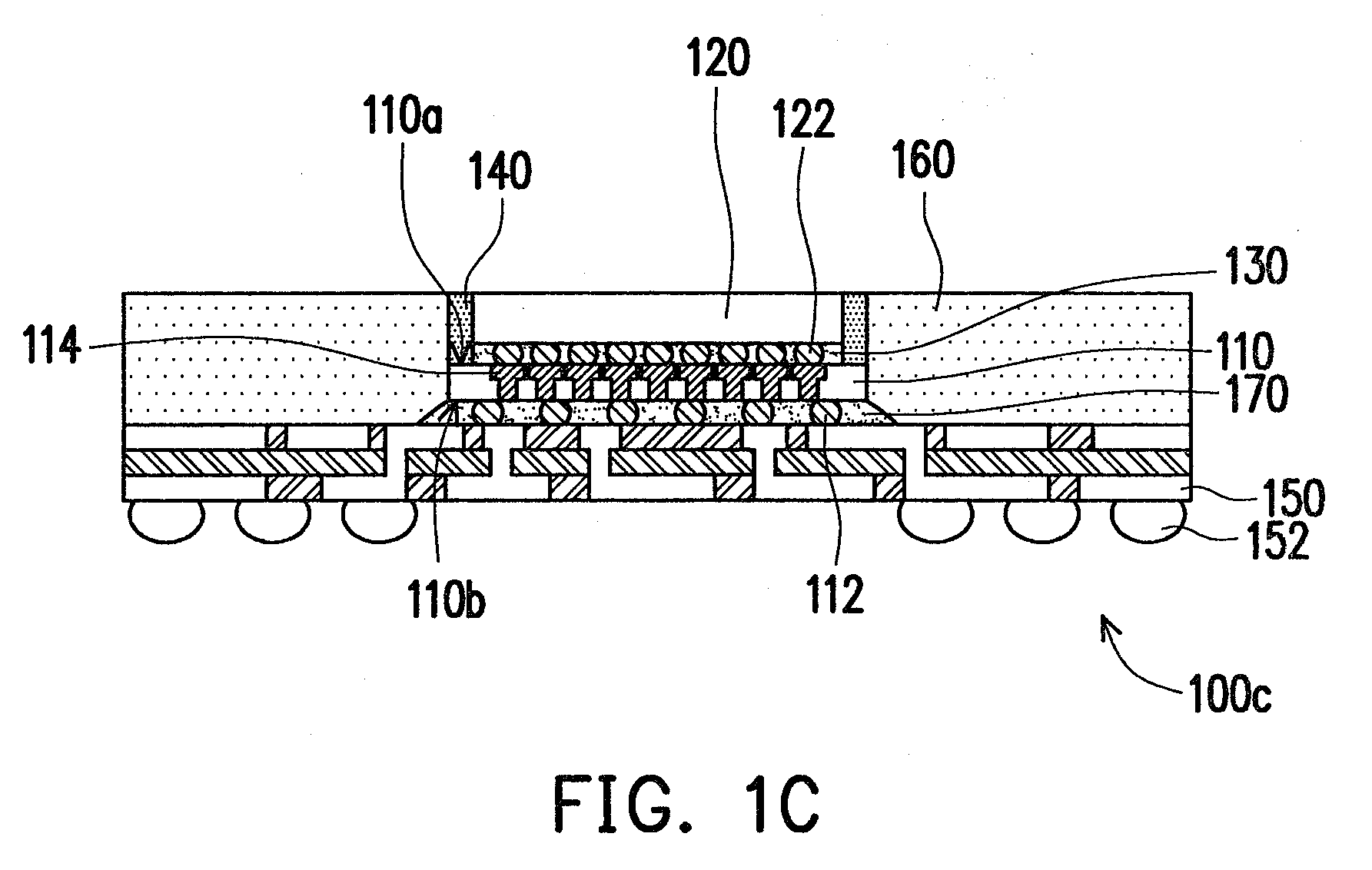

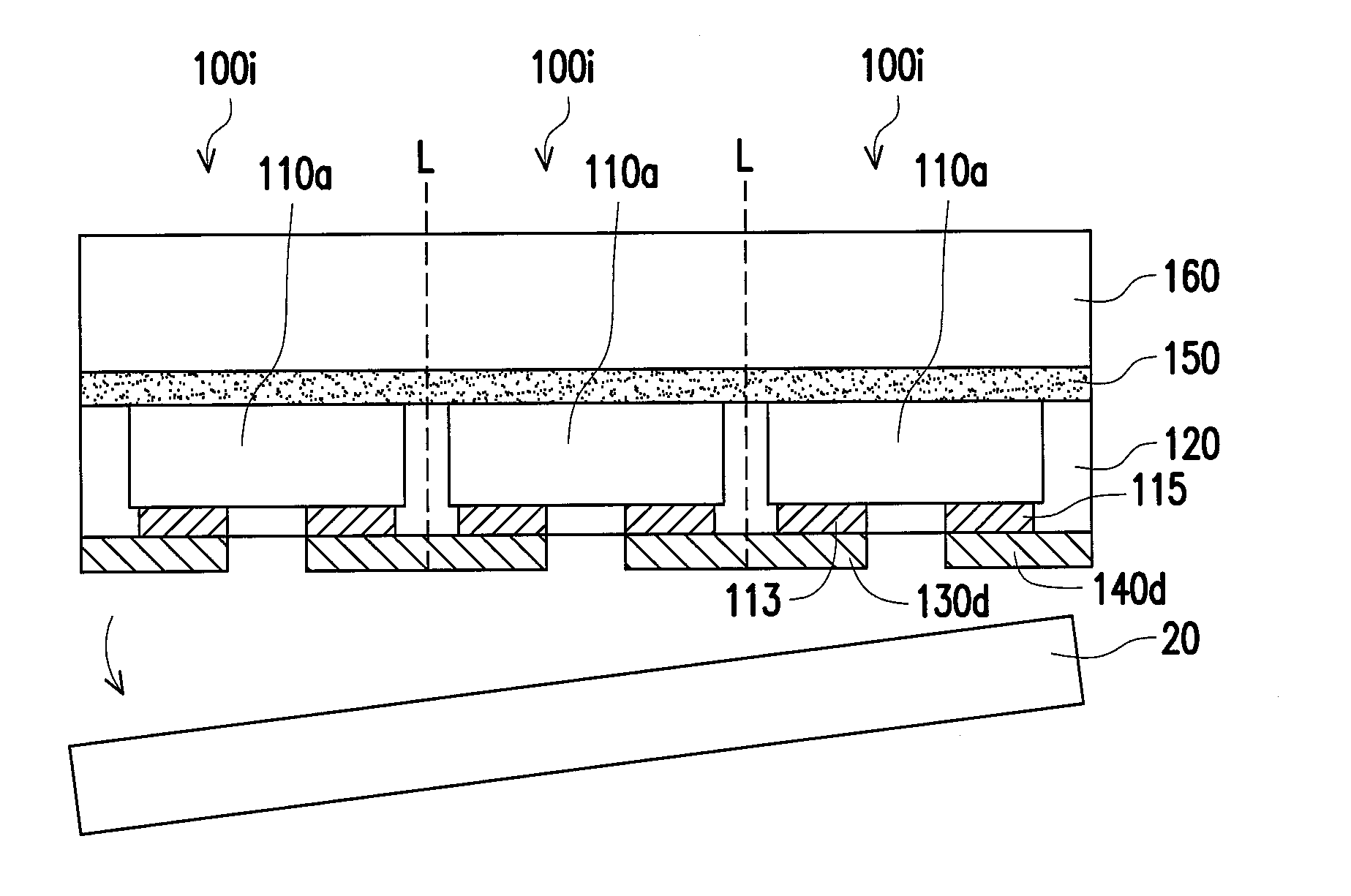

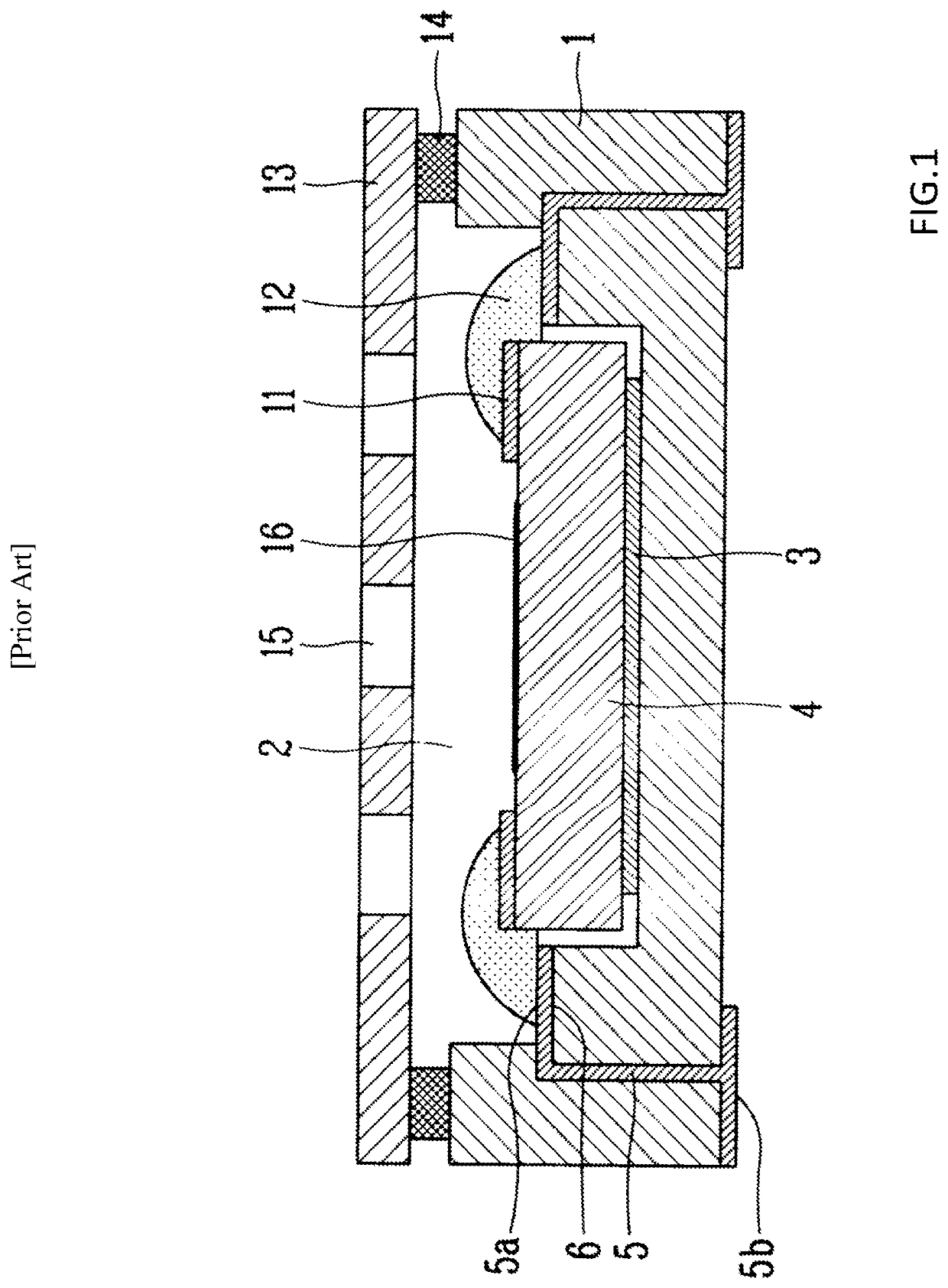

A package process is provided. First, a semiconductor substrate is disposed on a carrier, in which a surface of the carrier has an adhesive layer and the semiconductor substrate is bonded to the carrier by the adhesive layer. Next, a chip is bonded on the semiconductor substrate by flip chip technique and a first underfill is formed between the chip and the semiconductor substrate to encapsulate a plurality of first conductive bumps at the bottom of the chip. Then, a first molding compound is formed on the semiconductor substrate. The first molding compound at least encapsulates the side surface of the chip and the first underfill. Finally, the semiconductor substrate together with the chip and the first molding compound located thereon are separated from the adhesive layer of the carrier to form an array package structure.

Owner:ADVANCED SEMICON ENG INC

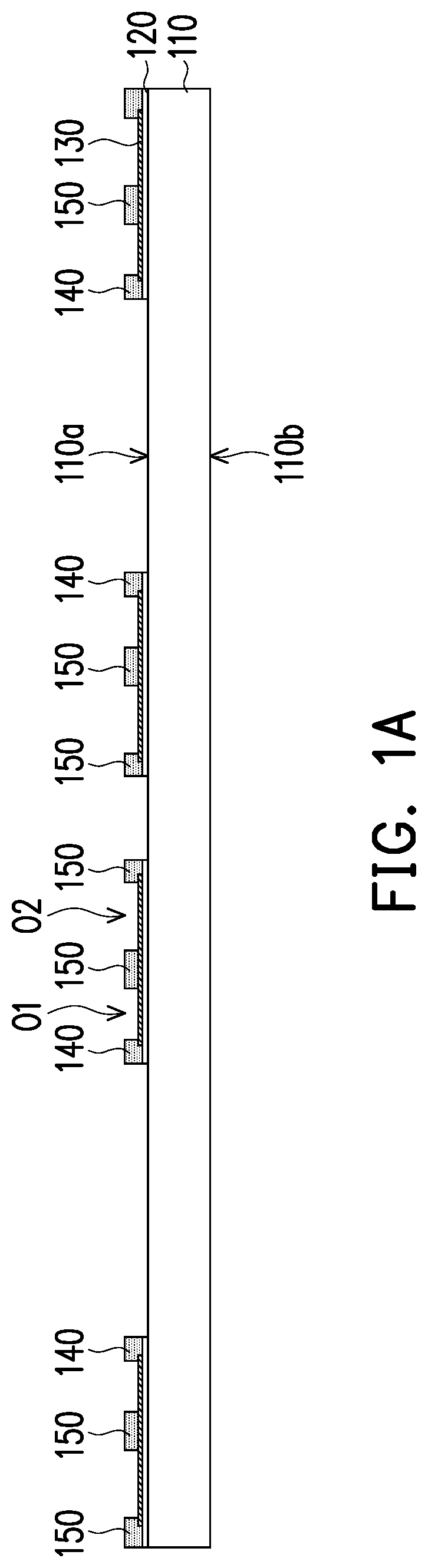

Light emitting device package structure and manufacturing method thereof

InactiveUS20150333227A1Reduce manufacturing costReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturingLight emitting devicePhysics

A light emitting device package structure and a manufacturing method thereof are provided. The light emitting device package structure includes a light emitting device and a protecting element. The light emitting device has an upper surface and a lower surface opposite to each other, a side surface connecting the upper surface and the lower surface and a first electrode pad and a second electrode pad located on the lower surface and separated from each other. The protecting element encapsulates the side surface of the light emitting device and exposes at least portion of the upper surface, at least portion of a first bottom surface of the first electrode pad and at least portion of a second bottom surface of the second electrode pad.

Owner:GENESIS PHOTONICS

Wafer-level packaging method and packaging structure thereof

ActiveCN103117232AAvoid displacementRealize the requirements of light, thin and shortSemiconductor/solid-state device detailsSolid-state devicesHigh densityBiomedical engineering

The invention relates to a wafer-level packaging method and a packaging structure thereof. The packaging method comprises the following steps: providing a wafer which contains chip units; carrying out first protrusion fabrication process on the front face of the wafer; carrying out grooving twice between adjacent protrusions of the adjacent chip units on the front face of the wafer, wherein the width of a first groove is larger than that of a second groove, the depth of the first groove is smaller than that of the second groove and smaller than the thickness of the chip units, and the centers of the second groove and the first groove are on the same straight line which is perpendicular to the surface of the wafer; filling coating materials in the first groove and the second groove; coating the back face of the wafer, wherein the height of the coating materials is higher than the back surface of the wafer; and carrying out simplified cutting. Through a wafer protrusion technology, wafer-level partial grooving and wafer-level coating material filling, high-density input / output ports of products and high reliability are achieved, the products are light, thin and short, productivity is high, and cost is low.

Owner:MEMSIC SEMICON WUXI

Manufacturing method for embedded type semiconductor package piece of element

ActiveCN103489796AImprove production process yieldReduce difficultySemiconductor/solid-state device manufacturingResistInsulation layer

The invention discloses a manufacturing method for an embedded type semiconductor package piece of an element. A metal substrate is provided. A metal layer is formed on the metal substrate and coats the metal substrate. The metal layer is provided with the upper surface, the lower surface and the first side surface, wherein the upper surface and the lower surface are mutually opposite and are connected through the first side surface. A patterning photo-resist layer is formed on the metal layer, and a part of the upper surface and a part of the lower surface are exposed out of the patterning photo-resist layer. A plurality of connecting pads are formed on the portion, exposed out of the patterning photo-resist layer, of the upper surface and the portion, exposed out of the patterning photo-resist layer, of the lower surface, and the patterning photo-resist layer coats second side surfaces of the connecting pads. The second side surfaces of the connecting pads are exposed after the patterning photo-resist layer is removed. A plurality of electronic elements are arranged on the connecting pads. An insulation layer is pressed on the metal layer in a combination mode and coats the electronic elements, the connecting pads and a part of the metal layer.

Owner:TRIPOD WUXI ELECTRONICS

Wafer-level packaging method and packaging structure thereof

InactiveCN103117231AAvoid displacementRealize the requirements of light, thin and shortSemiconductor/solid-state device detailsSolid-state devicesHigh densityBiomedical engineering

The invention relates to a wafer-level packaging method and a packaging structure thereof. The packaging method comprises the following steps: providing a wafer which contains chip units; carrying out protrusion fabrication process on the front face of the wafer; forming a first groove between adjacent protrusions of the adjacent chip units on the front face of the wafer; filling coating materials in the first groove, wherein after the filling, the coating materials in the first groove are aligned with the surfaces of the chip units; forming a second groove in the back face of the wafer, wherein the depth of the second groove is equal to the difference between the thickness of the wafer and the thickness of the coating materials in the first groove; filling coating materials in the second groove, wherein after the filling, the height of the coating materials is higher than the back surface of the wafer; and carrying out simplified cutting. Through a wafer protrusion technology, wafer-level partial grooving and wafer-level coating material filling, high-density input / output ports of products and high reliability are achieved, the products are light, thin and short, productivity is high, and cost is low.

Owner:MEMSIC SEMICON WUXI

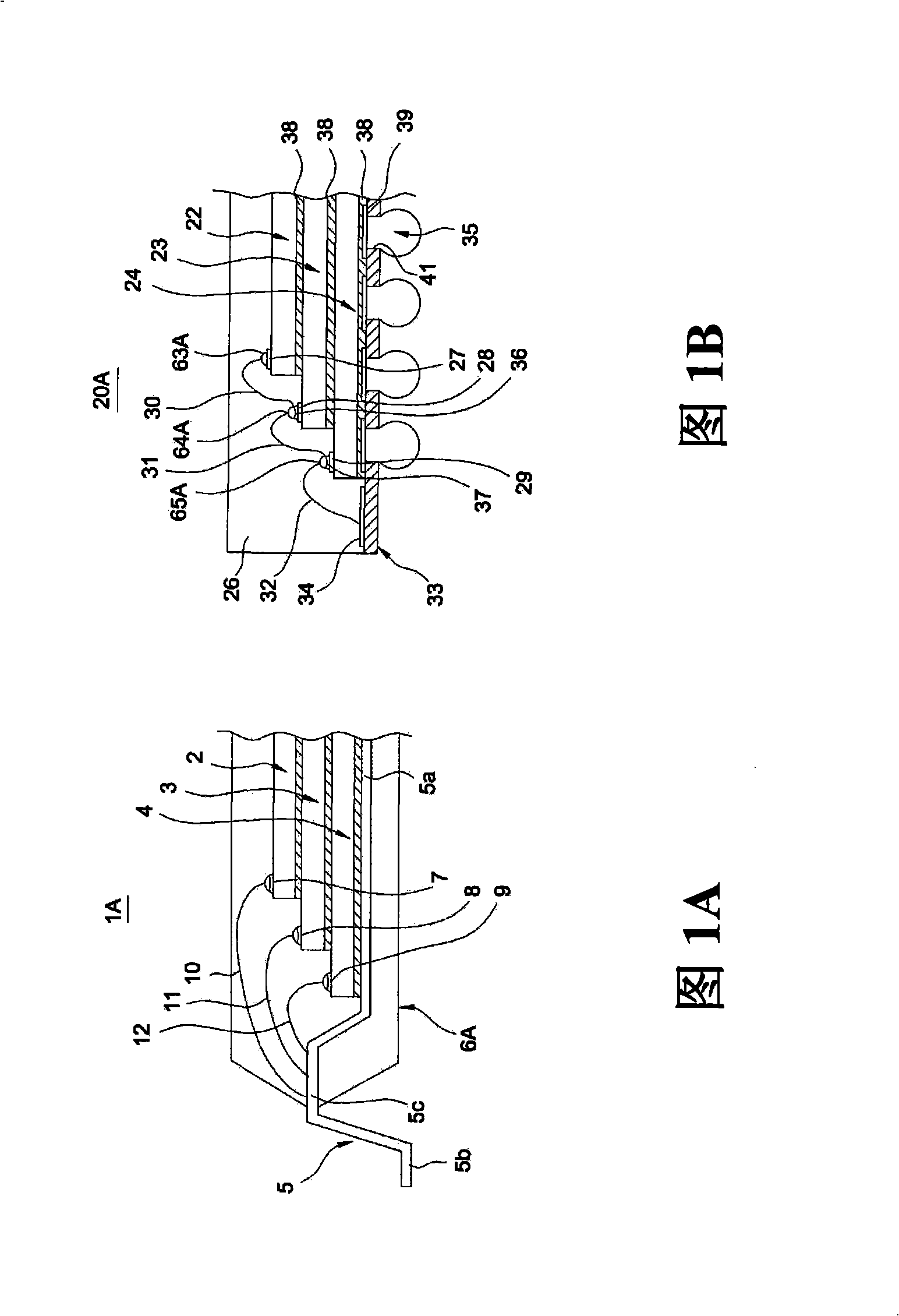

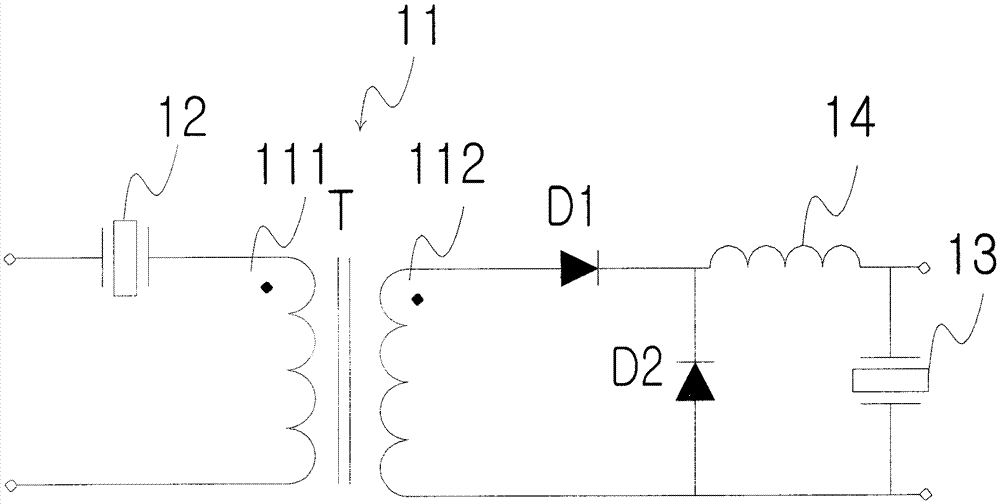

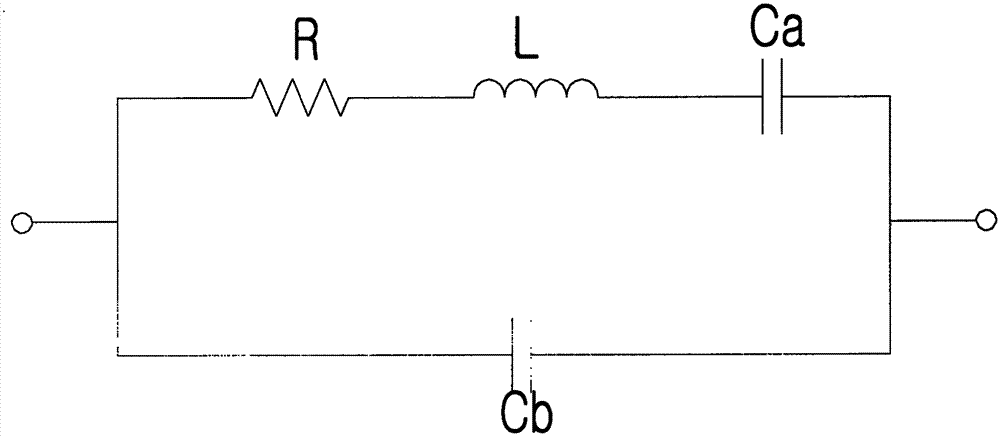

High-power output piezoelectric power converter

ActiveCN101938220AIncrease output powerAchieve the effect of high power outputAc-dc conversionPower factorResonance

The invention discloses a high-power output piezoelectric power converter, applying to the AC-DC or AC-AC piezoelectric power converter. In the invention, at least one third piezoelectric component replaces a capacitor arranged between a rectifying circuit and a power factor correcting circuit; at least one first piezoelectric component replaces a capacitor arranged in a resonance circuit; and at least one second piezoelectric component replaces a capacitor arranged on an output terminal of the rectifying circuit. The piezoelectric components have the advantages of small leakage current, high pressure resistance, good conversion efficiency, small volume and the like, thus reducing the danger of low pressure resistance and ignition owing to overheat in the common capacitor.

Owner:MIDAS WEI TRADING +1

High-power output piezoelectric power converter

ActiveCN101938220BIncrease output powerAchieve the effect of high power outputAc-dc conversionPower factorResonance

The invention discloses a high-power output piezoelectric power converter, applying to the AC-DC or AC-AC piezoelectric power converter. In the invention, at least one third piezoelectric component replaces a capacitor arranged between a rectifying circuit and a power factor correcting circuit; at least one first piezoelectric component replaces a capacitor arranged in a resonance circuit; and at least one second piezoelectric component replaces a capacitor arranged on an output terminal of the rectifying circuit. The piezoelectric components have the advantages of small leakage current, high pressure resistance, good conversion efficiency, small volume and the like, thus reducing the danger of low pressure resistance and ignition owing to overheat in the common capacitor.

Owner:MIDAS WEI TRADING +1

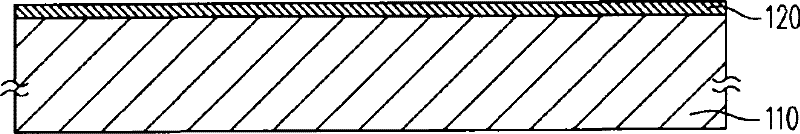

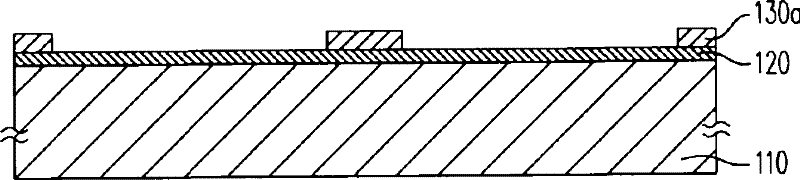

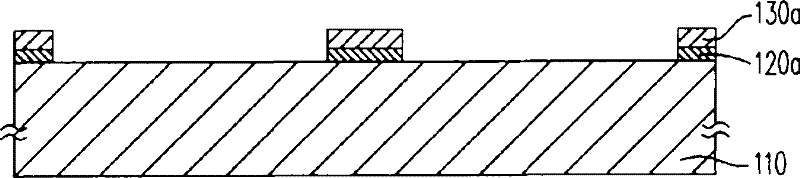

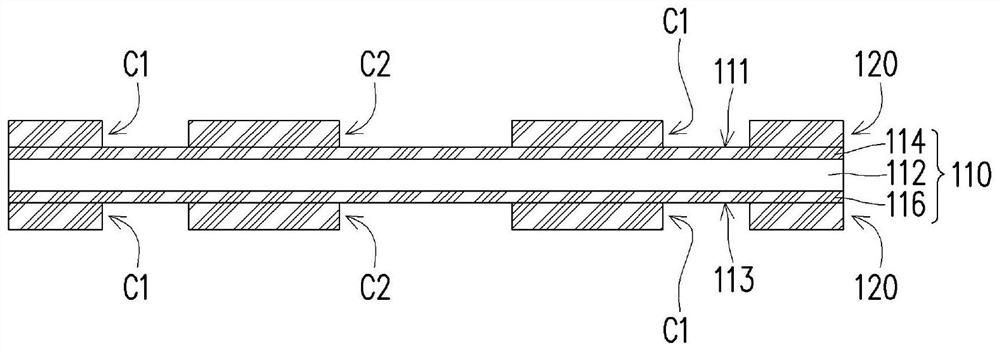

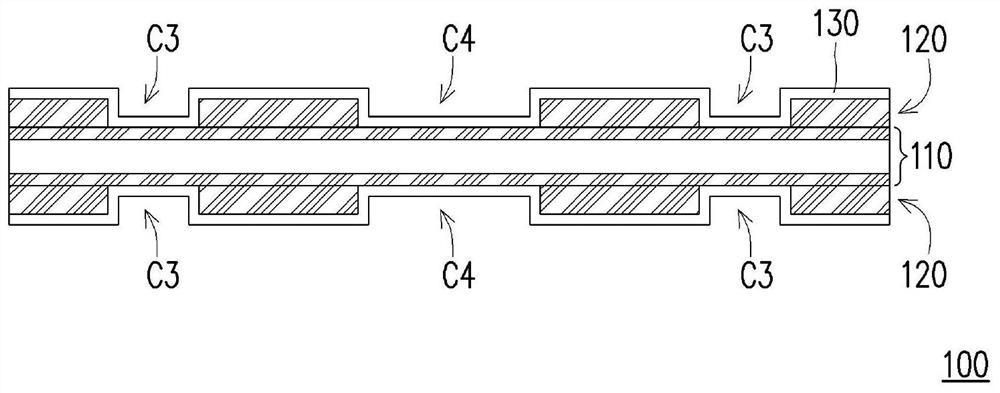

Packaging substrate and manufacturing method thereof

ActiveCN104576402AThin Package ThicknessShorten manufacturing process timePrinted circuit detailsSemiconductor/solid-state device detailsMetallurgyMetal foil

The invention discloses a manufacturing method for a packaging substrate. The method comprises the following steps: jointing two substrate metal layers; pressing two supporting layers on the substrate metal layers respectively; arranging two release metal films on the supporting layers respectively, wherein each release metal film comprises a first metal foil layer and a second metal foil layer which can be separated from each other; forming two first patterned metal layers on the release metal films respectively, wherein each first patterned metal layer comprises a connecting pad pattern; forming two dielectric layers on the release metal films respectively and covering the corresponding first patterned metal layers, wherein a conducting hole is formed in each dielectric layer and the dielectric layers are connected with the corresponding connecting pad patterns respectively; forming two second patterned metal layers on the dielectric layers respectively, wherein the second patterned metal layers at least cover the upper surfaces of the corresponding conducting holes; separating the substrate metal layers to form two packaging substrates independent of each other.

Owner:SUBTRON TECH

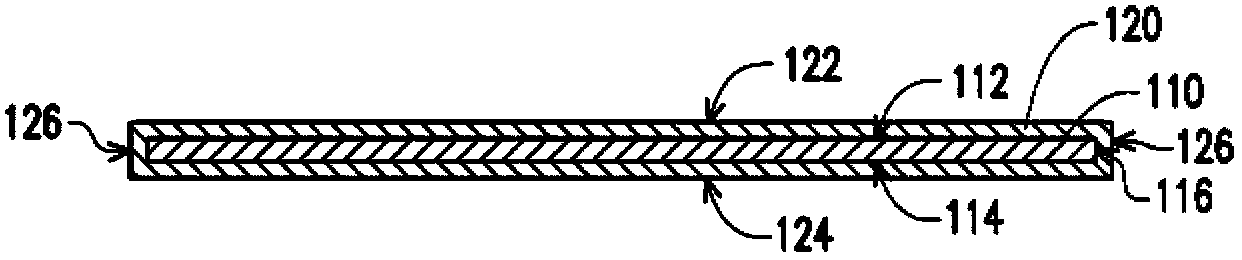

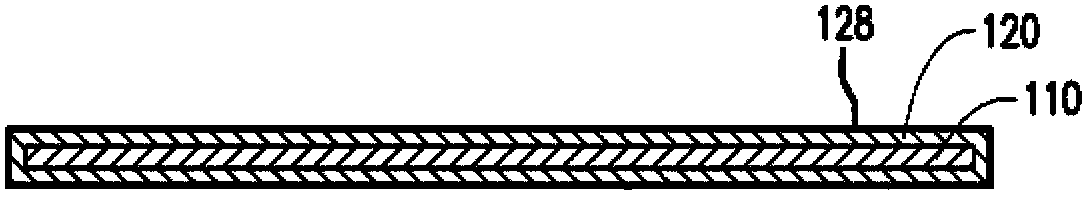

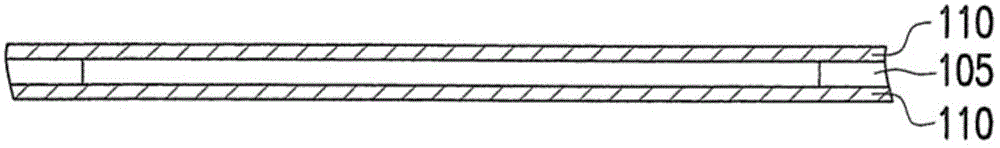

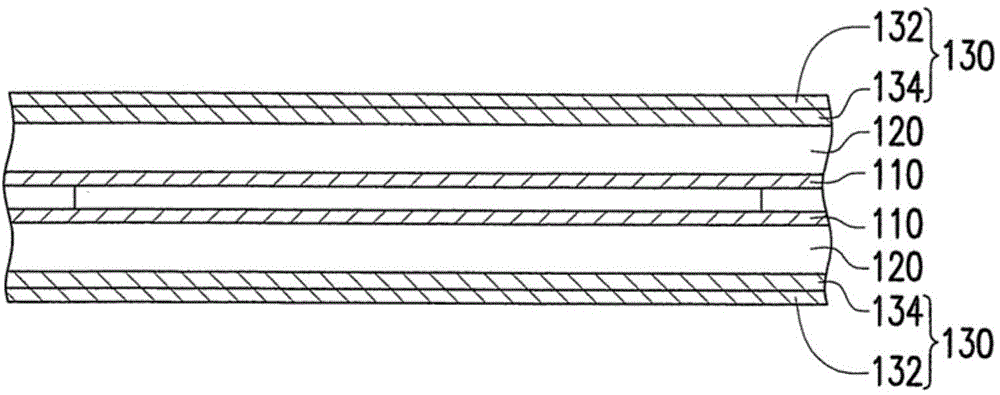

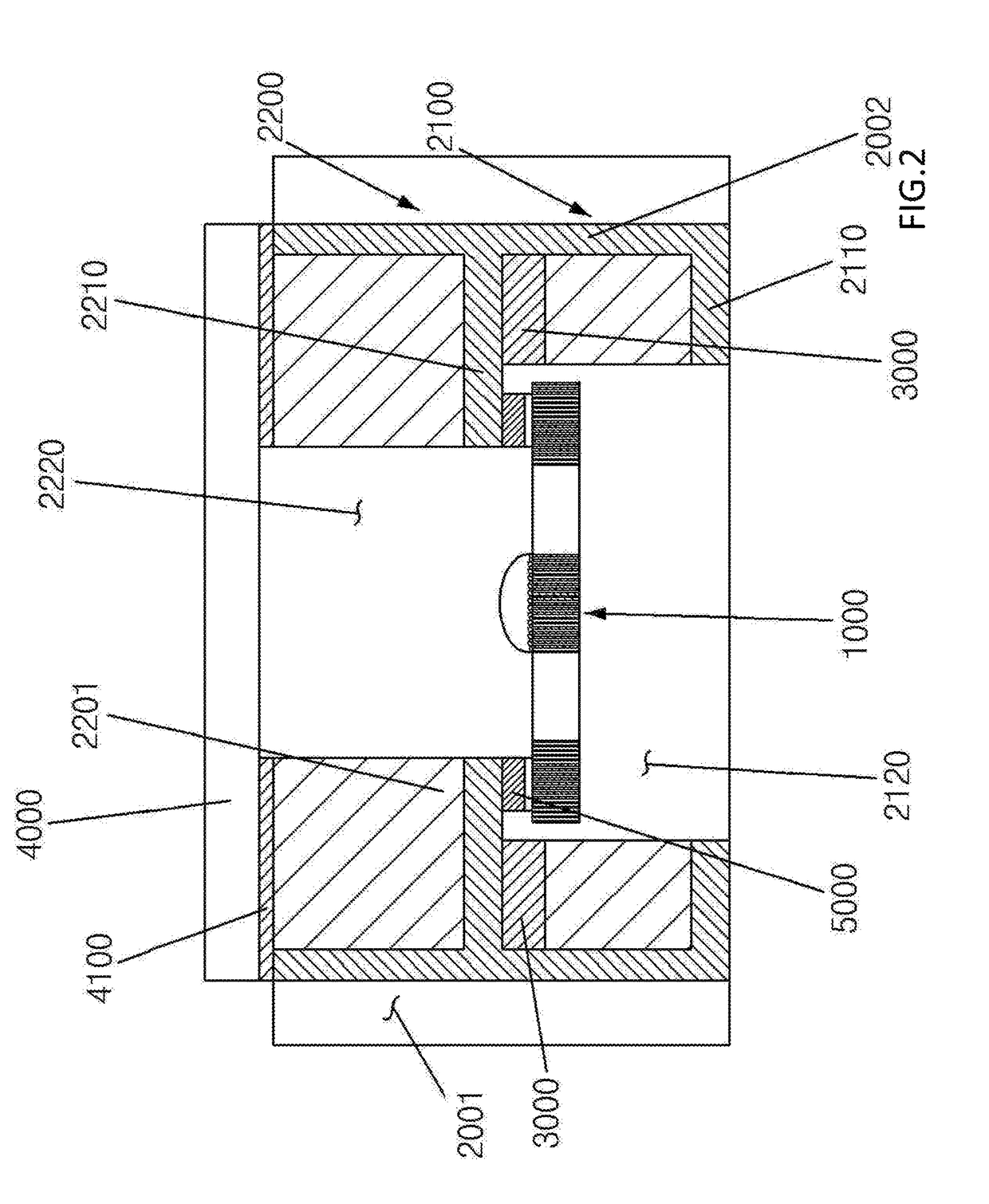

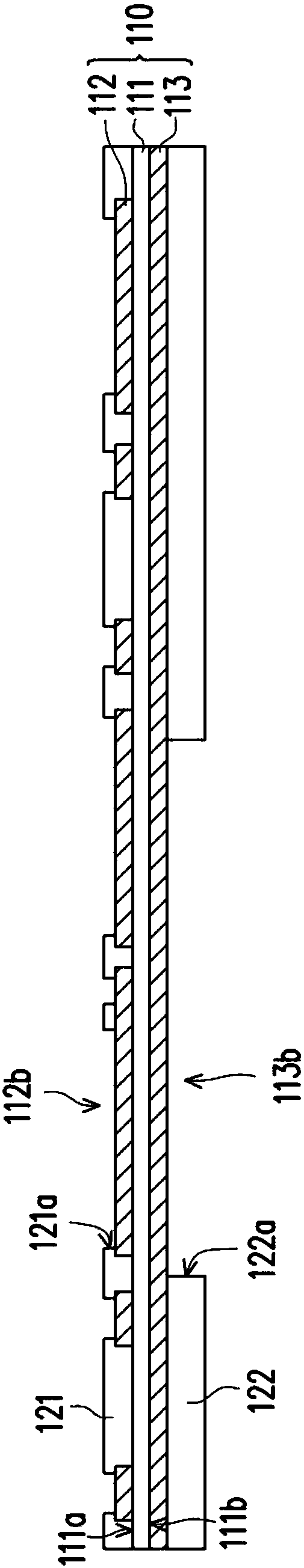

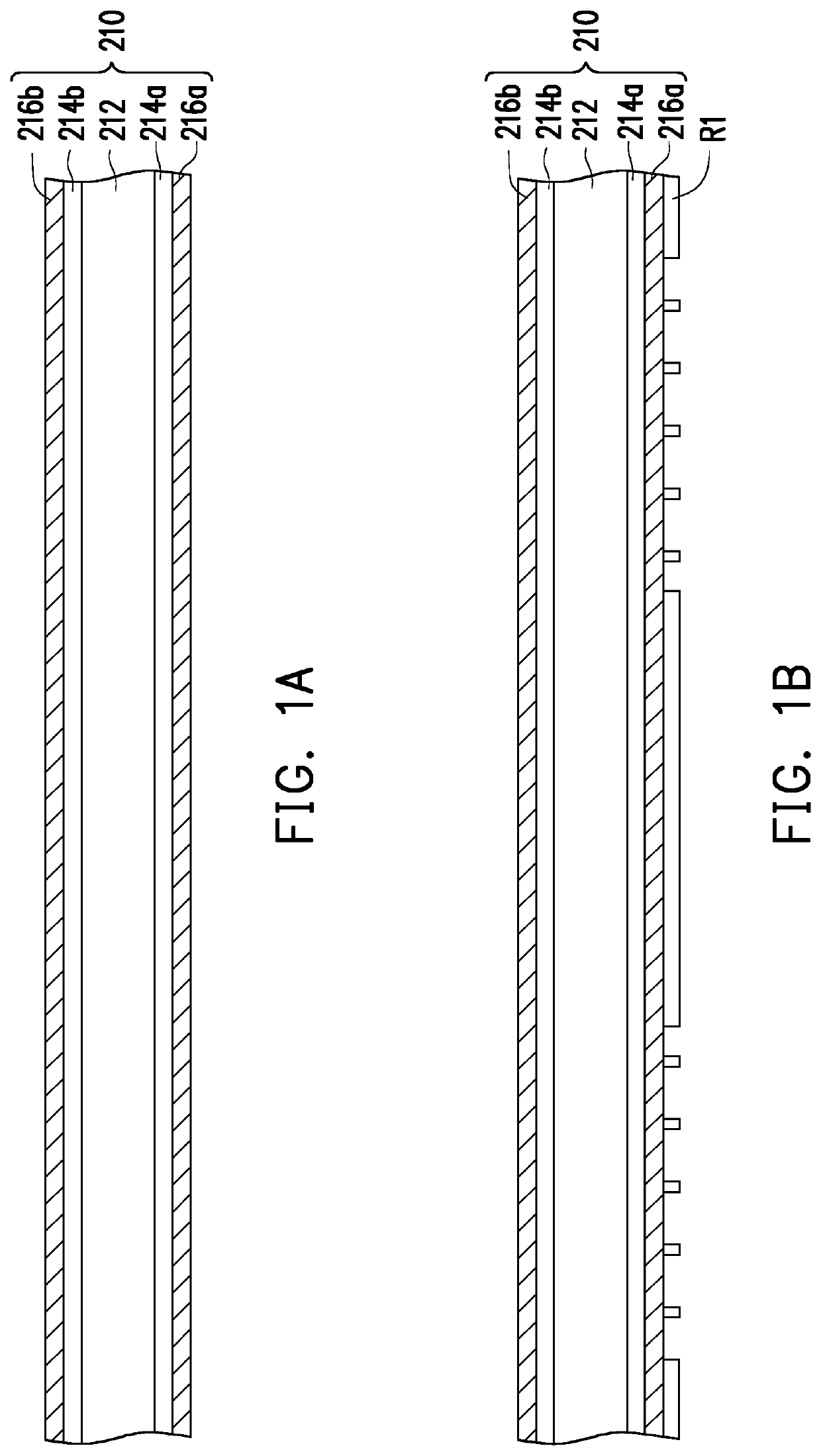

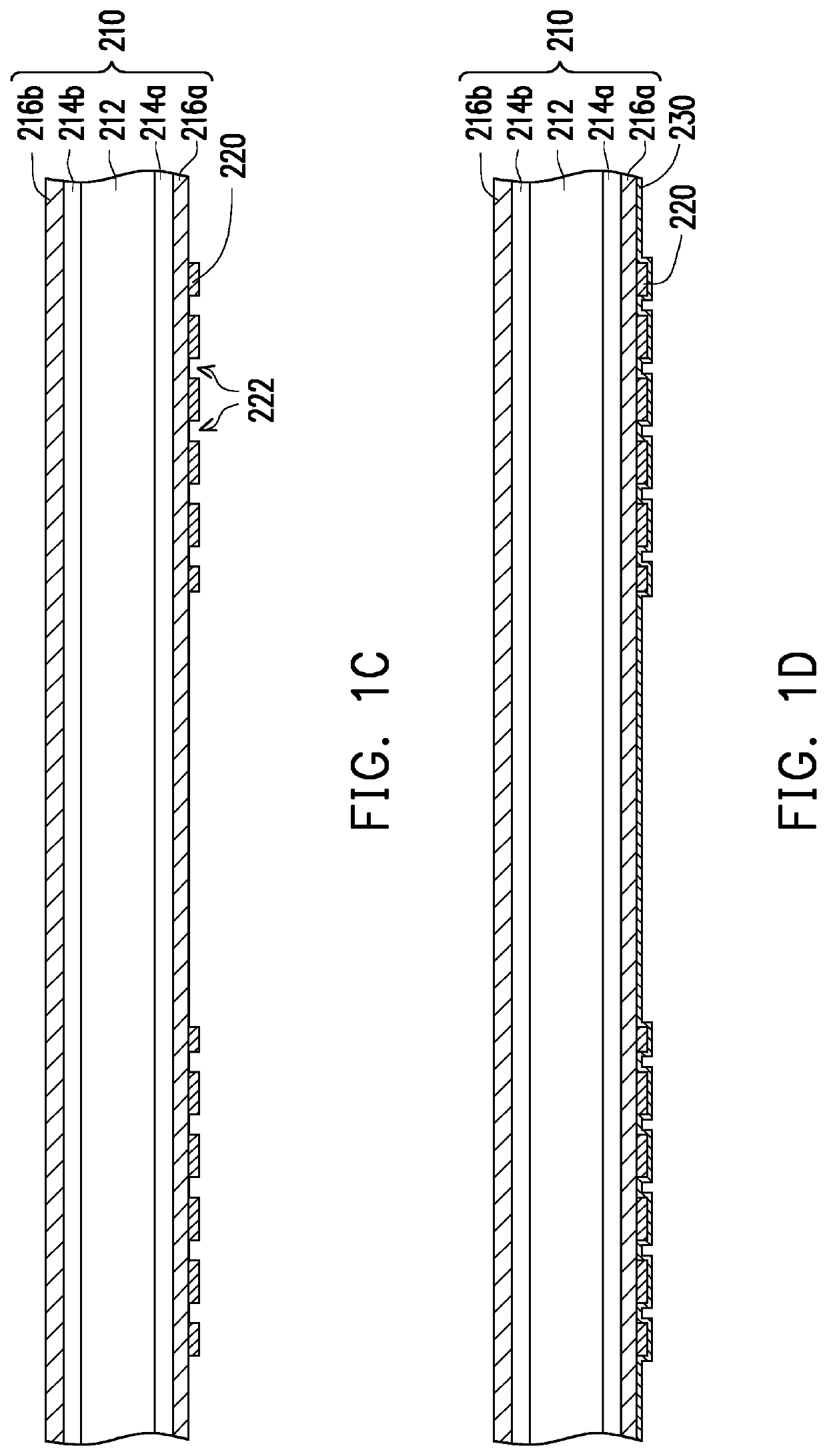

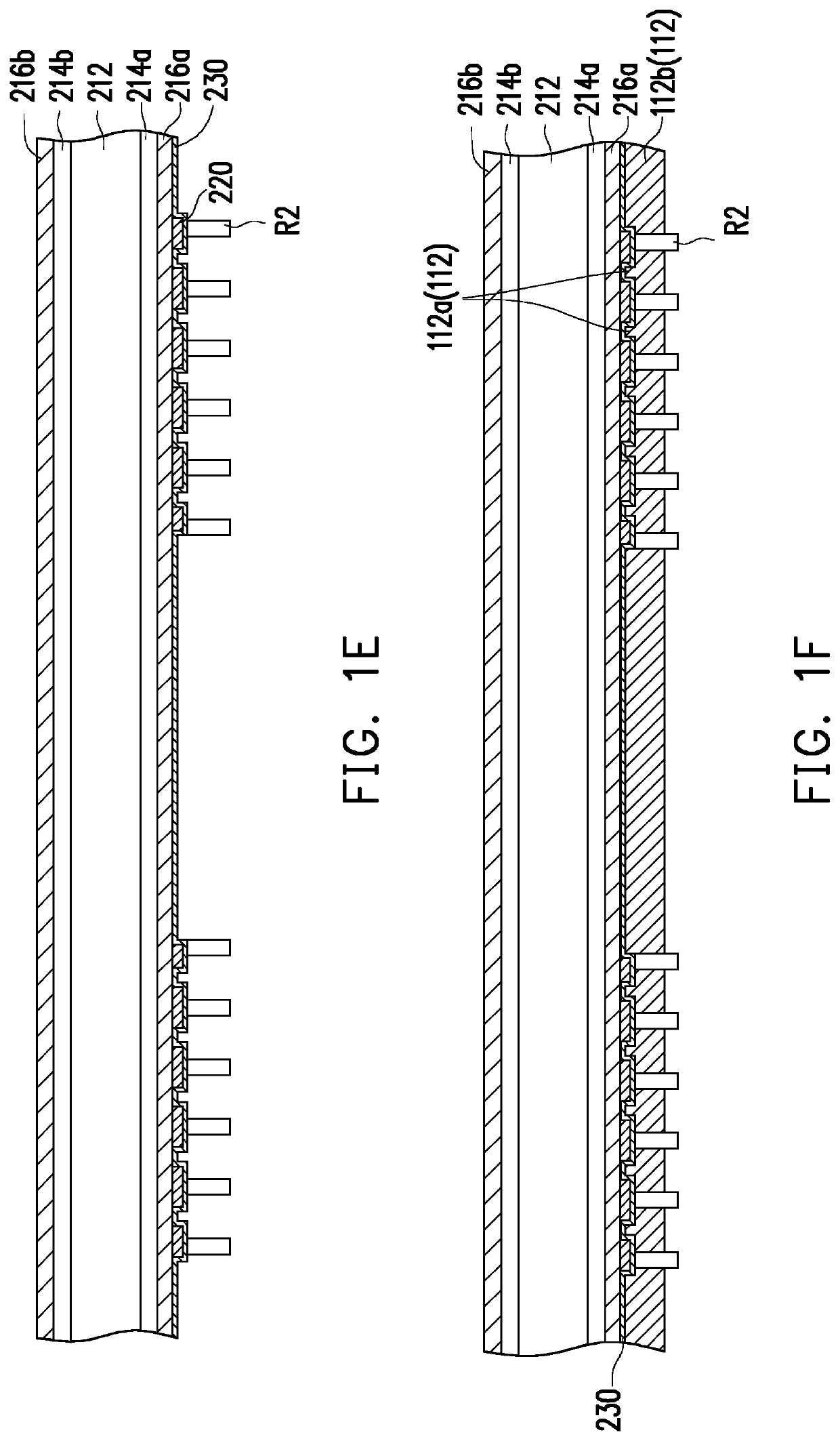

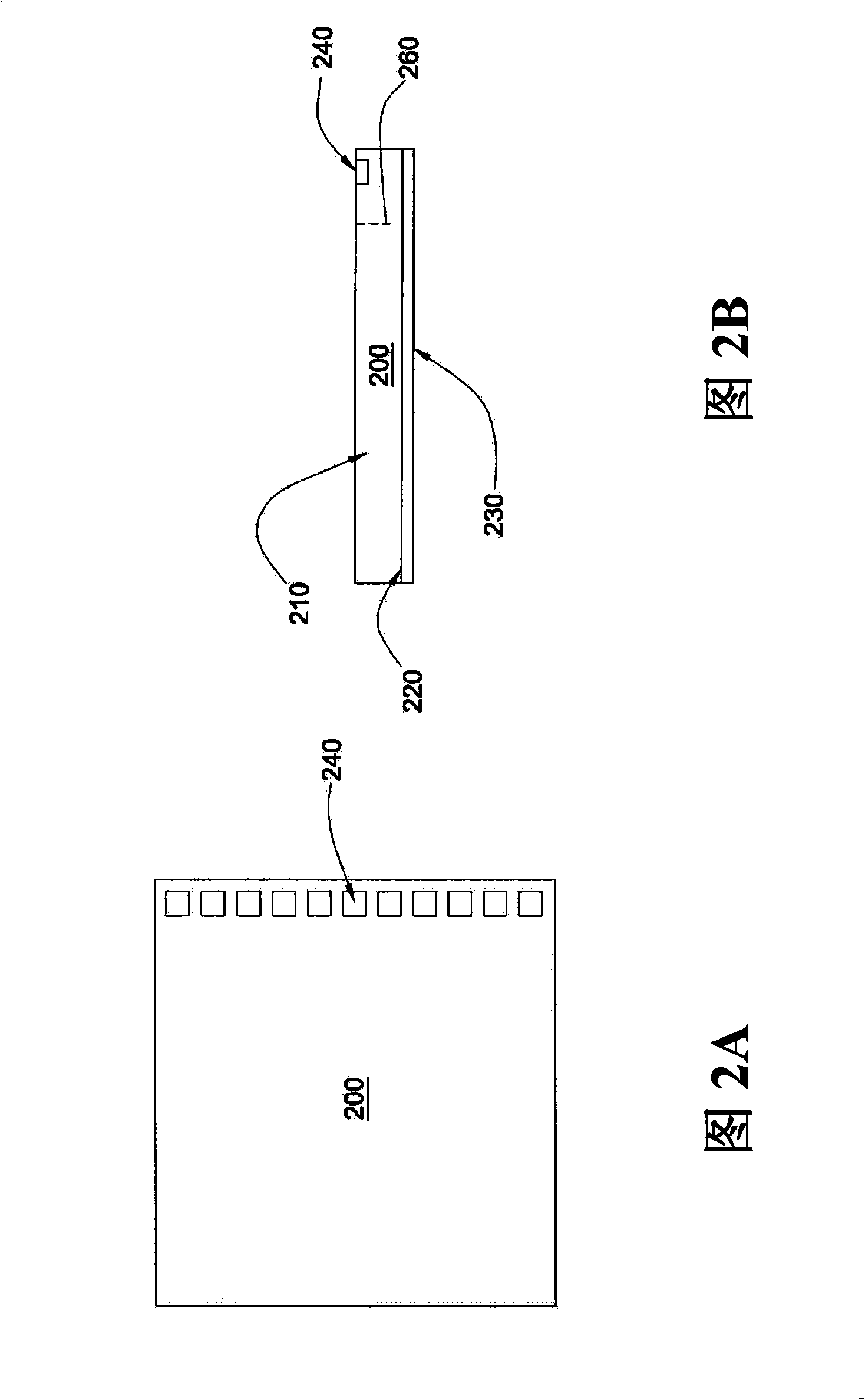

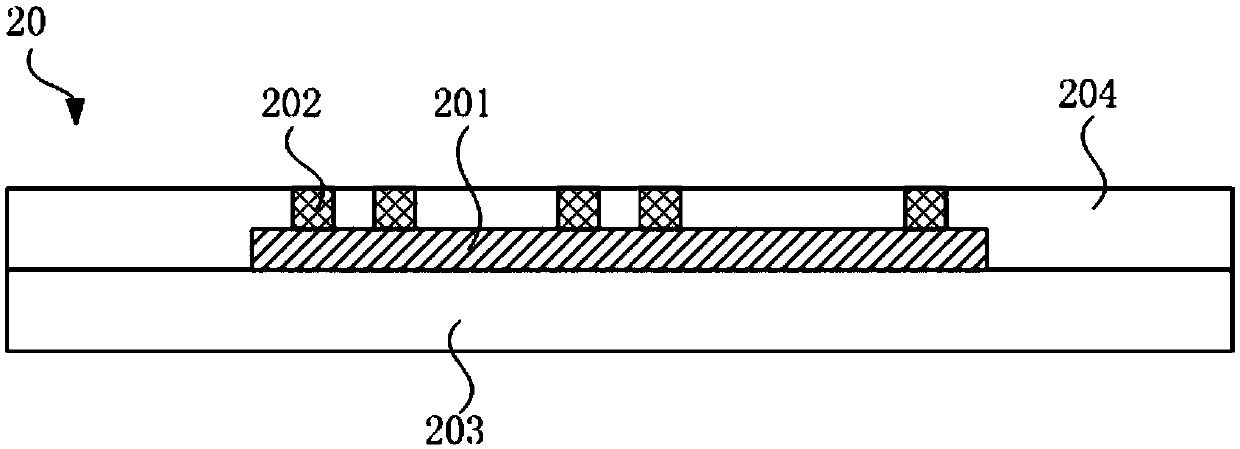

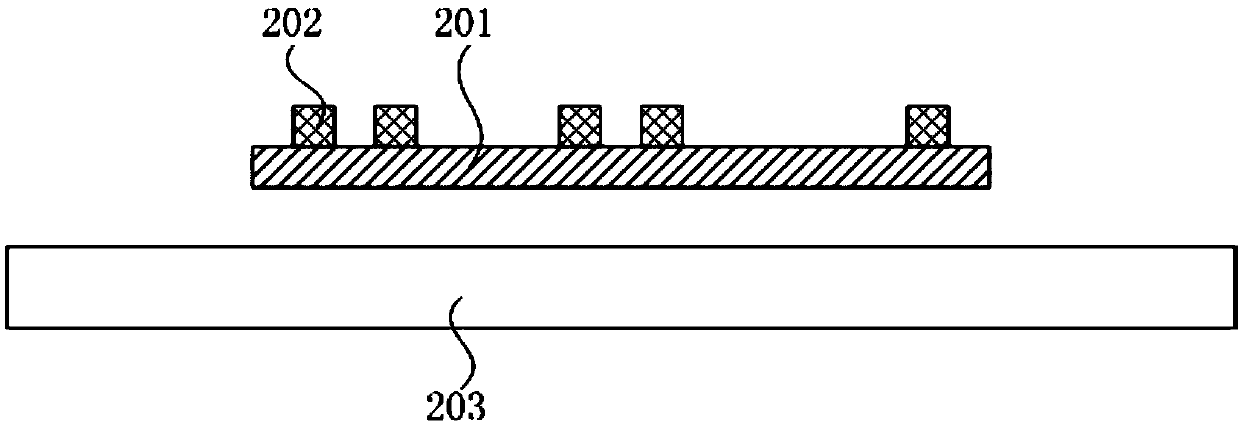

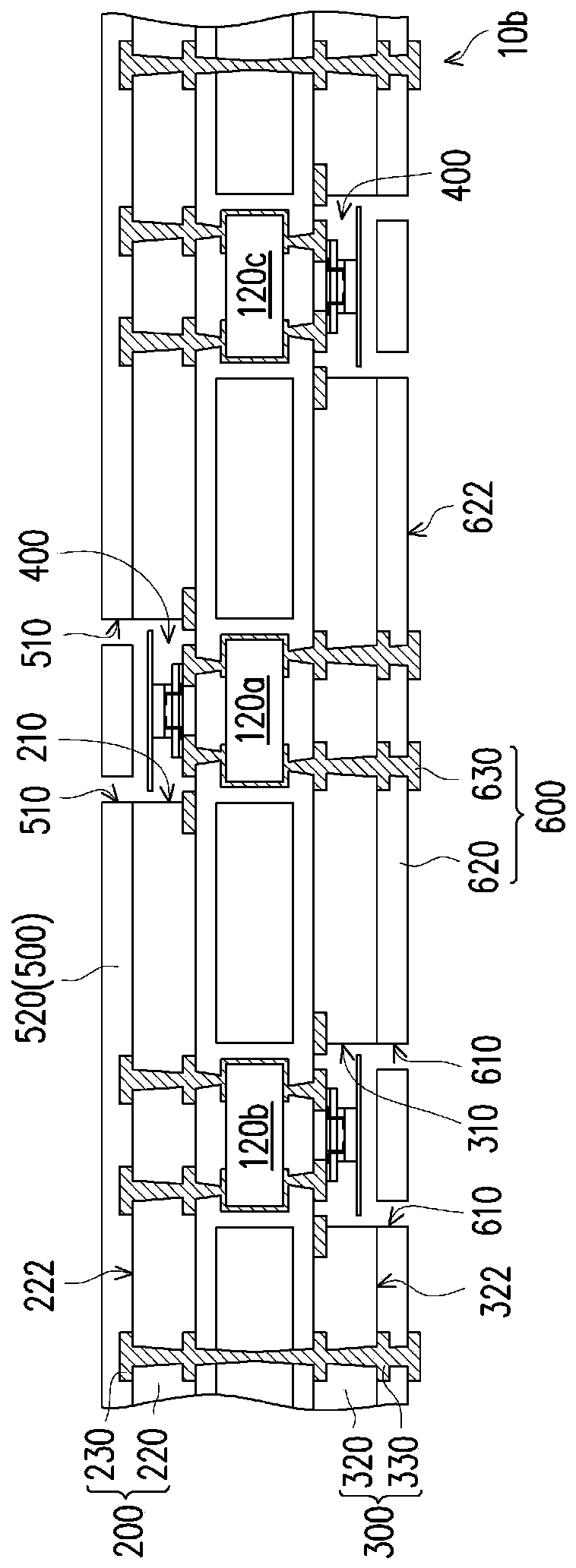

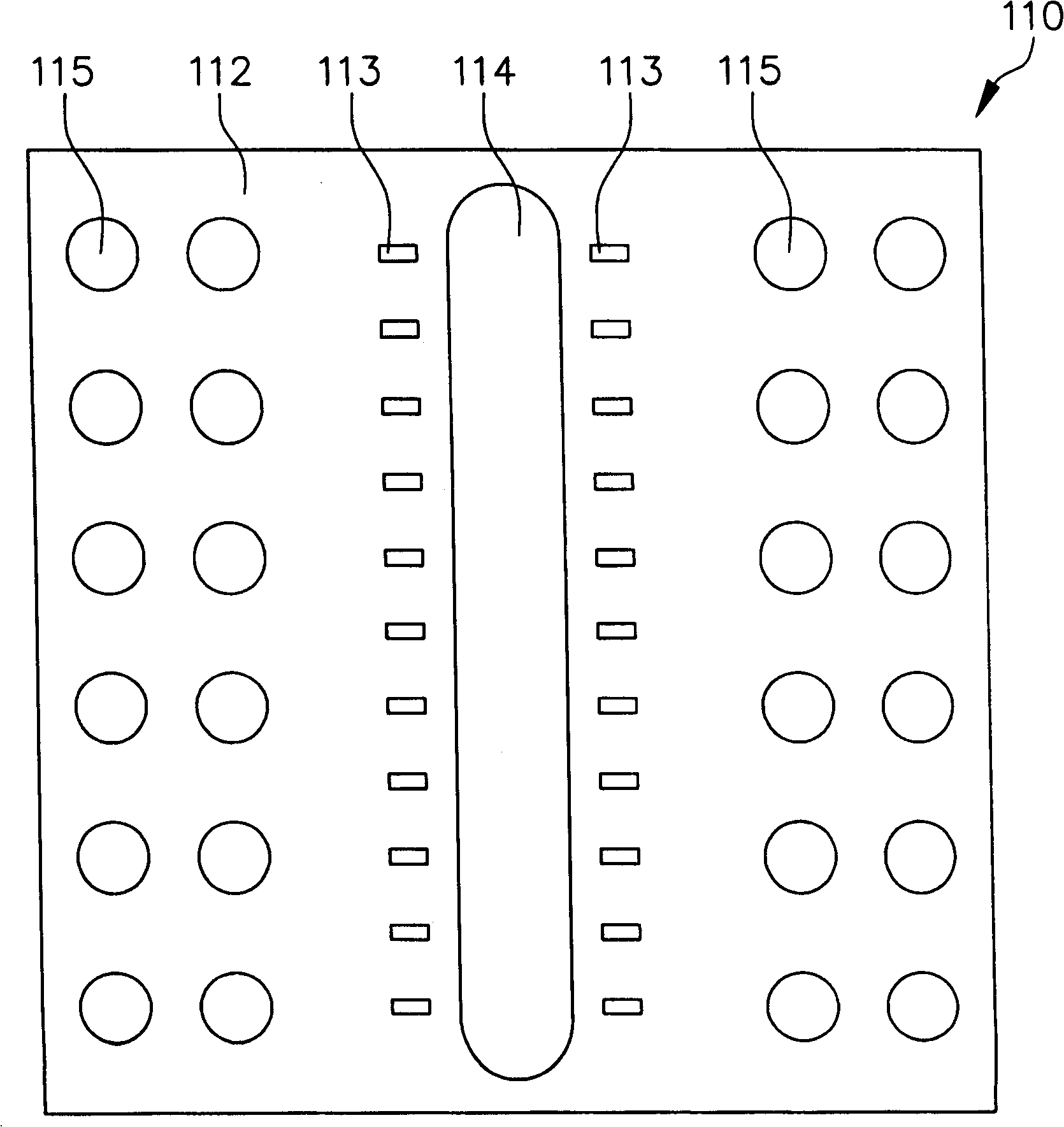

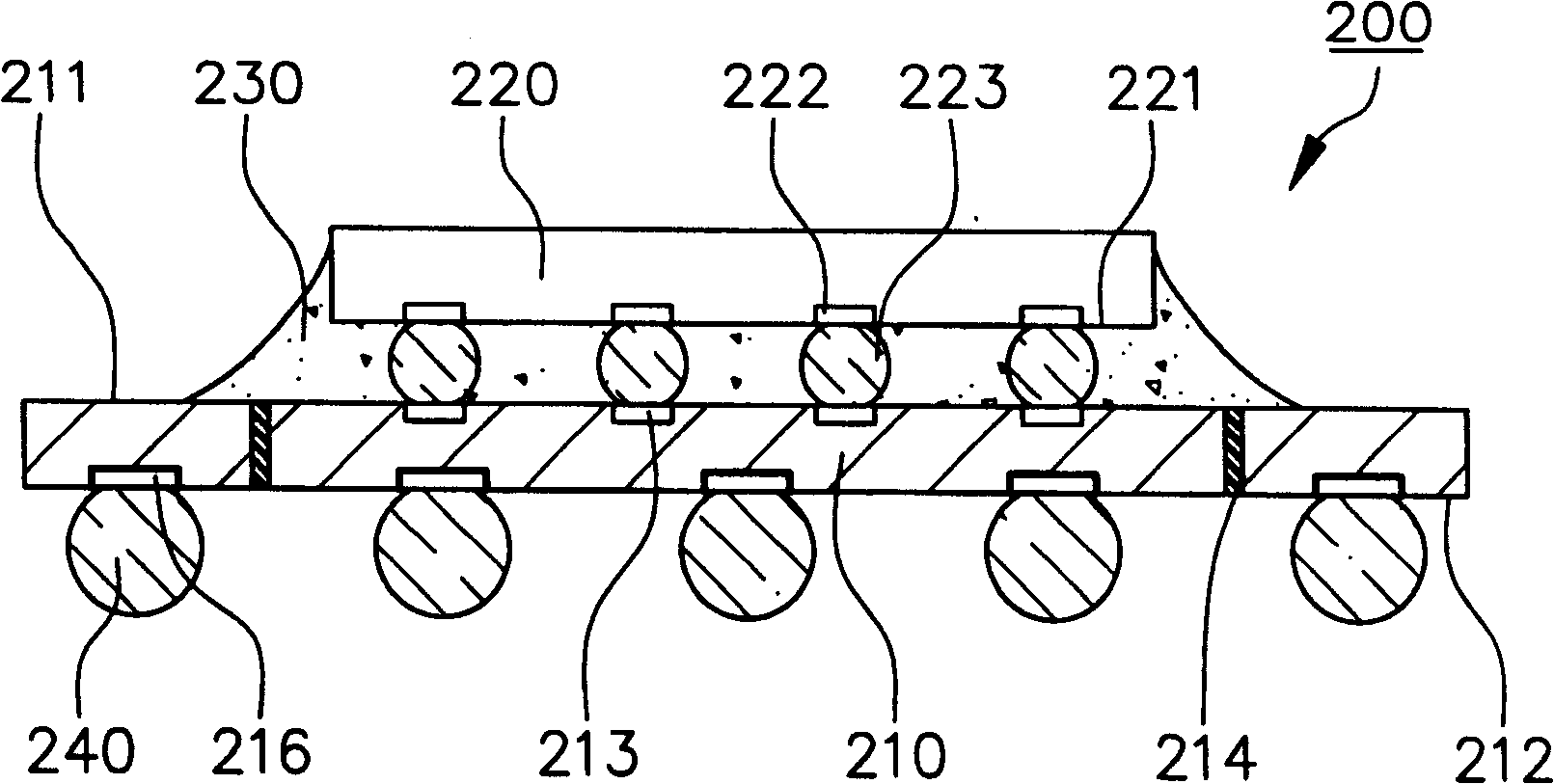

Micro sensor package and manufacturing method of micro sensor package

ActiveUS20180073999A1Prevent moisture penetrationSimple processPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringElectrical and Electronics engineering

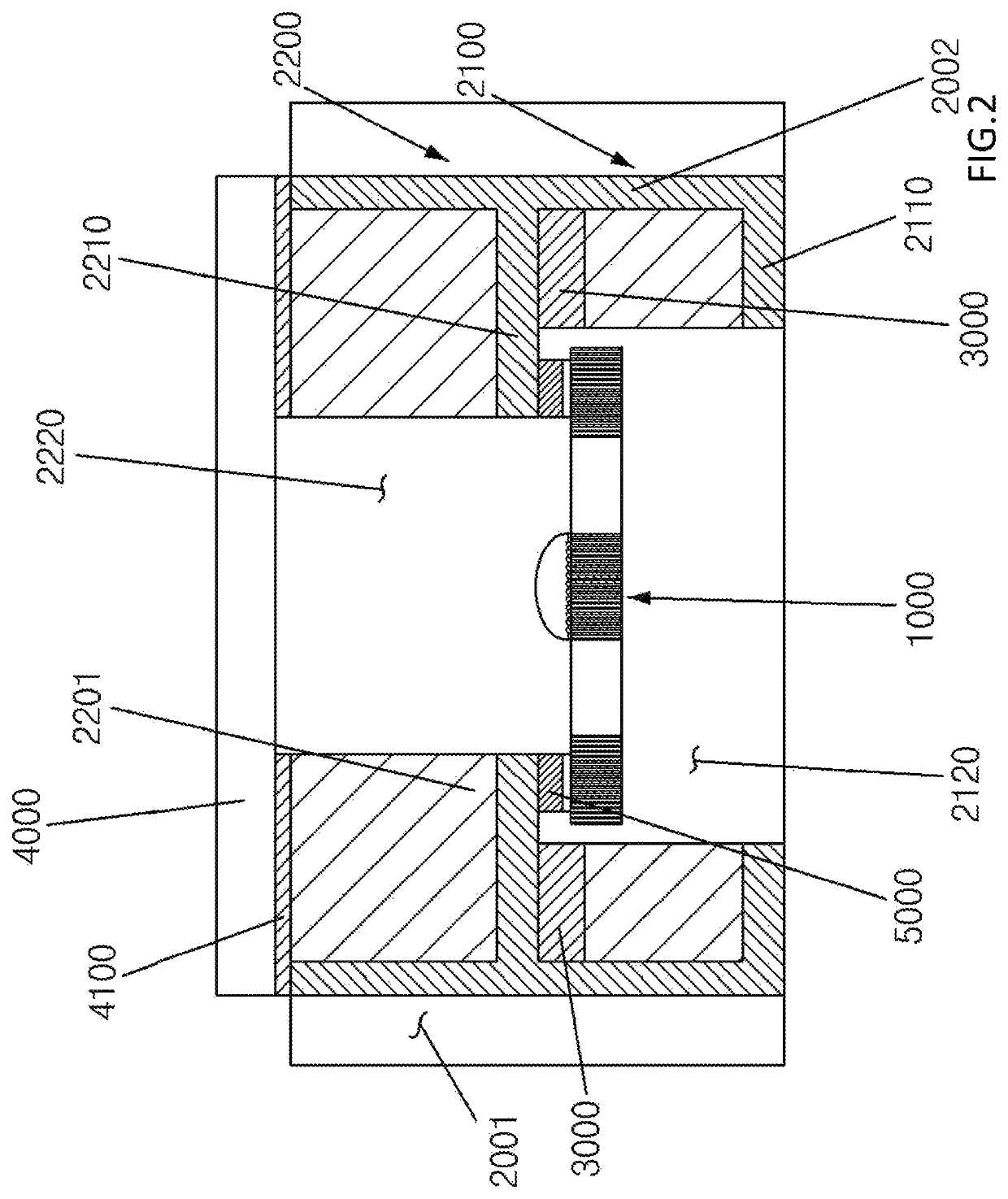

Disclosed is a microsensor package. Particularly, disclosed is a microsensor package, in which a sensing chip is packaged by using PCBs stacked on top of one another, whereby the thickness of the package slim can be kept slim, and at the same time, it can be manufactured at a low cost and can be easily manufactured.

Owner:POINT ENG

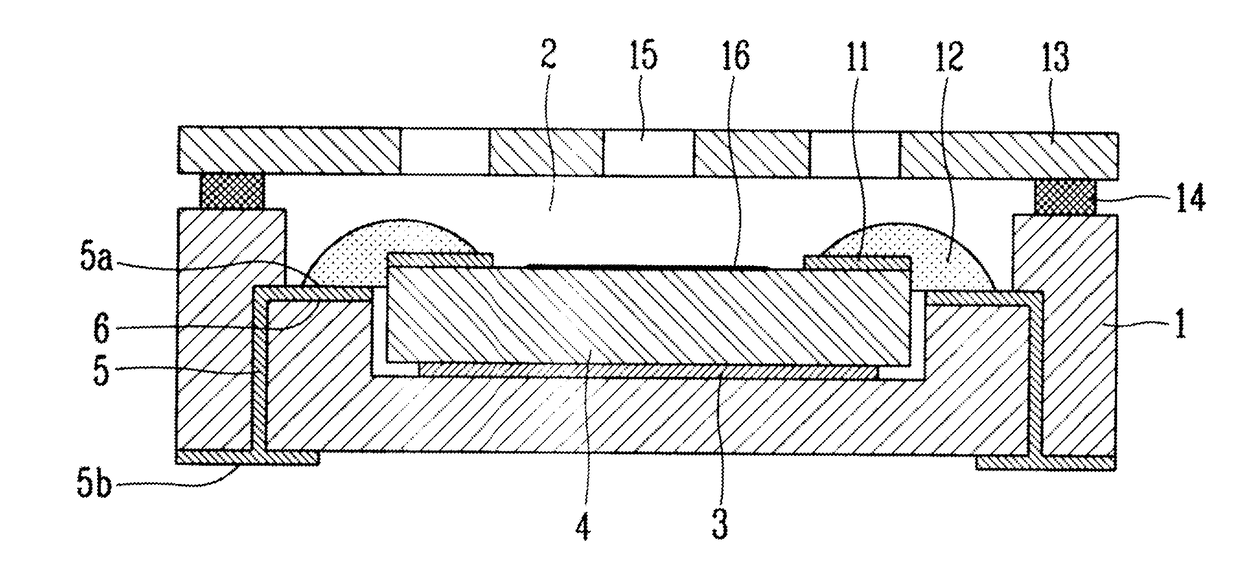

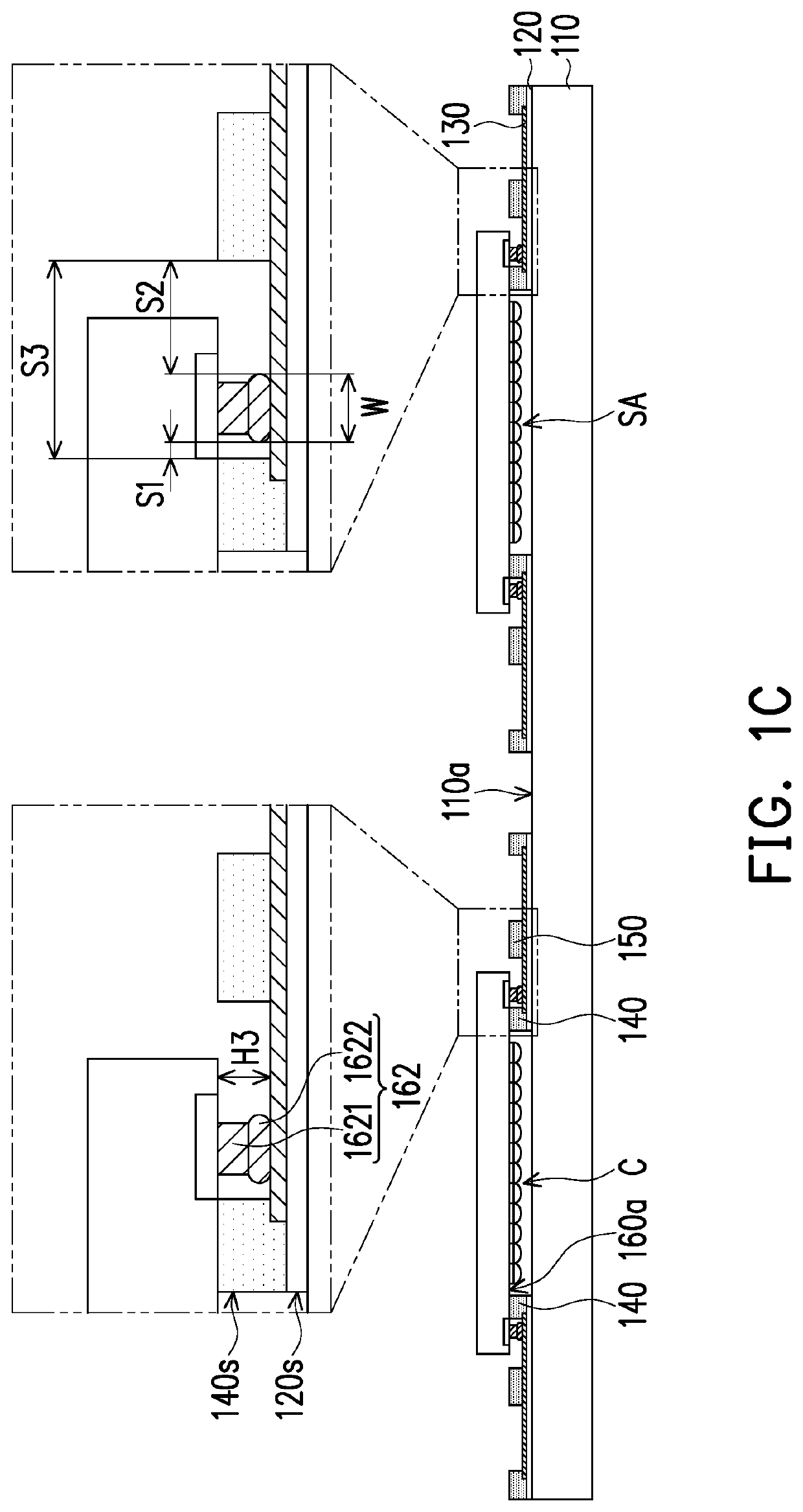

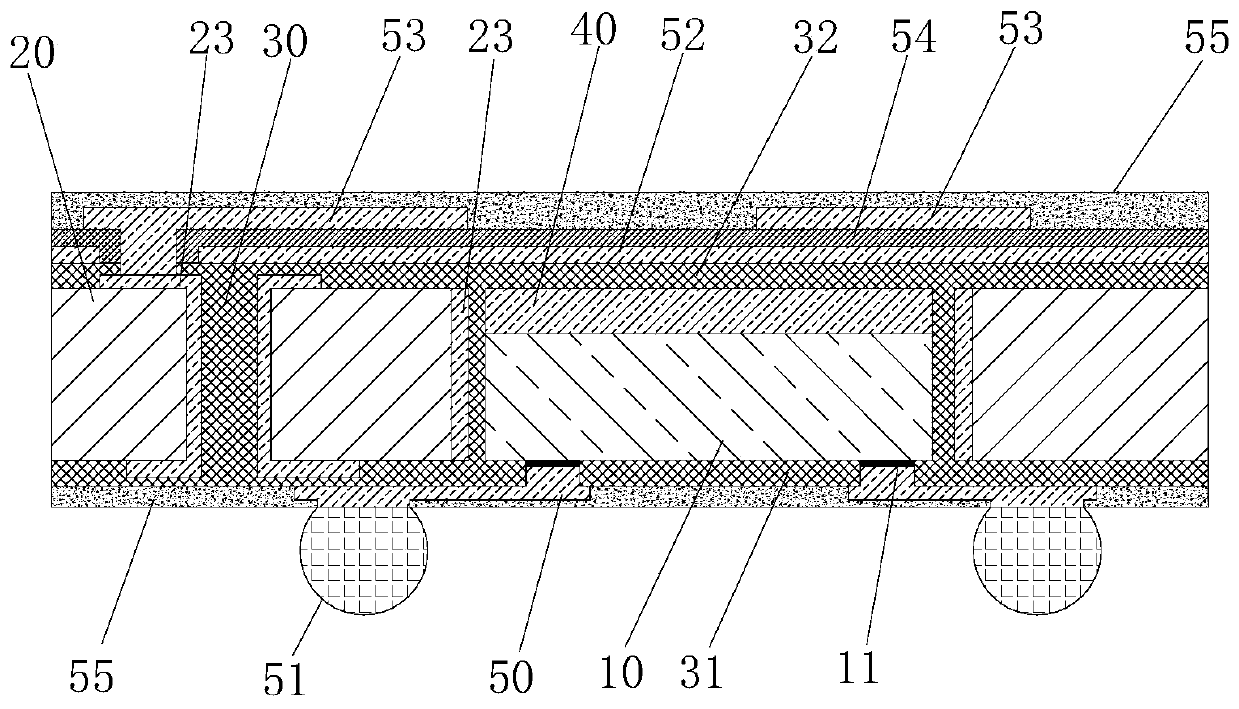

Semiconductor package structure and manufacturing method thereof

ActiveUS20210098517A1Reduce the possibilityThin Package ThicknessSolid-state devicesRadiation controlled devicesSemiconductor packageHemt circuits

A semiconductor package structure including a sensor die, a substrate, a light blocking layer, a circuit layer, a dam structure and an underfill is provided. The sensor die has a sensing surface. The sensing surface includes an image sensing area and a plurality of conductive bumps. The substrate is disposed on the sensing surface. The light blocking layer is located between the substrate and the sensor die. The circuit layer is disposed on the light blocking layer. The sensor die is electrically connected to the circuit layer by the conductive bumps. The dam structure is disposed on the substrate and surrounds the image sensing area. Opposite ends of the dam structure directly contact the sensor die and the light blocking layer. The underfill is disposed between the dam structure and the conductive bumps.

Owner:POWERTECH TECHNOLOGY

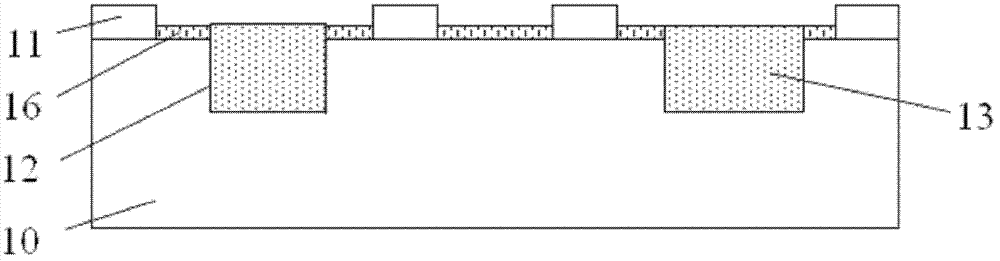

High-heat-resistant packaging substrate

InactiveCN110265365AExtended service lifeImprove cooling efficiencySemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

The invention discloses a high-heat-resistant packaging substrate. The high-heat-resistant packaging substrate comprises a base plate, a circuit board, a high-heat-resistant insulating layer, a patterned conductive layer and an anti-welding layer, wherein the circuit board is positioned on the upper surface of the base plate; the high-heat-resistant insulating layer is arranged above the circuit board; the patterned conductive layer is arranged at the upper portion of the high-heat-resistant insulating layer; an electronic element is arranged in the patterned conductive layer; and a thermal expansion coefficient of the high-heat-resistant insulating layer is between the thermal expansion coefficients of the base plate and the electronic element. The thermal expansion coefficient difference among the electronic element, the high-heat-resistant insulating layer and the base plate of the high-heat-resistant packaging substrate is gradually reduced, so that the phenomena that the electronic element falls off and is stripped can be avoided, and the service life of the packaging substrate is prolonged; the high-heat-resistant insulating layer is adopted, so that the heat-resistant strength of the substrate can be improved; the thickness of the circuit board is small, so that the subsequently finished packaging structure has relatively small packaging thickness, and the heat dissipation efficiency of the packaging substrate is improved; and the packaging substrate is suitable for industrial large-scale production.

Owner:江门建滔电子发展有限公司

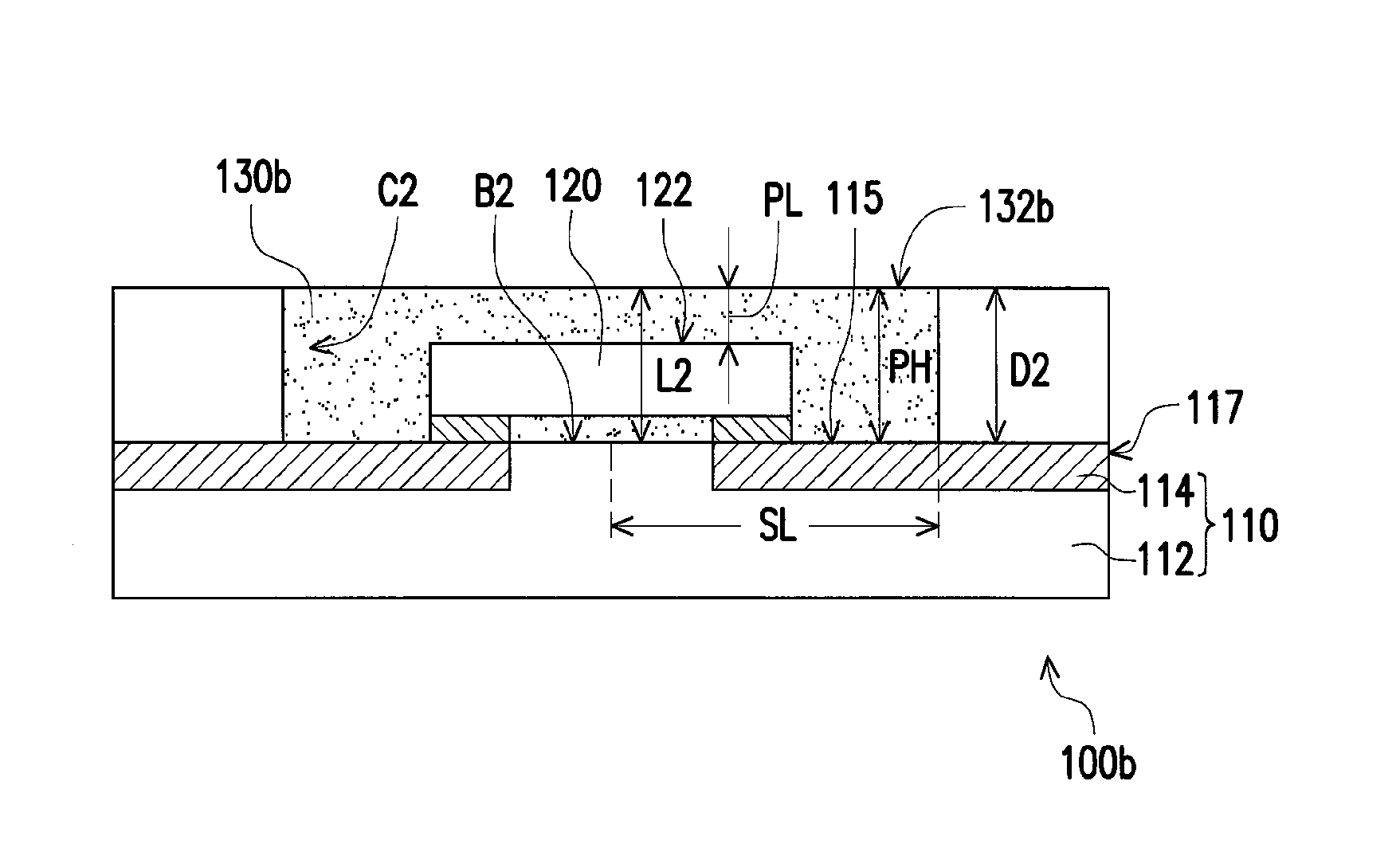

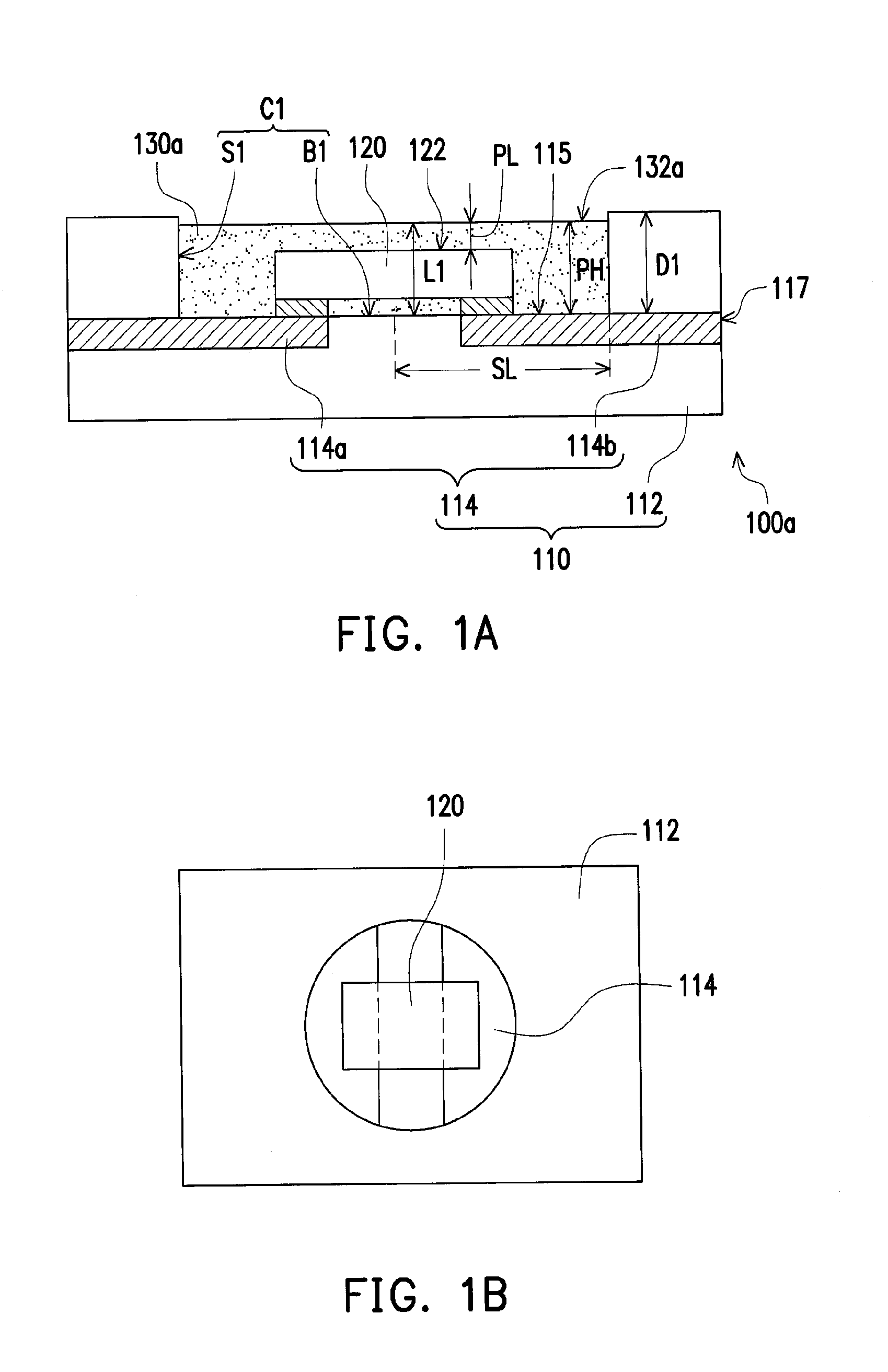

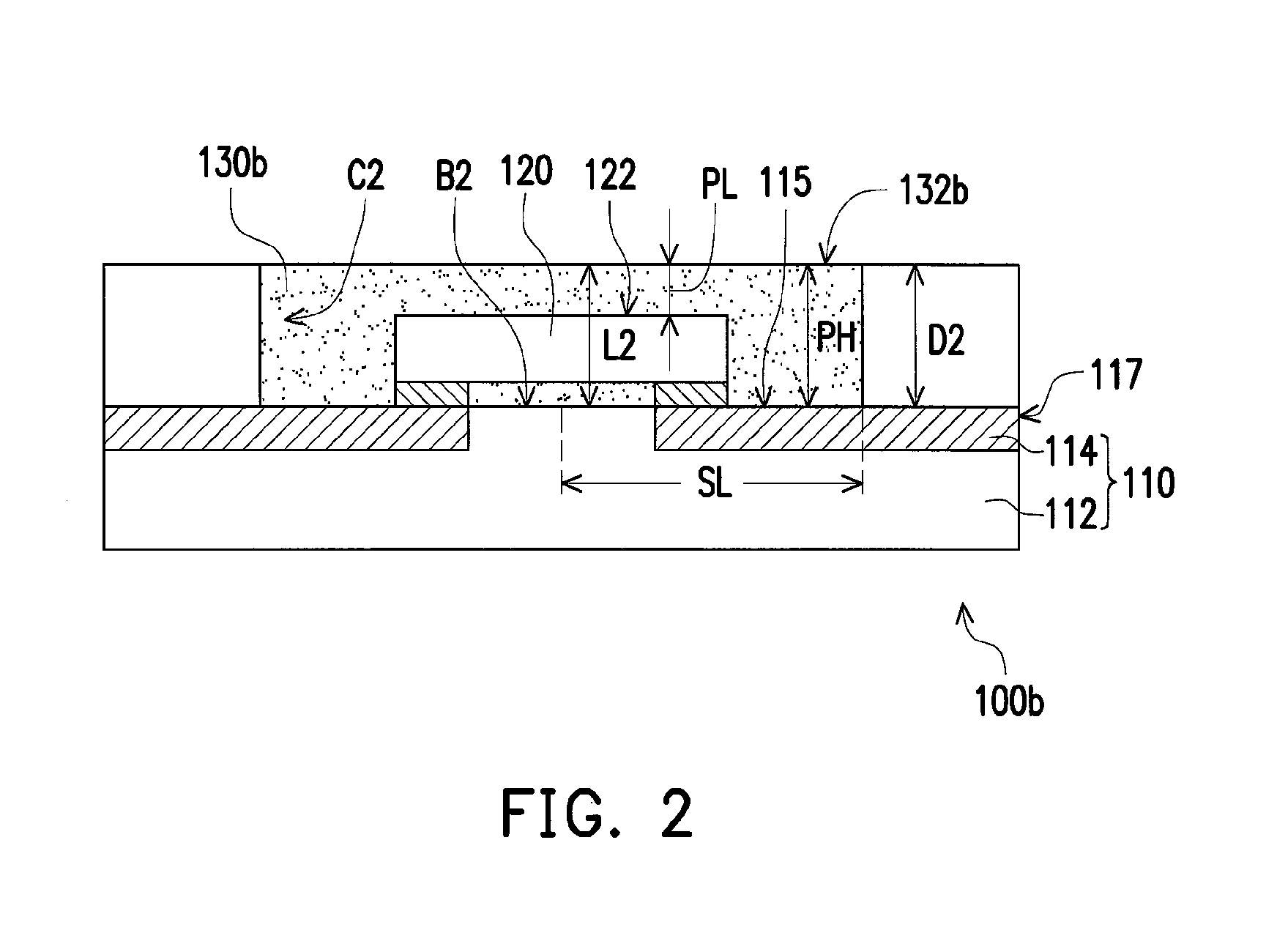

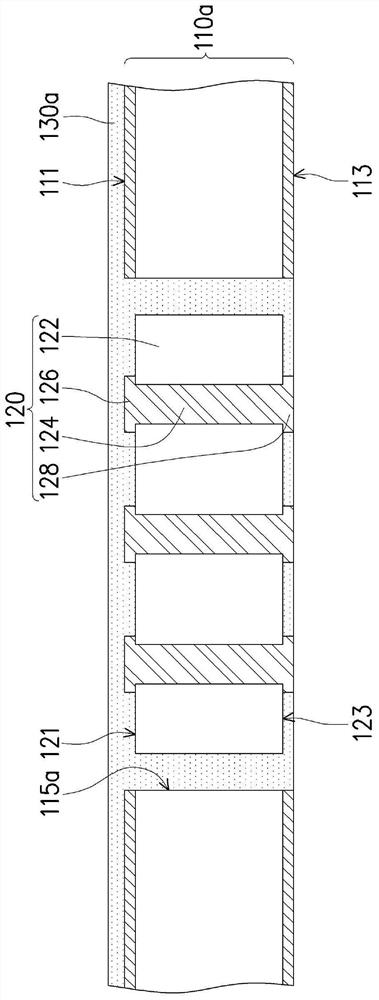

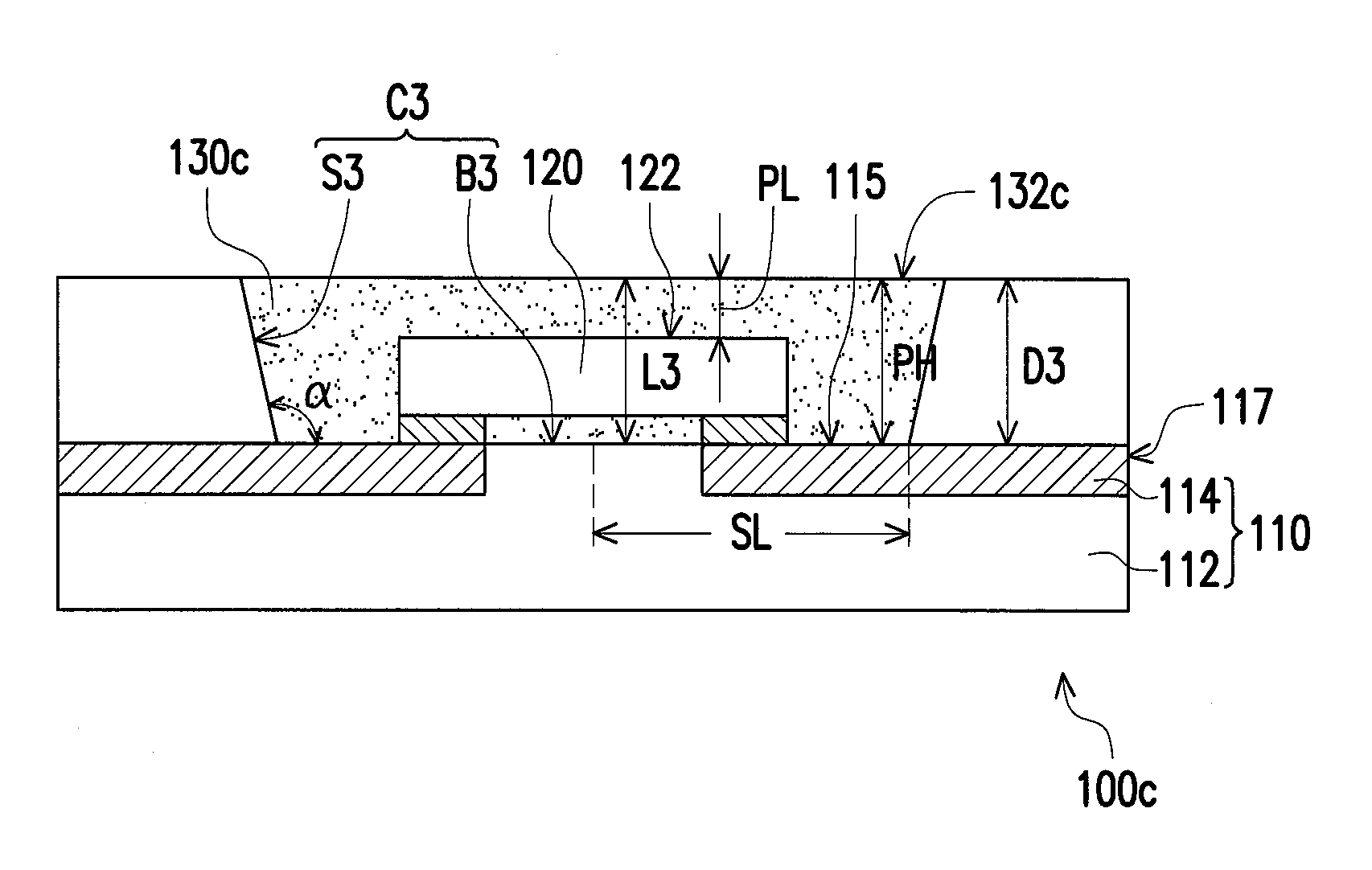

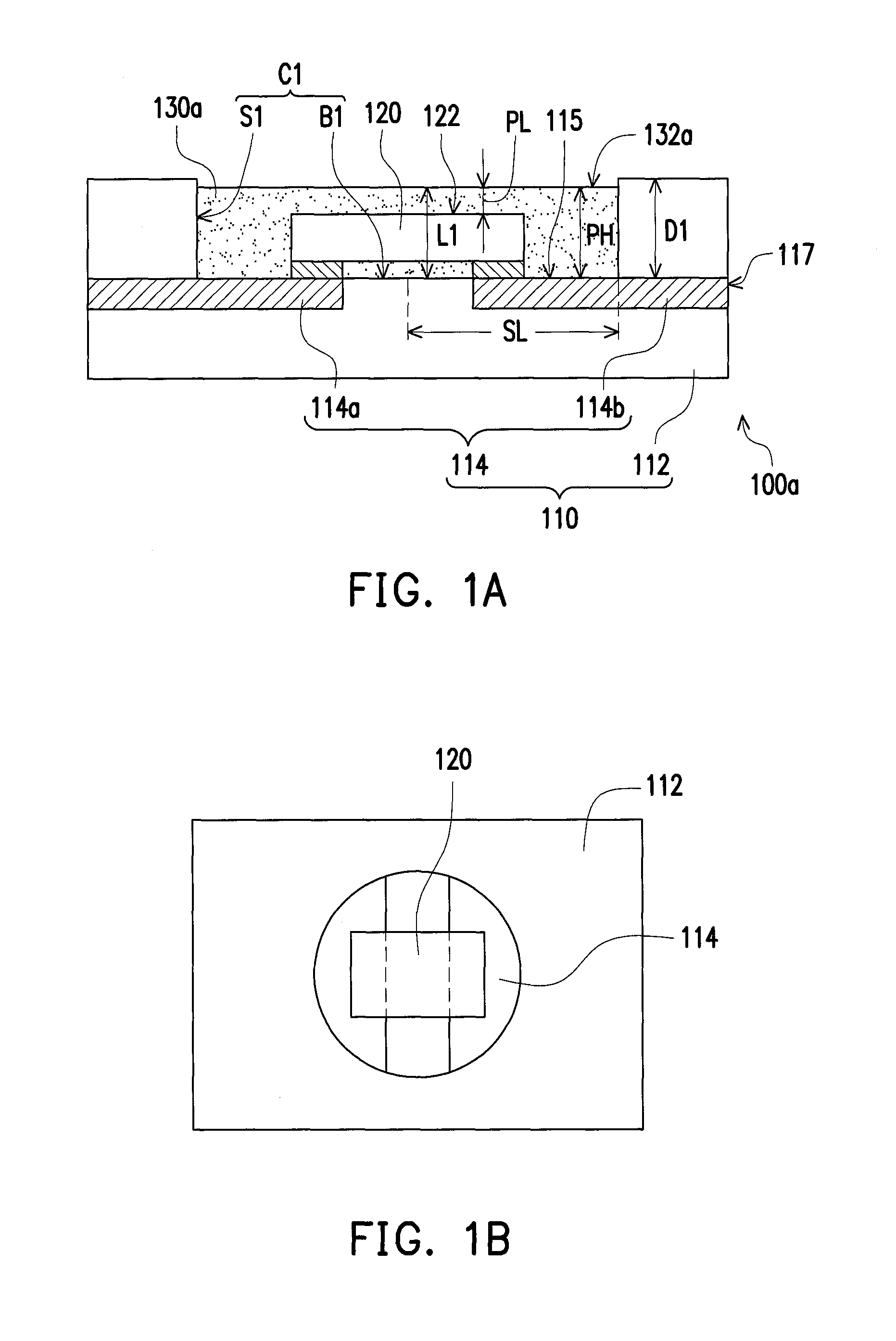

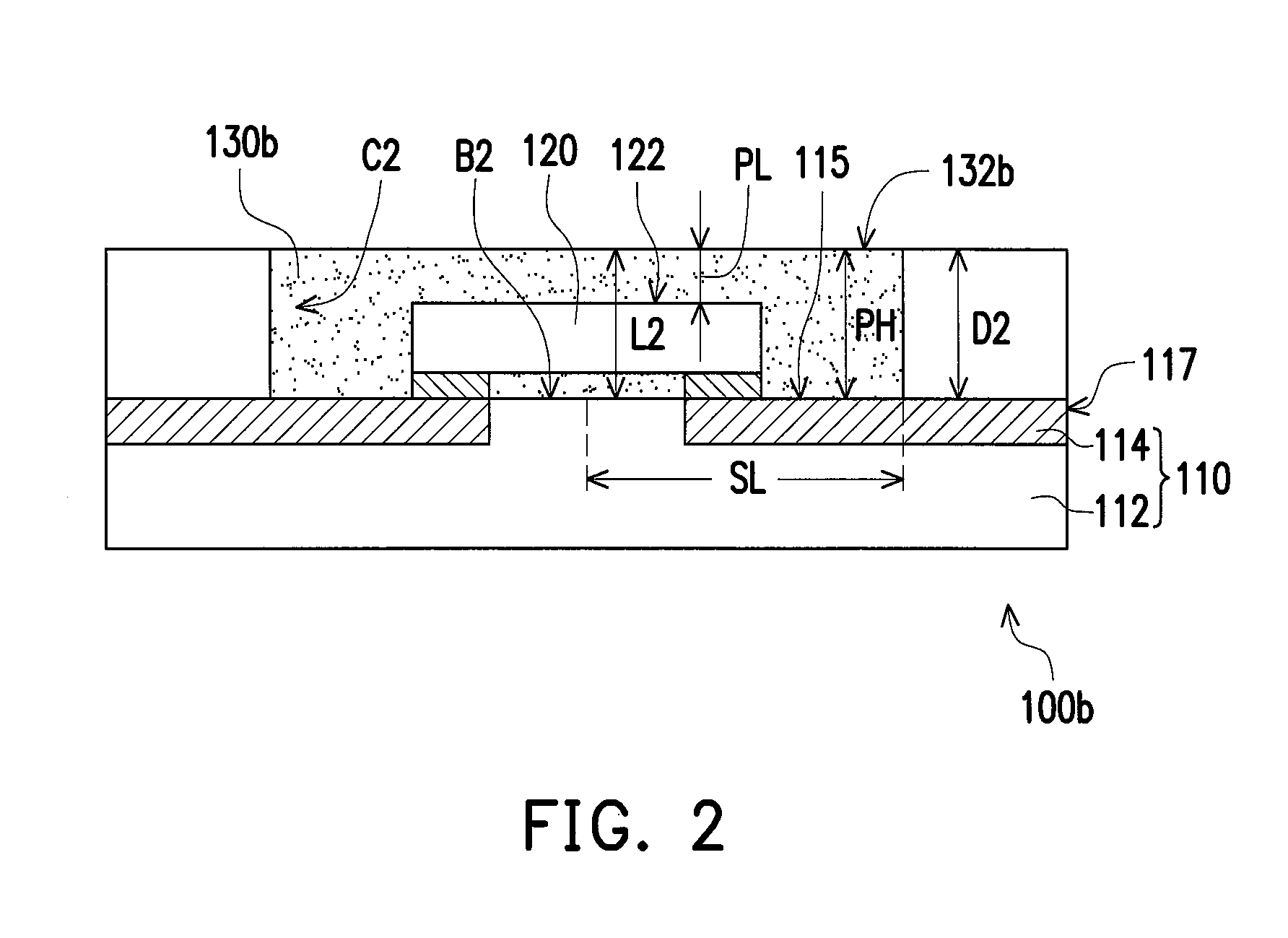

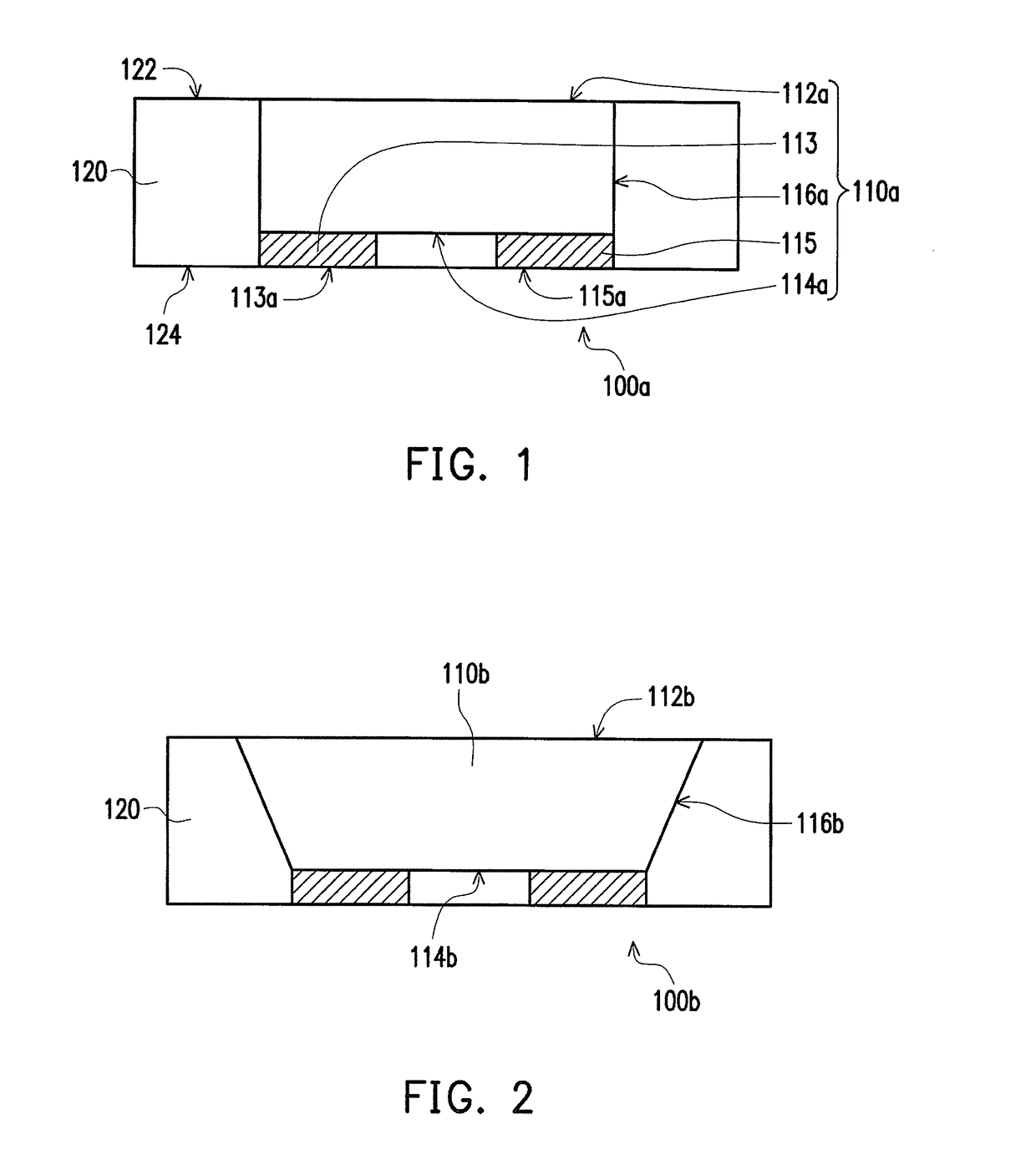

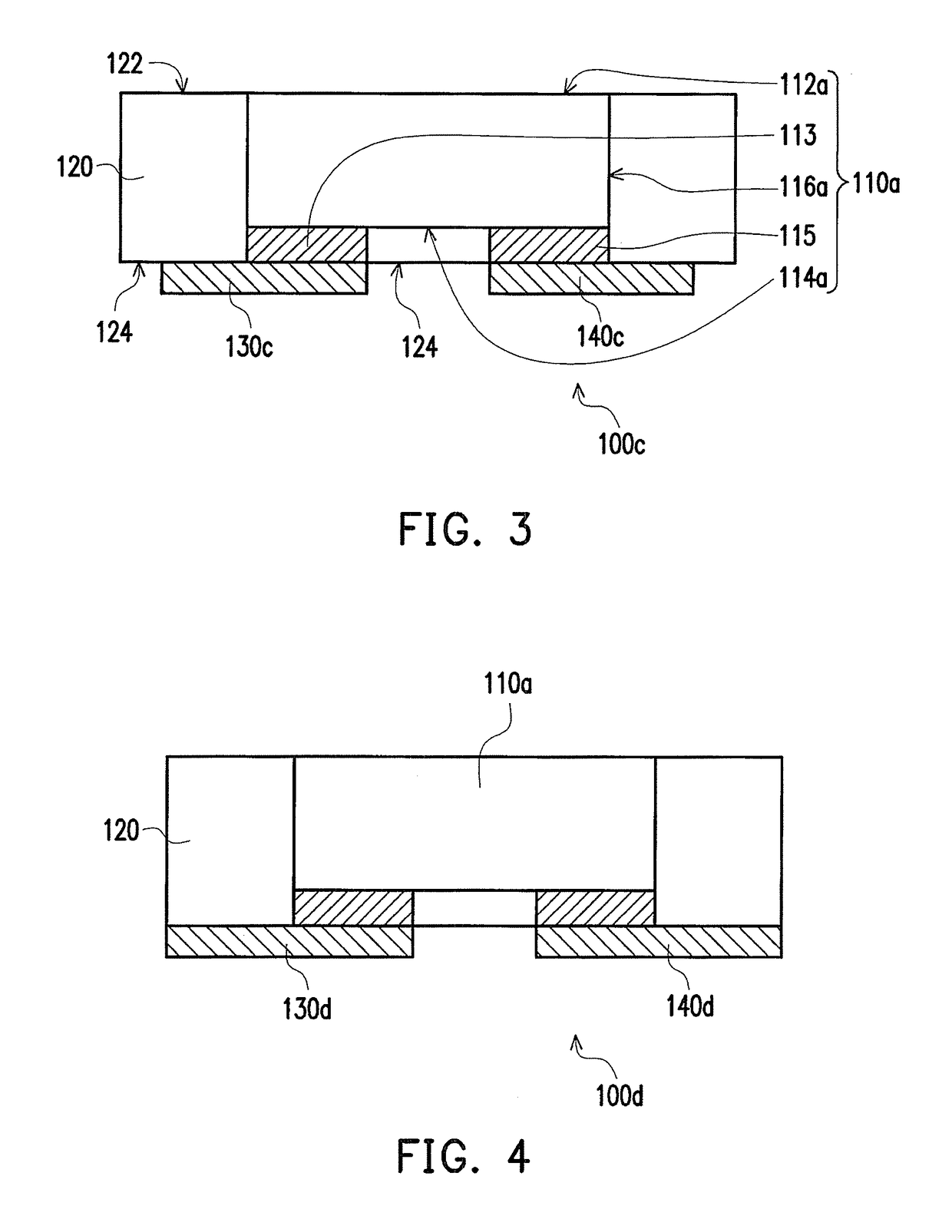

Light emitting diode package structure

InactiveUS20170062664A1Thin Package ThicknessHigh structural reliabilitySolid-state devicesSemiconductor devicesEngineeringThermal expansion

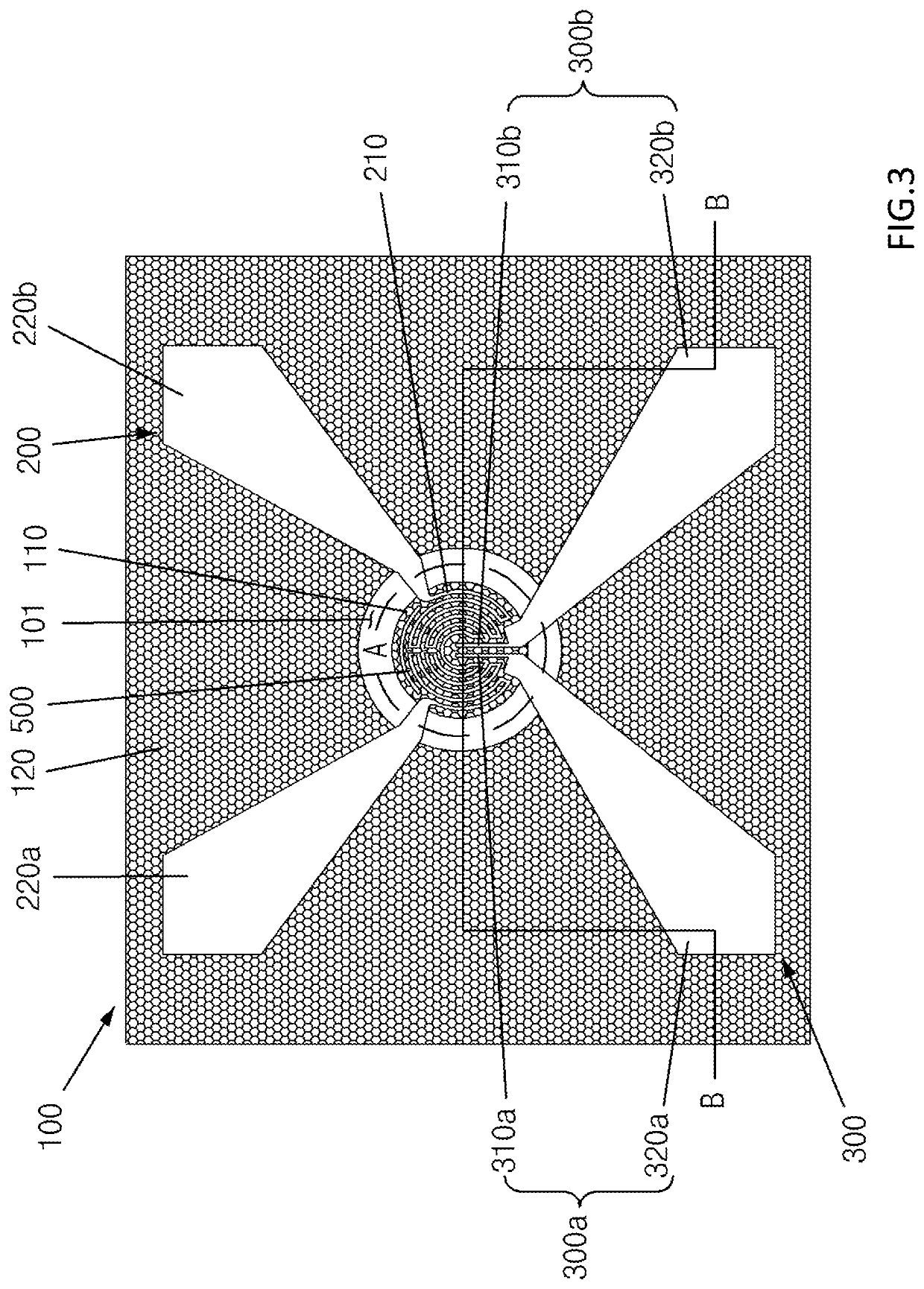

A LED package structure including a carrier substrate, a flip-chip LED and a molding compound is provided. The carrier substrate includes a main body and a patterned conductive layer embedded in the main body. The main body is composed of polymer material. The main body has a cavity, and a bottom surface of the cavity is aligned with an upper surface of the patterned conductive layer. A difference in coefficient of thermal expansion between the main body in a rubbery state and the patterned conductive layer is smaller than 30 ppm / ° C. The flip-chip LED is disposed inside the cavity and electrically connected to the patterned conductive layer. The molding compound is disposed inside the cavity and encapsulates the flip-chip LED. A vertical distance between a top surface of the molding compound and the bottom surface of the cavity is smaller than or equal to a depth of the cavity.

Owner:GENESIS PHOTONICS INC

Semiconductor package structure and manufacturing method

ActiveCN109216214AGood cooling effectWide applicabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

The present invention provides a semiconductor package structure and a manufacturing method. The semiconductor package structure includes a substrate, at least one electronic component, an encapsulant, and a redistribution wiring layer. The substrate includes a thermally conductive insulating layer, a patterned circuit layer, and a metal layer. The thermally conductive insulating layer has a firstsurface and a second surface opposite to each other. The patterned circuit layer is disposed on the thermally conductive insulating layer and exposes a portion of the first surface of the thermally conductive insulating layer. The metal layer is disposed on the thermally conductive insulating layer and completely covers the second surface of the thermally conductive insulating layer. The electronic component is disposed on the substrate and electrically connected to the patterned circuit layer. The encapsulant at least covers the electronic component. The redistribution circuit layer is disposed on the encapsulant and electrically connected to the electronic component, wherein the edge of the encapsulant is approximately flush with the edge of the substrate.

Owner:UNIMICRON TECH CORP +1

Chip and antenna integrated three-dimensional packaging structure and preparation method thereof

PendingCN111199957ACompact structureThin Package ThicknessSemiconductor/solid-state device detailsSolid-state devicesEngineeringConductive materials

The invention relates to a chip and antenna integrated three-dimensional packaging structure and a preparation method thereof. The chip and antenna integrated three-dimensional packaging structure comprises at least one chip, wherein the chip is provided with a first surface and a second surface, and the first surface is provided with a functional area and an electrode. The chip and antenna integrated three-dimensional packaging structure also comprises a glass substrate, wherein at least one through groove and at least one through hole are arranged on the glass substrate, and a metal conductive material is deposited in the inner walls of the through groove and the through hole; the chip and a heat dissipation metal block are embedded in the through groove through a bonding structure, andthe heat dissipation metal block is located on the second surface of the chip; the bonding structure is also filled in the through hole, a first wiring surface is formed on the first surface of the chip and one surface of the glass substrate, and a second wiring surface is formed on the surface of the heat dissipation metal block and the other surface of the glass substrate; the first wiring surface is provided with at least one metal circuit to be electrically connected with the electrode of the chip; the second wiring surface is provided with at least one grounding layer and at least one antenna layer, and the antenna layer is electrically connected with the metal conductive material on the through hole. The three-dimensional packaging structure has the advantages of compact structure, thin packaging thickness, short signal transmission line, low loss and high electrical property.

Owner:XIAMEN SKY SEMICON TECH CO LTD

Micro sensor package and manufacturing method of micro sensor package

ActiveUS10634634B2Thin Package ThicknessEasy to manufacturePrinted circuit assemblingSemiconductor/solid-state device detailsMechanical engineeringElectrical and Electronics engineering

Disclosed is a microsensor package. Particularly, disclosed is a microsensor package, in which a sensing chip is packaged by using PCBs stacked on top of one another, whereby the thickness of the package slim can be kept slim, and at the same time, it can be manufactured at a low cost and can be easily manufactured.

Owner:POINT ENG

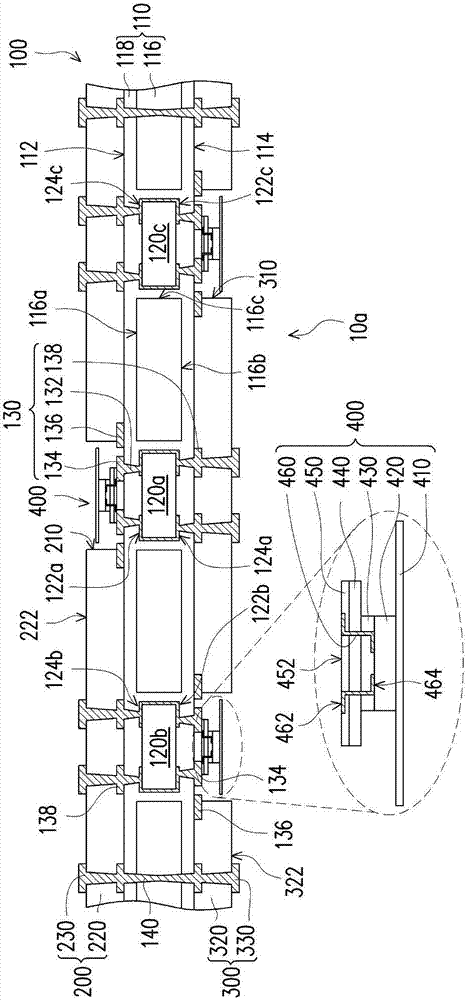

Circuit carrier with embedded substrate, manufacturing method thereof and chip package structure

ActiveUS20200075469A1Thin thicknessSmall volumeSemiconductor/solid-state device detailsSolid-state devicesHemt circuitsEngineering

A circuit carrier with embedded substrate includes a circuit structure and an embedded substrate. The circuit structure includes a first dielectric layer, a first patterned circuit layer, a trench, and a plurality of first bumps. The first dielectric layer has a first surface and a second surface opposite to each other. The first patterned circuit layer is embedded in the first surface. The first bumps are disposed on the first surface and electrically connected to the first patterned circuit layer. The trench exposes a portion of the first dielectric layer. The embedded substrate is disposed in the trench and includes a plurality of second bumps. A chip package structure includes the above circuit carrier with embedded substrate.

Owner:UNIMICRON TECH CORP

Packaging structure and manufacturing method thereof

ActiveCN107978575AAvoid electromagnetic interferenceThin Package ThicknessSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

The invention relates to a packaging structure and a manufacturing method thereof. The packaging structure comprises a circuit substrate, a first layer-adding line structure, a second layer-adding line structure, and a plurality of piezoelectric heat radiating units. The circuit substrate comprises a core layer, a plurality of electronic components, and a conducting unit. The electronic componentsare imbedded in the core layer, and the active surfaces of two adjacent electronic components respectively face towards the a first surface and a second surface of the core layer. The conducting unitis configured to the core layer and is electrically connected to the electronic components. The first and second layer-adding line structure are respectively configured to the first and second surface, and are respectively provided with at least one first opening and one second opening. Each piezoelectric heat radiating unit is corresponding to the active surface of the electronic component, andis electrically connected to the conducting unit, exposing from the first opening and the second opening. The invention is advantageous in that the electromagnetic wave interference among the electronic components can be prevented; the packaging is thin and volume can be small; the thin-type demand can be met.

Owner:UNIMICRON TECH CORP

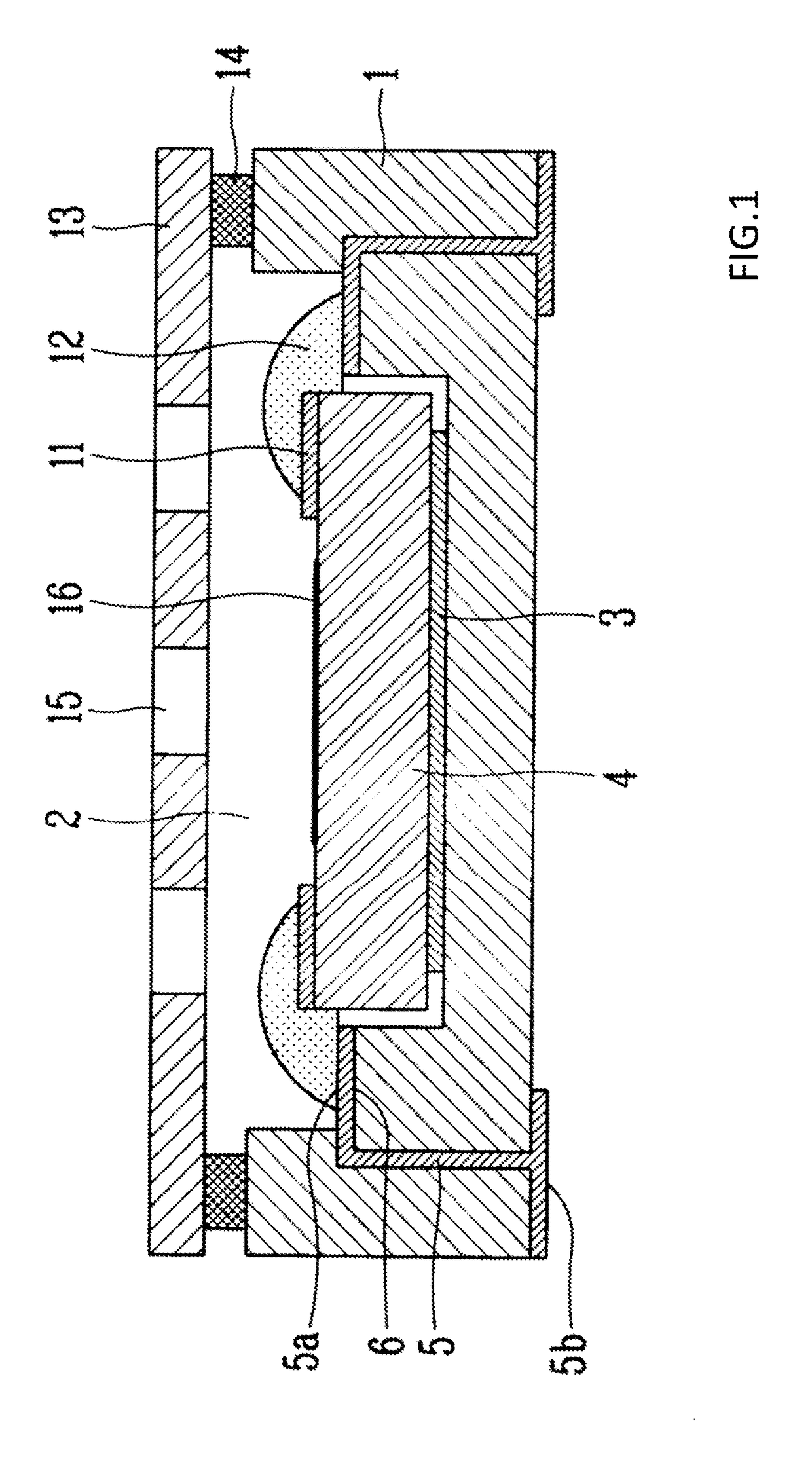

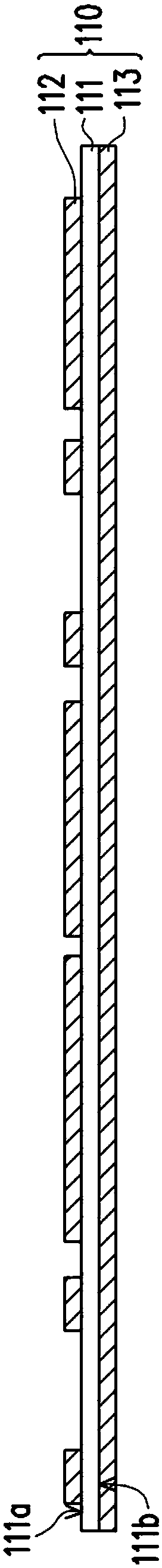

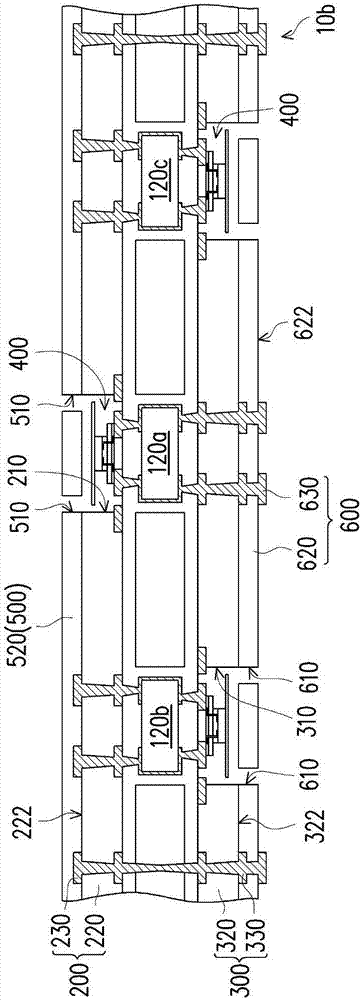

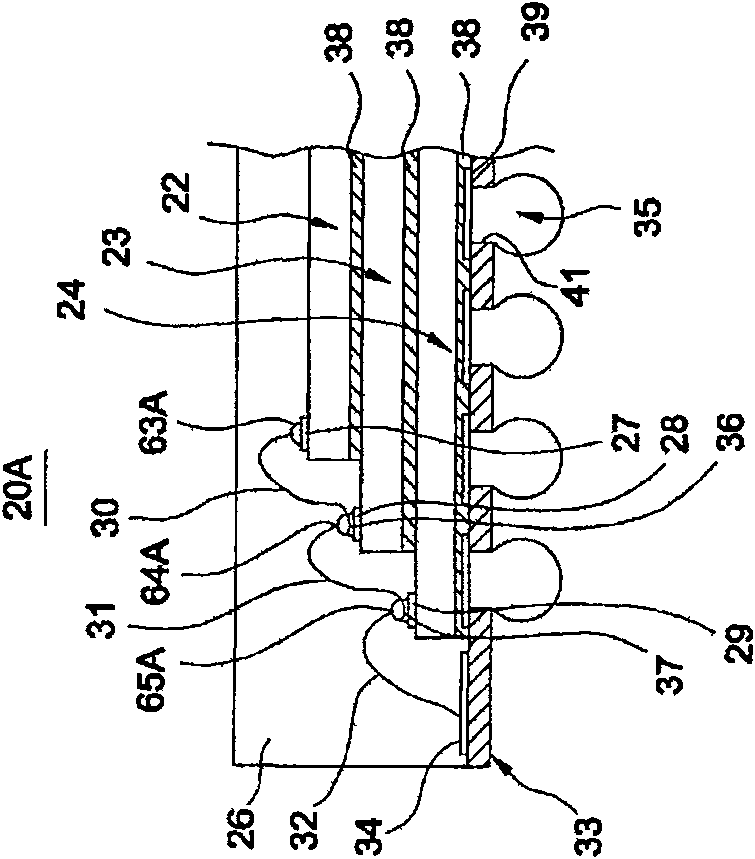

Stacking encapsulation structure with symmetric multi-chip migration up and down

ActiveCN101325194AHigh package densityThin Package ThicknessSemiconductor/solid-state device detailsSolid-state devicesColloidEngineering

The invention provides a multi-chip offset stacked package structure, which is symmetric on upper and lower sides. The multi-chip offset stacked package structure comprises a wire holder composed of a plurality of inner pin groups that are oppositely arranged and a chip bearing seat, wherein the chip bearing seat is positioned among the plurality of inner pin groups, and both the inner pin groups and the chip bearing seat have respective upper surfaces and low surfaces; a first multi-chip offset stacked package structure and a second multi-chip offset stacked package structure, which are respectively fixedly connected on the upper surface and the lower surface of the bearing seat of the chip; a plurality of metal wires for electronically connecting the first multi-chip offset stacked package structure and the second multi-chip offset stacked package structure with the inner pin groups; and a sealant for coating the first multi-chip offset stacked package structure, the second multi-chip offset stacked package structure, the inner pin groups and the bearing seat of the chip, and exposing outer pins.

Owner:CHIPMOS TECH INC

Package carrier and manufacturing method thereof

PendingCN113838829AImprove rigidityImprove packaging yieldSemiconductor/solid-state device detailsSolid-state devicesInterposerStructural engineering

The invention provides a package carrier and a manufacturing method thereof. The package carrier includes a substrate, at least one interposer, a conductive structure layer, a first build-up structure, and a second build-up structure. The interposer is disposed in the at least one opening of the substrate, and the interposer includes a glass substrate, at least one conductive via, at least one first pad, and at least one second pad. The conductive through hole penetrates through the glass substrate, and the first connecting pad and the second connecting pad are arranged on the upper surface and the lower surface, opposite to each other, of the glass substrate respectively and connected to the two opposite ends of the conductive through hole. The conductive structure layer is arranged on the substrate and is structurally and electrically connected with the first connecting pad and the second connecting pad. The first layer-adding structure and the second layer-adding structure are respectively configured on the first surface and the second surface of the substrate and are electrically connected with the conductive structure layer. The packaging carrier plate provided by the invention has better coplanarity.

Owner:UNIMICRON TECH CORP

Light emitting diode package structure

ActiveUS9496461B2Thin Package ThicknessHigh structural reliabilitySolid-state devicesSemiconductor devicesEngineeringThermal expansion

A LED package structure including a carrier substrate, a flip-chip LED and a molding compound is provided. The carrier substrate includes a main body and a patterned conductive layer embedded in the main body. The main body is composed of polymer material. The main body has a cavity, and a bottom surface of the cavity is aligned with an upper surface of the patterned conductive layer. A difference in coefficient of thermal expansion between the main body in a rubbery state and the patterned conductive layer is smaller than 30 ppm / ° C. The flip-chip LED is disposed inside the cavity and electrically connected to the patterned conductive layer. The molding compound is disposed inside the cavity and encapsulates the flip-chip LED. A vertical distance between a top surface of the molding compound and the bottom surface of the cavity is smaller than or equal to a depth of the cavity.

Owner:GENESIS PHOTONICS

Stacking encapsulation structure with symmetric multi-chip migration up and down

ActiveCN100590866CHigh package densityThin Package ThicknessSemiconductor/solid-state device detailsSolid-state devicesEngineeringSealant

The invention provides a multi-chip offset stacked package structure, which is symmetric on upper and lower sides. The multi-chip offset stacked package structure comprises a wire holder composed of aplurality of inner pin groups that are oppositely arranged and a chip bearing seat, wherein the chip bearing seat is positioned among the plurality of inner pin groups, and both the inner pin groupsand the chip bearing seat have respective upper surfaces and low surfaces; a first multi-chip offset stacked package structure and a second multi-chip offset stacked package structure, which are respectively fixedly connected on the upper surface and the lower surface of the bearing seat of the chip; a plurality of metal wires for electronically connecting the first multi-chip offset stacked package structure and the second multi-chip offset stacked package structure with the inner pin groups; and a sealant for coating the first multi-chip offset stacked package structure, the second multi-chip offset stacked package structure, the inner pin groups and the bearing seat of the chip, and exposing outer pins.

Owner:CHIPMOS TECH INC

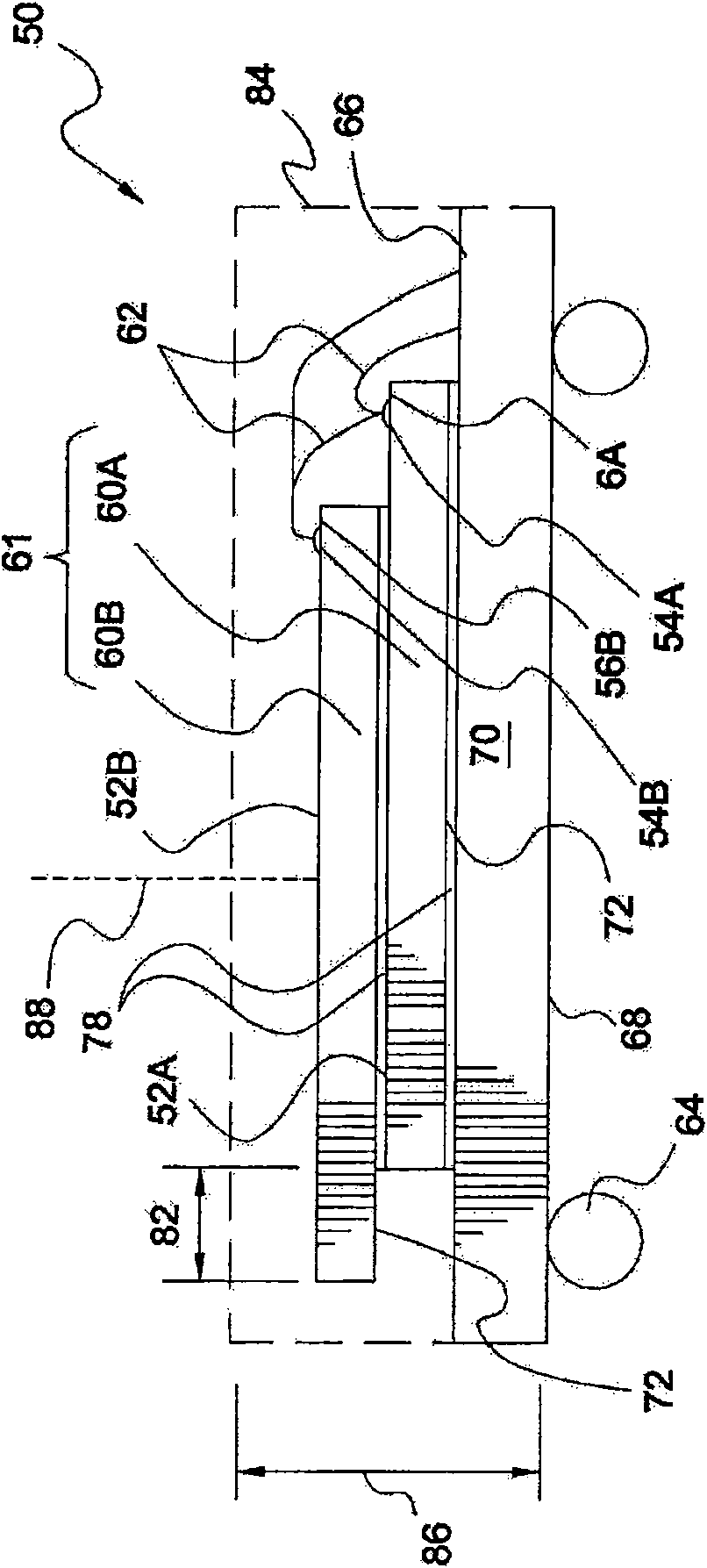

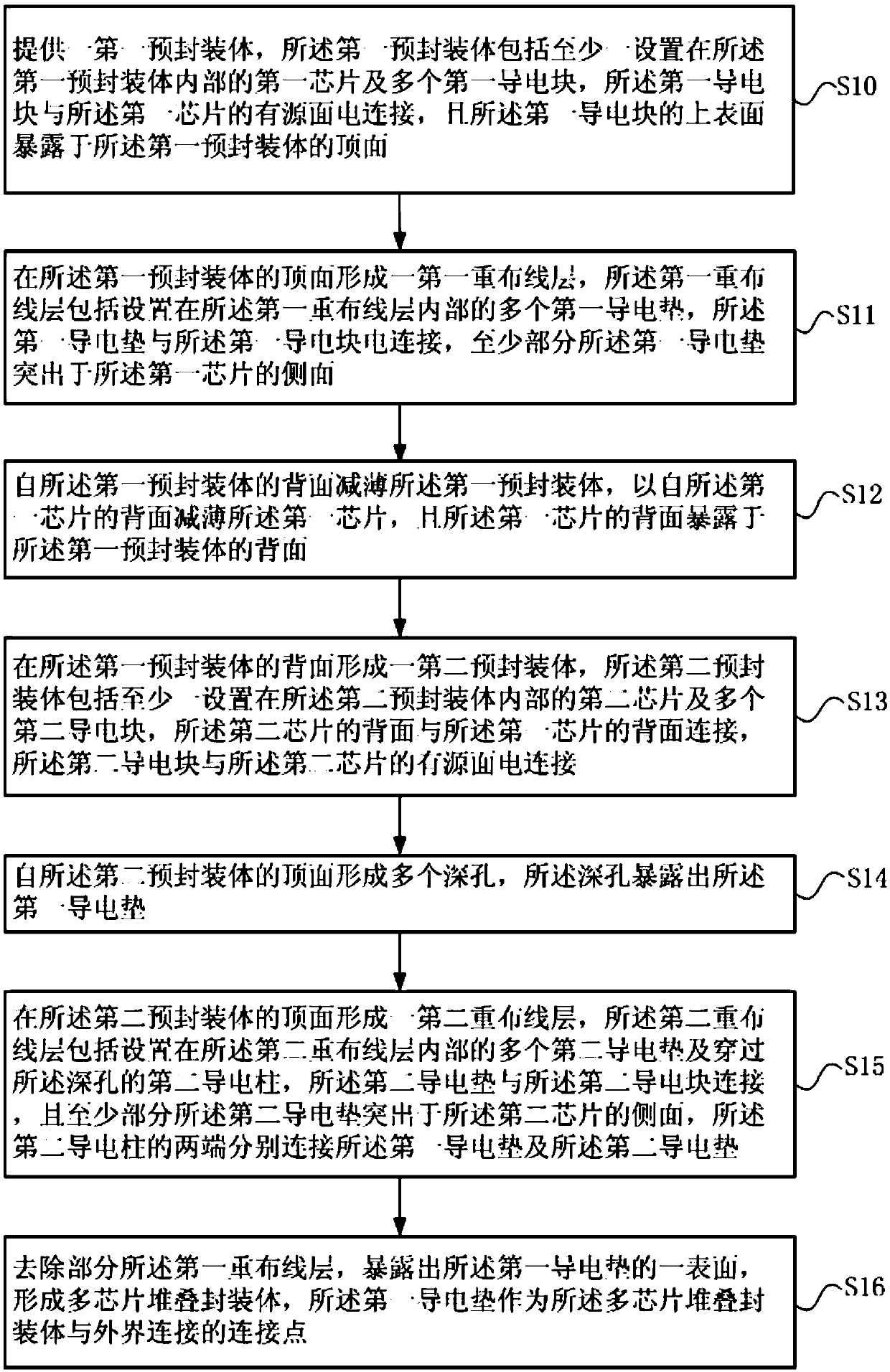

Multi-chip stacked packaging method and multi-chip stacked package body

PendingCN109659278AThin Package ThicknessReduce package sizeSemiconductor/solid-state device detailsSolid-state devicesThermal conductivityRedistribution layer

The invention provides a multi-chip stacked packaging method and a multi-chip stacked package body. The method has the advantages that the interconnection between the stacked chips is realized by useof the combination of the redistribution layer and the conductive pillars; the method replaces the commonly used routing technique and substrate inversion technique for traditional package of stackedchips; and compared with the traditional chip-stacked layer BGA package, the overall package thickness is quite small, the package size is quite small under the condition of the same number of chips,and good electrical conductivity, thermal conductivity and reliability are achieved.

Owner:HEFEI SMAT TECH CO LTD

Encapsulation structure and manufacturing method thereof

ActiveCN107978575BAvoid electromagnetic interferenceThin Package ThicknessSemiconductor/solid-state device detailsSolid-state devicesHemt circuitsEngineering

The invention relates to a packaging structure and a manufacturing method thereof. The packaging structure comprises a circuit substrate, a first layer-adding line structure, a second layer-adding line structure, and a plurality of piezoelectric heat radiating units. The circuit substrate comprises a core layer, a plurality of electronic components, and a conducting unit. The electronic componentsare imbedded in the core layer, and the active surfaces of two adjacent electronic components respectively face towards the a first surface and a second surface of the core layer. The conducting unitis configured to the core layer and is electrically connected to the electronic components. The first and second layer-adding line structure are respectively configured to the first and second surface, and are respectively provided with at least one first opening and one second opening. Each piezoelectric heat radiating unit is corresponding to the active surface of the electronic component, andis electrically connected to the conducting unit, exposing from the first opening and the second opening. The invention is advantageous in that the electromagnetic wave interference among the electronic components can be prevented; the packaging is thin and volume can be small; the thin-type demand can be met.

Owner:UNIMICRON TECH CORP

Light emitting device package structure and manufacturing method thereof

InactiveUS20180151781A1Thin Package ThicknessLow costSolid-state devicesSemiconductor/solid-state device manufacturingLight emitting deviceElectrode

A light emitting device package structure and a manufacturing method thereof are provided. The light emitting device package structure includes a light emitting device and a protecting element. The light emitting device has an upper surface and a lower surface opposite to each other, a side surface connecting the upper surface and the lower surface and a first electrode pad and a second electrode pad located on the lower surface and separated from each other. The protecting element encapsulates the side surface of the light emitting device and exposes at least portion of the upper surface, at least portion of a first bottom surface of the first electrode pad and at least portion of a second bottom surface of the second electrode pad.

Owner:GENESIS PHOTONICS

Piezoelectric Power Converter

ActiveCN101924479BIncrease output powerAchieve the effect of high power outputAc-dc conversion without reversalElectricityCapacitance

The invention discloses a piezoelectric power supply converter. A traditional capacitor is replaced by using a piezoelectric assembly. Because the piezoelectric assembly has higher capacitance than the traditional capacitor and can produce inverse voltage effect during power-on deformation and produce positive piezoelectric effect after the deformation to generate positive charges, the piezoelectric assembly has voltage amplification effect, achieves high-power output and can overcome the defects of low voltage, high leakage current and low power output of the traditional capacitor.

Owner:MIDAS WEI TRADING +1

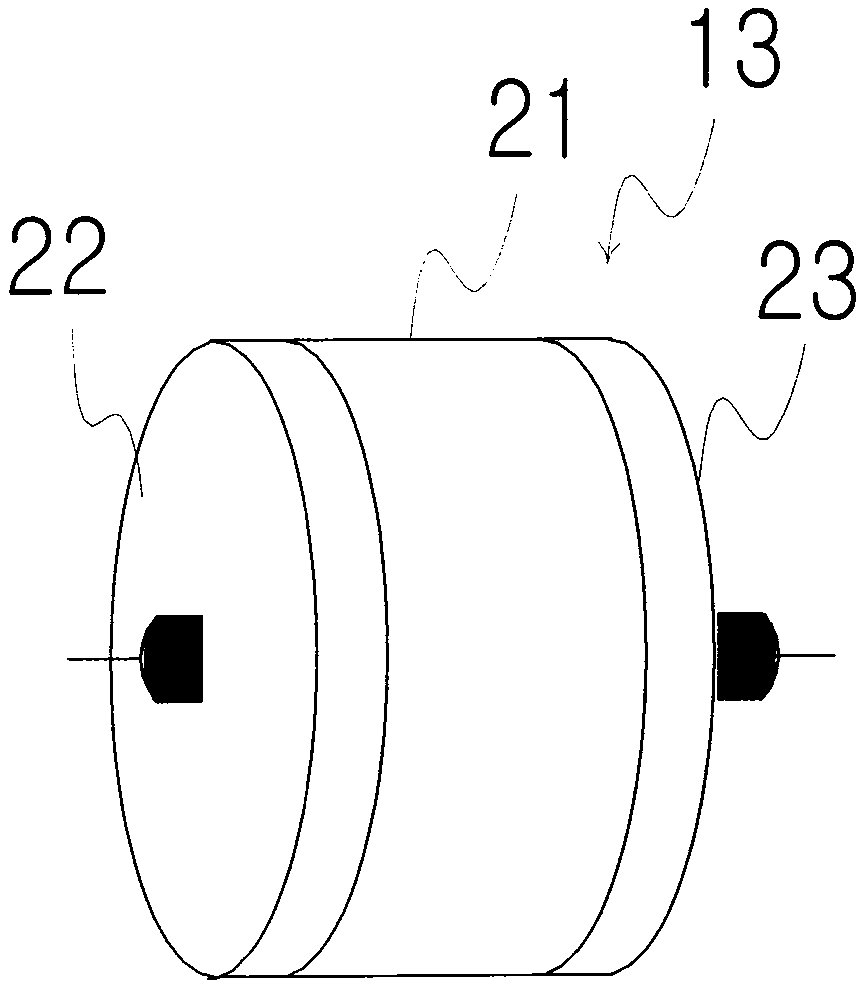

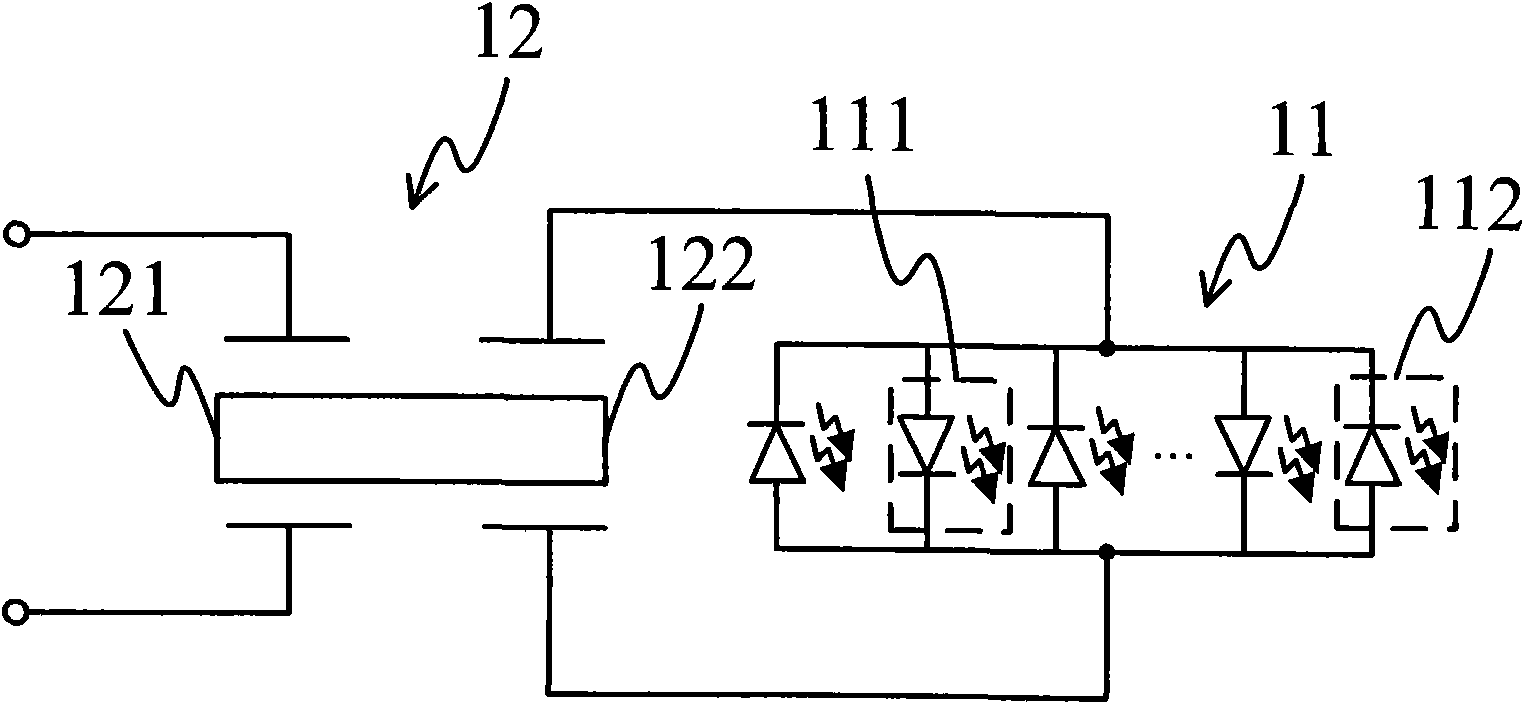

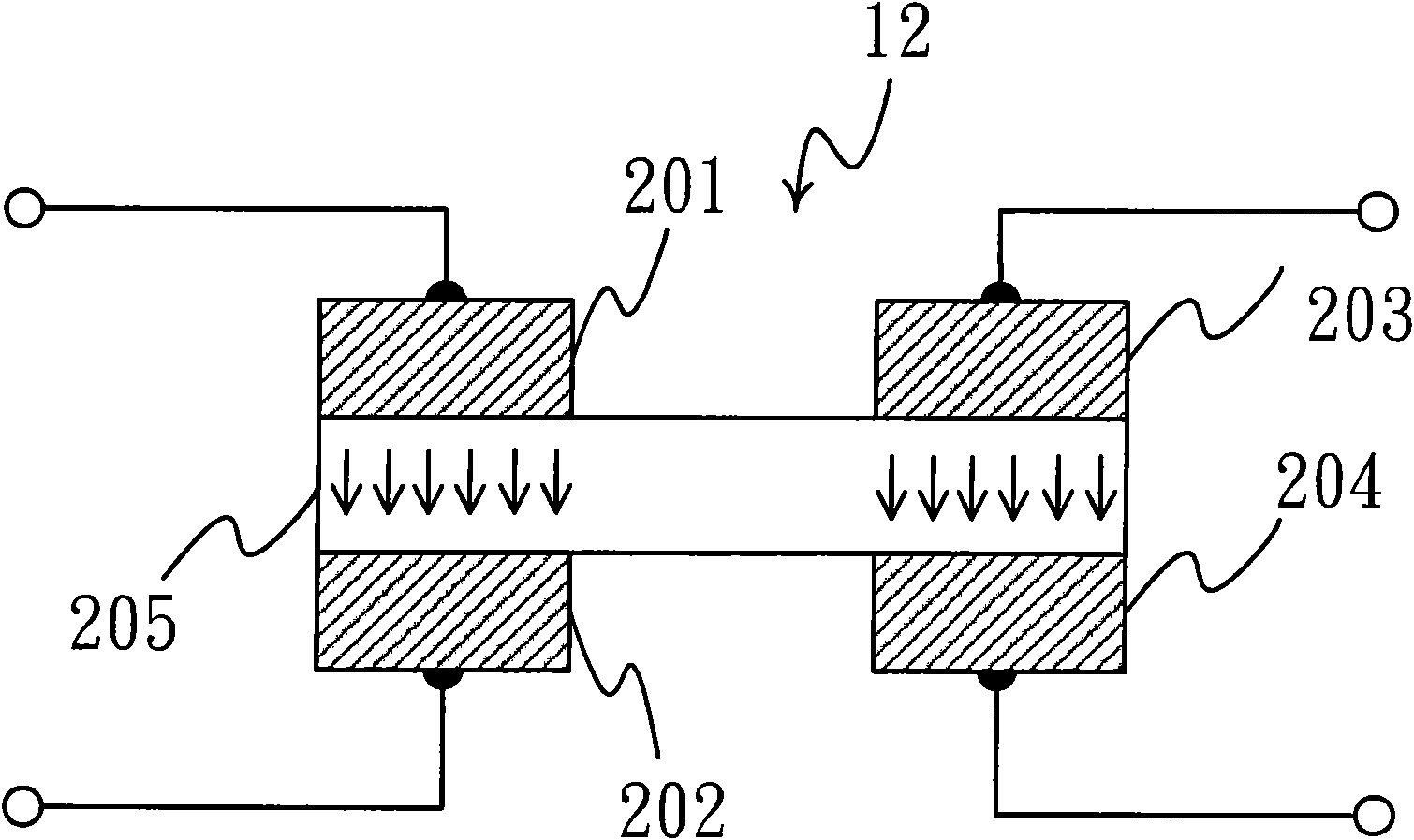

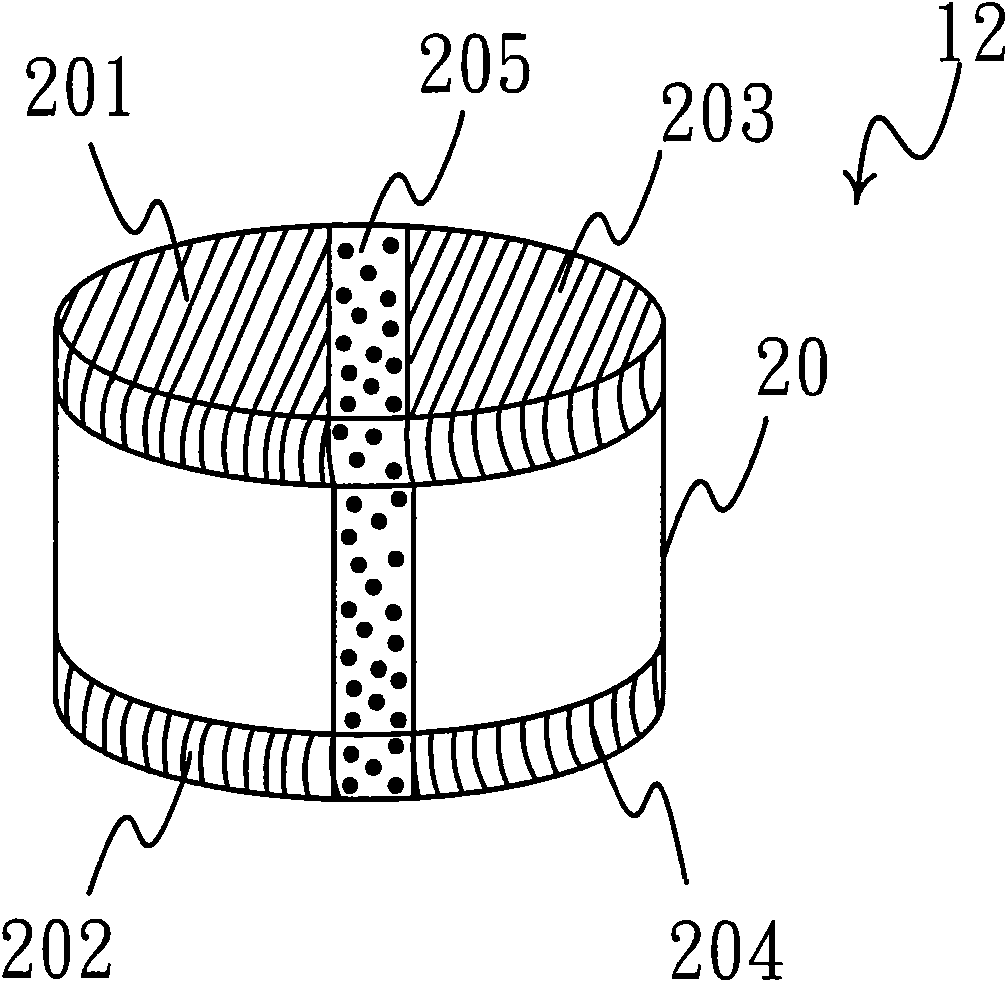

Lighting device for driving light-emitting diode by using insulated piezoelectric transformer

InactiveCN101998712AReduce lossImprove power conversion efficiencyPoint-like light sourceElectric circuit arrangementsPiezoelectric voltageEngineering

The invention discloses a lighting device for driving a light-emitting diode (LED) by using an insulated piezoelectric transformer. The lighting device comprises at least one insulated piezoelectric transformer connected to an LED module, the primary side of the insulated piezoelectric transformer receives pulse signals, the pulse signals are converted into an alternating current voltage in a piezoelectric voltage transformation mode, and the secondary side of the insulated piezoelectric transformer outputs the alternating current voltage to the LED module to drive lighting. Because of the advantages of low leakage current, good insulating property, high pressure resistance, low temperature, small volume, thin packing thickness, high conversion efficiency and the like, the insulated piezoelectric transformer can improve the lighting efficiency and even can reduce the volume effect of the whole lighting driving device.

Owner:MIDAS WEI TRADING +1

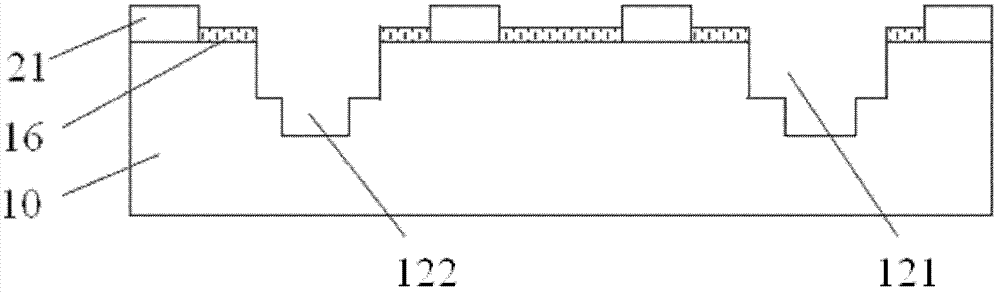

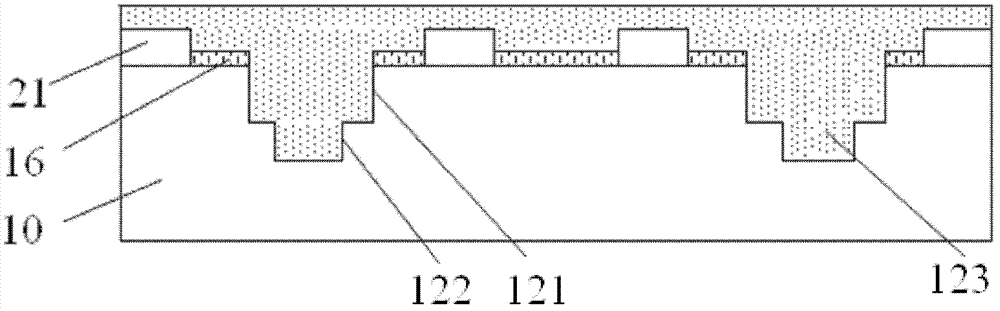

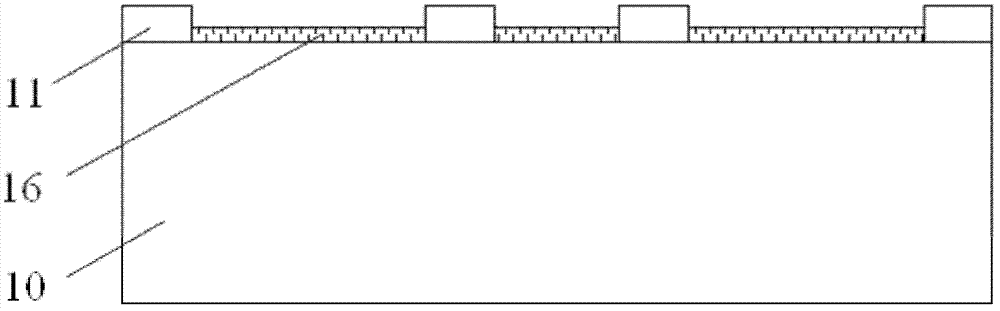

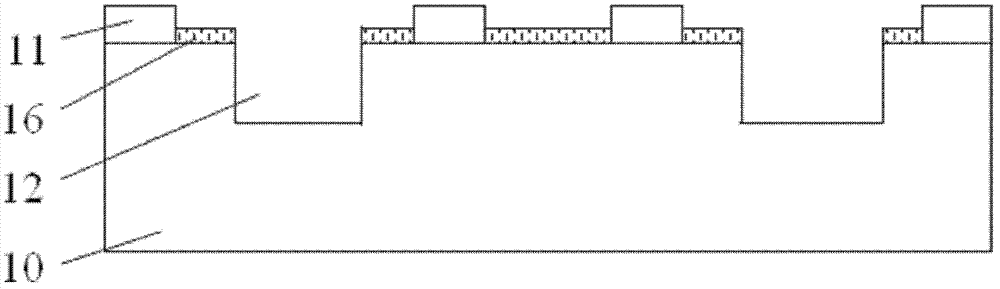

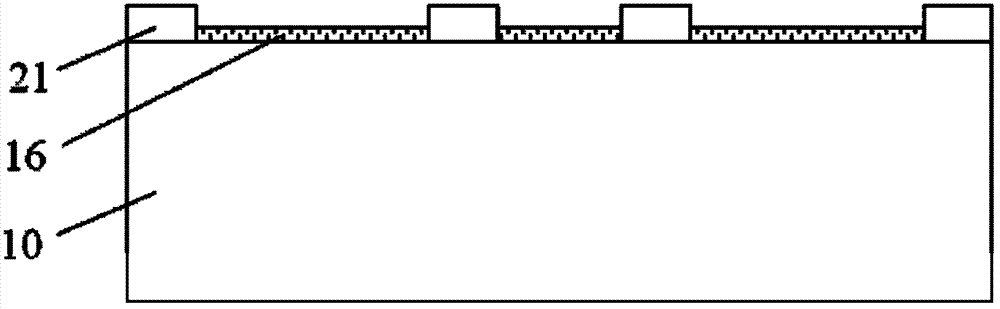

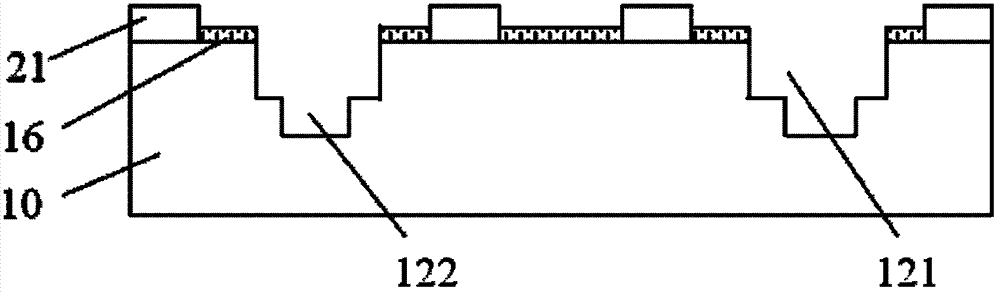

Semiconductor technology and the silicon substrate and chip packaging structure formed by applying this technology

InactiveCN101752261BThin Package ThicknessSemiconductor/solid-state device detailsSolid-state devicesPhotoresistSemiconductor technology

The invention provides a semiconductor process and a silicon substrate and a chip packaging structure formed by applying the process. First, a silicon substrate is provided. Next, a surface of the silicon substrate is partially exposed, and the surface of the silicon substrate is etched, so that the silicon substrate is formed with at least one stepped shape with a first notch having a first depth and a second notch having a second depth structure. The first depth is smaller than the second depth, and the aperture of the first notch is larger than the aperture of the second notch. A final insulating layer, a metal seed layer and a ladder-like structure are sequentially formed. A patterned photoresist layer is formed on the metal seed layer. A circuit layer is formed to cover part of the metal seed layer exposed above the first notch. Afterwards, the patterned photoresist layer and part of the metal seed layer under it are removed.

Owner:UNIMICRON TECH CORP

Chip packaging structure and manufacturing method thereof

PendingCN113192895ASmall body and weightLow manufacturing costSemiconductor/solid-state device detailsSolid-state devicesElectrically conductiveStructural engineering

The invention provides a chip packaging structure and a manufacturing method thereof. The manufacturing method of the chip packaging structure comprises the following steps that: a carrier plate on which a plurality of conductive blocks and at least one metal layer have been formed is provided, the carrier plate comprises a base material and a stainless steel layer sputtered on the base material, the base material is provided with a plurality of first grooves and at least one second groove surrounding the first grooves, the stainless steel layer conformally covers the first grooves and the second grooves to define a plurality of third grooves and at least one fourth groove, the third grooves are filled with the conductive blocks, the metal layer covers the stainless steel layer, the conductive blocks and the fourth grooves to define at least one fifth groove; at least one chip is arranged in the fifth groove; at least one circuit structure layer is formed on the carrier plate; the patterned circuit layer of the circuit structure layer is electrically connected with the plurality of electrodes of the chip; and the carrier plate and the circuit structure layer are separated to expose the conductive blocks and the metal layer.

Owner:何崇文

Wafer-level packaging method and packaging structure thereof

ActiveCN103117232BAvoid displacementRealize the requirements of light, thin and shortSemiconductor/solid-state device detailsSolid-state devicesHigh densityMechanical engineering

The invention relates to a wafer-level packaging method and a packaging structure thereof. The packaging method comprises the following steps: providing a wafer which contains chip units; carrying out first protrusion fabrication process on the front face of the wafer; carrying out grooving twice between adjacent protrusions of the adjacent chip units on the front face of the wafer, wherein the width of a first groove is larger than that of a second groove, the depth of the first groove is smaller than that of the second groove and smaller than the thickness of the chip units, and the centers of the second groove and the first groove are on the same straight line which is perpendicular to the surface of the wafer; filling coating materials in the first groove and the second groove; coating the back face of the wafer, wherein the height of the coating materials is higher than the back surface of the wafer; and carrying out simplified cutting. Through a wafer protrusion technology, wafer-level partial grooving and wafer-level coating material filling, high-density input / output ports of products and high reliability are achieved, the products are light, thin and short, productivity is high, and cost is low.

Owner:MEMSIC SEMICON WUXI

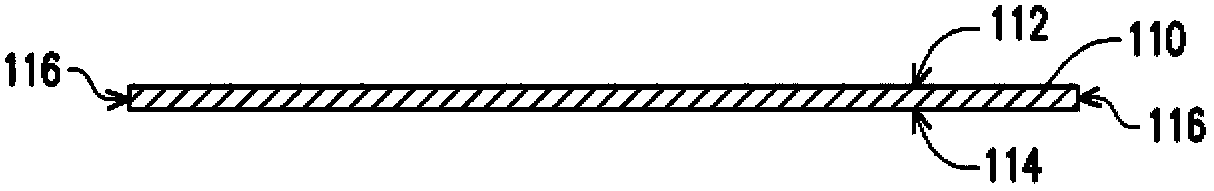

High-frequency IC circuit packing structure and its production

InactiveCN100438008CShorten the electrical conduction pathNo additional production cost requiredSemiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit

The invention is concerned with the conformation and the manufacture method of the high frequency integrated circuit, it comprising of: the base plate, the protruding chip and plural number of conducting filling. The base plat consists of the circuit layer and plural number of protruding containing via hole crossing from upper surface to bottom surface. The initiative surface of the protruding chip sticks to the upper surface of the base plate in order that the plural number of the protruding blocks of the protruding chip contains in the corresponding protruding containing via hole. The conducting filling forms in the protruding containing via hole in order to electric connect the protruding blocks to the circuit layer.

Owner:CHIPMOS TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com