Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

34results about How to "Reducing penalty" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

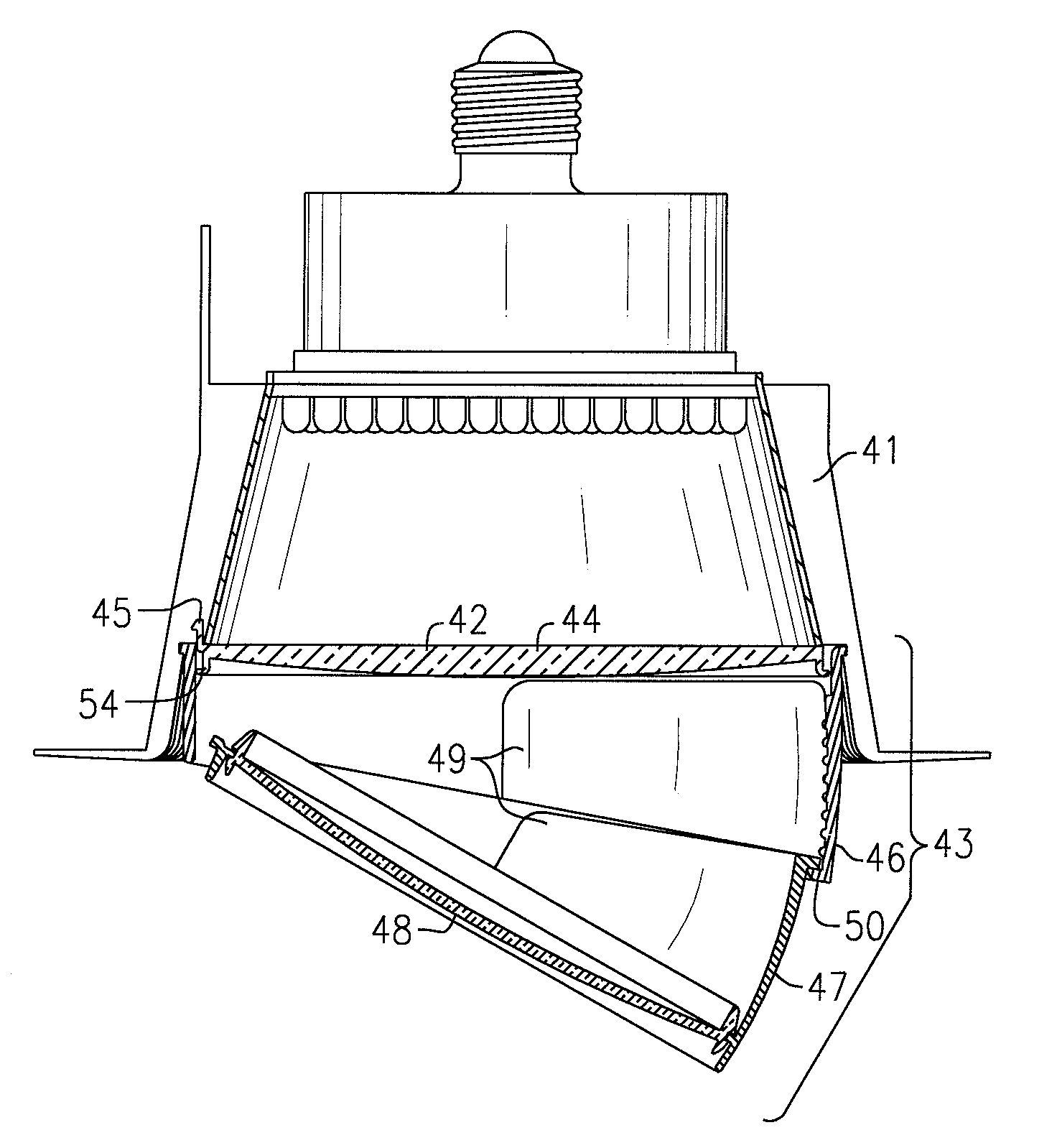

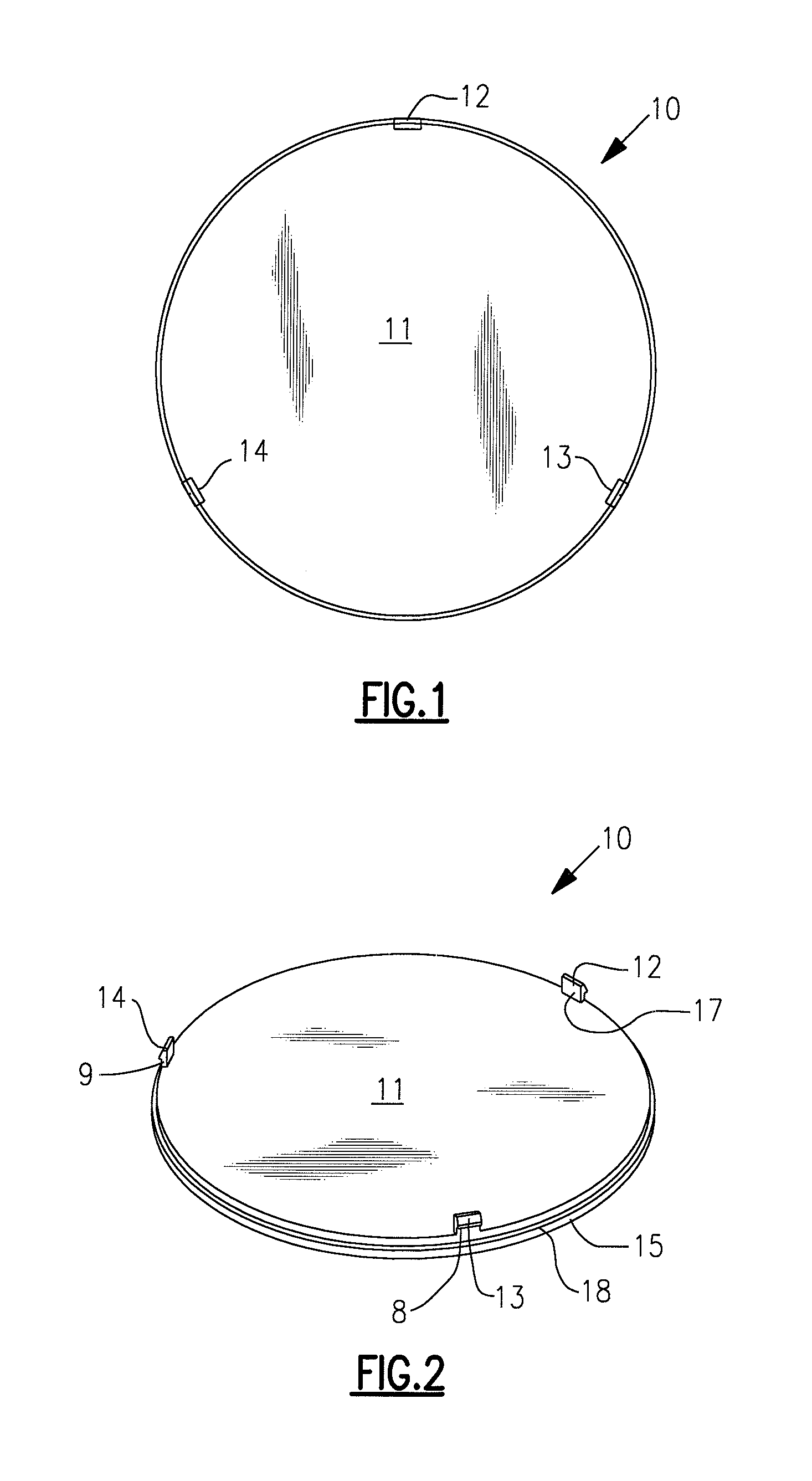

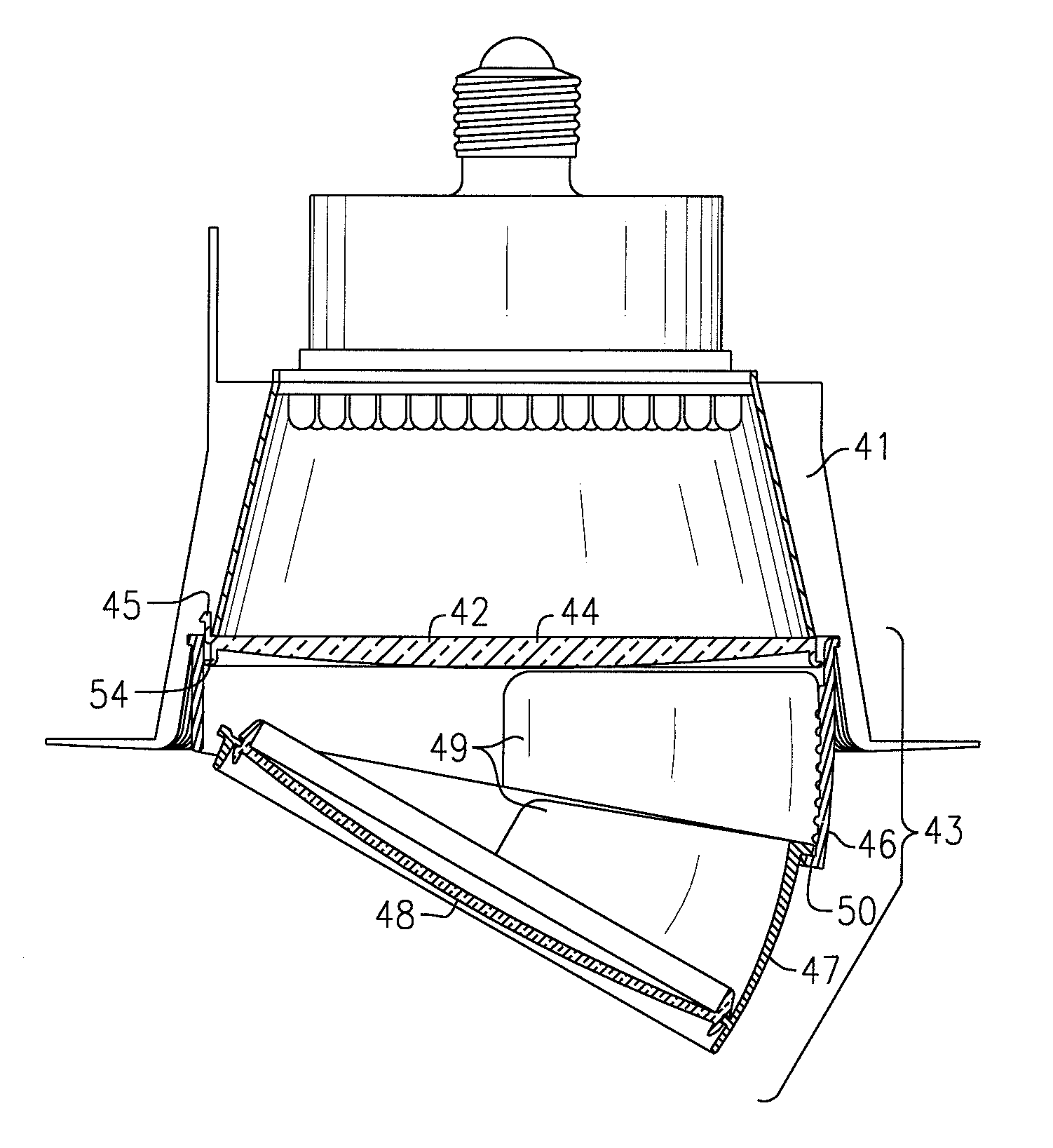

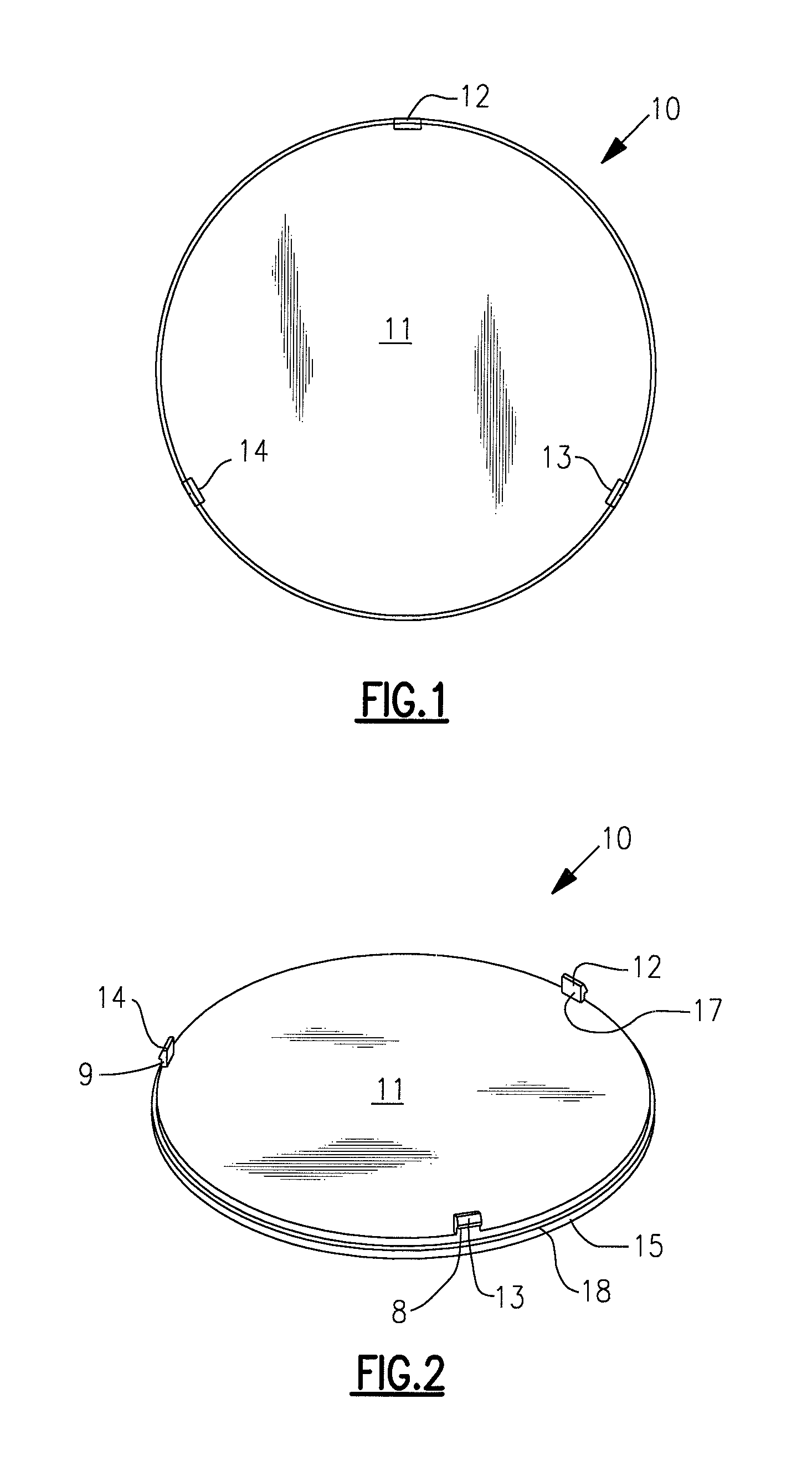

Light fixtures, lighting devices, and components for the same

ActiveUS20080137347A1Easy to removeGood adhesionPoint-like light sourceProtective devices for lightingLight equipmentEffect light

A diffuser for a lighting device comprises a diffuser region, a hook element and a nose element. A light fixture comprises a housing with an opening and a diffuser as described above, in which the nose element extends through the opening, optionally further comprising an accessory including at least one spring element engaging the hook element. A light fixture structure comprises a housing defining an opening and an first attachment element comprising a nose element, a hook element and a connection region, and optionally further comprising a diffuser engaging a first portion of the hook element, and / or an accessory which engages a second portion of the hook element. An eyeball accessory comprises first and second housing elements pivotably attached to each other. An accessory for a light fixture comprises a housing member and a spring element engageable with a fixture.

Owner:IDEAL IND LIGHTING LLC

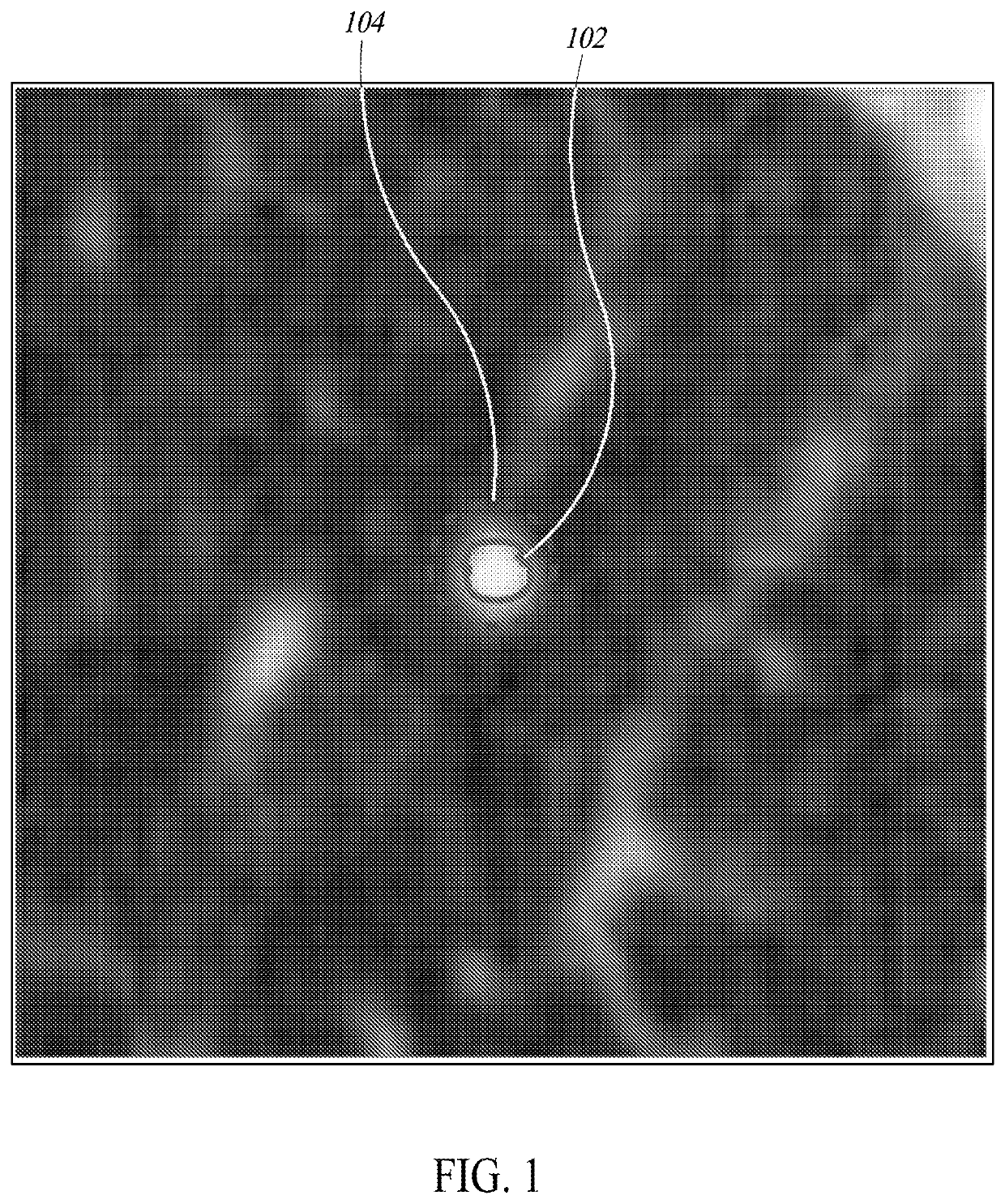

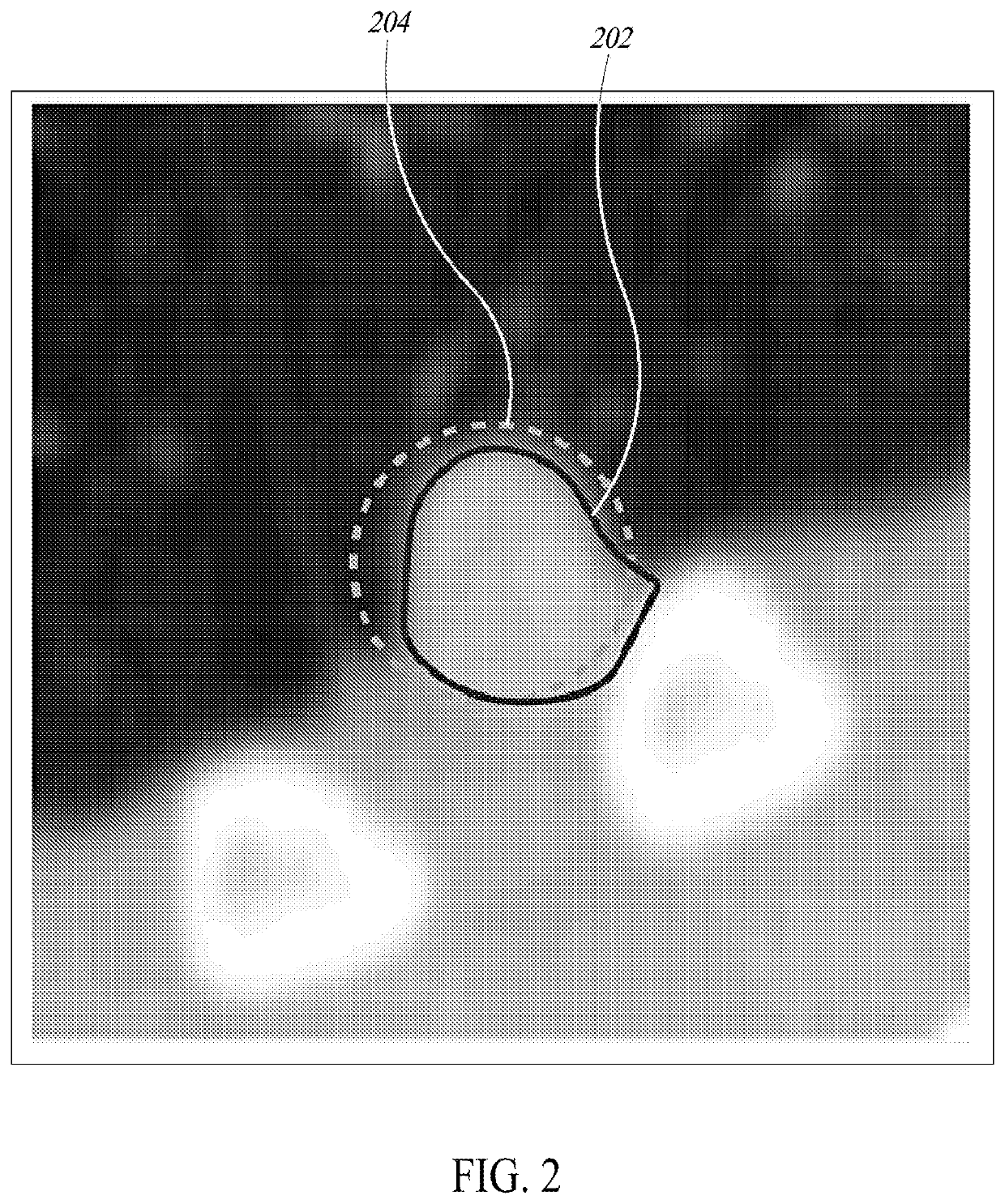

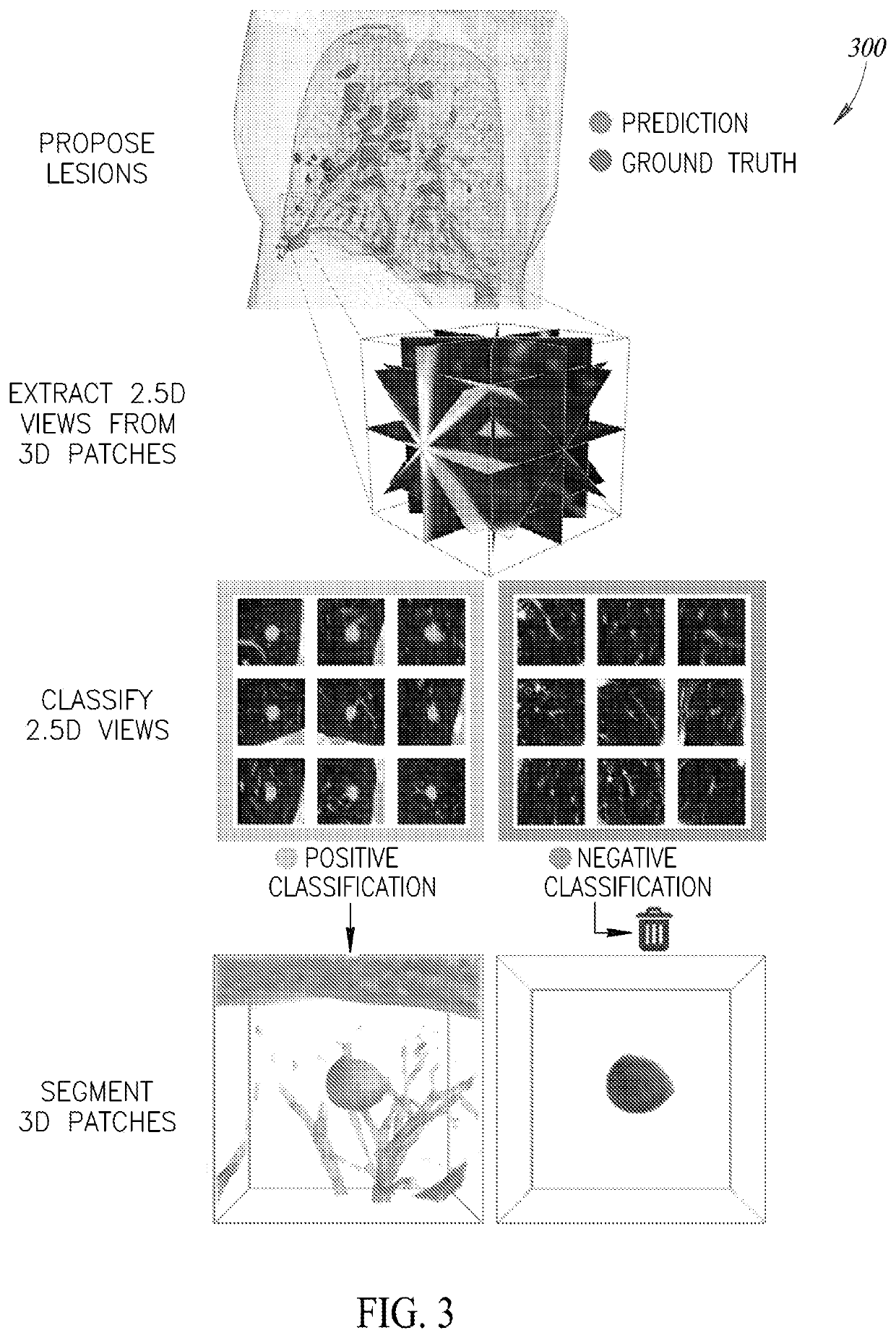

Automated lesion detection, segmentation, and longitudinal identification

InactiveUS20200085382A1Reducing penaltyImage enhancementQuantum computersComputed tomographyLesion detection

Computed Tomography (CT) and Magnetic Resonance Imaging (MRI) are commonly used to assess patients with known or suspected pathologies of the lungs and liver. In particular, identification and quantification of possibly malignant regions identified in these high-resolution images is essential for accurate and timely diagnosis. However, careful quantitative assessment of lung and liver lesions is tedious and time consuming. This disclosure describes an automated end-to-end pipeline for accurate lesion detection and segmentation.

Owner:ARTERYS INC

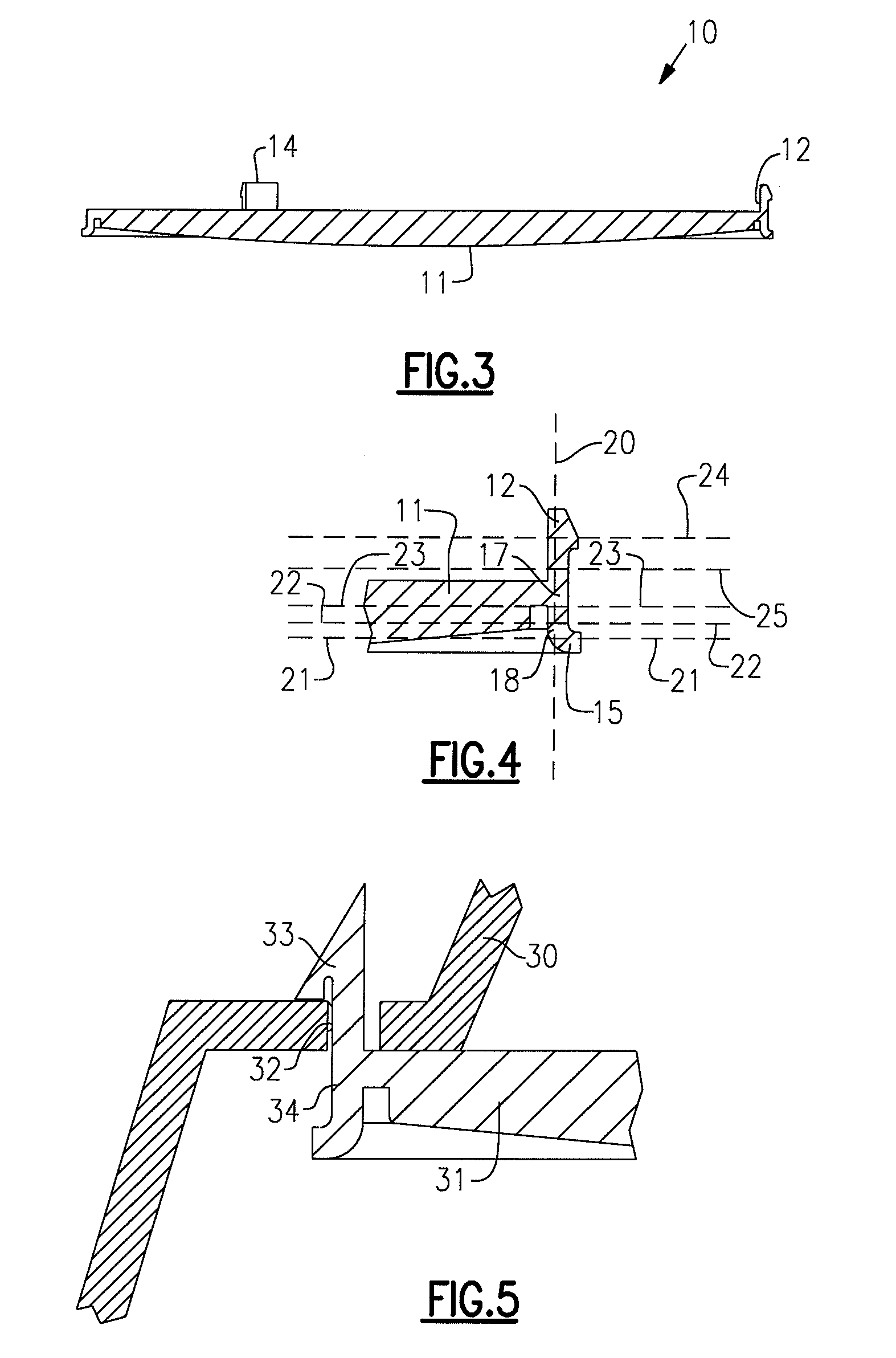

Light fixtures, lighting devices, and components for the same

ActiveUS8096670B2Readily be removed and attachedEasy typingPoint-like light sourceProtective devices for lightingLight equipmentEffect light

A diffuser for a lighting device comprises a diffuser region, a hook element and a nose element. A light fixture comprises a housing with an opening and a diffuser as described above, in which the nose element extends through the opening, optionally further comprising an accessory including at least one spring element engaging the hook element. A light fixture structure comprises a housing defining an opening and an first attachment element comprising a nose element, a hook element and a connection region, and optionally further comprising a diffuser engaging a first portion of the hook element, and / or an accessory which engages a second portion of the hook element. An eyeball accessory comprises first and second housing elements pivotably attached to each other. An accessory for a light fixture comprises a housing member and a spring element engageable with a fixture.

Owner:IDEAL IND LIGHTING LLC

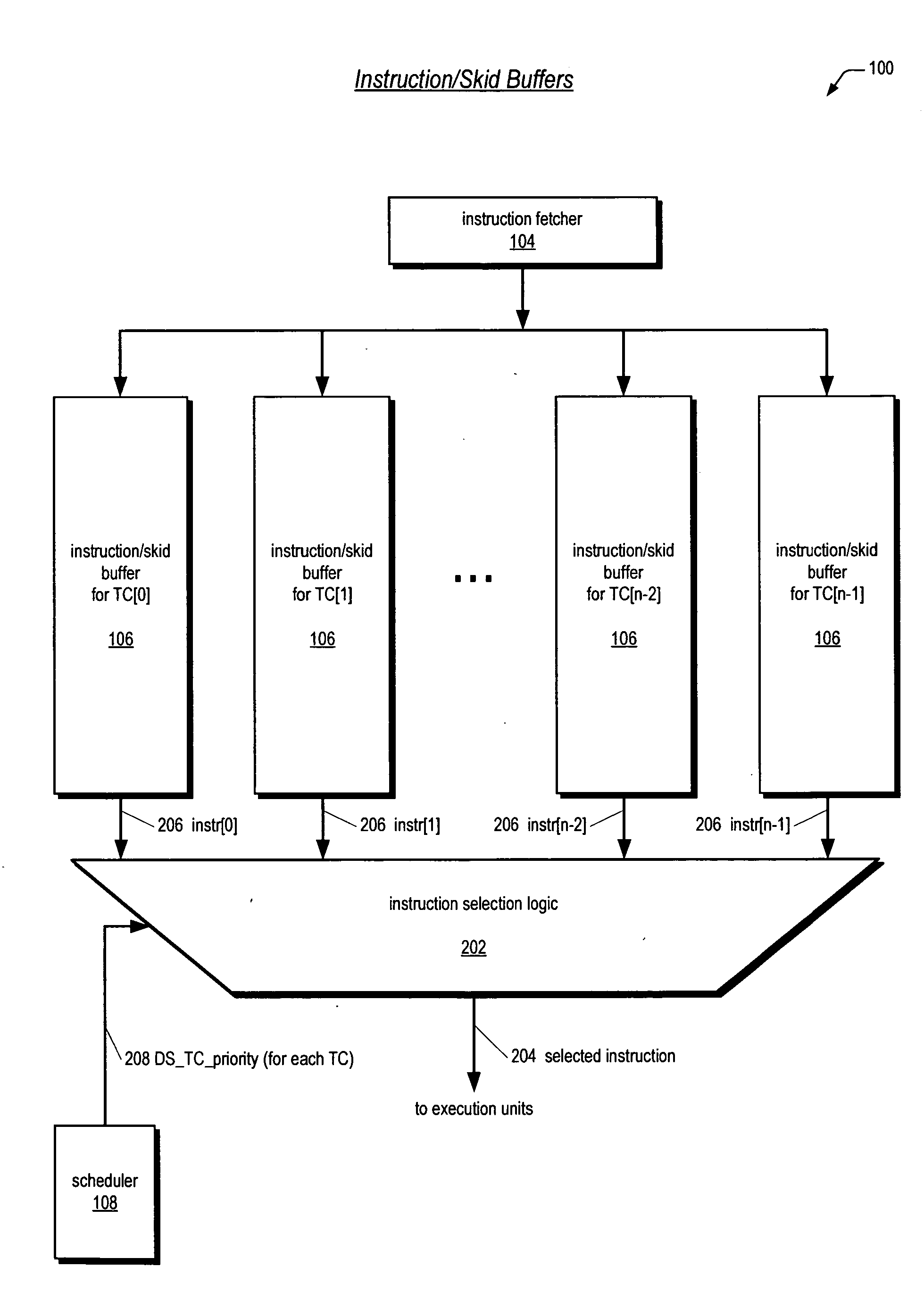

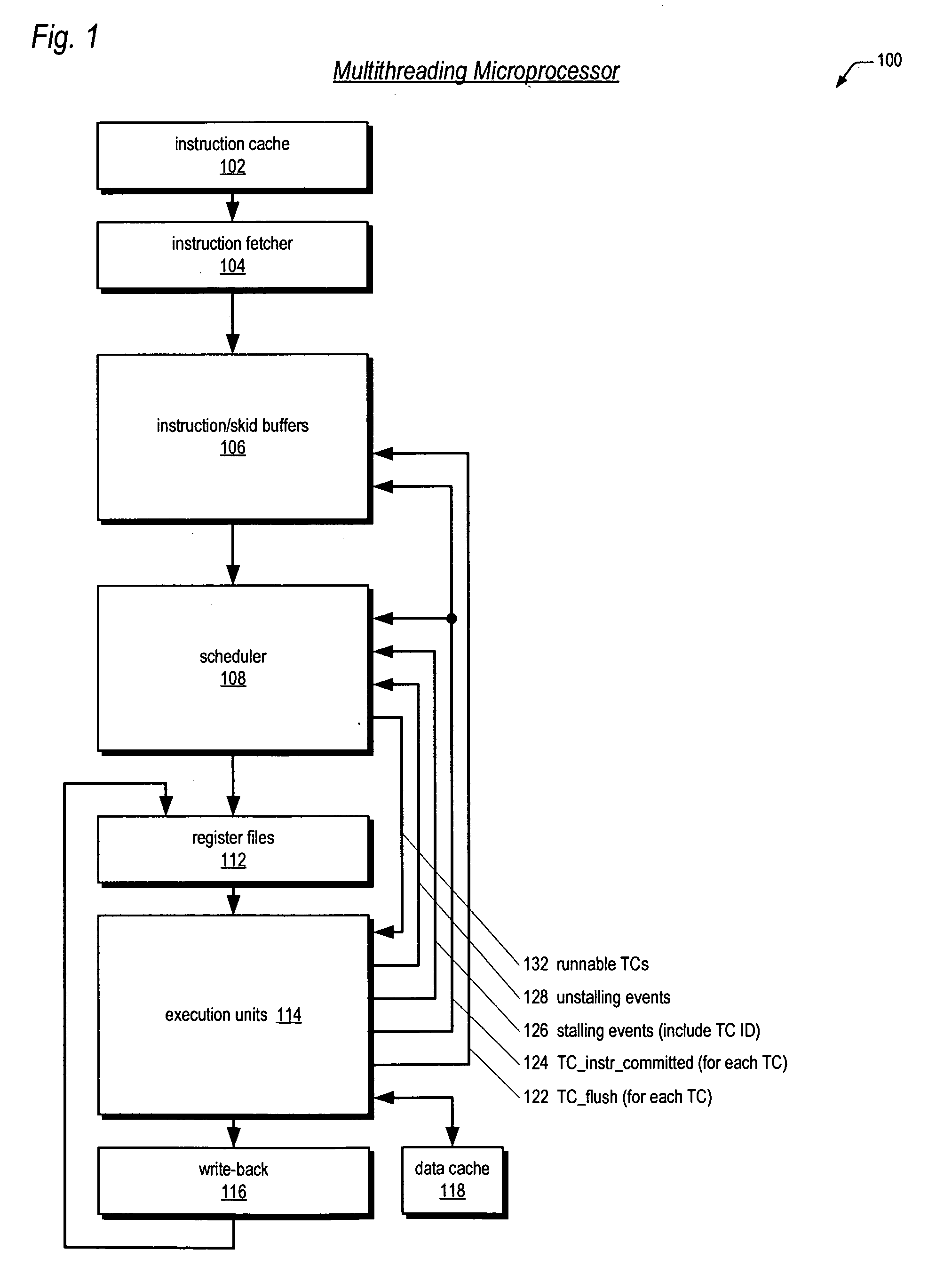

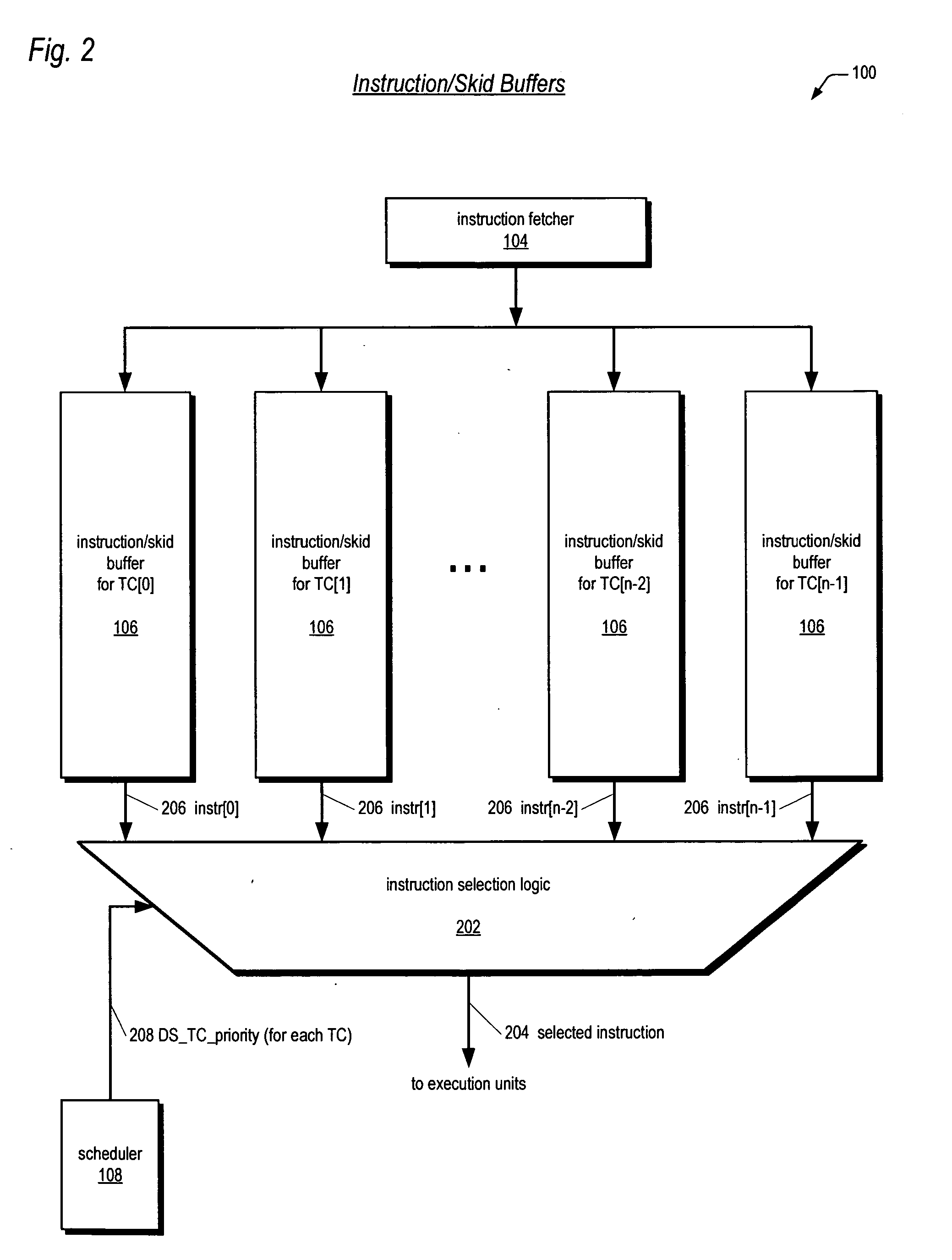

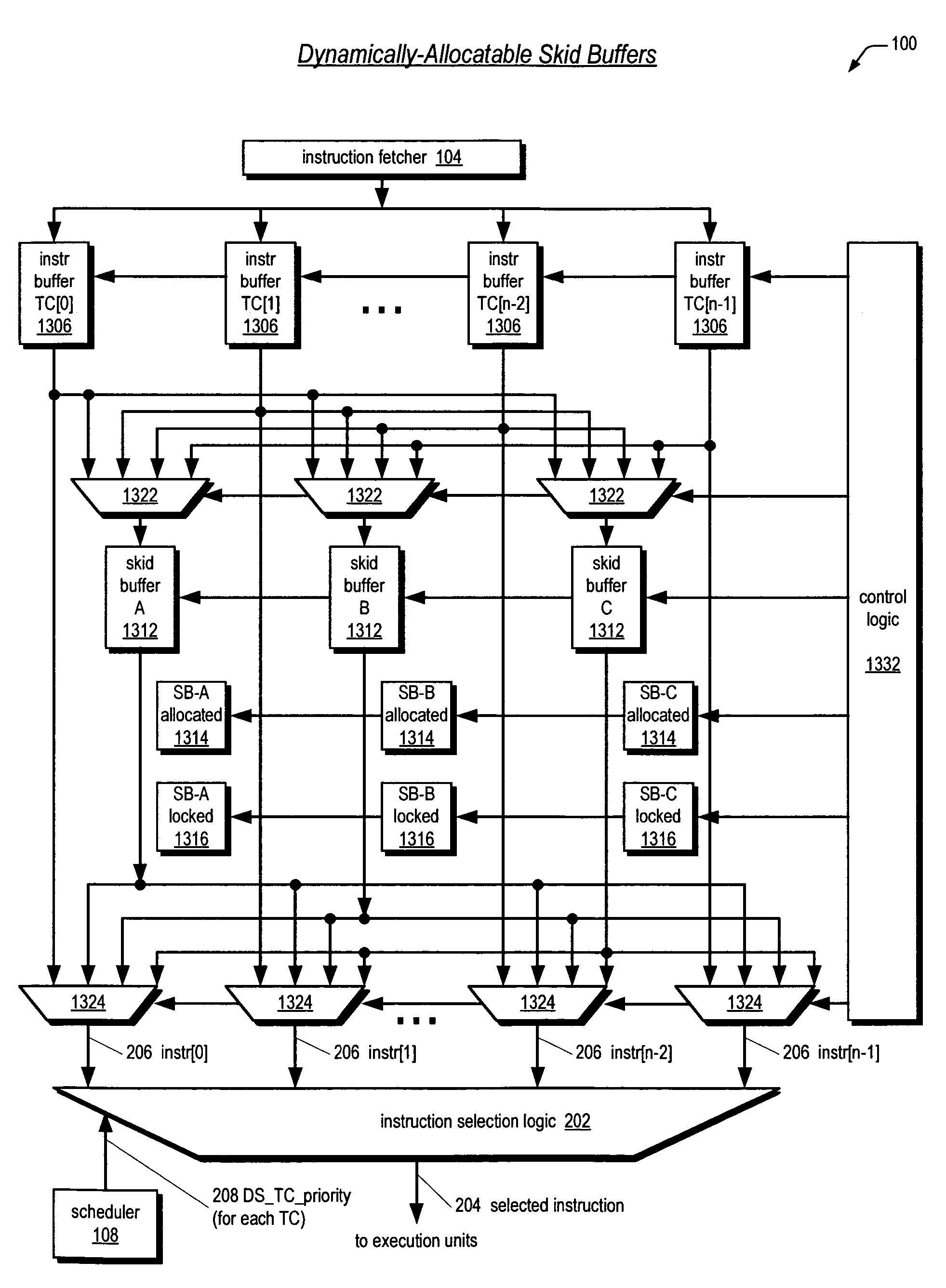

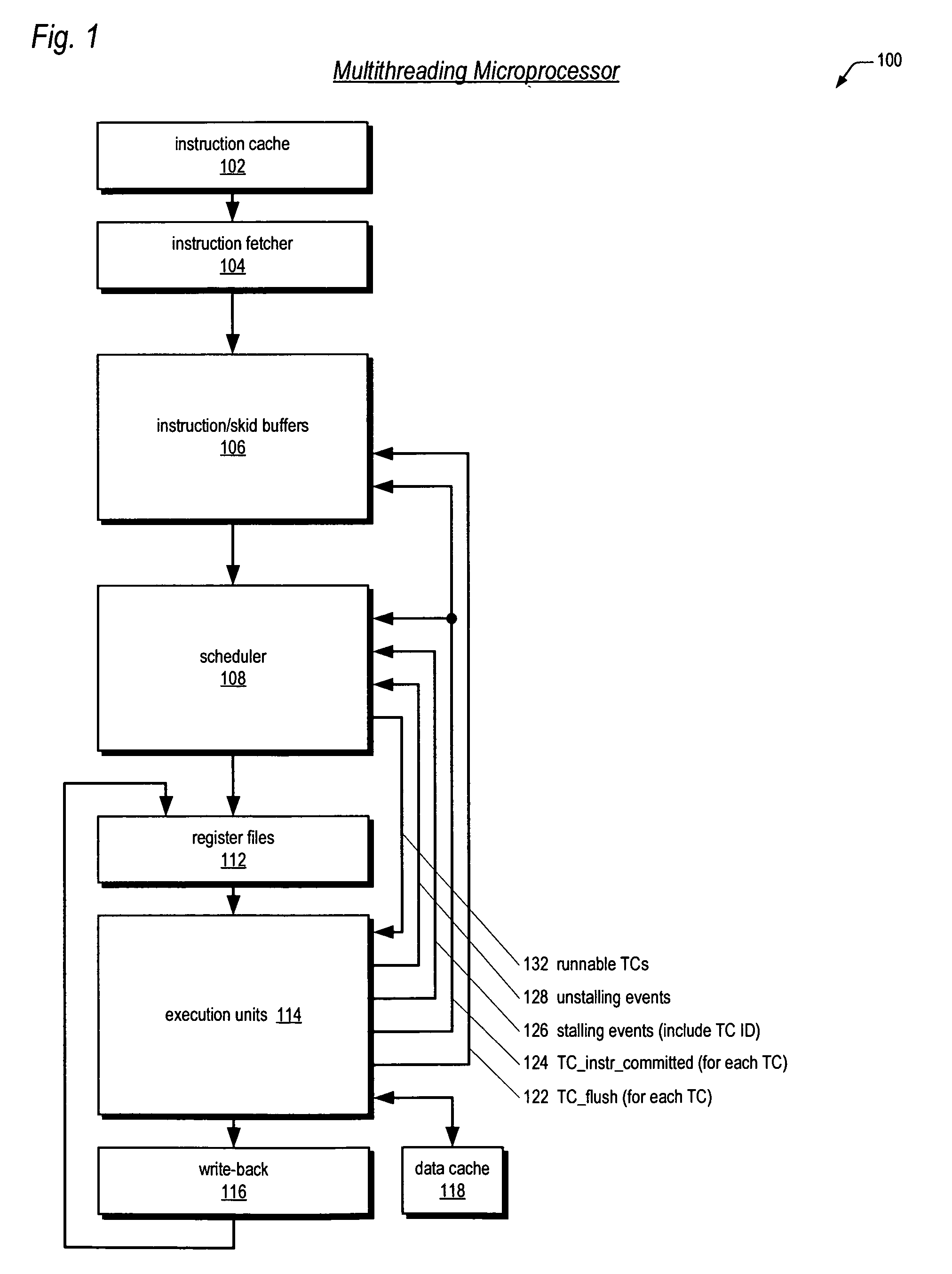

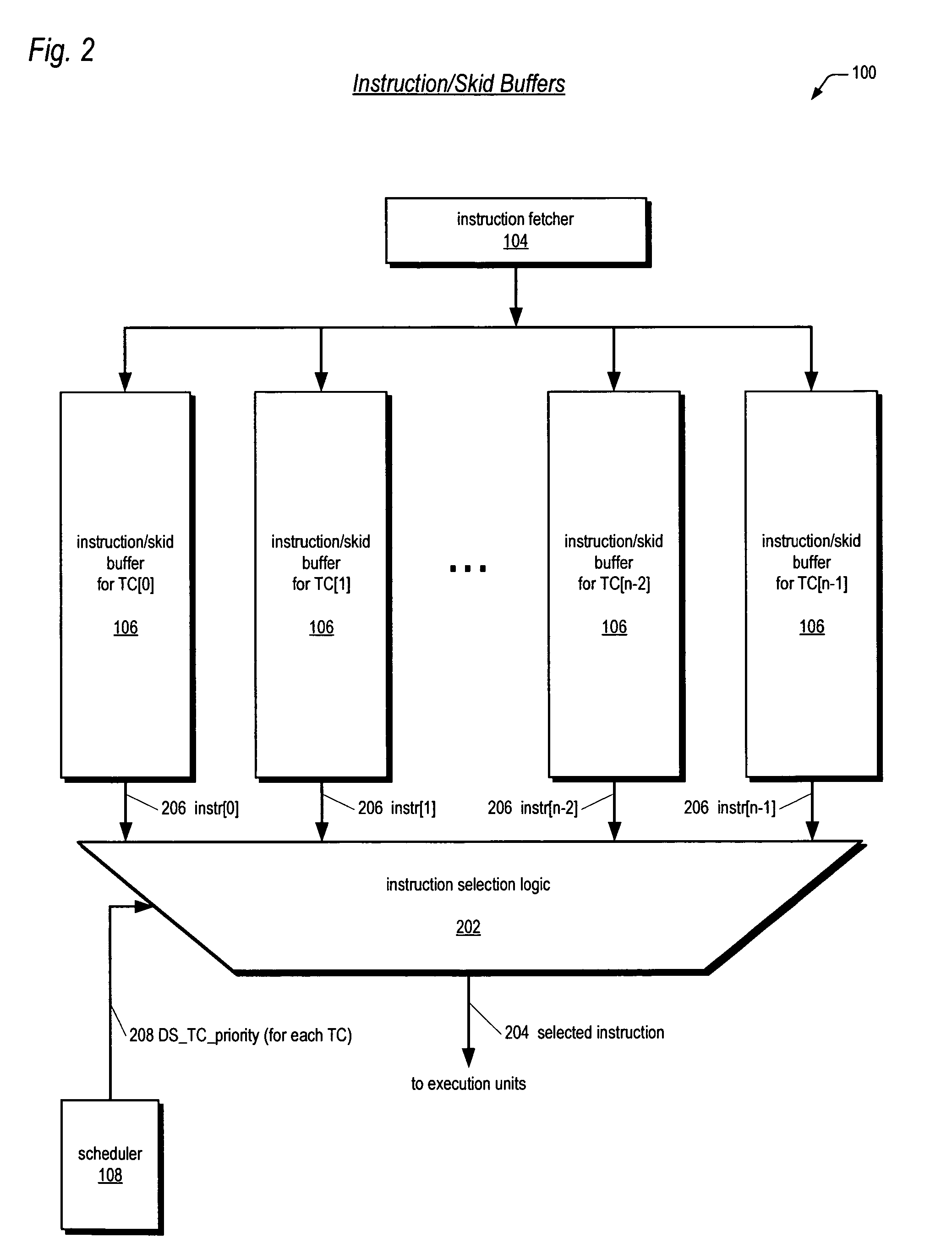

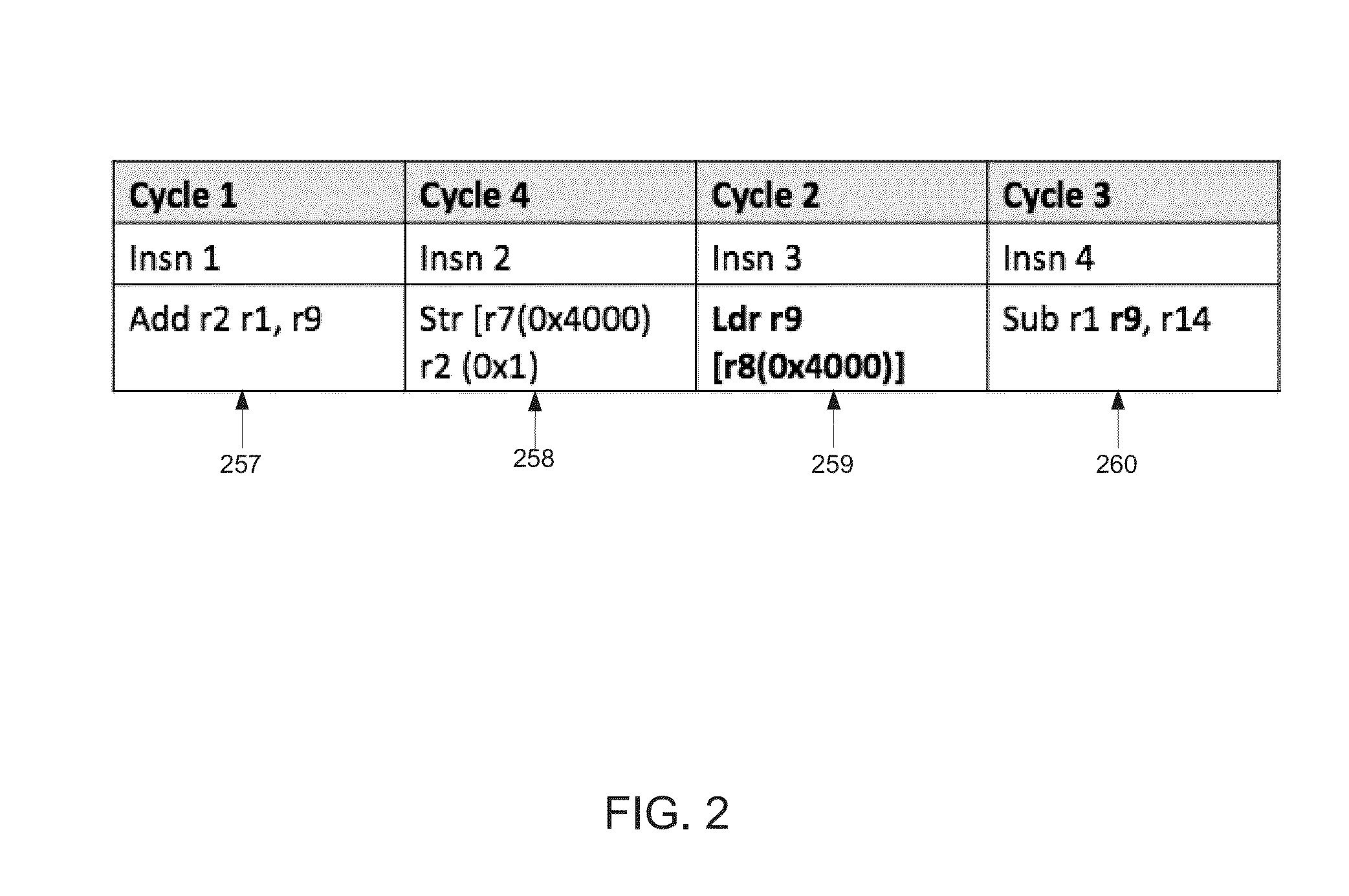

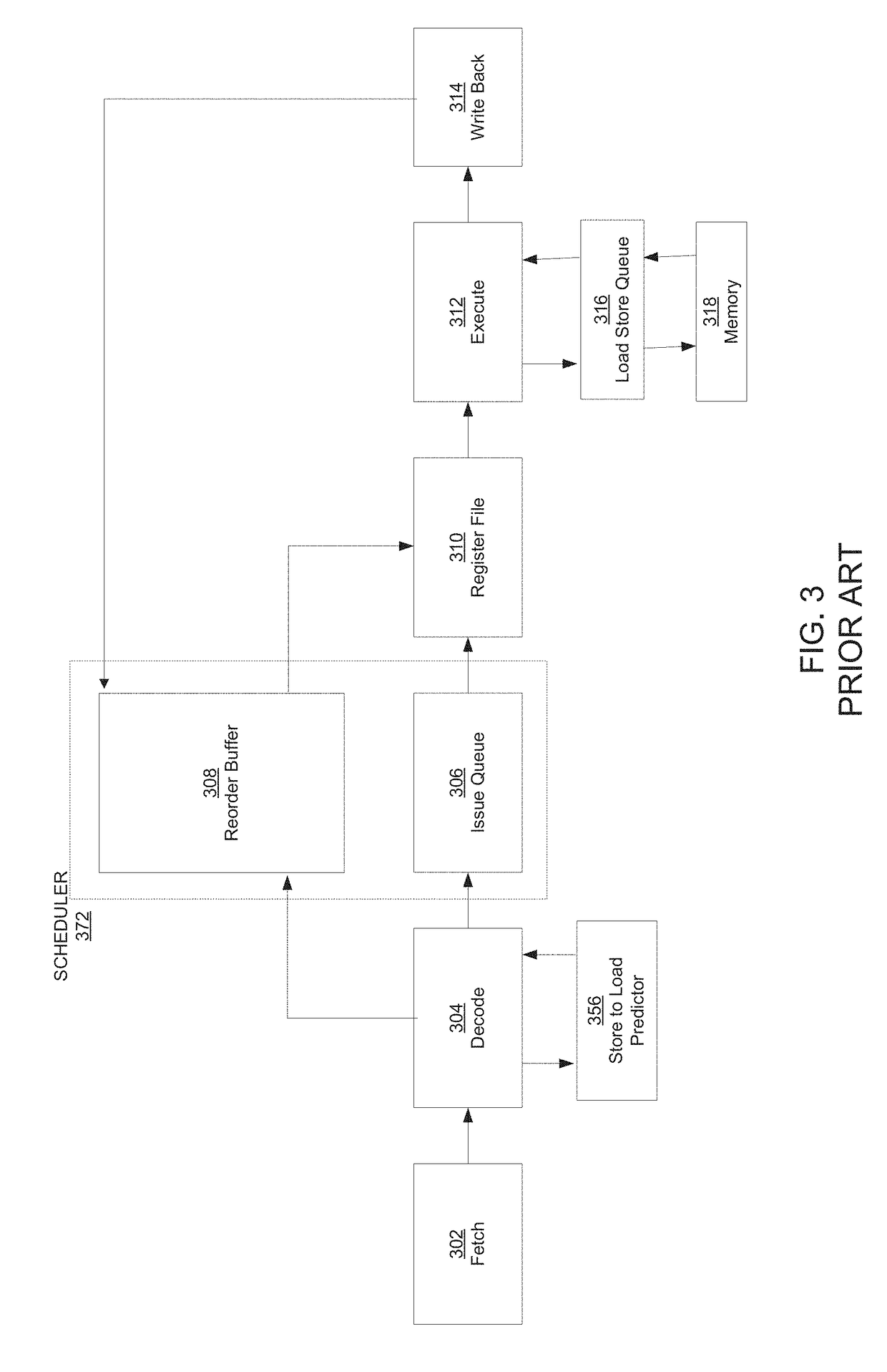

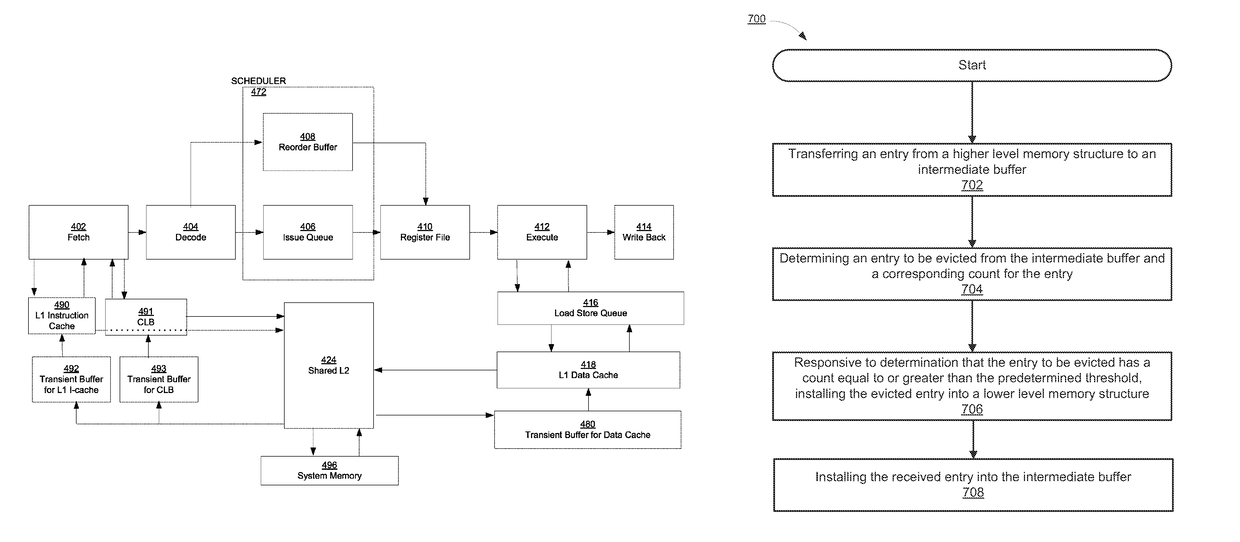

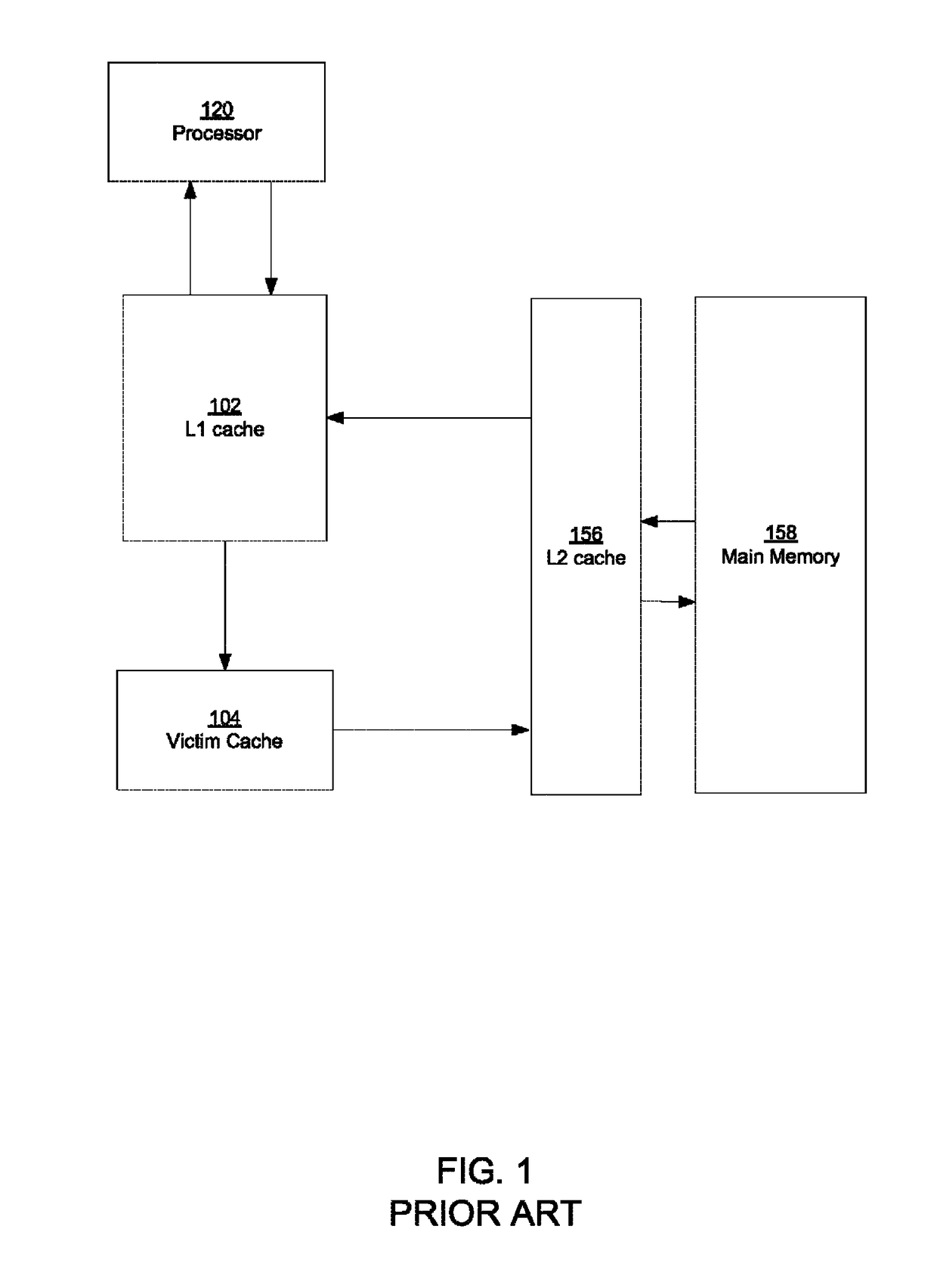

Instruction/skid buffers in a multithreading microprocessor

ActiveUS20060179274A1Reduce the amount requiredImprove processor performanceDigital computer detailsMemory systemsParallel computingControl logic

An apparatus for reducing instruction re-fetching in a multithreading processor configured to concurrently execute a plurality of threads is disclosed. The apparatus includes a buffer for each thread that stores fetched instructions of the thread, having an indicator for indicating which of the fetched instructions in the buffer have already been dispatched for execution. An input for each thread indicates that one or more of the already-dispatched instructions in the buffer has been flushed from execution. Control logic for each thread updates the indicator to indicate the flushed instructions are no longer already-dispatched, in response to the input. This enables the processor to re-dispatch the flushed instructions from the buffer to avoid re-fetching the flushed instructions. In one embodiment, there are fewer buffers than threads, and they are dynamically allocatable by the threads. In one embodiment, a single integrated buffer is shared by all the threads.

Owner:MIPS TECH INC

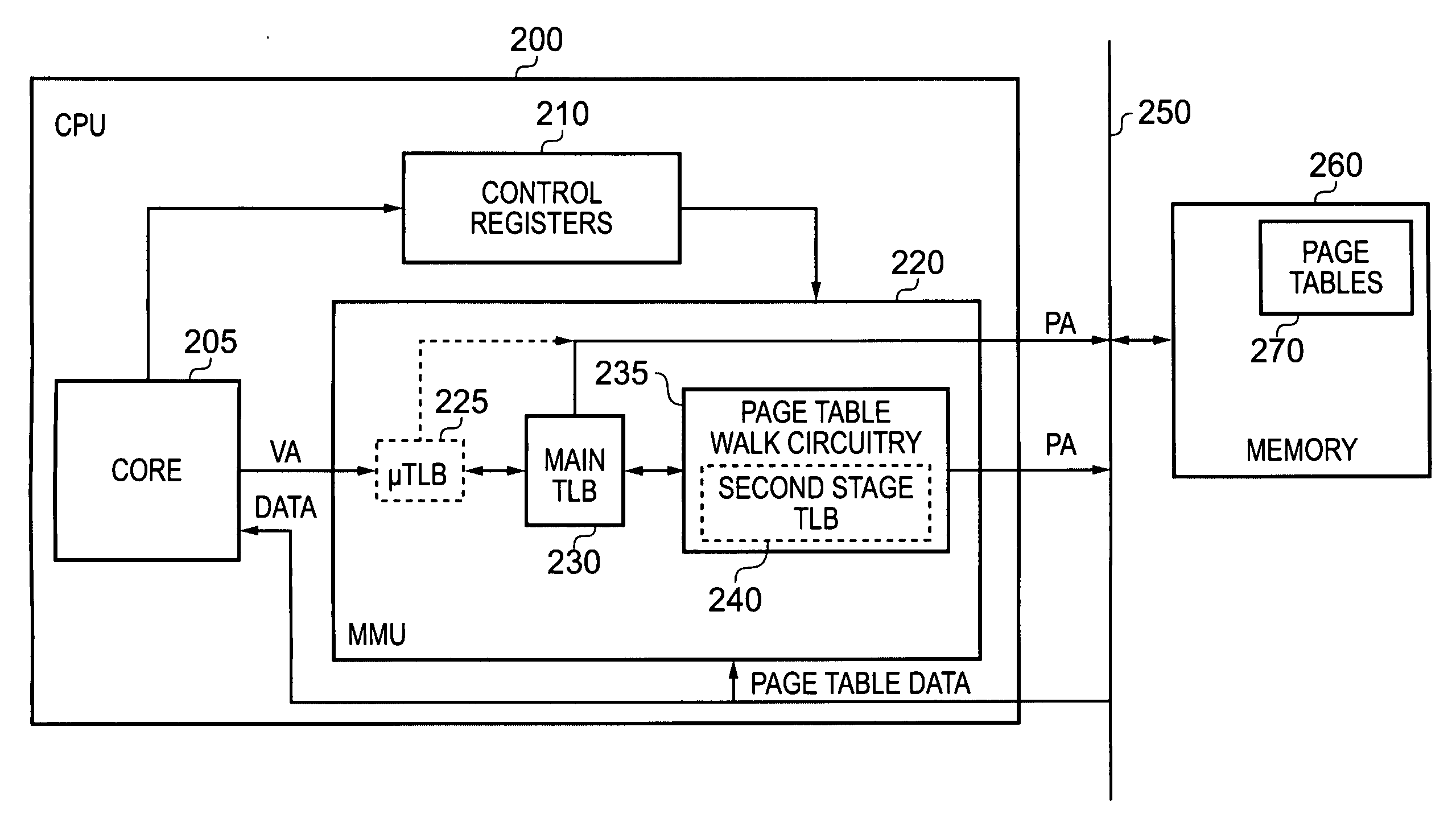

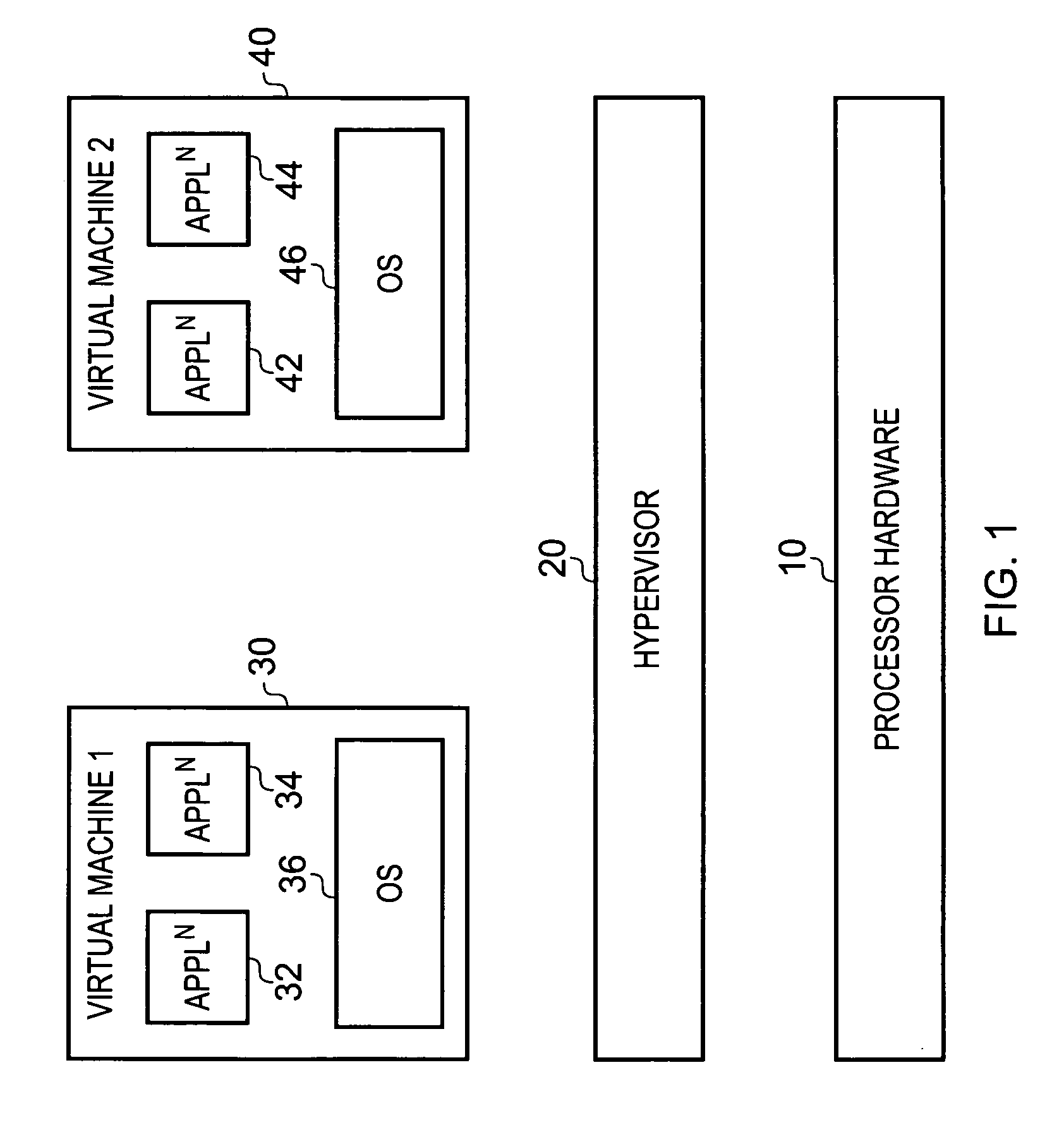

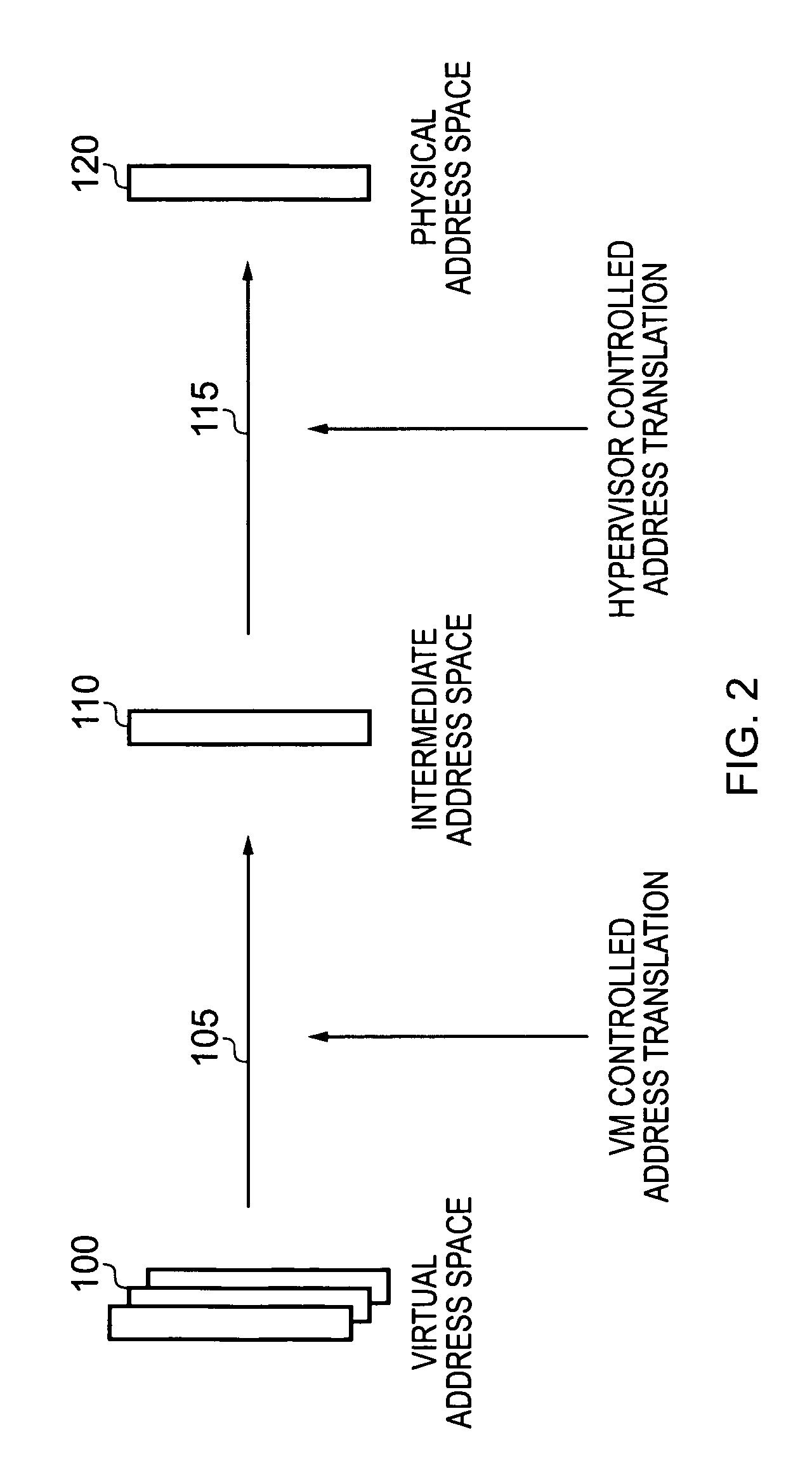

Data processing apparatus and method for handling address translation for access requests issued by processing circuitry

ActiveUS20090292899A1Improve efficiencyAccurate processingMemory adressing/allocation/relocationMicro-instruction address formationNetwork address translationVirtual address space

A data processing apparatus has address translation circuitry which is responsive to an access request specifying a virtual address, to perform a multi-stage address translation process to produce, via at least one intermediate address, a physical address in memory corresponding to the virtual address. The address translation circuitry references a storage unit, with each entry of the storage unit storing address translation information for one or more virtual addresses. Each entry has a field indicating whether the address translation information is consolidated address translation information or partial address translation information. If when processing an access request, it is determined that the relevant entry in the storage unit provides consolidated address translation information, the address translation circuitry produces a physical address directly from the consolidated address translation information. If on the other hand the relevant entry stores partial address translation information, the address translation circuitry produces an intermediate address from the partial address translation information and then performs the remainder of the multi-stage address translation process. Such an approach provides the performance benefits associated with a consolidated entry mechanism within the storage unit, whilst also allowing certain problem cases to be handled correctly and in an efficient manner.

Owner:ARM LTD

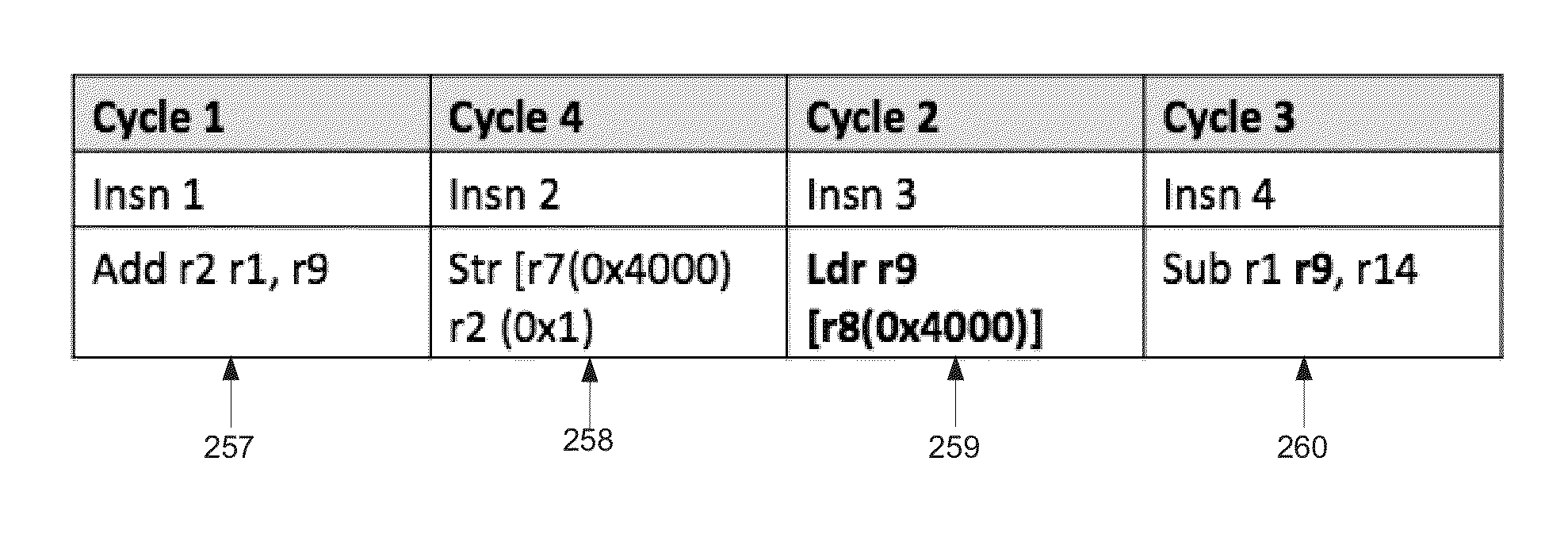

Instruction/skid buffers in a multithreading microprocessor that store dispatched instructions to avoid re-fetching flushed instructions

ActiveUS7853777B2Reduce the amount requiredPenalty associated with flushing instructions is reducedDigital computer detailsMemory systemsOperating systemControl logic

An apparatus for reducing instruction re-fetching in a multithreading processor configured to concurrently execute a plurality of threads is disclosed. The apparatus includes a buffer for each thread that stores fetched instructions of the thread, having an indicator for indicating which of the fetched instructions in the buffer have already been dispatched for execution. An input for each thread indicates that one or more of the already-dispatched instructions in the buffer has been flushed from execution. Control logic for each thread updates the indicator to indicate the flushed instructions are no longer already-dispatched, in response to the input. This enables the processor to re-dispatch the flushed instructions from the buffer to avoid re-fetching the flushed instructions. In one embodiment, there are fewer buffers than threads, and they are dynamically allocatable by the threads. In one embodiment, a single integrated buffer is shared by all the threads.

Owner:MIPS TECH INC

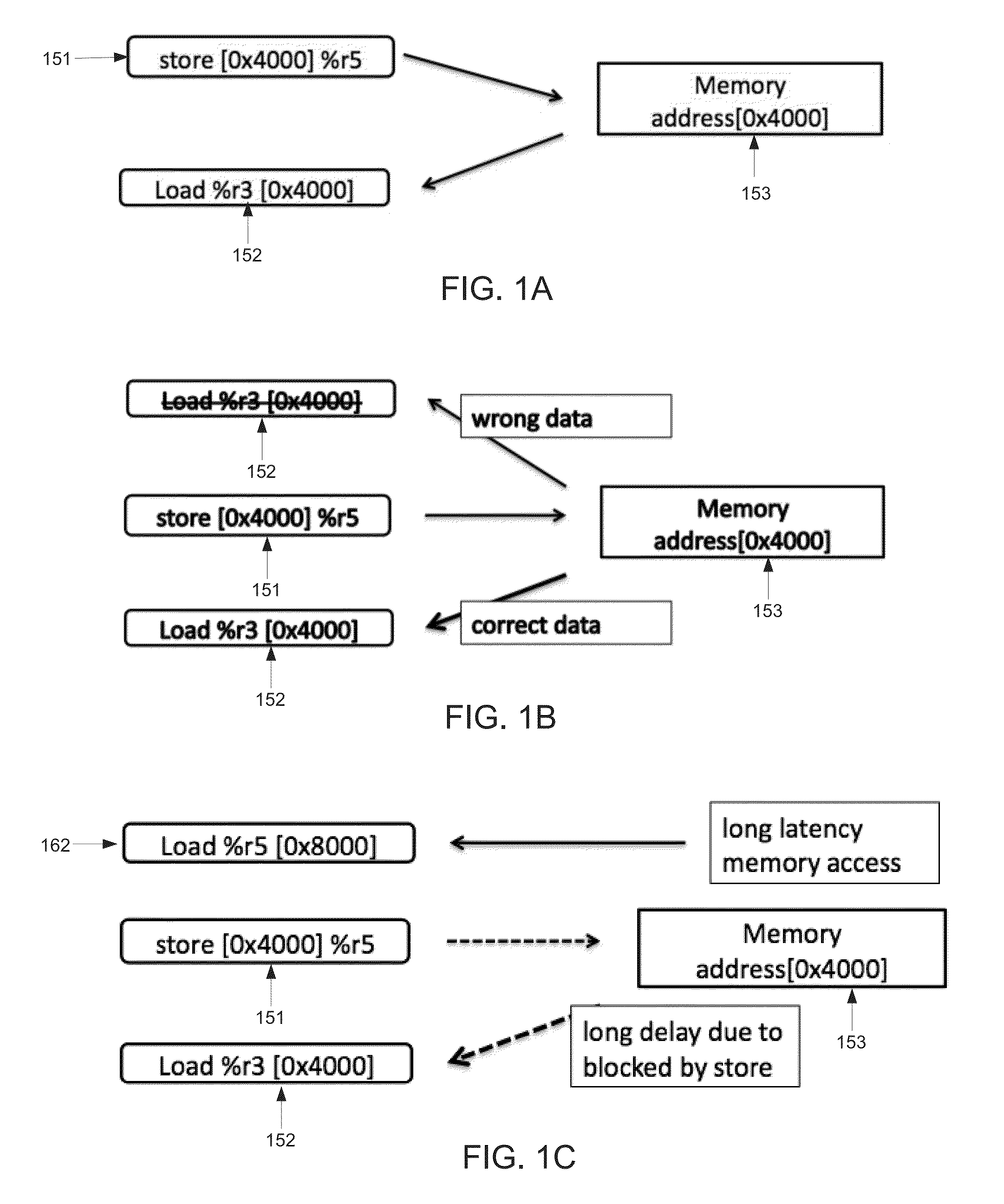

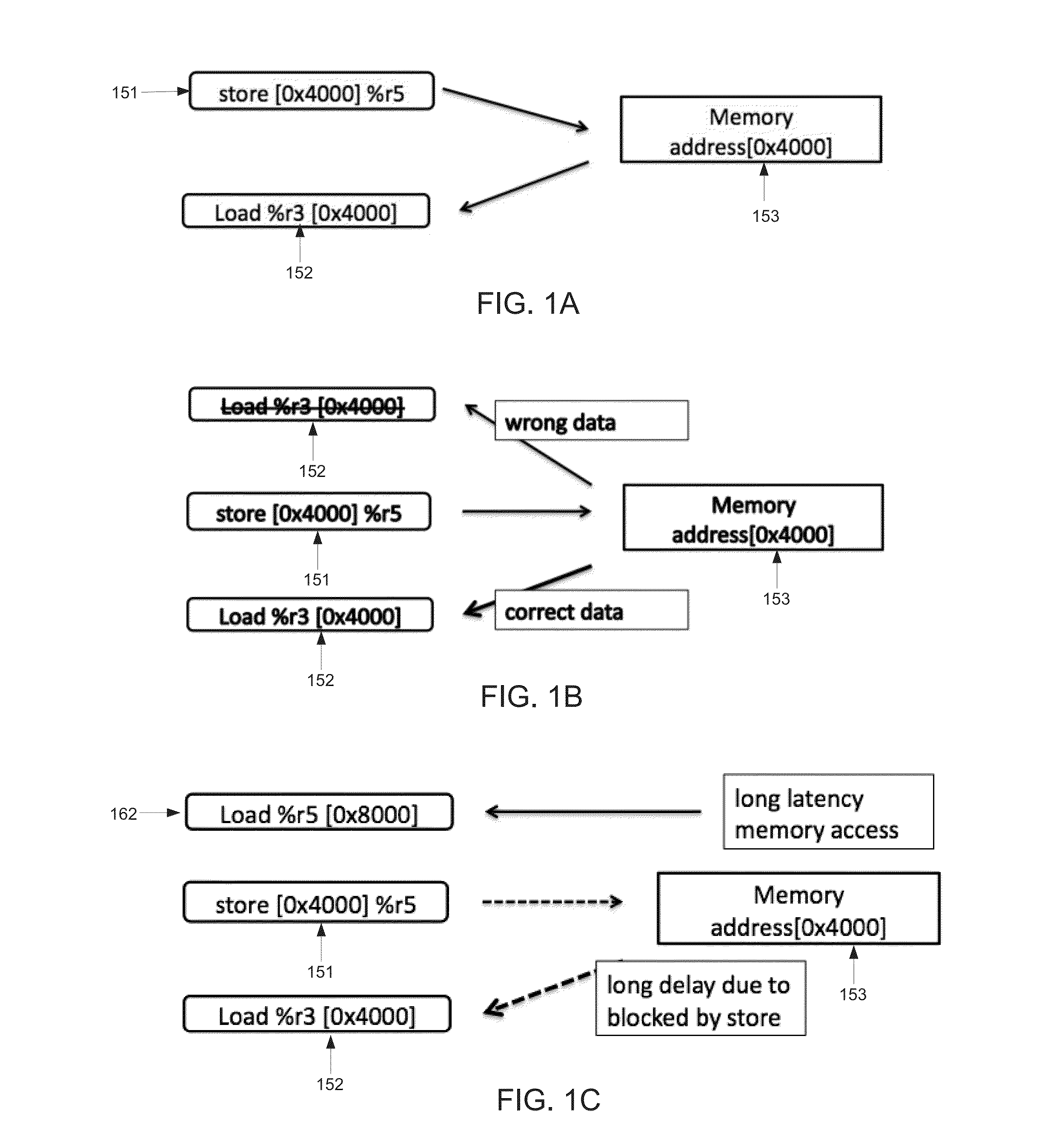

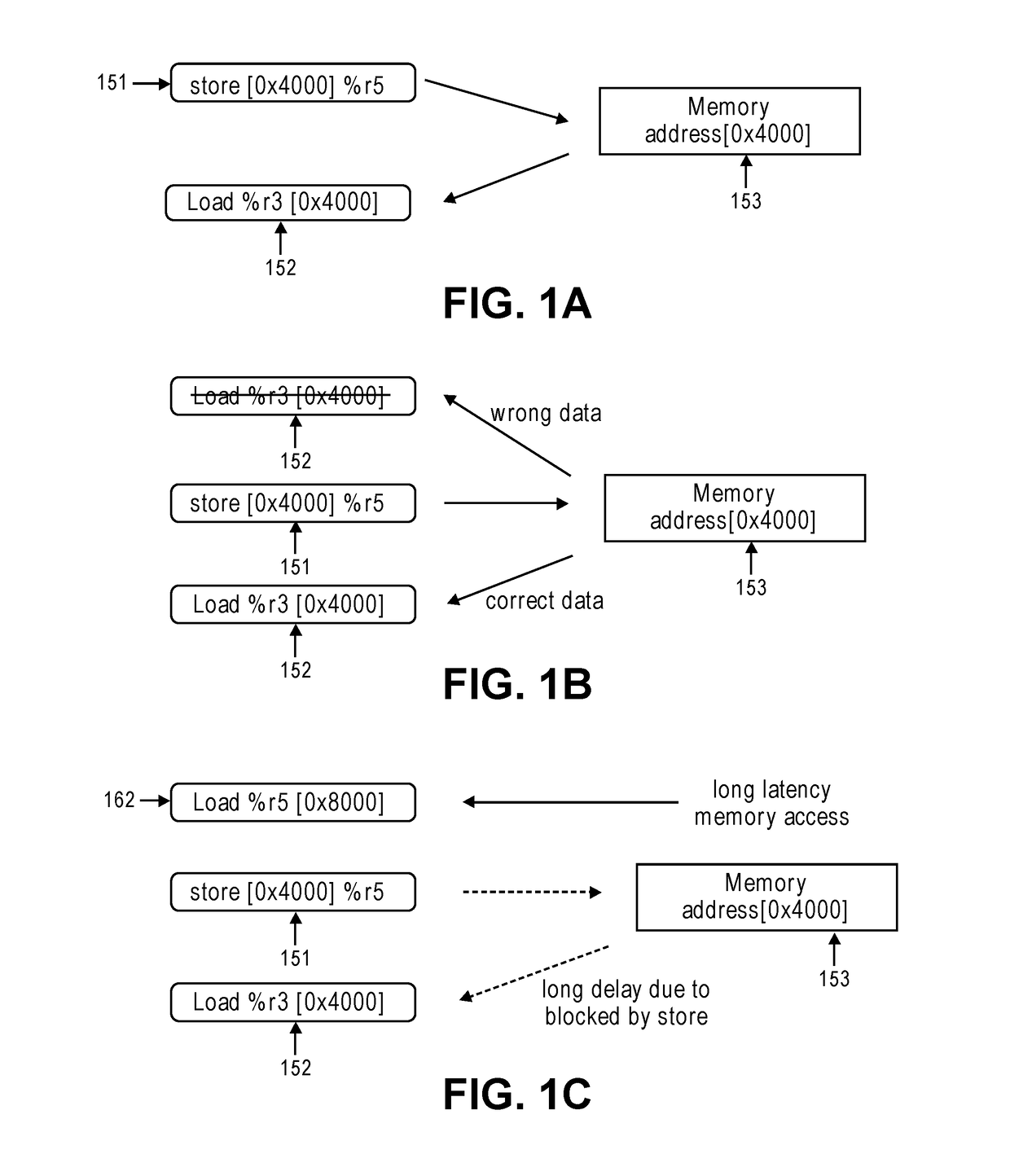

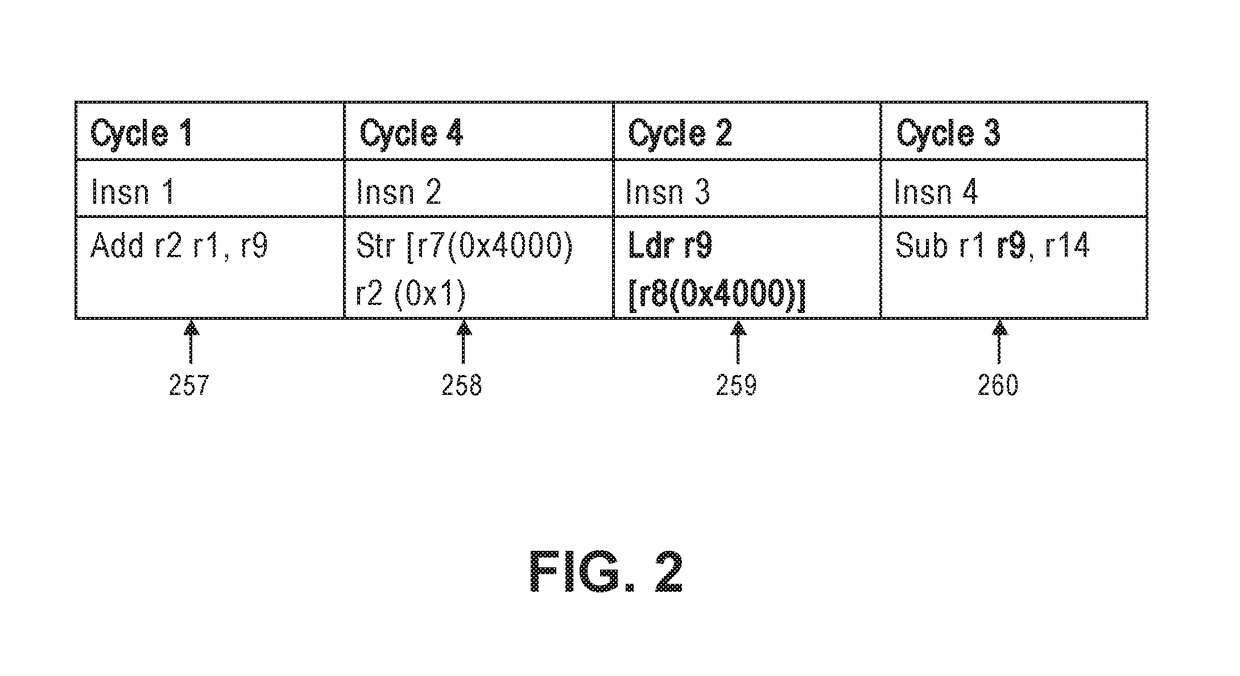

Method and apparatus for predicting forwarding of data from a store to a load

ActiveUS20140281408A1Prevent memory RAW delayLower performance requirementsDigital computer detailsMemory systemsData miningStore instruction

A method for gating a load operation based on entries of a prediction table is presented. The method comprises performing a look-up for the load operation in a prediction table to find a matching entry, wherein the matching entry corresponds to a prediction regarding a behavior of the load operation, and wherein the matching entry comprises: (a) a tag field operable to identify the matching entry; (b) a distance field operable to indicate a distance of the load operation to a prior aliasing store instruction; and (c) a confidence field operable to indicate a prediction strength generated by the prediction table. The method further comprises determining if the matching entry provides a valid prediction and, if valid, retrieving a location for the prior aliasing store instruction using the distance field. It finally comprises performing a gating operation on said load operation.

Owner:INTEL CORP

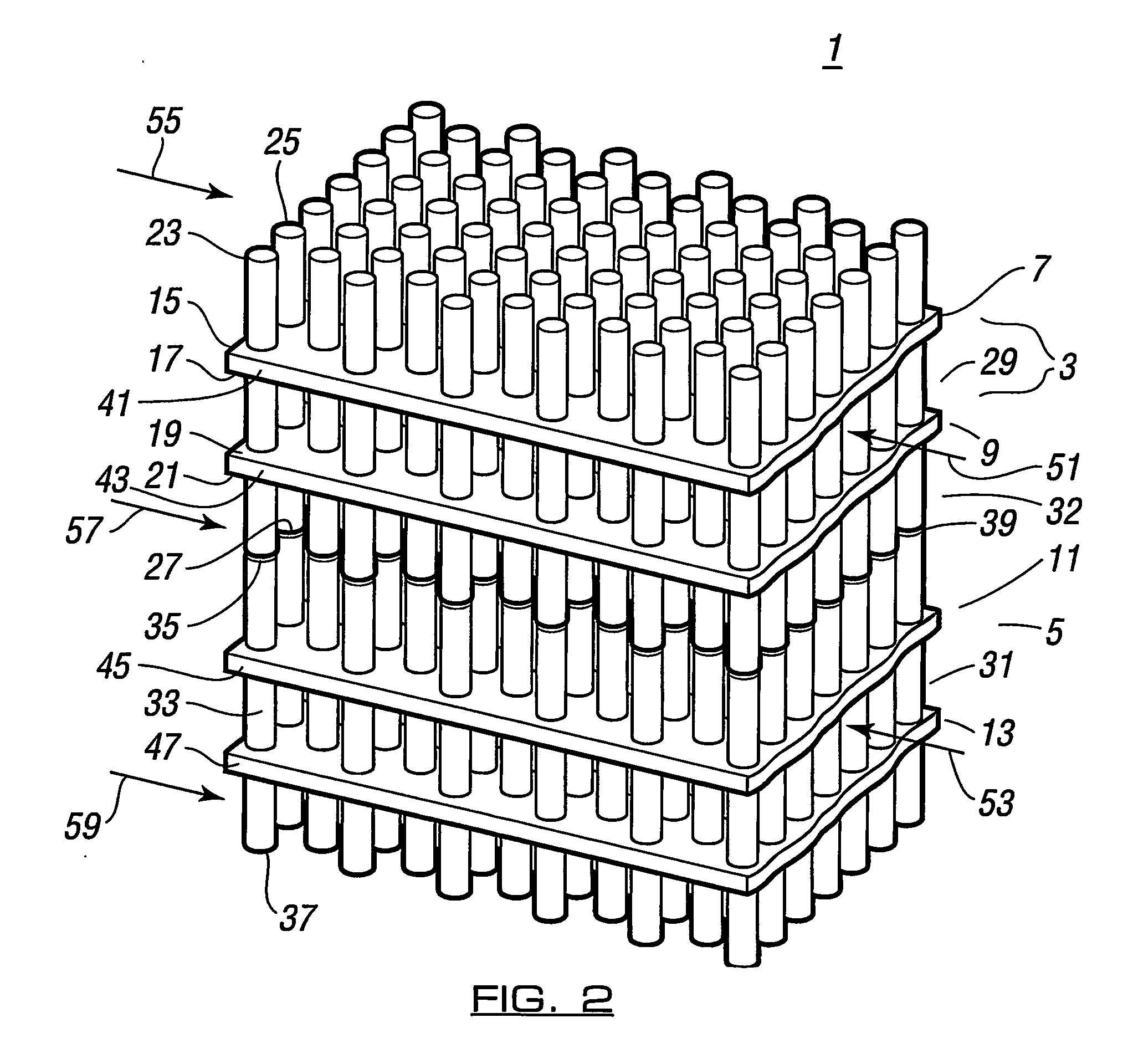

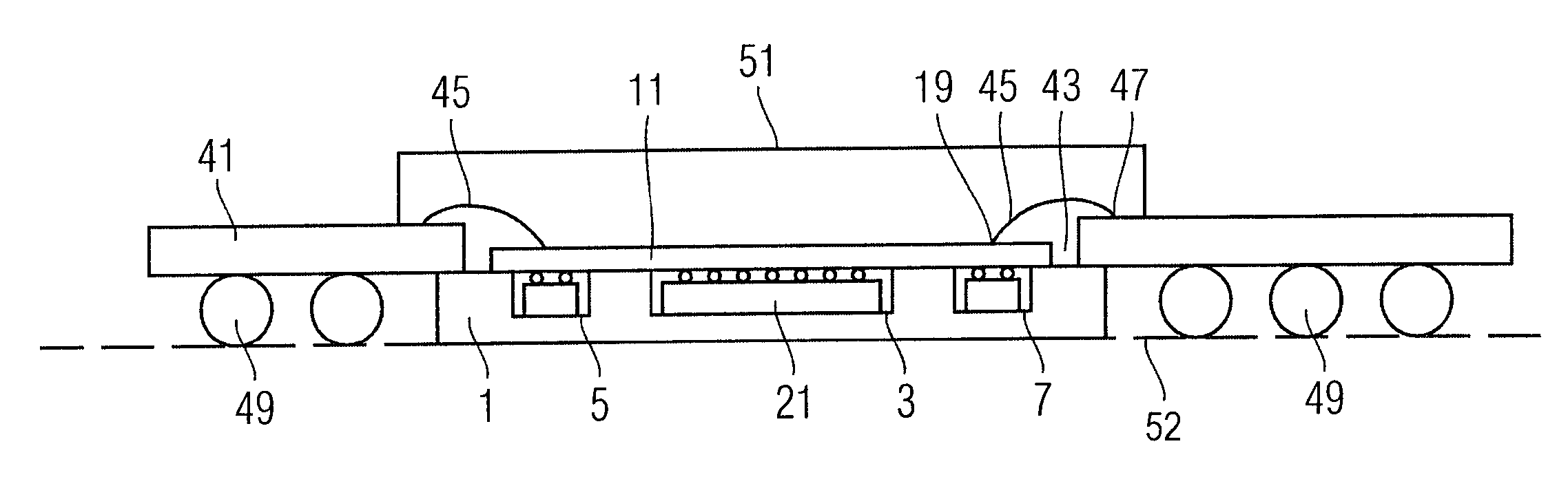

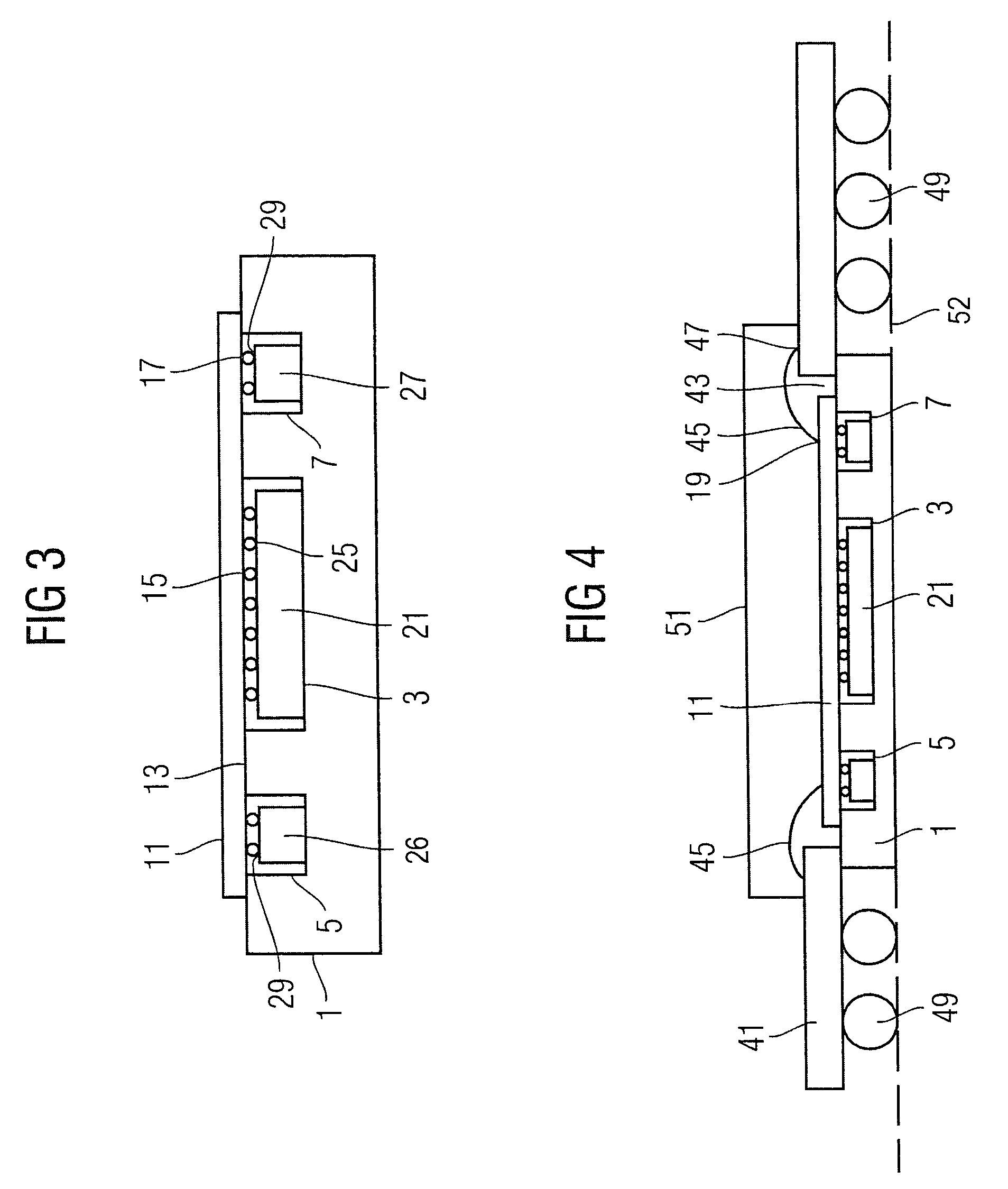

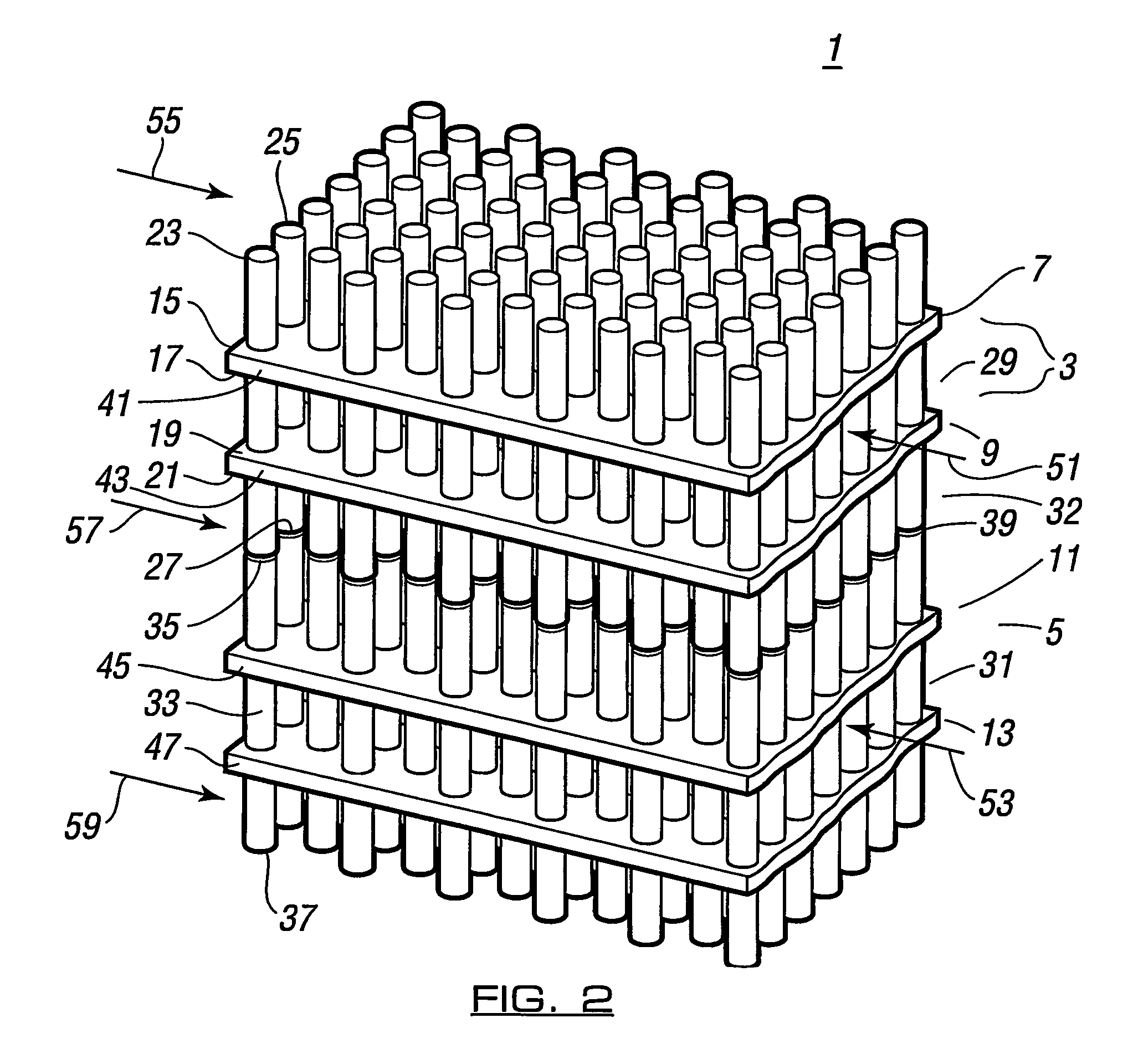

Heat exchanger and use thereof

ActiveUS20070084593A1Guaranteed robustness and reliabilityImprove heat transfer performanceLaminated elementsStationary plate conduit assembliesEngineeringHeat exchanger

A heat exchanger comprises a plurality of plates (7, 9, 11, 13) each having first (15, 19) and second (17, 21) heat transfer surfaces on reverse sides. The plates are arranged in a stack with spacings between mutually facing heat transfer surfaces of adjacent plates. Alternate spacings in the stack providing respectively, a first fluid path (51, 52) for a first fluid and a second fluid path (57, 59) for a second fluid. The plates are arranged in a plurality of groups, each comprising at least two plates. Pin means are provided in the form of a plurality of groups of pins (23). The pins of each pin group are arranged to bridge plates of a respective plate group.

Owner:HIFLUX

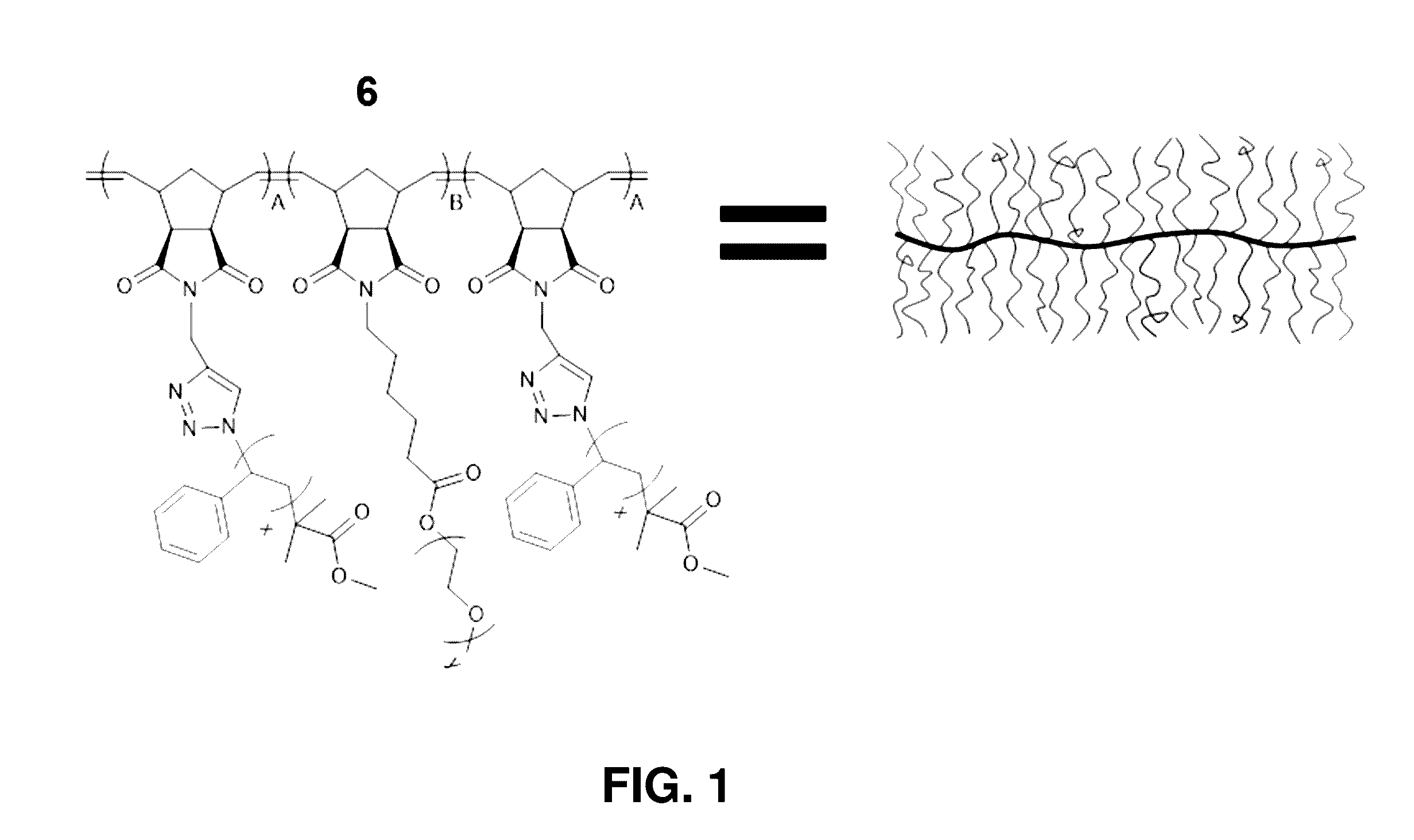

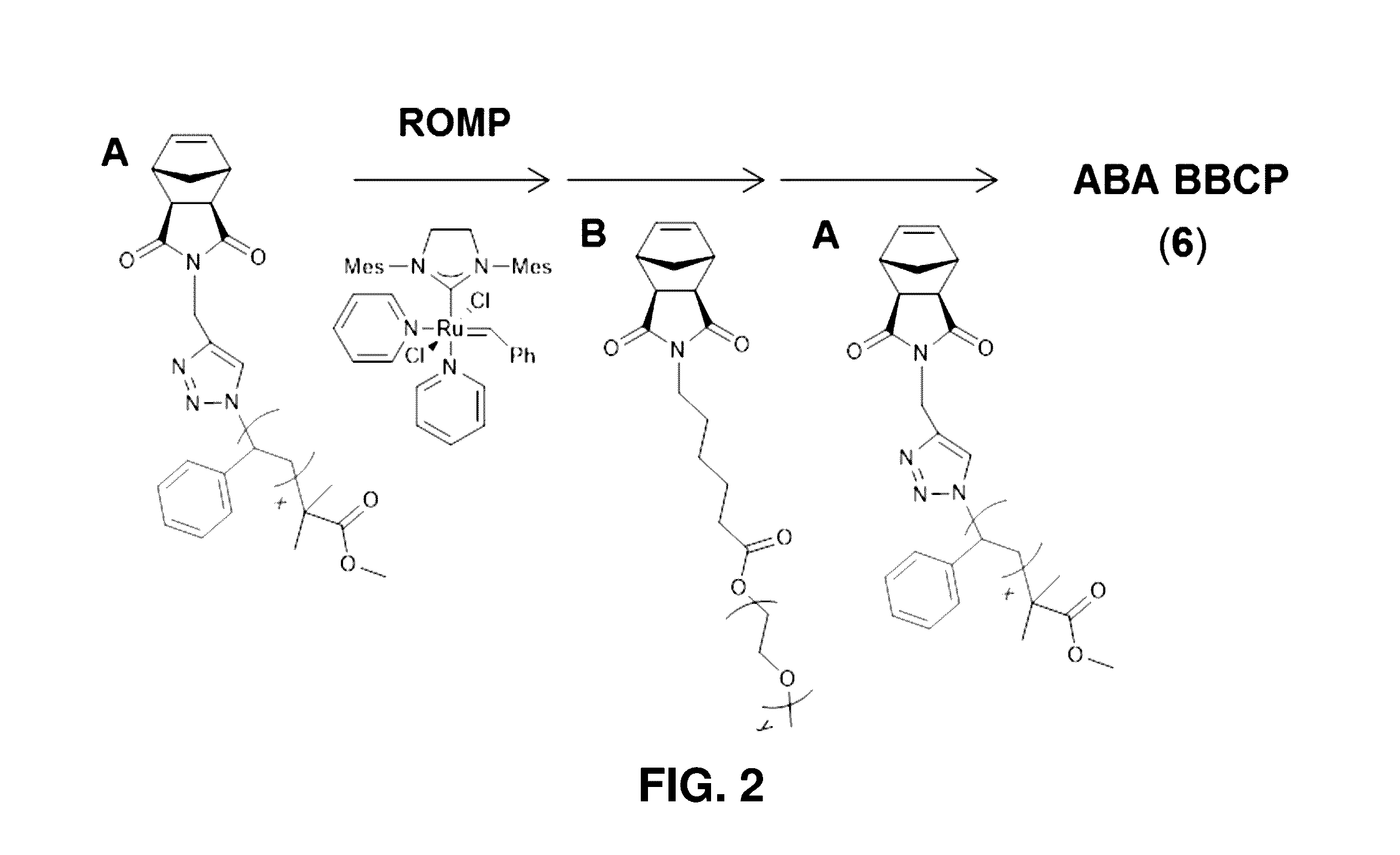

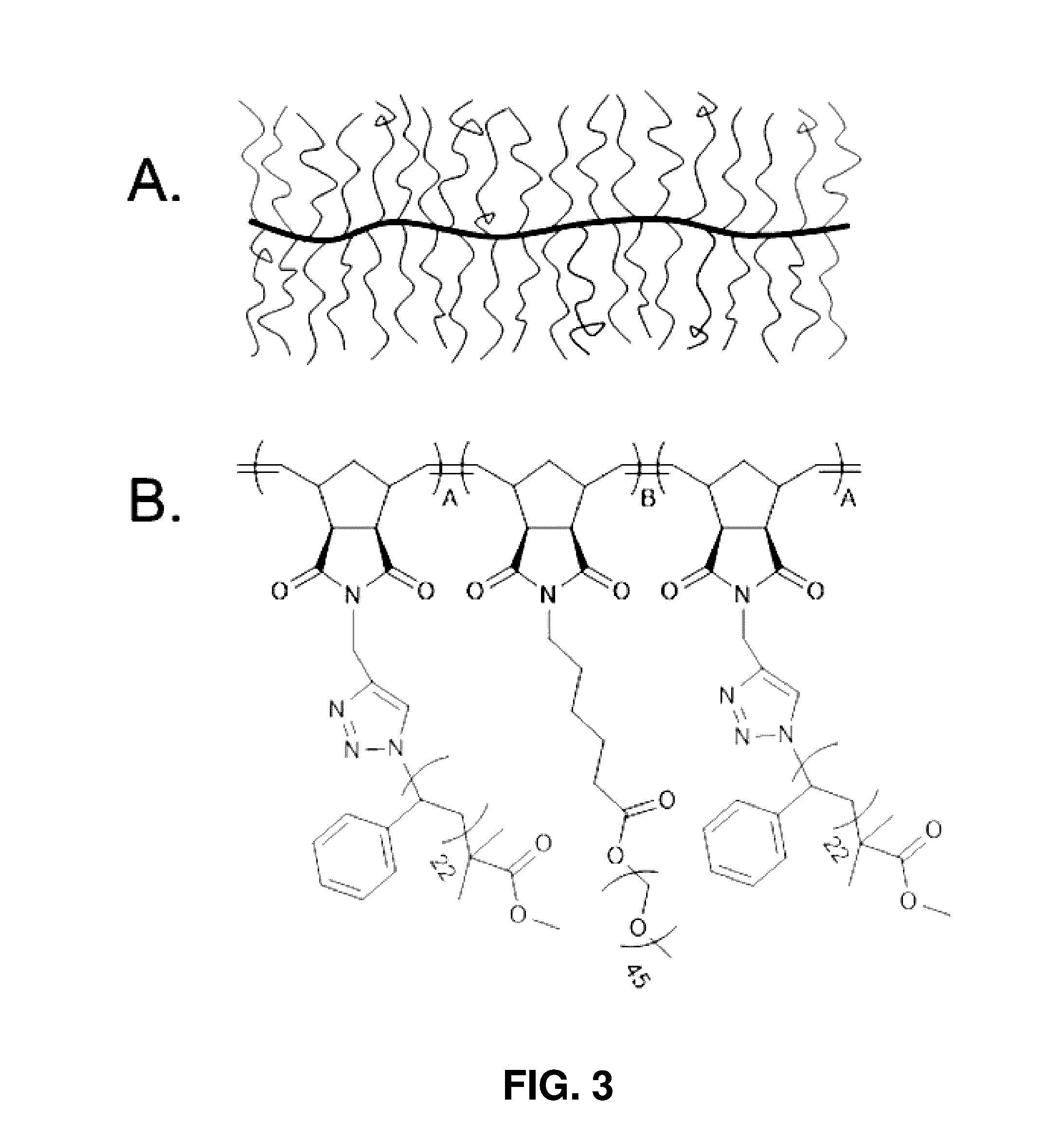

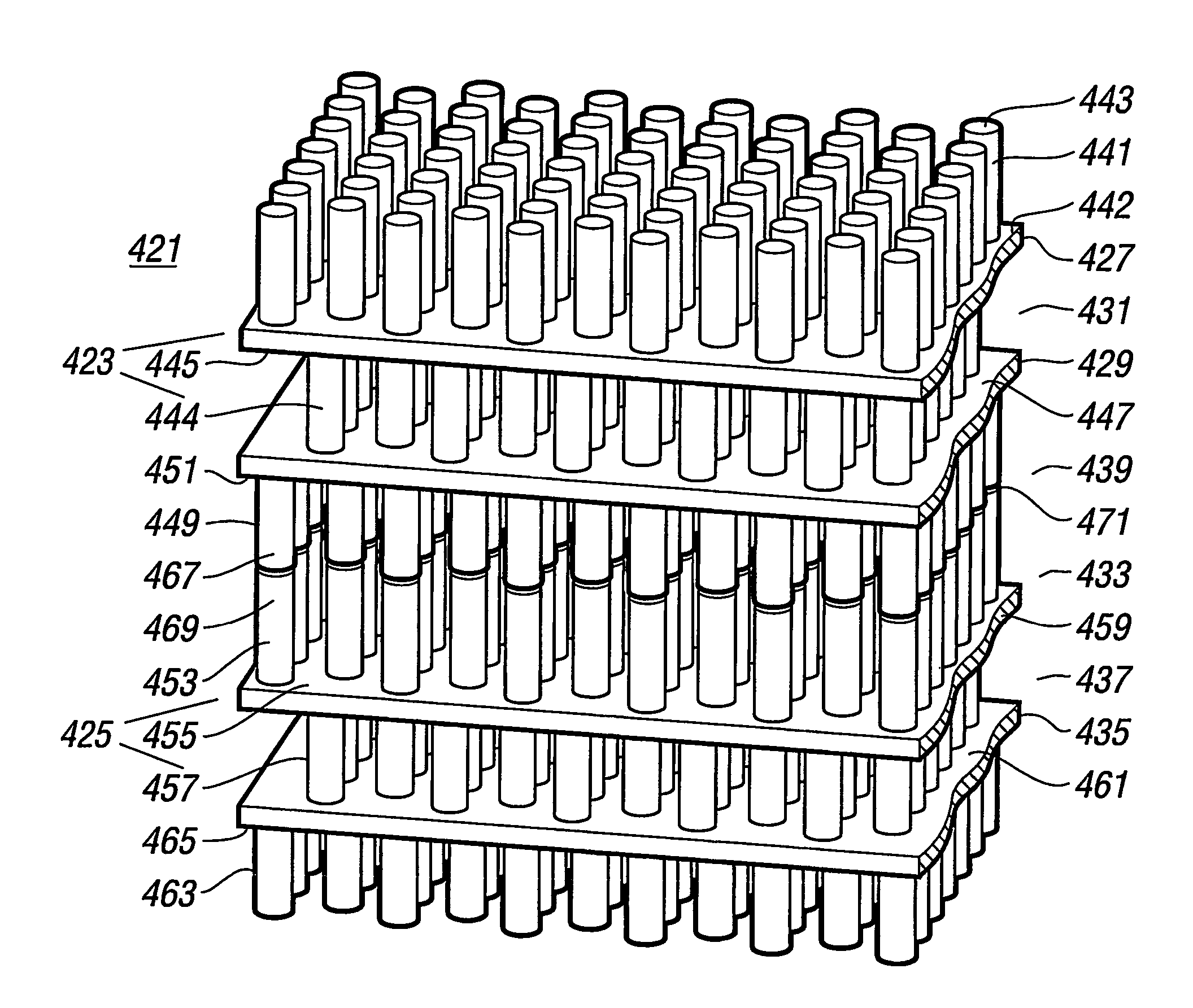

Triblock brush block copolymers

ActiveUS20160289392A1Useful mechanical and elastic strengthAdvantageousSolid electrolytesSecondary cellsPolymer scienceSide chain

Provided herein is a class of copolymers, including triblock brush copolymers having specific block configurations, for example, ABC triblock brush copolymers and ABA triblock brush copolymers. In an embodiment, for example, copolymers of the invention incorporate various polymer side chain groups which contribute beneficial physical, chemical, or electronic properties such as increased mechanical or elastic strength, improved ionic or electric conductivity. In some embodiments, the provided copolymers exhibit advantageous steric properties allowing for rapid self-assembly into a variety of morphologies that are substantially different than non-brush, block copolymers.

Owner:CALIFORNIA INST OF TECH

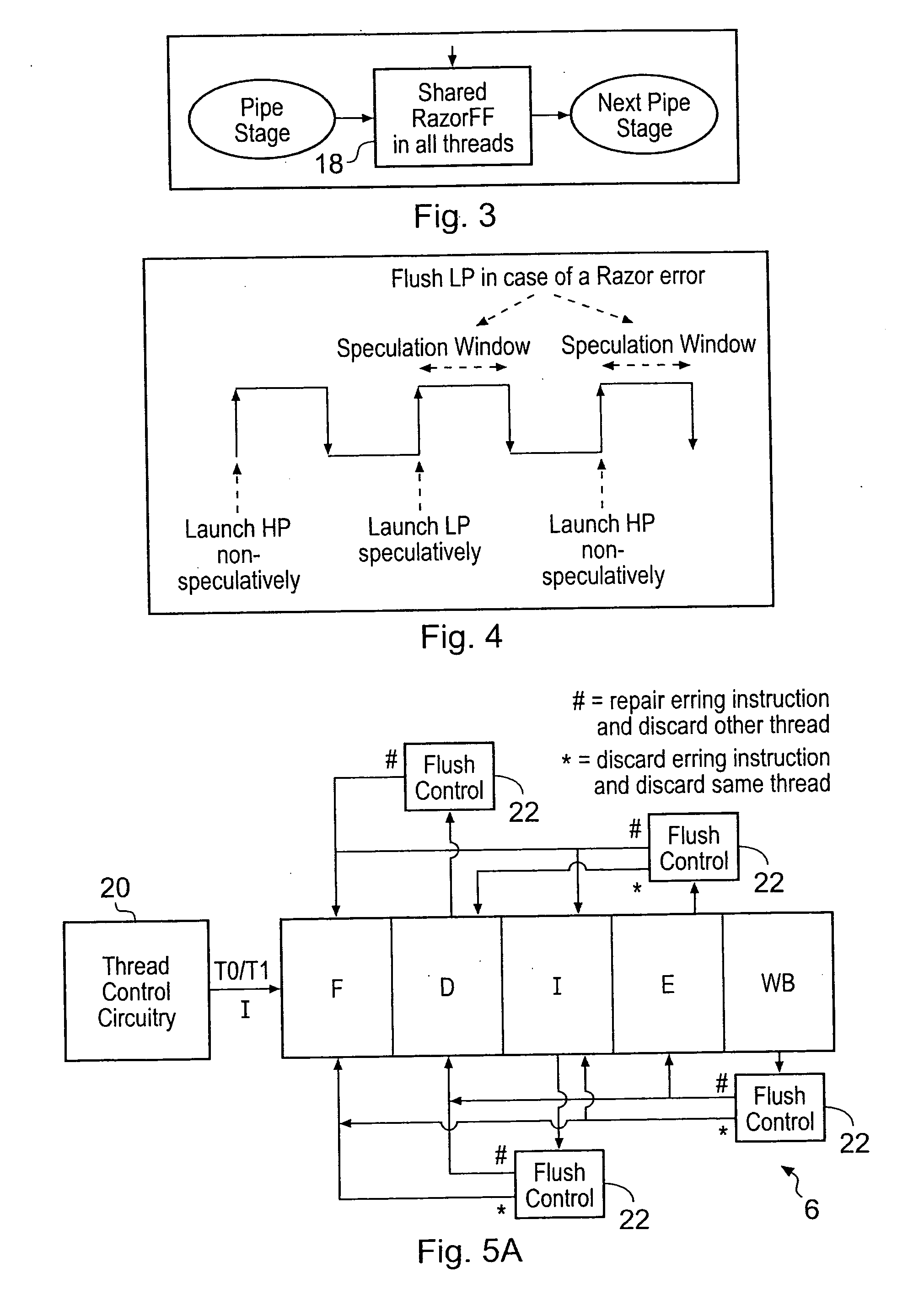

Error recovery following speculative execution with an instruction processing pipeline

ActiveUS20080250271A1Reduce performance impactReduce penaltyDigital computer detailsNon-redundant fault processingProgram instructionPrivilege level

An instruction processing pipeline 6 is provided. This has error detection and error recovery circuitry 20 associated with one or more of the pipeline stages. If an error is detected within a signal value within that pipeline stage, then it can be repaired. Part of the error recovery may be to flush upstream program instructions from the instruction pipeline 6. When multi-threading, only those instructions from a thread including an instruction which has been lost as a consequence of the error recovery need to be flushed from the instruction pipeline 6. Instruction can also be selected for flushing in dependence upon characteristics such as privileged level, number of dependent instructions etc. The instruction pipeline may additionally / alternatively be provided with more than one main storage element 26, 28 associated with each signal value with these main storage elements 26, 28 being used in an alternating fashion such that if a signal value has been erroneously captured and needs to be repaired, there is still available a main storage element 26, 28 to properly capture the signal value corresponding to the following program instruction. In this way flushes can be avoided.

Owner:ARM LTD

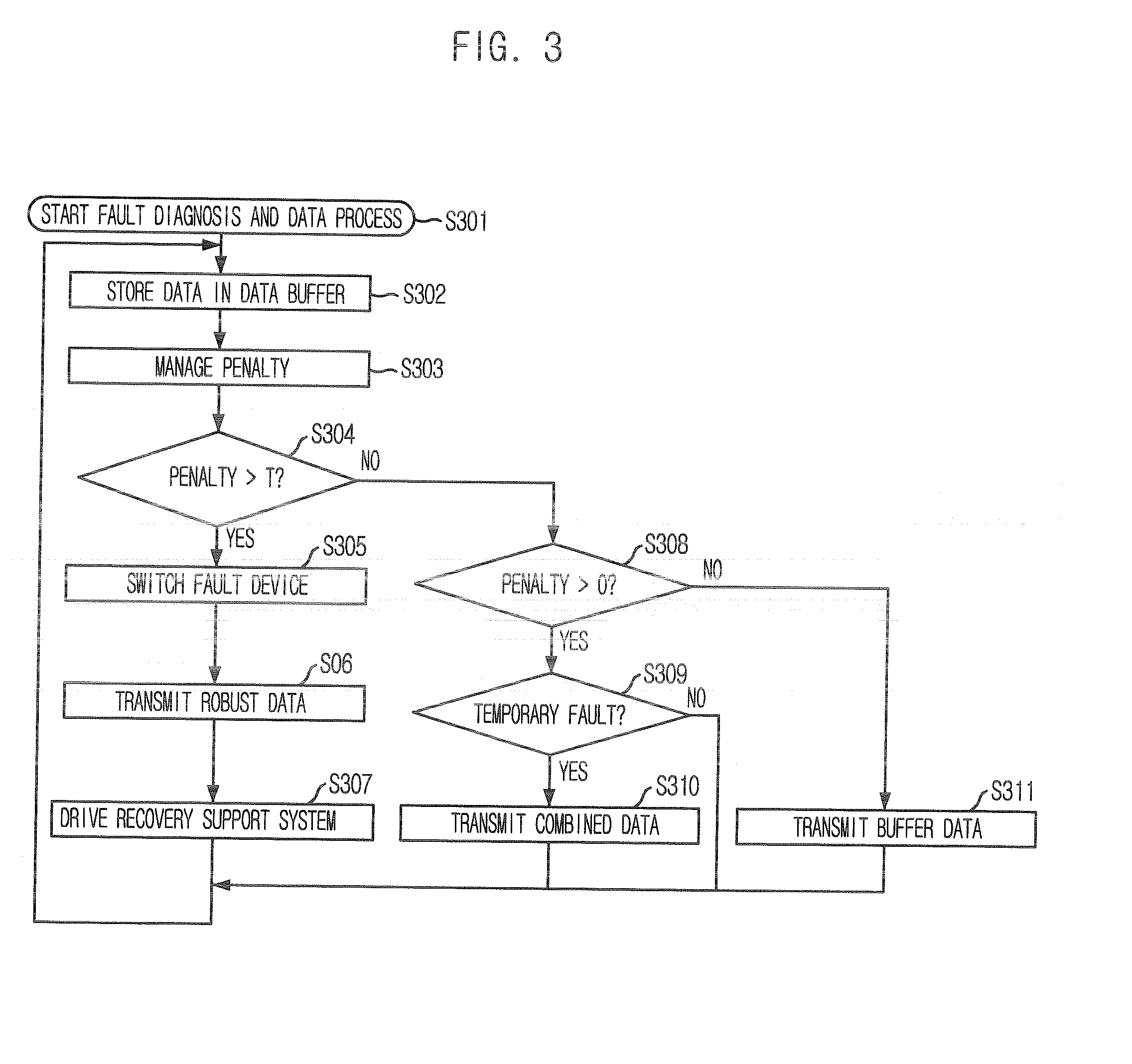

Apparatus and Method for Diagnosing Fault and Managing Data in Satellite Ground System

InactiveUS20080313488A1Reducing penaltyEfficient in operationFault responseTransmission monitoringData bufferSystem failure

Provided are an apparatus and a method for diagnosing fault and processing data of a satellite ground system. The apparatus and a method can prevent data loss of a satellite, and efficiently operate the satellite ground system using data buffer and penalty method when a temporary fault occurs. Data buffer stores data in fault situation and penalty method imposes high penalty in critical fault and low penalty in minor fault. System is managed according to penalty degree. The apparatus, includes: a satellite data processing and controlling means; a signal transforming means; a fault detecting and controlling means; a state displaying means for displaying a state of the satellite and the system; a penalty managing means for being notified whether the device has fault or not; a data storing means for storing and transmitting the data; and a system recovery supporting means.

Owner:ELECTRONICS & TELECOMM RES INST

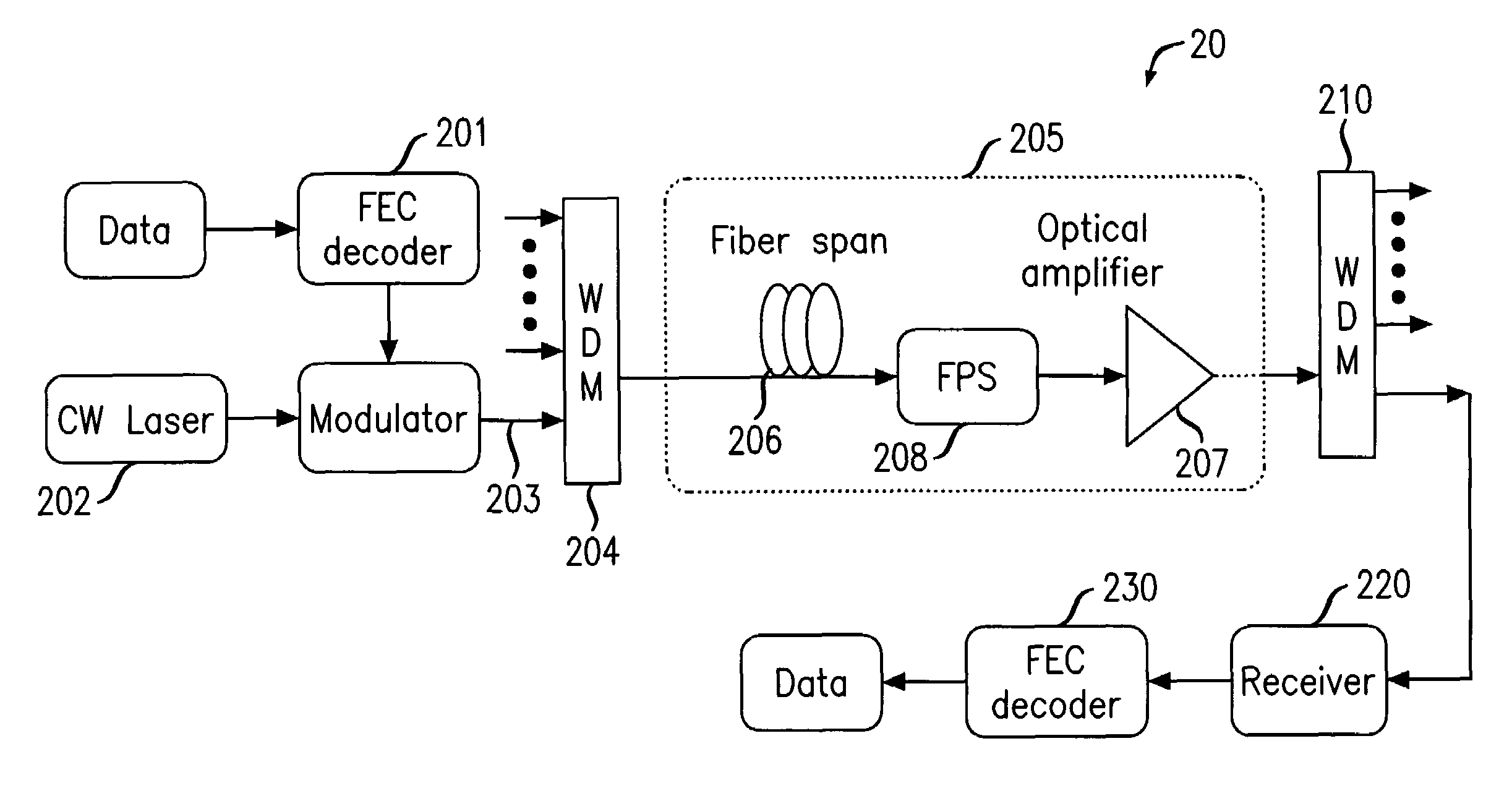

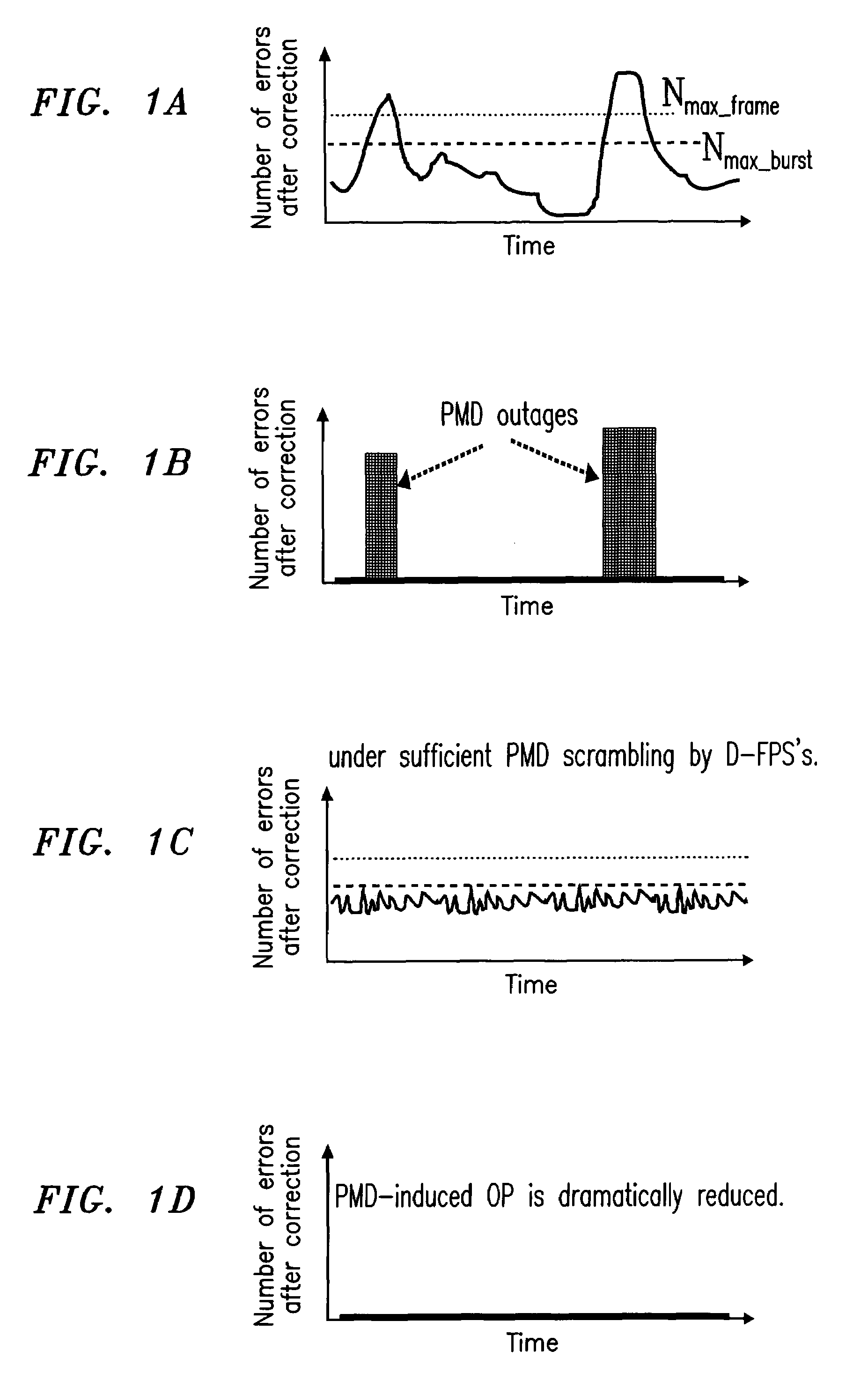

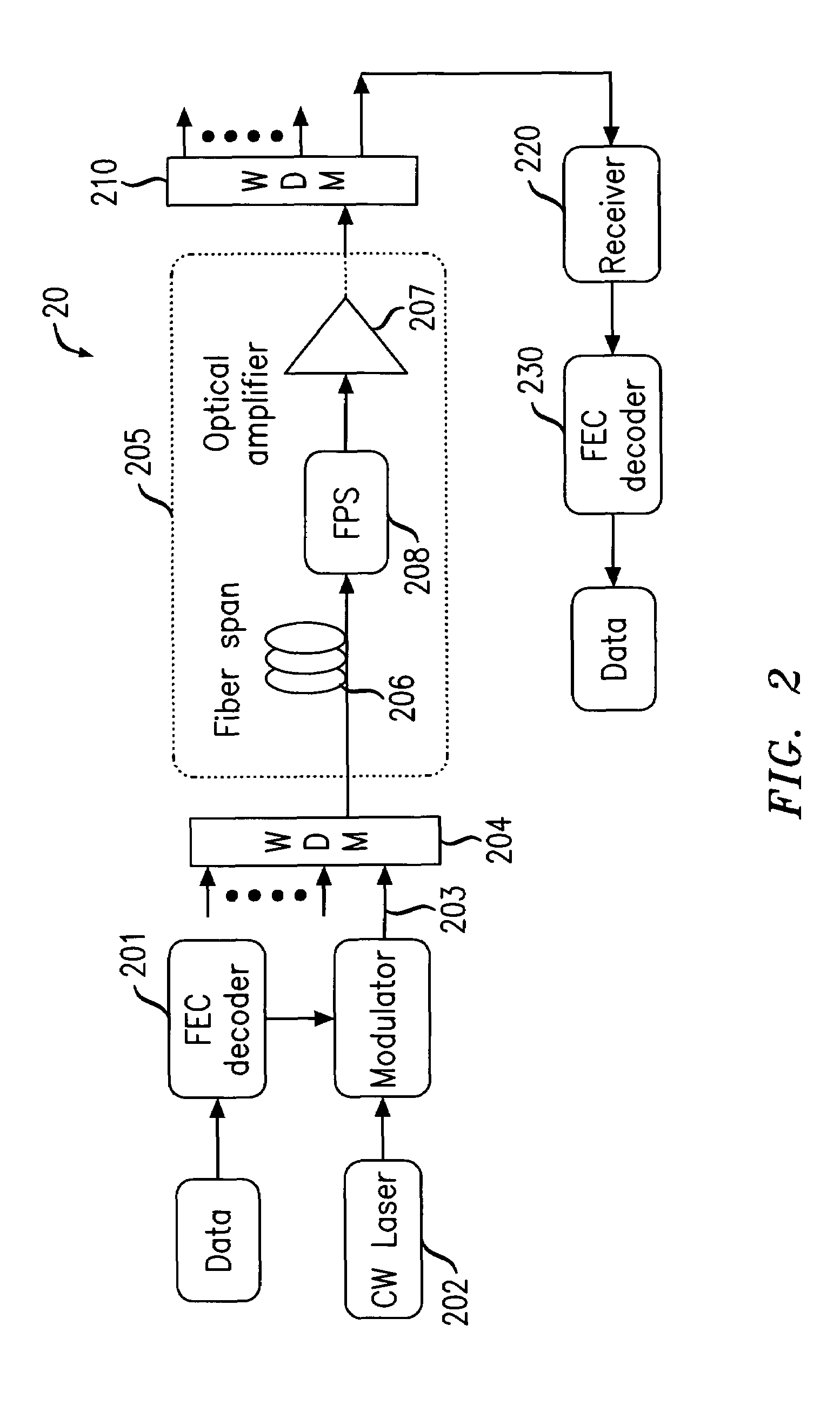

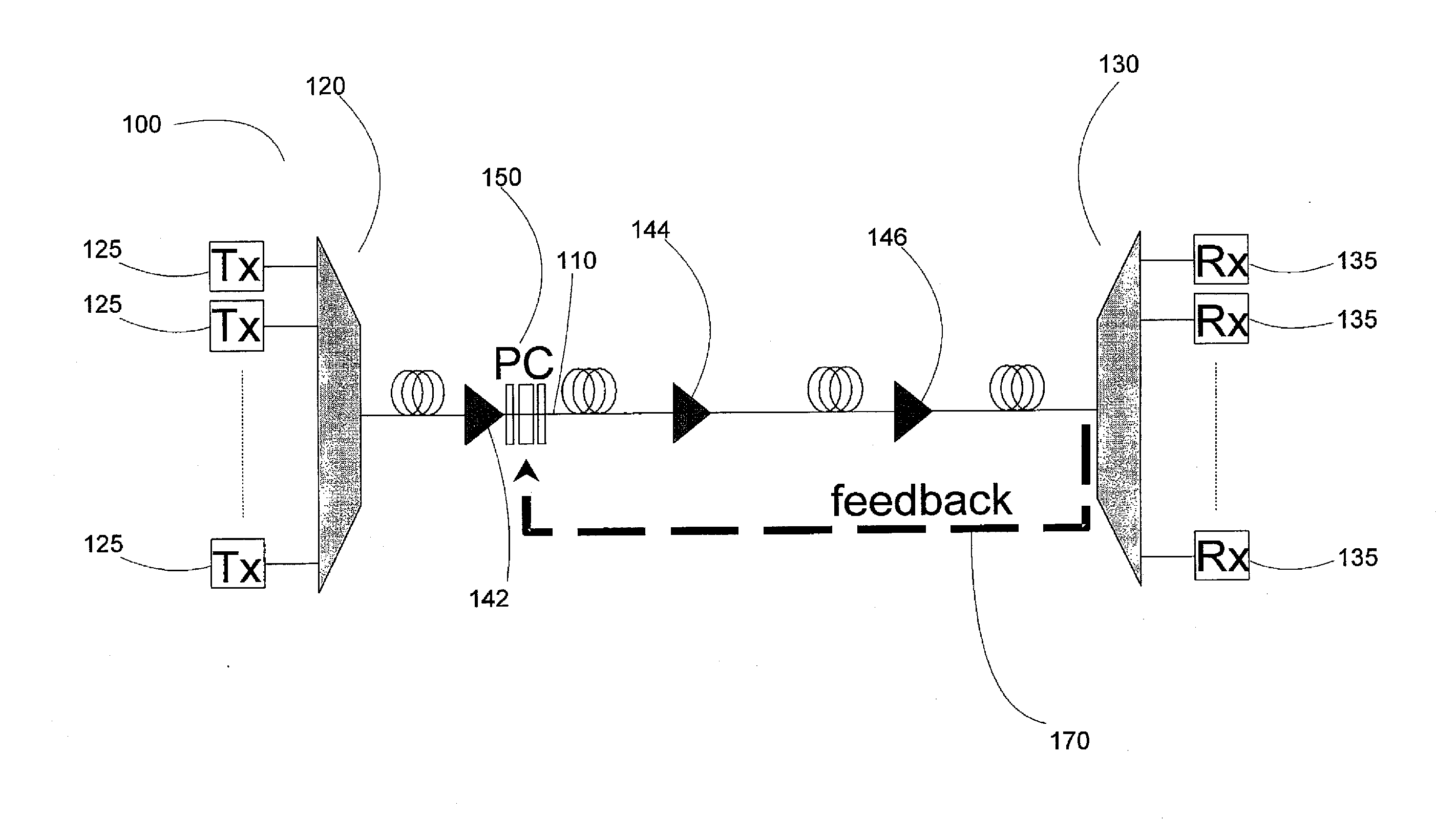

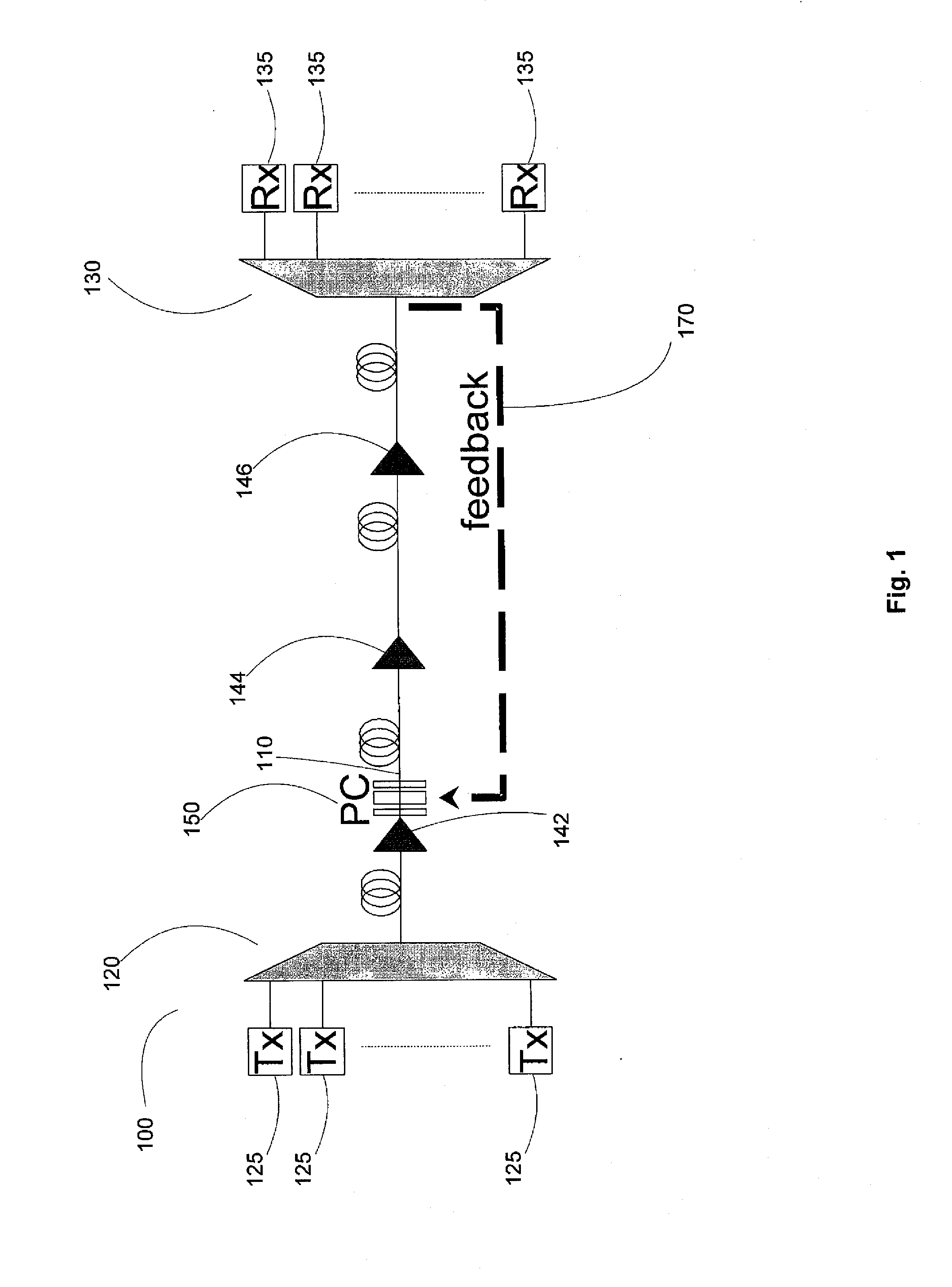

System and method for multi-channel mitigation of PMD/PDL/PDG

InactiveUS7010180B2Transmission errorImprove toleranceWavelength-division multiplex systemsPolarising elementsForward error correctionPolarization mode dispersion

A system and method for multi-channel PMD / PDL / PDG mitigation, the system including polarization scramblers adapted to vary the state of polarization of an optical signal propagated through the system to effectively vary the polarization mode dispersion experienced by the signal during each burst-error-correcting-period of the forward error correction used in the system.

Owner:LUCENT TECH INC +1

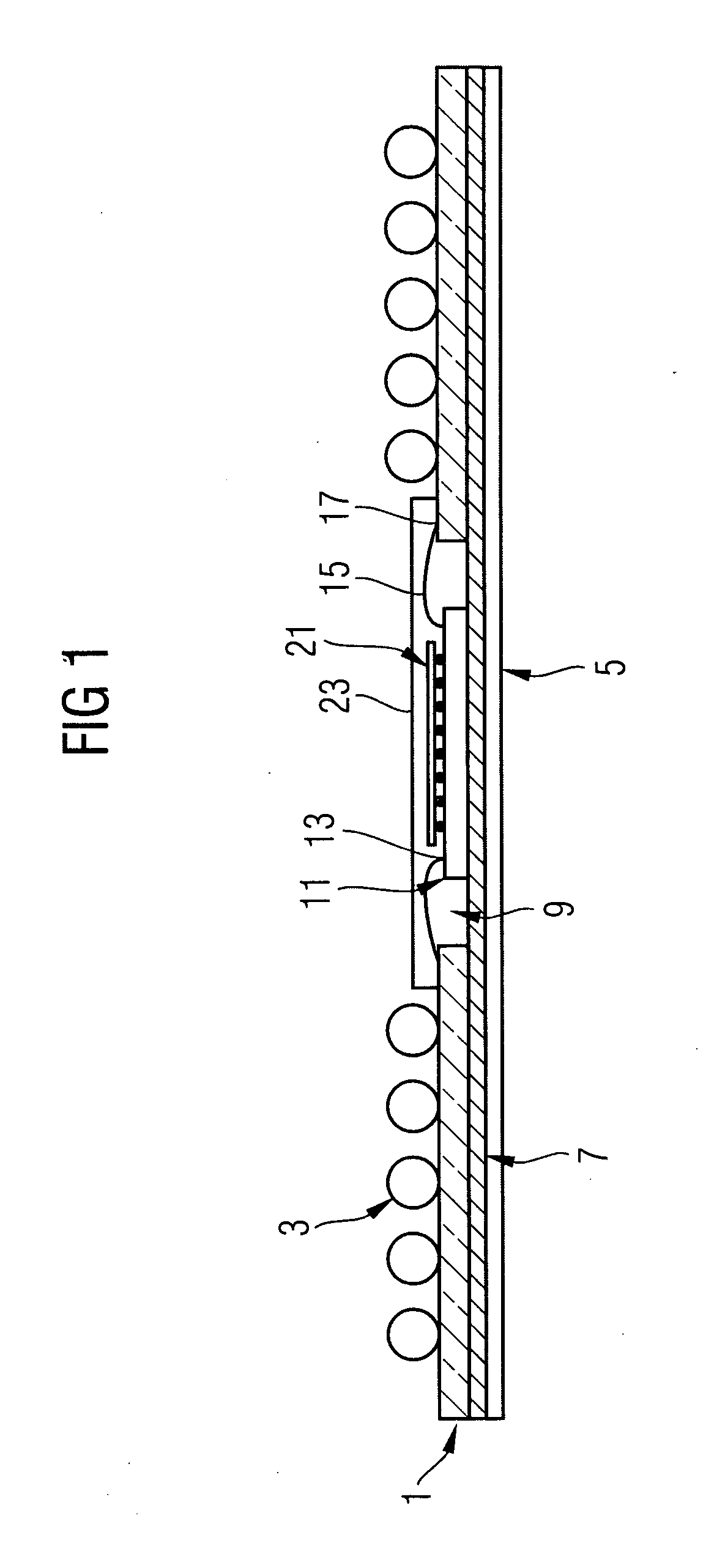

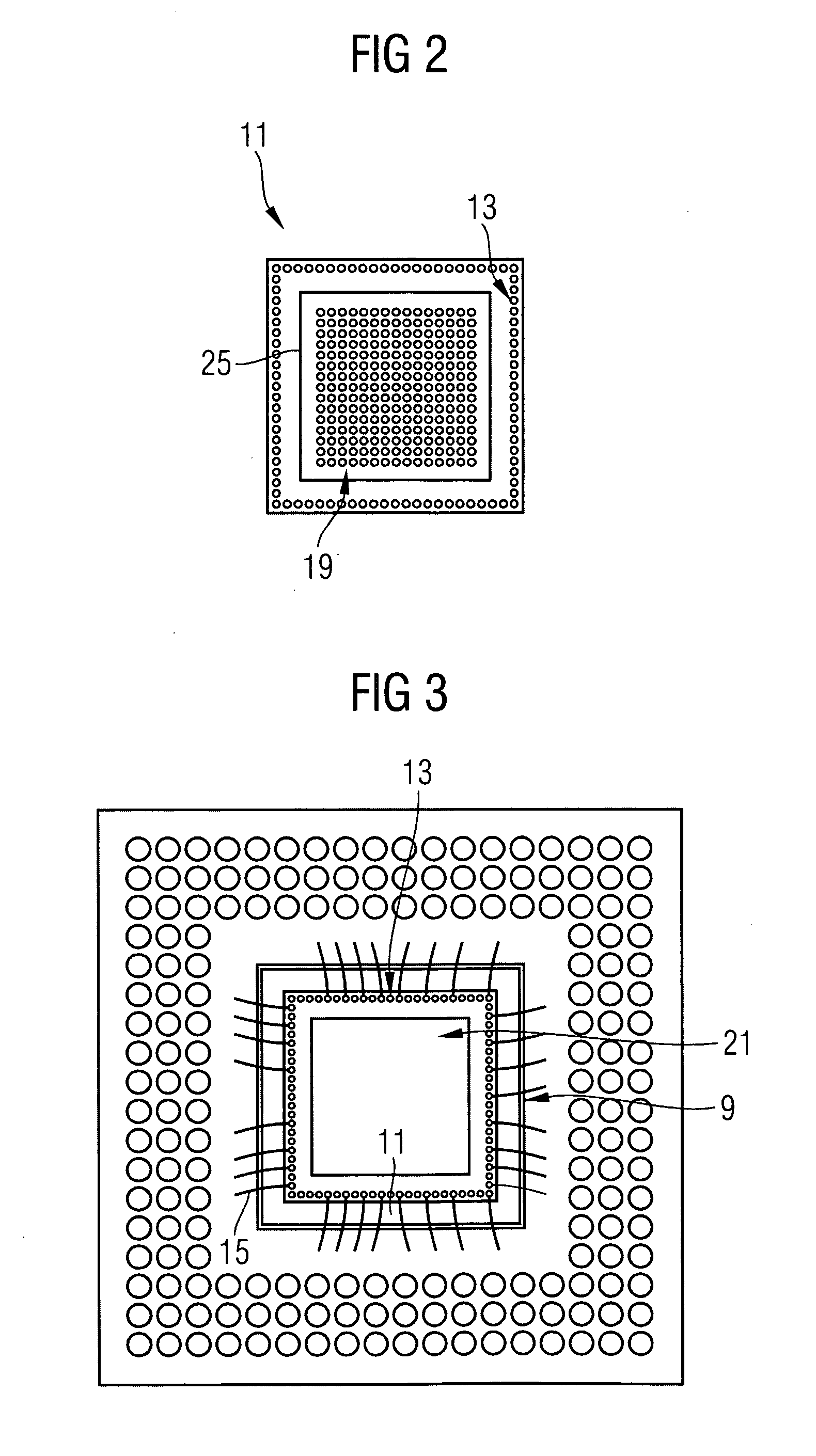

Integrated circuit package employing a heat-spreader member

InactiveUS7224058B2Reduced footprintReducing penaltySemiconductor/solid-state device detailsSolid-state devicesEngineeringHeat spreader

Owner:INFINEON TECH AG

Method and apparatus for predicting forwarding of data from a store to a load

InactiveUS20140281384A1Prevent memory RAW delayLower performance requirementsProgram controlArchitecture with single central processing unitData miningStore instruction

A method for gating a load operation based on entries of a prediction table is presented. The method comprises performing a look-up for the load operation in a prediction table to find a matching entry, wherein the matching entry corresponds to a prediction regarding a behavior of the load operation, and wherein the matching entry comprises: (a) a tag field operable to identify the matching entry; (b) a distance field operable to indicate a distance of the load operation to a prior aliasing store instruction; and (c) a confidence field operable to indicate a prediction strength generated by the prediction table. The method further comprises determining if the matching entry provides a valid prediction and, if valid, retrieving a location for the prior aliasing store instruction using the distance field. It finally comprises performing a gating operation on said load operation.

Owner:INTEL CORP

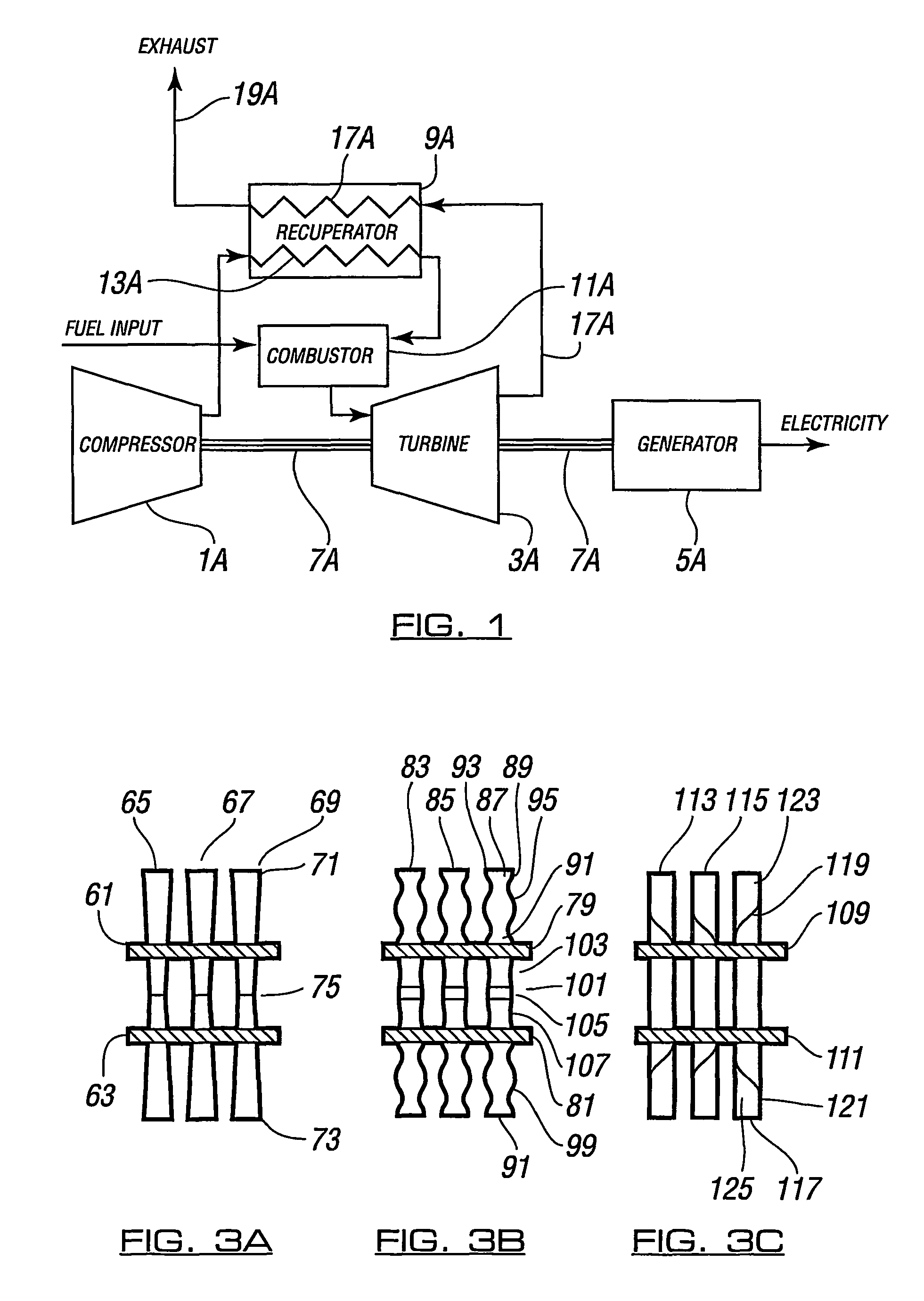

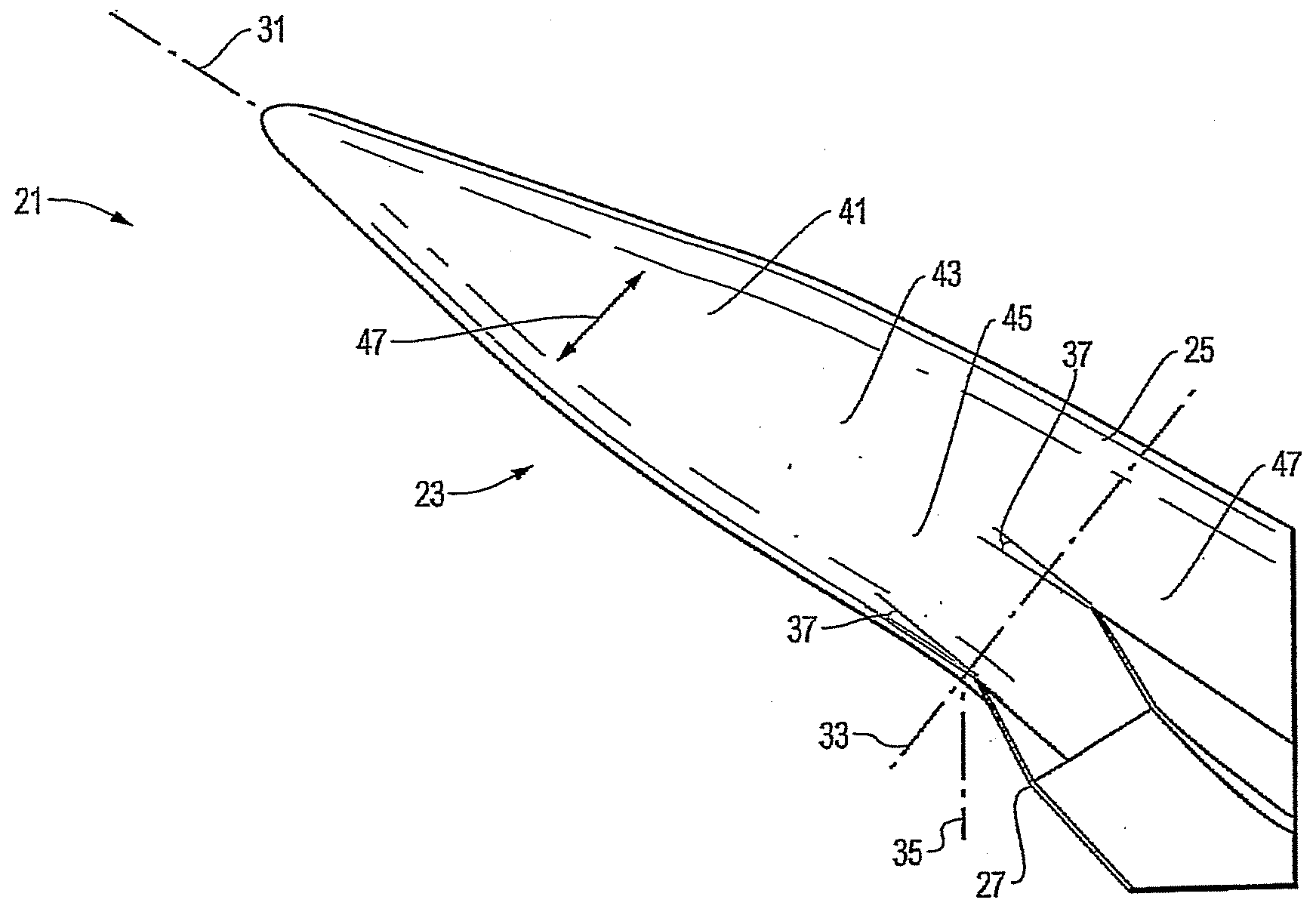

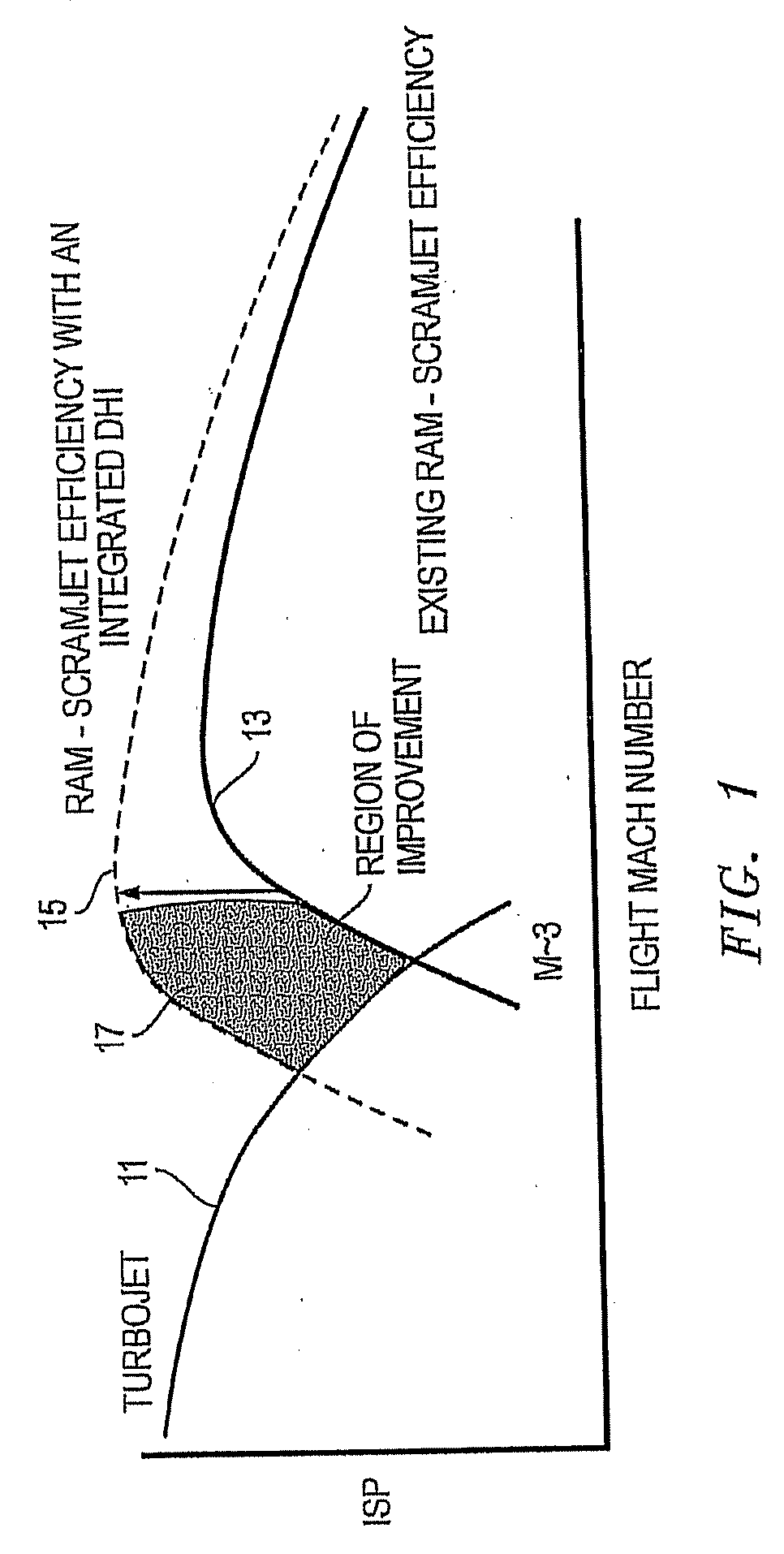

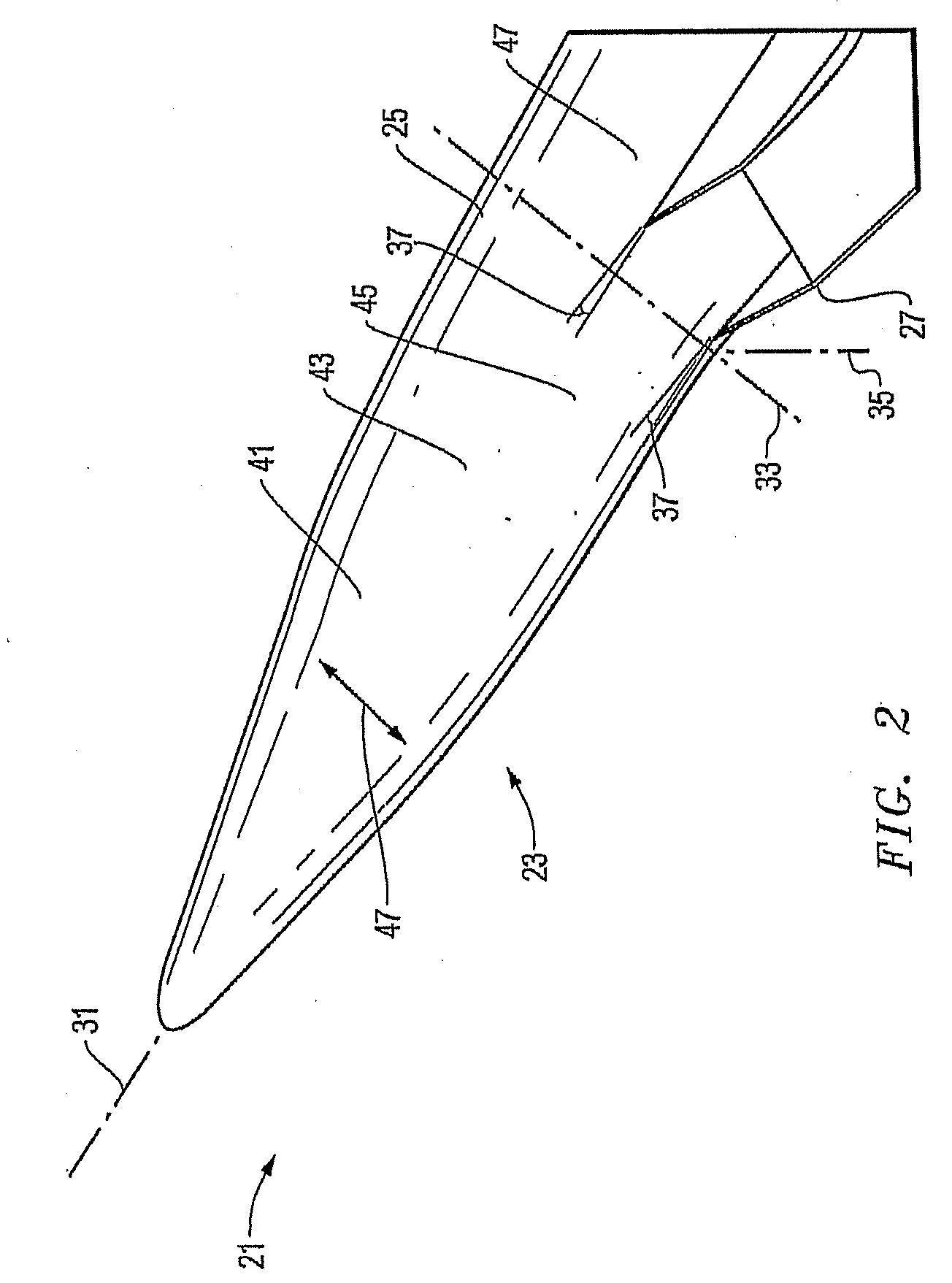

System, method, and apparatus for diverterless hypersonic inlet for integrated turbojet and ram-scramjet applications

ActiveUS20070136032A1Reduce penaltyFavorable air flow characteristicGeometric CADSustainable transportationAir breathingScramjet

A diverterless hypersonic inlet (DHI) for a high speed, air-breathing propulsion system reduces the ingested boundary layer flow, drag, and weight, and maintains a high capture area for hypersonic applications. The design enables high vehicle fineness ratios, low-observable features, and enhances ramjet operability limits. The DHI is optimized for a particular design flight Mach number. A forebody segment generates and focuses a system of multiple upstream shock waves at desired strengths and angles to facilitate required inlet and engine airflow conditions. The forebody contour diverts boundary layer flow to the inlet sides, effectively reducing the thickness of the boundary layer that is ingested by the inlet, while maintaining the capture area required by the hypersonic propulsion system. The cowl assembly is shaped to integrate with the forebody shock system and the thinned boundary layer region.

Owner:LOCKHEED MARTIN CORP

Heat exchanger with multi-plate structure and use thereof

ActiveUS8616269B2Guaranteed robustness and reliabilityImprove heat transfer performanceFuel cell auxillariesStationary conduit assembliesEngineeringHeat exchanger

A heat exchanger comprises a plurality of plates (7, 9, 11, 13) each having first (15, 19) and second (17, 21) heat transfer surfaces on reverse sides. The plates are arranged in a stack with spacings between mutually facing heat transfer surfaces of adjacent plates. Alternate spacings in the stack providing respectively, a first fluid path (51, 52) for a first fluid and a second fluid path (57, 59) for a second fluid. The plates are arranged in a plurality of groups, each comprising at least two plates. Pin means are provided in the form of a plurality of groups of pins (23). The pins of each pin group are arranged to bridge plates of a respective plate group.

Owner:HIFLUX

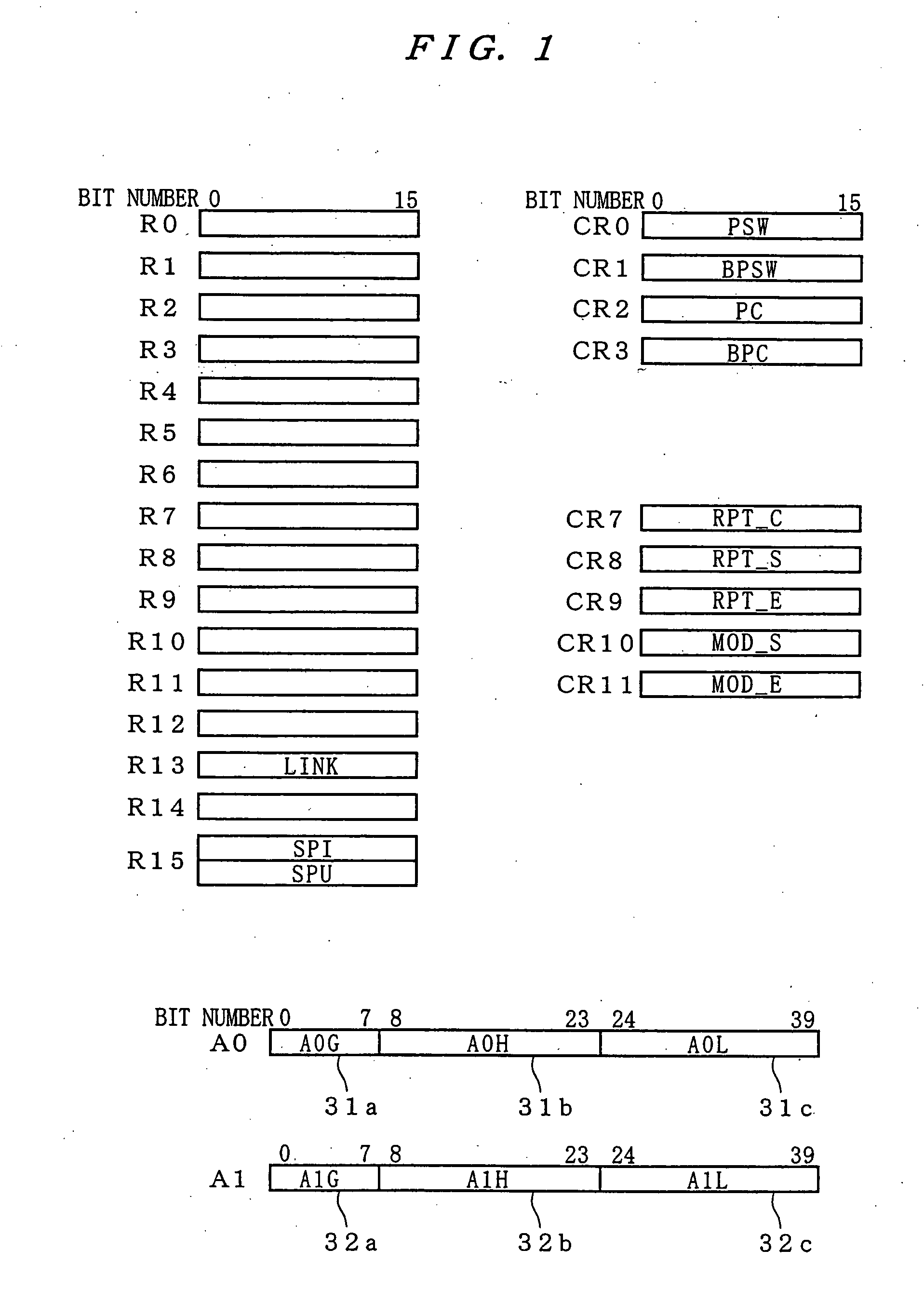

Data processor

InactiveUS20070174596A1Improve coding efficiencyReducing penaltyConditional code generationRegister arrangementsSignal onParallel computing

A data processor, and particularly in a data processor performing condition execution on the basis of flag information, aims at obtaining a data processor having excellent code efficiency, which can reduce branch penalty. In order to attain the aforementioned object, it is so structured that, when a first instruction decoded in a first decoder is an execution condition specifying instruction specifying the execution condition for a pair of second instructions executed in parallel, a first execution condition determination unit performs determination of the execution condition for the second instructions defined by the execution condition specifying instruction on the basis of the flag information and controls assertion / non-assertion of an execution inhibit signal on the basis of whether the execution condition defined by the execution condition specifying instruction is satisfied or not.

Owner:RENESAS TECH CORP

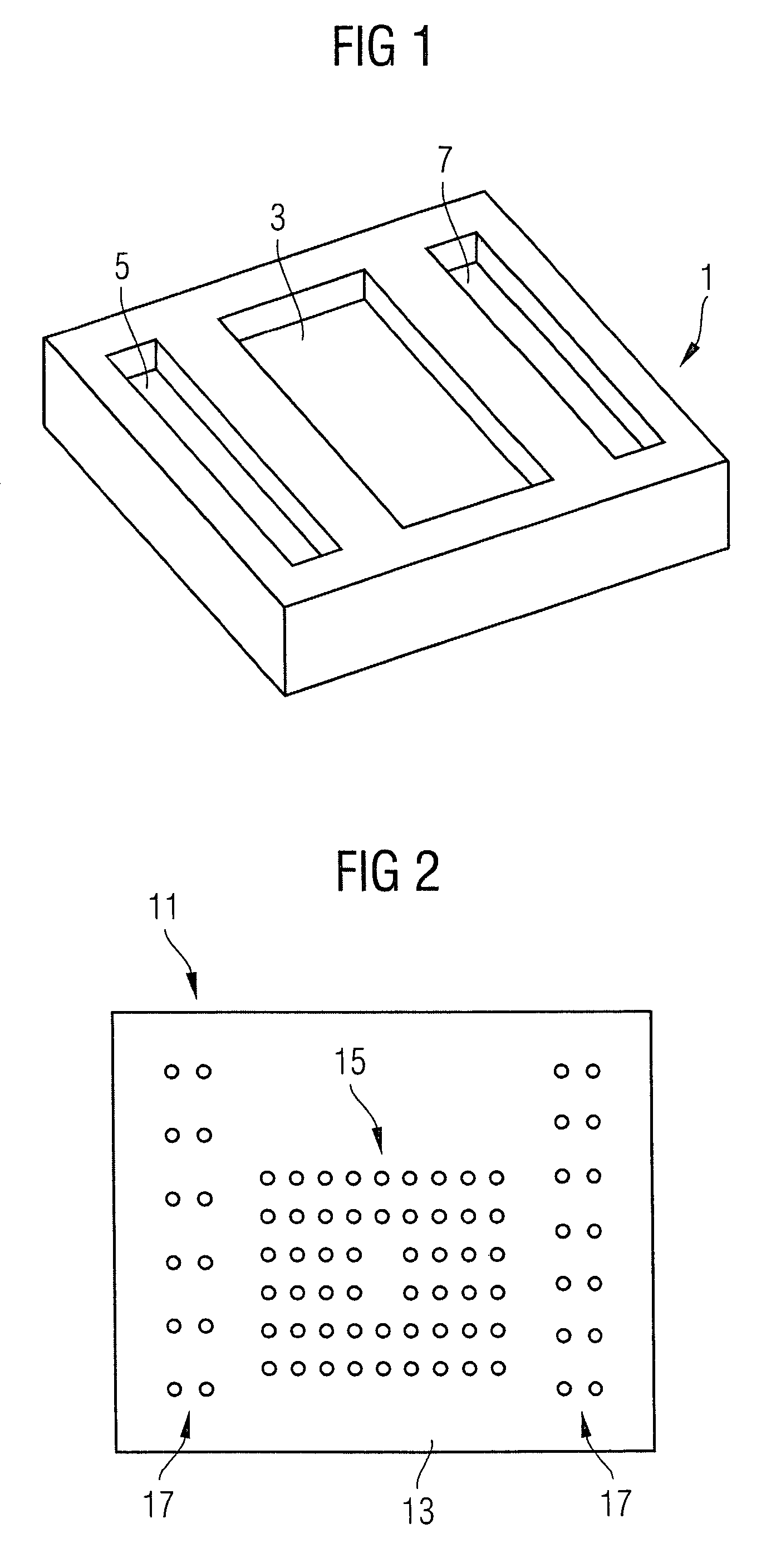

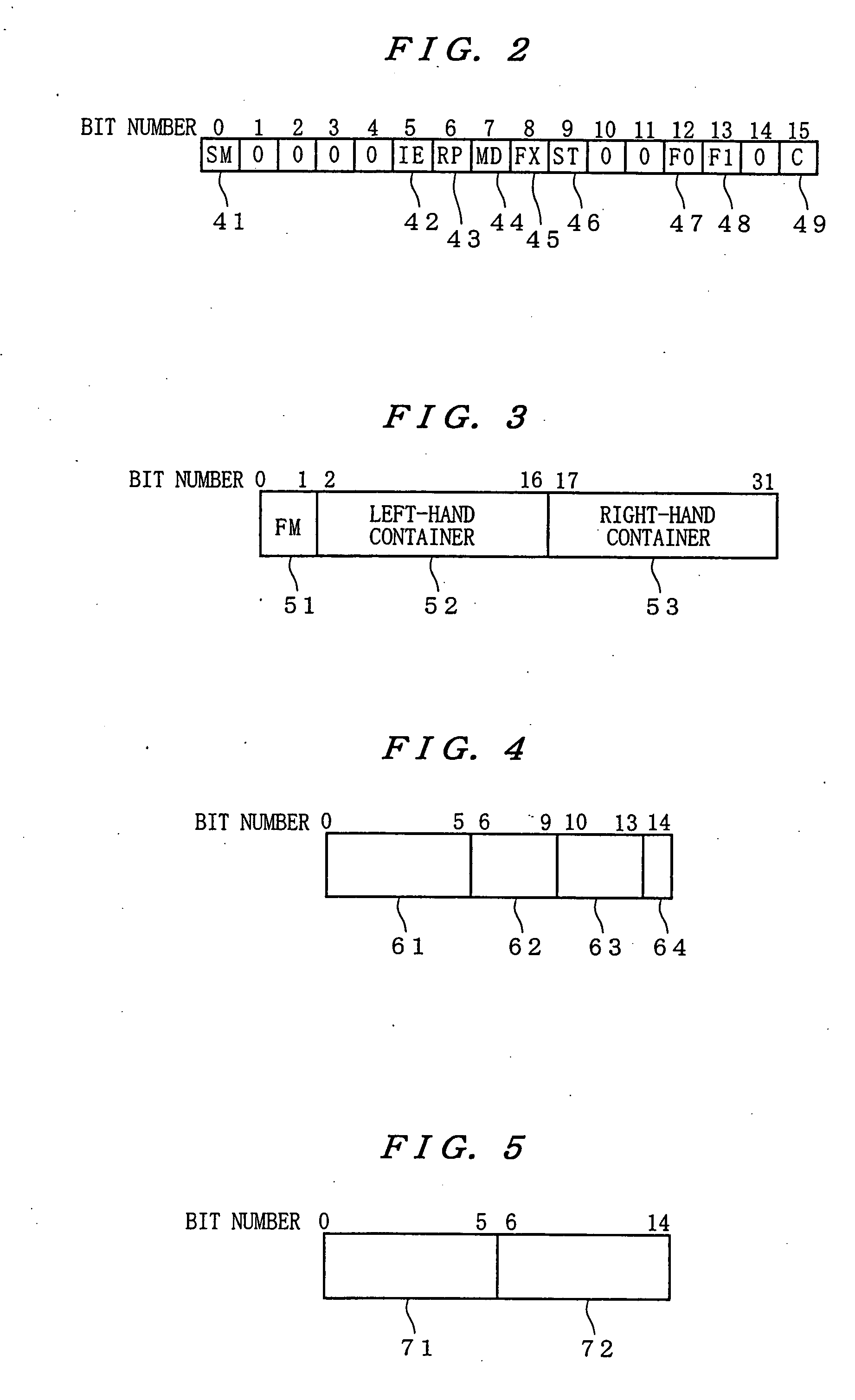

Integrated circuit package employing a flexible substrate

InactiveUS7659620B2Easy to optimizeReduced footprintSemiconductor/solid-state device detailsSolid-state devicesConductive materialsIntegrated circuit packaging

An integrated circuit package includes a flexible laminar substrate 1. The substrate 1 has a flexible layer 5 of heat conductive material on one of its faces. The layer 5 extends across an aperture 9 in the flexible substrate 1. A first integrated circuit 11 is mounted on the layer 5 within the aperture 9, and wire bonded to the substrate 1. A flip chip 21 is mounted on the first integrated circuit 11. The two integrated circuits 11, 21 are embedded in a resin body 23.

Owner:INFINEON TECH AG

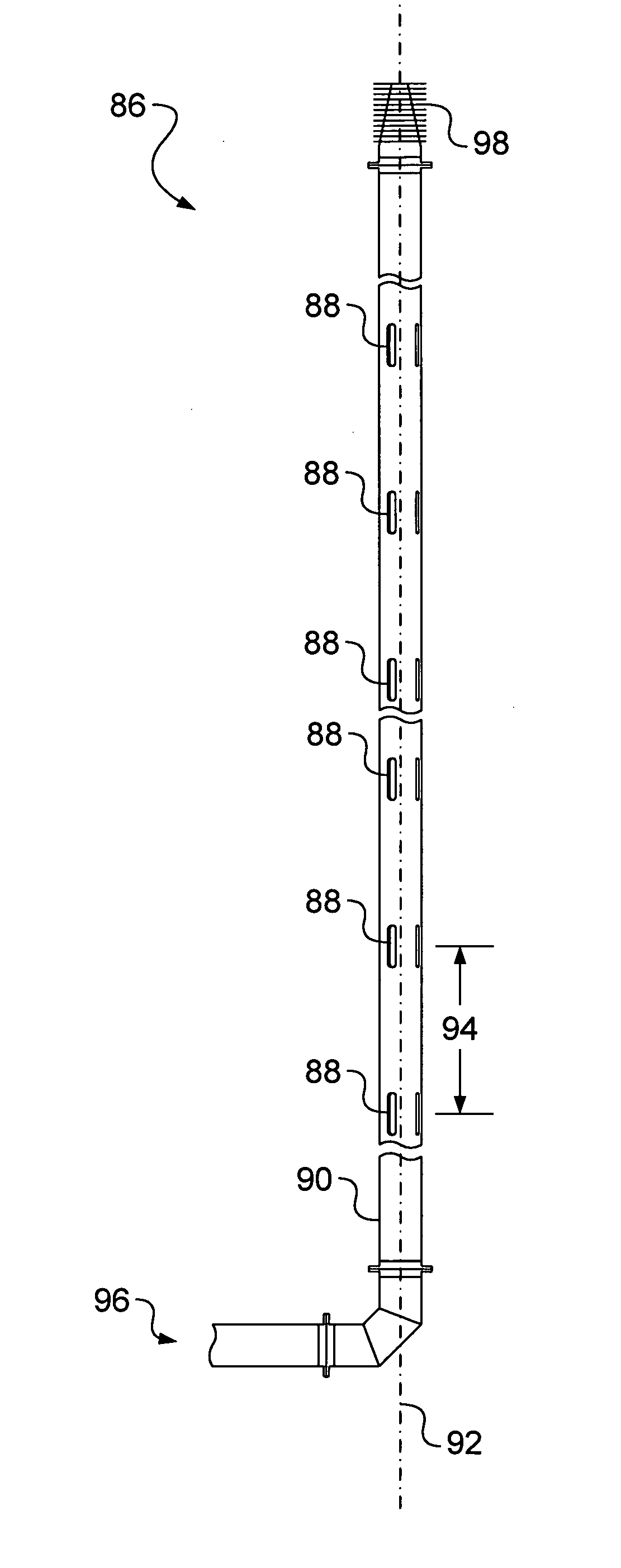

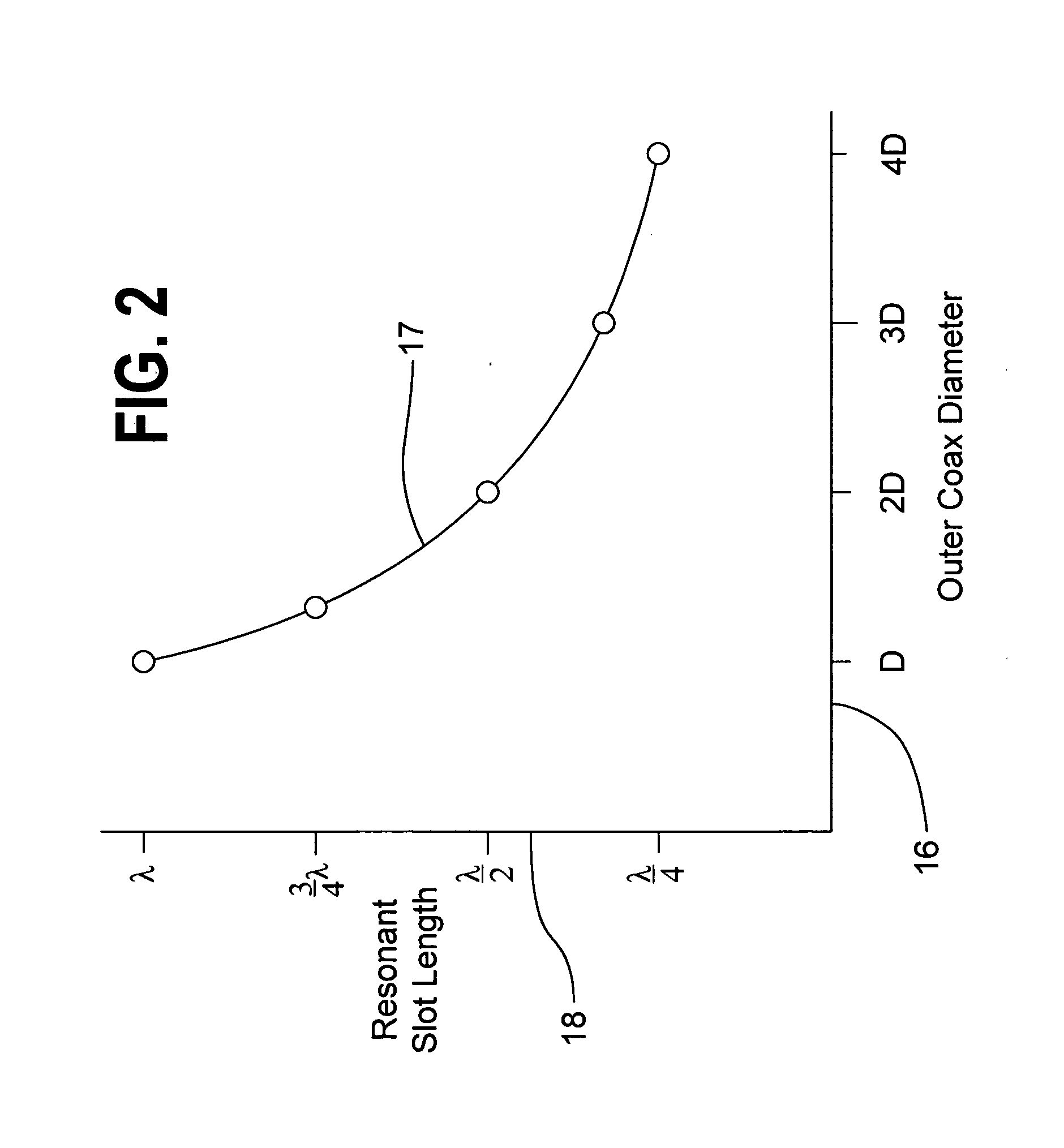

Apparatus and method to increase apparent resonant slot length in a slotted coaxial antenna

InactiveUS20050146474A1Increase capacitanceReducing penaltySlot antennasLeaky-waveguide antennasCapacitanceOblique angle

An oblique angle defining the slot face opposing a coupler in a slotted coaxial antenna increases the apparent slot length and therewith the capacitance of the driven element. The altered slot angle, in concert with a flattened facing surface on the associated coupler, increases the radiating efficiency of the antenna.

Owner:SPX CORP

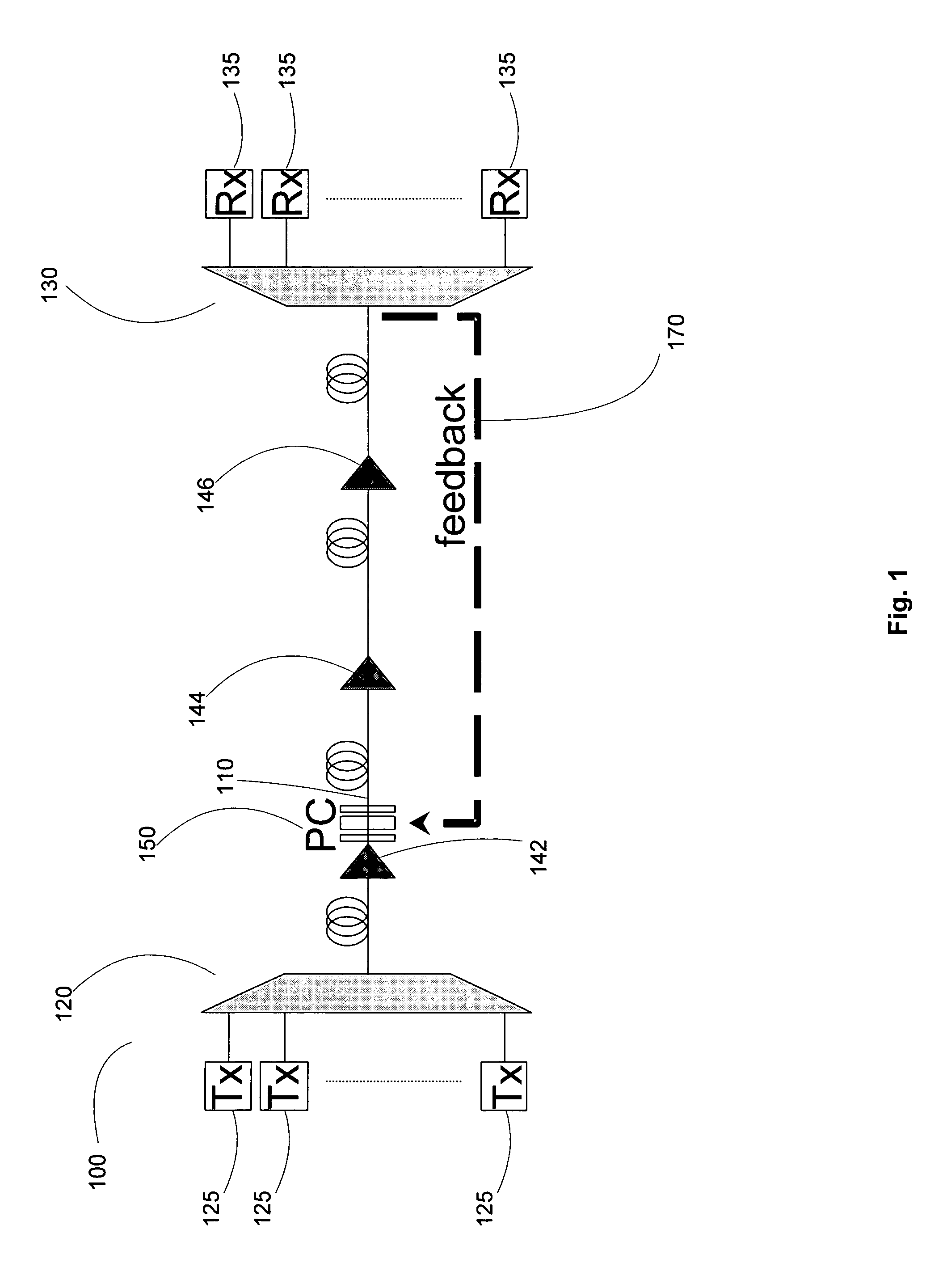

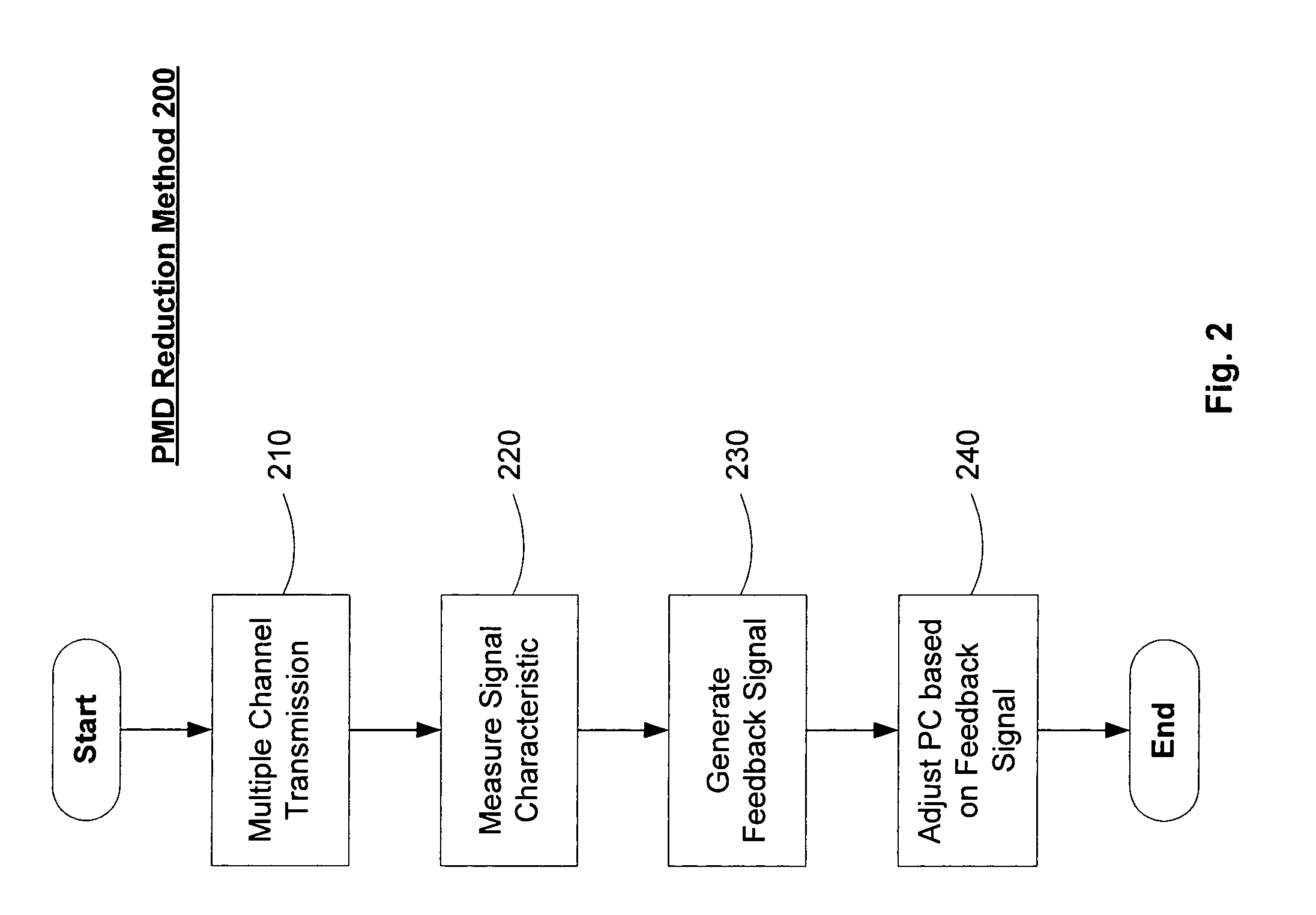

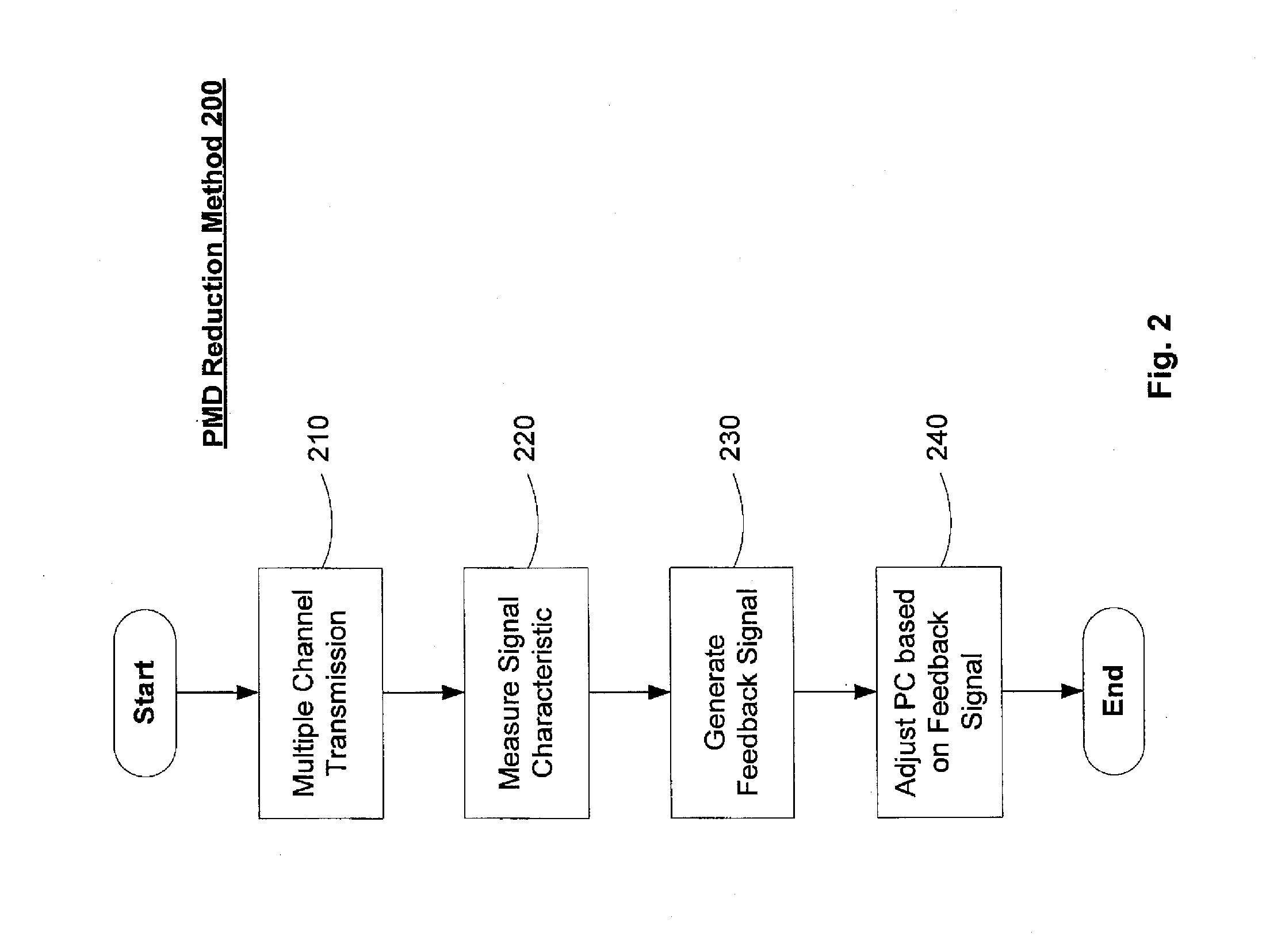

Method and apparatus for broadband mitigation of polarization mode dispersion

ActiveUS7869716B1Reducing penaltyReduce dispersionWavelength-division multiplex systemsMaterial analysis by optical meansBroadbandEngineering

Described is a method and system for reducing system penalty from polarization mode dispersion. The method includes receiving a plurality of signals at a receiving end of a transmission line, each signal being received on one of a plurality of channels of the transmission line and measuring a signal degradation of at least one of the channels of the transmission line. An amount of adjustment of a polarization controller is determined based on the signal degradation, the amount of adjustment being selected to reduce the polarization mode dispersion. The amount of adjustment is then transmitted to the polarization controller.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

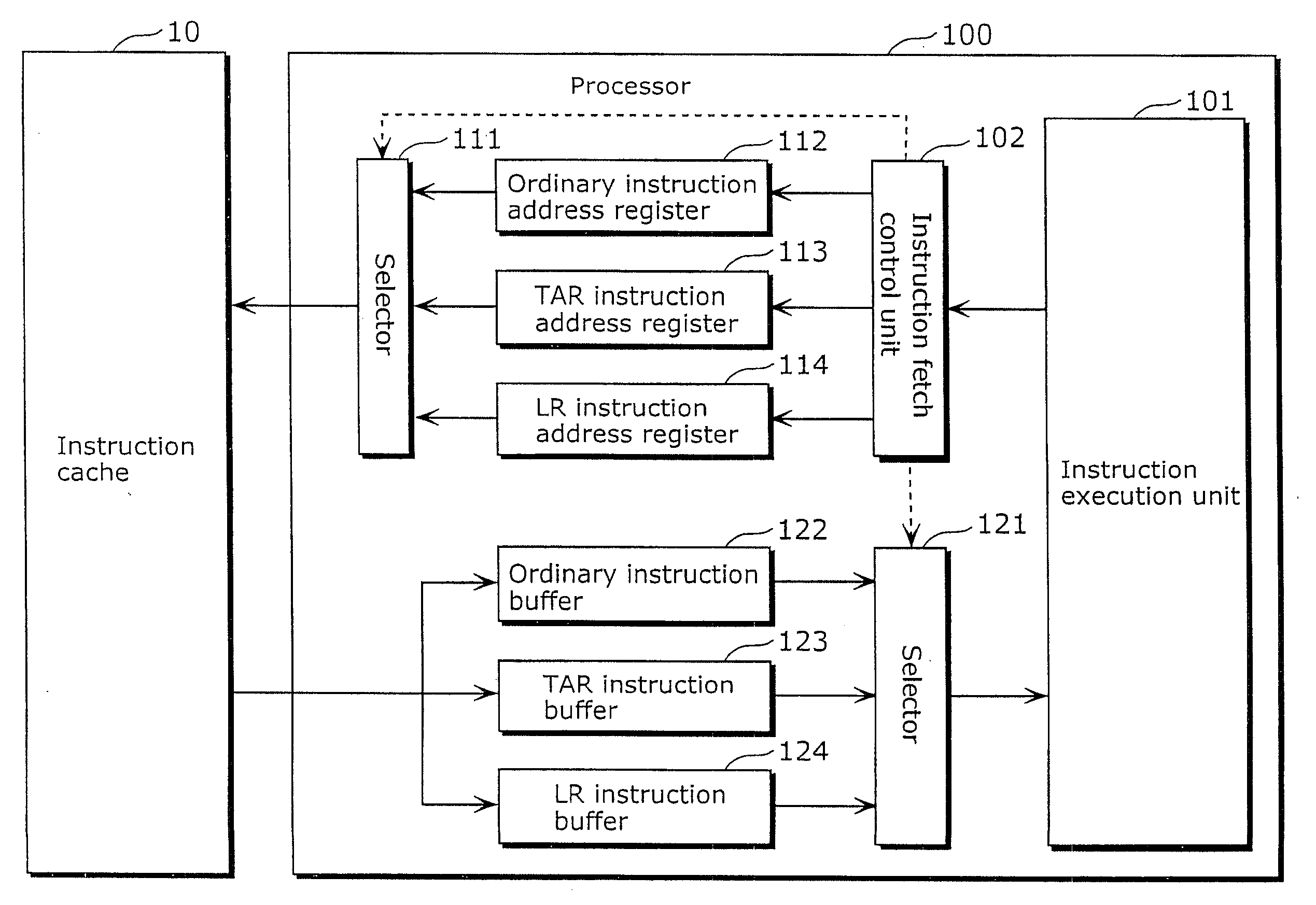

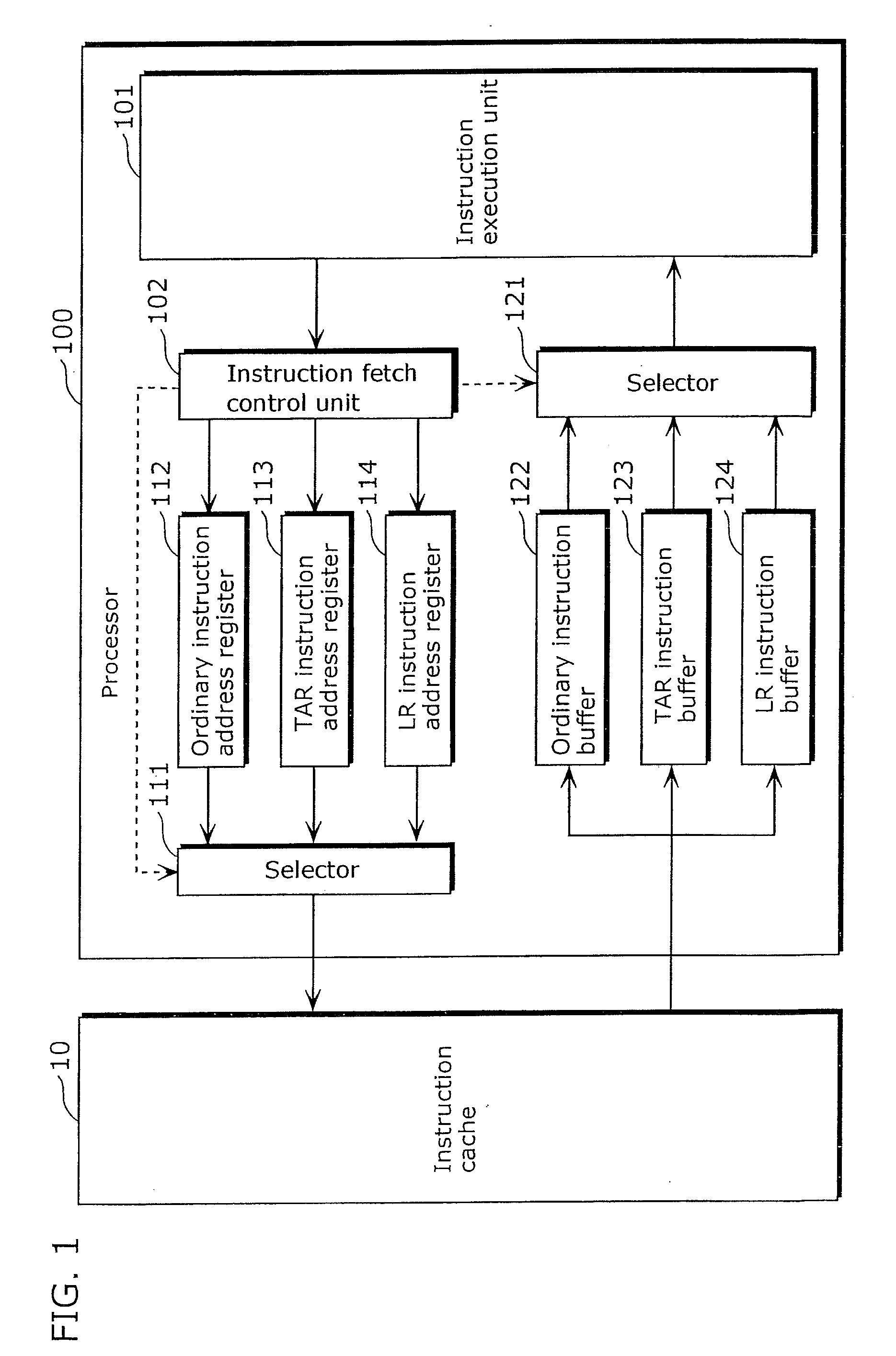

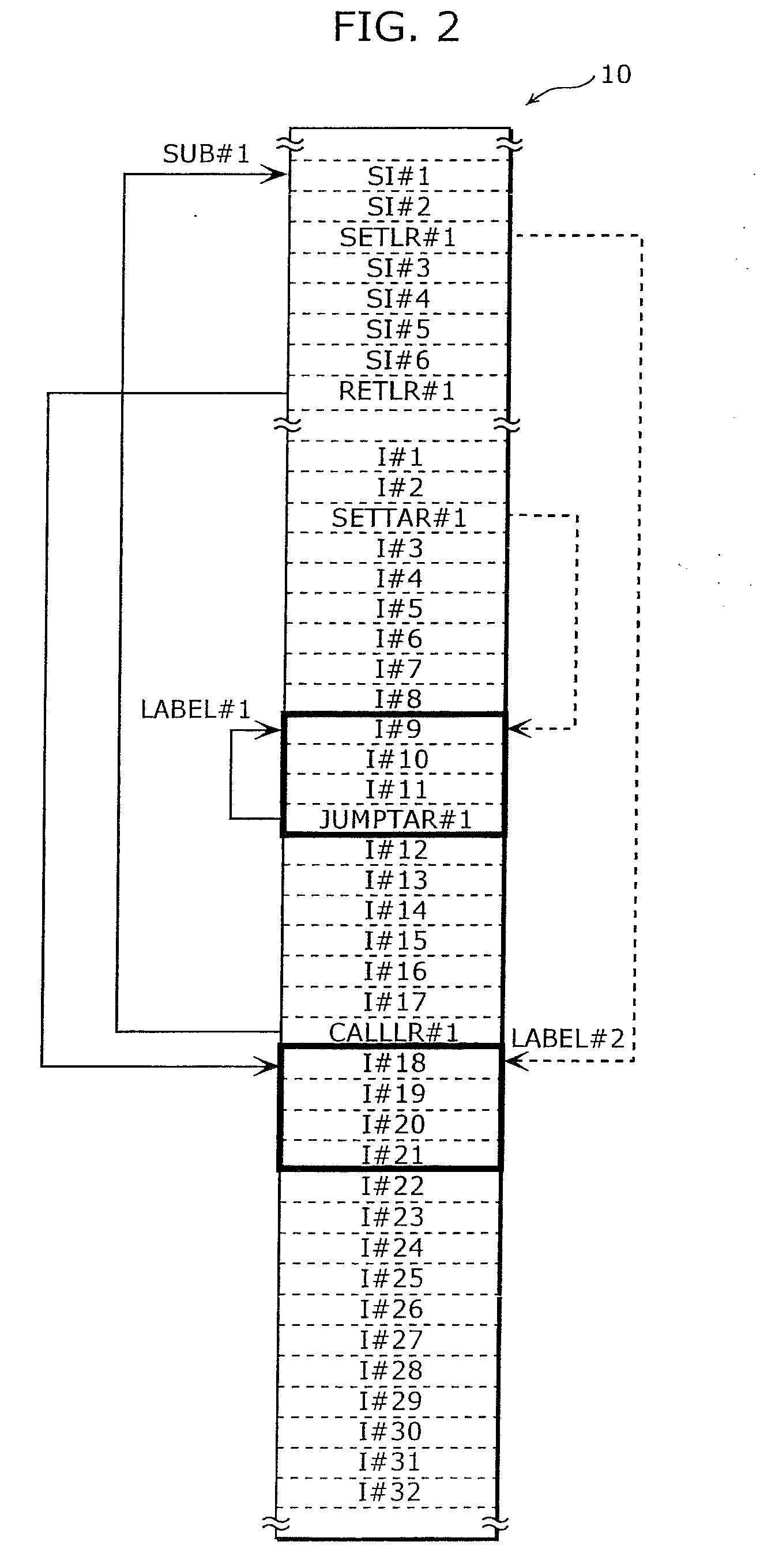

Processor

InactiveUS20090037696A1Reducing penaltyFill idle portionProgram control using stored programsDigital computer detailsComputer scienceInstruction buffer

A processor (100) includes an ordinary instruction buffer (122) for storing and supplying one or more instructions fetched from an instruction cache (10), a TAR instruction buffer (123) for storing the one or more instructions fetched from the instruction cache (10) and supplying them secondarily, a selector (121) for selecting either the ordinary instruction buffer (122) or the TAR instruction buffer (123) as an instruction supplying source, and an instruction fetch control unit (102) for fetching, when a TAR filling instruction is executed, one or more instructions specified by the TAR filling instruction, and for controlling the selector (121) to select the TAR instruction buffer (123), in the case where case one or more fetched instructions are repeatedly supplied, thereby to supply an instruction through the selector (121) from the TAR instruction buffer (123).

Owner:PANASONIC CORP

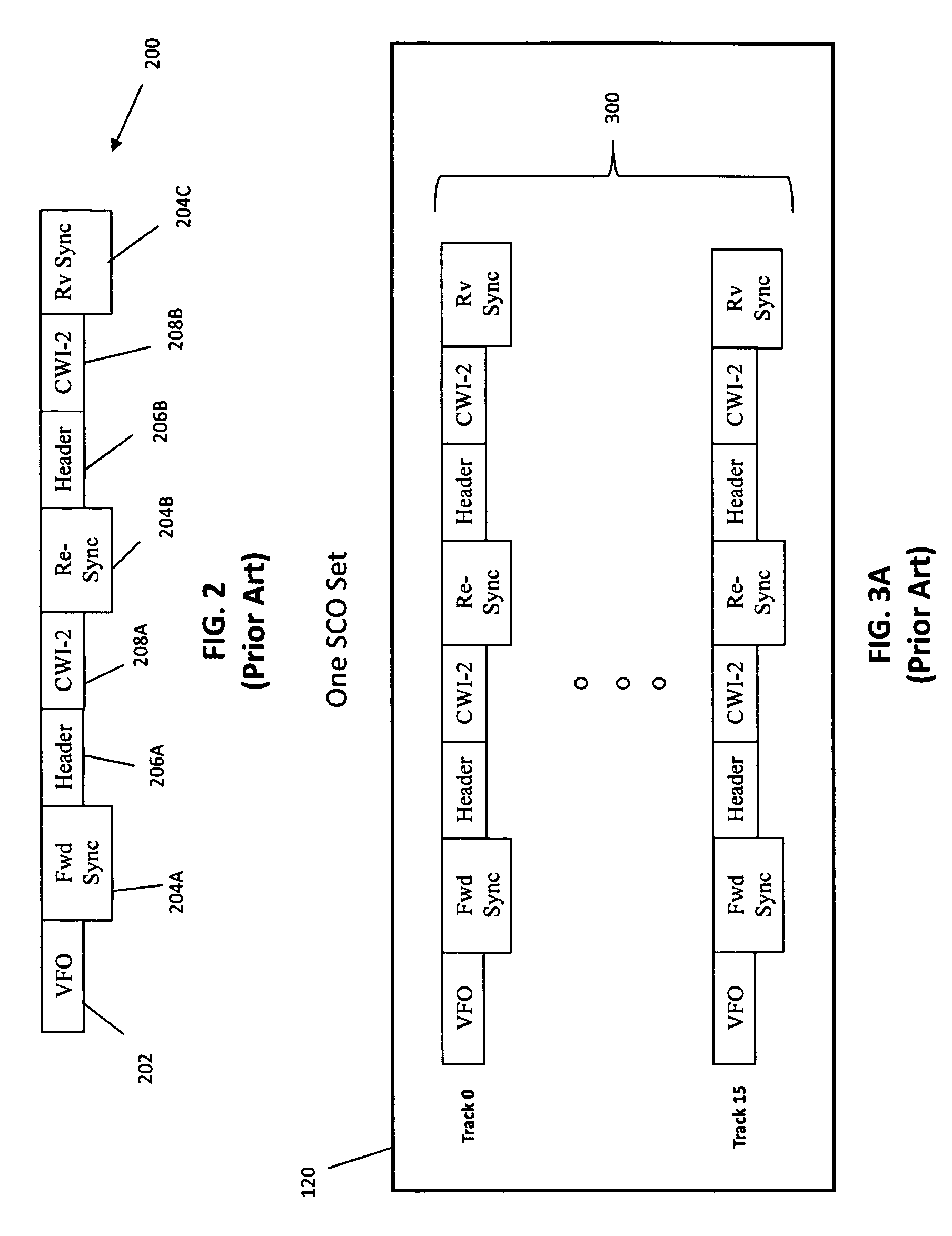

Rewriting codeword objects to magnetic data tape upon detection of an error

InactiveUS20100177420A1Reducing penaltyRecord information storageTape-like record carriersMagnetic tapeComputer science

During a read-after-write operation on magnetic tape, a first SCO is formed which includes two encoded processed user data units and is one of T SCOs in a first SCO set. The user data units are each one of T user data units in first and second user data unit sets, respectively, within the first SCO set. The first SCO set is written to the magnetic tape and is immediately read. When an error is detected in one of the user data units, a second SCO is formed to include the first user data unit and, only if an error is not detected in a user data unit in the other user data unit set, to not include the other user data unit, the second SCO being one of T SCOs in a second SCO set. Then, the second SCO set is rewritten to a later position on the tape later.

Owner:IBM CORP

Rewriting codeword objects to magnetic data tape upon detection of an error

InactiveUS8259405B2Reducing penaltyRecord information storageTape-like record carriersMagnetic tapeData tape

Owner:INT BUSINESS MASCH CORP

Apparatus and method for processing airflow with flowfield molded hypersonic inlet

ActiveUS20090094987A1Reducing penaltyImproved airflow characteristicsGeometric CADCosmonautic vehiclesShock waveJet engine

Owner:LOCKHEED MARTIN CORP

Method and Apparatus for Broadband Mitigation of Polarization Mode Dispersion

ActiveUS20110129215A1Reducing penaltyReduce dispersionWavelength-division multiplex systemsMaterial analysis by optical meansBroadbandPolarization mode dispersion

Described is a method and system for reducing system penalty from polarization mode dispersion. The method includes receiving a plurality of signals at a receiving end of a transmission line, each signal being received on one of a plurality of channels of the transmission line and measuring a signal degradation of at least one of the channels of the transmission line. An amount of adjustment of a polarization controller is determined based on the signal degradation, the amount of adjustment being selected to reduce the polarization mode dispersion. The amount of adjustment is then transmitted to the polarization controller.

Owner:AT&T INTPROP II LP

Microprocessor for gating a load operation based on entries of a prediction table

ActiveUS10198265B2Avoid delayLower performance requirementsConcurrent instruction executionTheoretical computer scienceStore instruction

A method for gating a load operation based on entries of a prediction table is presented. The method comprises performing a look-up for the load operation in a prediction table to find a matching entry, wherein the matching entry corresponds to a prediction regarding a behavior of the load operation, and wherein the matching entry comprises: (a) a tag field operable to identify the matching entry; (b) a distance field operable to indicate a distance of the load operation to a prior aliasing store instruction; and (c) a confidence field operable to indicate a prediction strength generated by the prediction table. The method further comprises determining if the matching entry provides a valid prediction and, if valid, retrieving a location for the prior aliasing store instruction using the distance field. The method finally comprises performing a gating operation on the load operation.

Owner:INTEL CORP

Integrated circuit package employing a flexible substrate

InactiveUS20060076655A1Easy to optimizeReduced footprintSemiconductor/solid-state device detailsSolid-state devicesConductive materialsEngineering

An integrated circuit package includes a flexible laminar substrate 1. The substrate 1 has a flexible layer 5 of heat conductive material on one of its faces. The layer 5 extends across an aperture 9 in the flexible substrate 1. A first integrated circuit 11 is mounted on the layer 5 within the aperture 9, and wire bonded to the substrate 1. A flip chip 21 is mounted on the first integrated circuit 11. The two integrated circuits 11, 21 are embedded in a resin body 23.

Owner:INFINEON TECH AG

Apparatus for gating a load operation based on entries of a prediction table

InactiveUS10152327B2Avoid delayLower performance requirementsConcurrent instruction executionParallel computingComputer science

An apparatus for gating a load operation is presented. The apparatus comprises a memory resident data structure, wherein the memory resident data structure is a prediction table comprising a plurality of entries, wherein a matching entry corresponding to the load operation within the prediction table comprises a prediction regarding a dependence of the load operation on a prior aliasing store instruction, and wherein the matching entry comprises: (a) a tag field operable to identify the matching entry; (b) a distance field operable to indicate a distance of the load operation to the prior aliasing store instruction; and (c) a confidence field operable to indicate a prediction strength generated by the prediction table, wherein the prediction strength influences a gating of the load operation.

Owner:INTEL CORP

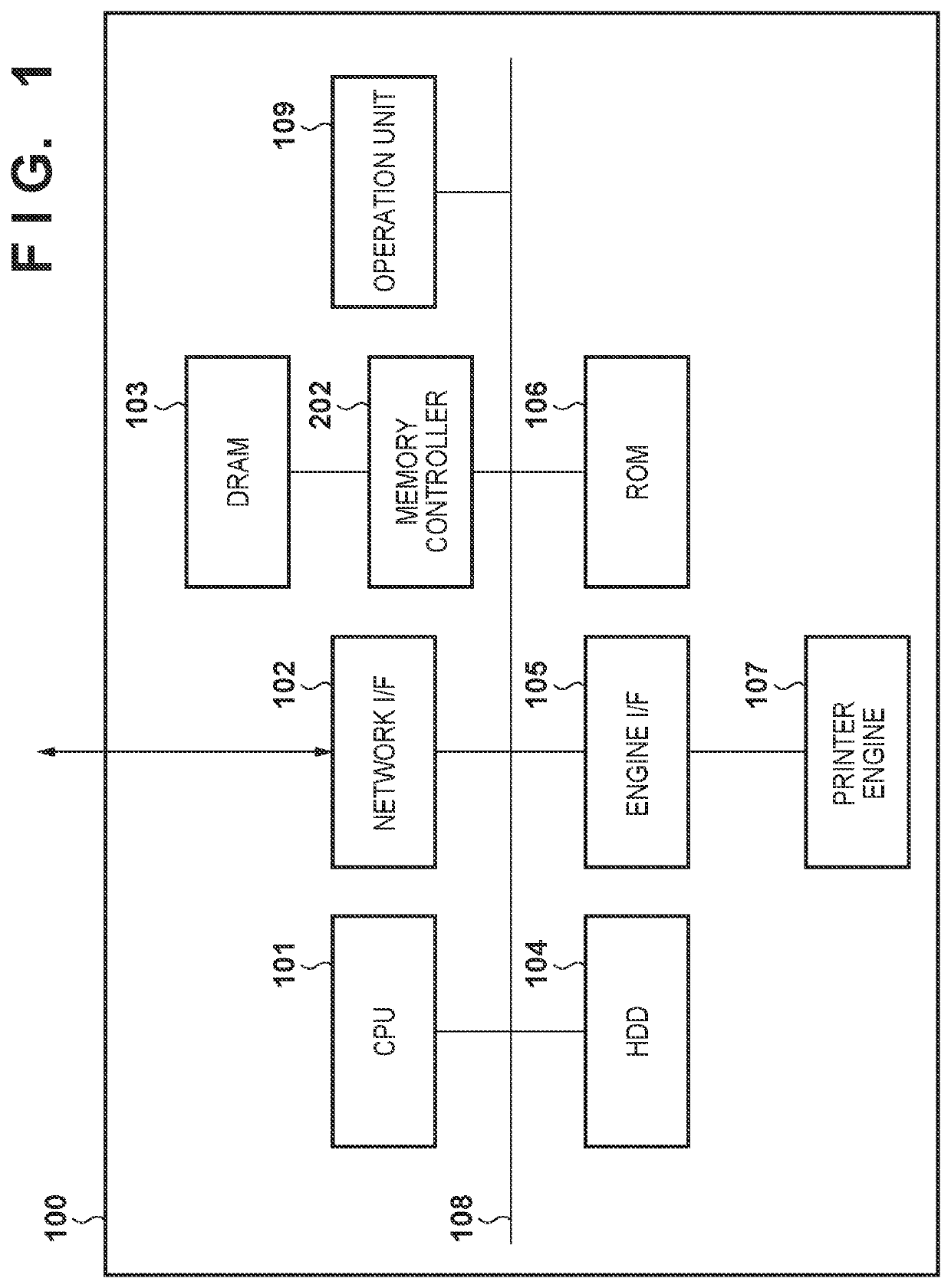

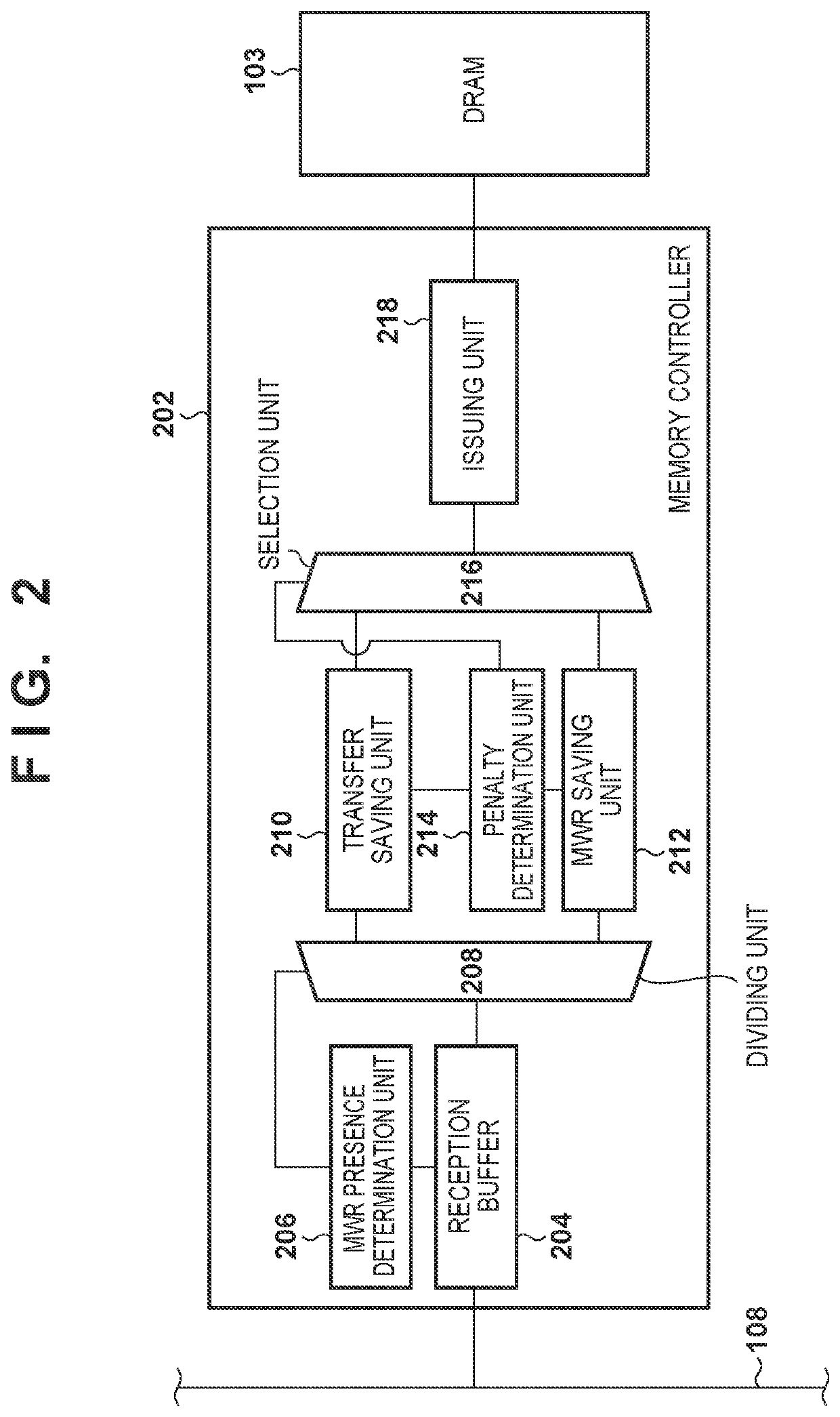

Memory controller and method performed by the memory controller

ActiveUS11385832B2Reduce influence penaltyLow efficiencyInput/output to record carriersDigital storageEngineeringMemory controller

A memory controller is capable of issuing a first write command for writing data of a predetermined size in a DRAM, and a second write command for writing data of a size smaller than the predetermined size in the DRAM. The memory controller comprises a receiving unit configured to receive a request to the DRAM from a bus; a determining unit configured to determine whether a command that is after the second write command when a reception sequence of a request is observed is issuable in a period until the second write command is issued after a preceding command is issued; and an issuing unit configured to issue a command determined to be issuable before the second write command.

Owner:CANON KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com