Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

42results about How to "Reduce calculation delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

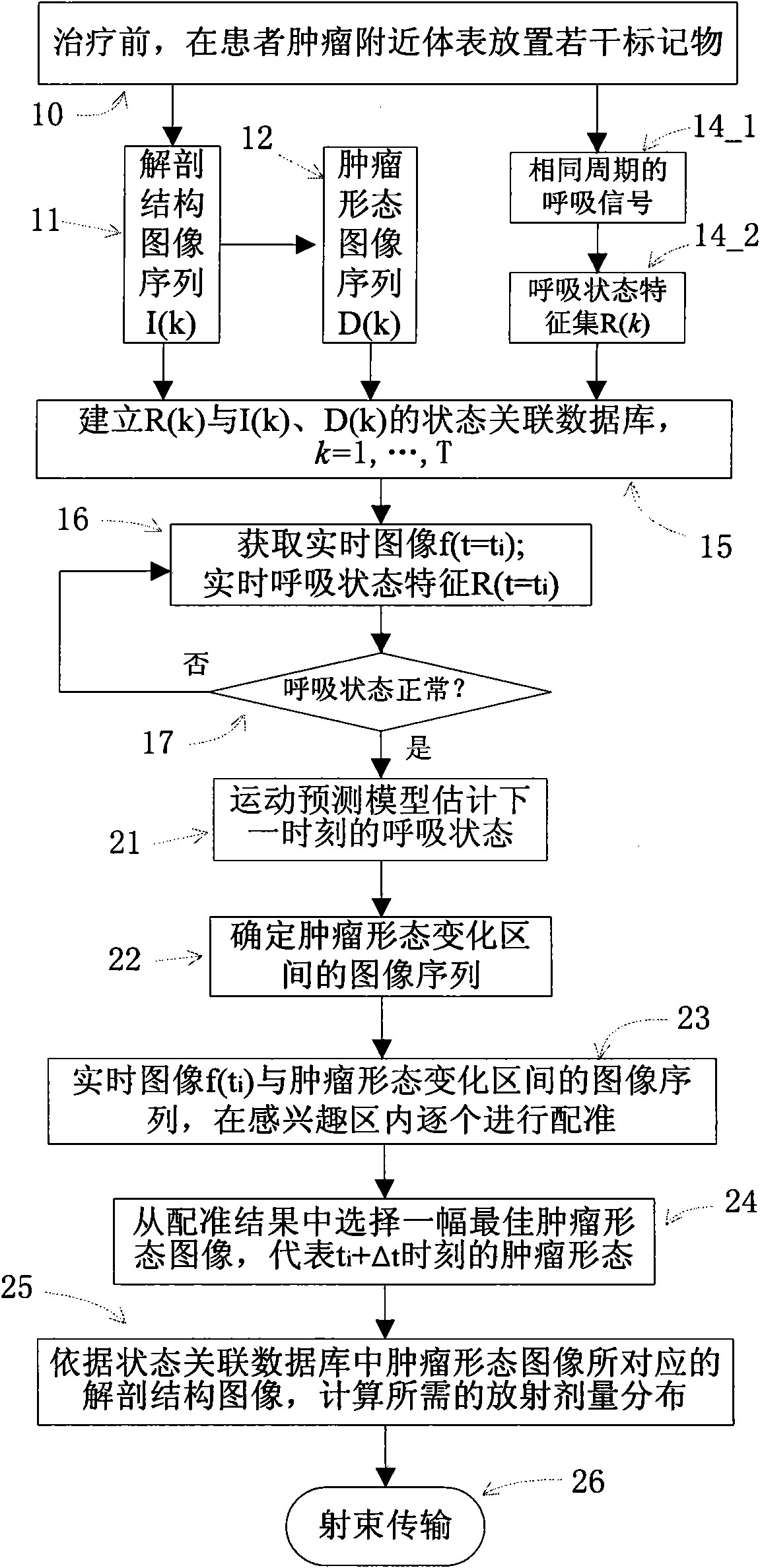

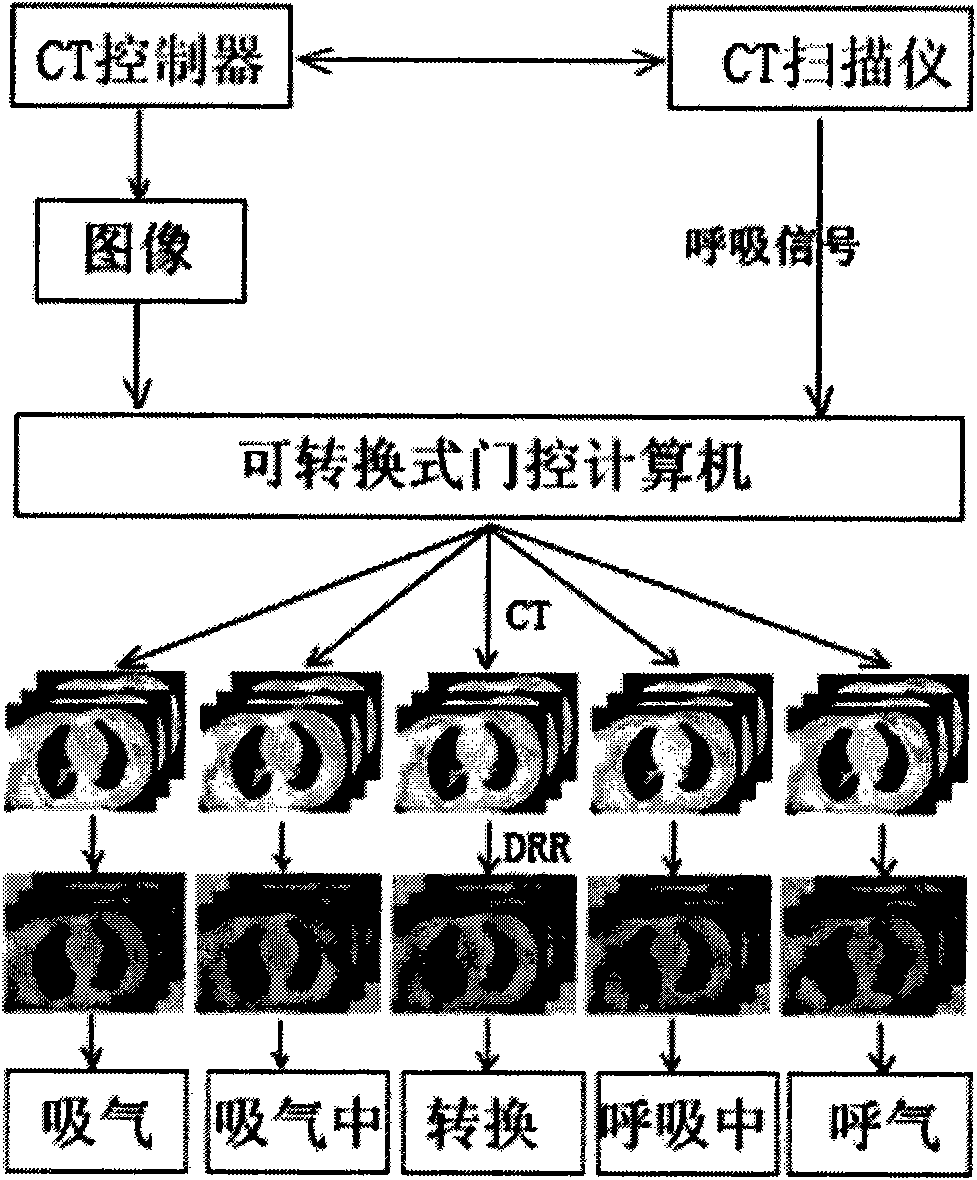

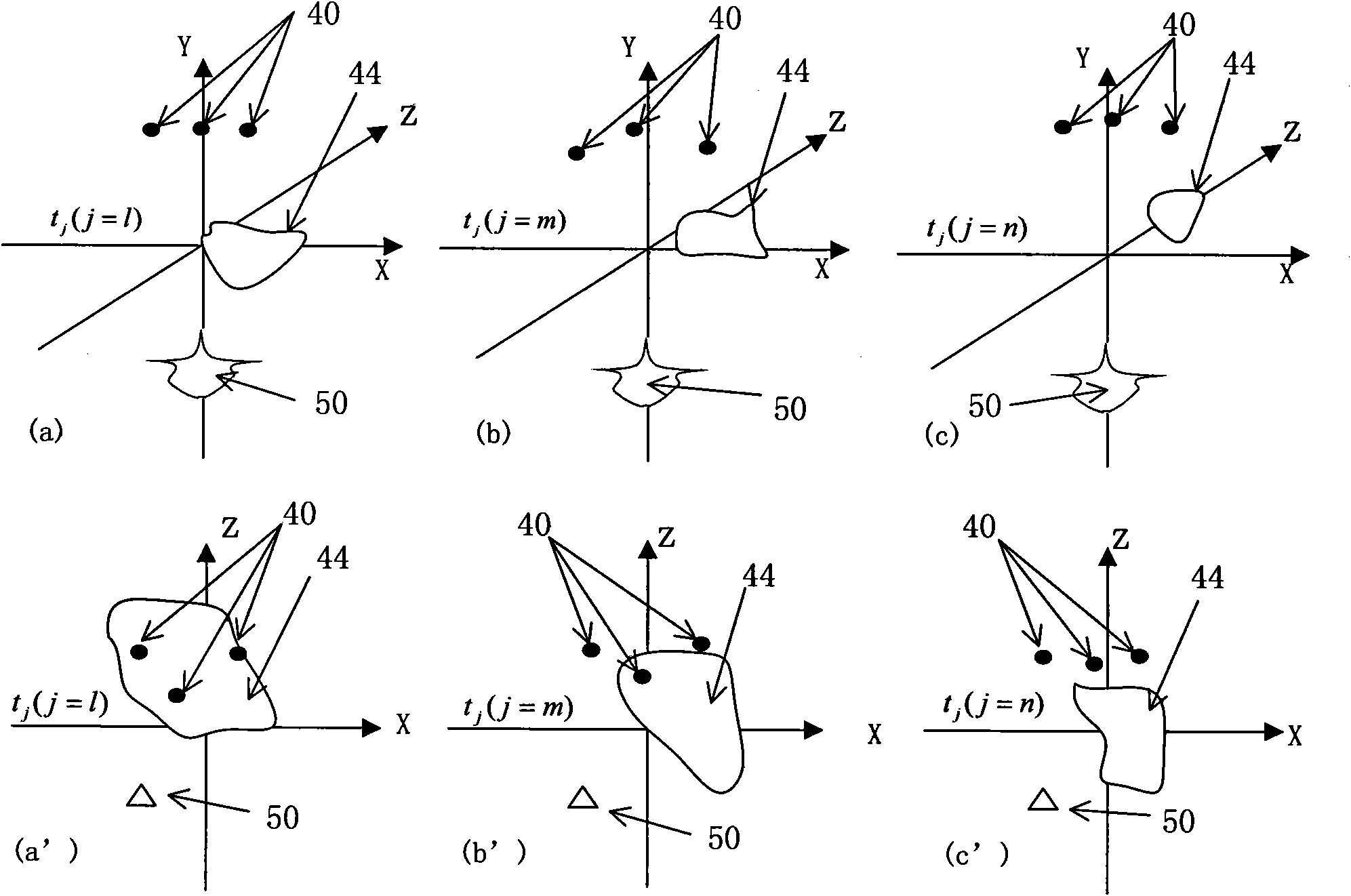

Image guiding and tracking method based on prediction

InactiveCN101628154AReal-time intensity modulation therapy effectContinuous treatmentSurgeryComputerised tomographsAnatomical structuresFeature set

The invention discloses an image guiding and tracking method based on prediction, which comprises the following steps: 1, inputting image sequences and a breathing status feature set of a tumor anatomical structure; 2, establishing a status association database; 3, acquiring real-time images and breathing status features; 4, predicting the delayed breathing status features, and determining the image sequences in a corresponding tumor shape varying section; 5, registering the real-time images with the image sequences in the tumor shape varying section one by one in an interested area; 6, selecting an optimal tumor shape image from registration results; and 7, outputting the image of the tumor anatomical structure. The image guiding and tracking method based on the prediction establishes the correlation between breath and tumor movement by the quantification and analysis on the breathing statuses, predicts the breath and tracks the movement according to the correlation, and improves the efficiency and the accuracy of tracking a dynamic tumor in real time.

Owner:SHEN ZHEN HYPER TECH SHENZHEN

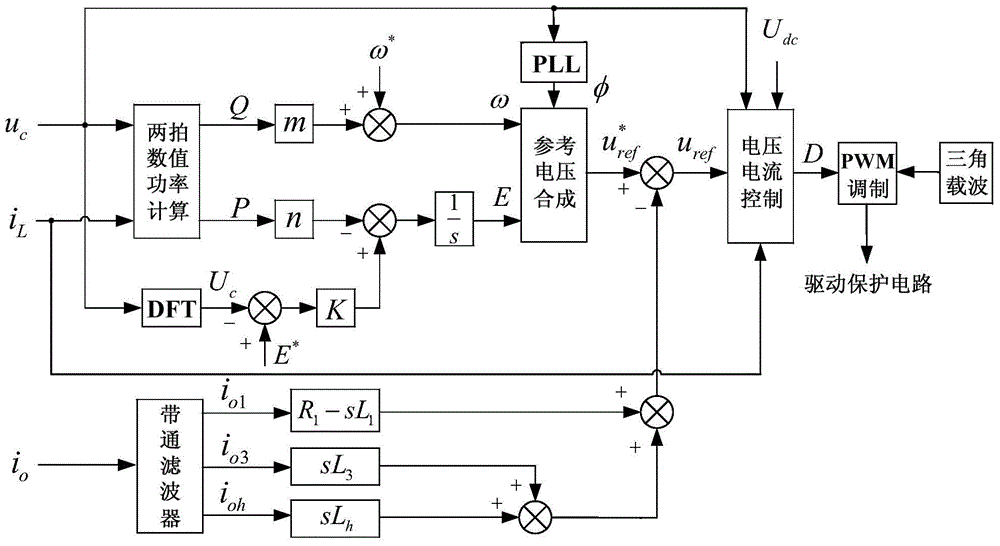

Microgrid multi-inverter parallel-control method based on frequency division virtual complex impedance

InactiveCN104578861AImprove dynamic performanceReduce calculation delayEnergy industrySingle network parallel feeding arrangementsLow voltageBand-pass filter

The invention discloses a microgrid multi-inverter parallel-control method based on frequency division virtual complex impedance, which is suitable for a multi-inverter parallel-control system with a nonlinear load for a low-voltage microgrid. The microgrid multi-inverter parallel-control method comprises the following steps: performing frequency division on a line current by virtue of a band pass filter by adopting a robust droop control strategy of resistance equivalent output impedance, simultaneously multiplying a fundamental current by a virtual complex impedance containing a resistance-capacitance component, designing that each parallel connection inverter output impedance is resistive in a fundamental band; and respectively multiplying each high-frequency current by different virtual inductive impedances, indicating that a harmonic frequency band inverter output impedance is inductive so as to be limited by the robust droop control strategy of resistance equivalent output impedance, so that the influence of a high-frequency harmonic current to inverter parallel-control is avoided. According to the microgrid multi-inverter parallel-control method, the defect of a conventional method is overcome, and good control effect is achieved in the multi-inverter parallel-control system with the nonlinear load for the low-voltage microgrid.

Owner:国网山东省电力公司聊城供电公司 +1

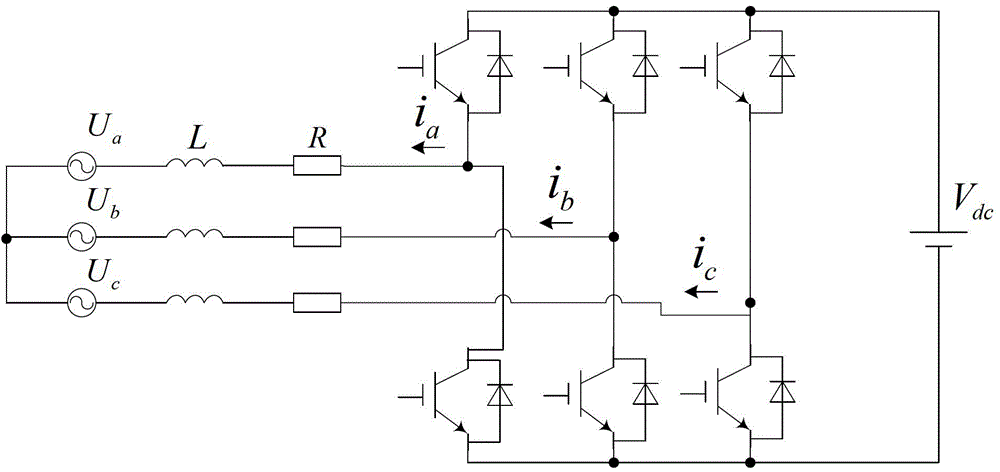

Grid-connected inverter control method under unbalanced and harmonic wave power grids

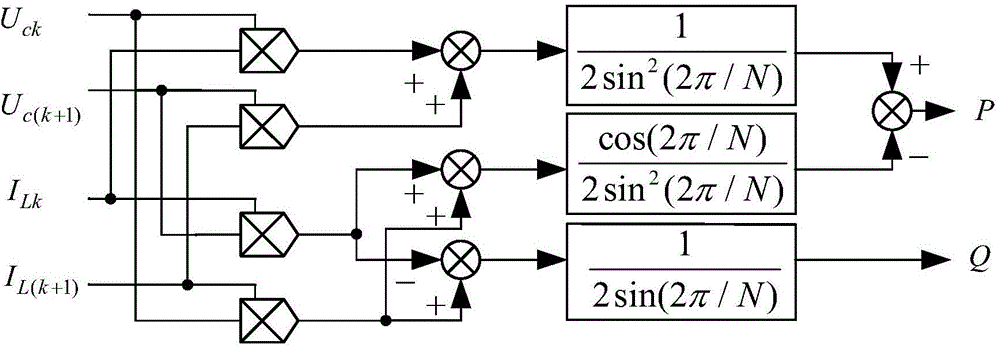

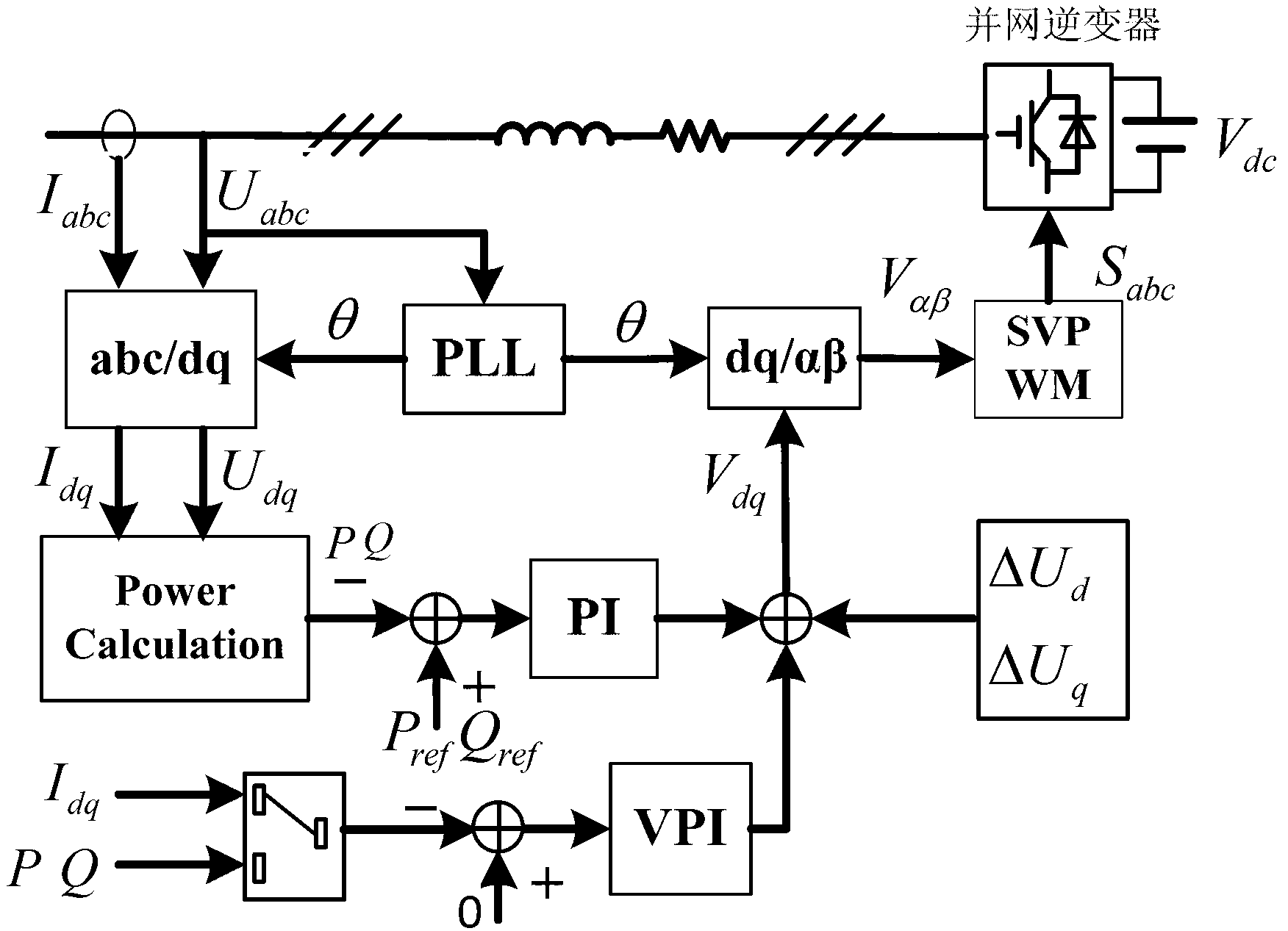

ActiveCN103326399AImprove stabilityImprove fault toleranceAc-dc conversionSingle network parallel feeding arrangementsEngineeringAlternating current

The invention discloses a grid-connected inverter control method under unbalanced and harmonic wave power grids. The grid-connected inverter control method adopts a VPI regulator to directly control frequency doubling harmonic wave frequency doubling component fluctuation of active power and reactive power, does not need to decompose positive sequences and negative sequences under multiple synchronous rotating coordinate systems to calculate power reference of frequency doubling components, therefore, reduces calculating delay and strengthens the dynamic response capacity. Meanwhile, due to the fact that the grid-connected inverter control method adopts the SVM-DPC strategy, the problem that the opening-closing frequency is changed is solved, and convenience is brought to selection of an alternating current filtering device. Therefore, the grid-connected inverter control method is suitable for single-phase or three-phase inverting devices, controlled by various PWMs, formed by other various high-frequency switch self-turn-off components under the unbalanced and harmonic wave power grids, and the one-phase or the three-phase inverting devices include grid-connected devices of power generation systems such as a wind energy power generation system, a solar energy power generation system and a fuel battery power generation system, a power electronic device of a flexible alternating current power transmission system and an inverter device in motor control.

Owner:ZHEJIANG UNIV

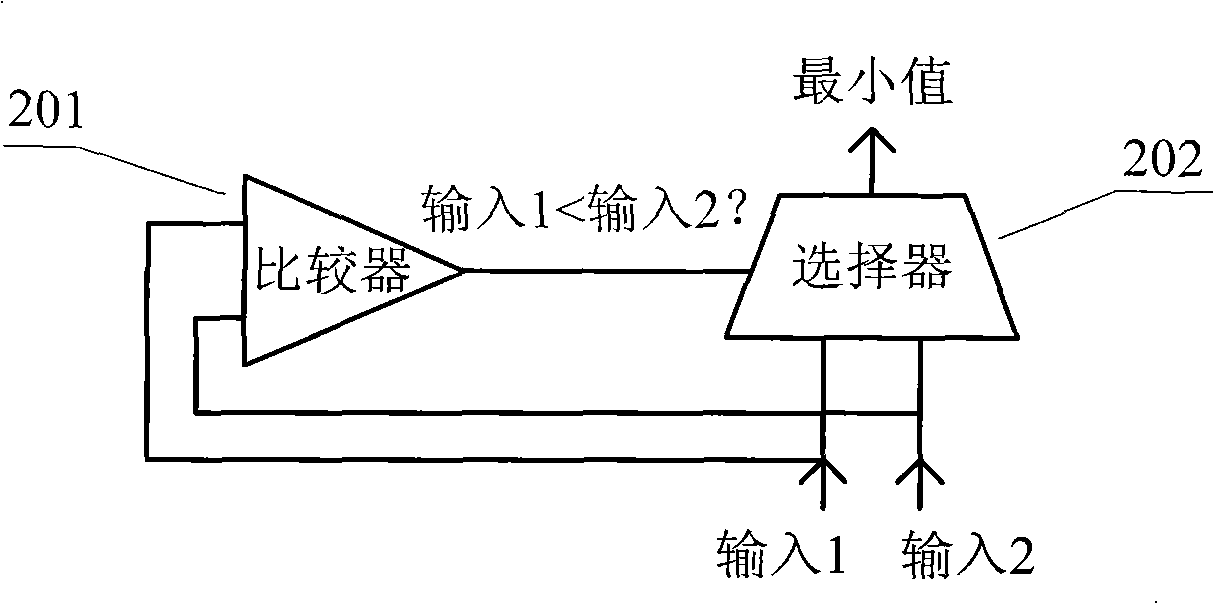

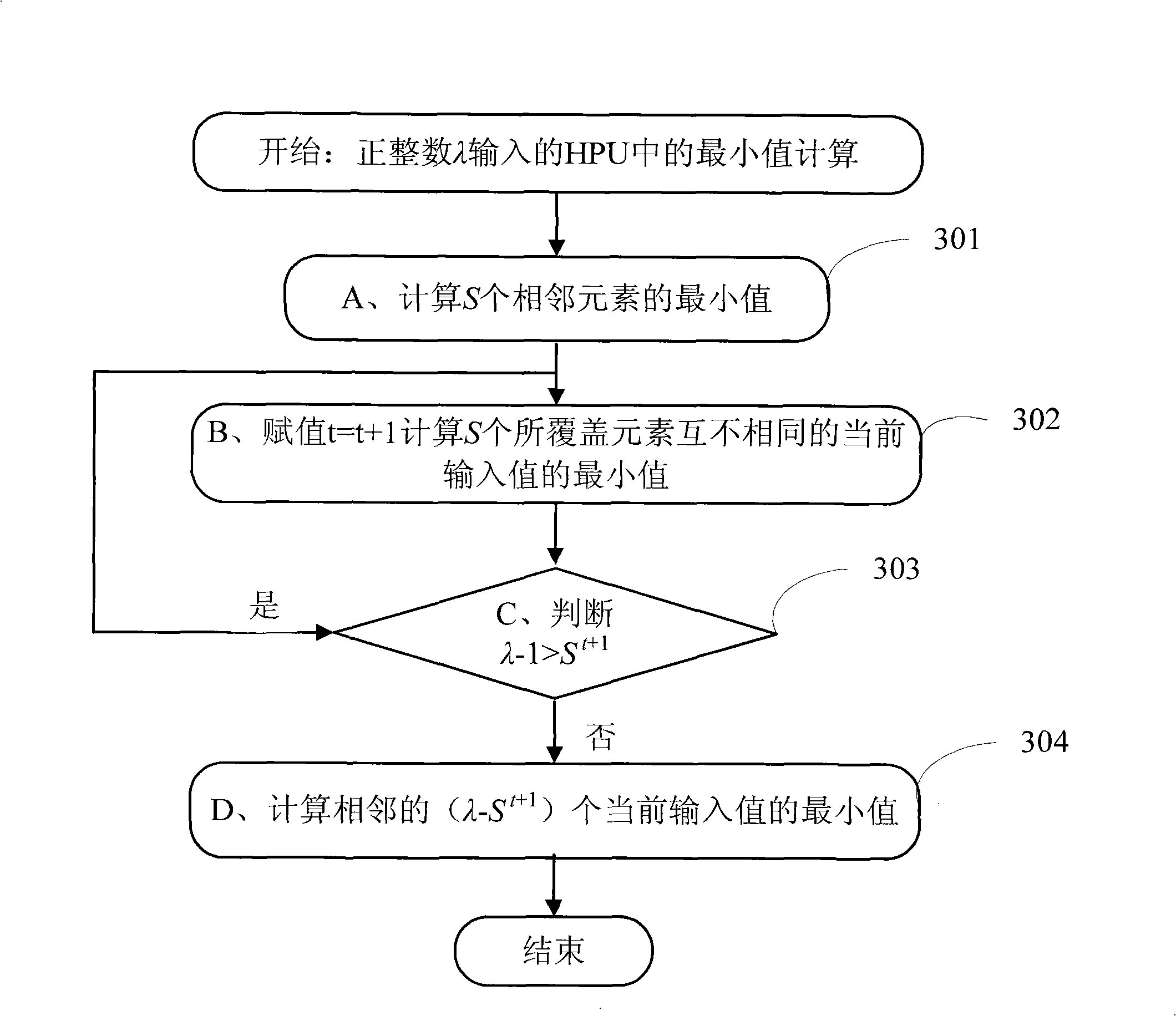

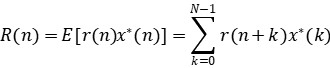

LDPC decoding circular hierarchical minimum calculation method and its realization device

InactiveCN101267209AHigh frequencyImprove throughputError preventionError correction/detection using multiple parity bitsTime delaysDecomposition

A method for calculating the least value of the circulating grading to the LDPC decoding and a realizing device thereof belong to the field of the digital information transmission technique. The method uses a fundamental least value calculating module which is composed of a comparator and a selector, and realizes the least value calculation of the horizontal calculating unit in the low-density check code encoder basing on the least summation algorithm and the improved algorithm. The designing process of the low-density check code encoder can be simplified, and the consumption quantity of the logical resource of the horizontal arithmetic unit in the encoder can be reduced. The least value calculating method basing on the invention and the realizing device thereof has the advantages of directly designing out the horizontal arithmetic unit of the production line, decomposition to the time delay path of the horizontal arithmetic unit, increase to the clock frequency of the encoder and increase to the capability of the turnover rate of decoding.

Owner:TSINGHUA UNIV

Simplified three-level space vector modulation method

InactiveCN103731055AEasy to judgeImprove reliabilityDc-ac conversion without reversalThree levelVoltage vector

The invention discloses a simplified three-level space vector modulation method. The method comprises the following steps of (1) obtaining a reference voltage synthesizing vector according to the three-phase voltage of a control system; (2) determining a large sector which the reference voltage synthesizing vector belongs to; (3) determining a small sector which the reference voltage synthesizing vector belongs to (4) calculating the action time of the reference voltage synthesizing vector in the small sector; (5) arranging the switching sequence of every vector in the small sector which the reference voltage synthesizing vector; (6) calculating the duty ratio according to the switching sequence. According to the simplified three-level space vector modulation method, by deprecating 6 large vectors and dividing voltage vector space through the other 21 fundamental space vectors, the quantity of the voltage vectors and sectors can be reduced, the space complexity can be reduced, the algorithm running time can be effectively shortened, the running efficiency can be improved and popularization and application of the three-level space vector modulation technology can be facilitated.

Owner:SOUTHEAST UNIV

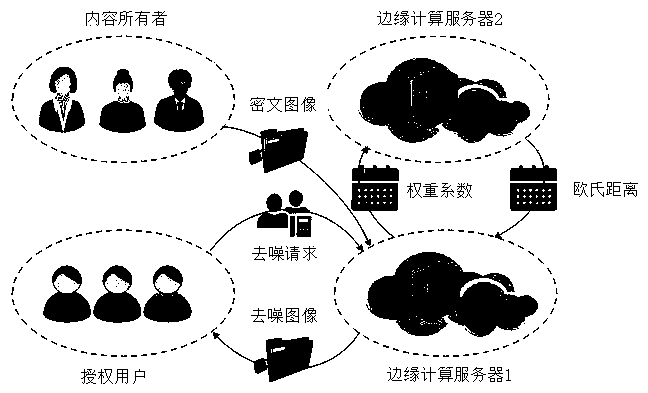

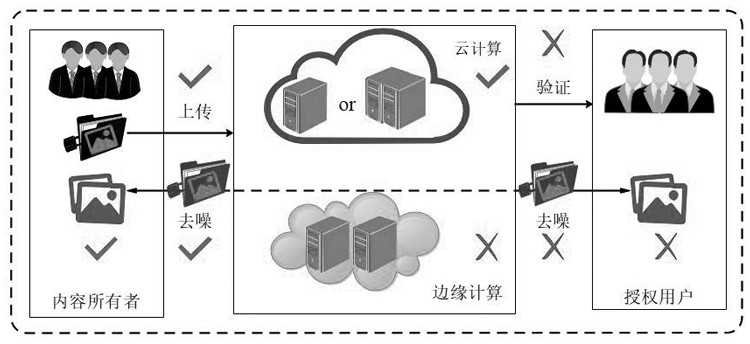

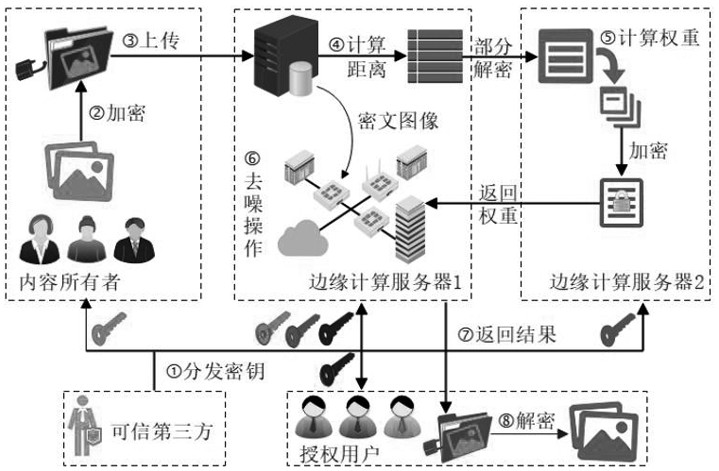

Privacy protection-based user authenticated outsourcing image denoising method

ActiveCN111241561AReduce lossesImprove securityImage enhancementImage analysisPlaintextImage denoising

The invention relates to a privacy protection-based user authenticated outsourcing image denoising method. The method comprises the following steps that: a trusted third party TTP allocates related keys to a content owner CO, an authorized user AU and two edge computing servers ES1 and ES2; the CO firstly uses a secret key distributed by the TTP to encrypt a noisy image, and sends the encrypted image to the first edge computing server ES1; the second edge computing server ES2 assists the first edge computing server ES1 to perform ciphertext image denoising, and a result obtained through calculation is sent to the first edge computing server ES1; and the AU makes an image use request to the corresponding CO, obtains the corresponding denoised ciphertext image from the first edge computing server ES1, and authorizes the user AU to decrypt and recover the required plaintext denoised image with the help of the private key of the AU. According to the invention, the image denoising service is provided while the user privacy data security is ensured; and moreover, the local calculation and communication overhead of the user is reduced, and the ciphertext denoising effect is almost equal to the plaintext domain performance.

Owner:FUZHOU UNIV

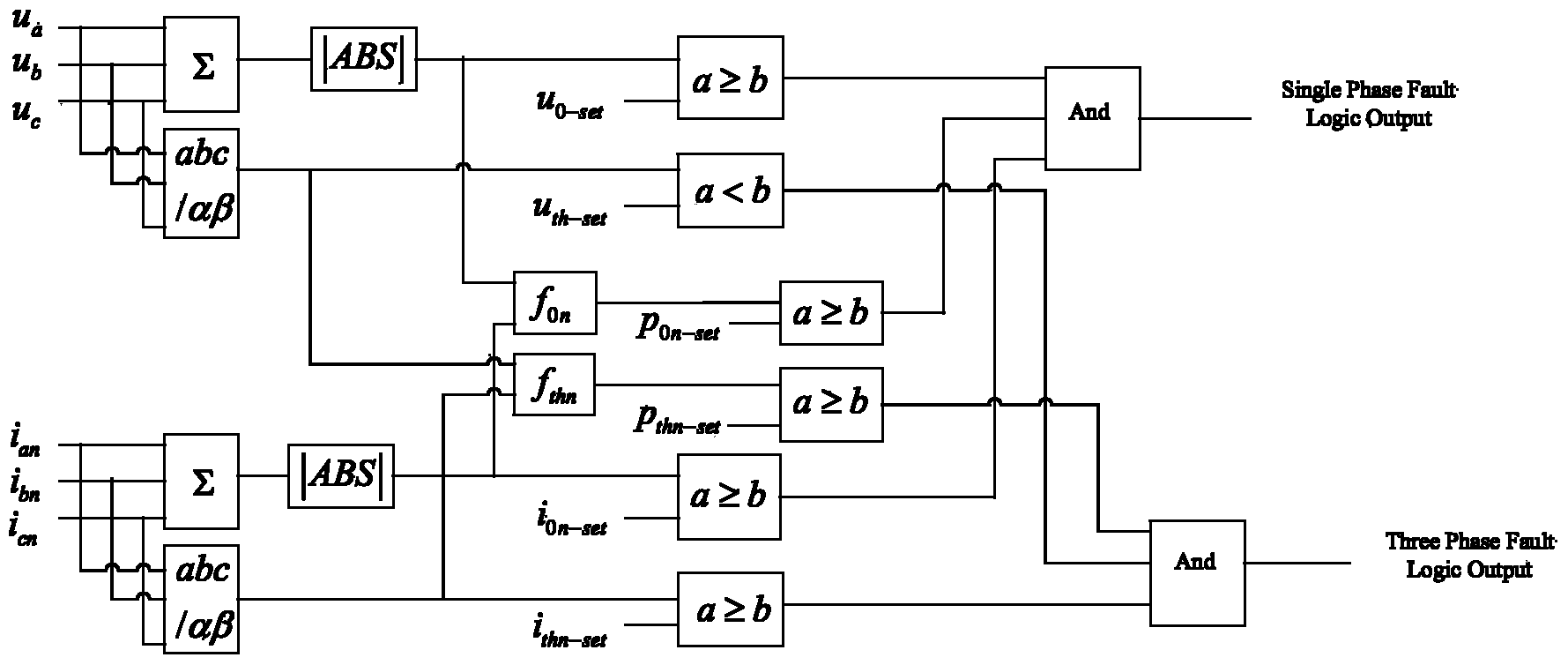

Alternating-current fault detection method for high-voltage direct-current power transmission

The invention provides an alternating-current fault detection method for high-voltage direct-current power transmission. The alternating-current fault detection method for high-voltage direct-current power transmission comprises the following steps of obtaining the three-phase voltage of a current conversion bus and three-phase currents of outgoing lines of the current conversion bus; obtaining a voltage zero-sequence component value and a rotating vector amplitude of the current conversion bus according to the three-phase voltage of the current conversion bus, and obtaining current zero-sequence component values and rotating vector amplitudes of the outgoing lines of the current conversion bus according to the three-phase currents of outgoing lines of the current conversion bus; obtaining power zero-sequence component values and power rotating vector amplitudes of the outgoing lines of the current conversion bus; comparing the values and the amplitudes with the set values and the set amplitudes respectively to obtain the fault detection result. The alternating-current fault detection method for high-voltage direct-current power transmission is high in speed and accuracy, and meets the requirement of high-voltage direct-current power transmission for fault detection, and valuable information is provided for the defense commutation failure of a control system for high-voltage direct-current power transmission.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING) +3

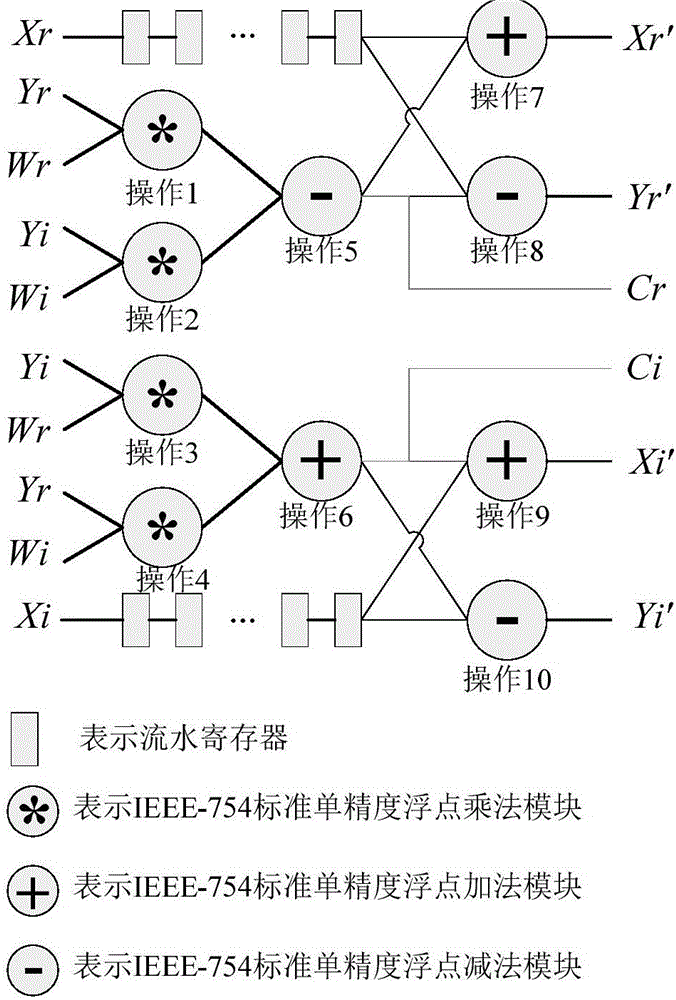

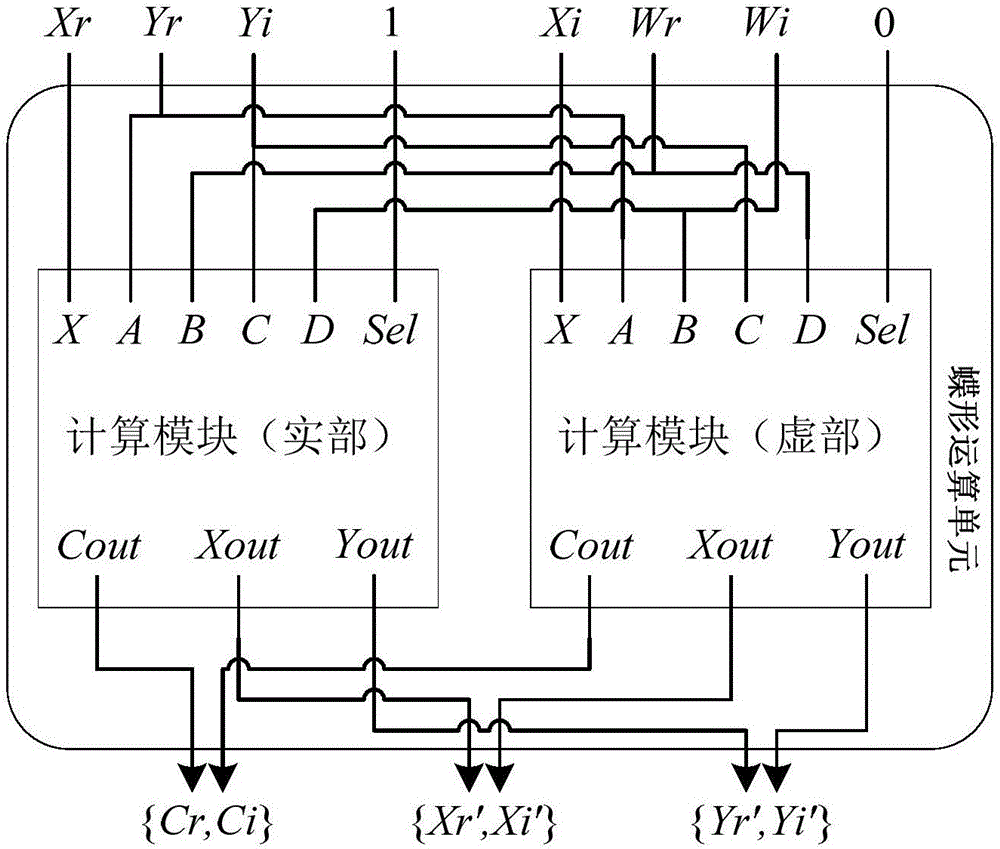

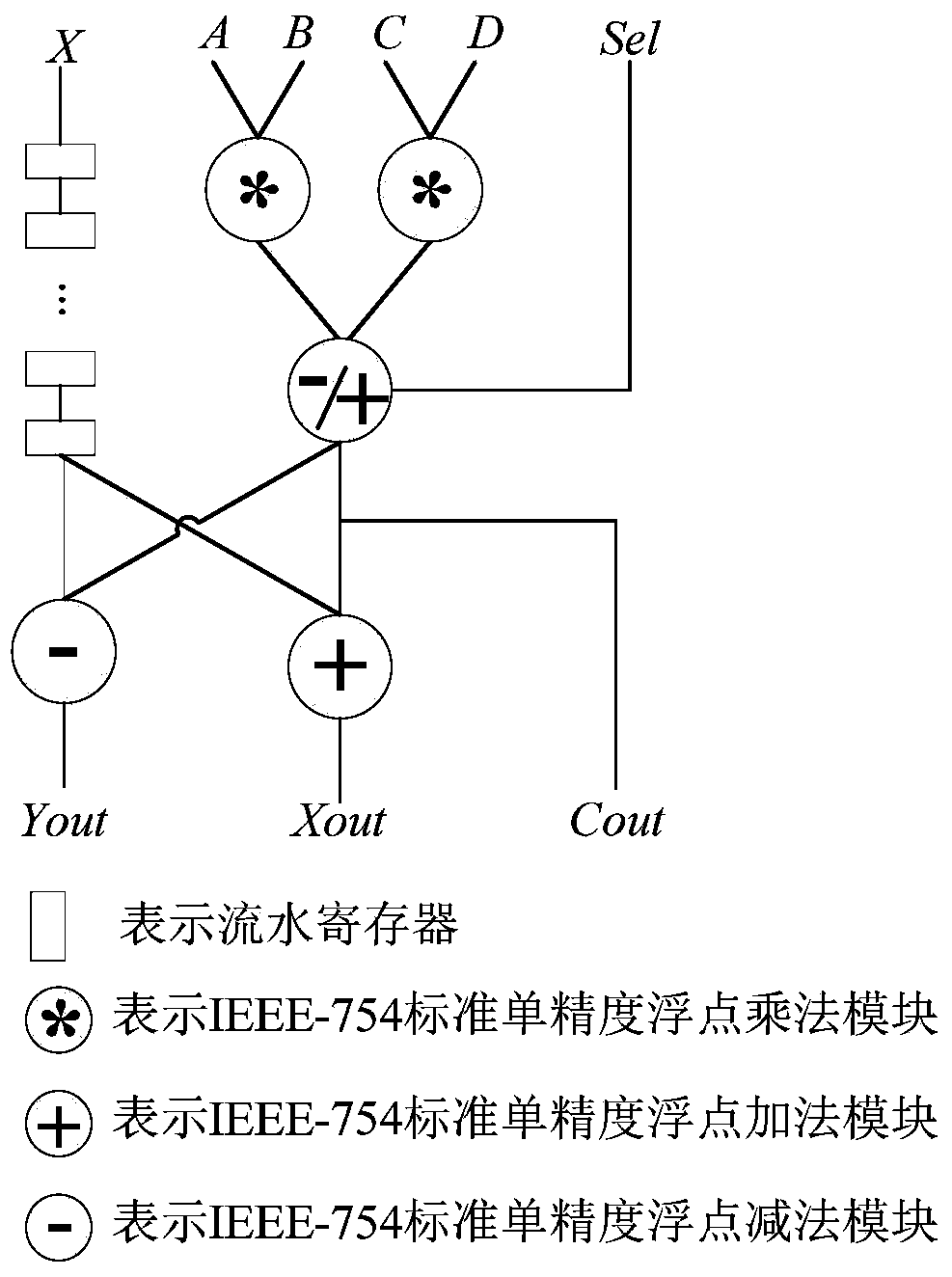

FFT (fast Fourier transform) butterfly operation hardware implementation circuit supporting complex multiplication

ActiveCN106168941AReduce overheadReduce normalizationComplex mathematical operationsFast Fourier transformHardware implementations

The invention discloses an FFT (fast Fourier transform) butterfly operation hardware implementation circuit supporting complex multiplication. The circuit comprises a real part calculation module and an imaginary part calculation module, wherein the real part calculation module is used for calculating a real part in complex multiplication and calculating real parts of X and Y in butterfly operation, and the imaginary part calculation module is used for calculating an imaginary part in complex multiplication and calculating imaginary parts of X and Y in butterfly operation. The circuit has the advantages of capabilities of reducing hardware cost, decreasing calculation delay and improving calculation accuracy and the like.

Owner:NAT UNIV OF DEFENSE TECH

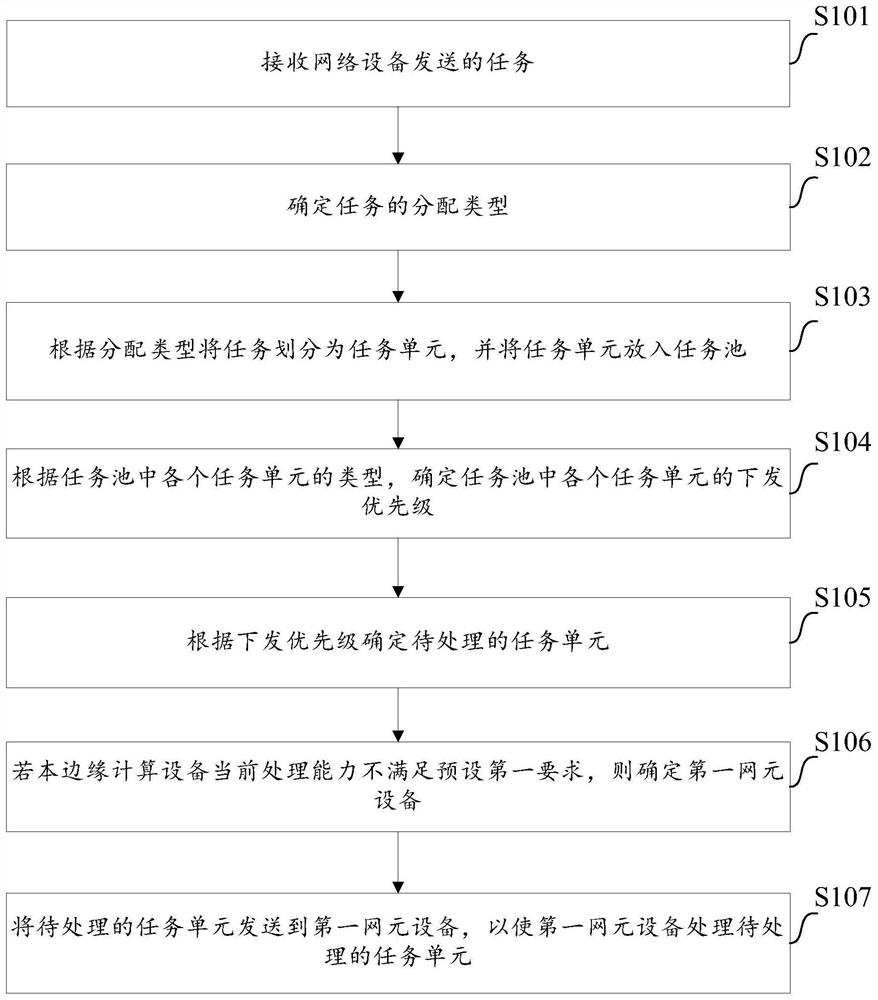

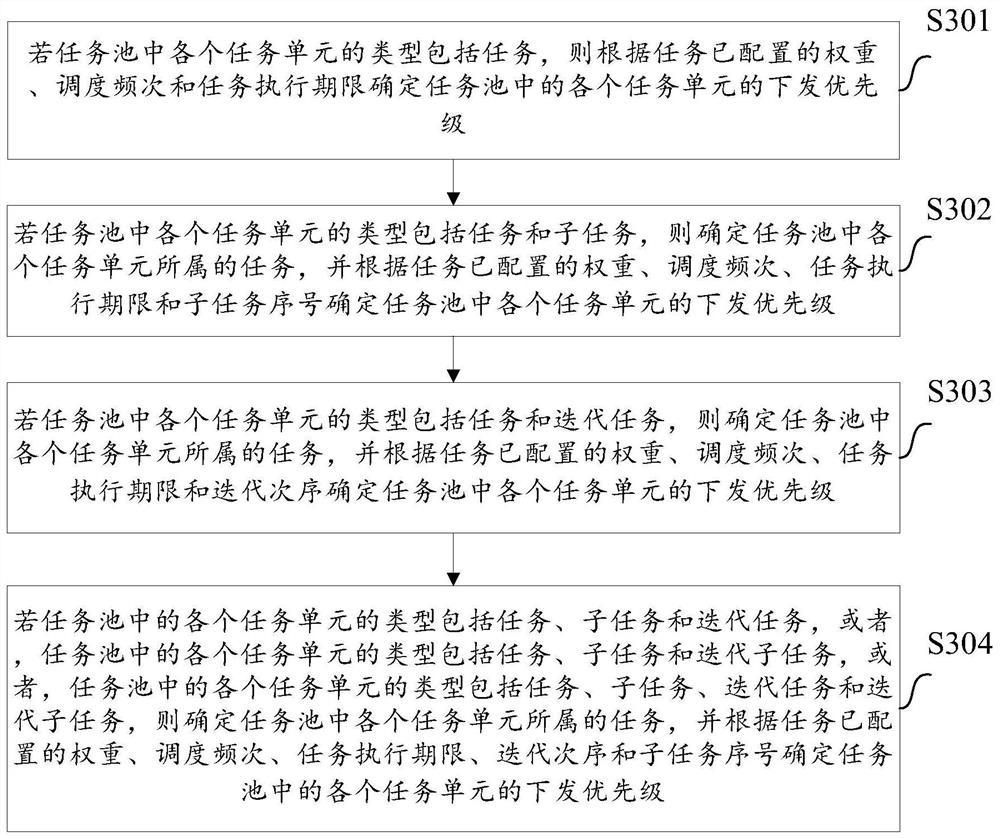

Task processing method, edge computing equipment, computer equipment, and medium

PendingCN113918314AIncrease computing powerReduce task calculation delayResource allocationProgram initiation/switchingEquipment computersComputer equipment

The invention provides a task processing method, edge computing equipment, computer equipment, and a computer-readable medium. The method comprises the following steps: receiving tasks sent by network equipment; determining distribution types of the tasks, dividing the tasks into task units according to the distribution types, and putting the task units into a task pool; according to the types of the task units in the task pool, determining the issuing priority of the task units in the task pool, wherein the types of the task units are the distribution types of the tasks to which the task units belongs; determining to-be-processed task units according to the issuing priority; if the current processing capability of edge computing equipment does not meet a preset first requirement, determining first network element equipment, and sending the to-be-processed task units to the first network element equipment. According to the invention, when computing power resources of the edge computing equipment are insufficient, the first network element equipment is selected from a peripheral network element group to carry out task transfer computing, so that the computing power of the edge computing equipment is improved, and the task computing delay can be reduced at the same time.

Owner:ZTE CORP

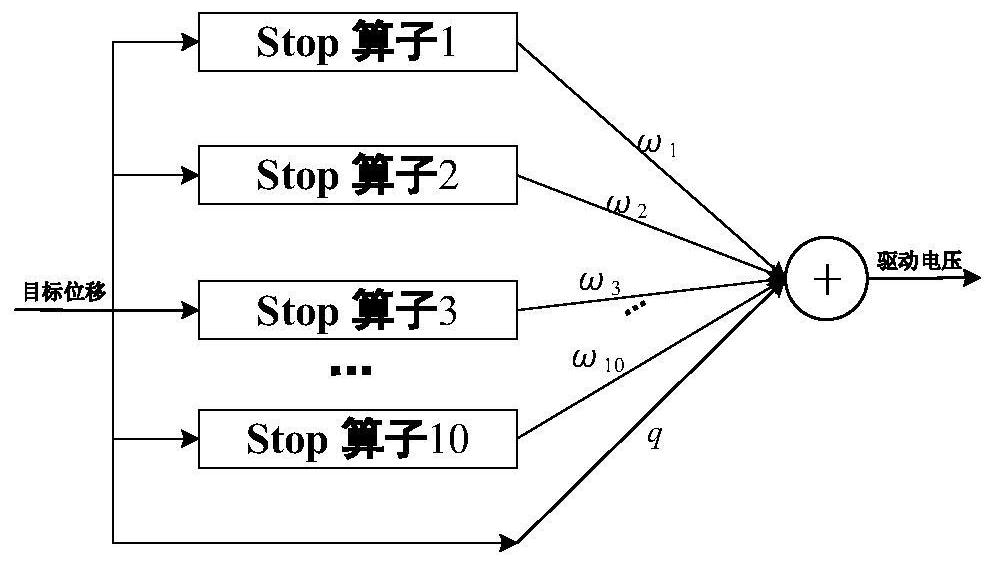

Three-point piezoelectric driving fast steering mirror hysteresis compensation control system based on FPGA

PendingCN112859703AReduce calculation delayQuick responseProgramme controlComputer controlSignal conditioningControl system

The invention discloses an FPGA-based three-point piezoelectric driving fast steering mirror hysteresis compensation control system, which comprises an FPGA hysteresis compensation control module, an SGS micro-displacement sensor, an SGS micro-displacement signal conditioning and acquisition circuit, a piezoelectric ceramic driving circuit, an upper computer and a three-point piezoelectric driving fast steering mirror, and is characterized in that the three-point piezoelectric driving large-aperture fast steering mirror is a controlled object, the SGS micro-displacement sensor is integrated in a piezoelectric ceramic actuator, the SGS micro-displacement signal conditioning and acquisition circuit is connected with the FPGA hysteresis compensation control module, the piezoelectric ceramic driving circuit is connected with the FPGA hysteresis compensation control module, and the upper computer is communicated with the FPGA through a 422 interface. According to the system, the parallel processing characteristic of the FPGA is fully utilized, deployment of a PI inverse model based on parallel connection of multiple Stop operators on the FPGA and parallel hysteresis compensation control of multiple piezoelectric ceramic actuators are completed, the calculation delay of the system is shortened, the response speed of the system is increased, and high-precision, real-time and synchronous multi-piezoelectric compensation and control are achieved.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

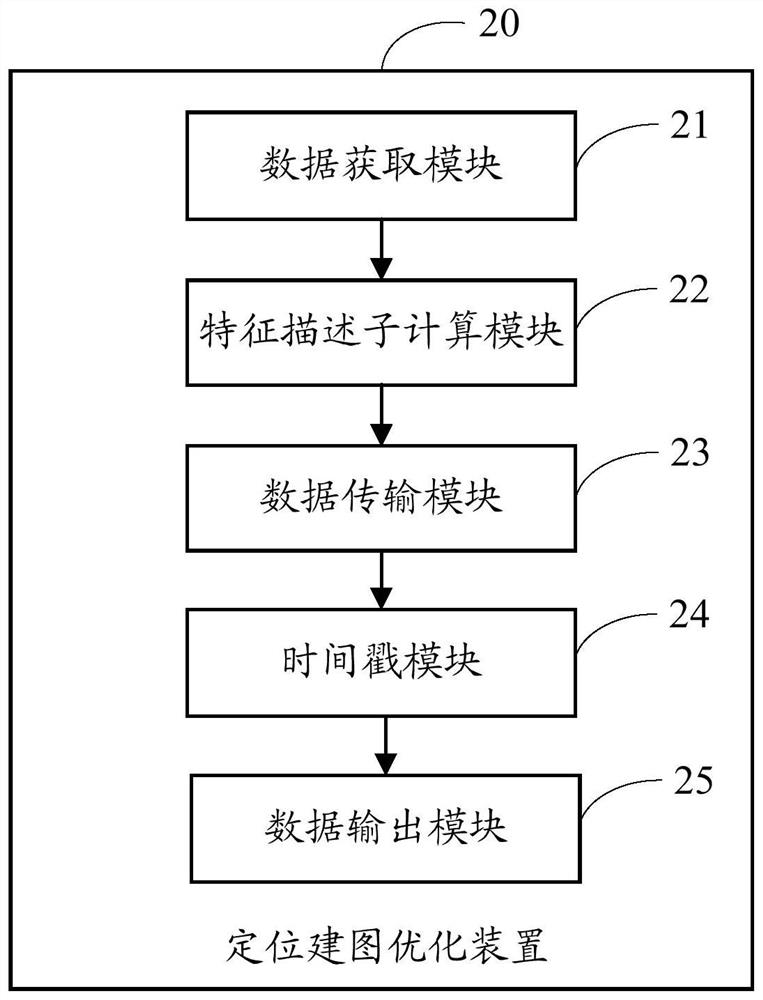

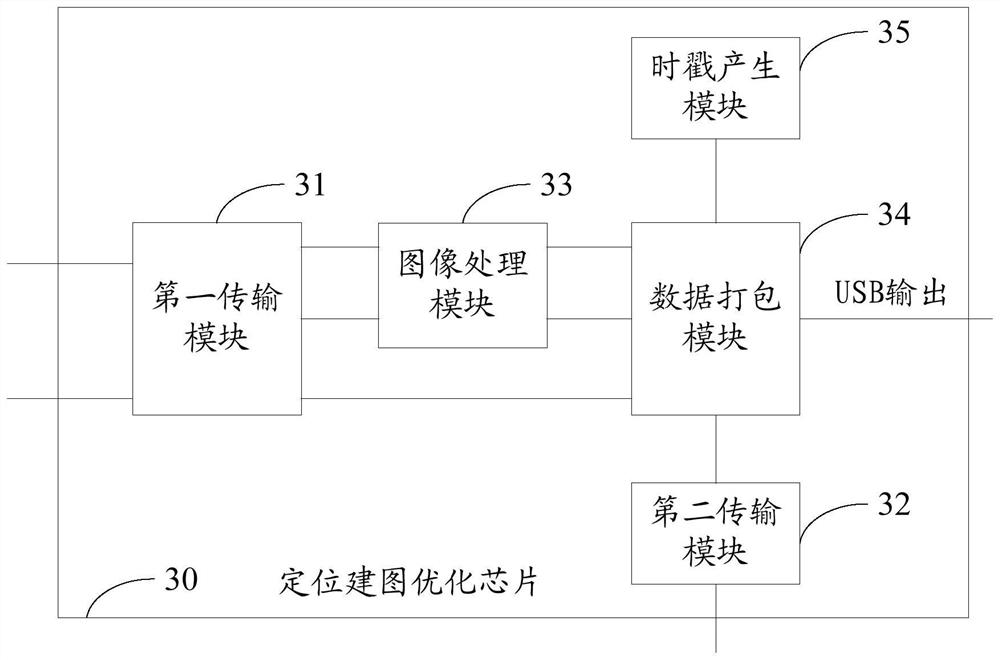

Positioning mapping optimization method and device and positioning mapping optimization chip

ActiveCN112000225AReduce computing loadSimplified Computational ComplexityInput/output for user-computer interactionImage analysisData packImaging processing

The invention is suitable for the technical field of head-mounted display equipment, and provides a positioning mapping optimization method and device and a positioning mapping optimization chip, andthe method comprises the steps: responding to a positioning mapping instruction, calling a first transmission module to obtain an input image and a depth image, and calling a second transmission module to obtain sensor data; sending the input image to an image processing module to enable the image processing module to calculate a feature descriptor according to the input image; in the data packaging module, calling a timestamp generation module to add a first time label in the feature descriptor, add a second time label in the depth image and add a third time label in the sensor data; and calling a data packaging module to align the feature descriptor, the depth image and the sensor data according to the first time label, the second time label and the third time label, packaging the aligned data and outputting the packaged data so as to execute a positioning mapping instruction through an SLAM algorithm. According to the invention, the calculation load during the execution of the SLAMalgorithm can be reduced.

Owner:唯羲科技有限公司

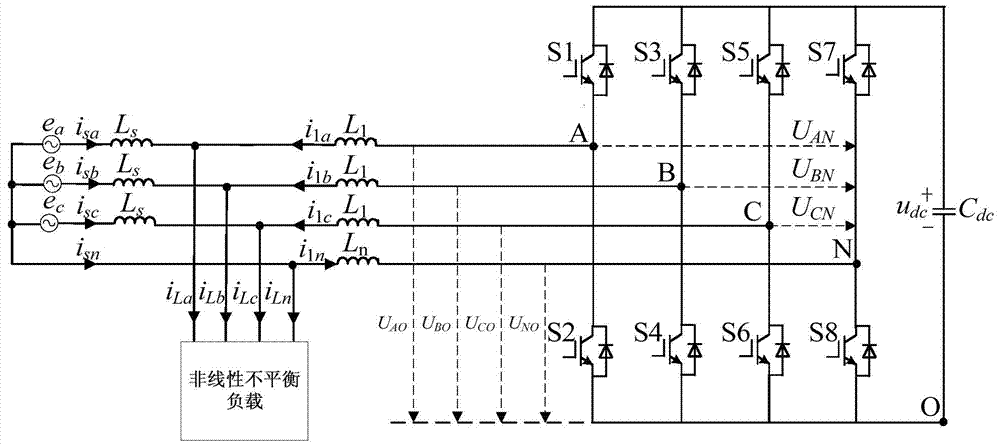

Method, device and system for modulating zero sequence voltage pulse width of three-phase four-legged APF (active power filter)

ActiveCN104753064APractical degree of simple engineeringImprove engineering practicalityActive power filteringAc network to reduce harmonics/ripplesCapacitanceLinear control

The invention provides a method, a device and a system for modulating a zero sequence voltage pulse width of a three-phase four-legged APF (active power filter). The method comprises the following steps of solving a zero sequence component according to a reference value of a voltage of midpoints of legs A, B and C of the three-phase four-legged arm APF to a midpoint of a leg N of the three-phase four-legged arm APF; controlling a pulse duty ratio according to a reference value of a voltage of a calculating point N of the three-phase four-legged APF to a point O of a cathode of a direct-current bus capacitor and a switch tube of the leg N; and solving a voltage of the midpoints of the legs A, B and C of the three-phase four-legged APF to the point O of the cathode of the direct-current bus capacitor and a corresponding duty ratio. A zero sequence voltage linear control pulse width modulation strategy is applied to the three-phase four-legged APF. Compared with the traditional 3D-SVPWM (three-dimensional space vector pulse width modulation) strategy, the zero sequence voltage linear control pulse width modulation strategy is easy to implement and can reduce calculation delay and requirements on main frequency; and the response speed of the three-phase four-legged APF can be increased further, the harmonic compensation accuracy of the three-phase four-legged APF can be improved, hardware investment is saved, and the method has an important practical significance on practical degree of a project of the three-phase four-legged APF.

Owner:WUHAN UNIV

Track ballast inspection system based on binocular vision and working method thereof

PendingCN112801975AHigh precisionSolve technical problems with large detection errorsImage enhancementImage analysisComputer hardwareOptical axis

The invention discloses a track ballast inspection system based on binocular vision, which is arranged on a rail and comprises a wheel driving module, a plurality of wheels, an MCU module, a storage module, a communication module, an FPGA module, a first CCD sensing module, a second CCD sensing module and a man-machine interaction module. The wheel driving module is electrically connected with a plurality of wheels and the MCU module, the MCU module is electrically connected with the communication module and the FPGA module, the FPGA module is electrically connected with the storage module, the first CCD sensing module, the second CCD sensing module and the man-machine interaction module, and the optical axis of the first CCD sensing module and the optical axis of the second CCD sensing module are perpendicular to a rail. The invention can solves the the technical problems of large detection error in the existing railway ballast manual detection, the technical problems of manpower fatigue, visual fatigue and considerable time cost caused by large workload of railway ballast detection, and the technical problems of manpower fatigue, visual fatigue and considerable time cost consumption caused by large workload of railway ballast inspection.

Owner:中科(湖南)先进轨道交通研究院有限公司

FFT calculation method, calculation module and chip for high-precision navigation

InactiveCN111562900AReduce calculation delayImprove resource utilizationDigital data processing detailsData selectionElectrical and Electronics engineering

The invention discloses an FFT calculation method for high-precision navigation. The FFT calculation method comprises the following steps: introducing an FFT8 butterfly-shaped accumulation calculationunit, four groups of butterfly-shaped accumulation and addition calculation units, a control unit and a data selection unit; obtaining the calculation type of the FFT calculation, employing an FFT8 butterfly-shaped accumulation calculation unit and four groups of butterfly-shaped accumulation-multiplication-addition calculation units to carry out calculation for a plurality of times, and completing the FFT calculation. The invention also discloses a calculation module for realizing the FFT calculation method for high-precision navigation, and a chip comprising the FFT calculation method for high-precision navigation and the calculation module. According to the method, logic resources are simplified into 30 adders, 4 multipliers and some simple control logics, and the maximum utilization rate of the adders and the multipliers is realized by adopting accurate pipeline control. Meanwhile, the calculation delay is relatively low, the resource utilization rate is higher, and the area of the chip module is effectively reduced.

Owner:长沙金维信息技术有限公司

Train braking method and device, storage medium and electronic equipment

ActiveCN113696875AReduce transmission delayReduce calculation delayBraking action transmissionElectric energy managementNetwork controlMechanical engineering

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

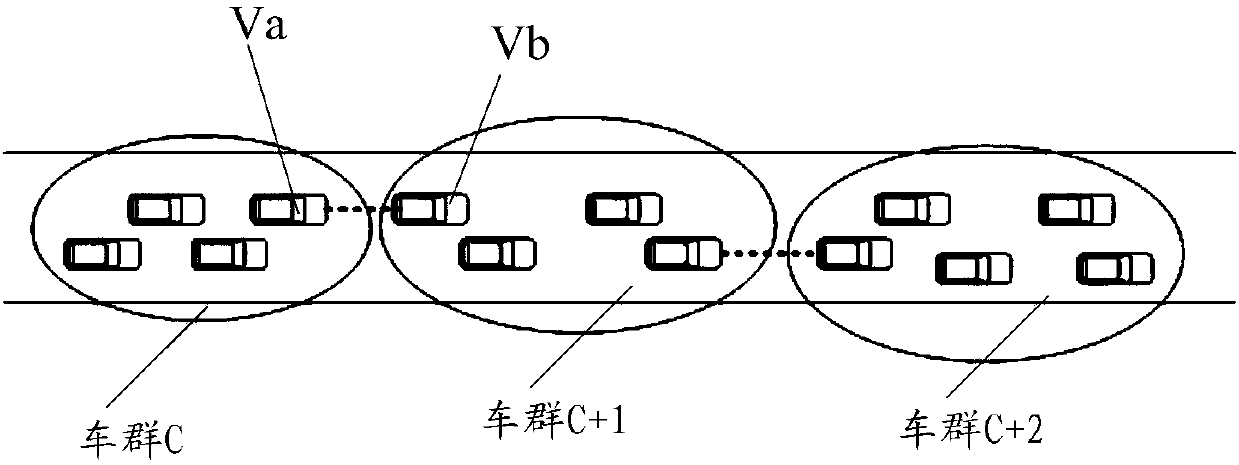

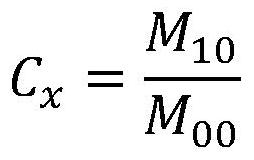

Target speed calculation method and device, MEC server and storage medium

ActiveCN109993965ASimplified amount calculationAvoid chain reactionDetection of traffic movementAnti-collision systemsCalculation methodsReal-time computing

Embodiments of the invention provide a target speed calculation method, a mobile edge calculation server and a storage medium. The target speed calculation method comprises the steps of determining whether an (i+1)th vehicle adjacent to an ith vehicle meets a predetermined boundary condition or not, wherein i is a positive integer; and when the (i+1)th vehicle meets the predetermined boundary condition, determining that the ith vehicle is a boundary for dividing a vehicle group; dividing the vehicle group on the basis of the boundary; and calculating target speeds of the vehicles in the vehicle group by the divided vehicle group according to a first risk threshold value corresponding to the vehicle group.

Owner:CHINA MOBILE COMM LTD RES INST +1

Automatic extraction method of initial frame image target in target tracking

PendingCN114782491ASmall amount of calculationReduce calculation delayImage enhancementImage analysisRadiologyMorphological processing

The invention discloses a method for automatically extracting an initial frame image target in target tracking, which comprises the following steps of: sequentially carrying out manual coordinate selection, image enhancement, significance detection and morphological processing on an input image, and then calculating a corrected coordinate; compared with other methods based on deep learning, the rapid automatic extraction method is small in calculation amount, low in calculation delay, adaptive and controllable in process, and very suitable for deployment and application of an embedded platform with computing power limitation.

Owner:武汉华中天经通视科技有限公司

A privacy-preserving user-authenticable outsourced image denoising method

ActiveCN111241561BReduce lossesImprove securityImage enhancementImage analysisPlaintextImage denoising

Owner:FUZHOU UNIV

Pop-out network processor and network data stack-out processing method

ActiveCN110417813BLower latencyReduce calculation delayTransmission format adaptationComputer hardwareNetworking hardware

An embodiment of the present invention provides a stacking network processor and a network data stacking processing method. The network processor includes: a storage module, including a header memory and a payload memory, for storing protocol headers and data payloads respectively; a framing module, It is used to obtain the corresponding protocol header and data load from the storage module according to the operation instruction, and after replacing or inserting the preset part of the obtained protocol header, output the data frame to be verified; the verification module is used to verify the After the data frame to be verified is verified, a verification result is obtained; the framing module is further configured to obtain a final data frame according to the data frame to be verified and the verification result, and output it to the network. The network processor does not need to store the entire final data frame before sending it, which can reduce the delay caused by storage. In addition, it is implemented through network hardware modules, which can effectively reduce the calculation delay.

Owner:极芯通讯技术(安吉)有限公司

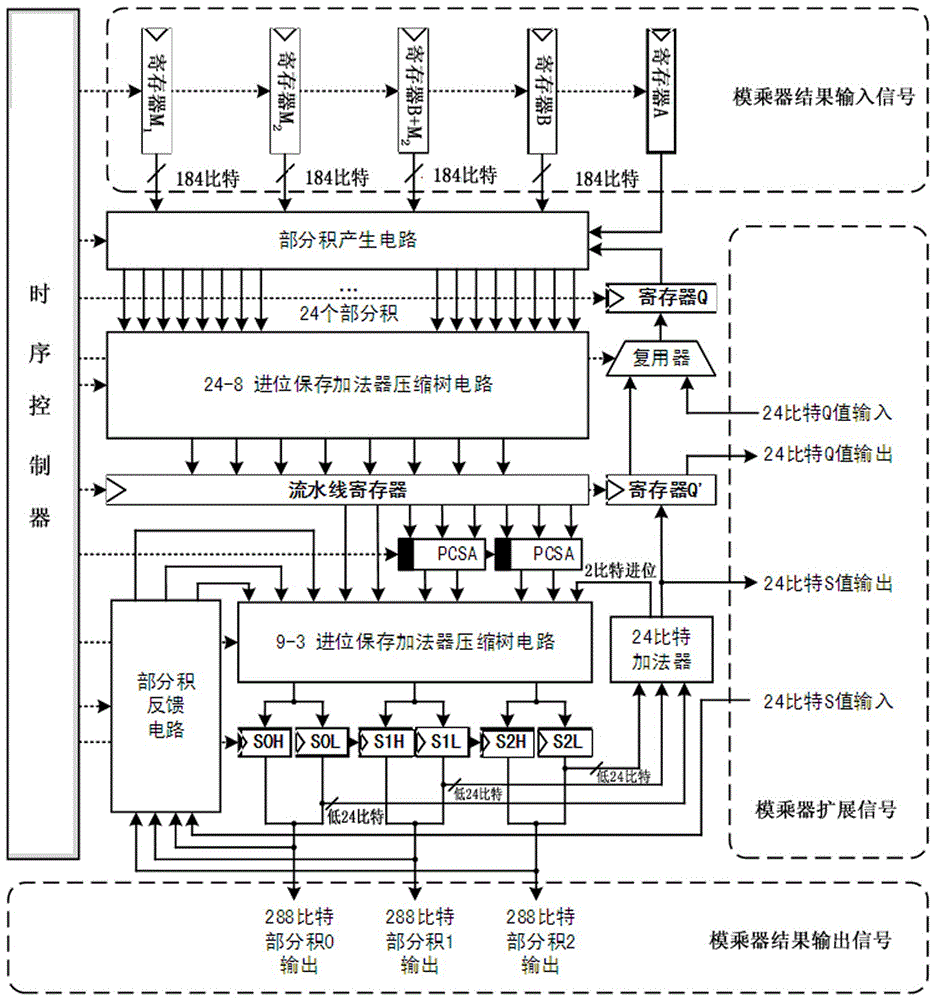

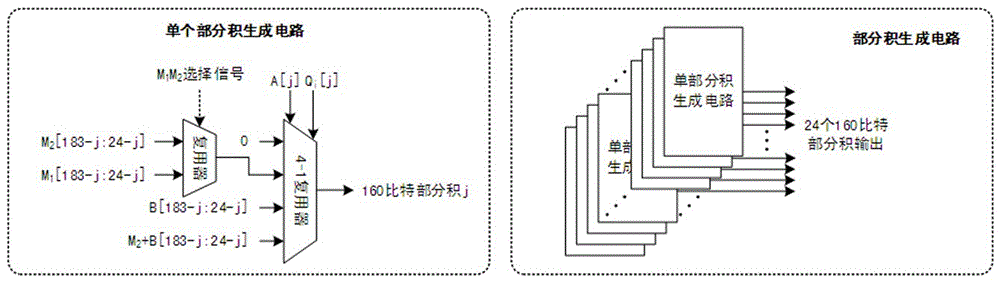

A Scalable Modular Multiplier Circuit Based on Improved Montgomery Modular Multiplication Algorithm

ActiveCN103914277BIncrease working frequencyAvoid overheadComputations using residue arithmeticComputer architectureTime delays

The invention belongs to the technical field of high-performance public key cryptographic integrated circuits and particularly relates to an extensible modular multiplier circuit based on an improved Montgomery modular multiplication algorithm. According to the extensible modular multiplier circuit based on the improved Montgomery modular multiplication algorithm, by introducing an extra parameter, the data bit width of a Montgomery field can be reduced, and further the hardware cost of a whole system can be reduced. The invention also designs a high-performance extensible multiplier circuit based on the improved Montgomery modular multiplication algorithm. The high-performance extensible multiplier circuit is mainly composed of a time schedule controller, a partial product generating circuit, a carry storage summator compressed tree circuit, a partial product feedback circuit, a modular multiplier extension correlated circuit and a time schedule controller. The high-performance extensible multiplier circuit achieves modular multiplication with a relatively large bit width through cooperation of a plurality of modular multipliers, thereby reducing computation time delay, achieving good extending performance and obviously improving the modular multiplication efficiency.

Owner:FUDAN UNIV

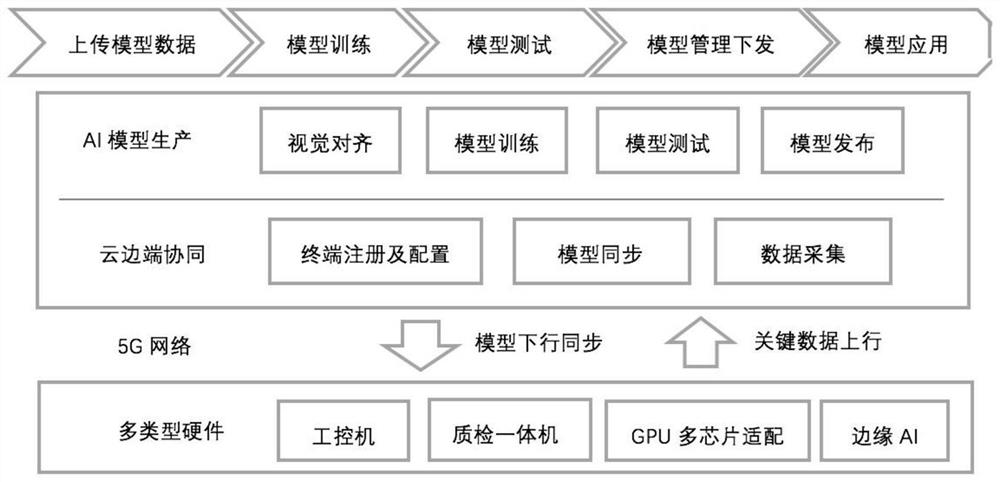

Edge application management method and system based on 5G + AI industrial vision

PendingCN113282302AFlexible deploymentIncrease productivityResource allocationSoftware simulation/interpretation/emulationEdge computingBusiness enterprise

The invention relates to the technical field of edge computing, in particular to an edge application management method and system based on 5G + AI industrial vision. The efficiency and quality can be improved for enterprises, and the cost is reduced; The method comprises a cloud platform ME orchestrator MEO, the cloud platform ME orchestrator MEO receives an uploaded ME instance packet, the ME instance packet further comprises a deployment mode indication, and the deployment mode indication adopts one of multiple deployment modes.

Owner:浙江九州未来信息科技有限公司

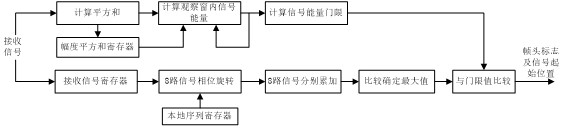

FPGA-based high-speed data transmission system frame synchronization parallel implementation method

ActiveCN112104586AReduce implementation complexityReduce calculation delayMulti-frequency code systemsComputation complexityData transmission systems

The invention discloses an FPGA-based high-speed data transmission system frame synchronization parallel implementation method, which has certain advantages compared with the existing method, and comprises the following steps of: firstly, introducing a stepping factor d into an MM algorithm to reduce the calculation complexity of the algorithm, change the estimation range and reduce the estimationprecision loss; then under a certain estimation precision, enabling the estimation range of the method to be larger than that of a Fitz algorithm, and therefore, because the method separates the estimation range from the estimation precision, the method irons out the defect that the high estimation precision is achieved at the cost of sacrificing the estimation range. Through experimental comparison, the method is more flexible and applicable than an MM algorithm and a Fitz algorithm.

Owner:湖南国科锐承电子科技有限公司

Grid-connected inverter control method under unbalanced and harmonic wave power grids

ActiveCN103326399BImprove stabilityImprove fault toleranceAc-dc conversionSingle network parallel feeding arrangementsGrid-tie inverterEngineering

The invention discloses a grid-connected inverter control method under unbalanced and harmonic wave power grids. The grid-connected inverter control method adopts a VPI regulator to directly control frequency doubling harmonic wave frequency doubling component fluctuation of active power and reactive power, does not need to decompose positive sequences and negative sequences under multiple synchronous rotating coordinate systems to calculate power reference of frequency doubling components, therefore, reduces calculating delay and strengthens the dynamic response capacity. Meanwhile, due to the fact that the grid-connected inverter control method adopts the SVM-DPC strategy, the problem that the opening-closing frequency is changed is solved, and convenience is brought to selection of an alternating current filtering device. Therefore, the grid-connected inverter control method is suitable for single-phase or three-phase inverting devices, controlled by various PWMs, formed by other various high-frequency switch self-turn-off components under the unbalanced and harmonic wave power grids, and the one-phase or the three-phase inverting devices include grid-connected devices of power generation systems such as a wind energy power generation system, a solar energy power generation system and a fuel battery power generation system, a power electronic device of a flexible alternating current power transmission system and an inverter device in motor control.

Owner:ZHEJIANG UNIV

A hardware implementation circuit of fft butterfly operation supporting complex multiplication

ActiveCN106168941BReduce overheadReduce normalizationComplex mathematical operationsFast Fourier transformHardware implementations

Owner:NAT UNIV OF DEFENSE TECH

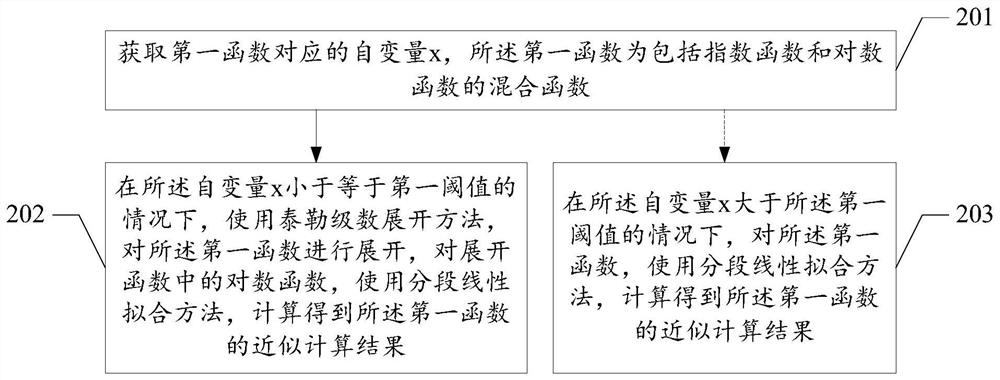

Approximate calculation method of mixed function, terminal equipment and storage medium

PendingCN113836487AApproximate computing fast implementationReduce calculation delayComplex mathematical operationsAlgorithmTerminal equipment

The embodiment of the invention discloses an approximate calculation method of a mixed function, terminal equipment and a storage medium, which are used for quickly realizing approximate calculation of the mixed function based on a Taylor series expansion method and a piecewise linear fitting method, do not have an iterative process, and are relatively small in calculation delay, relatively high in precision and relatively low in complexity. The method comprises the steps of obtaining an independent variable x corresponding to a first function, wherein the first function is a mixed function comprising an exponential function and a logarithmic function; when the independent variable x is smaller than or equal to a first threshold value, using a Taylor series expansion method for expanding the first function,using a piecewise linear fitting method for a logarithmic function in the expanded function, acquiring an approximate calculation result of the first function by calculation, wherein the independent variable x is larger than 0.

Owner:ZEKU TECH (BEIJING) CORP LTD

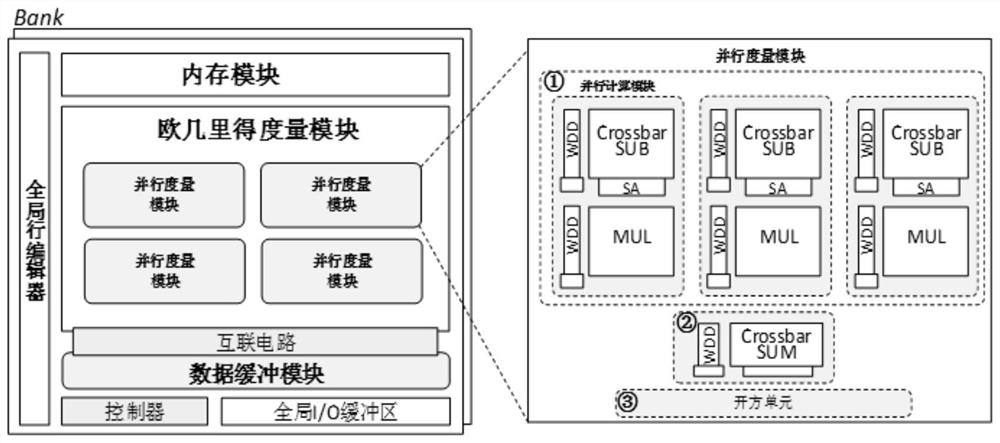

An underwater sensor and positioning system

ActiveCN109885279BSpeed up the calculation processRealize real-time underwater positioningDigital data processing detailsConcurrent computationEngineering

The disclosure provides an underwater sensor and a positioning system. Wherein, an underwater sensor includes a ReRAM and a controller, and the controller is connected to the ReRAM; the ReRAM includes a memory module and a Euclid measurement module; the memory module is used for buffering input data; the Euclid The Reed measurement module includes several parallel measurement modules, each parallel measurement module includes an addition calculation module, a square root calculation module and several parallel calculation modules; the parallel calculation module includes a first subtraction array and a first multiplication array; The parallel calculation module is used for parallel calculation of each addend in the Euclidean metric formula; the addition calculation module is used to complete the summation process of the operation results of each unit of the parallel calculation module, and use the result as the square root calculation Input data for the module.

Owner:无锡航征科技有限公司

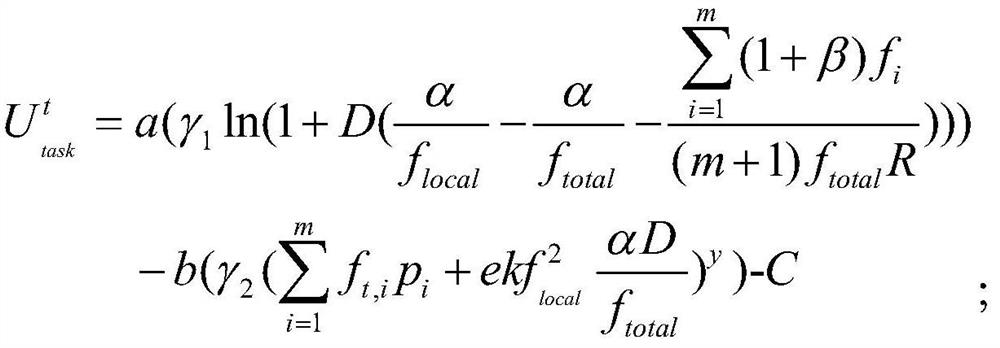

Agricultural Internet of Things task overall planning method and system

ActiveCN113259159AEfficient use ofReduce calculation delayData switching networksOperations researchIndustrial engineering

The invention relates to an agricultural Internet of Things task overall planning method and system, and the method comprises the steps that a maximum utility function of each task node is determined according to a mathematical module through the game relation between M service nodes and N task nodes; at the t' moment, the service nodes send a computing power efficiency strategy to the N task nodes according to the computing power demand of each task node; each task node obtains a computing power demand strategy of each task node through first iteration of set times according to the received computing power efficiency strategy and the corresponding maximized utility function; whether a second iteration stop condition is met or not is judged; if the second iteration stop condition is not met, updating is carried out according to the set step length, and the step that the service nodes send the computing power efficiency strategy to the N task nodes according to the computing power demand of each task node at the t moment is returned; and if the second iteration stop condition is met, a computing power efficiency strategy sent by each service node and a computing power demand strategy of each task node is determined. According to the invention, the calculation time delay is reduced.

Owner:AGRI INFORMATION INST OF CAS +1

Global pooling method of neural network and many-core system

PendingCN112446458AReduce storageReduce calculation delayNeural architecturesPhysical realisationPoint dataReal-time computing

The invention provides a global pooling method of a neural network and a many-core system. The method comprises the steps of receiving point data of to-be-processed data input by a previous network layer in sequence; and after each piece of point data is received, executing a preset pooling operation based on the currently received point data until pooling of all point data of the to-be-processeddata is completed. Based on the scheme provided by the invention, the point operation can be used for replacing the graph operation under the line pipeline operation of the many-core system, that is,after each point data is received, the point data is processed once to obtain the intermediate pooling result until the final pooling result of the to-be-processed data is finally obtained, so that the calculation delay is reduced.

Owner:LYNXI TECH CO LTD

Zero-sequence voltage pulse width modulation method, device and system for three-phase four-arm apf

ActiveCN104753064BPractical degree of simple engineeringImprove engineering practicalityActive power filteringAc network to reduce harmonics/ripplesCapacitanceVoltage pulse

Owner:WUHAN UNIV

An underwater sensor and a positioning system

ActiveCN109885279ACalculation speedReduce work energy consumptionDigital data processing detailsParallel computingComputer module

The invention provides an underwater sensor and a positioning system. The underwater sensor comprises a ReRAM and a controller, and the controller is connected with the ReRAM; wherein the ReRAM comprises a memory module and an Euclidean measurement module; the memory module is used for caching input data; the Euclidean measurement module comprises a plurality of parallel measurement modules, and each parallel measurement module comprises an addition calculation module, an extraction calculation module and a plurality of parallel calculation modules; the parallel computing module comprises a first subtraction array and a first multiplication array; the parallel computing module is used for performing parallel computing on each addend in the Euclidean metric formula; and the addition calculation module is used for completing a summation process of operation results of all units of the parallel calculation module and taking the results as input data of the evolution calculation module.

Owner:无锡航征科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com