Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

74results about How to "Raise the voltage difference" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

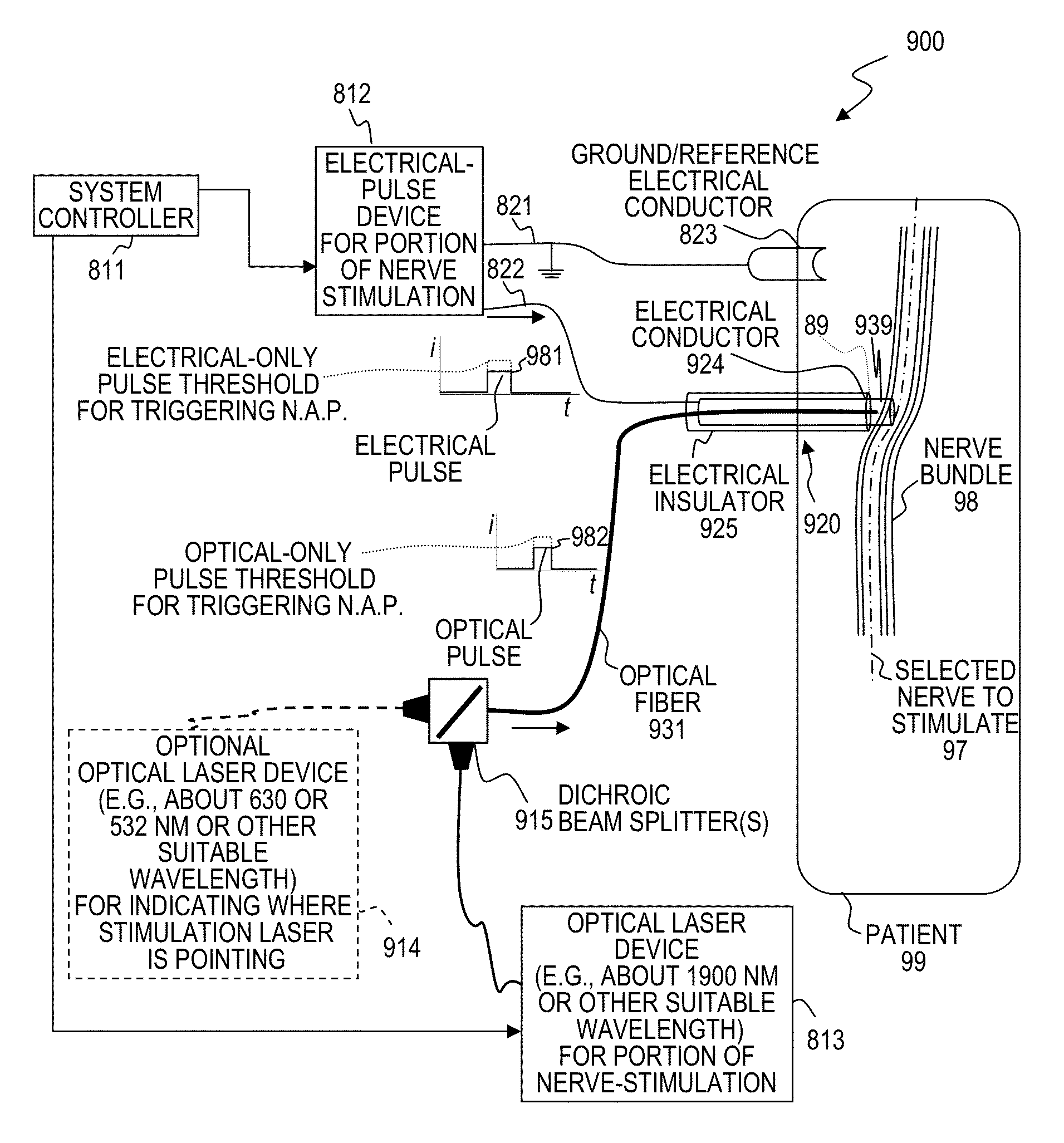

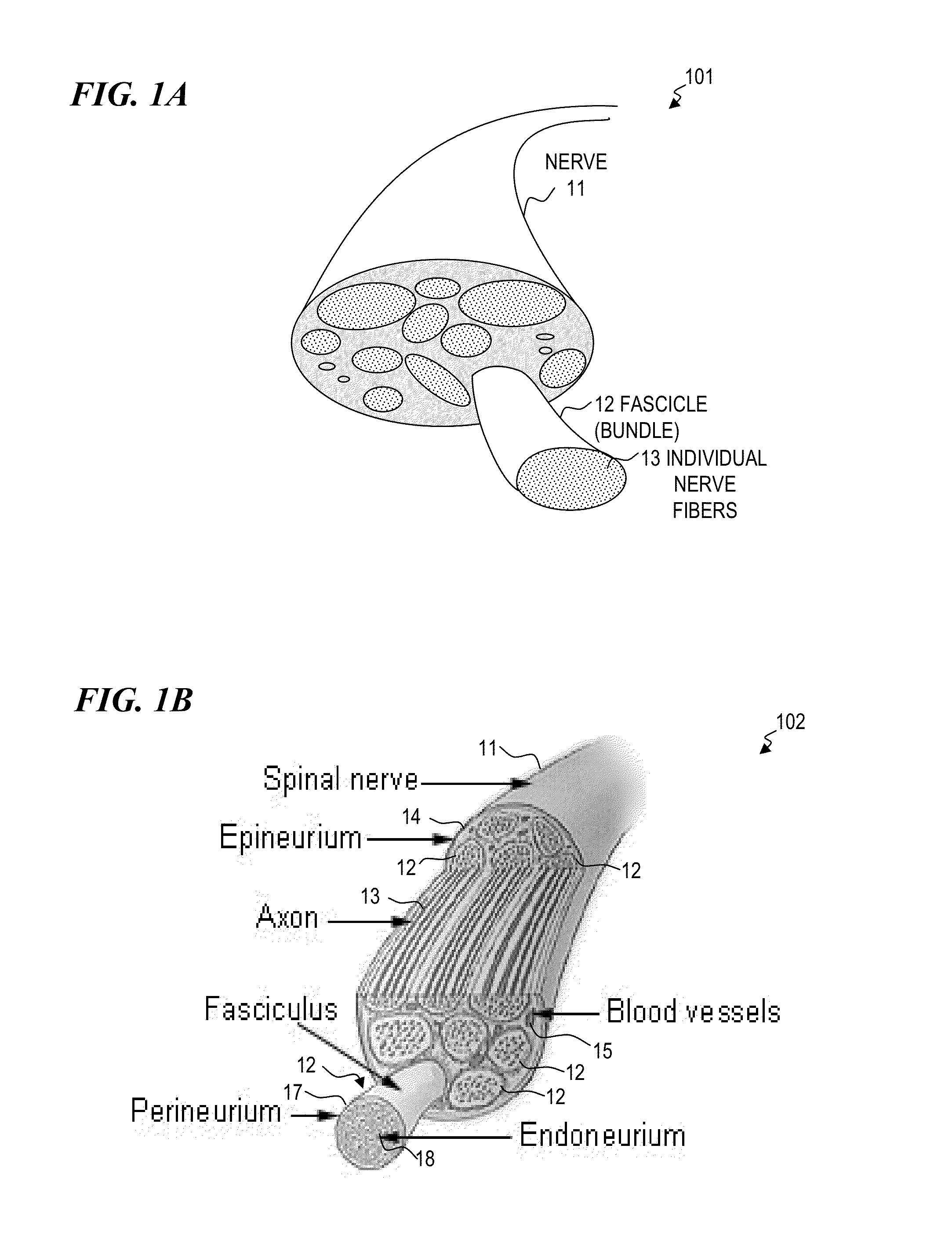

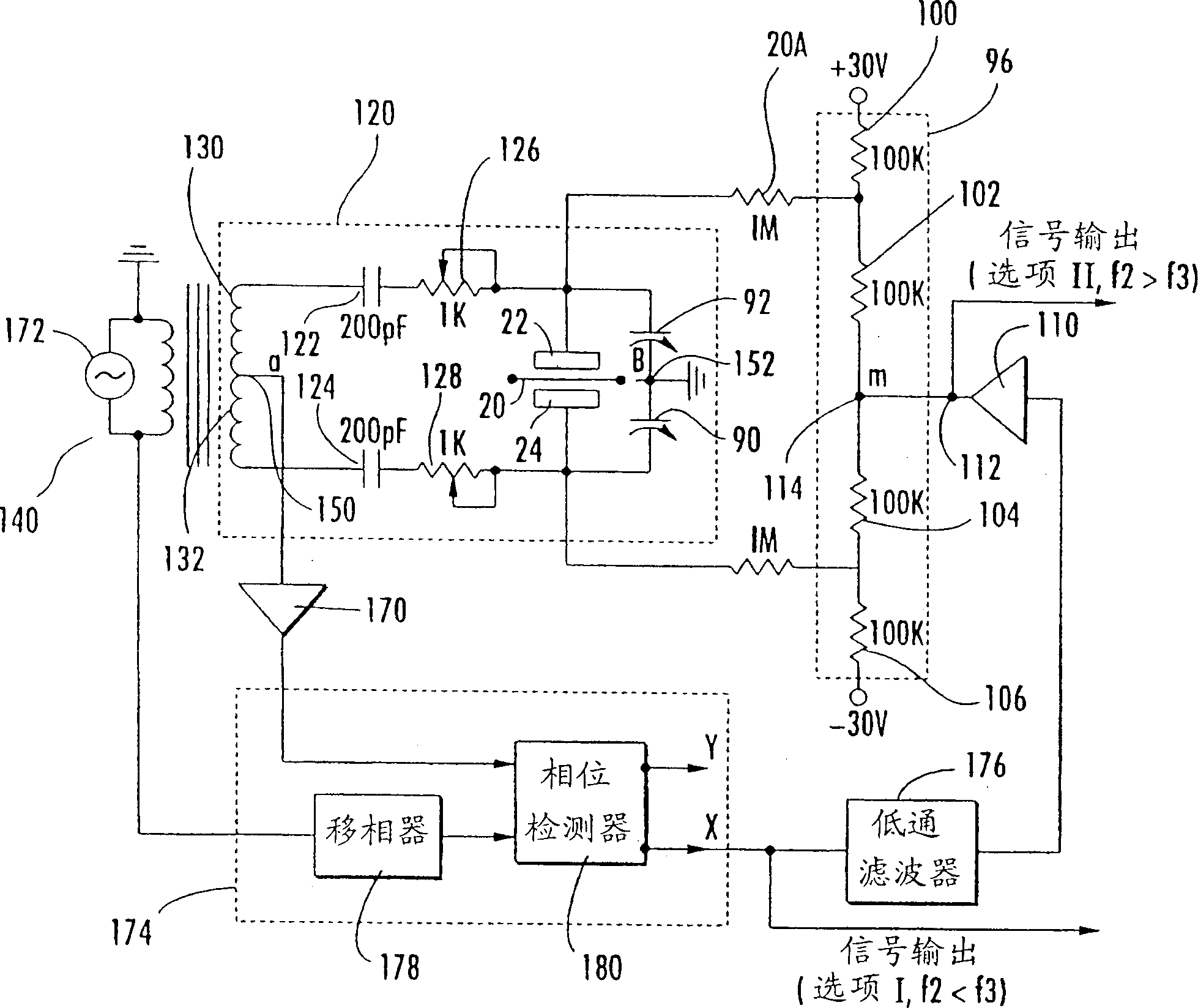

Nerve stimulator and method using simultaneous electrical and optical signals

ActiveUS20100114190A1Reduce amountLower Level RequirementsInternal electrodesImplantable neurostimulatorsEngineeringAction potential

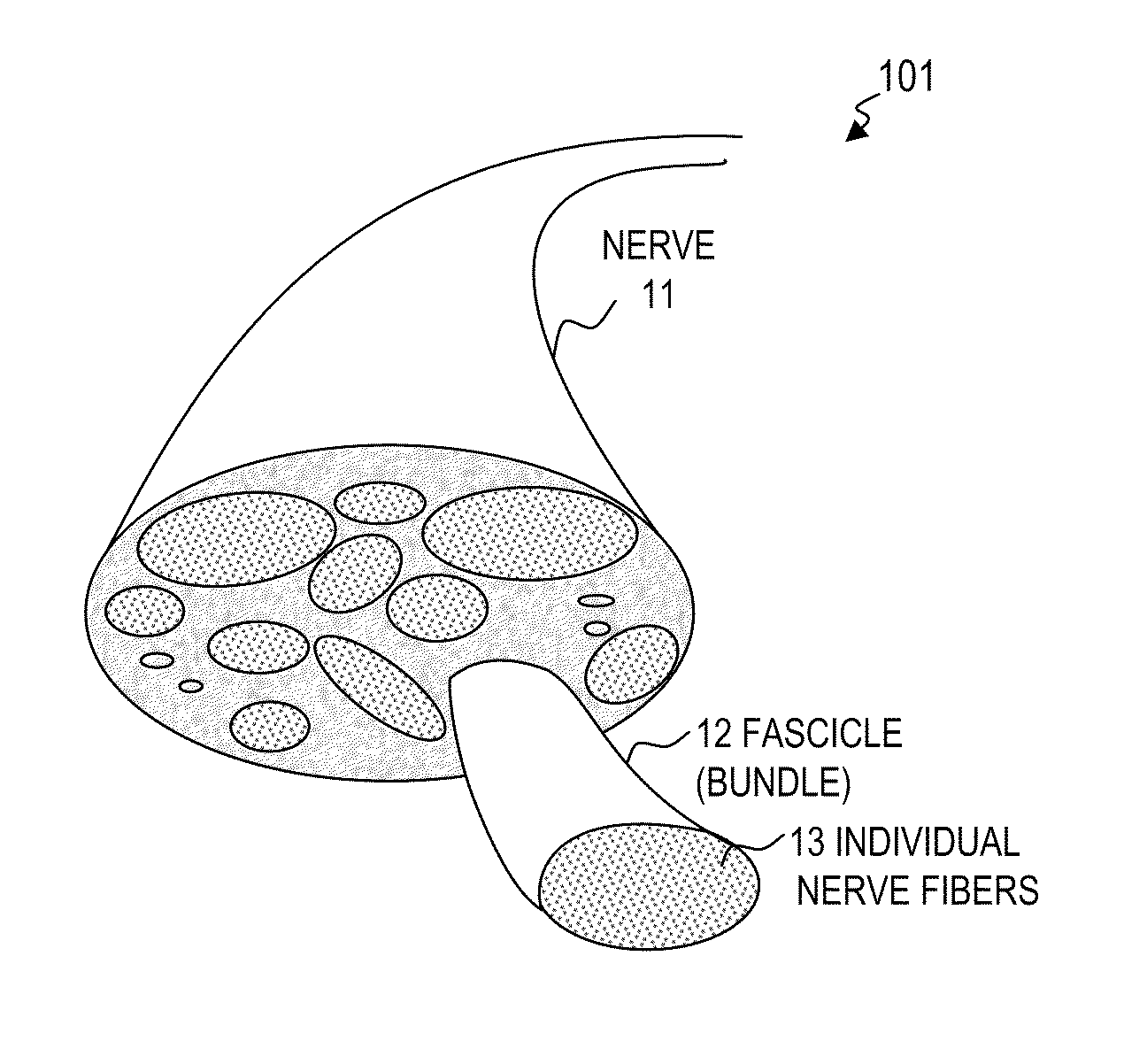

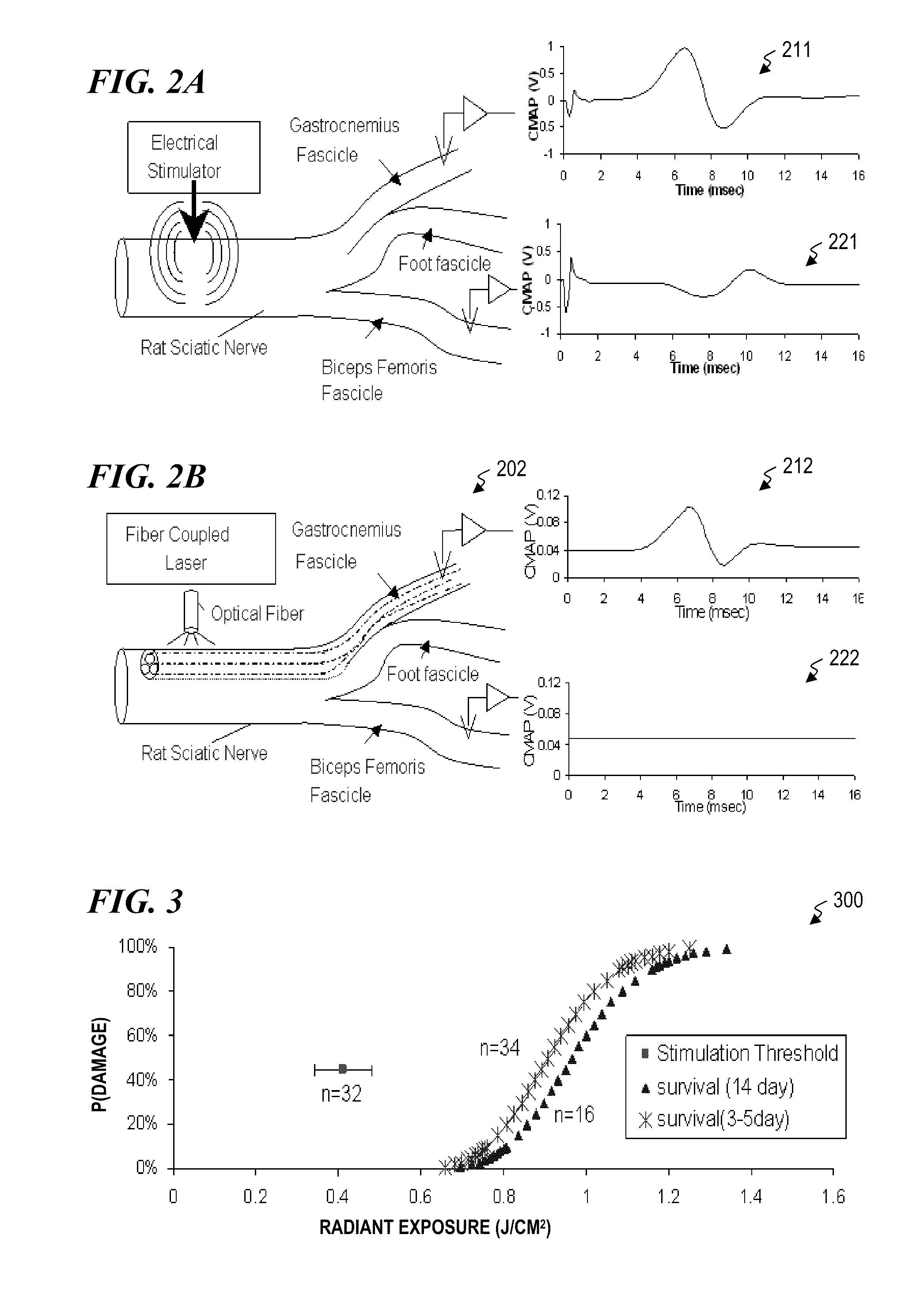

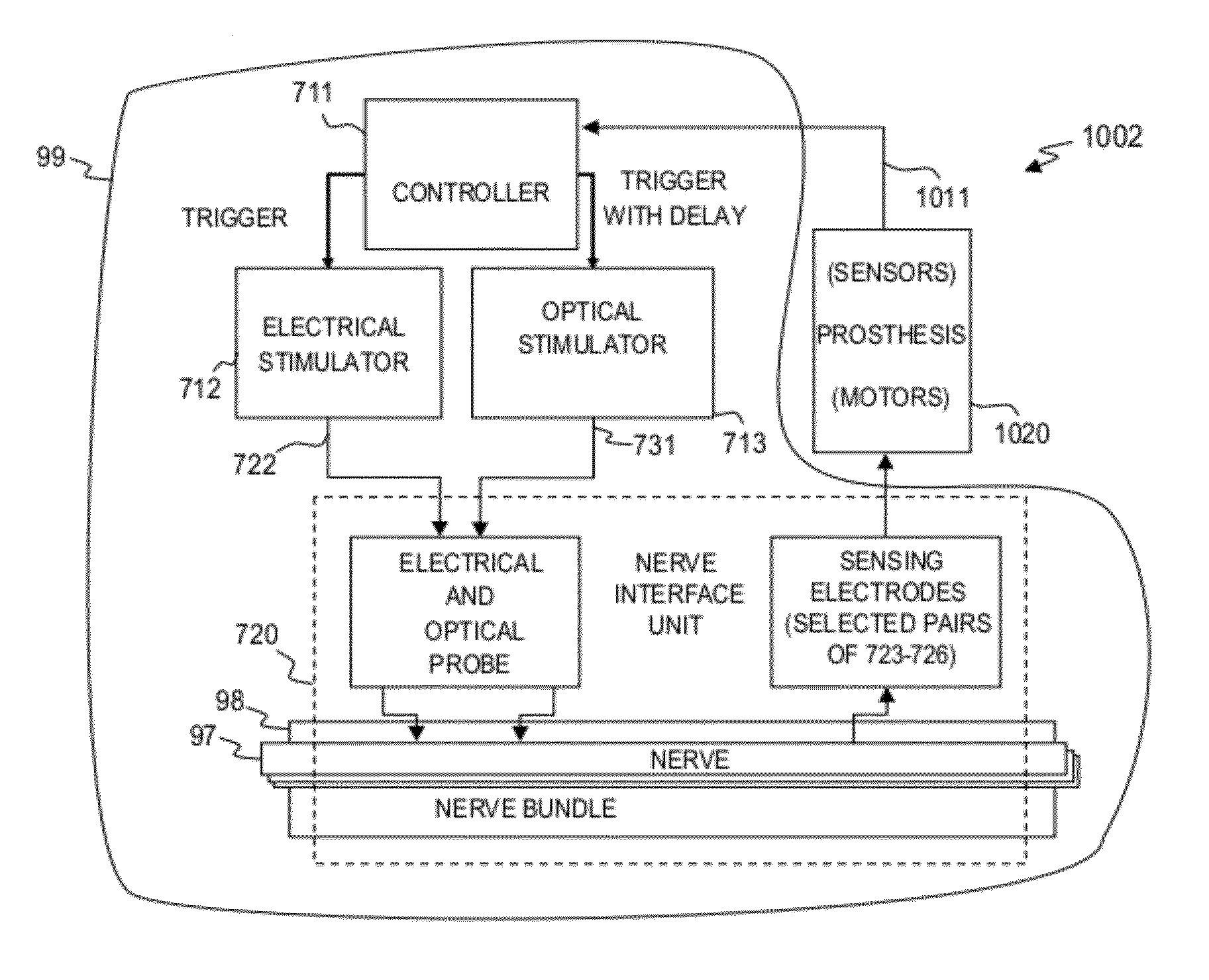

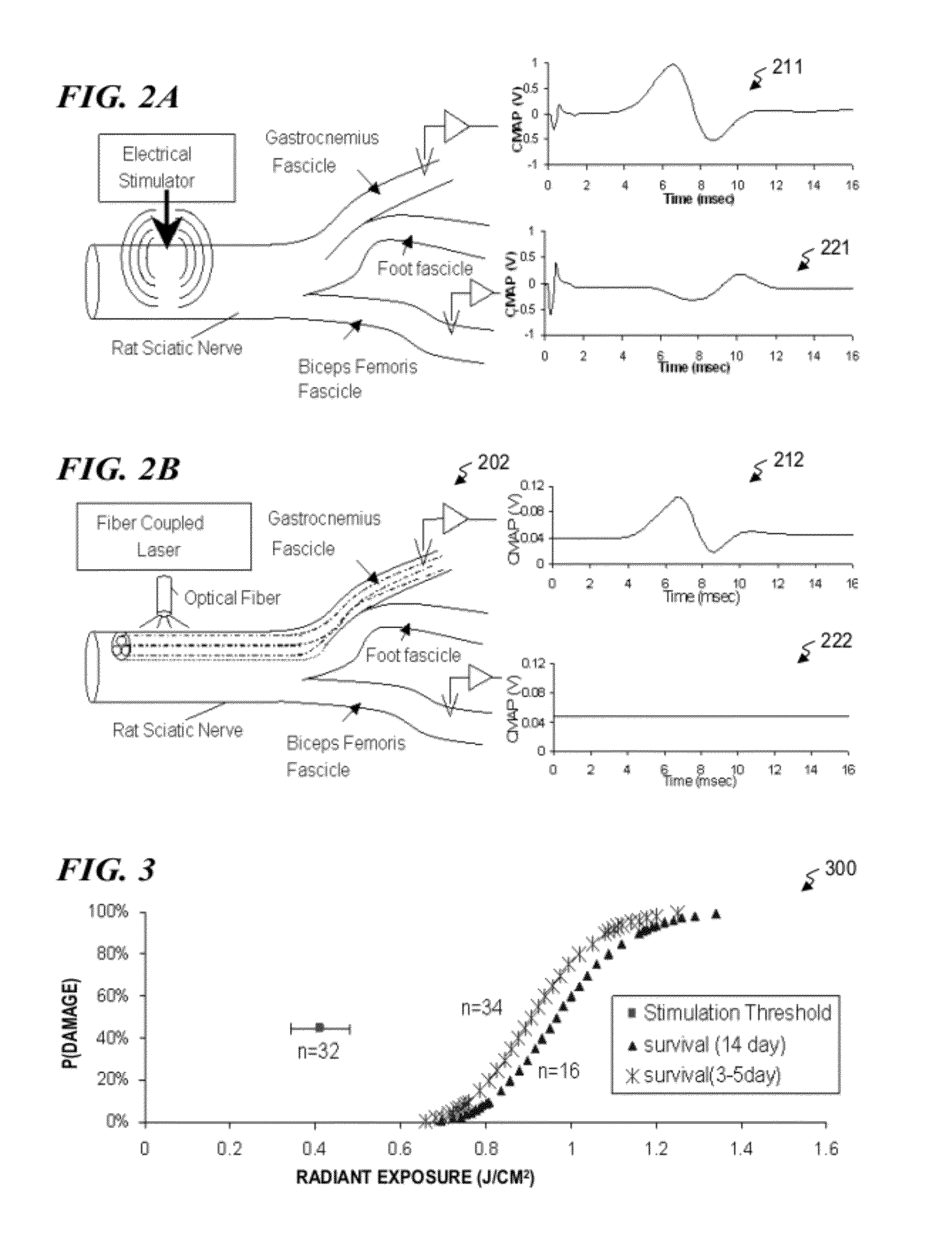

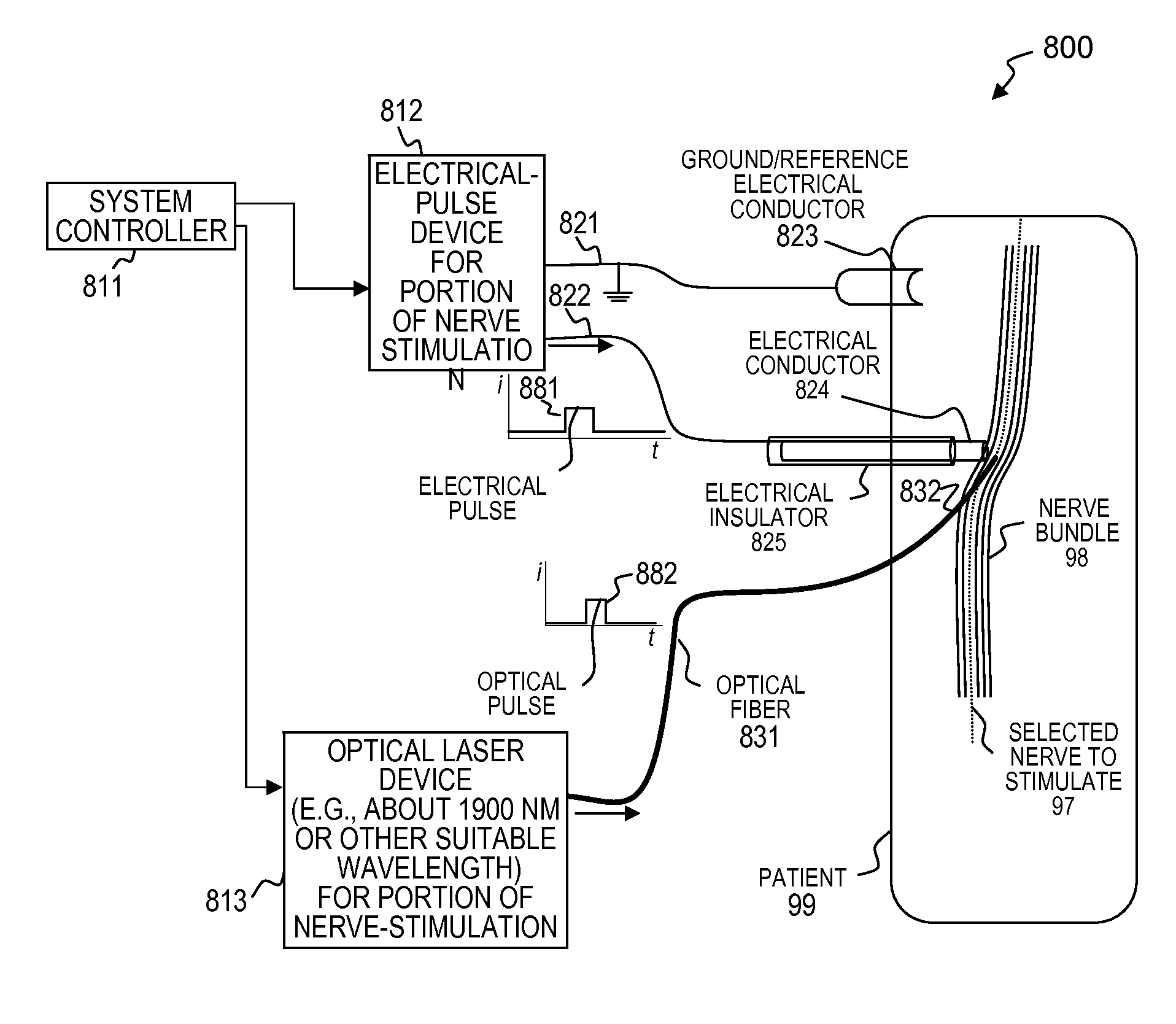

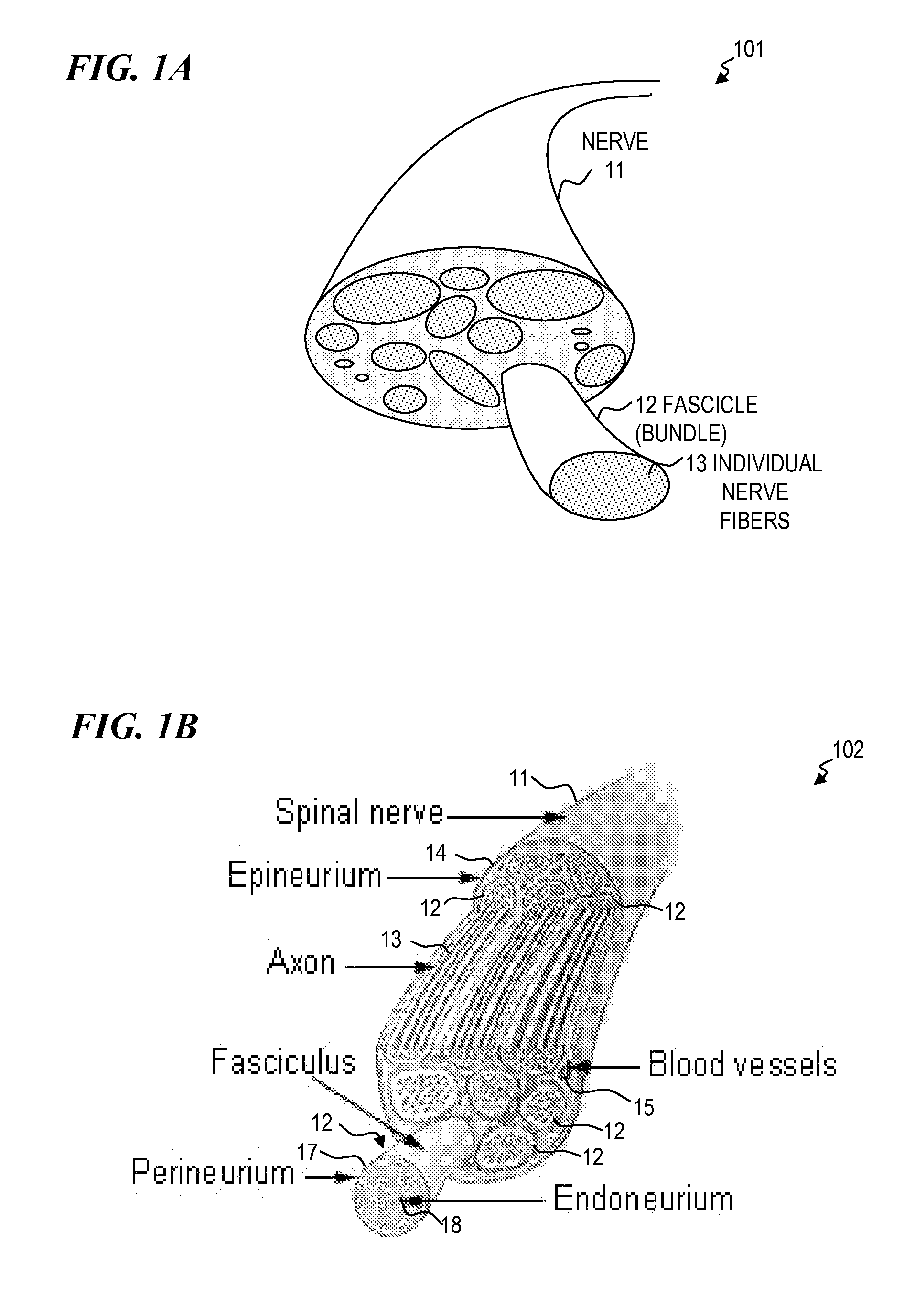

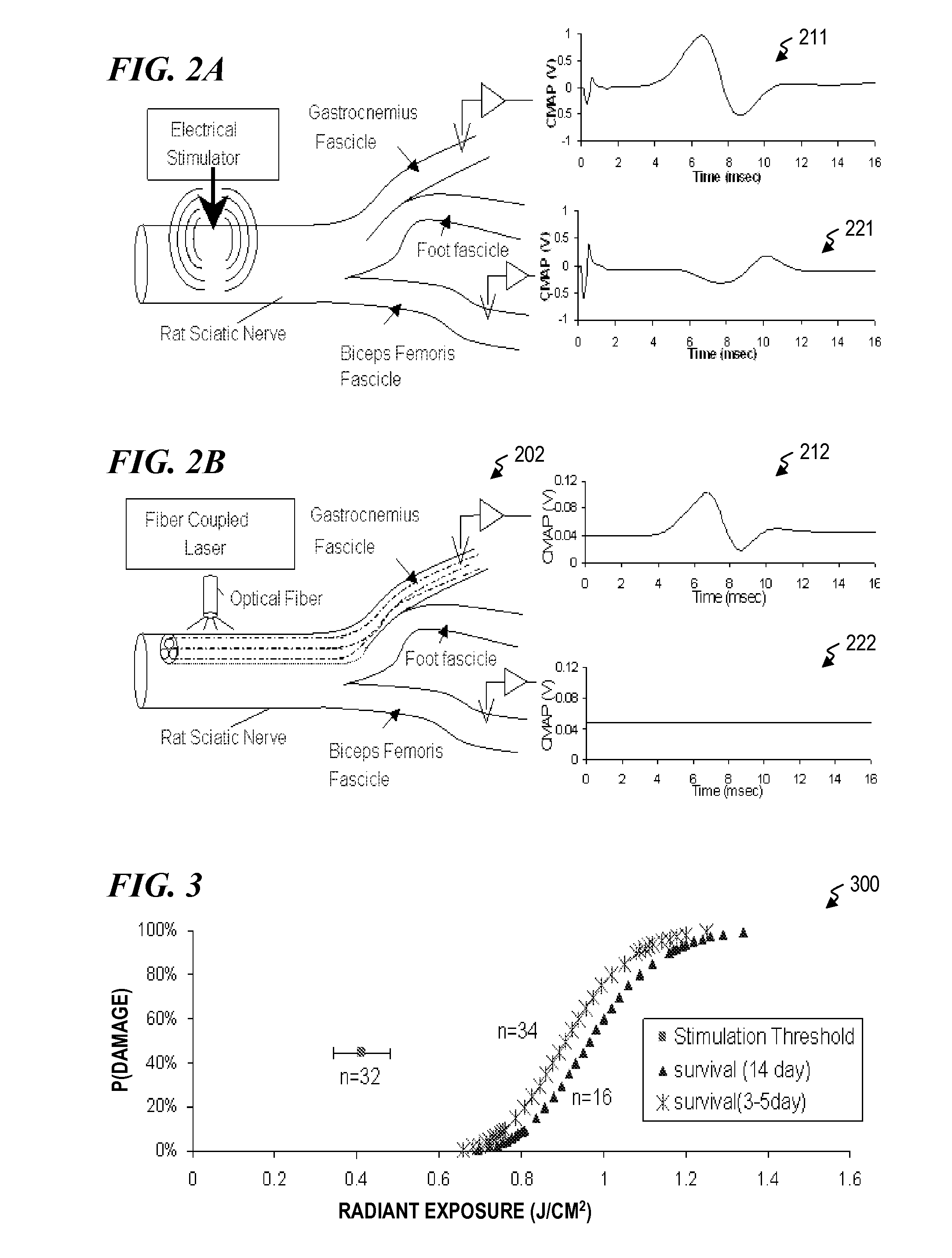

An apparatus and method for stimulating animal tissue (for example to trigger a nerve action potential (NAP) signal in a human patient) by application of both electrical and optical signals for treatment and diagnosis purposes. The application of an electrical signal before or simultaneously to the application of a NAP-triggering optical signal allows the use of a lower amount of optical power or energy than would otherwise be needed if an optical signal alone was used for the same purpose and effectiveness. The application of the electrical signal may precondition the nerve tissue such that a lower-power optical signal can be used to trigger the desired NAP, which otherwise would take a higher-power optical signal were the electric signal not applied. Some embodiments include an implanted nerve interface having a plurality of closely spaced electrodes placed transversely and / or longitudinally to the nerve and a plurality of optical emitters.

Owner:NERVESENSE LTD

Nerve stimulator and method using simultaneous electrical and optical signals

ActiveUS8160696B2Reduce amountReduced Optical Power RequirementsSurgical instrument detailsImplantable neurostimulatorsElectricityOptical power

An apparatus and method for stimulating animal tissue (for example to trigger a nerve action potential (NAP) signal in a human patient) by application of both electrical and optical signals for treatment and diagnosis purposes. The application of an electrical signal before or simultaneously to the application of a NAP-triggering optical signal allows the use of a lower amount of optical power or energy than would otherwise be needed if an optical signal alone was used for the same purpose and effectiveness. The application of the electrical signal may precondition the nerve tissue such that a lower-power optical signal can be used to trigger the desired NAP, which otherwise would take a higher-power optical signal were the electric signal not applied. Some embodiments include an implanted nerve interface having a plurality of closely spaced electrodes placed transversely and / or longitudinally to the nerve and a plurality of optical emitters.

Owner:NERVESENSE LTD

Nerve stimulator and method using simultaneous electrical and optical signals

ActiveUS20110172725A1Reduce amountDecrease in levelElectrotherapySurgical instrument detailsOptical powerNerves tissue

An apparatus and method for stimulating animal tissue (for example to trigger a nerve action potential (NAP) signal in a human patient) by application of both electrical and optical signals for treatment and diagnosis purposes. The application of an electrical signal before or simultaneously to the application of a NAP-triggering optical signal allows the use of a lower amount of optical power or energy than would otherwise be needed if an optical signal alone was used for the same purpose and effectiveness. The application of the electrical signal may precondition the nerve tissue such that a lower-power optical signal can be used to trigger the desired NAP, which otherwise would take a higher-power optical signal were the electric signal not applied. Some embodiments include an implanted nerve interface having a plurality of closely spaced electrodes placed transversely and / or longitudinally to the nerve and a plurality of optical emitters.

Owner:VANDERBILT UNIV +1

Semiconductor integrated circuit and control method for clock signal synchronization

InactiveUS20100117697A1Maximize low power consumption effectImprove Low Power PerformanceEnergy efficient ICTPulse automatic controlSynchronous controlEngineering

There is a need to ensure operation performance of a circuit region under DVFS control at low costs and highly precisely while a power-supply voltage change is made to the region. A first circuit (FVA) uses a first power-supply voltage (VDDA) for operation. A second circuit (NFVA) uses a second power-supply voltage (VDDB) for operation. A clock delay may be adjusted between paths for transmitting a clock to these circuits. When VDDA equals VDDB, a clock is distributed to FVA through a path that does not contain a delay device for phase adjustment. When the power-supply voltage for the FVA region is reduced, a clock is distributed to the FVA region based on a phase equivalent to one or two cycles of the clock displaced. Synchronization control is provided to synchronize clocks (CKAF and CKBF) and ensures operation so that a phase of two clocks to be compared fits in a range of design values while the power-supply voltage for the first circuit is changed.

Owner:RENESAS ELECTRONICS CORP

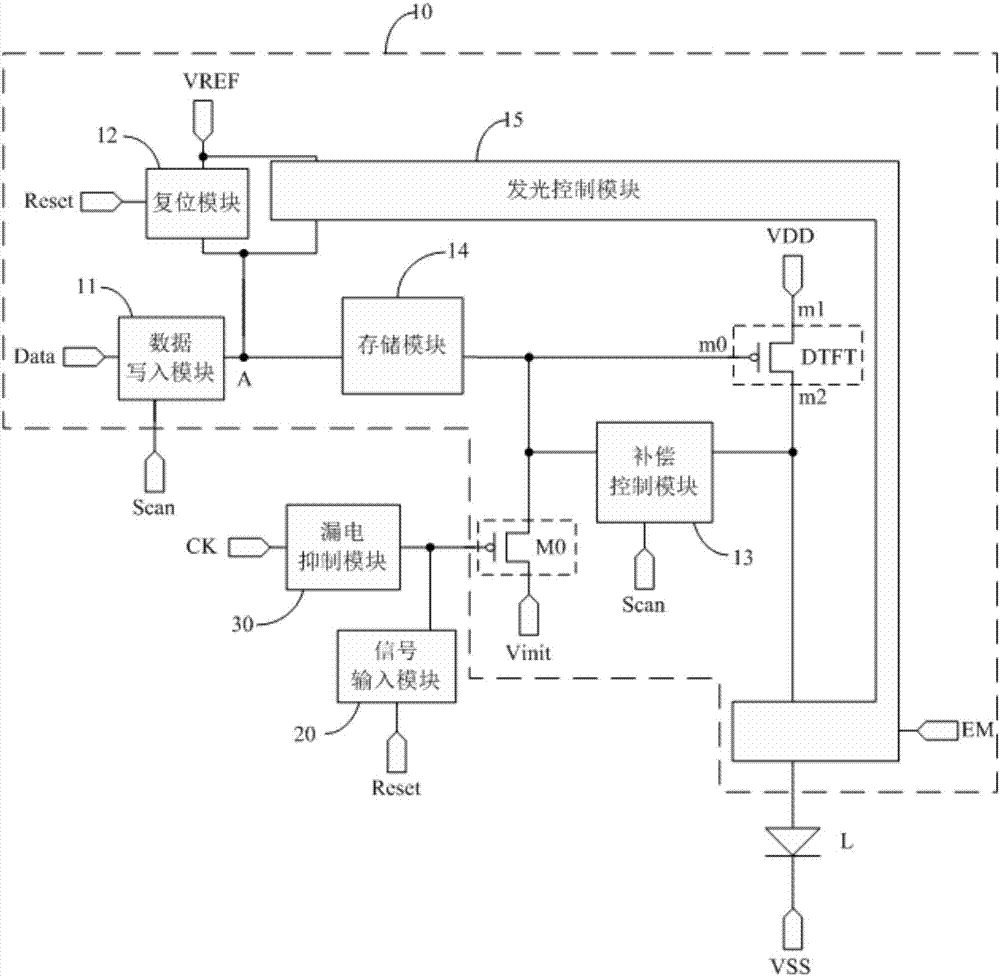

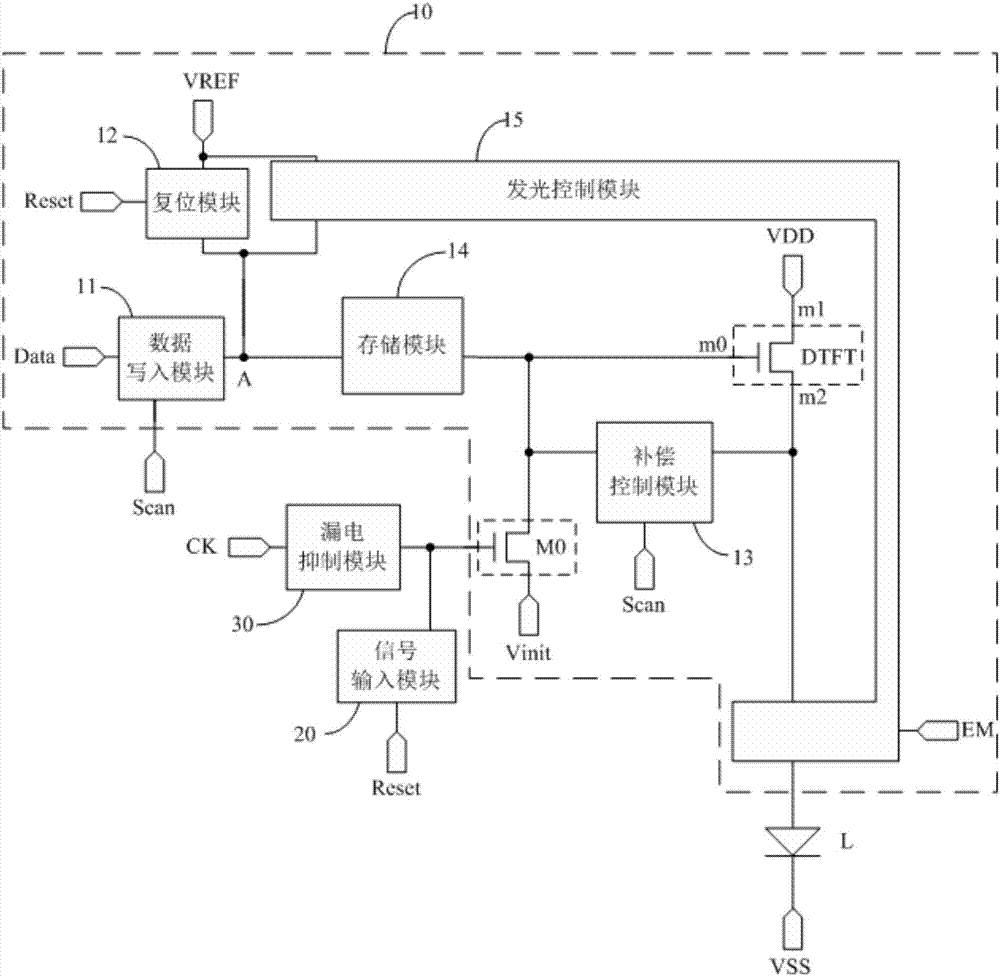

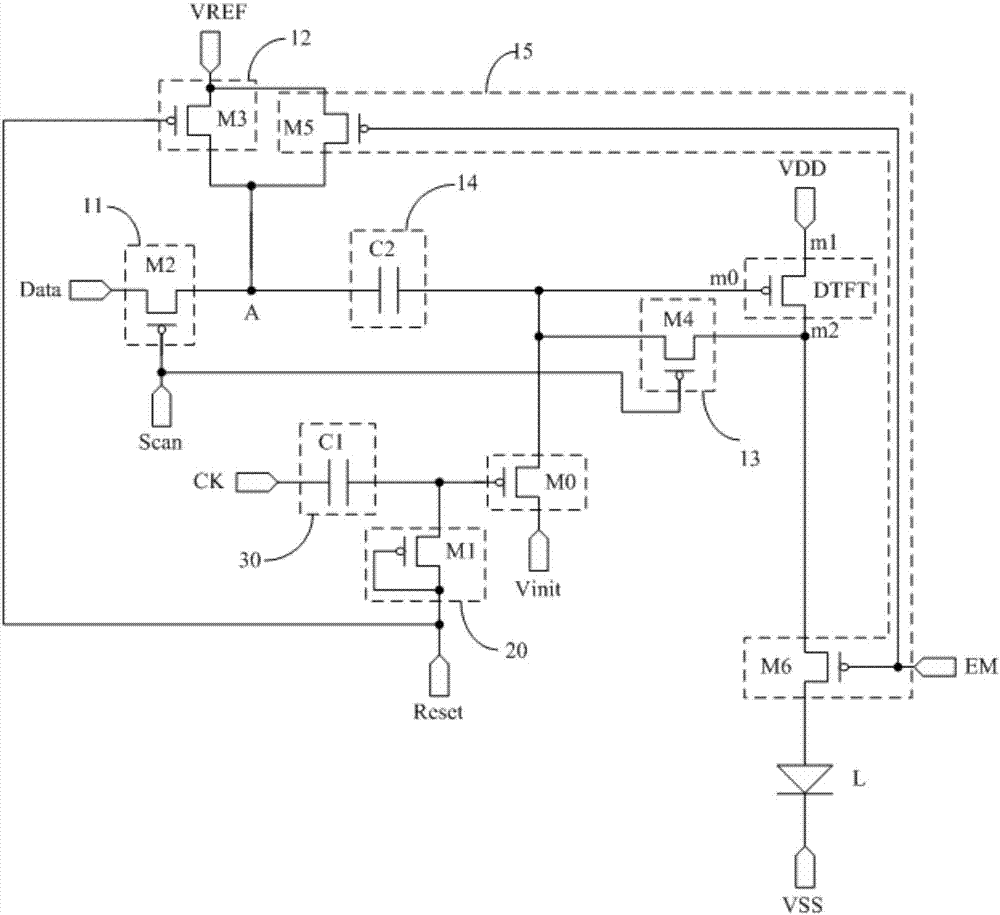

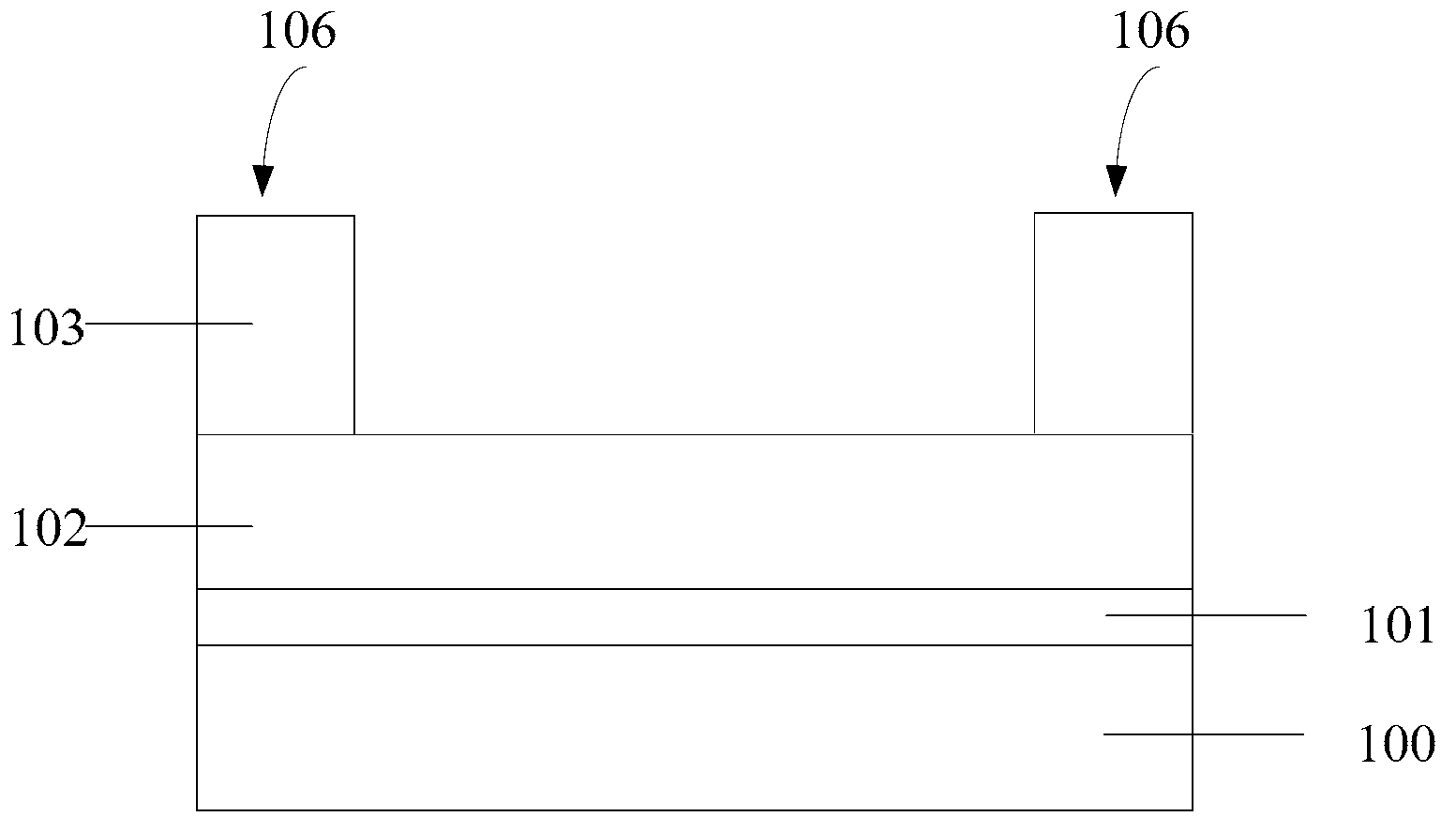

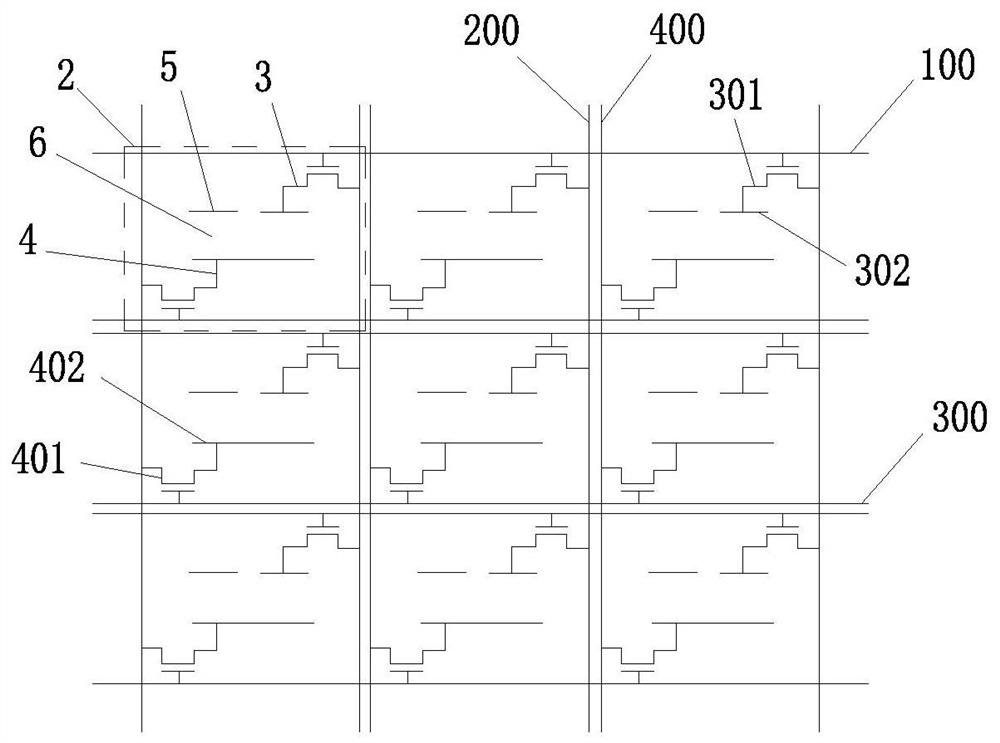

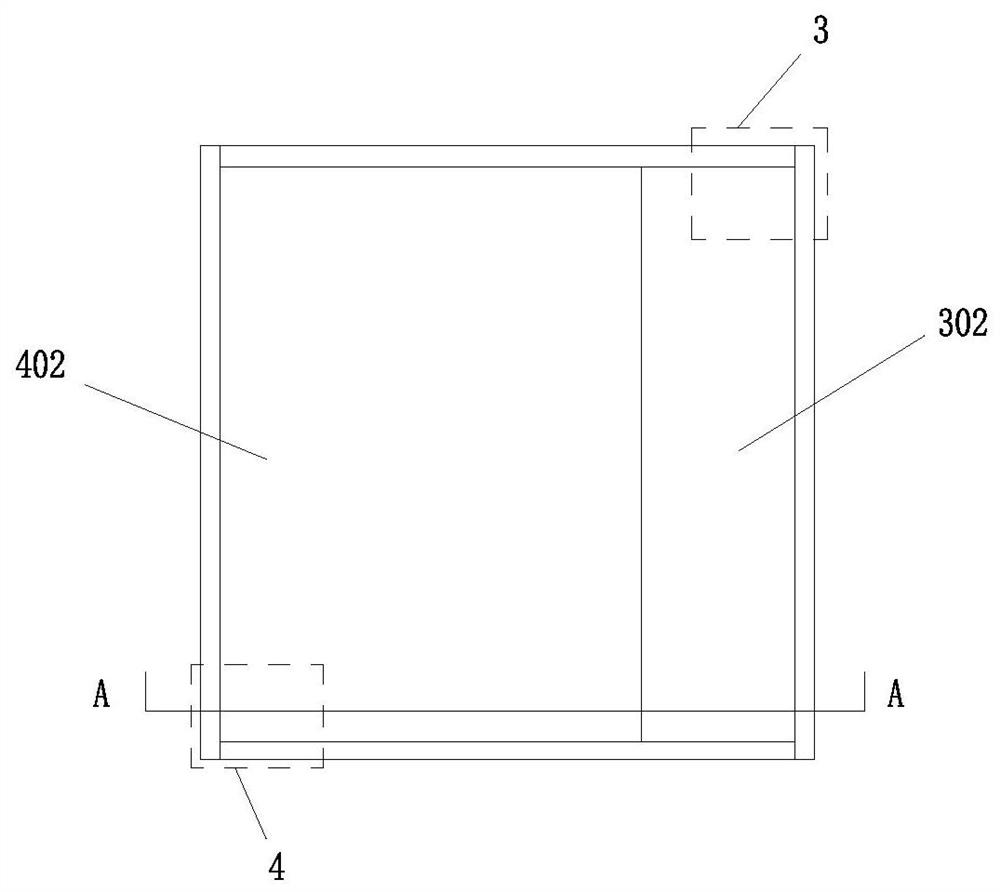

Pixel drive circuit and driving method thereof, and organic light-emitting display panel

ActiveCN106935198AImprove luminous brightnessRaise the voltage differenceStatic indicating devicesDriver circuitControl signal

The invention discloses a pixel drive circuit and a driving method thereof, and an organic light-emitting display panel. The pixel drive circuit comprises a light-emitting device, a pixel compensation circuit connected with the light-emitting device, a signal input module, and a leakage suppression module. A reset signal terminal is connected with a control electrode of an initialized transistor by the signal input module. The signal input module is used for providing a signal of the reset signal terminal for the control electrode of the initialized transistor under control of the reset signal terminal; and the leakage suppression module is used for increasing a voltage difference between the control electrode of the initialized transistor and a second electrode of the initialized transistor under control of a leakage control signal terminal. On the basis of mutual cooperation of the modules, the signal inputted into an initialized signal terminal by the initialized transistor can be controlled; and the initialized transistor enters a cut-off state by increasing the voltage difference between the control electrode and the second electrode of the initialized transistor. Therefore, formation of a leakage current path of the initialized transistor can be avoided; the brightness of the light-emitting device can be improved; and the scintillation phenomenon can be improved.

Owner:BOE TECH GRP CO LTD +1

Method and nerve stimulator using simultaneous electrical and optical signals

ActiveUS8498699B2Reduce amountReduced Optical Power RequirementsElectrotherapySurgical instrument detailsElectricityOptical power

An apparatus and method for stimulating animal tissue (for example to trigger a nerve action potential (NAP) signal in a human patient) by application of both electrical and optical signals for treatment and diagnosis purposes. The application of an electrical signal before or simultaneously to the application of a NAP-triggering optical signal allows the use of a lower amount of optical power or energy than would otherwise be needed if an optical signal alone was used for the same purpose and effectiveness. The application of the electrical signal may precondition the nerve tissue such that a lower-power optical signal can be used to trigger the desired NAP, which otherwise would take a higher-power optical signal were the electric signal not applied. Some embodiments include an implanted nerve interface having a plurality of closely spaced electrodes placed transversely and / or longitudinally to the nerve and a plurality of optical emitters.

Owner:VANDERBILT UNIV +1

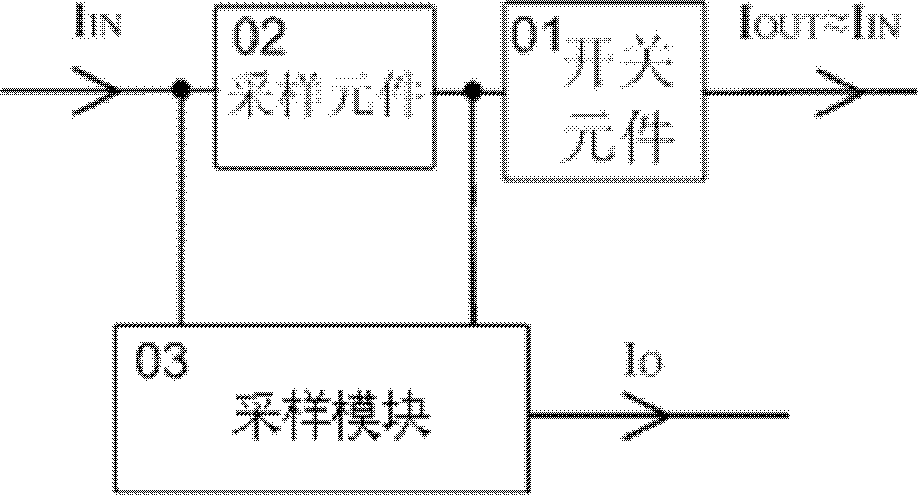

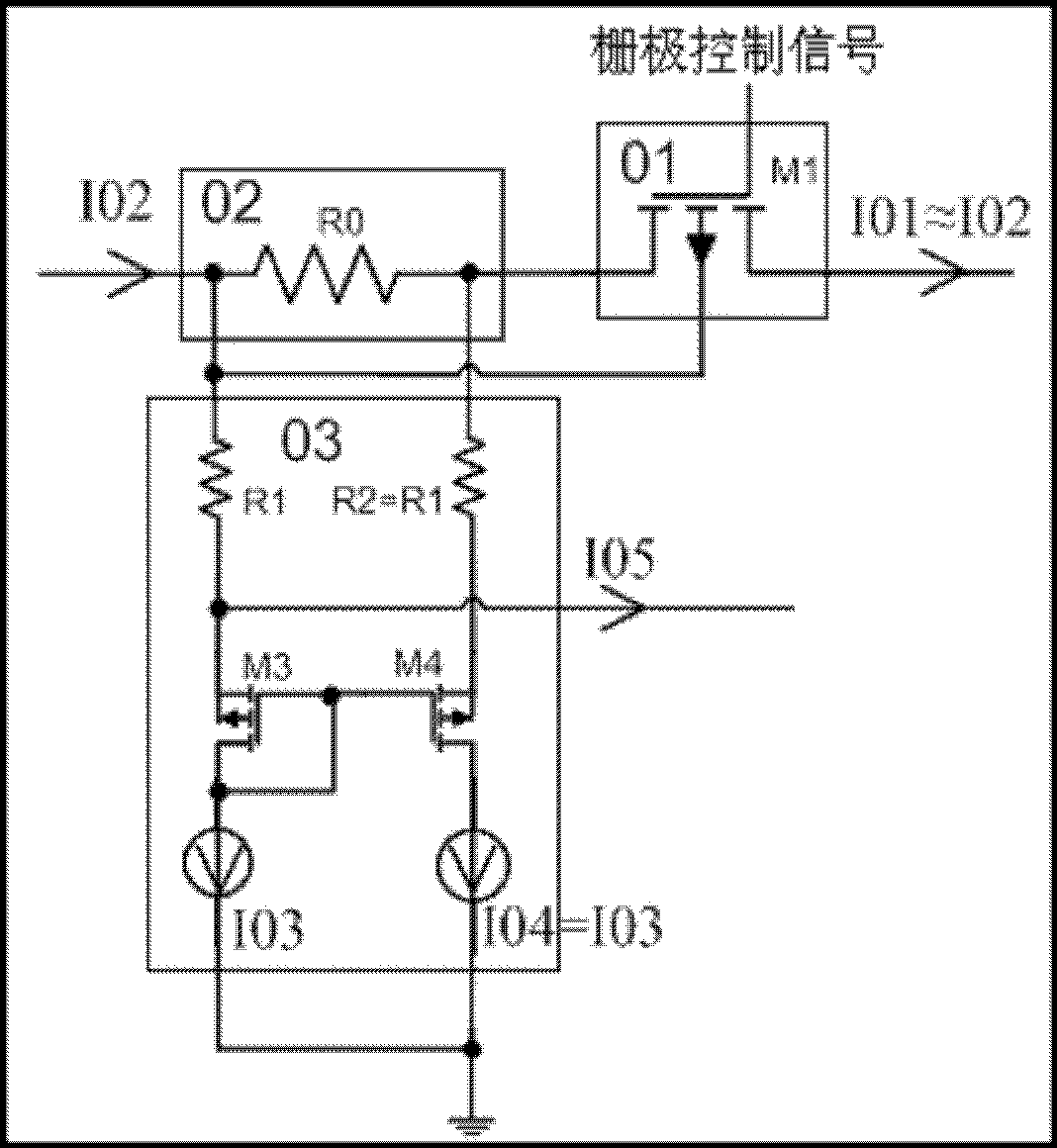

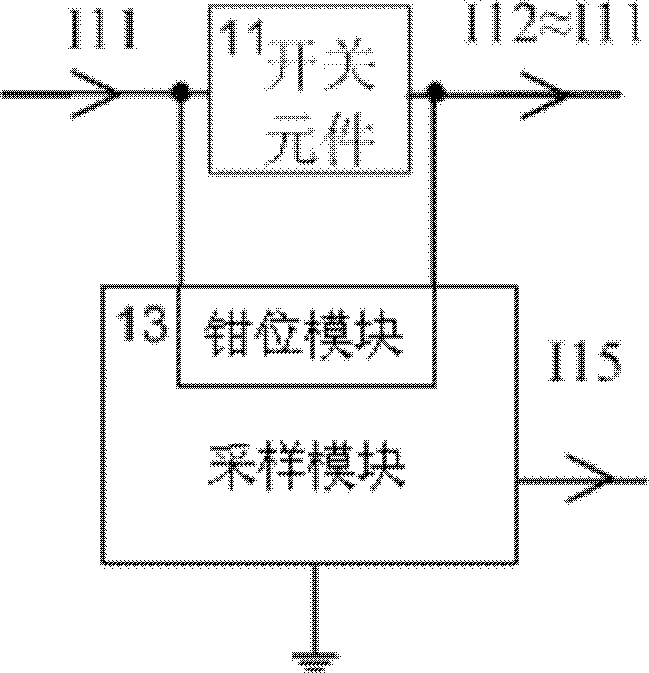

Current sampling circuit of metal oxide semiconductor field effect transistor (MOSFET) switch element

ActiveCN102495265AEliminate power lossExtended working voltage rangeCurrent/voltage measurementMOSFETHemt circuits

The invention discloses a current sampling circuit of a metal oxide semiconductor field effect transistor (MOSFET) switch element. A first end of the switch element is connected with a first input end of a sampling module and serves as a current input signal end, a second end of the switch element is connected with a second input end of the sampling module and serves as a current output signal end of the MOSFET switch element, and an output end of the sampling module serves as a sampling current output signal end. The sampling module directly samples voltage difference of the first end and the second end of the MOSFET switch element. Maximum voltage difference value allowed between the first input end and the second input end of the sampling module is a withstand voltage value between two input ends of the sampling module. A clamping module included in the sampling module increases the withstand voltage value of the sampling module so that a current path formed between the first input end and the second input end of the sampling module is blocked, and working voltage range of the current sampling circuit of the MOSFET switch element is improved.

Owner:HANGZHOU SILAN MICROELECTRONICS

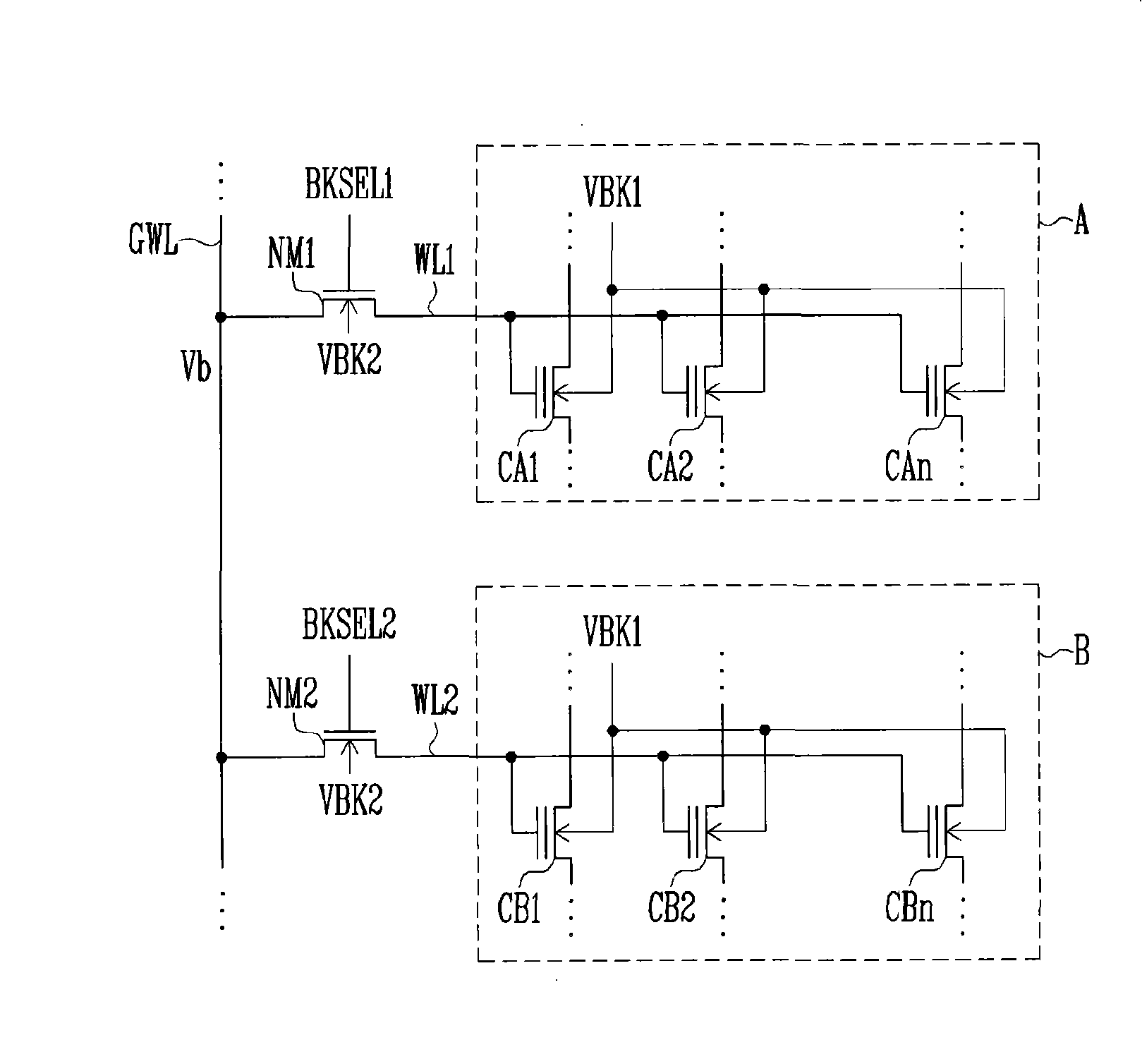

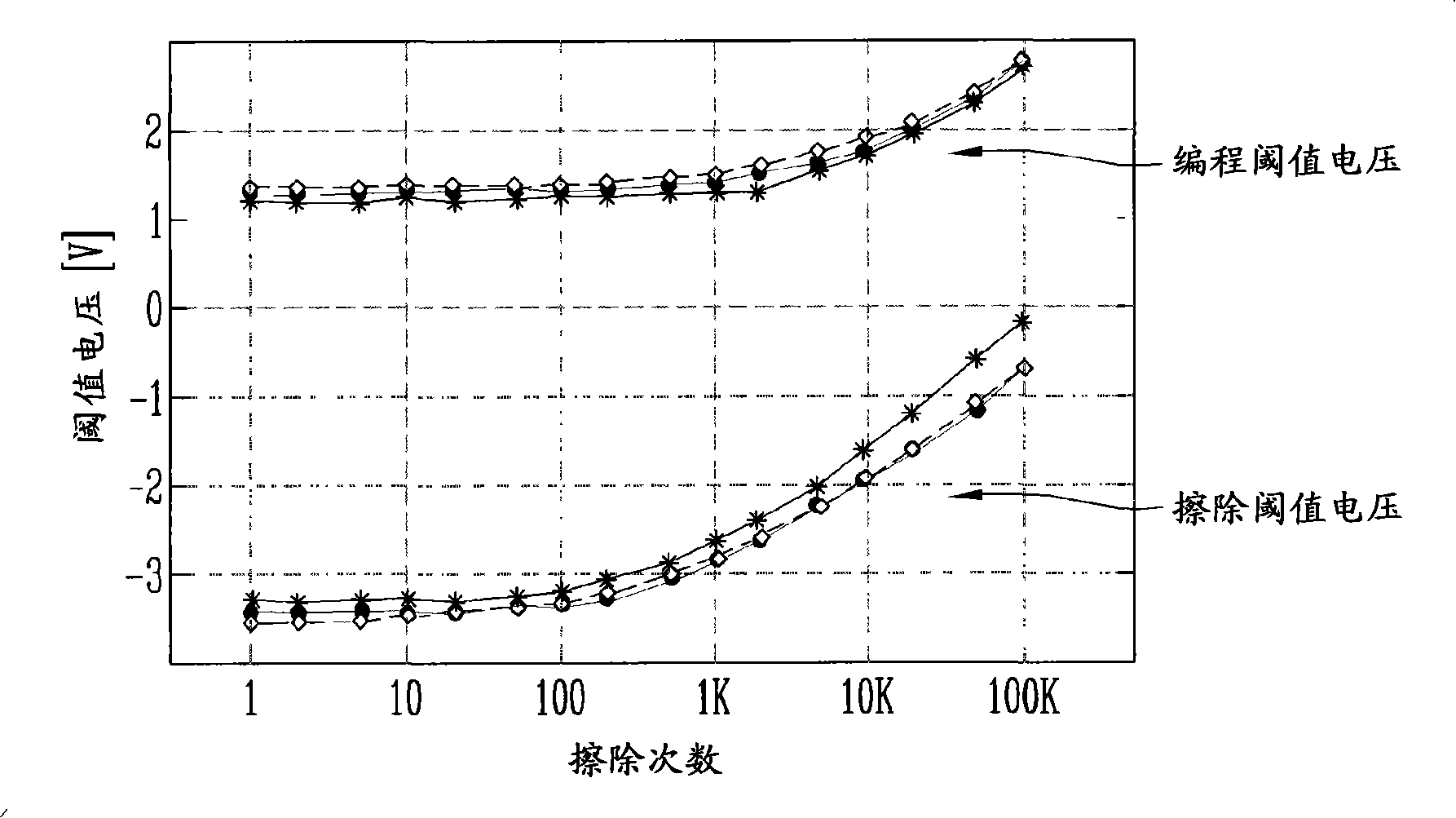

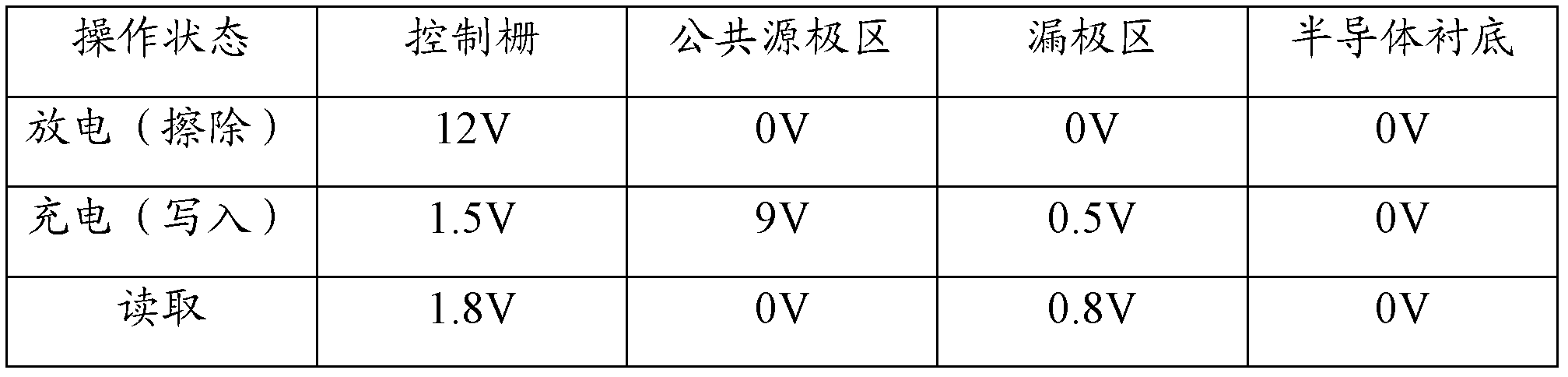

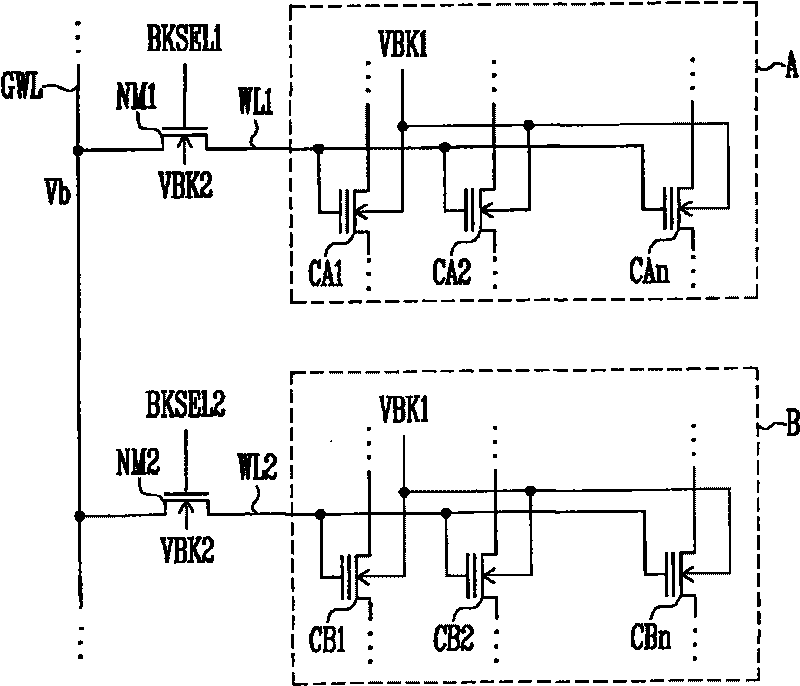

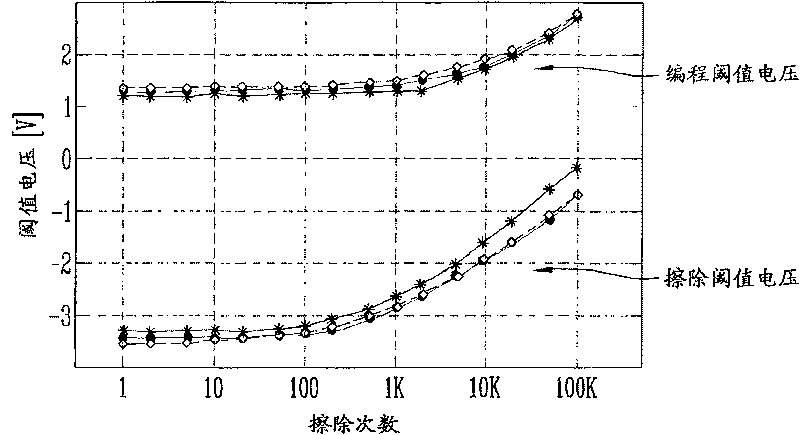

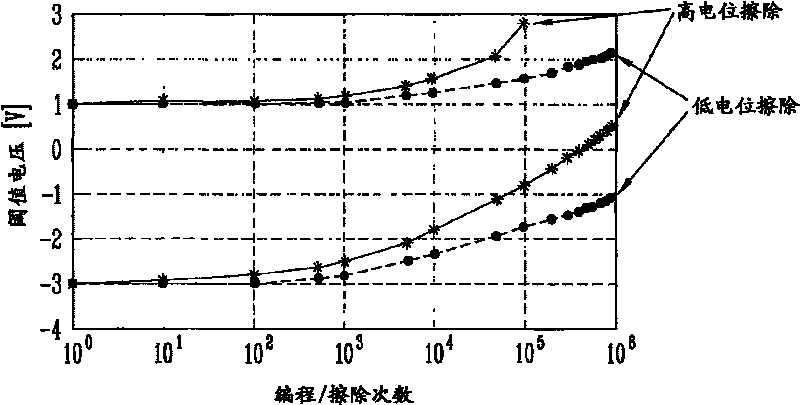

Flash memory device and method for controlling the same

ActiveCN101178937ARaise the voltage differenceIncrease the erase voltageRead-only memoriesVoltage generatorComputer science

The present invention provides a flash memory device and a method used for controlling erasing operation of the flash memory device.A non-volatile memory mechanism includes a first and a second memory cell blocks, wherein each memory cell block includes a plurality of memory cells, a local drain selection wire, a local source pole selection wire and a plurality of local character wires.A block selection unit respectively connects the set local character wires and an integral character wire to respond to block selective signals.A first voltage bias generator is allocated to be used for applying at least a first and a second erasing voltages which are positive ones to the integral character wire during the erasing manipulation period, wherein, the first erasing voltage is applied to the integral character wire during a first erasing try period of the erasing operation, the second erasing voltage is applied to the integral character wire during the second erasing try period, and a second erasing try is executed if a first erasing try does not make good erasing manipulation.A body voltage generator applies a body electric voltage to a body of the memory cell during the erasing manipulation period.

Owner:SK HYNIX INC

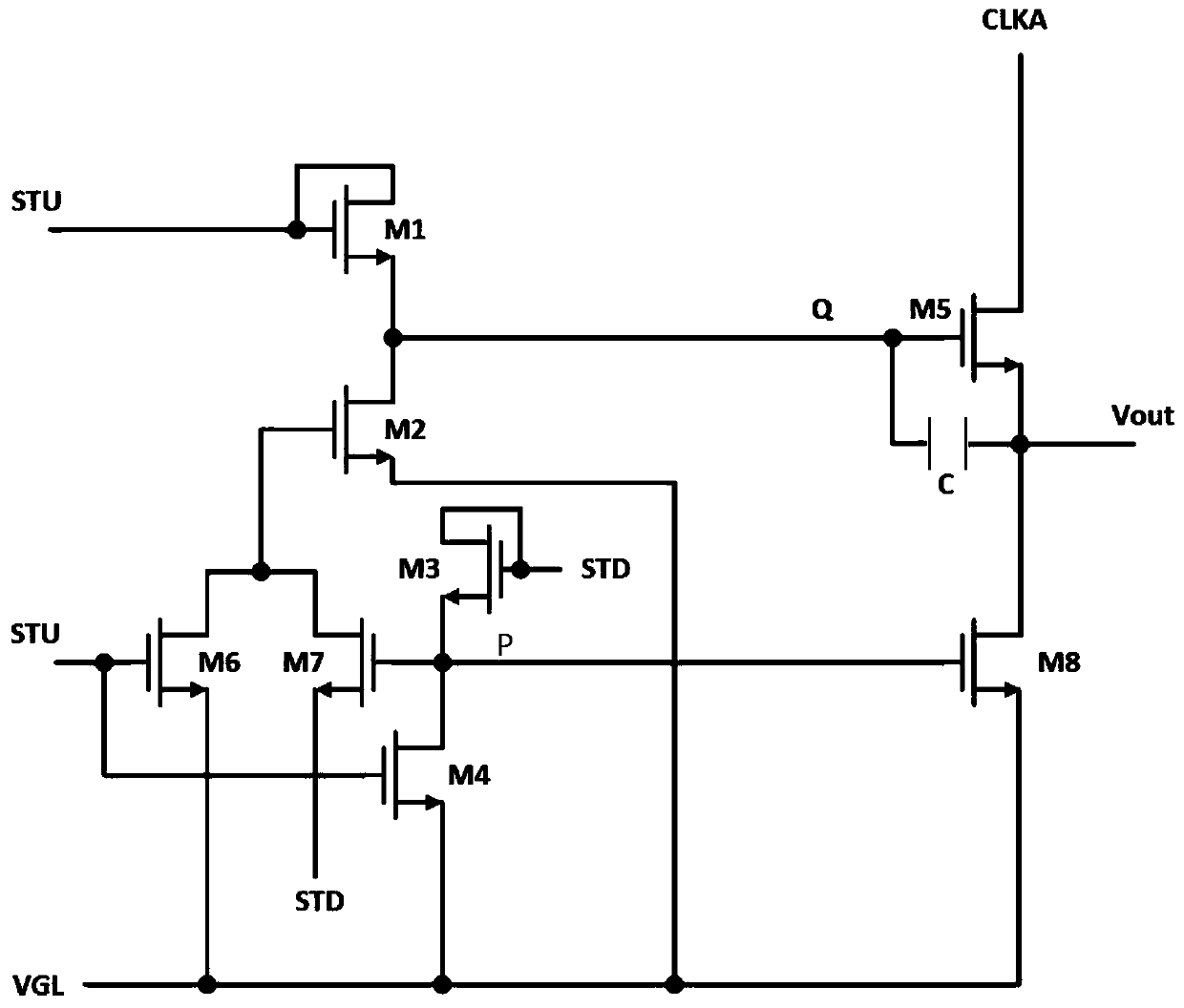

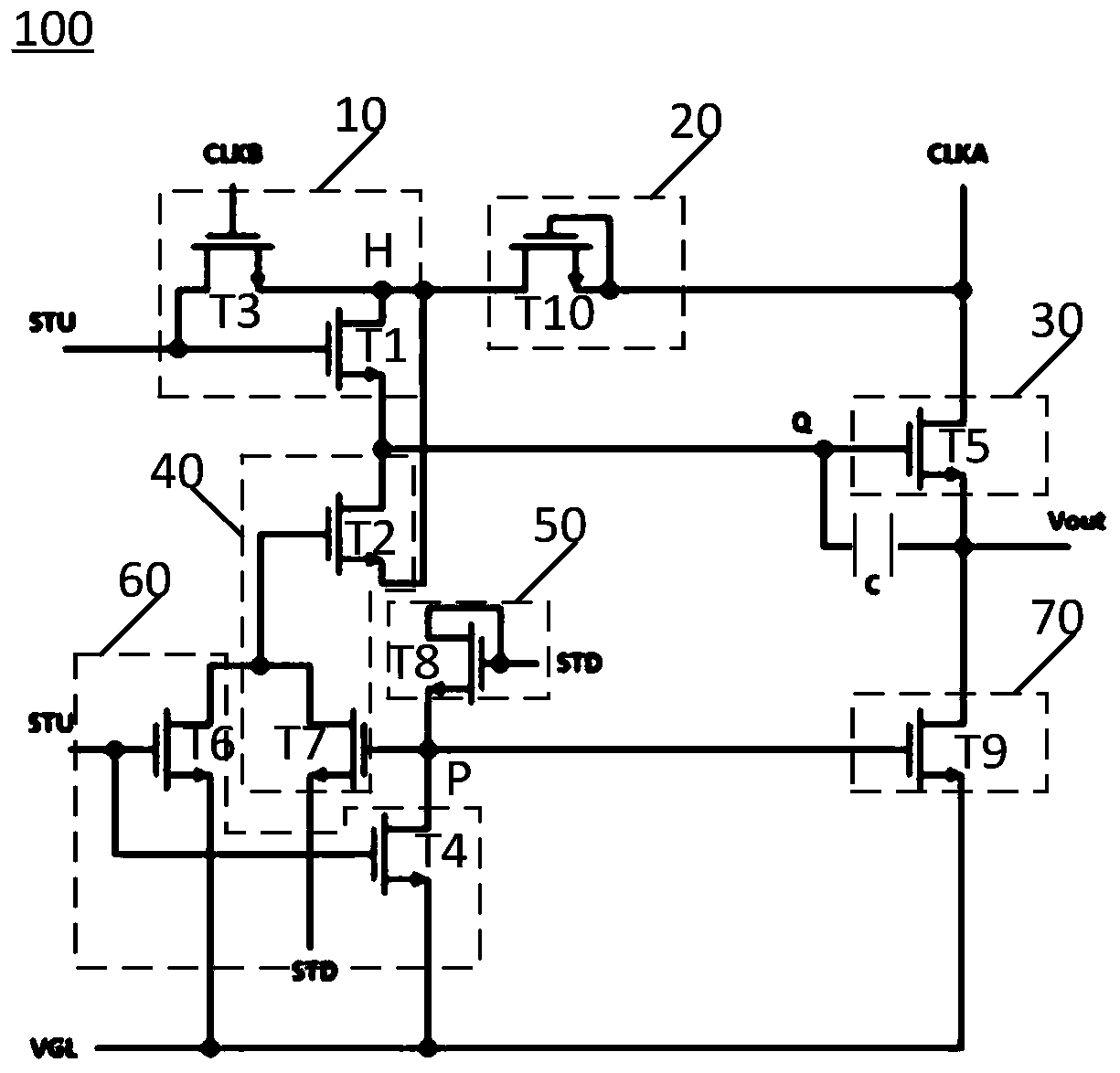

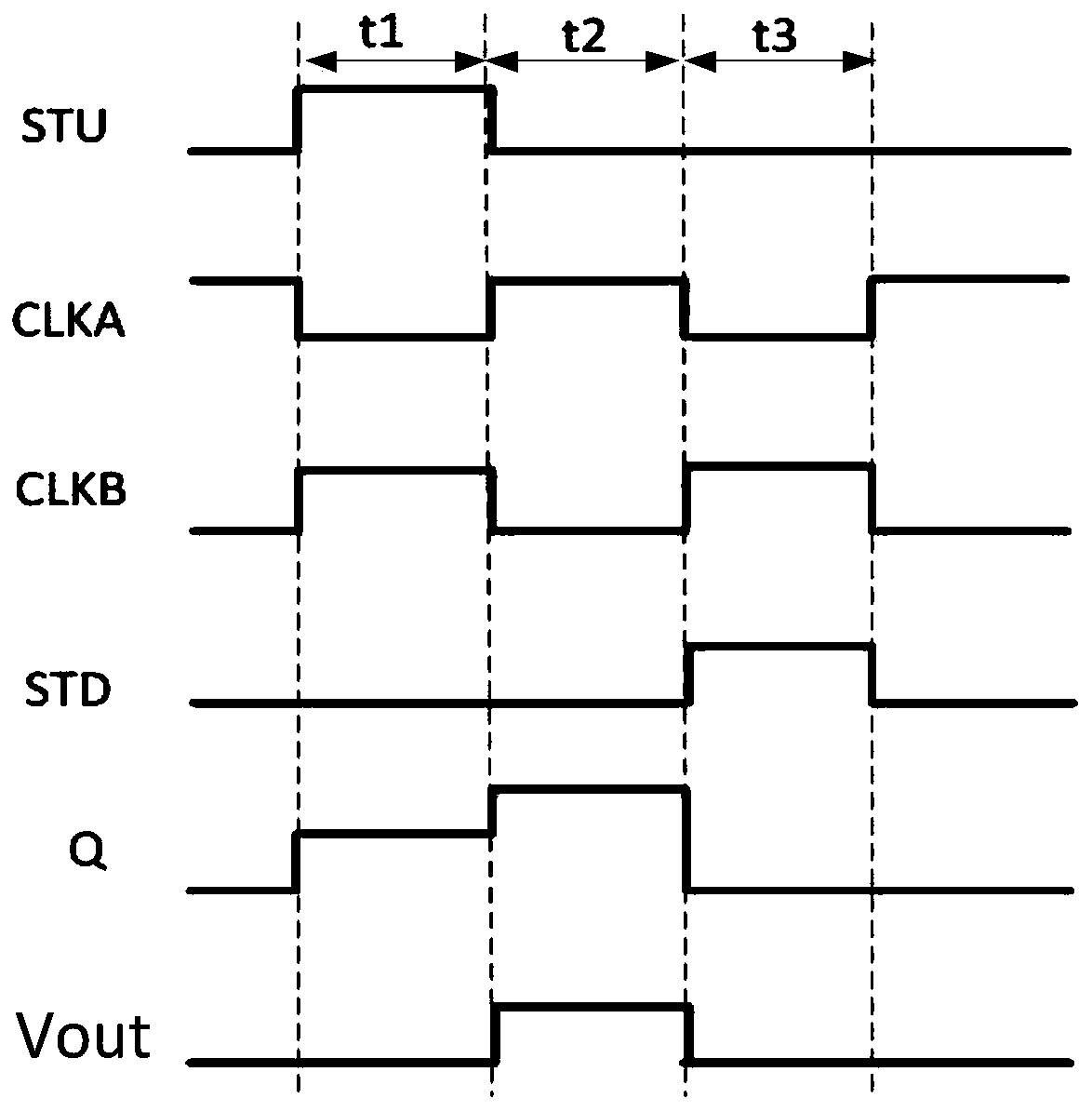

Shift register unit, gate drive circuit and display panel

PendingCN111179811AImprove stabilityRaise the voltage differenceStatic indicating devicesDigital storageShift registerDriver circuit

The invention provides a shift register unit, a gate drive circuit and a display panel. The shift register unit comprises a pull-up control module connected with an (n-1) th-stage scanning signal output end, a first node and a third node; a pull-up module connected with a first clock signal, wherein the first node is connected to the scanning signal output end of the current stage; an anti-creeping module connected with the first clock signal and the third node; a pull-down control module connected with a (n + 2) th-stage scanning signal output end and a second node; and a first pull-down module connected with a (n + 2) th-stage scanning signal output end, the first node, the second node and the third node. According to the shift register unit, the gate drive circuit and the display panel,electric leakage of a Q point can be avoided, and the stability of the shift register unit is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Memory devices having bit line precharge circuits and associated bit line precharge methods

ActiveCN1574084ARaise the voltage differenceExpand the detection areaDigital storageBit lineHemt circuits

A memory device having an off-current (Ioff) robust precharge control circuit and a bit line precharge method are provided. The precharge control circuit may be embodied as a delay circuit unit which receives and delays a precharge enable signal for a predetermined delay time; a NAND gate which receives the precharge enable signal and the output of the delay circuit; and an inverter which inverts the output of the NAND gate. The precharge control circuit may enable the word lines before disabling the precharge signal.

Owner:SAMSUNG ELECTRONICS CO LTD

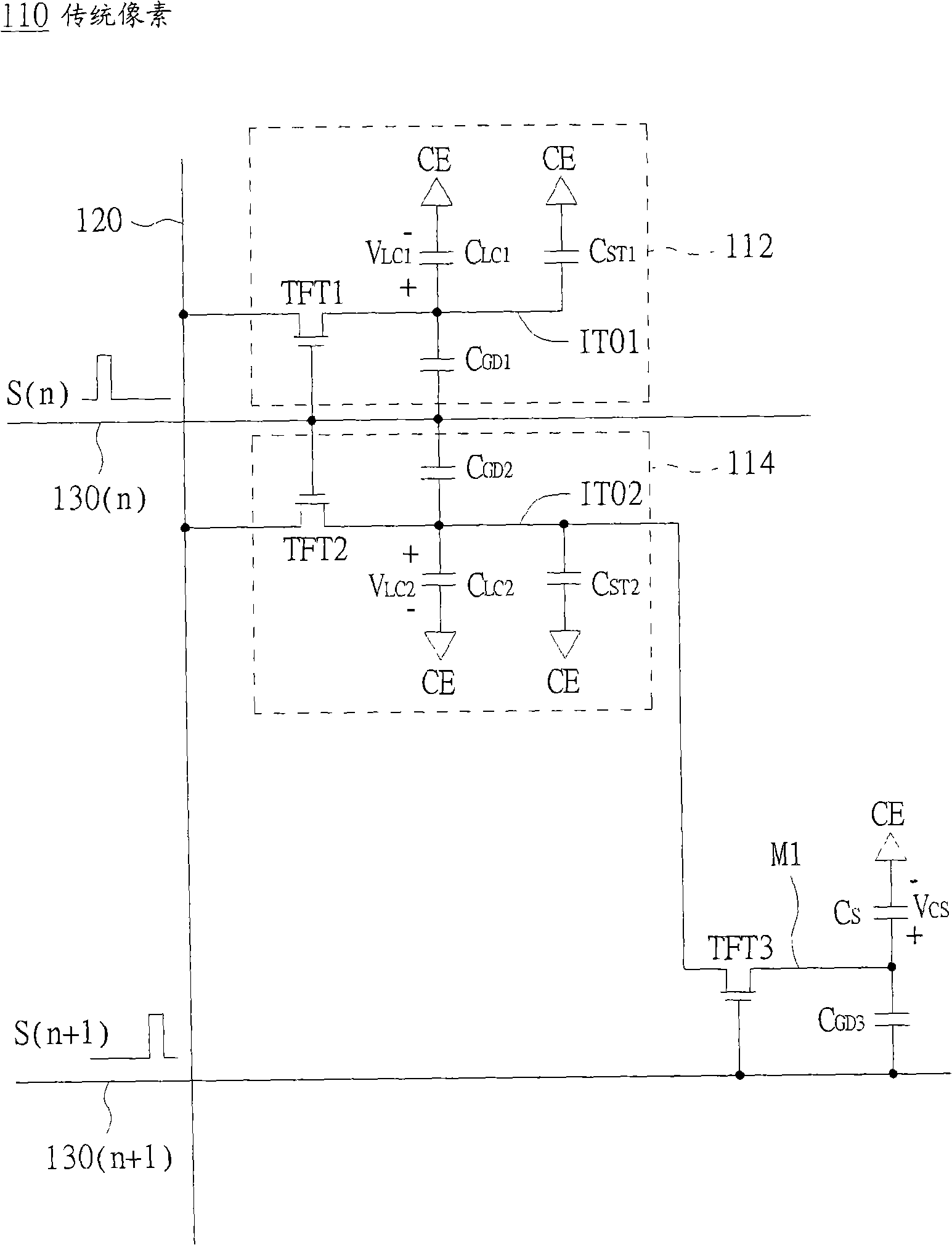

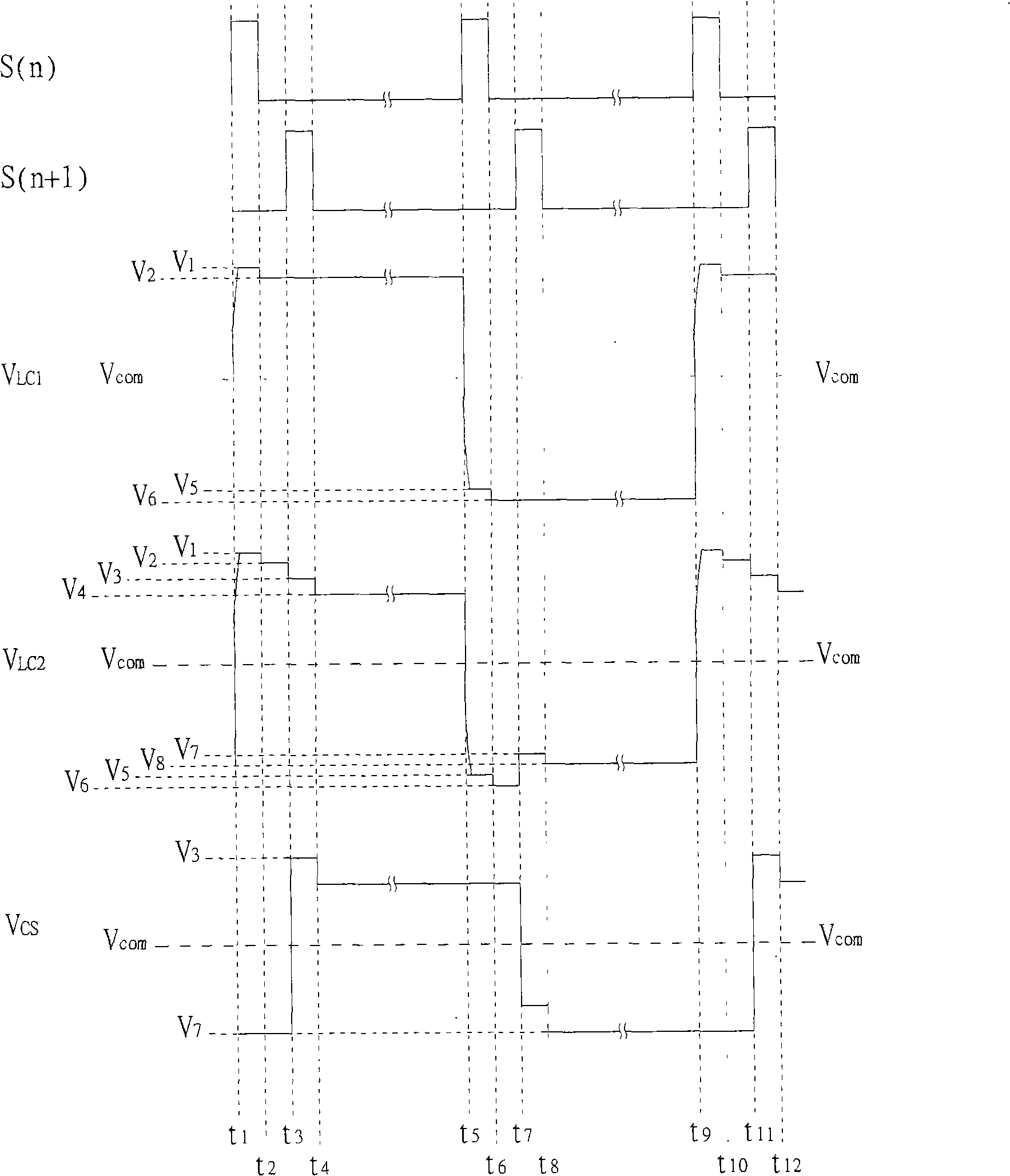

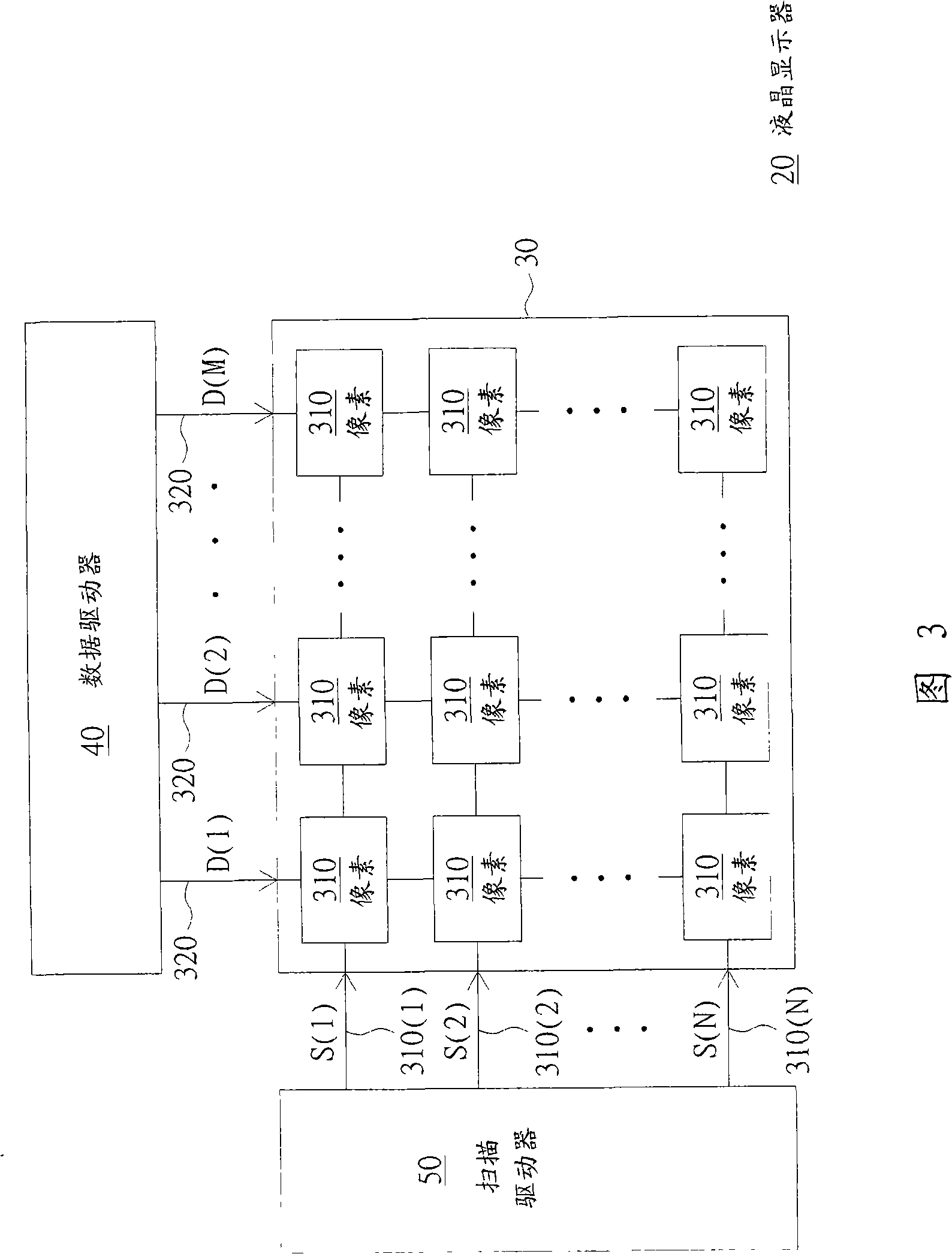

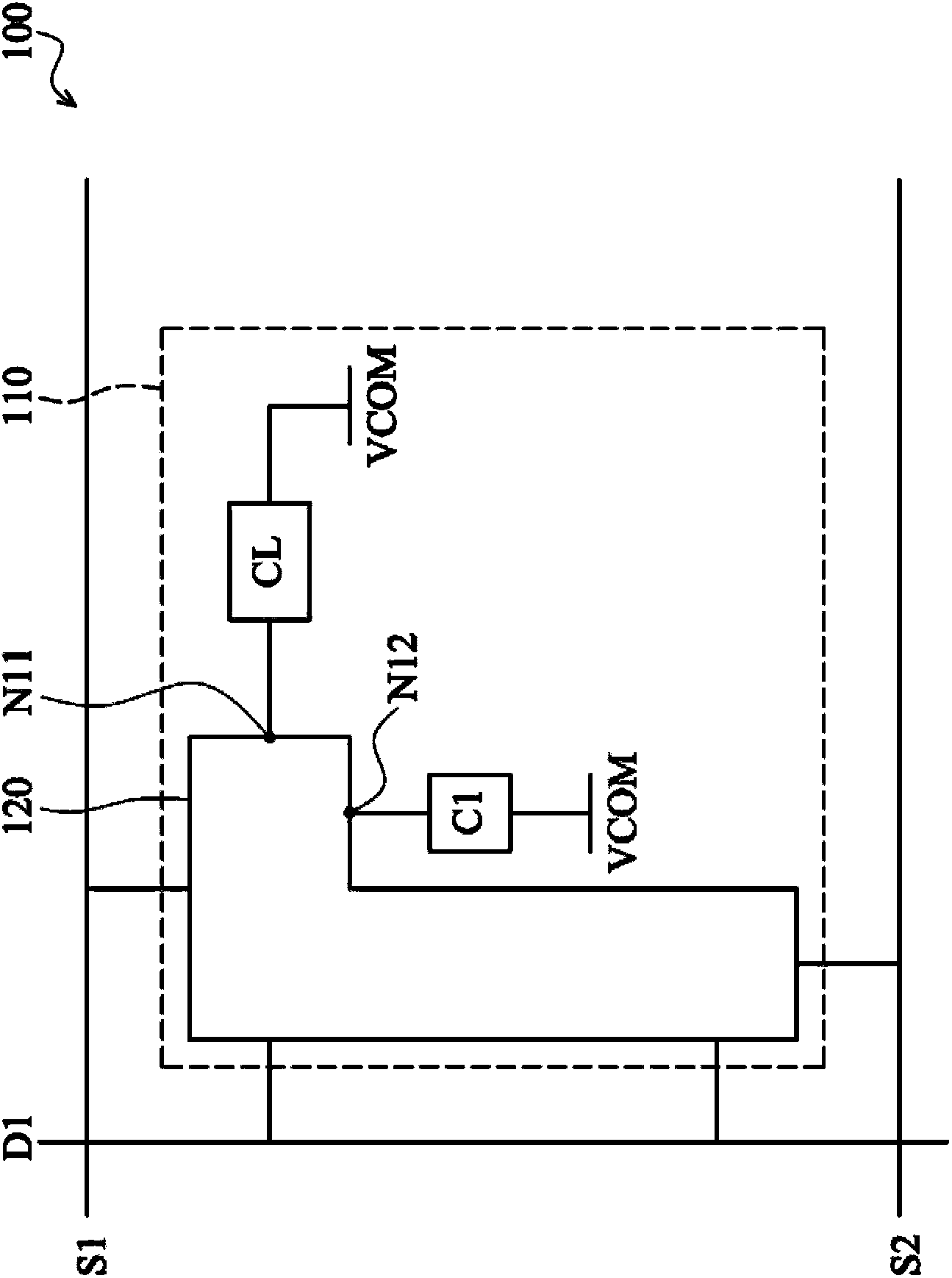

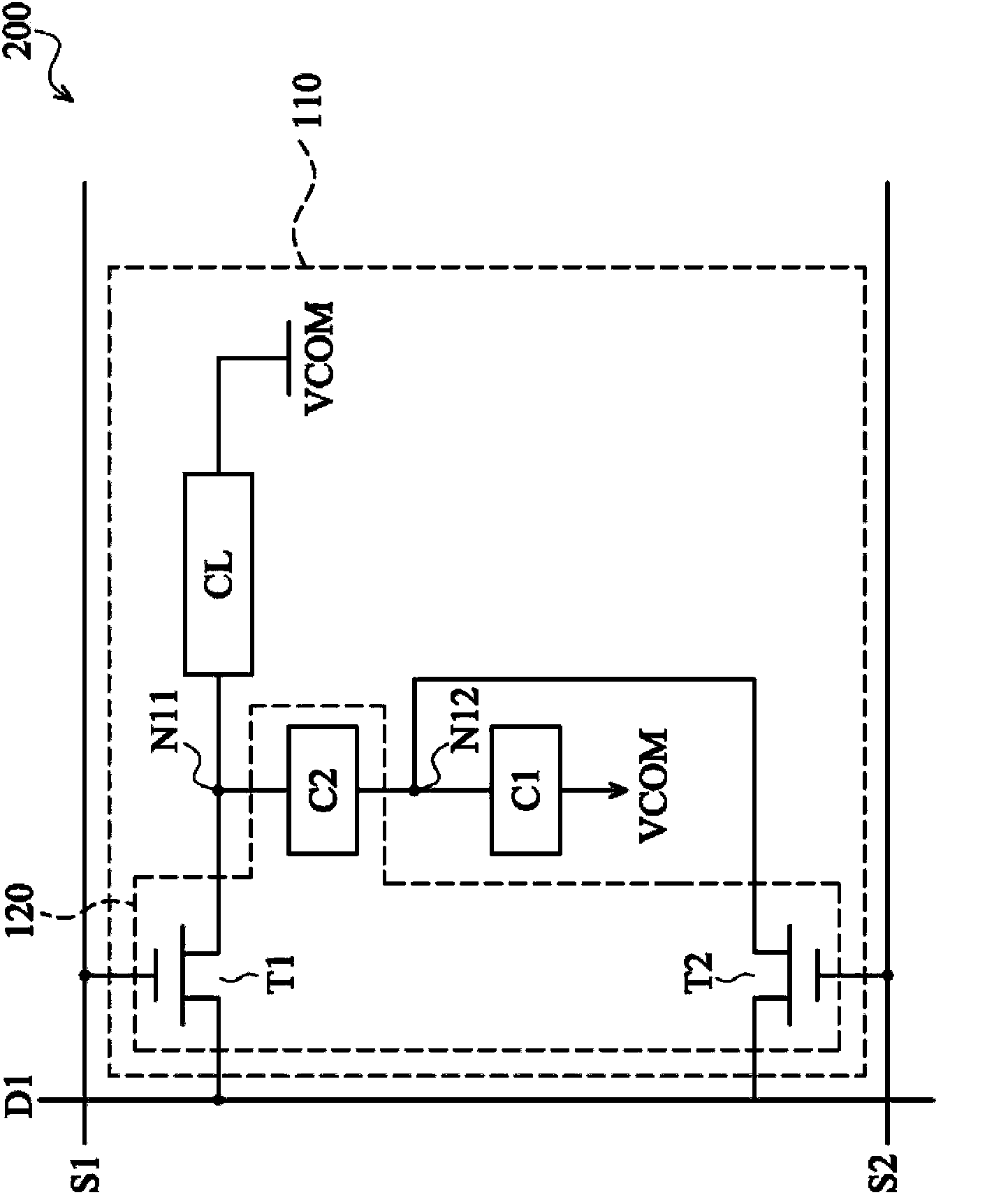

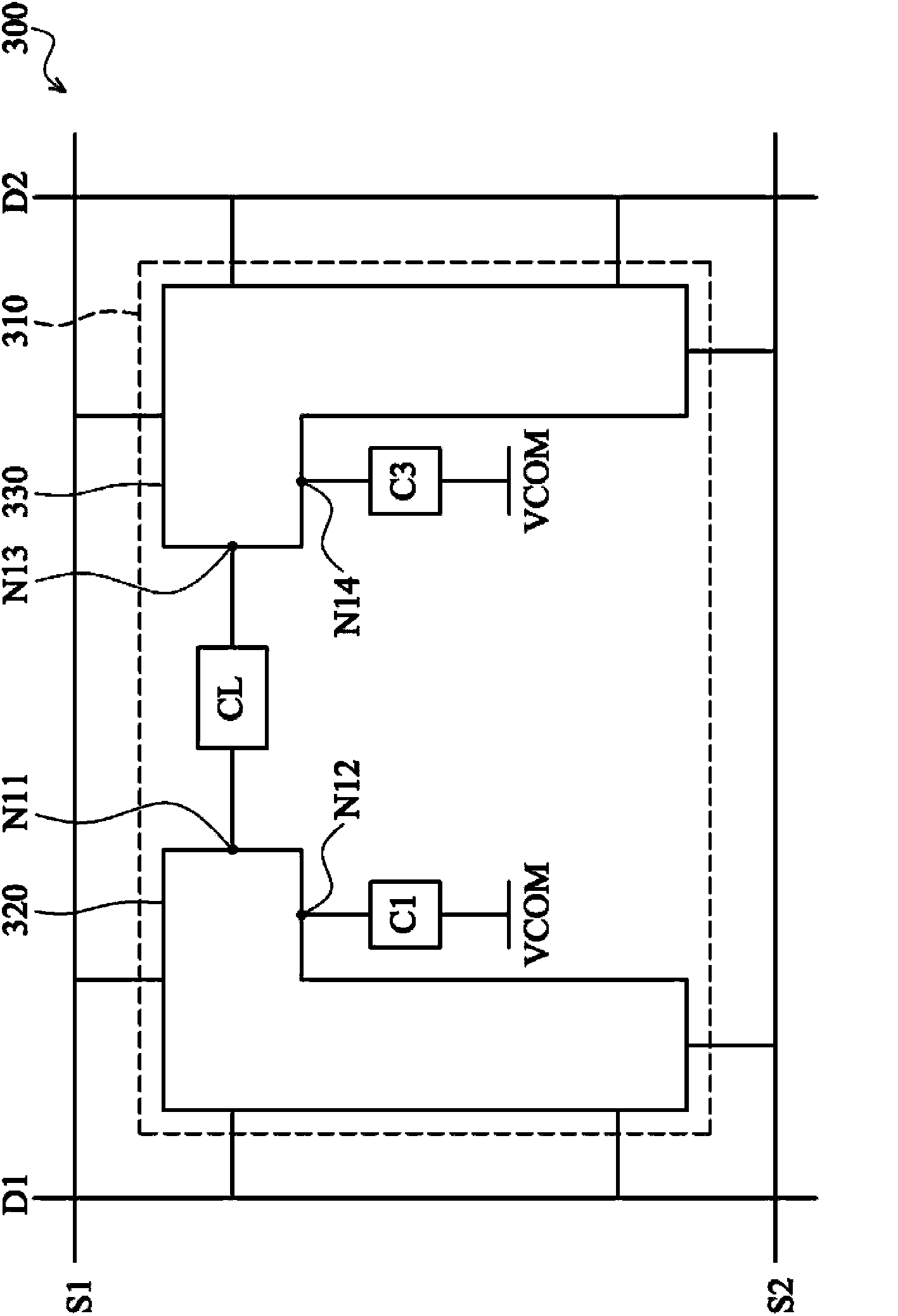

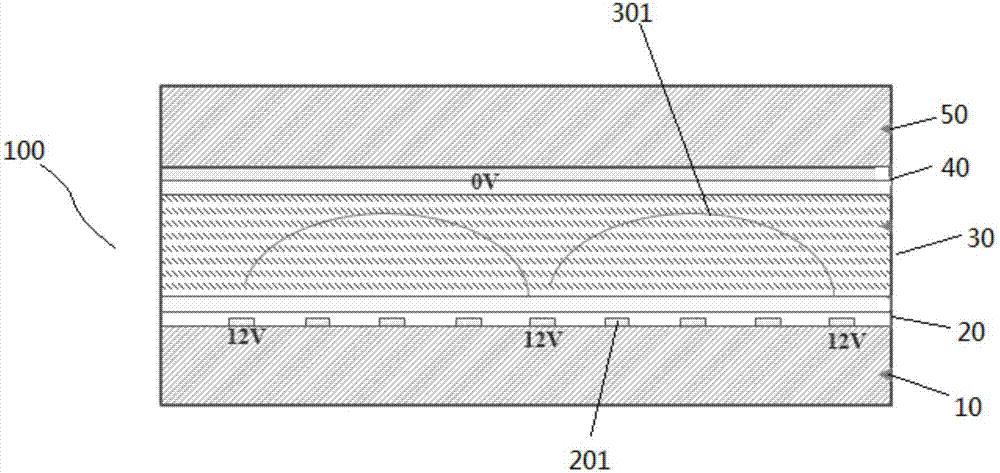

Liquid crystal display panel, LCD display and method for producing same

InactiveCN101290411AStrong penetrating powerIncrease screen brightnessStatic indicating devicesCapacitanceLiquid-crystal display

The invention provides a liquid crystal display panel, a liquid crystal display and a method for driving the same. The liquid crystal display panel comprises a data wire, a first scanning beam, a second scanning beam and a pixel, wherein, the second scanning beam is the next scanning beam adjacent to the first scanning beam; the pixel comprises a first sub-pixel, a second sub-pixel, a third switch, an auxiliary capacitor and a feedback capacitor; moreover, the first sub-pixel and the second sub-pixel are respectively comprise a first switch and a second switch; input ends of the first switch and the second switch are coupled with the data wire, controlled ends of the first switch and the second switch are coupled with the first scanning beam; and an output end of the third switch is coupled with a common electrode through the auxiliary capacitor and is coupled with an output end of the first switch through the feedback capacitor.

Owner:INNOLUX CORP

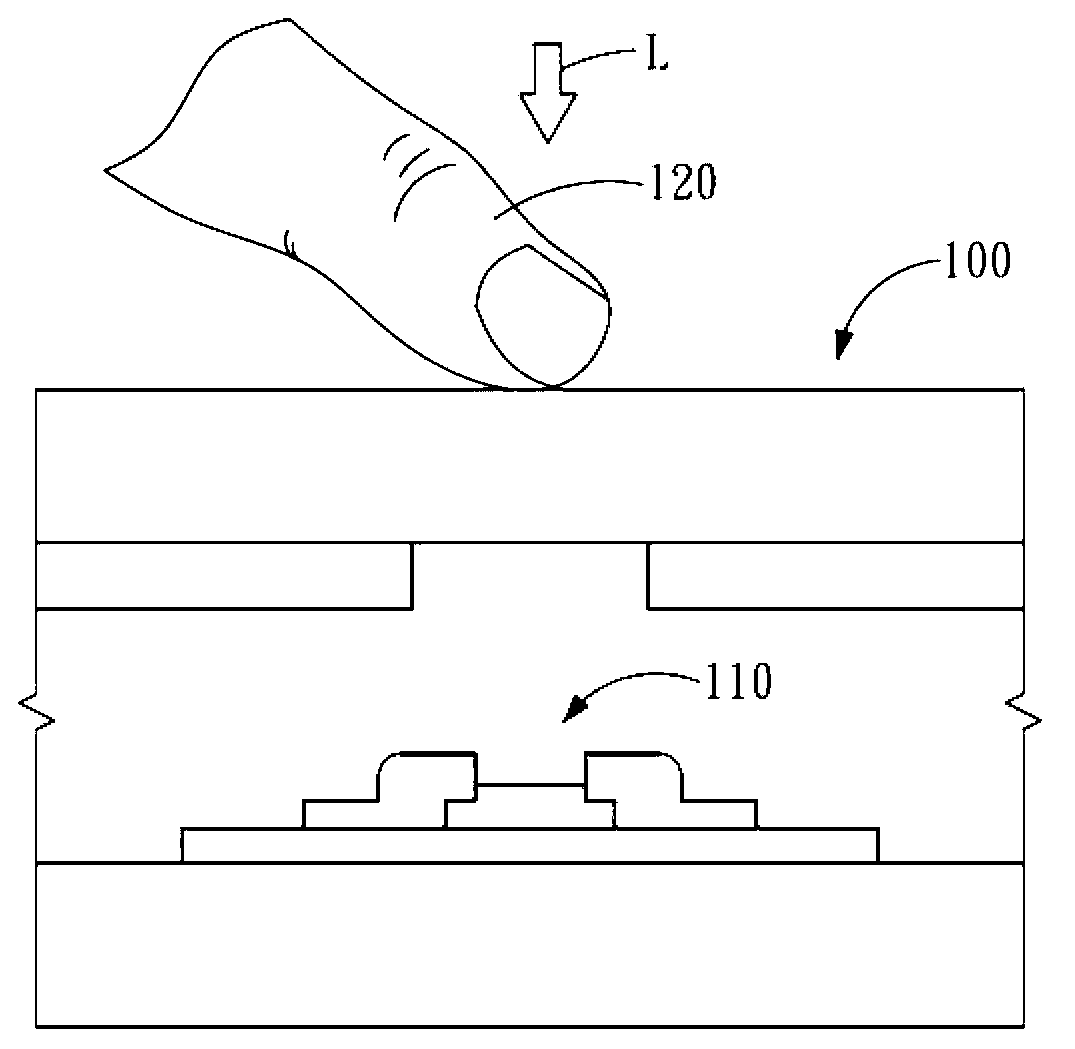

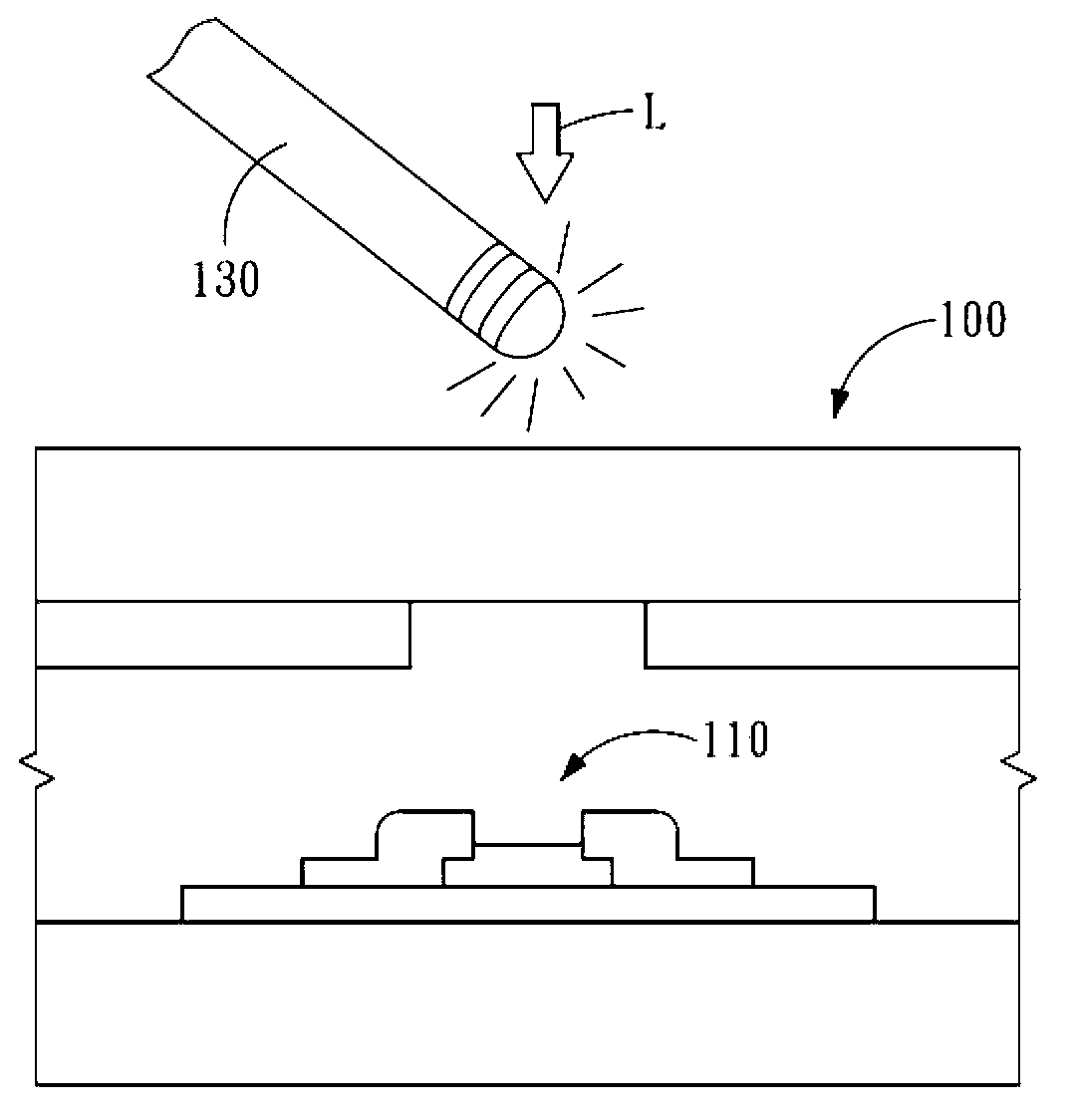

Optical touch control display panel

ActiveCN103150061AReduce signal varianceImprove uniformityInput/output processes for data processingCapacitanceControl signal

The invention provides an optical touch control display panel which comprises a plurality of reset signal lines, a plurality of scanning signal lines and a plurality of optical sensing touch control units. Each optical sensing touch control unit includes an optical sensing element and a storage capacitor. The optical sensing element includes a control end, an input end and a control end, and is used for outputting a sensing signal via an output end to the storage capacitor. The control ends of the optical sensing elements along a first direction are respectively connected to the different scanning signal lines and are used for receiving a control signal. The optical sensing elements along a second direction are divided into a plurality of groups, wherein the input ends of the optical sensing elements of each group are respectively connected to the different reset signal lines so that a reset signal is received by each group. Each optical sensing element outputs, based on the control signal, a charging signal corresponding to the reset signal to the storage capacitor so that voltages of the storage capacitor is reset.

Owner:AU OPTRONICS CORP

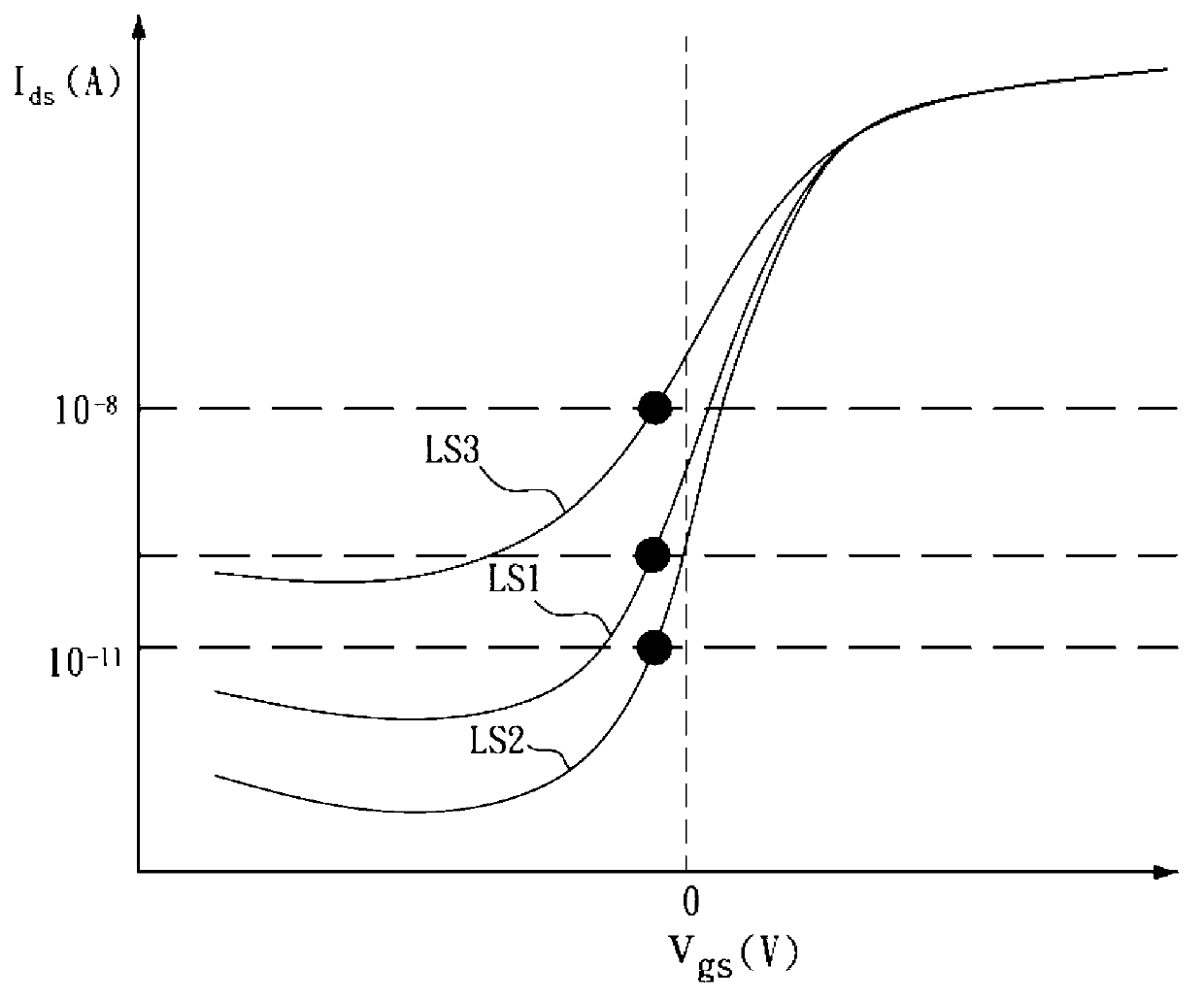

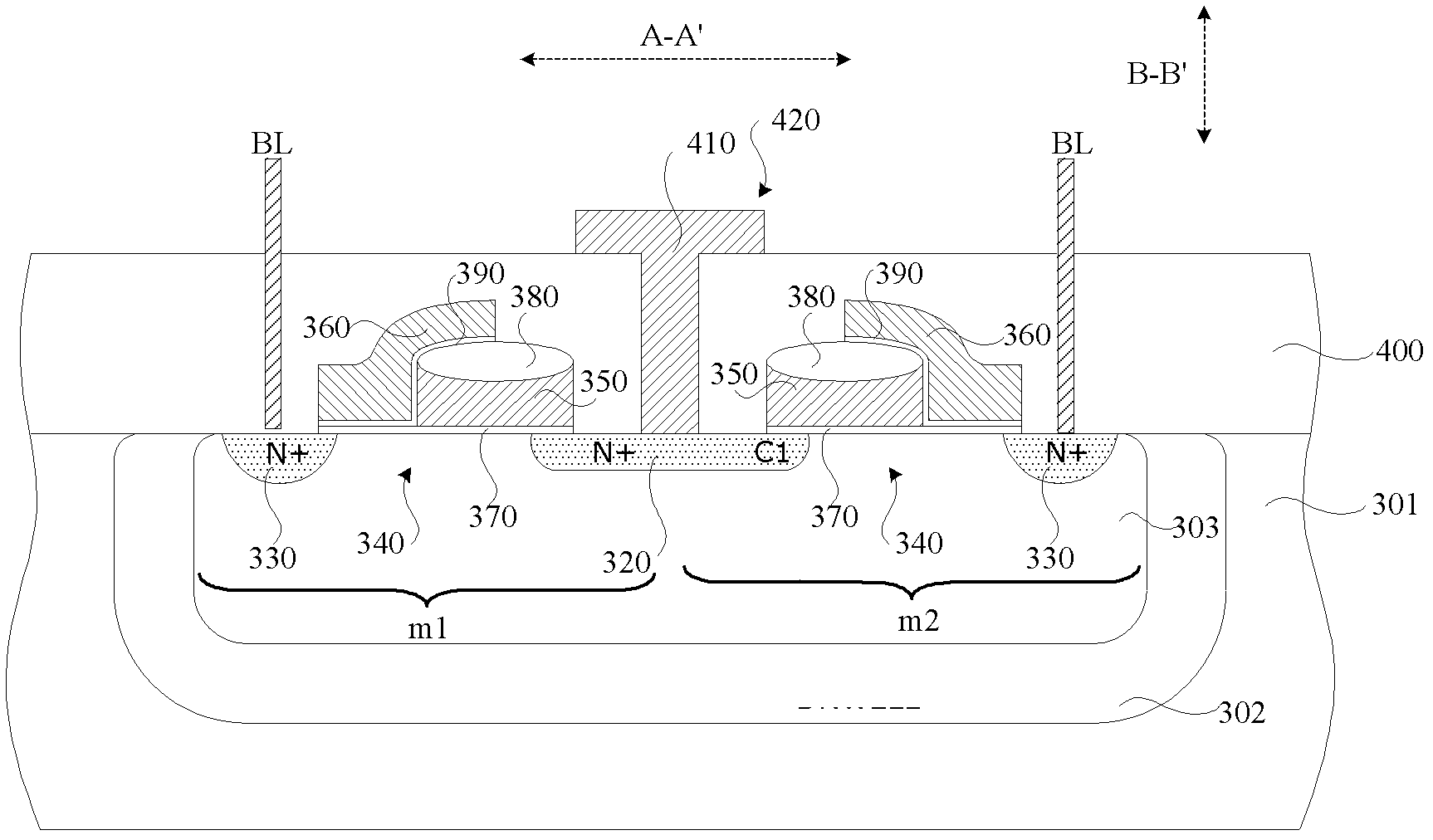

Splitting grid memory cell and operation method thereof

ActiveCN102437161ASmall sizeReduce the erase voltageSolid-state devicesRead-only memoriesDiffusionSemiconductor

A splitting grid memory cell and an operation method thereof are disclosed. The memory cell comprises: a semiconductor substrate, a floating grid, a control grid and a selection grid, wherein a first doped region, a second doped region and a third doped region are successively formed on the semiconductor substrate; a first diffusion region and a second diffusion region are formed in the third doped region; the floating grid is formed on the semiconductor substrate between the first diffusion region and the second diffusion region; a first side of the floating grid is overlapped with parts of the first diffusion region; the control grid is formed on the semiconductor substrate between a second side of the floating grid and the second diffusion region; an insulating oxide layer is formed between the control grid and the second side of the floating grid; the selection grid is formed on the semiconductor substrate in the first diffusion region; a doped type of the first doped region is the same with the doped type of the third doped region and is opposite to the doped type of the second doped region. By using the memory cell and the method of the invention, a size of the memory cell can be effectively reduced; a quality of the memory cell can be improved and manufacturing costs can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

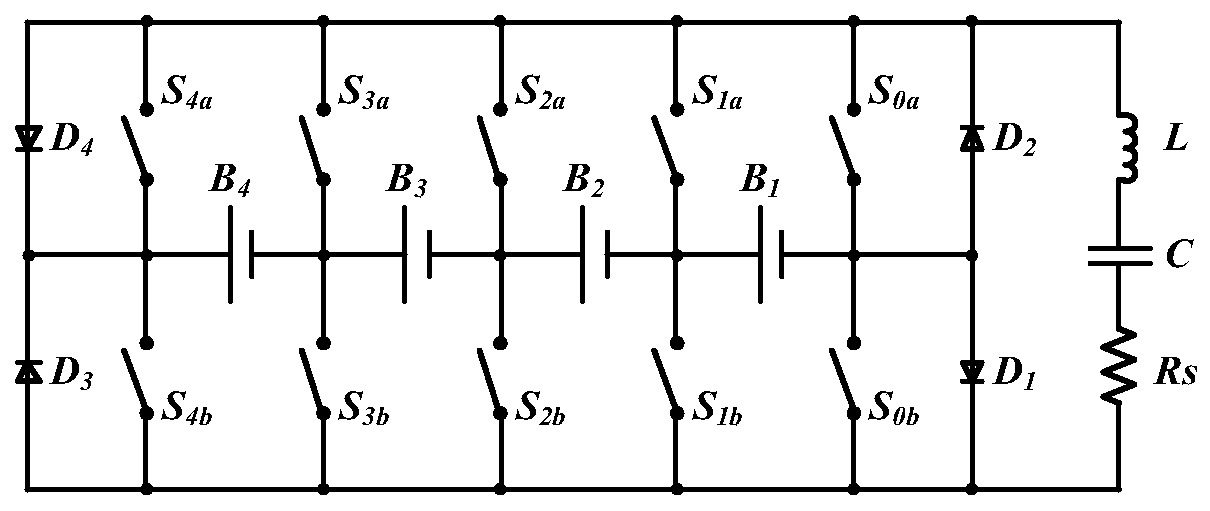

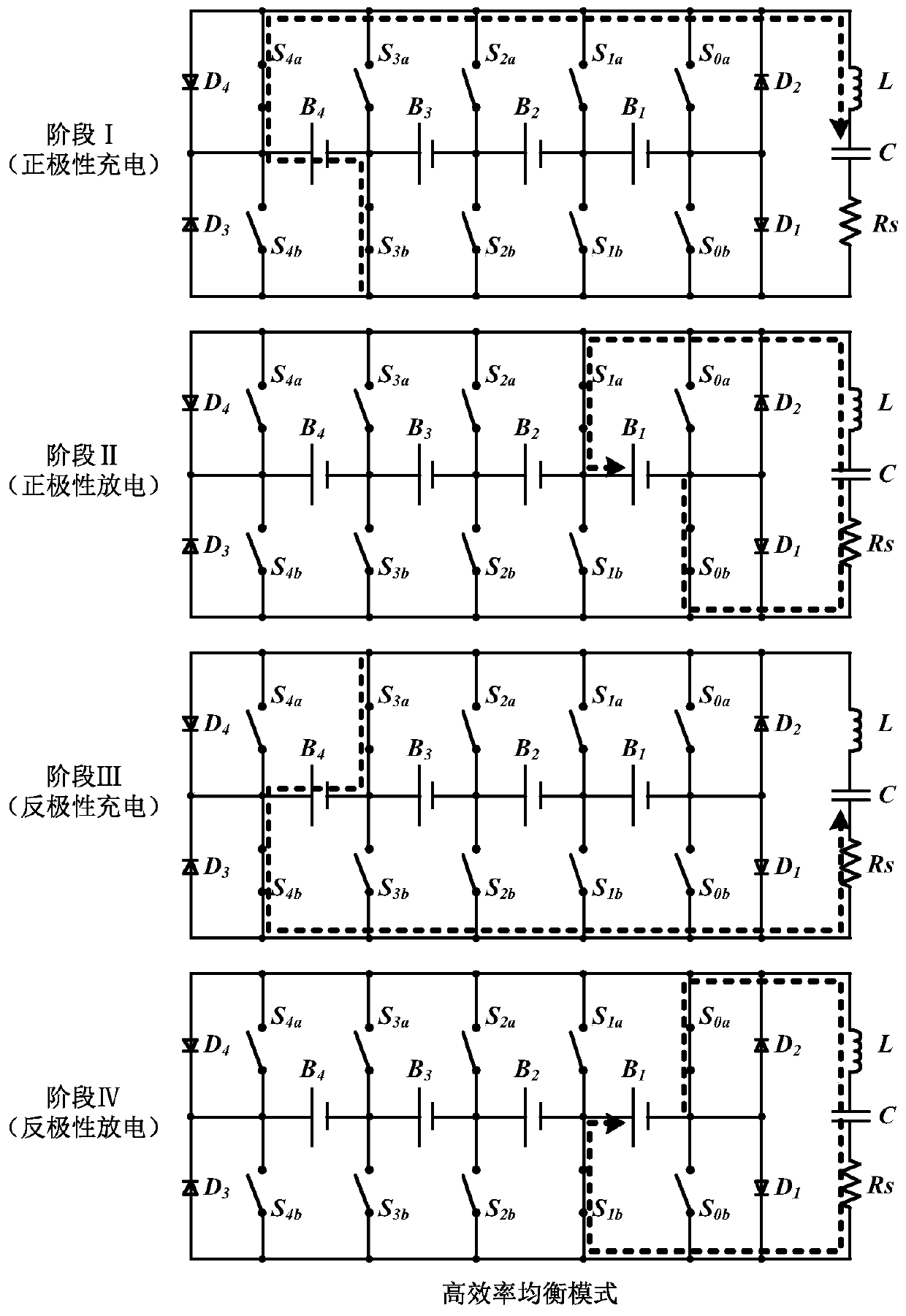

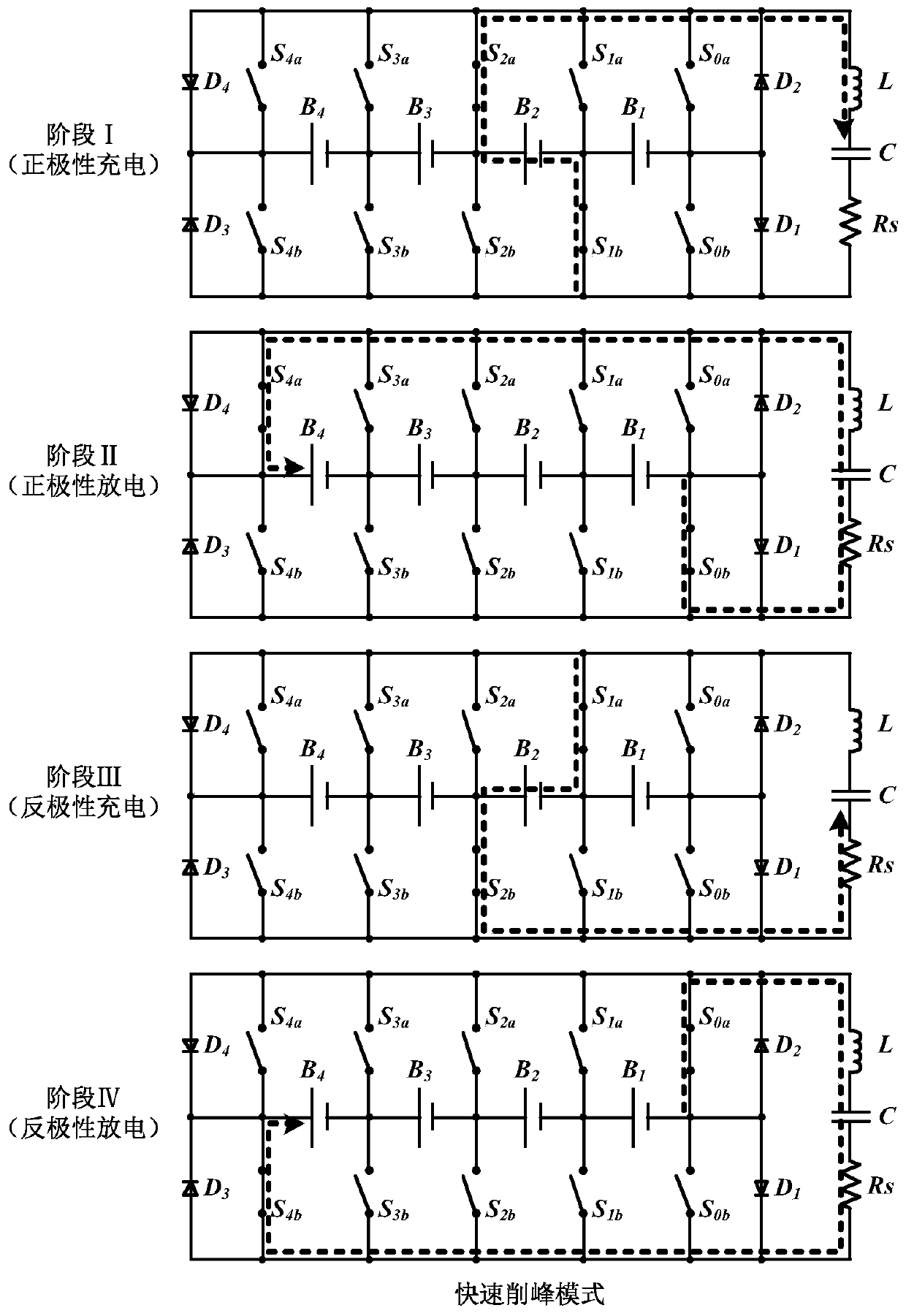

LC bipolar resonant-based Cells-to-Cells equalization circuit and control method thereof

PendingCN110034597APrevent overchargingIncrease capacityCharge equalisation circuitSecondary cells charging/dischargingMicrocontrollerCapacitance

The invention discloses an LC bipolar resonant-based Cells-to-Cells equalization circuit and a control method thereof. During the equalization process, a microcontroller outputs four paths of rectangular wave driving signal of which frequencies are half of an LC resonant frequency, the phase difference is 90 degree and the duty ratio is 25% so that an equalization source unit and an equalization target unit are bipolarly and circularly connected to an LC resonant branch by a switch network, the LC resonant branch circularly works in states of positive polarity charging, positive polarity discharging, reverse polarity charging and reverse polarity discharging, and zero-current switch equalization of which energy is transmitted from the source unit to the equalization target unit is achieved. By the equalization circuit, equivalent release of a residual voltage of a resonant capacity C during the equalization process is achieved, the equalization source unit and the equalization target unit both can be adjacent arbitrary sections of Cells, the equalization circuit has the advantages of high power density, high equalization efficiency and control flexibility, and modular manufacturingis easy.

Owner:SOUTH CHINA UNIV OF TECH

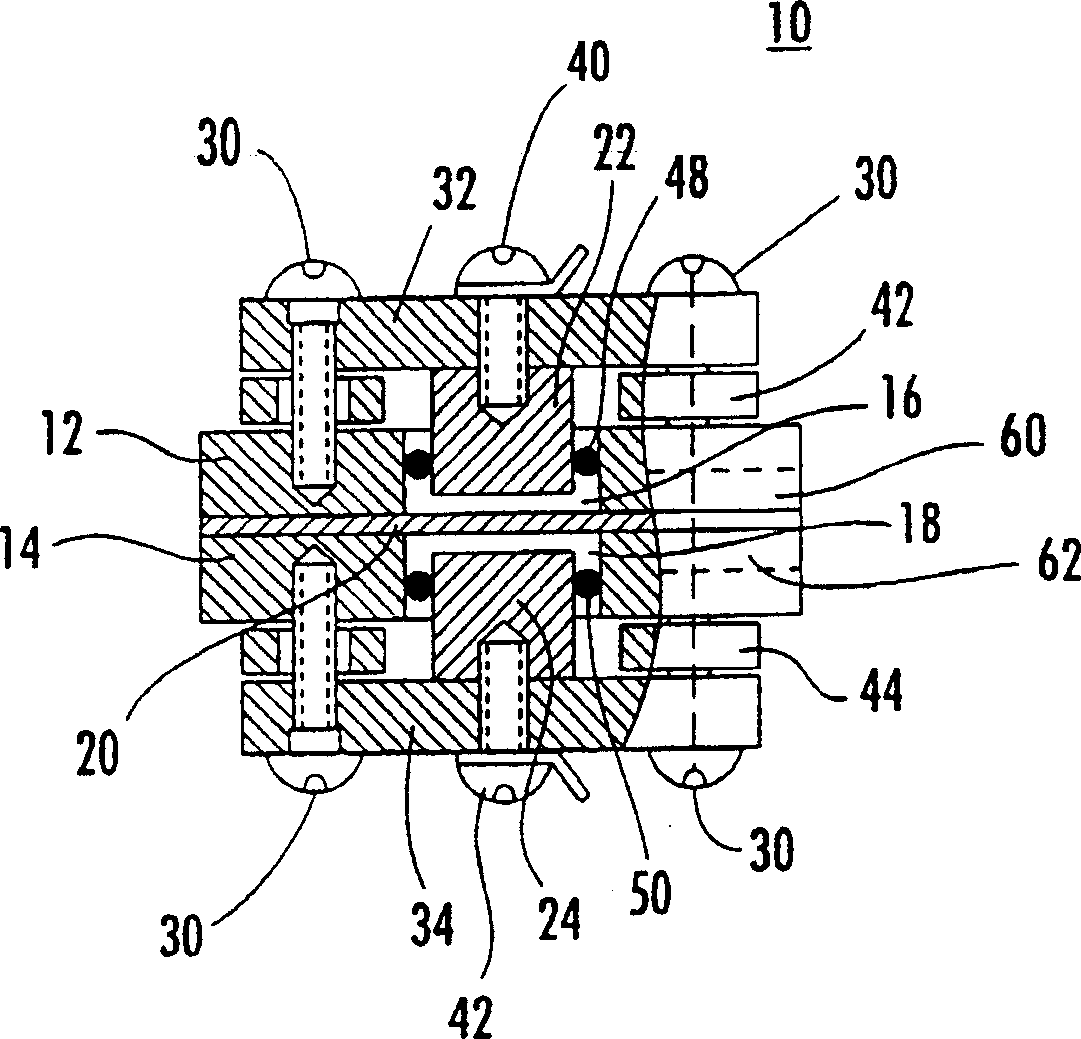

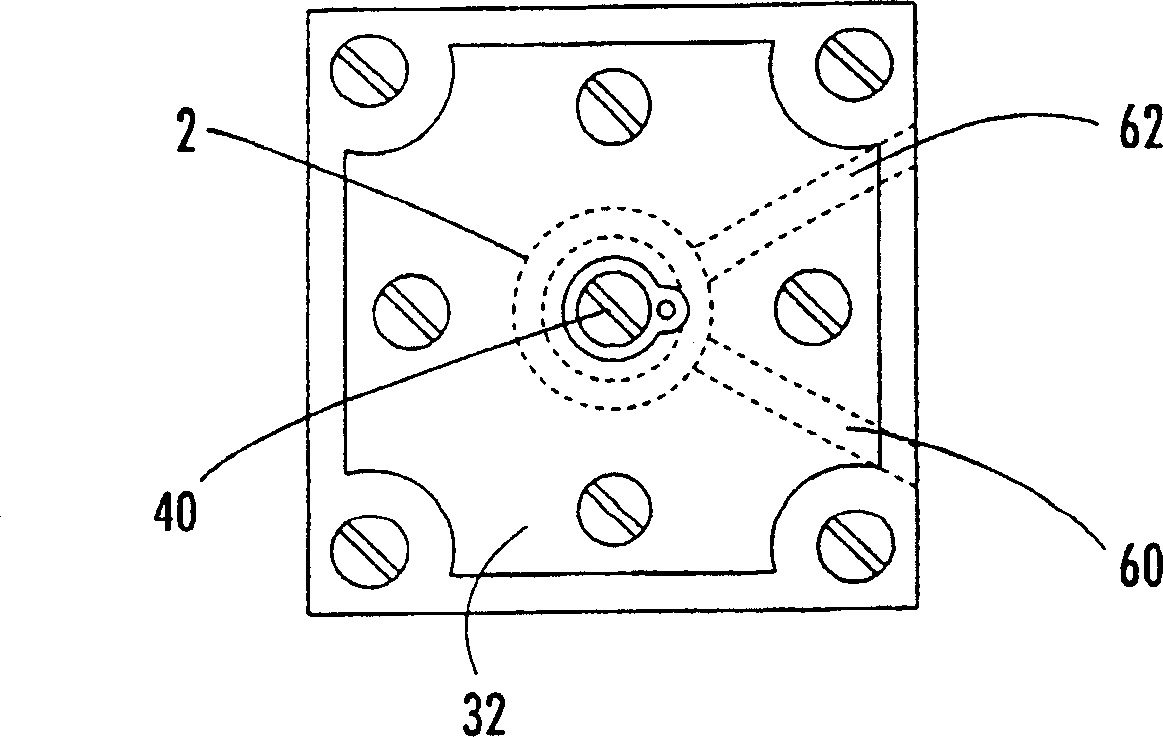

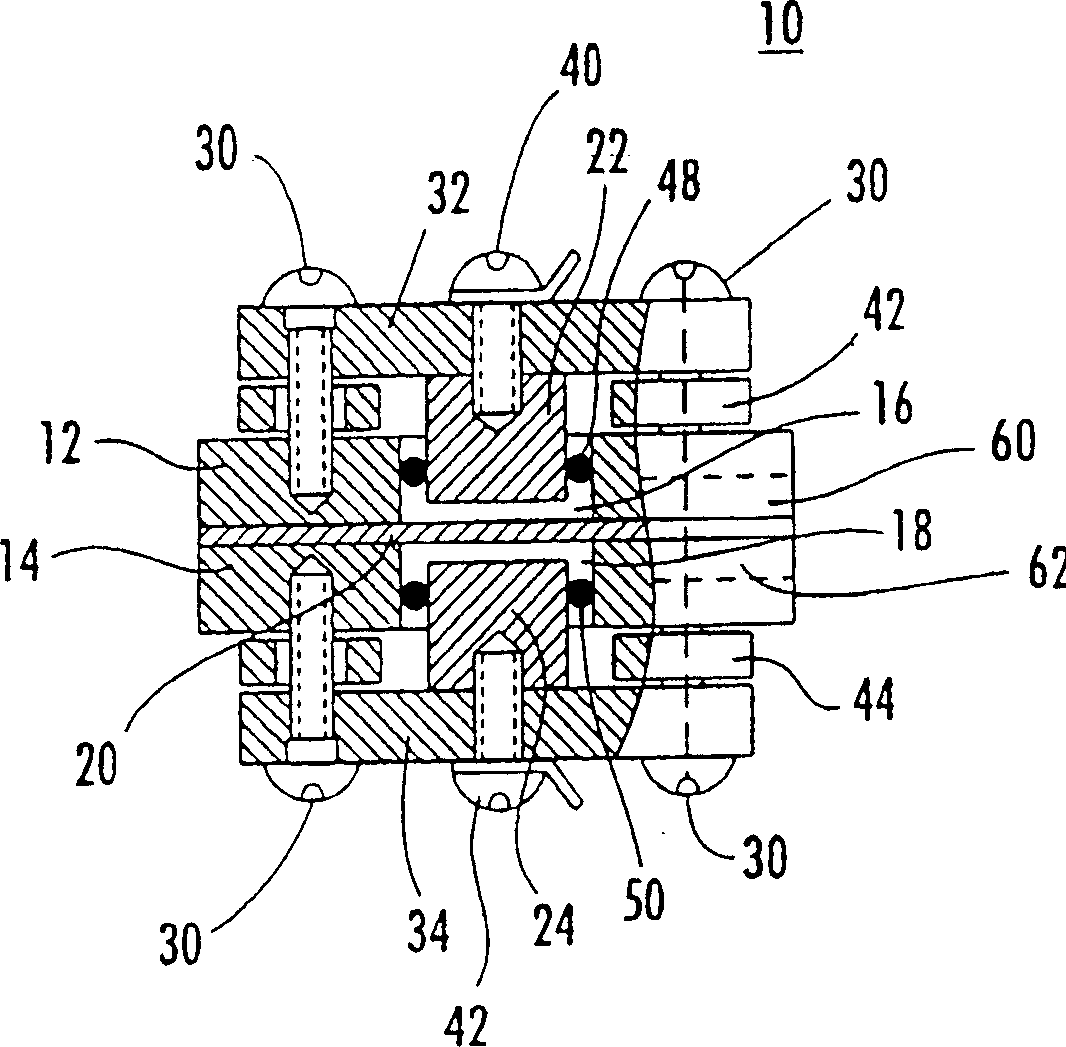

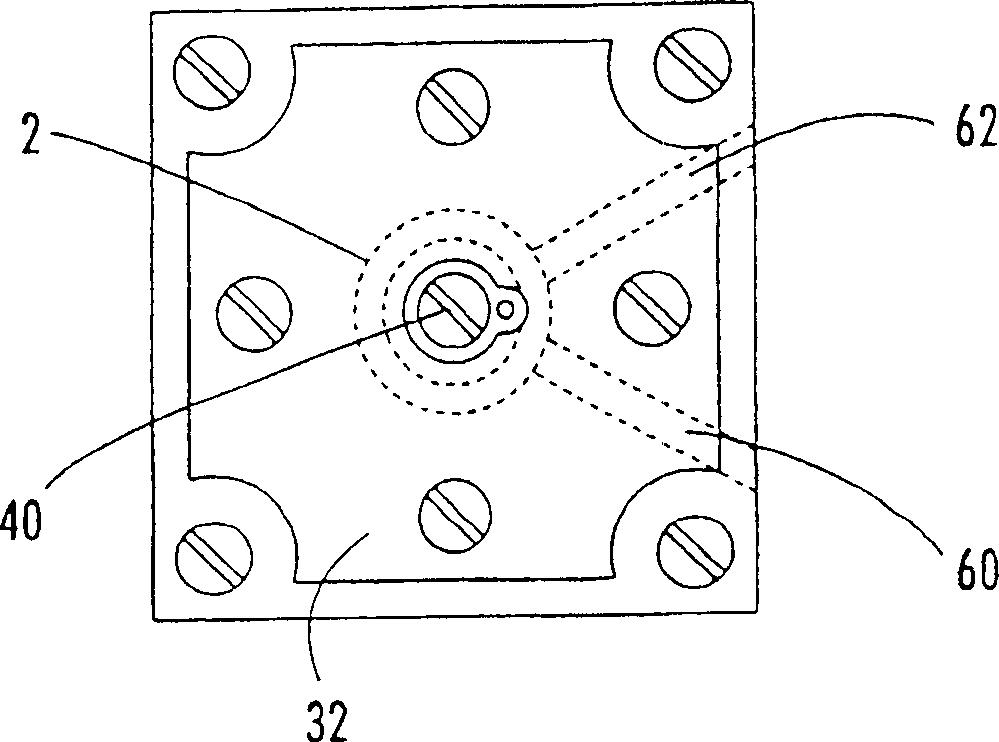

High sensitivity pressure sensor with long term stability

InactiveCN1511252AReduce voltage differenceCapacitance difference increasesPressure difference measurement between multiple valvesFluid pressure measurement using capacitance variationForce sensorCapacitor

A high sensitivity pressure sensor with long term stability including a housing with first and second chambers, a membrane (20) separating the first and second chambers, a first electrode located in the first chamber (16) and spaced from one side of the membrane forming a first capacitor therewith, and a second electrode located in the second chamber (18) and spaced from an opposite side of the membrane forming a second capacitor therewith.

Owner:PANAMETRICS

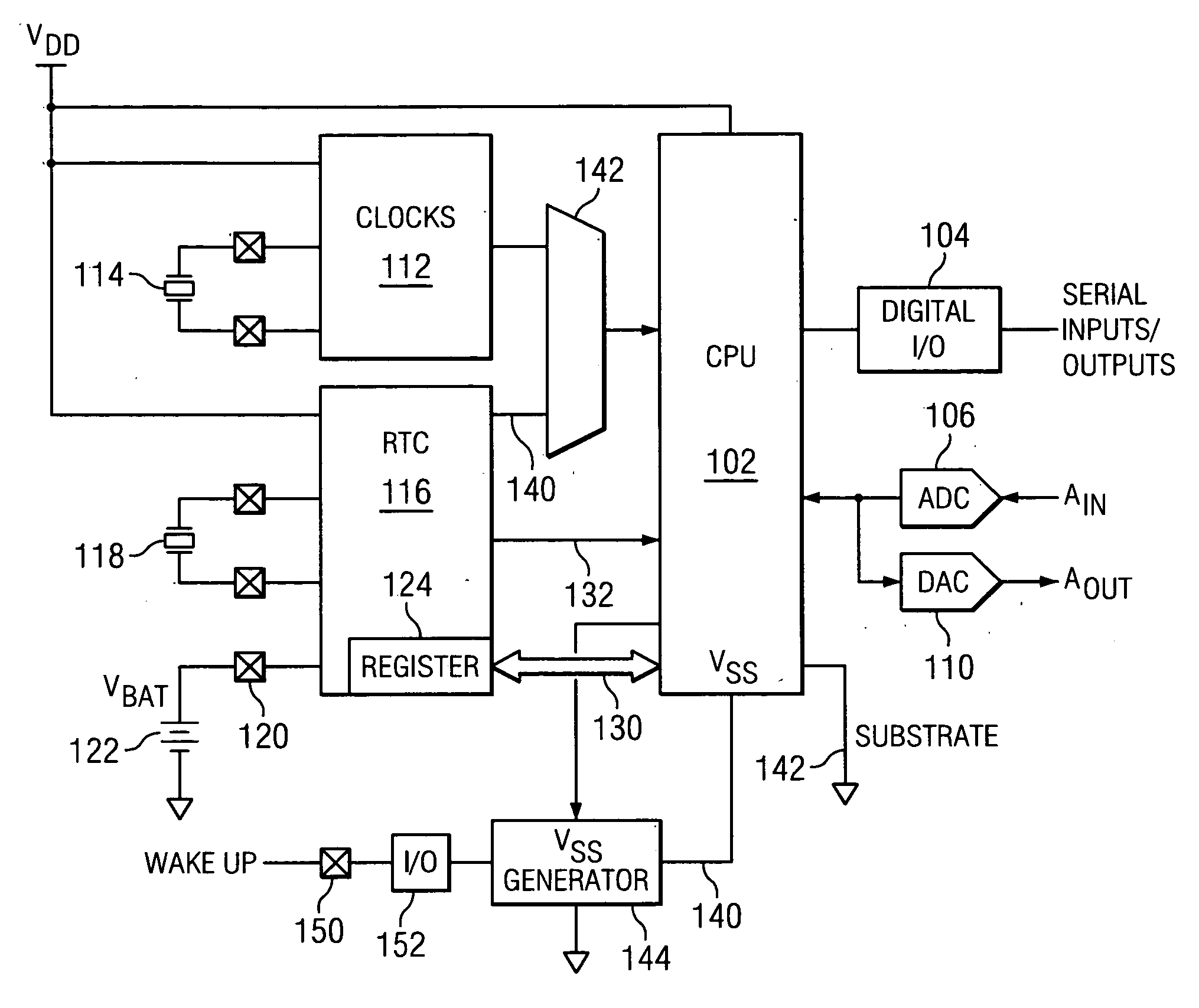

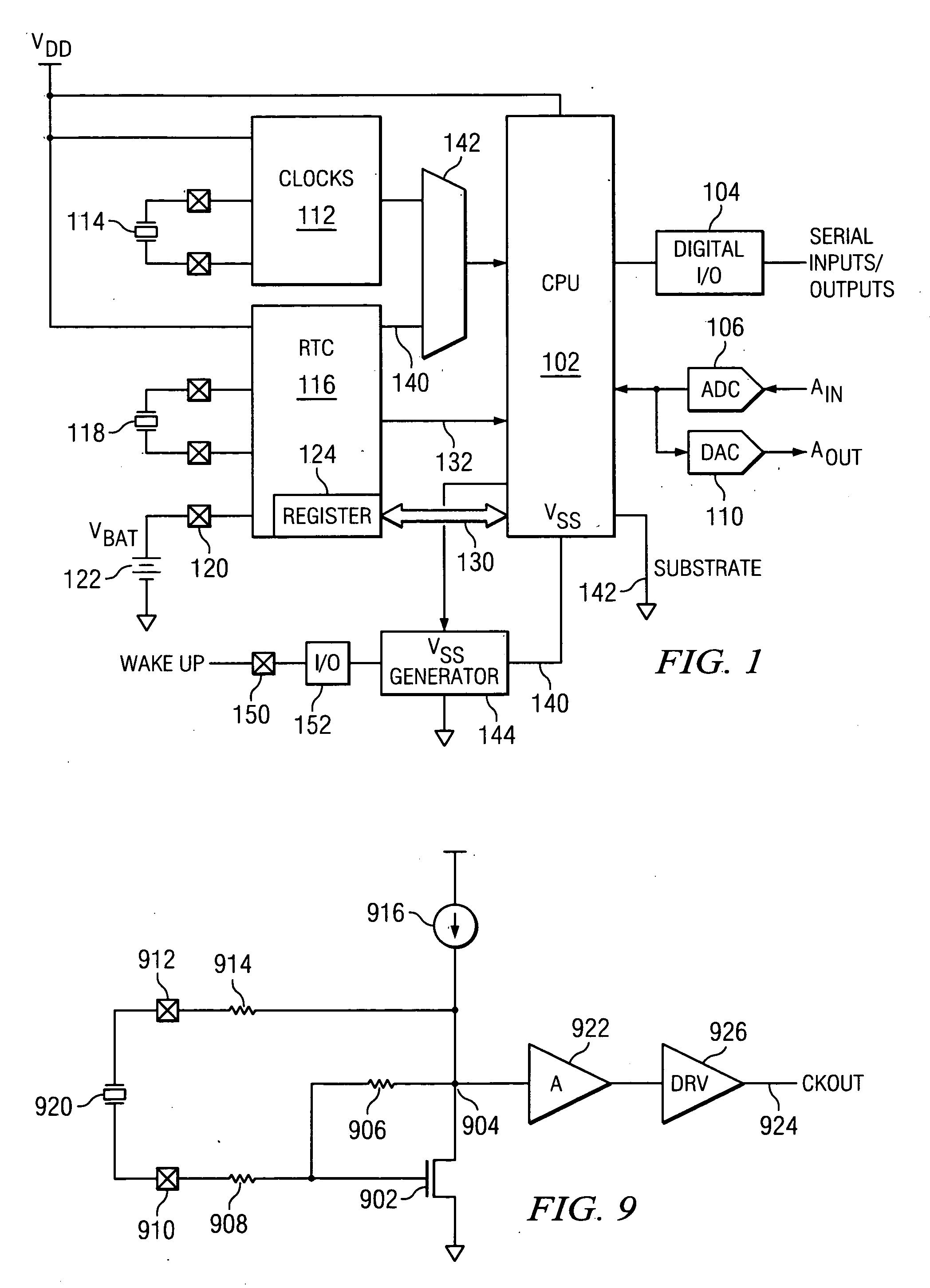

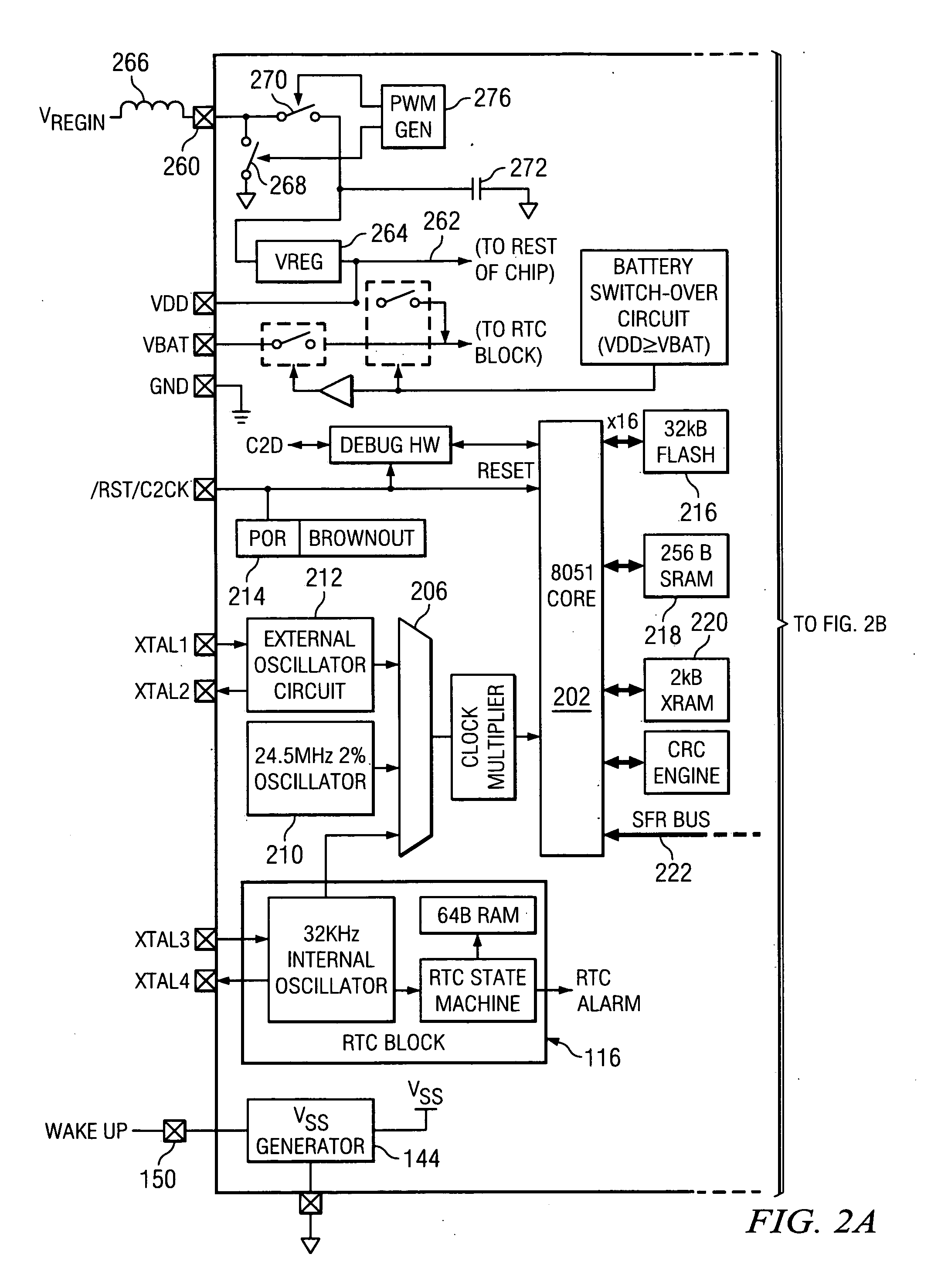

MCU with low power mode of operation

ActiveUS20070168681A1Raise the voltage differenceEnergy efficient ICTDigital data processing detailsPower modeVoltage generator

A low power system is disclosed for working in conjunction with a digital circuit that is disposed between positive and negative terminals. The system includes an internal voltage generator for increasing, for at least a first portion of the digital circuit, a voltage difference between the at least a first portion of the digital circuit and the voltage on at least one of the positive and negative terminals during a low power mode of operation. This allows the voltage across the at least first portion of the digital circuit to be less than the full voltage across the positive and negative terminals.

Owner:SILICON LAB INC

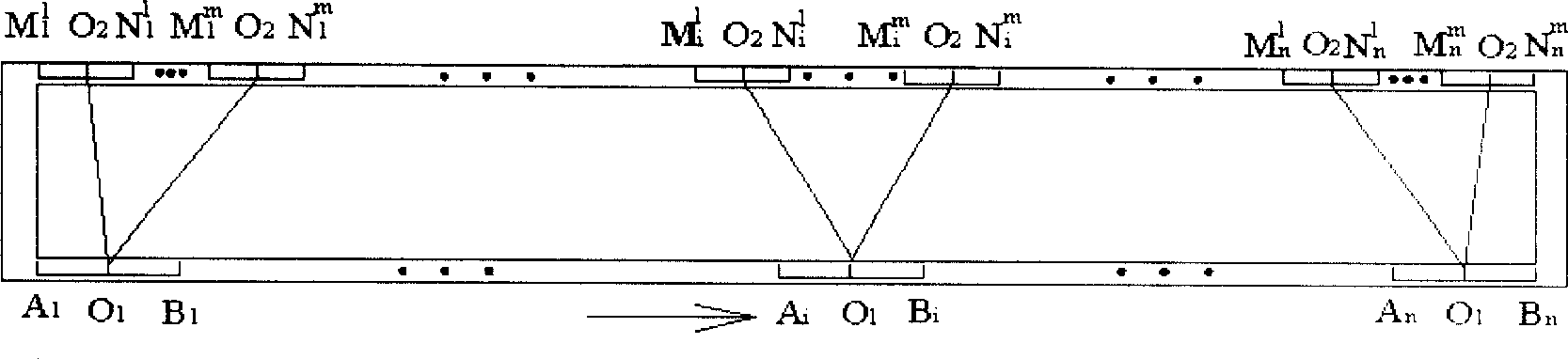

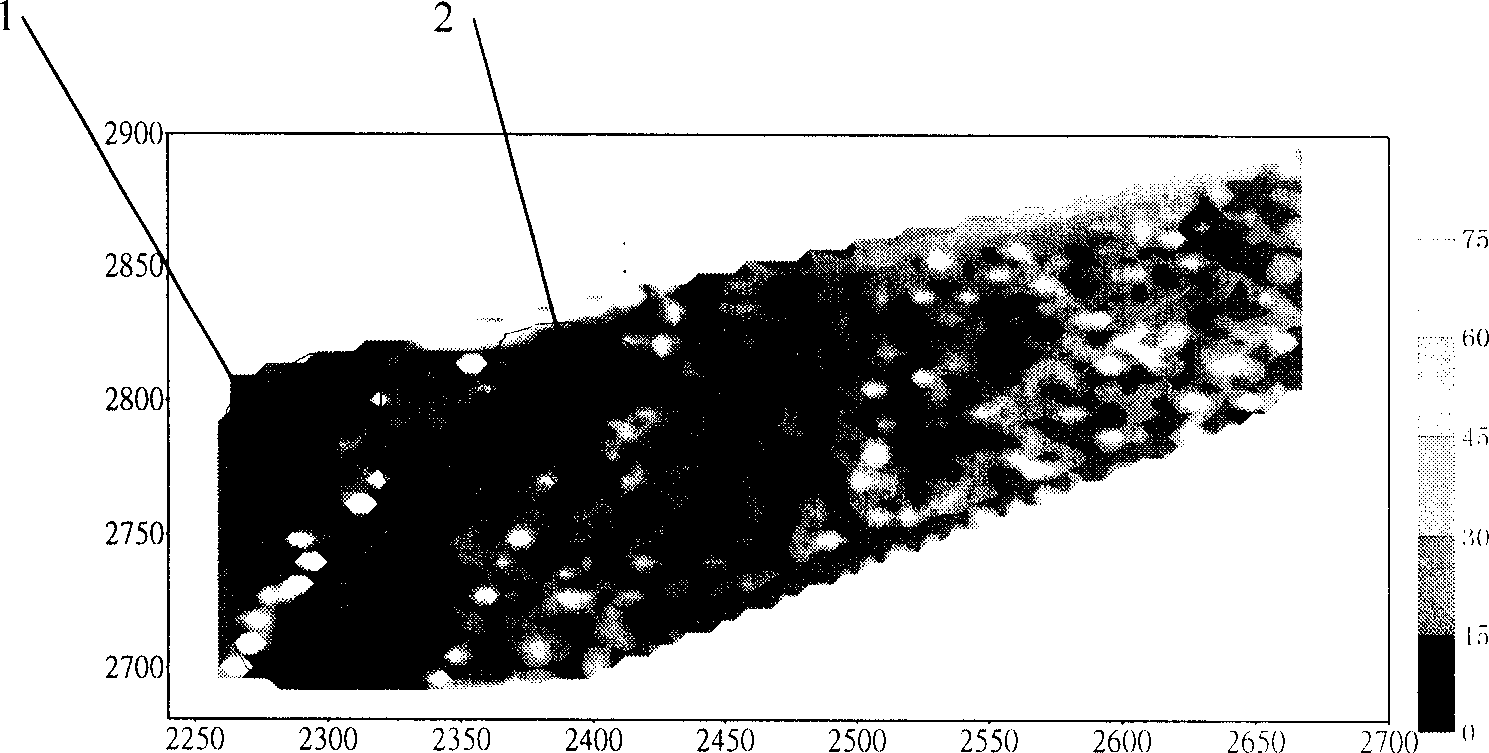

Bipolar-bipolar detection method for mine working face floor strata

The invention discloses a dual-pole-dual-pole detecting method of mine working surface bottom plate terrane, which arranges the power electrodes A and B into one channel, while their midpoint is 01; powers the AB and measure the current I between AB; arranges the measuring electrodes M and N in another channel while their midpoint is 02; measures the voltage ªñU between them; and fixes AB to keep the MN length; moves MN distantly; therefore, the connecting line of 01 and 02 can scan a certain area to form a sector; keeps the AB length to move it to another position and repeat the operation; therefore, said connecting line can scan a certain area to form another sector; moves to the whole channel to complete the measurement. According to measured data, the invention uses resistance CT method to reversely calculate and process image treatment to accurately set the water content and structure of working surface bottom plate terrance. The invention has the advantages as strong detecting signal, less safe hidden, and high detecting accuracy.

Owner:SHANDONG UNIV OF SCI & TECH

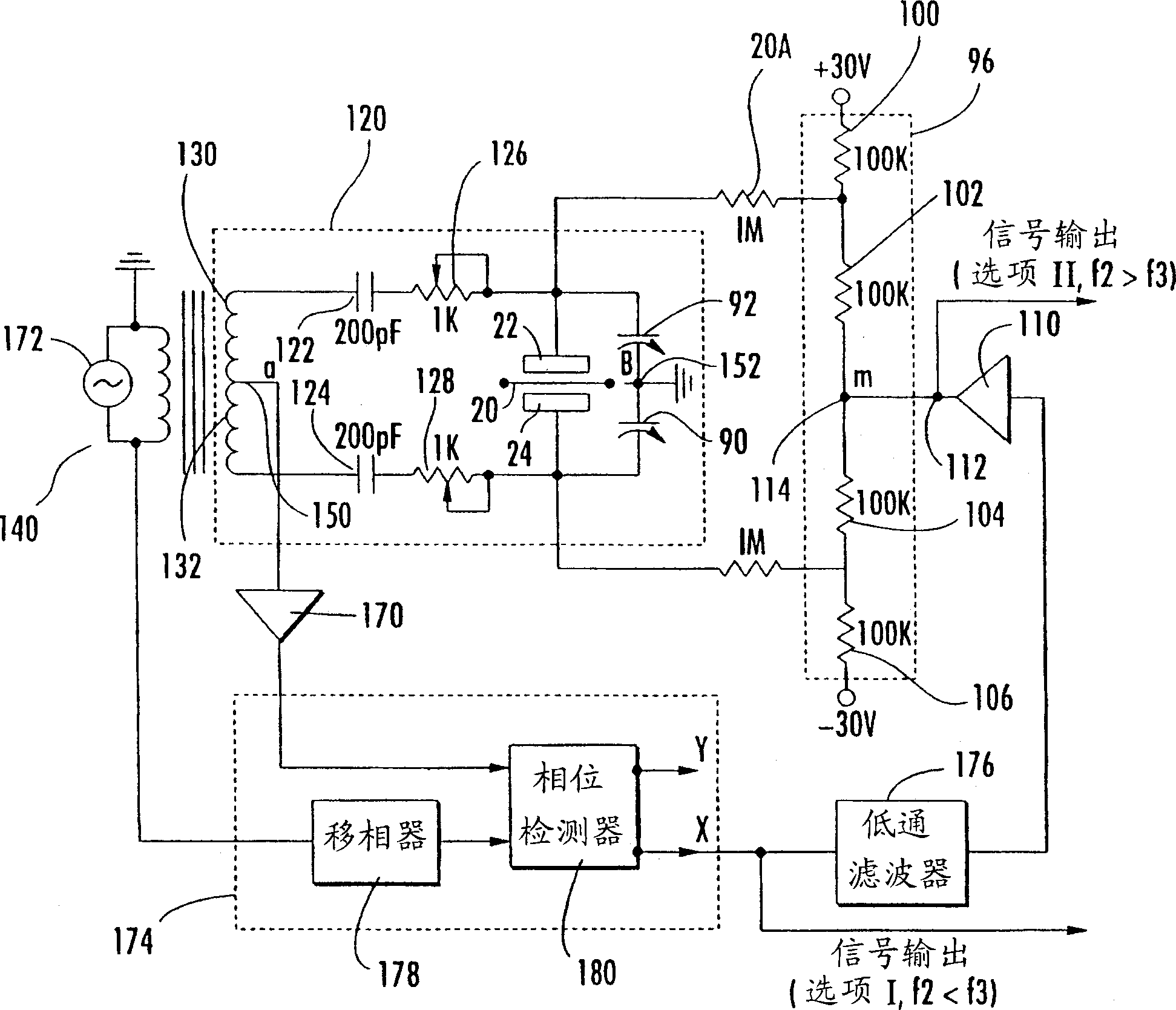

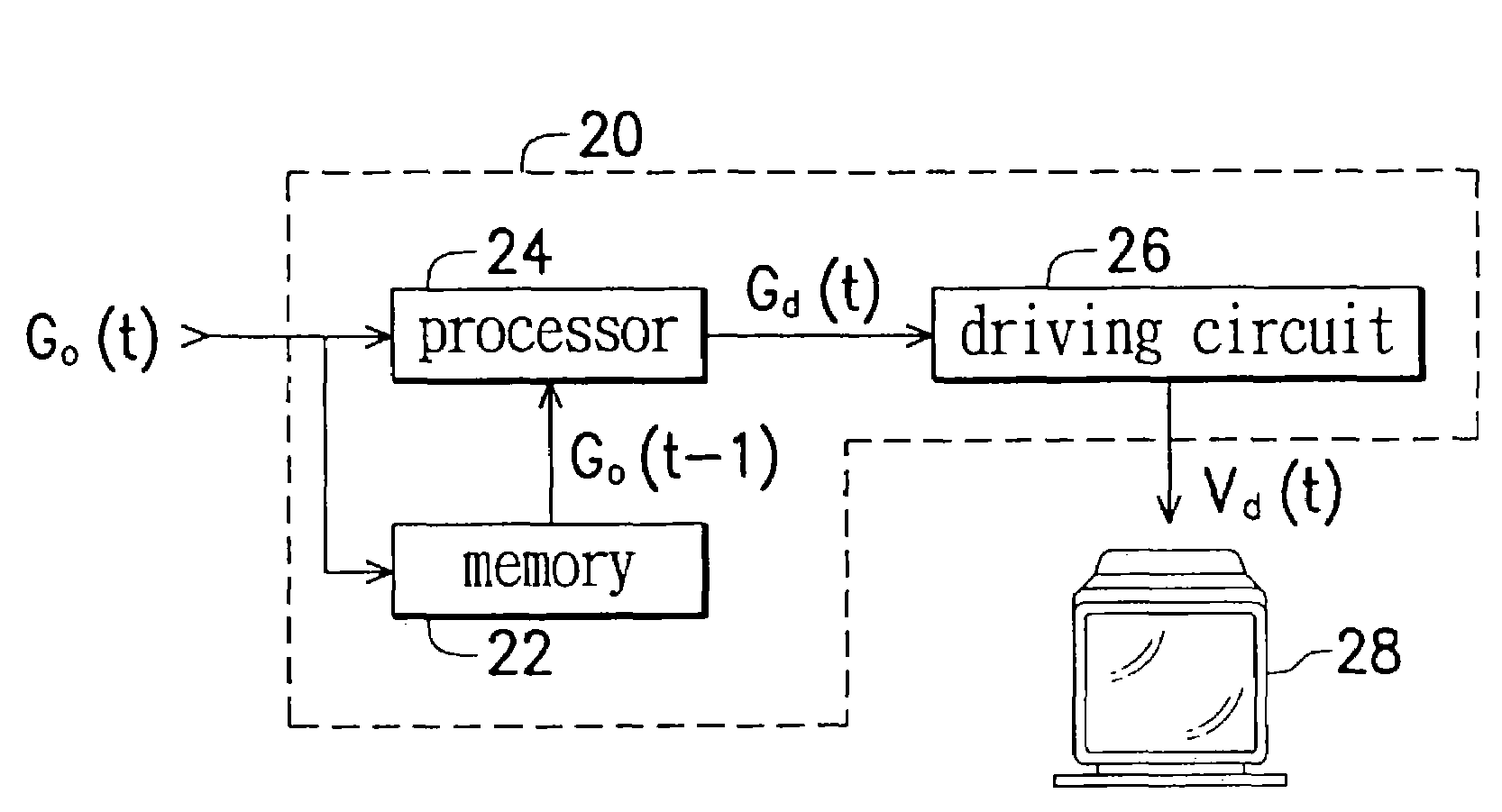

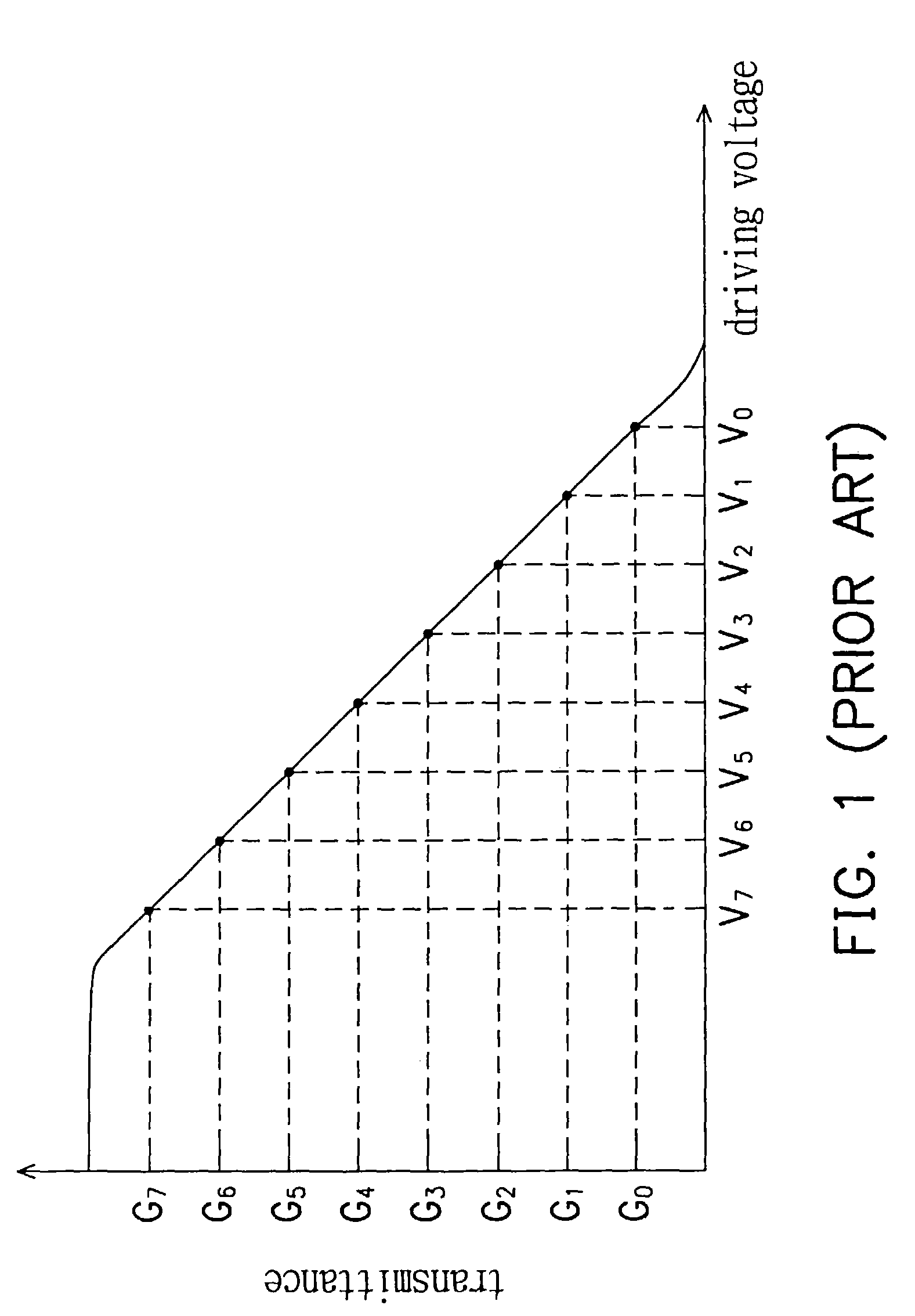

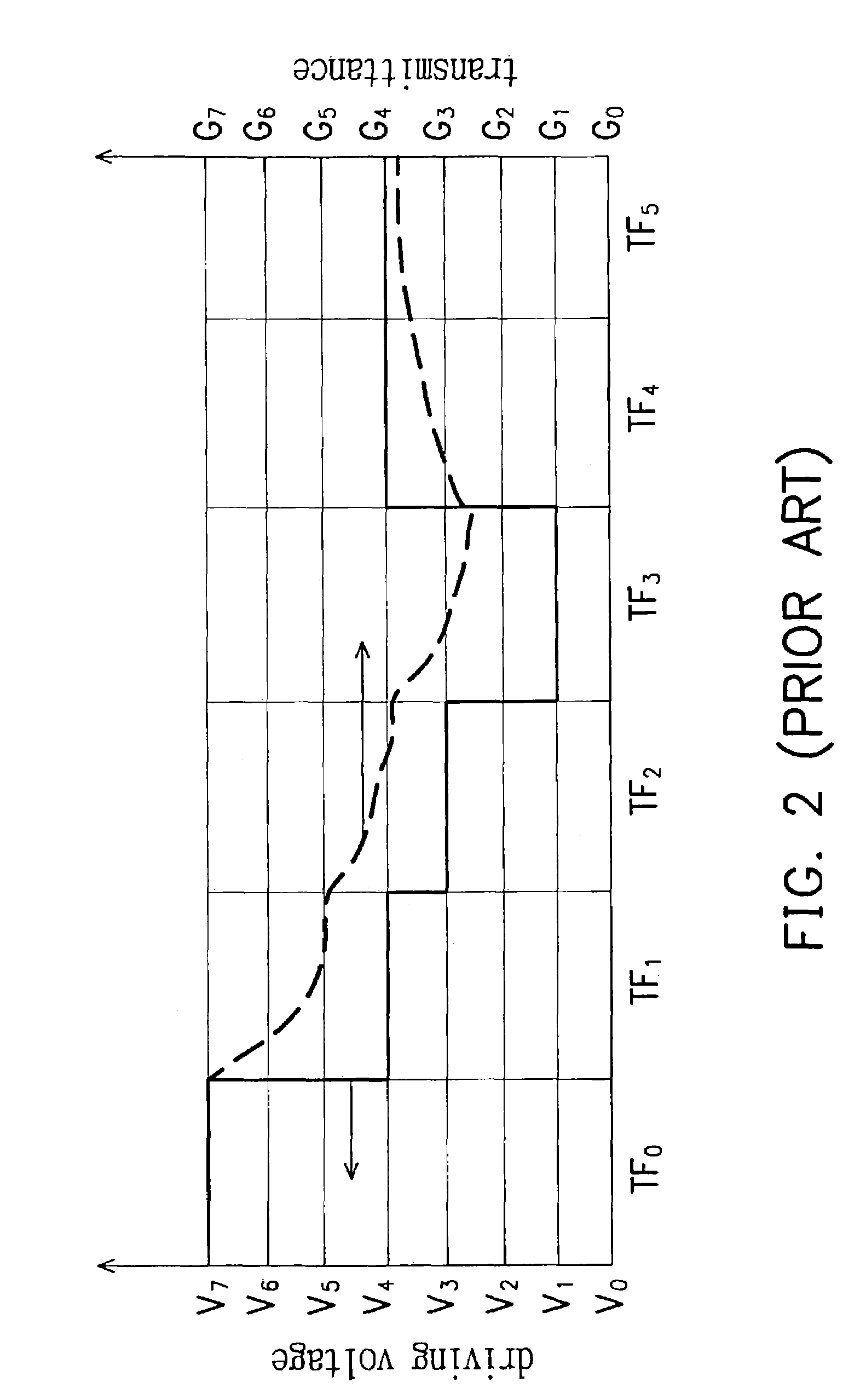

Method and apparatus for dynamic gray level switching

InactiveUS7248241B2High response rateRaise the voltage differenceStatic indicating devicesGray levelDisplay device

A method and apparatus for gray level dynamic switching. The method is applied to driving a display with at least one pixel. In the method of the present invention, a gray level sequence SG is provided. SG sequentially represents two or more desired gray levels Go(1), . . . , Go(T) of the pixel at consecutive time frames 1, . . . , T and comprises a current gray level Go(t) and a previous gray level Go(t−1) corresponding to time frames t and t−1, respectively. Then, the pixel is driven with an optimized driving force Vd(t) to change the pixel forward to a state corresponding to Go(t) according to Go(t) and Go(t−1). In the present invention, the optimized driving voltage Vd(t) is determined by equations of Vd(t)=Vo(t−1)+ODV and Vd(t)=a×Gd(m)3+b×Gd(m)2+c×Gd(m)+d, wherein the voltage ODV is a minimum voltage capable of obtaining one gray level transition in a determined response time.

Owner:HANNSTAR DISPLAY CORPORATION

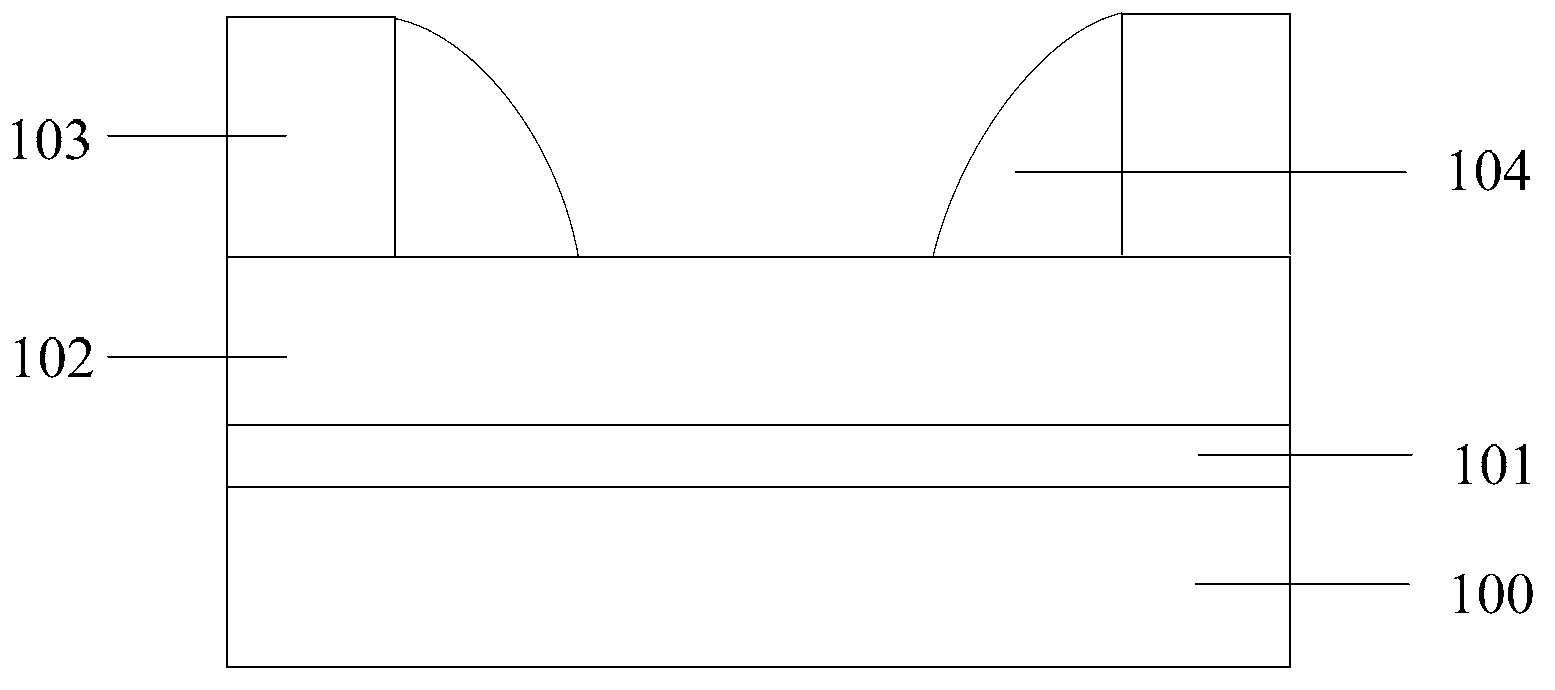

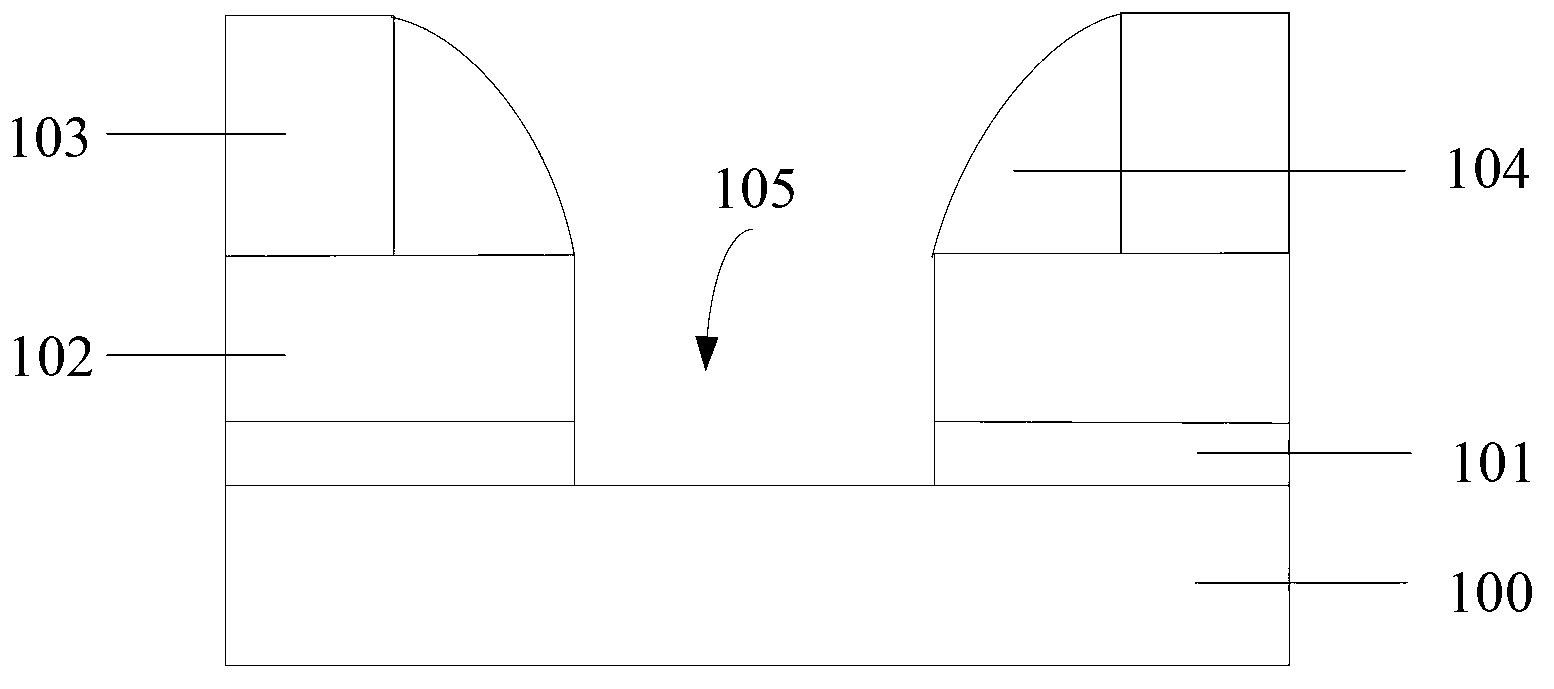

Split gate flash memory and forming method thereof

ActiveCN103021952AIncrease distanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringMedia layer

The invention provides a split gate flash memory and a forming method thereof. The forming method of the split gate flash memory includes that: a first media layer and a floating gate layer are sequentially formed on a substrate; a discrete second media layer is formed on the floating gate layer, and an area where the second media layer is located is a word line area; first side walls are formed around the second media layer, and areas between adjacent first side walls are source electrode line areas; the floating gate layer and the first media layer are etched to the substrate by using the first side walls as masks; source electrode lines are formed on the source electrode line areas; a floating gate and a floating gate media layer are formed by removing the second media layer, and the floating gate layer and the first media layer under the second media layer; a third media layer is formed on a floating gate side wall below the top tip of the floating gate which is adjacent to the word line area; a tunneling media layer is formed to cover the substrate, the third media layer, the floating gate, the first side walls and the surfaces of the source electrode lines; and word lines are formed on the tunneling media layer of the word line area. By using the forming method, erasure performance is improved, voltage applied on the word lines is reduced, and power consumption is saved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

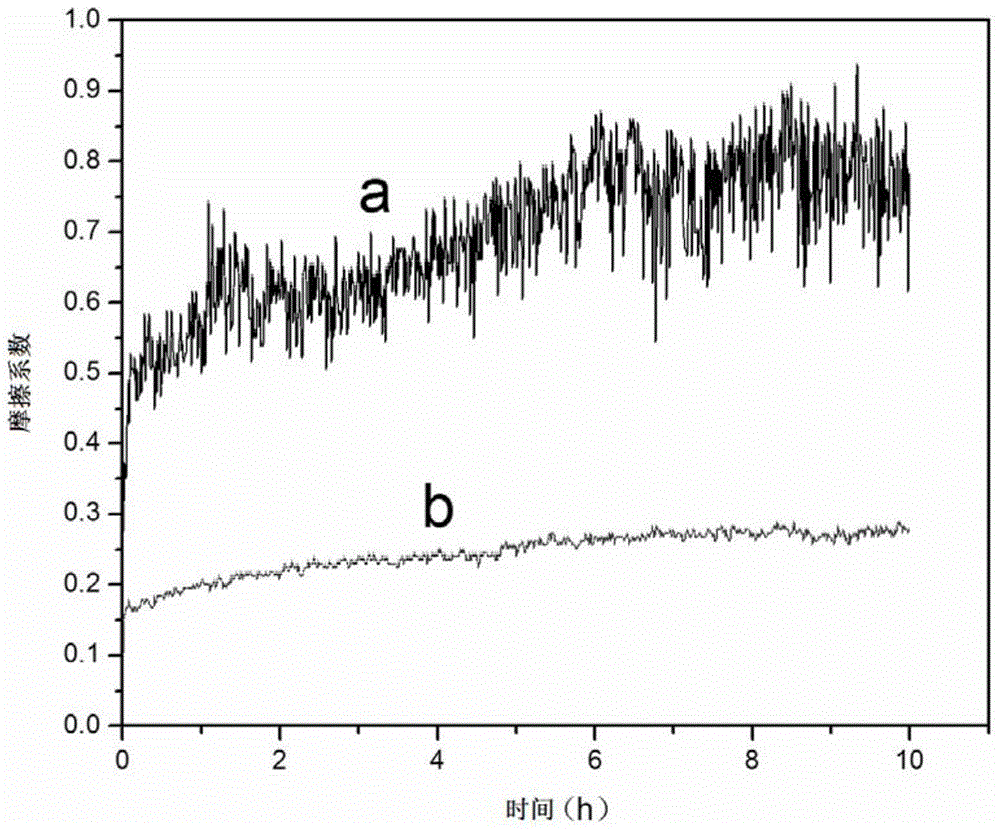

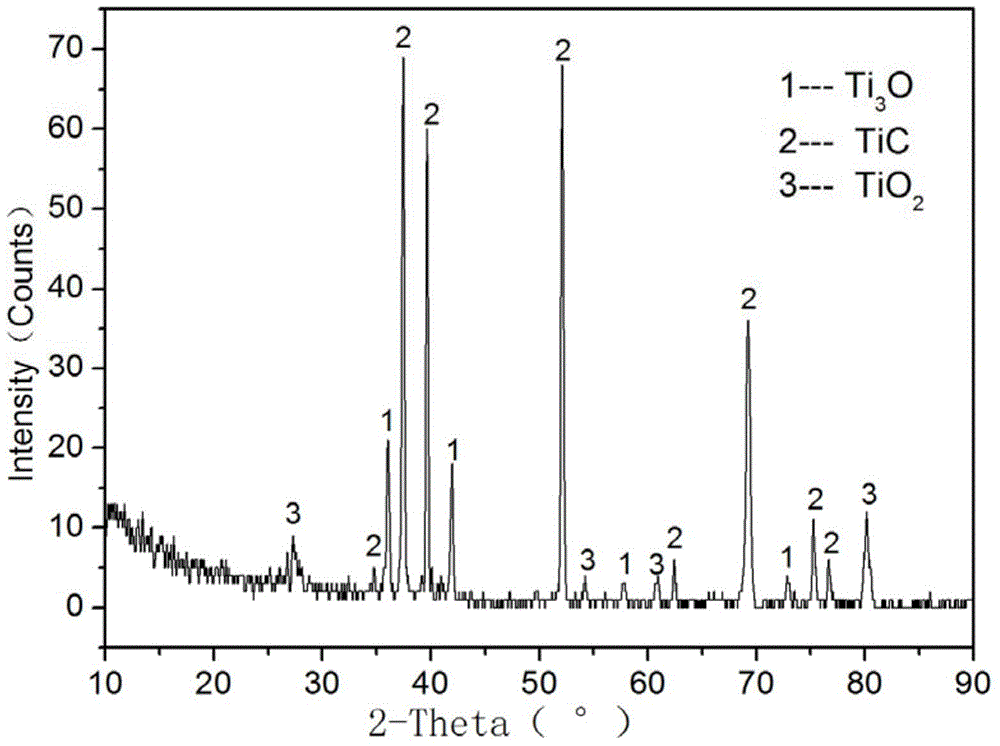

Hardening method of inner surface of cylinder barrel of titanium and titanium alloy hydraulic cylinder

InactiveCN104388891ATo achieve the purpose of anti-biteHigh bonding strengthSolid state diffusion coatingSuperimposed coating processHigh pressureBiological activation

The invention discloses a hardening method for an inner surface of a cylinder barrel of a titanium and titanium alloy hydraulic cylinder. The hardening method comprises the following steps: I, polishing the inner surface of the cylinder barrel of the hydraulic cylinder, then, removing greasy dirt and dehydrating; II, putting the dehydrated cylinder barrel, which is used as a cathode, of the hydraulic cylinder in a double-layer glow ion diffusion metalizing furnace, putting a graphite source electrode in the cylinder barrel of the hydraulic cylinder, in the presence of argon gas, generating glow under the high-voltage electric fields by utilizing an anode and a cathode to perform bombardment activation on the inner surface of the cylinder barrel of the hydraulic cylinder; III, after the bombardment activation is finished, introducing a gas mixture of the argon gas and oxygen gas into the double-layer glow ion diffusion metalizing furnace, generating double-layer glow under the high-voltage electric fields by utilizing the anode and the graphite source electrode as well as the anode and the cathode to perform oxyarburizing on the inner surface of the cylinder barrel of the hydraulic cylinder to obtain a composite membrane layer on the inner surface of the cylinder barrel of the hydraulic cylinder. The composite film layer prepared by the hardening method disclosed by the invention is high in bonding strength and good in wear resistance, and capable of effectively avoiding the titanium and titanium alloy occlusive locking problem.

Owner:西安赛福斯材料防护有限责任公司

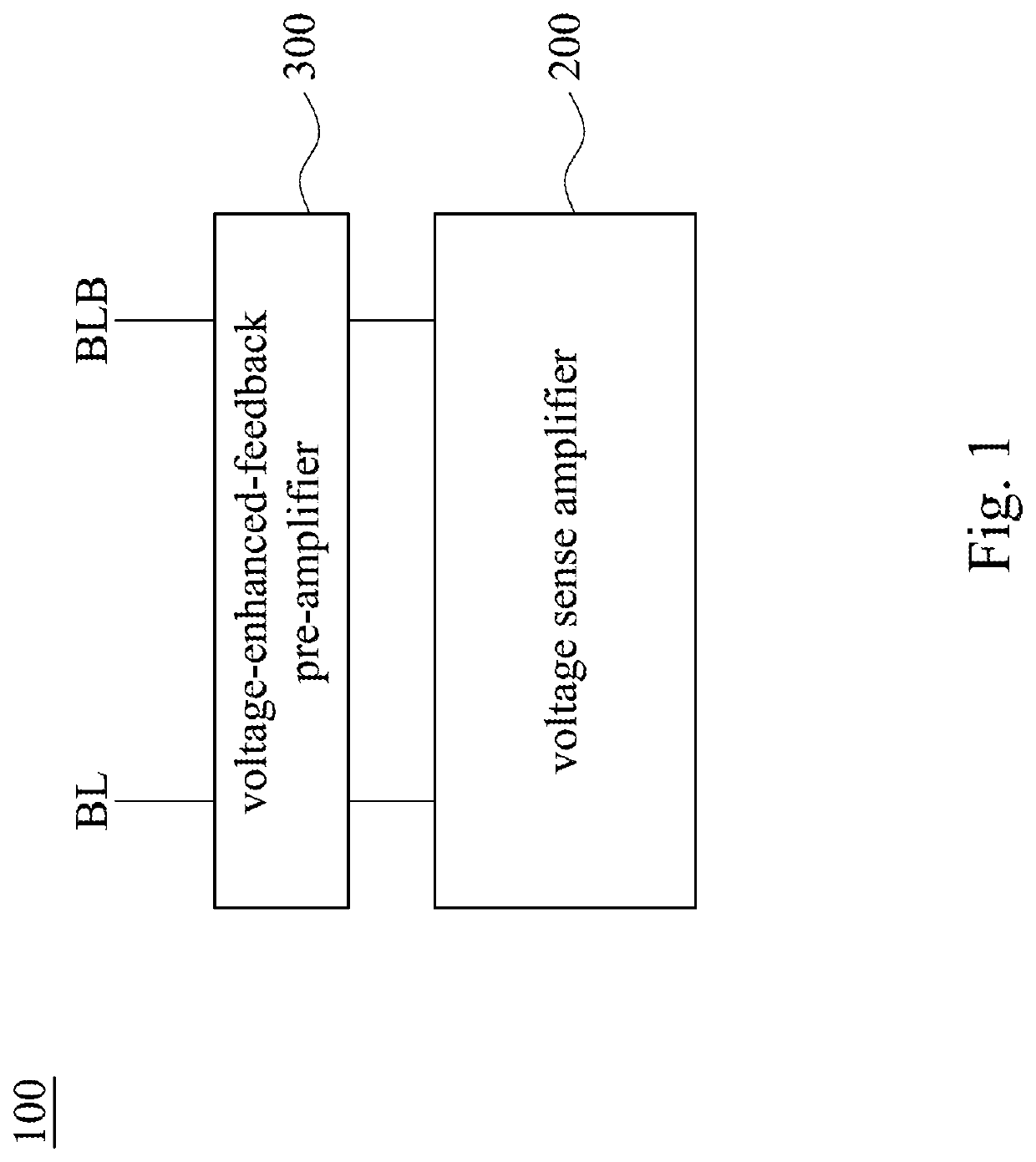

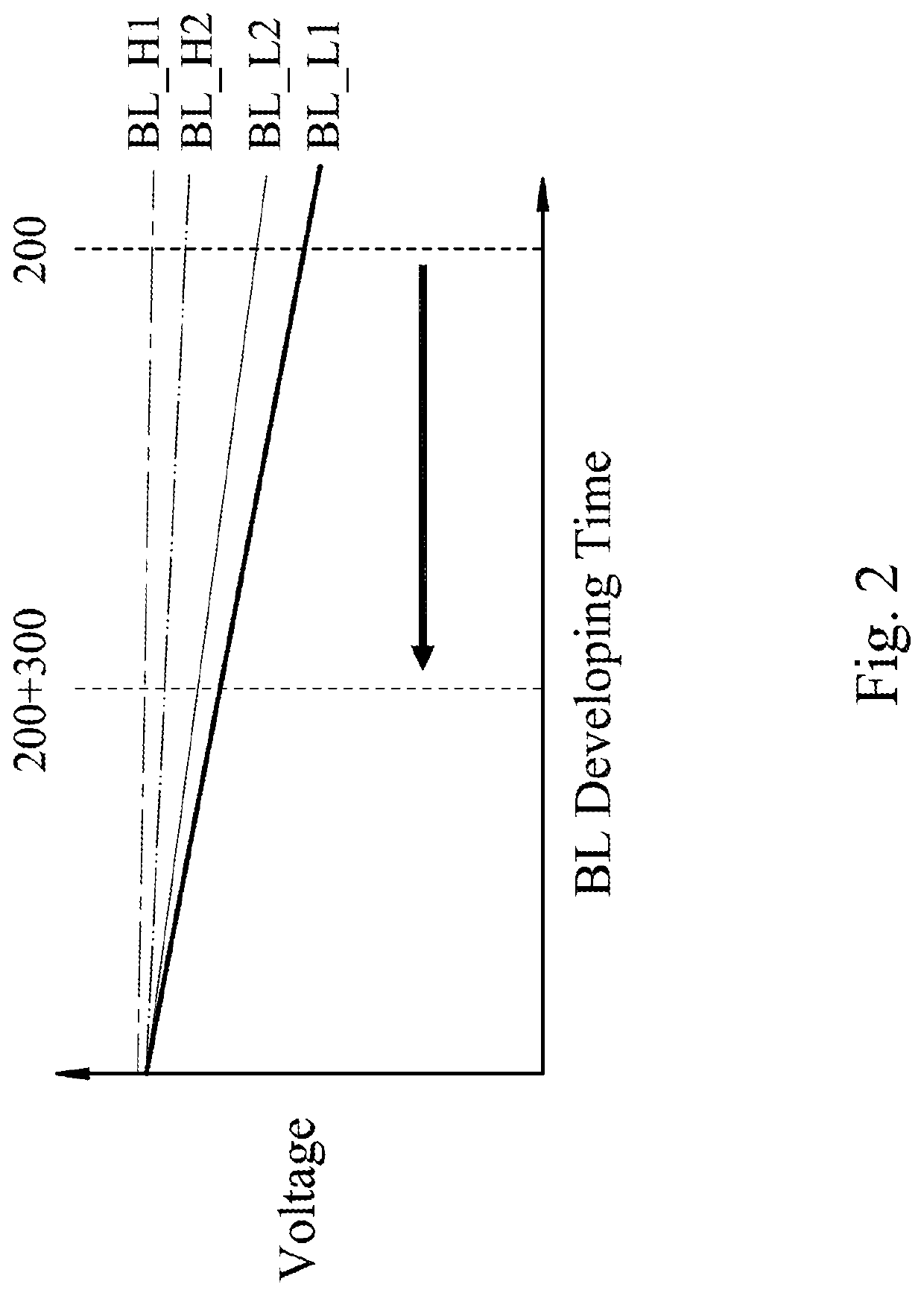

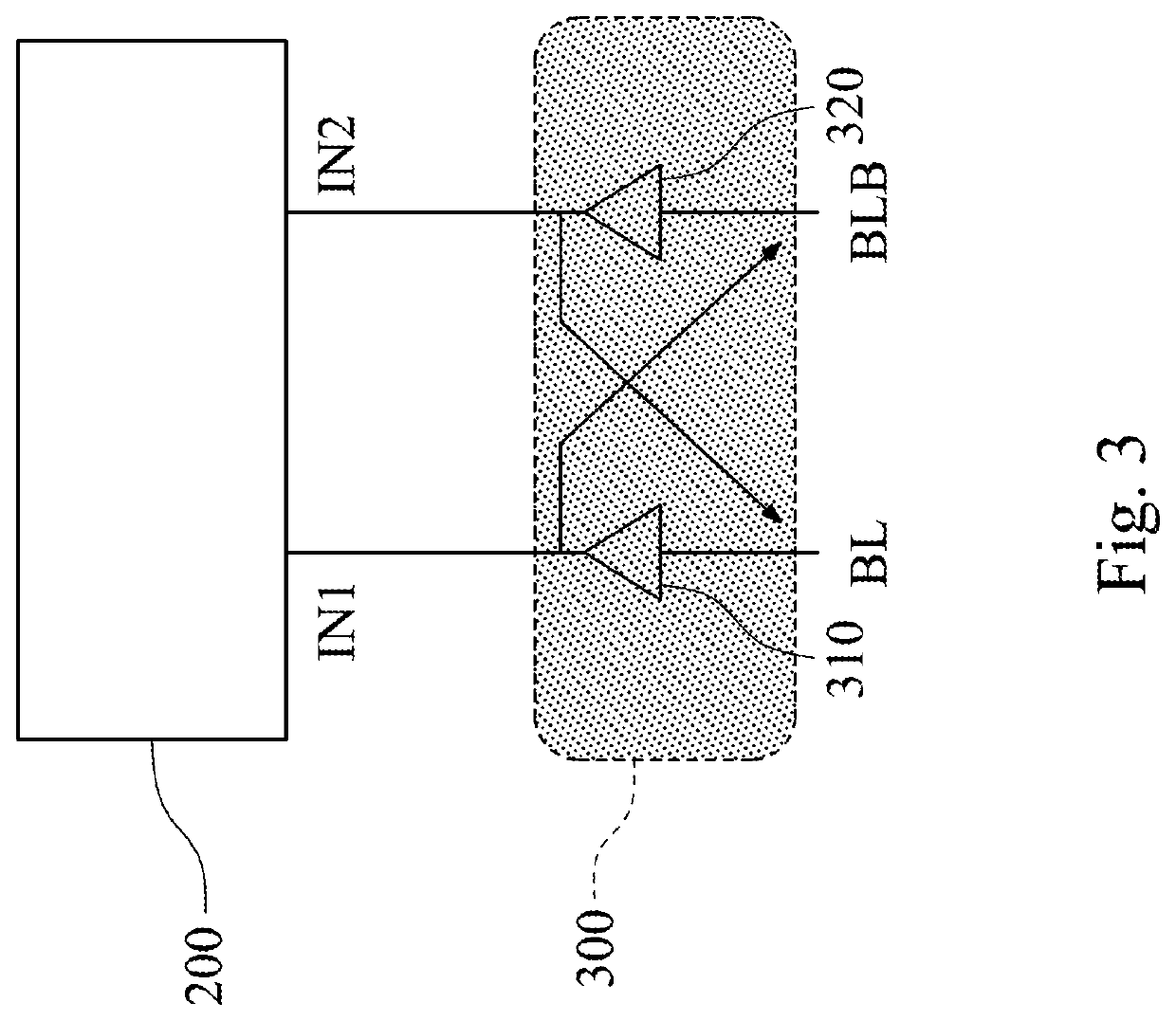

Voltage-enhanced-feedback sense amplifier of resistive memory and operating method thereof

ActiveUS20200105315A1Raise the voltage differenceSuppression pressure dropDigital storageBit lineVoltage drop

A voltage-enhanced-feedback sense amplifier of a resistive memory is configured to sense a first bit line and a second bit line. The voltage-enhanced-feedback sense amplifier includes a voltage sense amplifier and a voltage-enhanced-feedback pre-amplifier. The voltage-enhanced-feedback pre-amplifier is electrically connected to the voltage sense amplifier. A first bit-line amplifying module receives a voltage level of the second input node to suppress a voltage drop of the first bit line and amplifies a voltage level of the first input node according to a voltage level of the first bit line. A second bit-line amplifying module receives the voltage level of the first input node to suppress a voltage drop of the second bit line and amplifies the voltage level of the second input node according to a voltage level of the second bit line. A margin enhanced voltage difference is greater than a read voltage difference.

Owner:NATIONAL TSING HUA UNIVERSITY

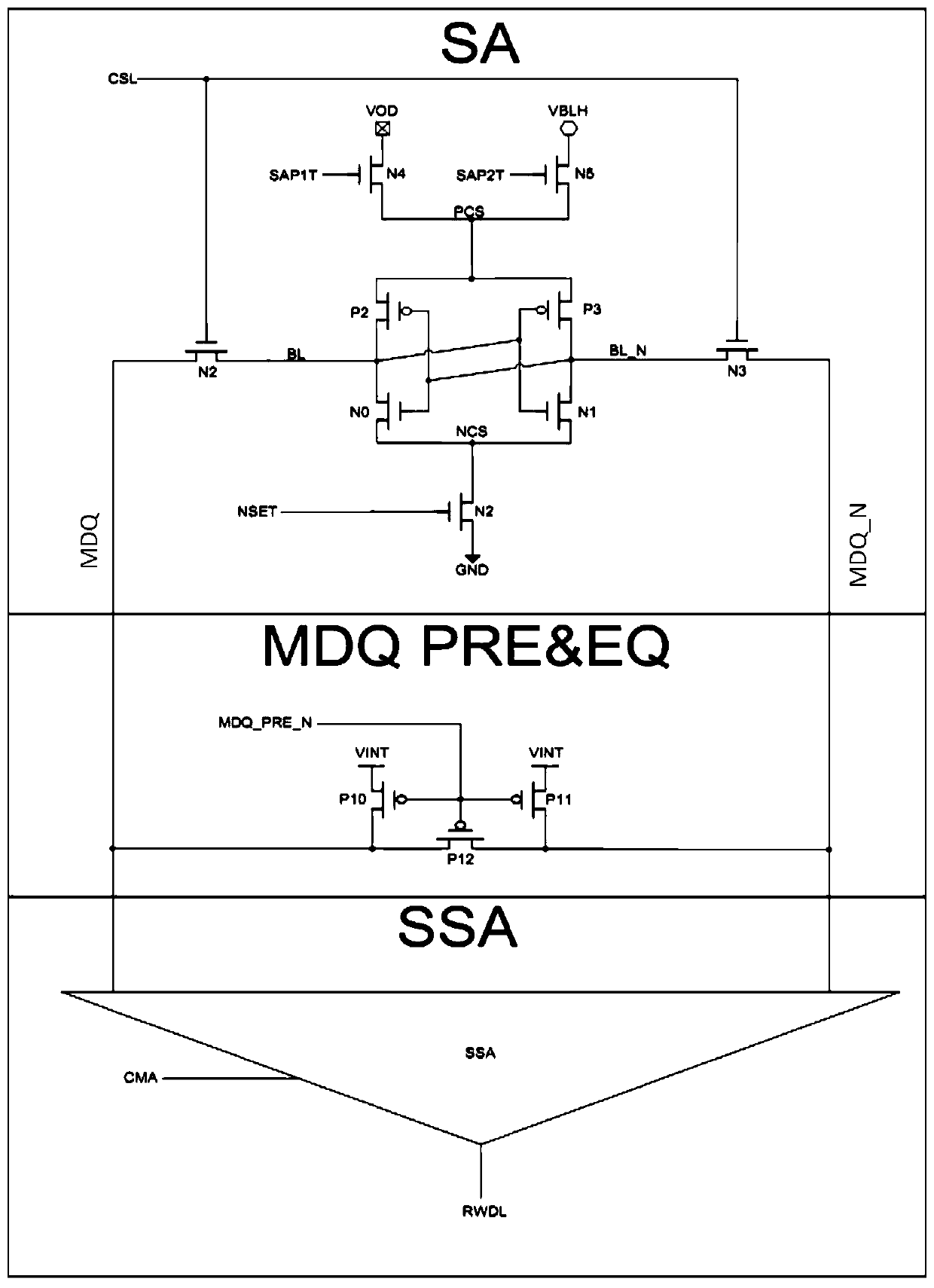

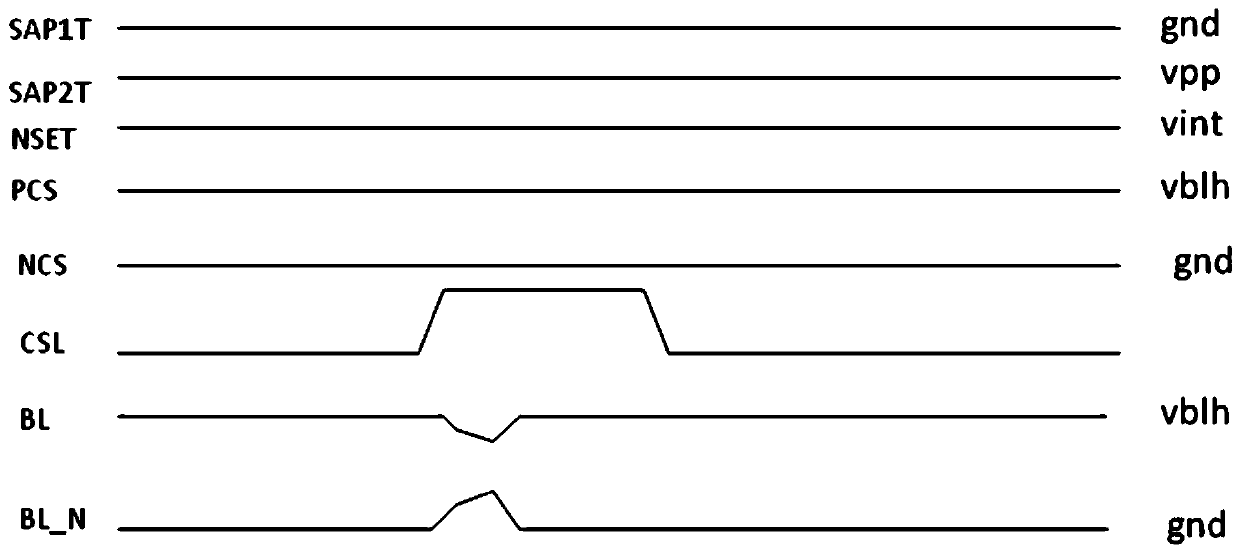

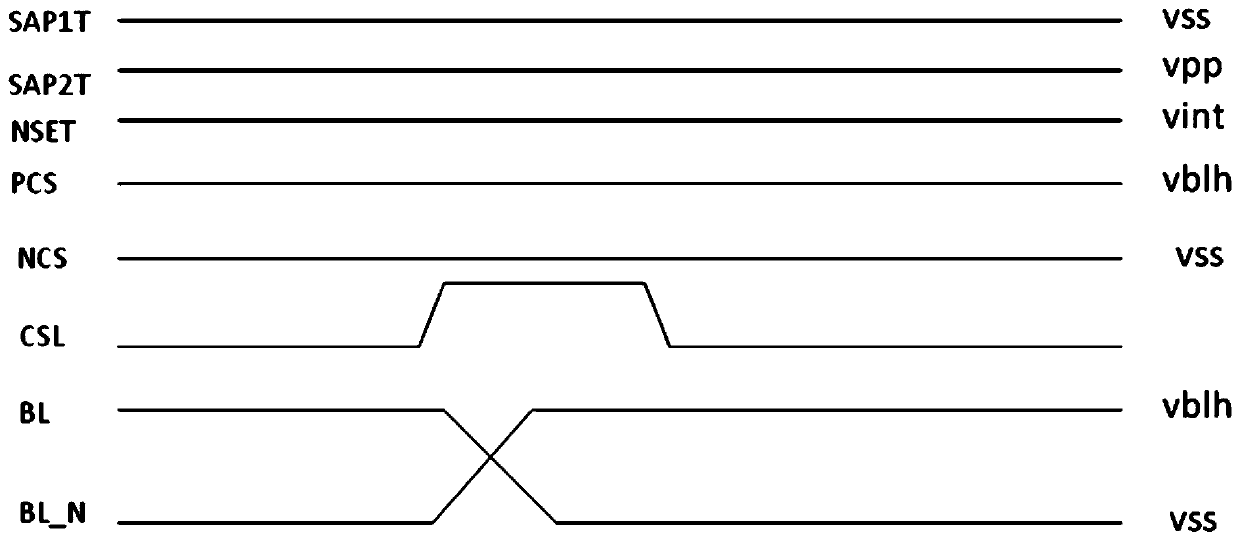

Read auxiliary circuit and method for improving read stability of sense amplifier in DRAM and sense amplifier

PendingCN109817263ARaise the voltage differenceIncreased resistance to coupling effectsRead-only memoriesAudio power amplifierControl signal

In order to improve the reading stability of a sensitive amplifier, the invention provides a reading auxiliary circuit method for improving the reading stability of the sensitive amplifier and the sensitive amplifier. Wherein the reading auxiliary circuit comprises an NMOS tube N6, the source end of the NMOS tube N6 is connected with negative voltage VNWL, the gate end of the NMOS tube N6 is connected with a control signal NSET2, and the drain end of the NMOS tube N6 is used for being connected with the drain end of a low-voltage pull-down tube N2 in the sensitive amplifier. In the CSL pulse period, firstly, the NOMS tube N2 is turned off, and the NMOS tube N6 is turned on, so that the NCS and the BL _ N are charged to a negative voltage VNWL; then, an NMOS tube N4 connected with the SAP1Tin the sensitive amplifier is opened; According to the invention, the NMOS tube N5 connected with the SAP2T in the sensitive amplifier is turned off, so that the PCS and the BL are charged to the VOD, the voltage difference between the BL and the BL _ N is further increased, and the capacity of the sensitive amplifier for resisting the coupling effect is improved.

Owner:XI AN UNIIC SEMICON CO LTD

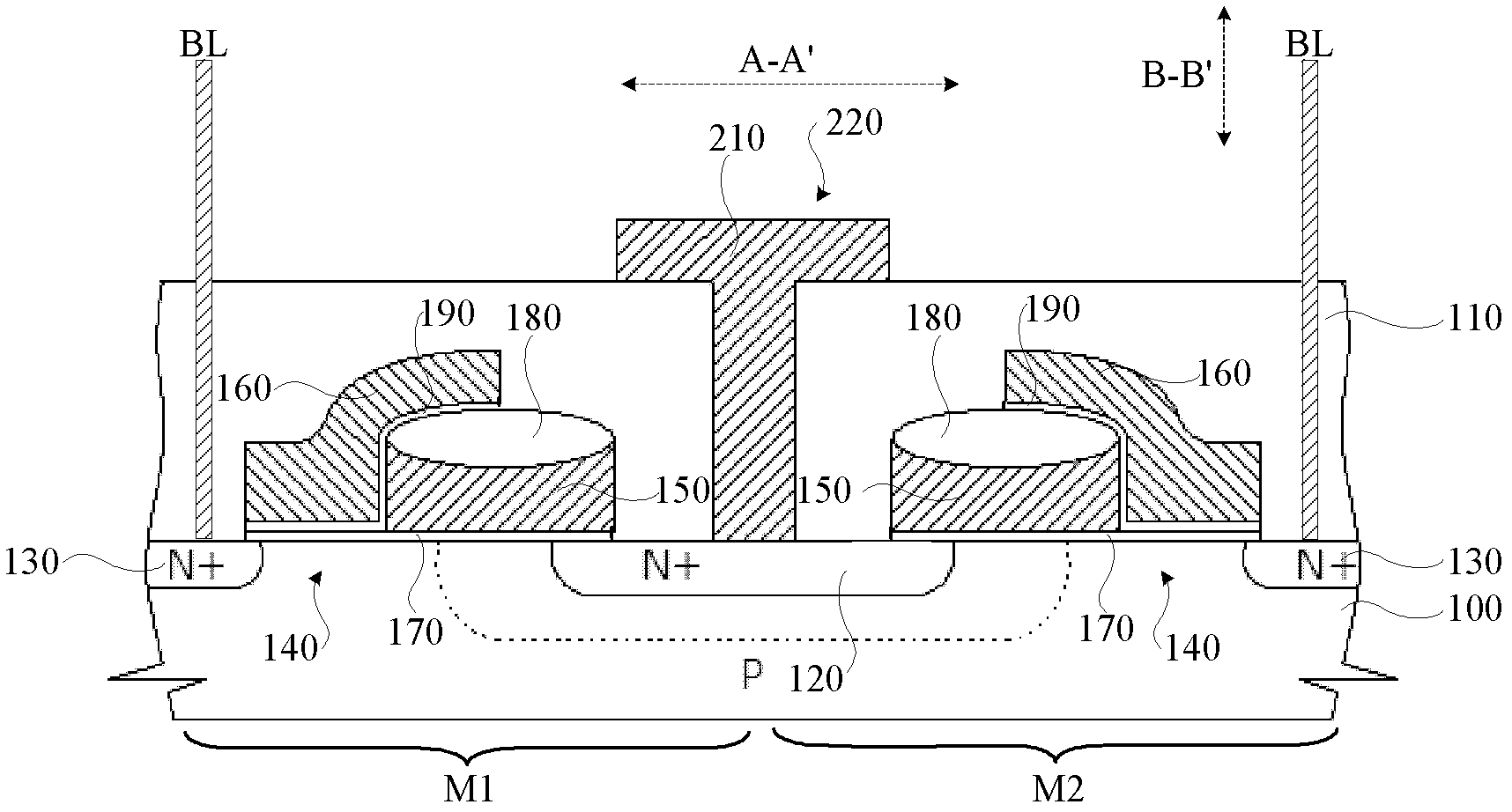

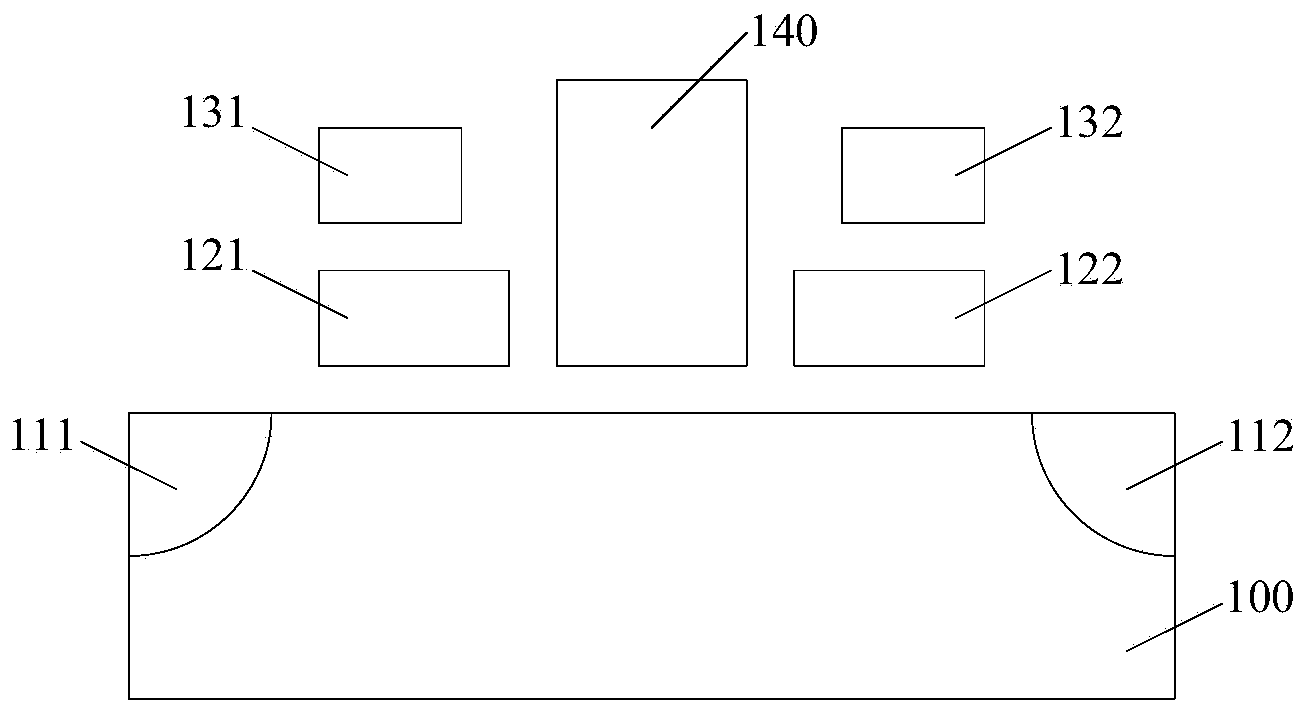

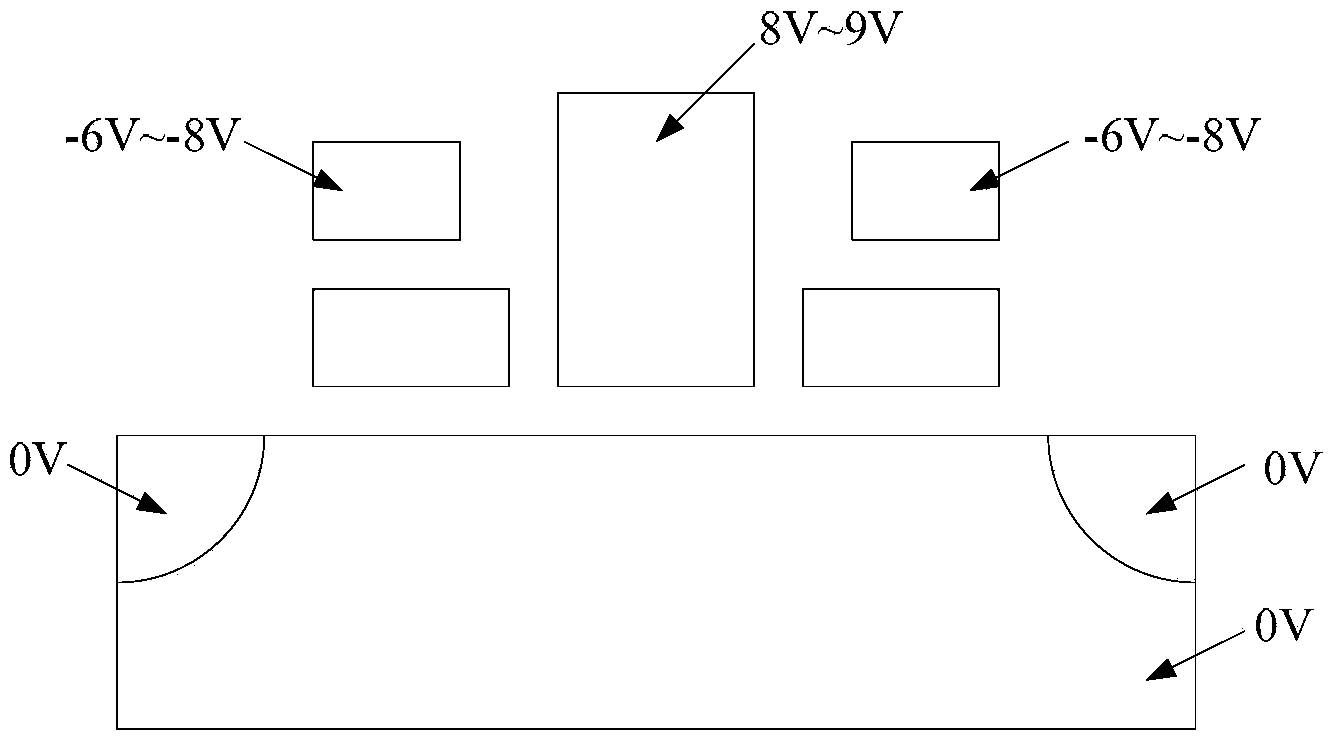

Storage unit and storage array erasing method

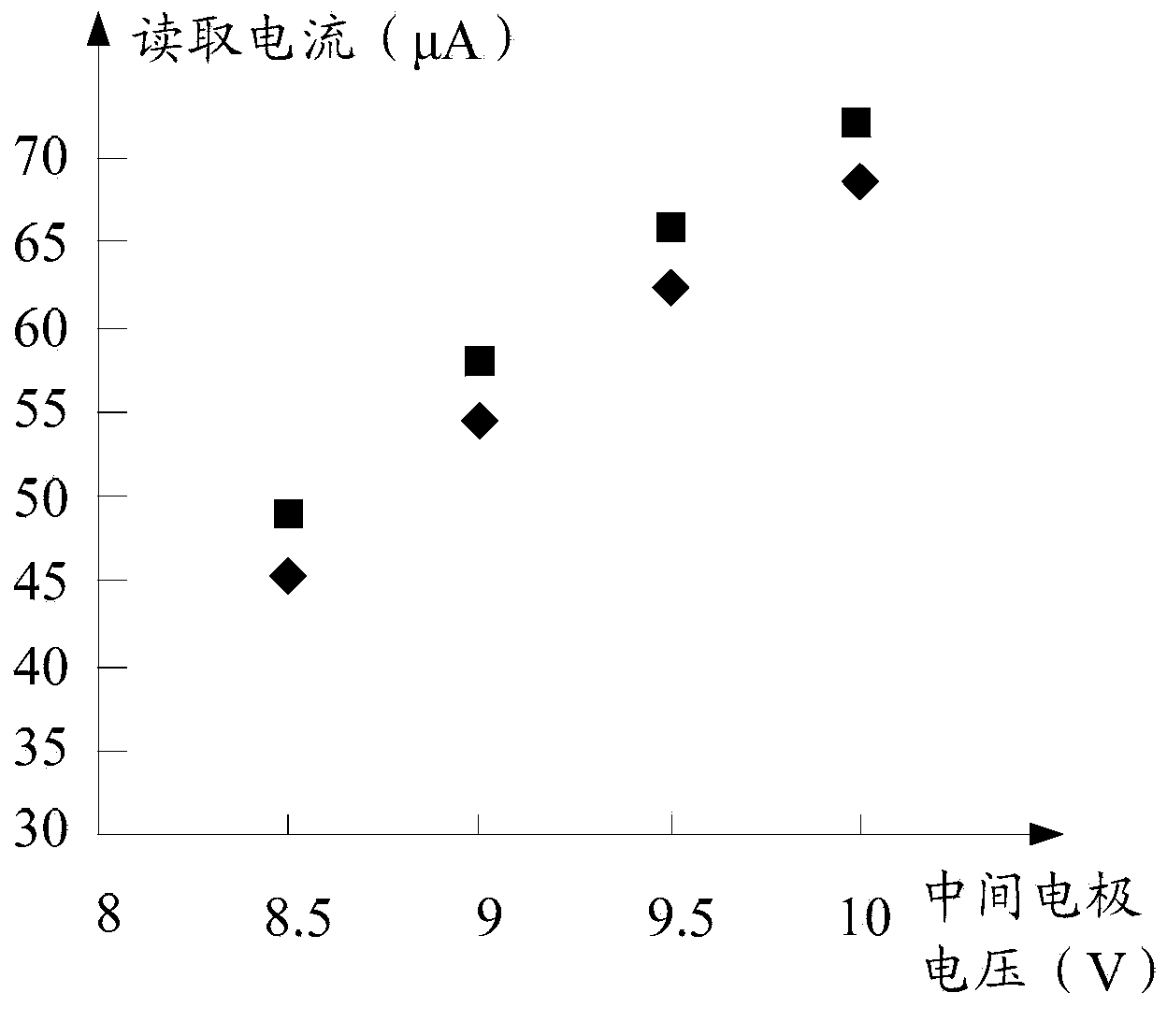

ActiveCN104183274ARaise the voltage differenceIncrease read currentRead-only memoriesStorage cellEngineering

The invention relates to a storage unit and a storage array erasing method. The storage unit comprises a P-type well region, a drain electrode, a source electrode, a first control grid electrode, a second control grid electrode and a middle electrode; the storage array erasing method comprises the following steps: applying first bias voltage to the P-type well region; applying second bias voltage to the drain electrode; applying third bias voltage to the source electrode; applying minus 6V-minus 8V voltage to the first control grid electrode; applying minus 6V-minus 8V voltage to the second control grid electrode; and applying 8V-9V voltage to the middle electrode, wherein the value of the first bias voltage is negative, and the values of the first bias voltage, the second first bias voltage and the third first bias voltage are equal. The storage unit and the storage array erasing method can improve the durability of the storage unit.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

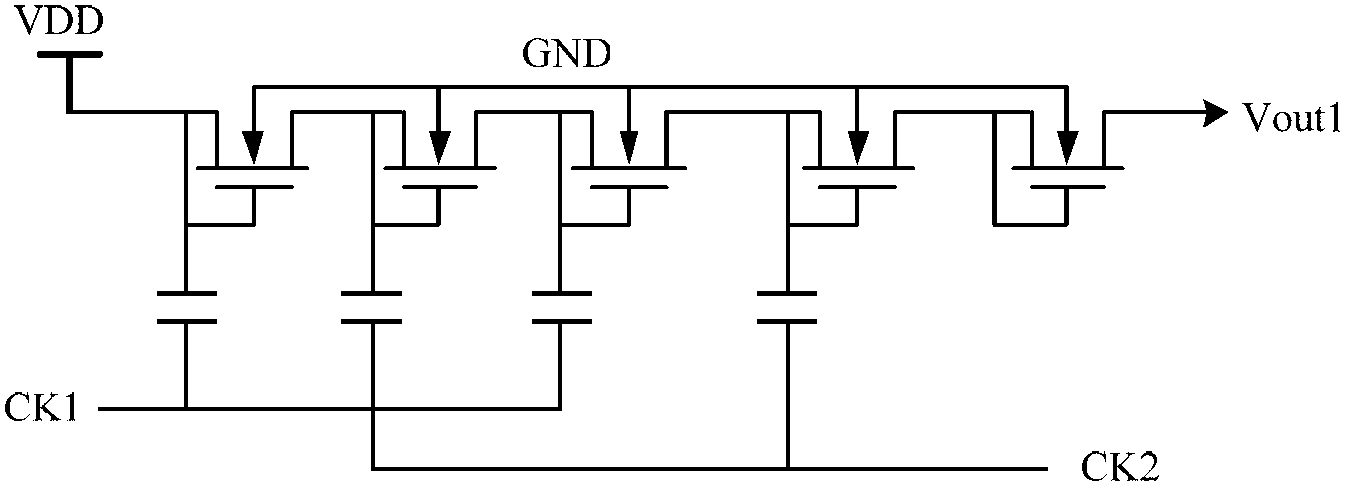

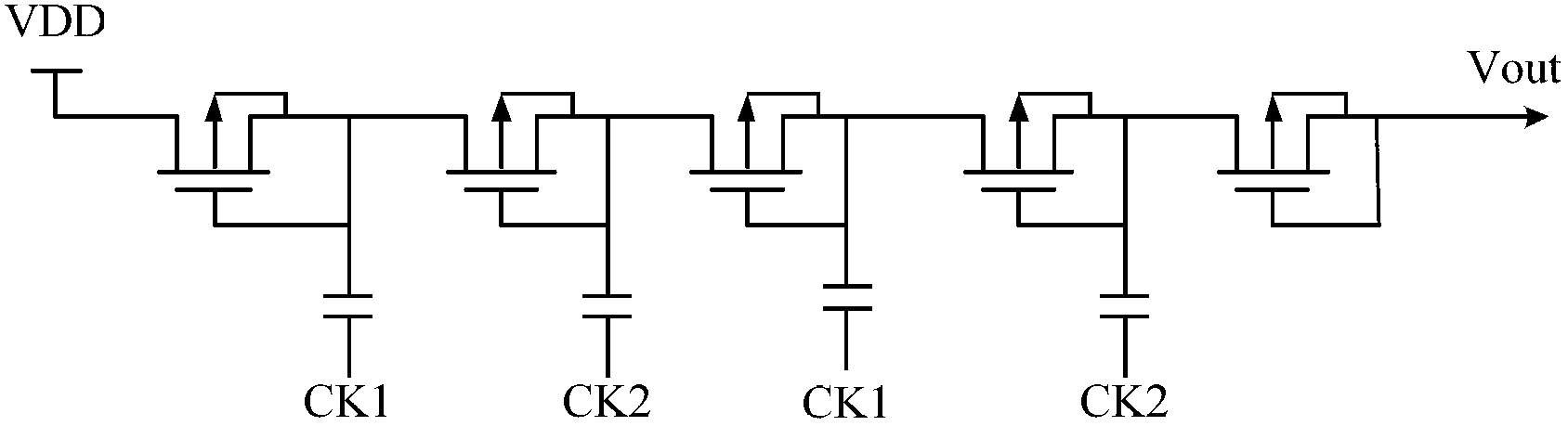

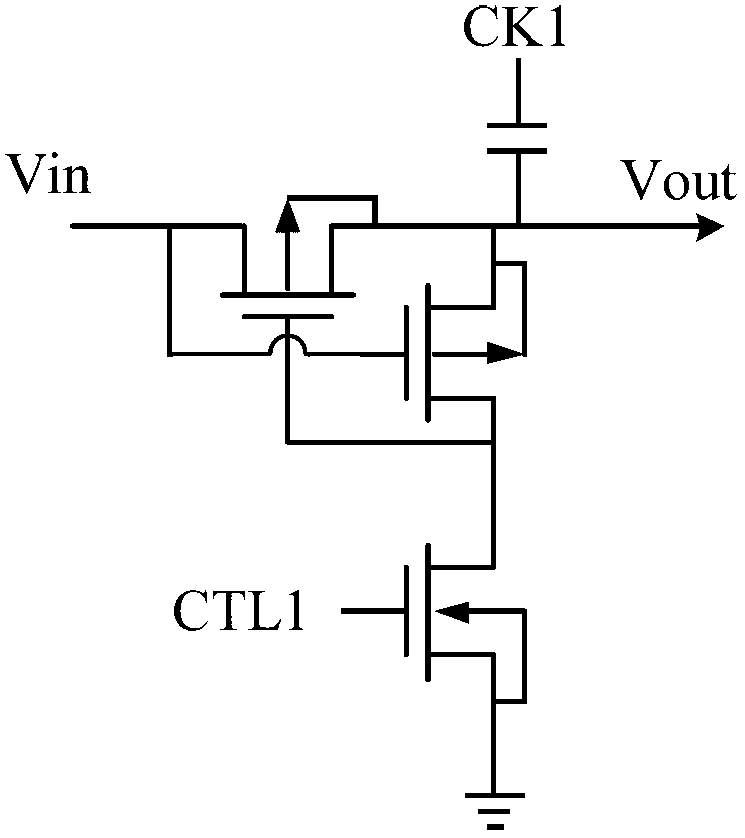

Positive high-voltage charge pump

ActiveCN102710122AImprove conduction performanceRaise the voltage differenceApparatus without intermediate ac conversionEngineeringAuxiliary circuit

The invention relates to the technical field of an integrated circuit, and discloses a positive high-voltage charge pump. The charge pump comprises a charge pump circuit which is connected in multi-level series and a one-level output circuit; and the input end of the output circuit is connected with the output end of the last level charge pump circuit. According to the charge pump provided by the invention, an auxiliary circuit is added to reduce the PMOS (P-channel Metal Oxide Semiconductor) grid voltage in the charge pump circuit and increase the voltage difference of the grid electrode and the source electrode, thus, the PMOS grid voltage can be zero when the switch is switched on, and the voltage loss can be reduced during switching on and the PMOS conductive performance can be improved, thereby enhancing the capability of switch pumping charge.

Owner:PEKING UNIV

Displayer and pixel driving method

ActiveCN103424903AShort reaction timeRaise the voltage differenceStatic indicating devicesSignal linesDisplay device

The invention discloses a displayer and a pixel driving method. The displayer comprises a pixel driving circuit which comprises a first switch element, a second switch element, a third switch element and a fourth switch element, the first switch element has a first end, a second end coupled to a first node and a light-emitting element, and a control end coupled to a second node, the second switch element has a first end coupled to a first signal source, a second end coupled to the first end of the first switch element, and a control end coupled to a first scanning signal line, the third switch element has a first end coupled to a second signal source, a second end coupled to the second node, and a control end coupled to a second scanning signal line, and the fourth switch element has a first end coupled to a third node, a second end coupled to a grounding end, and a control end coupled to the second scanning signal line.

Owner:INNOCOM TECH SHENZHEN +1

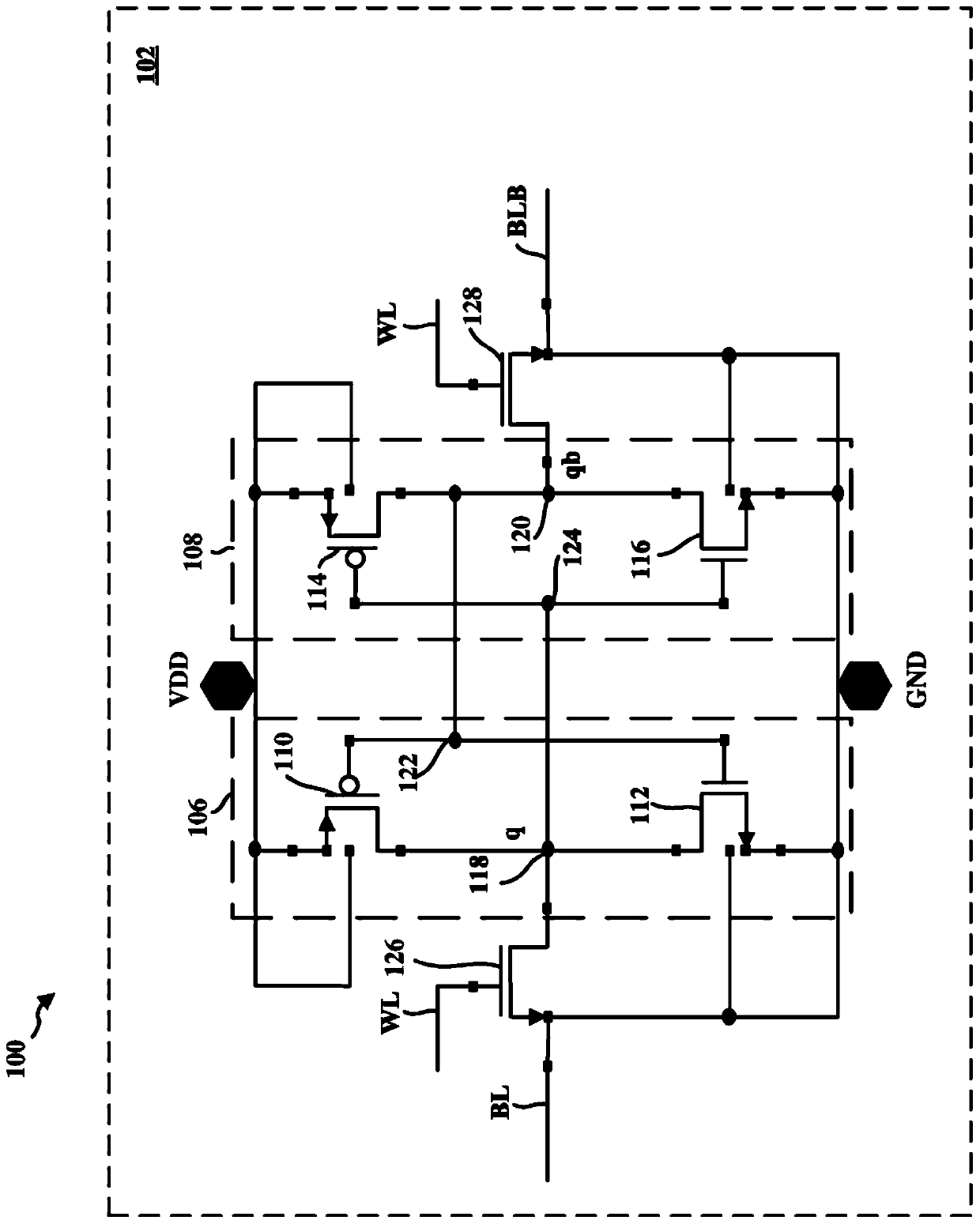

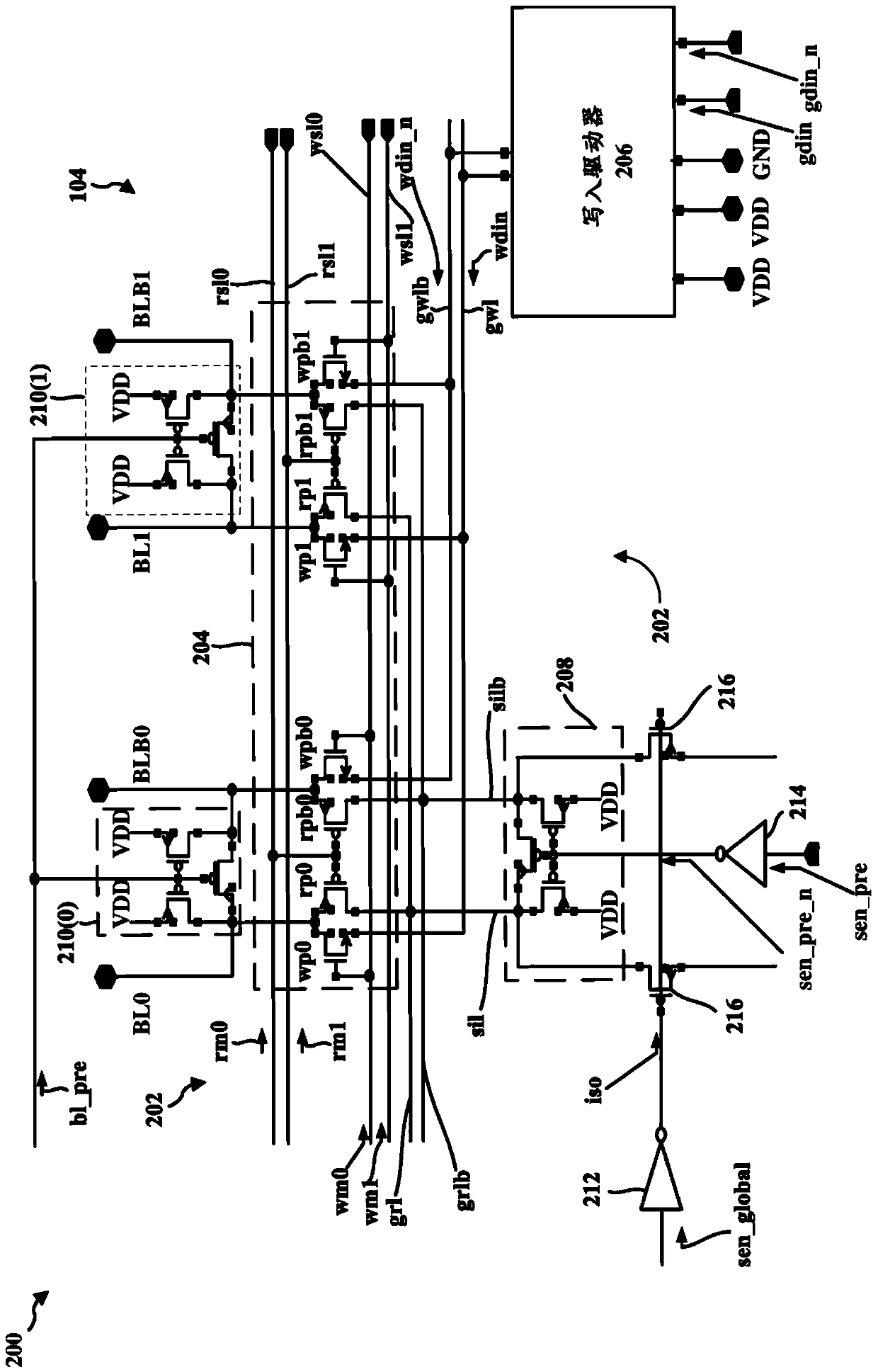

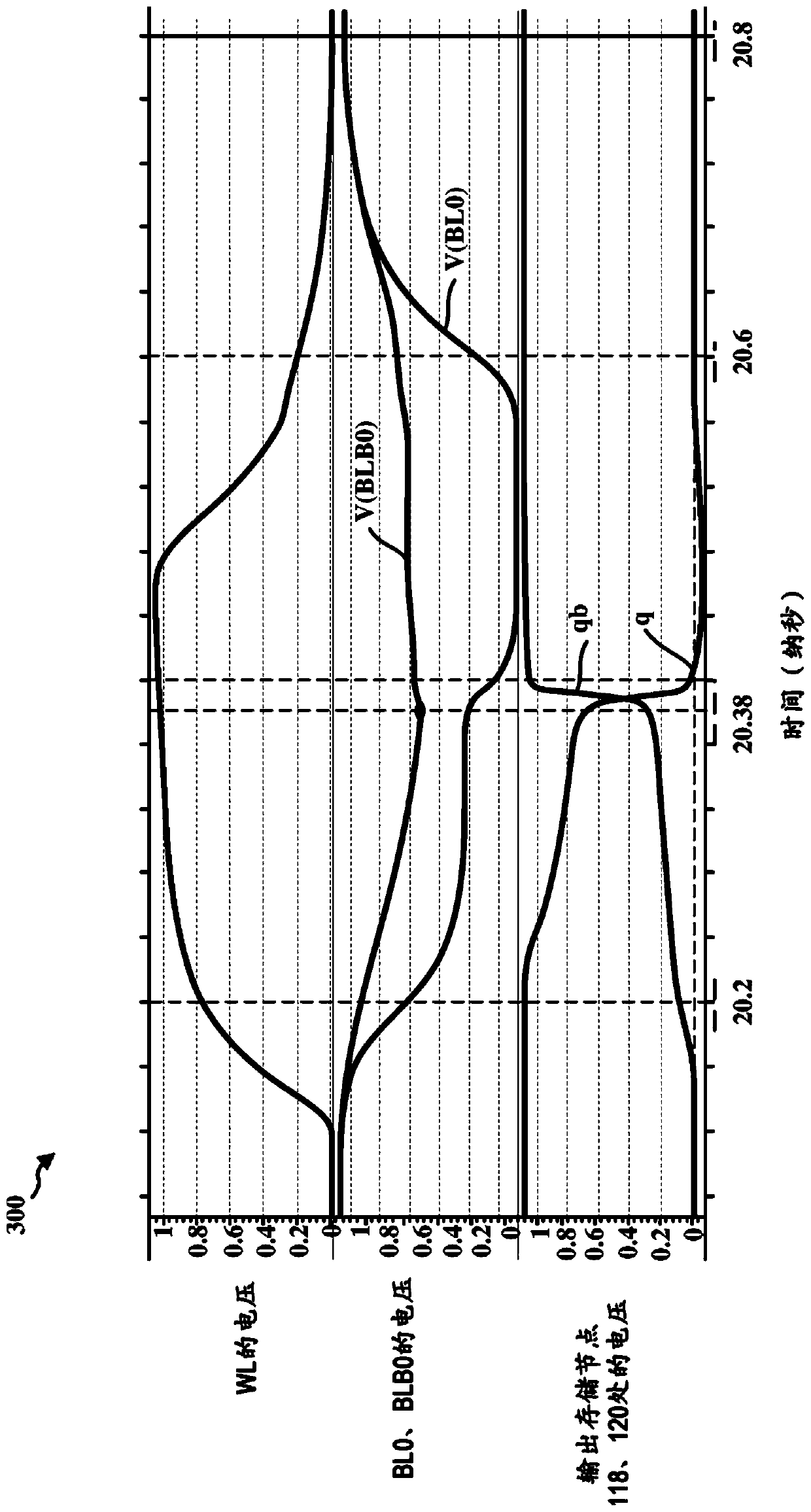

Area efficient write data path circuit for SRAM yield enhancement

PendingCN111164691AImprove reliabilityRaise the voltage differenceDigital storageDatapath circuitsCapacitance

A memory and method of performing a write operation in a memory are disclosed. In one aspect of the disclosure, the memory includes a memory cell, a pair of bit lines (BL; BLB) coupled to the memory cell, a multiplexer (404), and a pull-up circuit (418) coupled to the multiplexer. The multiplexer may be configured to select the pair of bit lines coupled to the memory cell during the write operation. To increase the write performance of the memory cell, the pull-up circuit is configured to select which of the pair of bit lines is a non zero bit line during the write operation and to clamp thenon-zero bit line through read pass transistors (rpO, rpbO) of the multiplexer to approximately a power rail voltage (VDD). Thus, the pull-up circuit (418) may increase the voltage difference betweenthe non-zero bit line and the zero bit line during the write operation and thus decrease the area and power consumed by a boost capacitance of a conventional write driver.

Owner:QUALCOMM INC

High sensitivity pressure sensor with long term stability

InactiveCN1250951CReduce voltage differenceCapacitance difference increasesPressure difference measurement between multiple valvesFluid pressure measurement using capacitance variationForce sensorCapacitor

A high sensitivity pressure sensor with long term stability including a housing with first and second chambers, a membrane (20) separating the first and second chambers, a first electrode located in the first chamber (16) and spaced from one side of the membrane forming a first capacitor therewith, and a second electrode located in the second chamber (18) and spaced from an opposite side of the membrane forming a second capacitor therewith.

Owner:PANAMETRICS

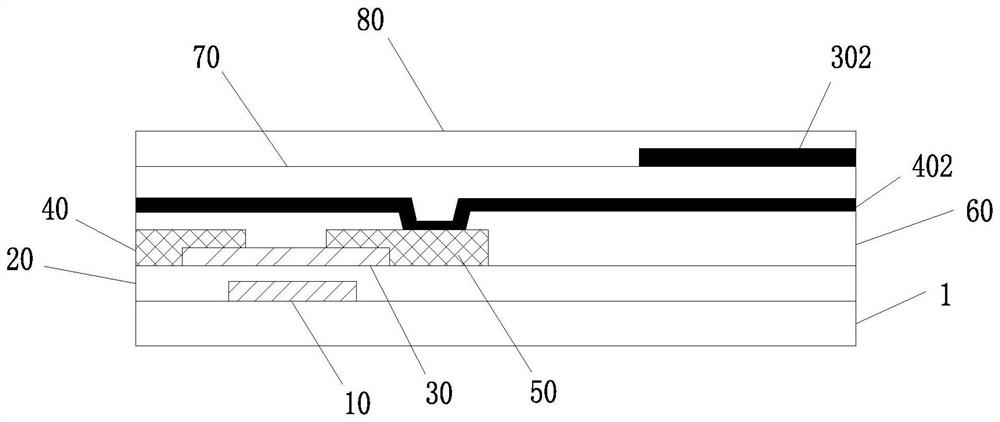

Display substrate and display device

PendingCN112379542AEasy to identifyIncrease the electric field strengthPrint image acquisitionNon-linear opticsCapacitanceDisplay device

The embodiment of the invention provides a display substrate and a display device, the display substrate comprises a substrate and a fingerprint identification unit arranged on the substrate, and thefingerprint identification unit comprises an excitation circuit and a reading circuit. The reading circuit is configured to form a first capacitor with a fingerprint to be identified and read a chargequantity signal of the first capacitor, and the excitation circuit comprises a first thin film transistor and a first electrode plate connected with the first thin film transistor. the first thin film transistor is configured to apply a driving voltage to the first electrode plate, and the first electrode plate is configured to boost the voltage of the fingerprint to be identified through the driving voltage; and the fingerprint identification effect is improved.

Owner:BOE TECH GRP CO LTD +1

Flash memory device and method for controlling erased operation

ActiveCN101178937BRaise the voltage differenceIncrease the erase voltageRead-only memoriesVoltage generatorMemory cell

The present invention provides a flash memory device and a method used for controlling erasing operation of the flash memory device.A non-volatile memory mechanism includes a first and a second memorycell blocks, wherein each memory cell block includes a plurality of memory cells, a local drain selection wire, a local source pole selection wire and a plurality of local character wires.A block selection unit respectively connects the set local character wires and an integral character wire to respond to block selective signals.A first voltage bias generator is allocated to be used for applyingat least a first and a second erasing voltages which are positive ones to the integral character wire during the erasing manipulation period, wherein, the first erasing voltage is applied to the integral character wire during a first erasing try period of the erasing operation, the second erasing voltage is applied to the integral character wire during the second erasing try period, and a seconderasing try is executed if a first erasing try does not make good erasing manipulation.A body voltage generator applies a body electric voltage to a body of the memory cell during the erasing manipulation period.

Owner:SK HYNIX INC

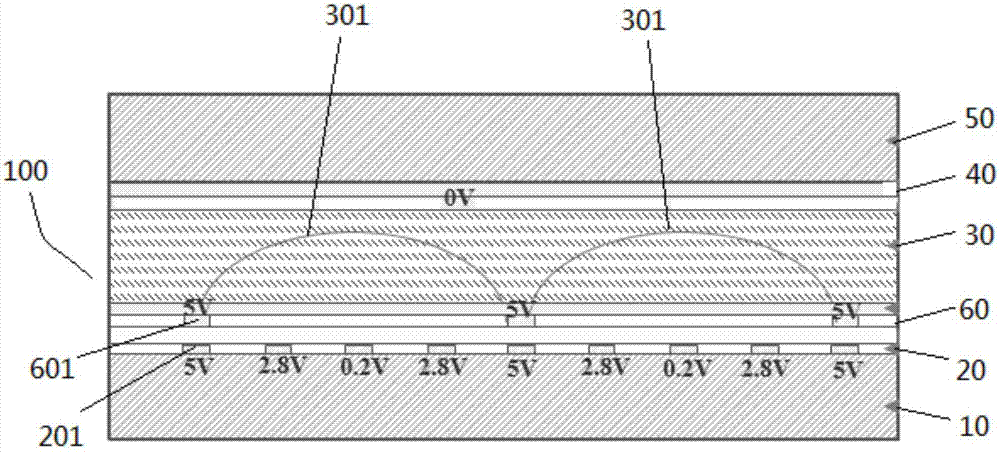

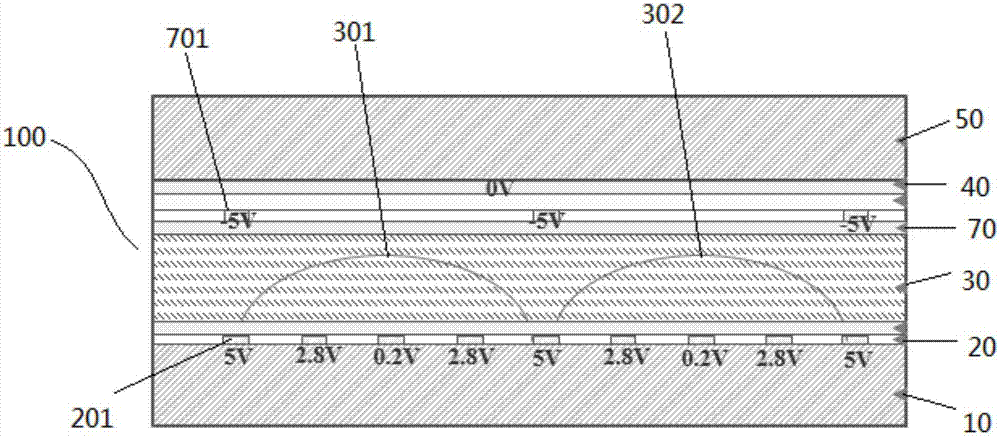

Liquid crystal lens structure, liquid crystal lens forming method, display panel and display device

ActiveCN107367882ARaise the voltage differenceIncrease optical path differenceNon-linear opticsOptical elementsLiquid-crystal displayDisplay device

The invention provides a liquid crystal lens structure which comprises a first substrate, a first electrode layer, a liquid crystal layer, a second electrode layer and a second substrate which are sequentially stacked. The first electrode layer comprises a plurality of first strip electrodes, the first electrode layer and the second electrode layer are mutually matched, a lens unit can be formed in the liquid crystal layer, the first strip electrodes close to two end points of the lens unit are correspondingly matched with second strip electrodes, and voltage can be applied to the first strip electrodes and the second strip electrodes. According to the liquid crystal lens structure, light rays passing the liquid crystal lens structure can have high optical path difference, good imaging effects are achieved, and power consumption is reduced. The invention further provides a display panel, a display device and a liquid crystal lens forming method applicable to the liquid crystal lens structure.

Owner:BOE TECH GRP CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com