Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

83results about How to "Minimize period" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

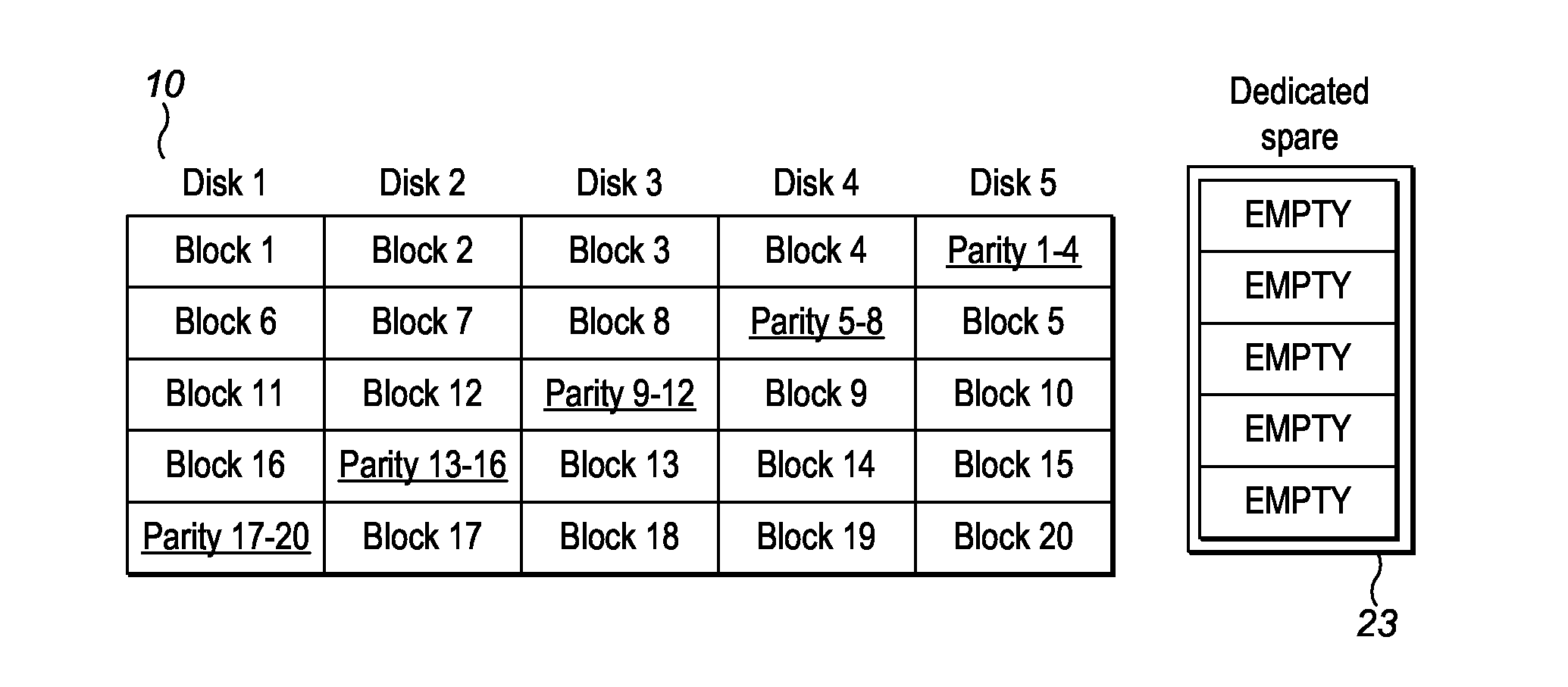

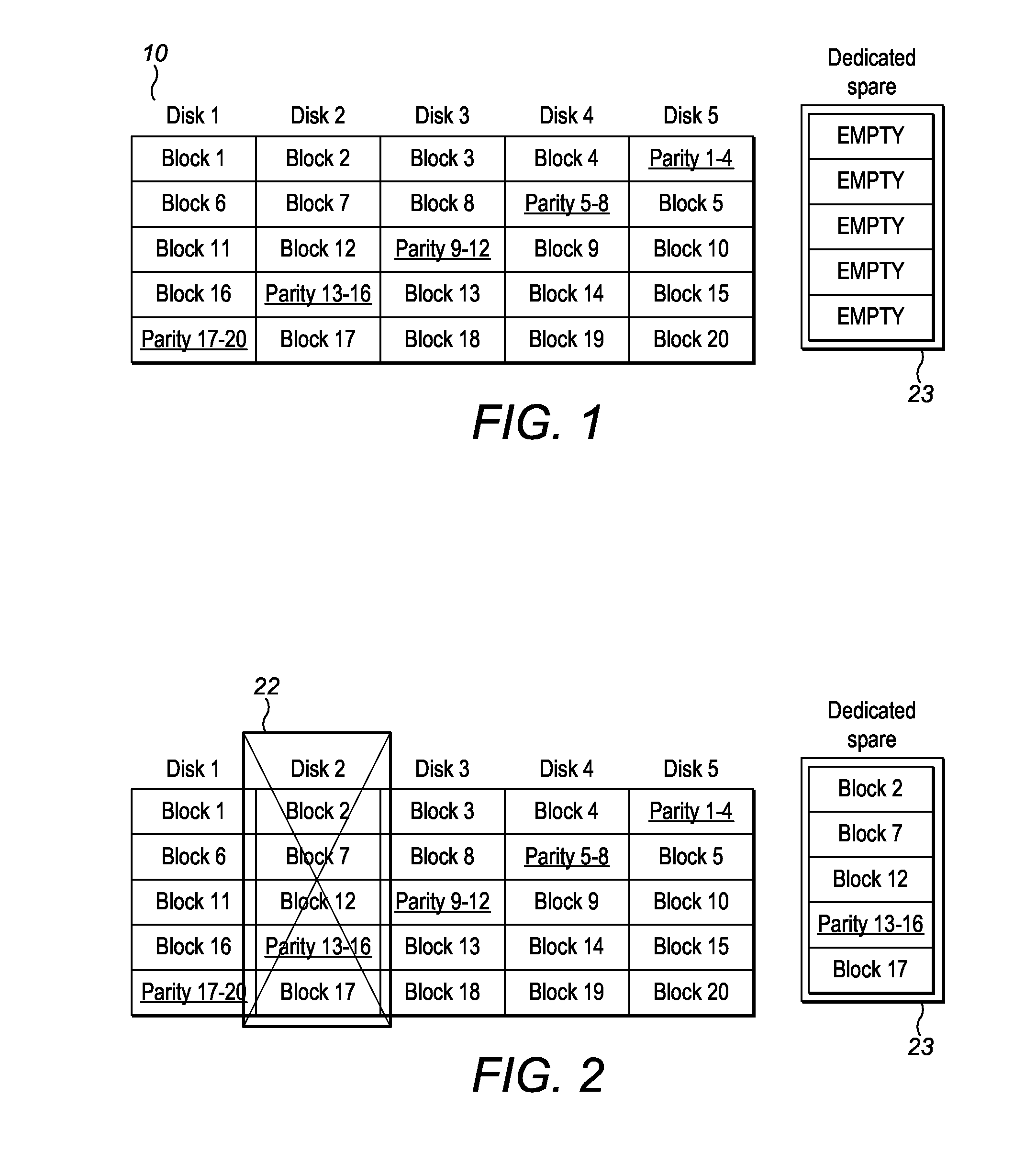

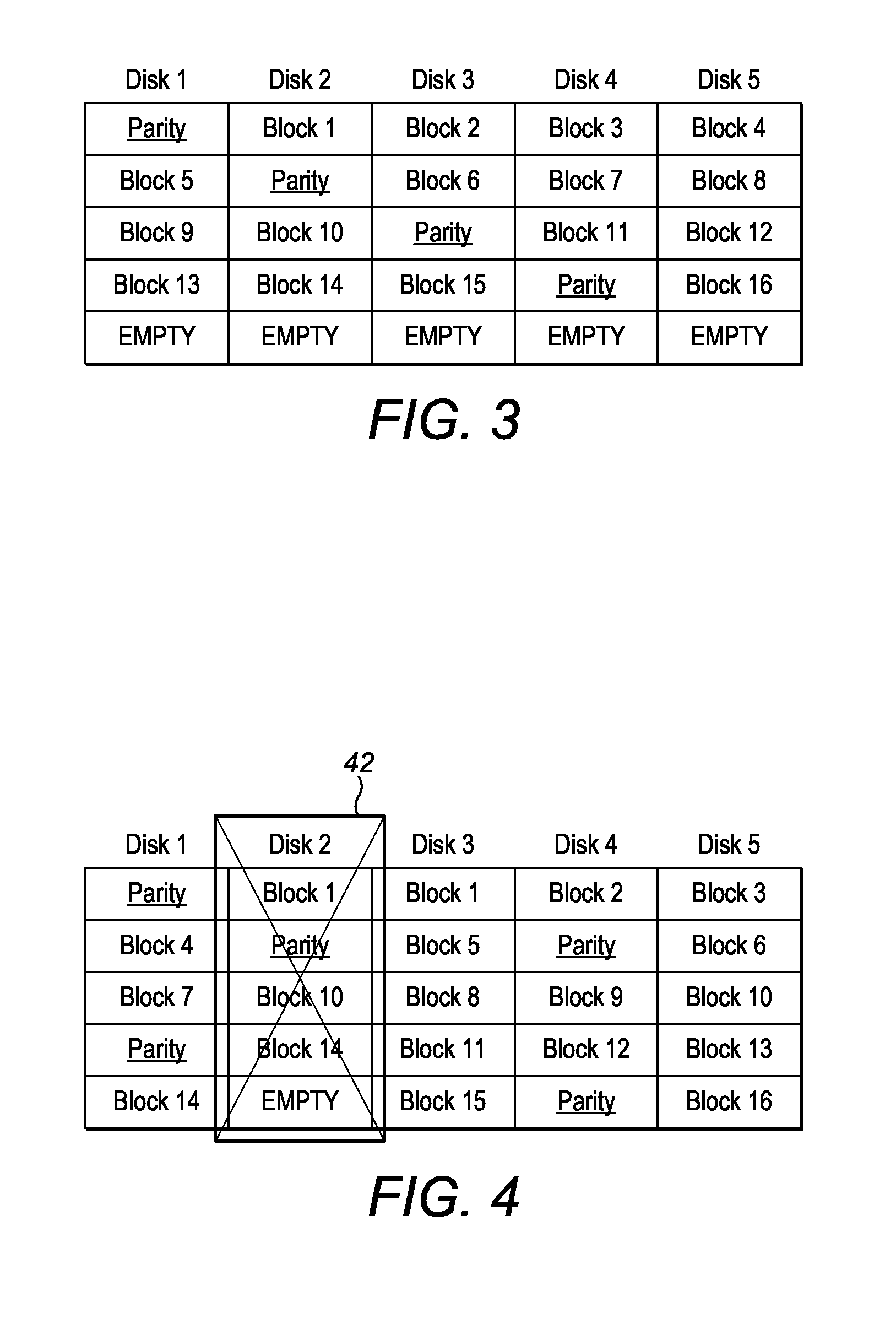

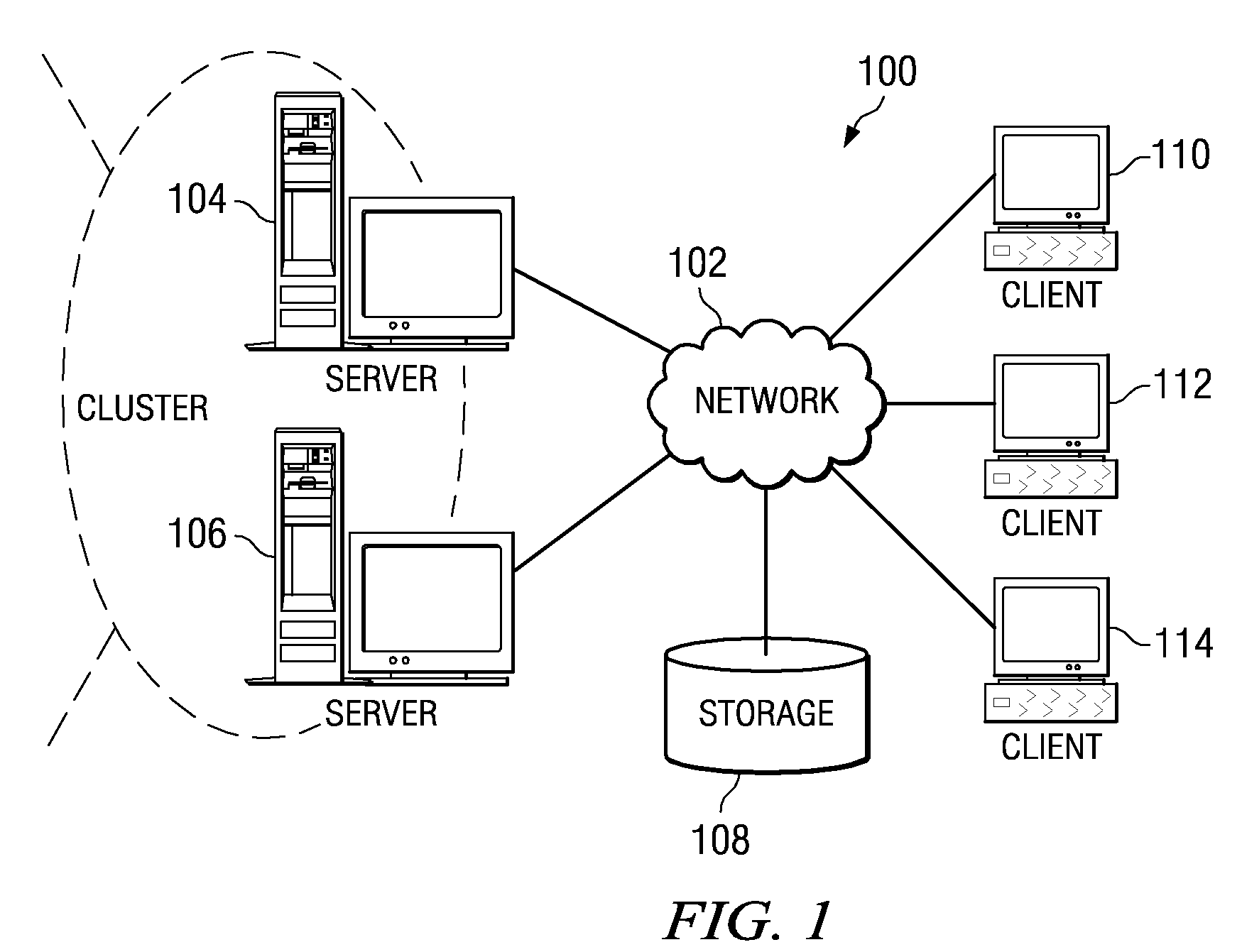

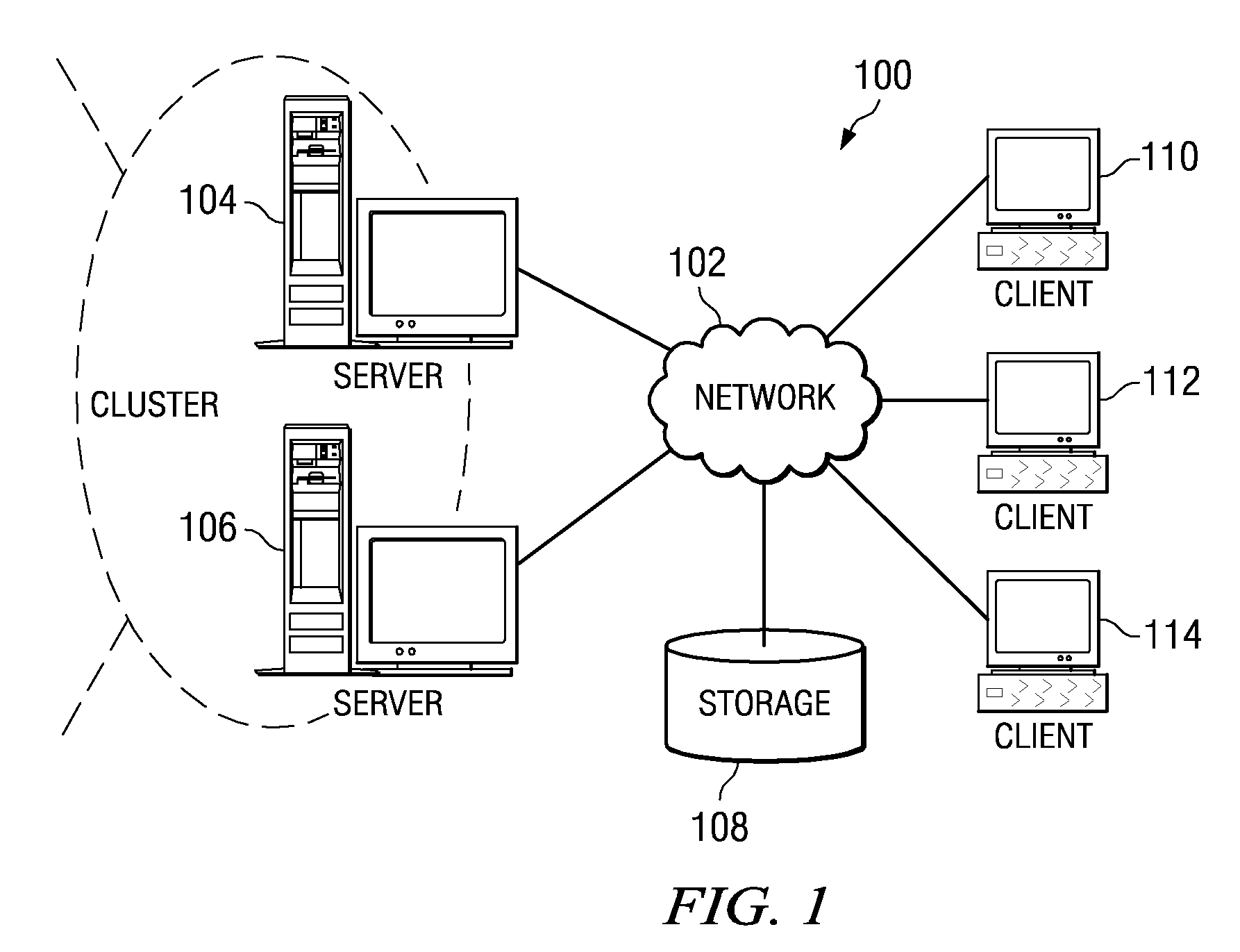

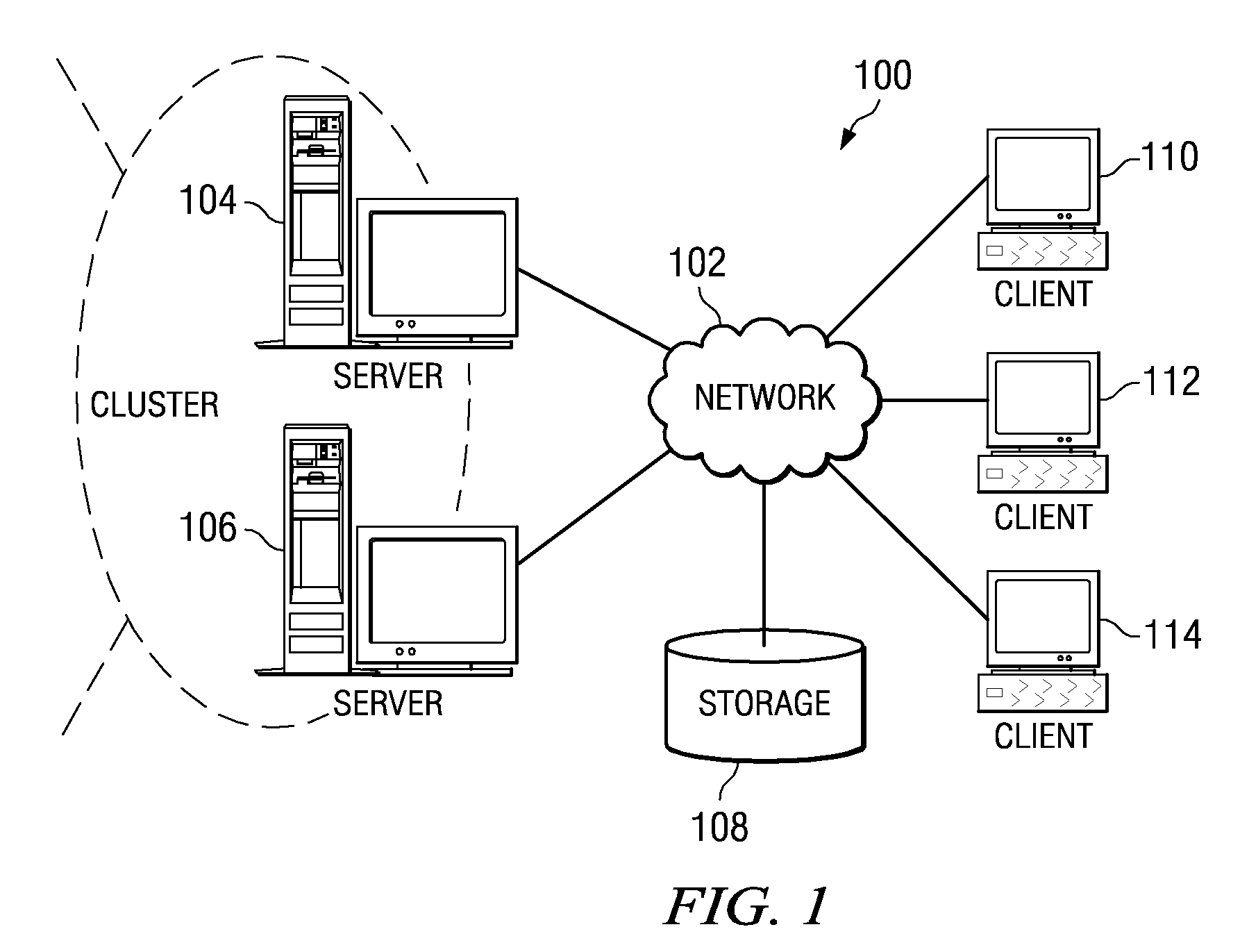

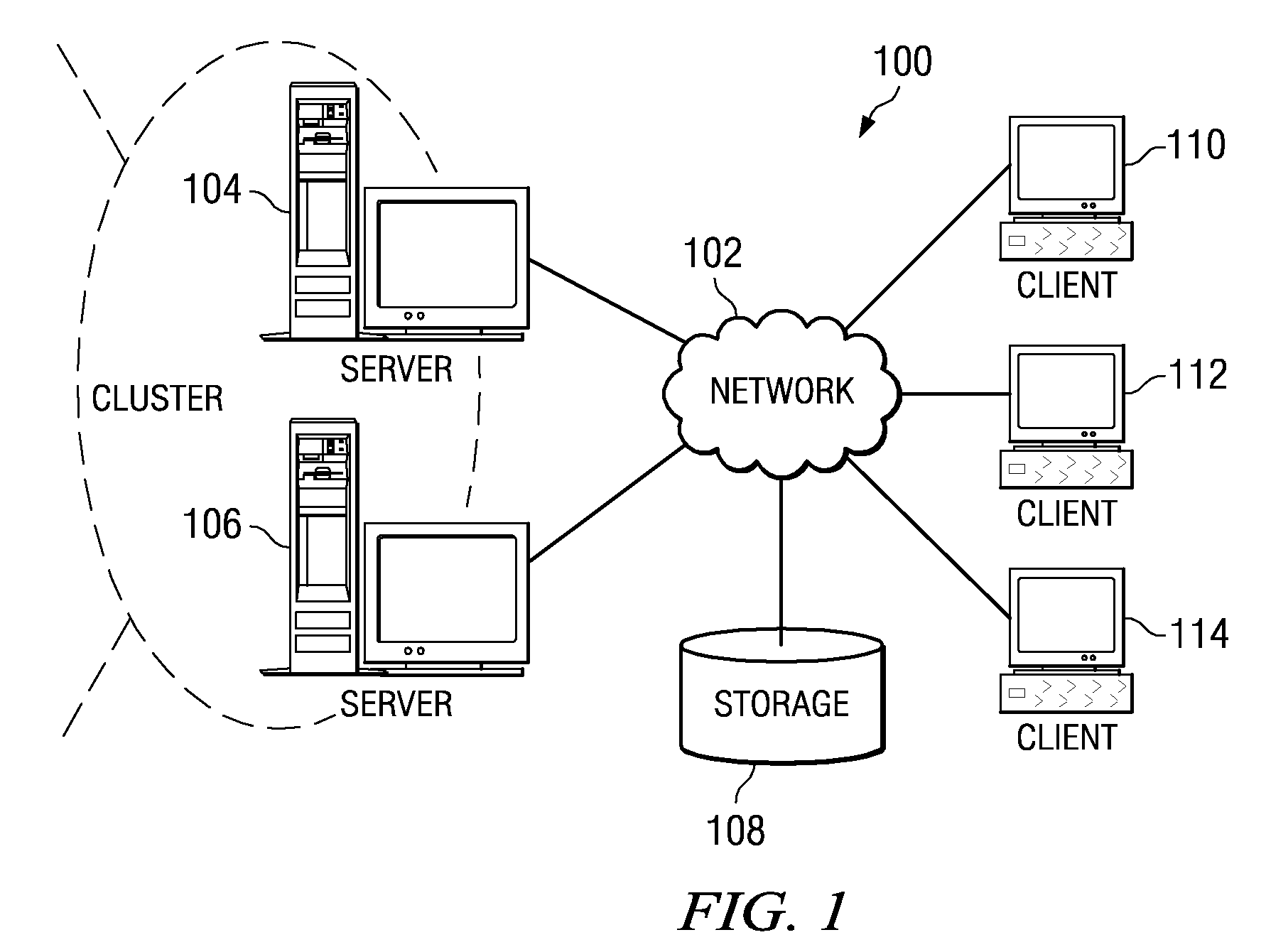

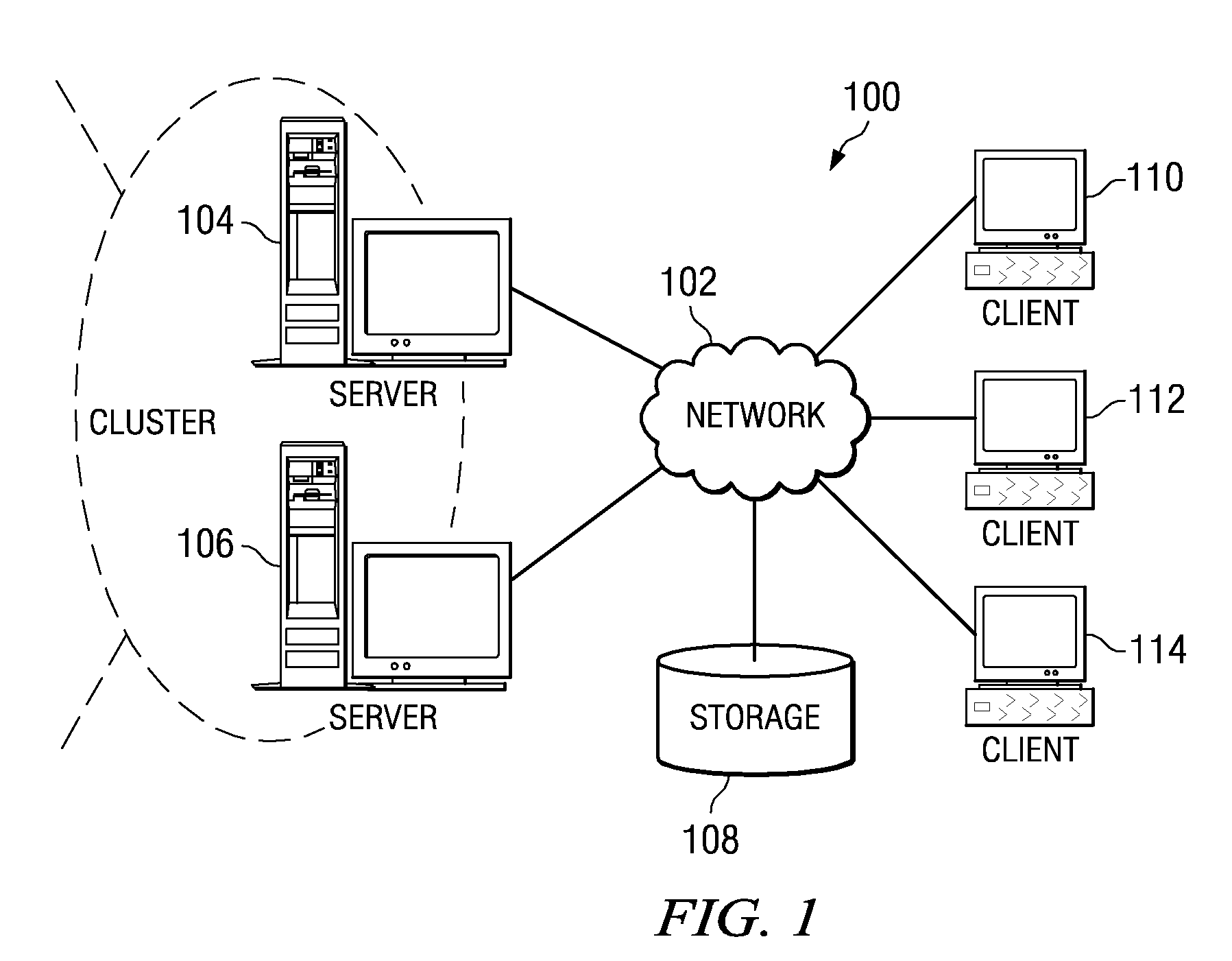

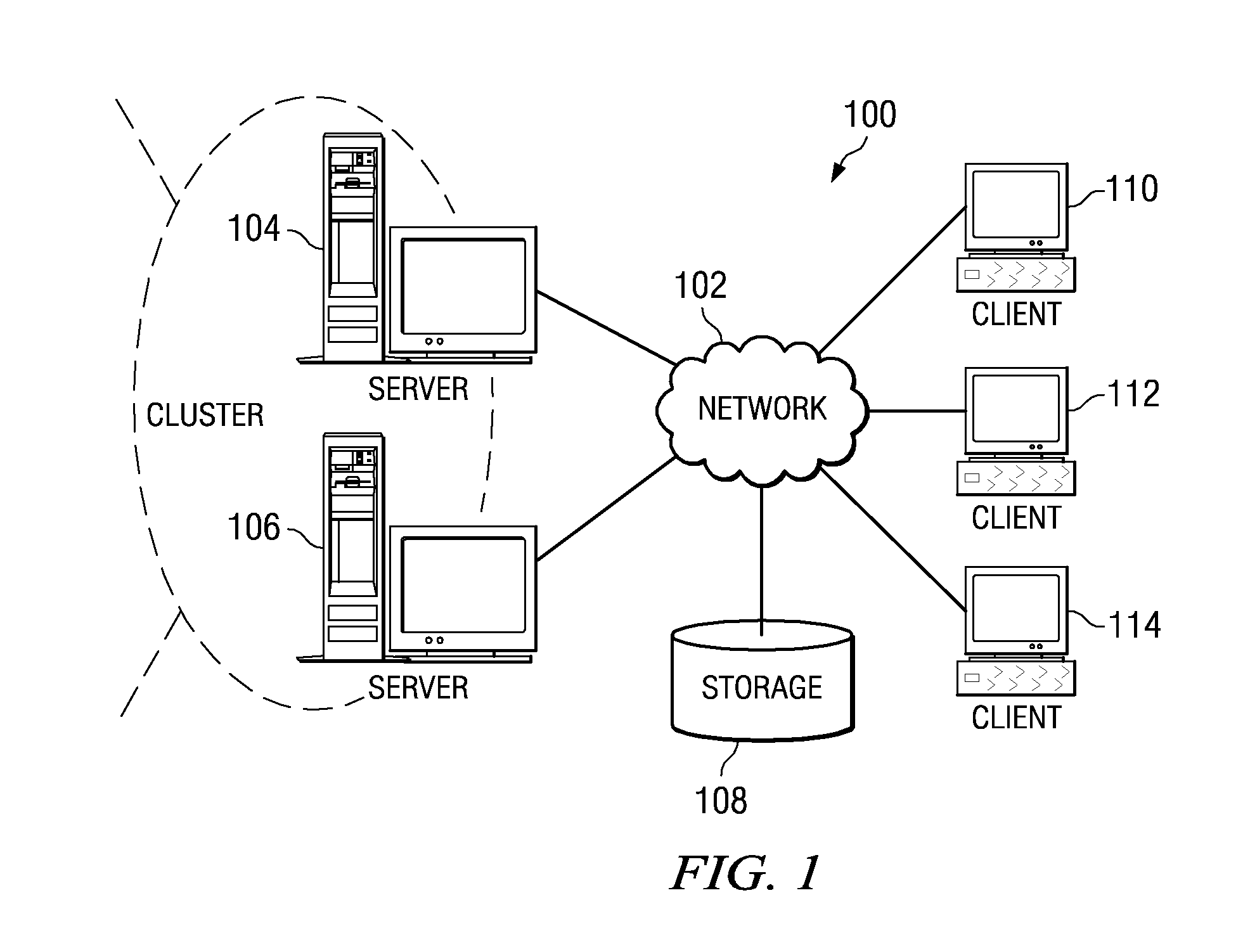

Controlling data storage in an array of storage devices

ActiveUS20140325262A1Reduce mismatchLow costRedundant hardware error correctionData storeDevice failure

Methods, apparatus and computer programs have been provided for mitigating a problem of non-optimal recovery from storage device failures. A method involves determining a required write performance for rebuilding data of a failed device, based at least partly on the potential read performance of storage devices in a data rebuild; and allocating a virtual storage area within available storage, which allocation of virtual storage is based at least partly on the required write performance. Data is rebuilt by writing to the allocated virtual storage area, and data recovery is completed by migrating this rebuilt data to at least one data storage device such as a spare physical storage device within the array.

Owner:GLOBALFOUNDRIES US INC

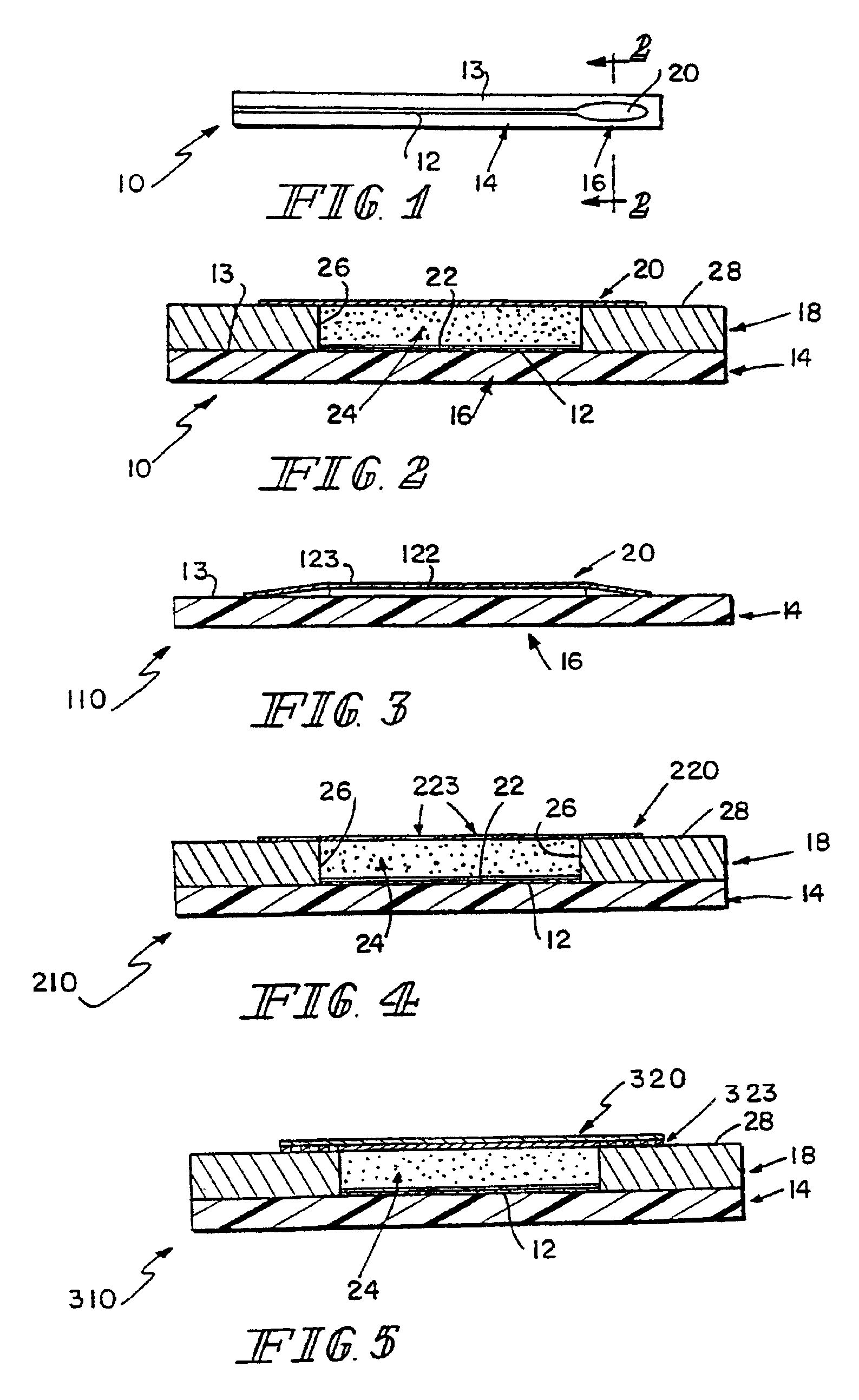

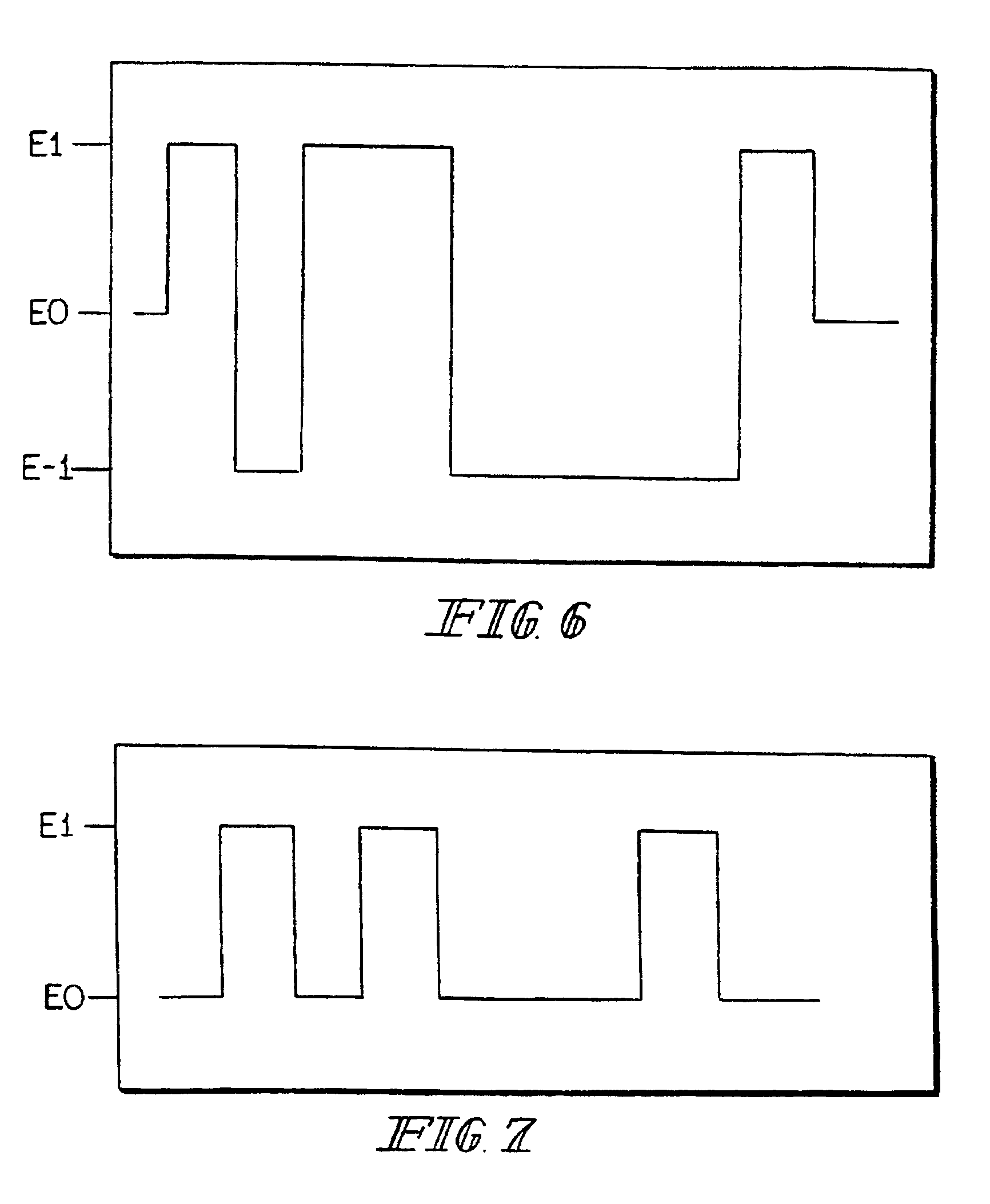

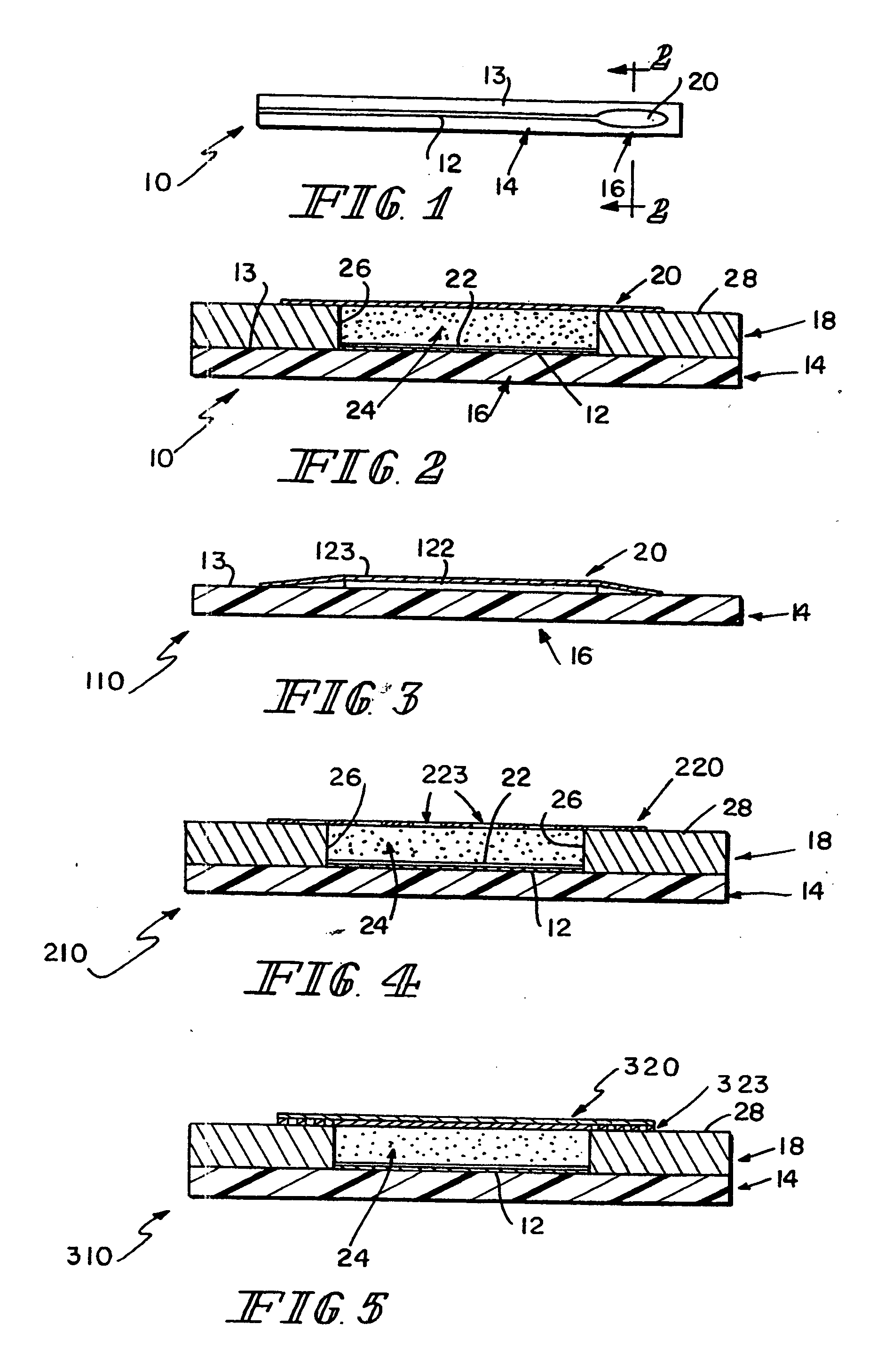

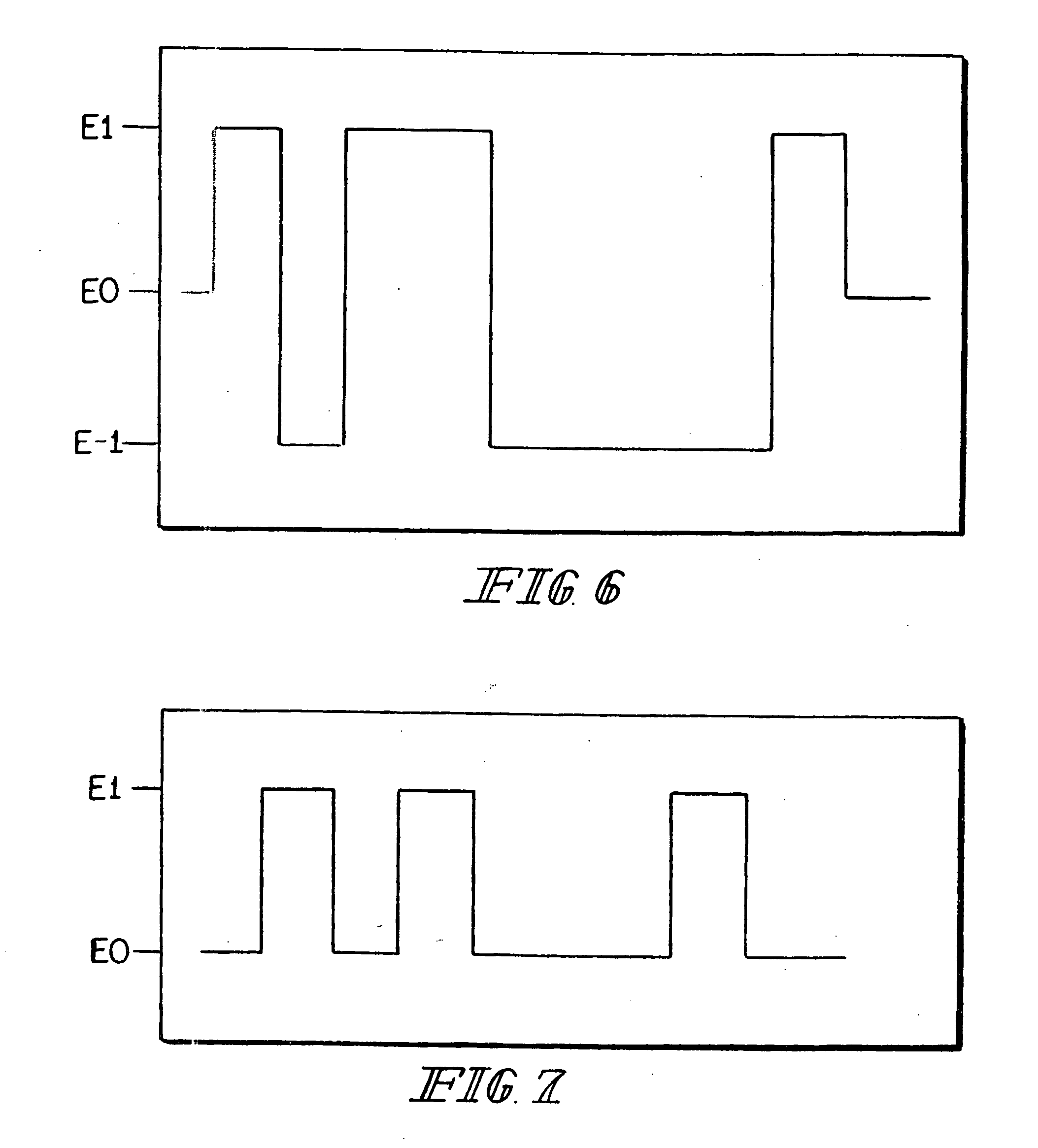

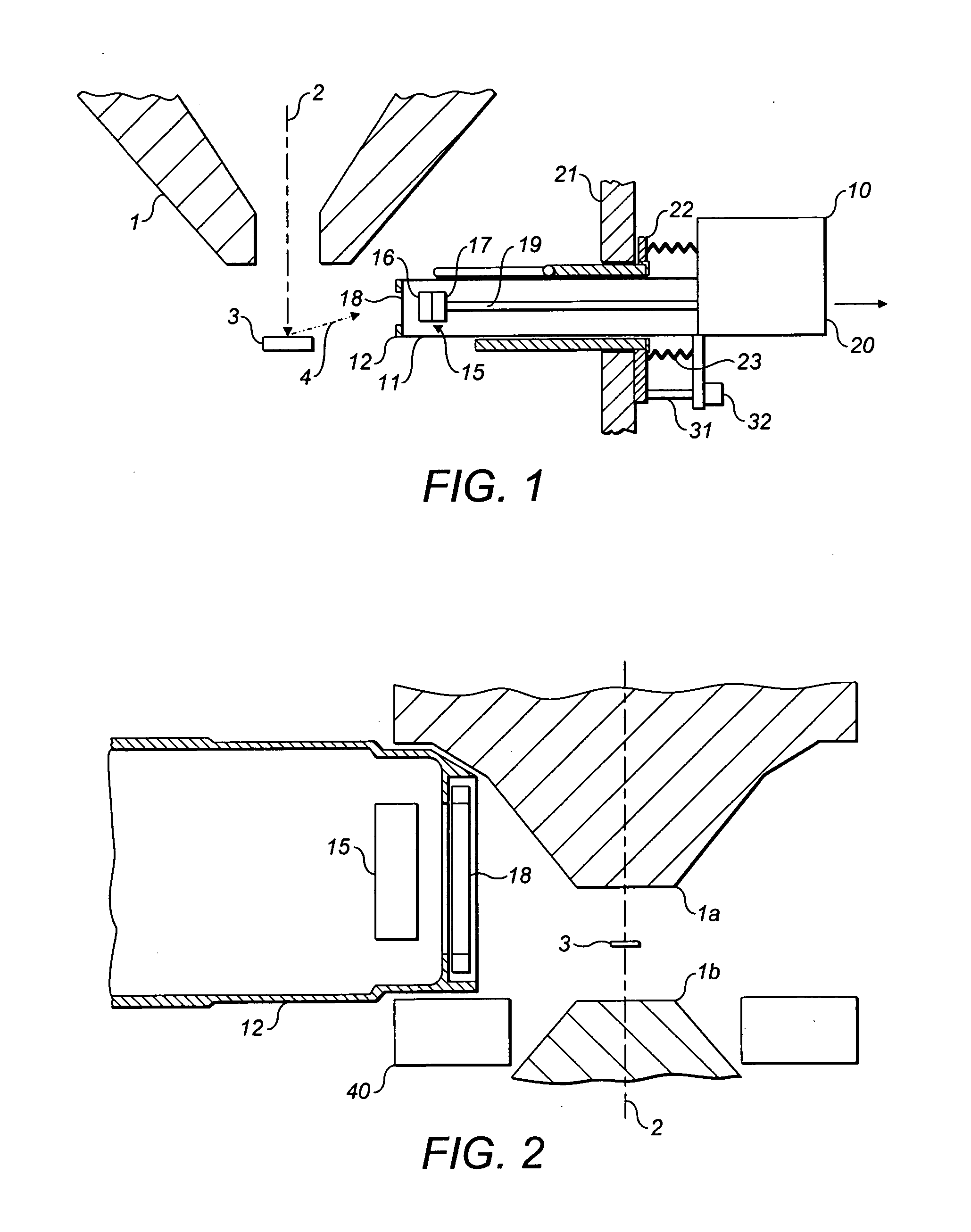

Small volume biosensor for continuous analyte monitoring

InactiveUS7045054B1Increase ratingsMinimize periodImmobilised enzymesBioreactor/fermenter combinationsRedox enzymesContinuous analysis

Sensors (10, 110, 210, 310, 410) and a method for detecting an analyte are described. Sensors (10, 110, 210, 310, 410) each have a volume of a hydrophilic medium (24) that retains an amount of analyte proportionate to the concentration of analyte in a biological fluid, electrodes (12) and a redox enzyme in contact with medium (24), and an electron transfer mediator. The fluid contacts sensors (10, 110, 210, 310, 410) and at initially predetermined intervals intermittently applies a potential to electrode (12) sufficient to oxidize the mediator and sensing current through electrode (12) as a function of the duration of the applied potential. The applied mediator oxidizing applied potential is maintained for a period of time sufficient to determine the rate of change of current with time through electrode (12). The current flow is correlated with the current flow for known concentrations of the analyte in medium (24).

Owner:ROCHE DIABETES CARE INC

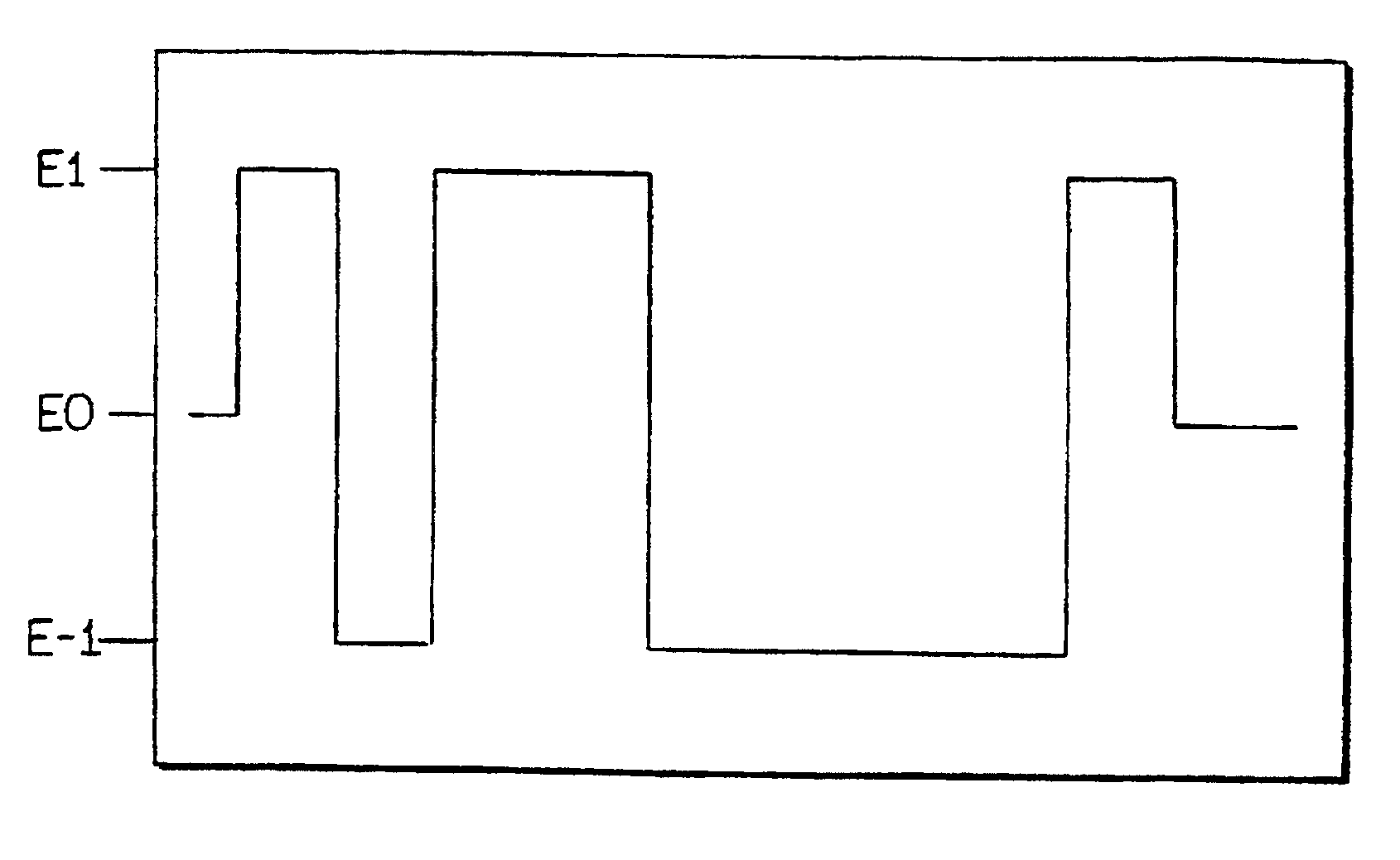

Electrochemical sensor and method for continuous analyte monitoring

InactiveUS20050211572A1Minimize periodLowImmobilised enzymesBioreactor/fermenter combinationsBiological fluidApplied potential

Sensors and a method for detecting an analyte are described. Sensors each have a volume of a hydrophilic medium that retains an amount of analyte proportionate to the concentration of analyte in a biological fluid, electrodes and a redox enzyme in contact with medium, and an electron transfer mediator. The fluid contacts sensors and at initially predetermined intervals intermittently applies a potential to electrode sufficient to oxidize the mediator and sensing current through electrode as a function of the duration of the applied potential. The applied mediator oxidizing applied potential is maintained for a period of time sufficient to determine the rate of change of current with time through electrode. The current flow is correlated with the current flow for known concentrations of the analyte in medium.

Owner:ROCHE DIABETES CARE INC

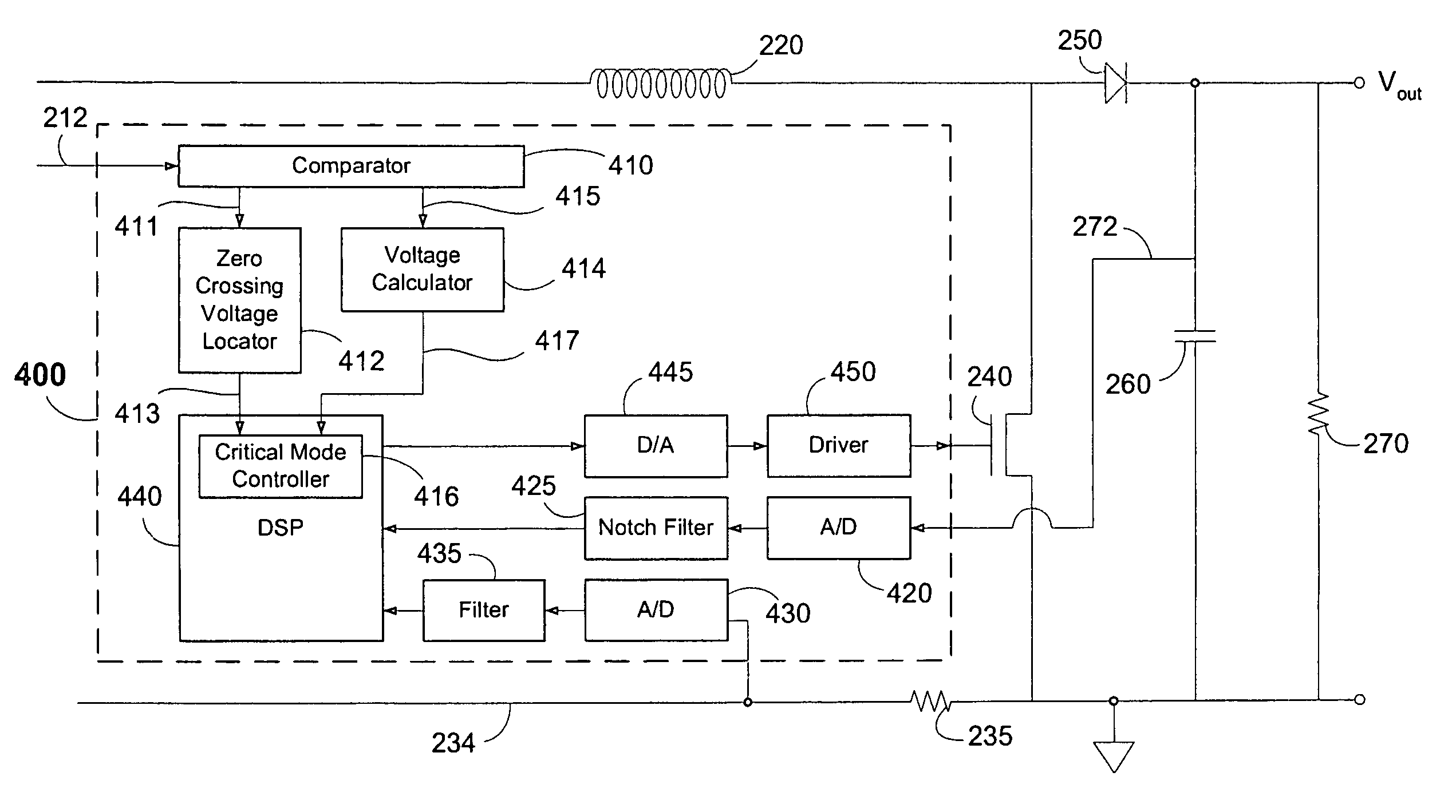

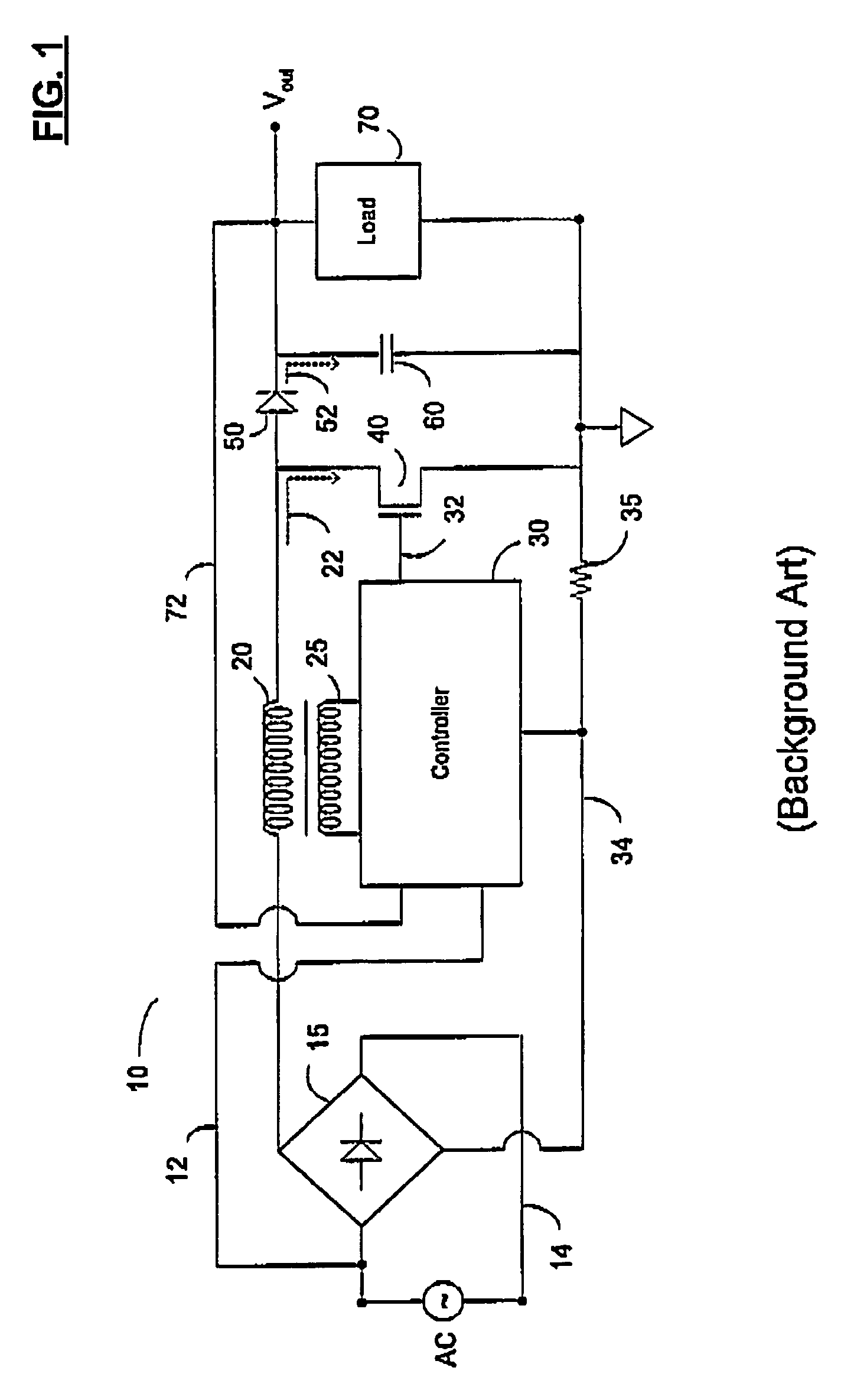

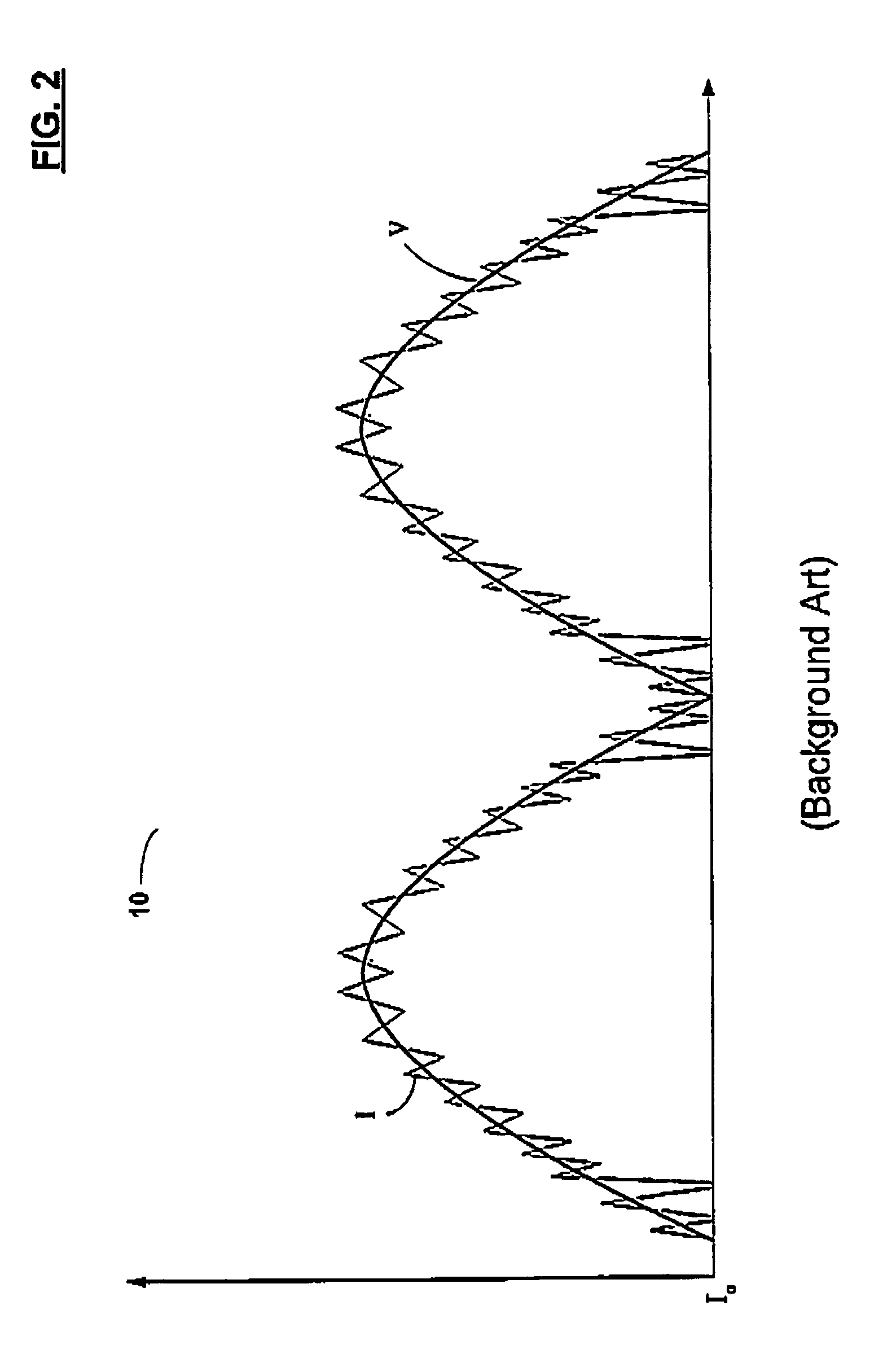

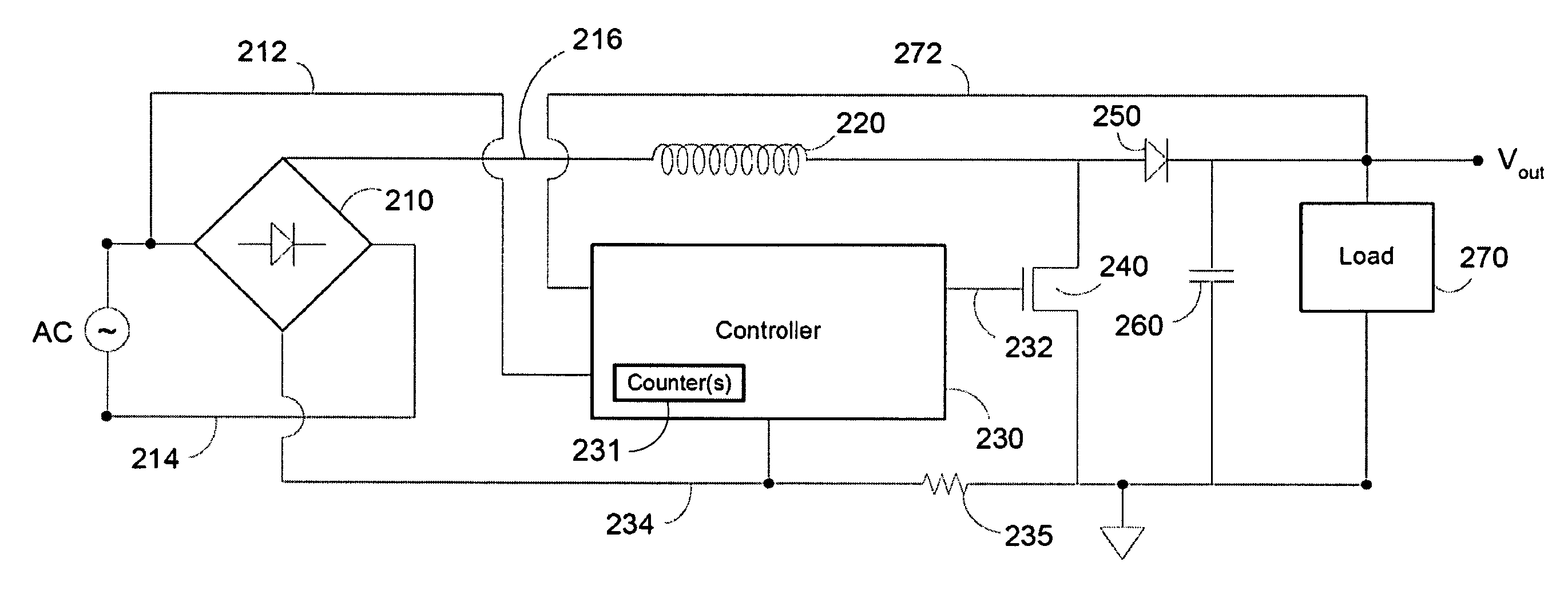

Circuits, systems, methods, and software for power factor correction and/or control

ActiveUS7292013B1Minimize periodMinimize powerAc-dc conversion without reversalEfficient power electronics conversionImage resolutionPower factor control

Circuits, systems, methods and software for controlling a power conversion and / or correcting and / or controlling a power factor in such conversion(s). The present invention generally takes a computational approach to reducing or minimizing zero current periods in the critical mode of power converter operation, and advantageously reduces zero current periods in the critical mode of power converter operation, thereby maximizing the power factor of the power converter in the critical mode and reducing noise that may be injected back into AC power lines. The present power factor controller allows for greater design flexibility, reduced design complexity, and reduced resolution and greater tolerance for error in certain parameter measurements useful in power factor correction and / or control.

Owner:MARVELL ASIA PTE LTD

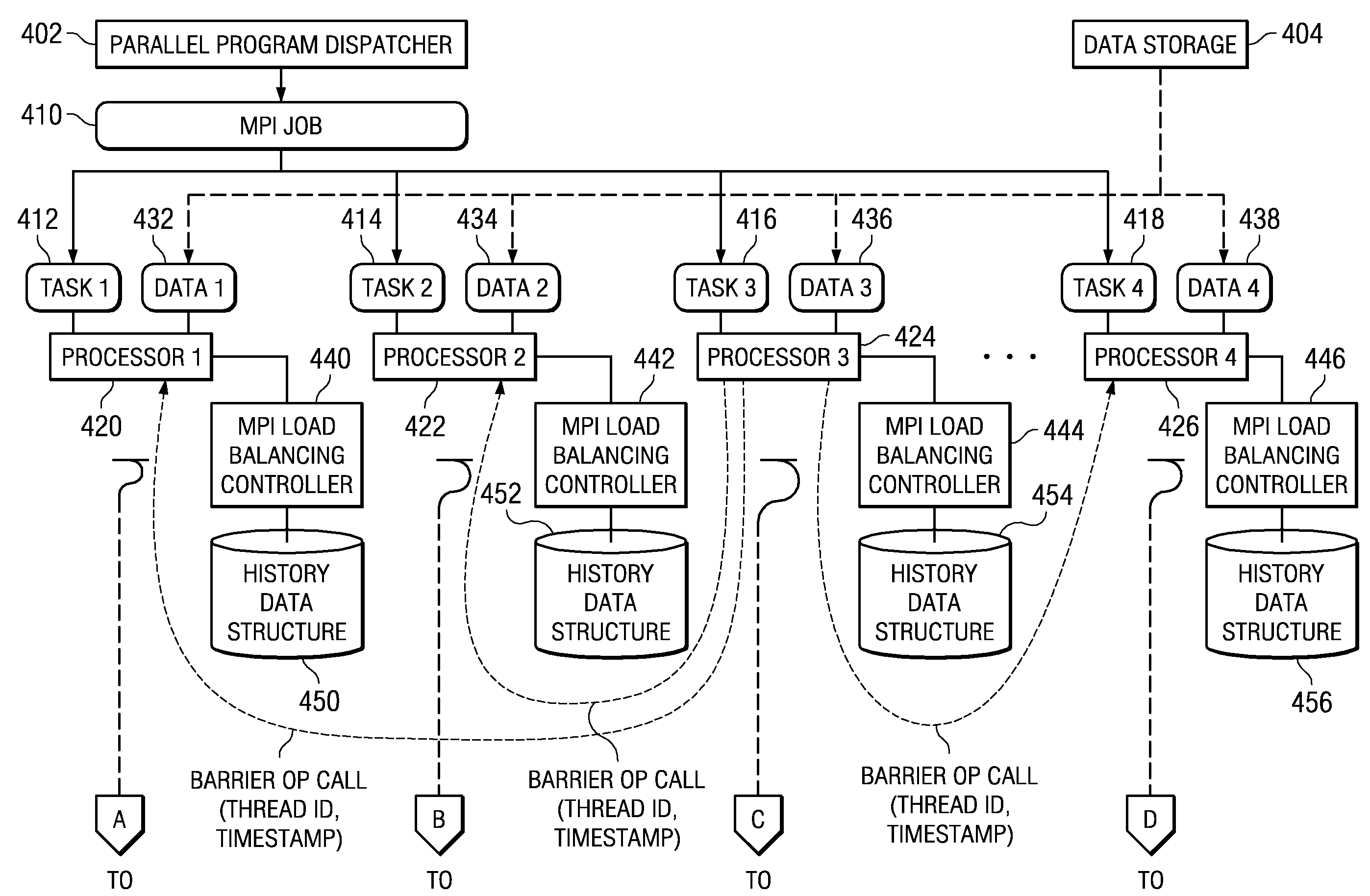

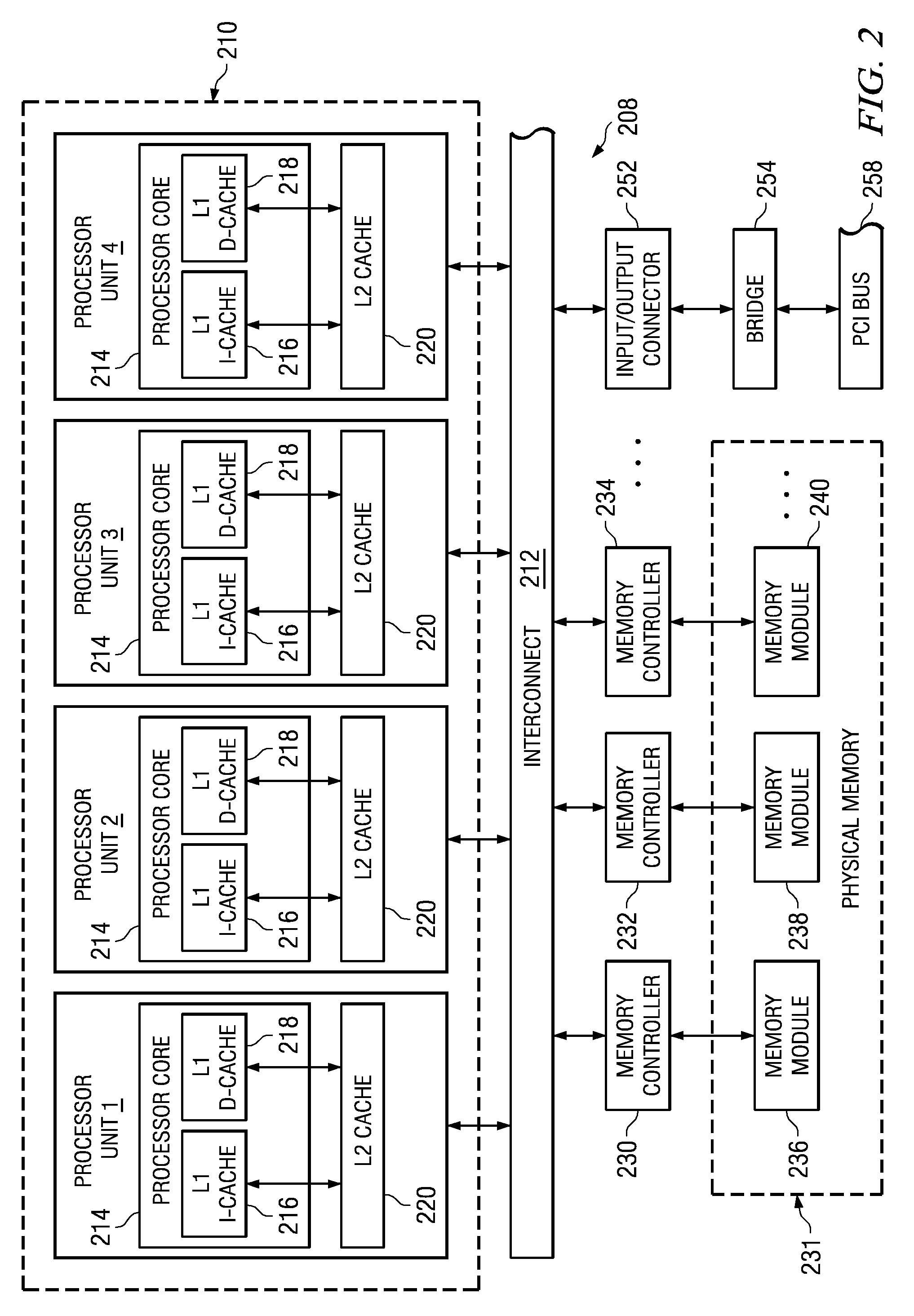

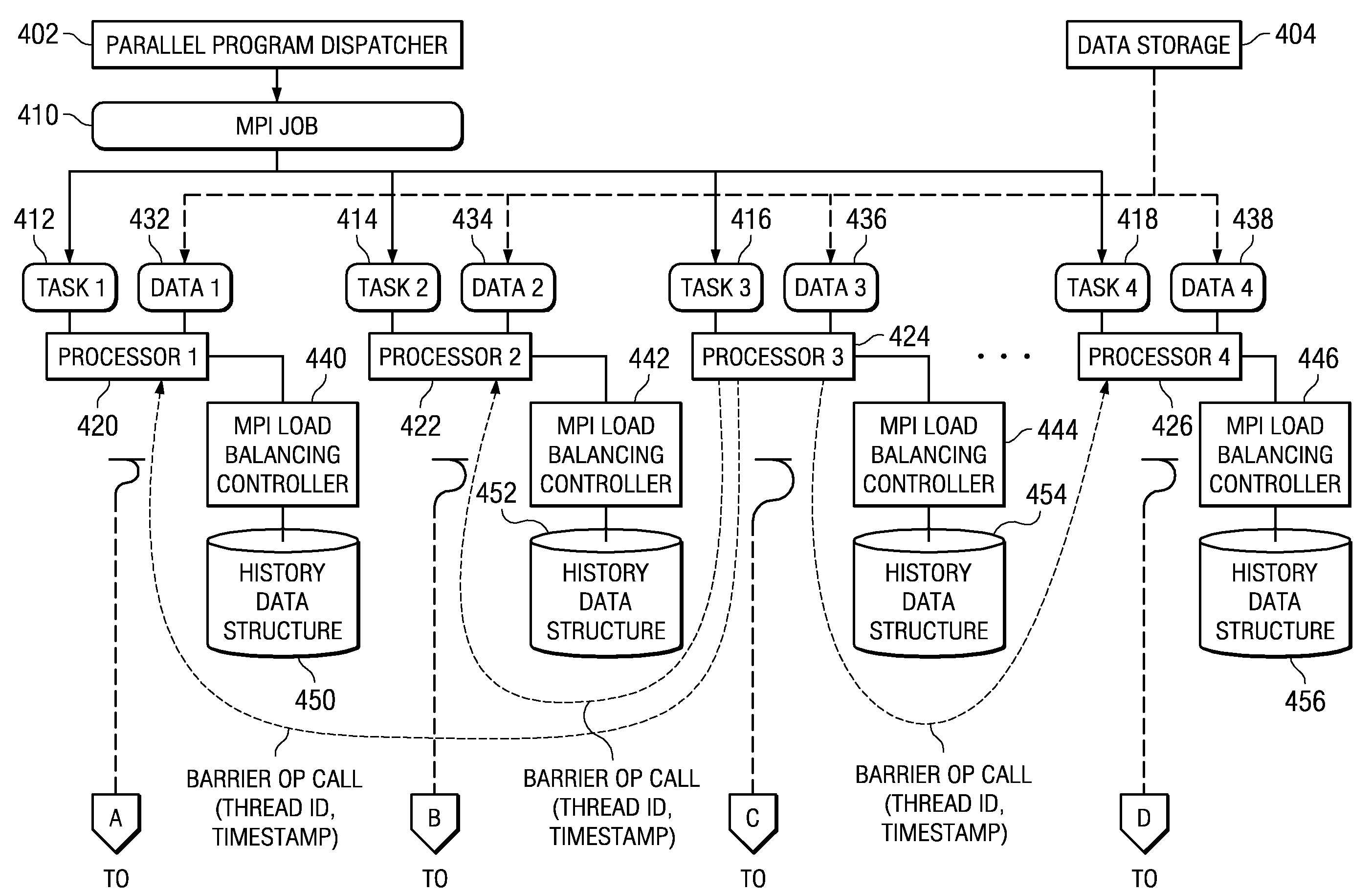

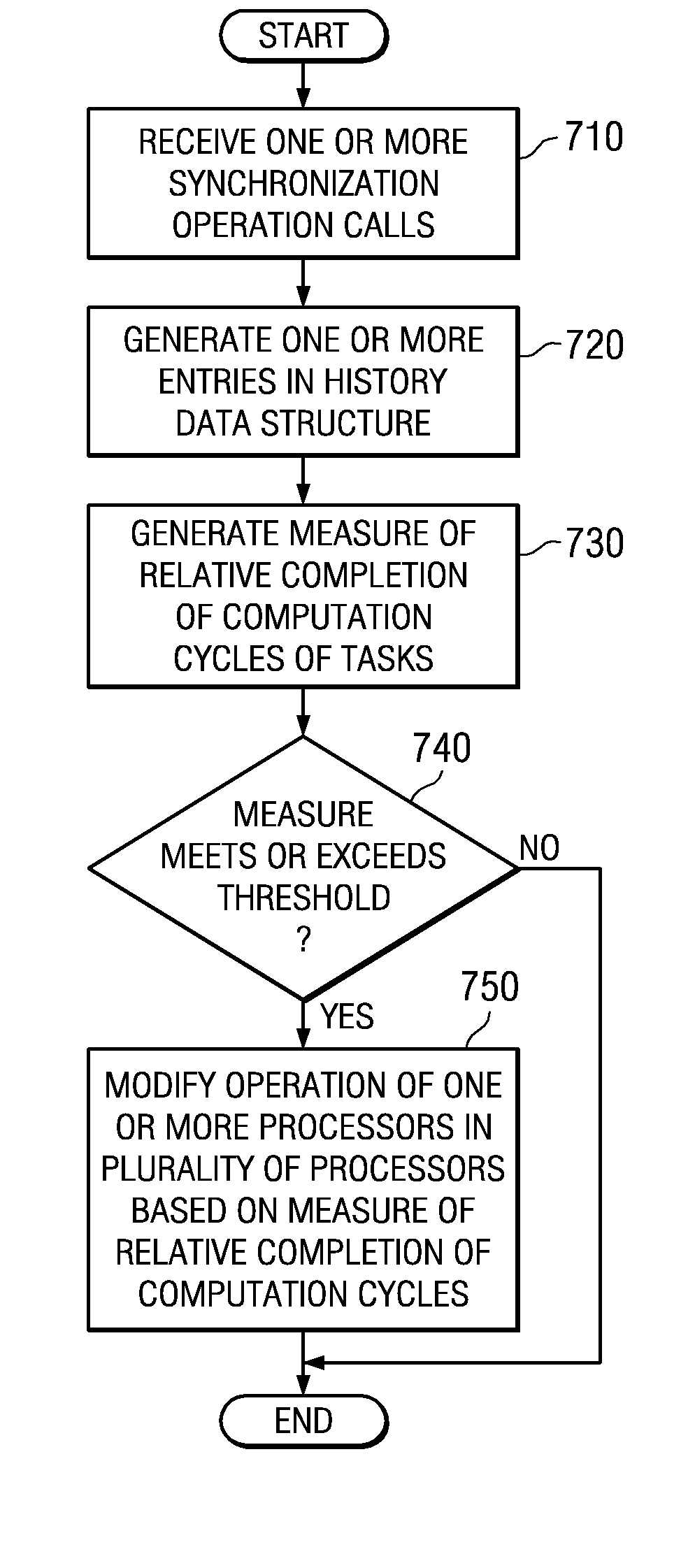

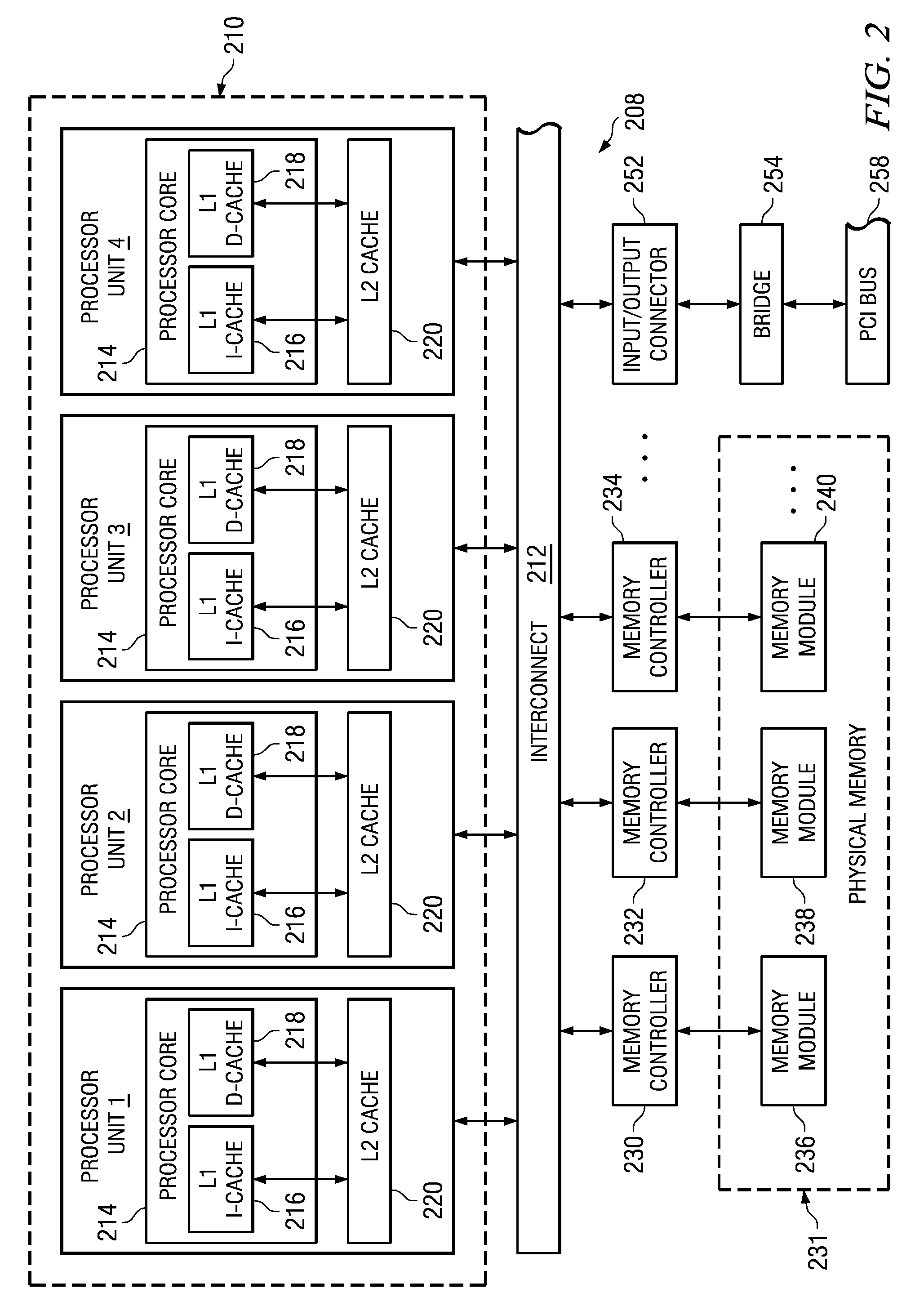

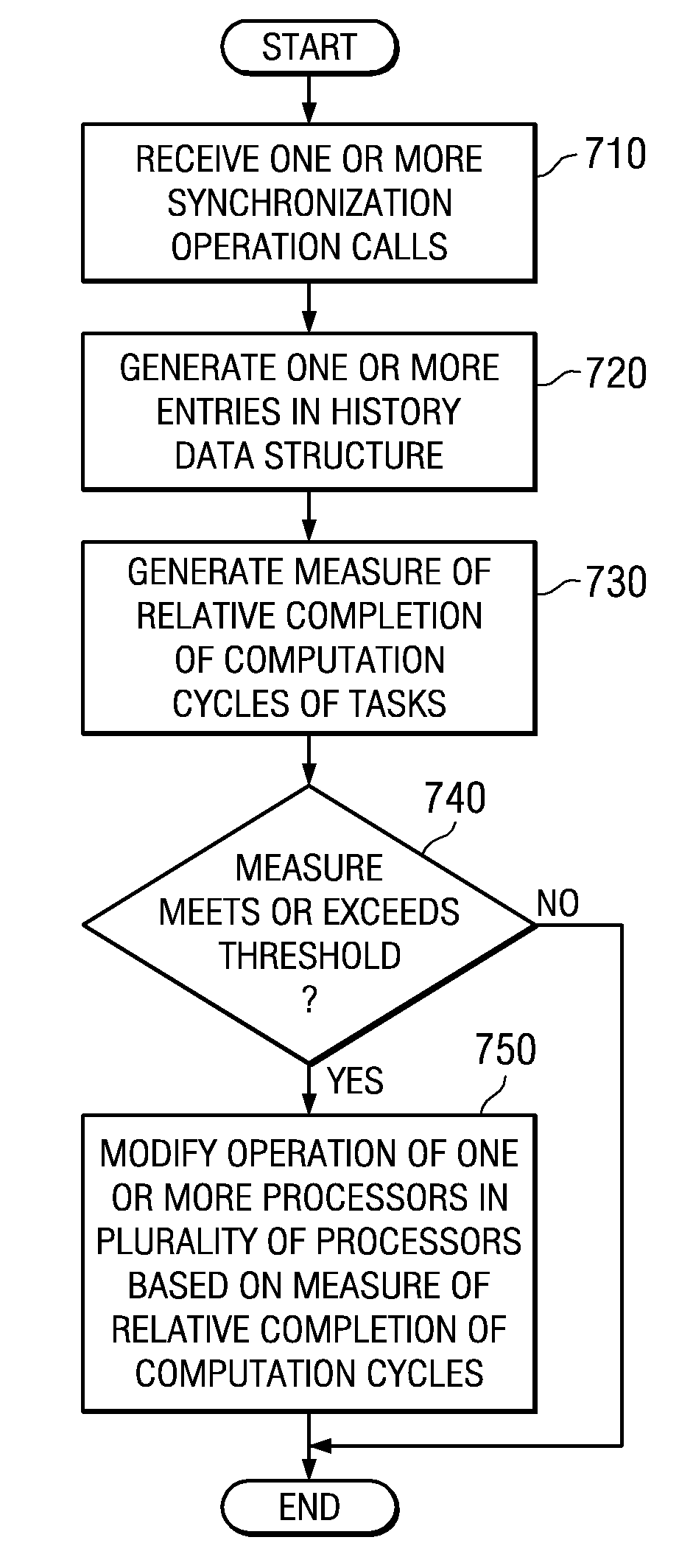

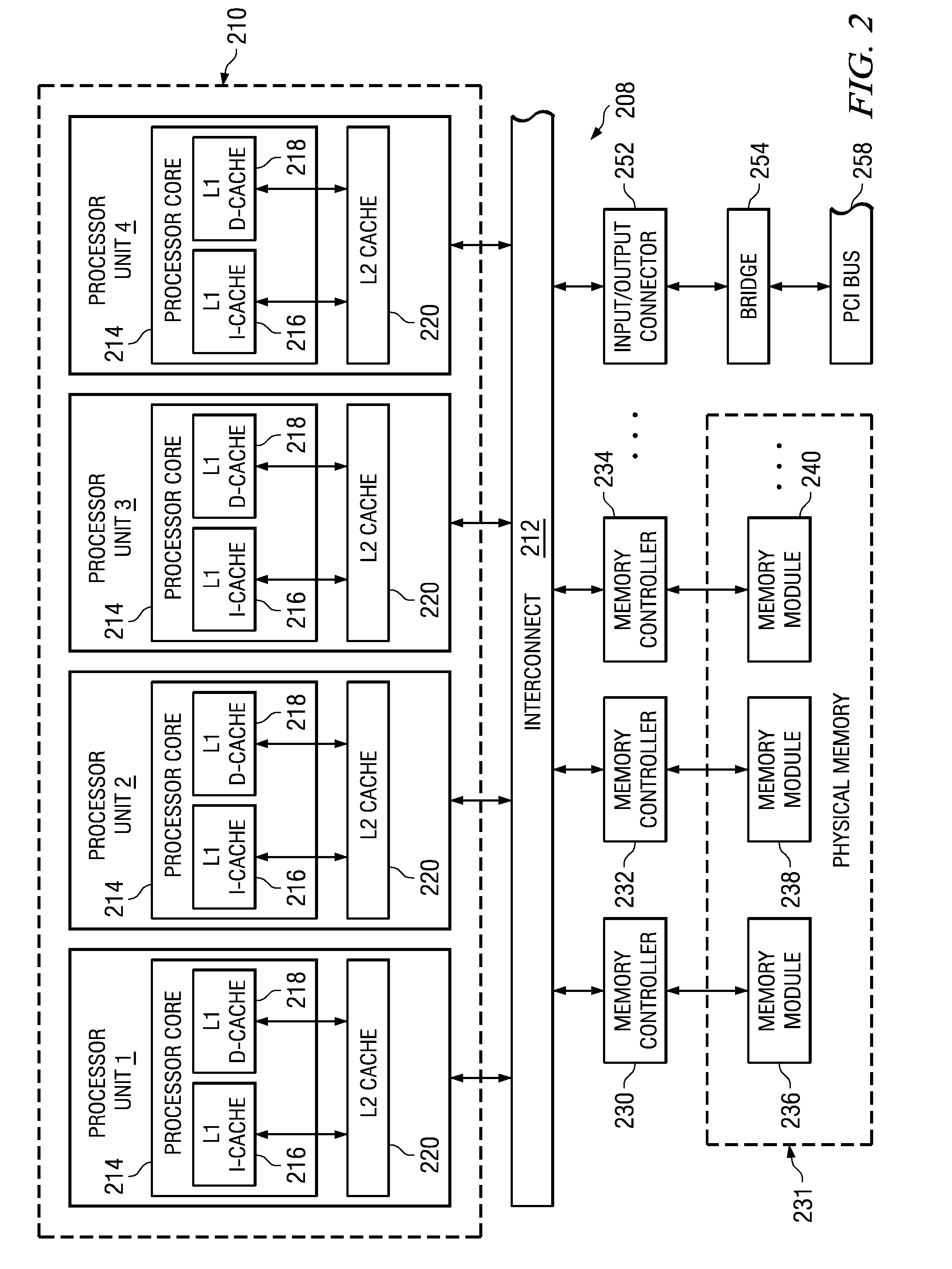

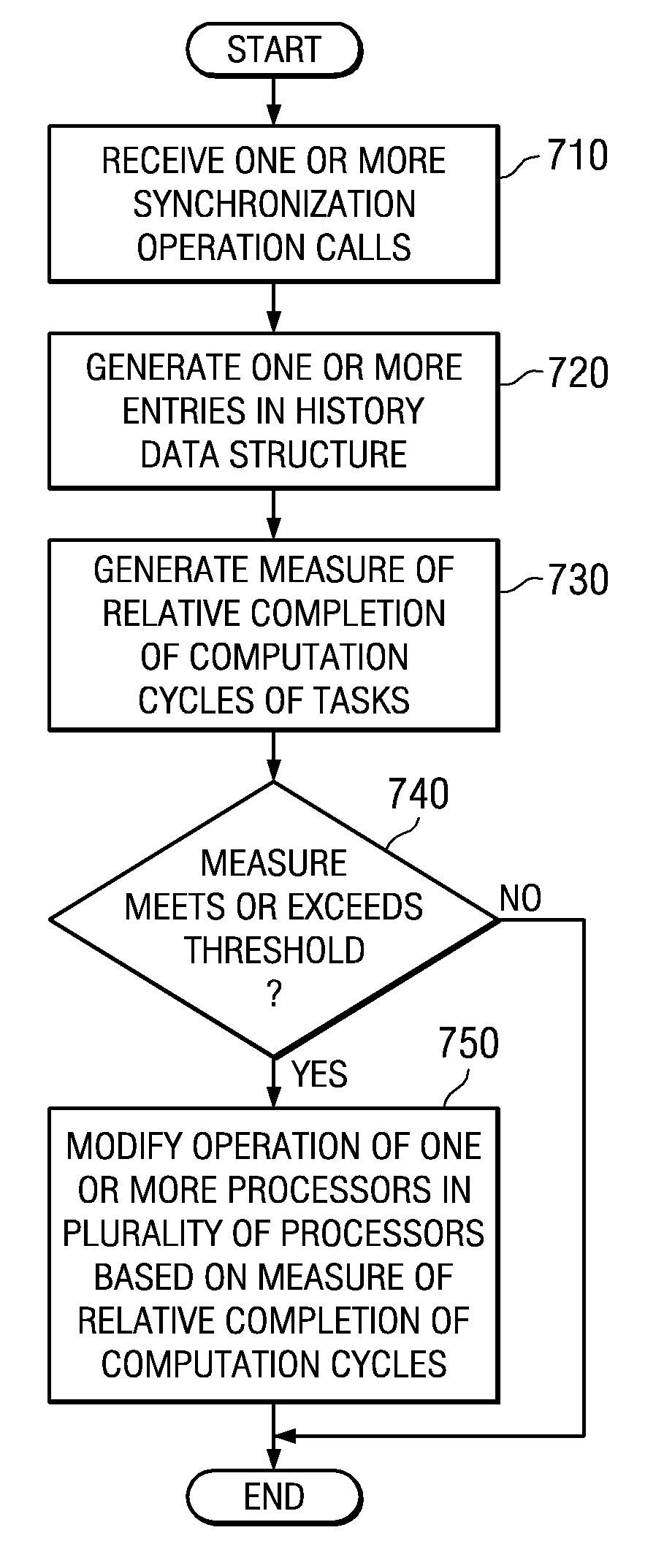

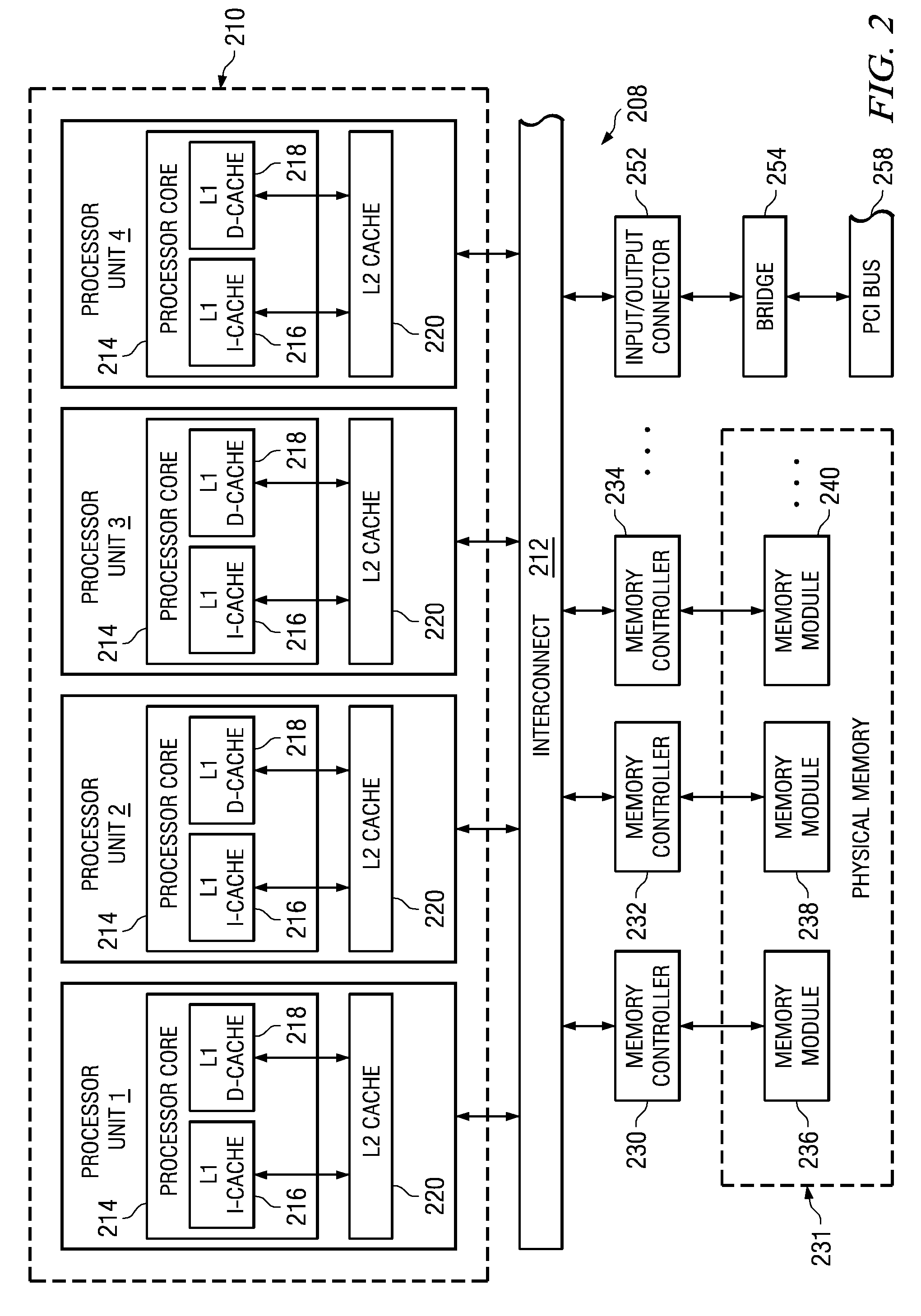

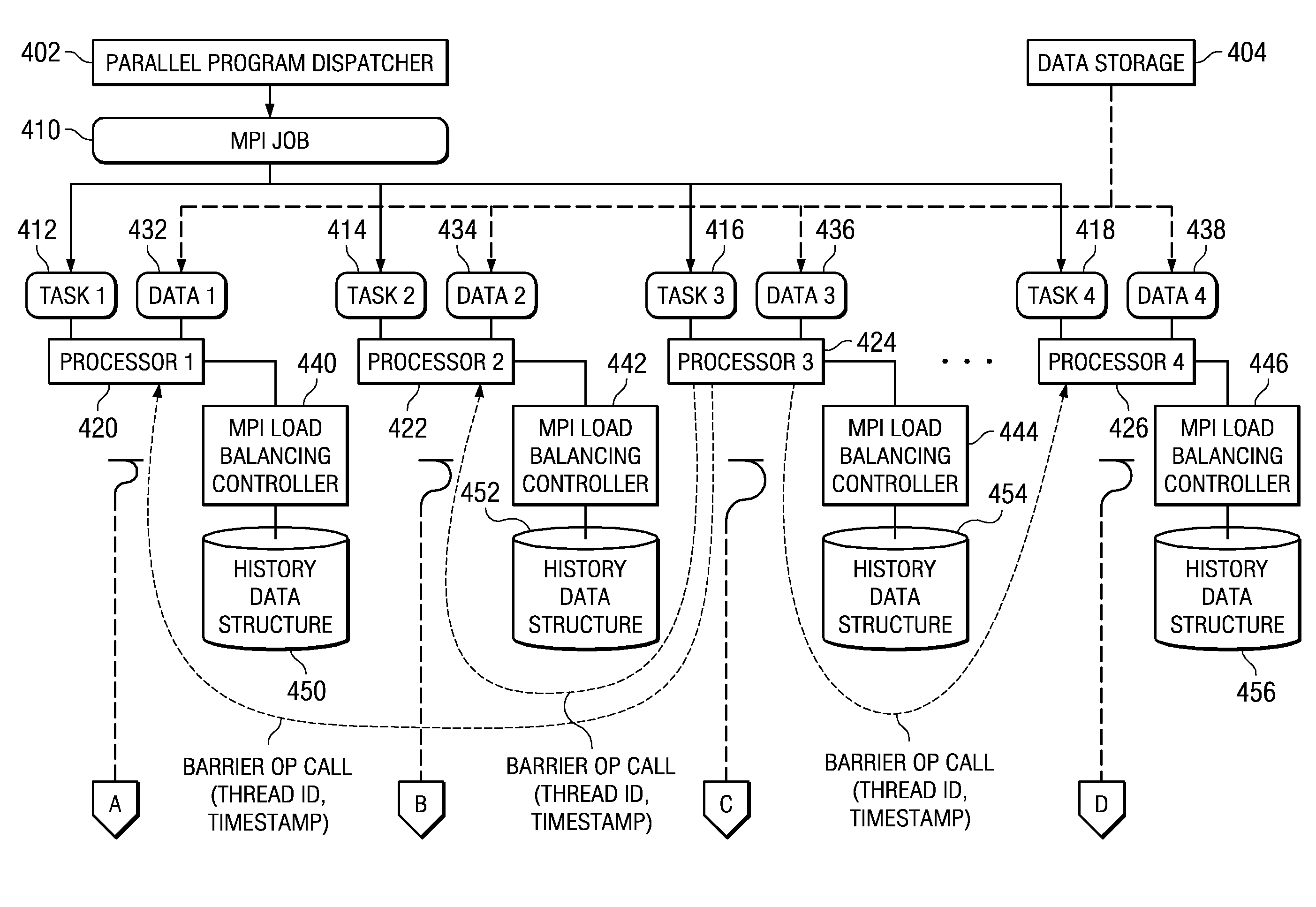

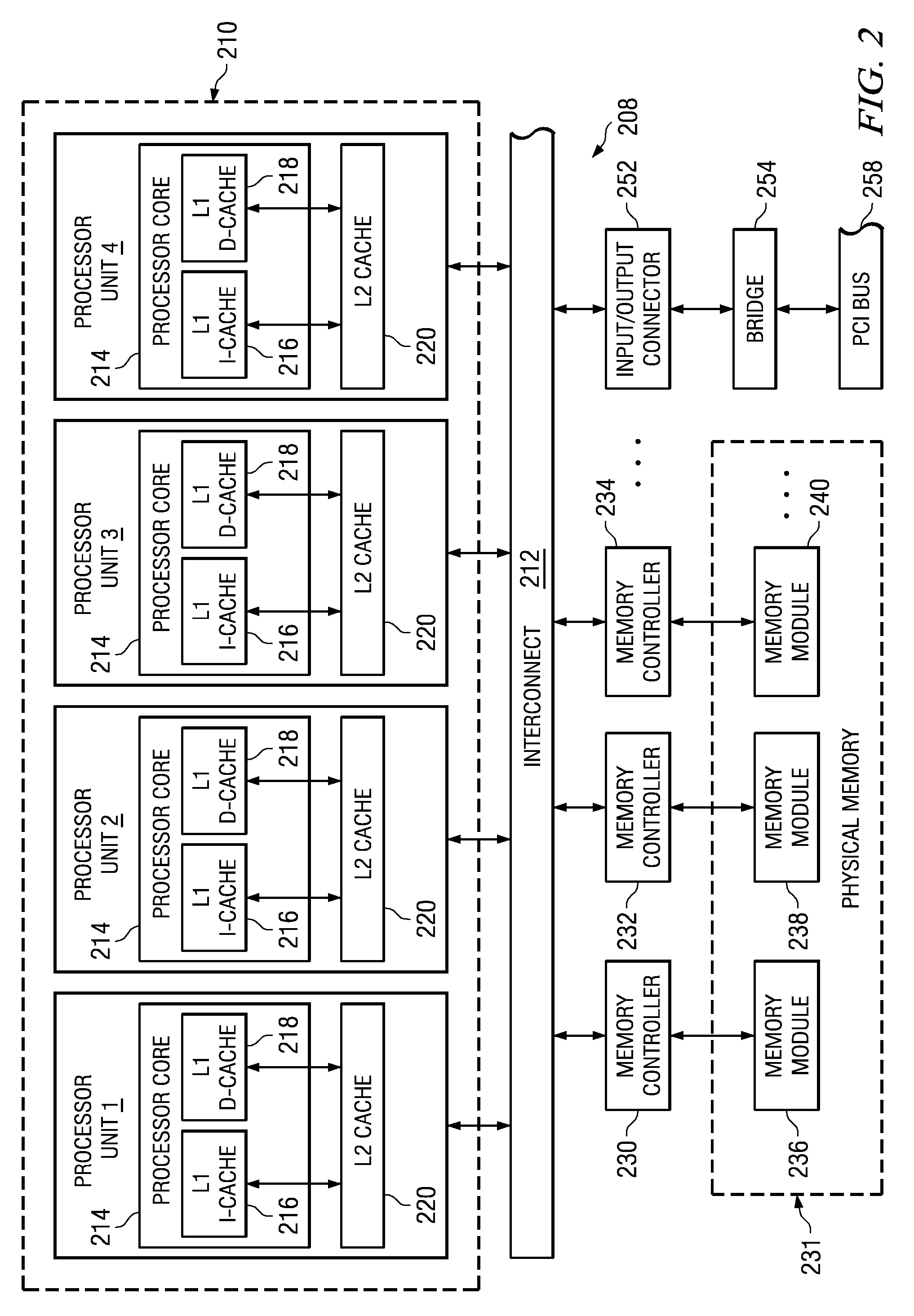

System and Method for Hardware Based Dynamic Load Balancing of Message Passing Interface Tasks By Modifying Tasks

InactiveUS20090064168A1Minimize periodWasted processor cyclesMultiprogramming arrangementsMemory systemsDynamic load balancingMessage Passing Interface

A system and method are provided for providing hardware based dynamic load balancing of message passing interface (MPI) tasks by modifying tasks. Mechanisms for adjusting the balance of processing workloads of the processors executing tasks of an MPI job are provided so as to minimize wait periods for waiting for all of the processors to call a synchronization operation. Each processor has an associated hardware implemented MPI load balancing controller. The MPI load balancing controller maintains a history that provides a profile of the tasks with regard to their calls to synchronization operations. From this information, it can be determined which processors should have their processing loads lightened and which processors are able to handle additional processing loads without significantly negatively affecting the overall operation of the parallel execution system. Thus, operations may be performed to shift workloads from the slowest processor to one or more of the faster processors.

Owner:IBM CORP

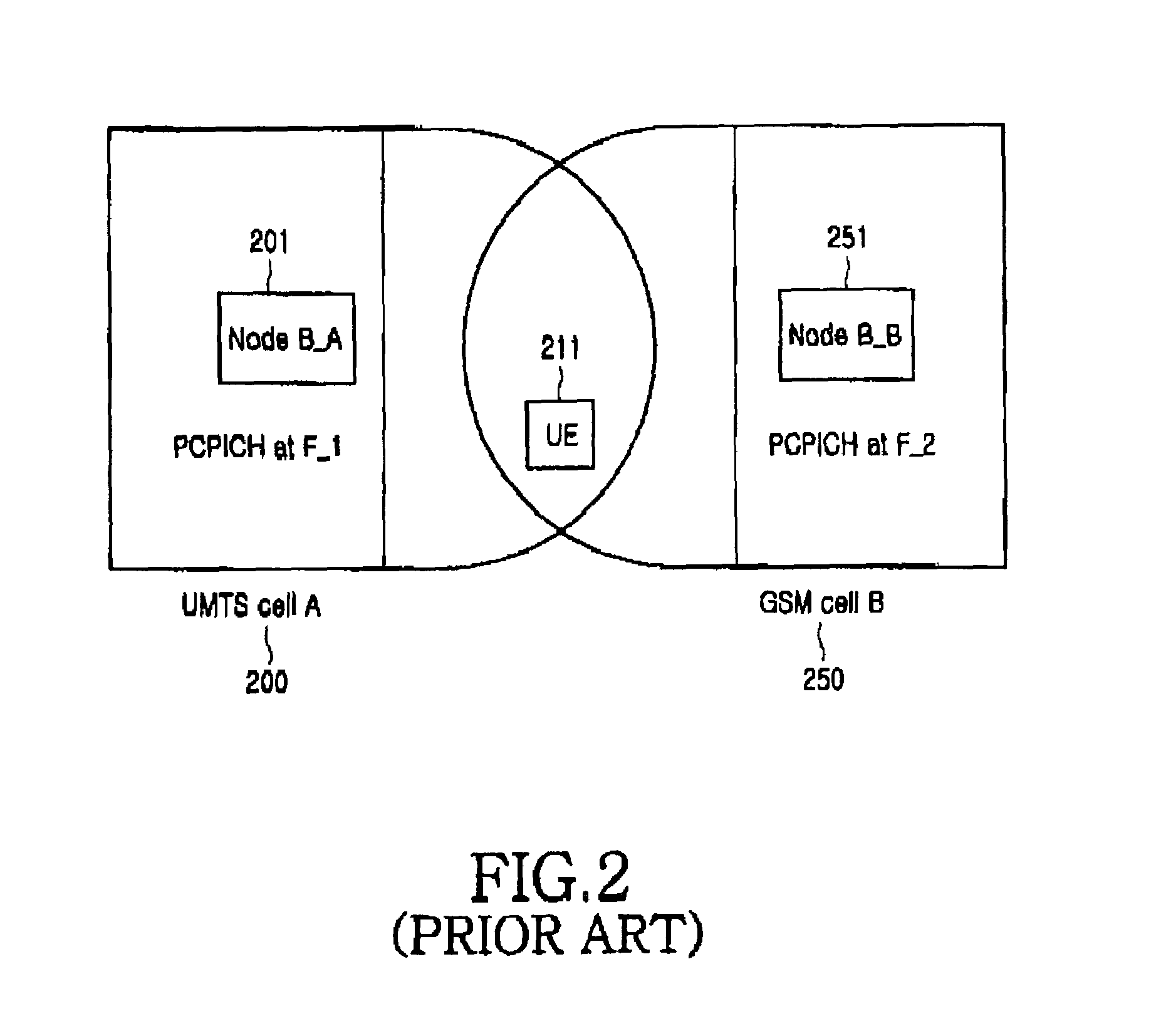

Apparatus and method for minimizing a non-transmittable period due to a compressed mode in a mobile communication system supporting HSDPA

InactiveUS7372842B2Minimize periodMaximize capacityError prevention/detection by using return channelTime-division multiplexRelevant informationTime segment

An apparatus and method for minimizing a non-transmittable period where high-speed packet data transmission is impossible. In the apparatus, a non-transmittable period calculator receives transmission gap-related information for a UE from a radio network controller, calculates a transmission gap starting point based on the transmission gap-related information, defines a period determined by excluding the downlink transmission period from the transmission gap starting point as the non-transmittable period, and suspends transmission of the high-speed packet data to the UE for the non-transmittable period. A scheduler performs scheduling on the high-speed packet data under the control of the non-transmittable period calculator so that transmission of the high-speed packet data to the UE is suspended for the downlink transmission period.

Owner:SAMSUNG ELECTRONICS CO LTD

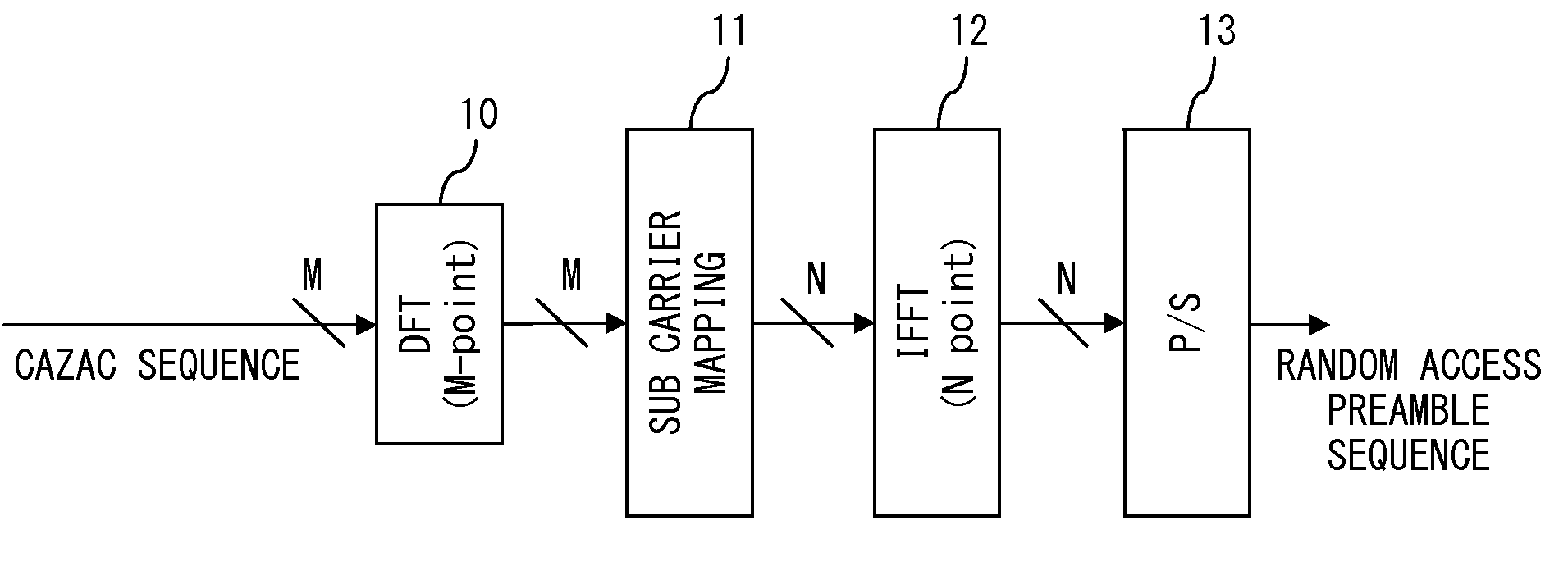

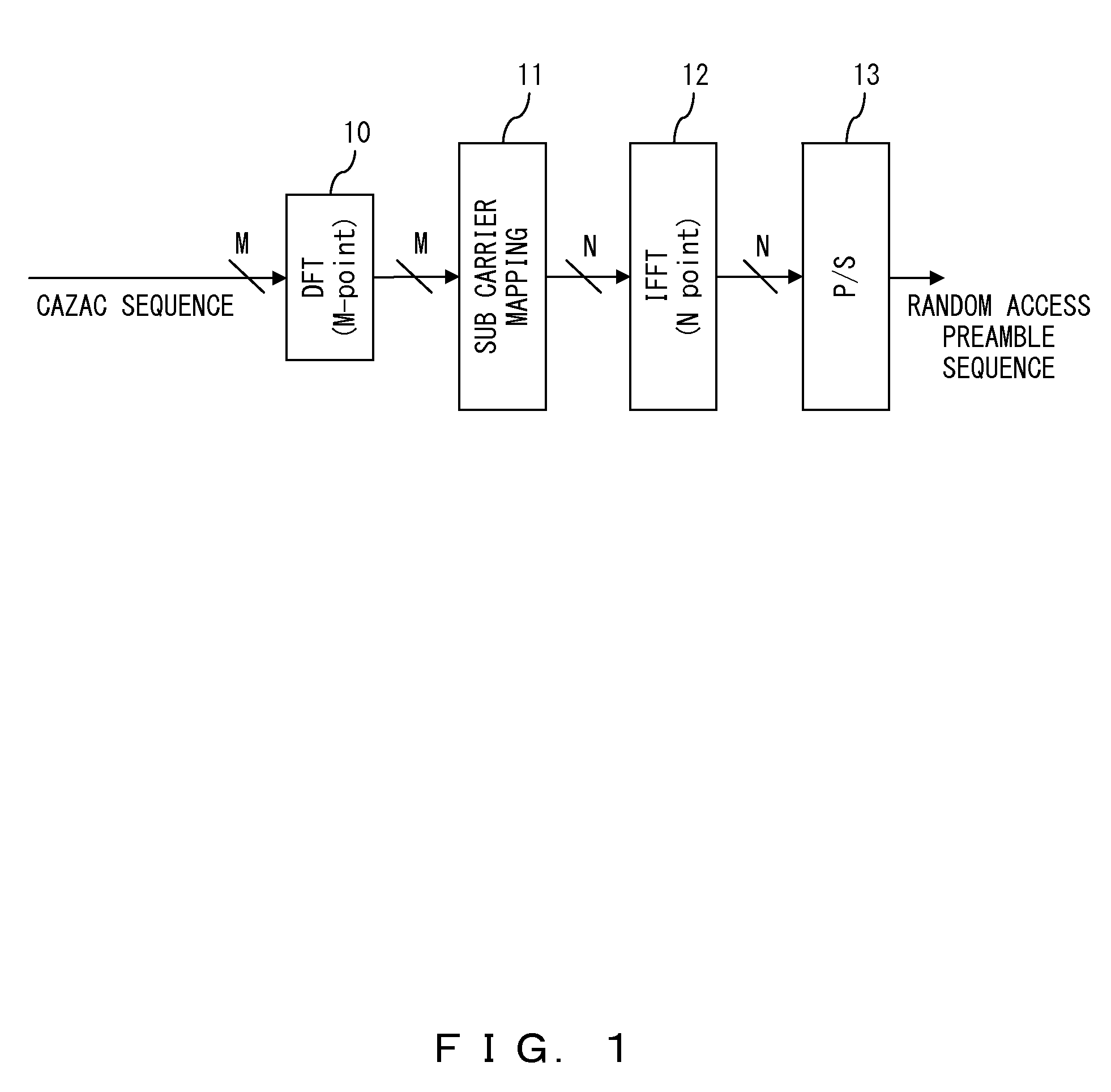

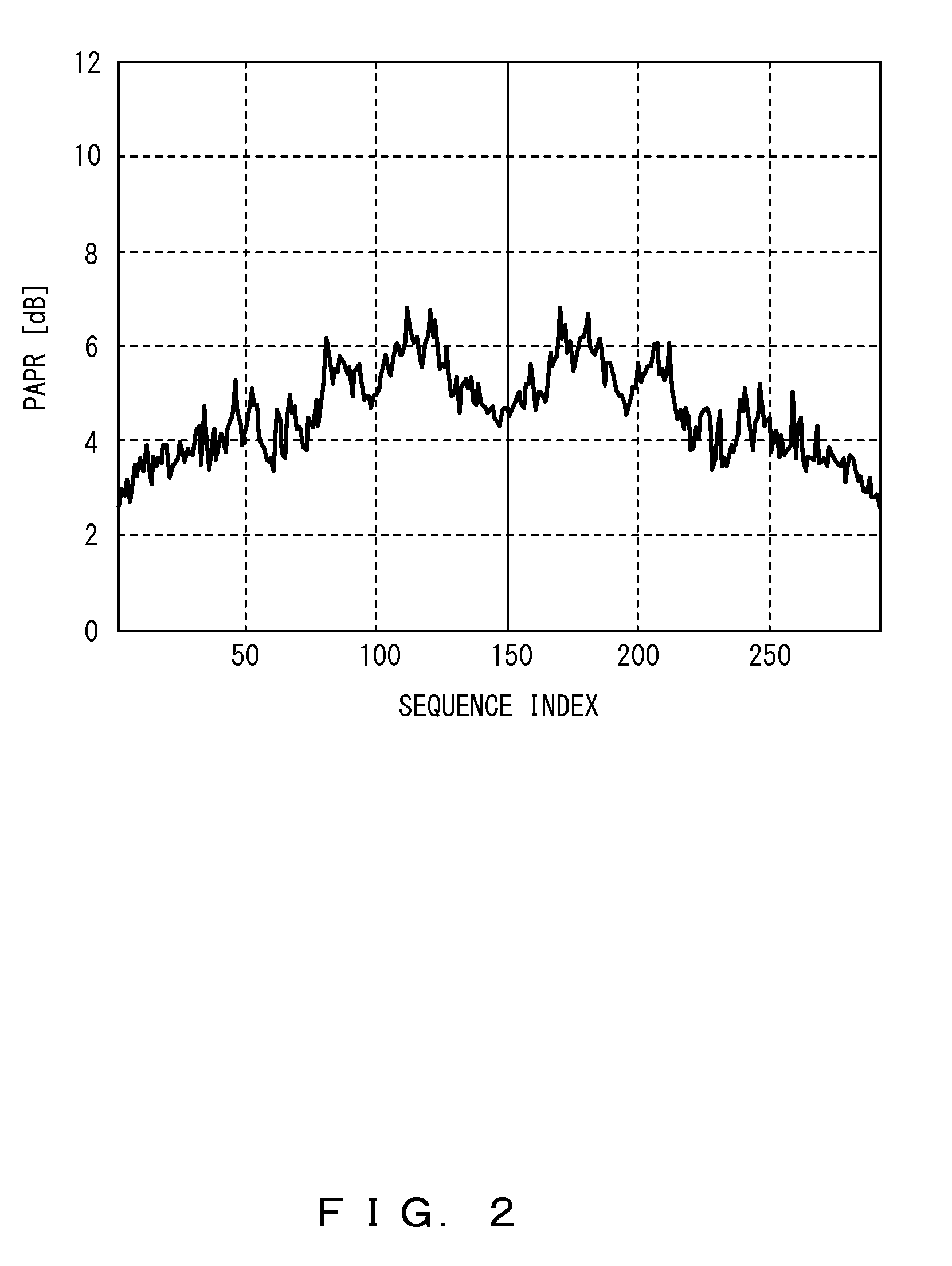

Wireless communication device

ActiveUS20090180443A1Minimize periodEffective performanceSynchronisation arrangementTime-division multiplexHandoverRandom access

Upon handover, a mobile station receives, from the movement origin base station, information on the movement destination base station and information relating to a sequence to be used for transmitting a random access signal to the movement destination base station. The mobile station receives a synchronization channel signal transmitted from the movement destination base station. The mobile station transmits the random access signal to the movement destination base station at a timing offset by a prescribed period from a timing of receiving a synchronization channel and at a frequency corresponding to that of the synchronization channel. A position of the timing / frequency used for transmitting the random access signal for the handover is used exclusively by the random access signal transmitted from the mobile terminal for which a handover is being performed or is used exclusively at the same time by a plurality of mobile stations for which handovers are performed.

Owner:FUJITSU LTD

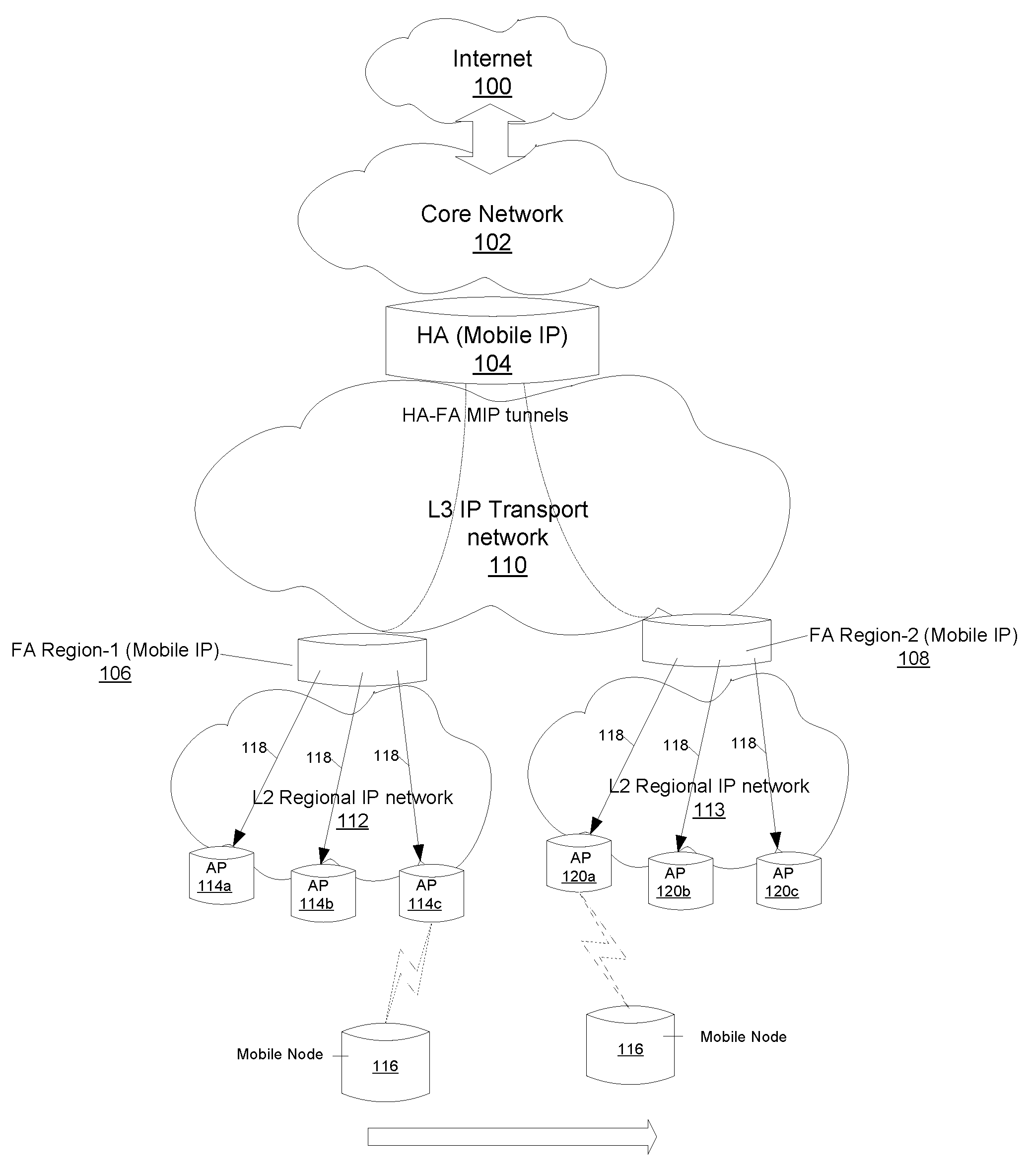

System and method to provide fast wide-area mobile IP handoffs

ActiveUS20100091732A1Effectively seamless wireless communicationMinimize communication disruption periodWireless network protocolsWireless commuication servicesMobile deviceMobile IP

A system, device, and method for real-time handoff in a mobile IP network is provided. In an embodiment, an indication that a mobile device is in a new network is sent out more often in a beacon than in an IRDP message in order to provide an effective seamless connectivity between service areas for wireless communications.

Owner:T MOBILE USA

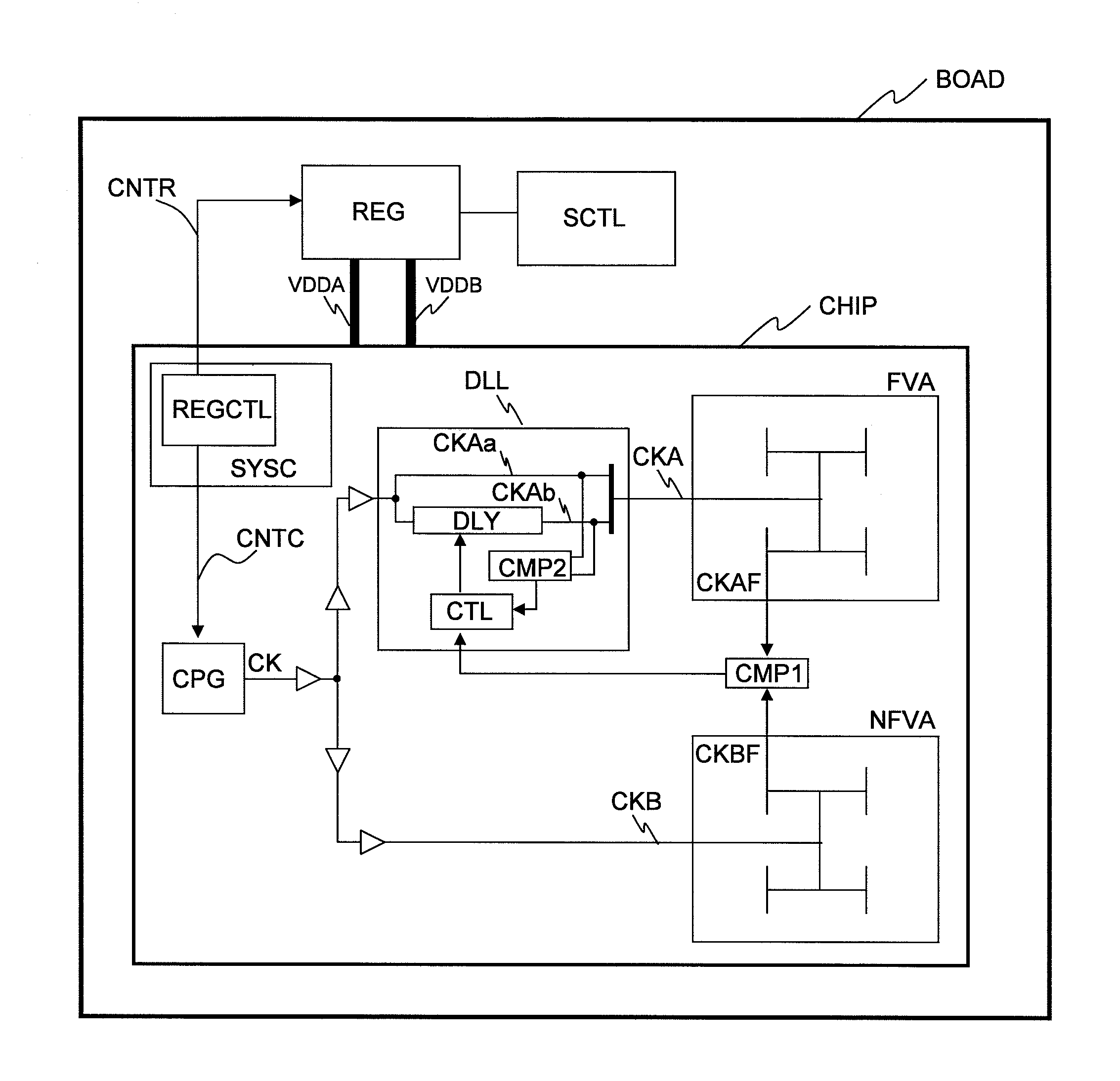

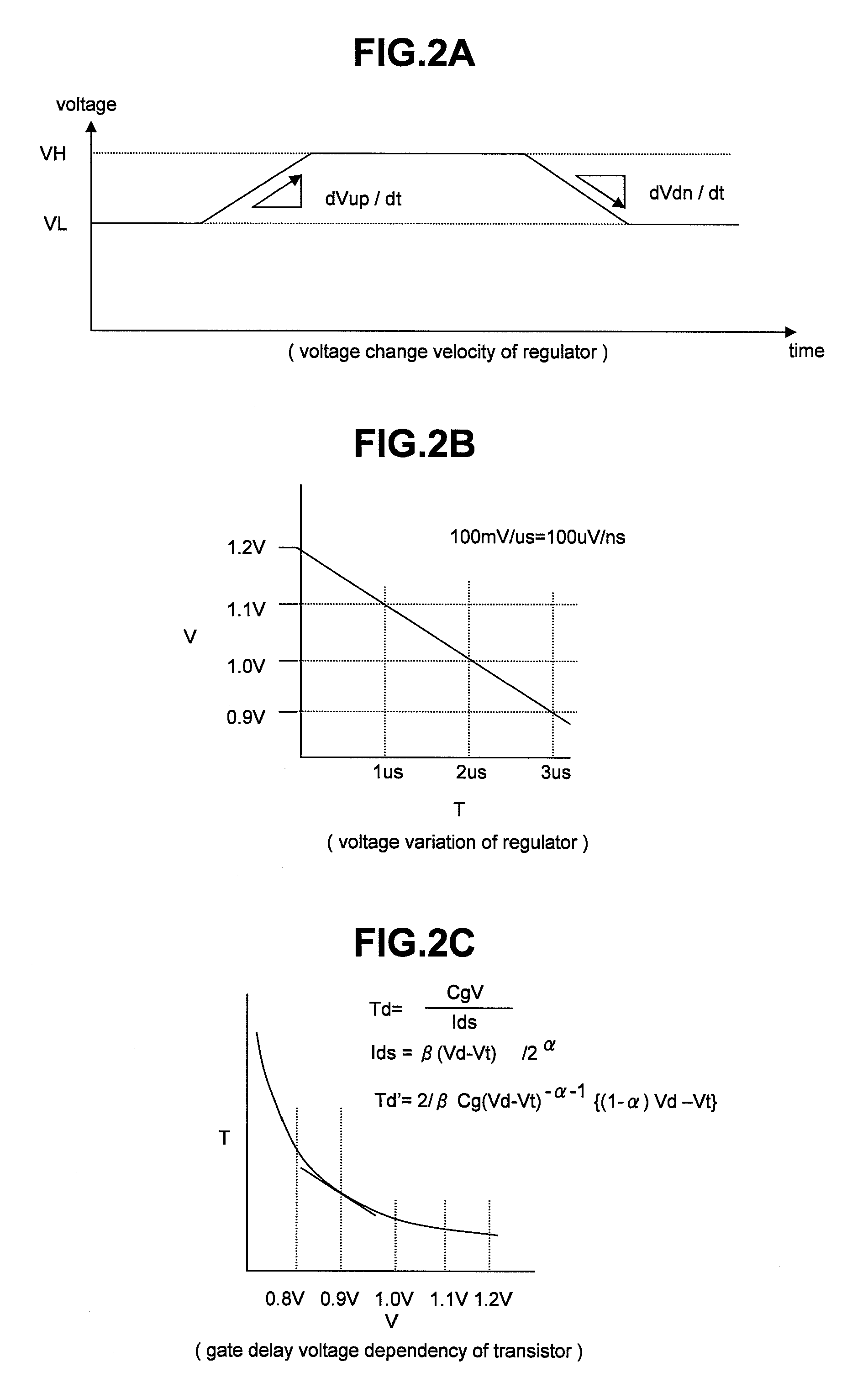

Semiconductor integrated circuit and control method for clock signal synchronization

InactiveUS20100117697A1Maximize low power consumption effectImprove Low Power PerformanceEnergy efficient ICTPulse automatic controlSynchronous controlEngineering

There is a need to ensure operation performance of a circuit region under DVFS control at low costs and highly precisely while a power-supply voltage change is made to the region. A first circuit (FVA) uses a first power-supply voltage (VDDA) for operation. A second circuit (NFVA) uses a second power-supply voltage (VDDB) for operation. A clock delay may be adjusted between paths for transmitting a clock to these circuits. When VDDA equals VDDB, a clock is distributed to FVA through a path that does not contain a delay device for phase adjustment. When the power-supply voltage for the FVA region is reduced, a clock is distributed to the FVA region based on a phase equivalent to one or two cycles of the clock displaced. Synchronization control is provided to synchronize clocks (CKAF and CKBF) and ensures operation so that a phase of two clocks to be compared fits in a range of design values while the power-supply voltage for the first circuit is changed.

Owner:RENESAS ELECTRONICS CORP

Method for Hardware Based Dynamic Load Balancing of Message Passing Interface Tasks

InactiveUS20090064165A1Minimize periodWasted processor cyclesDigital computer detailsMultiprogramming arrangementsDynamic load balancingMessage Passing Interface

A method for providing hardware based dynamic load balancing of message passing interface (MPI) tasks are provided. Mechanisms for adjusting the balance of processing workloads of the processors executing tasks of an MPI job are provided so as to minimize wait periods for waiting for all of the processors to call a synchronization operation. Each processor has an associated hardware implemented MPI load balancing controller. The MPI load balancing controller maintains a history that provides a profile of the tasks with regard to their calls to synchronization operations. From this information, it can be determined which processors should have their processing loads lightened and which processors are able to handle additional processing loads without significantly negatively affecting the overall operation of the parallel execution system. As a result, operations may be performed to shift workloads from the slowest processor to one or more of the faster processors.

Owner:IBM CORP

Method to Start a Process for Producing Hydrocarbons from Synthesis Gas

InactiveUS20080275144A1Minimize periodEasy to useHydrocarbon from carbon oxidesOrganic compound preparationSyngasHydrocarbon

Method to start a steady state process for producing normally gaseous, normally liquid and optionally normally solid hydrocarbons from synthesis gas, which process comprises the steps of: (i) providing the synthesis gas; and (ii) catalytically converting the synthesis gas at an elevated temperature and a steady state total reactor pressure to obtain the normally gaseous, normally liquid and optionally normally solid hydrocarbons; the method comprising admixing the synthesis gas of step (i) with one or more inert gases to form an admixture stream prior to catalytically converting the synthesis gas in step (ii) at the steady state total reactor pressure and wherein as the activity of the catalyst converting the synthesis gas proceeds towards a steady state, the amount of inert gas(es) in the admixture stream is reduced.

Owner:SHELL OIL CO

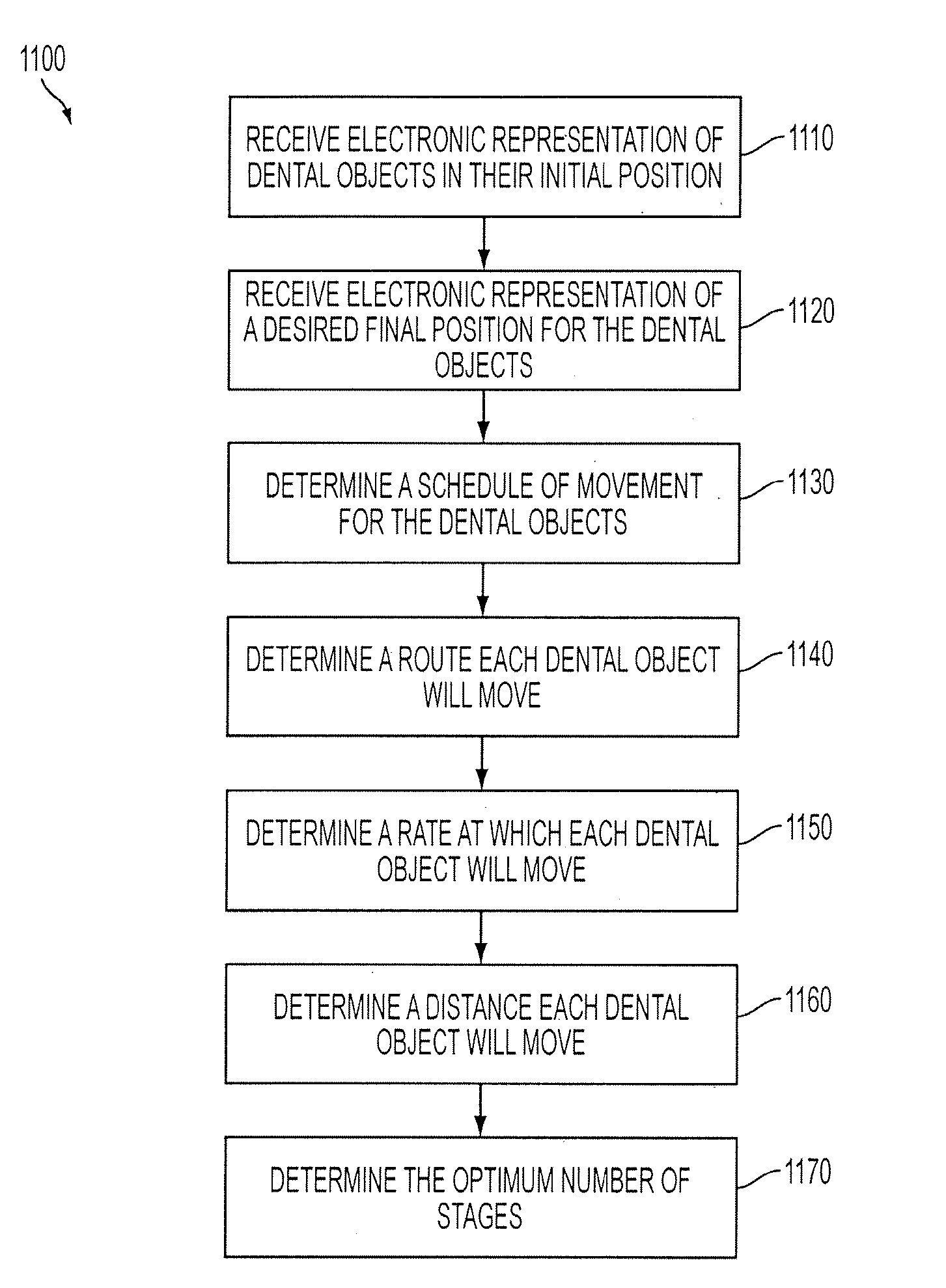

Automated treatment staging for teeth

ActiveUS20120035901A1Minimize periodOthrodonticsAnalogue computers for chemical processesMovement patternMaximum rate

Apparatus, system, and methods for utilizing one or more computing devices to stage the movement of teeth during an alignment treatment are disclosed. The computing device receives an electronic representation of the patient's teeth in their initial position and an electronic representation of the teeth a final position for each tooth. A route each tooth will travel to reach its final position is determined, and the teeth are scheduled to move according to a movement pattern. Moreover, the schedule of movement takes into account a maximum rate of tooth movement for each tooth, the path of movement for each tooth, the distance each tooth needs to move, any needed tooth staggering, any needed round-tripping or tooth movement slowing. The invention also includes techniques for determining an optimum number of stages for the treatment based on the schedule of movement.

Owner:ALIGN TECH

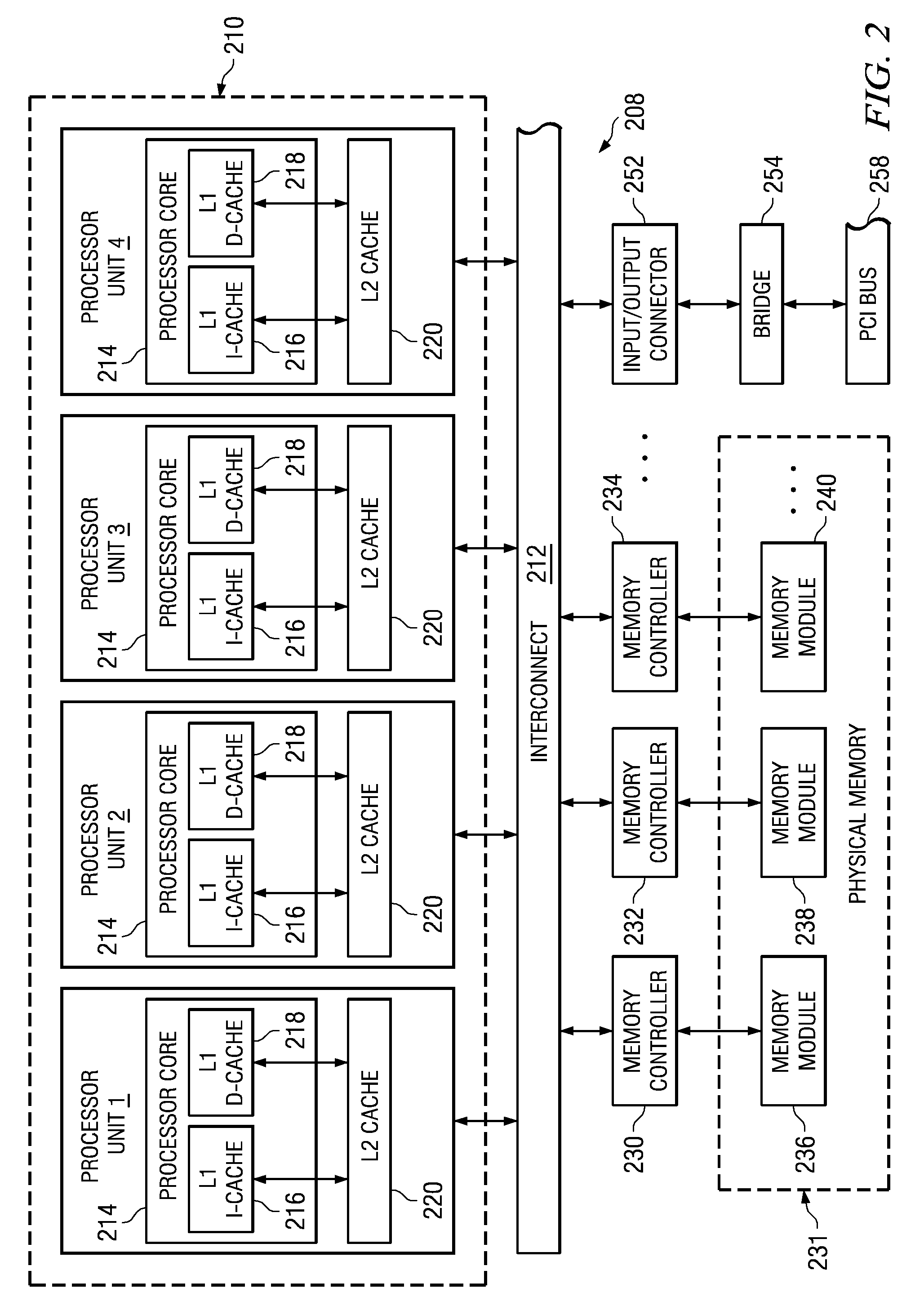

Hardware based dynamic load balancing of message passing interface tasks

InactiveUS8127300B2Minimize periodWasted processor cyclesDigital computer detailsMultiprogramming arrangementsDynamic load balancingMessage Passing Interface

Mechanisms for providing hardware based dynamic load balancing of message passing interface (MPI) tasks are provided. Mechanisms for adjusting the balance of processing workloads of the processors executing tasks of an MPI job are provided so as to minimize wait periods for waiting for all of the processors to call a synchronization operation. Each processor has an associated hardware implemented MPI load balancing controller. The MPI load balancing controller maintains a history that provides a profile of the tasks with regard to their calls to synchronization operations. From this information, it can be determined which processors should have their processing loads lightened and which processors are able to handle additional processing loads without significantly negatively affecting the overall operation of the parallel execution system. As a result, operations may be performed to shift workloads from the slowest processor to one or more of the faster processors.

Owner:INT BUSINESS MASCH CORP

Semiconductor integrated circuit and control method for clock signal synchronization

InactiveUS8183899B2Maximize low power consumption effectKeep for a long timeEnergy efficient ICTPulse automatic controlSynchronous controlEngineering

There is a need to ensure operation performance of a circuit region under DVFS control at low costs and highly precisely while a power-supply voltage change is made to the region. A first circuit (FVA) uses a first power-supply voltage (VDDA) for operation. A second circuit (NFVA) uses a second power-supply voltage (VDDB) for operation. A clock delay may be adjusted between paths for transmitting a clock to these circuits. When VDDA equals VDDB, a clock is distributed to FVA through a path that does not contain a delay device for phase adjustment. When the power-supply voltage for the FVA region is reduced, a clock is distributed to the FVA region based on a phase equivalent to one or two cycles of the clock displaced. Synchronization control is provided to synchronize clocks (CKAF and CKBF) and ensures operation so that a phase of two clocks to be compared fits in a range of design values while the power-supply voltage for the first circuit is changed.

Owner:RENESAS ELECTRONICS CORP

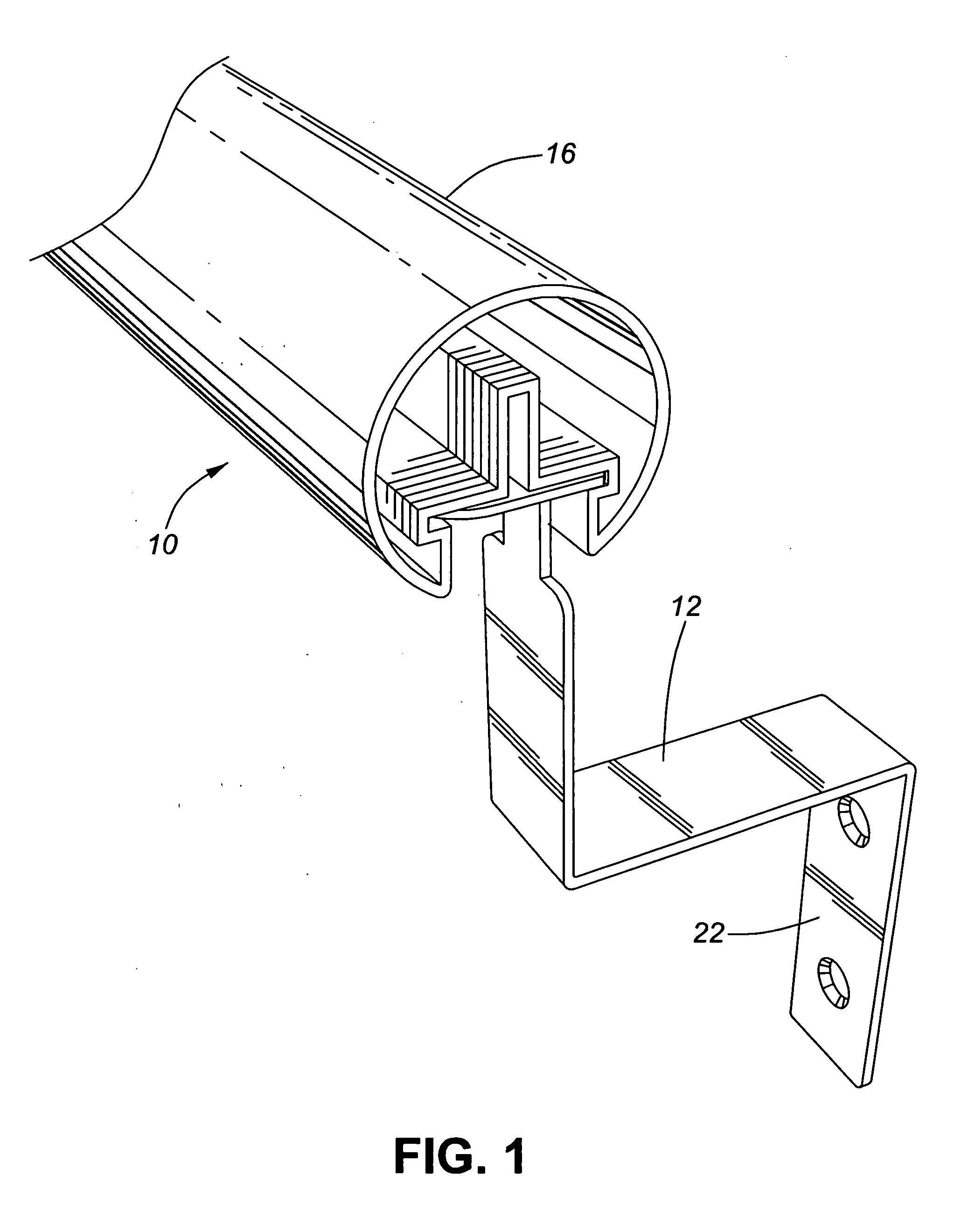

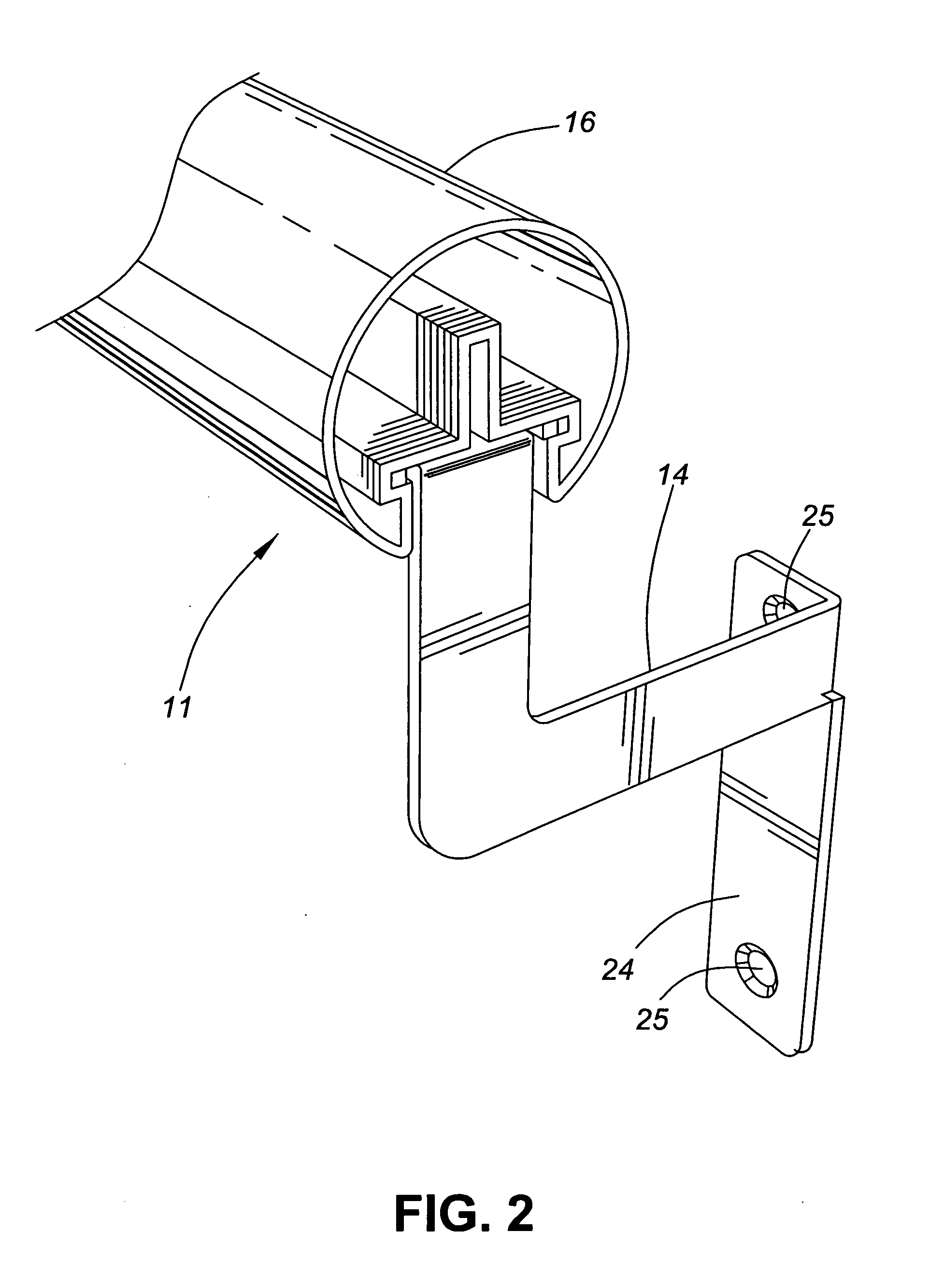

Handrail assembly and method

This invention relates to a handrail assembly that can be installed on any wall. The assembly consists of a handrail and a bracket. The bracket can be twist-locked inside the handrail at any point in the handrail because the handrail has a continuous T-shaped channel at the bottom. The T-shaped channel's bottom portion is narrower than the upper portion. The bracket has a head that is as wide as the T-shaped channel's bottom portion and as long as the T-shaped channel's upper portion. The head has one curved corner to facilitate turning and teeth to bite into the upper portion of the channel's wall. The head is lifted through the bottom portion into the upper portion of the channel, the bracket is rotated a quarter turn, and the bracket becomes immobilized. The head of the bracket acts as a cam. Union joints can join multiple lengths of handrails.

Owner:9220 6820 QUEBEC

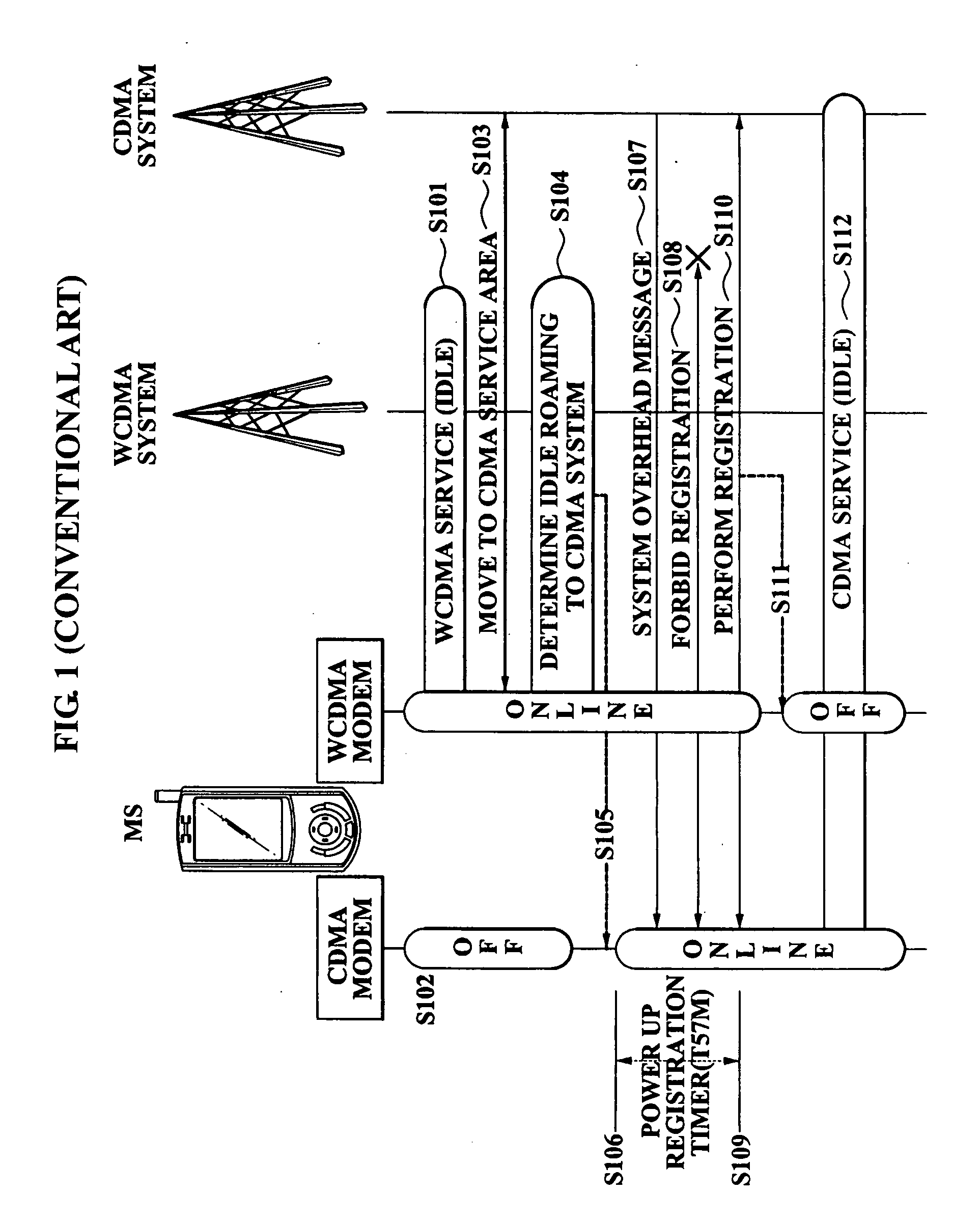

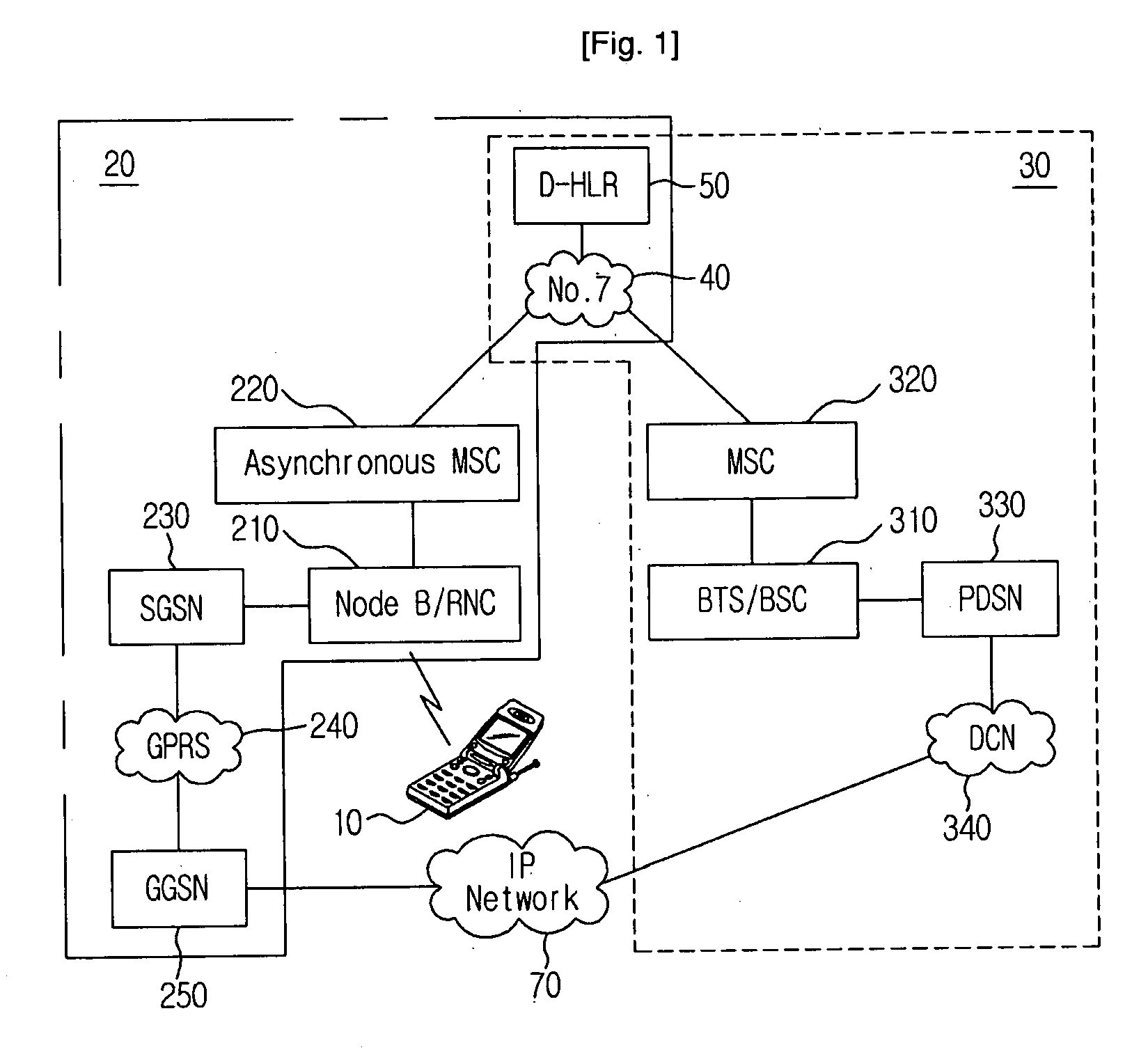

Inter-system handover

InactiveUS7983676B2Minimize periodRadio transmission for post communicationWireless commuication servicesCommunications systemComputer terminal

Owner:SK TELECOM CO LTD

Modifying an operation of one or more processors executing message passing interface tasks

InactiveUS8108876B2Minimize periodWasted processor cyclesProgram synchronisationMultiple digital computer combinationsMessage Passing InterfaceWaiting period

Mechanisms for modifying an operation of one or more processors executing message passing interface (MPI) tasks are provided. Mechanisms for adjusting the balance of processing work loads of the processors are provided so as to minimize wait periods for waiting for all of the processors to call a synchronization operation. Each processor has an associated hardware implemented MPI load balancing controller. The MPI Load balancing controller maintains a history that provides a profile of the tasks with regard to their calls to synchronization operations. From this information, it can be determined which processors should have their processing loads lightened and which processors are able to handle additional processing loads without significantly negatively affecting the overall operation of the parallel execution system. As a result, operations may be performed to shift workloads from the slowest processor to one or more of the faster processors.

Owner:INT BUSINESS MASCH CORP

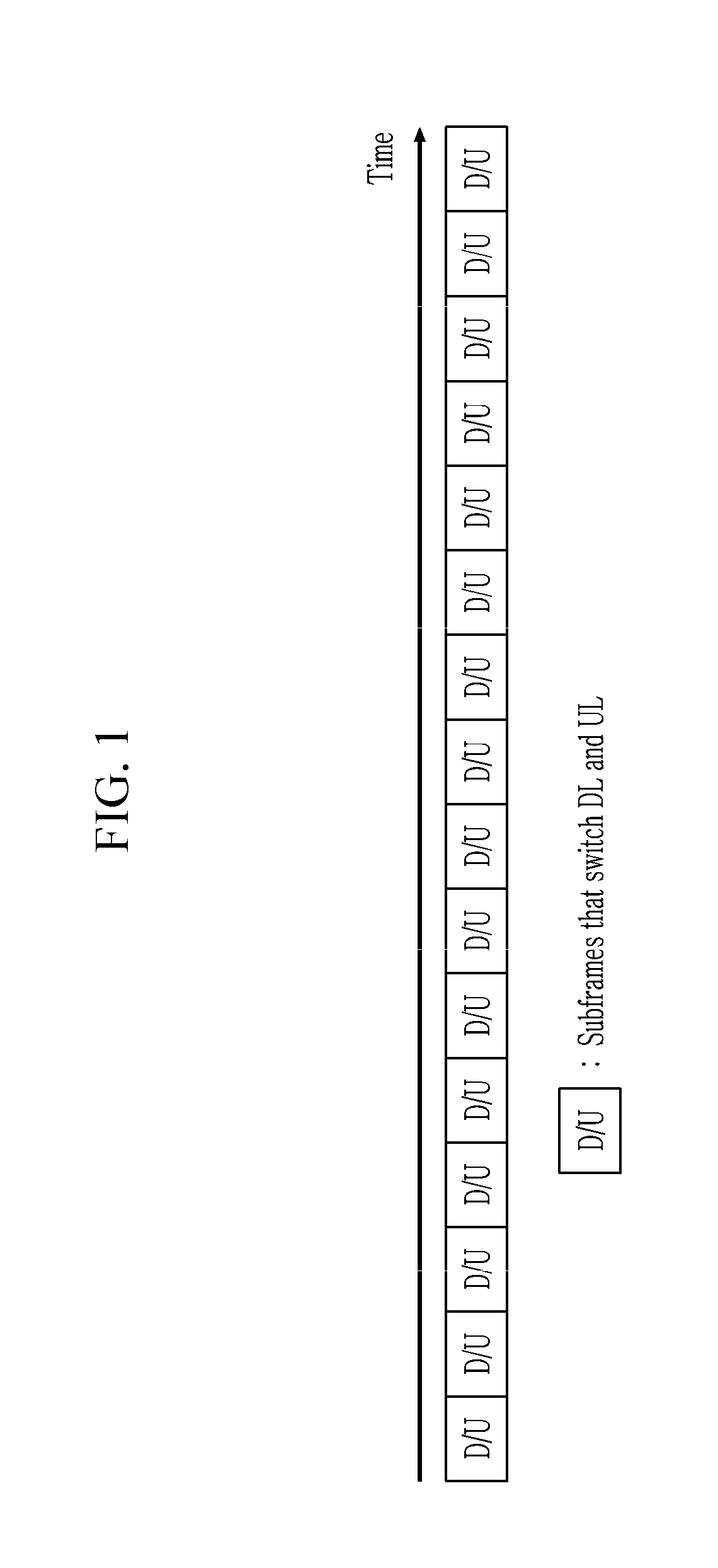

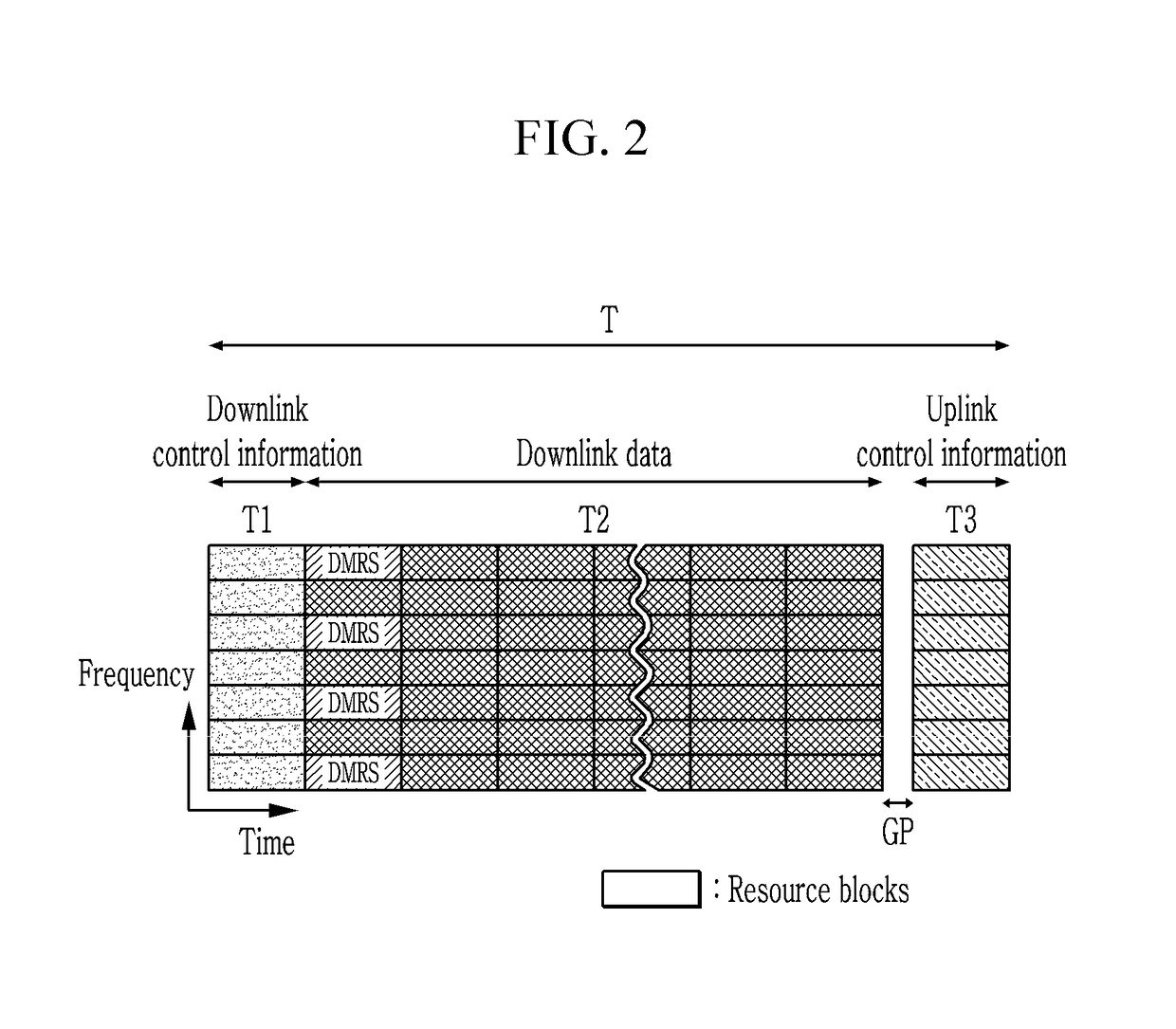

Resource allocation method and communication device

ActiveUS20180213529A1Minimize periodMaximize efficiencySignal allocationRadio transmission for post communicationTime domainResource allocation

A resource allocation method is provided in which a resource allocation apparatus using a time-division duplex communication scheme allocates resources for a subframe. The resource allocation method includes: allocating a first time region of the time domain of the subframe as a downlink control information region; and allocating the rest of the time domain of the subframe, apart from the first time region, as at least one region variably selected from among a downlink data region, an uplink data region, an uplink control information region, and a guard period (GP) region.

Owner:5G SIG CO LTD

Circuits, systems, methods, and software for power factor correction and/or control

ActiveUS7511460B1Minimize periodMinimize powerAc-dc conversion without reversalEfficient power electronics conversionImage resolutionPower factor control

Circuits, systems, methods and software for controlling a power conversion and / or correcting and / or controlling a power factor in such conversion(s). The present invention generally takes a computational approach to reducing or minimizing zero current periods in the critical mode of power converter operation, and advantageously reduces zero current periods in the critical mode of power converter operation, thereby maximizing the power factor of the power converter in the critical mode and reducing noise that may be injected back into AC power lines. The present power factor controller allows for greater design flexibility, reduced design complexity, and reduced resolution and greater tolerance for error in certain parameter measurements useful in power factor correction and / or control.

Owner:MARVELL ASIA PTE LTD

Controlling data storage in an array of storage devices

Methods, apparatus and computer programs have been provided for mitigating a problem of non-optimal recovery from storage device failures. A method involves determining a required write performance for rebuilding data of a failed device, based at least partly on the potential read performance of storage devices in a data rebuild; and allocating a virtual storage area within available storage, which allocation of virtual storage is based at least partly on the required write performance. Data is rebuilt by writing to the allocated virtual storage area, and data recovery is completed by migrating this rebuilt data to at least one data storage device such as a spare physical storage device within the array.

Owner:GLOBALFOUNDRIES U S INC

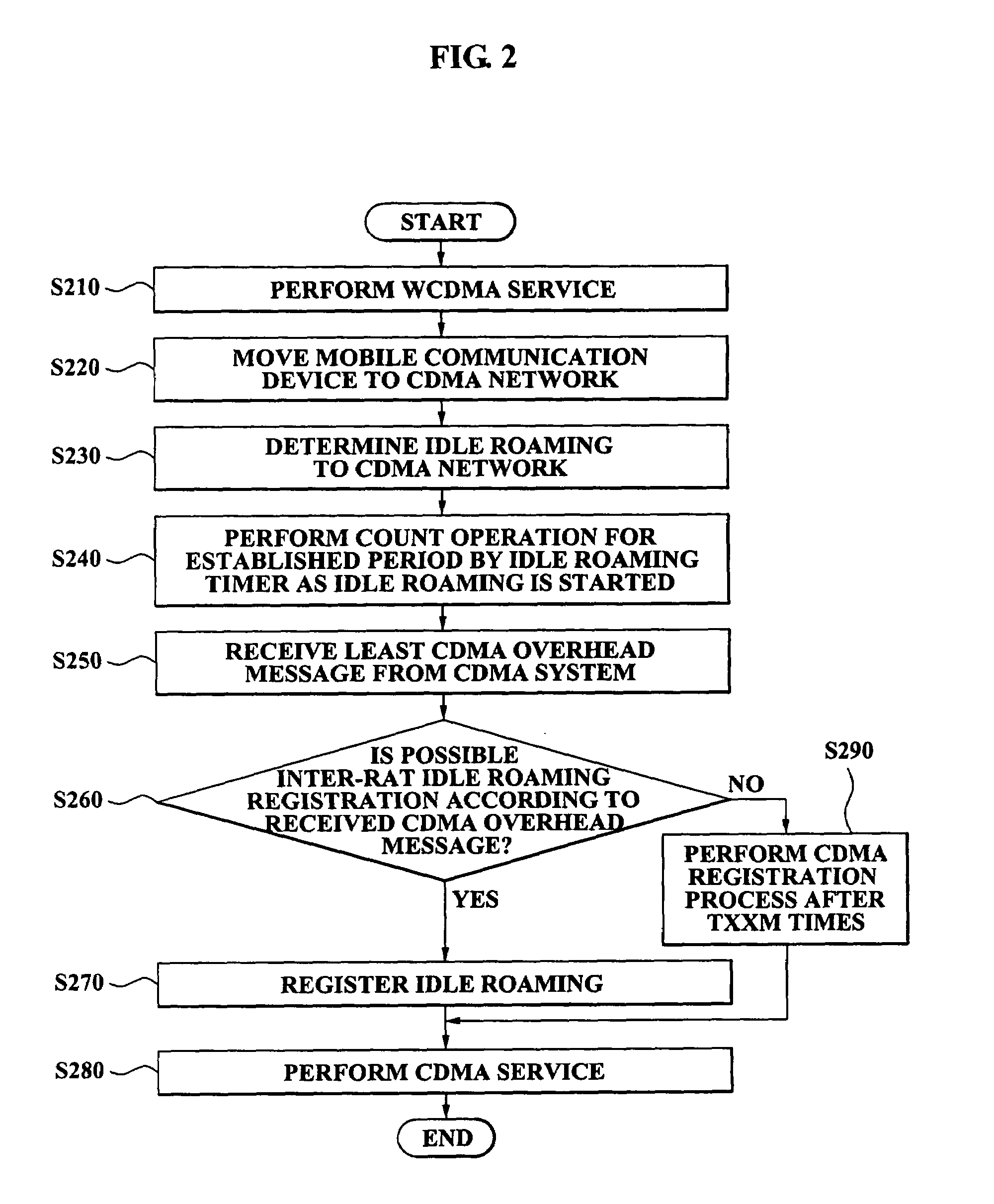

Method and apparatus for efficiently managing power-up timer for high-speed inter-radio access technology handover in mobile communication device

ActiveUS20070177546A1Maintain continuityQuality improvementEnergy efficient ICTRadio/inductive link selection arrangementsCdma networksRadio access technology

A method of an Inter-RAT handover between a WCDMA service and a CDMA service of a mobile communication device having a WCDMA modem and a CDMA modem, the method including: performing the WCDMA service in a WCDMA network; move from the WCDMA network to a CDMA network; determining an Inter-RAT idle roaming to the CDMA network; measuring, with a timer, a count period from a cut-off time of the WCDMA service according to the determination of the Inter-RAT idle roaming; and performing CDMA service registration according to the Inter-RAT idle roaming immediately after the cut-off time of the WCDMA service or after the count period set in the timer.

Owner:PANTECH CORP

Performing setup operations for receiving different amounts of data while processors are performing message passing interface tasks

InactiveUS8234652B2Minimize periodWasted processor cyclesDigital computer detailsMultiprogramming arrangementsMessage Passing InterfaceWaiting period

Mechanisms are provided for performing setup operations for receiving a different amount of data while processors are performing message passing interface (MPI) tasks. Mechanisms for adjusting the balance of processing workloads of the processors are provided so us to minimize wait periods for waiting for all of the processors to call a synchronization operation. An MPI load balancing controller maintains a history that provides a profile of the tasks with regard to their calls to synchronization operations. From this information, it can be determined which processors should have their processing loads lightened and which processors are able to handle additional processing loads without significantly negatively affecting the overall operation of the parallel execution system. As a result, setup operations may be performed while processors are performing MPI tasks to prepare for receiving different sized portions of data in a subsequent computation cycle based on the history.

Owner:INT BUSINESS MASCH CORP

Etching methods and apparatus for producing semiconductor devices

InactiveUS7030027B1Increase production efficiencyDecrease defective densitySemiconductor/solid-state device manufacturingChemistrySemiconductor

A multi-layered film on a semiconductor substrate is etched with a multi-step etching process by sequentially providing a plurality of process gases having different compositions in a chamber. A plasma discharge to excite the process gases is continued without an interruption during a switch to a different process gas. A relationship between different process gases desirable for the continuous plasma excitation is also disclosed. An apparatus suitable to practice this continuous plasma excitation process includes a process gas supply system having a gas reservoir. A mixture of at least two component gases is prepared and reserved in the reservoir, and is supplied to the etching chamber when it is needed.

Owner:KAWASAKI MICROELECTRONICS

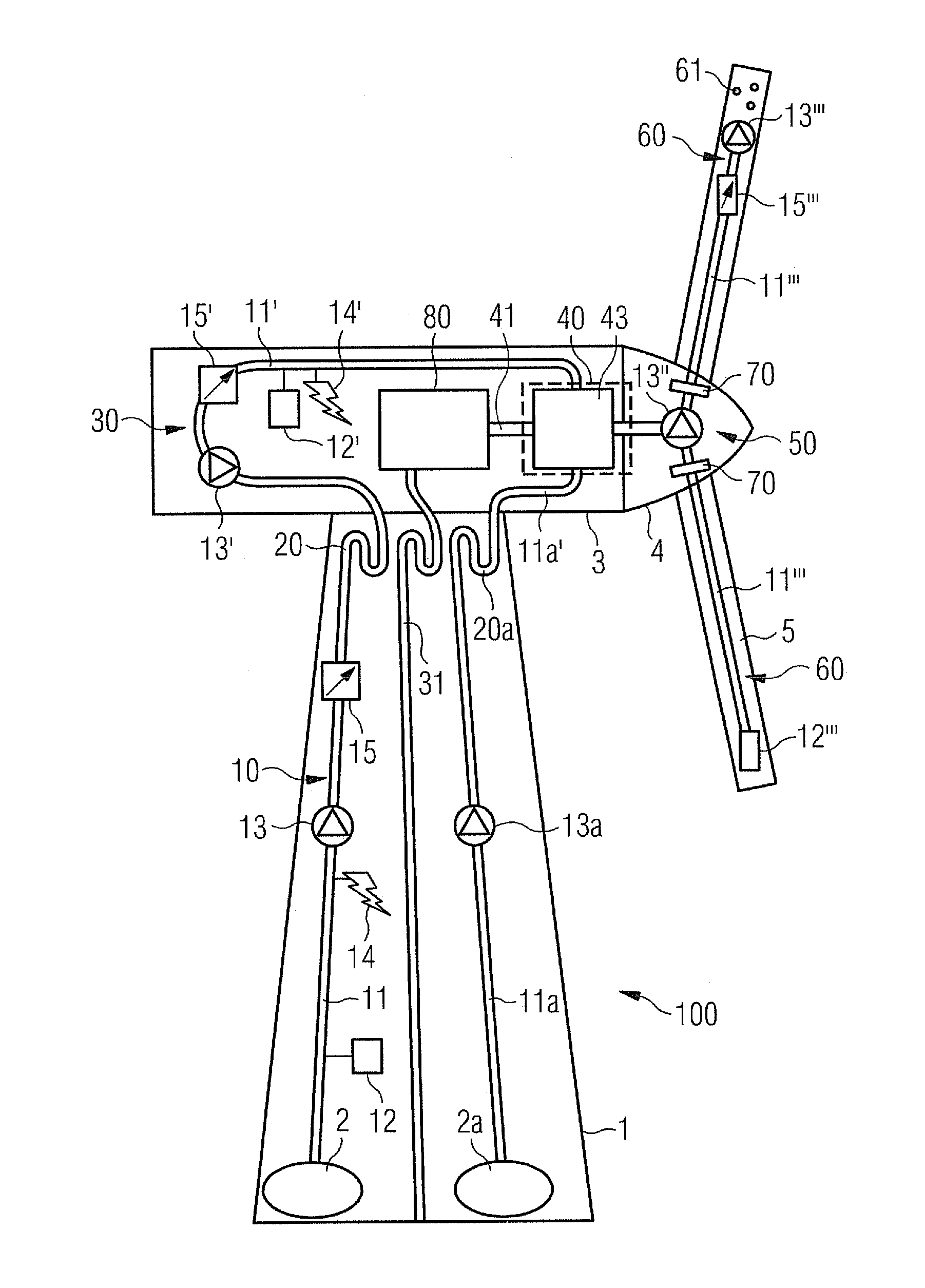

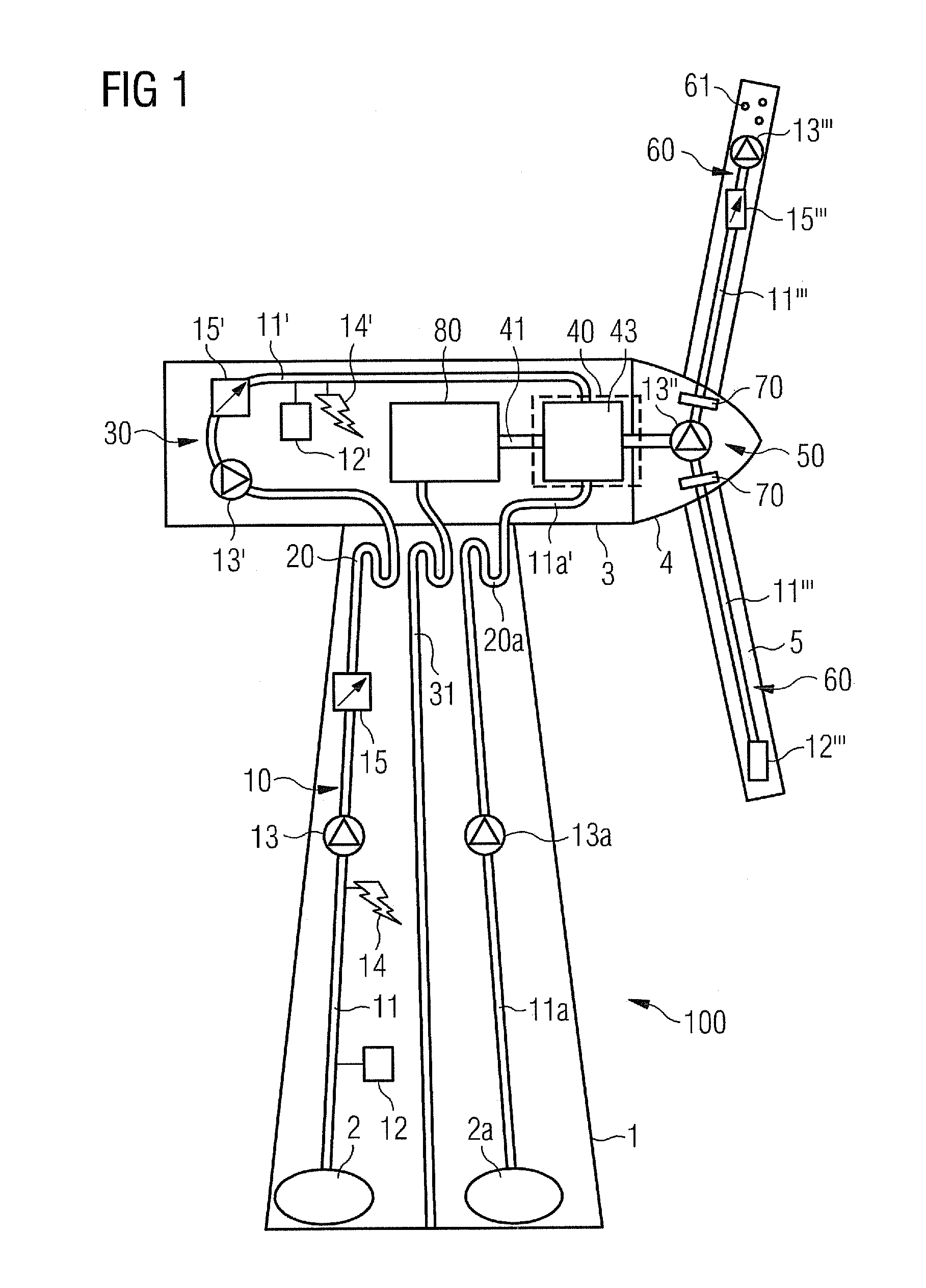

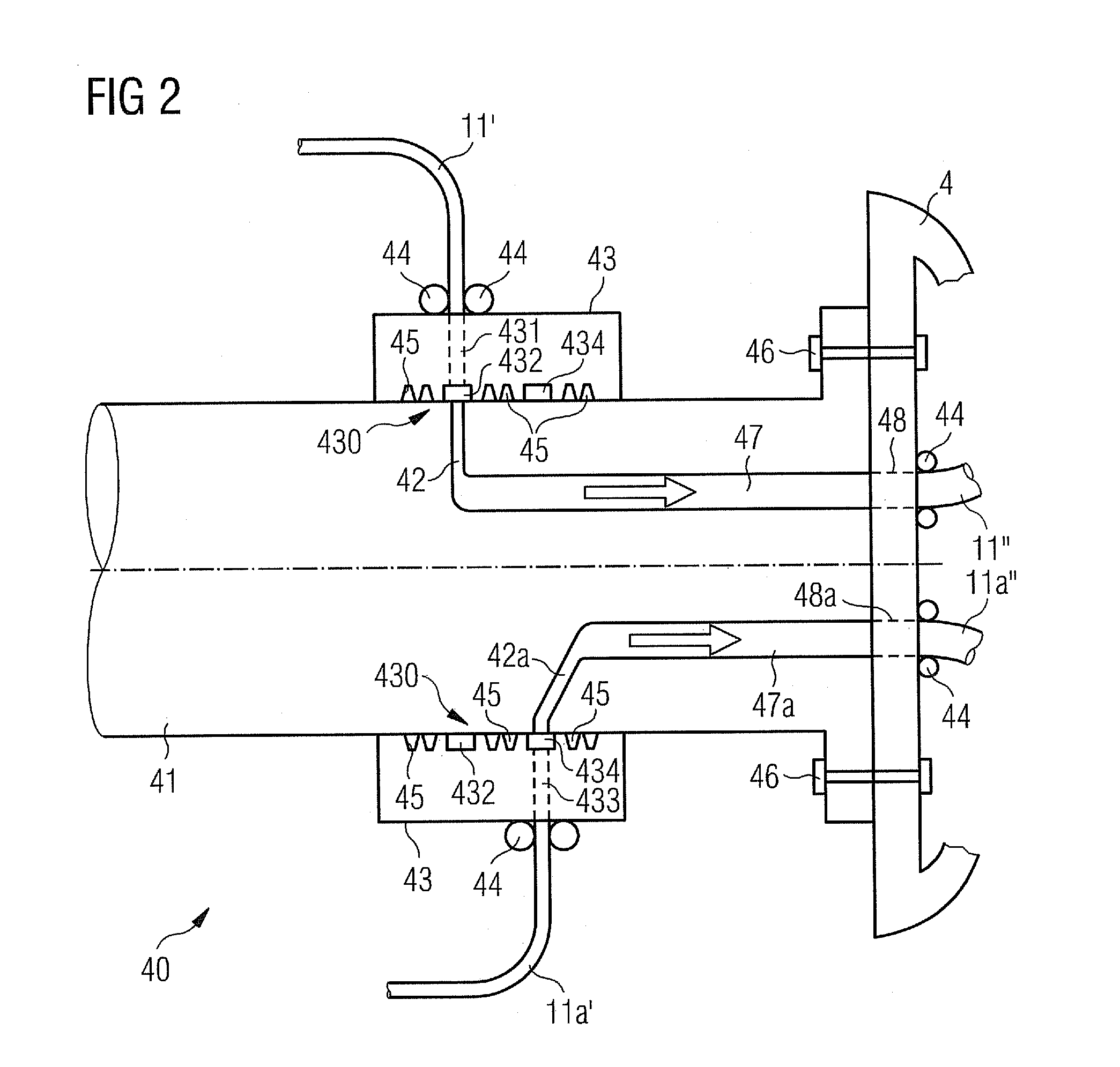

Wind turbine with liquid medium distribution system

A wind turbine with a tower, a nacelle, a main shaft, a hub and blades is provided. The wind turbine also includes a liquid medium distribution system for transport of liquid medium in the wind turbine. The liquid medium distribution system has a first distribution sub-system located in the tower, a second distribution sub-system located in the nacelle, a third distribution sub-system located in the hub, a tower-nacelle-interface connecting the first distribution sub-system to the second distribution sub-system, and a nacelle-hub-interface connecting the second distribution sub-system to the third distribution sub-system. Further, a method of transporting liquid medium in a wind turbine is provided.

Owner:SIEMENS AG

LNG carrier construction method

ActiveUS20150367915A1Reduce riskReduce unnecessary downtimeVessel partsHulls from prefabricated subunitsLiquefactionRegasification

A structural block is fabricated with necessary components and structure for LNG storage and / or process. The structural block may be an LNG tank with the same configuration as that in an LNG carrier. The structural block may also be a regasification plant or a liquefaction plant to be used for LNG process. An existing vessel, e.g. an LNG carrier, is cut apart to form a forward section and an aft section. The forward section and the aft section are moved away from each other to form a space therebetween. The structural block is then placed into the space and jointed to the forward and aft sections, by welding for example, to form an integrated new vessel. The structural block provides the new vessel with increased LNG storage and transportation capabilities as well as regasification and / or liquefaction process facilities to meet the increased demand for LNG storage, transportation and processing.

Owner:KEPPEL OFFSHORE & MARINE TECH CENT PTE LTD

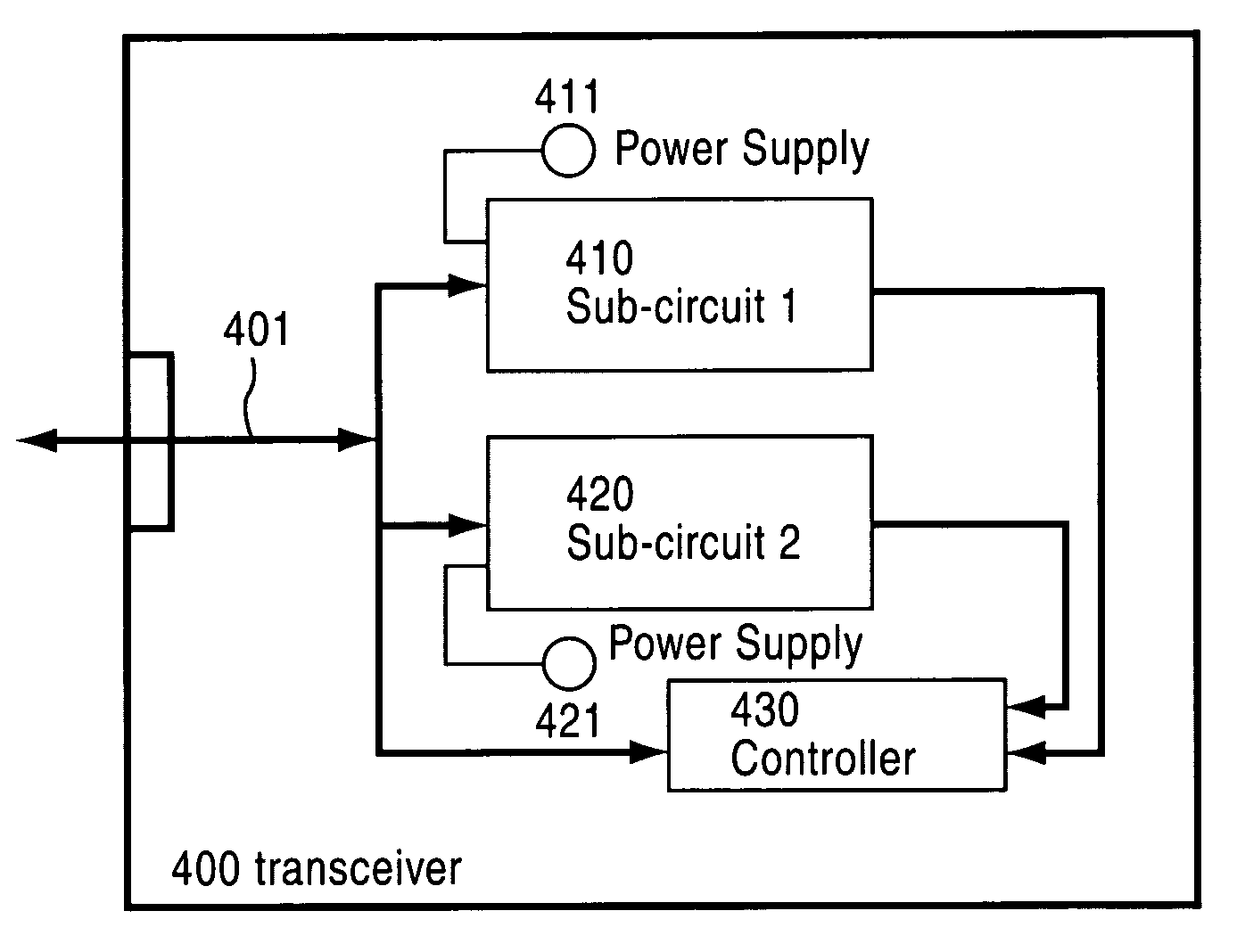

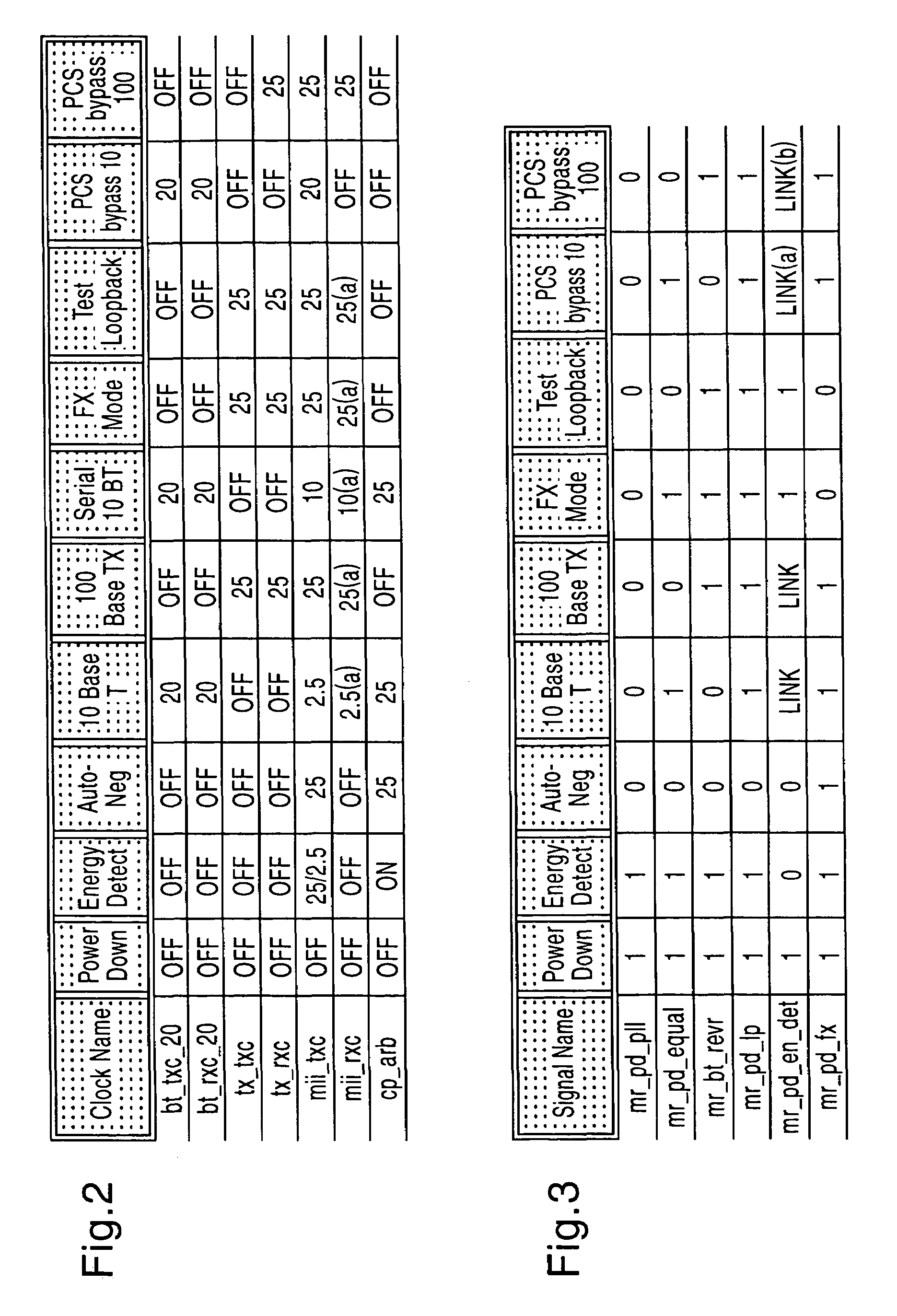

Method and circuits for power management in a transceiver

InactiveUS7079571B1Minimize power consumptionMinimize periodError preventionFrequency-division multiplex detailsTransceiverControl signal

A transceiver circuit having 10 mb and 100 mb transmit and receive circuitries using the power saving methods allows for power consumption of the transceiver circuit to be significantly reduced. This is accomplished by providing each defined subcircuit with its own power supply and means of activation and deactivation. However, the method for activating and deactivating digital subcircuits and analog subcircuits are different and therefore different types of control signals and methods are provided. Furthermore, there are two general types of power-saving situations. The first type is near total circuit power-down and the second type is partial circuit power-down. In yet another embodiment, a method for minimizing energy usage during the idle period is utilized.

Owner:AVAGO TECH INT SALES PTE LTD

Inter-System Handover

InactiveUS20080242304A1Minimize silent periodMinimize periodRadio/inductive link selection arrangementsRadio transmission for post communicationCommunications systemDual mode

A method of handover in a wireless communication system in which an asynchronous system and a synchronous system are mixed is disclosed. The method comprises the steps of: the asynchronous system ordering a dual mode mobile terminal to perform a handover from the asynchronous system to the synchronous system; when the handover order is received at the mobile terminal, the mobile terminal transmitting a frame or a preamble through a reverse traffic channel to the synchronous system, reporting to the synchronous system that the handover is completed and initiating a timer of the mobile terminal which is set according to a predetermined time; the mobile terminal switching from an asynchronous vocoder into a synchronous vocoder when the timer expires; and the wireless communication system switching vocoders of asynchronous and synchronous MSCs when the report is received.

Owner:SK TELECOM CO LTD

X-ray analyser

InactiveUS20120273679A1Reduce mechanical vibrationEasy to detectMaterial analysis using wave/particle radiationElectric discharge tubesX-rayX ray analysis

An x-ray analyser for a transmission electron microscope is described. The analyser has a silicon drift detector moveable in use between an analysis position and a retracted position. The analyser has a housing having an end portion within which the silicon drift detector is retained. The end portion is formed from a material with a relative magnetic permeability of less than 1.004. The analyser also has an automatic retraction system adapted to move the silicon drift detector from the analysis position to the retracted position upon receipt of a trigger signal indicative of a condition in which the power level received by the silicon drift detector from impinging x-rays or electrons is above a predetermined threshold.

Owner:OXFORD INSTR NANOTECH TOOLS

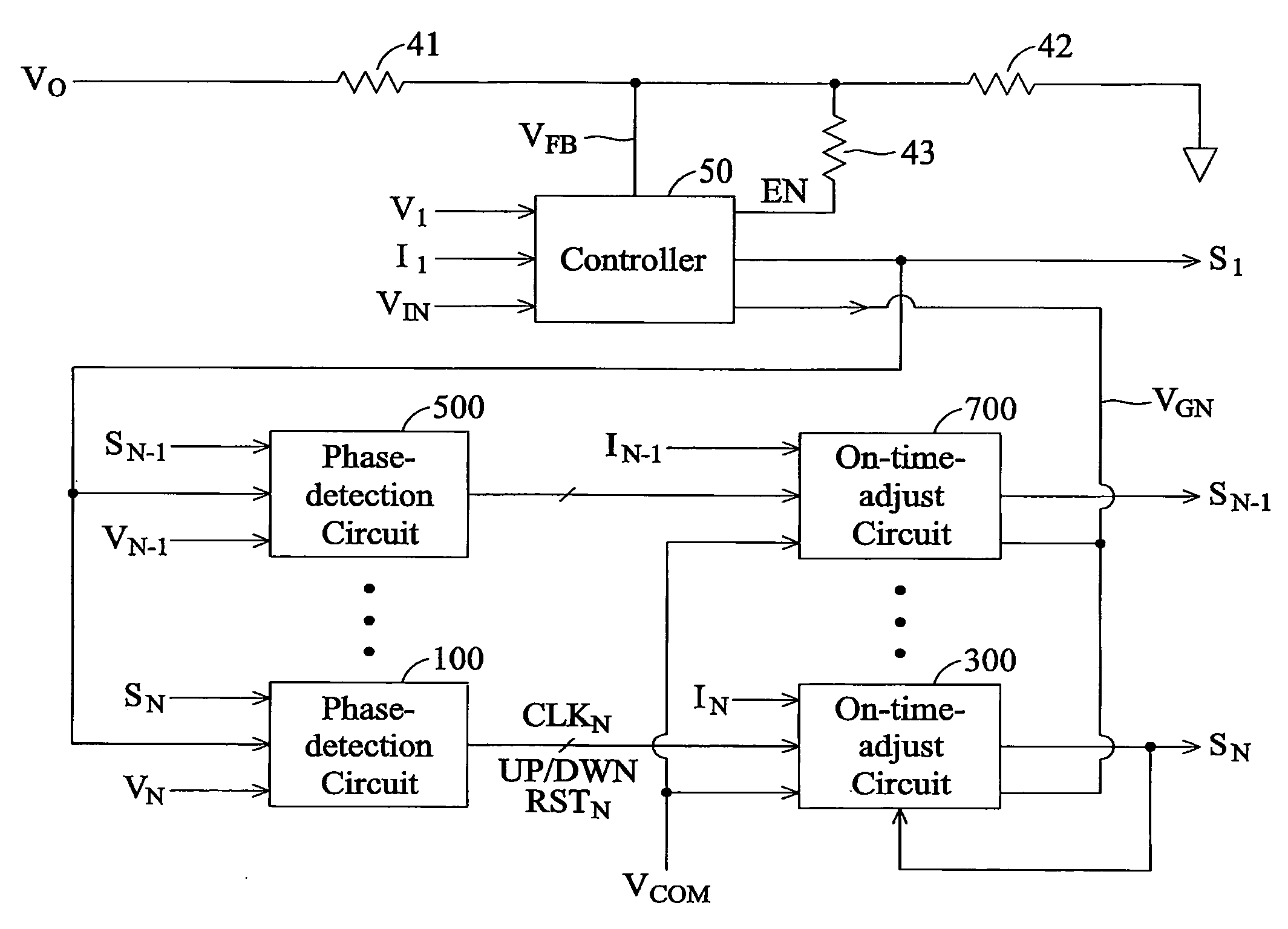

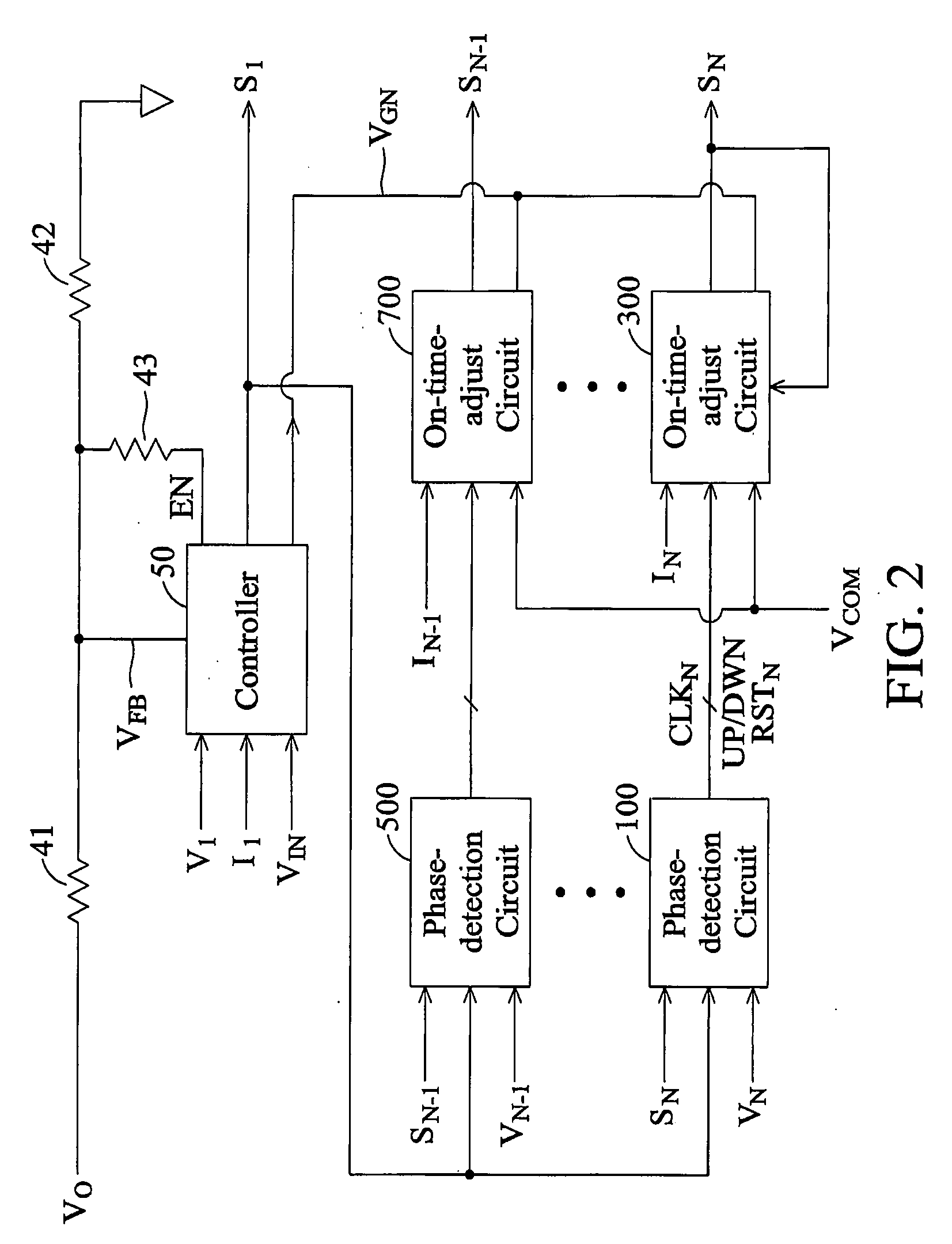

Control circuit for multi-phase, multi-channels pfc converter with variable switching frequency

ActiveUS20090091304A1Minimize periodEfficient power electronics conversionDc-dc conversionPower factor correctorStart signal

A switching control circuit for multi-phases PFC converters is provided. It includes a PFC-control circuit coupled to receive a first-inductor signal and a feedback signal for generating a first-switching signal. The first-switching signal is utilized to switch the first inductor for power factor correction. A phase-detection circuit detects the first-switching signal and a second-inductor signal for generating a start signal and a phase-lock signal. The start signal is developed to enable a second-switching signal. The second-switching signal is coupled to switch a second inductor. An on-time-adjust circuit is coupled to adjust the on time of the second-switching signal in accordance with the phase-lock signal. The phase-lock signal is correlated to the period between the end of the second-inductor signal and the start of the second-switching signal.

Owner:SEMICON COMPONENTS IND LLC

Hardware based dynamic load balancing of message passing interface tasks by modifying tasks

InactiveUS8312464B2Minimize periodWasted processor cyclesMultiprogramming arrangementsMemory systemsDynamic load balancingMessage Passing Interface

Mechanisms are provided for providing hardware based dynamic load balancing of message passing interface (MPI) tasks by modifying tasks. Mechanisms for adjusting the balance of processing workloads of the processors executing tasks of an MPI job are provided so as to minimize wait periods for waiting for all of the processors to call a synchronization operation. Each processor has an associated hardware implemented MPI load balancing controller. The MPI load balancing controller maintains a history that provides a profile of the tasks with regard to their calls to synchronization operations. From this information, it can be determined which processors should have their processing loads lightened and which processors are able to handle additional processing loads without significantly negatively affecting the overall operation of the parallel execution system. Thus, operations may be performed to shift workloads from the slowest processor to one or more of the faster processors.

Owner:INT BUSINESS MASCH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com