Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33results about How to "Improve prediction success rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

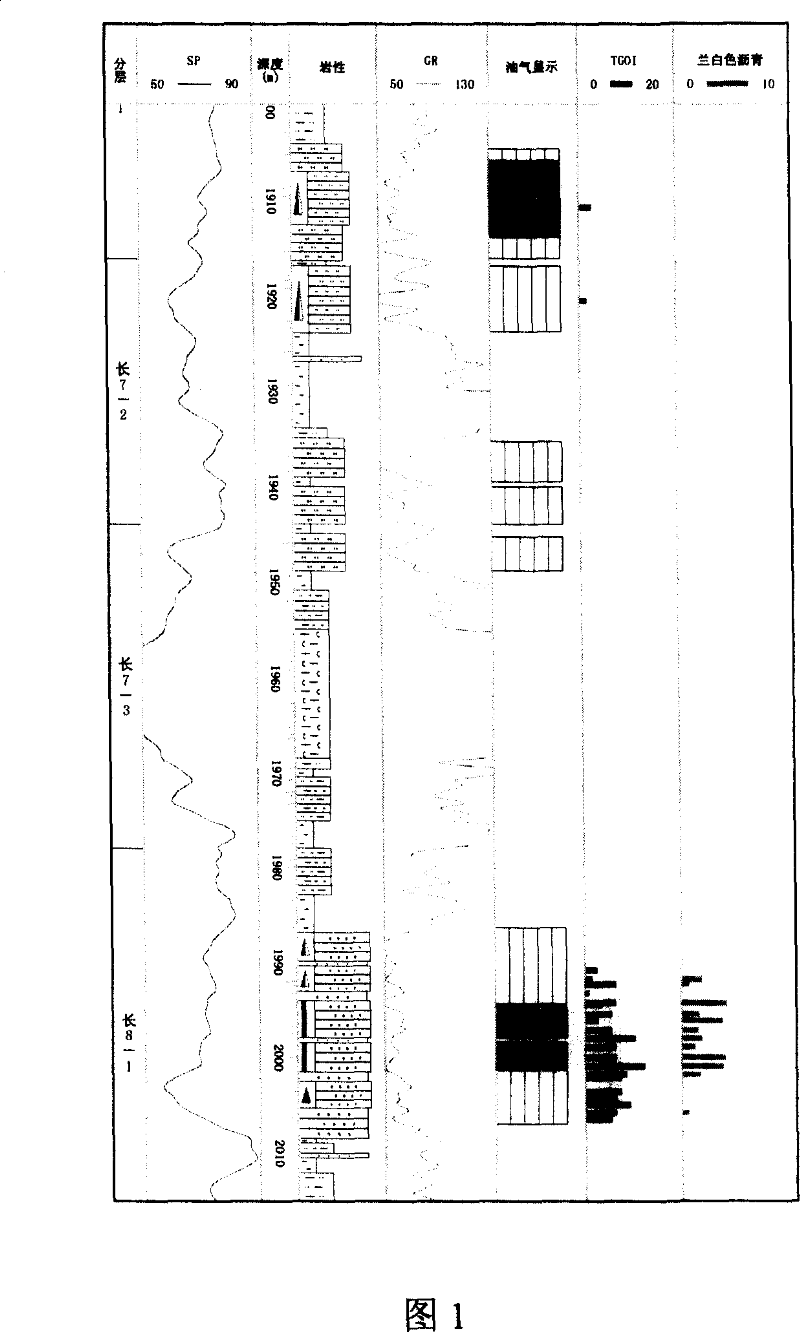

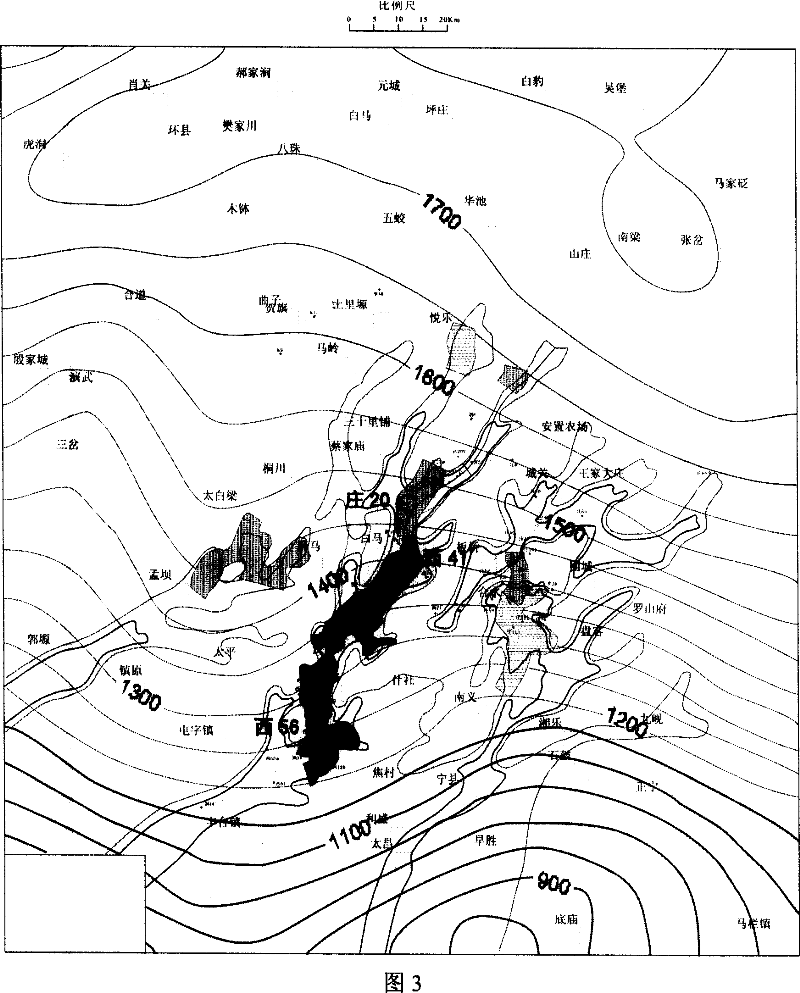

Method for recognizing oil layer by using petroleum inclusion and pitch and migration tracing

ActiveCN101038342AImprove prediction success rateEliminate distractionsMaterial analysis by optical meansSeismology for water-loggingPetroleumAsphalt

The invention relates to oil-gas prospecting technical field, especially using the petroleum inclusion and asphalt to distinguish the oil reservoir and fulfill the migration tracing. With the statistical data from the petroleum inclusion and asphalt, the invention may distinguish the oil reservoir during the drilling (including the prospecting and development) or later; and determine the petroleum migration direction, and trace its routing, search the prevailing migration channel etc. under multi-stage migration and accumulation, fulfill the multi-stage and multiple genesis statistics for petroleum inclusion, trace the oil-gas migration during different geologic phase, determine the oil-gas migration direction and prevailing channels during different stages, and the variation of physical and chemical conditions during migration, thereby recovers the history of oil-gas migration and accumulation, provides the important basis for finding the oil-gas distribution law and advantageous areas for oil-gas migration and accumulation.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

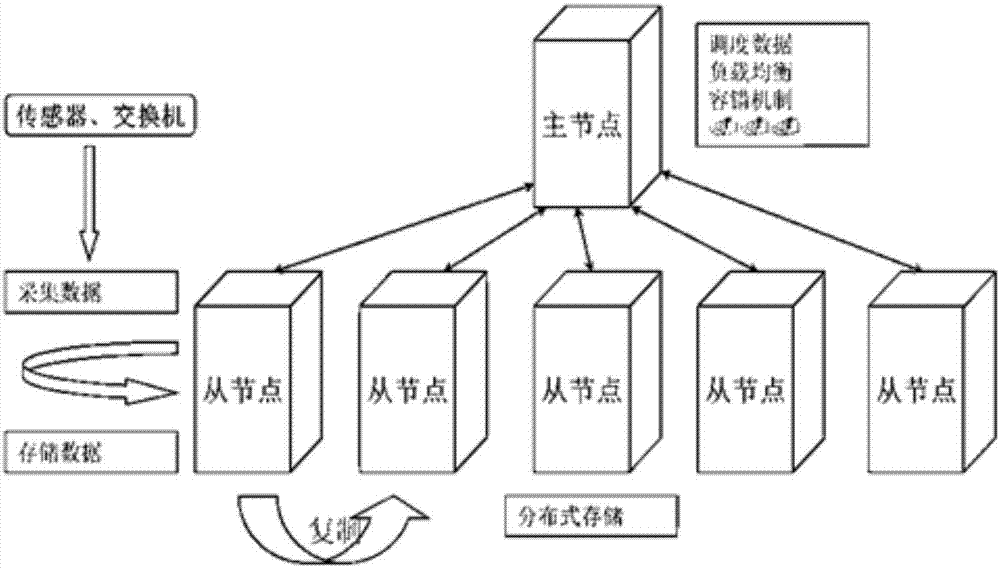

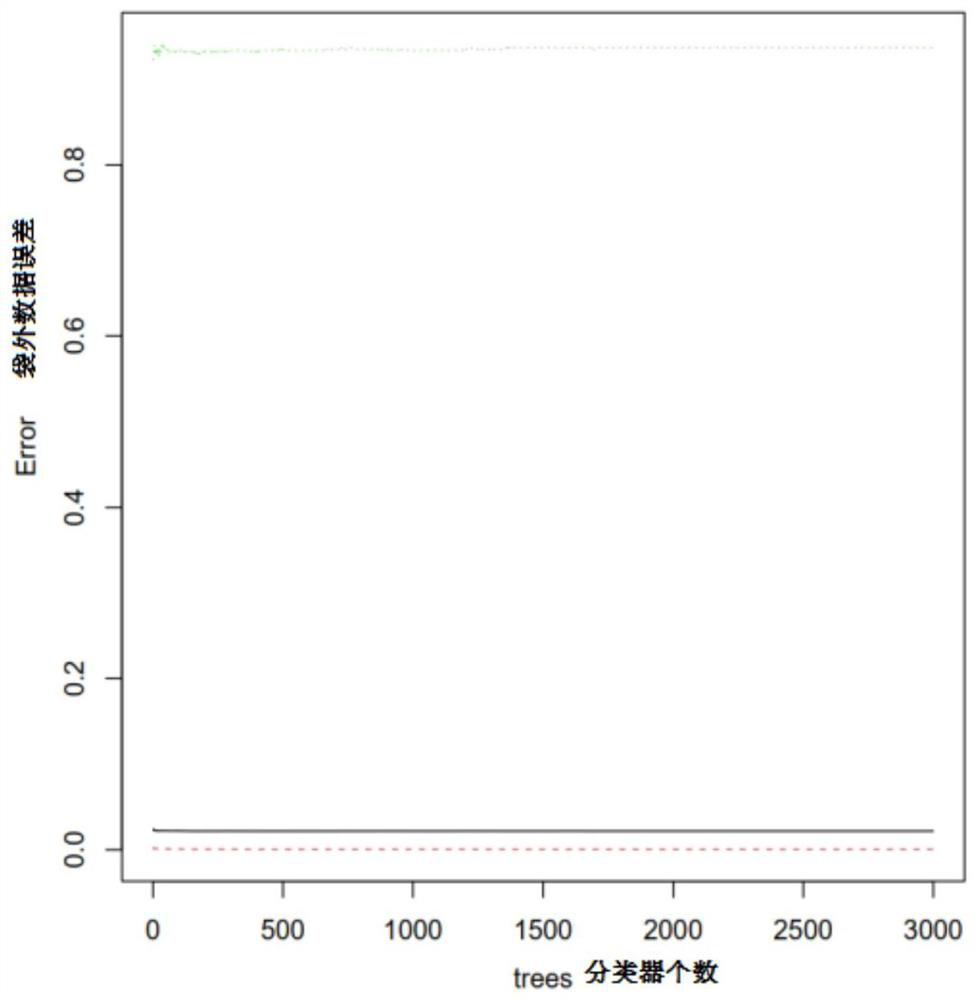

Multi-platform avionics big data system and method

InactiveCN107229695AGuaranteed real-timeReal-time acquisitionCharacter and pattern recognitionSpecial data processing applicationsAviationMulti platform

The invention discloses a multi-platform avionics big data system. The multi-platform avionics big data system comprises a data acquisition module, a data storage module, a data association analysis module and a data association analysis application module. The data acquisition module acquires a pcap data packet file from a data source 1, after acquisition and classification, the pcap data packet file is sent to the data storage module, and the data storage process is completed; the data association analysis module acquires training data from a data source 2, and establishes a data association model, and provides the data association model for the data association analysis application module for use, real-time prediction is completed, the result is displayed on the screen, and the data association analysis application module completes a real-time storage function by means of a cloud storage function implemented by the data storage module. In addition, the invention also discloses an implementing method for the multi-platform avionics big data system. The multi-platform avionics big data system is integrated with functions of data acquisition, data classified management, data storage, data analysis and the like, multi-source heterogeneous data is acquired and managed in a classified manner, and is stored to a resource cloud platform in real time, and the data real-time performance is guaranteed.

Owner:SHENZHEN UNIV

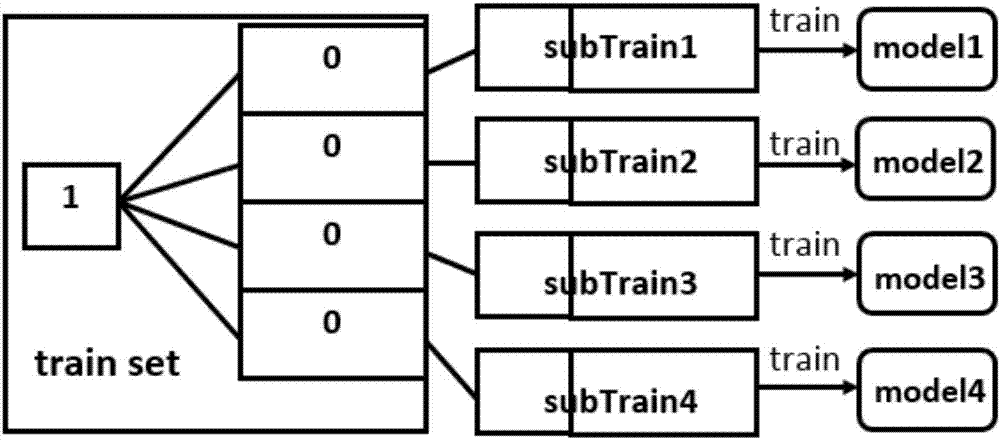

Method and device for building model and pushing message

InactiveCN105407158AImprove opening rateImprove prediction success rateTransmissionData miningComputer science

The invention discloses a method and device for building a model and pushing a message. The method for building the model comprises the following steps: obtaining user behaviour information of a user accessing a preset application in recent K days and K+1 days; constructing a training set according to the user behaviour information of the user in recent K days and K+1 days; and building a predication model according to the training set, wherein the predication model is used for determining the pushing time of the user about the preset application in the N+1th day according to the user behaviour information of the user accessing the preset application in the recent N days; and both K and N are preset parameters, which are integers more than 1. By means of the technical scheme, aiming at different users, the pushing message can be sent in a customized manner; and the opening rate for the user to open an application programme or the pushing message can be increased.

Owner:无线生活(杭州)信息科技有限公司

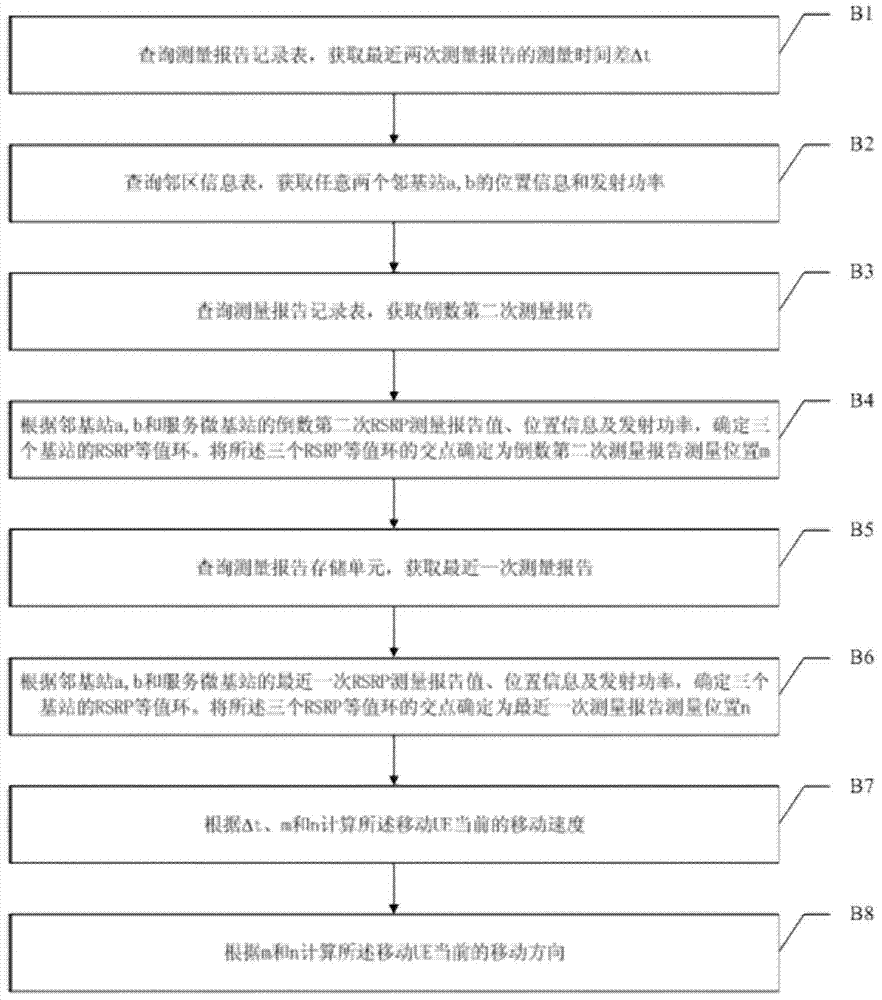

Mobile robustness optimization method and device based on mobile state information and adjacent region proximity

ActiveCN103796256AImprove prediction success rateImprove the success rate of switchingWireless communicationFrequency spectrumMicrocell

The invention discloses a mobile robustness optimization method and device based on mobile state information and adjacent region proximity and belongs to the technical field of wireless communication. In the method, a micro base station controller estimates real-time mobile state information of mobile UE according to cyclic measuring reports obtained from the mobile UE; then the mobile UE is subjected to switching control according to an adjacent region deploying environment, and frequent switching between a macrocell and a microcell of the mobile UE is avoided; and finally, during a switching process, switching preparing operation to a preparing target cell is brought forward, and according to the moving speed of the mobile UE and the PDCCH interruption point of the service microcell, the switching condition for avoiding ping-pong switching is computed. Compared with the prior art, the prediction success rate of the preparing target cell is improved, frequency spectrum resource using rate is improved, frequent switching between the macrocell and the microcell of the mobile UE is lowered, then network signaling expenditure is reduced, SToS rate is not increased, meanwhile, the switching success rate of the mobile UE can be improved, and then user experience is improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Method for predicting period of re-enriching remaining oil of water flooding reservoir into new reservoir

InactiveCN104727790AImprove prediction success rateEnhanced overall recoveryFluid removalSocial benefitsWater flooding

The invention provides a method for predicting a period of re-enriching remaining oil of a water flooding reservoir into a new reservoir. The method comprises the following steps of (1) gaining a value of water saturation of a researched oil reservoir; (2) selecting a corresponding oil and water delivery speed formula of the water flooding reservoir according to the value of the water saturation; and (3) calculating the maximum time of re-enriching the remaining oil of the water flooding reservoir into the new reservoir, namely the period of re-enriching the remaining oil of the water flooding reservoir into the new reservoir, by using the selected oil and water delivery speed formula of the water flooding reservoir. The method for predicting the period of re-enriching remaining oil of the water flooding reservoir into the new reservoir points out the direction for strategic adjustment of low-efficiency oil reservoir development at an ultra-high-water content stage, periodic oil reservoir injection-production development, capacity recovery and re-development of an oil reservoir which is about to be abandoned, and the like. Therefore, the method is wide in popularization and application prospect and high in economic benefit and social benefit.

Owner:CHINA PETROLEUM & CHEM CORP +1

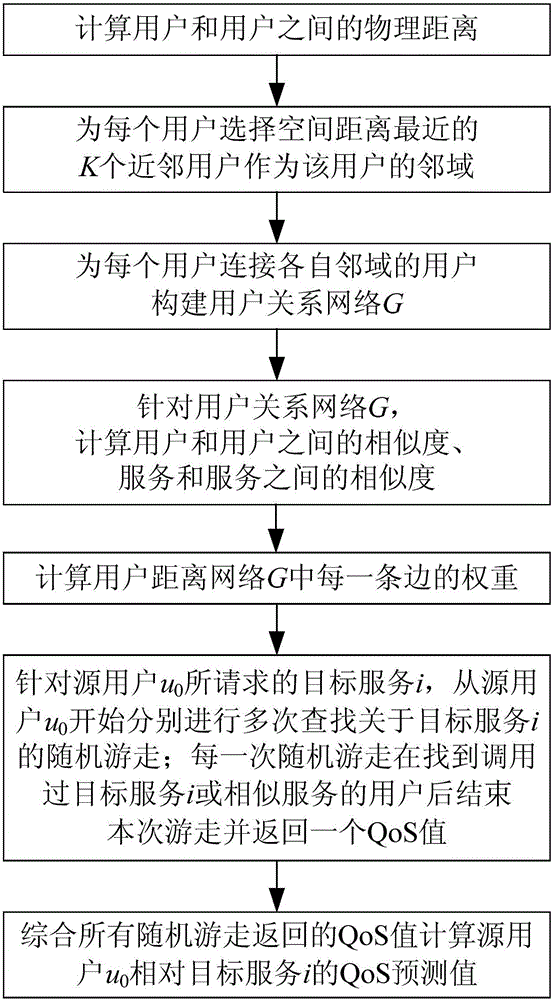

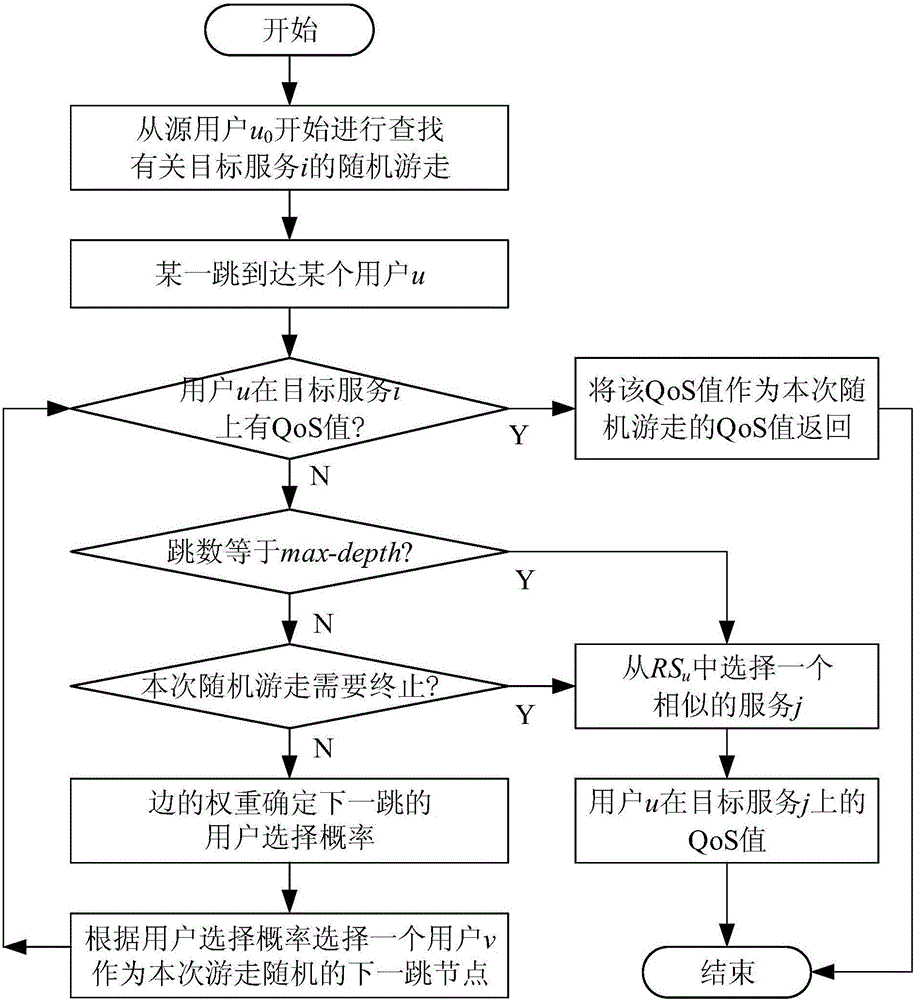

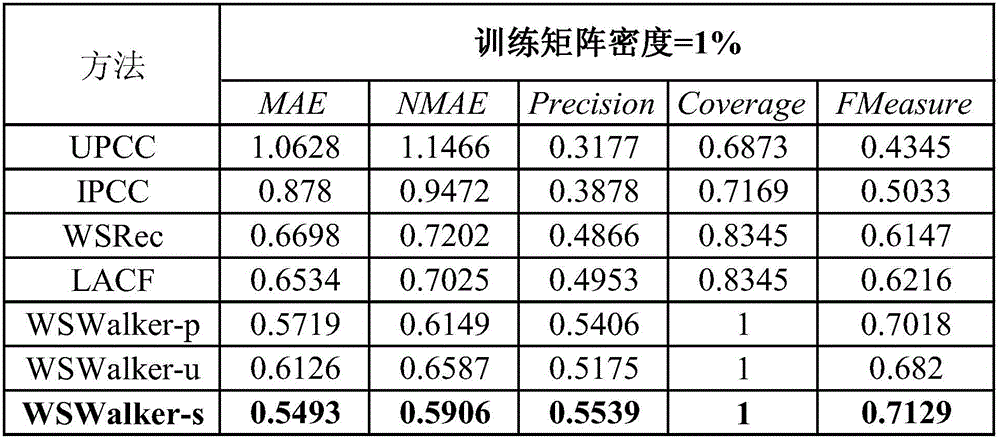

Web service quality prediction method based on random walk

InactiveCN105117325AGuaranteed success rateImprove prediction success rateHardware monitoringNeighborhood searchPredictive methods

The invention discloses a Web service quality prediction method based on random walk. The Web service quality prediction method comprises the following steps: on the basis of a user position, calculating a distance between users; selecting adjacent users for each user to form a neighborhood, and connecting neighborhood users to construct a user relationship network; calculating a similarity between the users and the similarity between services in the user relationship network; calculating the weight of each edge in the user relationship network; aiming at a target service requested by a source user to independently look up the random walk about the target service i for multiple times from the source user, randomly selecting a next-hop node by each hop in each-time random walk according to a certain probability, returning a QoS value after each-time walk is finished; and synthesizing all QoS values to calculate a quality prediction value, which is relative to the target service, of the source user. The Web service quality prediction method can balance coverage rate and the prediction precision of Web service quality prediction and has the advantages of being accurate in prediction, high in success rate, good in universality and favorable in evaluable confidence coefficient and interpretability.

Owner:HUNAN UNIV OF SCI & TECH

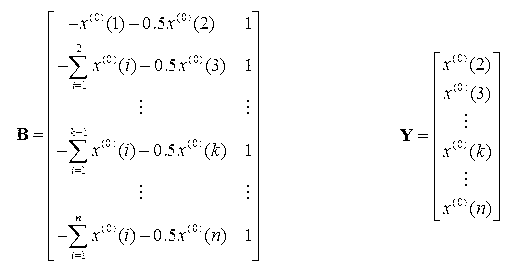

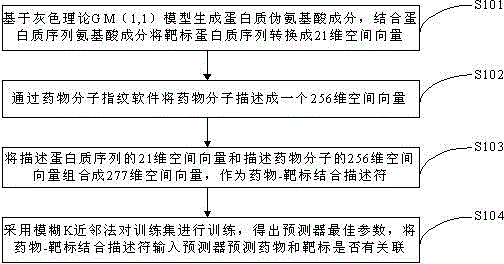

Method for predicating drug-target combination based on grey theory and molecular fingerprints

InactiveCN102930169AOvercome the disadvantage of needing to know the three-dimensional structure of the proteinImprove prediction success rateSpecial data processing applicationsFingerprintPseudo amino acid composition

The invention discloses a method for predicating drug-target combination based on the grey theory and molecular fingerprints. The method includes generating protein pseudo amino acid compositions based on a gray theory gray model (GM) (1,1) and converting target protein sequences into 21-dimensional spatial vectors combined with the protein sequence pseudo amino acid compositions; describing drug molecules into a 256-dimensional spatial vector through a drug molecular fingerprint software; combining the 21-dimensional spatial vectors of the protein sequences and the 256-dimensional spatial vector of the drug molecules into 277-dimensional spatial vectors to serve as drug-target combination descriptors; and training sets are trained through a fuzzy K-nearest neighboring method to obtain optimum parameters of a predictor and the drug-target combination descriptors are input into the predictor to predicate whether a drug is associated with a target. According to the method, three-dimensional structures of proteins are not needed to be measured, whether the drug and the proteins can be combined can be predicated by only adding drug molecular fingerprints on a protein one dimensional sequence, and the predication success rate is high.

Owner:JINGDEZHEN CERAMIC INSTITUTE

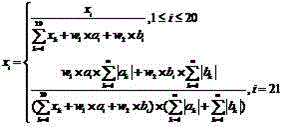

Data correcting method applying petroleum inclusion to carry out oil and gas migration tracking and ancient and present oil layer recognition

ActiveCN101776769AImprove prediction success rateMaterial analysis by optical meansSeismic signal processingMicroscopic observationCorrection method

The invention relates to a data correcting method applying a petroleum inclusion to carry out oil and gas migration tracking and ancient and present oil layer recognition, which is characterized in that for the petroleum inclusion of each cement, a correction formula of GOI and FOI statistic data is disclosed in the specification, wherein GOImc is the relative number of a corrected single cement (such as silicious cement) and an oil-bearing inclusion in a fissure thereof, and the GOIm is the original data; Cm represents the content of the cement and is an average value; and CC represents the content of carbonaceous asphalt and is the average value of the content of the carbonaceous asphalt. Similarly, the correction of FOI can be realized, the FOImc is the frequency of occurrence of the m cement after correction and the oil-bearing inclusion in the fissure thereof, and the FOIm is the original data. Microscopic observation is carried out on ordinary sheets or casting sheets, the contents of the cement and the carbonaceous asphalt corresponding to the petroleum inclusion are counted, and the number of statistical points is between 100 and 1000; and a fluorescence microscope is utilized to observe the dissolution phenomenon of the carbonaceous asphalt by oily asphalt so as to identify the carbonaceous asphalt, and the formula (2) and the formula (3) are utilized to correct the GOI and the FOI.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

Accurate digital indicator reading detection method

InactiveCN108875739AHigh probability of predicting successSave manpower and material resourcesCharacter and pattern recognitionNeural learning methodsLearning abilitiesData entry

The invention discloses an accurate digital indicator reading detection method in the technical field of mode recognition and artificial intelligence. The method comprises the following steps of: (1)data obtaining: shooting an instrument image which comprises a reading area by adoption of a camera device; (2) data processing: manually annotating an instrument reading value and carrying out randomrotation, stretching and translation transformation on the instrument image; (3) deep network model construction and training: inputting the instrument image and corresponding annotation data into adeep network model to carry out training; and (4) instrument reading detection: inputting the instrument image and returning a standard instrument reading image by a system. The method is capable of overcoming deficiencies of existing instrument reading extraction methods, sufficiently utilizing parameter learning ability of the deep network model, and accurately detecting digital indicator readings through distribution of learning data samples on the basis of adversarial learning ability of the deep network model and physical meaning of backpropagation residuals, has the characteristics of being strong in practicability and high in correctness, and has a relatively good practical value.

Owner:深圳市云识科技有限公司 +1

Soil adsorbed hydrocarbon low-temperature desorption apparatus and method

ActiveCN1667408AImprove prediction success rateAchieve quantitative desorptionComponent separationDesorptionGas phase

The invention relates to a soil adsorbed hydrocarbons cryogenic temperature desorption apparatus and its method.The method comprises following steps: injecting water without gas into the apparatus; mixing water and soil to mud absorbed into the apparatus; then injecting water without gas and adjusting temperature head to normal temperature and normal pressure; collecting desorption gas sample and detecting them in gas-chromatography.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

Novel protein sequence representation method based on gene ontology information

ActiveCN106845149AImprove prediction success rateReduce dimensionalityProteomicsGenomicsGene ontologyAntibacterial peptide

The invention relates to a novel protein sequence representation method based on gene ontology information, comprising: using BLAST program to search Swiss-Prot database for all similar protein sequences of protein sequence P, inputting all proteins in a training dataset into GO (gene ontology) database, and searching for GO information of each protein; searching the gene ontology database for targeting gene ontology information of P protein; defining the P protein as discrete vectors of M elements according to M labels that a prediction problem has. The protein GO information in a sequence set is fused into novel P protein vector description, and the dimensionality of the GO method is reduced greatly; by applying the method to protein subcellular multi-label positioning prediction and antibacterial peptide functional multi-label prediction, it is possible to significantly increase the prediction success rate of a related predictor; the novel protein sequence representation method based on gene ontology information has a promising application prospect.

Owner:上海司默迪医学信息科技有限公司

Method for predicting success rate of scarred uterus trial-production

InactiveCN105243267AProtect your healthEasy to operateSpecial data processing applicationsObstetricsObstetric history

The present invention relates to the technical field of obstetrics and gynecology medical science, and particularly to a method for predicting the success rate of scarred uterus trial-production. The method comprises: collecting data of a pregnant woman, including antepartum parity, an antepartum BMI (Body Mass Index), a cervix prenatal situation, and whether PROM (premature rupture of membranes) occurs or not; performing calculation by using P = 1 / [1+exp(-0.785+1.3259x1-1.5061x2-1.2449x31-1.4211x32+0.7617x4)]*100%; and predicting the success rate of the pregnant woman uterus trial-production according to a P value, so as to provide a reference index for the pregnant woman and doctors. The method is easy in data collection, high in prediction success rate, and especially suitable for vagina trial-production prediction of Chinese pregnant women with a scarred uterus.

Owner:东莞市塘厦医院

Sandstone bottom water reservoir water cone quantitative-description method

The invention provides a sandstone bottom water reservoir water cone quantitative-description method. The sandstone bottom water reservoir water cone quantitative-description method comprises the steps of 1 collecting an oil reservoir characterization parameter of a researched oil reservoir, 2 describing a model formula by selecting a corresponding water cone or a water ridge according to well type and 3 utilizing the selected water cone or the water ridge to describe the model formula and calculate the morphological parameter and volume of the water cone or the water ridge. By means of the sandstone bottom water reservoir water cone quantitative-description method, the morphologies of the water cone or the water ridge of the oil reservoir at different position in different periods can be predicted, and the residual oil distribution rule of the sandstone bottom water reservoir can be determined. The sandstone bottom water reservoir water cone quantitative-description method has the advantages of being high in prediction success rate, simple and convenient to used and practical.

Owner:CHINA PETROLEUM & CHEM CORP +1

Six-stage pipeline processor based on RISC-V instruction set

PendingCN114721724AReduce cavitationImprove branch prediction success rateConcurrent instruction executionEnergy efficient computingData memoryInstruction memory

The invention relates to the field of computer components, in particular to a six-level assembly line processor based on an RISC-V instruction set, which comprises a six-level assembly line, a first register, a data memory and an instruction memory, and is characterized in that an instruction fetching module, a decoding module, a distribution module, a transmitting module, an execution module and a write-back module of the six-level assembly line are connected in sequence; the data memory is connected with the execution module and the write-back module, the first register is connected with the distribution module and the write-back module, and the instruction memory is connected with the instruction fetching module. The characteristic of out-of-order execution of double-instruction decoding emission is achieved, and a reference model is provided for superscalar parallel design of the RISC-V processor. And a Gshare branch prediction circuit is provided, so that the branch prediction success rate is improved. The register is renamed, so that assembly line cavitation caused by reading after writing and writing after writing is remarkably reduced. And a complete branch prediction failure repair circuit is provided, so that the time loss caused by branch prediction failure is reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Risk assessment method for unqualified products

InactiveCN114611919ATake advantage ofEasy to guide designCharacter and pattern recognitionResourcesFeature extractionFeature parameter

The invention discloses a risk assessment method for unqualified products, and the method comprises the following steps: (1) carrying out the data preprocessing, data screening and feature extraction of pre-collected product large-class sample data, and obtaining feature parameters corresponding to the unqualified products; (2) randomly segmenting data of all samples into a training set and a verification set according to a proportion of 7: 3; (3) establishing a Logistic regression model according to the characteristic parameters, evaluating the Logistic regression model by adopting an ROC curve and an AUC value, and calculating an optimal truncation value of an unqualified product probability according to a Youden index; and (4) inputting the characteristic parameters of the to-be-tested product into the Logistic regression model to obtain the disqualification condition of the to-be-tested product. The method is accurate in prediction result, high in speed and good in adaptability to a large amount of detection data.

Owner:GUANGDONG TESTING INST OF PROD QUALITY SUPERVISION

Crop cultivation mode analysis optimization method with real-time database and advanced control algorithm

ActiveCN106803209AImprove predictive performanceGood forecastForecastingSupport vector machineAgricultural science

The invention discloses a crop cultivation mode analysis optimization method with a real-time database and an advanced control algorithm. Physiological factors and environmental factors of crop cultivation are introduced, and through a canonical correlation analysis method and a support vector machine, environmental parameters and physiological parameters are analyzed and processed to obtain an optimal parameter combination; sample data corresponding to the optimal parameter combination are input to the support vector machine to be trained, a crop cultivation model capable of predicting the crop growing state is built, and the obtained crop cultivation model is utilized to optimize a crop cultivation mode. The crop cultivation mode analysis optimization method with the real-time database and the advanced control algorithm simplifies the crop cultivation mode, can solve the problem in the prior art that correlation calculation is too complicated, can accurately predict the growth of crop that is cultivated, and optimize a crop cultivation process.

Owner:HANGZHOU QIUSHI ARTIFICIAL ENVIRONMENT

Concealed resource prediction method and rock electromagnetic logging system

ActiveCN110703344ARealize broadband complex impedance measurementImprove prediction success rateElectric/magnetic detection for well-loggingDetection using electromagnetic wavesWell loggingBroadband

The invention discloses a concealed resource prediction method and a rock electromagnetic logging system which are applied to the technical field of mineral and oil-gas resource exploration. Accordingto the rock electromagnetic logging system, by the adoption of a broadband (0.001-10,000 Hz) sweep frequency mode, rock broadband complex impedance measurement can be realized, and potential mineralor oil-gas resources are predicted through acquired rock electromagnetic characteristic factors separately or in combination with geochemical characteristics.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

Soil adsorbed hydrocarbon low-temperature desorption apparatus and method

ActiveCN1308678CImprove prediction success rateAchieve quantitative desorptionComponent separationDesorptionGas phase

The invention relates to a soil adsorbed hydrocarbons cryogenic temperature desorption apparatus and its method.The method comprises following steps: injecting water without gas into the apparatus; mixing water and soil to mud absorbed into the apparatus; then injecting water without gas and adjusting temperature head to normal temperature and normal pressure; collecting desorption gas sample and detecting them in gas-chromatography.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

Logarithm normalization method for improving local prediction ability of neural network

InactiveCN105550425AImprove prediction success rateGeometric CADNeural learning methodsNerve networkNetwork output

The invention discloses a logarithm normalization method for improving local prediction ability of a neural network. The method comprises the following steps of: determining input and output of the neural network according to a prediction object, specifically, generating an input value of a training sample as a neural network input value through a sampling method, and calculating an output value of each training sample through a computational fluid mechanics method, namely, designing a target value, as a neural network output value; performing normalization for the neural network input value through a linear normalization method; determining a threshold value of the neural network output value, and performing normalization for the neural network output value through a logarithm normalization method. Compared with the conventional linear normalization method, the logarithm normalization method provided by the invention improves prediction success rate of the neural network by 17.1%.

Owner:TIANJIN UNIV

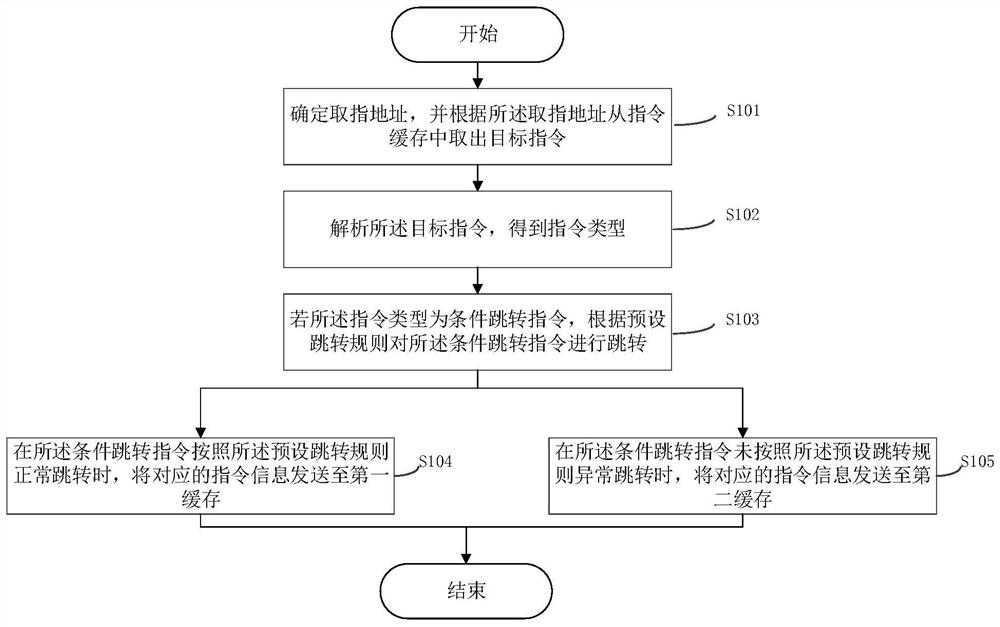

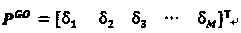

Conditional jump instruction processing method and system and related device

PendingCN113760366AImprove prediction success rateImprove instruction execution efficiencyConcurrent instruction executionEnergy efficient computingProgramming languageHandling system

The invention provides a conditional jump instruction processing method. The method comprises the following steps: determining an instruction fetching address, and fetching a target instruction from an instruction cache according to the instruction fetching address; analyzing the target instruction to obtain an instruction type; if the instruction type is a conditional jump instruction, controlling the conditional jump instruction to jump according to a preset jump rule; when the conditional jump instruction jumps normally according to the preset jump rule, sending corresponding instruction information to a first cache; and when the conditional jump instruction jumps abnormally not according to the preset jump rule, sending the corresponding instruction information to a second cache. According to the invention, the problem that a dynamic prediction method is easily influenced by an algorithm, resources, a compiler and application adaptation can be solved, and the instruction execution efficiency of a processor is improved. The invention further provides a conditional jump instruction processing system, a computer readable storage medium and electronic equipment, which have the above beneficial effects.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

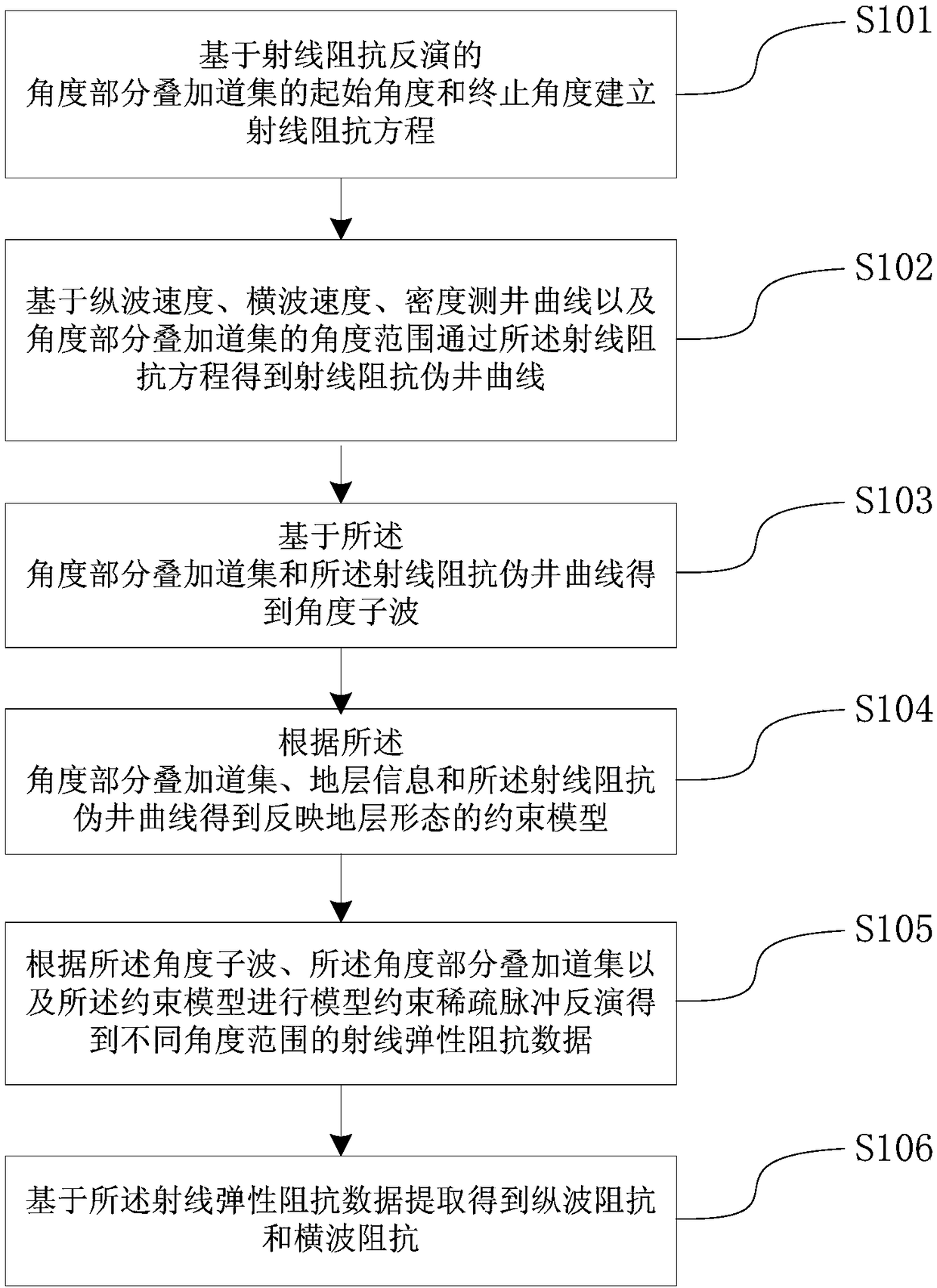

A data processing method for post-drilling data

ActiveCN106291712BReduce exploration riskReduce uncertaintySeismic signal processingSeismology for water-loggingState predictionData acquisition

The invention discloses a post-drilling data processing method. The method comprises the following steps: data acquisition is carried out, a pre-drilling calculation analysis result for an exploratory well is acquired, and post-drilling data of the exploratory well are acquired; post-drilling data are pretreated, the post-drilling data are calculated and analyzed to acquire a post-drilling calculation analysis result corresponding to the pre-drilling calculation analysis result; comparative analysis is carried out, based on the comparative analysis on the pre-drilling calculation analysis result and the post-drilling calculation analysis result, a comprehensive analysis processing result for the post-drilling data is acquired, wherein the comprehensive analysis processing result comprises rationality judgment on the pre-drilling calculation analysis result and / or reasons for deviation of the pre-drilling calculation analysis result. The method of the invention can reduce uncertainty of the pre-drilling geological data calculation analysis result, the geological state prediction success rate can be improved, and the oil-gas exploration risks are finally reduced.

Owner:CHINA PETROLEUM & CHEM CORP +1

Method for predicating drug-target combination based on grey theory and molecular fingerprints

InactiveCN102930169BOvercome the disadvantage of needing to know the three-dimensional structure of the proteinImprove prediction success rateSpecial data processing applicationsProtein targetDrug target

The invention discloses a method for predicating drug-target combination based on the grey theory and molecular fingerprints. The method includes generating protein pseudo amino acid compositions based on a gray theory gray model (GM) (1,1) and converting target protein sequences into 21-dimensional spatial vectors combined with the protein sequence pseudo amino acid compositions; describing drug molecules into a 256-dimensional spatial vector through a drug molecular fingerprint software; combining the 21-dimensional spatial vectors of the protein sequences and the 256-dimensional spatial vector of the drug molecules into 277-dimensional spatial vectors to serve as drug-target combination descriptors; and training sets are trained through a fuzzy K-nearest neighboring method to obtain optimum parameters of a predictor and the drug-target combination descriptors are input into the predictor to predicate whether a drug is associated with a target. According to the method, three-dimensional structures of proteins are not needed to be measured, whether the drug and the proteins can be combined can be predicated by only adding drug molecular fingerprints on a protein one dimensional sequence, and the predication success rate is high.

Owner:JINGDEZHEN CERAMIC UNIV

Method for recognizing oil layer by using petroleum inclusion and pitch and migration tracing

ActiveCN100547436CImprove prediction success rateEliminate distractionsMaterial analysis by optical meansSeismology for water-loggingWell drillingChemical condition

The invention relates to oil-gas prospecting technical field, especially using the petroleum inclusion and asphalt to distinguish the oil reservoir and fulfill the migration tracing. With the statistical data from the petroleum inclusion and asphalt, the invention may distinguish the oil reservoir during the drilling (including the prospecting and development) or later; and determine the petroleum migration direction, and trace its routing, search the prevailing migration channel etc. under multi-stage migration and accumulation, fulfill the multi-stage and multiple genesis statistics for petroleum inclusion, trace the oil-gas migration during different geologic phase, determine the oil-gas migration direction and prevailing channels during different stages, and the variation of physical and chemical conditions during migration, thereby recovers the history of oil-gas migration and accumulation, provides the important basis for finding the oil-gas distribution law and advantageous areas for oil-gas migration and accumulation.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

Mobile Robustness Optimization Method and Device Based on Mobile State Information and Adjacent Cell Proximity

ActiveCN103796256BImprove prediction success rateImprove the success rate of switchingWireless communicationFrequency spectrumMicrocell

The invention discloses a mobile robustness optimization method and device based on mobile state information and adjacent region proximity and belongs to the technical field of wireless communication. In the method, a micro base station controller estimates real-time mobile state information of mobile UE according to cyclic measuring reports obtained from the mobile UE; then the mobile UE is subjected to switching control according to an adjacent region deploying environment, and frequent switching between a macrocell and a microcell of the mobile UE is avoided; and finally, during a switching process, switching preparing operation to a preparing target cell is brought forward, and according to the moving speed of the mobile UE and the PDCCH interruption point of the service microcell, the switching condition for avoiding ping-pong switching is computed. Compared with the prior art, the prediction success rate of the preparing target cell is improved, frequency spectrum resource using rate is improved, frequent switching between the macrocell and the microcell of the mobile UE is lowered, then network signaling expenditure is reduced, SToS rate is not increased, meanwhile, the switching success rate of the mobile UE can be improved, and then user experience is improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

A method for predicting the success rate of scarred uterus trial delivery

InactiveCN105243267BProtect your healthEasy to operateElectronic clinical trialsObstetricsObstetric history

The present invention relates to the technical field of obstetrics and gynecology, in particular to a method for predicting the success rate of trial delivery of a scarred uterus, by analyzing the prenatal parity of pregnant women, prenatal body mass index, dilation of the cervix, and premature rupture of membranes. Data collection, and then use P=1 / [1+exp (‑0.785+1.3259x1‑1.5061x2‑1.2449x31‑1.4211x32+0.7617x4)]*100% to calculate, and predict the success rate of vaginal trial delivery according to the P value , to provide a reference index for pregnant women and doctors, data collection is easy, and the prediction success rate is high, especially suitable for the prediction of vaginal trial labor of pregnant women with scarred uterus in our country.

Owner:东莞市塘厦医院

A Novel Solution to the Unbalanced Problem of Protein Training Set Integrating Genetic Information

InactiveCN104899478BImprove prediction success rateObvious biological significanceSpecial data processing applicationsData setData expansion

The present invention provides a new solution to the imbalance problem of the protein training set fused with genetic information. The amino acids in the conserved region in the protein P sequence are kept unchanged, and the amino acids in the non-conserved region are sequentially converted according to the probability of mutation of the PSSM matrix to other amino acids. into other amino acids, so that 20 virtual proteins containing the genetic information of protein P can be obtained, and the small number of subsets in the unbalanced data set can be expanded to make the unbalanced data set into a balanced data set, which is conducive to training related predictors , which can improve the prediction success rate of the predictor. Different from the existing methods for solving unbalanced data, the present invention can integrate protein evolution information and directly expand from the sequence instead of interpolating in the discrete digital model describing the sequence information, which has obvious biological significance, so it can significantly improve The prediction success rate of related predictors has a wide application space.

Owner:JINGDEZHEN CERAMIC UNIV

A Protein Sequence Representation Method Based on Gene Ontology Information

ActiveCN106845149BImprove prediction success rateReduce dimensionalityProteomicsGenomicsGene ontologyAntibacterial peptide

Owner:上海司默迪医学信息科技有限公司

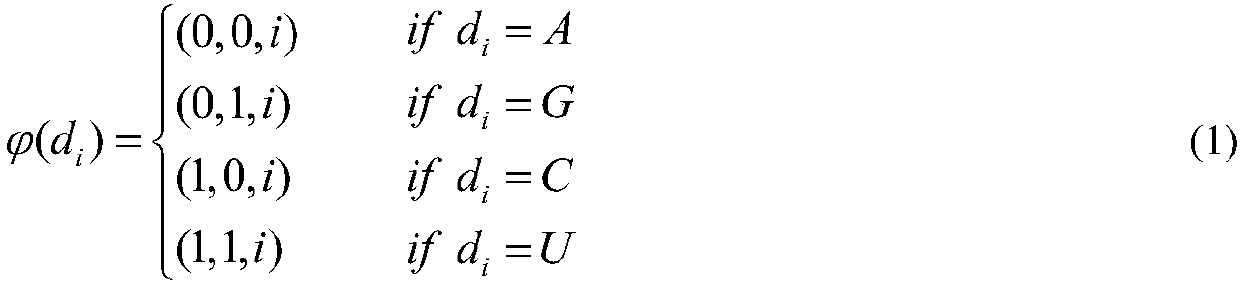

An RNA-Seq Description Method Fused with Local and Global Features

ActiveCN105224825BImprove prediction success rateSpecial data processing applicationsCorrelation coefficientRNA modification

The invention provides an RNA sequence description method that combines local and global features, constructs an RNA sequence physicochemical matrix PCM by combining nucleotide duplex structure information and other physical and chemical properties, and the matrix contains RNA sequence structure information and sequence order information. By establishing a gray model for each row of data in the matrix and calculating its autocorrelation factor and cross-correlation factor between rows to obtain the local information of the sequence, convert the PCM into a two-dimensional image, and calculate the geometric distance of the image to obtain the global sequence information. Combining the obtained factors describing sequence local information and global information, a discrete vector description model of RNA sequence is obtained. The method is used in the prediction of RNA attribute types and RNA modification sites, can significantly improve the prediction success rate of related predictors, and has broad application prospects.

Owner:JINGDEZHEN CERAMIC INSTITUTE

Crop cultivation mode analysis and optimization method based on real-time database and advanced control algorithm

ActiveCN106803209BSimplify the way of breedingAccurately predict growthForecastingAdaptive controlAlgorithmCrop cultivation

The invention discloses a crop cultivation mode analysis optimization method with a real-time database and an advanced control algorithm. Physiological factors and environmental factors of crop cultivation are introduced, and through a canonical correlation analysis method and a support vector machine, environmental parameters and physiological parameters are analyzed and processed to obtain an optimal parameter combination; sample data corresponding to the optimal parameter combination are input to the support vector machine to be trained, a crop cultivation model capable of predicting the crop growing state is built, and the obtained crop cultivation model is utilized to optimize a crop cultivation mode. The crop cultivation mode analysis optimization method with the real-time database and the advanced control algorithm simplifies the crop cultivation mode, can solve the problem in the prior art that correlation calculation is too complicated, can accurately predict the growth of crop that is cultivated, and optimize a crop cultivation process.

Owner:HANGZHOU QIUSHI ARTIFICIAL ENVIRONMENT

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com