Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

616results about How to "Ensure performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

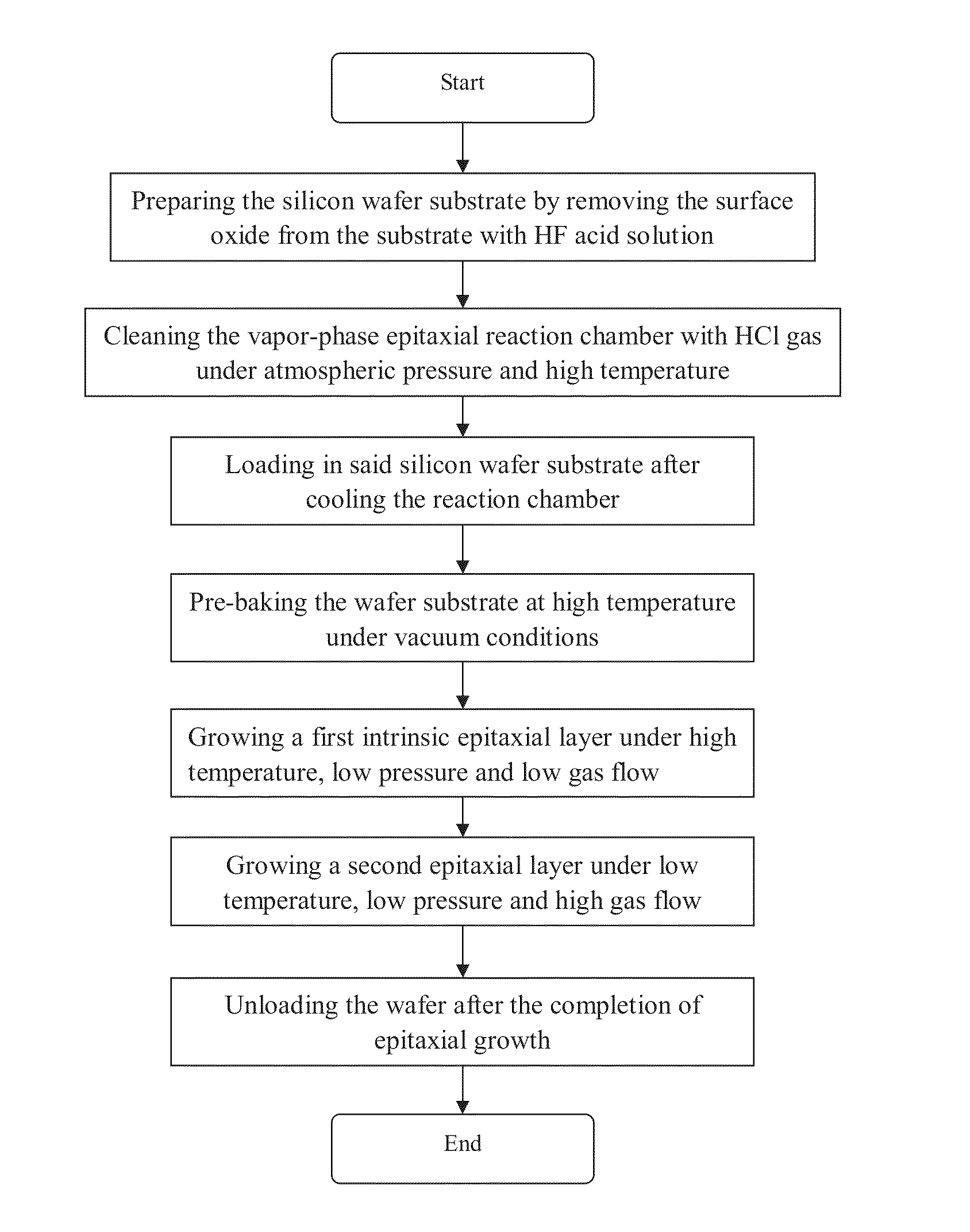

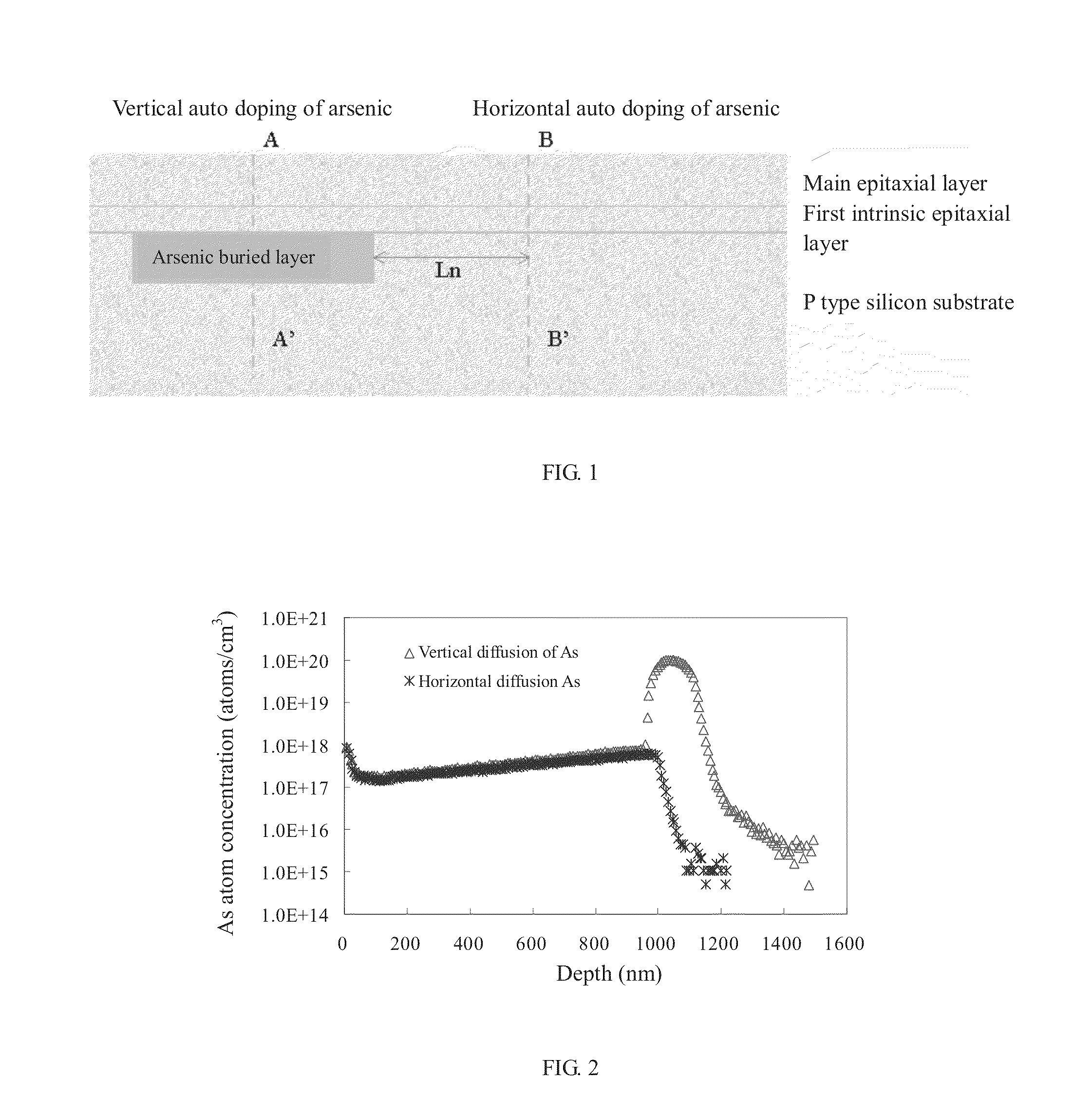

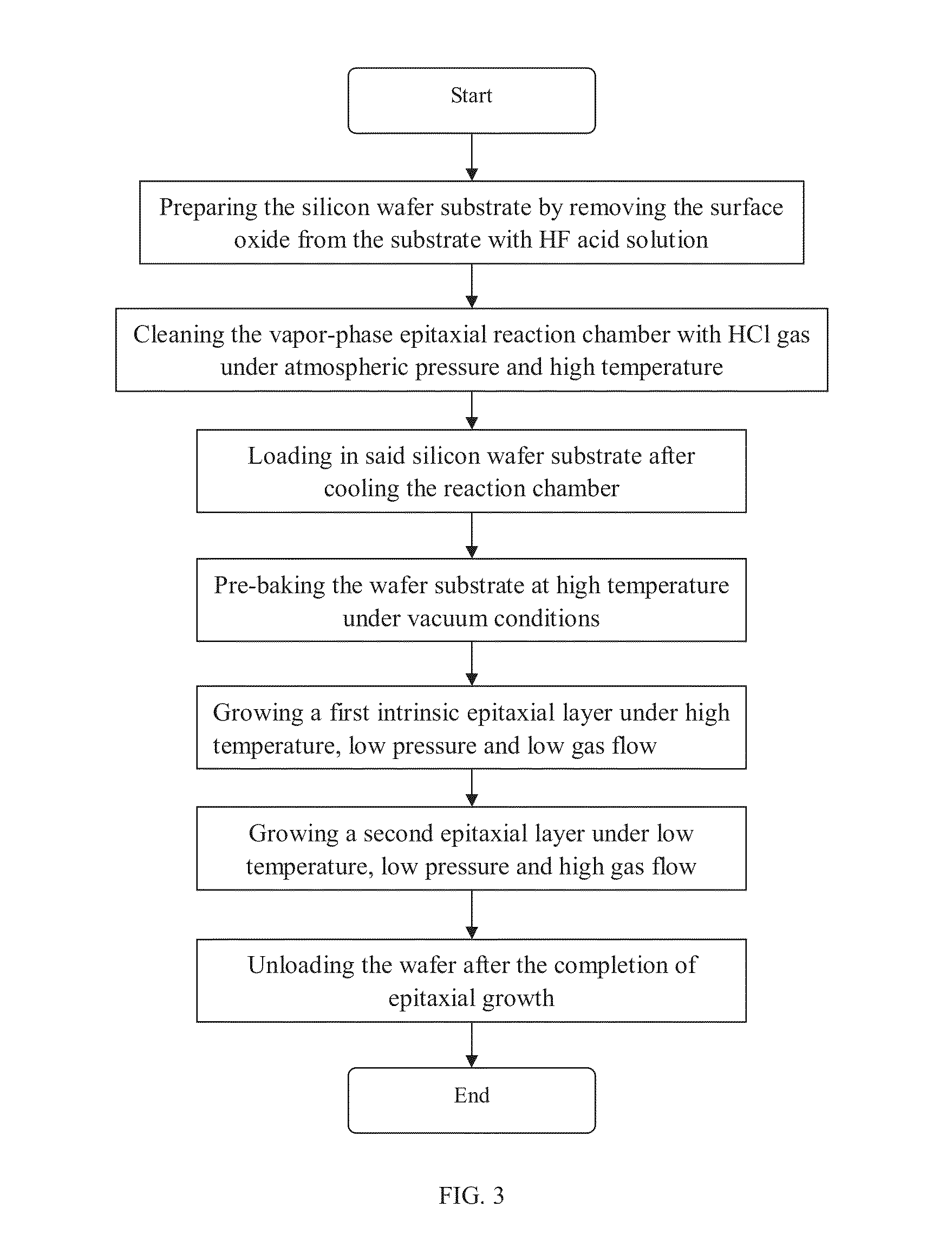

Method of epitaxial growth effectively preventing auto-doping effect

ActiveUS20130145984A1Improve equipment reliabilityInhibited DiffusionPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantMoisture

This invention relates to a method of epitaxial growth effectively preventing auto-doping effect. This method starts with the removal of impurities from the semiconductor substrate having heavily-doped buried layer region and from the inner wall of reaction chamber to be used. Then the semiconductor substrate is loaded in the cleaned reaction chamber to be pre-baked under vacuum conditions so as to remove moisture and oxide from the surface of said semiconductor substrate before the extraction of the dopant atoms desorbed from the surface of the semiconductor substrate. Next, under high temperature and low gas flow conditions, a first intrinsic epitaxial layer is formed on the surface of said semiconductor substrate where the dopant atoms have been extracted out. Following this, under low temperature and high gas flow conditions, a second epitaxial layer of required thickness is formed on the structural surface of the grown intrinsic epitaxial layer. Last, silicon wafer is unloaded after cooling. This method can prevent auto-doping effect during the epitaxial growth on semiconductor substrate and thus ensure the performance and enhance the reliability of the devices in peripheral circuit region.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

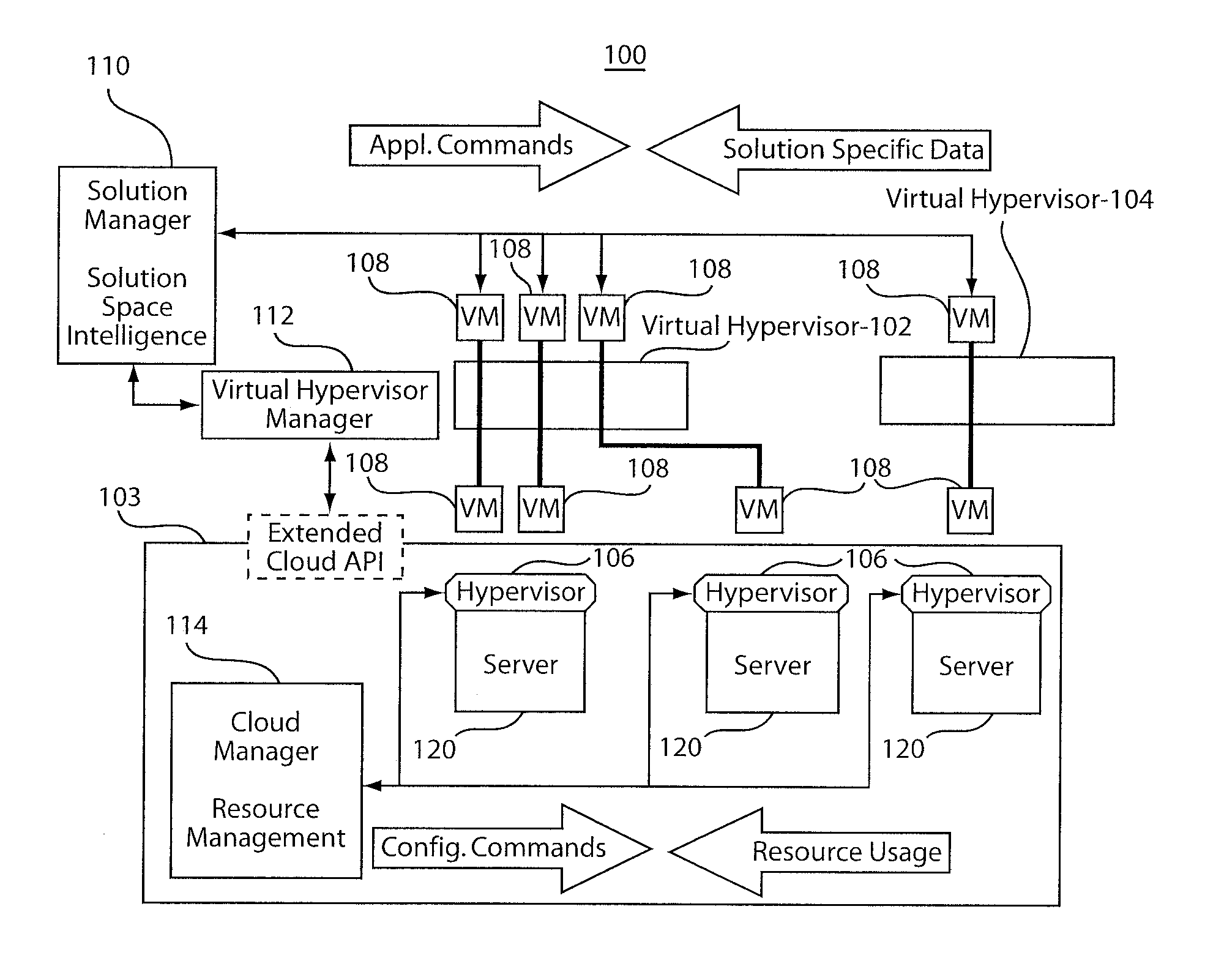

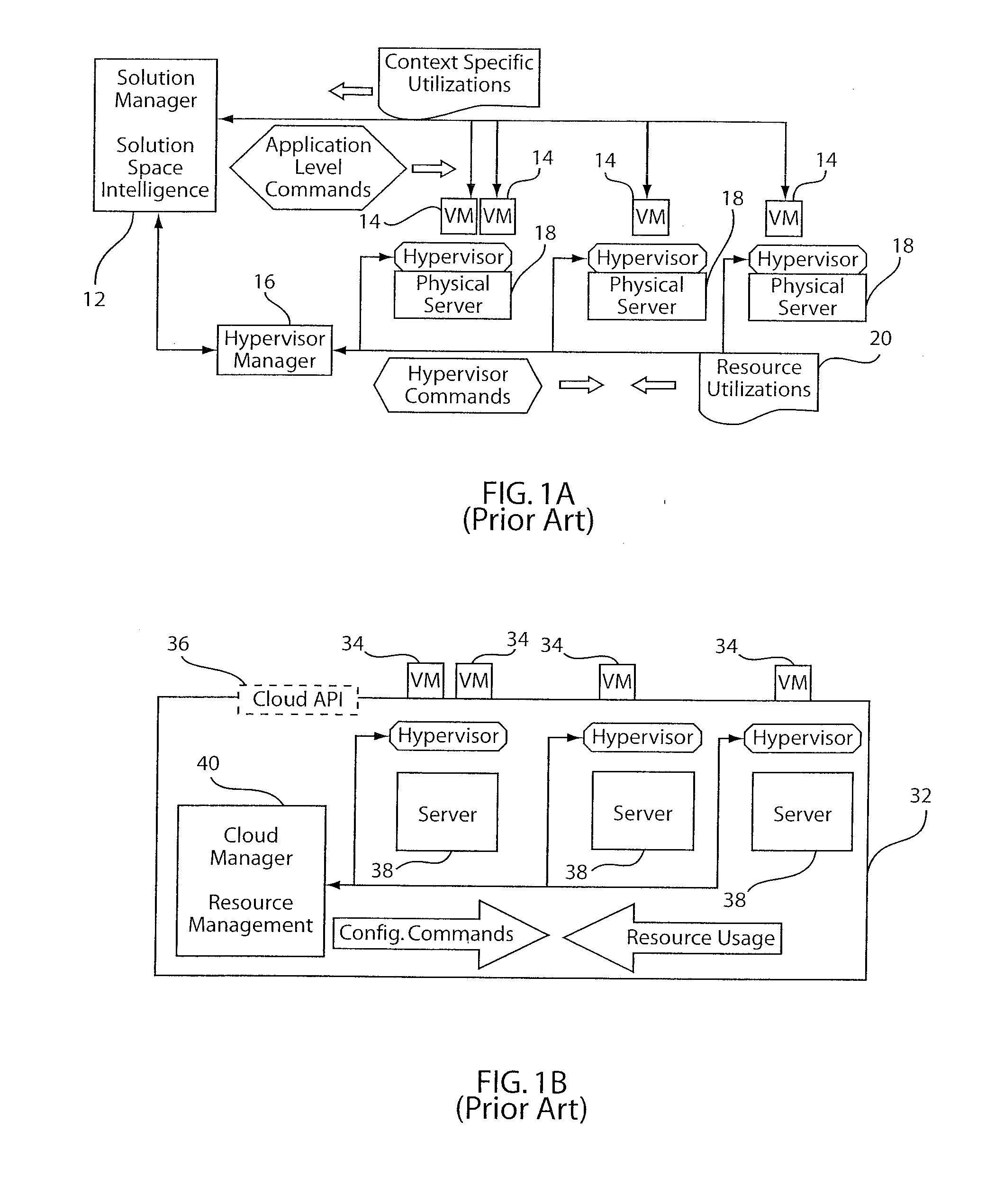

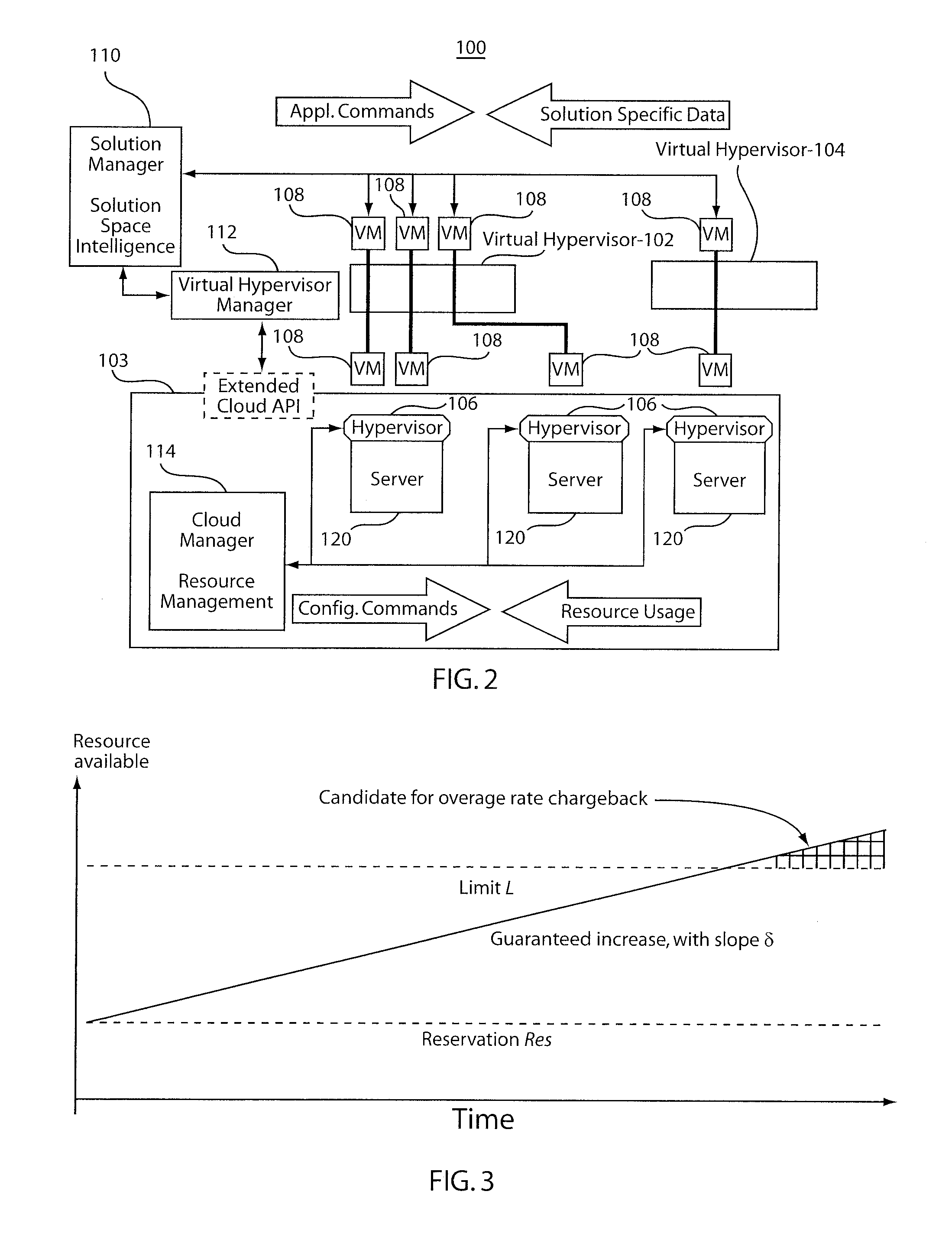

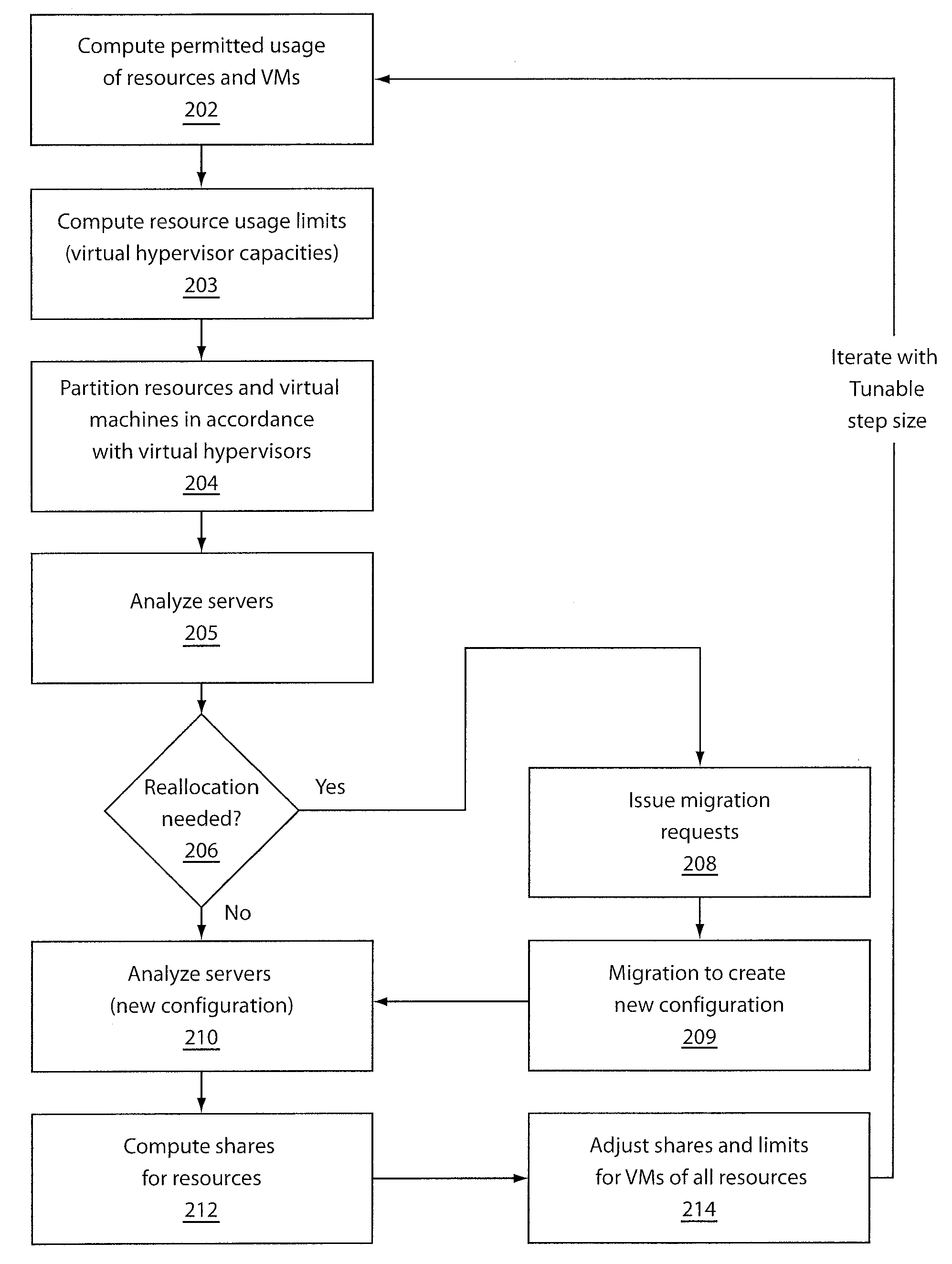

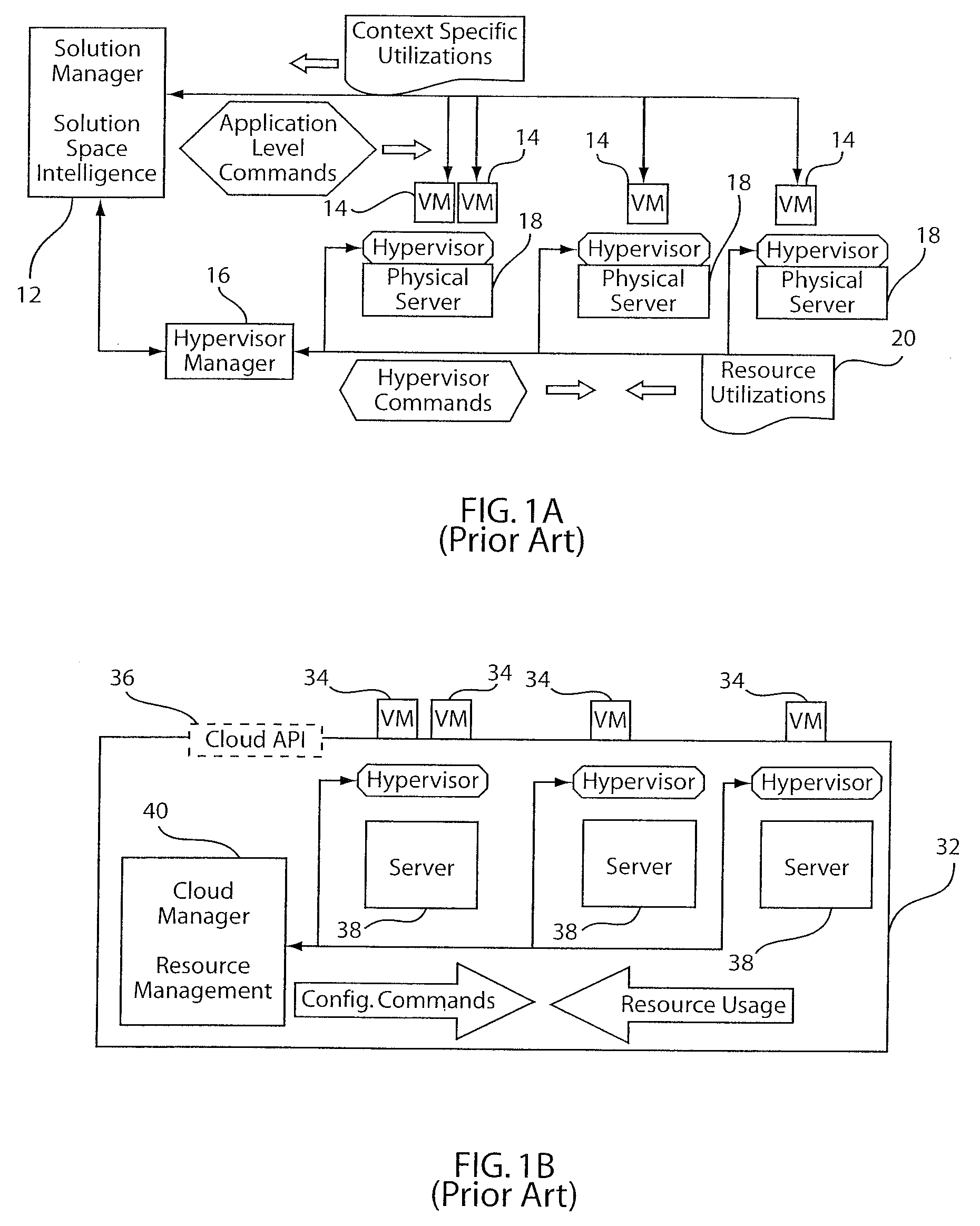

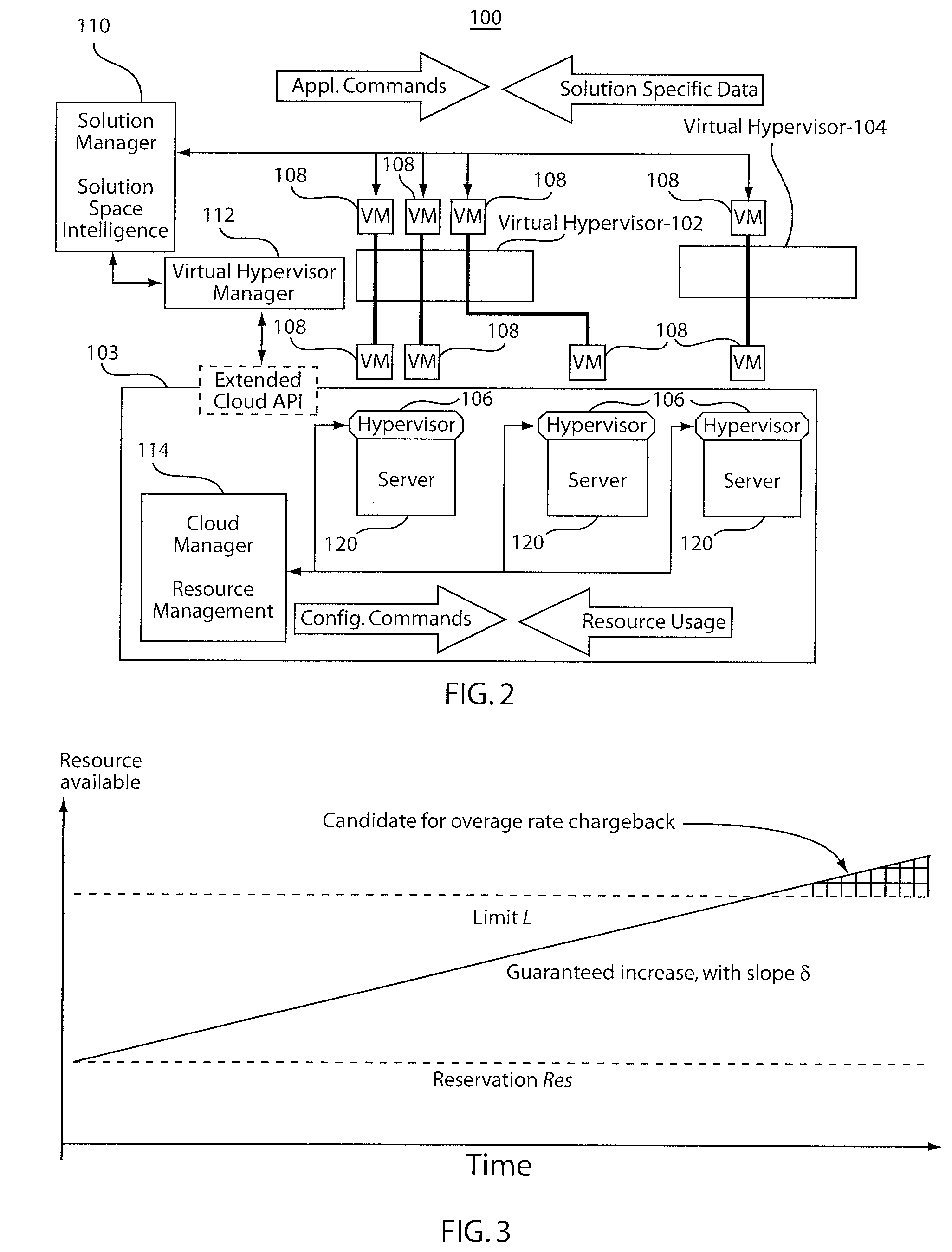

System and method for fair and economical resource partitioning using virtual hypervisor

ActiveUS20110185064A1Easy to controlEnsure performanceEnergy efficient ICTDigital computer detailsAbstraction layerNetwork service

A system and method for allocating resources in a cloud environment includes determining permitted usage of virtual machines and partitioning resources between network servers in accordance with a virtual hyperviser generated in accordance with an abstraction layer configured as an interface between a solution manager and an interface to a cloud network. Resource usage limits are determined for each virtual machine associated with the virtual hyperviser, and the servers are analyzed through the virtual hypervisers to determine if the virtual machines need to be migrated. If reallocation is needed, virtual machine migration requests are issued to migrate virtual machines into a new configuration at the virtual hypervisor abstraction level. The servers are reanalyzed to determine if migration of the new configuration is needed. Shares are computed to enforce balance requirements, and virtual machine shares and limits are adjusted for resources according to the computed shares.

Owner:IBM CORP

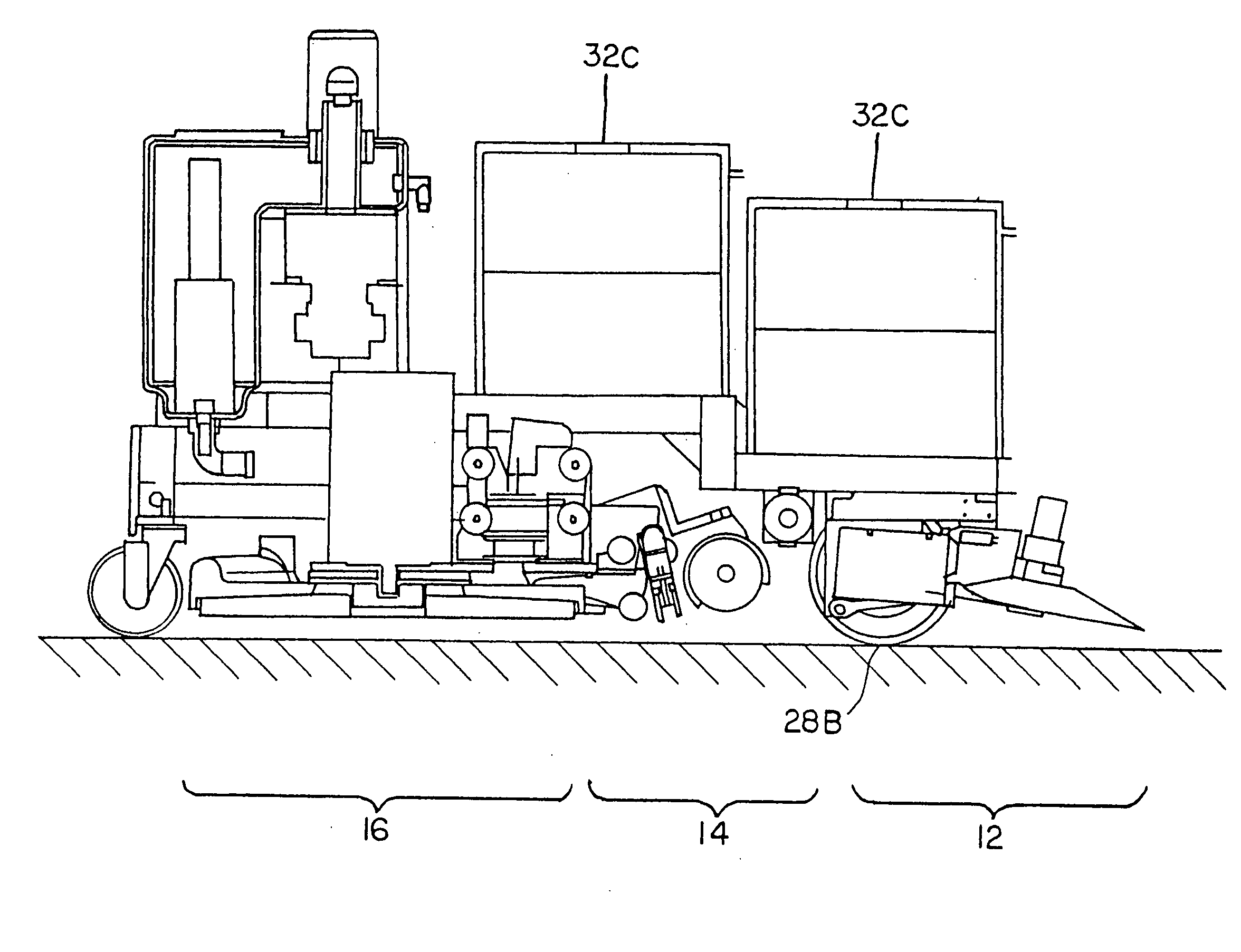

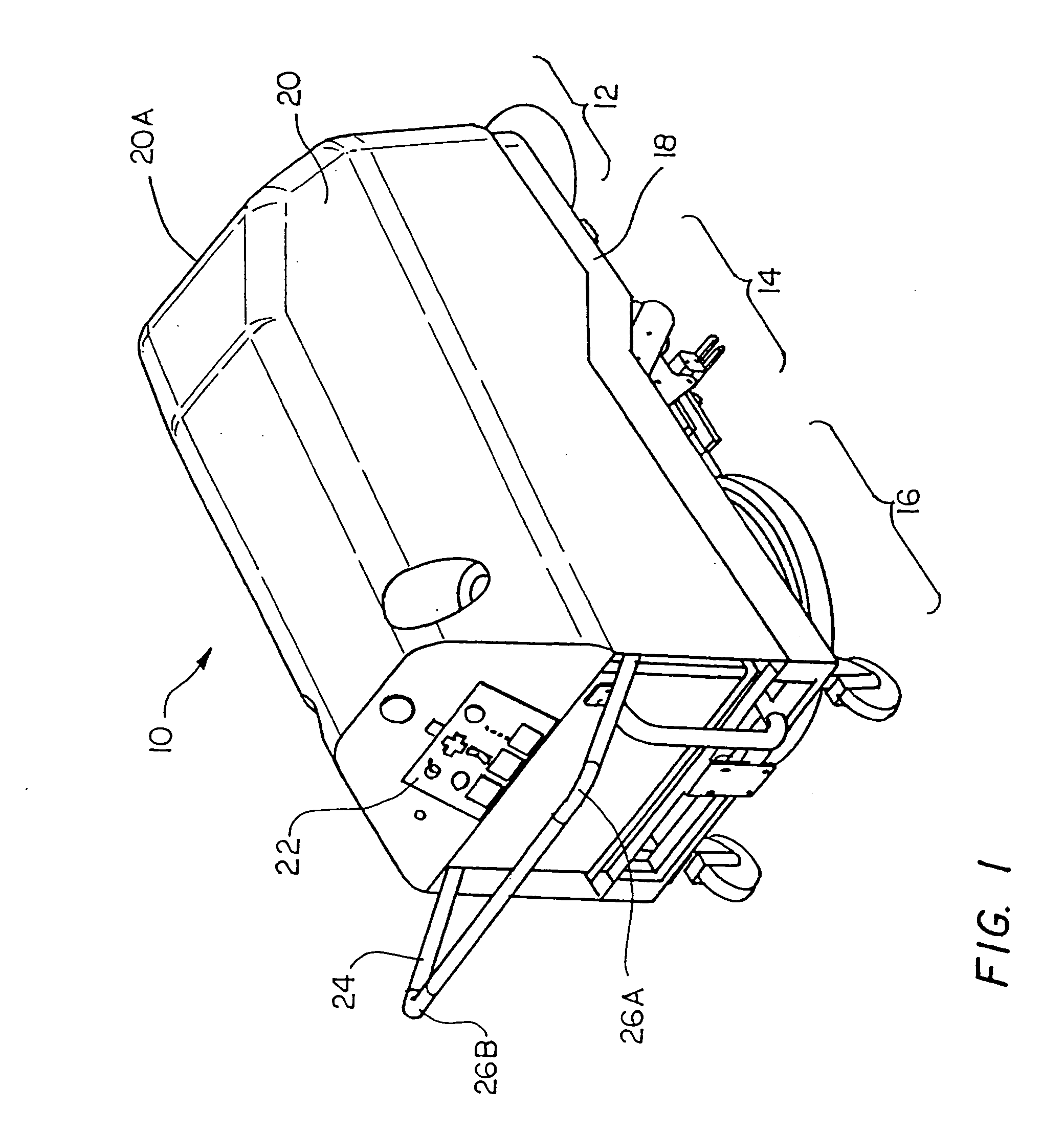

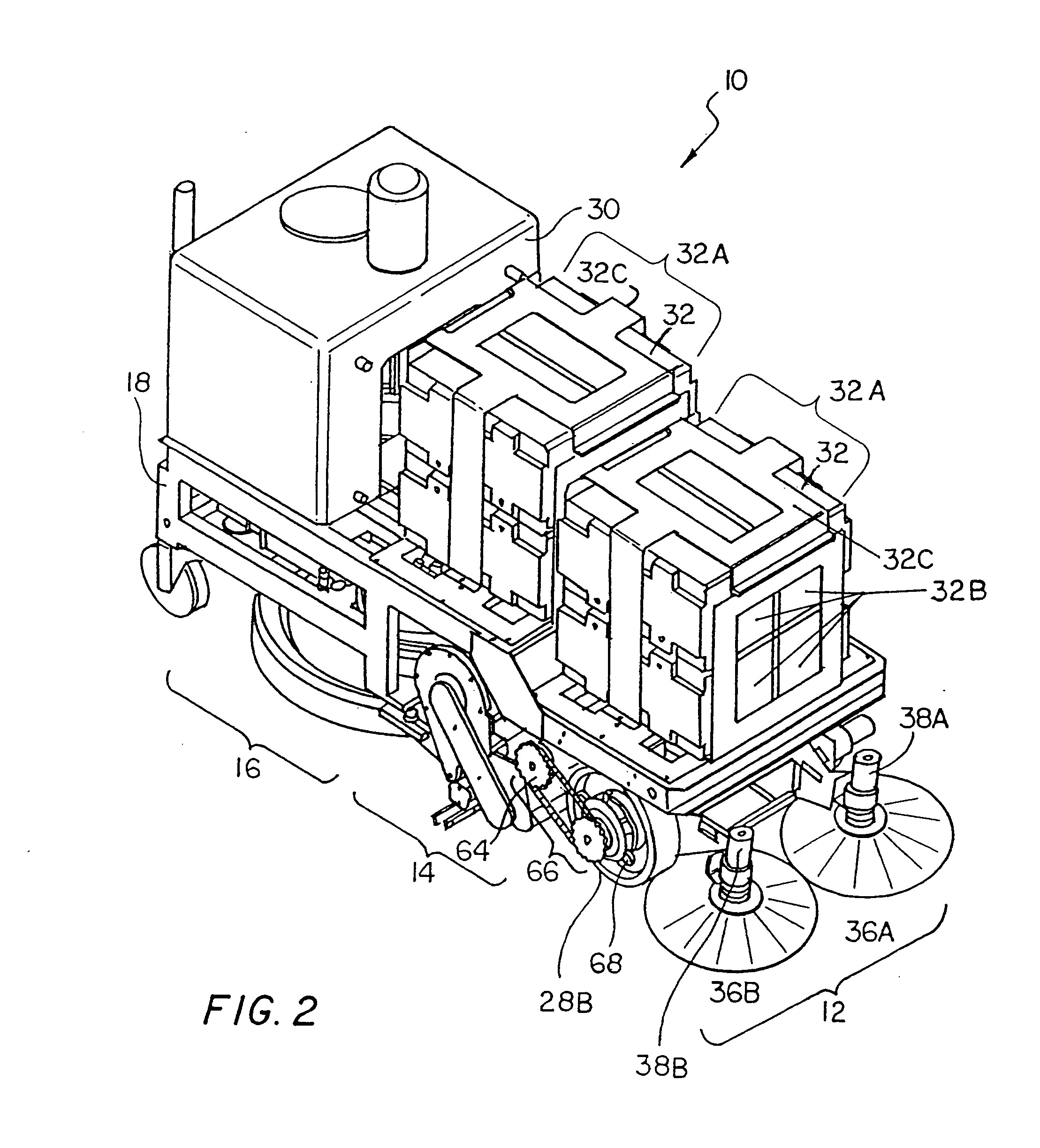

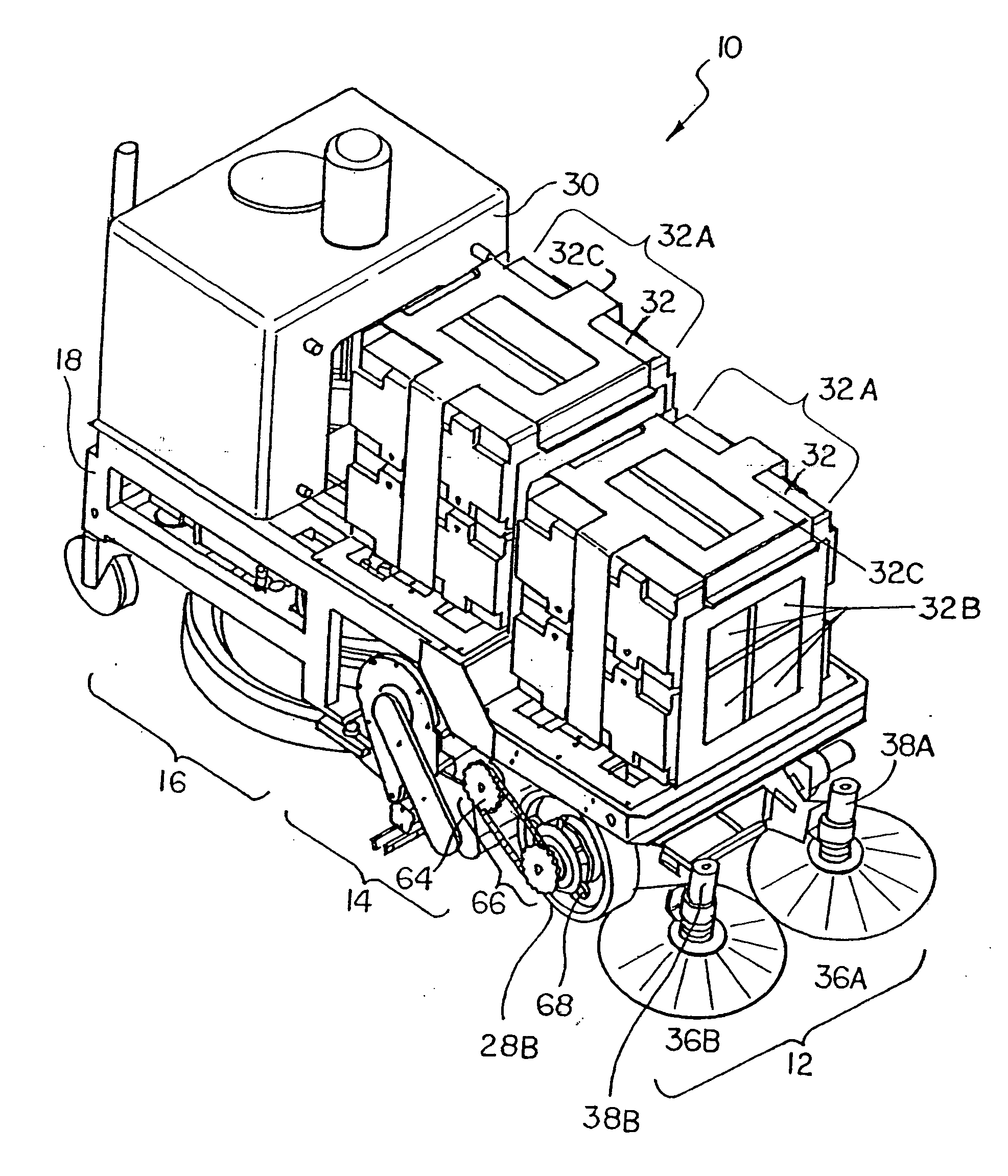

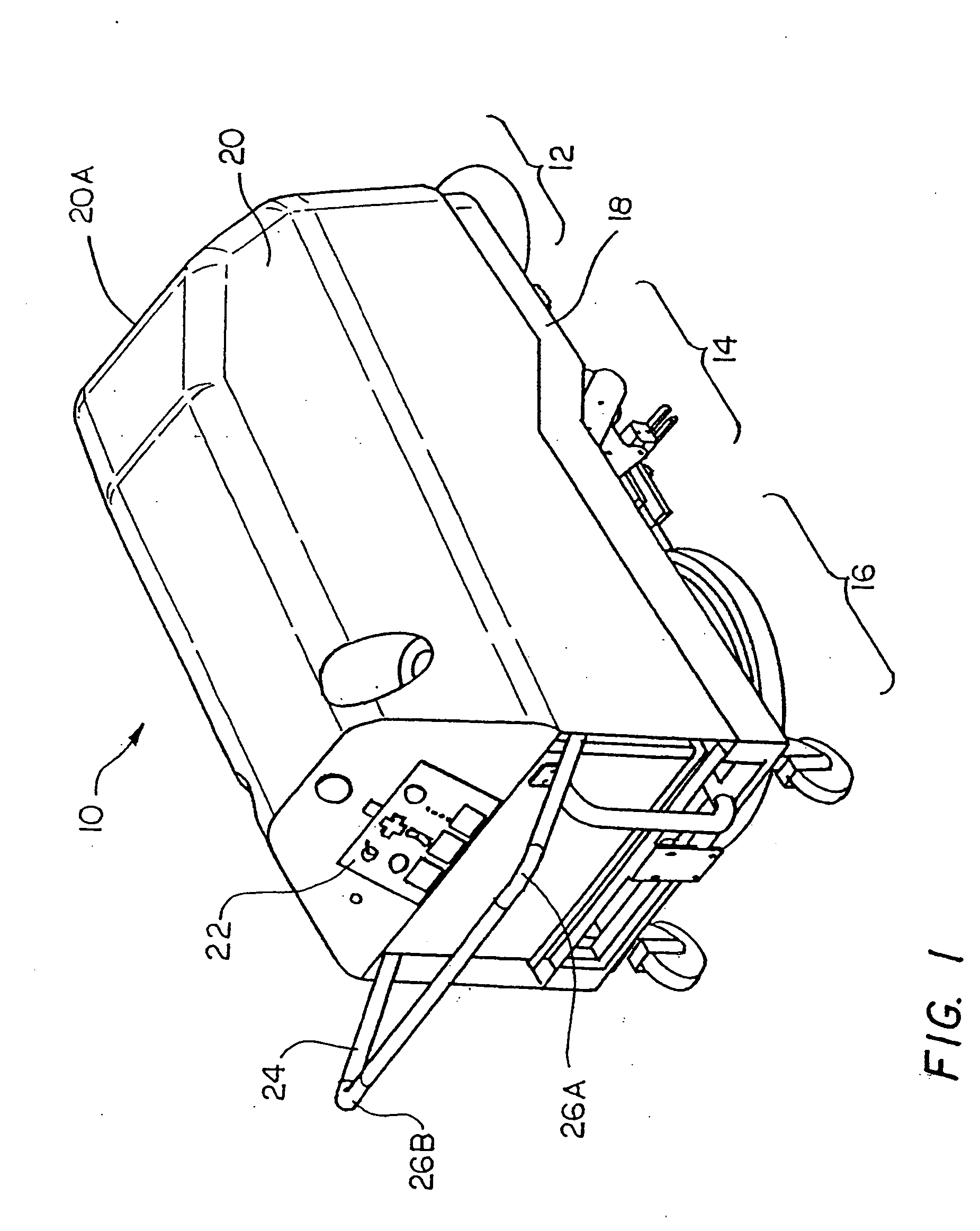

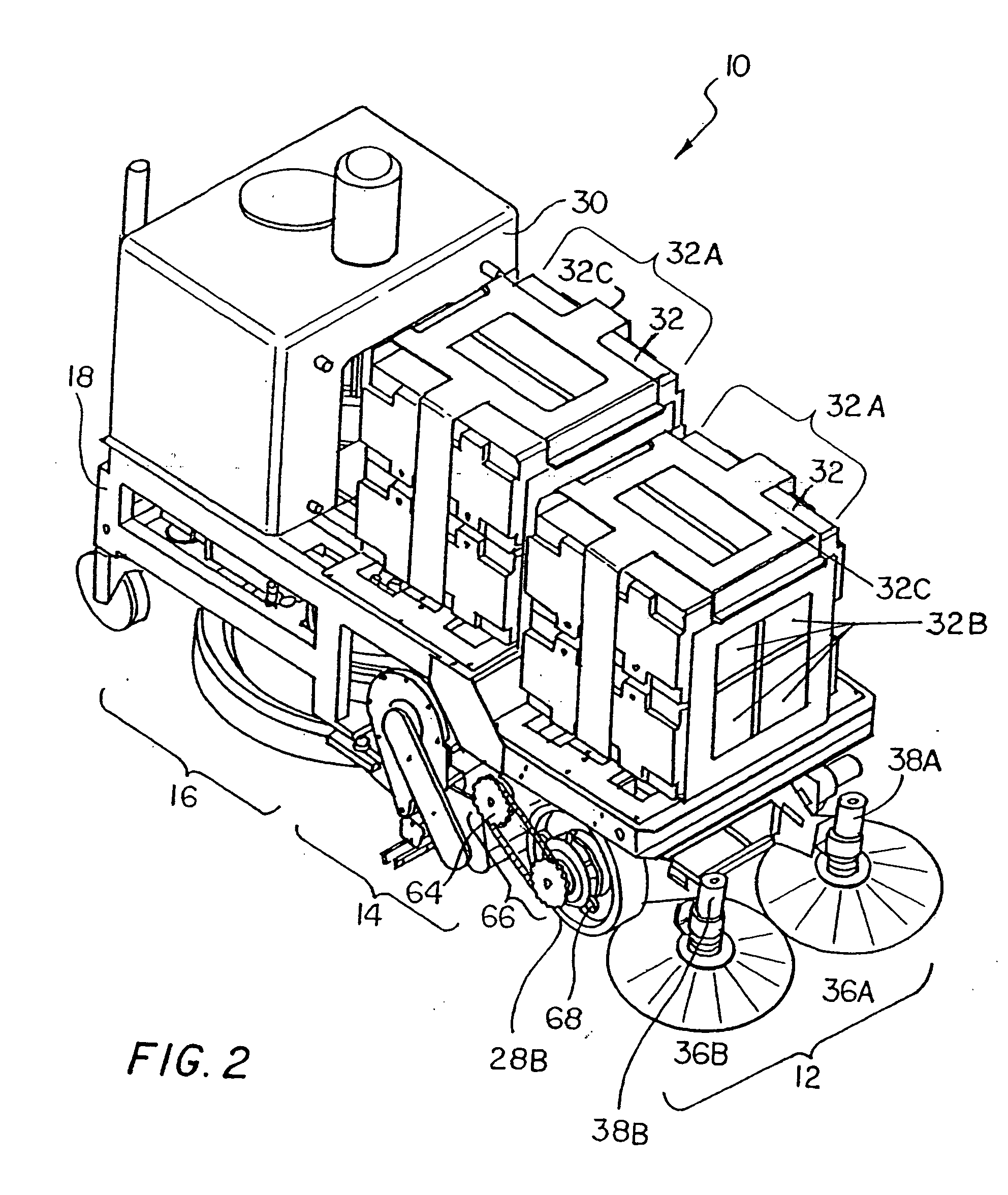

Floor cleaning apparatus with control circuitry

InactiveUS20050028316A1Easy to operateImprove performanceLiquid processingBrush bodiesEngineeringControl circuit

A floor cleaner is provided for cleaning a floor, where the floor cleaner has a front and a rear and includes: a sweeper for sweeping the floor; a scrubber, connected to the sweeper and located in the rear of the sweeper, for wetting and cleaning the floor; and a burnisher, connected to the scrubber and located in the rear of the scrubber, for burnishing the floor.

Owner:JOHNSONDIVERSEY INC

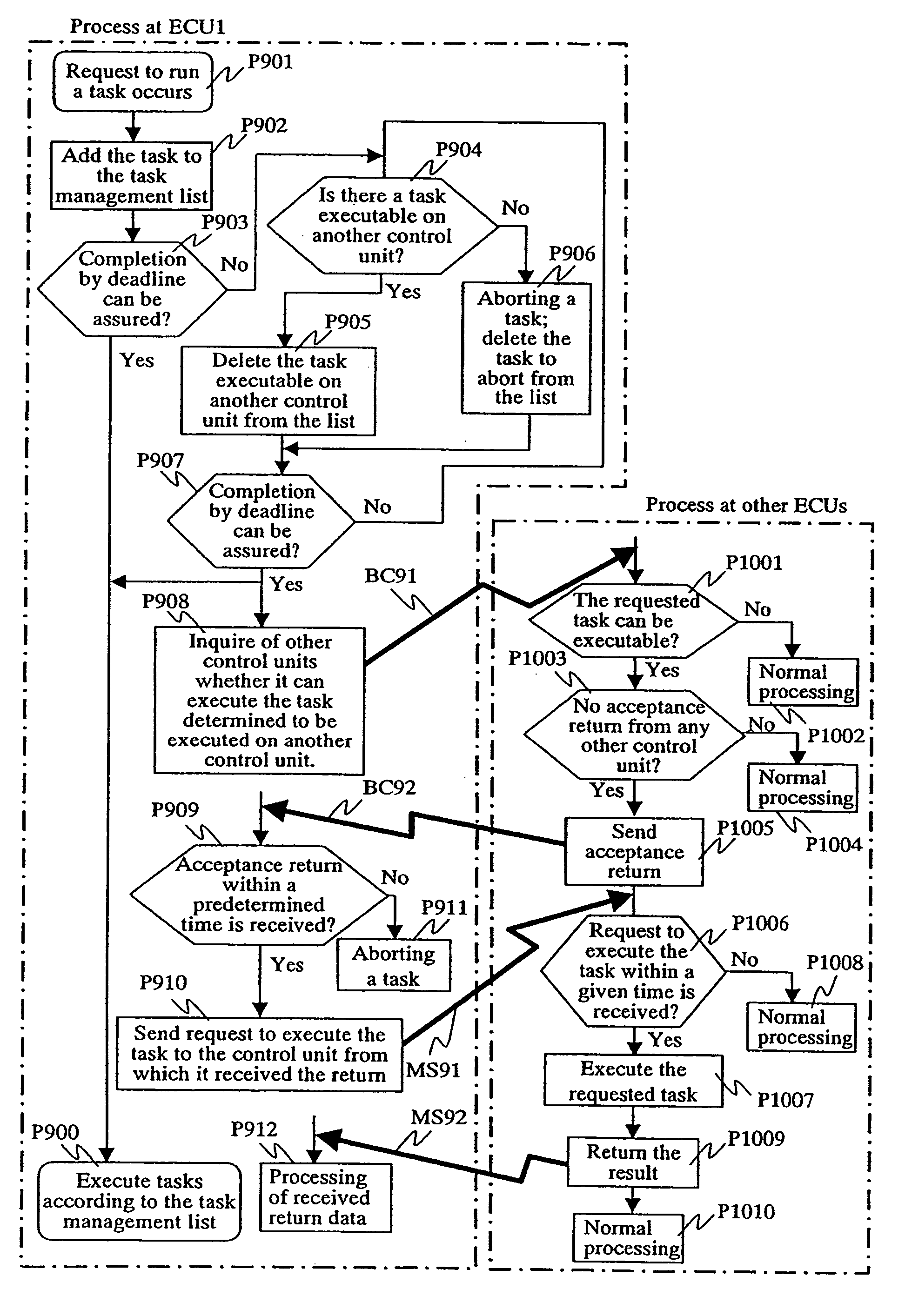

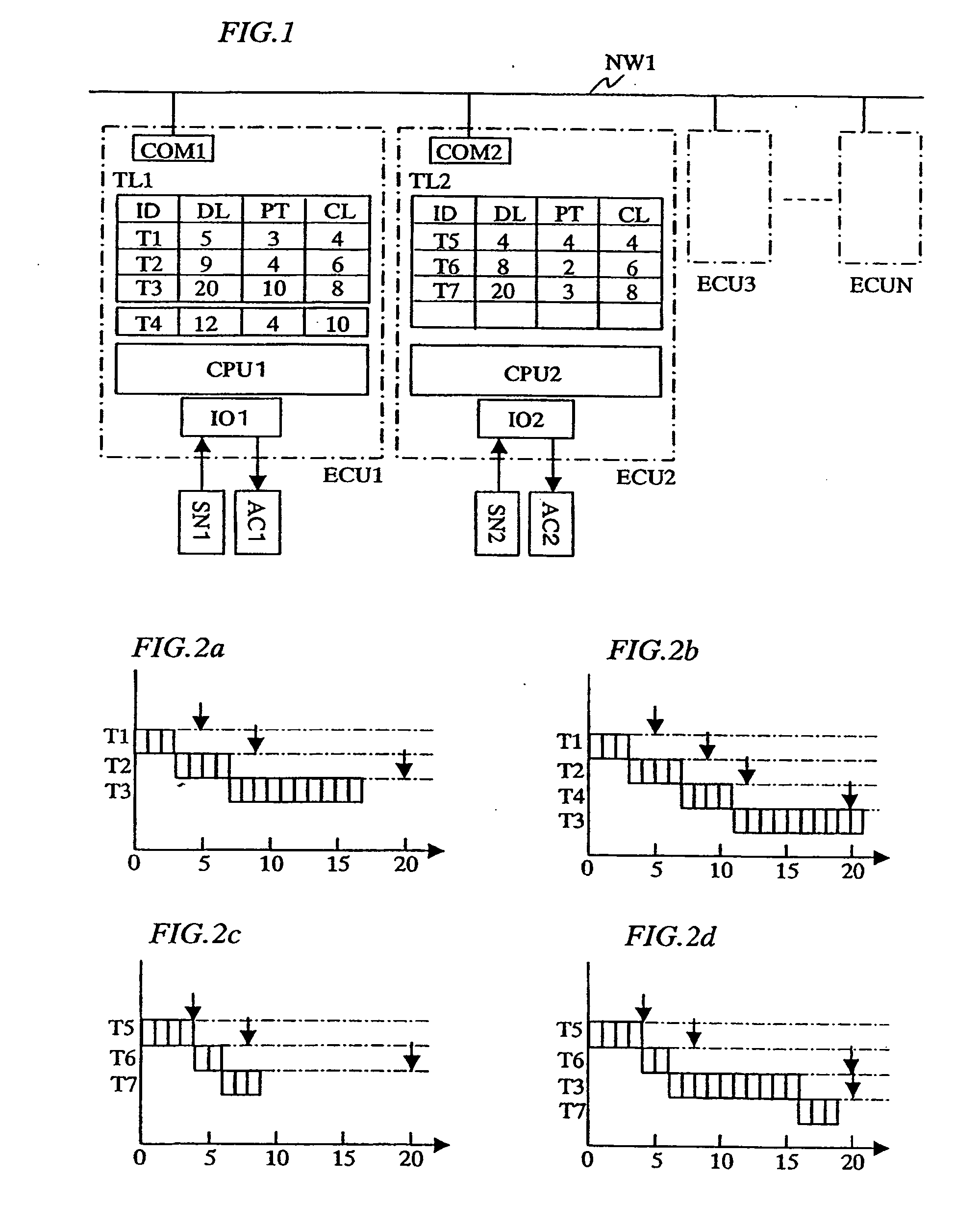

Distributed control system

InactiveUS20060101465A1Easy to operateEnsure performanceProgramme controlMultiprogramming arrangementsFault toleranceTask completion

In a distributed control system where a plurality of control units are connected via a network, the invention allows for efficient operation of each control unit, while ensuring real-time processing. To provide a distributed control system in which ensured real-time processing and enhanced fault tolerance are achieved, information of a deadline or task run cycle period as time required until task completion is given for each task and a control unit on which a task will be executed is selected according to the deadline or task cycle period. A first control circuit and related sensors and actuators are connected by a dedicated path on which fast response time is easy to ensure and another control circuit and related sensors and actuators are connected via a network. When the first control circuit operates normally with sufficient throughput, the first control circuit is used for control; in case the first control circuit fails or if its throughput is insufficient, another control circuit is used.

Owner:HITACHI LTD

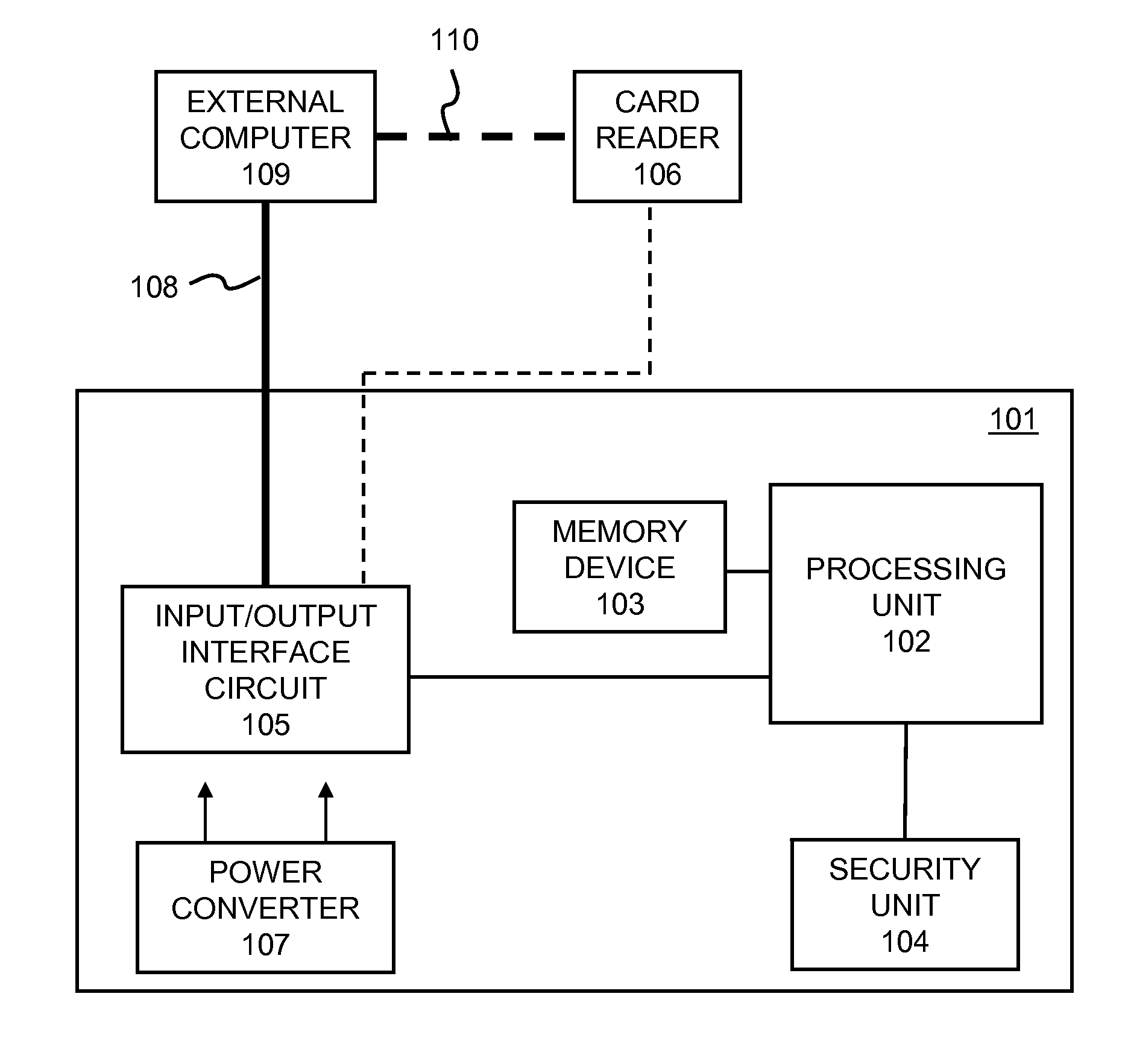

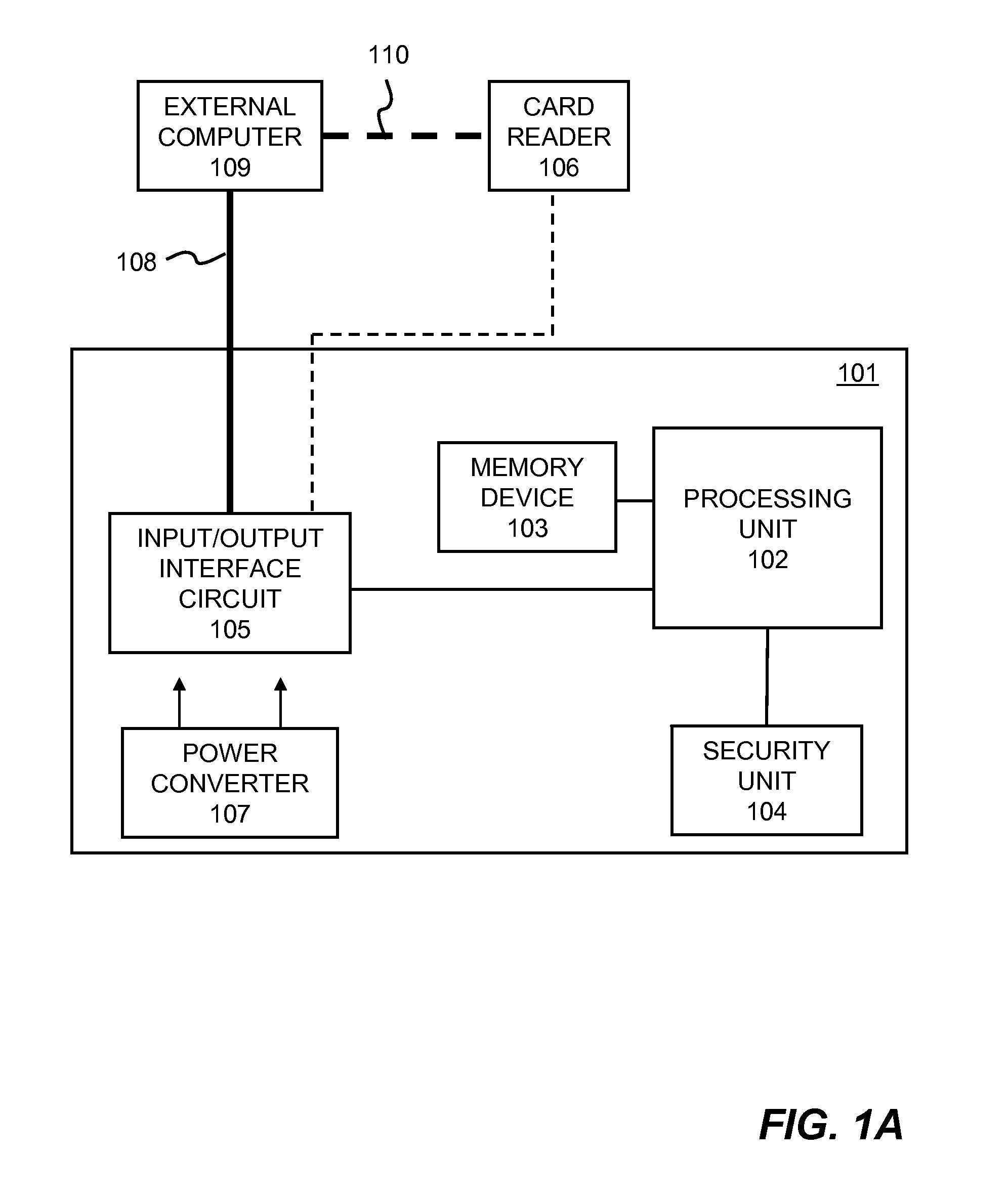

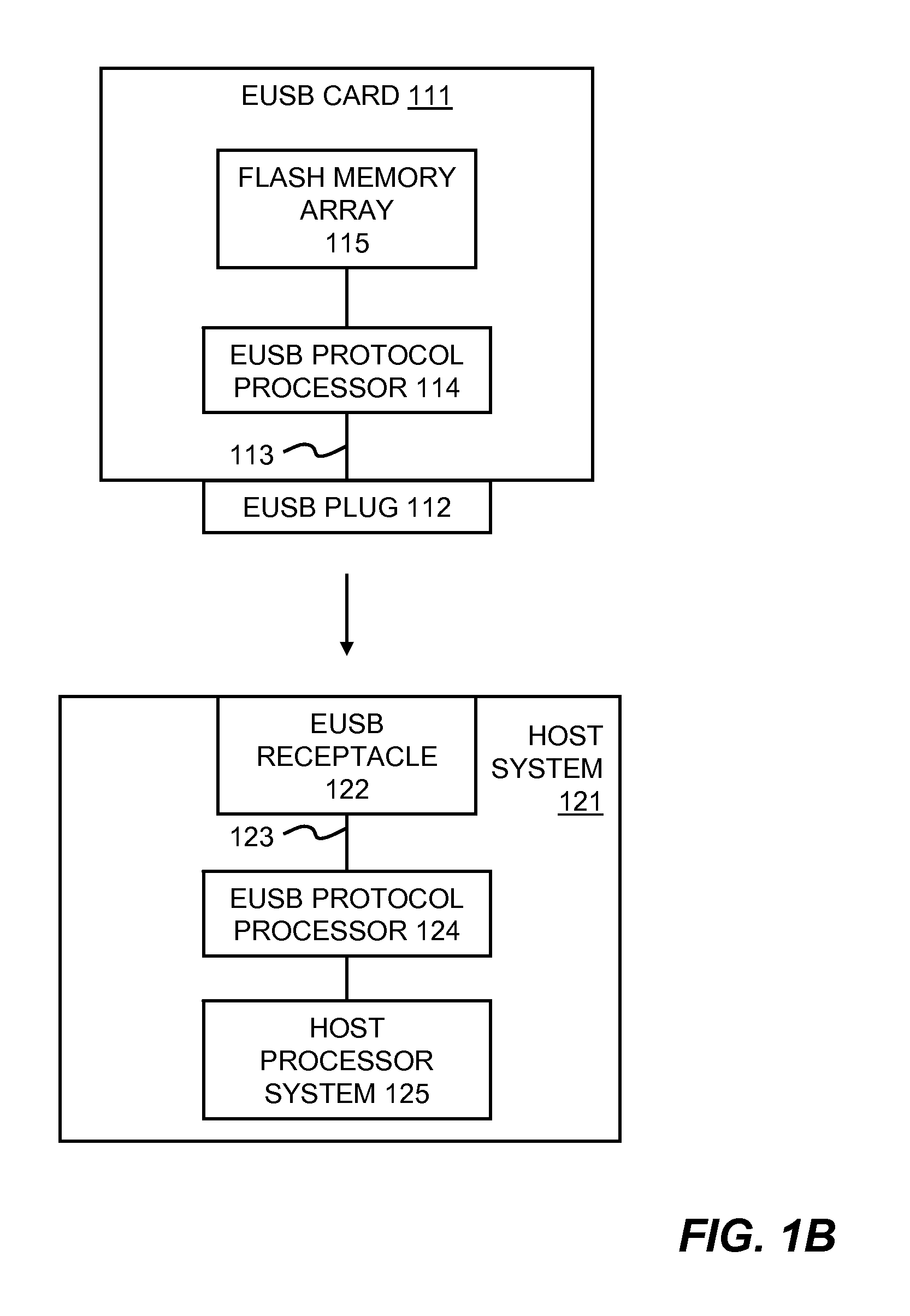

Methods and systems for storing and accessing data in uas based flash-memory device

ActiveUS20100185808A1Improve efficiencyEnsure performanceMemory adressing/allocation/relocationRead-only memoriesTransceiverRandom access memory

Methods and systems for storing and accessing data in UAS based flash memory device are disclosed. UAS based flash memory device comprises a controller and a plurality of non-volatile memories (e.g., flash memory) it controls. Controller is configured for connecting to a UAS host via a physical layer (e.g., plug and wire based on USB 3.0) and for conducting data transfer operations via two sets of logical pipes. Controller further comprises a random-access-memory (RAM) buffer configured for enabling parallel and duplex data transfer operations through the sets of logical pipes. In addition, a Smart Storage Switch configured for connecting multiple non-volatile memory devices is included in the controller. Finally, a security module / engine / unit is provided for data security via user authentication data encryption / decryption of the device. Furthermore, the flash memory device includes an optical transceiver configured for optical connection to a host also configured with an optical transceiver.

Owner:SUPER TALENT TECH CORP

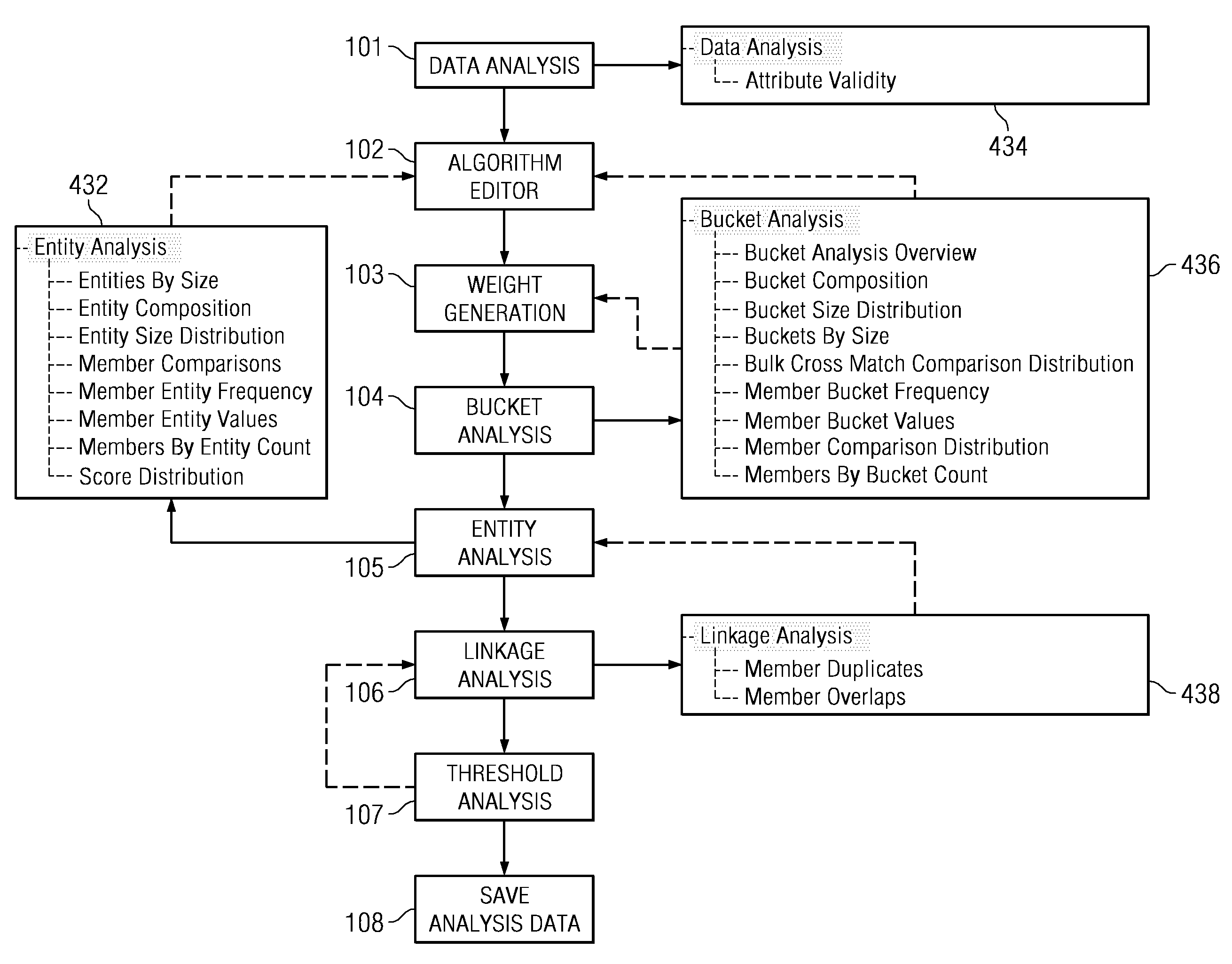

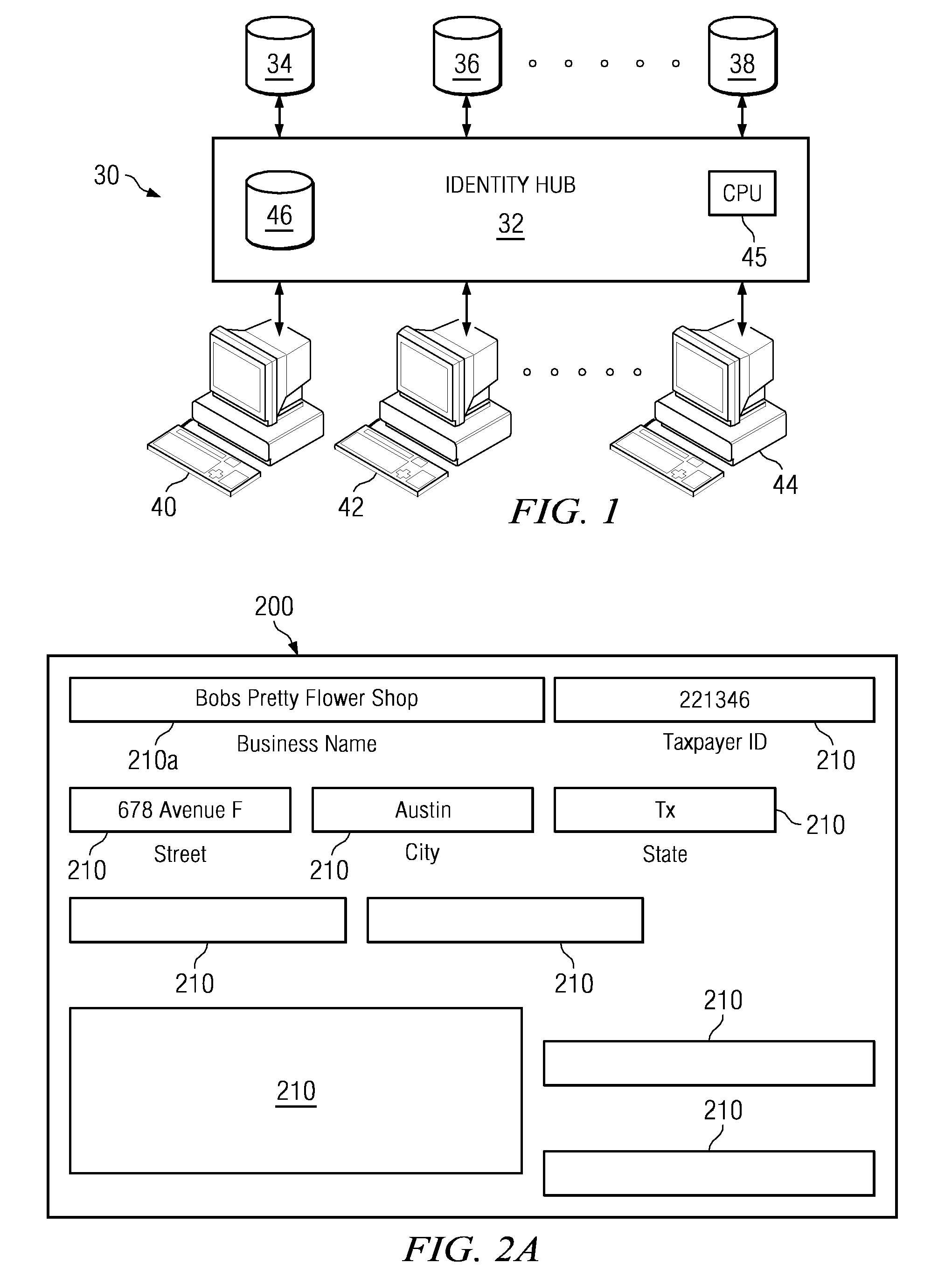

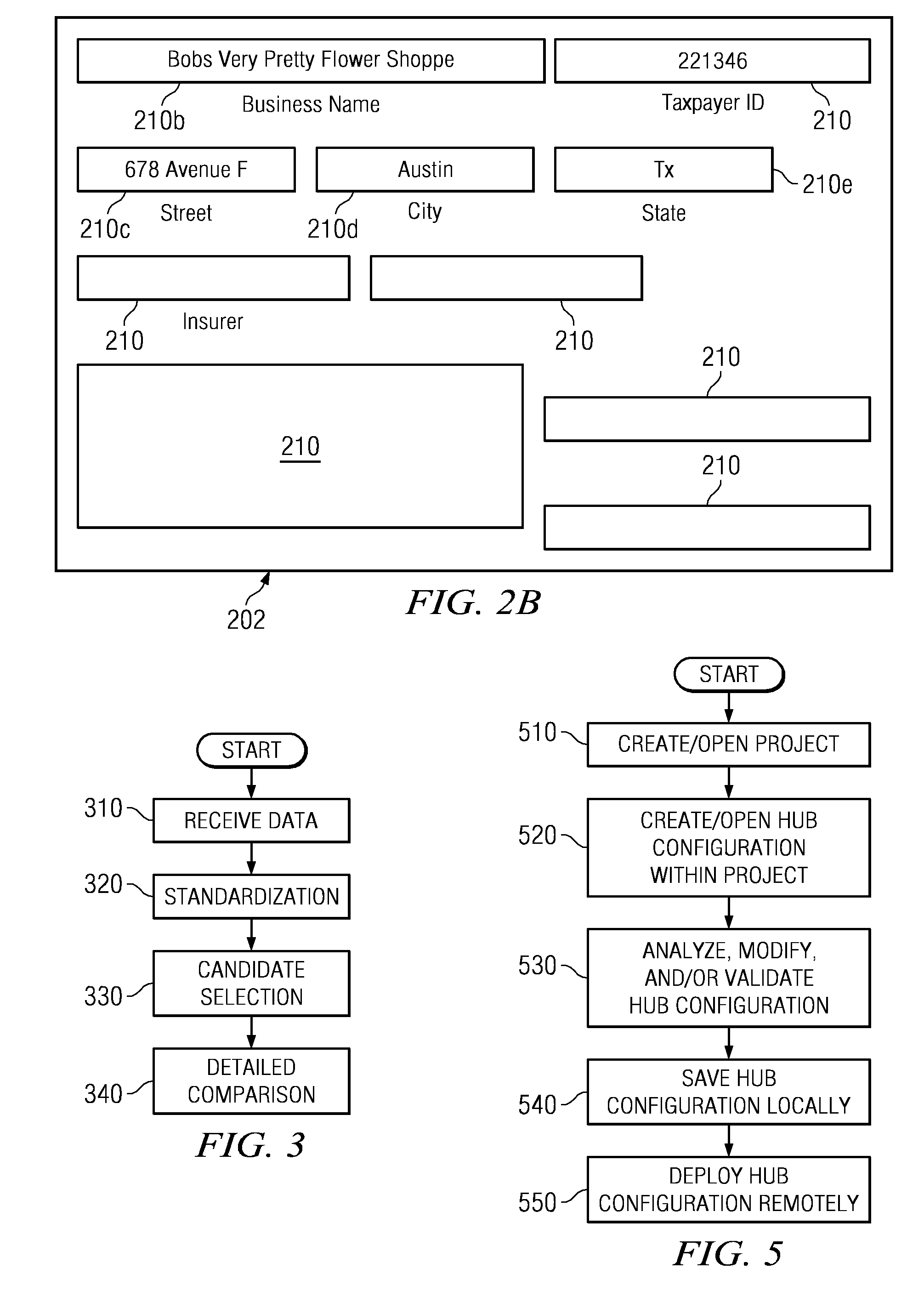

Method and system for analysis of a system for matching data records

InactiveUS20090089630A1Ensure performanceDigital data information retrievalError detection/correctionGraphicsReal time analysis

Embodiments disclosed herein provide a system and method for analyzing an identity hub. Particularly, a user can connect to the identity hub, load an initial set of data records, create and / or edit an identity hub configuration locally, analyze and / or validate the configuration via a set of analysis tools, including an entity analysis tool, a data analysis tool, a bucket analysis tool, and a linkage analysis tool, and remotely deploy the validated configuration to an identity hub instance. In some embodiments, through a graphical user interface, these analysis tools enable the user to analyze and modify the configuration of the identity hub in real time while the identity hub is operating to ensure data quality and enhance system performance.

Owner:IBM CORP

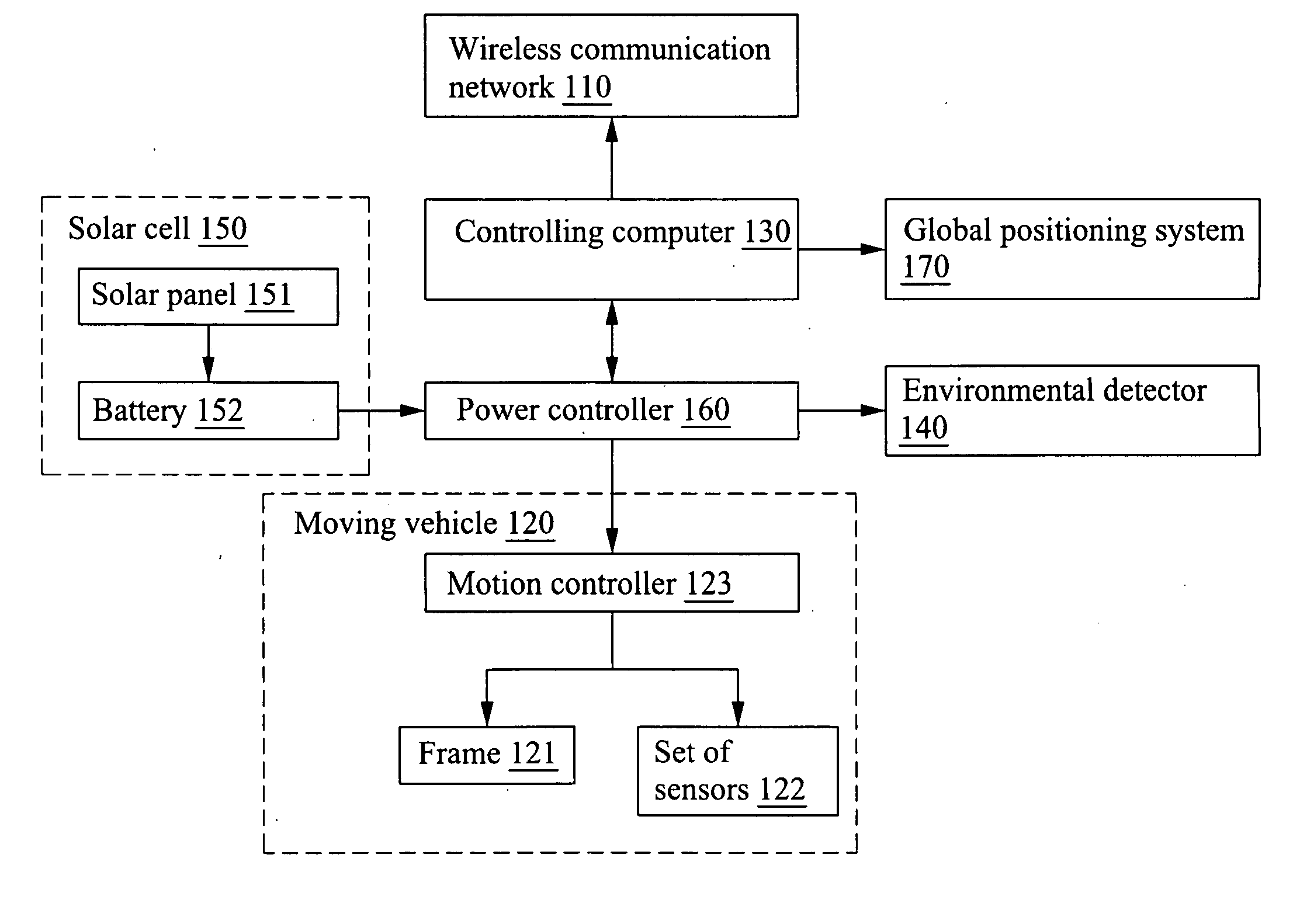

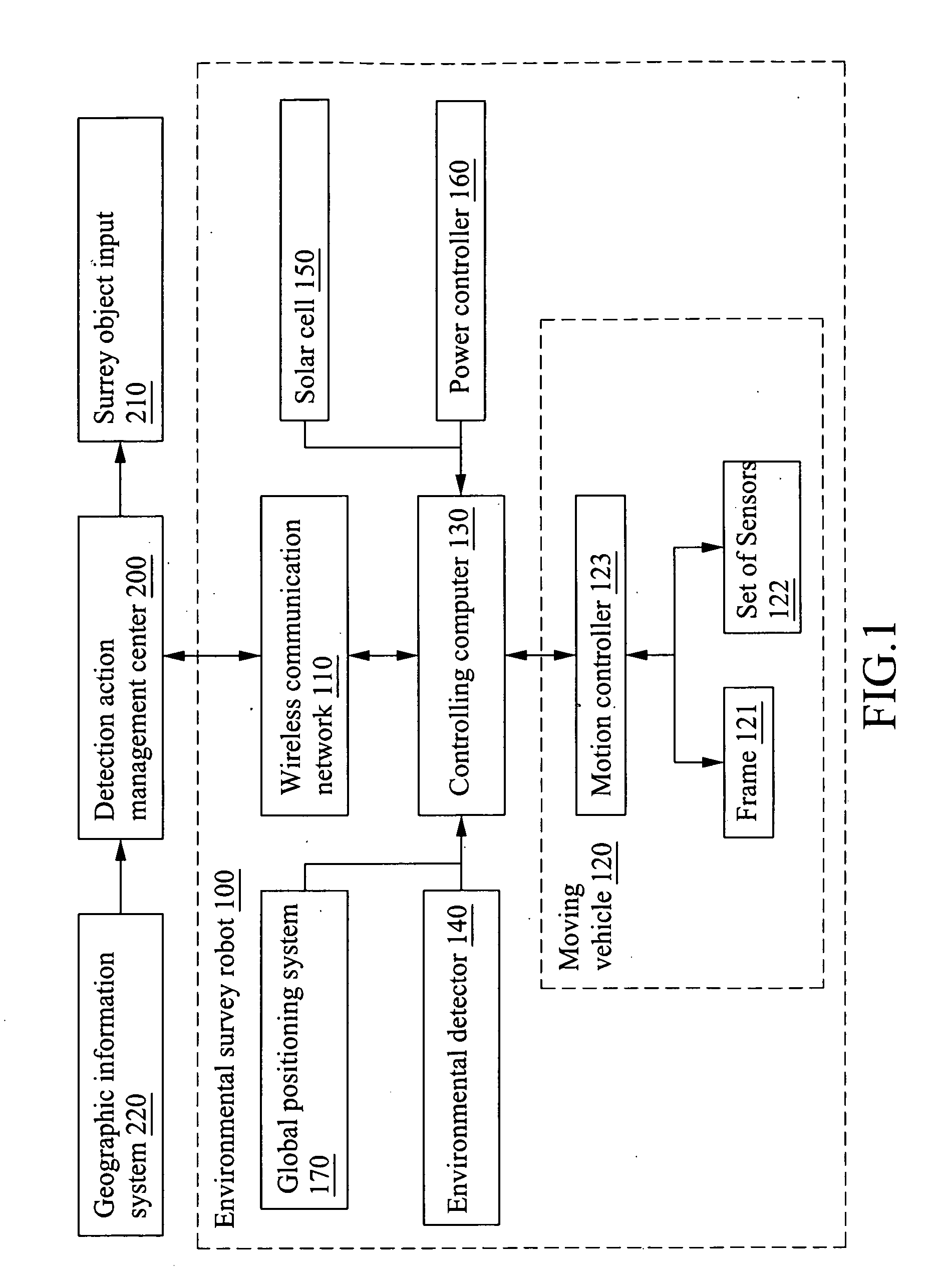

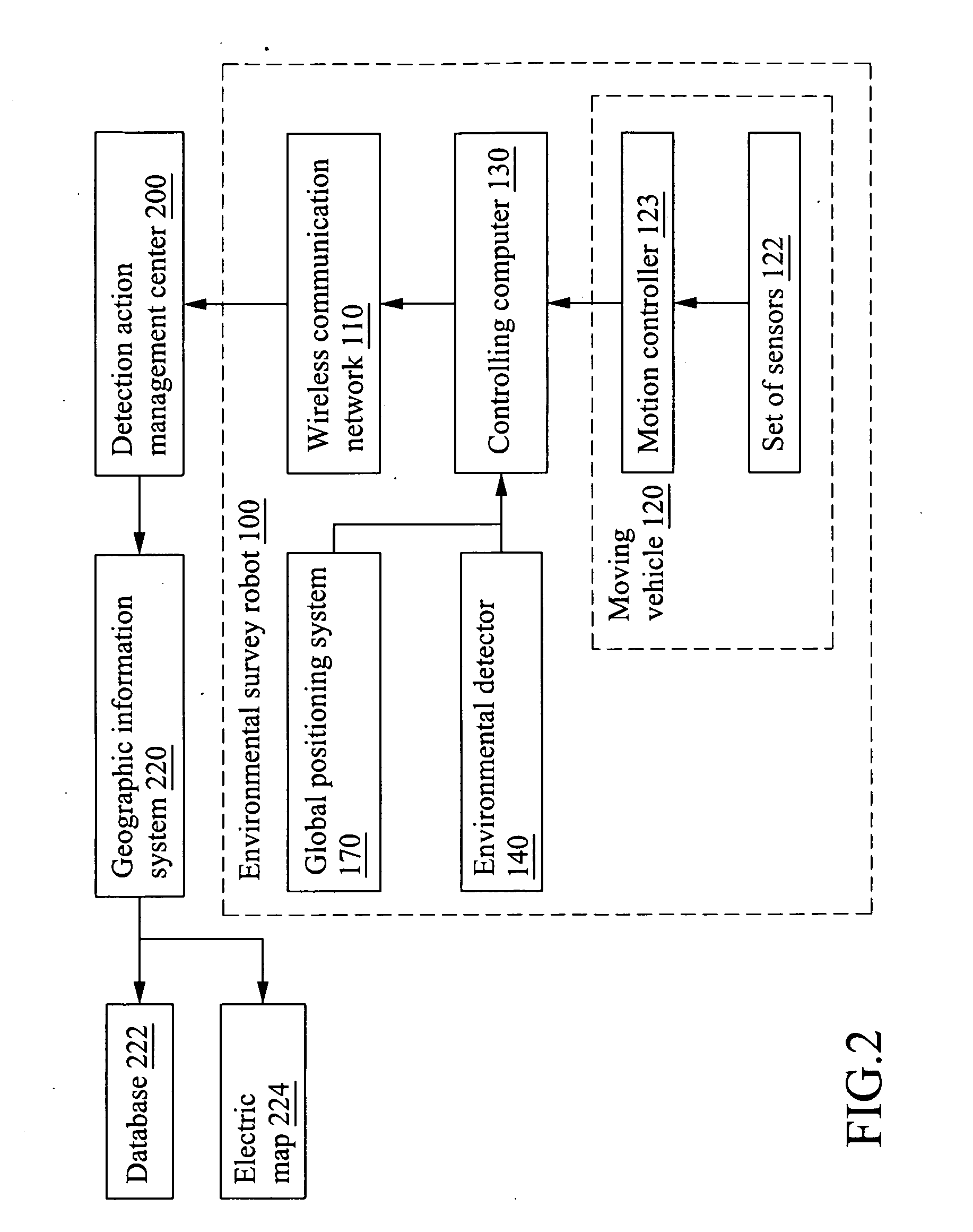

Environmental survey robot

InactiveUS20100030417A1Less obstacleIncrease the areaProgramme controlComputer controlMobile vehiclePower controller

An environmental survey robot suitable for wireless communicating with a survey action management center having a geographic information system to scheme an advance route with multiple check points is provided. The environmental survey robot includes a moving vehicle, a controlling computer, a wireless communication network, a Global positioning system, an environment detector, a solar cell and a power controller. The wireless communication network receives the advance route from the detecting action management center, and the controlling computer autonomously controls the moving vehicle to move in accordance with the advance route. The environmental detector is suitable for detecting the environment information and sending the same to the controlling computer. When the electricity of the solar cell is less than a predetermined value, the power controller will send the signal to the controlling computer such that the action controller will stop the action of the moving vehicle.

Owner:INST NUCLEAR ENERGY RES ROCAEC

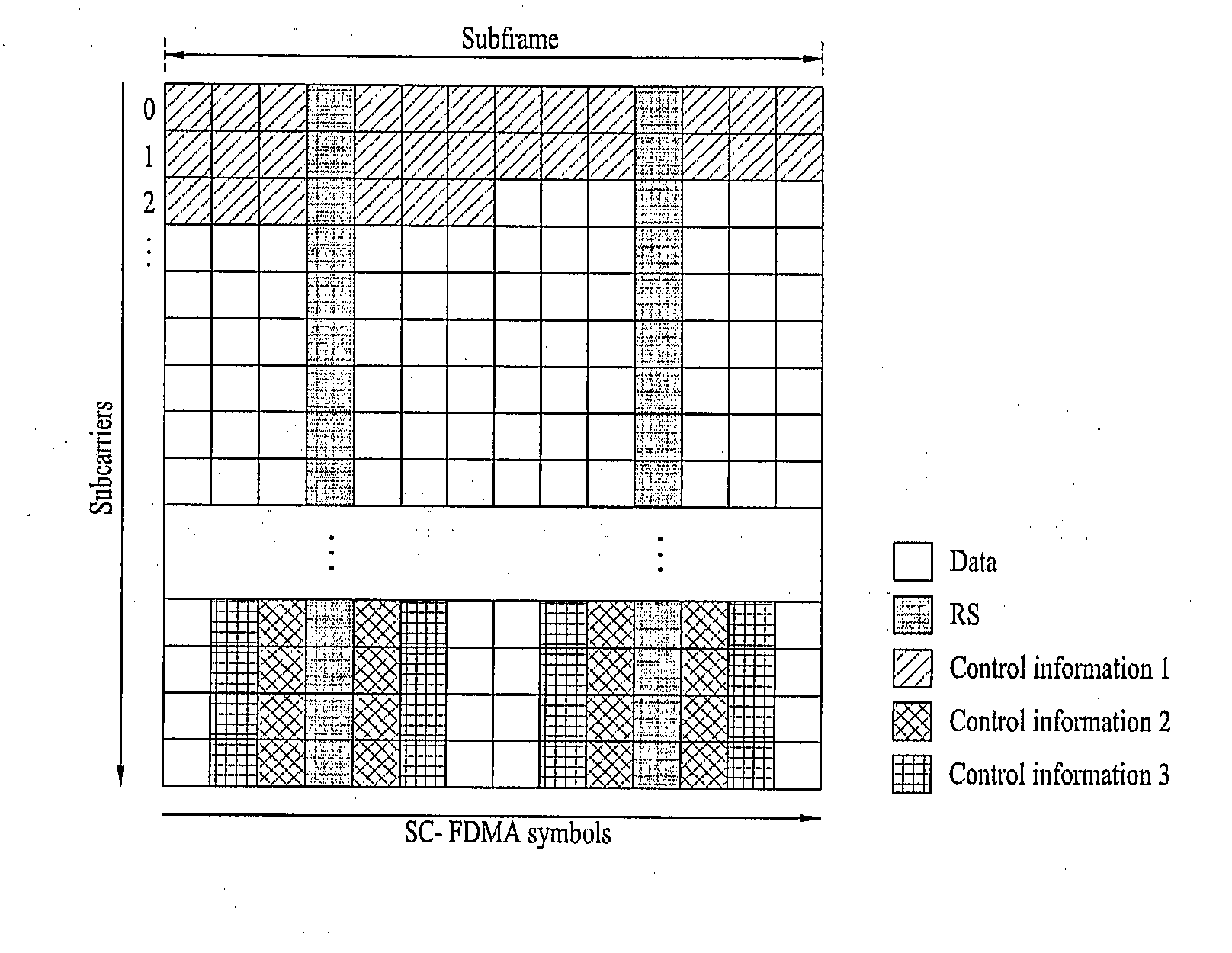

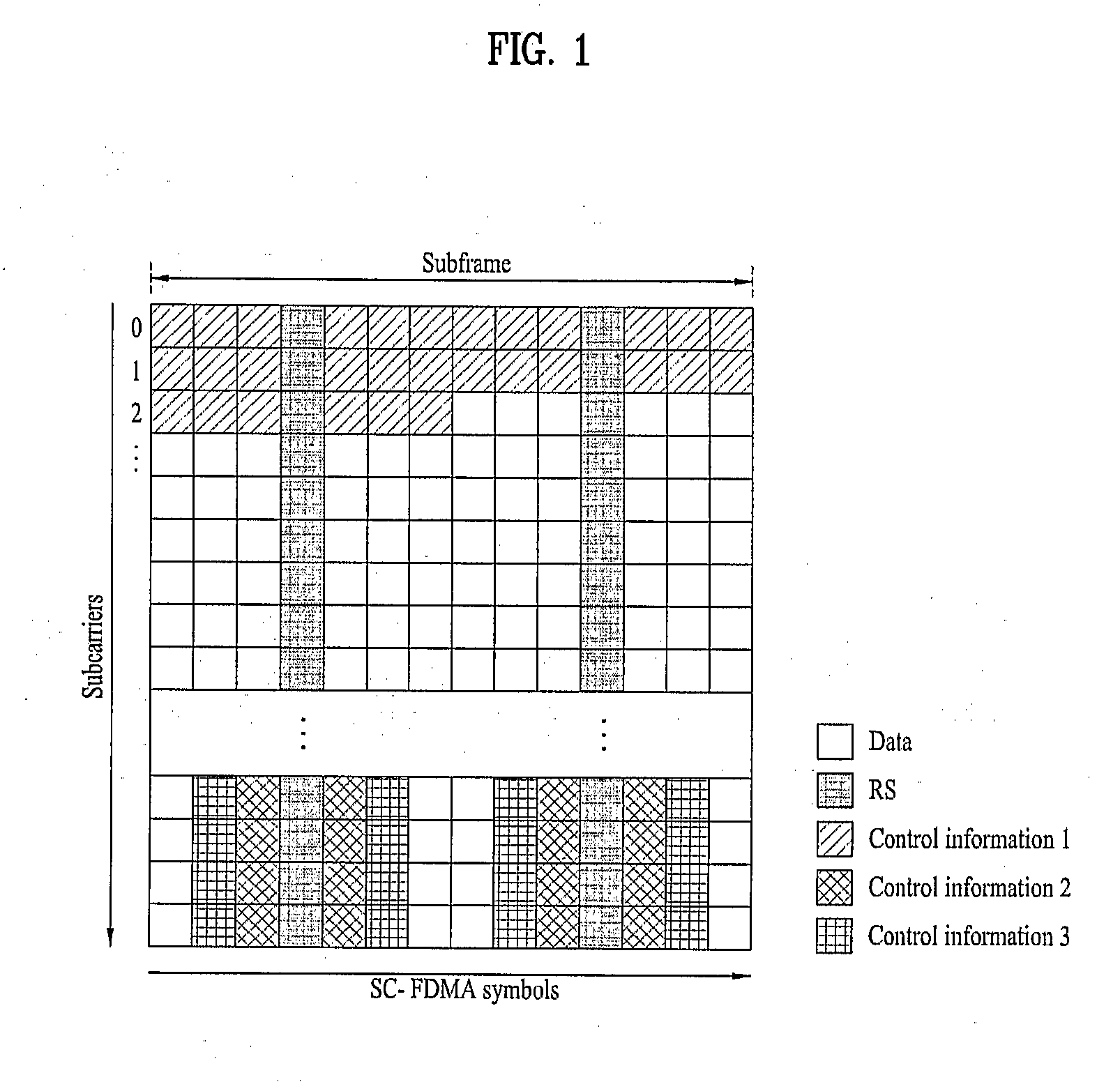

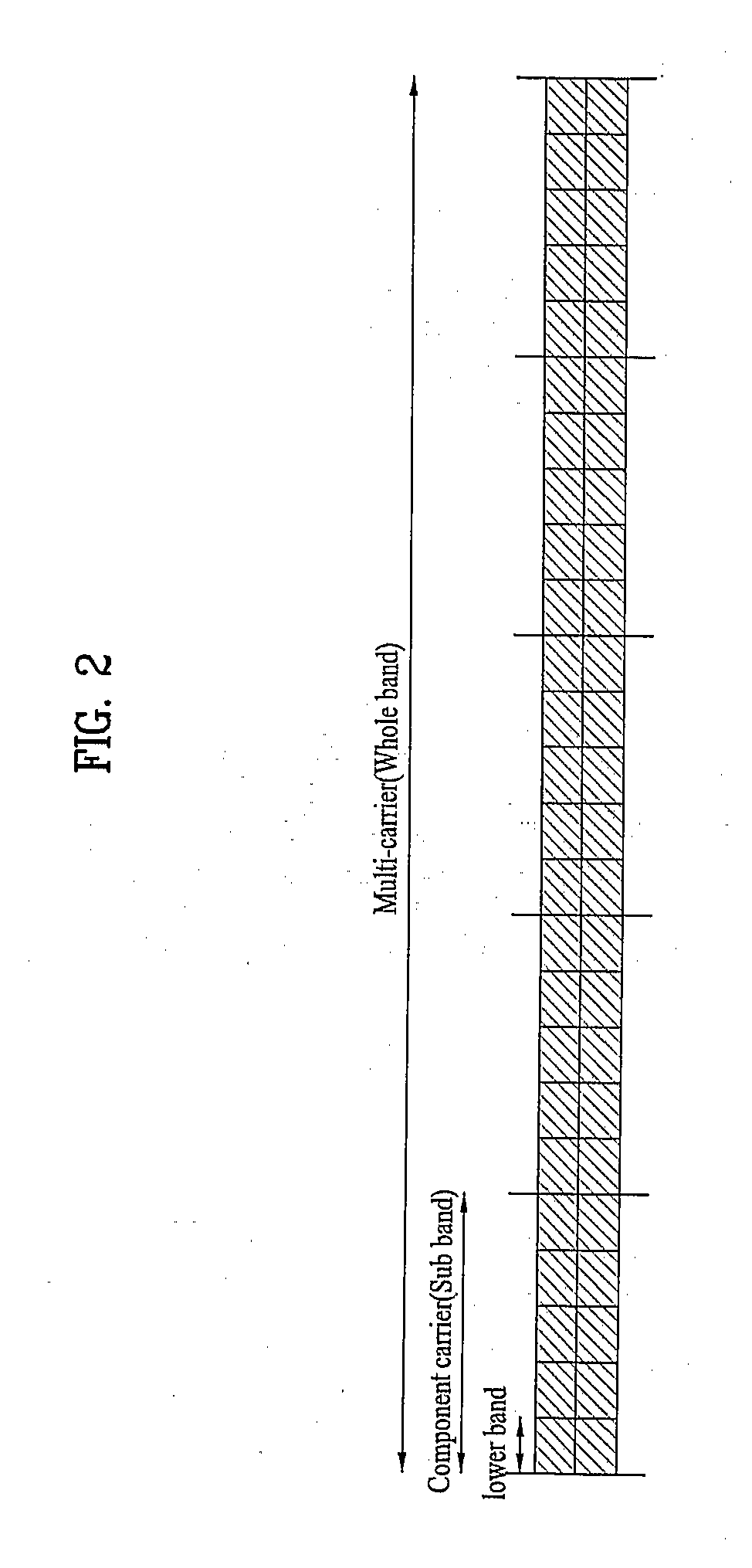

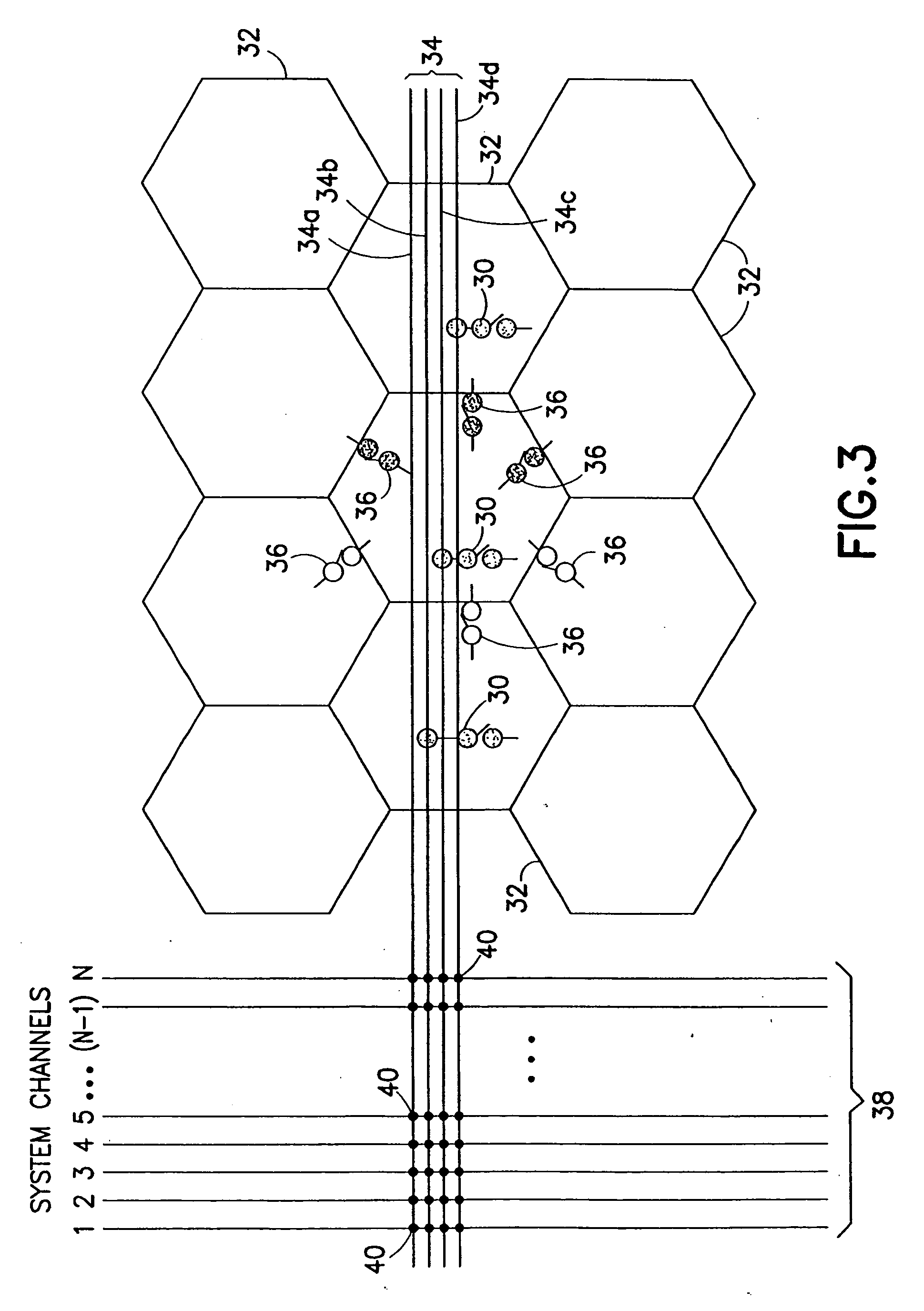

Method for transmitting control information about downlink multiple carriers in a wireless communication system

ActiveUS20110128942A1Ensure performanceFrequency-division multiplex detailsTransmission path divisionCommunications systemCarrier signal

A method for transmitting uplink control information in a wireless communication system is disclosed. The method includes receiving one or more downlink component carriers among N downlink component carriers created by dividing a multi-carrier by an integer N, and transmitting control information about the received one or more downlink component carriers in one or more uplink component carriers among N uplink component carriers created by dividing a multi-carrier by the integer N, wherein the control information about the received one or more downlink component carriers is distributed equally or unequally to the one or more uplink component carriers and the control information includes at least one of a Channel Quality Information / Precoding Matrix Index (CQI / PMI), an ACKnowledgment / Negative ACKnowledgment (ACK / NACK), and a Rank Indication (RI).

Owner:LG ELECTRONICS INC

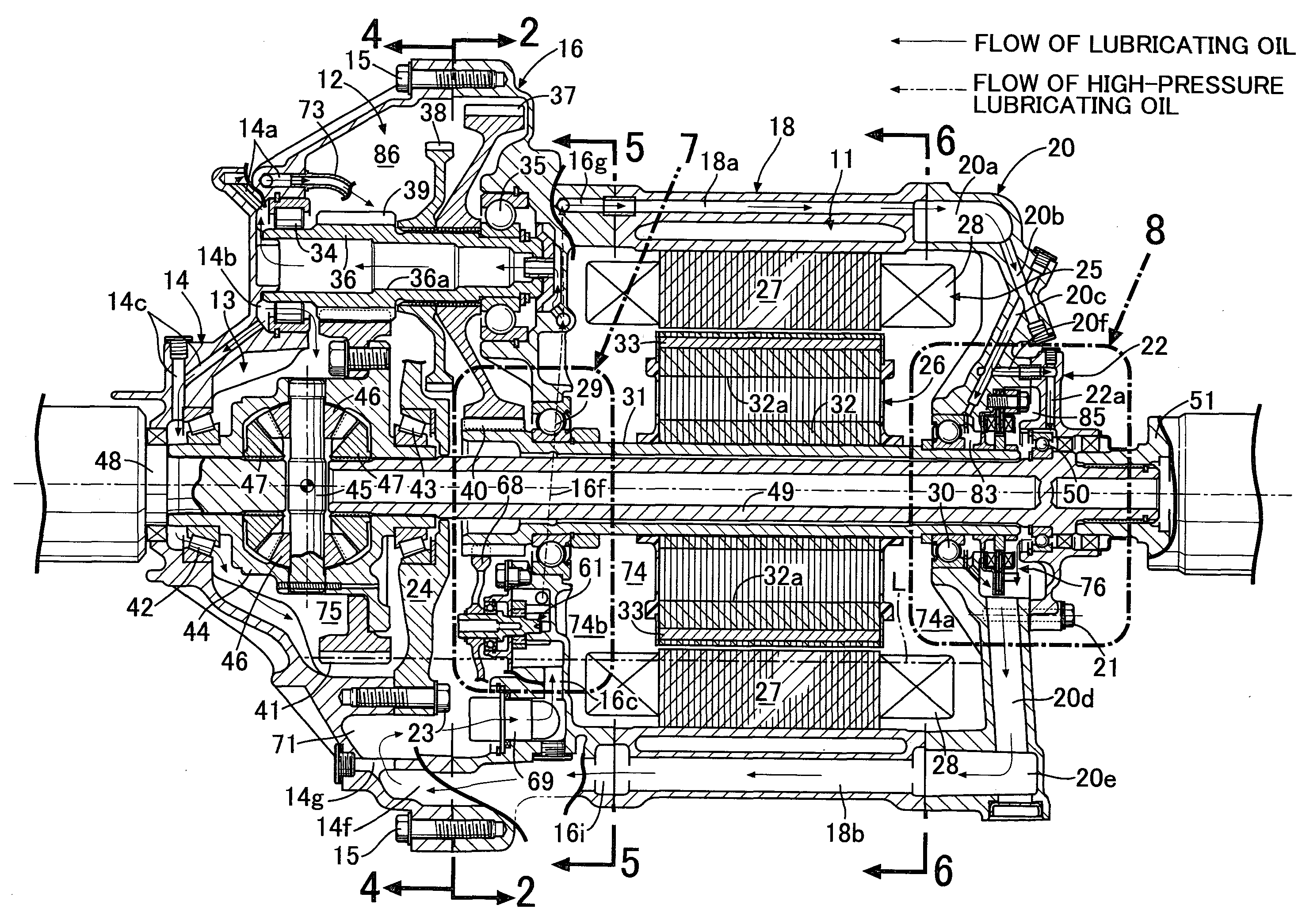

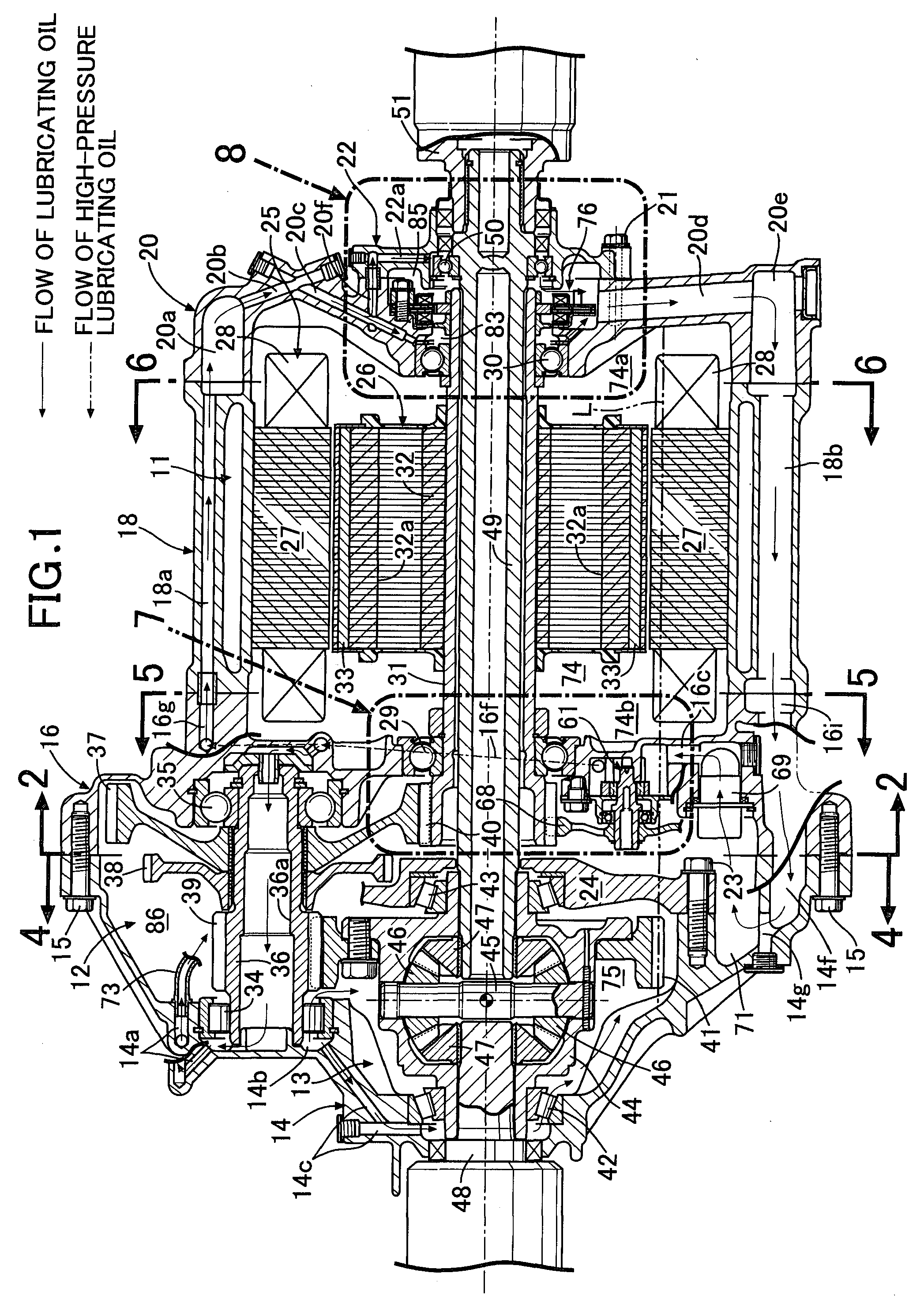

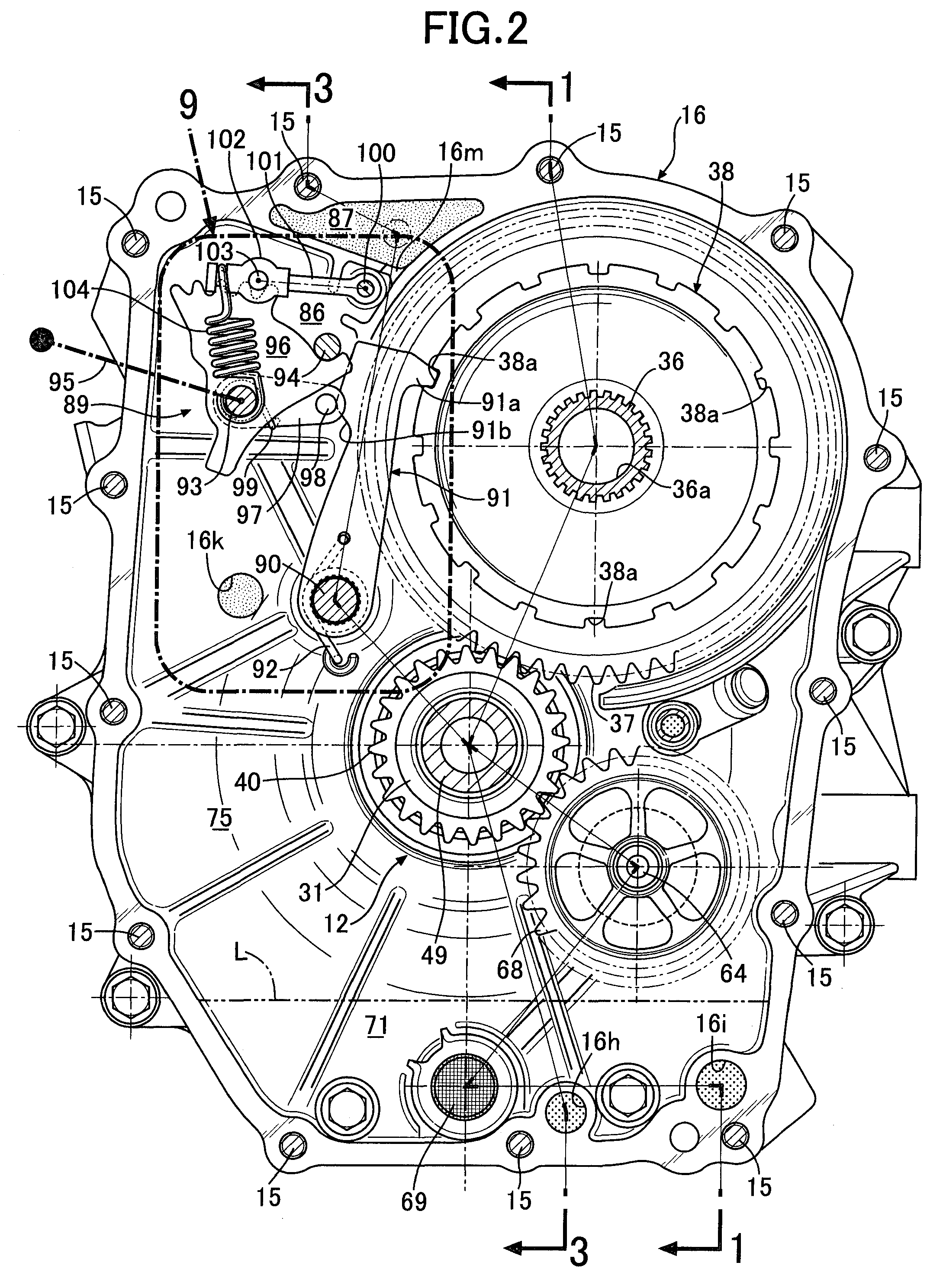

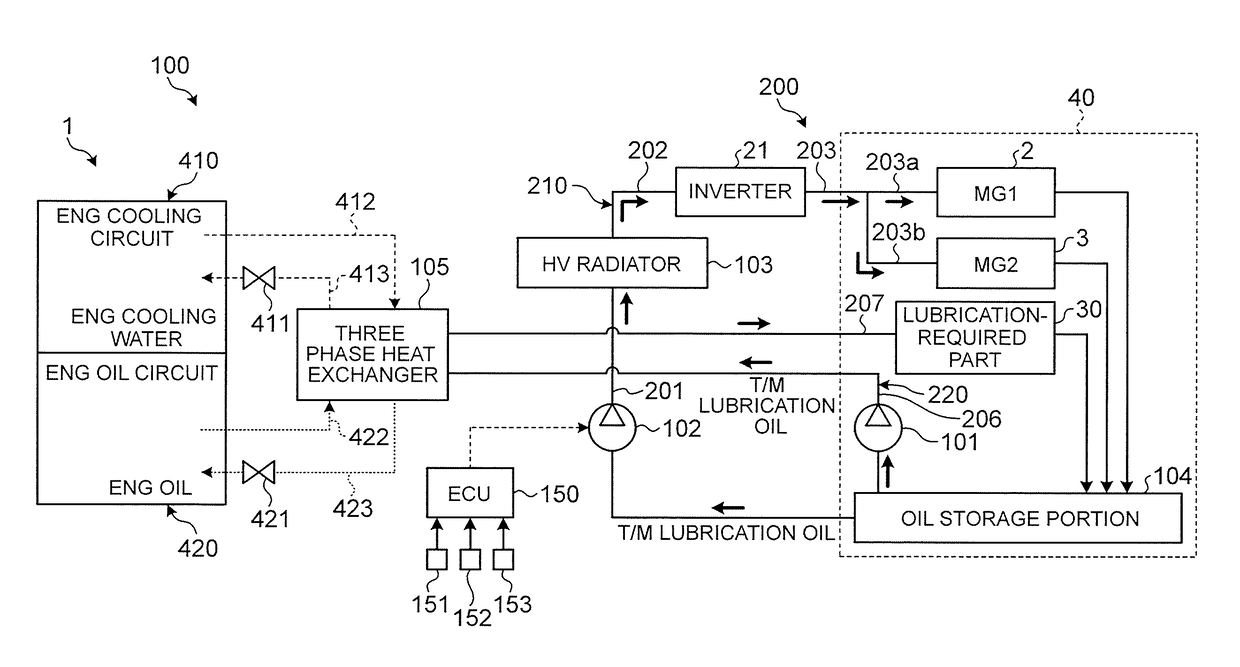

Motor-type power device

ActiveUS20090127954A1Suppress stirring resistance of oilEnsure performanceGearboxesGear lubrication/coolingEngineeringCentrifugal force

Due to a centrifugal force in a vehicle width direction due to turning of an automobile, oil in an electric motor housing chamber housing an electric motor and oil in a transmission housing chamber housing a reduction gear and a differential gear flows to-and-fro via oil communication passages that penetrate a partitioning wall. An opening on the transmission housing chamber side of the oil communication passages is spaced from the partitioning wall. Hence, when oil moves from the transmission housing chamber side to the electric motor housing chamber side, it is possible to prevent the oil quantity on the electric motor housing chamber side from increasing excessively and suppress an increase in resistance to oil stirring by a rotor of the electric motor while retaining a constant oil amount on the transmission housing chamber side to ensure lubricating performance for the reduction gear and the differential gear.

Owner:HONDA MOTOR CO LTD

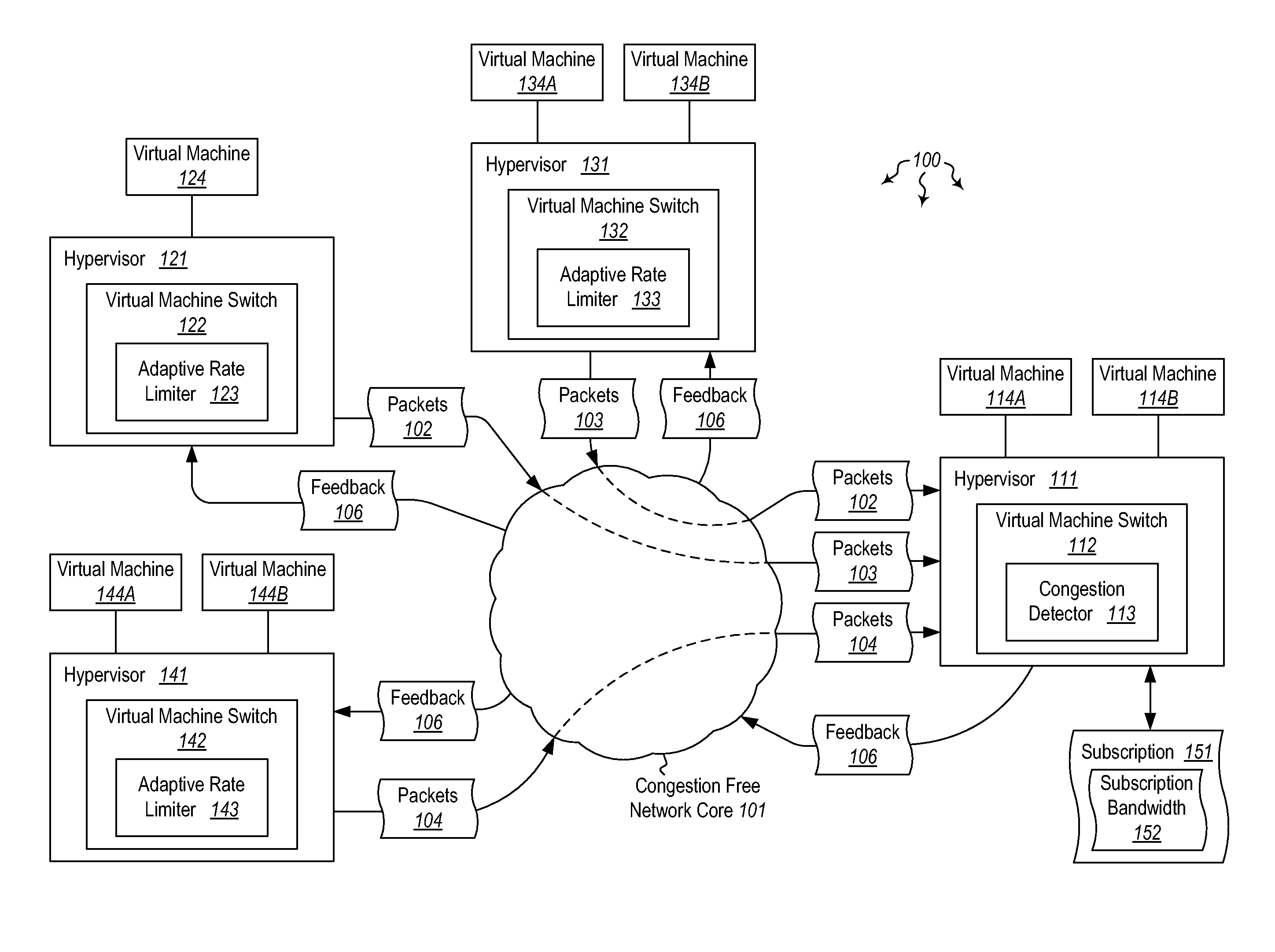

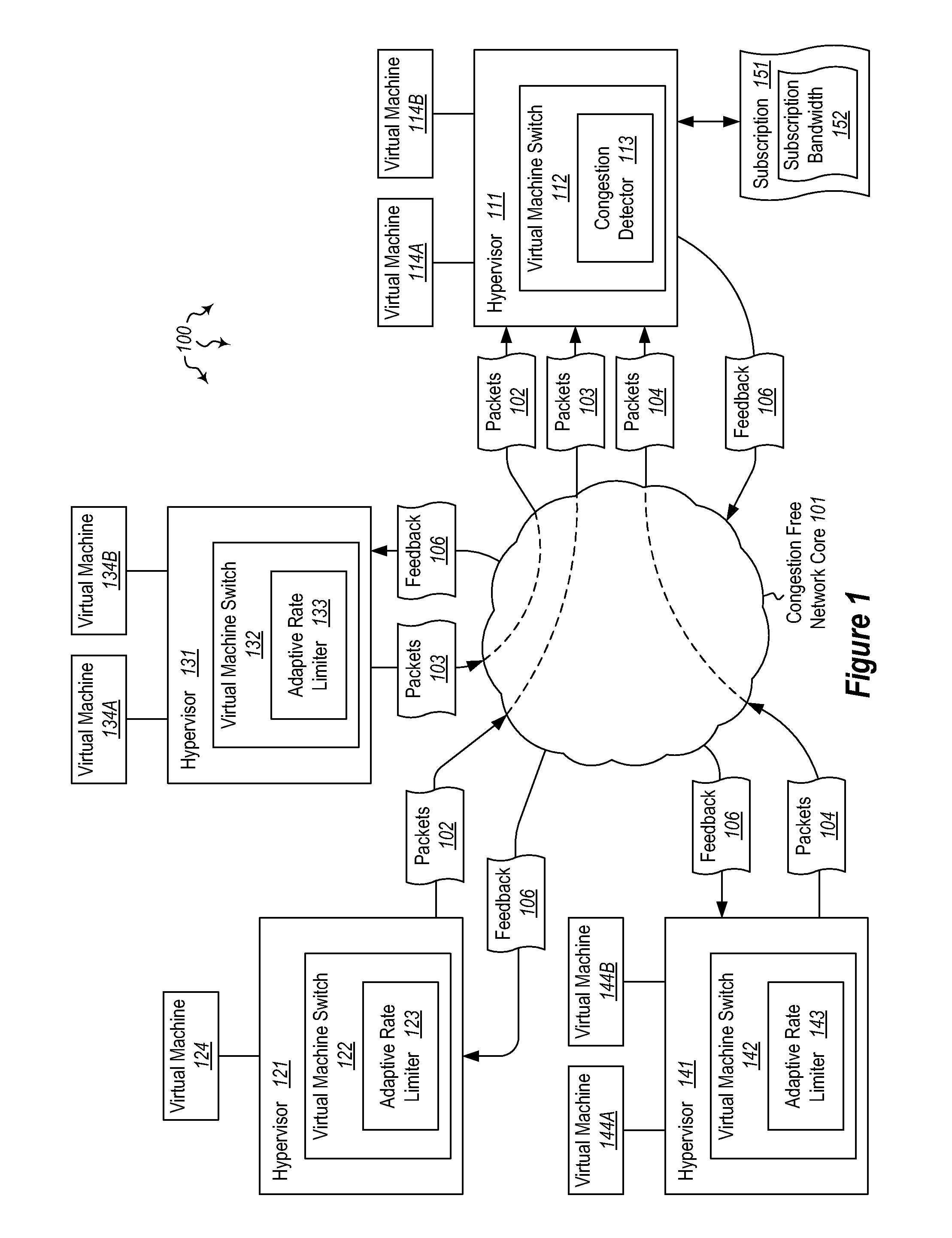

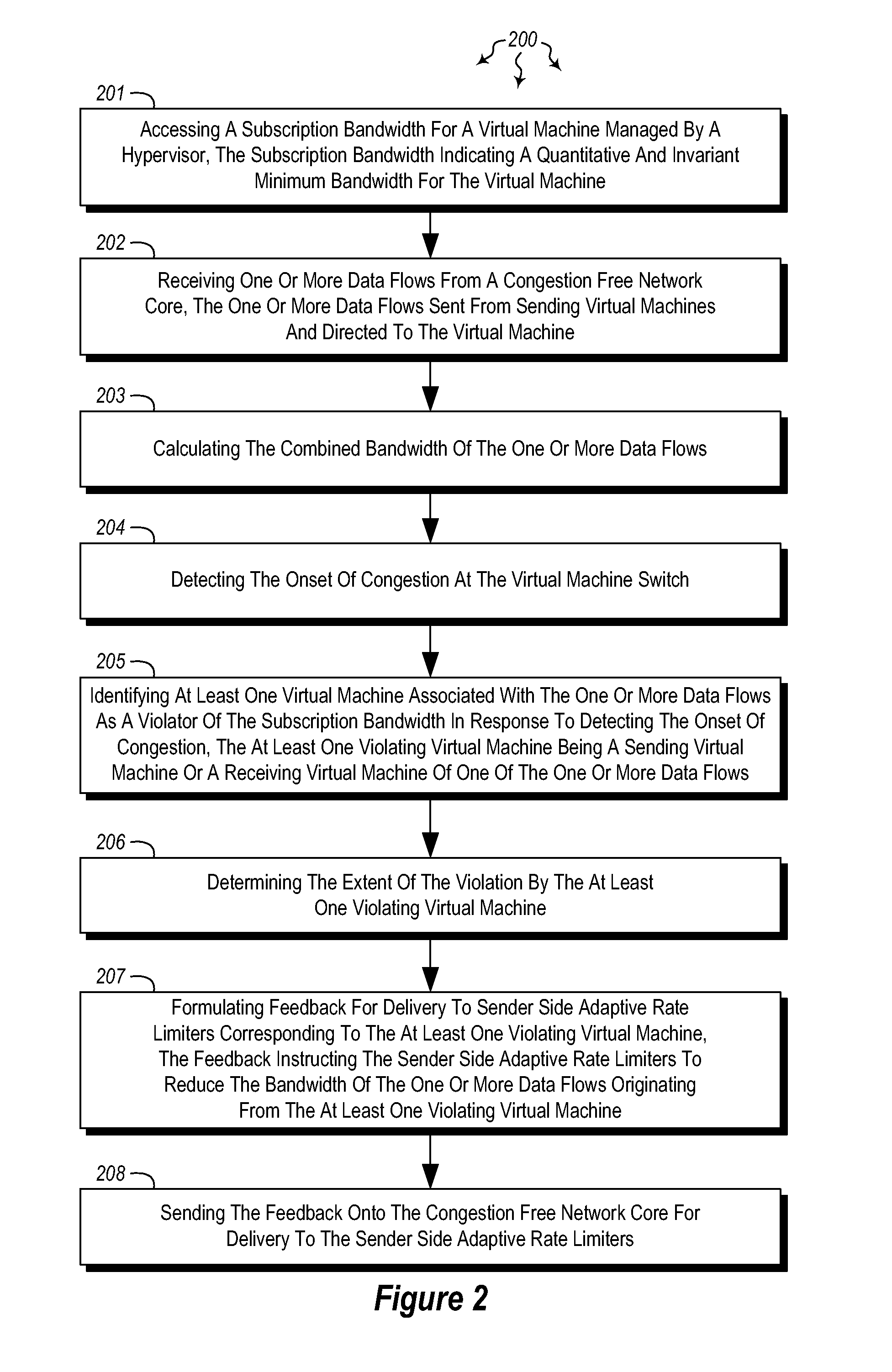

Ensuring predictable and quantifiable networking performance

ActiveUS20130343191A1Ensure performanceError preventionTransmission systemsTraffic capacityEdge based

The ensuring of predictable and quantifiable networking performance. Embodiments of the invention combine a congestion free network core with a hypervisor based (i.e., edge-based) throttling design to help insure quantitative and invariable subscription bandwidth rates. A lightweight shim layer in a hypervisor can adaptively throttle the rate of VM-to-VM traffic flow. A receiving hypervisor can detect congestion and communicate back to sending hypervisors that rates are to be regulated. In response, sending hypervisors can reduce transmission rate to mitigate congestion at the receiving hypervisor. In some embodiments, the principles are extended to any message processors communicating over a congestion free network.

Owner:MICROSOFT TECH LICENSING LLC

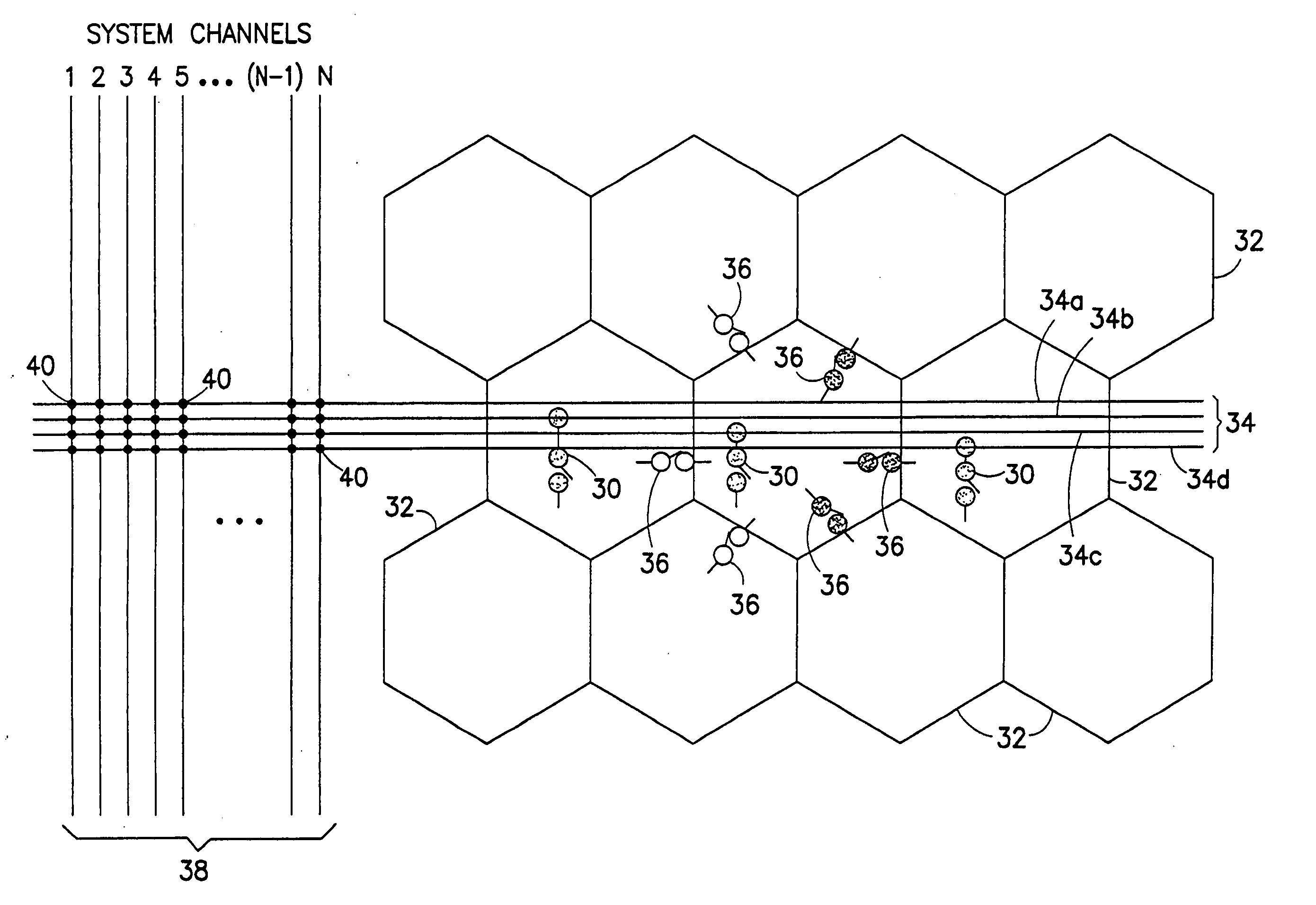

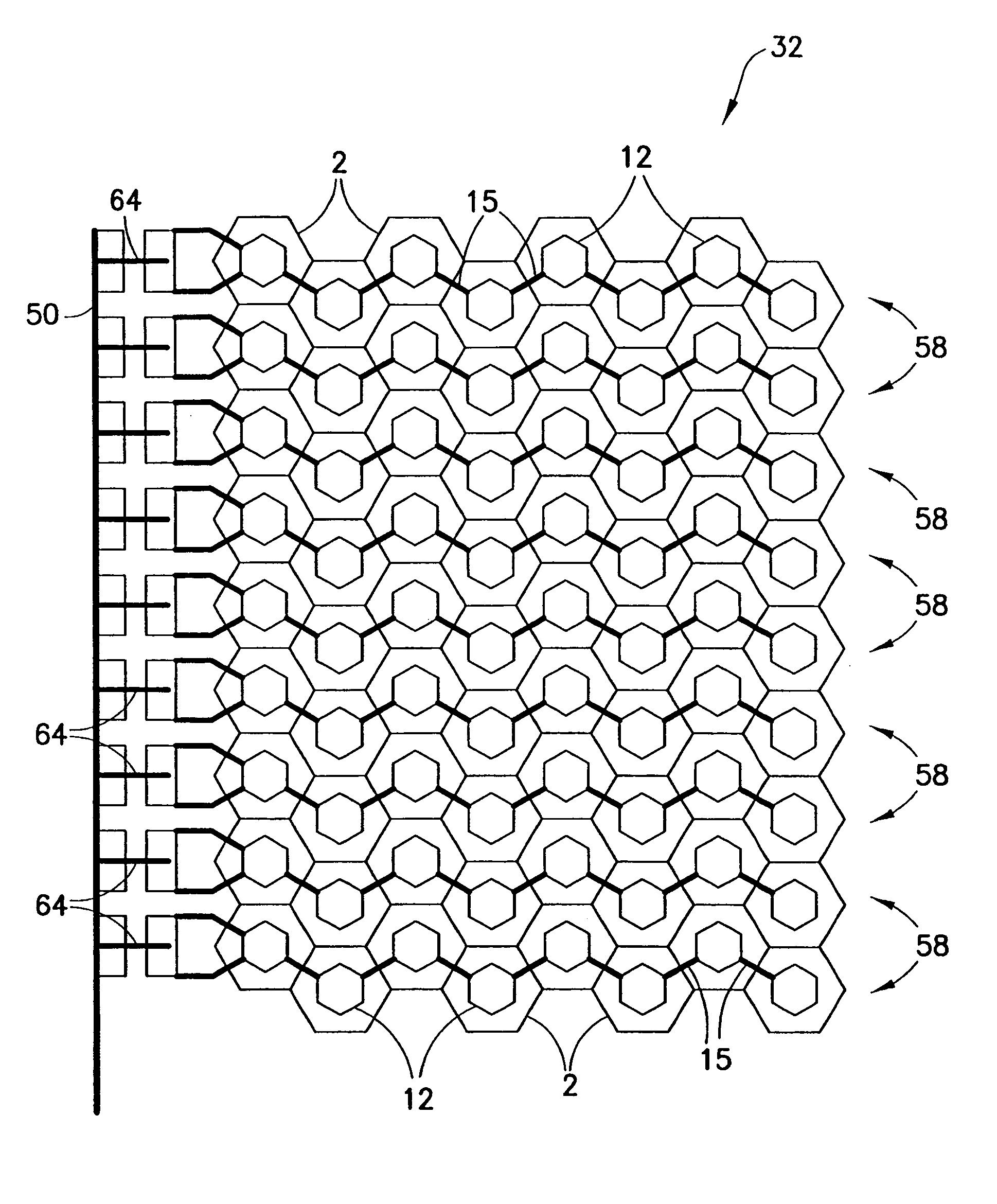

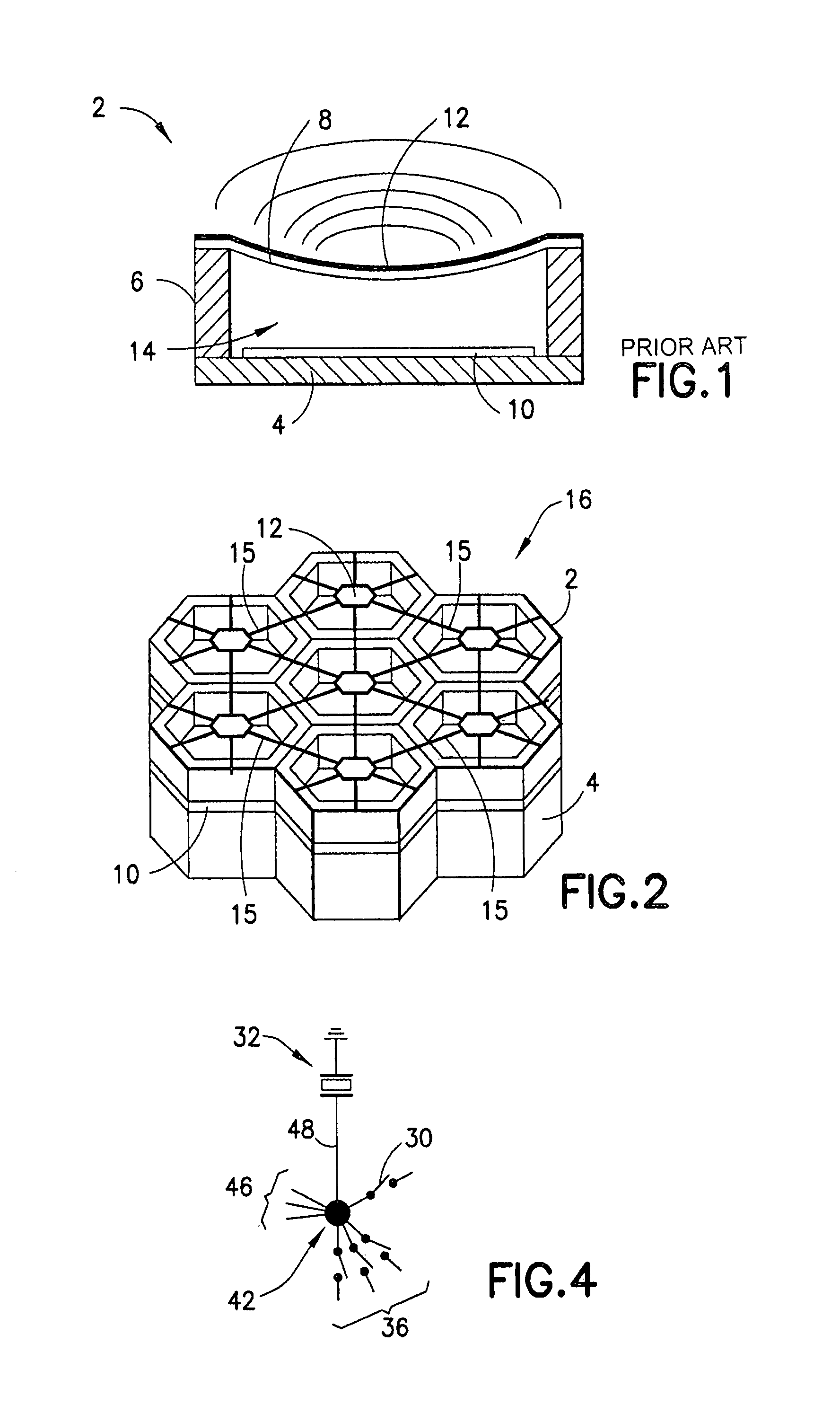

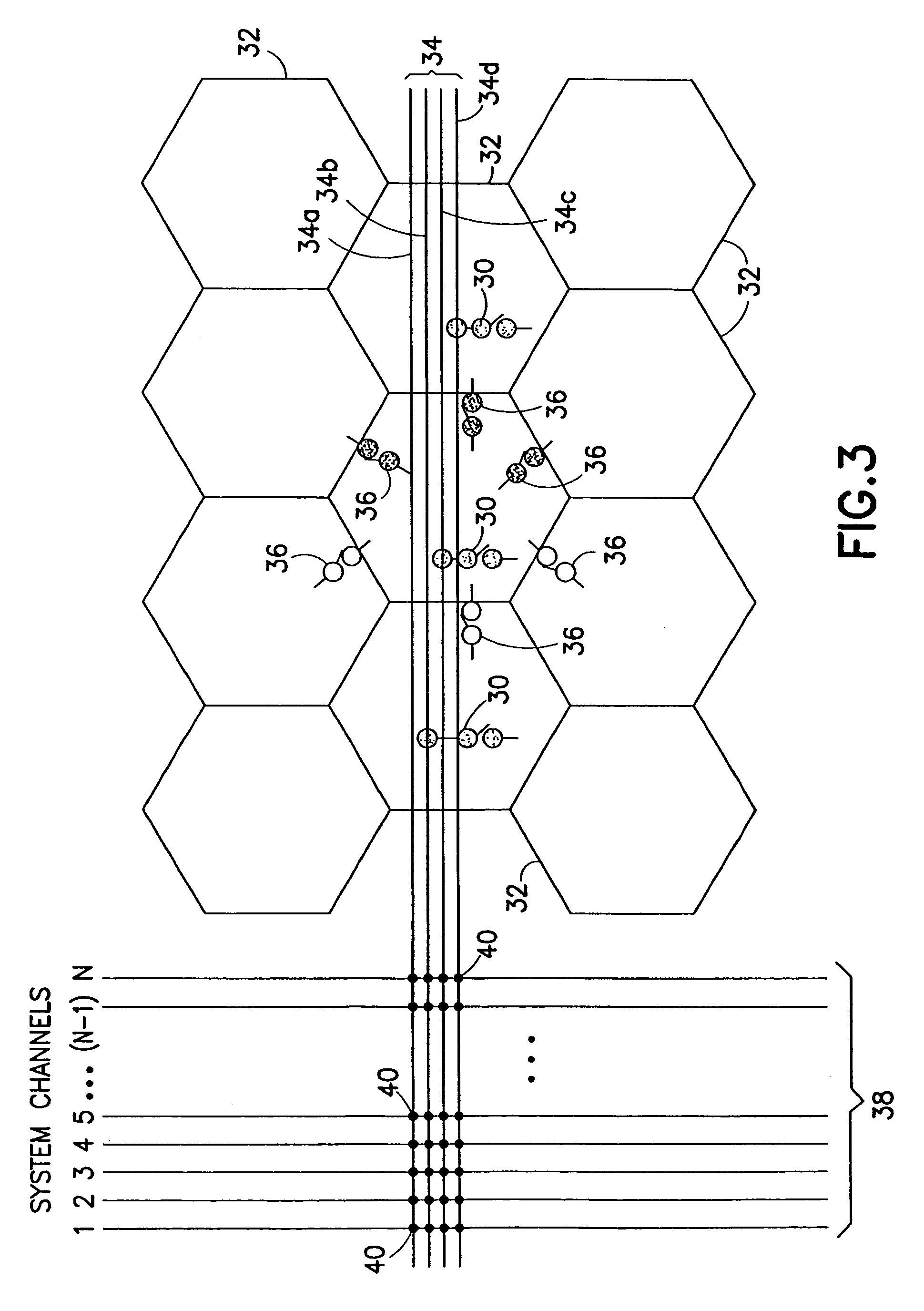

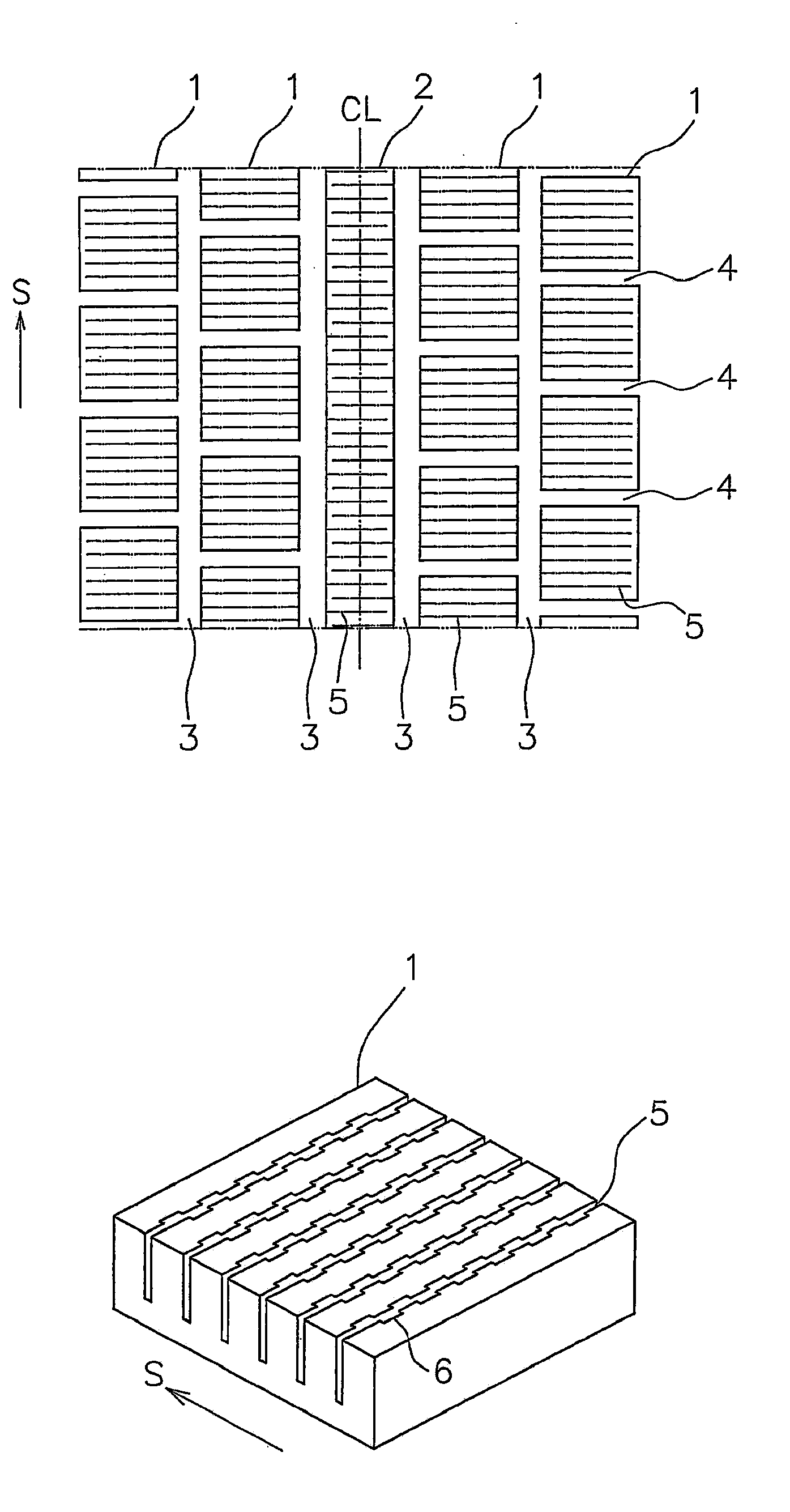

Isolation of short-circuited sensor cells for high-reliability operation of sensor array

ActiveUS20060145059A1Simple and cost-effectiveLower performance requirementsMaterial analysis using sonic/ultrasonic/infrasonic wavesTransducer detailsSensor arrayCurrent sensor

A device comprising an array of sensors and a multiplicity of bus lines, each sensor being electrically connected to a respective bus line and comprising a respective multiplicity of groups of micromachined sensor cells, the sensor cell groups of a particular sensor being electrically coupled to each other via the bus line to which that sensor is connected, each sensor cell group comprising a respective multiplicity of micromachined sensor cells that are electrically interconnected to each other and not switchably disconnectable from each other, the device further comprising means for isolating any one of the sensor cell groups from its associated bus line and in response to any one of the micromachined sensor cells of that sensor cell group being short-circuited to ground. In one implementation, the isolating means comprise a multiplicity of fuses. In another implementation, the isolating means comprise a multiplicity of short circuit protection modules, each module comprising a current sensor circuit and an electrical isolation switch.

Owner:GENERAL ELECTRIC CO

System and method for fair and economical resource partitioning using virtual hypervisor

ActiveUS8433802B2Easy to controlEnsure performanceEnergy efficient ICTDigital computer detailsAbstraction layerVirtual machine

A system and method for allocating resources in a cloud environment includes determining permitted usage of virtual machines and partitioning resources between network servers in accordance with a virtual hypervisor generated in accordance with an abstraction layer configured as an interface between a solution manager and an interface to a cloud network. Resource usage limits are determined for each virtual machine associated with the virtual hypervisor, and the servers are analyzed through the virtual hypervisors to determine if the virtual machines need to be migrated. If reallocation is needed, virtual machine migration requests are issued to migrate virtual machines into a new configuration at the virtual hypervisor abstraction level. The servers are reanalyzed to determine if migration of the new configuration is needed. Shares are computed to enforce balance requirements, and virtual machine shares and limits are adjusted for resources according to the computed shares.

Owner:IBM CORP

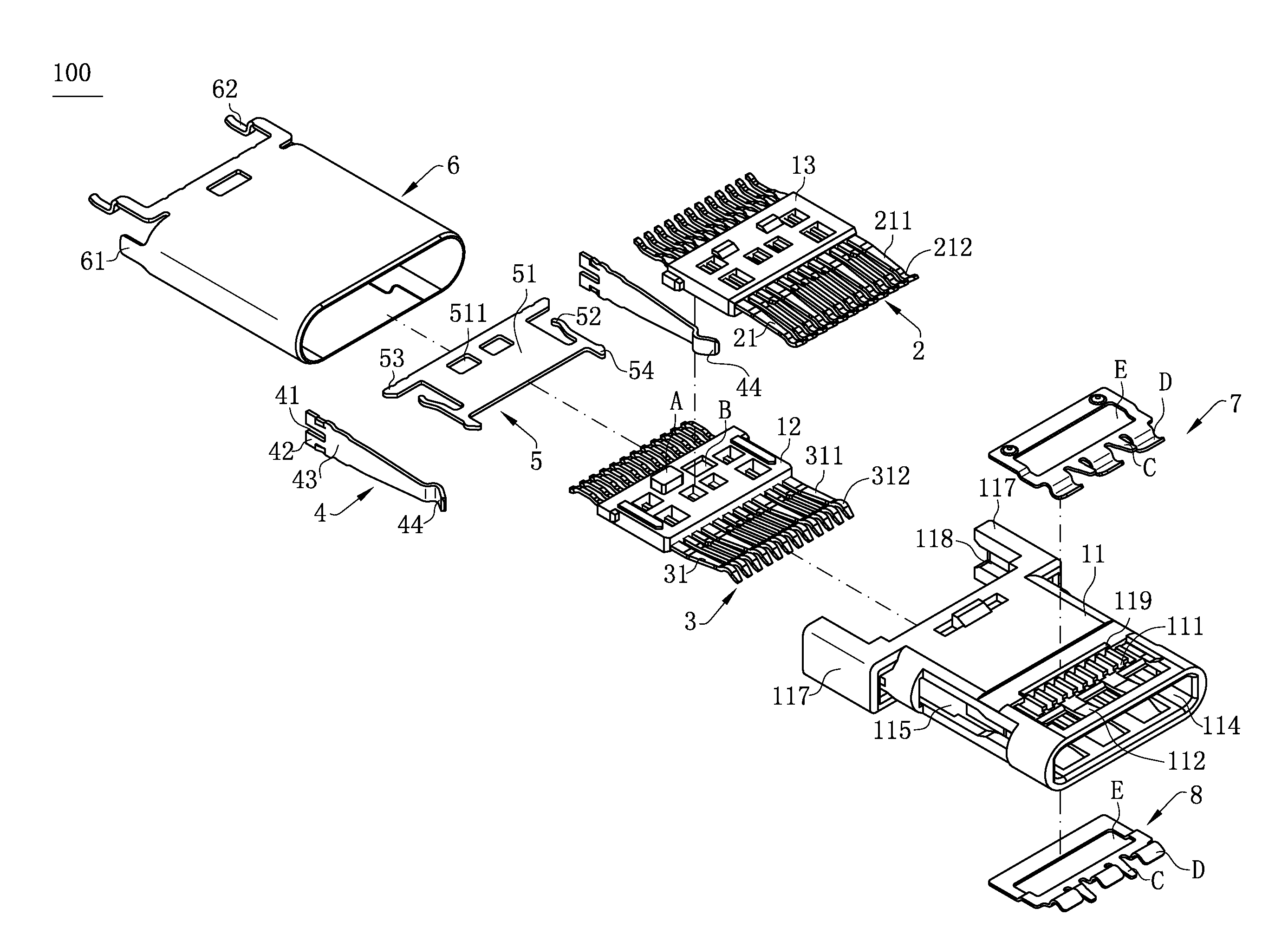

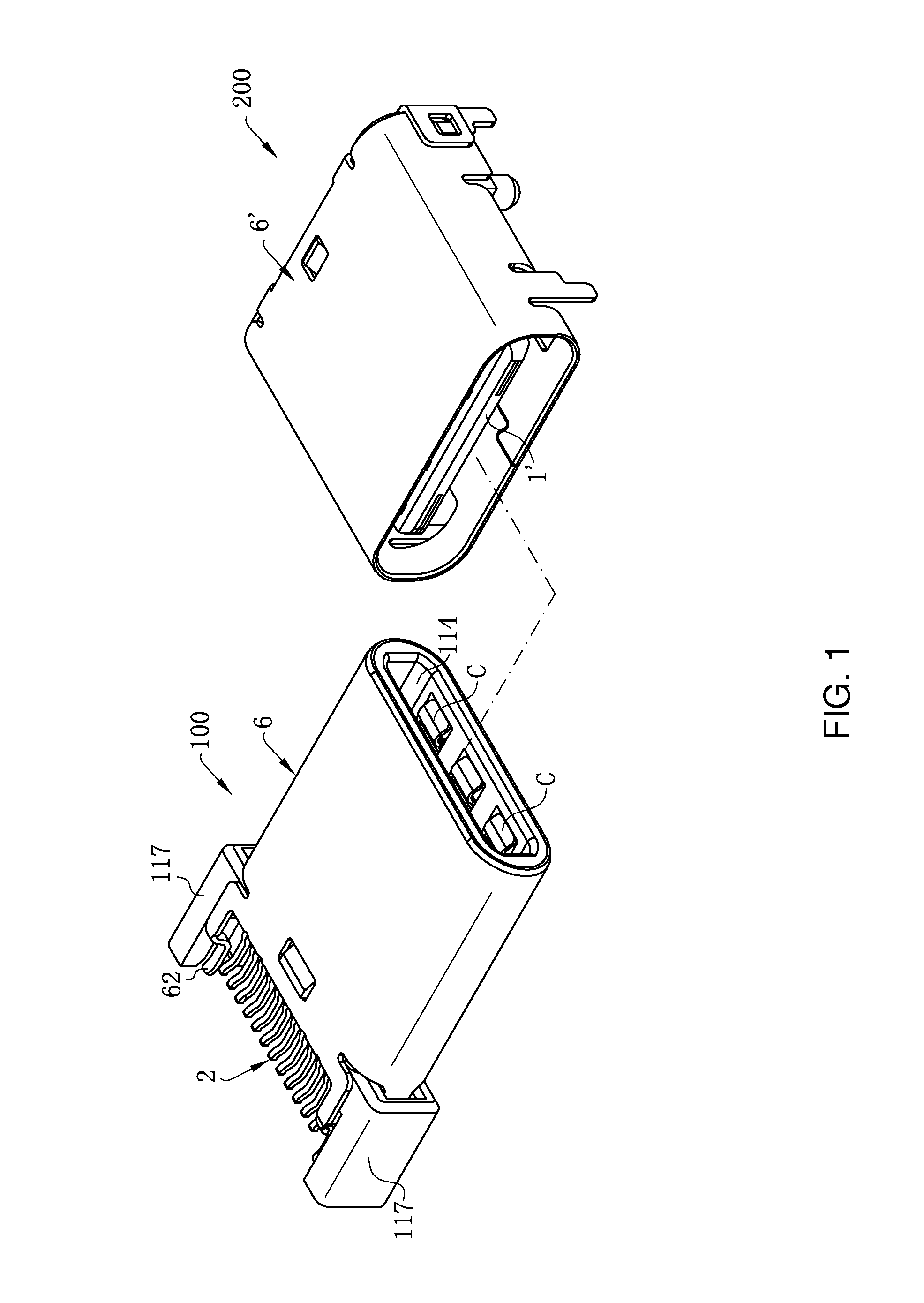

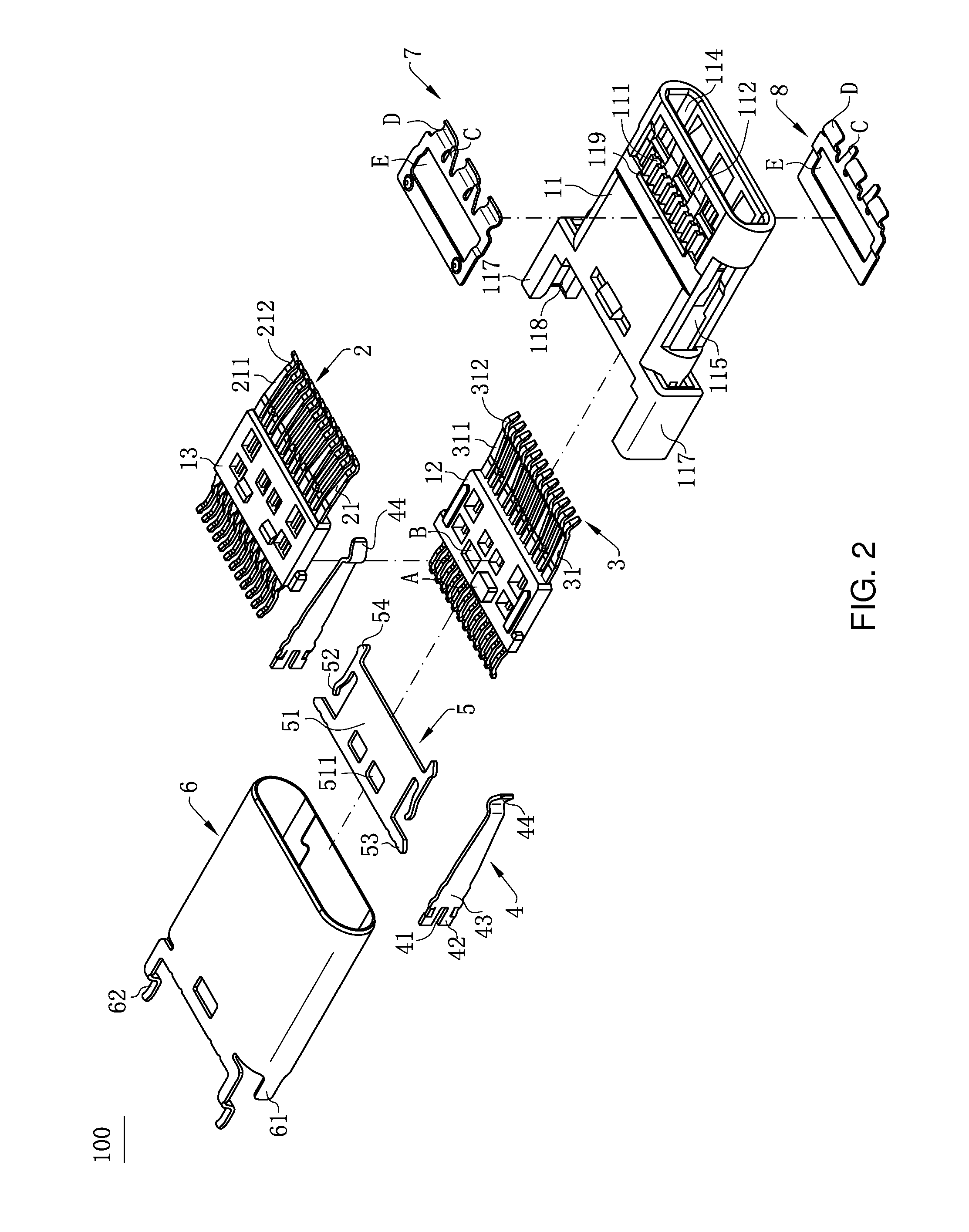

Mating connector

ActiveUS9281626B2Improve anti-interference abilityStable insertion forceCoupling protective earth/shielding arrangementsMating connectionCase contact

A mating connector includes a plastic body, a first terminal group and a second terminal group received in the plastic body, a retaining elastic sheet retained at the plastic body and located at a side of the first terminal group and the second terminal group, a middle shielding sheet located between the first terminal group and the second terminal group, and a shielding case contacting the middle shielding sheet. An urging portion is extended from the middle shielding sheet and abuts the retaining elastic sheet. The middle shielding sheet shields an interference signal between plate surfaces of the first and second terminal groups. The retaining elastic sheet shields an interference signal between side surfaces of the first and second terminal groups.

Owner:LOTES

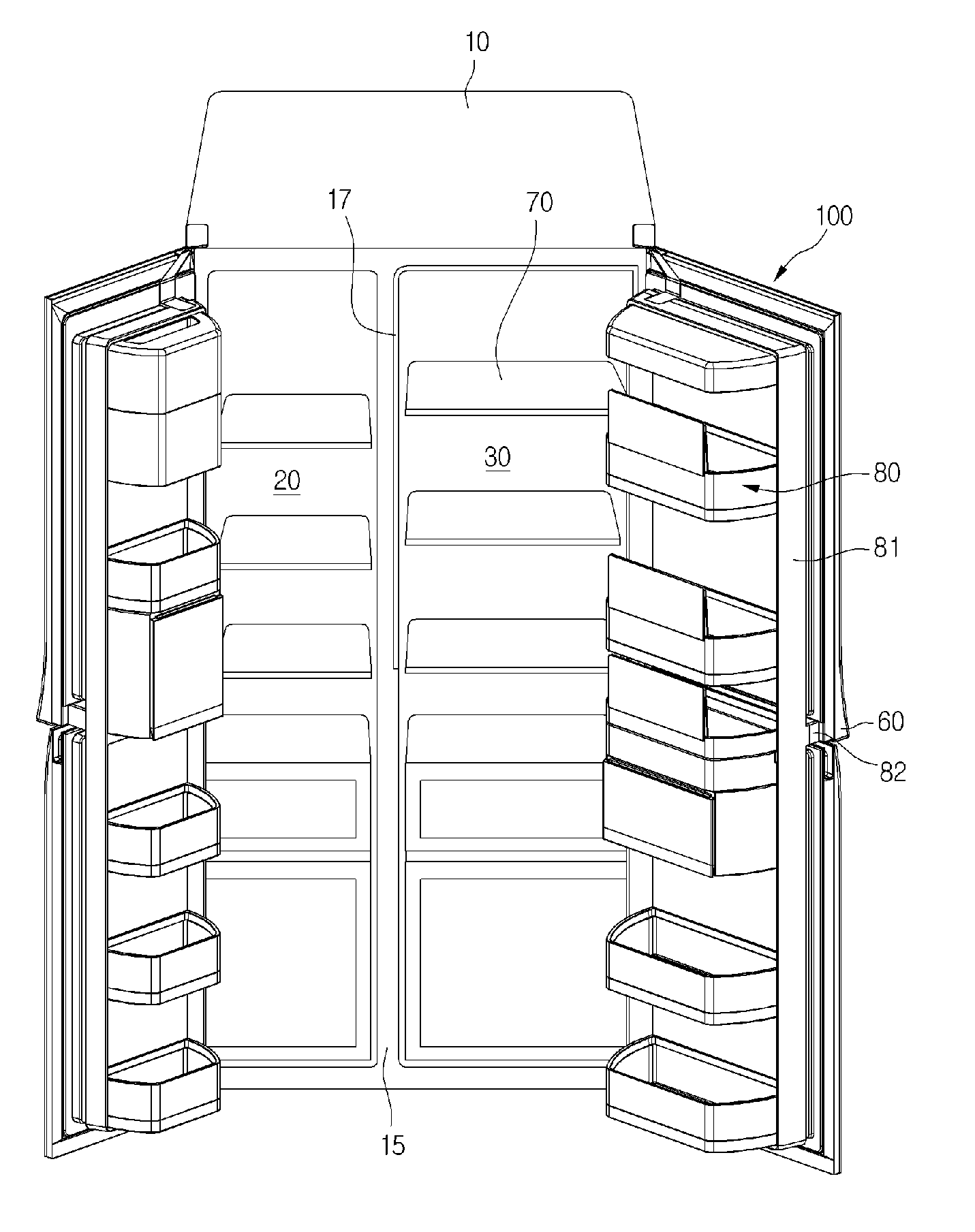

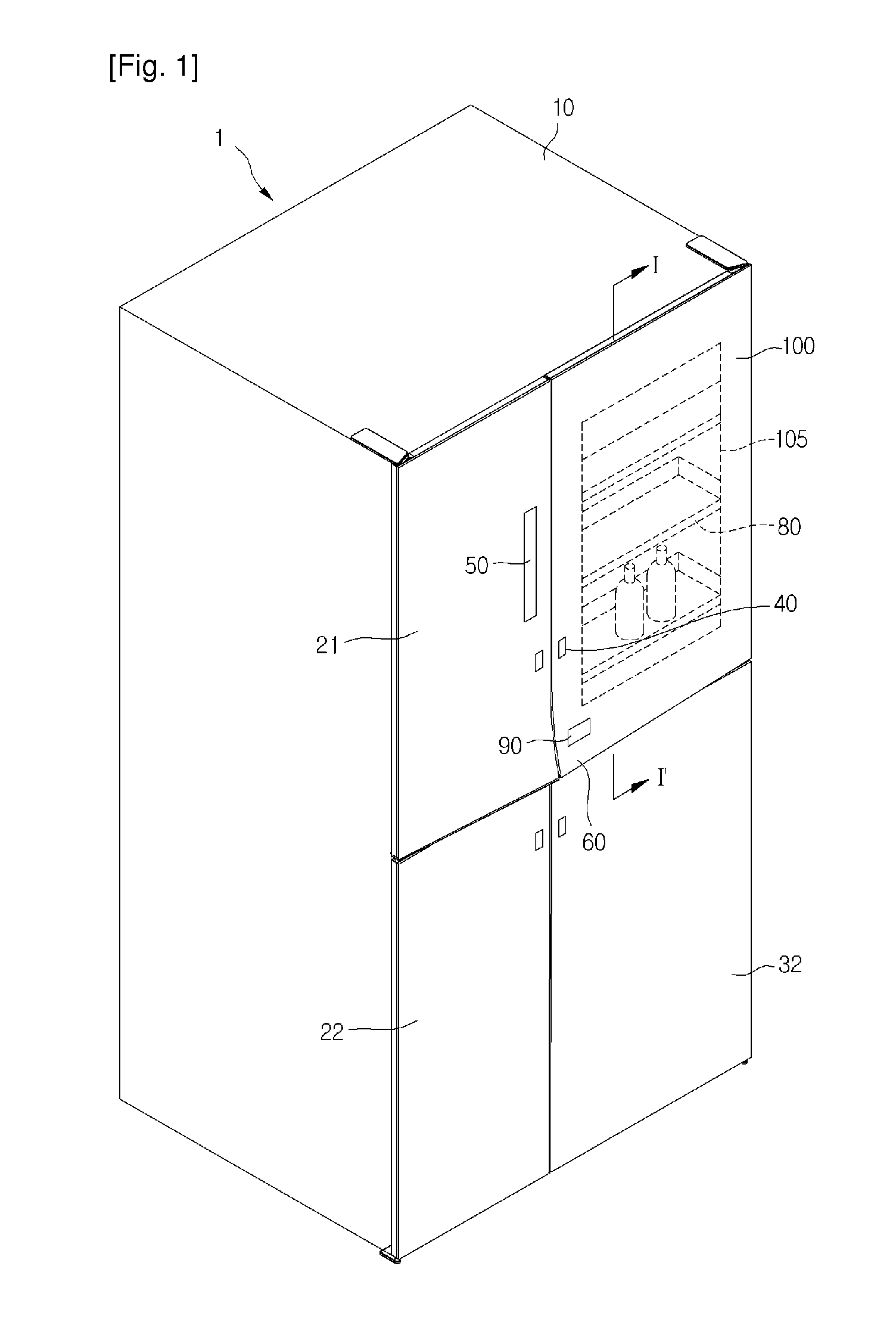

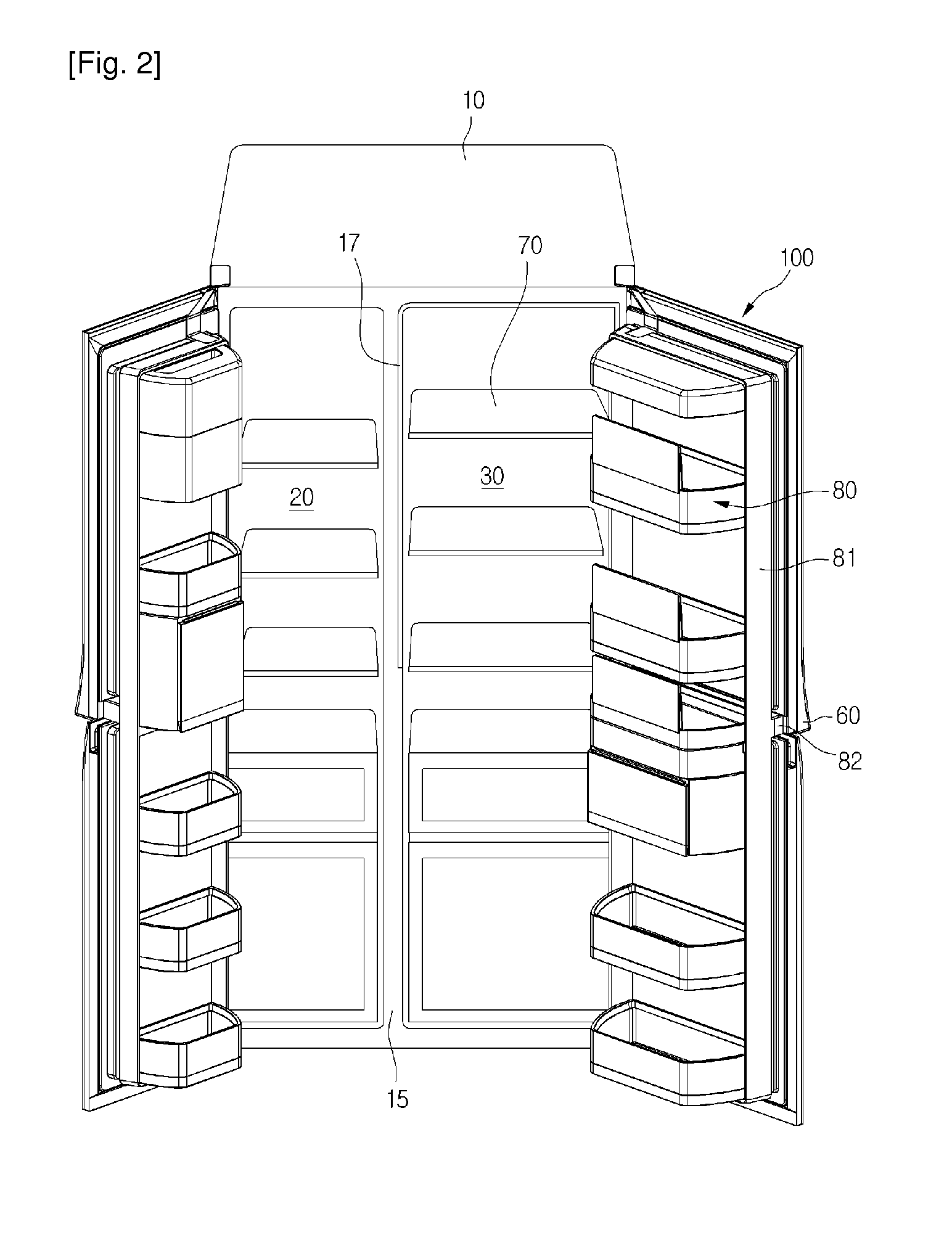

Refrigerator and method for controlling the same

ActiveUS20120286638A1Precise positioningImprove user convenienceShow cabinetsLighting and heating apparatusElectrical and Electronics engineeringEngineering

Provided is a refrigerator, which includes a refrigerating compartment, a freezing compartment, and a door assembly. The freezing compartment is adjacent to the refrigerating compartment. The door assembly selectively opens the refrigerating compartment and the freezing compartment. The door assembly includes a glass member defining a frontal exterior thereof and allowing an inside of the refrigerating compartment or the freezing compartment to be seen therethrough when the door assembly is closed, a deposition treated layer formed on a rear surface of the glass member to allow light to partially pass through the glass member, and a transparent plate spaced a predetermined distance from the glass member. Gas for insulation is injected in a space formed between the glass member and the transparent plate, and the space is sealed.

Owner:LG ELECTRONICS INC

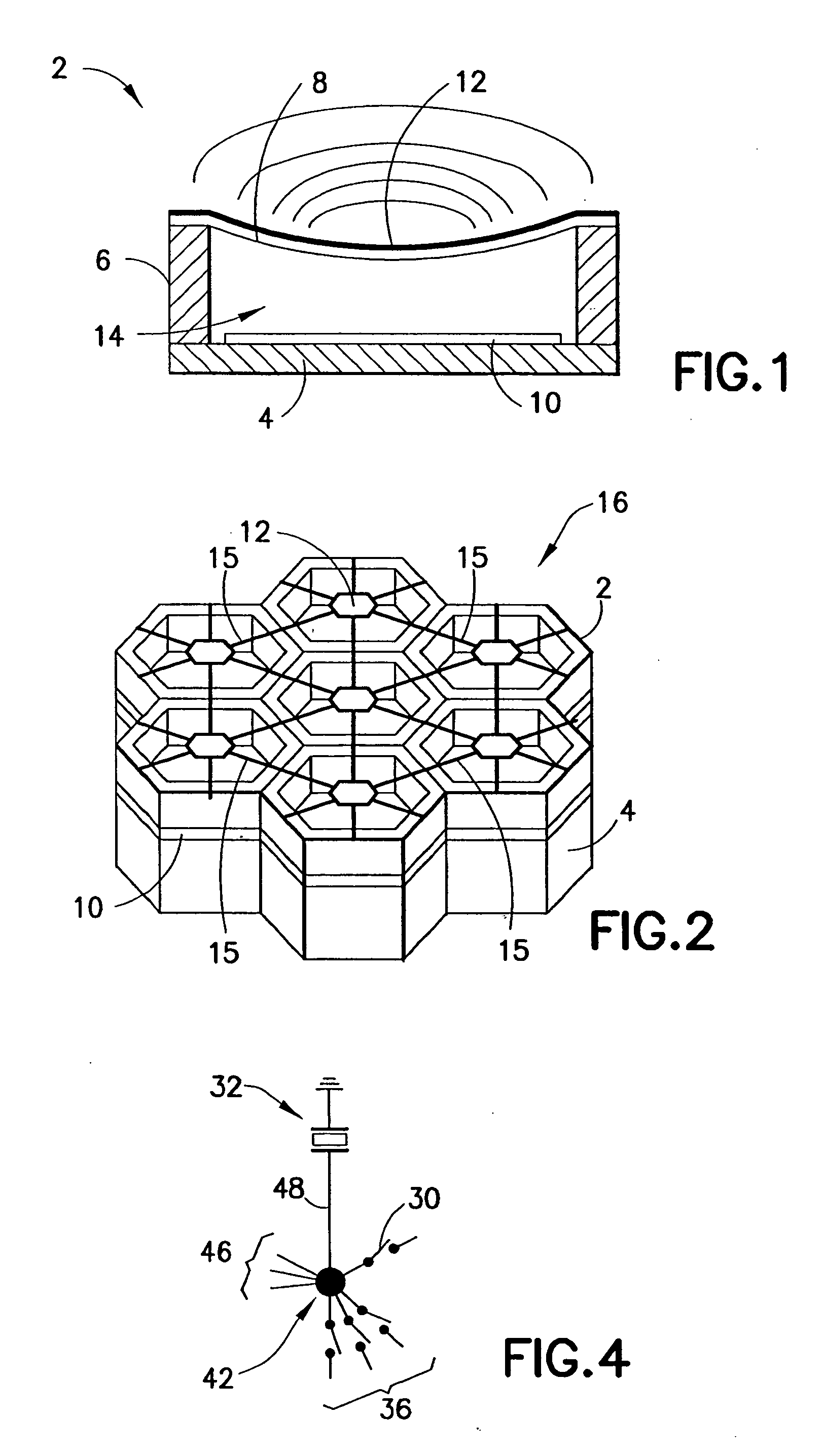

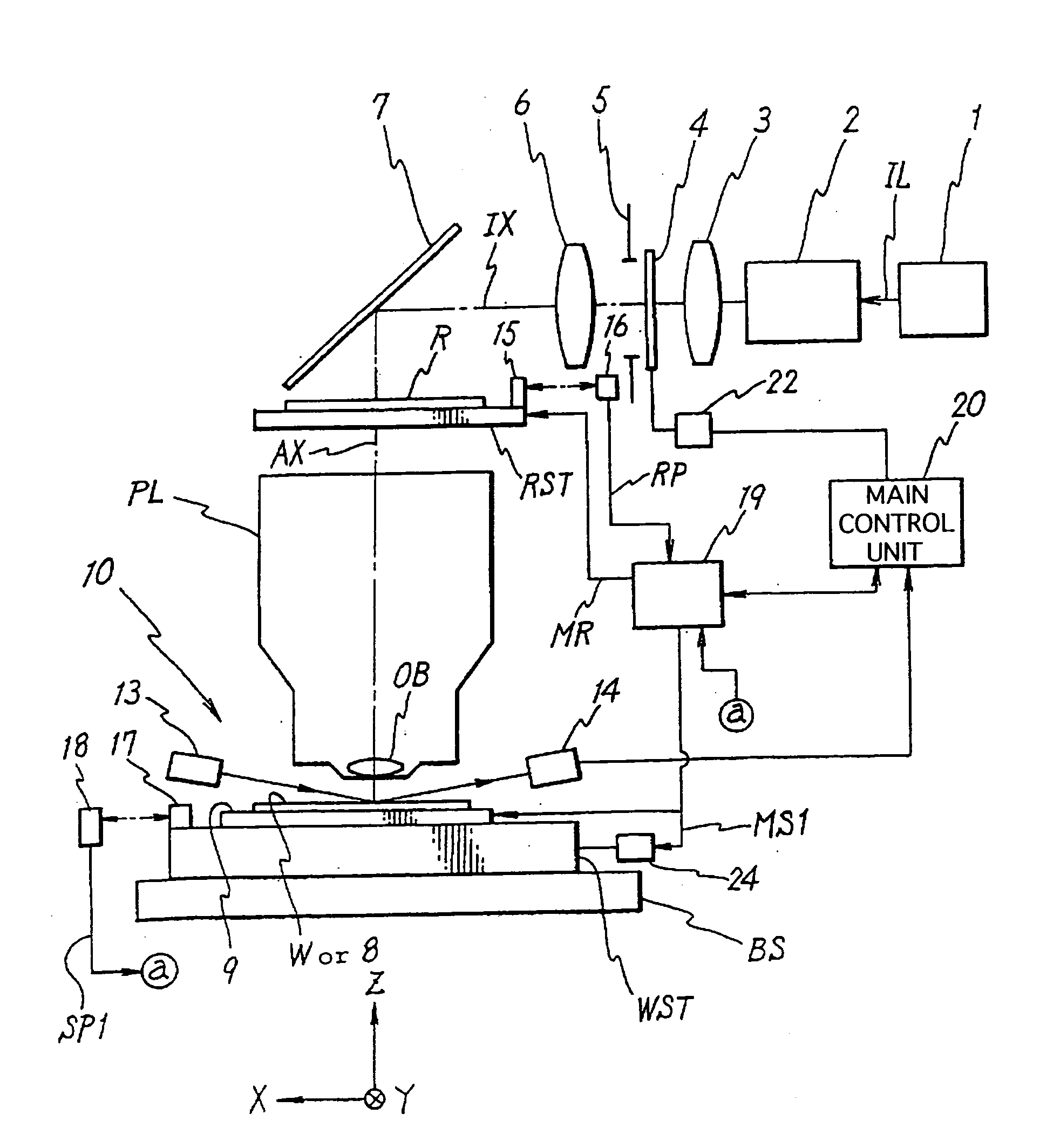

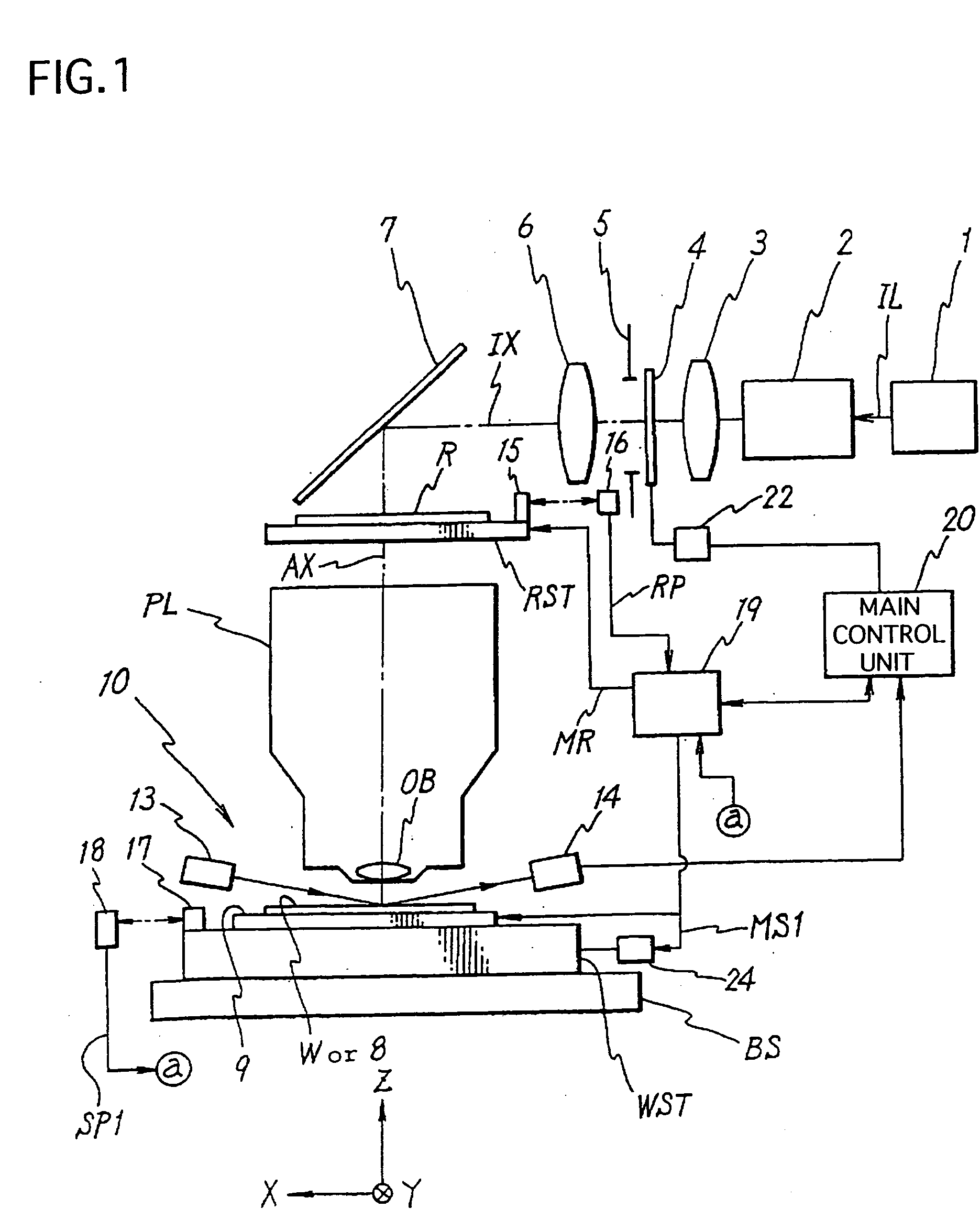

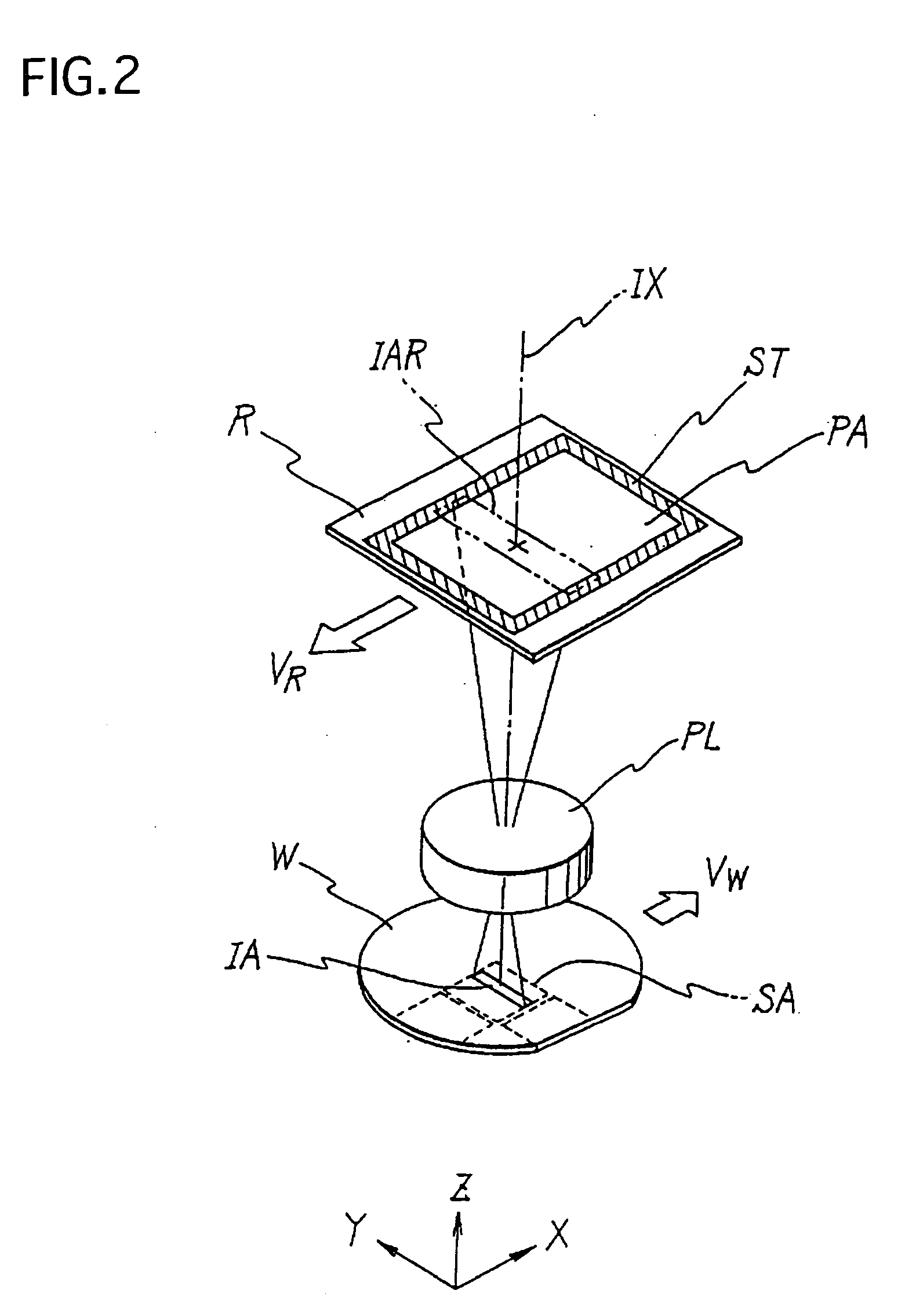

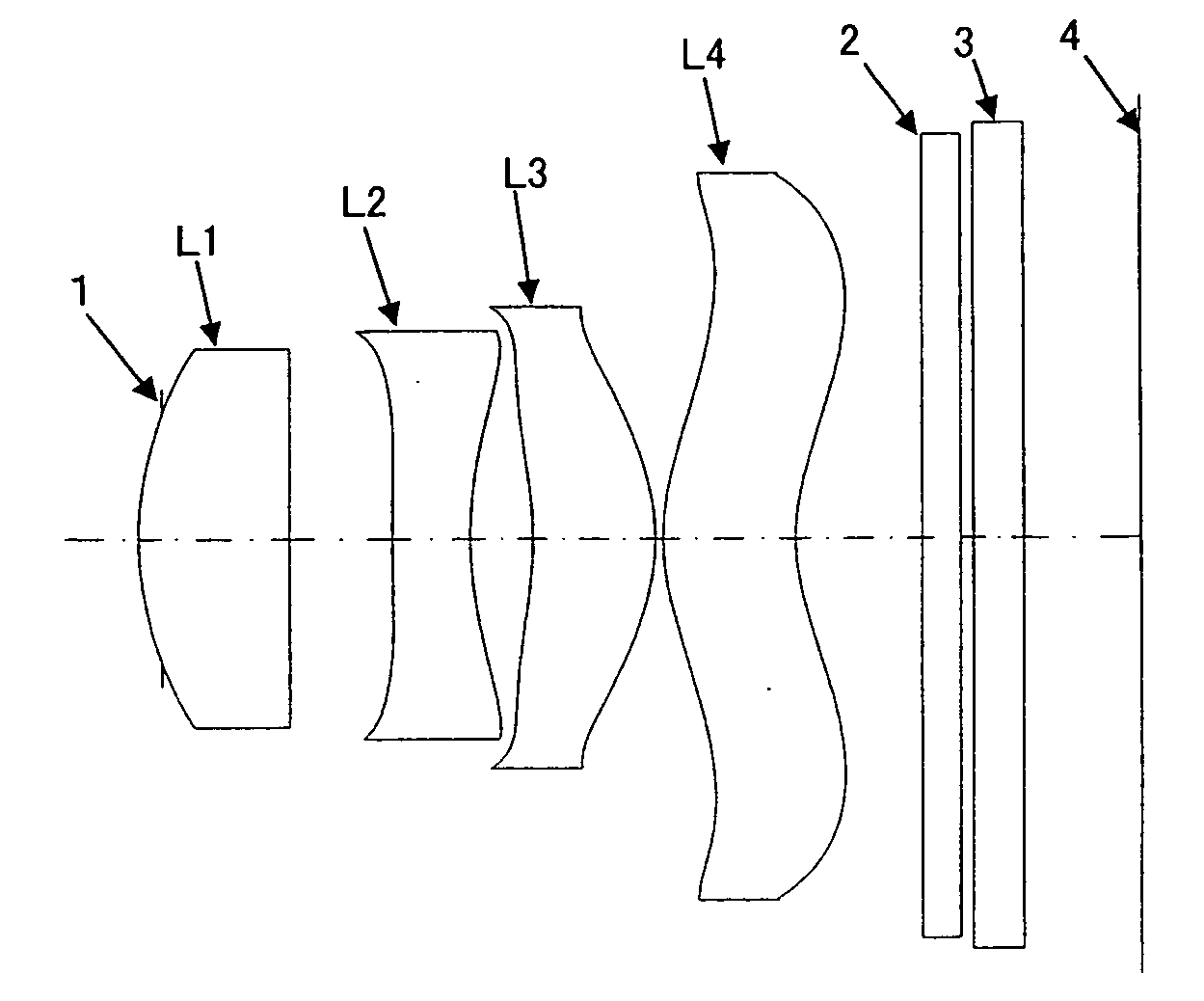

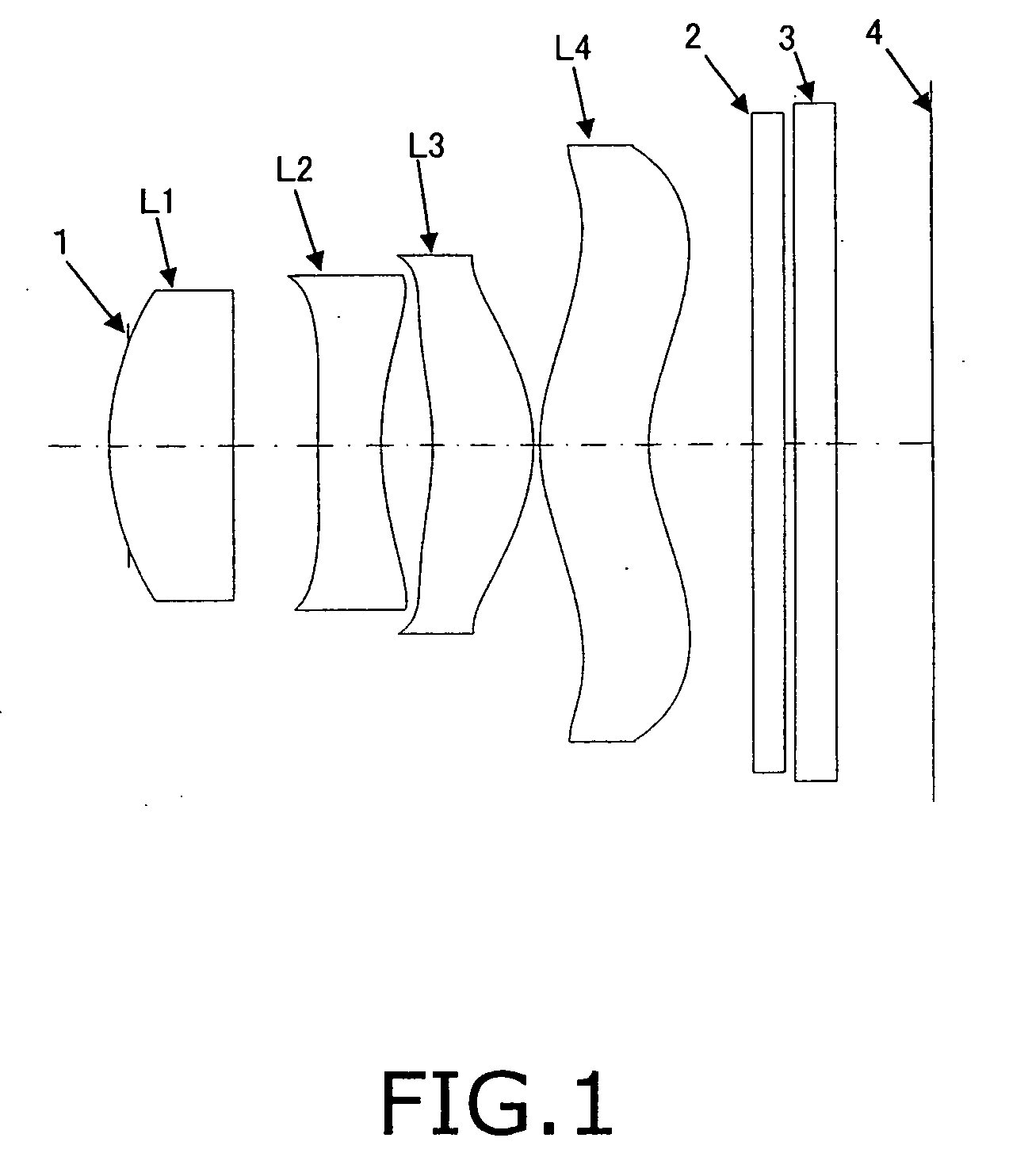

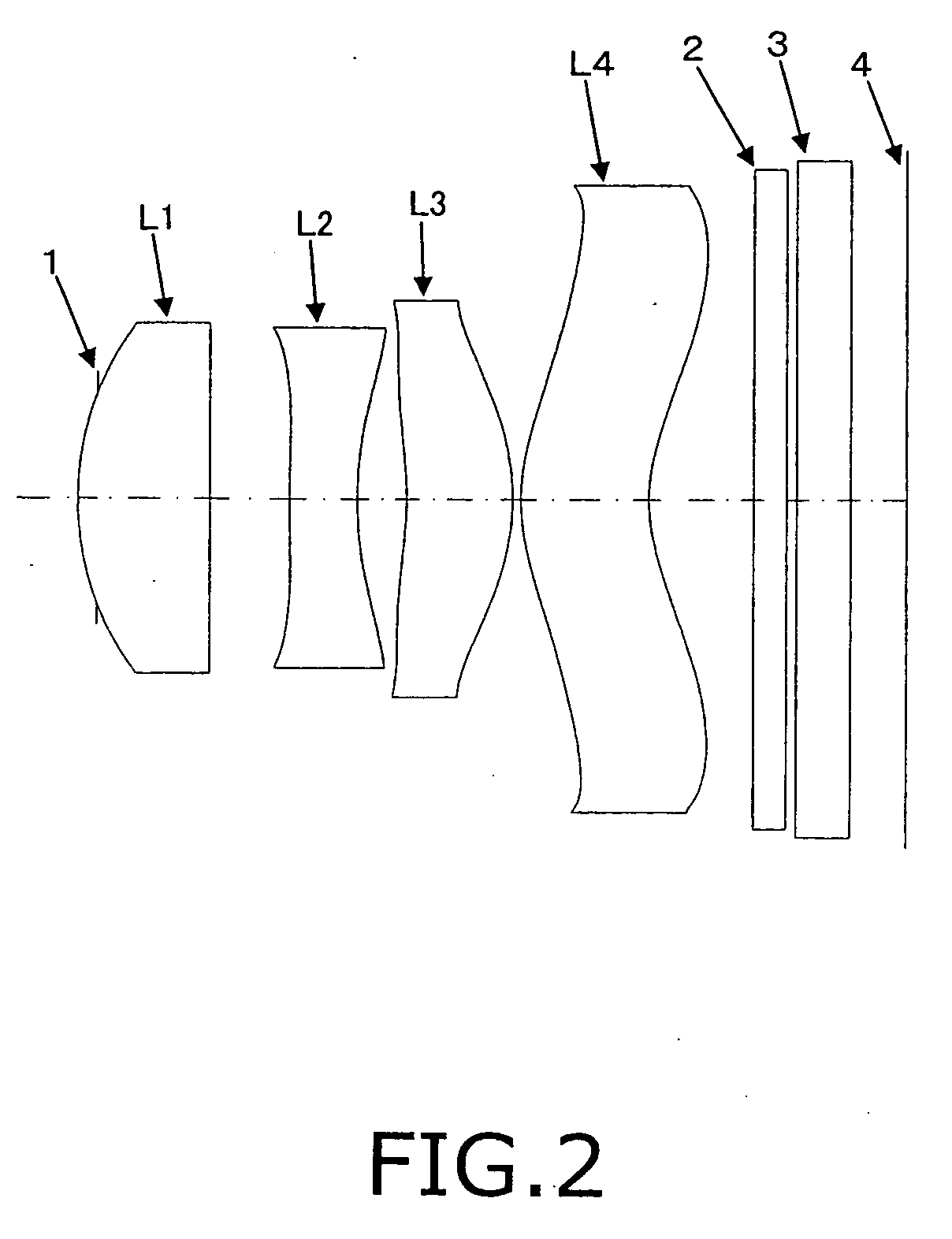

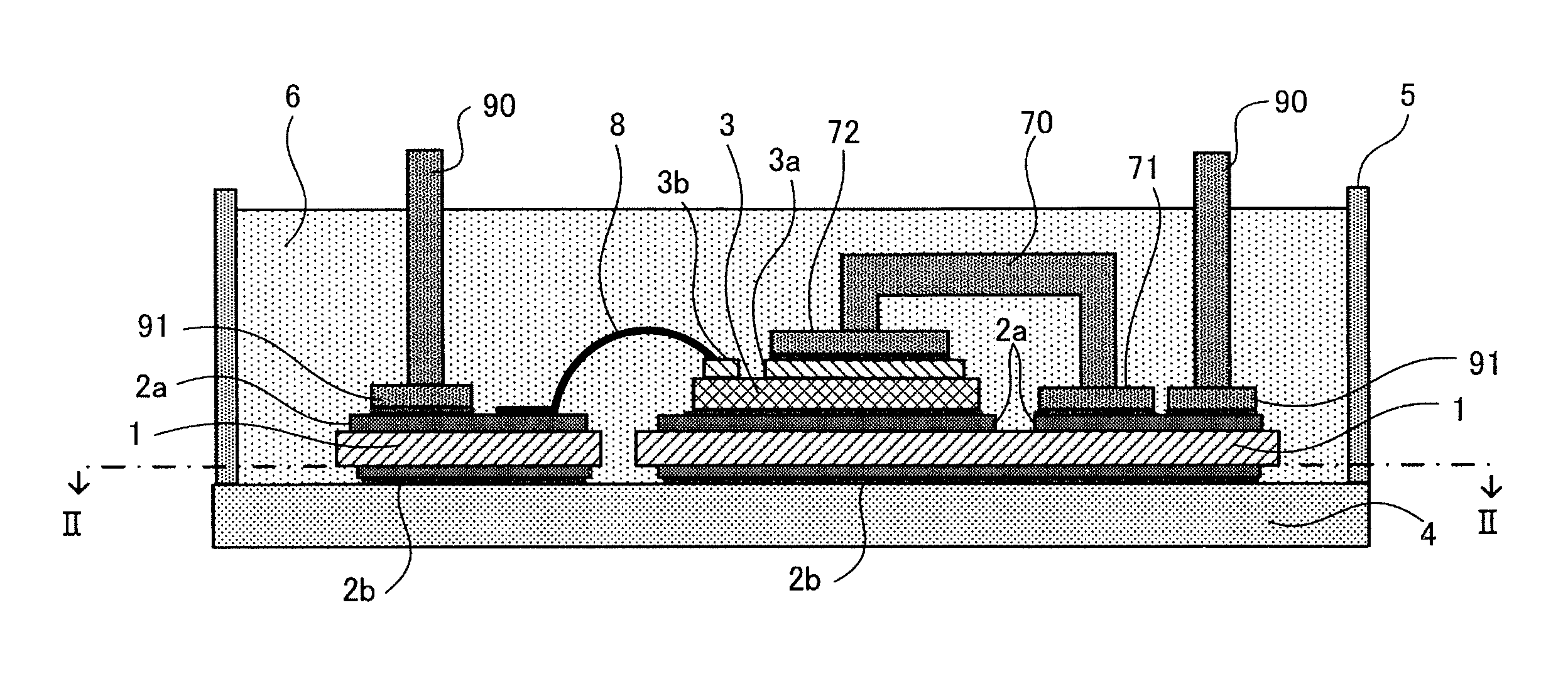

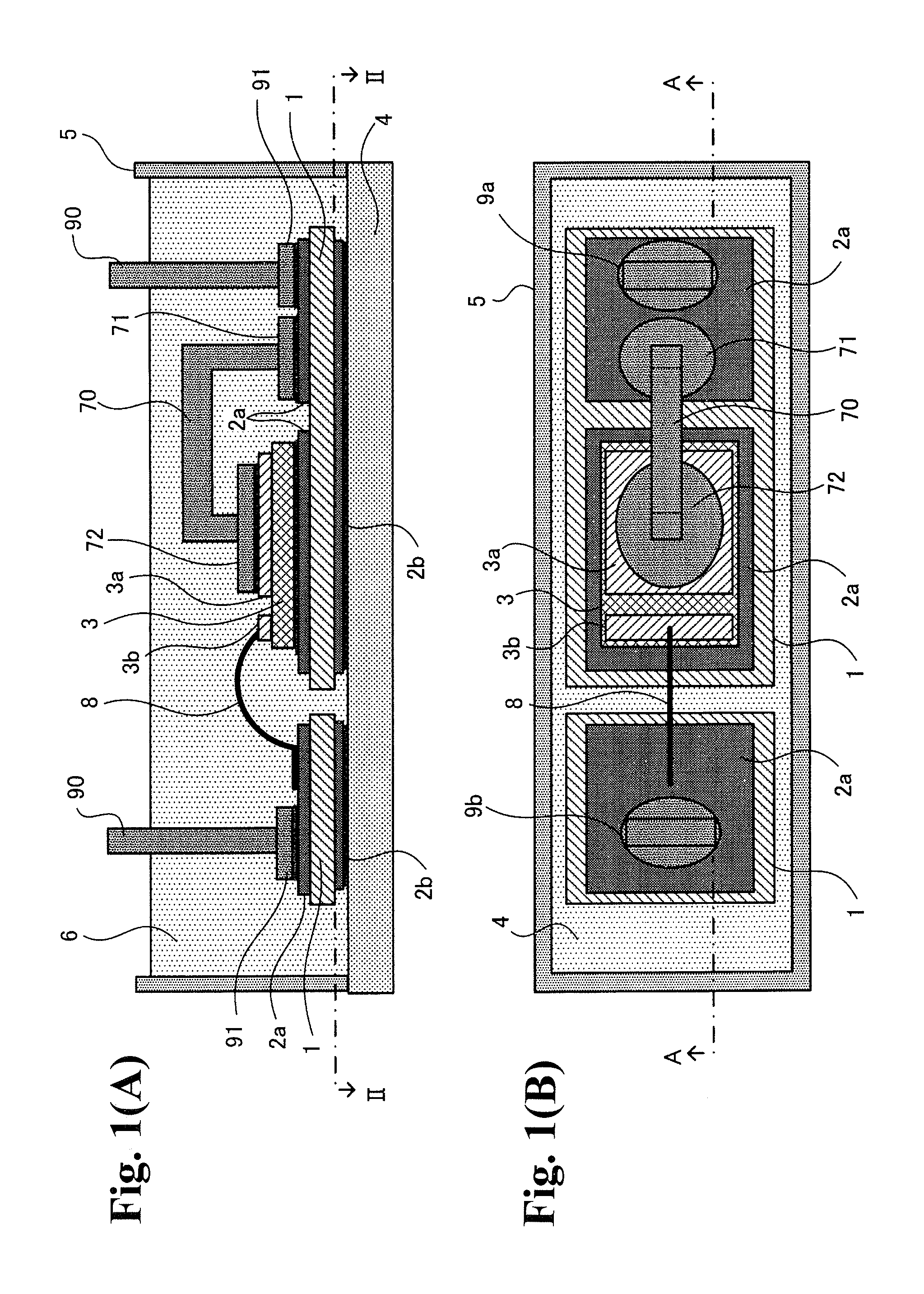

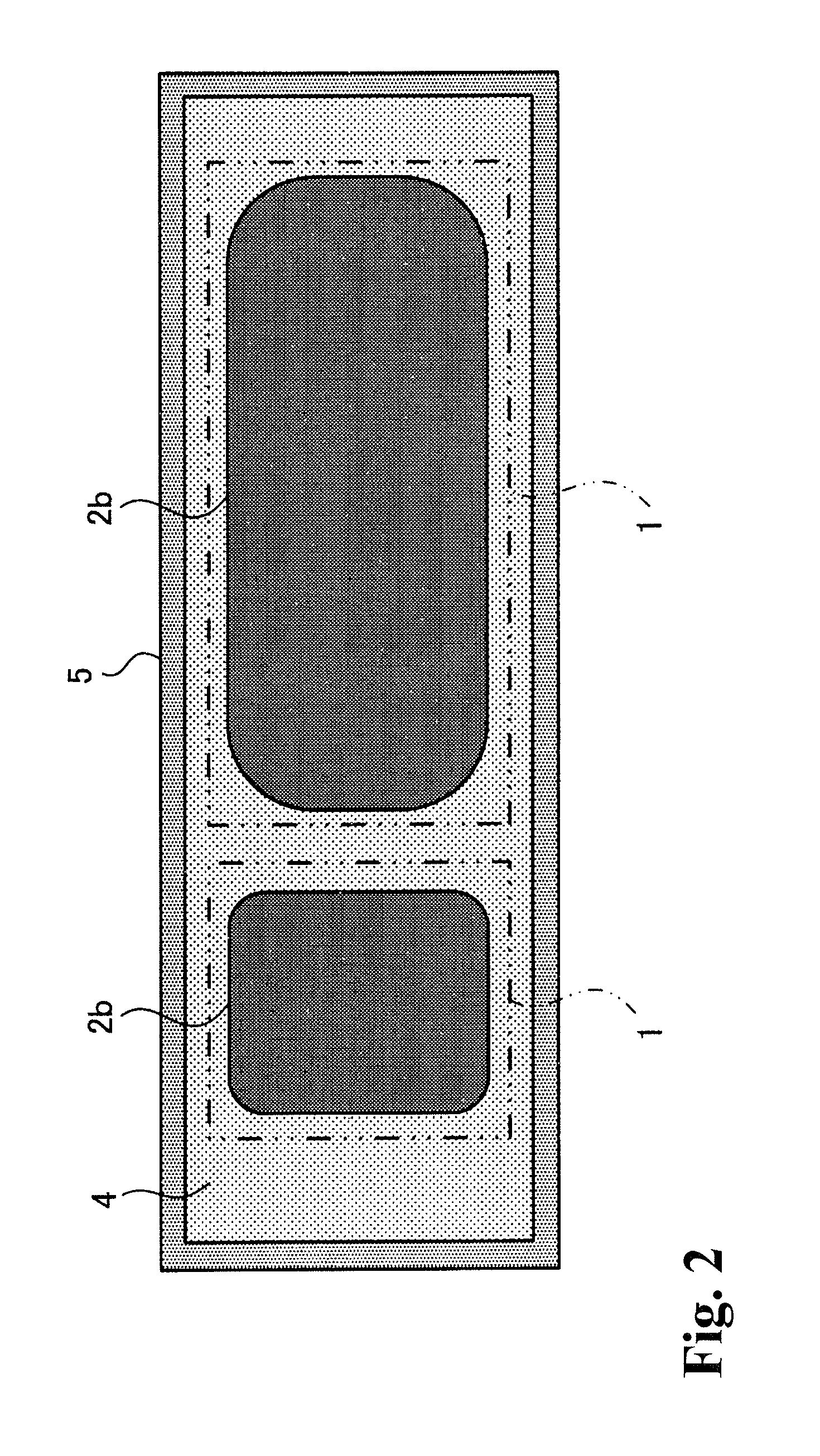

Projection exposure apparatus and method

InactiveUS20050094115A1Cleaning effect can be moreImprove cleaning effectMaterial analysis by optical meansPhotomechanical exposure apparatusPhysicsExposure

Pattern transfer can be performed with improved exposure accuracy, by reducing the contamination caused by the attachment of a photosensitive agent or the like on an optical member of a projection optical member or the like. The pattern transfer onto a substrate W is performed after cleaning the objective member OB disposed at a given position by a cleaning device 8 at the time when pattern transfer is not performed, or while making flow a gas in a space between the substrate W and the optical member OB by a contamination protection device 98. Alternatively, the optical member OB disposed at a given position is inspected for contamination by a contamination inspection device 84 at the time when pattern transfer is not performed, and the pattern transfer or the cleaning or replacement of the optical member is performed based on the result.

Owner:NIKON CORP

Isolation of short-circuited sensor cells for high-reliability operation of sensor array

ActiveUS7293462B2Simple and cost-effectiveLower performance requirementsMaterial analysis using sonic/ultrasonic/infrasonic wavesTransducer detailsSensor arrayElectricity

A device comprising an array of sensors and a multiplicity of bus lines, each sensor being electrically connected to a respective bus line and comprising a respective multiplicity of groups of micromachined sensor cells, the sensor cell groups of a particular sensor being electrically coupled to each other via the bus line to which that sensor is connected, each sensor cell group comprising a respective multiplicity of micromachined sensor cells that are electrically interconnected to each other and not switchably disconnectable from each other, the device further comprising means for isolating any one of the sensor cell groups from its associated bus line and in response to any one of the micromachined sensor cells of that sensor cell group being short-circuited to ground. In one implementation, the isolating means comprise a multiplicity of fuses. In another implementation, the isolating means comprise a multiplicity of short circuit protection modules, each module comprising a current sensor circuit and an electrical isolation switch.

Owner:GENERAL ELECTRIC CO

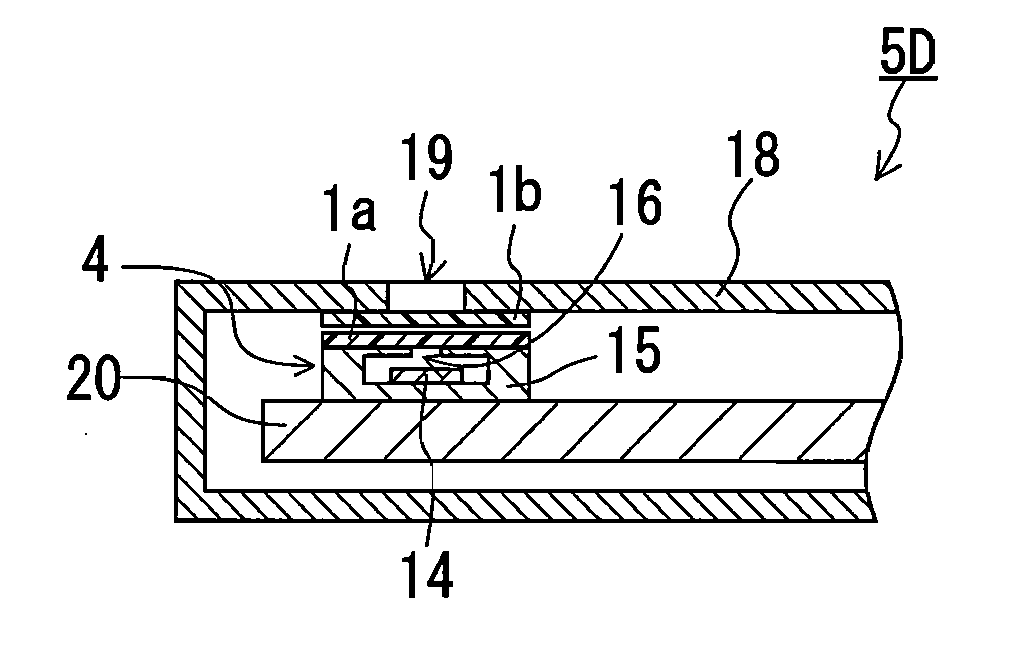

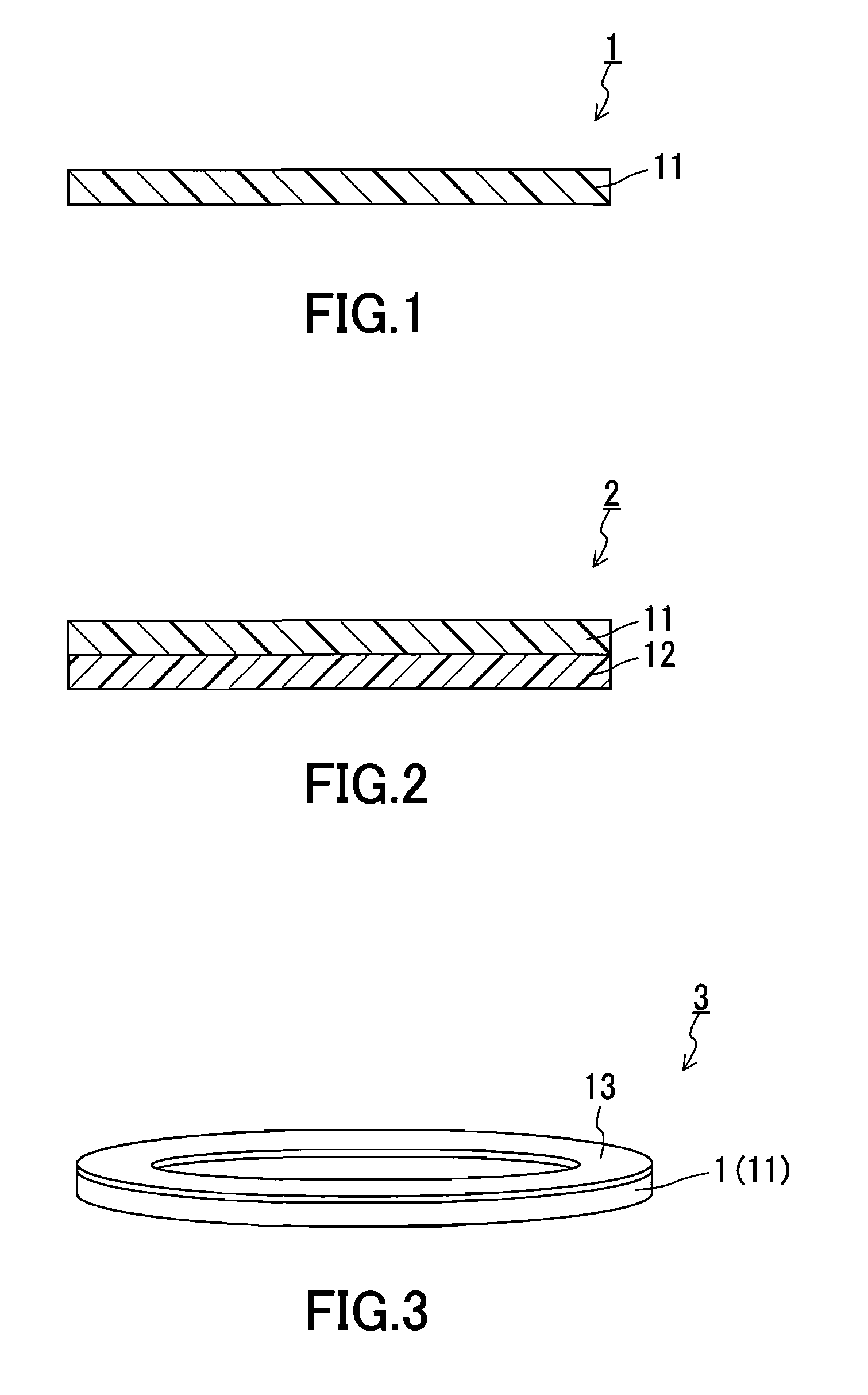

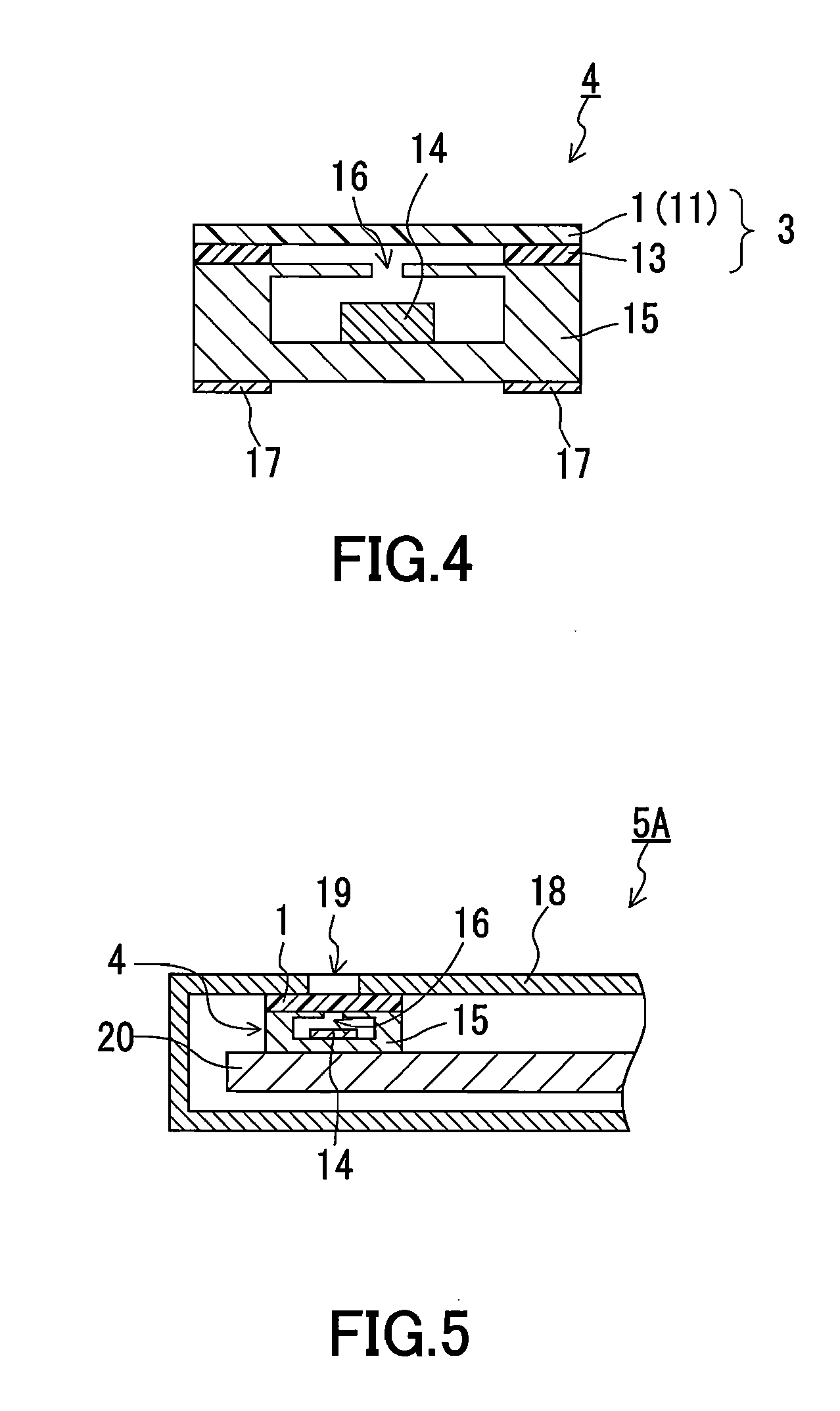

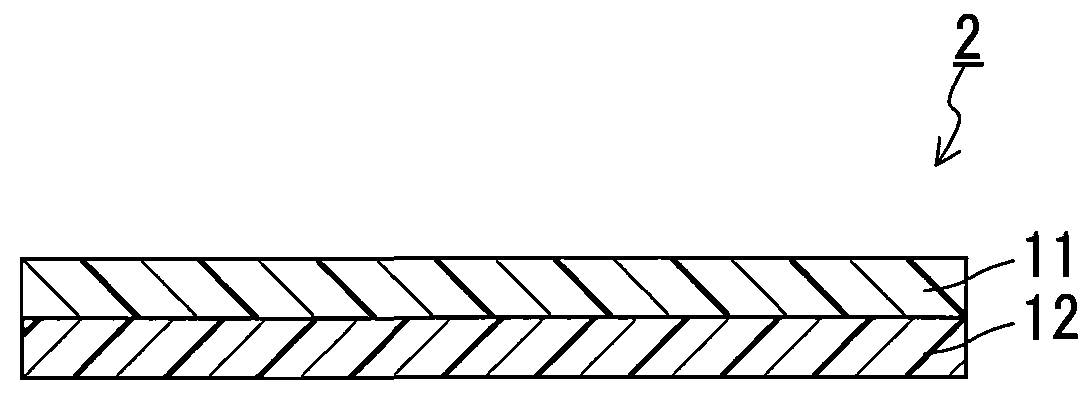

Sound-transmitting membrane for microphone, sound-transmitting membrane member for microphone provided with the membrane, microphone, and electronic device provided with microphone

ActiveUS20110255728A1Suppress water condensationEnsure microphone performancePiezoelectric/electrostrictive microphonesElectrostatic transducer microphonesForeign matterAcoustic transmission

The present invention provides a sound-transmitting membrane for a microphone, to be disposed to a sound-collecting opening of the microphone so as to allow sound to transmit through the membrane while preventing a foreign matter from entering into the microphone through the opening. This membrane for a microphone prevents the entry of a foreign matter, such as fine dust and water vapor, that is difficult for conventional sound-transmitting membranes to block, and ensures the microphone performance. This membrane for a microphone is composed of a nonporous film or a multilayer membrane including a nonporous film, has a surface density of 30 g / m2 or less, and has a sound transmission loss of less than 3 dB in a frequency range of 300 to 4000 Hz.

Owner:NITTO DENKO CORP

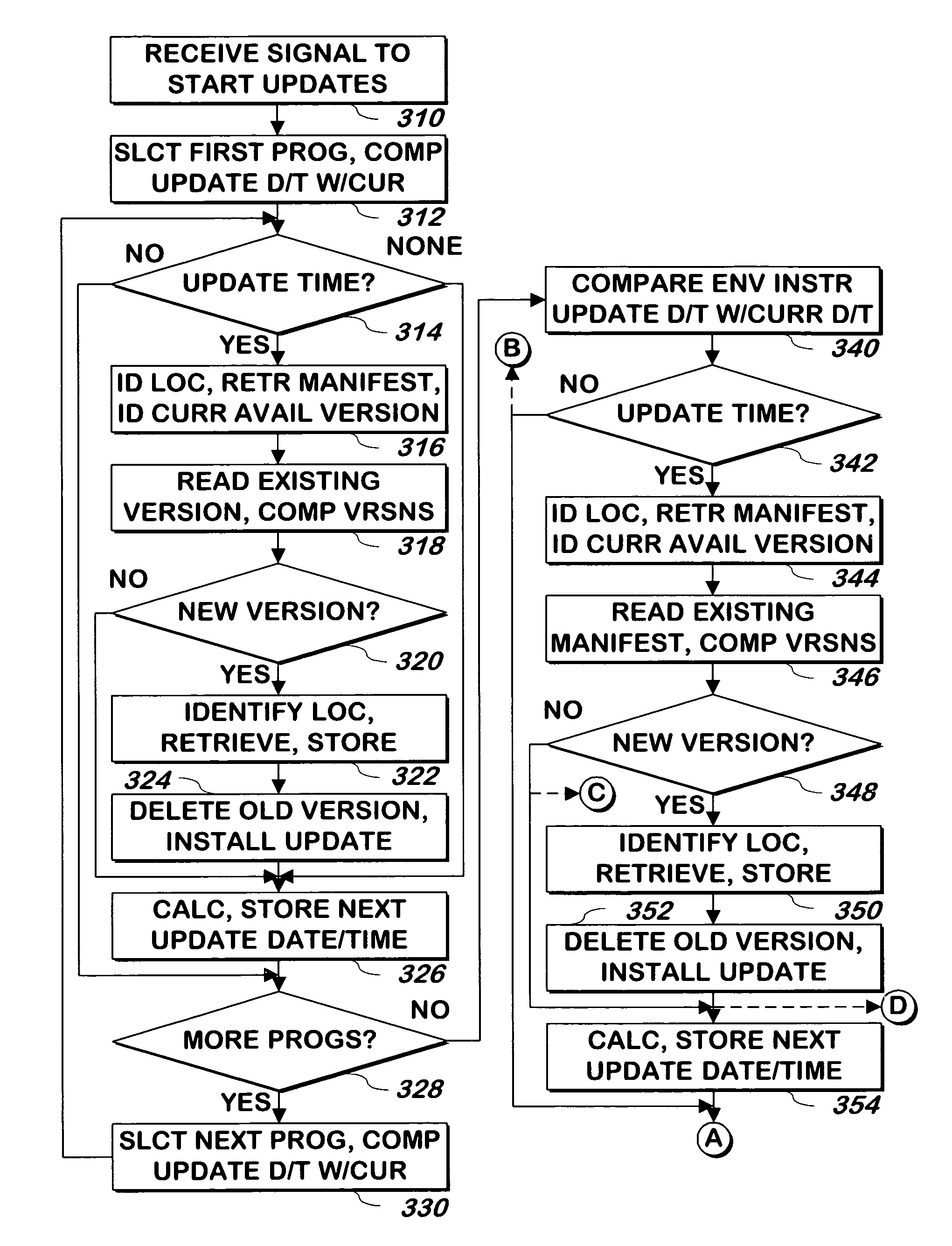

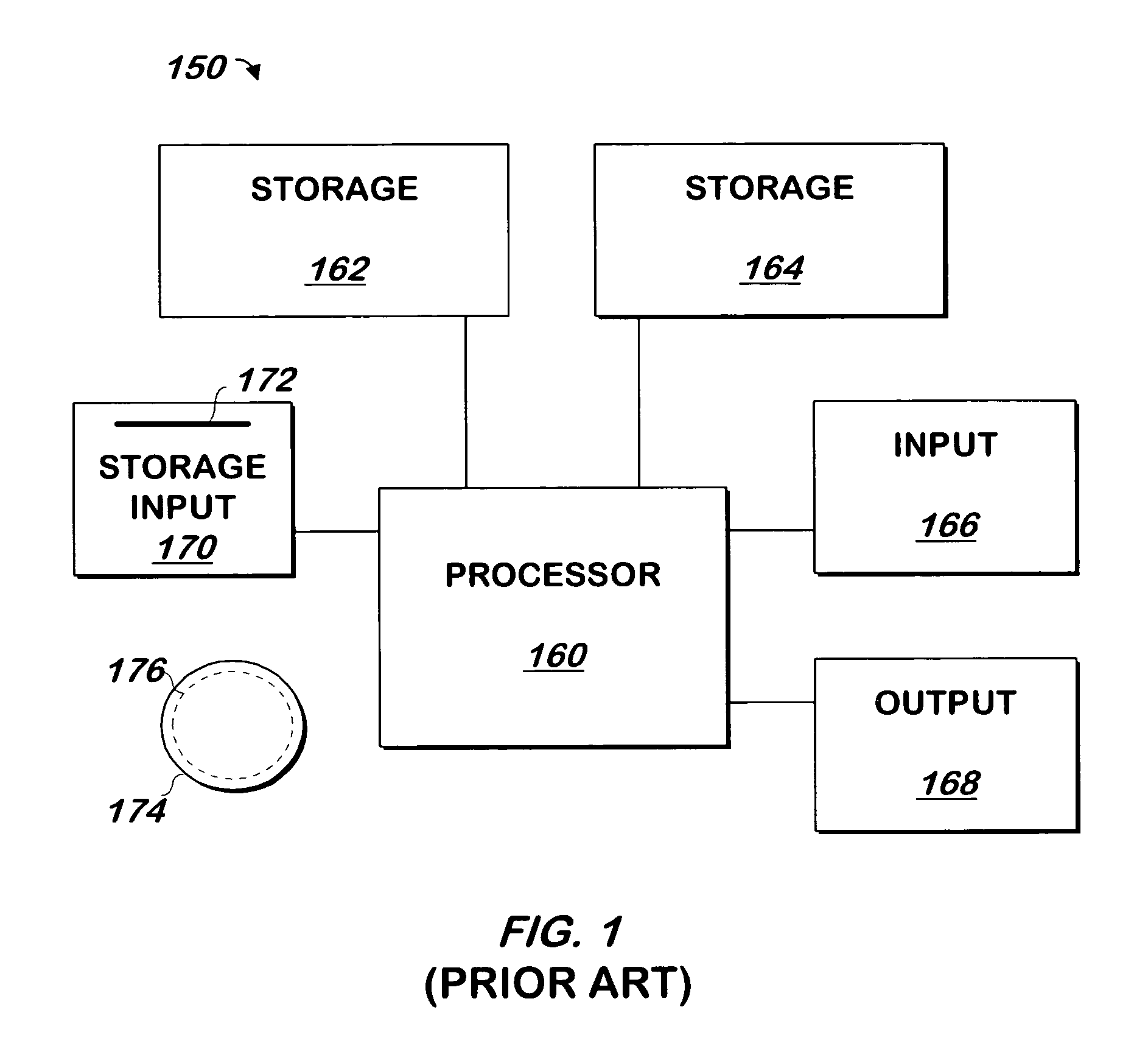

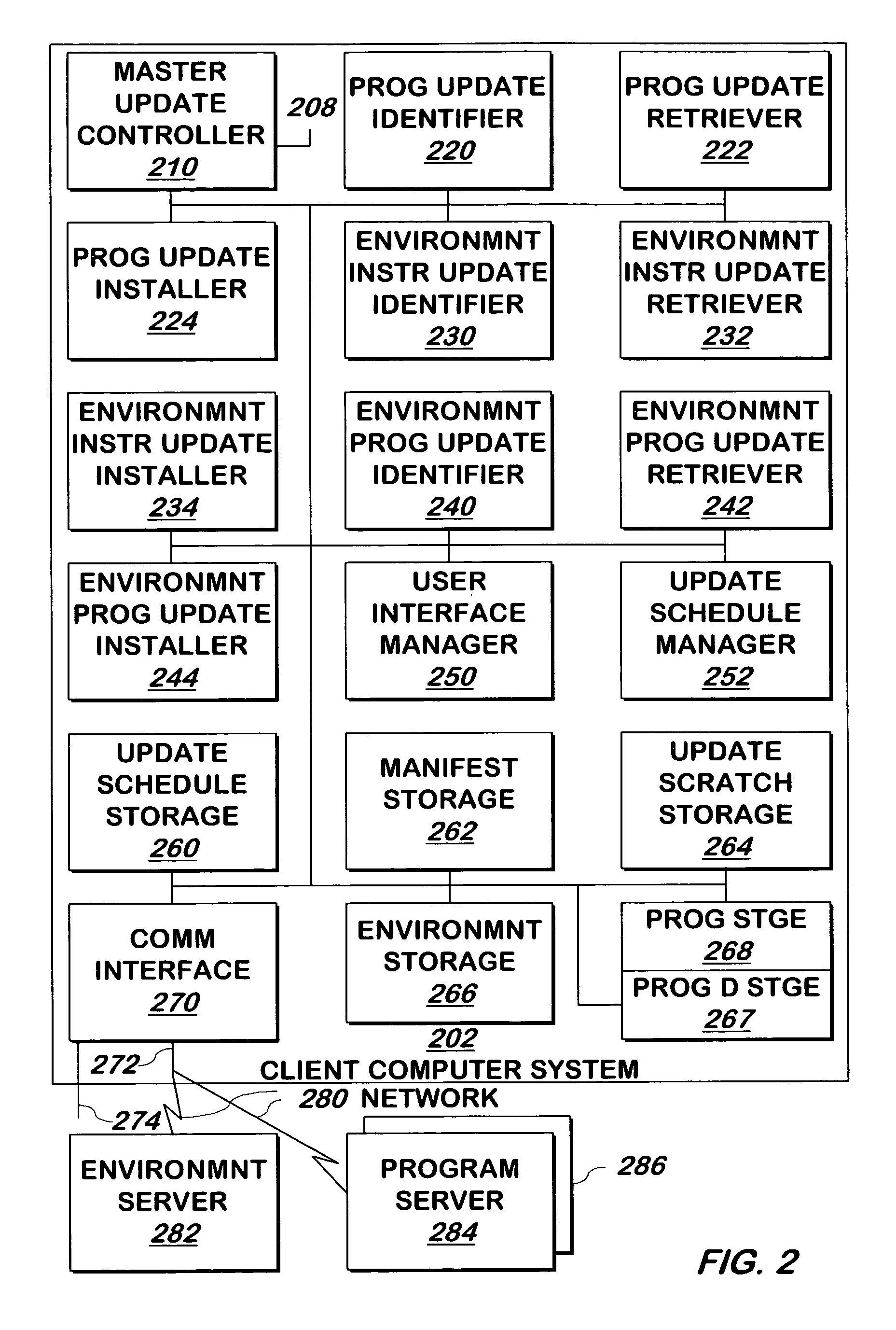

System and method for updating one or more programs and their environment

ActiveUS7934210B1Ensure performanceQuick updateDigital computer detailsProgram loading/initiatingComputer science

A system and method automatically updates one or more programs and some or all of an environment in which the one or more programs run, to latest versions of the programs and the environment, or portion thereof.

Owner:ADOBE SYST INC

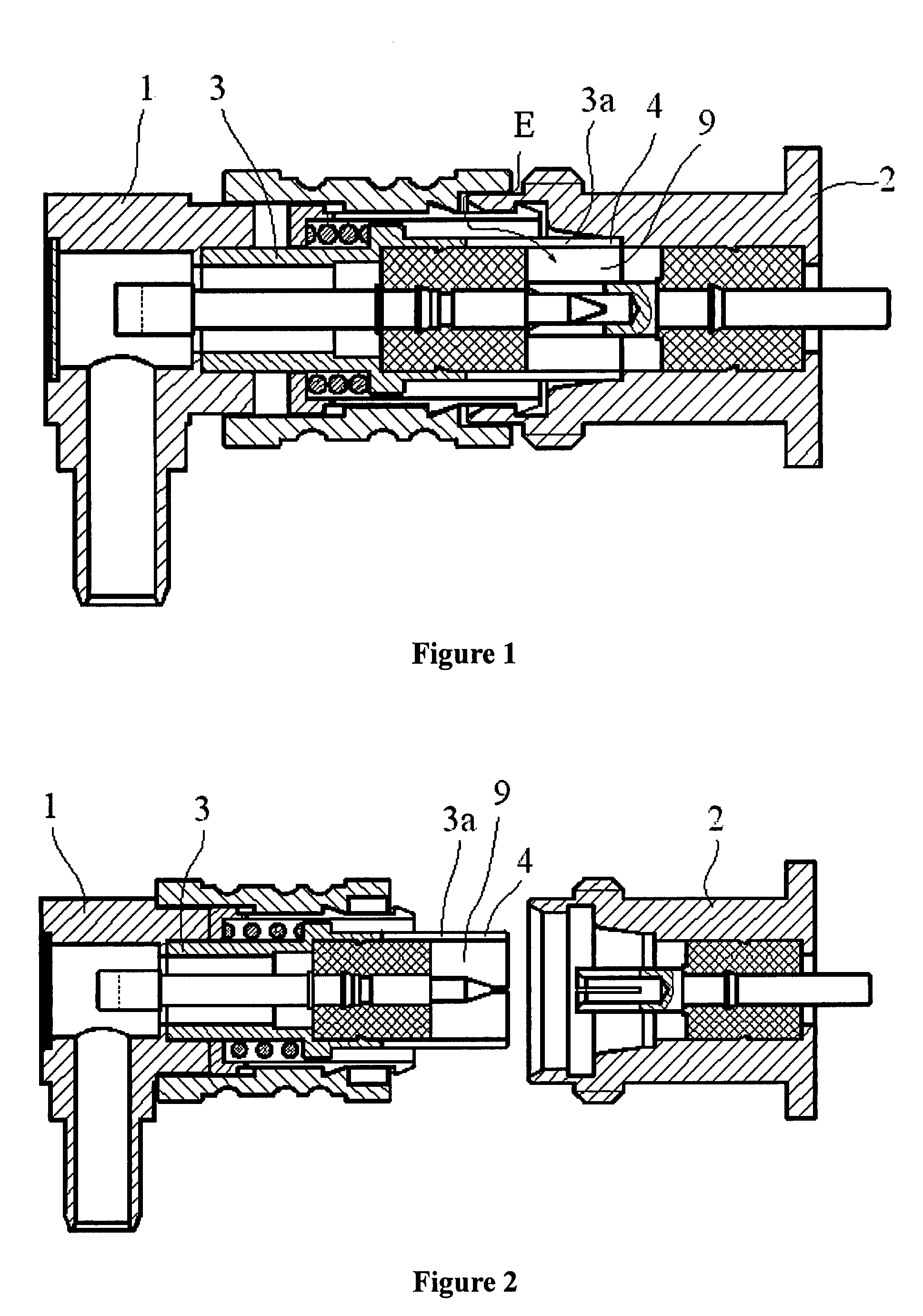

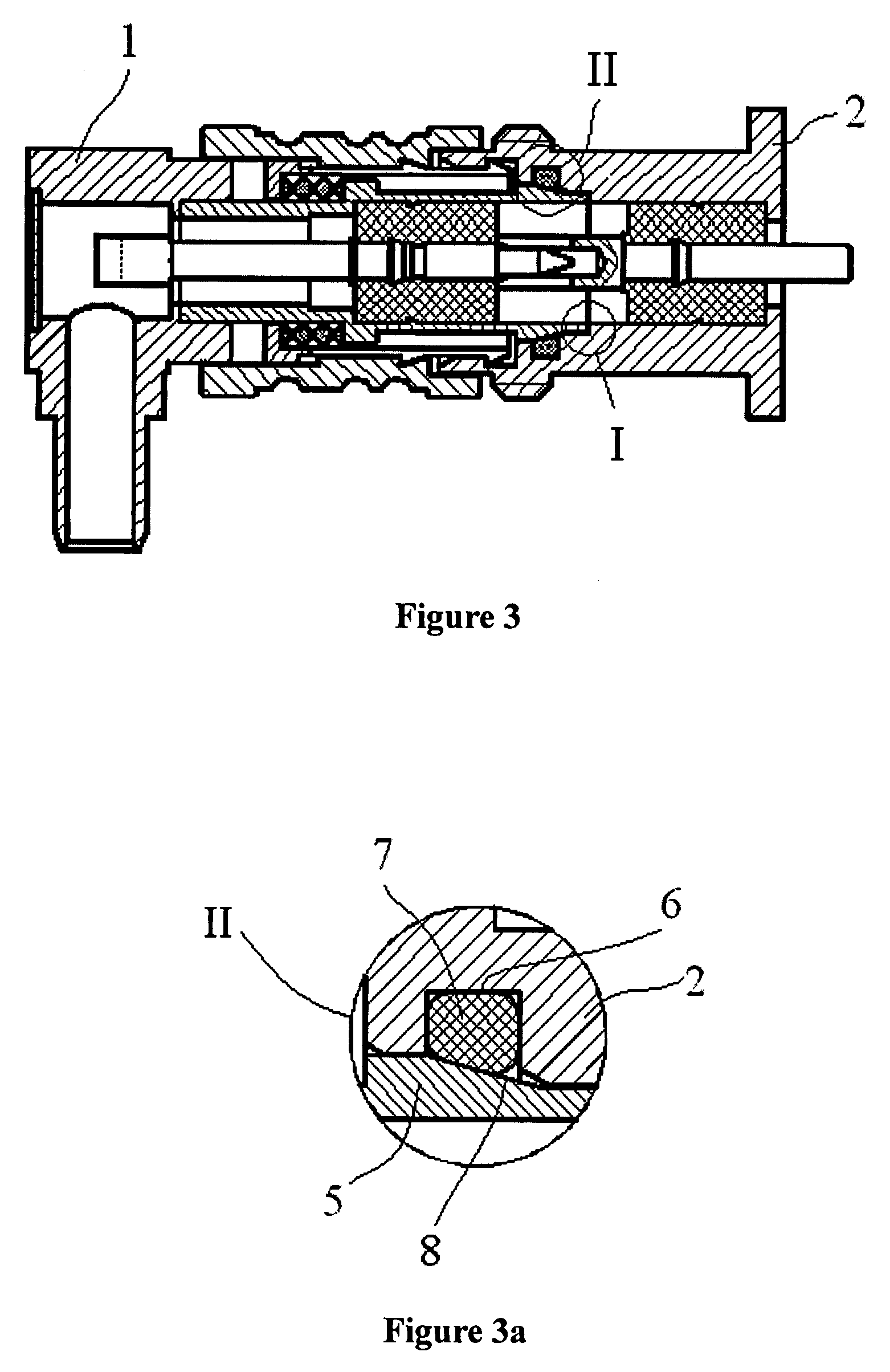

Airtight RF coaxial connector with self-locking by snap-fastening

InactiveUS7481673B1Increase stiffnessReduce leakageElectrically conductive connectionsTwo pole connectionsElectrical conductorSelf locking

An airtight RF coaxial connector with self-locking by snap-fastening is disclosed. The front end of the plug outer conductor is in the shape of continuous circles, forming an overall ring; the front end of the plug outer conductor is provided with a ring-shaped bulge with right angle trapezoid shaped cross section, the hypotenuse of the trapezoid being faced with the front side of the socket connector, and the right angle side of the trapezoid being positioned normal to the longitudinal axis of the socket connector on the back side of the connector; the inner part of the socket connector is provided with a groove provided with a sealing ring; and the distance between the mid-point of the ring bulge and the front contact surface of the plug outer conductor corresponds to that between the mid-point of the groove and the front contact surface of the socket connector. The abolishment of the four-way slits at the front end of the plug outer conductor not only increases the stiffness of the outer conductor, but also decreases the leakage of RF. When the connector is in connection, the conical surface of the plug outer conductor will automatically extrude the sealing ring on the inner side of the socket outer conductor so as to realize ideal sealing effects.

Owner:QU JINLIANG +1

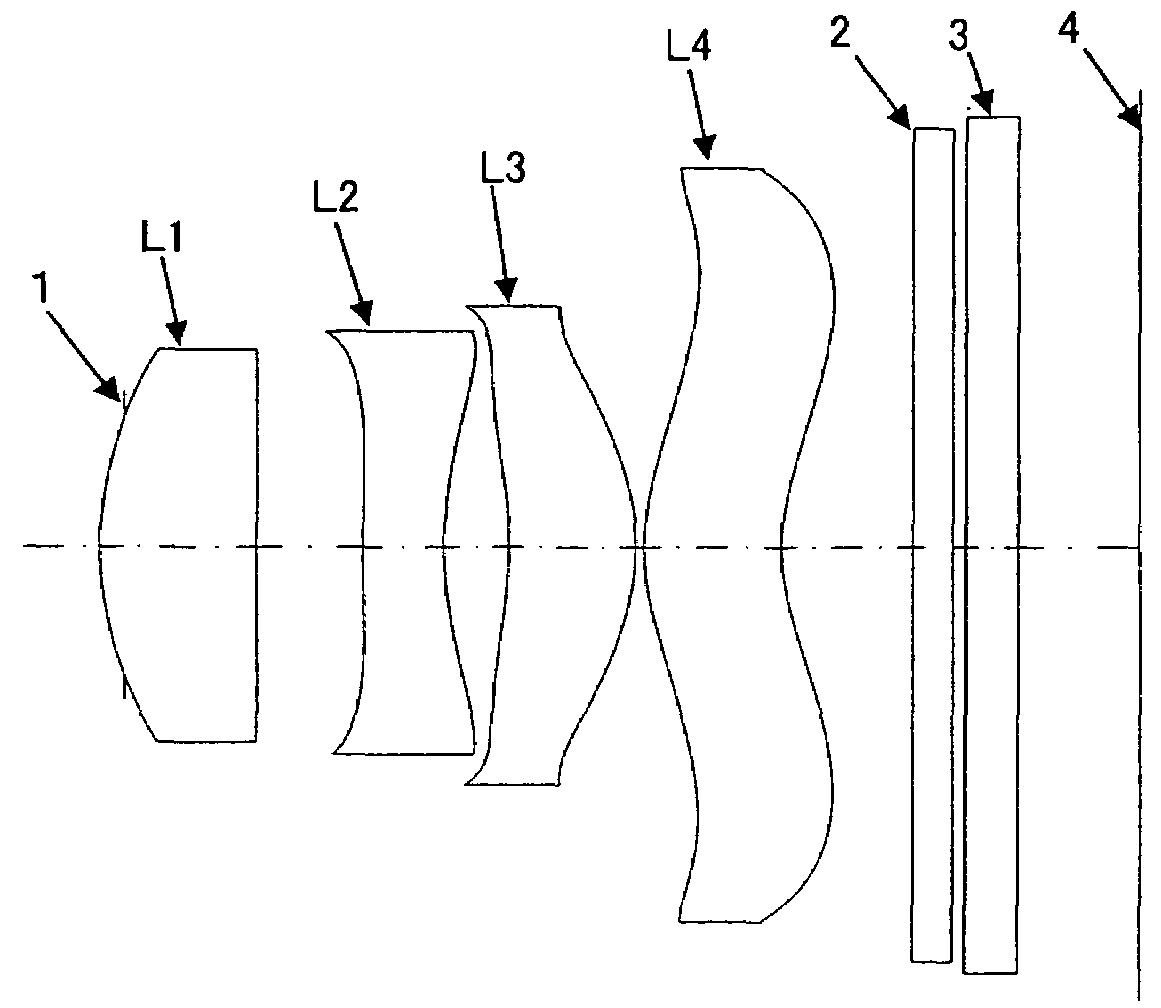

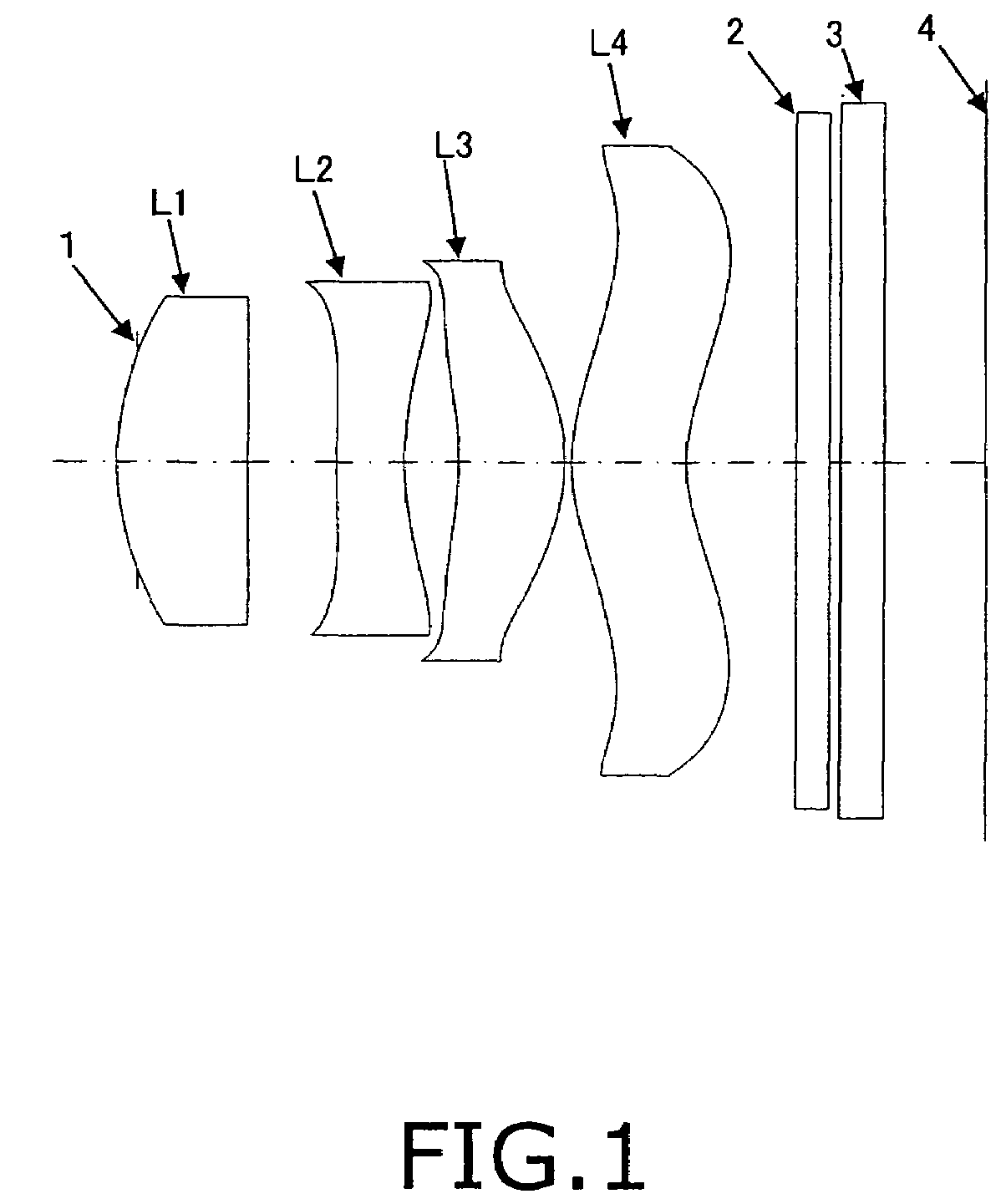

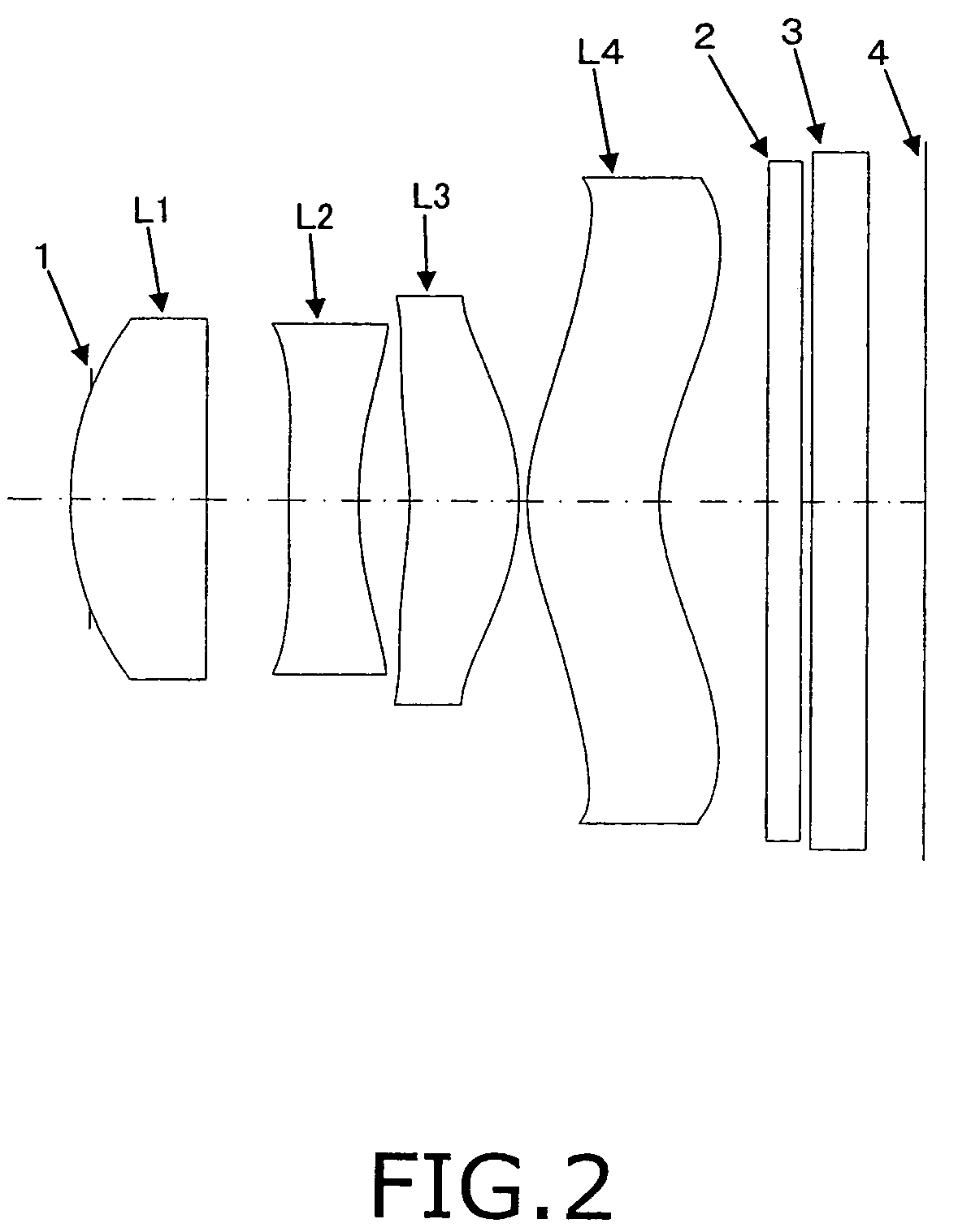

Imaging lens array

Owner:LARGAN PRECISION

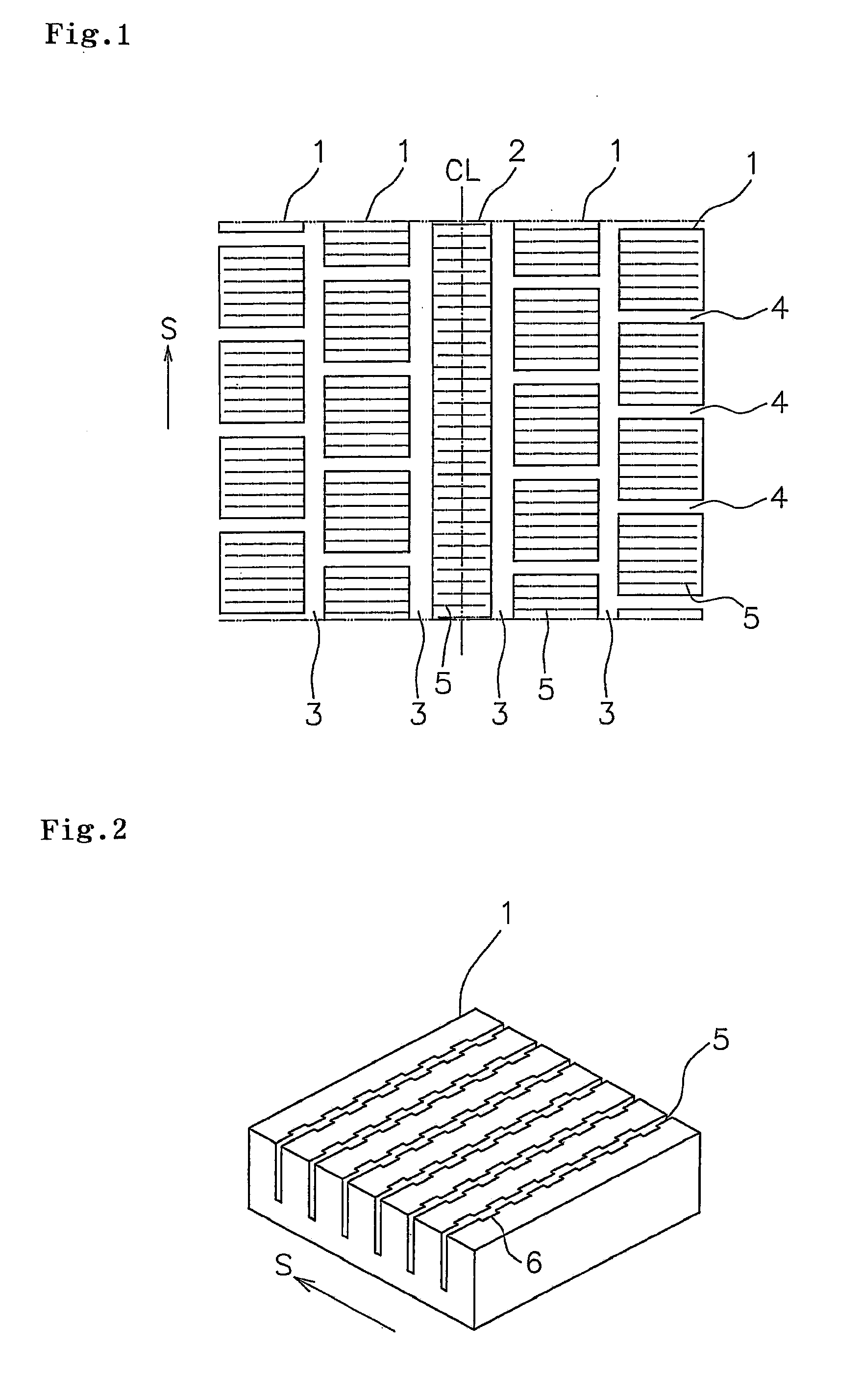

Pneumatic Tire

InactiveUS20100084062A1Increasing dry steering stability performanceImprove rigidityTyre tread bands/patternsNon-skid devicesRoad surfaceEngineering

An object of the present invention is to provide a pneumatic tire capable of ensuring both of the ice braking performance and the ice turning performance while increasing the dry steering stability performance. To achieve the above object, a sipe extending in a width direction of the tire is formed a land portion, the sipe having: pluralities of wide portions each having an inclined plane that begins from the tread surface of a road surface, and terminates in the half way of a sipe wall while inclining so that a sipe width decreases toward the groove bottom of the sipe, and a pair of side faces connecting the inclined plane and the sipe wall therebetween, wherein the pluralities of wide portions are located alternately on both sipe walls along a longitudinal direction of the sipe.

Owner:TOYO TIRE & RUBBER CO LTD

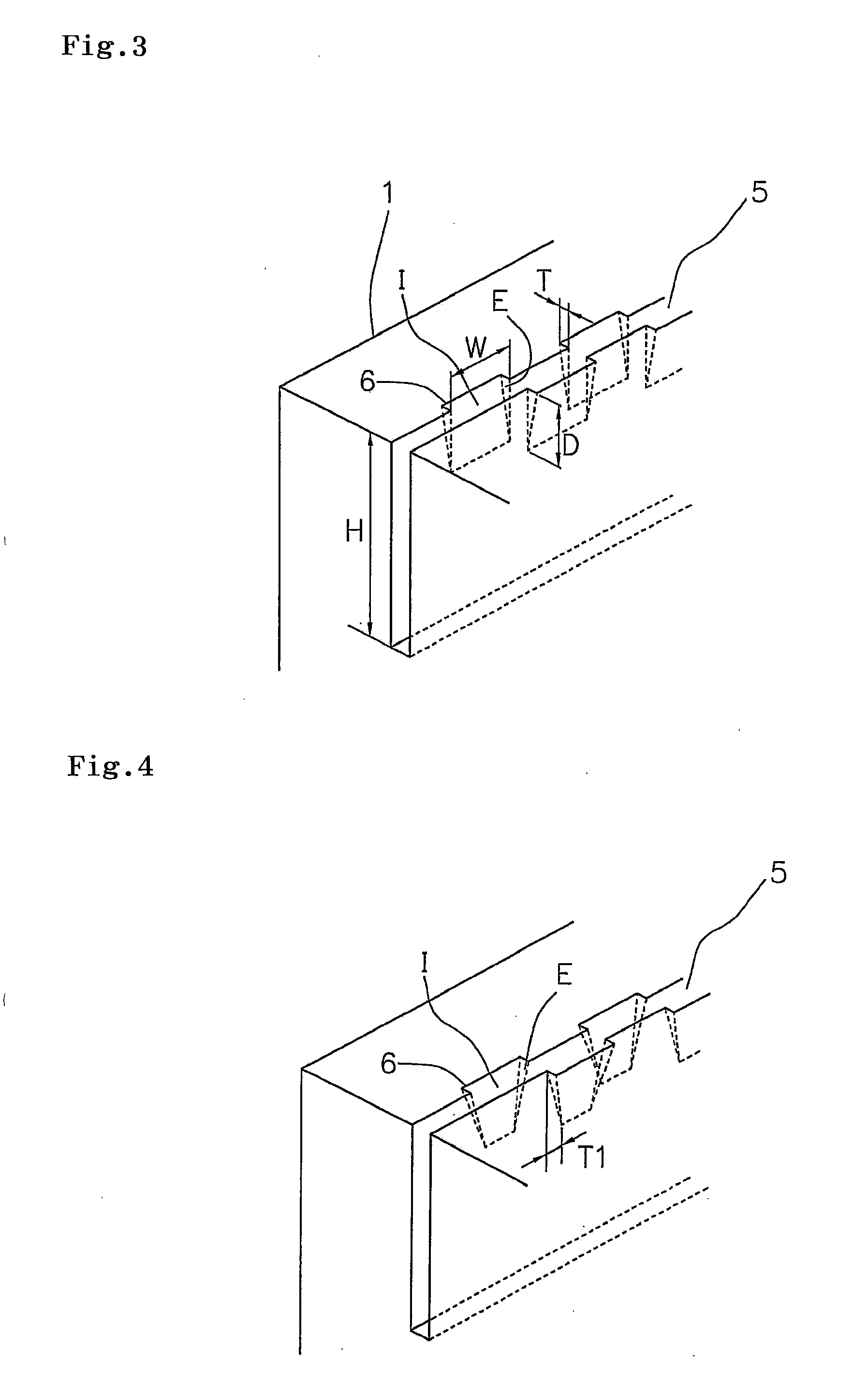

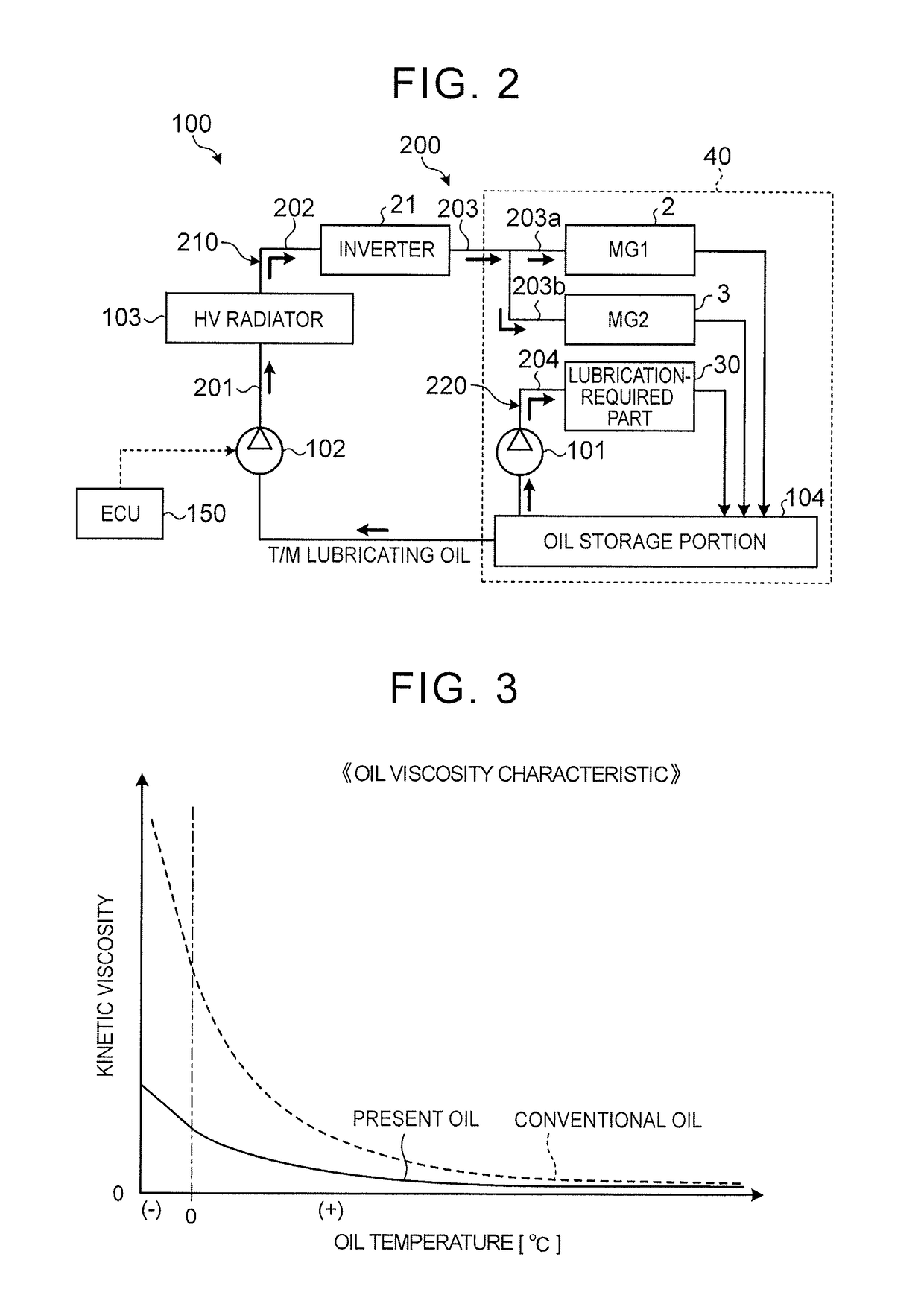

Vehicular cooling system

InactiveUS20170175612A1Small sizeEnsure performanceHybrid vehiclesLiquid coolingLubricationPetroleum engineering

An cooling system including an oil circulation circuit includes a first circuit including an electric oil pump that discharges oil as a coolant to be supplied to an inverter and respective motors, and an HV radiator that cools the oil to be supplied to the inverter and the respective motors, and a second circuit including a mechanical oil pump that discharges the oil to be supplied to a lubrication-required part without passing through the HV radiator.

Owner:TOYOTA JIDOSHA KK

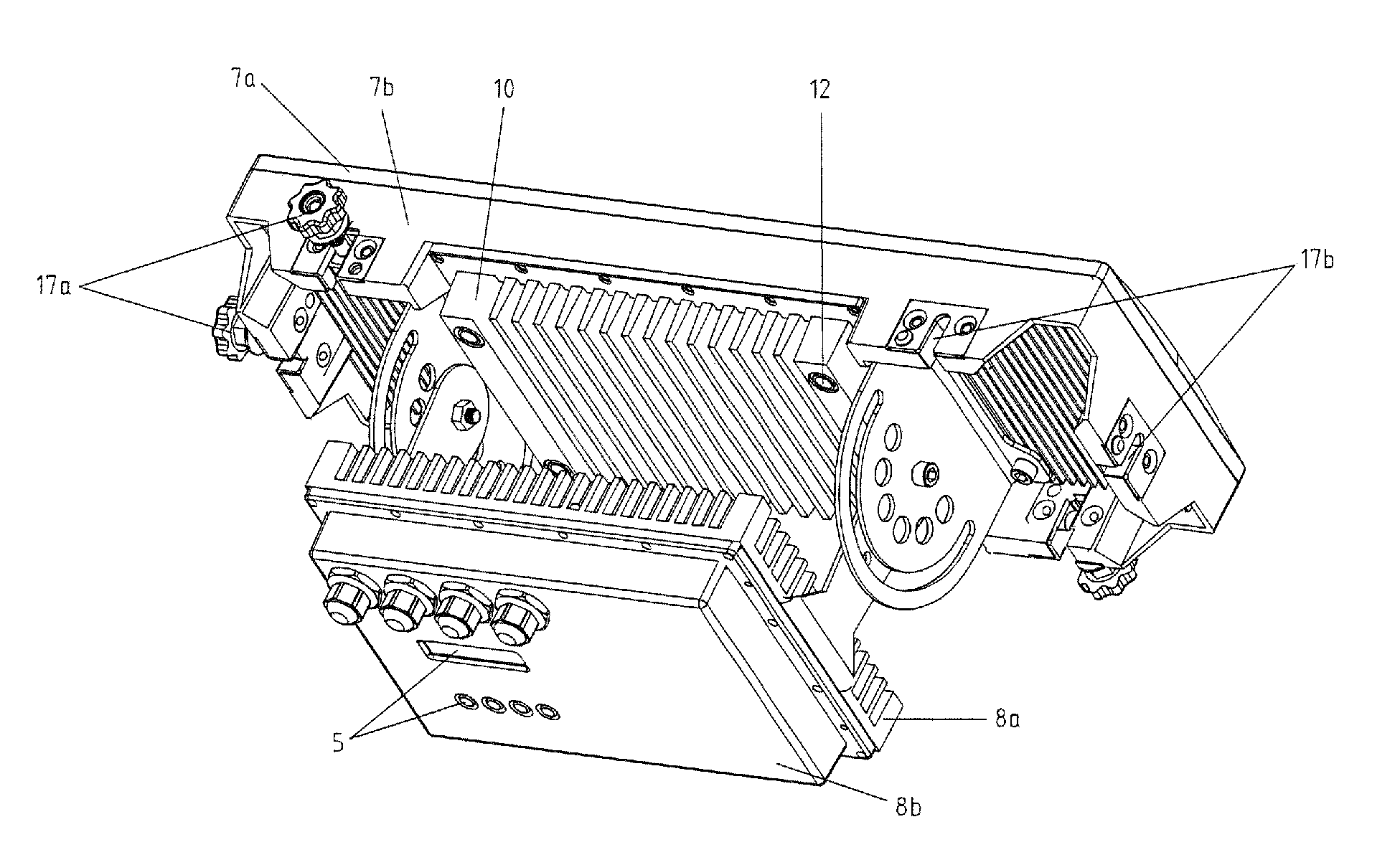

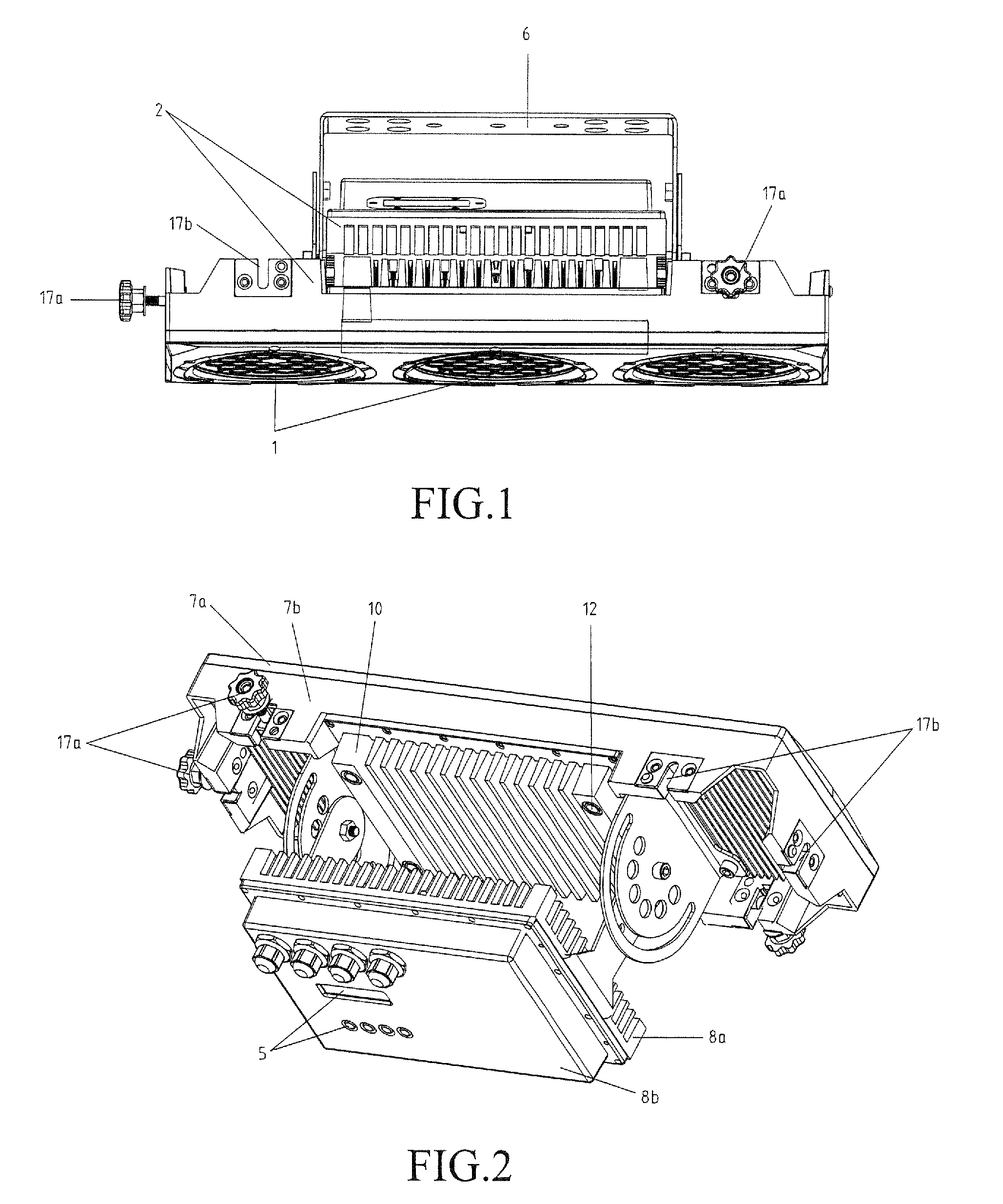

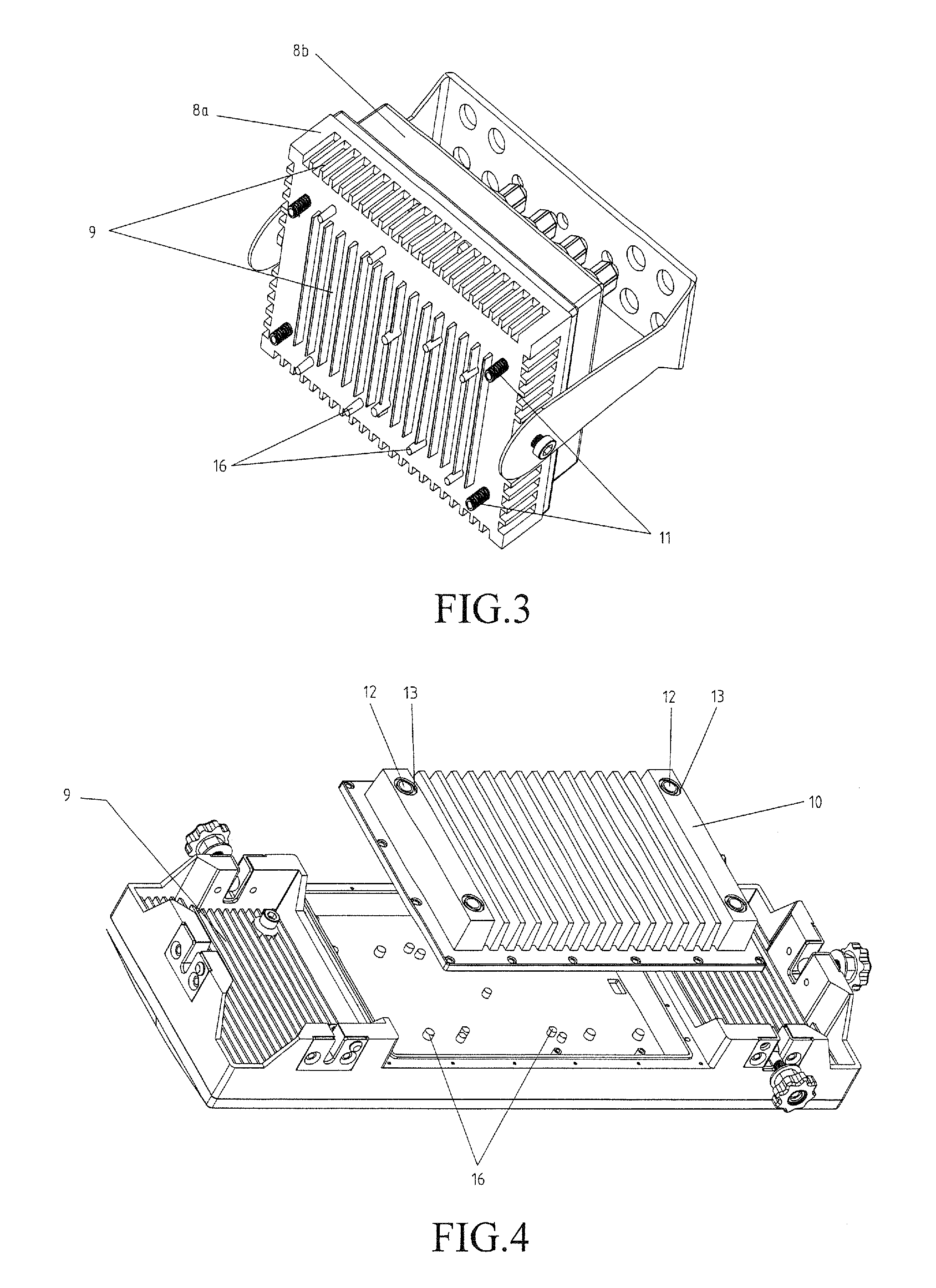

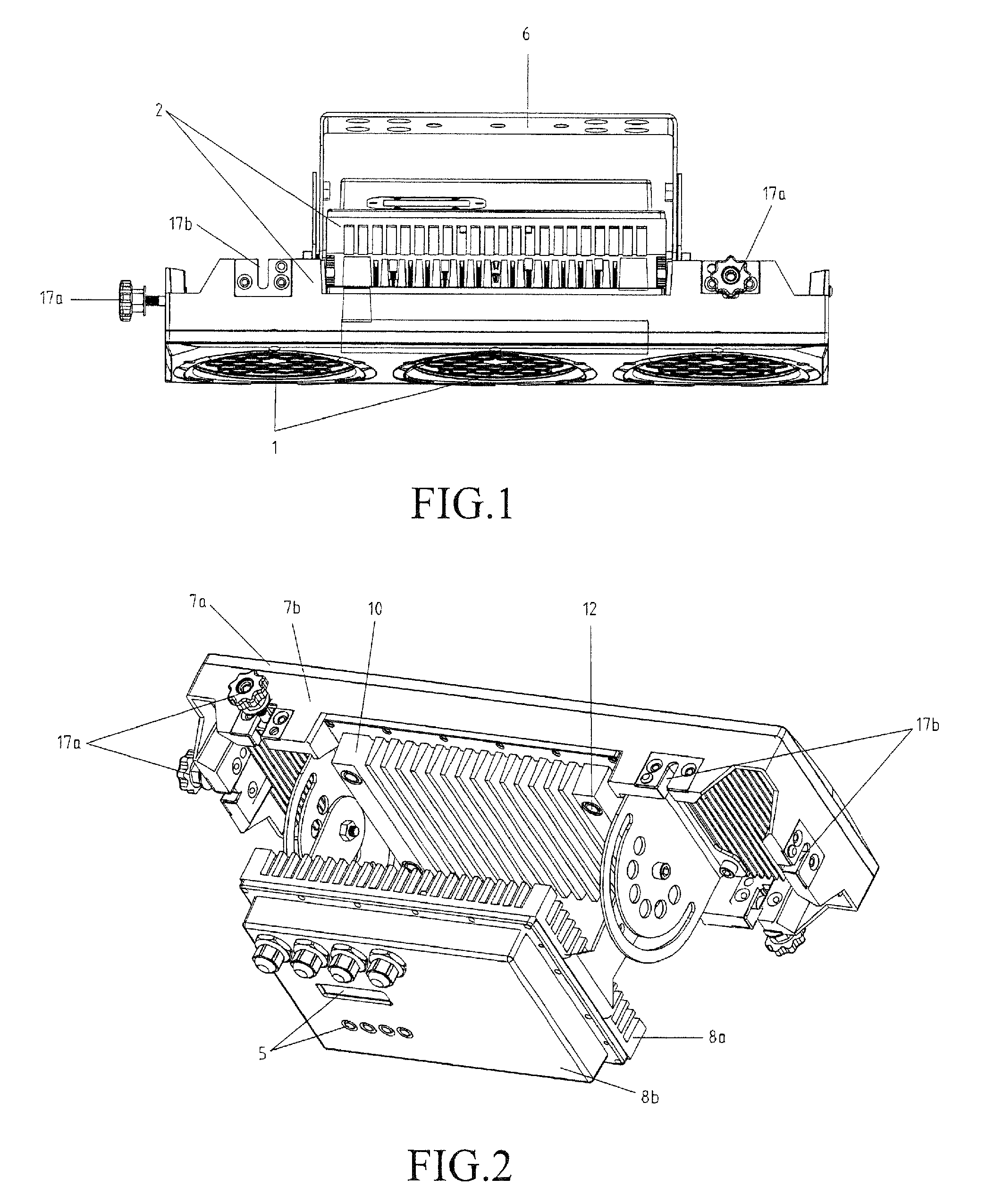

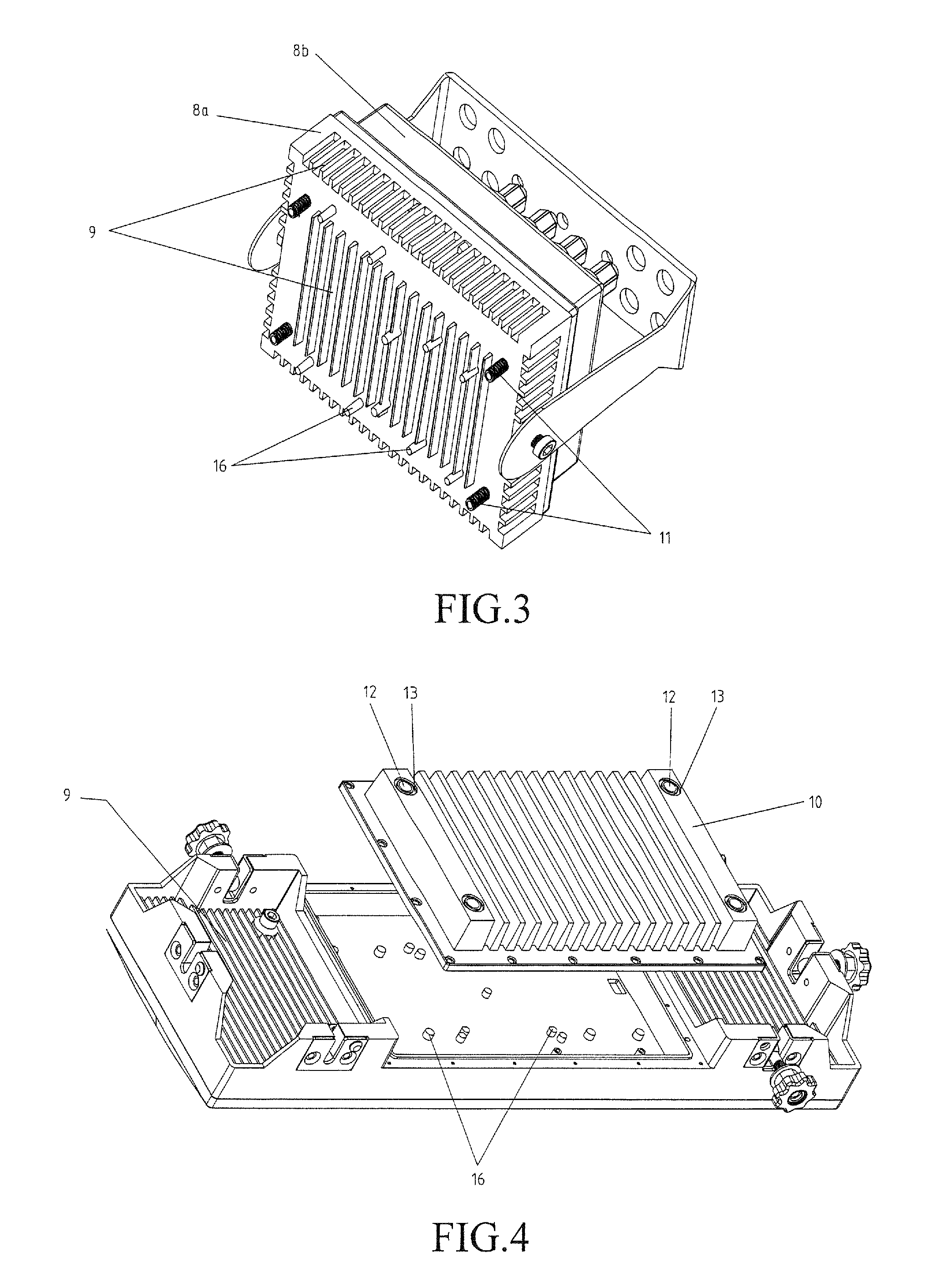

Divided LED lamp

InactiveUS20100315824A1Solve the low heat dissipation efficiencyGuaranteed uptimePlanar light sourcesLighting support devicesLED lampElectronics

A divided LED lamp includes an LED assembly, a casing assembly, LED electronics, power and signal cables, a control panel including a display screen and operation buttons, and a bracket for mounting the lamp. The casing assembly includes a first casing member and a second casing member. At least one cable tube is formed between the first casing member and the second casing member. The power and signal cables that connect the LED assembly received in the first casing member and the LED electronics received in the second casing member are received through the cable tube. This arrangement allows the LED assembly and the LED electronics to be received in individual and independent casing members and are associated with respective individual heat dissipation fins or heat radiators, so as to realize high efficiency of heat dissipation, stabilized operation, and extended lifespan.

Owner:GUANGZHOU YAJIANG PHOTOELECTRIC EQUIP CO LTD

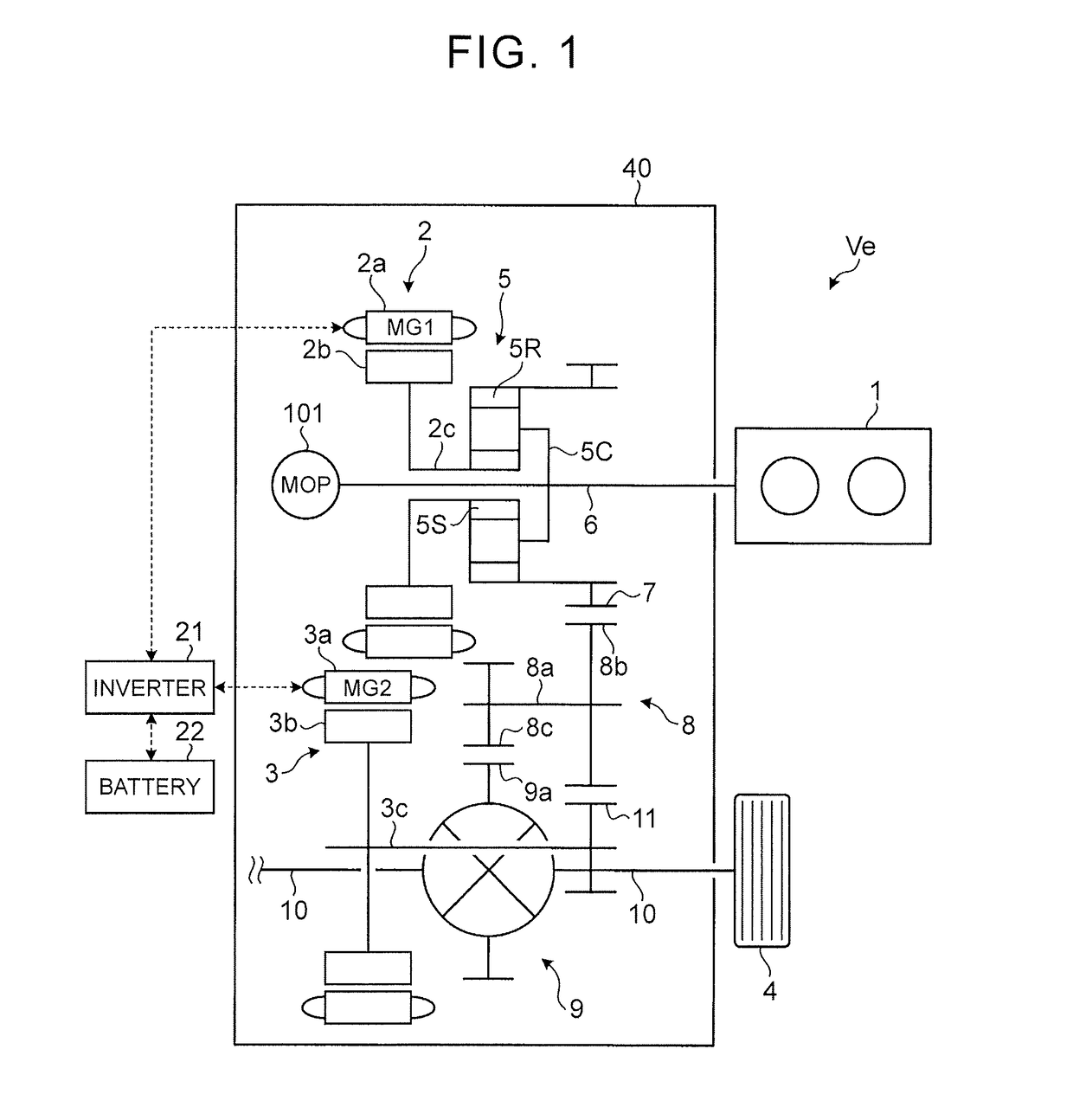

Imaging lens array

ActiveUS20070081259A1Improve performanceHigh precisionLensOptical elementsImaging qualityImaging lens

Owner:LARGAN PRECISION

Semiconductor device and method of manufacturing the same

InactiveUS20140048918A1Increase lifespanSuppress and prevent of crackSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical conductor

A semiconductor device has a connection structure in which a power semiconductor chip is mounted on an insulating substrate having conductor patterns bonded to front and rear surfaces thereof, and the insulating substrate is connected to a heat-dissipating base member to dissipate heat generated from the power semiconductor chip to outside. The conductor pattern on the rear surface bonded to the heat-dissipating base member has a bonding portion having a rectangular shape and a predetermined curvature radius in vicinity of corners.

Owner:FUJI ELECTRIC CO LTD

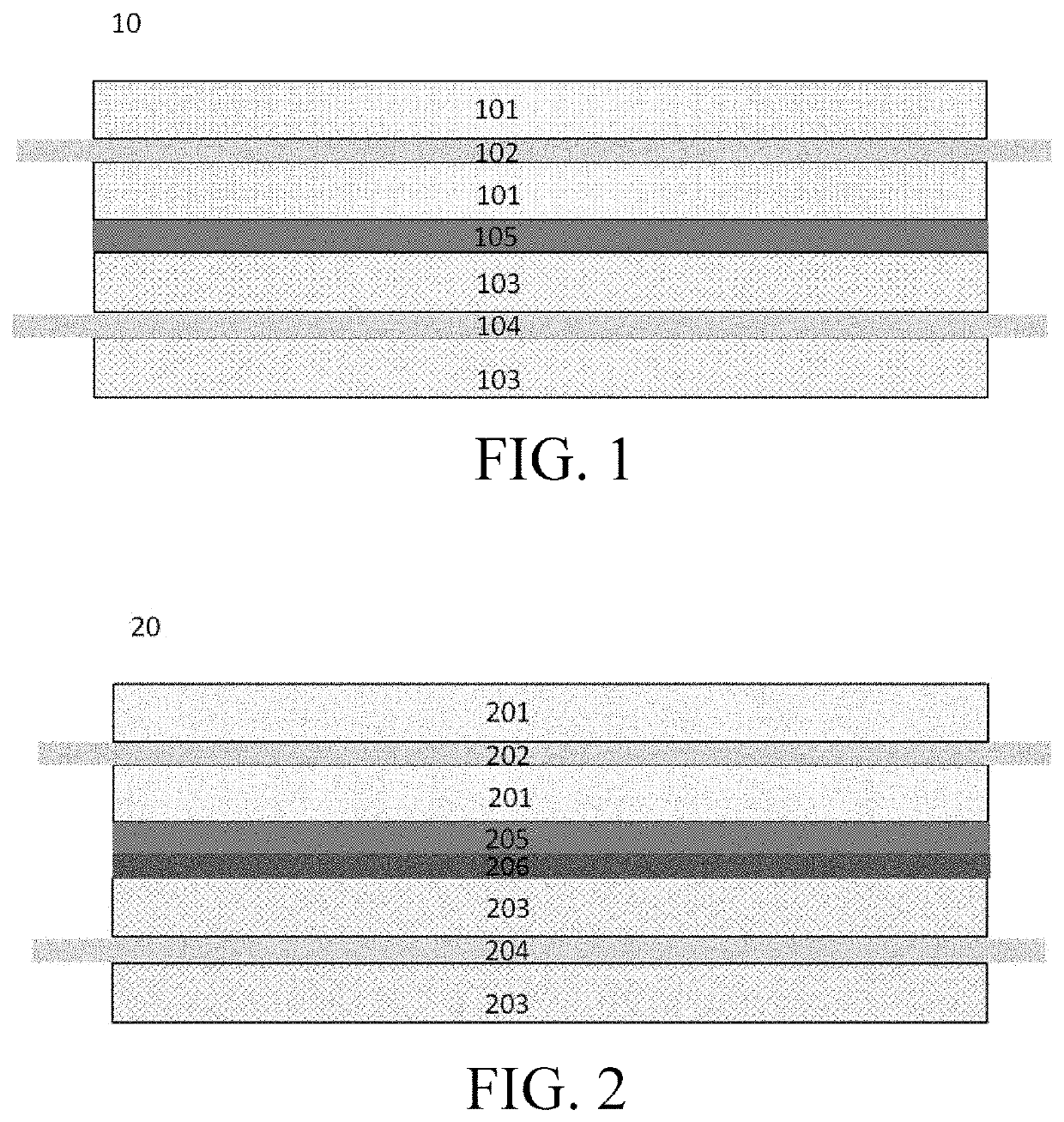

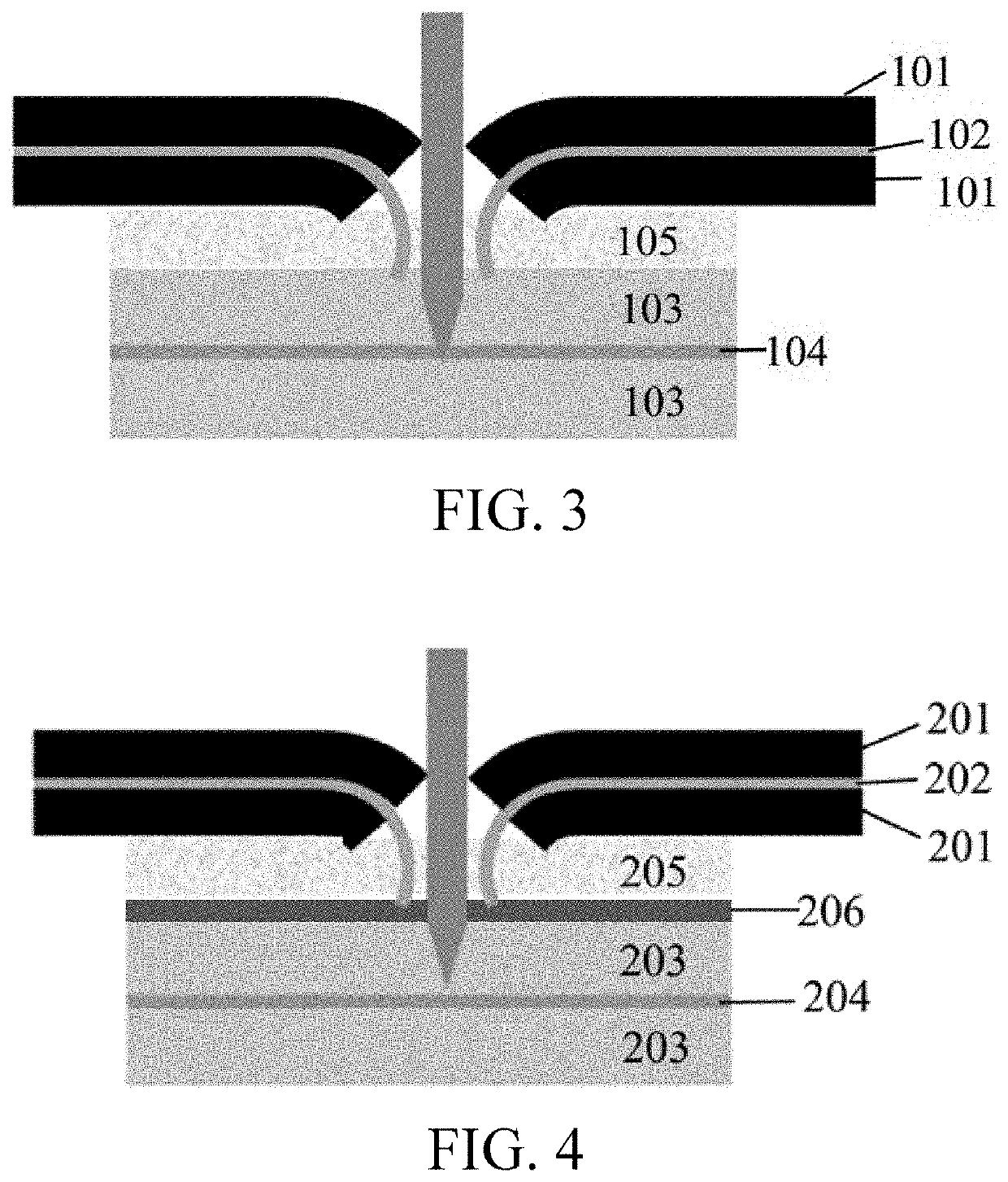

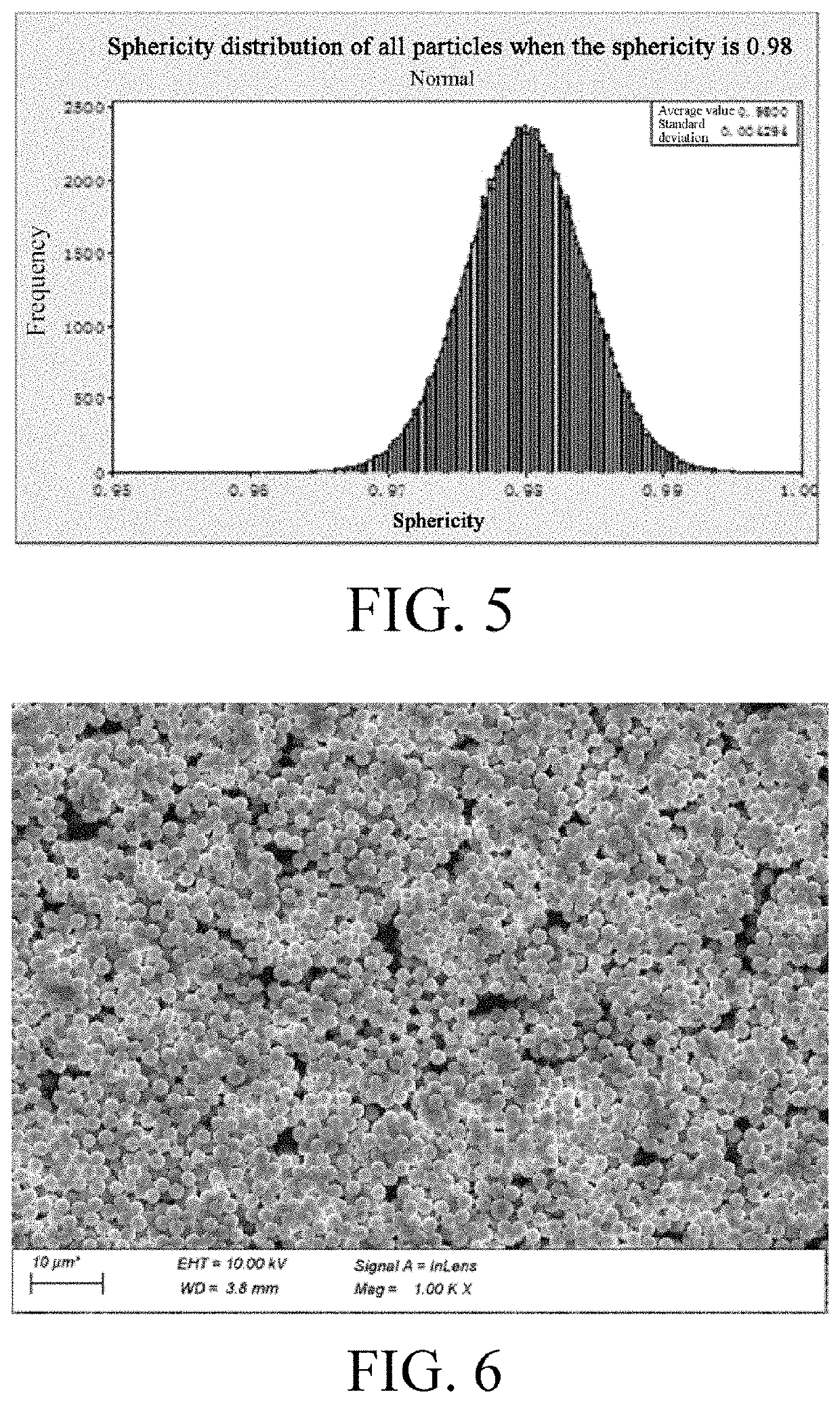

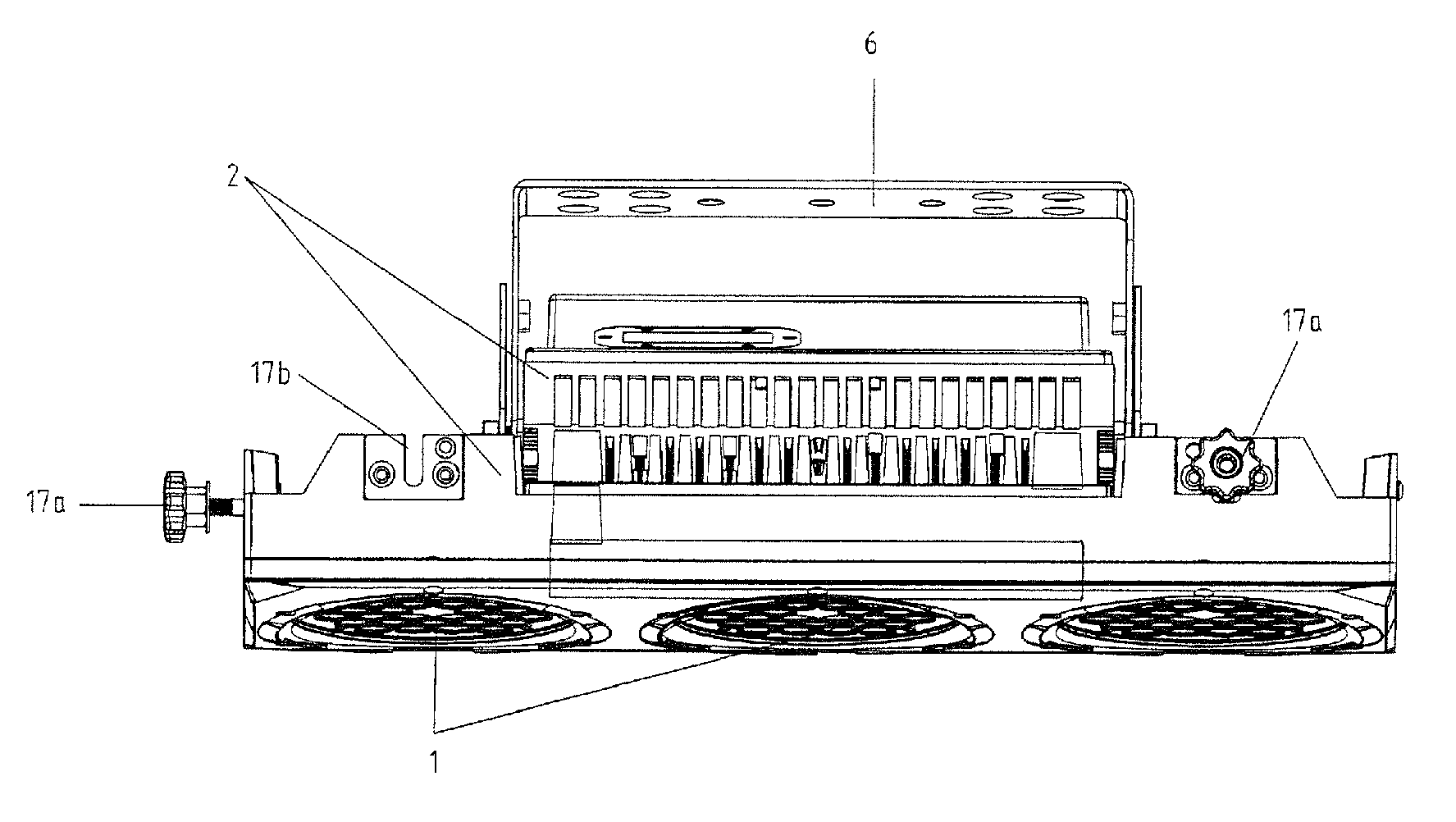

Electrochemical device

InactiveUS20190393466A1Satisfy safety performance requirementsPromote meltingCell electrodesLi-accumulatorsConductive polymerElectrochemistry

This application relates to an electrochemical device having safety performance. Specifically, this application provides an electrochemical device, including: an anode, the anode comprising an anode active material layer; a separator; and a polymer layer, wherein the polymer layer is disposed between the anode active material layer and the separator. The polymer layer comprises polymer particles, and the polymer particles according to some embodiments of this application have a sphericity of about 0.70 to about 1.0. This application effectively protects the anode by providing a non-conductive or poorly conductive inactive substance (for example, non-conductive polymer particles) between the anode active material layer and the separator, so as to ensure that is the electrochemical device does not generate an internal short circuit when being impacted, penetrated or squeezed by an external force, which causes a failure of the electrochemical device.

Owner:NINGDE AMPEREX TECH

Divided LED lamp

InactiveUS8425091B2Solve the low heat dissipation efficiencyGuaranteed uptimePlanar light sourcesPoint-like light sourceEngineeringLED lamp

A divided LED lamp includes an LED assembly, a casing assembly, LED electronics, power and signal cables, a control panel including a display screen and operation buttons, and a bracket for mounting the lamp. The casing assembly includes a first casing member and a second casing member. At least one cable tube is formed between the first casing member and the second casing member. The power and signal cables that connect the LED assembly received in the first casing member and the LED electronics received in the second casing member are received through the cable tube. This arrangement allows the LED assembly and the LED electronics to be received in individual and independent casing members and are associated with respective individual heat dissipation fins or heat radiators, so as to realize high efficiency of heat dissipation, stabilized operation, and extended lifespan.

Owner:GUANGZHOU YAJIANG PHOTOELECTRIC EQUIP CO LTD

Floor cleaning apparatus

InactiveUS20050015915A1Operation moreEasy to operateBrush bodiesMachine detailsMechanical engineeringScrubber

A floor cleaner is provided for cleaning a floor, where the floor cleaner has a front and a rear and includes: a sweeper for sweeping the floor; a scrubber, connected to the sweeper and located in the rear of the sweeper, for wetting and cleaning the floor; and a burnisher, connected to the scrubber and located in the rear of the scrubber, for burnishing the floor.

Owner:JOHNSONDIVERSEY INC

Sound-transmitting membrane for microphone, sound-transmitting membrane member for microphone provided with the membrane, microphone, and electronic device provided with microphone

ActiveUS9253297B2Condensation suppressionEnsure performancePiezoelectric/electrostrictive microphonesElectrostatic transducer microphonesAcoustic transmissionForeign matter

Owner:NITTO DENKO CORP

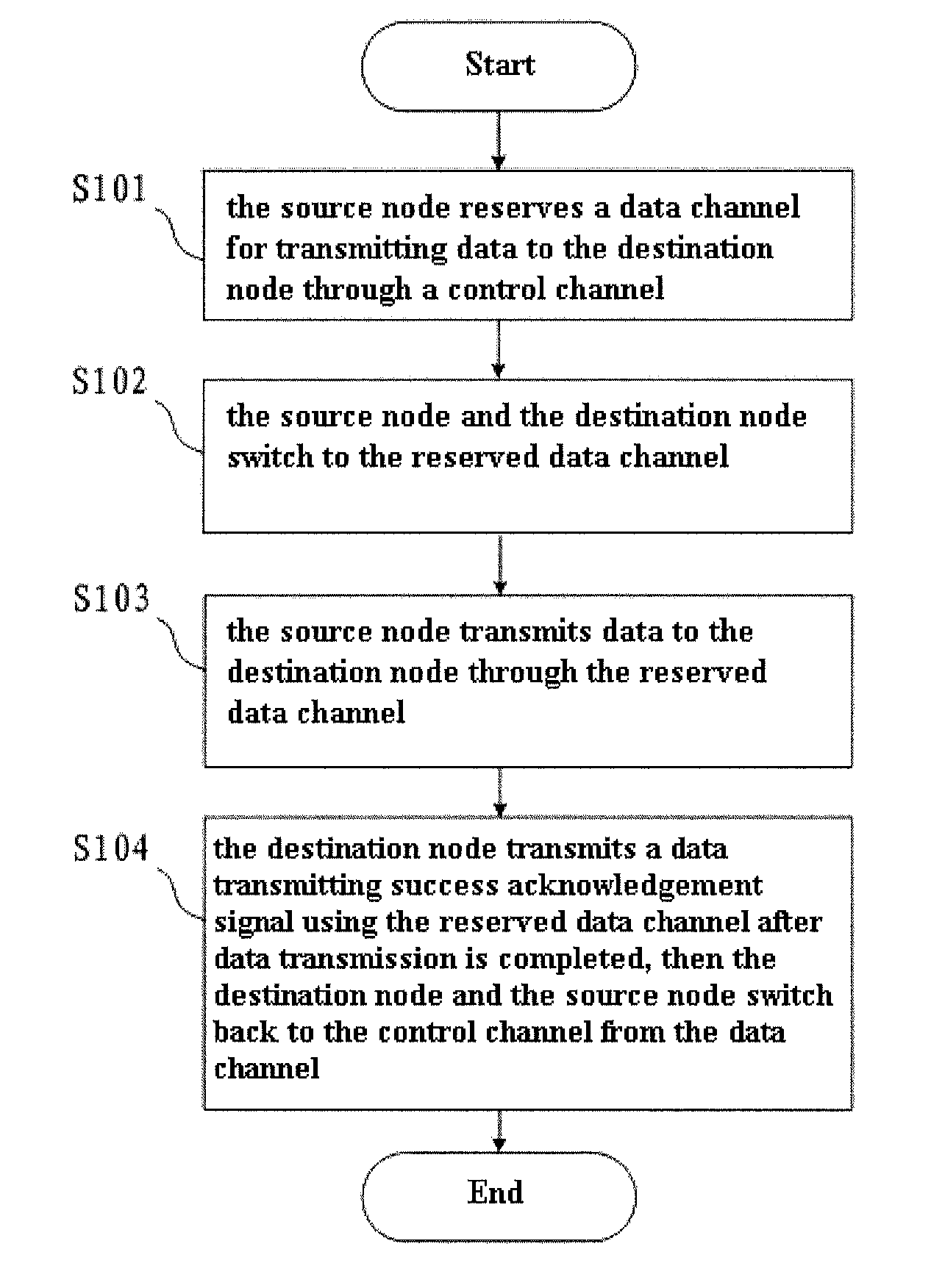

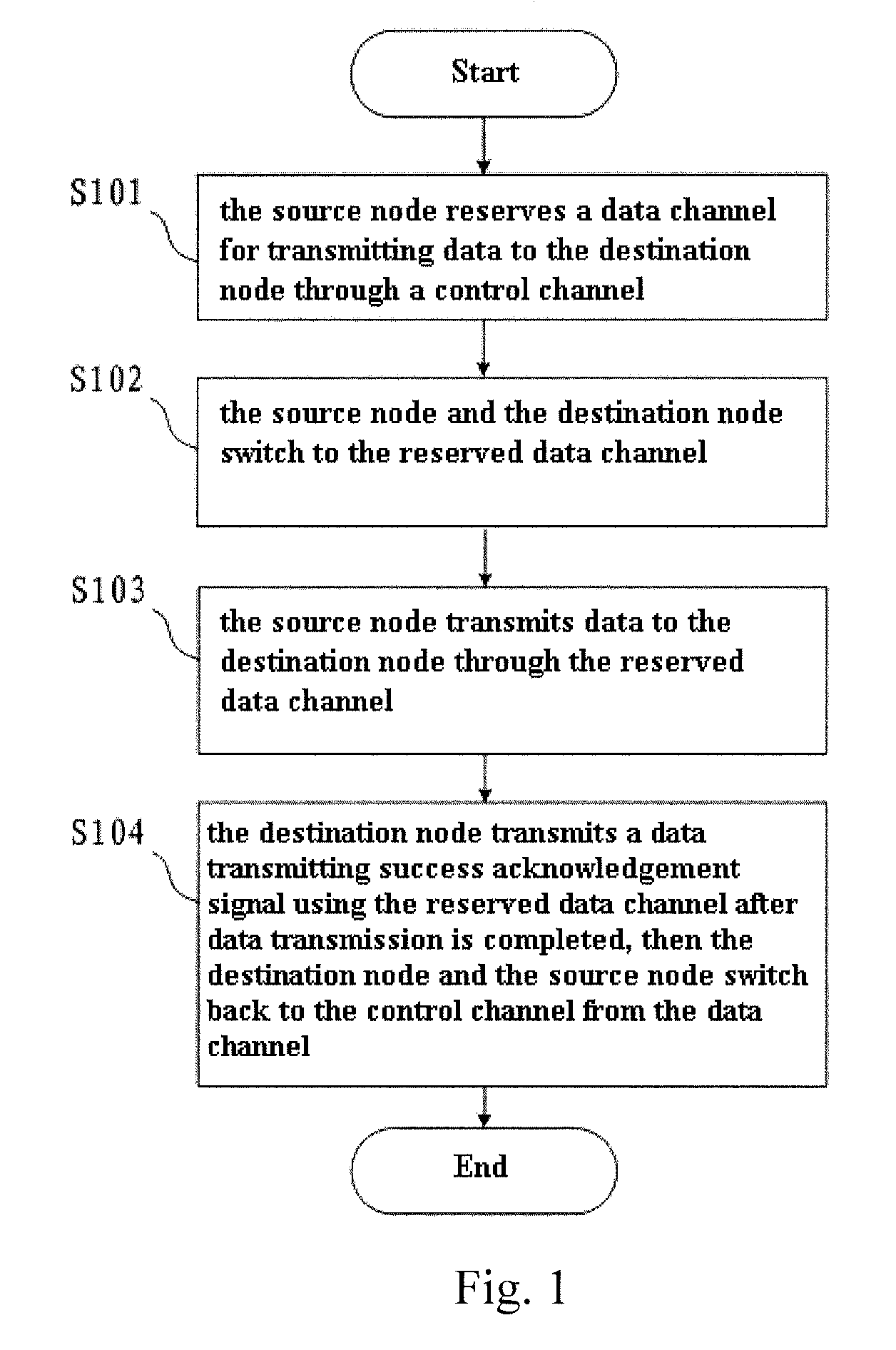

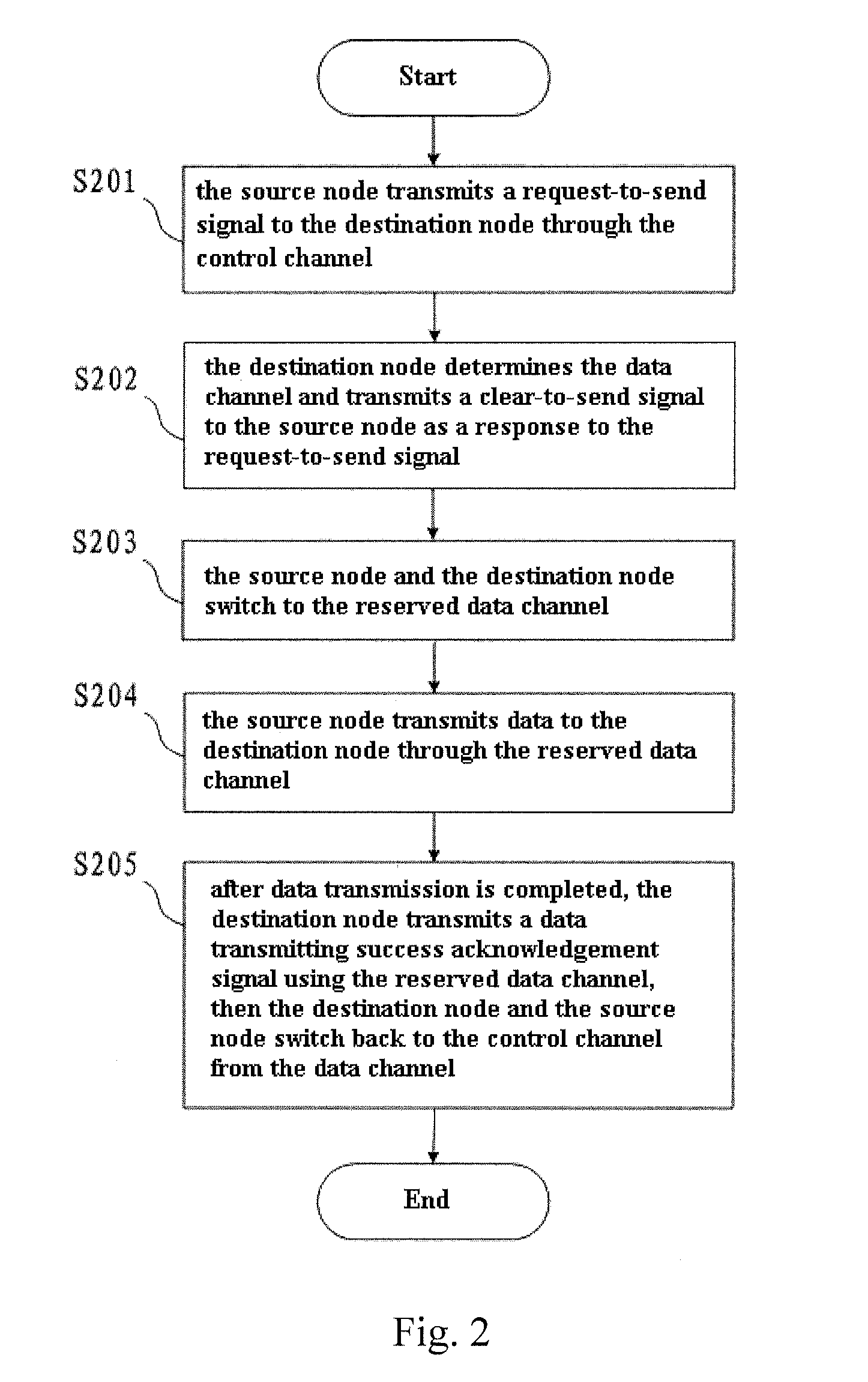

Communication method and node used in wireless communication network

InactiveUS20120020312A1Small control information overheadEnsuring communication performanceError preventionWireless commuication servicesControl channelData transmission

A wireless communication network includes a plurality of peer nodes, the plurality of nodes communicating with each other through a control channel and a plurality of data channels, the communication method including: a source node in the plurality of nodes reserves a data channel used for transmitting data to a destination node in the plurality of nodes through the control channel; the source node and the destination node switch to the reserved data channel; the source node transmits the data to the destination node through the reserved data channel; and after the data transmission between the source node and the destination node is completed, the destination node sends a data transmitting success acknowledgement signal to the source node through the reserved data channel, and then both of the destination node and the source node switch to the control channel from the reserved data channel for operation.

Owner:FUJITSU LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com