Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

485 results about "Abstraction layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

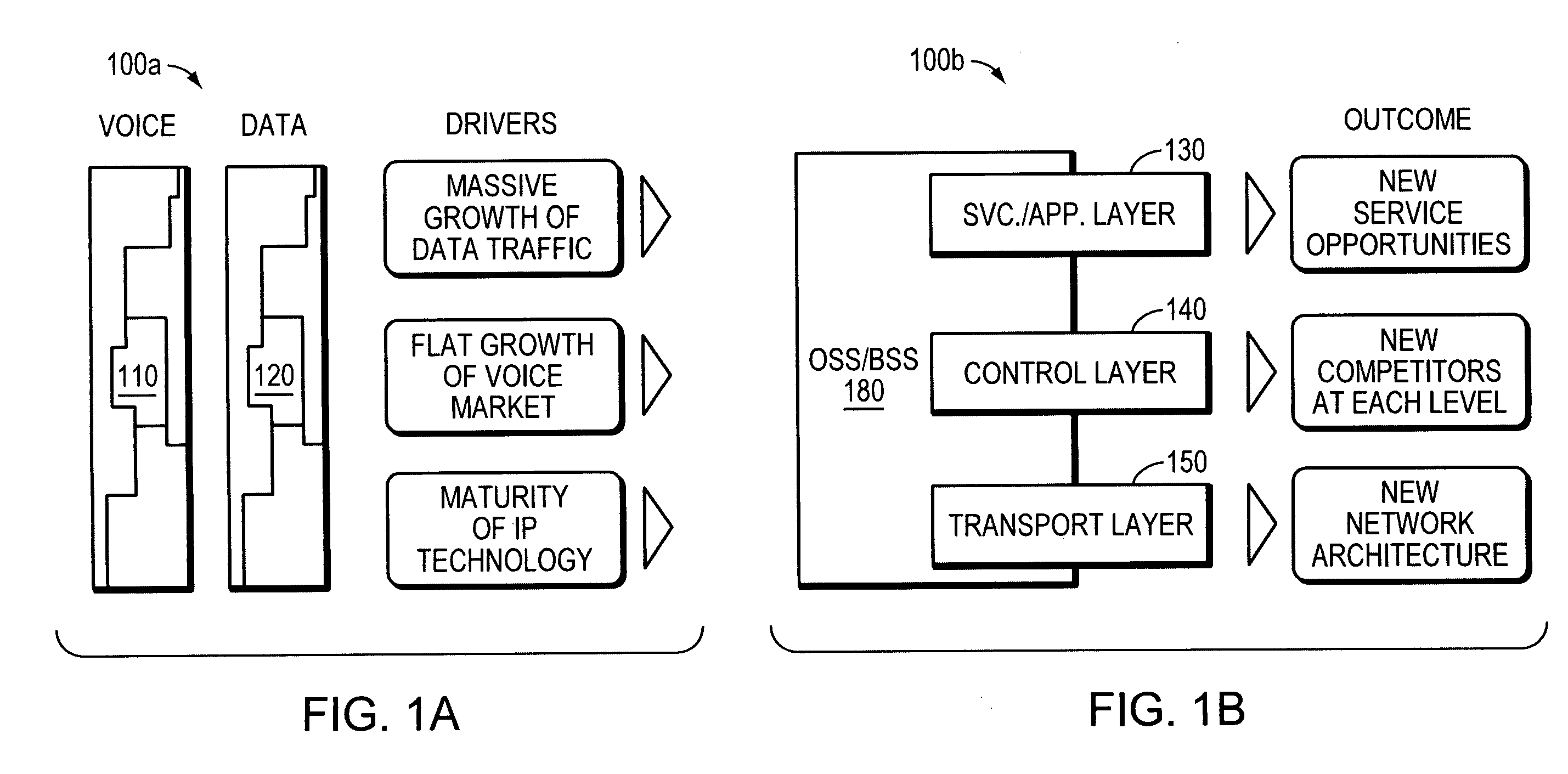

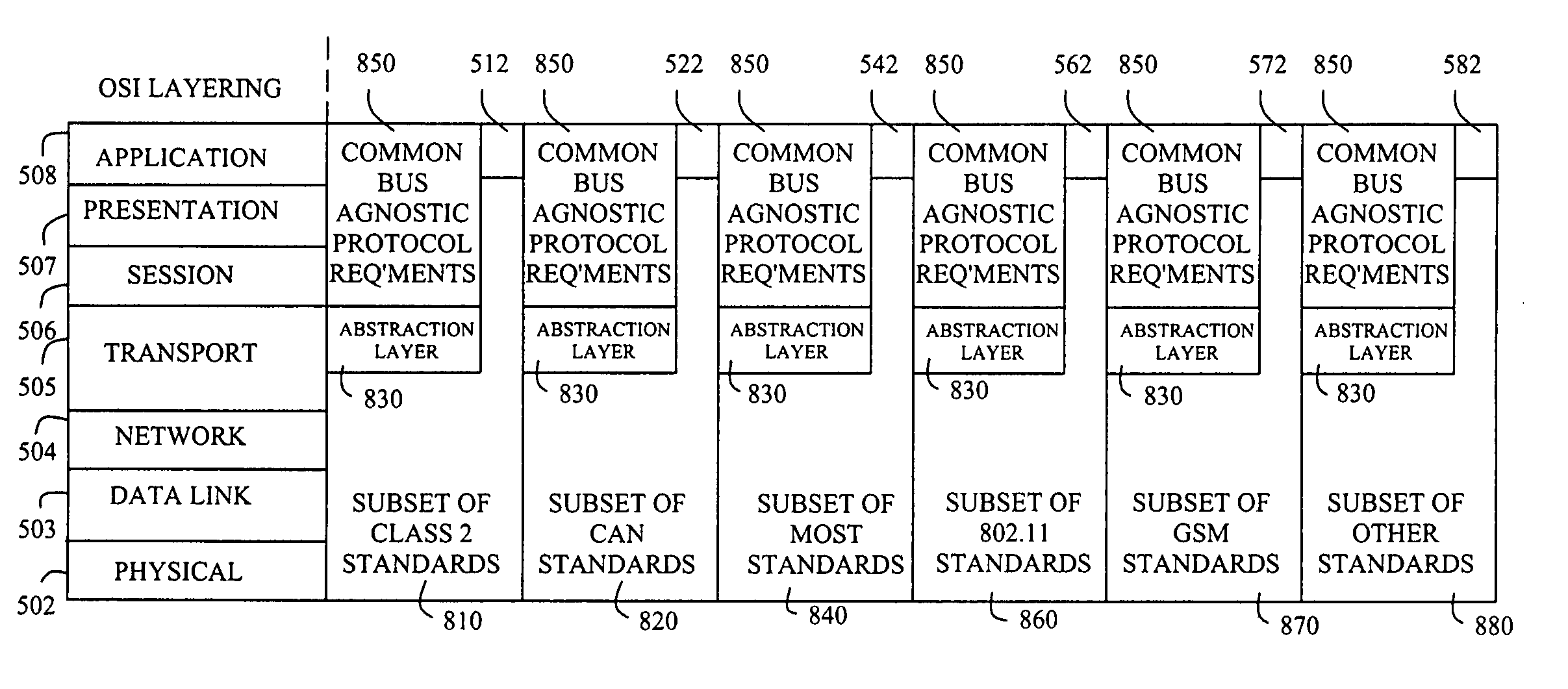

In computing, an abstraction layer or abstraction level is a way of hiding the working details of a subsystem, allowing the separation of concerns to facilitate interoperability and platform independence. Examples of software models that use layers of abstraction include the OSI model for network protocols, OpenGL and other graphics libraries.

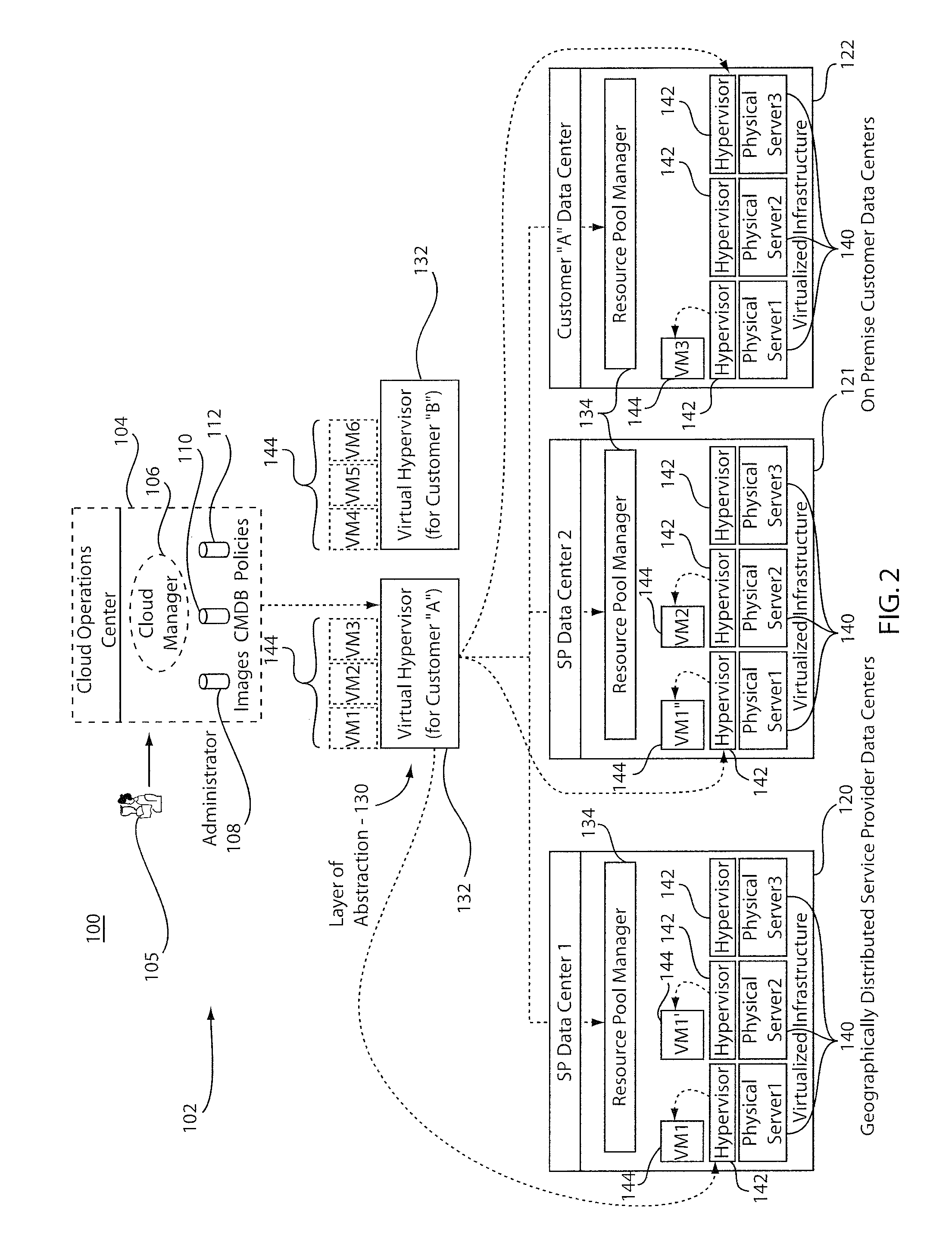

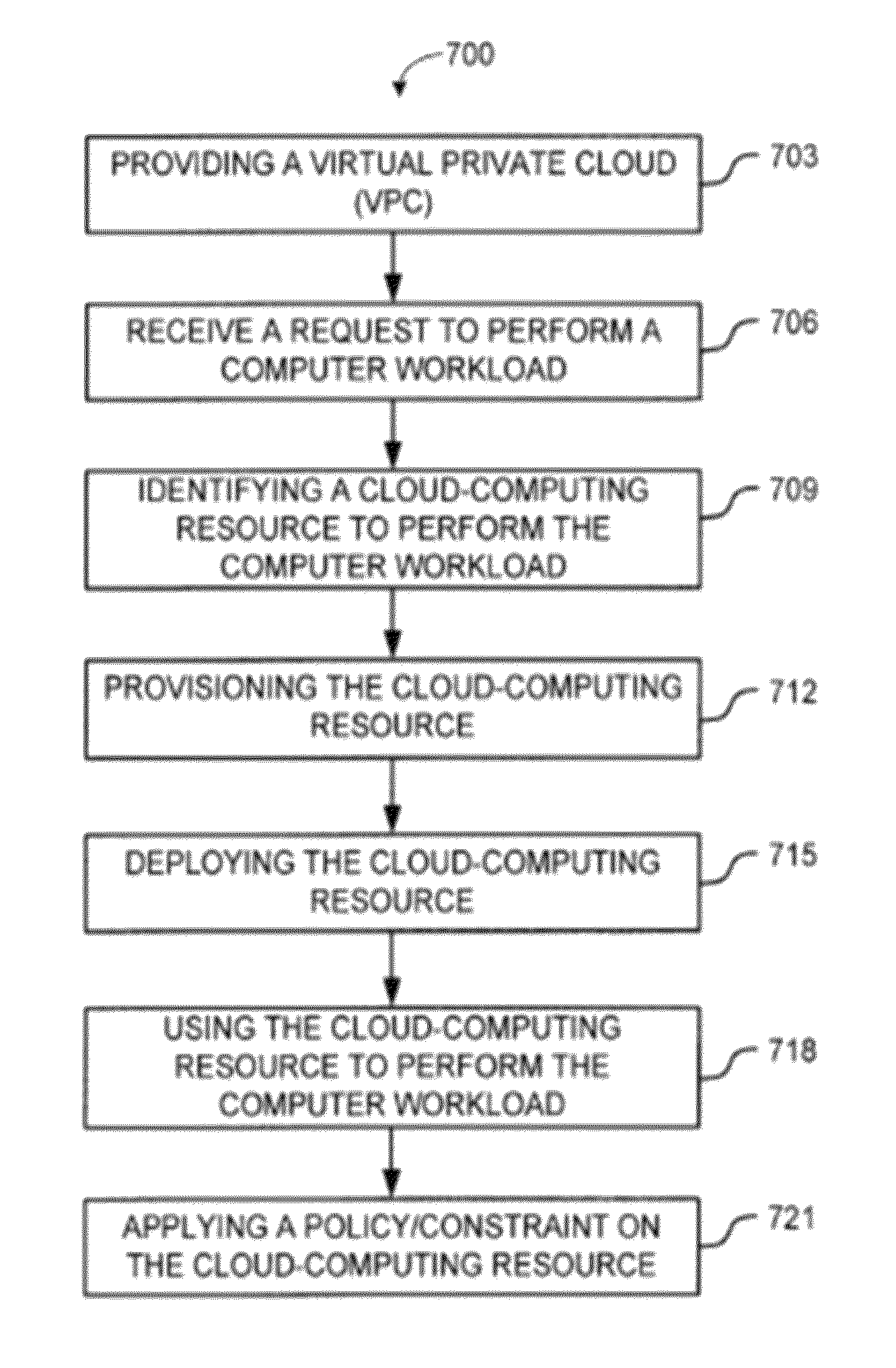

System and method for a cloud computing abstraction layer with security zone facilities

ActiveUS20120185913A1Rapid and dynamic deployment and scalingShorten the timeComputer security arrangementsHybrid transportVirtualizationAbstraction layer

In embodiments of the present invention improved capabilities are described for a virtualization environment adapted for development and deployment of at least one software workload, the virtualization environment having a metamodel framework that allows the association of a policy to the software workload upon development of the workload that is applied upon deployment of the software workload. This allows a developer to define a security zone and to apply at least one type of security policy with respect to the security zone including the type of security zone policy in the metamodel framework such that the type of security zone policy can be associated with the software workload upon development of the software workload, and if the type of security zone policy is associated with the software workload, automatically applying the security policy to the software workload when the software workload is deployed within the security zone.

Owner:DXC US AGILITY PLATFORM INC

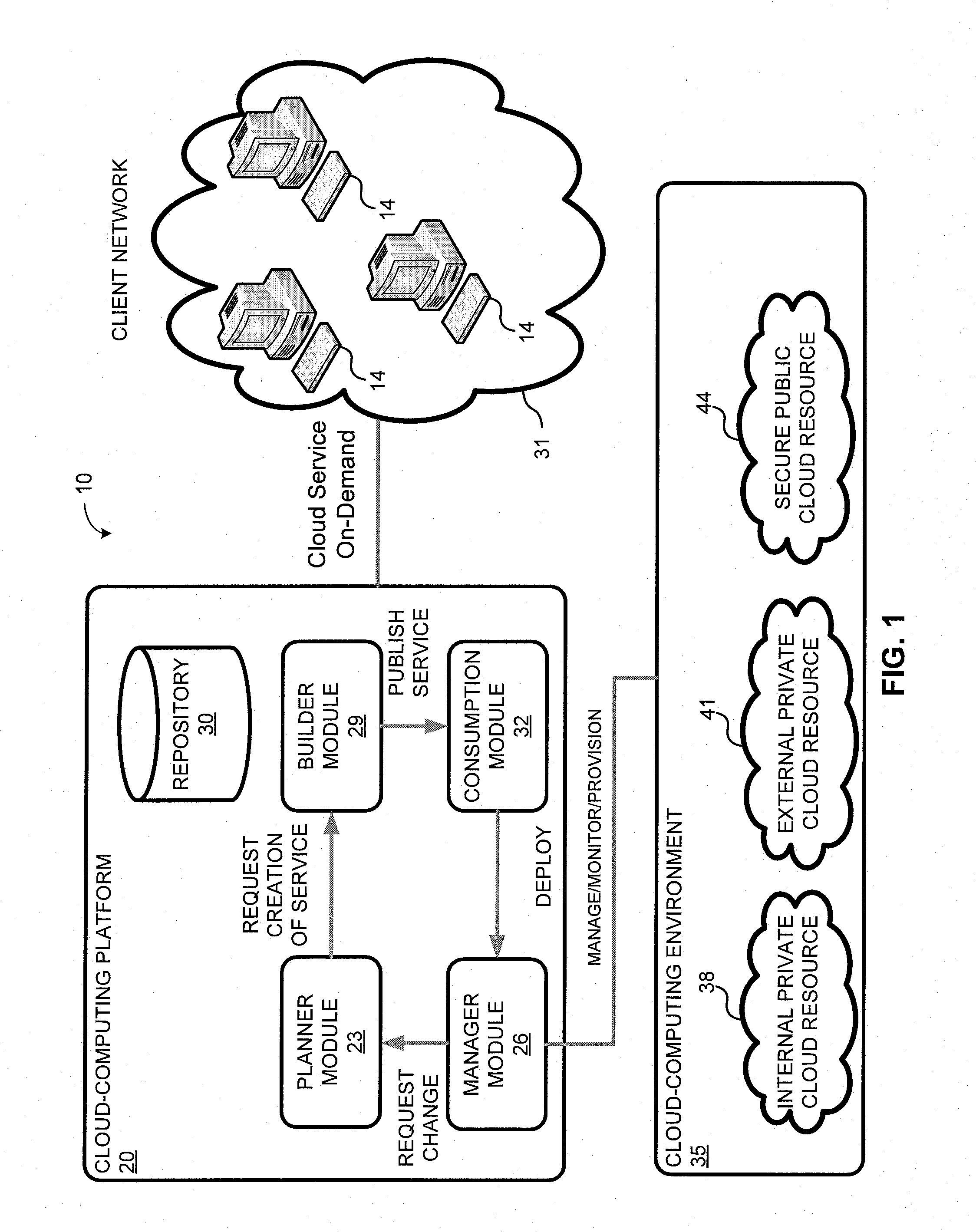

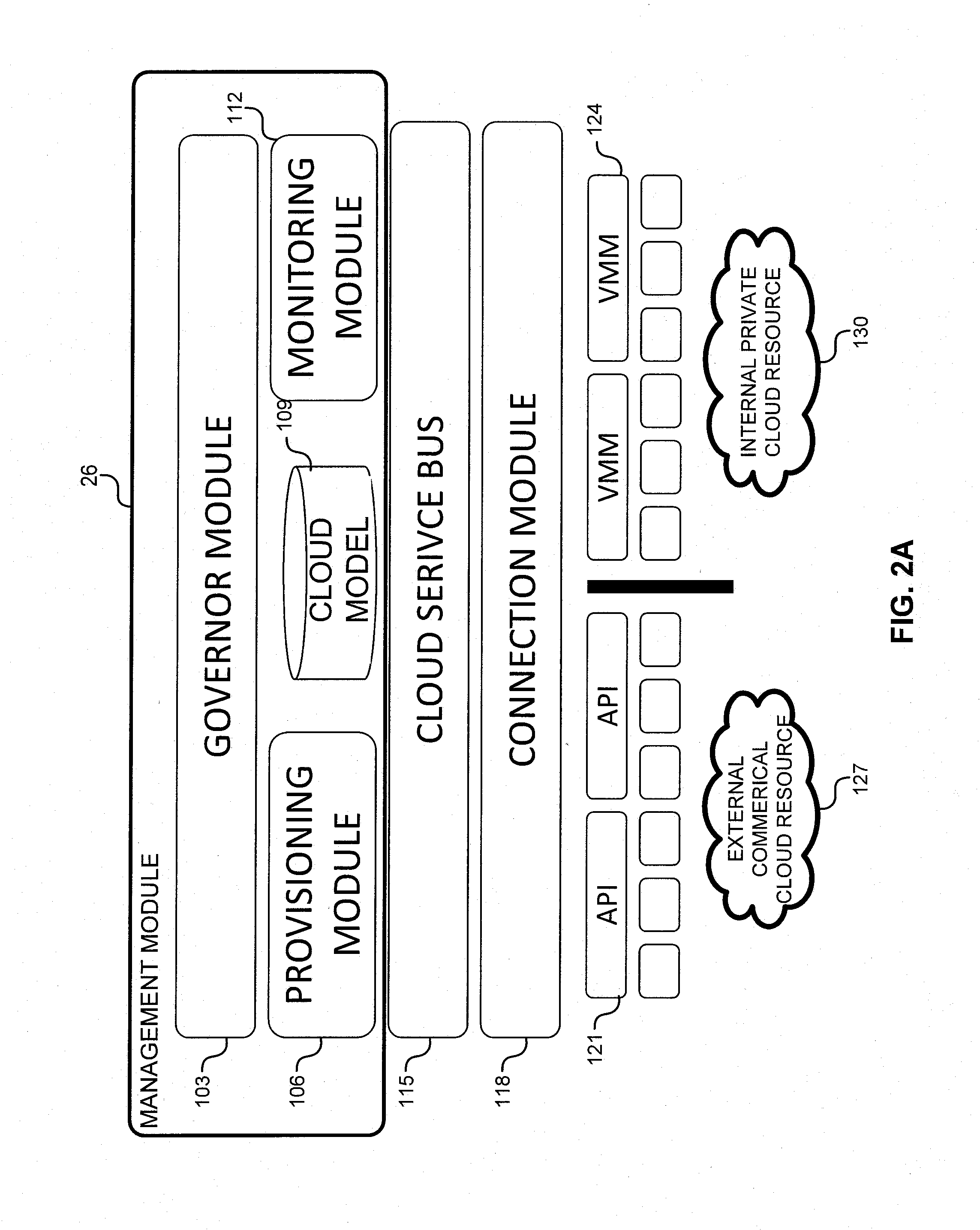

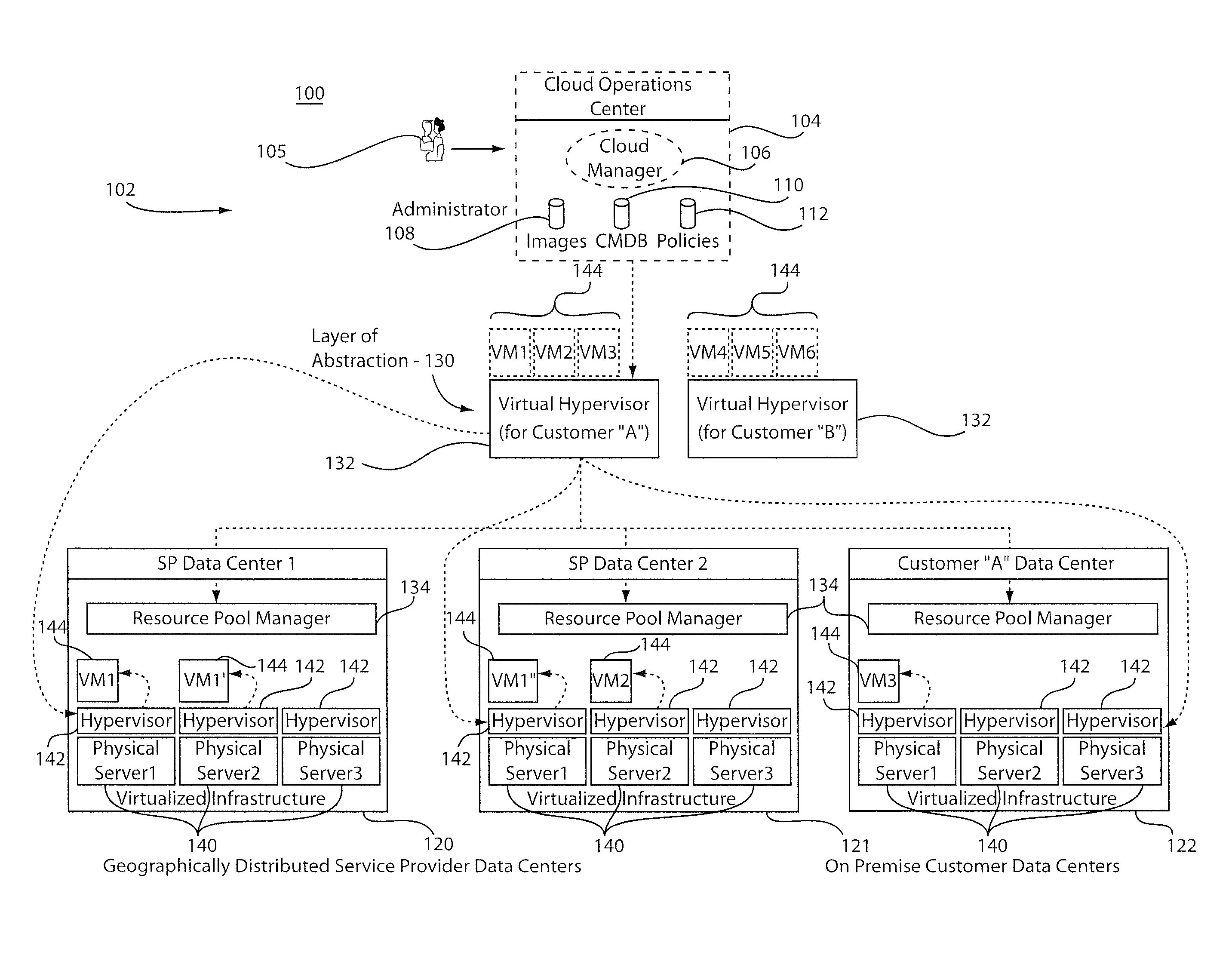

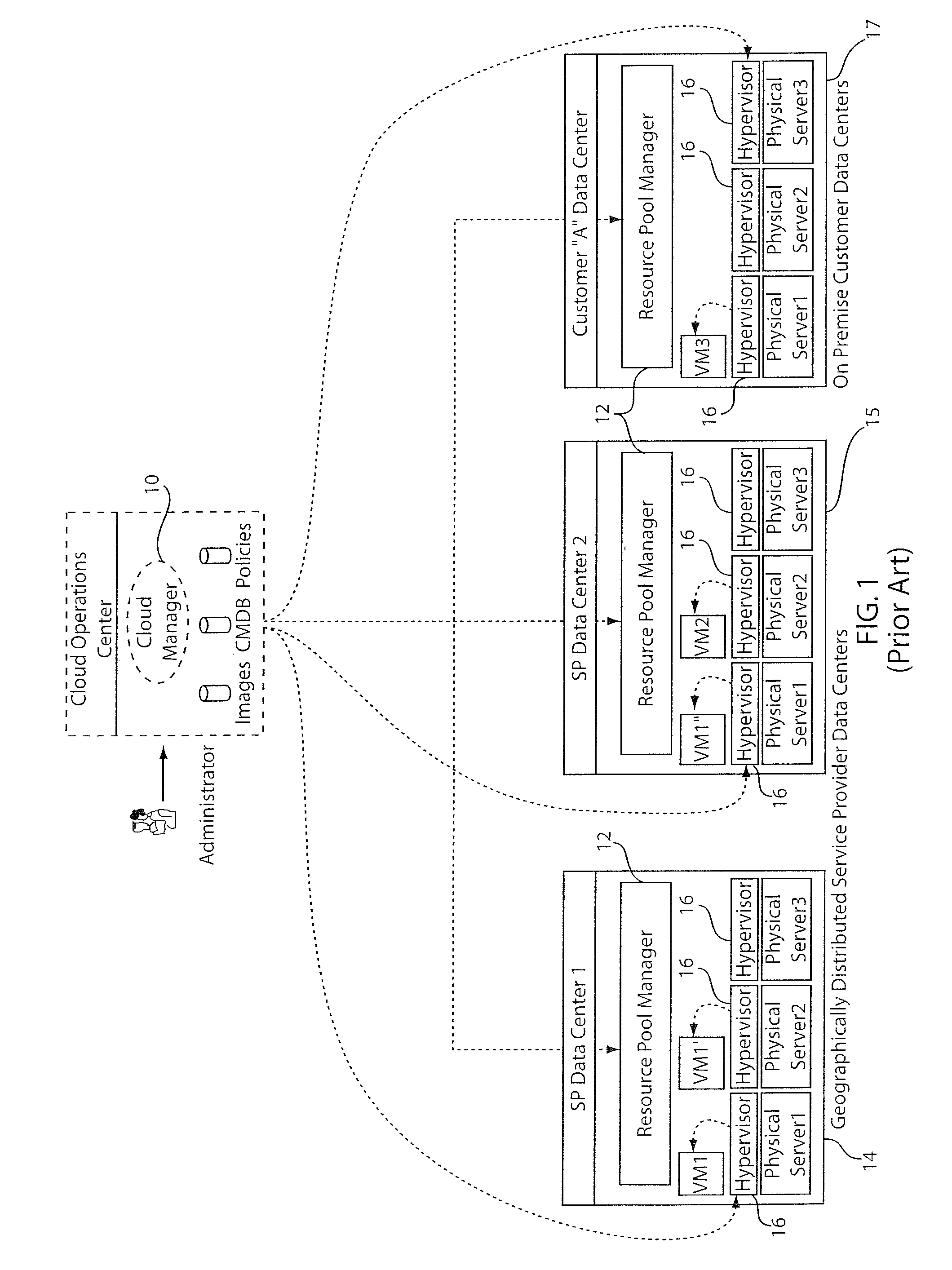

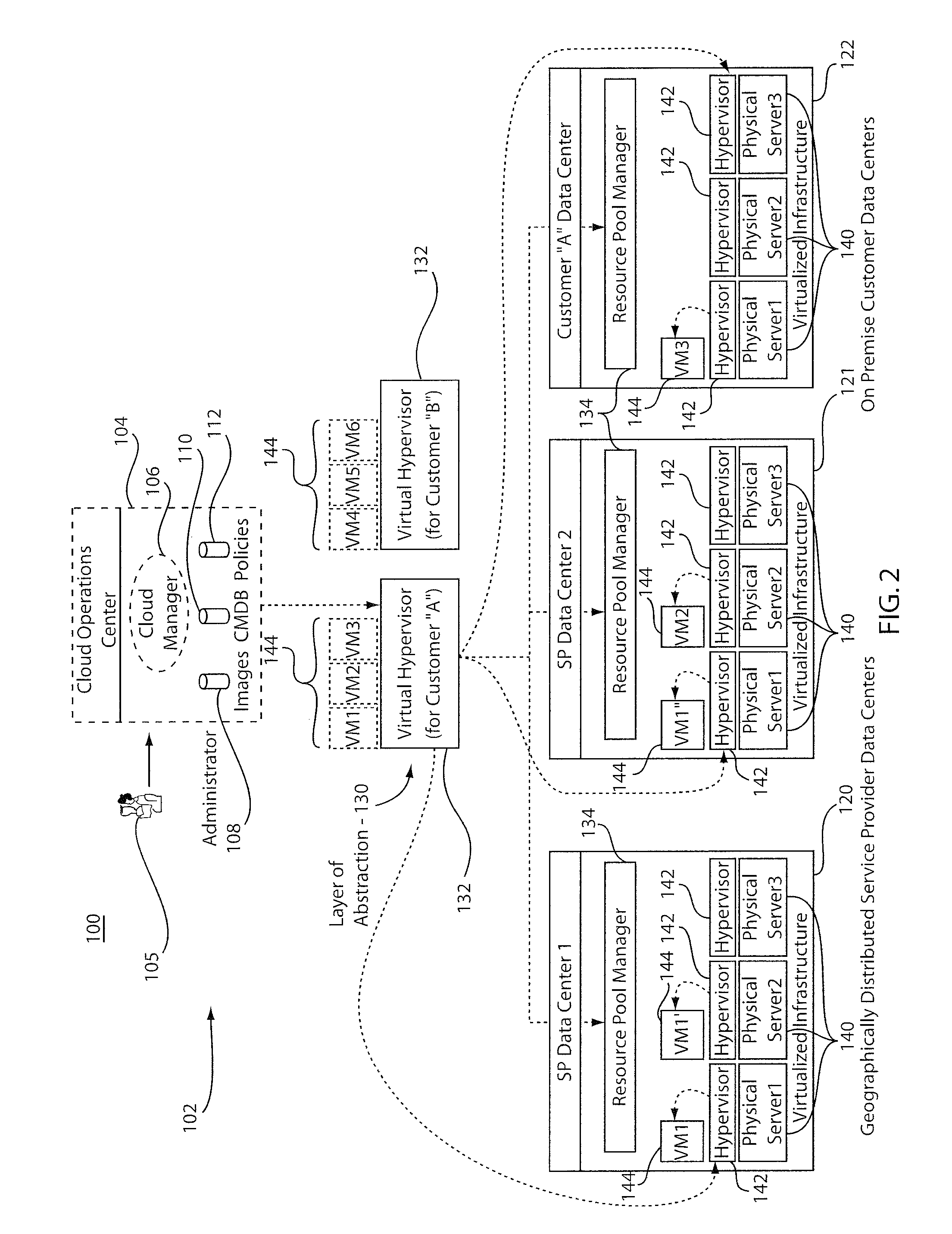

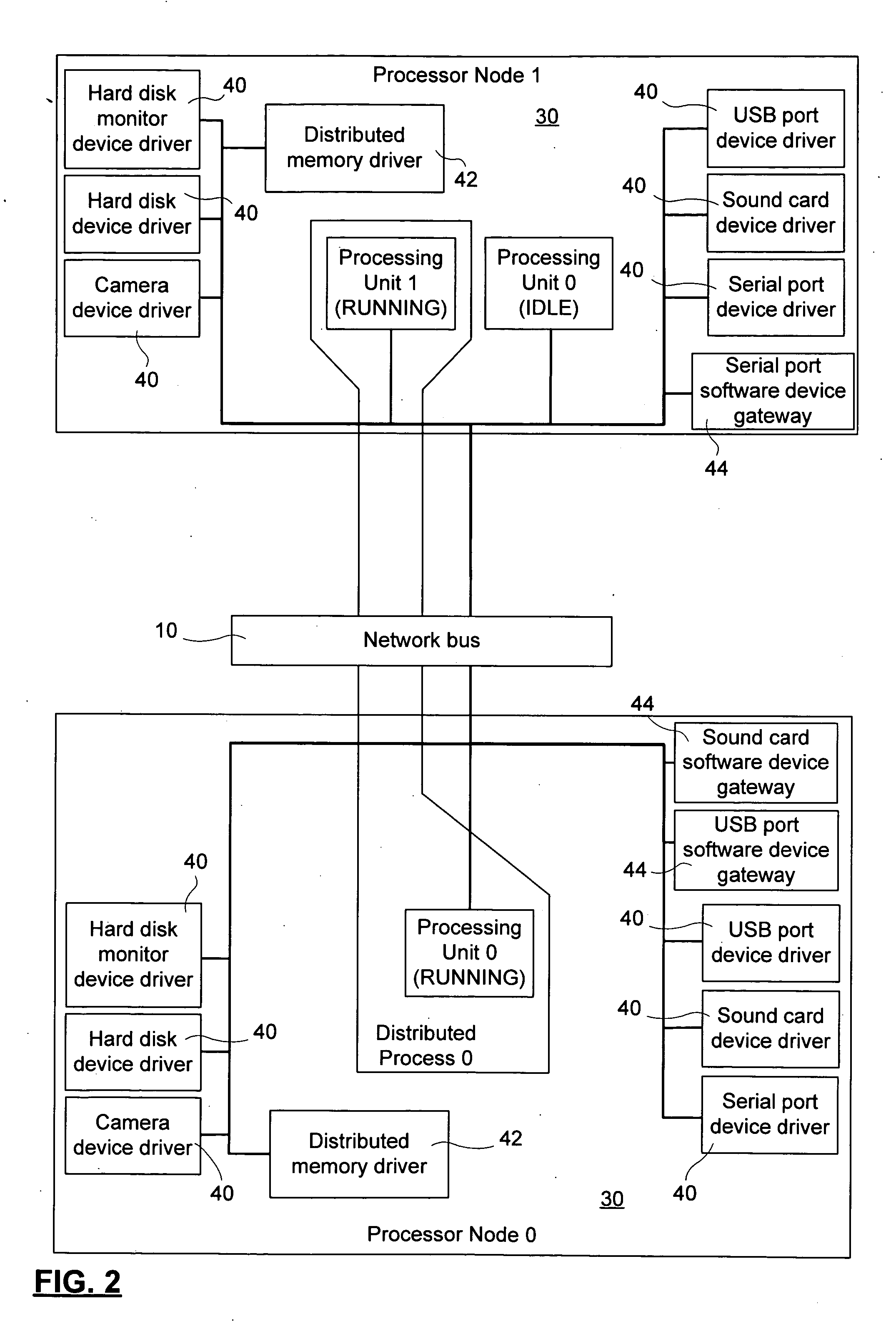

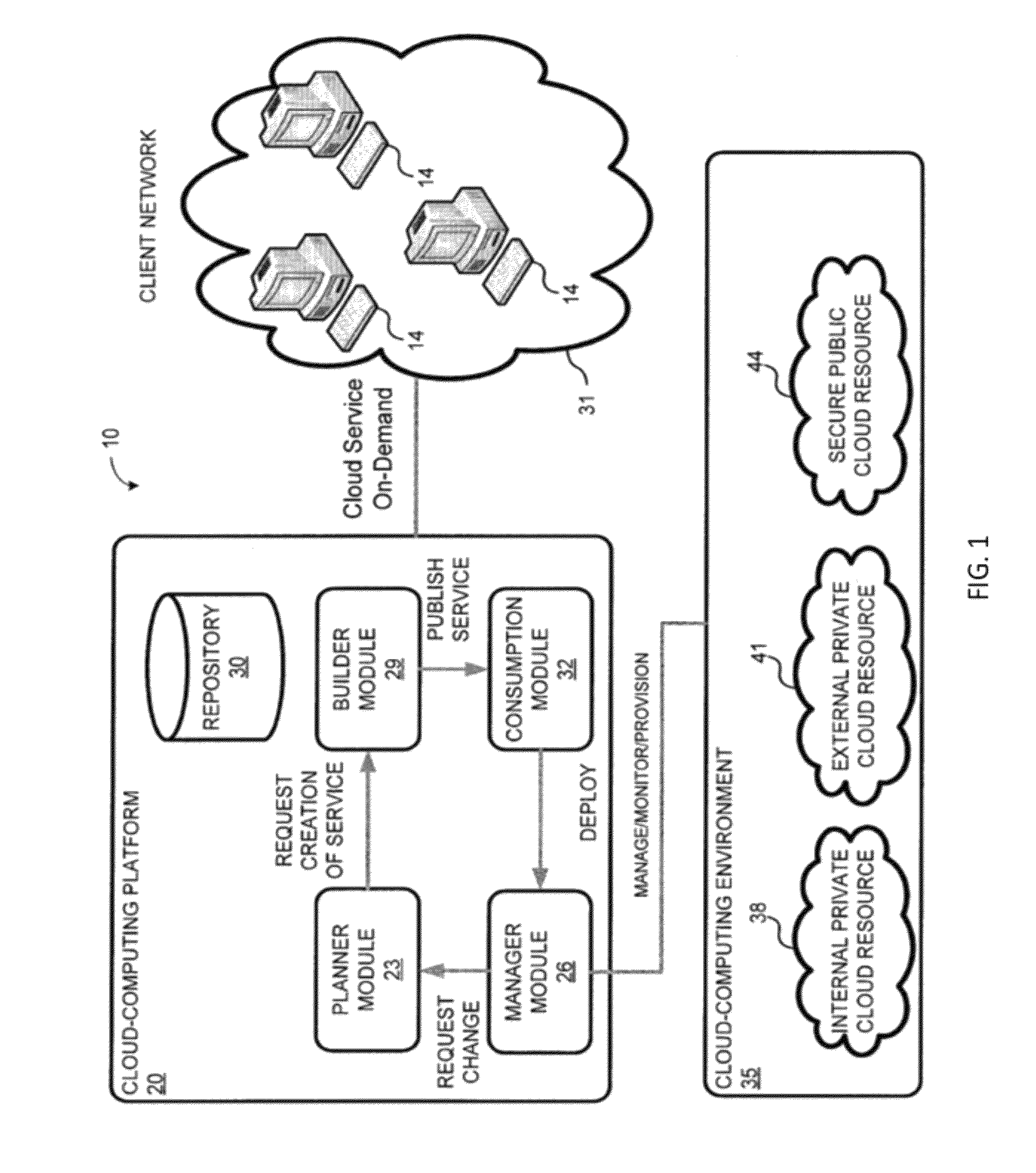

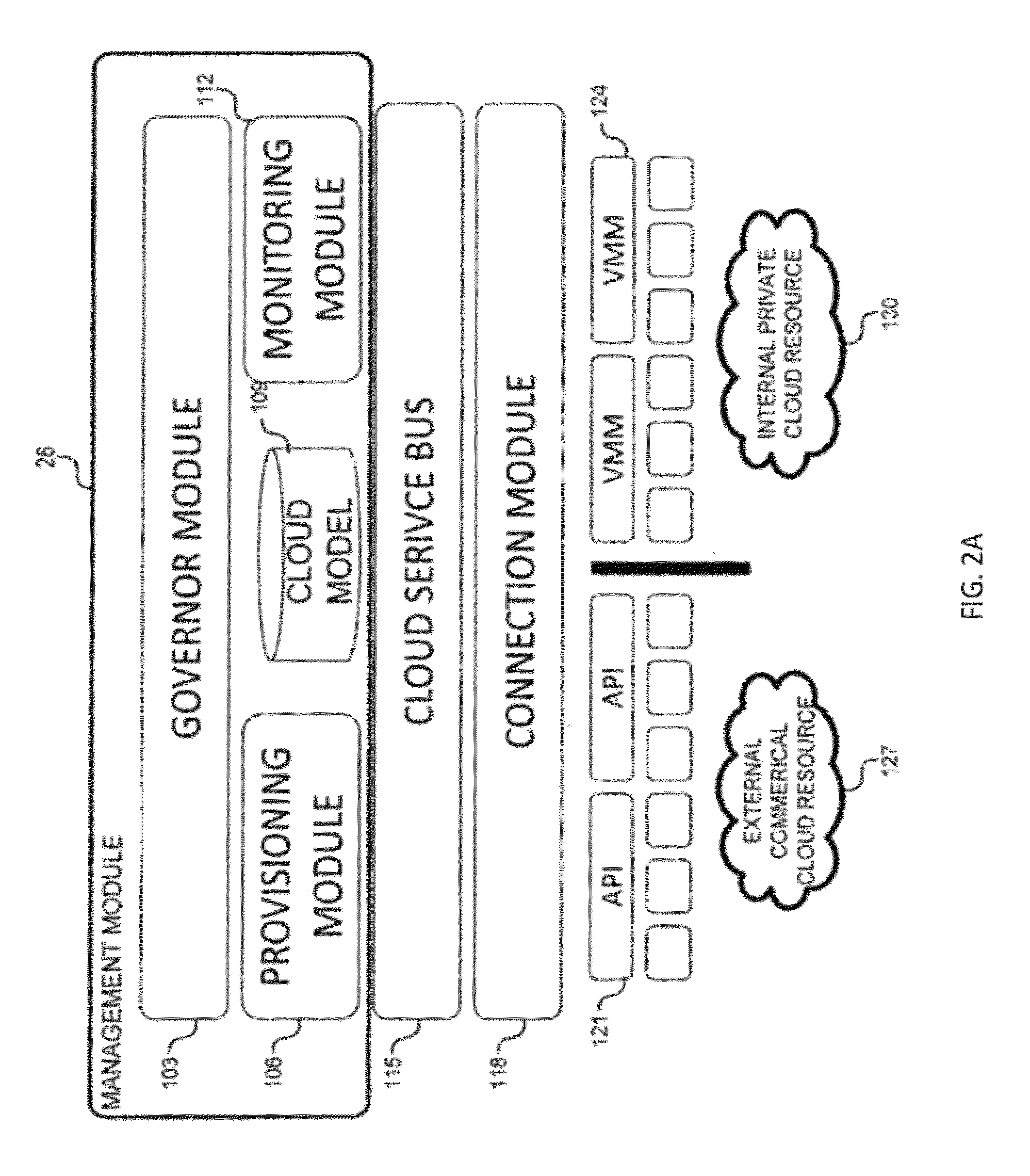

System and method for a cloud computing abstraction layer

ActiveUS20110231899A1Rapid and dynamic deployment and scalingShorten the timeDigital computer detailsComputer security arrangementsAbstraction layerWorkload

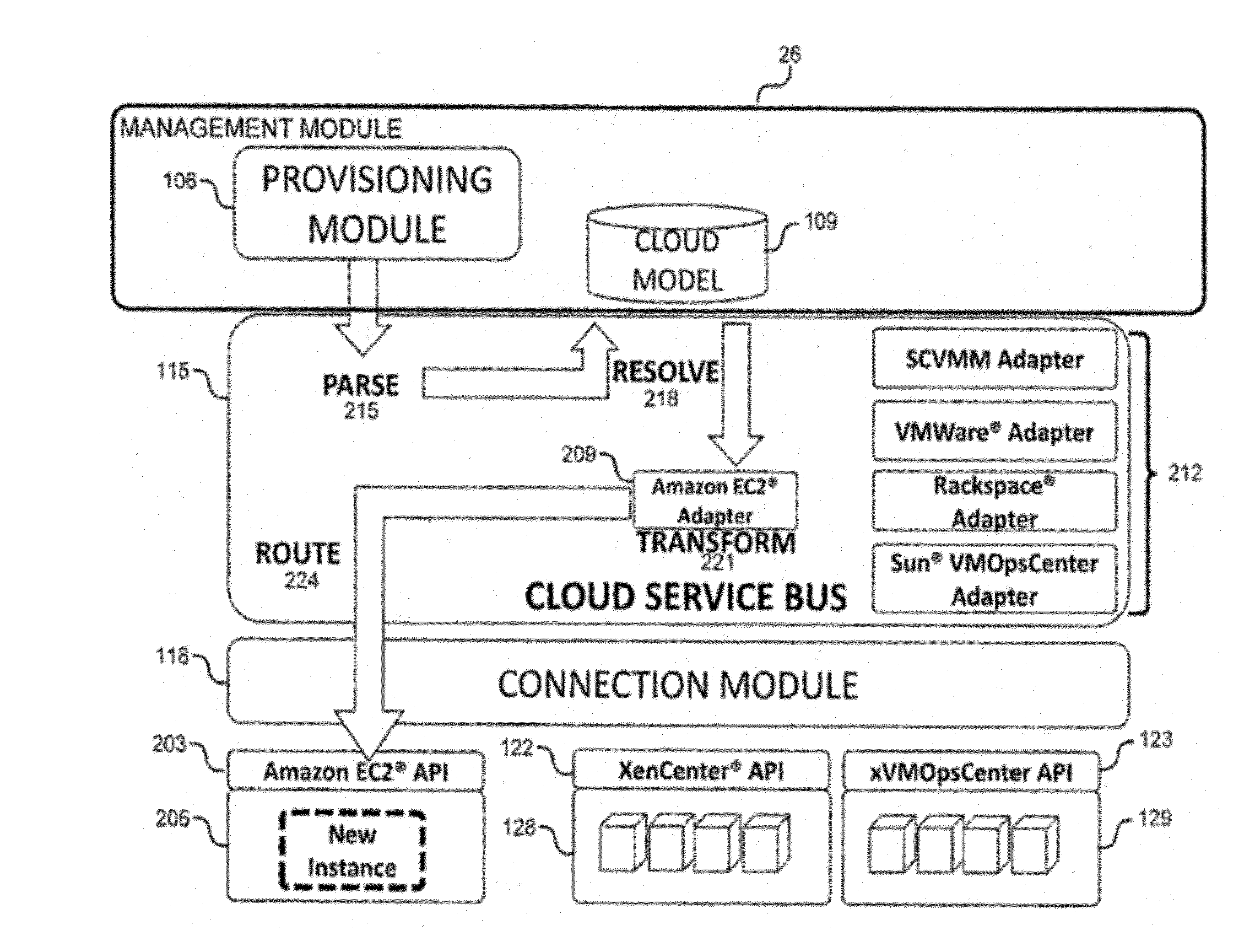

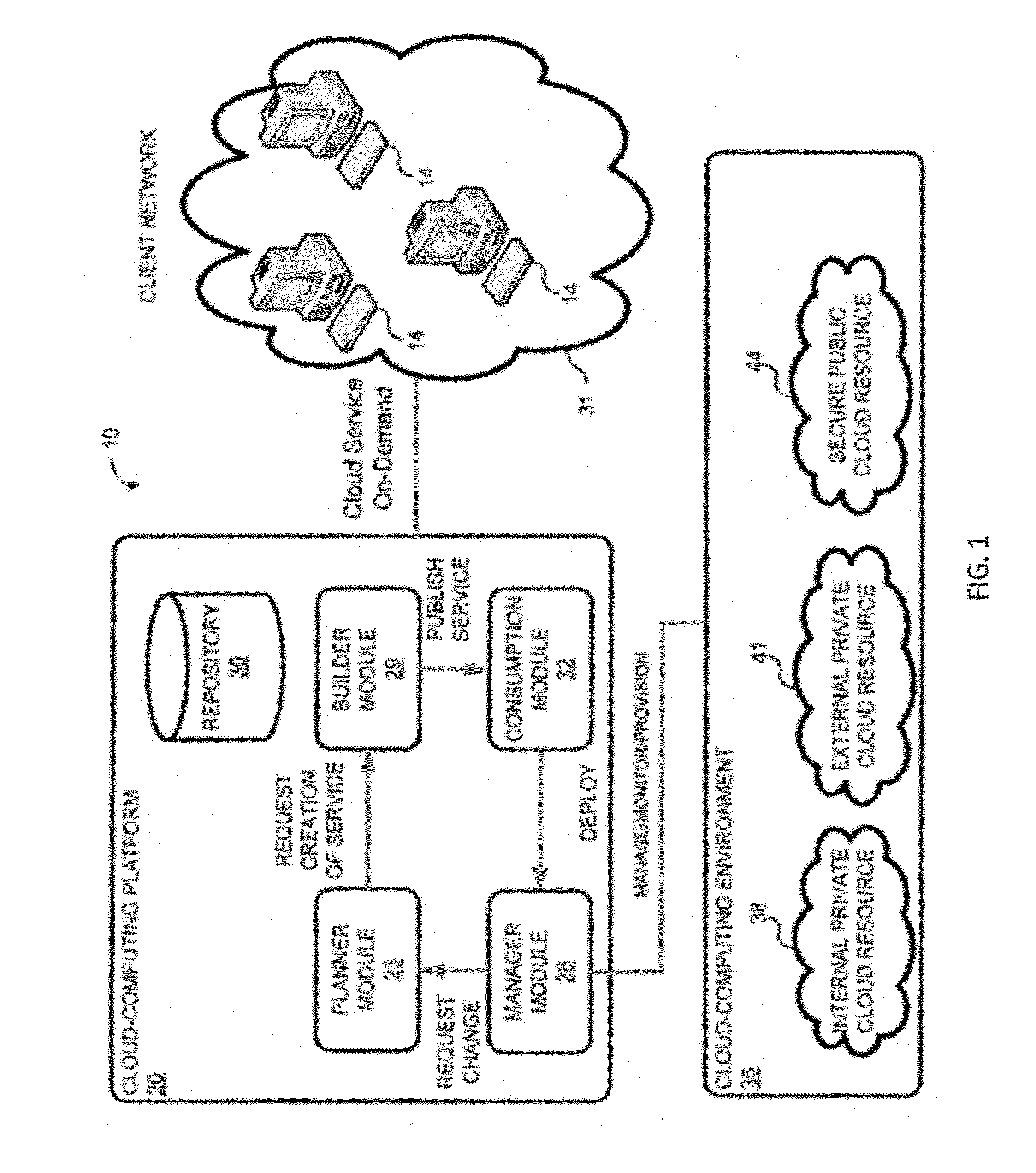

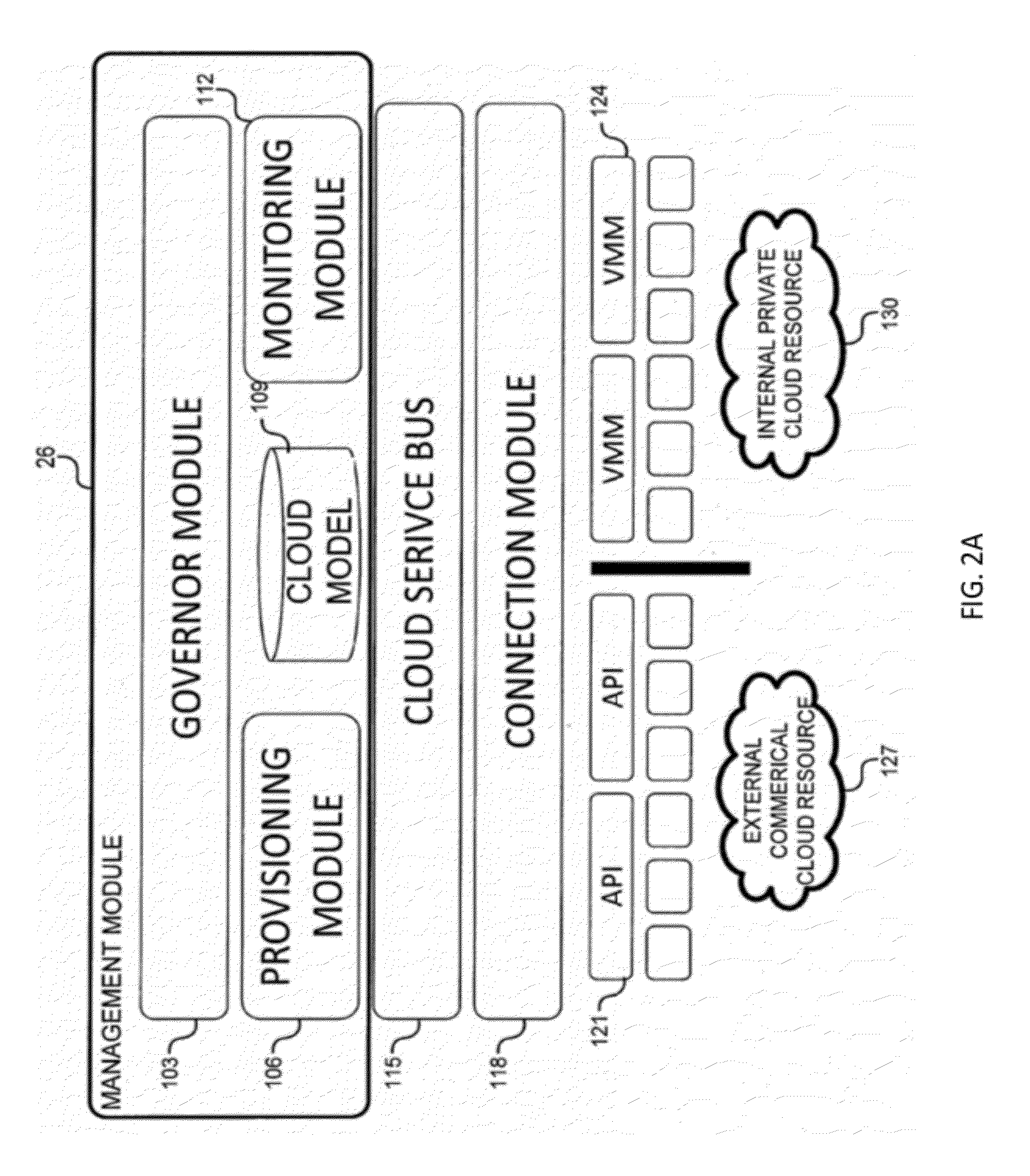

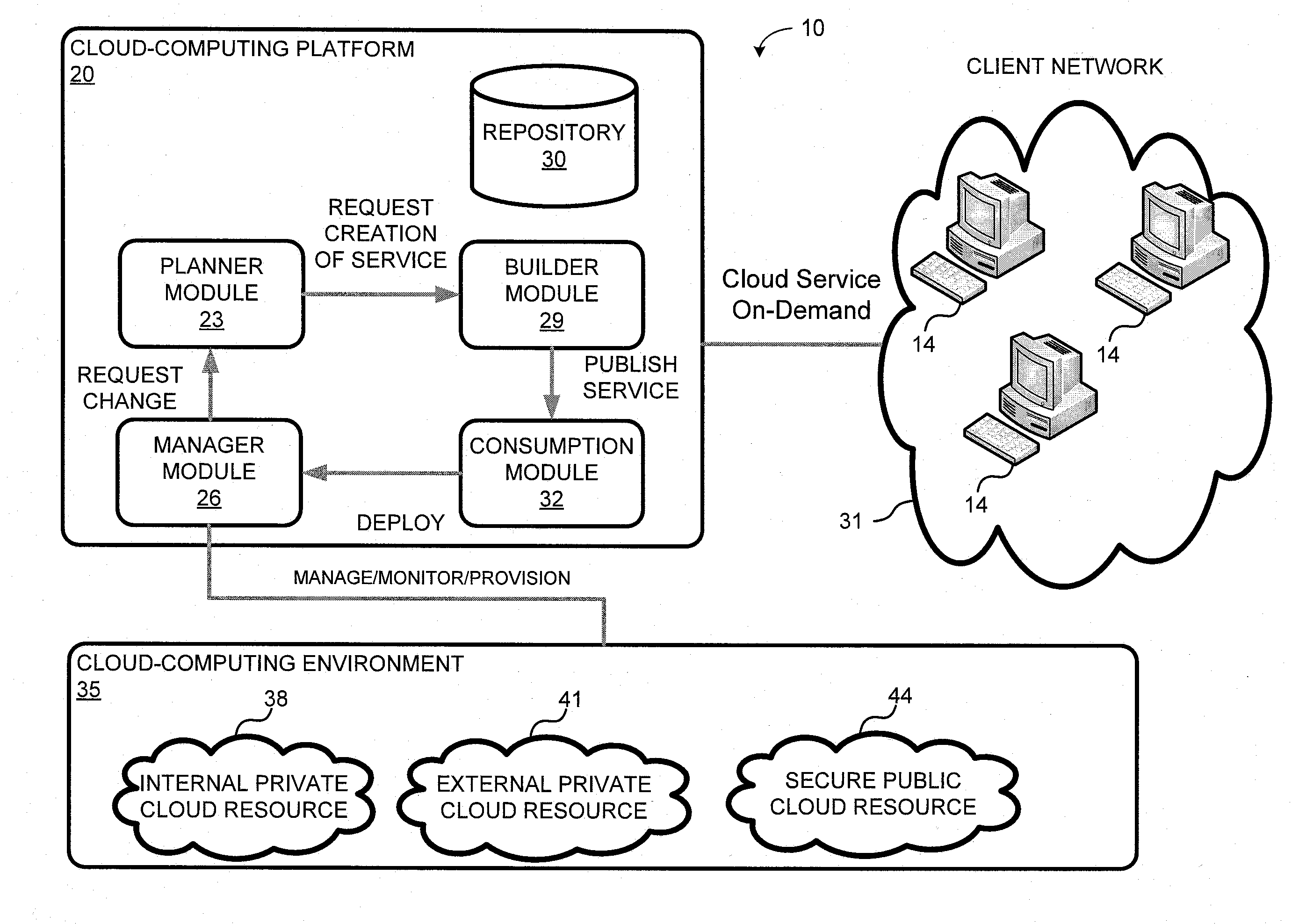

According to one system of the invention, the system provides a cloud-computing service from a cloud-computing environment comprising a plurality of cloud-computing resources. The system may comprise: a management module configured to manage a cloud-computing resource of the plurality of cloud-computing resources as a cloud-computing service, wherein the cloud-computing service performs a computer workload; an adapter configured to connect to the cloud-computing resource to the system and translate a management instruction received from the management module into a proprietary cloud application program interface call for the cloud-computing resource; a cloud service bus configured to route the management instruction from the management module to the adapter; a consumption module configured to allow a user to subscribe the cloud-computing service; a planning module configured to plan the cloud-computing service; and a build module configured to build the cloud-computing service from the cloud-computing resource and publish the cloud-computing service to the consumption module.

Owner:DXC US AGILITY PLATFORM INC

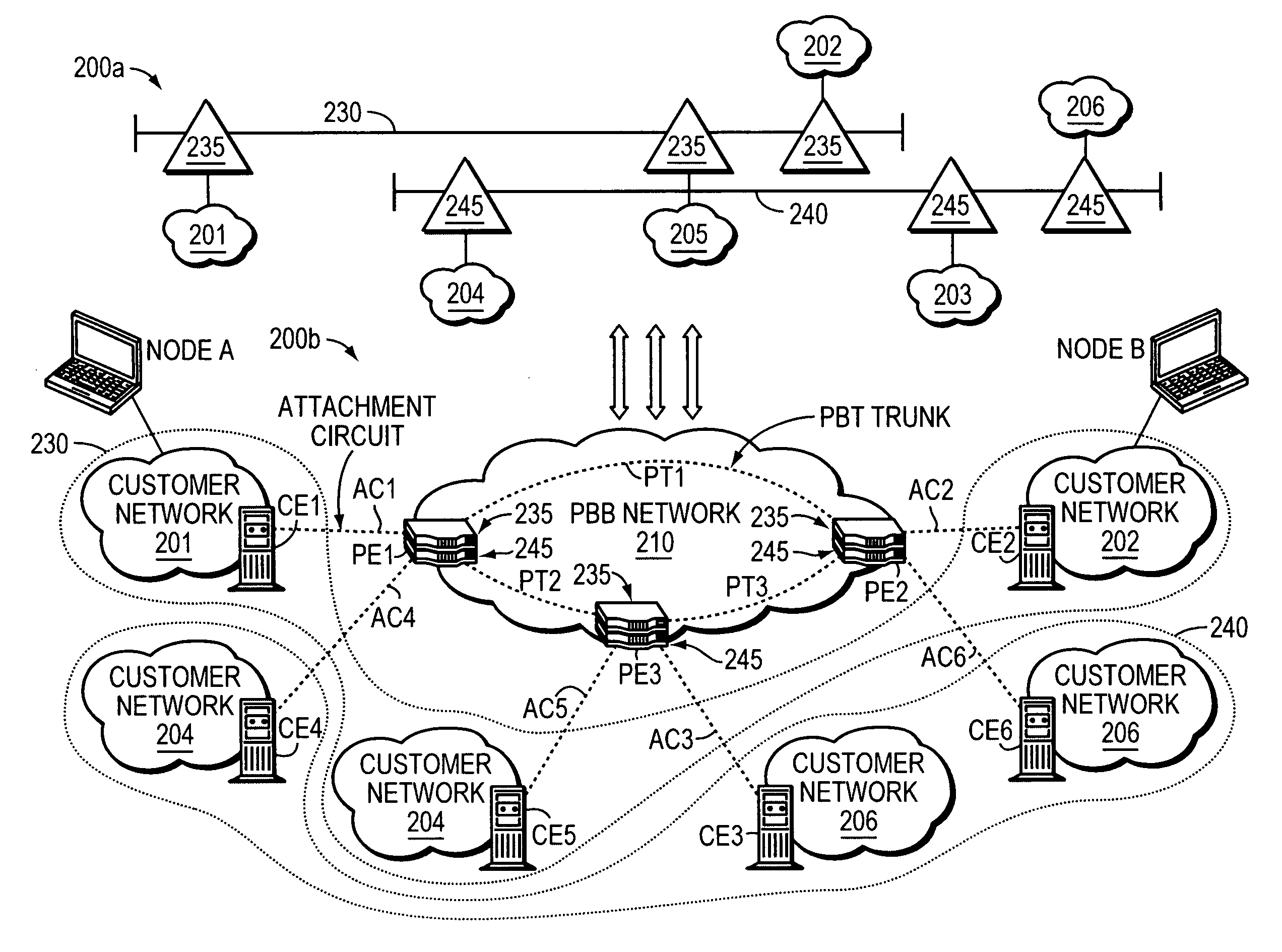

Software control plane for switches and routers

ActiveUS20080219268A1Bridging the gapImprove convenienceError preventionTransmission systemsQuality of serviceAbstraction layer

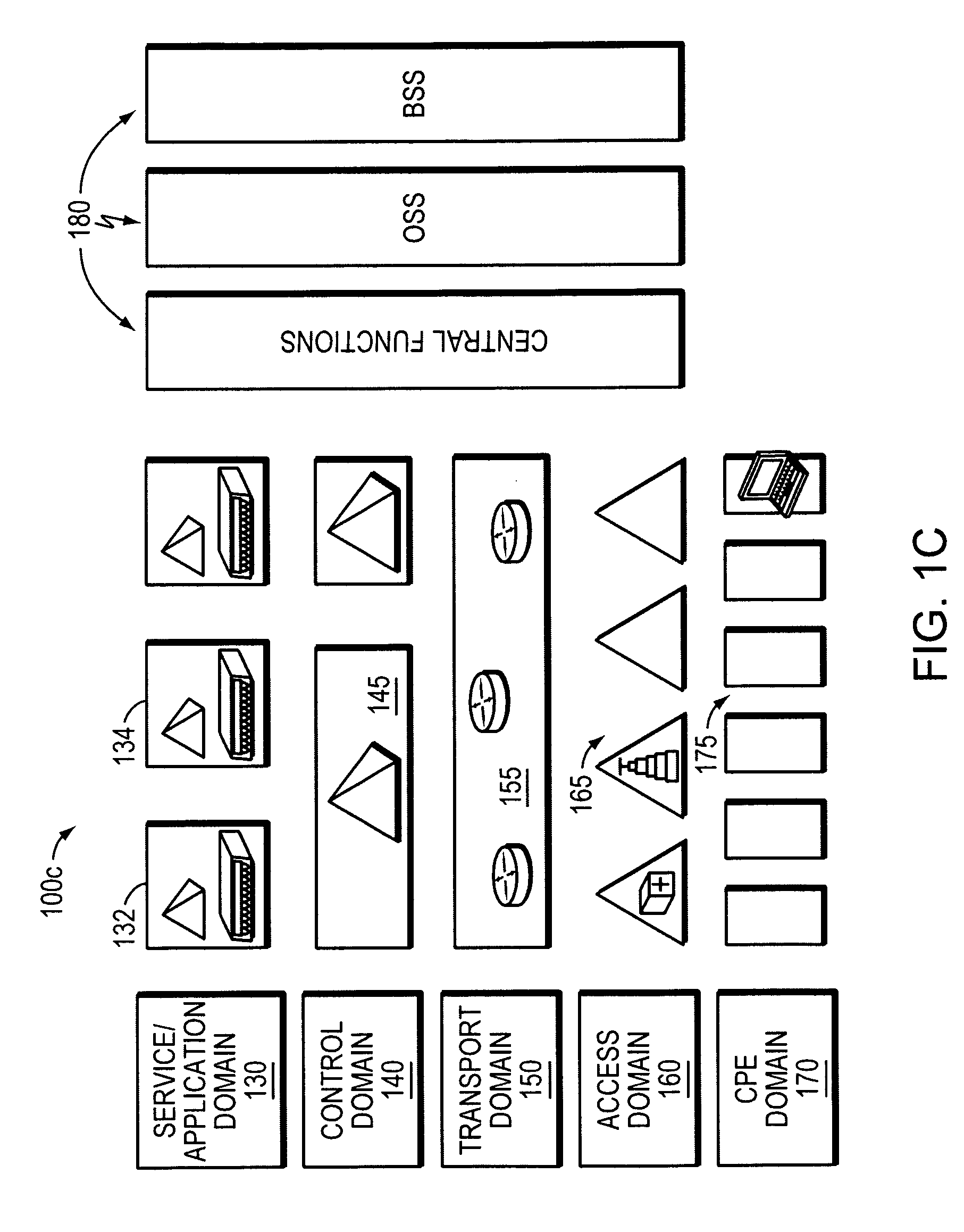

A Provider Network Controller (PNC) addresses the challenges in building services across Next Generation Network (NGN) architectures and creates an abstraction layer as a bridge, or glue, between the network transport and applications running over it. The PNC is a multi-layer, multi-vendor dynamic control plane that implements service activation and Layer 0-2 management tools for multiple transport technologies including Carrier Ethernet, Provider Backbone Transport (PBT), Multi-protocol Label Switching (MPLS), Transport MPLS (T-MPLS), optical and integrated networking platforms. Decoupling transport controls and services from the network equipment simplifies service creation and provides options for carriers to choose best-in-class equipment that leverages the PNC to enable rapid creation and management of transports and services. The PNC provides Service-Oriented Architecture (SOA) interfaces to abstract transport objects expressly designed to support both wholesale and retail services, and supports service offerings with varied bandwidth and Quality of Service (QoS) requirements, thus achieving enterprise Ethernet economics.

Owner:EXTREME NETWORKS INC

Mobile device management

ActiveUS20080070495A1Broadcast transmission systemsTransmissionAbstraction layerKnowledge management

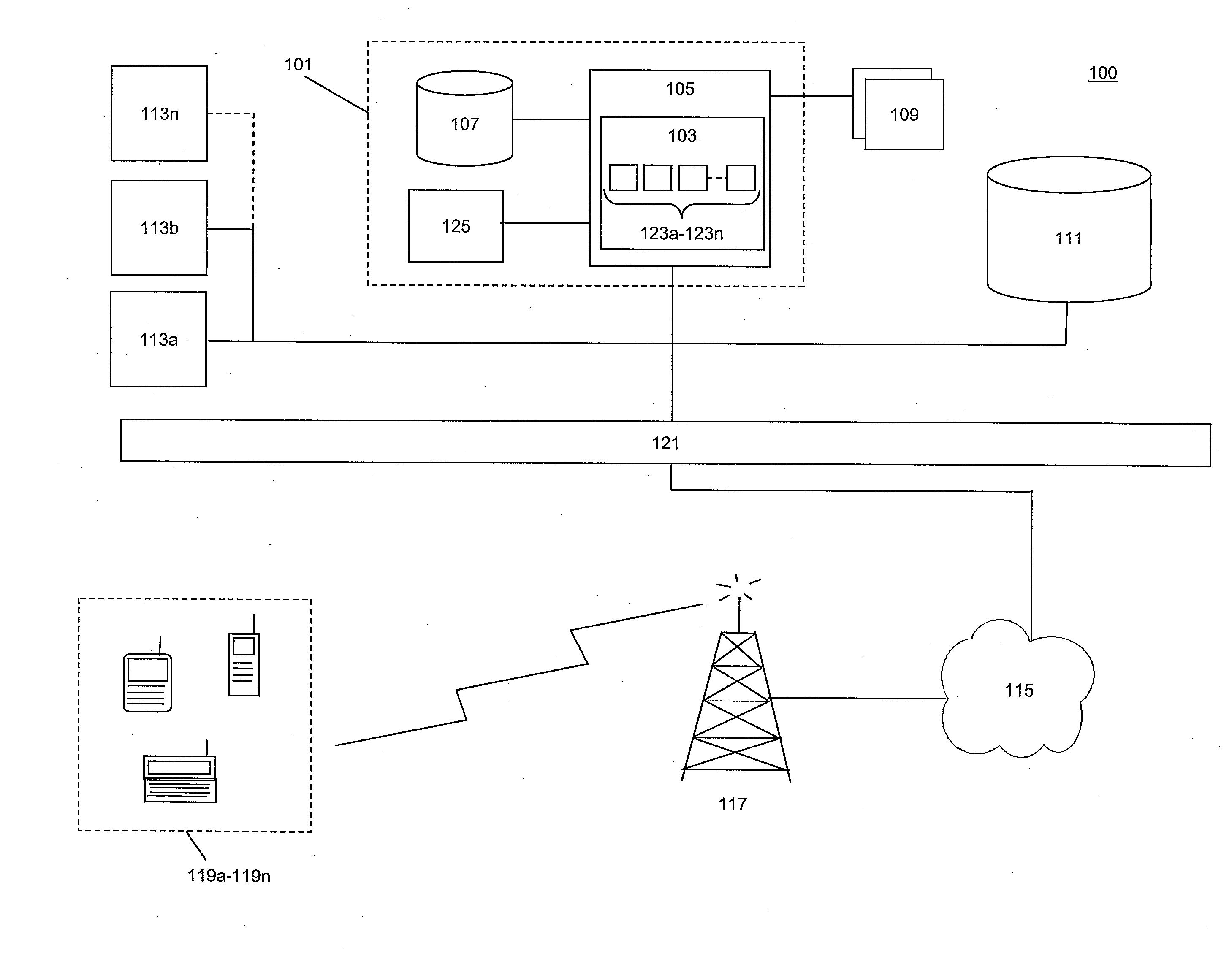

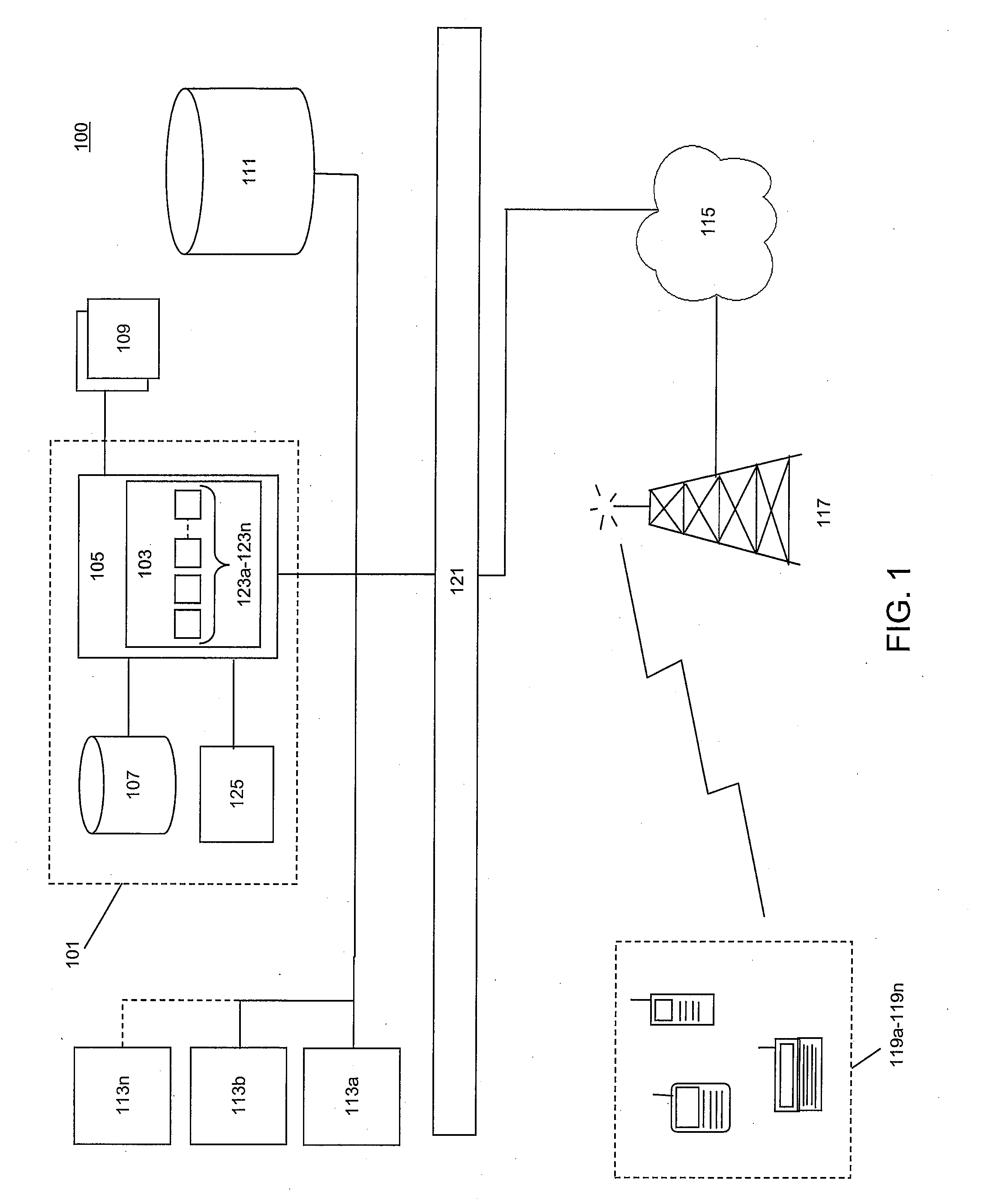

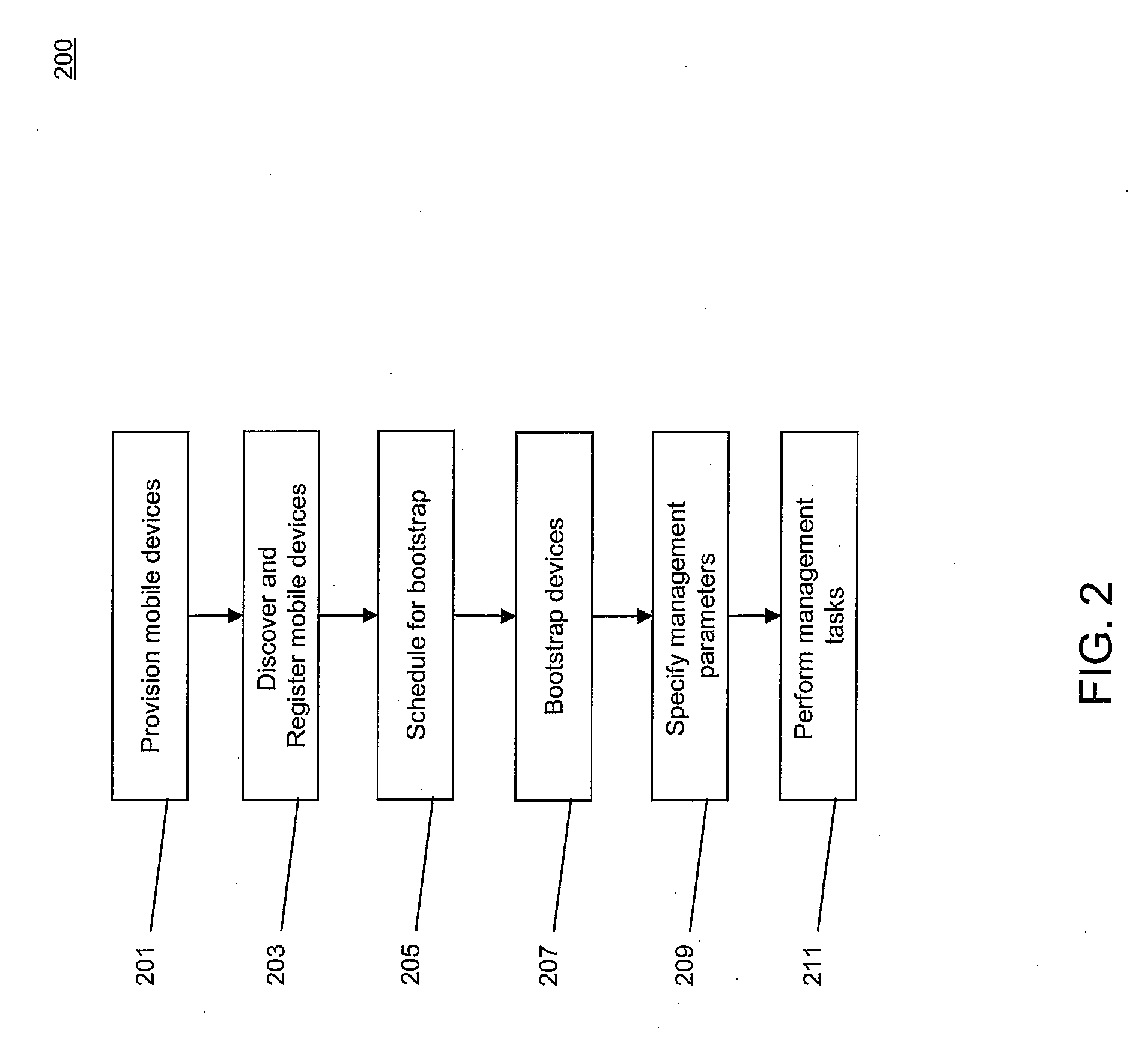

The invention provides systems and methods for managing mobile devices of supported by different platforms. In some embodiments, the invention provides this management capability by utilizing one or more agents or modules native to the platforms themselves to provide interaction with individual mobile. In some embodiments, the invention provides an abstraction layer by which management tasks or other functions relating to mobile devices of different types may be generally defined and translated for application to mobile devices supported by different platforms. In some embodiments, the invention utilizes existing organizational structure of an enterprise or organization to define management permission for mobile device administrators and end users as well as to define policy configuration schemes for mobile devices. In some embodiments, the invention tracks the lifecycle of mobile devices within an enterprise or organization as assets within the organization.

Owner:CA TECH INC

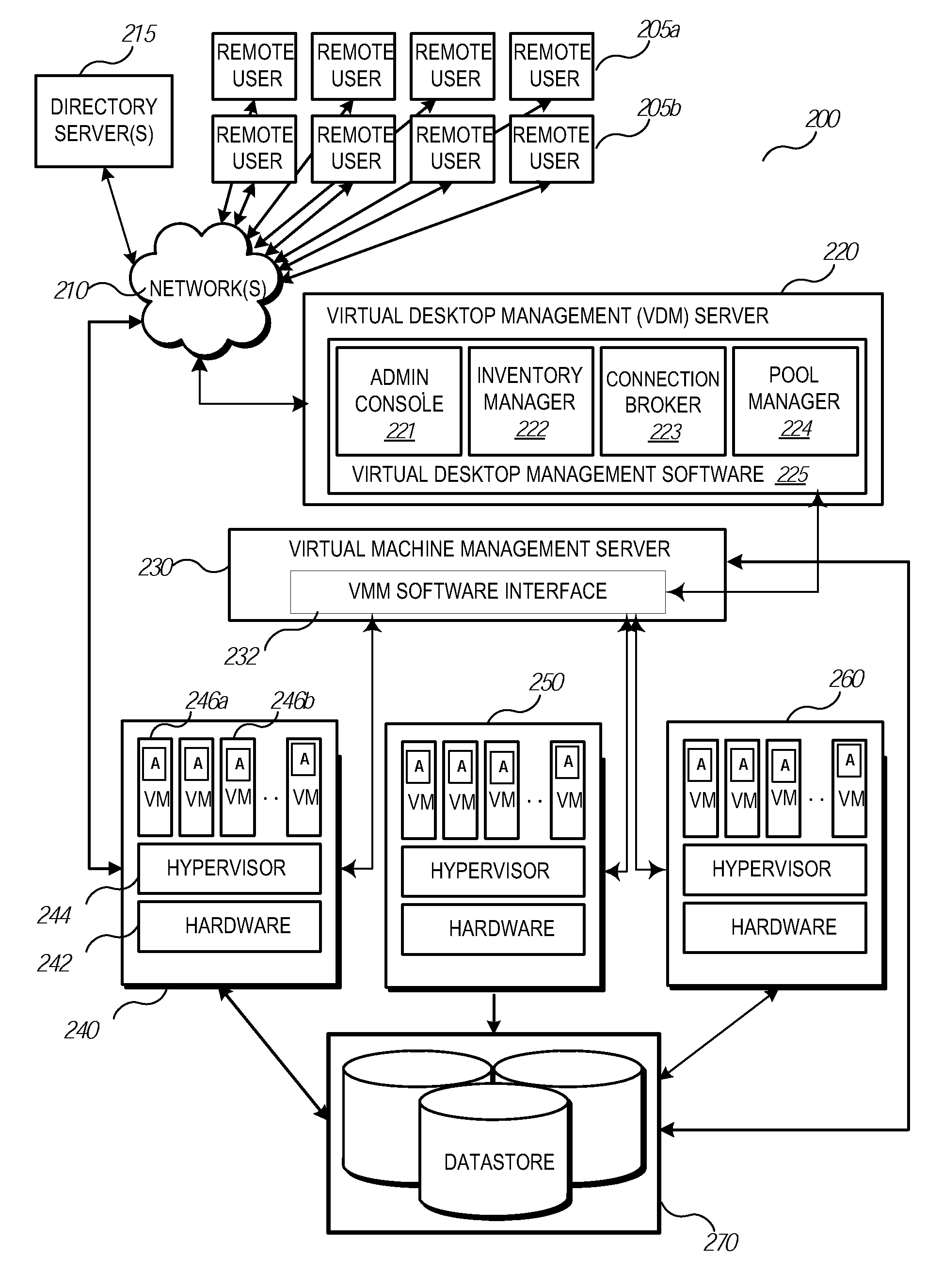

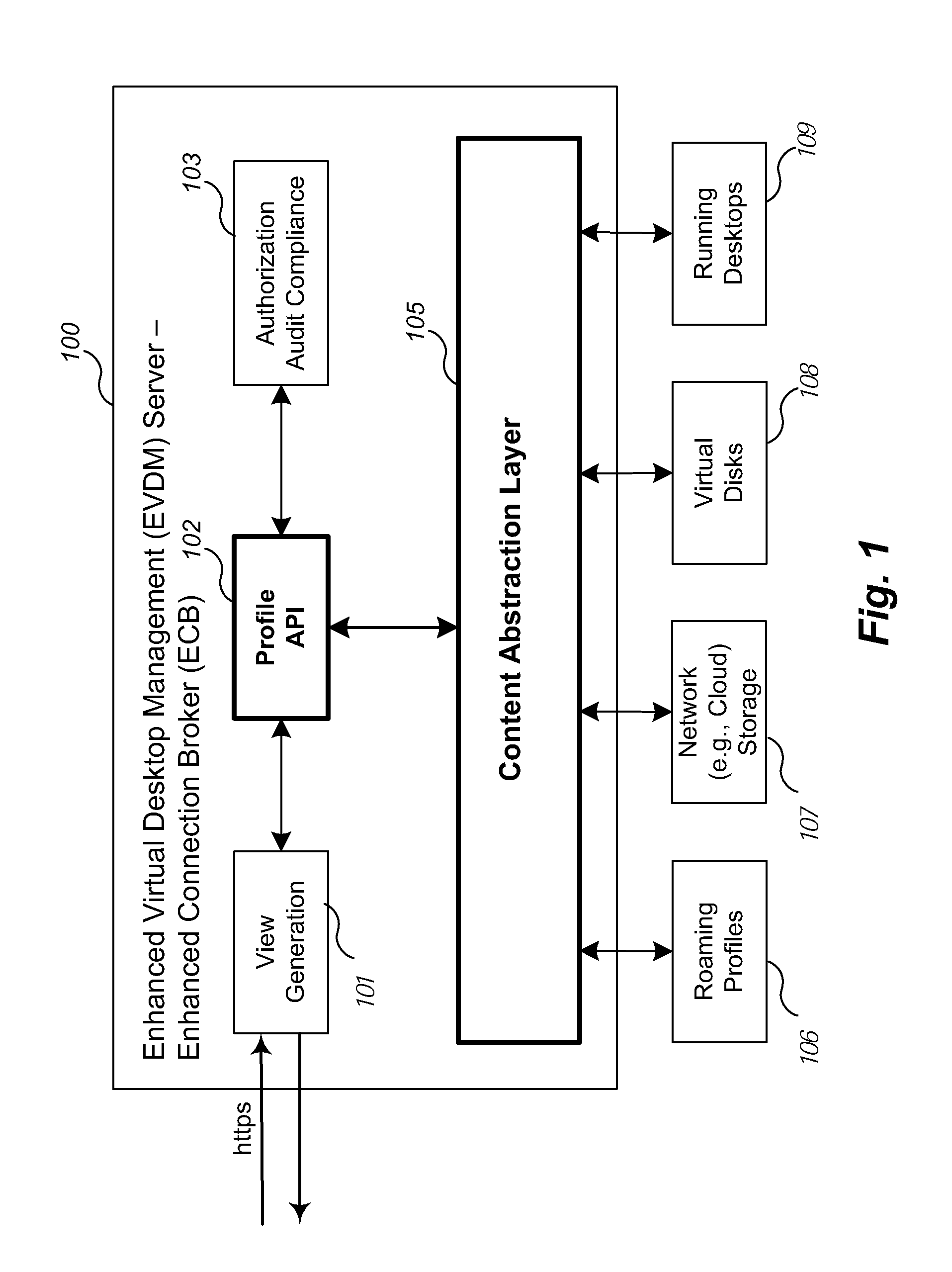

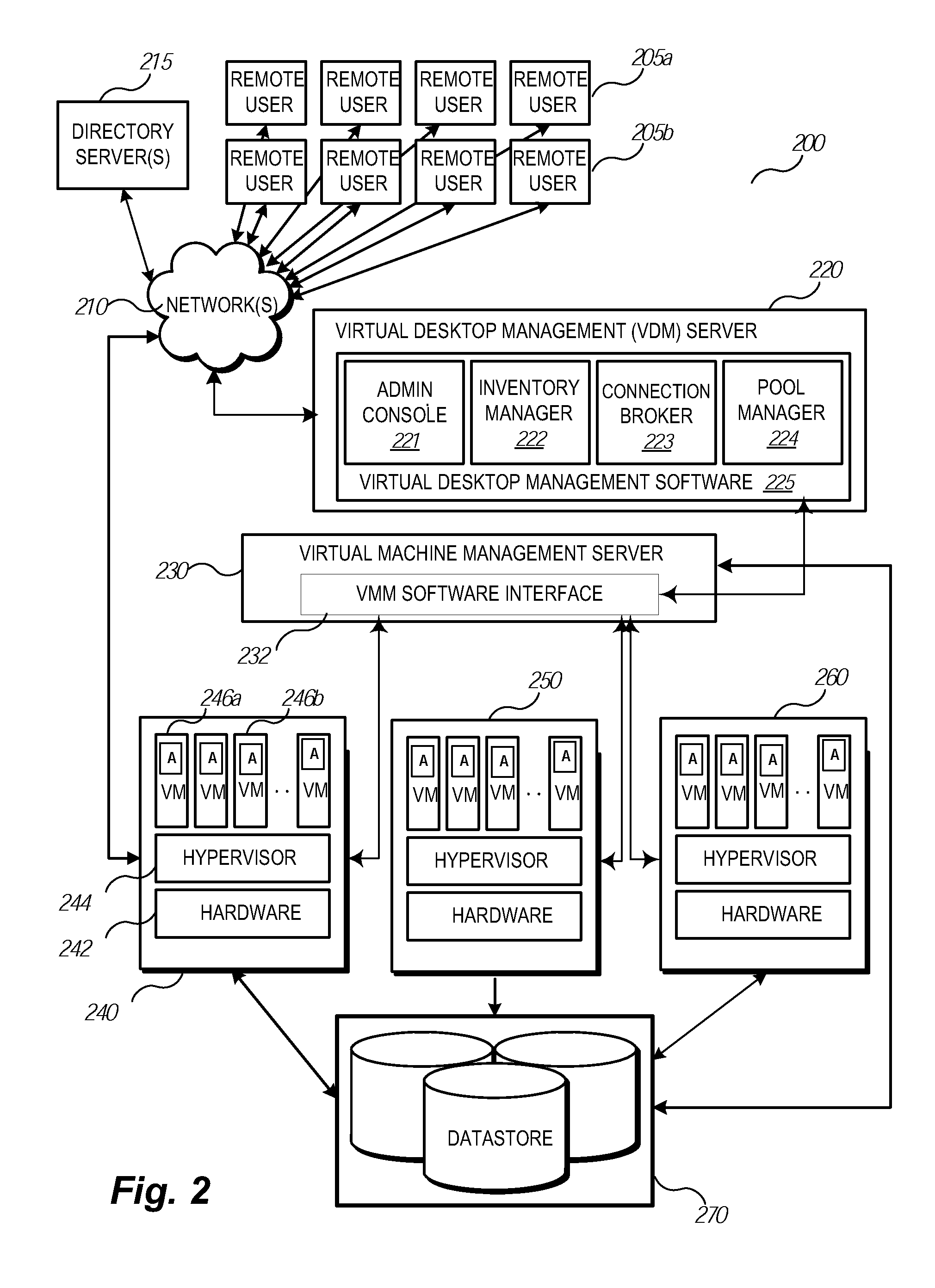

Accessing Virtual Disk Content of a Virtual Machine Without Running a Virtual Desktop

ActiveUS20110185355A1Multiprogramming arrangementsMultiple digital computer combinationsAbstraction layerData center

Methods, systems, and techniques for facilitating access to content stored remotely, for example, as part of a virtual machine infrastructure or elsewhere in a networked environment, using a uniform mechanism are provided. Example embodiments provide an Enhanced Virtual Desktop Management Server / System with a Content Abstraction Layer which enables users to access their data stored as part of a virtual machine environment, or replicated otherwise on a network, using a generic API. The API can be incorporated into a web browser or other third party interface to provide access to the users' data without needing to remote a bitmap representation of a virtual desktop display. Accordingly, users can access their data, applications, and settings regardless of the type of access device and regardless of whether the corresponding virtual desktop is running in the data center, provisioned in the datacenter but running on a client device, or not running at all.

Owner:VMWARE INC

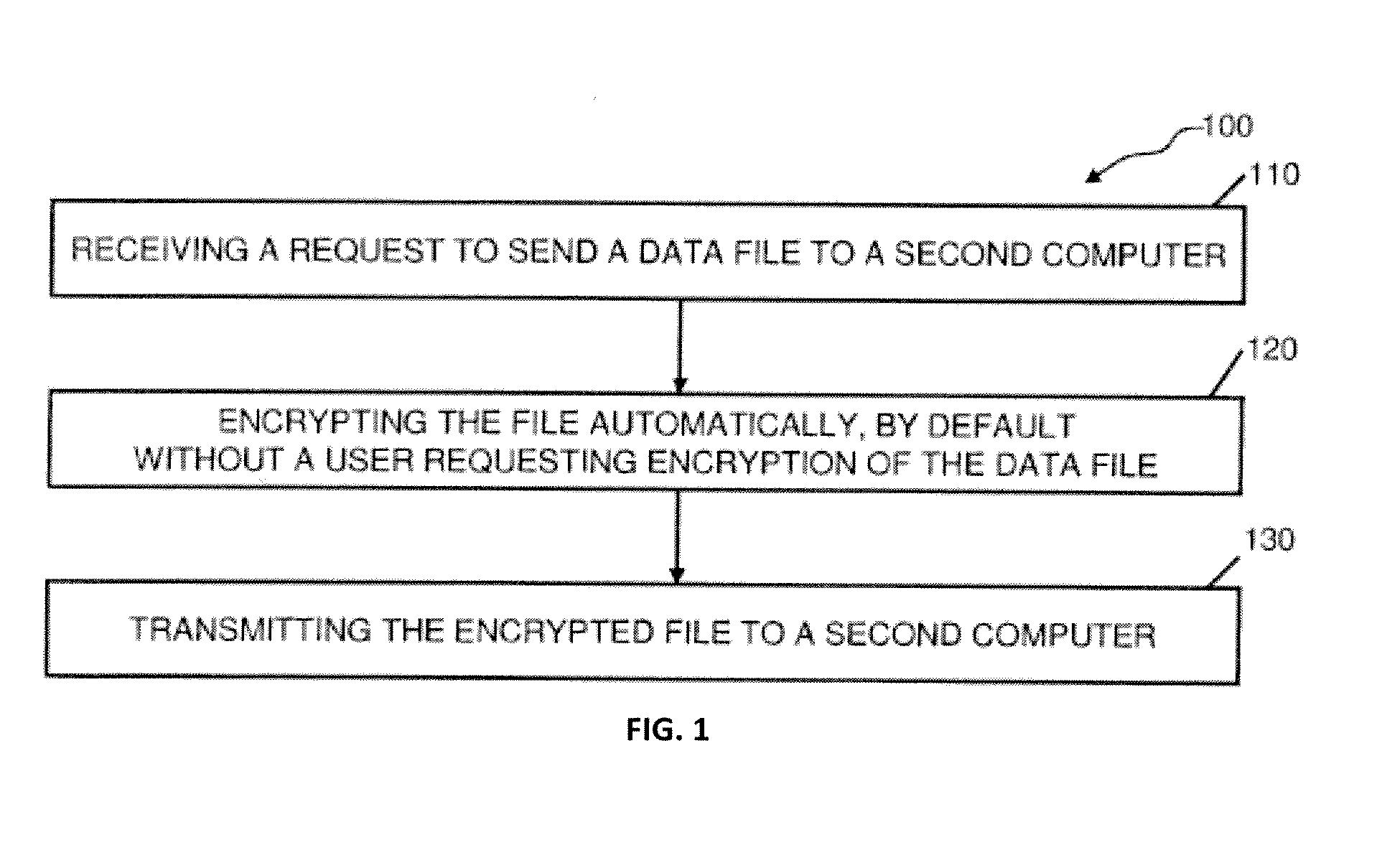

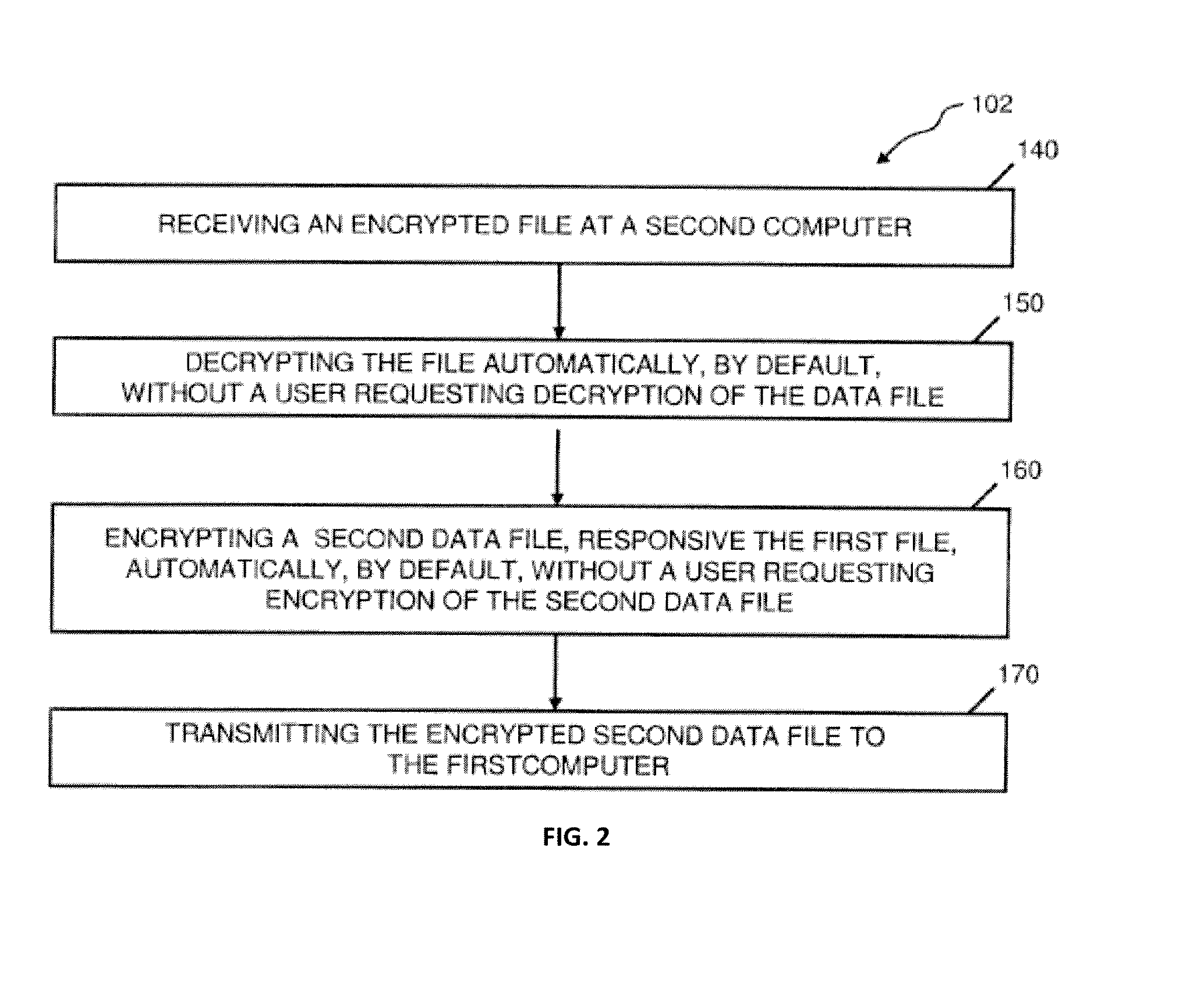

Abstraction layer for default encryption with orthogonal encryption logic session object; and automated authentication, with a method for online litigation

InactiveUS20140304505A1Reduce decreaseData processing applicationsUser identity/authority verificationAbstraction layerSubject matter

Embodiments herein provide methods, apparatus, computer program products, software and means for (1) an abstraction layer for default encryption, (2) with orthogonal encryption logic session object, and (3) automated authentication, (4) with a method for online litigation. In some cases subject matter disclosed herein relates to default data encryption; use a user's registration data to generate an encryption logic and related executable code, including servers and client applications; encryption as an automatic background task occurring through variable encryption logic, with authentication; embodiments are also described for conducting online litigation through pleadings formed as meta-files that trigger litigation related algorithms in order to automate and coordinate litigation.

Owner:VERIDICOM DE

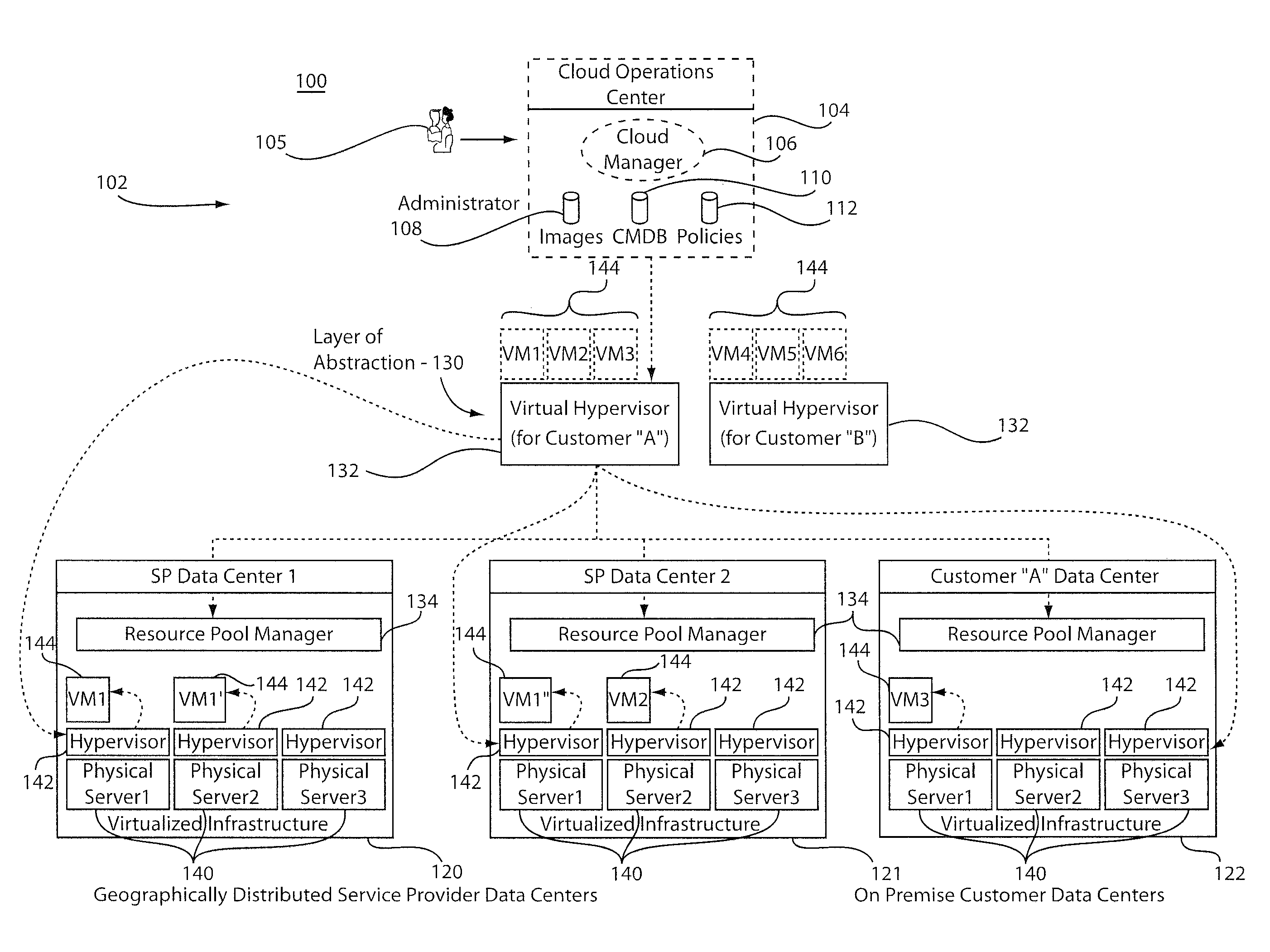

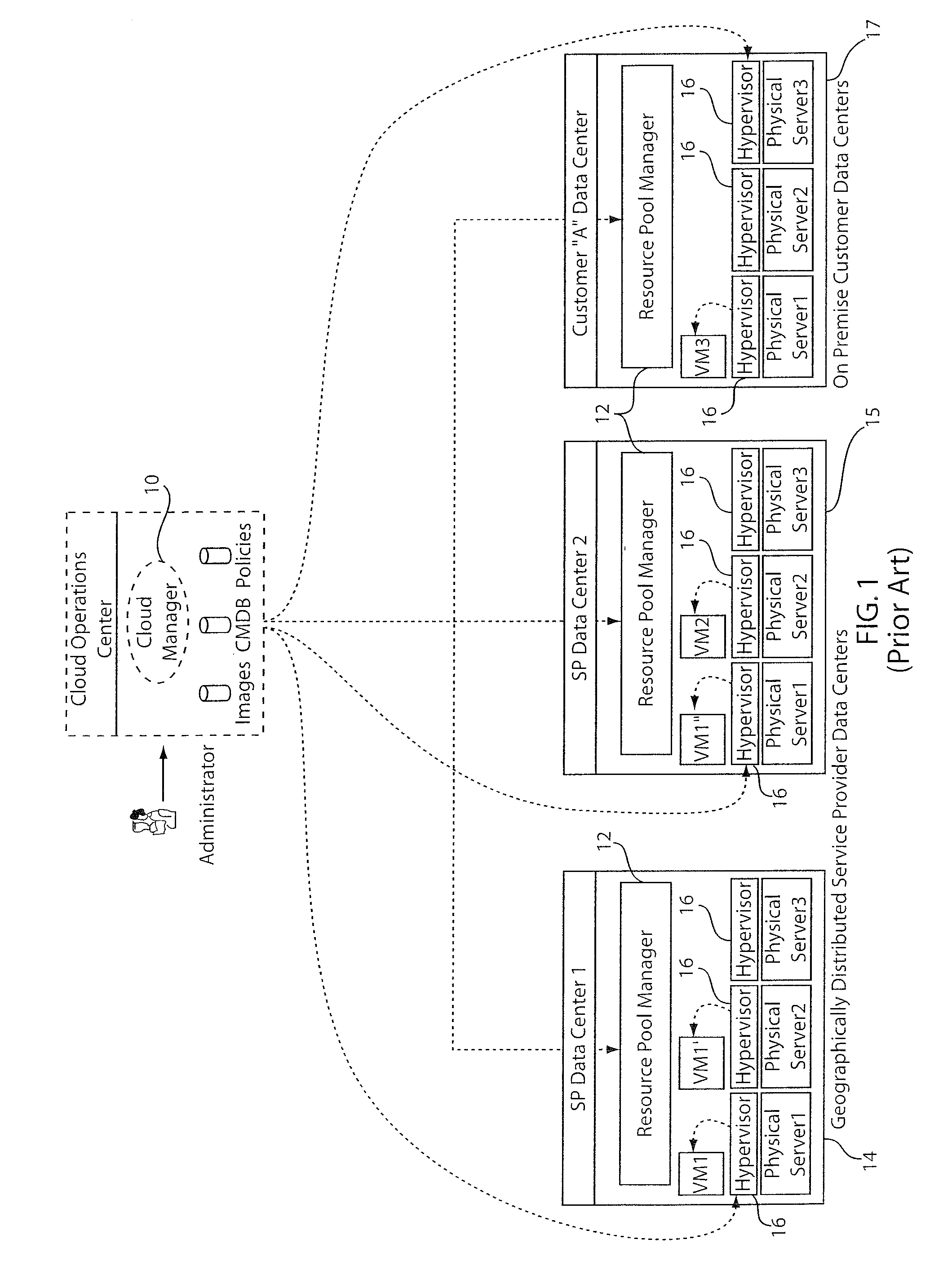

Method and system for abstracting non-functional requirements based deployment of virtual machines

ActiveUS20110185063A1Reduce complexityResource allocationMemory adressing/allocation/relocationAbstraction layerNon-functional requirement

A system and method for allocating resources in a cloud environment includes providing an abstraction layer between a cloud environment and one or more data centers by generating a virtual hypervisor as an application programming interface. Responsive to a workload request by the one or more data centers, resources are partitioned and virtual machines are instantiated in the one or more data centers using the virtual hypervisor such that non-functional requirements of the workload are addressed at the abstraction level using the virtual hypervisor.

Owner:IBM CORP

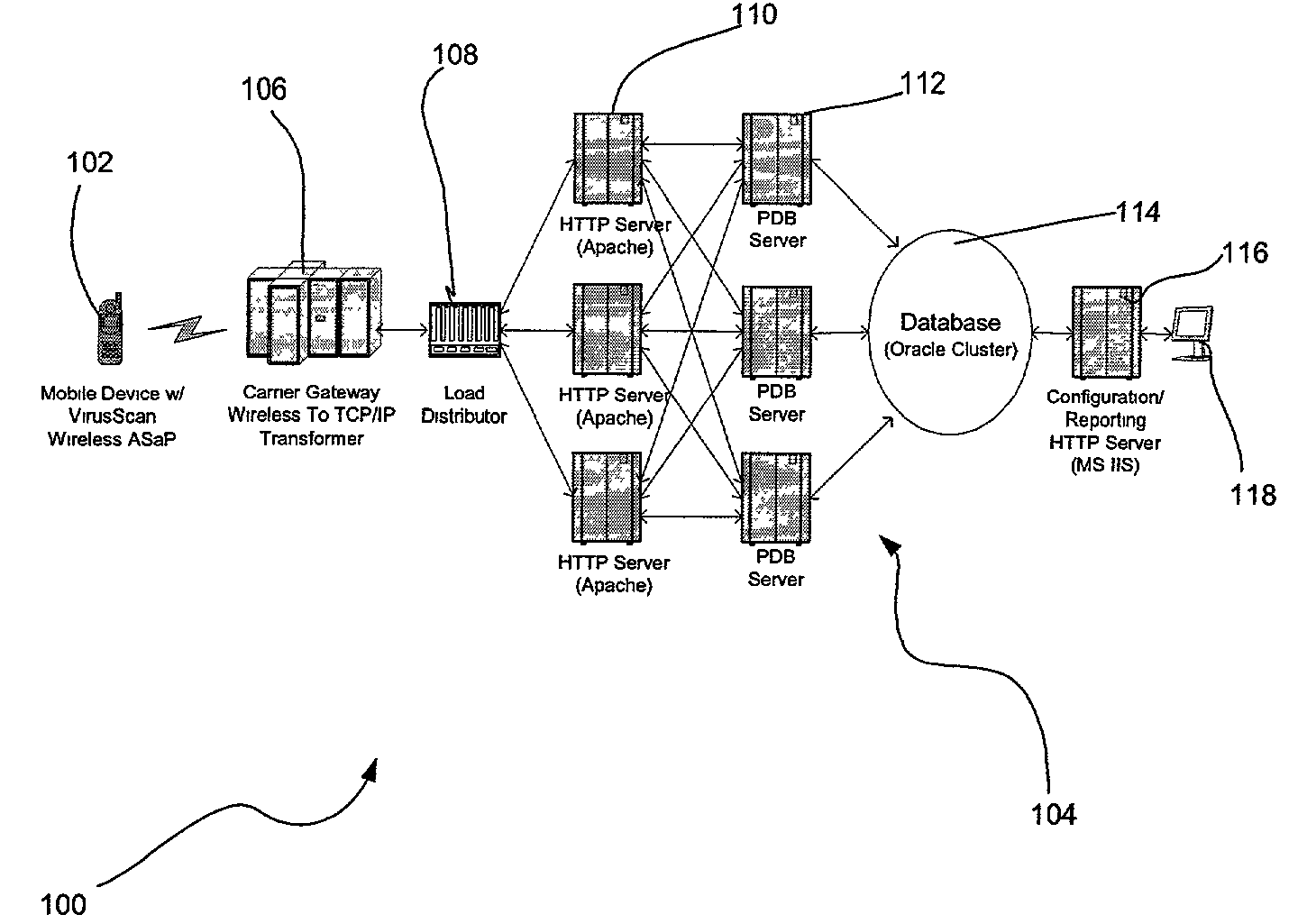

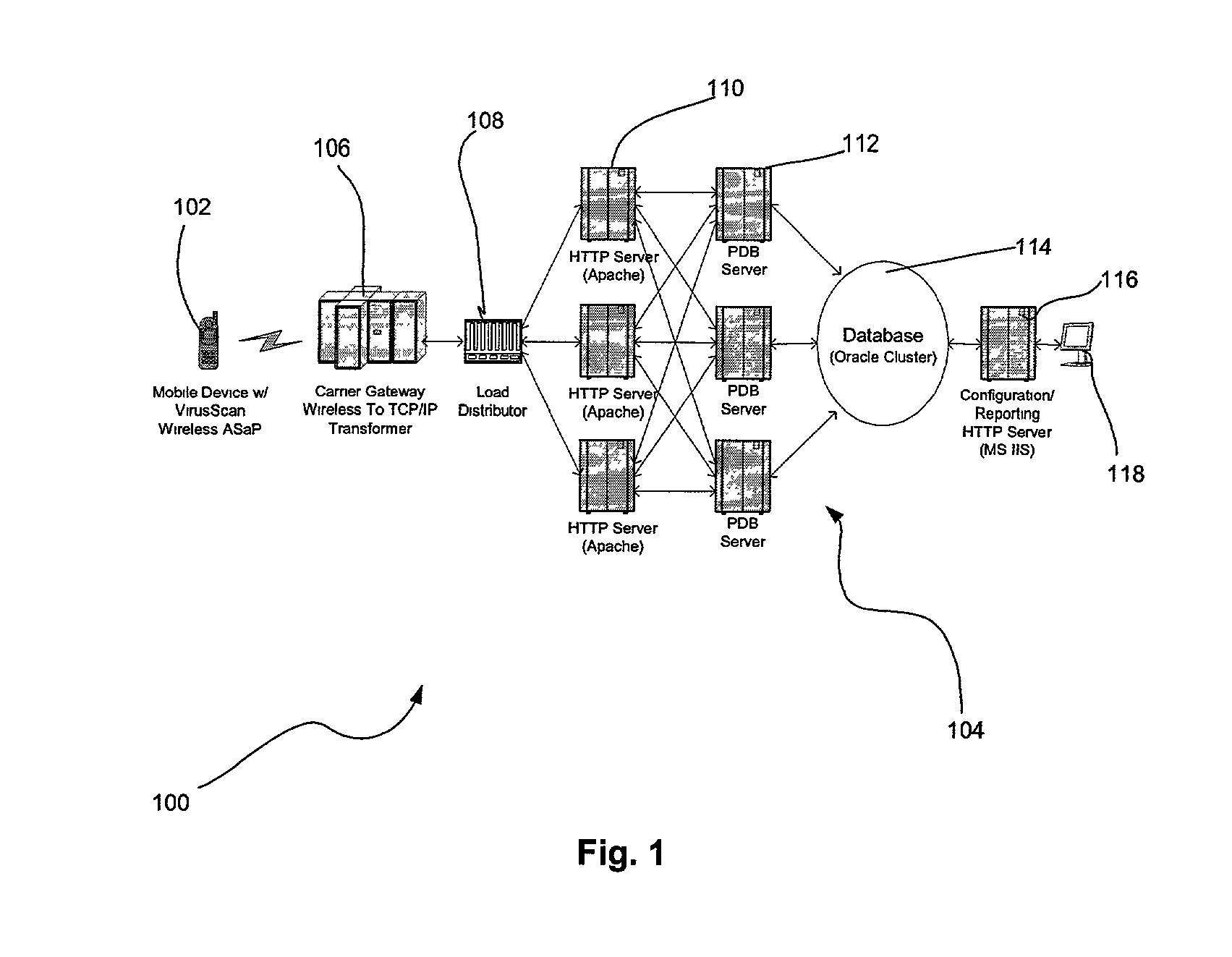

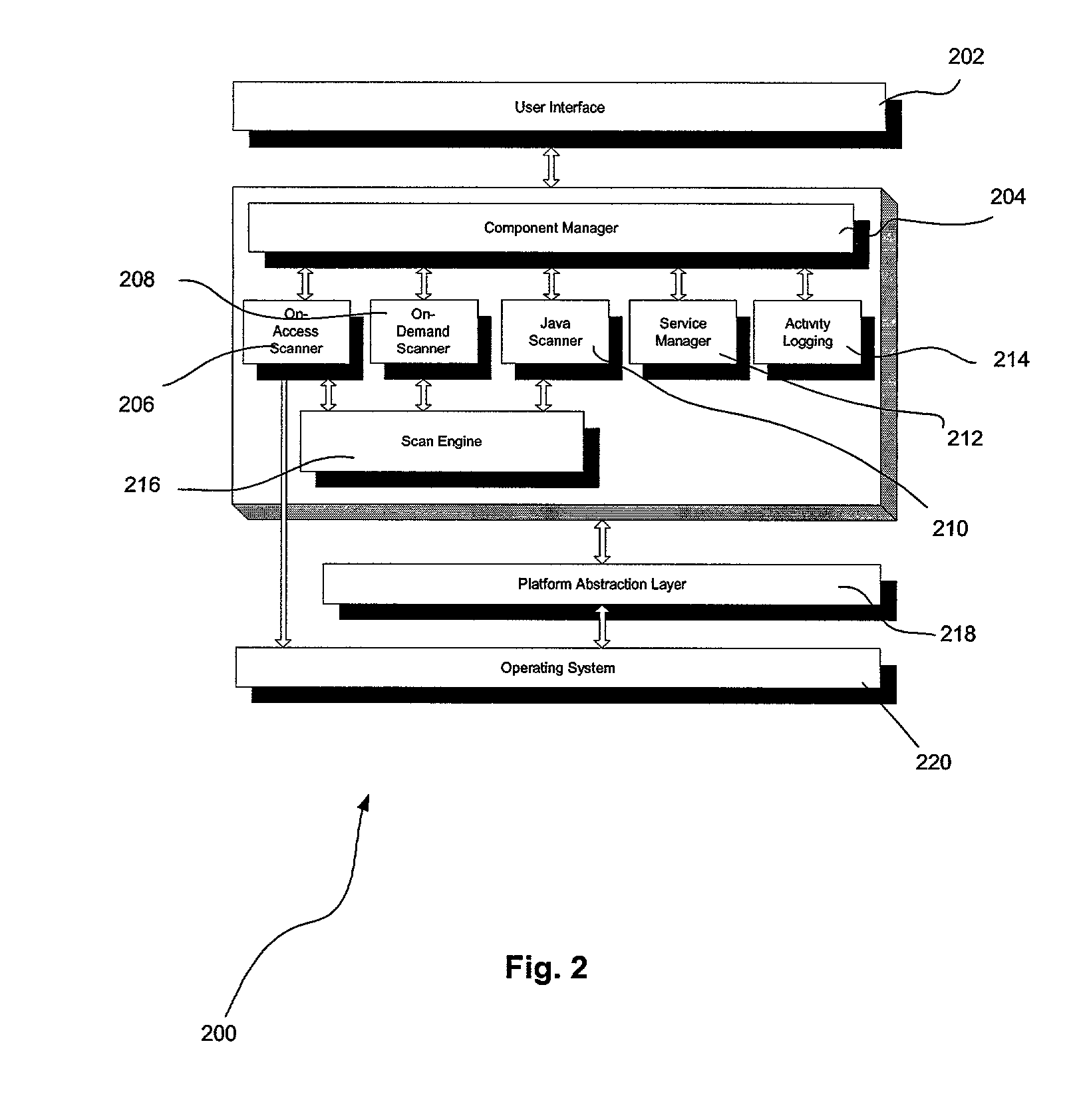

Platform abstraction layer for a wireless malware scanning engine

InactiveUS7096368B2Memory loss protectionUnauthorized memory use protectionAbstraction layerComputer module

A system, method and computer program product are provided for scanning a mobile wireless device for malware. Initially, a platform abstraction layer of a mobile wireless device is called. Further, an anti-malware scanner-related function module on the mobile wireless device is initiated utilizing the platform abstraction layer. Such platform abstraction layer enables the anti-malware scanner-related function module to be initiated on any of a plurality of different mobile wireless devices.

Owner:MCAFEE LLC

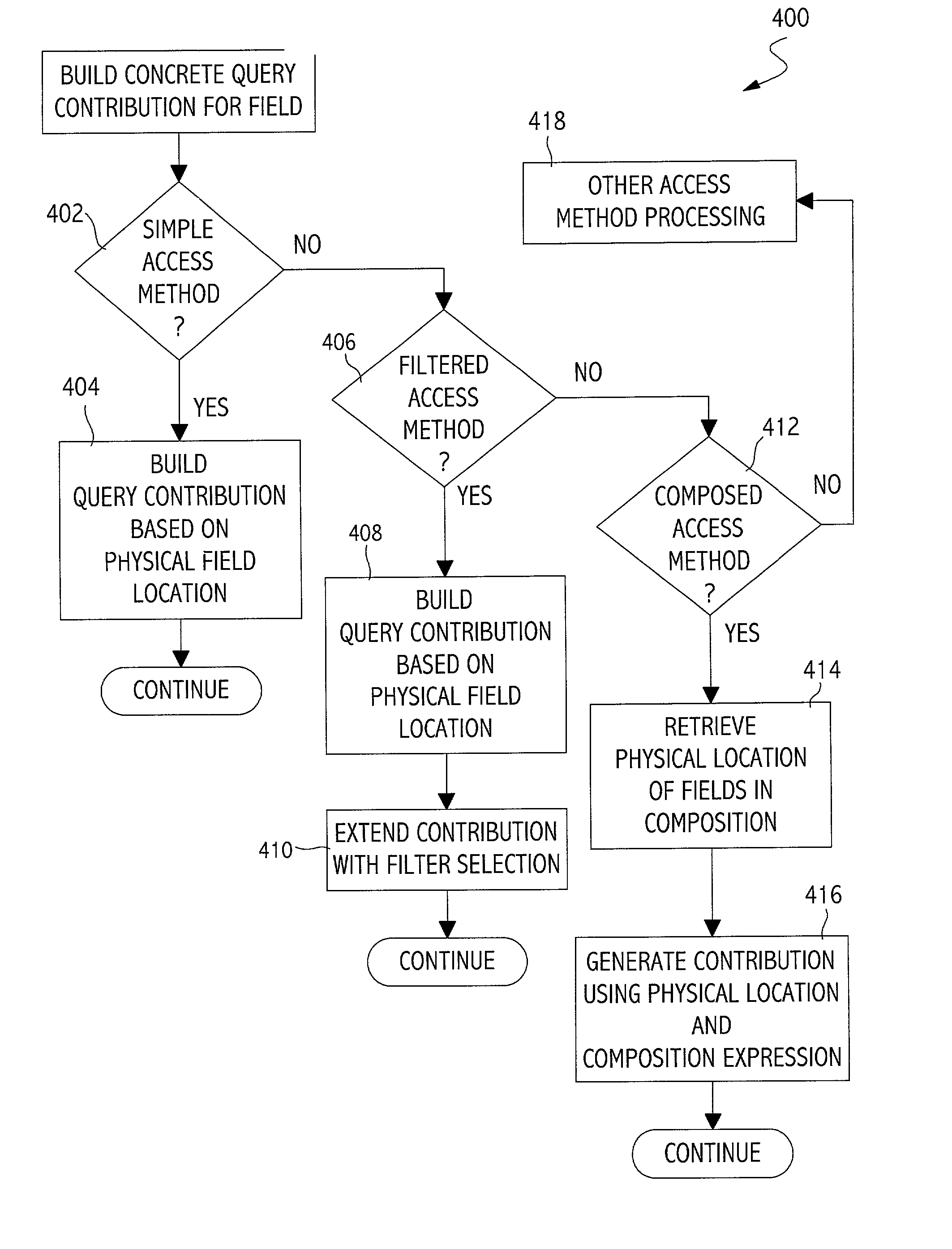

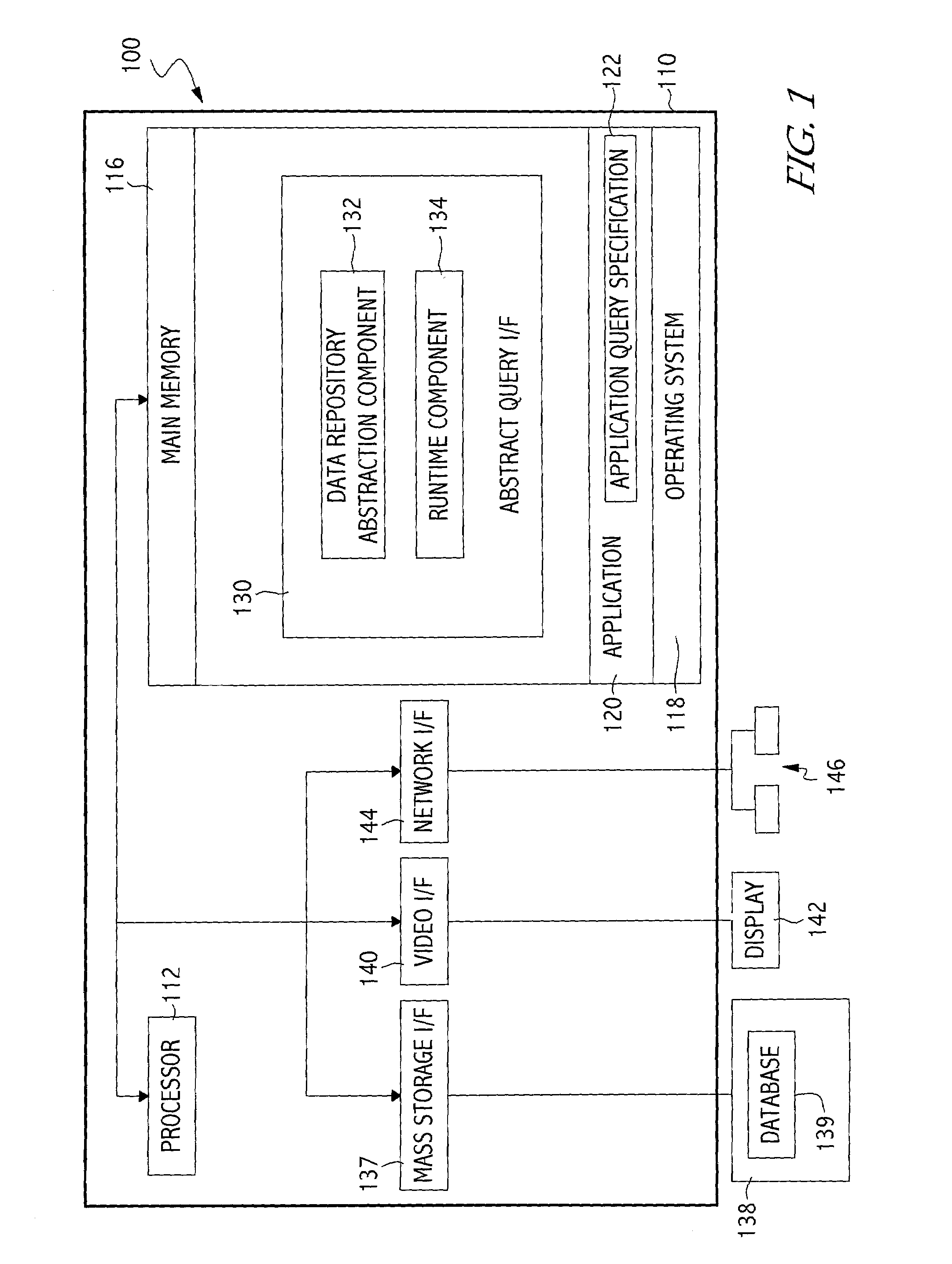

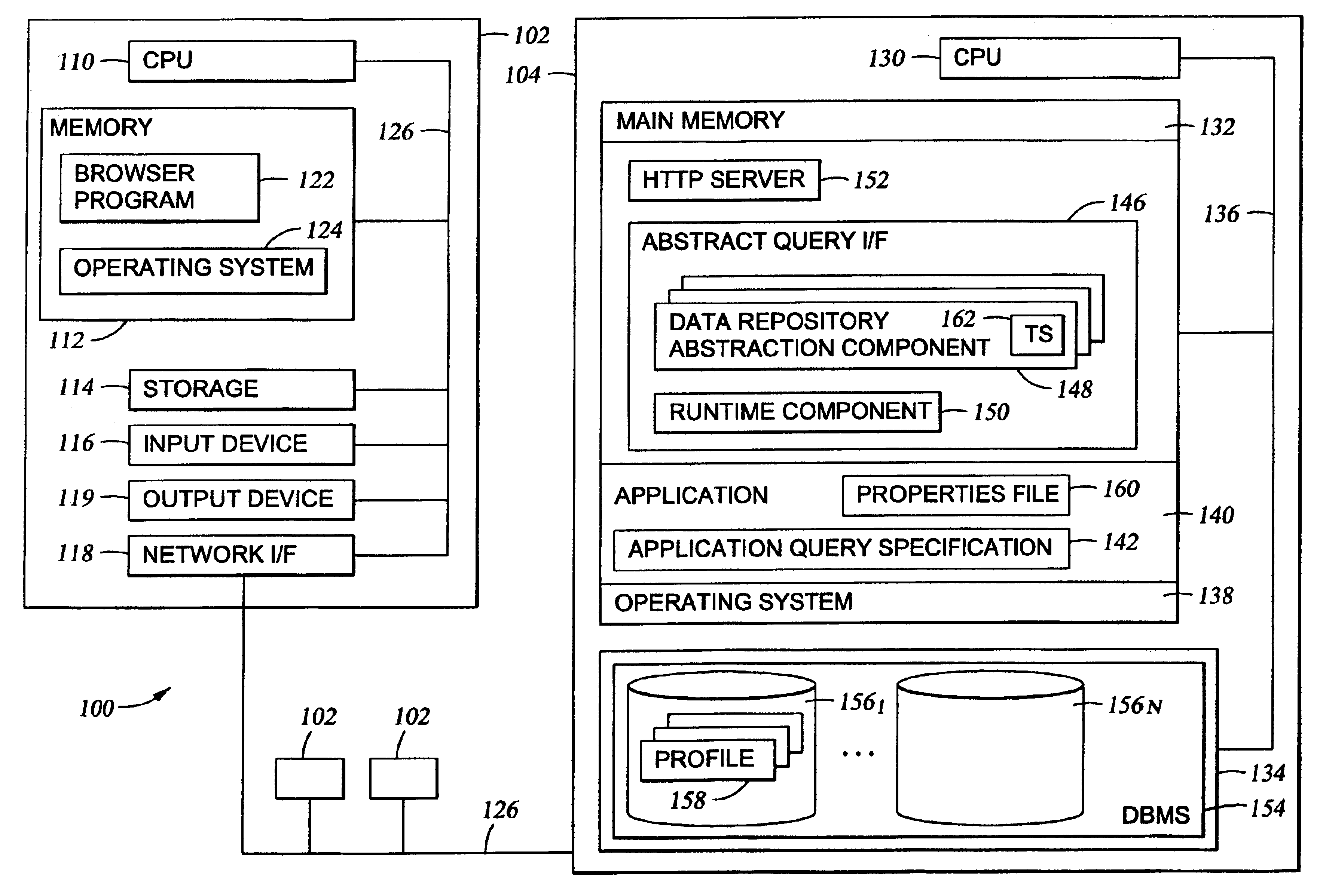

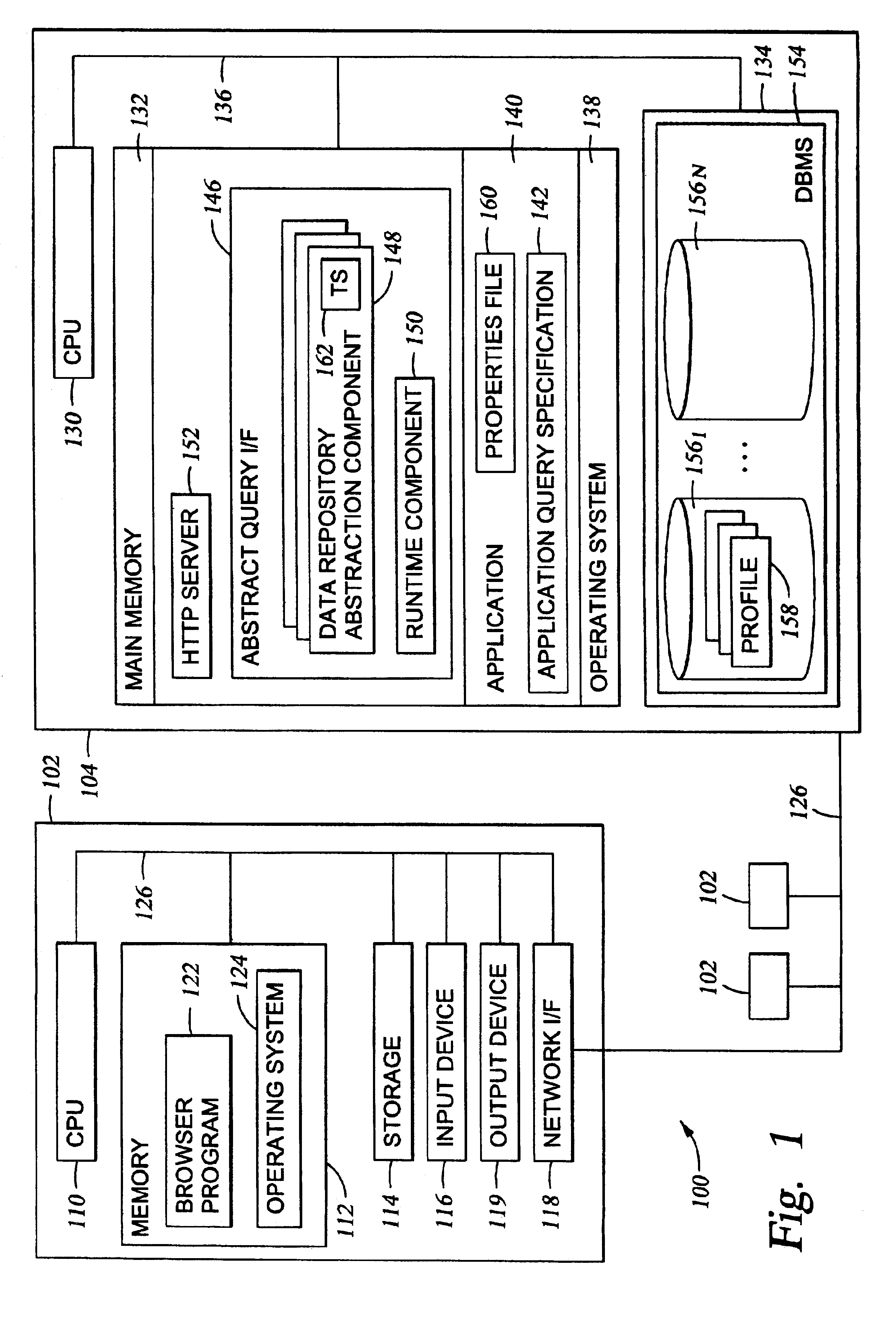

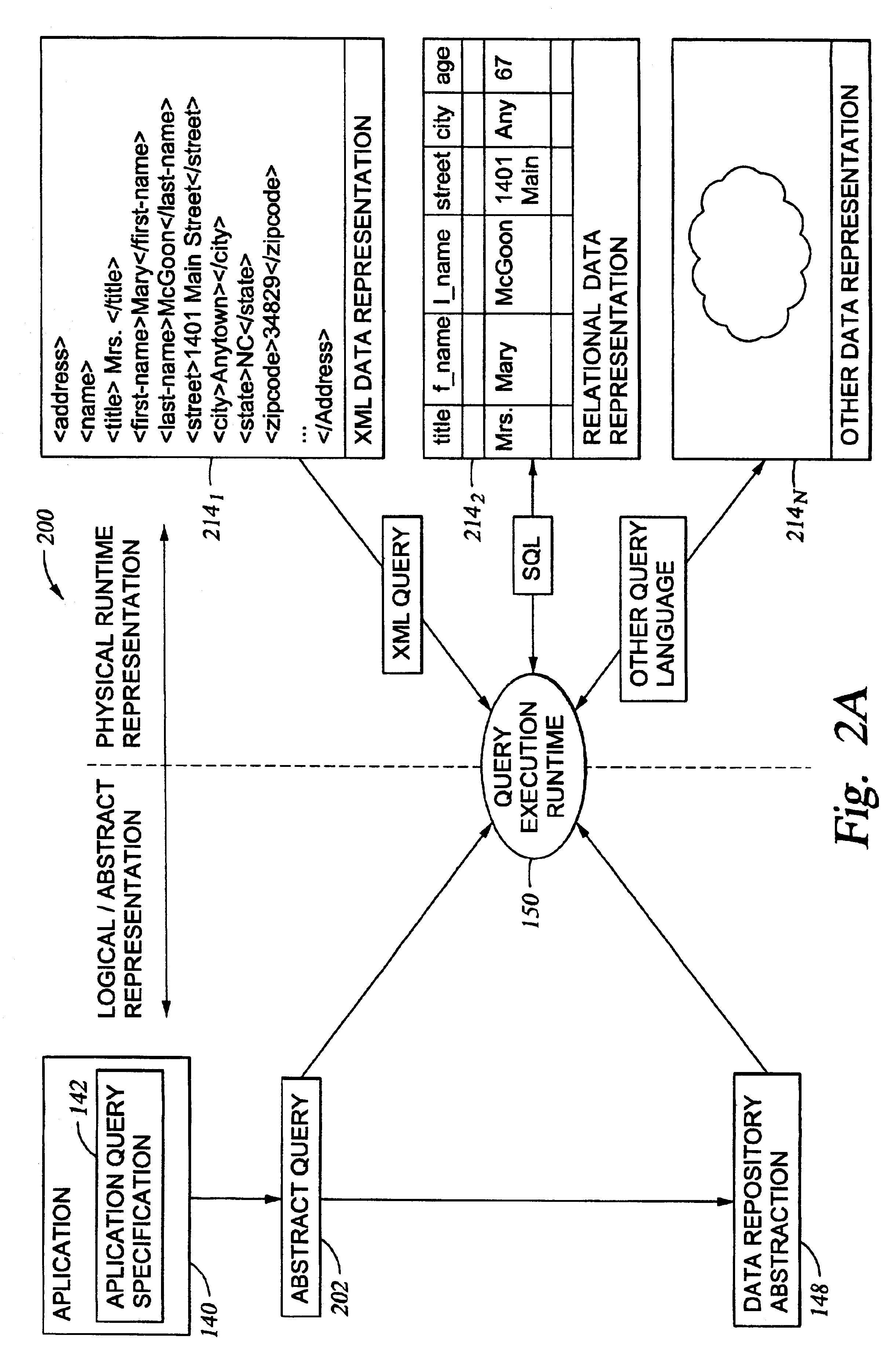

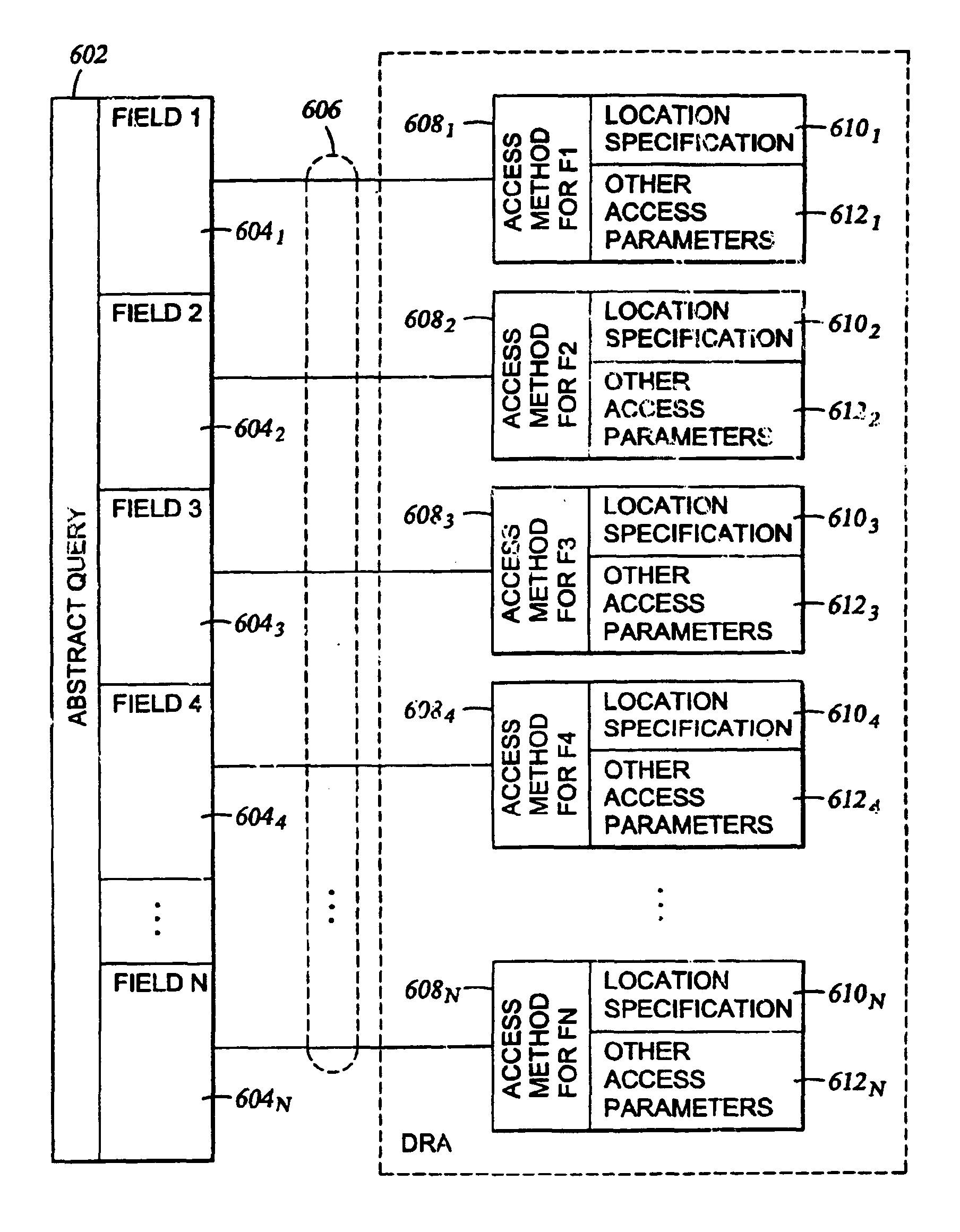

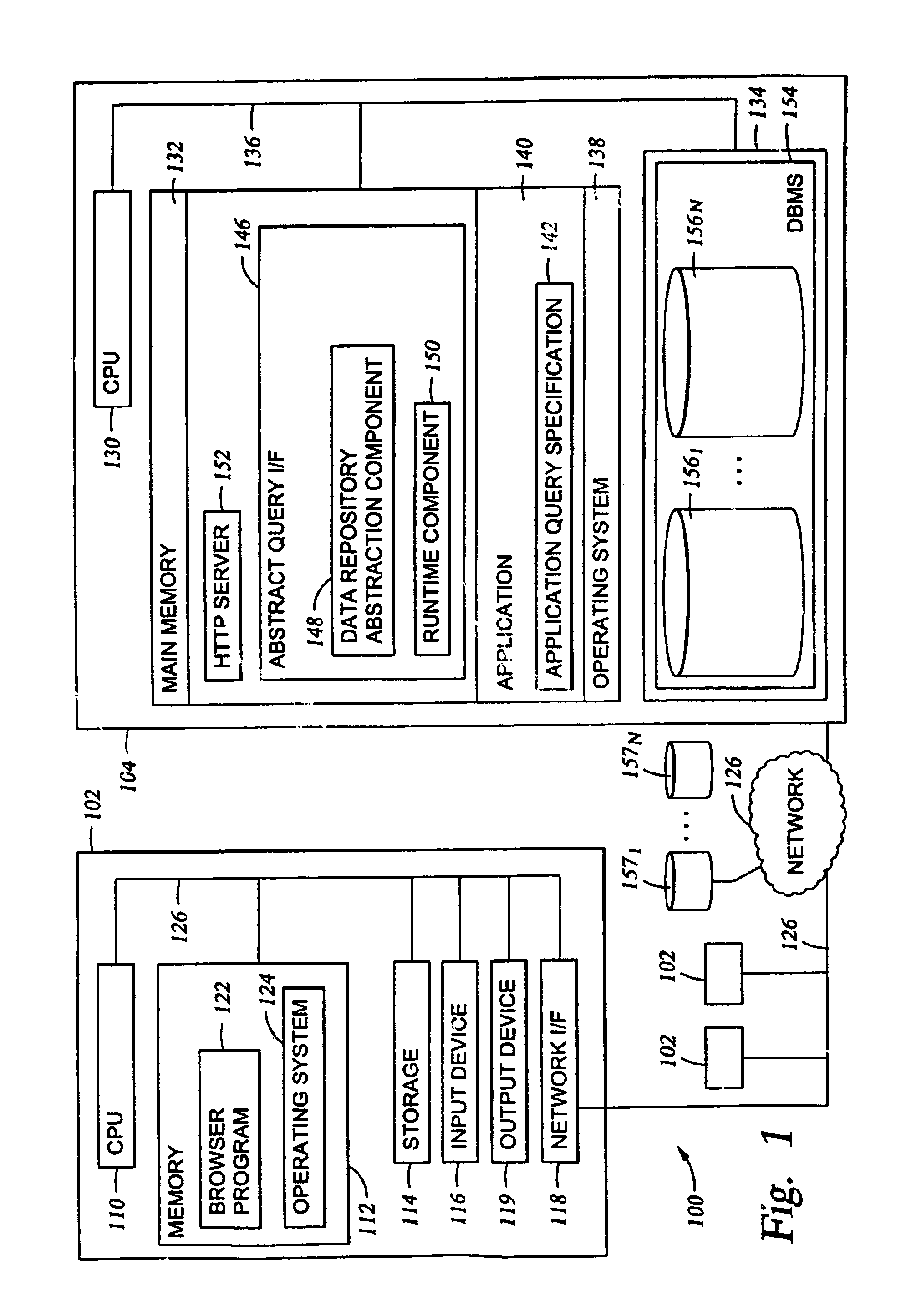

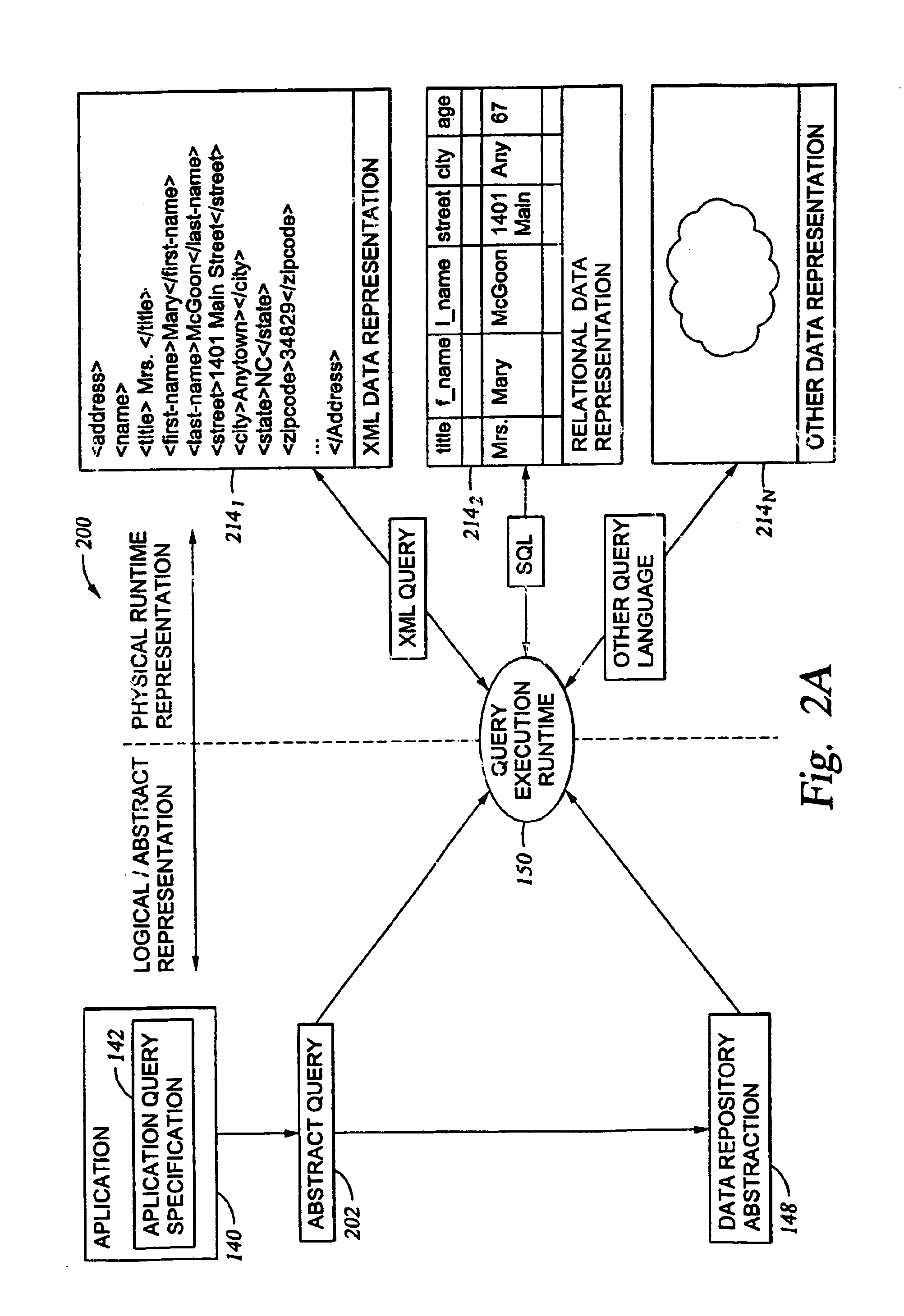

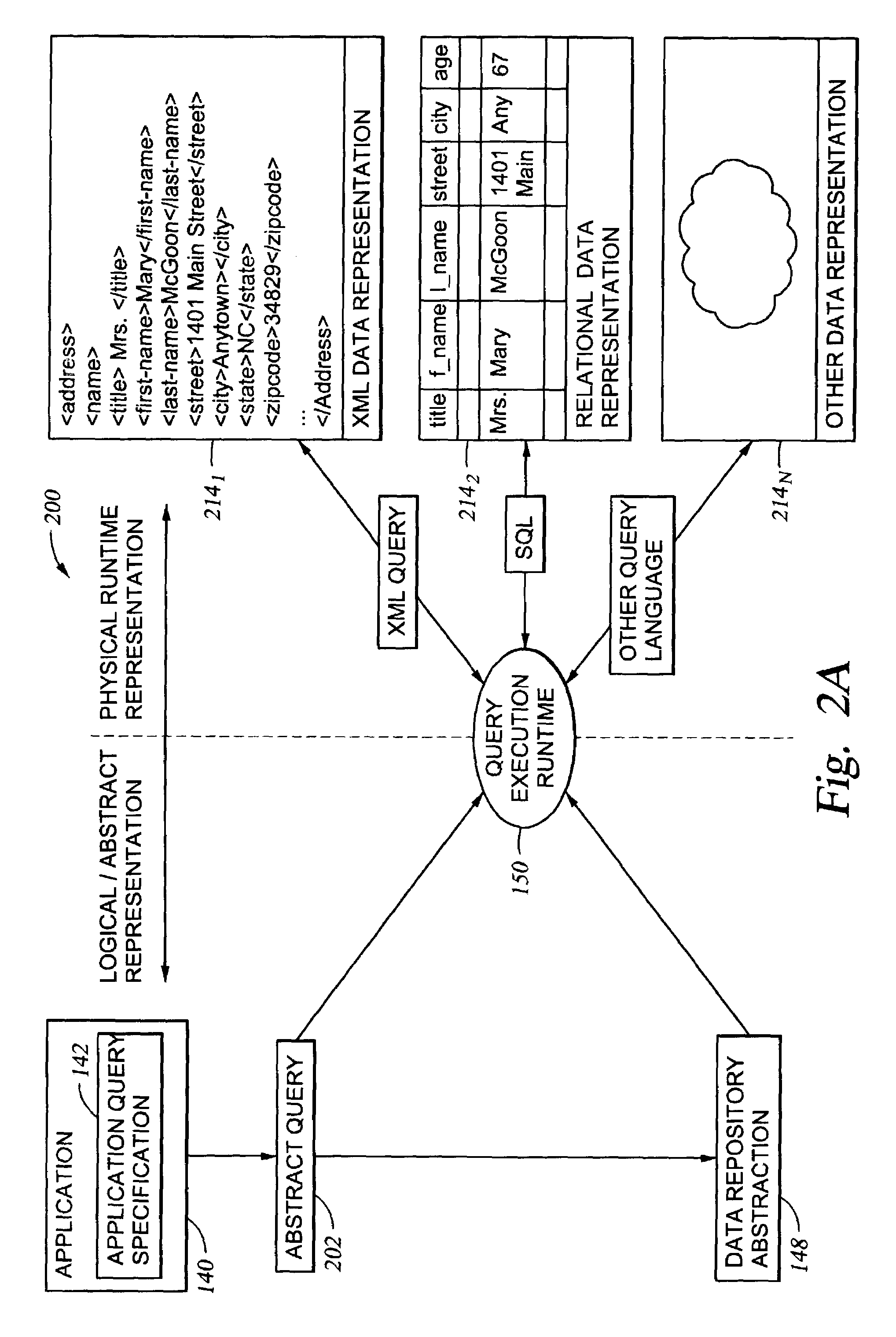

Application portability and extensibility through database schema and query abstraction

InactiveUS6996558B2Data processing applicationsDigital data information retrievalExtensibilityAbstraction layer

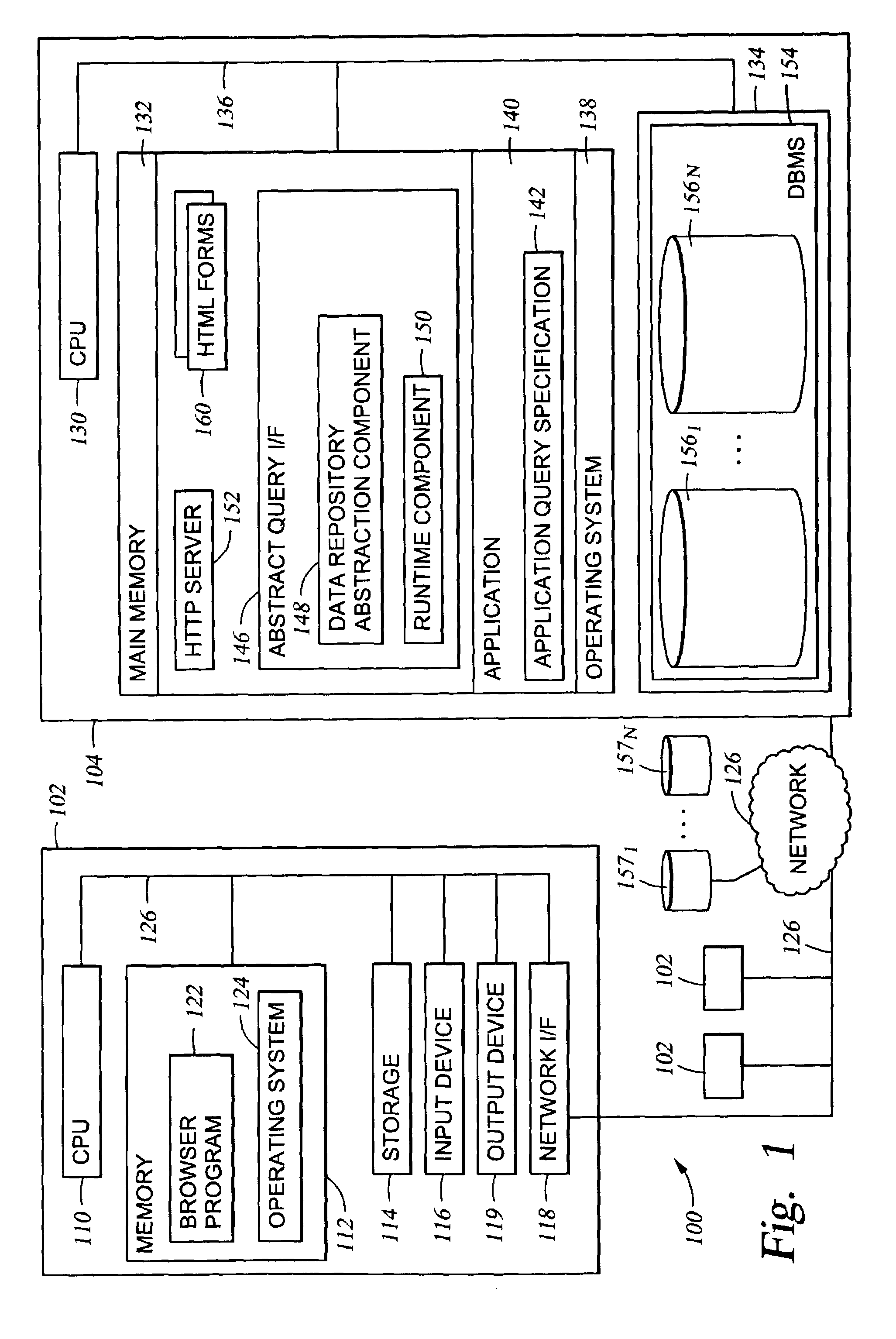

The present invention generally is directed to a system, method and article of manufacture for accessing data independent of the particular manner in which the data is physically represented. In one embodiment, a data repository abstraction layer provides a logical view of the underlying data repository that is independent of the particular manner of data representation. A query abstraction layer is also provided and is based on the data repository abstraction layer. A runtime component performs translation of an abstract query into a form that can be used against a particular physical data representation.

Owner:WORKDAY INC

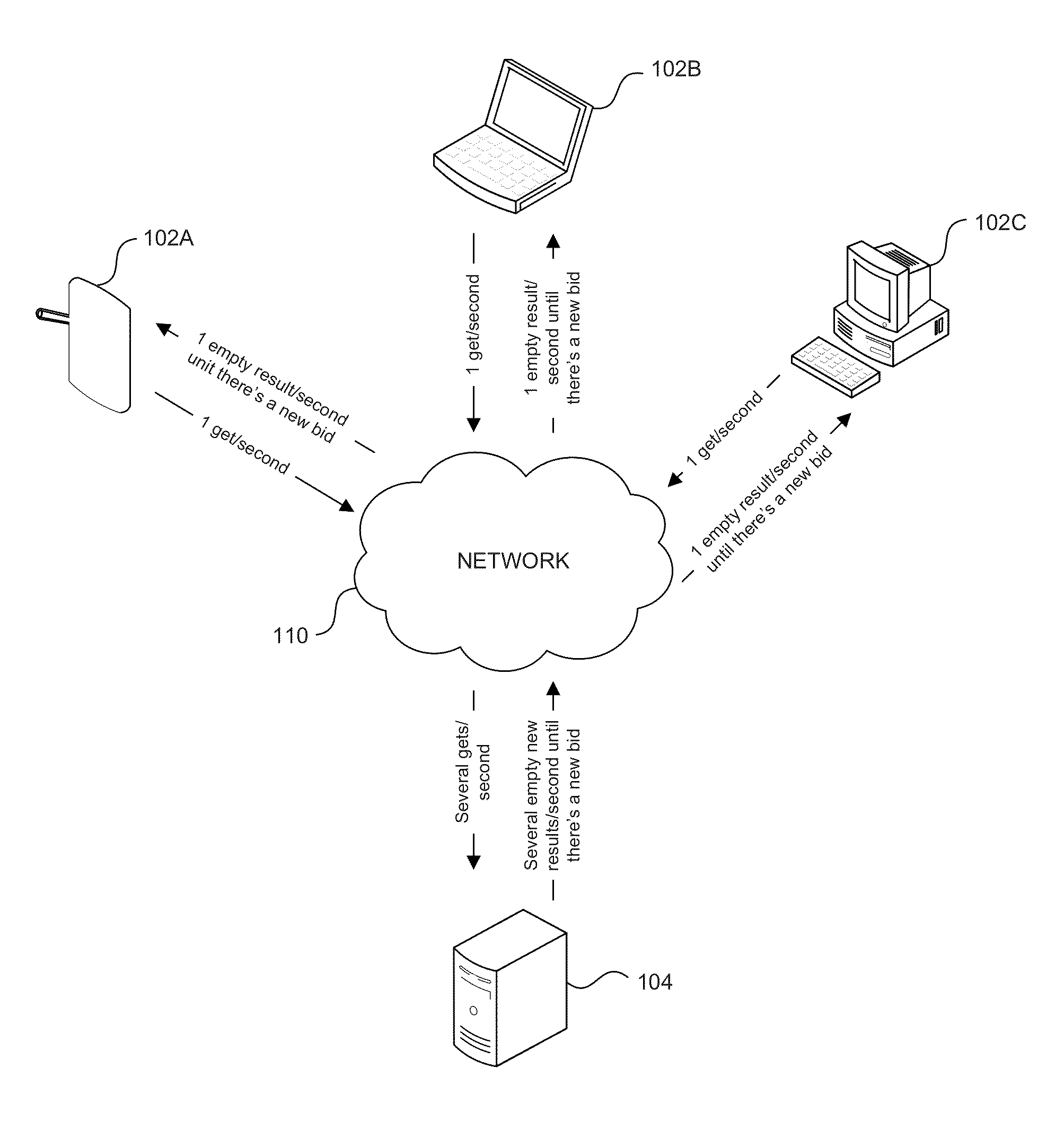

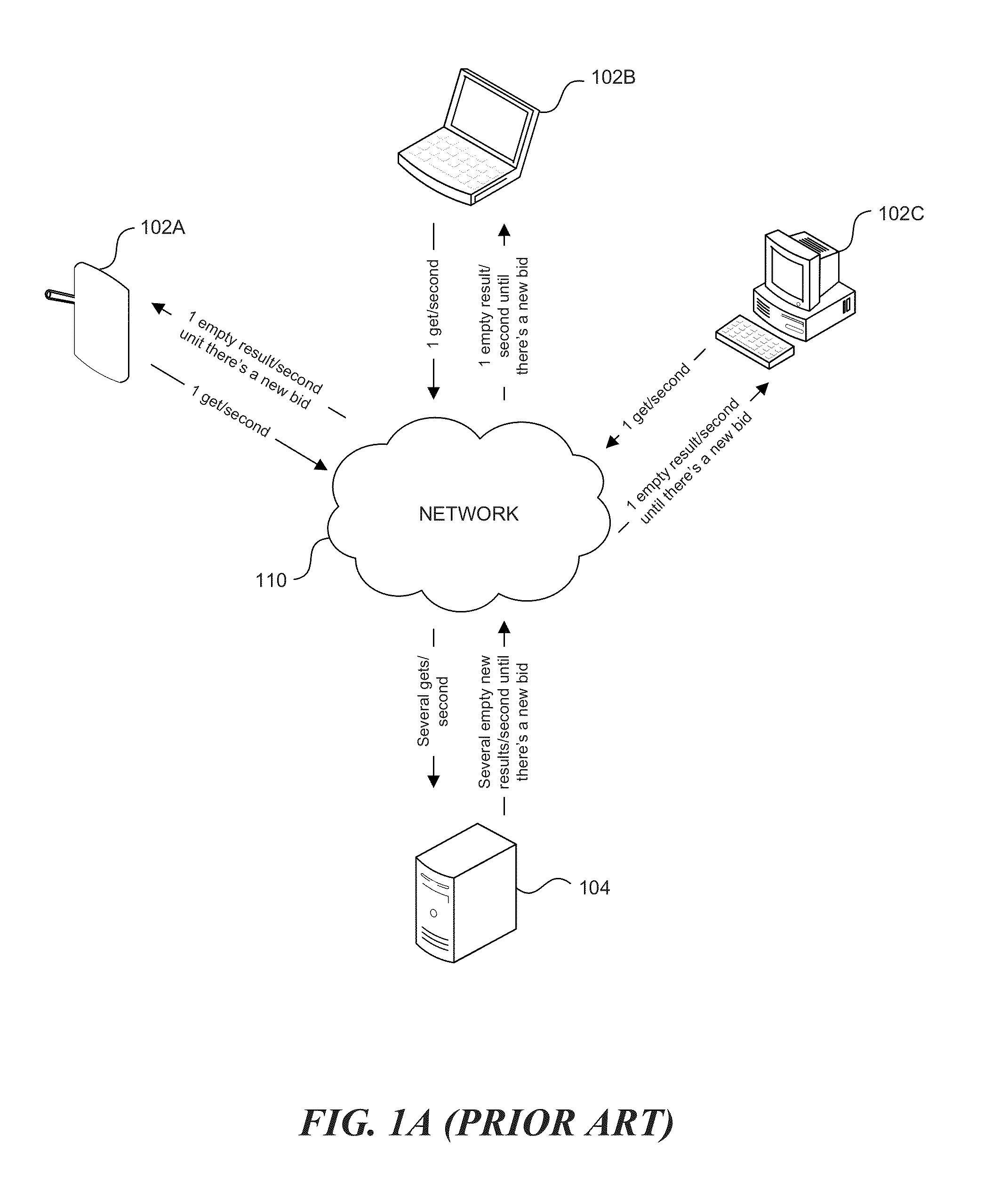

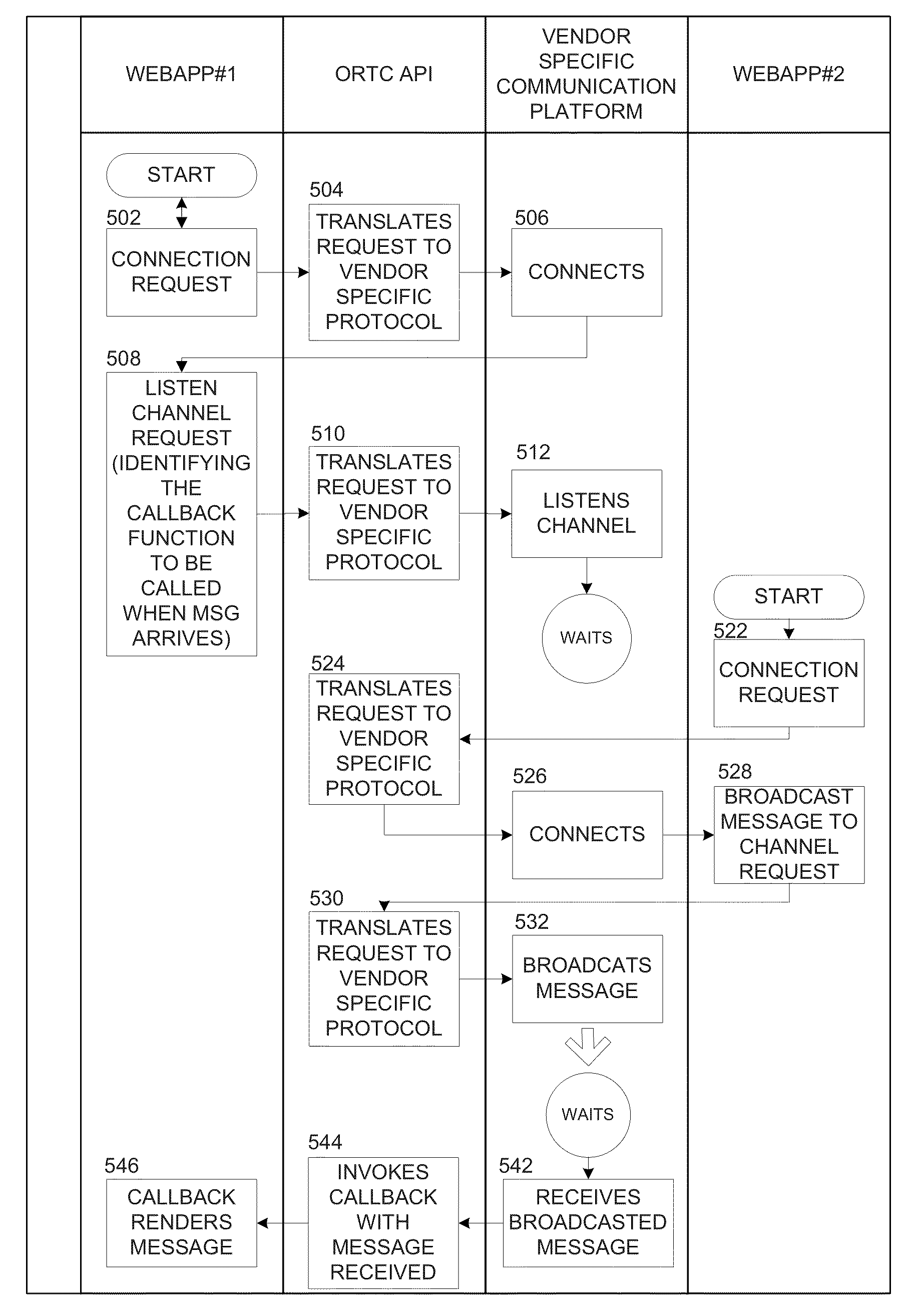

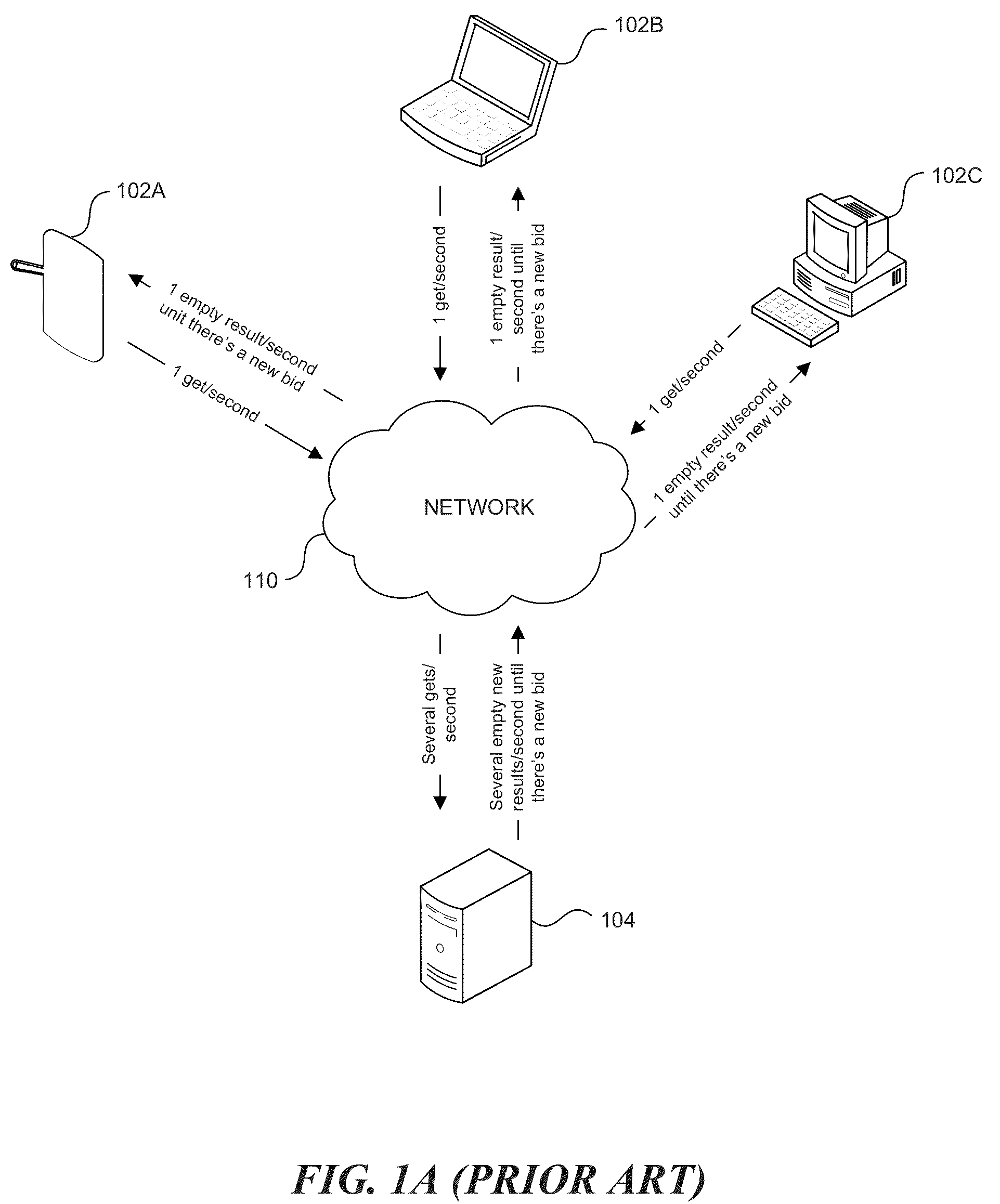

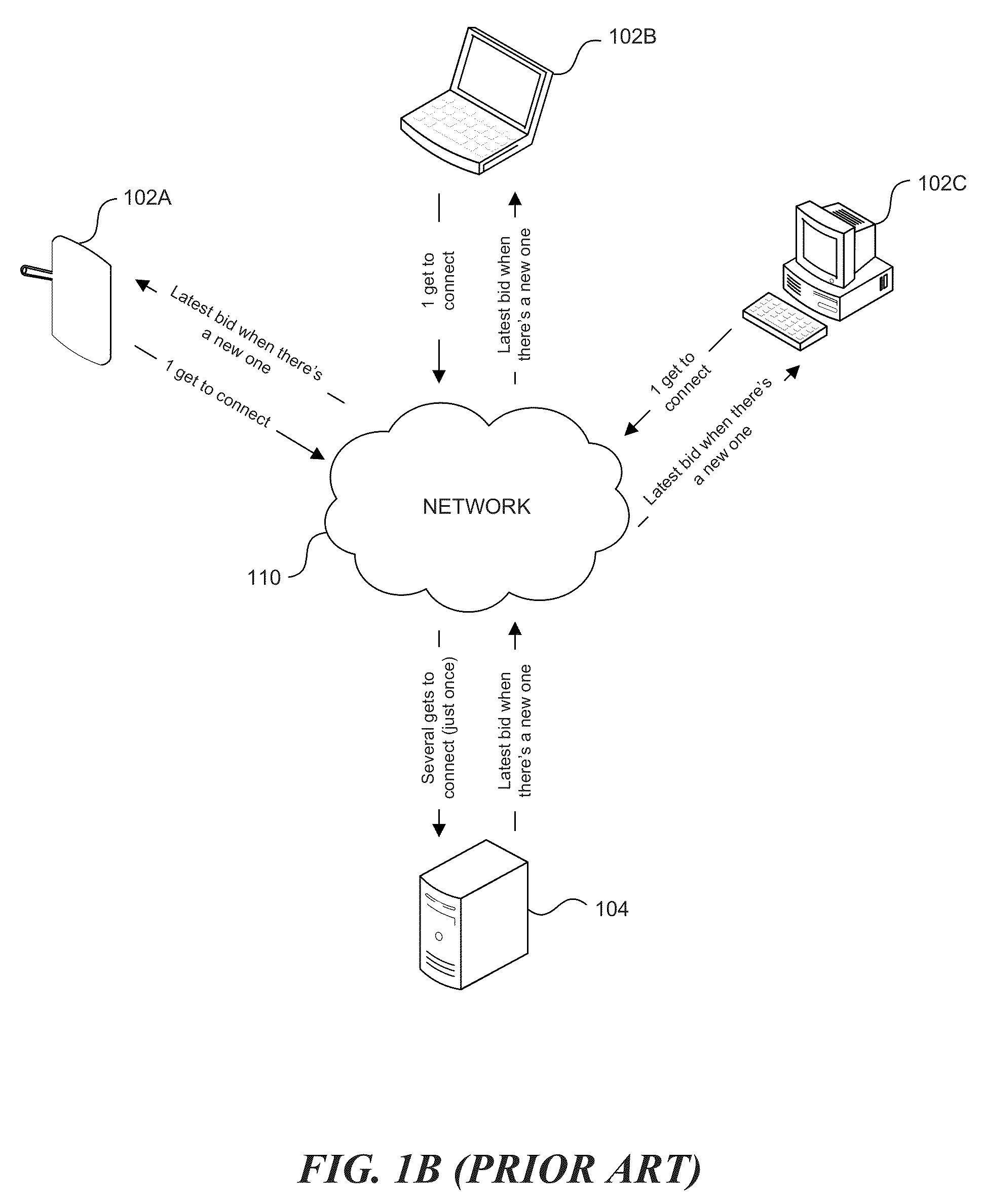

Methods and systems for access to real-time full-duplex web communications platforms

InactiveUS20130058262A1Relieve pressureConsistent interfaceNatural language data processingBroadcast service distributionAbstraction layerClient-side

At least one embodiment of this invention pertains to an abstraction layer that provides a consistent interface, with client-side and server-side implementations, to allow web client to interact with other web clients (that are connected to a common interactive event) in real-time over standard web ports without the web clients being tied to a specific real-time communications platform. At least some embodiments described herein contemplate methods and systems for establishing web communication among multiple web clients by providing a layer of abstraction between the web clients and the interactive session using interfaces to an Open Real-Time Connectivity (ORTC) layer. The system may use authentication methods to validate the web communications. The system may be implemented on a scalable, load-balanced, and fault-tolerant network.

Owner:IBT TECHAS E SISTEMAS LTDA

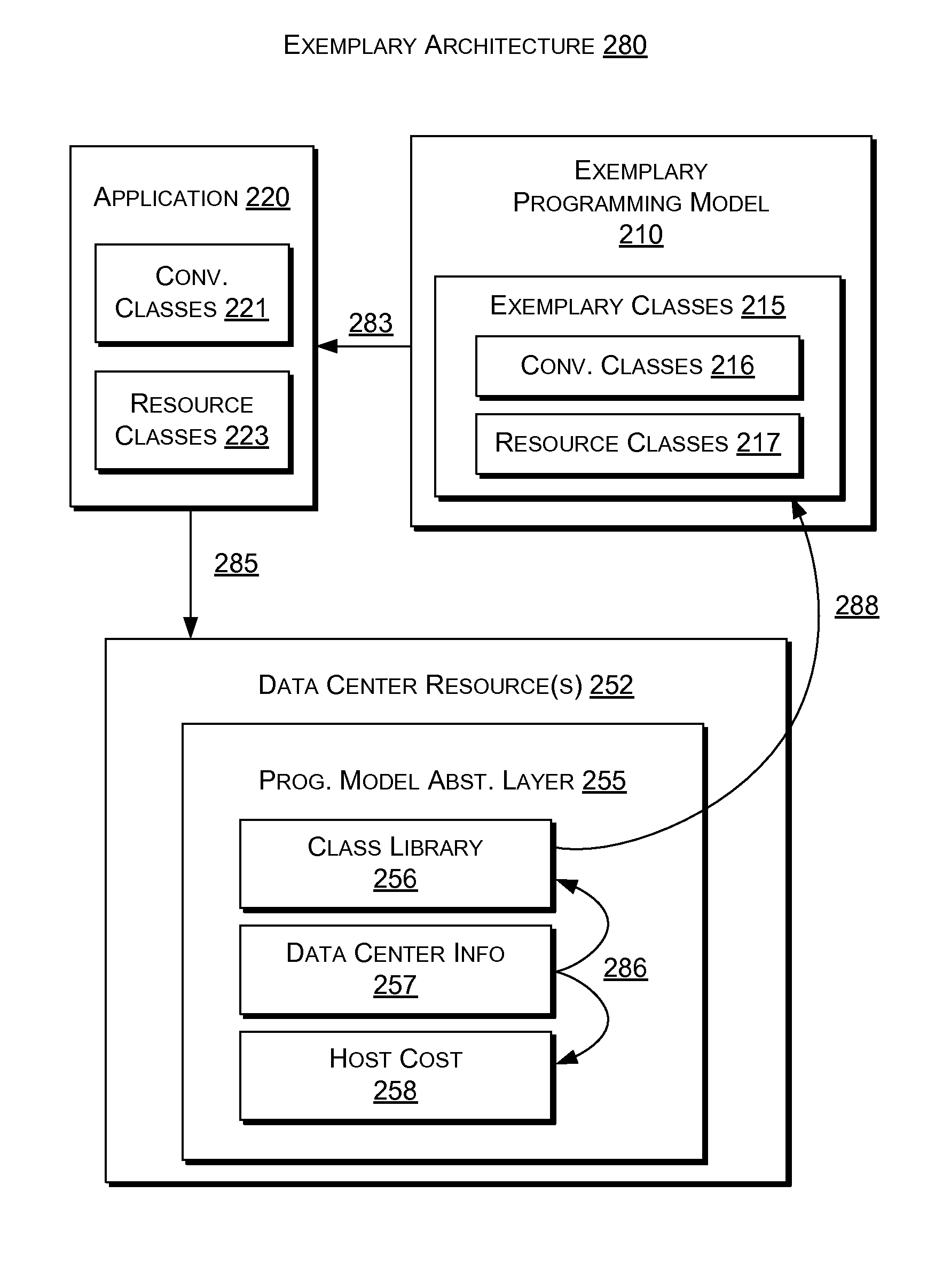

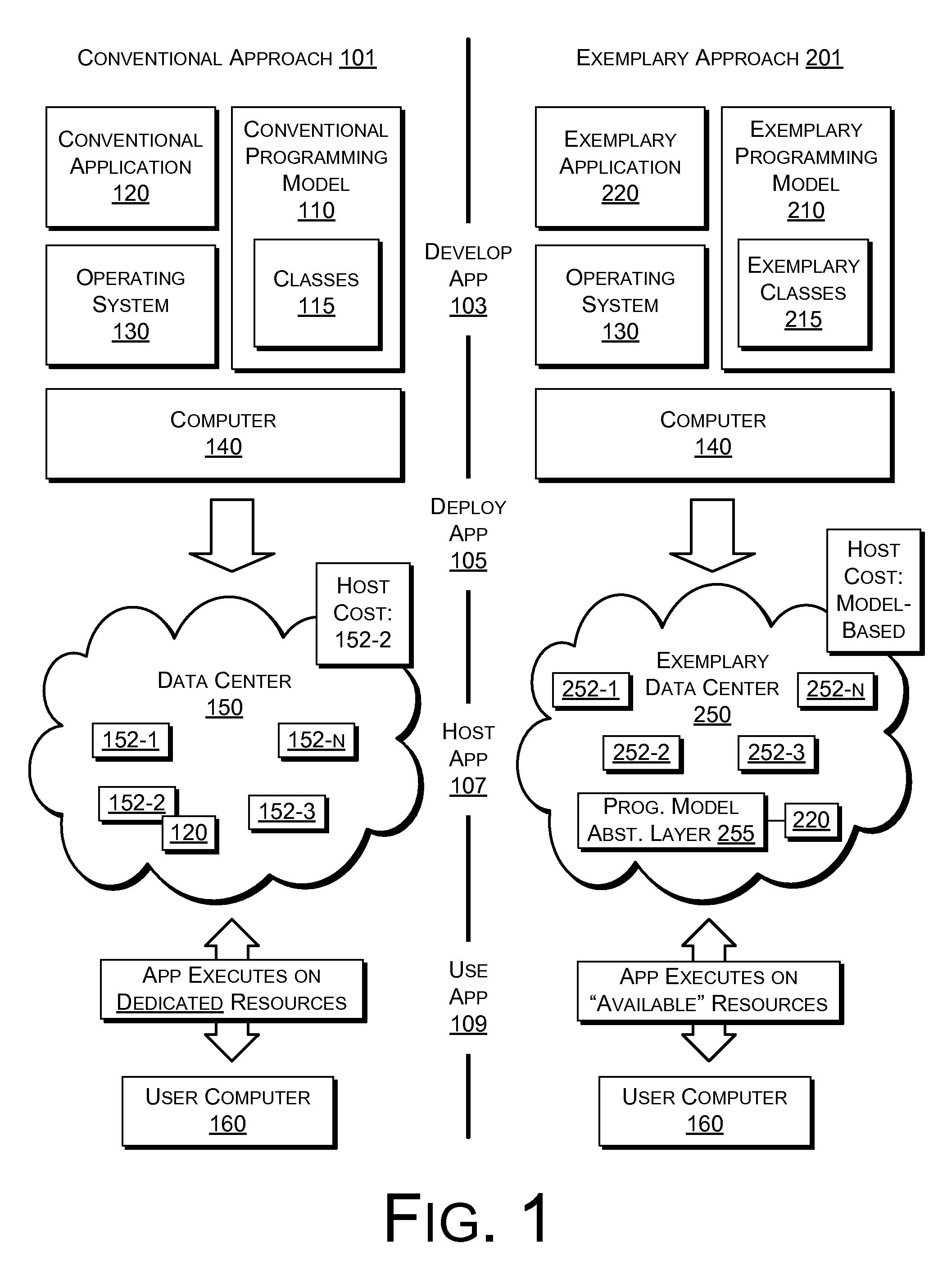

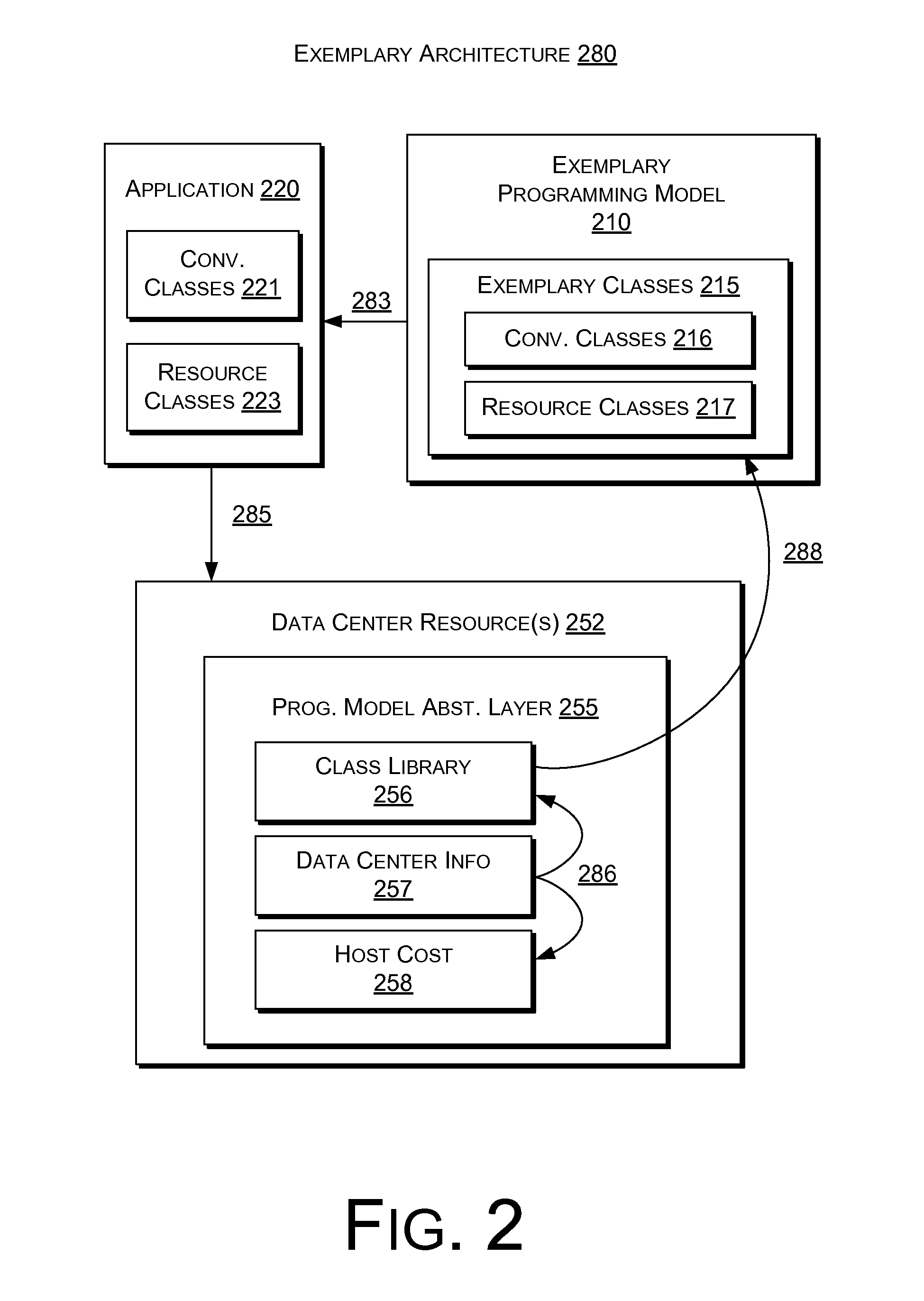

Data center programming model

An exemplary method includes hosting a service at a data center, the service relying on at least one software component developed according to a programming model and the data center comprising a corresponding programming model abstraction layer that abstracts resources of the data center; receiving a request for the service; and in response to the request, assigning at least some of the resources of the data center to the service to allow for fulfilling the request wherein the programming model abstraction layer performs the assigning based in part on reference to a resource class in the at least one software component, the resource class modifiable to account for changes in one or more resources of the data center. Various other devices, systems and methods are also described.

Owner:MICROSOFT TECH LICENSING LLC

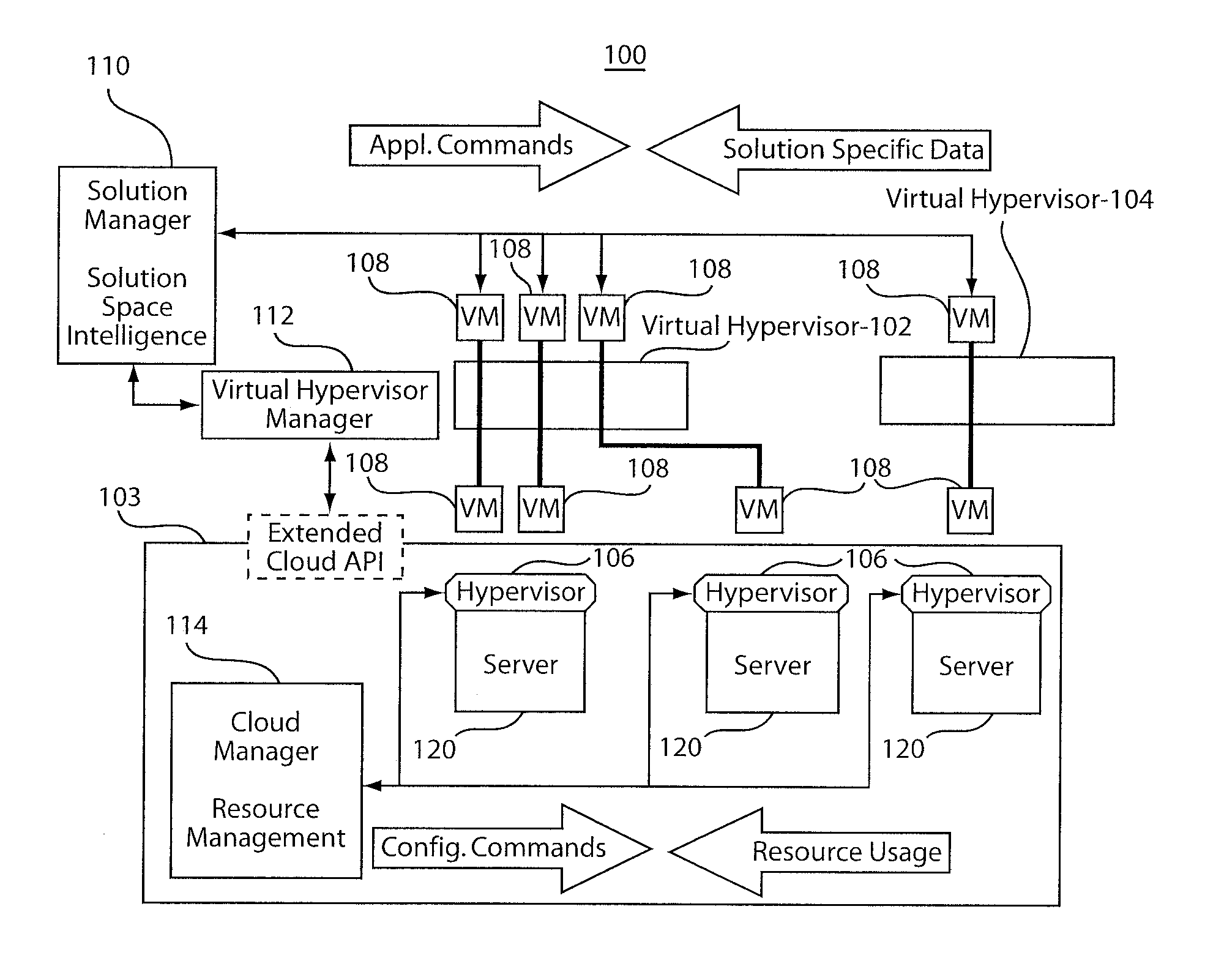

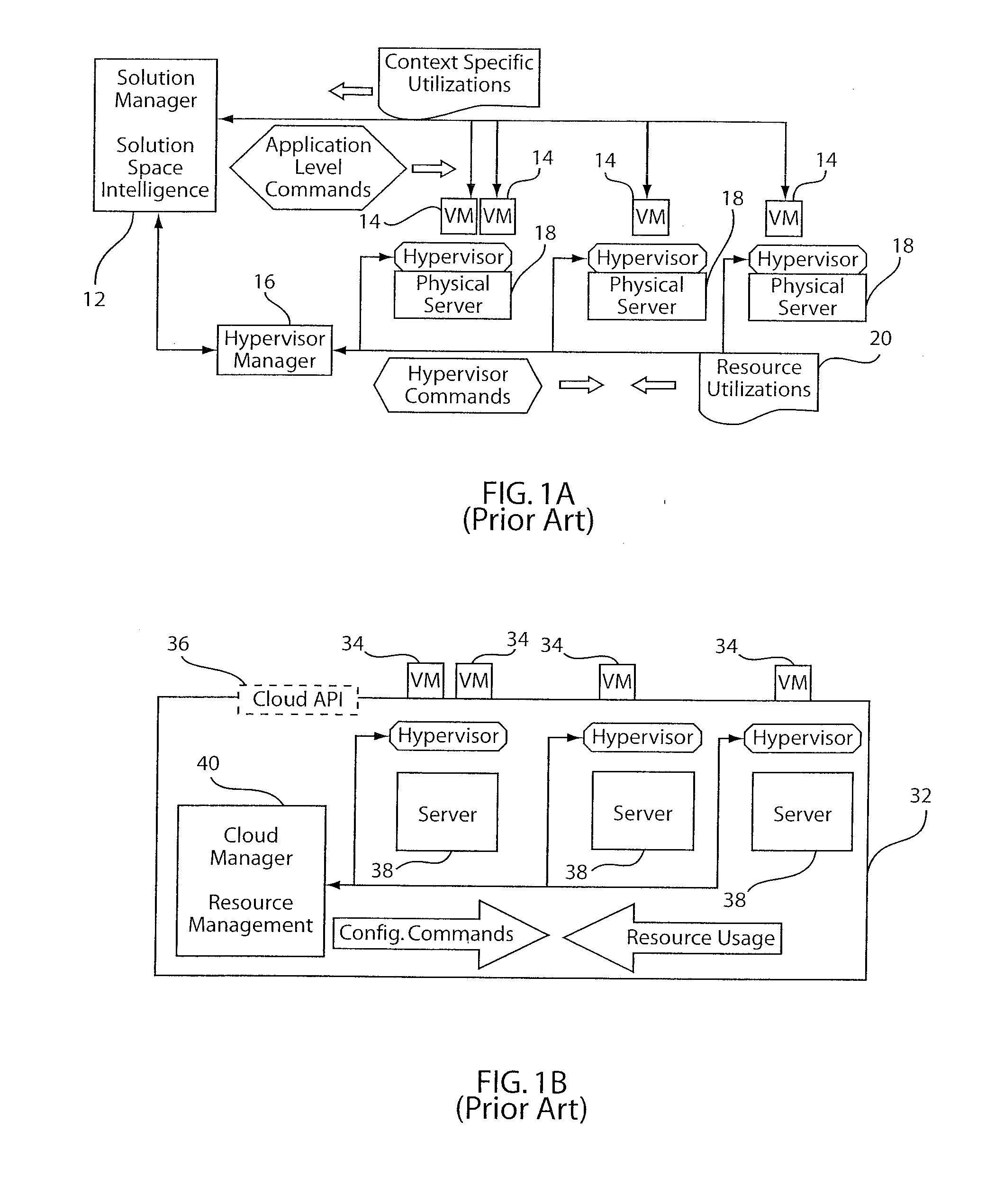

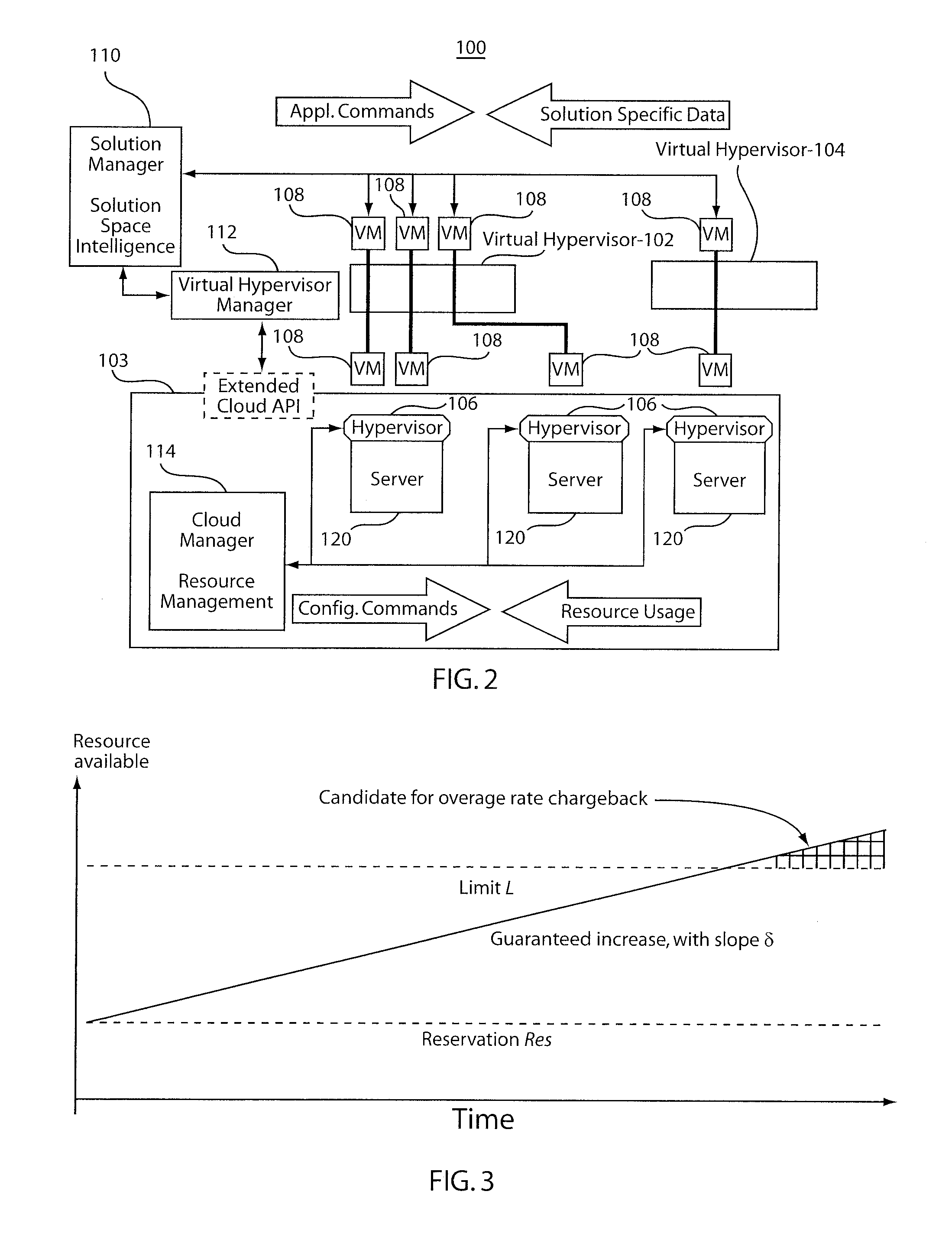

System and method for fair and economical resource partitioning using virtual hypervisor

ActiveUS20110185064A1Easy to controlEnsure performanceEnergy efficient ICTDigital computer detailsAbstraction layerNetwork service

A system and method for allocating resources in a cloud environment includes determining permitted usage of virtual machines and partitioning resources between network servers in accordance with a virtual hyperviser generated in accordance with an abstraction layer configured as an interface between a solution manager and an interface to a cloud network. Resource usage limits are determined for each virtual machine associated with the virtual hyperviser, and the servers are analyzed through the virtual hypervisers to determine if the virtual machines need to be migrated. If reallocation is needed, virtual machine migration requests are issued to migrate virtual machines into a new configuration at the virtual hypervisor abstraction level. The servers are reanalyzed to determine if migration of the new configuration is needed. Shares are computed to enforce balance requirements, and virtual machine shares and limits are adjusted for resources according to the computed shares.

Owner:IBM CORP

Dynamic end user specific customization of an application's physical data layer through a data repository abstraction layer

ActiveUS6928431B2Data processing applicationsDigital data information retrievalAbstraction layerData set

A system, method and article of manufacture are provided for accessing data independent of the particular manner in which the data is physically represented. In one embodiment, a plurality of data repository abstractions provide different logical views of the same underlying data repository. The plurality of data repository abstractions may each be associated with different users, thereby exposing a different set of data to each user. A runtime component performs translation of abstract queries into a form that can be used against a particular physical data representation.

Owner:IBM CORP

Remote data access and integration of distributed data sources through data schema and query abstraction

InactiveUS6954748B2Data processing applicationsDigital data information retrievalAbstraction layerData access

The present invention generally is directed to a system, method and article of manufacture for accessing data independent of the particular manner in which the data is physically represented. In one embodiment, a data repository abstraction layer provides a logical view of the underlying data repository that is independent of the particular manner of data representation. In one embodiment, the data repository abstraction layer specifies a location of data in a repository and a method for accessing the data. A query abstraction layer is also provided and is based on the data repository abstraction layer. A runtime component performs translation of an abstract query into a form that can be used against a particular physical data representation.

Owner:WORKDAY INC

Method and system for abstracting non-functional requirements based deployment of virtual machines

ActiveUS8301746B2Reduce complexityMultiprogramming arrangementsMultiple digital computer combinationsAbstraction layerNon-functional requirement

A system and method for allocating resources in a cloud environment includes providing an abstraction layer between a cloud environment and one or more data centers by generating a virtual hypervisor as an application programming interface. Responsive to a workload request by the one or more data centers, resources are partitioned and virtual machines are instantiated in the one or more data centers using the virtual hypervisor such that non-functional requirements of the workload are addressed at the abstraction level using the virtual hypervisor.

Owner:IBM CORP

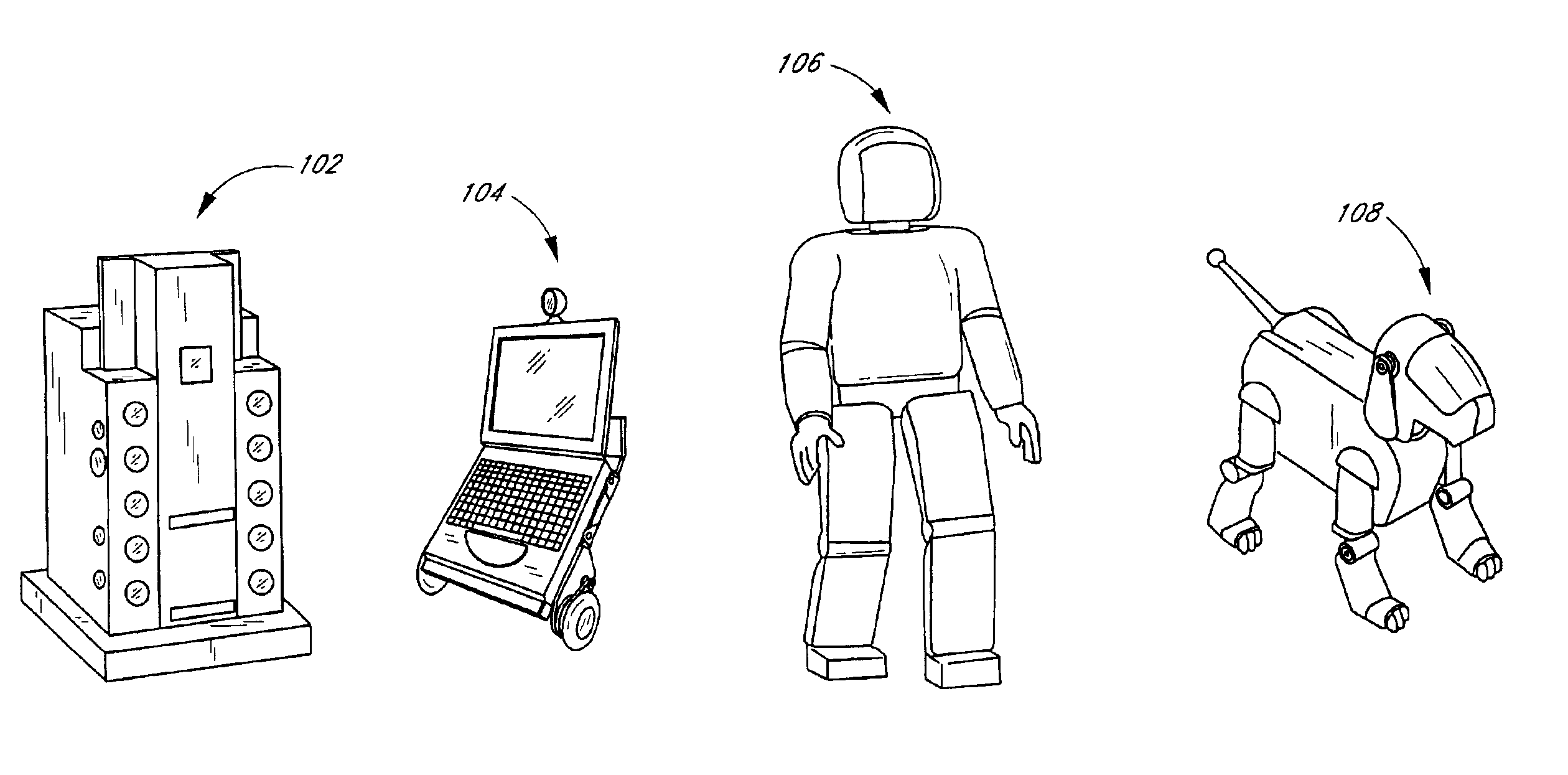

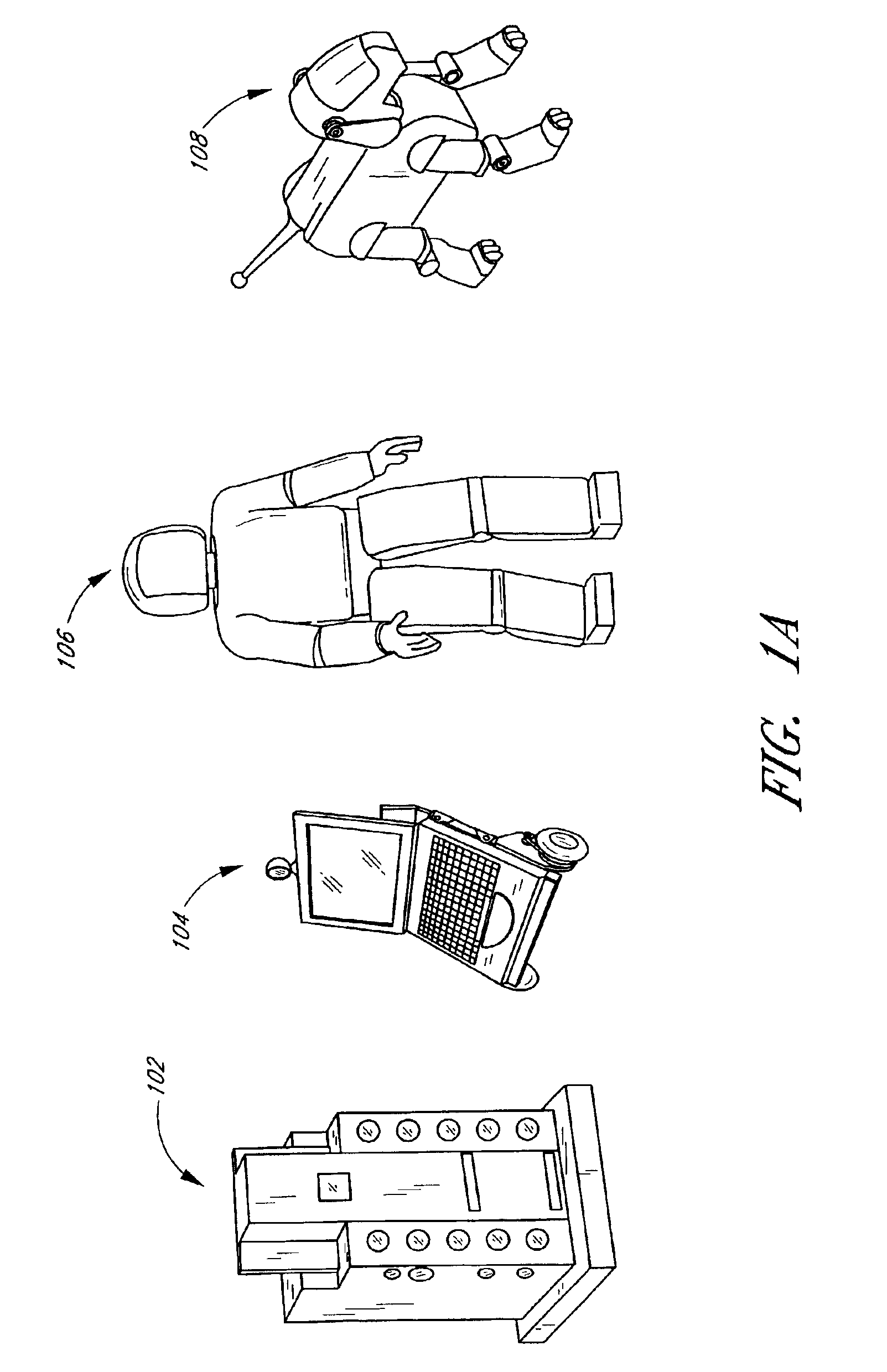

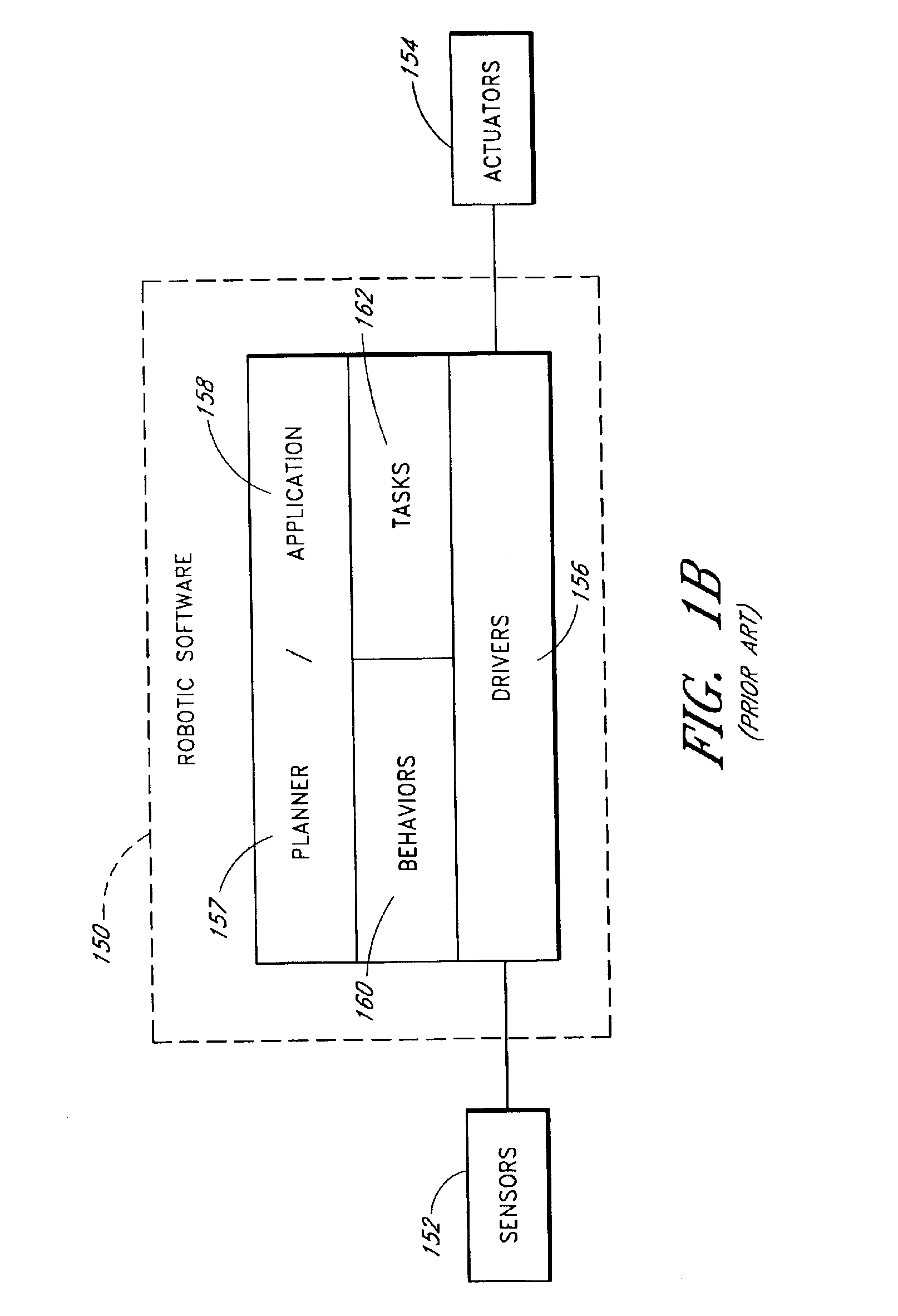

Hardware abstraction layer for a robot

InactiveUS6889118B2Reduced portabilityEfficiently permittingProgramme-controlled manipulatorAutonomous decision making processAbstraction layerOperational system

Owner:IROBOT CORP

Method and protocol for diagnostics of arbitrarily complex networks of devices

InactiveUS20050251604A1Removal costPreserving abilityNetworks interconnectionNetwork connectionsAbstraction layerCommunications software

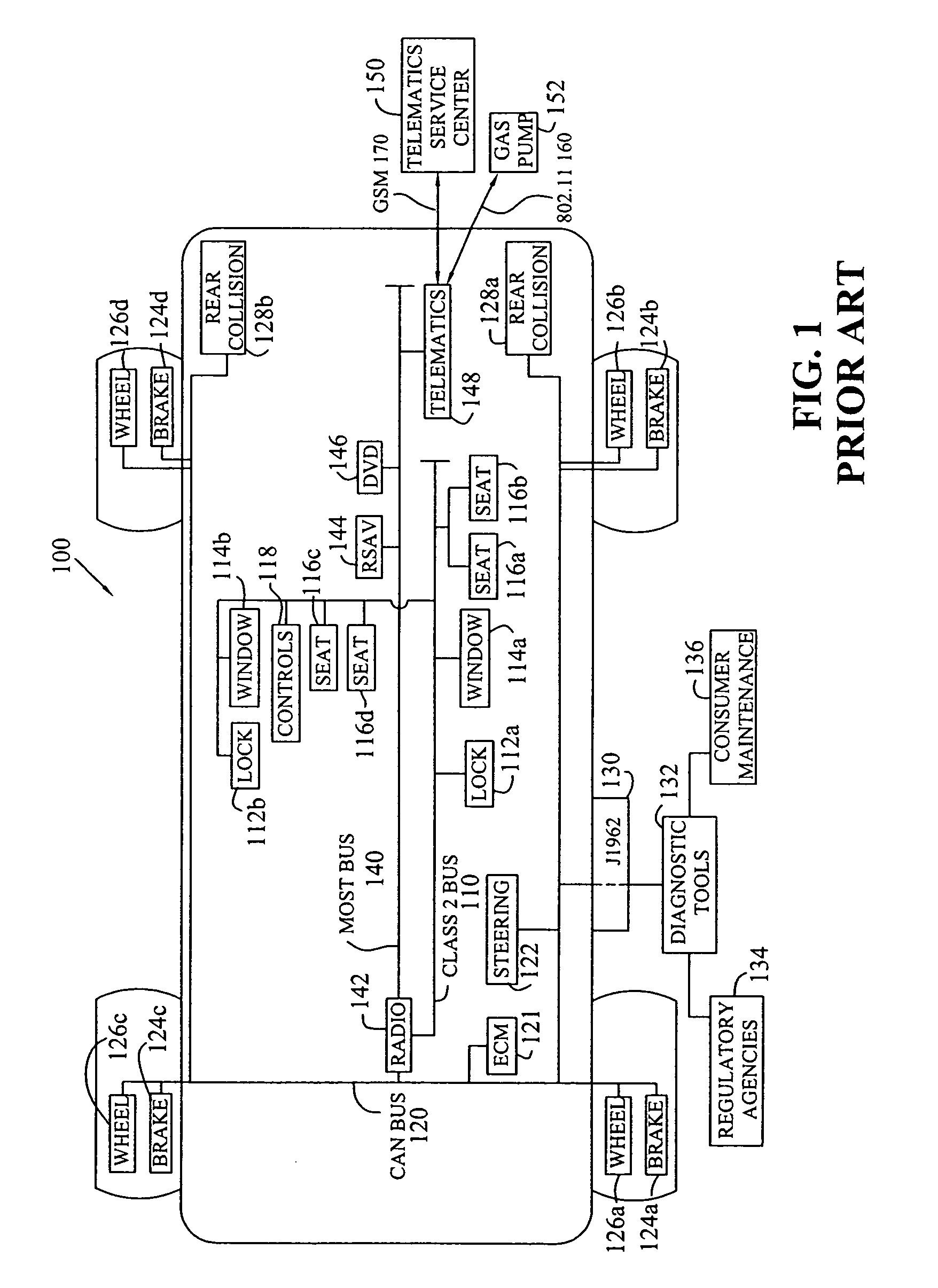

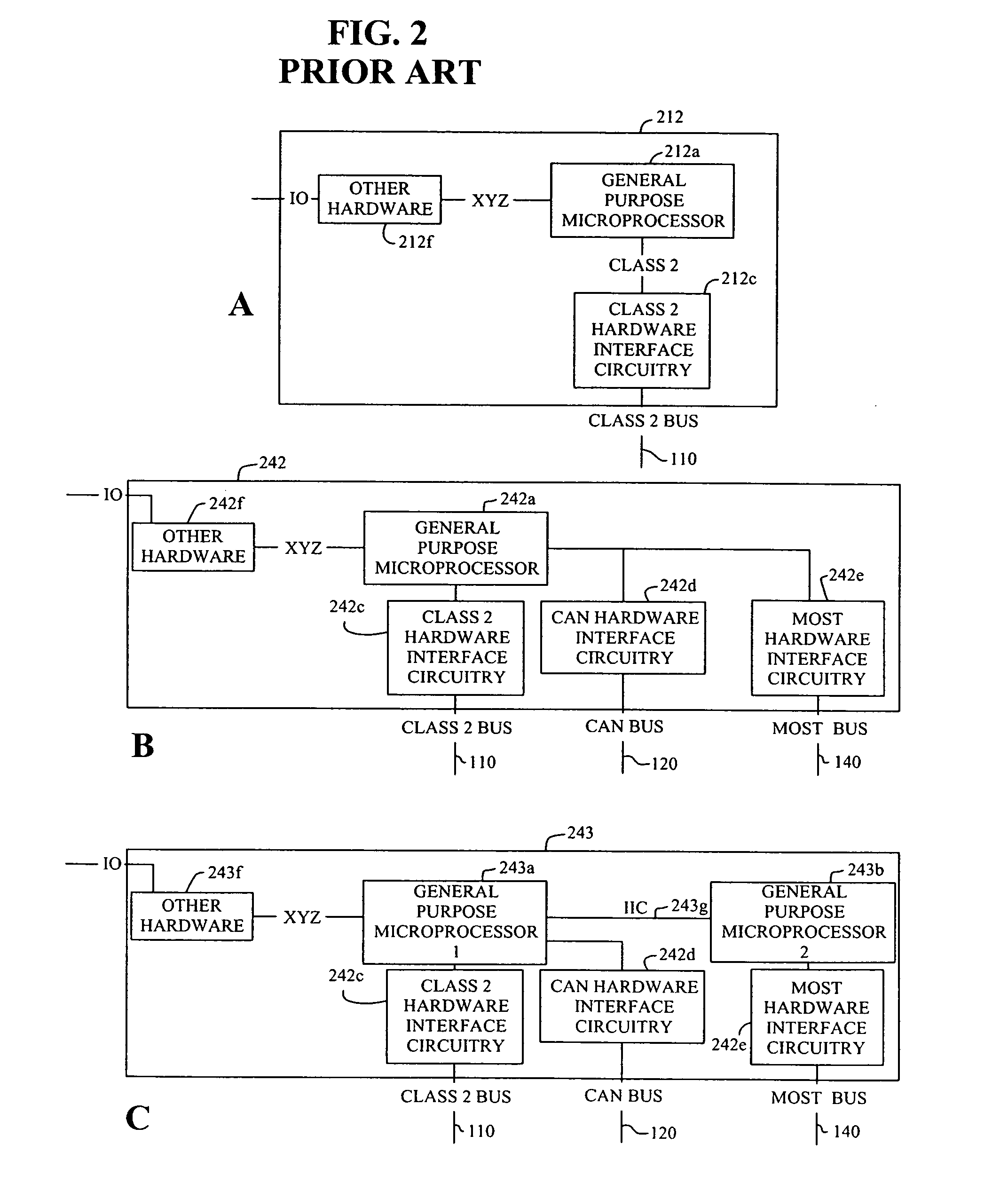

The present invention includes a network having a plurality of communication buses, at least two of the plurality of buses utilizing different communication bus protocols; a plurality of computer devices, at least one of the plurality of computer devices coupled to at least one of the plurality of communication buses and containing computer device software having an architecture including bus communication software for communicating with at least one of the plurality of communication buses; and an abstraction layer in communication with the bus communication software and capable of abstracting messages from the communication bus protocols, the plurality of computer devices including at least one gateway computer device coupled to multiple of the plurality of communication buses and containing computer device software having an architecture further including a gateway in communication with the abstraction layer and capable of routing the abstracted messages between computer devices coupled to the multiple communication buses to which the at least one gateway computer device is coupled.

Owner:APTIV TECH LTD

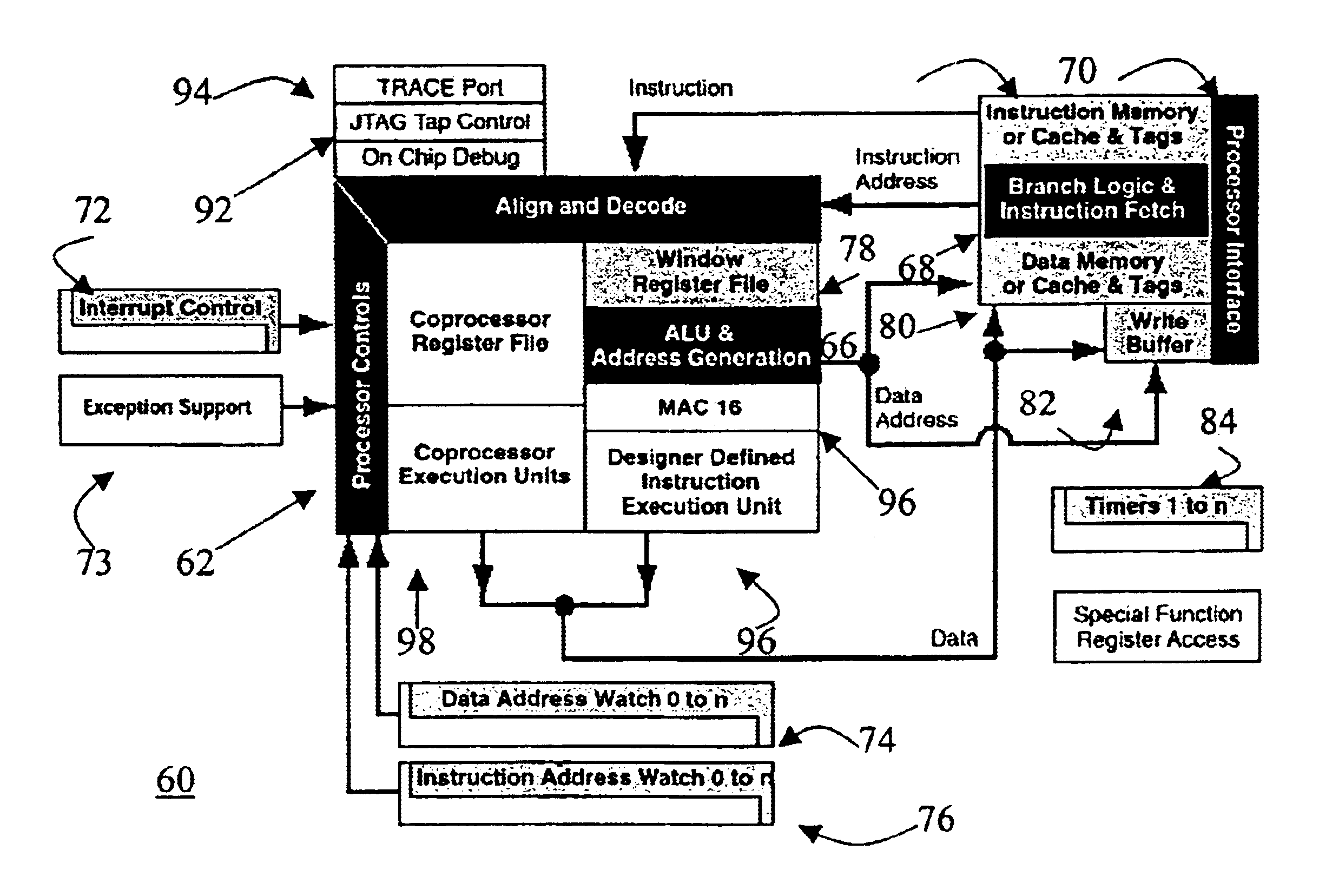

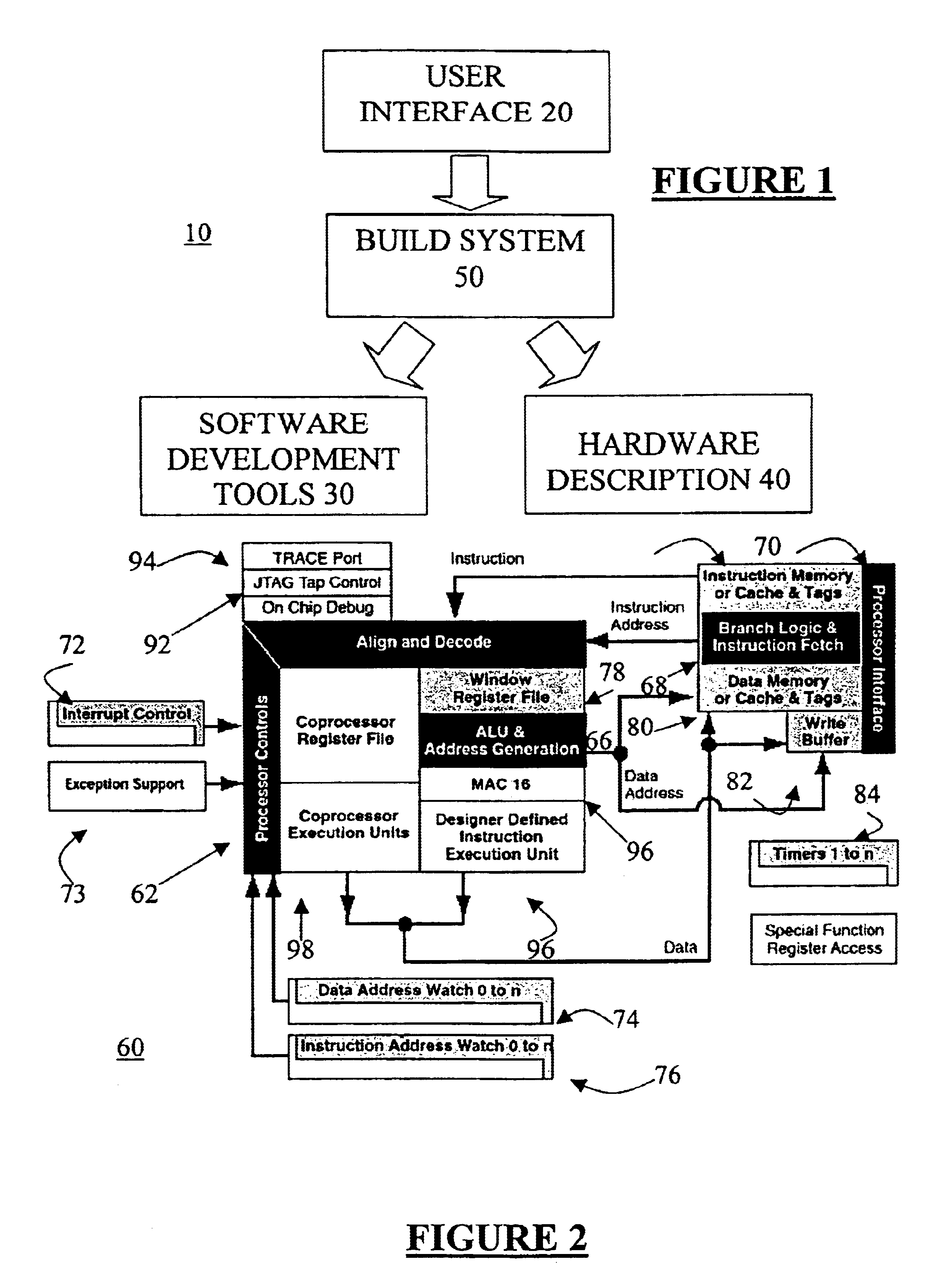

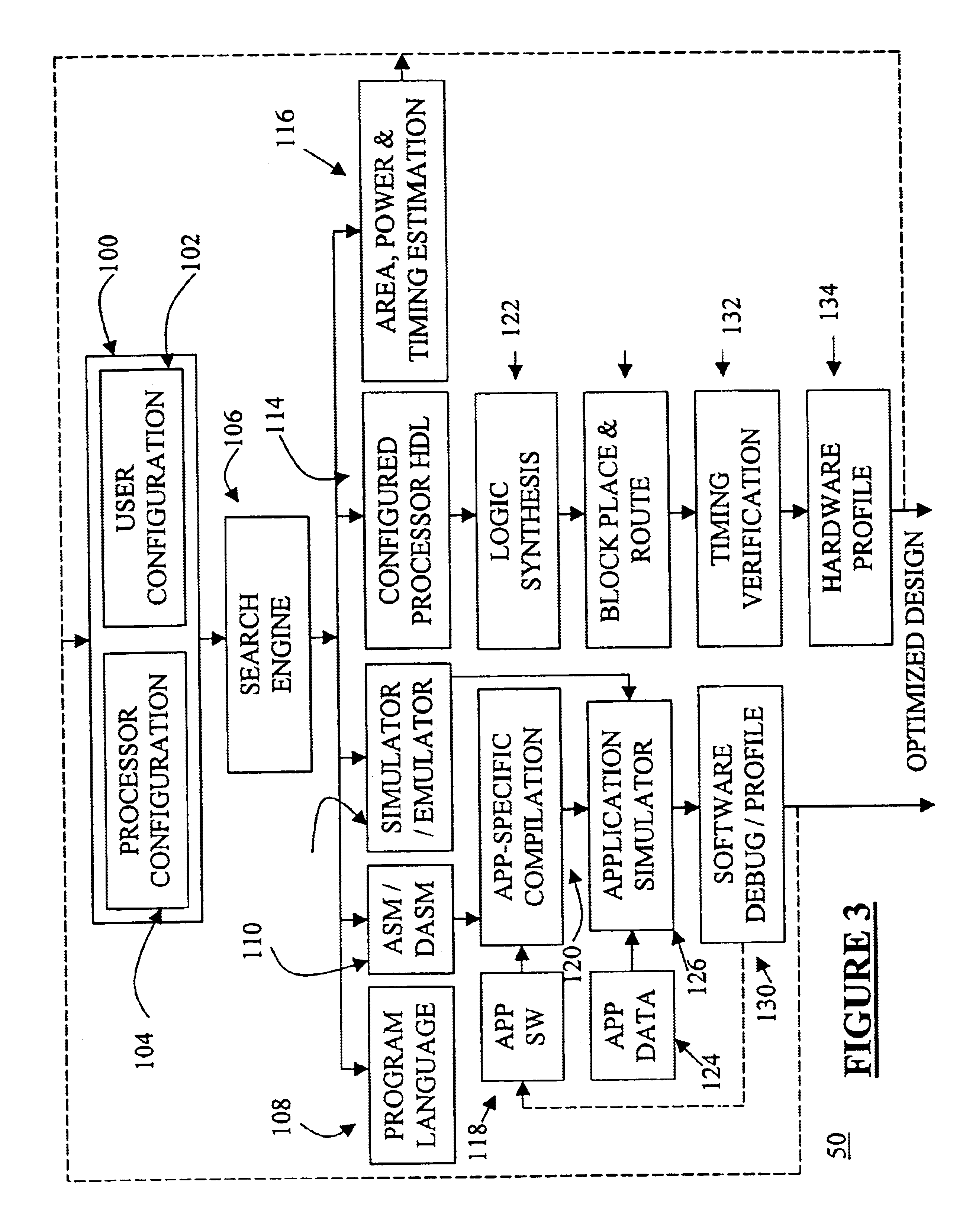

Abstraction of configurable processor functionality for operating systems portability

InactiveUS6763327B1Easily reimplementedEasily reimplementable portionSoftware simulation/interpretation/emulationSpecial data processing applicationsComputer hardwareStandardization

A hardware abstraction layer operates as a system architectural layer between a real-time operating system and an underlying configurable processor. The hardware abstraction layer provides an abstraction of processor-specific functionality to the operating system. In particular, it abstracts configurable processor features visible to the operating system to provide a uniform, standardized interface between the operating system and the configurable processor on which it runs. Thus, an operating system running on top of the hardware abstraction layer will work on all configurations of the processor which differ from one another only in the configuration parameters covered by the hardware abstraction layer. The hardware abstraction layer may be generated using the same information that is used to describe the features being configured in the configurable processor. Automatic generation of the HAL greatly eases use of the HAL and the configurable processor, since the user is not required to manually write the HAL or adapt an existing one based on the processor configuration parameters.

Owner:TENSILICA

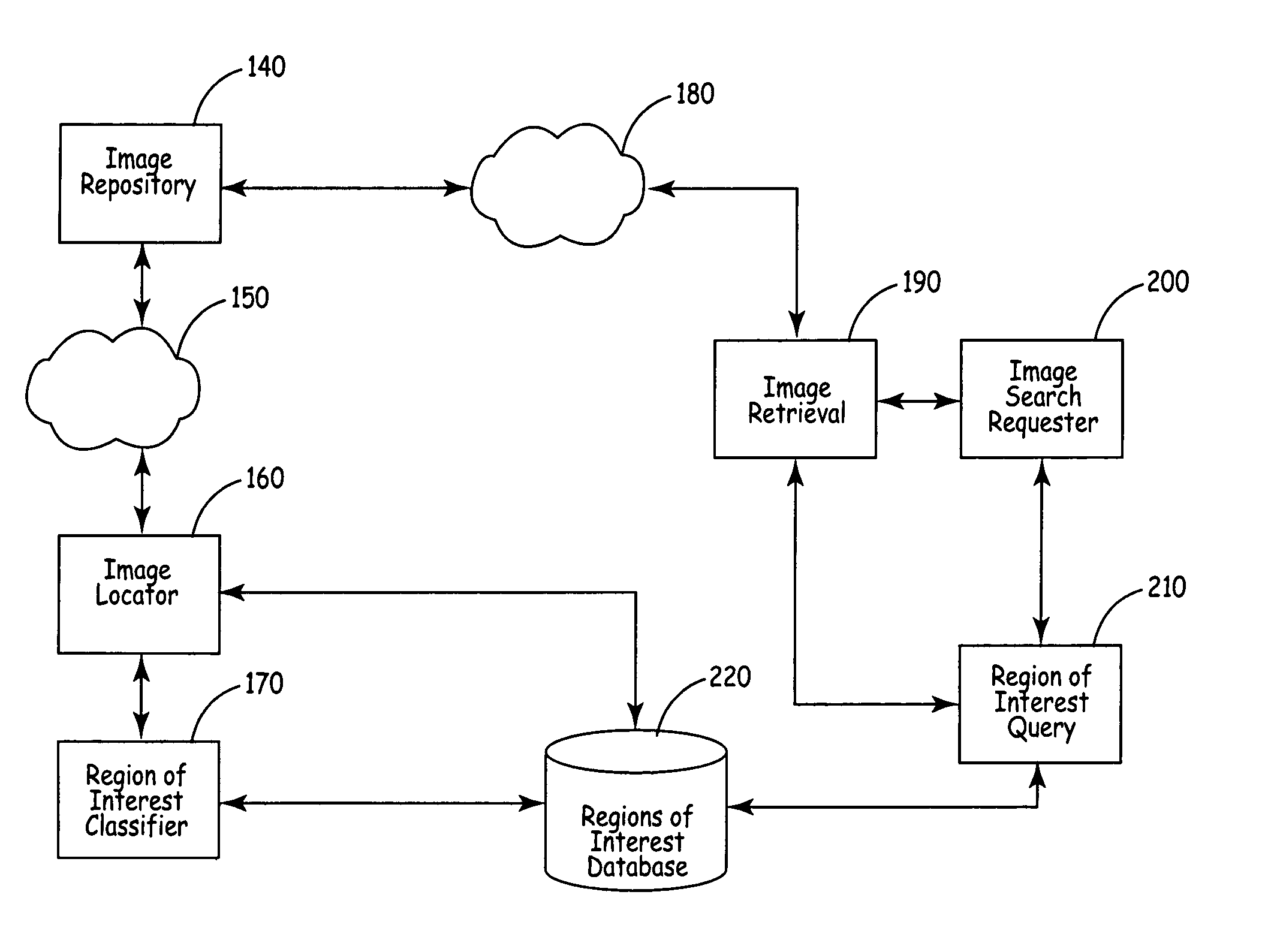

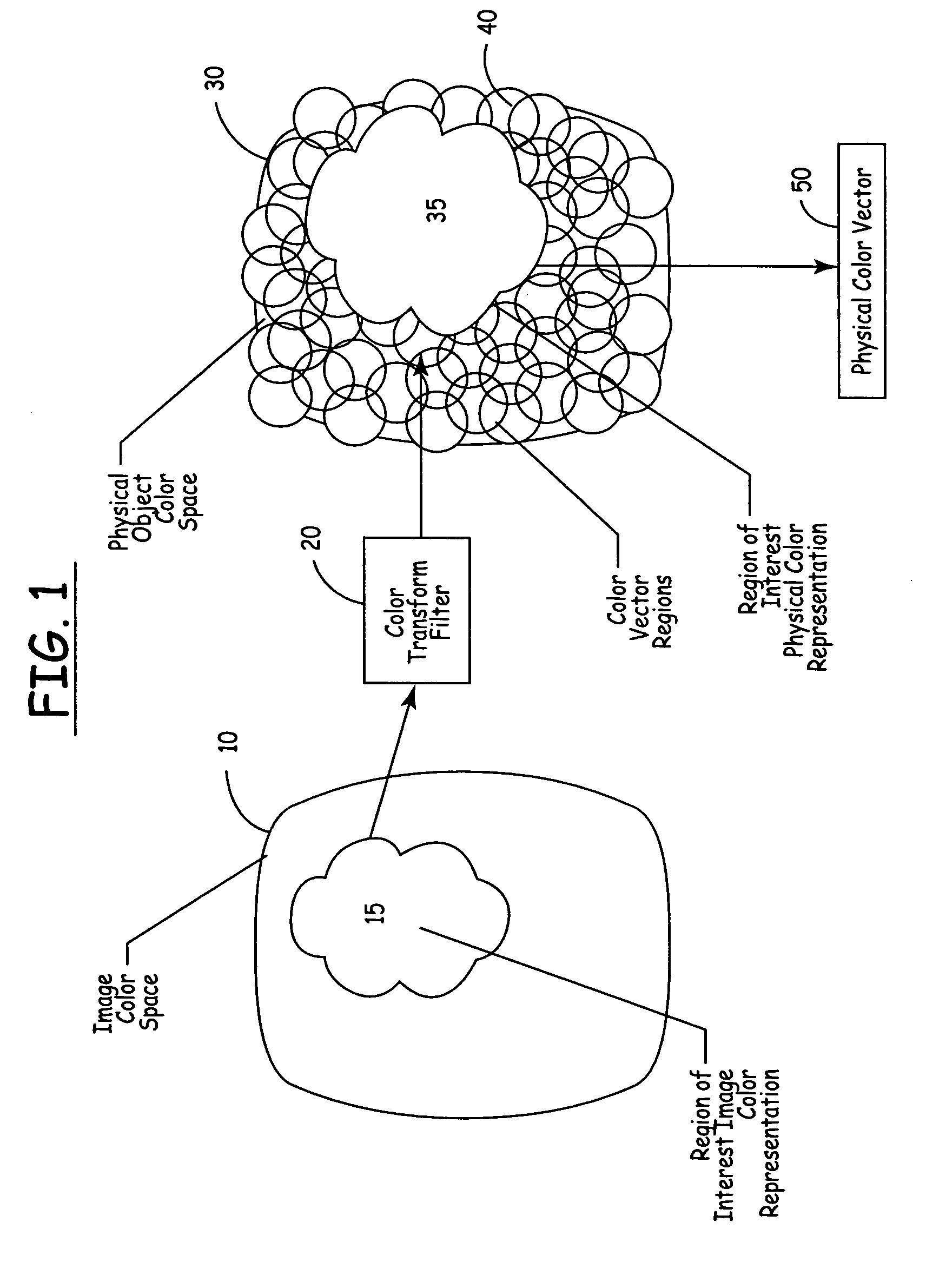

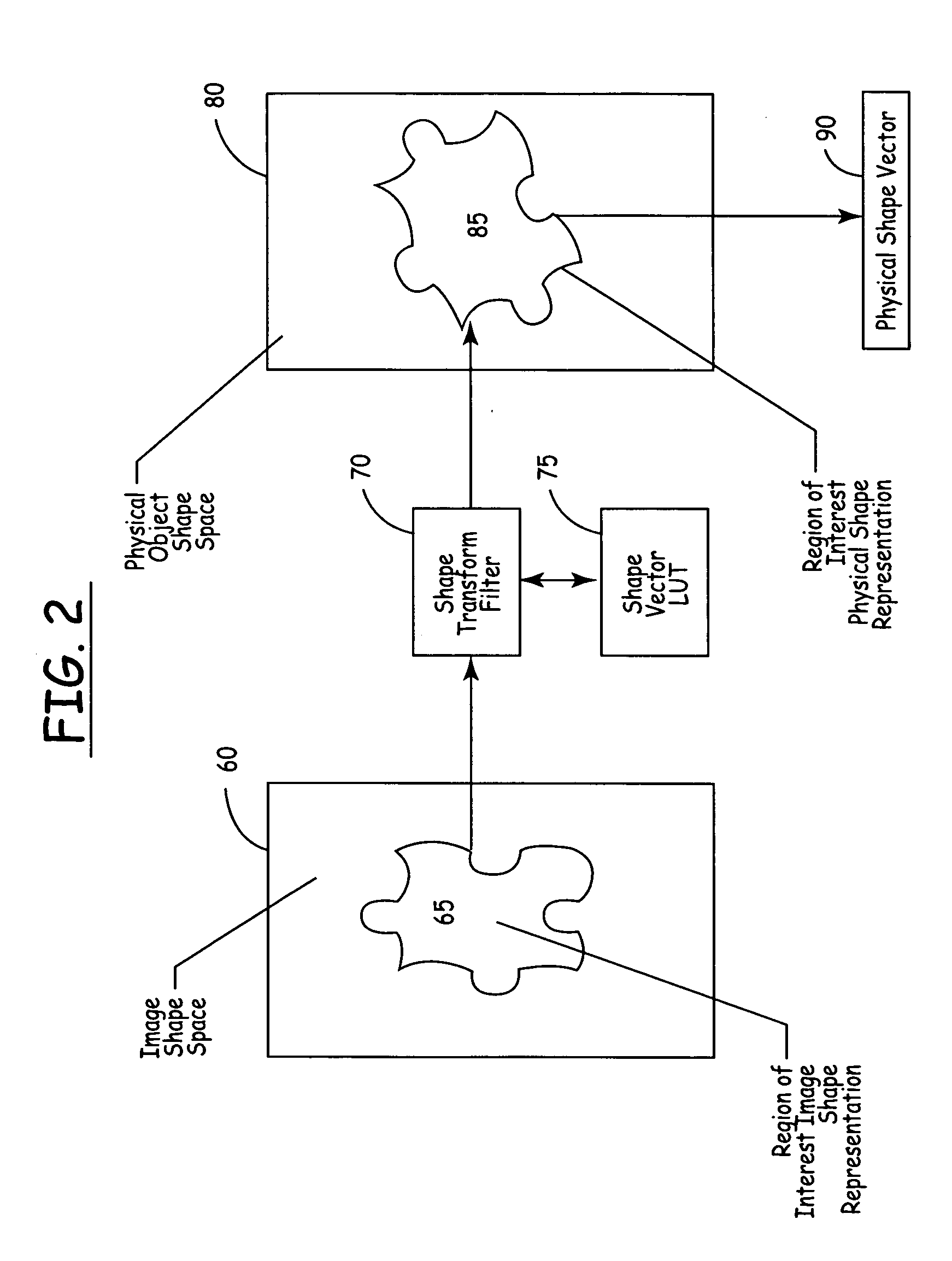

Methods and apparatus for automated true object-based image analysis and retrieval

ActiveUS20050271304A1Data processing applicationsDigital data processing detailsAbstraction layerScalable system

The present invention is an automated and extensible system for the analysis and retrieval of images based on region-of-interest (ROI) analysis of one or more true objects depicted by an image. The system uses a Regions Of Interest (ROI) database that is a relational or analytical database containing searchable vectors that represent the images stored in a repository. Entries in the ROI database are created by an image locator and ROI classifier that work in tandem to locate images within the repository and extract the relevant information that will be stored in the ROI database. Unlike existing region-of-interest search systems, the ROI classifier analyzes objects in an image to arrive at the actual features of the true object, instead of merely describing the features of the image of that object. Graphical searches are performed by the collaborative workings of an image retrieval module, an image search requestor and an ROI query module. The image search requestor is an abstraction layer that translates user or agent search requests into the language understood by the ROI query.

Owner:GOOGLE LLC

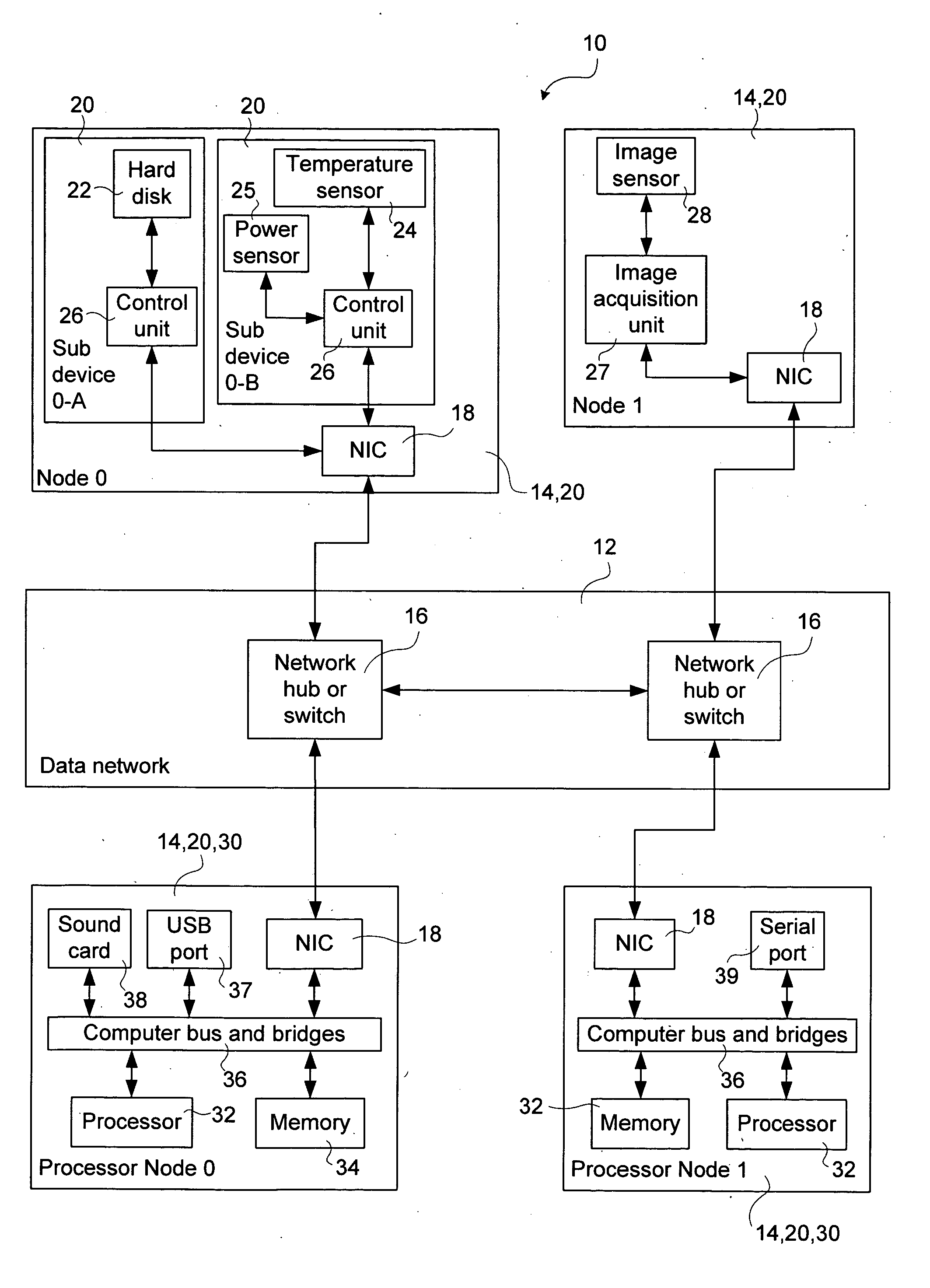

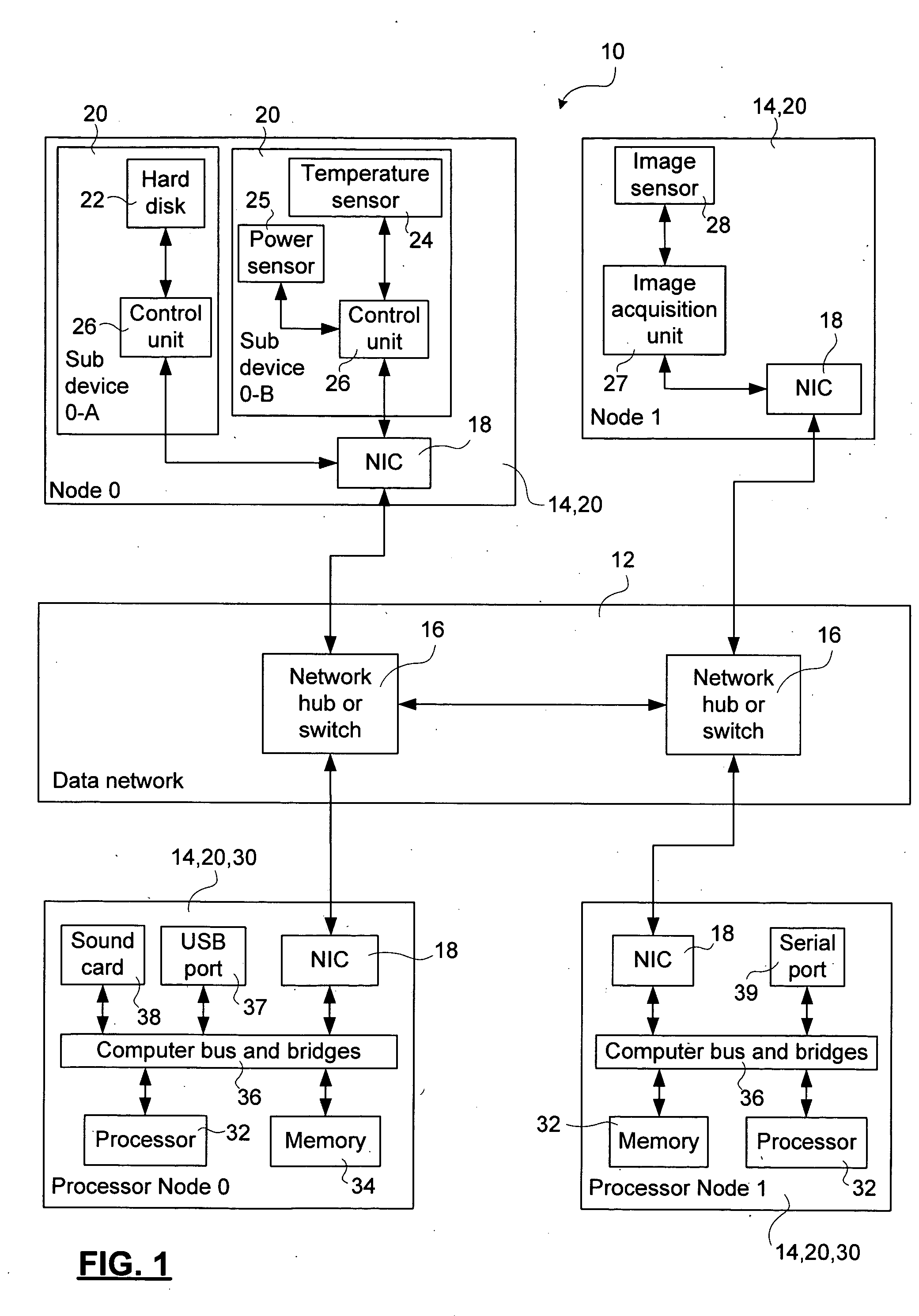

Methods and apparatus for enabling bus connectivity over a data network

ActiveUS20060059287A1Facilitate communicationSelectively leverage operating system capabilitiesProgram synchronisationMemory addressAbstraction layer

A method and system for interconnecting peripherals, processor nodes, and hardware devices to a data network to produce a network bus providing OS functionality for managing hardware devices connected to the network bus involves defining a network bus driver at each of the processor nodes that couples hardware device drivers to a network hardware abstraction layer of the processor node. The network bus can be constructed to account for the hot-swappable nature of the hardware devices using a device monitoring function, and plug and play functionality for adding and, removing device driver instances. The network bus can be used to provide a distributed processing system by defining a shared memory space at each processor node. Distributed memory pages are provided with bus-network-wide unique memory addresses, and a distributed memory manager is added to ensure consistency of the distributed memory pages, and to provide a library of functions for user mode applications.

Owner:PLEORA TECH

System and method for a cloud computing abstraction layer with security zone facilities

ActiveUS9069599B2Rapid and dynamic deployment and scalingShorten the timeResource allocationHybrid transportVirtualizationAbstraction layer

In embodiments of the present invention improved capabilities are described for a virtualization environment adapted for development and deployment of at least one software workload, the virtualization environment having a metamodel framework that allows the association of a policy to the software workload upon development of the workload that is applied upon deployment of the software workload. This allows a developer to define a security zone and to apply at least one type of security policy with respect to the security zone including the type of security zone policy in the metamodel framework such that the type of security zone policy can be associated with the software workload upon development of the software workload, and if the type of security zone policy is associated with the software workload, automatically applying the security policy to the software workload when the software workload is deployed within the security zone.

Owner:DXC US AGILITY PLATFORM INC

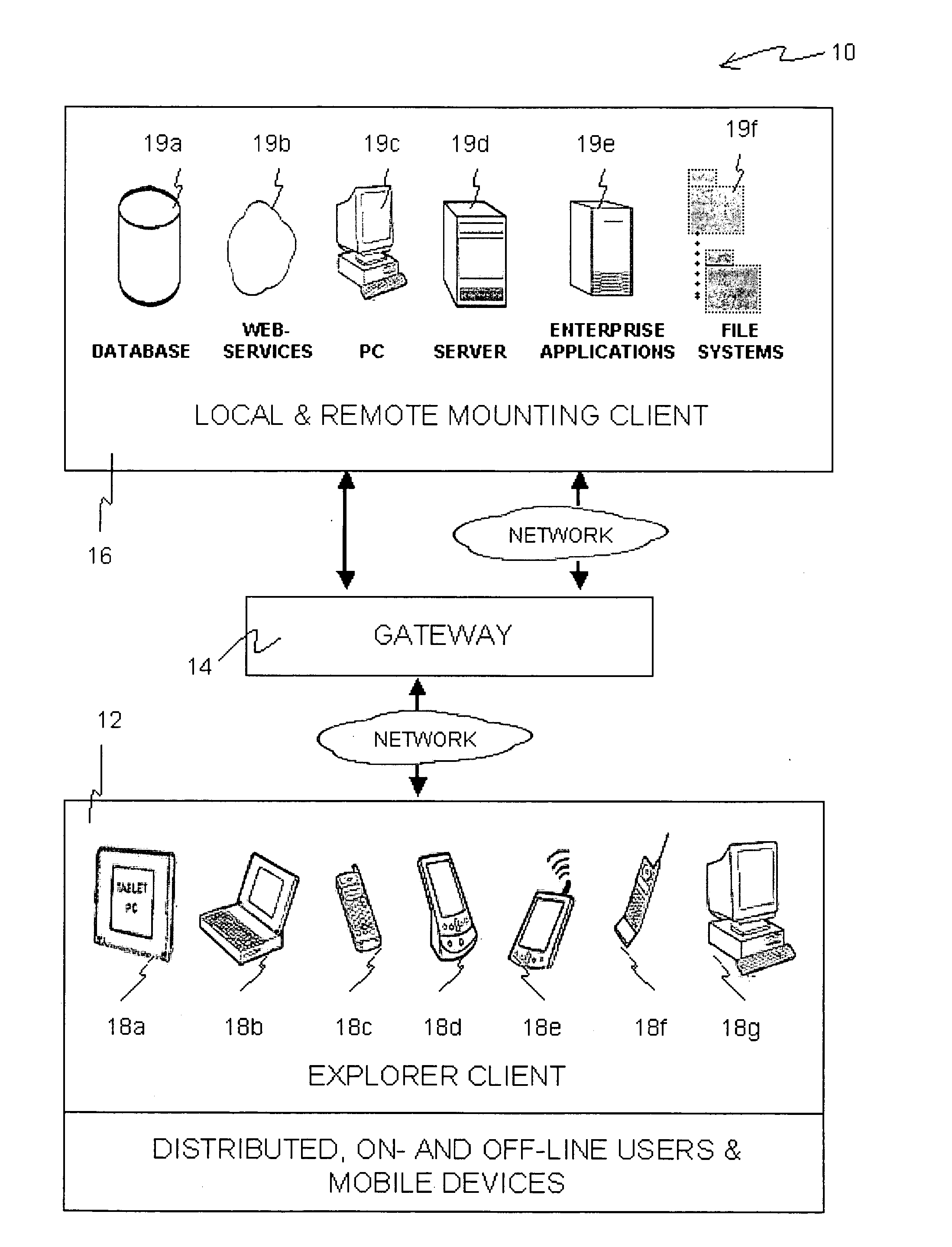

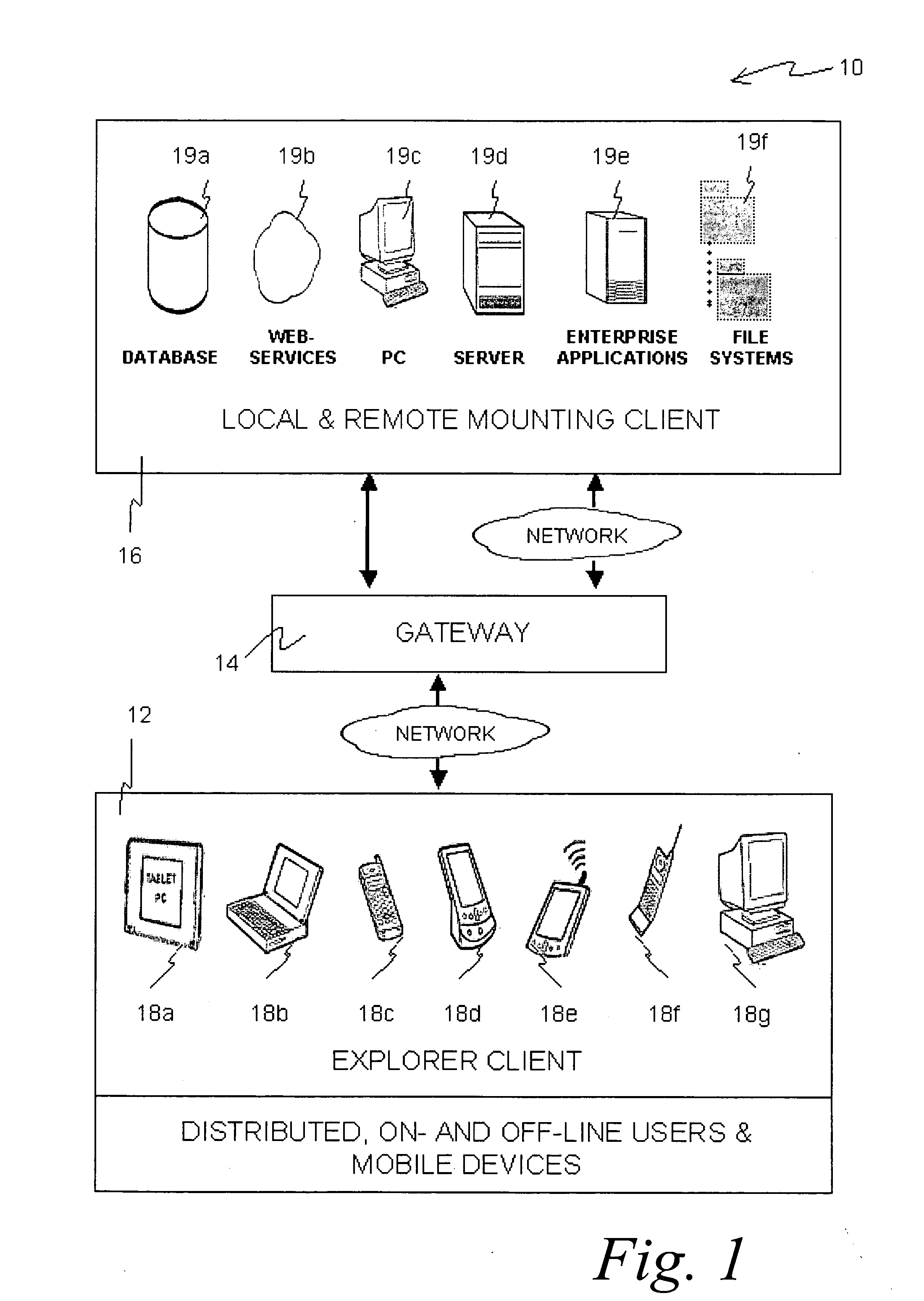

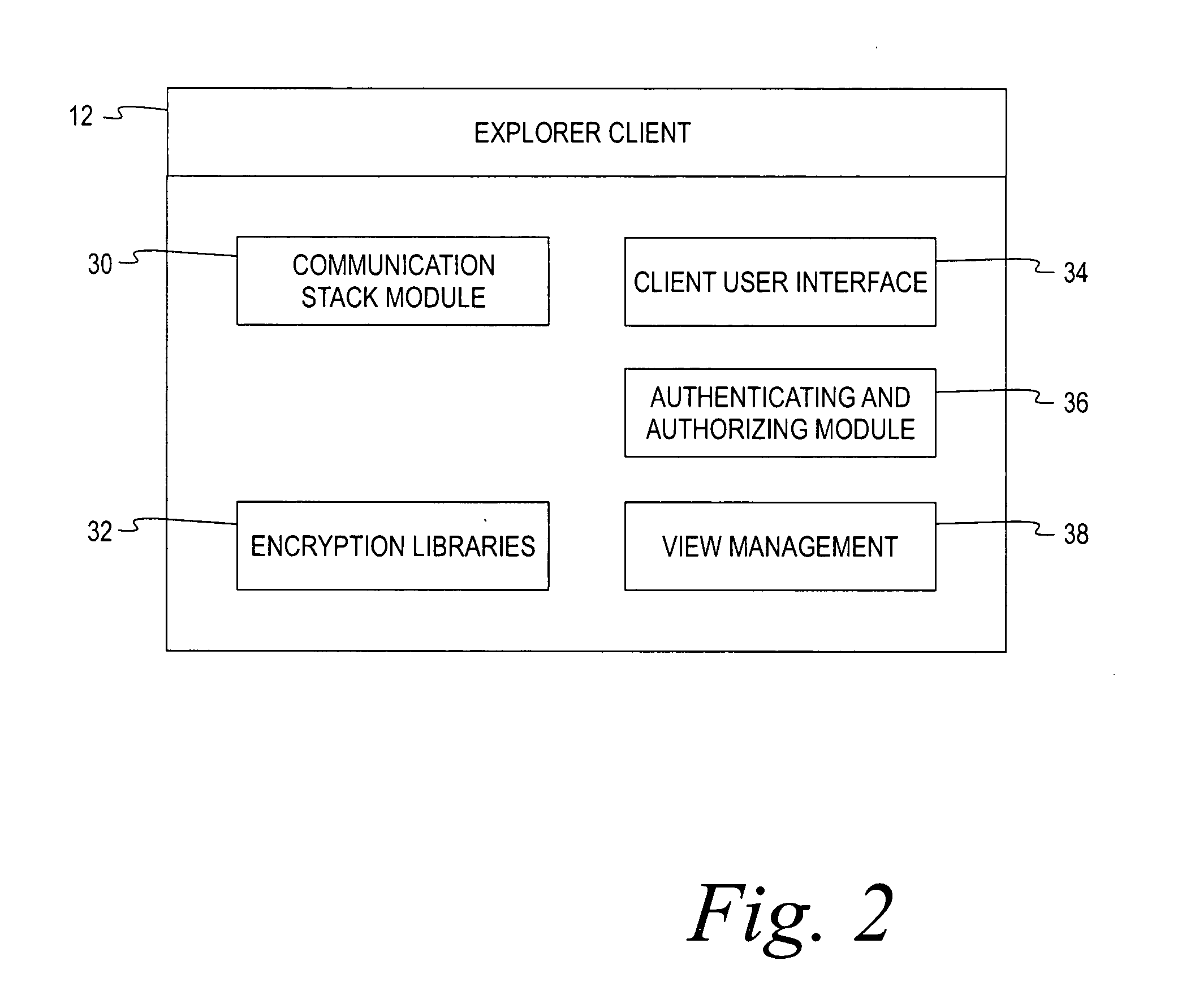

Content management across shared, mobile file systems

InactiveUS20060080397A1Multiple digital computer combinationsSecuring communicationAbstraction layerFlash file system

A content management system and method are disclosed having one or more shared file systems located on one or more networks having a firewall. The content management system includes an explorer client, a mounting client, and a gateway. The gateway is in communication with both the explorer client and the mounting client. The explorer client forms a profile of a user device by determining the characteristics of the user device. The mounting client determines the capabilities of the one or more file systems and where content resides on each of the one or more file systems. The gateway then creates a virtual abstraction layer based on the profile of the user device and the capabilities of the one or more file systems.

Owner:RPX CORP

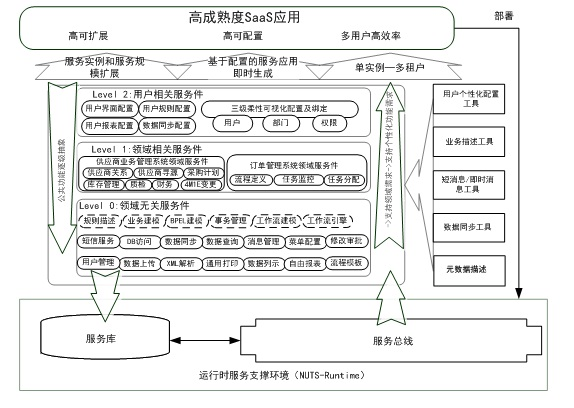

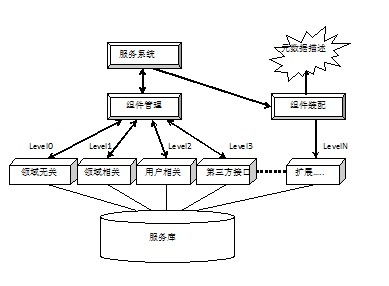

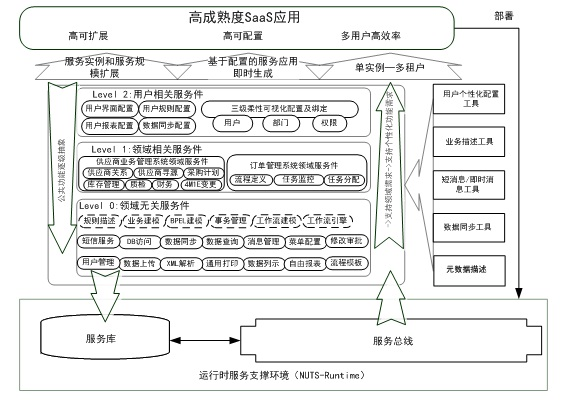

Service software construction method and system adapting to multiple business abstraction levels

InactiveCN101794226AReduced domain knowledge requirementsImprove reusabilityData switching networksSpecific program execution arrangementsAbstraction layerService-orientation

The invention discloses a service software construction method and a system adapting to multiple business abstraction levels. The invention is based on business-oriented frameworks, and constructs the service component resources by a stage-by-stage abstraction method, and a software system is constructed on the basis. According to the application requirements of different business abstraction levels, the invention also provides construction way atom component unrelated to the field, a composite component reconstruction way related to the field, and a configuration way related to the user business. Thus, the construction and the management of the software can aim at different business requirements and abstraction levels, and a proper method can be utilized to adapt to quick reconstruction of large-scale multiple tenants and software, namely quick reconstruction of service mode applications, thereby ensuring the efficiency, economical efficiency and reliability of software production.

Owner:SHANDONG UNIV

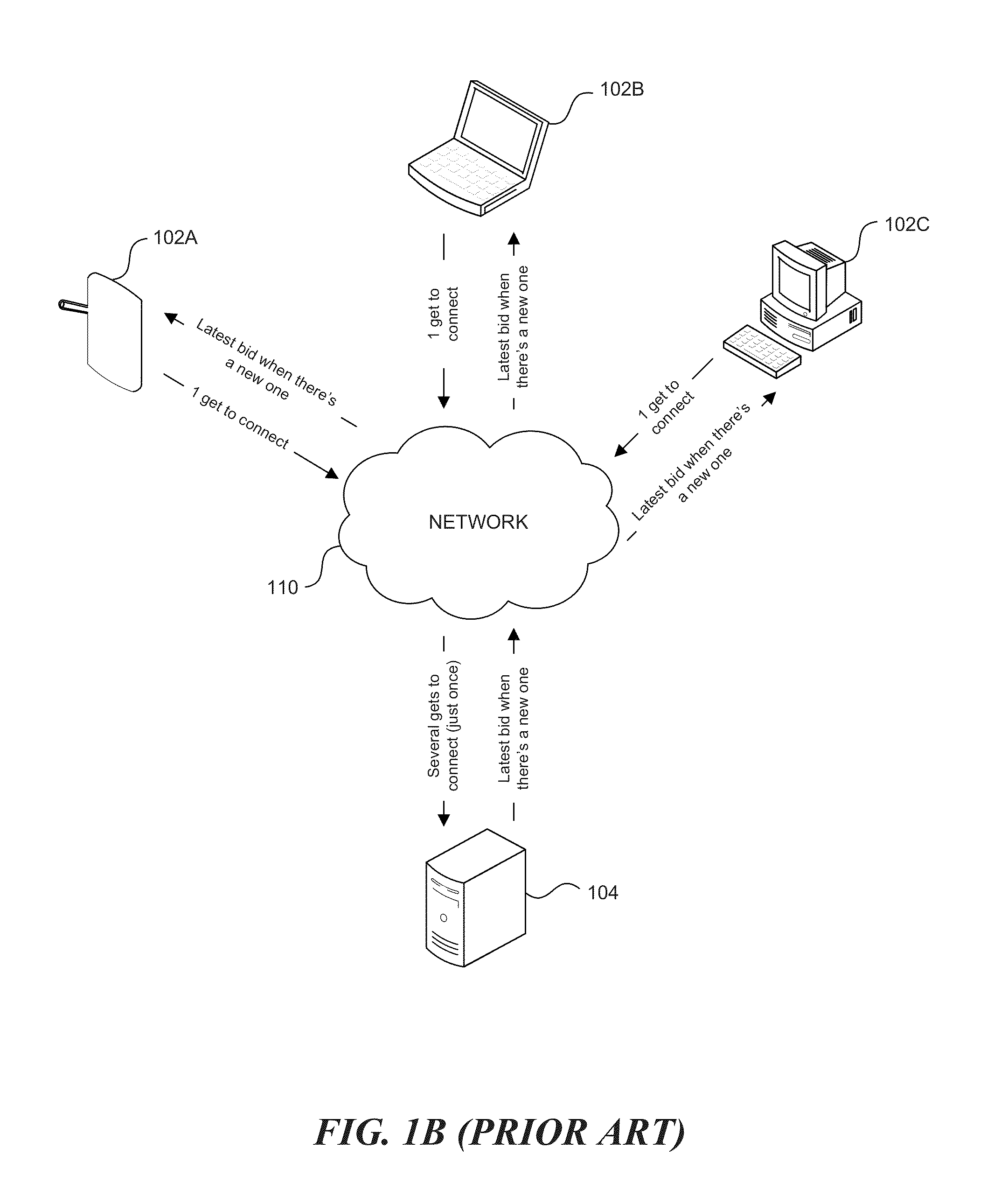

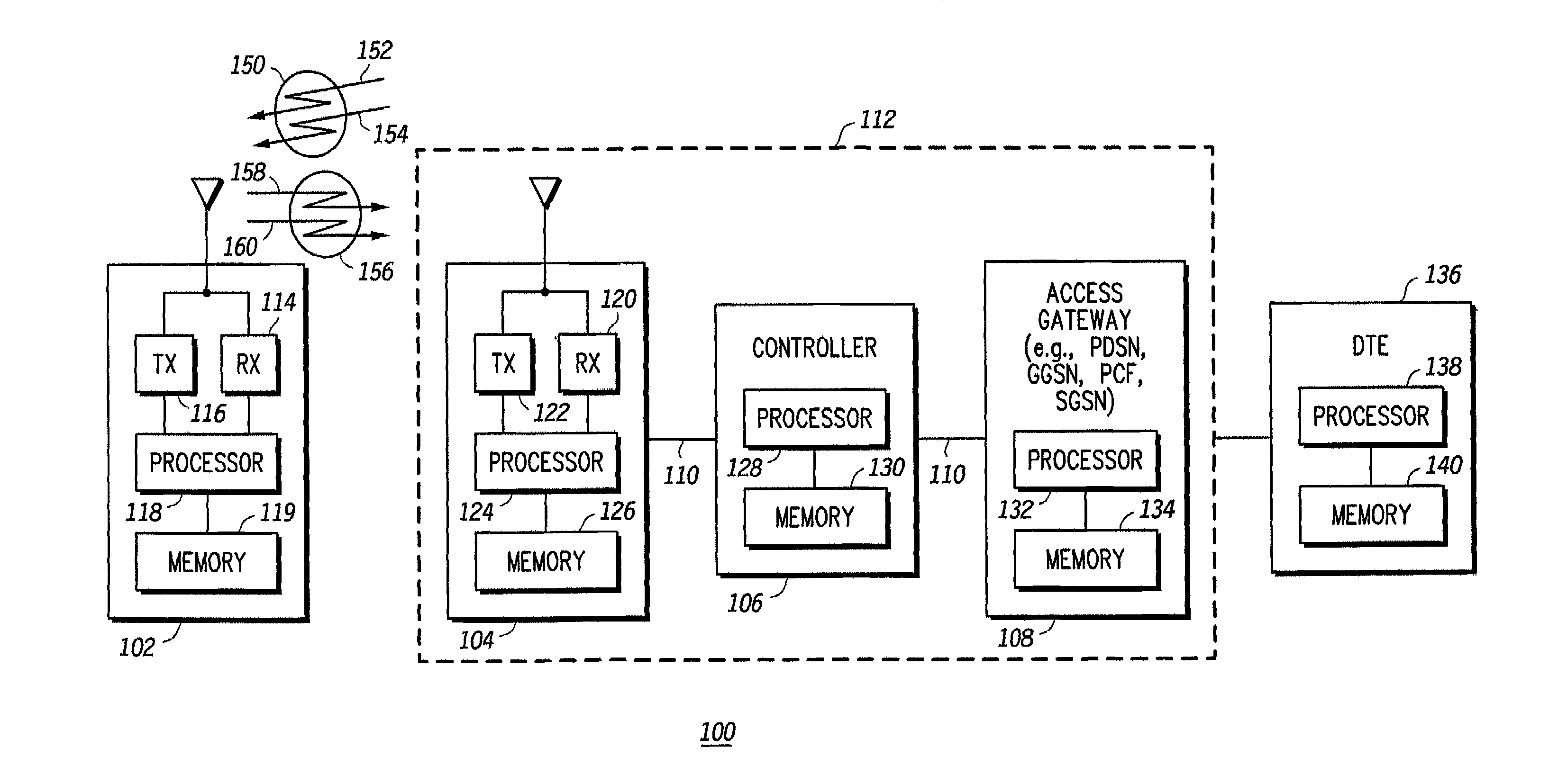

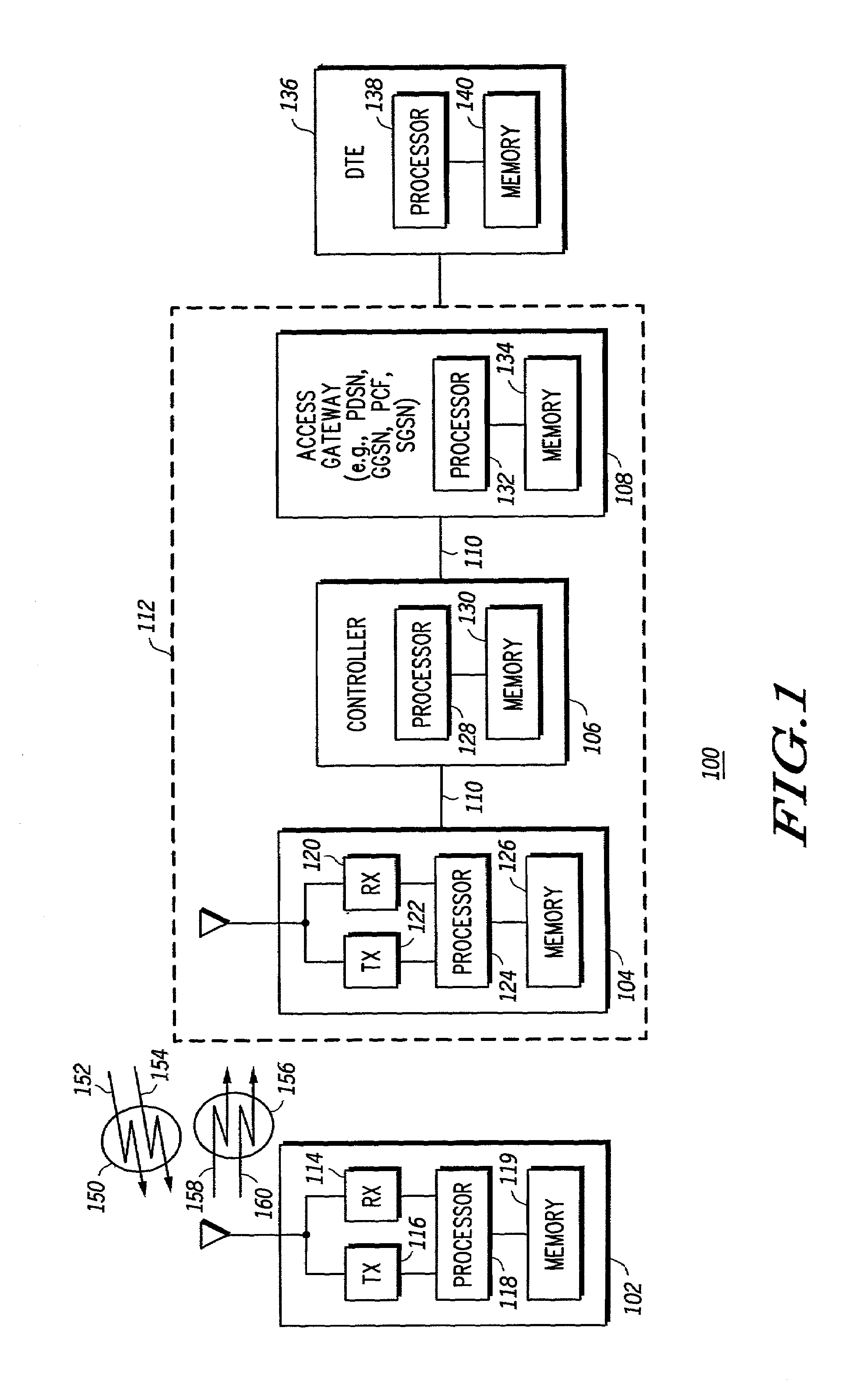

Method and apparatus for transmitting data in a communication system

ActiveUS7165112B2Network traffic/resource managementMultiple digital computer combinationsAbstraction layerSystem capacity

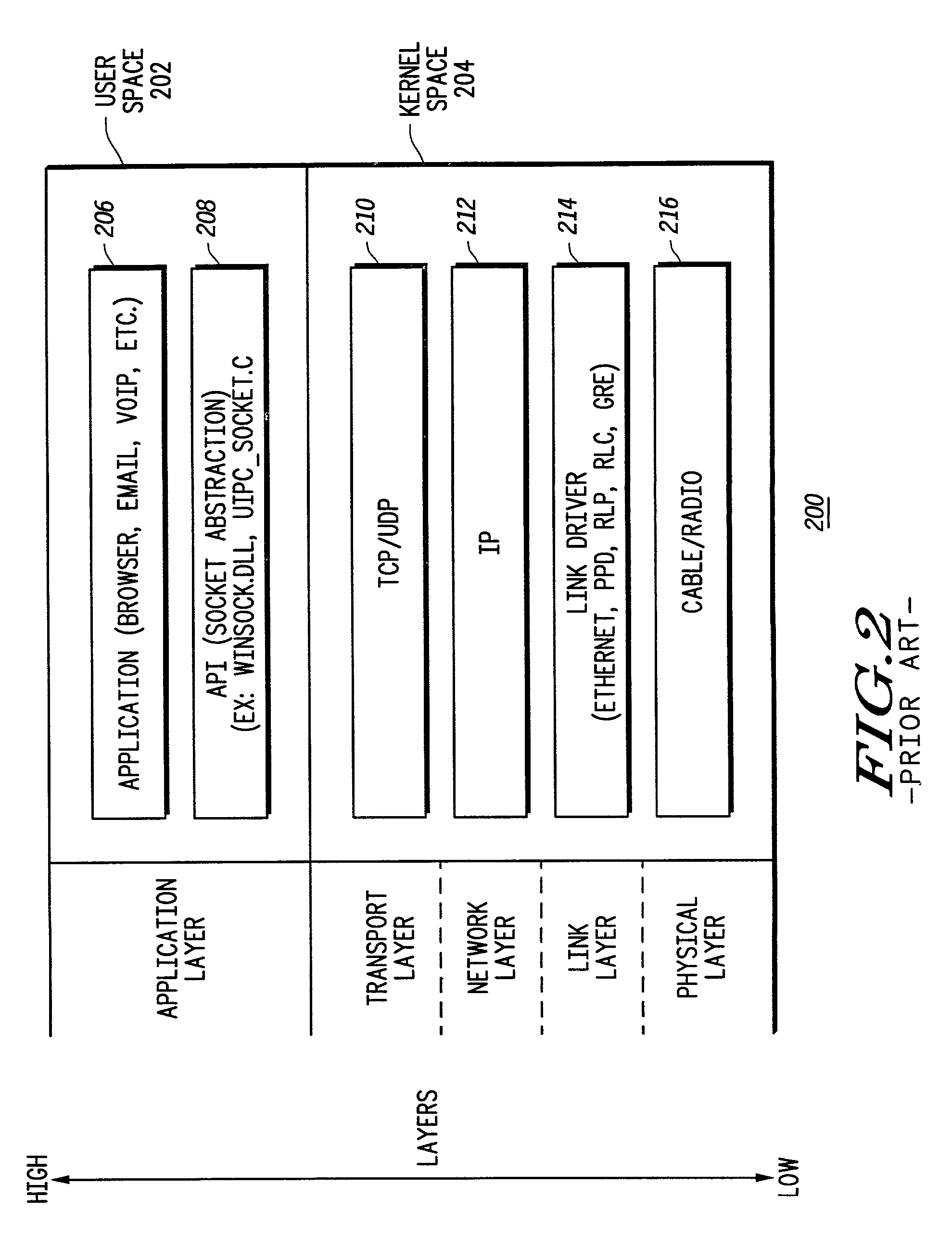

A communication system distributes the functions of a socket abstraction layer of the prior art between a socket abstraction layer included in an client communication device, such as a mobile subscriber, and a socket abstraction layer in a an agent communication device, such as an infrastructure serving the mobile subscriber. By so distributing the functions of the socket abstraction layer, headers may be reduced in signaling between the client communication device and the corresponding agent communication device as part of call set ups and tear downs and in the exchange of payloads between the client and agent communication devices. By reducing the required headers, overhead is reduced and bandwidth is conserved in communications between the client and agent communication devices, such as in over-the-air communications between a mobile subscriber and an infrastructure serving the mobile subscriber, with resulting increases in system capacity and improvements in system efficiency.

Owner:GOOGLE TECH HLDG LLC

Dealing with composite data through data model entities

ActiveUS7054877B2Data processing applicationsDigital data processing detailsAbstraction layerTheoretical computer science

The present invention is generally directed to a system, method and article of manufacture for accessing data represented abstractly through an abstraction model. In one embodiment, a data repository abstraction layer provides a logical view of an underlying data repository that is independent of the particular manner of data representation. A query abstraction layer is also provided and is based on the data repository abstraction layer. A runtime component performs conversion of an abstract query (i.e., a request for results or a request to modify data) into a form that can be used against a particular physical data representation. Abstract and / or physical queries are transformed according to model entities which define a relationship between logical fields of the data repository abstraction layer.

Owner:HUAWEI TECH CO LTD

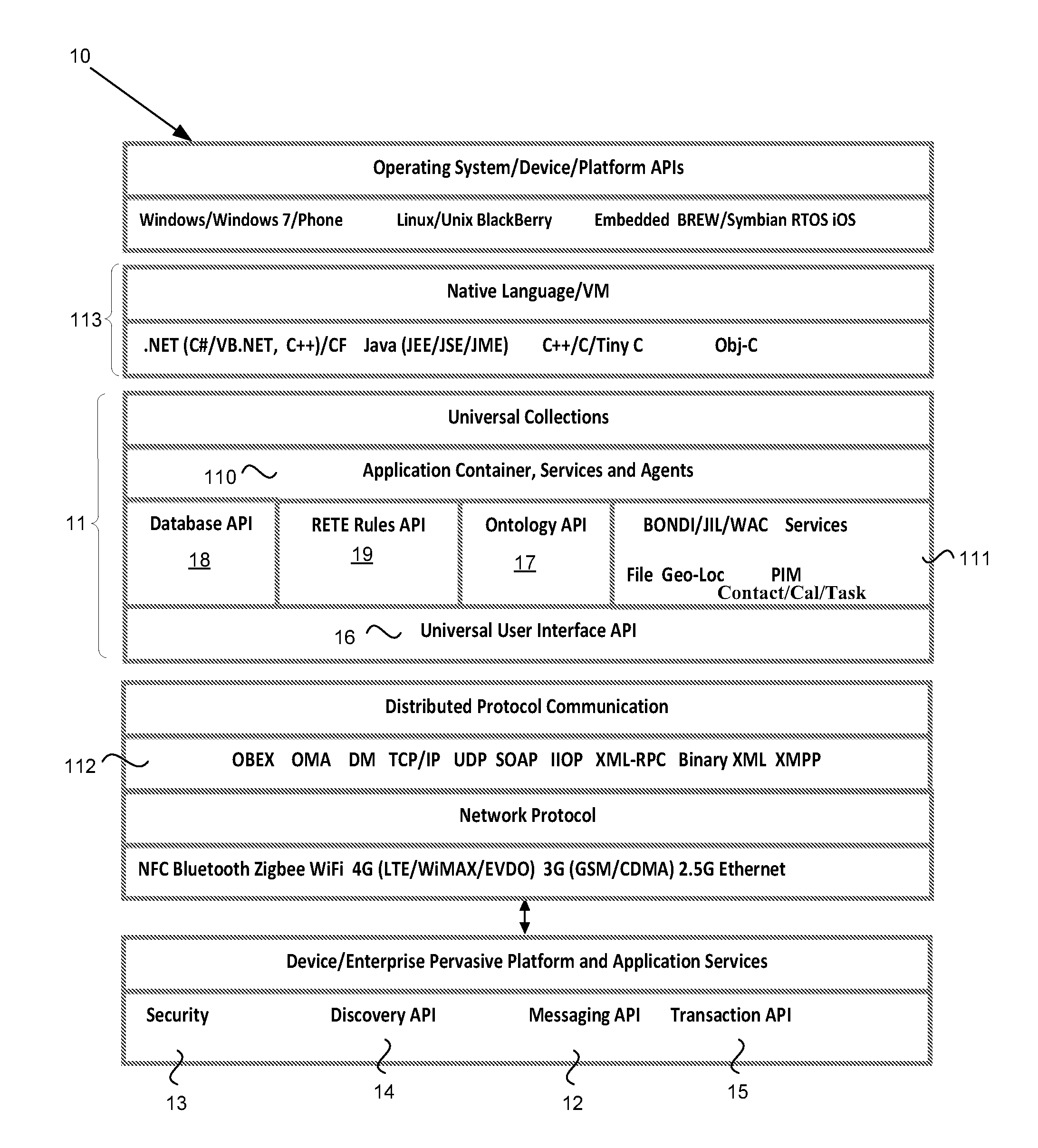

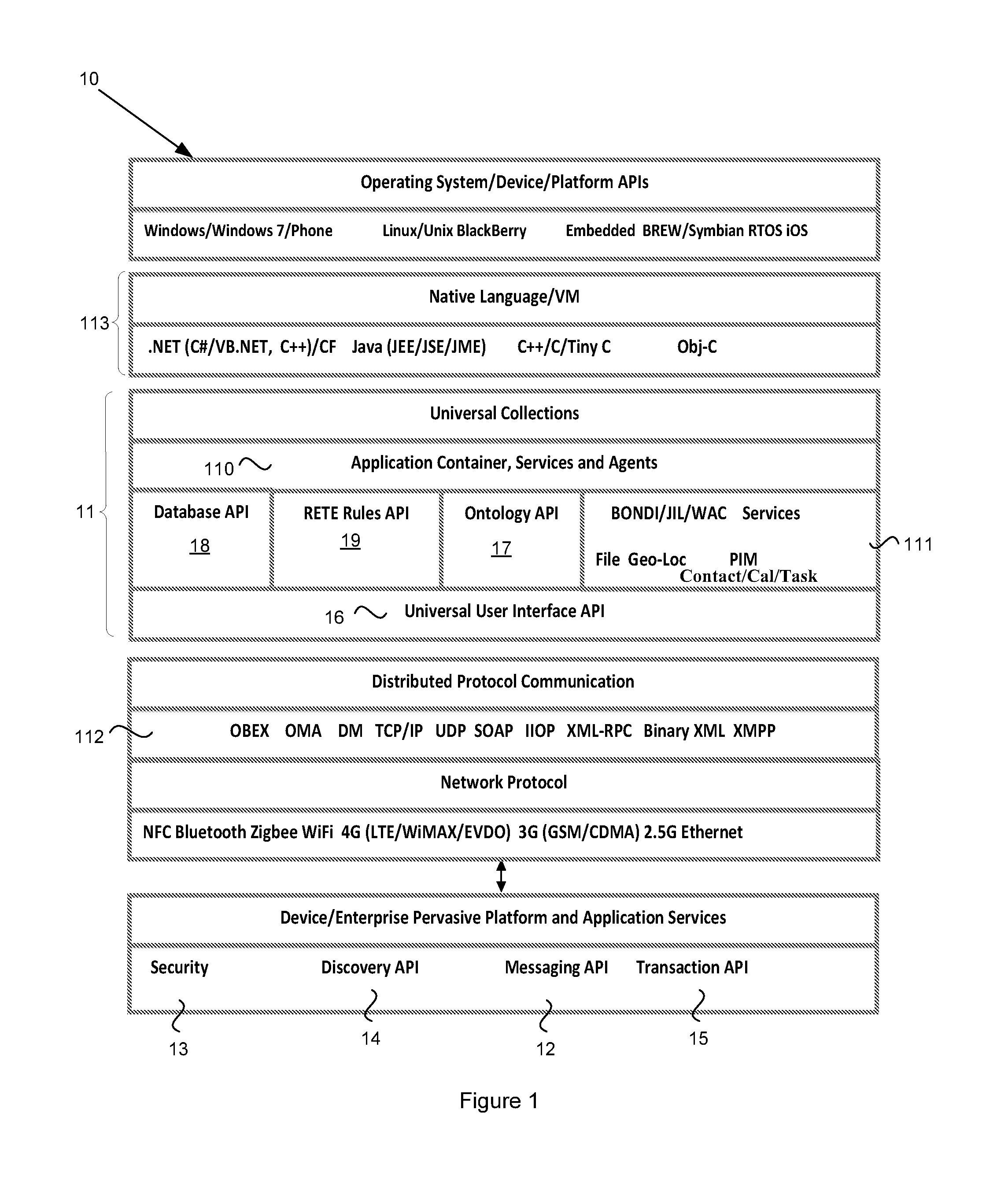

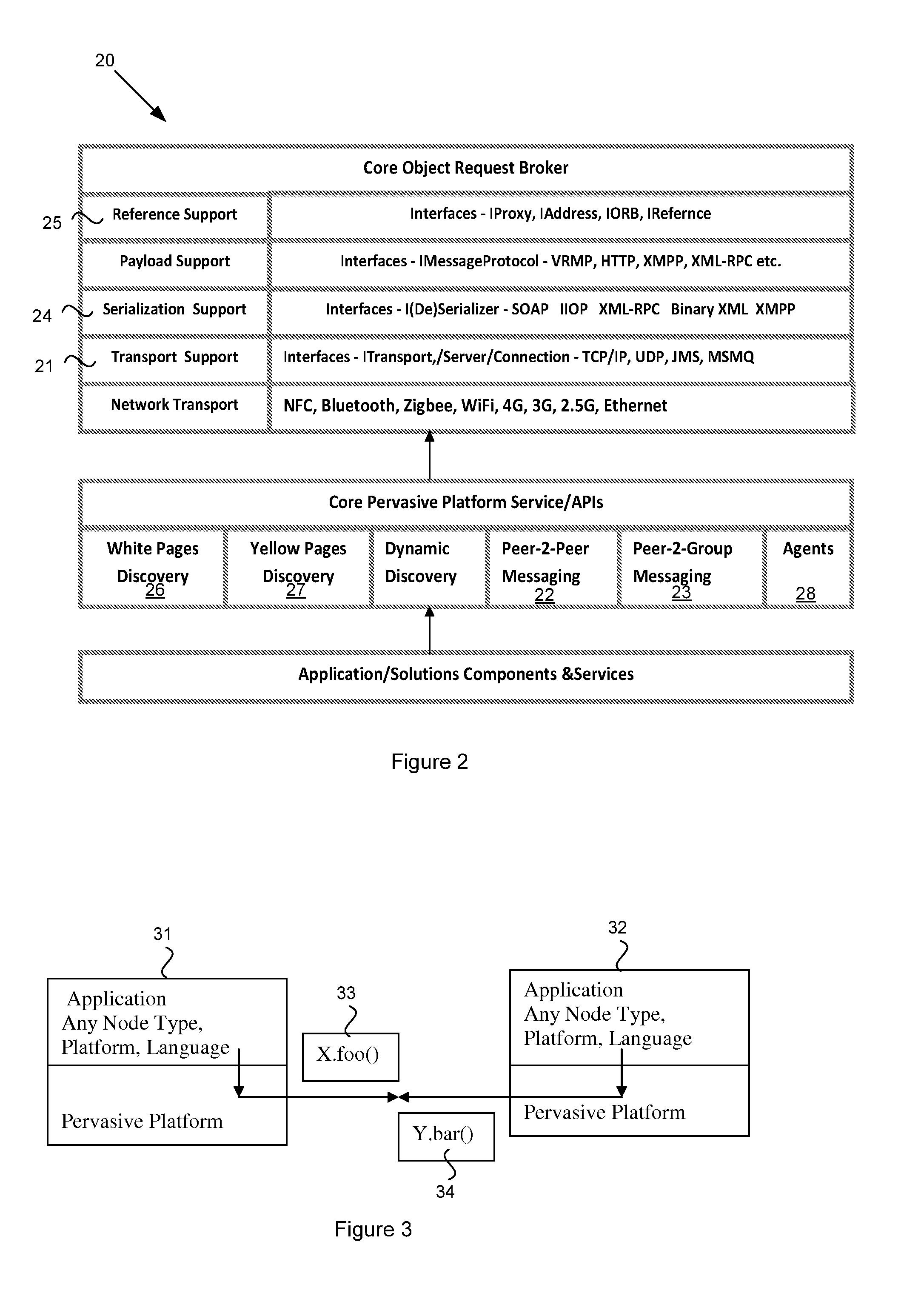

Architecture for pervasive software platform-based distributed knowledge network (DKN) and intelligent sensor network (ISN)

InactiveUS20120311614A1Multiprogramming arrangementsTransmissionAbstraction layerApplication software

A device API Abstraction layer is provided that is configured to operate as an interface between one or more applications operating on a device and an operating platform of the device. The device API abstraction layer comprises a universal set of APIs that enables the applications to execute irrespective of the operating system and software platform of the host device.

Owner:OPEN INVENTION NEWTORK LLC

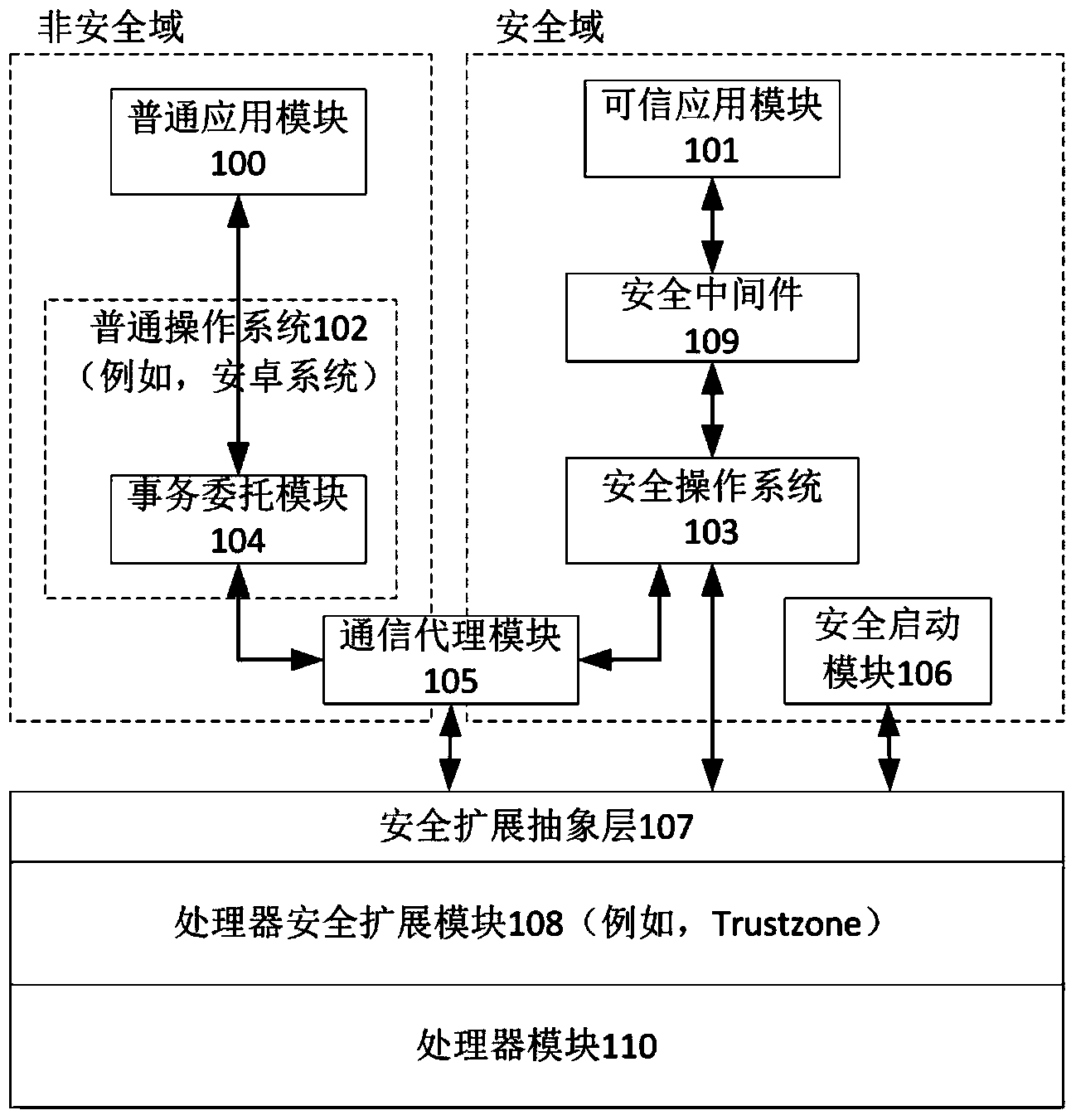

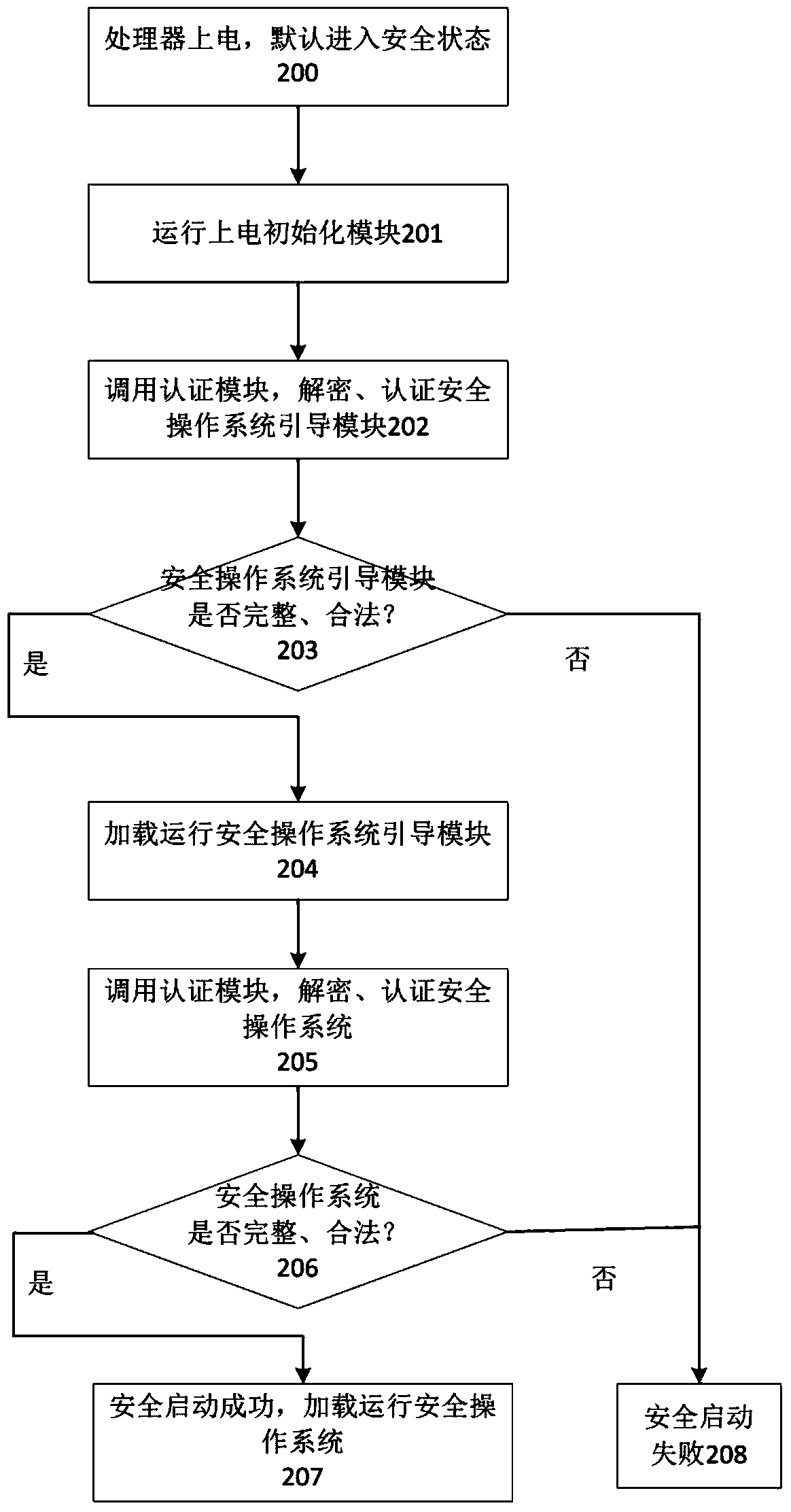

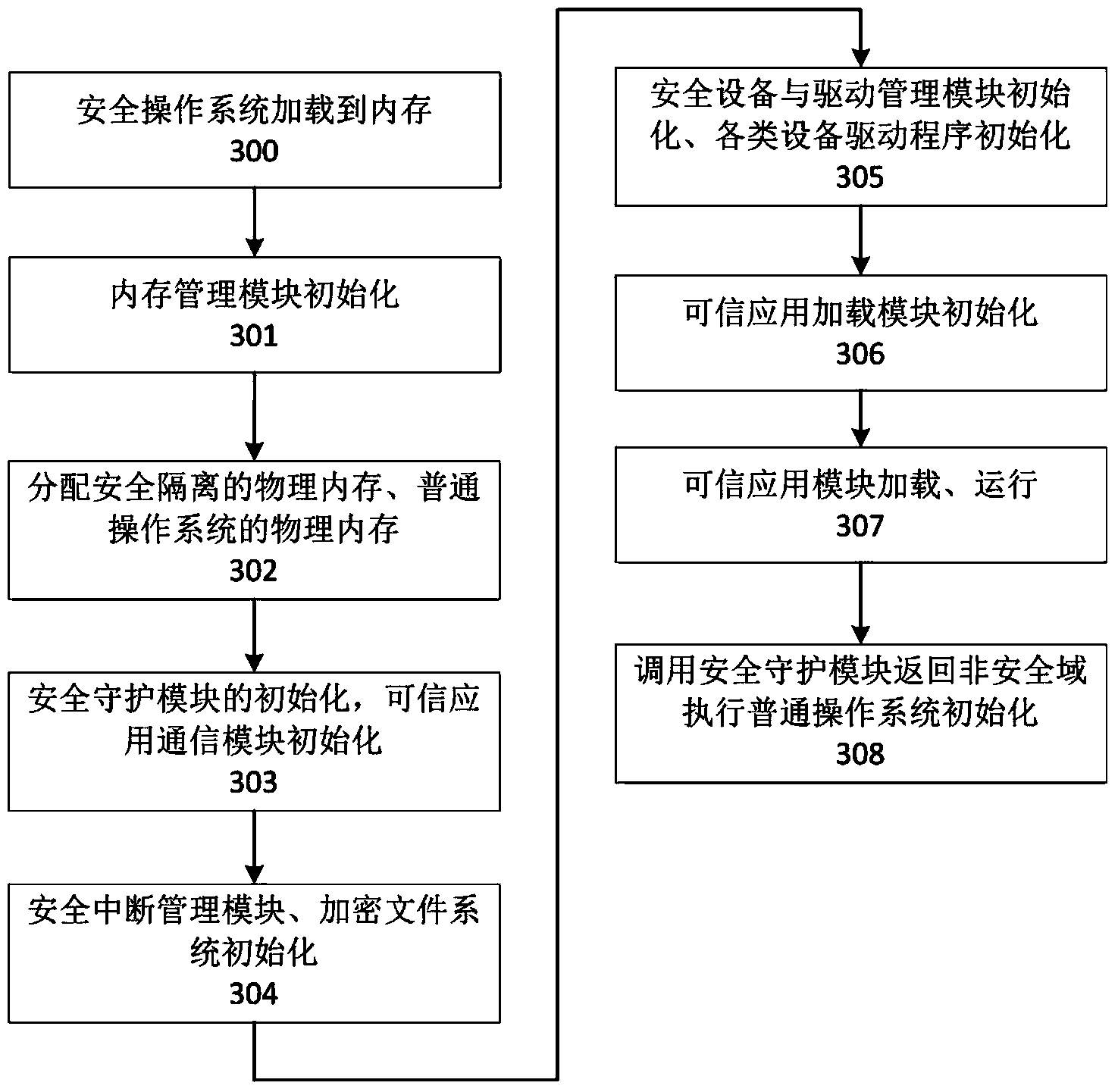

Intelligent terminal isolation system and intelligent terminal isolation method both based on processor safety extension

InactiveCN104318182AAchieve security isolationEnsure safetyInternal/peripheral component protectionSubstation equipmentAbstraction layerOperational system

Disclosed are an intelligent terminal isolation system and an intelligent terminal isolation method both based on processor safety extension. The intelligent terminal isolation system comprises a safety starting module, a transaction commission module, a communication agent module, a safety extension abstraction layer, a safety operating system, safety middleware, credible application modules and a common application module. The safety starting module simply initializes hardware environment of an intelligent terminal, and authenticates and guides the safety operating system. The communication agent module is responsible for encapsulation and communication of bottom layer data of the credible application modules and the common application module. The safety extension abstraction layer provides a uniform calling interface to the safety operating system. The safety operating system provides mutually independent operation space for the credible application modules in a whole safety domain and manages all software and hardware resources in the safety domain. The safety middleware is a core library related to implementation of safety functions and transaction commissions and provides related functional interfaces to credible applications. The intelligent terminal isolation system and the intelligent terminal isolation method aim to provide a complete safety isolation mechanism to the intelligent terminal and improve safety of software operation environment.

Owner:INST OF INFORMATION ENG CHINESE ACAD OF SCI

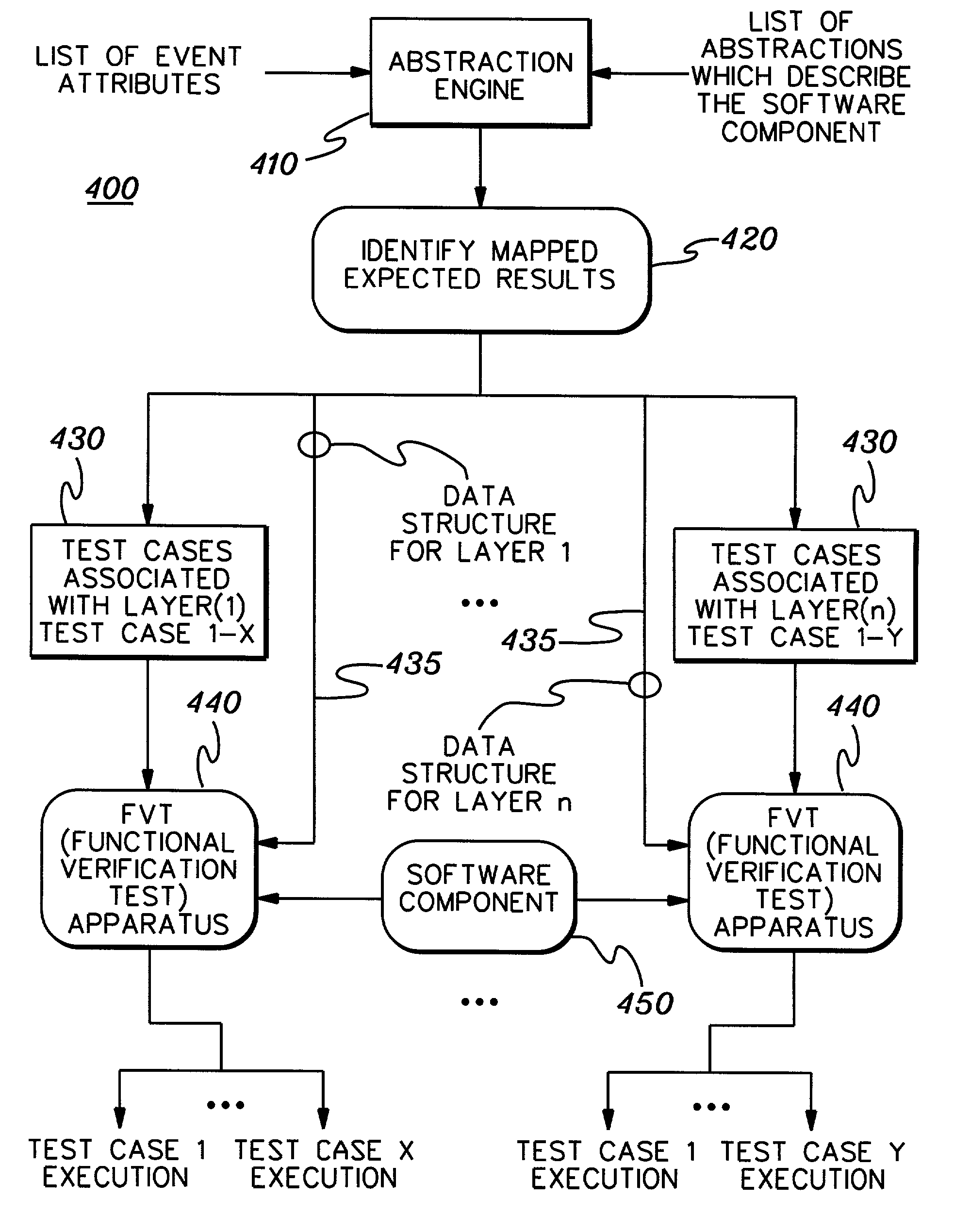

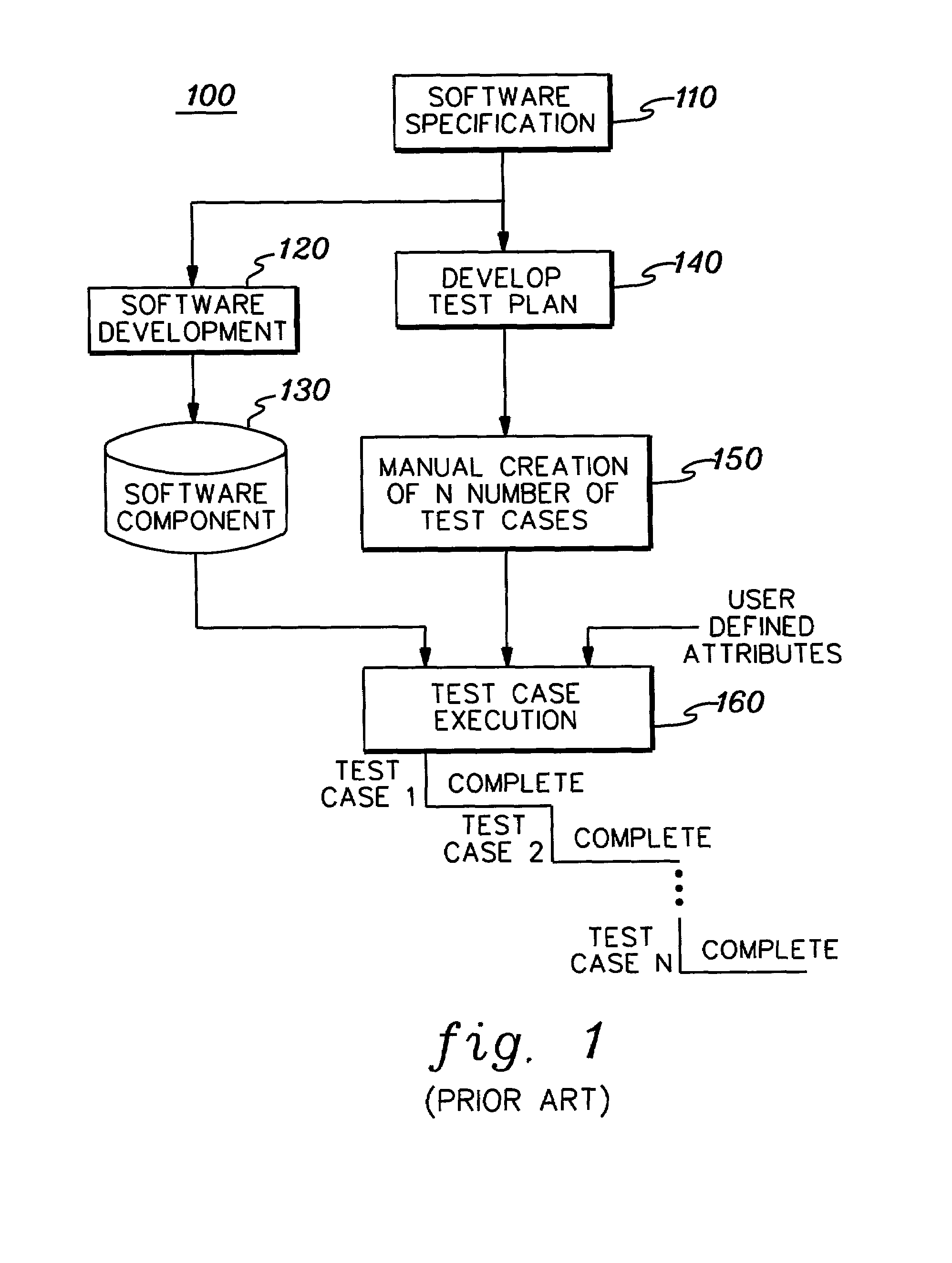

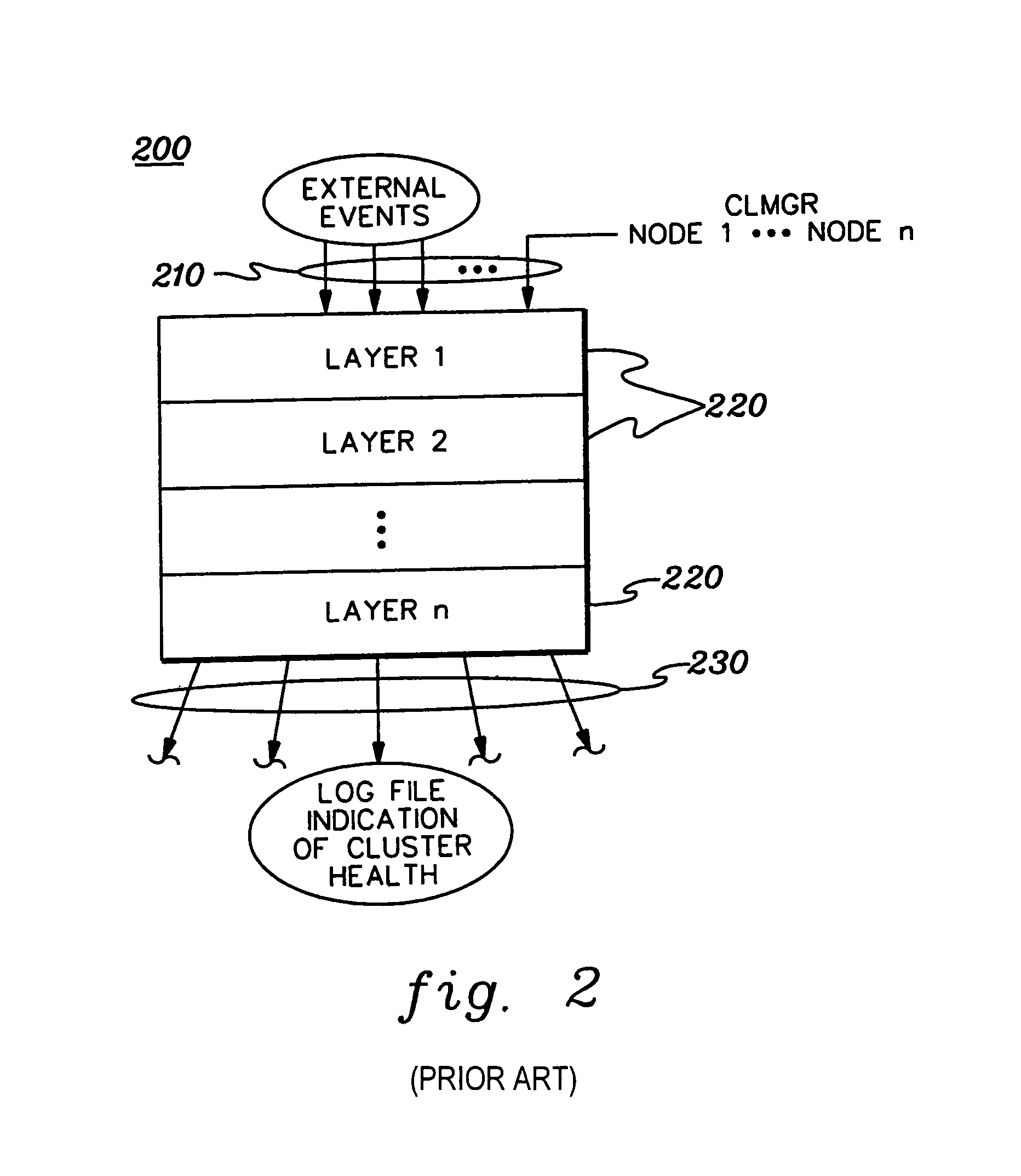

Method and apparatus for testing and evaluating a software component using an abstraction matrix

InactiveUS6986125B2Cost changeElectronic circuit testingSoftware testing/debuggingAbstraction layerFunctional testing

A functional testing and evaluation technique is provided employing an abstraction matrix that describes a complex software component to be tested. The abstraction matrix includes at least one test case scenario and mapped expected results therefore. Test cases are derived from the at least one test case scenario and used to test the software component, thereby generating test results. The test results are automatically evaluated using the abstraction matrix. The evaluating includes comparing a test case to the at least one test case scenario of the abstraction matrix and if a match is found, comparing the test result for that test case with the mapped expected result therefore in the abstraction matrix.

Owner:IBM CORP

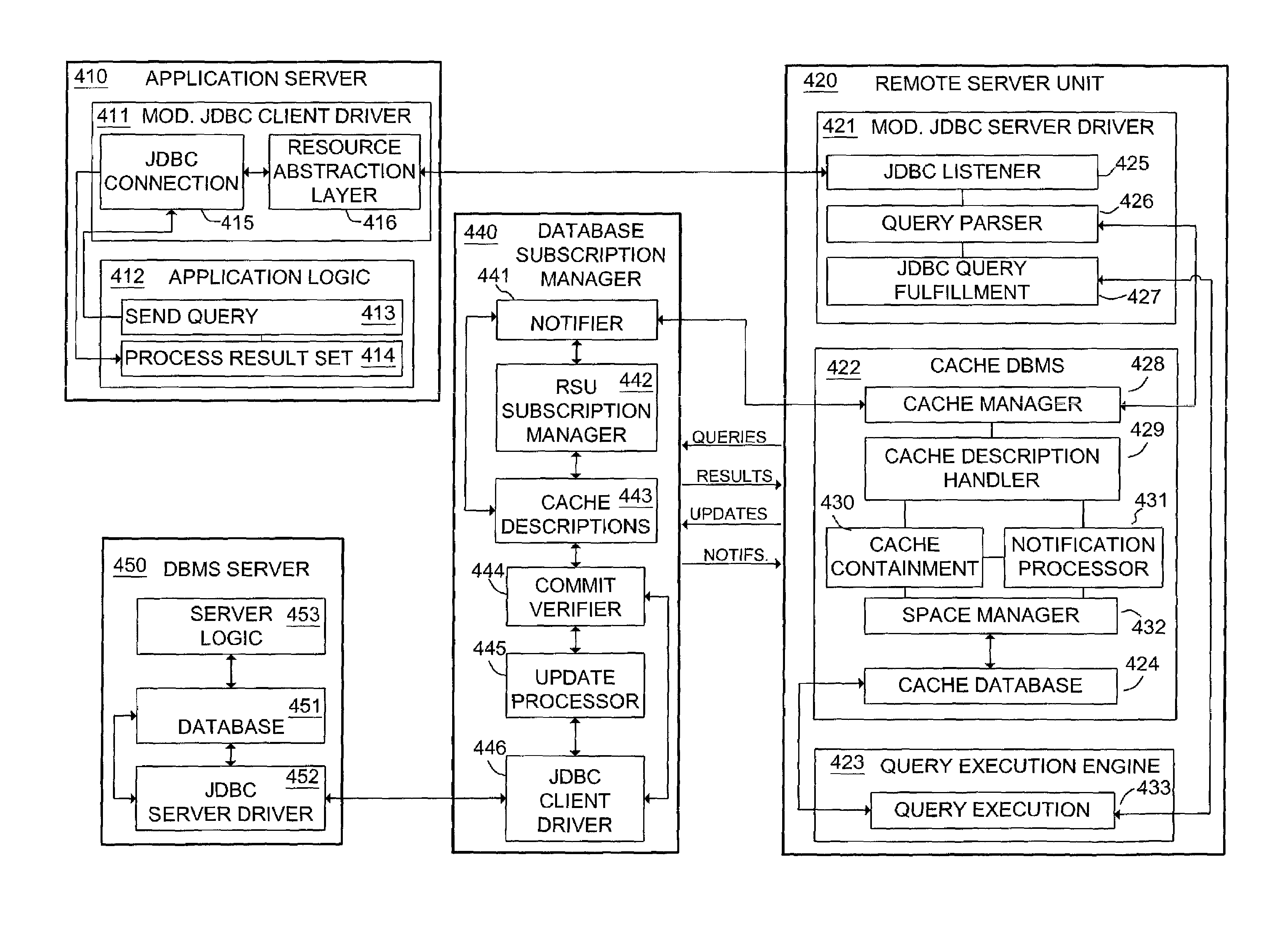

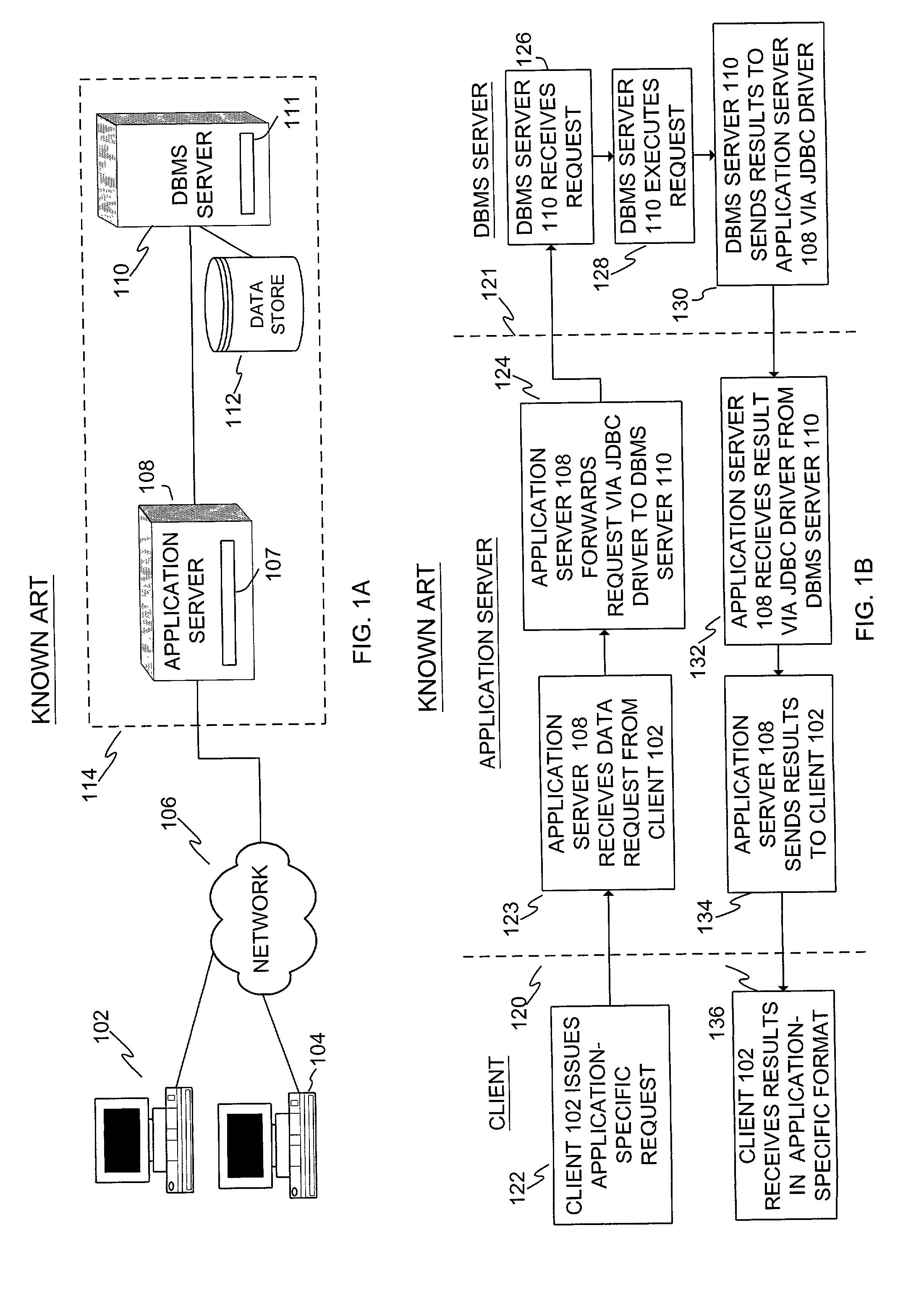

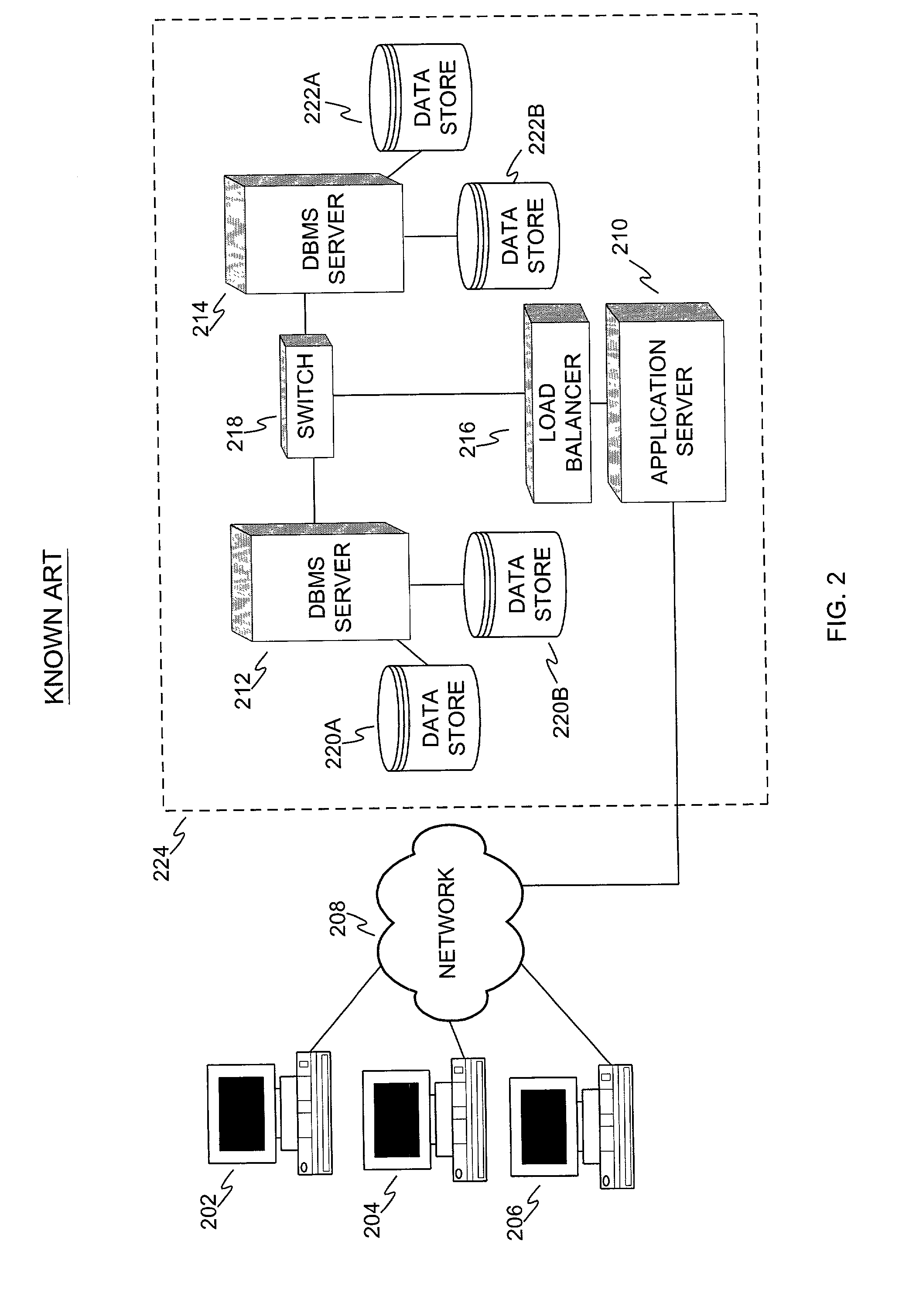

Systems and methods for managing distributed database resources

ActiveUS7162467B2Quality improvementLow costData processing applicationsDigital data processing detailsAbstraction layerCentral database

A system and method are described for implementing a distributed database caching system with the capability to support and accelerate read and update transactions to and from one or more central Database Management System (DBMS) servers for multiple concurrent users. The system and method include a resource abstraction layer in a database client driver in communication with remote server units (RSUs) having a cache database. RSUs respond to user requests using the cache database if possible. If the cache database does not have the needed data, the RSU sends the request to a database subscription manager (DSM) in communication with the DBMS server. The DSM responds to the request and sends predicate data based on queries processed by the DBMS server for use in updating the cache databases.

Owner:GOPIVOTAL

Methods and systems for access to real-time full-duplex web communications platforms

InactiveUS8797920B2Relieve pressureNatural language data processingBroadcast service distributionAbstraction layerClient-side

At least one embodiment of this invention pertains to an abstraction layer that provides a consistent interface, with client-side and server-side implementations, to allow web client to interact with other web clients (that are connected to a common interactive event) in real-time over standard web ports without the web clients being tied to a specific real-time communications platform. At least some embodiments described herein contemplate methods and systems for establishing web communication among multiple web clients by providing a layer of abstraction between the web clients and the interactive session using interfaces to an Open Real-Time Connectivity (ORTC) layer. The system may use authentication methods to validate the web communications. The system may be implemented on a scalable, load-balanced, and fault-tolerant network.

Owner:IBT TECHAS E SISTEMAS LTDA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com