Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

129results about How to "Capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

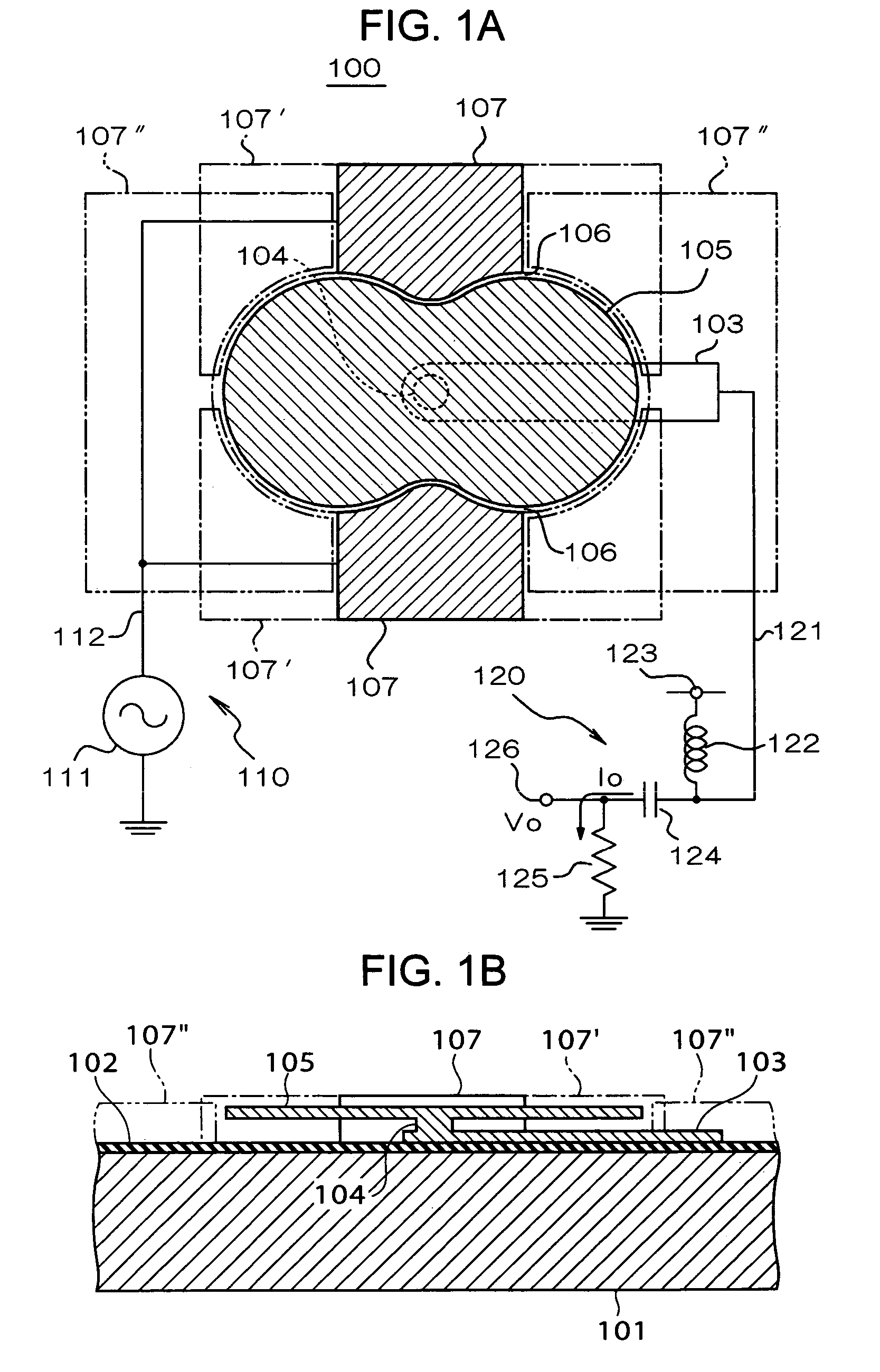

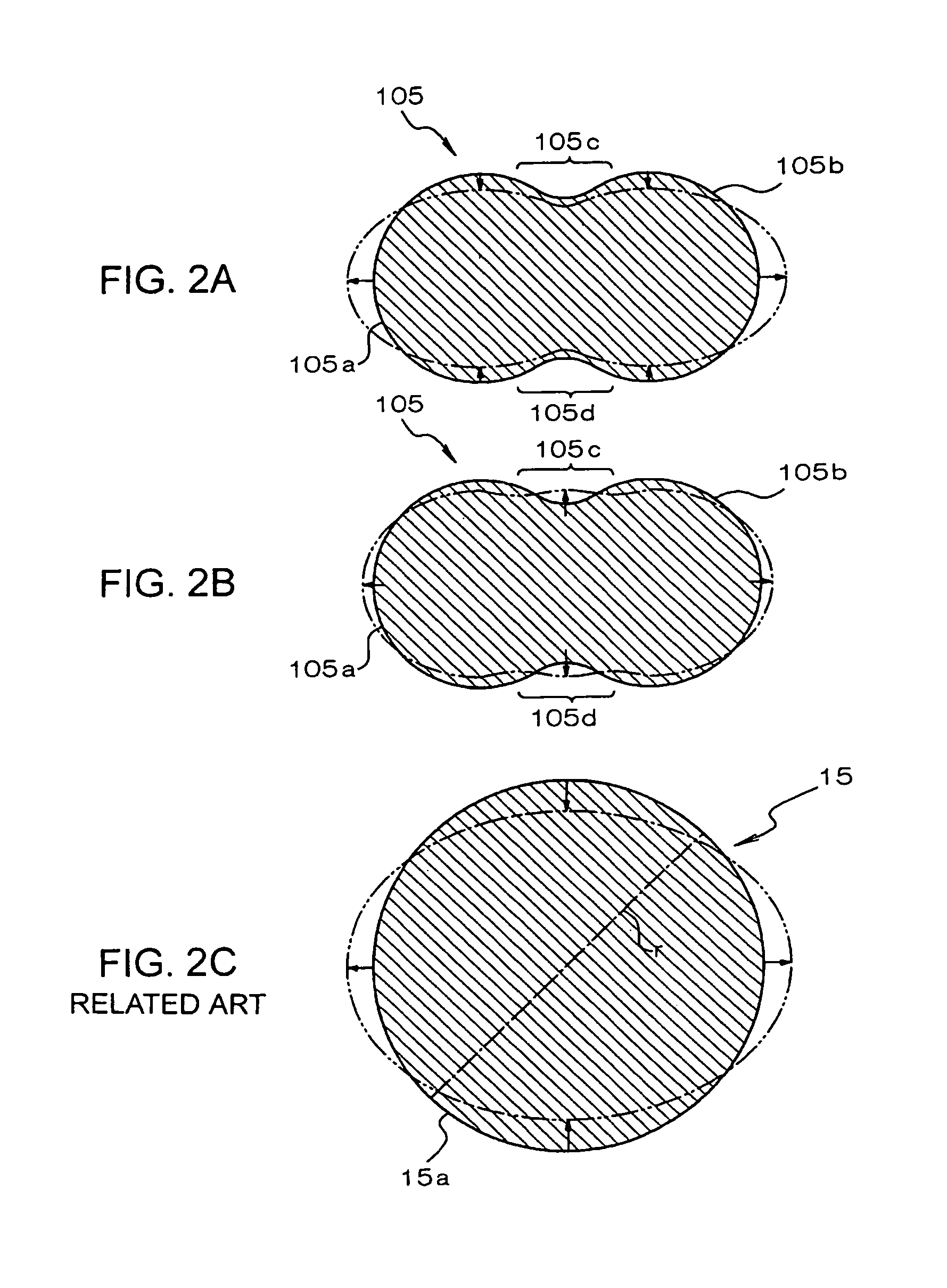

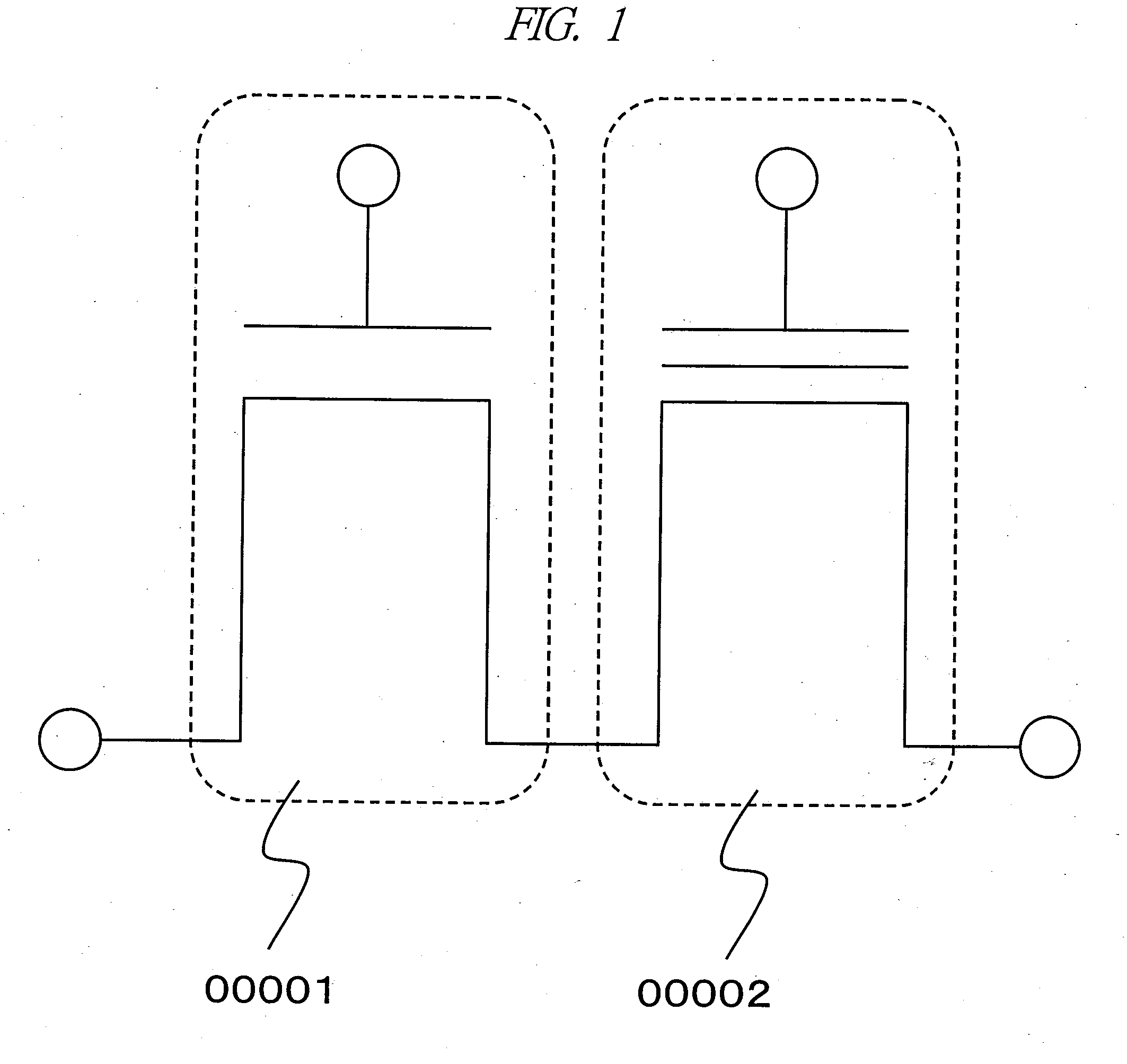

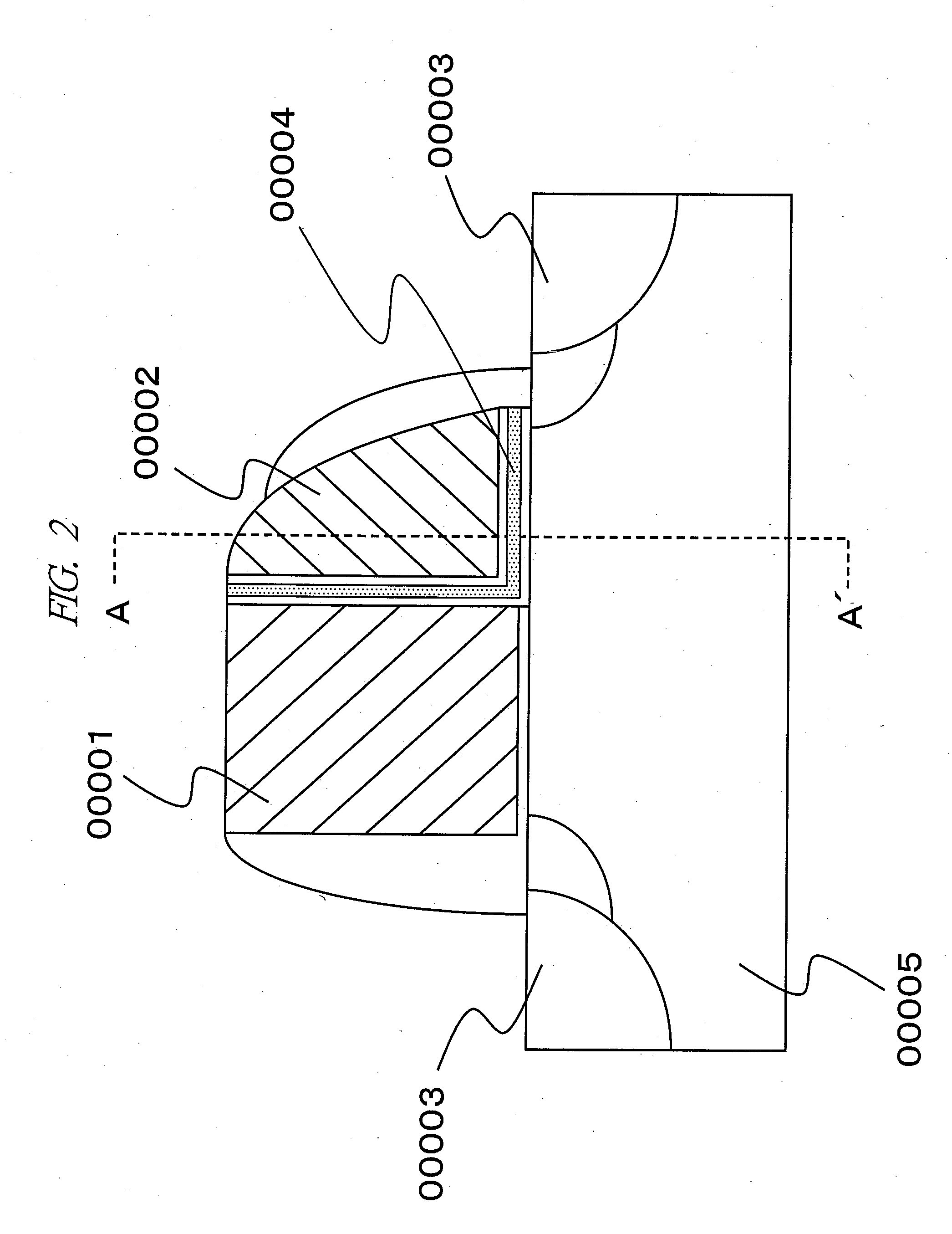

Micromechanical electrostatic resonator

InactiveUS7215061B2CapacitanceLarge capacitancePiezoelectric/electrostriction/magnetostriction machinesDecorative surface effectsCapacitanceAlternating current

Owner:SEIKO EPSON CORP

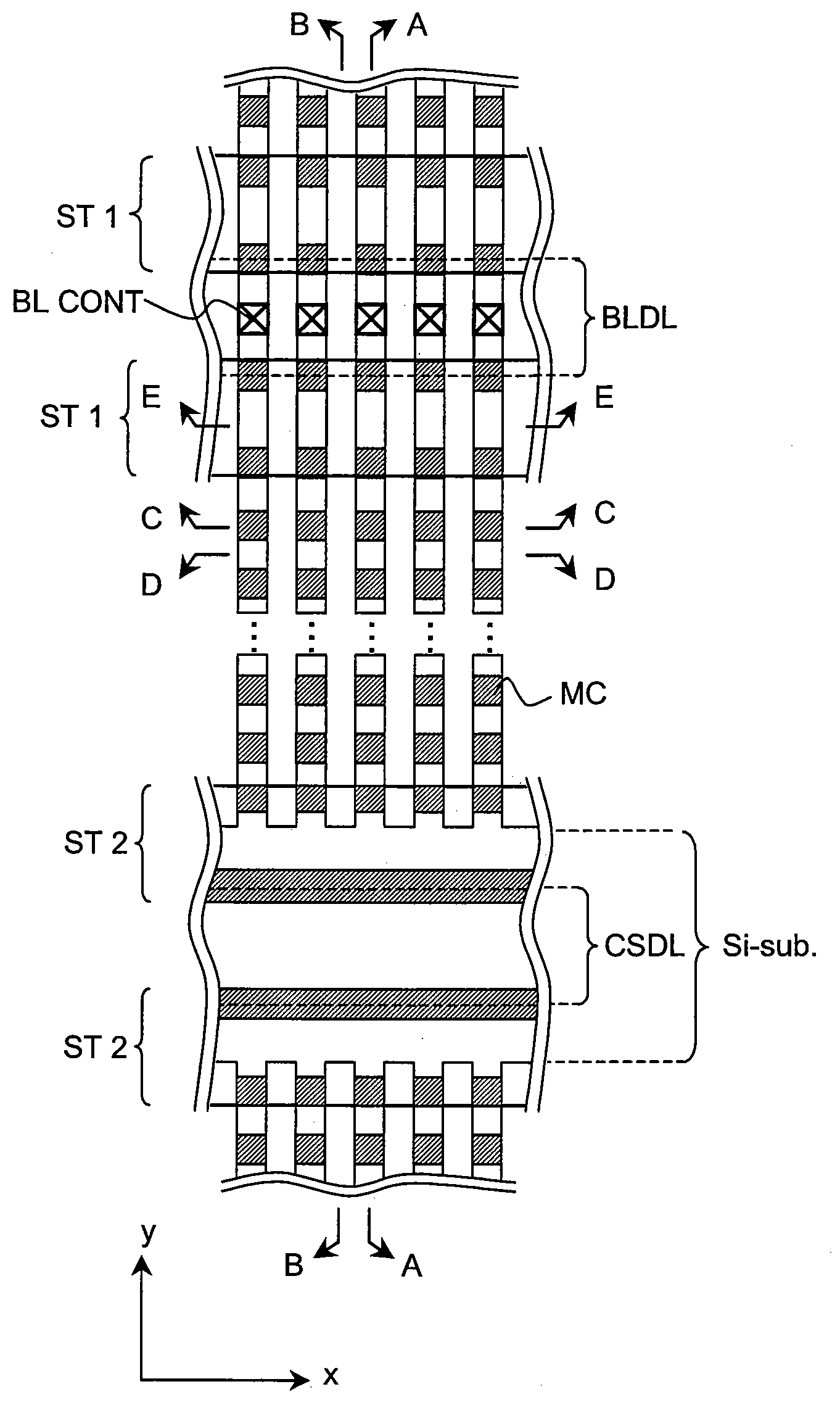

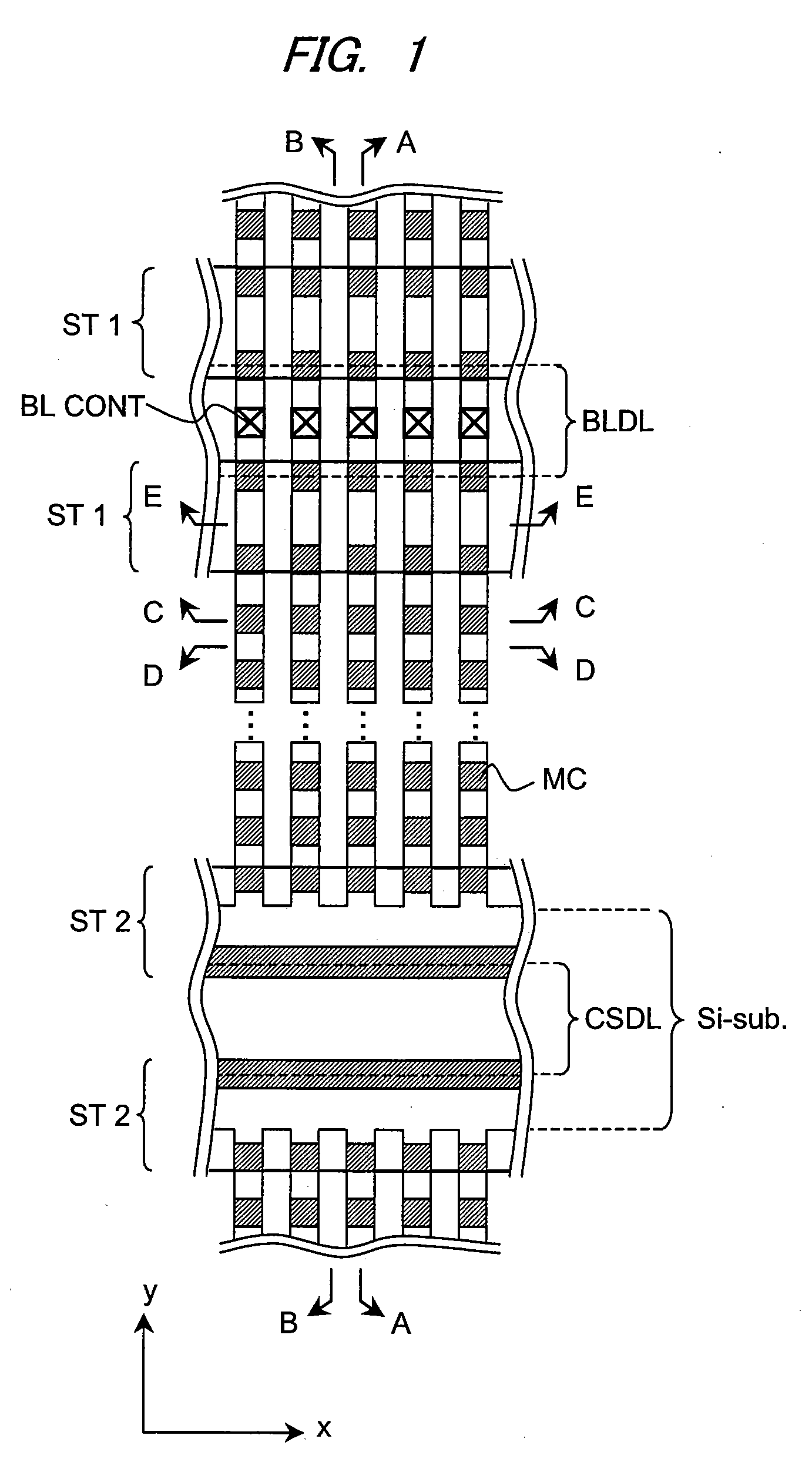

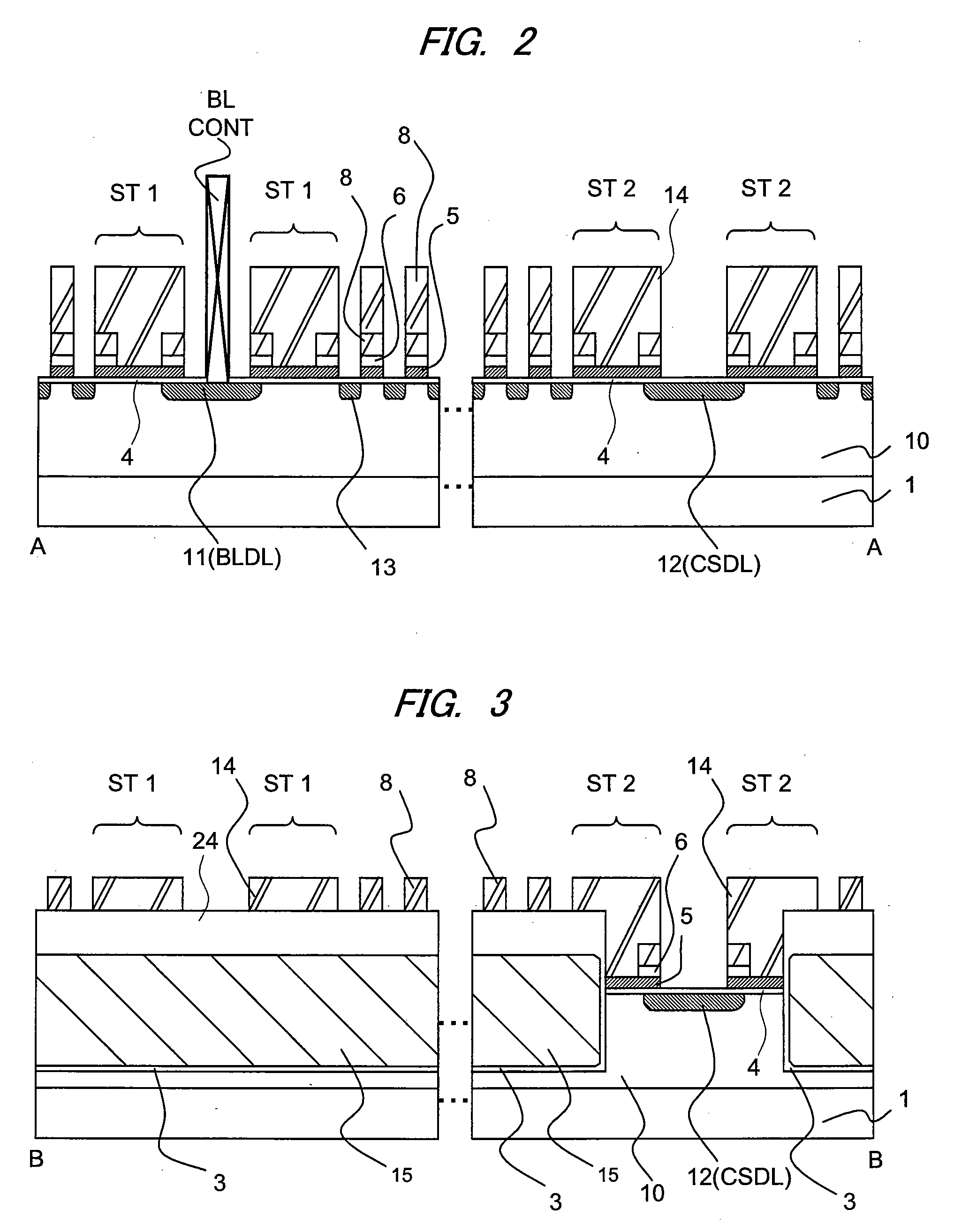

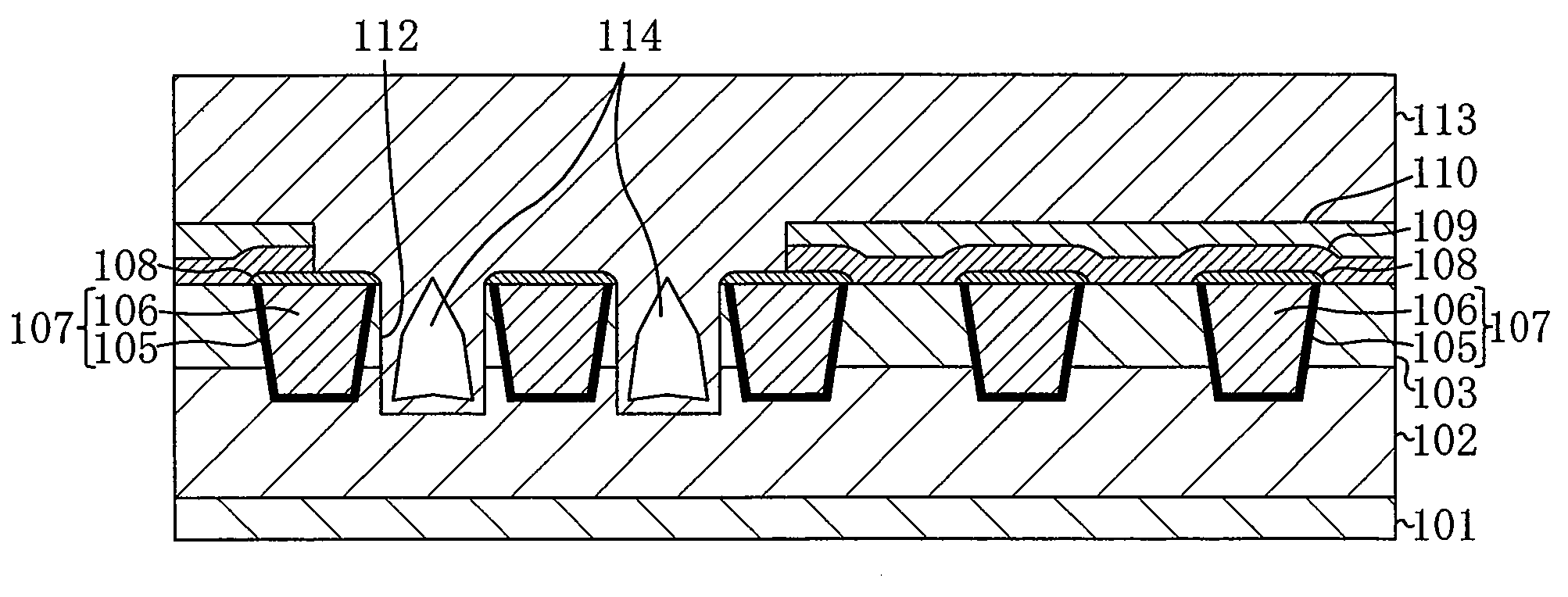

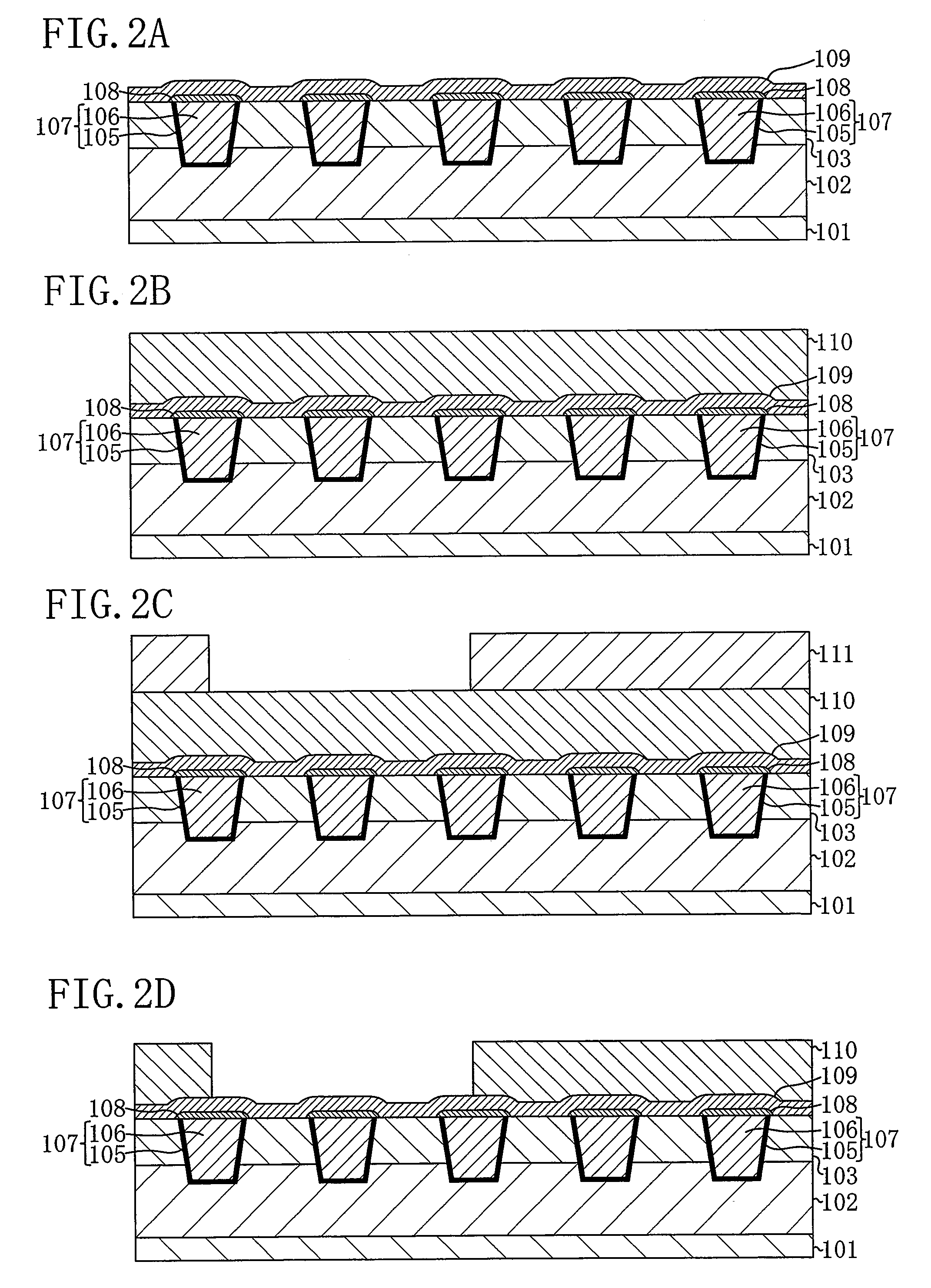

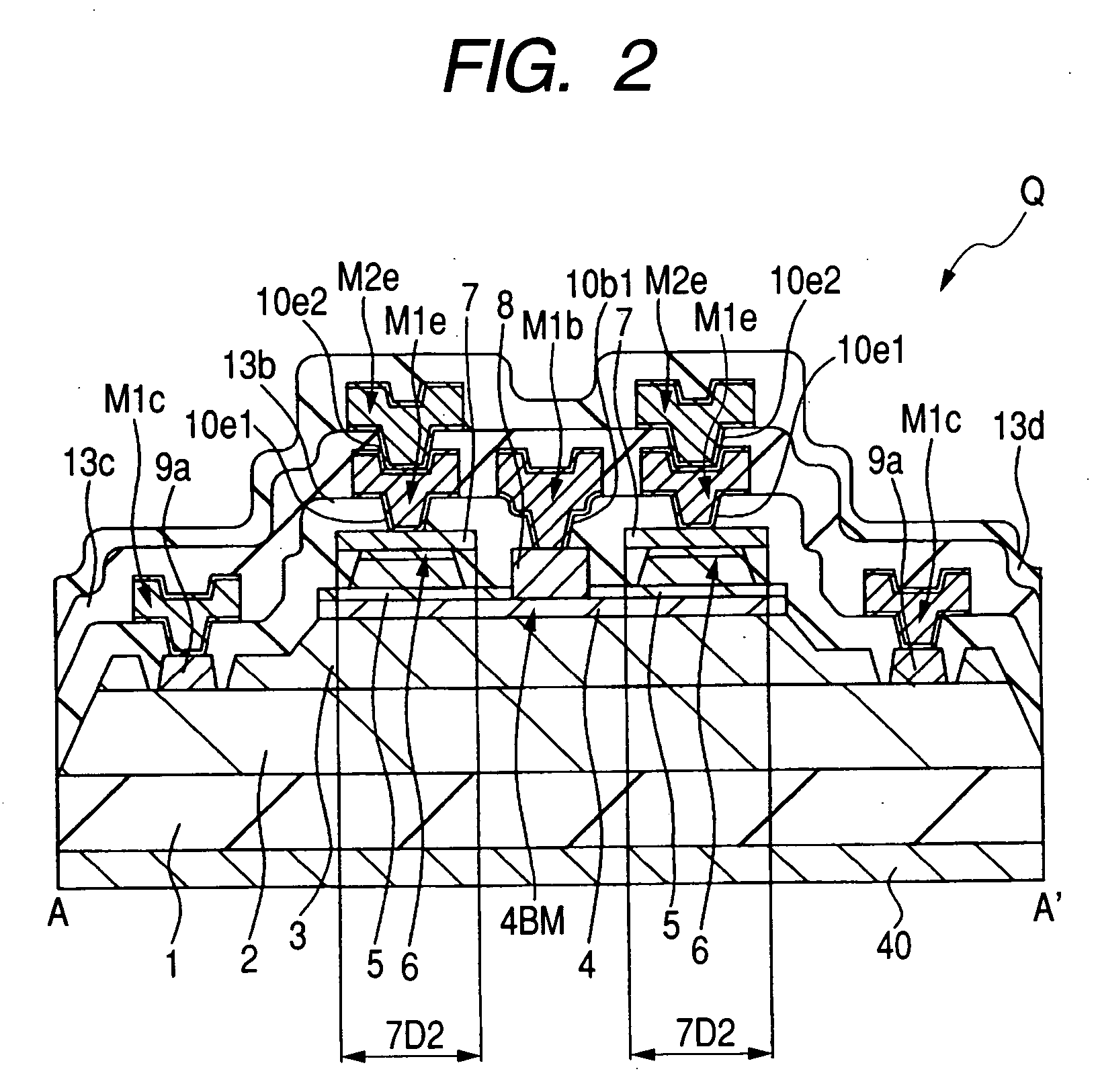

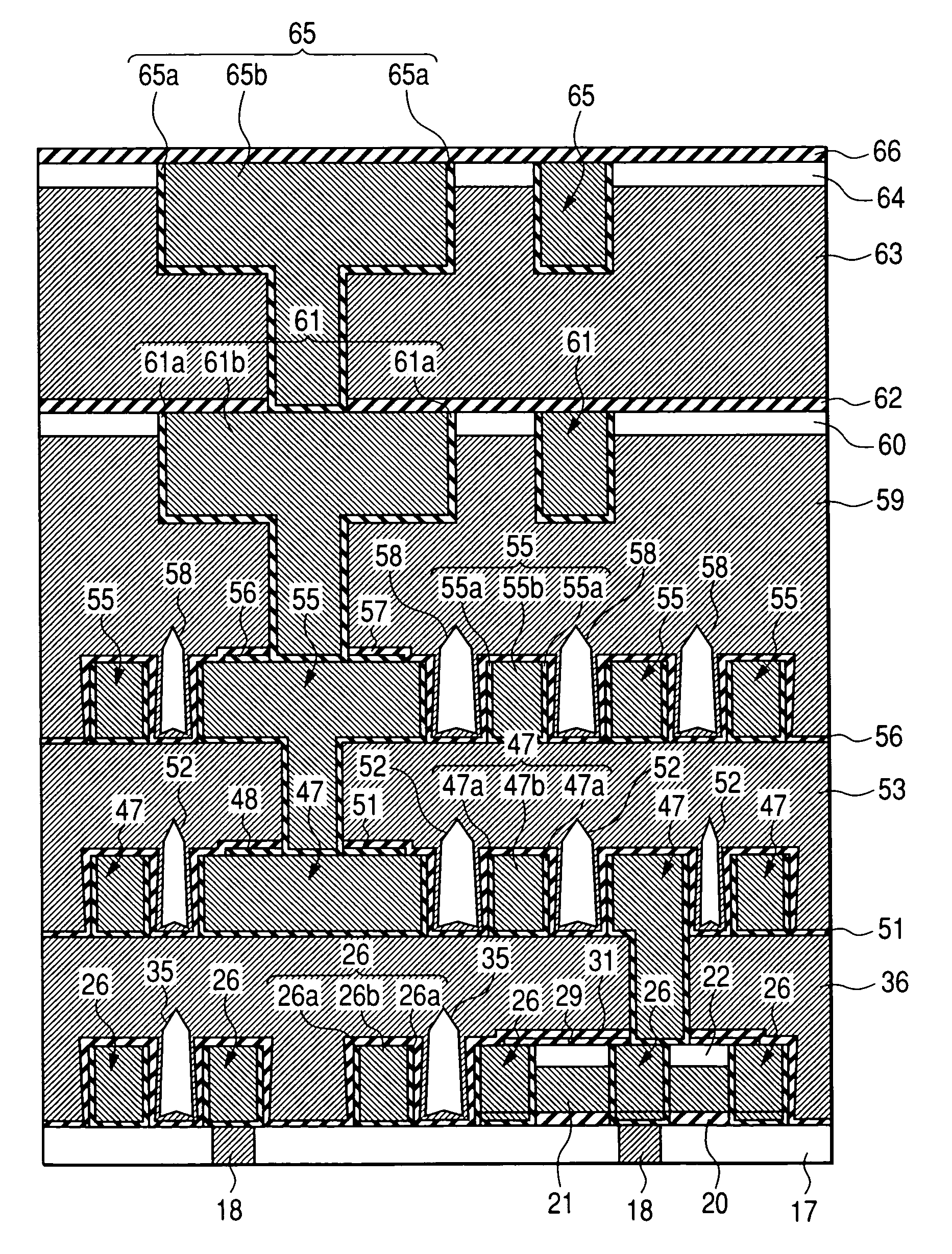

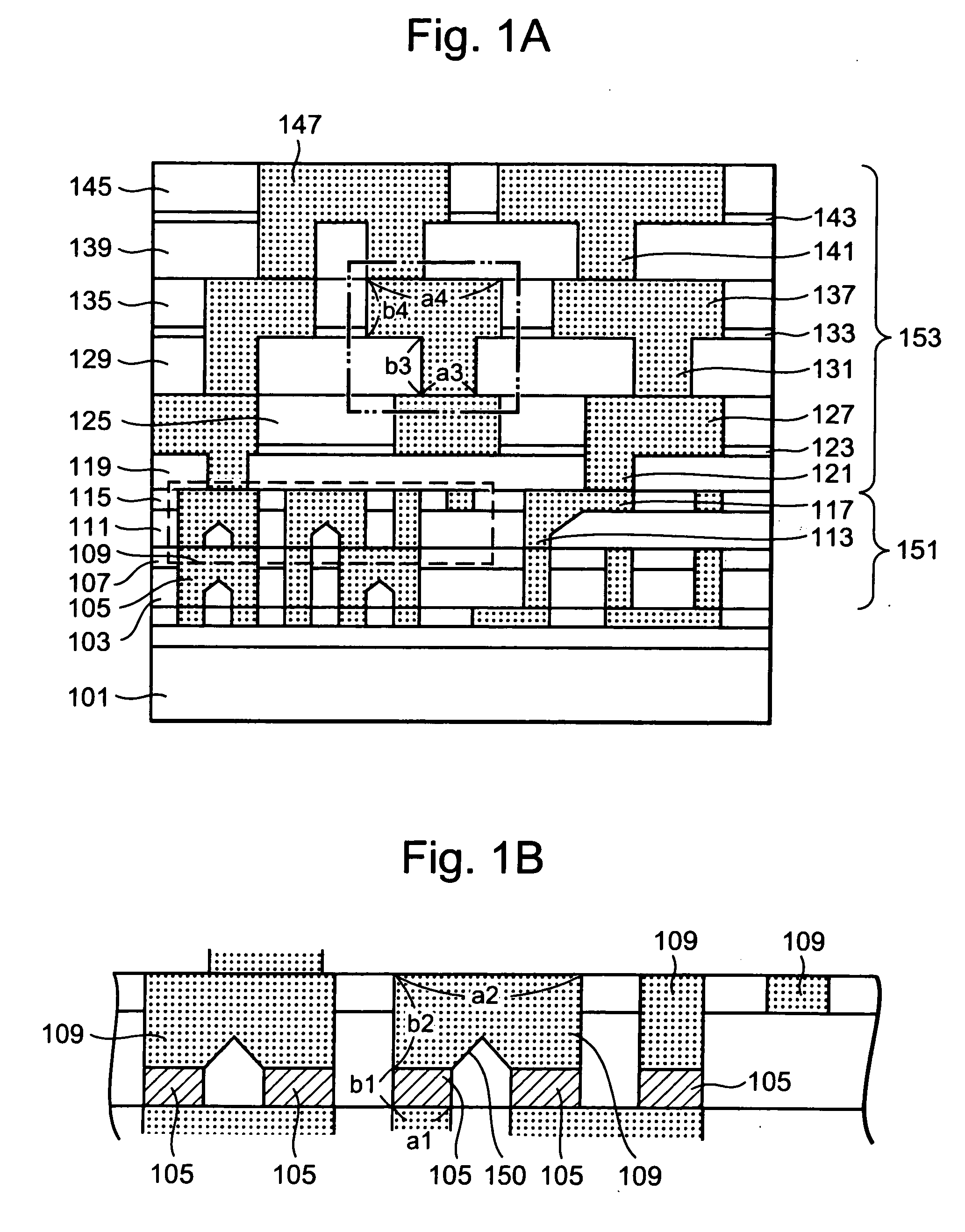

Nonvolatile semiconductor memory device and manufacturing method thereof

InactiveUS20070257305A1Improve reliability of flashDecreasing threshold voltage changeTransistorSolid-state devicesPotential changeGate insulator

By decreasing the threshold voltage shift due to the potential change of the cells adjacent in a word line direction, the reliability of a flash memory can be enhanced. Memory cells of a flash memory are formed in p-type wells of a semiconductor substrate and include gate insulator films, floating gates, high-K insulator films, and control gates (word lines). The floating gates and control gates (word lines) are isolated by high-K insulator films. The plurality of memory cells arrayed in row a direction are isolated by isolation trenches extending in a column direction. In the isolation trenches, a silicon oxide film is embedded. In the silicon oxide film, an air gap is provided. A lower end of the air gap extends near to the bottom of the isolation trench, and its upper end extends further above the upper surface of the high-K insulator film covering the floating gate.

Owner:RENESAS TECH CORP

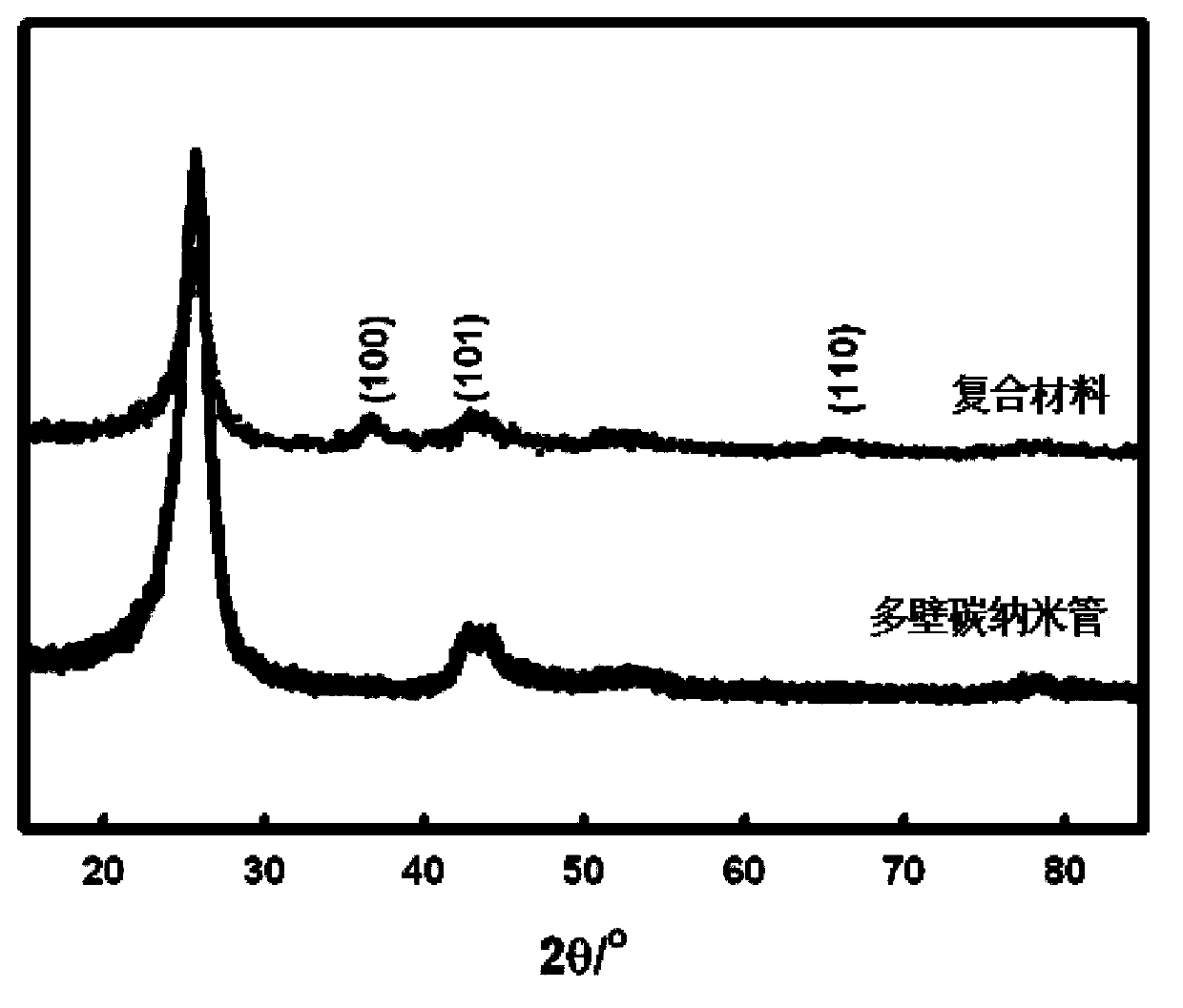

Manganese dioxide/carbon nanocomposite, and preparation method and application thereof

InactiveCN103972518AEasy to operateShort timeMaterial nanotechnologyHybrid capacitor electrodesFuel cellsSupercapacitor

The invention provides a manganese dioxide / carbon nanocomposite and a preparation method and application thereof. The preparation method comprises the following concrete steps: mixing an aqueous solution of permanganate, a carbon carrier and an aqueous solution of a divalent manganese salt; carrying out a reaction to produce a precipitate; and carrying out washing and drying so as to obtain the manganese dioxide / carbon nanocomposite. The preparation method has the advantages of easiness, rapidness, environment friendliness and easy realization of scale-up synthesis. The prepared manganese dioxide / carbon nanocomposite is applicable to a super-capacitor, a metal-air battery and a fuel battery.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI

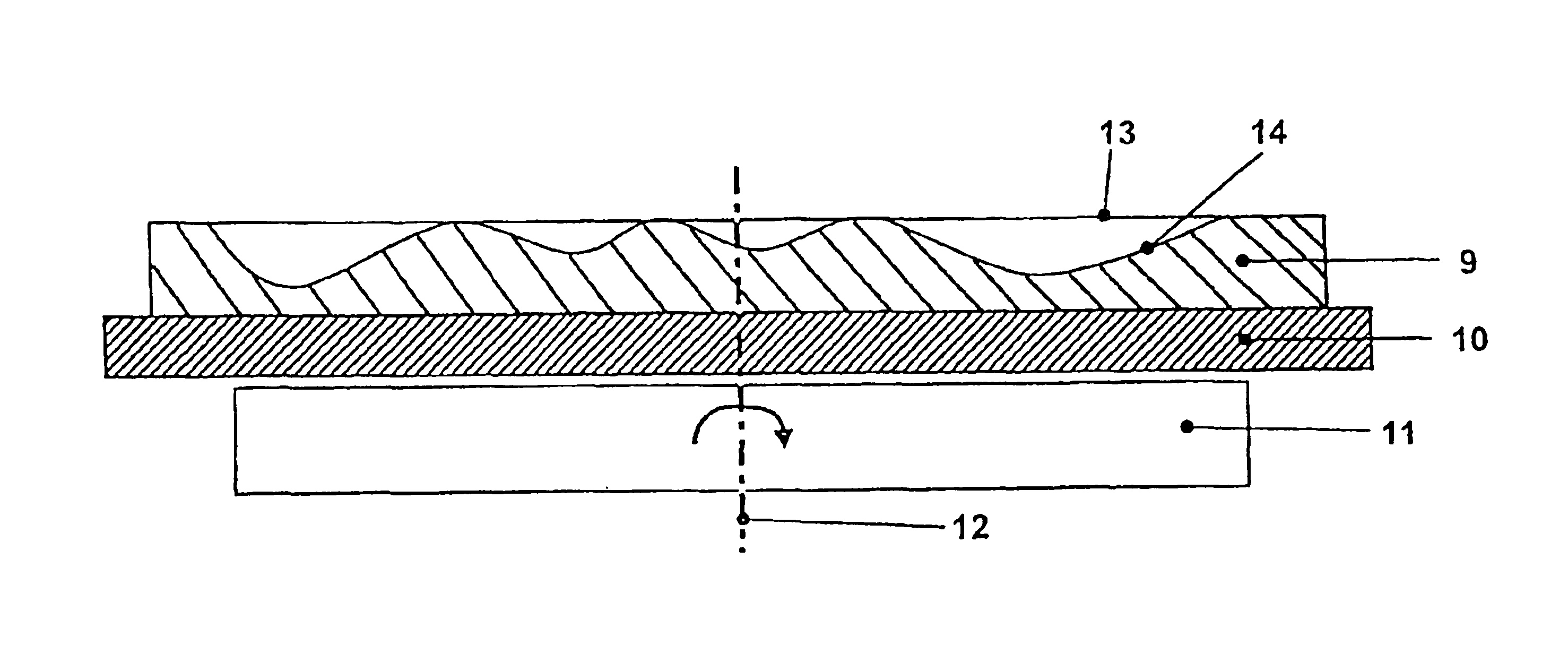

Target comprising thickness profiling for an RF magnetron

InactiveUS6916407B2CapacitanceImprove thermal conductivityCellsElectric discharge tubesOptoelectronicsVacuum chamber

Method for sputtering from a dielectric target (9) in a vacuum chamber (2) with a high frequency gas discharge, the target (9) being mounted on a cooled metallic back plate (10) and this back plate forming an electrode (10) supplied with high frequency, includes a target thickness (Td) profiled (15) differently over the surface such that in the regions of a desired decrease of the sputtering rate the target thickness (Td) is selected to be greater than in the remaining regions.

Owner:ESEC

Method for fabricating semiconductor device

InactiveUS7741228B2Lower Reliability RequirementsLow reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering physics

After a first insulating film is formed on a substrate, a wiring groove is formed in the first insulating film, and then a wire is formed inside the wiring groove. Subsequently, a protection film is formed on the first insulating film and on the wire, and then a hard mask film is formed on the protection film. After that, the hard mask film is patterned. Subsequently, the protection film and the first insulating film are partially removed using the patterned hard mask film to form an air gap groove, and then a second insulating film is formed to close an upper portion of the air gap groove for forming an air gap.

Owner:PANASONIC CORP +1

Semiconductor device and manufacturing method of the same

ActiveUS20060281298A1CapacitanceReduce capacitanceSemiconductor/solid-state device manufacturingLow-k dielectricCapacitance

In a semiconductor device, capacitance between copper interconnections is decreased and the insulation breakdown is improved simultaneously, and a countermeasure is taken for misalignment via by a manufacturing method including the steps of forming an interconnection containing copper as a main ingredient in an insulative film above a substrate, forming insulative films and a barrier insulative film for a reservoir pattern, forming an insulative film capable of suppressing or preventing copper from diffusing on the upper surface and on the lateral surface of the interconnection and above the insulative film and the insulative film, forming insulative films of low dielectric constant, in which the insulative film is formed such that the deposition rate above the opposing lateral surfaces of the interconnections is larger than the deposition rate therebelow to form an air gap between the adjacent interconnections and, finally, planarizing the insulative film by interlayer CMP.

Owner:KOKUSA ELECTRIC CO LTD

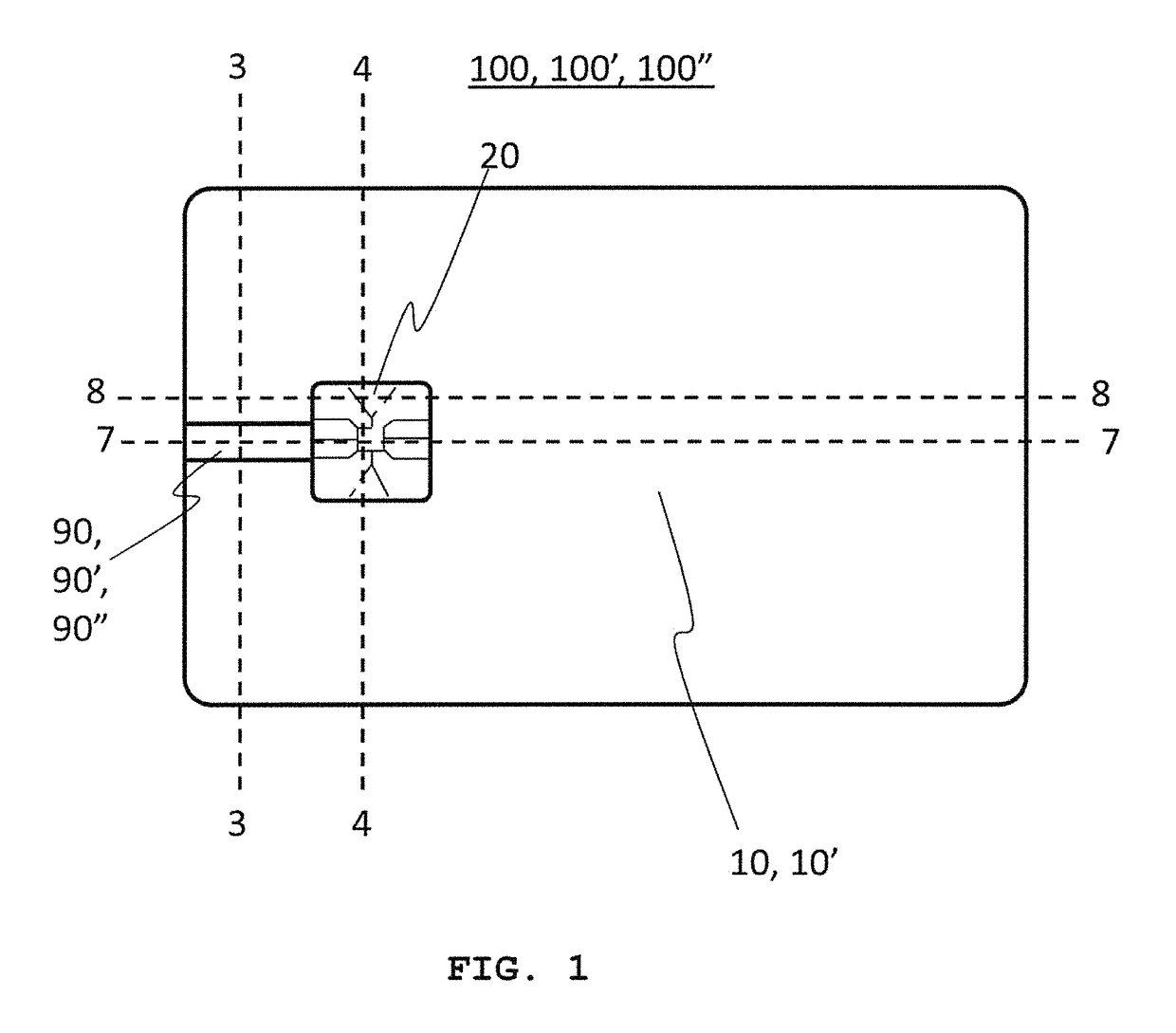

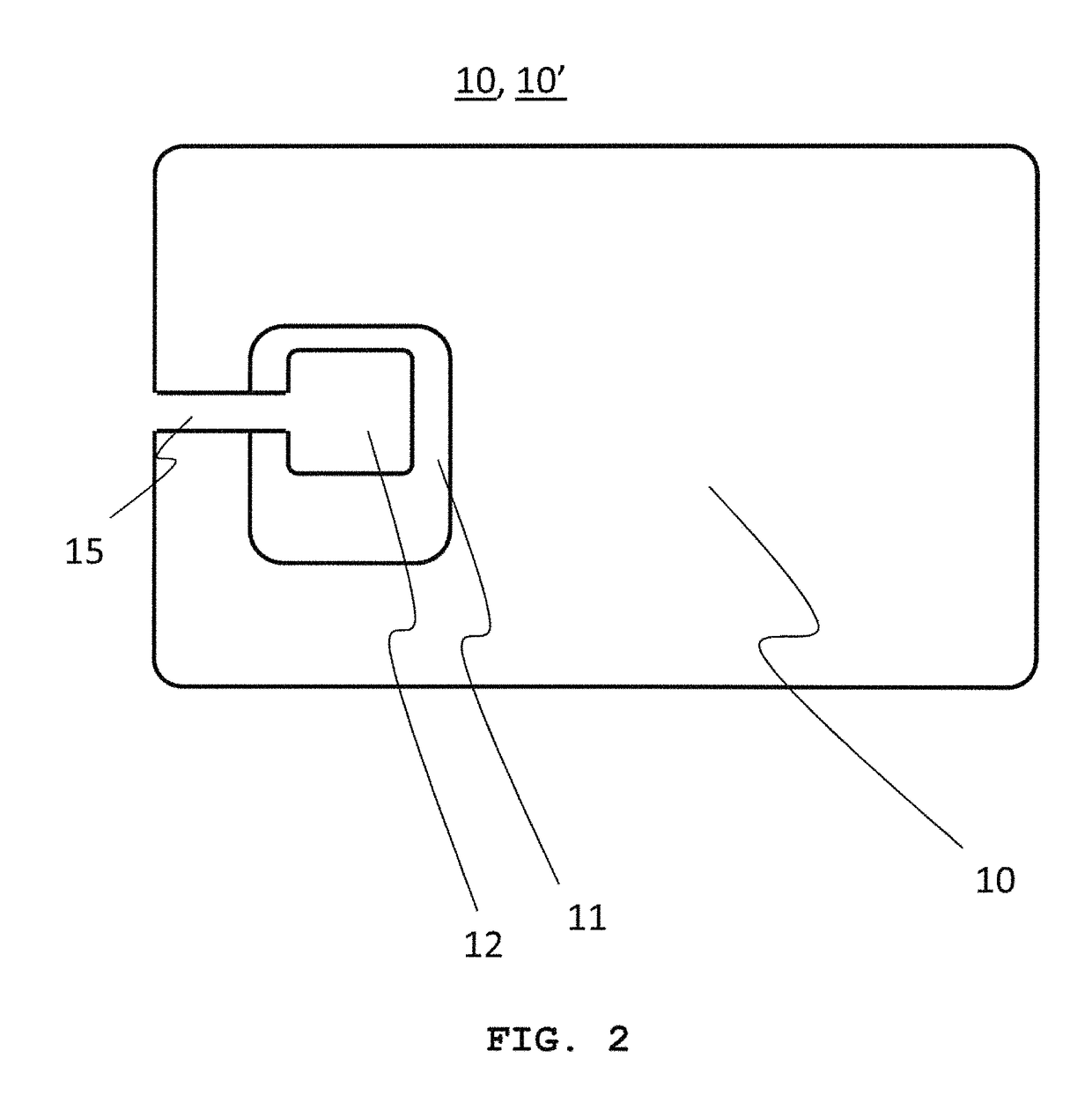

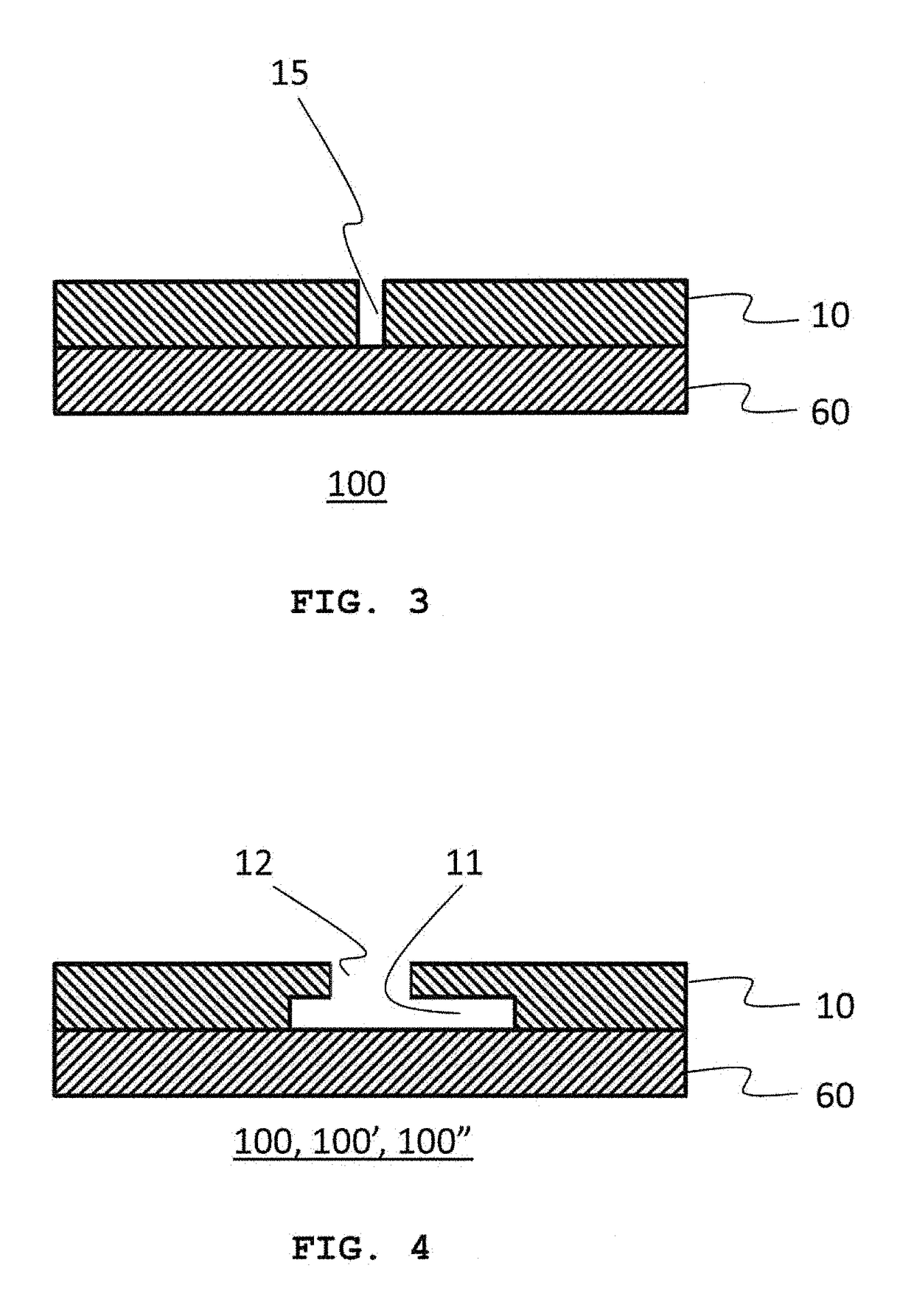

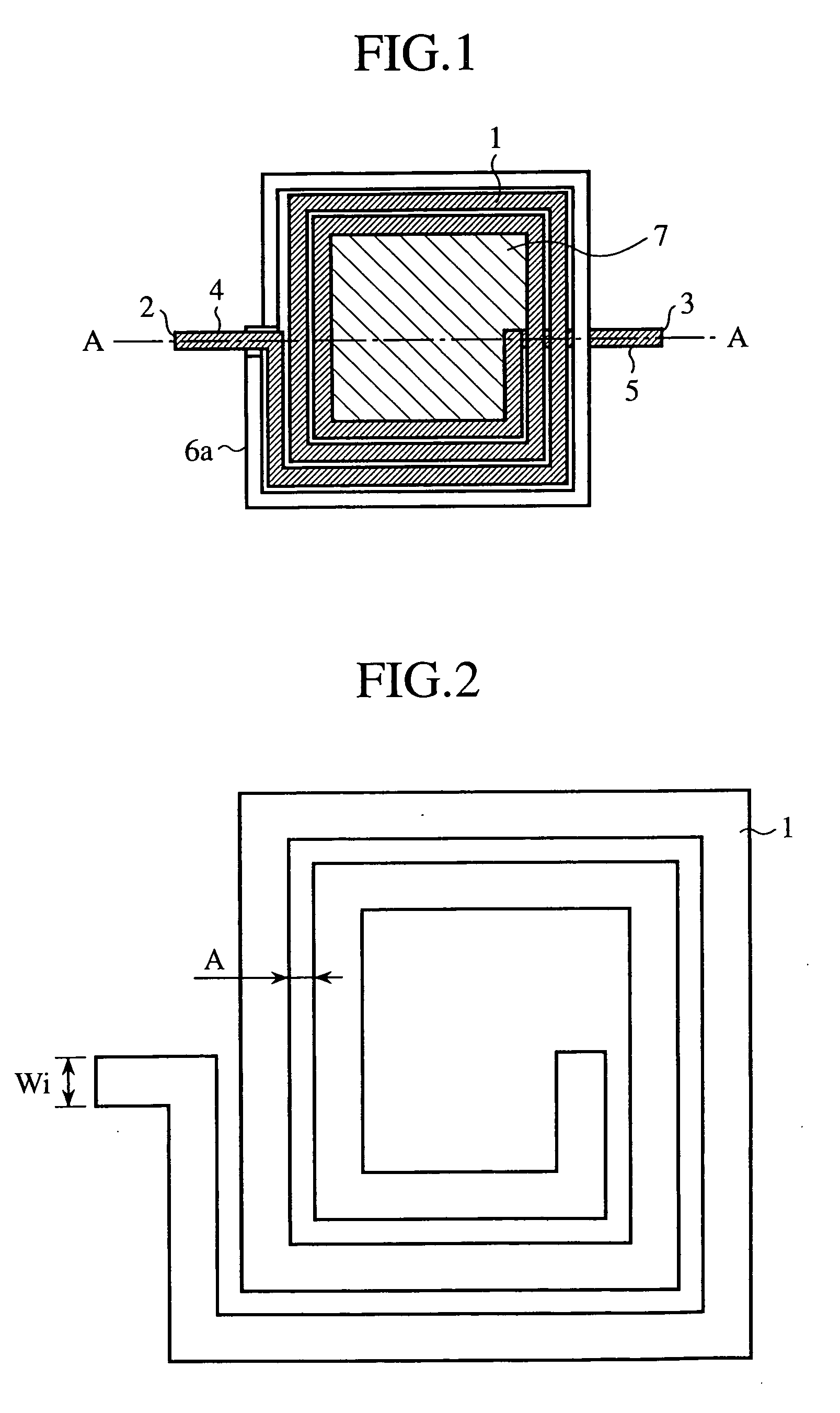

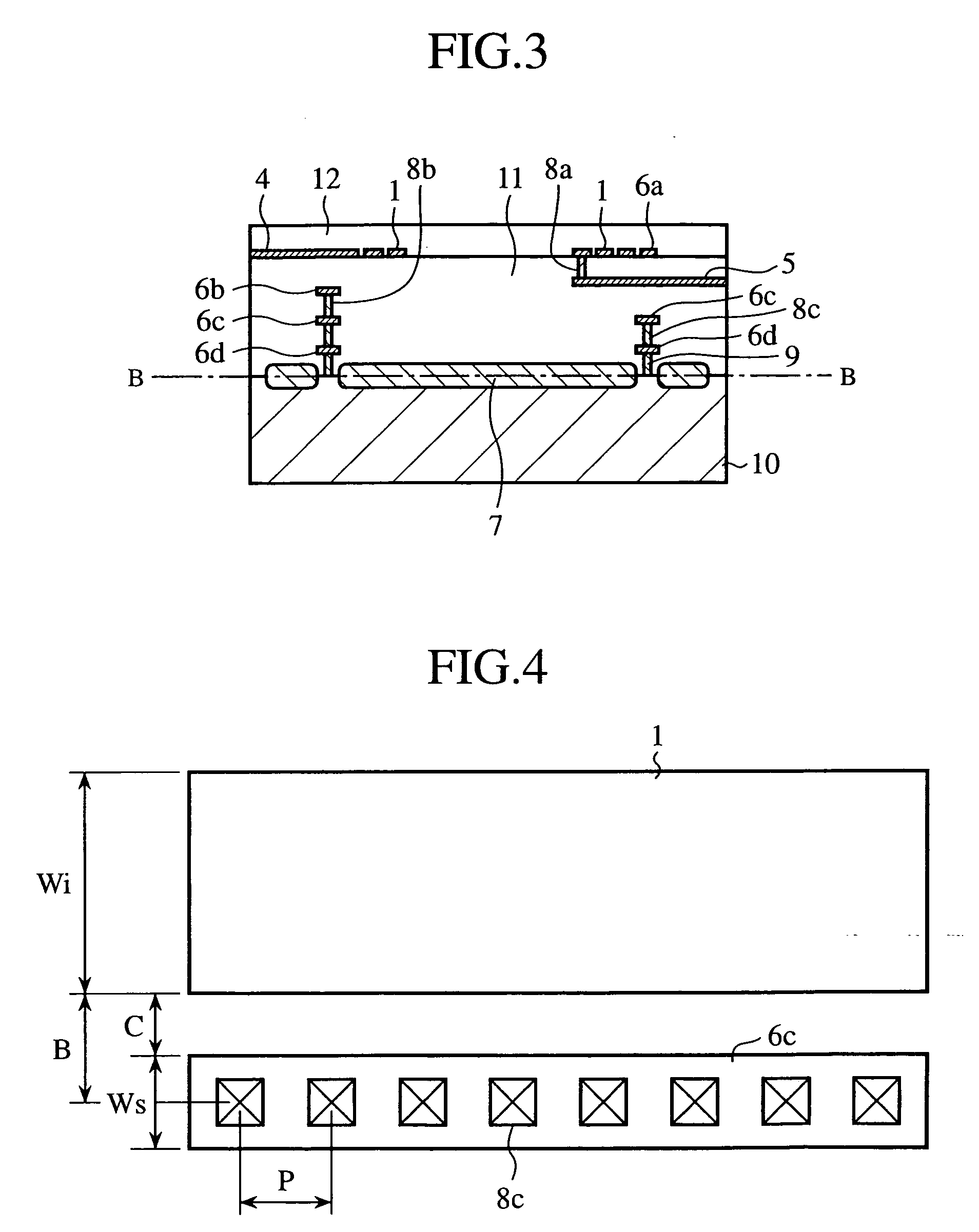

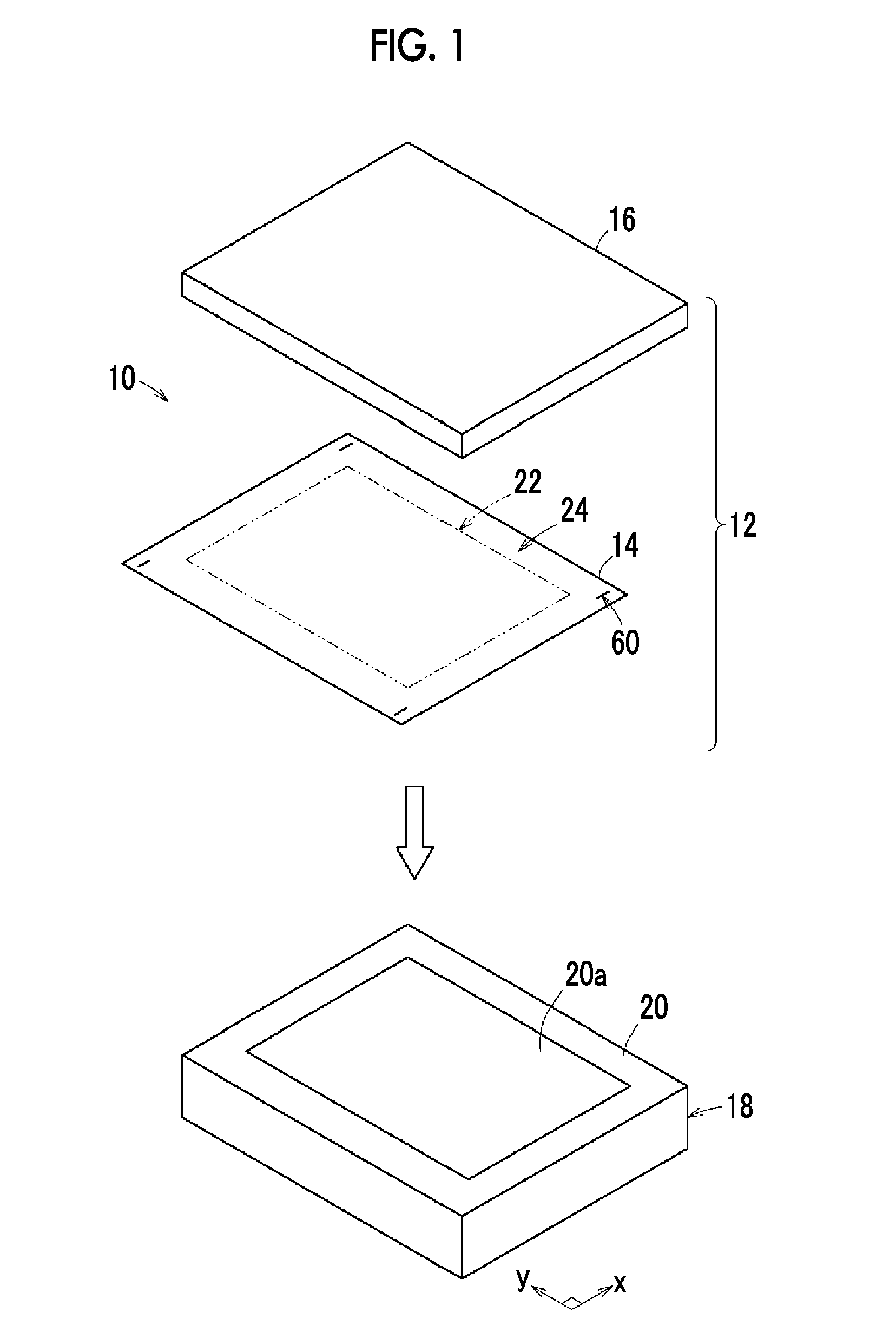

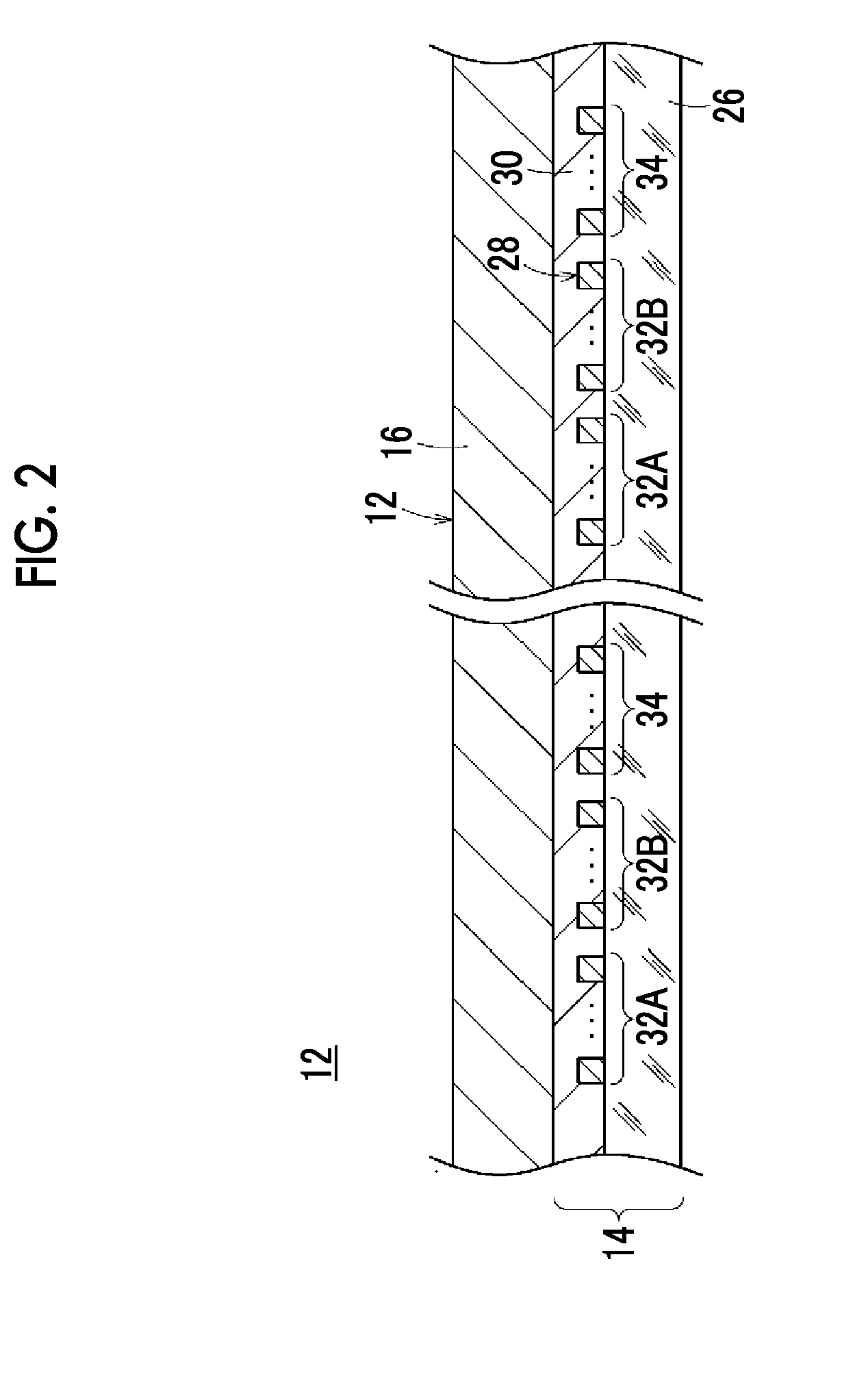

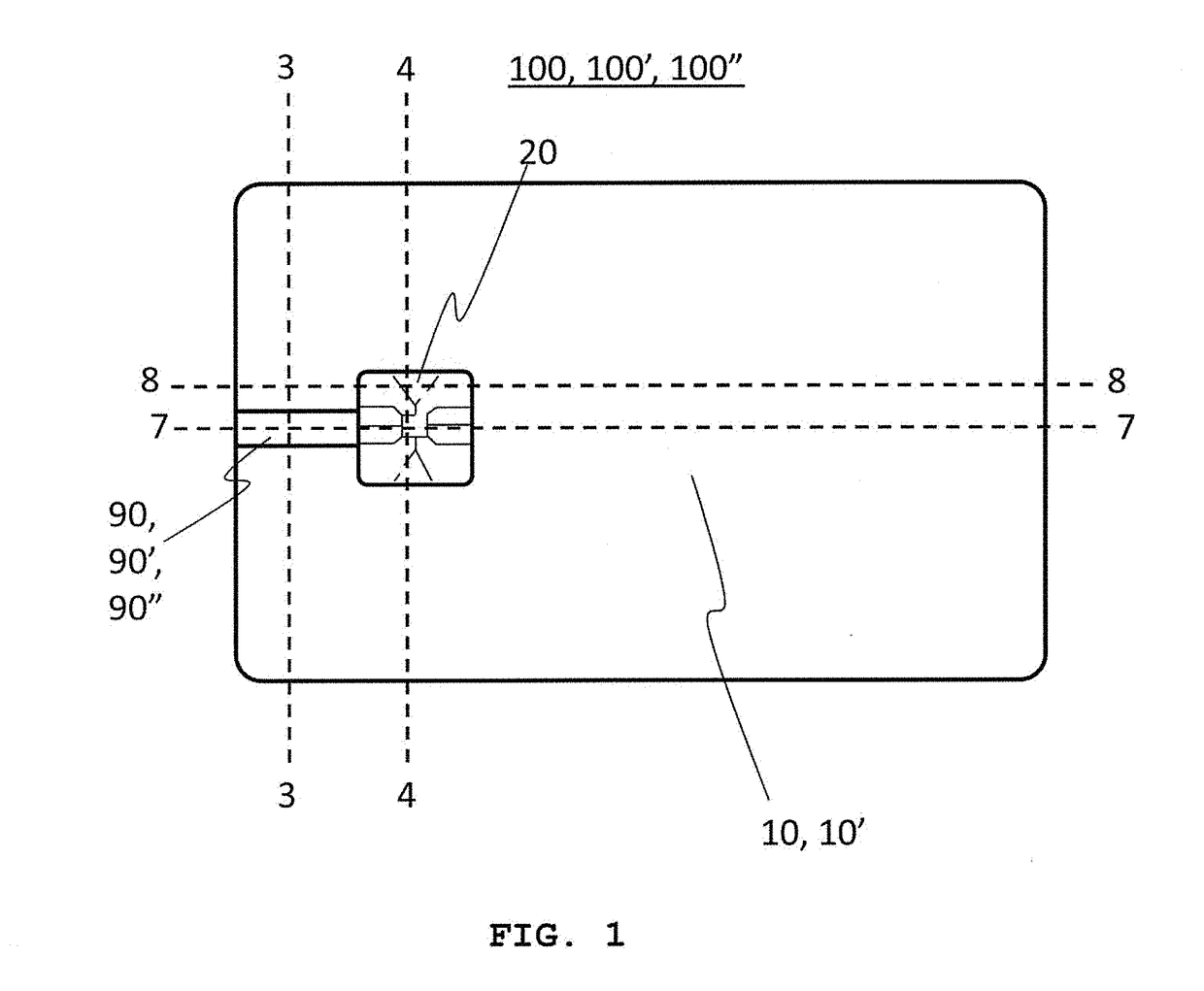

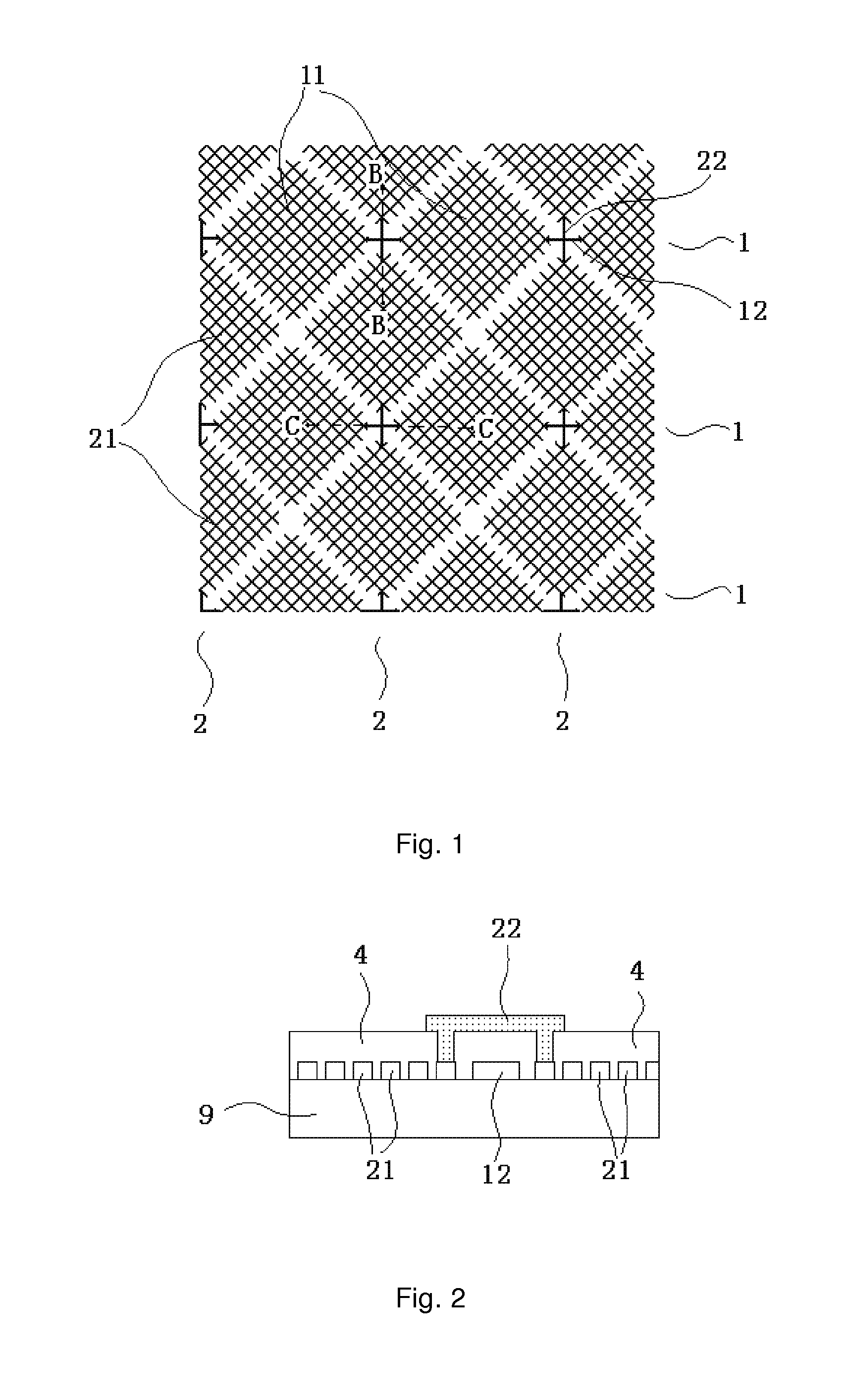

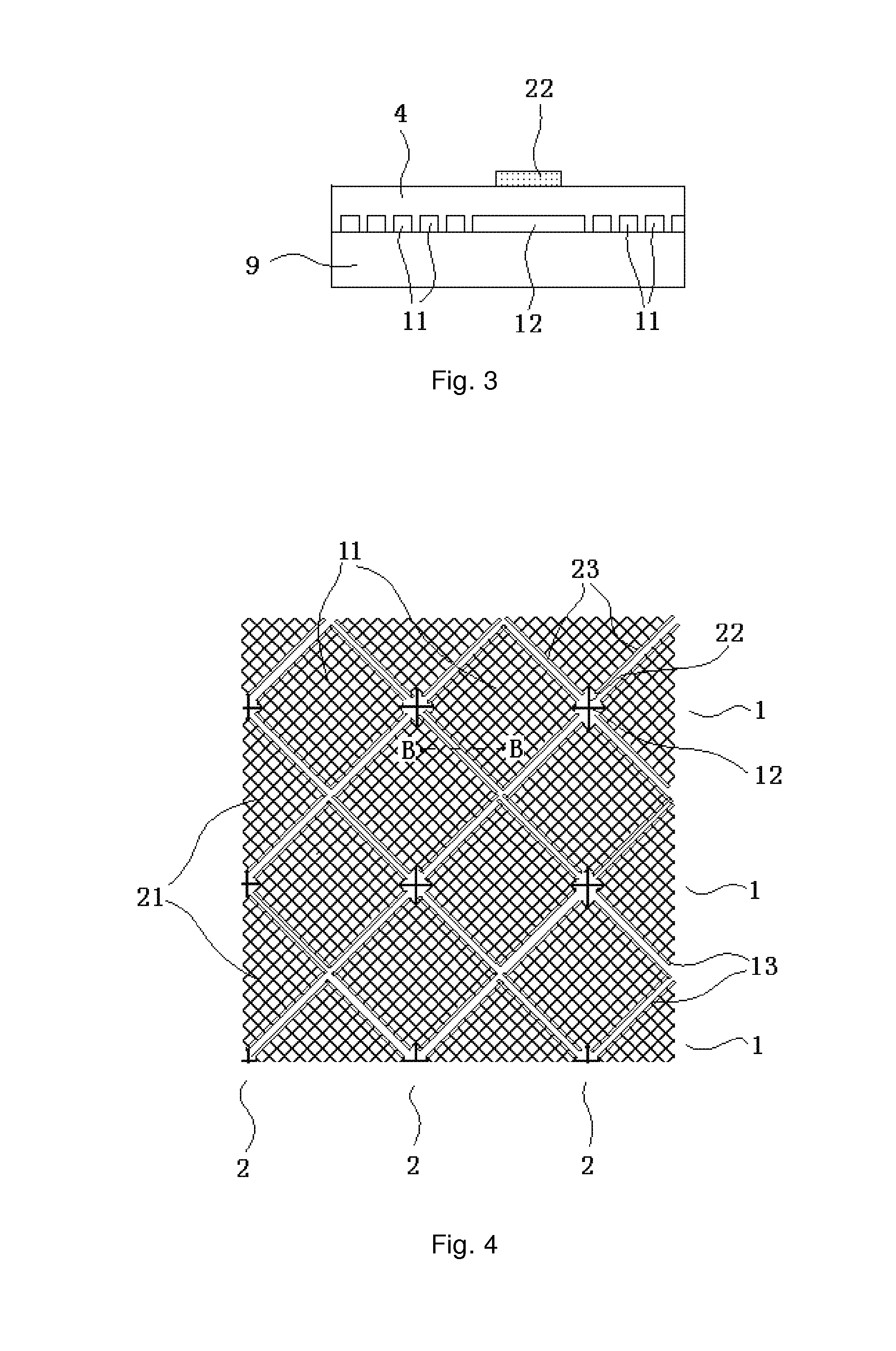

Metal contactless smart card and method for fabricating the same

ActiveUS20170308785A1Improving Impedance MatchingCapacitanceRecord carriers used with machinesInformation cardsContactless smart cardRadio frequency

A metal contactless smart card includes a first metal layer having a first slit, a second layer, a radio-frequency integrated circuit chip module, and an inlay having an antenna. A nonconductive insert may be fitted in the slit. The first metal layer may include an inlay recess where the inlay may be received and a through-hole where the chip may be inserted. The second layer of the smart card may be made of metal and may also include a slit.

Owner:KANG SOO HYANG

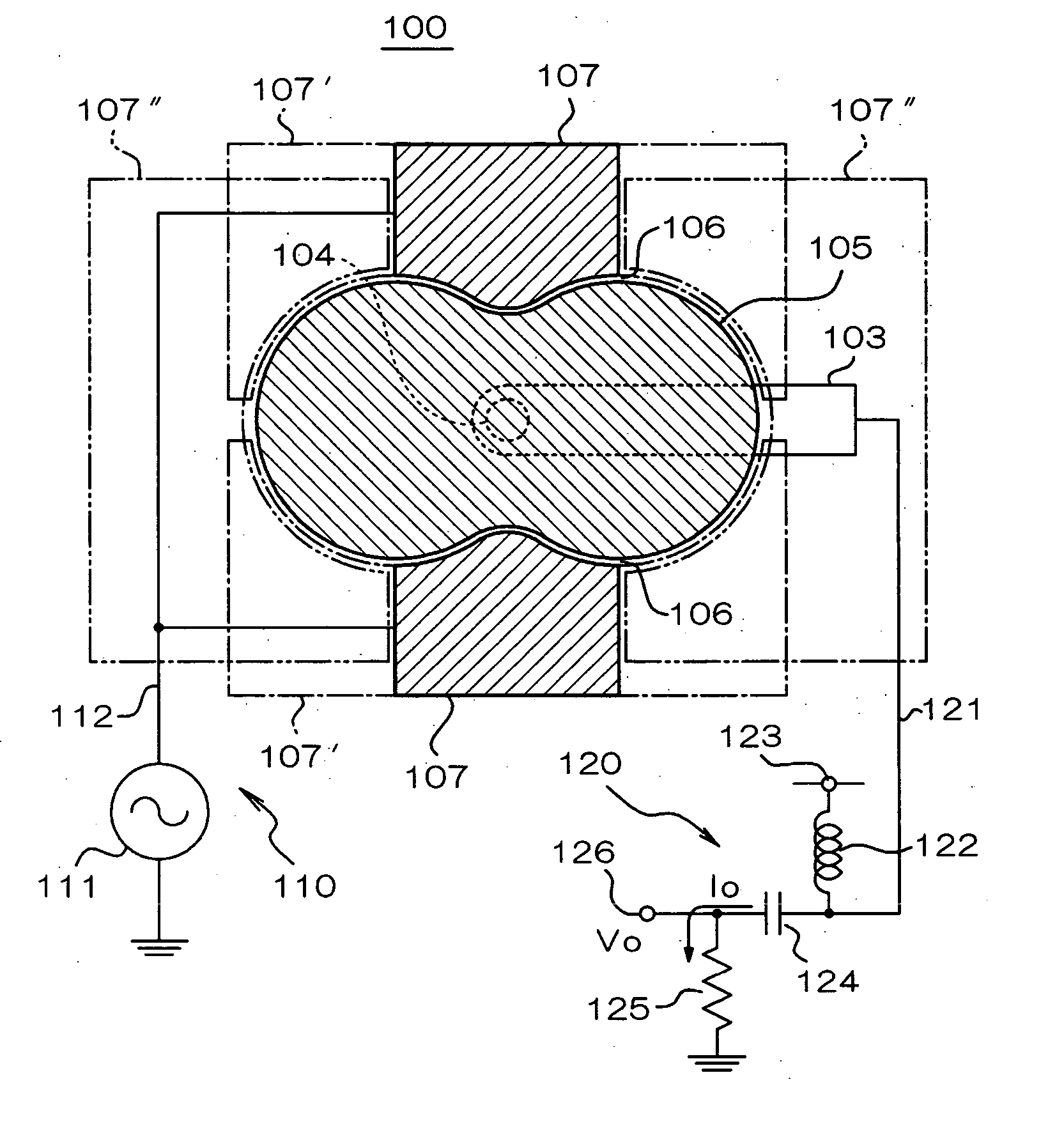

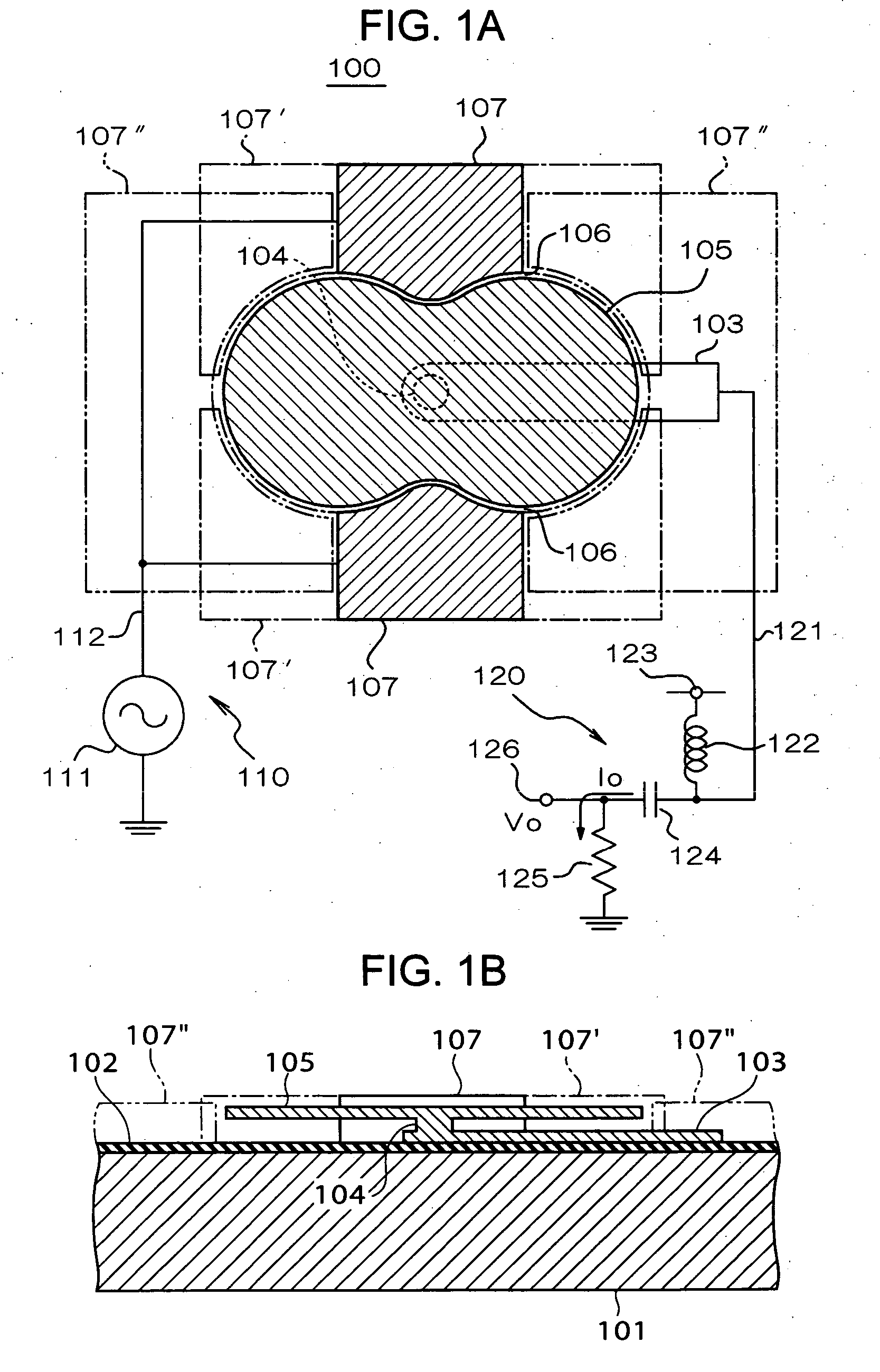

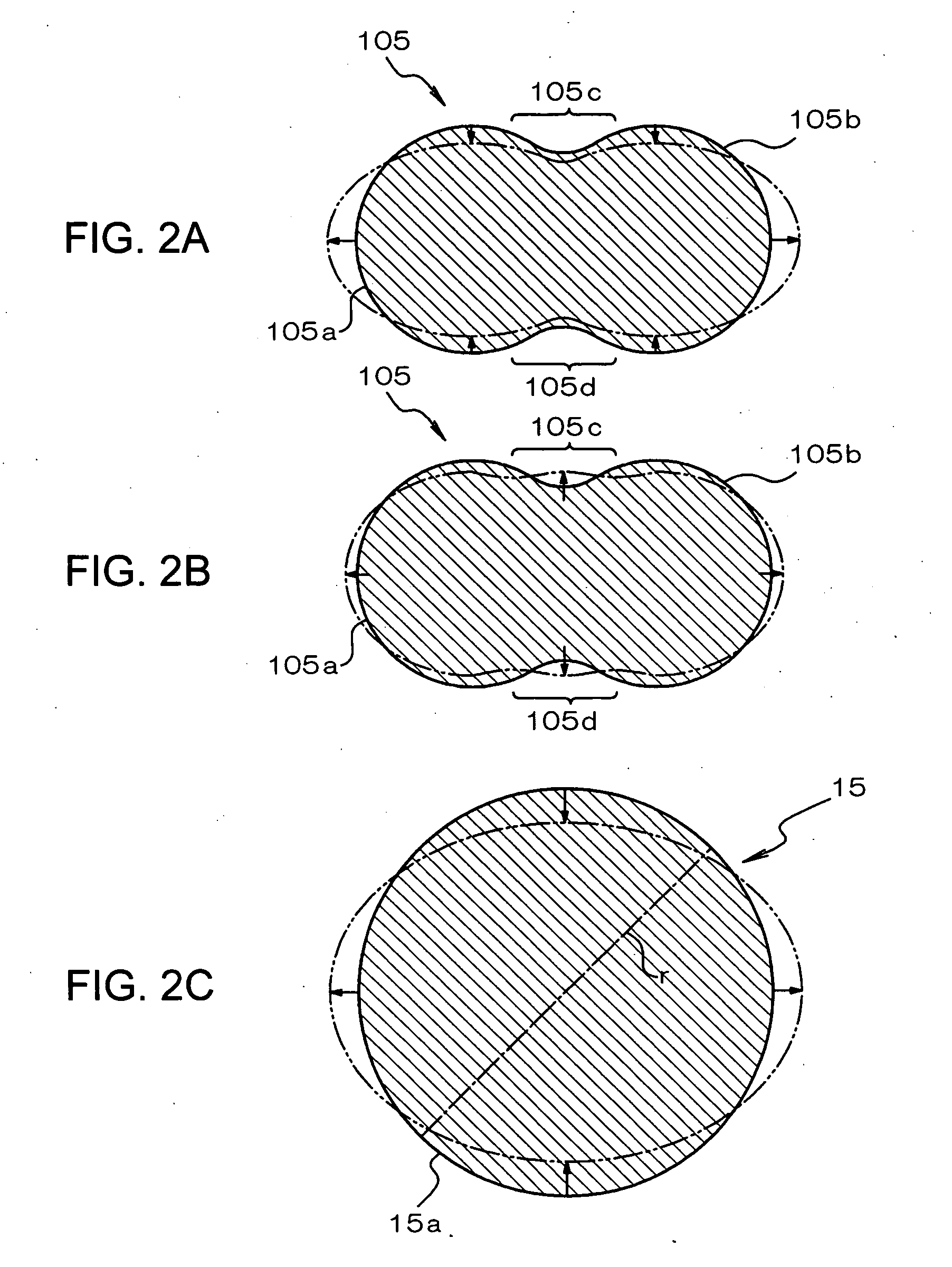

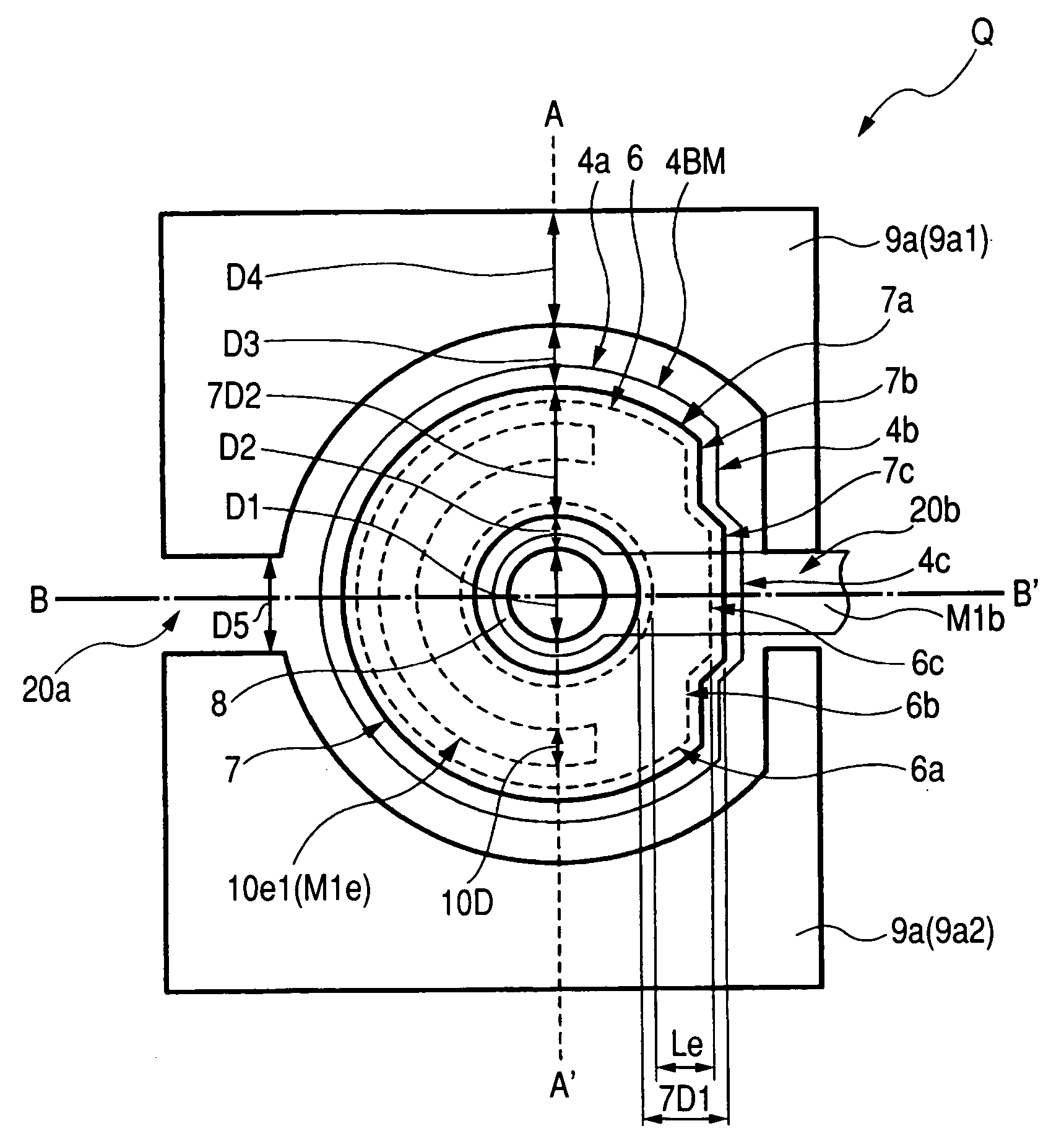

Micromechanical electrostatic resonator

InactiveUS20050151442A1CapacitanceLarge capacitancePiezoelectric/electrostriction/magnetostriction machinesDecorative surface effectsCapacitanceAlternating current

Exemplary embodiments of the invention provide a micromechanical electrostatic resonator which designs high frequency, increases a ratio of output voltage to input voltage, and designs low drive voltage or reduced power consumption. A micromechanical electrostatic resonator of exemplary embodiments includes a plate-shaped vibration body, a pair of electrodes arranged oppositely to each other at both sides of the vibration body with a gap from an outer circumferential portion of the vibration body, a feeding device to apply in-phase alternating-current power to the pair of electrodes, and a detecting device to obtain an output corresponding to a change in capacitance between the vibration body and the electrodes. The planar shape of the vibration body takes a shape having a curved outline which comprises a neck portion.

Owner:SEIKO EPSON CORP

Metal contactless smart card and method for fabricating the same

ActiveUS10140569B2CapacitanceImproving Impedance MatchingRecord carriers used with machinesInformation cardsComputer moduleEngineering

A metal contactless smart card includes a first metal layer having a first slit, a second layer, a radio-frequency integrated circuit chip module, and an inlay having an antenna. A nonconductive insert may be fitted in the slit. The first metal layer may include an inlay recess where the inlay may be received and a through-hole where the chip may be inserted. The second layer of the smart card may be made of metal and may also include a slit.

Owner:ICK INT INC

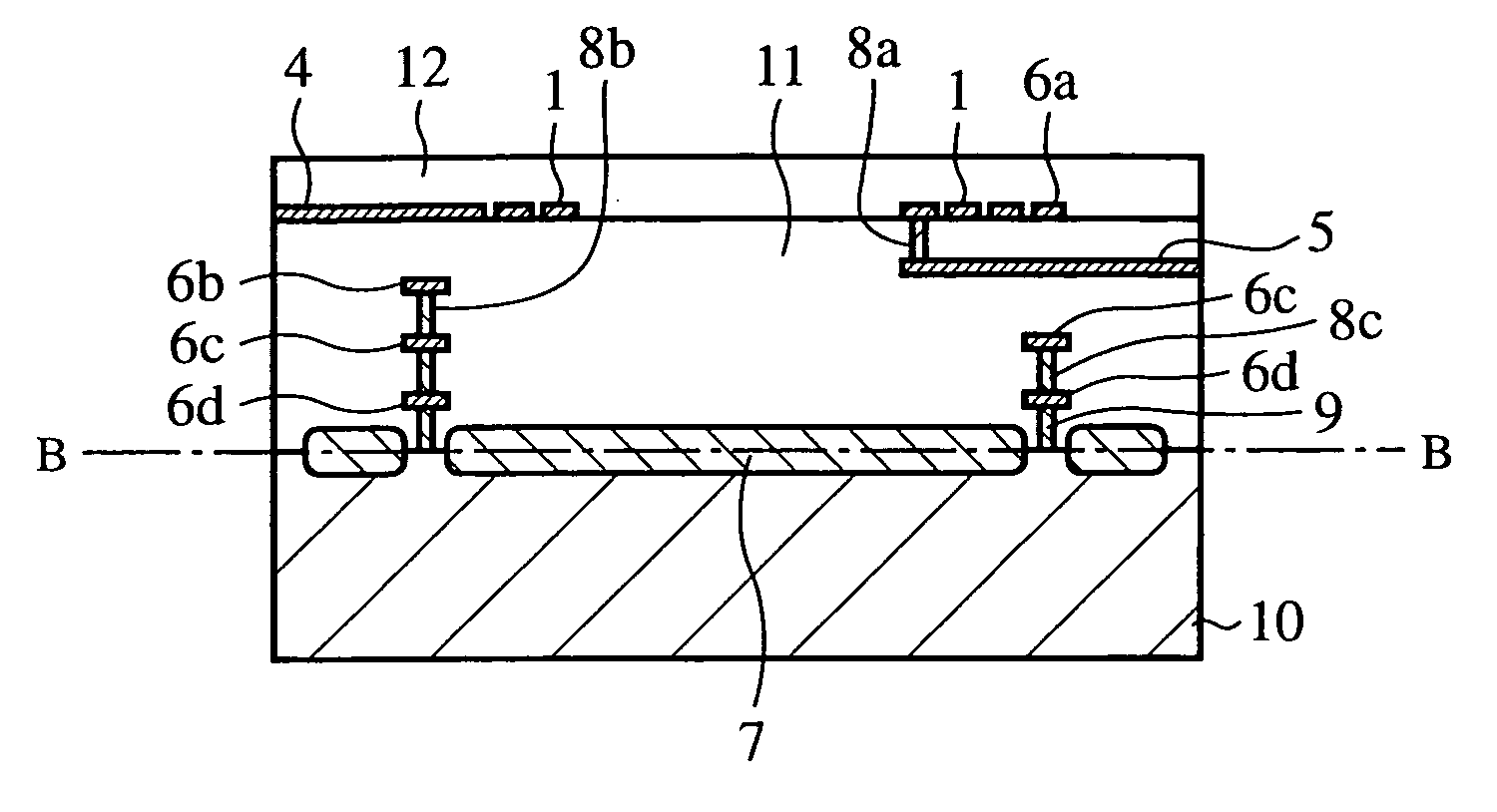

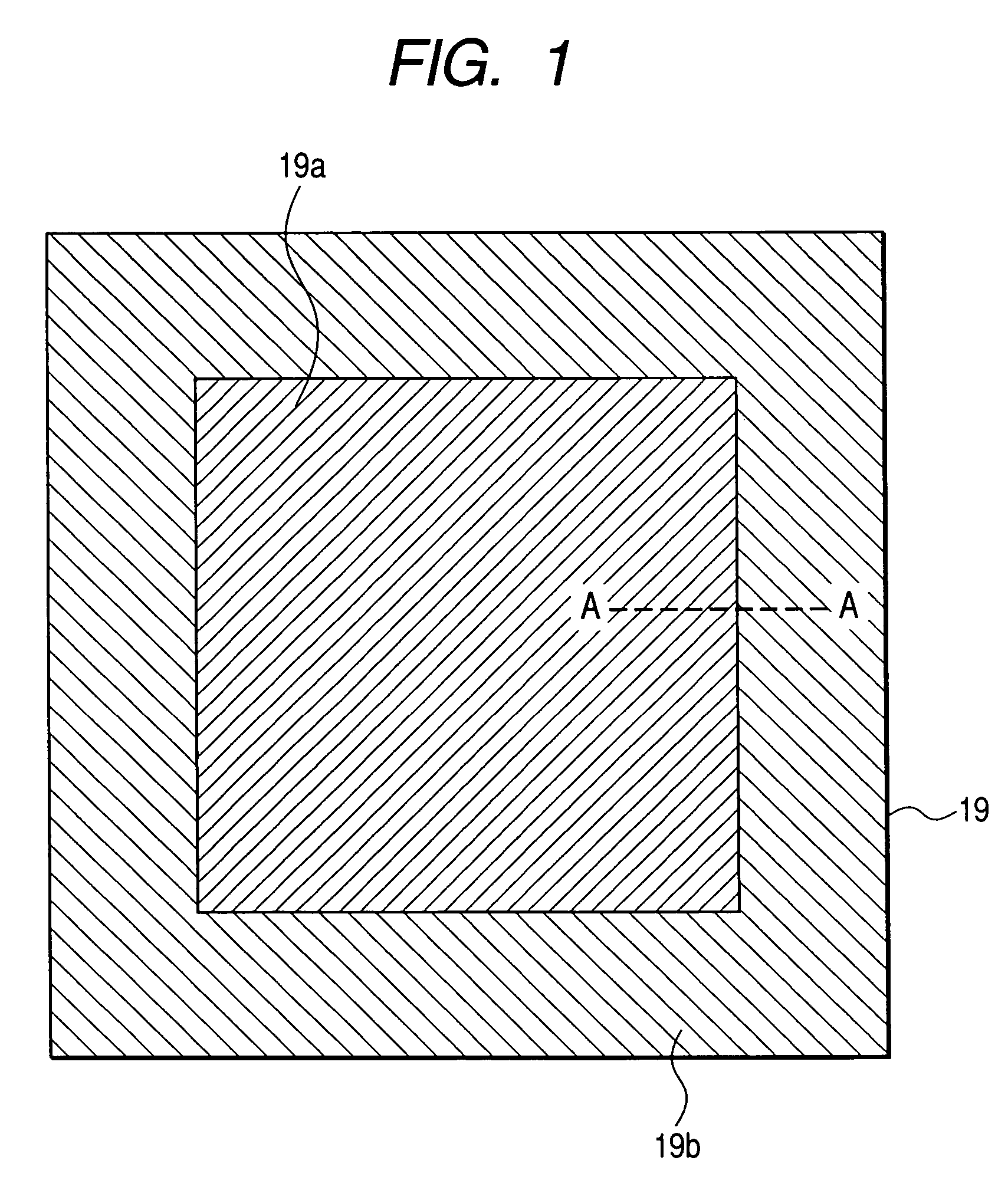

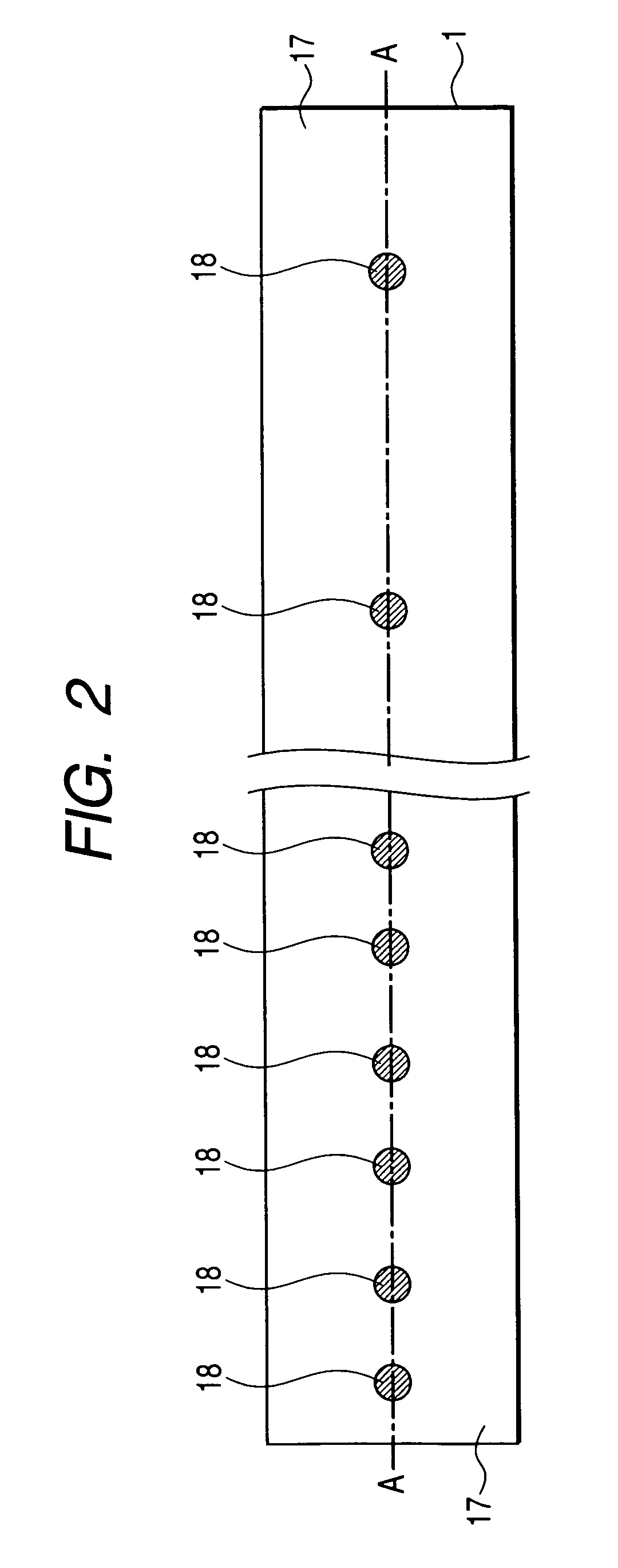

Semiconductor device

InactiveUS20050247999A1Electromagnetic interferenceReduce electromagnetic interferenceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDevice material

A semiconductor device includes: an inductor (1) provided with a conductor interconnection formed spirally on a semiconductor substrate (10); and a shield (6a) that is provided with a continuous conductor interconnection provided along the outer periphery of the spiral pattern of the inductor (1) while opening a portion of the conductor interconnection, and that is electrically connected to ground potential.

Owner:MITSUBISHI ELECTRIC CORP

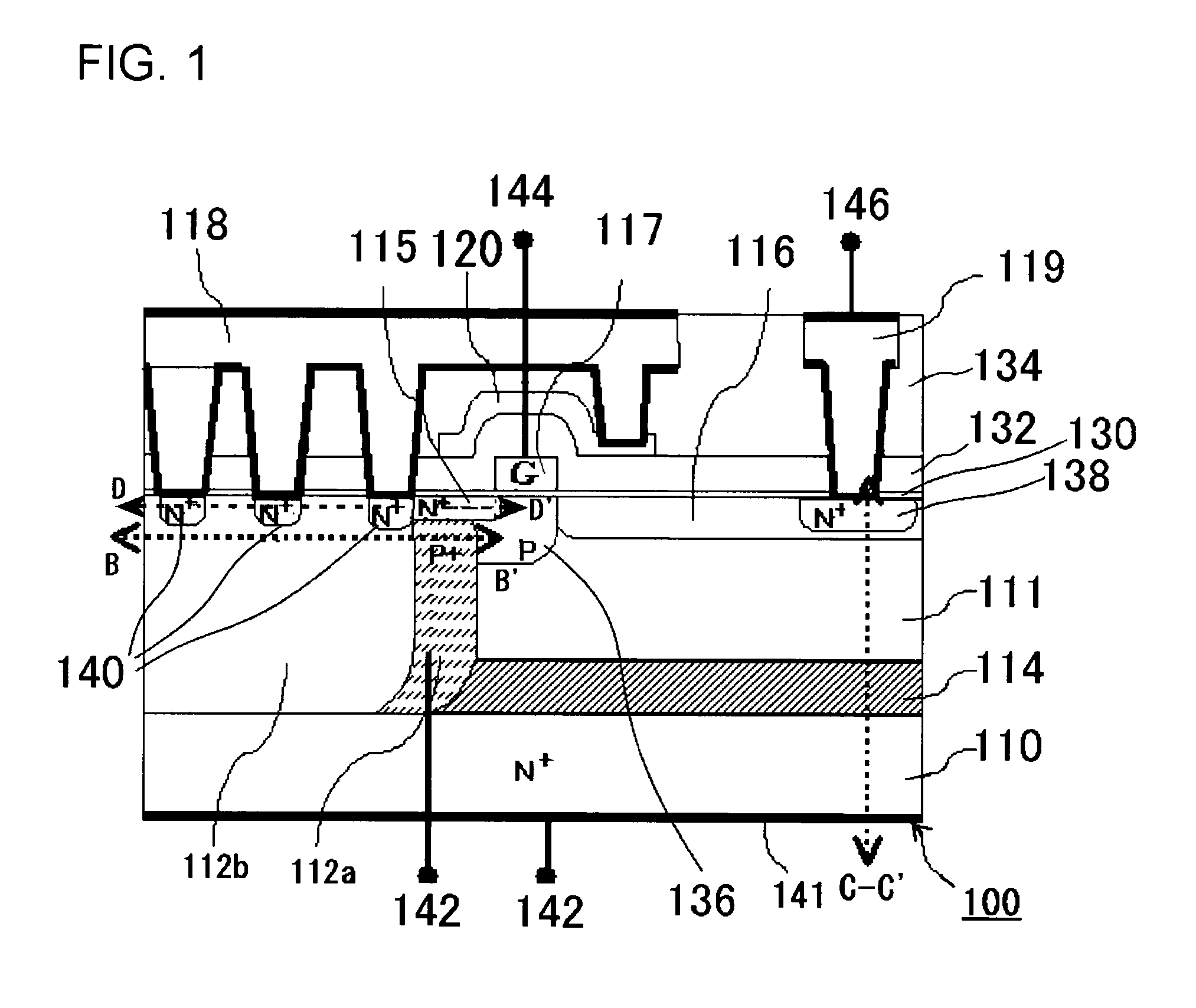

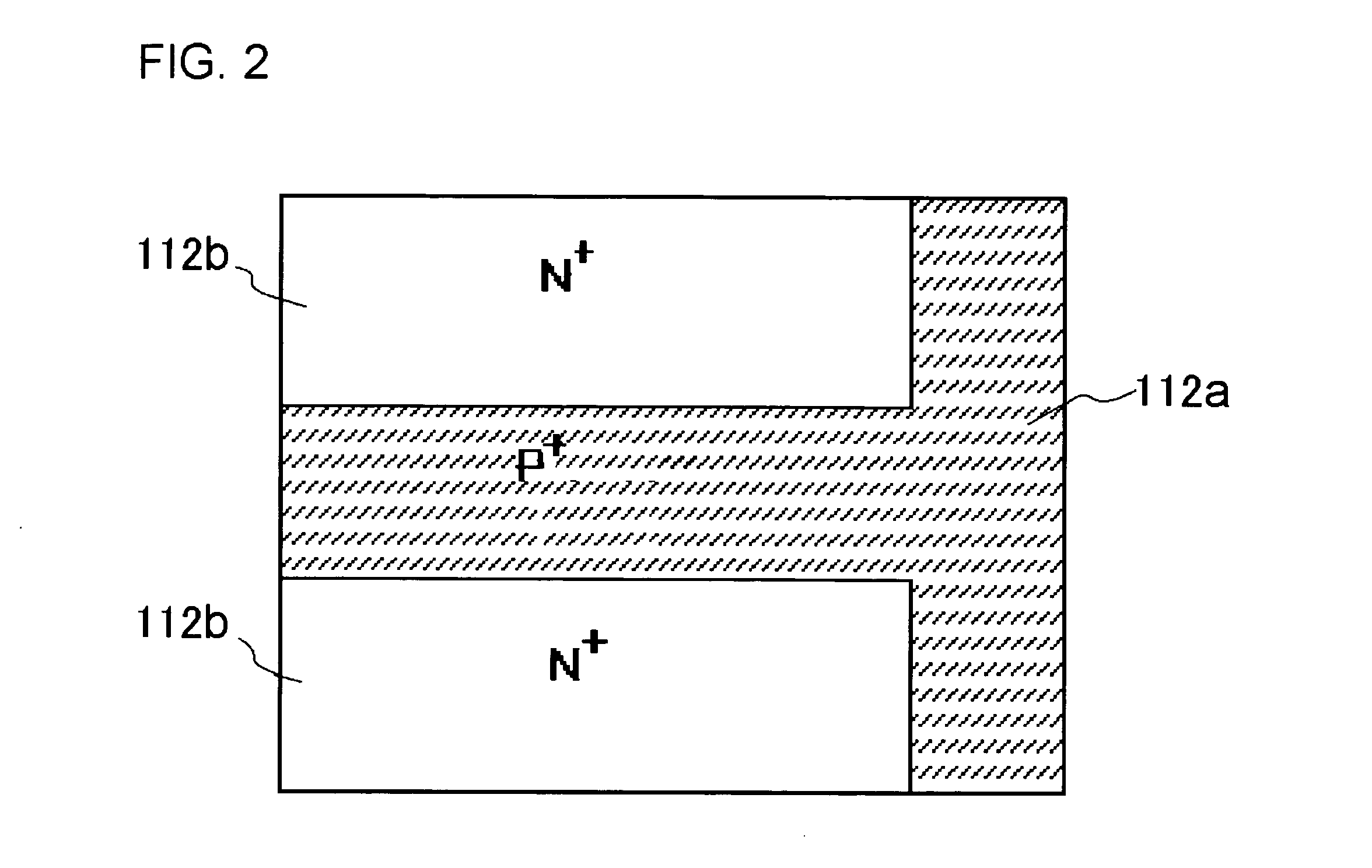

Semiconductor device

InactiveUS20050269601A1Extending of the semiconductor substrate can be preventedHigh film thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETHigh concentration

The semiconductor device comprises: a semiconductor substrate (N+ substrate 110) containing a first conductivity type impurity implanted therein; a second conductivity type impurity-implanted layer (P+ implanted layer 114) at relatively high concentration, formed on the semiconductor substrate (N+ substrate 110); a second conductivity type impurity epitaxial layer (P− epitaxial layer 111) at relatively low concentration, formed on the second conductivity type impurity-implanted layer (P+ implanted layer 114); and a field effect transistor 100 (N-channel type lateral MOSFET 100)composed of a pair of impurity diffusion regions (N+ source diffusion layer 115 and N− drain layer 116) provided in the second conductivity type impurity epitaxial layer (P− epitaxial layer 111) and a gate electrode 117 provided over a region sandwiched with the pair of impurity diffusion regions (N+ source diffusion layer 115 and N− drain layer 116).

Owner:RENESAS ELECTRONICS CORP

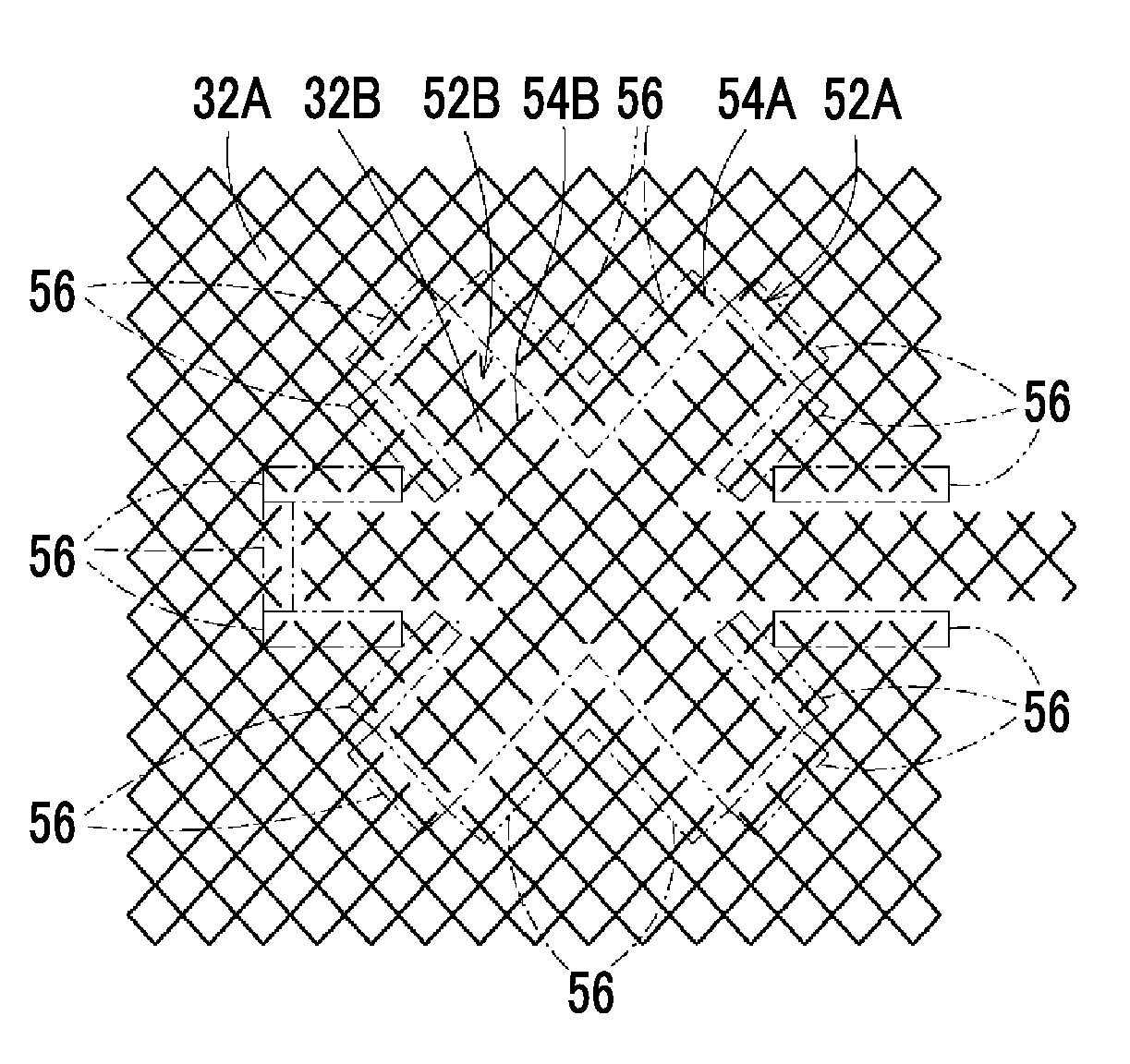

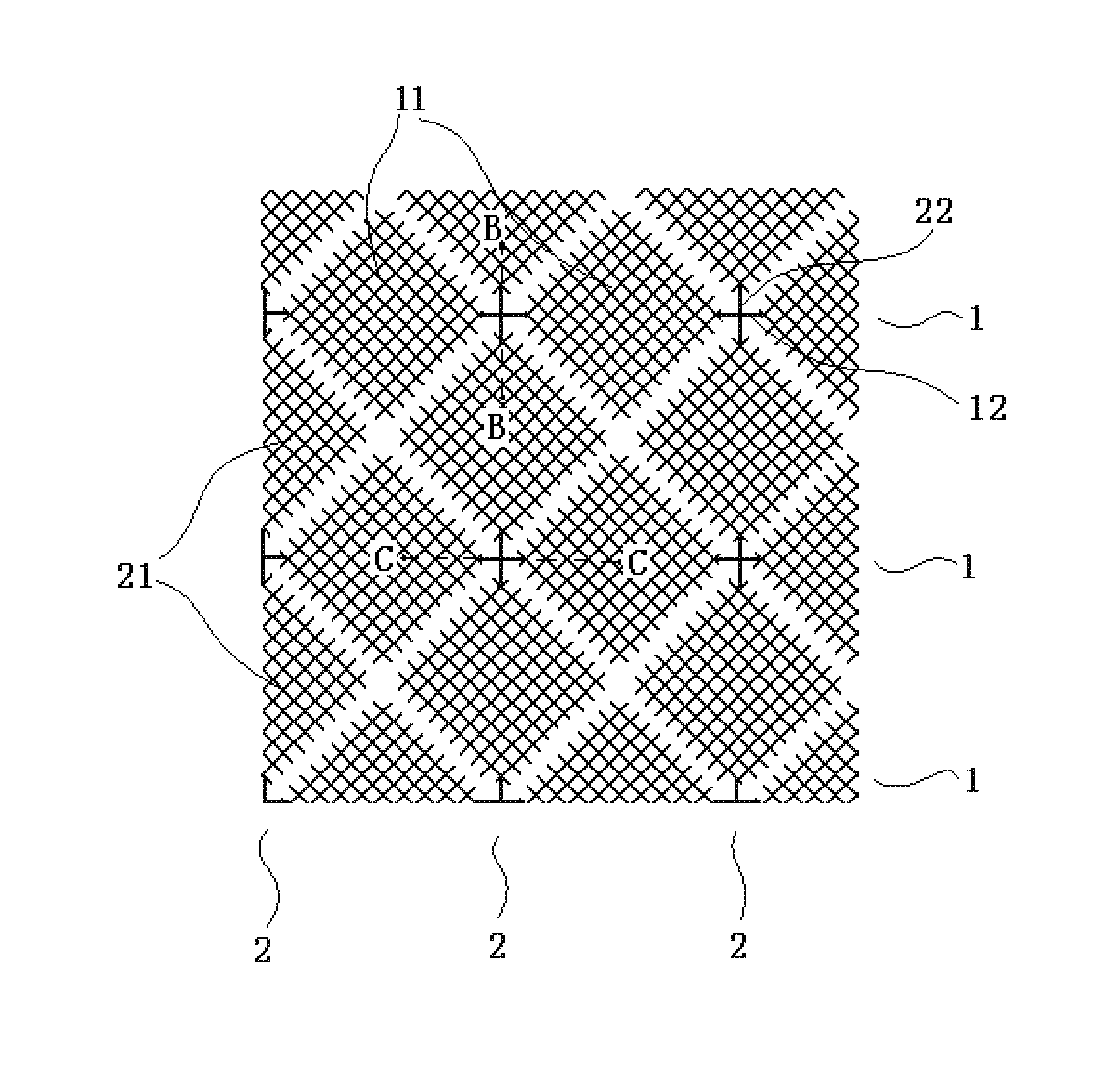

Conductive film and touch panel

ActiveUS20160274727A1Cut surfaceImprove accuracyInput/output processes for data processingThin metalCapacitance

Provided are a conductive film and a touch panel in which an extraction electrode that is formed in a visible region is inconspicuous to improve visibility, the initial capacitance between electrodes is increased to improve the accuracy of detection, and the electrodes are formed on only one main surface of a base to reduce costs. The conductive film includes a transparent base, first and second electrodes 32A and 32B that are formed on a main surface of the transparent base so as to face each other, and an extraction electrode 34 that is formed on the main surface of the transparent base and extends from the second electrode 32B. The first electrode 32A has a shape which surrounds a portion of the second electrode 32B. At least the extraction electrode 34 is formed in a mesh pattern 38 including a plurality of grids 36 which are formed by thin metal wires.

Owner:FUJIFILM CORP

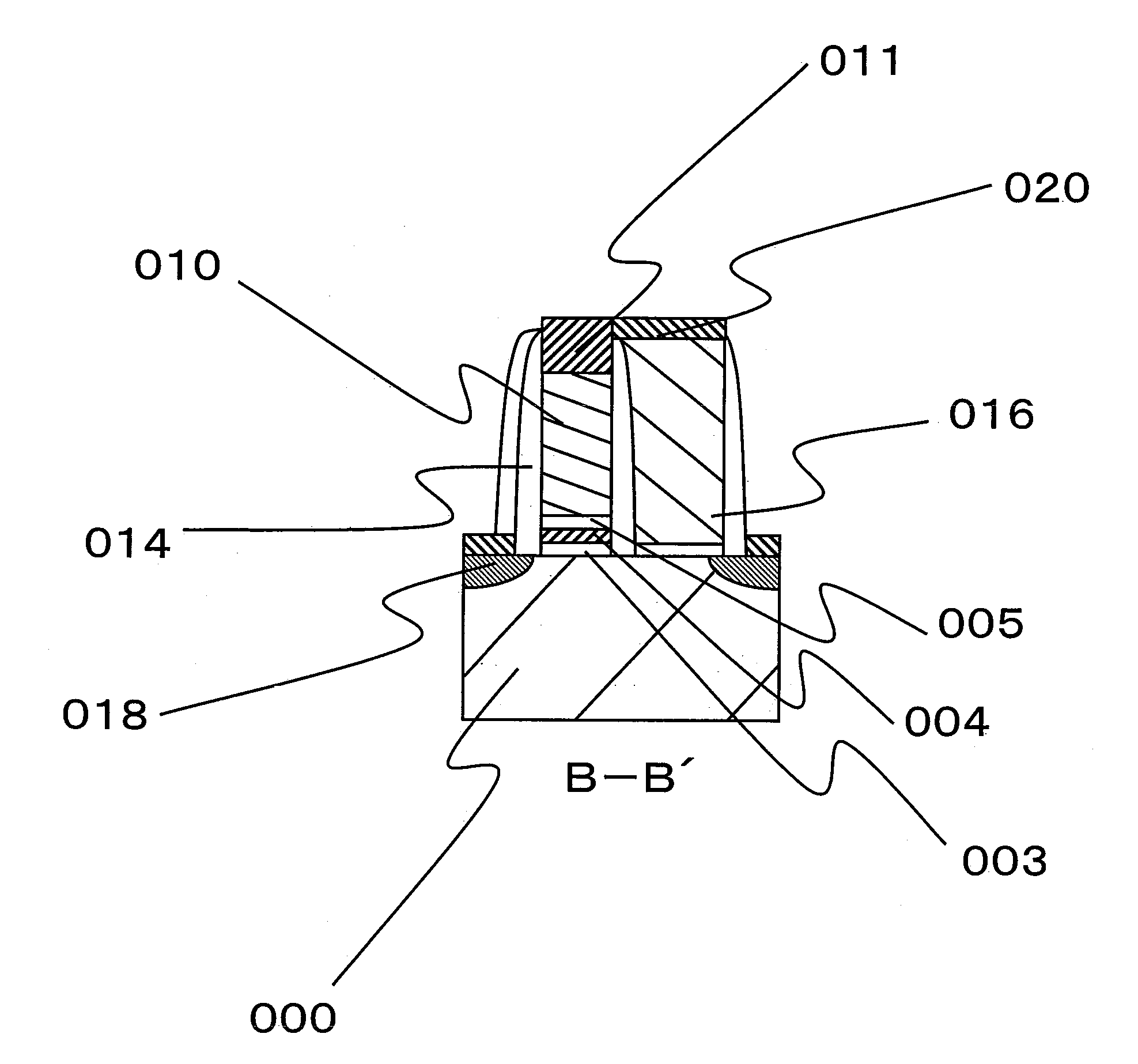

Semiconductor device, manufacturing method of the same, and electronic device

InactiveUS20060108665A1Improve featuresReduce areaTransistorHigh frequency amplifiersLower limitDevice material

The invention is directed to improve characteristics of an HBT (Hetero-junction Bipolar Transistor). An HBT has a collector layer, a base layer, and an emitter layer formed in order on a main surface of a substrate made of a compound semiconductor and a collector electrode, a base electrode, and an emitter electrode electrically connected to the collector layer, the base layer, and the emitter layer, respectively, and further has an emitter contact layer formed between the emitter electrode and the emitter layer. The plane shape of the emitter contact layer and the emitter electrode is an almost annular shape surrounding the base electrode in a plane parallel with the main surface of the substrate, and the lower limit of the emitter contact layer is 1.2 μm or larger.

Owner:RENESAS TECH CORP

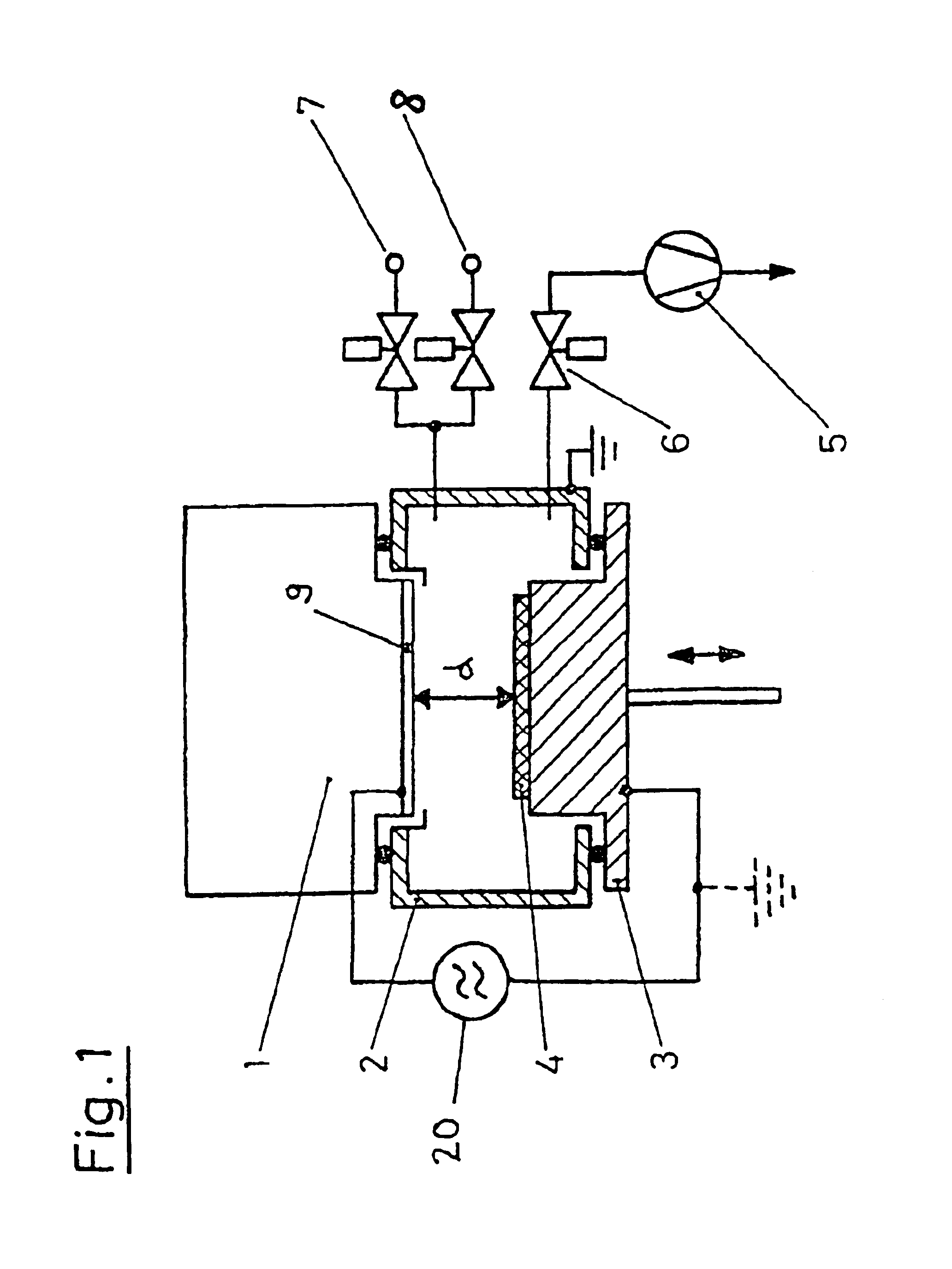

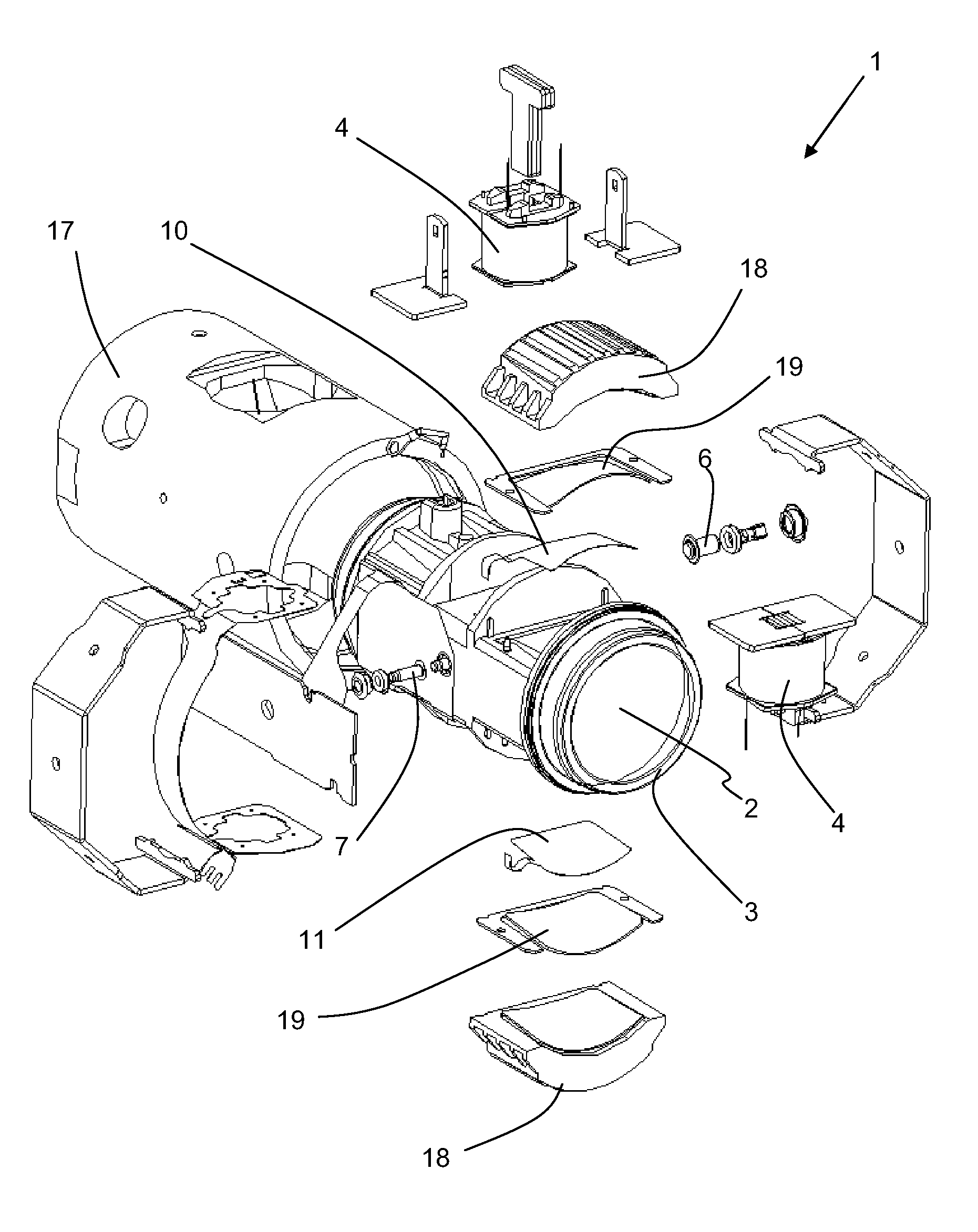

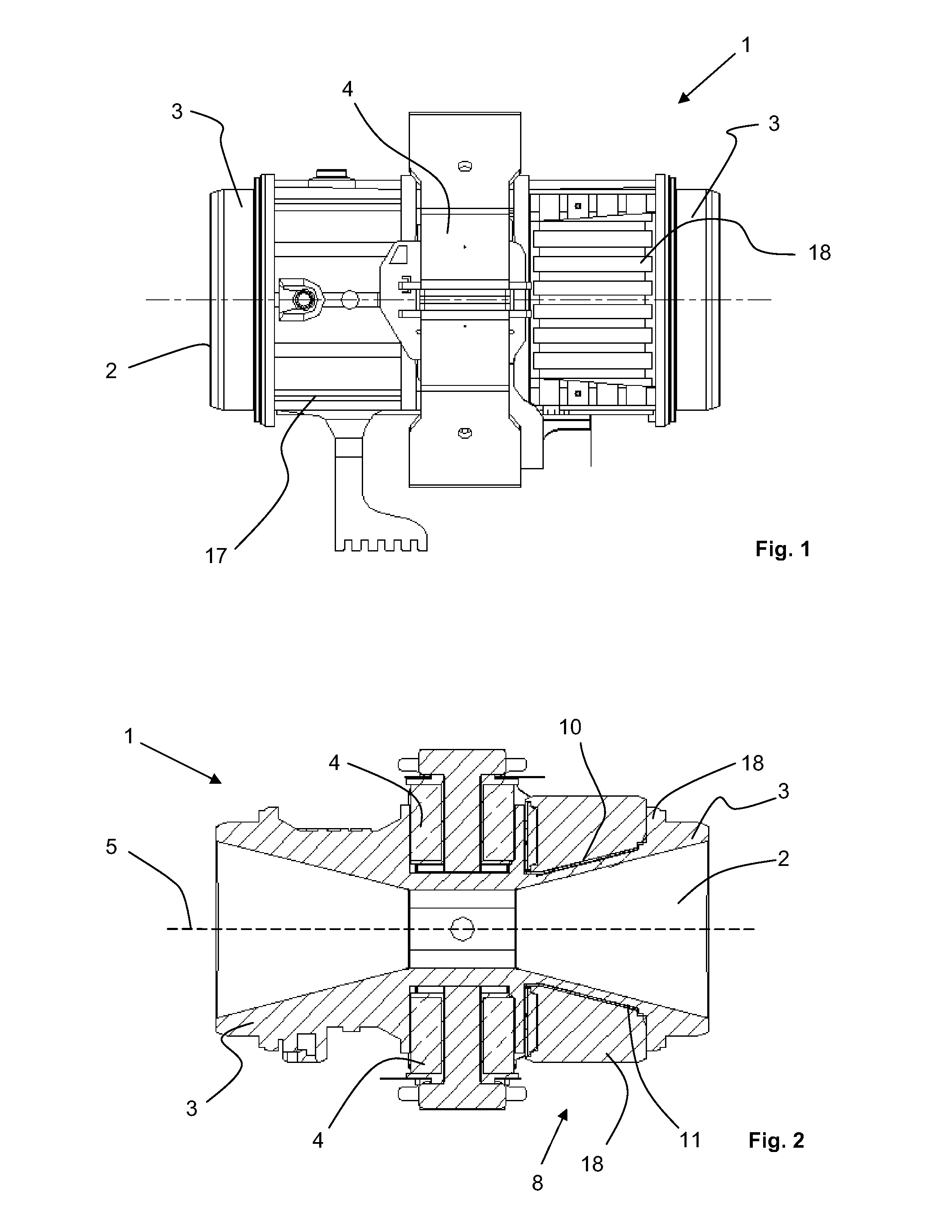

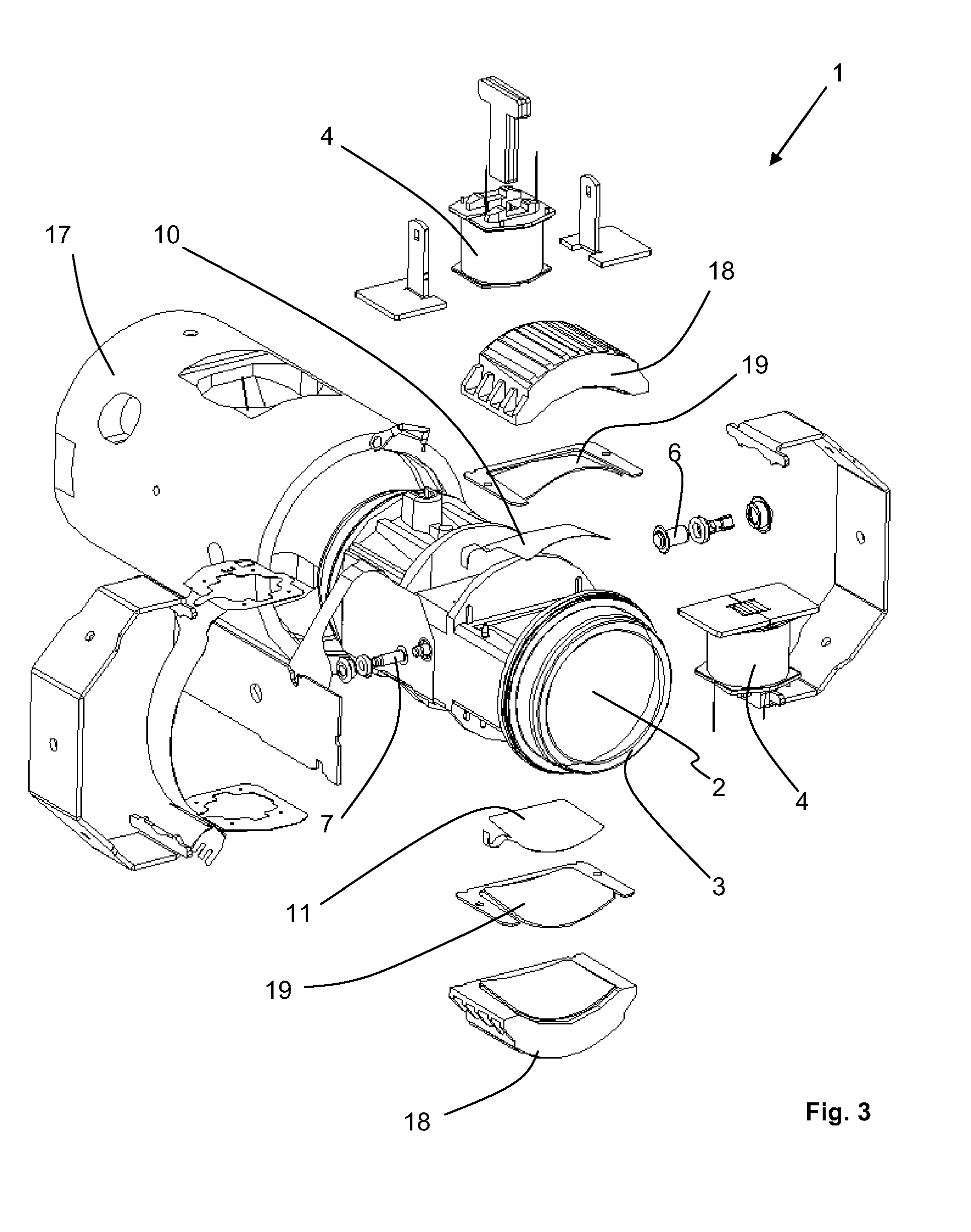

Magnetic inductive flow meter

ActiveUS20150168188A1Increase capacityEnhanced couplingVolume meteringVolume/mass flow by electromagnetic flowmetersCapacitive couplingParasitic capacitance

A magnetoinductive flowmeter for measuring the flow rate of a flowing, conductive medium with a capacitive measuring apparatus for detecting empty pipes is provided. In order to improve the detection of empty pipes and, in particular, the capacitive coupling to the medium, the invention provides for the measuring apparatus for detecting empty pipes to comprise a sheet-like electrode in each case and a counterelectrode which form a measurement capacitance CMess which is dependent on the medium and on the degree of filling of the measuring tube; for the measuring tube to have a wall thickness which is reduced in order to maximize the measurement capacitance CMess at least in the region of the electrode and the counterelectrode; and for the measuring tube to be surrounded by a metal supporting housing, wherein, in order to maintain the pressure resistance of the measuring tube, a hollow-walled supporting body for minimizing the influence of parasitic capacitances on the measurement capacitance CMess is arranged in each case in the region of the reduced wall thickness between the electrode and the inner wall of the supporting housing and between the counterelectrode and the inner wall of the supporting housing and supports the measuring tube against the supporting housing in each case.

Owner:IMF ELECTRONIC GMBH

High frequency MOS transistor, method of forming the same, and method of manufacturing a semiconductor device including the same

InactiveUS20060011981A1On-resistance of the transistor is decreasedImprove featuresSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceLDMOS

In a high frequency LDMOS transistor, a gate structure is formed on a substrate. A drain, doped with first type impurities at a first concentration, is formed on the substrate spaced apart from the gate structure. A buffer well, doped with the first type impurities at a second concentration lower than the first concentration, surrounds side and lower portions of the drain. A lightly doped drain, doped with the first type impurities at a third concentration lower than the second concentration, is formed between the buffer well and the gate structure. A source, doped with the first type impurities at the first concentration, is formed on the substrate adjacent to the gate structure and opposite to the drain with respect to the gate structure. Accordingly, an on-resistance decreases while a breakdown voltage increases in the LDMOS transistor without increasing a capacitance between the gate structure and the drain.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and manufacturing method of the same

ActiveUS7501347B2High insulation breakdown voltageCapacitanceSemiconductor/solid-state device manufacturingCapacitanceCountermeasure

In a semiconductor device, capacitance between copper interconnections is decreased and the insulation breakdown is improved simultaneously, and a countermeasure is taken for misalignment via by a manufacturing method including the steps of forming an interconnection containing copper as a main ingredient in an insulative film above a substrate, forming insulative films and a barrier insulative film for a reservoir pattern, forming an insulative film capable of suppressing or preventing copper from diffusing on the upper surface and on the lateral surface of the interconnection and above the insulative film and the insulative film, forming insulative films of low dielectric constant, in which the insulative film is formed such that the deposition rate above the opposing lateral surfaces of the interconnections is larger than the deposition rate therebelow to form an air gap between the adjacent interconnections and, finally, planarizing the insulative film by interlayer CMP.

Owner:KOKUSA ELECTRIC CO LTD

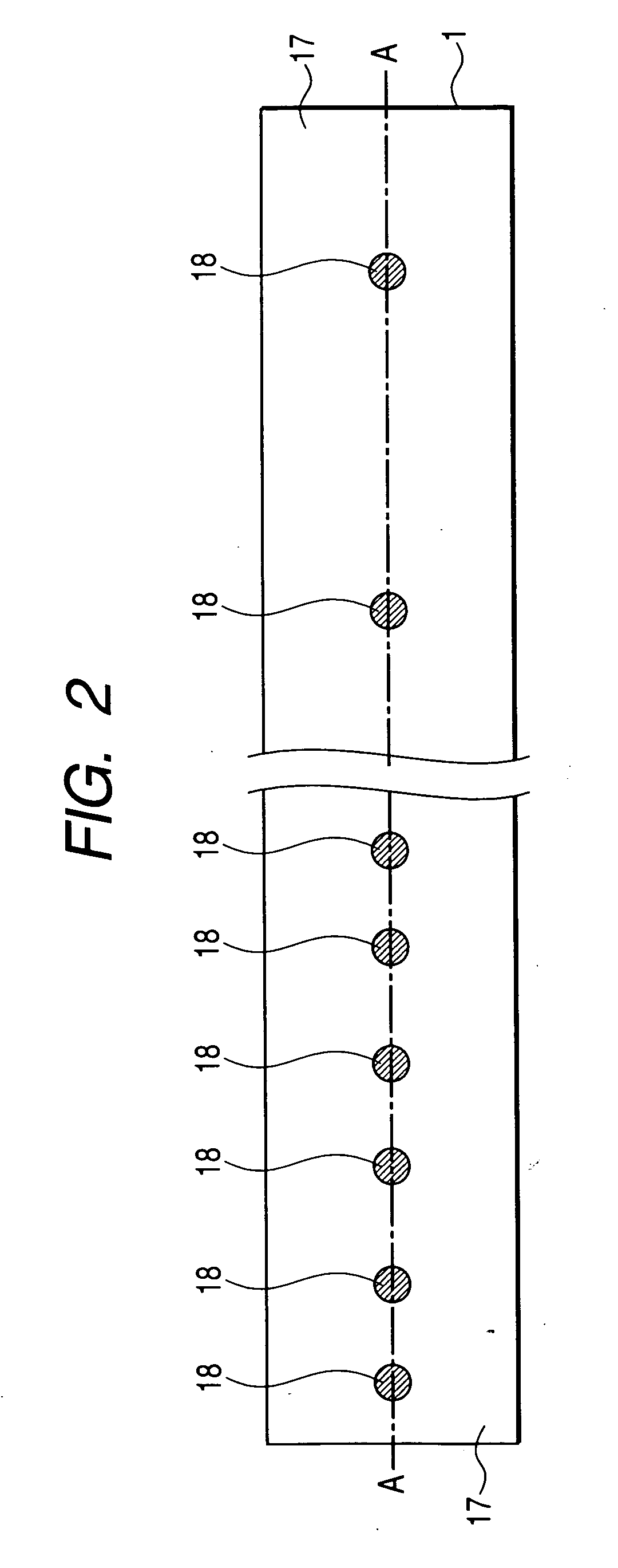

Strip conductor arrangement and method for producing a strip conductor arrangement

InactiveUS7033926B2Reduce capacitanceCapacitanceSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorBand shape

An interconnect arrangement comprises a substrate made from a first insulating material with a substrate surface, at least two interconnects which are arranged next to one another in the substrate, a buffer layer made from a second insulating material above the substrate and comprising a buffer-layer surface, which is parallel to the substrate surface, at least one cavity, which is arranged between the interconnects and, with respect to the buffer-layer surface, extends deeper into the substrate than the interconnects, and a covering layer made from a third insulating material, which is arranged above the buffer layer and completely closes off the cavity with respect to the buffer-layer surface.

Owner:INFINEON TECH AG

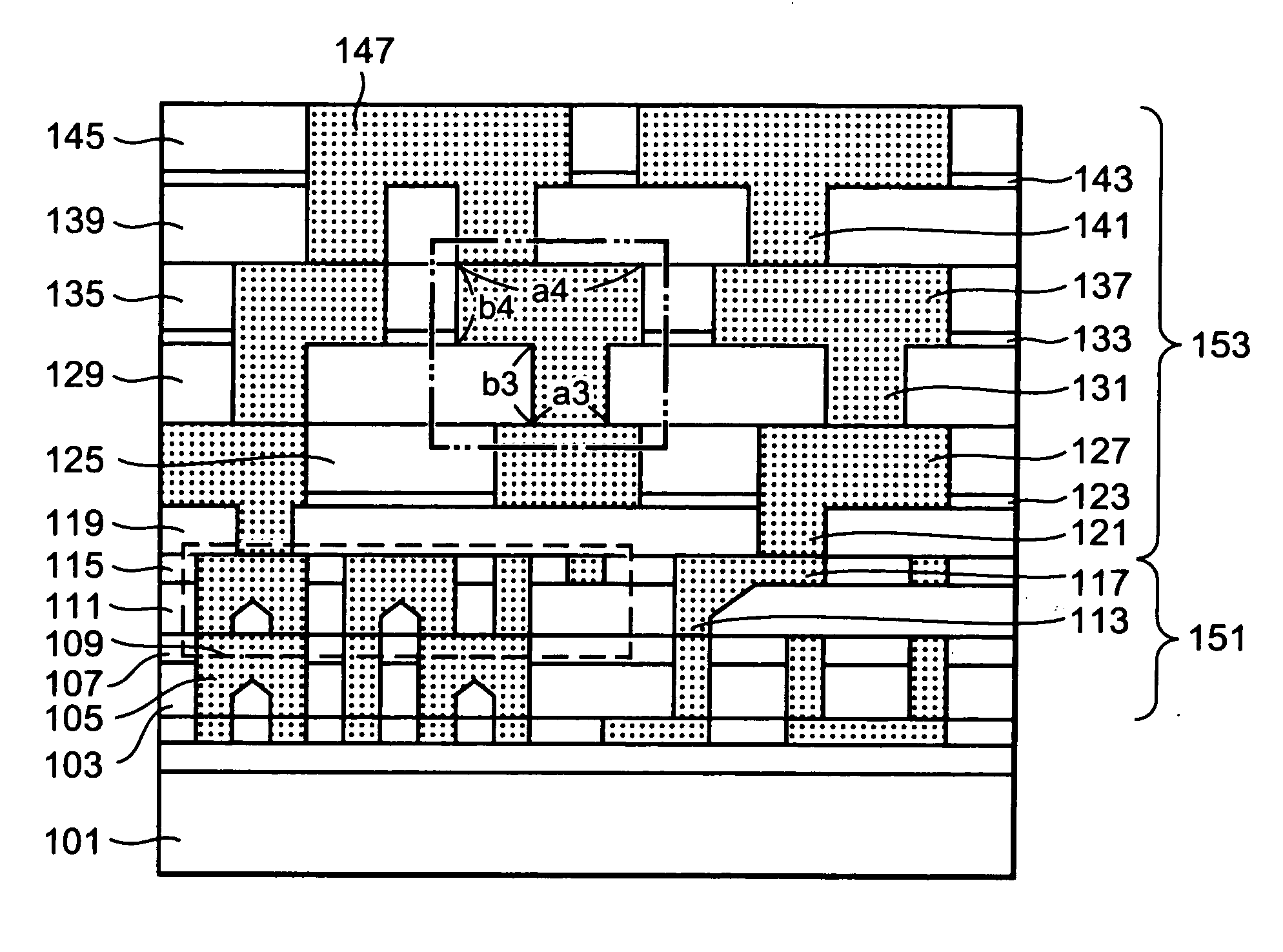

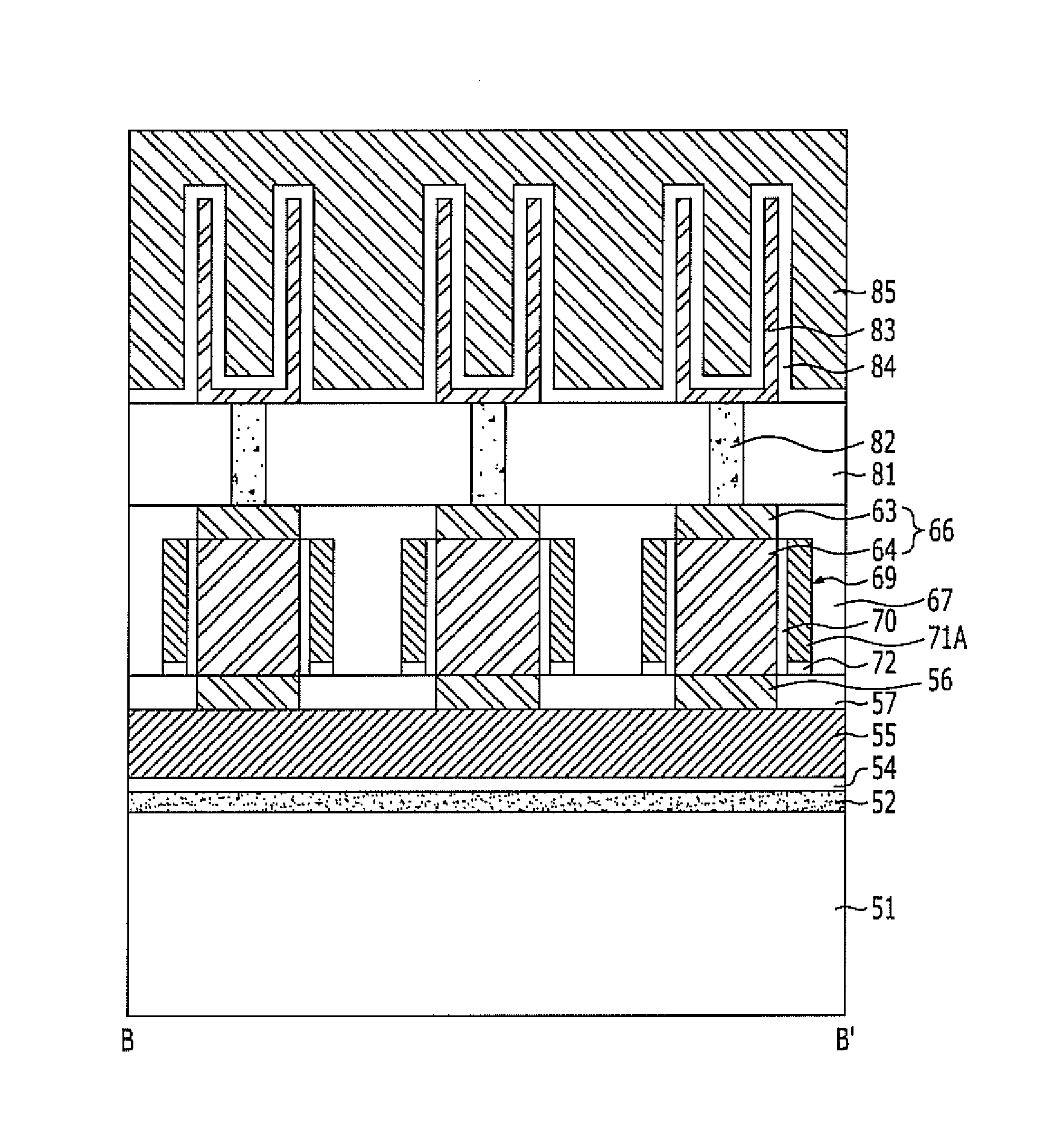

Semiconductor device having dual damascene structure

ActiveUS20090121360A1Reduce capacitanceImprove assembly yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

The semiconductor device includes multilayer wirings of a dual damascene structure. The multilayer wirings include a first wiring layer formed on a semiconductor substrate and a second wiring layer formed on the first wiring layer. The first wiring layer includes a first insulation film, plural first vias provided in the first insulation film, a second insulation film provided on the first insulation film, and a first wiring provided on the first vias and connected to those first vias in the second insulation film. The second wiring layer includes a third insulation film, plural second vias provided in the third insulation film, an adhesive layer provided on the third insulation film, a fourth insulation film provided on the adhesive layer, and a second wiring provided on the second vias and connected to those second vias in the fourth insulation film. In the first wiring layer, the aspect ratio L of a wiring having the minimum wiring width and the via aspect ratio V are in a relationship of L≧V and in the second wiring layer, the aspect ratio L of a wiring having the minimum wiring width and the via aspect ratio V is in a relationship of L<V.

Owner:RENESAS ELECTRONICS CORP

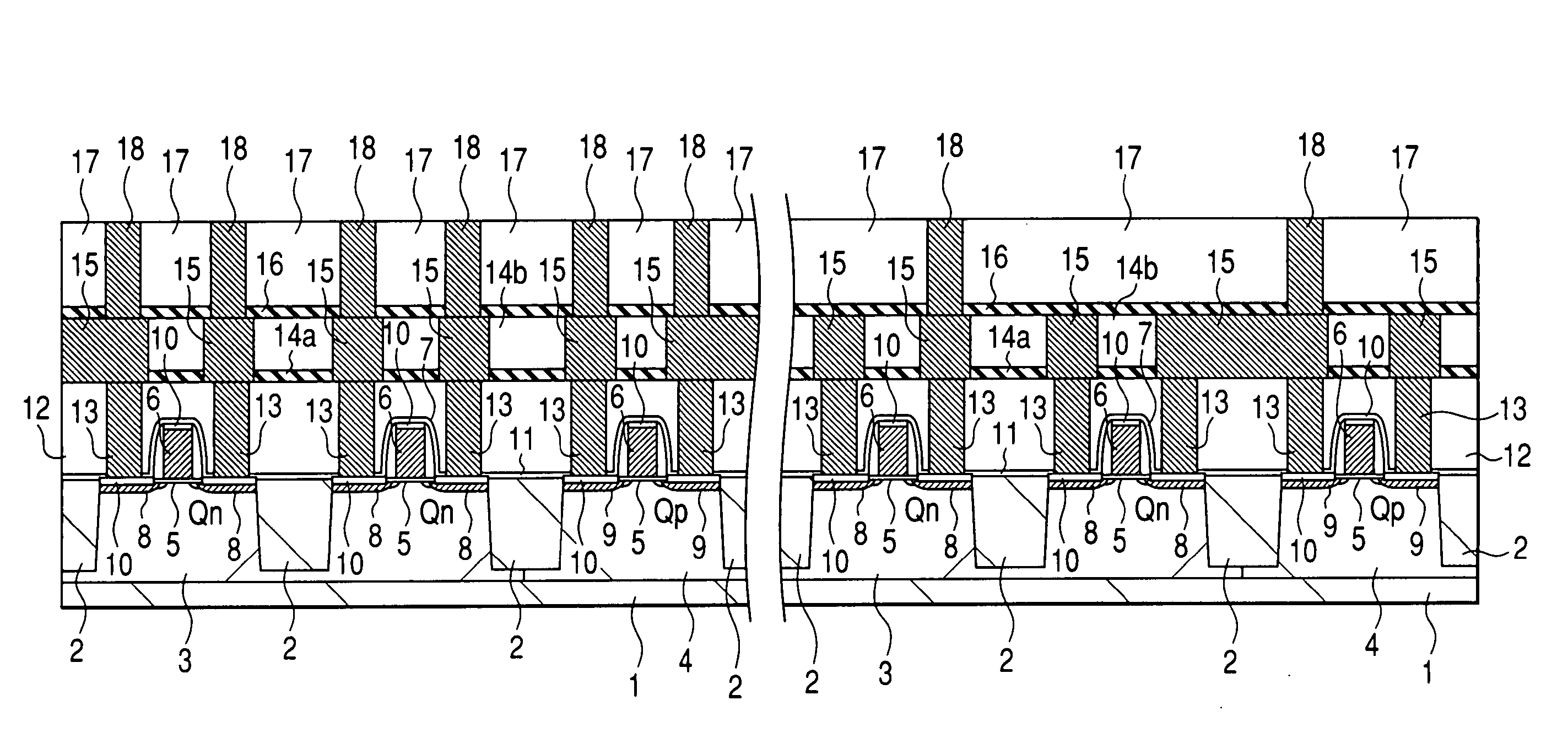

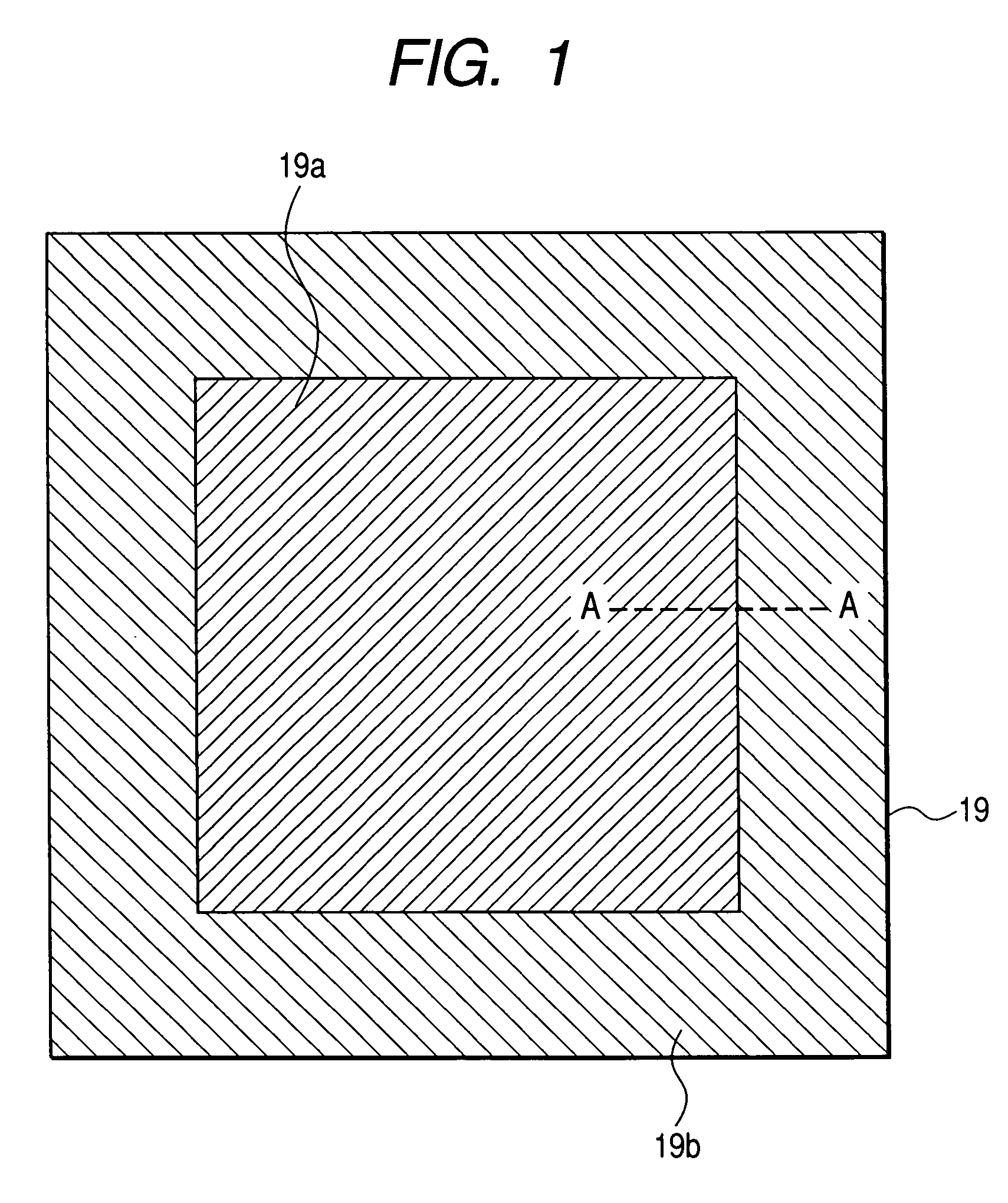

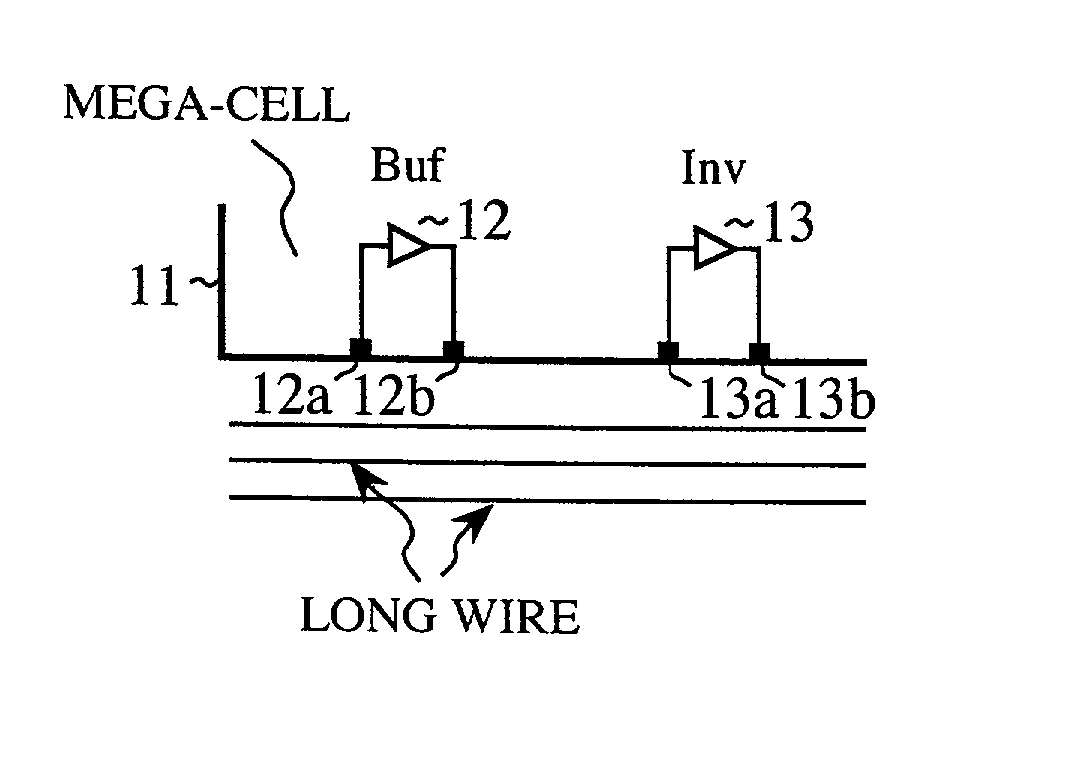

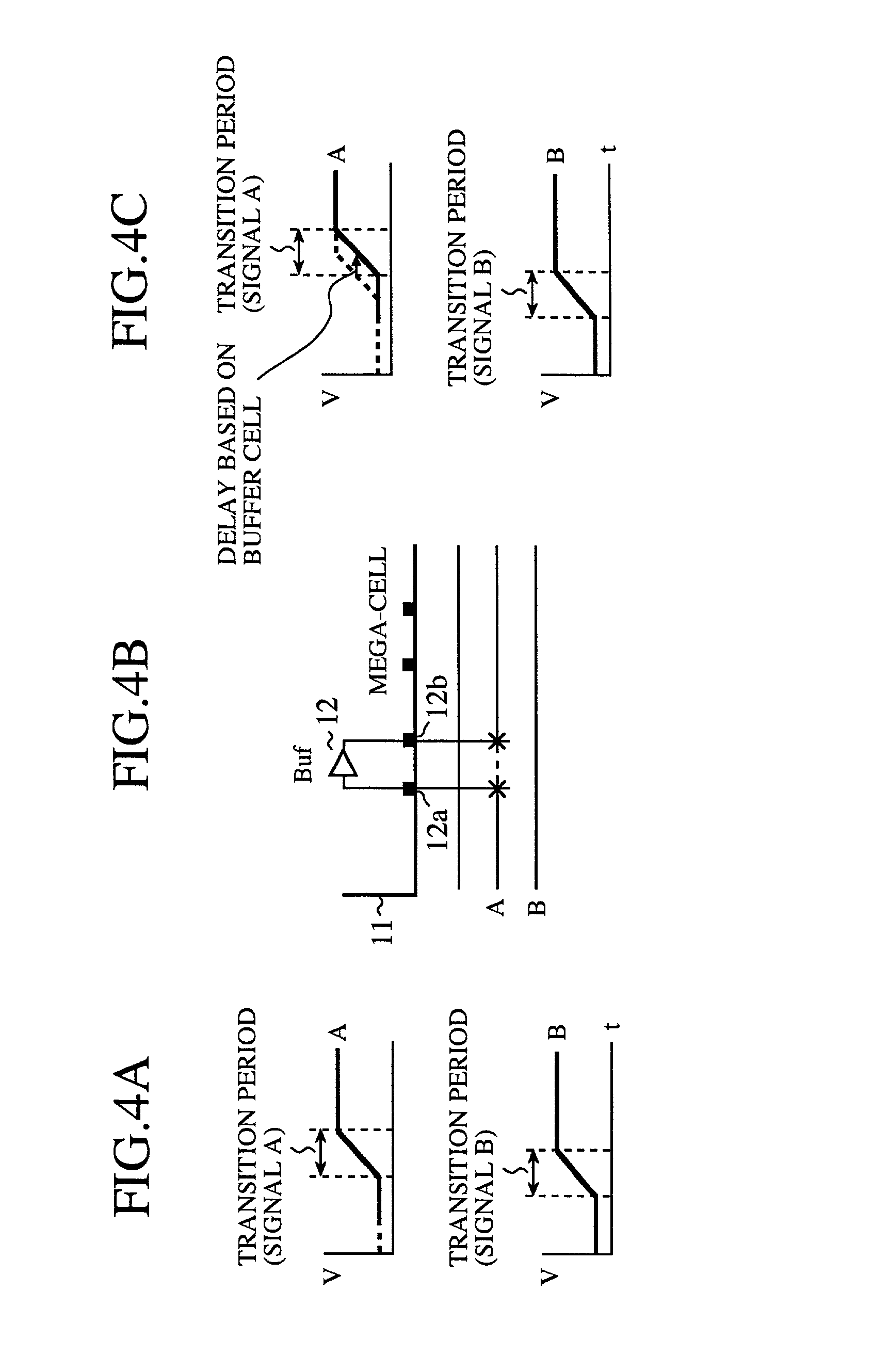

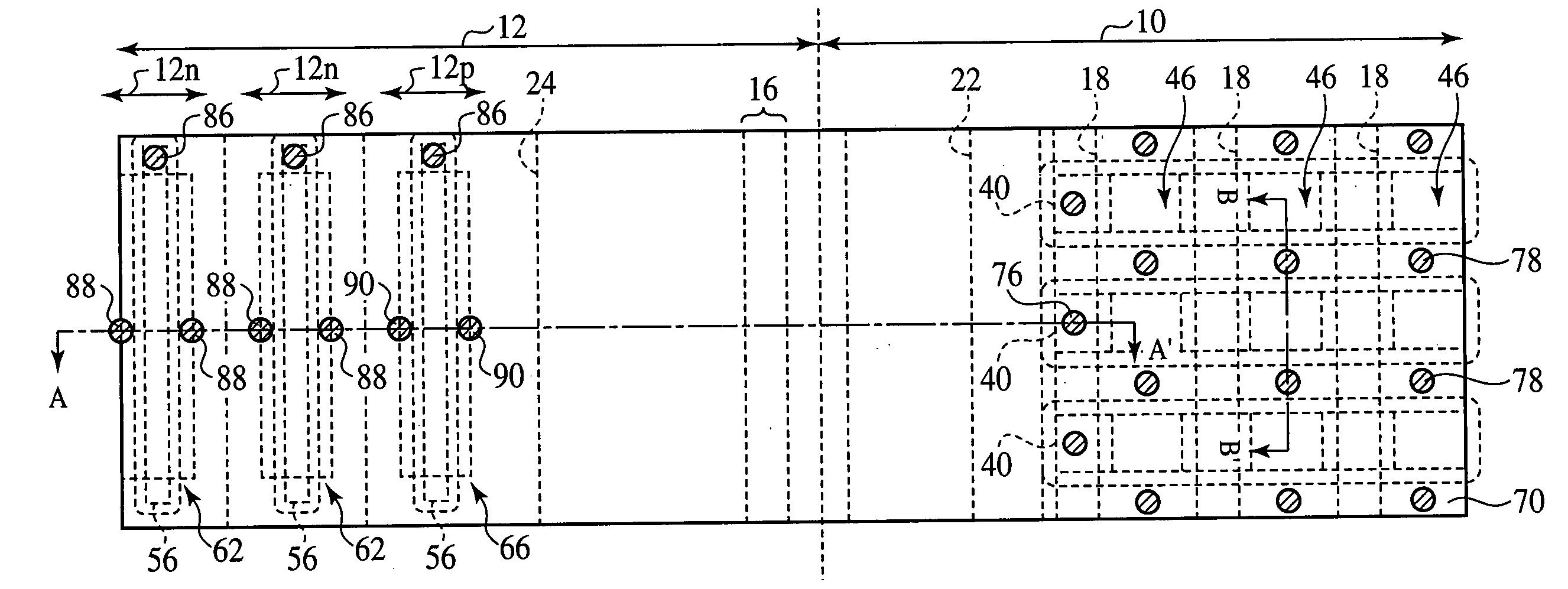

Automatic cell placement and routing apparatus and automatic cell placement and routing method used for the apparatus

InactiveUS20020046389A1CapacitanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

A buffer cell and an inverter cell are embedded in advance in an internal open space of each of mega-cells and IO cells composing a semiconductor integrated circuit. Thereafter, in cases where it is expected that a cross-talk noise is generated in a signal transmitting through a particular wire of the semiconductor integrated circuit, one mega-cell or one IO cell, which is placed in a position nearest to a generation position of the cross-talk noise, is selected from the mega-cells and the IO cells, and the buffer cell or the inverter cell embedded in the selected mega-cell or the selected IO cell is inserted into the particular wire. Therefore, because the capacitance between the particular wire and each wire adjacent to the particular wire is reduced, the cross-talk noise can be reduced.

Owner:RENESAS ELECTRONICS CORP

Nonvolatile semiconductor storage device and manufacturing method of the same

ActiveUS20080142876A1Improve reliabilityHigh speedSolid-state devicesRead-only memoriesCapacitanceTrapping

A charge trapping layer in an element isolation region and that in an isolation region between a memory transistor and a selection transistor are removed so that the charges are not injected or trapped in the regions. Also, in an element isolation region, gate electrodes of each memory transistor are united at a position higher than a gate electrode of the selection transistor from a surface of a silicon substrate in an element isolation region, thereby reducing the capacitance between the memory transistor and the selection transistor.

Owner:RENESAS ELECTRONICS CORP

Metal contactless smart card and method for fabricating the same

ActiveUS20180232617A1CapacitanceImproving Impedance MatchingRecord carriers used with machinesInformation cardsEngineeringRadio frequency

A metal contactless smart card includes a first metal layer having a first slit, a second layer, a radio-frequency integrated circuit chip module, and an inlay having an antenna. A nonconductive insert may be fitted in the slit. The first metal layer may include an inlay recess where the inlay may be received and a through-hole where the chip may be inserted. The second layer of the smart card may be made of metal and may also include a slit.

Owner:KANG SOO HYANG

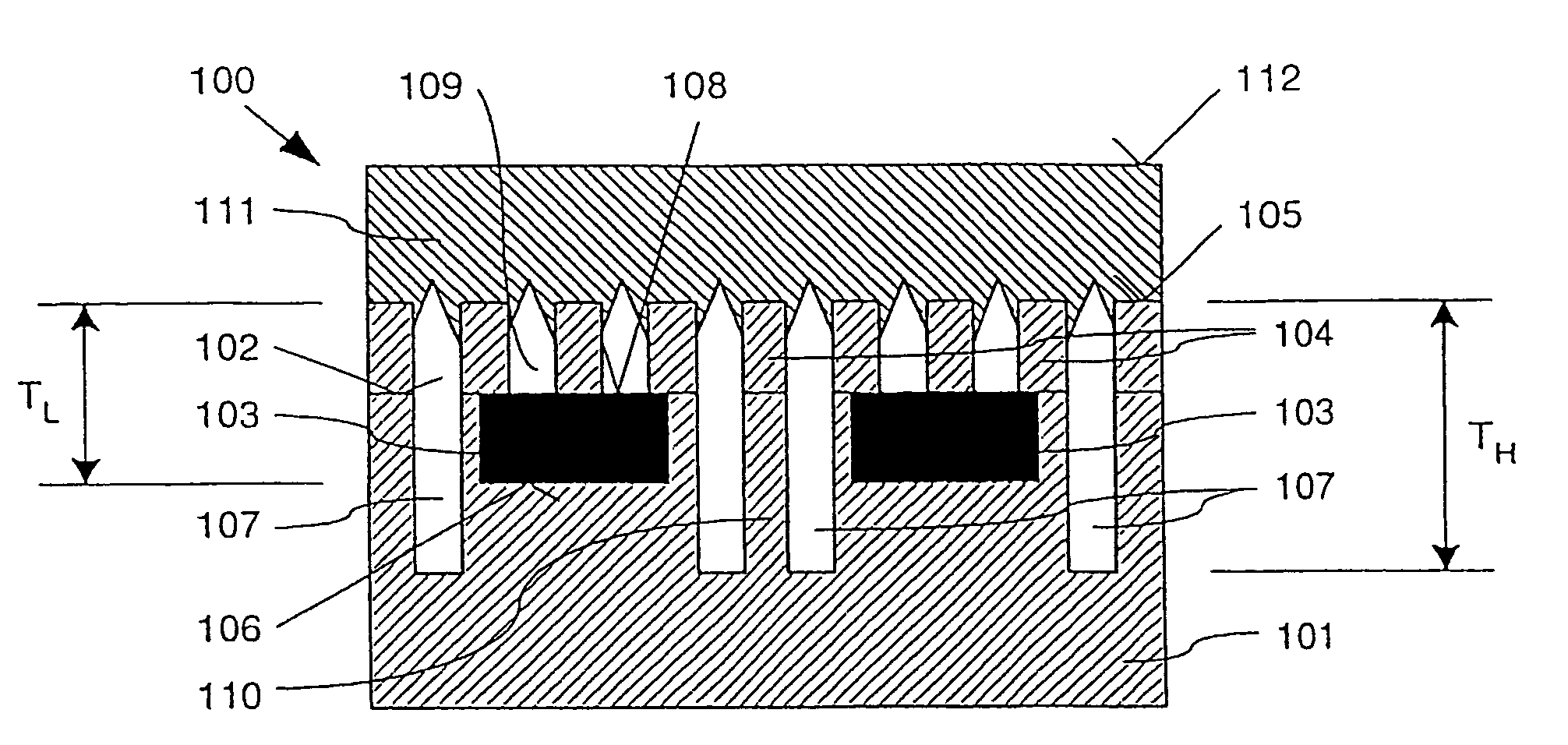

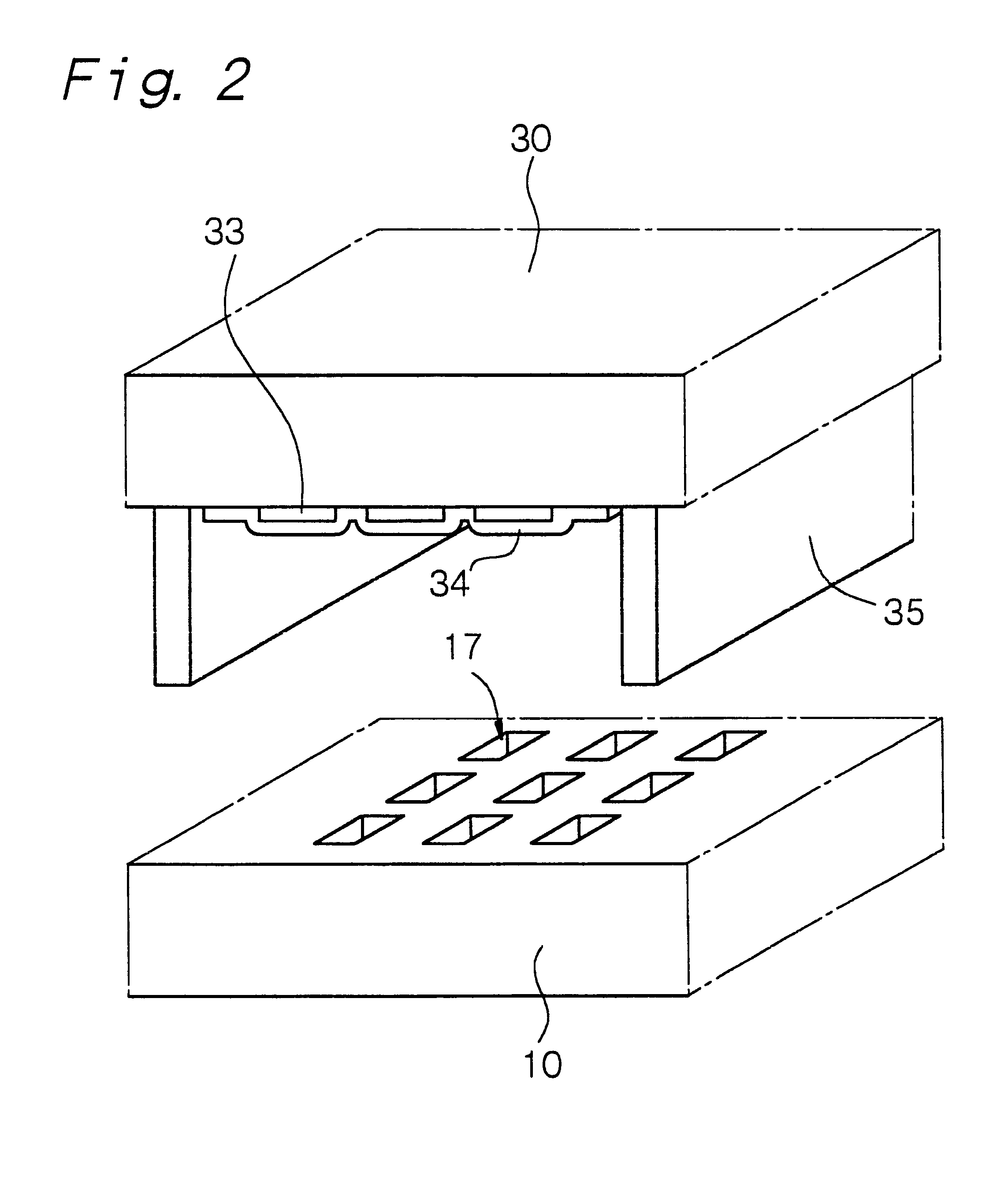

Cold cathode field emission device and cold cathode field emission display

InactiveUS6278228B1Improve efficiencyCapacitanceControl electrodesElectrode and associated part arrangementsField emission deviceField emission display

A cold cathode field emission device having an electron emission layer (14), an insulating layer and a gate electrode (12) which are laminated one on another with the insulating layer positioned between the gate electrode, and the electron emission layer (14), and further having an opening portion which penetrates through at least the insulating layer and the electron emission layer, the electron emission layer having an edge portion for emitting electrons, the edge portion being projected on a wall surface of the opening portion, and the electron emission layer being connected to a power source through a resistance layer (23).

Owner:SONY CORP

Touch substrate and touch screen

ActiveUS20160246405A1CapacitanceImprove signal-to-noise ratioInput/output processes for data processingTouchscreenMetal mesh

The present invention provides a touch substrate and a touch screen. The touch substrate comprises first electrodes and electrodes which intersect with each other, each first electrode includes a plurality of first metal meshes, adjacent first metal meshes are connected through a connection portion, each second electrode includes a plurality of second metal meshes, adjacent second metal meshes are connected through a connection bridge, the first metal meshes, the second metal meshes and the connection portion are in the same layer, and an insulation layer is provided between the layer in which the connection portion is located and the layer in which the connection bridge is located, at least a part of edges of the first metal mesh is provided with a first side strip thereat, the first side strip is adjacent to a corresponding second metal mesh and is connected to the first metal mesh.

Owner:BOE TECH GRP CO LTD +1

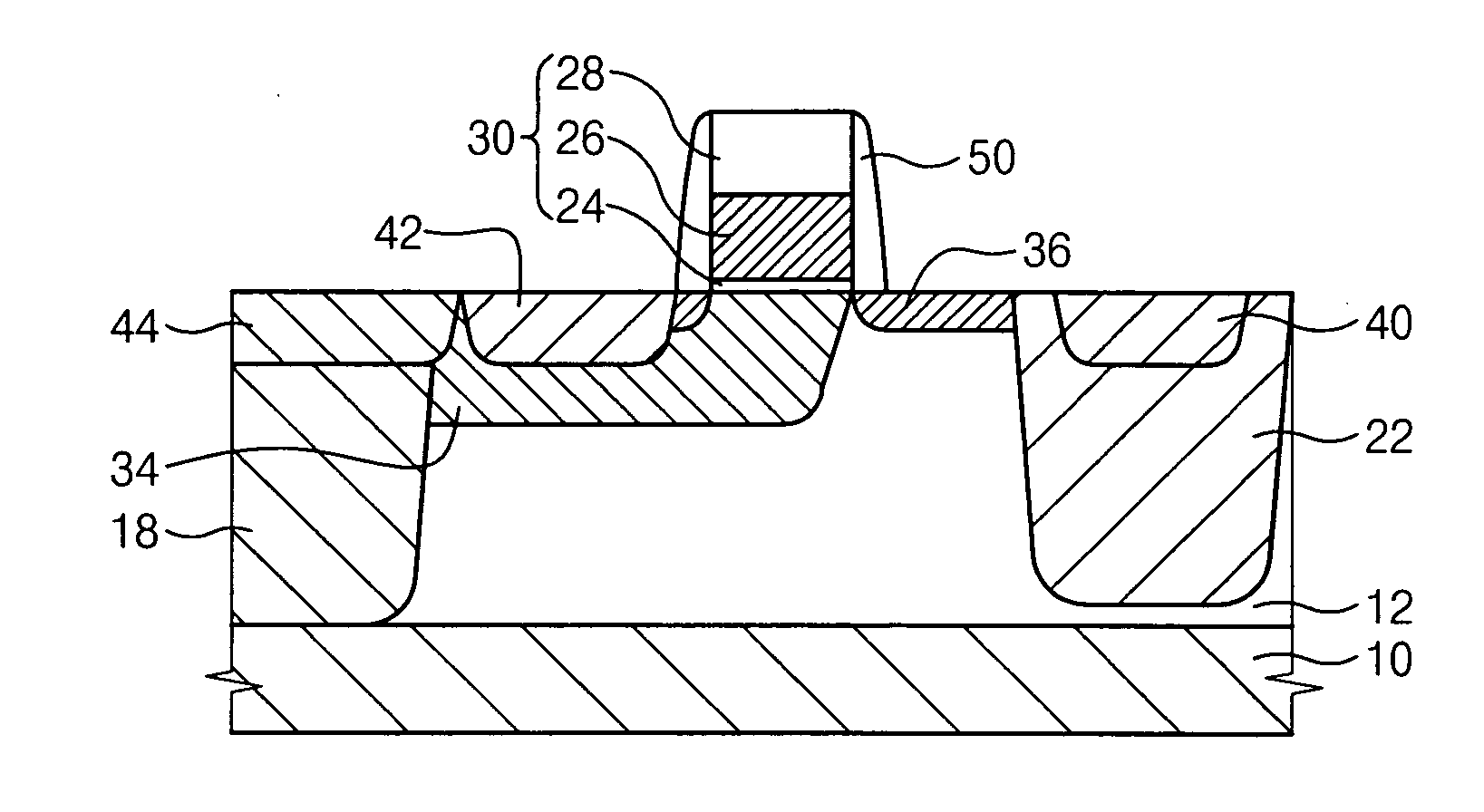

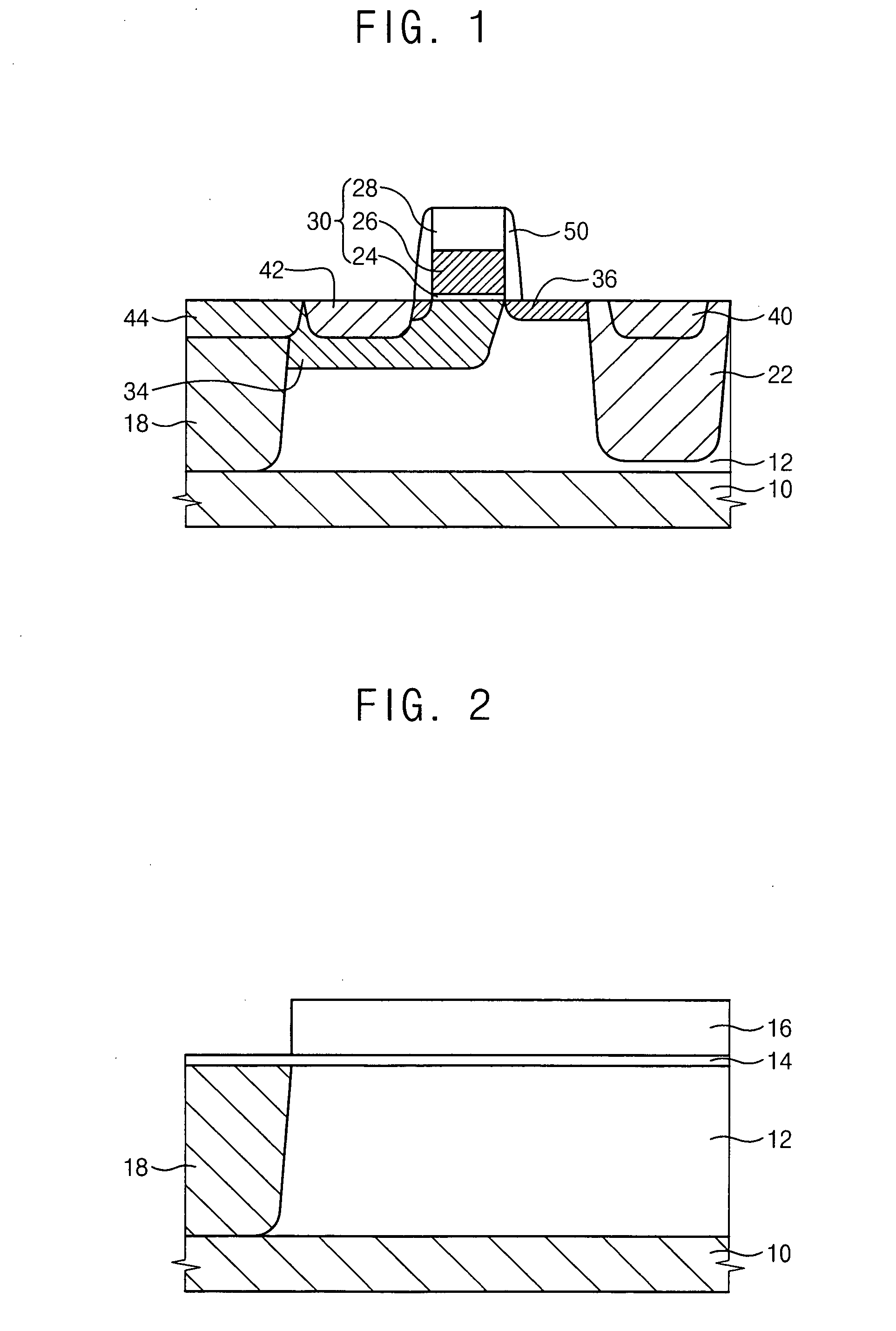

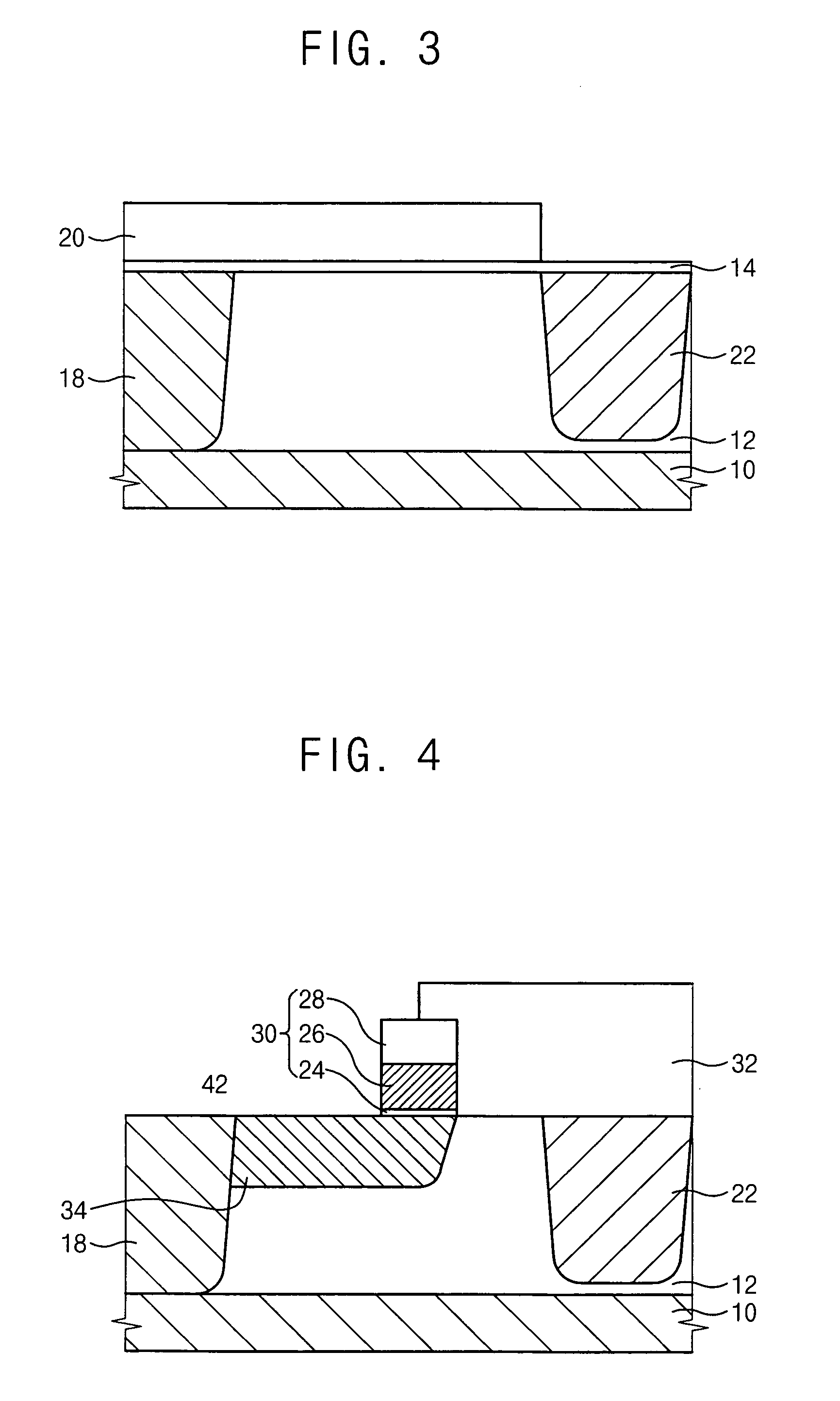

Semiconductor device and method for fabricating the same

InactiveUS20060220097A1Improve accuracyHigh-accuracy patterningTransistorSolid-state devicesCell regionSilicon

The semiconductor device comprises a silicon substrate 14 having a step formed in the surface which makes the surface in a flash memory cell region 10 lower than the surface in a peripheral circuit region 12; a device isolation region 20a formed in a trench 18 in the flash memory cell region 10; a device isolation region 20c formed in a trench 24 deeper than the trench 18 in the peripheral circuit region 12; a flash memory cell 46 including a floating gate 32 and a control gate 40 formed on the device region defined by the device isolation region 20a; and transistors 62, 66 formed on the device regions defined by the device isolation region 20c.

Owner:FUJITSU MICROELECTRONICS LTD

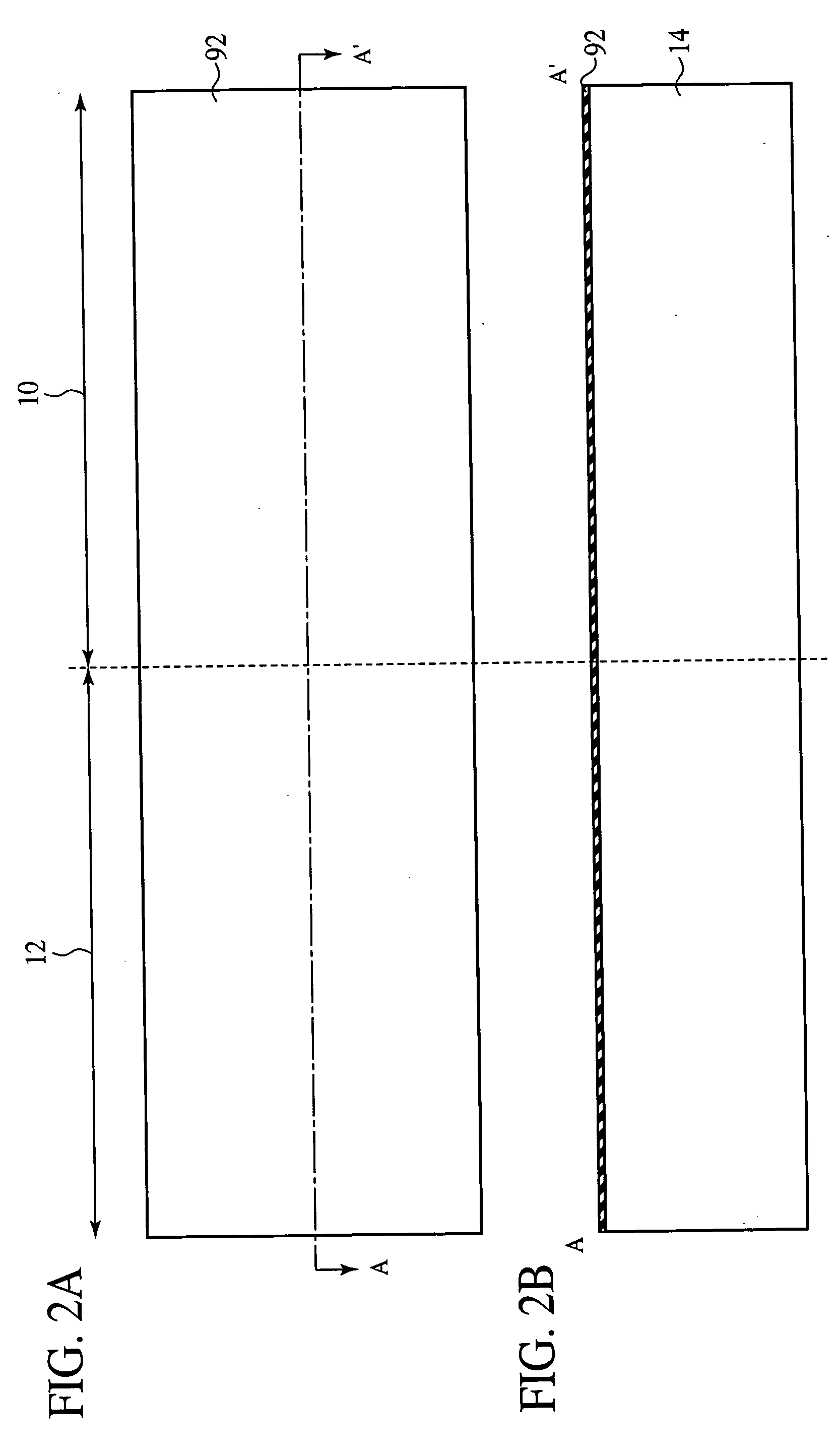

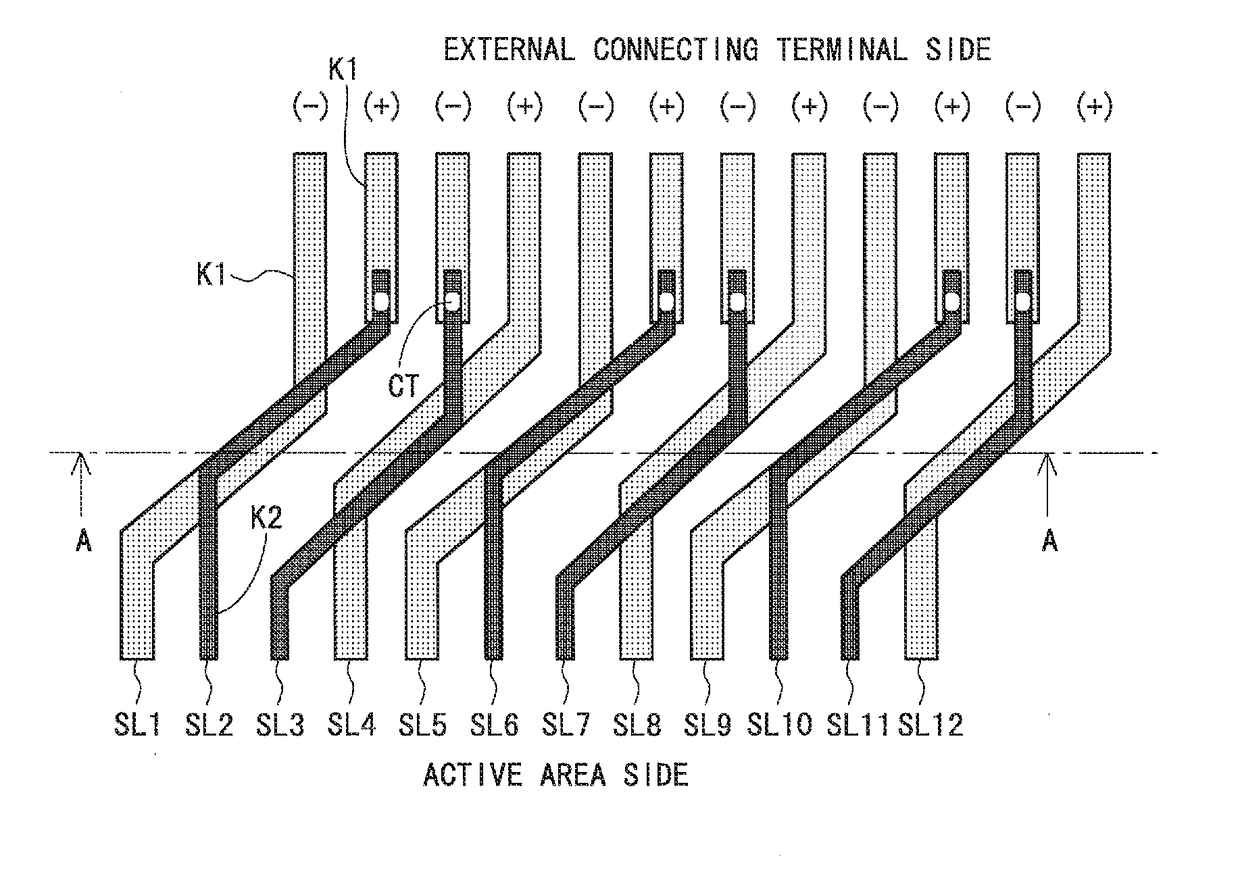

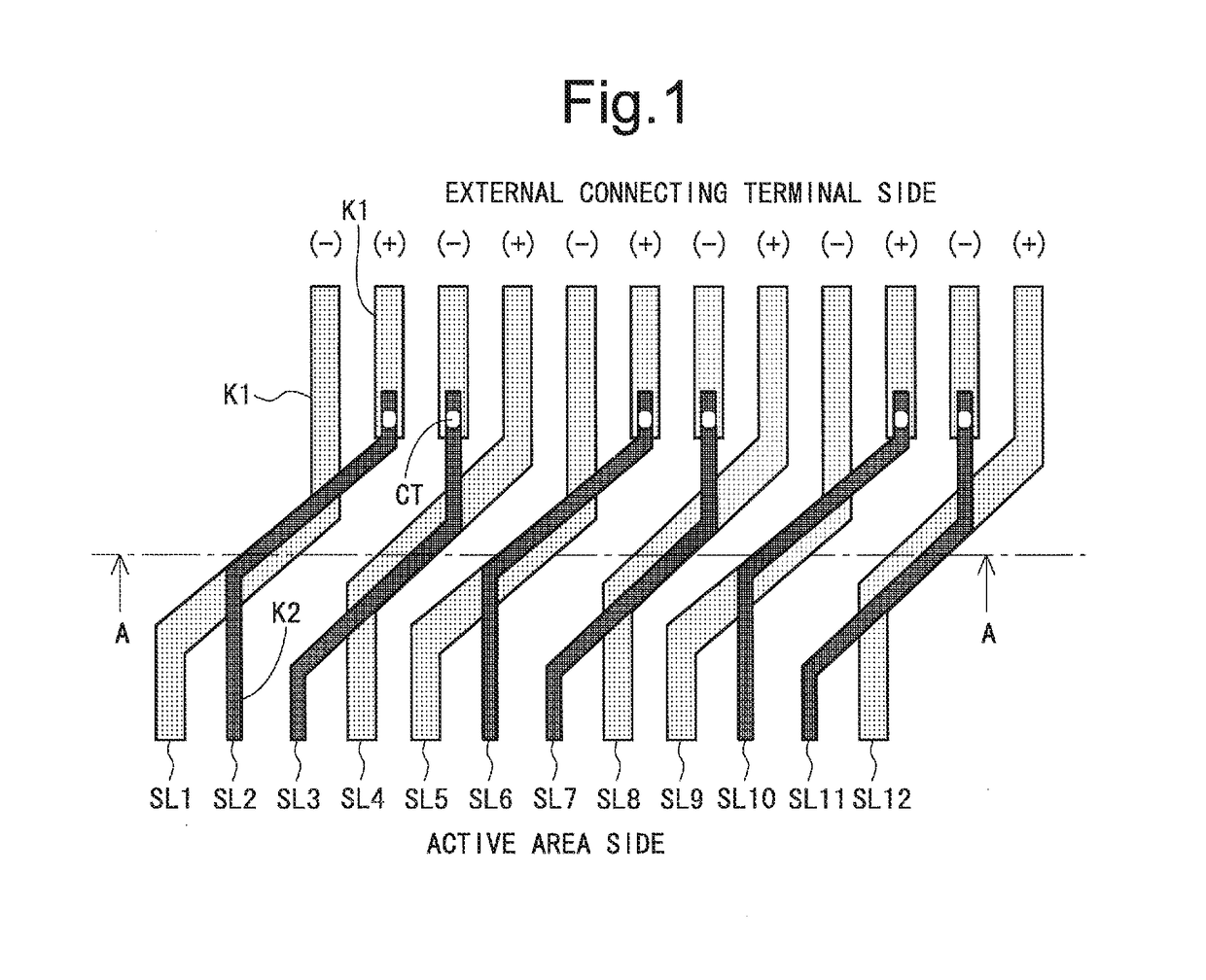

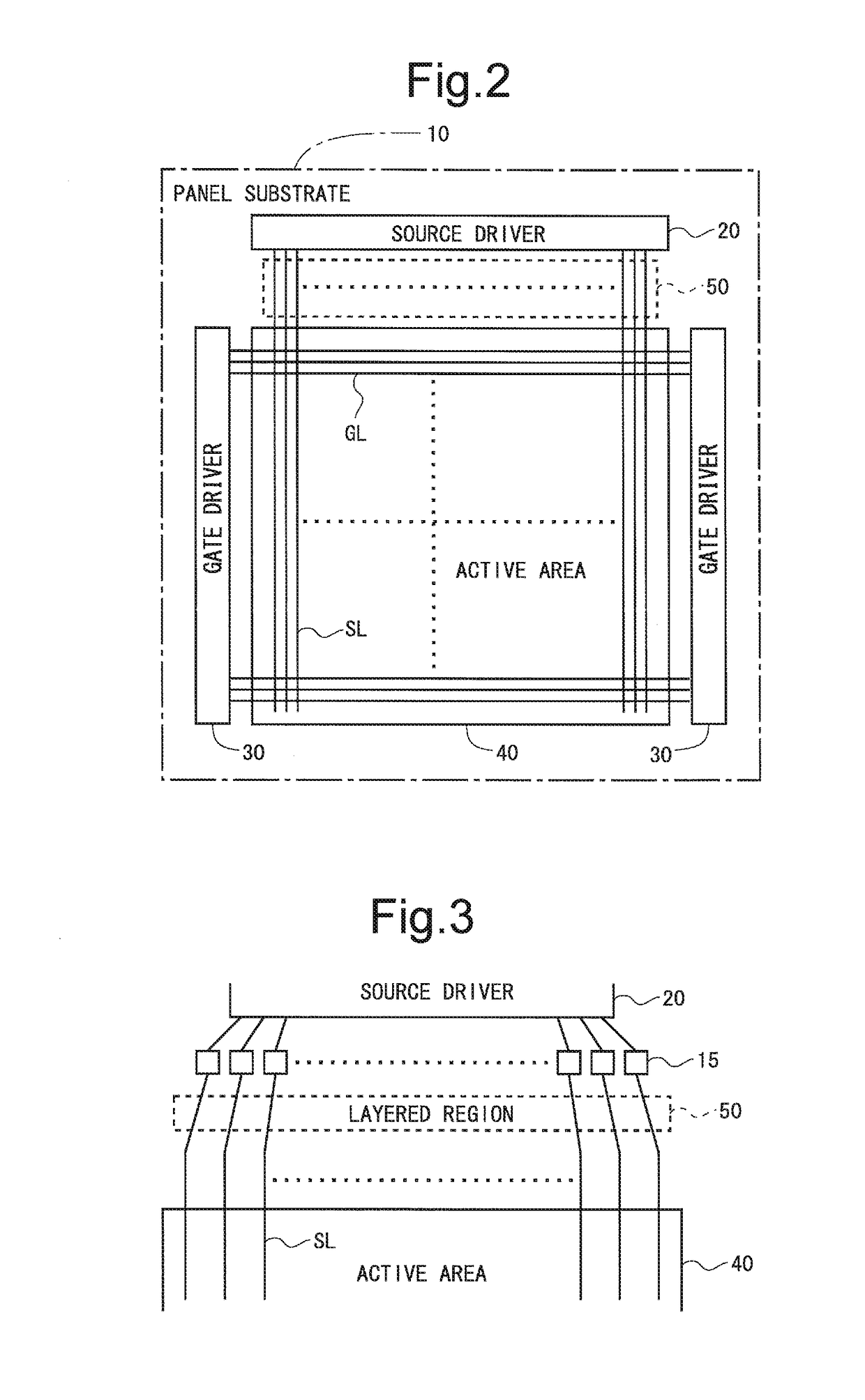

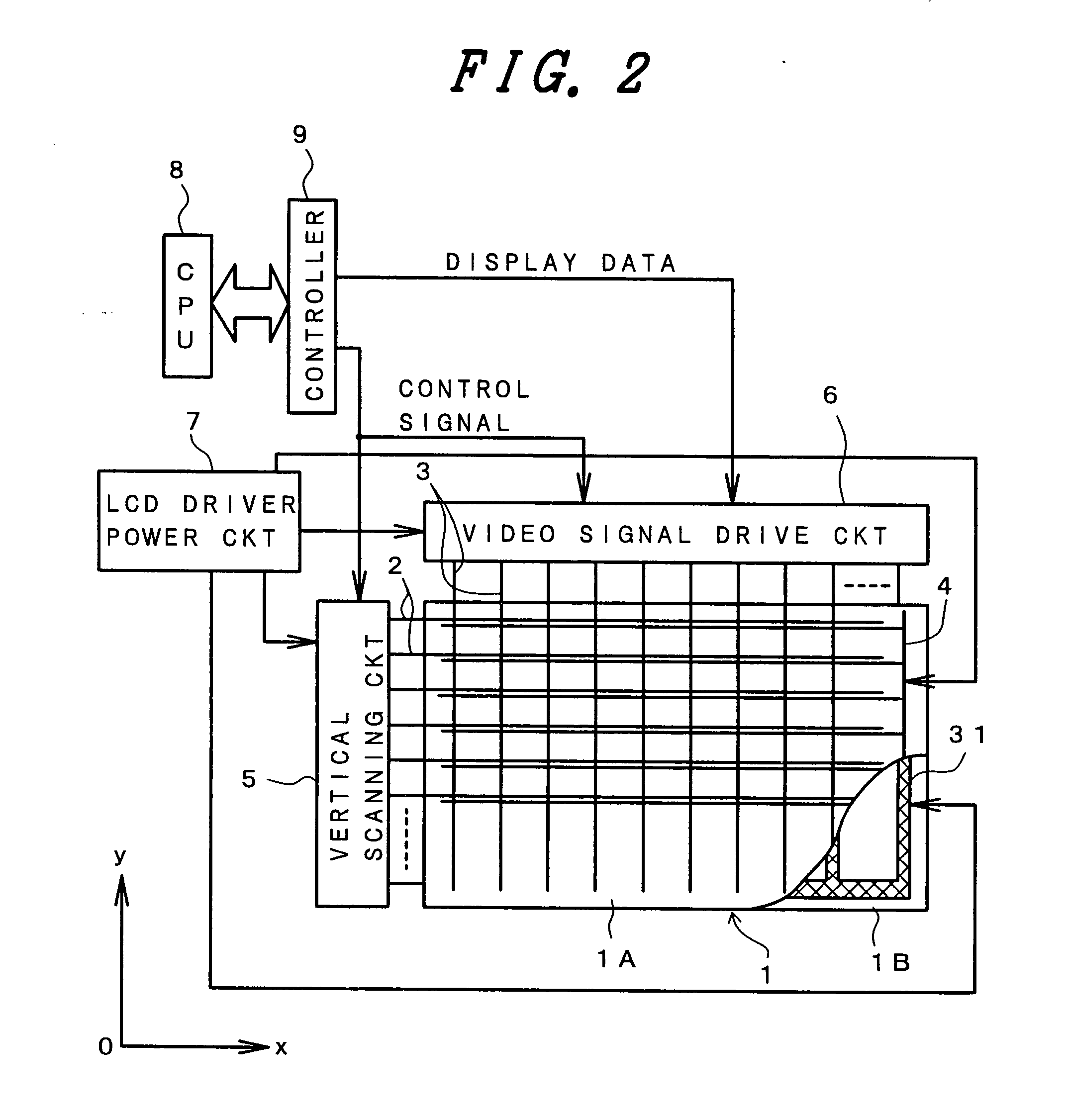

Display device

ActiveUS20170336688A1Display quality be deteriorateEliminate residual electric chargeStatic indicating devicesNon-linear opticsCapacitanceEngineering

An object of the present invention is to suppress deterioration of display quality due to difference in wiring resistance and capacitance between the layers in a display device having a layered wiring structure. In a display device having a layered wiring structure of P layers, and employing a Q-column reversal driving method in which a polarity of a video signal is reversed every Q source bus lines (SL), the plurality of source bus lines SL are wired to the plurality of layers such that taking source bus lines (SL) of a number equal to a double of a least common multiple of P and Q as one group, the number of source bus lines (SL) to which positive video signals are applied matches the number of source bus lines (SL) to which negative video signals are applied in each of the layers in each of horizontal scanning periods.

Owner:SHARP KK

Magnetoresistive effect element, thin-film magnetic head with the element and manufacturing method of the head

InactiveUS20070127165A1Reduce capacitanceSufficient effectNanomagnetismElectrical transducersCapacitanceEngineering

An MR effect element that can obtain the sufficient back flux-guide effect under the condition of reducing the capacitance between the upper and lower electrode layers is provided. The element comprises: an MR effect multilayer provided on the lower electrode layer; an insulating layer surrounding a rear side surface and side surfaces opposed to each other in track width direction of the MR effect multilayer; and an upper electrode layer provided on the MR effect multilayer and the insulating layer, the insulating layer having a concave portion filled with a portion of the upper electrode layer, the concave portion positioned near the rear side surface of the MR effect multilayer, and a bottom point of a concave of the concave portion positioned at the same level or a lower level in stacking direction compared to an upper surface of the free layer.

Owner:TDK CORPARATION

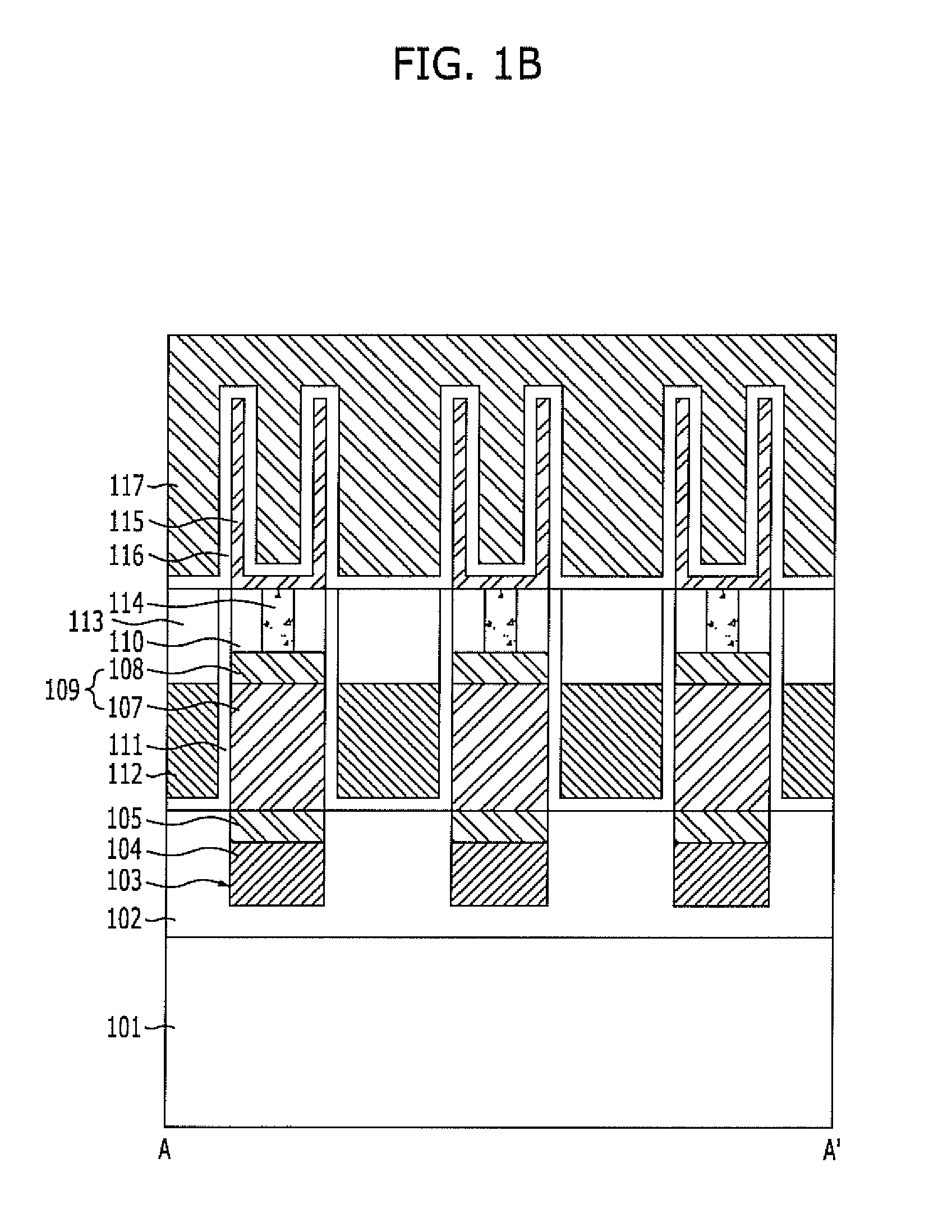

Semiconductor device with buried bit line and method for fabricating the same

ActiveUS20130234242A1Lower resistanceCapacitanceSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor devicePartial filling

A semiconductor device includes trenches defined in a substrate, buried bit lines partially filling the trenches, a first source / drain layer filling remaining portions of the trenches on the buried bit lines, stack patterns having a channel layer and a second source / drain layer stacked therein and bonded to the first source / drain layer, wherein the channel layer contacts with the first source / drain layer, and word lines crossing with the buried bit lines and disposed adjacent to sidewalls of the channel layer.

Owner:SK HYNIX INC

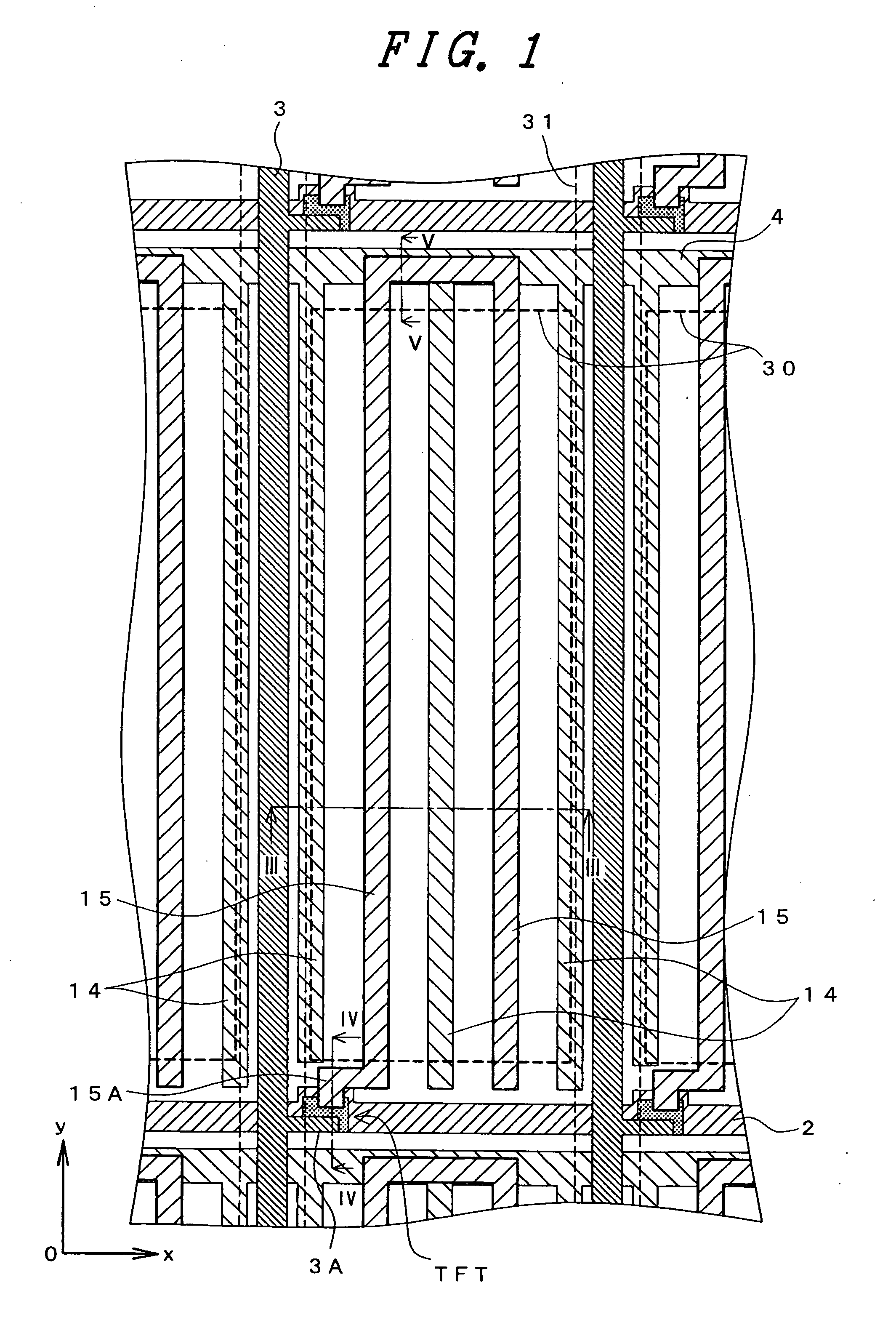

Active-matrix liquid crystal display

InactiveUS20050225692A1Avoid loadSmall sizeNon-linear opticsIn planeActive-matrix liquid-crystal display

An active matrix liquid crystal display device having a pair of substrates with liquid crystal layer therebetween, a plurality of video signal lines and a plurality of scan lines formed on one of the pair of substrates and a plurality of pixel electrodes connected to the video signal line through an active device and a plurality of color filters formed on another of the pair of substrates. A shield electrode which overlaps with one of the video signal lines in plane view is arranged between the one of the video signal lines and one of the color filters, and a planarization layer is arranged between one of the pixel electrodes and the shield electrode.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

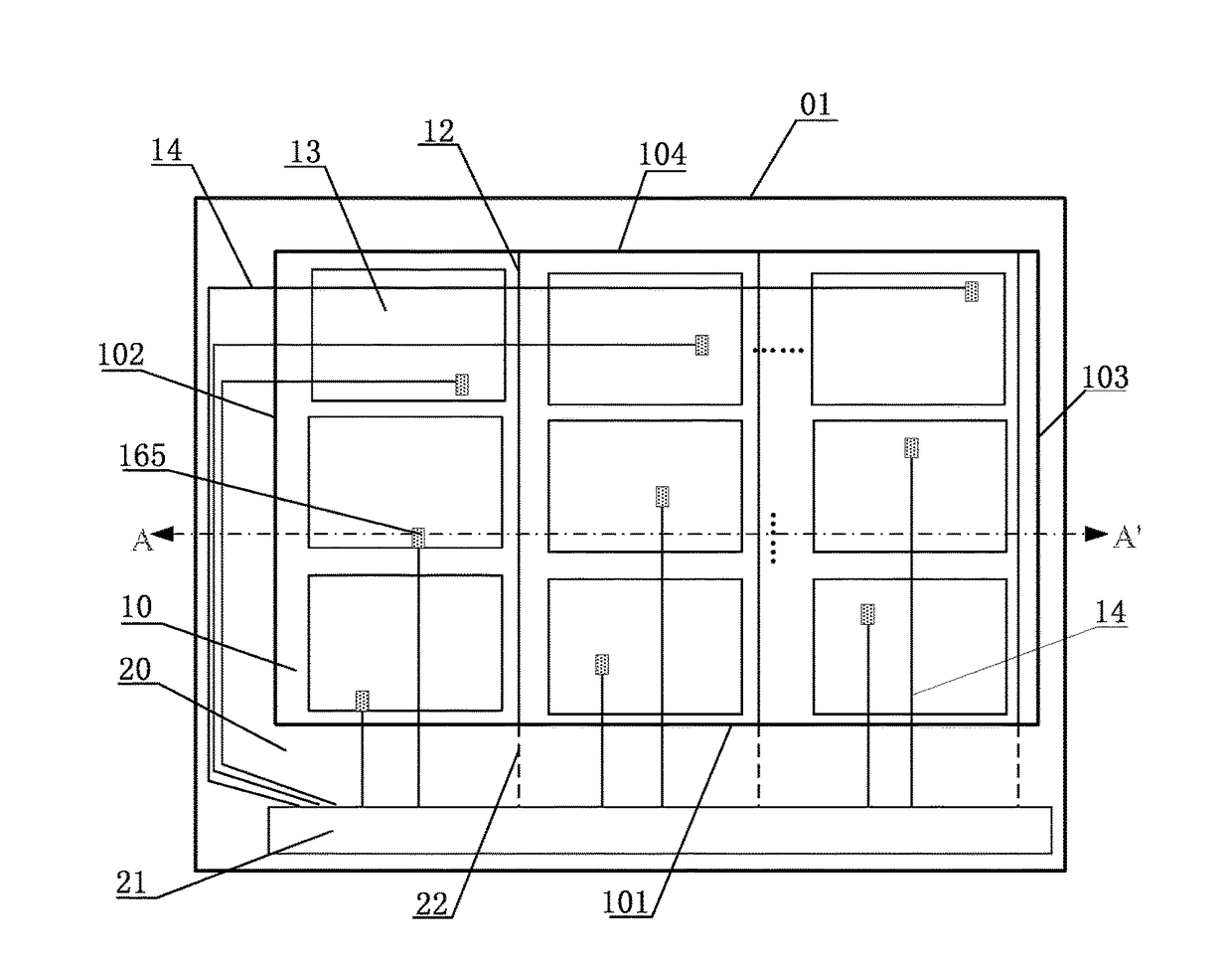

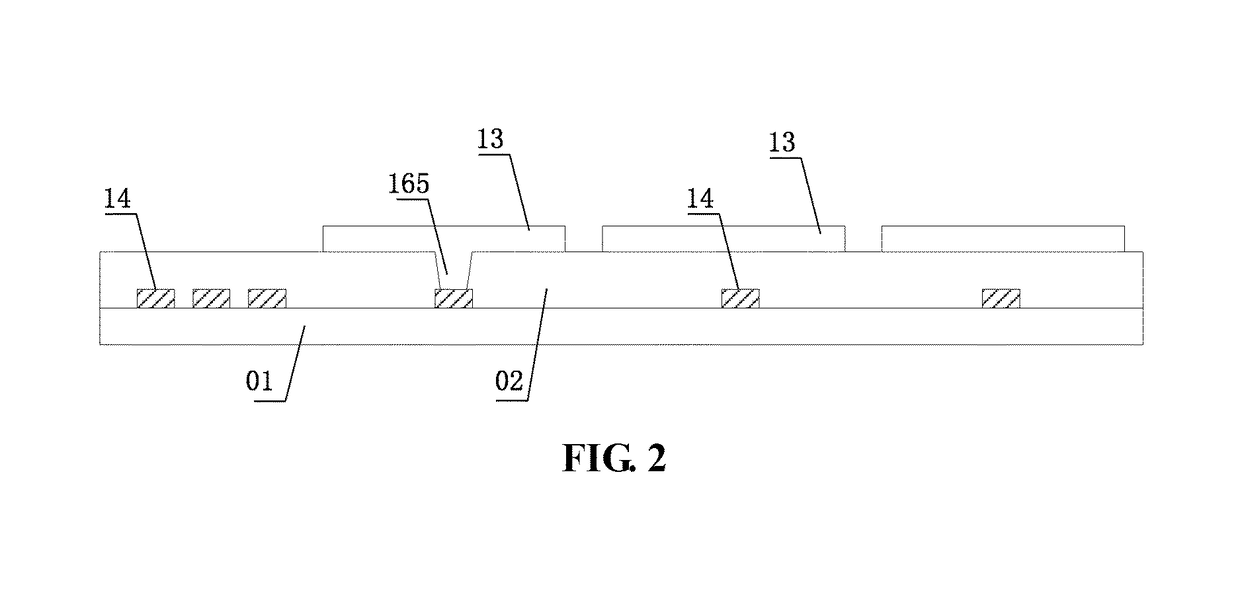

Array substrate, touch display panel and touch display device

InactiveUS20170192558A1Increase capacitanceReduce the likelihood of occurrenceStatic indicating devicesInput/output processes for data processingSignal linesData lines

The present disclosure discloses an array substrate, touch display panel and touch display device. The array substrate comprises a substrate, a display region and a non-display region surrounding the display region. A driver chip is provided in the non-display region. The display region comprises a plurality of data lines. Each of the plurality of data lines is electrically connected to the driver chip via a respective one of a plurality of first connection lines; and a plurality of touch electrode blocks. The plurality of touch electrode blocks are electrically connected to the driver chip via a plurality of touch signal lines. In the non-display region, the plurality of touch signal lines are not overlapped with the plurality of first connection lines in a direction perpendicular to the substrate.

Owner:SHANGHAI AVIC OPTOELECTRONICS +1

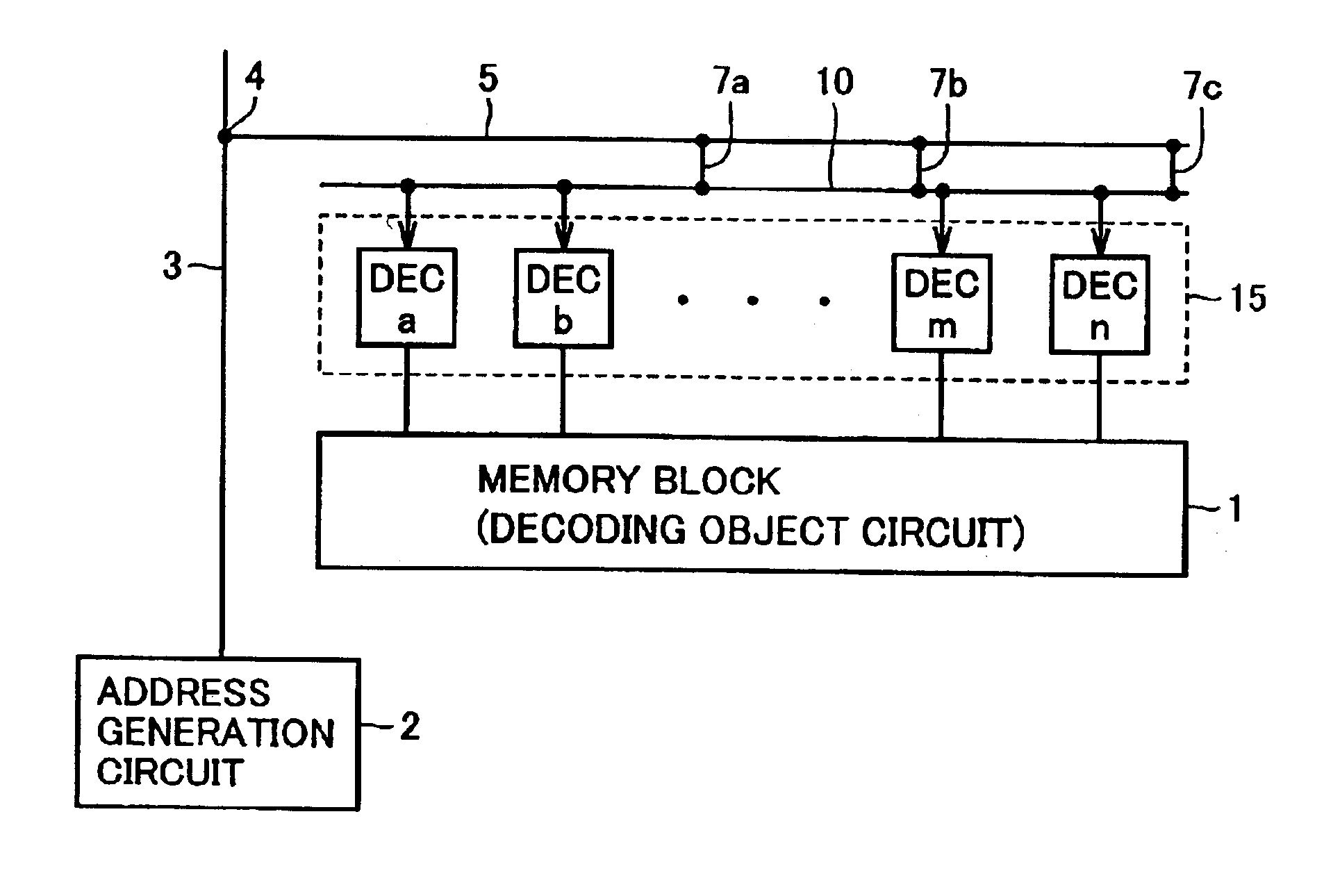

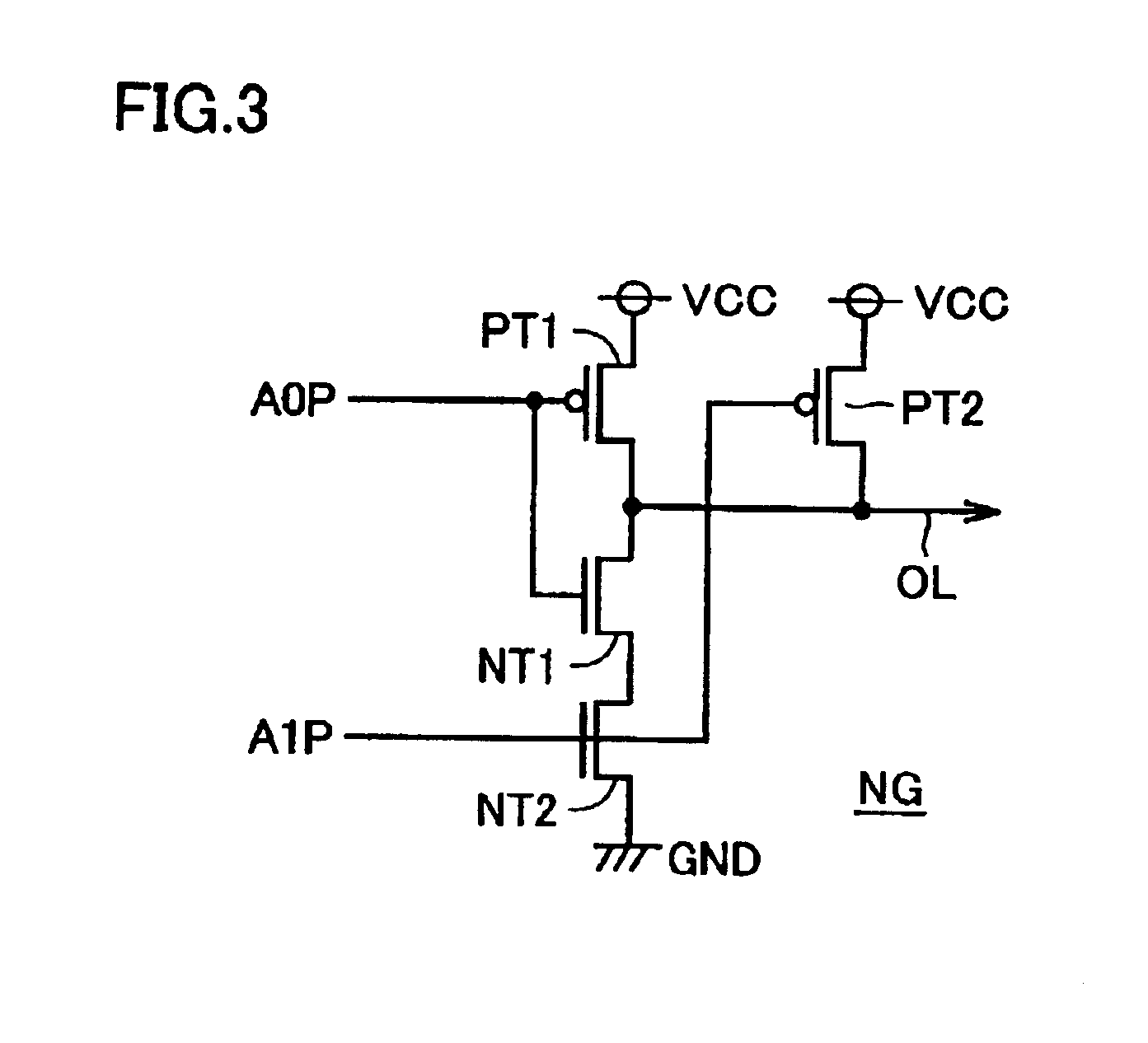

Semiconductor circuit device capable of high speed decoding

InactiveUS6806738B2Reduce the differenceQuick changeReliability increasing modificationsSolid-state devicesCapacitanceLine resistance

An address signal is transferred from an address bus transmitting an address from an address generation circuit, to a real address bus connecting to a decoder for decoding an applied address signal, via a branch node, a branch address bus and contacts. The real address bus and the branch address bus are electrically connected at a plurality of points using the contacts. The branch address bus functions as a lining or backing signal line to the real address bus, and a line resistance and line capacitance of the real address bus can be equivalently reduced. A variation in signal propagation delay over an entire decoding circuits is suppressed.

Owner:RENESAS TECH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com