Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1080results about "Dielectric/insulating layers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

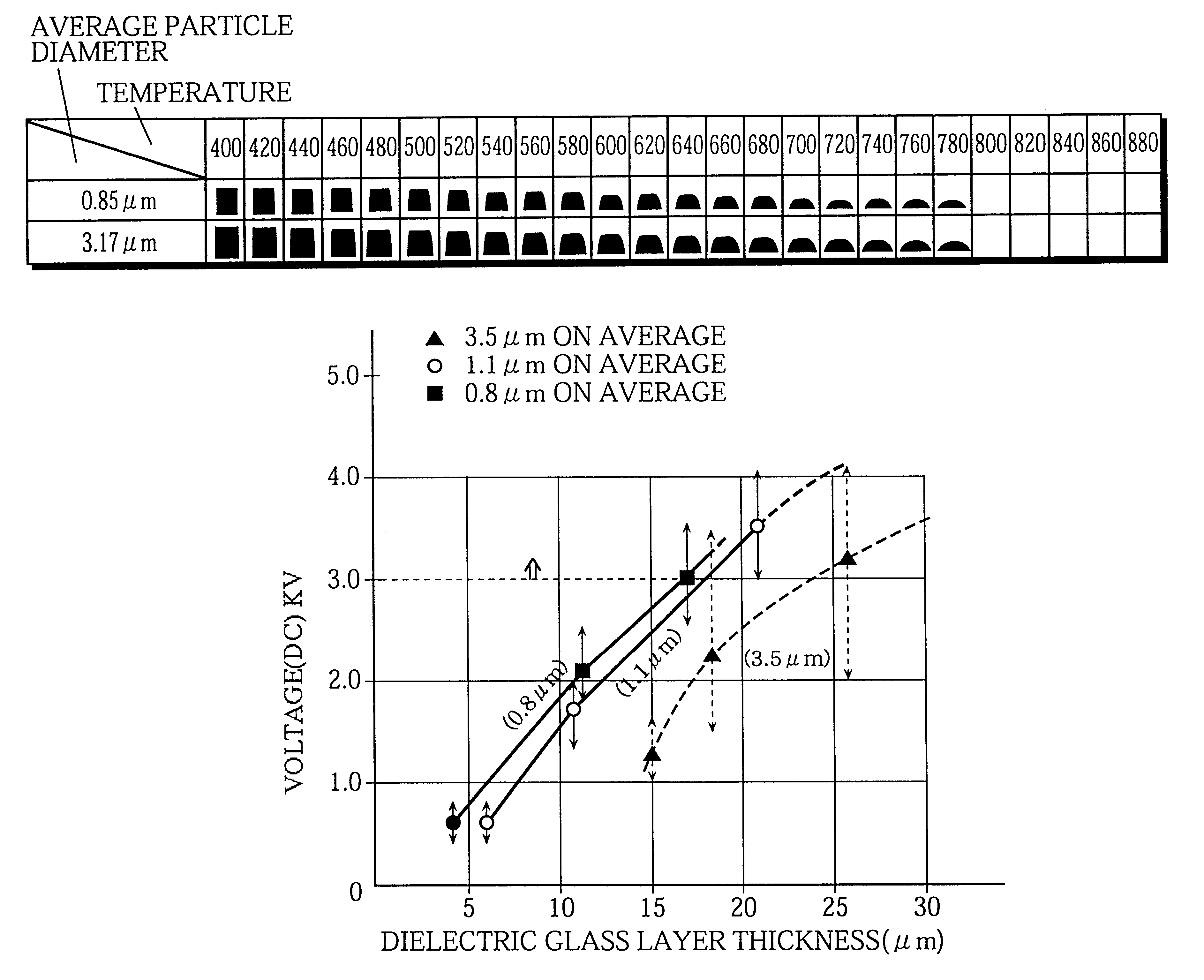

Manufacturing method of plasma display panel that includes adielectric glass layer having small particle sizes

InactiveUS6439943B1Alternating current plasma display panelsVessels or leading-in conductors manufactureScreen printingMetallurgy

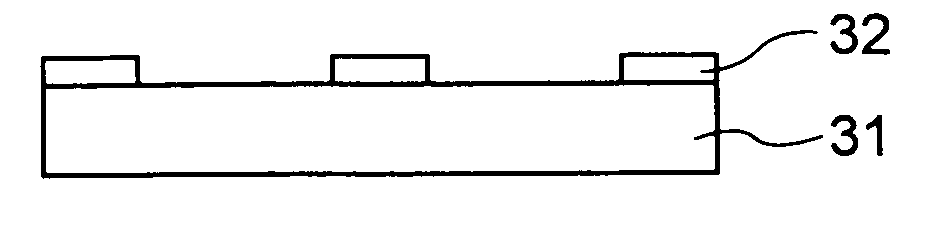

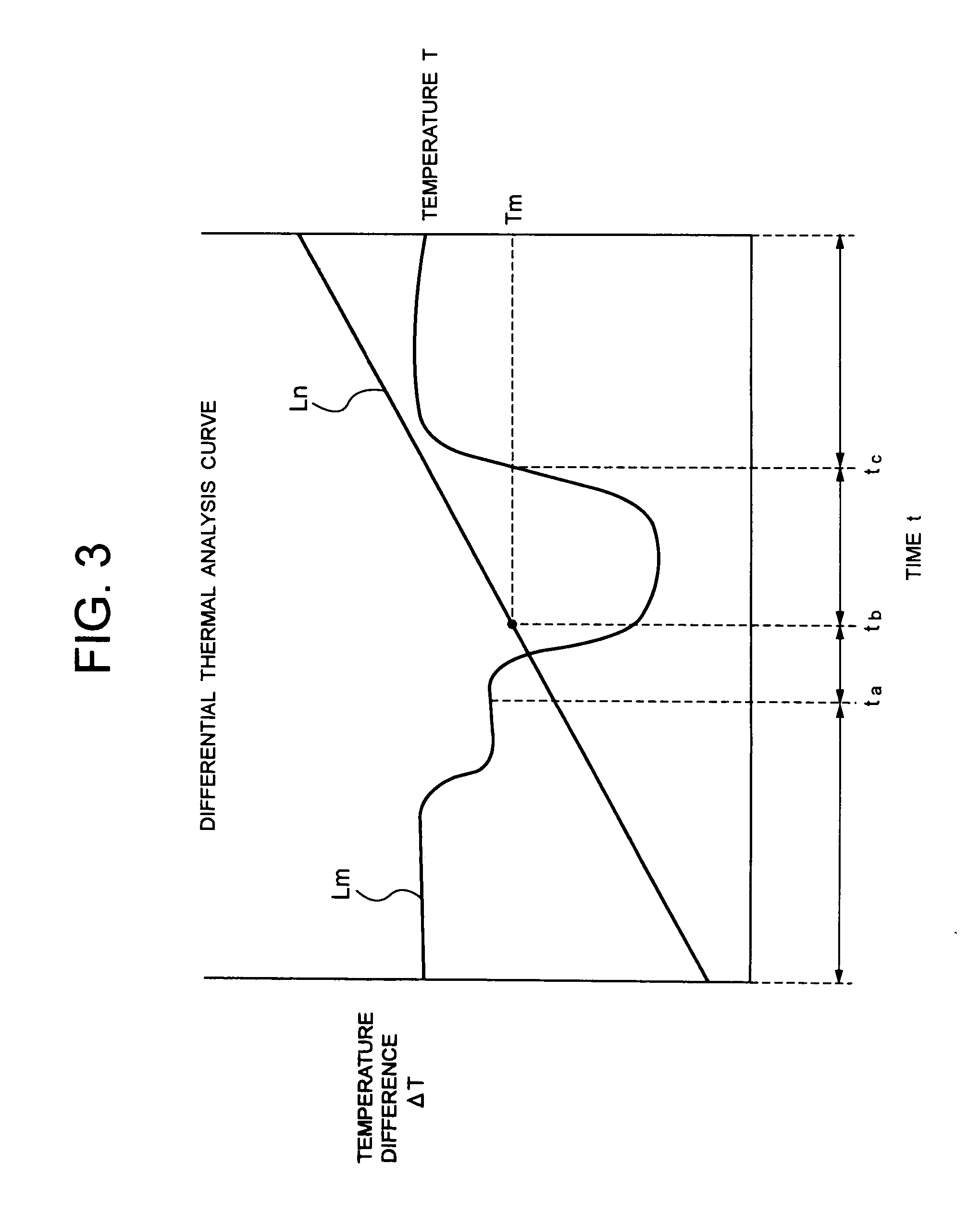

The object of the present invention is to provide a high-intensity, reliable plasma display panel even when the cell structure is fine by resolving the problems such as a low visible light transmittance and low voltage endurance of a dielectric glass layer. The object is realized by forming the dielectric glass layer in the manner given below. A glass paste including a glass powder is applied on the front glass substrate or the back glass substrate, according to a screen printing method, a die coating method, a spray coating method, a spin coating method, or a blade coating method, on each of which electrodes have been formed, and the glass powder in the applied glass paste is fired. The average particle diameter of the glass powder is 0.1 to 1.5 mum and the maximum particle diameter is equal to or smaller than three times the average particle diameter.

Owner:PANASONIC CORP

Glass composition and its applications

InactiveUS20090199897A1Reduce the temperatureLow air tightness requirementsConductive layers on insulating-supportsSustain/scan electrodesVanadium oxideMaterials science

Owner:HITACHI POWDERED METALS COMPANY

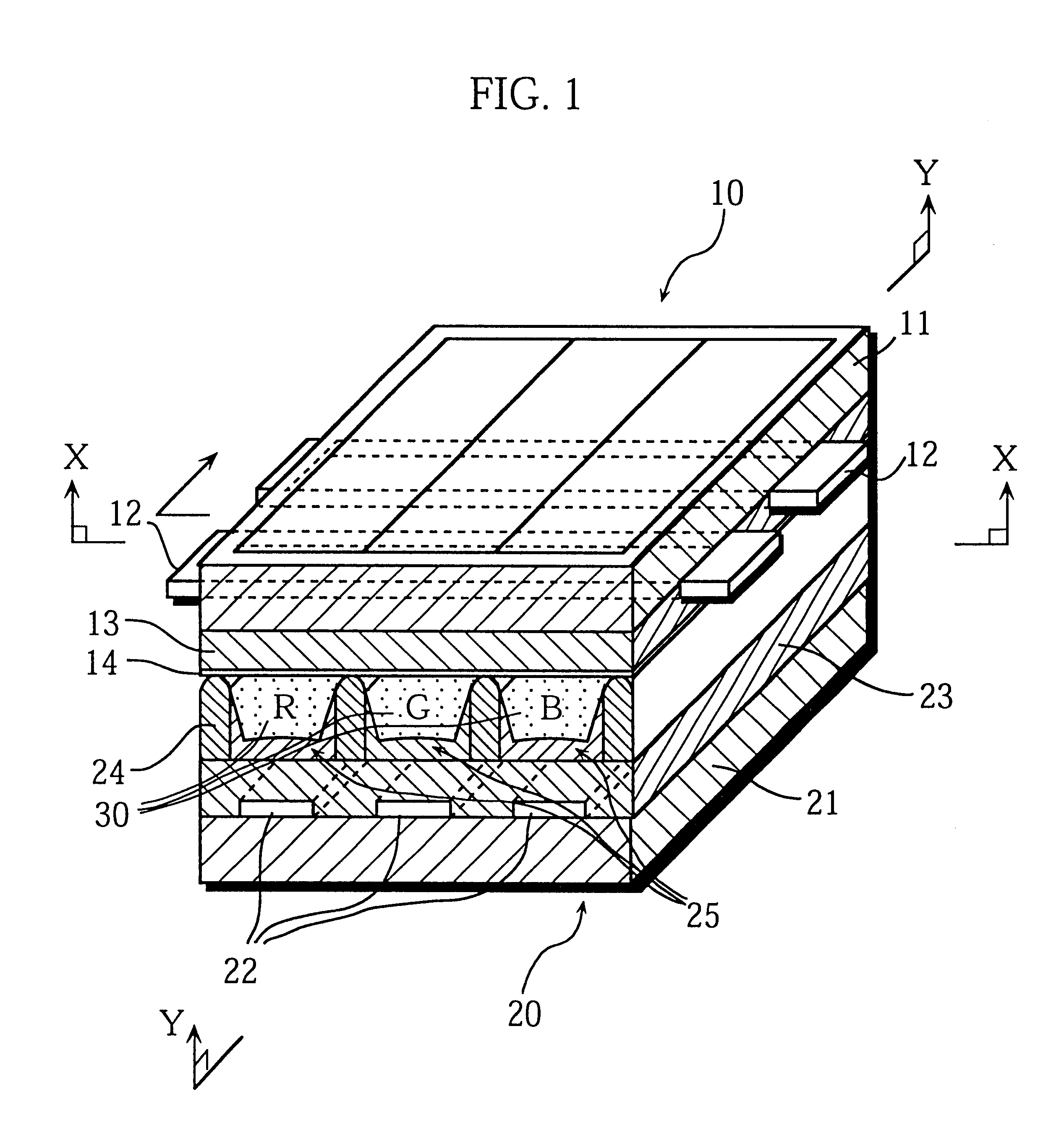

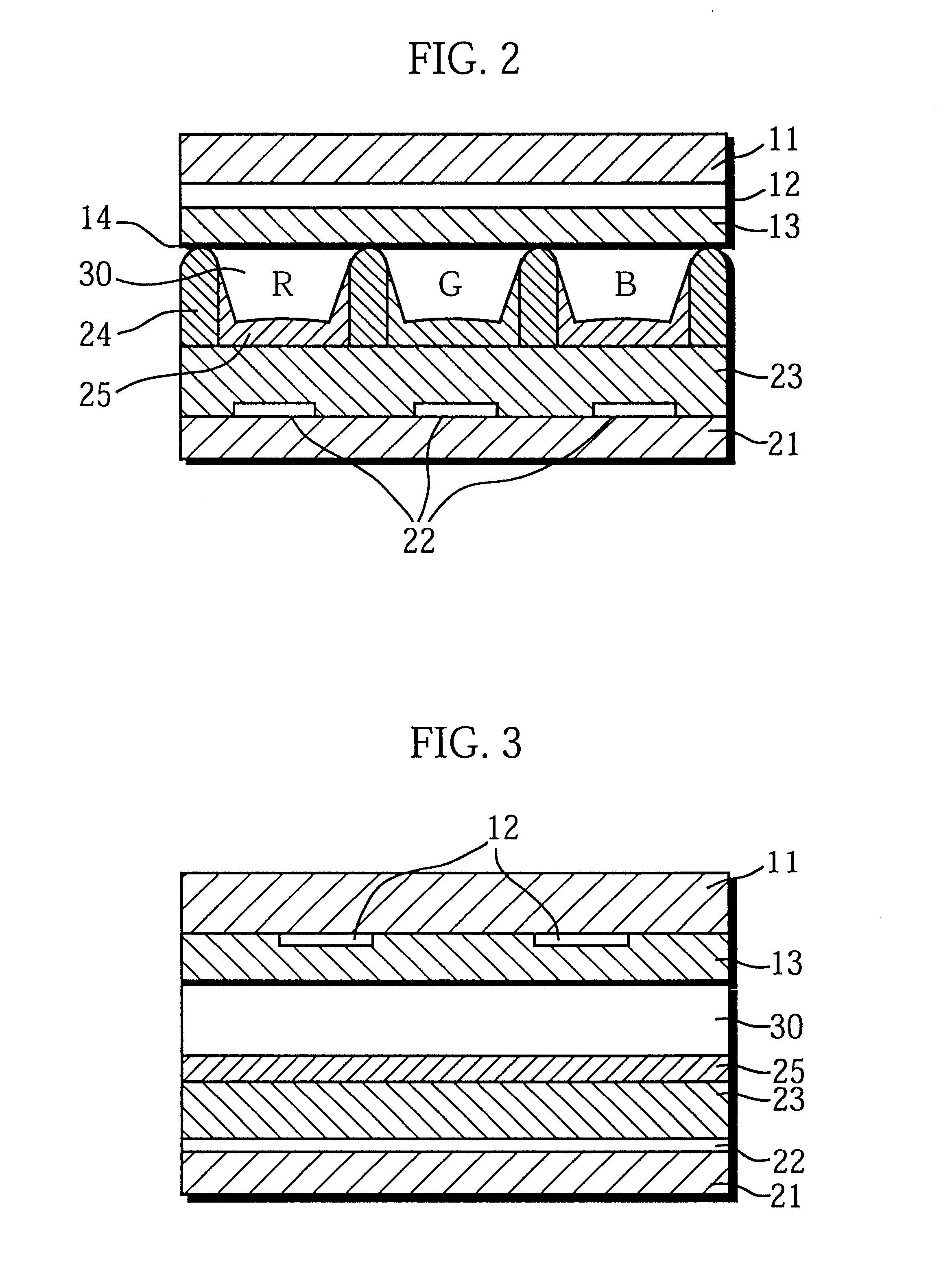

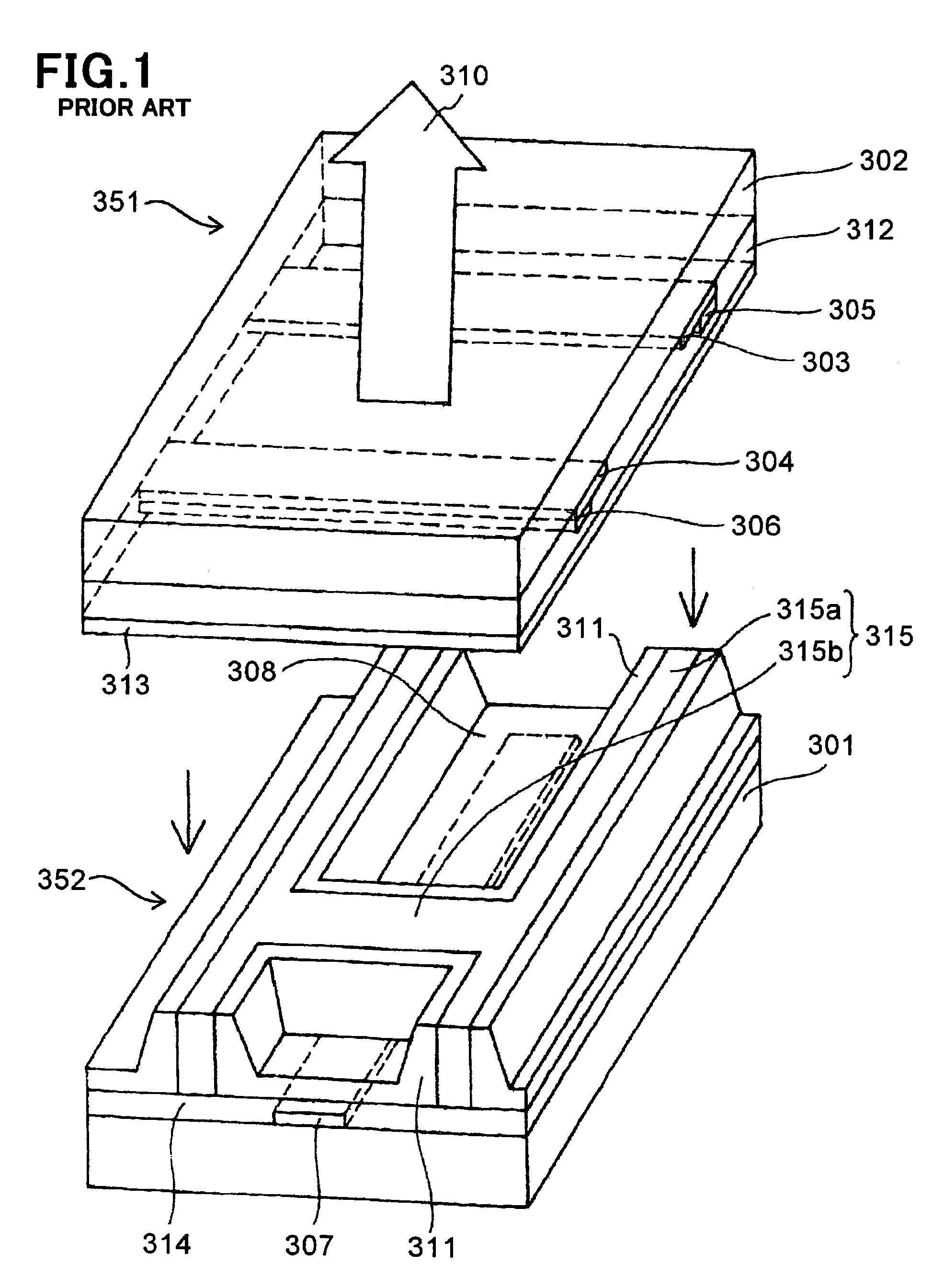

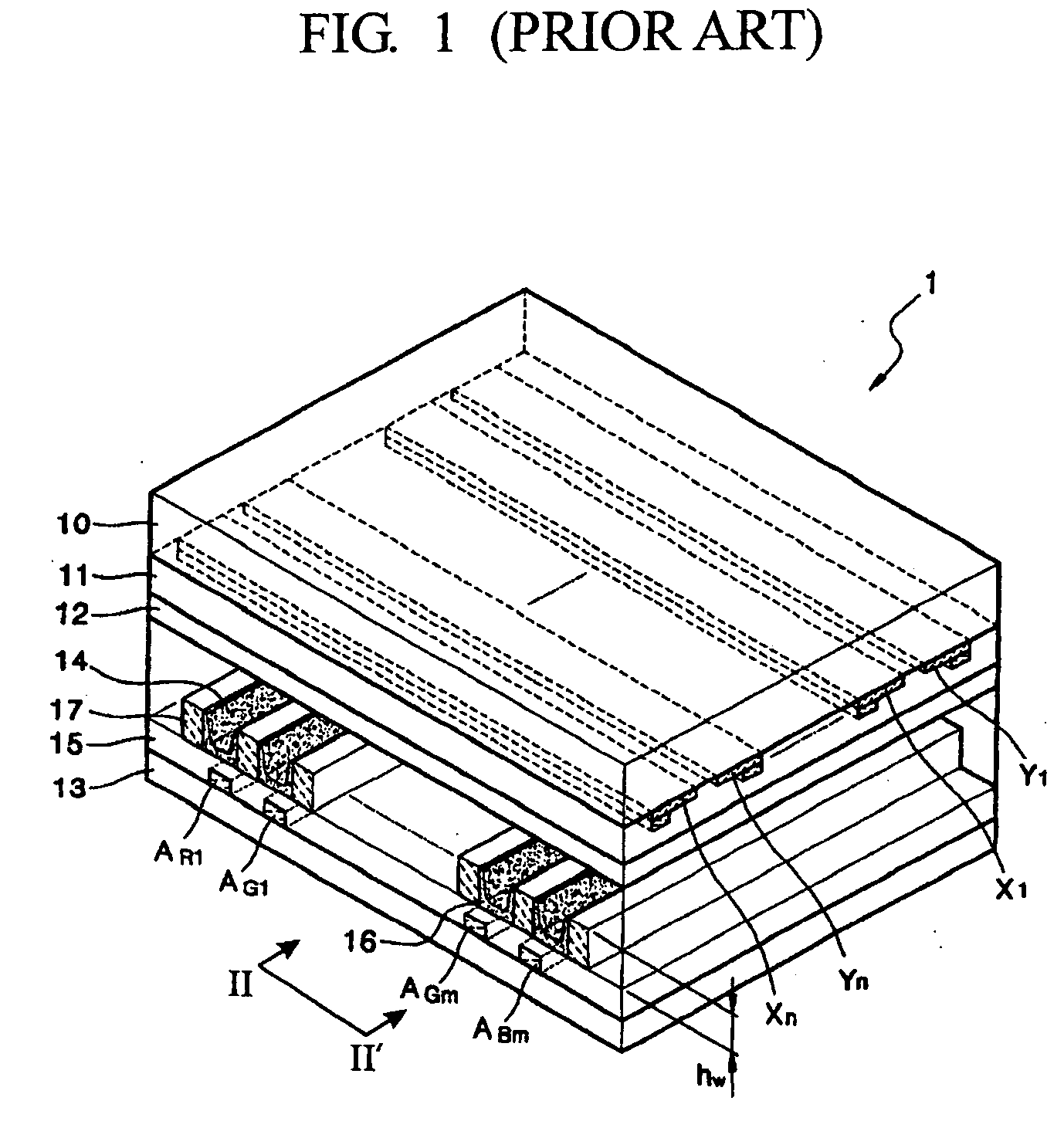

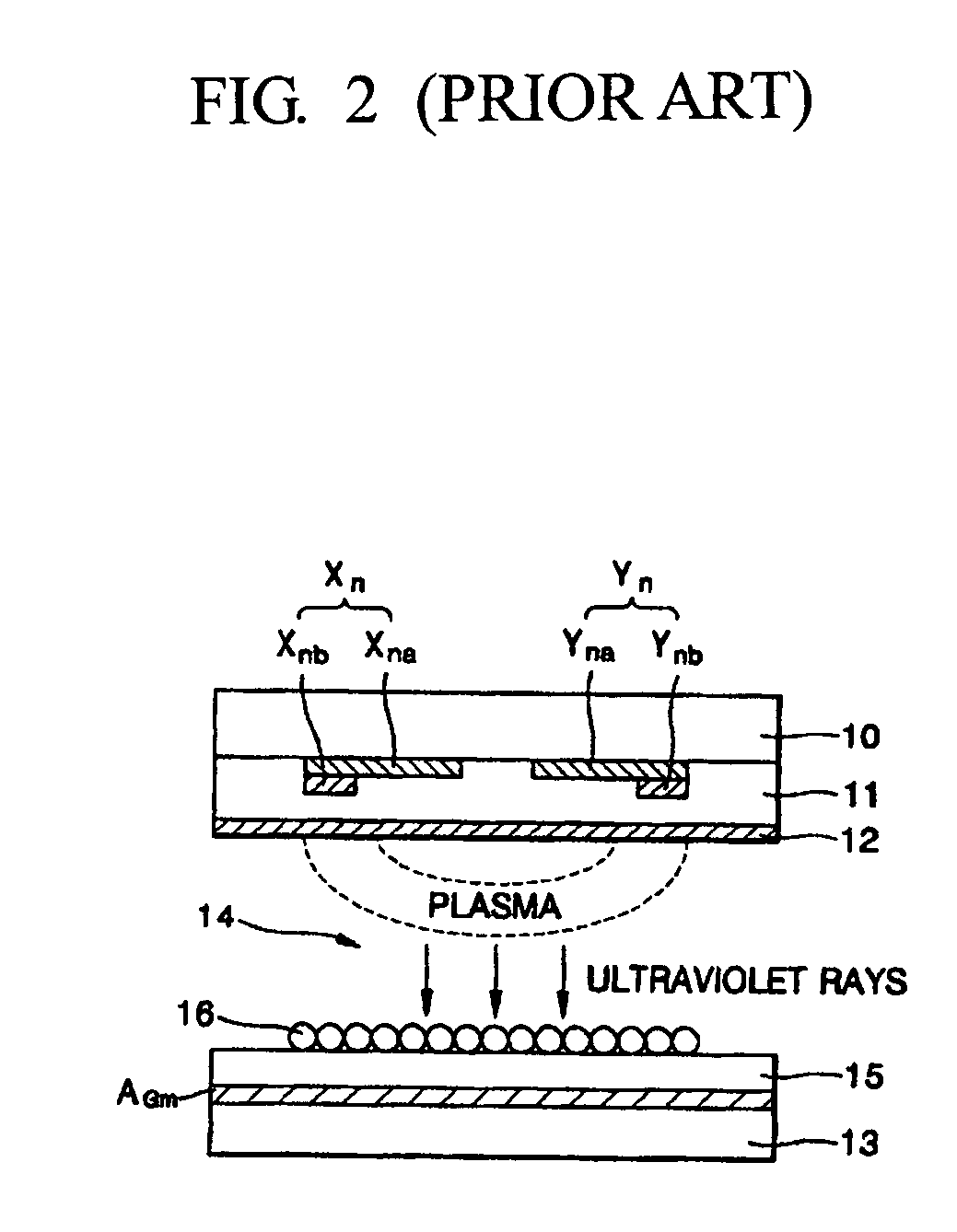

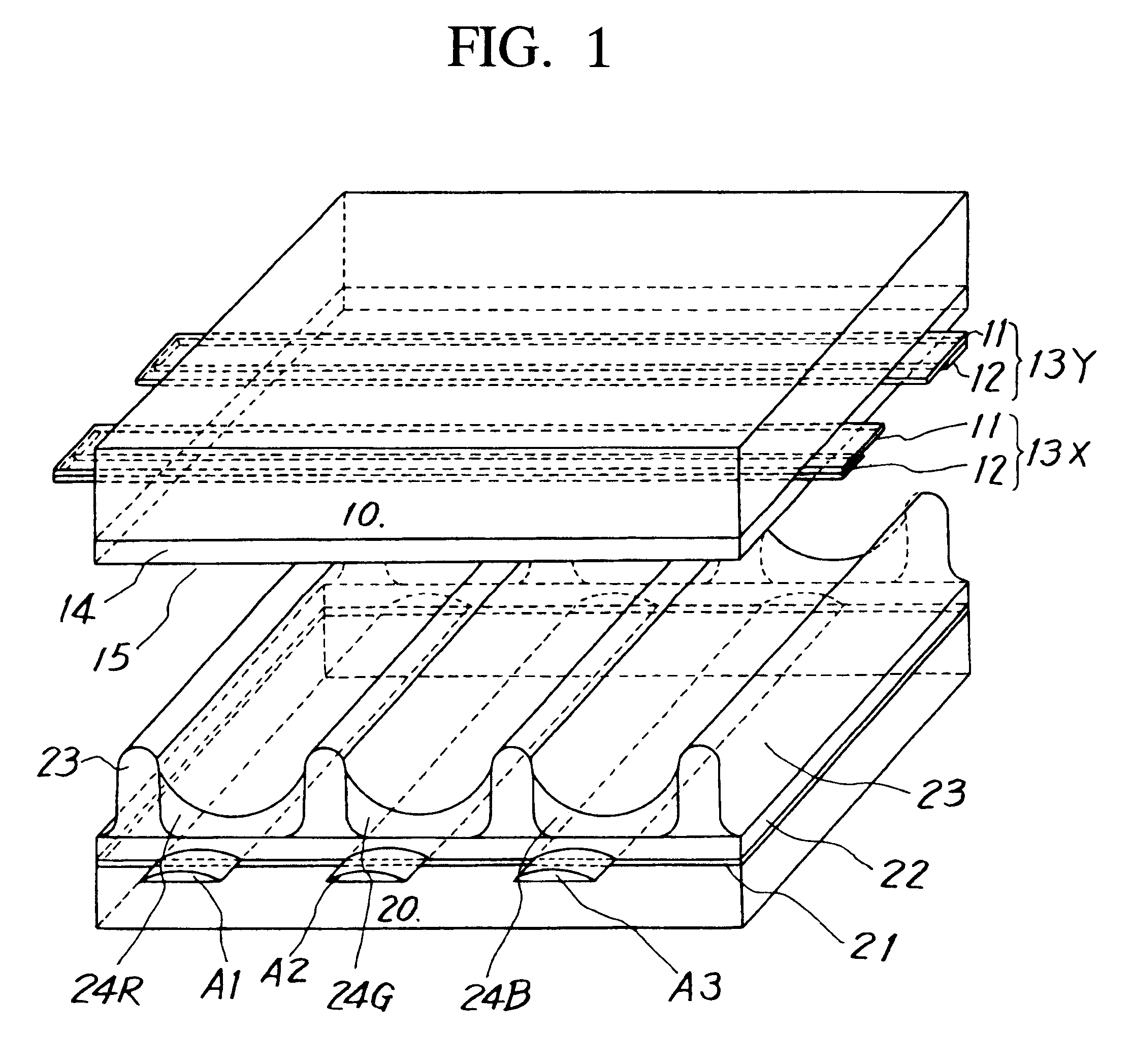

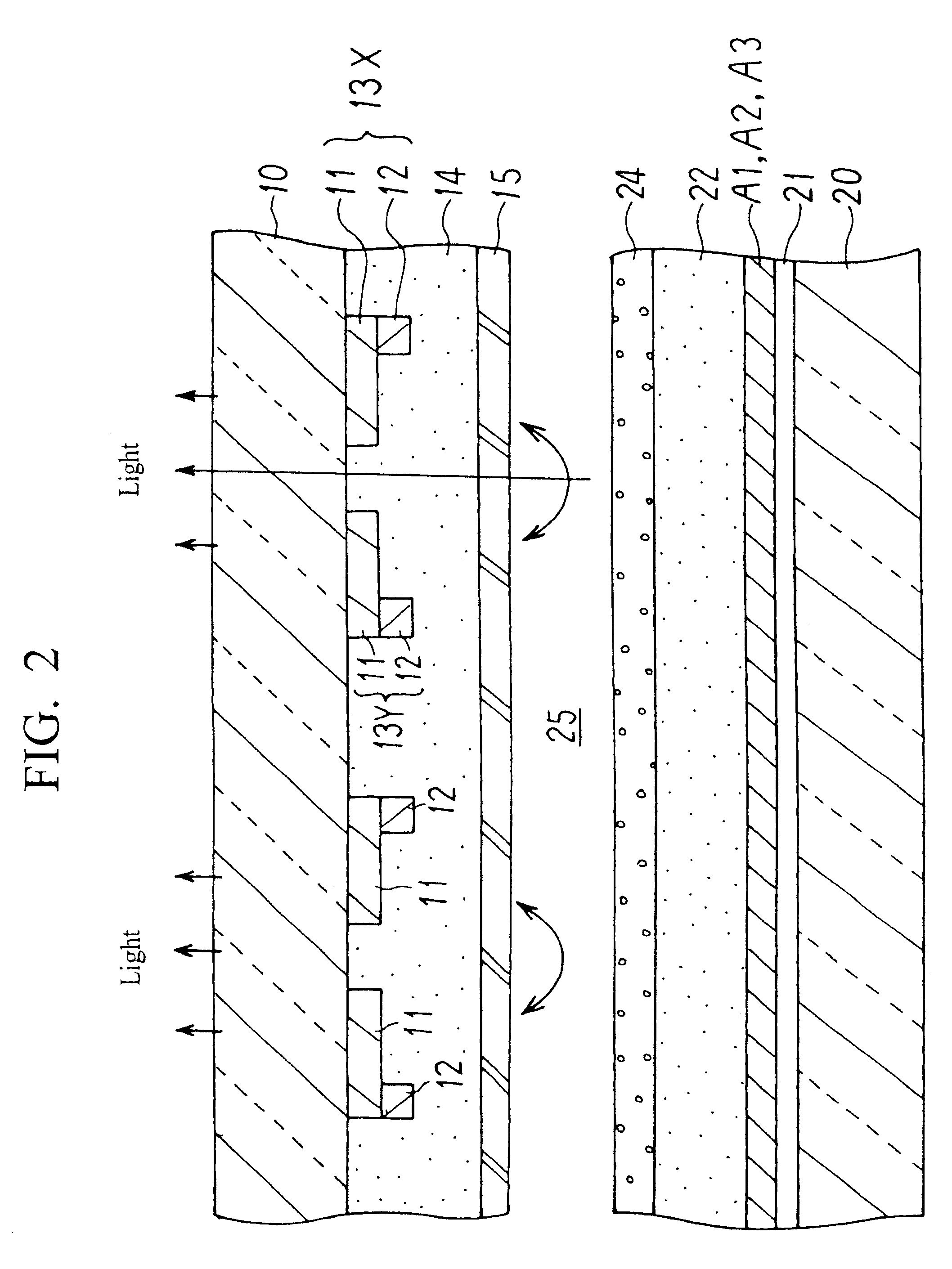

Plasma display panel

InactiveUS7239085B2Suppress brightness changesReduce brightnessAddress electrodesSustain/scan electrodesFluorescencePhosphor

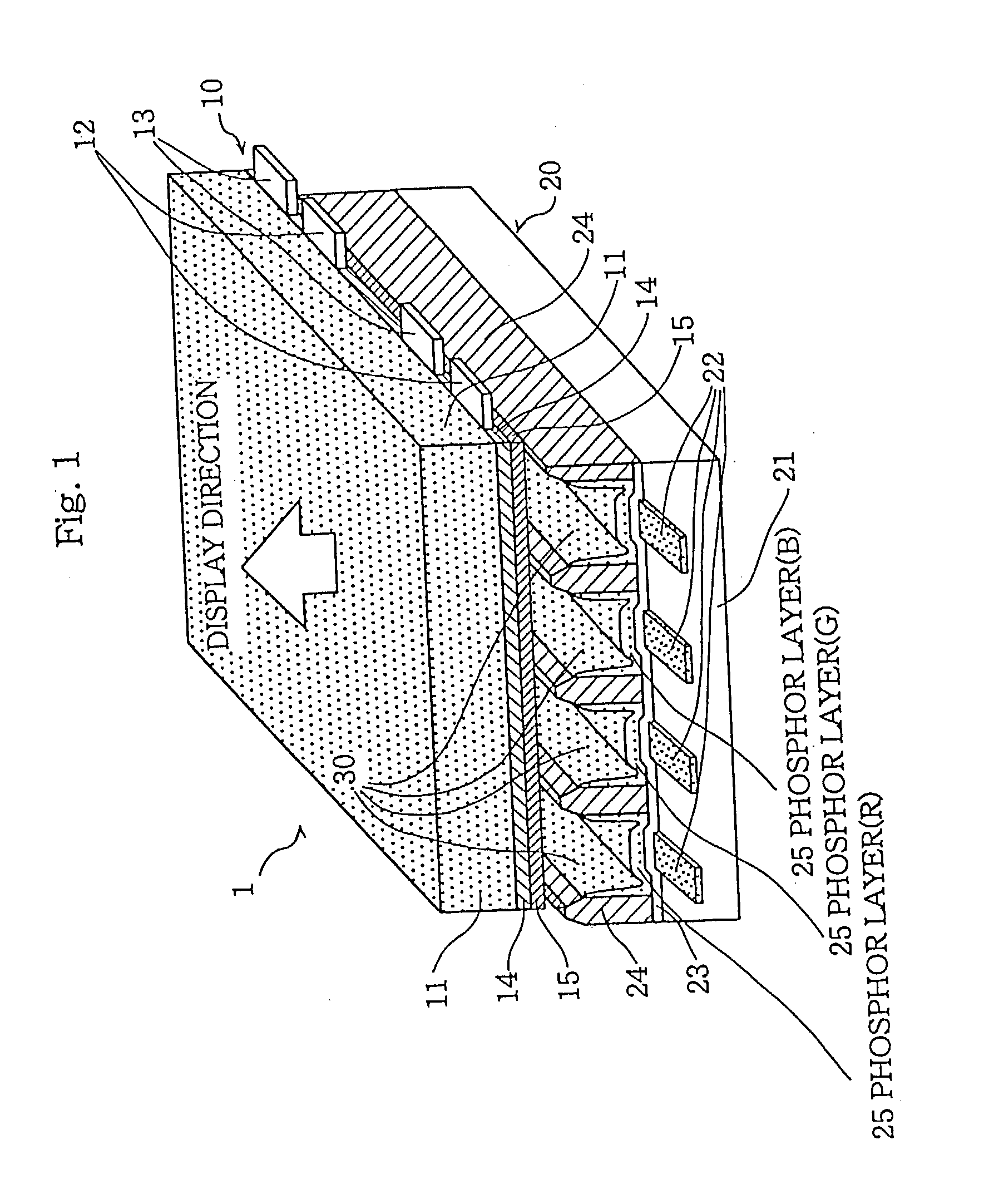

A plasma display panel includes a first substrate, and a second substrate facing the first substrate. The first substrate includes a transparent substrate, a scanning electrode and a common electrode both formed on the transparent substrate, and a dielectric layer covering the transparent substrate, the scanning electrode and the common electrode therewith. The second substrate includes an electrically insulating substrate, data electrodes formed on the electrically insulating substrate, partition walls formed on the electrically insulating substrate, and a phosphor layer covering the electrically insulating substrate and the data electrodes therewith between adjacent partition walls. The phosphor layer includes a blue-phosphor layer composed of phosphor which emits a blue light. The blue-phosphor layer is composed of a mixture of two or more phosphors each of which emits a blue light and has an initial brightness and variation of brightness with the lapse of time both different from one another.

Owner:PANASONIC CORP

Glass composition and paste composition suitable for a plasma display panel, and plasma display panel

InactiveUS20050242725A1Reduce residual stressAlternating current plasma display panelsCoatingsTransmittanceTransparent conducting film

A glass composition that is lead-free, and that, when used in a PDP, suppresses coloration of a dielectric layer, a transparent conductive film and a glass substrate, and suppresses reduction in transmittance of the dielectric layer. The glass composition is includes GeO2 0.1-20 wt %, B2O3 3-35 wt %, ZnO 4-45 wt %, Bi2O3 10-80 wt %, is free of PbO, and SiO2 content is not more than 0.5 wt %. It is preferable to further include in the glass composition Al2O3 up to 8 wt % and at least one selected from the group consisting of MgO, CaO, SrO, and BaO, up to 20 wt %.

Owner:PANASONIC CORP

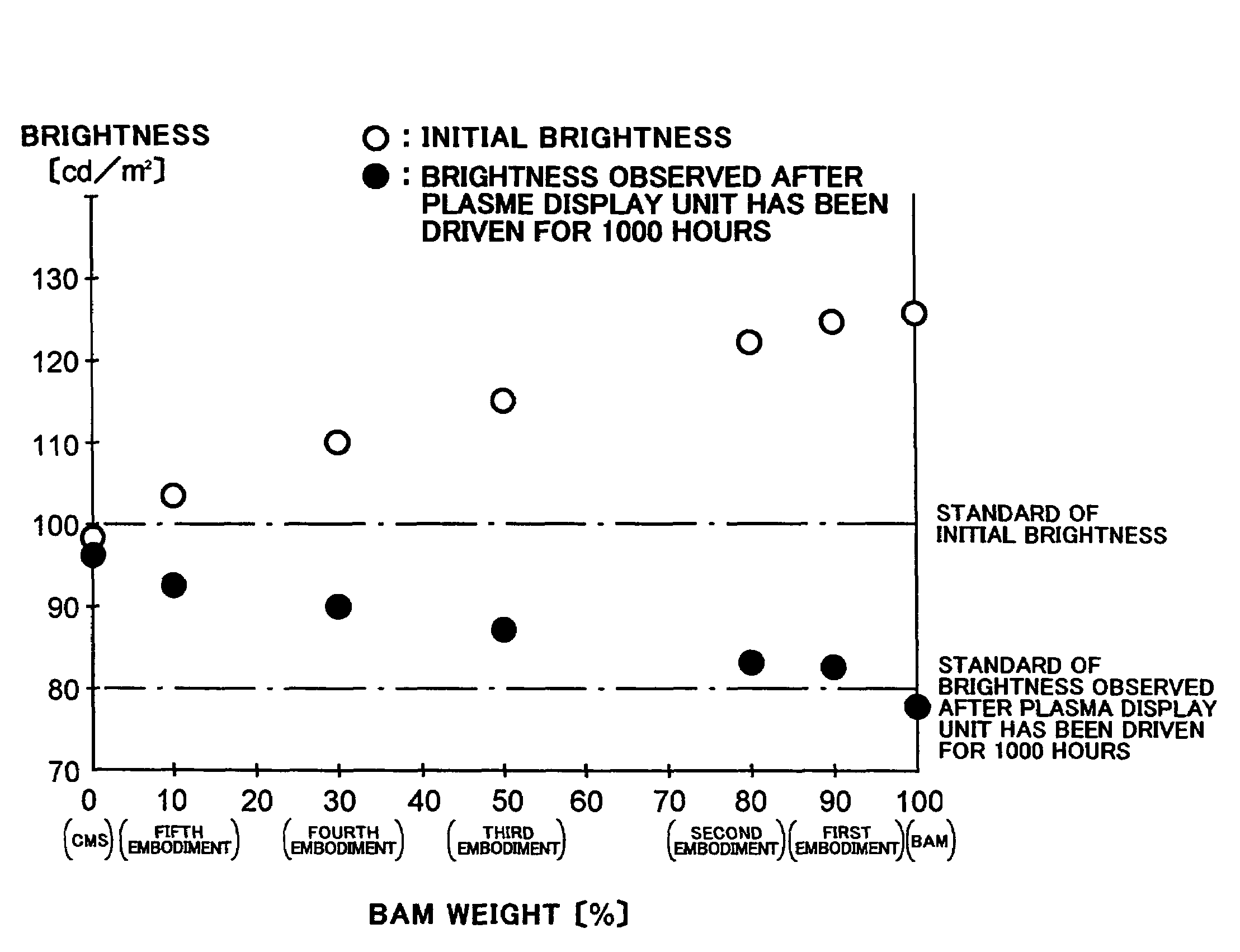

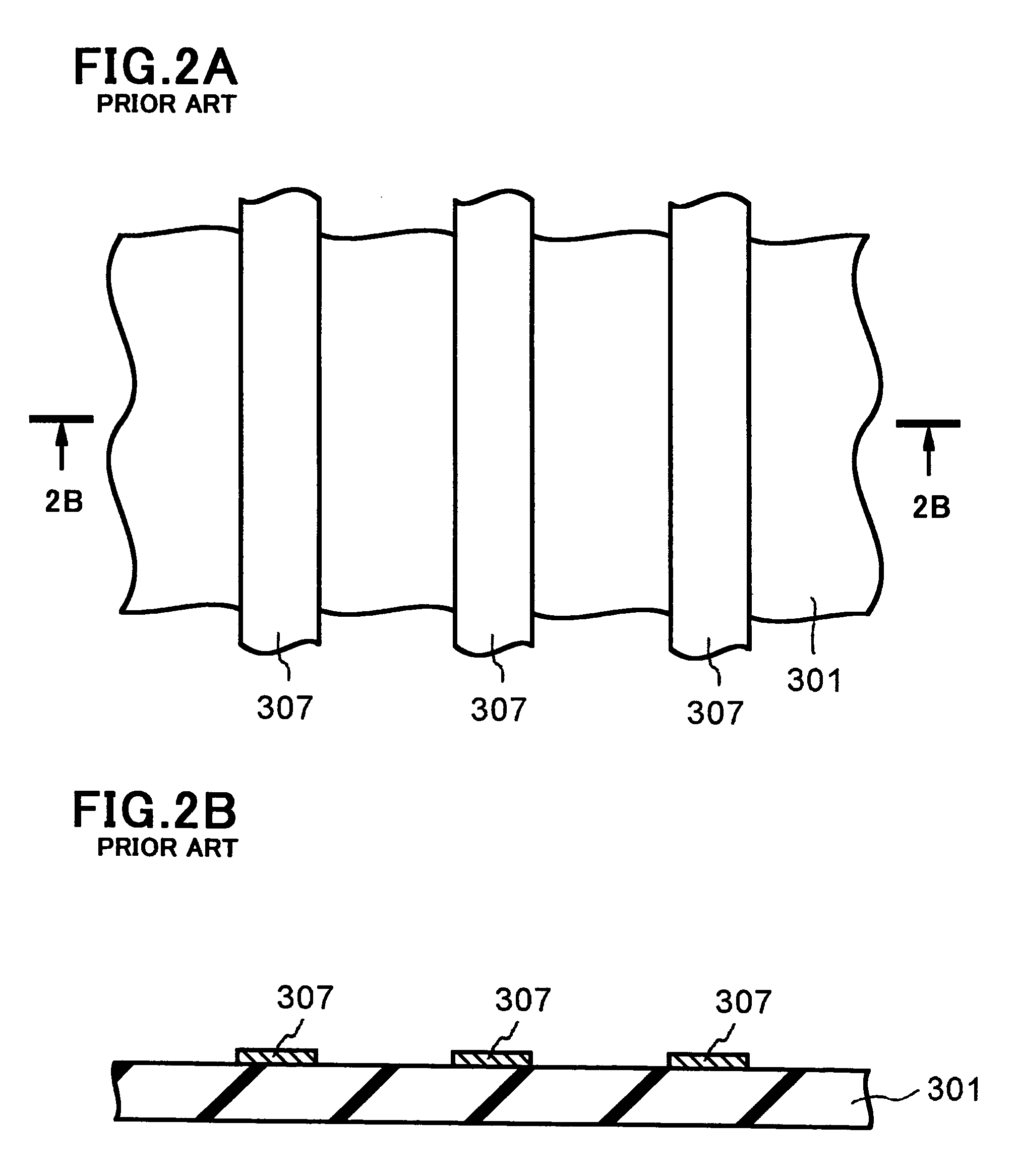

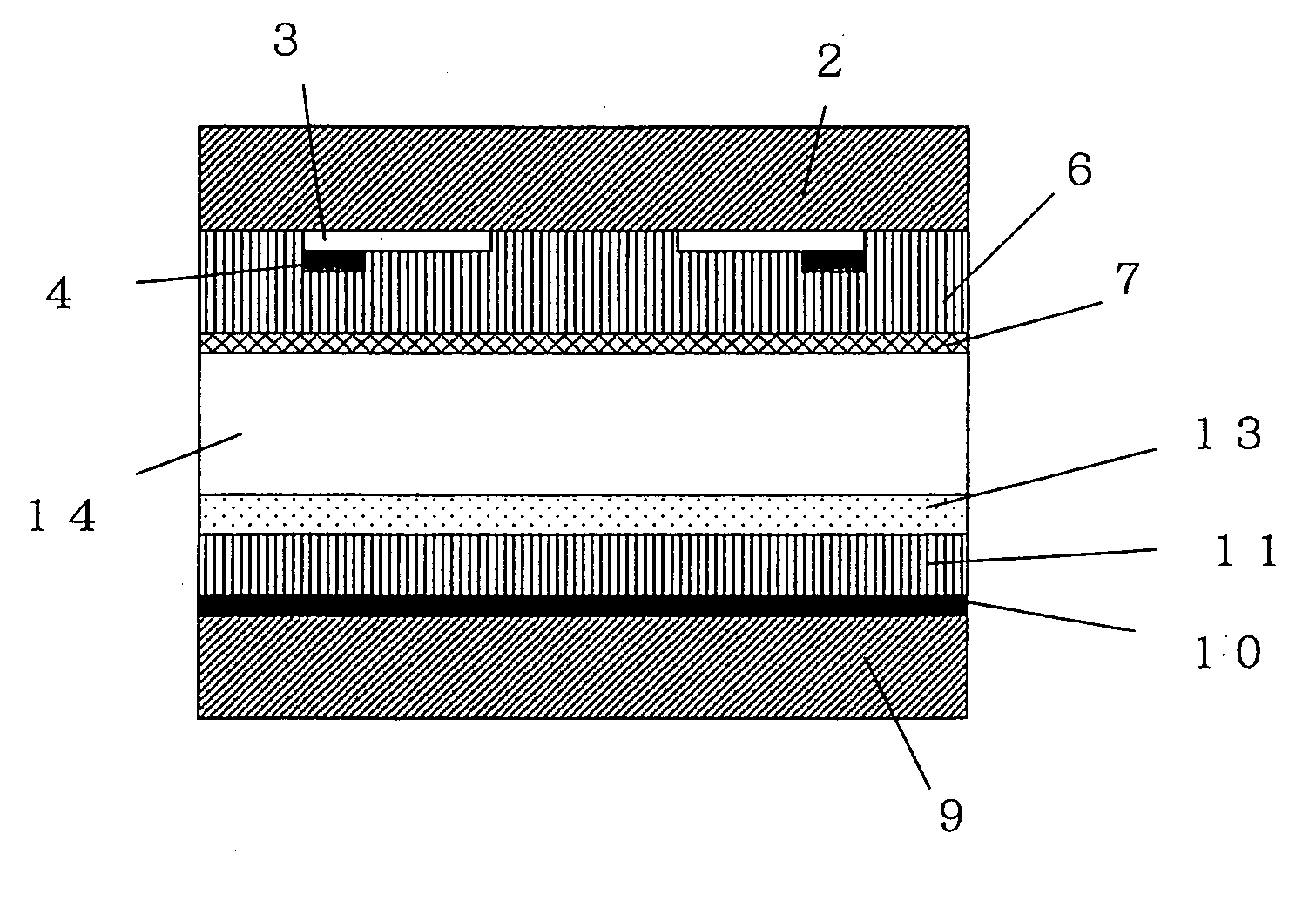

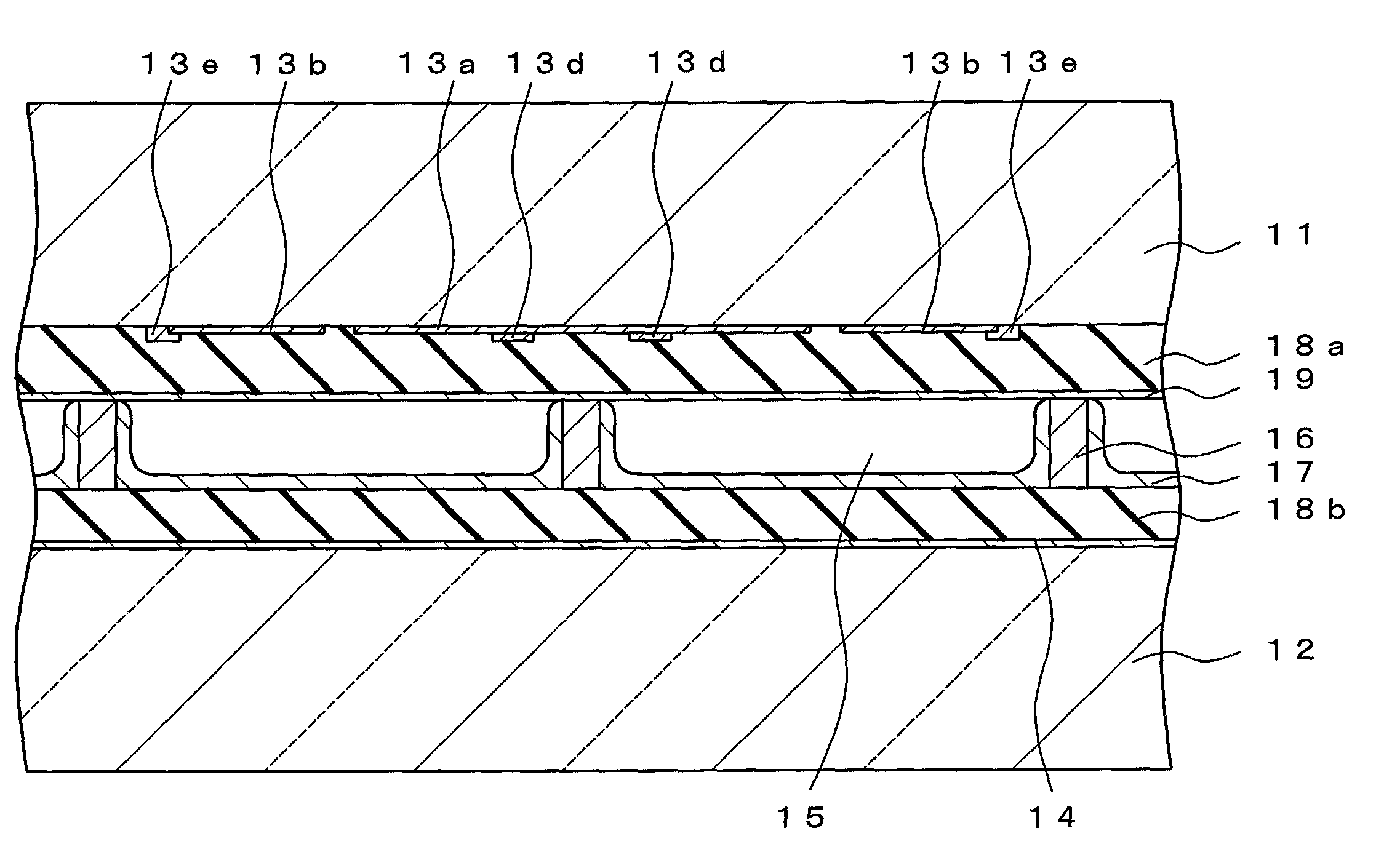

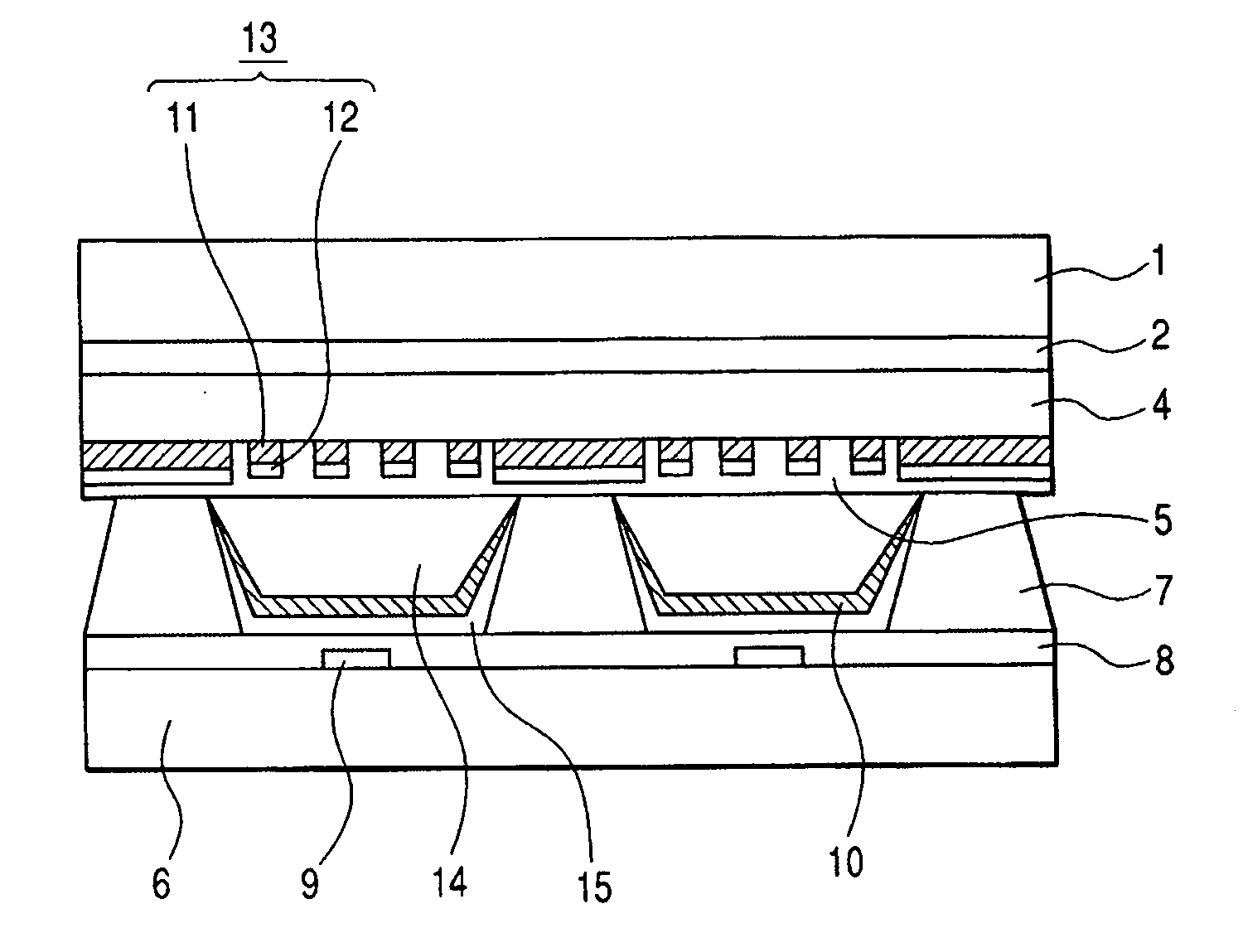

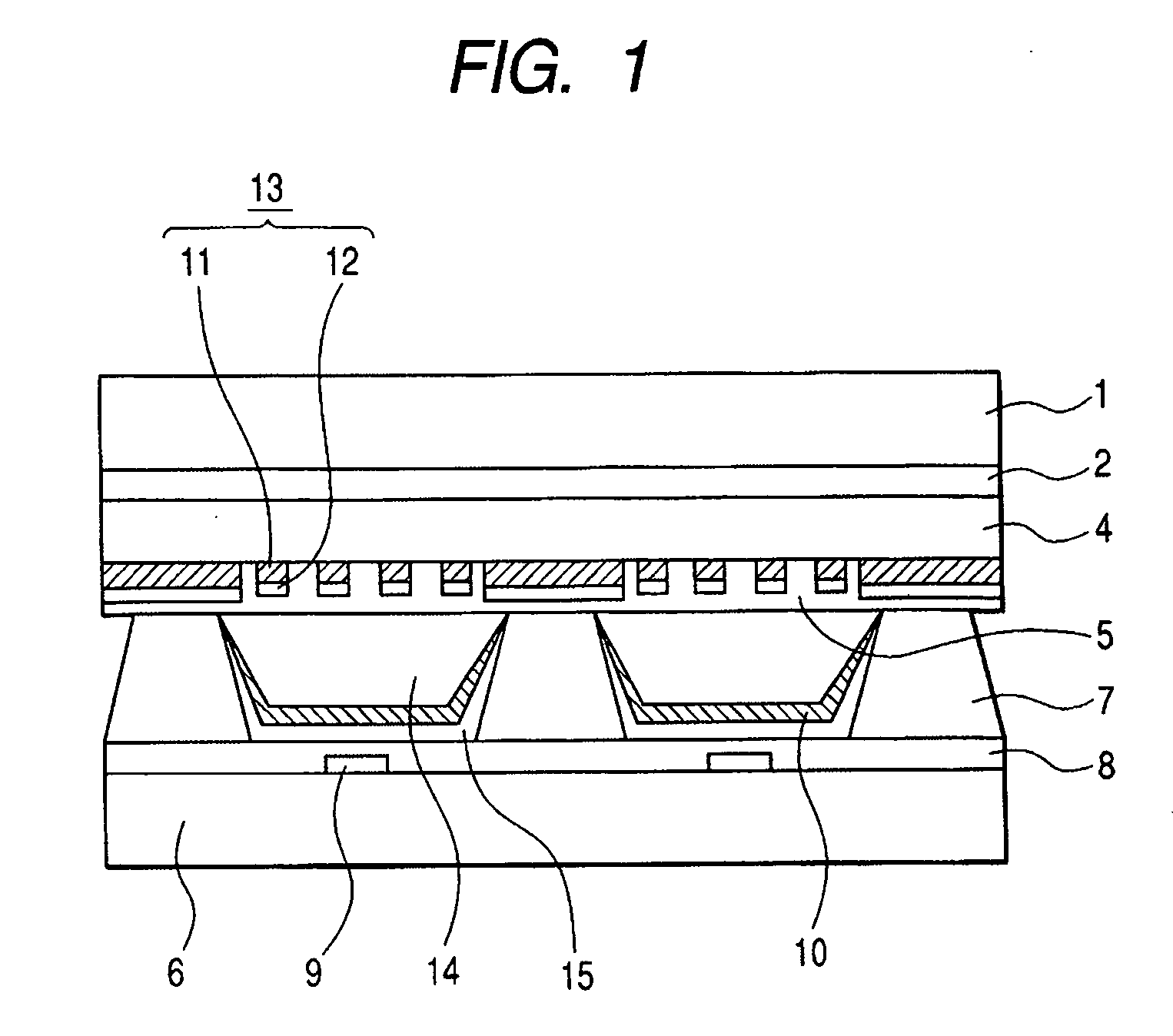

Plasma display panel and process for manufacturing its substrate structure

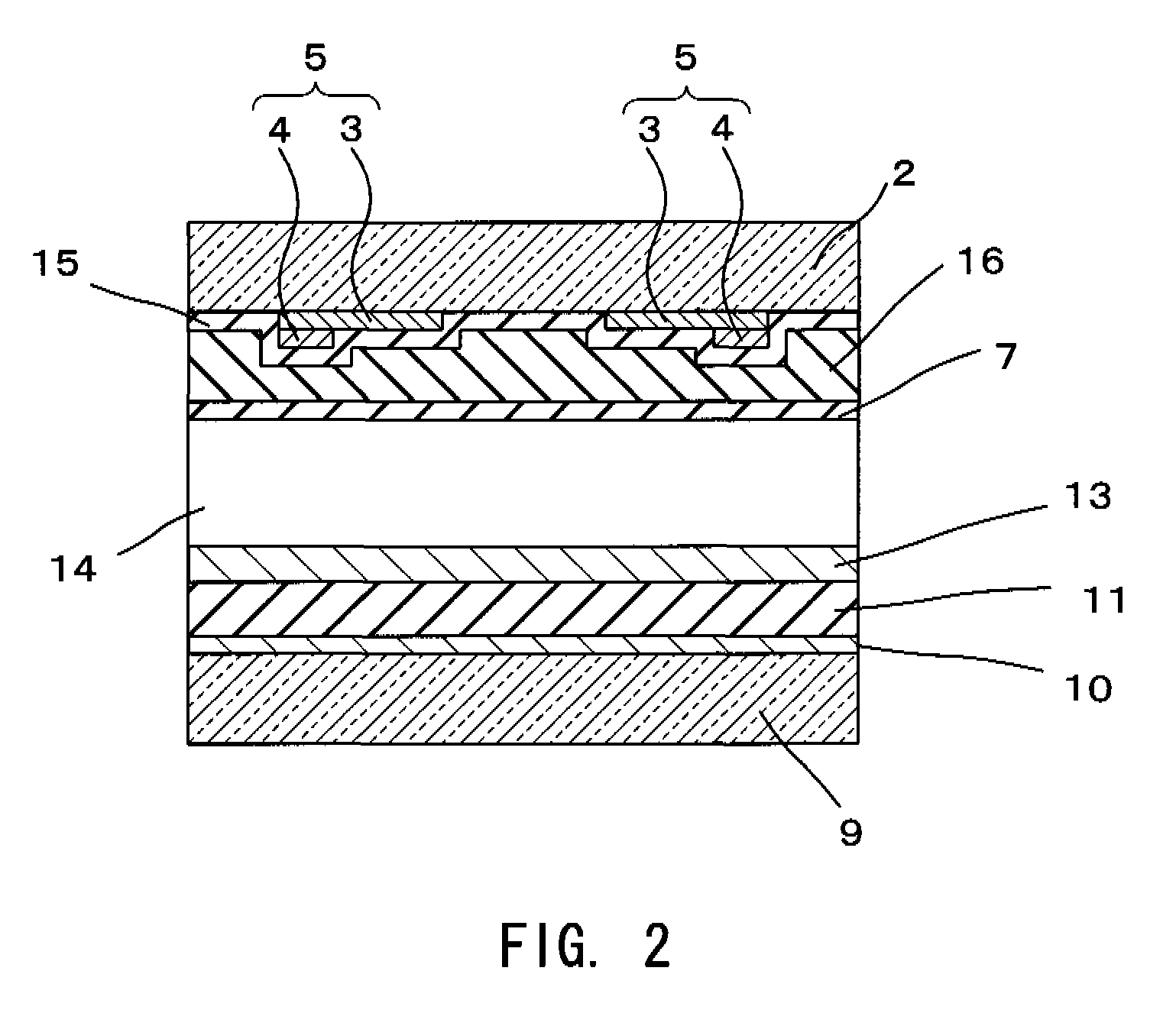

InactiveUS20010054871A1Improve reflectivityLow dielectric constantAlternating current plasma display panelsVessels or leading-in conductors manufactureOptoelectronicsDielectric layer

A plasma display panel includes a dielectric layer in which a filler for enhancing reflectance is dispersed. To increase luminescence efficiency, the filler consists of flakes oriented in parallel to the surface of the dielectric layer.

Owner:HITACHI PLASMA PATENT LICENSING

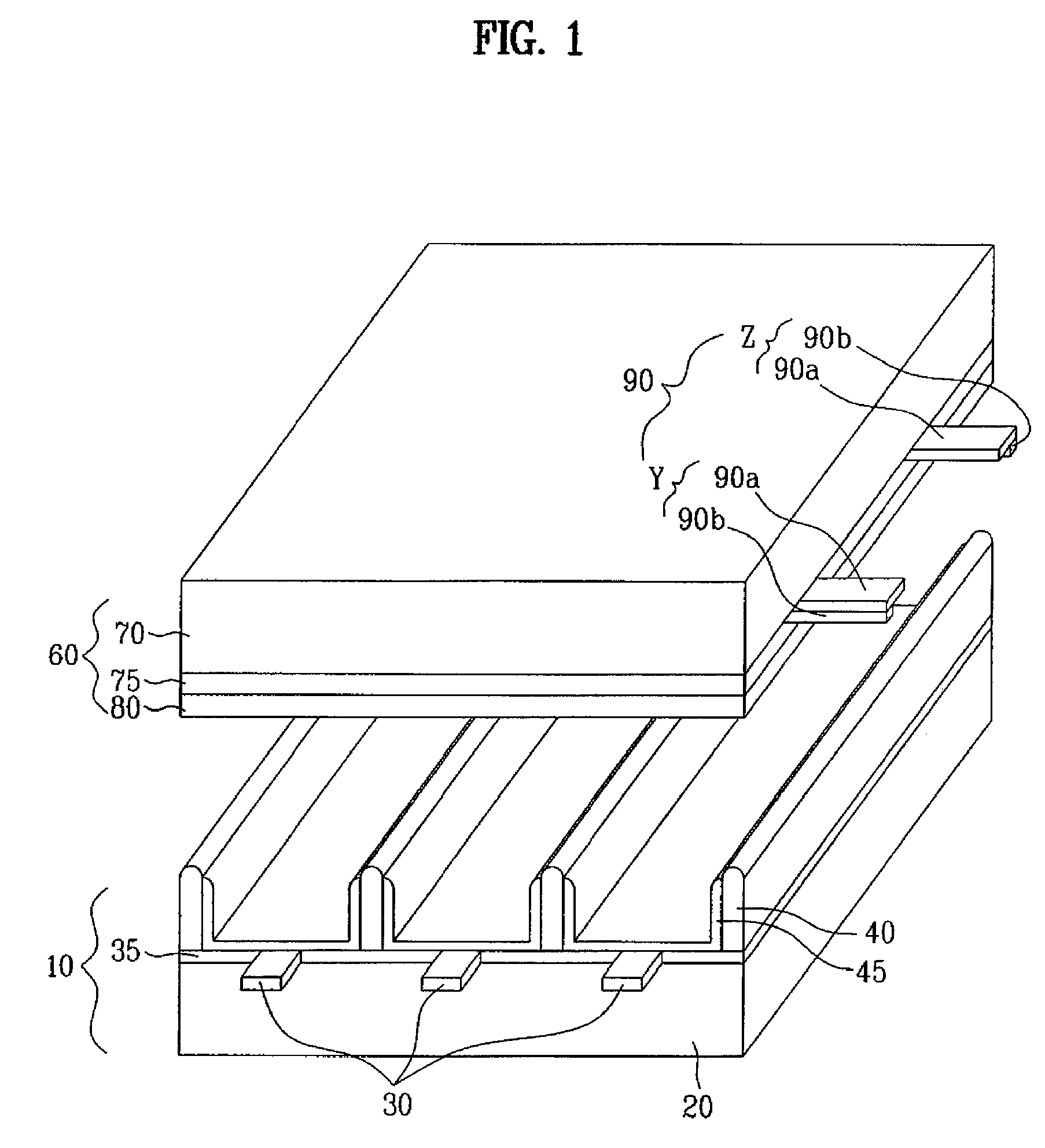

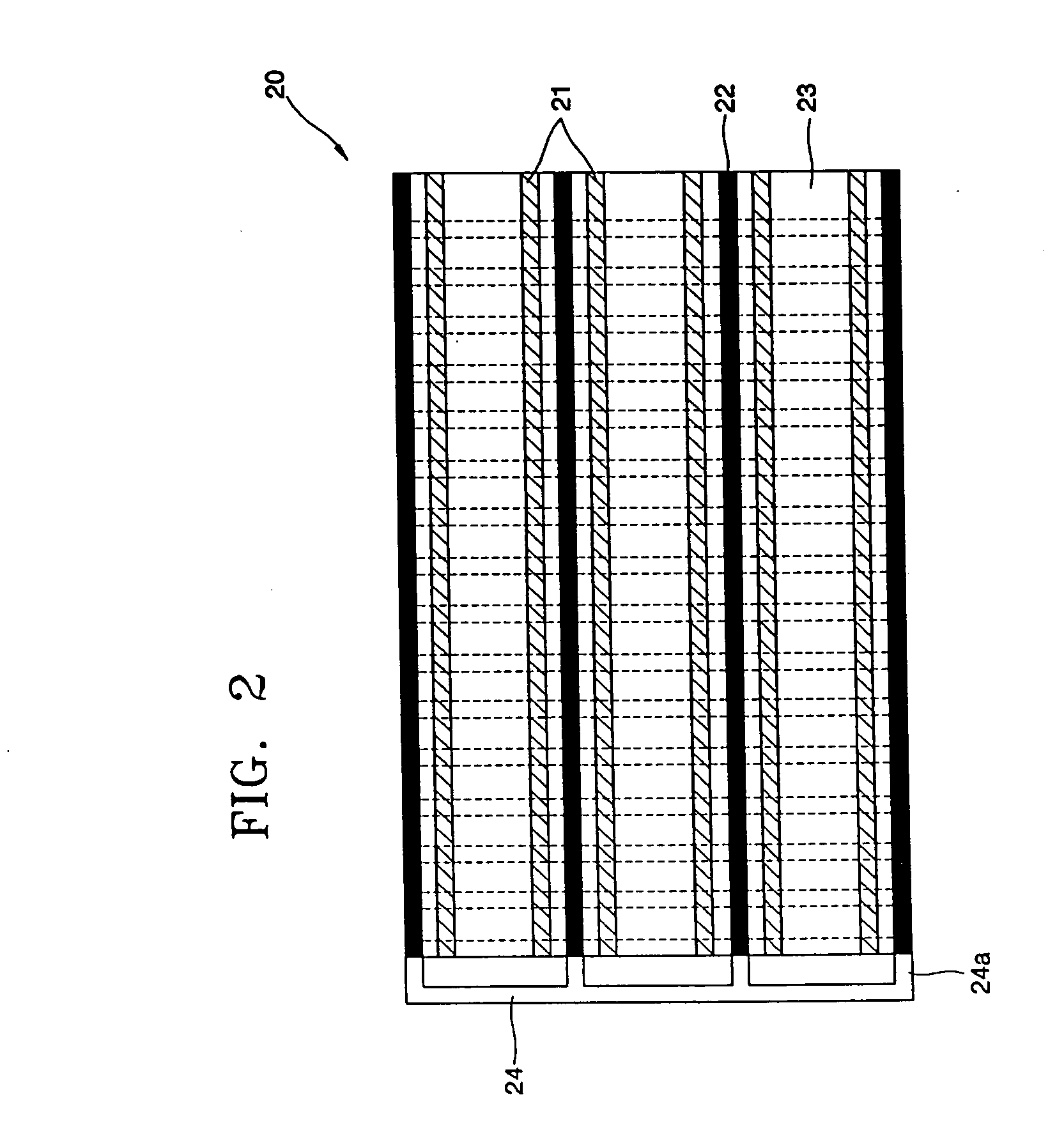

Plasma display panel

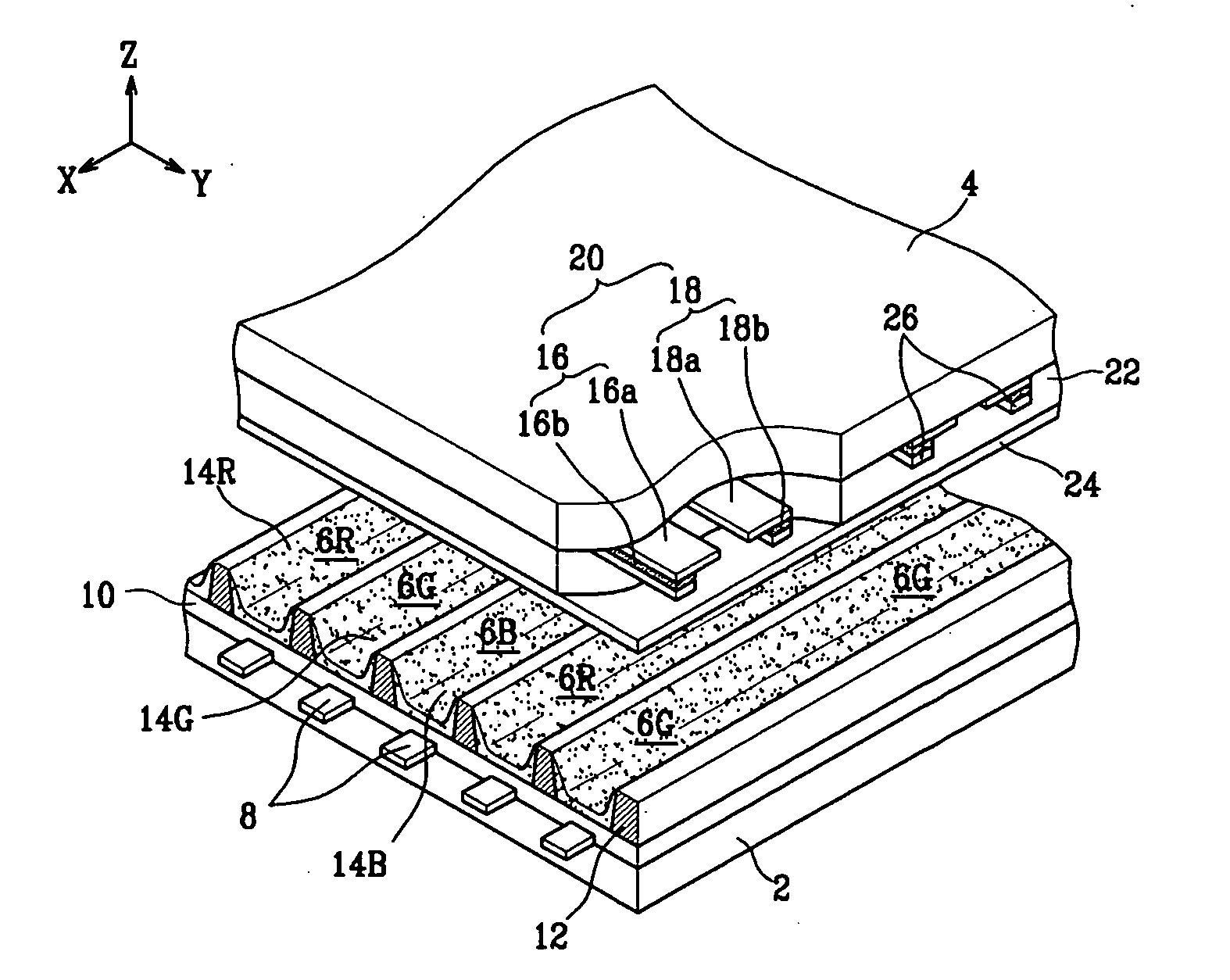

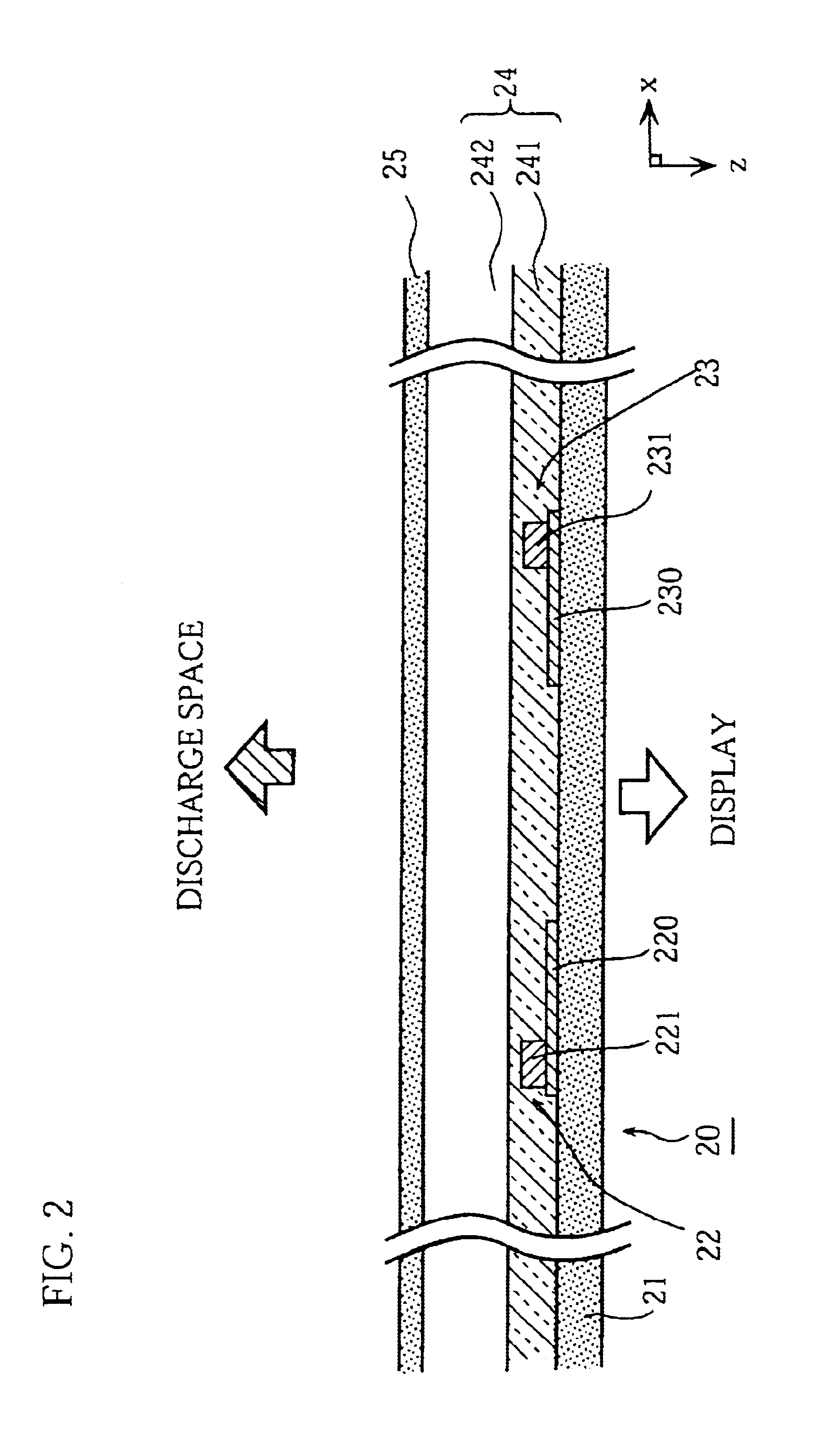

InactiveUS20050116646A1Reduce distanceIncrease speedAddress electrodesSustain/scan electrodesLow voltagePlasma display

A plasma display panel capable of being fast driven with low voltage by reducing a distance between an address electrode and a Y electrode. The plasma display panel includes a pair of substrates, discharge electrodes, and an address electrode. The substrates are arranged at a predetermined interval to face each other and form a plurality of discharge spaces between facing surfaces of the substrates. The discharge electrodes are arranged at predetermined intervals between the substrates. The address electrode is arranged a predetermined distance apart from the discharge electrodes in a direction where the substrates are arranged, and defines each of the discharge spaces in cooperation with the discharge electrodes.

Owner:SAMSUNG SDI CO LTD

Glass composition for covering electrodes and glass paste containing the same

InactiveUS20060276322A1Improve reliabilityImprove pressure resistanceSustain/scan electrodesGas discharge fillingPolymer chemistryElectrode

Owner:PANASONIC CORP

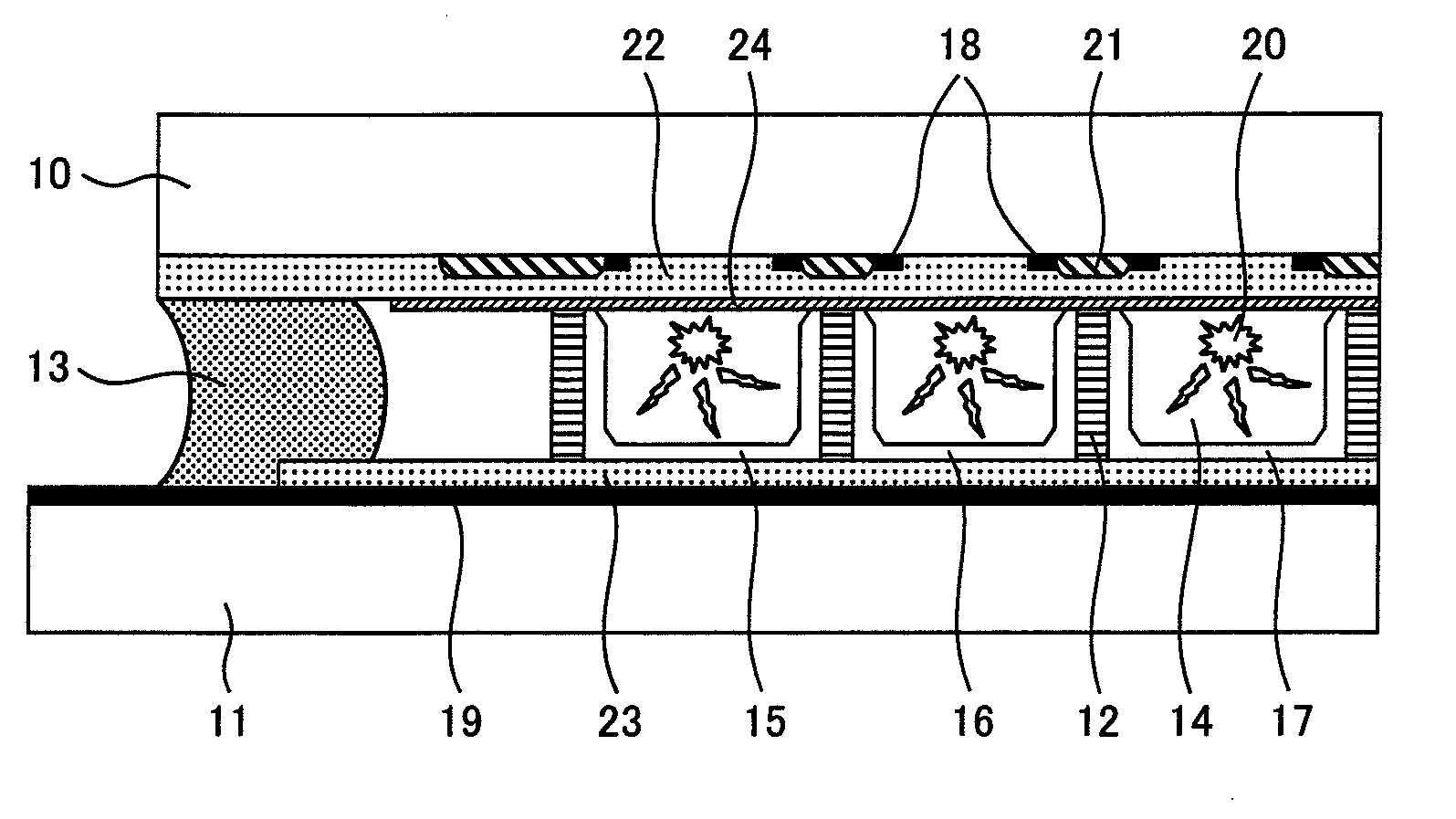

Plasma display panel and method for manufacturing the same

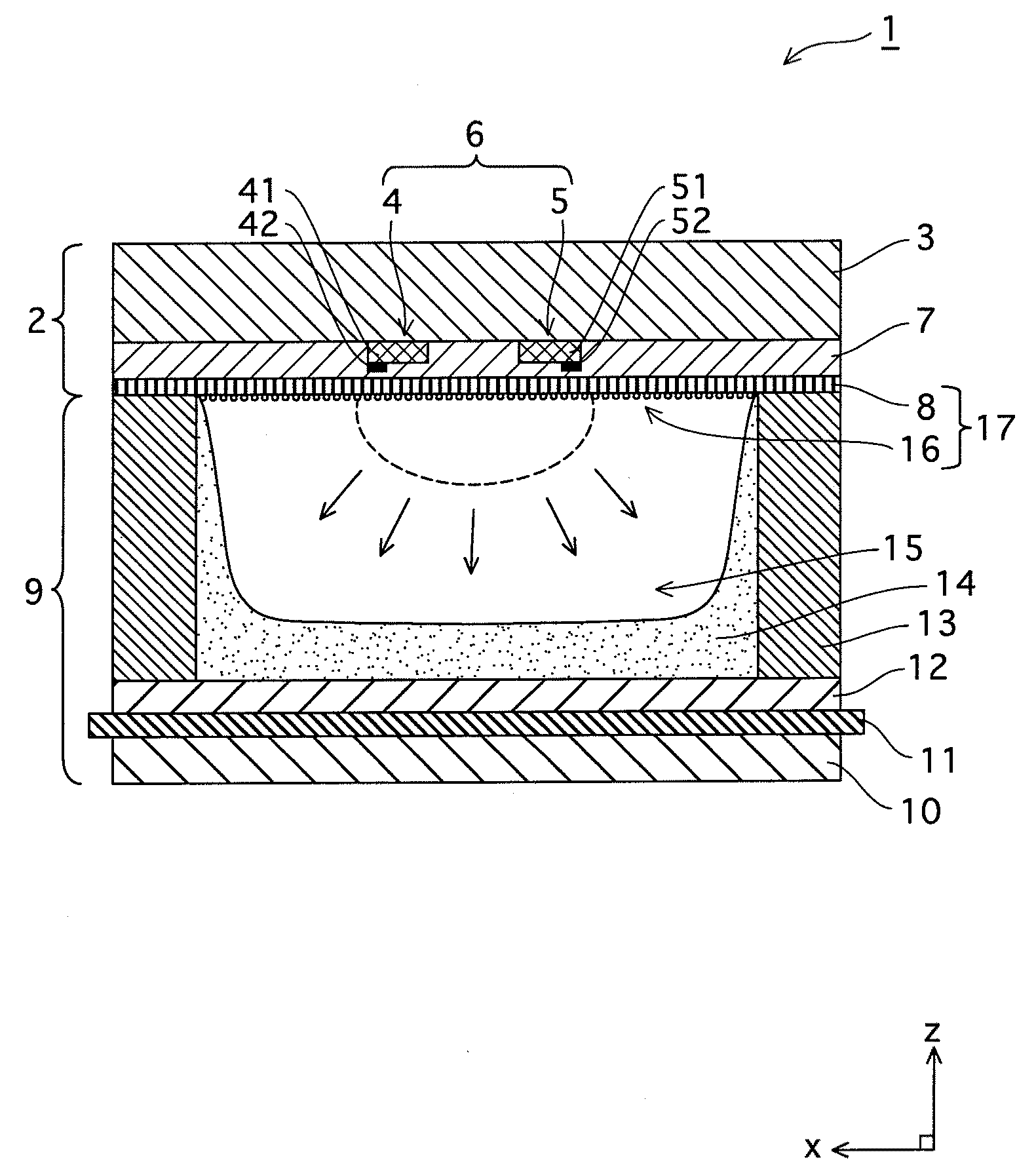

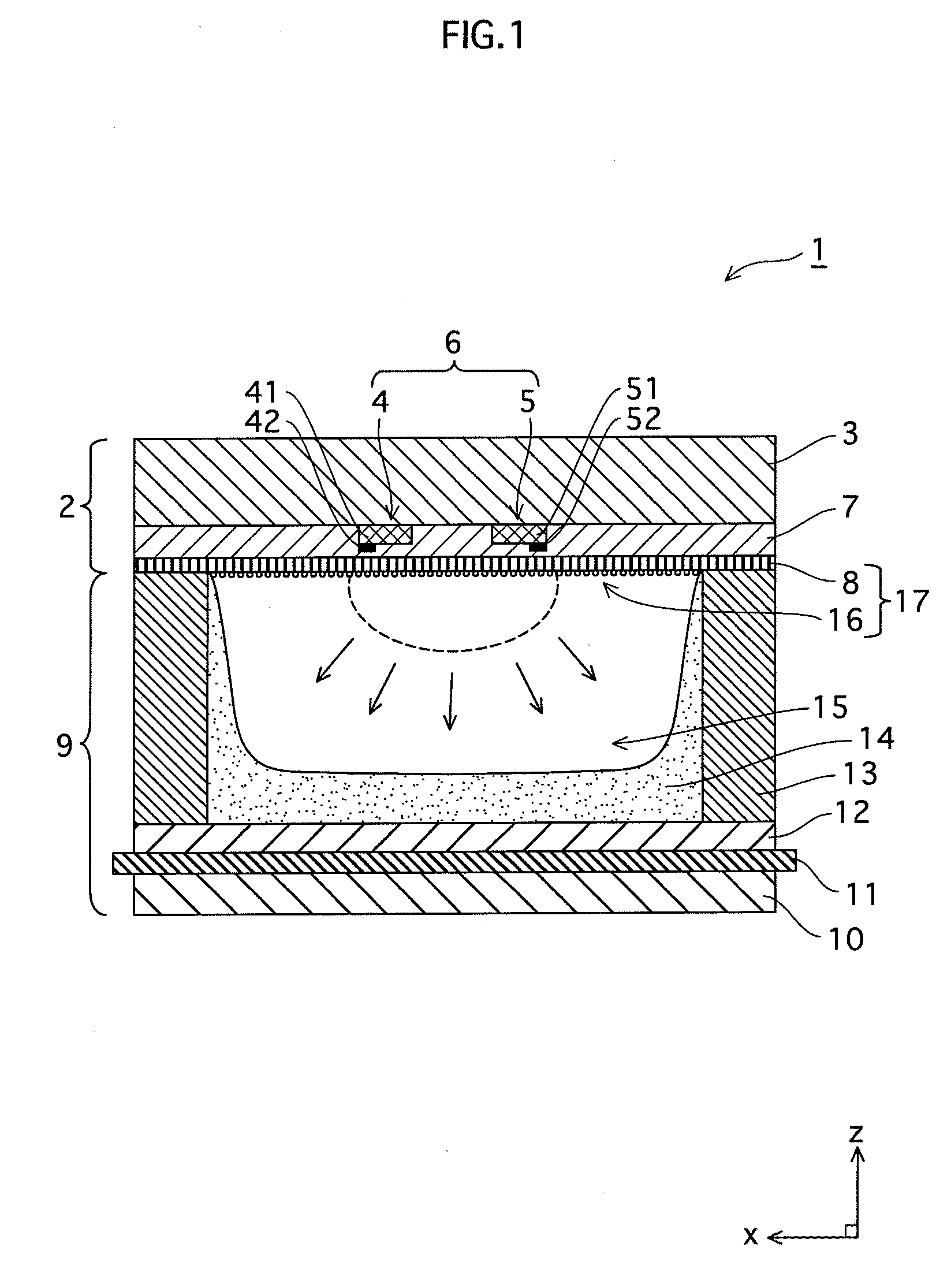

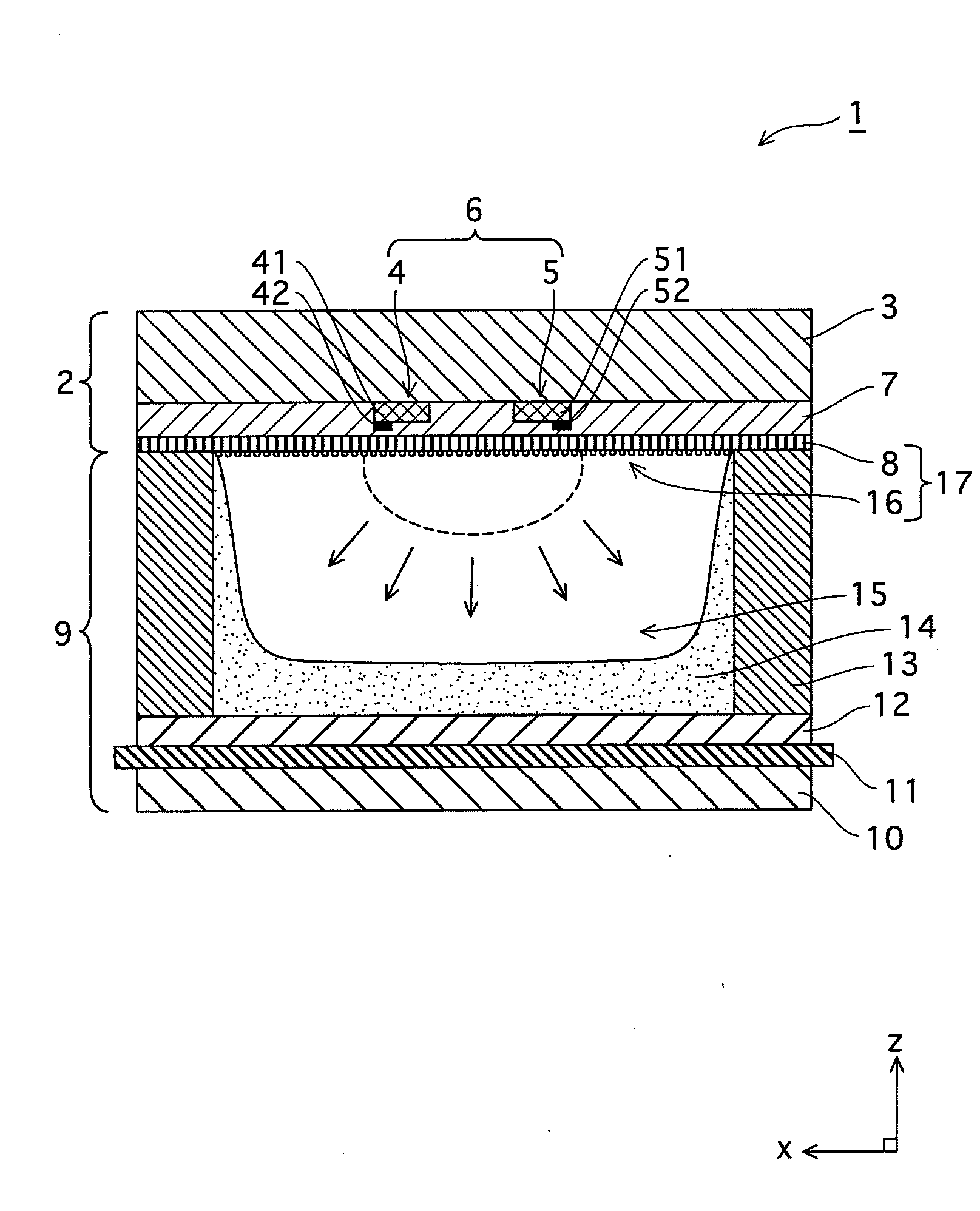

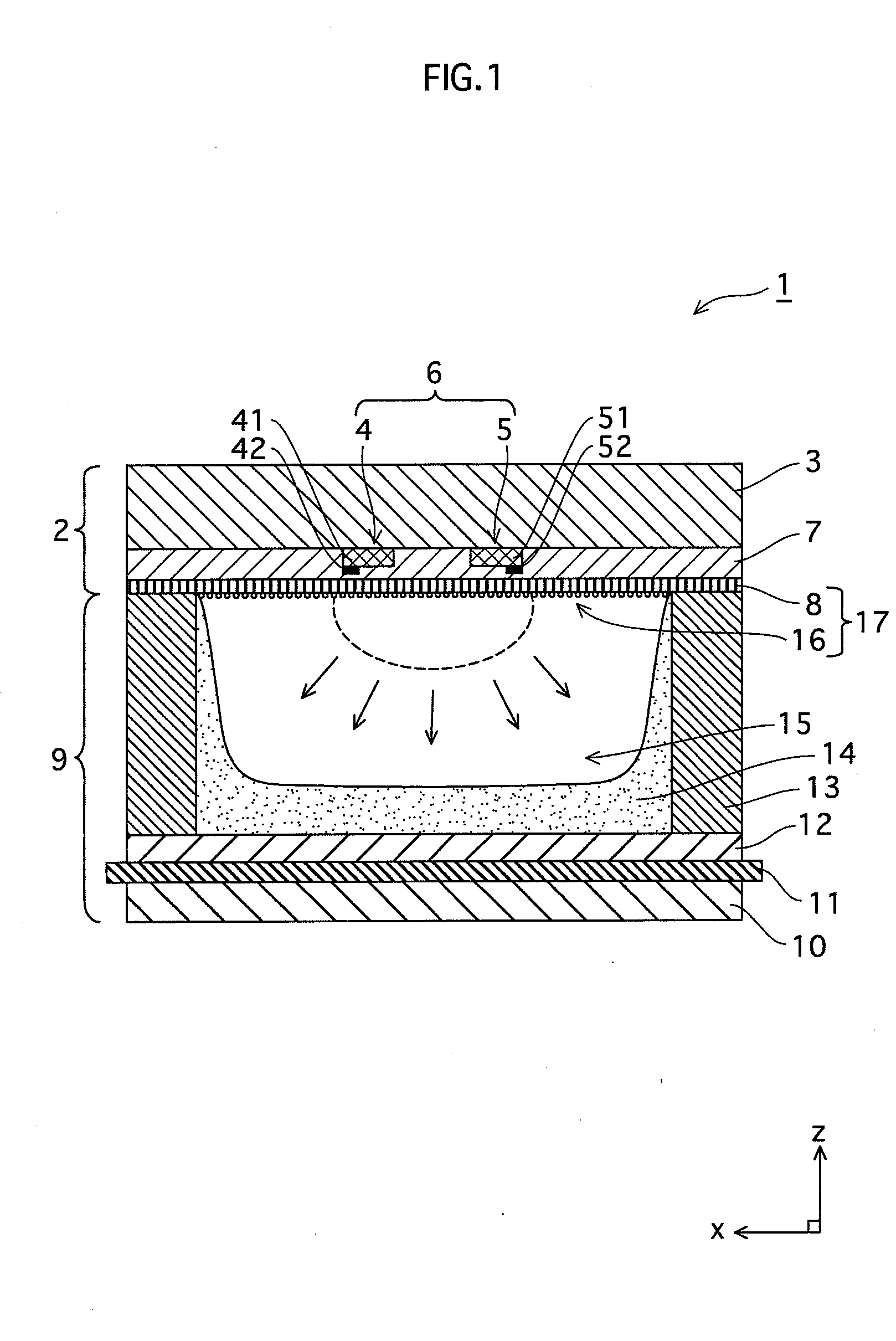

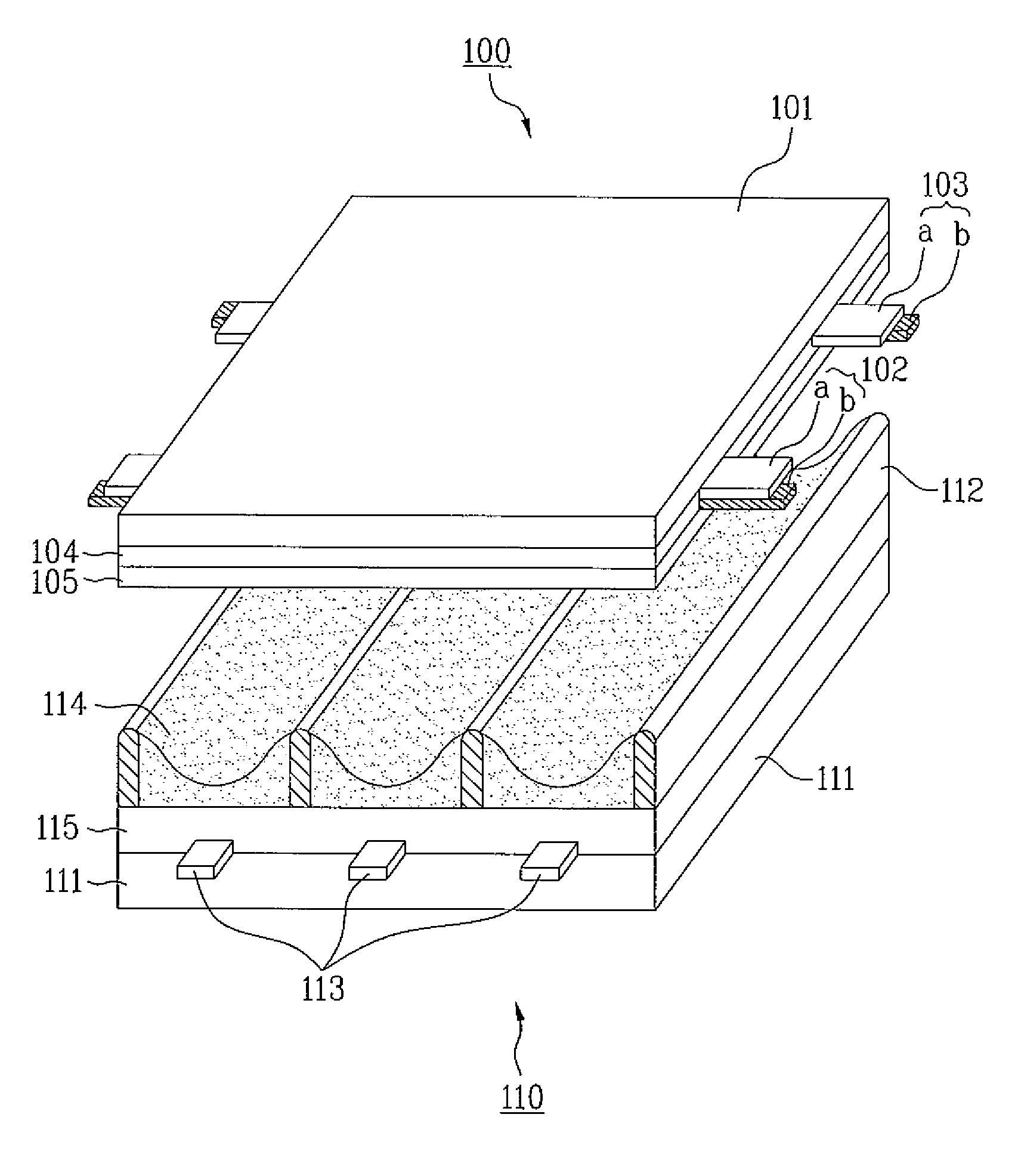

ActiveUS20090140652A1Large secondary electron emission coefficientLaunch evenlyTube/lamp screens manufactureAddress electrodesLow voltagePlasma display

“Discharge delay” and “dependence of discharge delay on temperatures” are solved by improving a protective layer, thus a PDP can be driven at a low voltage. Furthermore, the PDP can display excellent images by suppressing “dependence of discharge delay on space charges.” Liquid-phase magnesium alkoxide (Mg (OR)2) or acetylacetone magnesium ate whose purity is 99.95% or more is prepared, and is hydrolyzed by adding a small amount of acids to the solution. Thus, a gel of magnesium hydroxide that is a magnesium oxide precursor is formed. Burning the gel in atmosphere at 700° C. or more produces powder containing MgO particles 16a-16d having the NaCl crystal structure with (100) and (111) crystal faces or with (100), (110) and (111) crystal faces. By pasting the powder on a dielectric layer 7 or a surface layer 8, the MgO powder 16 is formed so as to serve as the protective layer.

Owner:PANASONIC CORP

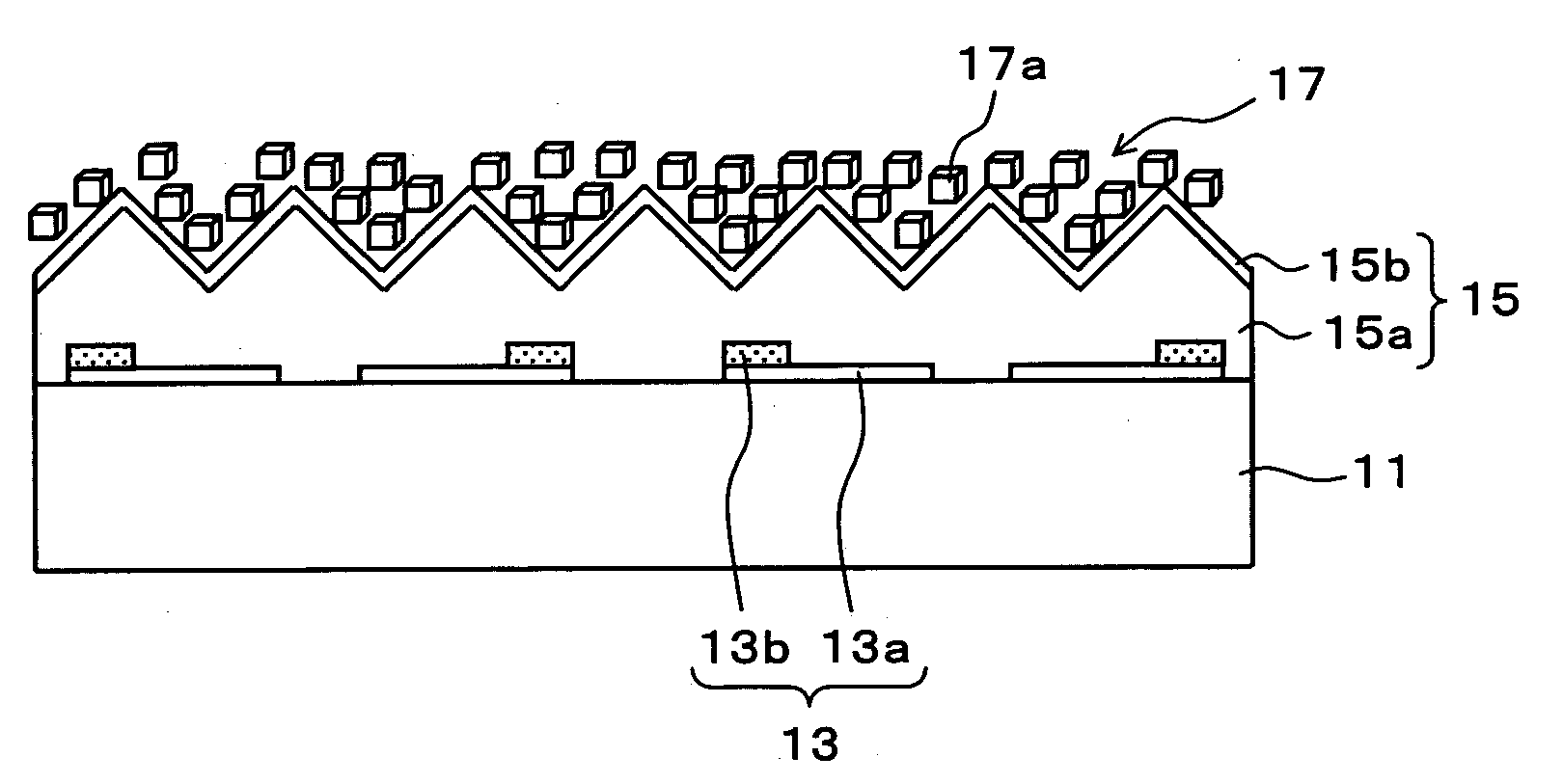

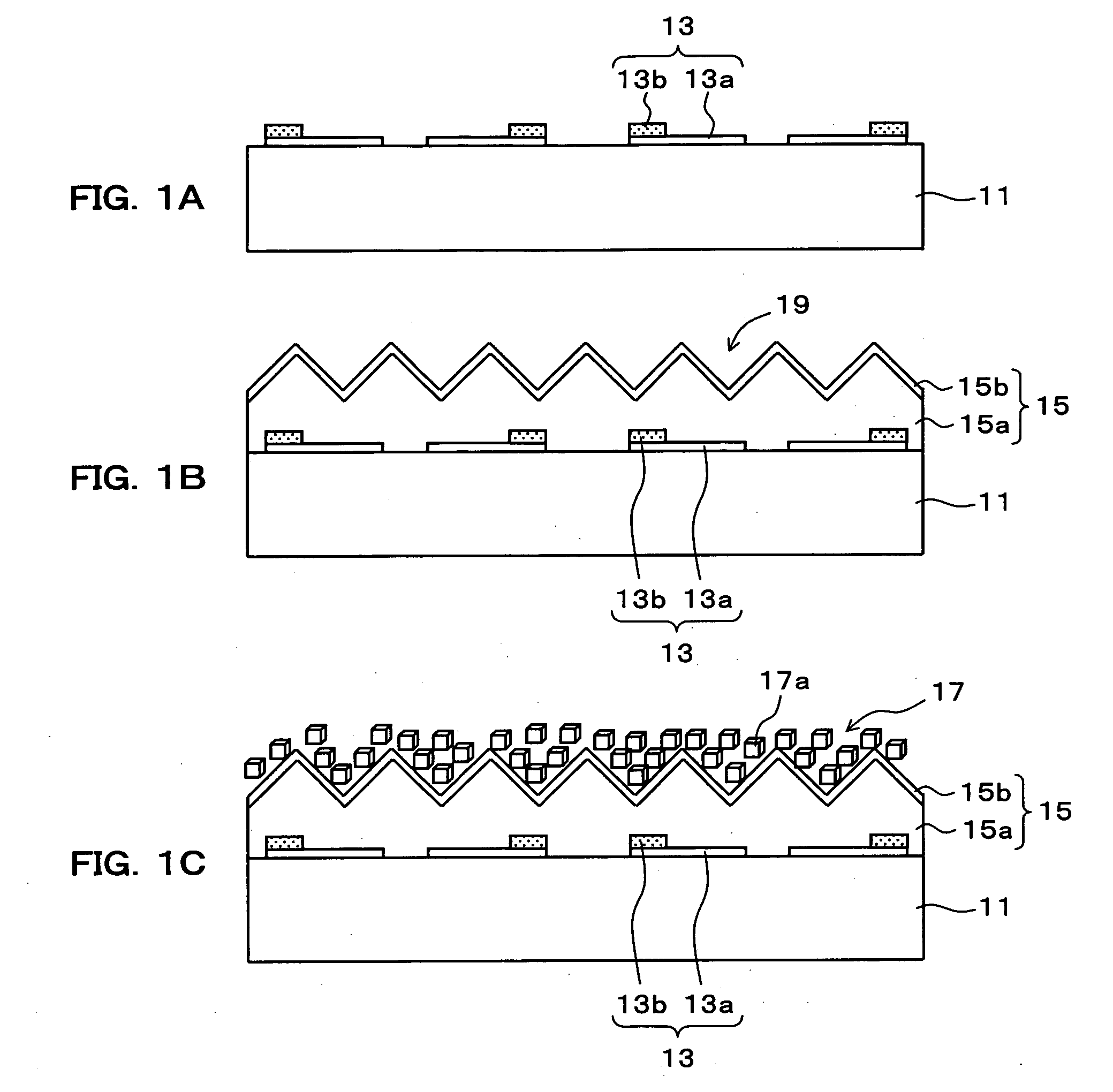

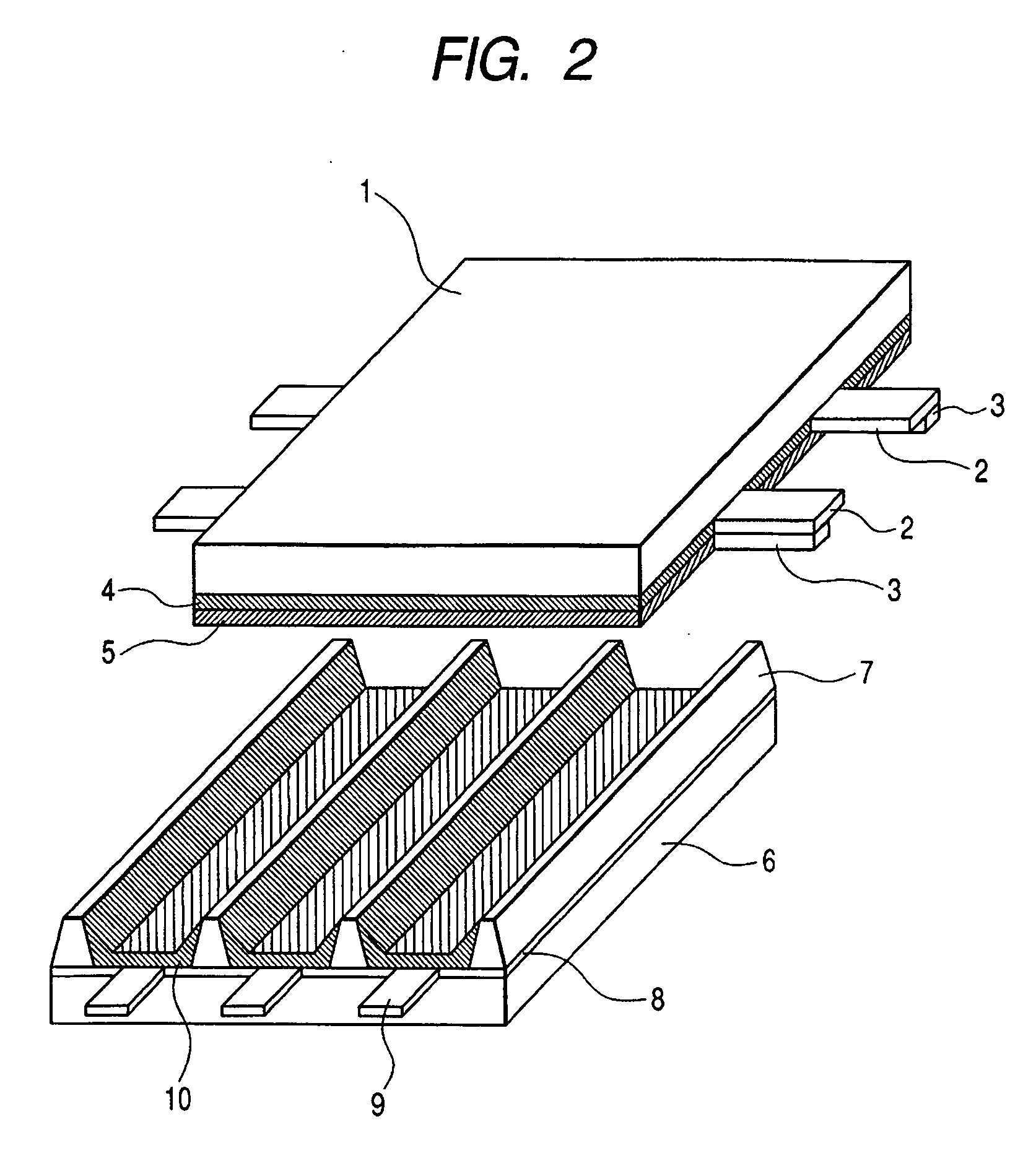

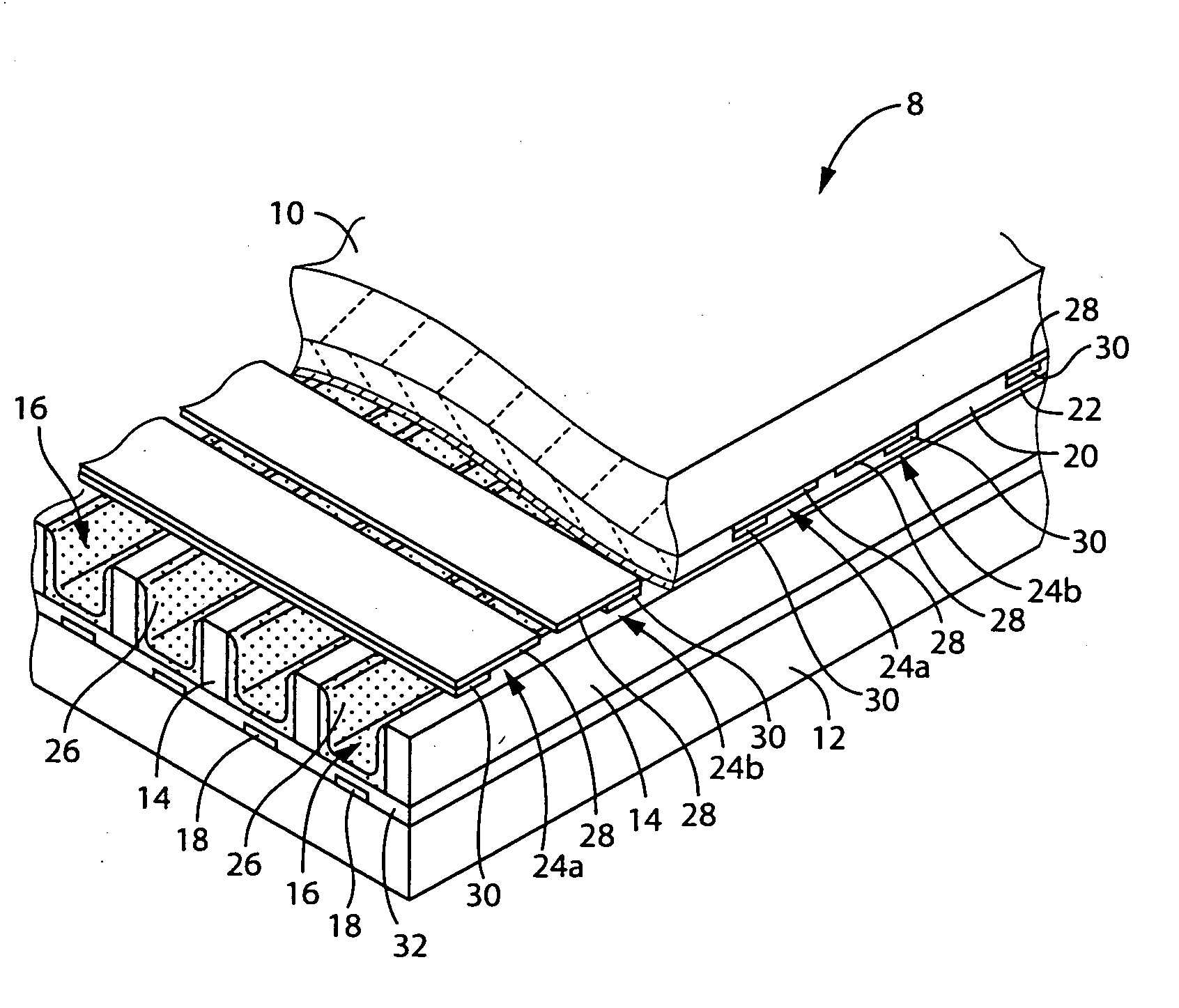

Method for producing substrate assembly for plasma display panel, and plasma display panel

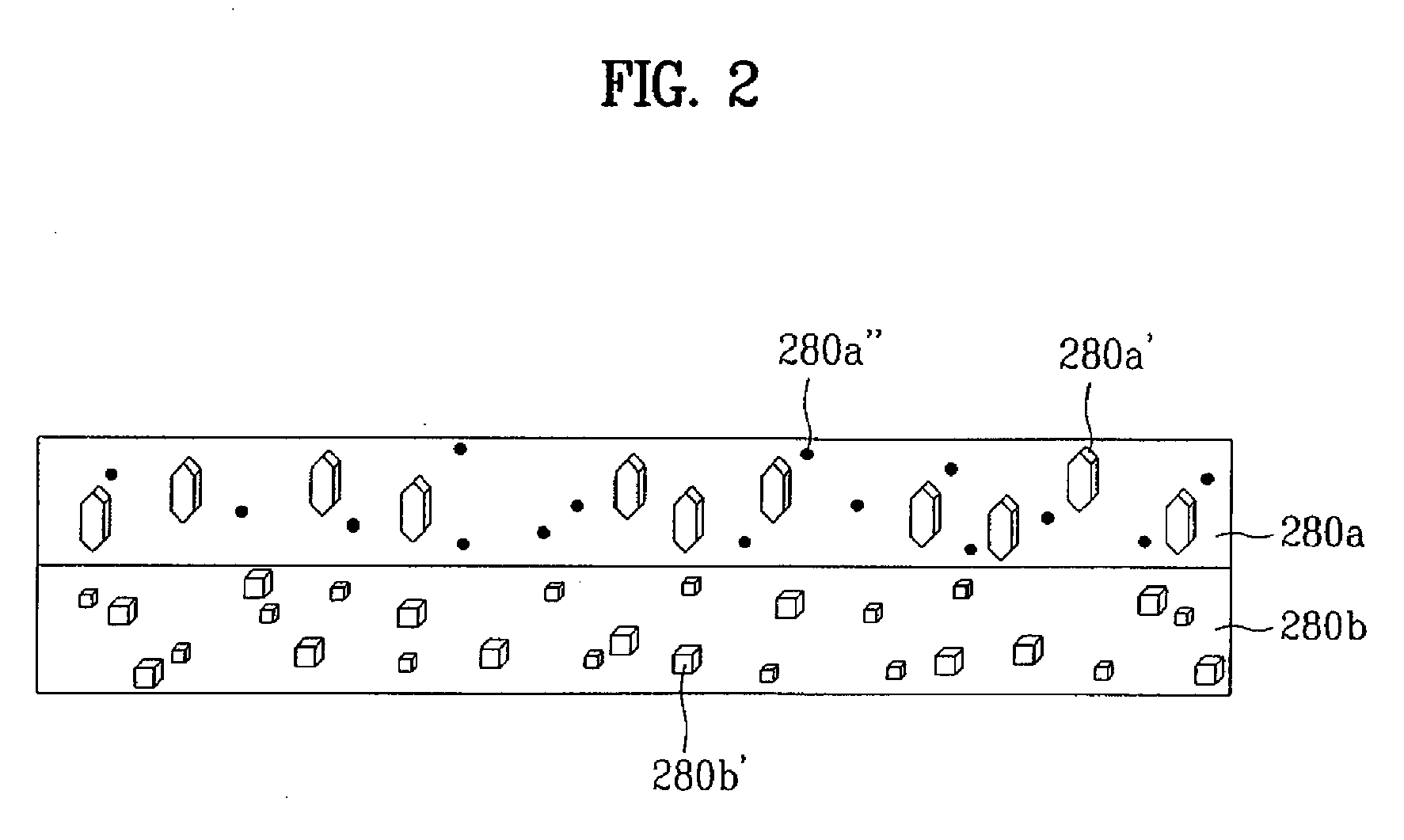

InactiveUS20080049382A1Form evenlyAddress electrodesSustain/scan electrodesRough surfaceOptoelectronics

A method for producing a substrate assembly for a plasma display panel includes the steps of applying a suspension to a dielectric layer covering display electrodes formed on a substrate, the suspension containing a dispersion medium and a large number of magnesium oxide crystals dispersed in the dispersion medium, and thereafter evaporating the dispersion medium to form a layer of the magnesium oxide crystals on the dielectric layer, wherein the dielectric layer has a rugged surface structure having uniformly-dispersed projections and depressions, the rugged surface structure being capable of trapping the magnesium oxide crystals.

Owner:FUJITSU HITACHI PLASMA DISPLAY LTD

Plasma display panel and manufacturing method thereof

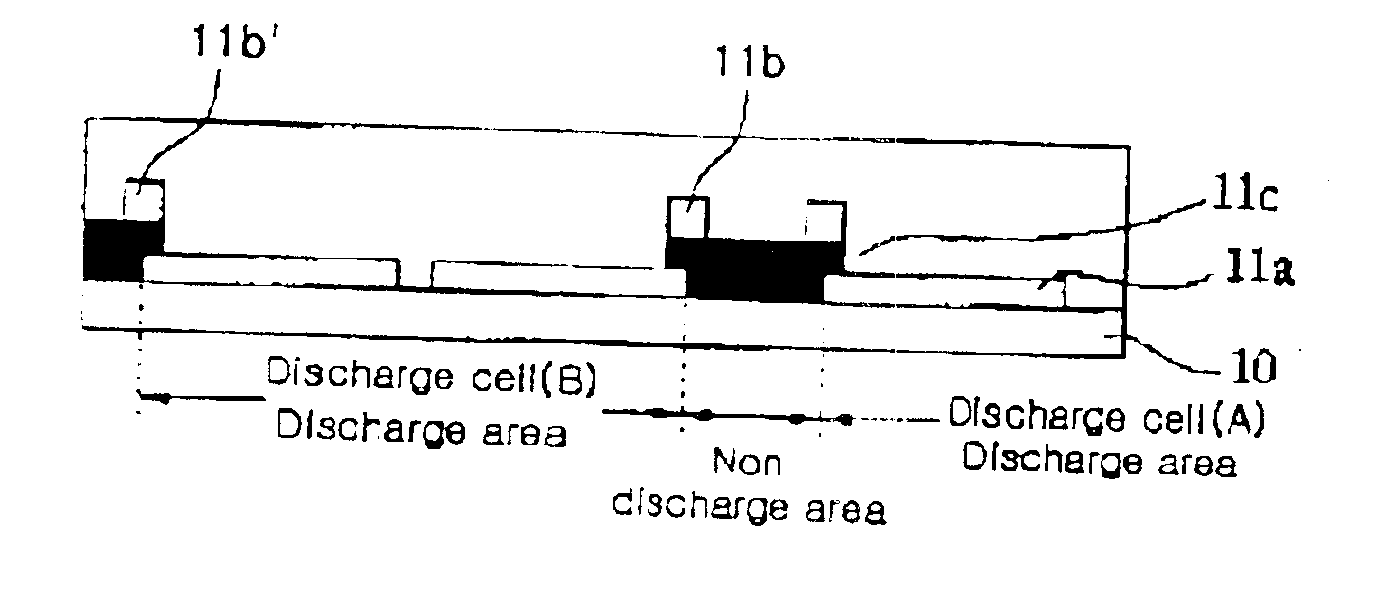

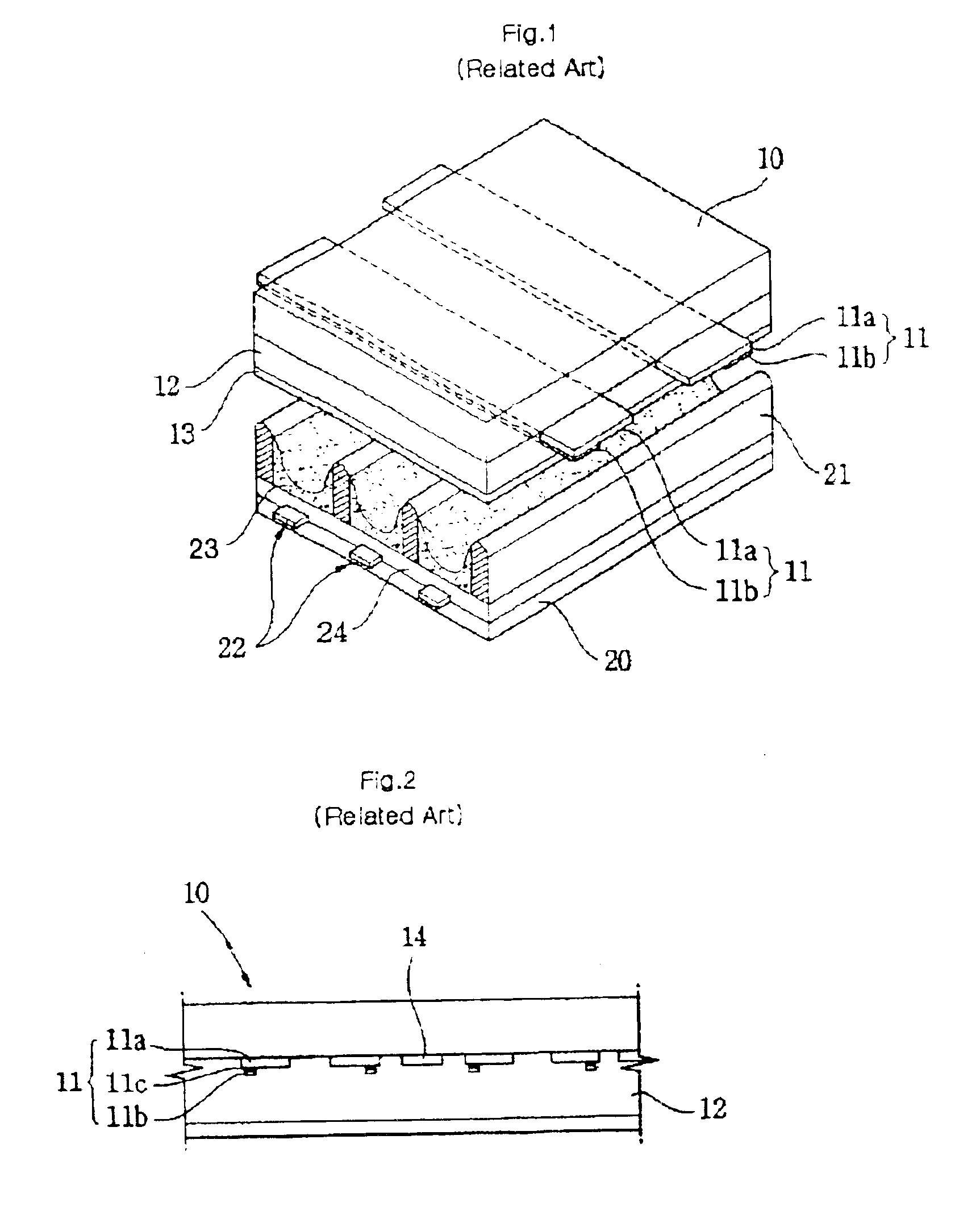

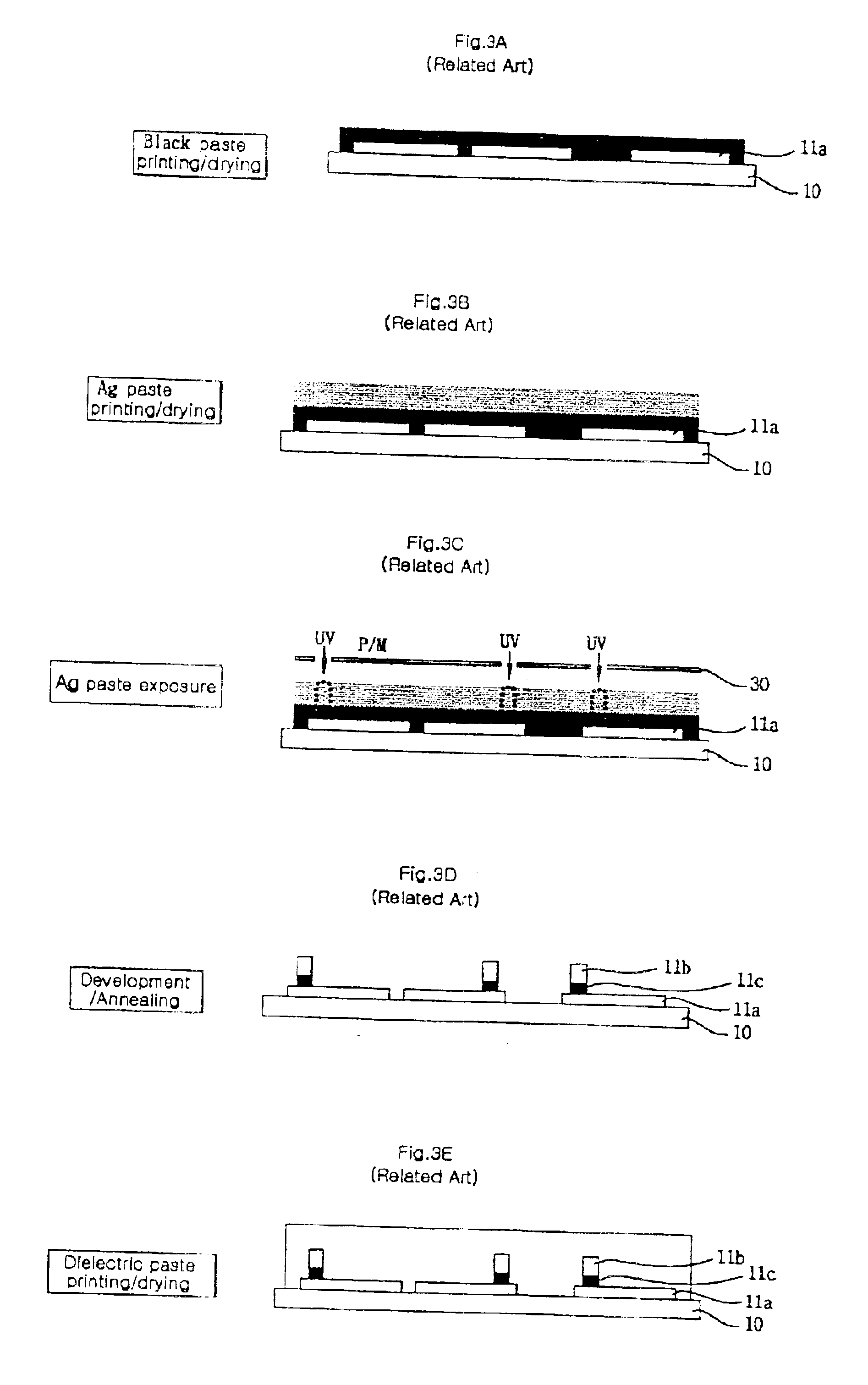

InactiveUS6838828B2Simple manufacturing processIncrease brightnessTube/lamp screens manufactureAddress electrodesEngineeringBrightness perception

The present invention relates to plasma display panel and manufacturing method thereof to simplify the manufacturing steps and reduce cost of production. In the present invention, a black layer formed between a transparent electrode and a bus electrode is formed together with a black matrix at the same time. In this case, the black layer is formed together with the black matrix in one. Cheap nonconductive oxide is used as a black powder of a black layer. Specifically, in case the black layer and the black matrix are formed in one, the bus electrode is shifted to a non-discharge area to improve the brightness of the plasma display panel.

Owner:LG ELECTRONICS INC

Plasma display panel

InactiveUS20050001551A1Maximize discharge efficiencyImprove efficiencyAddress electrodesSustain/scan electrodesPhosphorPlasma display

A plasma display panel. A first substrate and a second substrate are provided opposing one another with a predetermined gap therebetween. Address electrodes are formed on the second substrate. Barrier ribs are mounted between the first substrate and the second substrate, the barrier ribs defining a plurality of discharge cells and a plurality of non-discharge regions. Phosphor layers are formed within each of the discharge cells. Discharge sustain electrodes are formed on the first substrate. The non-discharge regions are formed in areas encompassed by discharge cell abscissas that pass through centers of adjacent discharge cells and discharge cell ordinates that pass through centers of adjacent discharge cells, the non-discharge regions having a width that is at least as large as a width of an end of barrier ribs. Also, a transverse barrier rib is formed extending between each pair of adjacent rows of discharge cells.

Owner:SAMSUNG SDI CO LTD

Plasma display panel

InactiveUS20050212430A1Improve discharge efficiencyEfficiently usSustain/scan electrodesFloating electrodesCarbon nanotubeSurface roughness

A plasma display panel with reinforcing electrodes arranged at both ends of discharge cells along a direction address electrodes are formed and coupled to display electrodes. The reinforcing electrodes may comprise carbon-based material such as carbon nanotubes or graphite, and they may be stacked in two or more layers and covered with a dielectric layer and a protective layer. The dielectric layer may be interposed between the reinforcing electrodes and the display electrodes. The dielectric layer may expose the reinforcing electrodes so that the protective layer covers the reinforcing electrodes. A portion of the protective layer corresponding to the reinforcing electrodes has a surface roughness of about 300 nm to about 700 nm.

Owner:SAMSUNG SDI CO LTD

Plasma display panel

InactiveUS6897610B1Improve the display effectReduce power consumptionAlternating current plasma display panelsCold-cathode tubesEngineeringPermittivity

The present invention provides a plasma display panel in which a space between a first plate and a second plate facing each other is filled with a discharge gas, a plurality of pairs of display electrodes made of Ag or Cu are formed on a surface of the first plate facing the second plate, and the surface of the first plate is covered with a dielectric layer covering the plurality of pairs of display electrodes, where the dielectric layer is made of a glass that contains at least ZnO and 10 wt % or less of R2O and does not substantially contain PbO and Bi2O3, and a product of permittivity ε and loss factor tan δ of the dielectric layer is 0.12 or less, wherein R is selected from a group consisting of K, Rb, Cs, Cu, and Ag.

Owner:PANASONIC CORP

Plasma display panel and method for manufacturing the same

InactiveUS20090146566A1Increase dependenceLarge secondary electron emission coefficientTube/lamp screens manufactureAddress electrodesLow voltageSpace charge

“Discharge delay” and “dependence of discharge delay on temperatures” are solved by improving a protective layer, thus a PDP can be driven at a low voltage. Furthermore, the PDP can display excellent images by suppressing “dependence of discharge delay on space charges.” Liquid-phase magnesium alkoxide (Mg(OR)2) or acetylacetone magnesium ate whose purity is 99.95% or more is prepared, and is hydrolyzed by adding a small amount of acids to the solution. Thus, a gel of magnesium hydroxide that is a magnesium oxide precursor is formed. Burning the gel in atmosphere at 700° C. or more produces powder containing MgO particles 16a-16d having the NaCl crystal structure with (100) and (111) crystal faces or with (100), (110) and (111) crystal faces. By pasting the powder on a dielectric layer 7 or a surface layer 8, the MgO powder 16 is formed so as to serve as the protective layer.

Owner:PANASONIC CORP

Plasma display panel and method for producing the same

InactiveUS20070096653A1Lower firing voltageIncrease contrastAddress electrodesSustain/scan electrodesEngineeringDielectric layer

Disclosed is a plasma display panel with improved discharge characteristics. The plasma display panel comprises an upper panel and a lower panel integrally joined to the upper panel through barrier ribs wherein the upper panel includes a dielectric layer, a first protective film formed on one surface of the dielectric layer and composed of magnesium oxide, and a second protective film formed on the first protective film and composed of crystalline magnesium oxide.

Owner:LG ELECTRONICS INC

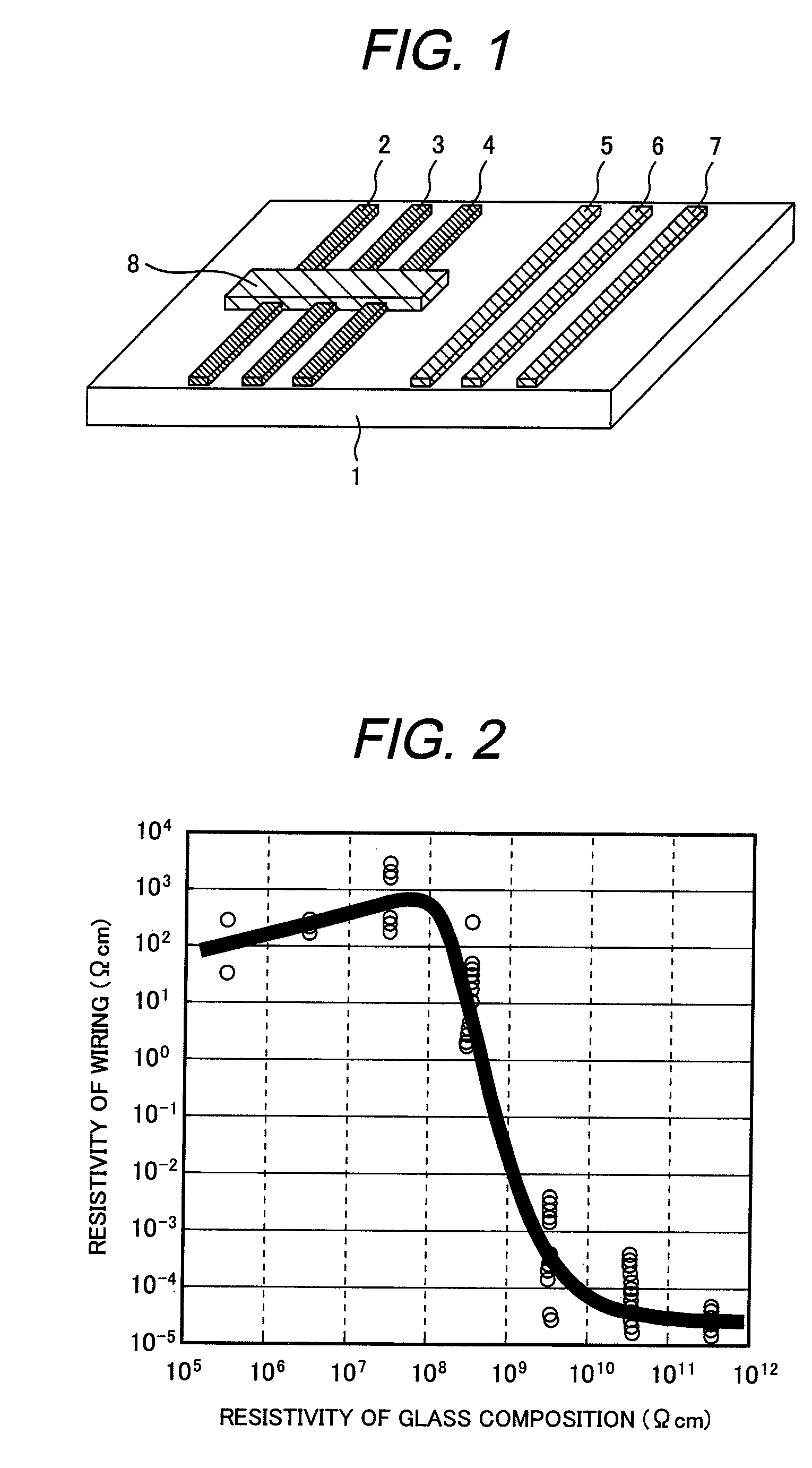

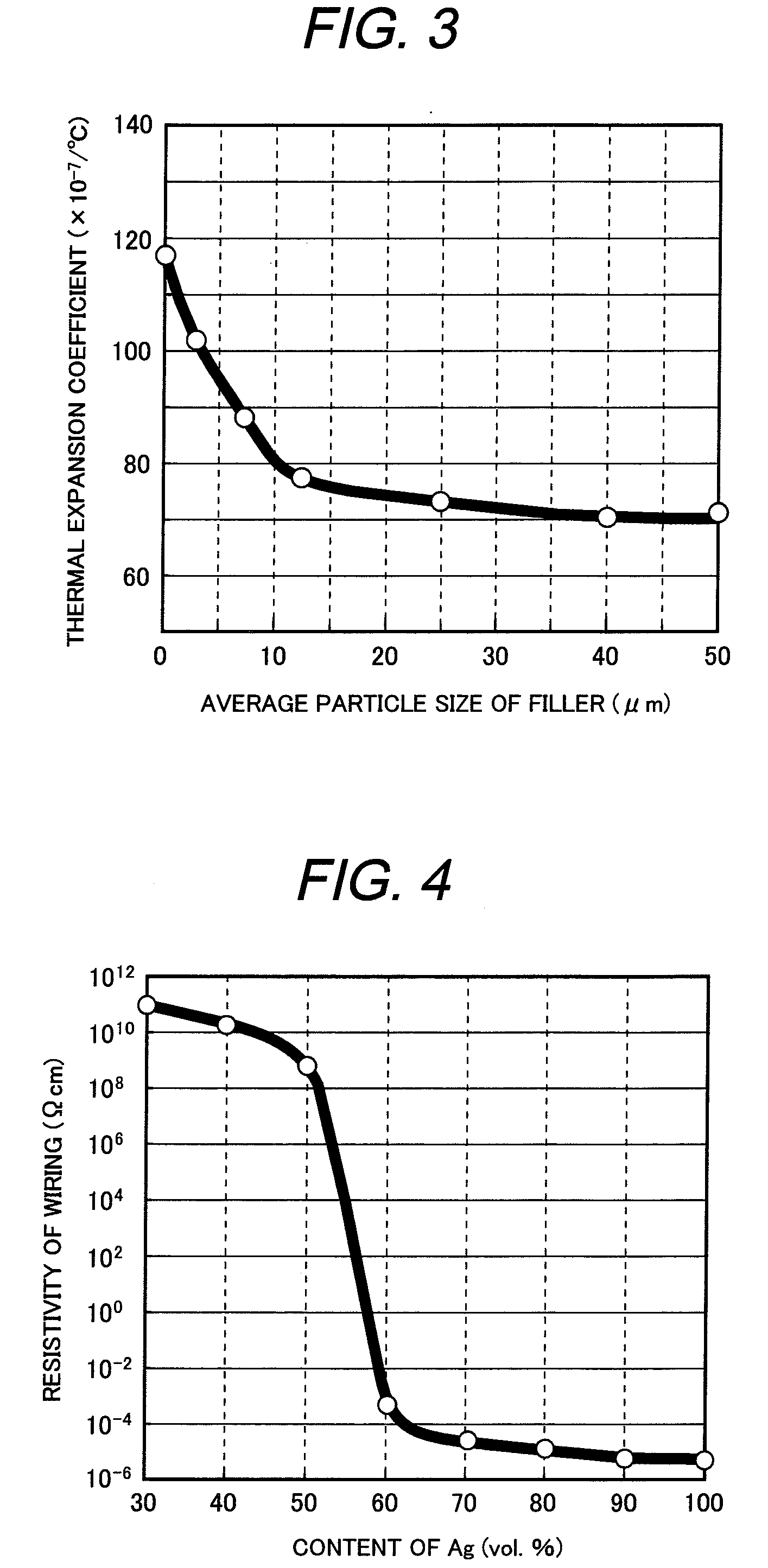

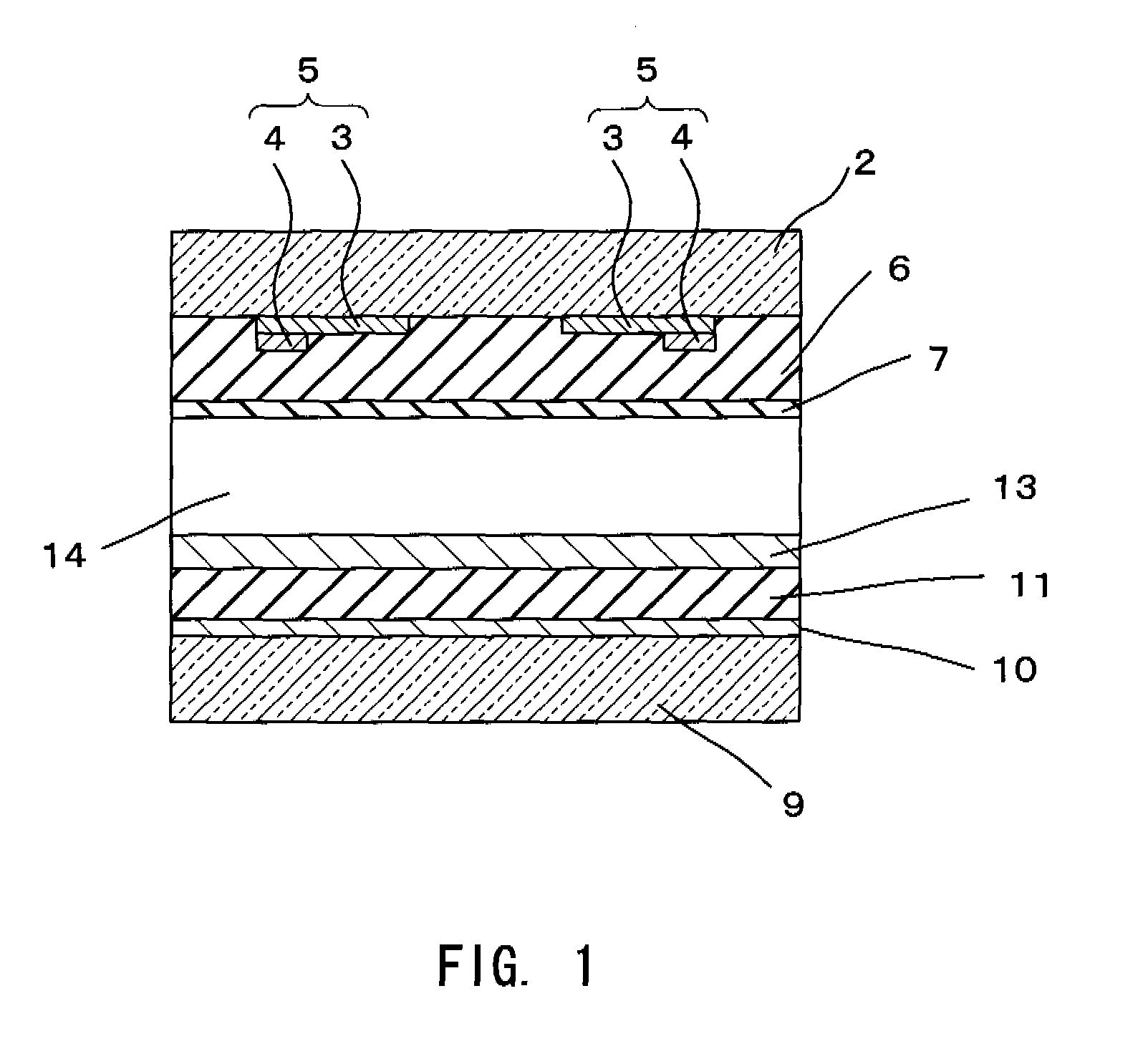

Method of making plasma display panel with dielectric layer suppressing reduced electrode conductivity

InactiveUS6296539B1Drop in conductivitySuppresses resistance riseAddress electrodesSustain/scan electrodesIndiumIndium tin oxide

The present invention relates to a plasma display panel comprising transparent electrodes and a dielectric layer covering said transparent electrodes on at least one substrate of a pair of substrates facing each other with a discharge space therebetween, the main constituent of the transparent electrodes is included in the dielectric layer. Further, the main constituent of the transparent electrode is indium oxide and indium oxide is included in the dielectric layer. By including the main constituent of the transparent electrodes in the dielectric layer, it is believed that the drop in conductivity caused by diffusion of the dielectric substance in the transparent electrodes during high-temperature processing is prevented.

Owner:HITACHT MAXELL LTD

Plasma display panel and method for producing the same

InactiveUS20070152593A1Improved secondary electron emission characteristicReduce ignition voltageAddress electrodesSustain/scan electrodesEngineeringSecondary electrons

A plasma display panel with low firing voltage is disclosed. The plasma display panel includes an upper panel and a lower panel facing each other through barrier ribs wherein the upper panel includes a first protective film composed of magnesium oxide and a second protective film formed on the first protective film and composed of a secondary electron-emitting material.

Owner:LG ELECTRONICS INC

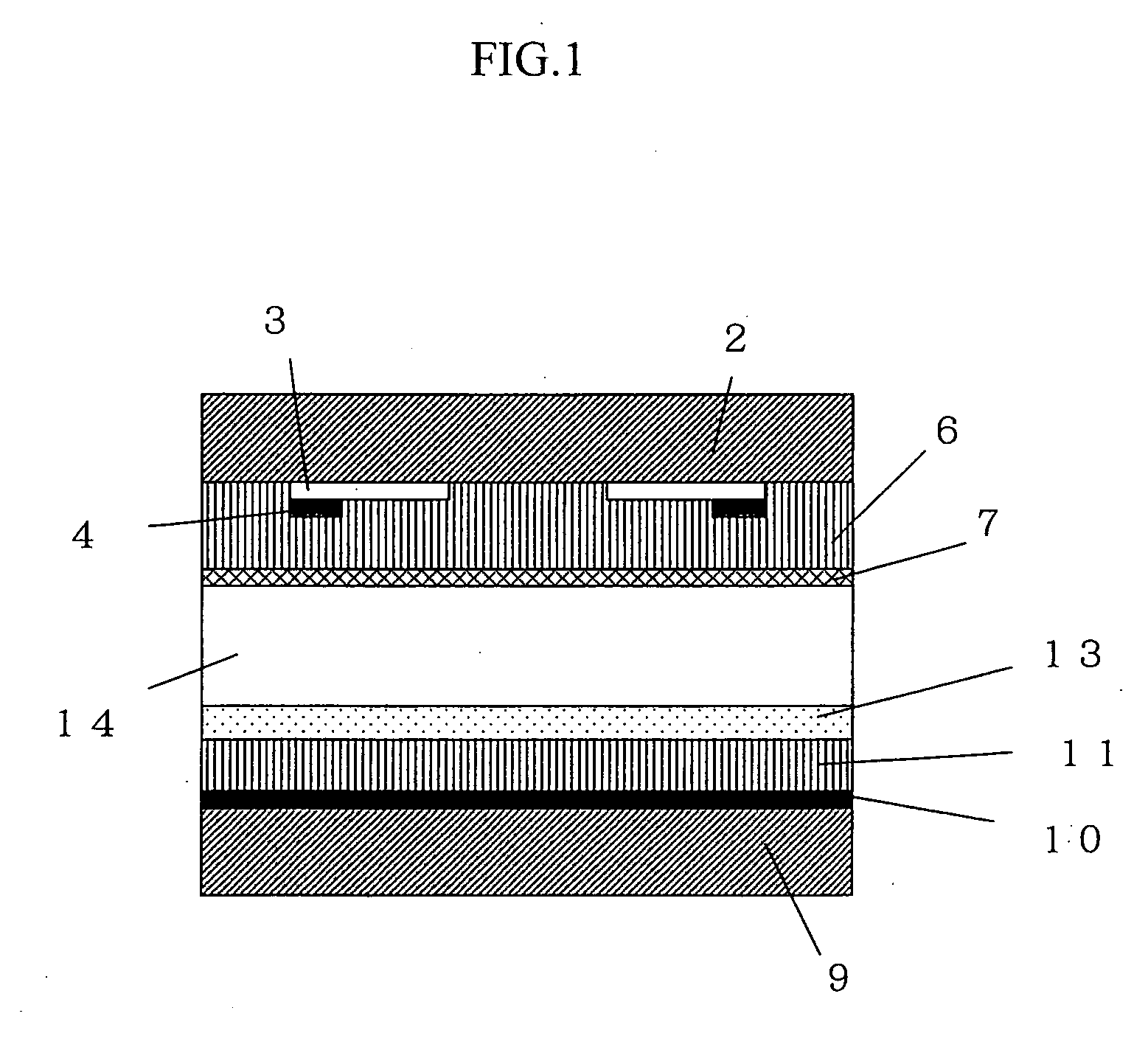

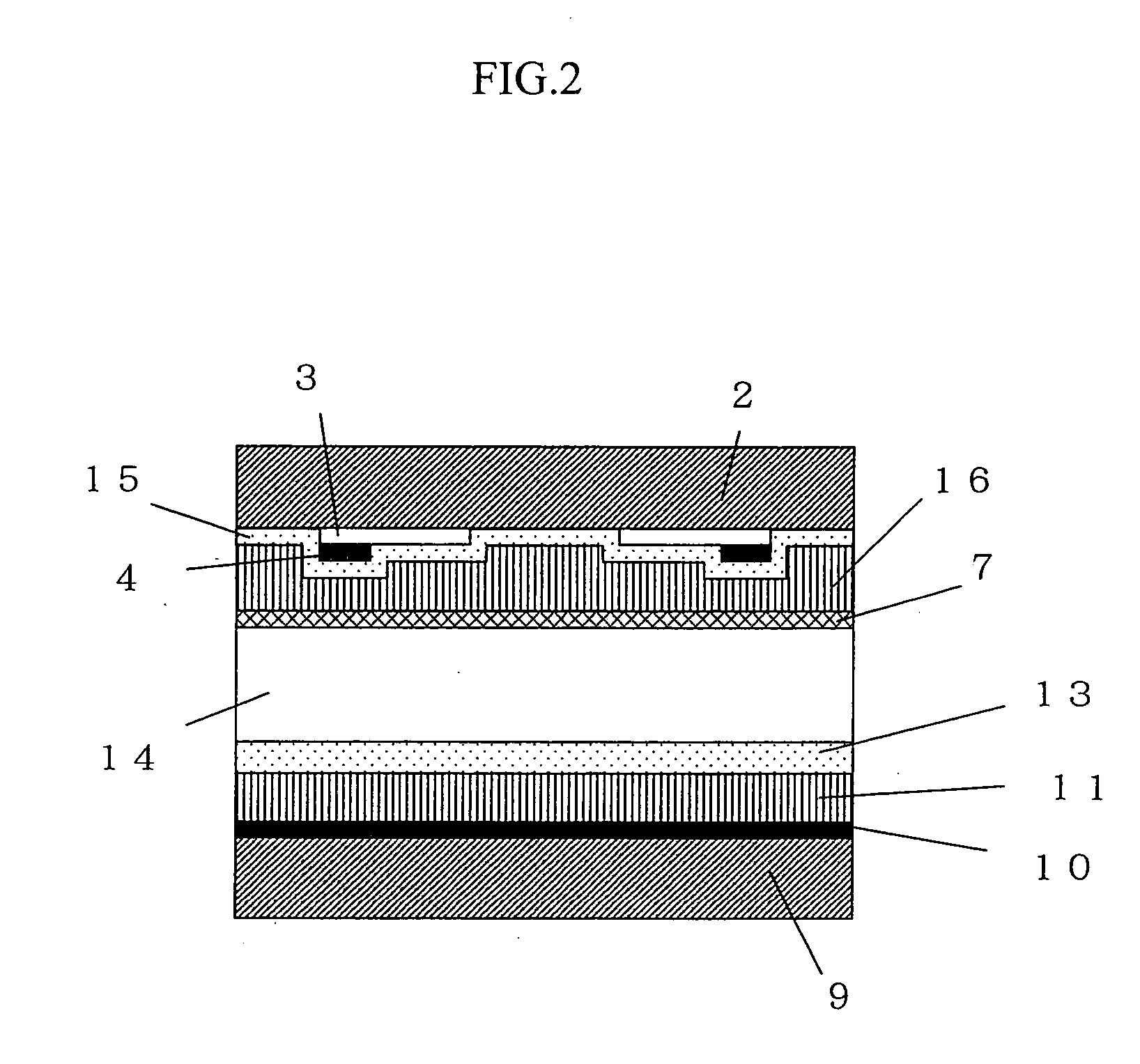

Surface-discharge type display device with reduced power consumption

A surface-discharge type display device is provided that can reduce power consumption during sustain discharge and suppress the occurrence of illumination failures. A display electrode and a display scan electrode are aligned on a substrate, and a dielectric layer is formed on the substrate so as to cover the display electrode and the display scan electrode. An area having a lower relative permittivity than the dielectric layer is formed in an area surrounded on three sides by the display electrode, the display scan electrode, and the substrate. The dielectric layer allows sufficient wall charges for surface discharge to be accumulated, whereas the lower relative permittivity area allows the capacitance between the display electrode and the display scan electrode to be decreased. Accordingly, the power consumption during sustain discharge is reduced without causing illumination failures.

Owner:PANASONIC CORP

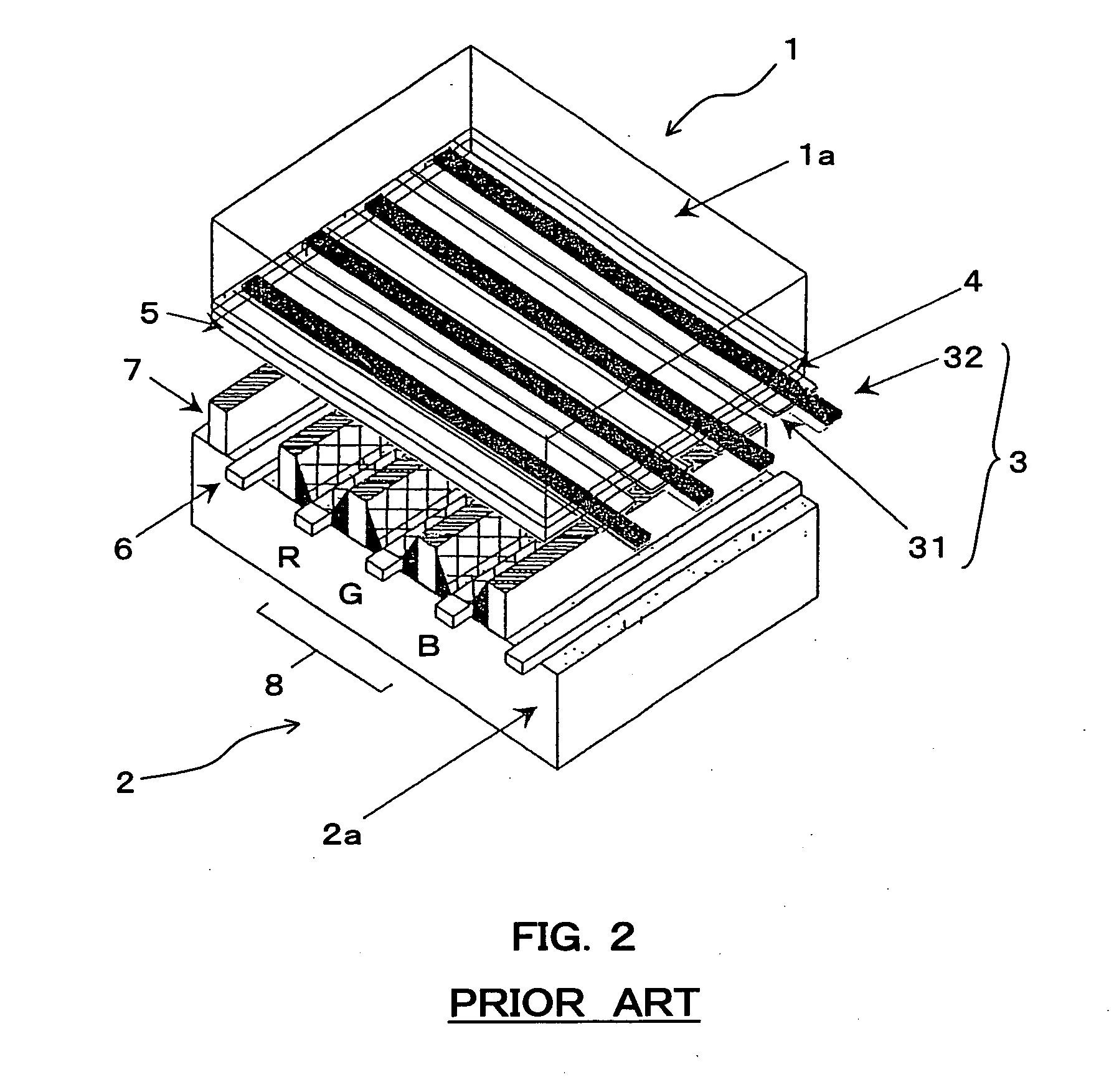

Alternating current driven type plasma display device and method for production thereof

InactiveUS6657396B2Increase cumulativeIncrease brightnessSustain/scan electrodesStatic indicating devicesAlternating currentPlasma display

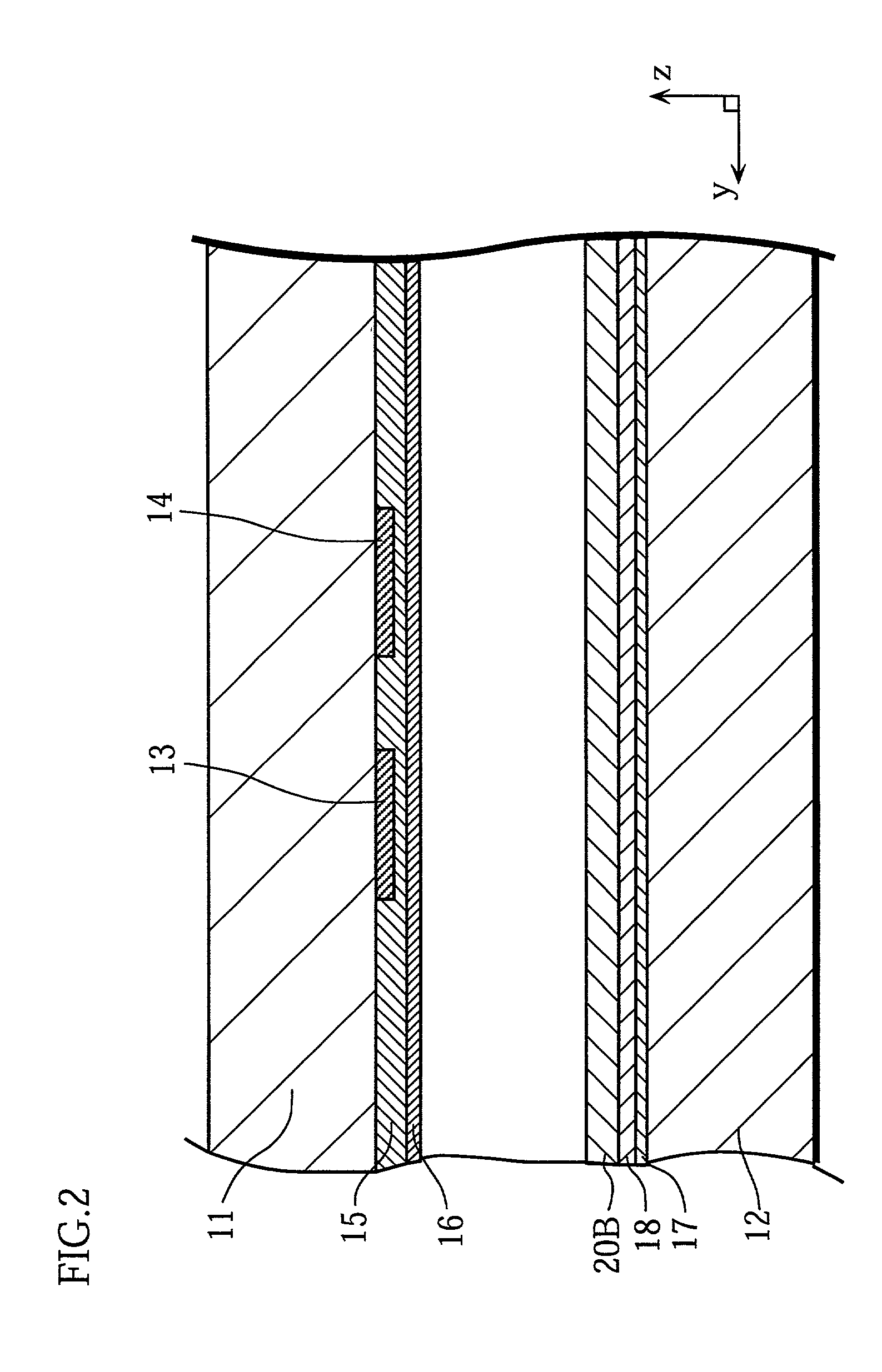

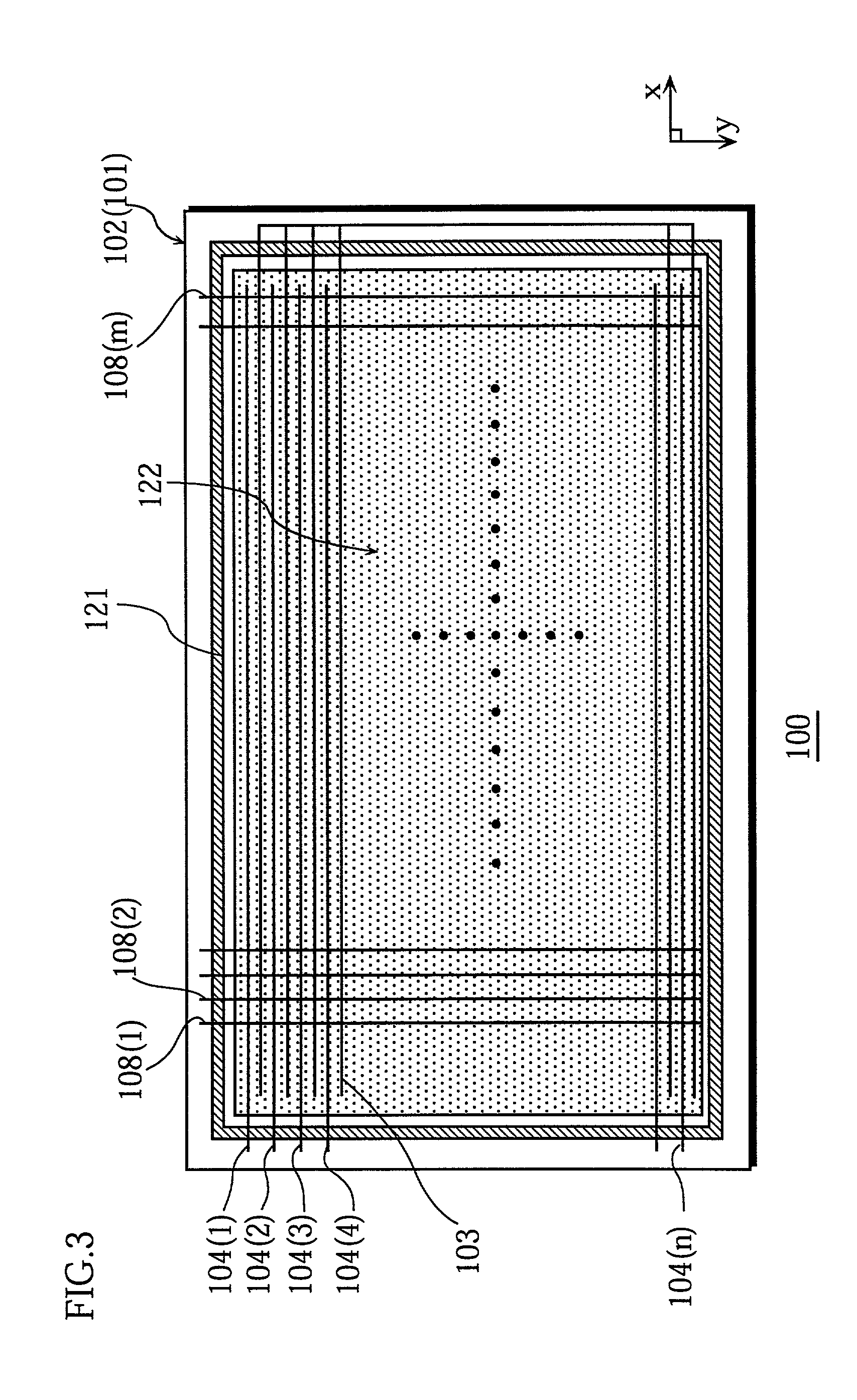

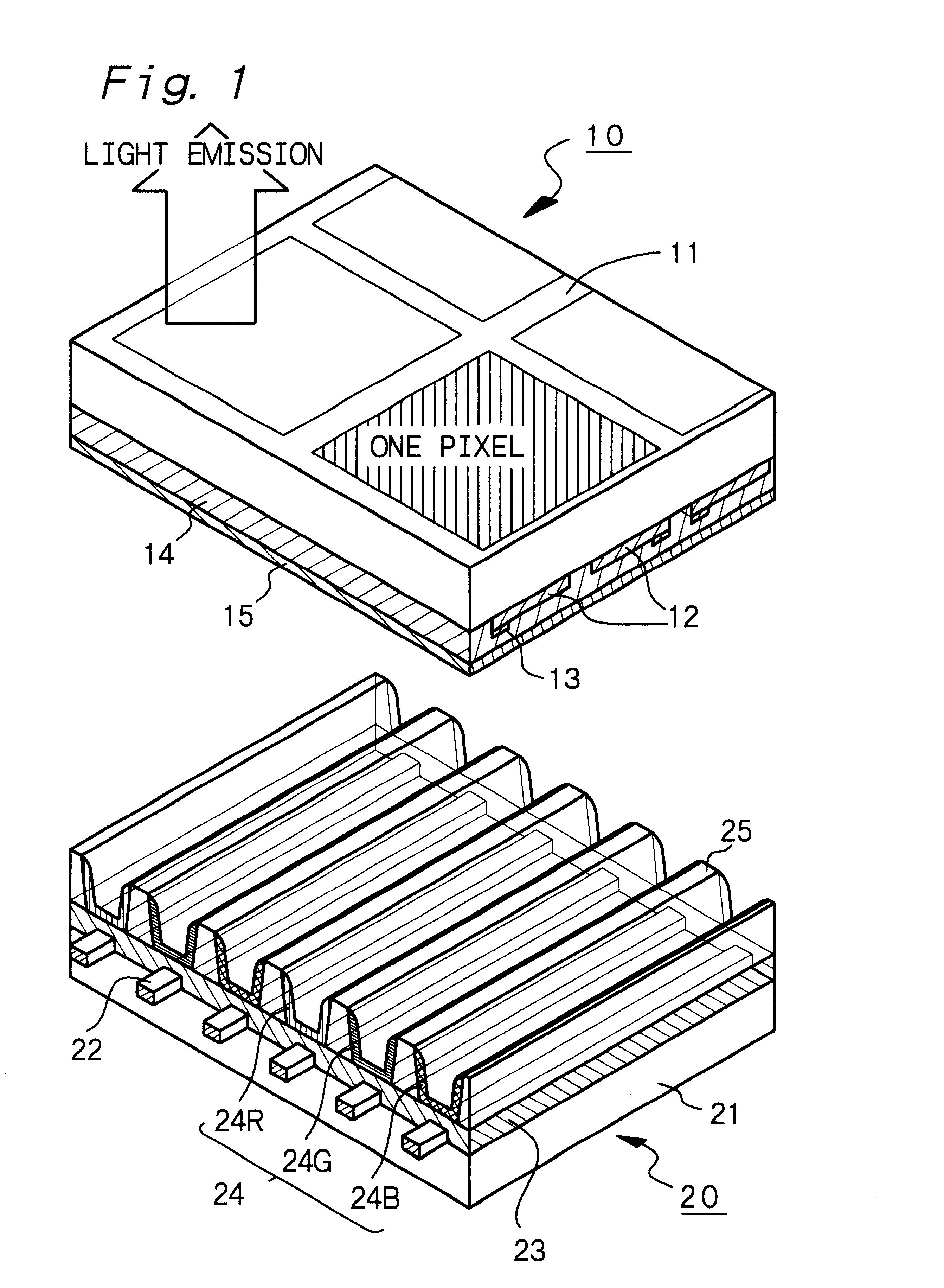

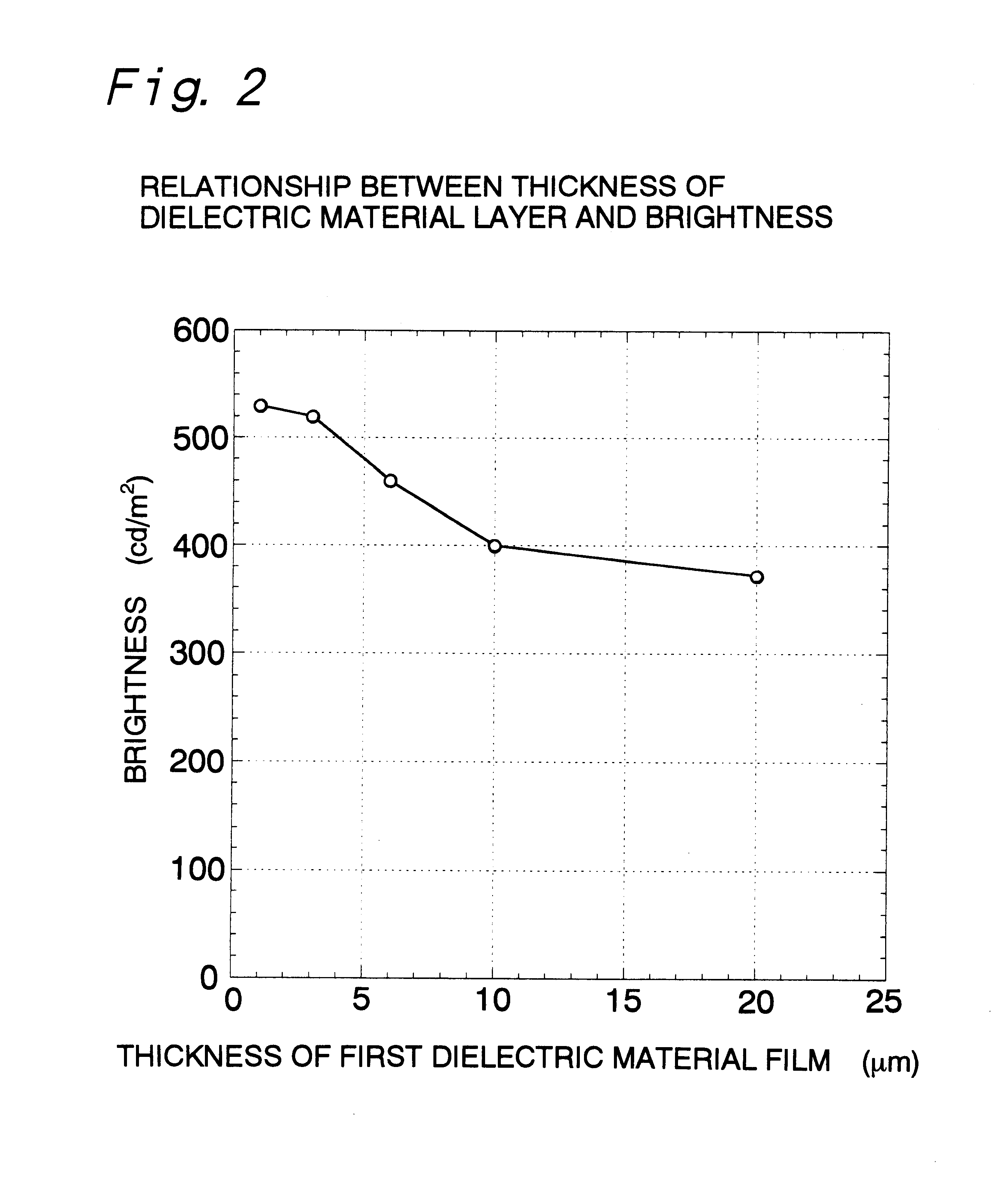

An alternating current driven type plasma display device comprising a first panel and a second panel, said first panel having sustain electrodes formed on a first substrate and a dielectric material layer formed on the first substrate and the sustain electrodes, wherein the first panel and the second panel are bonded to each other in their circumferential portions,characterized in that the dielectric material layer has a thickness of 1.5x10<-5 >m or less.

Owner:SONY CORP

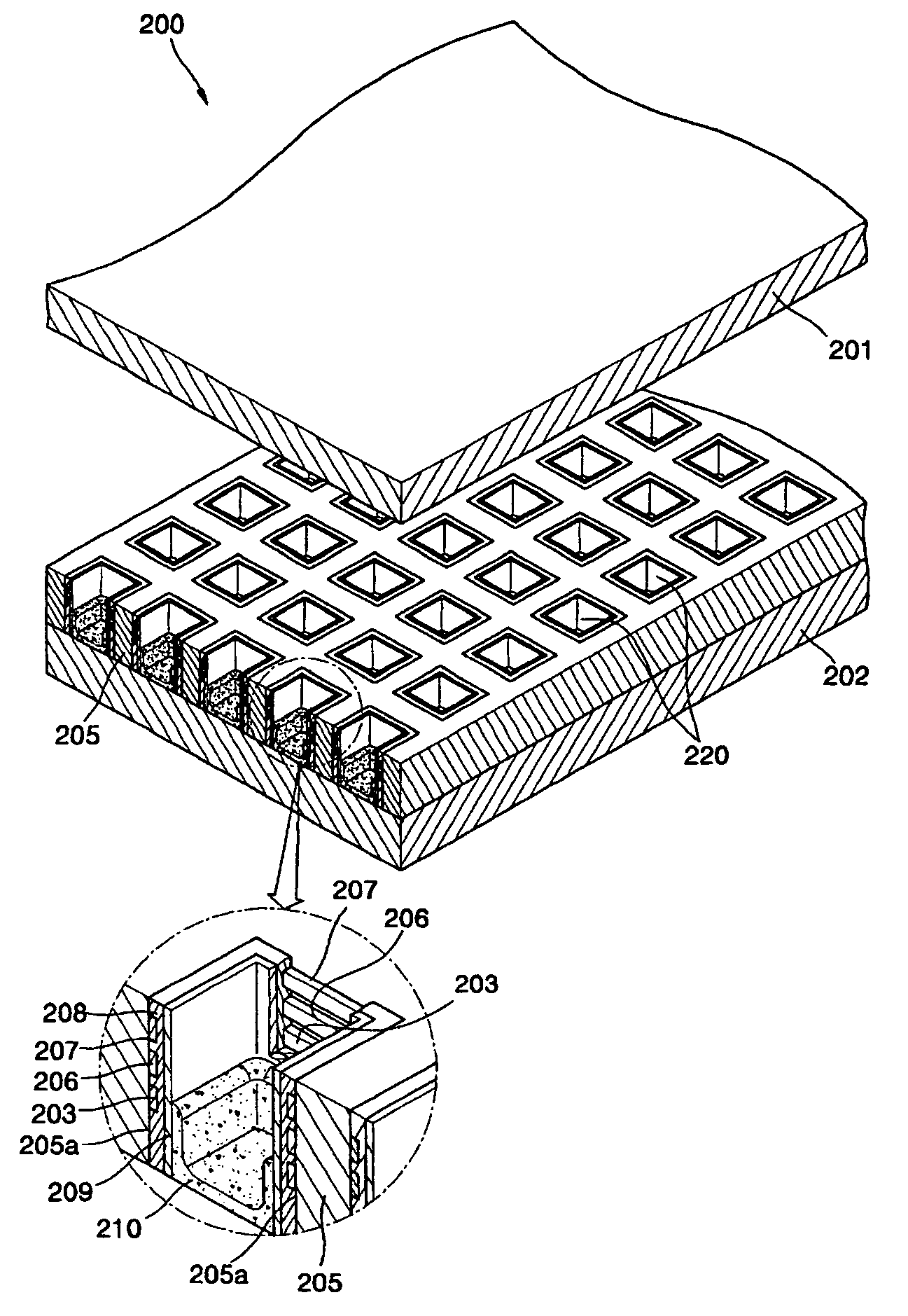

Plasma display panel and field emission display

InactiveUS20080129188A1Effective dispersionHigh definitionNanostructure manufactureSustain/scan electrodesField emission displayDisplay device

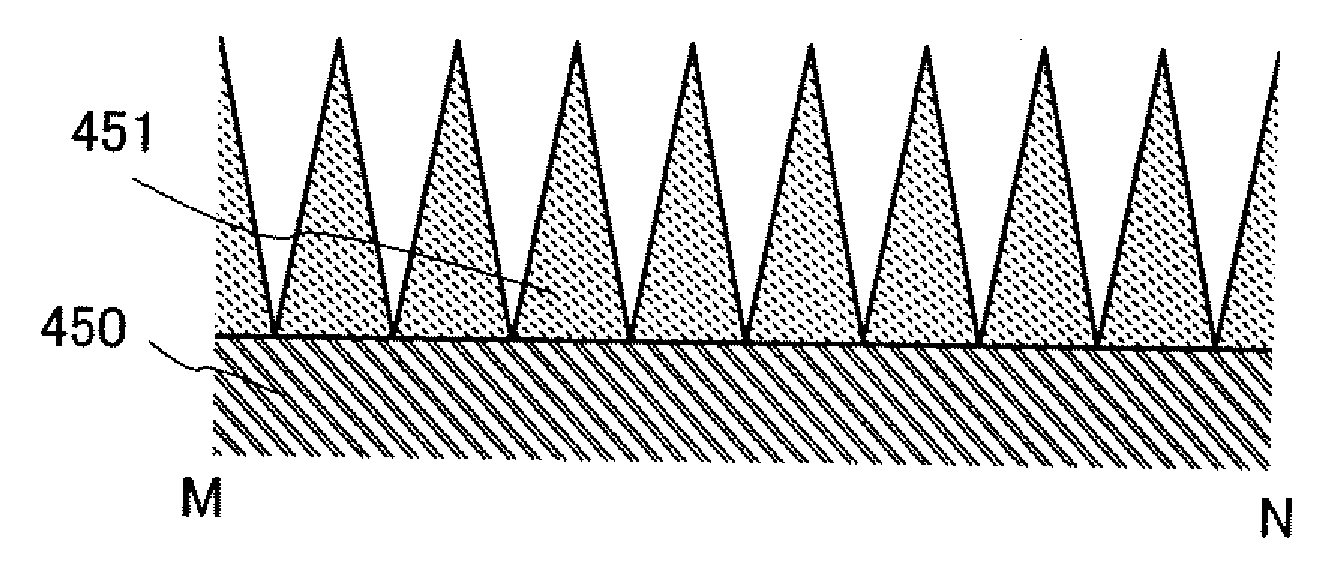

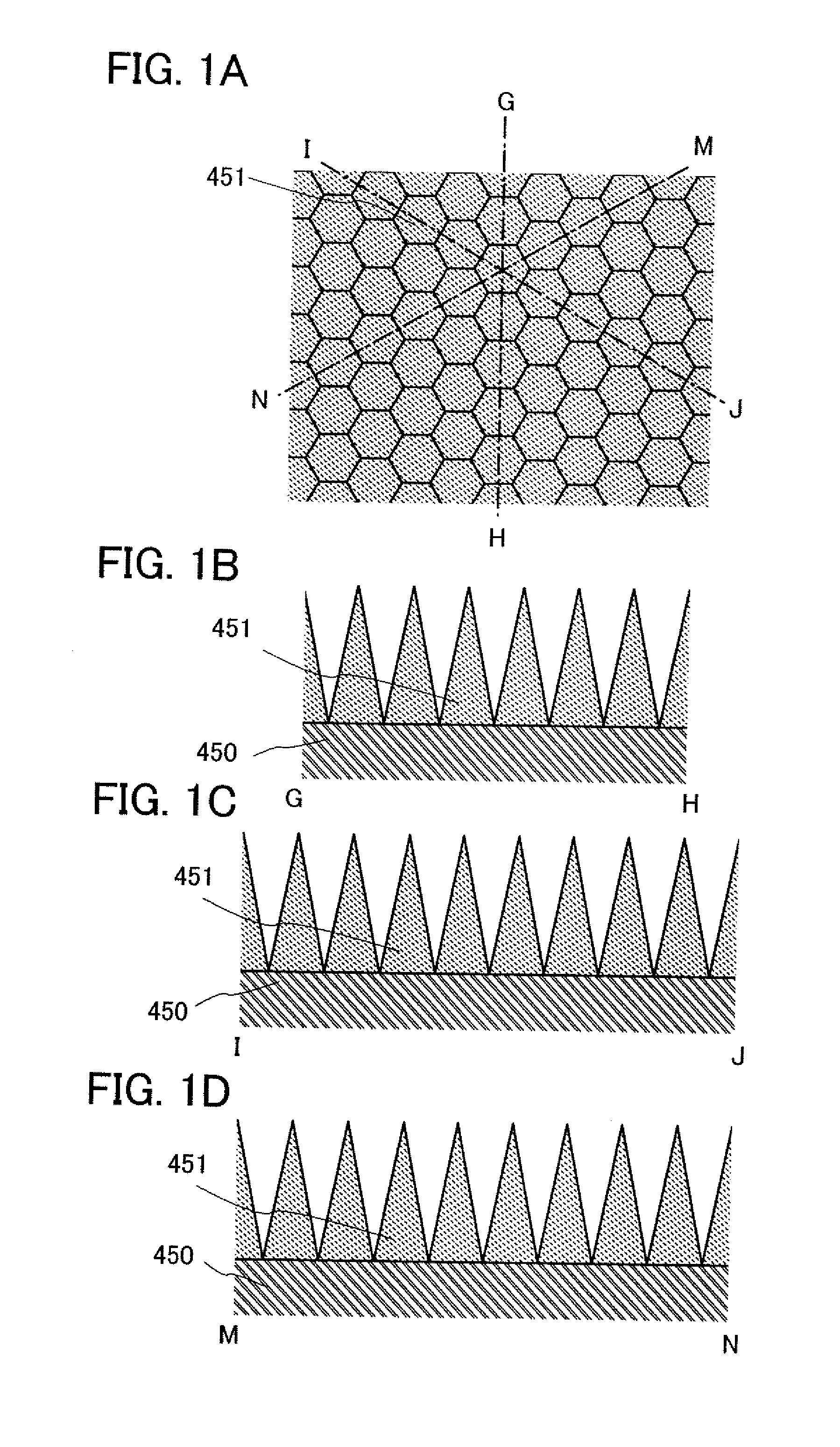

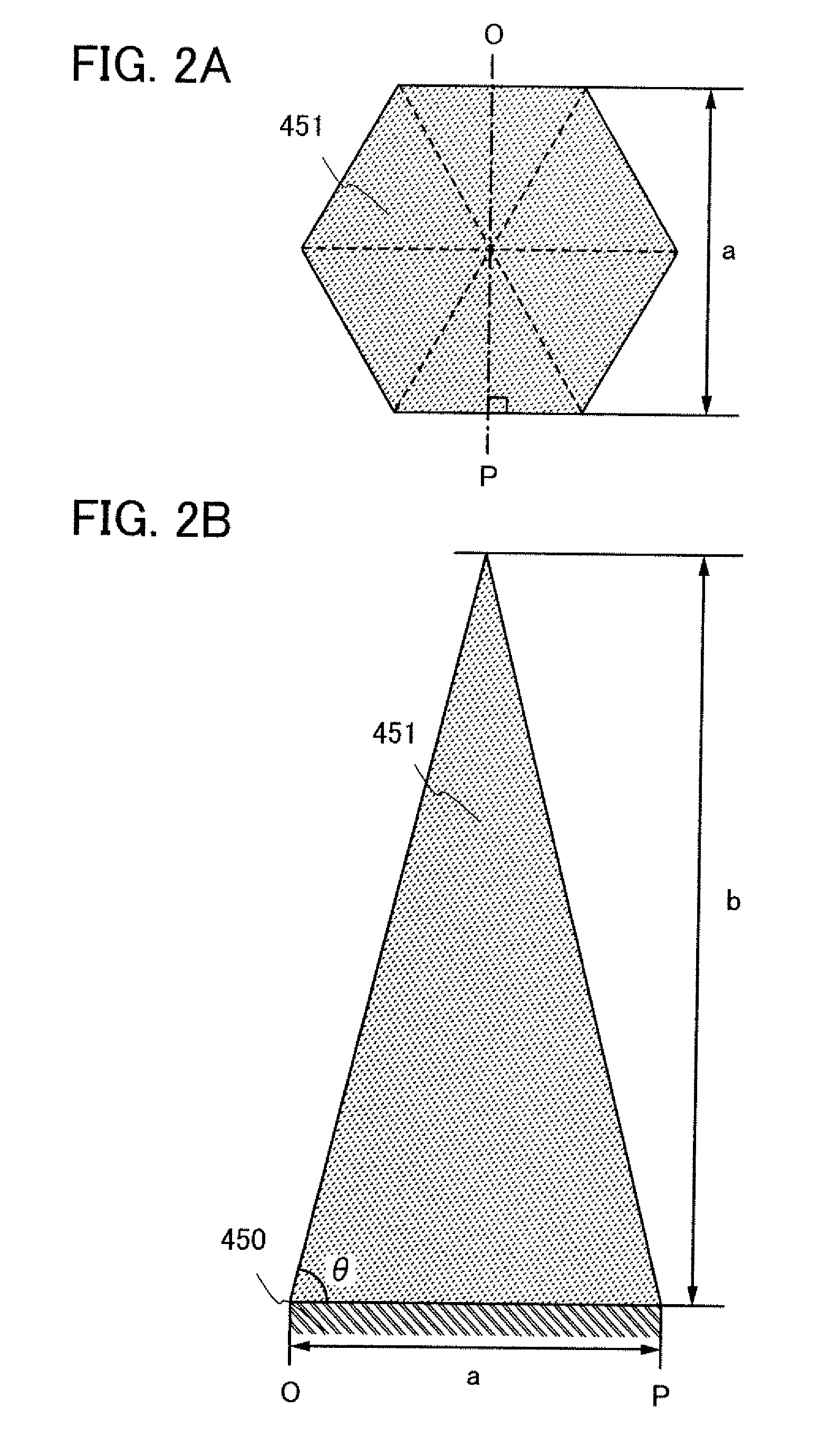

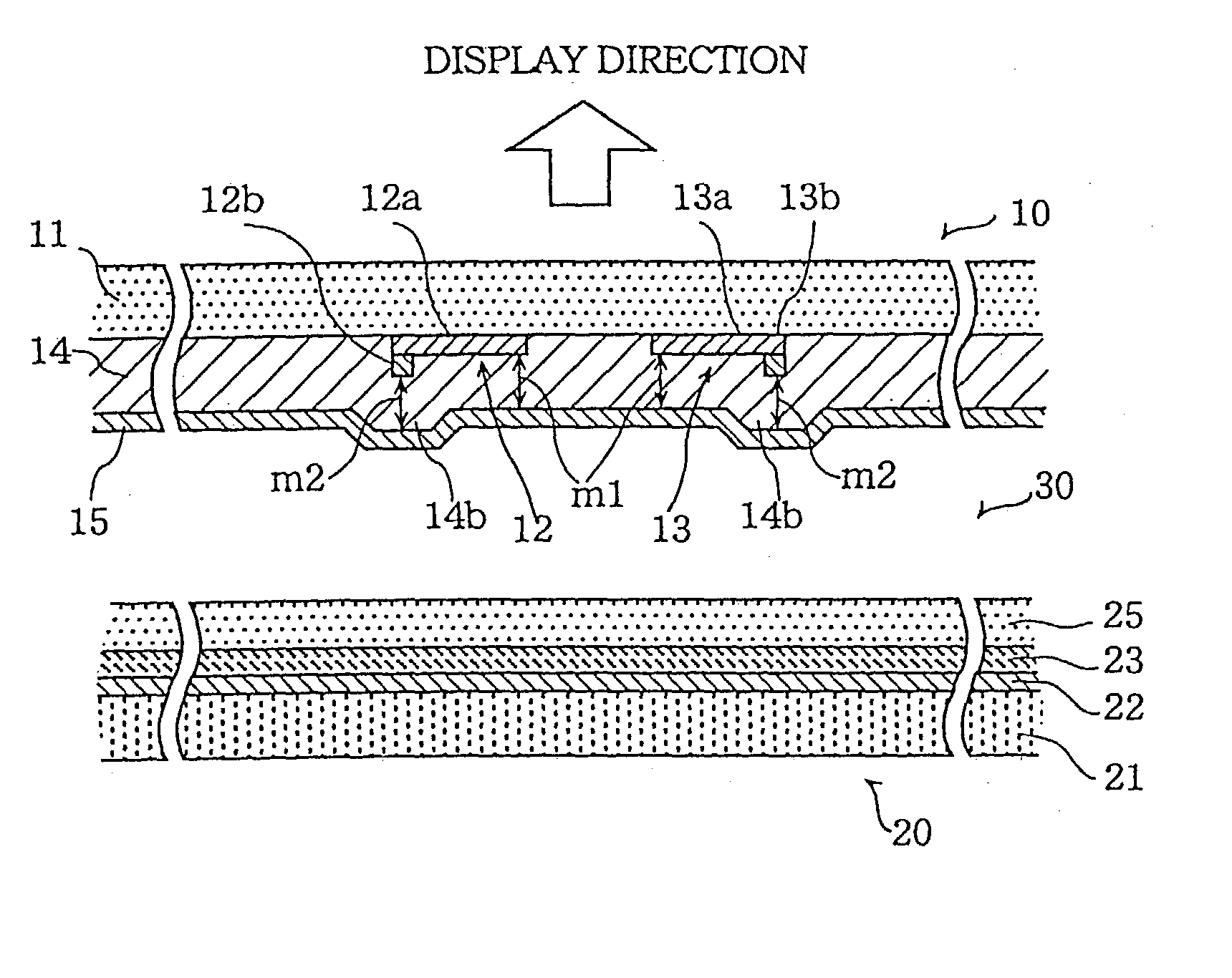

To provide a plasma display panel and a field emission display having an anti-reflection function which can further reduce reflection of incident light from an external source. By providing an anti-reflection layer which geometrically includes a plurality of adjacent hexagonal pyramid-shaped projections, reflection of light is prevented. The reflective index changes from a surface side of display screen to an out side (an atmosphere side) due to a physical shape of a hexagonal pyramid. The plurality of hexagonal pyramid-shaped projections can be provided densely without any space remaining, and six surfaces of side of the hexagonal pyramid-shaped projection are each provided at different angles to a base surface. Therefore, light ray can be effectively scattered in many directions.

Owner:SEMICON ENERGY LAB CO LTD

Plasma display panel and method for its manufacure

InactiveUS20030038599A1Improve luminous efficiencyReduce manufacturing costAlternating current plasma display panelsVessels or leading-in conductors manufactureDielectricPhosphor

A plasma display panel that requires lower consumption power to drive is proved. This plasma display has a good luminance efficacy, is less tending to yellowing of glass and deterioration of phosphors, and is manufactured at a low cost. The dielectric layers and ribs of the PDP are made from a silicone resin containing polysiloxane bond. Preferably, the silicon resin should have siloxane bond joined with methyl group, ethyl group or phenyl group. It is also preferable that a sealing member is made from a silicone resin.

Owner:PANASONIC CORP

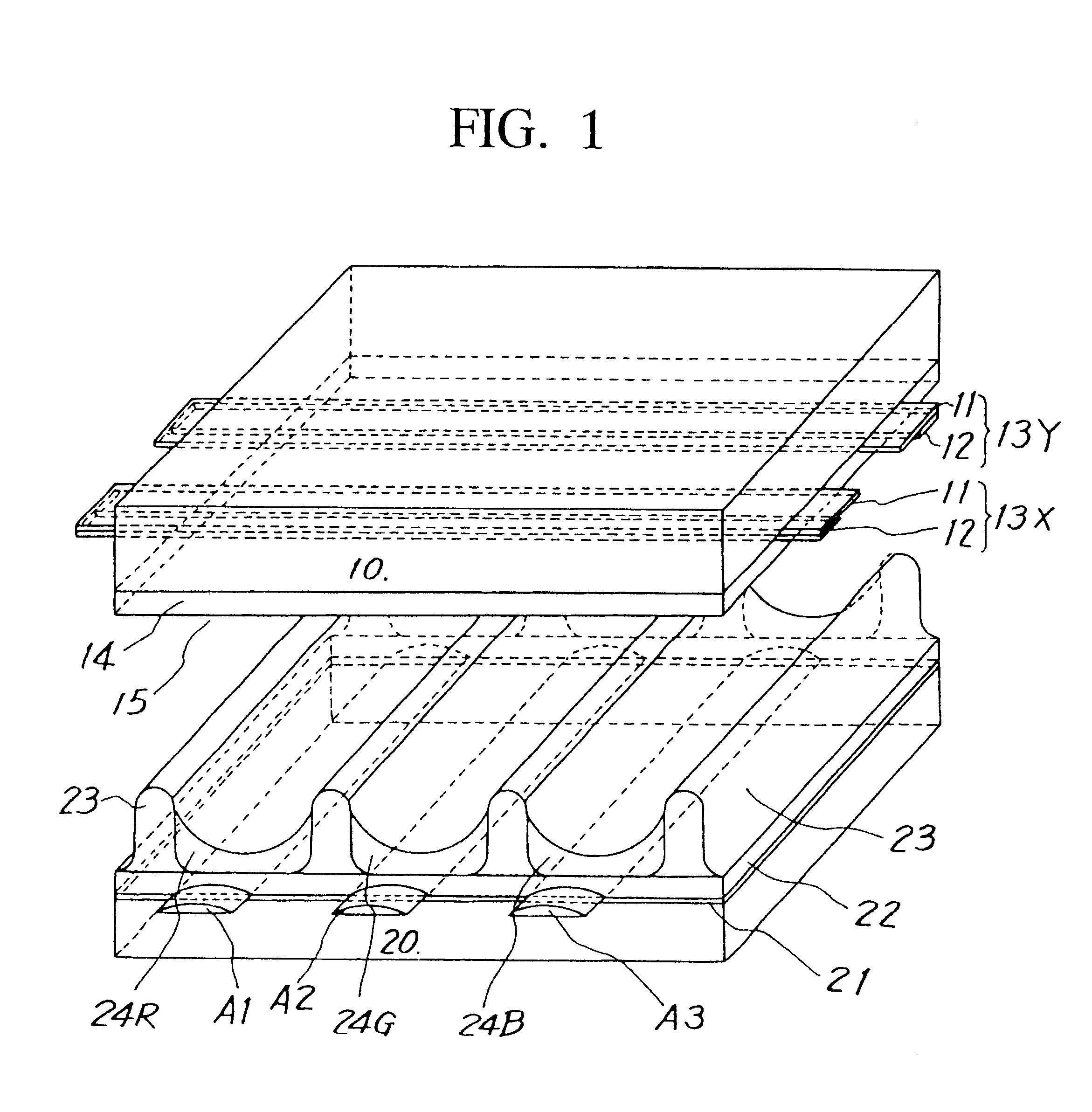

Plasma display panel using color filters to improve contrast

InactiveUS20060175971A1Increase contrastAddress electrodesSustain/scan electrodesImage contrastEngineering

A plasma display panel is provided. The plasma display panel includes a front substrate; a rear substrate arranged to face the front substrate, a dielectric layer arranged between the front and the rear substrates and at least a portion of the dielectric layer having a first color, plurality of barrier ribs arranged between the front and the rear substrates and at least a portion of the plurality of barrier ribs having a second color, plurality of light absorbing layers arranged between the front substrate and the plurality of barrier ribs, wherein the first and the second colors are subtractive-mixed with each other. The dielectric layer and the plurality of barrier ribs are colored with two complementary colors that essentially filter out nearly all light. Accordingly, it is possible to reduce outdoor daylight reflection and improve image contrast

Owner:SAMSUNG SDI CO LTD

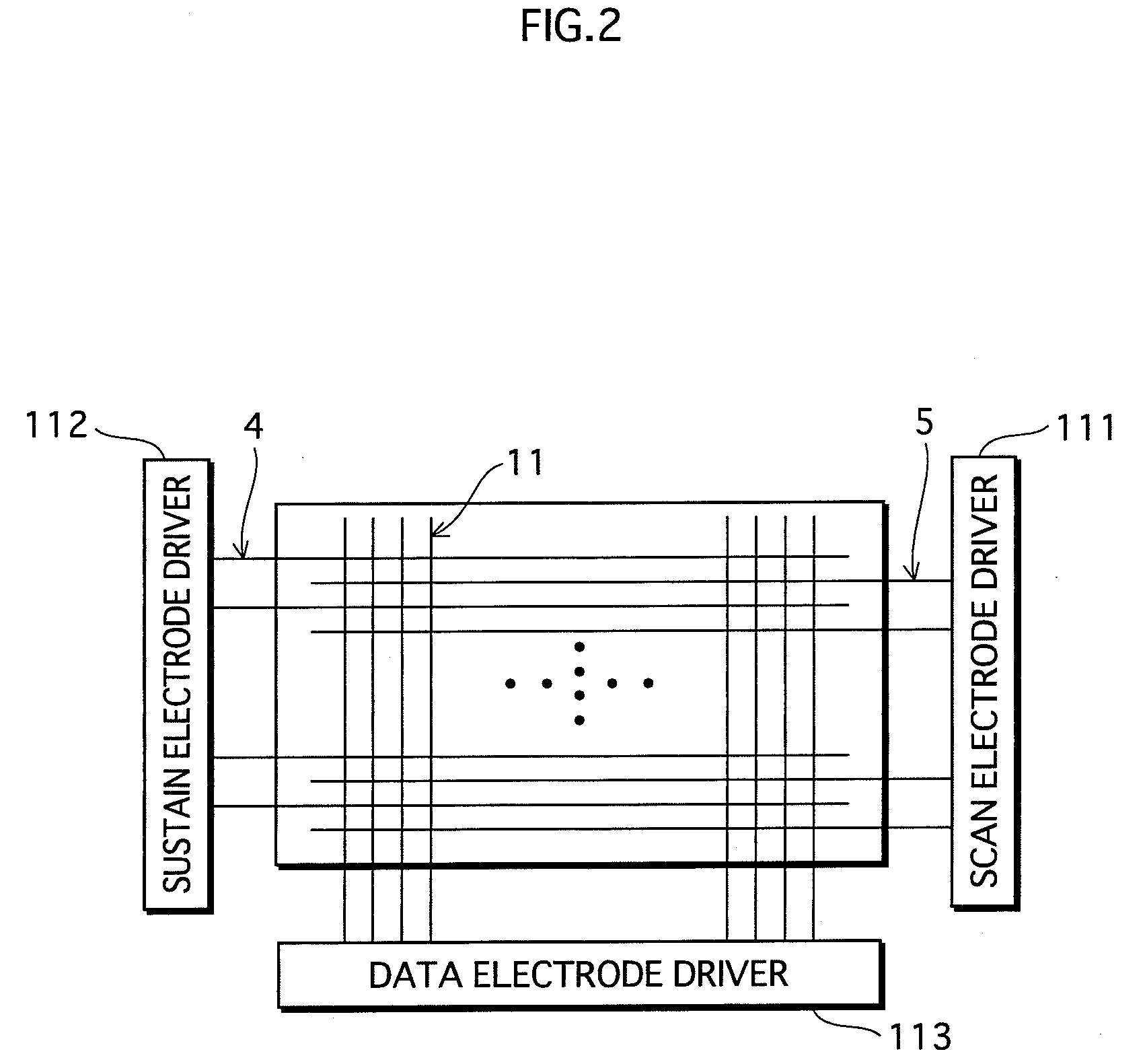

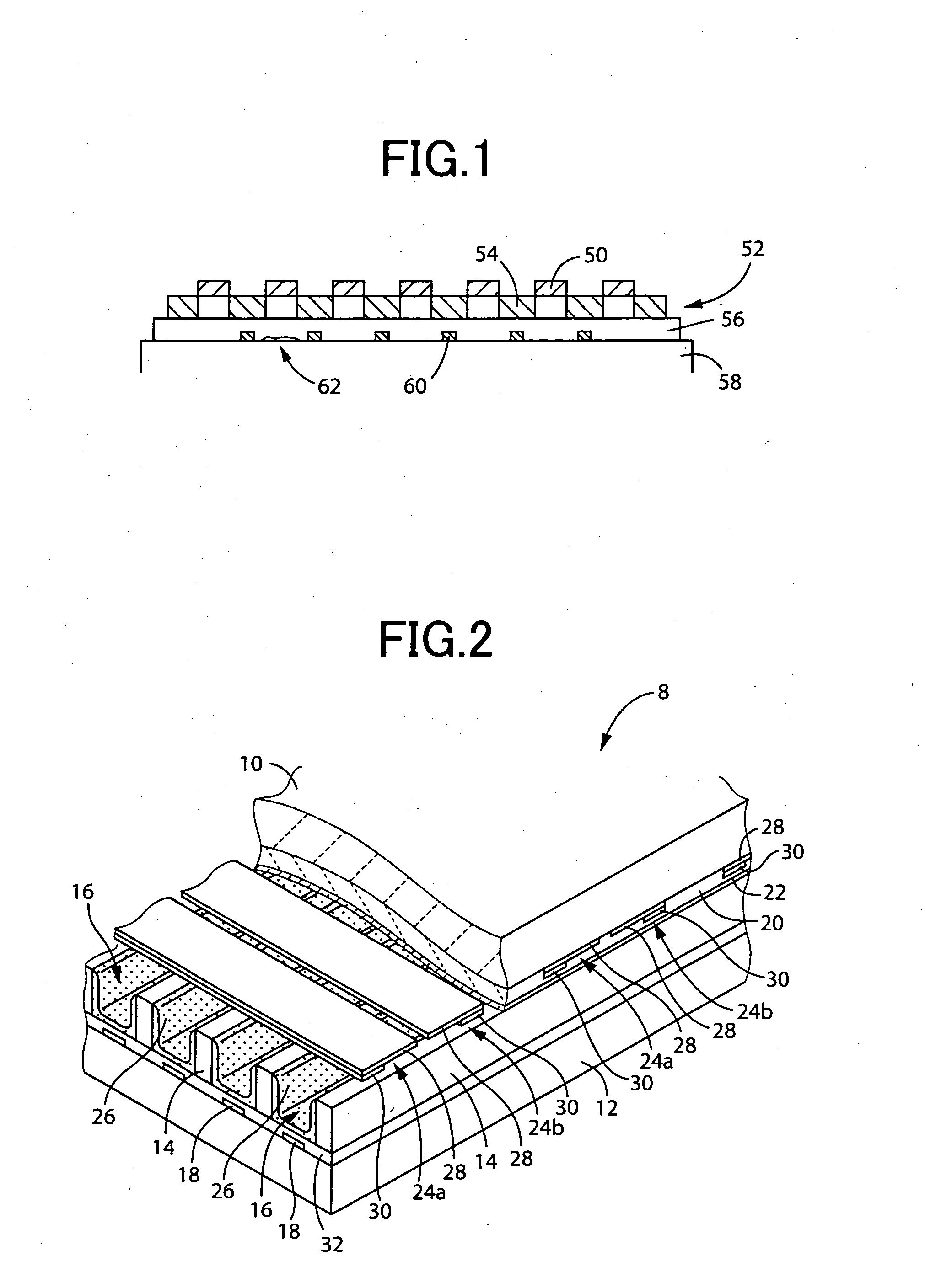

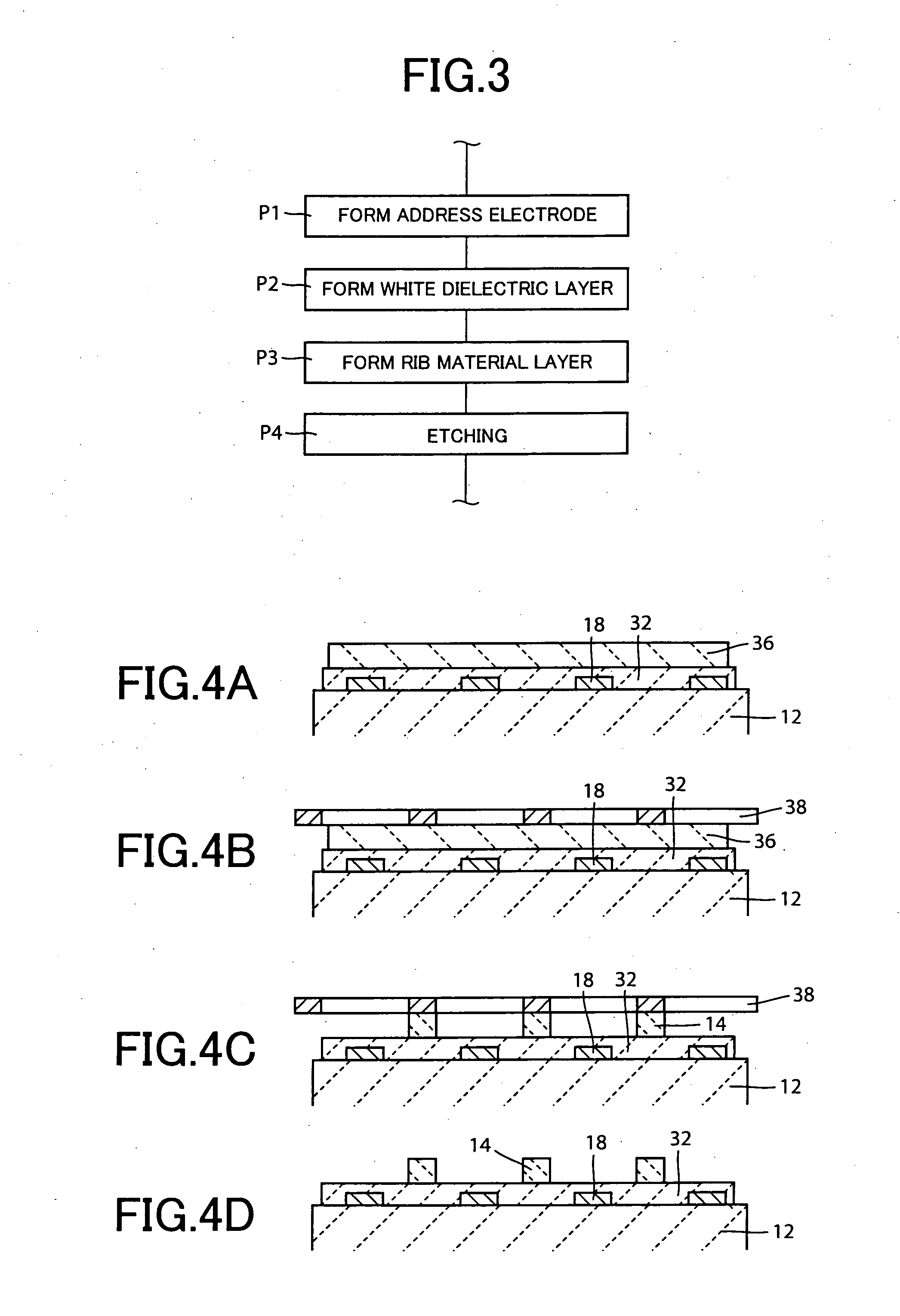

Method of manufacturing plasma display panel and method of manufacturing plasma display apparatus

InactiveUS20050130547A1Shorten the timeReduce manufacturing costGas discharge electrodesAlternating current plasma display panelsSilver pasteFrit

Address electrode patterns are formed on a rear surface glass substrate using a silver paste for forming address electrodes, and these patterns are dried. The average particle size of the silver powder in the silver paste is approximately 10 nm, and the softening point of the glass frit is approximately 420° C. The content ratio of the glass frit in the silver paste is set to 5 wt %. Then, a dielectric layer pattern is formed by using glass paste for forming a white dielectric layer so as to cover the address electrode patterns, and this dielectric layer pattern is dried. The glass frit in the glass paste has a softening point of approximately 540° C. Then, the address electrode patterns and the dielectric layer patterns are baked at a temperature of 540° C. Thus, the resin components in the address electrode patterns and the dielectric layer pattern are burnt away, and the glass frit components are softened so as to be fixed onto the rear surface glass substrate.

Owner:PANASONIC CORP

Phosphor and plasma display panel using the same

InactiveUS20060152135A1Improved after-glow characteristicIncrease contrastAddress electrodesSustain/scan electrodesHemt circuitsPhysical chemistry

A phosphor for a plasma display panel (PDP) has a decay time of about 1 ms or less when a Xe concentration is about 10 wt % to about 30 wt % based on the total weight of a discharge gas. A phosphor composition includes the same and a PDP includes a phosphor layer comprising the phosphor or the phosphor composition. When the phosphor or the phosphor composition are used, a low gray scale and low discharge problem due to a green phosphor of a PDP may be solved, a permanent afterimage due to a green phosphor is reduced, and a color reproduction range is significantly broadened compared to a conventional green phosphor of a PDP. In addition, the circuit of the PDP is simplified since colors are not individually subjected to gamma correction but are corrected using a single white gamma. Furthermore, the contrast in a light room is also improved due to the use of phosphor powders with color.

Owner:SAMSUNG SDI CO LTD

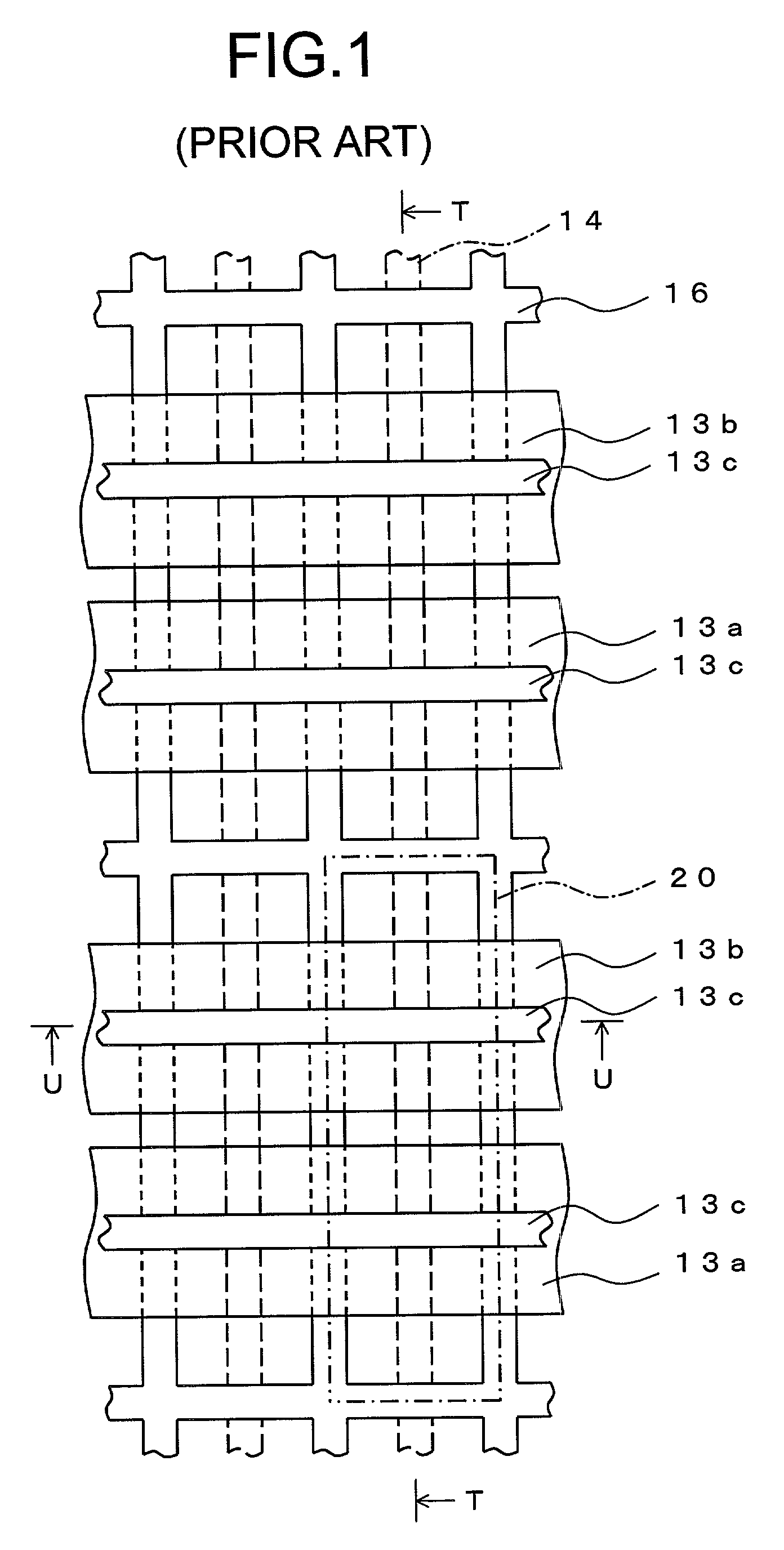

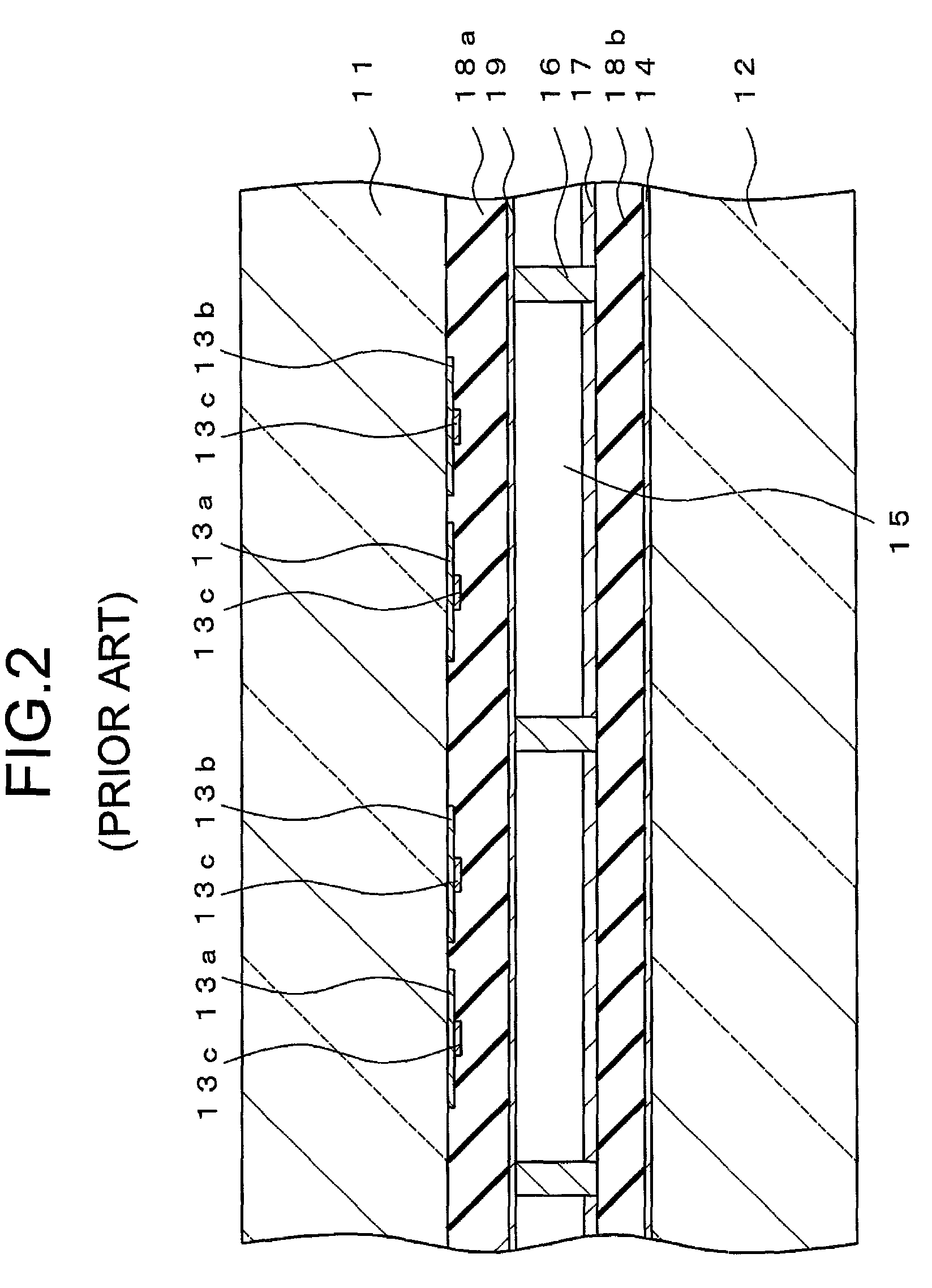

Plasma display panel and method for fabricating the same

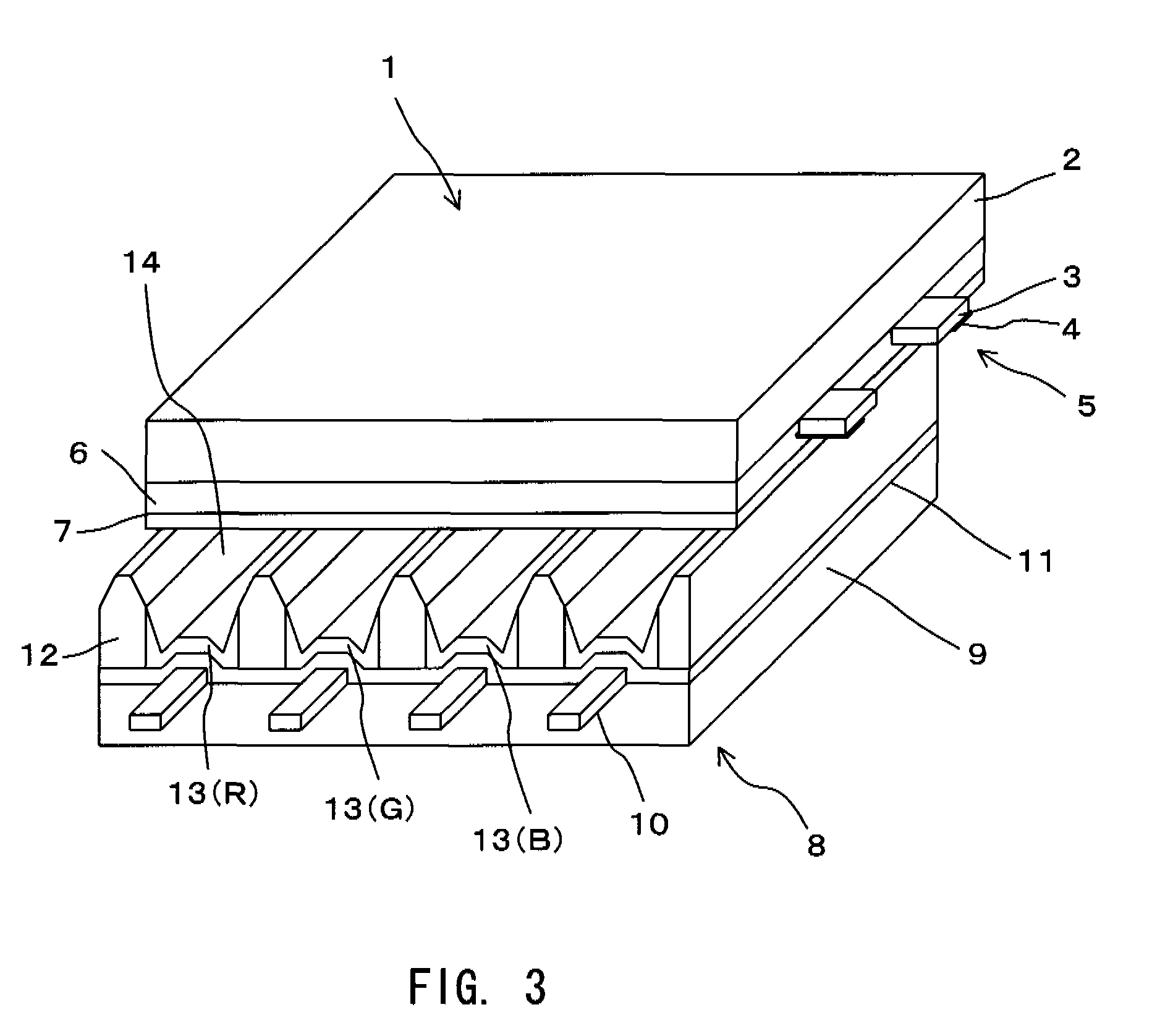

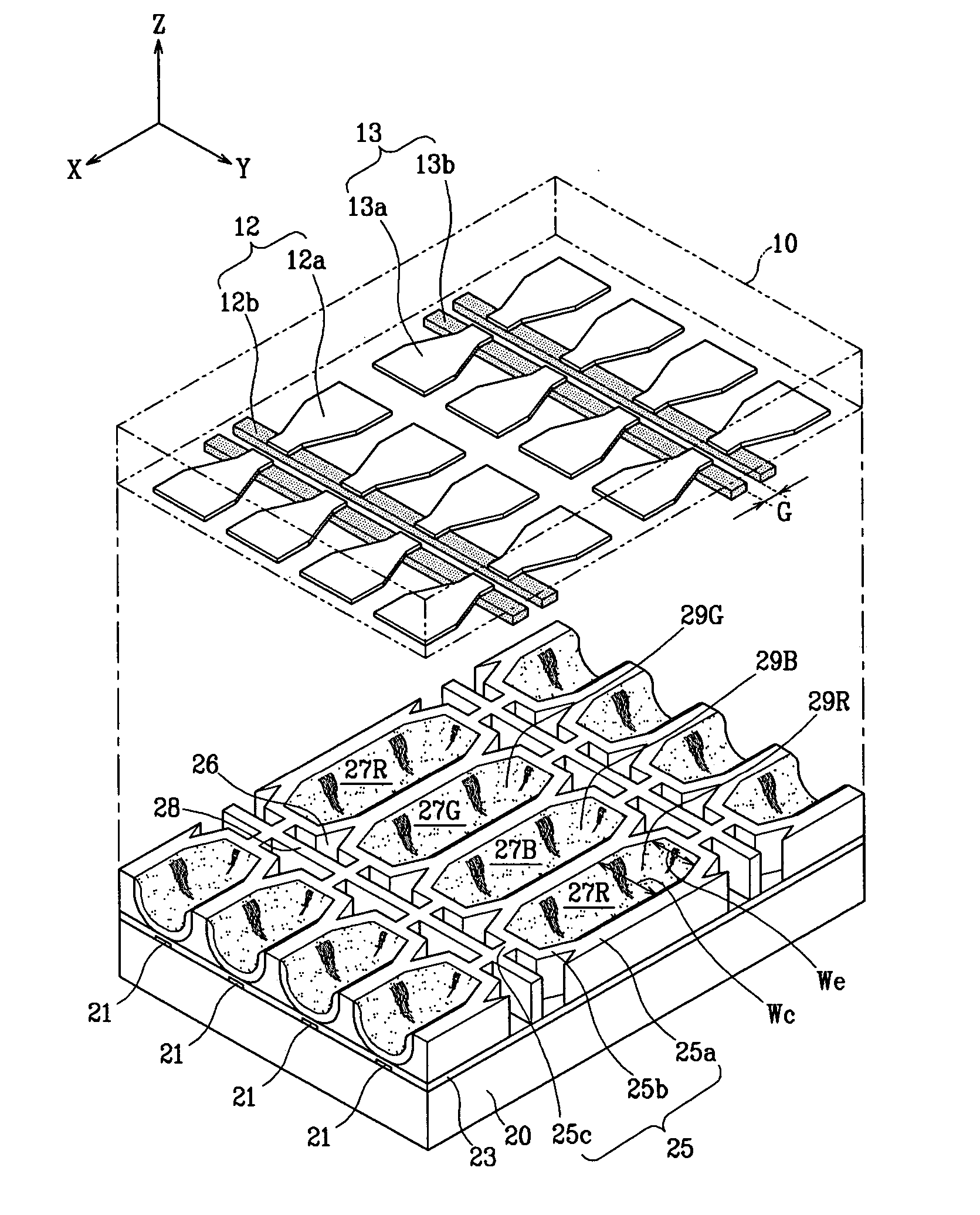

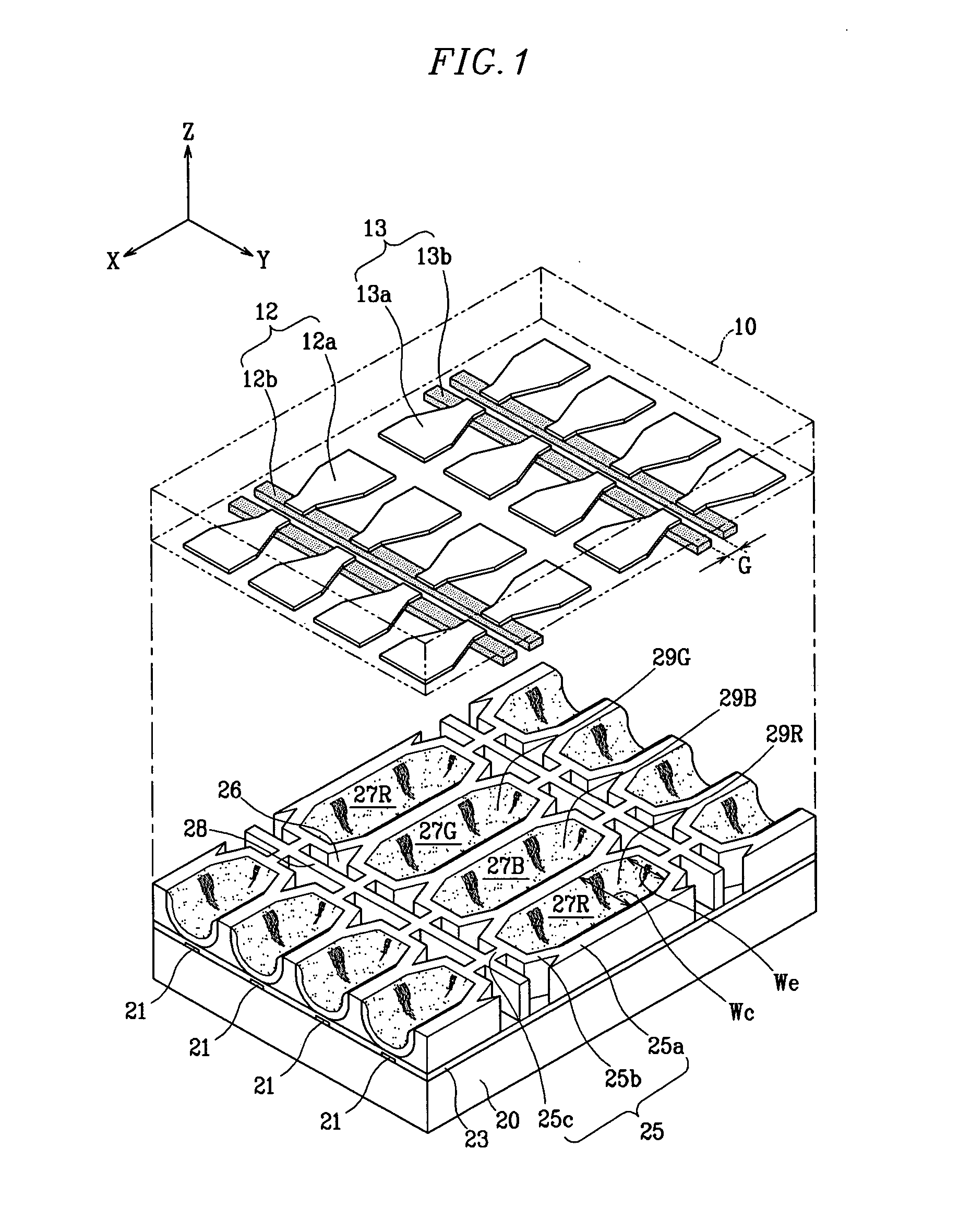

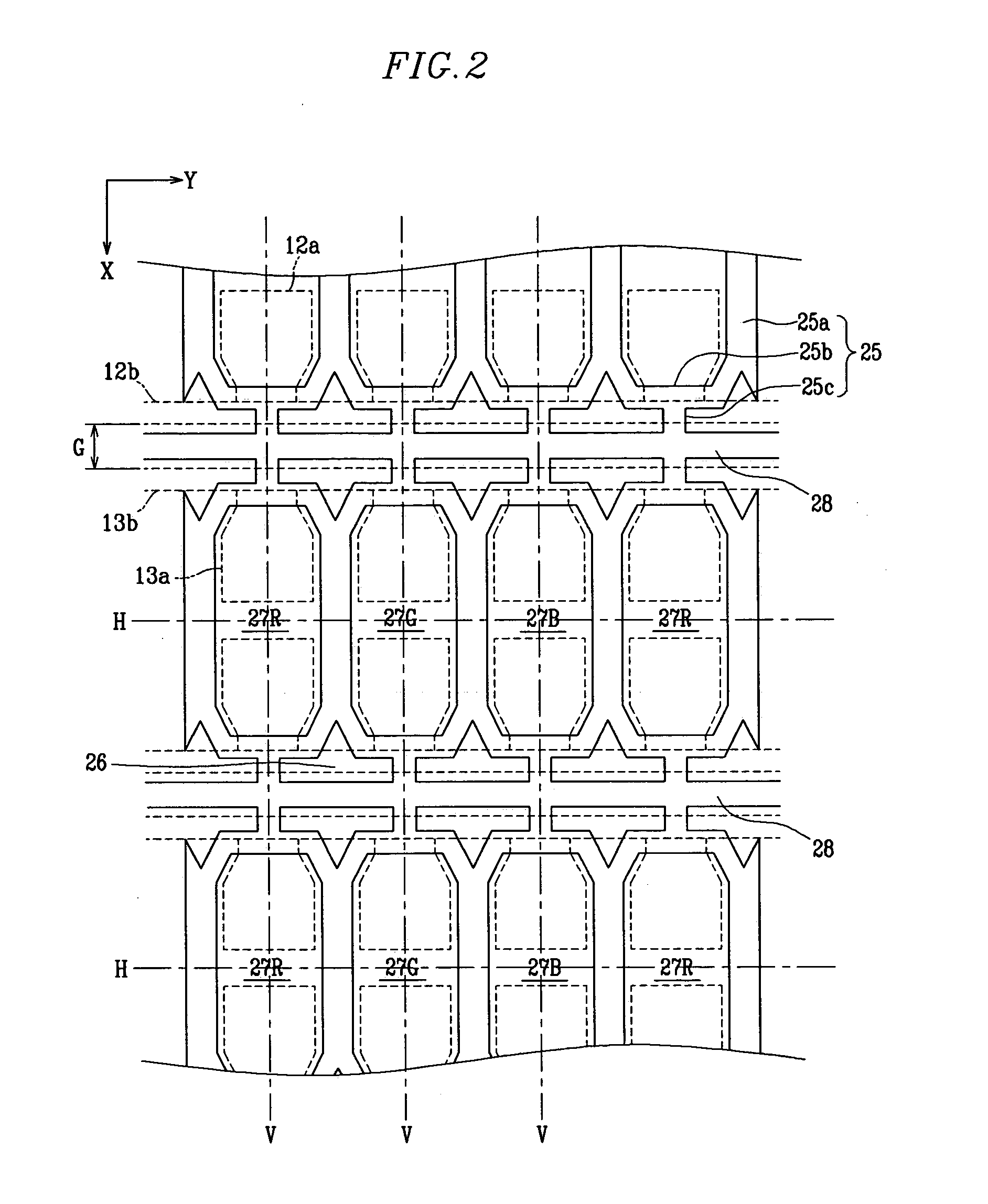

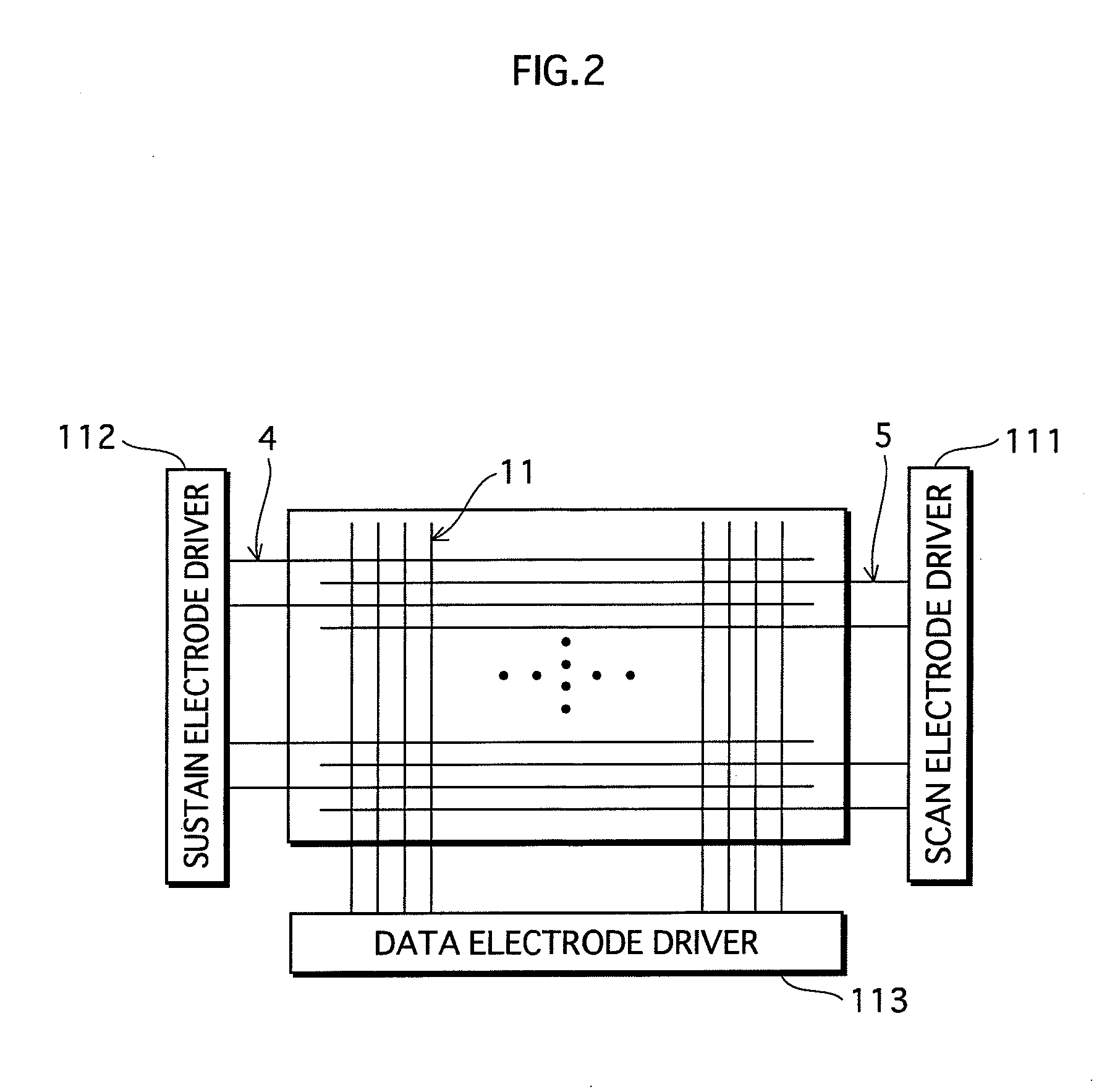

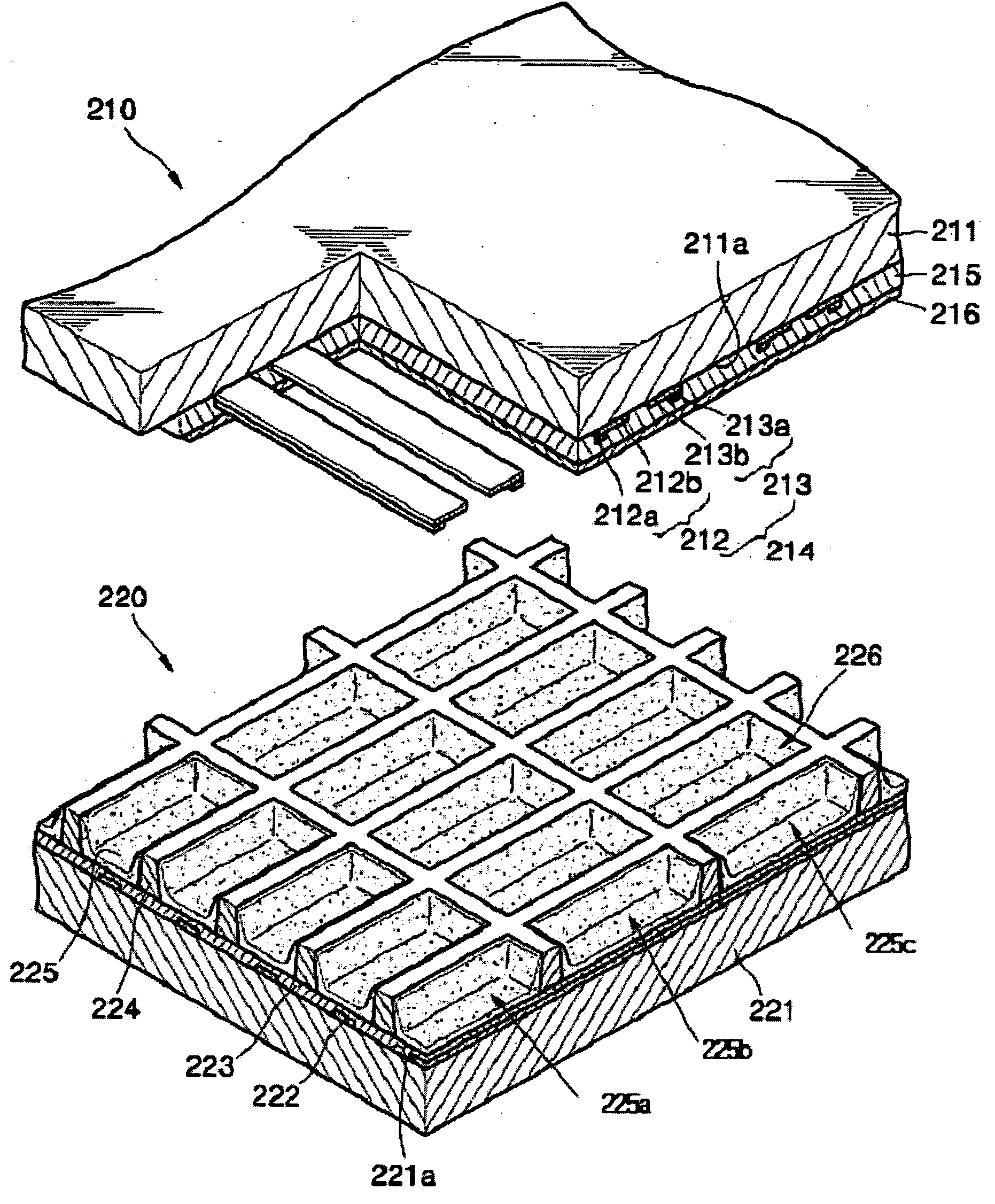

InactiveUS7002296B2Improve efficiencyLess power consumptionAddress electrodesSustain/scan electrodesEngineeringPlasma display

Ribs for defining pixel cells are formed in the shape of a lattice, and sustain electrodes and scan electrodes are disposed near the ribs. The electrodes are spaced apart in each pixel cell, and the sustain electrode and the scan electrode are each cut away between pixel cells arranged in the row direction to provide each pixel cell with individually separated electrodes. In addition, between pixel cells adjacent to each other in the row direction, the sustain electrodes and the scan electrodes are connected to each other by means of a sustain-side bus electrode and a scan-side bus electrode, respectively. This makes it possible to provide a high luminous efficiency.

Owner:PANASONIC CORP

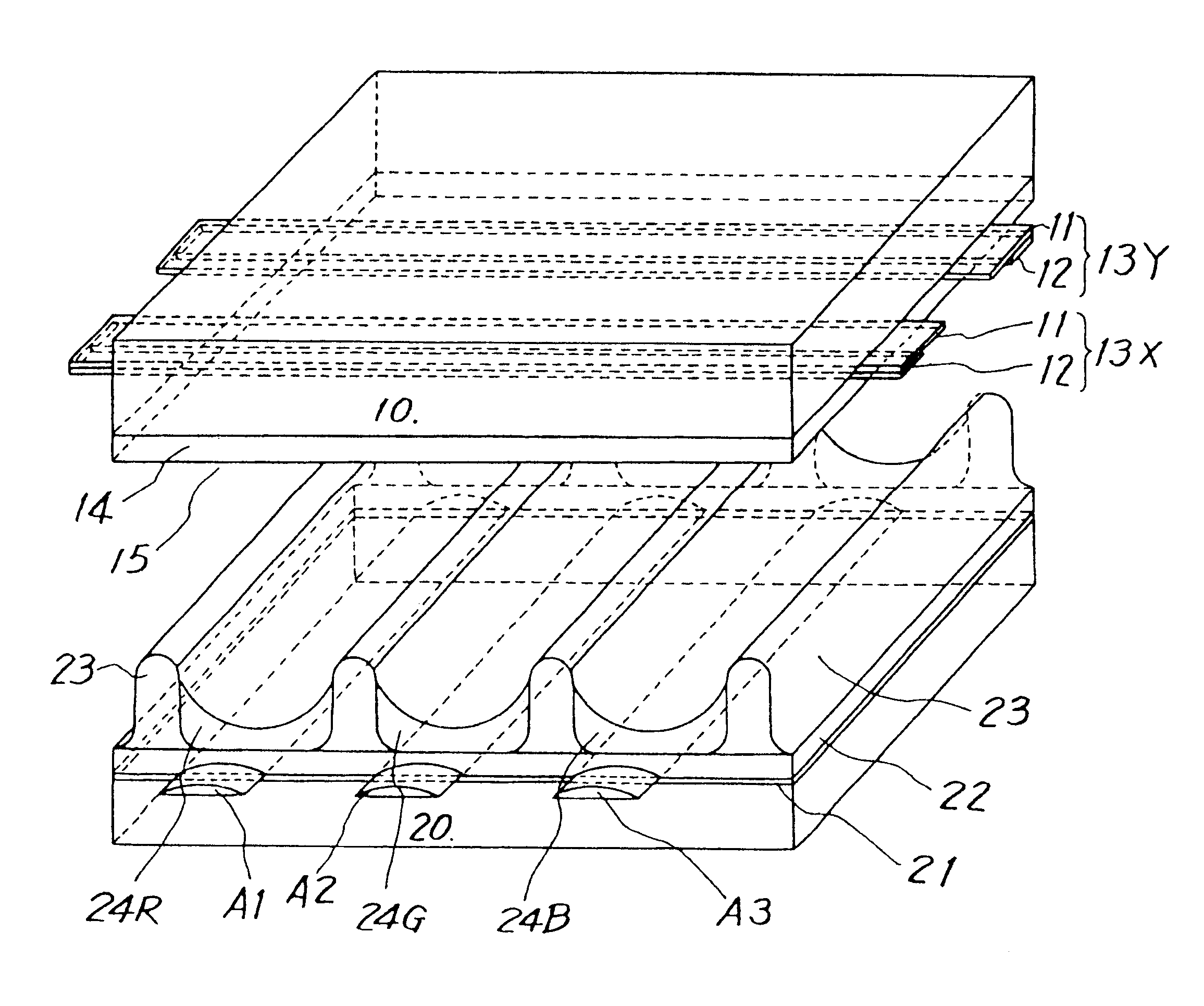

Plasma display panel using color filters to improve contrast

InactiveUS20050040767A1Prevents external reflection of lightIncrease contrastAddress electrodesSustain/scan electrodesImage contrastFluorescence

A plasma display panel is provided. The plasma display panel includes a front substrate, an X electrode and a Y electrode alternately formed on the front substrate, a dielectric layer formed to cover the X and Y electrodes, a rear substrate installed to face the front substrate, address electrodes formed on the rear substrate and intersecting the X and Y electrodes, barrier ribs formed between the front and rear substrates, and red, green, and blue fluorescent layers applied in discharge cells defined by the barrier ribs. The dielectric layer and the barrier ribs are colored with two complementary colors that essentially filter out nearly all light. Accordingly, it is possible to reduce outdoor daylight reflection and improve image contrast by an improved design over the use of black stripes.

Owner:SAMSUNG SDI CO LTD

Plasma display panel and image display system using same

InactiveUS20070001602A1Degradation in display luminance being suppressedIncrease display contrastAddress electrodesSustain/scan electrodesPhosphorFluorescence

A plasma display panel has plural discharge cells between two opposing first and second substrates. Each of the discharge cells includes at least one pair of electrodes for generating a discharge for display, a discharge gas and a phosphor film for emitting visible light by being excited by ultraviolet rays produced by the discharge of the discharge gas. Laminated members are dispersed in a plane within each of the discharge cells inside the first substrate from which visible light for display is emitted, and each of the laminated members includes a light absorption layer disposed on a side of the first substrate on which ambient light is incident and a light reflection layer disposed on a phosphor-film side of the laminated members. A visible-light-reflection layer is disposed on a surface of the phosphor film on a side thereof opposite from a space in which the discharge is generated.

Owner:MAXELL HLDG LTD

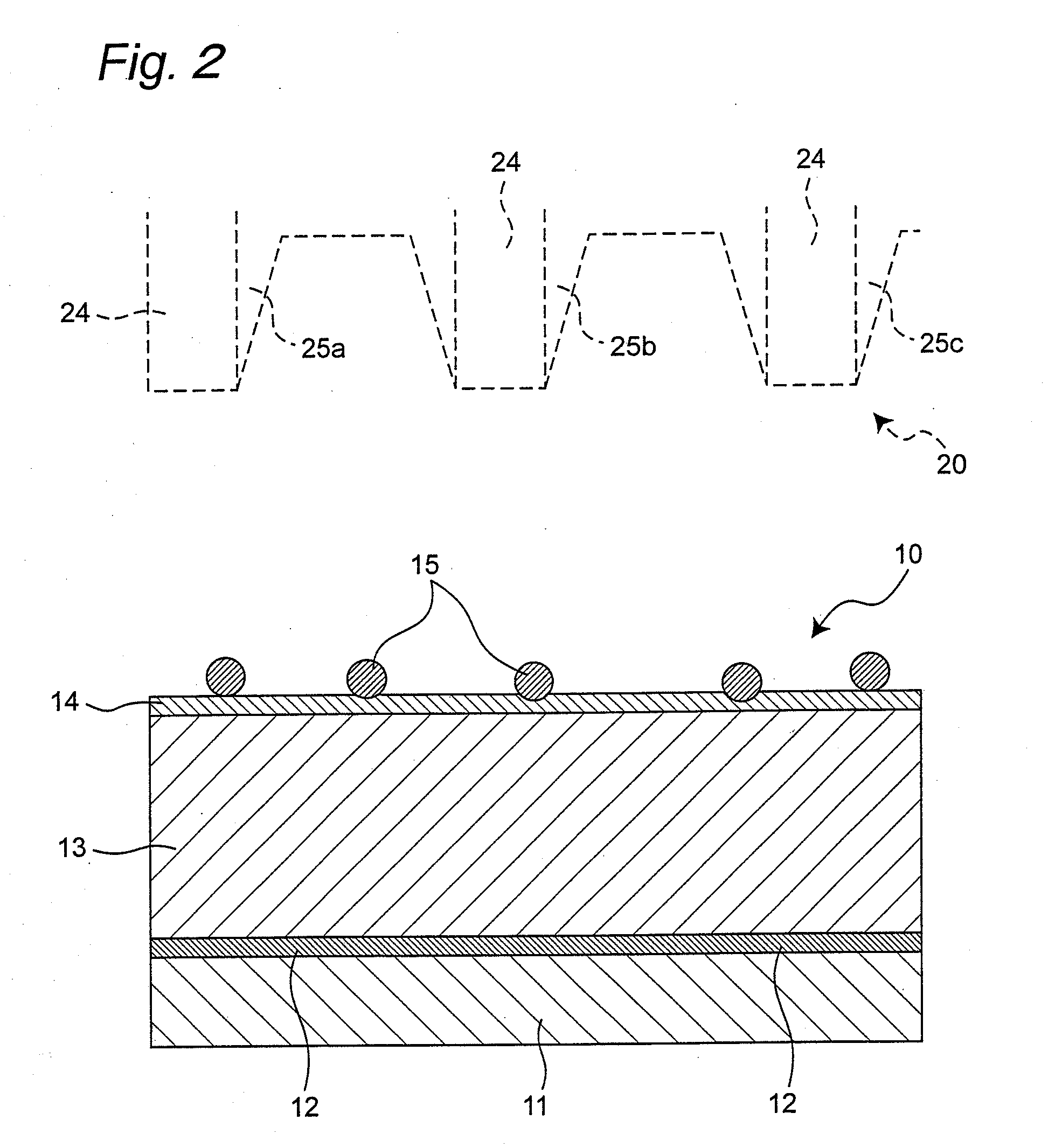

Front panel for plasma display panel and method for producing the same, and plasma display panel

InactiveUS20080290800A1Suppress incidentImprove stabilitySustain/scan electrodesAlternating current plasma display panelsEngineeringProtection layer

The present invention provides a front panel for a plasma display panel which can suppress the incidence of chipping of the barrier rib of a rear panel for a PDP, can enhance the stability of initial electron emission in a dielectric layer, and can reduce a voltage required for maintaining a wall charge. The front panel for a plasma display panel includes a substrate, a plurality of electrodes formed on the substrate, a dielectric layer formed to cover the respective electrodes and the substrate, a dielectric-protection layer formed to cover the dielectric layer, and powder components dispersed on the dielectric-protection layer, wherein an annealed layer having a thickness of 10 to 300 nm is formed on at least the exposed surface of each of the powder components, wherein said exposed surface does not contact the dielectric-protection layer.

Owner:PANASONIC CORP

Plasma display panel with dielectric layer suppressing reduced electrode conductivity

InactiveUS6344713B1Suppresses resistance riseReduce discharge voltageAddress electrodesSustain/scan electrodesIndiumDielectric layer

The present invention relates to a plasma display panel comprising transparent electrodes and a dielectric layer covering said transparent electrodes on at least one substrate of a pair of substrates facing each other with a discharge space therebetween, the main constituent of the transparent electrodes is included in the dielectric layer. Further, the main constituent of the transparent electrode is indium oxide and indium oxide is included in the dielectric layer. By including the main constituent of the transparent electrodes in the dielectric layer, it is believed that the drop in conductivity caused by diffusion of the dielectric substance in the transparent electrodes during high-temperature processing is prevented.

Owner:HITACHT MAXELL LTD

Lead-free acid-resistant glass composition and glass paste comprised of the same

InactiveUS20080185962A1Softening pointRestrain lowering of acid resistanceAddress electrodesSustain/scan electrodesFree acidMaterials science

Lead-free acid-resistant glass composition includes 5-25% of SiO2, 4-30% of B2O3, 7-30% of ZnO, 15-70% of Bi2O3, 0-15% of Al2O3, 5-20% of BaO in weight percentage, and being substantially lead-free.

Owner:NORITAKE CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com