Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30 results about "Worst-case execution time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The worst-case execution time (WCET) of a computational task is the maximum length of time the task could take to execute on a specific hardware platform.

Generational real-time garbage collection

InactiveUS20060294165A1Improved real-time garbage collectionImprove utilizationSpecial data processing applicationsMemory systemsTime rangeRefuse collection

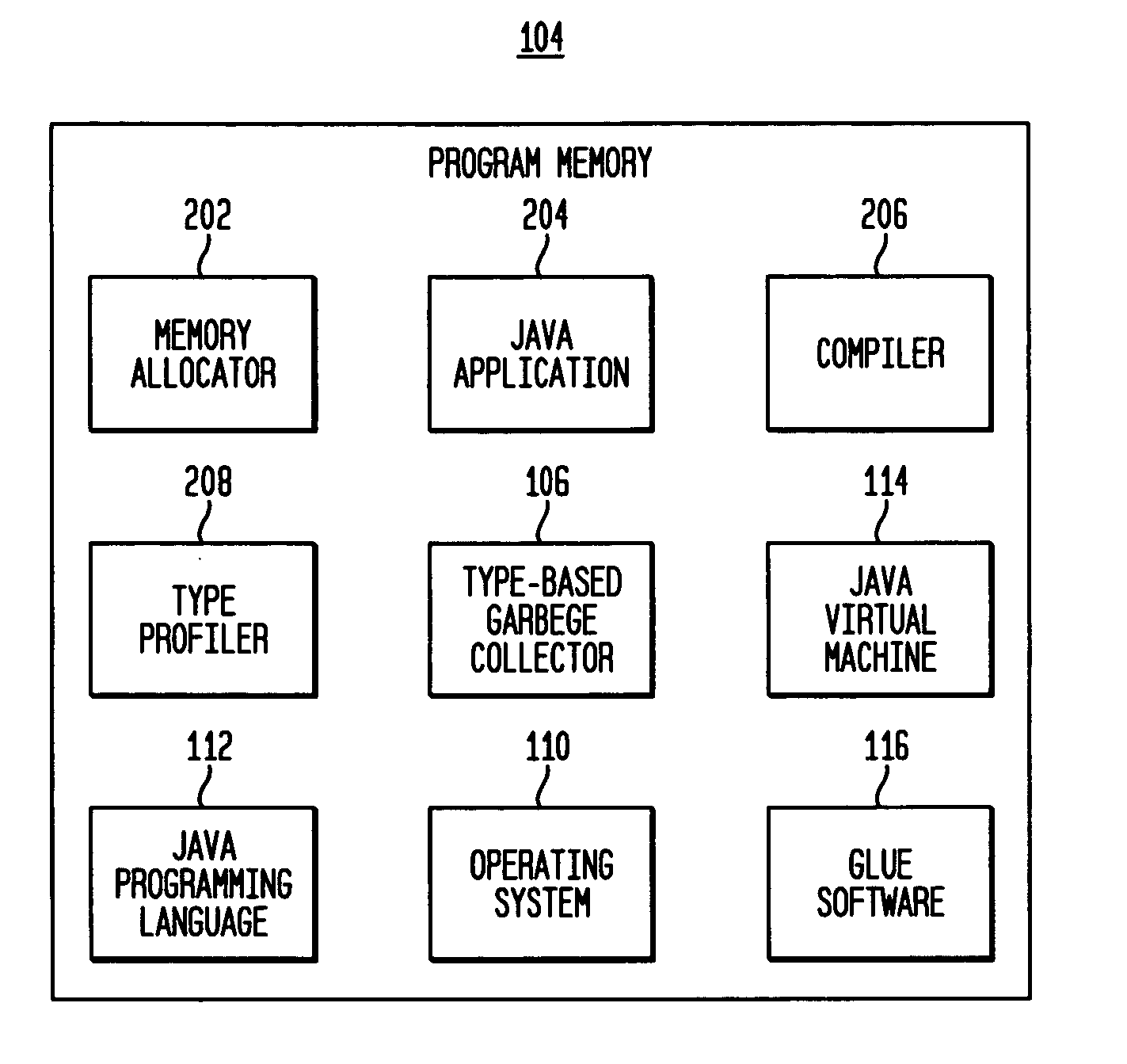

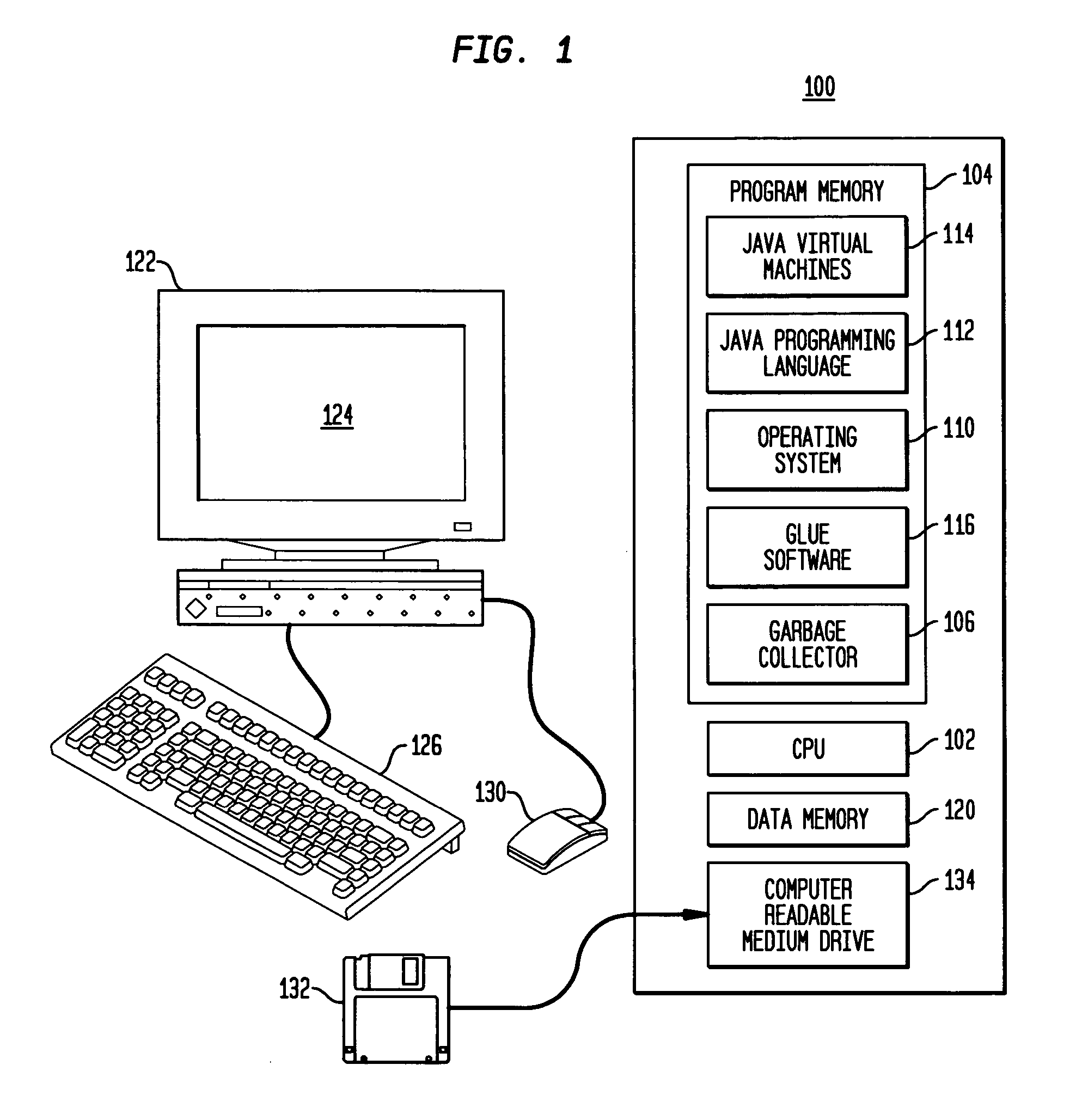

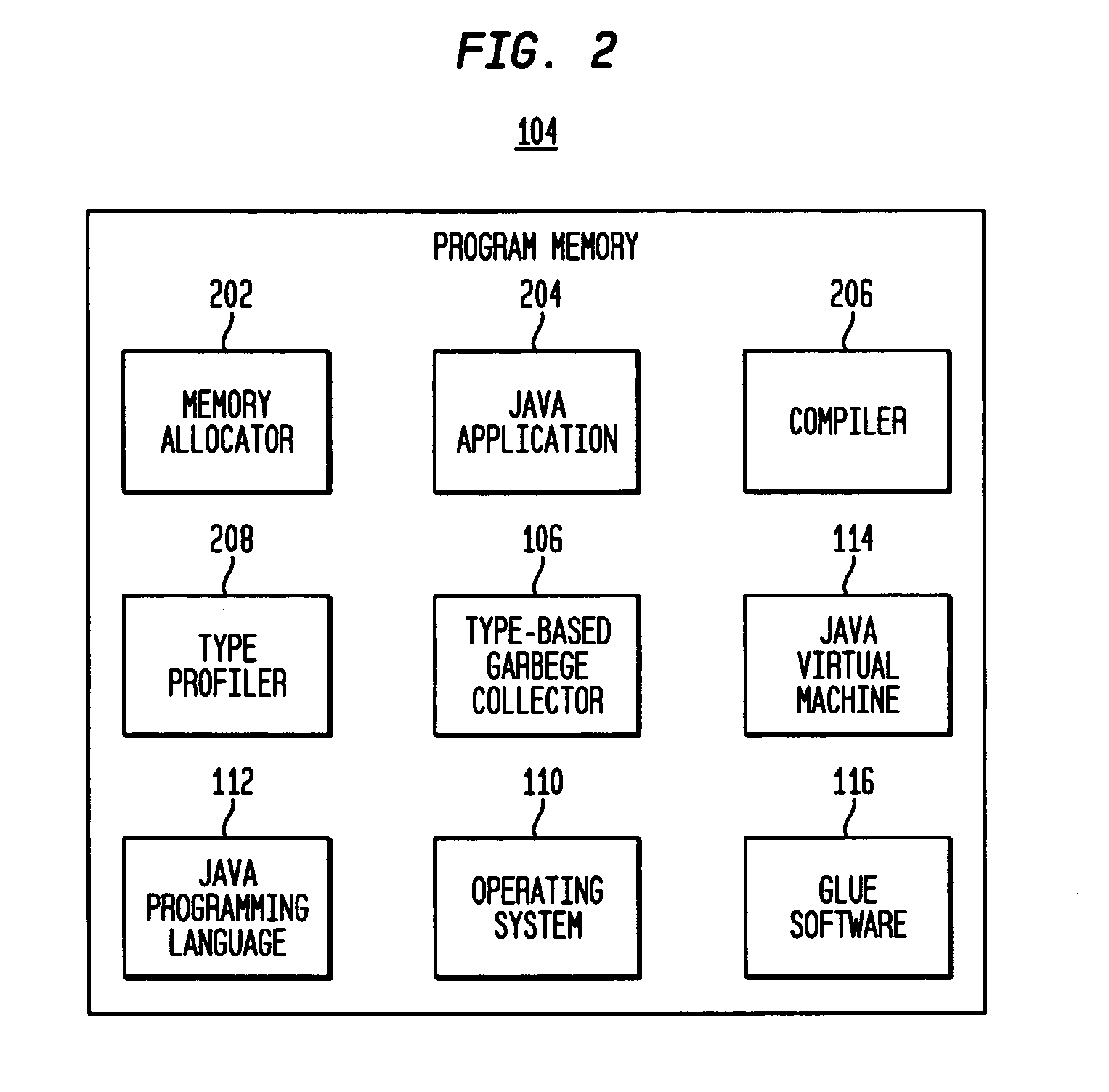

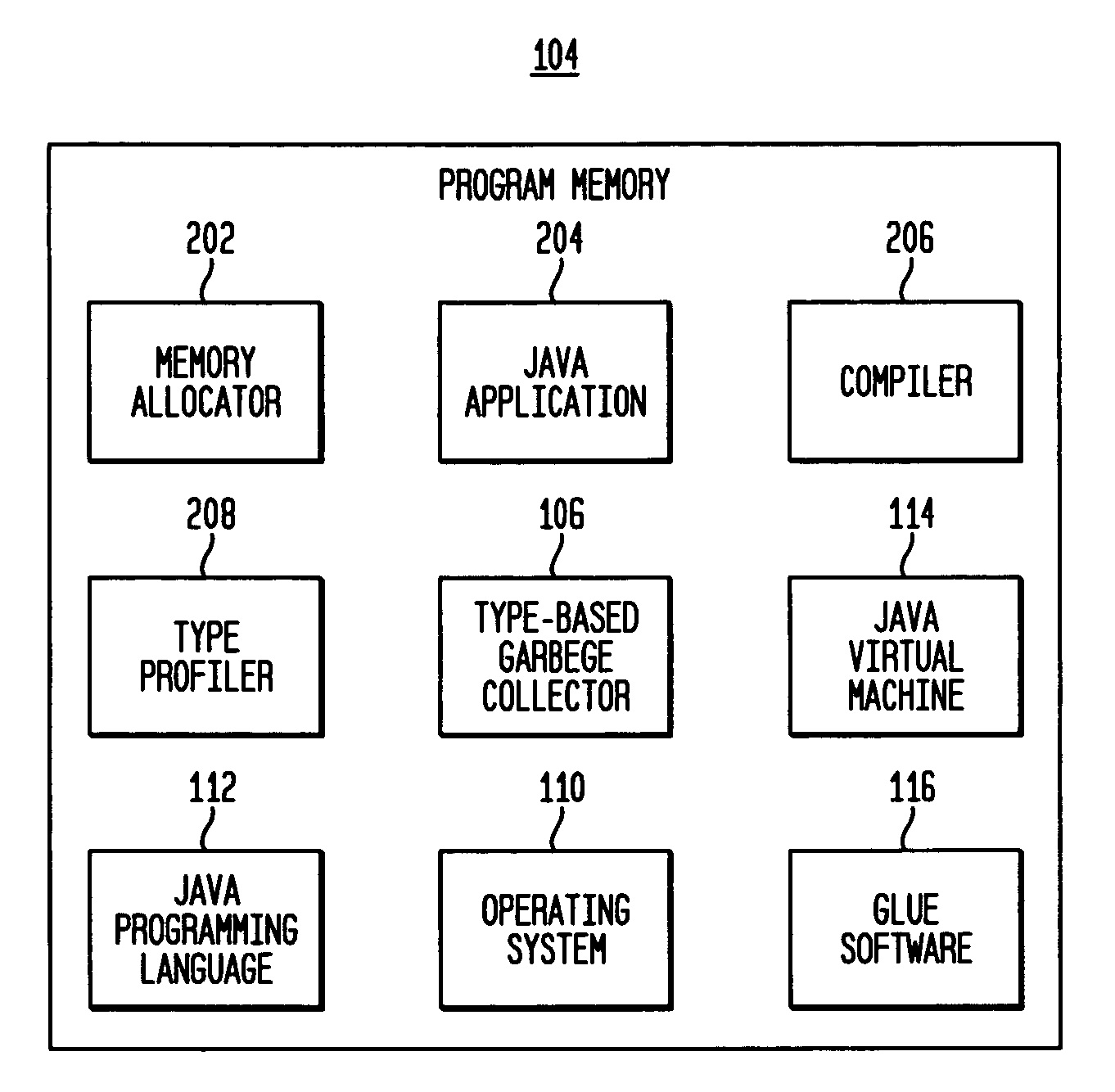

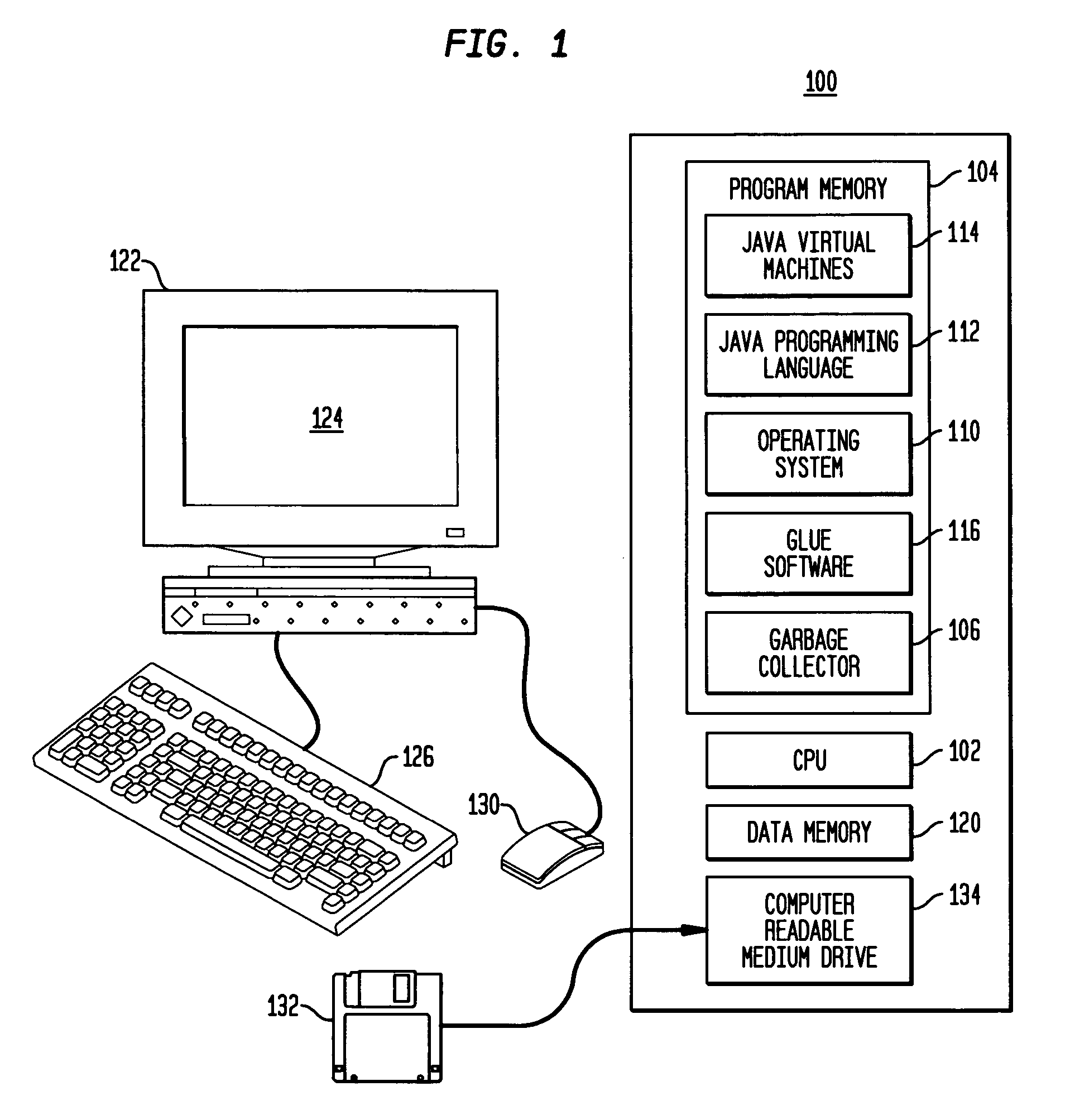

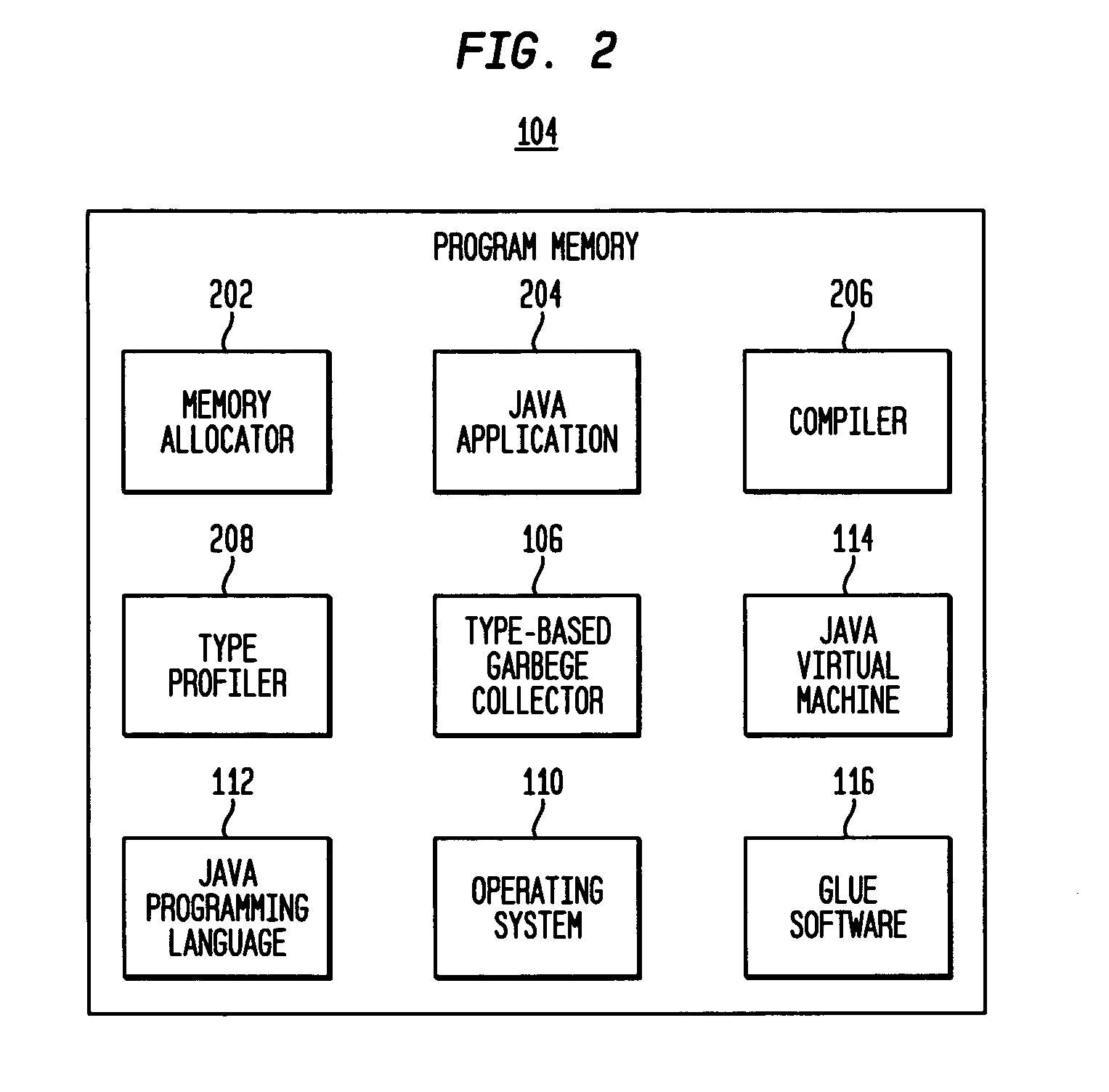

Disclosed are a partial heap garbage collector, and a partial heap garbage collection method, that during collection checks the time remaining (or equivalently the time taken so far, or the work done so far) to complete the partial heap collection. In a preferred embodiment, the partial heap collection is guaranteed to complete within a fixed time interval. For example, this guarantee may be obtained by applying a worst-case execution time (WCET) and sizing a nursery so that complete evacuation of the nursery can always be achieved on time. As an alternative, a technique, referred to as syncopation, may be used to allow generational collection to be used despite variance in program behavior over the short time scales in which a nursery can be collected. Syncopation may be accomplished via allocation control or via collection control.

Owner:IBM CORP

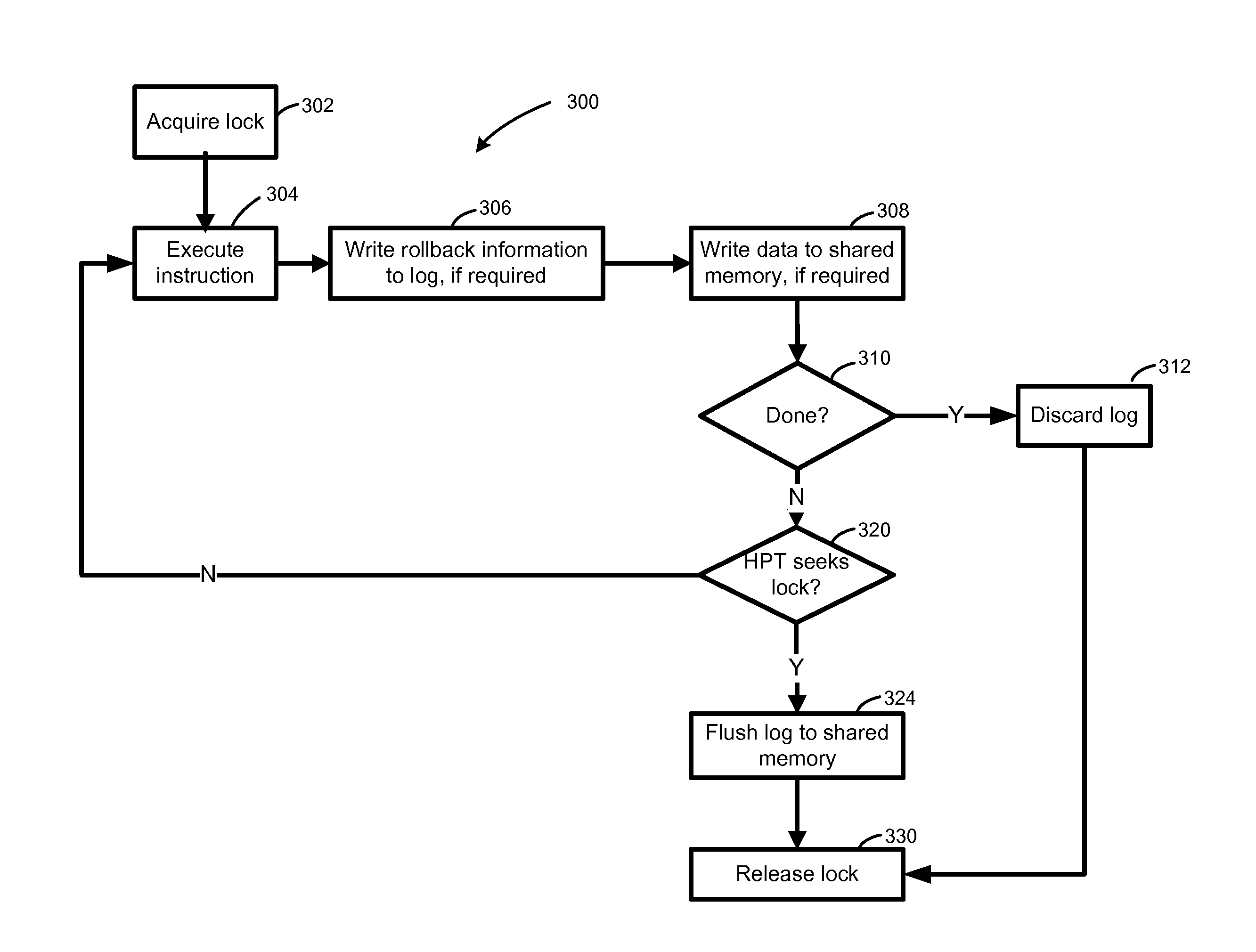

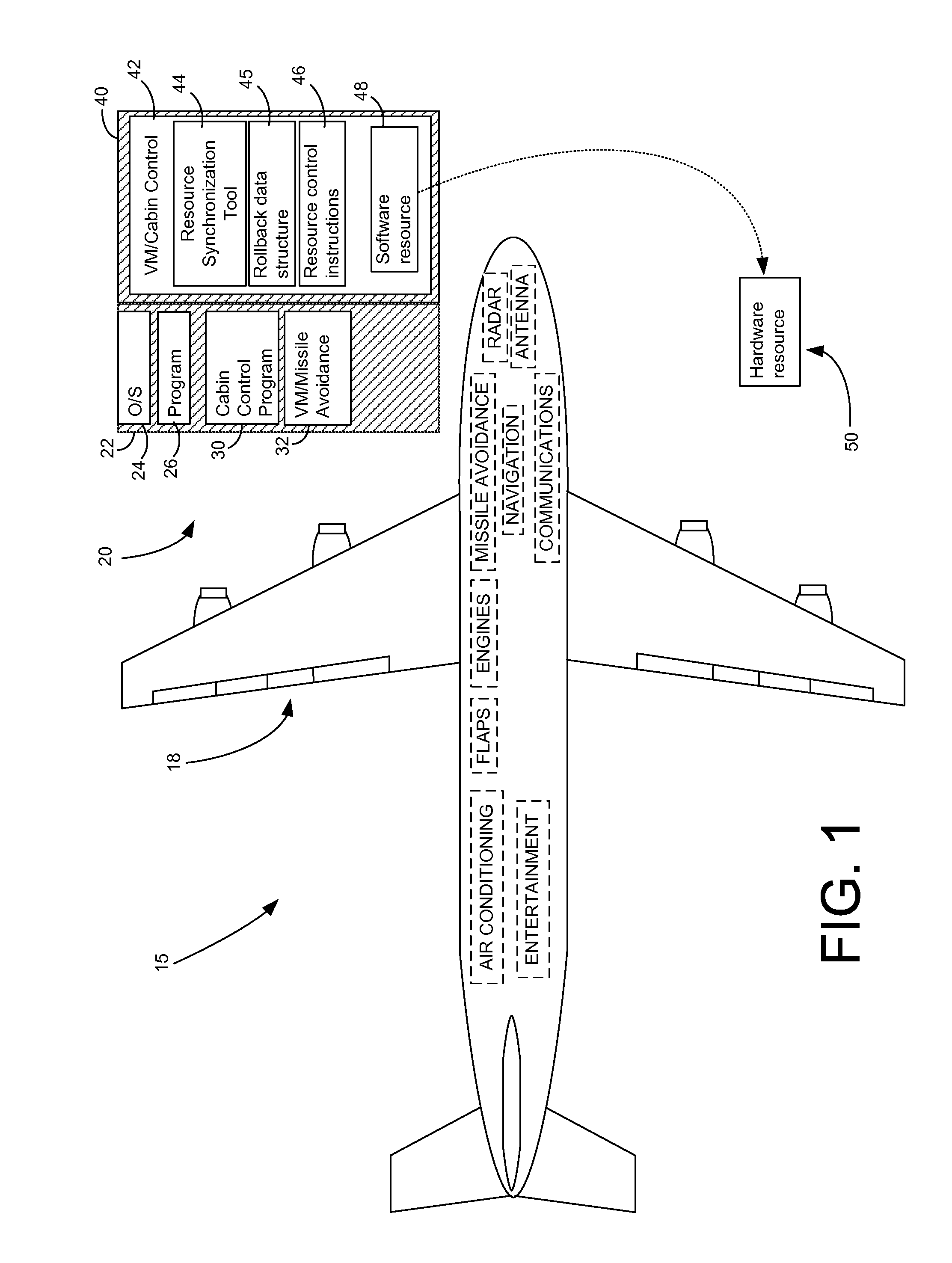

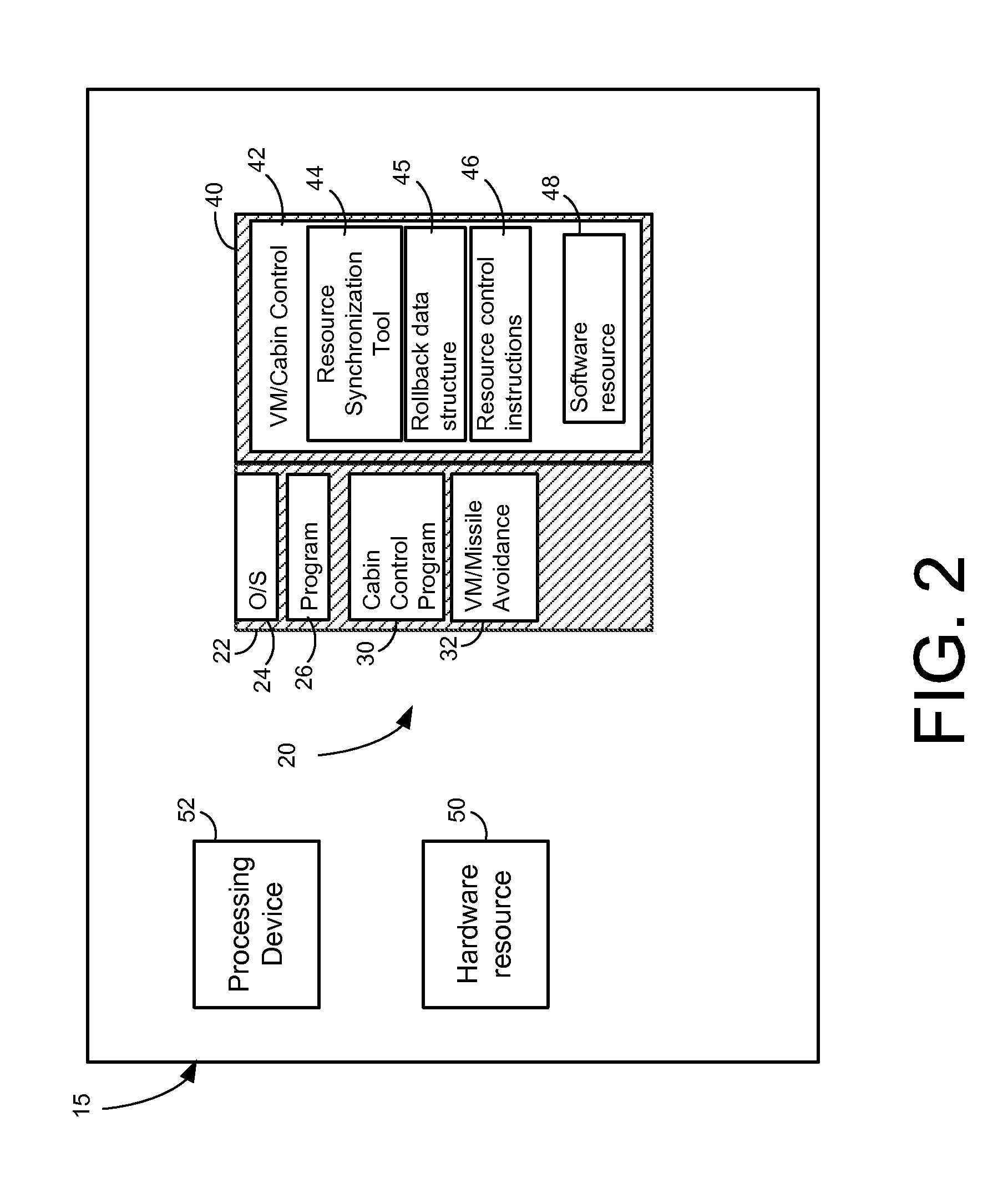

Priority rollback protocol

InactiveUS20120005684A1Detrimental to execution timeLow priorityMultiprogramming arrangementsMemory systemsWorst-case execution timeDistributed computing

Mechanisms for enforcing limits to resource access are provided. In some embodiments, synchronization tools are used to reduce the worst case execution time of selected processing sequences. In one example, instructions from a first processing sequence are rolled back using rollback information stored in a data structure if a higher priority processing sequence seeks access to the resource.

Owner:FIJI SYST

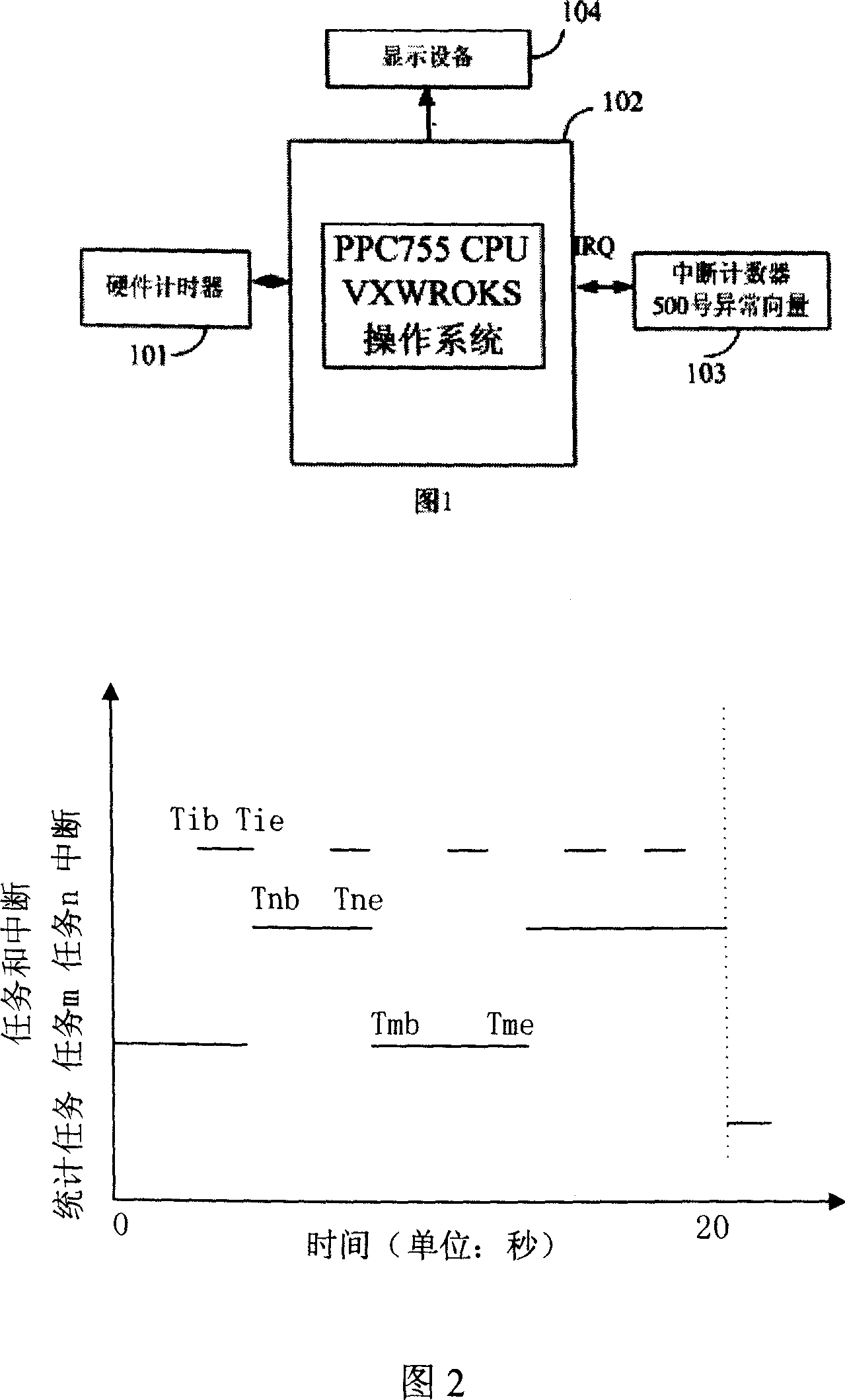

Method for measuring task CPU occupancy rate in multitasking operation system

ActiveCN101145125AAccurate occupancy measurementAccurate measurementHardware monitoringMultiprogramming arrangementsOccupancy rateStart time

The present invention provides a method to measure the CPU occupancy factor of a multi-task operation system, and the method comprises the procedures that (a) a high-priority timing statistic task is established to clear up all statistics, and a statistic interval is arranged; (b) the time points at the entrance of the interrupt processing routine and at the exit of the interrupt processing routine are recorded; the difference between the two time points is an once-execution time of the interrupt processing routine, and the time is accumulated; (c) when switching the task, the task starting time point when the task is switched in and the task ending time point when the task is switched off are respectively recorded; the time difference of the same task between the task ending time point and the task starting time point deducted by the interrupt processing routine execution time contained in the task execution process is the once-execution time of the task, and the time is accumulated; (d) when the statistic interval is ended, the total execution time of each task is mounted to the total execution time of the interrupt processing routine to get the total execution time of the system in the statistic interval, thereby calculating the CPU occupancy factor of every task and the interruption.

Owner:ZTE CORP

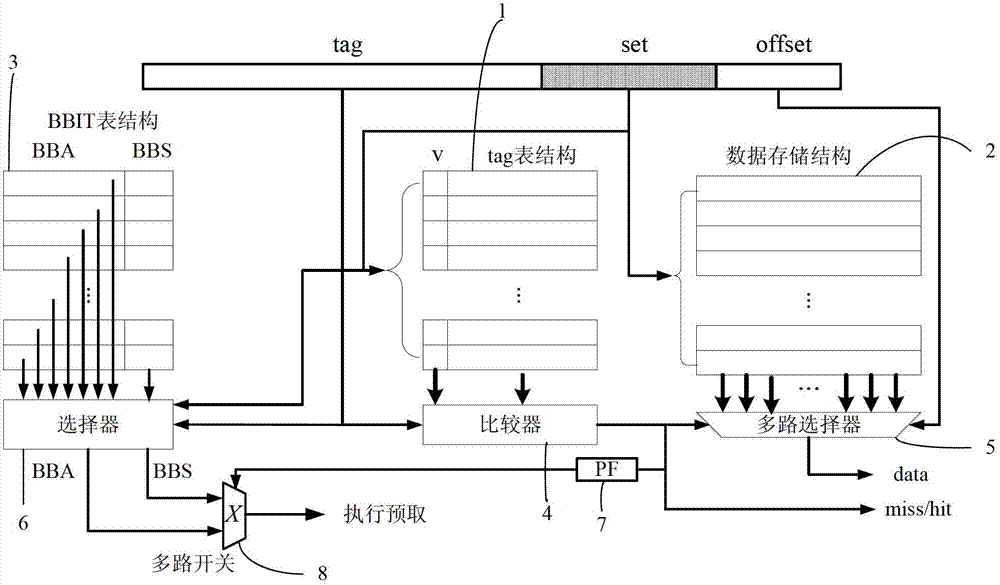

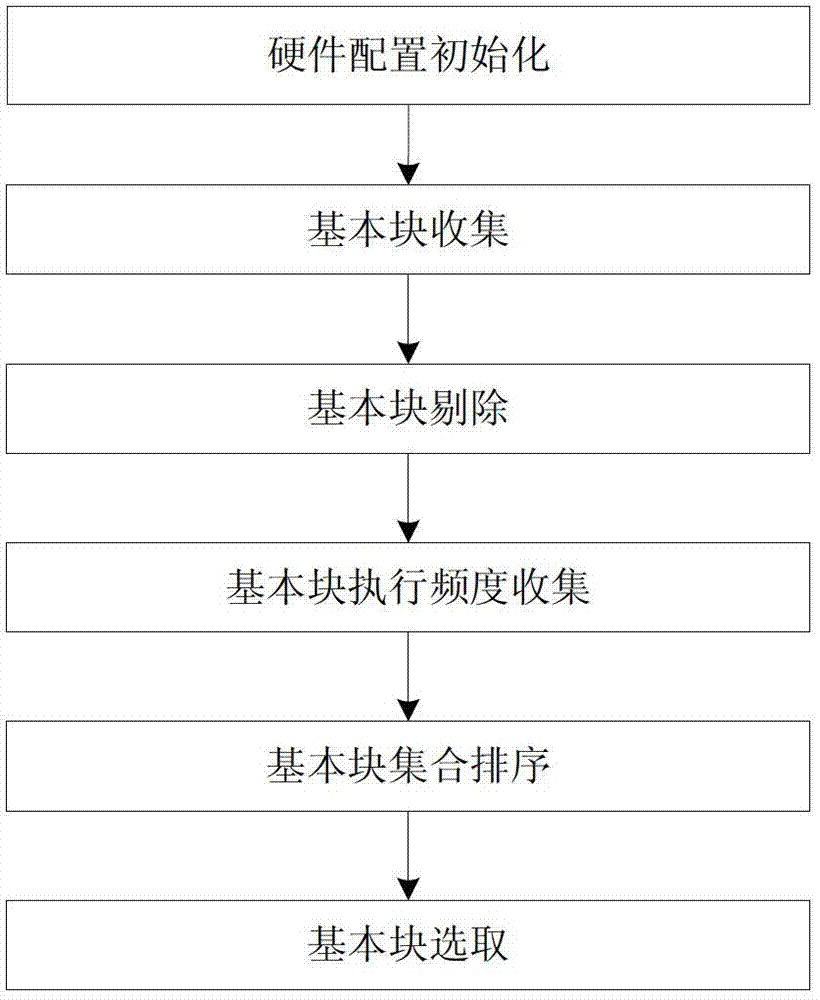

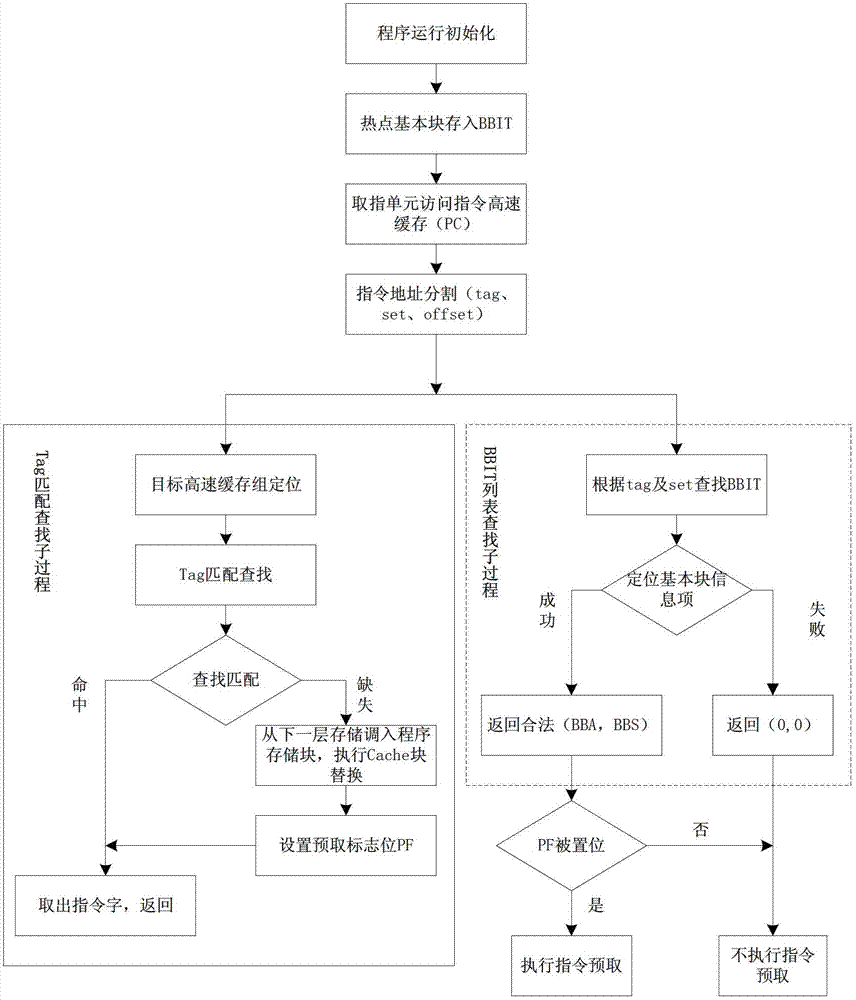

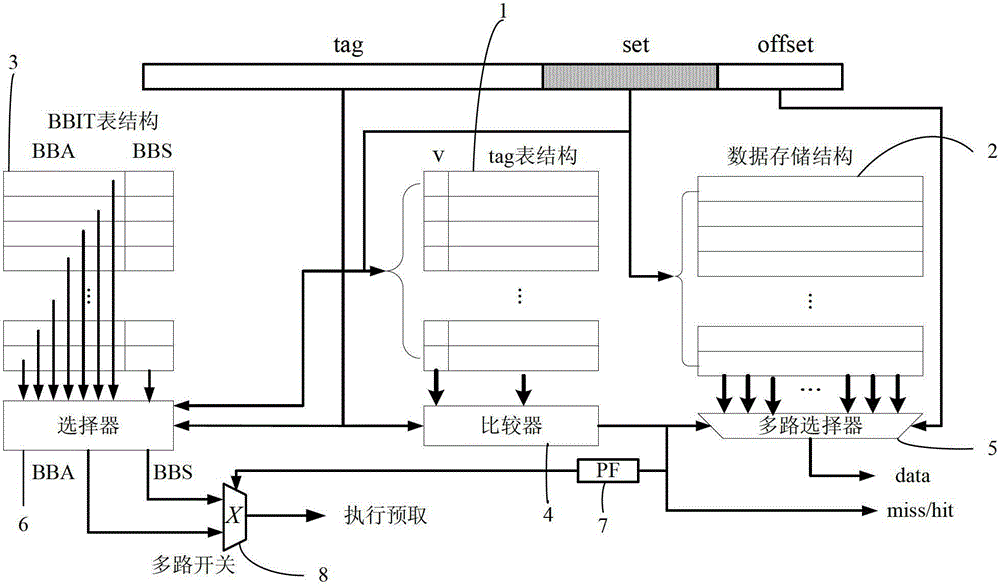

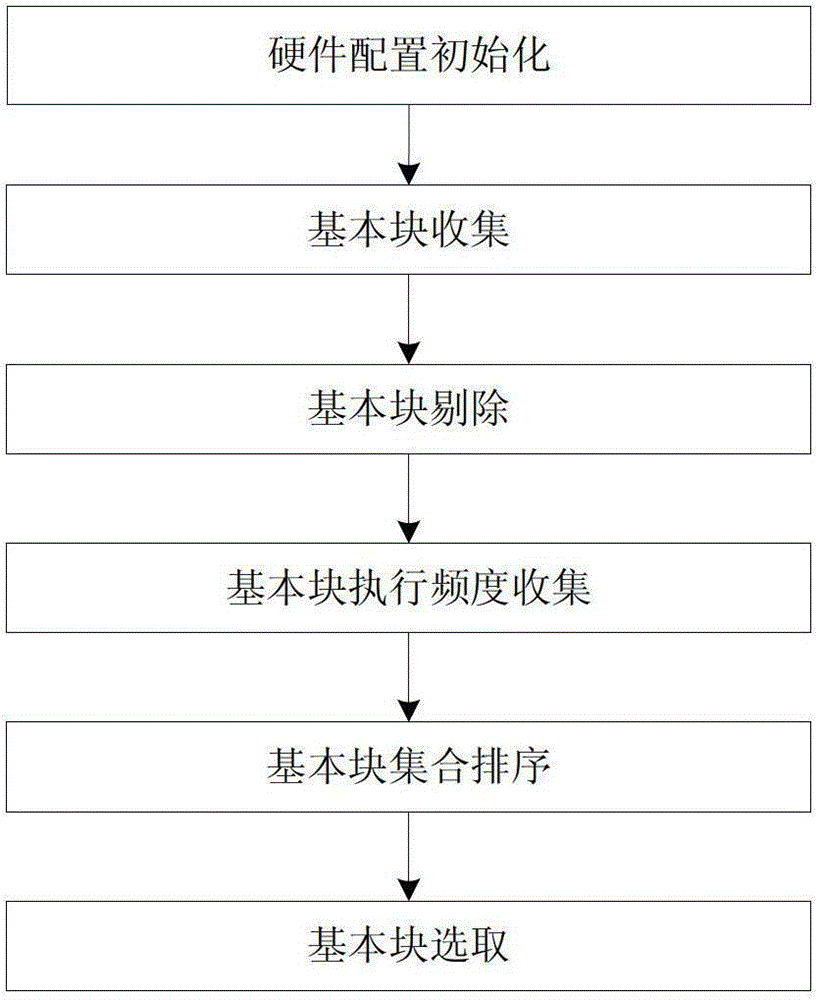

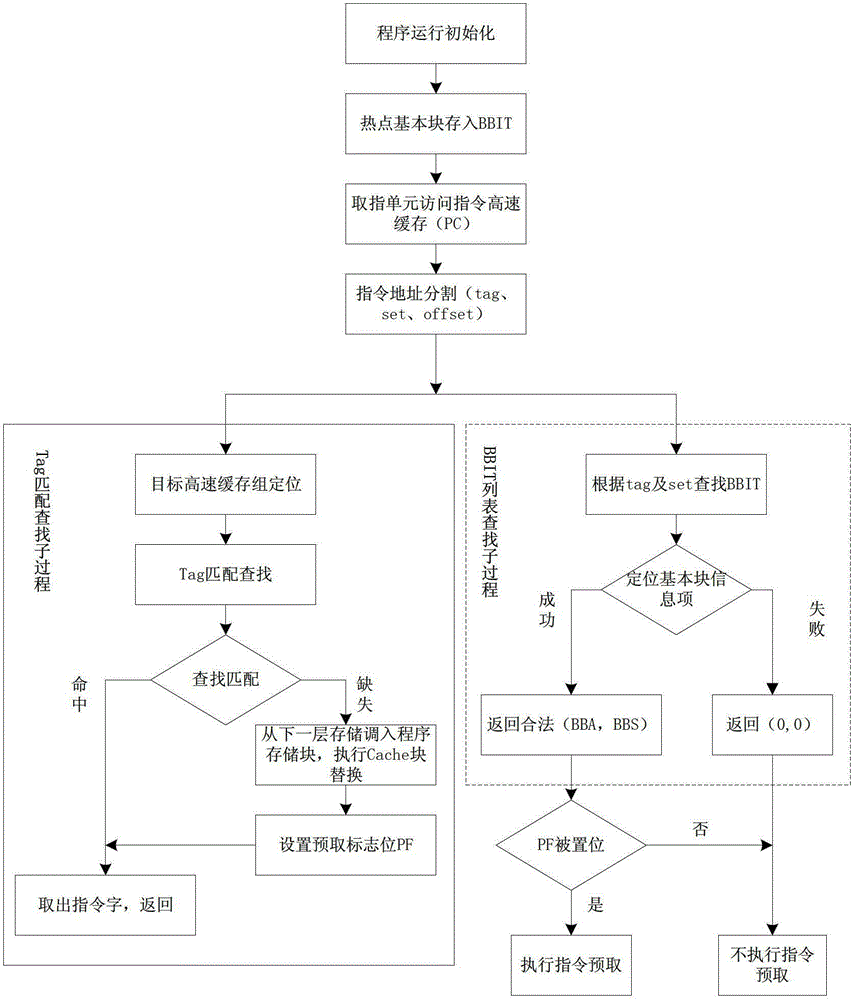

Instruction prefetching content selecting method for optimizing WCET (worst-case execution time) of real-time task

ActiveCN103207772AReduce design overheadReduce overheadMachine execution arrangementsHardware structureCache access

The invention provides an instruction prefectching content selecting method for optimizing WCET (worst-case execution time) of a real-time task. A hardware structure of a basic-block information table (BBIT) is added in high-speed caching hardware of an existing instruction. The instruction prefectching content selecting method includes: initializing hardware configuration, collecting a static routine base block set via a compiler or a static routine character analyzing tool, removing base blocks only covering one storage block, collecting execution frequentness of every program base block under worst-case execution condition, sequencing the program base blocks according to the execution frequentness, selecting information of an appointed amount of program base blocks according to the sequence, and storing the information in the BBIT. During a high-speed cache accessing process, high-speed instruction cache and the BBIT are searched at the same time, high-speed instruction cache accessing loss under the worst-case execution condition can be effectively avoided, requirements on the real-time task are met, and meanwhile, the instruction prefectching content selecting method can effectively reduce hardware design cost, and is simple and direct to realize.

Owner:BEIHANG UNIV

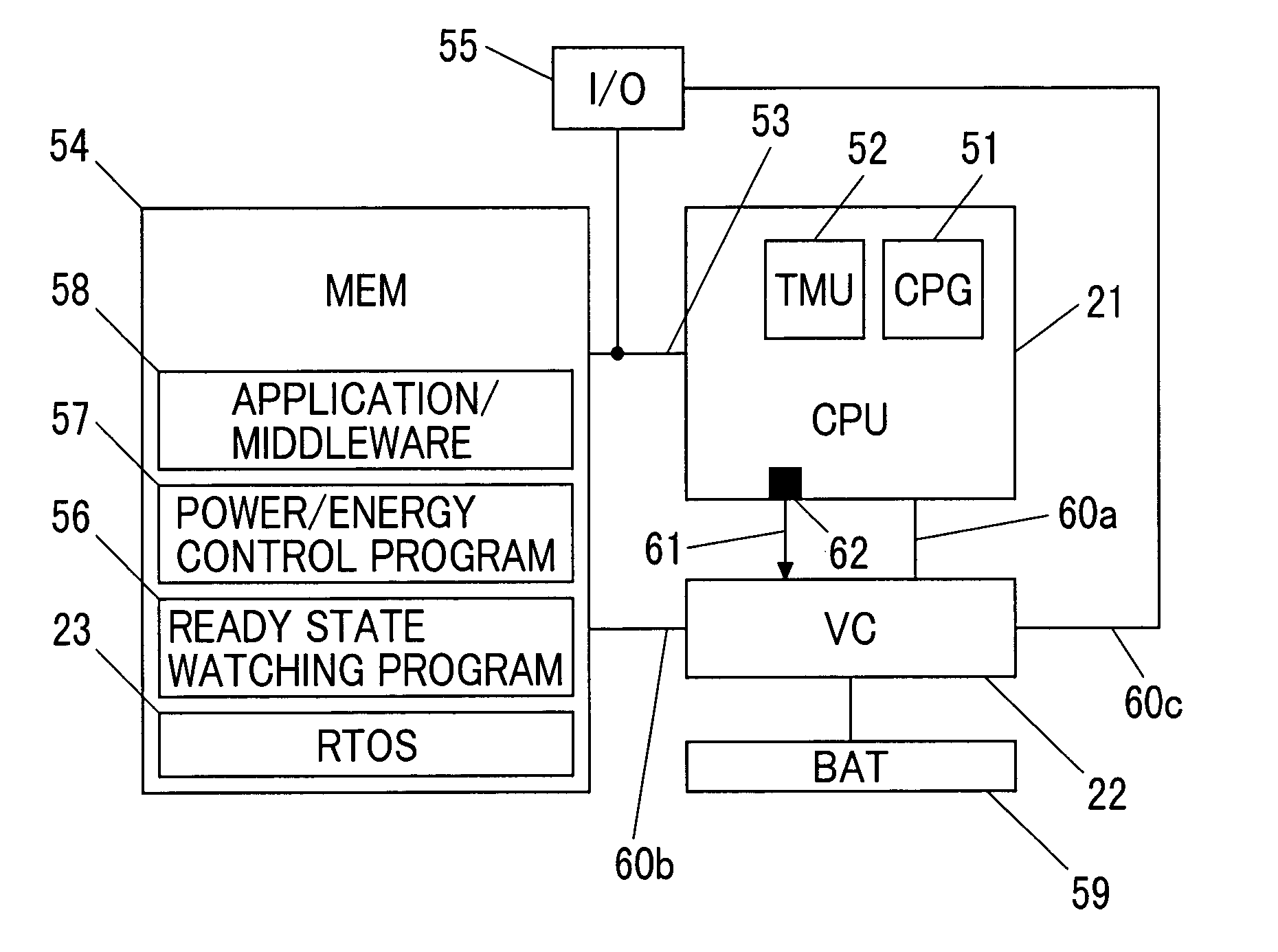

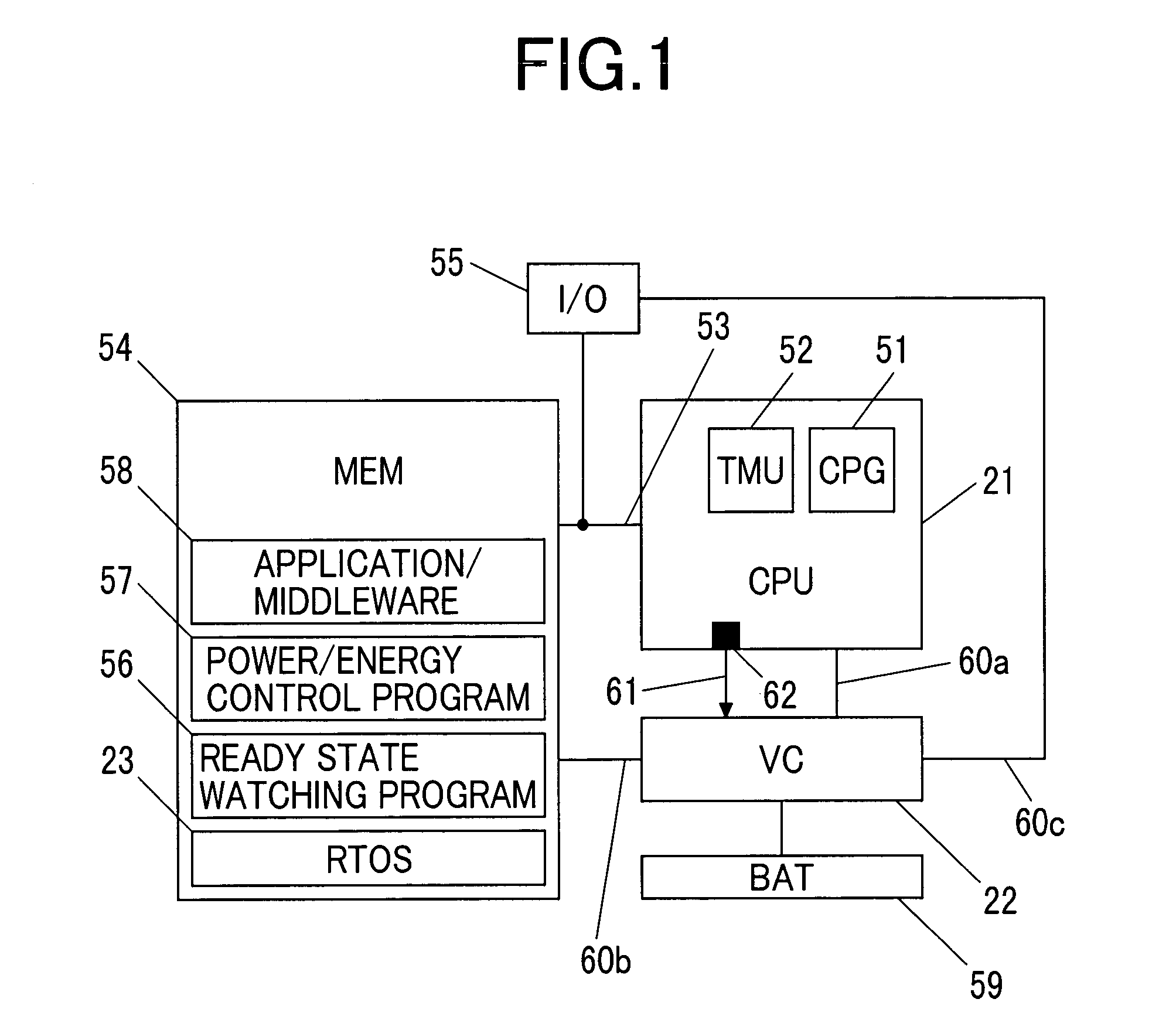

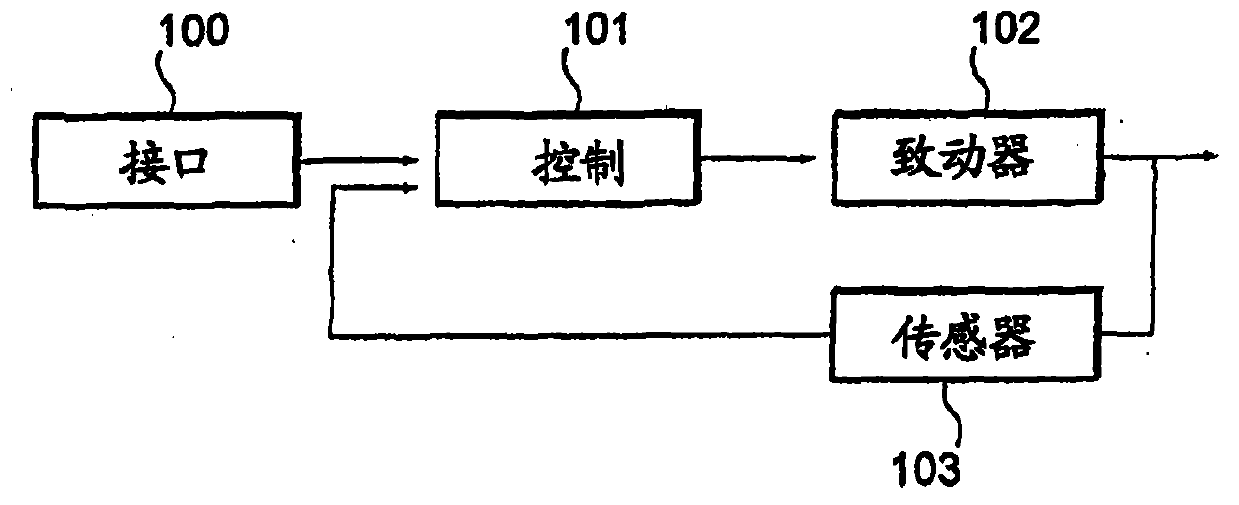

System for adjusting a clock frequency based on comparing a required process times and a worst case execution times and adjusting a voltage and clock frequency based on a number of ready state application tasks

ActiveUS7146513B2Reduce power consumptionEnergy efficient ICTProgram initiation/switchingInformation processingClock rate

An information processing system that can reduce its power consumption by means of robust power controlling even upon occurrence of an interruption / exception processing. If it is found that there is no task set in the ready state as a result of watching the number of tasks set in the ready state by the RTOS or ready state watching task, the system controls the RTOS or ready state watching task so as to lower the power while the current active task controls the power according to the preset WCET of each application slice. On the contrary, if there is any task set in the ready state, the system controls so as to raise the power and the current active task comes to control the power according to the virtual WCET that is earlier than the WCET of each application slice. And, if there is no task set in the ready state and there is no current active task, the system controls so that the RTOS or both of the ready state watching task and sleep task lower the power. This is why the present invention can reduce the power consumption of the subject information processing system.

Owner:MAXELL HLDG LTD

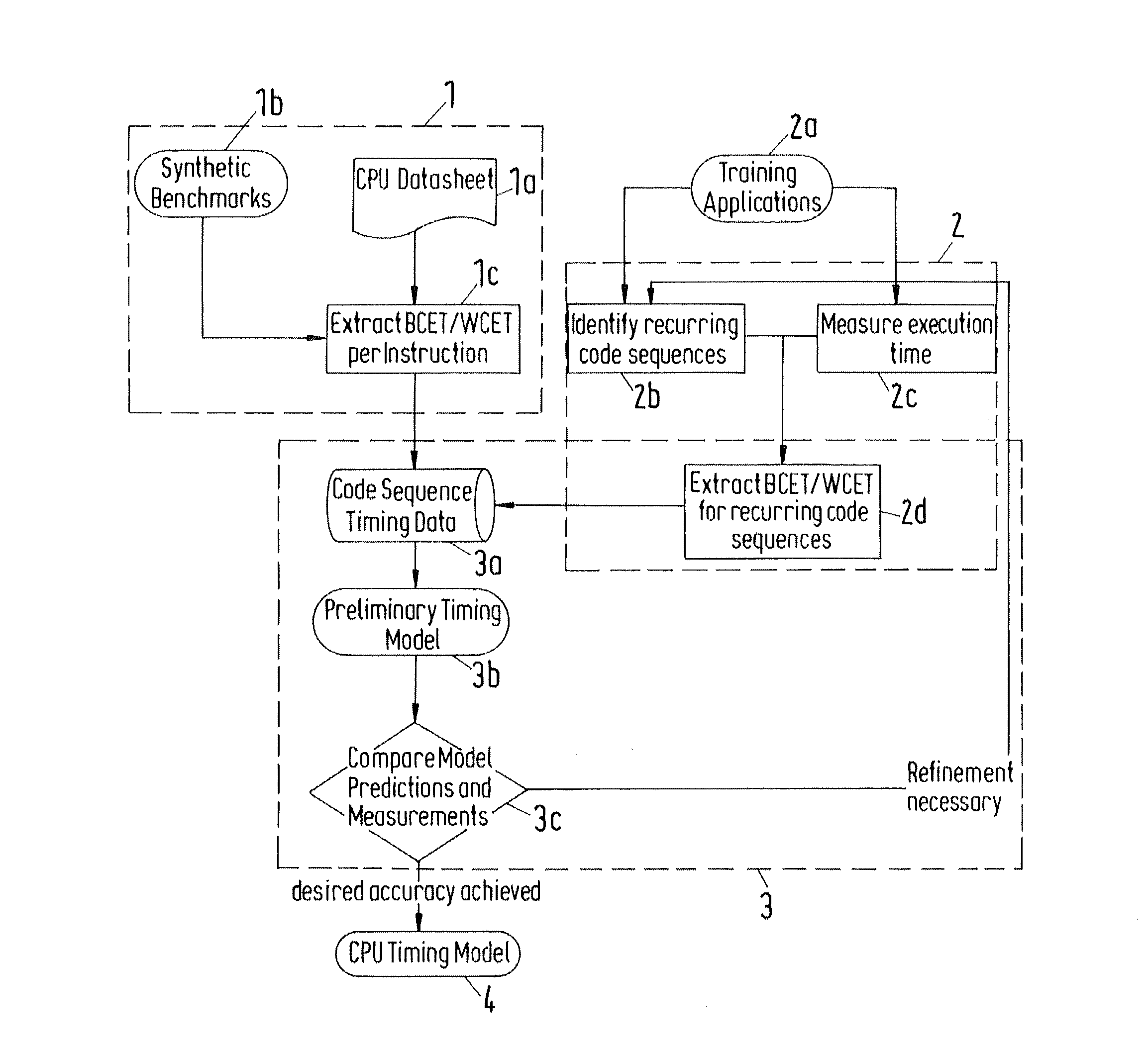

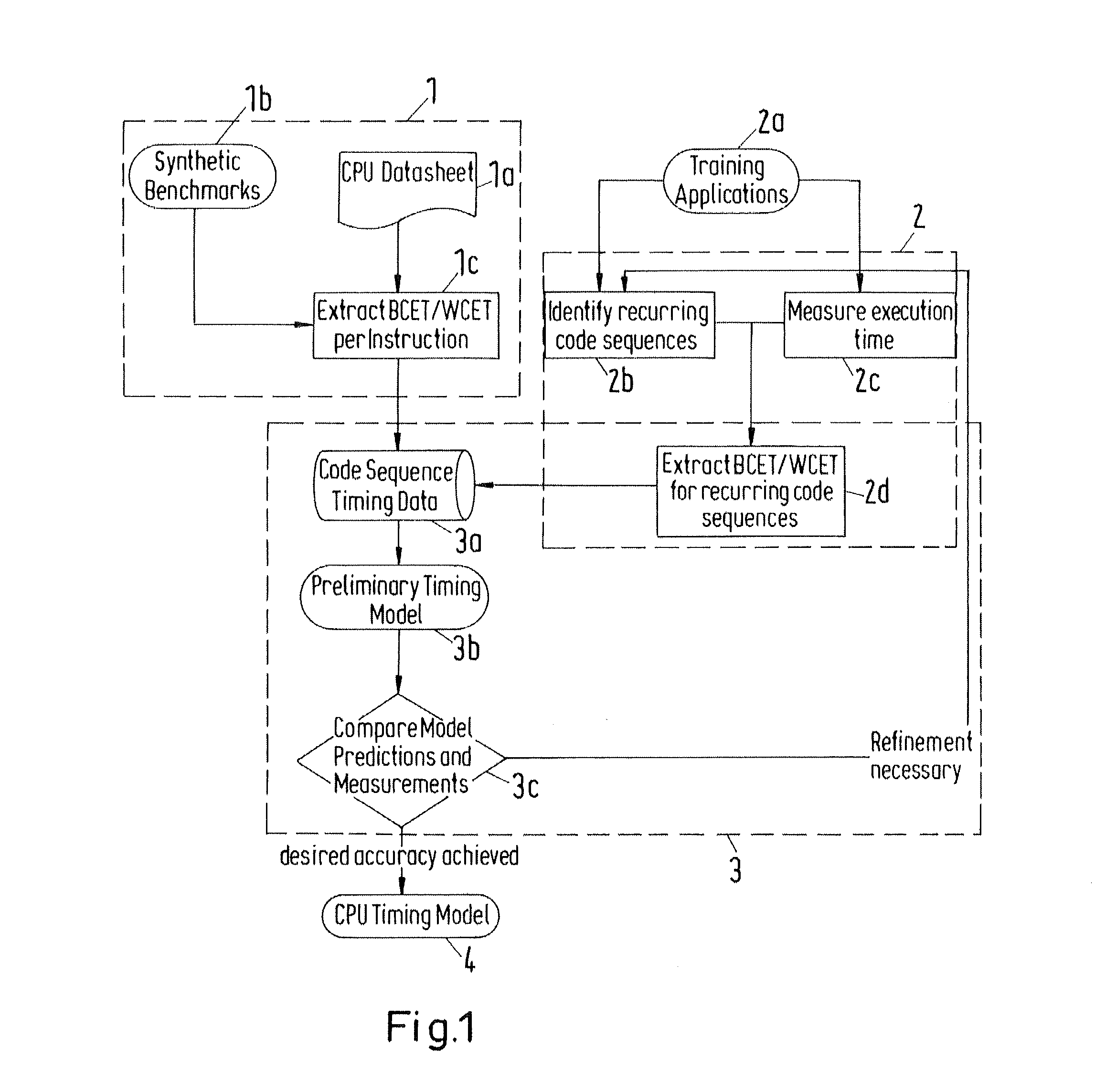

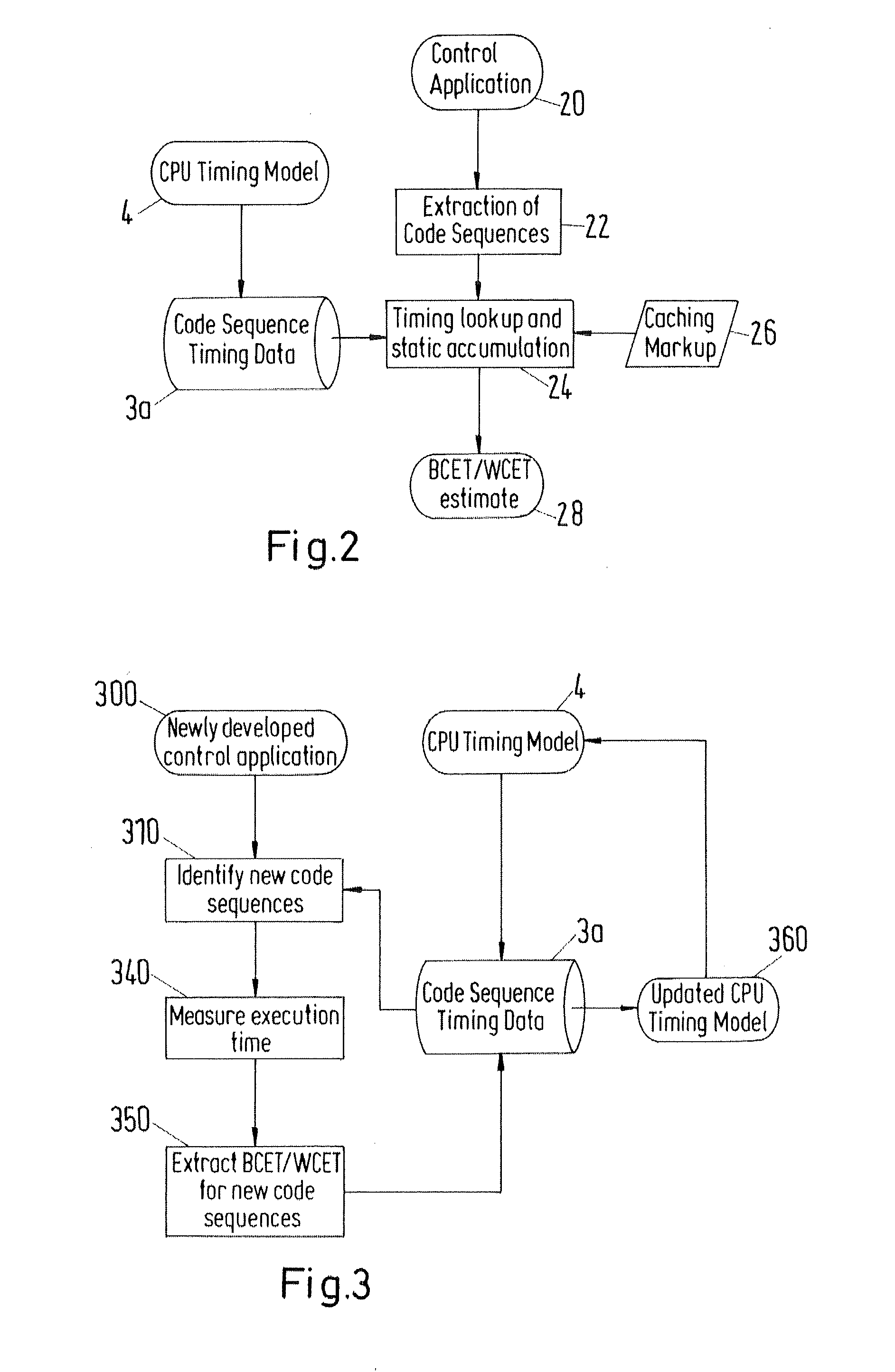

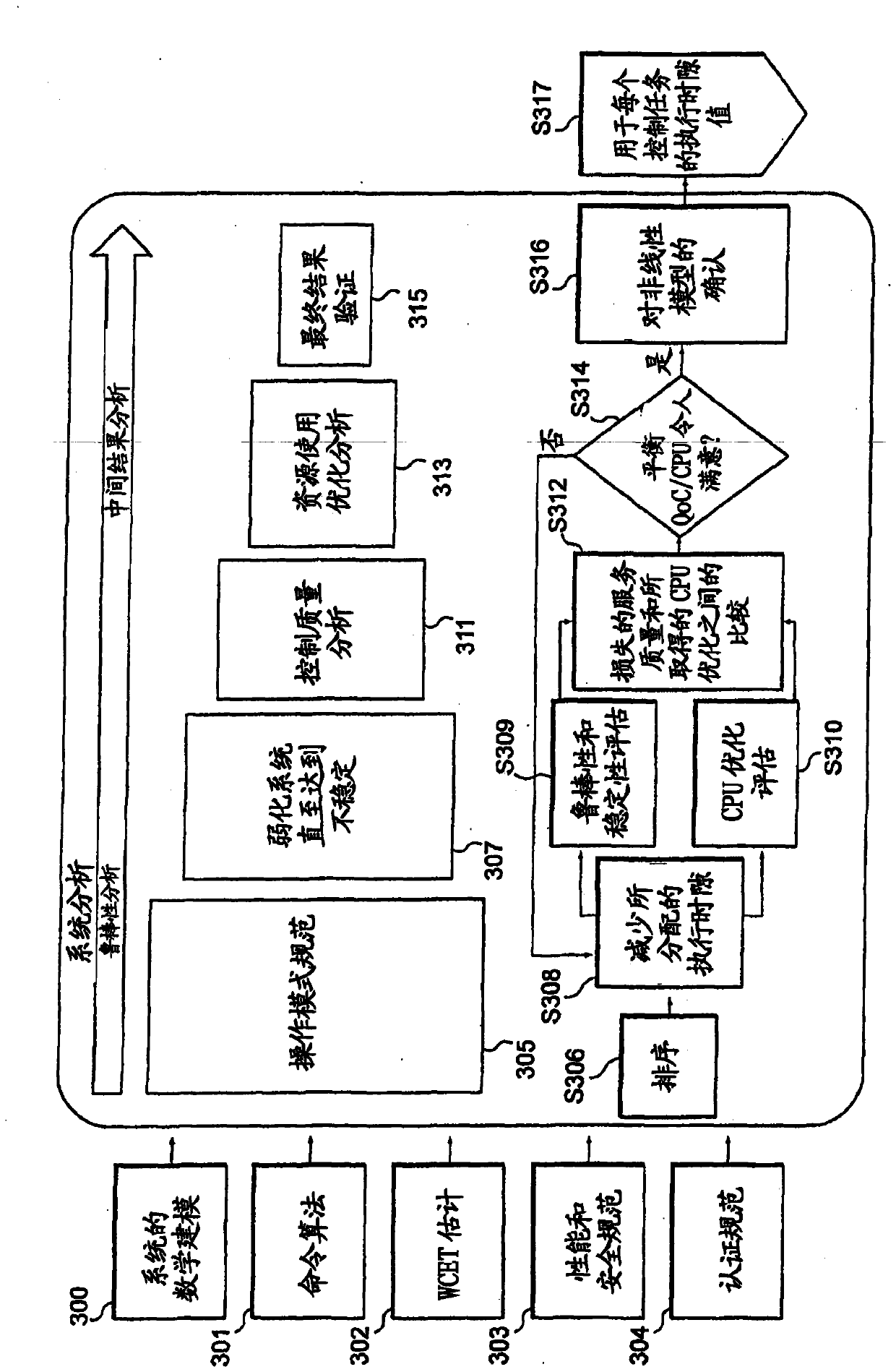

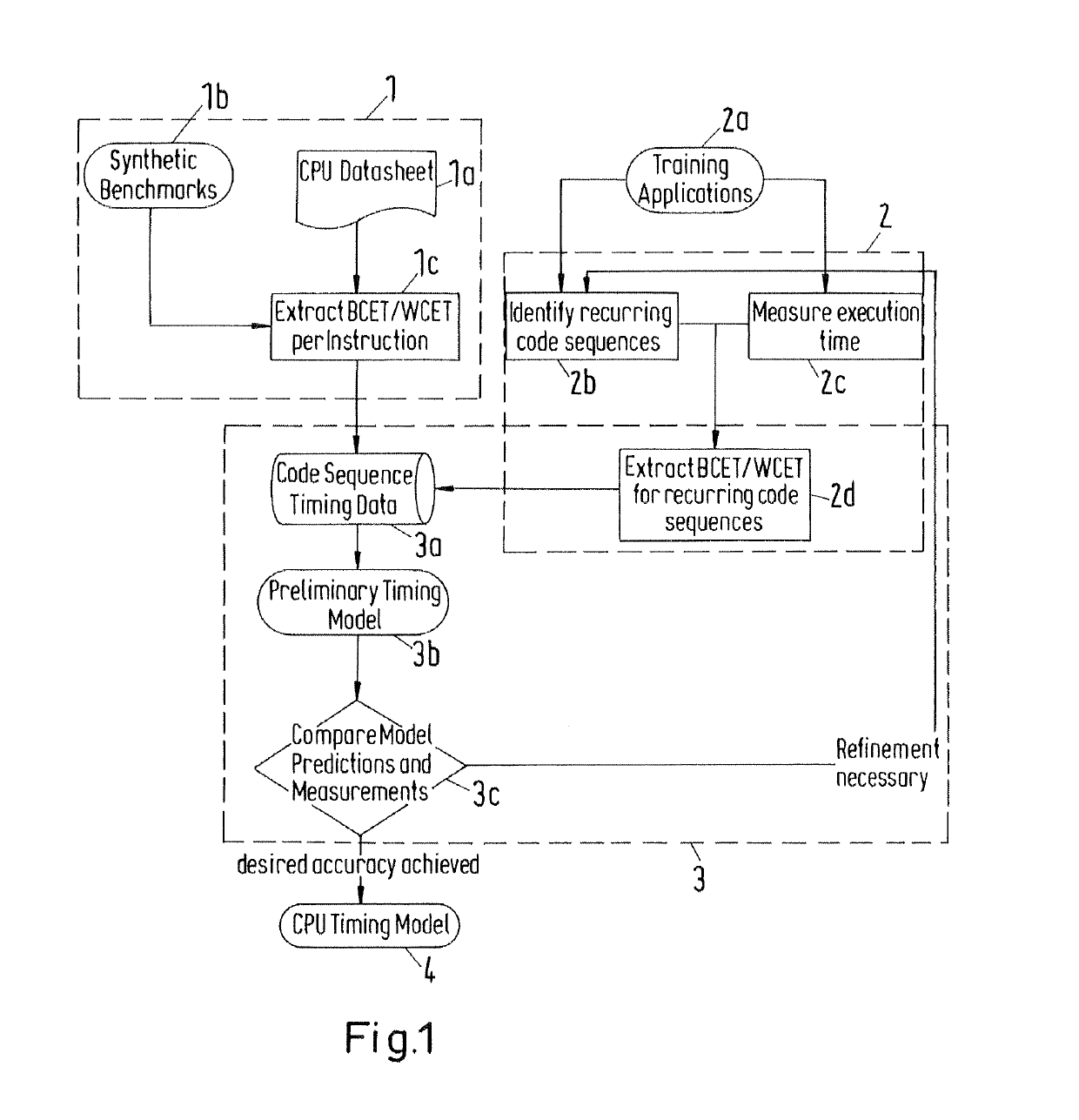

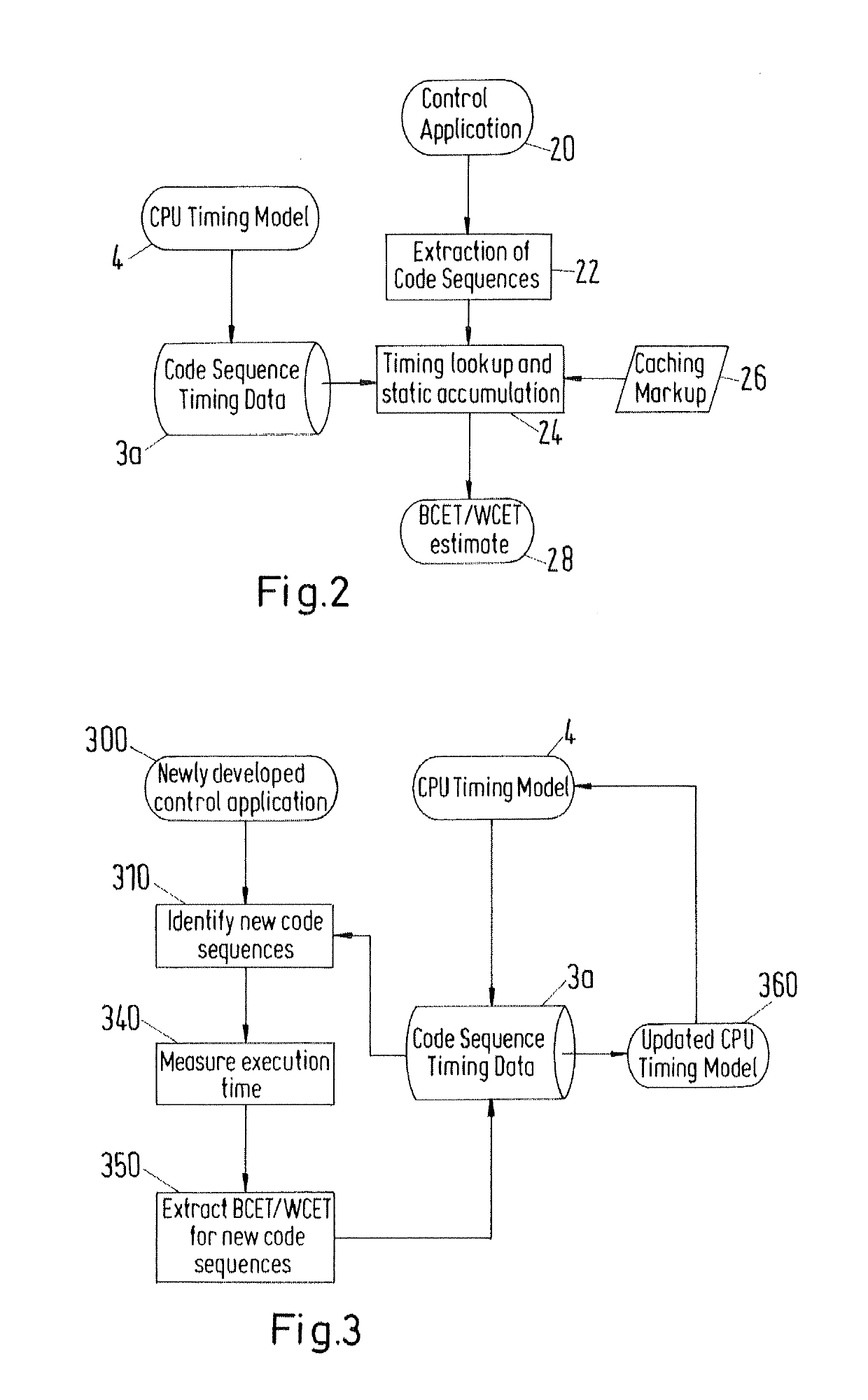

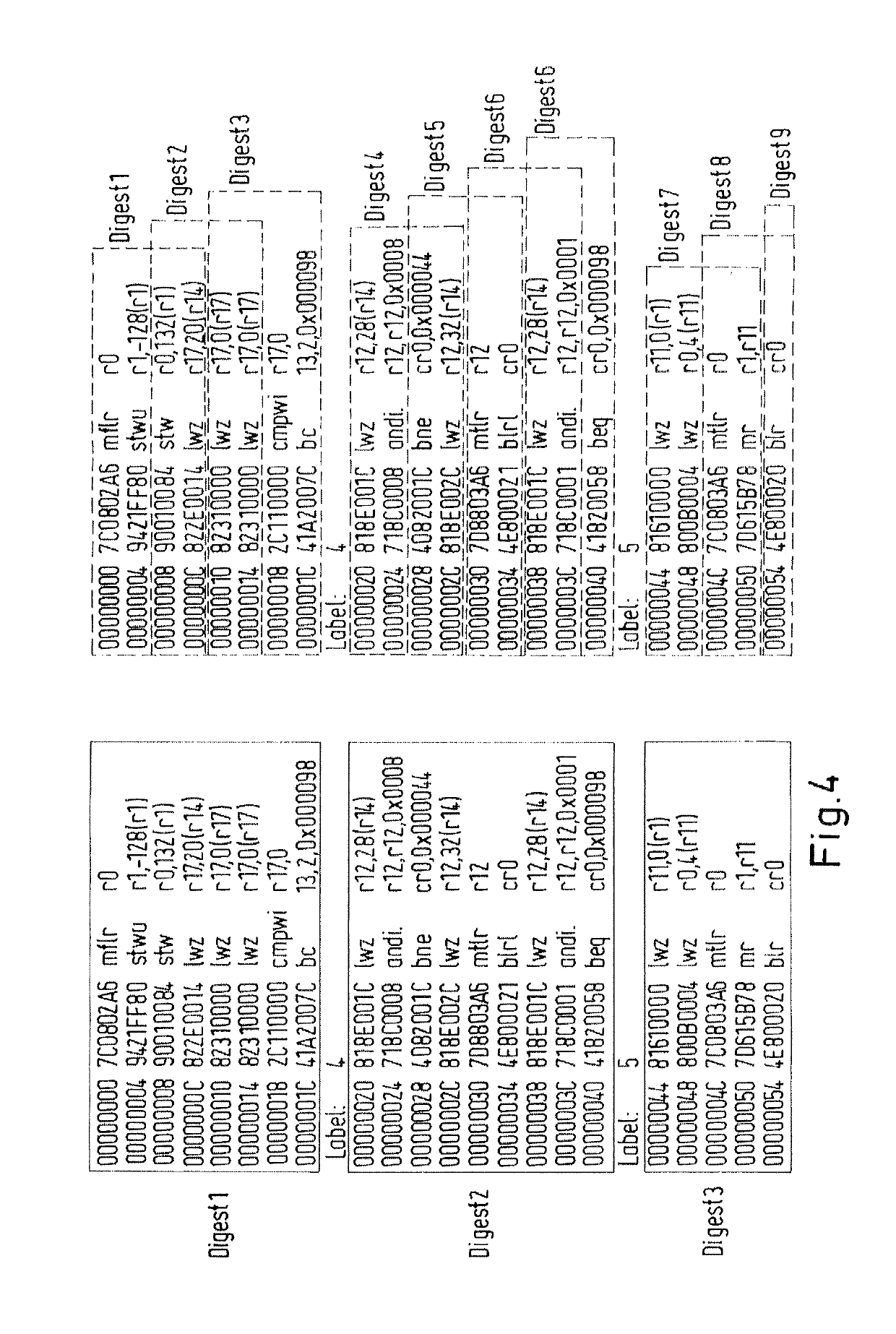

System and method for an optimized operation of real-time embedded solutions in industrial automation

ActiveUS20150286203A1Easy to operateProgramme controlComputer controlTime controlApplication software

A system and method for optimized operation of real-time control applications. The system and method being configured for identifying and processing recurring code sequences in control applications to quantify the execution time of control applications, wherein for each set up and / or control application a timing data structure is generated to determine the execution time of control applications in industrial automation, determining execution times of control applications based on recurring code sequences that are automatically extracted from a set of training applications and / or identified in the respective application, automatically generating test data to determine their on-target execution times for refinement of the timing data structure, decomposing the structure of the respective control application into code sequences for which the created data timing structure and timing model respectively provide execution time estimates, and determining at least an estimate for the best-case execution time and / or the worst-case execution time of the control application.

Owner:ABB (SCHWEIZ) AG

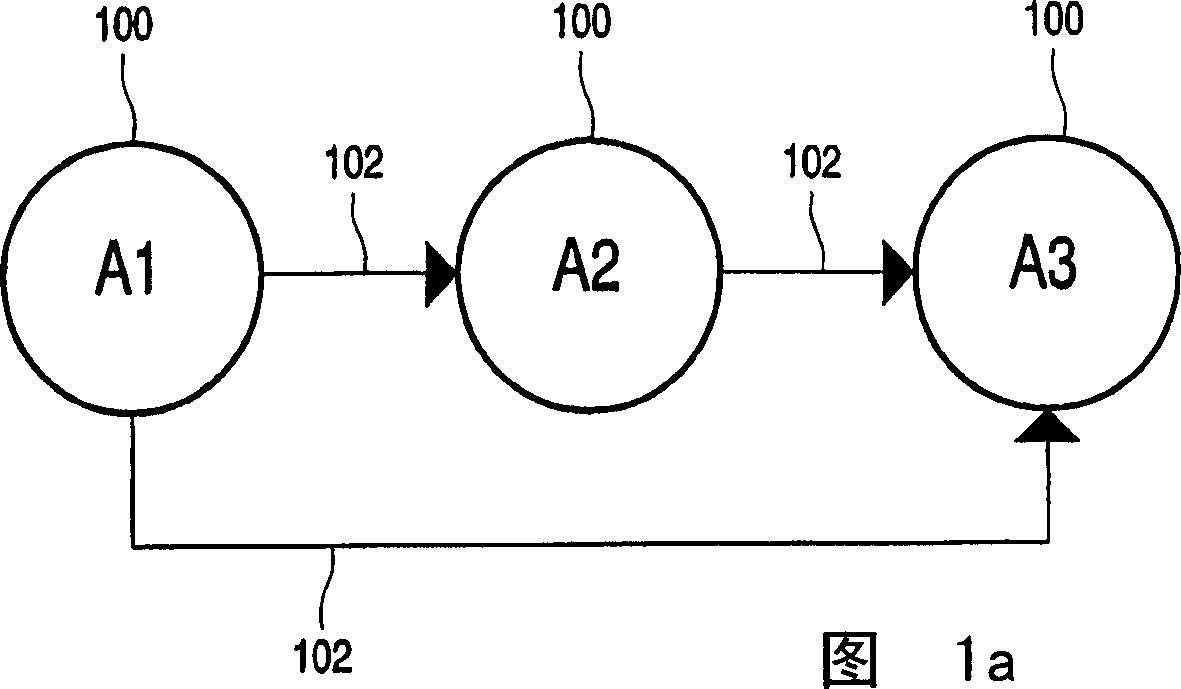

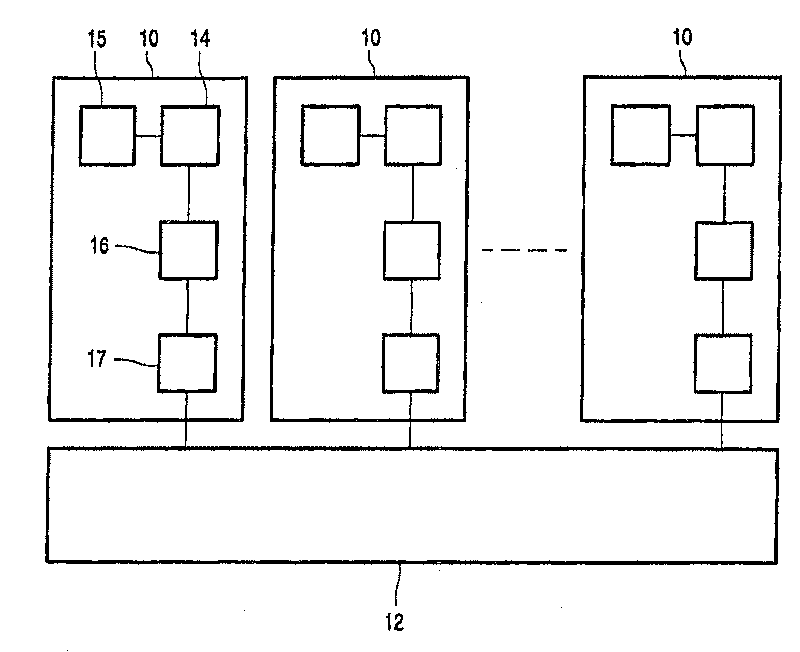

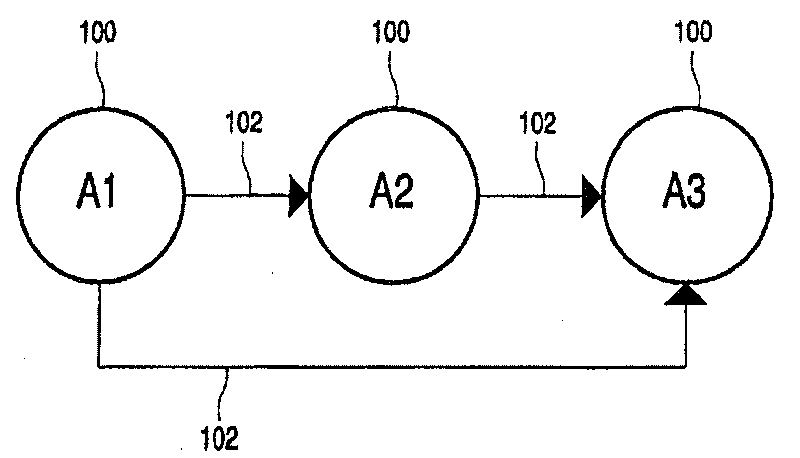

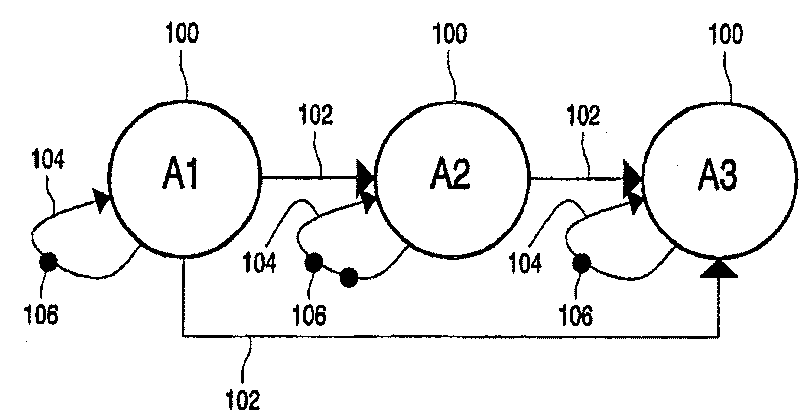

Signal processing apparatus

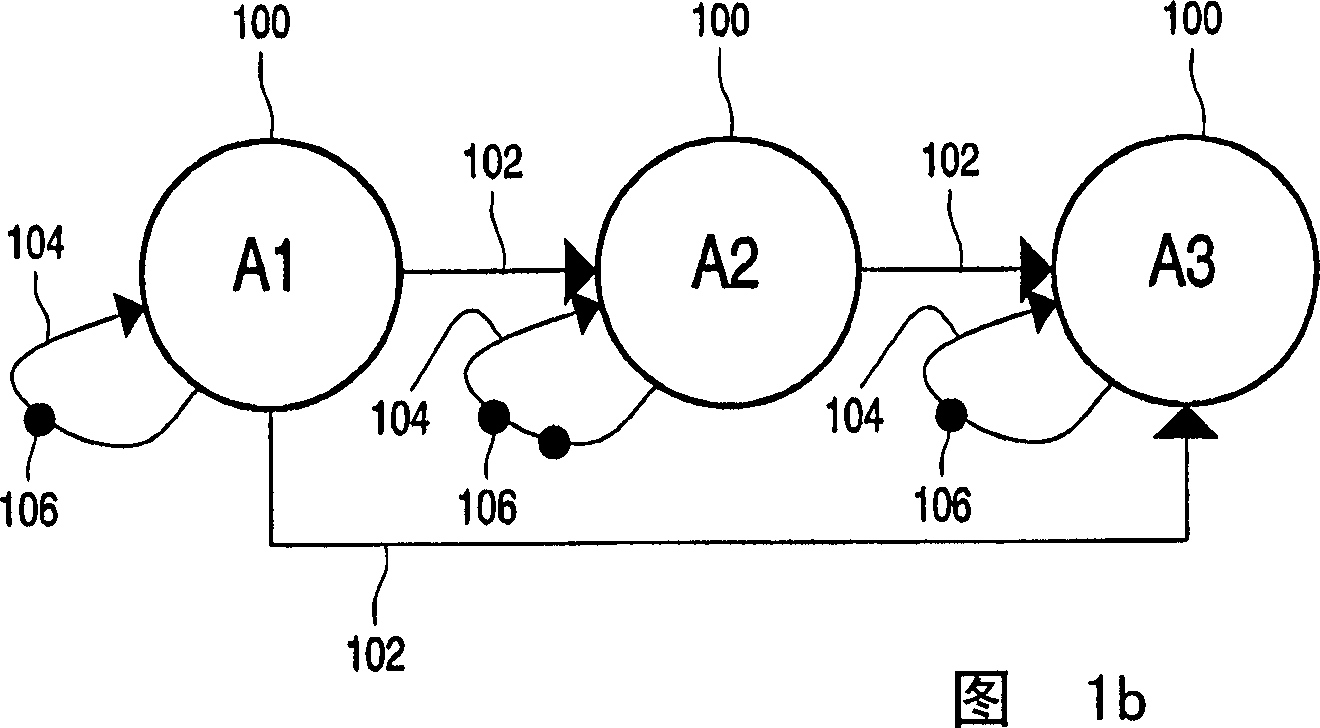

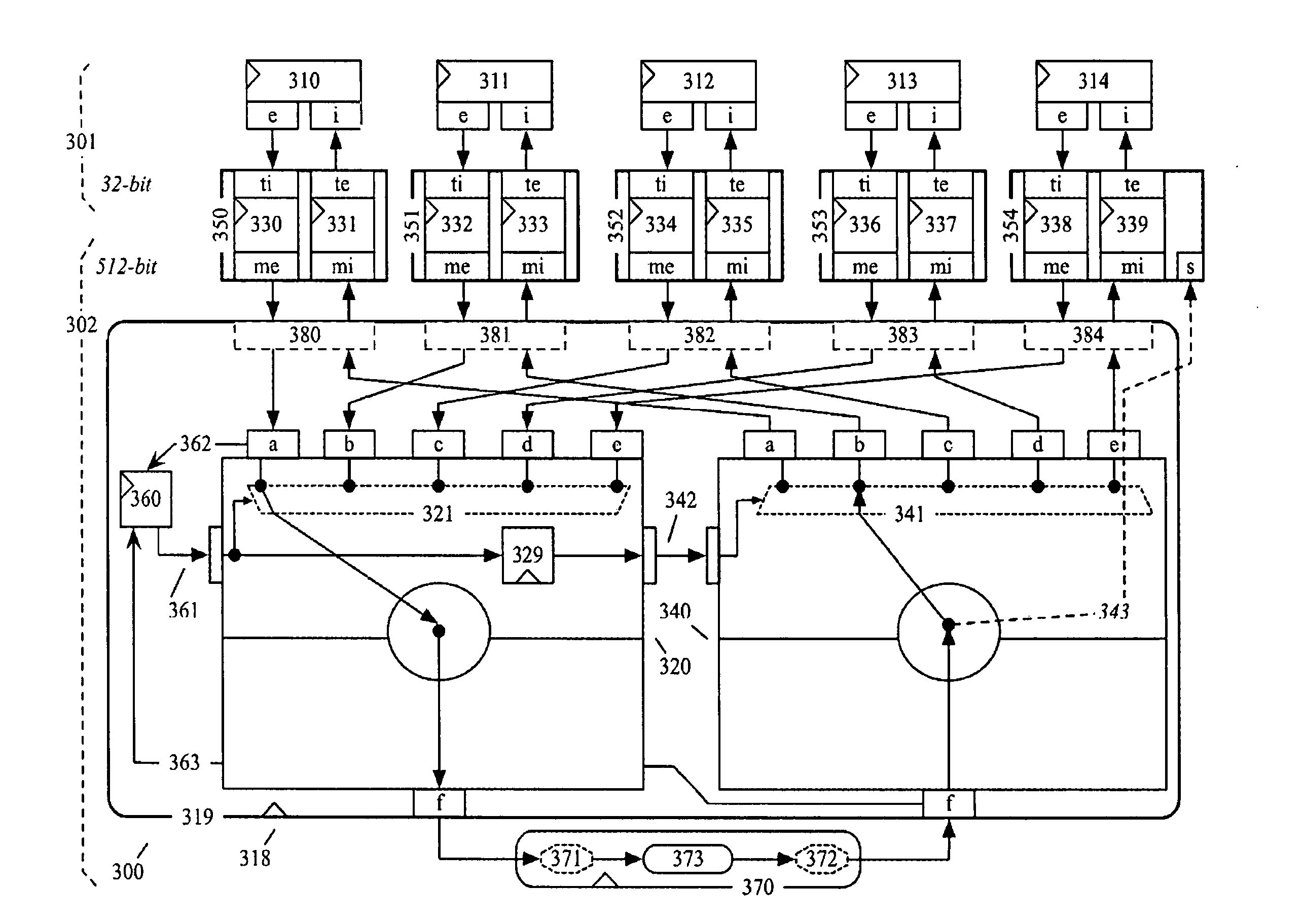

Signal stream processing jobs contain tasks (100), each task (100) to be performed by repeated execution of an operation that processes a chunk of data from a stream. Each job comprises a plurality of the tasks (100) in stream communication with one another. A plurality of processing units (10), which are mutually coupled for the communication of signal streams execute that tasks. A preliminary computation is performed for each job individually, to determine execution parameters required for the job to support a required minimum stream throughput rate if each task of the job is executed in a respective context wherein opportunities to start execution of the task occur separated at most by a cycle time T defined for the task. At run time combination of jobs is selected for execution. Groups of the tasks of the selected combination of jobs are assigned to respective ones of the processing units (10), checking that for each particular processing unit (10) a sum of worst case execution times for the tasks assigned to that particular processing unit (10) does not exceed the defined cycle time T defined for any of the tasks (100) assigned to the particular processing unit (10). The processing unit (10) execute the selected combination of jobs concurrently, each processing unit (10) time multiplexing execution of the group of tasks (100) assigned to that processing unit (10).

Owner:NXP BV

Generational real-time garbage collection

InactiveUS7548940B2Improve utilizationImprove throughputSpecial data processing applicationsMemory systemsRefuse collectionLitter

Disclosed are a partial heap garbage collector, and a partial heap garbage collection method, that during collection checks the time remaining (or equivalently the time taken so far, or the work done so far) to complete the partial heap collection. In a preferred embodiment, the partial heap collection is guaranteed to complete within a fixed time interval. For example, this guarantee may be obtained by applying a worst-case execution time (WCET) and sizing a nursery so that complete evacuation of the nursery can always be achieved on time. As an alternative, a technique, referred to as syncopation, may be used to allow generational collection to be used despite variance in program behavior over the short time scales in which a nursery can be collected. Syncopation may be accomplished via allocation control or via collection control.

Owner:INT BUSINESS MASCH CORP

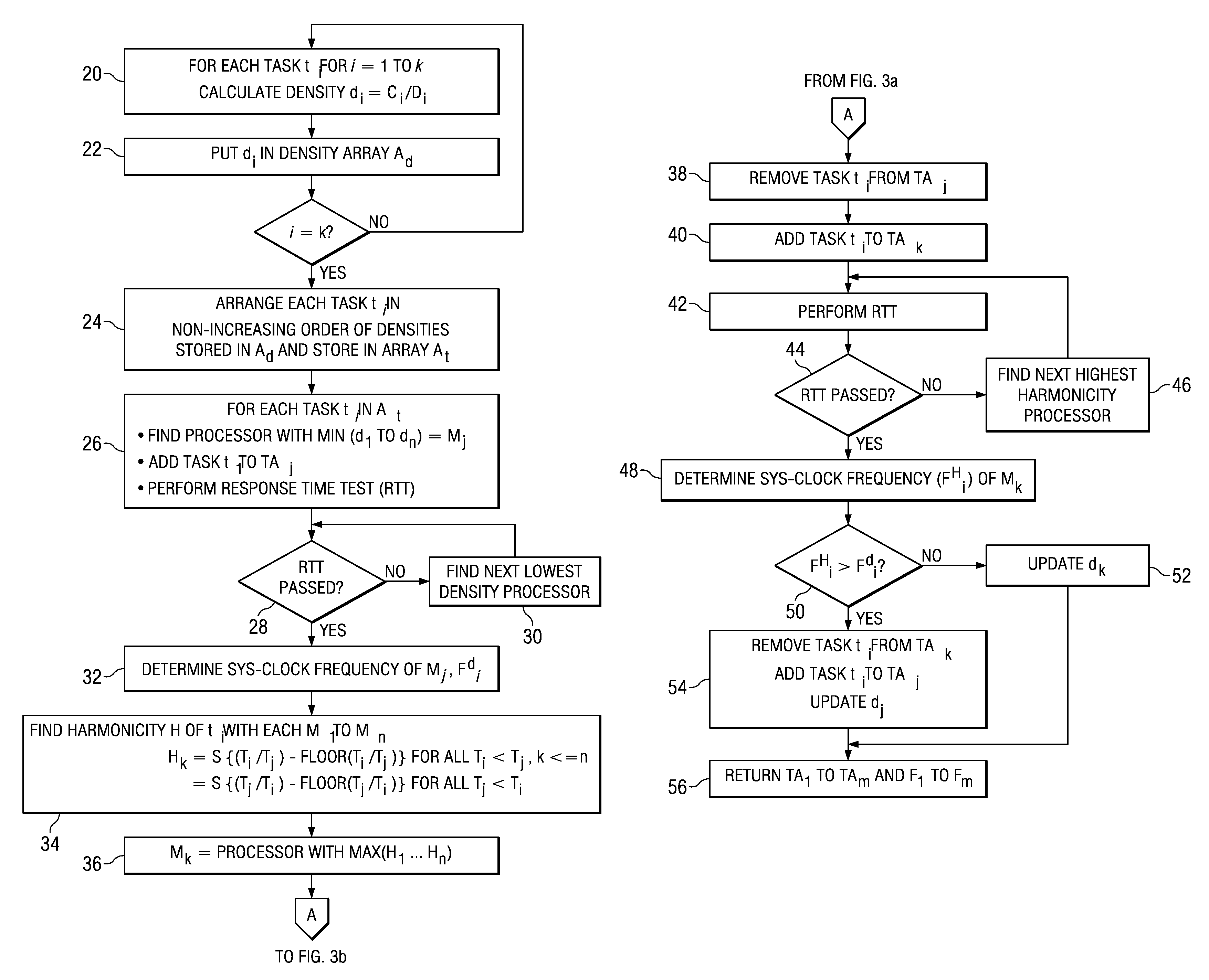

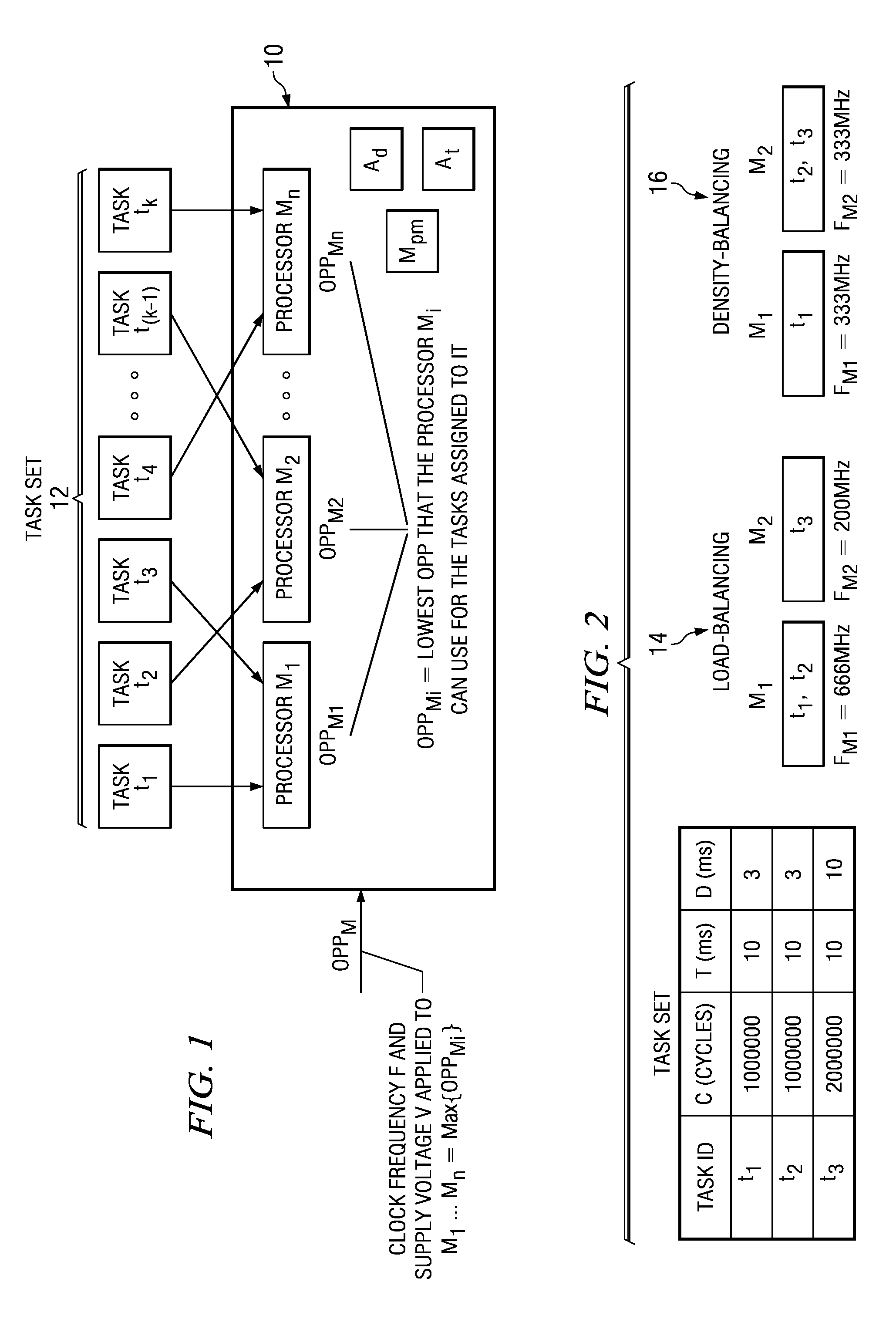

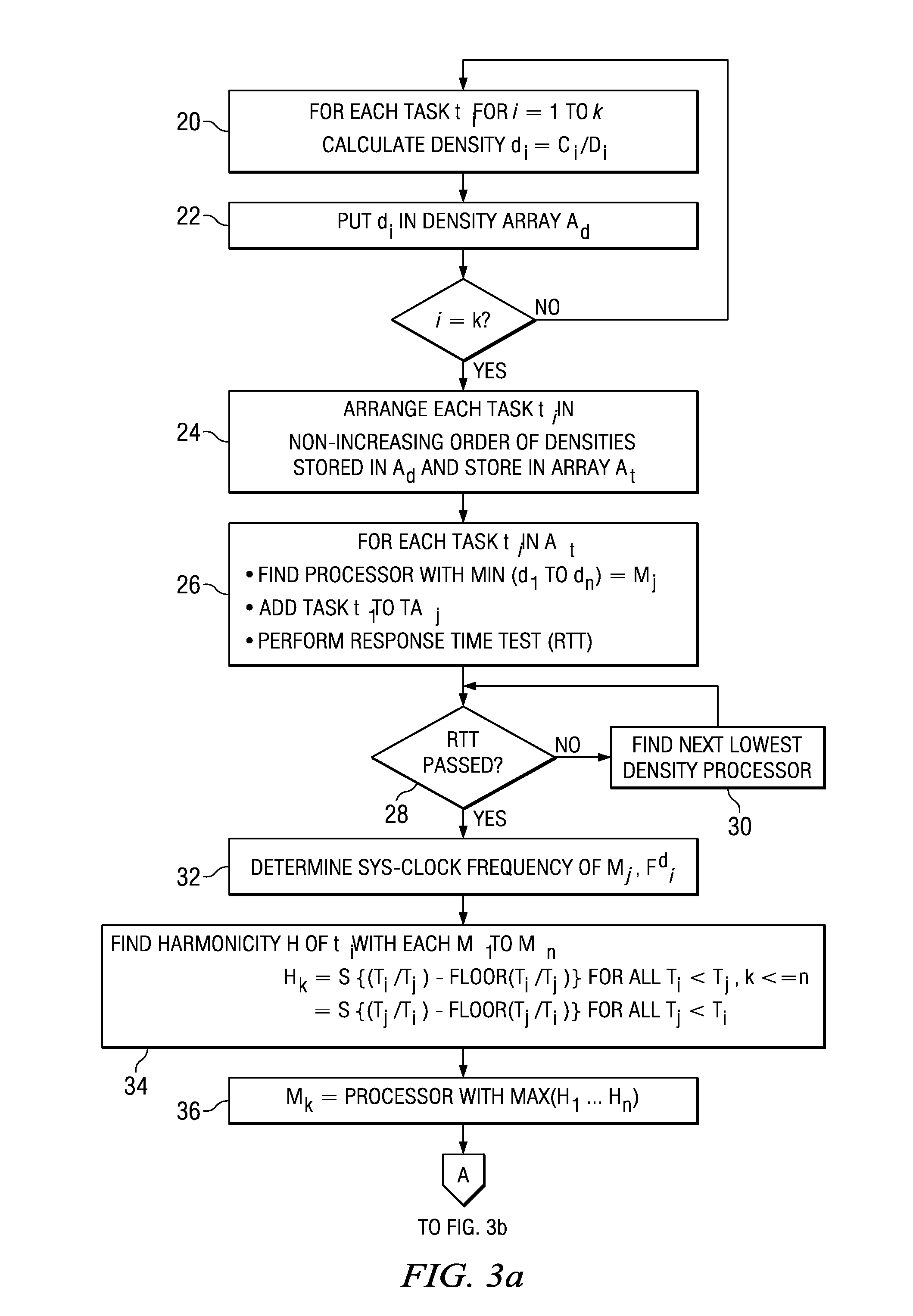

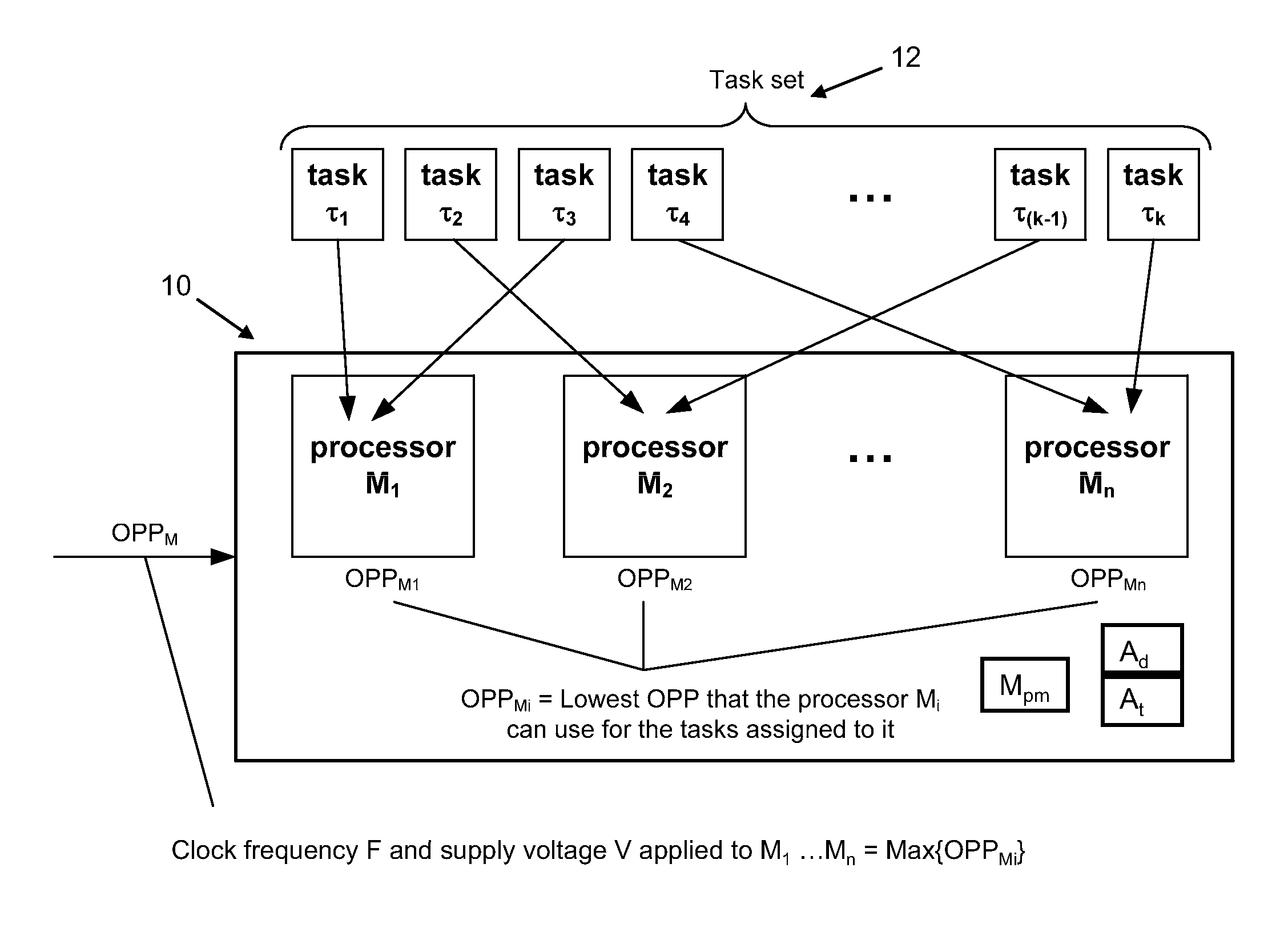

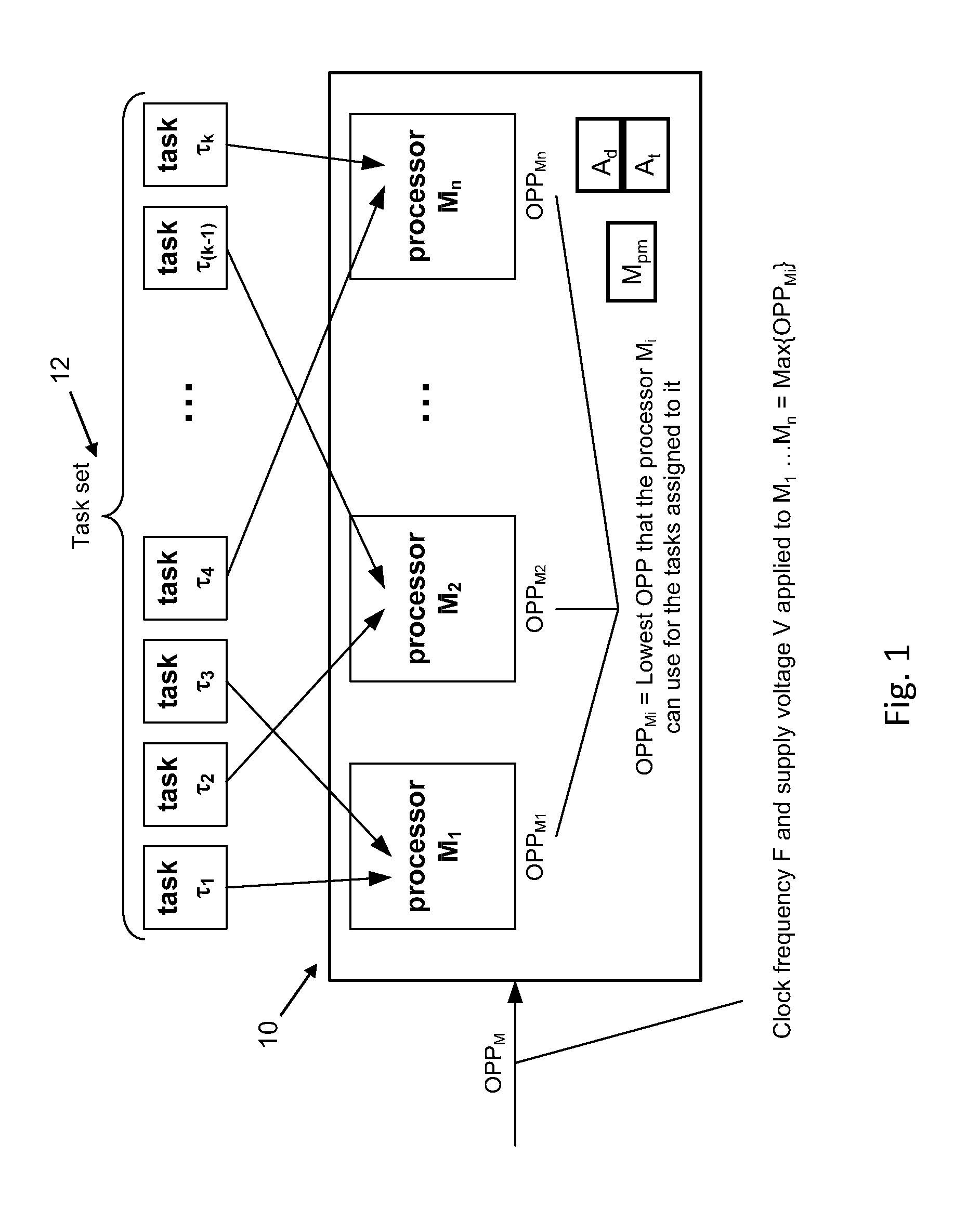

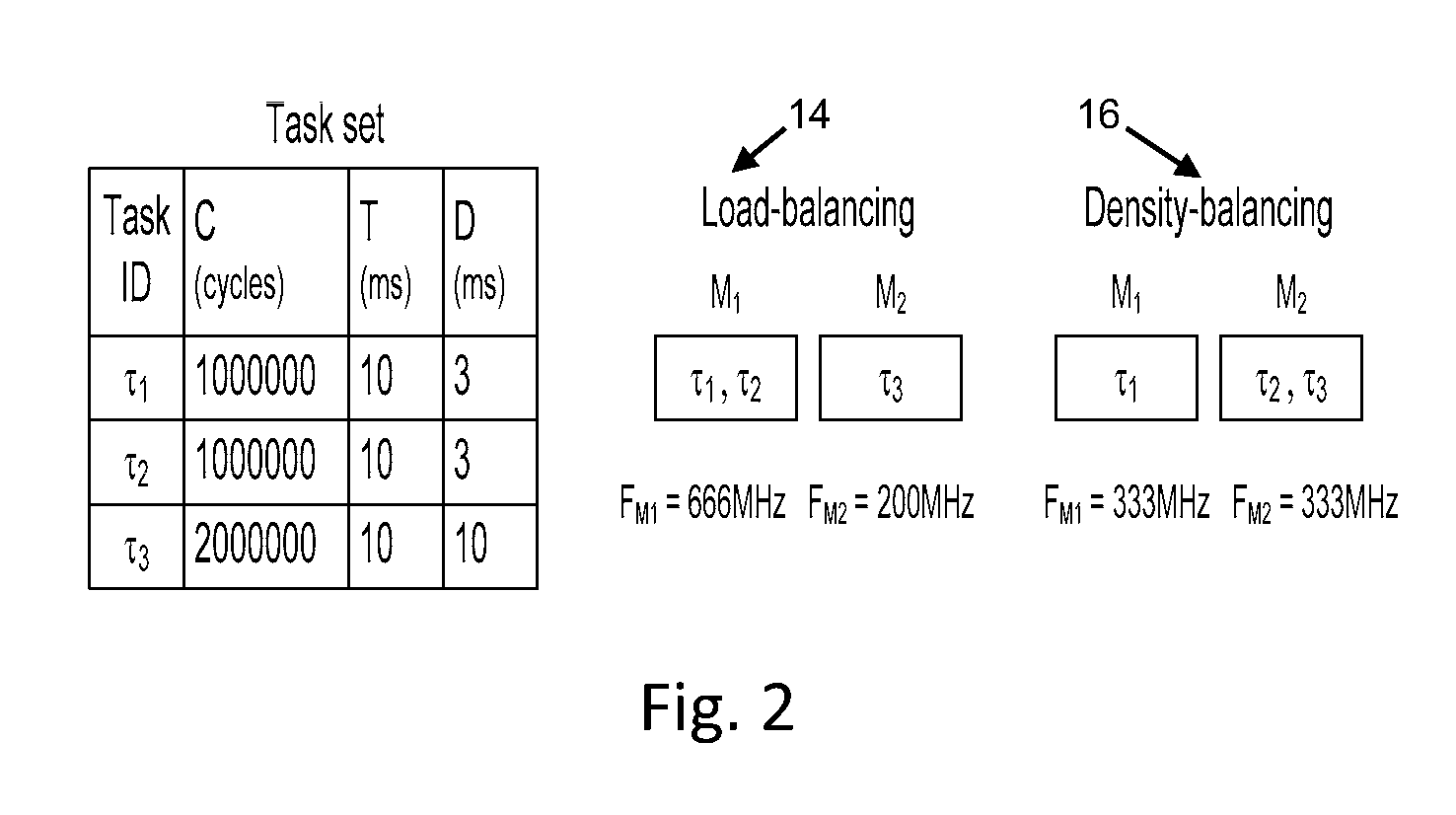

System and method of task allocation in multiprocessing environment based on minimum density or maximum harmonicity that results in lower clock frequency

Systems and Methods for task allocation in a multiprocessor environment employing power management techniques are described wherein tasks are allocated relative to the density given by the ratio of worst-case-execution time and deadline of a task and also the harmonicity of a task's period with respect to a task-set. Tasks are allocated to a given processor based on either minimum density or maximum harmonicity depending on which allocation results in a lower clock frequency. Assigning a task to the processor with lowest density results in balancing the density across processors while assigning task to the processor with maximum harmonicity attempts to maximize the utilization of the processor.

Owner:TEXAS INSTR INC

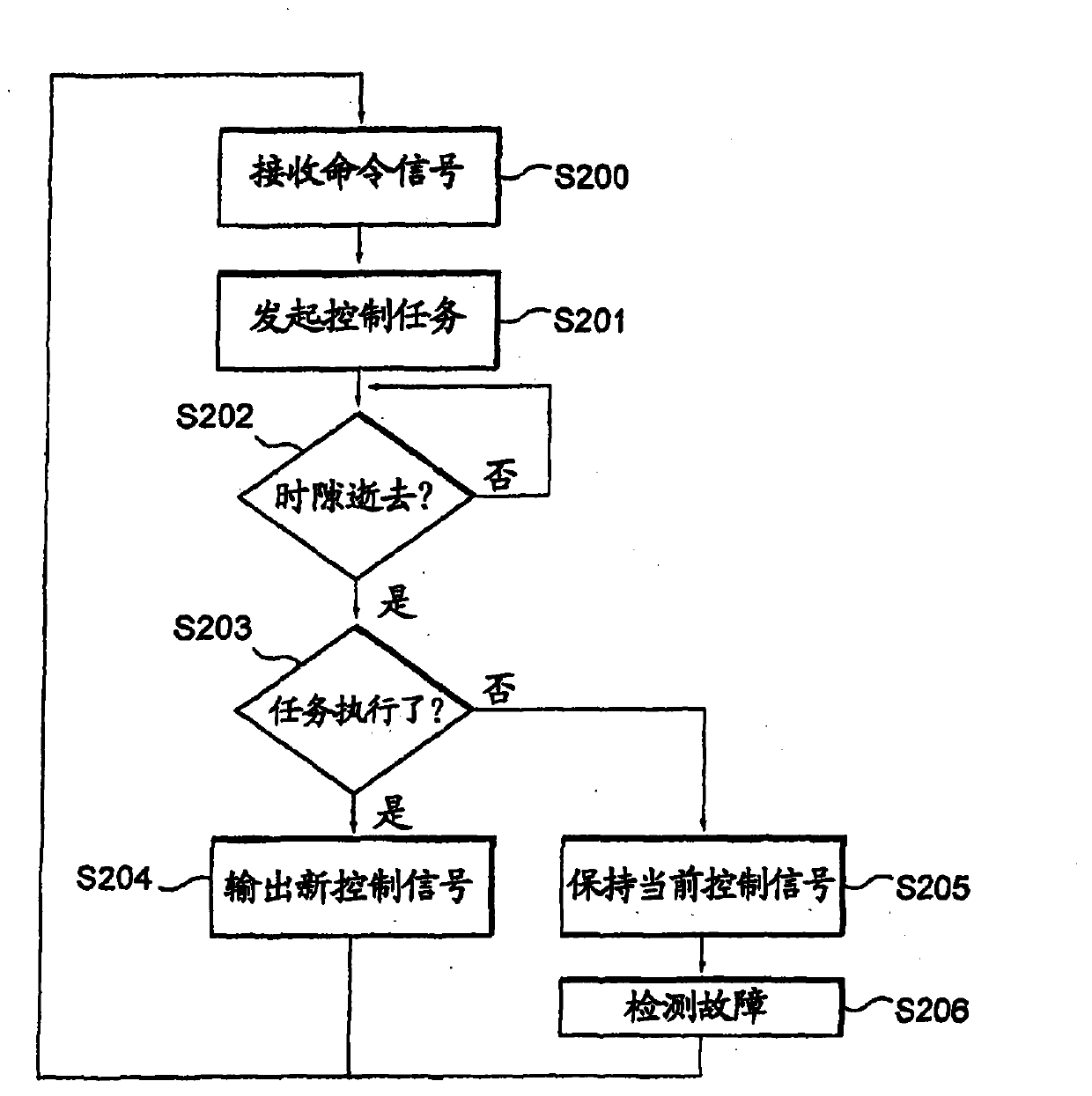

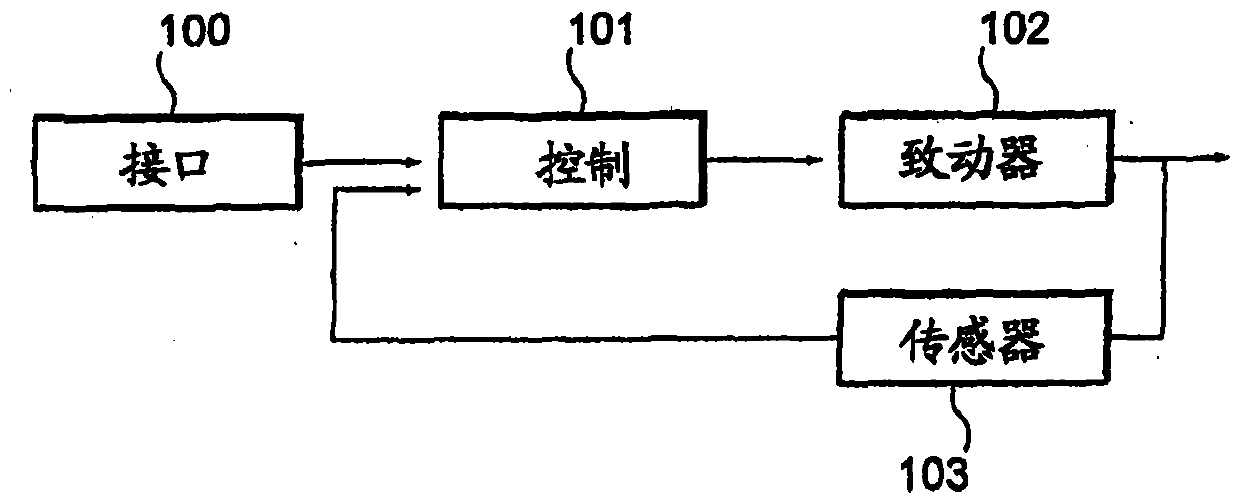

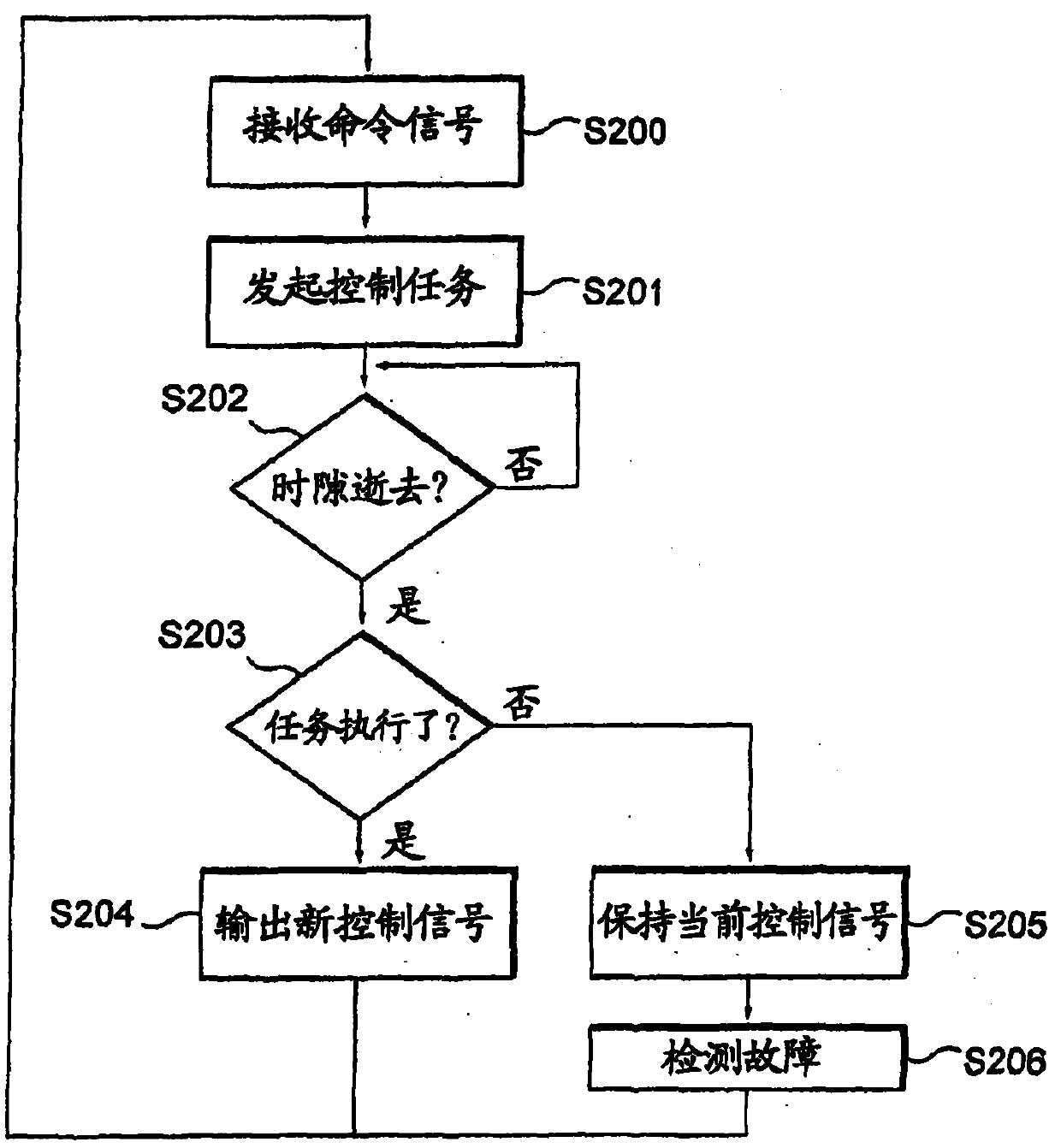

Robust system control method with short execution deadlines

InactiveCN102981405AProgramme controlProgram initiation/switchingControl systemWorst-case execution time

A method of controlling a system comprising the following steps: - launching a task, said task being associated with a worst case execution time; and - monitoring the end of the task after a time slot allocated to the execution of the task; wherein said time slot is shorter than said worst case execution time.

Owner:AIRBUS OPERATIONS (SAS)

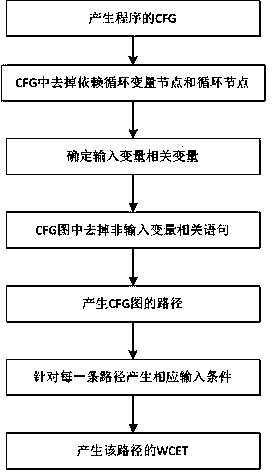

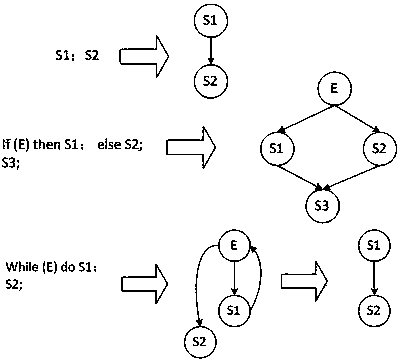

Automatic method for exactly analyzing WCET (Worst-Case Execution Time) of task

InactiveCN104391684AImprove estimation accuracySpecific program execution arrangementsLoop controlTheoretical computer science

The invention relates to an automatic method for exactly analyzing WCET (Worst-Case Execution Time) of a task, which comprises the following steps: 1) generating a no loop control flow graph NLCFG of a program; 2) utilizing the NLCFG to confirm a depending input variable and a corresponding node thereof; 3) confirming a depending cyclic variable, a depending non-input branch variable and non-depending input nodes corresponding to the depending cyclic variable and the depending non-input branch variable; 4) deleting the non-depending input nodes and generating an ICFG (input control flow graph); 5) generating all paths of the ICFG; 6) generating an input condition for each path and the WCET corresponding to each path. The condition of each path and the corresponding WCET can be utilized to accurately estimate the WCET of the task.

Owner:LUOYANG INST OF SCI & TECH

Systems and methods of task allocation in a multiprocessing environment having power management

Systems and Methods for task allocation in a multiprocessor environment employing power management techniques are described wherein tasks are allocated relative to the density given by the ratio of worst-case-execution time and deadline of a task and also the harmonicity of a task's period with respect to a task-set. Tasks are allocated to a given processor based on either minimum density or maximum harmonicity depending on which allocation results in a lower clock frequency. Assigning a task to the processor with lowest density results in balancing the density across processors while assigning task to the processor with maximum harmonicity attempts to maximize the utilization of the processor.

Owner:TEXAS INSTR INC

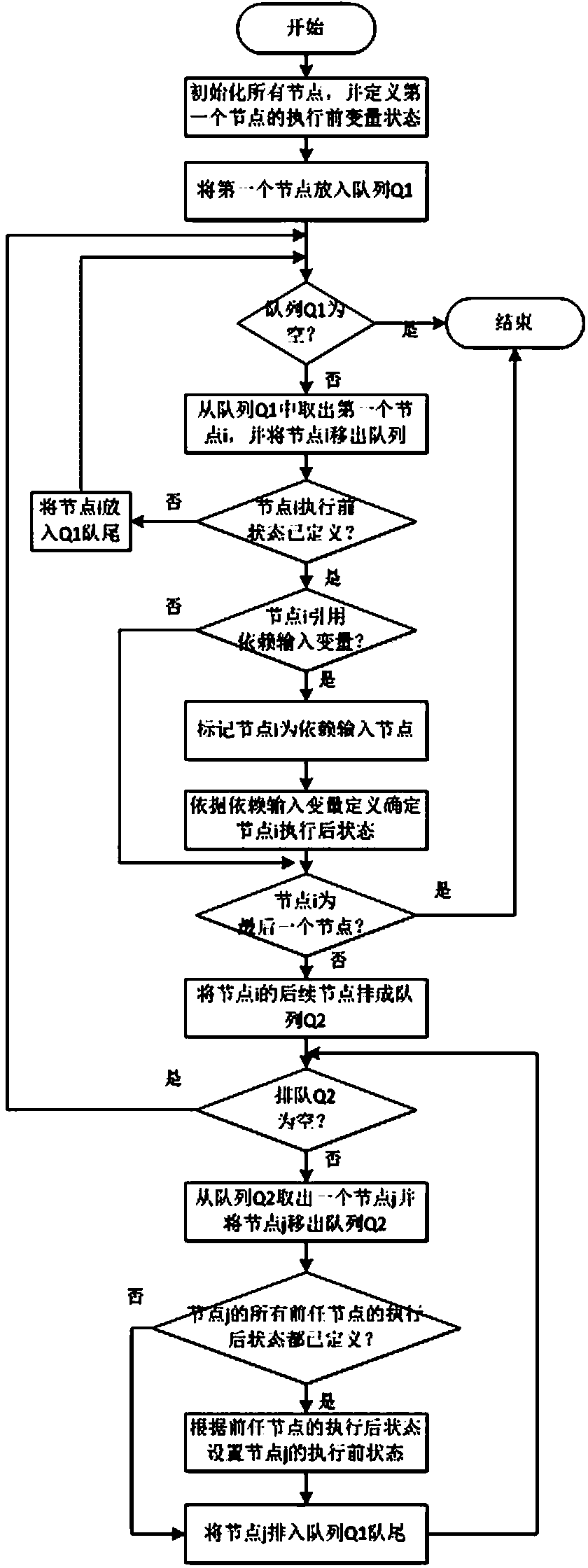

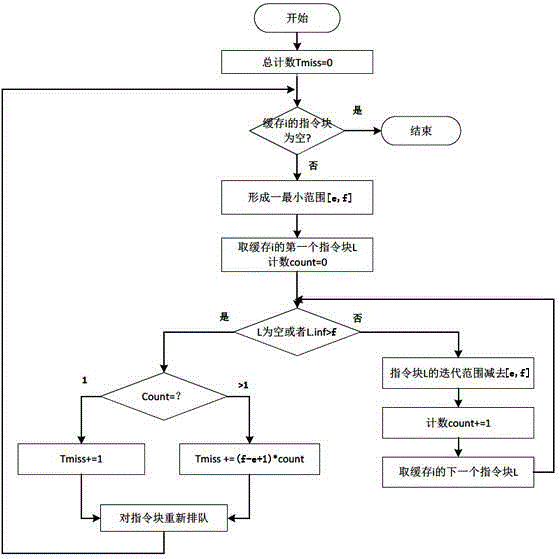

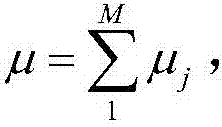

Analysis method for accurately calculating WCET (worst case execution time) of task high-speed cache

InactiveCN104679521AImprove estimation accuracySpecific program execution arrangementsWorst-case execution timeBasic block

The invention relates to an analysis method for accurately calculating WCET (worst case execution time) of a task high-speed cache. The method comprises the following steps of firstly, generating the iteration range of a basic block; then, according to the iteration range of the basic block, calculating the iteration range of an instruction block, and finding the minimum iteration range of all instruction blocks from the calculated iteration range of the instruction block; according to the minimum iteration range of the instruction blocks, calculating the loss times, and removing the minimum iteration range; finally, according to the minimum iteration range, calculating the total maximum loss times of the high-speed cache, so as to calculate the WCET of the task high-speed cache. The method has the advantage that the estimating accuracy of the WCET of the high-speed cache can be obviously improved.

Owner:LUOYANG INST OF SCI & TECH

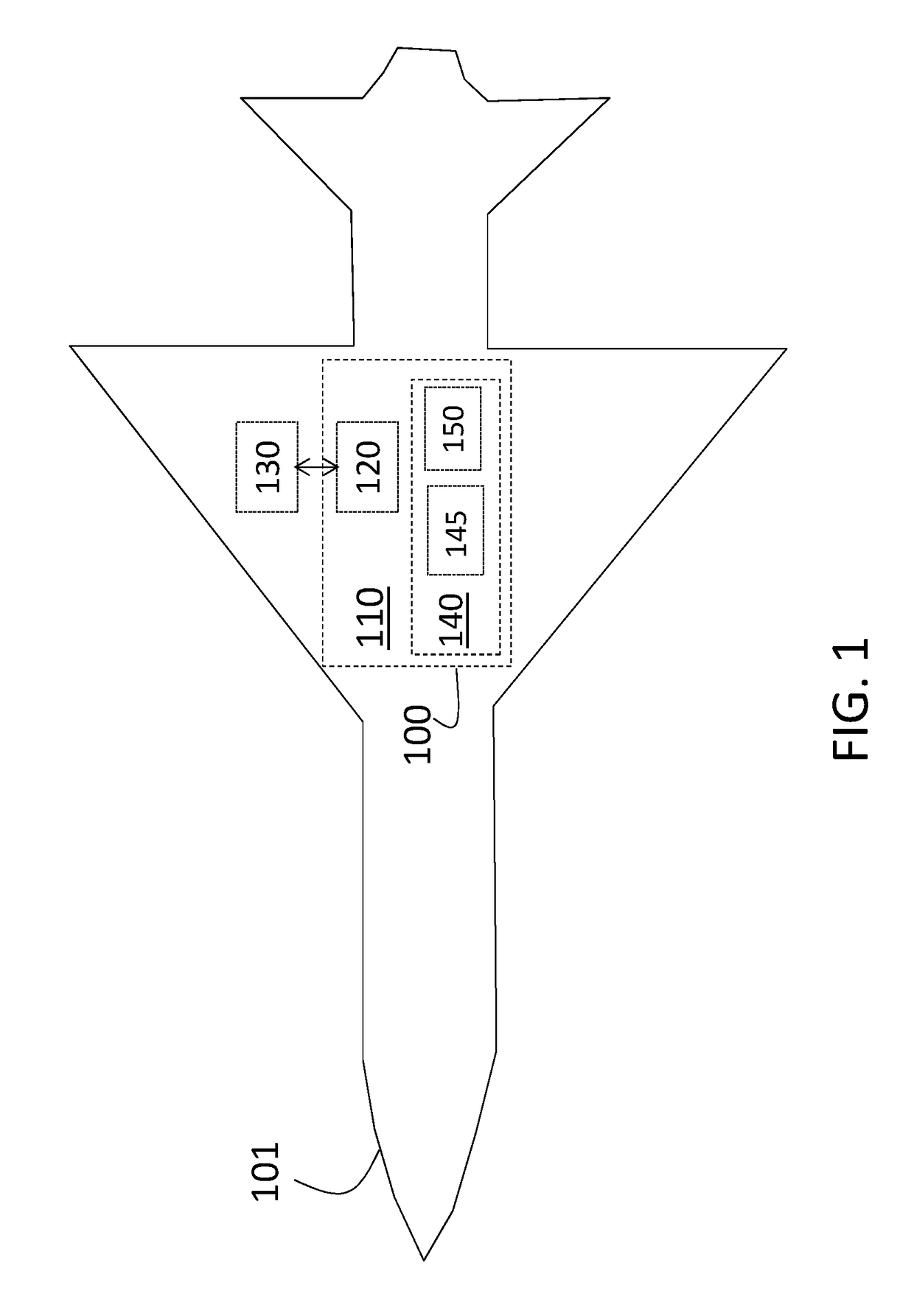

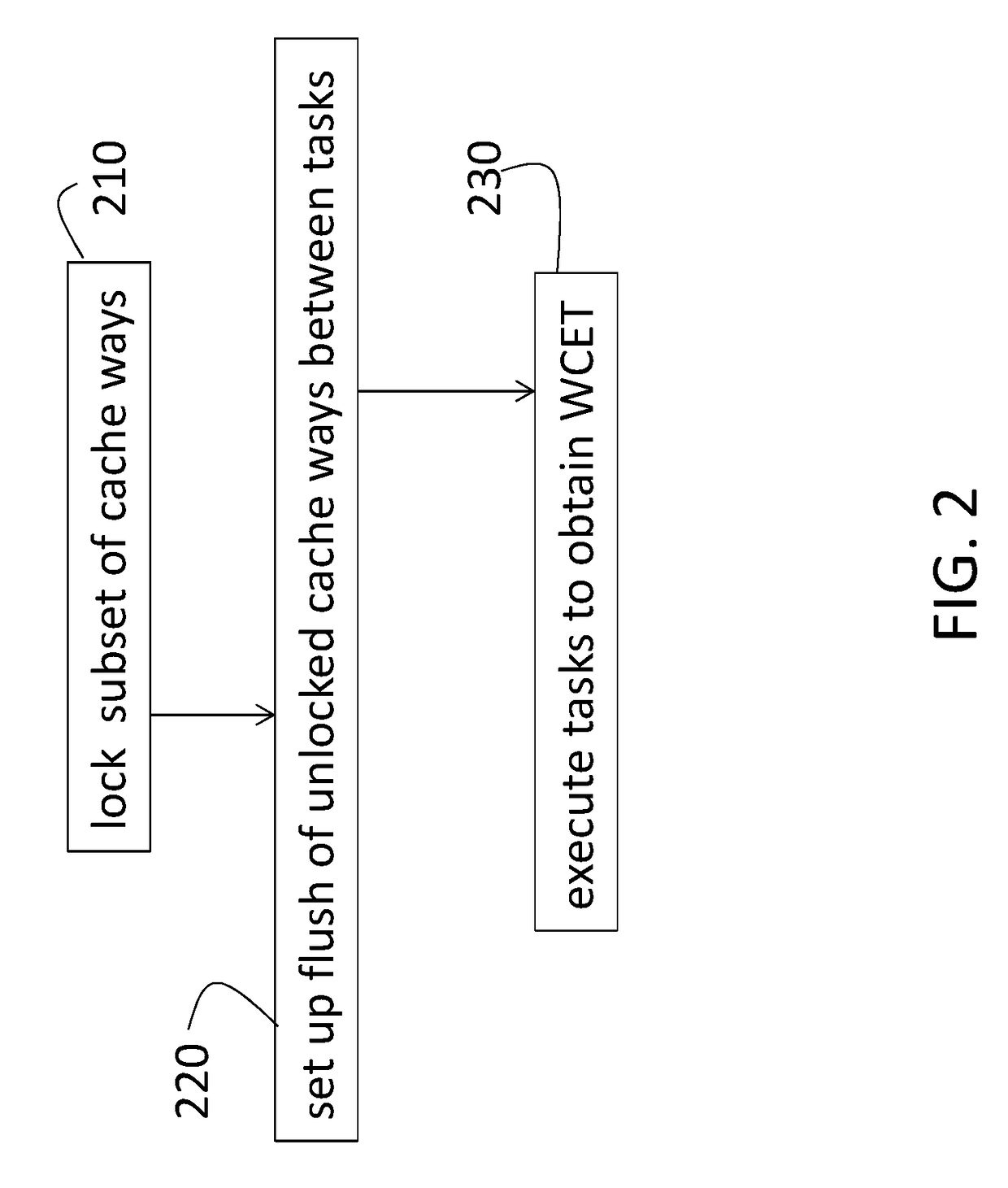

Deterministic timing evaluation

InactiveUS20180173622A1Memory architecture accessing/allocationMemory adressing/allocation/relocationWorst-case execution timeSoftware

A method and system to perform deterministic timing analysis of a plurality of software tasks involves cache memory that is shared by the plurality of software tasks. Real memory is accessible by the plurality of software tasks. A task scheduler establishes a cache flush between executions of consecutive tasks among the plurality of software tasks. The cache flush includes movement of data in the cache memory to the real memory. A processor executes the plurality of software tasks to obtain a worst case execution time (WCET) associated with each of the plurality of software tasks.

Owner:HAMILTON SUNDSTRAND CORP

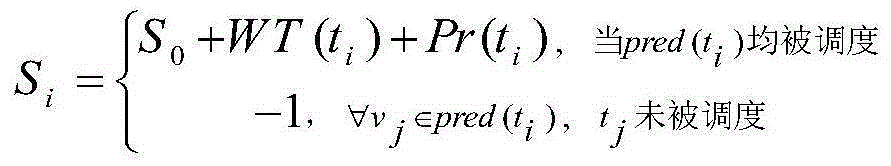

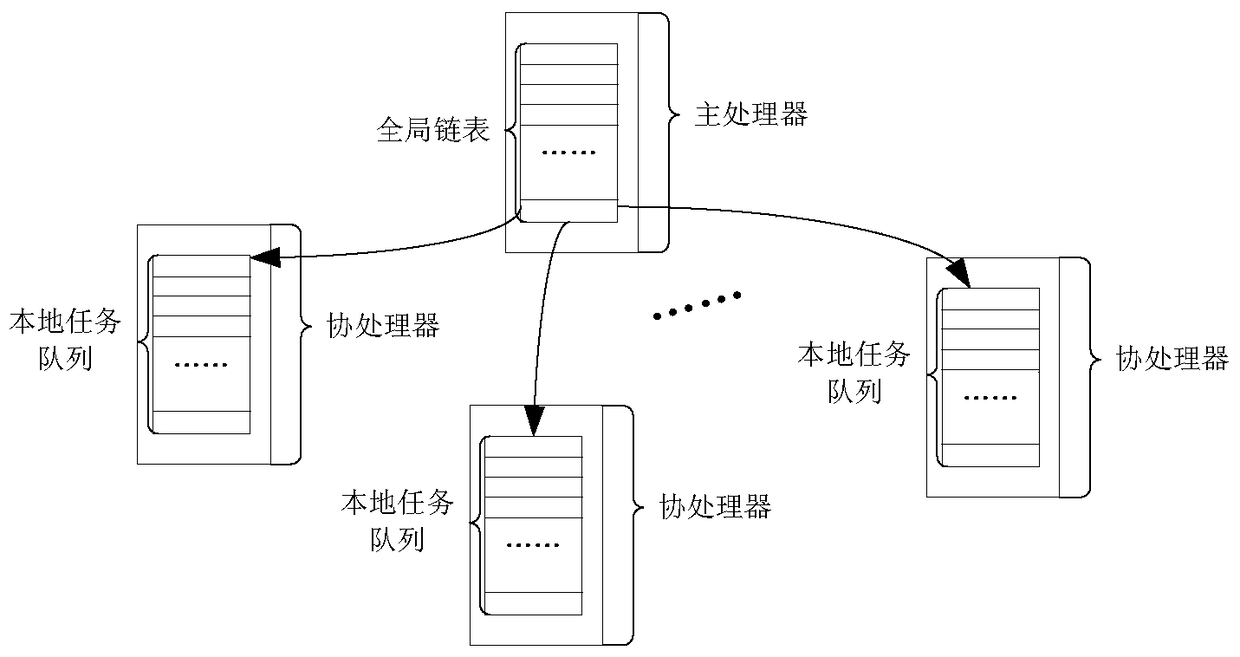

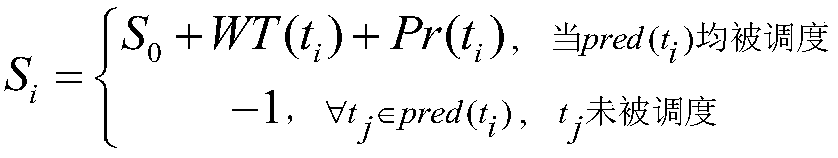

Task scheduling method based on task application signal and execution cost value of processor core

ActiveCN105117281AReduced execution timeReduce overheadProgram initiation/switchingWorst-case execution timeOperating system

The invention relates to a task scheduling method based on a task application signal and an execution cost value of a processor core. The task scheduling method comprises the following steps: (1) the task application signal: a global linked list and a processor core scheduling queue are adopted to record a task; (2) the execution cost value of the processor core: each processor core maintains one execution cost value vector, and the processor core calculates to obtain the execution cost value of each task in the global linked list, and stores the execution cost value of each task into the execution cost value vector; and (3) task scheduling probability: the processor core calculates the probability for scheduling the task to the processor core scheduling queue from the global linked list according to the execution cost value of the task and the application signal of the task. The global linked list and the processor core scheduling queue are adopted to record tasks, the application signal intensity of the task and the task execution cost value of the processor core are used as task scheduling criterions, cost generated in a task transfer process can be effectively reduced, and task execution time is shortened.

Owner:HARBIN ENG UNIV

Computing architecture with peripherals

InactiveUS20160275015A1Memory architecture accessing/allocationMemory adressing/allocation/relocationFinite-state machineWorst-case execution time

A shared memory computing device optimised for worst case execution time analysis that has at least one interconnect master, N cache modules and N processor cores. Each cache module has a finite state machine that employs an update-type cache coherency policy. Each processor core is assigned a different one of the N fully associative cache modules as its private cache. Furthermore, the execution time of memory transfer requests issued by each of the N processor cores is not modified by: (a) the unrelated memory transfer requests issued by any of the other N processor cores; or (b) the unrelated memory transfer requests issued by at least one other interconnect master.

Owner:SYNAPTIC LAB

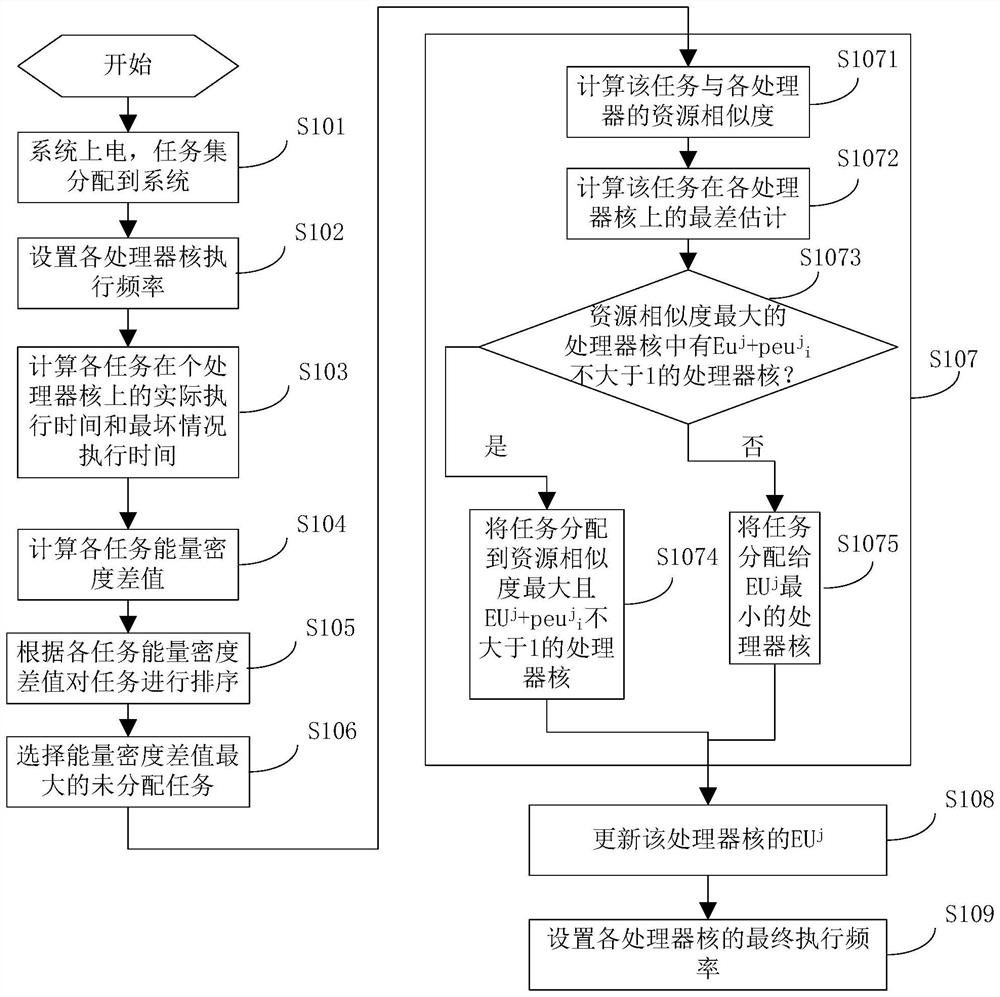

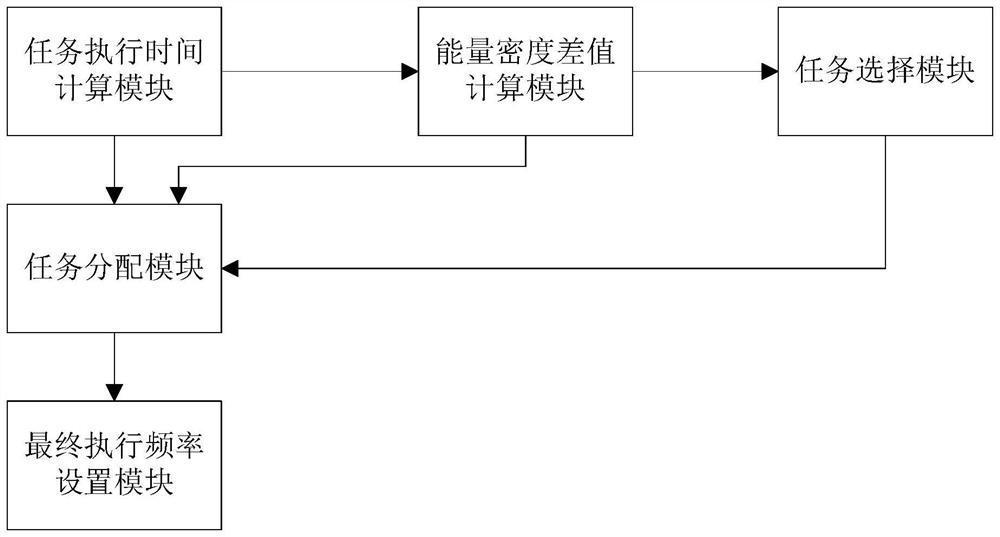

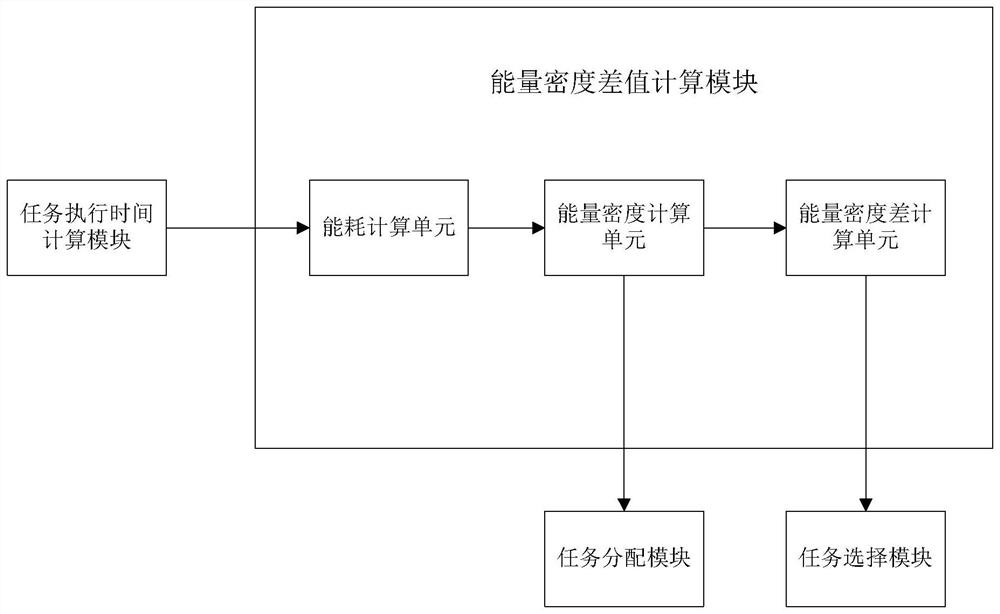

Heterogeneous multi-core system task allocation method and device based on shared resource access

The invention discloses a heterogeneous multi-core system task allocation method based on shared resource access, which comprises the following steps of: calculating worst-case execution time and actual execution time of each task on each processor core; calculating the energy density of each task on each processor and the energy density difference value of each task; and sequentially selecting the unallocated task with the maximum energy density difference, and allocating the task to the processor core with the maximum resource similarity with the task in the selectable processor cores. The invention further discloses a heterogeneous multi-core system task allocation device based on shared resource access, in the technical scheme, the task allocation sequence is selected according to the energy density difference values of the tasks from large to small, and the energy consumption of processor cores of the heterogeneous multi-core system can be effectively reduced.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

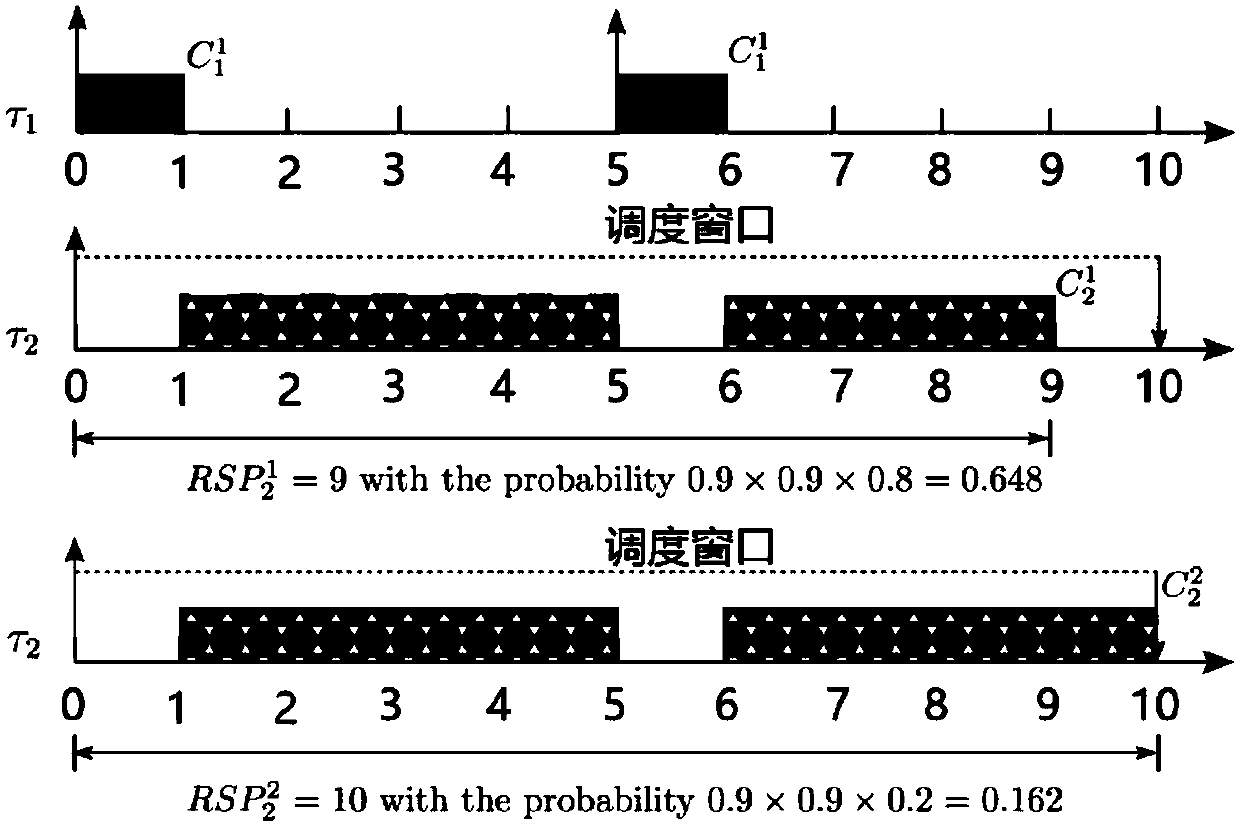

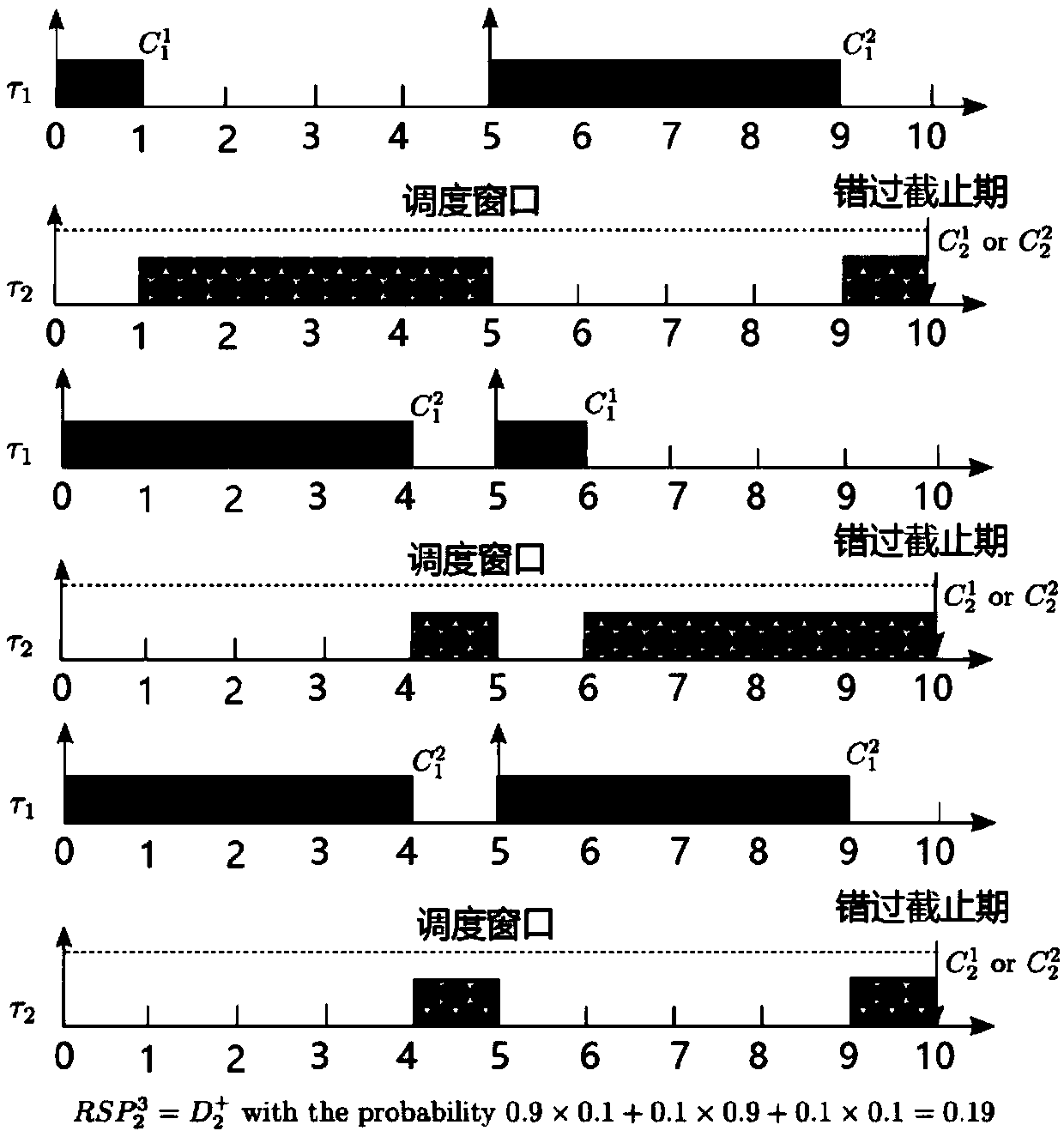

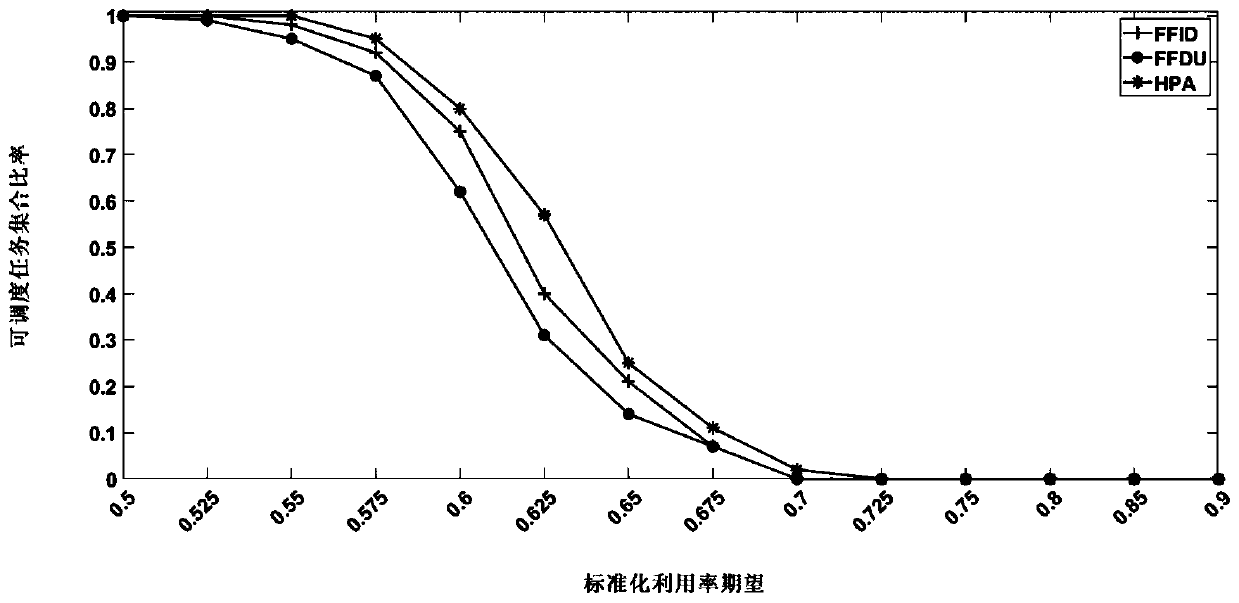

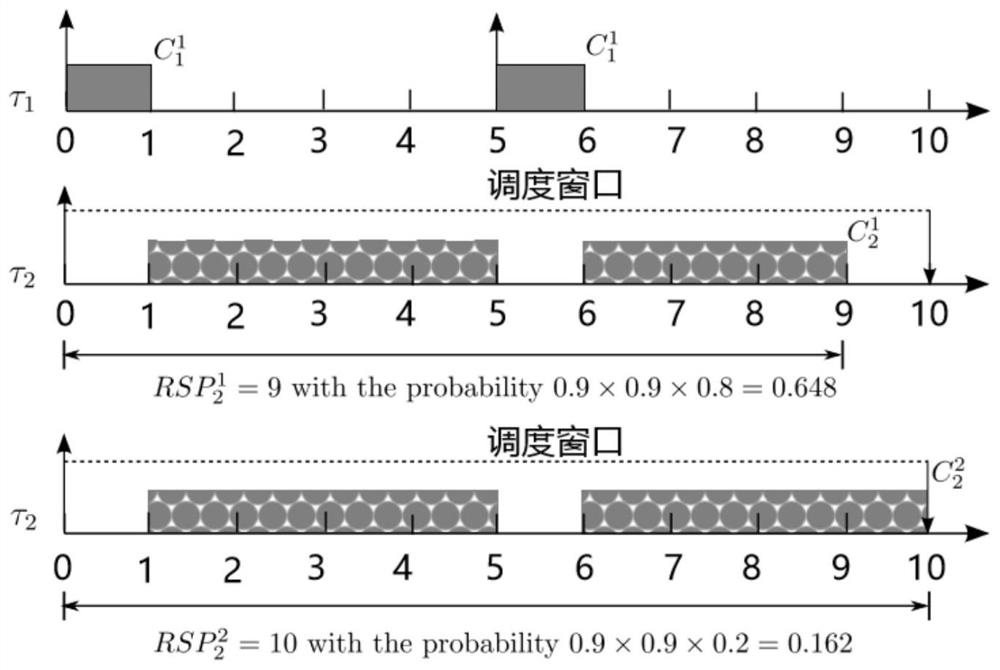

Probabilistic real-time task scheduling method based on pWCET shaping

ActiveCN108845870AValue reductionReduce computational complexityProgram initiation/switchingResource allocationComputation complexityRound complexity

The invention provides a probabilistic real-time task scheduling method based on pWCET (probabilistic worst case execution time) shaping, and belongs to the technical field of real-time systems. A probabilistic real-time task scheduling scheme based on the pWCET shaping is proposed, so that the goals of properly isolating the influence between probabilistic real-time tasks and lowering the calculation complexity of system schedulability analysis are achieved. According to the method, the pWCET of the probabilistic real-time tasks is shaped, and budget allocation is performed on the basis of the shaped pWCET, so that while the probabilistic real-time requirements of the tasks are met, the influence between the probabilistic real-time tasks can be properly isolated, and the schedulability ofthe whole task set is remarkably improved. In addition, the value of the shaped pWCET is obviously reduced compared with that of original pWCET; the calculation complexity of the schedulability analysis can be lowered; and the efficiency is remarkably improved.

Owner:DALIAN UNIV OF TECH

Signal processing apparatus

Owner:NXP BV

A Task Scheduling Method Based on Task Application Signal and Processor Core Execution Cost

ActiveCN105117281BReduced execution timeReduce overheadProgram initiation/switchingWorst-case execution timeOperating system

Owner:HARBIN ENG UNIV

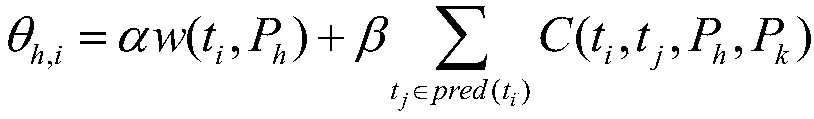

A Fast Estimation Method of Worst Execution Time wcet Based on Distribution Function

InactiveCN104572103BOvercome the disadvantage of needing to run the program to obtain the measurement value sampleEasy to implementSoftware testing/debuggingSpecific program execution arrangementsEstimation methodsObject code

The invention provides a distribution function-based WCET (Worst Case Execution Time) quick estimation method. The method comprises the following steps: disassembling a DSP (Digital Signal Processor) project objective code (out file) to obtain a disassembled file F; analyzing the disassembled file F to acquire each divided basic block to obtain a basic block set B of a program; recognizing relation between every two basic blocks in the basic block set B to construct a program flow graph C; calculating execution time T of each basic block; obtaining weighted program flow graph Cw by weighting the basic block execution time T and the basic block execution frequency Ts; analyzing the weighted program flow graph Cw to obtain a path with the maximum total weight value and taking the maximum total weight value as the WCET. The defect that a program is required to be operated to obtain a test sample in the prior art is overcome, and the problems of more manual intervention and irrationality of a beta distribution parameter estimation method in the conventional PERT (Program Evaluation and Review Technique) are solved.

Owner:XIAN INSTITUE OF SPACE RADIO TECH +1

An Analysis Method of Precise Computing Task Cache Wcet

InactiveCN104679521BImprove estimation accuracySpecific program execution arrangementsWorst-case execution timeAnalysis method

The invention relates to an analysis method for accurately calculating WCET (worst case execution time) of a task high-speed cache. The method comprises the following steps of firstly, generating the iteration range of a basic block; then, according to the iteration range of the basic block, calculating the iteration range of an instruction block, and finding the minimum iteration range of all instruction blocks from the calculated iteration range of the instruction block; according to the minimum iteration range of the instruction blocks, calculating the loss times, and removing the minimum iteration range; finally, according to the minimum iteration range, calculating the total maximum loss times of the high-speed cache, so as to calculate the WCET of the task high-speed cache. The method has the advantage that the estimating accuracy of the WCET of the high-speed cache can be obviously improved.

Owner:LUOYANG INST OF SCI & TECH

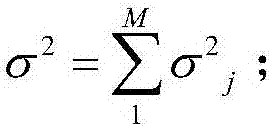

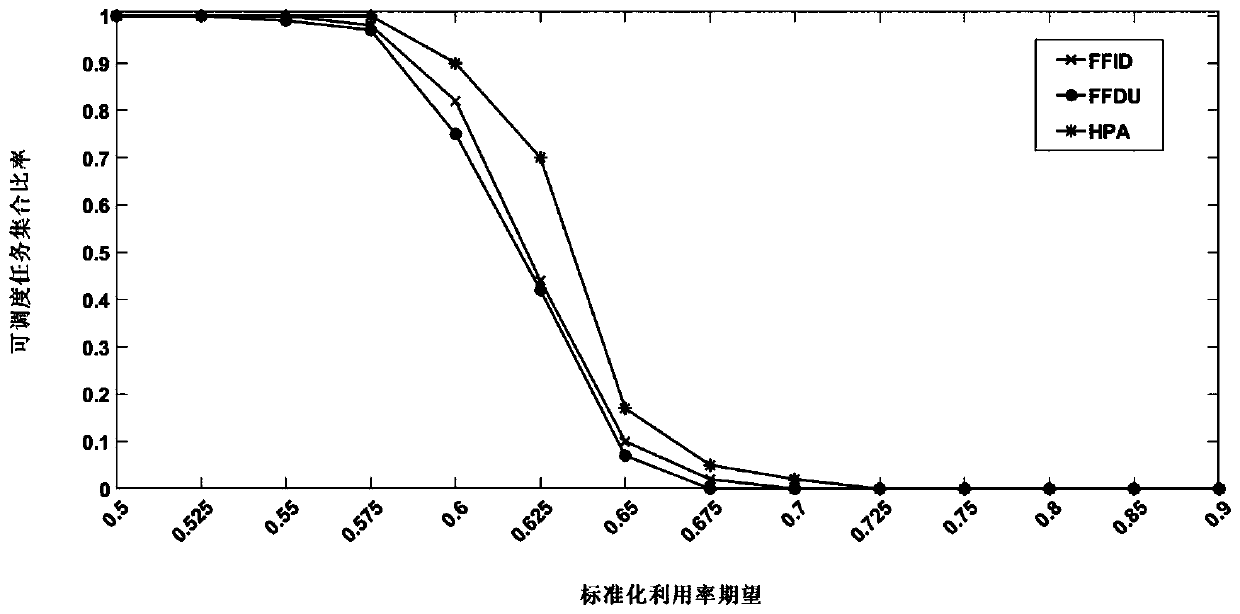

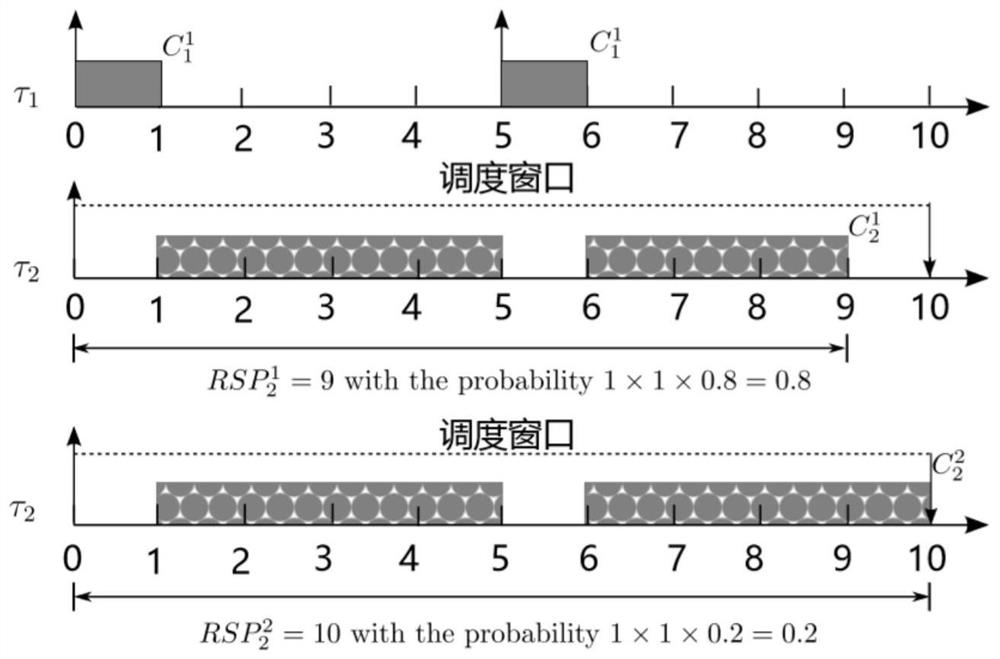

Harmonious perception multiprocessor scheduling method for multi-probabilistic parameter real-time tasks

ActiveCN110865886ASolve FragmentationGuaranteed probabilistic real-time demandResource allocationProcessor schedulingMulti processor

The invention discloses a harmonious perception multiprocessor scheduling method for multi-probabilistic parameter real-time tasks, and belongs to the technical field of real-time systems. The harmonious perception multiprocessor scheduling method comprises three steps of calculating a harmony coefficient between every two tasks in a task set, dividing all tasks in a real-time task set containingn independent probabilities into p task subsets based on the harmony coefficient, and generating a real-time task set scheduling scheme oriented to multiple probabilistic parameters. The fragmentationproblem of CPU resource utilization in multi-probabilistic parameter real-time task multiprocessor scheduling based on probabilistic worst case execution time and probabilistic minimum arrival interval time is solved. The worst task execution time and the minimum arrival interval time in the task scheduling model are probabilistic, and the model application range is wider. In addition, the harmony relationship between the task load and the task is comprehensively considered in the task scheduling process, and the schedulability and the resource utilization rate of the system are improved.

Owner:DALIAN UNIV OF TECH

A probabilistic real-time task scheduling method based on pwcet shaping

ActiveCN108845870BValue reductionReduce computational complexityProgram initiation/switchingResource allocationComputation complexityRound complexity

The invention provides a probabilistic real-time task scheduling method based on pWCET shaping, which belongs to the technical field of real-time systems. The present invention proposes a probabilistic real-time task scheduling scheme based on probabilistic worst-case execution time shaping to achieve the goal of properly isolating the influence between probabilistic real-time tasks and reducing the computational complexity of system schedulability analysis. The present invention shapes the pWCET of the probabilistic real-time task and allocates the execution budget based on the shaped pWCET. While meeting the probabilistic real-time requirements of each task, it can properly isolate the influence between the probabilistic real-time tasks, so that the entire task set The schedulability is significantly improved. In addition, the value of pWCET after shaping is significantly lower than that of the original pWCET, which can reduce the computational complexity of schedulability analysis and significantly improve efficiency.

Owner:DALIAN UNIV OF TECH

An instruction prefetch content selection method for optimizing real-time task wcet

ActiveCN103207772BReduce design overheadReduce overheadMachine execution arrangementsHardware structureCache access

The invention provides an instruction prefectching content selecting method for optimizing WCET (worst-case execution time) of a real-time task. A hardware structure of a basic-block information table (BBIT) is added in high-speed caching hardware of an existing instruction. The instruction prefectching content selecting method includes: initializing hardware configuration, collecting a static routine base block set via a compiler or a static routine character analyzing tool, removing base blocks only covering one storage block, collecting execution frequentness of every program base block under worst-case execution condition, sequencing the program base blocks according to the execution frequentness, selecting information of an appointed amount of program base blocks according to the sequence, and storing the information in the BBIT. During a high-speed cache accessing process, high-speed instruction cache and the BBIT are searched at the same time, high-speed instruction cache accessing loss under the worst-case execution condition can be effectively avoided, requirements on the real-time task are met, and meanwhile, the instruction prefectching content selecting method can effectively reduce hardware design cost, and is simple and direct to realize.

Owner:BEIHANG UNIV

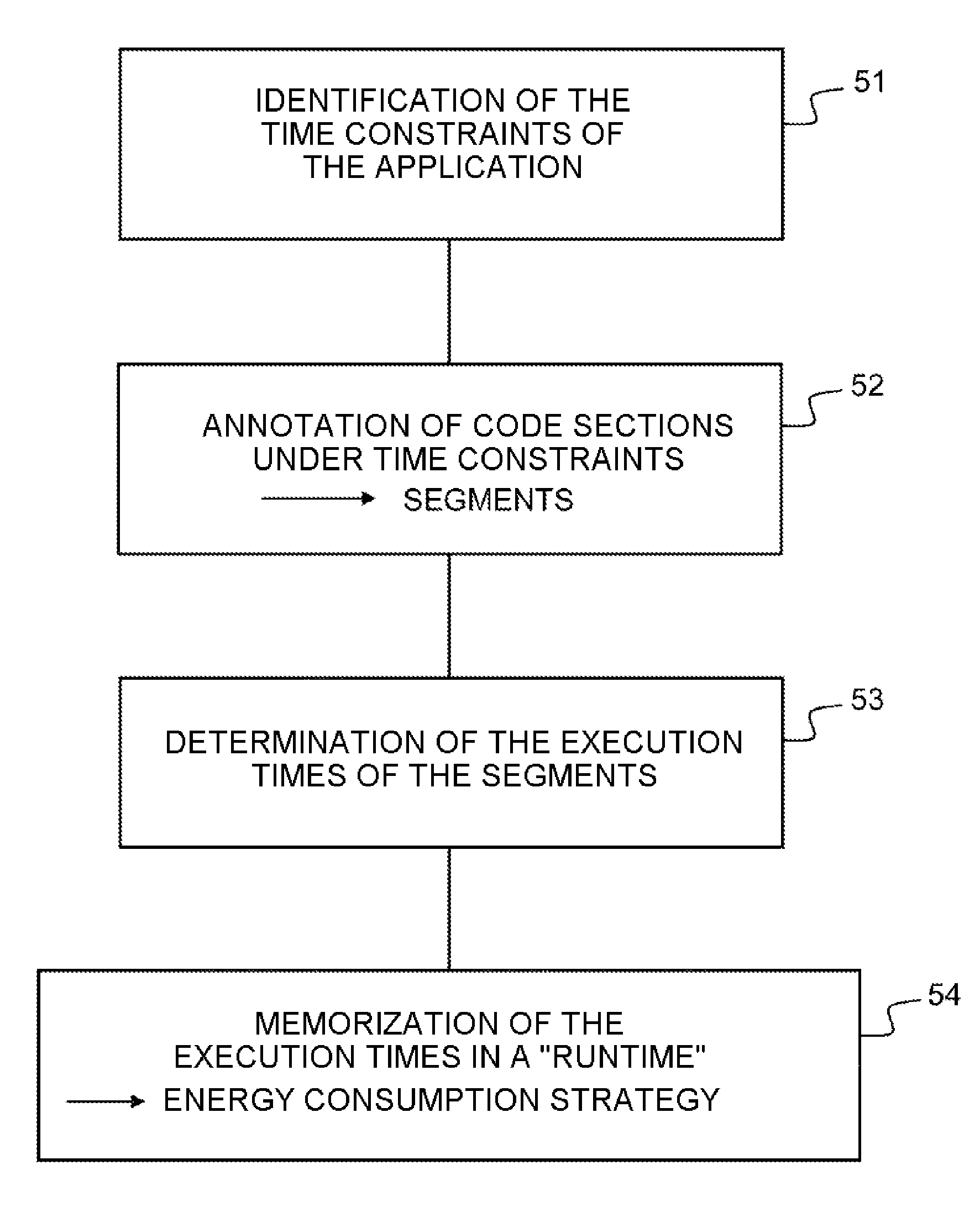

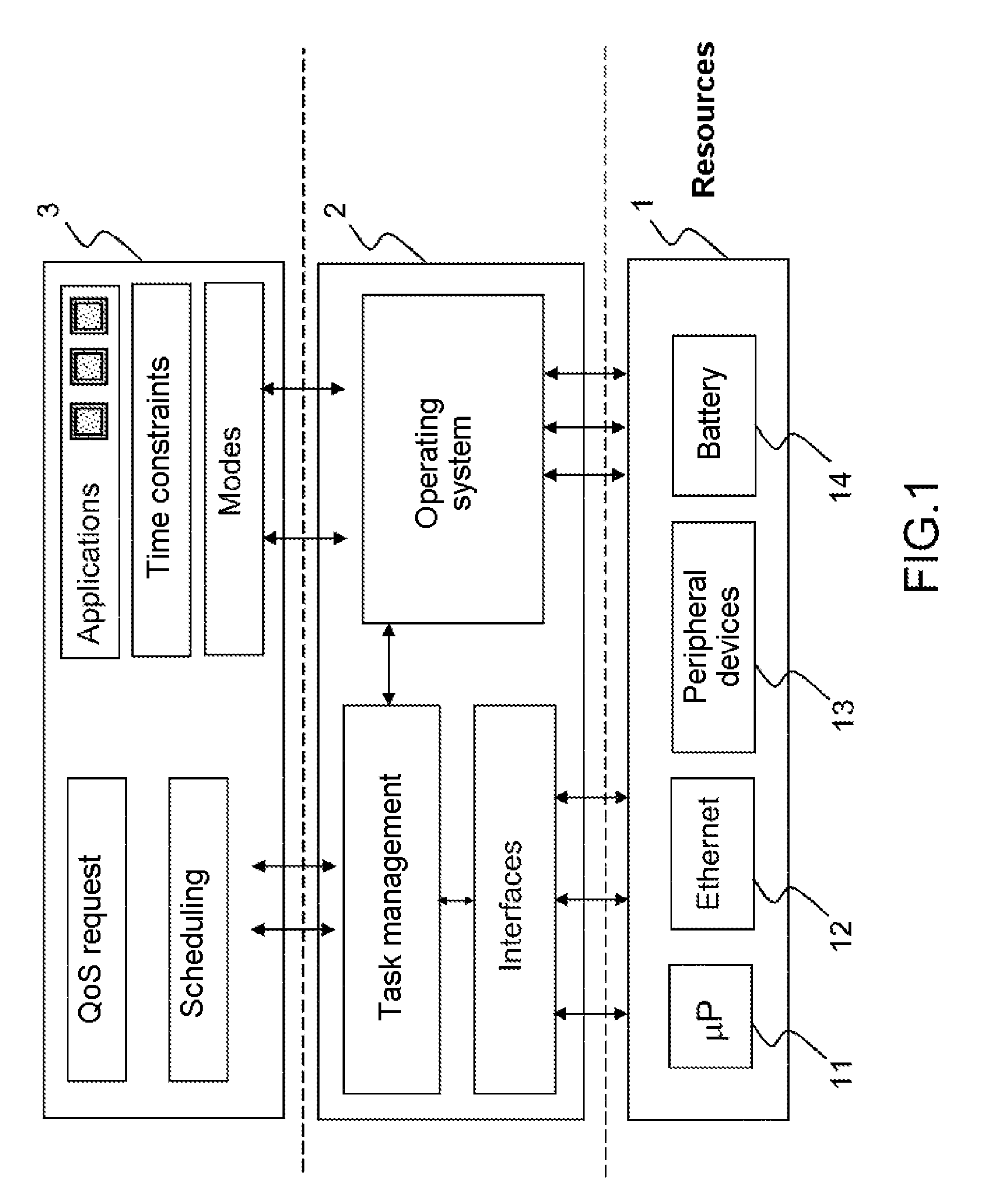

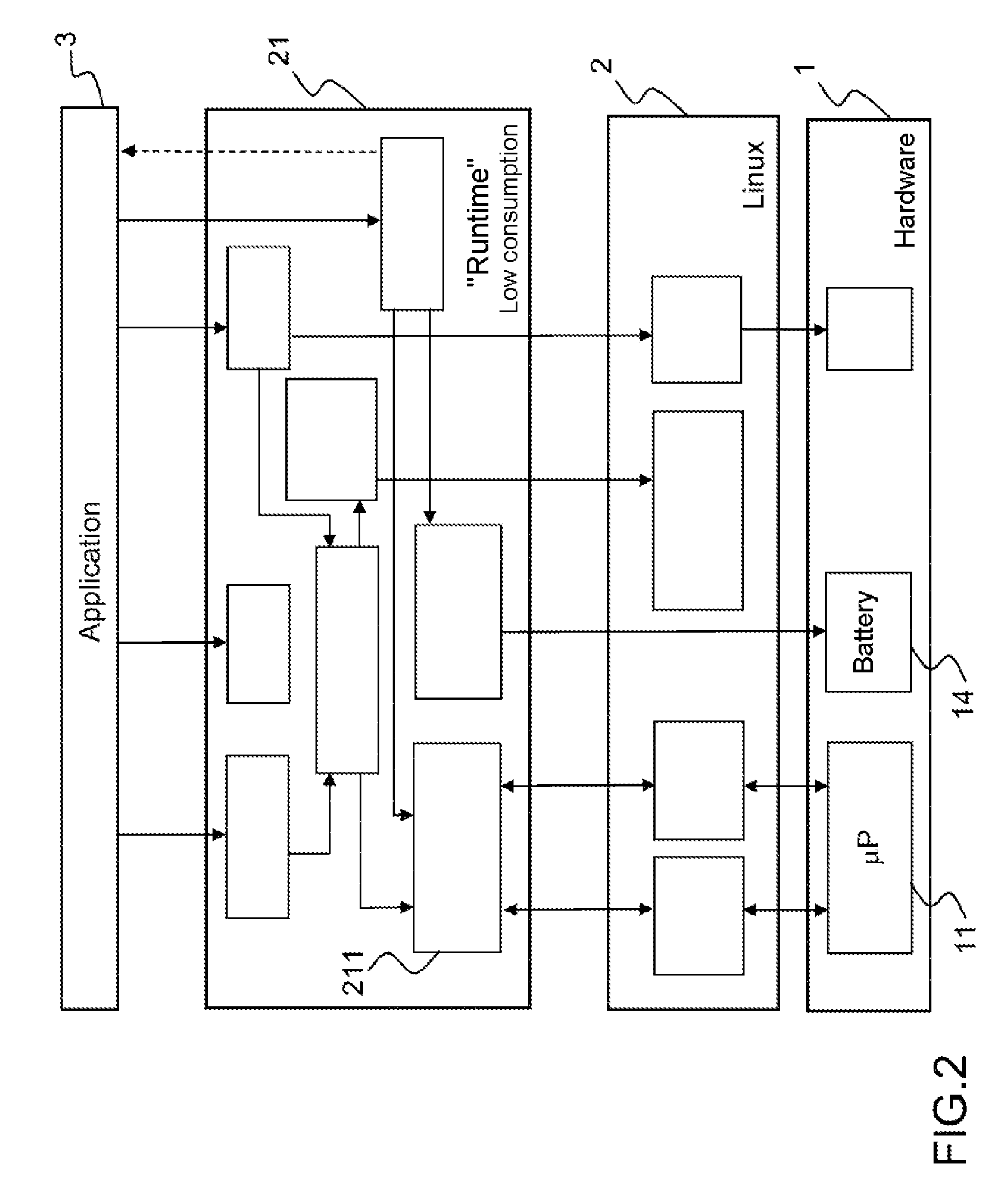

Method of managing the energy consumption of an application executable in various environments and software architecture implementing such a method

InactiveUS9285849B2Energy efficient ICTProgram initiation/switchingOperational systemApplication software

The application being executable by hardware comprising a set of processors using an operating system, a method comprises at least the following steps: a first step of identifying the time constraints of the application; a second step of annotating code sections of the application that are subject to a time constraint, said annotating being performed by means of software markers, the software markers delimiting code segments; a third step of determining the worst case execution times of the segments in a given set of execution modes; a fourth step of memorizing the execution times of the segments in an execution library for each execution mode, said library being able to be interfaced with said hardware, said operating system and said application and to execute an energy management strategy by controlling the state of the processors.

Owner:THALES SA

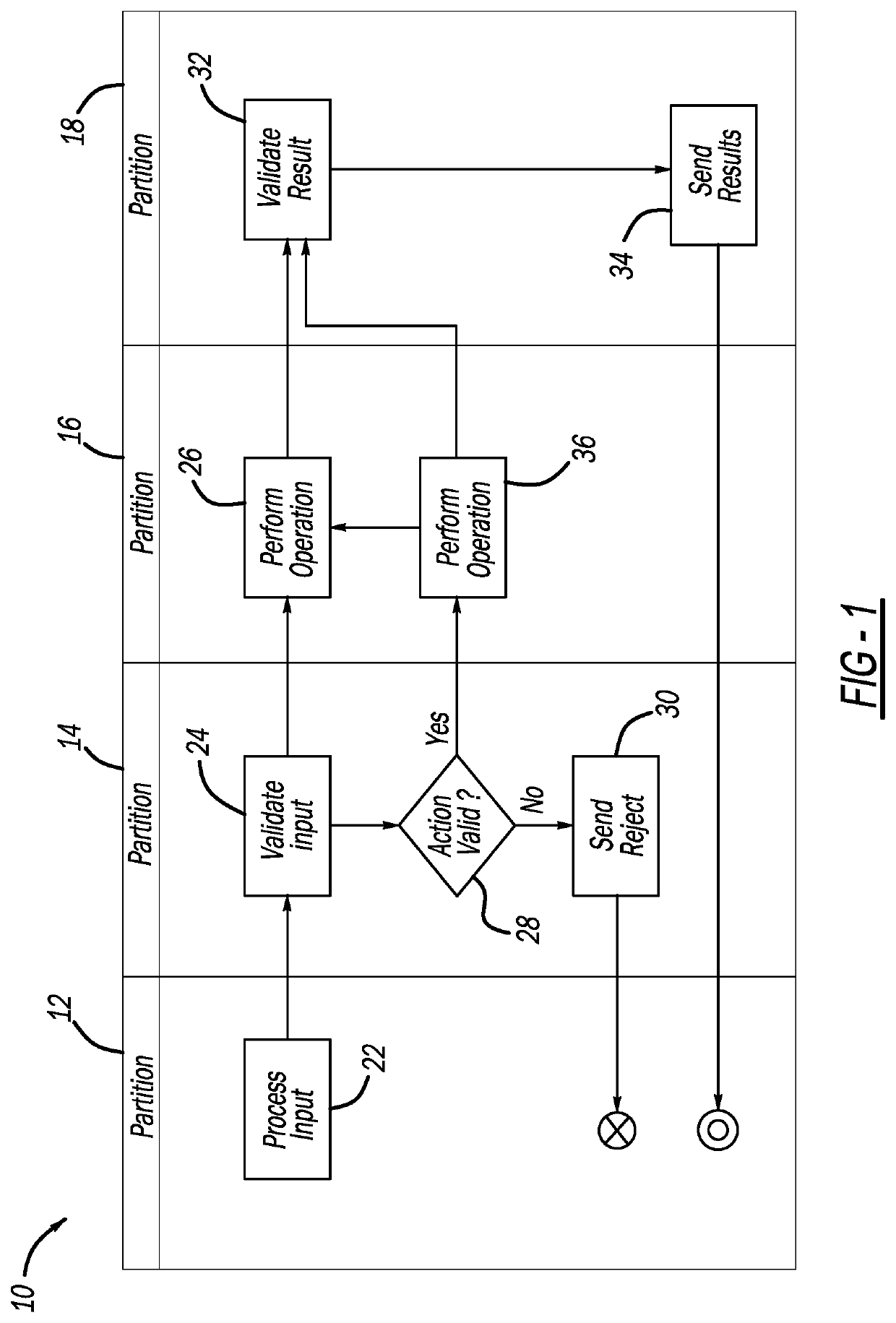

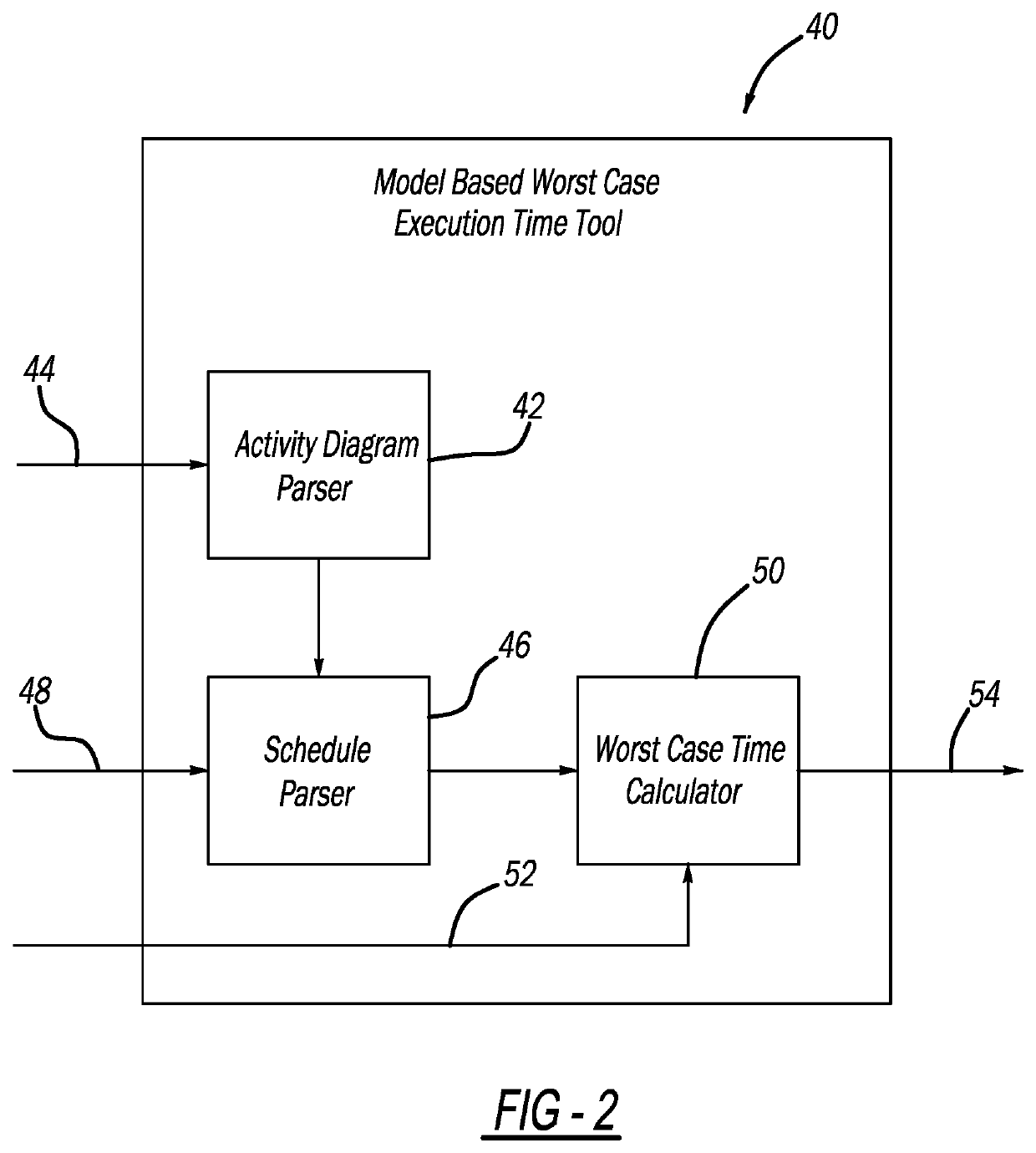

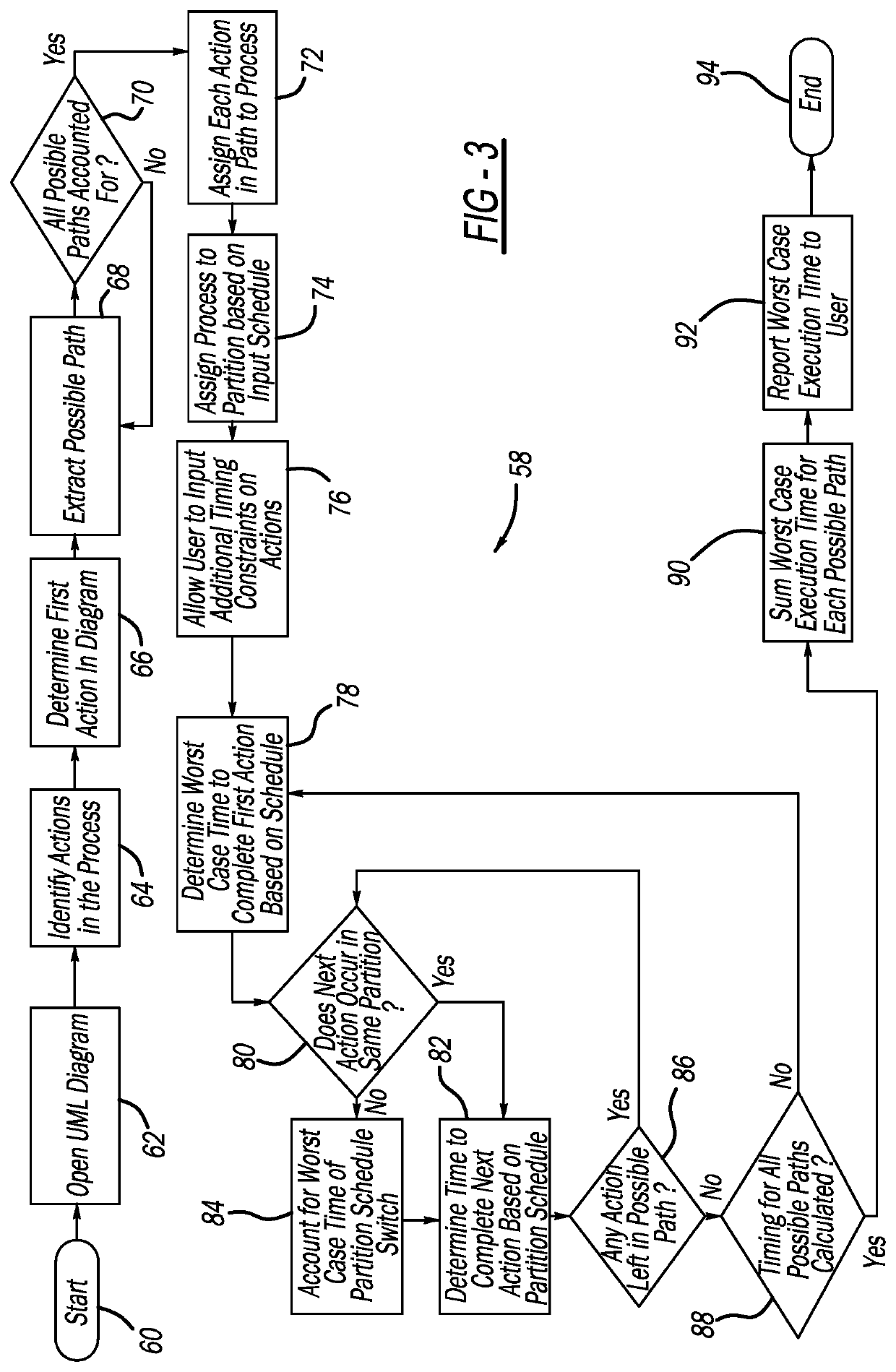

Model-based worst case execution time analysis for partitioned systems

A system and method for calculating worst case execution times for actions in a process that is partitioned into a number of sub-processes that perform certain ones of the actions and operate on their own partition schedule independent of the other partitions. The method includes providing a unified modeling language (UML) activity diagram including the actions in the process, identifying each action in the diagram, determining each possible processing path for the actions in the process, assigning each action in each path to one of the sub-processes in the partitions, determining the time that each action will take through each path based on the partition schedule, and integrating the times for performing the actions in each of the paths. The method reports a longest time for performing the process along each path based on the integration of the times.

Owner:NORTHROP GRUMMAN SYST CORP

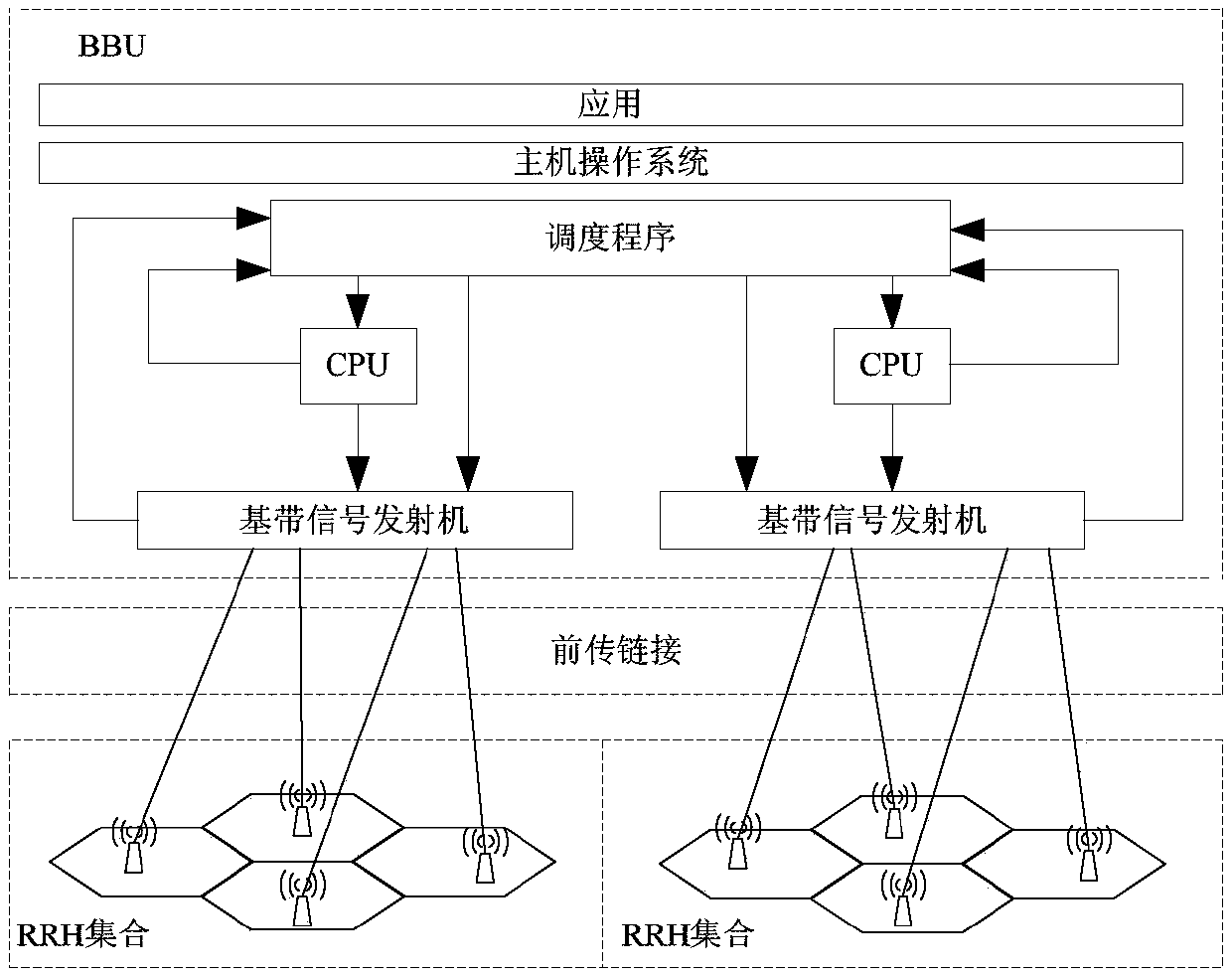

Data packet scheduling method and device

The embodiment of the application provides a data packet scheduling method and device. The method includes the following steps: executing a first judgement operation, wherein the first judgement operation includes: determining whether a ratio of a worst case execution time (WCET) corresponding to a first service data packet of first user equipment to be scheduled in a current scheduling period toa relative cut-off time is greater than a preset value; if the ratio is greater than the preset value, abandoning the scheduling of the first service data packet, taking a second service data packetof second user equipment to be scheduled as a new first service data packet, and returning to execute the first judgement operation until the ratio of the WCET corresponding to the new first service data packet to the relative cut-off time is not greater than the preset value, and scheduling the new first service data packet. Thereby, compared with scheduling algorithms in the prior art, a high utilization rate of the scheduling processing capability of the data packet scheduling device can be realized in the data packet scheduling method provided by the embodiment.

Owner:BEIJING UNIV OF POSTS & TELECOMM

Robust system control method with short execution time

A robust system control method with short execution time limit. A method of controlling a system is provided, comprising the steps of: initiating a task, the task being associated with a worst case execution time; and monitoring the end of the task after a time slot allocated to execution of the task; wherein the time slot Shorter than the worst case execution time stated.

Owner:AIRBUS OPERATIONS (SAS)

System and method for an optimized operation of real-time embedded solutions in industrial automation

A system and method for optimized operation of real-time control applications. The system and method being configured for identifying and processing recurring code sequences in control applications to quantify the execution time of control applications, wherein for each set up and / or control application a timing data structure is generated to determine the execution time of control applications in industrial automation, determining execution times of control applications based on recurring code sequences that are automatically extracted from a set of training applications and / or identified in the respective application, automatically generating test data to determine their on-target execution times for refinement of the timing data structure, decomposing the structure of the respective control application into code sequences for which the created data timing structure and timing model respectively provide execution time estimates, and determining at least an estimate for the best-case execution time and / or the worst-case execution time of the control application.

Owner:ABB (SCHWEIZ) AG

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com