Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38 results about "Single event latchup" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Single Event Latchup. Single event latchup (SEL) is a condition that causes loss of device functionality due to a single-event induced current state. Kolasinski et al. first observed SEL in 1979 during ground testing.[4] SELs are hard errors, and are potentially destructive (i.e., may cause permanent damage).

CMOS device with zero soft error rate

InactiveUS20070080406A1Action being takenReduce impactTransistorSolid-state devicesCMOSSingle event latchup

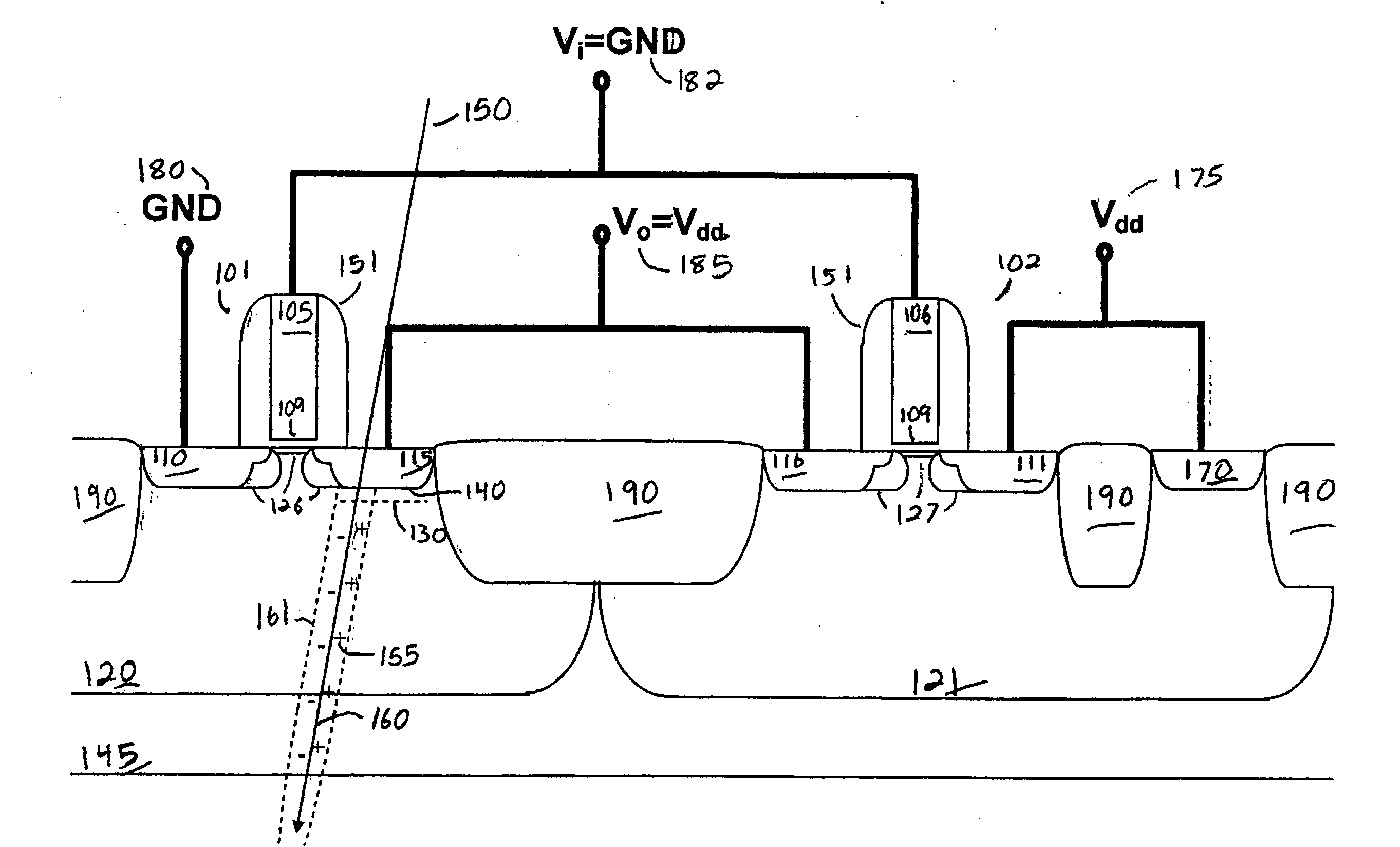

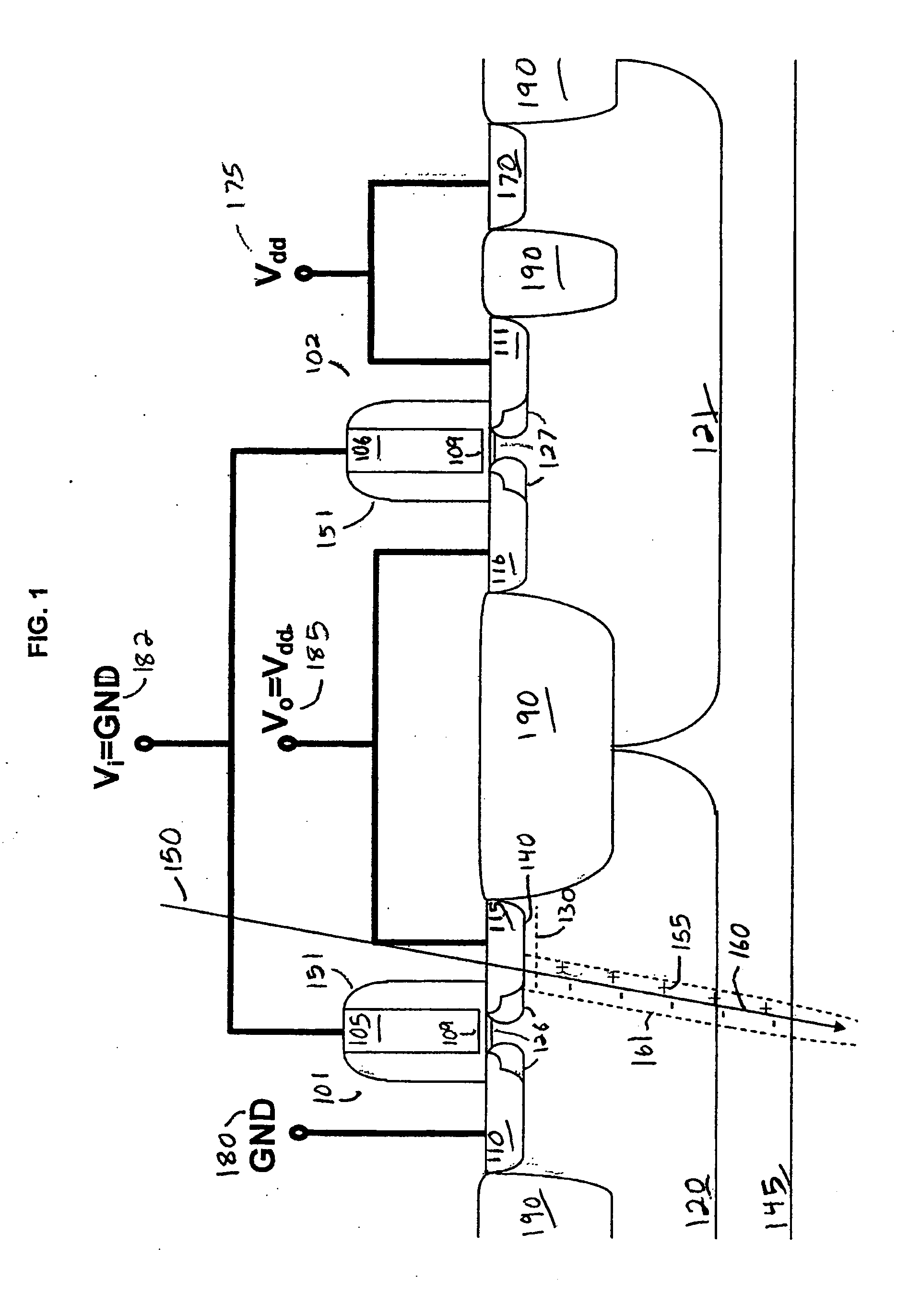

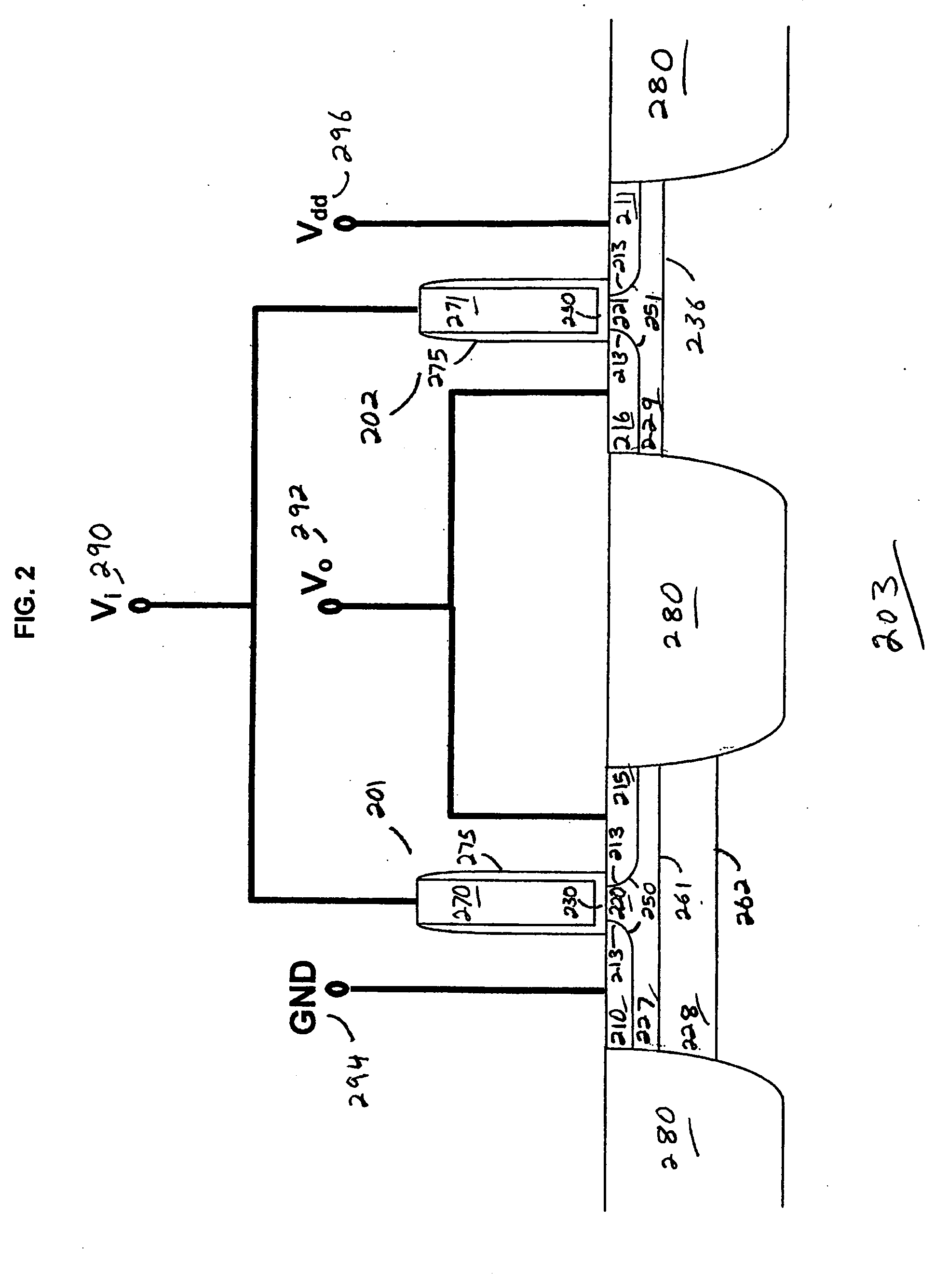

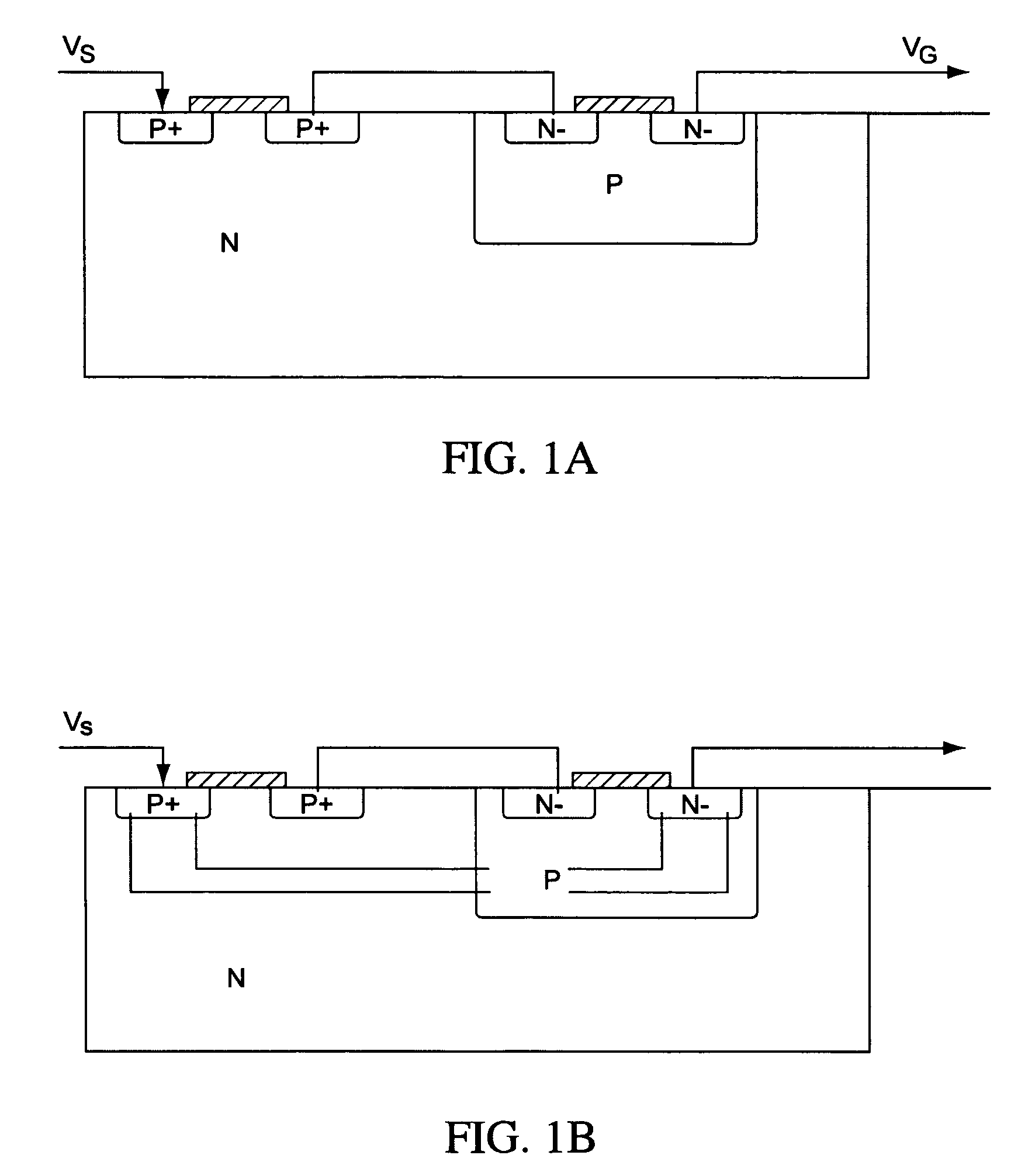

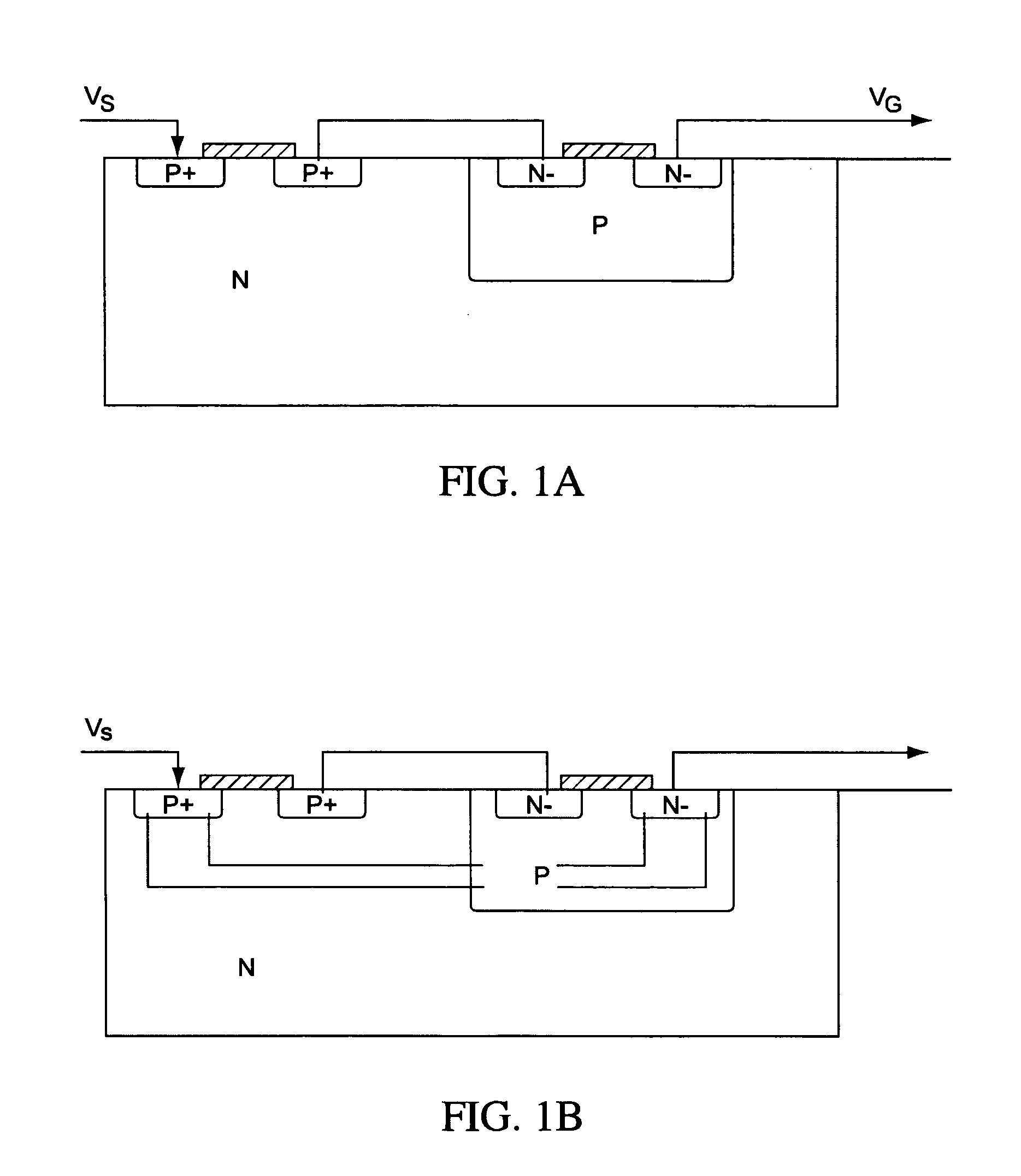

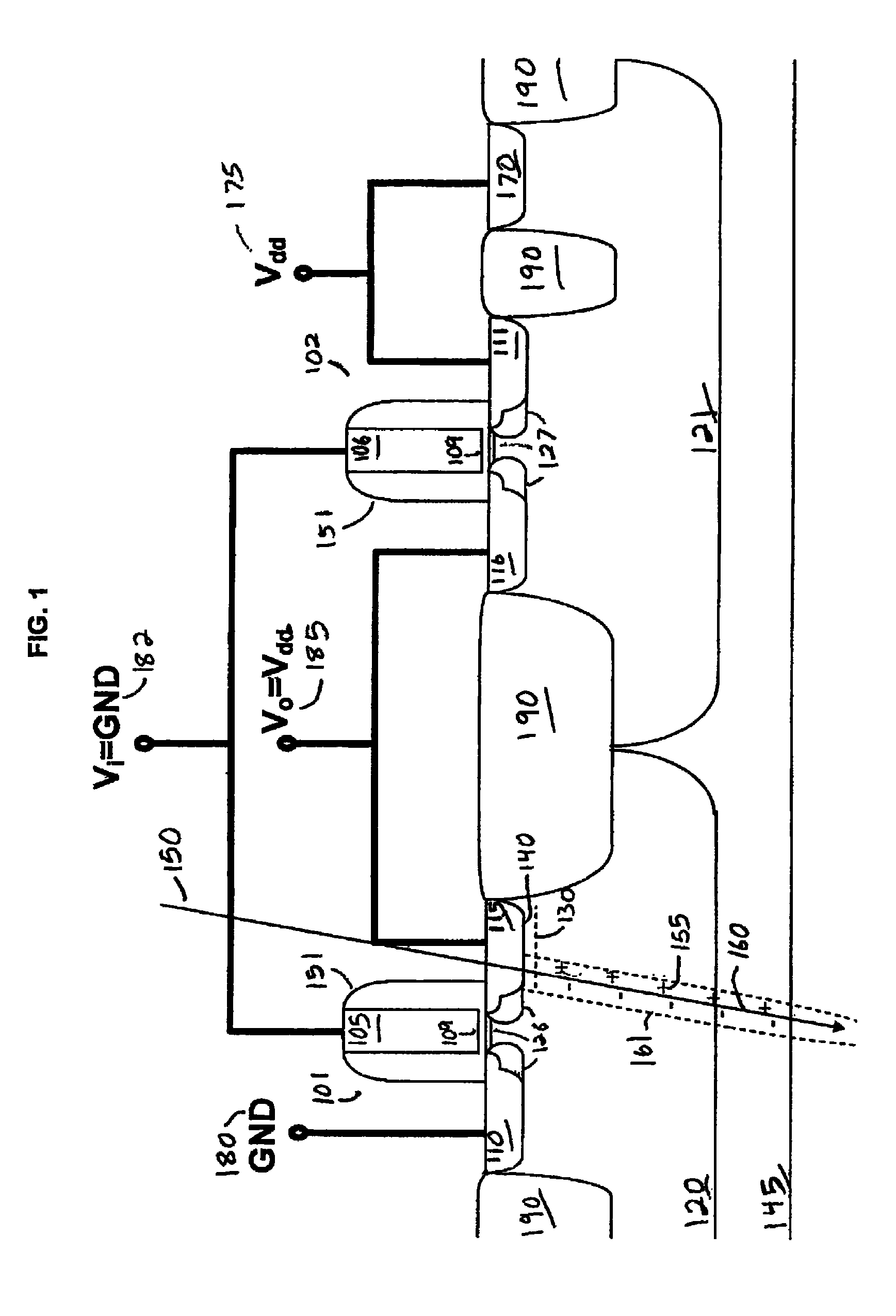

A CMOS device and method of manufacture is provided for producing an integrated circuit that is not susceptible to various soft errors such as single-event upsets, multi-bit upsets or single-event latchup. The CMOS device and method utilizes a new and novel well architecture in conjunction with metal source / drain electrodes to eliminate soft errors. In one embodiment, the CMOS device uses a first metal source / drain material for the NMOS device and a second metal source / drain material for the PMOS device. The CMOS device further uses a multi-layered well-structure with a shallow N-well and a buried P-well for the PMOS device and a shallow P-well and a buried N-well for the NMOS device.

Owner:AVOLARE 2 LLC

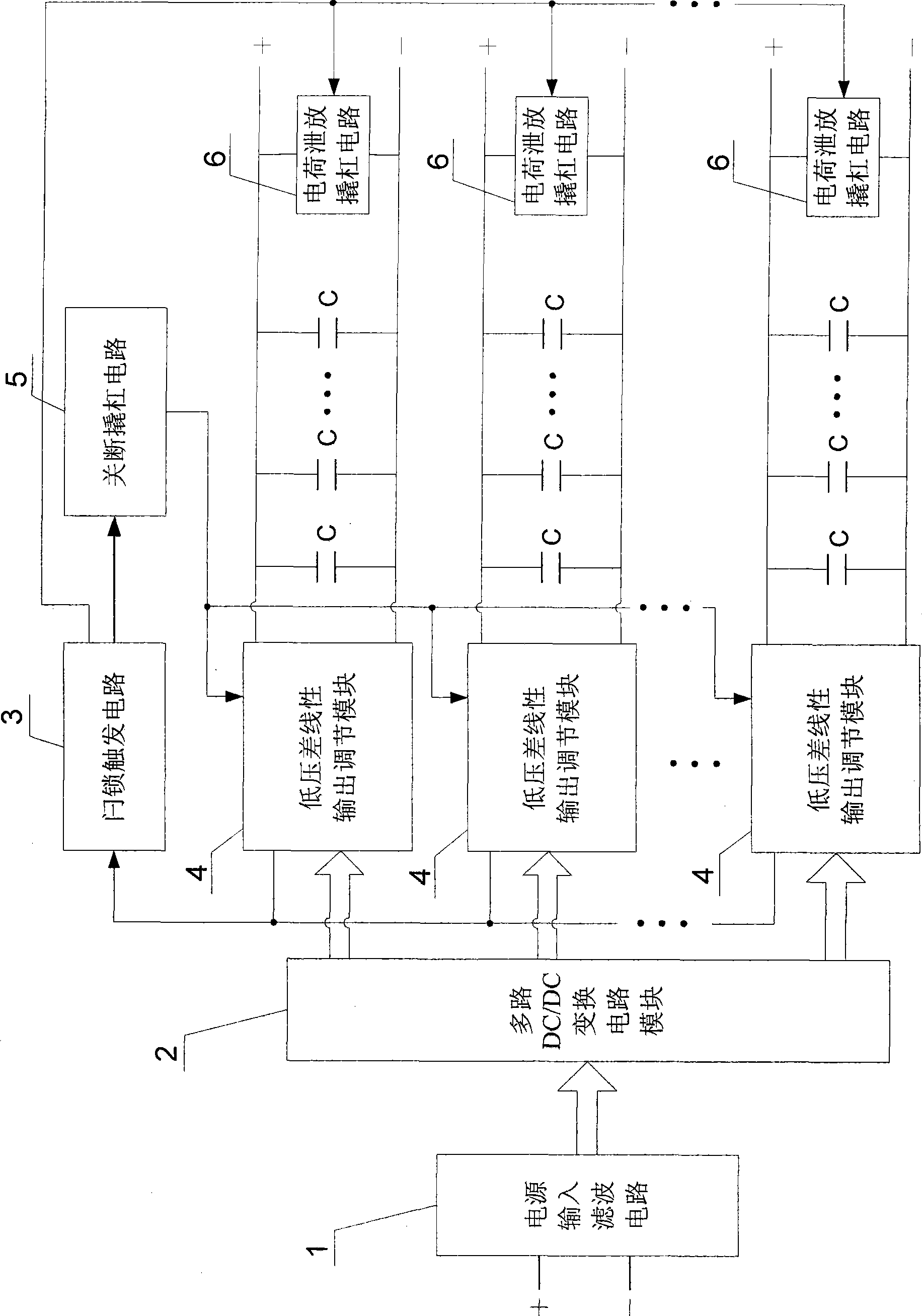

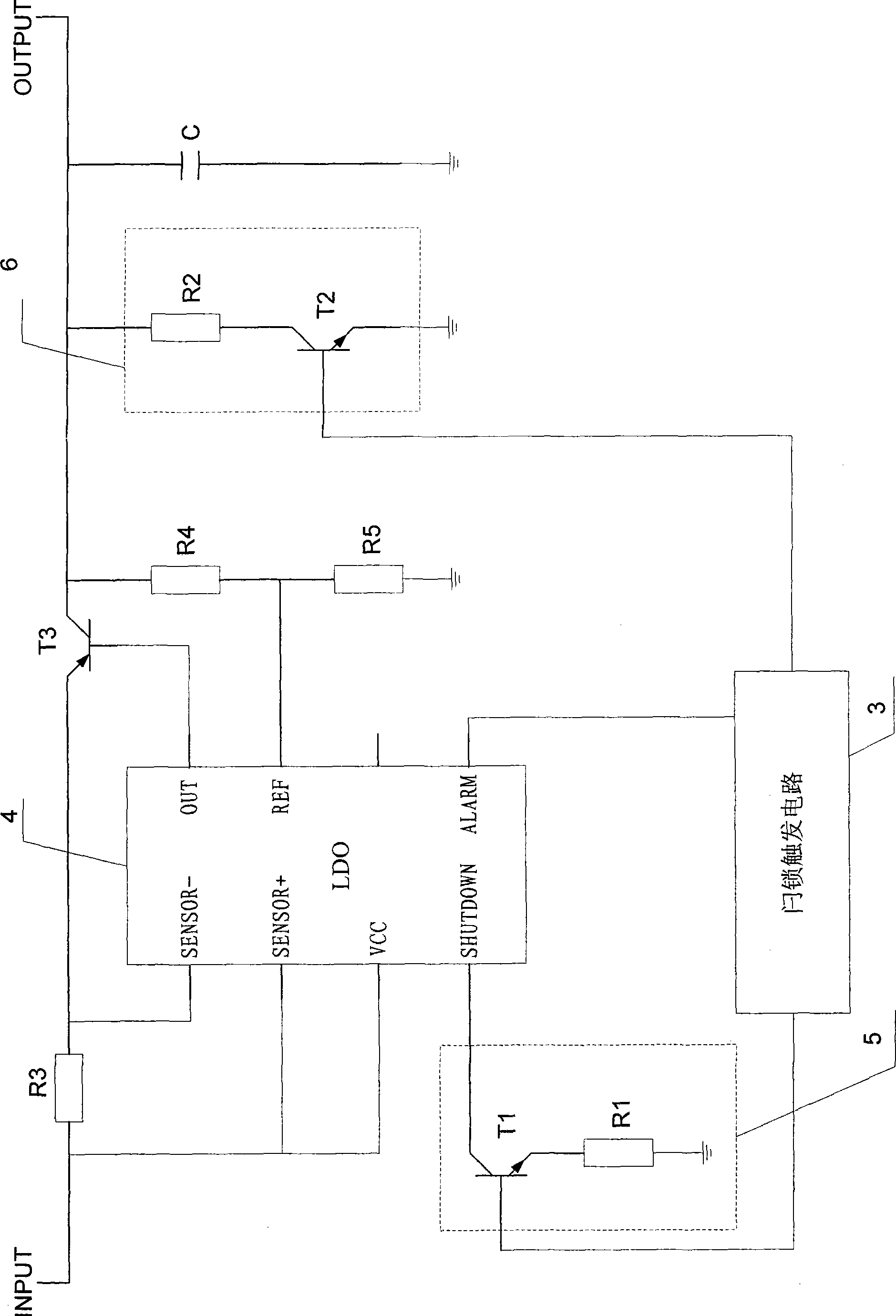

Multipath output electrical power suitable for space environment

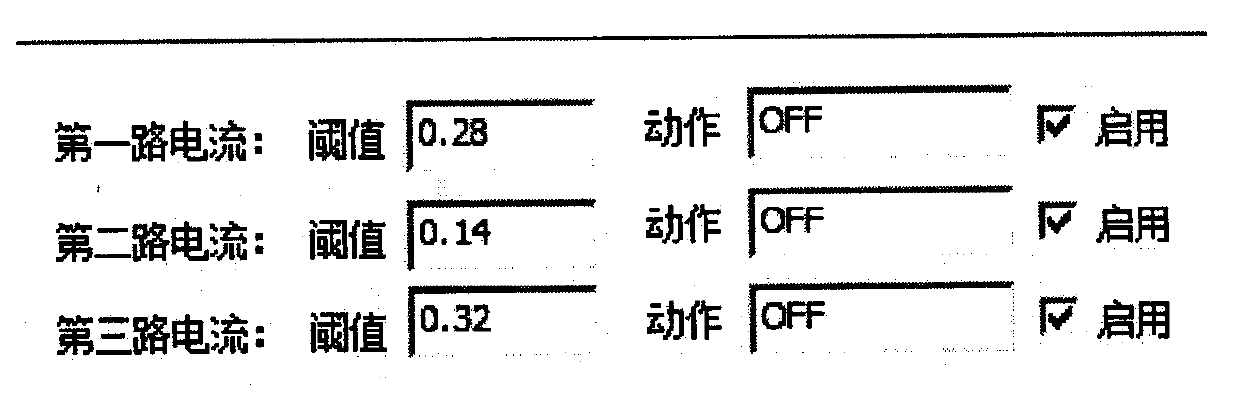

InactiveCN101505093AMeet the design requirementsReduce design requirementsDc-dc conversionArrangements responsive to excess currentSingle event latchupLoad circuit

The invention discloses a multi-output power supply suitable to be used in a spatial environment, which belongs to the filed of power supply devices. The invention aims to solve the problem that the prior power supply circuit cannot realize the effective protection of a load, nor the detection and protection of a single event latchup event according to the special requirements of the spatial environment. A multipath DC / DC conversion circuit module of the invention has the functions of bus input overcurrent protection and output voltage protection, is connected with a higher-level power supply through a power input filter circuit and connected with a load circuit through n low dropout voltage linear output regulator modules, and outputs an alarming signal to a latch trigger circuit when the current in the load exceeds a preset upper limit of the current so that the latch trigger circuit can control and turn off the n low dropout voltage linear output regulator modules by turning off crow bar circuits and control the n charge-dissipation crow bar circuits to be turned on to release the excessive charges of a load capacitor quickly. The multi-output power supply is used in a spatial environment, and is particularly applicable to the design of modularized joints of a space robot.

Owner:HARBIN INST OF TECH

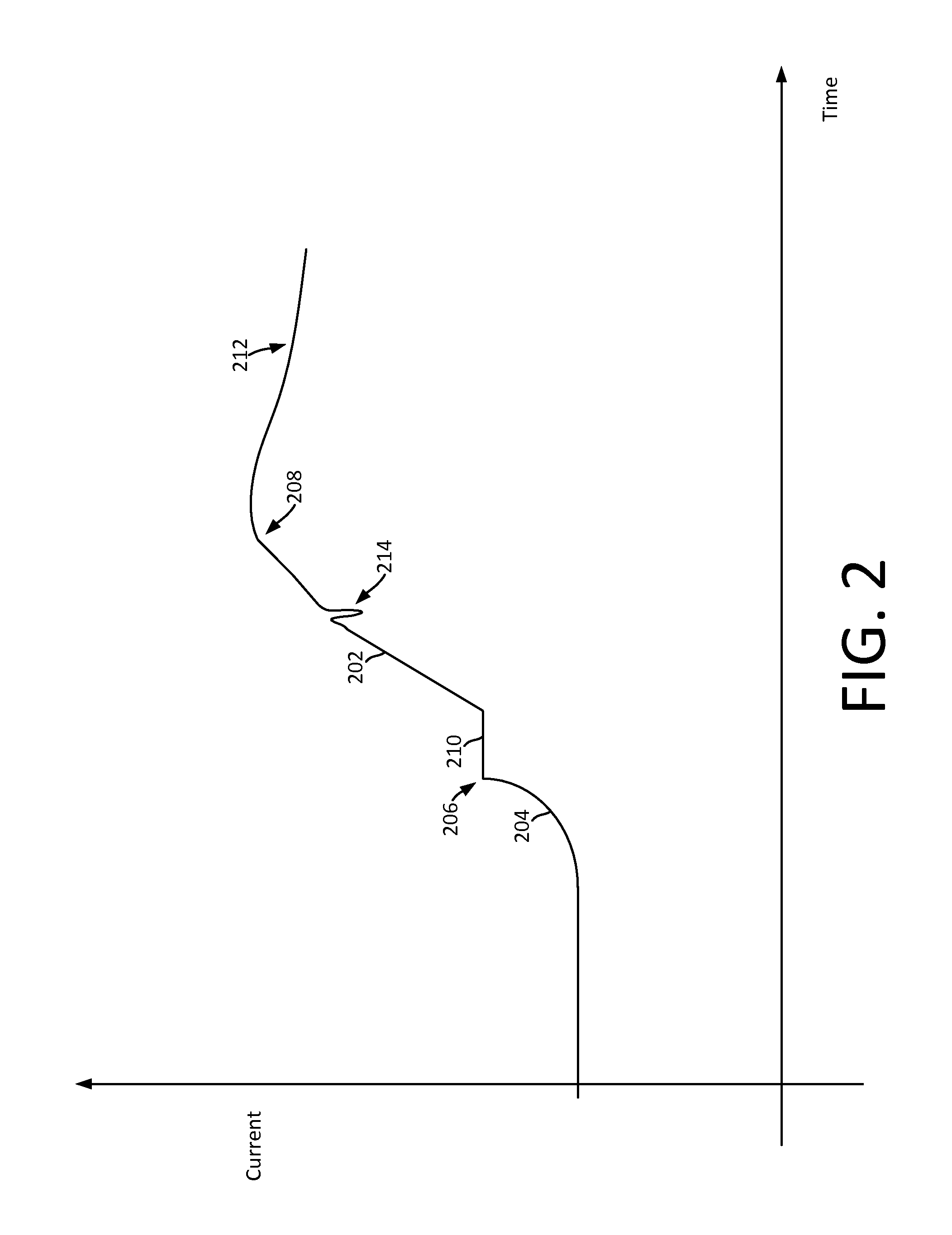

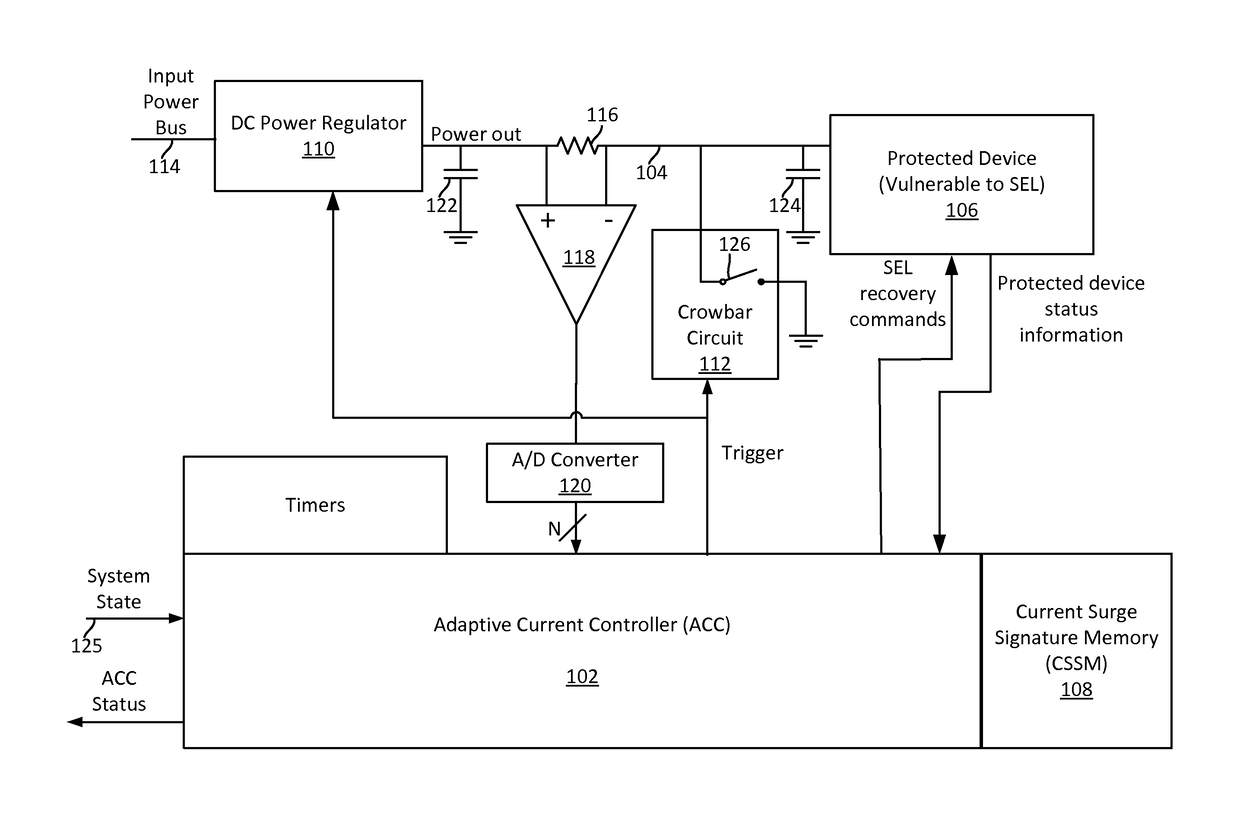

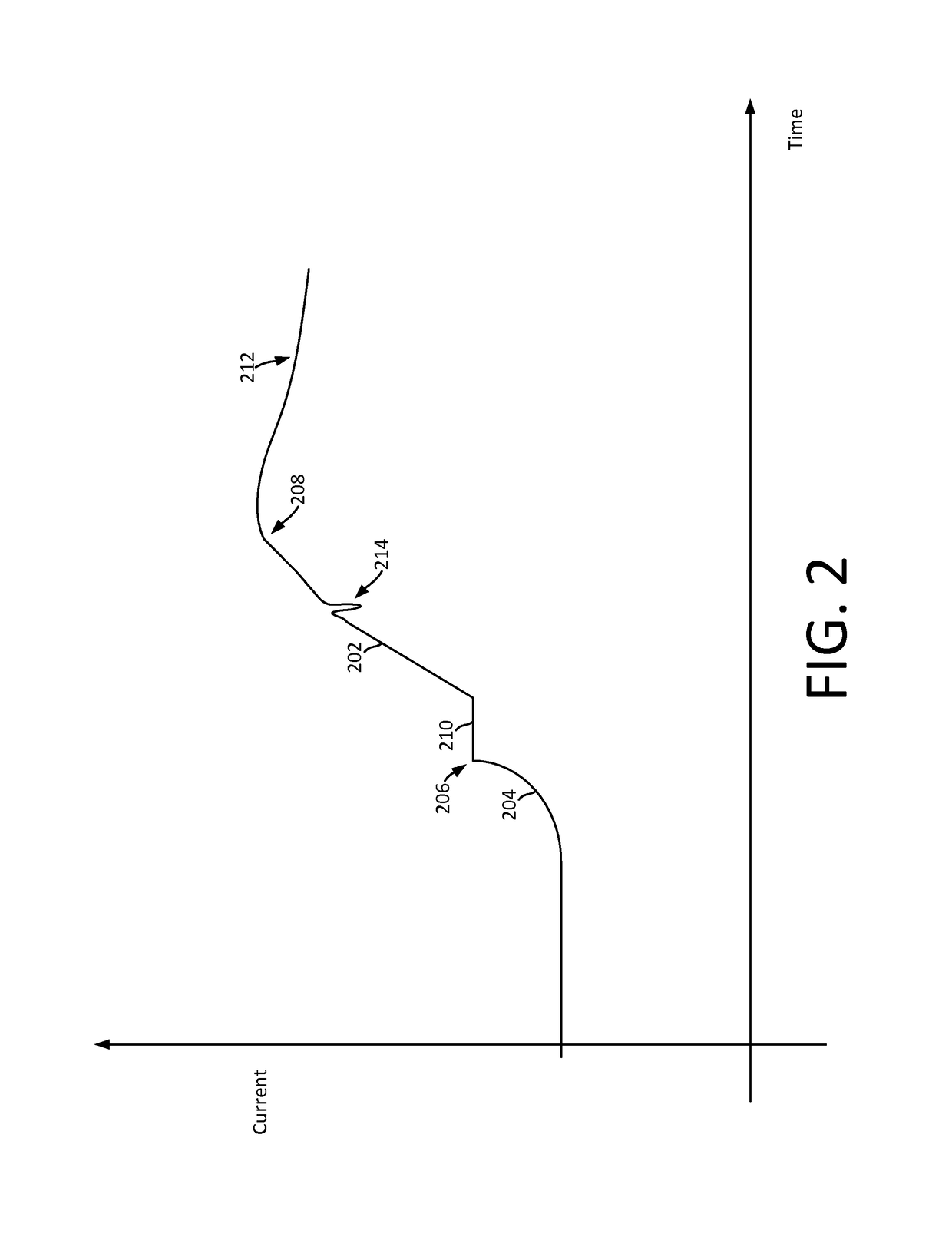

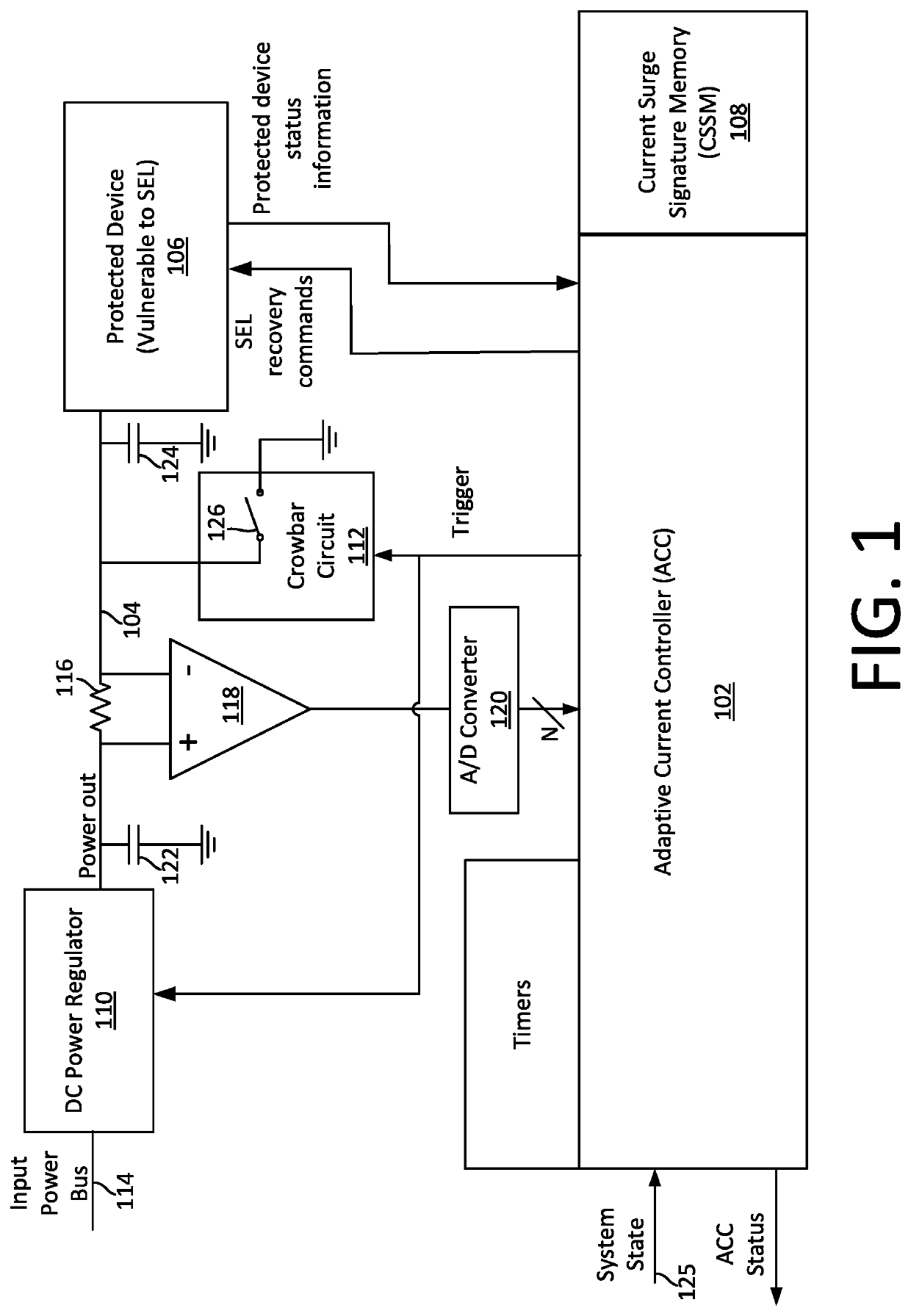

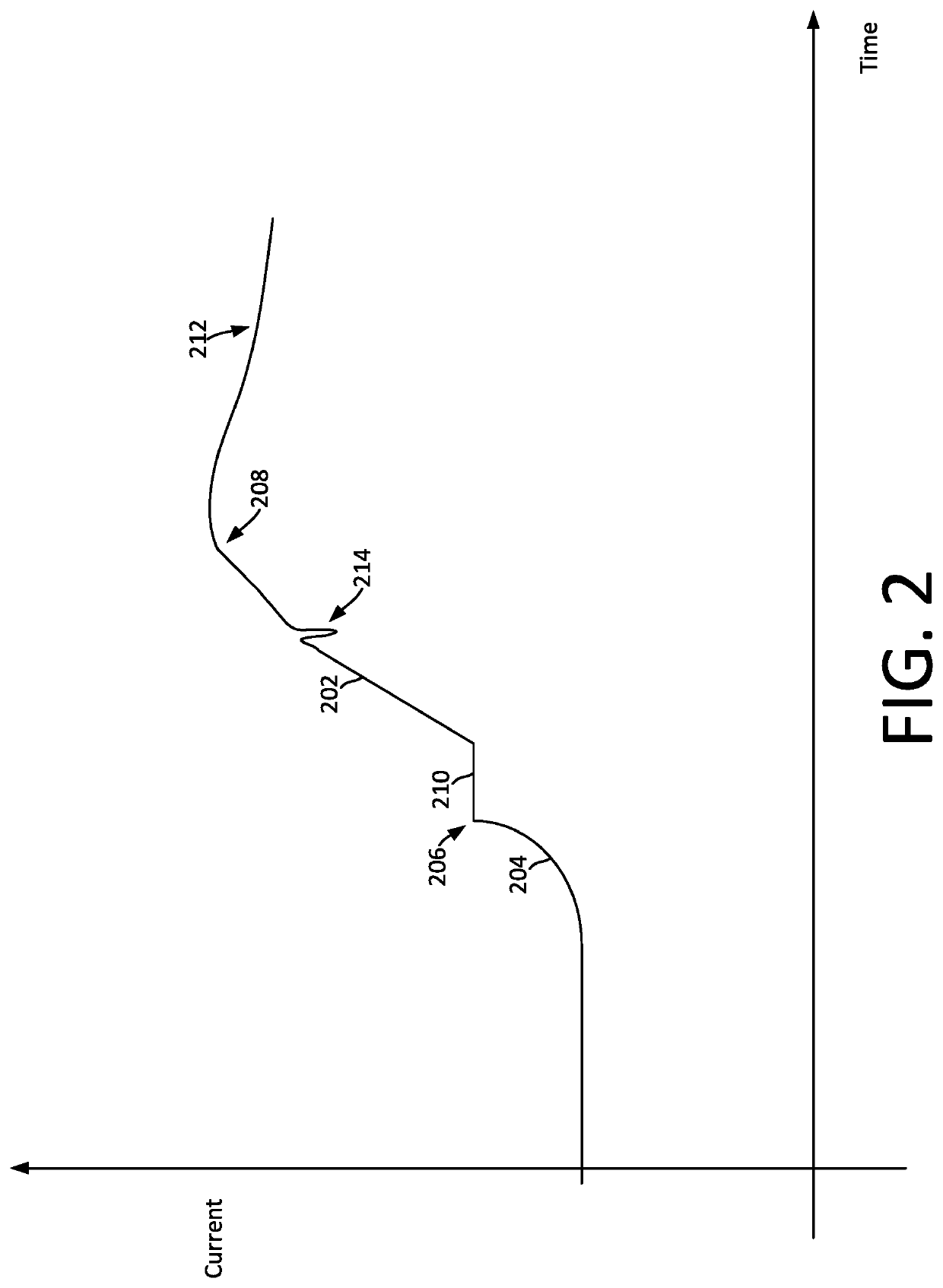

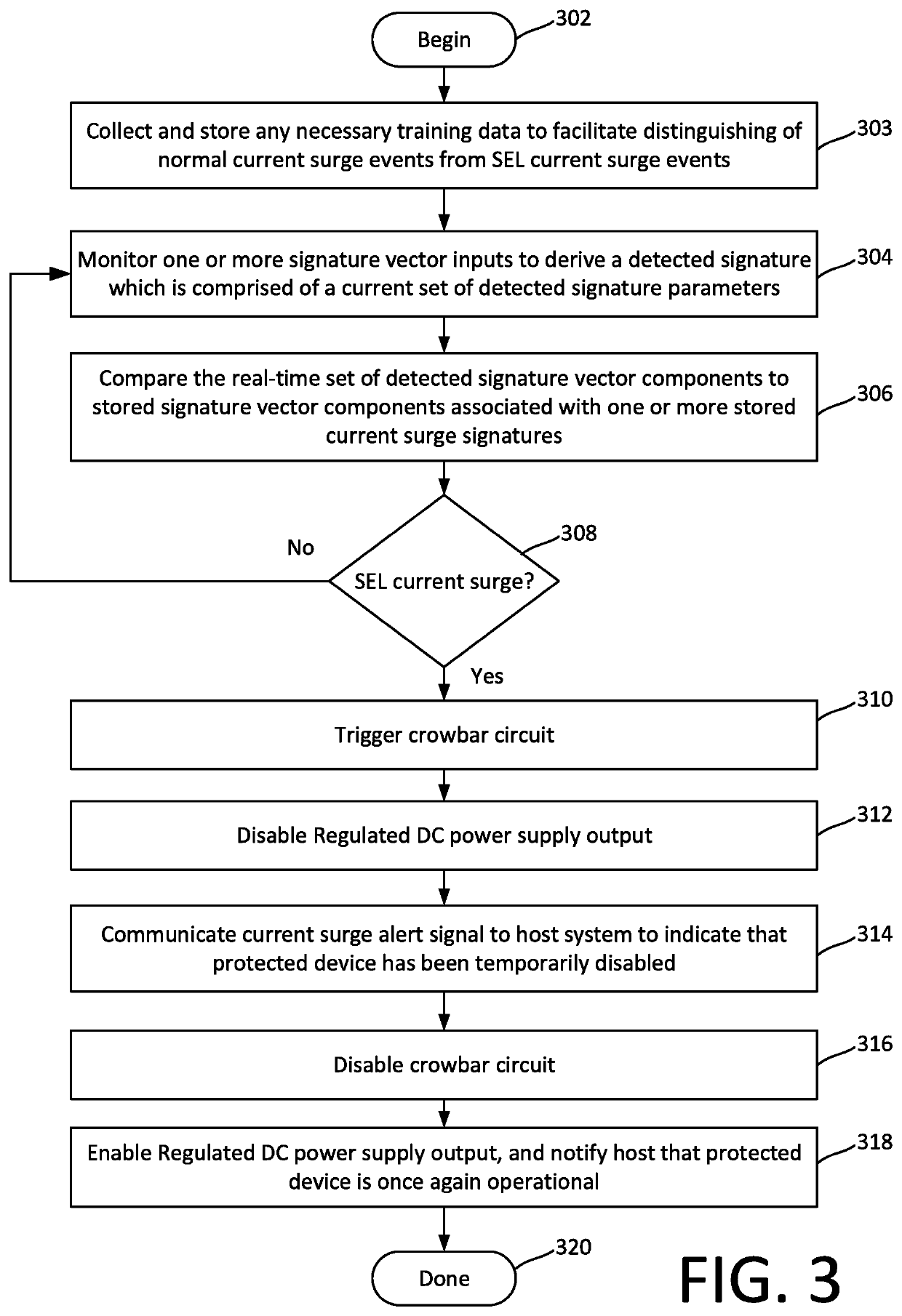

Single event latchup (SEL) current surge mitigation

ActiveUS20170033554A1Electrical testingEmergency protective arrangements for automatic disconnectionSingle event latchupData signal

Method and system for Single Event Latchup (SEL) current surge mitigation involves monitoring data signals for a protected device and deriving from them a detected signature comprised of one or more detected signature vector components. The detected signature vector components are compared to previously stored signature vector components. Based on the comparing, the system selectively differentiates between the occurrence of standard power surges associated with normal operation of the protected device, and a non-standard current surge which requires cycling power of the protected device for continued proper functioning of the protected device.

Owner:HARRIS CORP

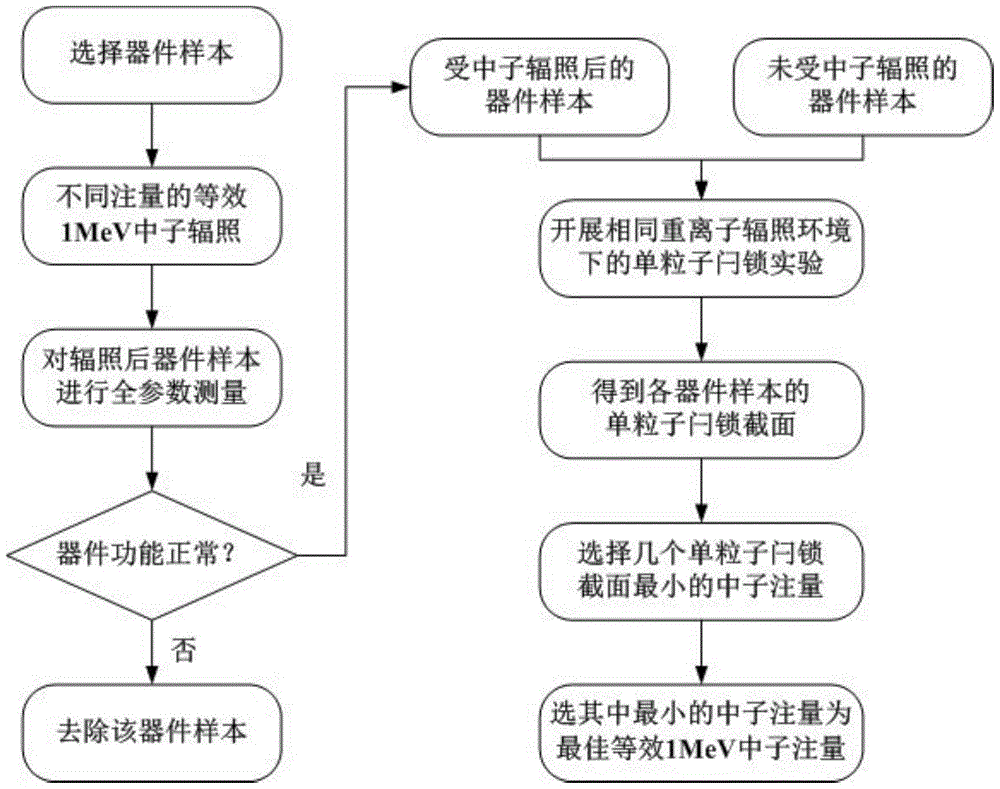

Reinforcement method for single event latchup resistance of CMOS device

ActiveCN105679658AAvoid export restrictionsLow costSemiconductor/solid-state device manufacturingIndividual semiconductor device testingSingle event latchupCMOS

The invention discloses a reinforcement method for the single event latchup resistance of a CMOS device. Neutron irradiation is carried out on the CMOS device; a displacement damage is introduced in the neutron irradiation; and a current gain of a parasitical bipolar transistor in an inverter of the CMOS device is reduced, so that P-N-P-N latchup is not generated. The reinforcement method is an external reinforcement method; processing steps to produce the device will not be increased; there is no need to redesign a device layout for the single event latchup effect; and complexity of an original system will not be increased. Thus, the fixed size of the device will not be changed, and a peripheral circuit will not be increased either.

Owner:NORTHWEST INST OF NUCLEAR TECH

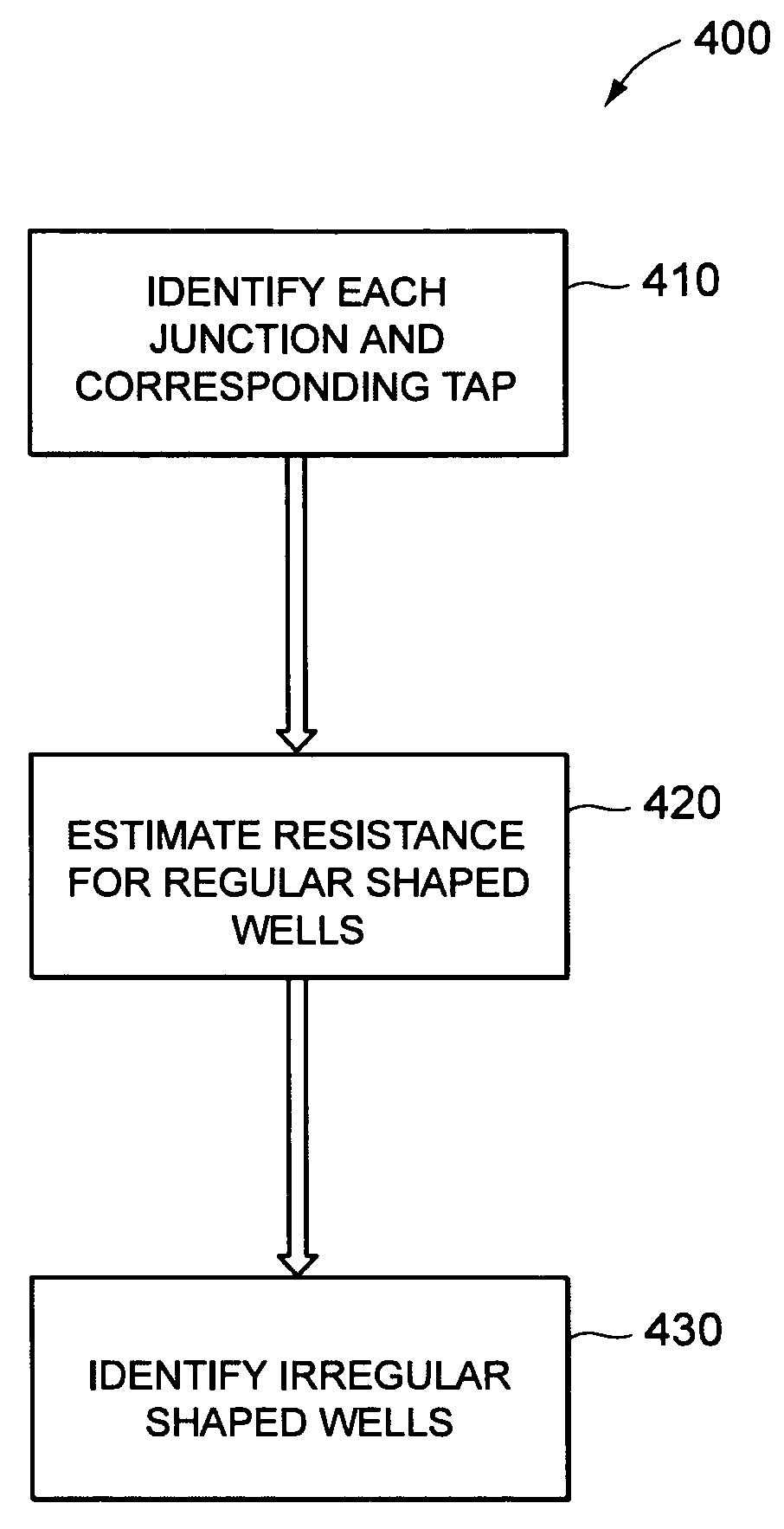

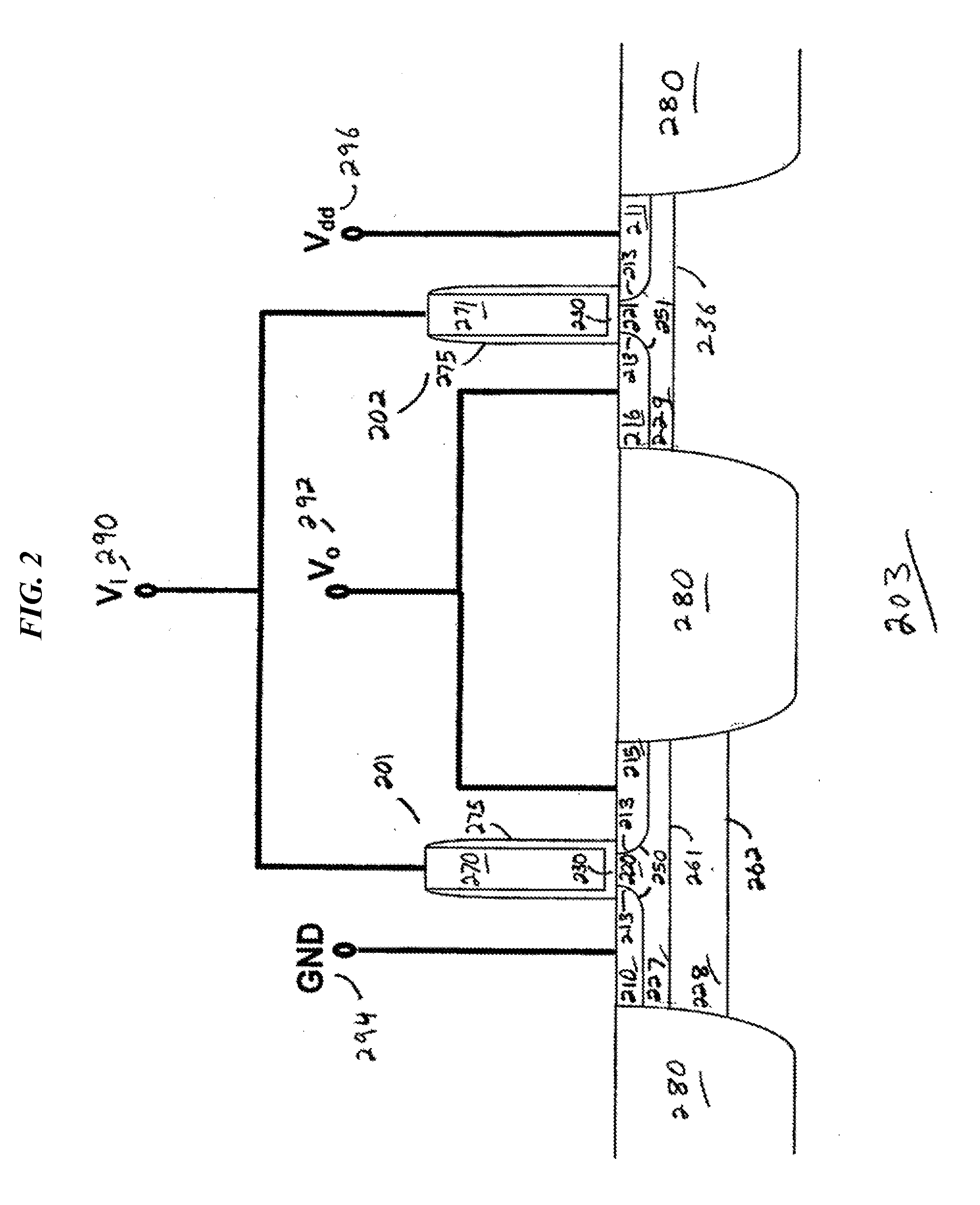

Method for improved single event latch up resistance in an integrated circuit

ActiveUS7474011B2Semiconductor/solid-state device detailsSolid-state devicesSingle event latchupJunction point

Owner:INTEGRATED DEVICE TECH INC

Method for improved single event latch up resistance in an integrated circuit

ActiveUS20080122473A1Electronic circuit testingSemiconductor/solid-state device detailsSingle event latchupElectrical resistance and conductance

A process and system for estimating the occurrence of single event latch-up in an integrated circuit. The process involves determining the resistance between each junction and the closest appropriate tap in a regular shaped well. Each junction occurring in an irregular-shaped well is also identified. Finally, the method may make suggestions for lowering the probability that single event latch-up may occur in the integrated circuit.

Owner:INTEGRATED DEVICE TECH INC

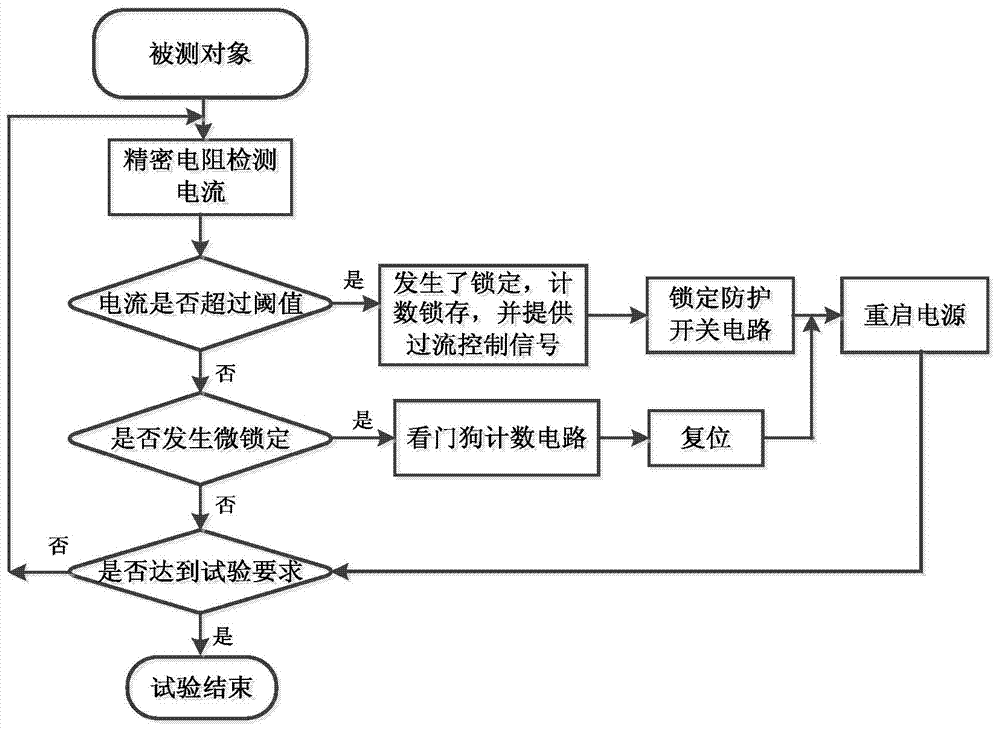

On-track monitoring method for space single event latchup effect

InactiveCN103701087AEnables lock-in monitoringNormal supply voltageArrangements responsive to excess currentSingle event latchupElectrical resistance and conductance

The invention belongs to the technical field of space radiation effect and strengthening, and particularly relates to an on-track monitoring method for space single event latchup effect. The method is based on a precision resistor, an over-current detection circuit, a counting latch, a latchup protection switching circuit, a power system and a watch dog counting circuit, wherein the watch dog counting circuit comprises two stages; the precision resistor is connected with the over-current detection circuit; the over-current detection circuit is also connected with the counting latch and the latchup protection switching circuit; the latchup protection switching circuit is also connected with the watch dog counting circuit and the power system. The monitoring method can realize space single event latchup effect monitoring of different track environment, and simultaneously provides a quick and accurate universality method for monitoring and evaluating deep space detection single event latchup effect.

Owner:LANZHOU INST OF PHYSICS CHINESE ACADEMY OF SPACE TECH

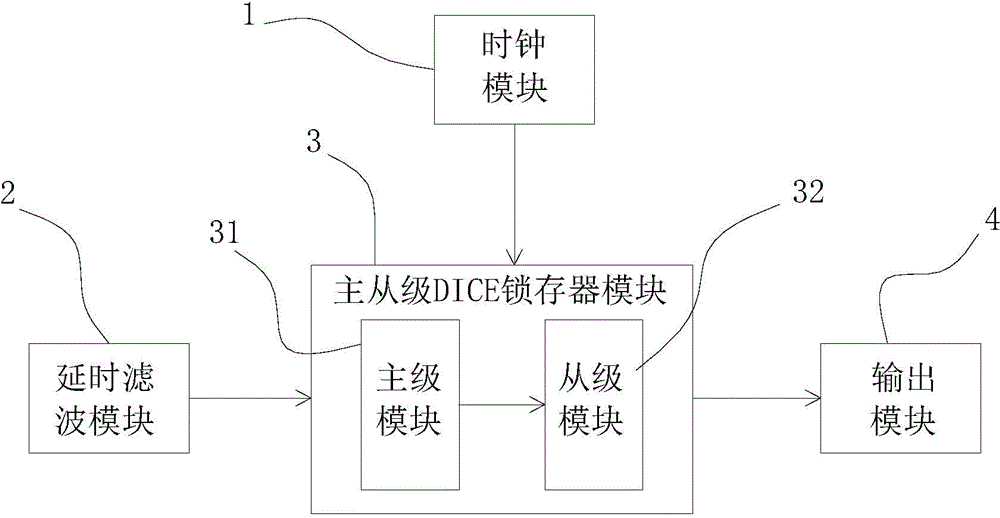

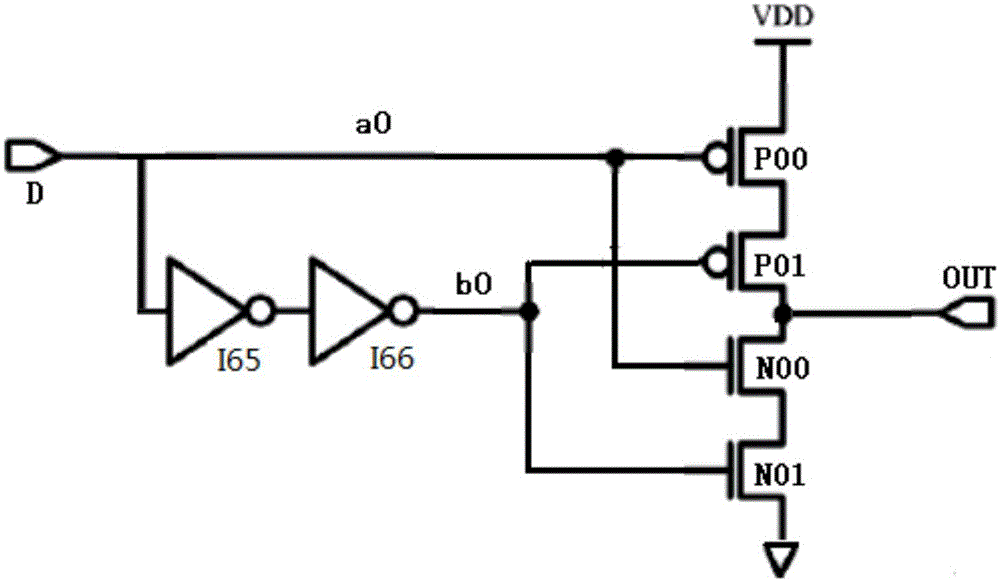

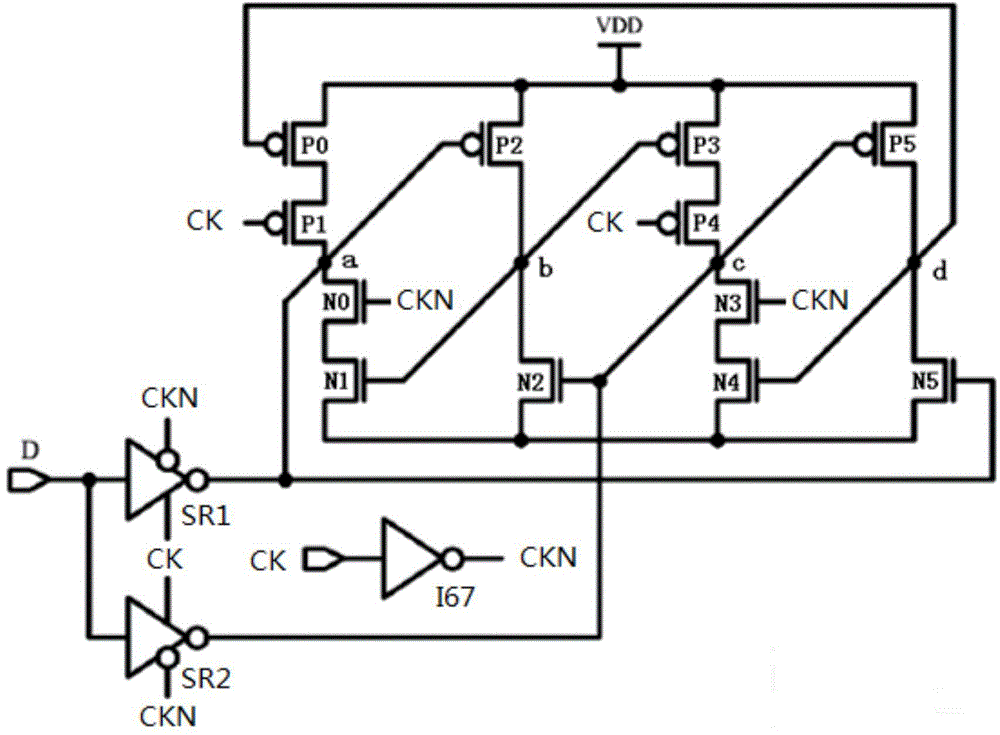

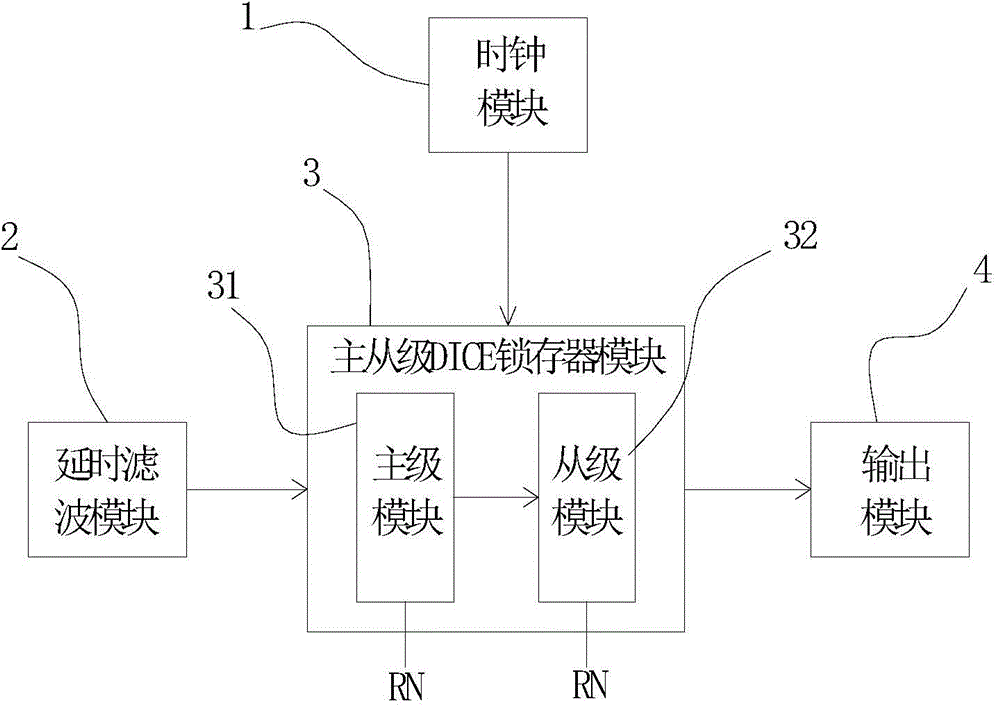

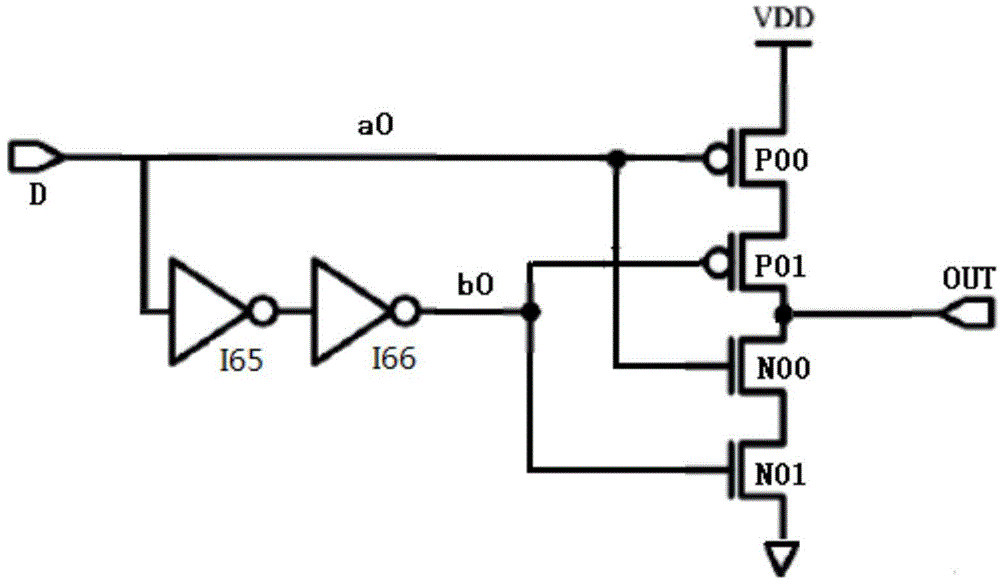

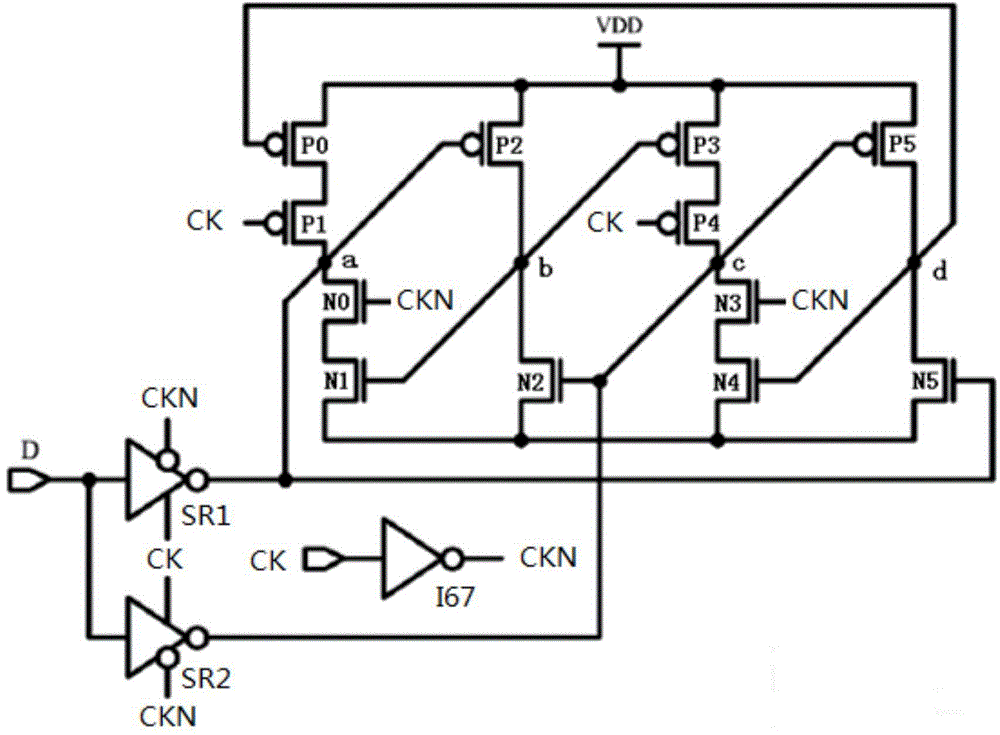

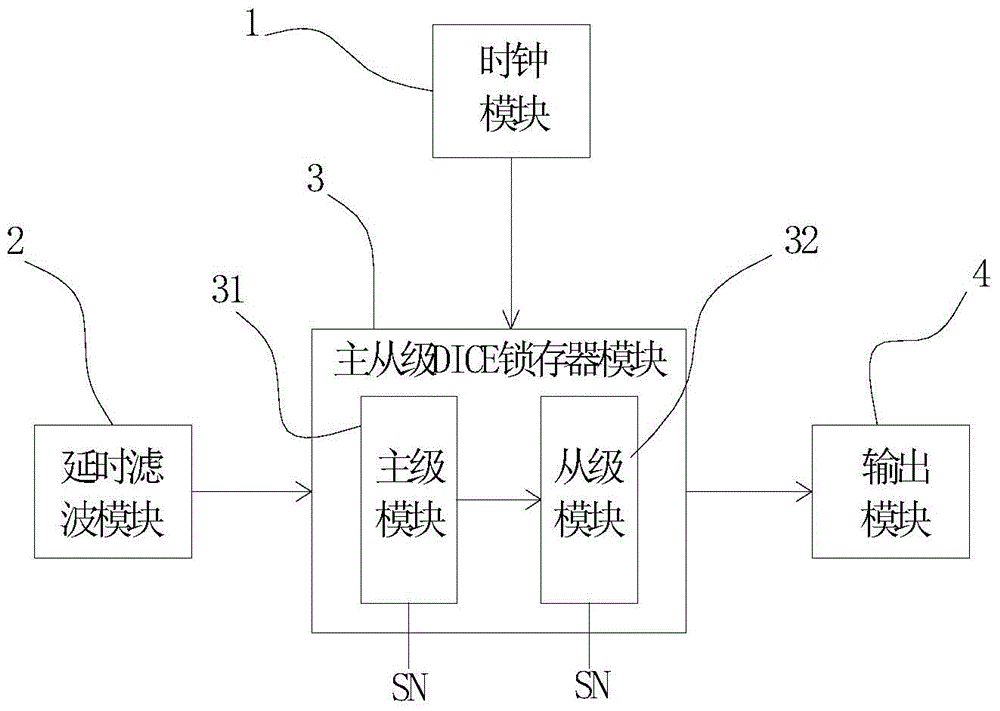

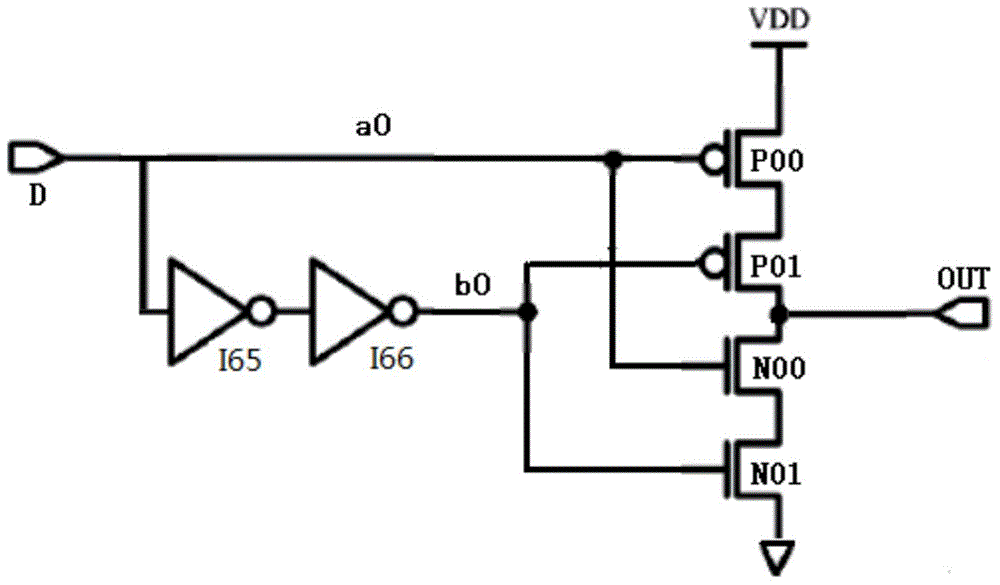

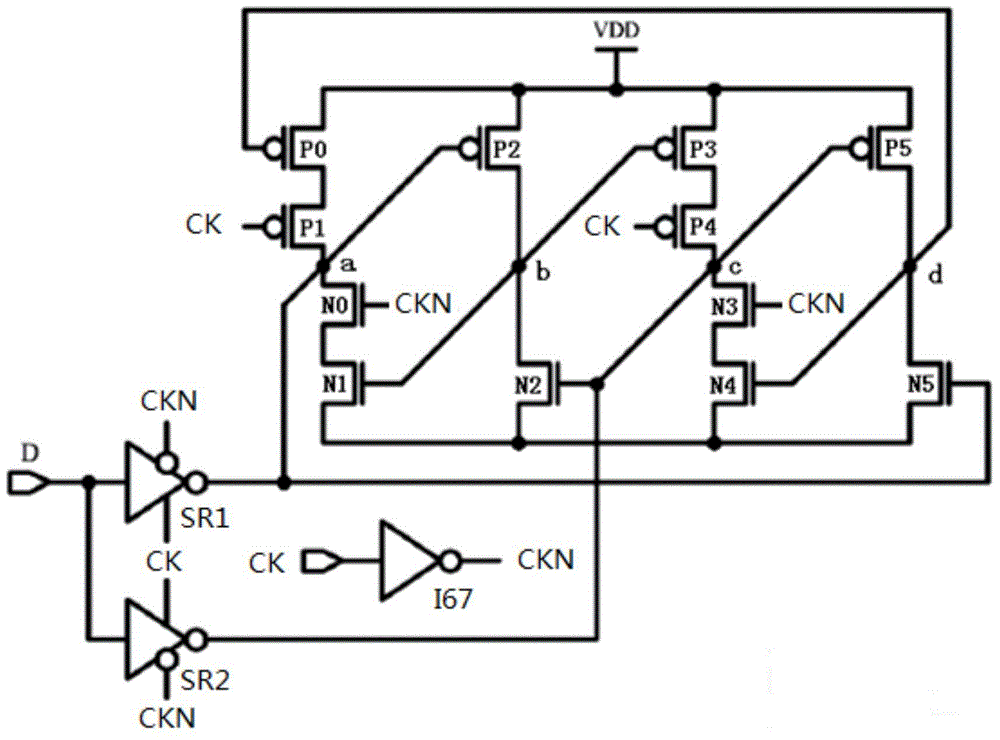

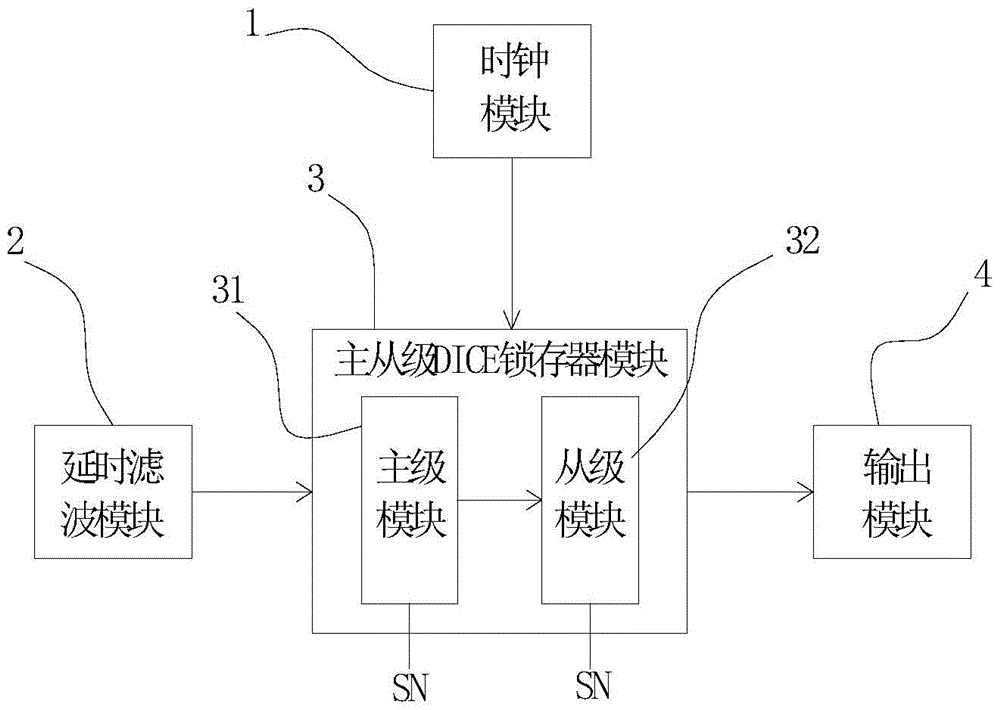

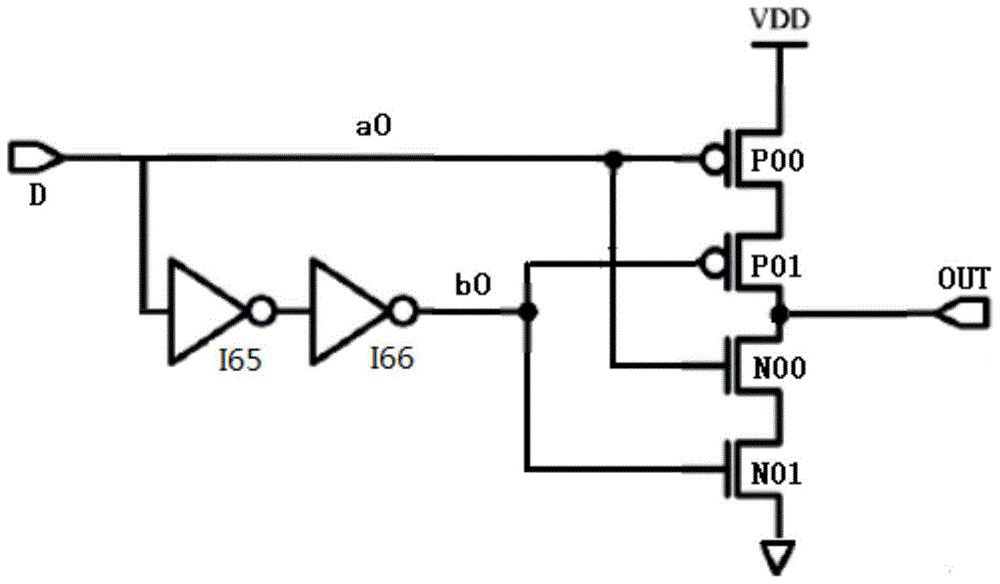

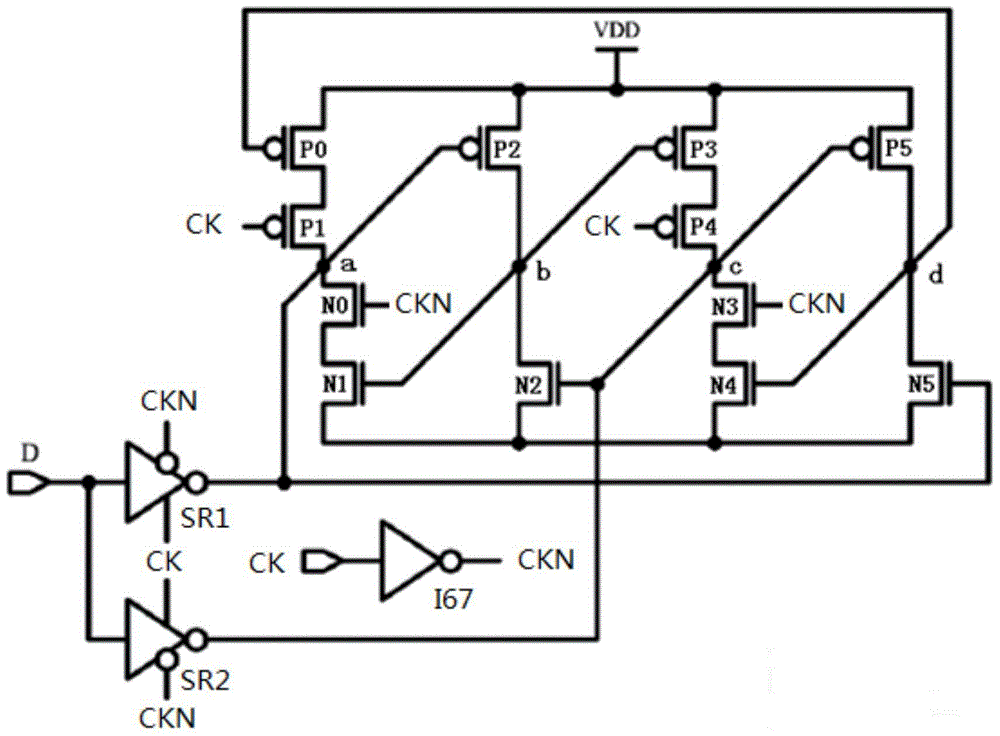

Delay flip-flop

ActiveCN104821805AThe output is normalReduce widthElectric pulse generatorSingle event latchupProcessor register

A delay flip-flop comprises a clock module, a delay filtering module, a master-slave DICE latch module and an output module, wherein the master-slave DICE latch module outputs a corresponding data signal to the data output module according to a clock signal that is output from the clock module and an outer data signal that is received through the delay filtering module. The master-slave DICE latch module is composed of a master-grade module and a slave-grade module. The delay filtering module is used for preventing entering of a transient pulse which is caused by a single event effect into the register. The master-slave DICE latch module is used for correcting inner node upset which is caused by the single-particle effect. The delay filtering module performs a function of preventing a single event transient pulse. The master-slave DICE latch module prevents overturning of an inner storage node, thereby performing a function of preventing single event upset. A protective belt structure is added in layout design. The structure of the delay flip-flop effectively restrains single event latchup, and facilitates reduction of a single event transient pulse width in a circuit.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

System and method for detecting single event latchup in integrated circuits

InactiveUS20070229096A1Electric discharge tubesIndividual semiconductor device testingSingle event latchupIntegrated circuit layout

A method for testing an integrated circuit for potential latchup sites includes applying a voltage to the integrated circuit, measuring a current through the integrated circuit, applying at least one radiation beam to at least one area of the integrated circuit, and detecting an occurrence of a latchup by detecting an increase of the current through the integrated circuit upon applying the at least one radiation beam to the at least one area of the integrated circuit.

Owner:INTEGRATED DEVICE TECH INC

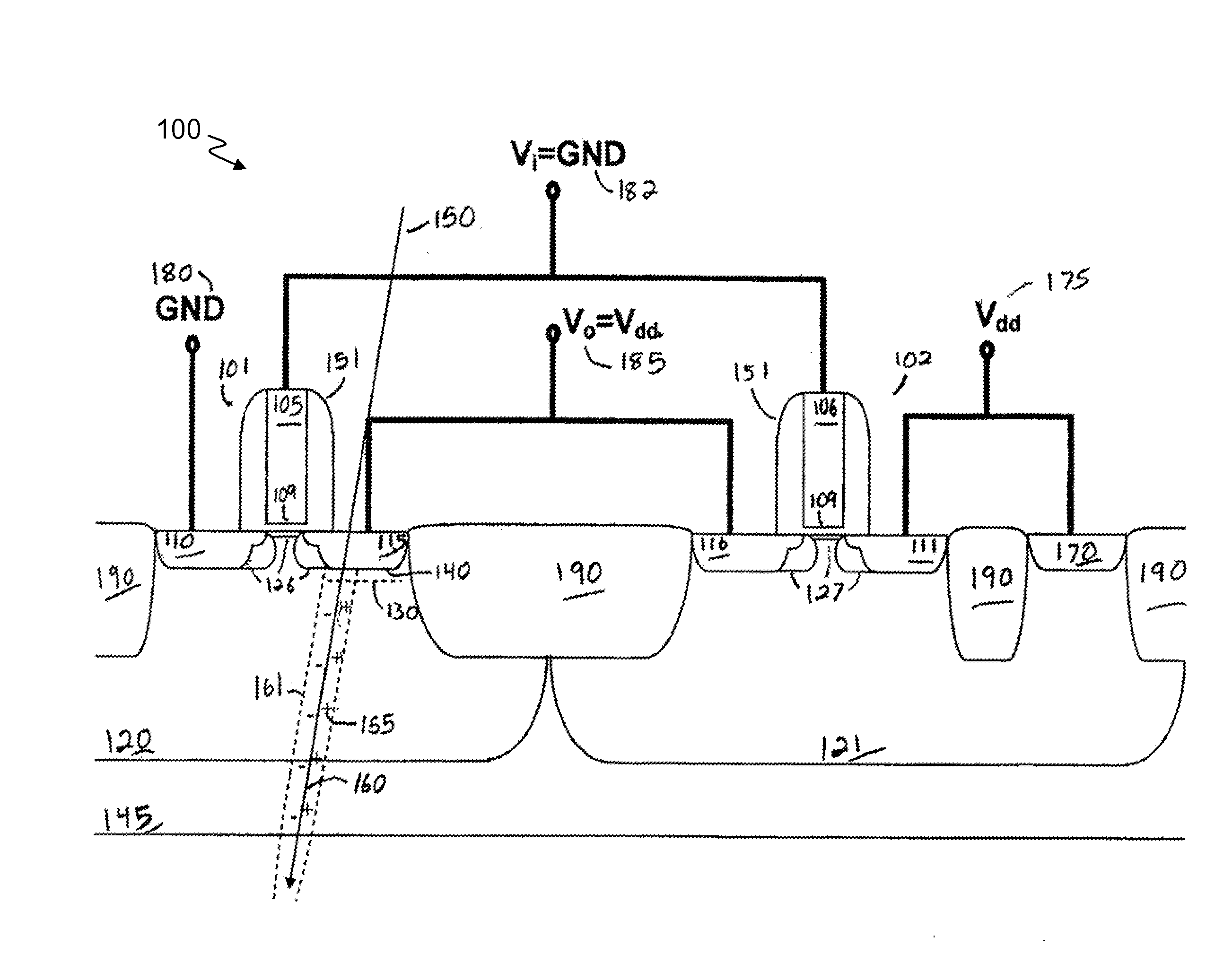

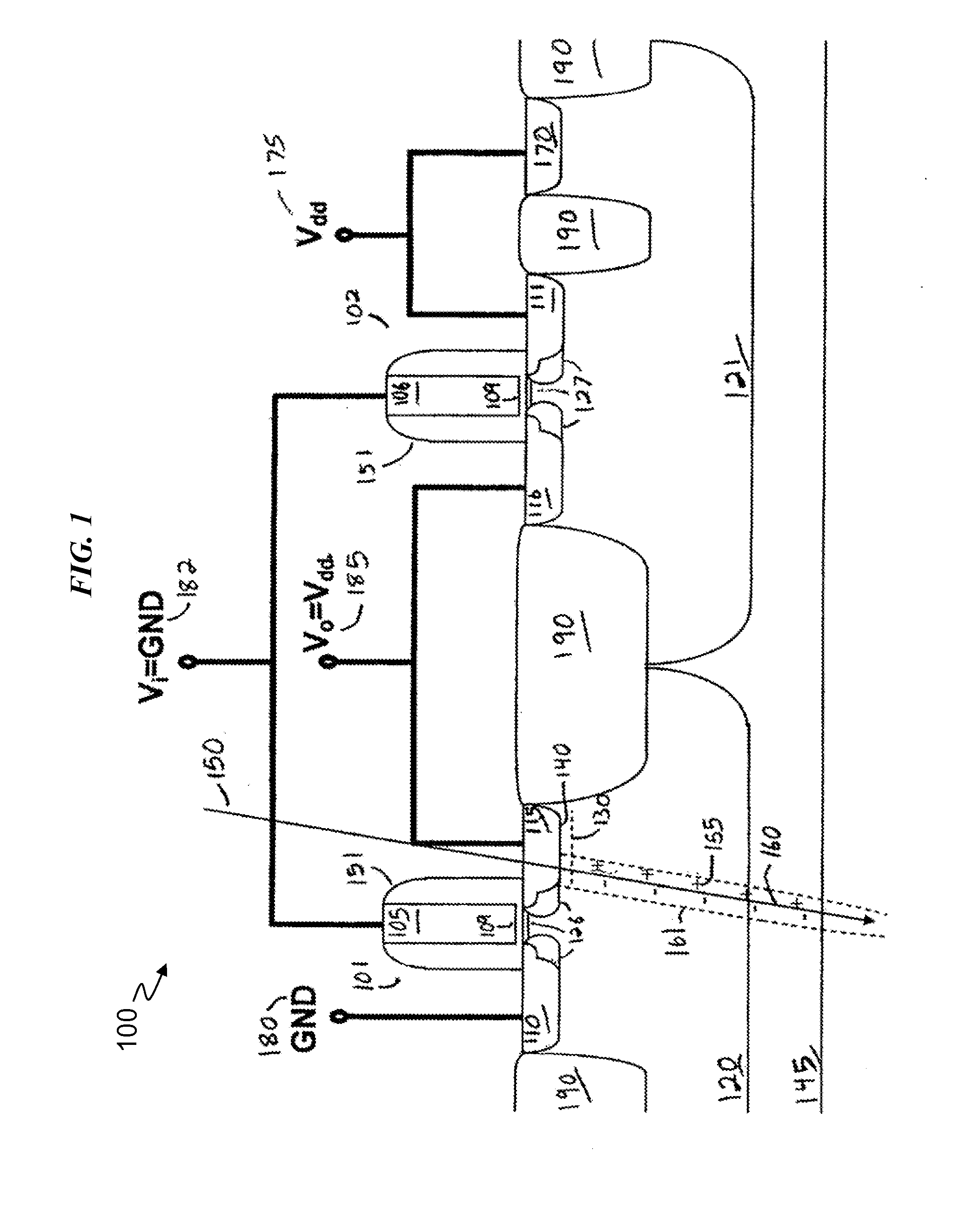

CMOS device with zero soft error rate

InactiveUS7821075B2Action being takenReduce impactTransistorSolid-state devicesSingle event latchupCMOS

A CMOS device and method of manufacture is provided for producing an integrated circuit that is not susceptible to various soft errors such as single-event upsets, multi-bit upsets or single-event latchup. The CMOS device and method utilizes a new and novel well architecture in conjunction with metal source / drain electrodes to eliminate soft errors. In one embodiment, the CMOS device uses a first metal source / drain material for the NMOS device and a second metal source / drain material for the PMOS device. The CMOS device further uses a multi-layered well-structure with a shallow N-well and a buried P-well for the PMOS device and a shallow P-well and a buried N-well for the NMOS device.

Owner:AVOLARE 2 LLC

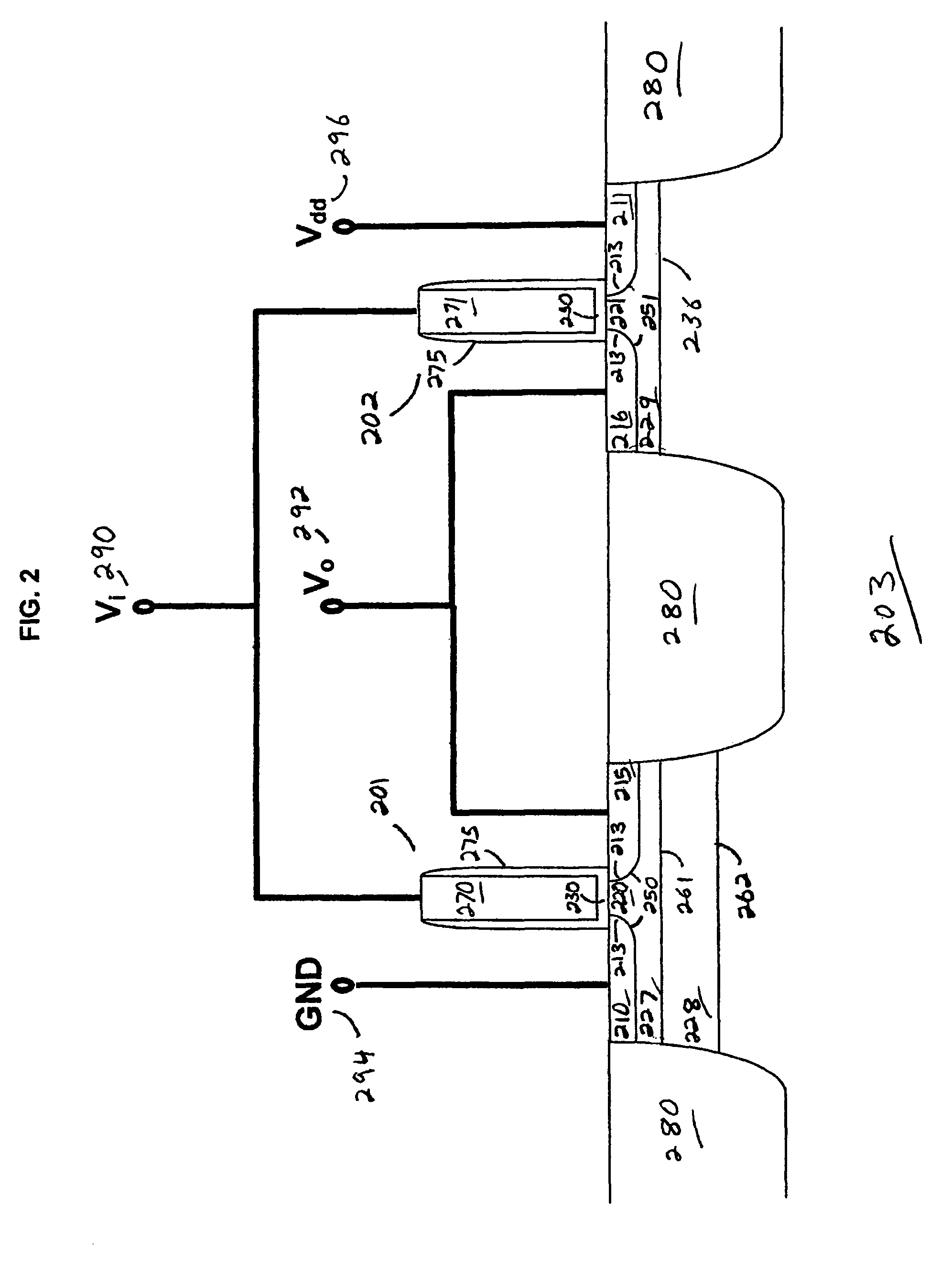

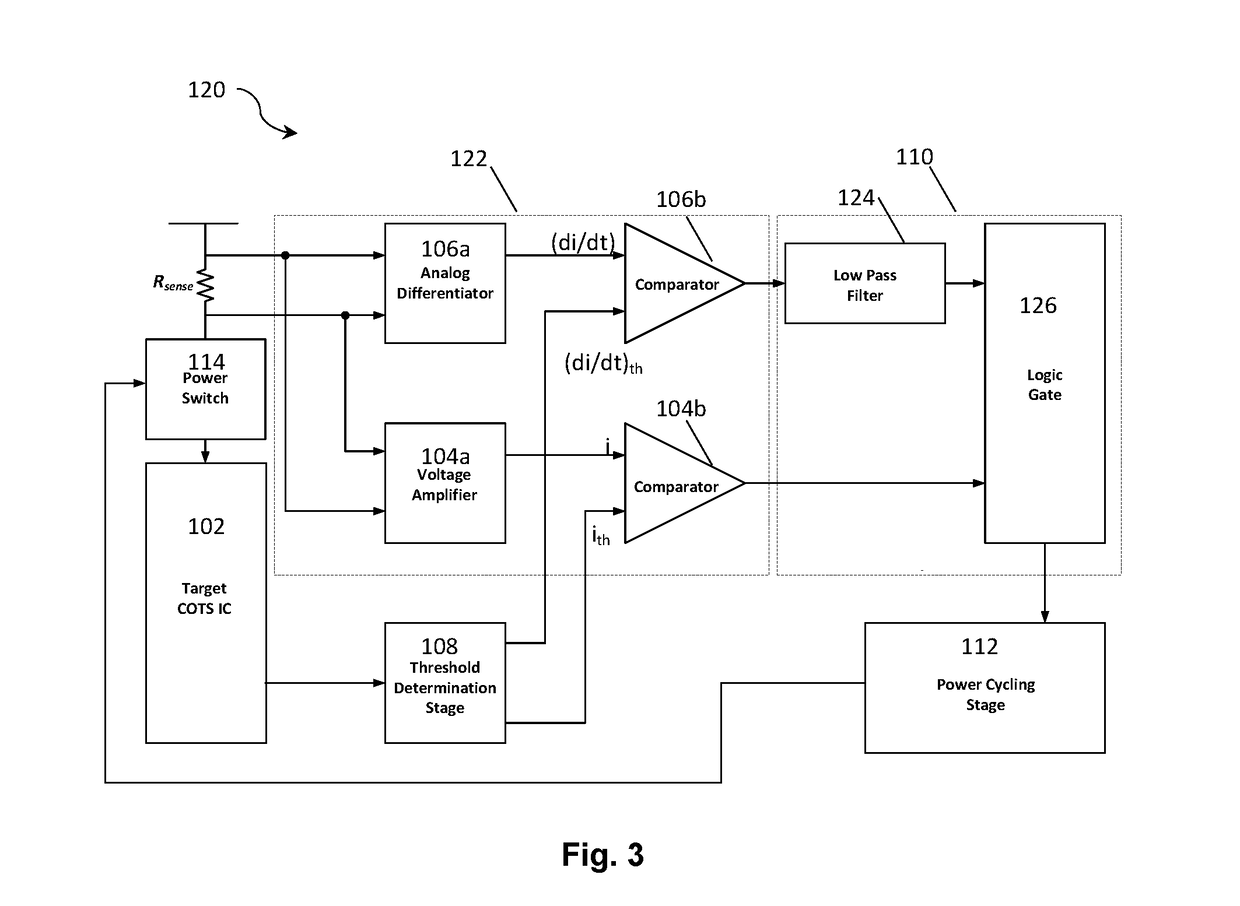

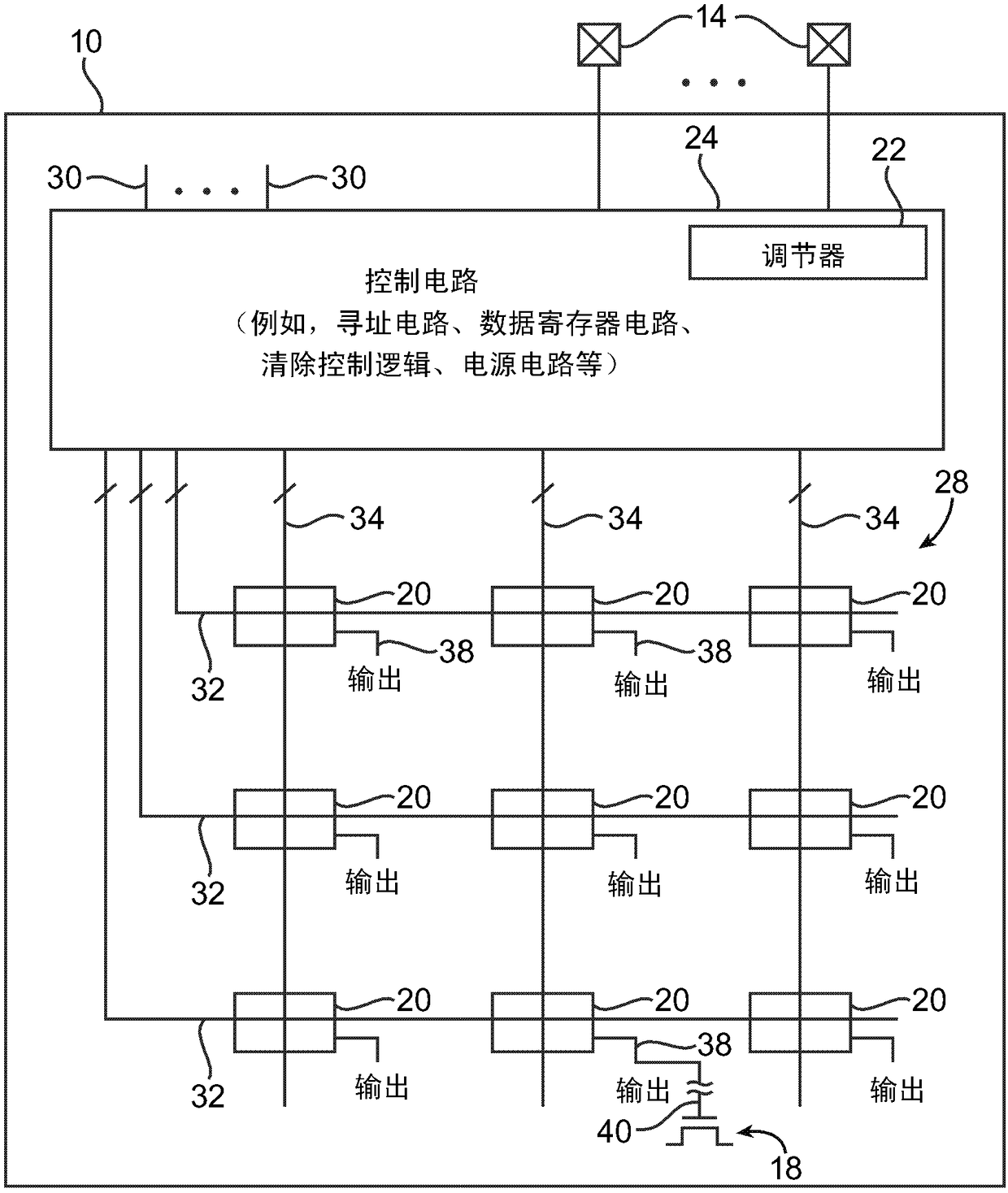

Adaptive single event latchup (SEL) current surge mitigation

ActiveUS20180248351A1Guaranteed uptimeFalse alarm rateEmergency protective arrangement detailsEmergency protective arrangements for automatic disconnectionSingle event latchupDevice status

Method for SEL mitigation involves determining one or more base sets of signature vector components for each of a plurality of signal loading conditions experienced by a protected device in an operating state, each set of base signature vector components together comprising a base signature vector. The method further involves monitoring signature vector components for the protected device to determine a detected signature vector which is comprised of a set of detected signature vector components. The detected signature vector is compared to a dynamically selected base signature vector which is associated with the device state and signal loading condition which are currently active to differentiate between the occurrence of standard current surges associated with normal operation of the protected device and a non-standard current surge.

Owner:HARRIS CORP

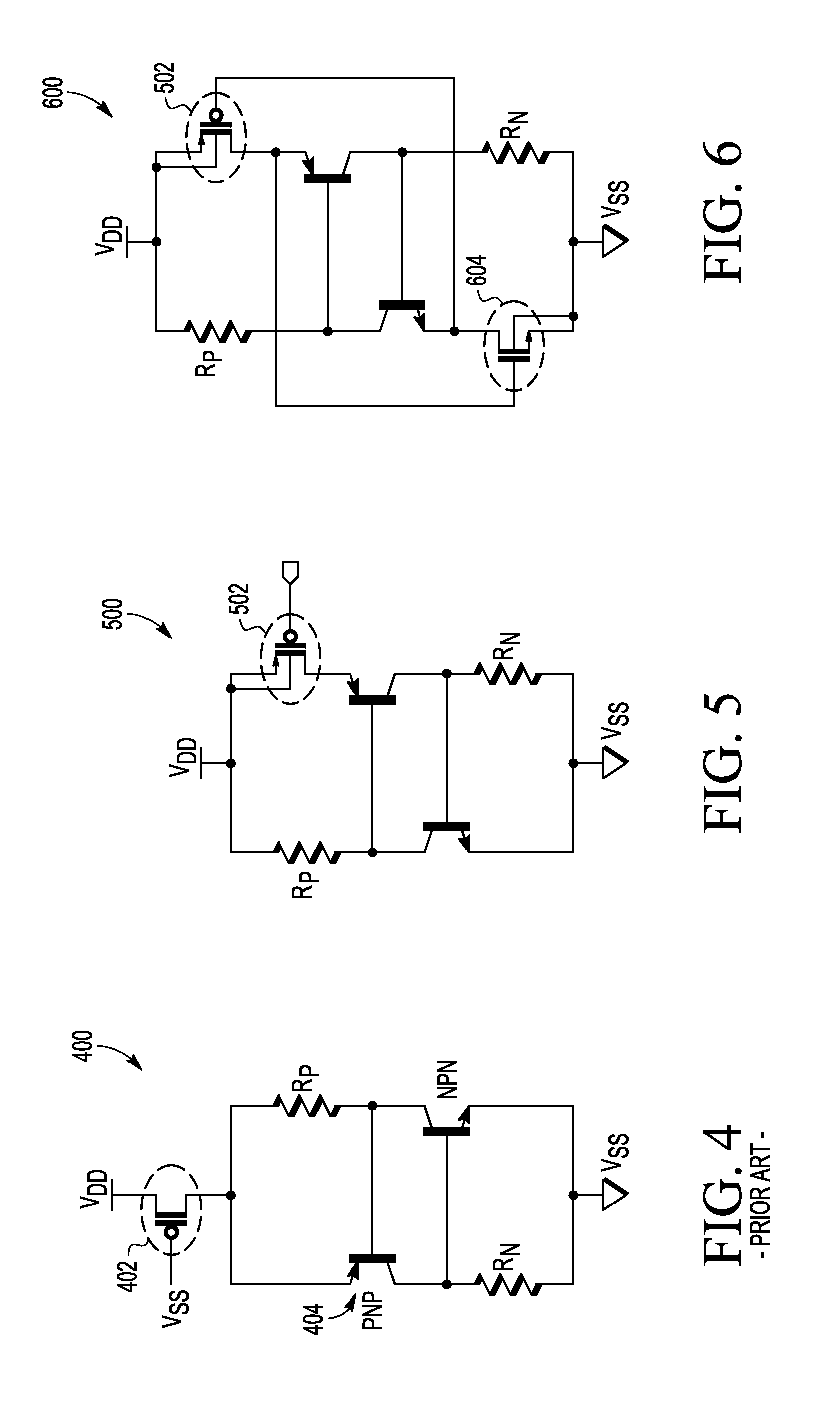

Single event latch-up prevention techniques for a semiconductor device

A technique for addressing single-event latch-up (SEL) in a semiconductor device includes determining a location of a parasitic silicon-controlled rectifier (SCR) in an integrated circuit design of the semiconductor device. In this case, the parasitic SCR includes a parasitic pnp bipolar junction transistor (BJT) and a parasitic npn BJT. The technique also includes incorporating a first transistor between a first power supply node and an emitter of the parasitic pnp BJT in the integrated circuit design. The first transistor includes a first terminal coupled to the first power supply node, a second terminal coupled to the emitter of the parasitic pnp BJT, and a control terminal. The first transistor is not positioned between a base of the pnp BJT and the first power supply node. The first transistor limits current conducted by the parasitic pnp bipolar junction transistor following an SEL.

Owner:NXP USA INC

Delay flip-flop with reset terminal

ActiveCN104821804AThe output is normalStable stateElectric pulse generatorSingle event latchupProcessor register

A delay flip-flop with a reset terminal comprises a clock module, a delay filtering module, a master-slave DICE latch module and an output module, wherein the master-slave DICE latch module outputs a corresponding data signal to the data output module according to a clock signal that is output from the clock module and an outer data signal that is received through the delay filtering module. The master-slave DICE latch module is provided with the reset terminal. The delay filtering module is used for preventing entering of a transient pulse which is caused by a single event effect into the register. The master-slave DICE latch module is used for correcting inner node upset which is caused by the single-particle effect. The reset terminal is used for resetting the output end. The delay filtering module performs a function of preventing a single event transient pulse. The master-slave DICE latch module prevents overturning of an inner storage node, thereby performing a function of preventing single event upset. A protective belt structure is added in layout design. The structure of the delay flip-flop effectively restrains single event latchup, and facilitates reduction of a single event transient pulse width in a circuit.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

System and method for detecting single event latchup in integrated circuits

InactiveUS7830165B2Individual semiconductor device testingContactless circuit testingSingle event latchupIntegrated circuit layout

A method for testing an integrated circuit for potential latchup sites includes applying a voltage to the integrated circuit, measuring a current through the integrated circuit, applying at least one radiation beam to at least one area of the integrated circuit, and detecting an occurrence of a latchup by detecting an increase of the current through the integrated circuit upon applying the at least one radiation beam to the at least one area of the integrated circuit.

Owner:INTEGRATED DEVICE TECH INC

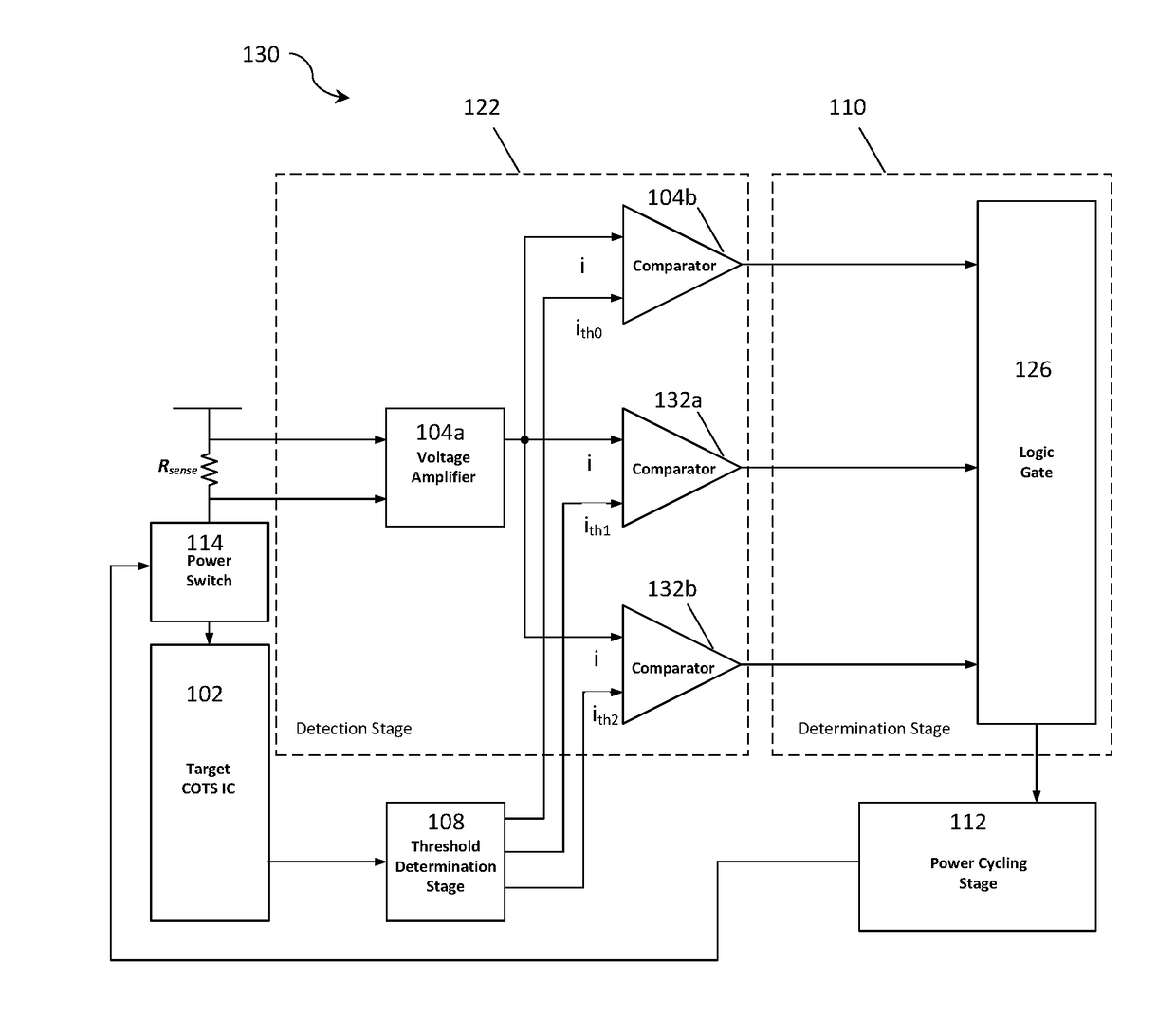

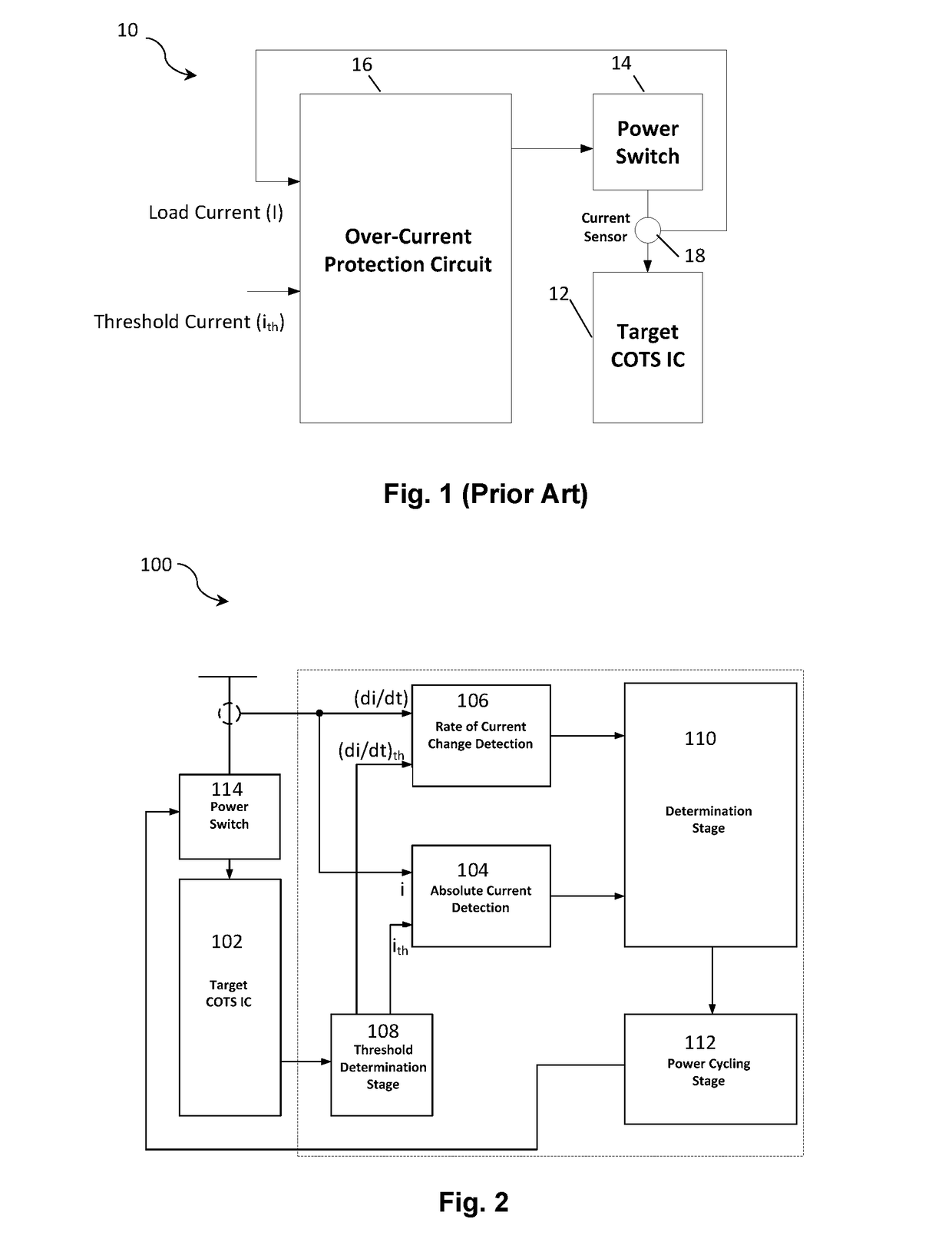

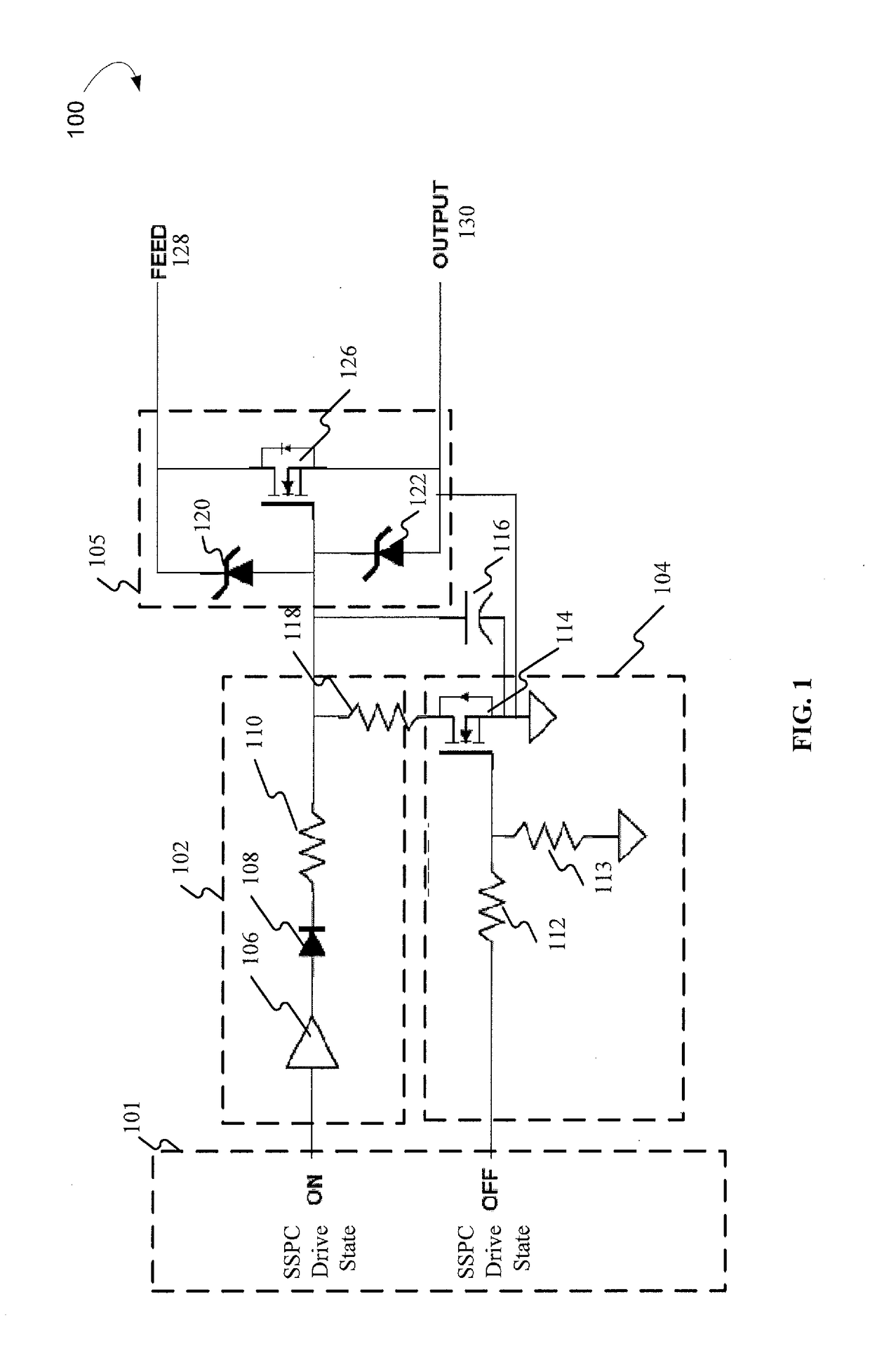

Electronic circuit for single-event latch-up detection and protection

ActiveUS20170237250A1Early detectionFast disablingSolid-state devicesEmergency protection detectionSingle event latchupComputer module

An electronic circuit for single-event latch-up (SEL) detection and protection of a target integrated circuit (IC) is disclosed. The circuit comprises: a first detector configured for detecting an absolute load current (i) and comparing the absolute load current (i) with a threshold current (ith); a second detector configured for detecting a rate of change of load current (di / dt) and comparing the rate of change of load current (di / dt) with a threshold current change rate (di / dt)th; and a determination module for triggering a power shut-down to the target IC if the absolute load current (i) exceeds the threshold current (ith) and / or the rate of change of load current (di / dt) exceeds the threshold current change rate (di / dt)th.

Owner:ZERO ERROR SYST PTE LTD

D flip-flop with set terminal

ActiveCN104811162AThe output is normalReduce widthElectric pulse generatorSingle event latchupExternal data

The invention relates to a D flip-flop with a set terminal. The D flip-flop comprises a clock module, a delay filtering module, a master-slave DICE latch module and an output module, wherein the master-slave DICE latch module is used for outputting corresponding data signals to a data output module according to clock signals output from the clock module and external data signals received through the delay filtering module. The master-slave DICE latch module is provided with the set terminal; the delay filtering module is used for preventing transient pulses caused by a single event effect from entering inside a register; the master-slave DICE latch module is used for correcting internal node upsetting caused by the single event effect; the set terminal is used for setting an output terminal to be 1; the delay filtering module plays a role in resisting SET (Single Event Transient), the master-slave DICE latch module is used for preventing internal storage nodes from upsetting and plays a role in resisting SEU (Single Event Upset), and a guard band structure is added during layout designing, is used for effectively inhibiting SEL (Single Event Latchup) and is also beneficial to the reduction of SET pulse width in a circuit.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

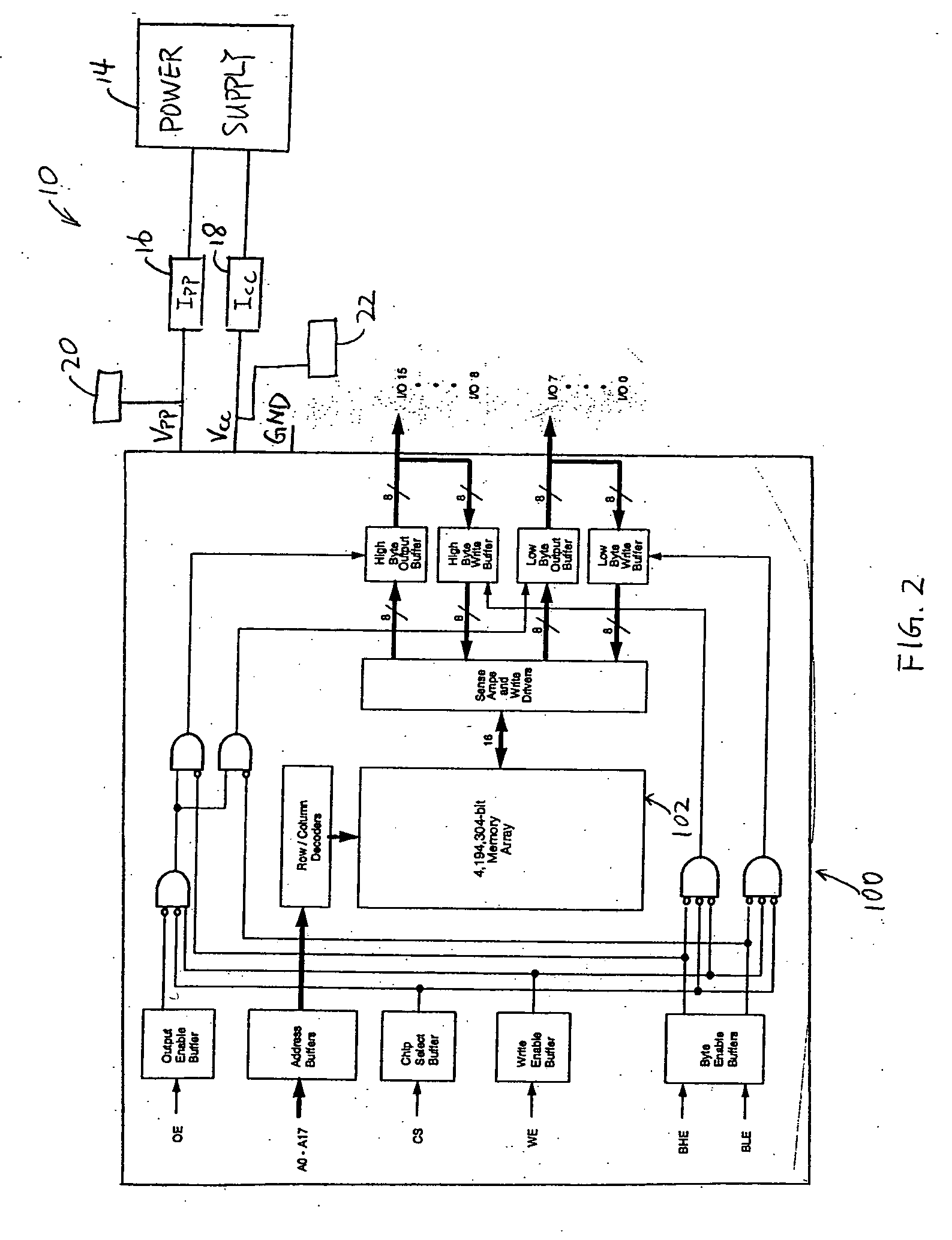

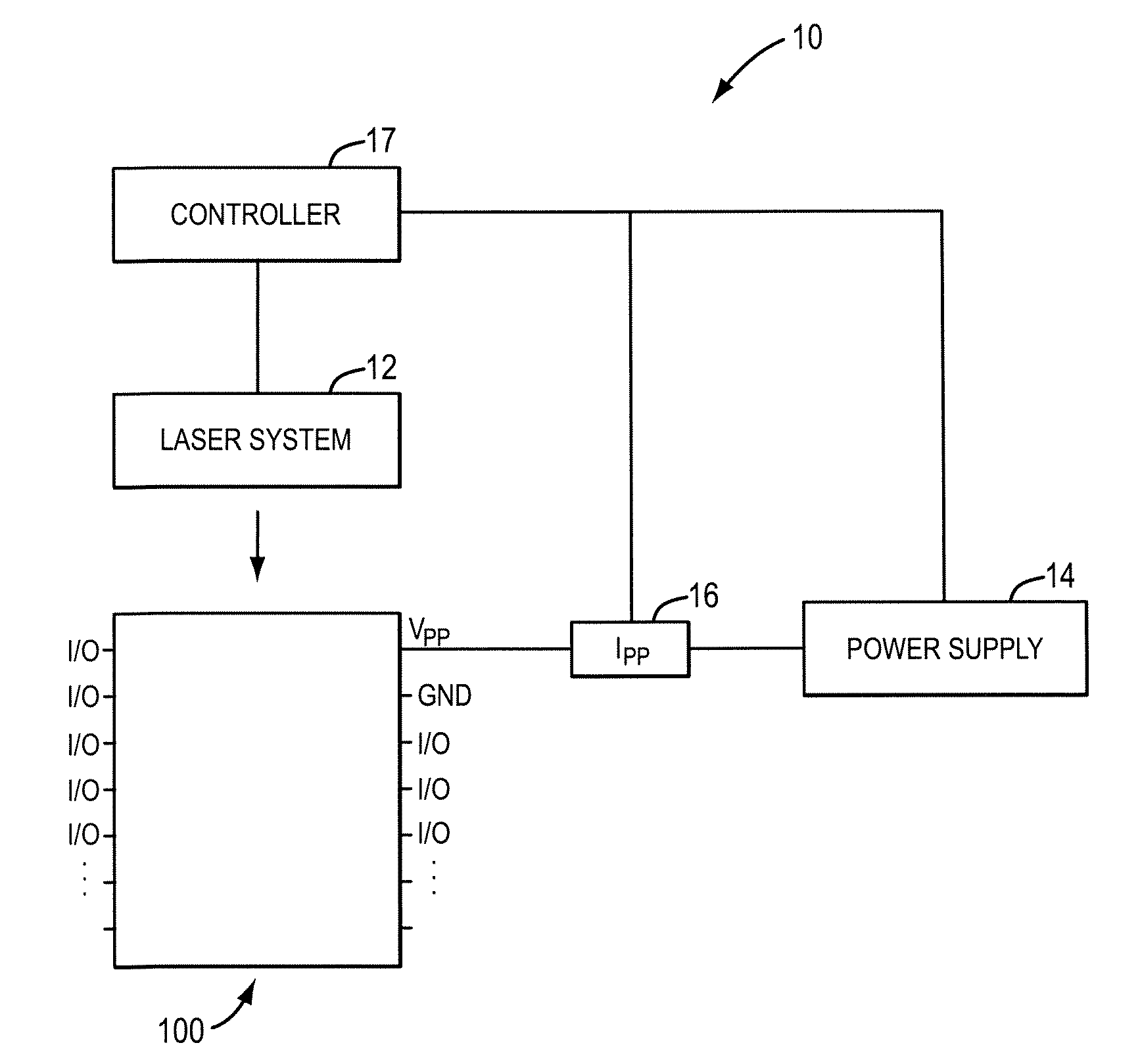

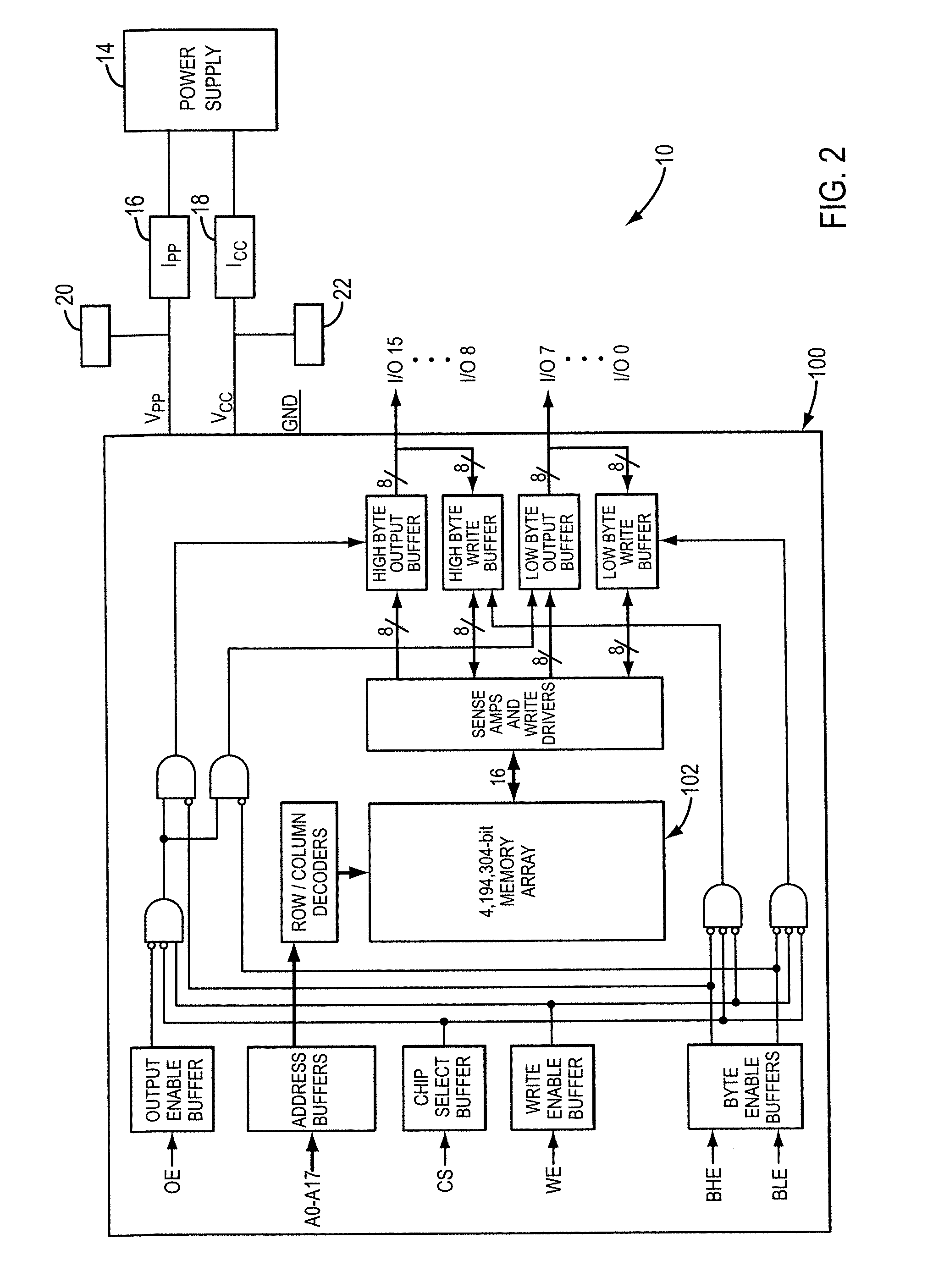

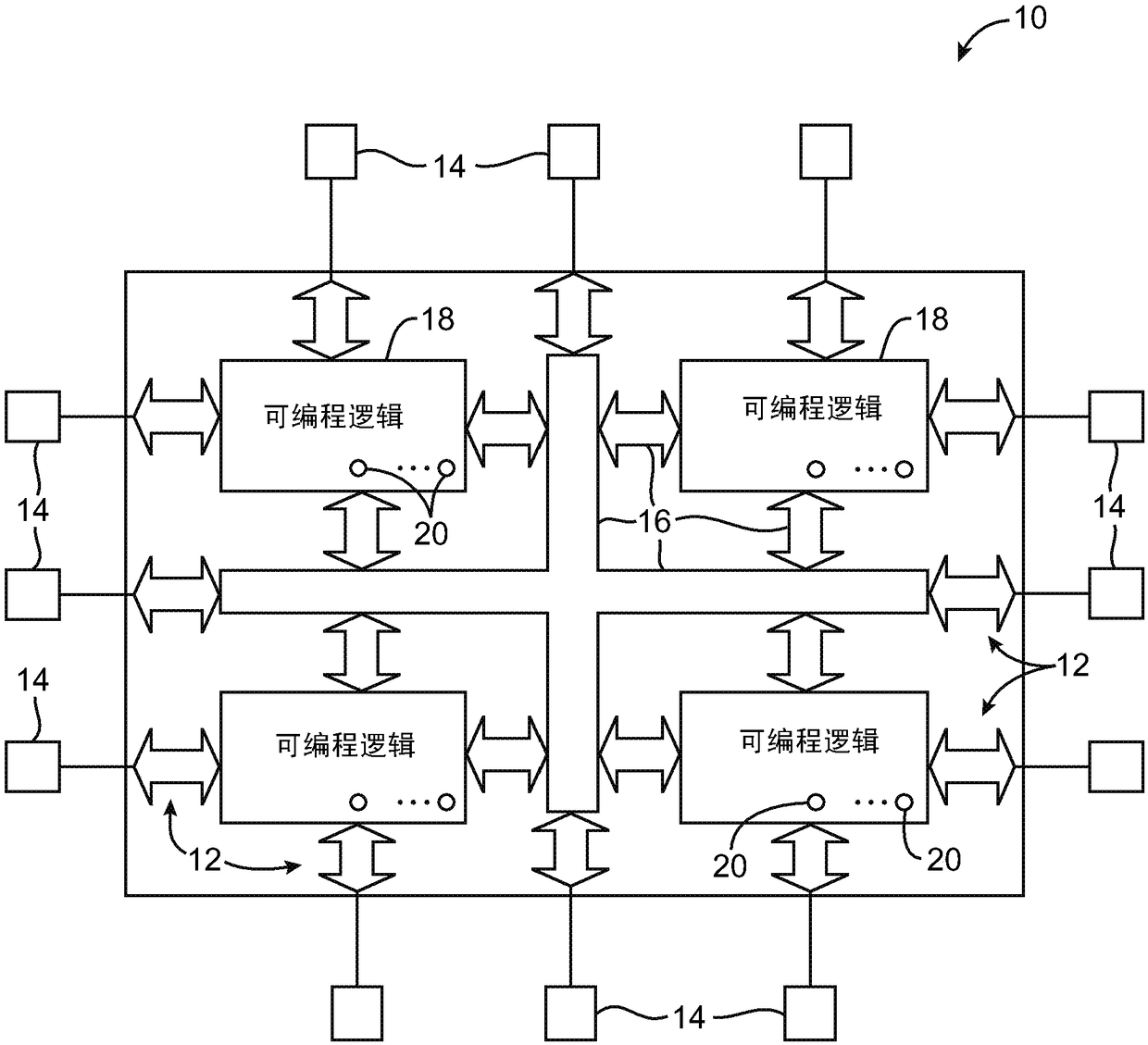

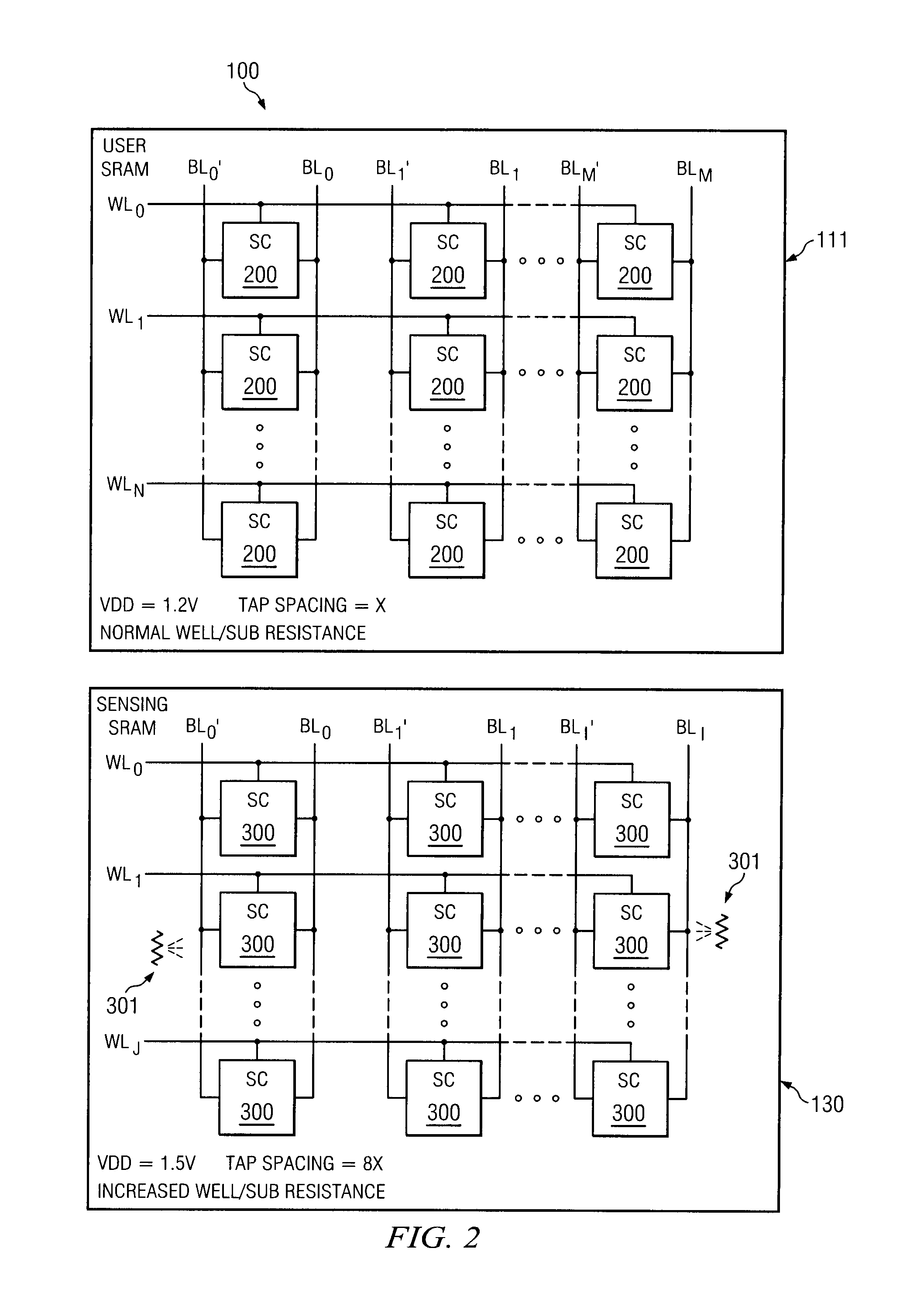

Memory with single-event latchup prevention circuitry

Provided is an integrated circuit. The integrated circuit includes an array of random-access memory cells is provided. Each memory cell may include inverting circuits formed from pull-up transistors and pull-down transistors and also access transistors coupled to the inverting circuits. The pull-up transistors may be formed in an n-well. The memory cells may also be coupled to single event latch-up (SEL) prevention circuitry. The SEL prevention circuitry may include a clamping circuit, a voltage sensing circuit, and a driver circuit. In response to a single event alpha particle strike at one of the memory cells, a temporary voltage rise may be presented at the clamping circuit. The voltage sensing circuit may detect the voltage rise and direct the driver circuit to bias the n-well into deep reverse bias region. Operated in this way, the SEL prevention circuitry can mitigate SEL while minimizing memory cell leakage.

Owner:INTEL CORP

Single event latchup (SEL) current surge mitigation

ActiveUS9960593B2Electrical testingEmergency protective arrangements for automatic disconnectionSingle event latchupSignature vector

Method and system for Single Event Latchup (SEL) current surge mitigation involves monitoring data signals for a protected device and deriving from them a detected signature comprised of one or more detected signature vector components. The detected signature vector components are compared to previously stored signature vector components. Based on the comparing, the system selectively differentiates between the occurrence of standard power surges associated with normal operation of the protected device, and a non-standard current surge which requires cycling power of the protected device for continued proper functioning of the protected device.

Owner:HARRIS CORP

Integrated circuit with automatic deactivation upon exceeding a specific ion linear energy transfer (LET) value

ActiveUS8896978B2Digital storageConductive pattern formationSingle event latchupLinear energy transfer

Integrated circuits as well as fabrication and operating methods are presented in which user circuitry of the IC is selectively disabled in response to detection of a single event latchup condition in a sensing circuit that is prone to latchup in response to ionic radiation at a specific linear energy transfer level.

Owner:TEXAS INSTR INC

Method of manufacturing a CMOS device with zero soft error rate

InactiveUS20110034016A1Action being takenReduce impactSolid-state devicesSemiconductor/solid-state device manufacturingSingle event latchupCMOS

Owner:AVOLARE 2 LLC

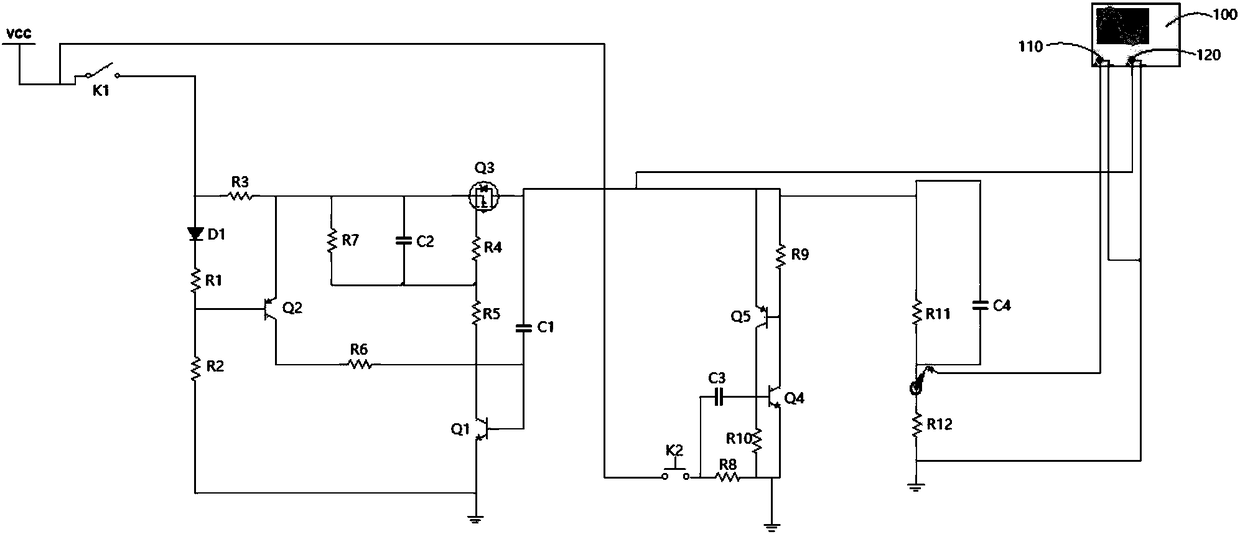

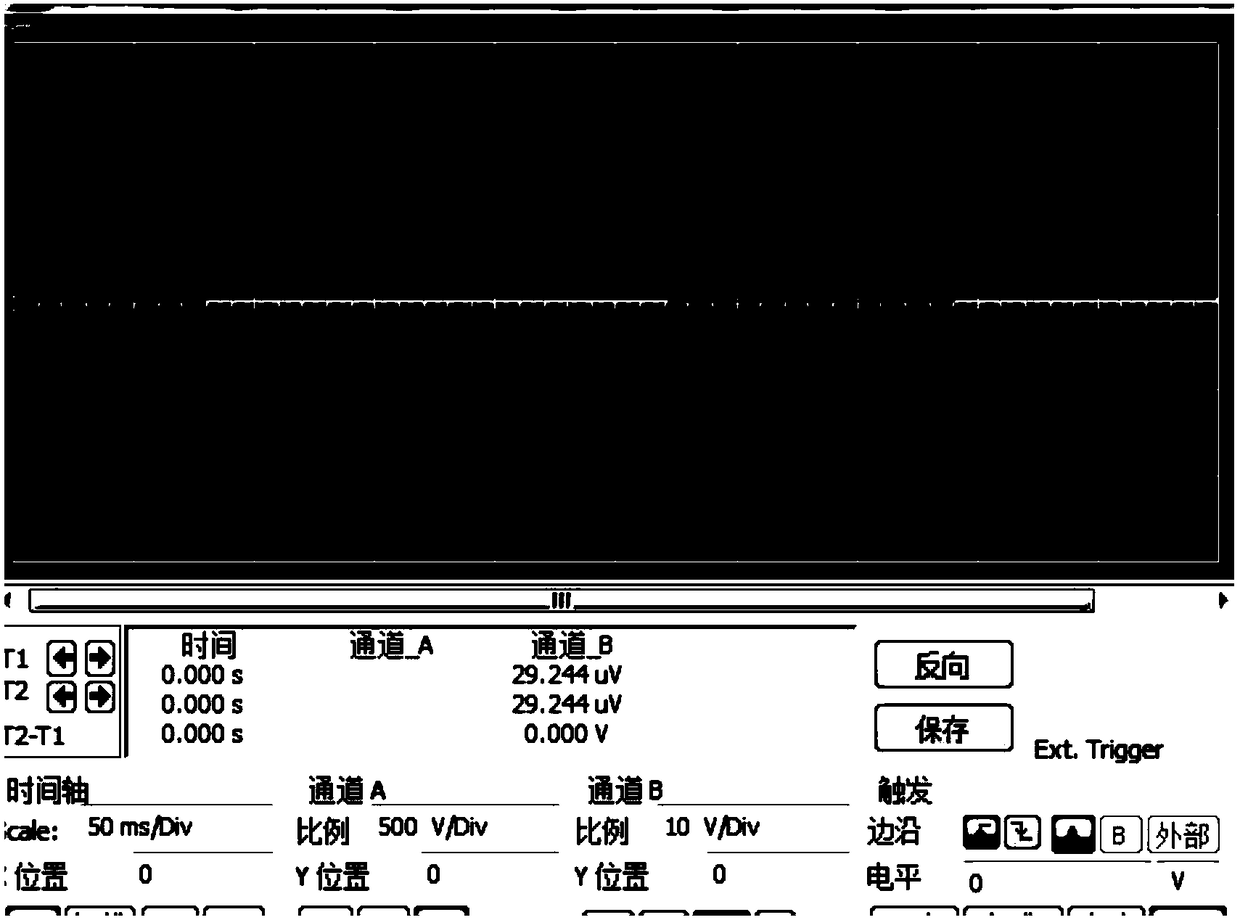

CMOS image sensor single event latchup effect test method

PendingCN110361618AIncreased sensitivityLatch-up real-time monitoringElectrical testingTelevision systemsSingle event latchupCMOS

The invention provides a CMOS image sensor single event latchup effect test method. The method is composed of a CMOS image sensor, a CMOS image sensor test board, an FPGA, a PC, a current and voltagemonitoring board and a test system of a power supply. The method can evaluate the single-particle sensitivity of different circuit modules of the CMOS image sensor and analyze specific reasons of latch from the circuit level; in the ground simulation space environment irradiation test, the current and voltage values of different circuit units are collected online in real time, and meanwhile, darkfield images are also collected; and according to dark field images obtained when the latch occurs and the current and voltage changes of the different circuit units, the specific position and circuitmodule where the latch occurs are analyzed. The method is high in real-time performance, and simple and fast, can monitor the single event latchup effect of the CMOS image sensor in real time, meanwhile, can protect the normal operation of the CMOS image sensor after the latch occurs, and can more accurately locate the circuit module of the CMOS image sensor where the single event latchup occurs.

Owner:XINJIANG TECHN INST OF PHYSICS & CHEM CHINESE ACAD OF SCI

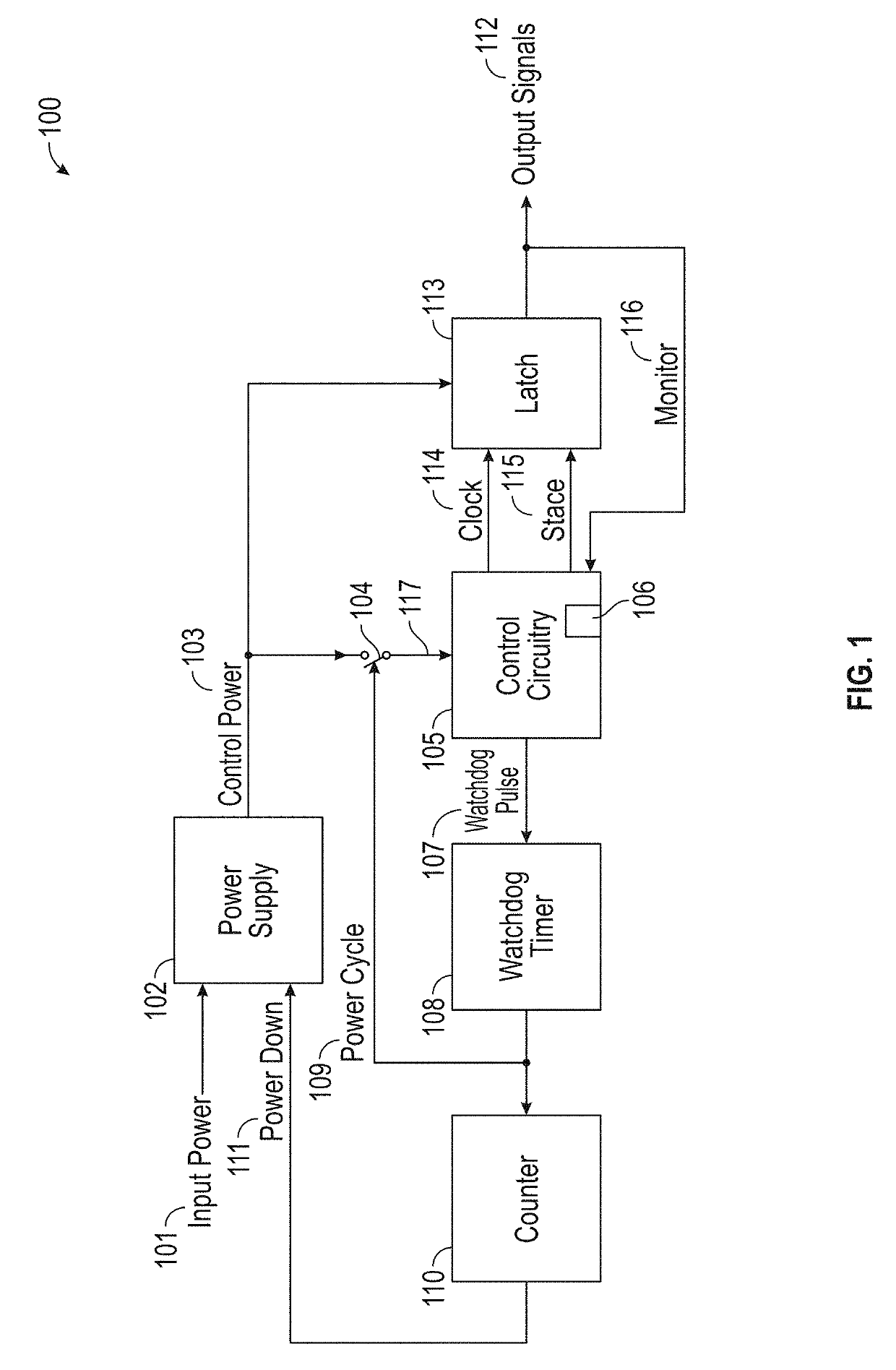

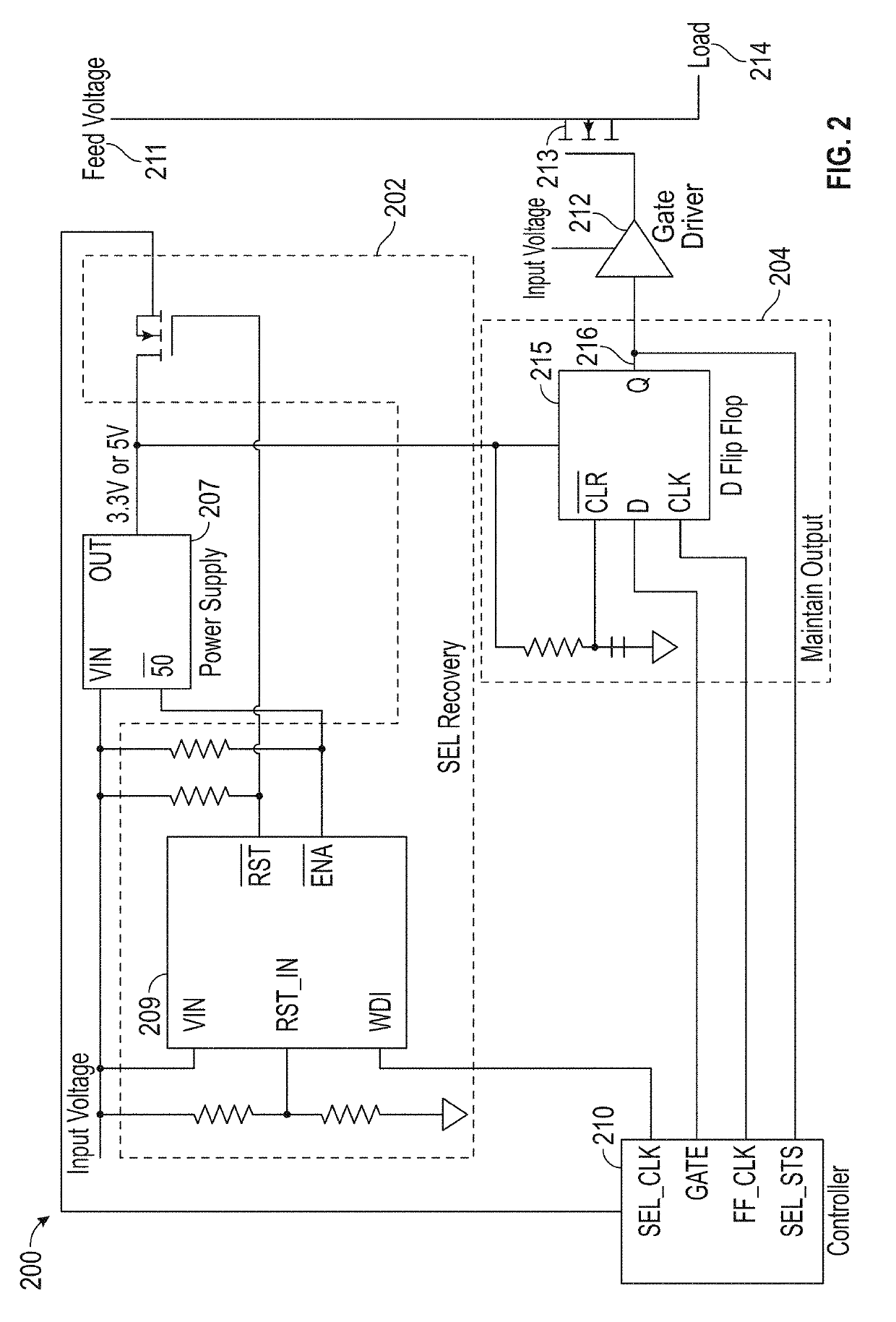

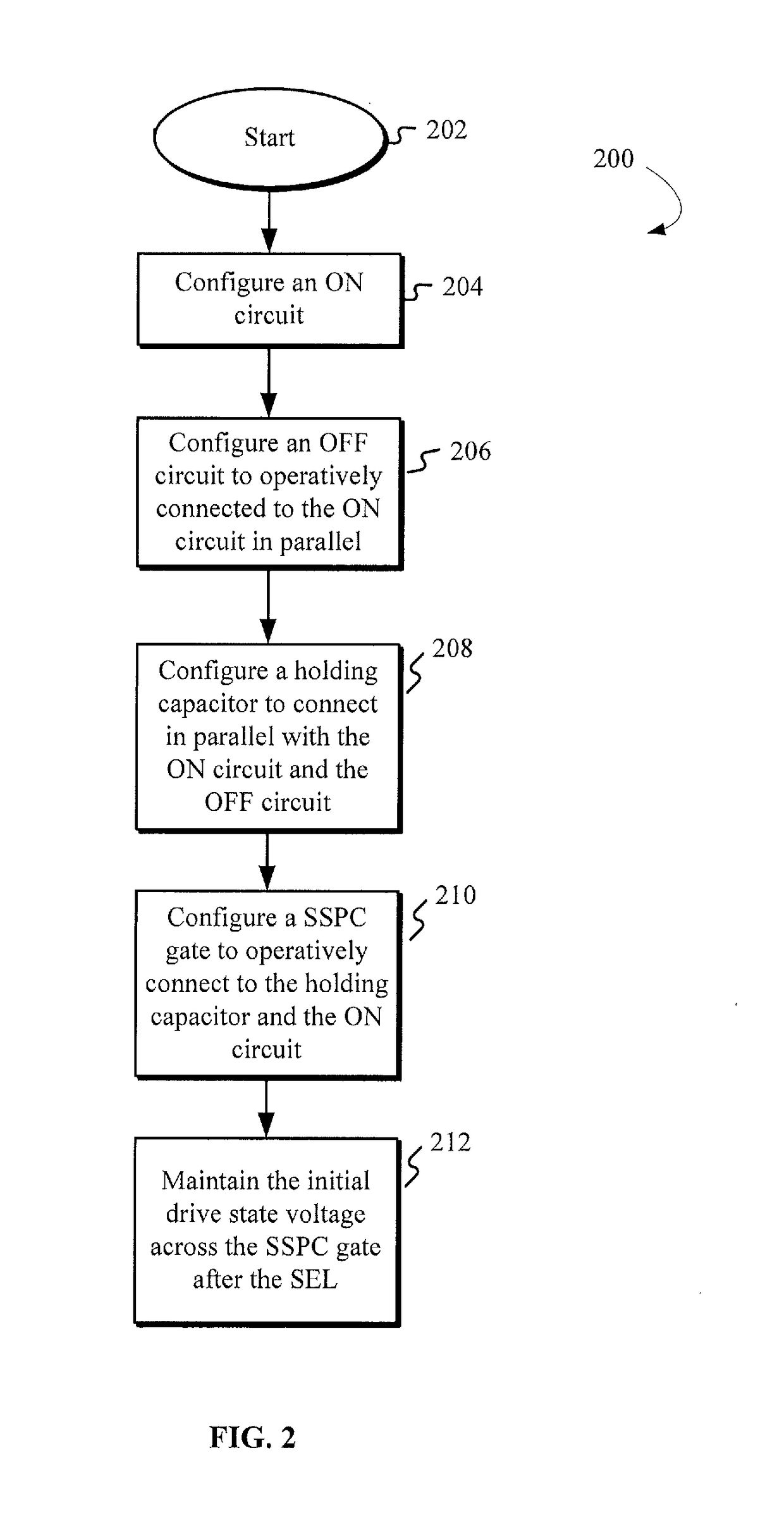

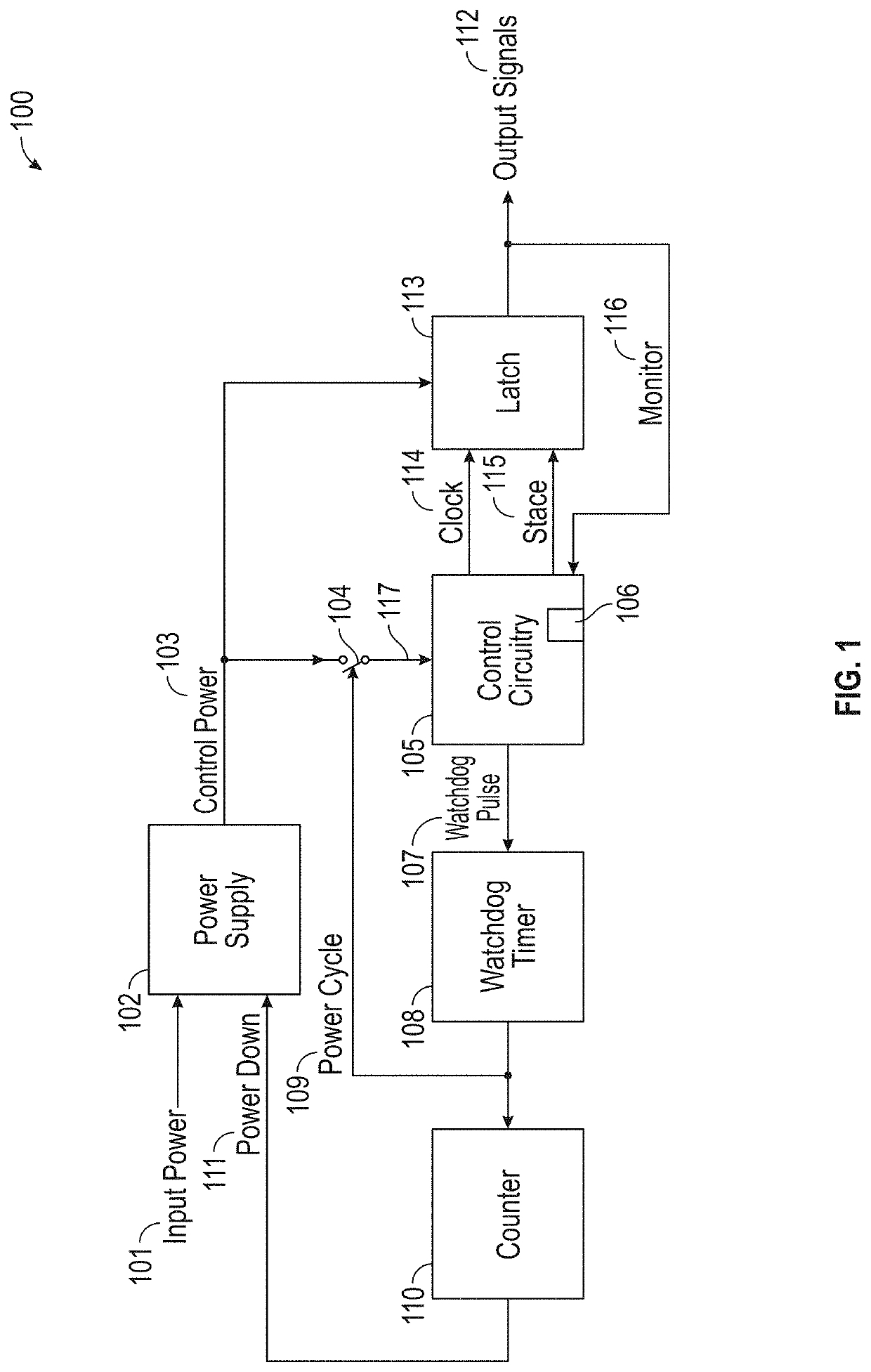

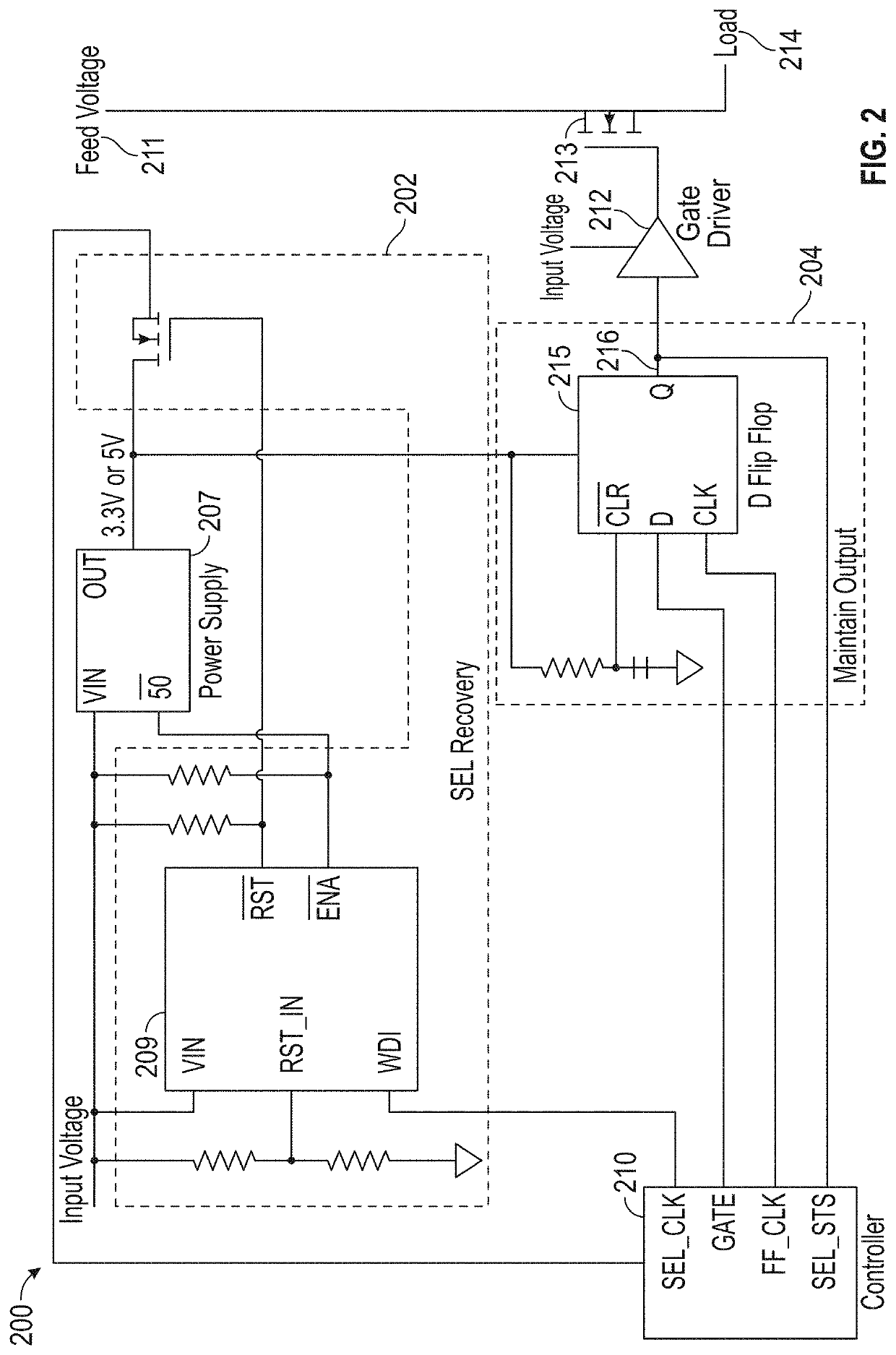

Single event latchup recovery with state protection

ActiveUS20190278660A1Electronic switchingNon-redundant fault processingSingle event latchupPower cycle

An apparatus that includes a single event latchup (SEL) recovery circuit, a microprocessor operatively connected with the SEL recovery circuit, and an output maintenance circuit that maintains a state of the microprocessor prior to a power cycle of the microprocessor. The apparatus is configured to detect a SEL event or other fault via a watchdog circuit, initiate a power cycle of the microprocessor, retain a latch state from the microprocessor, and determine whether the microprocessor was restarted due to an SEL event. Responsive to determining that the microprocessor has failed to restart due to a persistent fault, the apparatus determines whether a prepower cycle limit is reached within a predetermined span of time, and selectively provide power to a load based on the latch state and the power cycle limit determination.

Owner:HAMILTON SUNDSTRAND CORP

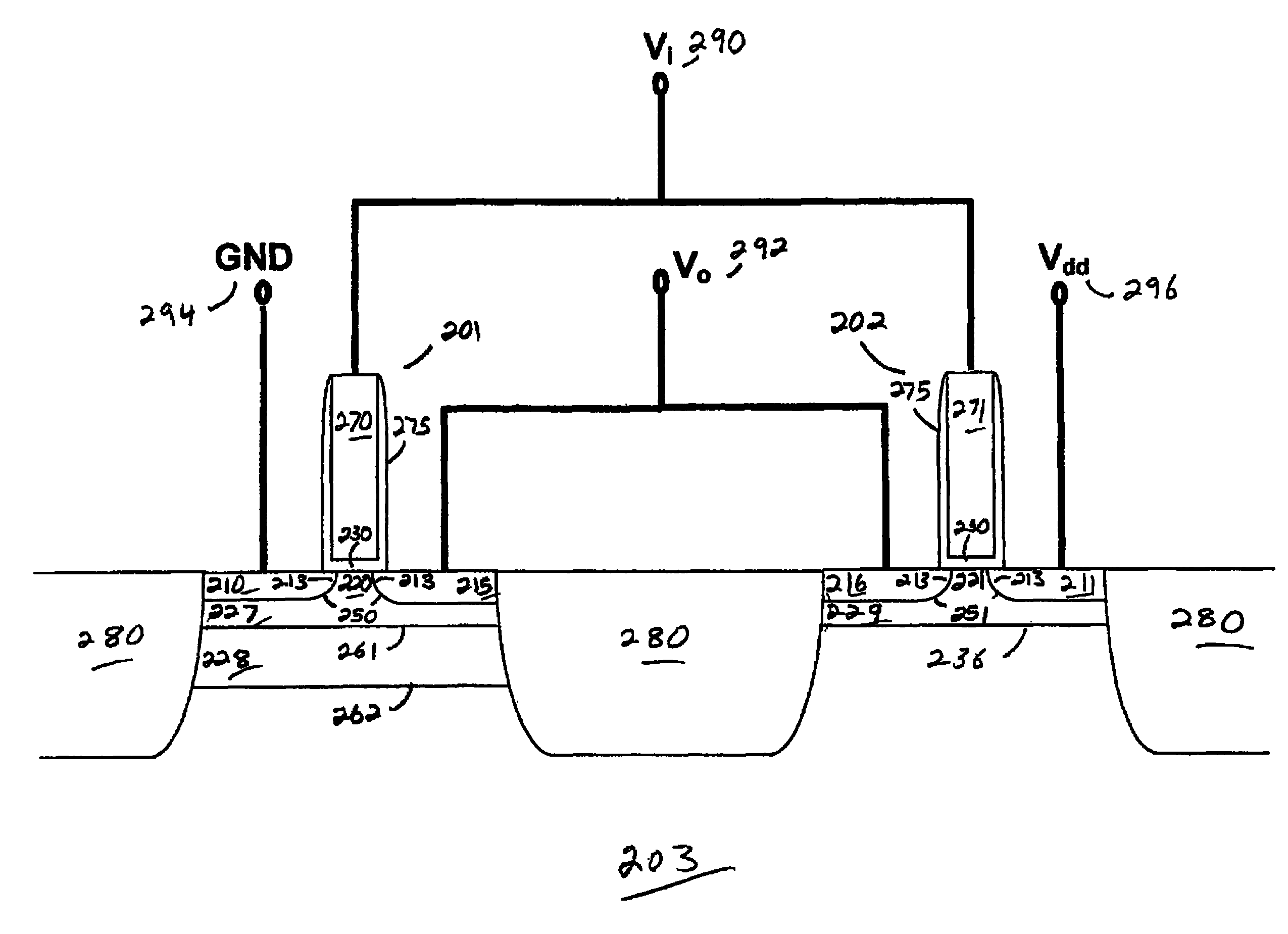

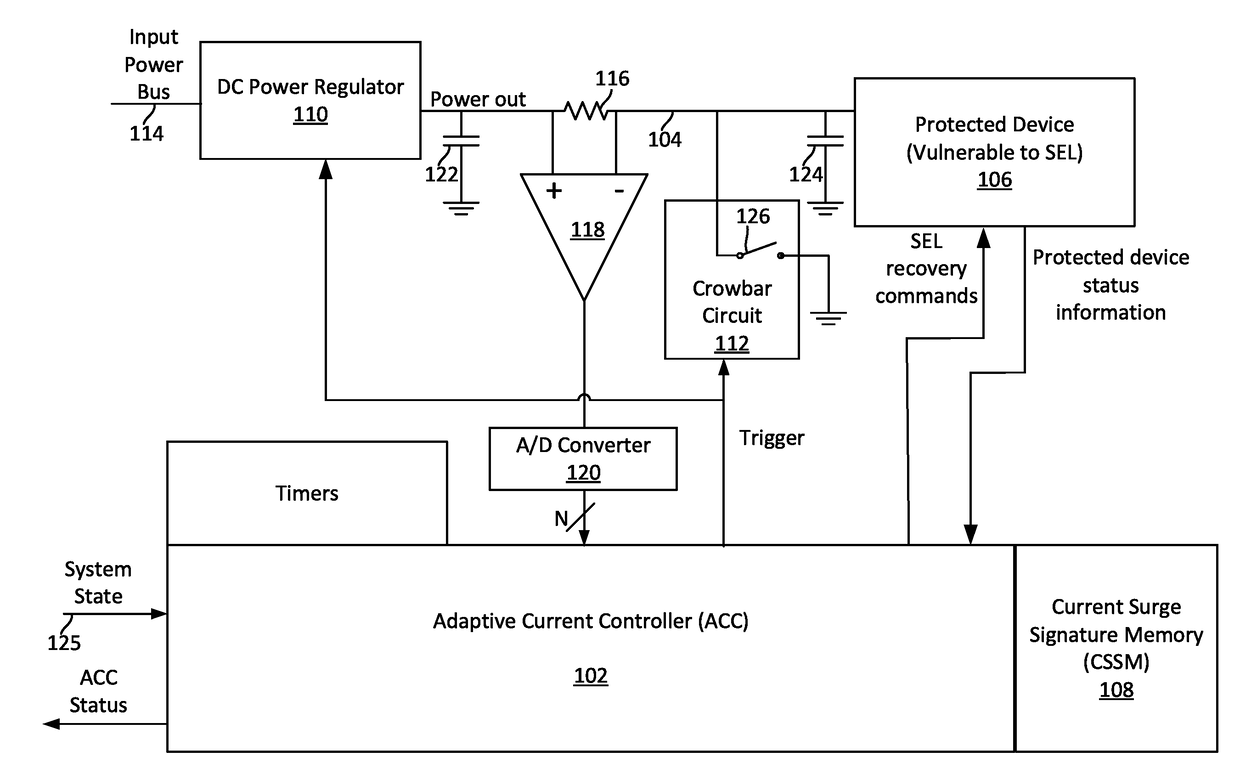

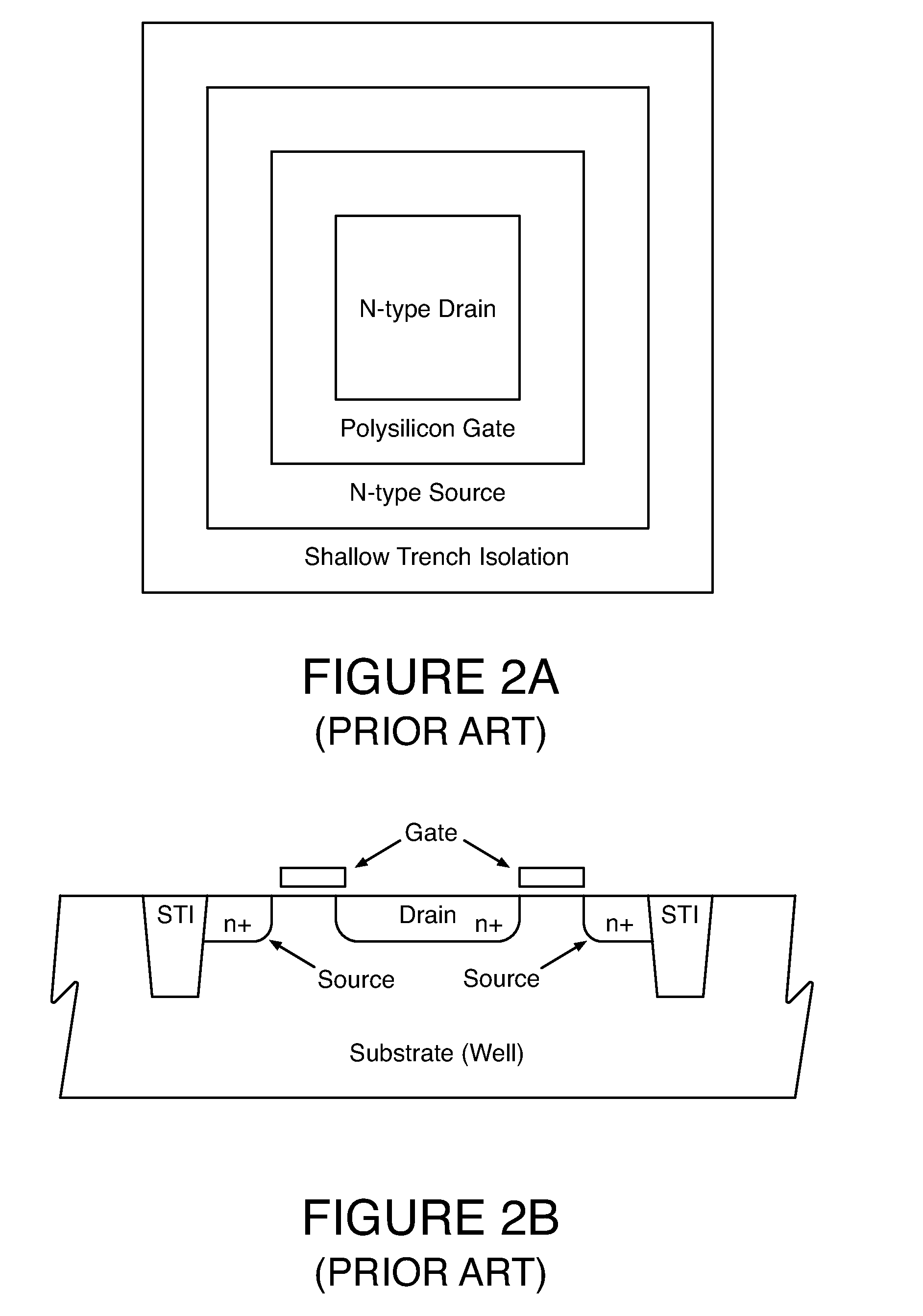

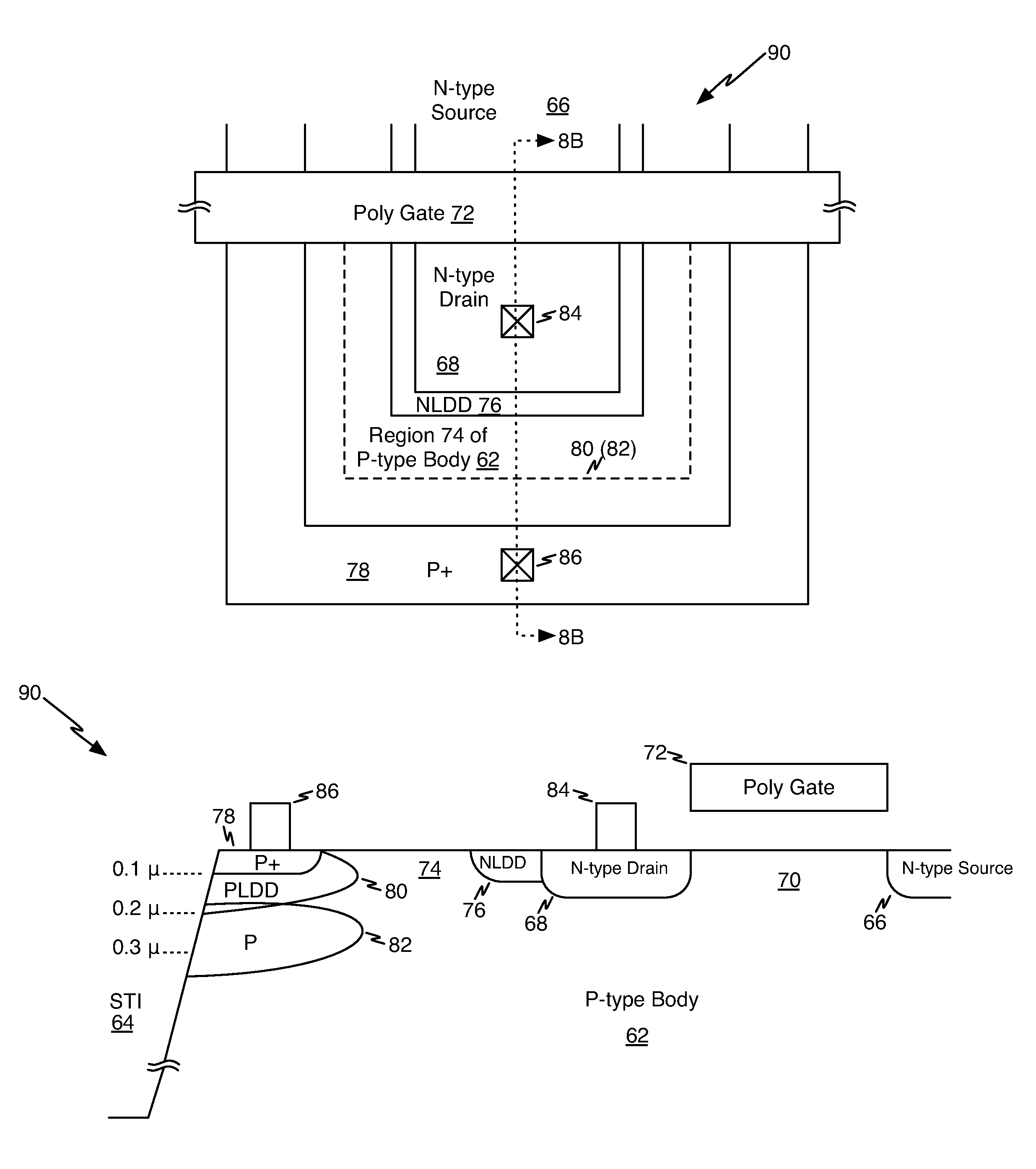

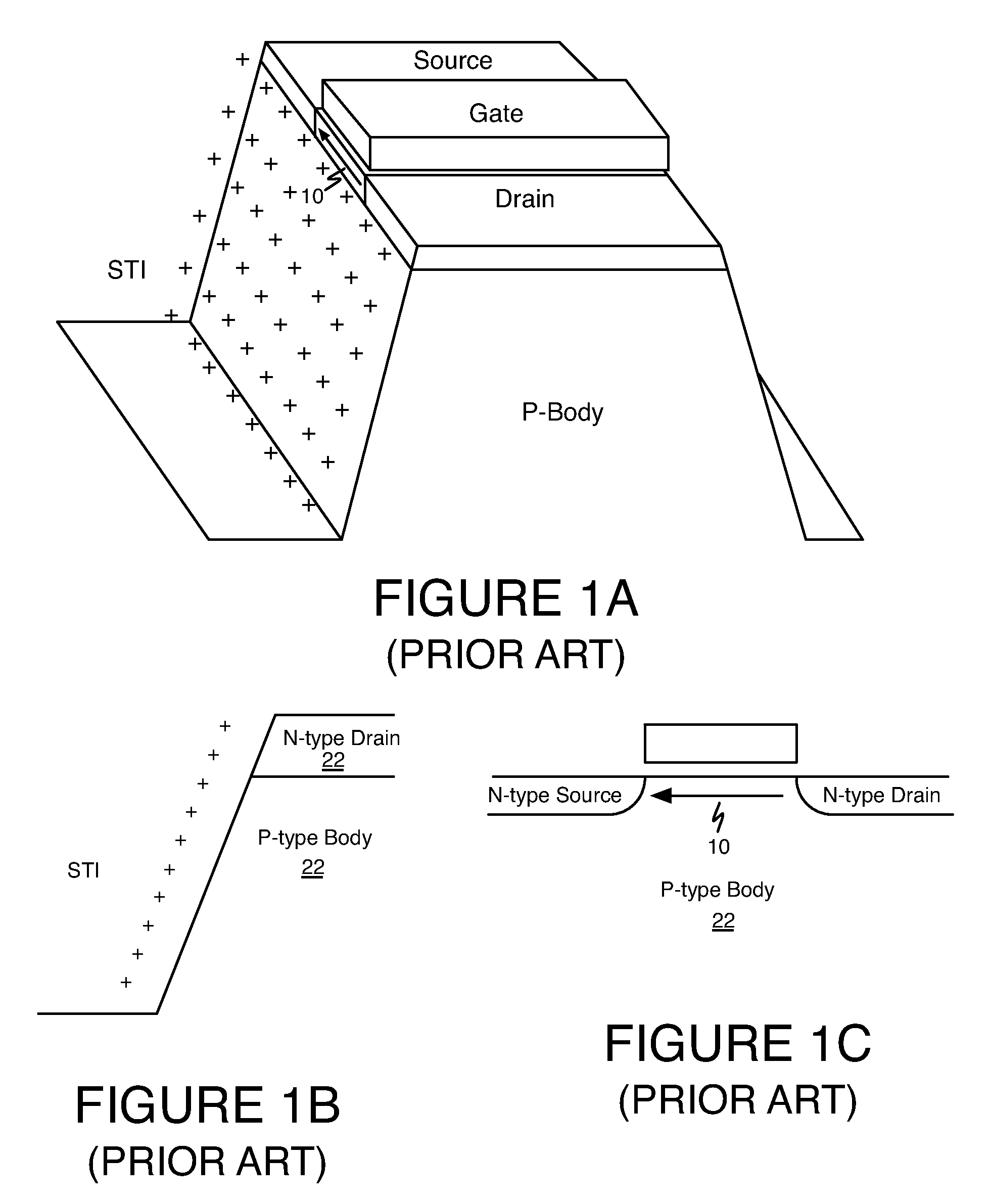

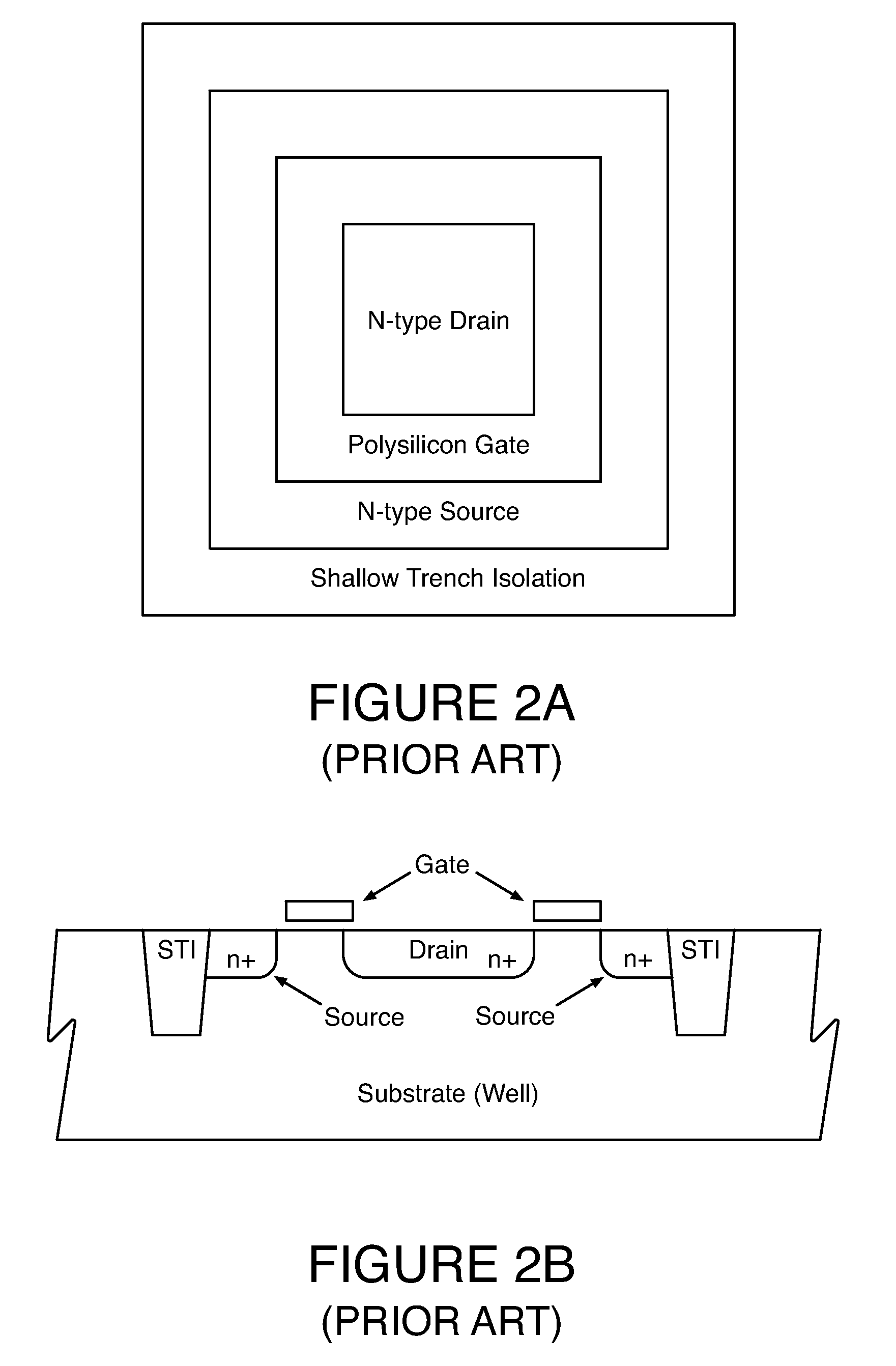

TID Hardened and Single Even Transient Single Event Latchup Resistant MOS Transistors and Fabrication Process

ActiveUS20140291771A1Lower impedanceLower resistanceTransistorSolid-state devicesSingle event latchupBody contact

A radiation-hardened transistor is formed in a p-type body. An active region is disposed within the p-type body and has a perimeter defined by a shallow-trench isolation region filled with a dielectric material. Spaced-apart source and drain regions are disposed in the active region, forming a channel therebetween. A polysilicon gate is disposed above, aligned with, and insulated from the channel region. A p-type isolation ring is disposed in the p-type body separating outer edges of at least one of the source and drain regions from the perimeter of the active region. A body contact is disposed in the p-type isolation ring.

Owner:MICROSEMI SOC

TID hardened and single event transient single event latchup resistant MOS transistors and fabrication process

ActiveUS9093517B2Increase the parasitic V<subImprove immunitySemiconductor devicesSingle event latchupBody contact

A radiation-hardened transistor is formed in a p-type body. An active region is disposed within the p-type body and has a perimeter defined by a shallow-trench isolation region filled with a dielectric material. Spaced-apart source and drain regions are disposed in the active region, forming a channel therebetween. A polysilicon gate is disposed above, aligned with, and insulated from the channel region. A p-type isolation ring is disposed in the p-type body separating outer edges of at least one of the source and drain regions from the perimeter of the active region. A body contact is disposed in the p-type isolation ring.

Owner:MICROSEMI SOC

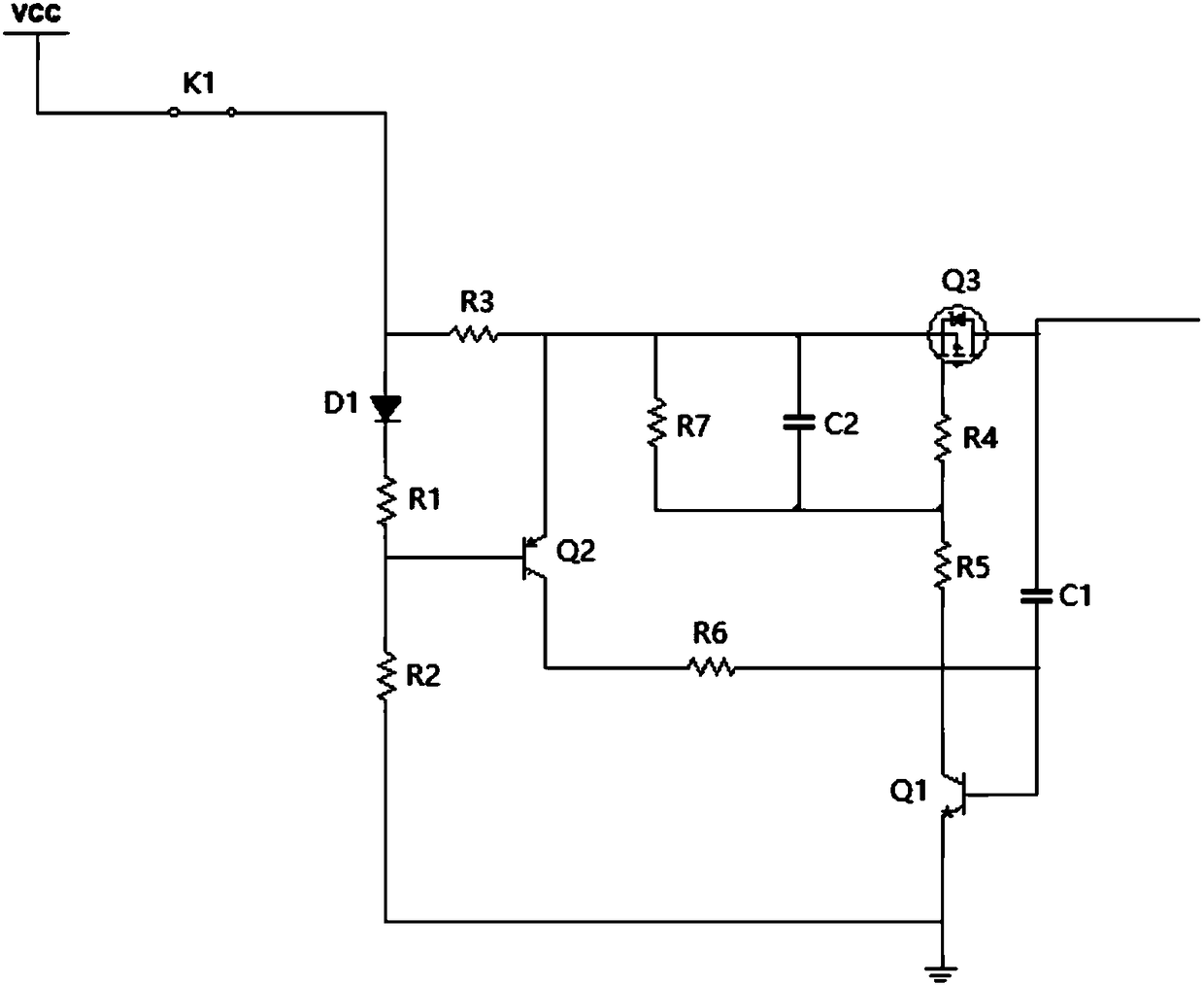

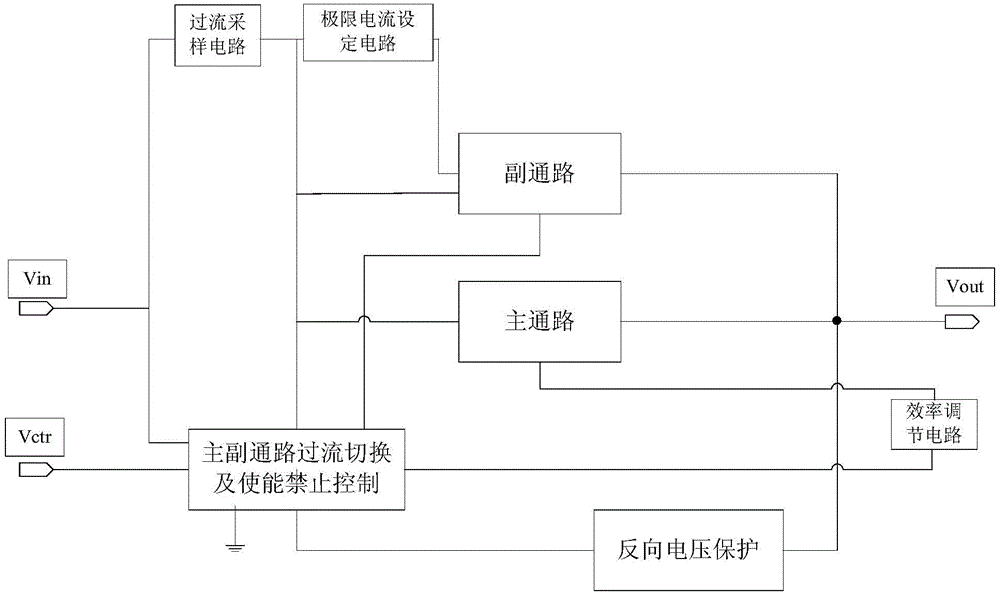

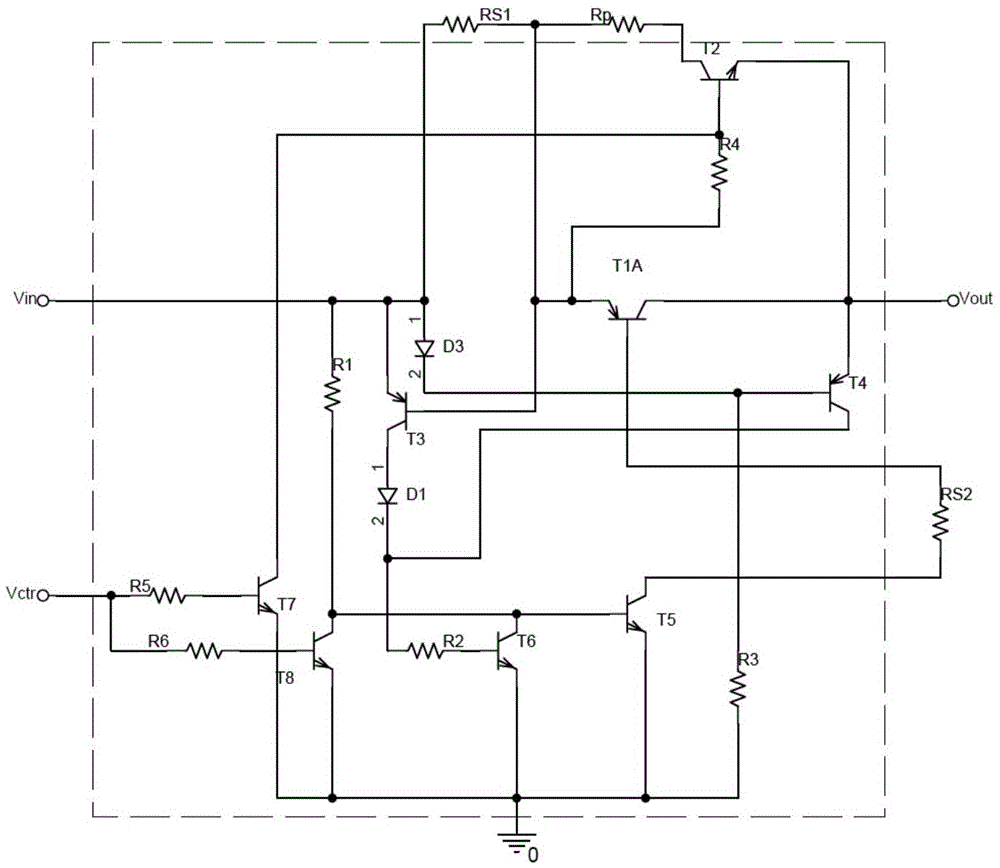

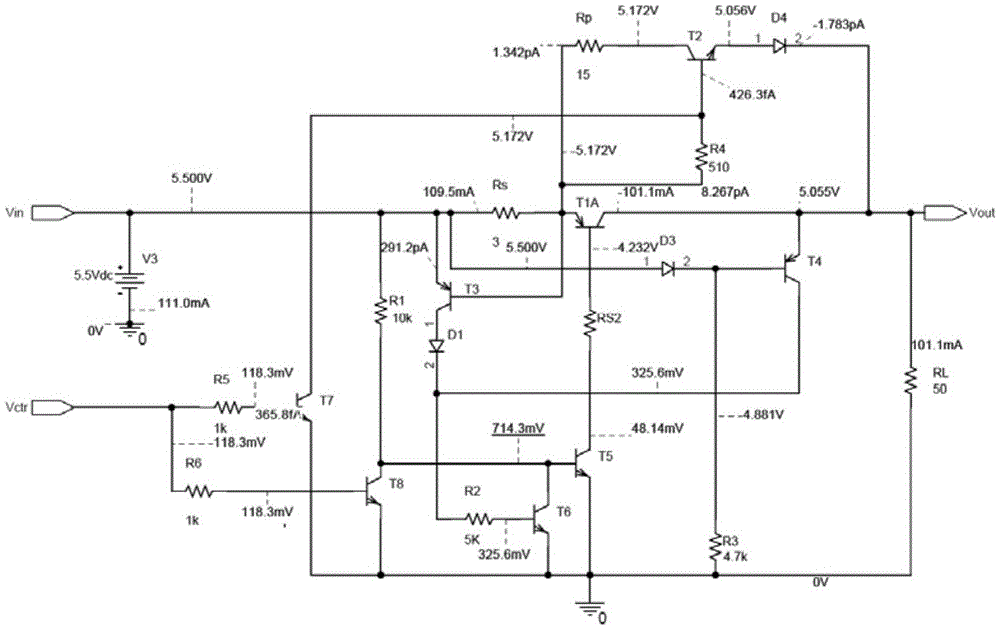

Circuit module capable of preventing surge and single event latchup for on-satellite equipment

PendingCN108494240AReduce sizeSmall pressure dropPower conversion systemsSingle event latchupVoltage drop

The invention discloses a circuit module capable of preventing surge and single event latchup for on-satellite equipment. The circuit module comprises a power switch K1, a diode D1, resistors R1, R2,R3, R4, R5, R6 and R7, triodes Q1 and Q2, capacitors C1 and C2 and a power field effect transistor Q3. The circuit module integrates an anti-surge circuit and a single event latchup preventing circuitto enable the circuit module to have an anti-surge function and a single event latchup prevention function simultaneously, thereby effectively reducing voltage drop of the power end, improving equipment efficiency, reducing equipment power consumption and improving global stability of the system.

Owner:BEIJING PENGYU SIRUI TECH CO LTD

Single event latchup mitigation with sample and hold

Owner:HAMILTON SUNDSTRAND CORP

Adaptive single event latchup (SEL) current surge mitigation

ActiveUS10886723B2Emergency protective arrangement detailsEmergency protective arrangements for automatic disconnectionSingle event latchupDevice status

Method for SEL mitigation involves determining one or more base sets of signature vector components for each of a plurality of signal loading conditions experienced by a protected device in an operating state, each set of base signature vector components together comprising a base signature vector. The method further involves monitoring signature vector components for the protected device to determine a detected signature vector which is comprised of a set of detected signature vector components. The detected signature vector is compared to a dynamically selected base signature vector which is associated with the device state and signal loading condition which are currently active to differentiate between the occurrence of standard current surges associated with normal operation of the protected device and a non-standard current surge.

Owner:HARRIS CORP

An output controllable low dropout overcurrent protection circuit

ActiveCN103474951BGuaranteed low dropout power supply requirementsIncreased flexibility of useDc-dc conversionArrangements responsive to excess currentSingle event latchupElectrical resistance and conductance

Owner:BEIJING INST OF SPACECRAFT SYST ENG

A D flip-flop with set terminal

ActiveCN104811162BThe output is normalReduce widthElectric pulse generatorSingle event latchupProcessor register

The invention relates to a D flip-flop with a set terminal. The D flip-flop comprises a clock module, a delay filtering module, a master-slave DICE latch module and an output module, wherein the master-slave DICE latch module is used for outputting corresponding data signals to a data output module according to clock signals output from the clock module and external data signals received through the delay filtering module. The master-slave DICE latch module is provided with the set terminal; the delay filtering module is used for preventing transient pulses caused by a single event effect from entering inside a register; the master-slave DICE latch module is used for correcting internal node upsetting caused by the single event effect; the set terminal is used for setting an output terminal to be 1; the delay filtering module plays a role in resisting SET (Single Event Transient), the master-slave DICE latch module is used for preventing internal storage nodes from upsetting and plays a role in resisting SEU (Single Event Upset), and a guard band structure is added during layout designing, is used for effectively inhibiting SEL (Single Event Latchup) and is also beneficial to the reduction of SET pulse width in a circuit.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

Single event latchup recovery with state protection

ActiveUS10713118B2Reliability increasing modificationsElectronic switchingSingle event latchupPower cycle

An apparatus that includes a single event latchup (SEL) recovery circuit, a microprocessor operatively connected with the SEL recovery circuit, and an output maintenance circuit that maintains a state of the microprocessor prior to a power cycle of the microprocessor. The apparatus is configured to detect a SEL event or other fault via a watchdog circuit, initiate a power cycle of the microprocessor, retain a latch state from the microprocessor, and determine whether the microprocessor was restarted due to an SEL event. Responsive to determining that the microprocessor has failed to restart due to a persistent fault, the apparatus determines whether a prepower cycle limit is reached within a predetermined span of time, and selectively provide power to a load based on the latch state and the power cycle limit determination.

Owner:HAMILTON SUNDSTRAND CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com