Delay flip-flop with reset terminal

A technology of clearing the terminal and trigger, applied in the direction of pulse generation, electrical components, generating electrical pulses, etc., can solve problems such as affecting subsequent operations, adverse system work, system errors or crashes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Below in conjunction with accompanying drawing, invention is described in further detail.

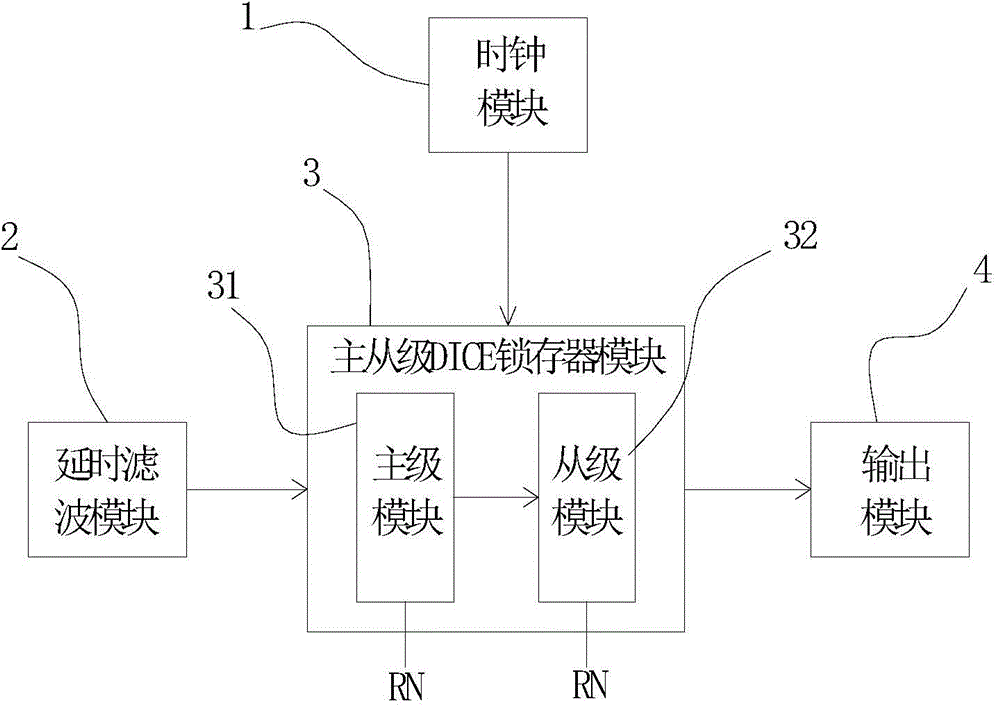

[0031] Such as figure 1 As shown, a D flip-flop with a reset terminal according to an embodiment of the present invention includes a clock module 1 , a delay filter module 2 , a master-slave DICE latch module 3 , and an output module 4 . The master-slave DICE latch module includes a master module 31 and a slave module 32 . Both the master and slave stages are reinforced with DICE, and a delay filter module 2 is added to the data end.

[0032] The clock signal output of the clock module 1 is connected to the clock signal input of the master-slave DICE latch module 3, the data input of the delay filter module 2 is connected to the data source, and the data output is connected to the master-slave DICE latch The data input end of the module 3 is connected, and the data output end of the master-slave DICE latch module 3 is connected to the signal input end of the output module 4 . ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com