Memory with single-event latchup prevention circuitry

A technology of single-event locking and memory cells, which is applied in the field of integrated circuits and integrated circuit memory components, and can solve problems such as damaging devices and circuit failures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

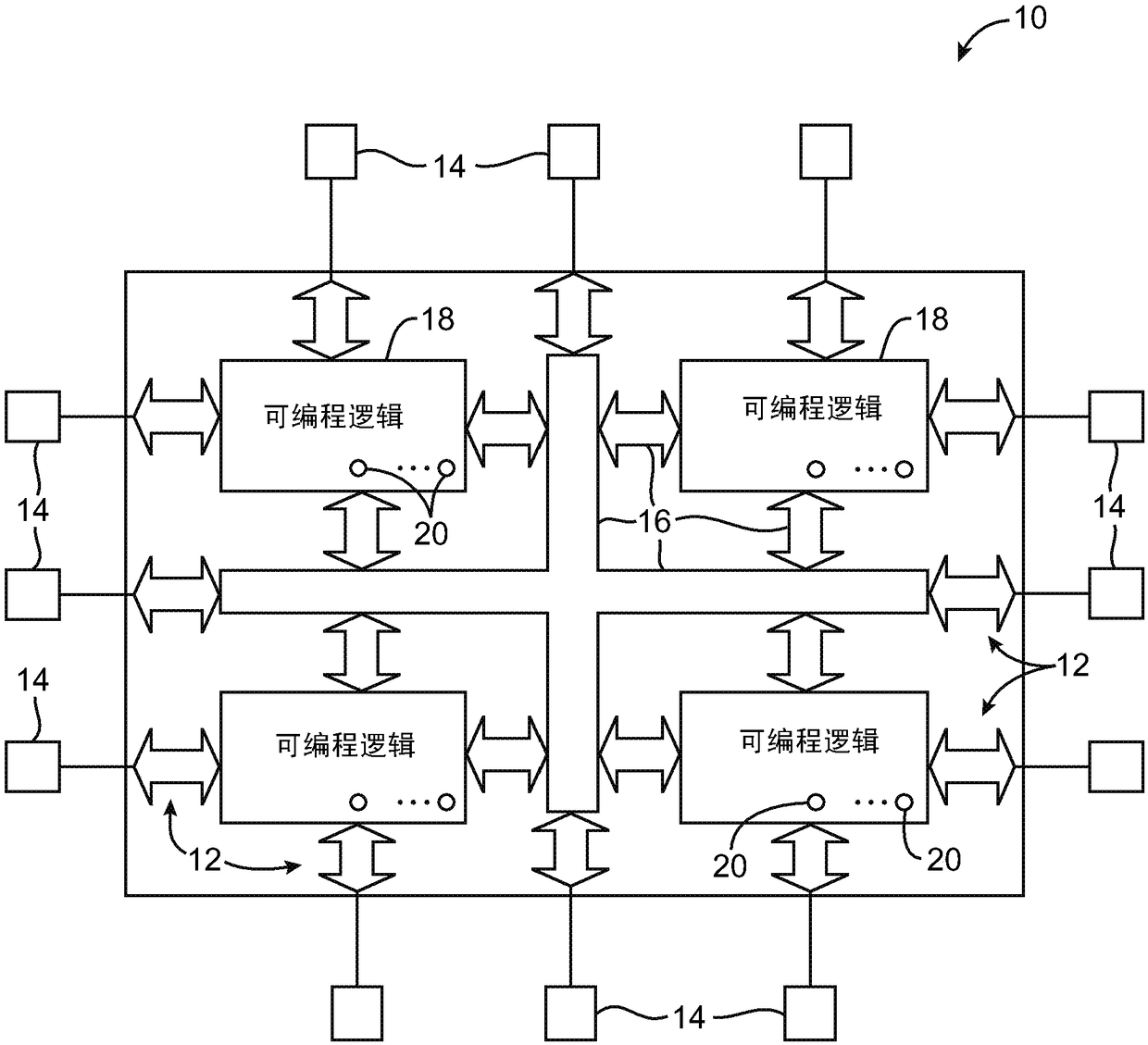

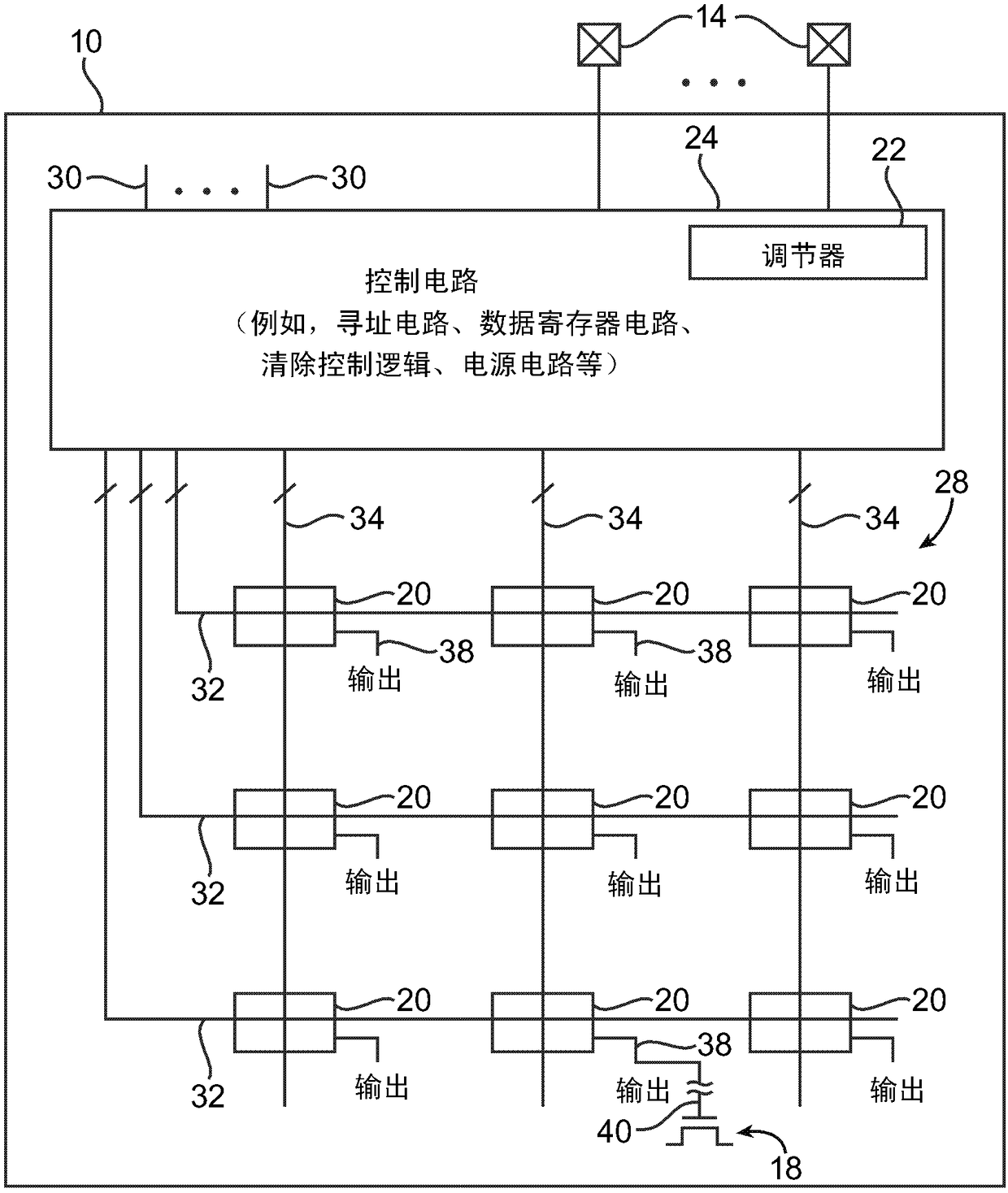

[0020] Embodiments of the invention relate to integrated circuit memory elements that may be subject to single event lock-up (SEL). According to an embodiment, an SEL prevention circuit is provided that detects a lock signal using a sense amplifier. In response to detecting the lockout signal, drivers in the SEL prevention circuit can then force the n-well within the memory element into a deep reverse biased region to temporarily turn off any parasitic components that may have turned on during single event lockup. In another suitable arrangement, the n-well of the memory element may be constantly biased to an elevated voltage level to permanently turn off the parasitic components to completely eliminate latch-up.

[0021] It will be appreciated by those skilled in the art that the present exemplary embodiment may be practiced without some or all of these specific details. In other instances, well known operations have not been described in detail in order not to unnecessarily...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com