Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38 results about "Single-ended signaling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

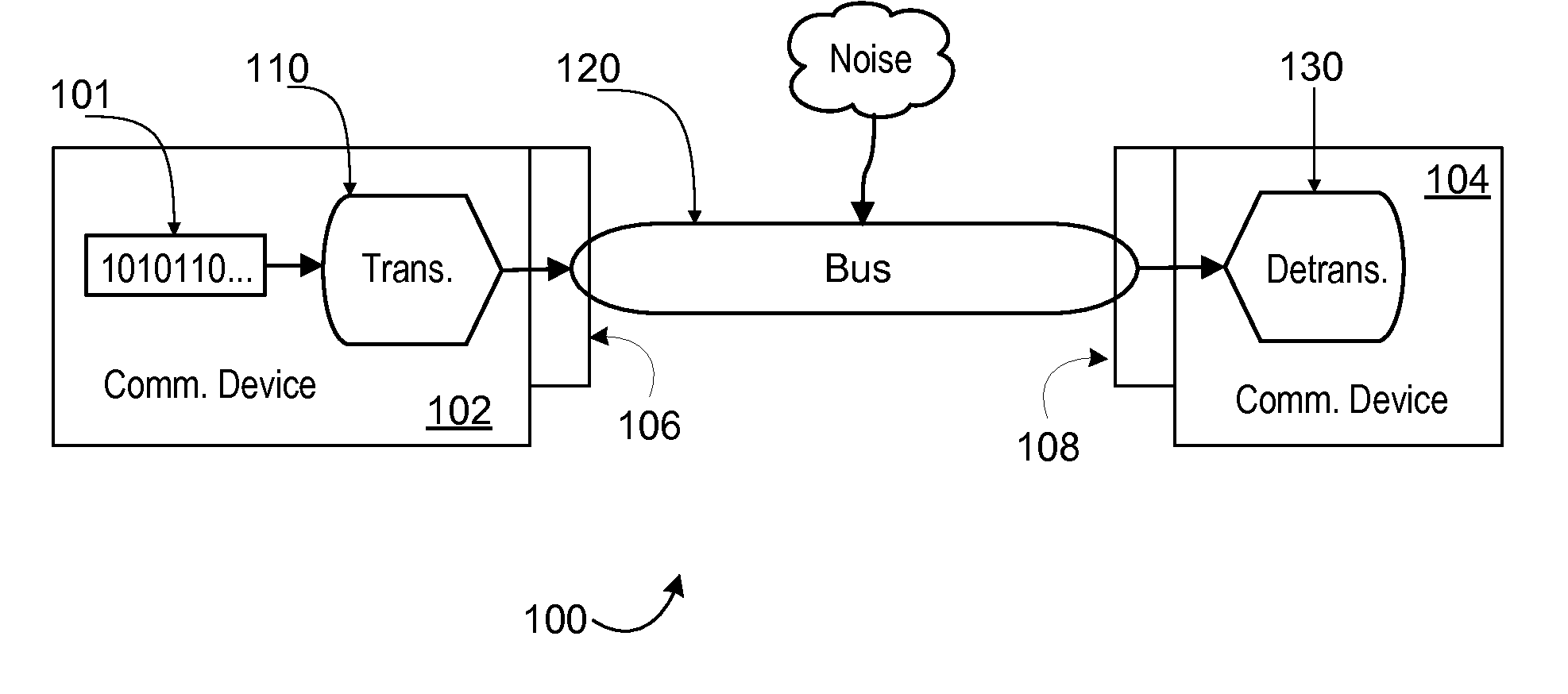

Single-ended signaling is the simplest and most commonly used method of transmitting electrical signals over wires. One wire carries a varying voltage that represents the signal, while the other wire is connected to a reference voltage, usually ground.

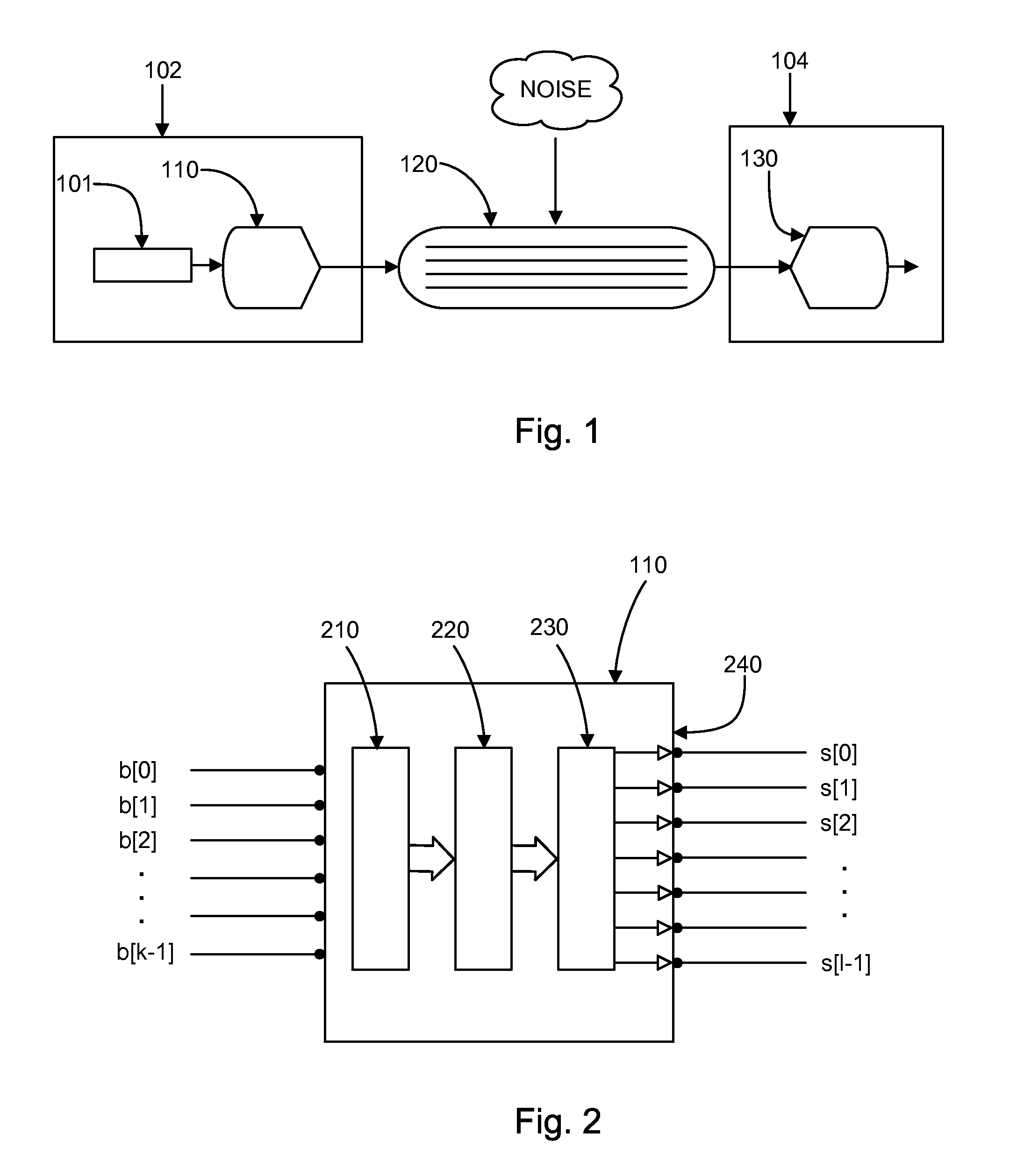

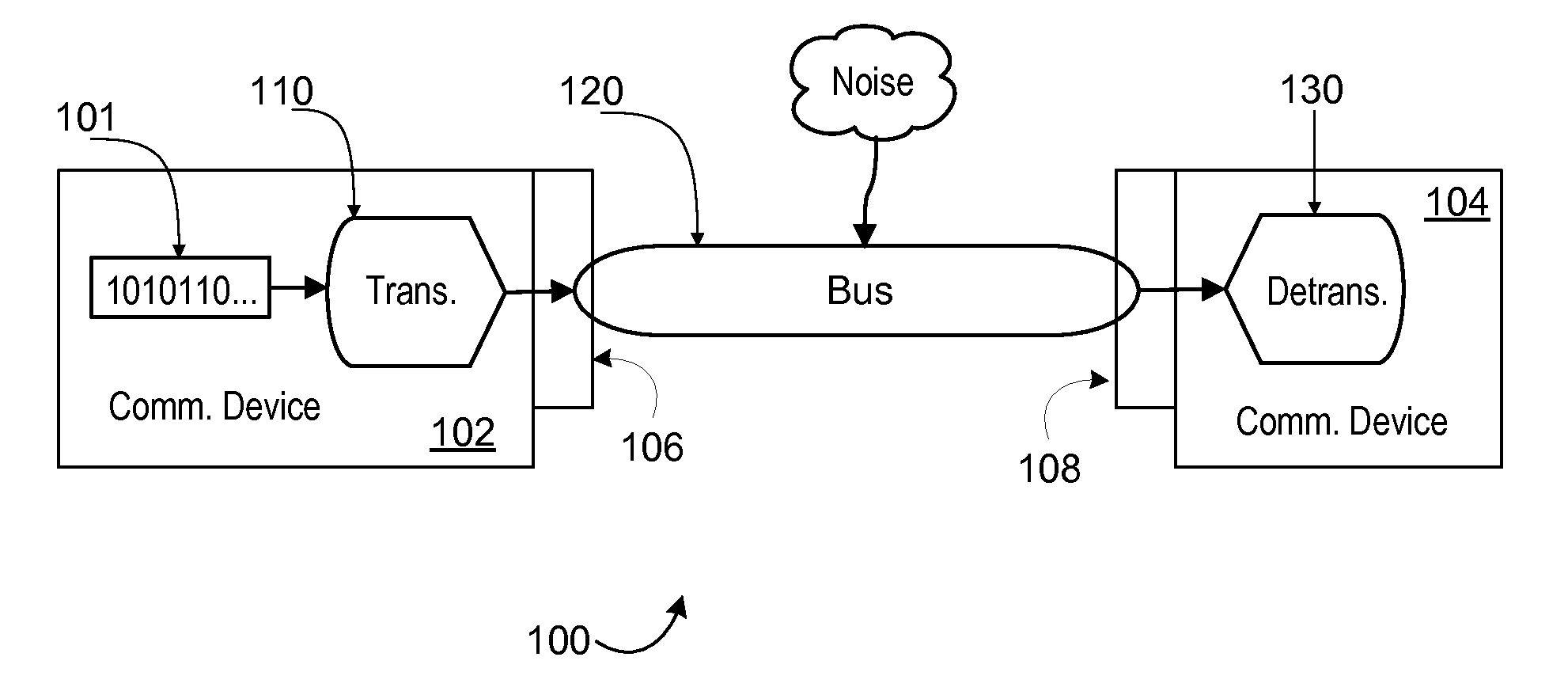

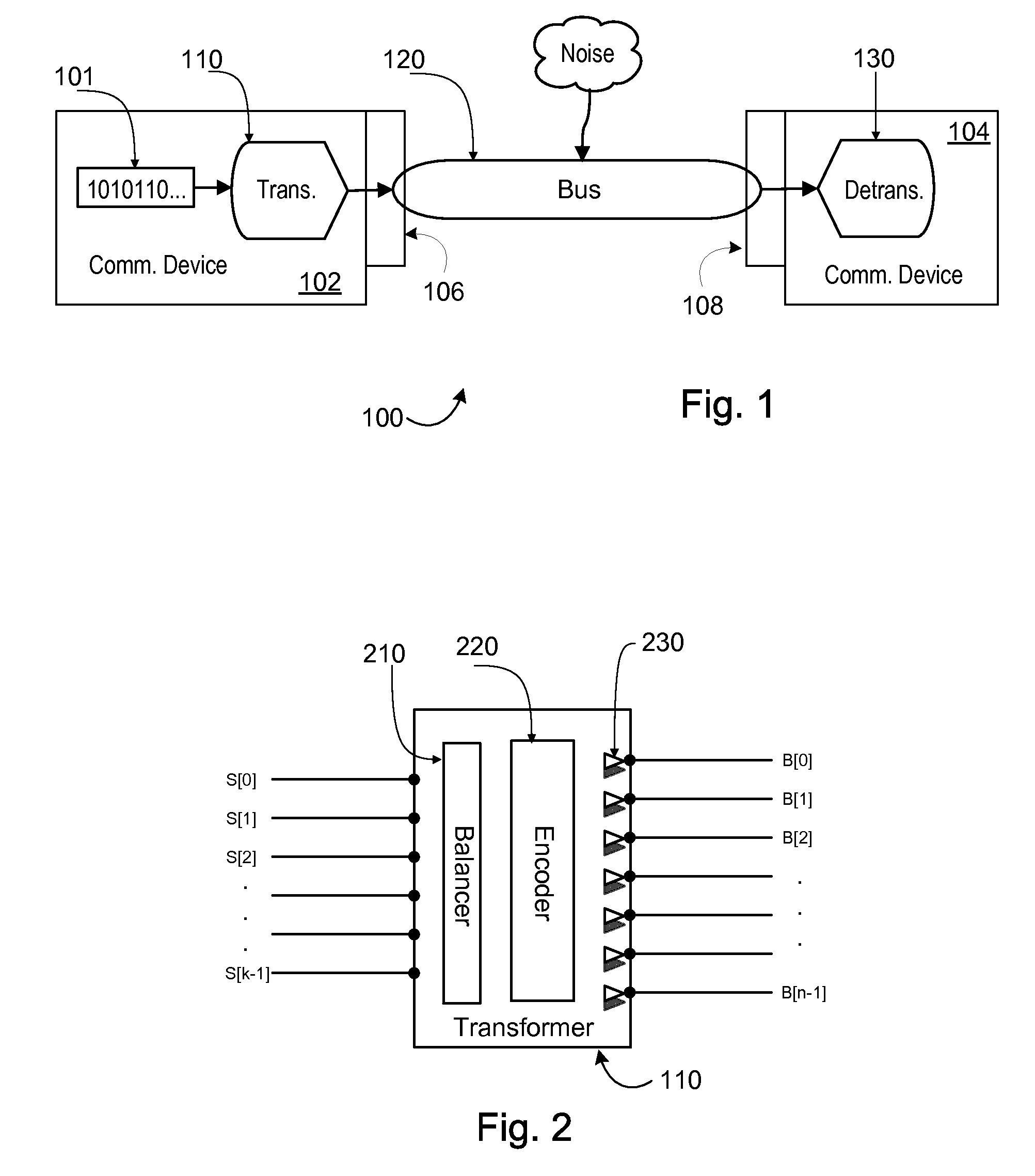

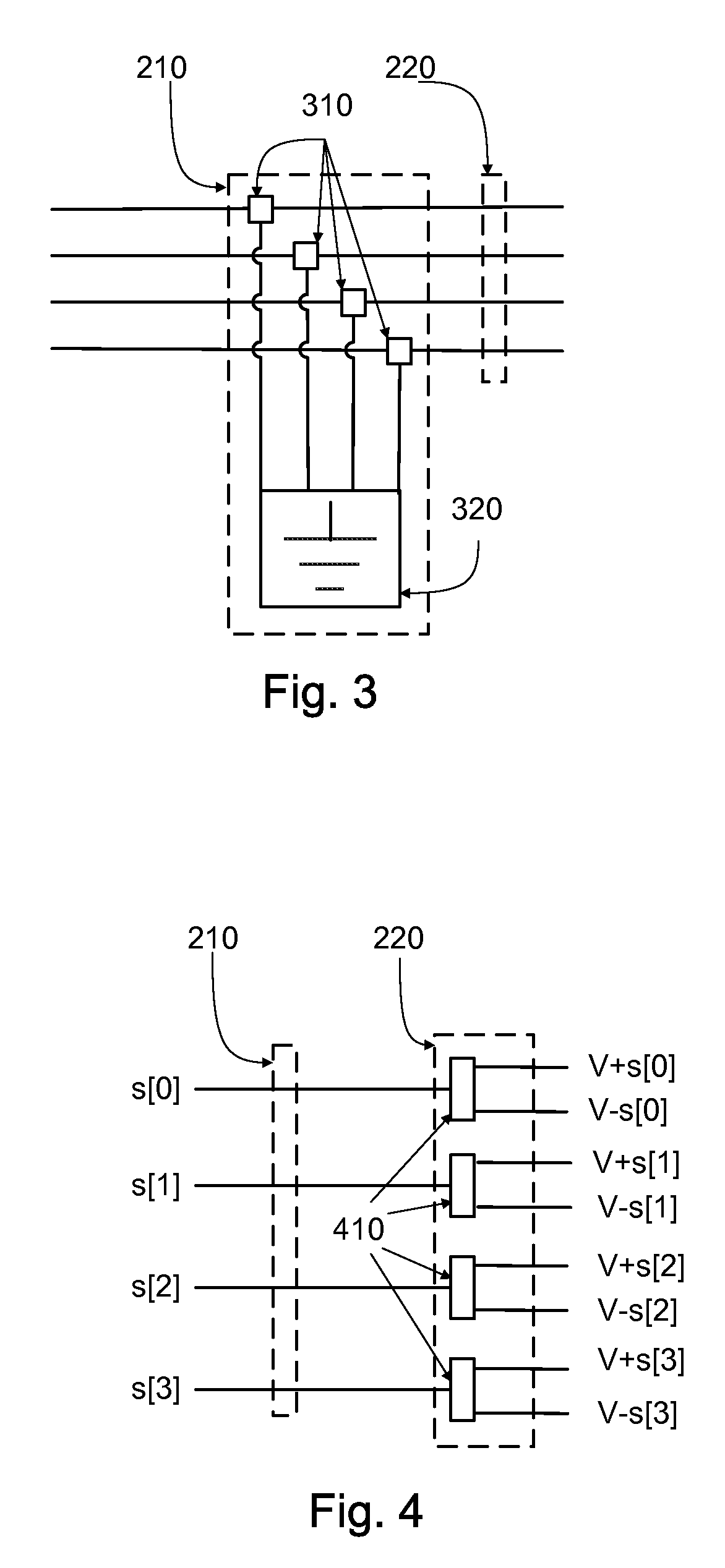

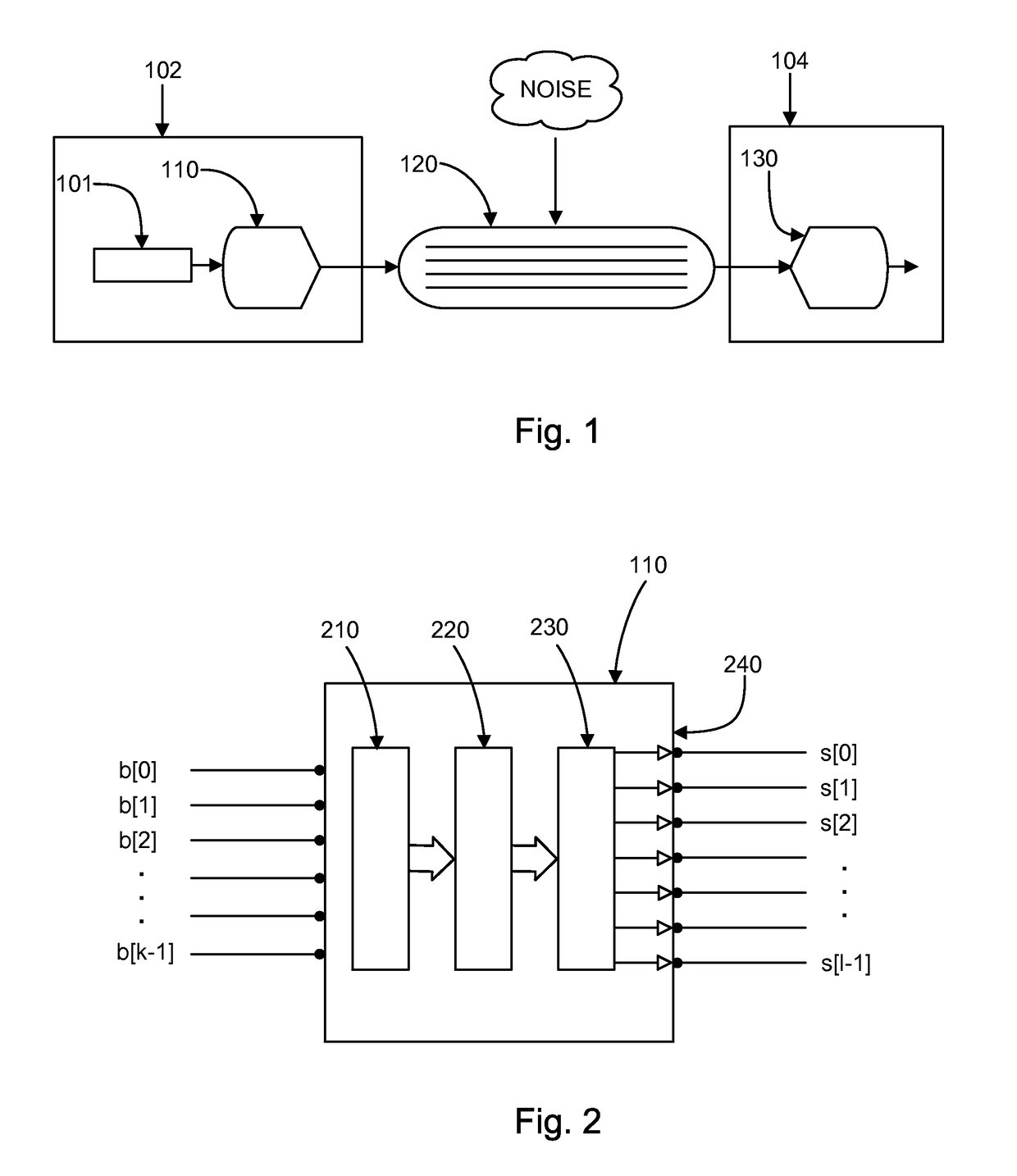

Orthogonal differential vector signaling

ActiveUS20110268225A1Enhanced signalImprove the immunityTransmission path divisionSecret communicationPhysical spaceTransformer

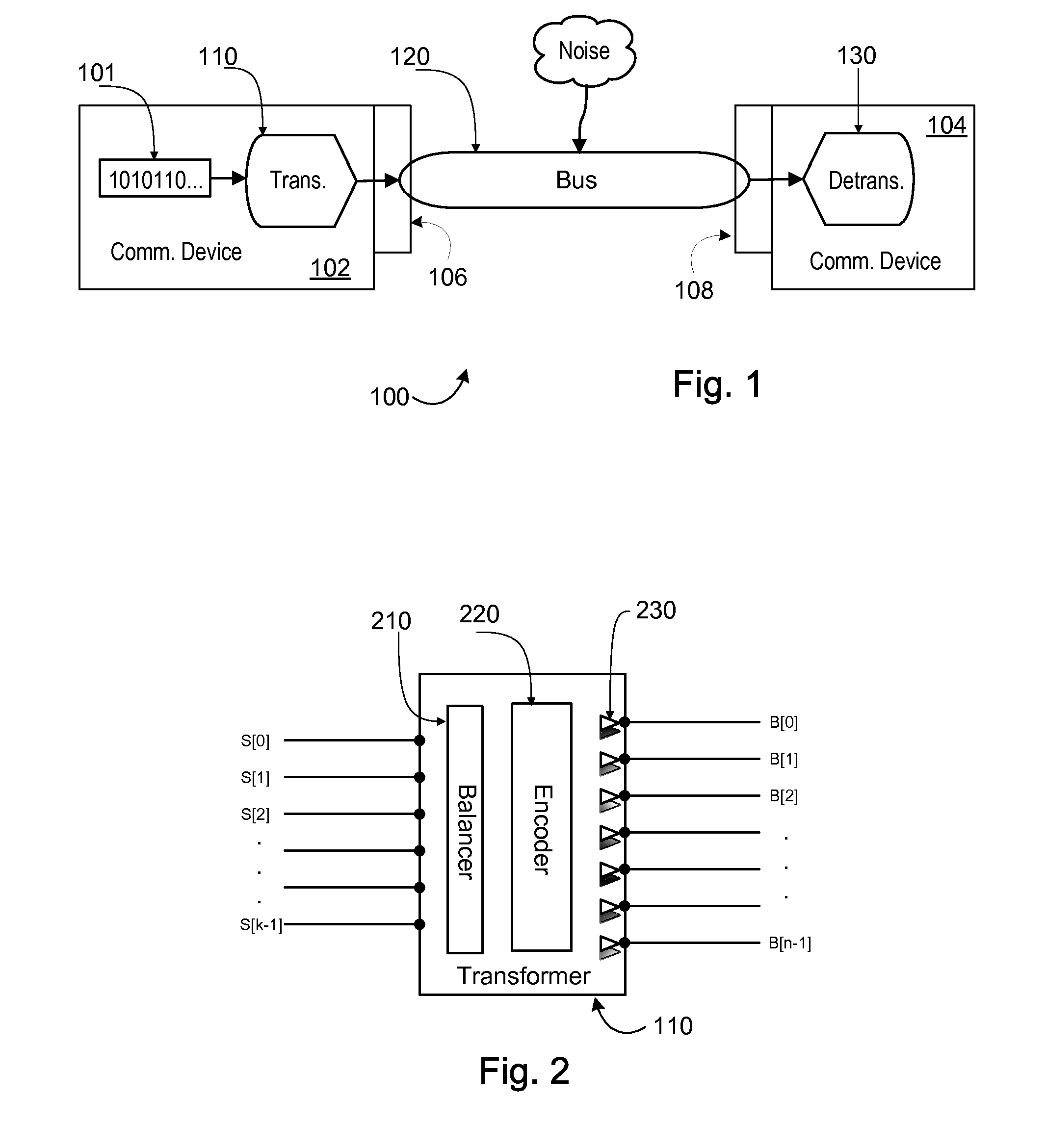

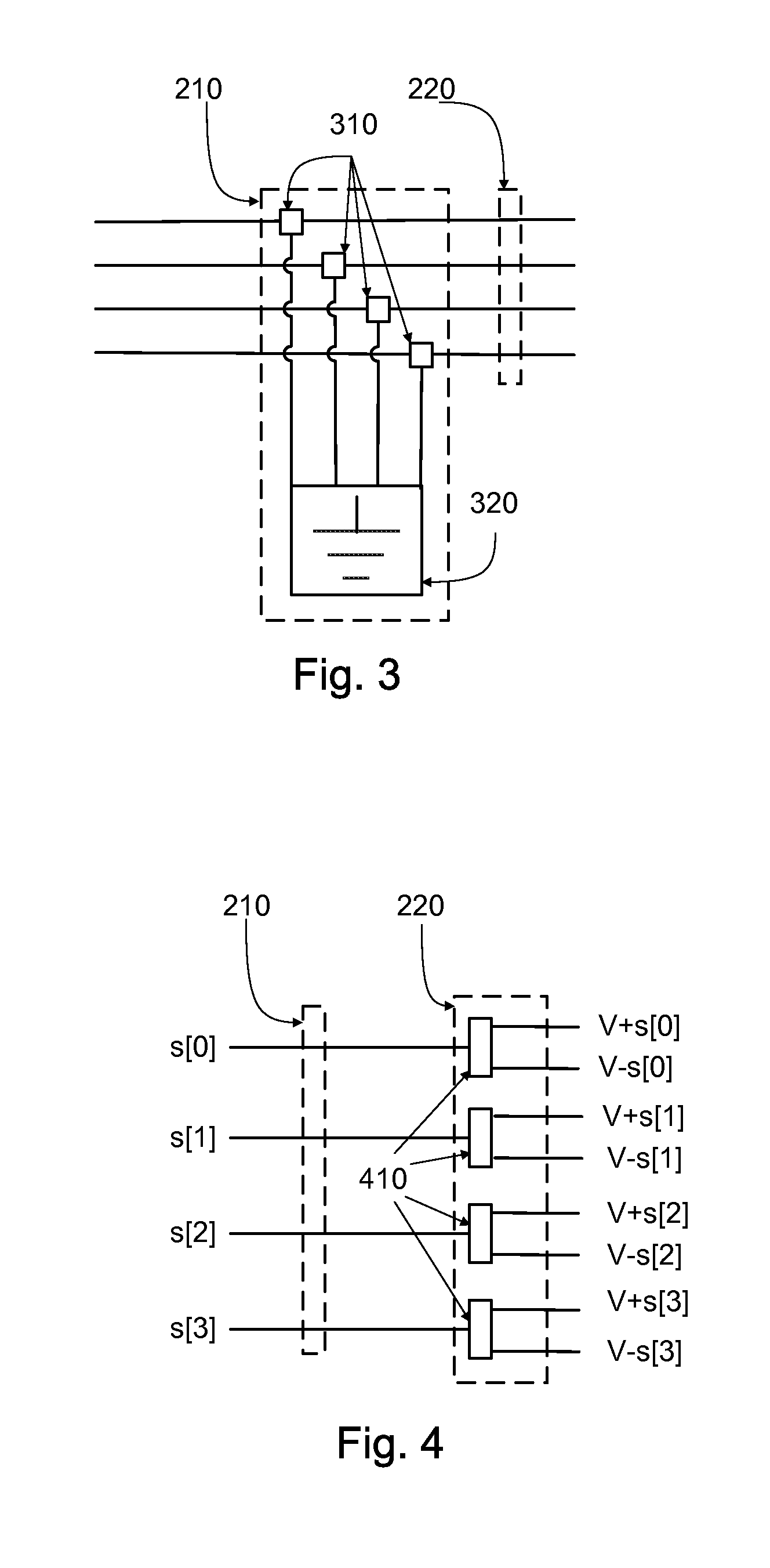

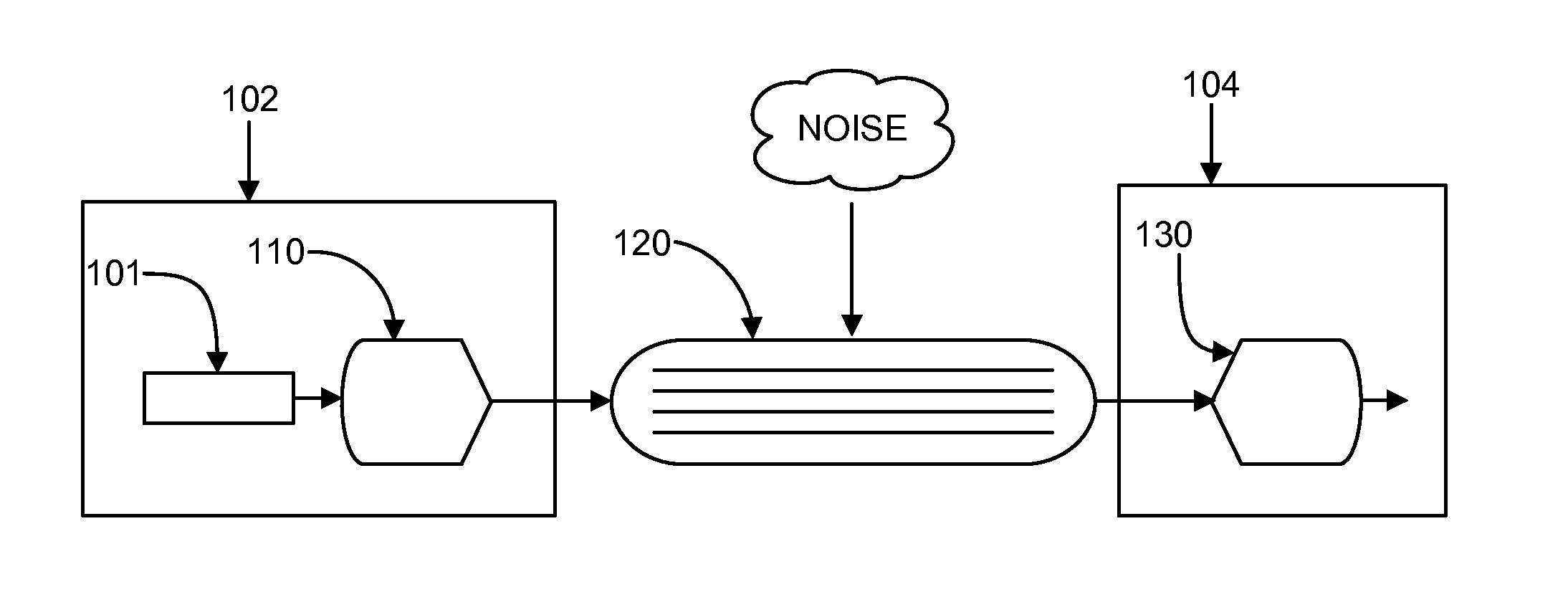

Using a transformation based at least in part on a non-simple orthogonal or unitary matrix, data may be transmitted over a data bus in a manner that is resilient to one or more types of signal noise, that does not require a common reference at the transmission and acquisition points, and / or that has a pin-efficiency that is greater than 50% and may approach that of single-ended signaling. Such transformations may be implemented in hardware in an efficient manner. Hybrid transformers that apply such transformations to selected subsets of signals to be transmitted may be used to adapt to various signal set sizes and / or transmission environment properties including noise and physical space requirements of given transmission environments.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

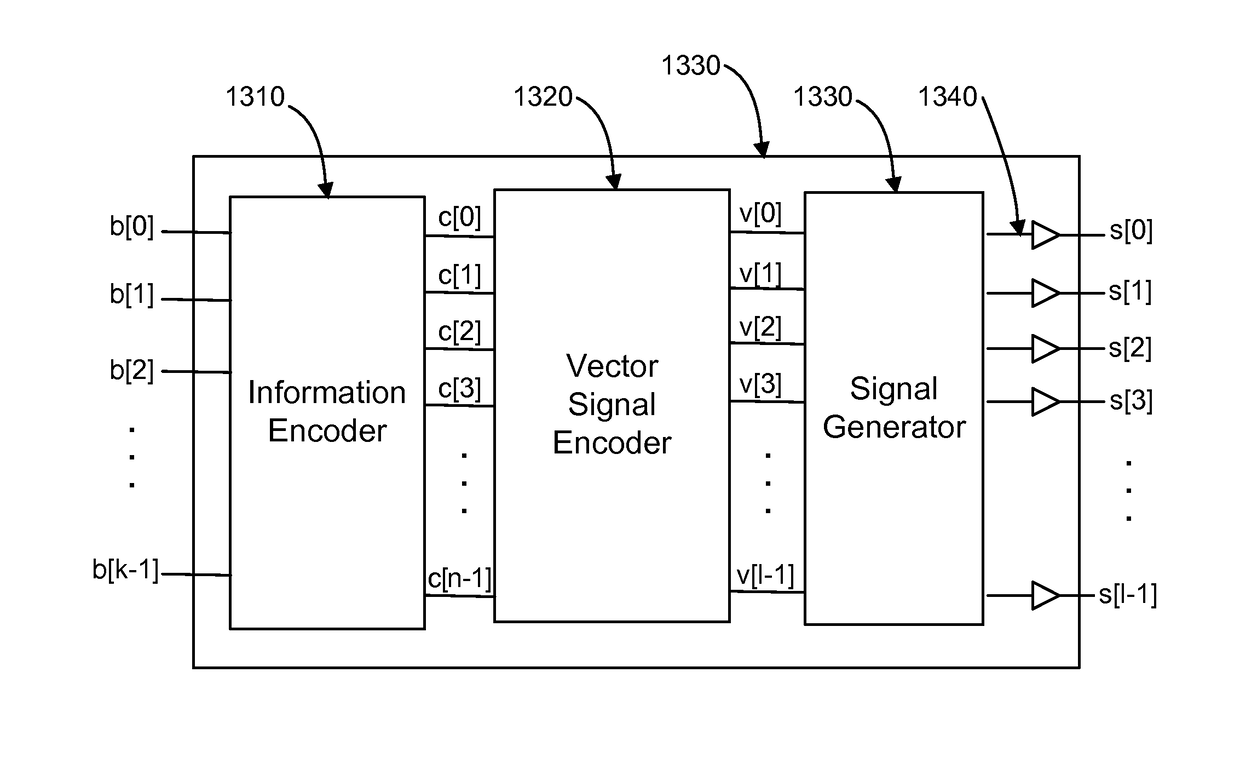

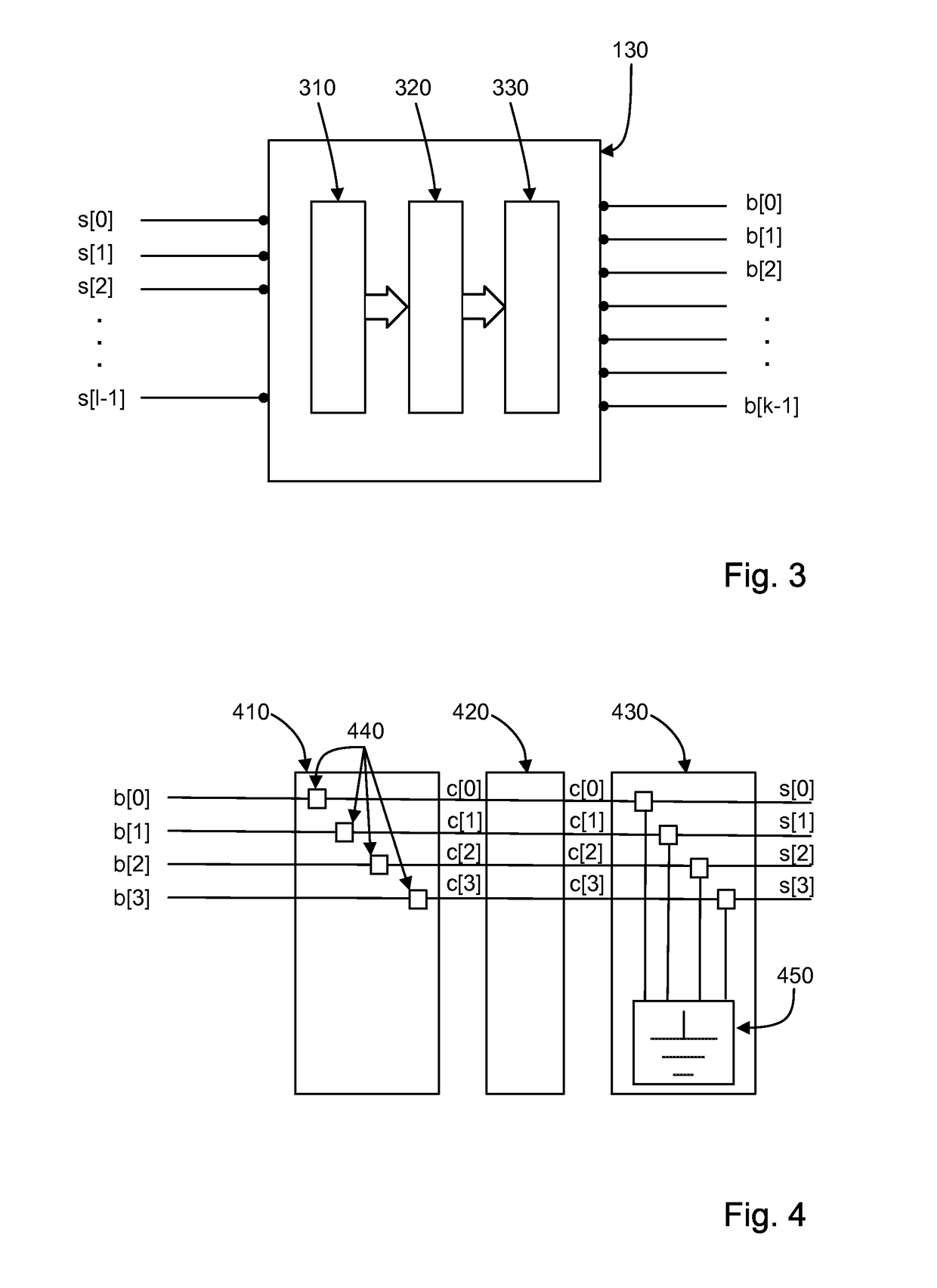

Error control coding for orthogonal differential vector signaling

ActiveUS20110299555A1Error preventionTime-division multiplexForward error correctionComputer science

Using a transformation based, at least in part, on a non-simple orthogonal matrix, data may be transmitted over a data bus in a manner that is resilient to one or more types of signal noise, that does not require a common reference at the transmission and acquisition points, and / or that has a pin-efficiency that is greater than 50% and may approach that of single-ended signaling. Such transformations may be implemented in hardware in an efficient manner. The transformation may be combined with methods from forward error correction to lower the required transmission power.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

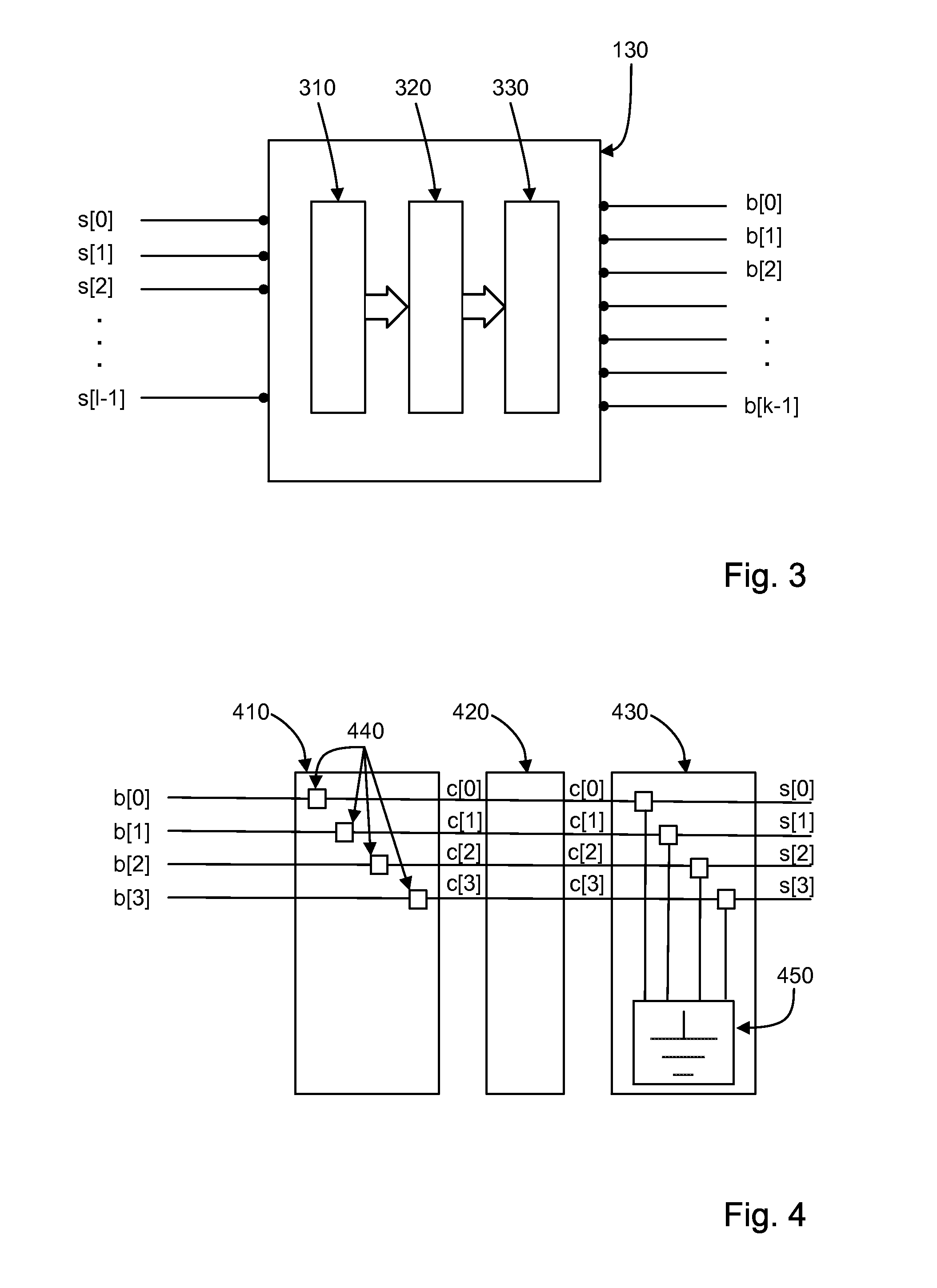

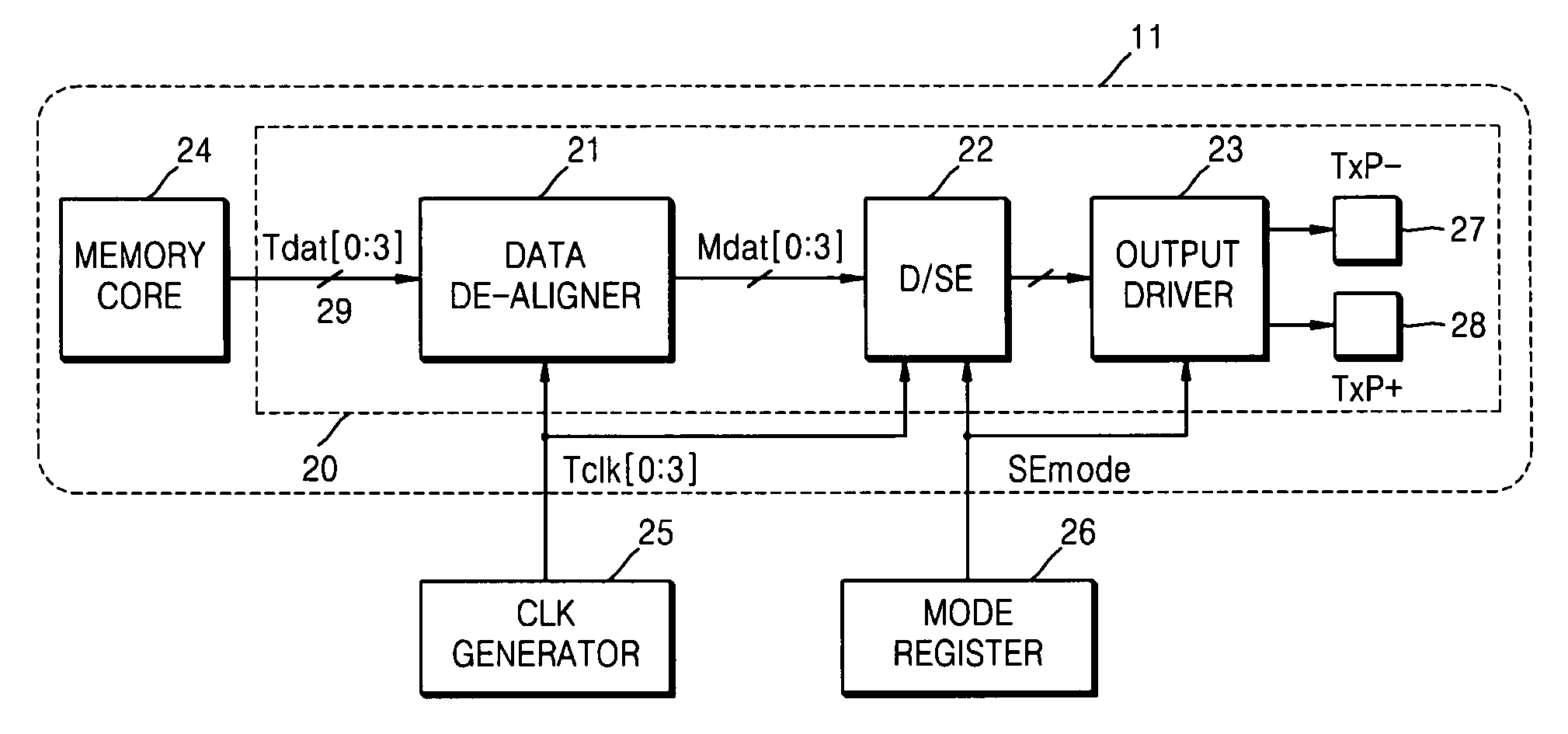

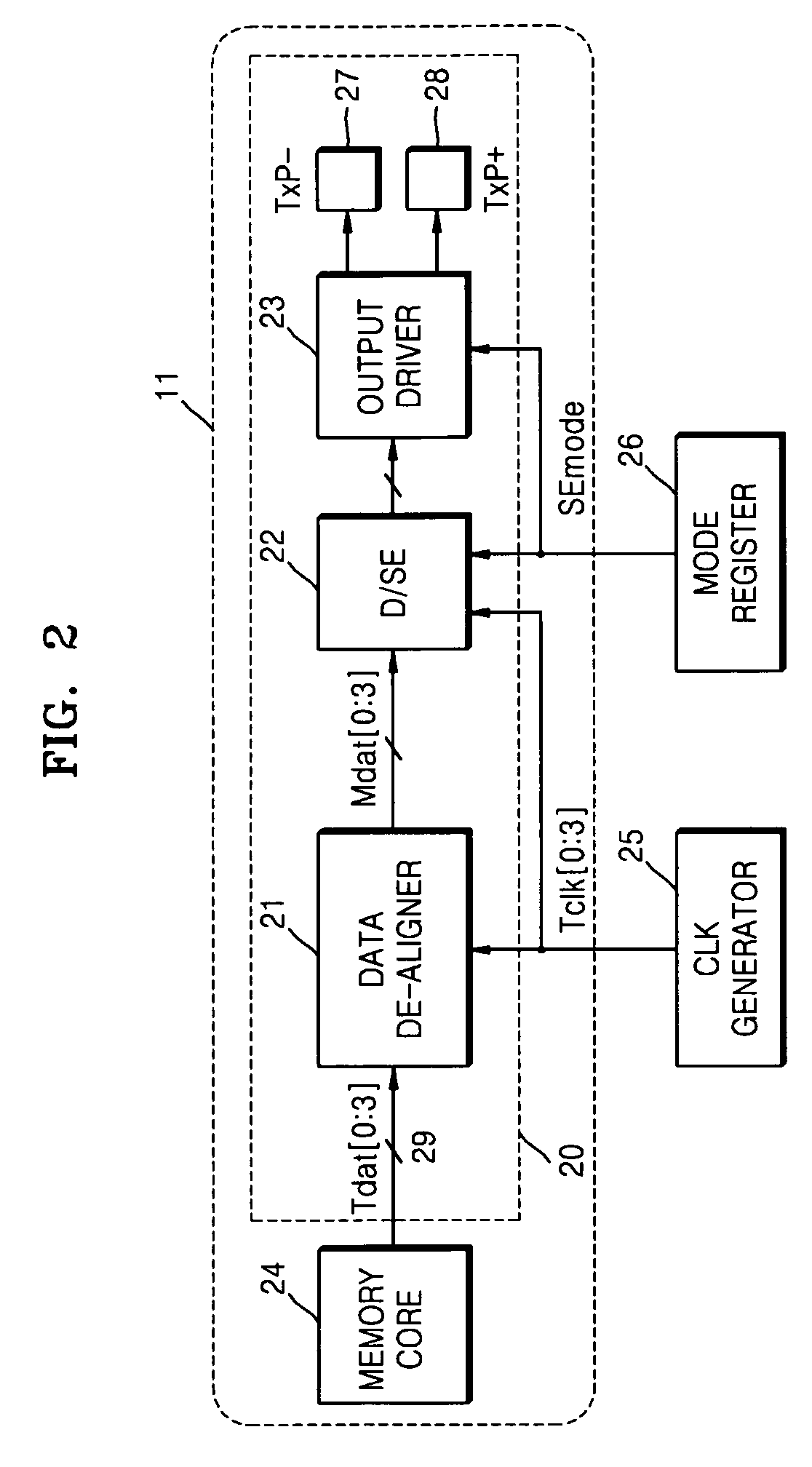

System and method for selectively performing single-ended and differential signaling

In a communication system, data is selectively transmitted using single-ended or differential signaling. The data is transmitted in relation to a plurality of clock signals having different relative phases. When the data is transmitted using single-ended signaling, data on adjacent signal lines undergo logic transitions at different times in relation to the plurality of clock signals.

Owner:SAMSUNG ELECTRONICS CO LTD

Orthogonal differential vector signaling

ActiveUS9288089B2Increase valueImprove energy consumptionBaseband system detailsTransmission path divisionPhysical spaceAlgorithm

Using a transformation based at least in part on a non-simple orthogonal or unitary matrix, data may be transmitted over a data bus in a manner that is resilient to one or more types of signal noise, that does not require a common reference at the transmission and acquisition points, and / or that has a pin-efficiency that is greater than 50% and may approach that of single-ended signaling. Such transformations may be implemented in hardware in an efficient manner. Hybrid transformers that apply such transformations to selected subsets of signals to be transmitted may be used to adapt to various signal set sizes and / or transmission environment properties including noise and physical space requirements of given transmission environments.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

Error control coding for orthogonal differential vector signaling

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

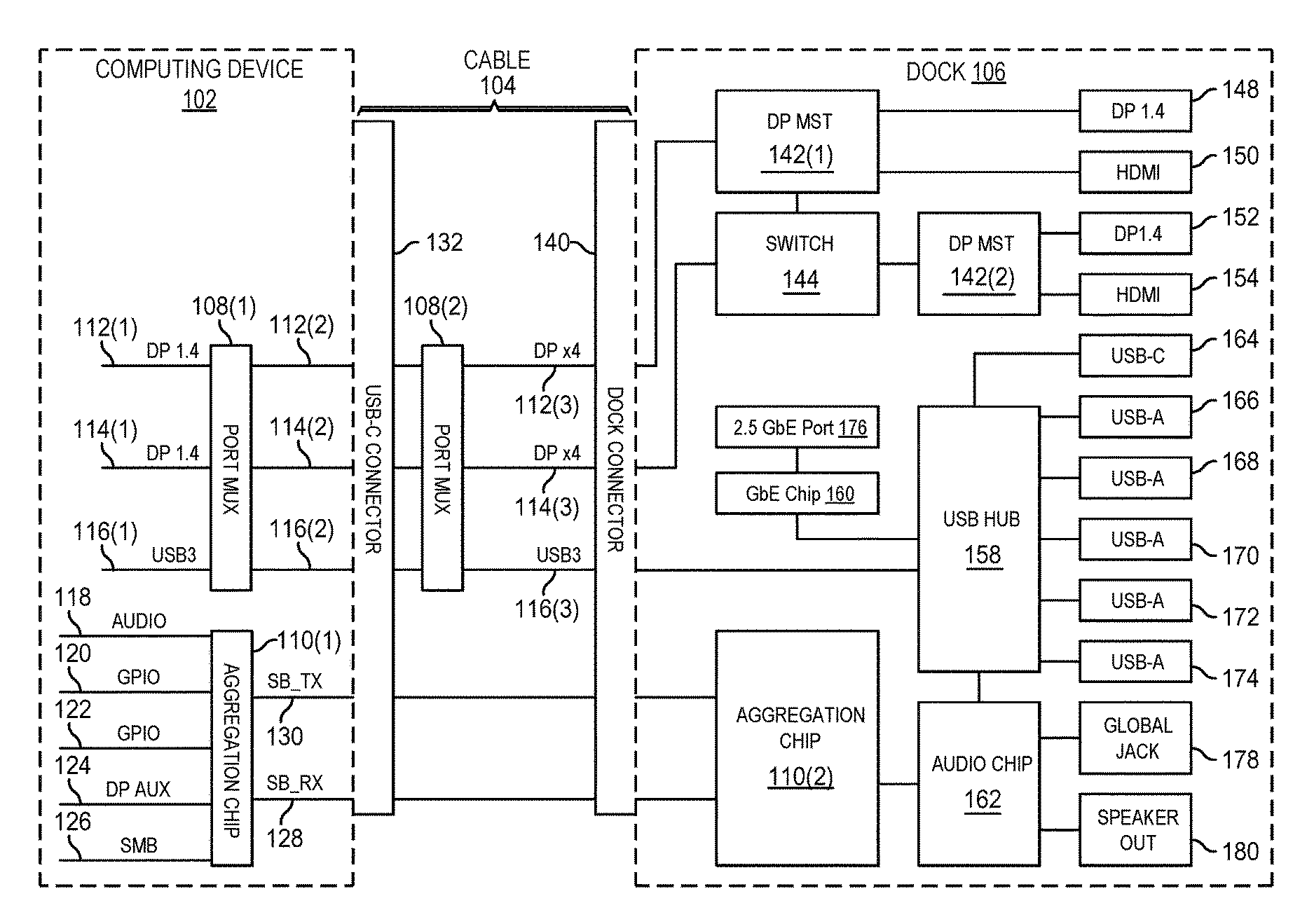

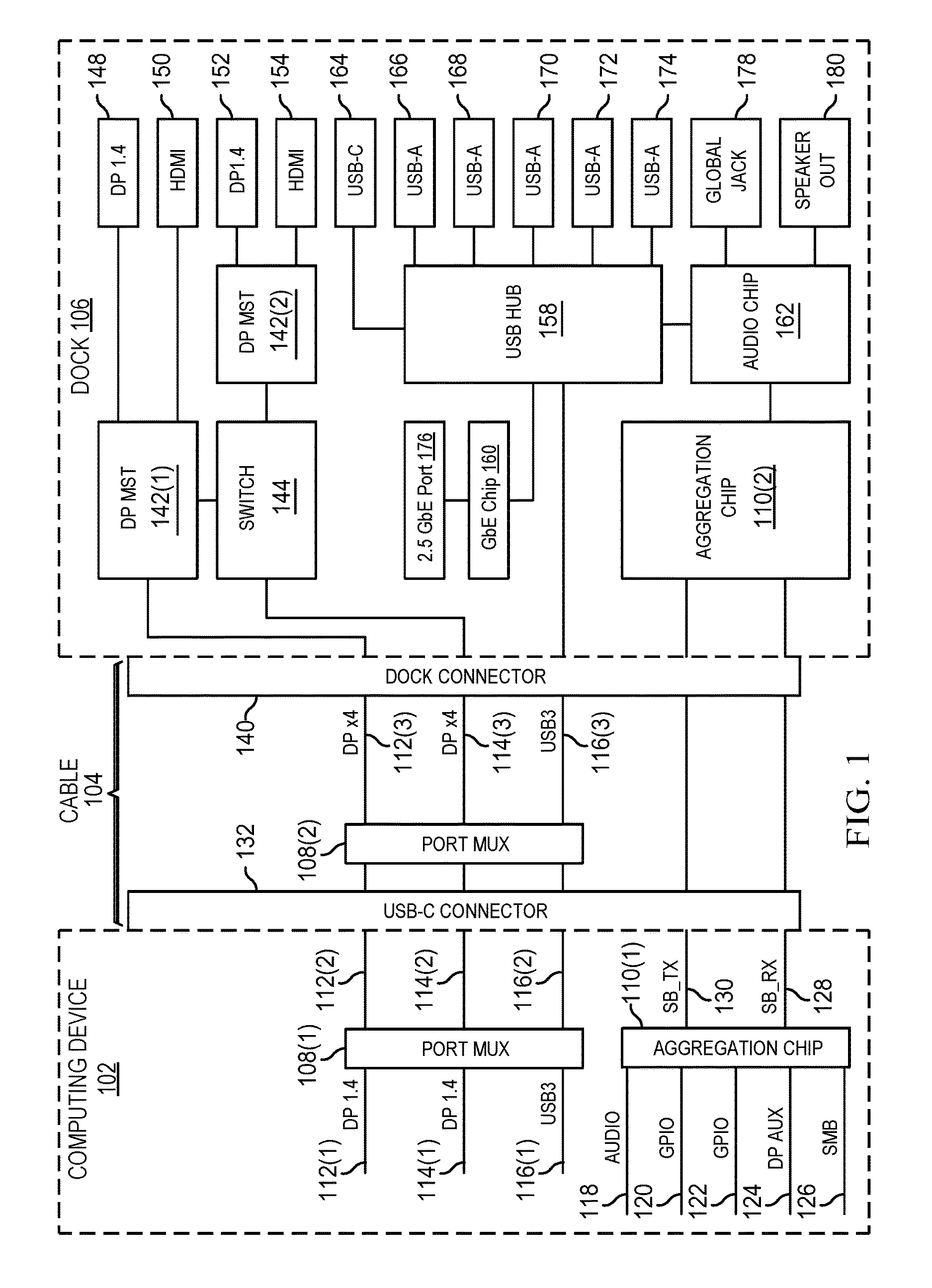

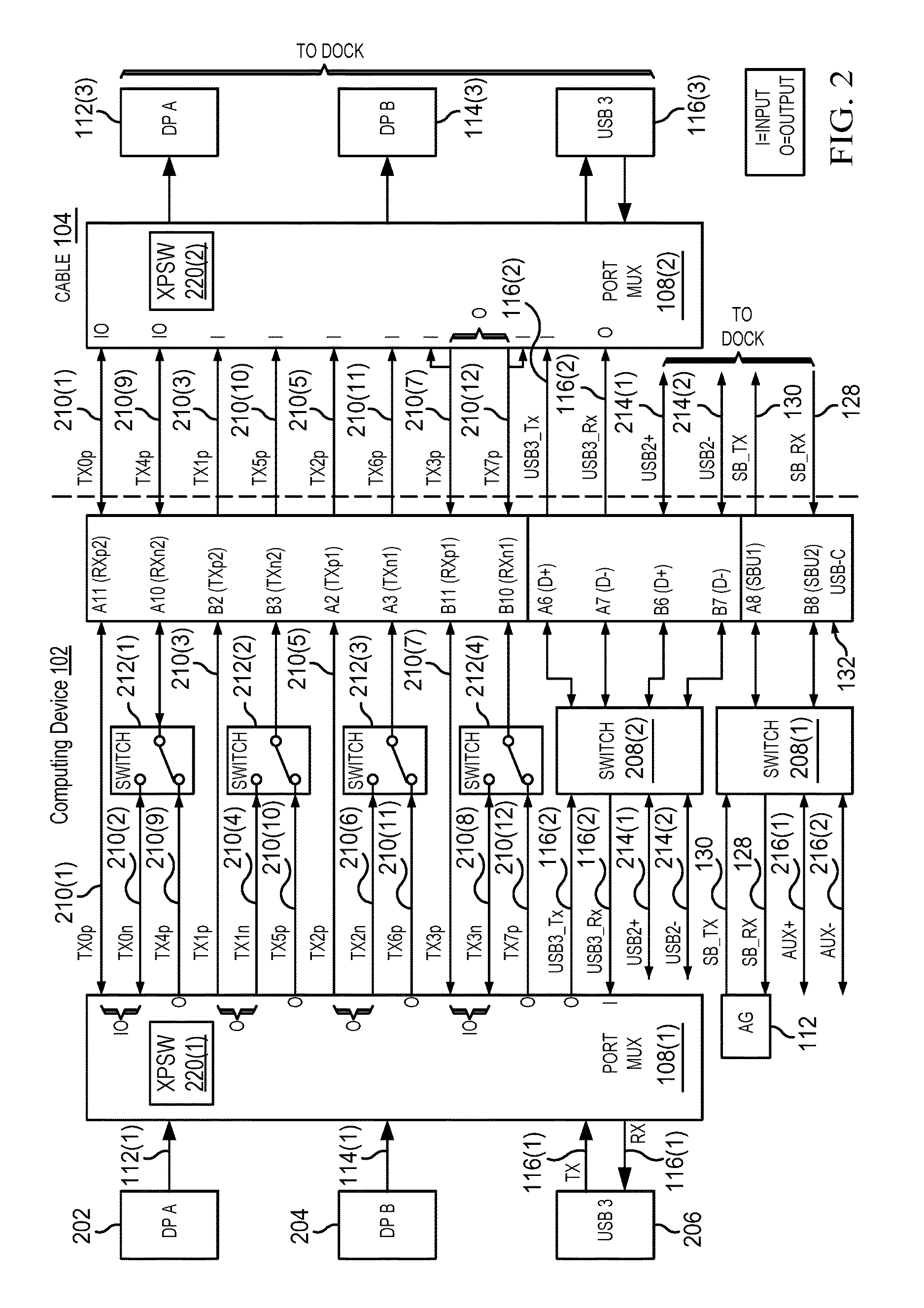

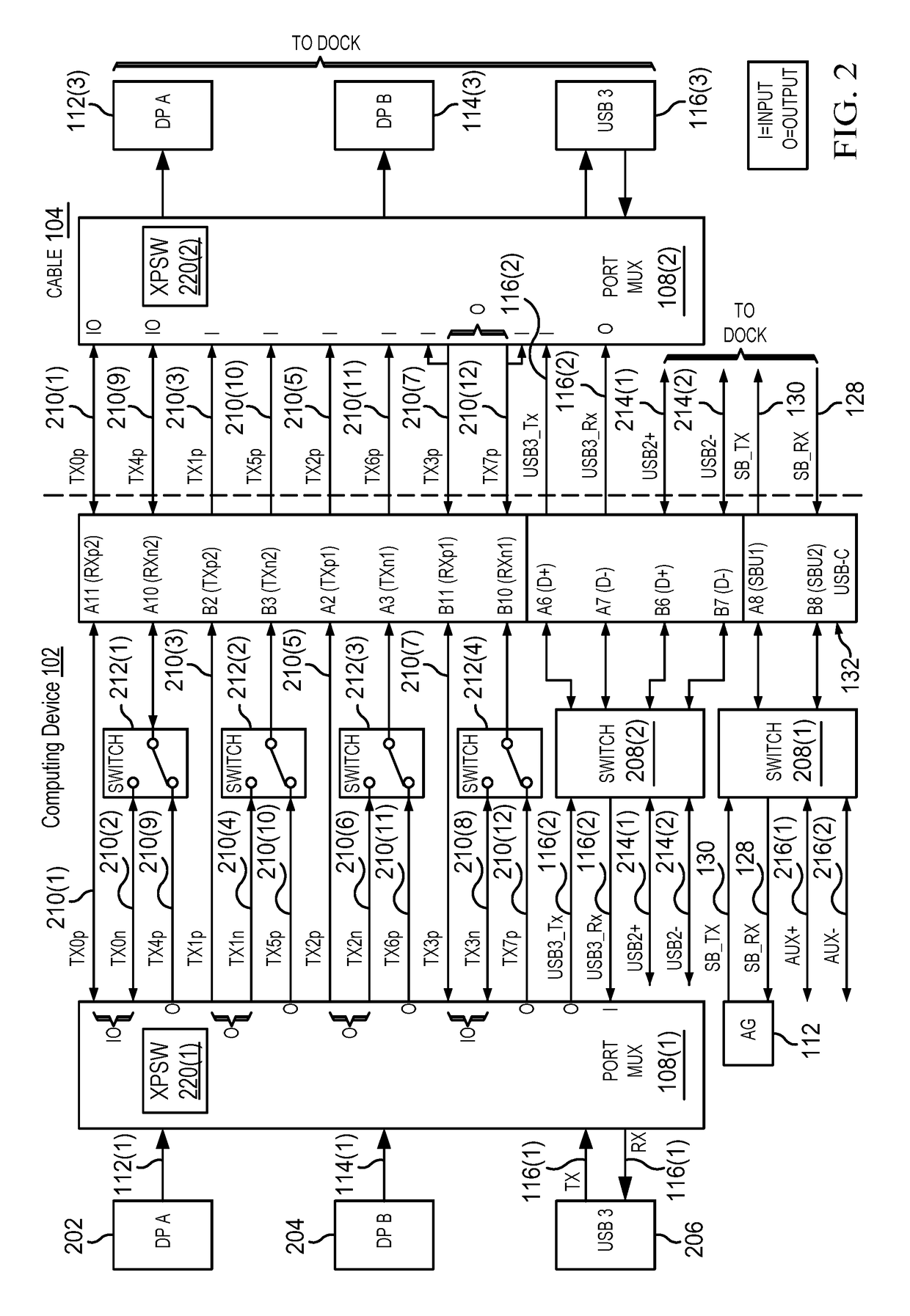

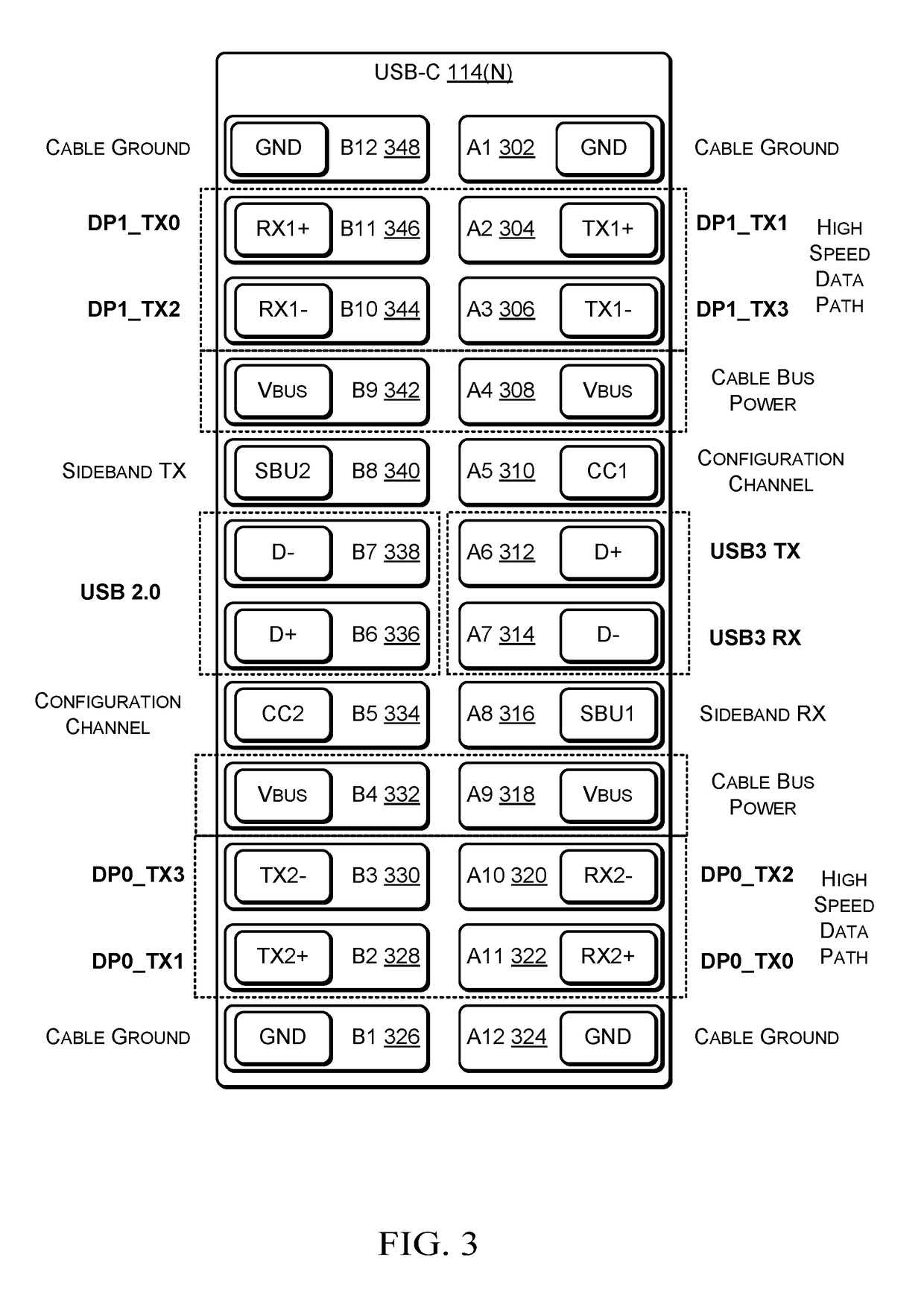

Increasing data throughput of a universal serial bus (USB) type-c port

A computing device may include a universal serial bus (USB) port, a port controller, and a first port multiplexer. The port controller may determine that a connector of a cable has been connected to the port of the computing device and determine that the cable includes a second port multiplexer. The port controller may send a first instruction to the first port multiplexer to select a single-ended signaling configuration and send a second instruction to the second port multiplexer to select the single-ended signaling configuration. In the single-ended configuration, the first port multiplexer may receive a set of differential signals, convert the set of differential signals to a corresponding set of single-ended signals, and output the set of single-ended signals to the port.

Owner:DELL PROD LP

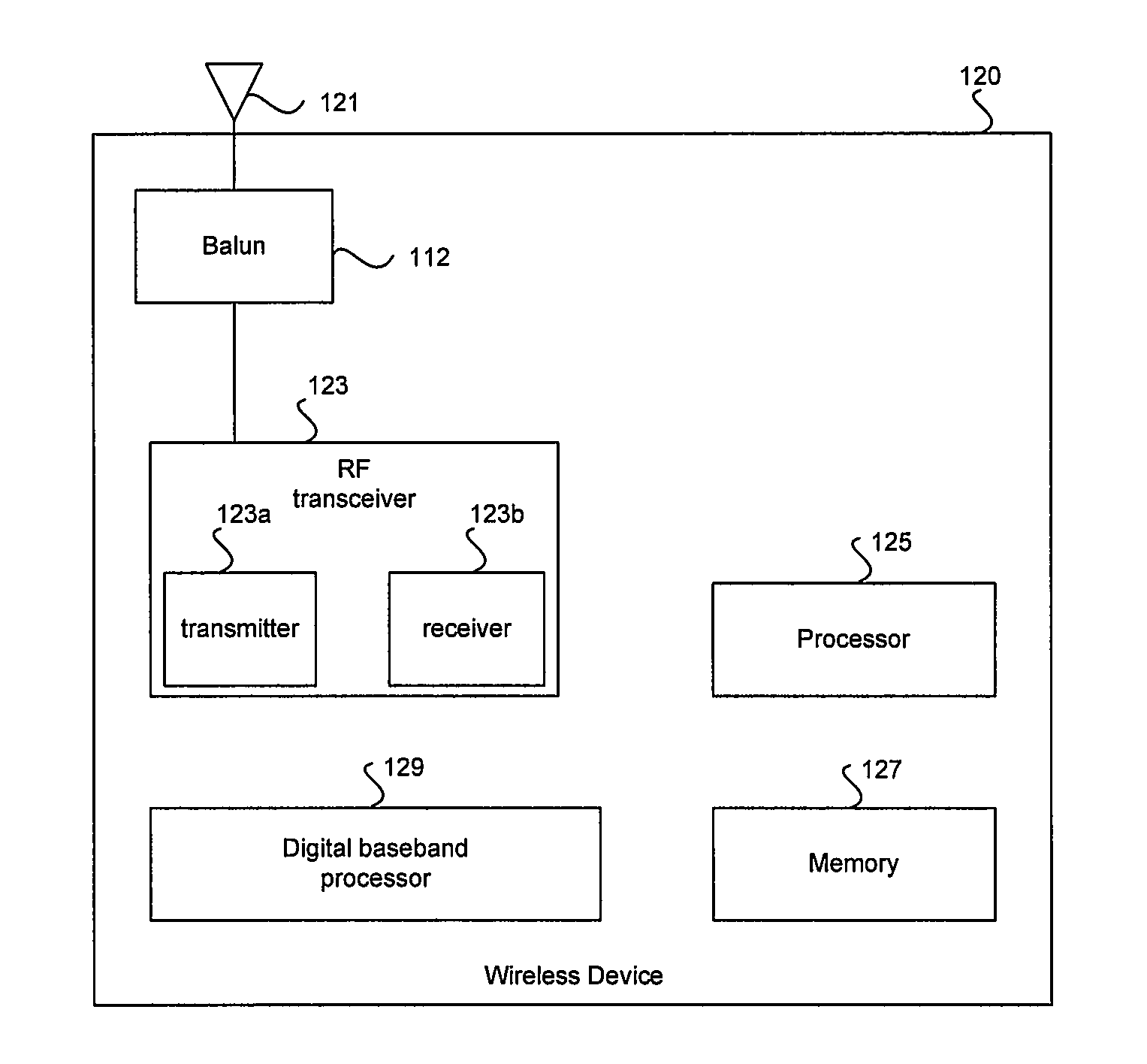

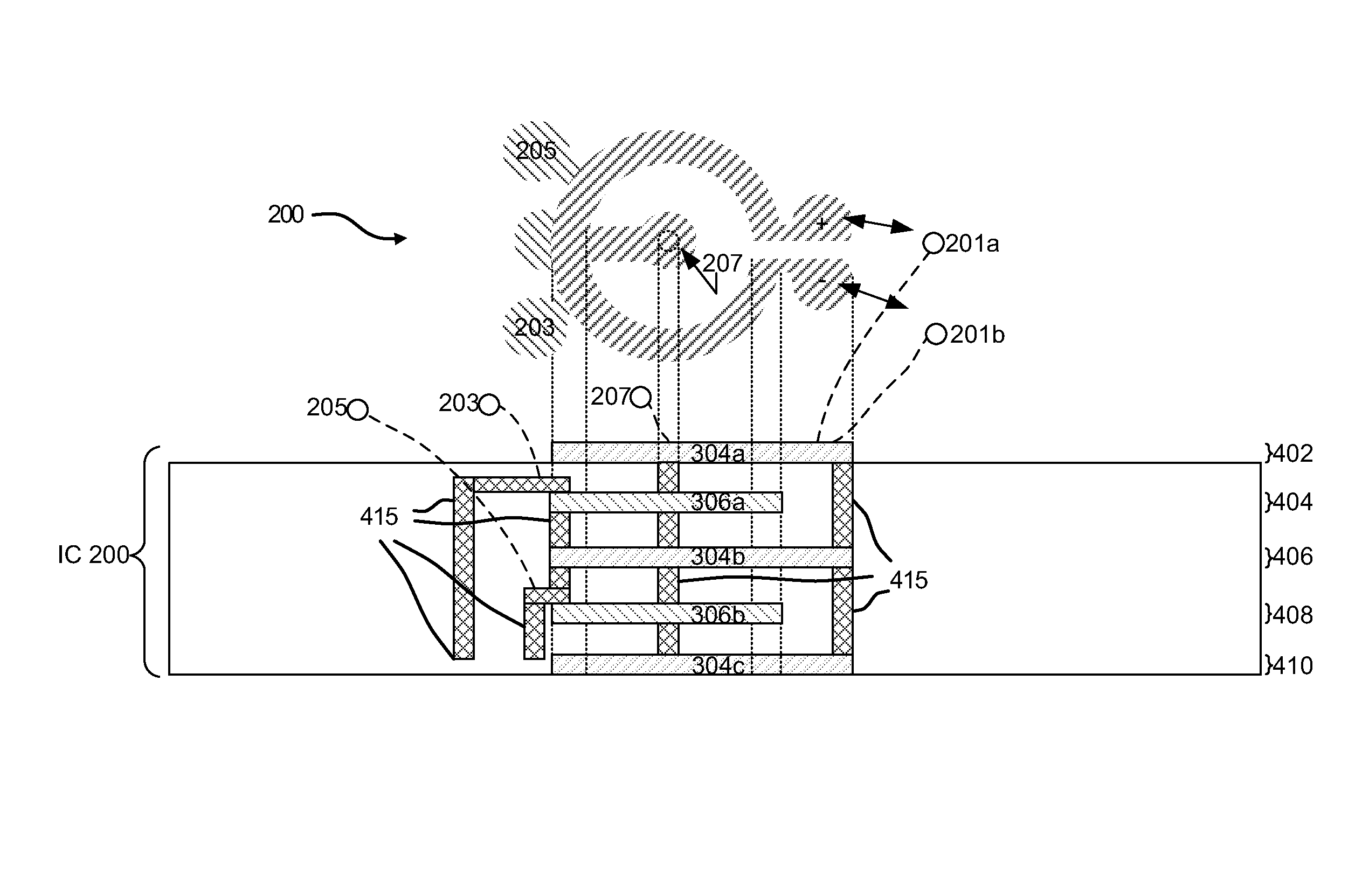

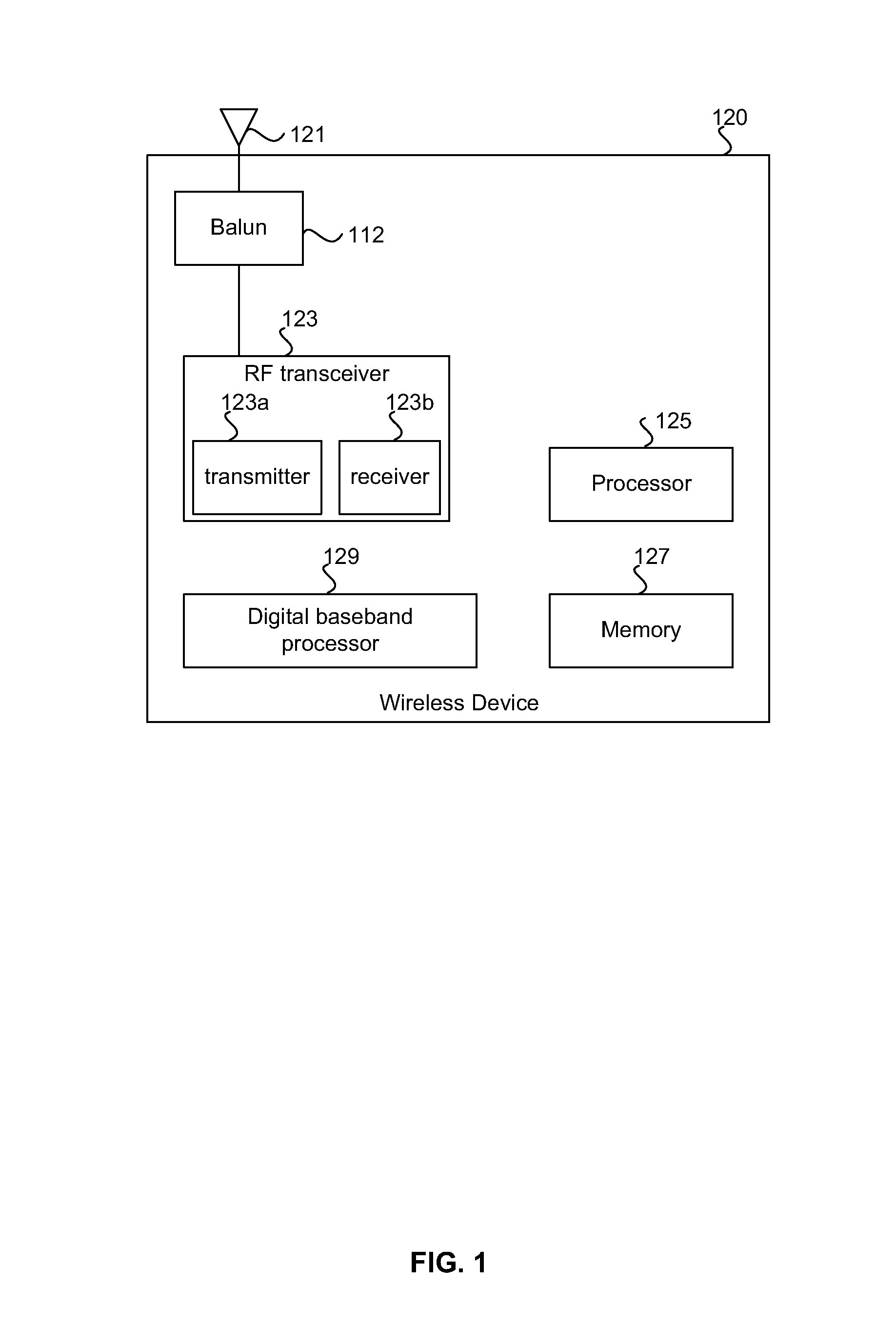

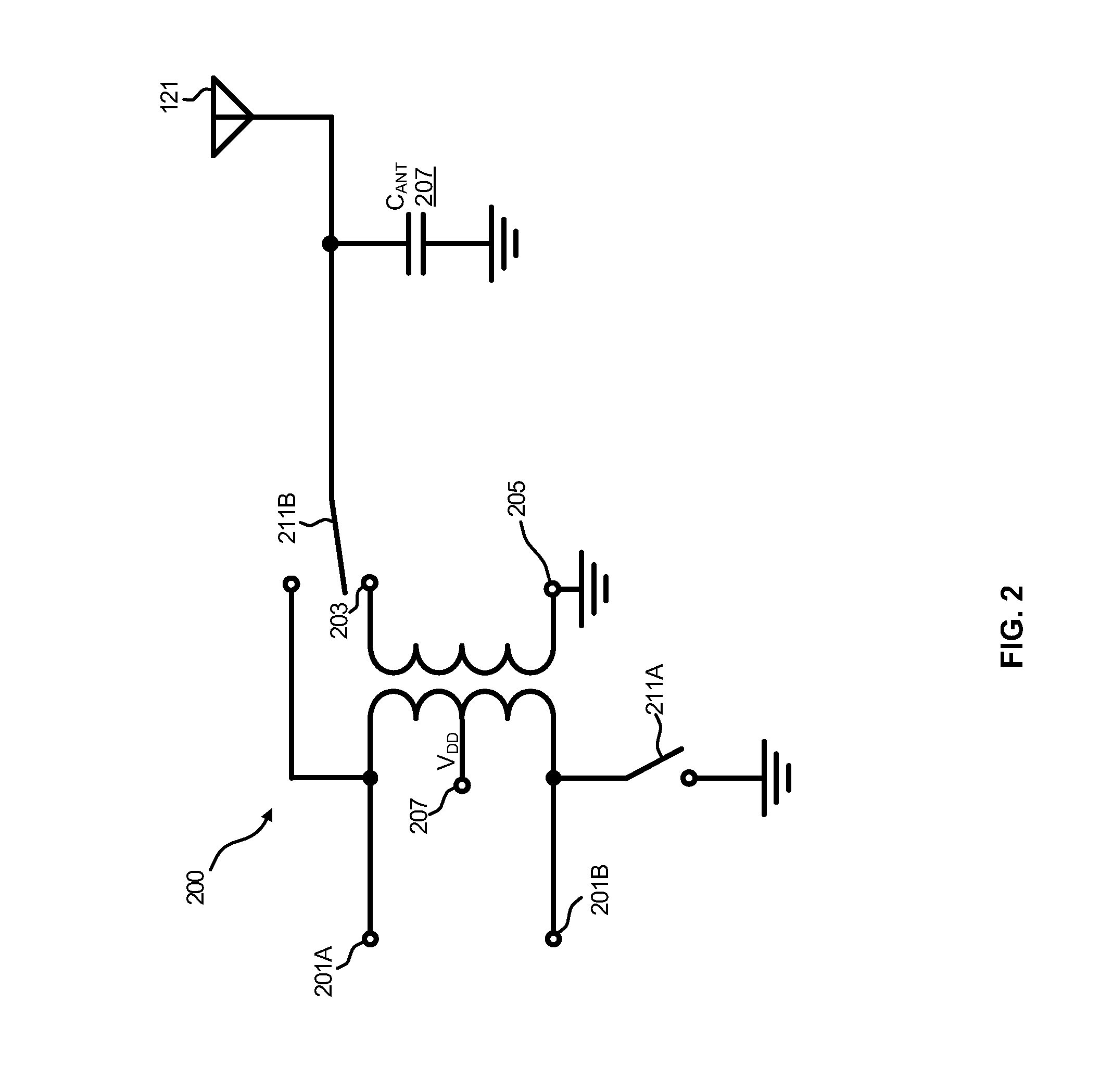

Method and system for configurable differential or single-ended signaling in an integrated circuit

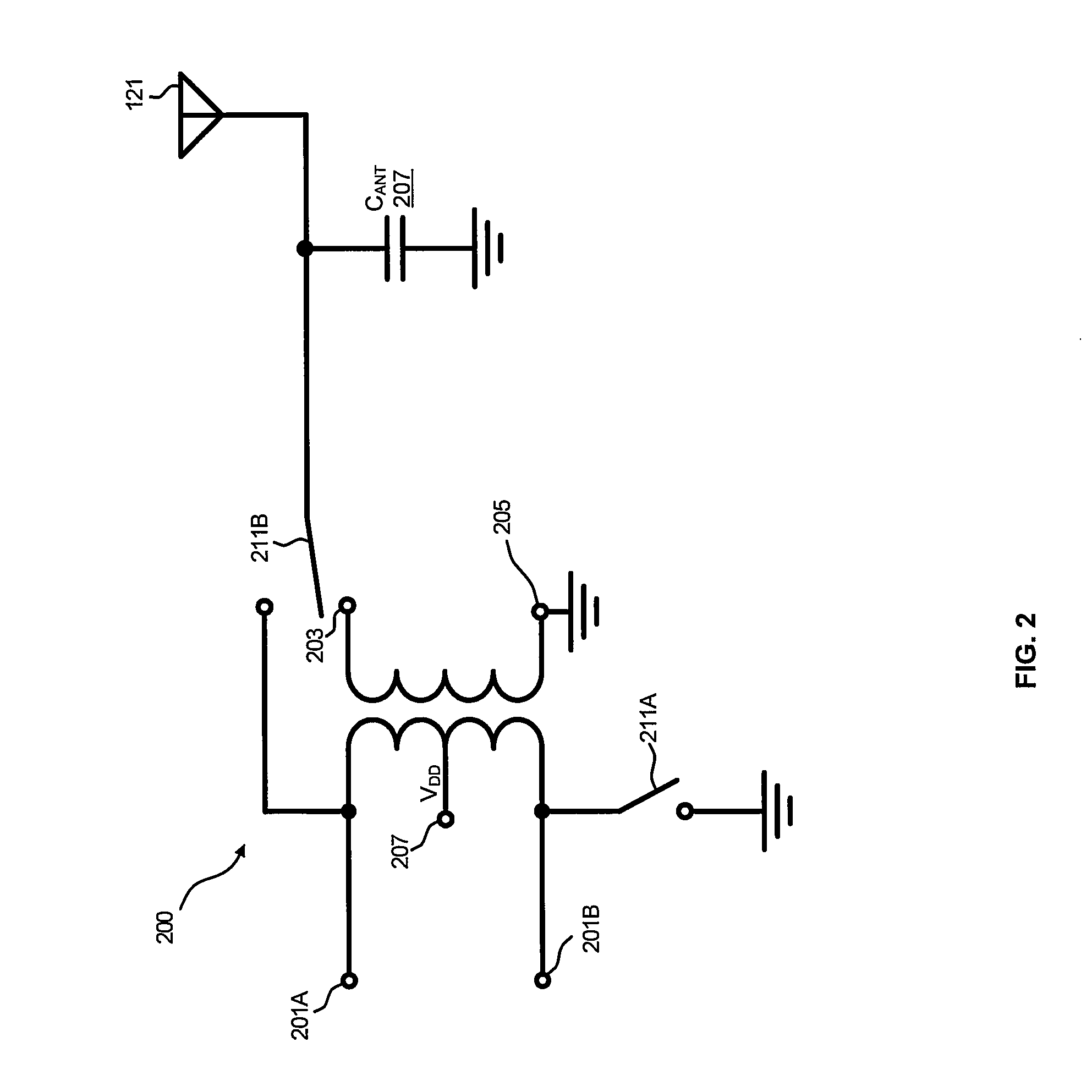

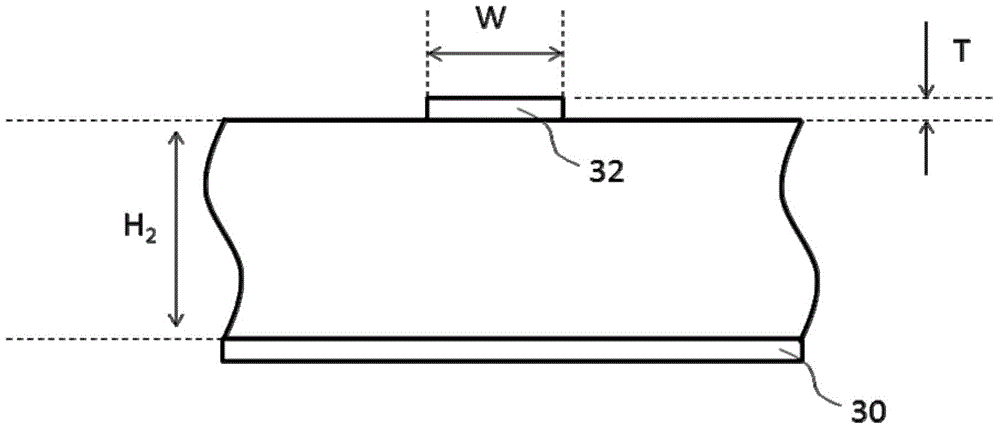

Aspects of a method and system for configurable differential or single-ended signaling in an integrated circuit. In this regard, a balun comprising one or more loops fabricated in a plurality of metal layers in an integrated circuit may enable conversion between unbalanced and balanced signals. In this regard, balanced signal output by a power amplifier may be converted to a balanced signal for transmission via an antenna. Similarly, an unbalanced signal received by an antenna may be converted to a balanced signal for amplification by an amplifier with a balanced input. The loops may be fabricated in transmission line media such as microstrip and / or stripline. The loops may comprise ferromagnetic material which may be deposited on and / or within the IC. Signals converted via the balun may be in the 61 GHz-61.5 GHz ISM band.

Owner:AVAGO TECH INT SALES PTE LTD

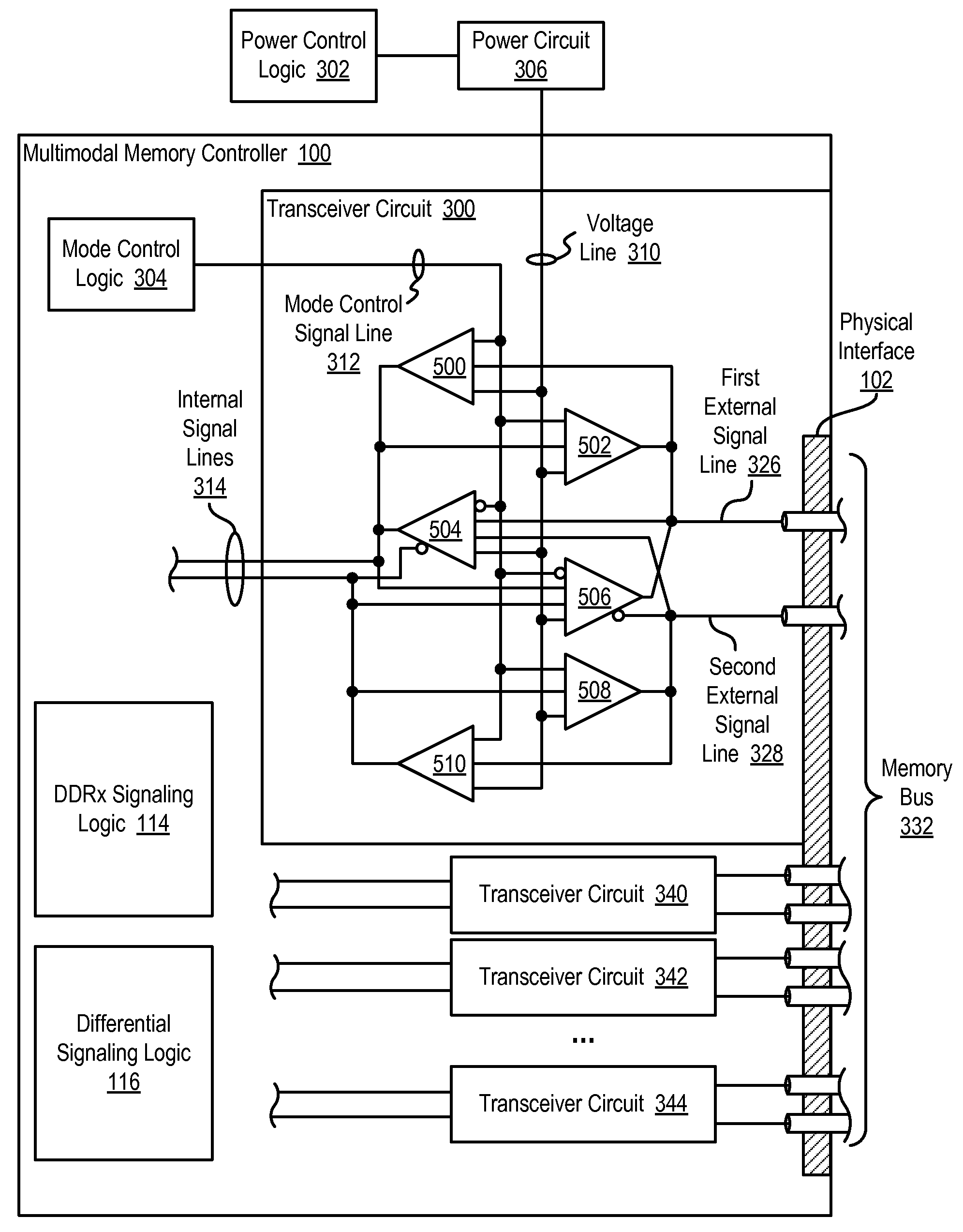

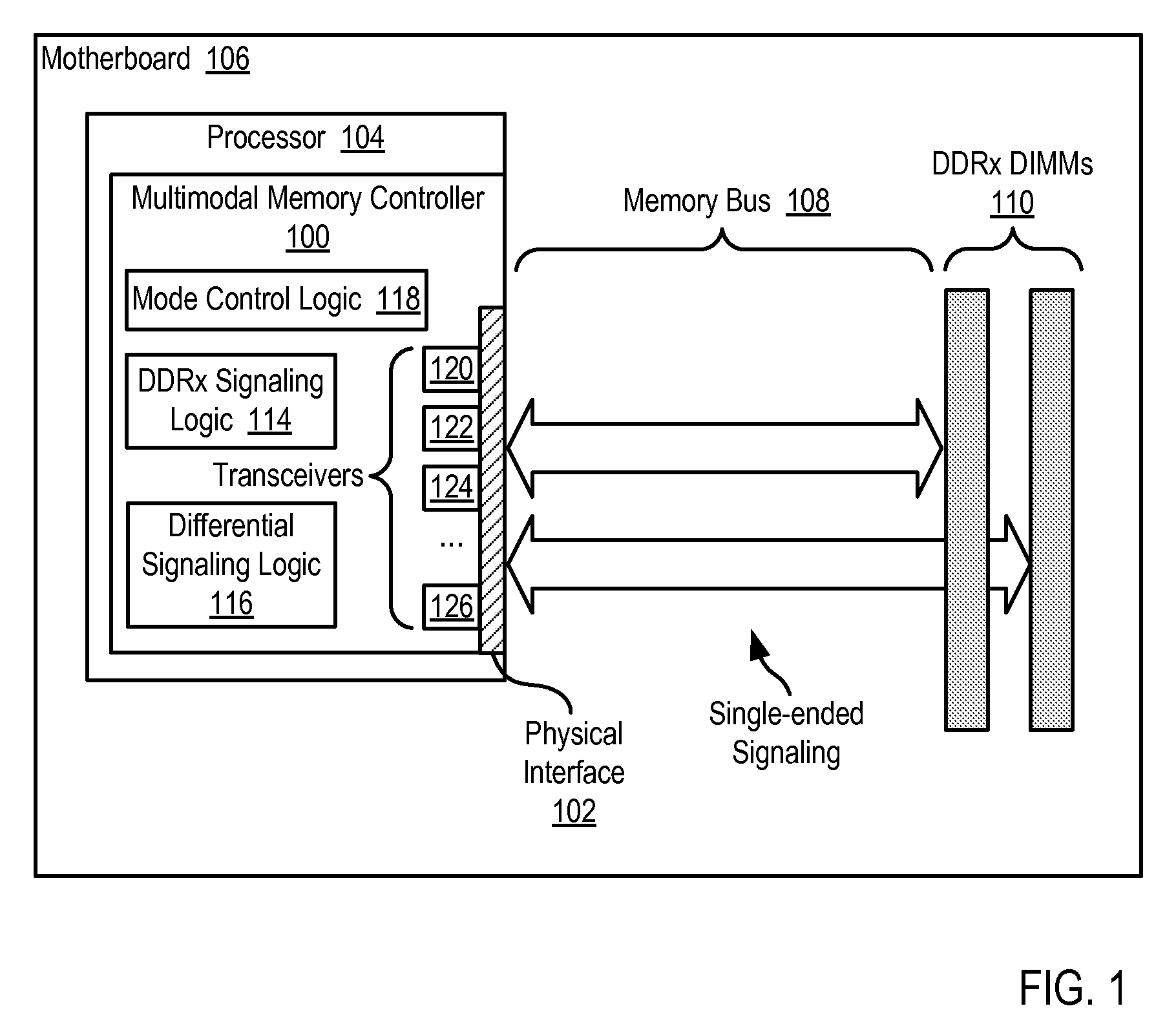

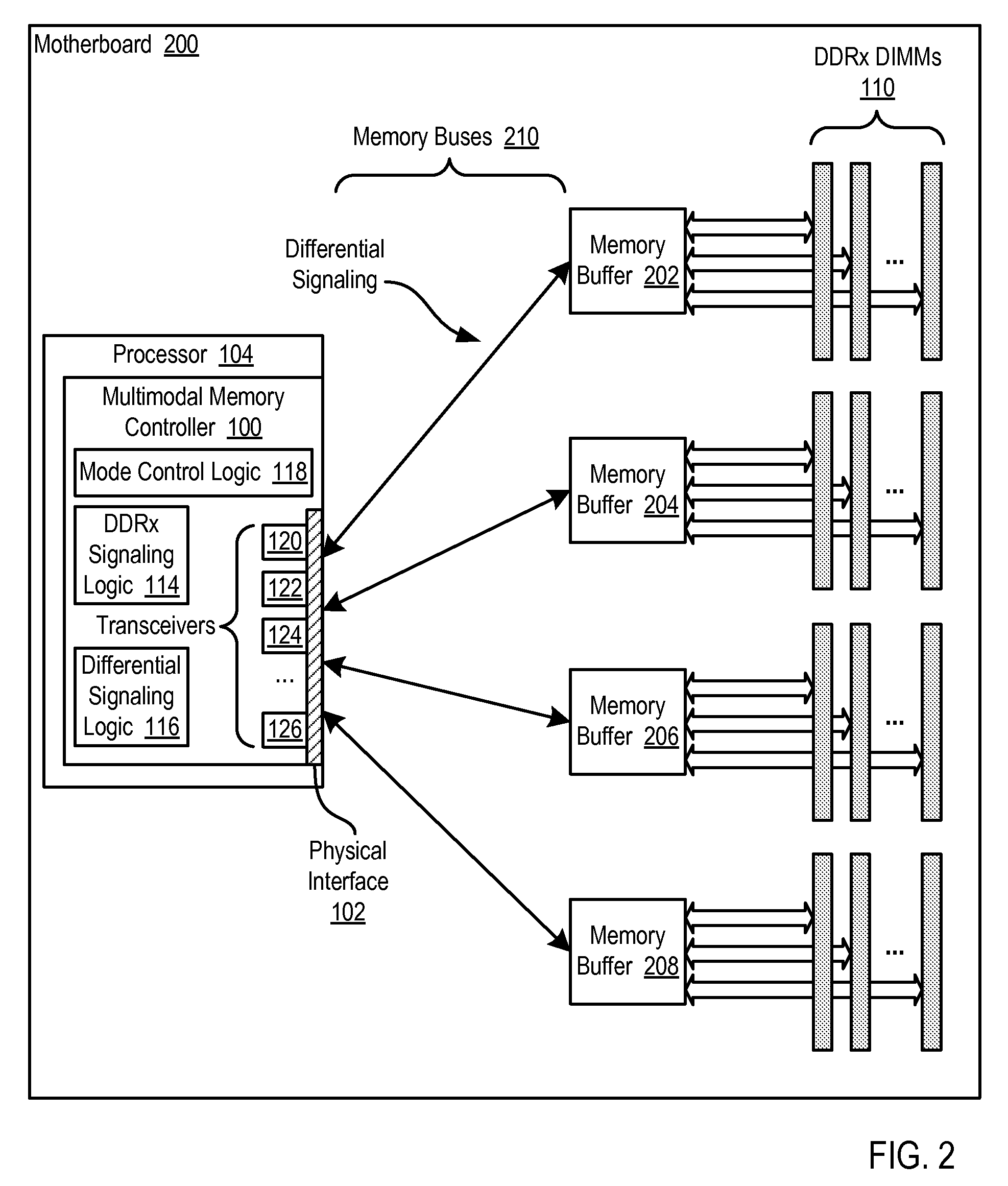

Multimodal memory controllers

Design structures embodied in machine readable medium are provided. Embodiments of the design structures include a multimodal memory controller comprising: a transceiver circuit having at least one internal signal line, a first external signal line, a second external signal line, and a mode control signal line, the mode control signal line having asserted upon it a mode control signal, and the transceiver circuit configured to operate the external signal lines for single-ended signaling at a first voltage when the mode control signal is a first value and to operate the external signal lines for differential signaling at a second voltage when the mode control signal is a second value.

Owner:IBM CORP

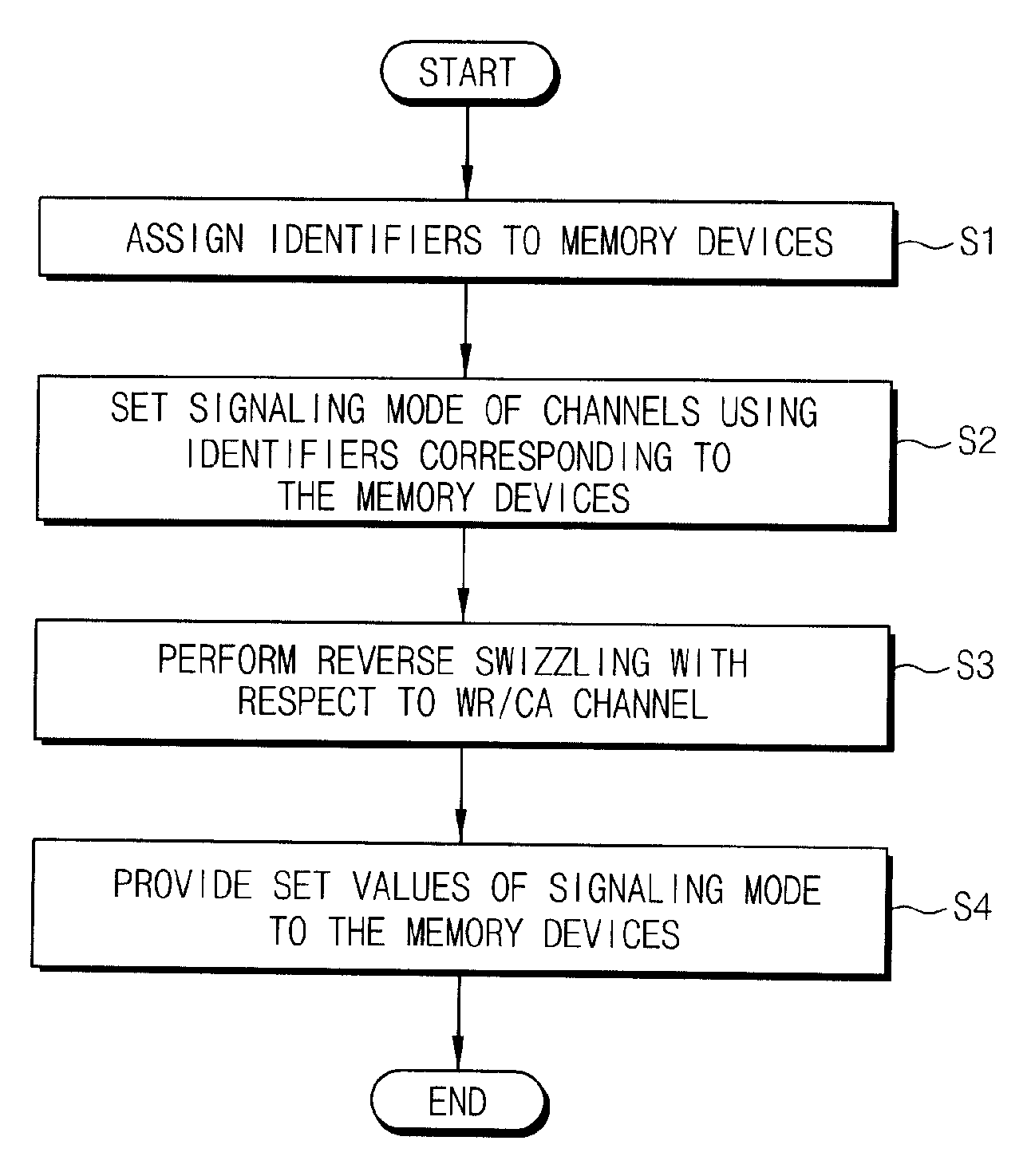

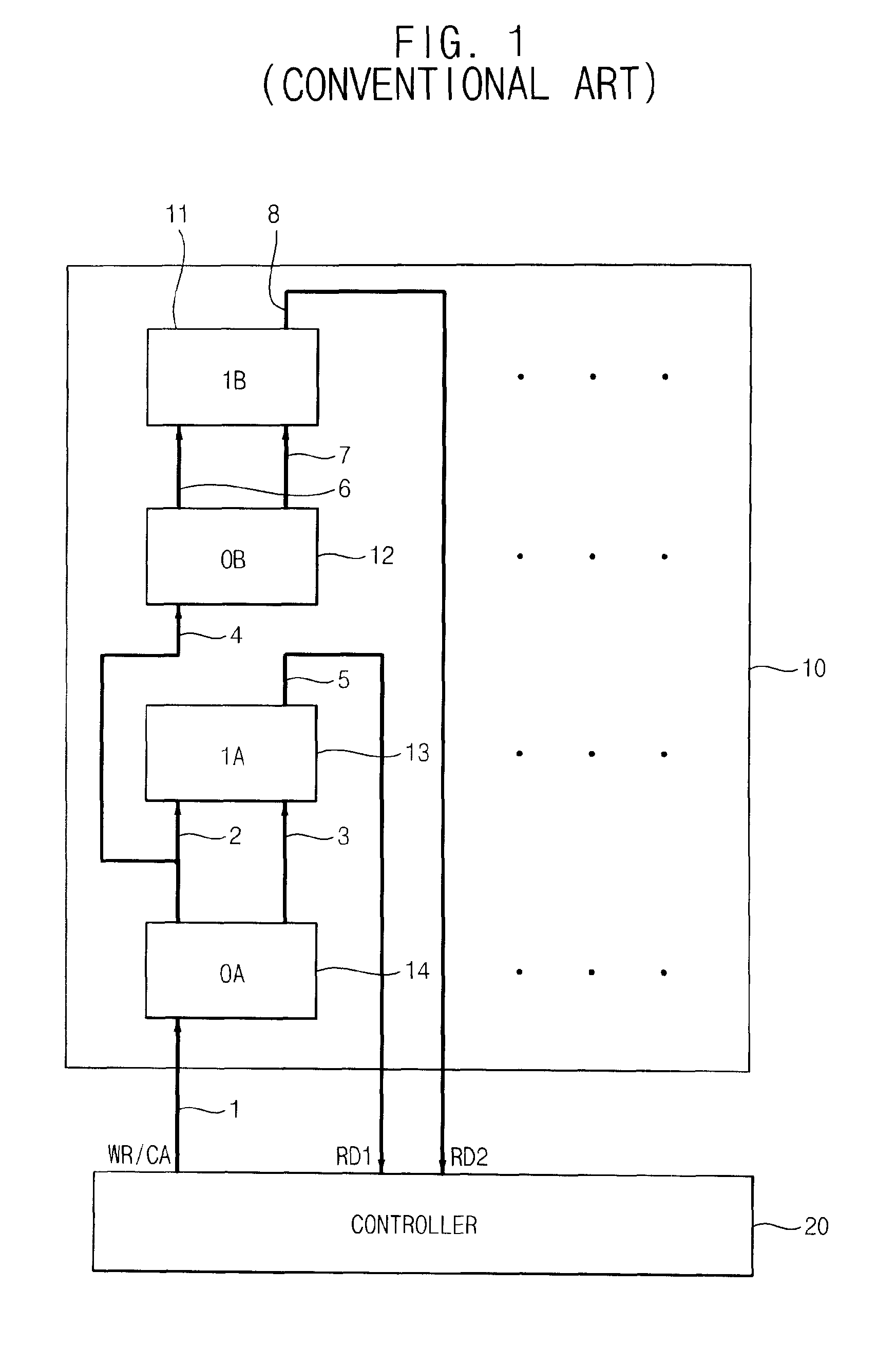

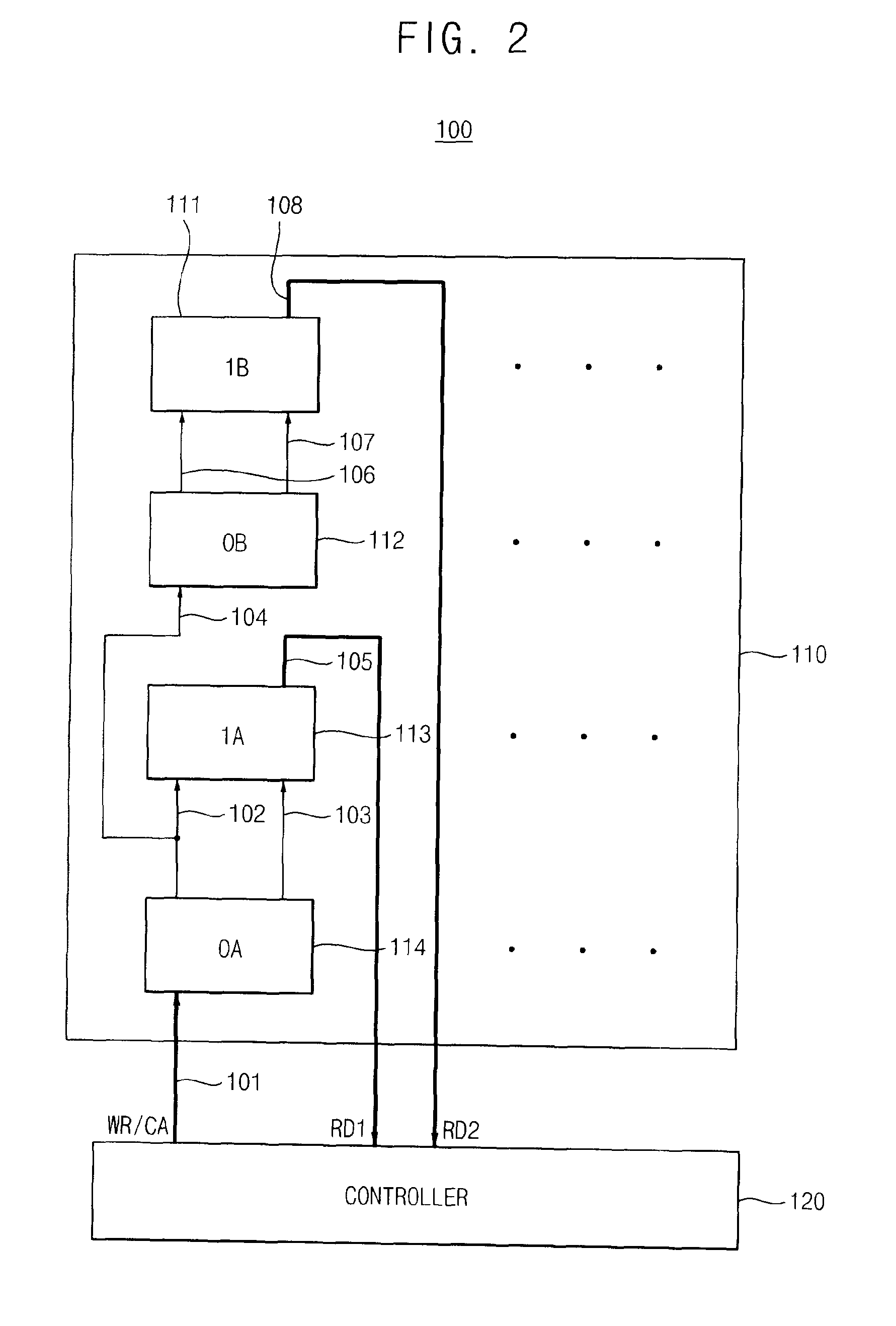

Memory system having low power consumption

InactiveUS7930492B2Reduce power consumptionMemory adressing/allocation/relocationDigital storageDifferential signalingComputer module

A memory system selectively sets signaling modes based on stack position information. The memory system includes a memory module having at least one semiconductor memory device and a memory controller configured to set a signaling mode based on stack position information of each of the semiconductor memory devices. A signaling between the memory controller and each of the semiconductor memory devices is performed in a differential signaling mode, and a signaling among the semiconductor memory devices is performed in a single-ended signaling mode. Accordingly, the memory system has reduced power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

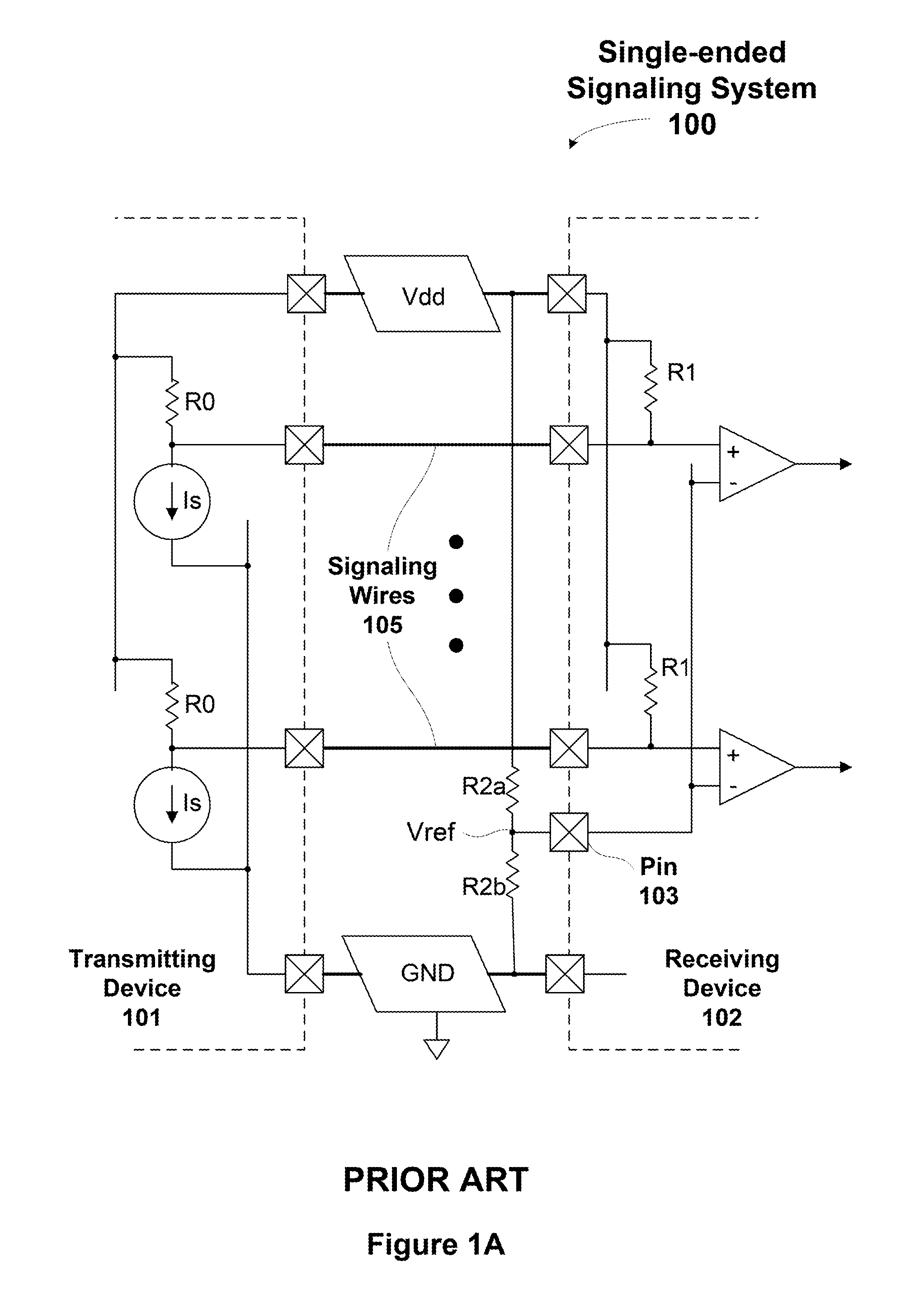

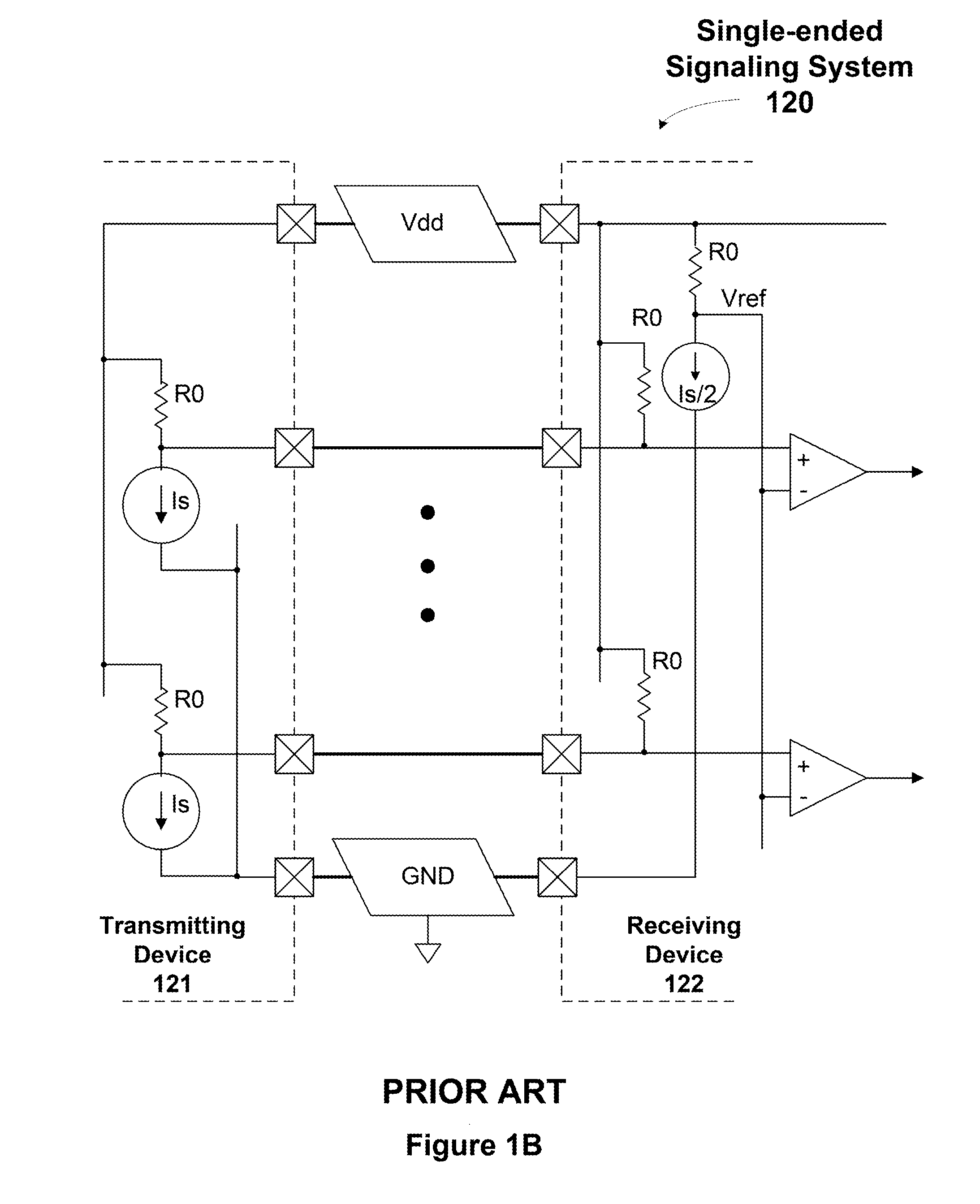

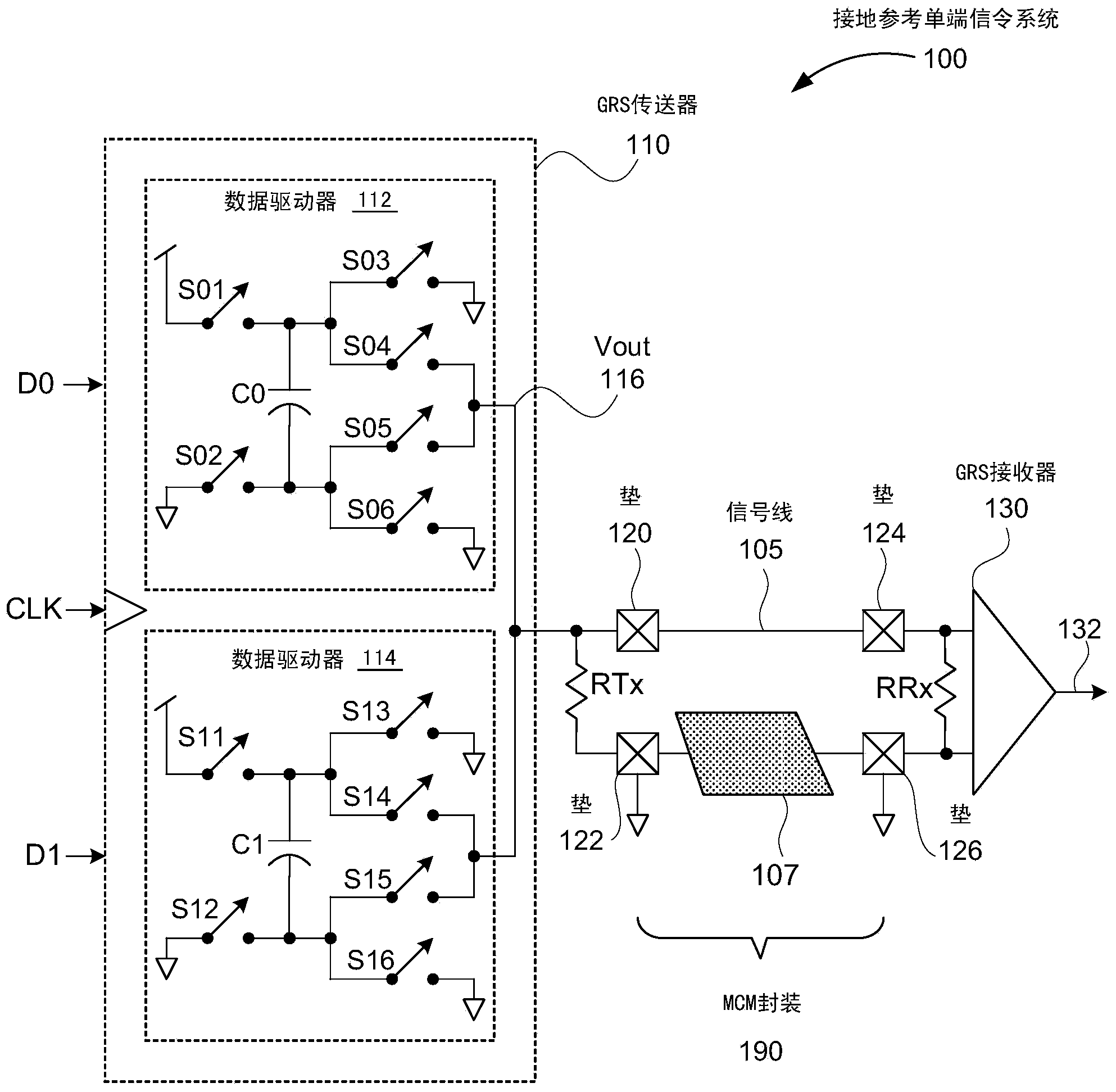

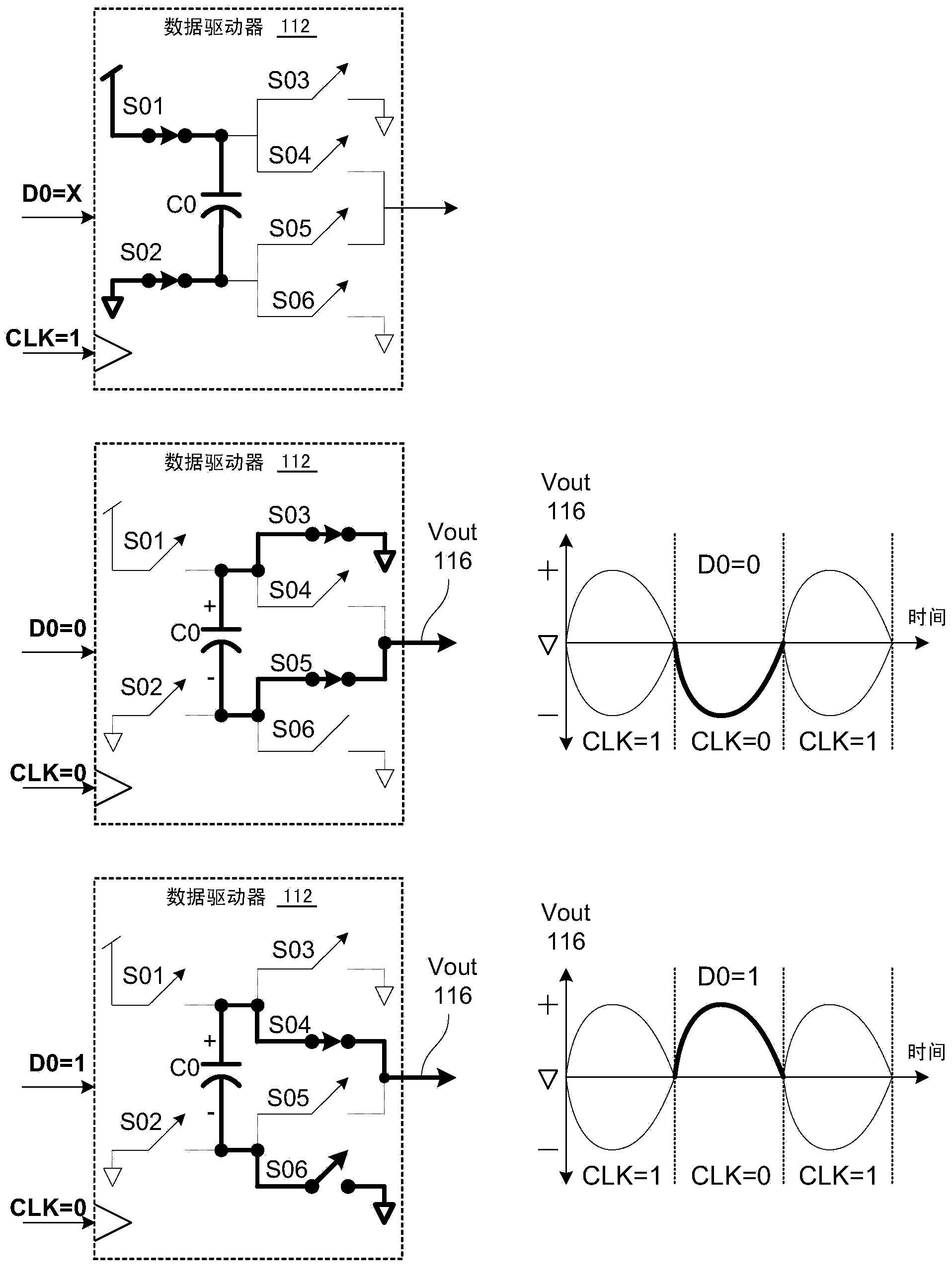

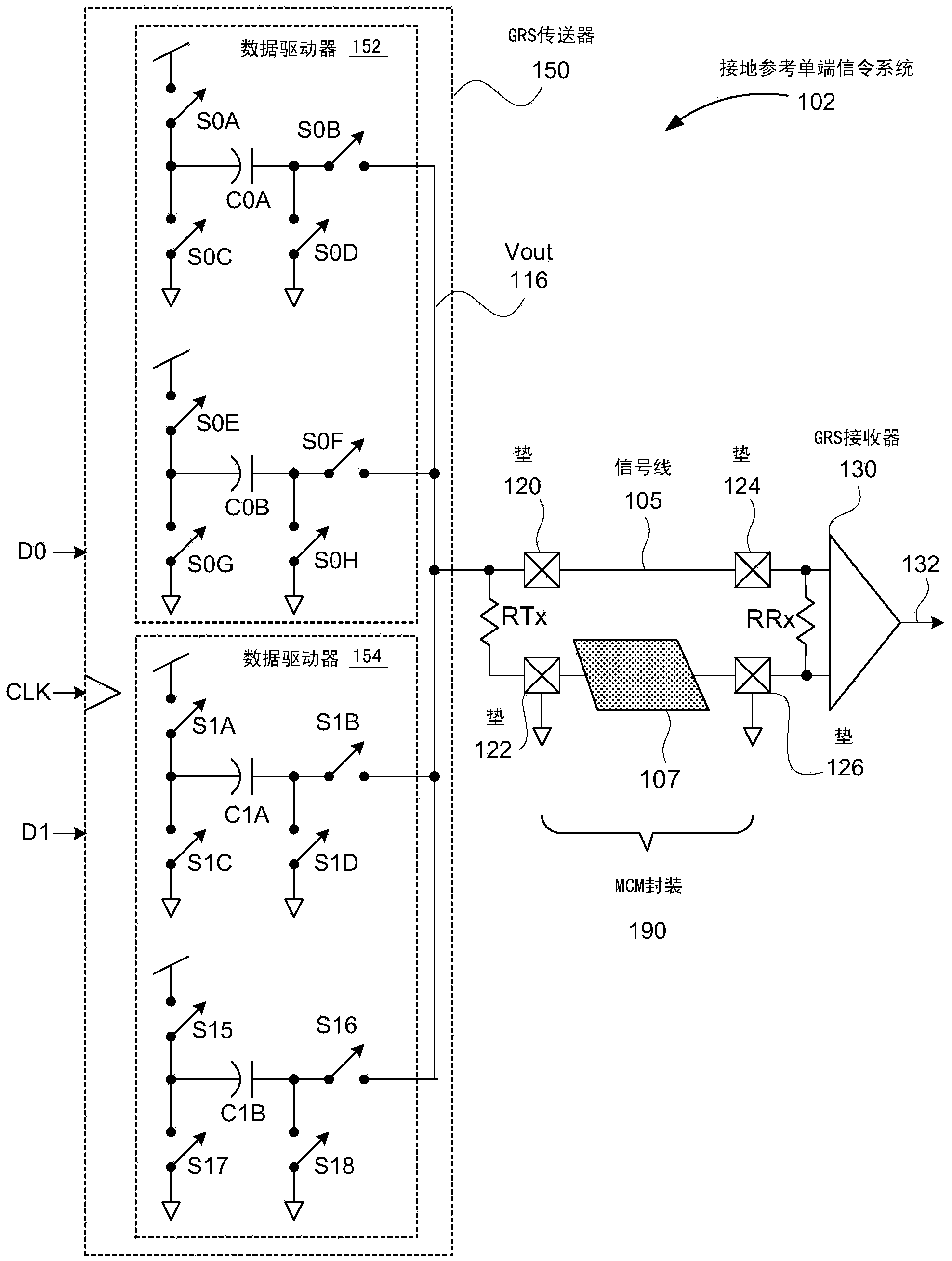

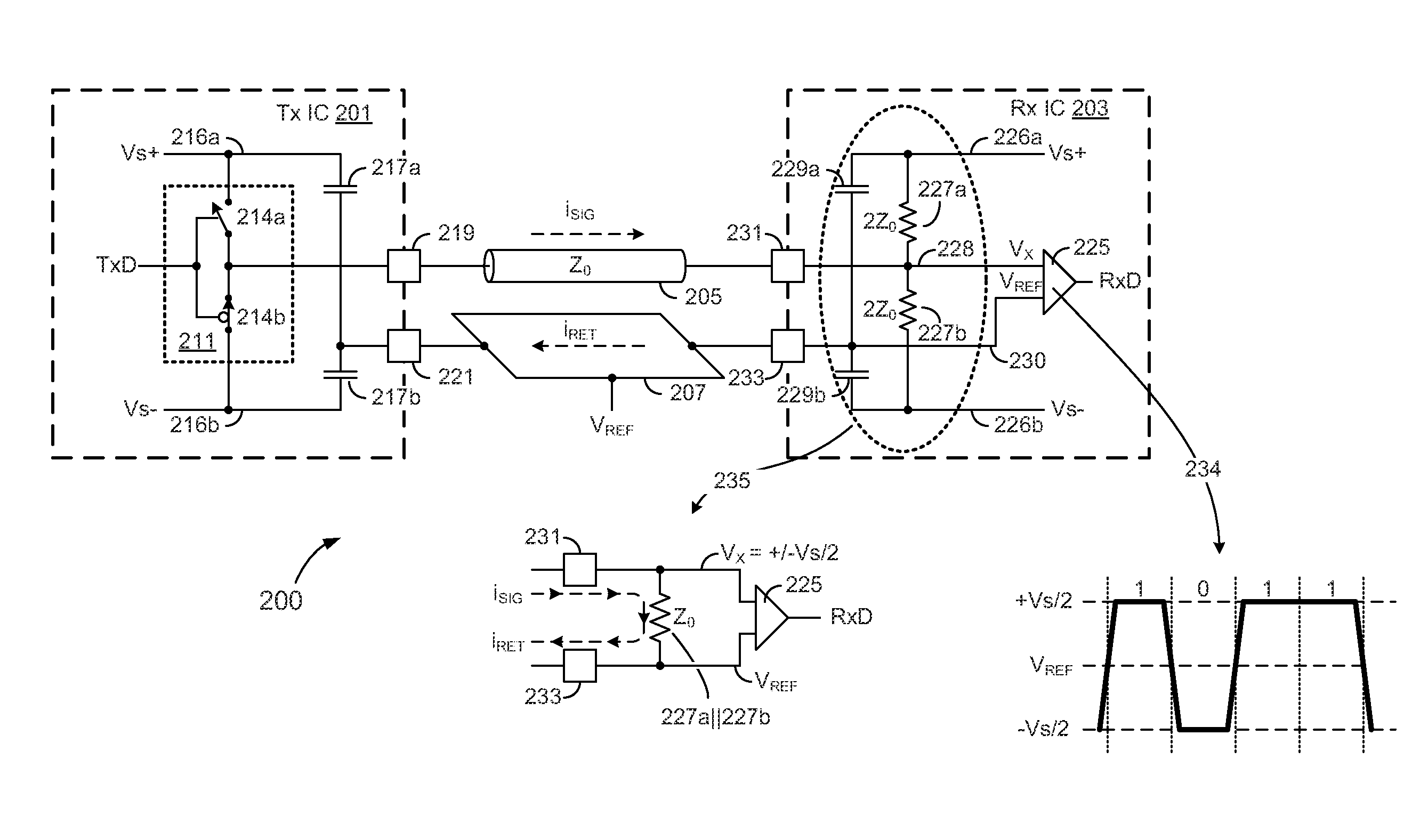

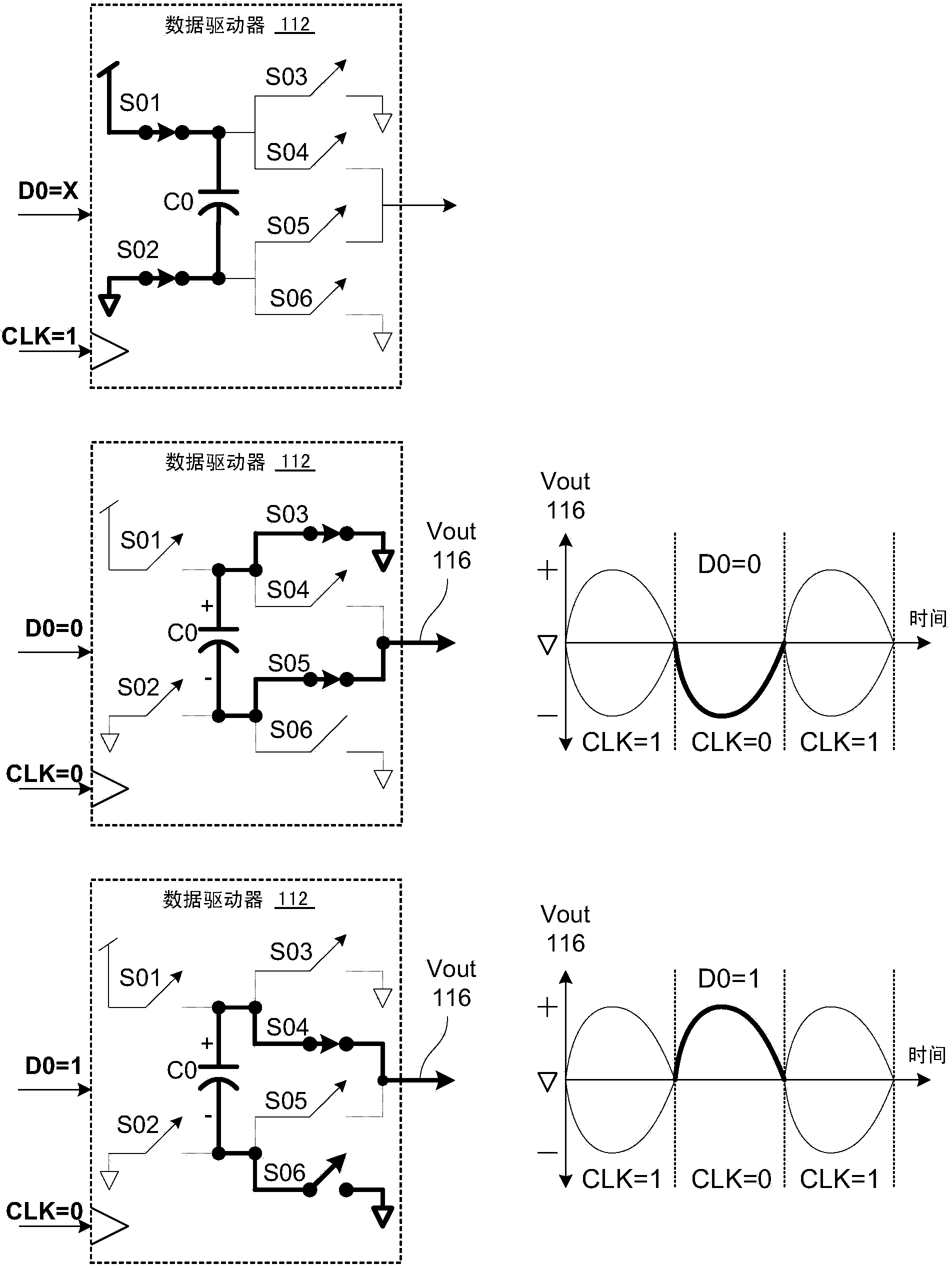

Ground referenced single-ended signaling

ActiveUS8611437B2Minimize generation of noiseLower impedanceMultiple-port networksDelay line applicationsMultiplexerEngineering

One embodiment of the present invention sets forth a mechanism for transmitting and receiving ground-referenced single-ended signals. A transmitter combines a direct current (DC) to DC converter including a flying capacitor with a 2:1 clocked multiplexer to drive a single-ended signaling line. The transmitter drives a pair of voltages that are symmetric about the ground power supply level. Signaling currents are returned to the ground plane to minimize the generation of noise that is a source of crosstalk between different signaling lines. Noise introduced through the power supply is correlated with the switching rate of the data and may be reduced using an equalizer circuit.

Owner:NVIDIA CORP

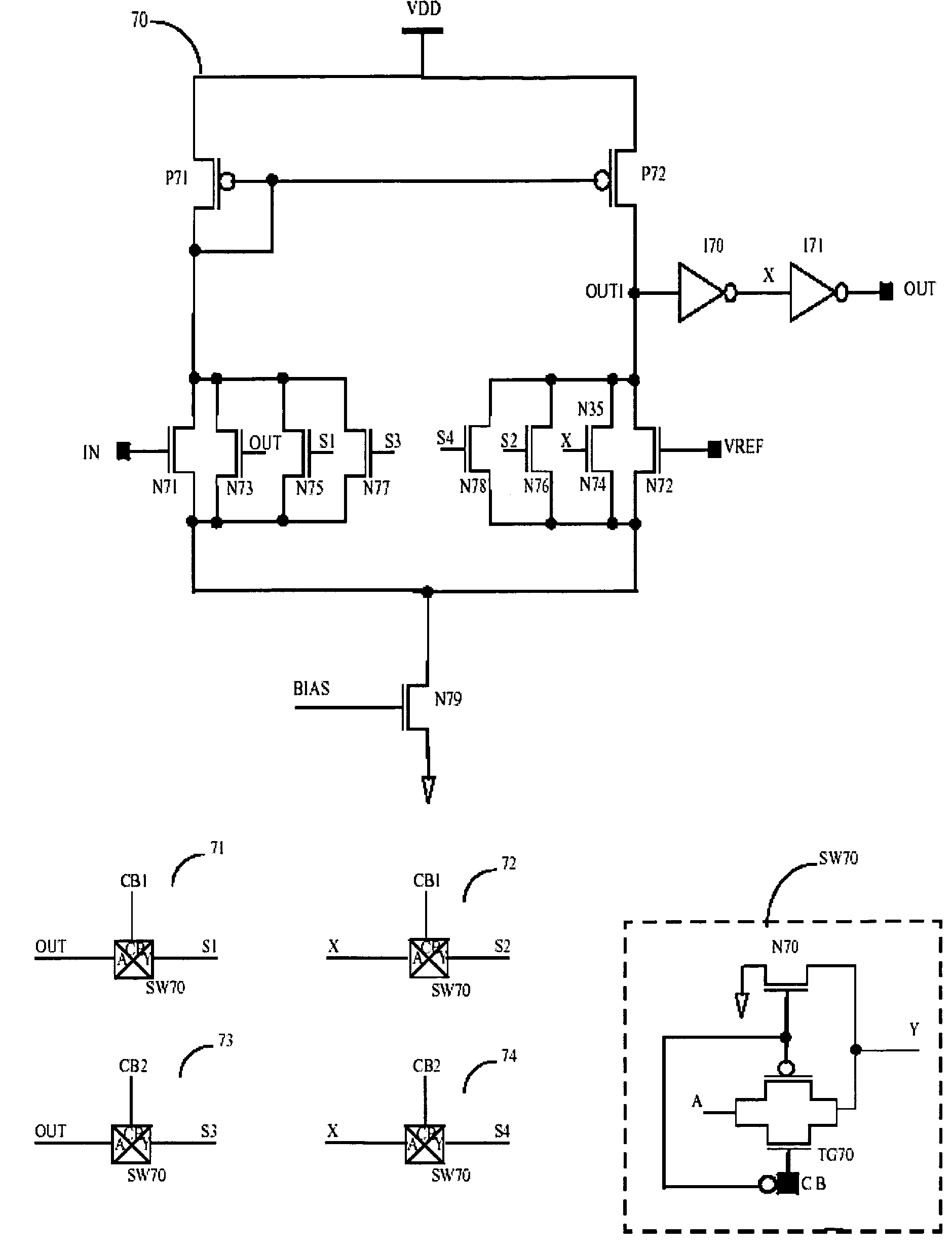

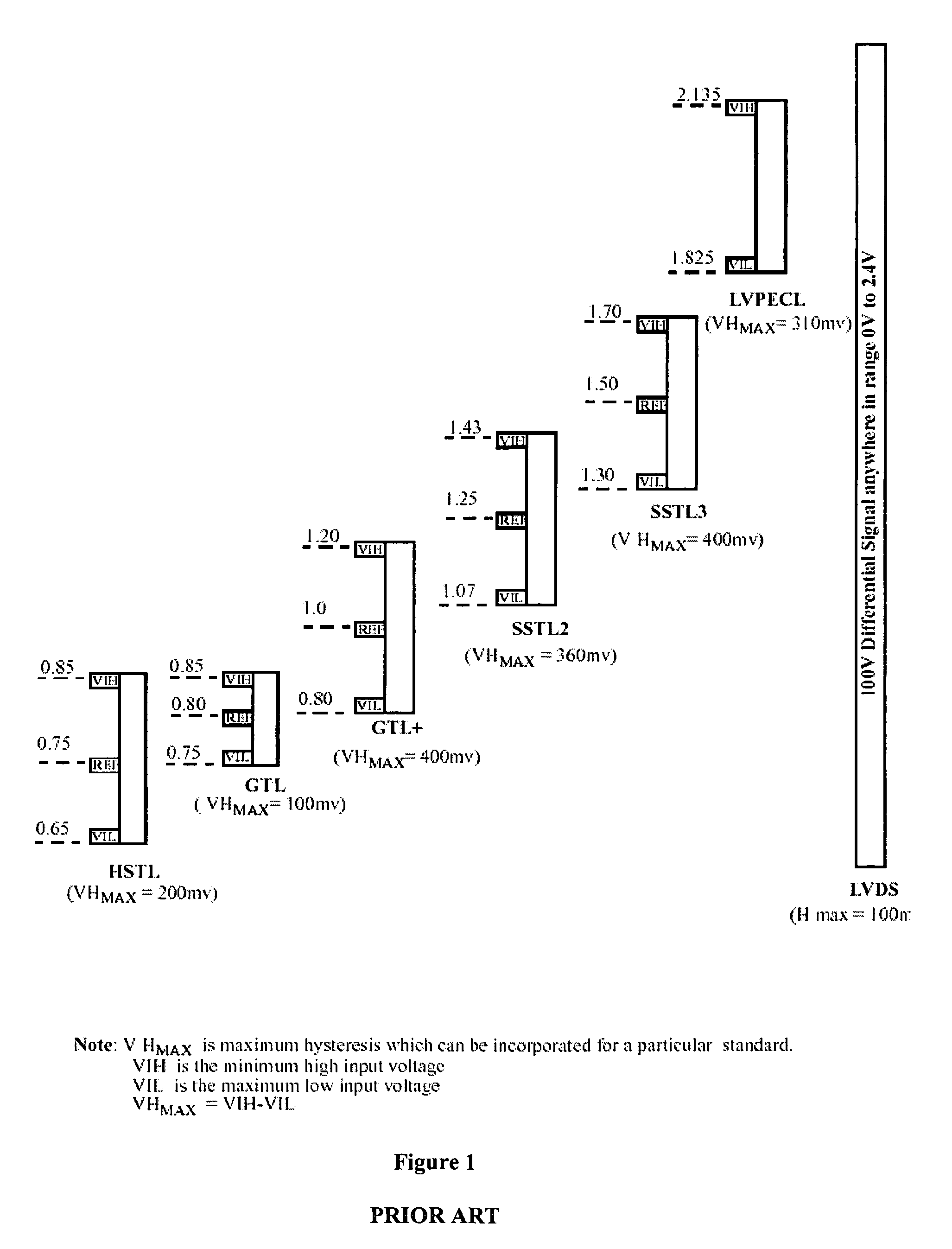

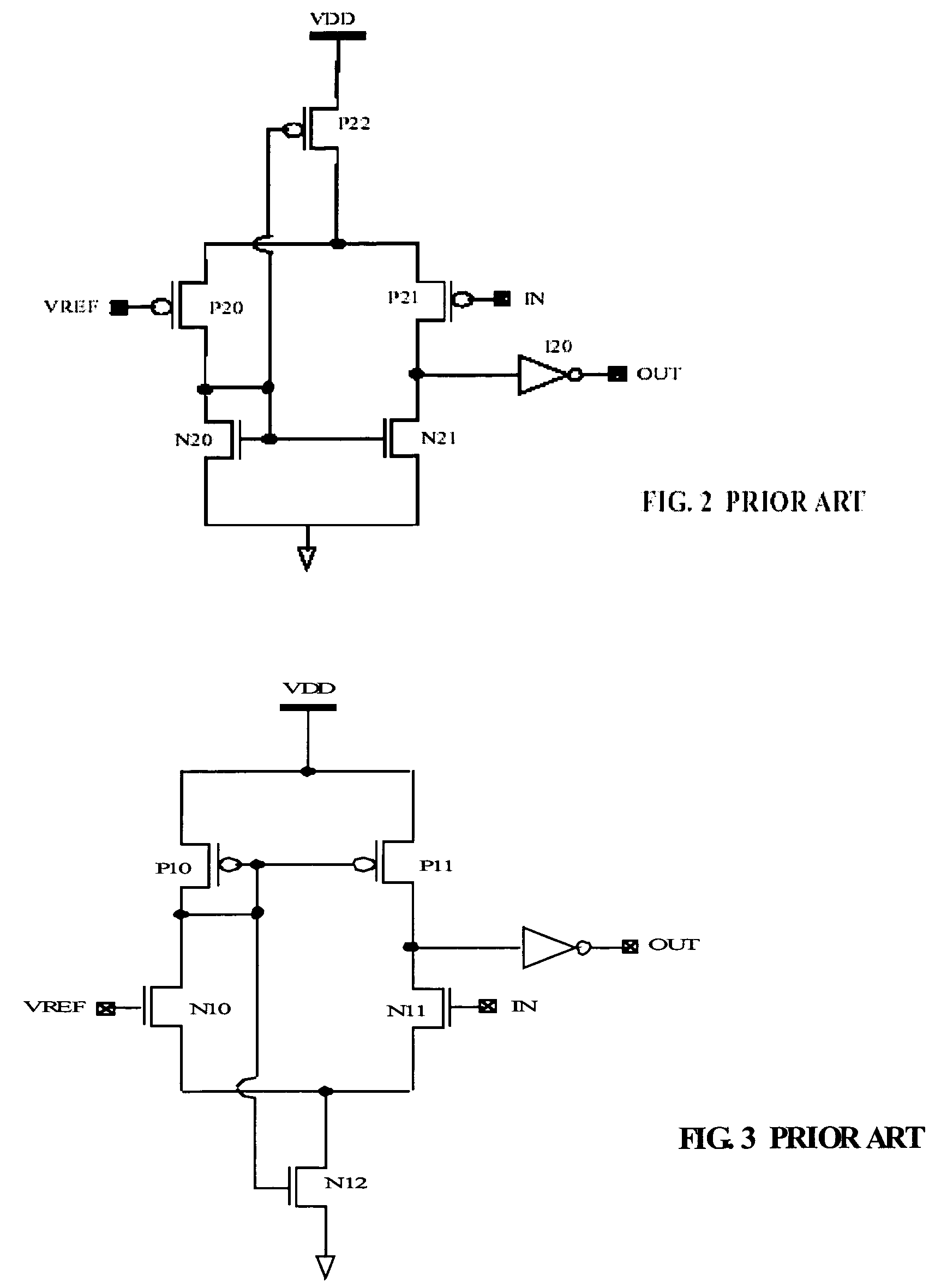

Input/output block with programmable hysteresis

An Input Output Block (IOB) provides programmable hysteresis to support multiple IO standards including a differential amplifier having one input coupled to an input signal and its second input coupled to a complementary input signal in the case of differential signalling, or to a reference voltage for the case of single-ended signalling, a pair of series coupled digital inverters coupled to one output of said differential amplifier, one or more transistors coupled in parallel with each input transistor of the differential amplifier, each transistor of each parallel coupled set being of a different size relative to the corresponding input transistor, the control terminal of each parallel coupled transistor in each set being coupled to the output of one of said series coupled inverters such that positive feedback is provided directly or indirectly through a selection switch, and hysteresis control bits that symmetrically enable or disable each said selection switch to provide a programmable level of hysteresis that is determined by the combination of selection switches that are enabled and the relative sizes of the corresponding parallel coupled transistors.

Owner:STMICROELECTRONICS PVT LTD

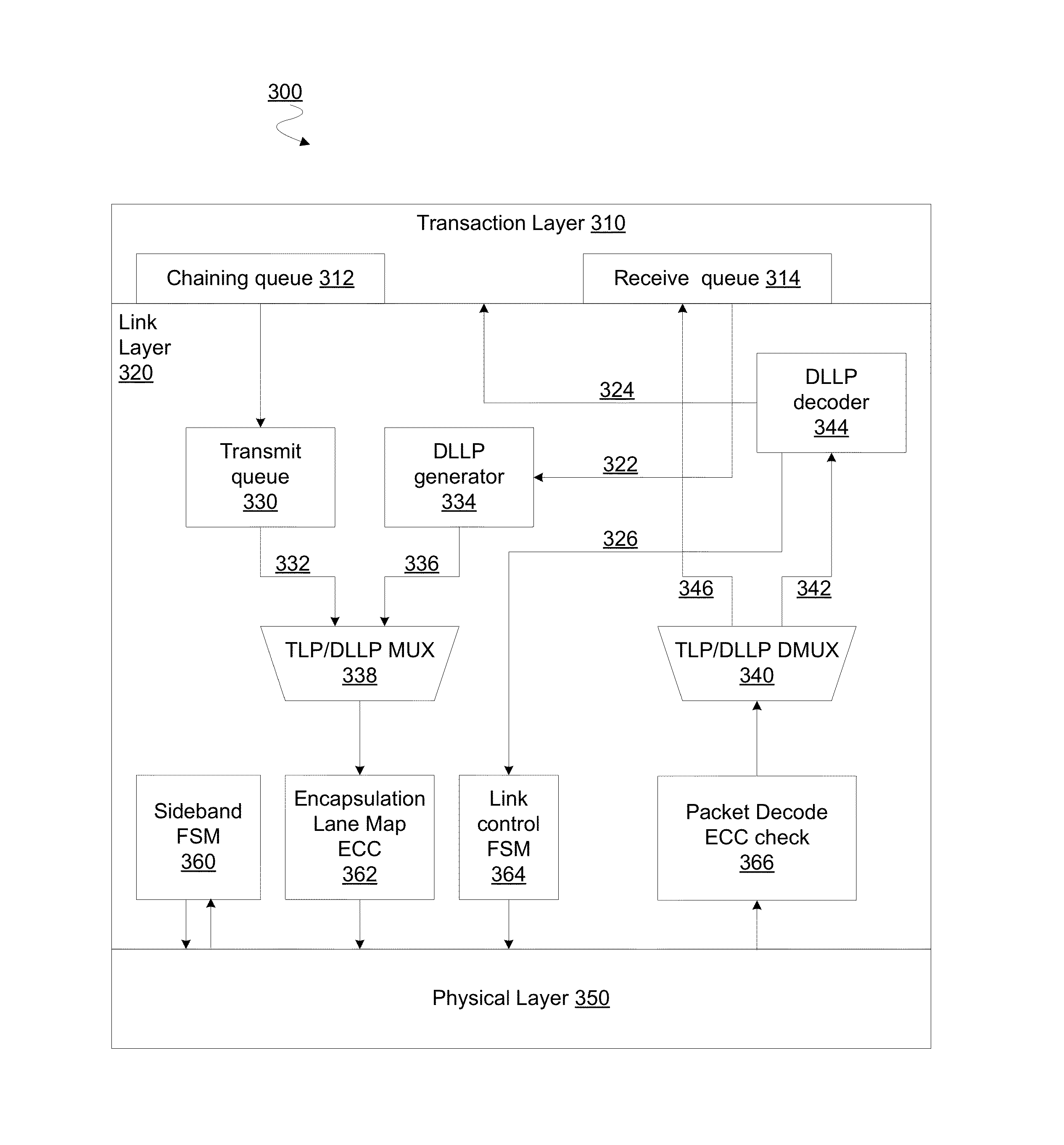

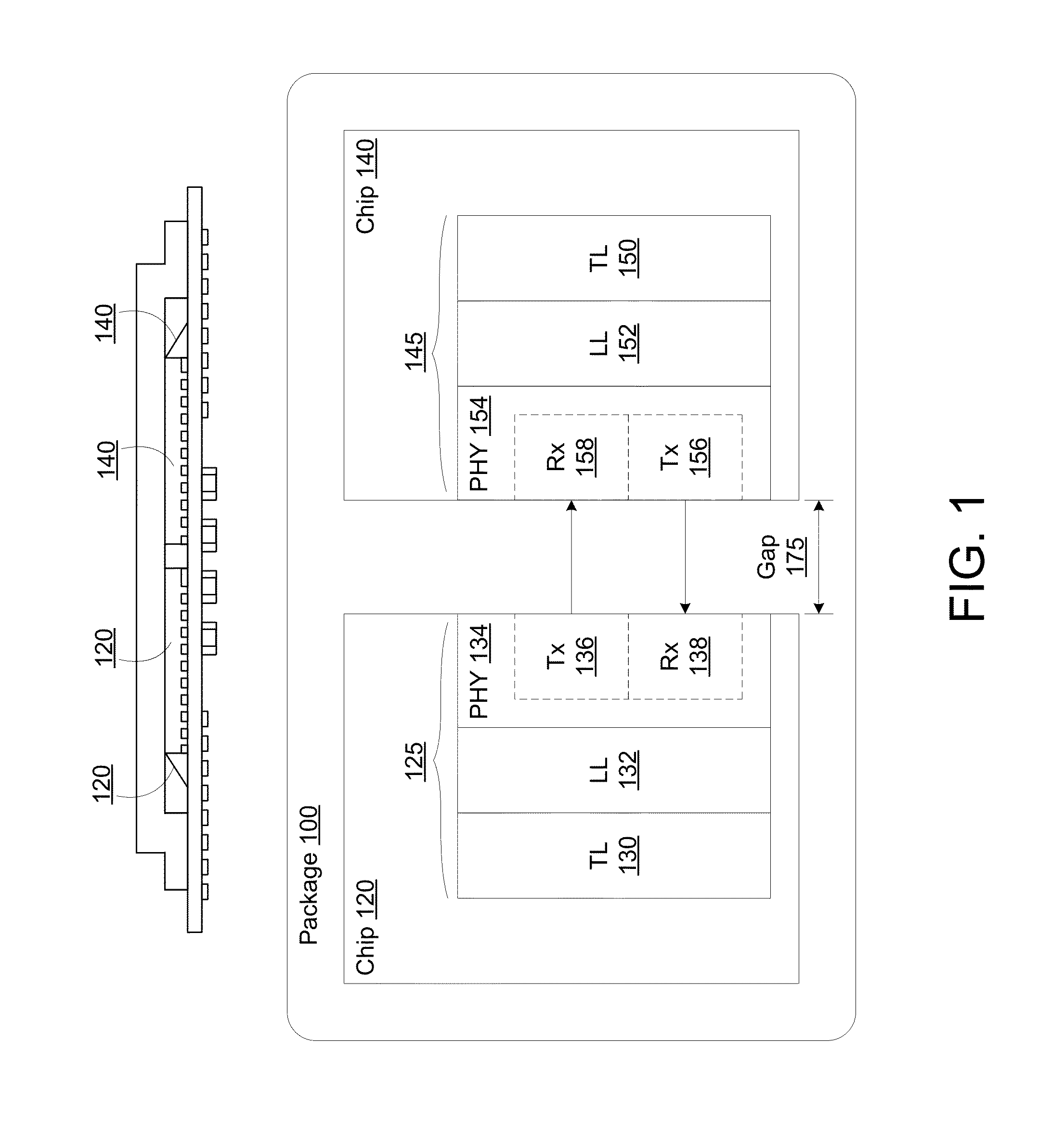

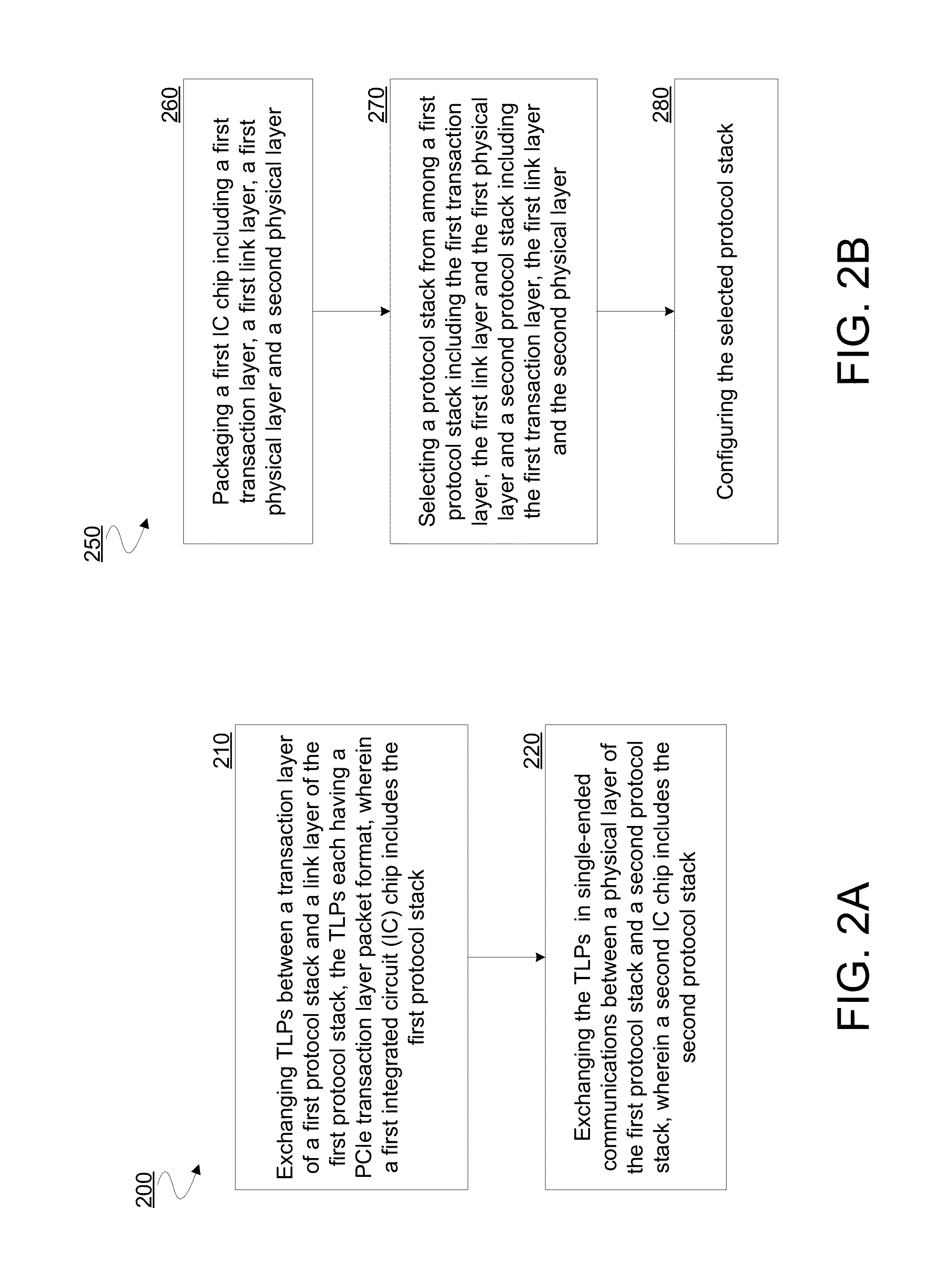

Method, apparatus and system for configuring a protocol stack of an integrated circuit chip

ActiveUS20150269108A1Energy efficient computingElectric digital data processingComputer hardwareDifferential signaling

Techniques and mechanisms for configuring an integrated circuit (IC) chip to implement a protocol stack. In an embodiment, a transaction layer of the IC chip is operable to exchange with a link layer of the IC chip transaction layer packets (TLPs) having a format compatible with one defined in a Peripheral Component Interconnect Express™ (PCIe™) specification. Configuration circuitry of the IC chip provides for configuration of a first protocol stack including the transaction layer, circuitry of the link layer and a first physical layer of the IC chip. The configuration circuitry further provides for an alternative configuration of a second protocol stack including the transaction layer, circuitry of the link layer and a second physical layer of the IC chip. In another embodiment, the first protocol stack supports single-ended signaling to communicate TLP information, whereas the second protocol stack supports differential signaling to communicate TLP information.

Owner:SK HYNIX NAND PROD SOLUTIONS CORP

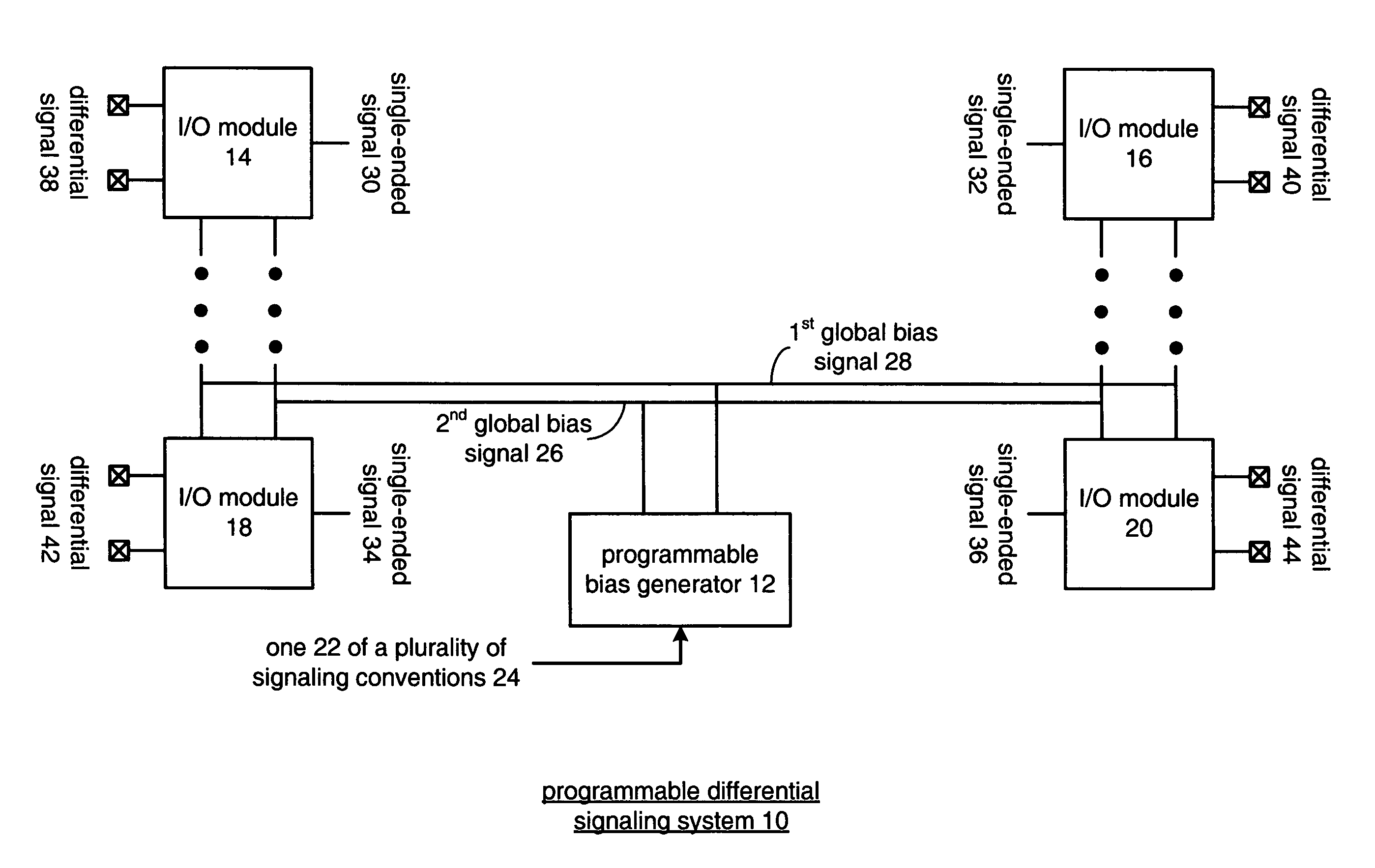

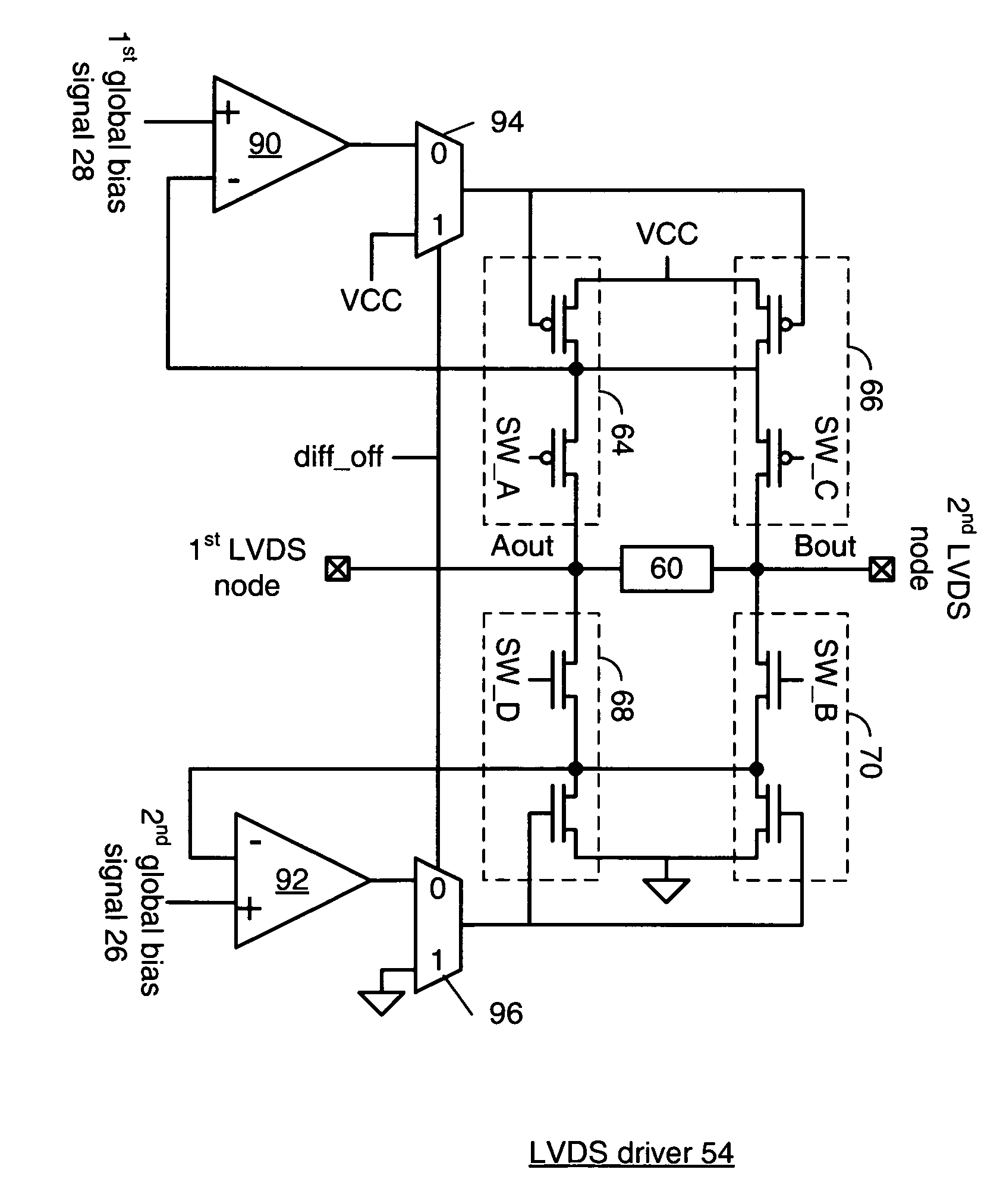

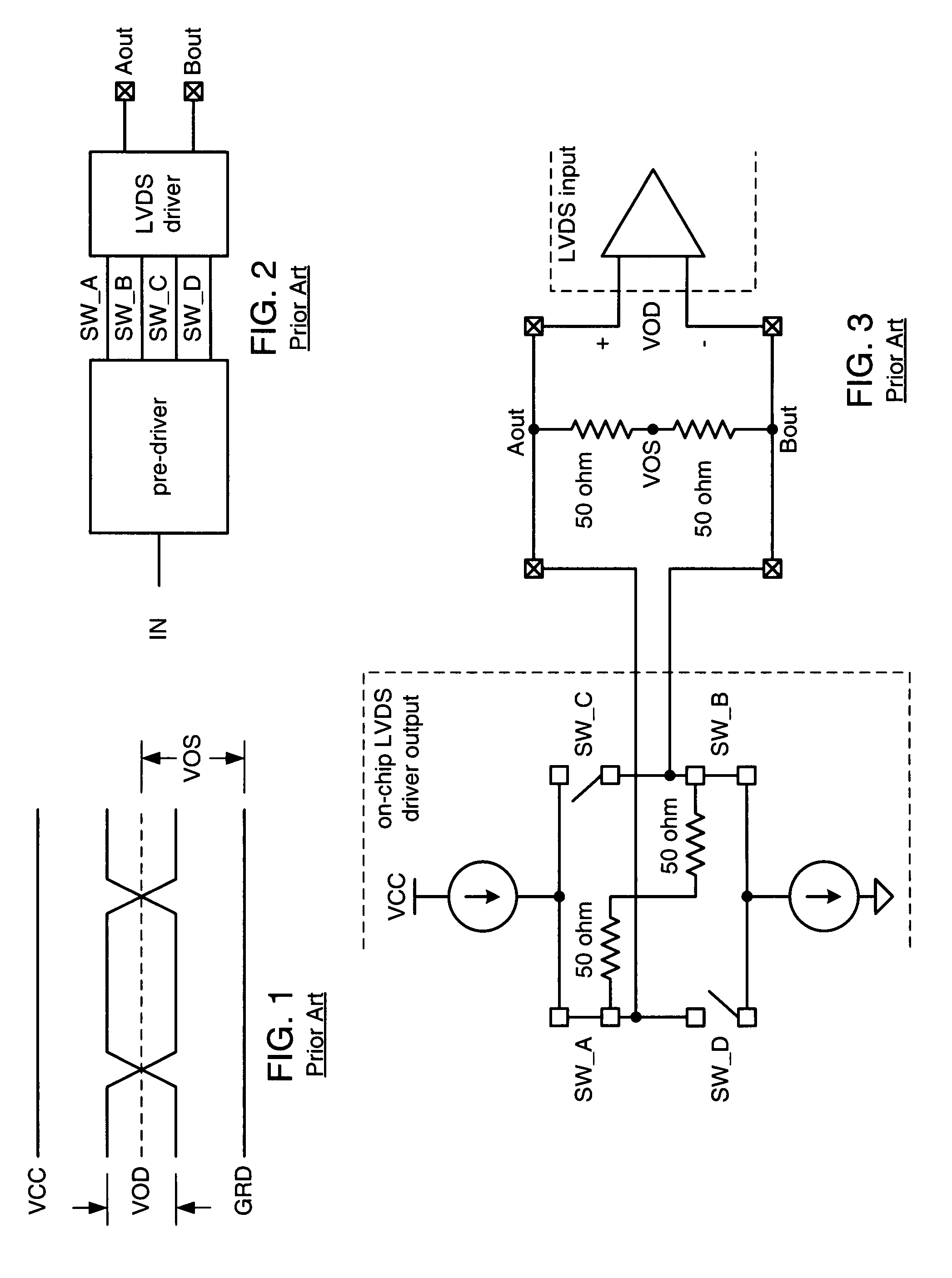

Programmable differential signaling system

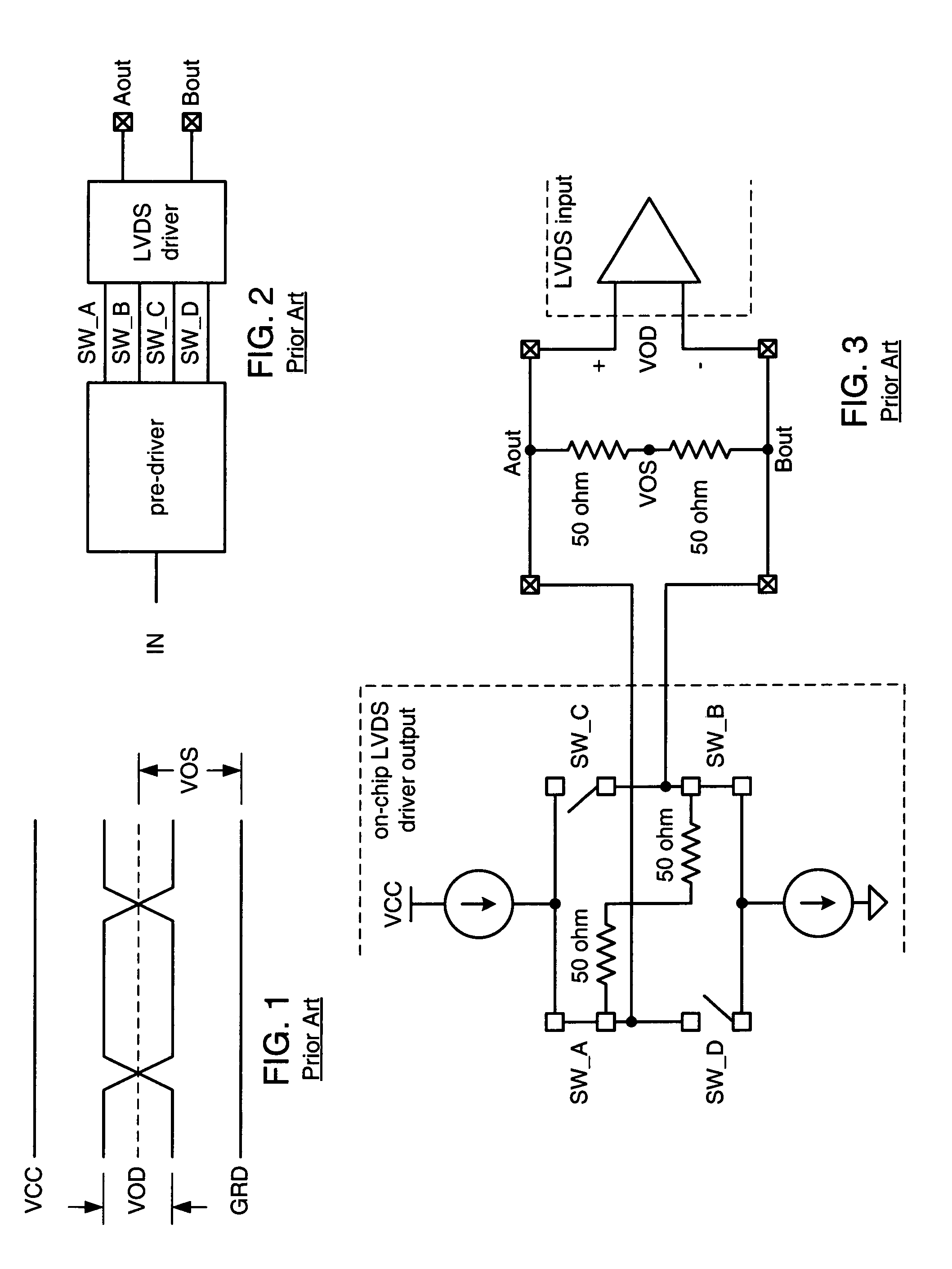

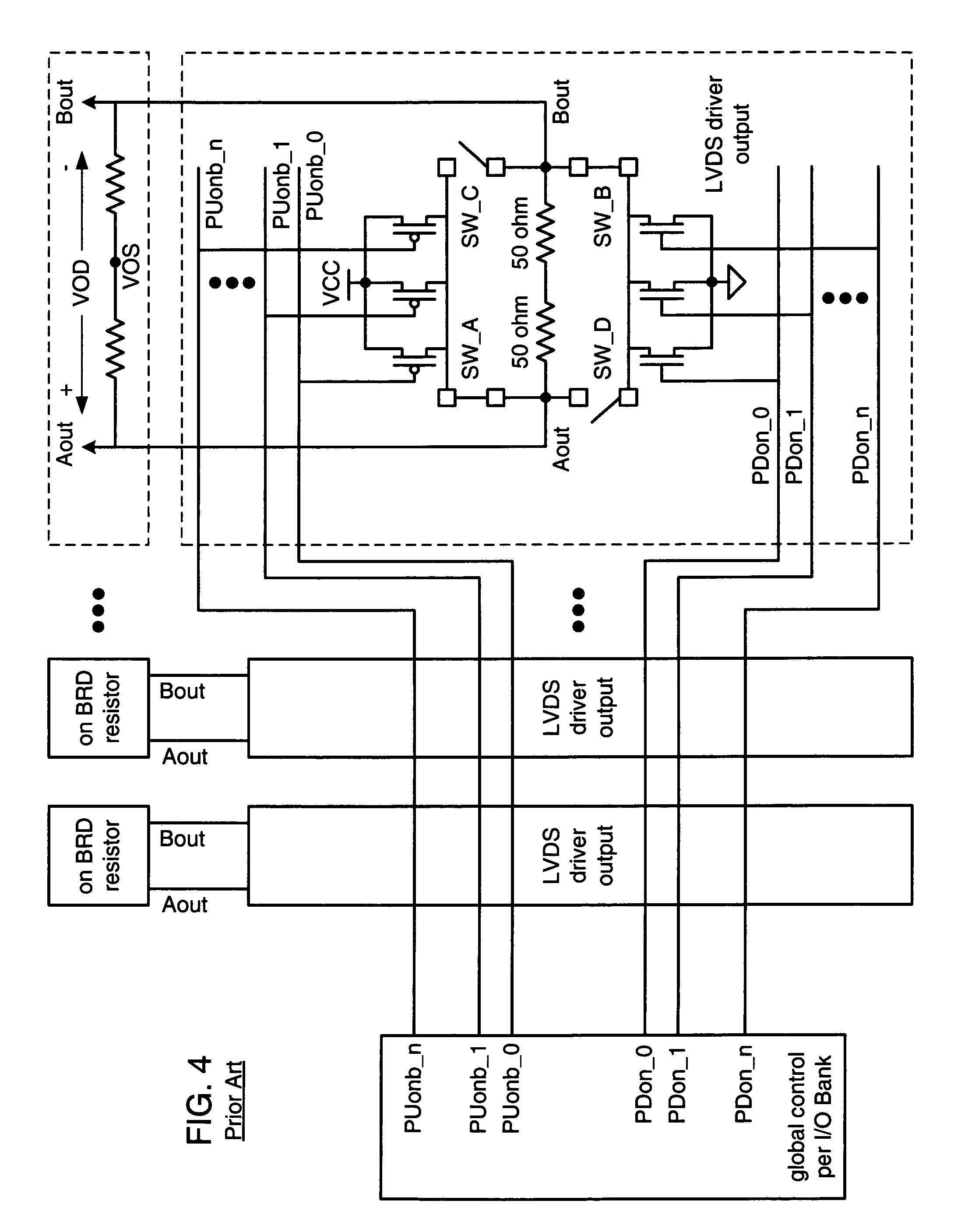

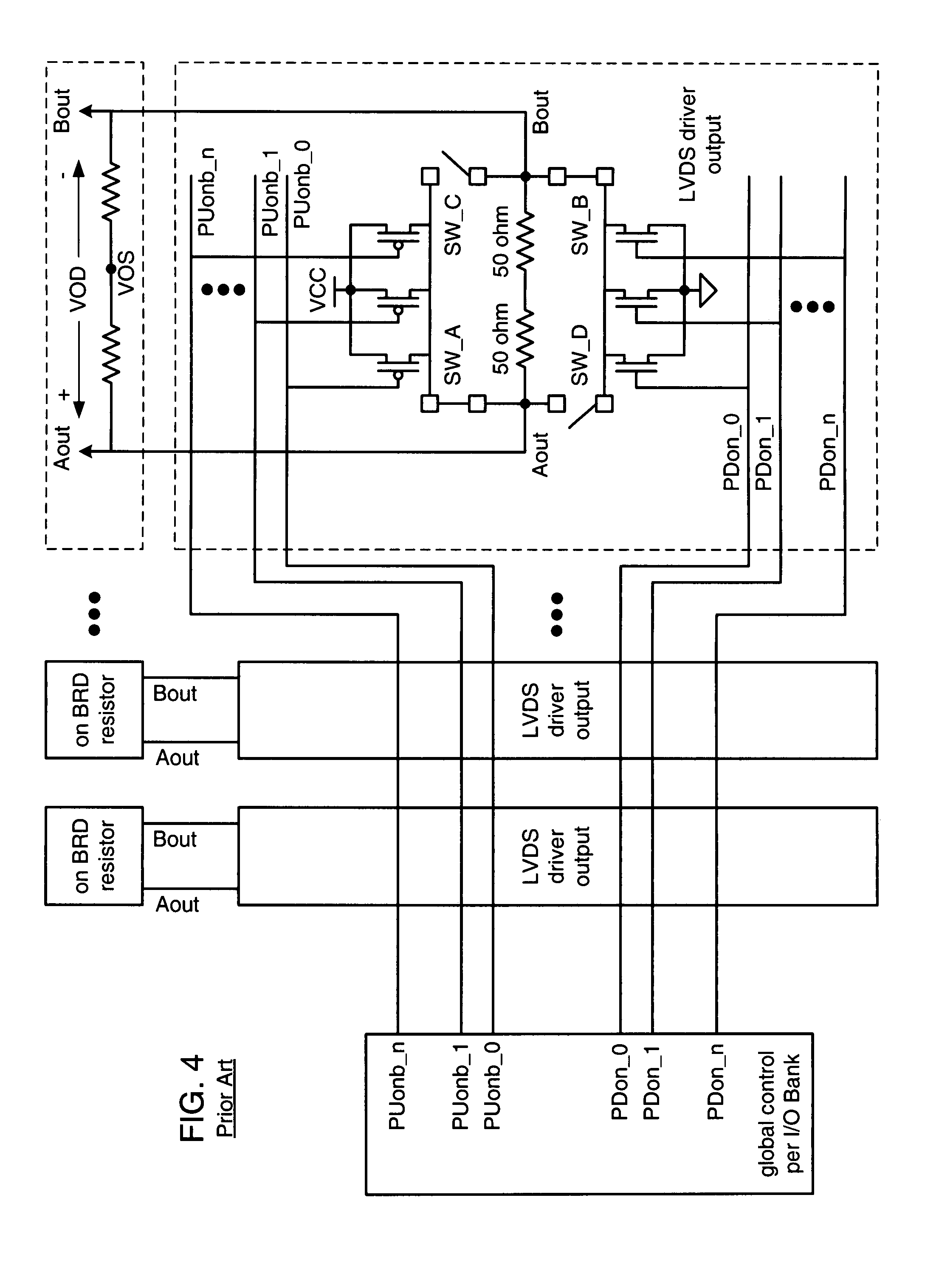

ActiveUS7265586B1Transmission line coupling arrangementsLogic circuits using elementary logic circuit componentsDifferential signalingSingle-ended signaling

A programmable differential signaling system includes a programmable bias generator and a plurality of input / output modules. The programmable bias generator is operably coupled to generate a first global bias signal and a second global signal based on desired signal properties of one of a plurality of differential signaling conventions. The a plurality of input / output modules is operably coupled to convert between differential signaling and single ended signaling, wherein actual signal properties of the differential signaling are regulated based on the first and second global bias signals to substantially equal the desired signal properties.

Owner:XILINX INC

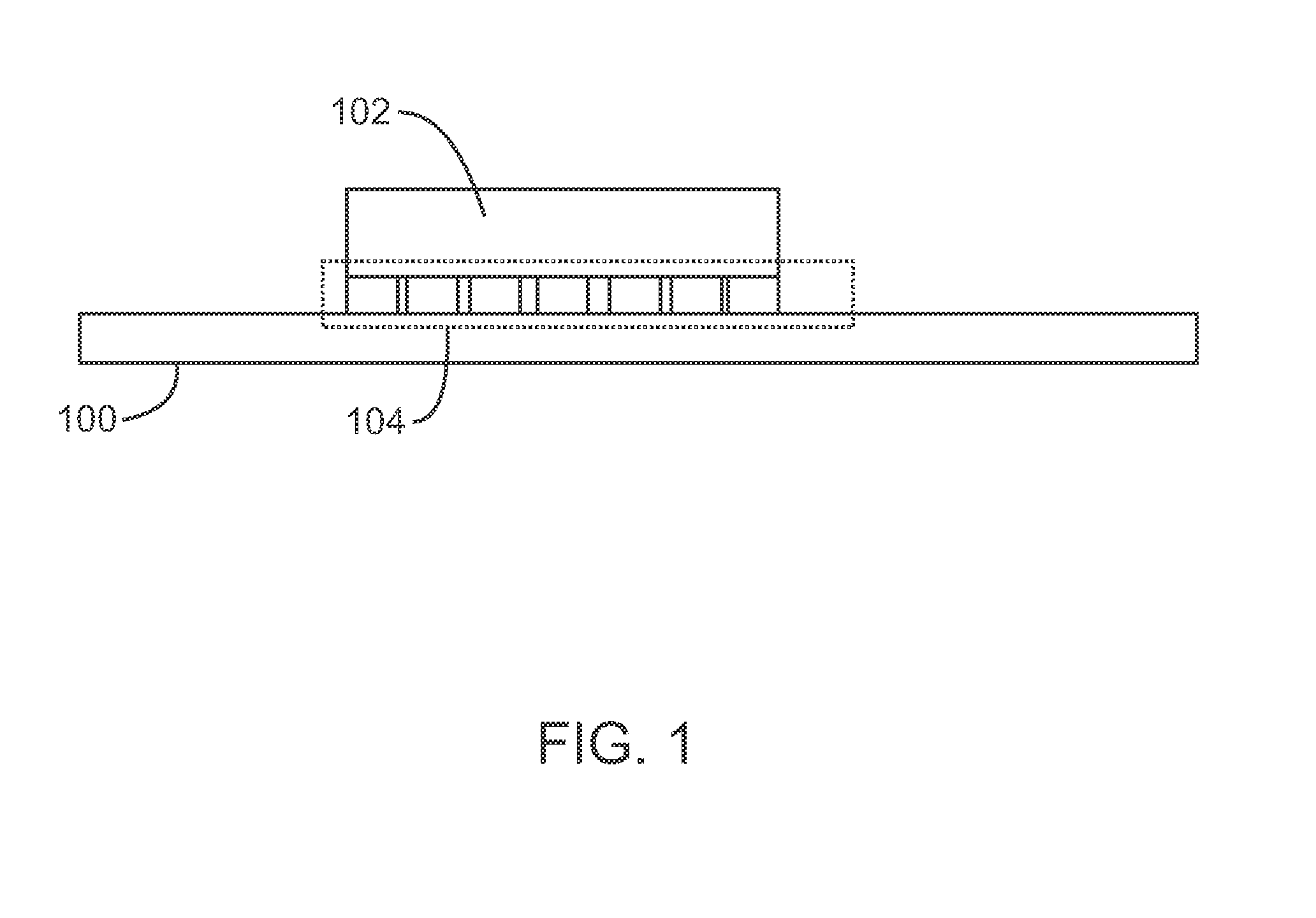

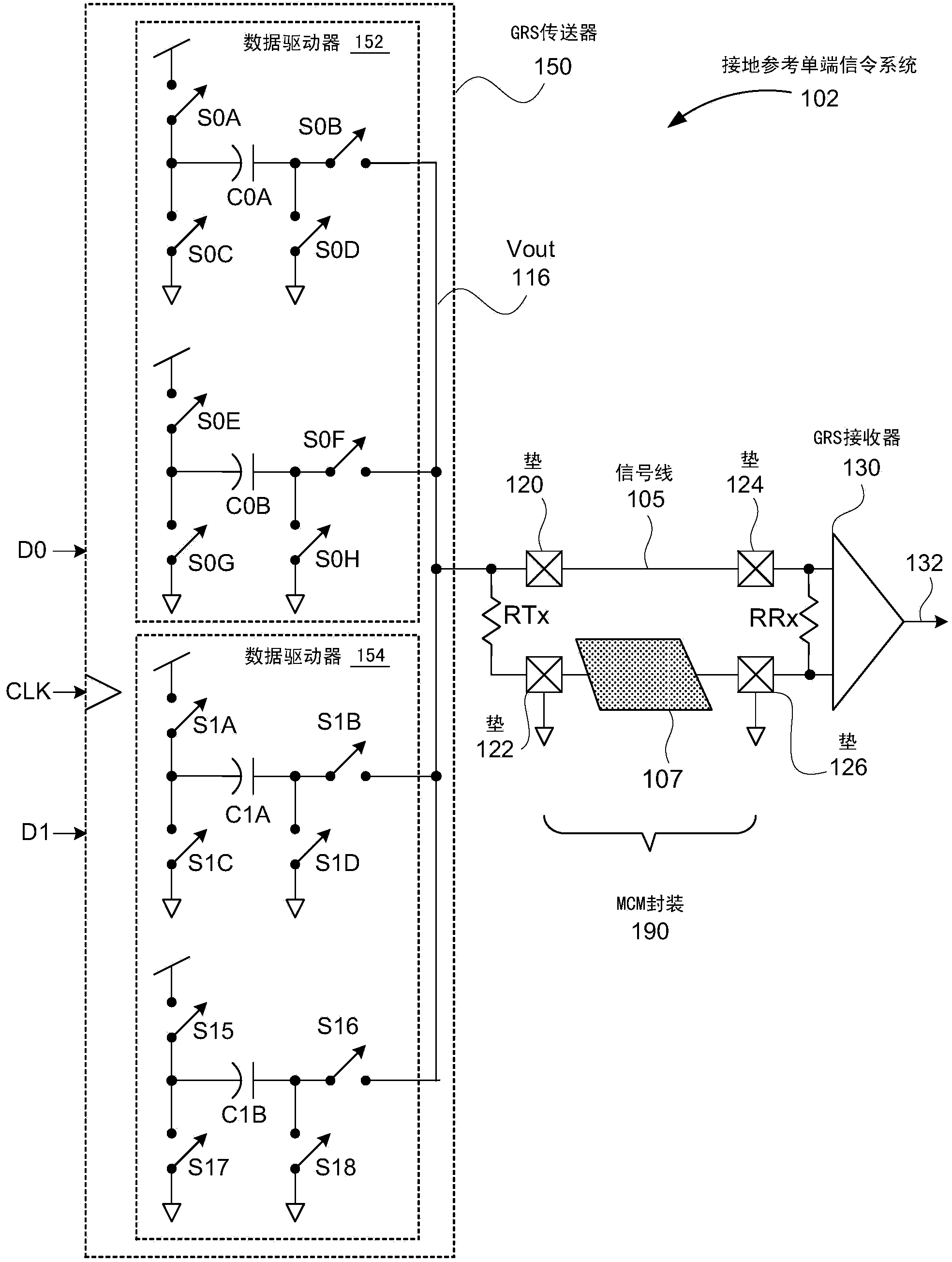

Ground-referenced single-ended signaling connected graphics processing unit multi-chip module

InactiveCN104050618ASemiconductor/solid-state device detailsSolid-state devicesComputer moduleComputer science

A system of interconnected chips comprising a multi-chip module (MCM) includes a first processor chip, a graphics processing cluster (GPC) chip, and an MCM package configured to include the first processor chip, the GPC chip, and an interconnect circuit. The first processor chip is configured to include a first ground-referenced single-ended signaling interface circuit. A first set of electrical traces fabricated within the MCM package and configured to couple the first single-ended signaling interface circuit to the interconnect circuit. The GPC chip is configured to include a second single-ended signaling interface circuit and to execute shader programs. A second set of electrical traces fabricated within the MCM package and configured to couple the second single-ended signaling interface circuit to the interconnect circuit. In one embodiment, each single-ended signaling interface advantageously implements ground-referenced single-ended signaling.

Owner:NVIDIA CORP

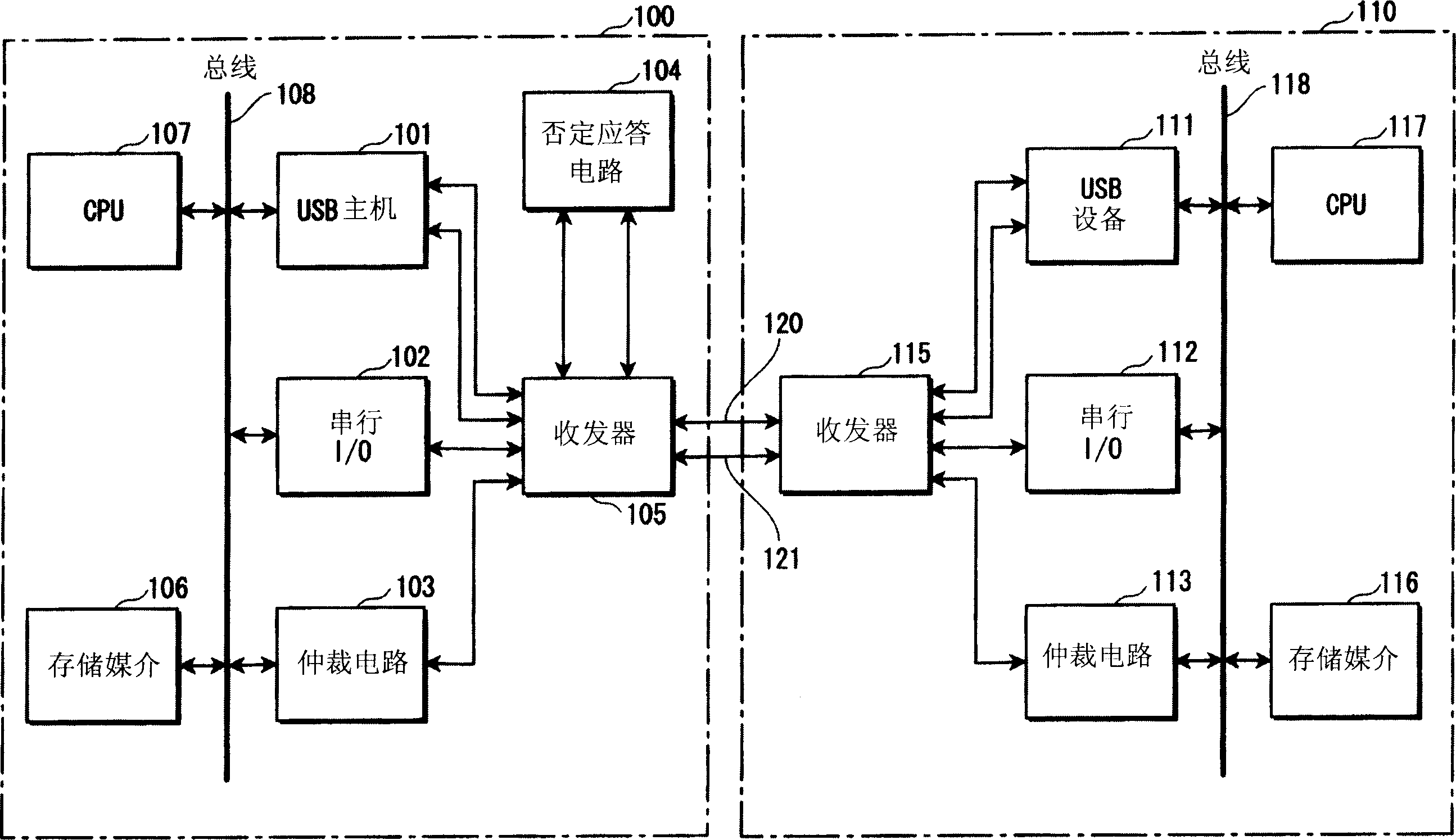

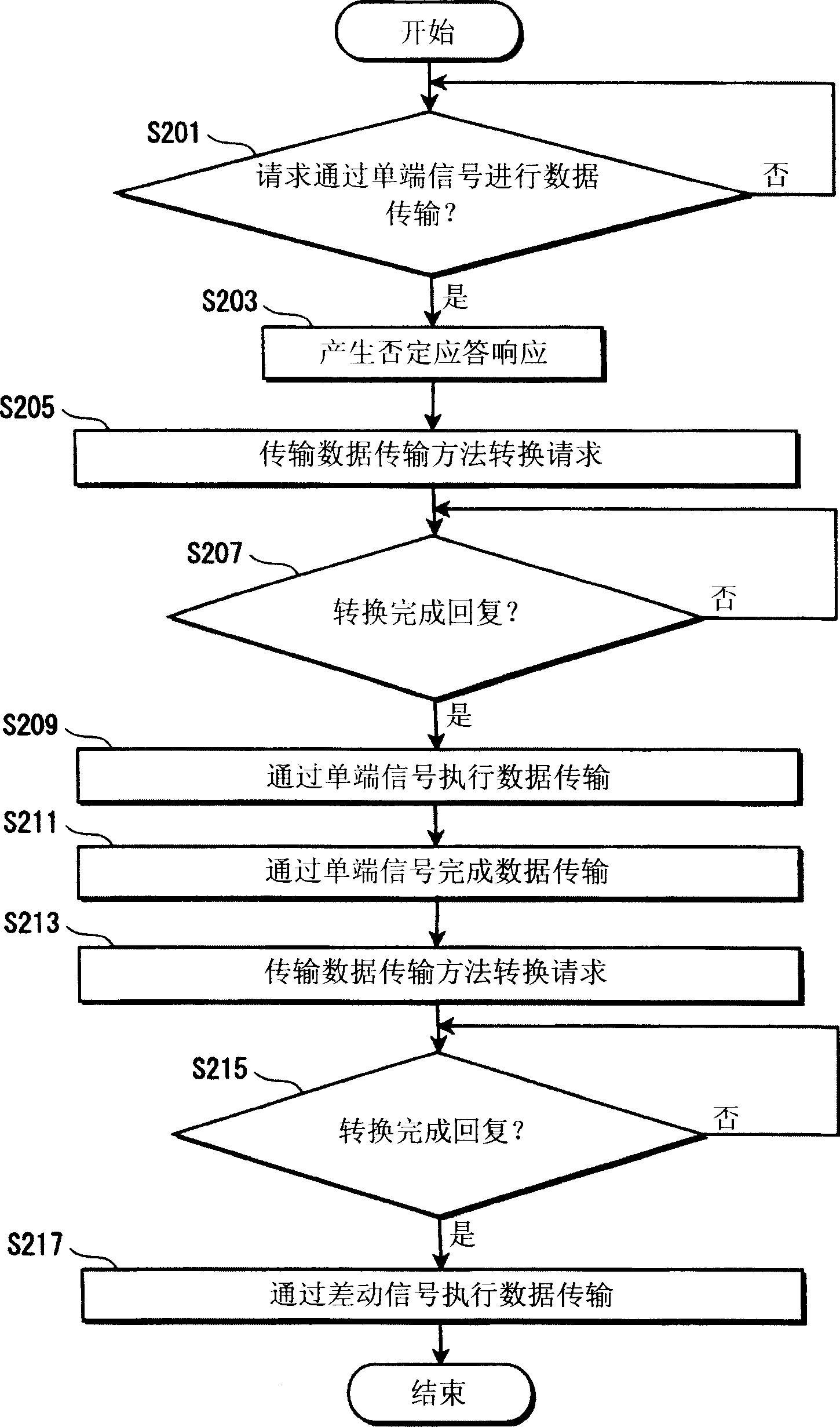

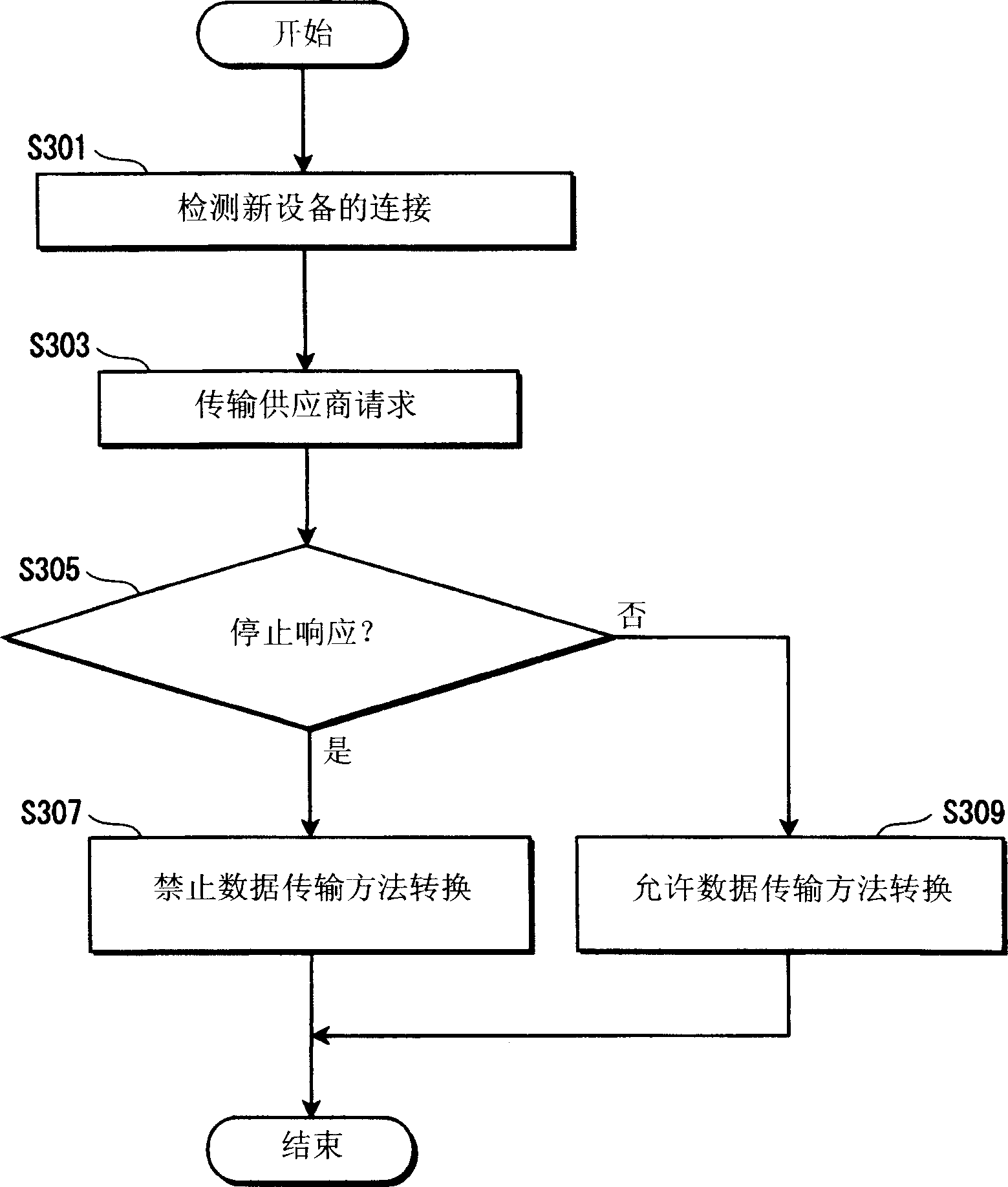

Communication apparatus, switching method, and switching program

To provide a communication apparatus which selectively performs a data transfer by differential signaling and a data transfer by single-ended signaling using a USB cable, where a USB host in the communication apparatus can recognize USB connection even when differential signaling is switched to single-ended signaling. The communication apparatus performs the data transfer by differential signaling using two data transfer signal lines in the USB cable, and the data transfer by single-ended signaling using one of the two data transfer signal lines. The communication apparatus includes a NAK circuit which, when differential signaling is switched to single-ended signaling, outputs a NAK response to the USB host to have the USB host recognize the USB connection.

Owner:PANASONIC CORP

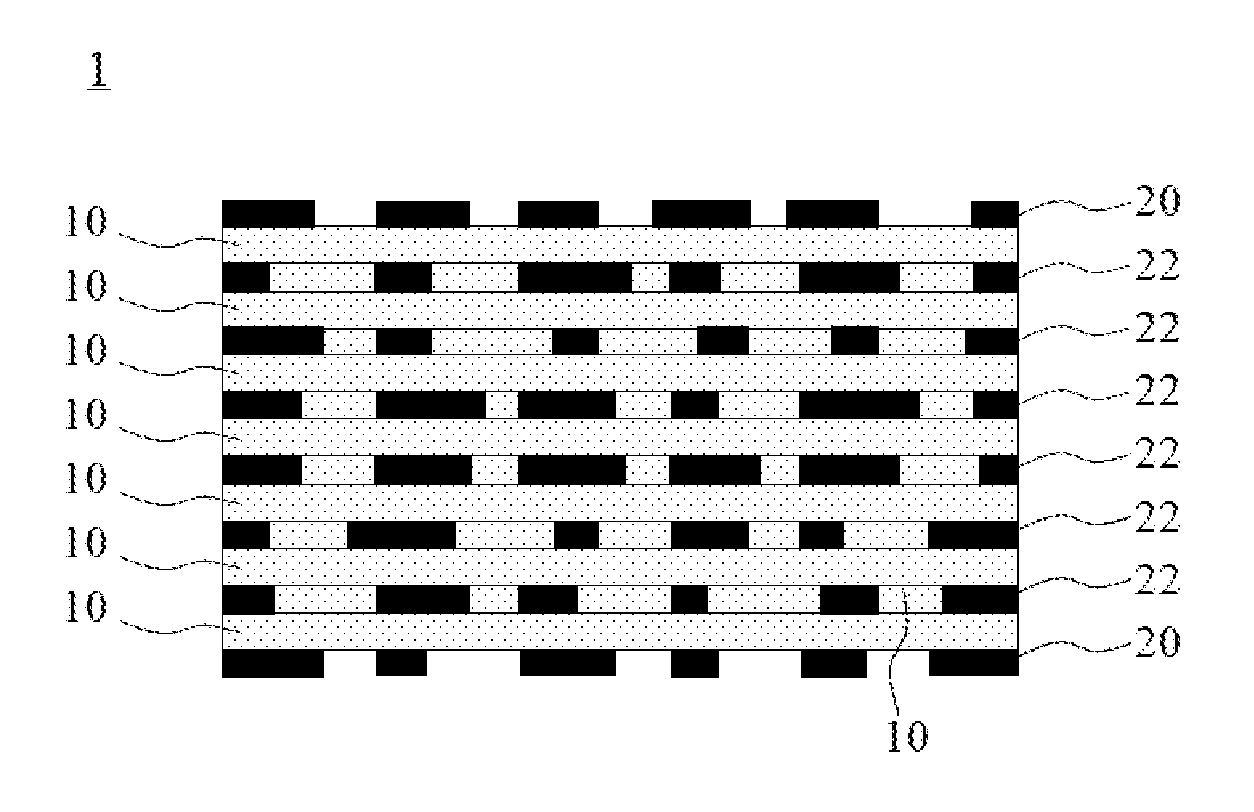

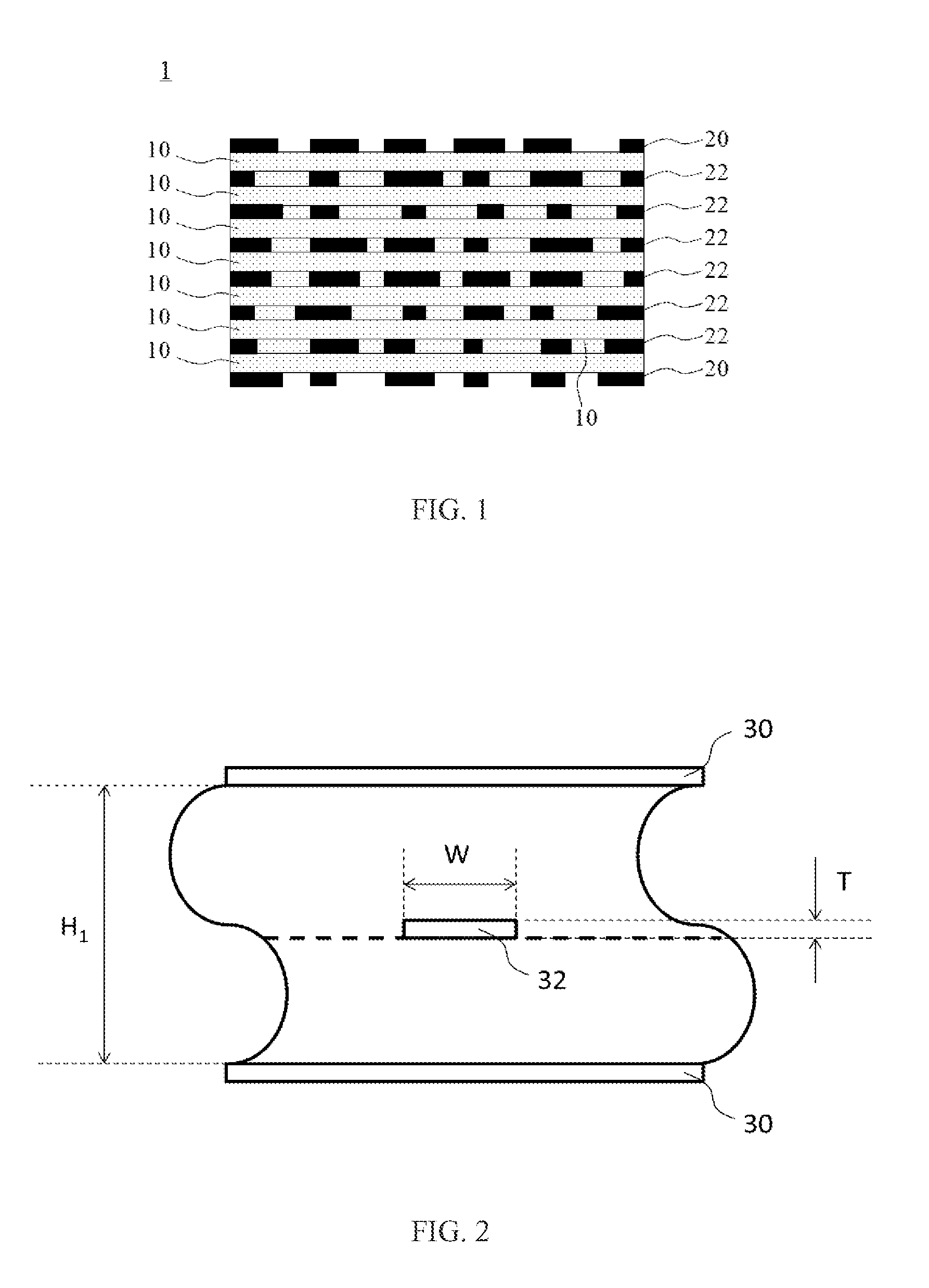

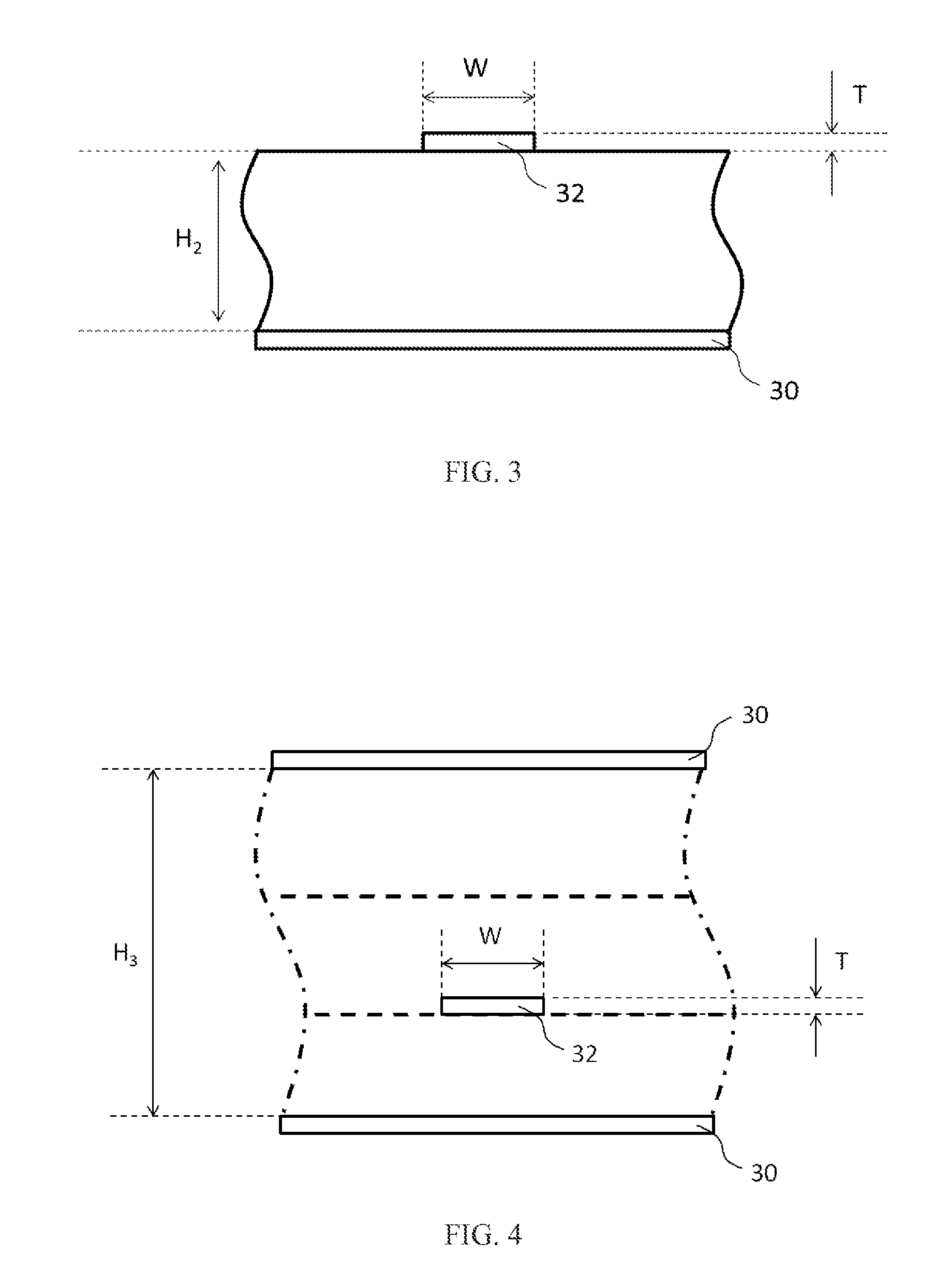

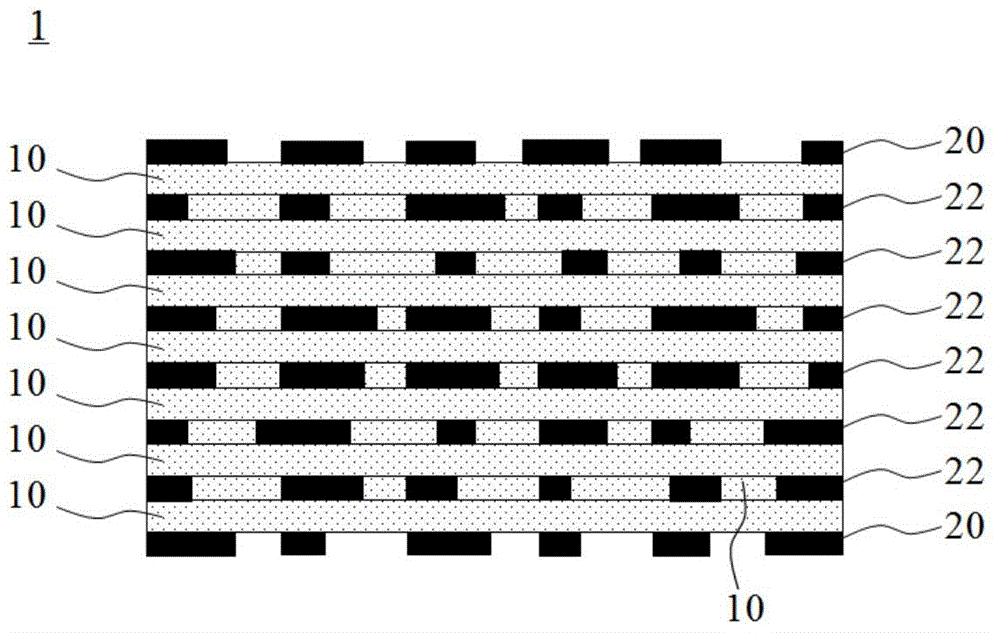

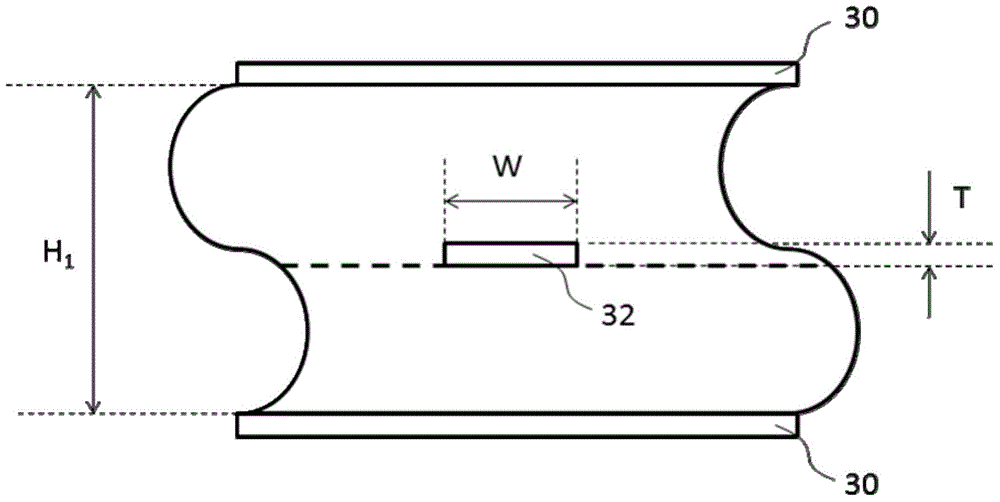

Multi-layer printed circuit boards suitable for layer reduction design

ActiveUS20160120018A1Function increaseHigh yield rateMultiple-port networksHigh frequency circuit adaptationsGlass fiberInsulation layer

A multi-layer printed circuit board comprises: at least two insulation layers, respectively having glass fiber cloth and cured resin covering thereon, the insulation layers being stacked on each other; an internal trace layer formed between two neighboring insulation layers; and an external trace layer formed on an outer surface of the outermost insulation layer; wherein the insulation layers have a dielectric constant of 3.4 or less, and the internal and external trace layers have a trace width between 40 and 75 micrometers, such that the multi-layer printed circuit board has a characteristic impedance between 45 and 55 Ω in single-ended signaling and between 90 and 110 Ω in differential signaling.

Owner:ELITE MATERIAL

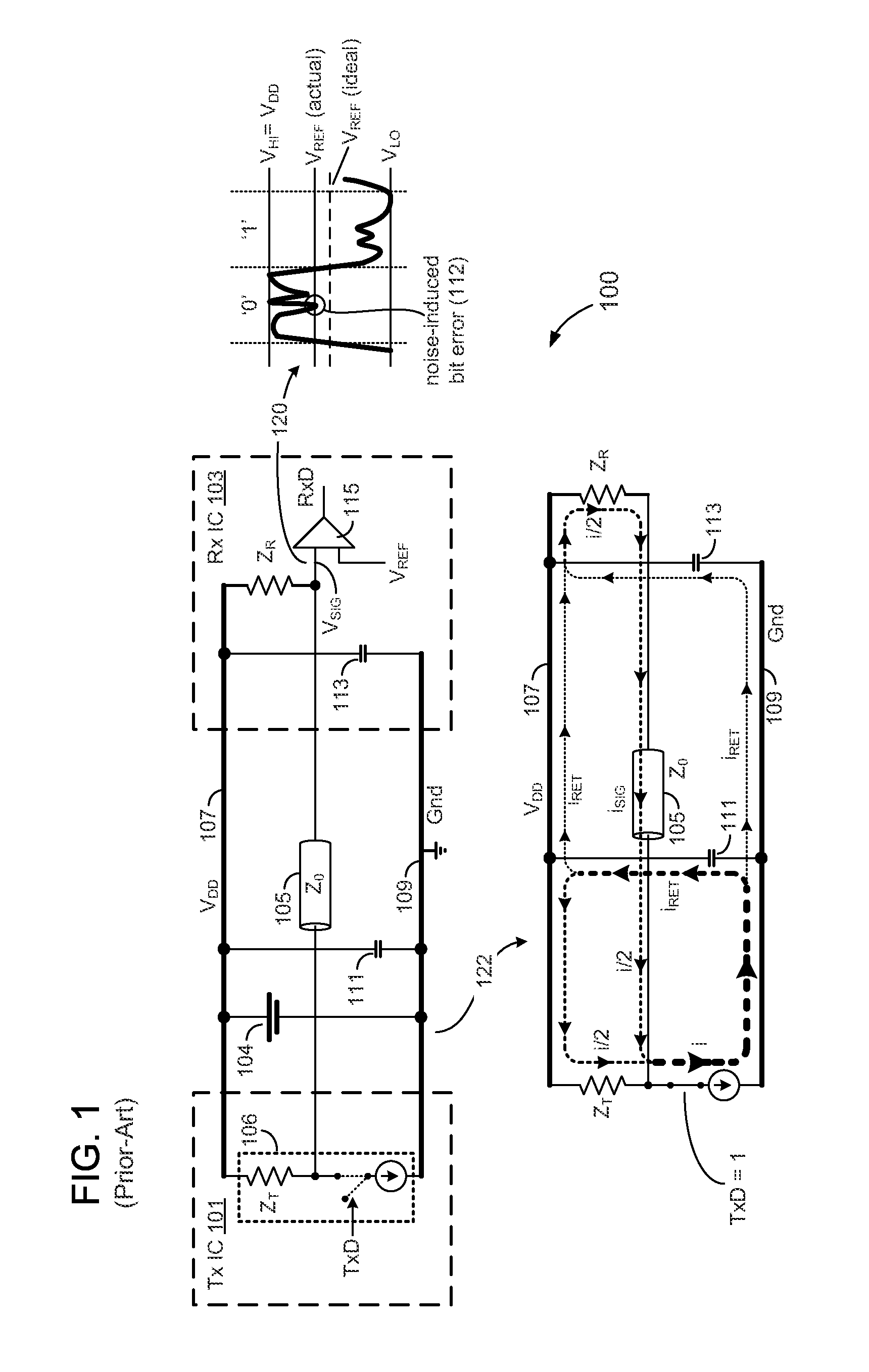

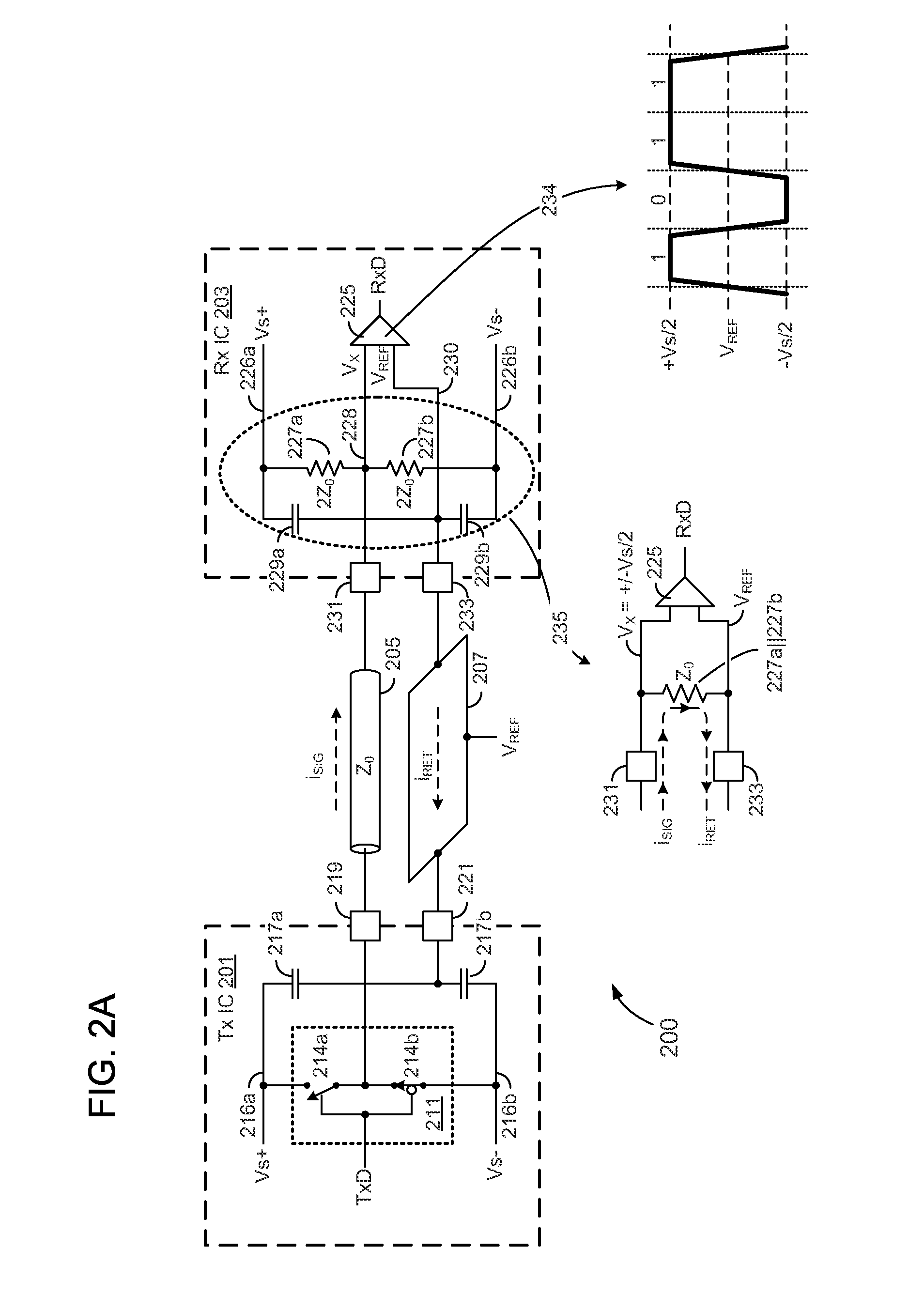

Single-ended signaling with parallel transmit and return current flow

ActiveUS8513976B2Reliability increasing modificationsMultiple input and output pulse circuitsElectrical conductorReturn current

A single-ended signaling system in which transmitted and returned signal currents are enabled to flow substantially parallel to one another and thereby maintain a substantially uniform impedance along the length of a single-ended signal conductor. A reference plane is disposed substantially parallel to a single-ended signaling conductor and coupled to the signaling conductor within a signal-receiving IC and to signaling supply voltage nodes within a signal-transmitting IC. By this arrangement, an signal current flowing to or from the receiving IC via the signaling conductor is conducted to the reference plane, thereby enabling a signal-return current to flow back to or back from the transmitting IC along a single path that is substantially parallel to the signal conductor.

Owner:RAMBUS INC

Multi-layer printed circuit boards suitable for layer reduction design

ActiveCN105682337AImprove signal transmission characteristicsHigh frequency circuit adaptationsPrinted circuit aspectsGlass fiberInsulation layer

A multi-layer printed circuit board comprises: at least two insulation layers, respectively having glass fiber cloth and cured resin covering thereon, the insulation layers being stacked on each other; an internal trace layer formed between two neighboring insulation layers; and an external trace layer formed on an outer surface of the outermost insulation layer; wherein the insulation layers have a dielectric constant of 3.4 or less, and the internal and external trace layers have a trace width between 40 and 75 micrometers, such that the multi-layer printed circuit board has a characteristic impedance between 45 and 55 [Omega] in single-ended signaling and between 90 and 110 [Omega] in differential signaling.

Owner:ELITE MATERIAL

Method and Apparatus for Far End Crosstalk Reduction in Single Ended Signaling

InactiveUS20140174812A1Liquid/solution decomposition chemical coatingPrinted circuit manufactureElectrical conductorEngineering

A method of reducing crosstalk. The method may include forming a first contact over a first vertical conductor. The method may include forming a second contact over a second vertical conductor. The method may include forming a third contact over a third vertical conductor. The method may include forming a capacitive coupler between the first contact, the second contact, and the third contact, wherein the capacitive coupler is to cancel crosstalk received at the second vertical conductor and third vertical conductor from the first vertical conductor.

Owner:INTEL CORP

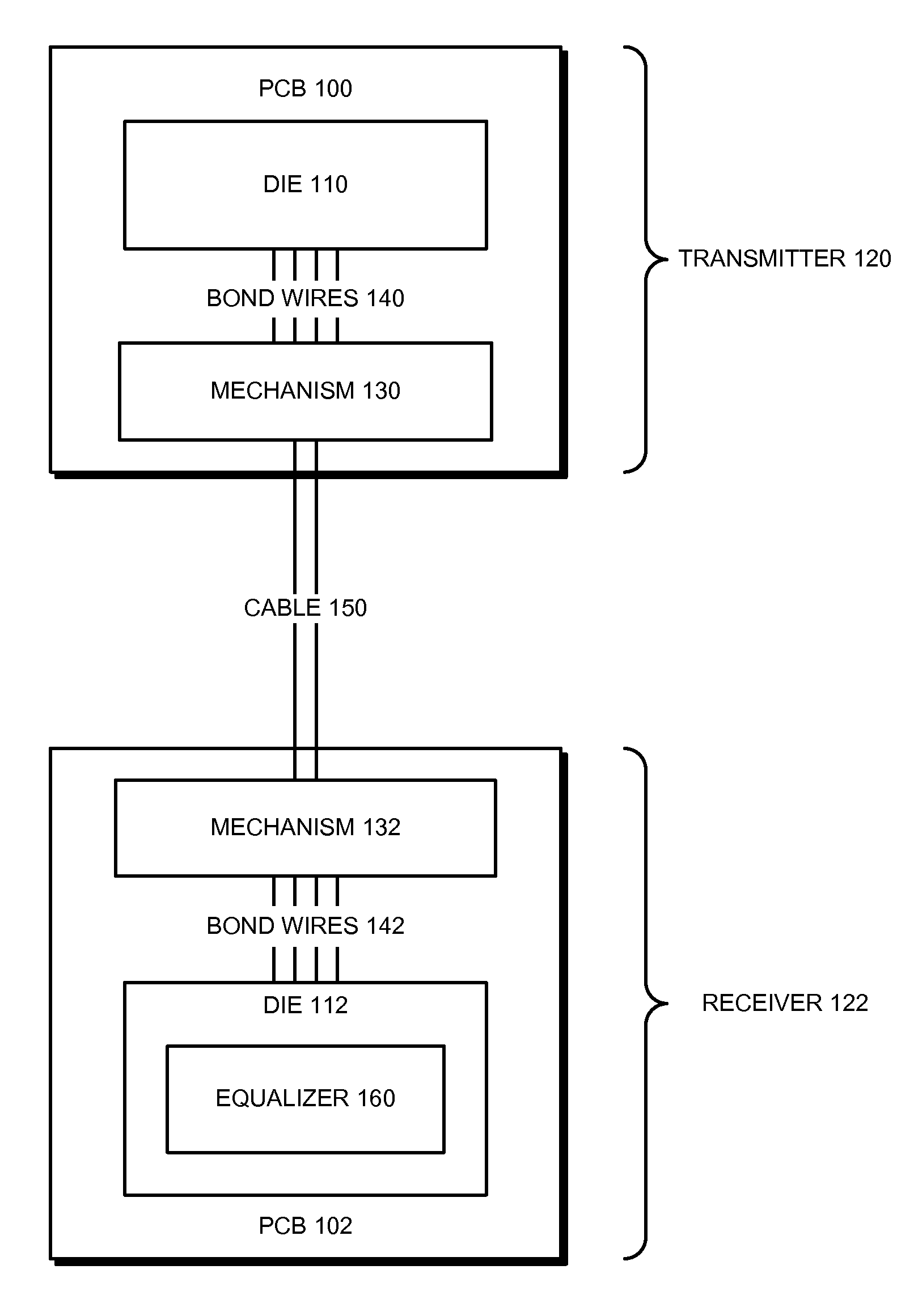

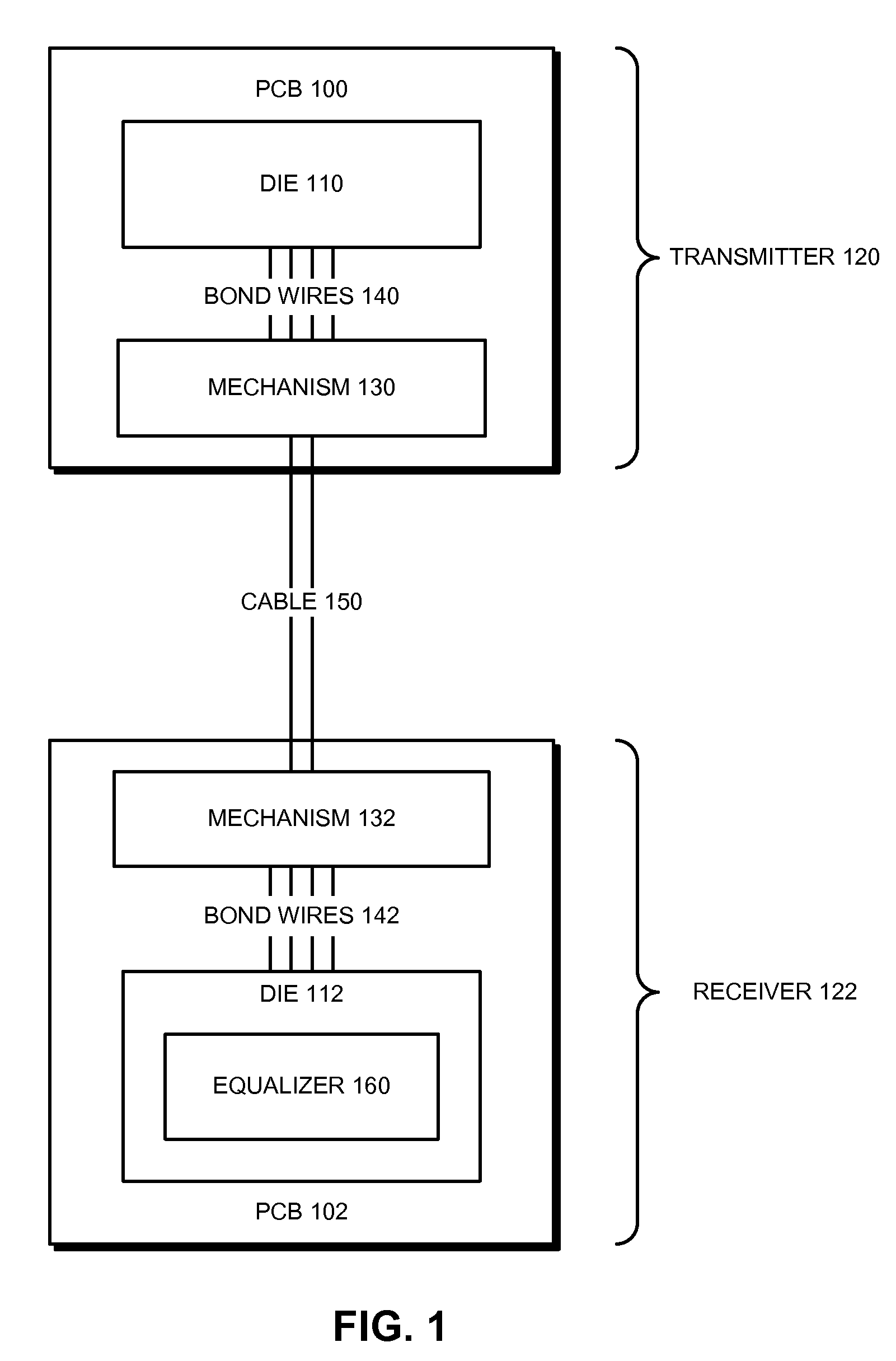

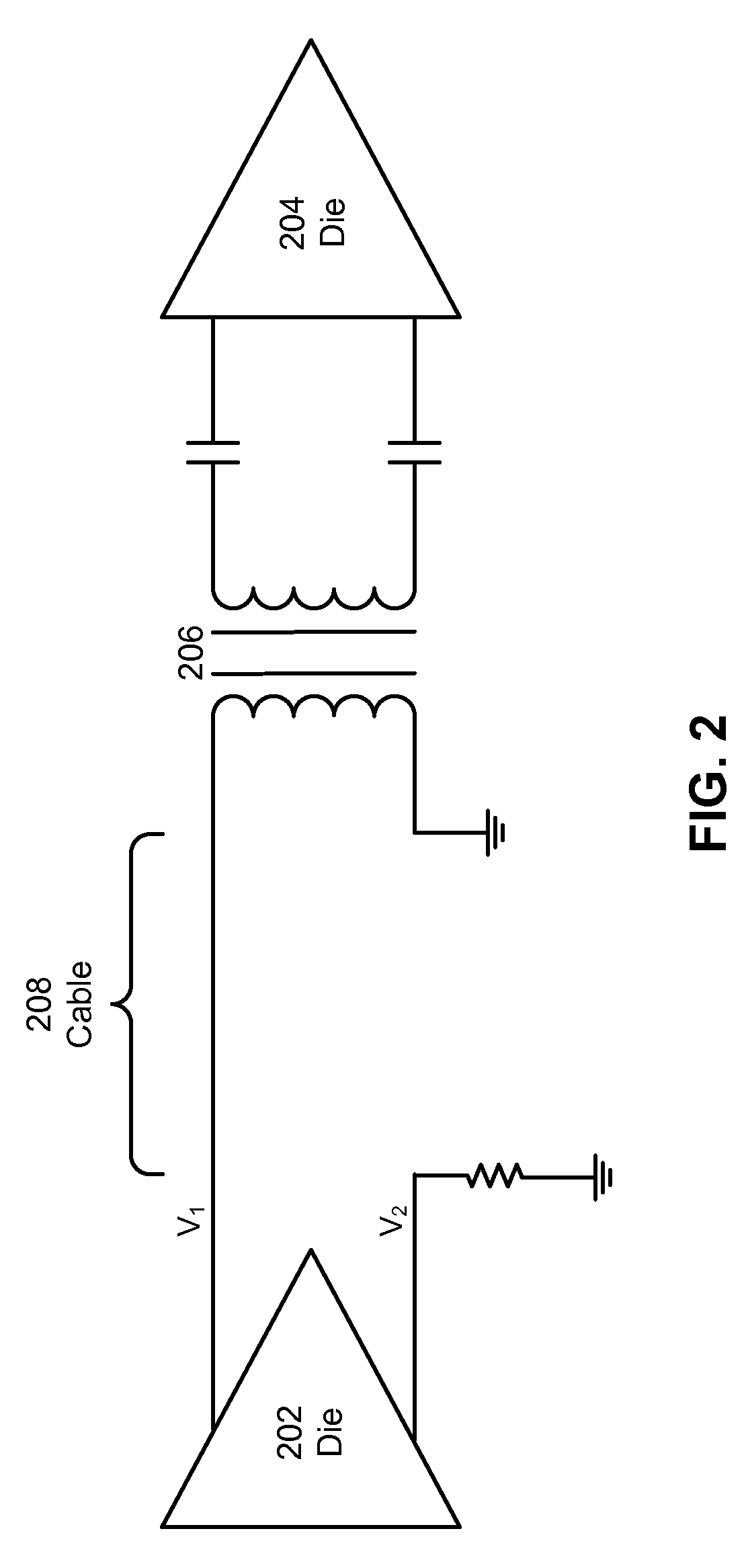

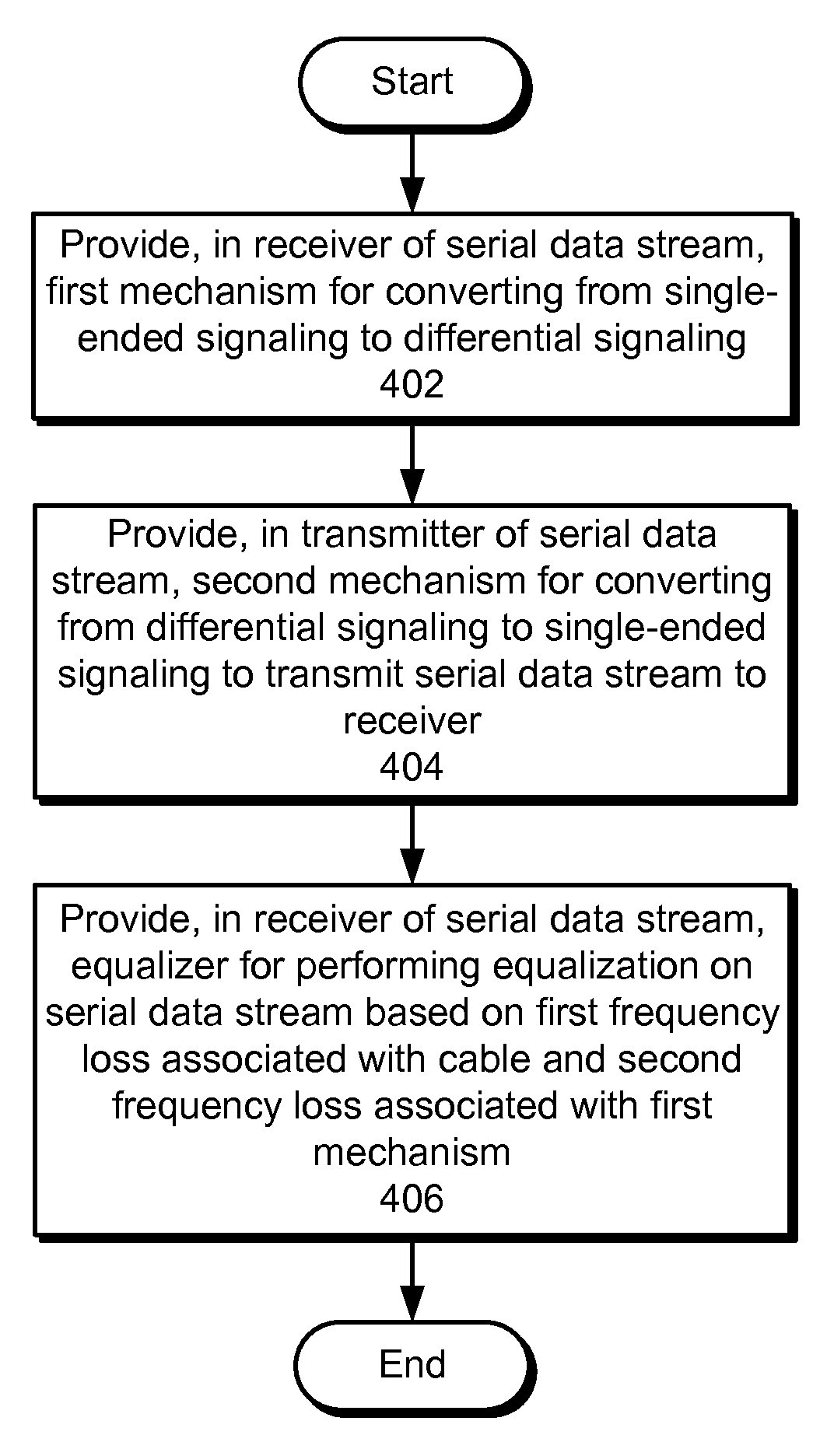

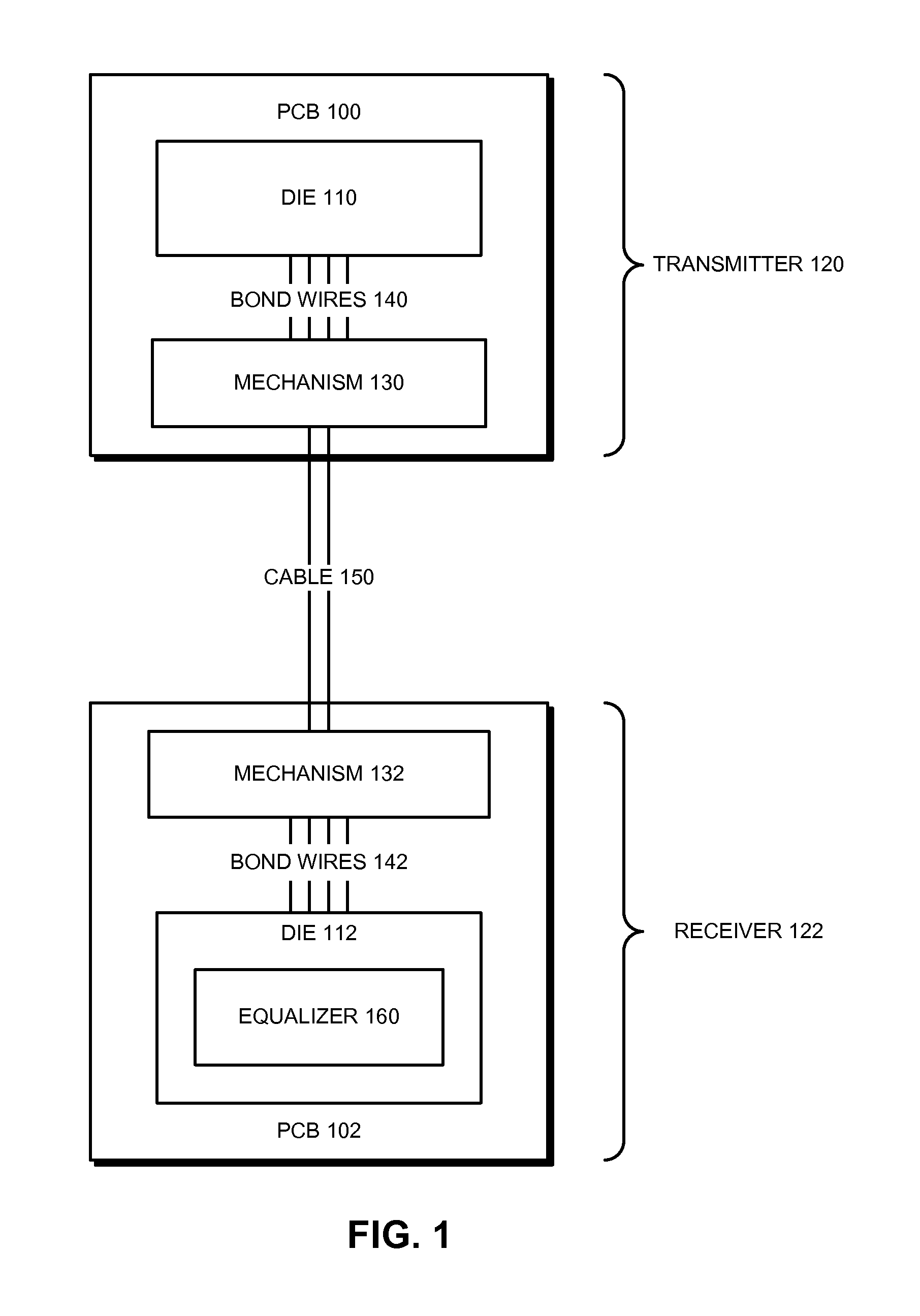

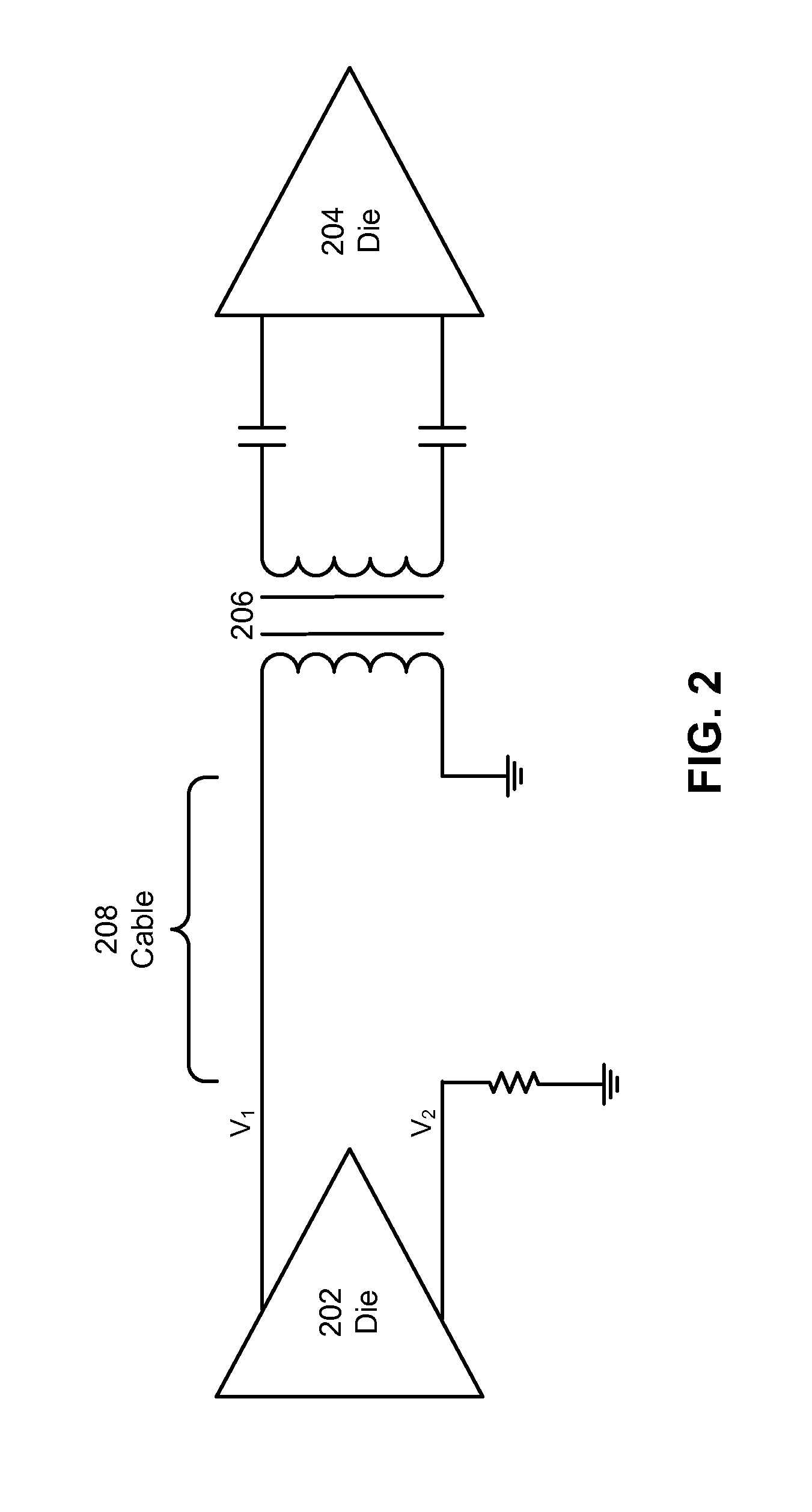

Signal conversion during transmission of serial data streams

ActiveUS8737521B2Facilitate transmissionFacilitates rejectionMultiple-port networksError preventionComputer hardwareData stream

The disclosed embodiments provide a system that facilitates transmission of a serial data stream. The system may include, in a receiver of the serial data stream, a first mechanism for converting from single-ended signaling to differential signaling, wherein the first mechanism facilitates rejection of common mode noise in the serial data stream. For example, the first mechanism may be a balun and / or a common-mode choke.

Owner:APPLE INC

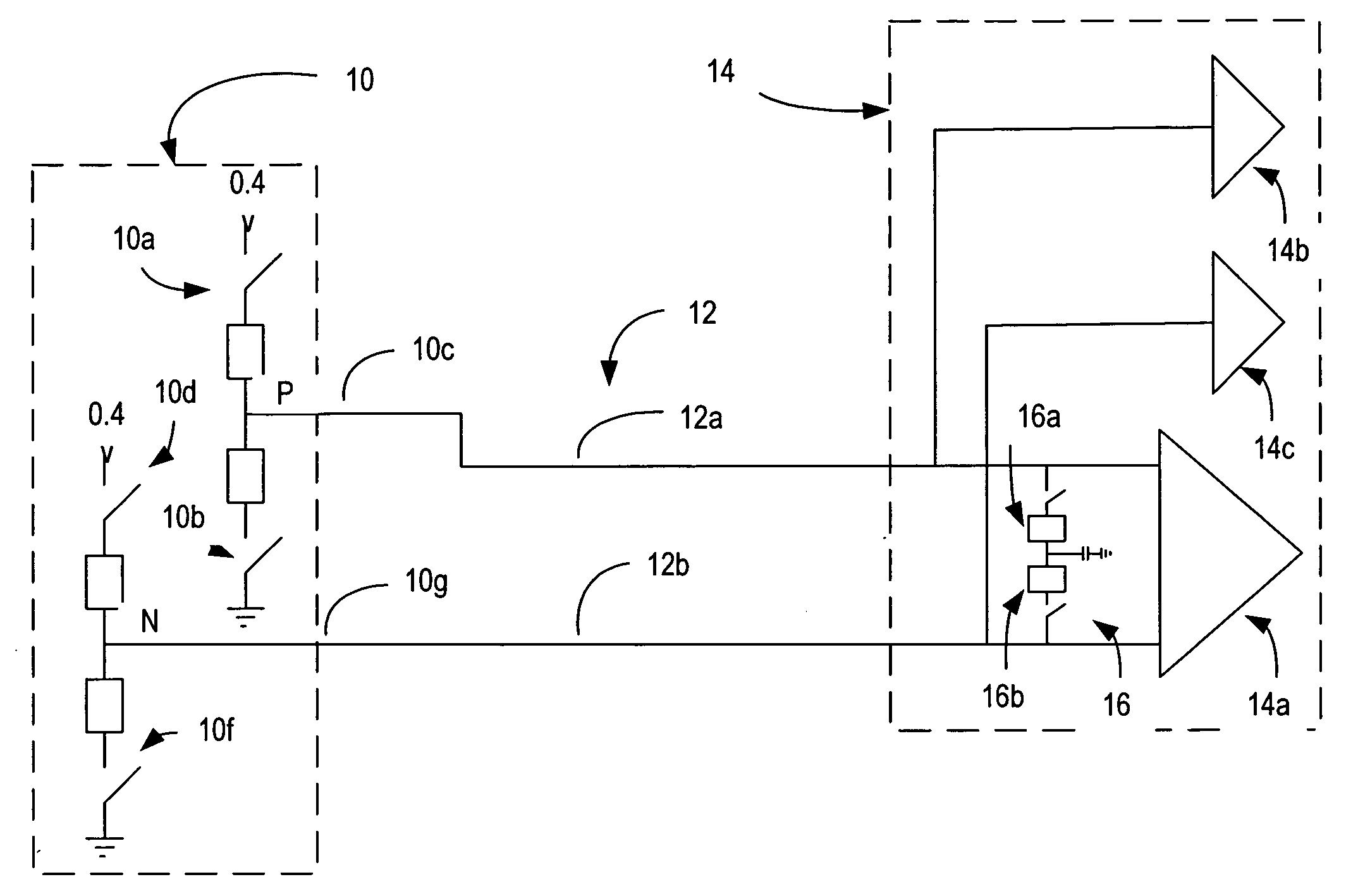

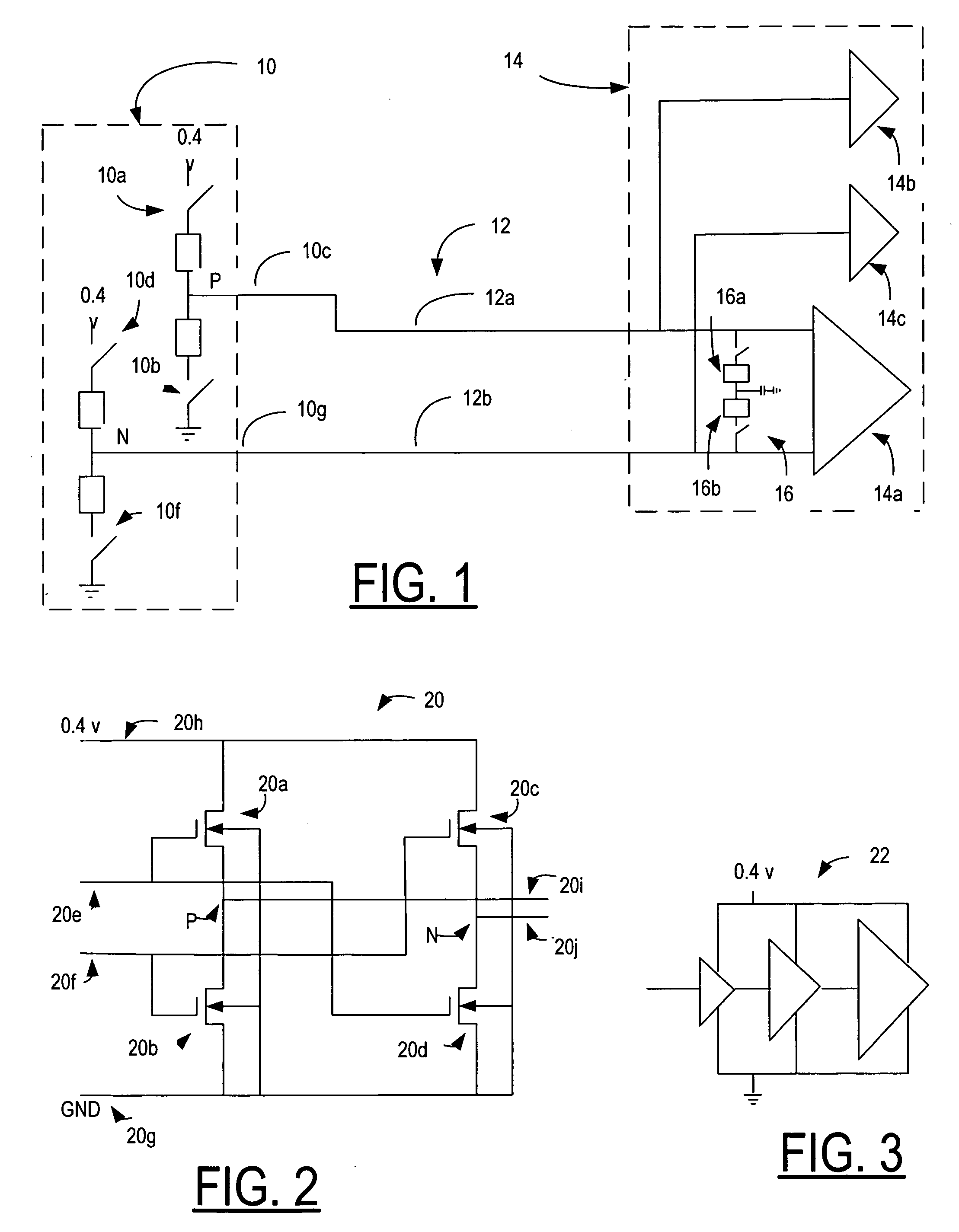

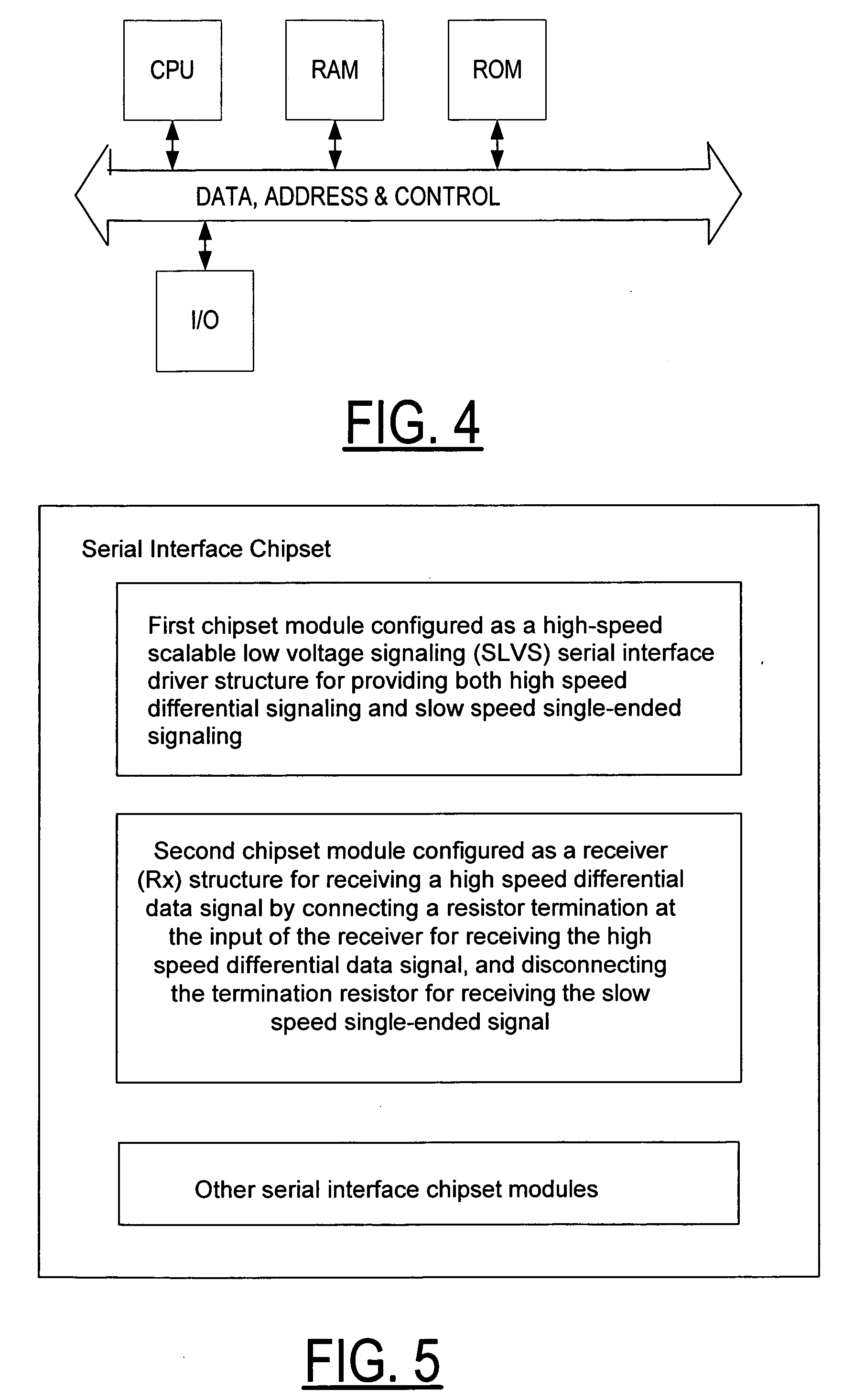

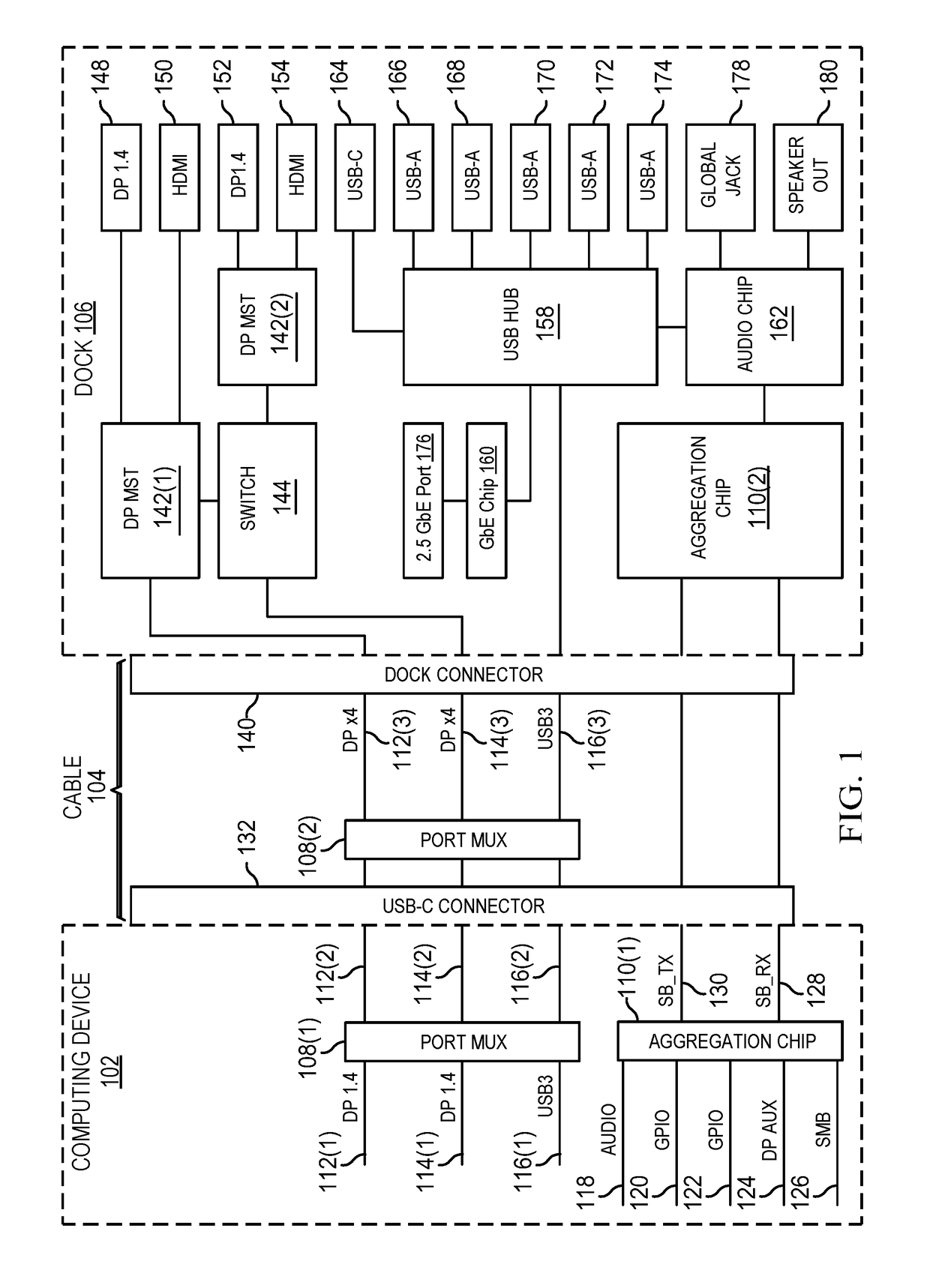

Control and slow data transmission method for serial interface

InactiveUS20080133799A1Increase speedSimple structureTransmission line coupling arrangementsInput/output processes for data processingCMOSDifferential signaling

A scalable low voltage signaling (SLVS) serial interface structure is configured as a 0.4V NMOS totem-pole driver structure for both high speed differential signaling and slow speed single-ended signaling using the same 0.4V NMOS totem-pole driver structure. An un-terminated receiver (Rx) and a CMOS inverter comparator powered from a 0.4 volt supply, is used for receiving the slow speed single-ended 0-100 mega bits per second (Mbps) signaling in a data link. A terminated receiver (Rx) and a differential comparator powered from a 0.4 volt supply, is used for receiving the high speed differential 2 giga bits per second (Gbps) signaling in the data link.

Owner:NOKIA CORP

Increasing data throughput of a universal serial bus (USB) type-C port

A computing device may include a universal serial bus (USB) port, a port controller, and a first port multiplexer. The port controller may determine that a connector of a cable has been connected to the port of the computing device and determine that the cable includes a second port multiplexer. The port controller may send a first instruction to the first port multiplexer to select a single-ended signaling configuration and send a second instruction to the second port multiplexer to select the single-ended signaling configuration. In the single-ended configuration, the first port multiplexer may receive a set of differential signals, convert the set of differential signals to a corresponding set of single-ended signals, and output the set of single-ended signals to the port.

Owner:DELL PROD LP

Method and system for configurable differential or single-ended signaling in an integrated circuit

Aspects of a method and system for configurable differential or single-ended signaling in an integrated circuit. In this regard, a balun comprising one or more loops fabricated in a plurality of metal layers in an integrated circuit may enable conversion between unbalanced and balanced signals. In this regard, balanced signal output by a power amplifier may be converted to a balanced signal for transmission via an antenna. Similarly, an unbalanced signal received by an antenna may be converted to a balanced signal for amplification by an amplifier with a balanced input. The loops may be fabricated in transmission line media such as microstrip and / or stripline. The loops may comprise ferromagnetic material which may be deposited on and / or within the IC. Signals converted via the balun may be in the 61 GHz-61.5 GHz ISM band.

Owner:AVAGO TECH INT SALES PTE LTD

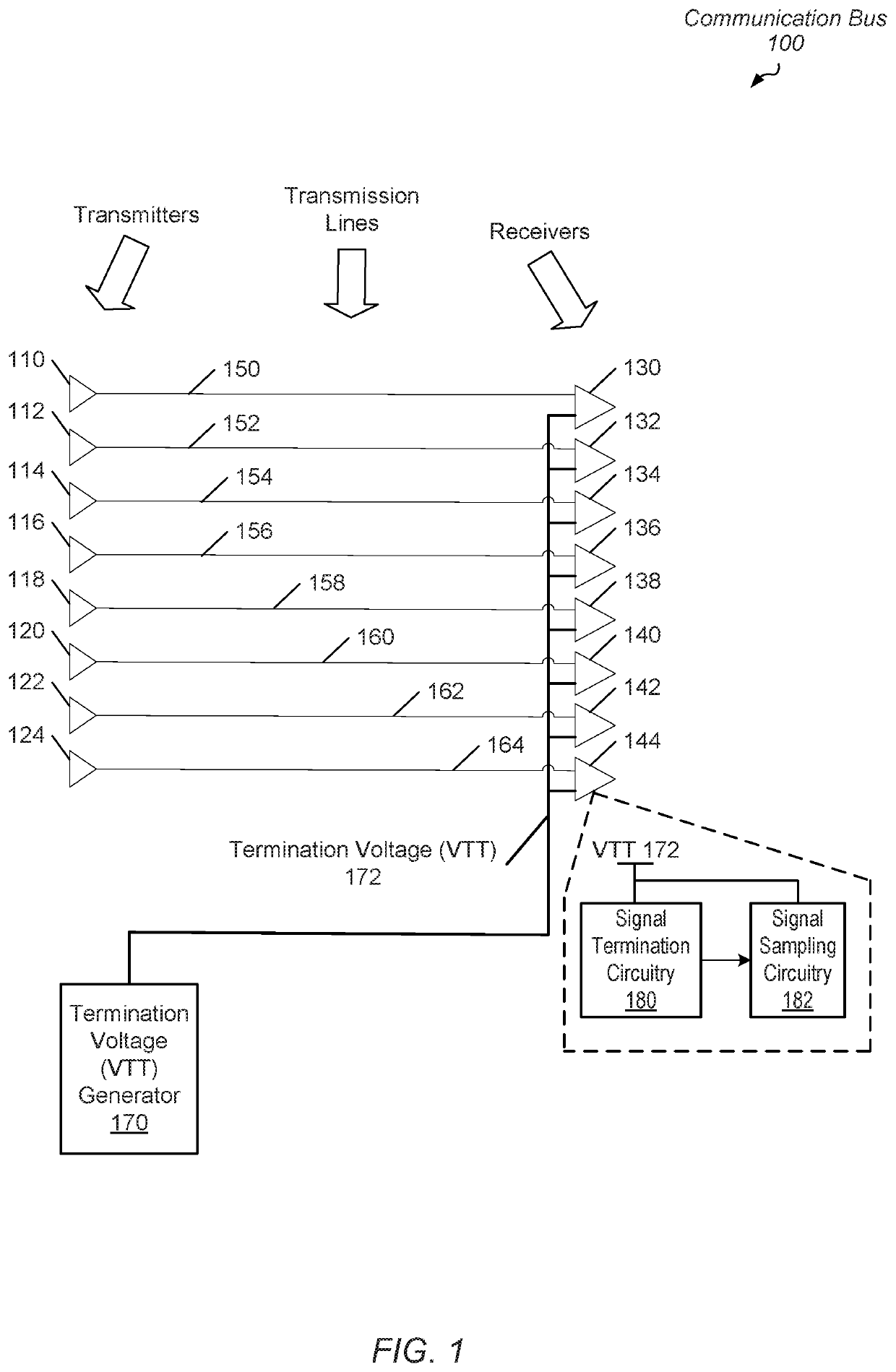

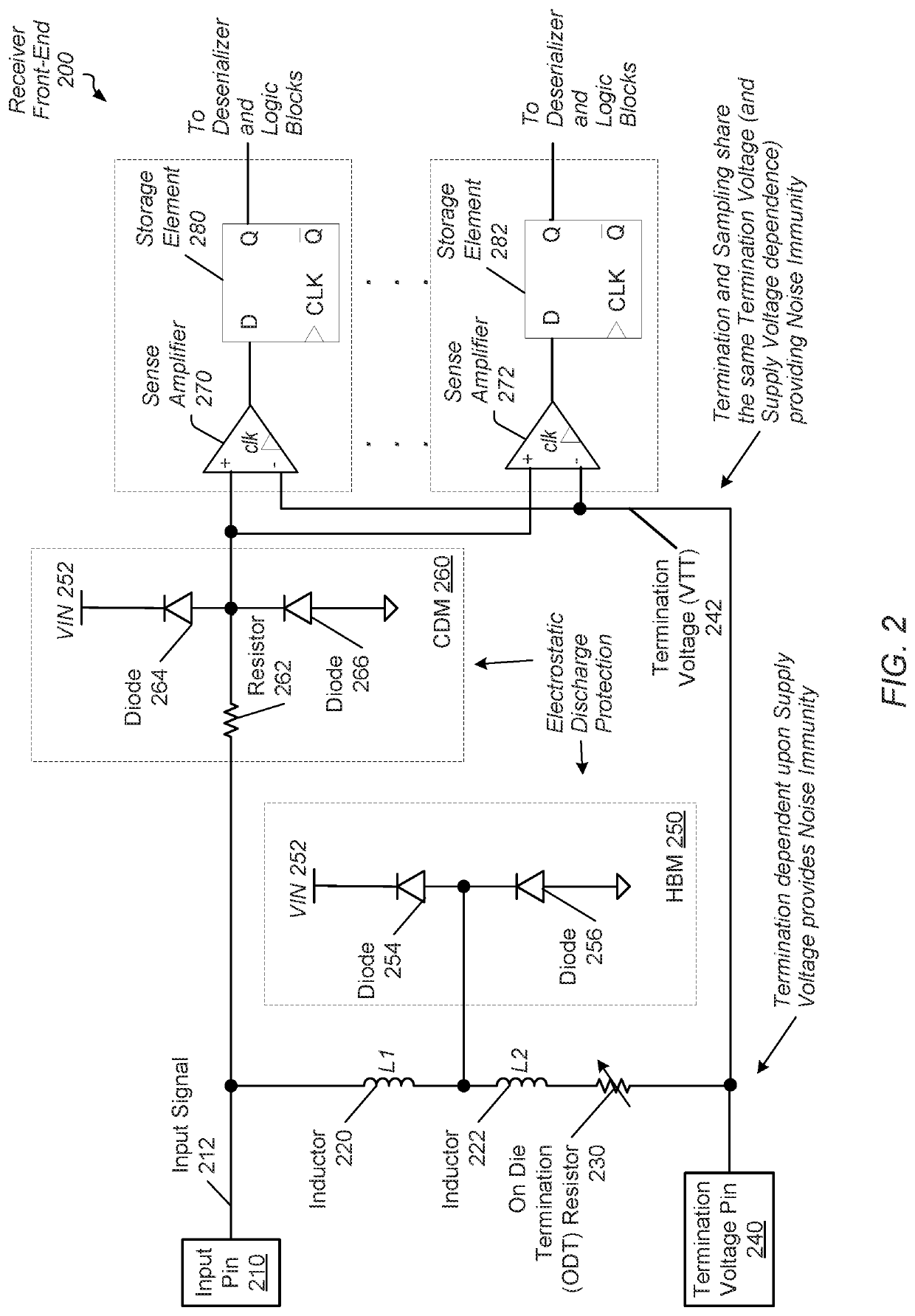

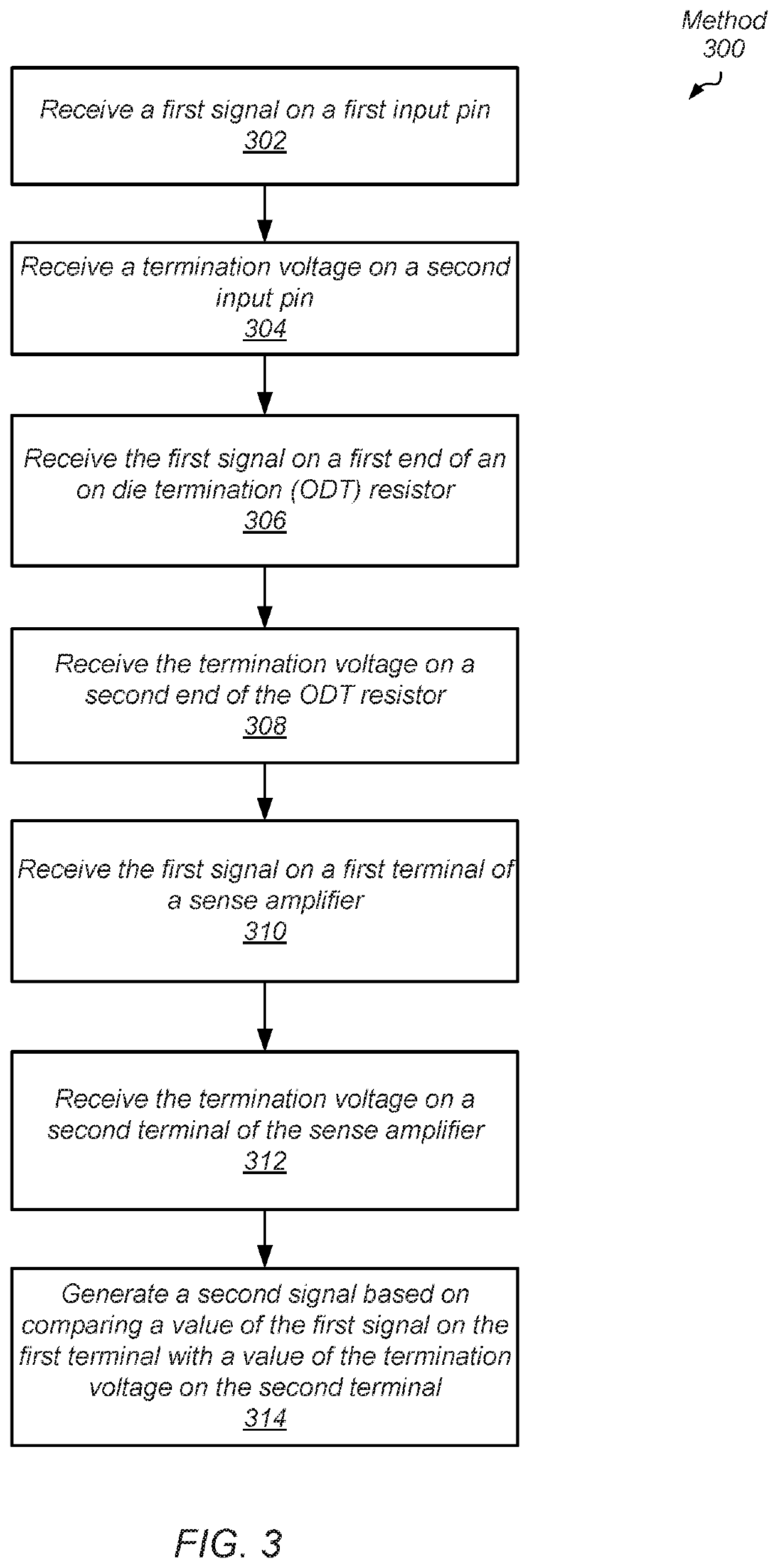

Pseudo differential receiving mechanism for single-ended signaling

ActiveUS10749552B2Analogue/digital conversionElectric signal transmission systemsTerminal voltageData signal

Owner:ADVANCED MICRO DEVICES INC

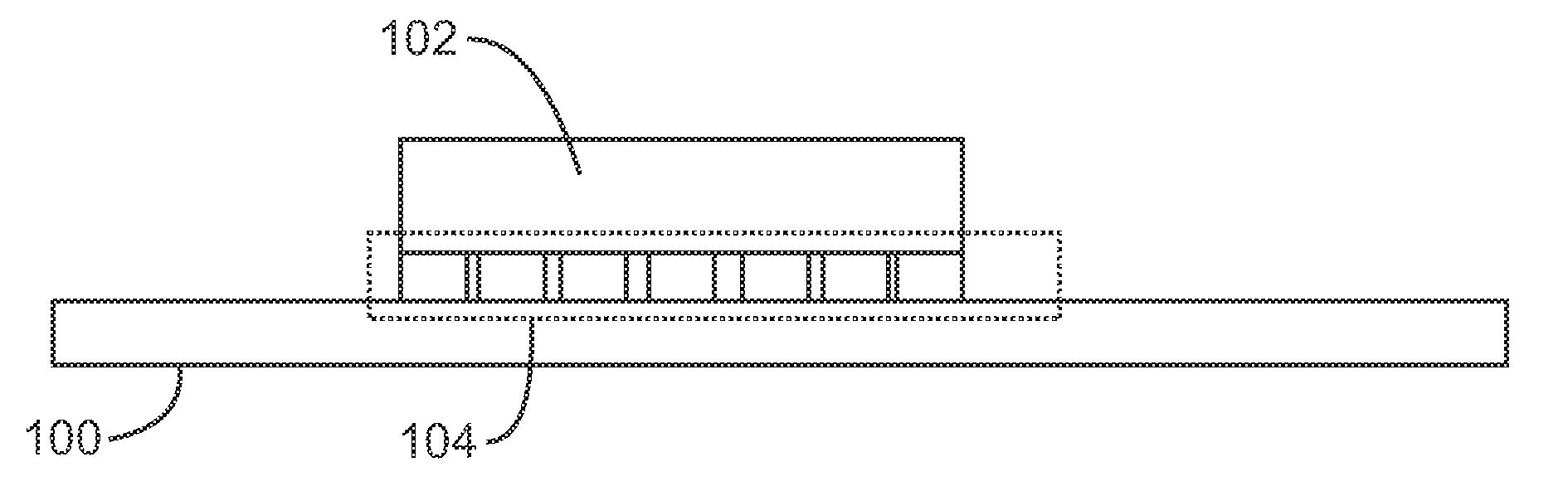

On-package multiprocessor ground-referenced single-ended interconnect

ActiveCN104050130ADigital storageElectrical connection printed elementsComputer moduleComputer science

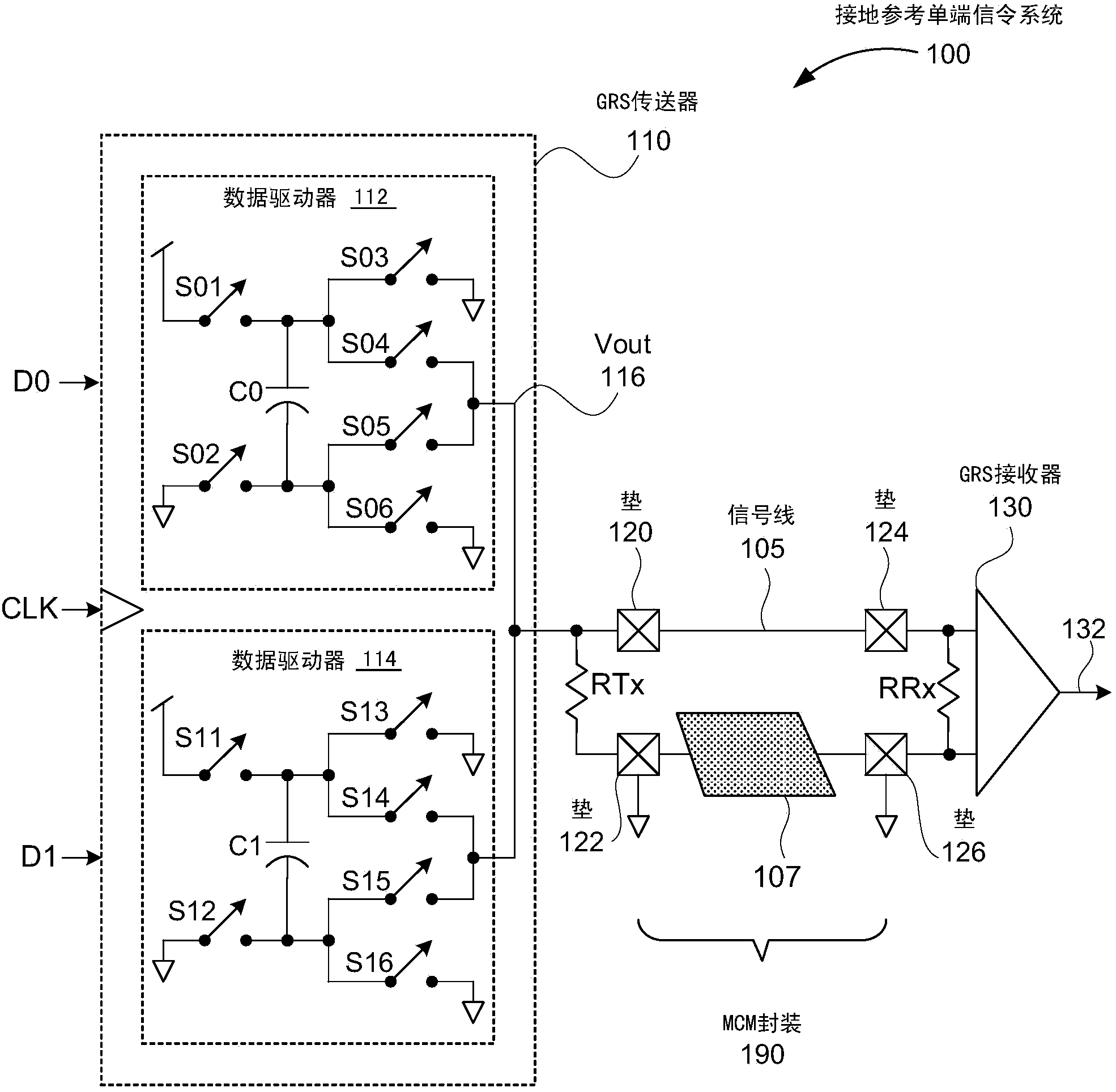

A system of interconnected chips comprising a multi-chip module (MCM) includes a first processor chip, a second processor chip, and an MCM package configured to include the first processor chip, the second processor chip, and an interconnect circuit. The first processor chip is configured to include a first ground-referenced single-ended signaling (GRS) interface circuit. A first set of electrical traces fabricated within the MCM package and configured to couple the first GRS interface circuit to the interconnect circuit. The second processor chip is configured to include a second GRS interface circuit. A second set of electrical traces fabricated within the MCM package and configured to coupled the second GRS interface circuit to the interconnect circuit.

Owner:NVIDIA CORP

Programmable differential signaling system

ActiveUS7479805B1Transmission line coupling arrangementsLogic circuit coupling/interface arrangementsDifferential signalingEngineering

A programmable differential signaling system includes a programmable bias generator and a plurality of input / output modules. The programmable bias generator is operably coupled to generate a first global bias signal and a second global signal based on desired signal properties of one of a plurality of differential signaling conventions. The a plurality of input / output modules is operably coupled to convert between differential signaling and single ended signaling, wherein actual signal properties of the differential signaling are regulated based on the first and second global bias signals to substantially equal the desired signal properties.

Owner:XILINX INC

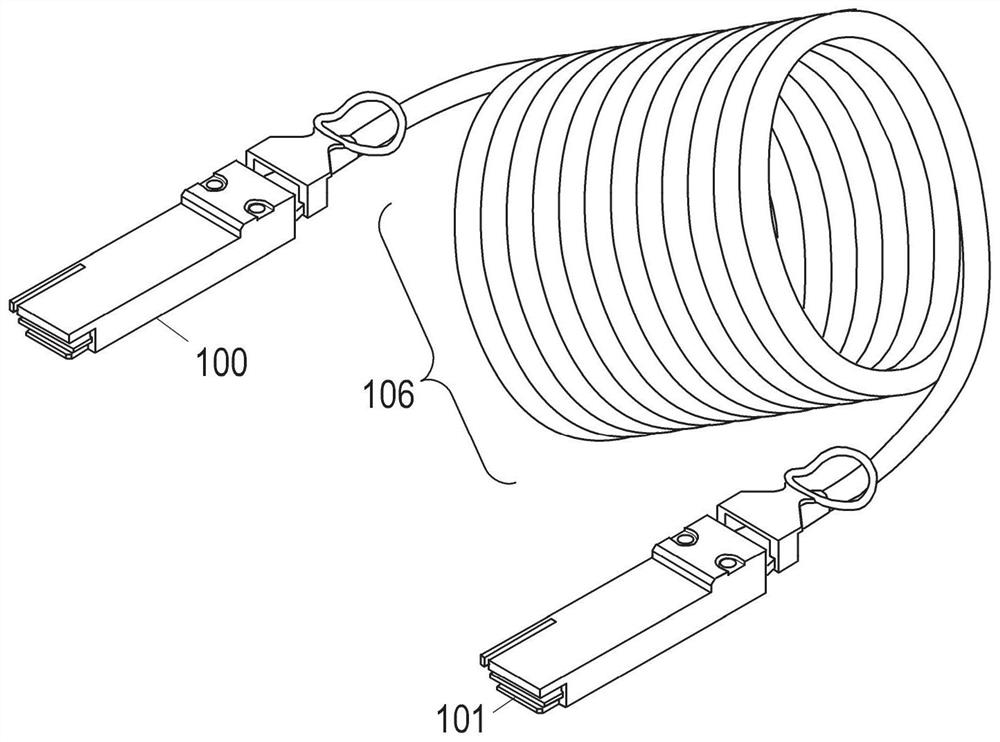

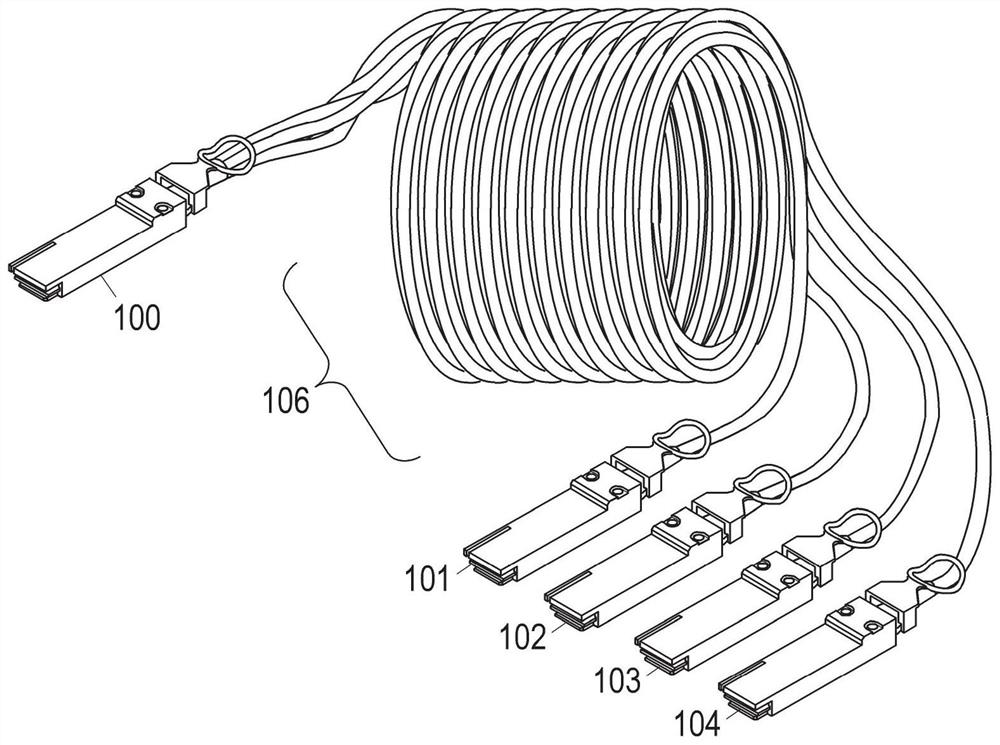

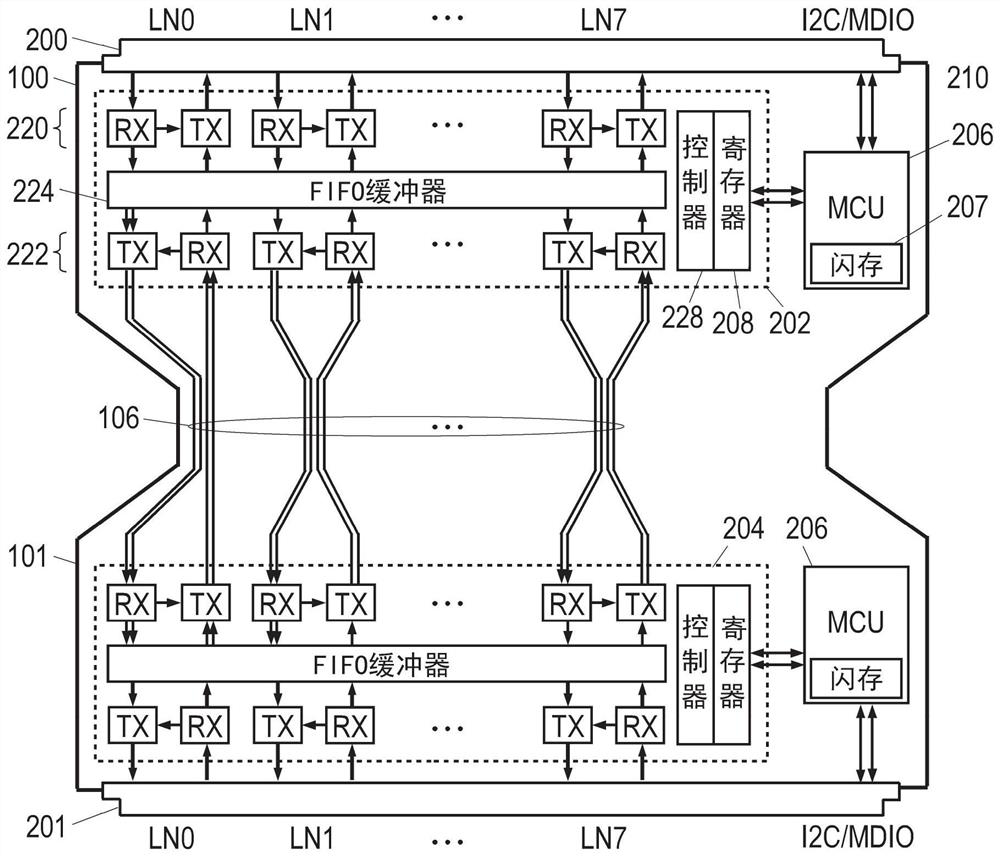

Single-ended signaling between differential ethernet interfaces

ActiveCN112653490ABroadband local area networksLine-transmission monitoring/testingTransceiverData stream

Mass-manufactured cables suitable for large communication centers may convert from differential PAM4 interface signaling to parallel single-ended NRZ transit signaling at 53.125 GBd to provide bidirectional data rates up to 800 Gbps and beyond. One illustrative cable embodiment includes: electrical conductors connected between a first connector and a second connector, each adapted to fit into an Ethernet port of a corresponding host device to receive an electrical input signal to the cable conveying an outbound data stream from the host device and to provide an electrical output signal from the cable conveying an inbound data stream to that host device. The electrical input and output signals employ differential PAM4 modulation to convey the inbound and outbound data streams. Each of the first and second connectors includes transceivers to perform clock and data recovery on the electrical input signal to extract and re-modulate the outbound data stream for transit via the electrical conductors as respective pairs of electrical transit signals employing single-ended NRZ modulation.

Owner:CREDO TECH GRP LTD

Signal conversion during transmission of serial data streams

ActiveUS20130235921A1Facilitate transmissionFacilitates rejectionMultiple-port networksError preventionComputer hardwareData stream

The disclosed embodiments provide a system that facilitates transmission of a serial data stream. The system may include, in a receiver of the serial data stream, a first mechanism for converting from single-ended signaling to differential signaling, wherein the first mechanism facilitates rejection of common mode noise in the serial data stream. For example, the first mechanism may be a balun and / or a common-mode choke.

Owner:APPLE INC

Pseudo differential receiving mechanism for single-ended signaling

ActiveUS20200099406A1Analogue/digital conversionElectric signal transmission systemsTerminal voltageData signal

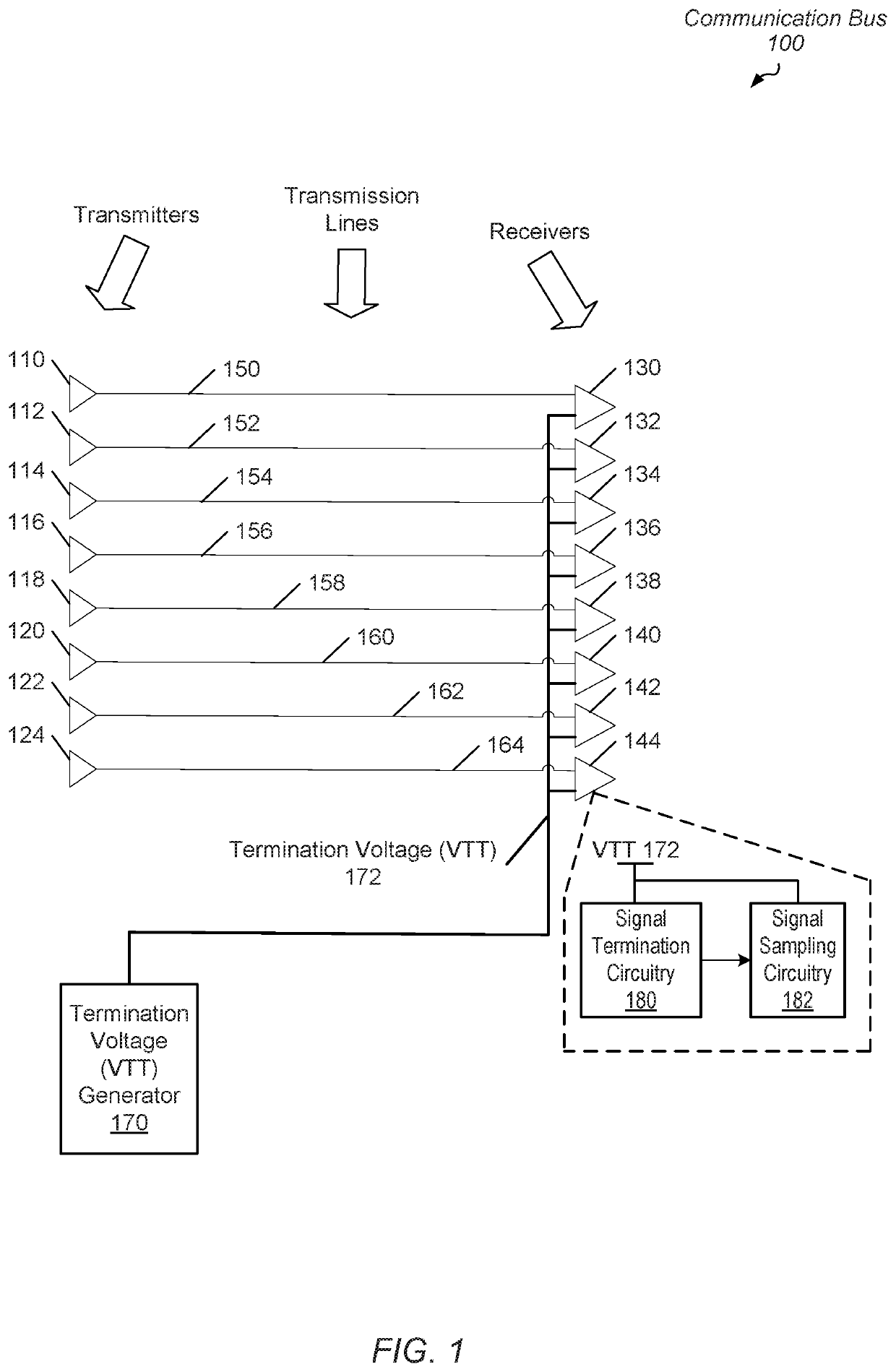

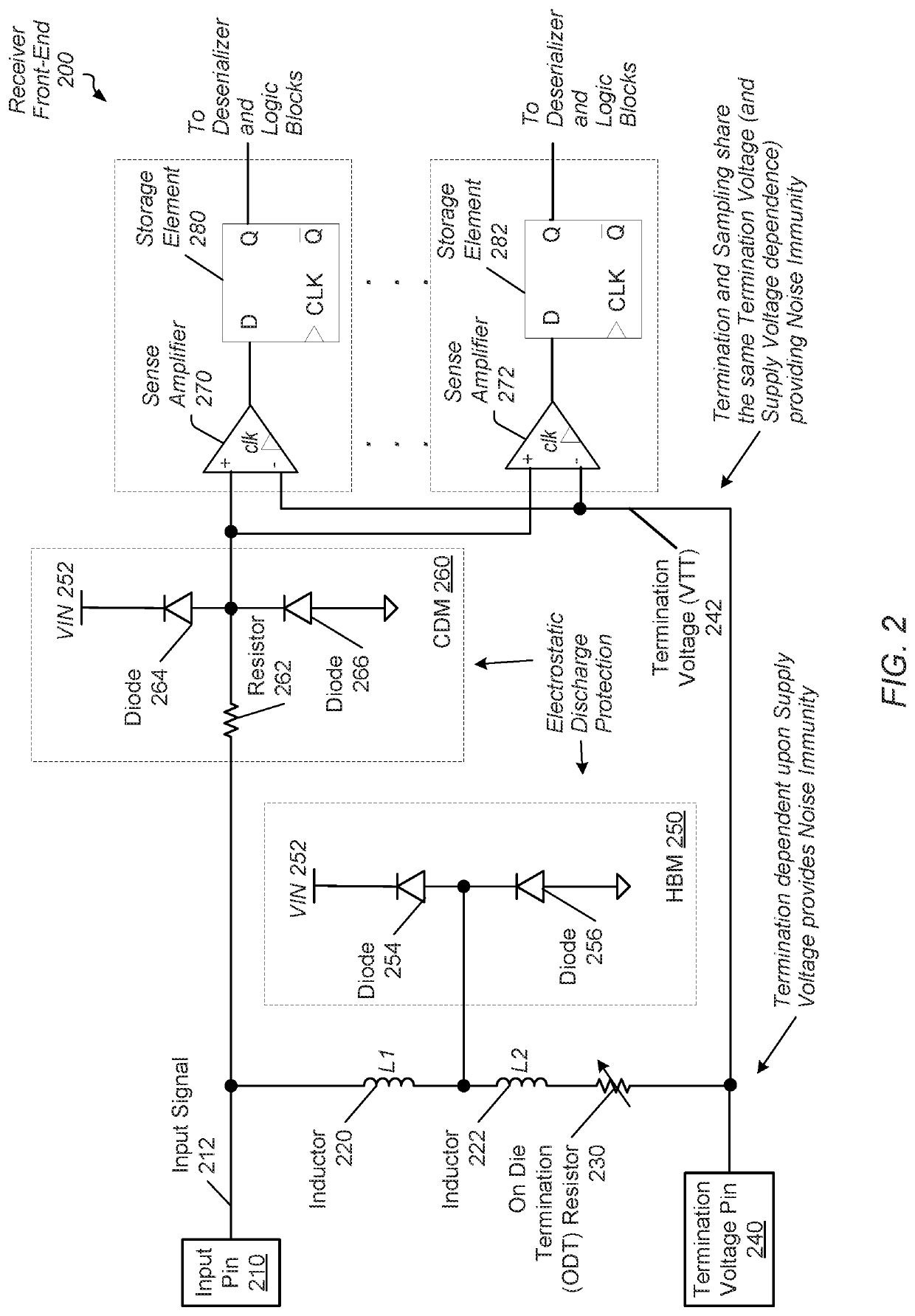

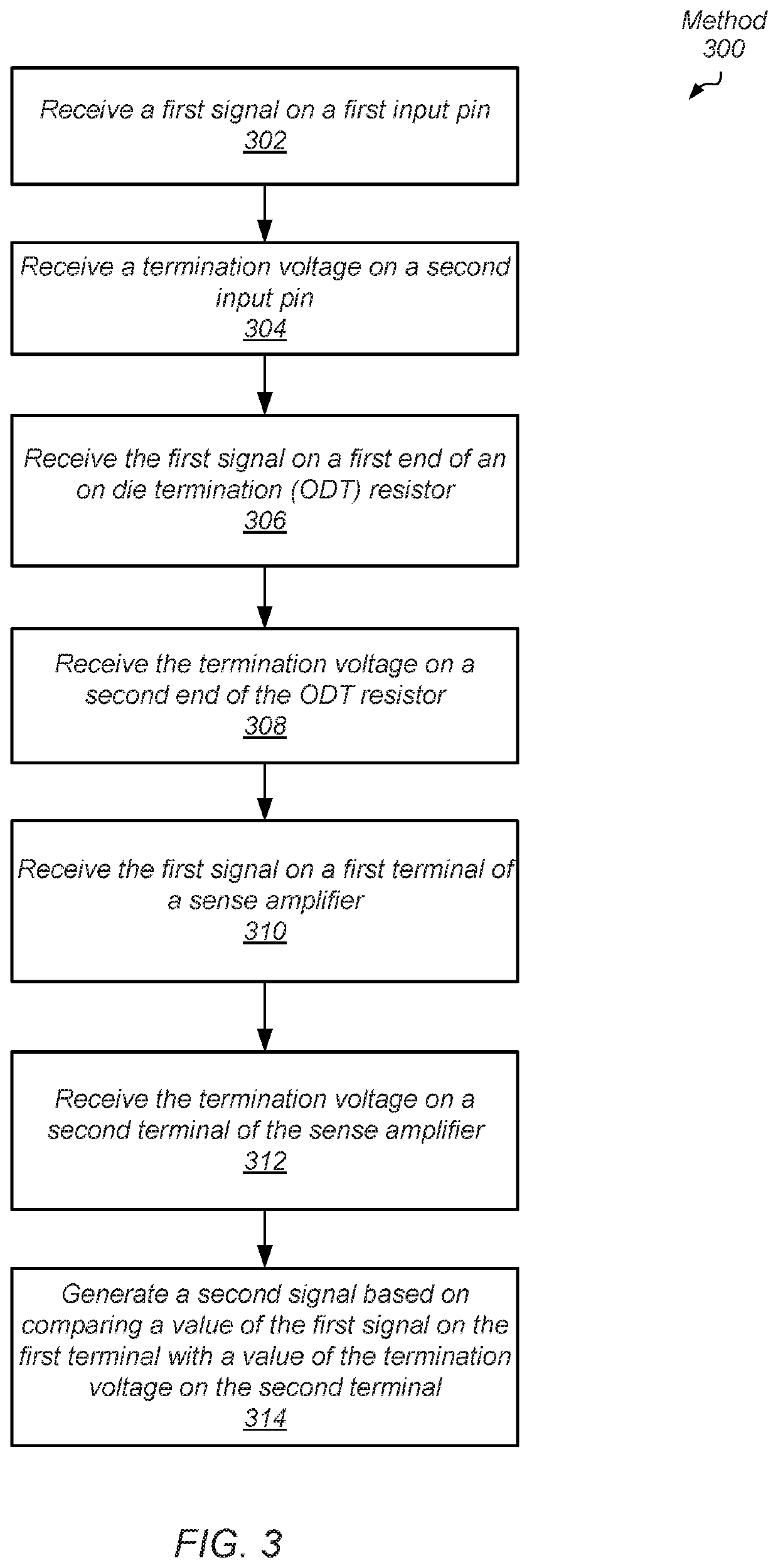

Systems, apparatuses, and methods for performing efficient data transfer in a computing system are disclosed. A computing system includes multiple transmitters sending singled-ended data signals to multiple receivers. A termination voltage is generated and sent to the multiple receivers. The termination voltage is coupled to each of signal termination circuitry and signal sampling circuitry within each of the multiple receivers. Any change in the termination voltage affects the termination circuitry and affects comparisons performed by the sampling circuitry. Received signals are reconstructed at the receivers using the received signals, the signal termination circuitry and the signal sampling circuitry.

Owner:ADVANCED MICRO DEVICES INC

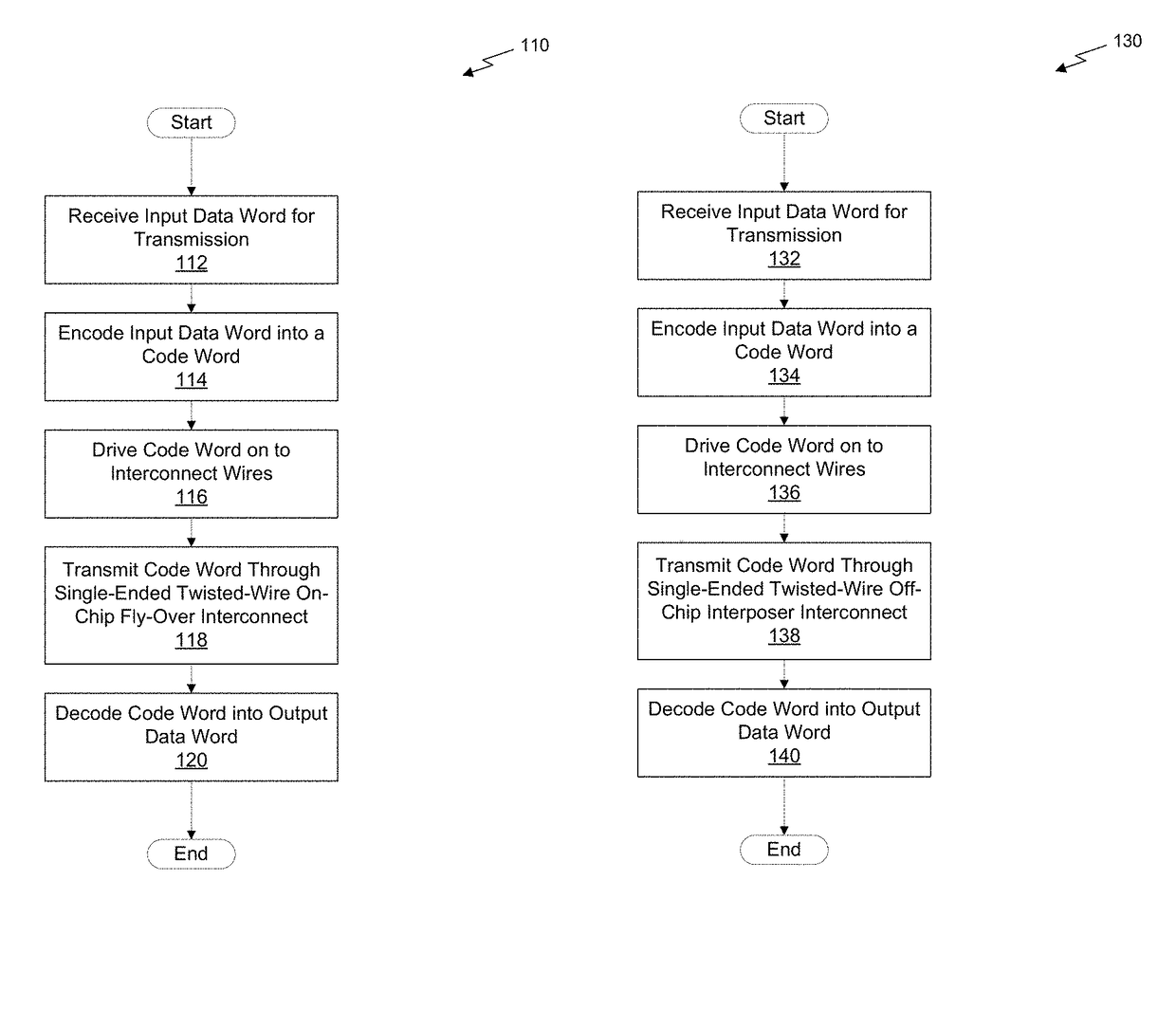

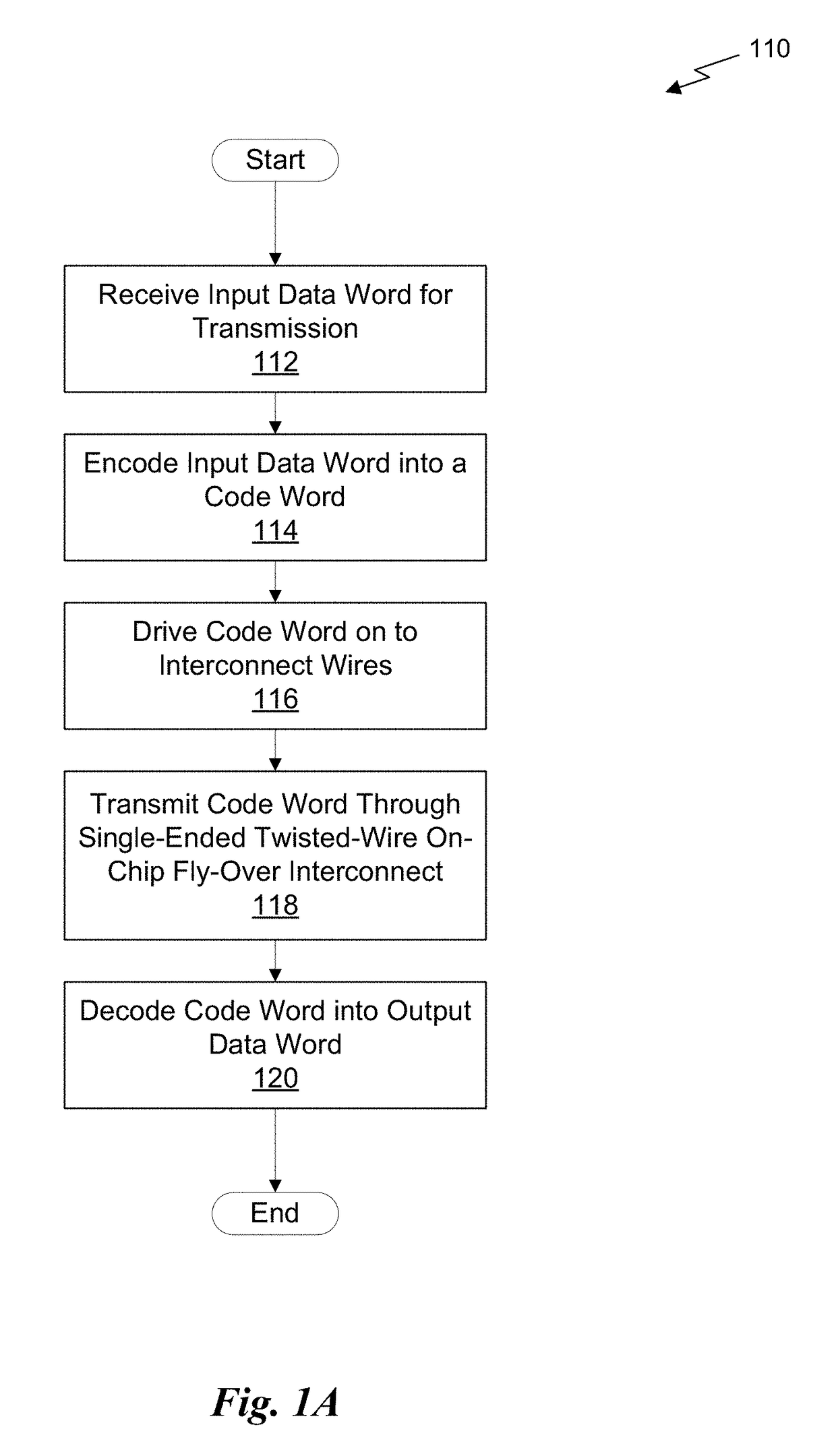

System and method for cross-talk cancellation in single-ended signaling

ActiveUS9882605B2Reduce crosstalkFrequency-division multiplex detailsCross-talk reductionData transmissionComputer science

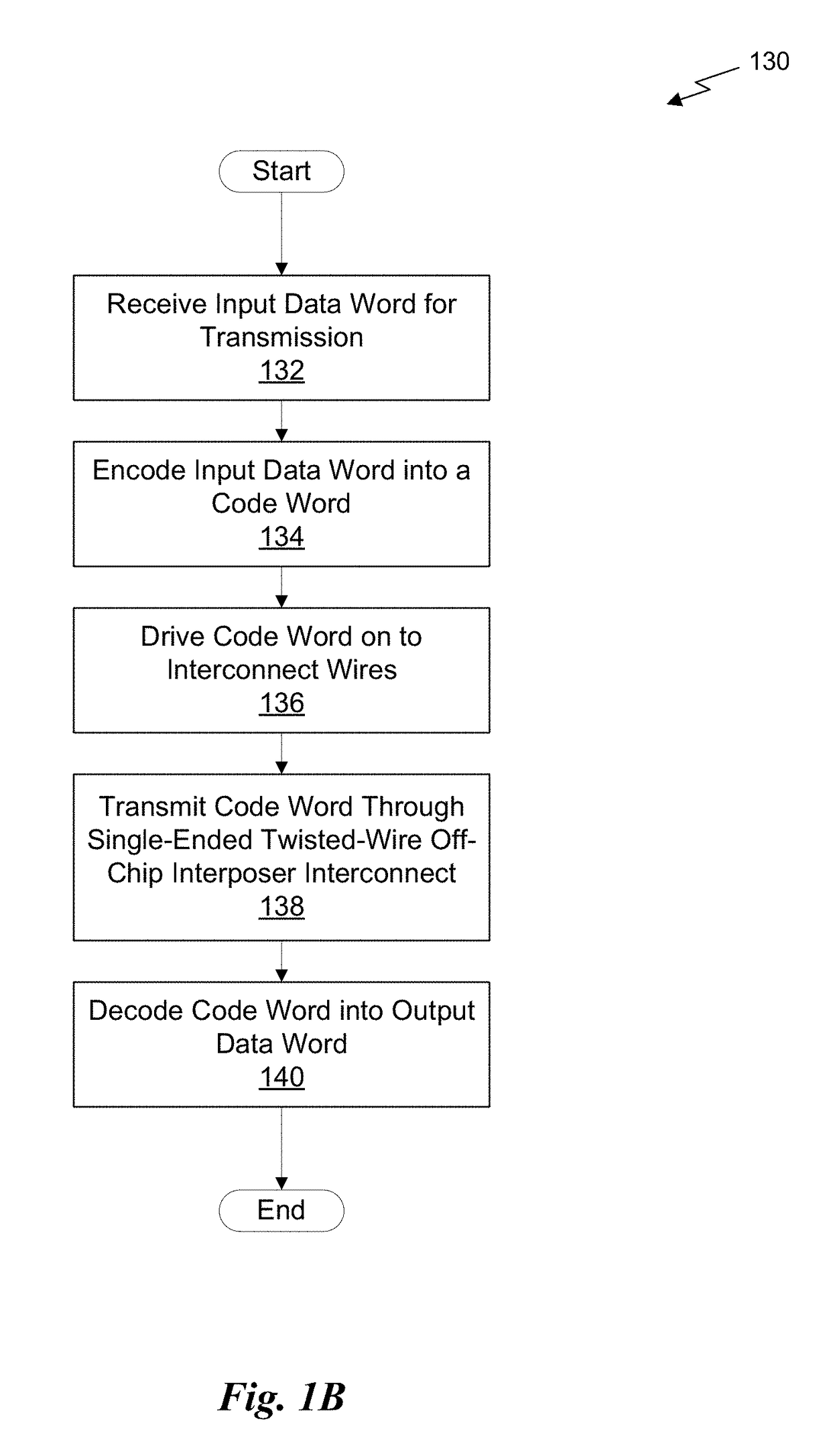

A method for transmitting data advantageously reduces cross-talk in high-speed data transmission. The method comprises receiving an input data word, encoding the input data word into a code word, and driving the code word on to an interconnect for transmission. The code word is generating using a balanced coding scheme, and the interconnect is a single-ended, twisted-wire interposer interconnect. A receiver circuit decodes the code word to generate an output data word.

Owner:NVIDIA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com