Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

267 results about "Frequency-locked loop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

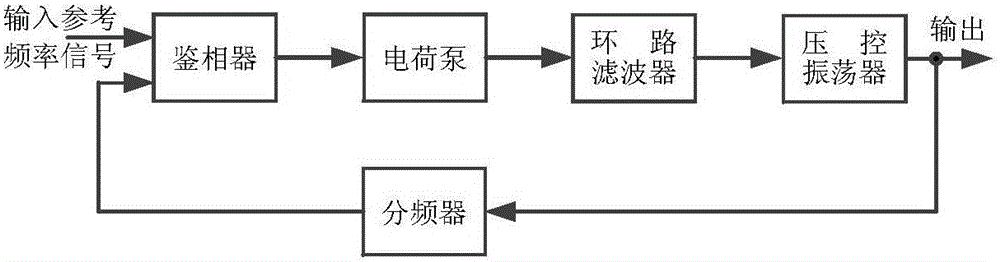

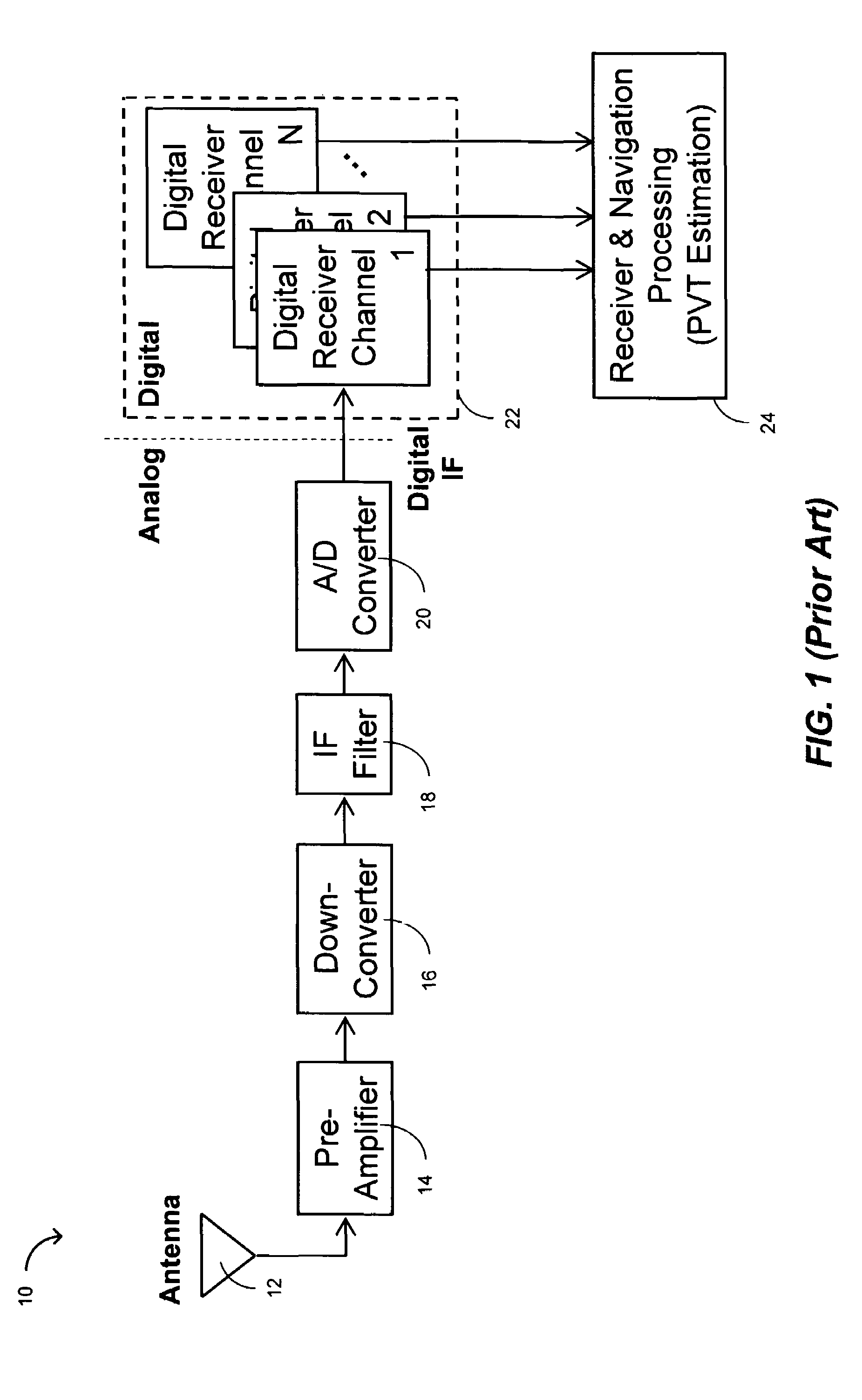

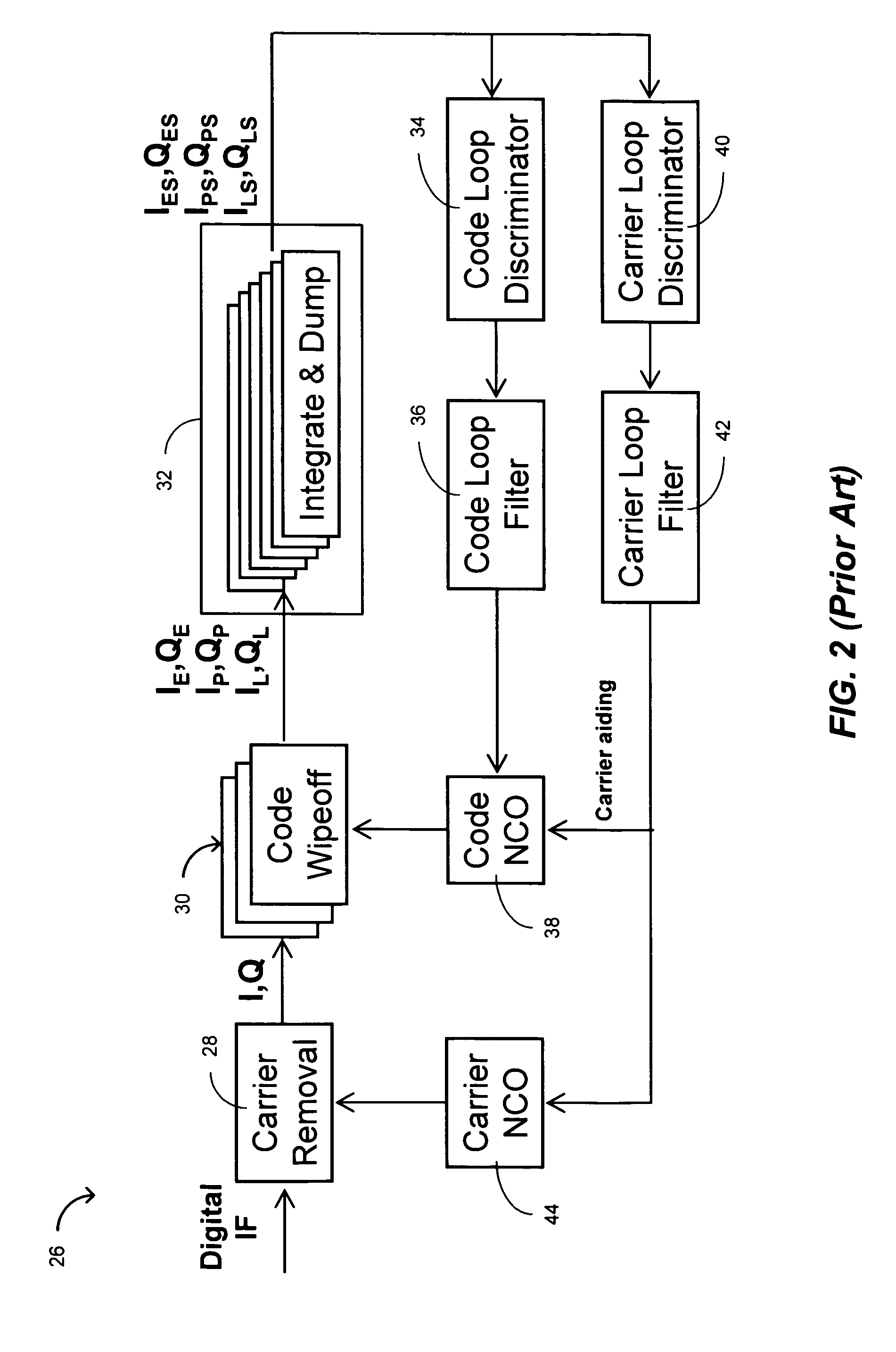

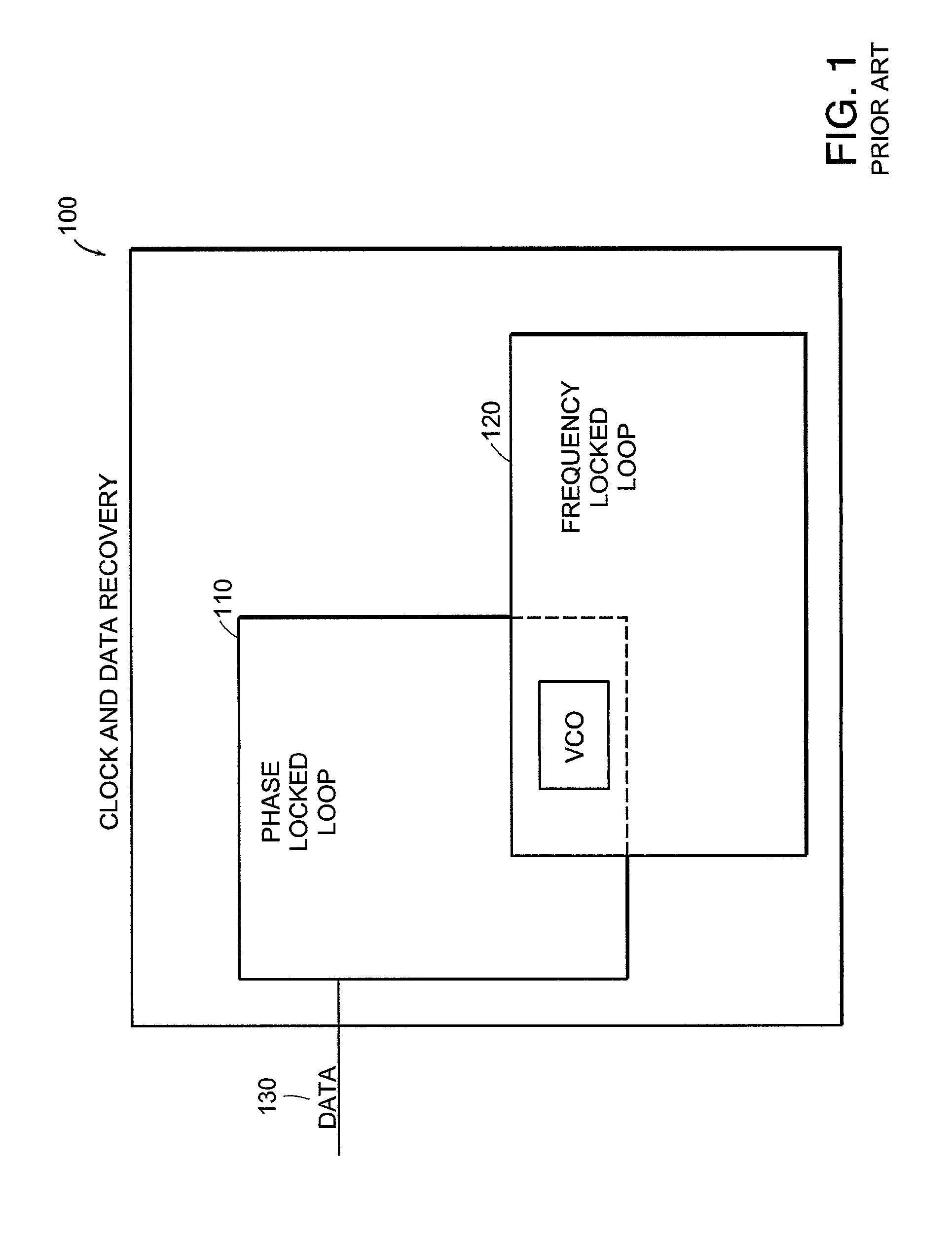

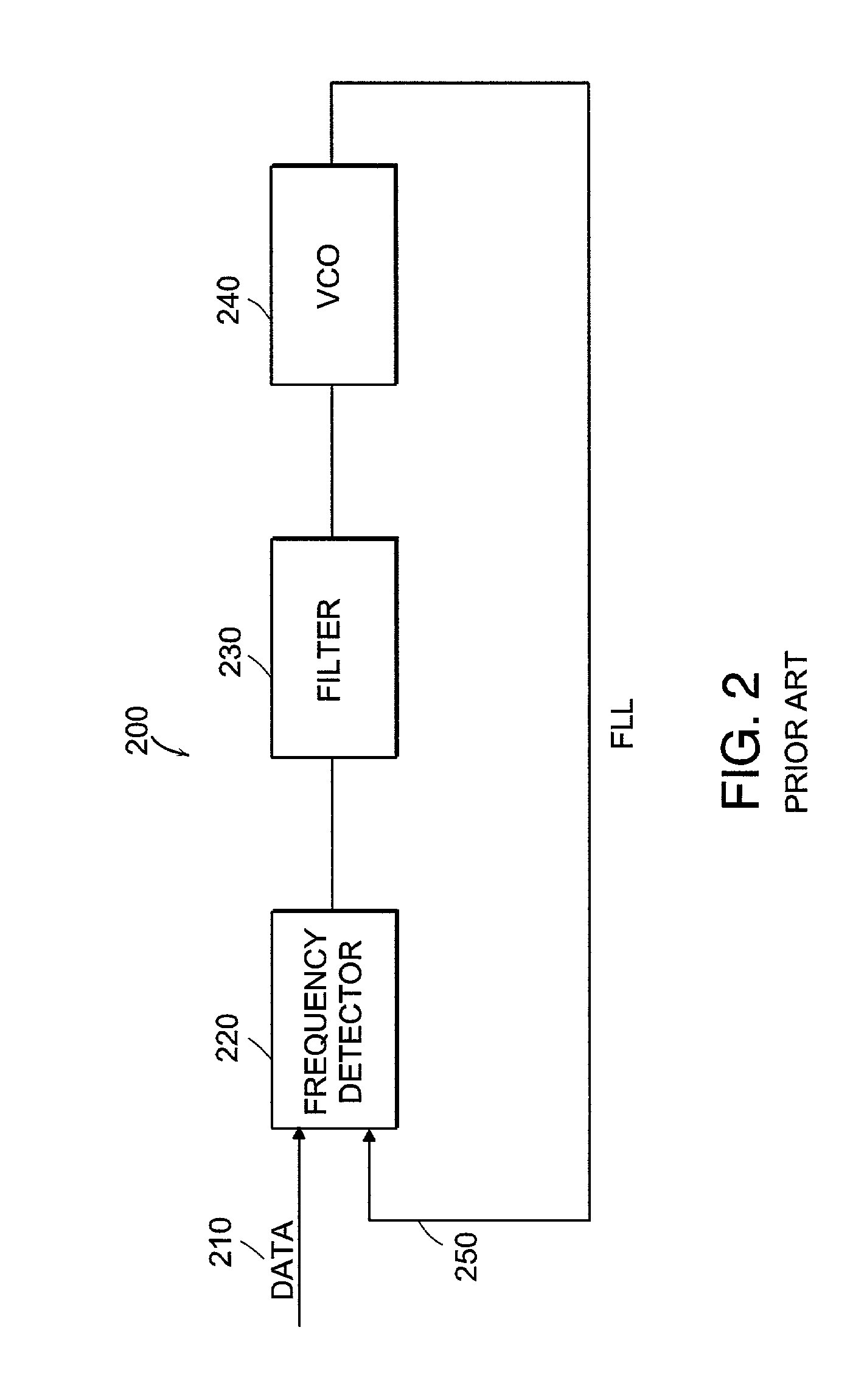

A frequency-lock, or frequency-locked loop (FLL), is an electronic control system that generates a signal that is locked to the frequency of an input or "reference" signal. This circuit compares the frequency of a controlled oscillator to the reference, automatically raising or lowering the frequency of the oscillator until its frequency (but not necessarily its phase) is matched to that of the reference.

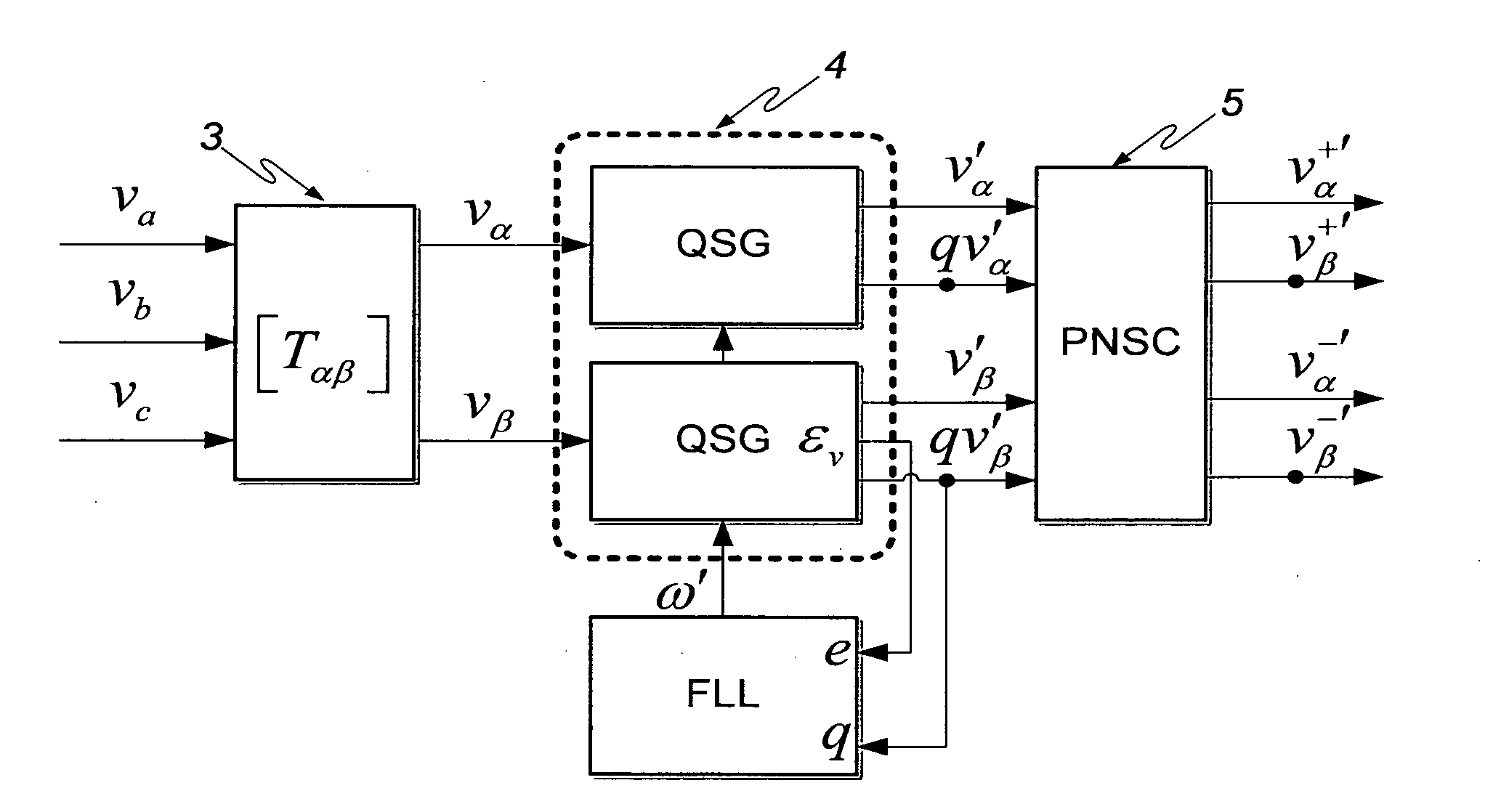

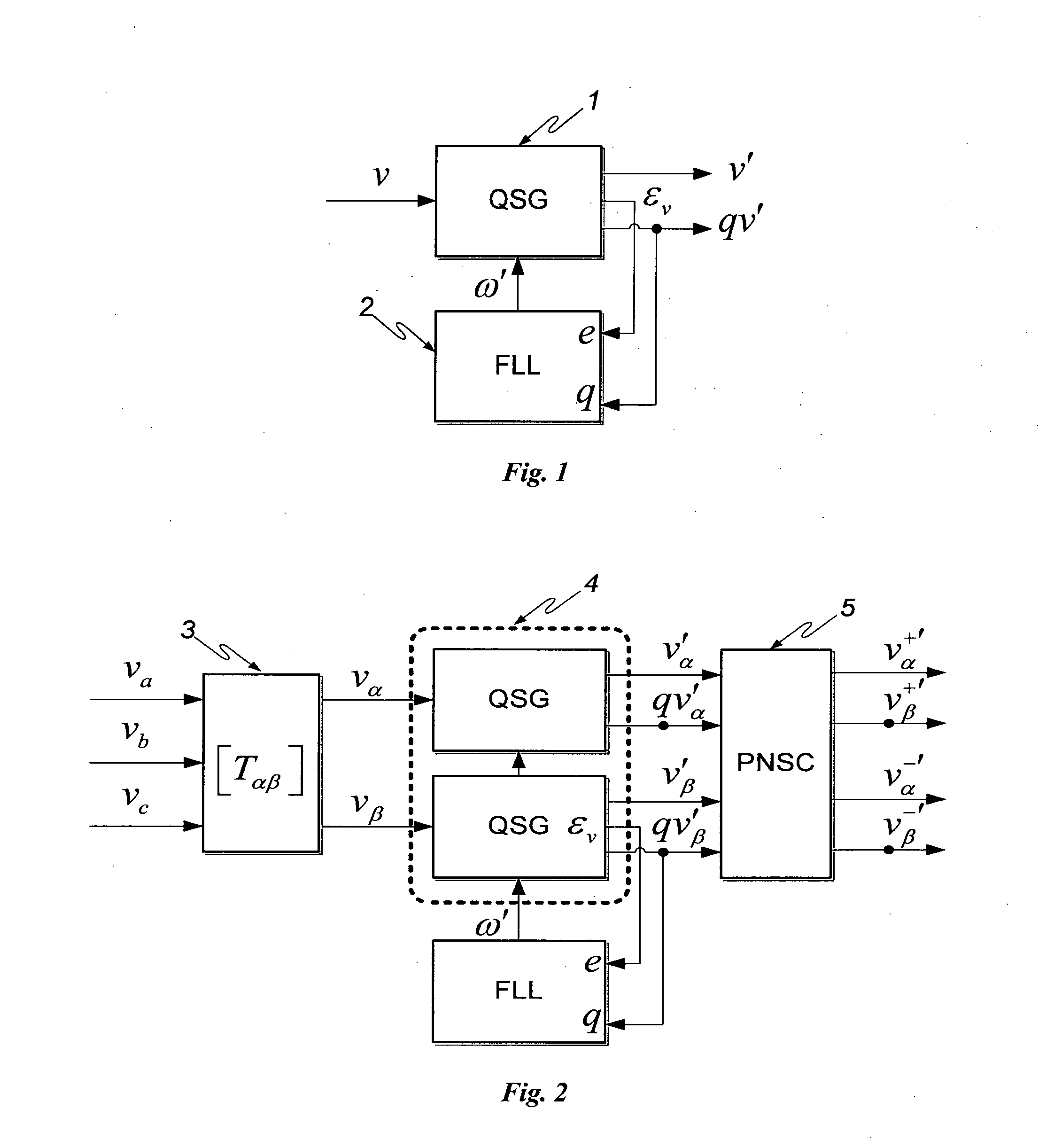

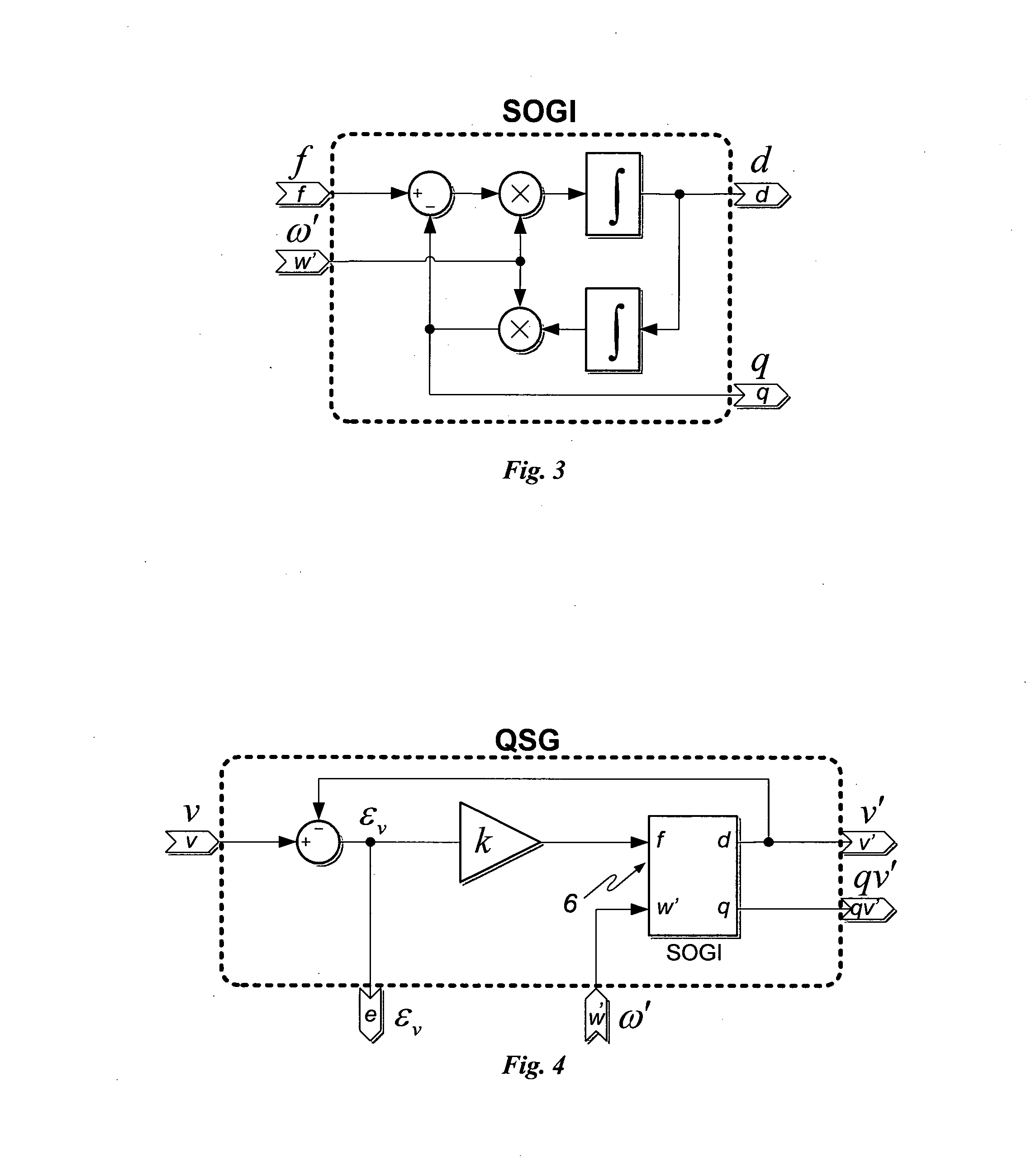

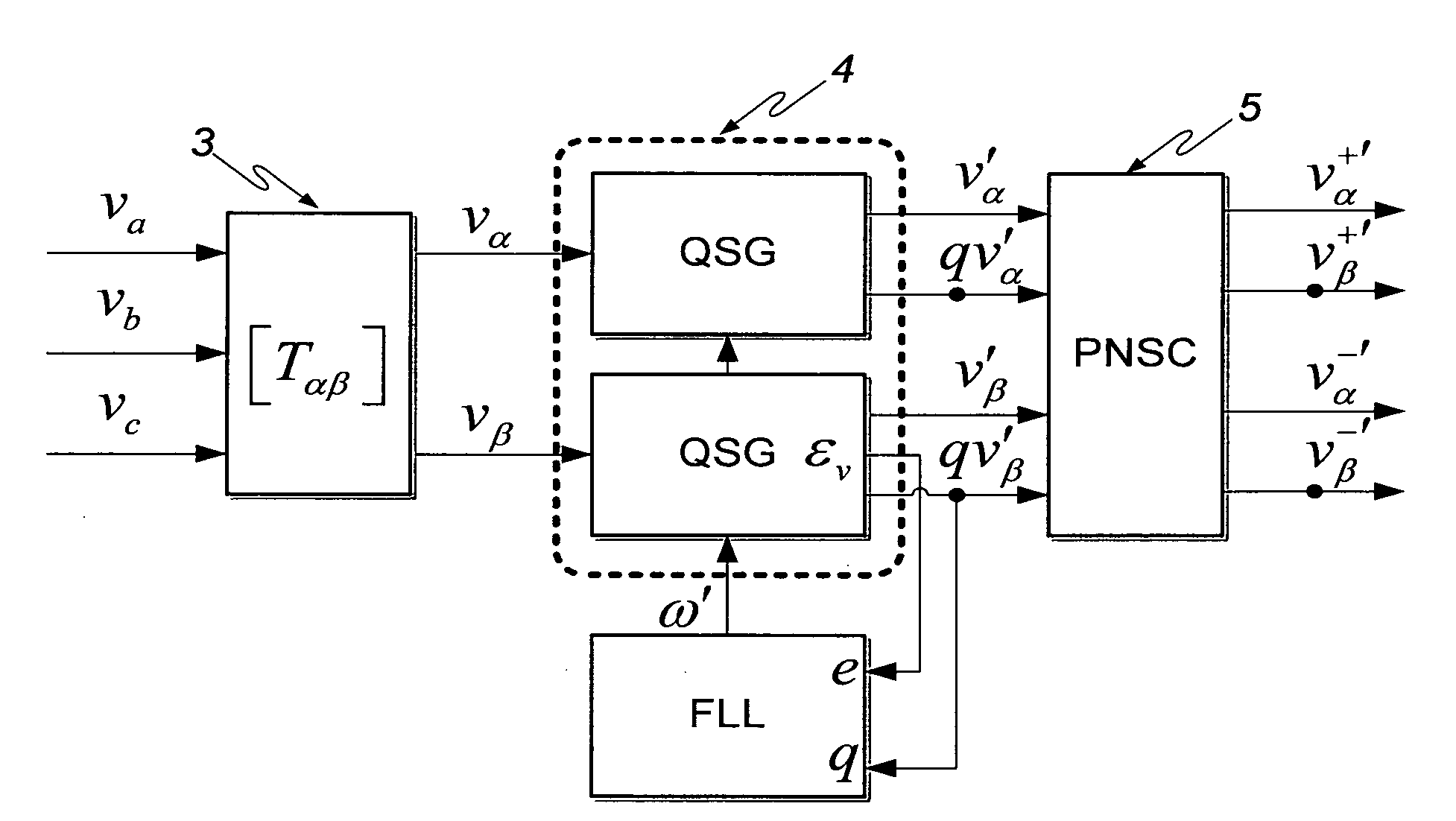

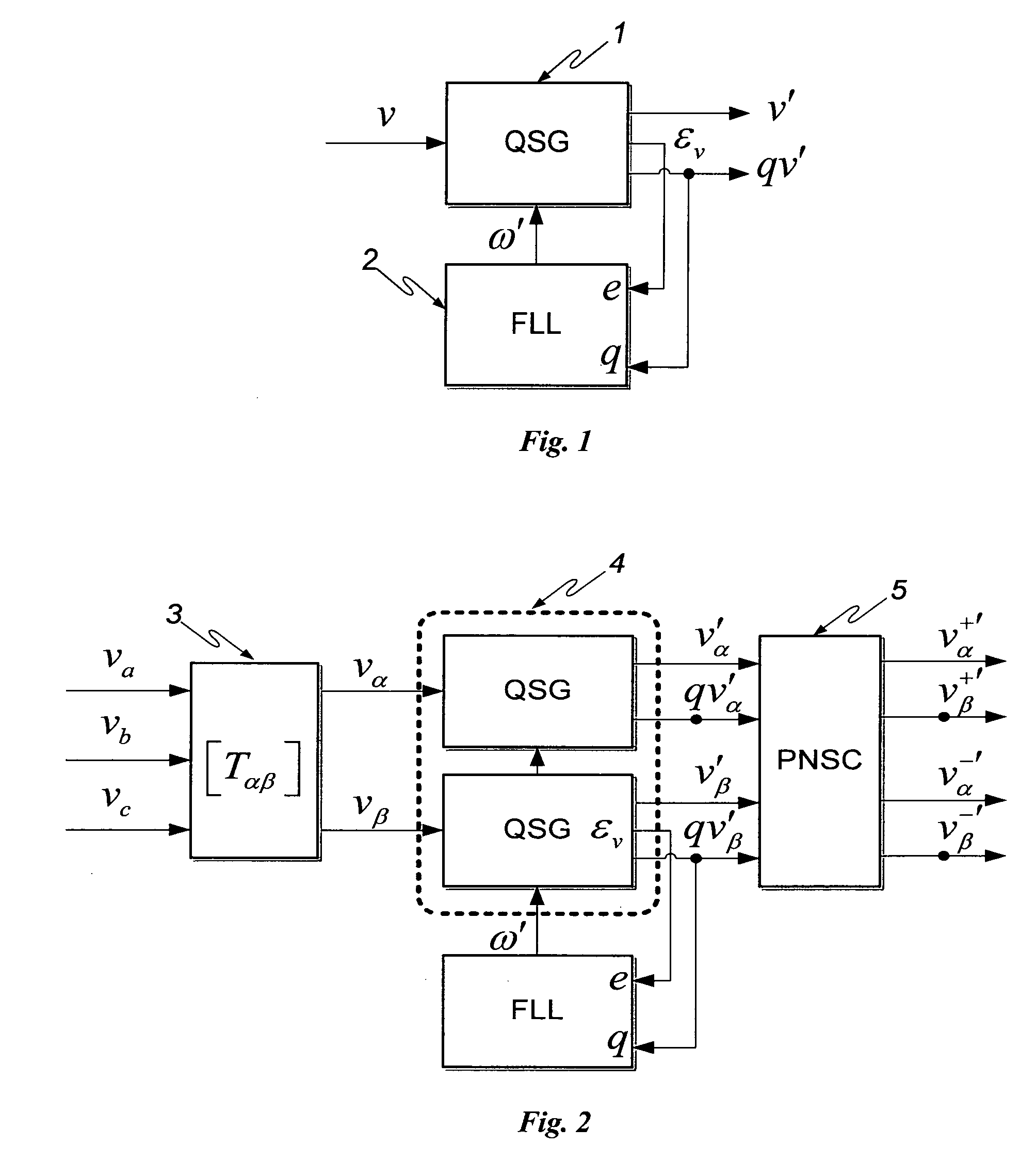

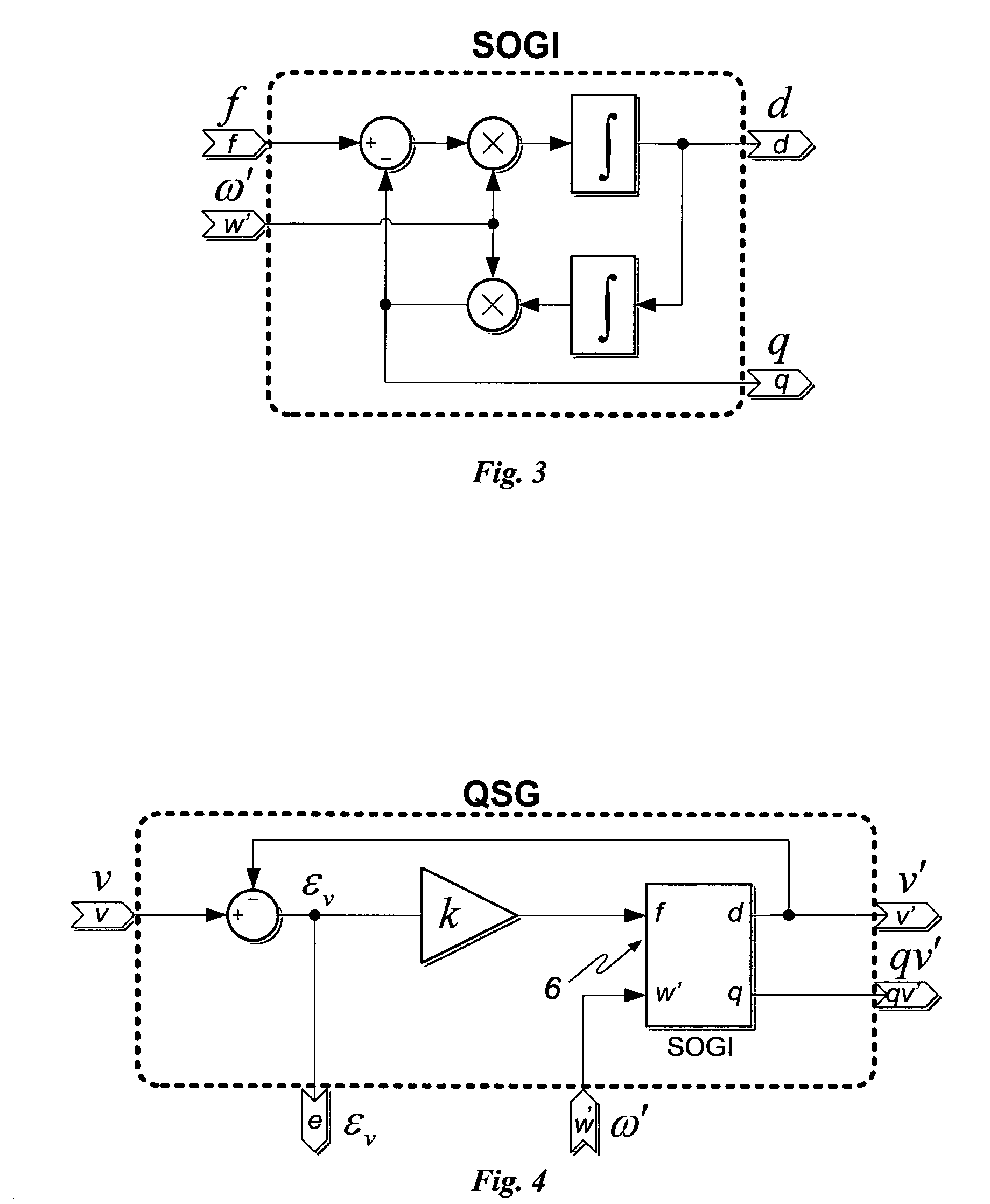

Advanced real-time grid monitoring system and method

ActiveUS20100213925A1Efficient and robustIncreased computational burdenCurrent/voltage measurementVoltage-current phase anglePower qualityElectric power system

This invention deals with an advanced Real-time Grid Monitoring System (RTGMS) suitable for both single-phase and three-phase electric power systems. This invention provides an essential signal processing block to be used as a part of complex systems either focused on supervising and diagnosing power systems or devoted to control power processors interacting with the grid. This invention is based on a new algorithm very suitable for real-time characterization of the grid variables under distorted and unbalanced grid conditions. The main characteristic of this invention is the usage of a frequency-locked loop, based on detecting the grid frequency, for synchronizing to the grid variables. It results in a very robust system response in relation to existing technique based on the phase-angle detection since grid frequency is much more stable variable than the grid voltage / current phase-angle, mainly during grid faults. Moreover, the algorithm supporting this invention is very efficient and can be implemented in regular industrial microprocessors. These features make the RTGMS object of this invention ideal to be applied in the control of distributed generation systems (DGS), flexible AC transmission systems (FACTS), power quality conditioners (PQC) and uninterruptible power supplies (UPS). In all these systems, the fast and precise real time detection of the voltage and / or current sequence components under grid fault conditions is a crucial matter.

Owner:GAMESA INNOVATION & TECH SA

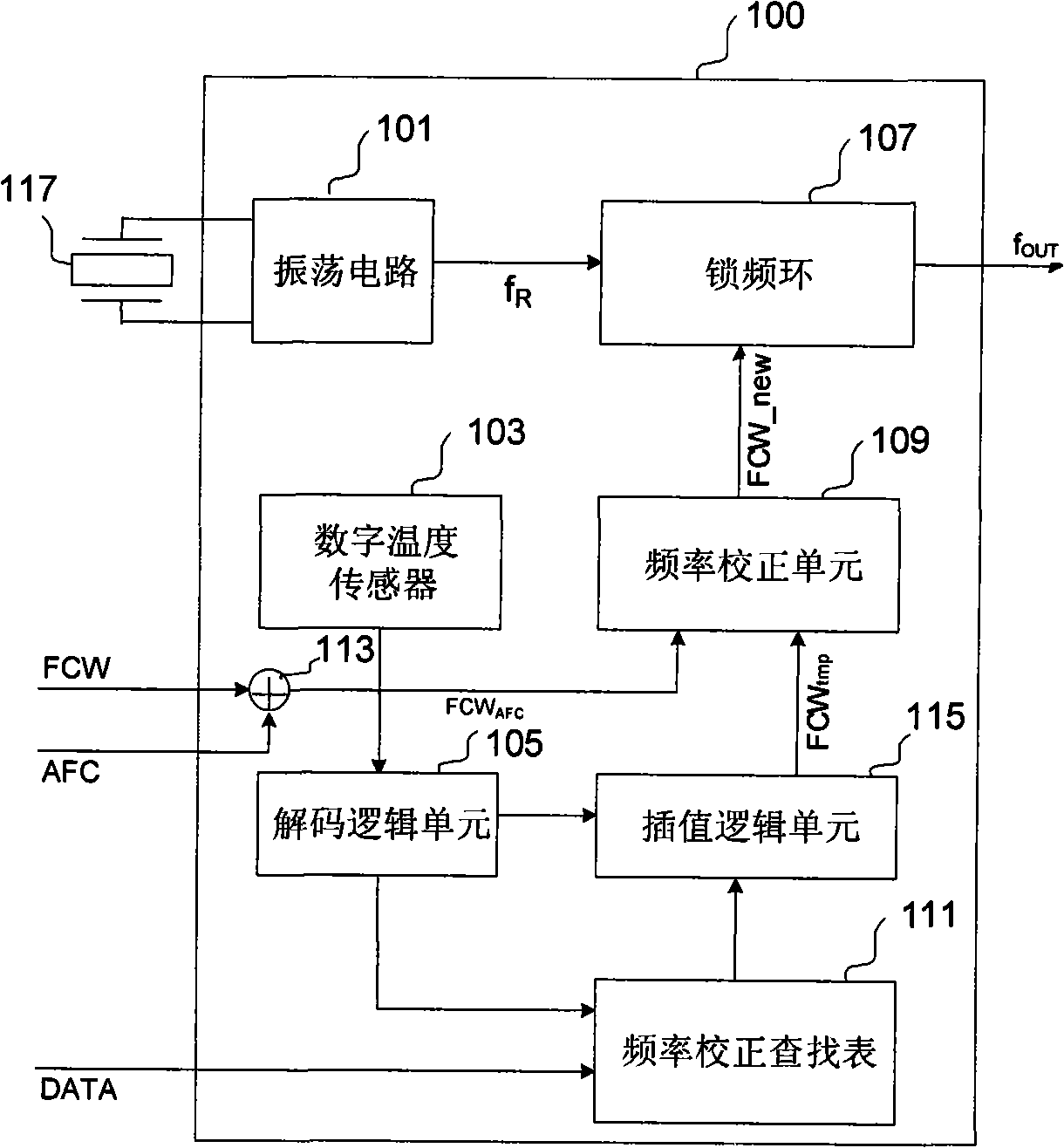

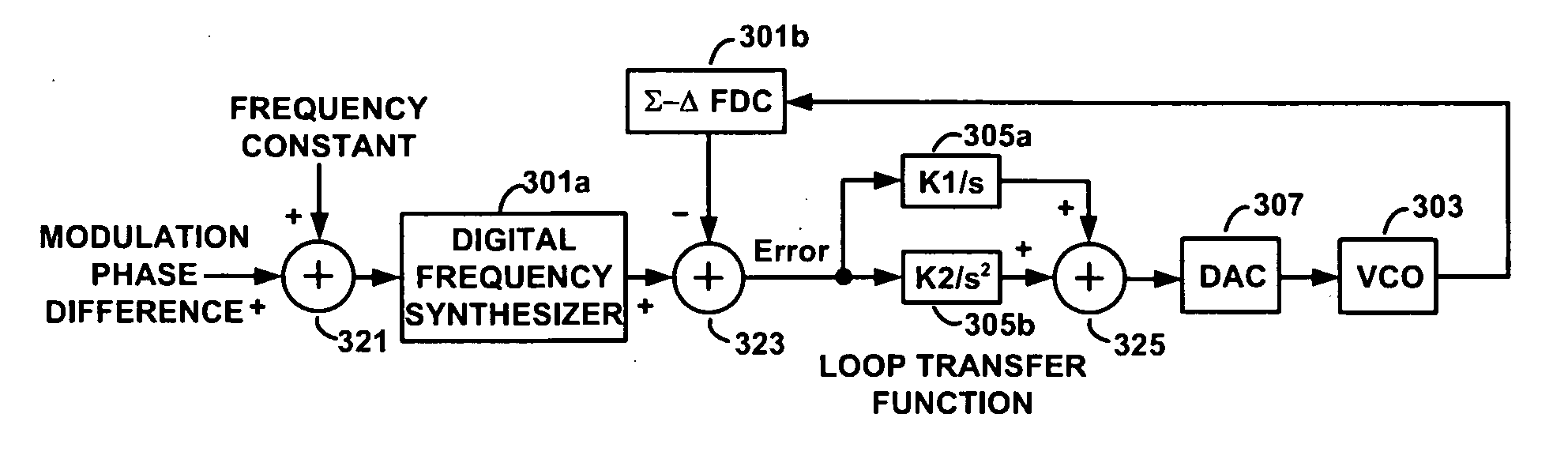

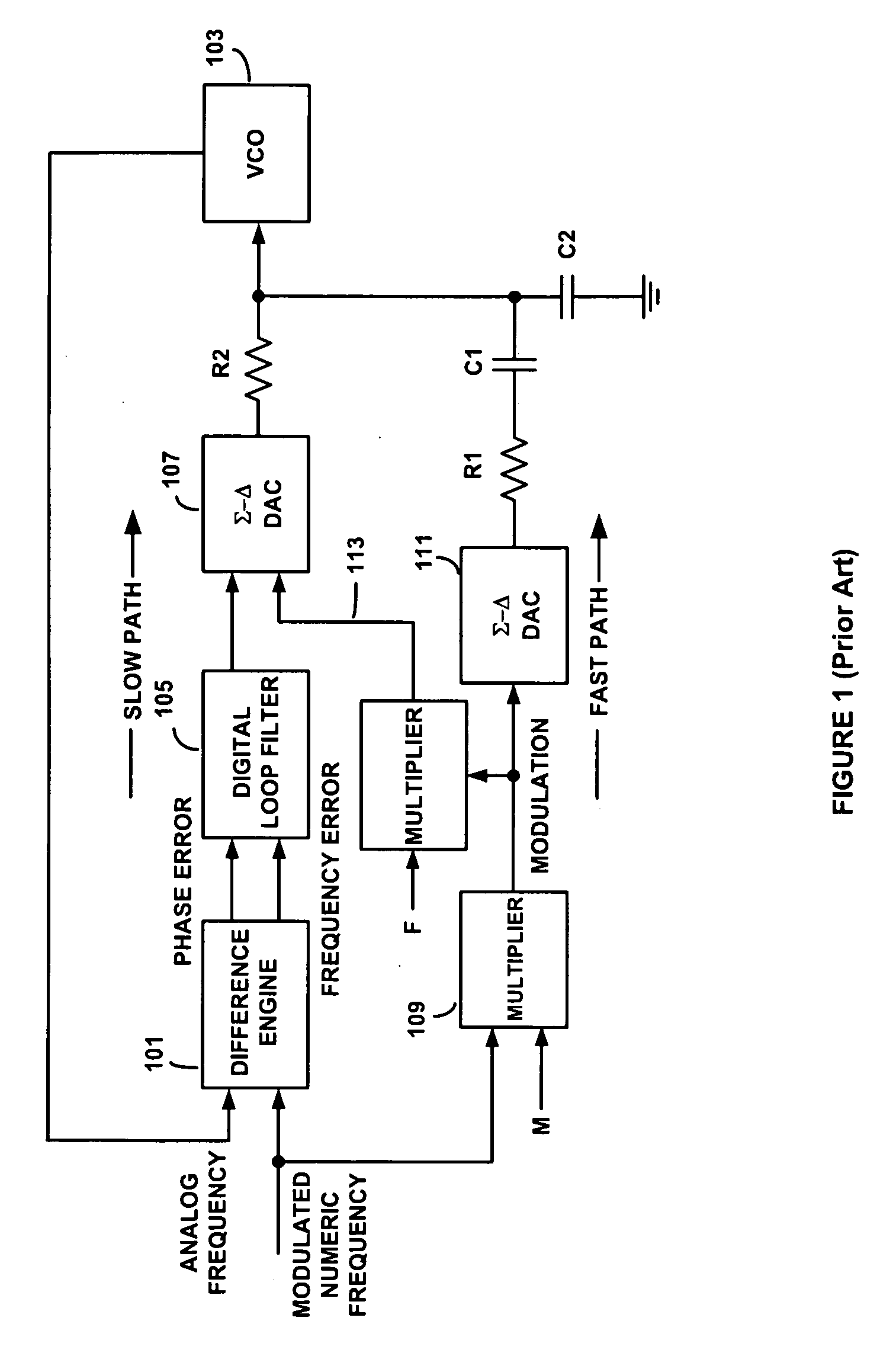

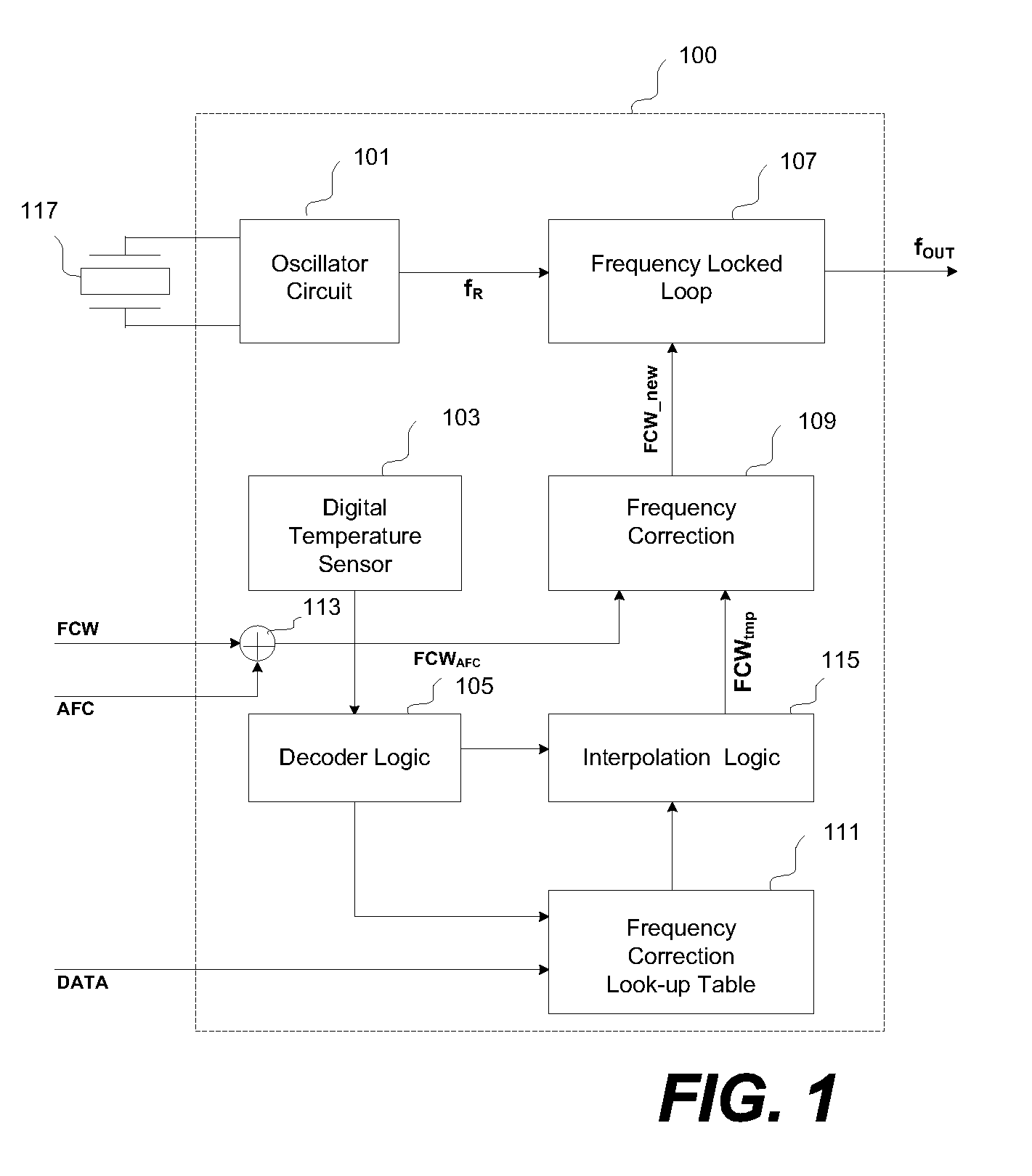

Frequency synthesizer

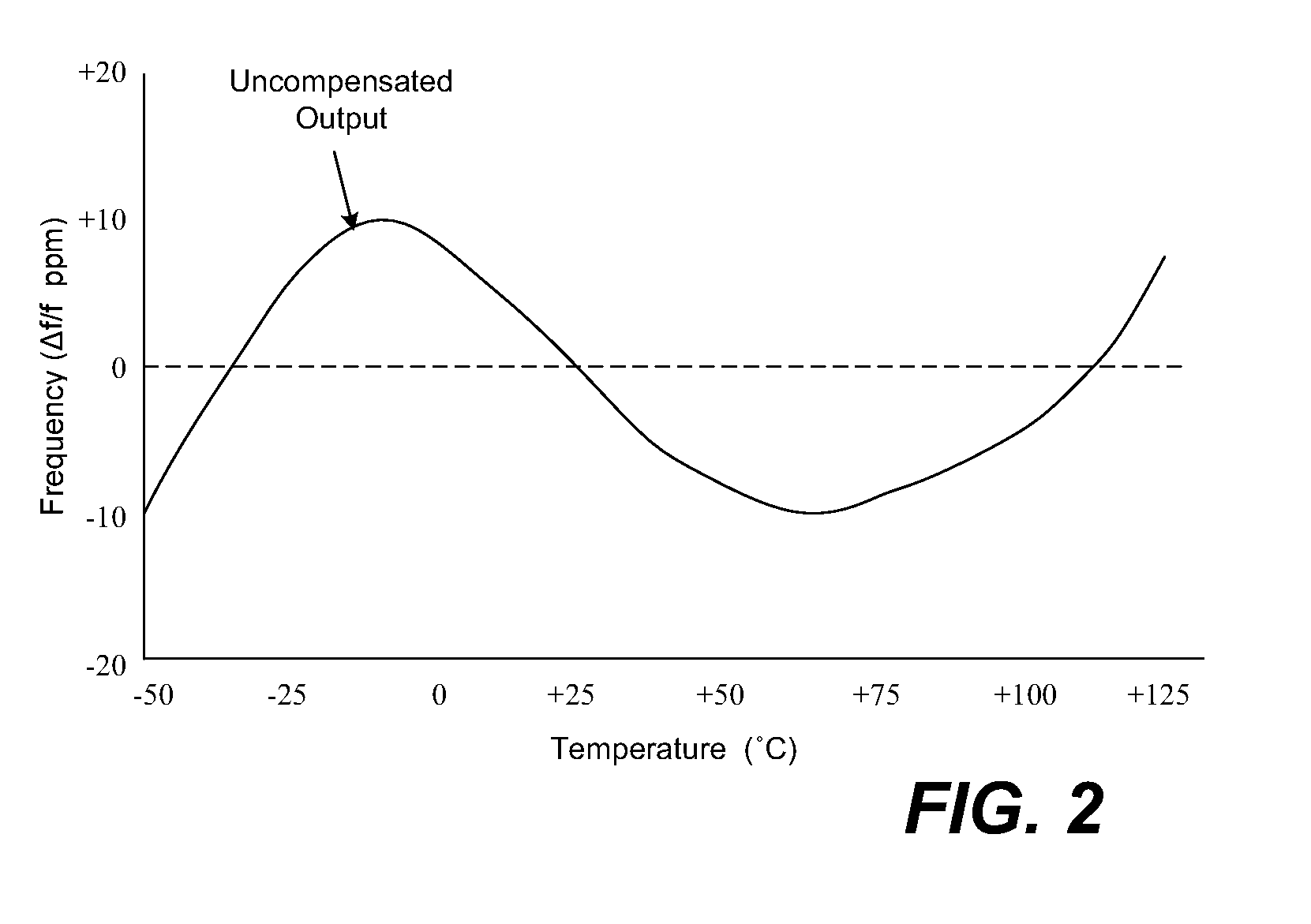

InactiveCN101272142ATo achieve temperature compensationGenerator stabilizationOscillations generatorsFrequency synthesizerFrequency modulation

The invention discloses a frequency synthesizer comprising a frequency-locked loop which runs based on the reference frequency of a crystal oscillator, a frequency correction unit and an interpolation logic unit; wherein, the frequency correction unit generates a digital frequency correction control word based on a first parameter and a second parameter; the first parameter is a combination of an automatic frequency correction word and a fixed frequency control word. The interpolation logic unit is used for generating the second parameter which expresses the temperature changing compensation; wherein, when the first parameter is a constant, the frequency-locked loop generates a fixed clock signal or when the first parameter is a binary sequence which expresses the frequency changing of a modulating signal, the frequency-locked loop generates a frequency modulating signal; temperature compensation to the frequency excursion of a reference clock can be realized by controlling the frequency correction control word.

Owner:曹秀娟

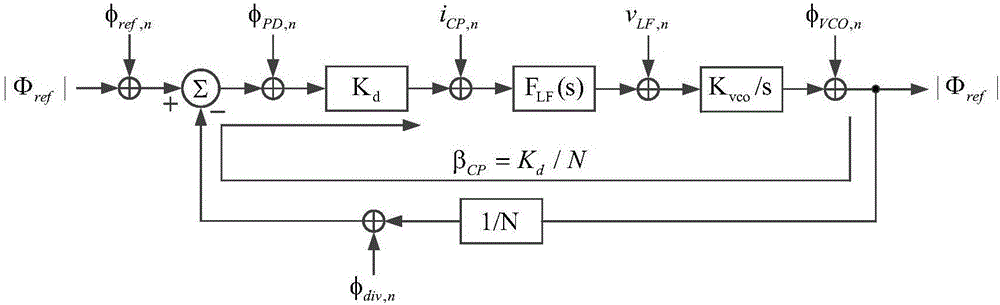

Bandwidth control in a mostly-digital pll/fll

InactiveUS20090108891A1Minimize disturbanceFaster frequency switching timePulse automatic controlLoop filterLoop bandwidth

Methods and apparatus for controlling a controlled oscillator using a phase-locked loop (PLL) or frequency-locked loop (FLL) having a digital loop filter with programmable filter parameters. An exemplary PLL (or FLL) includes a digital loop filter having one or more of the programmable filter parameters, which are changed by increments during operation in order to minimize disturbances (e.g., settling transients) as the loop bandwidth of the PLL is varied from a narrow loop bandwidth to a wide loop bandwidth, or vice versa. By changing the loop filter parameters in increments the loop bandwidth can be varied with substantially no perturbation. The end result is a much faster frequency switching time, improved settling dynamics, and predictable and stable loop operating performance. According to another aspect of the invention, one or more of the programmable filter parameters are changed in order to oppose a change in tuning sensitivity of the controlled oscillator (e.g., in order to maintain a constant loop bandwidth). By holding the loop bandwidth constant, switching time is maintained substantially constant under all conditions. This allows design and production margins to be reduced in a frequency agile system, and also relaxes the tuning sensitivity linearity requirements of the controlled oscillator.

Owner:PANASONIC CORP

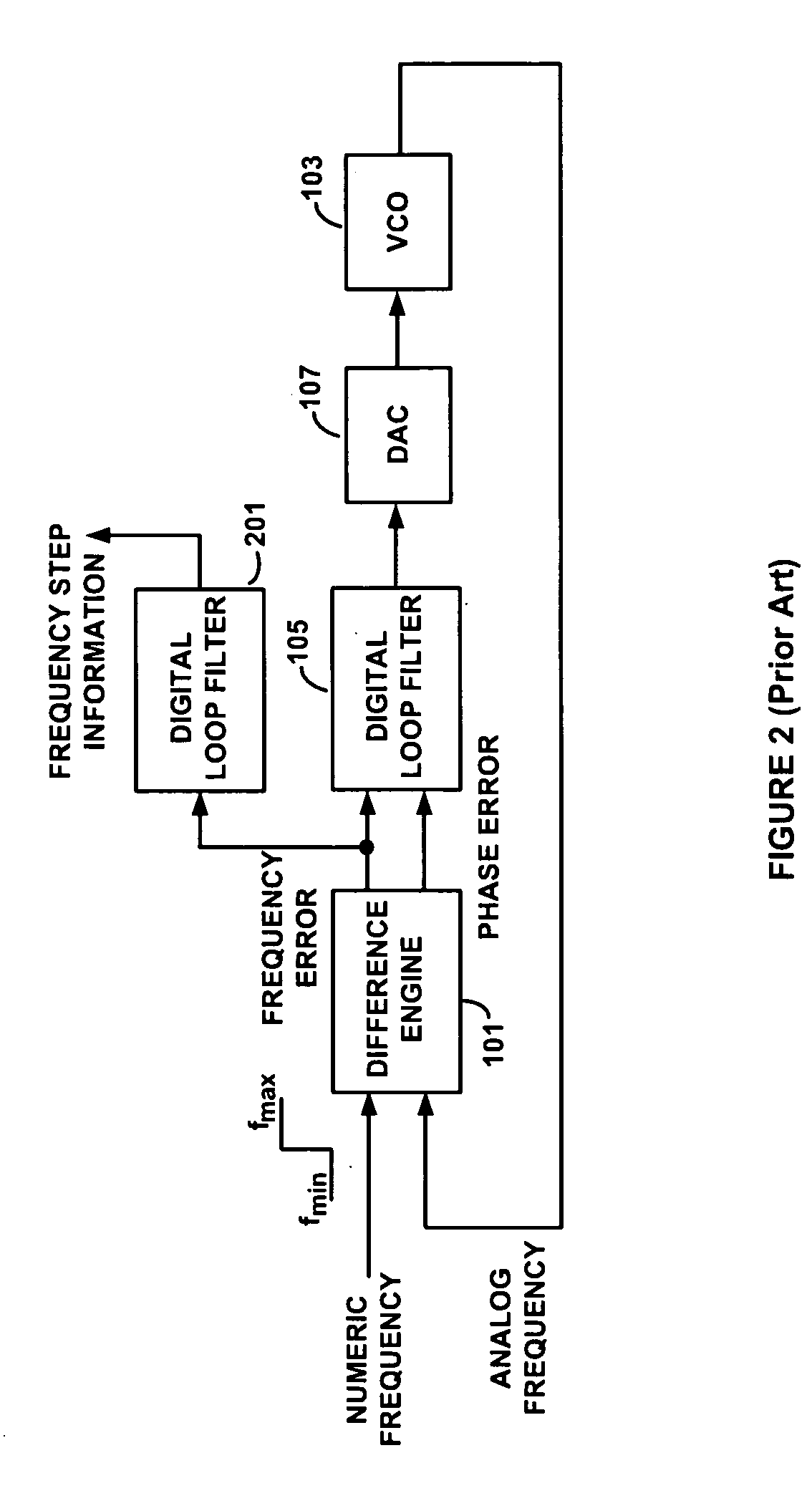

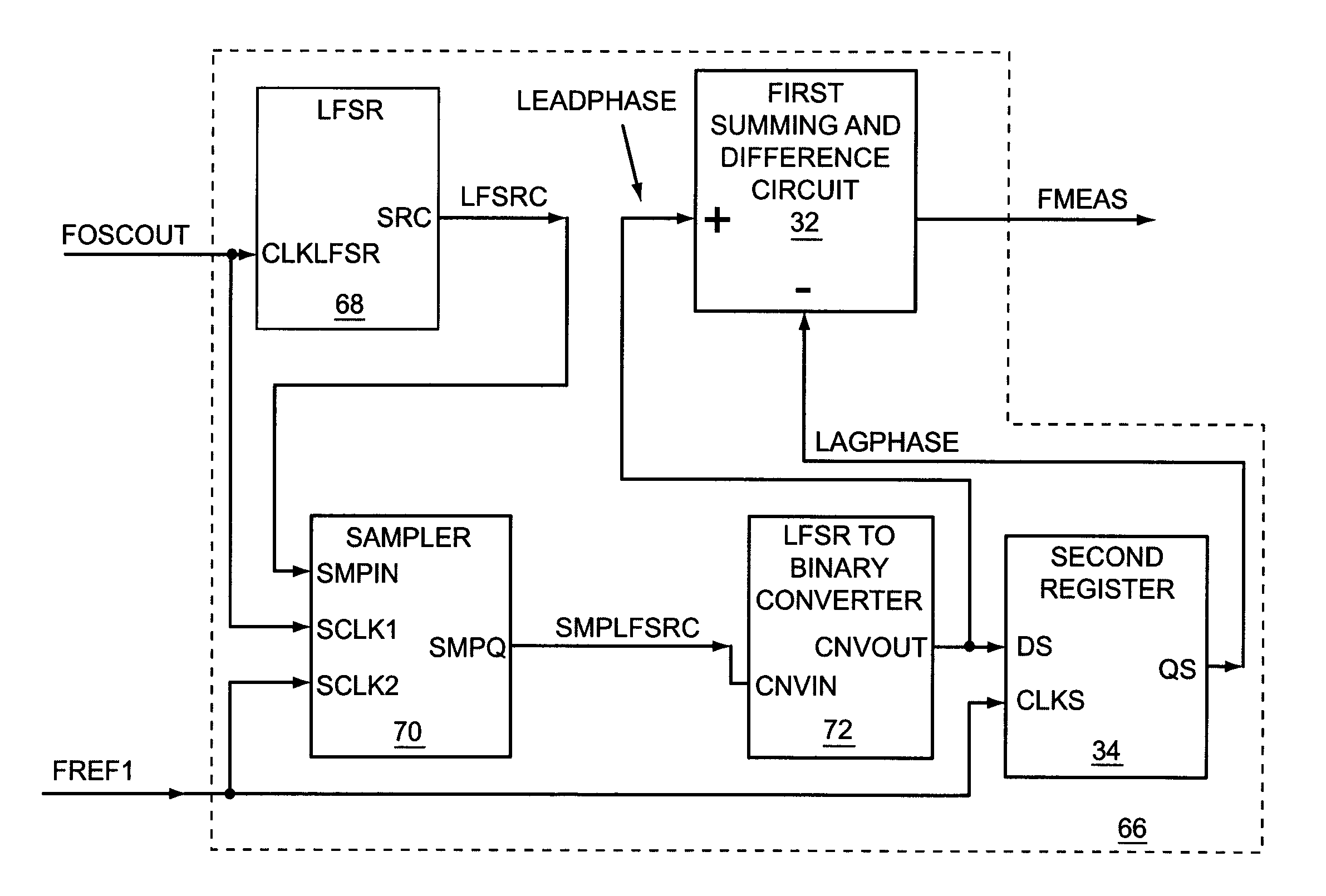

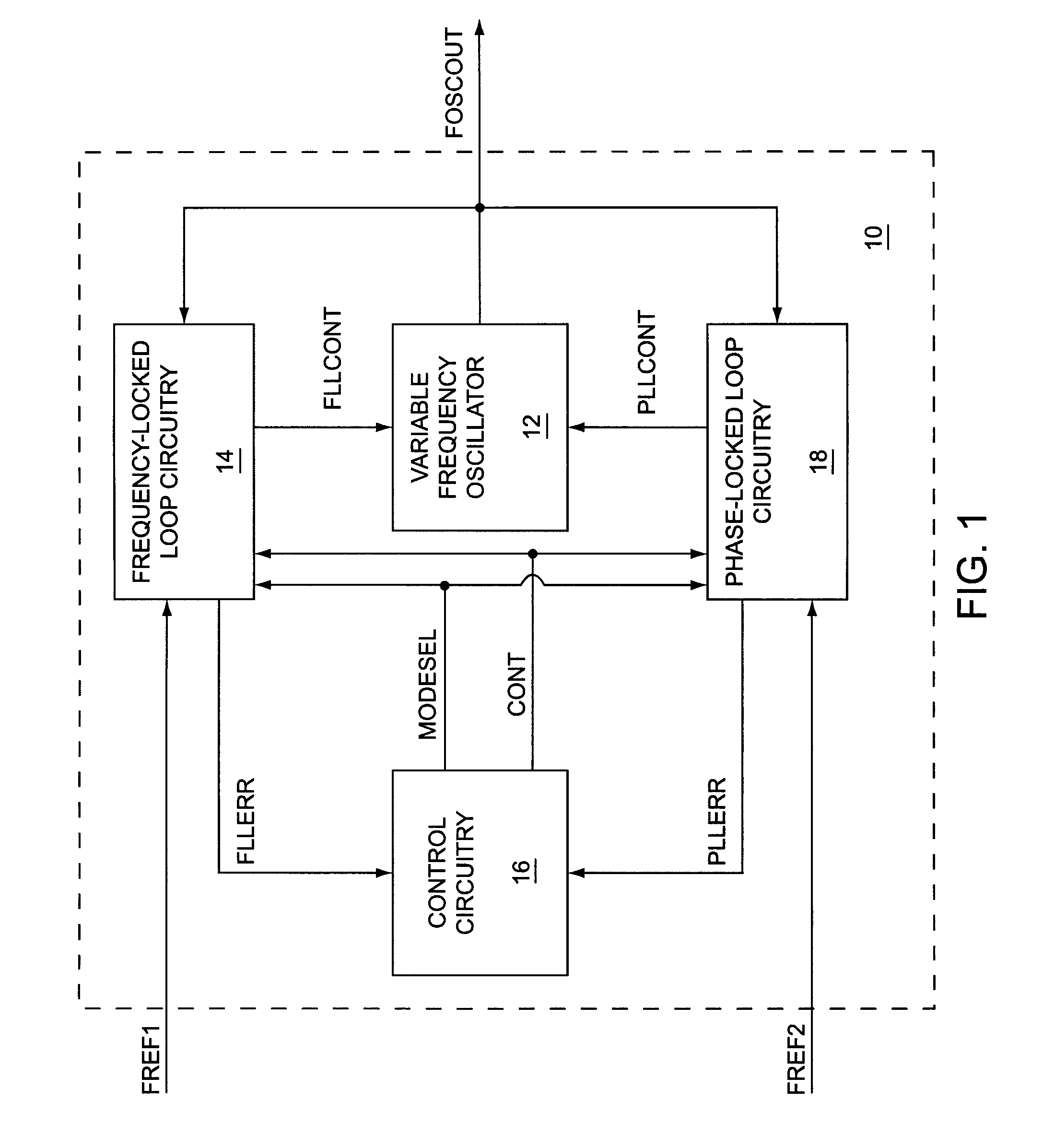

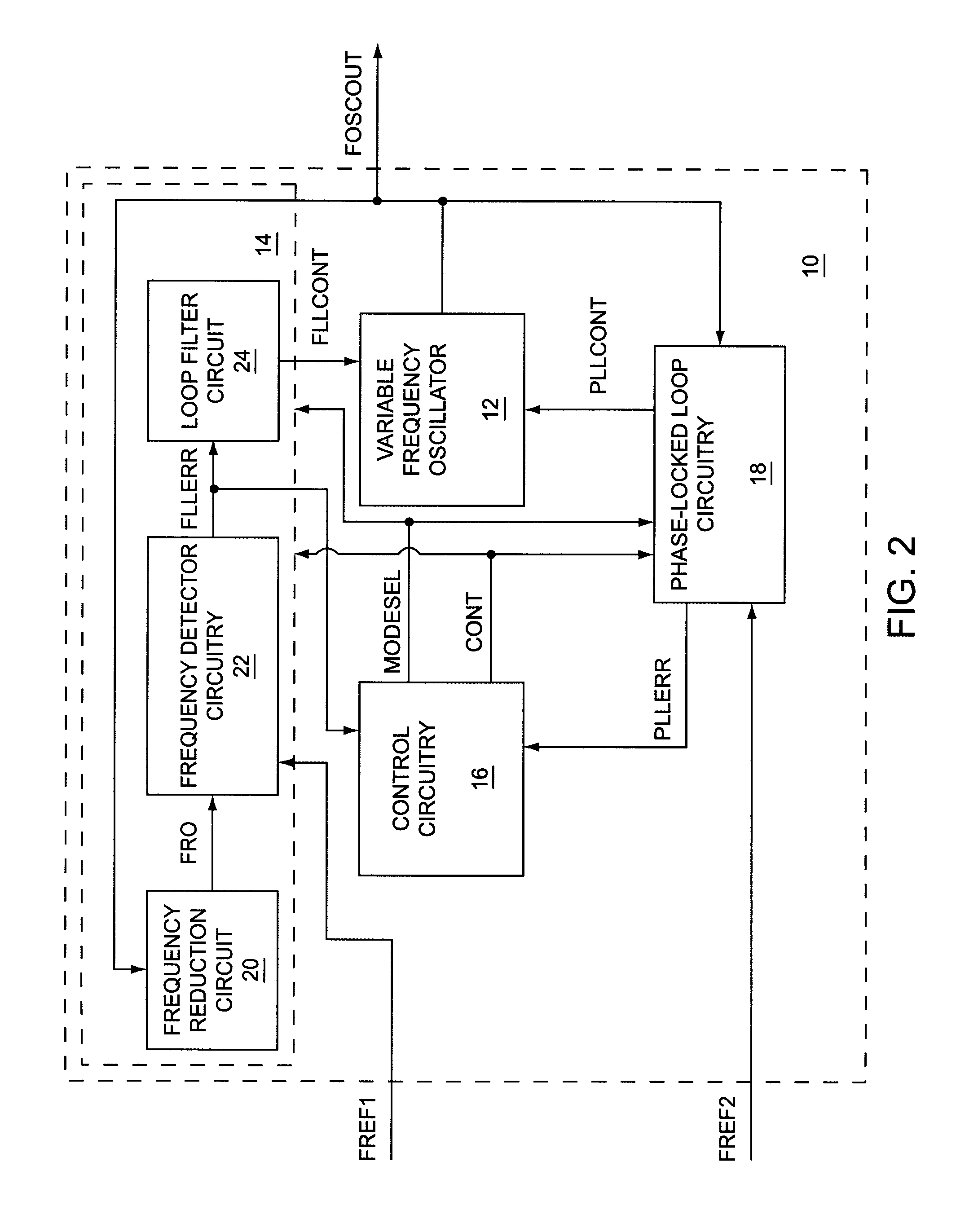

Frequency measurement based frequency locked loop synthesizer

ActiveUS7750685B1Fast settling timeReduce frequencyMultiple input and output pulse circuitsPulse automatic controlFrequency measurementsEngineering

A first embodiment of the present invention relates to a frequency and phase locked loop (FPLL) synthesizer having a frequency-locked loop (FLL) operating mode and a phase-locked loop (PLL) operating mode. The FLL operating mode is used for rapid coarse tuning of the FPLL synthesizer and is followed by the PLL operating mode for fine tuning and stabilization of the frequency of an output signal from the FPLL synthesizer. A second embodiment of the present invention relates to a high resolution frequency measurement circuit that is capable of directly measuring the frequency of a high frequency signal to provide a high resolution frequency measurement using a lower frequency reference signal, and may include linear feedback shift register (LFSR) circuitry and LFSR-to-binary conversion circuitry. A third embodiment of the present invention relates to an FPLL having an FLL that includes the high resolution frequency measurement circuit.

Owner:QORVO US INC

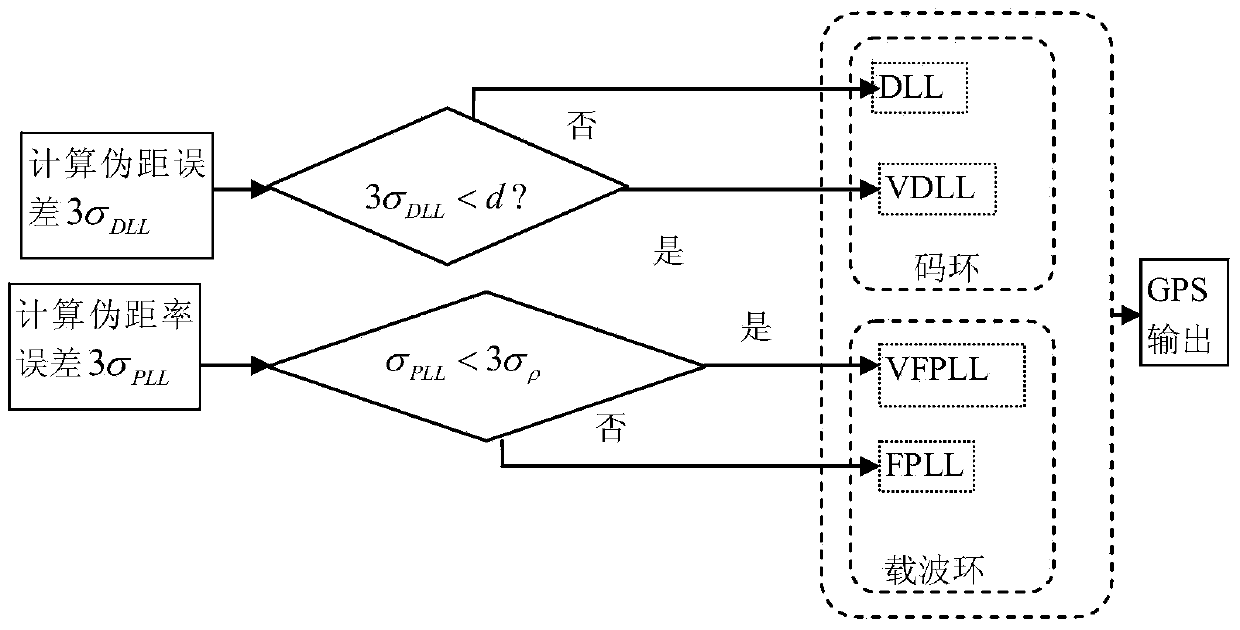

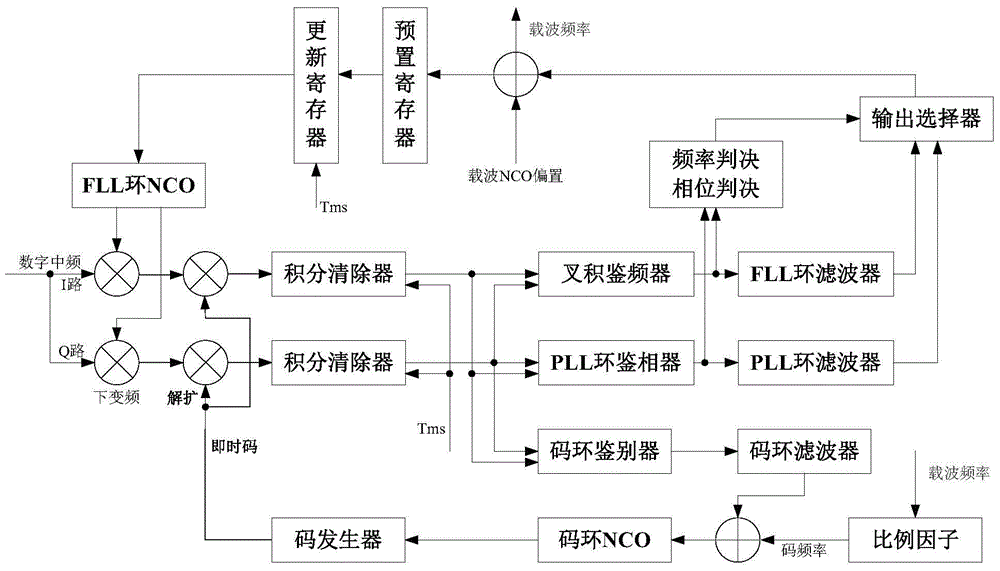

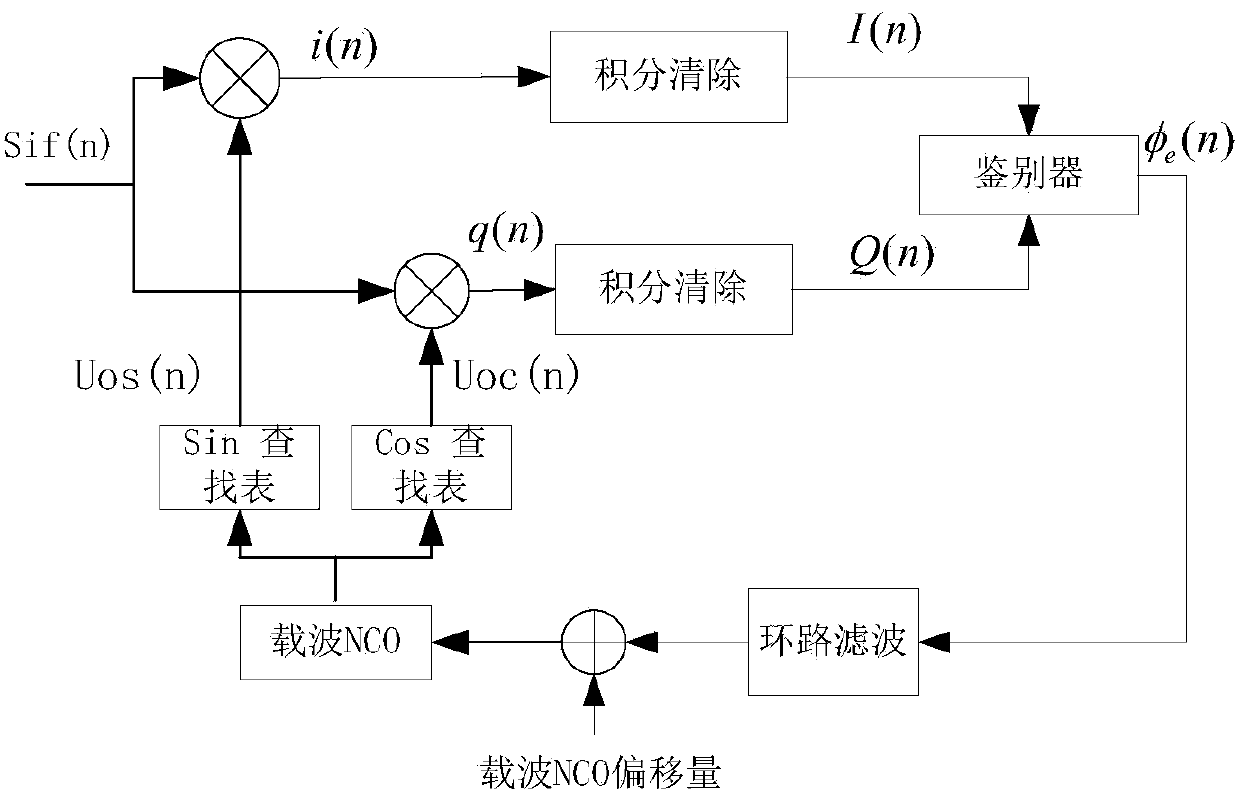

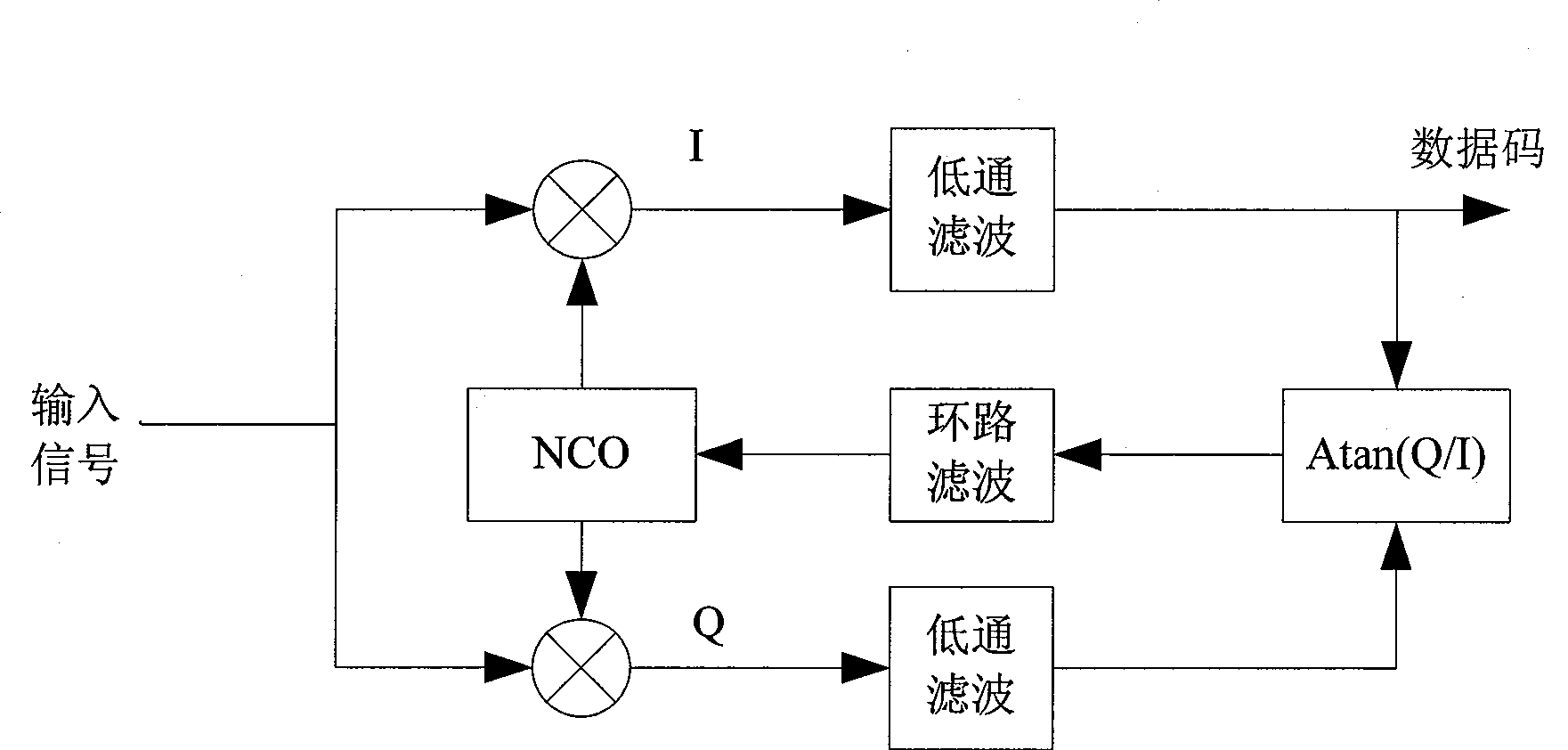

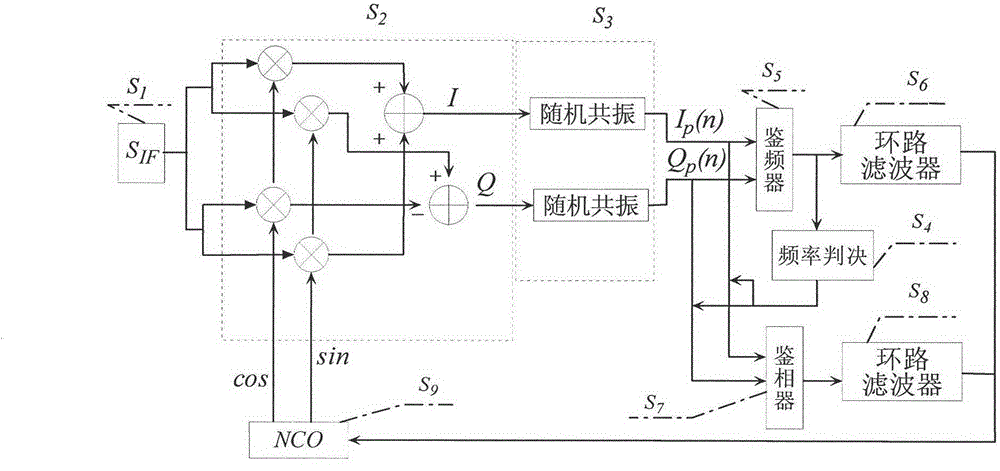

Signal tracing algorithm of GNSS receiver

InactiveCN103809191AQuickly restore locked stateReliable Signal TrackingSatellite radio beaconingVector trackingUsability

The invention discloses a signal tracing algorithm of a GNSS receiver. The signal tracing algorithm is capable of overcoming the phase-locked loop lock loosing problem by means of a frequency locking / phase locking cascade tracking loop, after the phase-locked loop is unlocked, a frequency locking loop helps the phase-locked loop to restore quickly, and moreover, a loop filter reset scheme is designed to control the error between the output value of the loop filter and the Doppler observed value at the last time, so that the phase-locked loop is fastened to restore from the lock loos state. The signal tracing algorithm automatically switches between a vector tracking loop and a scalar tracking loop according to the signal environment so as to improve the usability and dynamic property of the receiver. Whether the signal to noise ratio is low or the signal is momently interrupted due to shield, the performance of the receiver is not lower than the ordinary GNSS receiver, the influence of the accumulative error caused by the signal failure or interference of a satellite on the other satellite signal processing channels is avoided, and the system stability and the location output reliability are improved.

Owner:ZHEJIANG SCI-TECH UNIV

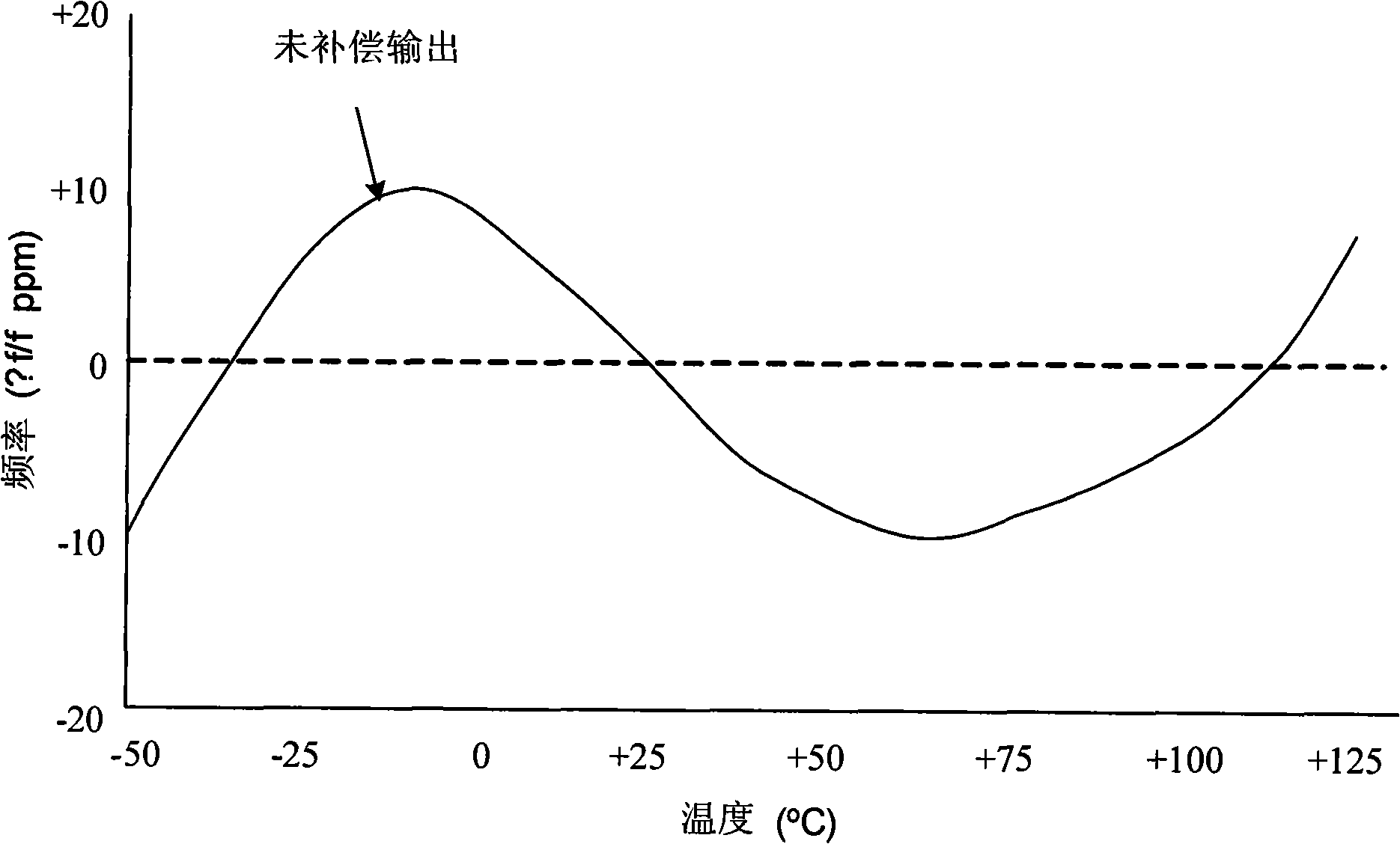

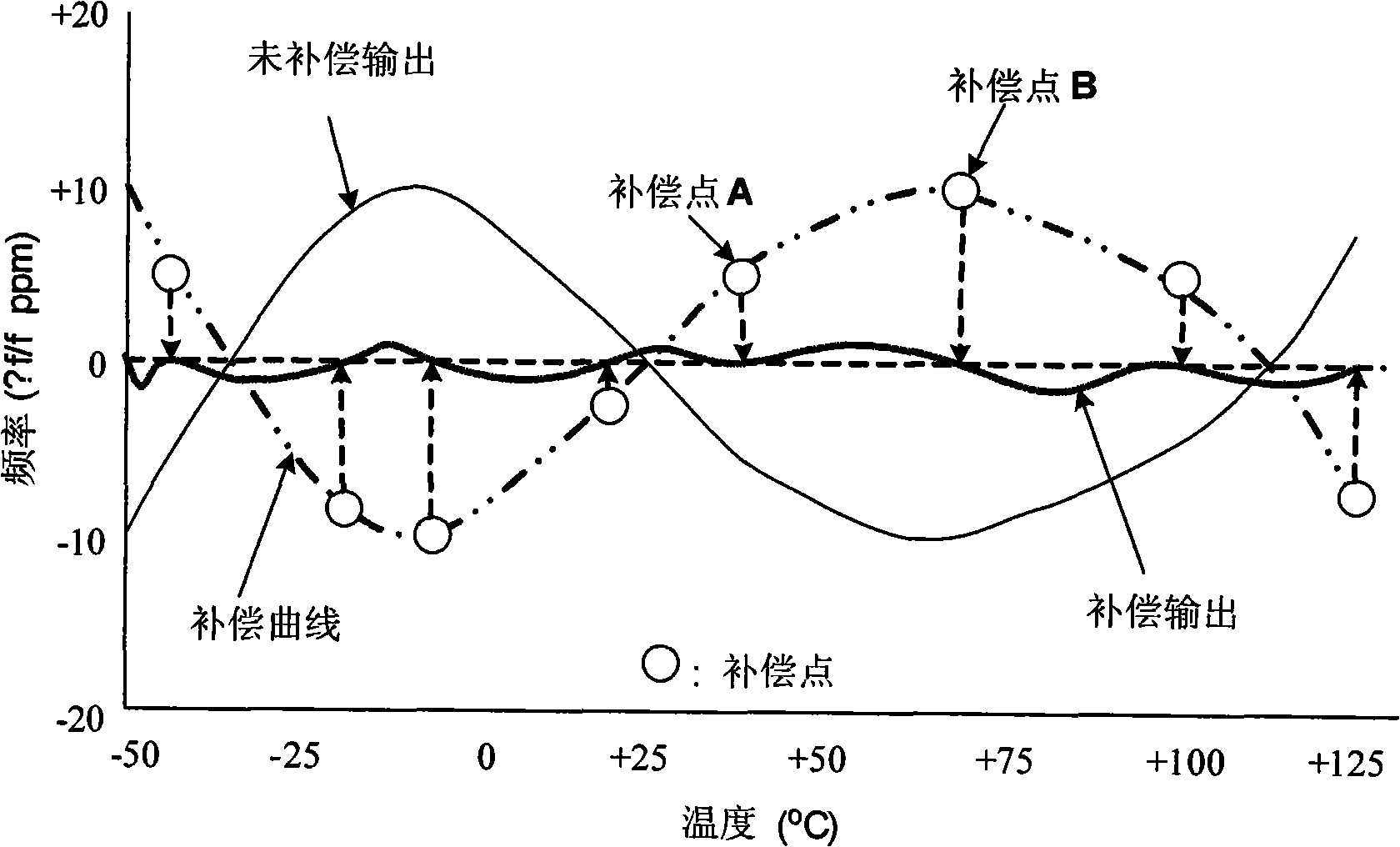

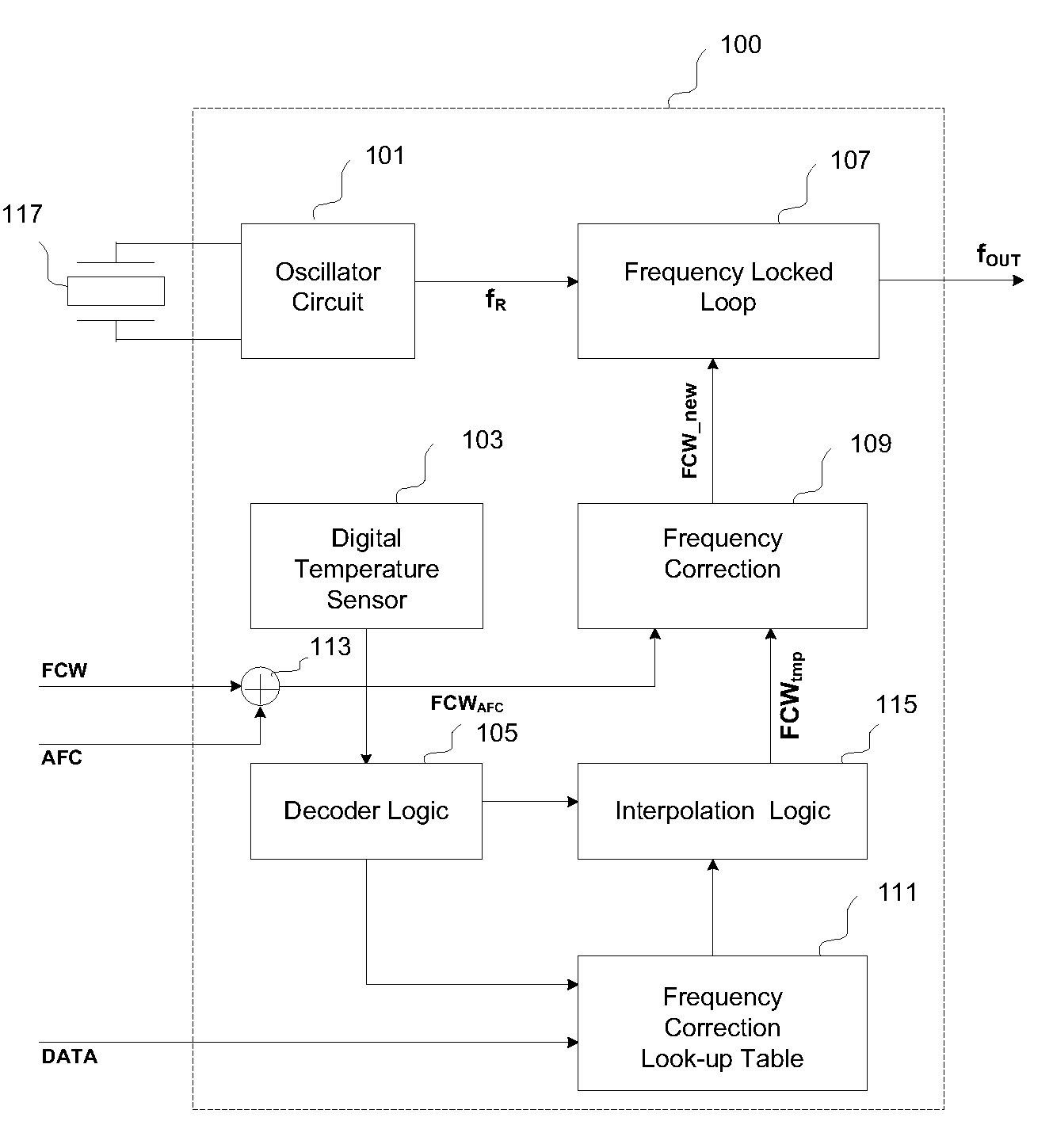

Method and apparatus for compensating temperature changes in an oscillator-based frequency synthesizer

InactiveUS7579919B1Pulse automatic controlAngle modulation detailsFrequency synthesizerBase frequency

Architectures for compensating the frequency drift of an oscillator based frequency synthesizer circuit due to the change of temperature are disclosed. By applying a digitally controlled frequency word which represents the frequency difference between an output signal of a crystal oscillator and a temperature-compensated signal obtained from the output of a frequency synthesizer, the generated frequency signal is controlled so as to be temperature compensated over a wide temperature range. In one embodiment, a frequency locked loop is provided to perform functions to compensate for possible drifts in the reference signal. The frequency locked loop receives a digital frequency corrected control word based on at least a first parameter and a second parameter, wherein the first parameter is a combination of a fixed frequency control word and an automatic frequency correction word, and the second parameter is derived from an external source.

Owner:CAO WEIXUN

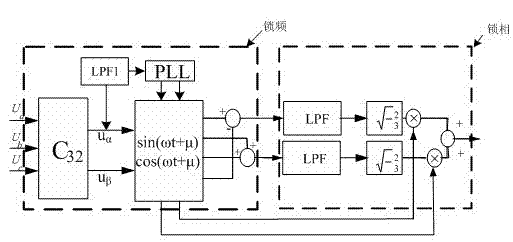

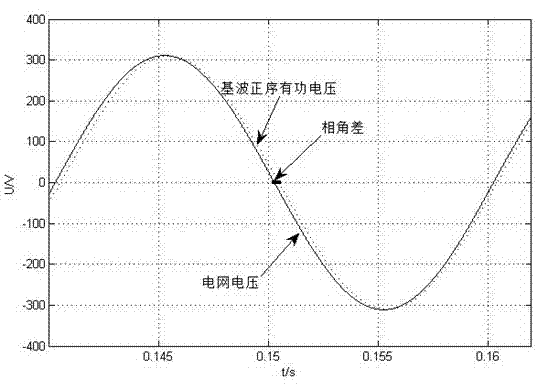

Quick detection method of grid voltage fundamental wave positive sequence phase angle

InactiveCN102735938AAccurate detectionGuaranteed uptimeVoltage-current phase angleHarmonicPower grid

The invention relates to a quick detection method of a grid voltage fundamental wave positive sequence phase angle, wherein the fundamental wave positive sequence voltage of a grid is obtained through two loops such as a frequency locking loop and a phase locking loop and a phase angle of fundamental wave voltage positive sequence component is extracted from a signal when the frequency of the grid voltage changes and the three-phase voltage is asymmetric or distorted. According to the quick detection method of the grid voltage fundamental wave positive sequence phase angle disclosed by the invention, when the frequency of the grid voltage is unstable and the waveform is distorted, the interference of harmonic component and fundamental wave negative sequence component is removed through the frequency locking loop and the phase locking loop, and the phase angle of grid voltage fundamental wave positive sequence component is exactly detected, thus the quick detection method disclosed by the invention not only has high detection precision, but also has quicker dynamic response speed, and can ensure the normal operation of various power electronic devices.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

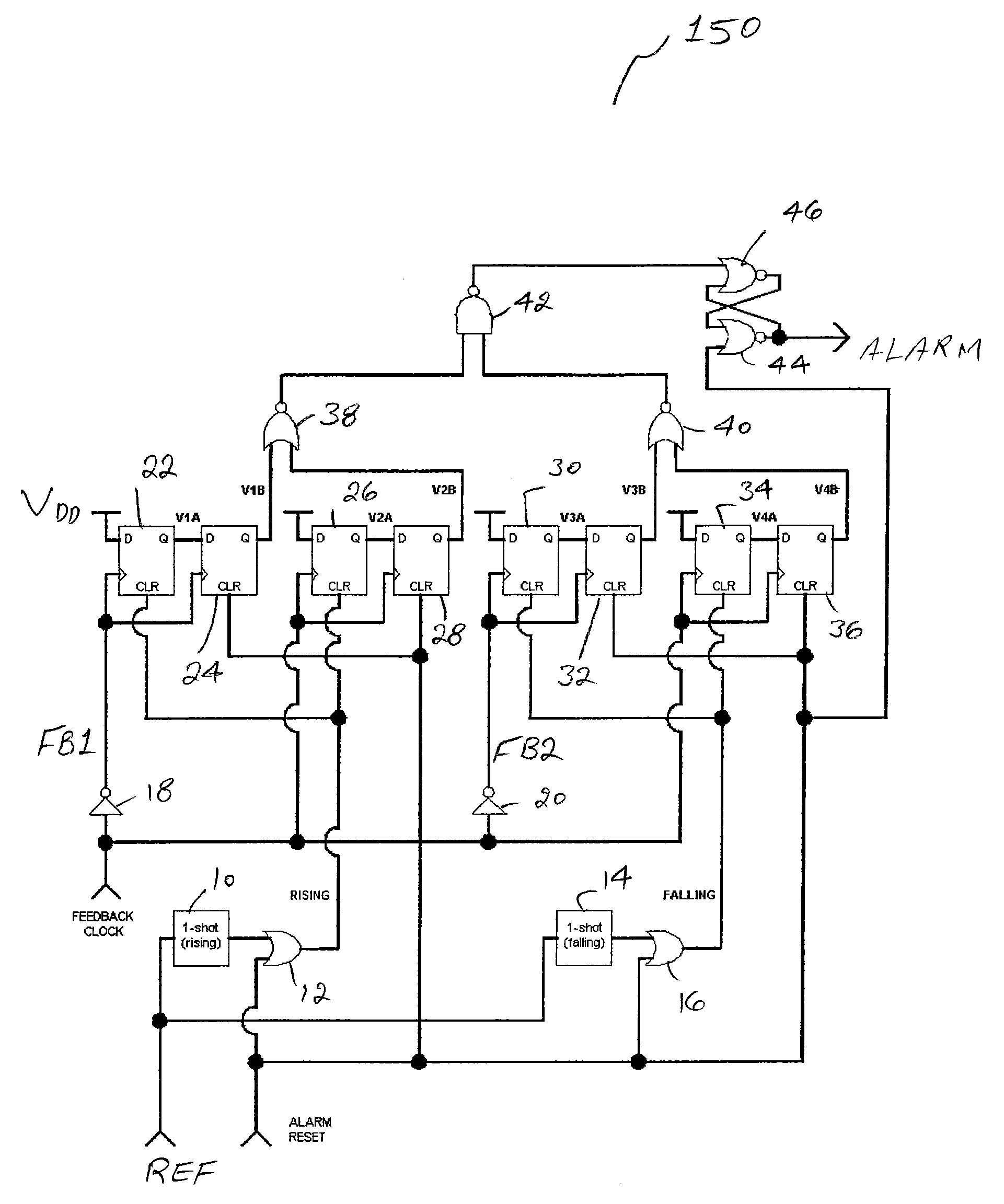

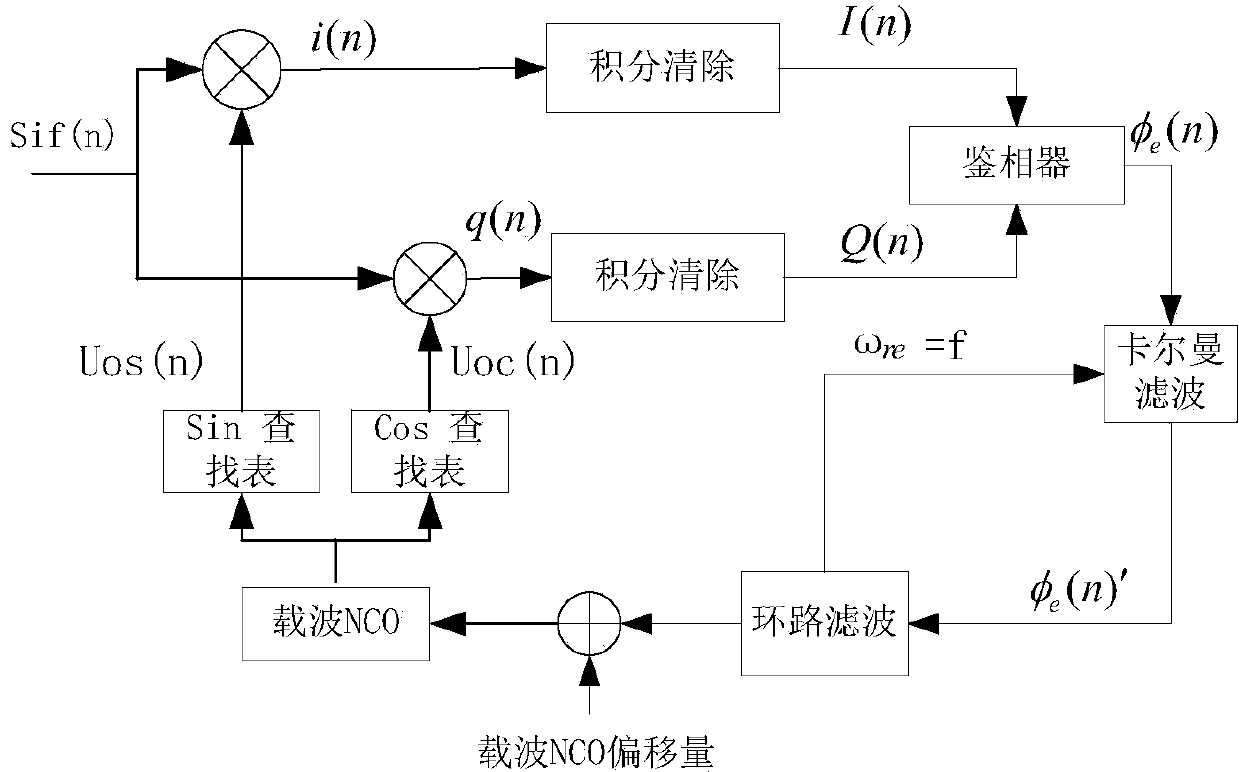

Means to detect a missing pulse and reduce the associated PLL phase bump

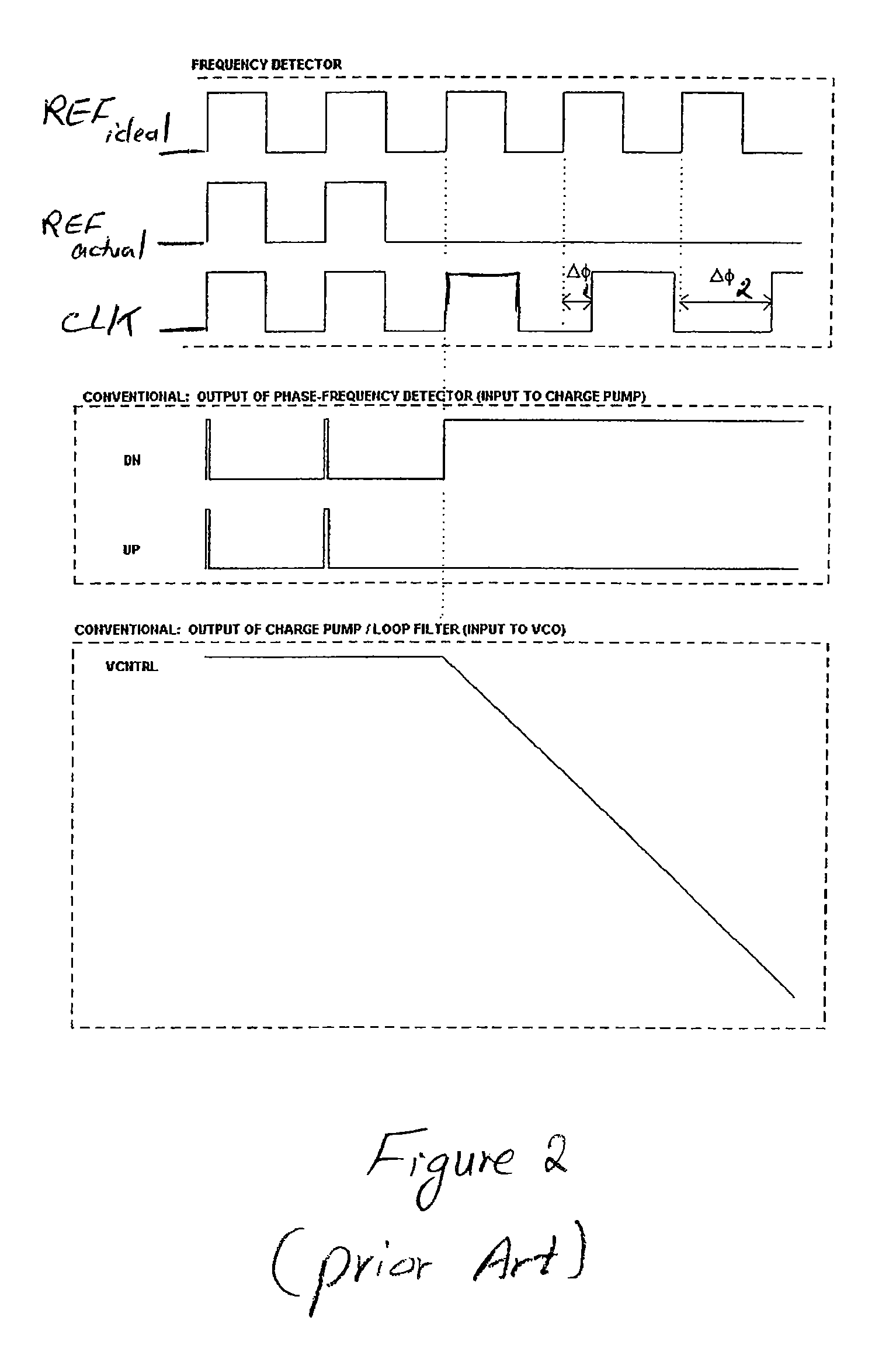

A phase / frequency locked loop (PLL) includes circuitry adapted to detect missing pulses of a reference clock and to control the phase bump of the PLL. The circuitry includes, in part, first and second flip-flops, as well as a one-shot block. The first flip-flop has a data input terminal responsive to a voltage supply, and a clock terminal responsive to an inverse of feedback clock. The second flip-flop has a data input terminal responsive to an output of the first flip-flop, and a clock terminal responsive to the inverse of the feedback clock. The one-shot block generates a pulse in response to a rising edge of the reference clock that is used to generate the feedback clock. The one-shot block generates an output signal applied to a reset terminal of the first flip-flop.

Owner:EXAR CORP

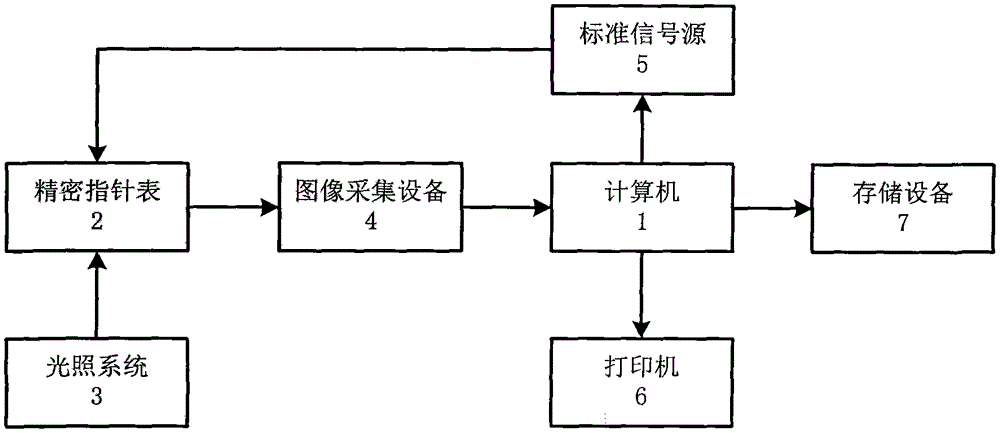

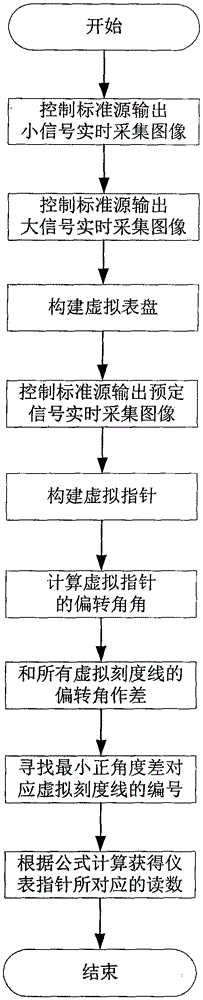

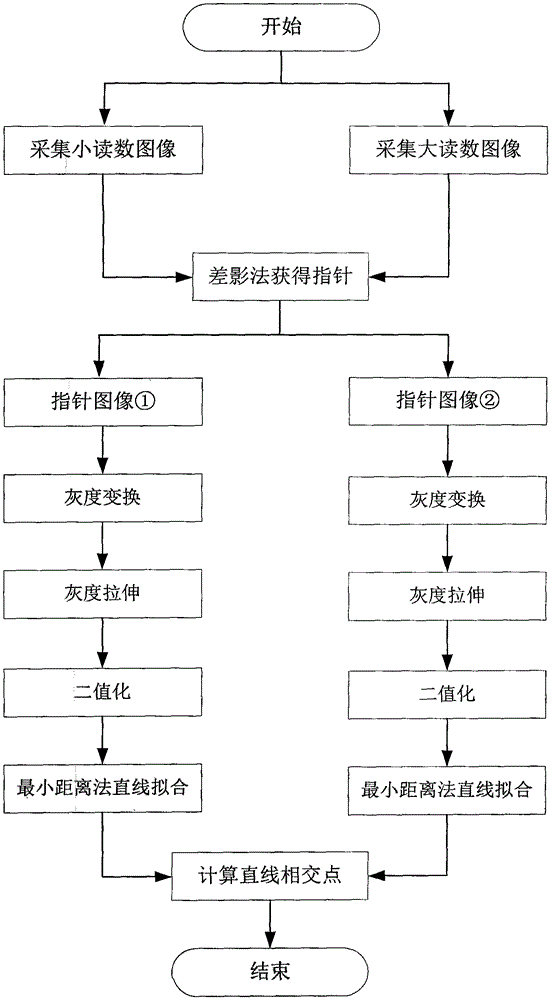

Virtual watch plate based pointer reading identifying method

ActiveCN105091922AReduce labor intensityAvoid human errorInstrumentsSignal-to-noise ratio (imaging)Machine vision

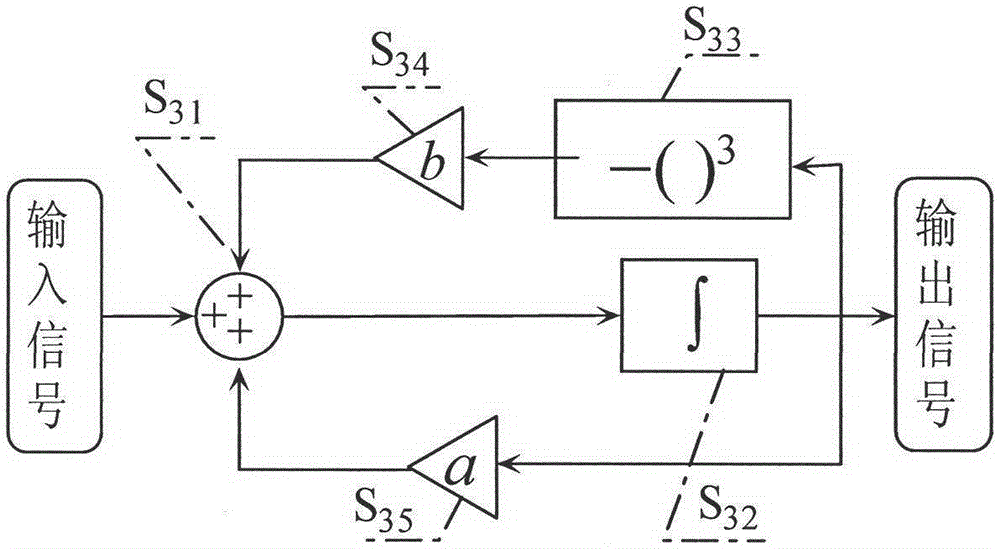

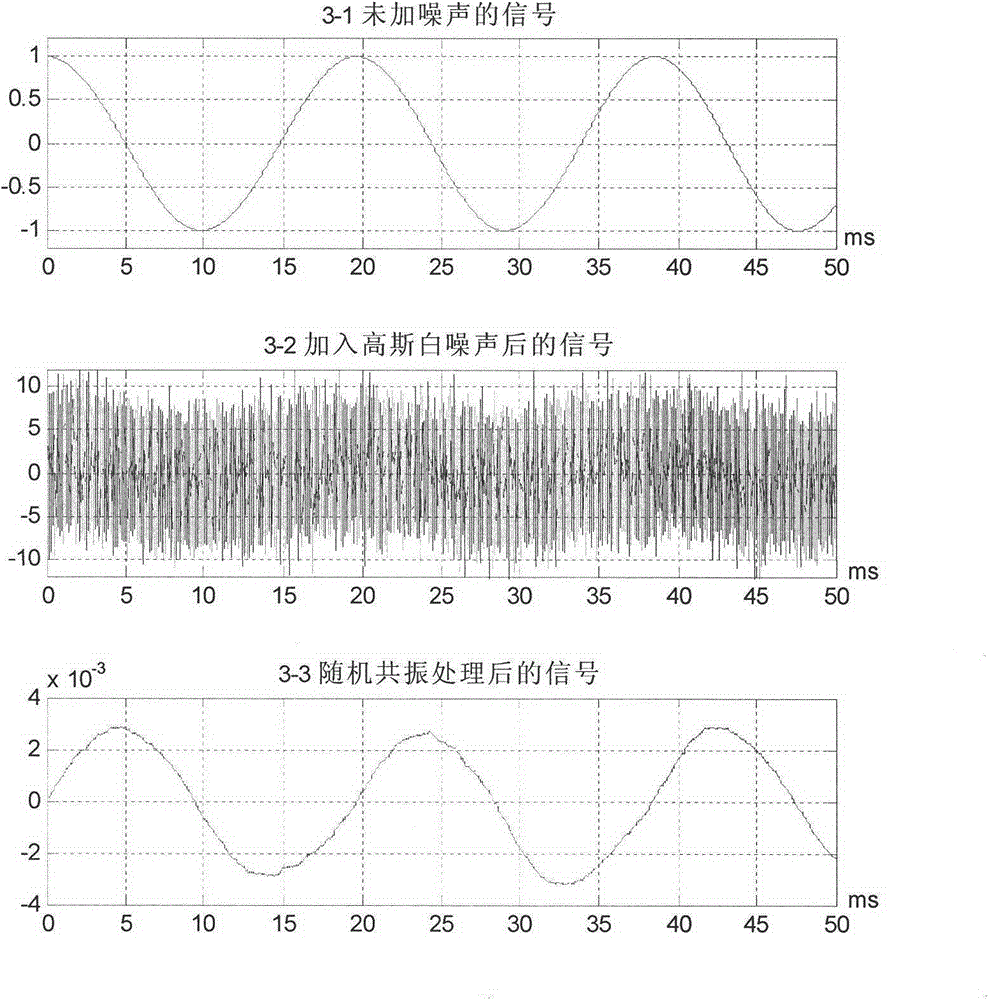

The invention discloses a GNSS carrier loop circuit tracking method based on a stochastic resonance algorithm. According to the invention, the signal to noise ratio of receiving signals is increased by integral accumulation and multiplication feedback treatment on input signals; rough tracking of frequency of the receiving signals is performed by utilizing a second-order frequency locking loop; and precise tracking is performed on the signals subjected to rough tracking by adopting a third-order phase locking loop. Therefore, precise carrier loop circuit tracking on the GNSS signals is realized in a low carrier-to-noise ratio. According to the invention, an advantage of the stochastic resonance algorithm in an aspect of improving the signal to noise ratio and an advantage of anti-interference and robustness of the cooperation of the second order frequency locking loop and the third-order phase locking loop are integrated effectively. The method is simple in hardware implementation and stable in signal tracking, and can realize stable and reliable tracking of highly dynamic satellite signals by a receiver in a severe environment.

Owner:GUANGDONG UNIV OF TECH

Spread-spectrum clock signal generator

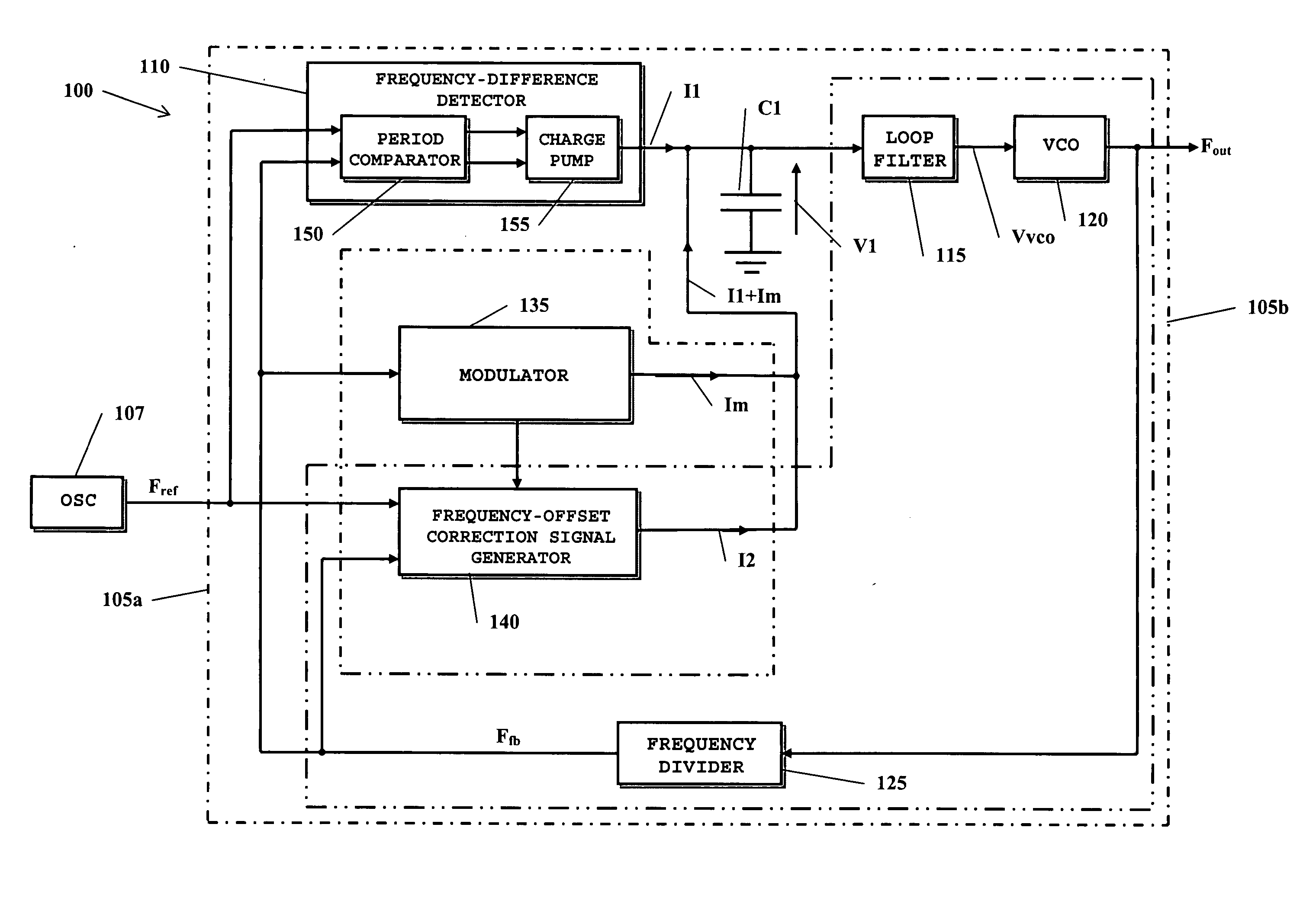

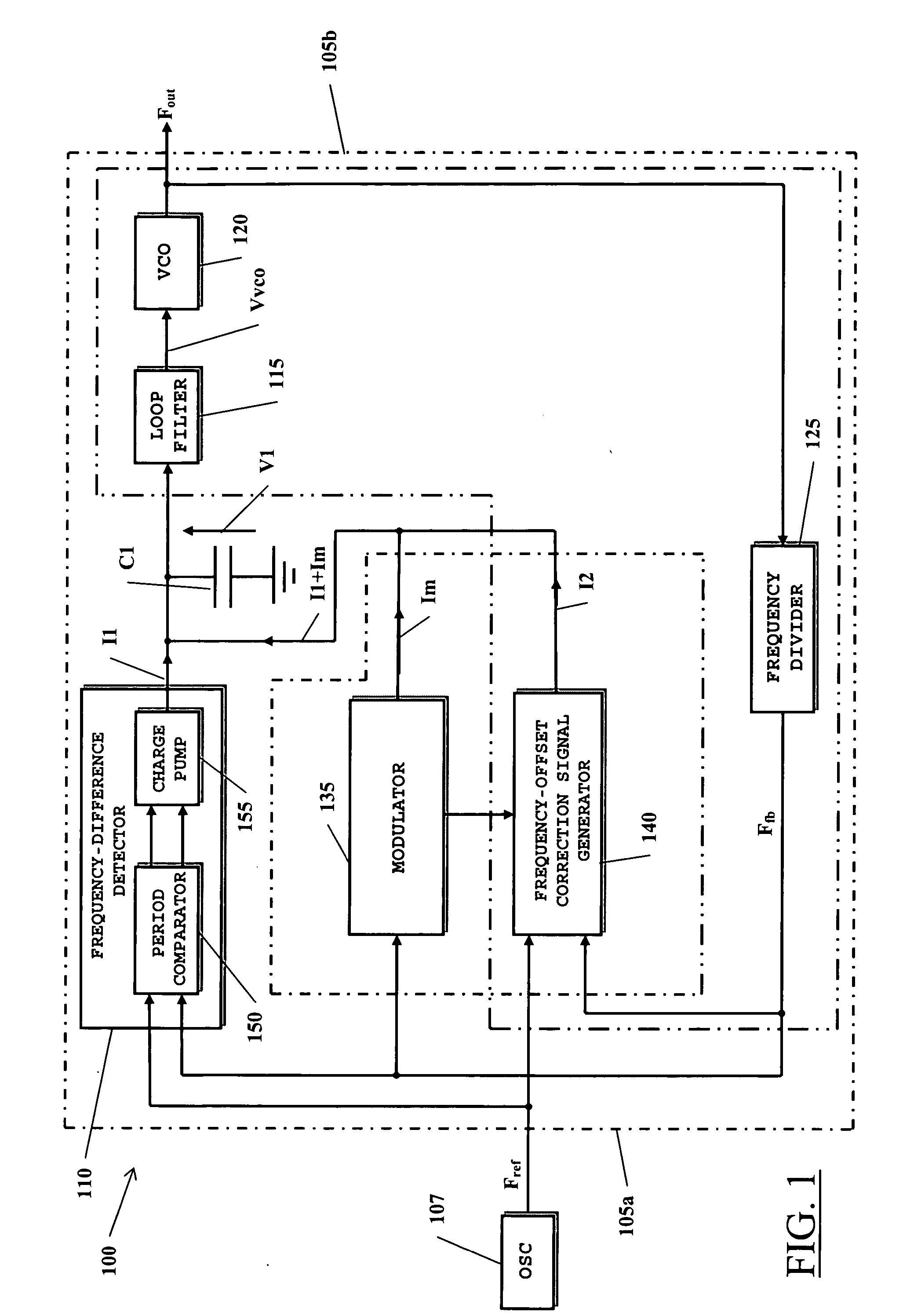

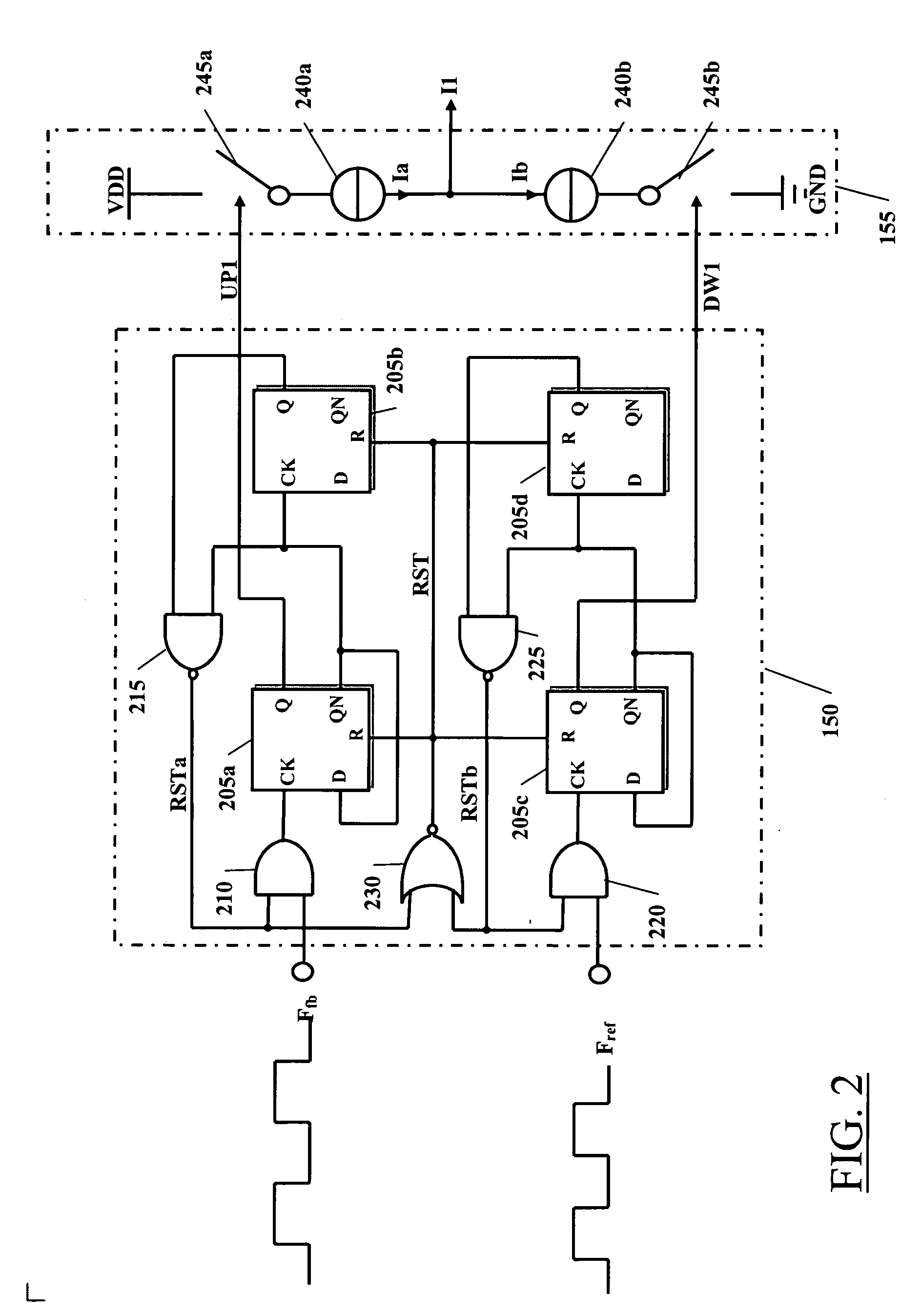

InactiveUS20050013343A1Reduce electromagnetic radiationPulse automatic controlAngle modulation detailsSignal generatorMean frequency

A spread-spectrum clock signal generator comprises a circuit loop receiving a reference signal at a reference frequency and adapted to generate an output signal at an output frequency dependent on and locked to the reference frequency, and a modulator circuit generating a modulation signal at a modulation frequency; the modulation signal is injected into the circuit loop to induce a modulation of the frequency of the output signal with respect to the frequency dependent on the reference frequency. The circuit loop is a frequency-locked loop and has a bandwidth sufficiently higher than the modulation frequency, so that the output frequency tracks the modulation signal. Frequency-offset correction means are further provided, for evaluating a frequency offset between an average frequency of the output signal and the frequency dependent on the reference frequency, and for generating a frequency-offset correction signal which is injected into the circuit loop for correcting the evaluated frequency offset.

Owner:ACCENT INC

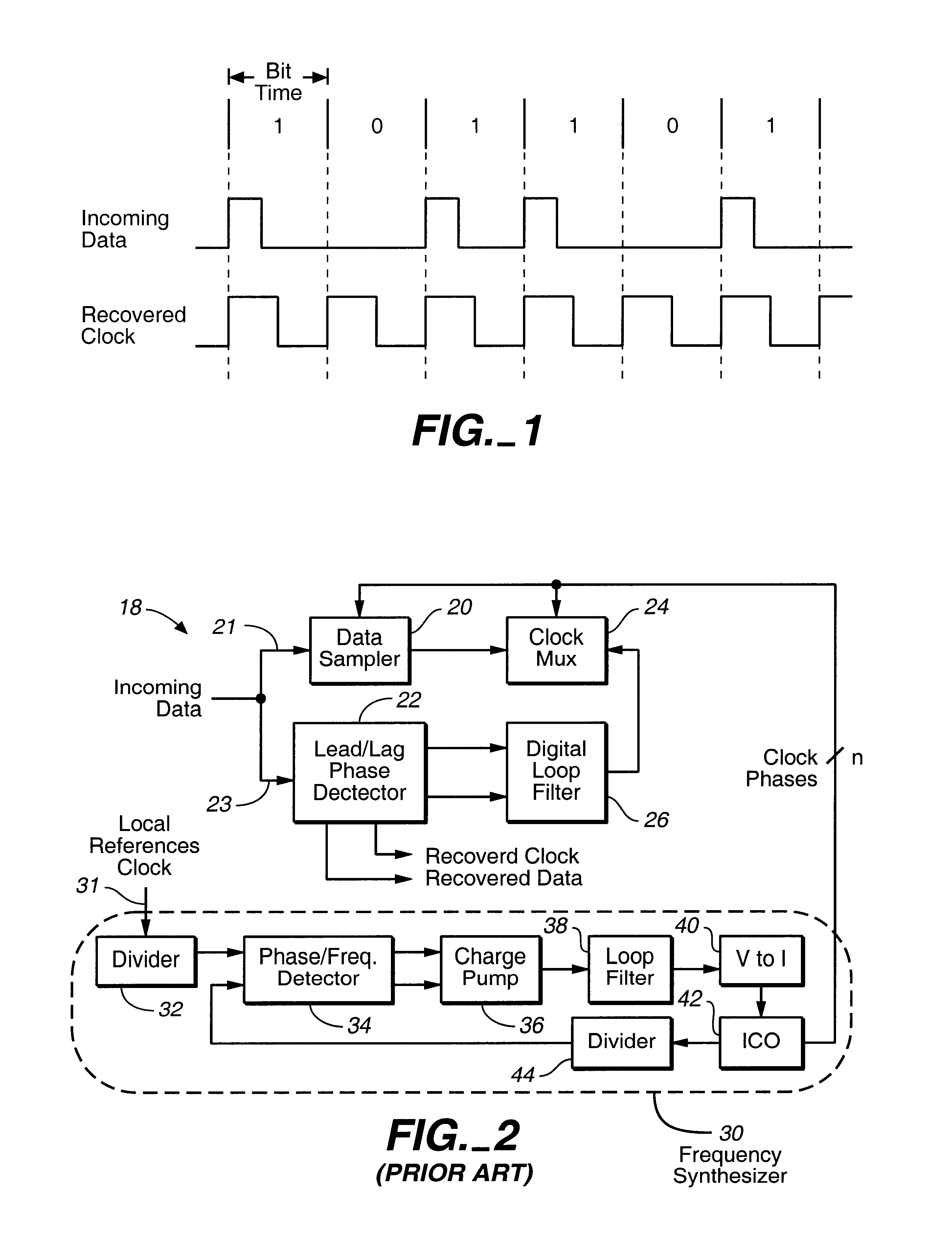

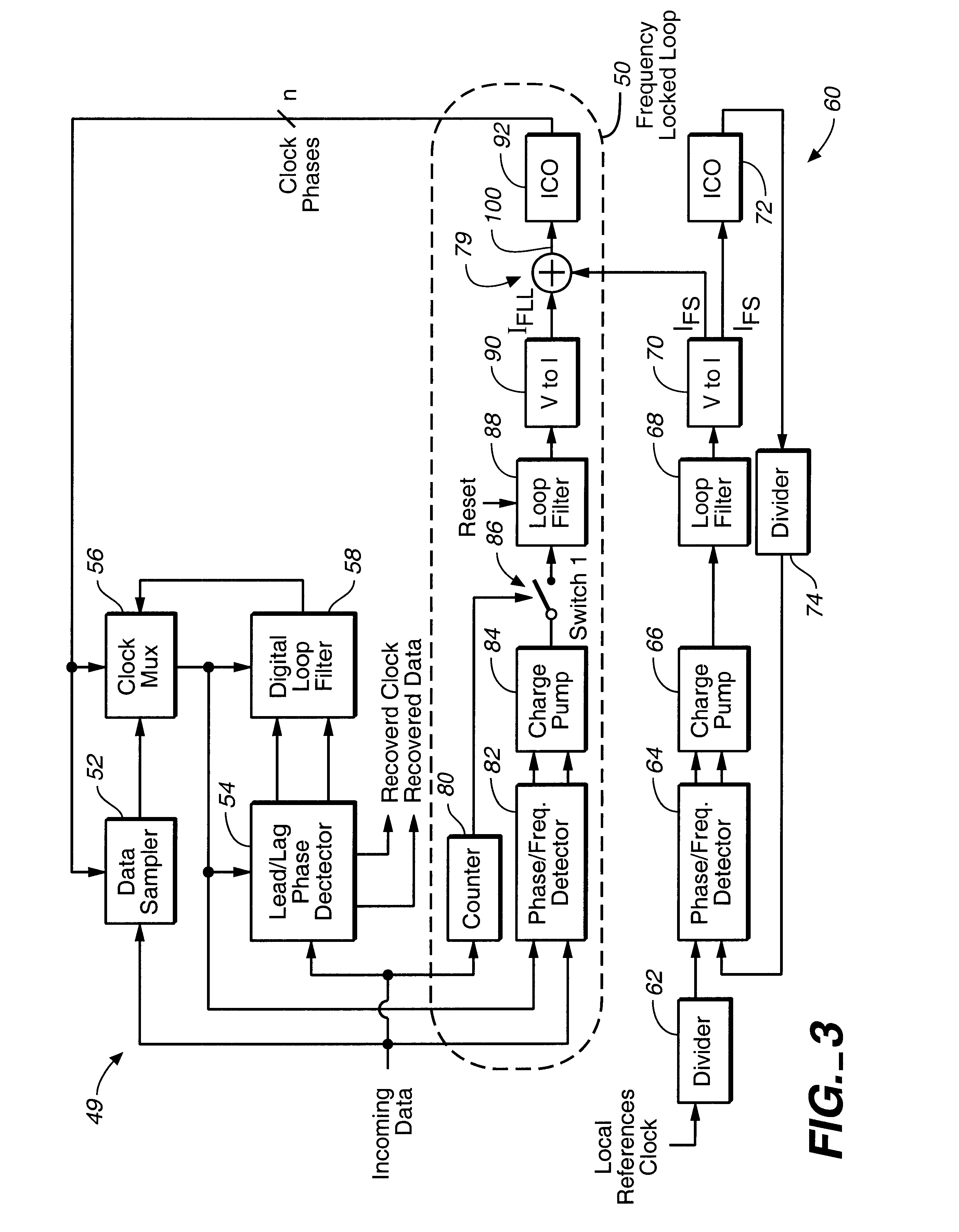

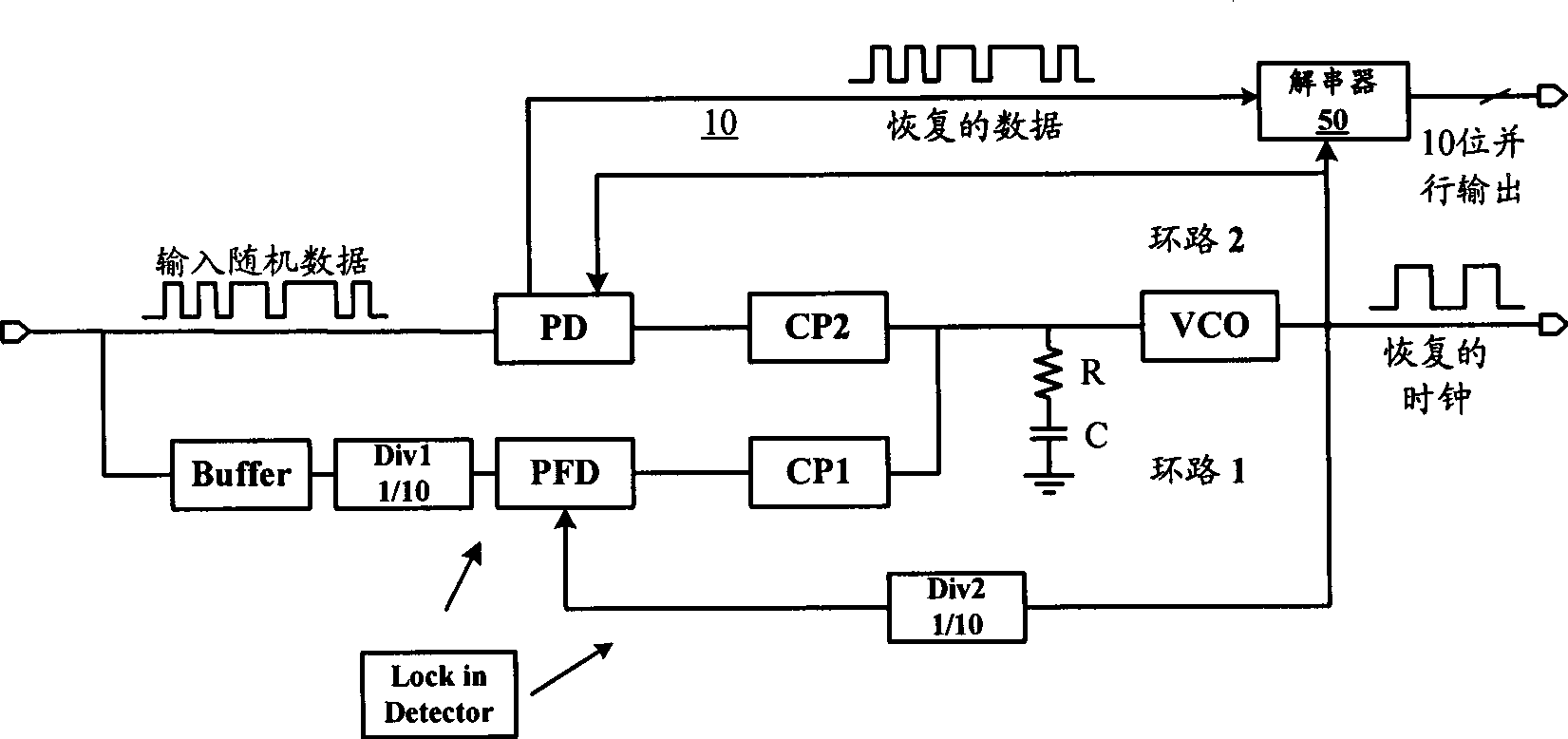

Modified first-order digital PLL with frequency locking capability

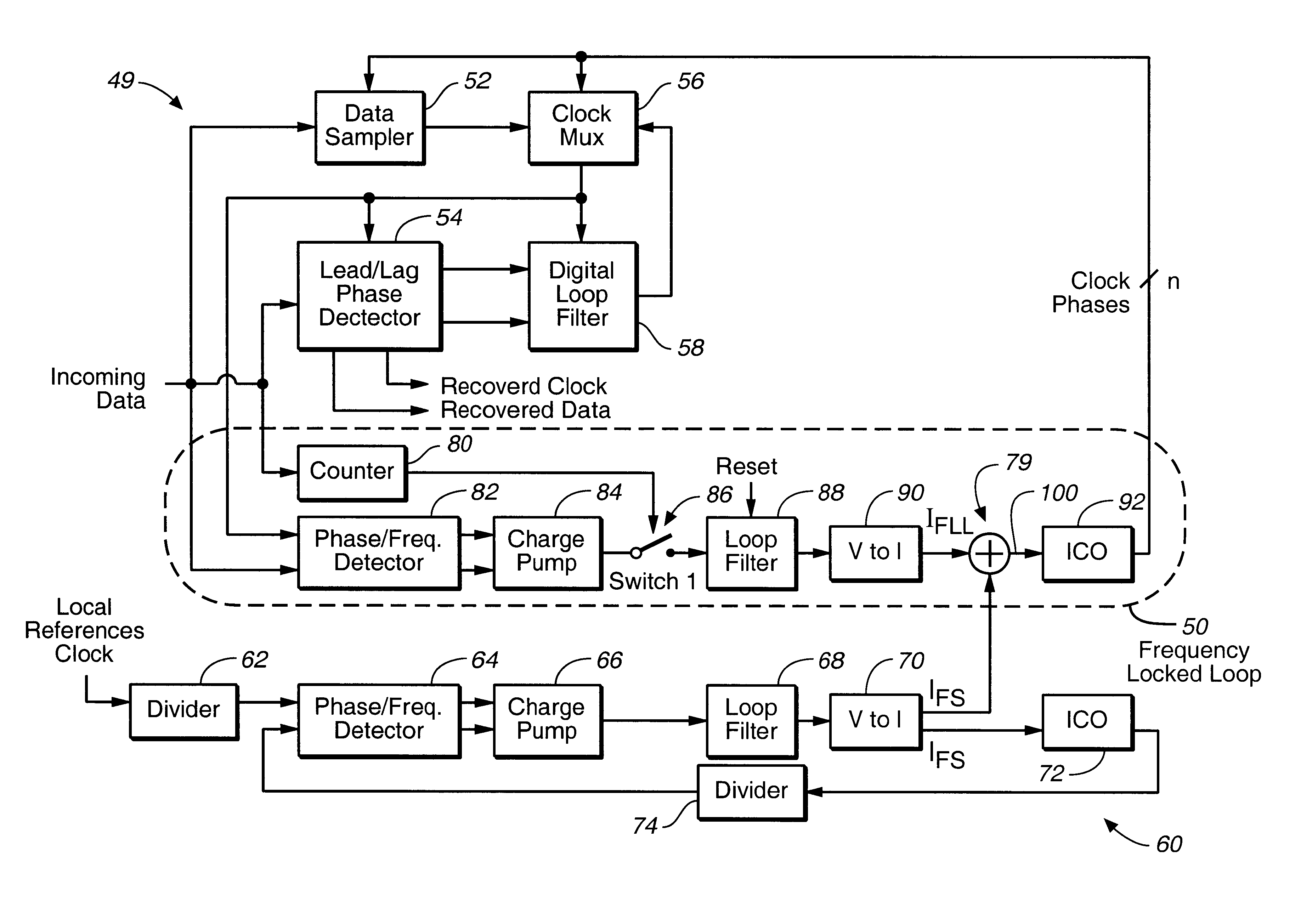

InactiveUS6606365B1Selective operationPulse automatic controlSynchronisation signal speed/phase controlData streamPhase locked loop circuit

A first-order digital PLL configured to accommodate a large frequency difference between a clock signal embedded in an incoming data stream received by a phase-locked loop and a local reference clock signal received by a phase-locked loop circuit. The PLL includes a data sampler which receives the incoming data stream, a frequency-locked loop (FLL) which receives the incoming data stream and is connected to the data sampler, and a frequency synthesizer which receives the local reference clock signal and is connected to the FLL. The FLL is provides a signal having a frequency which is substantially equal to the frequency of the local reference clock signal when no incoming data stream is received by the FLL, and provides a signal having a frequency which is substantially equal to the frequency of the incoming data stream when the FLL receives the incoming data stream.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

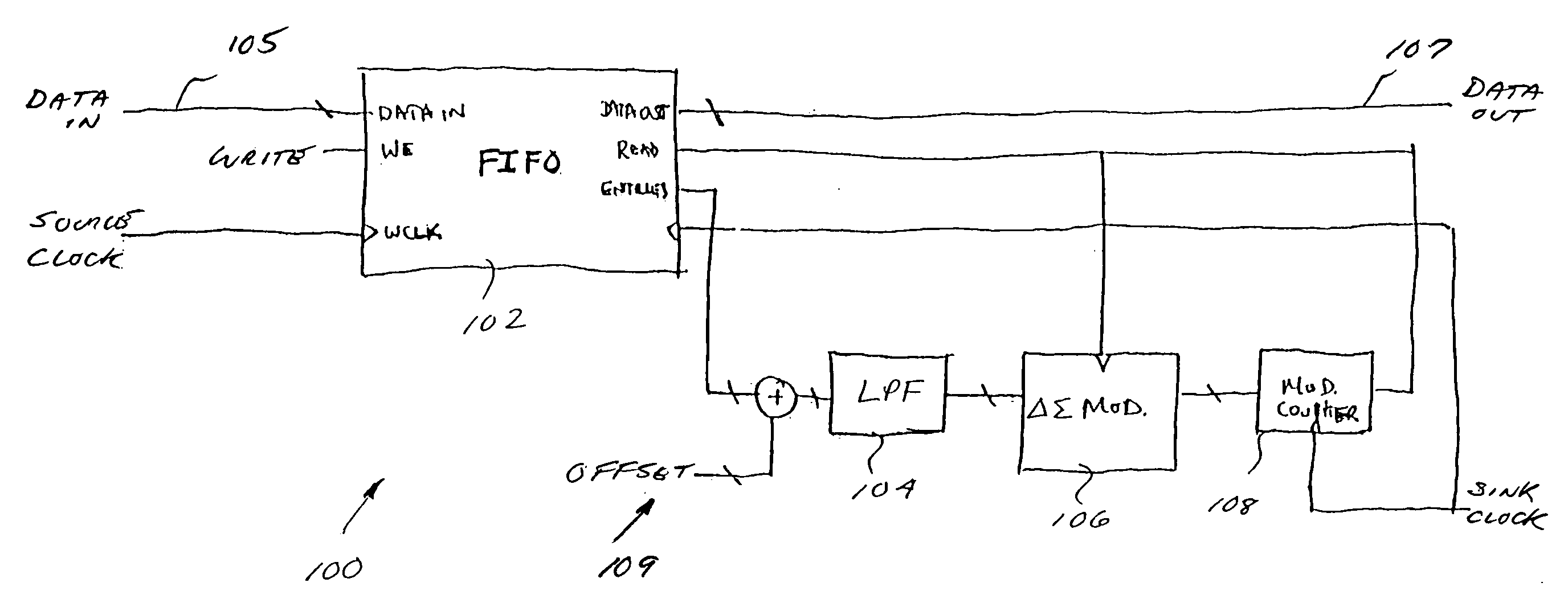

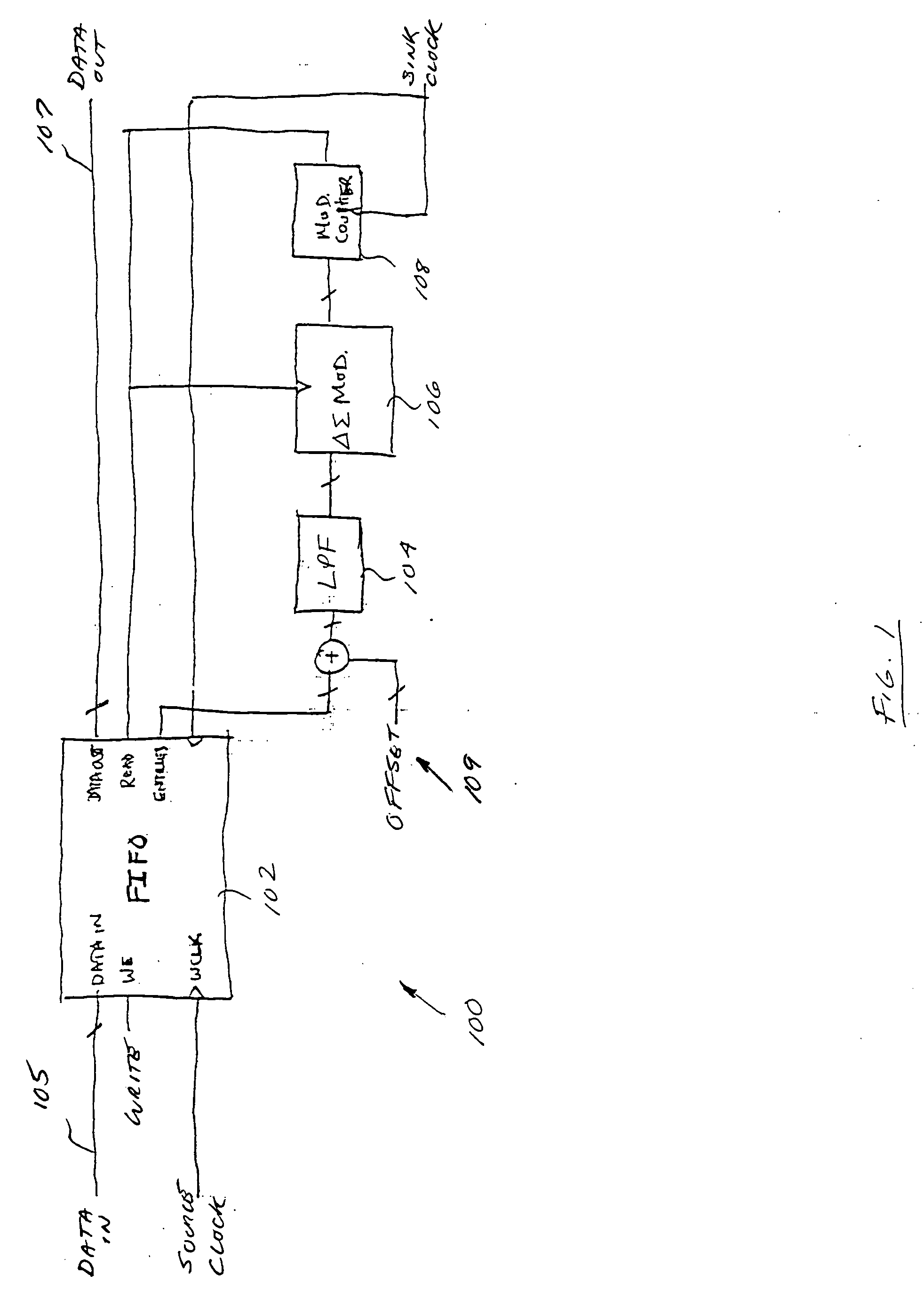

Noise shaped interpolator and decimator apparatus and method

ActiveUS20050207480A1Suppress phase noiseReduce presenceSynchronisation information channelsDigital technique networkNoise shapingEngineering

Improved interpolator and decimator apparatus and methods, including the addition of an elastic storage element in the signal path. In one exemplary embodiment, the elastic element comprises a FIFO which advantageously allows short term variation in sample clocks to be absorbed, and also provides a feedback mechanism for controlling a delta-sigma modulated modulo-N counter based sample clock generator. The elastic element combined with a delta-sigma modulator and counter creates a noise-shaped frequency lock loop without additional components, resulting in a much simplified interpolator and decimator.

Owner:STMICROELECTRONICS SRL

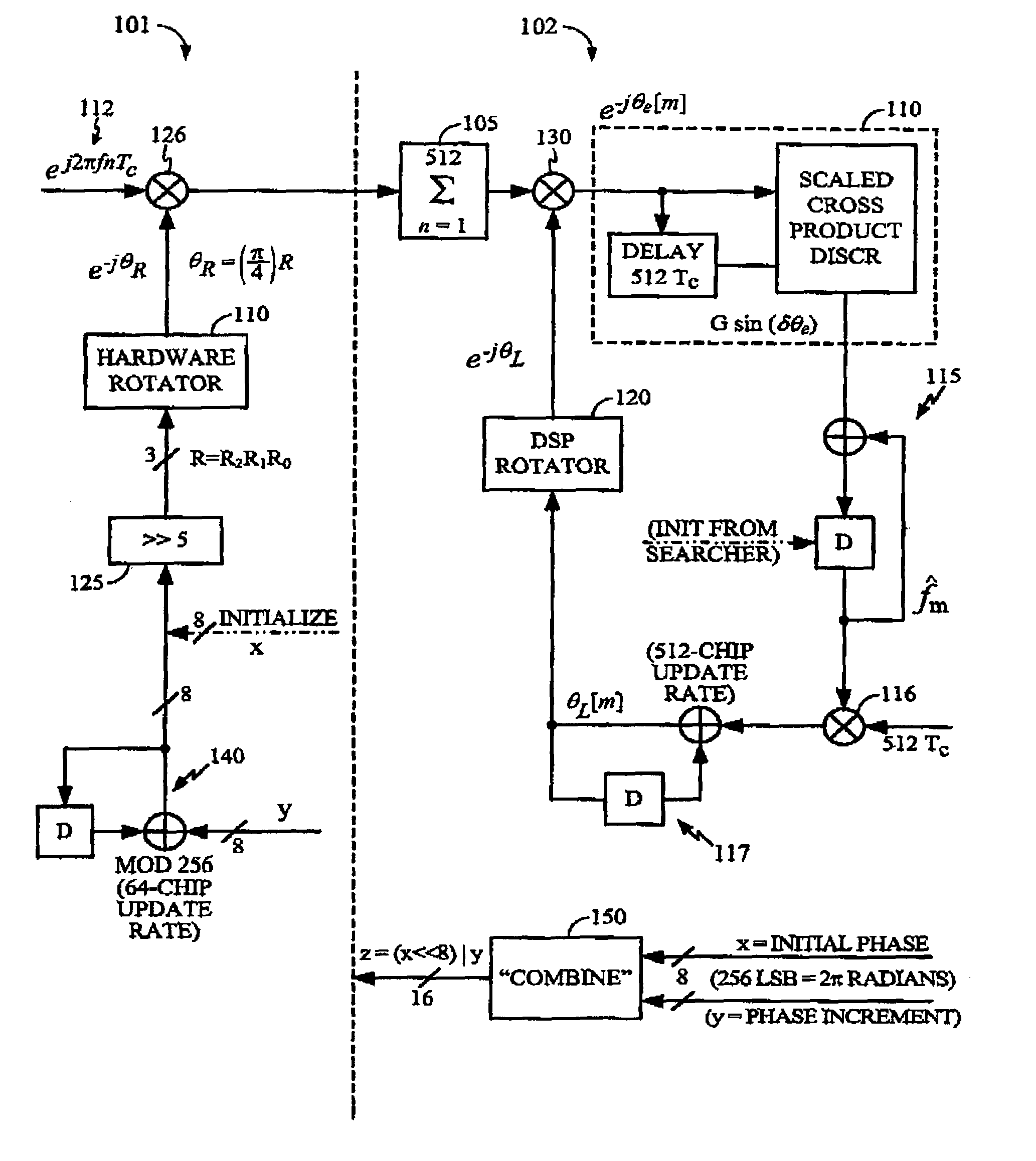

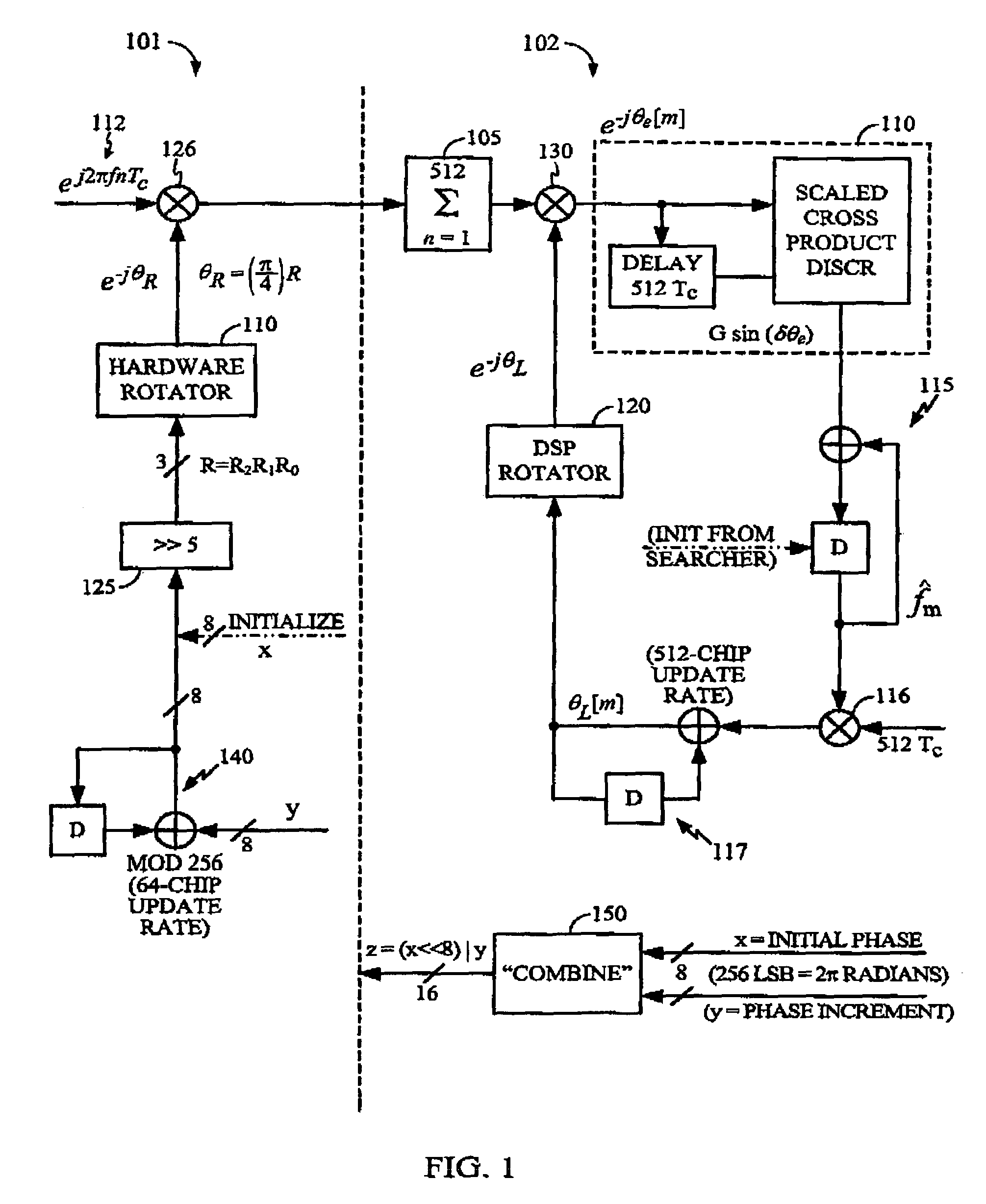

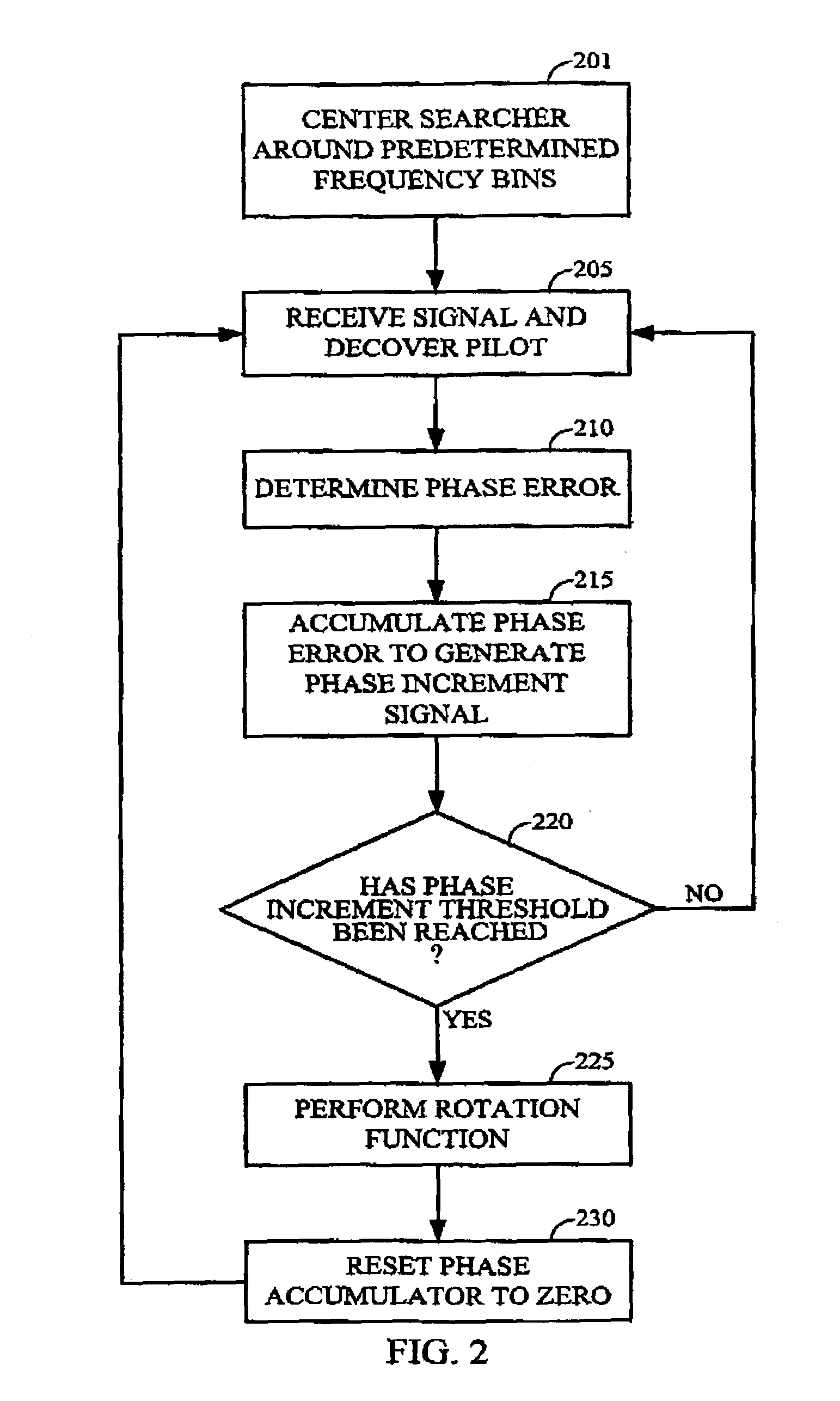

Frequency searcher and frequency-locked data demodulator using a programmable rotator

ActiveUS7020225B2Amplitude-modulated carrier systemsPhase-modulated carrier systemsControl signalEngineering

A searcher is centered on frequency bins to search for an incoming signal. The frequency locked loop generates an initial phase signal and a phase increment signal that are input to an accumulator. The accumulator accumulates the phase increments over a predetermined interval. After the interval, the accumulator generates a control signal that instructs a rotator to perform a phase rotation function.

Owner:QUALCOMM INC

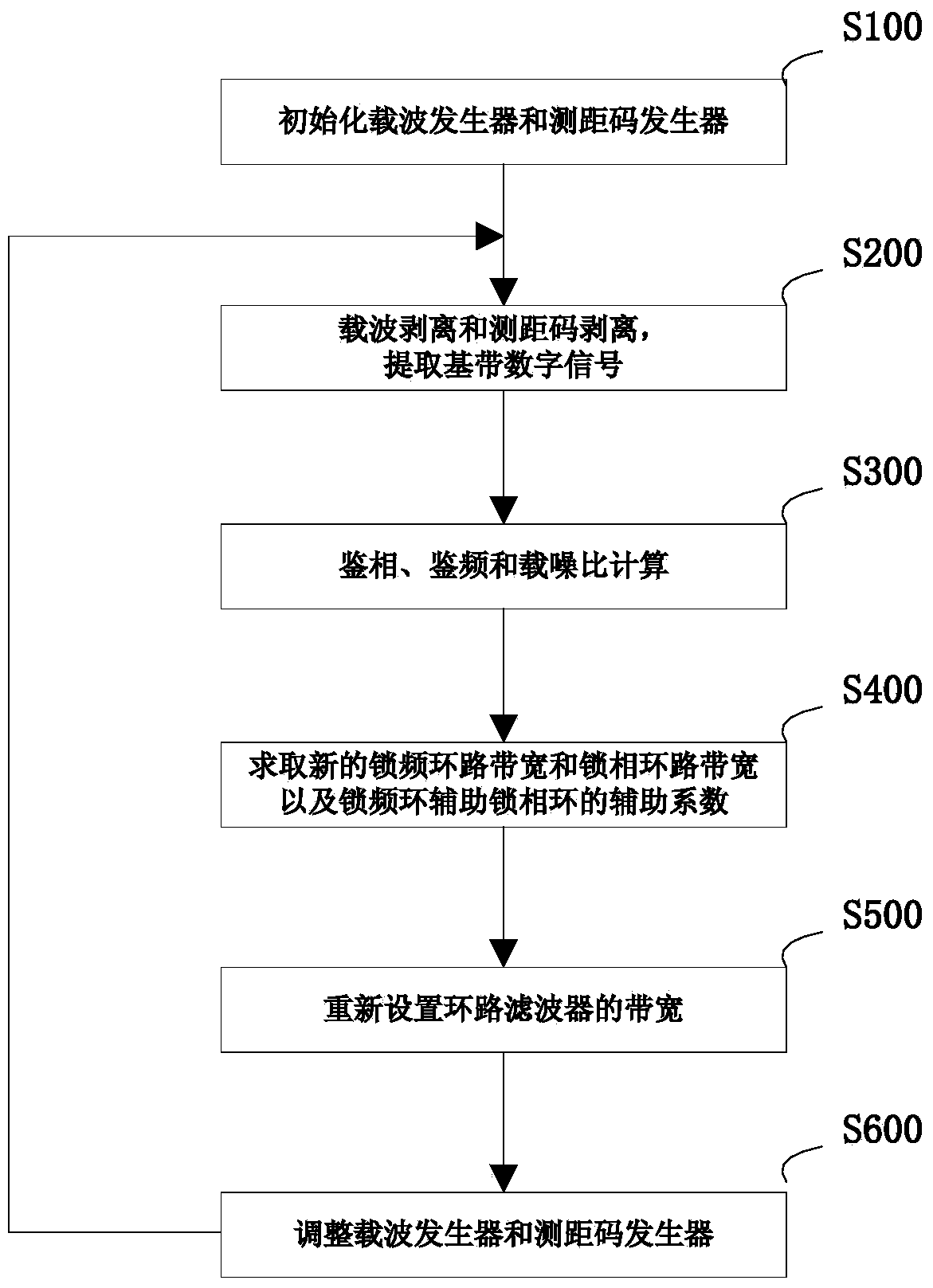

Adaptive tracking method for receiver in high-dynamic environment

ActiveCN104215981AAdjust bandwidthReduce tracking errorSatellite radio beaconingLoop filterSelf adaptive

The invention discloses an adaptive tracking method for a receiver in a high-dynamic environment. According to the adaptive tracking method, bandwidths of loop filters for a frequency-locked loop, a phase-locked loop and an auxiliary phase-locked loop of the frequency-locked loop are adjusted by detecting the dynamic property and the signal-to-noise property of tracking signals of the receiver in real time, so that optimum values of the bandwidths are kept; meanwhile, a dynamic application range of a tracking loop is widened by adjusting an auxiliary coefficient of the auxiliary phase-locked loop of the frequency-locked loop, so that stability of the tracking loop in the high-dynamic environment is improved. The adaptive tracking method for the receiver in the high-dynamic environment has the advantages that the adaptive tracking method is capable of enabling the receiver to adjust own parameters timely in a dynamic change environment, errors of tracking satellite navigation signals are kept within a small range, and the shortcomings of large tracking errors and proneness to lock loss of the receiver in the prior art are overcome.

Owner:SICHUAN JIUZHOU ELECTRIC GROUP

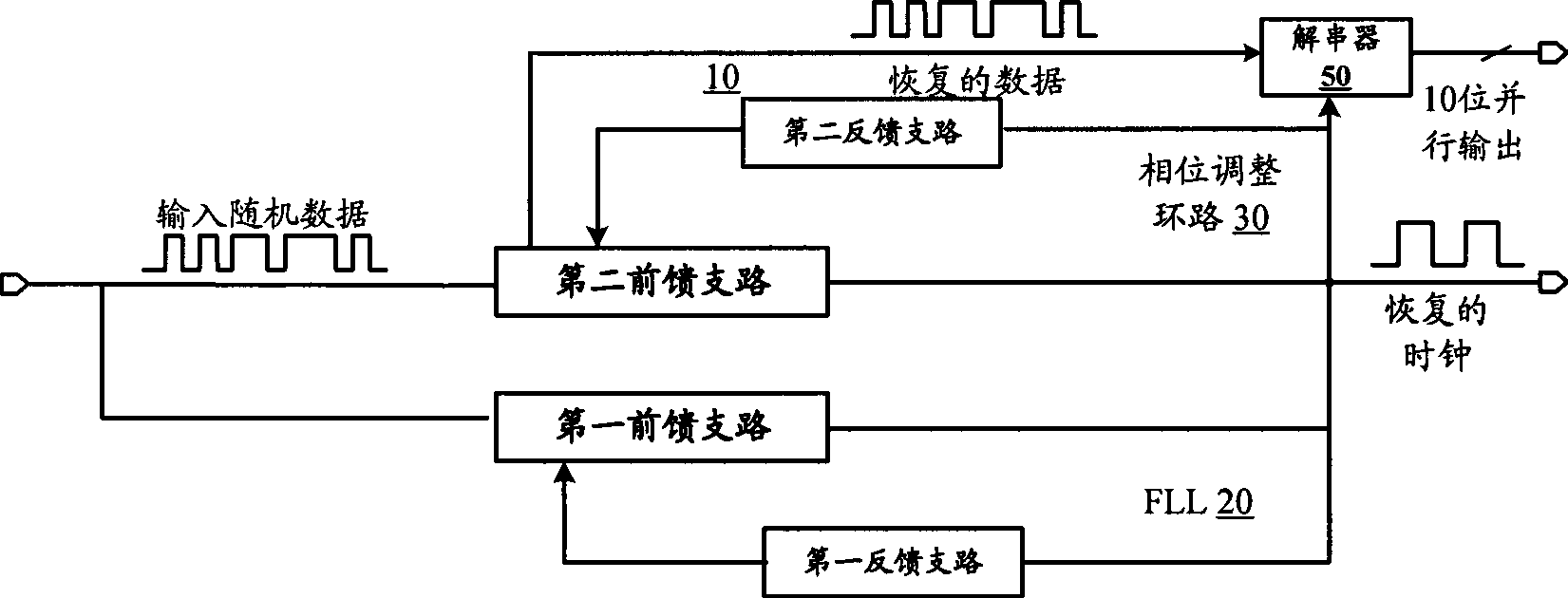

Time clock and data recovery circuit and integrated chip having the circuit

InactiveCN101394181ASimple structureLow costPulse automatic controlCathode-ray tube indicatorsEngineeringData recovery circuit

The invention provides a clock and data recovery circuit and an integrated chip provided with the circuit. The clock and data recovery circuit comprises a data channel, a frequency locking loop and a phasing loop, wherein the frequency locking loop utilizes a training signal to generate a clock signal which is locked on an expected frequency; the phasing loop utilizes the training signal to adjust the clock signal which is locked on the expected frequency to an expected phase; and the data channel utilizes recovery data of synchronous transmission of the clock signal which is locked on the expected frequency, and the clock signal which is adjusted on the expected phase. The invention has the advantages of simple structure, low cost, and easy realization.

Owner:ANALOGIX CHINA SEMICON

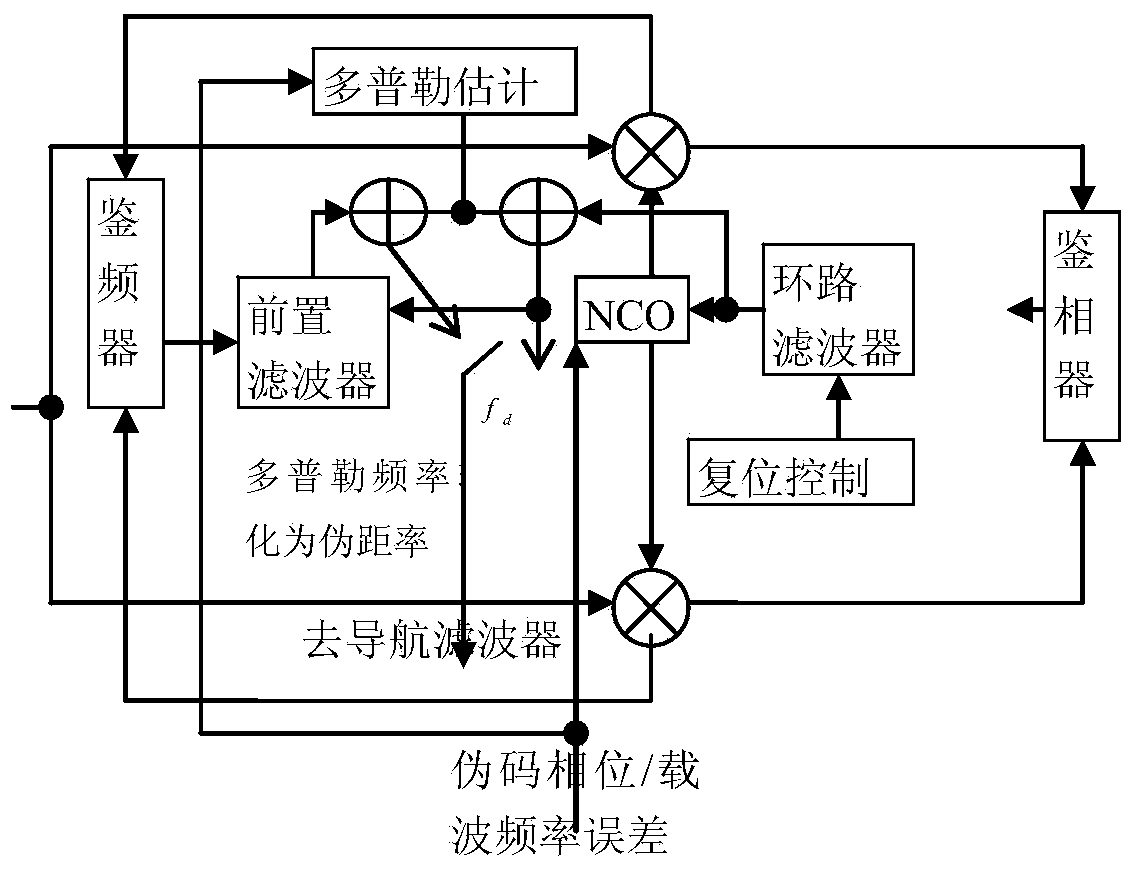

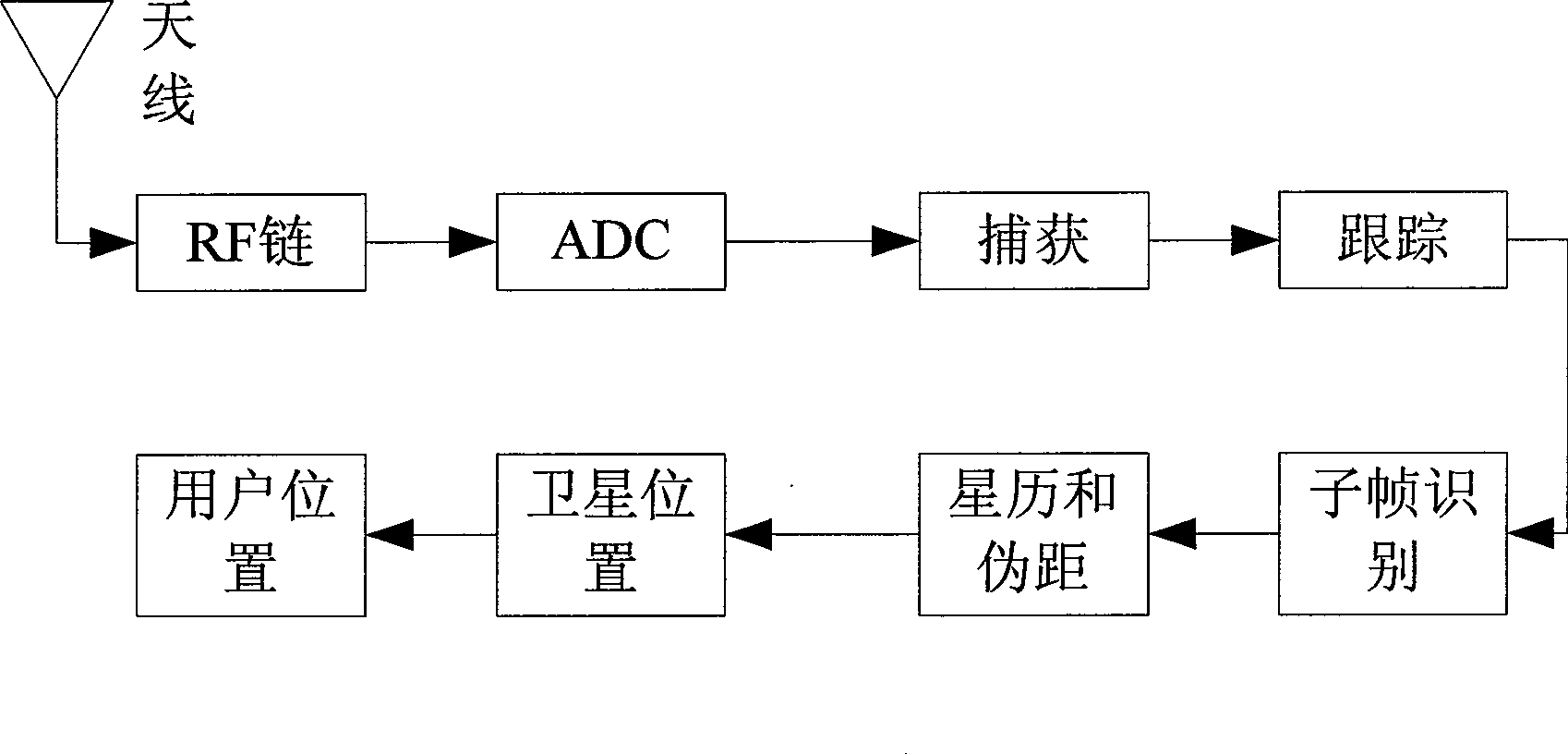

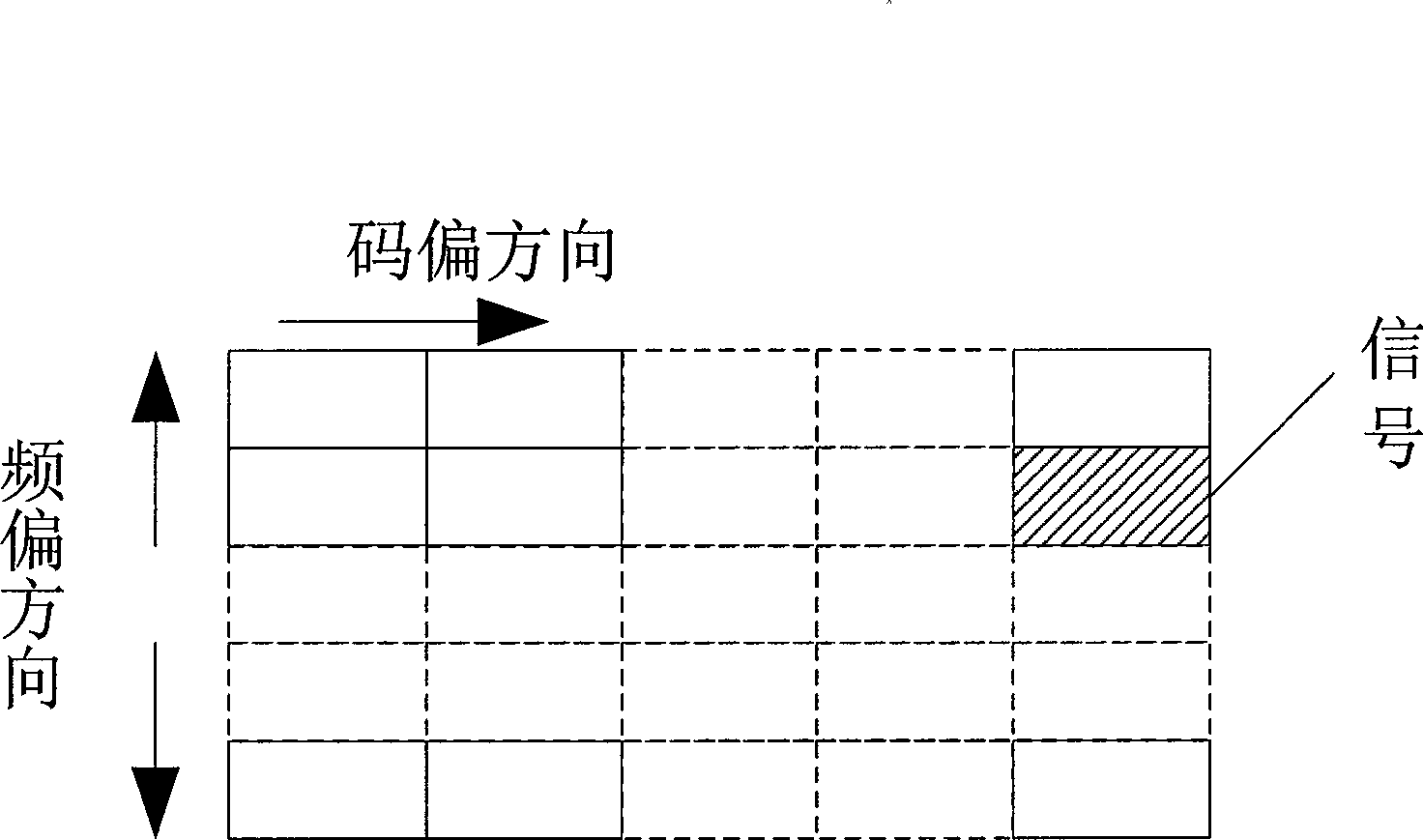

Baseband signal processing method used for GPS satellite navigation

InactiveCN105277955AHigh pseudorange accuracyImprove detection rateSatellite radio beaconingBand widthBaseband

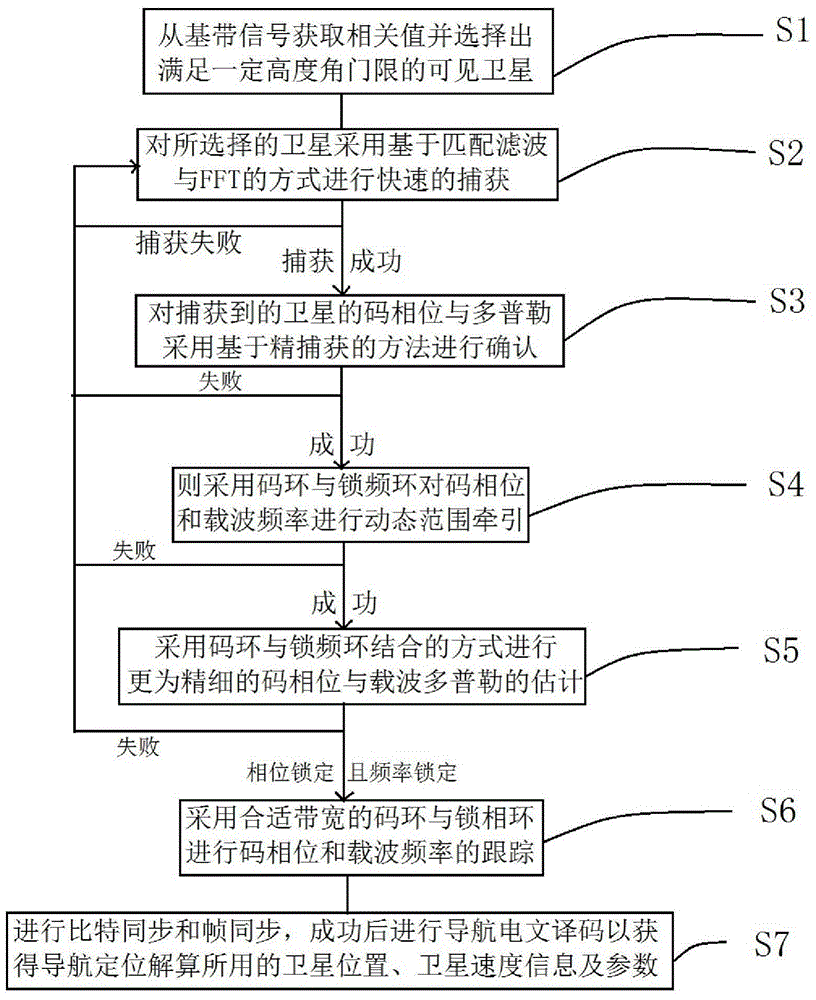

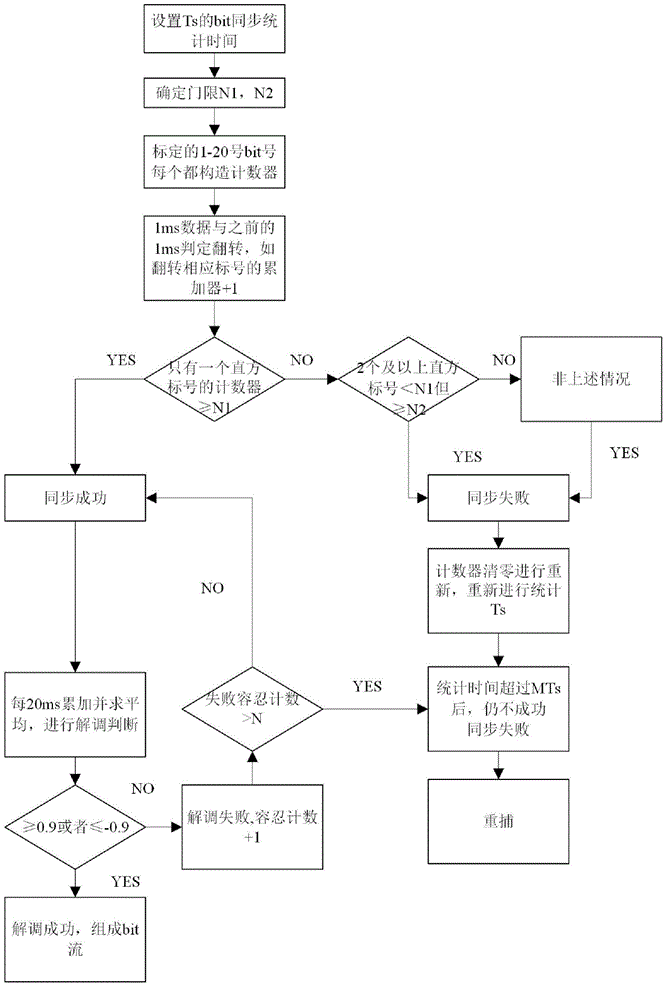

The present invention discloses a baseband signal processing method used for GPS satellite navigation. The method comprises rapidly capturing a selected satellite by using a method based on matched filtering and an FFT, thus to obtain code phase and Doppler information under large range uncertainty; confirming the code phase and Doppler information of the captured satellite by adopting a method based on fine capture; carrying out dynamic range traction on a code phase and a carrier frequency by adopting a code loop and a frequency-locked loop; tracking the code phase and the carrier frequency by adopting the code loop and the frequency-locked loop of proper bandwidths; and carrying out bit synchronization and frame synchronization, and carrying out navigation message decoding after success, thus to obtain satellite position and speed informaton and parameters used by navigational positioning calculation. With adoption of the baseband signal processing method used for GPS satellite navigation, high-quality raw observed quantities of a pseudorange and a carrier phase can be output, the precision of the pseudorange and the carrier phase is raised, and the reliability is also raised.

Owner:SHANGHAI HUACE NAVIGATION TECH

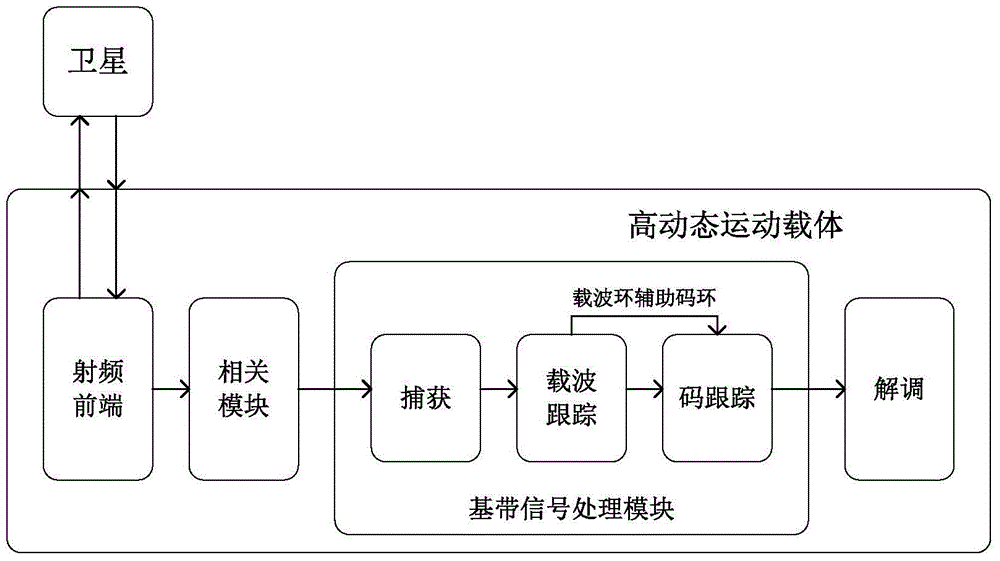

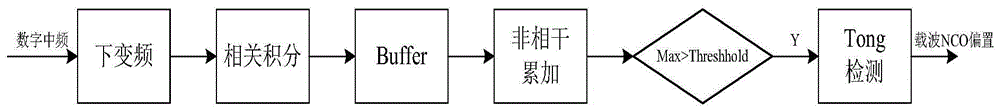

Method for capturing, tracking and receiving Beidou signal of high-dynamic movement carrier

InactiveCN104570016AEliminate DynamicsRealize code phase trackingSatellite radio beaconingNumerically controlled oscillatorCarrier signal

The invention provides a method for capturing, tracking and receiving a Beidou signal of a high-dynamic movement carrier. Through the adoption of the method, a satellite signal can be quickly captured and tracked, the capturing time is shortened, the tracking reliability is ensured, and the signal loss is avoided. The method comprises the following steps: Step 1, capturing a satellite signal of the high-dynamic movement carrier, using repeated uncorrelated accumulation and Tong detection, and obtaining a rough carrier frequency and a pseudo code phase of a received signal; Step 2, using a second-order FLL (frequency locked loop) for tracking the received signal during initial tracking so as to obtain frequency tracking errors, and at the same time, selecting a frequency tracking error for feeding back and rectifying the output carrier wave frequency of a numerically controlled oscillator (NCO) of the FLL by an output selector; Step 3, when the frequency tracking error is smaller than a preset threshold, using a third-order PLL for tracking so as to obtain phase tracking errors, at the same time, selecting the phase tracking error for feeding back and rectifying the output phase of the numerically controlled oscillator (NCO) of the FLL by the output selector, and realizing accurate tracking; Step 4, when the phase tracking error of the third-order PLL is greater than the preset threshold, returning to the Step 2 to perform the second-order FLL tracking, and completing carrier tracking.

Owner:北京航天科工世纪卫星科技有限公司

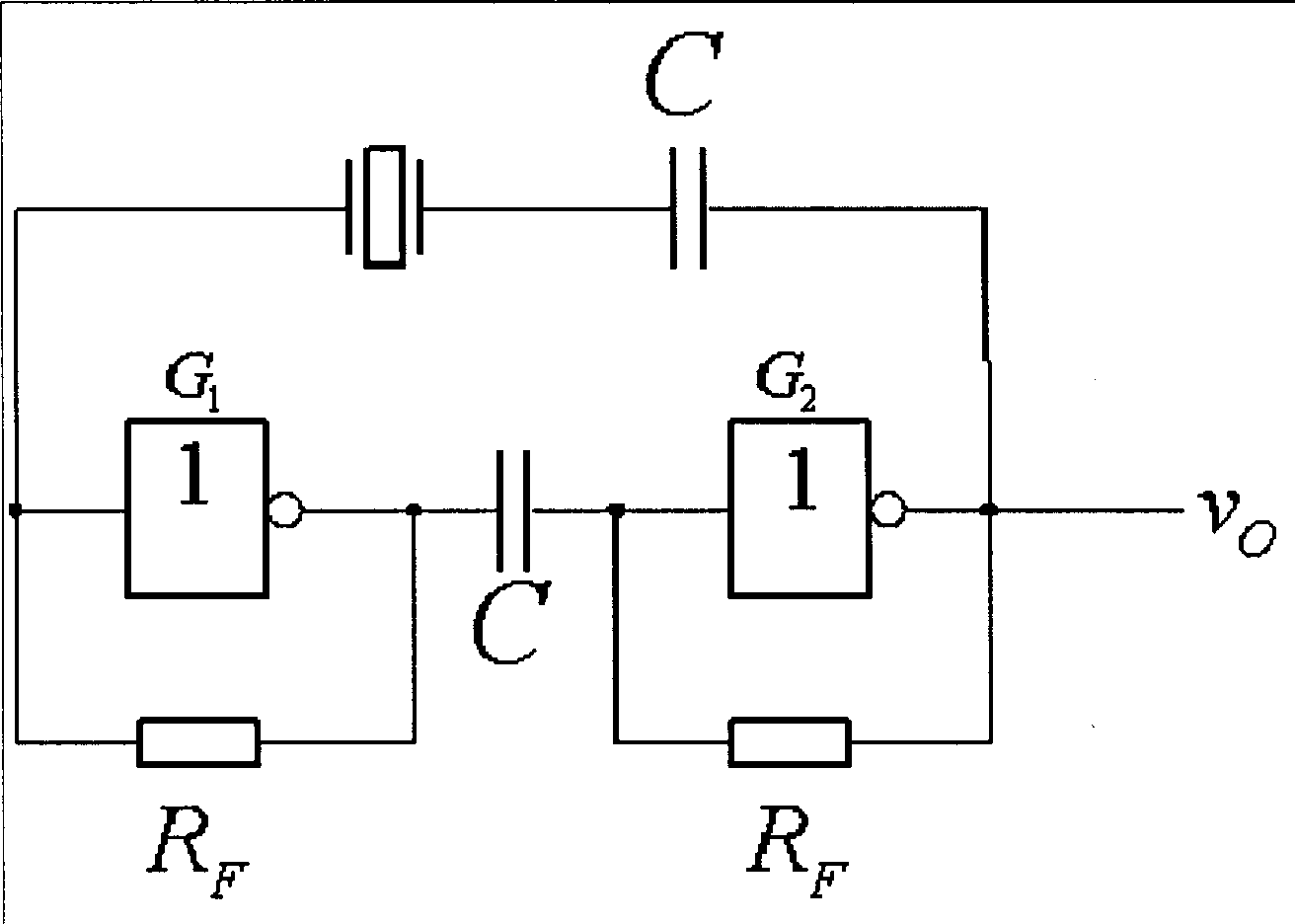

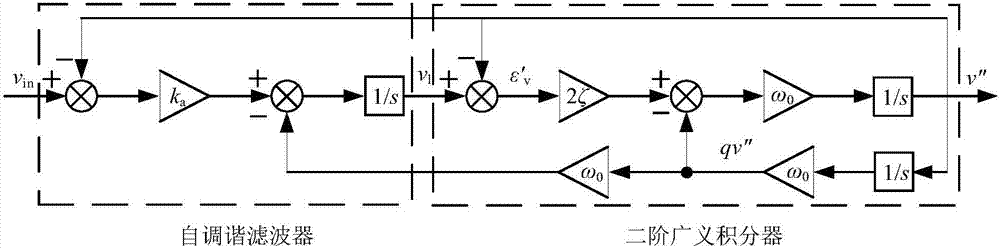

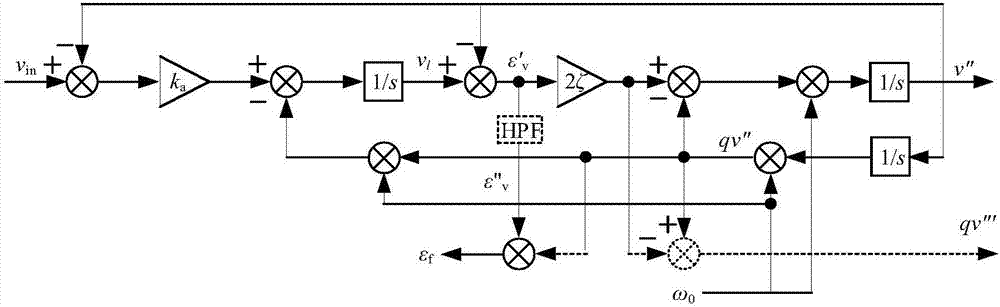

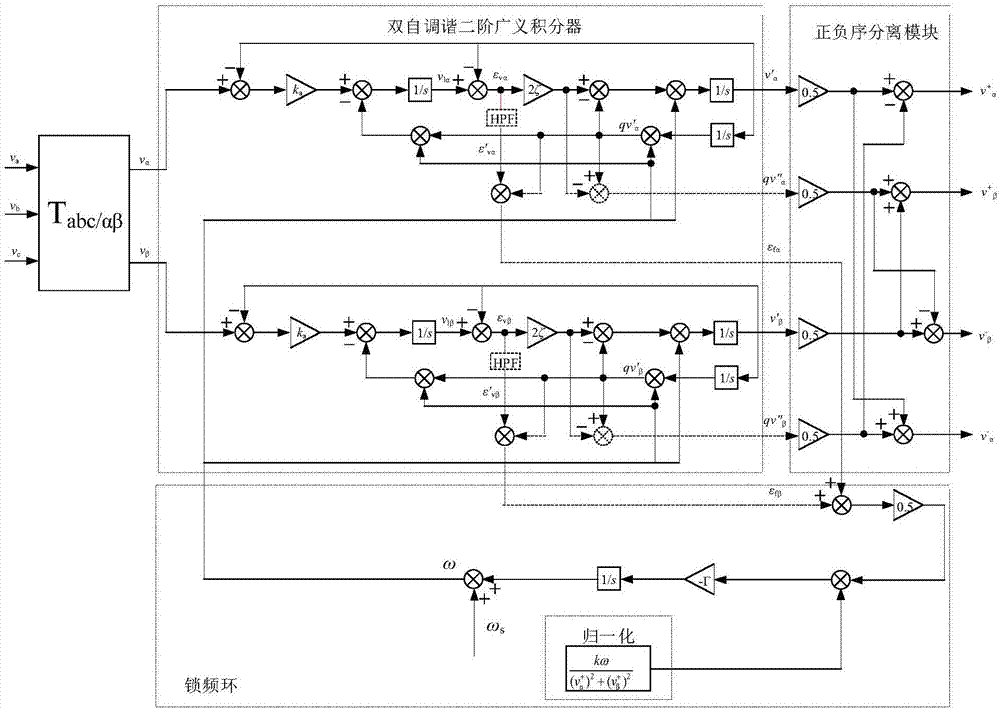

Frequency locked loop method based on double self-tuning second-order generalized integrators

ActiveCN106953634AEliminate disturbanceEliminate distractionsPulse automatic controlClimate change adaptationIntegratorNew energy

The invention discloses a frequency locked loop method based on double self-tuning second-order generalized integrators. A self-tuning filter is cascaded with the second-order generalized integrator to obtain a third-order structure of the self-tuning second-order generalized integrator, so that the self-tuning second-order generalized integrator has good filtering property in the case of serious distortion of a power grid; a differencing node and a first-order high-pass filter is imported in the structure of the self-tuning second-order generalized integrator, so that the self-tuning second-order generalized integrator has the ability of eliminating DC component disturbance; and the adaptive control of nonlinear closed loop of frequency is converted into a linear design effect by using an amplitude normalization algorithm, and the programming implementation of DSP is facilitated. The frequency locked loop method disclosed by the invention is not only suitable for normal working conditions of the power grid, and is still suitable for the faulty power grid, the structure is simple, and the method is easy to implement, thereby having a wide application prospect in new energy grid connection and other fields.

Owner:QINHUANGDAO HONGXIANG WELDING IND CO LTD

Second-order generalized integrator structure based on frequency locking loop and phase-locked loop synchronization method

ActiveCN107786201AImprove filtering effectImprove phase lock accuracyPulse automatic controlComplex mathematical operationsIntegratorHarmonic

The invention provides a second-order generalized integrator structure based on a frequency locking loop and a phase-locked loop synchronization method. The structure comprises a second-order generalized integrator, a frequency locking loop based on the second-order generalized integrator and a feedback loop; the second-order generalized integrator is used for receiving a voltage input signal of asingle-phase power grid and outputting a first orthogonal output signal and a second orthogonal output signal, wherein the voltage input signal comprises an input voltage signal and input frequency;the frequency locking loop based on the second-order generalized integrator is used for obtaining adjustment frequency and a third orthogonal output signal and a fourth orthogonal output signal according to the first orthogonal output signal; and the feedback loop is used for feeding back the adjustment frequency to the second-order generalized integrator to serve as new input frequency. The second-order generalized integrator structure based on the frequency locking loop provided by the invention improves the filtering ability of the DC components in the voltage signal, meanwhile improves the phase locking accuracy when the input signal contains the DC components and has better harmonic filtering ability.

Owner:CHINA AGRI UNIV

Carrier wave tracking method and loop for GPS signal receiver

ActiveCN103592662AImprove tracking accuracySimple calculationSatellite radio beaconingDiscriminatorPhase difference

The invention provides a carrier wave tracking method and loop for a GPS signal receiver. The method comprises the steps that 101) a GPS satellite signal is received by an antenna, and down conversion and related processing are implemented on the received GPS satellite signal to obtain related results; 102) the related results are input into a discriminator to calculate the frequency or phase difference between the received signal and a local signal, wherein the discriminator is a frequency discriminator when a carrier loop is a frequency locked loop, and the discriminator is a phase discriminator when the carrier loop is a phase locked loop; 103) a discrimination result is filtered via a Kalman filter; and 104) an output result after filtering update is then input into a loop filter for filtering, a carrier-wave Doppler frequency is further output, and local carrier waves are generated according to the carrier-wave Doppler frequency and a carrier-wave frequency. According to the invention, the carrier loop in the tracking loop is improved and optimized via improved Kalman filtering, thereby simplifying calculation while greatly improving the tracking precision for high-sensitivity GPS signals.

Owner:CHINA AEROSPACE KEGONG INFORMATION TECH RES INST

Means To Detect A Missing Pulse And Reduce The Associated PLL Phase Bump

A phase / frequency locked loop (PLL) includes circuitry adapted to detect missing pulses of a reference clock and to control the phase bump of the PLL. The circuitry includes, in part, first and second flip-flops, as well as a one-shot block. The first flip-flop has a data input terminal responsive to a voltage supply, and a clock terminal responsive to an inverse of feedback clock. The second flip-flop has a data input terminal responsive to an output of the first flip-flop, and a clock terminal responsive to the inverse of the feedback clock. The one-shot block generates a pulse in response to a rising edge of the reference clock that is used to generate the feedback clock. The one-shot block generates an output signal applied to a reset terminal of the first flip-flop.

Owner:EXAR CORP

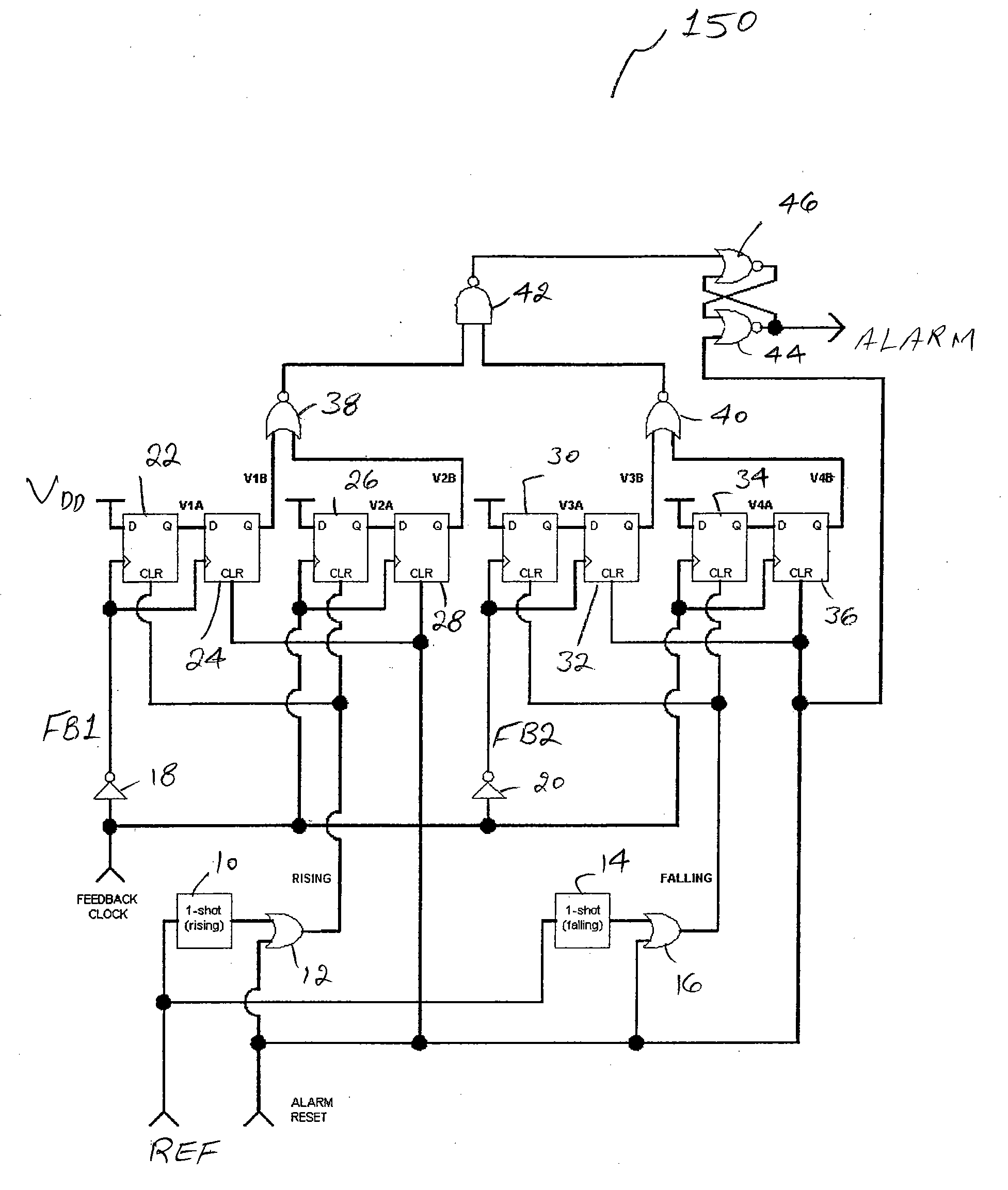

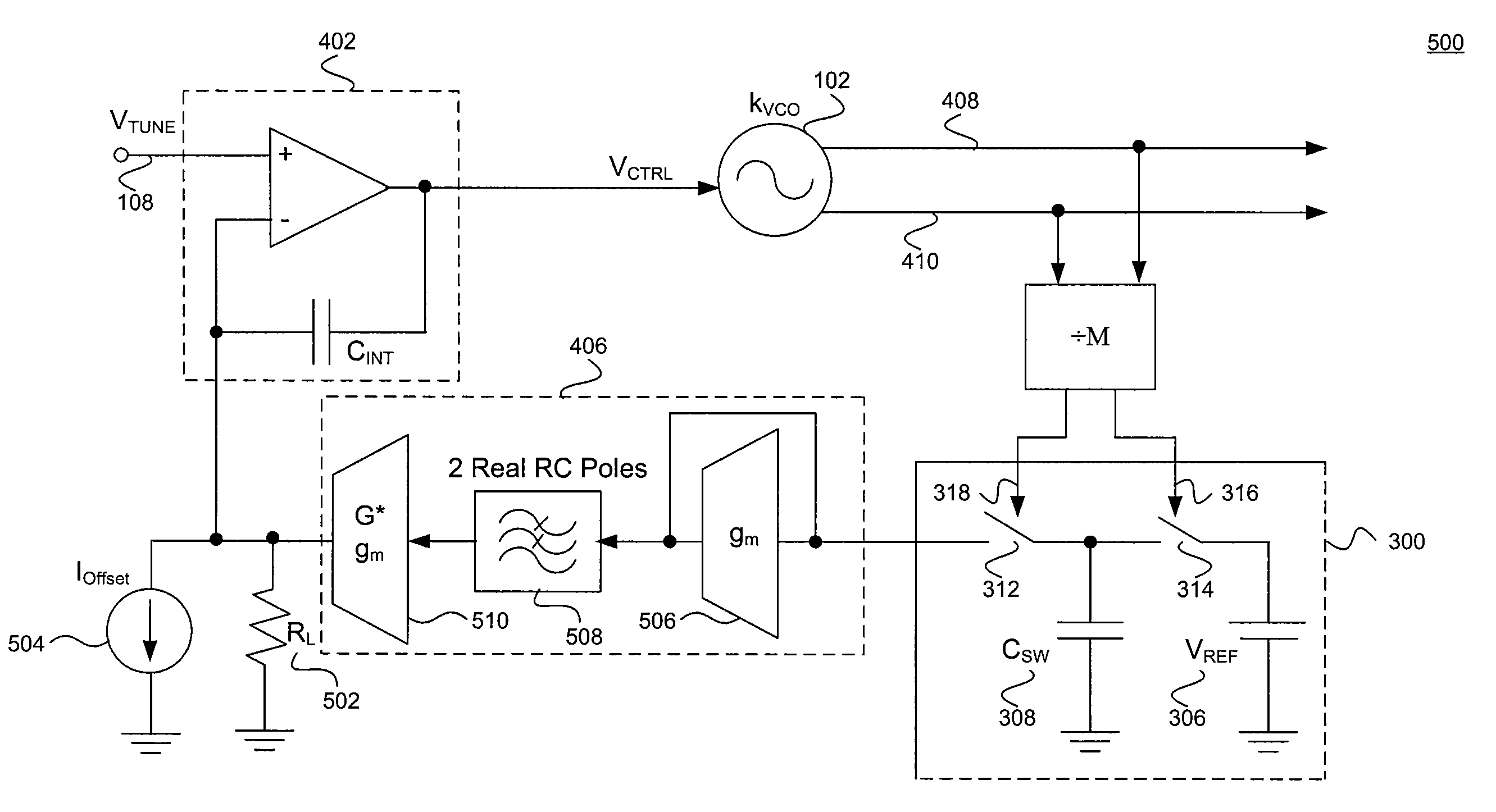

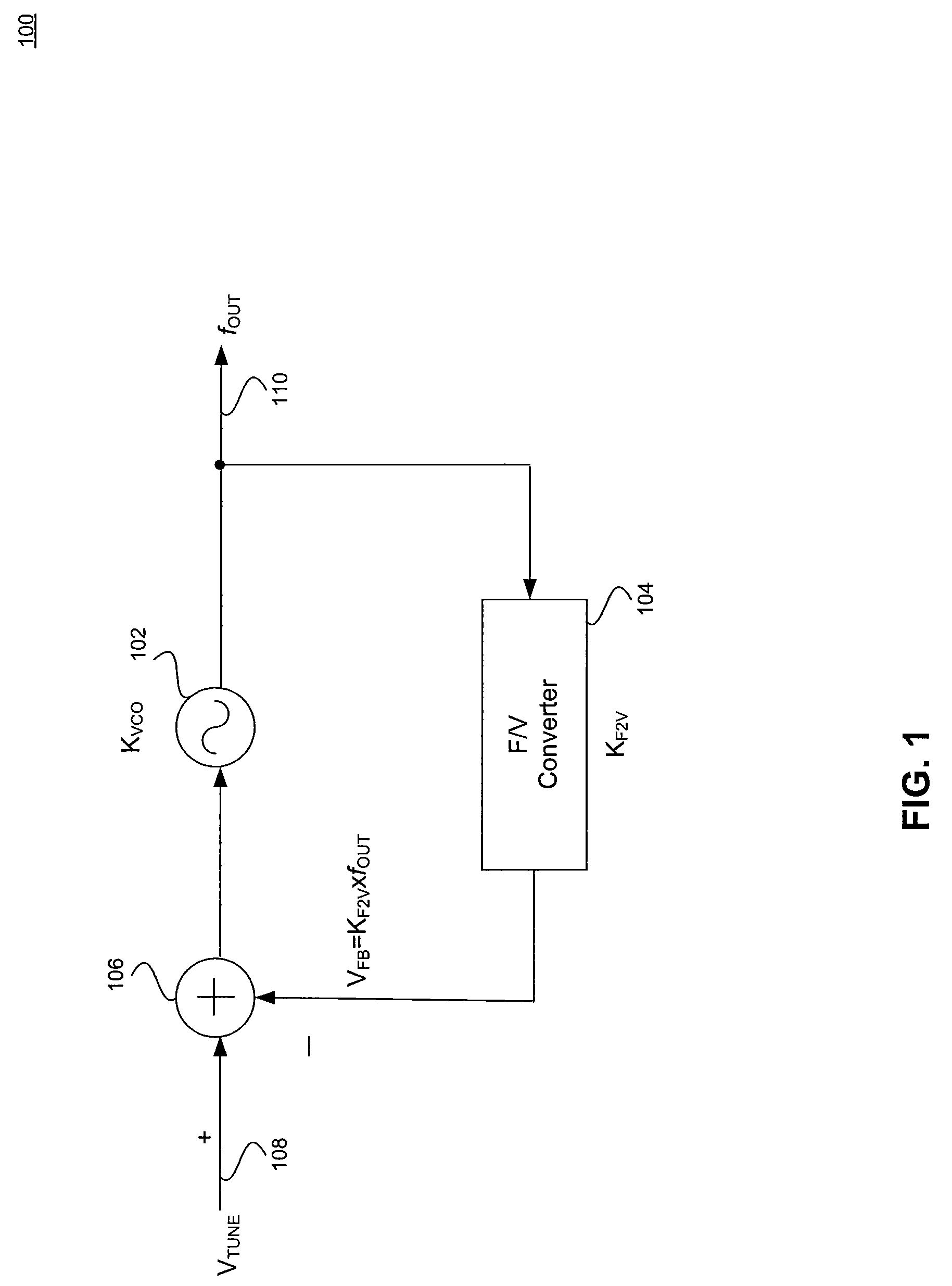

Feedback-based linearization of voltage controlled oscillator

Embodiments of the present invention enable a feedback-based VCO linearization technique. Embodiments include a frequency locked loop formed by feeding back a VCO's output into the VCO's input in negative phase by means of a frequency-to-voltage (F / V) converter. Embodiments enable constant VCO gain over a wide input tuning range and across PVT variations. Further, embodiments can be nested within a PLL, for example, with negligible area and power consumption overhead.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

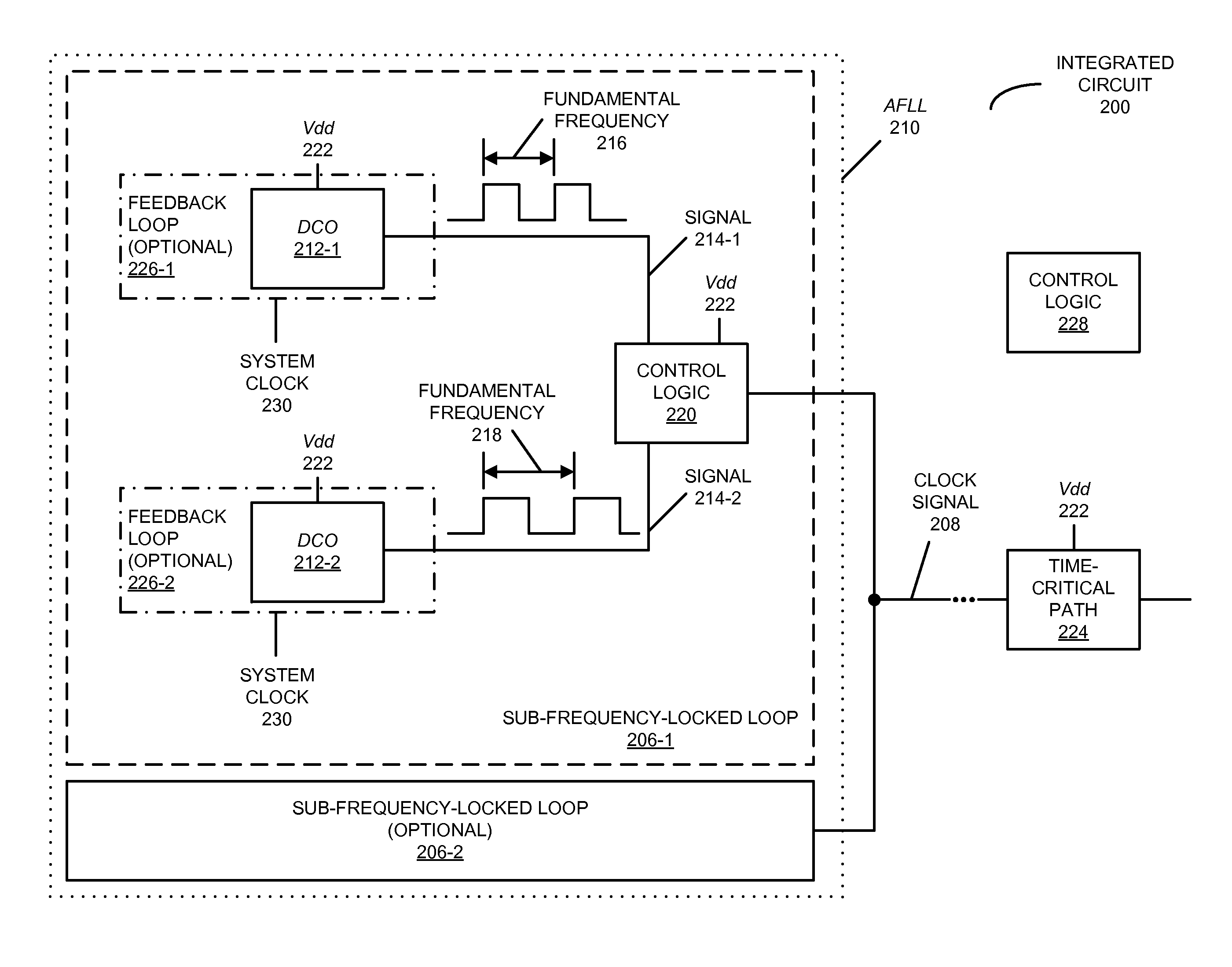

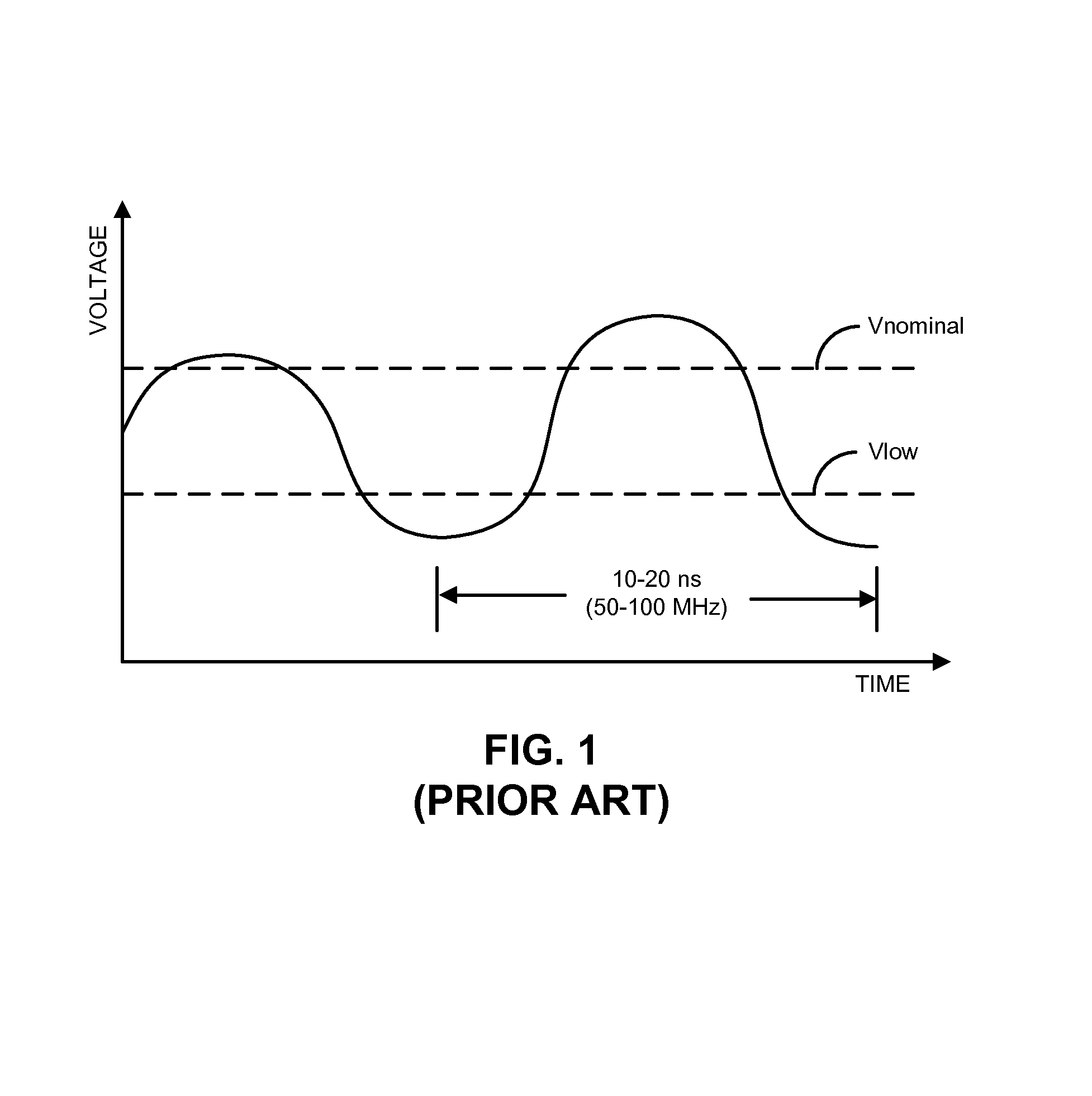

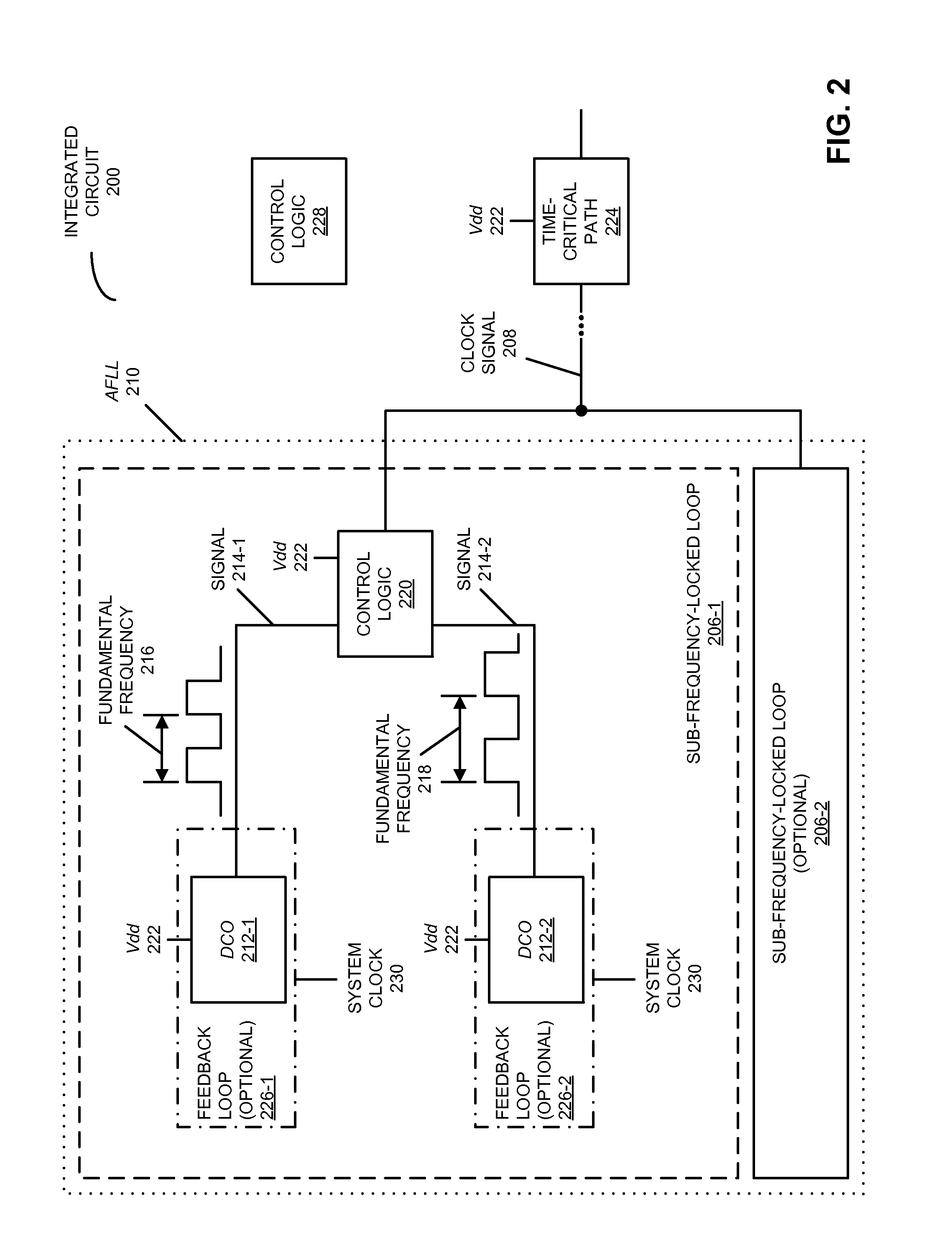

Noise suppression using an asymmetric frequency-locked loop

ActiveUS8604852B1Reduce the impactReduce impactPulse automatic controlElectric pulse generatorNon symmetricTime critical

In an integrated circuit that provides a clock signal, an asymmetric frequency-locked loop (AFLL) includes a first digitally controlled oscillator (DCO) that outputs a first signal having a first fundamental frequency, and a second DCO that outputs a second signal having a second fundamental frequency that is less than the first fundamental frequency. Moreover, the AFLL includes control logic that selects one of the first DCO and the second DCO based on an instantaneous value of a power-supply voltage and an average power-supply voltage so that an impact of power-supply voltage variations on a time-critical path in the integrated circuit is reduced. For example, the control logic may select the first DCO if the instantaneous value of the power-supply voltage is greater than the average power-supply voltage; otherwise, the control logic may select the second DCO.

Owner:ORACLE INT CORP

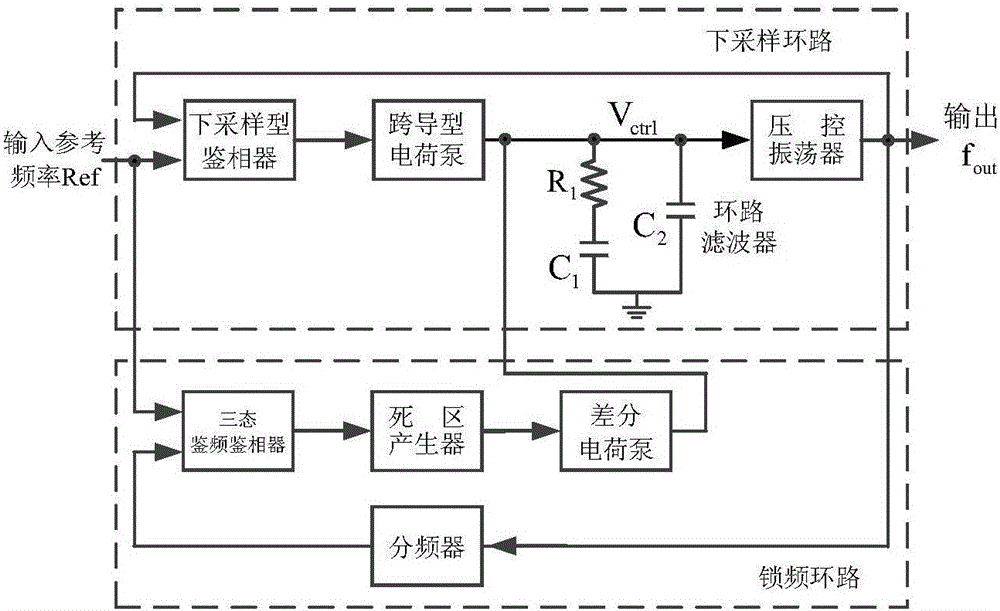

Downsampling phase locked loop for preventing in-band noise from being amplified to square times of frequency dividing ratio

The invention discloses a down-sampling phase-locked loop that prevents in-band noise from being amplified to the square of the frequency division ratio. Down-sampling phase detector, transconductance charge pump, loop filter, and voltage-controlled oscillator; frequency-locked loop, including, three-state frequency detector, dead-zone generator, differential charge pump, and frequency converter. When the down-sampling phase-locked loop circuit of the present invention is locked, the frequency-locked loop does not work, and the down-sampling loop does not contain a frequency divider, so from the reference frequency signal, the frequency and phase detector and the charge pump The noise of the phase-locked loop will not be amplified to the square of the frequency division ratio at the output of the phase-locked loop. It can be widely used in clock generation circuits based on phase-locked loops in analog integrated circuits, especially clock generation with high frequency and low phase noise. .

Owner:NO 24 RES INST OF CETC

Carrier wave tracking system and method of GPS coarse / capturing code signal

InactiveCN101435866AFast stabilizationReduce tracking error jitterPosition fixationSatellite radio beaconingNumerical controlDiscriminator

The invention provides a carrier tracking system of a GPS coarse / acquisition code signal and a method thereof. The system comprises an input signal, a loop circuit, a frequency discriminator in the loop circuit, a phase discriminator, a loop circuit filter and a numerical controlled oscillator (NCO), wherein the loop circuit is used for processing the input signal, and is combined by a frequency locked loop and a phase locked loop; the loop filter filters the output of the phase discriminator and phase discriminator; the numerical controlled oscillator (NCO) is connected with the output of the loop circuit filter. The system combines the frequency locked loop and the phase locked loop, when a frequency error is larger, the frequency locked loop plays the major role to be favorable for improving the bandwidth of a tracked loop, so that phase locking can be more easily; when the frequency error is smaller, the phase locked loop dominates to make the loop bandwidth smaller, so as to reduce noise influence and improve tracking precision.

Owner:许军

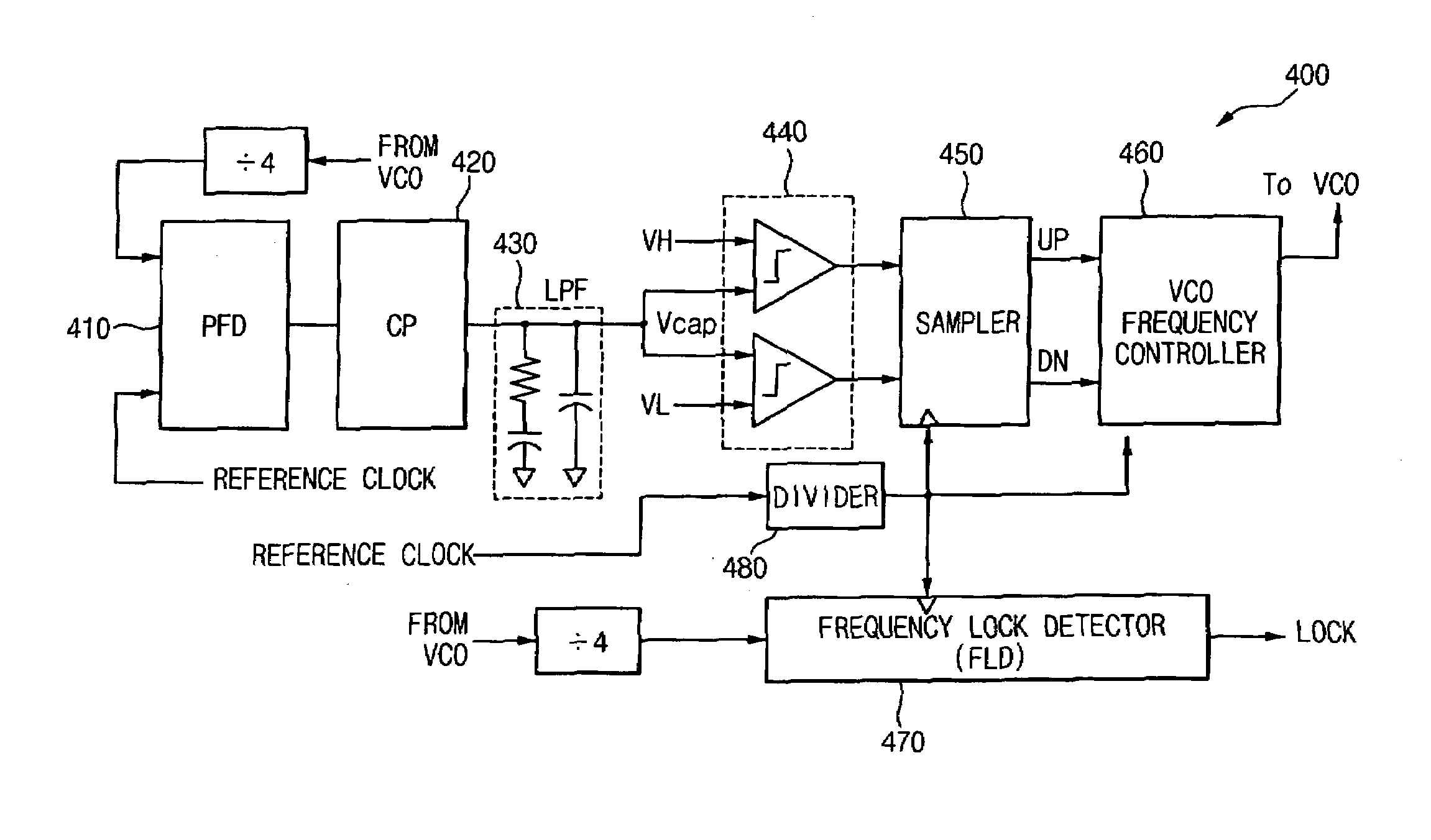

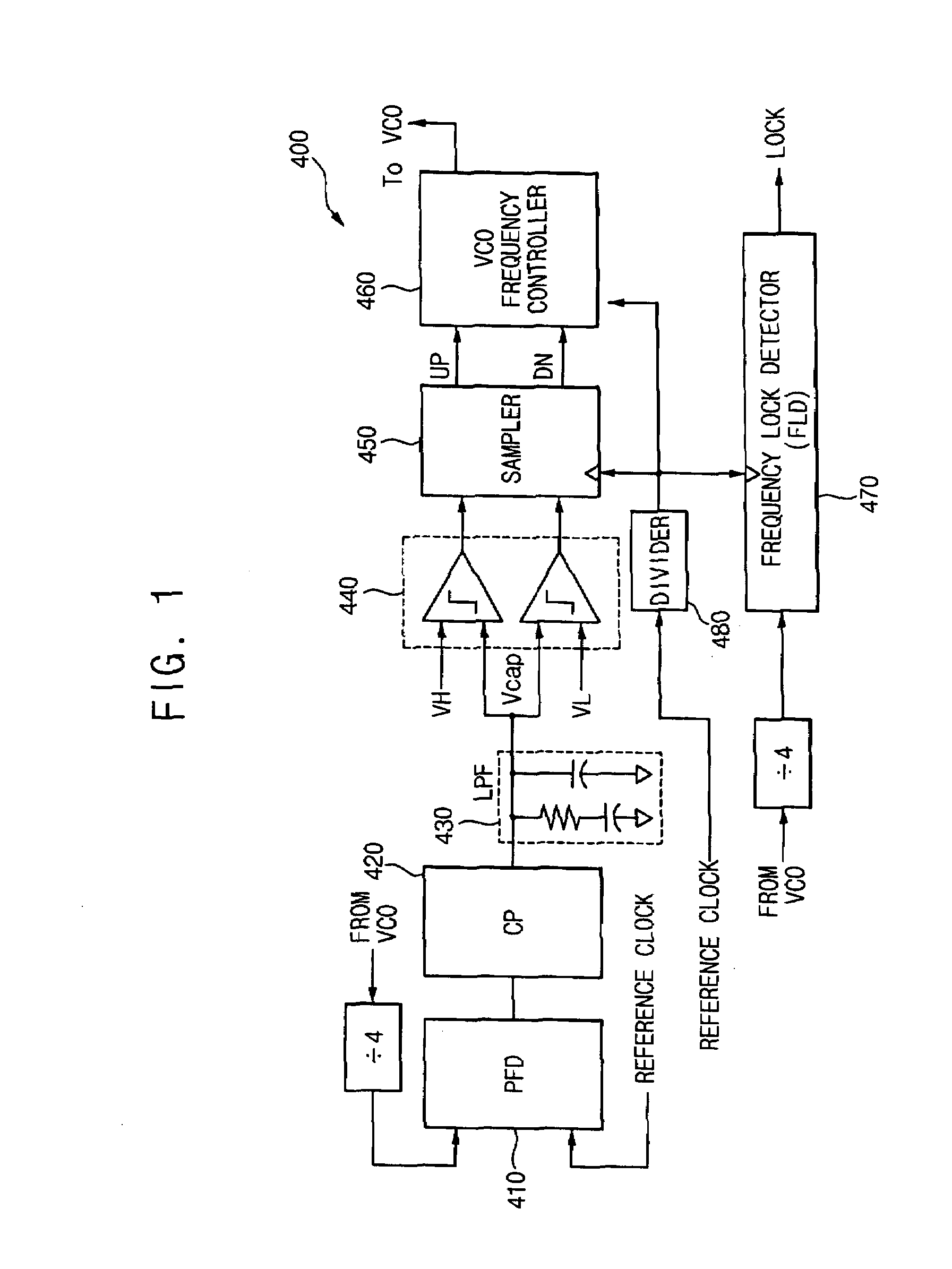

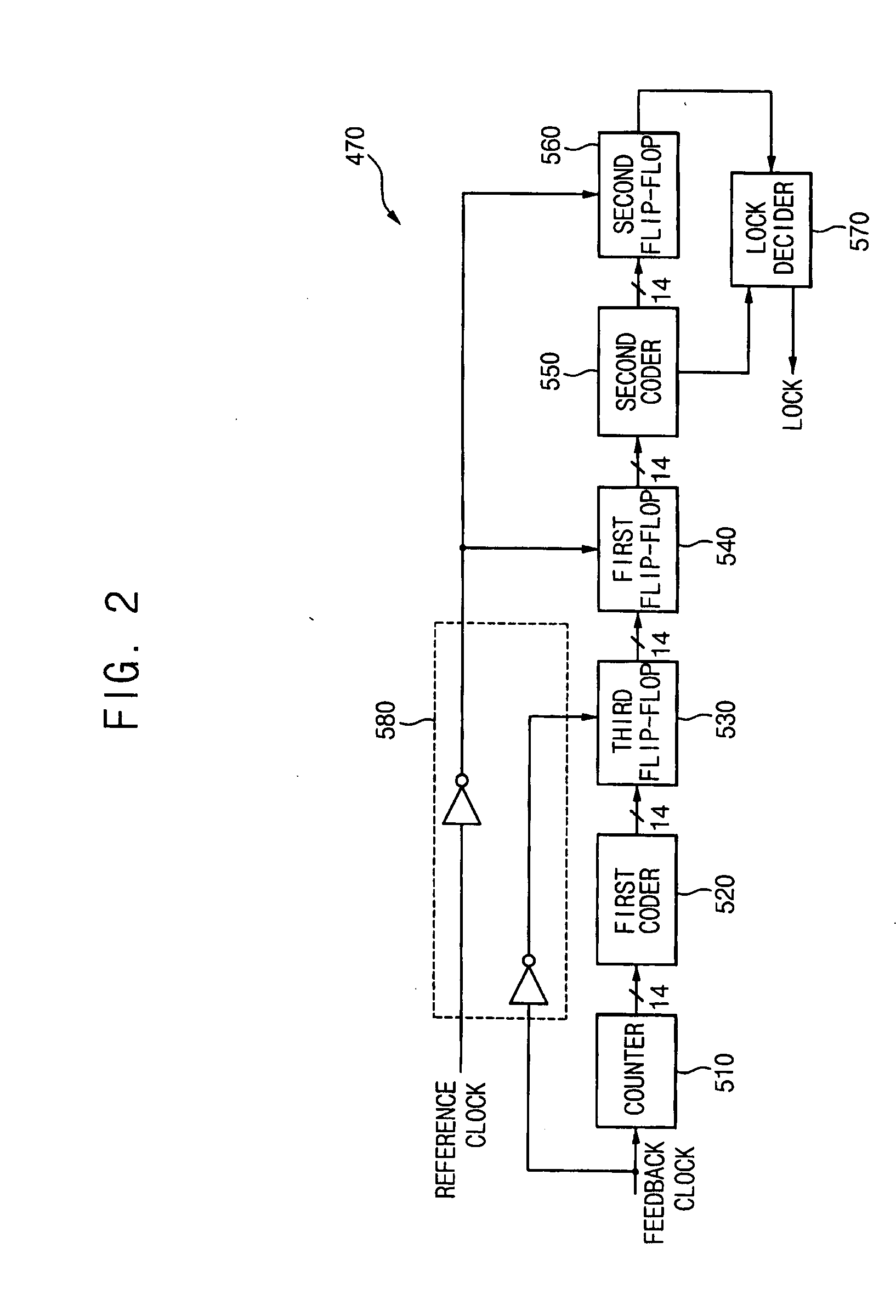

Thermometer code generator, and frequency-locked loop including the same

ActiveUS20080048904A1Improve reliabilitySimple structureElectric signal transmission systemsPulse automatic controlComputer scienceFrequency-locked loop

A thermometer code generator includes n bit storing stages that are coupled to each other, where n is an integer greater than 1, and the n bit storing stages store a thermometer code, and are adapted to increase the stored thermometer code by 1 in synchronization with a clock signal when an up signal is active, to decrease the stored thermometer code by 1 in synchronization with the clock signal when a down signal is active, and to maintain the stored thermometer code in synchronization with the clock signal when both of the up signal and the down signal are inactive.

Owner:SAMSUNG ELECTRONICS CO LTD

Advanced real-time grid monitoring system and method

ActiveUS8067932B2Increased computational burdenGood rejectionVoltage-current phase angleSingle output arrangementsPower qualityElectric power system

This invention deals with an advanced Real-time Grid Monitoring System (RTGMS) suitable for both single-phase and three-phase electric power systems. This invention provides an essential signal processing block to be used as a part of complex systems either focused on supervising and diagnosing power systems or devoted to control power processors interacting with the grid. This invention is based on a new algorithm very suitable for real-time characterization of the grid variables under distorted and unbalanced grid conditions. The main characteristic of this invention is the usage of a frequency-locked loop, based on detecting the grid frequency, for synchronizing to the grid variables. It results in a very robust system response in relation to existing technique based on the phase-angle detection since grid frequency is much more stable variable than the grid voltage / current phase-angle, mainly during grid faults. Moreover, the algorithm supporting this invention is very efficient and can be implemented in regular industrial microprocessors. These features make the RTGMS object of this invention ideal to be applied in the control of distributed generation systems (DGS), flexible AC transmission systems (FACTS), power quality conditioners (PQC) and uninterruptible power supplies (UPS). In all these systems, the fast and precise real time detection of the voltage and / or current sequence components under grid fault conditions is a crucial matter.

Owner:GAMESA INNOVATION & TECH SA

GNSS carrier loop circuit tracking method based on stochastic resonance algorithm

InactiveCN105093243AEasy to implementStable trackingSatellite radio beaconingSignal-to-noise ratio (imaging)Carrier signal

The invention discloses a GNSS carrier loop circuit tracking method based on a stochastic resonance algorithm. According to the invention, the signal to noise ratio of receiving signals is increased by integral accumulation and multiplication feedback treatment on input signals; rough tracking of frequency of the receiving signals is performed by utilizing a second-order frequency locking loop; and precise tracking is performed on the signals subjected to rough tracking by adopting a third-order phase locking loop. Therefore, precise carrier loop circuit tracking on the GNSS signals is realized in a low carrier-to-noise ratio. According to the invention, an advantage of the stochastic resonance algorithm in an aspect of improving the signal to noise ratio and an advantage of anti-interference and robustness of the cooperation of the second order frequency locking loop and the third-order phase locking loopare integrated effectively. The method is simple in hardware implementation and stable in signal tracking, and can realize stable and reliable tracking of highly dynamic satellite signals by a receiver in a severe environment.

Owner:PEKING UNIV

Method and apparatus for frequency discriminator and data demodulation in frequency lock loop of digital code division multiple access (CDMA) receivers

InactiveUS7702040B1Good estimateCarrier regulationSatellite radio beaconingDiscriminatorCode division multiple access

An embodiment and method of the present invention includes a frequency lock loop (FLL) having an improved frequency error estimation and a low bit error rate (BER) in data demodulation by calculating and using an improved averaged phase rotation using ‘valid’ phase rotation samples.

Owner:CSR TECH INC

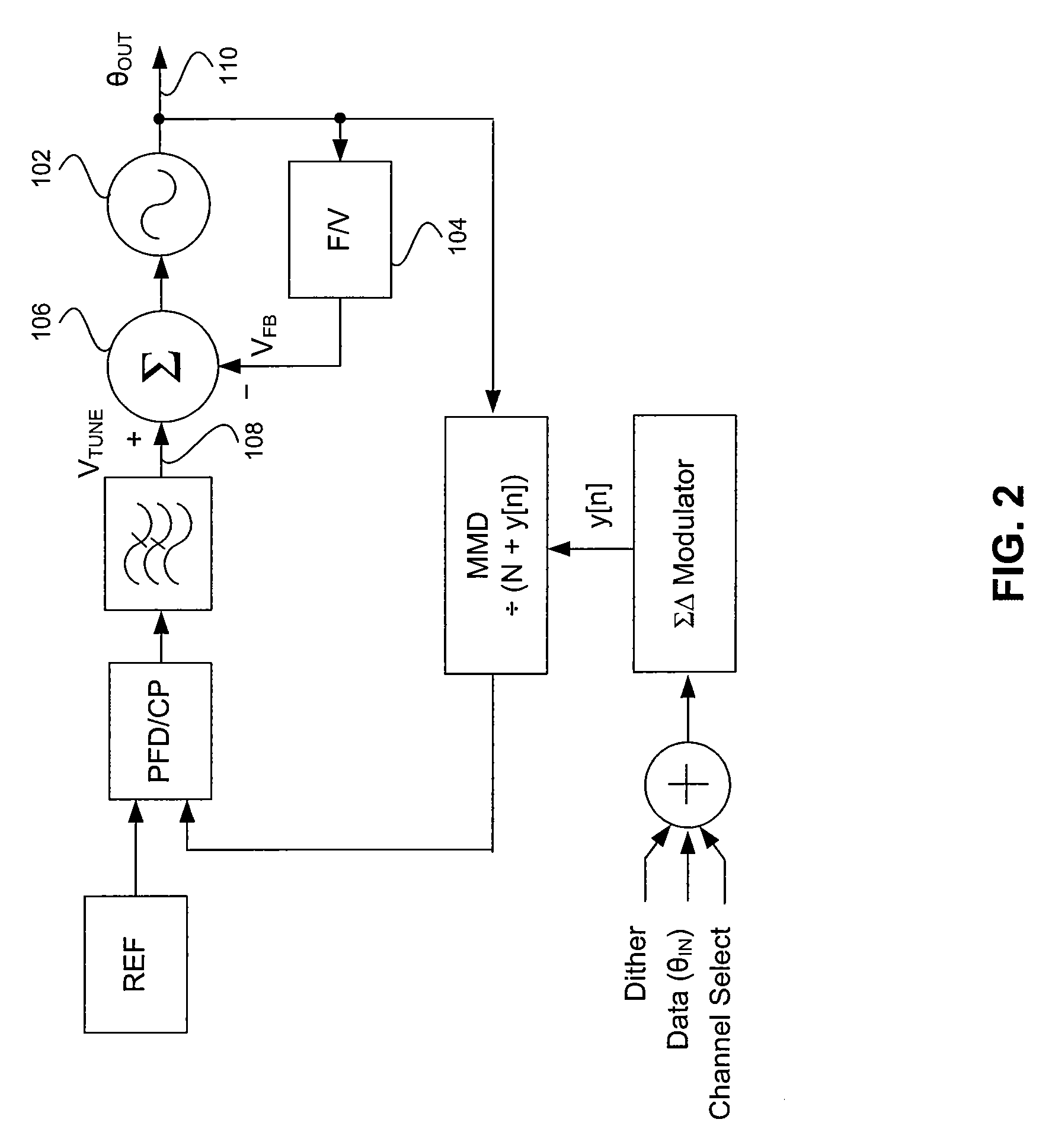

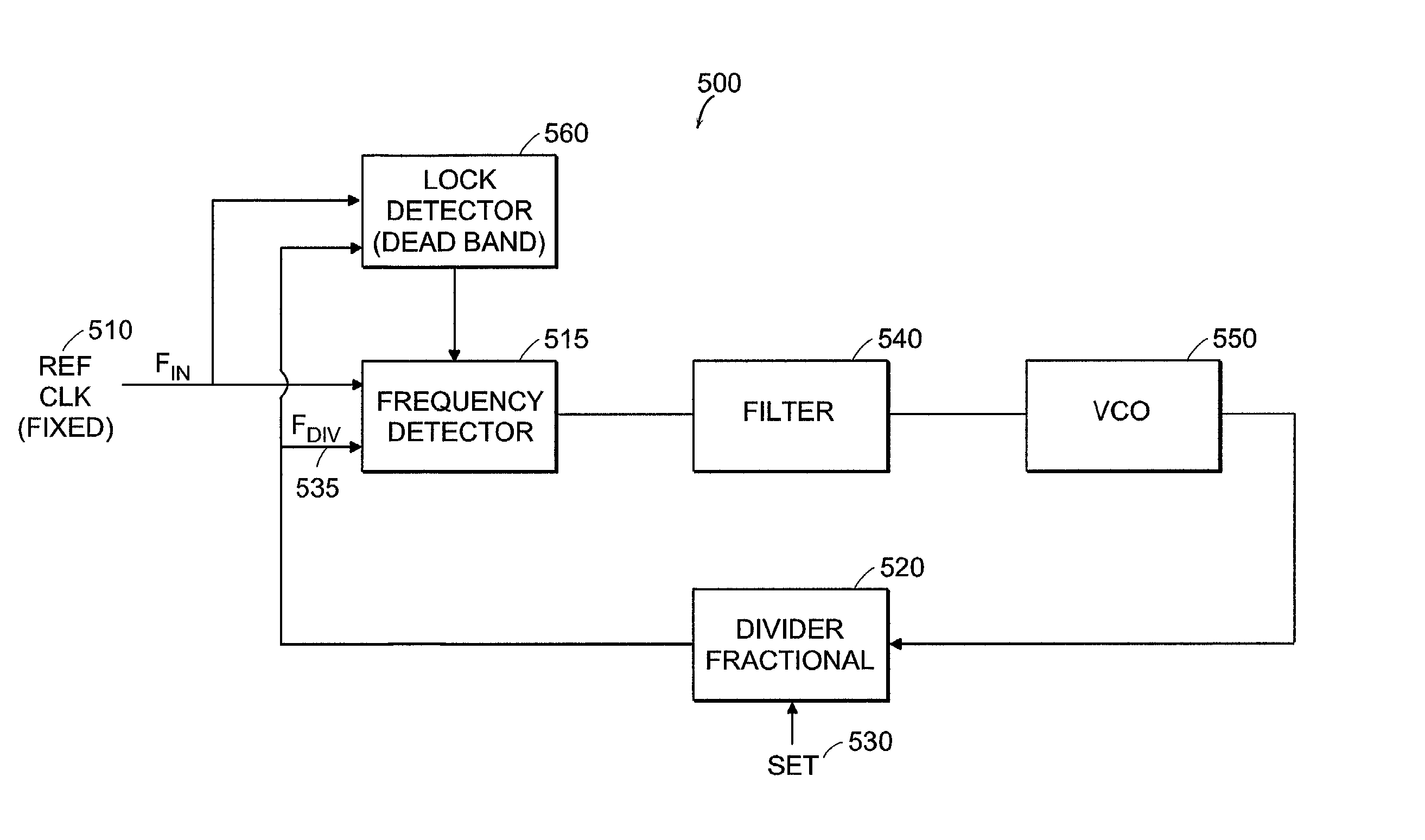

Fractional-n frequency synthesizer

InactiveUS20030007585A1Pulse automatic controlAngle demodulation by phase difference detectionDetector circuitsFrequency synthesizer

A frequency locked loop for providing an output signal having an output frequency within a predetermined range of a non-integer multiple of a reference frequency. The frequency locked loop includes a voltage element, such as a voltage controlled oscillator, which produces the output signal at the output frequency. The frequency locked loop further includes a fractional divider which is operably coupled to the voltage controlled oscillator. Further, the frequency locked loop includes a frequency detector, such as a rotational frequency detector, which is operably coupled to the fractional divider. The frequency detector receives the reference signal, such as a fixed clock signal, and the output of the fractional divider signal and outputs a frequency detector signal. In one embodiment, the rotational frequency detector responds to cycle slips of 2pi radians between the reference frequency and the output signal of the fractional divider. The frequency detector produces a signal which either increases or decreases charge on a capacitor which is read by the voltage element. The frequency locked loop may further incorporate a lock detector circuit for disabling the frequency detector when the output frequency is within the predetermined range.

Owner:2550 - ANALOG DEVICES

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com