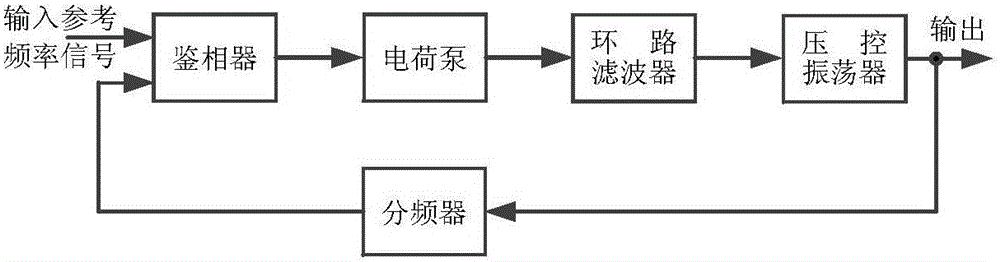

Downsampling phase locked loop for preventing in-band noise from being amplified to square times of frequency dividing ratio

A frequency division ratio, phase-locked loop technology, applied in the direction of automatic power control, electrical components, etc., can solve the problem of enlarging the frequency division ratio square times, and achieve the effect of less design difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings; it should be understood that the preferred embodiments are only for illustrating the present invention, rather than limiting the protection scope of the present invention.

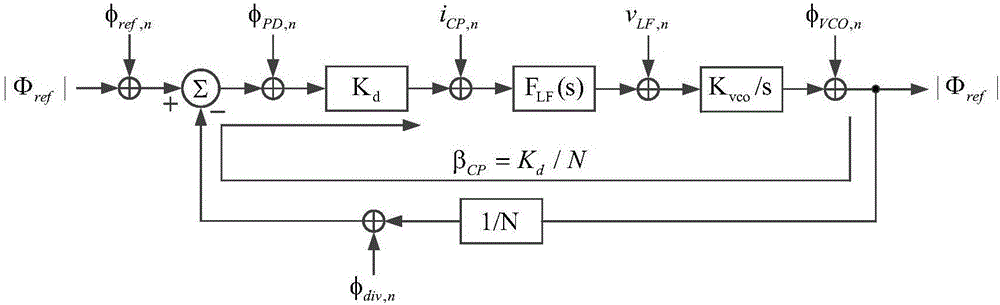

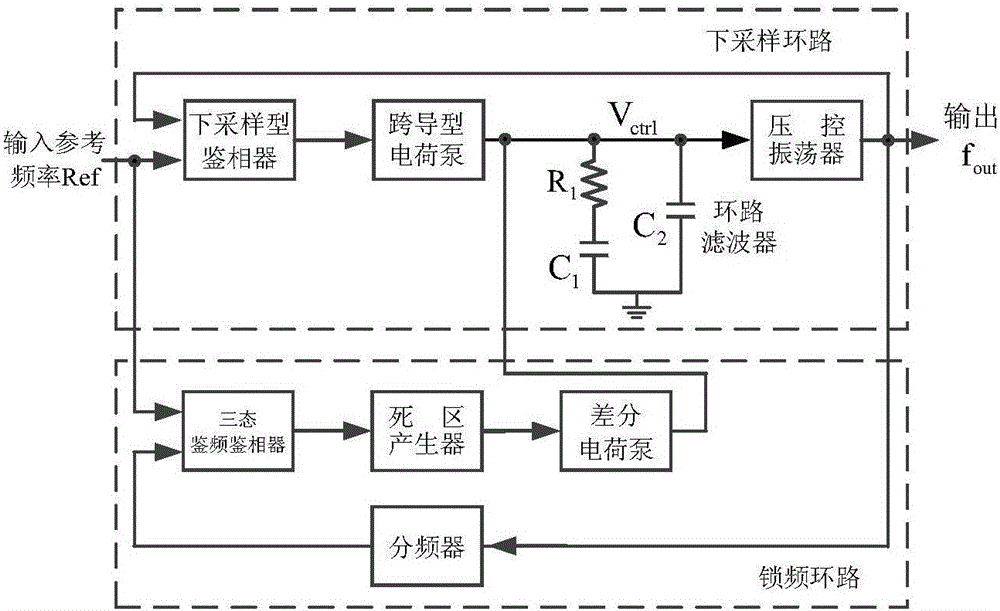

[0040] A down-sampling phase-locked loop structure that prevents in-band noise from being amplified to the square of the frequency division ratio. It is directly applied to clock generation circuits based on phase-locked loops in analog integrated circuits, especially for high frequency and low Phase noise clock generation, which includes downsampling loop and frequency-locked loop. The frequency-locked loop is responsible for reducing the difference between the product of the reference frequency and the frequency division ratio and the output frequency of the voltage-controlled oscillator. When this If the difference is small enough, the frequency-locked loop stops work...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com